TPS2556, TPS2557

JAJS440B - NOVEMBER 2009 - REVISED DECEMBER 2016

# TPS255x 高精度、可変電流制限の電力分配スイッチ

# 1 特長

- USBの電流制限要件に適合

- 電流制限を500mA~5A (標準値)の間で変更可能

- 4.5Aにおいて±6.5%の電流制限精度

- 過電流への高速な応答: 3.5µs (標準値)

- 22mΩのハイサイドMOSFET

- 動作電圧: 2.5V~6.5V

- スタンバイ時の最大消費電流: 2µA

- ソフト・スタート内蔵

- システム・レベルの15kVおよび8kV ESD耐性

- UL認定済み: ファイルNo. E169910およびCB IEC60950-1-am2 ed2.0

# 2 アプリケーション

- USBポートおよびハブ

- デジタルTV

- セットトップ・ボックス

- VOIP電話

# 3 概要

TPS255xは、正確な電流制限が必要な、または大きな容量性負荷や短絡が発生する可能性があるアプリケーション向けの電力分配スイッチです。これらのデバイスは、外付け抵抗により電流制限スレッショルドを500mA~5A (標準値)の範囲でプログラム可能です。この電源スイッチの立ち上がりおよび立ち下がり時間は、オン/オフ時の電流サージを最小限に抑えるように制御されます。

TPS255xデバイスは、出力負荷が電流制限スレッショルドを超過したときに、定電流モードを使用して、出力電流を安全なレベルに制限します。過電流および過熱状態の間、FAULTロジック出力はLOWにアサートされます。

#### 製品情報(1)

| 型番              | パッケージ    | 本体サイズ(公称)     |  |  |

|-----------------|----------|---------------|--|--|

| TPS2556、TPS2557 | VSON (8) | 3.00mm×3.00mm |  |  |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にある注文情報を参照してください。

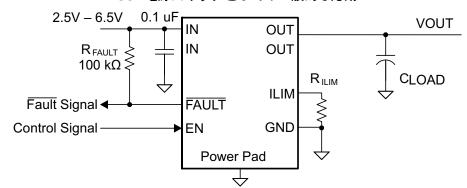

# USB電源スイッチとしての一般的な応用

Copyright © 2016, Texas Instruments Incorporated

# 目次

| 1 | 特長1                                  |    | 9.3 Feature Description        | 11 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | アプリケーション1                            |    | 9.4 Device Functional Modes    |    |

| 3 | 概要1                                  | 10 | Application and Implementation | 13 |

| 4 | 改訂履歴2                                |    | 10.1 Application Information   | 13 |

| 5 | Device Comparison Table3             |    | 10.2 Typical Applications      | 13 |

| 6 | Pin Configuration and Functions      | 11 | Power Supply Recommendations   | 18 |

| 7 | Specifications4                      | 12 | Layout                         | 19 |

| • | 7.1 Absolute Maximum Ratings         |    | 12.1 Layout Guidelines         | 19 |

|   | 7.2 ESD Ratings                      |    | 12.2 Layout Example            | 19 |

|   | 7.3 Recommended Operating Conditions |    | 12.3 Thermal Considerations    |    |

|   | 7.4 Thermal Information              | 13 | デバイスおよびドキュメントのサポート             |    |

|   | 7.5 Electrical Characteristics 5     |    | 13.1 関連リンク                     |    |

|   | 7.6 Switching Characteristics        |    | 13.2 ドキュメントの更新通知を受け取る方法        |    |

|   | 7.7 Typical Characteristics          |    | 13.3 コミュニティ・リソース               |    |

| 8 | Parameter Measurement Information 10 |    | 13.4 商標                        |    |

| 9 | Detailed Description 11              |    | 13.5 静電気放電に関する注意事項             |    |

|   | 9.1 Overview 11                      |    | 13.6 用語集                       |    |

|   | 9.2 Functional Block Diagram 11      | 14 | メカニカル、パッケージ、および注文情報            | 21 |

|   |                                      |    |                                |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Revision A (Feburary 2012) から Revision B に変更

**Page**

| 「製品情報」表、「デバイス比較表」、「ピン構成および機能」セクション、「仕様」セクション、「ESD定格」表、「アプリケーションと<br>実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セク<br>ション、「メカニカル、パッケージ、および注文情報」セクション 追加 |                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| データシートの末尾にあるパッケージ・オプションの追記を参照し、「注文情報」表を削除                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Added Thermal Information table                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changed R <sub>0JC(top)</sub> value in <i>Thermal Information</i> table From: 10.7°C/W To: 54.5°C/W                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                          |

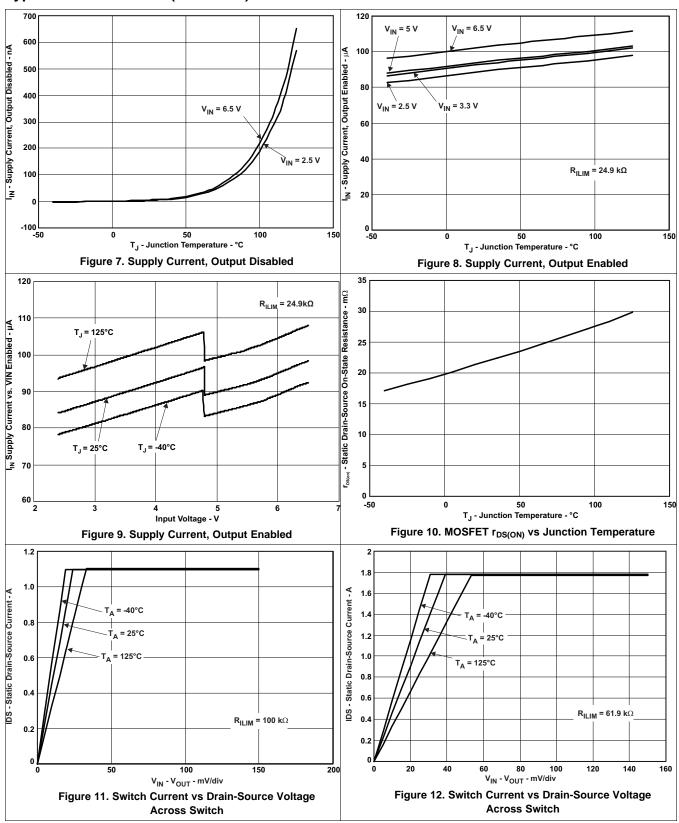

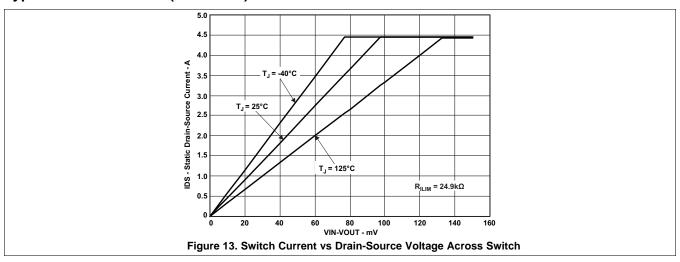

| Changed Figure 11 title From: Current Limit Threshold Vs R <sub>ILM</sub> To: Switch Current vs Drain-Source Voltage Across Switch                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changed Figure 12 title From: Current Limit Threshold Vs R <sub>ILM</sub> To: Switch Current vs Drain-Source Voltage Across Switch                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                         | 実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクション 追加 1 データシートの末尾にあるパッケージ・オプションの追記を参照し、「注文情報」表を 削除 Added <i>Thermal Information</i> table Changed R <sub>0JC(top)</sub> value in <i>Thermal Information</i> table From: 10.7°C/W To: 54.5°C/W Changed Figure 11 title From: Current Limit Threshold Vs R <sub>ILM</sub> To: Switch Current vs Drain-Source Voltage Across Switch |

# 2009年11月発行のものから更新

Page

| • | Changed V <sub>EN</sub> to V <sub>EN</sub> in <i>Recommended Operating Conditions</i> table | 4 |

|---|---------------------------------------------------------------------------------------------|---|

| • | Changed V <sub>EN</sub> to V <sub>EN</sub> in Recommended Operating Conditions table        | 4 |

# 5 Device Comparison Table

| 33 mΩ, SINGLE      | 80 mΩ, SINGLE   | 80 mΩ, DUAL     | 80 mΩ, DUAL    | 80 mΩ, TRIPLE   | 80 mΩ, QUAD     | 80 mΩ, QUAD    |

|--------------------|-----------------|-----------------|----------------|-----------------|-----------------|----------------|

|                    |                 |                 | 1-0-0-1        |                 | <del></del>     |                |

| TPS201xA 0.2 A-2 A | TPS2014 600 mA  |                 |                | 1 0 1           |                 | 100            |

| TPS202x 0.2 A-2 A  | TPS2015 1 A     | TPS2042B 500 mA | TPS2080 500 mA |                 |                 |                |

| TPS203x 0.2 A-2 A  | TPS2041B 500 mA | TPS2052B 500 mA | TPS2081 500 mA | TPS2043B 500 mA | ''              | ''             |

|                    | TPS2051B 500 mA | TPS2046B 250 mA | TPS2082 500 mA | TPS2053B 500 mA | TPS2044B 500 mA | TPS2085 500 mA |

|                    | TPS2045A 250 mA | TPS2056 250 mA  | TPS2090 250 mA | TPS2047B 250 mA | TPS2054B 500 mA | TPS2086 500 mA |

|                    | TPS2049 100 mA  | TPS2062 1 A     | TPS2091 250 mA | TPS2057A 250 mA | TPS2048A 250 mA | TPS2087 500 mA |

|                    | TPS2055A 250 mA | TPS2066 1 A     | TPS2092 250 mA | TPS2063 1 A     | TPS2058 250 mA  | TPS2095 250 mA |

|                    | TPS2061 1 A     | TPS2060 1.5 A   |                | TPS2067 1 A     |                 | TPS2096 250 mA |

|                    | TPS2065 1 A     | TPS2064 1.5 A   |                |                 |                 | TPS2097 250 mA |

|                    | TPS2068 1.5 A   |                 |                |                 |                 |                |

|                    | TPS2069 1.5 A   |                 |                |                 |                 |                |

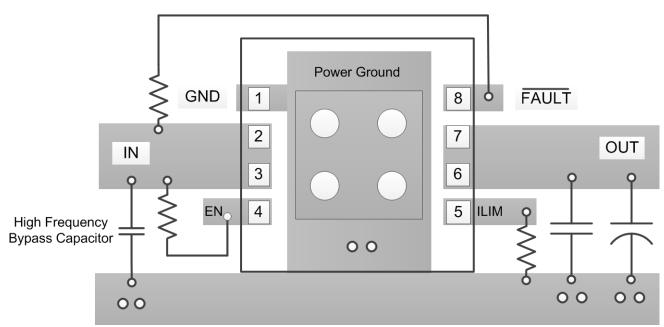

# 6 Pin Configuration and Functions

TPS2556:  $\overline{\text{EN}}$  pin is active low. TPS2557: EN pin is active high.

#### **Pin Functions**

|           | PIN      |          | PIN |                                                                                                                                     | I/O | DESCRIPTION |

|-----------|----------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

| NAME      | TPS2556  | TPS2557  | 1/0 | DESCRIPTION                                                                                                                         |     |             |

| EN        | 4        | _        | I   | Enable input: Logic low turns on power switch. Applicable to the TPS2556.                                                           |     |             |

| EN        | _        | 4        | I   | Enable input: Logic high turns on power switch. Applicable to the TPS2557.                                                          |     |             |

| FAULT     | 8        | 8        | 0   | Active-low open-drain output: Asserted during overcurrent or overtemperature conditions.                                            |     |             |

| GND       | 1        | 1        |     | Ground connection: Connect externally to PowerPAD.                                                                                  |     |             |

| ILIM      | 5        | 5        | 0   | External resistor used to set current-limit threshold. TI recommends 20 k $\Omega$ $\leq$ R <sub>ILIM</sub> $\leq$ 187 k $\Omega$ . |     |             |

| IN        | 2, 3     | 2, 3     | 1   | Input voltage: Connect a 0.1-µF or greater ceramic capacitor from IN to GND as close to the IC as possible.                         |     |             |

| OUT       | 6, 7     | 6, 7     | 0   | Power-switch output.                                                                                                                |     |             |

| PowerPAD™ | PowerPAD | PowerPAD | _   | Internally connected to GND. Used to heat-sink the part to the circuit board traces. Connect PowerPAD to GND pin externally.        |     |             |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                       |                                         | MIN                     | MAX                | UNIT |

|---------------------------------------|-----------------------------------------|-------------------------|--------------------|------|

| Voltage                               | IN, OUT, EN or EN, ILIM, and FAULT pins | -0.3                    | 7                  | V    |

| Voltage from IN to OUT                |                                         | -7                      | 7                  | V    |

| Continuous output current             |                                         | Internal                | Internally limited |      |

| Continuous FAULT sink current         |                                         | 25                      |                    | mA   |

| ILIM source current                   |                                         | Internally limited      |                    |      |

| Continuous total power dissipation    |                                         | See Thermal Information |                    |      |

| Maximum junction temperature          |                                         | -40                     | OTSD2              | °C   |

| Storage temperature, T <sub>stg</sub> |                                         | -65                     | 150                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                                            |                         |                                                                     | VALUE  | UNIT |

|--------------------------------------------|-------------------------|---------------------------------------------------------------------|--------|------|

|                                            |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000  |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Electrostatio discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) |        | \/   |

|                                            | Electrostatic discharge | IEC 61000-4-2 contact discharge (3)                                 | ±8000  | V    |

|                                            |                         | IEC 61000-4-2 air discharge <sup>(3)</sup>                          | ±15000 |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

|                   |                                        |         | MIN | N MAX | UNIT |

|-------------------|----------------------------------------|---------|-----|-------|------|

| $V_{IN}$          | Input voltage, IN                      |         | 2.5 | 6.5   | V    |

| VEN               | Fachla valtana                         | TPS2556 | (   | 6.5   |      |

| $V_{EN}$          | Enable voltage                         | TPS2557 | (   | 6.5   | V    |

| V <sub>IH</sub>   | High-level input voltage on Enable pin |         | 1.1 | 1     | V    |

| $V_{IL}$          | Low-level input voltage on Enable pin  |         |     | 0.66  | V    |

| I <sub>OUT</sub>  | Continuous output current (OUT pin)    |         | (   | 5     | Α    |

|                   | Continuous FAULT sink current          |         | (   | ) 10  | mA   |

| R <sub>ILIM</sub> | Recommended resistor limit             |         | 20  | ) 187 | kΩ   |

| T <sub>J</sub>    | Operating virtual junction temperature |         | -40 | ) 125 | °C   |

<sup>(2)</sup> Voltages are referenced to GND unless otherwise noted.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Surges per EN61000-4-2, 1999 applied between USB and output ground of the TPS2556EVM (HPA423) evaluation module (see *Using the TPS2556EVM-423 and TPS2557EVM-423*). These were the test levels, not the failure threshold.

## 7.4 Thermal Information

|                       |                                              | TPS255x    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DRB (VSON) | UNIT |

|                       |                                              | 8 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 41.5       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 54.5       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 16.4       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.7        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 16.6       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.6        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

over recommended operating conditions,  $V_{EN} = 0 \text{ V}$  or  $V_{EN} = V_{IN}$  (unless otherwise noted)<sup>(1)</sup>

|                     | PARAMETER                                              | TEST COND                                                                                    | ITIONS                                                | MIN  | TYP  | MAX      | UNIT |

|---------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|------|------|----------|------|

| POWER               | SWITCH                                                 |                                                                                              |                                                       | •    |      | <u> </u> |      |

| _                   | Otatia dania anno an atata annistra                    | $T_J = 25^{\circ}C$                                                                          |                                                       |      | 22   | 25       | 0    |

| r <sub>DS(ON)</sub> | Static drain-source on-state resistance                | -40°C ≤T <sub>J</sub> ≤ 125°C                                                                |                                                       |      |      | 35       | mΩ   |

|                     | Enable pin turn on and off threshold                   |                                                                                              |                                                       | 0.66 |      | 1.1      | V    |

|                     | Enable input hysteresis (2)                            |                                                                                              |                                                       |      | 55   |          | mV   |

| I <sub>EN</sub>     | Input current                                          | $V_{EN} = 0 \text{ V or } 6.5 \text{ V, } V_{\overline{EN}} = 0 \text{ V or } 6.5 \text{ V}$ | 6.5 V                                                 | -0.5 |      | 0.5      | μΑ   |

|                     | Current-limit threshold (Maximum DC output             | $R_{ILIM} = 24.9 \text{ k}\Omega$                                                            |                                                       | 4130 | 4450 | 4695     |      |

| I <sub>OS</sub>     | current I <sub>OUT</sub> delivered to load) and short- | $R_{ILIM} = 61.9 \text{ k}\Omega$                                                            |                                                       | 1590 | 1785 | 1960     | mA   |

|                     | circuit current, OUT connected to GND                  | R <sub>ILIM</sub> = 100 kΩ                                                                   | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |      |      |          |      |

| I <sub>IN_OFF</sub> | Supply current, low-level output                       | $V_{IN} = 6.5 \text{ V}$ , No load on OUT, $V_{EN}$                                          | = 6.5 V or V <sub>EN</sub> = 0 V                      |      | 0.1  | 2        | μΑ   |

|                     | Complete company binds because output                  | V 05 V No look on OUT                                                                        | = 6.5 V. No load on OLIT                              | 120  | μΑ   |          |      |

| I <sub>IN_ON</sub>  | Supply current, high-level output                      | V <sub>IN</sub> = 6.5 V, No load on OUT                                                      | $R_{ILIM} = 100 \text{ k}\Omega$                      |      | 85   | 110      | μΑ   |

| I <sub>REV</sub>    | Reverse leakage current                                | $V_{OUT} = 6.5 \text{ V}, V_{IN} = 0 \text{ V}, T_{J} = 25 \text{ s}$                        | °C                                                    |      | 0.01 | 1        | μΑ   |

| UVLO                | Low-level input voltage (IN pin)                       | V <sub>IN</sub> rising                                                                       |                                                       |      | 2.35 | 2.45     | V    |

|                     | UVLO hysteresis (IN pin) <sup>(2)</sup>                |                                                                                              |                                                       |      | 35   |          | mV   |

| FAULT F             | LAG                                                    |                                                                                              |                                                       |      |      |          |      |

| $V_{OL}$            | Output low voltage (FAULT pin)                         | I <sub>FAULT</sub> = 1 mA                                                                    |                                                       |      |      | 180      | mV   |

|                     | Off-state leakage                                      | V <sub>FAULT</sub> = 6.5 V                                                                   |                                                       |      |      | 1        | μΑ   |

|                     | FAULT deglitch                                         | FAULT assertion or deassertion or condition                                                  | due to overcurrent                                    | 6    | 9    | 13       | ms   |

| THERMA              | L SHUTDOWN                                             |                                                                                              |                                                       |      |      |          |      |

| OTSD2               | Thermal shutdown threshold                             |                                                                                              |                                                       | 155  |      |          | °C   |

| OTSD                | Thermal shutdown threshold in current-limit            |                                                                                              |                                                       | 135  |      |          | °C   |

|                     | Hysteresis (2)                                         |                                                                                              |                                                       |      | 20   |          | °C   |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be considered separately.

<sup>(2)</sup> These parameters are provided for reference only, and do no constitute part of TI's published specifications for purposes of TI's product warranty.

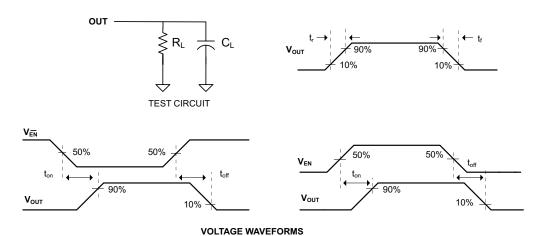

# 7.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                          | TEST CONDITI                                           | ONS                                                    | MIN | TYP | MAX | UNIT |

|------------------|------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| •                | Diag time cutout                   | $C_1 = 1 \mu F, R_1 = 100 \Omega$ , (see               | V <sub>IN</sub> = 6.5 V                                | 2   | 3   | 4   |      |

| t <sub>R</sub>   | Rise time, output                  | Figure 15)                                             | V <sub>IN</sub> = 2.5 V                                | 1   | 2   | 3   | ms   |

|                  | Fall time a sustaint               | $C_L = 1 \mu F, R_L = 100 \Omega$ , (see               | V <sub>IN</sub> = 6.5 V                                | 0.6 | 0.8 | 1   |      |

| t <sub>F</sub>   |                                    |                                                        | V <sub>IN</sub> = 2.5 V                                | 0.4 | 0.6 | 0.8 | ms   |

| t <sub>ON</sub>  | Turnon time                        | $C_L = 1 \mu F$ , $R_L = 100 \Omega$ , (see F          | $C_L = 1 \mu F$ , $R_L = 100 \Omega$ , (see Figure 15) |     |     | 9   | ms   |

| t <sub>OFF</sub> | Turnoff time                       | $C_L = 1 \mu F$ , $R_L = 100 \Omega$ , (see Figure 15) |                                                        |     |     | 6   | ms   |

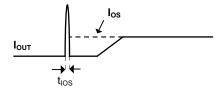

| t <sub>IOS</sub> | Response time to short circuit (1) | V <sub>IN</sub> = 5 V (see Figure 16)                  |                                                        |     | 3.5 |     | μs   |

<sup>(1)</sup> These parameters are provided for reference only, and do no constitute part of TI's published specifications for purposes of TI's product warranty.

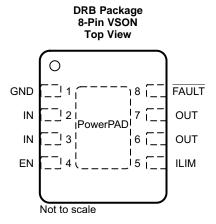

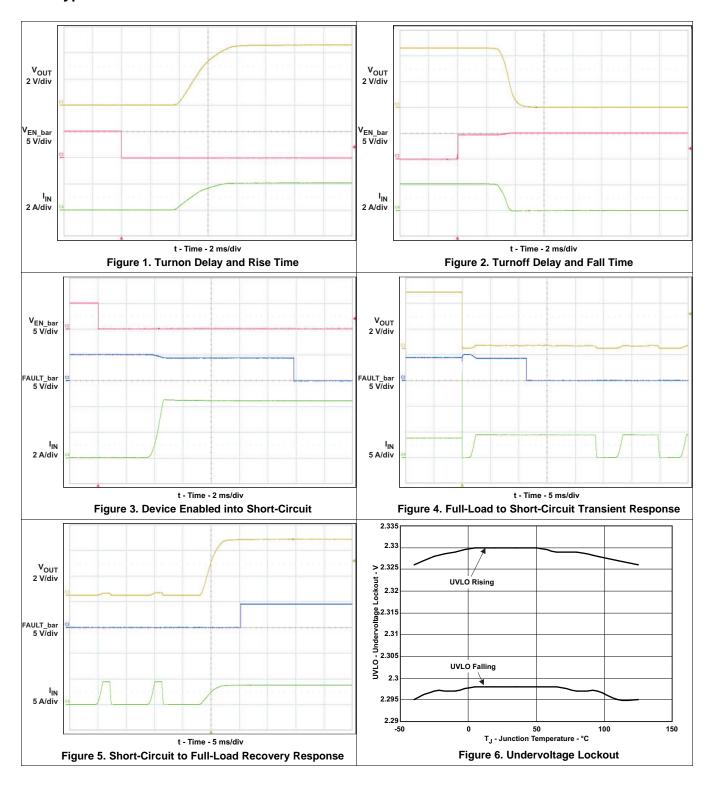

# 7.7 Typical Characteristics

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# 8 Parameter Measurement Information

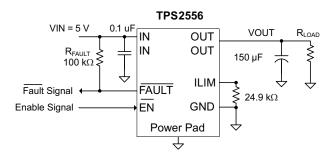

Figure 14. Typical Characteristics Reference Schematic

Figure 15. Test Circuit and Voltage Waveforms

Figure 16. Response Time to Short Circuit Waveform

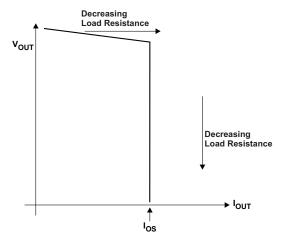

Figure 17. Output Voltage vs Current-Limit Threshold

# 9 Detailed Description

#### 9.1 Overview

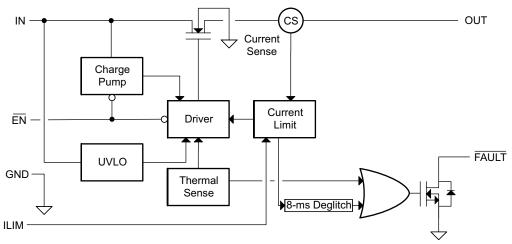

The TPS2556 and TPS2557 are current-limited, power-distribution switches using N-channel MOSFETs for applications where short circuits or heavy capacitive loads are encountered. These devices allow the user to program the current-limit threshold from 500 mA to 5 A (typical) through an external resistor. These devices incorporate an internal charge pump and the gate drive circuitry necessary to drive the N-channel MOSFET. The charge pump supplies power to the driver circuit and provides the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltages as low as 2.5 V and requires little supply current. The driver controls the gate voltage of the power switch. The driver incorporates circuitry that controls the rise and fall times of the output voltage to limit large current and voltage surges and provides built-in soft-start functionality. The TPS255x family limits the output current to the programmed current-limit threshold (I<sub>OS</sub>) during an overcurrent or short-circuit event by reducing the charge pump voltage driving the N-channel MOSFET and operating it in the linear range of operation. The result of limiting the output current to I<sub>OS</sub> reduces the output voltage at OUT because N-channel MOSFET is no longer fully enhanced.

# 9.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 9.3 Feature Description

#### 9.3.1 Overcurrent Conditions

The TPS255x responds to overcurrent conditions by limiting their output current to I<sub>OS</sub>. When an overcurrent condition is detected, the device maintains a constant output current and the output voltage reduces accordingly. Two possible overload conditions can occur.

The first condition is when a short circuit or partial short circuit is present when the device is powered up or enabled. The output voltage is held near zero potential with respect to ground and the TPS255x ramps the output current to  $I_{OS}$ . The TPS255x limits the current to  $I_{OS}$  until the overload condition is removed or the device begins to thermal cycle.

The second condition is when a short circuit, partial short circuit, or transient overload occurs while the device is enabled and powered on. The device responds to the overcurrent condition within time  $t_{IOS}$  (see Figure 16). The current-sense amplifier is overdriven during this time and momentarily disables the internal N-channel MOSFET. The current-sense amplifier recovers and ramps the output current to  $I_{OS}$ . Similar to the previous case, the TPS255x limits the current to  $I_{OS}$  until the overload condition is removed or the device begins to thermal cycle.

The TPS255s thermal cycles if an overload condition is present long enough to activate thermal limiting in any of the above cases. The device turns off when the junction temperature exceeds 135°C (minimum) while in current limit. The device remains off until the junction temperature cools 20°C (typical) and then restarts. The TPS255x cycles on and off until the overload is removed (see Figure 5).

# **Feature Description (continued)**

# 9.3.2 FAULT Response

The FAULT open-drain output is asserted (active low) during an overcurrent or overtemperature condition. The TPS255s asserts the FAULT signal until the fault condition is removed and the device resumes normal operation. The TPS255s is designed to eliminate false FAULT reporting by using an internal delay *deglitch* circuit for overcurrent (9-ms typical) conditions without the need for external circuitry. This ensures that FAULT is not accidentally asserted due to normal operation such as starting into a heavy capacitive load. The deglitch circuitry delays entering and leaving current-limit induced fault conditions. The FAULT signal is not deglitched when the MOSFET is disabled due to an overtemperature condition but is deglitched after the device has cooled and begins to turn on. This unidirectional deglitch prevents FAULT oscillation during an overtemperature event.

# 9.3.3 Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted on and off cycling due to input voltage droop during turnon.

# 9.3.4 Enable (EN OR EN)

The logic enable controls the power switch and device supply current. The supply current is reduced to less than 2-µA when a logic high is present on EN or when a logic low is present on EN. A logic low input on EN or a logic high input on EN enables the driver, control circuits, and power switch. The enable input is compatible with both TTL and CMOS logic levels.

#### 9.3.5 Thermal Sense

The TPS255x self-protects by using two independent thermal sensing circuits that monitor the operating temperature of the power switch and disable operation if the temperature exceeds recommended operating conditions. The TPS255x operates in constant-current mode during an overcurrent conditions, which increases the voltage drop across power switch. The power dissipation in the package is proportional to the voltage drop across the power switch, which increases the junction temperature during an overcurrent condition. The first thermal sensor (OTSD) turns off the power switch when the die temperature exceeds 135°C (minimum) and the part is in current limit. Hysteresis is built into the thermal sensor, and the switch turns on after the device has cooled approximately 20°C.

The TPS255x also has a second ambient thermal sensor (OTSD2). The ambient thermal sensor turns off the power switch when the die temperature exceeds 155°C (minimum) regardless of whether the power switch is in current limit and turns on the power switch after the device has cooled approximately 20°C. The TPS255x continues to cycle off and on until the fault is removed.

# 9.4 Device Functional Modes

There are no other functional modes.

# 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 10.1 Application Information

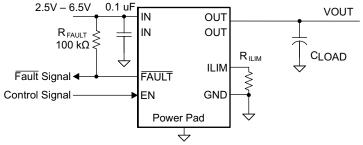

The TPS2556 and TPS2557 are precision power-distribution switches for applications where heavy capacitive loads and short circuits are expected to be encountered. The following design procedures can be used to choose the input and output capacitors as well as to calculate the current limit programming resistor value for a typical design. Additional application examples are provided including an auto-retry circuit and a two-level current limit circuit.

# 10.2 Typical Applications

#### 10.2.1 Current-Limiting Power-Distribution Switch

Copyright © 2016, Texas Instruments Incorporated

Figure 18. Typical Current-Limiting Application

# 10.2.1.1 Design Requirements

For this example, use the parameters listed in Table 1 as the input parameters.

**Table 1. Design Parameters**

| PARAMETER                     | VALUE   |

|-------------------------------|---------|

| Input voltage                 | 5 V     |

| Output voltage                | 5 V     |

| Above a minimum current limit | 3000 mA |

| Below a maximum current limit | 5000 mA |

# 10.2.1.2 Detailed Design Procedure

#### 10.2.1.2.1 Input and Output Capacitance

Input and output capacitance improves the performance of the device; the actual capacitance must be optimized for the particular application. TI recommends a 0.1-µF or greater ceramic bypass capacitor between IN and GND as close to the device as possible for local noise decoupling for all applications. This precaution reduces ringing on the input due to power-supply transients. Additional input capacitance may be needed on the input to reduce voltage overshoot from exceeding the absolute-maximum voltage of the device during heavy transient conditions. This is especially important during bench testing when long, inductive cables are used to connect the evaluation board to the bench power supply.

Output capacitance is not required, but TI recommends placing a high-value electrolytic capacitor on the output pin when large transient currents are expected on the output.

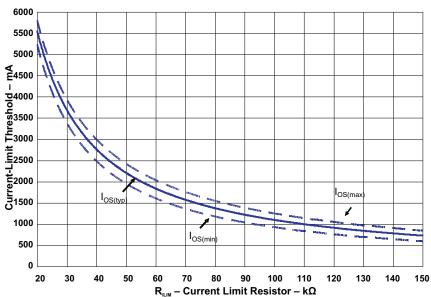

#### 10.2.1.2.2 Programming the Current-Limit Threshold

The overcurrent threshold is user programmable through an external resistor. The TPS255x uses an internal regulation loop to provide a regulated voltage on the ILIM pin. The current-limit threshold is proportional to the current sourced out of ILIM. The recommended 1% resistor for  $R_{ILIM}$  is  $20~k\Omega \le R_{ILIM} \le 187~k\Omega$  to ensure stability of the internal regulation loop. Many applications require that the minimum current limit is above a certain current level or that the maximum current limit is below a certain current level, so it is important to consider the tolerance of the overcurrent threshold when selecting a value for  $R_{ILIM}$ . Equation 1 approximates the resulting overcurrent threshold for a given external resistor value ( $R_{ILIM}$ ). See *Electrical Characteristics* for specific current limit settings. The traces routing the  $R_{ILIM}$  resistor to the TPS255x must be as short as possible to reduce parasitic effects on the current-limit accuracy.

$$I_{OSmax}(mA) = \frac{99038V}{R_{ILIM}^{0.947}k\Omega}$$

$$I_{OSnom}(mA) = \frac{111704V}{R_{ILIM}^{1.0028}k\Omega}$$

$$I_{OSmin}(mA) = \frac{127981V}{R_{ILIM}^{1.0708}k\Omega}$$

(1)

Figure 19. Current-Limit Threshold vs R<sub>ILIM</sub>

#### 10.2.1.2.2.1 Designing Above a Minimum Current Limit

Some applications require that current limiting cannot occur below a certain threshold. For this example, assume that 3 A must be delivered to the load so that the minimum desired current-limit threshold is 3000 mA. Use the  $I_{OS}$  equations and Figure 19 to select  $R_{ILIM}$ .

$$\begin{split} I_{OSmin}(mA) &= 3000mA \\ I_{OSmin}(mA) &= \frac{127981V}{R_{ILIM}^{1.0708}k\Omega} \\ R_{ILIM}(k\Omega) &= \left(\frac{127981V}{I_{OSmin}mA}\right)^{\frac{1}{1.0708}} \\ R_{ILIM}(k\Omega) &= 33.3k\Omega \end{split}$$

Select the closest 1% resistor less than the calculated value:  $R_{ILIM} = 33.2 \text{ k}\Omega$ . This sets the minimum current-limit threshold at 3000 mA . Use the  $I_{OS}$  equations, Figure 19, and the previously calculated value for  $R_{ILIM}$  to calculate the maximum resulting current-limit threshold.

$$\begin{split} R_{ILIM}(k\Omega) &= 33.2 k\Omega \\ I_{OSmax}(mA) &= \frac{99038 V}{R_{ILIM}^{0.947} k\Omega} \\ I_{OSmax}(mA) &= \frac{99038 V}{33.2^{0.947} k\Omega} \\ I_{OSmax}(mA) &= 3592 mA \end{split}$$

The resulting maximum current-limit threshold is 3592 mA with a 33.2-k $\Omega$  resistor.

#### 10.2.1.2.2.2 Designing Below a Maximum Current Limit

Some applications require that current limiting must occur below a certain threshold. For this example, assume that the desired upper current-limit threshold must be below 5000 mA to protect an upstream power supply. Use the  $I_{OS}$  equations and Figure 19 to select  $R_{ILIM}$ .

$$\begin{split} I_{OSmax}(mA) &= 5000mA \\ I_{OSmax}(mA) &= \frac{99038V}{R_{ILIM}^{0.947}k\Omega} \\ R_{ILIM}(k\Omega) &= \left(\frac{99038V}{I_{OSmax}mA}\right)^{\frac{1}{0.947}} \\ R_{ILIM}(k\Omega) &= 23.4k\Omega \end{split}$$

Select the closest 1% resistor greater than the calculated value:  $R_{ILIM}$  = 23.7 k $\Omega$ . This sets the maximum current-limit threshold at 5000 mA . Use the  $I_{OS}$  equations, Figure 19, and the previously calculated value for  $R_{ILIM}$  to calculate the minimum resulting current-limit threshold.

$$\begin{split} R_{ILIM}(k\Omega) &= 23.7 k\Omega \\ I_{OSmin}(mA) &= \frac{127981 V}{R_{ILIM}^{1.0708} k\Omega} \\ I_{OSmin}(mA) &= \frac{127981 V}{23.7^{1.0708} k\Omega} \\ I_{OSmin}(mA) &= 4316 mA \end{split}$$

(5)

The resulting minimum current-limit threshold is 4316 mA with a 23.7-k $\Omega$  resistor.

#### 10.2.1.2.2.3 Accounting for Resistor Tolerance

The analysis of resistor selection focused only on the TPS255x performance and assumed an exact resistor value. However, resistors sold in quantity are not exact and are bounded by an upper and lower tolerance centered around a nominal resistance. The additional  $R_{\rm ILIM}$  resistance tolerance directly affects the current-limit threshold accuracy at a system level. Table 2 shows a process that accounts for worst-case resistor tolerance assuming 1% resistor values. Using the selection process outlined, determine the upper and lower resistance bounds of the selected resistor. Then calculate the upper and lower resistor bounds to determine the threshold limits. It is important to use tighter tolerance resistors (0.5% or 0.1%) when precision current limiting is desired.

Table 2. Common R<sub>ILIM</sub> Resistor Selections

| DESIRED NOMINAL    | IDEAL RESISTOR | CLOSEST 1%             | RESISTOR E | BOUNDS (kΩ) | Ios ACTU | I <sub>OS</sub> ACTUAL LIMITS (mA) |      |  |

|--------------------|----------------|------------------------|------------|-------------|----------|------------------------------------|------|--|

| CURRENT LIMIT (mA) | (k $\Omega$ )  | RESISTOR ( $k\Omega$ ) | 1% LOW     | 1% HIGH     | MIN      | NOM                                | MAX  |  |

| 750                | 146.9          | 147                    | 145.5      | 148.5       | 605      | 749                                | 886  |  |

| 1000               | 110.2          | 110                    | 108.9      | 111.1       | 825      | 1002                               | 1166 |  |

| 1250               | 88.2           | 88.7                   | 87.8       | 89.6        | 1039     | 1244                               | 1430 |  |

| 1500               | 73.6           | 73.2                   | 72.5       | 73.9        | 1276     | 1508                               | 1715 |  |

| 1750               | 63.1           | 63.4                   | 62.8       | 64          | 1489     | 1742                               | 1965 |  |

| 2000               | 55.2           | 54.9                   | 54.4       | 55.4        | 1737     | 2012                               | 2252 |  |

| 2250               | 49.1           | 48.7                   | 48.2       | 49.2        | 1975     | 2269                               | 2523 |  |

| 2500               | 44.2           | 44.2                   | 43.8       | 44.6        | 2191     | 2501                               | 2765 |  |

| 2750               | 40.2           | 40.2                   | 39.8       | 40.6        | 2425     | 2750                               | 3025 |  |

| 3000               | 36.9           | 36.5                   | 36.1       | 36.9        | 2689     | 3030                               | 3315 |  |

| 3250               | 34             | 34                     | 33.7       | 34.3        | 2901     | 3253                               | 3545 |  |

| 3500               | 31.6           | 31.6                   | 31.3       | 31.9        | 3138     | 3501                               | 3800 |  |

| 3750               | 29.5           | 29.4                   | 29.1       | 29.7        | 3390     | 3764                               | 4068 |  |

| 4000               | 27.7           | 27.4                   | 27.1       | 27.7        | 3656     | 4039                               | 4349 |  |

| 4250               | 26             | 26.1                   | 25.8       | 26.4        | 3851     | 4241                               | 4554 |  |

| 4500               | 24.6           | 24.9                   | 24.7       | 25.1        | 4050     | 4446                               | 4761 |  |

| 4750               | 23.3           | 23.2                   | 23         | 23.4        | 4369     | 4773                               | 5091 |  |

| 5000               | 22.1           | 22.1                   | 21.9       | 22.3        | 4602     | 5011                               | 5331 |  |

| 5250               | 21.1           | 21                     | 20.8       | 21.2        | 4861     | 5274                               | 5595 |  |

| 5500               | 20.1           | 20                     | 19.8       | 20.2        | 5121     | 5539                               | 5859 |  |

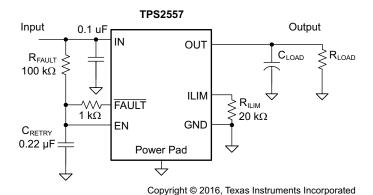

## 10.2.1.2.3 Auto-Retry Functionality

Some applications require that an overcurrent condition disables the part momentarily during a fault condition and re-enables after a pre-set time. This auto-retry functionality can be implemented with an external resistor and capacitor. During a fault condition, FAULTpulls EN low. The part is disabled when EN is pulled below the turn-off theshold, and FAULT goes high impedance allowing C<sub>RETRY</sub> to begin charging. The part re-enables when the voltage on EN reaches the turn-on threshold. The auto-retry time is determined by the resistor and capacitor time constant. The part continues to cycle in this manner until the fault condition is removed. The time between retries is given in Equation 6.

$$T_{BR} = -R_{FAULT} \times C_{RETRY} \times LN (1 - V_{EN} / (V_{IN} - V_{OL})) + T_{FAULT}$$

where

- V<sub>EN</sub> is the EN pin typical threshold voltage

- V<sub>IN</sub> is the input voltage

- V<sub>OI</sub> is the FAULT pin typical saturation voltage

- T<sub>FAULT</sub> is the internal FAULT typical deglitch time

The retry duty cycle is calculated with Equation 7, and the average current is D  $\times$  I<sub>OS</sub>.

$$D = T_{FAULT} / (T_{FAULT} + T_{BR})$$

(7)

(6)

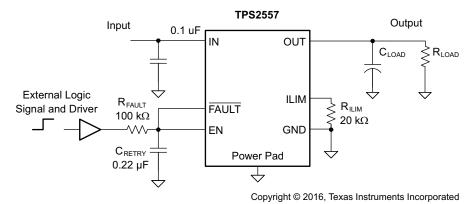

Figure 20. Auto-Retry Functionality

Some applications require auto-retry functionality and the ability to enable and disable with an external logic signal. The figure below shows how an external logic signal can drive EN through R<sub>FAULT</sub> and maintain auto-retry functionality. The resistor and capacitor time constant determines the auto-retry time-out period.

Figure 21. Auto-Retry Functionality With External EN Signal

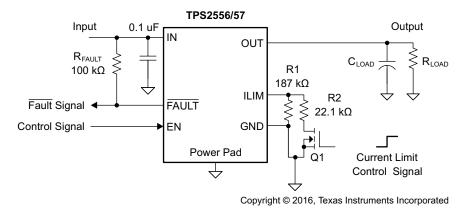

#### 10.2.1.2.4 Two-Level Current-Limit Circuit

Figure 22. Two-Level Current-Limit Circuit

Some applications require different current-limit thresholds depending on external system conditions. Figure 22 shows an implementation for an externally-controlled, two-level current-limit circuit. The current-limit threshold is set by the total resistance from ILIM to GND (see *Programming the Current-Limit Threshold*). A logic-level input enables and disables MOSFET Q1 and changes the current-limit threshold by modifying the total resistance from ILIM to GND. Additional MOSFET and resistor combinations can be used in parallel to Q1 and R2 to increase the number of additional current-limit levels.

#### **NOTE**

ILIM must never be driven directly with an external signal.

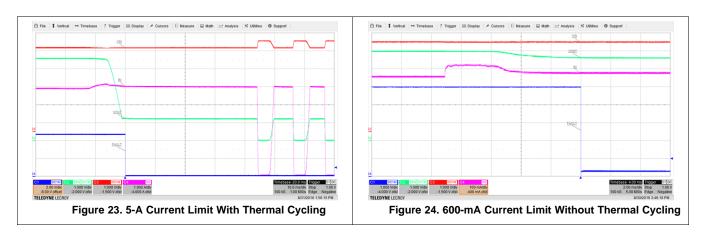

# 10.2.1.3 Application Curve

In Figure 23, the load current setpoint is 5.05 A, as programmed by the 22.1-k $\Omega$  resistor. Load current is stepped mildly from approximately 4.9 A to 5.2 A. The internal FAULT timer runs and after 9 ms, FAULT goes low and current continues to be regulated at approximately 5 A. Due to the high power dissipation within the device, thermal cycling occurs.

In Figure 24, the load current setpoint is 597 mA, as programmed by the 187-k $\Omega$  resistor. Load current is stepped mildly from approximately 560 mA to 620 mA. The internal FAULT timer runs and after 9 ms, FAULT goes low and current continues to be regulated at approximately 580 mA.

# 11 Power Supply Recommendations

The TPS255x operates from 2.5 V to 6.5 V. TI recommends operating from either a 3.3-V  $\pm$  10% or 5-V  $\pm$  10% power supply. The load capacity of the power supply must be greater than the maximum current limit ( $I_{OS}$ ) setting of the TPS255x.

# 12 Layout

## 12.1 Layout Guidelines

- TI recommends placing the 100-nF bypass capacitor near the IN and GND pins, and make the connections using a low-inductance trace.

- TI recommends placing a high-value electrolytic capacitor and a 100-nF bypass capacitor on the output pin

when large transient currents are expected on the output.

- The traces routing the R<sub>ILIM</sub> resistor to the device must be as short as possible to reduce parasitic effects on the current limit accuracy.

- The PowerPAD must be directly connected to PCB ground plane using wide and short copper trace.

# 12.2 Layout Example

Figure 25. TPS255x Layout Example

(9)

#### 12.3 Thermal Considerations

The low on-resistance of the N-channel MOSFET allows small surface-mount packages to pass large currents. It is good design practice to estimate power dissipation and junction temperature. This analysis gives an approximation for calculating junction temperature based on the power dissipation in the package. However, thermal analysis is strongly dependent on additional system level factors. Such factors include air flow, board layout, copper thickness and surface area, and proximity to other devices dissipating power. Good thermal design practice must include all system level factors in addition to individual component analysis.

Begin by determining the  $r_{DS(ON)}$  of the N-channel MOSFET relative to the input voltage and operating temperature. As an initial estimate, use the highest operating ambient temperature of interest and read  $r_{DS(ON)}$  from the typical characteristics graph. Using this value, the power dissipation can be calculated by Equation 8.

$$P_D = r_{DS(ON)} \times I_{OUT}^2$$

#### where

- P<sub>D</sub> = Total power dissipation (W)

- $r_{DS(ON)}$  = Power switch on-resistance ( $\Omega$ )

Finally, calculate the junction temperature with Equation 9.

$$T_J = P_D \times R_{\theta JA} + T_A$$

#### where

- T<sub>A</sub> = Ambient temperature (°C)

- R<sub>θJA</sub> = Thermal resistance (°C/W)

Compare the calculated junction temperature with the initial estimate. If they are not within a few degrees, repeat the calculation using the  $refined\ r_{DS(ON)}$  from the previous calculation as the new estimate. Two or three iterations are generally sufficient to achieve the desired result. The final junction temperature is highly dependent on thermal resistance, and thermal resistance is highly dependent on the individual package and board layout.

# 13 デバイスおよびドキュメントのサポート

#### 13.1 関連リンク

次の表に、クイック・アクセス・リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびサンプル注文またはご購入へのクイック・アクセスが含まれます。

# 表 3. 関連リンク

| 製品      | プロダクト・フォルダ | サンプルとご購入 | 技術資料    | ツールとソフトウェア | サポートとコミュニティ |

|---------|------------|----------|---------|------------|-------------|

| TPS2556 | ここをクリック    | ここをクリック  | ここをクリック | ここをクリック    | ここをクリック     |

| TPS2557 | ここをクリック    | ここをクリック  | ここをクリック | ここをクリック    | ここをクリック     |

# 13.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 13.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることが できます。技術サポート用の連絡先情報も参照できます。

## 13.4 商標

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 13.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

## 13.6 用語集

SLYZ022 — TI用語集.

この用語集には、用語や略語の一覧および定義が記載されています。

# 14 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com 2-Dec-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| TPS2556DRBR           | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | FULL NIPDAU<br>  NIPDAU       | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBR.A         | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBR.B         | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBRG4         | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBRG4.A       | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBRG4.B       | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBT           | Active | Production    | SON (DRB)   8  | 250   SMALL T&R       | Yes  | FULL NIPDAU<br>  NIPDAU       | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBT.A         | Active | Production    | SON (DRB)   8  | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2556DRBT.B         | Active | Production    | SON (DRB)   8  | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2556             |

| TPS2557DRBR           | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBR.A         | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBR.B         | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBRG4         | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBRG4.A       | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBRG4.B       | Active | Production    | SON (DRB)   8  | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBT           | Active | Production    | SON (DRB)   8  | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBT.A         | Active | Production    | SON (DRB)   8  | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

| TPS2557DRBT.B         | Active | Production    | SON (DRB)   8  | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 2557             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

# PACKAGE OPTION ADDENDUM

www.ti.com 2-Dec-2025

(5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

(6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS2556, TPS2557:

Automotive: TPS2556-Q1, TPS2557-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 18-Jun-2025

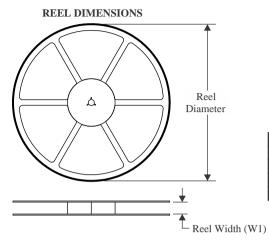

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO PI BO BO Cavity AO

|    | -                                                         |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

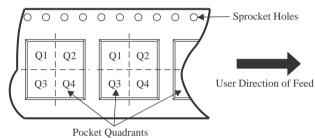

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2556DRBR   | SON             | DRB                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2556DRBRG4 | SON             | DRB                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2556DRBT   | SON             | DRB                | 8 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2557DRBR   | SON             | DRB                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2557DRBRG4 | SON             | DRB                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS2557DRBT   | SON             | DRB                | 8 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 18-Jun-2025

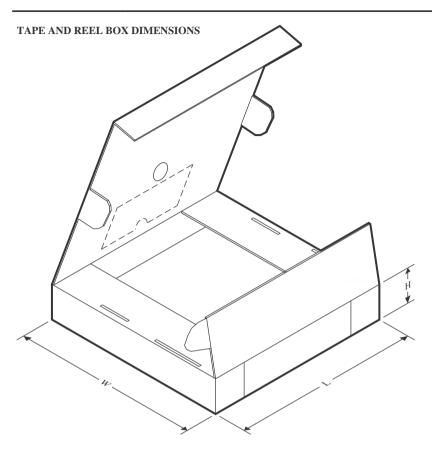

# \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS2556DRBR   | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 33.0        |

| TPS2556DRBRG4 | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 33.0        |

| TPS2556DRBT   | SON          | DRB             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| TPS2557DRBR   | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 33.0        |

| TPS2557DRBRG4 | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 33.0        |

| TPS2557DRBT   | SON          | DRB             | 8    | 250  | 210.0       | 185.0      | 35.0        |

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4203482/L

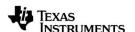

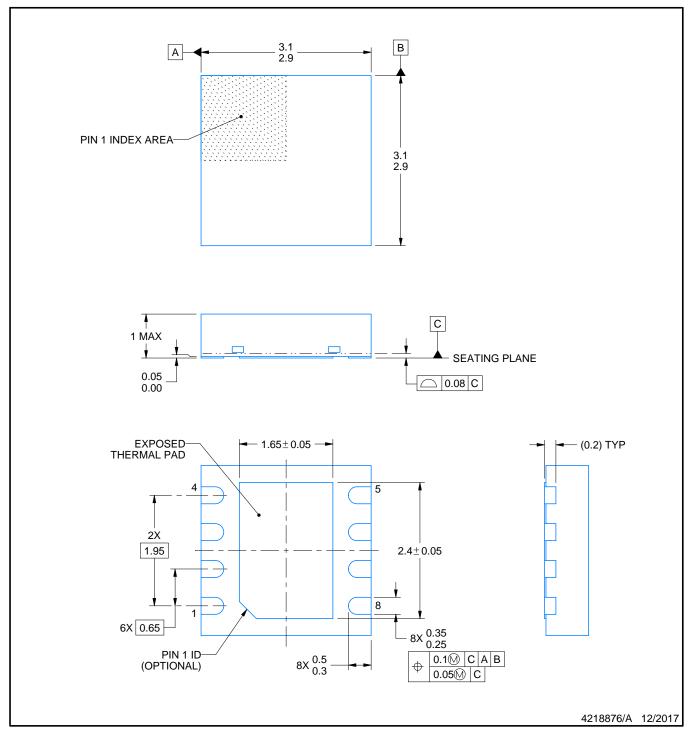

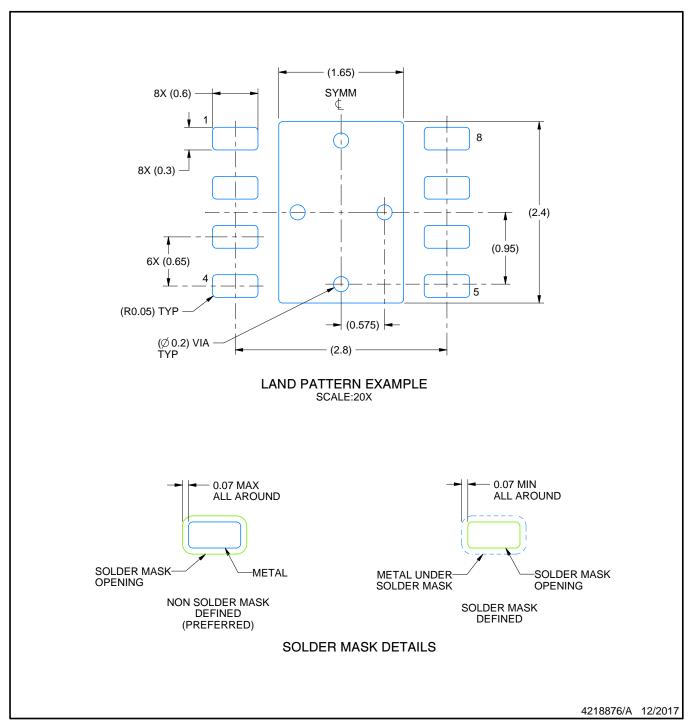

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日: 2025 年 10 月