# TPS23881B タイプ 4、4 ペア、8 チャネル PoE 2 PSE コントローラ、自律モード、200mΩ R<sub>SENSE</sub> 内蔵

## 1 特長

- PoE 2 タイプ 3 またはタイプ 4 Power Over Ethernet アプリケーション用の IEEE 802.3bt PSE ソリューション

- 8 つの独立した PSE チャネル

- 自律動作を抵抗で選択可能

- 外部 MCU 不要

- テキサス・インスツルメンツの FirmPSE システム フームウェアと互換

- プログラム可能な SRAM メモリ

- $\pm 2.5\%$  の精度で電力制限をプログラム可能

- 200mΩ の電流検出抵抗

- レガシー PD 容量の測定

- 2 ペアまたは 4 ペアのポート電力割り当てを選択可能

- 15.4W、30W、45W、60W、75W、90W

- シングルおよびデュアルシグネチャの PD 互換性

- ポートごとに専用の 14 ビット積算電流 ADC

- DC 分離用のノイズ耐性 MPS

- 2% の電流センシング精度

- 1 ビットまたは 3 ビットの高速ポートシャットダウン入力

- 自動クラス検出および電力測定

- 突入および動作フォールドバック保護

- 柔軟なプロセッサ制御の動作モード

- 自動、半自動、手動 / 診断

- ポートごとの電圧監視およびテレメトリ

- 40°C～+125°C の動作温度範囲

- 超低アルファ (ULA) のパッケージ (TPS23881B1A)

## 2 アプリケーション

- ビデオレコーダ (NVR、DVR など)

- 小規模企業向けスイッチ

- キャンパス / 分岐スイッチ

## 3 説明

TPS23881B は、IEEE 802.3bt 規格に従ってイーサネットケーブルに電力を重畠するための 8 チャネル給電機器 (PSE) コントローラです。8 つの個別の電源チャネルは、2 ペア (1 チャネル) または 4 ペア (2 チャネル) の PoE ポートの任意の組み合わせに構成できます。本 PSE コントローラは、有効なシグネチャを持つ受電デバイス (PD) の検出、相互識別の完了、電力の供給を行うことができます。

TPS23881B は TPS2388 に対して、電流センス抵抗値の低減、選択可能な自律動作、SRAM のプログラム可能性、プログラム可能な電力制限、容量測定、テキサス・インスツルメンツの FirmPSE システム フームウェアとの互換性に関して改良を加えた製品です（「デバイス比較表」を参照）。

プログラム可能な SRAM により、I<sup>2</sup>C を経由して現場でフームウェアをアップグレードでき、IEEE 準拠と、最新の PoE 対応デバイスとの相互運用性を保証できます。ポートごとに専用 ADC を備えているため、ポート電流を連続的に監視でき、また分類測定を同時に実行することでポートのターンオン時間を短縮できます。ポートの電力制限を  $\pm 2.5\%$  精度でプログラム可能ため、最大供給電力を 100W を超えることなく 90W から 125W を超える値に設定できます。200mΩ の電流センス抵抗と外部 FET を使うアーキテクチャにより、サイズ、効率、熱、ソリューションコストの要件のバランスが取れた設計が可能です。

### パッケージ情報

| 部品番号      | パッケージ (1) | 本体サイズ (公称)      |

|-----------|-----------|-----------------|

| TPS23881B | VQFN (56) | 8.00mm × 8.00mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

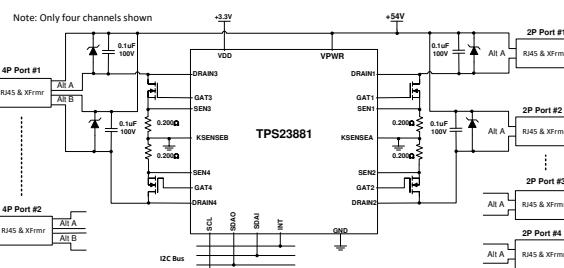

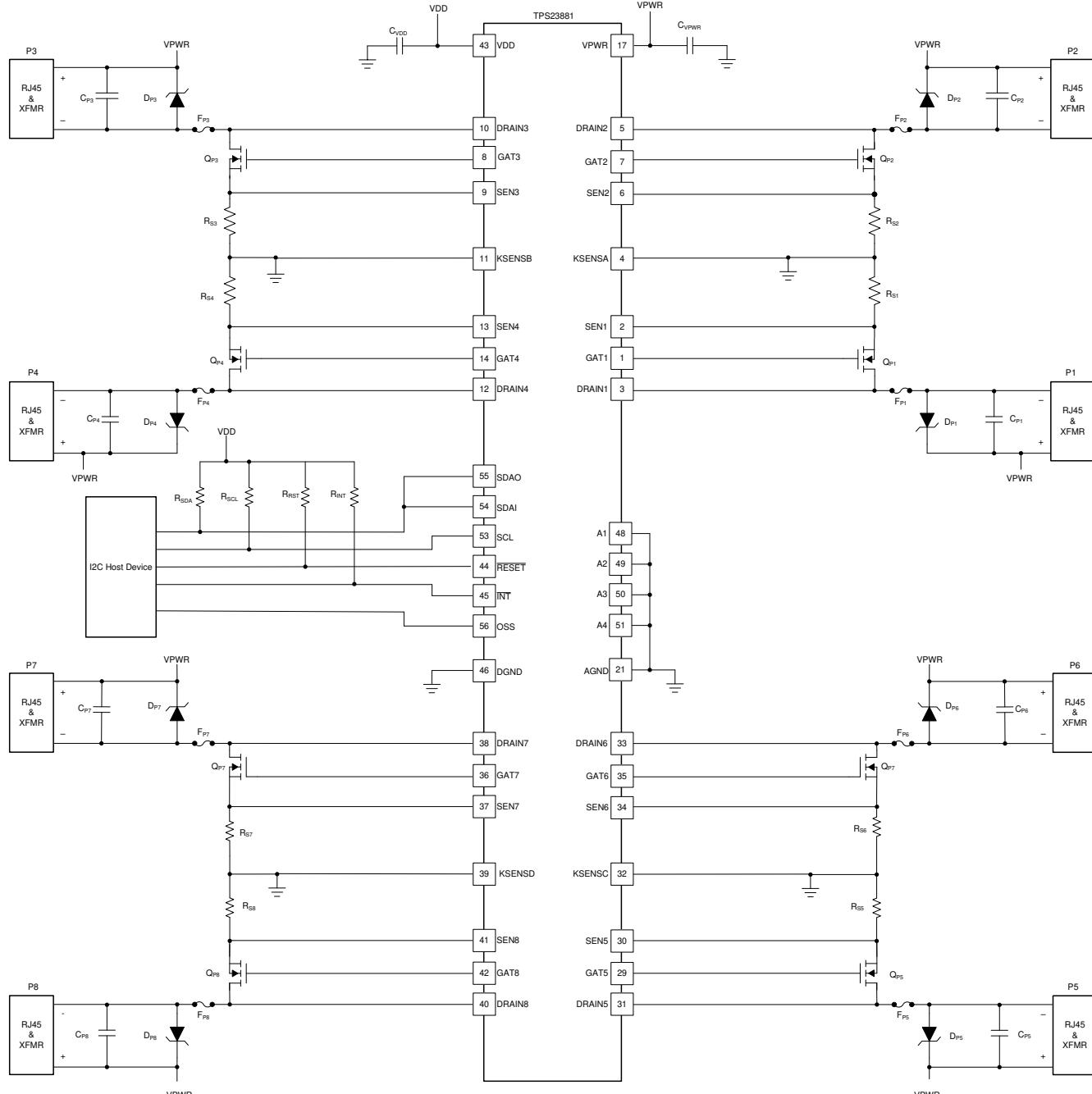

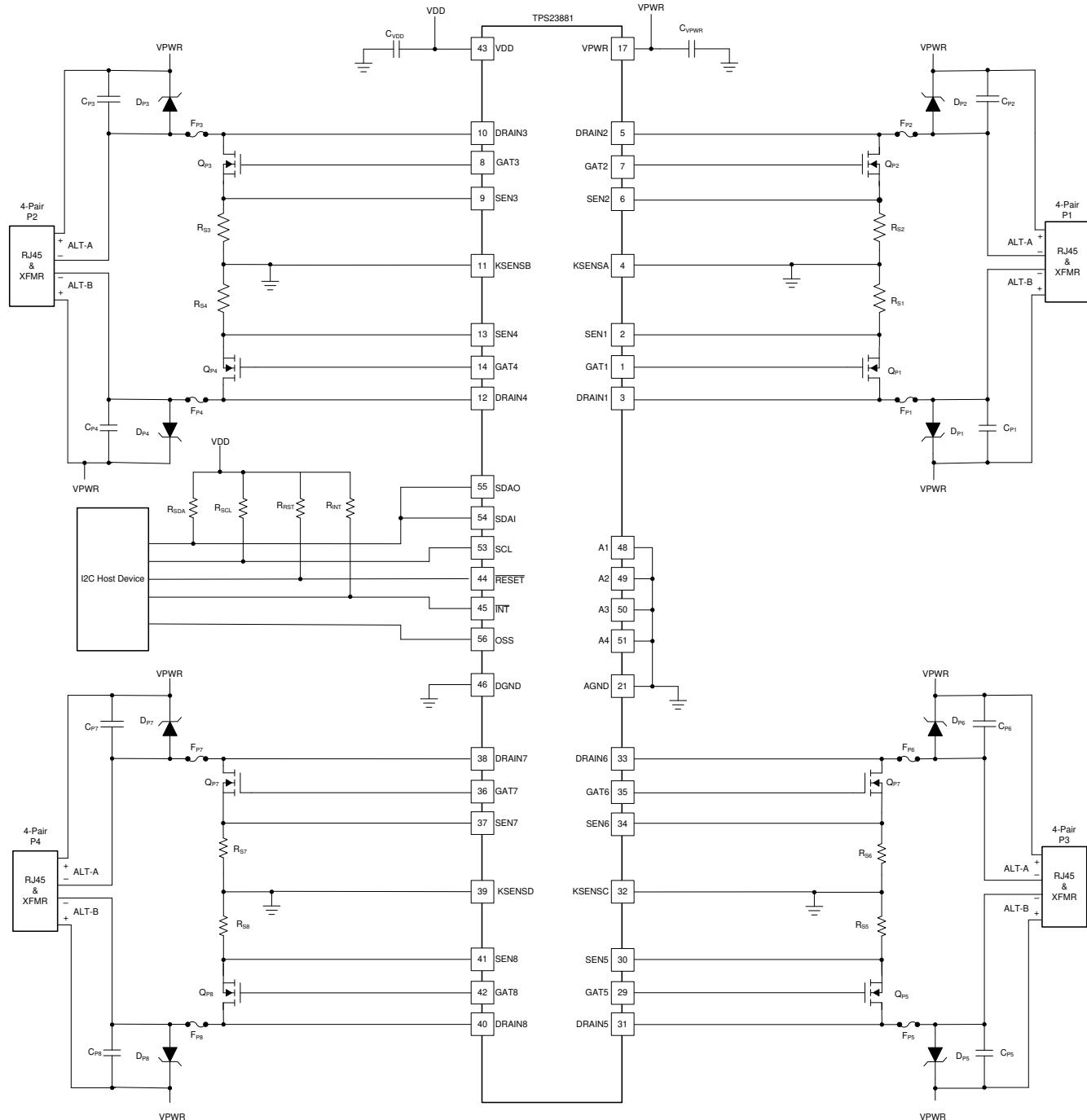

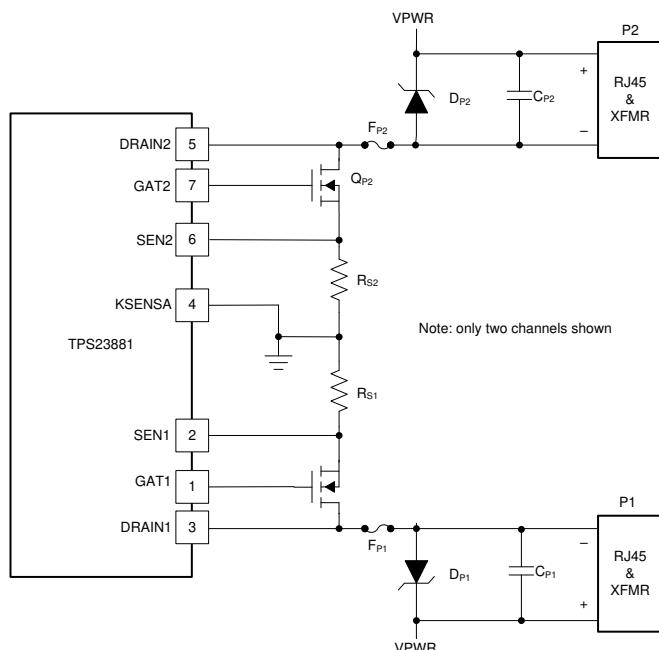

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                    |           |                                     |            |

|--------------------|-----------|-------------------------------------|------------|

| <b>1 特長</b>        | <b>1</b>  | 8.3 機能説明.....                       | 31         |

| <b>2 アプリケーション</b>  | <b>1</b>  | 8.4 デバイスの機能モード.....                 | 34         |

| <b>3 説明</b>        | <b>1</b>  | 8.5 I <sup>2</sup> C プログラミング.....   | 36         |

| <b>4 デバイス比較表</b>   | <b>3</b>  | 8.6 レジスタ マップ.....                   | 39         |

| <b>5 ピン構成および機能</b> | <b>4</b>  | <b>9 アプリケーションと実装</b> .....          | <b>133</b> |

| 5.1 ピンの詳細説明.....   | 5         | 9.1 アプリケーション情報.....                 | 133        |

| <b>6 仕様</b>        | <b>7</b>  | 9.2 代表的なアプリケーション.....               | 135        |

| 6.1 絶対最大定格.....    | 7         | 9.3 電源に関する推奨事項.....                 | 142        |

| 6.2 ESD 定格.....    | 7         | 9.4 レイアウト.....                      | 143        |

| 6.3 推奨動作条件.....    | 7         | <b>10 デバイスおよびドキュメントのサポート</b> .....  | <b>146</b> |

| 6.4 熱に関する情報.....   | 7         | 10.1 ドキュメントのサポート.....               | 146        |

| 6.5 電気的特性.....     | 8         | 10.2 ドキュメントの更新通知を受け取る方法.....        | 146        |

| 6.6 代表的特性.....     | 16        | 10.3 サポート・リソース.....                 | 146        |

| <b>7 パラメータ測定情報</b> | <b>21</b> | 10.4 商標.....                        | 146        |

| 7.1 タイミング図.....    | 21        | 10.5 静電気放電に関する注意事項.....             | 146        |

| <b>8 詳細説明</b>      | <b>25</b> | 10.6 用語集.....                       | 146        |

| 8.1 概要.....        | 25        | <b>11 改訂履歴</b> .....                | <b>146</b> |

| 8.2 機能ブロック図.....   | 30        | <b>12 メカニカル、パッケージ、および注文情報</b> ..... | <b>147</b> |

## 4 デバイス比較表

| 主要な機能                                 | TPS23881                                     | TPS23881B                                     | TPS23882B                     |

|---------------------------------------|----------------------------------------------|-----------------------------------------------|-------------------------------|

| テキサス・インスツルメンツの FirmPSE システム フームウェアと互換 | 該当なし                                         | あり                                            | あり                            |

| ピン互換                                  | あり                                           | あり                                            | あり                            |

| PSE のチャネル数                            | 8                                            | 8                                             | 8                             |

| サポートされている IEEE 802.3 PSE タイプ          | PoE 2<br>802.3bt タイプ 3 または 4<br>(2 または 4 ペア) | PoE 2<br>802.3bt タイプ 3 または 4<br>(2 または 4 ペア)  | PoE 2<br>802.3bt タイプ 3 (2 ペア) |

| R <sub>SENSE</sub>                    | 0.200Ω                                       | 0.200Ω                                        | 0.200Ω                        |

| 自律動作<br>抵抗を選択可能                       | 該当なし                                         | あり<br>2 ペア: 15.5W または 30W<br>4 ペア: 30W、最大 90W | あり<br>2 ペア: 15.5W または 30W     |

| 2 ペアの P <sub>CUT</sub> プログラマブル範囲      | 2W ~ 65W                                     | 2W ~ 65W                                      | 2W ~ 65W                      |

| 4 ペアの P <sub>CUT</sub> プログラマブル範囲      | 4W ~ 127W                                    | 4W ~ 127W                                     | 該当なし                          |

| 90+W 4 ペア P <sub>CUT</sub> 精度         | ±2.5%                                        | ±2.5%                                         | 該当なし                          |

| チャネル容量測定範囲                            | 1μF ~ 12μF                                   | 1μF~12μF                                      | 1μF~12μF                      |

| ULA パッケージング                           | あり (TPS23881A)                               | あり (TPS23881B1A)                              | 該当なし                          |

| I <sup>2</sup> C プログラム可能な SRAM メモリ    | 16kB                                         | 16kB                                          | 16kB                          |

## 5 ピン構成および機能

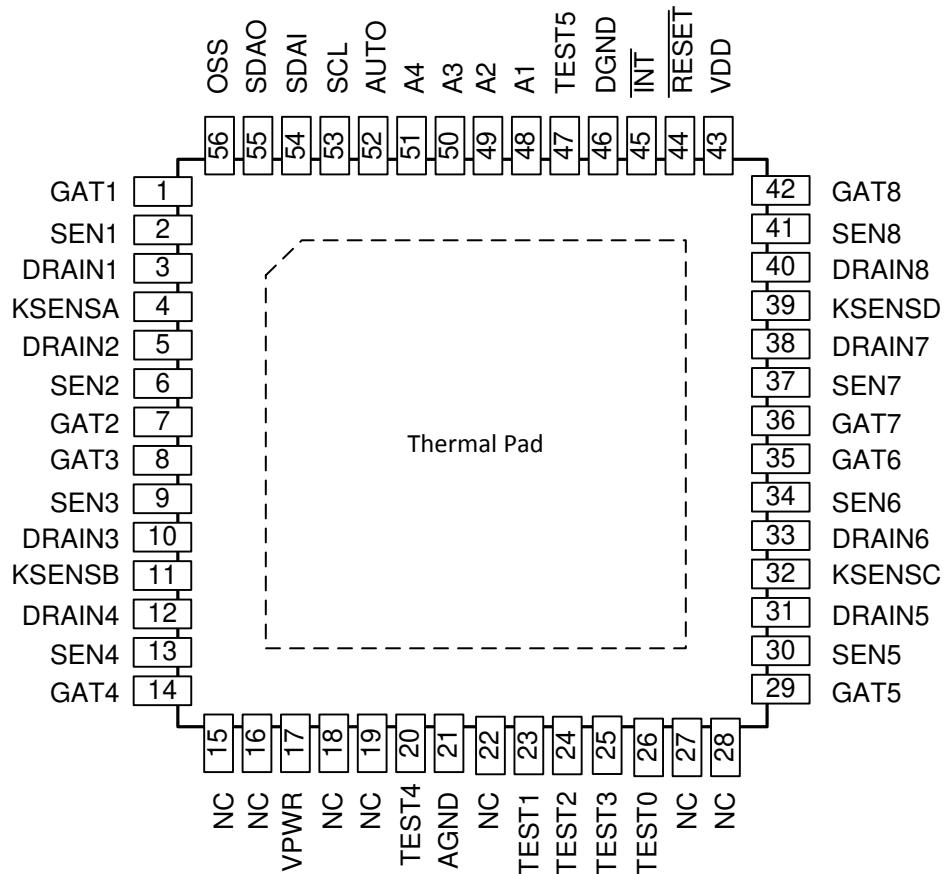

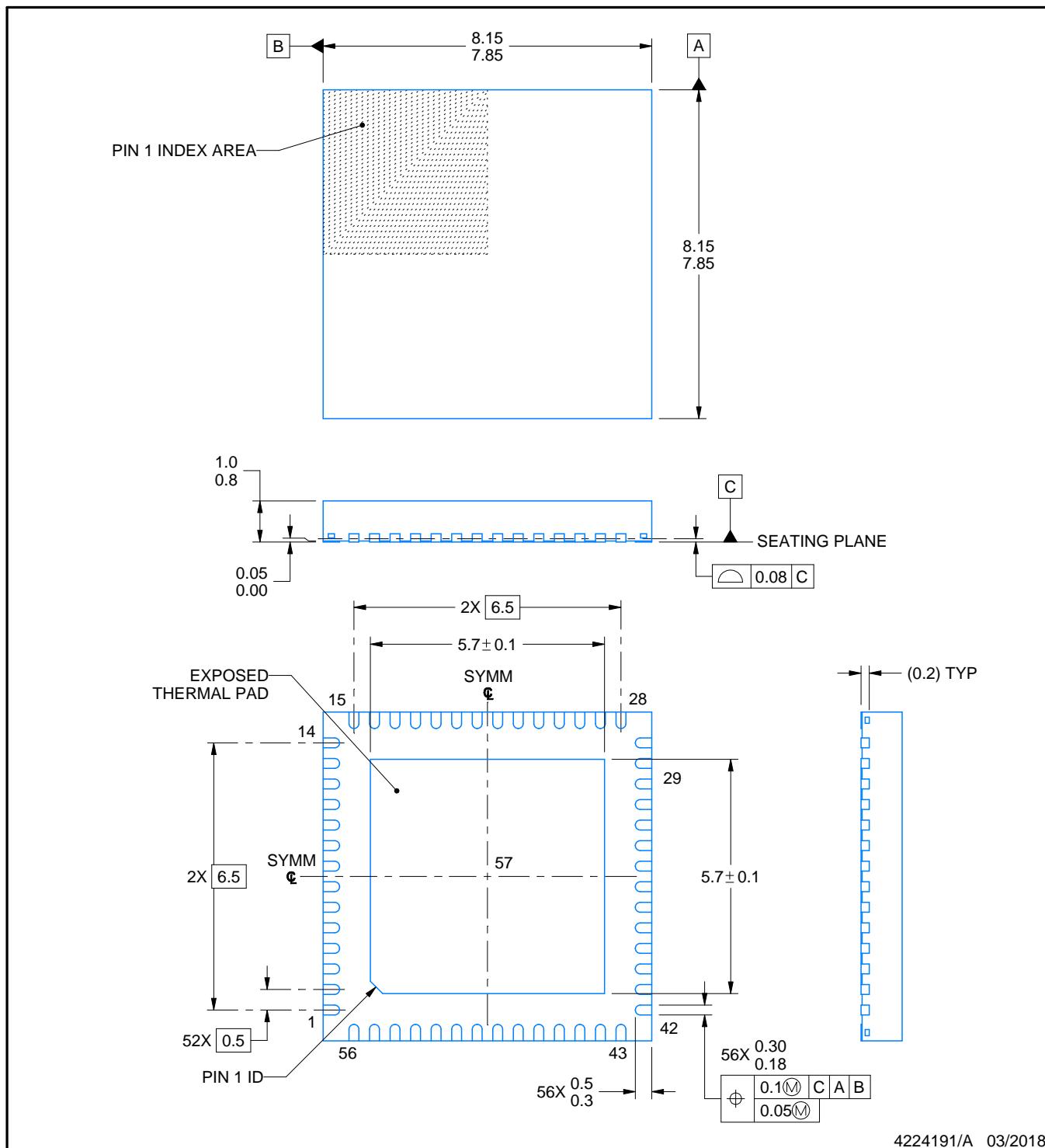

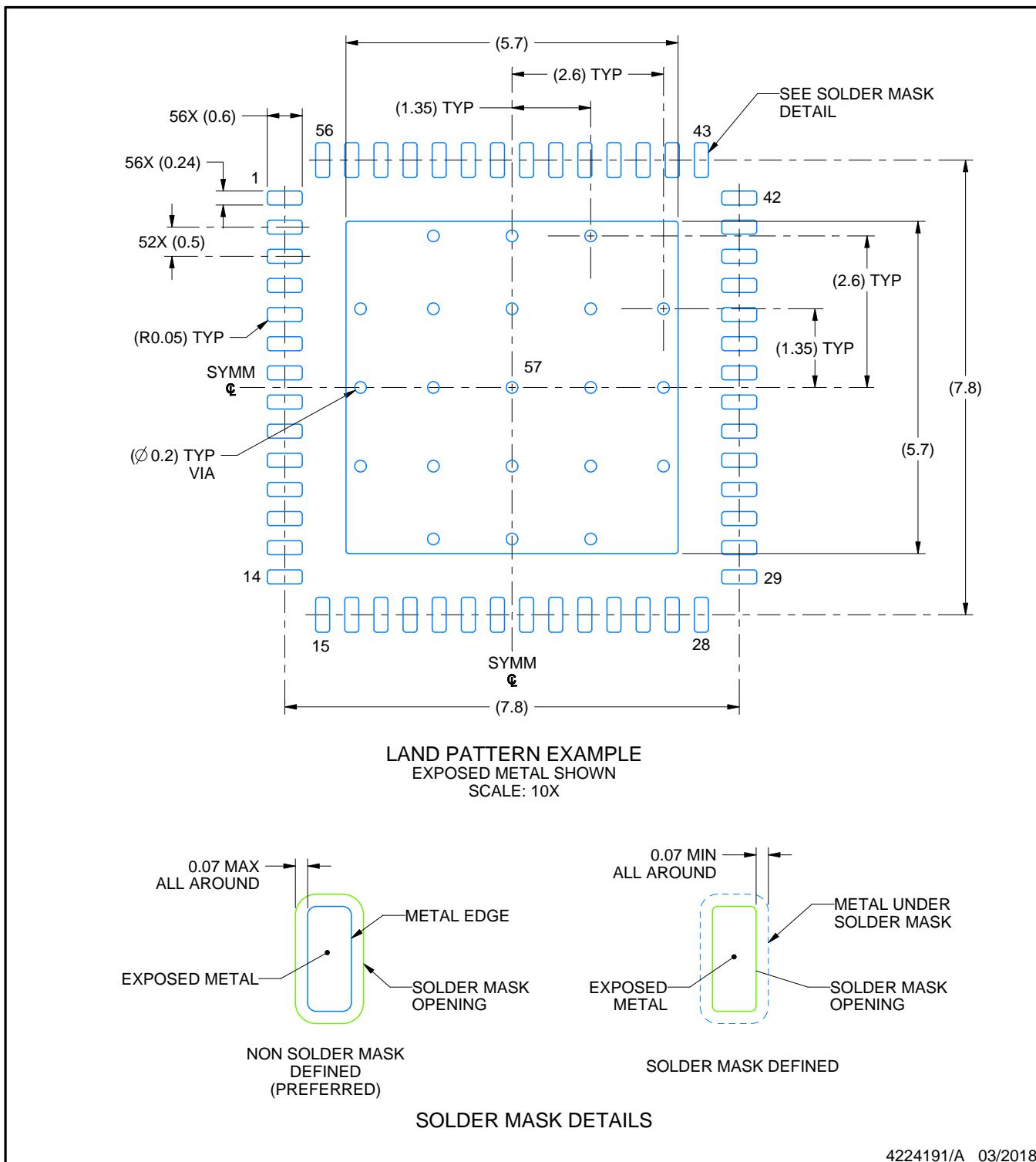

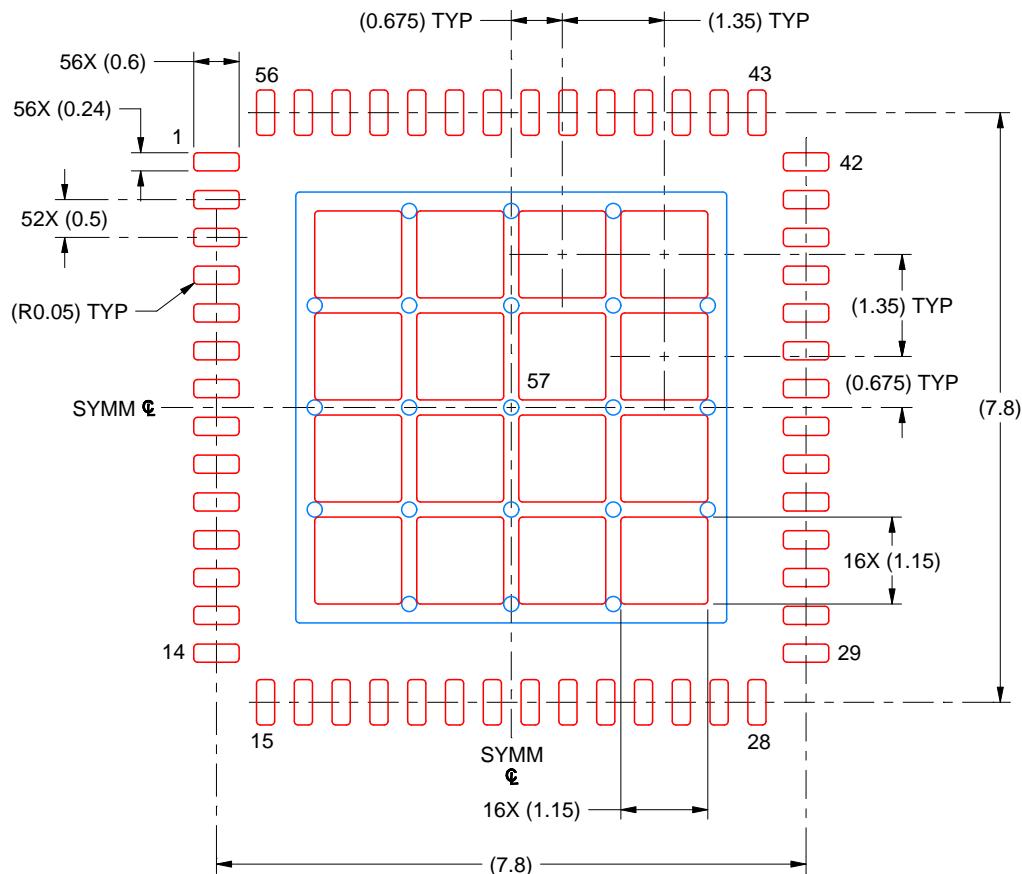

図 5-1. TPS23881B1 RTQ パッケージ(露出サーマルパッド付き)、56 ピン VQFN(上面図)

表 5-1. ピンの機能

| ピン       |                              | I/O | 説明                                                               |

|----------|------------------------------|-----|------------------------------------------------------------------|

| 名称       | 番号                           |     |                                                                  |

| A1-A4    | 48 ~ 51                      | I   | I <sup>2</sup> C A1-A4 アドレスライン。これらのピンは、内部で VDD にプルアップされています。     |

| AGND     | 21                           | —   | アナログ グランド。GND プレーンと露出サーマルパッドに接続します。                              |

| DGND     | 46                           | —   | デジタル グランド。GND プレーンと露出サーマルパッドに接続します。                              |

| DRAIN1-8 | 3, 5, 10, 12, 31, 33, 38, 40 | I   | チャネル 1 ~ 8 出力電圧モニタ                                               |

| GAT1-8   | 1, 7, 8, 14, 29, 35, 36, 42  | O   | チャネル 1-8 ゲートドライブ出力                                               |

| INT      | 45                           | O   | 割り込み出力。割り込みレジスタのビットがアサートされると、このピンは low にアサートされます。この出力はオープンドレンです。 |

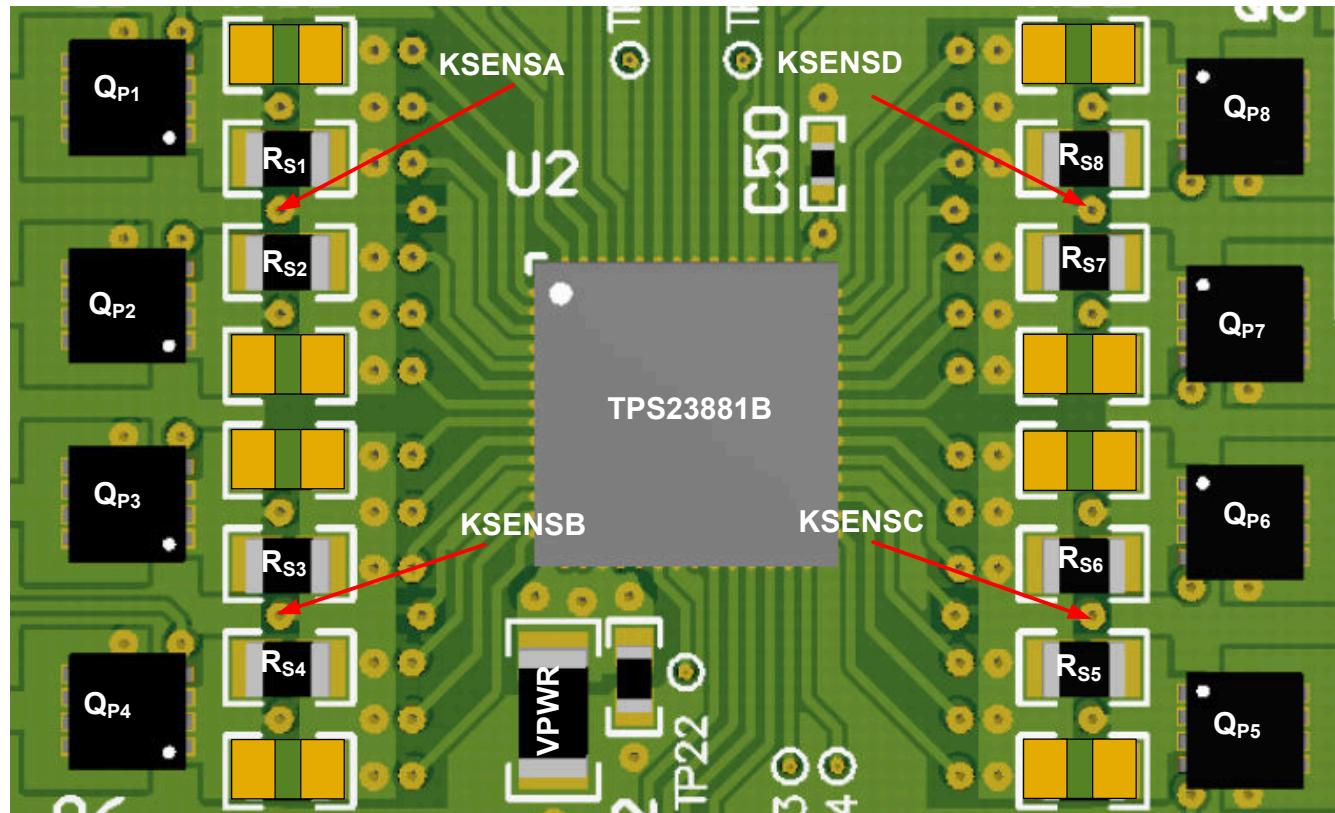

| KSENSA/B | 4, 11                        | I   | SEN1-4 のケルビン ポイント接続                                              |

| KSENSC/D | 32, 39                       | I   | SEN5-8 のケルビン ポイント接続                                              |

**表 5-1. ピンの機能(続き)**

| ピン       |                             | I/O | 説明                                                                                                                  |

|----------|-----------------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号                          |     |                                                                                                                     |

| NC       | 15, 16, 18, 19              | O   | 接続の無いピン。これらのピンは、VPWR からの電圧勾配を制御するために、VPWR の 1/3 および 2/3 で内部的にバイアスされます。オープンのままにします。                                  |

|          | 22, 27, 28, 52              | —   | 接続の無いピンオープンのままにします。                                                                                                 |

| OSS      | 56                          | I   | チャネル 1 ~ 8 の高速シャットダウン。このピンは、内部で DGND にプルダウンされています。                                                                  |

| RESET    | 44                          | I   | リセット入力。Low にアサートすると、TPS23881 はリセットされます。このピンは内部で VDD にプルアップされています。                                                   |

| SCL      | 53                          | I   | I <sup>2</sup> C バス用シリアル クロック入力                                                                                     |

| SDAI     | 54                          | I   | I <sup>2</sup> C バス用シリアル データ入力。このピンは、非絶縁型システムまたは双方向 I <sup>2</sup> C アイソレータを搭載したシステムの SDAO に接続できます。                 |

| SDAO     | 55                          | O   | I <sup>2</sup> C バス用シリアル データ出力。このピンは、非絶縁型システムまたは双方向 I <sup>2</sup> C アイソレータを搭載したシステムの SDAI に接続できます。この出力はオープンドレインです。 |

| 自動       | 52                          | I/O | 自律モードイネーブル/選択ピン。                                                                                                    |

| SEN1-8   | 2, 6, 9, 13, 30, 34, 37, 41 | I   | チャネル 1-8 電流センス入力                                                                                                    |

| TEST0-5  | 20, 23, 24, 25, 26, 47      | I/O | 内部的にテスト目的でのみ使用されます。オープンのままにします。                                                                                     |

| サーマル・パッド | —                           | —   | 正しく動作させるには、DGND 端子と AGND 端子を露出したサーマル パッドに接続する必要があります。                                                               |

| VDD      | 43                          | —   | デジタル電源。0.1μF ピンから DGND ピンへのバイパス。                                                                                    |

| VPWR     | 17                          | —   | アナログ 54V の正の電源。0.1μF ピンから AGND ピンへのバイパス。                                                                            |

## 5.1 ピンの詳細説明

以下の説明は、ピン配置と機能ブロック図を参照してください。

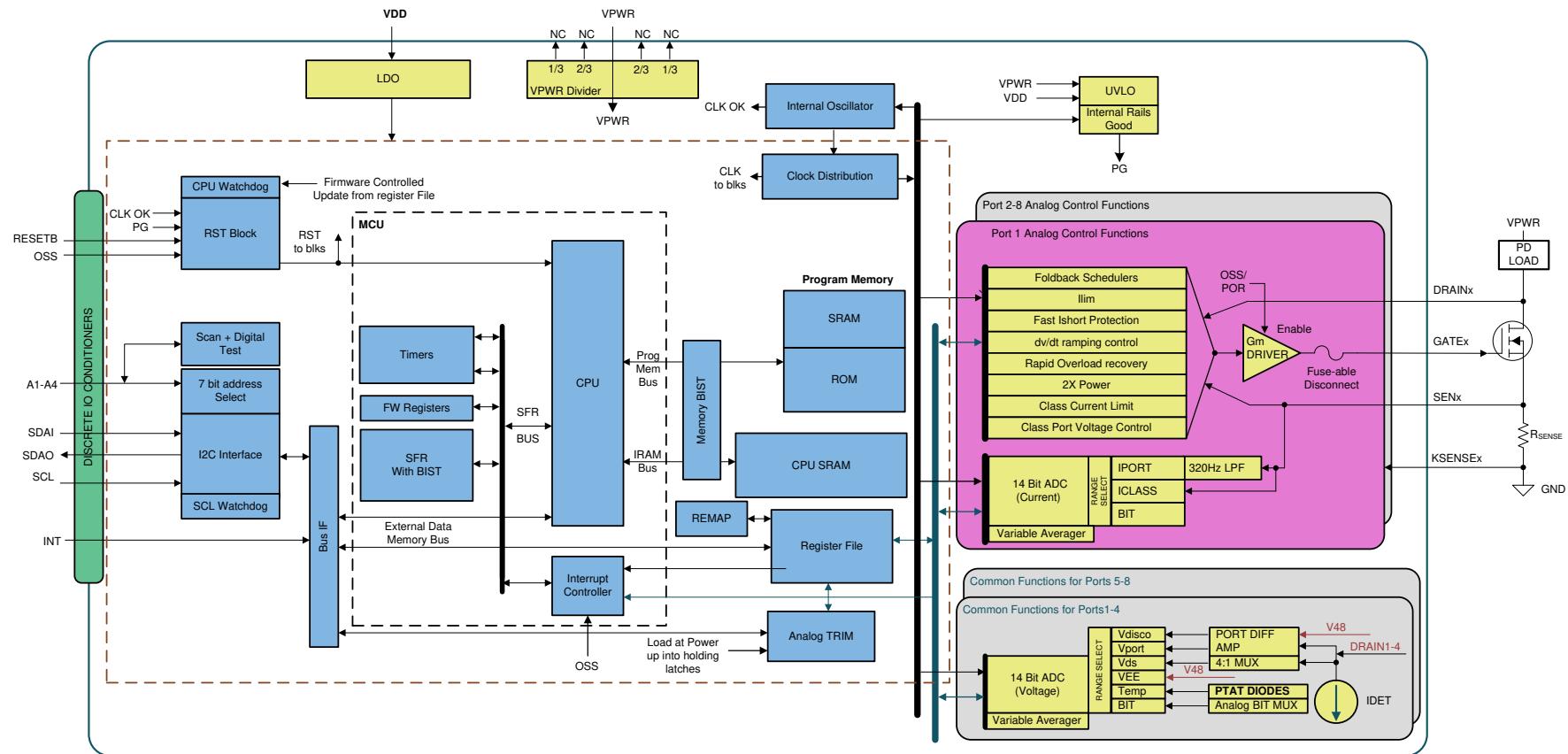

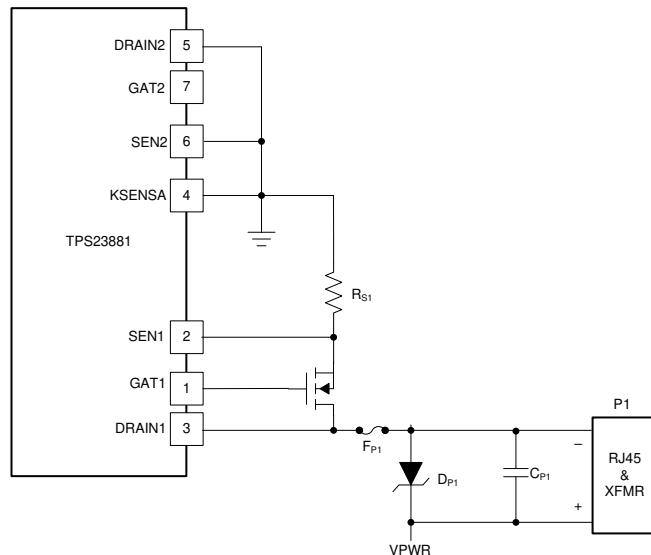

**DRAIN1-DRAIN8:** チャネル 1 ~ 8 出力電圧モニタと検出。ポート電圧の測定、ポート電圧の監視、ポートパワー グッドの検出、フォールドバック動作に使用されます。検出プローブの電流もこのピンに流れます。

TPS23881B は革新的な 4 点技術を使用して信頼性の高い PD 検出を行い、無効な負荷への電力供給を防止します。この検出は、DRAINn ピンを使用して 2 つの異なる電流レベルをシンクして行い、PD 電圧は VPWR から DRAINn まで測定します。新しい検出サイクルを開始する前にポート電圧が 2.5V を超える場合は、内部 100kΩ 抵抗がポートと並列に接続され、検出サイクルが開始される前にポートコンデンサが放電されるように 400ms の検出バックオフ期間が適用されます。

任意の動作モードでは、検出中またはポートがオンの間を除き、各 DRAINn ピンと VPWR の間に内部抵抗があります。ポート n を使用しない場合は、DRAINn をフローティングのままにするか、GND に接続できます。

**GAT1-GAT8:** チャネル 1 ~ 8 のゲート駆動出力を使用して、外部 N チャネル MOSFET ゲート制御を行います。ポートがオンのときは、低電流ソースによって MOSFET がオンになり、正の方向に駆動されます。GATn は、いずれかの入力電源が low である場合、または過電流タイムアウトが発生した場合、low になります。手動シャットダウン入力を使用してポートをオフにすると、GATn も low になります。未使用の場合は、フローティングのままにします。

設計の堅牢性向上のため、電流フォールドバック機能により、低抵抗負荷または短絡発生時およびポートがオンになった際の突入期間中の MOSFET の消費電力が制限されます。また、直接短絡が発生して MOSFET が 1μs 未満で強制的にオフになるなどの主要な異常を解消する高速過負荷保護コンパレータも搭載されています。

適切な MOSFET 制御を確保するため、GATn ピンと近くにある DRAINn ピン、GND、またはケルビン ポイント接続との間の回路のリーク パスは、最小限に抑える必要があります (250nA 未満)。

**INT:** 割り込みレジスタのビットがアサートされると、この割り込み出力ピンが low にアサートされます。この出力はオープンドレインです。

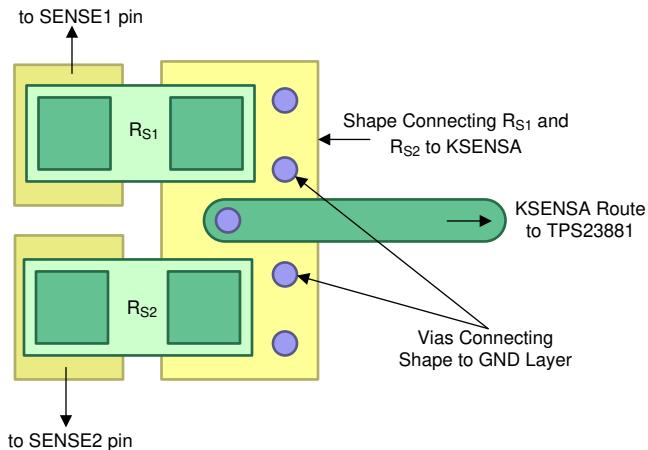

**KSENSA、KSENSB、KSENSC、KSENSD:** 関連する電流検出抵抗の両端で差動電圧測定を行うために使用されるケルビン ポイント接続。

各 KSENS は、次のように、2 つの隣接する SEN ピンで共有されます。KSENSA、SEN1 と SEN2、KSENSB と SEN3 と SEN4、KSENSC と SEN5 と SEN6、KSENSD と SEN7 と SEN8。測定精度を最適化するには、適切な PCB レイアウト手法に従うことを確認します。

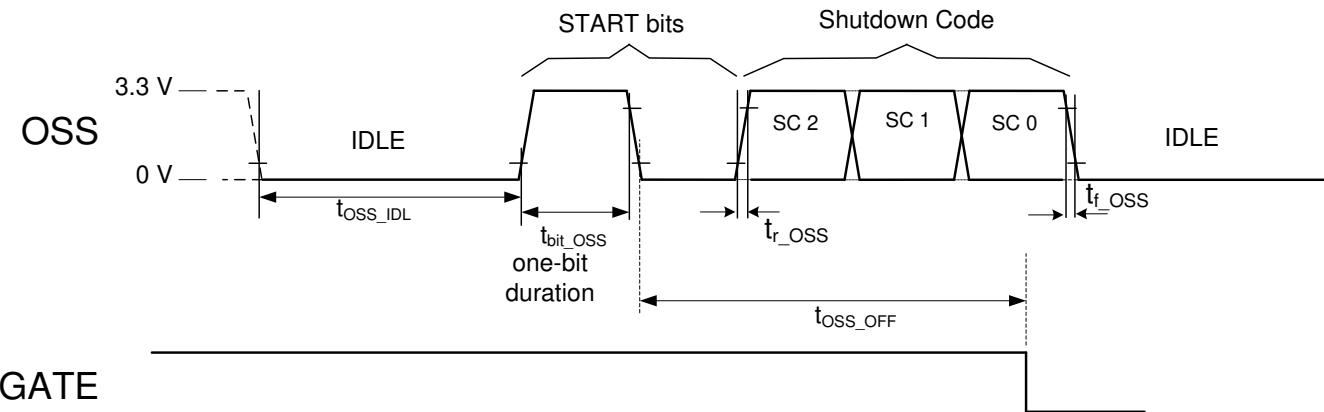

**OSS:** 高速シャットダウン、アクティブ high。このピンは、内部に  $1\mu\text{s} \sim 5\mu\text{s}$  のデグリッチ フィルターが内蔵され、内部的に DGND にプルダウンされています。

電源オフの手順は、Reset コマンド (1Ah レジスタ) を使用したポートリセットと同様です。3 ビットの OSS 機能により、OSS ピンに一連のパルスを印加して、個別または複数のポートを最大 8 レベルの優先度でオフにできます。

**RESET:** リセット入力、アクティブ low。アサートされると、TPS23881B はリセットされ、すべてのポートがオフになり、レジスタが強制的に電源投入時の状態になります。このピンは内部で VDD にプルアップされており、 $1\mu\text{s}$  から  $5\mu\text{s}$  へのグリッチ除去フィルタは内蔵されています。設計者は、外付け RC ネットワークを使用して、ターンオンを遅延させることができます。また、RESET 入力とは独立した内部パワー オンリセットも備えています。

**SCL:** I<sup>2</sup>C バス用シリアル クロック入力。

**SDAI:** I<sup>2</sup>C バス用シリアル データ入力。

**SDAO:** オープンドレインの I<sup>2</sup>C バス出力データ ライン。外付け抵抗プルアップが必要です。TPS23881B は、独立した SDAO ラインと SDAI ラインを使用して、光絶縁型 I<sup>2</sup>C インターフェイスを実現できます。

**自動: 自律モード選択ピン:** このピンをフローティングにすると、自律動作がディスエーブルこのピンを抵抗 ( $R_{AUTO}$ ) を介して GND に接続すると、選択可能なポート電力割り当てレベルで自律動作が可能になります。 $R_{AUTO}$  を接続する場合、Auto ピンと GND の間に  $10\text{nF}$  のコンデンサが必要です。

**A4-A1:** I<sup>2</sup>C バスのアドレス入力これらのピンは、内部で VDD にプルアップされています。詳細については、[セクション 8.6.2.13](#) を参照してください。

**SEN1-8:KSENSn** に対するチャネル電流センス入力 (KSENSn の説明を参照)。差動測定は、KSENSA-D ケルビン ポイント接続を使用して実行します。GND との間に  $0.200\Omega$  電流センス抵抗を接続することで、外部 MOSFET の電流を監視します。現在のフォールドバック エンジンまたは分類時に使用されます。ADC 変換による負荷電流を監視することに使用できます。

TPS23881B が分類測定を行うと、電流は外部 MOSFET を流れます。この動作によりデバイスの熱濃度を防ぐことができます。TPS23881B が複数のポートで同時に分類測定を実行できます。フォールドバック機能付きの電流制限については、SEN1-8 ピンに  $2\mu\text{S}$  アナログ フィルタが内部的にあり、グリッチ フィルタリングを提供します。ADC を介した測定の場合、SEN1-8 ピンにアンチエイリアシング フィルタがあります。これには、ポート電源電流監視、ポートポリシング、DC 切断が含まれます。

このポートを使用しない場合は、SENn を GND に接続します。

**VDD:3.3V** ロジック電源入力。

**VPWR:** 高電圧電源入力。公称 54V。

**AGND および DGND:** 内部アナログ回路とデジタル回路のグランド リファレンス。内部的には接続されていません。どちらのピンも、システムの GND プレーンへの低抵抗パスを必要とします。堅牢な GND プレーンを使用してデバイスのサーマル パッドから熱を抽出する場合は、これらのピンを PCB 上のサーマル パッド接続を介して互いに接続できます。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                              |                                    | 最小値  | 最大値 | 単位 |

|------------------------------|------------------------------------|------|-----|----|

| 電圧                           | VPWR                               | -0.3 | 70  | V  |

|                              | VDD                                | -0.3 | 4   | V  |

|                              | OSS、RESET、A1-A4、SDAI、SDAO、SCL、INT  | -0.3 | 4   | V  |

|                              | SEN1-8、KSENSA、KSENSB、KSENSC、KSENSD | -0.3 | 3   | V  |

|                              | GATE1-8                            | -0.3 | 13  | V  |

|                              | DRAIN1-8                           | -0.3 | 70  | V  |

|                              | TEST0-3、ATST_DCPL0、DTST_DCPL1      | -0.3 | 4   | V  |

|                              | AGND - DGND                        | -0.3 | 0.3 | V  |

|                              | シンク電流 INT、SDA                      |      | 20  | mA |

| リード温度ケースから 1/6mm 離れた点で 10 秒間 |                                    |      | 260 | °C |

| T <sub>stg</sub>             | 保存温度                               | -65  | 150 | °C |

(1) 「絶対最大定格」の範囲を超える動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |      |                                                               | 値     | 単位 |

|--------------------|------|---------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>  | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、JEDEC 規格 JESD22-C101 準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

(1) JEDEC document JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC document JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                          | 最小値 | 公称値 | 最大値 | 単位   |

|-------------------|--------------------------|-----|-----|-----|------|

| V <sub>VDD</sub>  |                          | 3   | 3.3 | 3.6 | V    |

| V <sub>VPWR</sub> |                          | 44  | 54  | 57  | V    |

|                   | VPWR の電圧スルーレート           |     |     | 1   | V/μs |

| f <sub>SCL</sub>  | I <sup>2</sup> C クロック周波数 |     |     | 400 | kHz  |

| T <sub>J</sub>    | 接合部温度                    | -40 |     | 125 | °C   |

### 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | TPS23881         | 単位   |

|-----------------------|---------------------|------------------|------|

|                       |                     | RTQ パッケージ (VQFN) |      |

|                       |                     | 56 ピン            |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 25.3             | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 9.7              | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 3.7              | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.2              | °C/W |

## 6.4 热に関する情報 (続き)

| 热評価基準 <sup>(1)</sup> |                   | TPS23881         | 単位   |

|----------------------|-------------------|------------------|------|

|                      |                   | RTQ パッケージ (VQFN) |      |

|                      |                   | 56 ピン            |      |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 3.7              | °C/W |

| $R_{θJC(bot)}$       | 接合部からケース(底面)への熱抵抗 | 0.5              | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 電気的特性

特に記載がない限り、条件は  $-40 < T_J < 125^{\circ}\text{C}$  です。 $V_{\text{VDD}} = 3.3\text{V}$ 、 $V_{\text{VPWR}} = 54\text{V}$ 、 $V_{\text{DGND}} = V_{\text{AGND}}$ 、 $\text{DGND}$ 、 $\text{KSENSA}$ 、 $\text{KSENSB}$ 、 $\text{KSENSC}$ 、 $\text{KSENSD}$  を  $\text{AGND}$  に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{\text{SENSE}} = 0.200\Omega$ 、 $\text{KSENSA}$  (SEN1 または SEN2) との間、 $\text{KSENSB}$  (SEN3 または SEN4) との間、 $\text{KSENCS}$  (SEN5 または SEN6) または  $\text{KSENSD}$  (SEN7 または SEN8) に接続。標準値は  $25^{\circ}\text{C}$  状態です。特に記述のない限り、すべての電圧は  $\text{AGND}$  を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ                         | テスト条件                       | 最小値                                                | 標準値   | 最大値   | 単位    |      |

|-------------------------------|-----------------------------|----------------------------------------------------|-------|-------|-------|------|

| <b>入力電源 VPWR</b>              |                             |                                                    |       |       |       |      |

| $I_{\text{VPWR}}$             | VPWR 消費電流                   | $V_{\text{VPWR}} = 54\text{V}$                     | 10    | 12.5  | mA    |      |

| $V_{\text{UVLOPW\_F}}$        | VPWR UVLO 立ち下がりスレッショルド      | 内部発振器が動作していないか確認します                                | 14.5  | 17.5  | V     |      |

| $V_{\text{UVLOPW\_R}}$        | VPWR UVLO 立ち上がりスレッショルド      |                                                    | 15.5  | 18.5  | V     |      |

| $V_{\text{PUV\_F}}$           | VPWR 低電圧立ち下がりスレッショルド        | $V_{\text{PUV}}$ スレッショルド                           | 25    | 26.5  | 28    | V    |

| <b>入力電源 VDD</b>               |                             |                                                    |       |       |       |      |

| $I_{\text{VDD}}$              | VDD 消費電流                    |                                                    | 6     | 12    | mA    |      |

| $V_{\text{UVDD\_F}}$          | VDD UVLO 立ち下がりスレッショルド       | チャネルのデアサーション                                       | 2.1   | 2.25  | 2.4   | V    |

| $V_{\text{UVDD\_R}}$          | VDD UVLO 立ち上がりスレッショルド       |                                                    | 2.45  | 2.6   | 2.75  | V    |

| $V_{\text{UVDD\_HYS}}$        | ヒステリシス VDD UVLO             |                                                    |       | 0.35  |       | V    |

| $V_{\text{UVW\_F}}$           | VDD UVLO 警告スレッショルド          | $V_{\text{DD}}$ 立ち下がり                              | 2.6   | 2.8   | 3     | V    |

| <b>A/D コンバータ</b>              |                             |                                                    |       |       |       |      |

| $T_{\text{CONV\_I}}$          | 変換時間                        | すべての範囲、各チャネル                                       | 0.64  | 0.8   | 0.96  | ms   |

| $T_{\text{CONV\_V}}$          | 変換時間                        | すべての範囲、各チャネル                                       | 0.82  | 1.03  | 1.2   | ms   |

| $T_{\text{INT\_CUR}}$         | 積分時間、電流                     | 各チャネル、チャネルのオン電流                                    | 82    | 102   | 122   | ms   |

| $T_{\text{INT\_DET}}$         | 積分時間、検出                     |                                                    | 13.1  | 16.6  | 20    | ms   |

| $T_{\text{INT\_channelV}}$    | 積分時間、チャネル電圧                 | チャンネル パワー                                          | 3.25  | 4.12  | 4.9   | ms   |

| $T_{\text{INT\_inV}}$         | 積分時間、入力電圧                   |                                                    | 3.25  | 4.12  | 4.9   | ms   |

|                               | 入力電圧変換のスケール ファクタと精度         | $V_{\text{VPWR}} = 57\text{V}$                     | 15175 | 15565 | 15955 | カウント |

|                               |                             |                                                    | 55.57 | 57    | 58.43 | V    |

|                               |                             | $V_{\text{VPWR}} = 44\text{V}$                     | 11713 | 12015 | 12316 | カウント |

|                               |                             |                                                    | 42.89 | 44    | 45.10 | V    |

|                               | パワード チャネルの電圧変換のスケール ファクタと精度 | $V_{\text{VPWR}} - V_{\text{DRAInN}} = 57\text{V}$ | 15175 | 15565 | 15955 | カウント |

|                               |                             |                                                    | 55.57 | 57    | 58.43 | V    |

|                               |                             | $V_{\text{VPWR}} - V_{\text{DRAInN}} = 44\text{V}$ | 11713 | 12015 | 12316 | カウント |

|                               |                             |                                                    | 42.89 | 44    | 45.10 | V    |

| $\delta V/V_{\text{Channel}}$ | 電圧読み取り精度                    |                                                    | -2.5  |       | 2.5   | %    |

## 6.5 電気的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、 $KSENSA$ 、 $KSENSB$ 、 $KSENSC$ 、 $KSENSD$  を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{SENSE} = 0.200\Omega$ 、 $KSENSA$  (SEN1 または SEN2) との間、 $KSENSB$  (SEN3 または SEN4) との間、 $KSENSC$  (SEN5 または SEN6) または  $KSENSD$  (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ                  |                     | テスト条件                                                                                          | 最小値   | 標準値   | 最大値           | 単位   |

|------------------------|---------------------|------------------------------------------------------------------------------------------------|-------|-------|---------------|------|

| $\delta I/I_{Channel}$ | パワード チャネルの電流変換係数と精度 | チャネル電流 = 770mA                                                                                 | 8431  | 8604  | 8776          | カウント |

|                        |                     | チャネル電流 = 100mA                                                                                 | 754.5 | 770   | 785.4         | mA   |

|                        |                     | チャネル電流 = 100mA                                                                                 | 1084  | 1118  | 1152          | カウント |

|                        |                     | チャネル電流 = 100mA                                                                                 | 97    | 100   | 103           | mA   |

| $\delta I/I_{Channel}$ | 電流読み取り精度            | チャネル電流 = 100mA                                                                                 | -3    | 3     | %             |      |

|                        |                     | チャネル電流 = 770mA                                                                                 | -2    | 2     |               |      |

| $\sigma I$             | パワー チャネル電流、フルスケール出力 | チャネル電流 = 1.5A、 $2 \times FBn = 1$                                                              | 14959 | 15671 | カウント          |      |

|                        |                     | チャネル電流 = 1.5A、 $2 \times FBn = 1$                                                              | 1.34  | 1.400 |               |      |

| $\sigma I$             | 現在の読み取りの再現性         | フルスケール読み取り値                                                                                    | -7.5  | 7.5   | mA            |      |

| $\delta R/R_{Channel}$ | 抵抗の読み取り精度           | $15\text{k}\Omega \leq R_{Channel} \leq 33\text{k}\Omega$ 、 $C_{Channel} \leq 0.25\mu\text{F}$ | -7    | 7     | %             |      |

| $I_{bias}$             | 検知ピンのバイアス電流         | チャネルがオンまたはクラス中にオンになります                                                                         | -2.5  | 0     | $\mu\text{A}$ |      |

### GATE 1-8

|                   |                                                |                                                                                        |    |      |                  |

|-------------------|------------------------------------------------|----------------------------------------------------------------------------------------|----|------|------------------|

| $V_{GOH}$         | ゲート駆動電圧                                        | $V_{GATEn}, I_{GATE} = -1\mu\text{A}$                                                  | 10 | 12.5 | V                |

| $I_{GO-}$         | パワーオンリセット、OSS 検出、またはチャネル ターンオフ コマンドによるゲートシンク電流 | $V_{GATEn} = 5\text{V}$                                                                | 60 | 100  | 190 mA           |

| $I_{GO\ short-}$  | チャネル短絡時のゲートシンク電流                               | $V_{GATEn} = 5\text{V}, V_{SENn} \geq V_{short}$ (または $2X$ モードの場合は $V_{short2x}$ )     | 60 | 100  | 190 mA           |

| $I_{GO+}$         | ピーク ソース電流                                      | $V_{GATEn} = 0\text{V}$ 、デフォルト選択                                                       | 39 | 50   | 63 $\mu\text{A}$ |

| $t_{D\_off\_OSS}$ | 1ビット OSS 入力からのゲート ターンオフ時間                      | OSS から $V_{GATEn} < 1\text{V}$ の範囲、 $V_{SENn} = 0\text{V}$ 、 $MbitPrty = 0$            | 1  | 5    | $\mu\text{s}$    |

| $t_{OSS\_OFF}$    | 3ビット OSS 入力からのゲート ターンオフ時間                      | スタートビットの立ち下がりエッジから $V_{GATEn} < 1\text{V}$ まで、 $V_{SENn} = 0\text{V}$ 、 $MbitPrty = 1$ | 72 | 104  | $\mu\text{s}$    |

| $t_{P\_off\_CMD}$ | チャネル ターンオフ コマンドからのゲート ターンオフ時間                  | チャネル オフ コマンド ( $POFFn=1$ ) から $V_{GATEn} < 1\text{V}$ 、 $V_{SENn} = 0\text{V}$ まで      |    | 300  | $\mu\text{s}$    |

| $t_{P\_off\_RST}$ | /RESET LOW からのゲート ターンオフ時間                      | /RESET LOW から $V_{GATEn} < 1\text{V}$ 、 $V_{SENn} = 0\text{V}$ まで                      | 1  | 5    | $\mu\text{s}$    |

### DRAIN 1-8

|                  |                     |                                               |     |      |     |            |

|------------------|---------------------|-----------------------------------------------|-----|------|-----|------------|

| $V_{PGT}$        | パワー グッド スレッショルド     | $V_{DRAINn}$ で測定                              | 1   | 2.13 | 3   | V          |

| $V_{SHT}$        | 短絡 FET スレッショルド      | $V_{DRAINn}$ で測定                              | 4   | 6    | 8   | V          |

| $R_{DRAIN}$      | DRAINn と VPWR の間の抵抗 | 検出中またはチャネルがオンである間を除く任意の動作モード (デバイスのリセット状態を含む) | 80  | 100  | 190 | k $\Omega$ |

| <b>AUTOCLASS</b> |                     |                                               |     |      |     |            |

| $t_{Class\_ACS}$ | 自動クラス検出の開始          | クラスの開始から測定されます                                | 90  | 100  | ms  |            |

| $t_{AUTO\_PSE1}$ | 自動クラス電力測定の開始        | インラッシュ終了時から測定                                 | 1.4 | 1.6  | s   |            |

|                  |                     | チャネルがすでに電力を供給されている間に MACx ビットを設定して測定されます      |     | 10   | ms  |            |

| $t_{AUTO}$       | 自動クラス電力測定の持続時間      |                                               | 1.7 | 1.8  | 1.9 | s          |

## 6.5 電気的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、KSENSA、KSENSB、KSENSC、KSENSD を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{SENSE} = 0.200\Omega$ 、KSENSA (SEN1 または SEN2) との間、KSENSB (SEN3 または SEN4) との間、KSENSC (SEN5 または SEN6) または KSENSD (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ              |                                | テスト条件                                                           | 最小値  | 標準値 | 最大値 | 単位   |

|--------------------|--------------------------------|-----------------------------------------------------------------|------|-----|-----|------|

| $t_{AUTO\_window}$ | 自動クラス パワー測定スライディング ウィンドウ       |                                                                 | 0.15 | 0.3 |     | s    |

| $P_{AC}$           | AutoClass チャネル電力変換のスケーリング係数と精度 | $VPWR = 52\text{V}$ 、 $VDRAINn = 0\text{V}$ 、<br>チャネル電流 = 770mA | 76   | 80  | 84  | カウント |

|                    |                                | $VPWR = 50\text{V}$ 、 $VDRAINn = 0\text{V}$ 、<br>チャネル電流 = 100mA | 9    | 10  | 11  |      |

## 6.5 電気的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、 $KSENZA$ 、 $KSENSB$ 、 $KSENSC$ 、 $KSENSD$  を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{SENSE} = 0.200\Omega$ 、 $KSENZA$  (SEN1 または SEN2) との間、 $KSENSB$  (SEN3 または SEN4) との間、 $KSENSC$  (SEN5 または SEN6) または  $KSENSD$  (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ             |                        | テスト条件                                                                            | 最小値  | 標準値  | 最大値  | 単位               |

|-------------------|------------------------|----------------------------------------------------------------------------------|------|------|------|------------------|

| <b>検出</b>         |                        |                                                                                  |      |      |      |                  |

| $I_{DISC}$        | 検出電流                   | 最初と 3 番目の検出ポイント<br>$V_{VPWR}-VDRAINn = 0\text{V}$                                | 145  | 160  | 190  | $\mu\text{A}$    |

|                   |                        | 2 番目と 4 番目の検出ポイント $V_{VPWR} - VDRAINn = 0\text{V}$                               | 235  | 270  | 300  |                  |

| $\Delta I_{DISC}$ | 2 回目 - 1 回目の検出電流       | $V_{VPWR} - VDRAINn = 0\text{V}$                                                 | 98   | 110  | 118  | $\mu\text{A}$    |

| $V_{det\_open}$   | オープン回路検出電圧             | $V_{VPWR} - VDRAINn$ として測定                                                       | 23.5 | 26   | 29   | $\text{V}$       |

| $R_{REJ\_LOW}$    | 抵抗除去 low 範囲            |                                                                                  | 0.86 |      | 15   | $\text{k}\Omega$ |

| $R_{REJ\_HI}$     | 除去抵抗高範囲                |                                                                                  | 33   |      | 100  | $\text{k}\Omega$ |

| $R_{ACCEPT}$      | 許容抵抗範囲                 |                                                                                  | 19   | 25   | 26.5 | $\text{k}\Omega$ |

| $R_{SHORT}$       | 短絡チャネルのスレッショルド         |                                                                                  |      |      | 360  | $\Omega$         |

| $R_{OPEN}$        | オープンチャネルスレッショルド        |                                                                                  | 400  |      |      | $\text{k}\Omega$ |

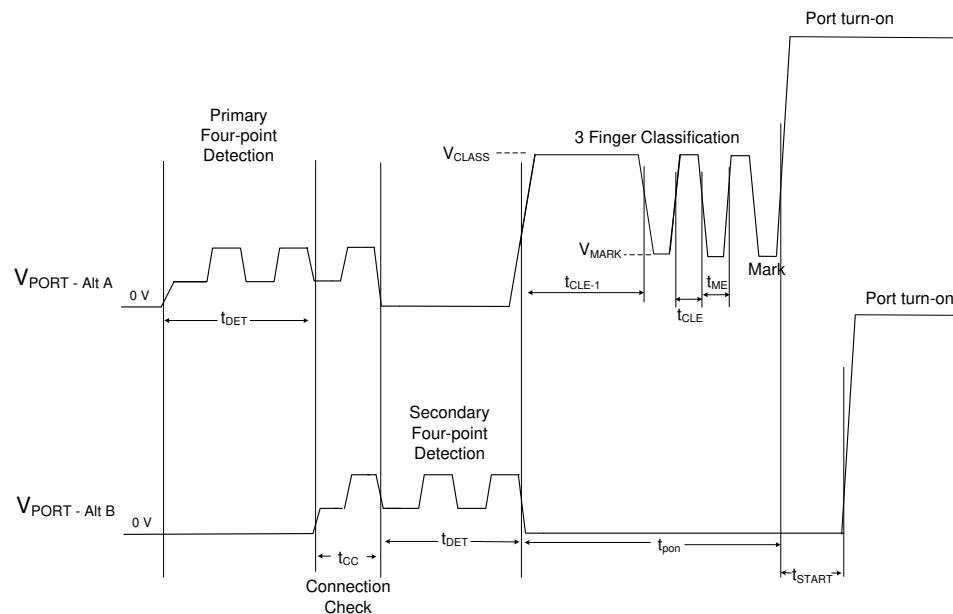

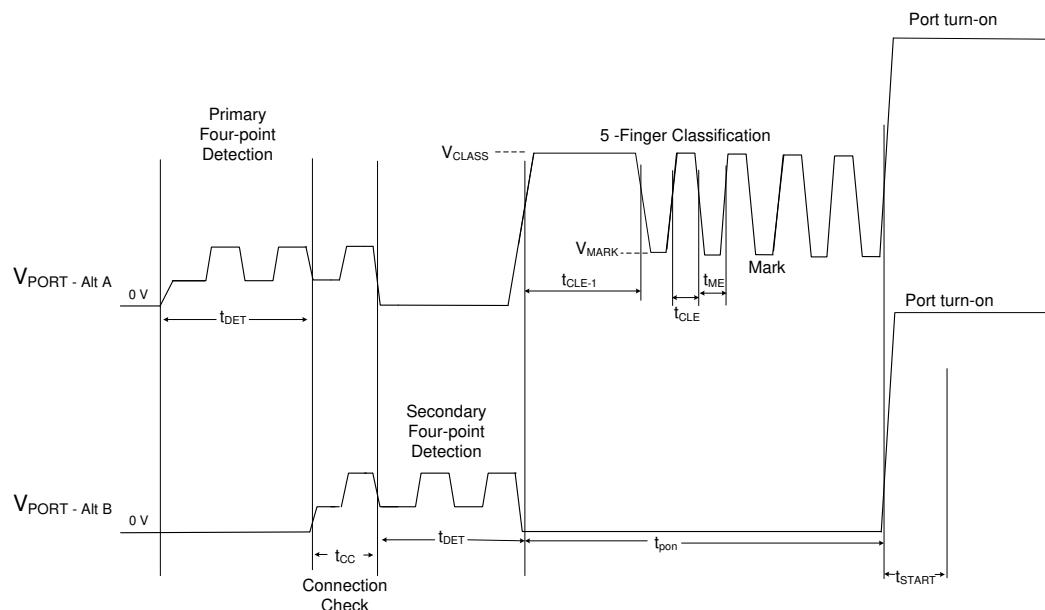

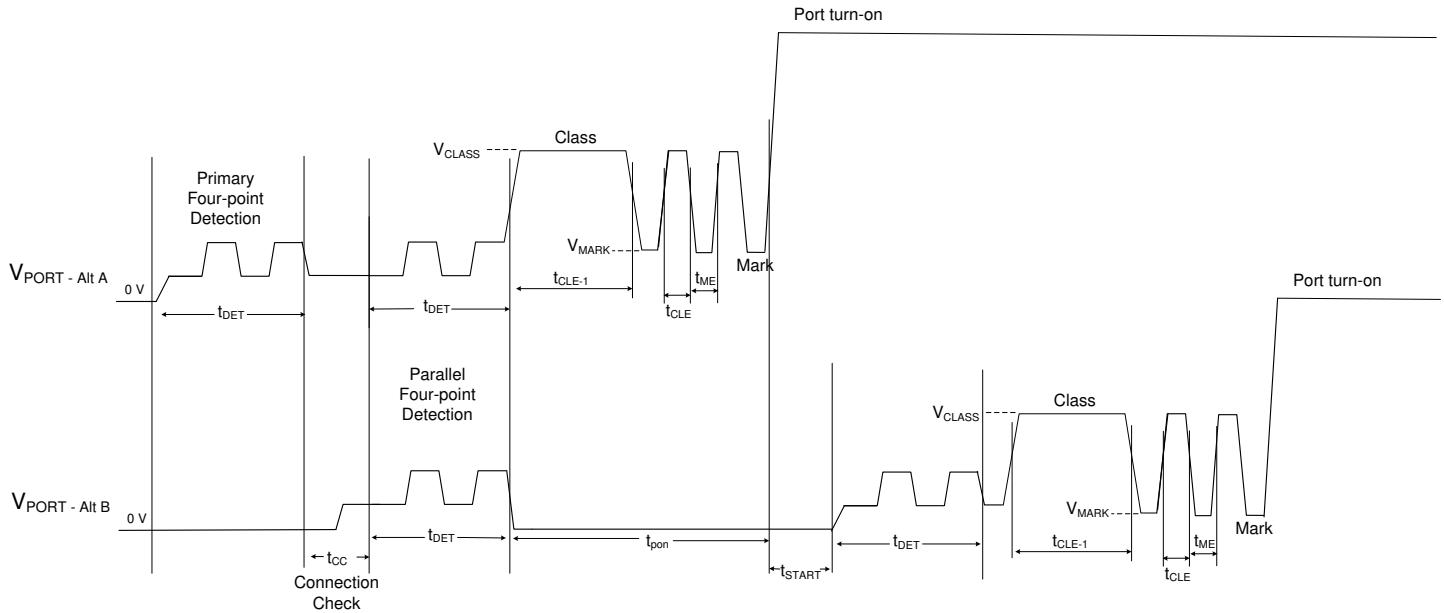

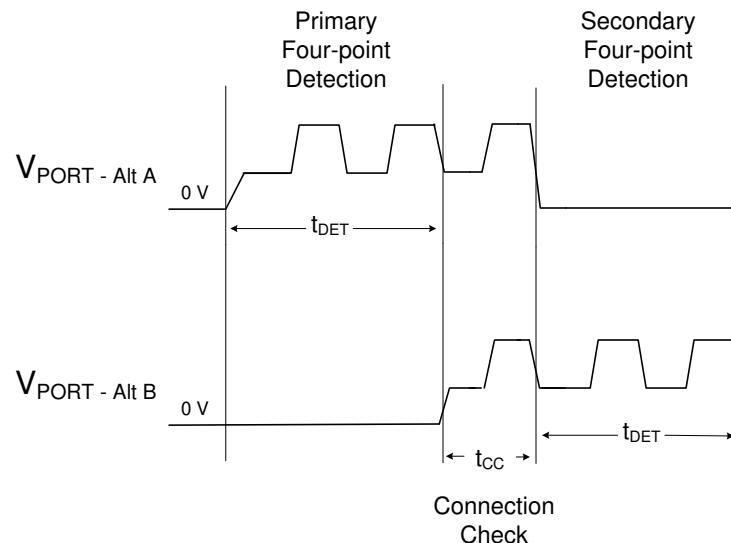

| $t_{DET}$         | 検出時間                   | 検出完了までの時間、 $4Pxx = 0$                                                            | 275  | 350  | 425  | $\text{ms}$      |

| $t_{CC}$          | 接続チェック期間               | 有効な検出後、接続チェック完了までの時間、 $4Pxx = 1$                                                 |      | 150  | 400  | $\text{ms}$      |

| $t_{DET\_BOFF}$   | 検出試行間のバックオフの一時停止を検出します | $V_{VPWR} - VDRAINn > 2.5\text{V}$                                               | 300  | 400  | 500  | $\text{ms}$      |

|                   |                        | $V_{VPWR} - VDRAINn < 2.5\text{V}$                                               | 20   |      | 100  | $\text{ms}$      |

| $t_{DET\_DLY}$    | 検出遅延                   | コマンドまたは PD の接続からチャネル検出への完了 $4Pxx = 0$                                            |      |      | 590  | $\text{ms}$      |

|                   | 容量測定                   | $C_{port} = 10\mu\text{F}$                                                       | 8.5  | 10   | 11.5 | $\mu\text{F}$    |

| <b>分類</b>         |                        |                                                                                  |      |      |      |                  |

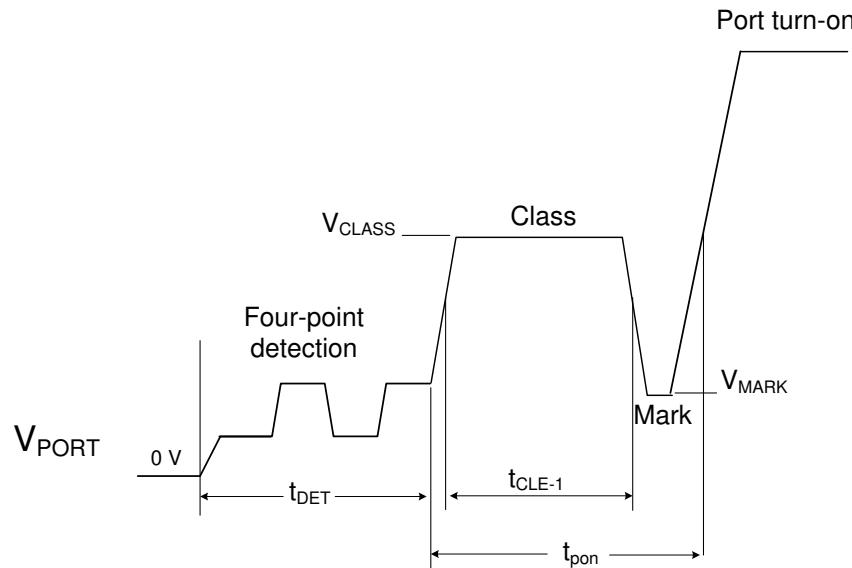

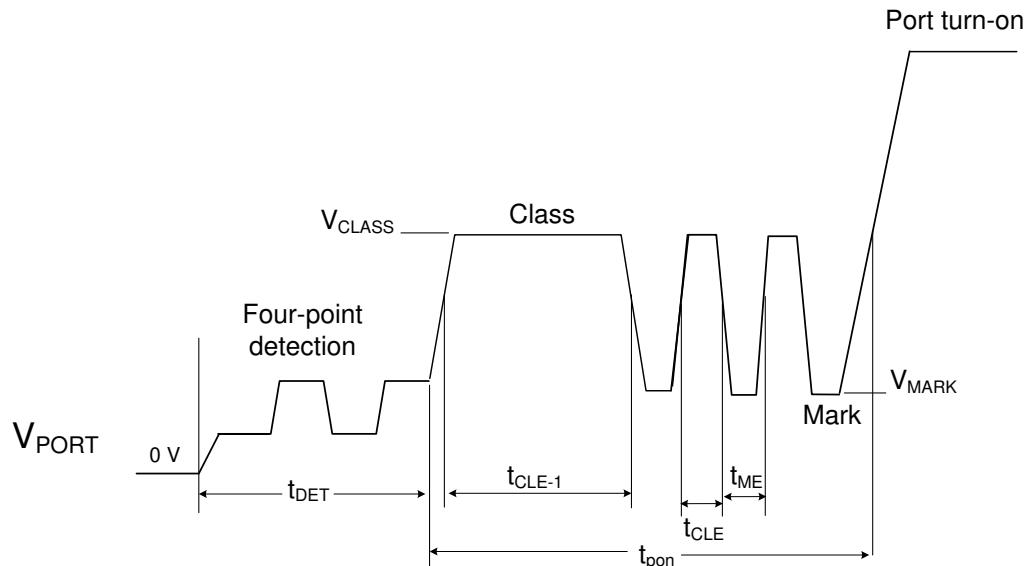

| $V_{CLASS}$       | 分類電圧                   | $V_{VPWR} - VDRAINn, VSENn \geq 0\text{mV}$<br>$I_{channel} \geq 180\mu\text{A}$ | 15.5 | 18.5 | 20.5 | $\text{V}$       |

| $I_{CLASS\_Lim}$  | 分類電流制限                 | $V_{VPWR} - VDRAINn = 0\text{V}$                                                 | 65   | 75   | 90   | $\text{mA}$      |

| $I_{CLASS\_TH}$   | 分類スレッショルド電流            | クラス 0-1                                                                          | 5    |      | 8    | $\text{mA}$      |

|                   |                        | クラス 1-2                                                                          | 13   |      | 16   | $\text{mA}$      |

|                   |                        | クラス 2-3                                                                          | 21   |      | 25   | $\text{mA}$      |

|                   |                        | クラス 3-4                                                                          | 31   |      | 35   | $\text{mA}$      |

|                   |                        | クラス 4-クラス過電流保護                                                                   | 45   |      | 51   | $\text{mA}$      |

| $t_{LCE}$         | 分類期間 (1 本目のフィンガー)      | 検出完了まで表示されます                                                                     | 95   |      | 105  | $\text{ms}$      |

| $t_{CLE2-5}$      | 分類期間 (2 ~ 5 目のフィンガー)   | マーク完了から                                                                          | 6.5  |      | 12   | $\text{ms}$      |

| <b>マーク</b>        |                        |                                                                                  |      |      |      |                  |

| $V_{MARK}$        | マーク電圧                  | $4\text{mA} \geq I_{Channel} \geq 180\mu\text{A}$<br>$V_{VPWR} - VDRAINn$        | 7    |      | 10   | $\text{V}$       |

| $I_{MARK\_Lim}$   | マークシンク電流制限             | $V_{VPWR} - VDRAINn = 0\text{V}$                                                 | 60   | 75   | 90   | $\text{mA}$      |

| $t_{ME}$          | マーク期間                  |                                                                                  | 6    |      | 12   | $\text{ms}$      |

## 6.5 電気的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、KSENZA、KSENSB、KSENSC、KSENSD を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{SENSE} = 0.200\Omega$ 、KSENZA (SEN1 または SEN2) との間、KSENSB (SEN3 または SEN4) との間、KSENSC (SEN5 または SEN6) または KSENSD (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ                    |                                           | テスト条件                  | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------------|-------------------------------------------|------------------------|-----|-----|-----|----|

| <b>DC 接続解除</b>           |                                           |                        |     |     |     |    |

| $V_{IMIN}$               | DC 切断スレッショルド                              | DCDTxx = 0             | 0.8 | 1.3 | 1.8 | mV |

|                          |                                           | DCDTxx = 1             | 0.4 | 0.9 | 1.4 | mV |

| $t_{MPDO}$               | PD 電力シグネチャ ドロップアウト時間制限を維持                 | TMPDO = 00             | 320 | 400 | ms  |    |

|                          |                                           | TMPDO = 01             | 75  | 100 | ms  |    |

|                          |                                           | TMPDO = 10             | 150 | 200 | ms  |    |

|                          |                                           | TMPDO = 11             | 600 | 800 | ms  |    |

| $t_{MPS}$                | PD 有効性のため電源シグネチャ時間を保持                     |                        |     | 2.5 | 3   | ms |

| <b>ポート電源ポリシング</b>        |                                           |                        |     |     |     |    |

| $\delta P_{CUT}/P_{CUT}$ | PCUT 公差                                   | POL ≤ 15W              | 0   | 5   | 10  | %  |

| $\delta P_{CUT}/P_{CUT}$ | PCUT 公差                                   | 15W < POL < 90W        | 0   | 3   | 6   | %  |

| $\delta P_{CUT}/P_{CUT}$ | PCUT 公差                                   | POL ≥ 90W              | 0   | 2.5 | 5   | %  |

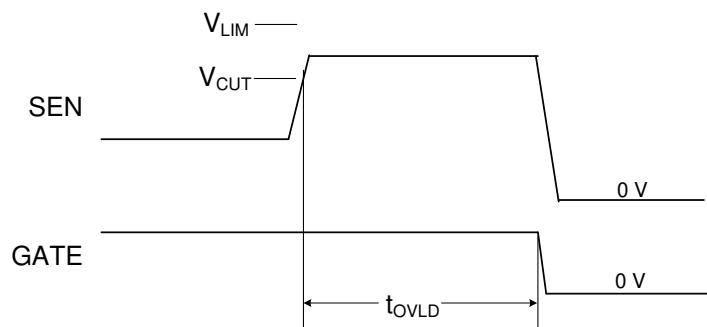

| $t_{OVLD}$               | PCUT 時間制限                                 | TOVLD = 00             | 50  | 70  |     | ms |

|                          |                                           | TOVLD = 01             | 25  | 35  |     |    |

|                          |                                           | TOVLD = 10             | 100 | 140 |     |    |

|                          |                                           | TOVLD = 11             | 200 | 280 |     |    |

| <b>ポート電流突入</b>           |                                           |                        |     |     |     |    |

| $V_{Inrush}$             | 突入電流制限、 $ALTIRNn = 0$                     | VVPWR - VDRAINn = 1V   | 19  | 30  | 41  | mV |

|                          |                                           | VVPWR - VDRAINn = 10V  | 19  | 30  | 41  |    |

|                          |                                           | VVPWR - VDRAINn = 15V  | 33  | 44  | 55  |    |

|                          |                                           | VVPWR - VDRAINn = 30 V | 80  | 90  |     |    |

|                          |                                           | VVPWR - VDRAINn = 55 V | 80  | 90  |     |    |

|                          | 突入電流制限、 $ALTIRNn = 1$                     | VVPWR - VDRAINn = 1V   | 19  | 30  | 41  |    |

|                          |                                           | VVPWR - VDRAINn = 10V  | 36  | 47  | 58  |    |

|                          |                                           | VVPWR - VDRAINn = 15V  | 53  | 64  | 75  |    |

|                          |                                           | VVPWR - VDRAINn = 30V  | 80  | 90  |     |    |

|                          |                                           | VVPWR - VDRAINn = 55 V | 80  | 90  |     |    |

| $t_{START}$              | スタートアップ時の最大電流制限期間                         | TSTART = 00            | 50  | 70  |     | ms |

|                          |                                           | TSTART = 01            | 25  | 35  |     |    |

|                          |                                           | TSTART = 10            | 100 | 140 |     |    |

| <b>ポートの電流フォールドバック</b>    |                                           |                        |     |     |     |    |

| $V_{LIM}$                | ILIM 1X の制限値、 $2xFB = 0$ および $ALTFBn = 0$ | VDRAINn = 1V           | 80  | 90  |     | mV |

|                          |                                           | VDRAINn = 15V          | 80  | 90  |     |    |

|                          |                                           | VDRAINn = 30V          | 51  | 58  | 65  |    |

|                          |                                           | VDRAINn = 50V          | 23  | 30  | 37  |    |

|                          | ILIM 1X の制限値、 $2xFB = 0$ および $ALTFBn = 1$ | VDRAINn = 1V           | 80  | 90  |     |    |

|                          |                                           | VDRAINn = 25V          | 80  | 90  |     |    |

|                          |                                           | VDRAINn = 40V          | 45  | 51  | 57  |    |

|                          |                                           | VDRAINn = 50V          | 23  | 30  | 37  |    |

## 6.5 電気的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、KSENSA、KSENSB、KSENSC、KSENSD を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{SENSE} = 0.200\Omega$ 、KSENSA (SEN1 または SEN2) との間、KSENSB (SEN3 または SEN4) との間、KSENSC (SEN5 または SEN6) または KSENSD (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ       |                                            | テスト条件                  | 最小値 | 標準値 | 最大値 | 単位 |

|-------------|--------------------------------------------|------------------------|-----|-----|-----|----|

| $V_{LIM2X}$ | ILIM 2X の制限値、 $2xFBn = 1$ および $ALTFBn = 0$ | $VDRAINn = 1\text{V}$  | 245 | 250 | 262 | mV |

|             |                                            | $VDRAINn = 10\text{V}$ | 164 | 180 | 196 |    |

|             |                                            | $VDRAINn = 30\text{V}$ | 51  | 58  | 64  |    |

|             |                                            | $VDRAINn = 50\text{V}$ | 23  | 30  | 37  |    |

|             | ILIM 2X の制限値、 $2xFBn = 1$ および $ALTFBn = 1$ | $VDRAINn = 1\text{V}$  | 245 | 250 | 262 |    |

|             |                                            | $VDRAINn = 20\text{V}$ | 139 | 147 | 155 |    |

|             |                                            | $VDRAINn = 40\text{V}$ | 45  | 51  | 57  |    |

|             |                                            | $VDRAINn = 50\text{V}$ | 23  | 30  | 37  |    |

| $t_{LIM}$   | $ILIM$ 時間制限<br><br>$2xFBn = 1$             | $2xFBn = 0$            | 55  | 60  | 65  | ms |

|             |                                            | $TLIM = 00$            | 55  | 60  | 65  |    |

|             |                                            | $TLIM = 01$            | 15  | 16  | 17  |    |

|             |                                            | $TLIM = 10$            | 10  | 11  | 12  |    |

|             |                                            | $TLIM = 11$            | 6   | 6.5 | 7   |    |

### 短絡回路の検出

|                   |                                   |                                                                           |     |     |               |

|-------------------|-----------------------------------|---------------------------------------------------------------------------|-----|-----|---------------|

| $V_{short}$       | 1X モードおよび突入時の $I_{SHORT}$ スレッショルド |                                                                           | 205 | 245 | mV            |

| $V_{short2X}$     | 2X モードでの $I_{SHORT}$ スレッショルド      |                                                                           | 280 | 320 |               |

| $t_{D\_off\_SEN}$ | SENn 入力からのゲートターンオフ時間              | $2xFBn = 0$ 、 $VDRAINn = 1\text{V}$<br>$VSENn$ パルス $\sim 0.425\text{V}$ 。 |     | 0.9 | $\mu\text{s}$ |

|                   |                                   | $2xFBn = 1$ 、 $VDRAINn = 1\text{V}$<br>$VSENn$ パルス $\sim 0.62\text{V}$ 。  |     | 0.9 |               |

### 電流障害回復 (バックオフ) タイミング

|                    |                                                  |                                                  |     |   |     |   |

|--------------------|--------------------------------------------------|--------------------------------------------------|-----|---|-----|---|

| $t_{ed}$           | 誤差遅延タイミング。エラー状態が原因で電源が切断された後、次のチャネルへの電源供給試行までの遅延 | $P_{CUT}$ , $I_{LIM}$ or $I_{Inrush}$ フォルト半自動モード | 0.8 | 1 | 1.2 | s |

| $\delta I_{fault}$ | 電流フォルト付き $I_{channel}$ のデューティサイクル                |                                                  | 5.5 |   | 6.7 | % |

### サーマルシャットダウン

|  |           |      |     |     |                  |

|--|-----------|------|-----|-----|------------------|

|  | シャットダウン温度 | 温度上昇 | 135 | 146 | $^\circ\text{C}$ |

|  | ヒステリシス    |      |     | 7   | $^\circ\text{C}$ |

## 6.5 電気的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、DGND、KSENSA、KSENSB、KSENSC、KSENSD を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{SENSE} = 0.200\Omega$ 、KSENSA (SEN1 または SEN2) との間、KSENSB (SEN3 または SEN4) との間、KSENSC (SEN5 または SEN6) または KSENSD (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ                                                 | テスト条件                               | 最小値                                              | 標準値  | 最大値 | 単位  |

|-------------------------------------------------------|-------------------------------------|--------------------------------------------------|------|-----|-----|

| <b>デジタル I/O (特に記述のない限り、SCL、SDAI、A1-A4、/RESET、OSS)</b> |                                     |                                                  |      |     |     |

| $V_{IH}$                                              | デジタル入力 High                         |                                                  | 2.1  |     | V   |

| $V_{IL}$                                              | デジタル入力 Low                          |                                                  | 0.9  |     | V   |

| $V_{IT\_HYS}$                                         | 入力電圧ヒステリシス                          |                                                  | 0.17 |     | V   |

| $V_{OL}$                                              | デジタル出力 Low                          | 9mA の SDAO                                       |      | 0.4 | V   |

|                                                       | デジタル出力 Low                          | 3mA での /INT                                      |      | 0.4 | V   |

| $R_{pullup}$                                          | VDD へのプルアップ抵抗                       | /RESET、A1-A4、TEST0                               | 30   | 50  | kΩ  |

| $R_{pulldown}$                                        | DGND へのプルダウン抵抗                      | OSS、TEST1、TEST2                                  | 30   | 50  | kΩ  |

| $t_{FLT\_INT}$                                        | /INT アサーションのフォールト                   | チャネルターンオフからの割り込みフォルトを内部レジスタに登録するための時間            | 50   | 500 | μs  |

| $T_{RESETmin}$                                        | /RESET 入力の最小パルス幅                    |                                                  |      | 5   | μs  |

| $T_{bit\_OSS}$                                        | 3 ビット OSS ビット周期                     | MbitPrty = 1                                     | 24   | 25  | 26  |

| $t_{OSS\_IDL}$                                        | 3 ビット モードでの連続シャットダウン コード送信までのアイドル時間 | MbitPrty = 1                                     | 48   | 50  | μs  |

| $t_{r\_OSS}$                                          | 3 ビット モードでの OSS の入力立ち上がり時間          | 0.8V → 2.3V、MbitPrty = 1                         | 1    | 300 | ns  |

| $t_{f\_OSS}$                                          | 3 ビット モードでの OSS の入力立ち下がり時間          | 2.3V → 0.8V、MbitPrty = 1                         | 1    | 300 | ns  |

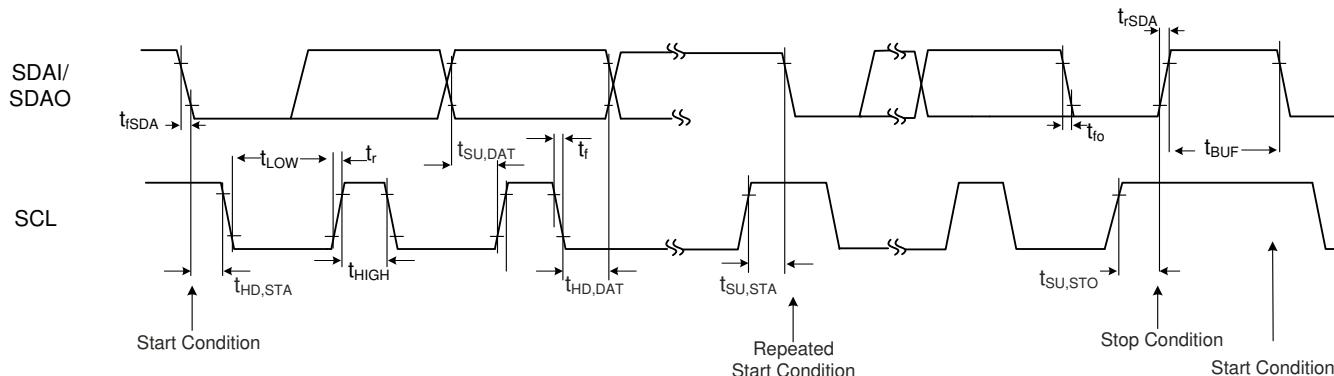

| <b>I2C のタイミング要件</b>                                   |                                     |                                                  |      |     |     |

| $t_{POR}$                                             | デバイスパワーオンリセット遅延                     |                                                  |      | 20  | ms  |

| $f_{SCL}$                                             | SCL クロック周波数                         |                                                  | 10   | 400 | kHz |

| $t_{LOW}$                                             | クロック LOW 期間                         |                                                  | 0.5  |     | μs  |

| $t_{HIGH}$                                            | クロック HIGH 期間                        |                                                  | 0.26 |     | μs  |

| $t_{fo}$                                              | SDAO 出力立ち下がり時間                      | SDAO、2.3V → 0.8V、CB = 10pF、10kΩ を 3.3V にプルアップ    | 10   | 50  | ns  |

|                                                       |                                     | SDAO、2.3V → 0.8V、CB = 400 pF、3.3V への 1.3kΩ プルアップ | 10   | 50  | ns  |

| $C_{I2C}$                                             | SCL 静電容量                            |                                                  |      | 10  | pF  |

| $C_{I2C\_SDA}$                                        | SDAI、SDAO 静電容量                      |                                                  |      | 6   | pF  |

| $t_{SU,DATW}$                                         | データセットアップ時間 (書き込み操作)                |                                                  | 50   |     | ns  |

| $t_{HD,DATW}$                                         | データホールド時間 (書き込み動作)                  |                                                  | 0    |     | ns  |

| $t_{HD,DATR}$                                         | データホールド時間 (読み取り動作)                  |                                                  | 150  | 400 | ns  |

| $t_{rSDA}$                                            | SDAI の入力立ち下がり時間                     | 2.3V → 0.8V                                      | 20   | 120 | ns  |

| $t_{rSDA}$                                            | SDAI の入力立ち上がり時間                     | 0.8V → 2.3V                                      | 20   | 120 | ns  |

| $t_r$                                                 | SCL の入力立ち上がり時間                      | 0.8V → 2.3V                                      | 20   | 120 | ns  |

| $t_f$                                                 | SCL の入力立ち下がり時間                      | 2.3V → 0.8V                                      | 20   | 120 | ns  |

| $t_{BUF}$                                             | STOP 条件と START 条件の間のバスフリー時間         |                                                  | 0.5  |     | μs  |

| $t_{HD,STA}$                                          | (繰り返し) START 条件の後のホールド時間。           |                                                  | 0.26 |     | μs  |

| $t_{SU,STA}$                                          | 再スタート条件のセットアップ時間                    |                                                  | 0.26 |     | μs  |

## 6.5 電気的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、KSENSA、KSENSB、KSENSC、KSENSD を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_{SENSE} = 0.200\Omega$ 、KSENSA (SEN1 または SEN2) との間、KSENSB (SEN3 または SEN4) との間、KSENSC (SEN5 または SEN6) または KSENSD (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

| パラメータ          | テスト条件                   | 最小値 | 標準値  | 最大値 | 単位            |

|----------------|-------------------------|-----|------|-----|---------------|

| $t_{SU,STO}$   | ストップ条件のセットアップ時間         |     | 0.26 |     | $\mu\text{s}$ |

| $t_{DG}$       | 抑制されたスパイク パルス幅、SDAI、SCL |     | 50   |     | $\text{ns}$   |

| $t_{WDT\_I2C}$ | I2C ウオッチドッグ トリップ遅延      | 1.1 | 2.2  | 3.3 | 秒             |

## 6.6 代表的特性

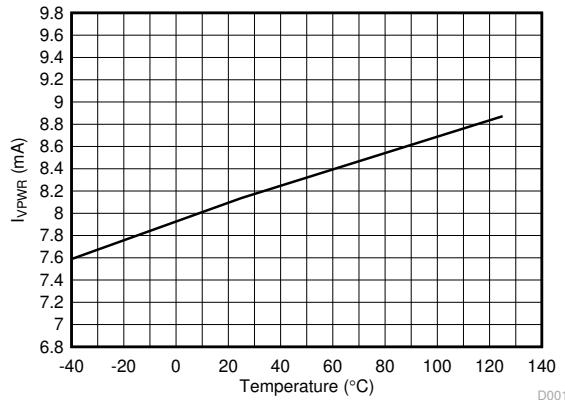

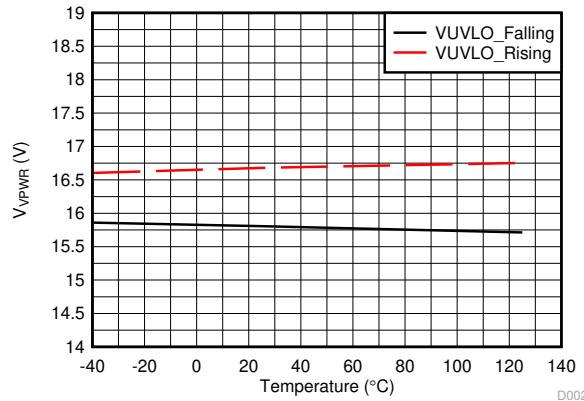

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、 $KSENSA$ 、 $KSENSB$ 、 $KSENSC$ 、 $KSENSD$  を  $AGND$  に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_S = 0.200\Omega$ 、 $KSENSA$  ( $SEN1$  または  $SEN2$ ) との間、 $KSENSB$  ( $SEN3$  または  $SEN4$ ) との間、 $KSENSC$  ( $SEN5$  または  $SEN6$ ) または  $KSENSD$  ( $SEN7$  または  $SEN8$ ) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は  $AGND$  を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

図 6-1. VPWR 消費電流と温度との関係

図 6-2. VPWR UVLO スレッショルドと温度との関係

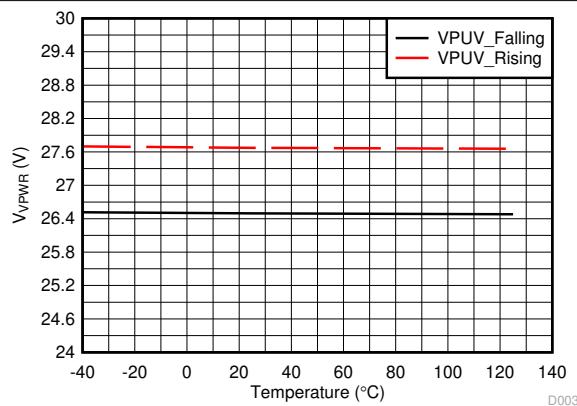

図 6-3. VPUV スレッショルドと温度との関係

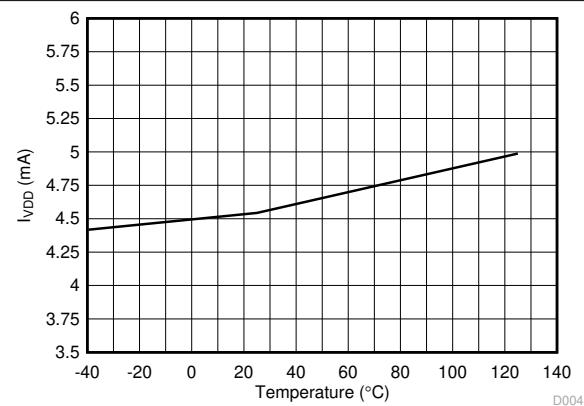

図 6-4. VDD 消費電流と温度との関係

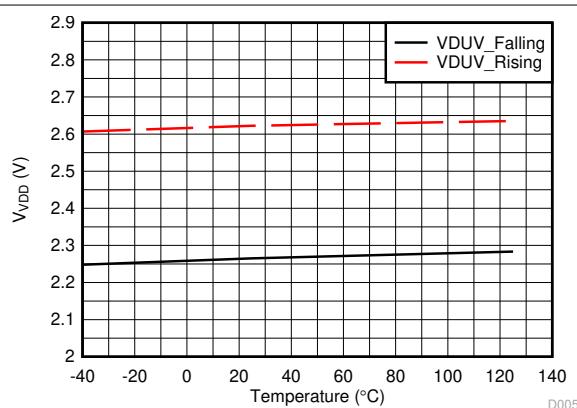

図 6-5. VDUV スレッショルドと温度との関係

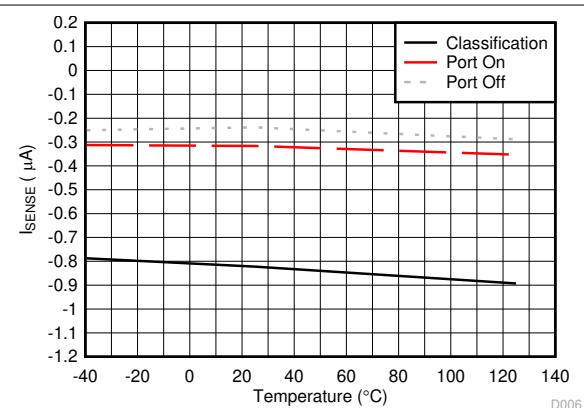

図 6-6. 検出ピンバイアス電流と温度との関係

## 6.6 代表的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^{\circ}\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、KSENSA、KSENSB、KSENCS、KSENSD を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_S = 0.200\Omega$ 、KSENSA (SEN1 または SEN2) との間、KSENSB (SEN3 または SEN4) との間、KSENCS (SEN5 または SEN6) または KSENSD (SEN7 または SEN8) に接続。標準値は  $25^{\circ}\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

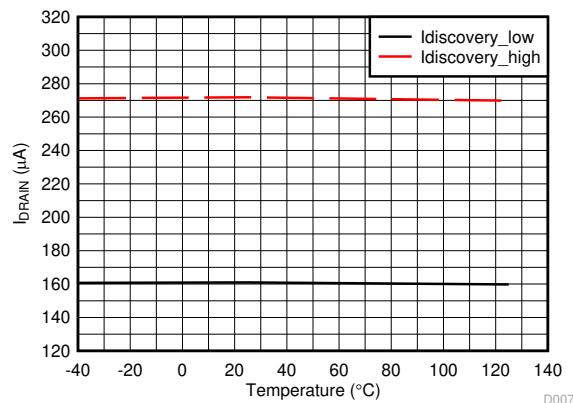

図 6-7. 検出電流と温度との関係

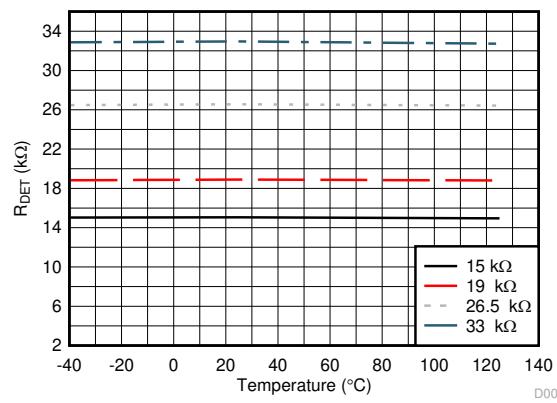

図 6-8. 検出抵抗測定値と温度との関係

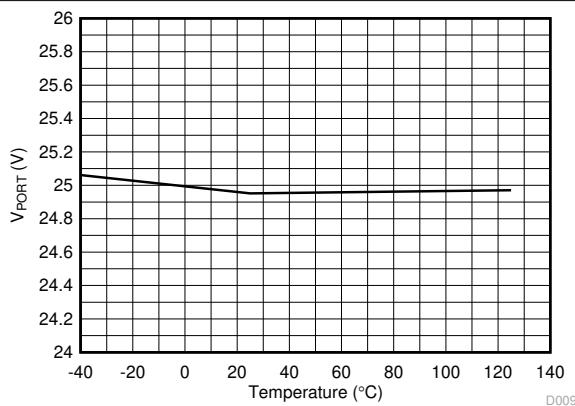

図 6-9. 検出開路電圧と温度との関係

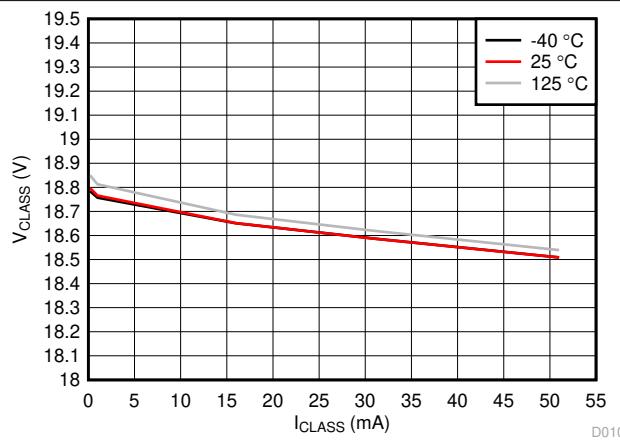

図 6-10. 分類電圧と  $I_{CLASS}$  および温度との関係

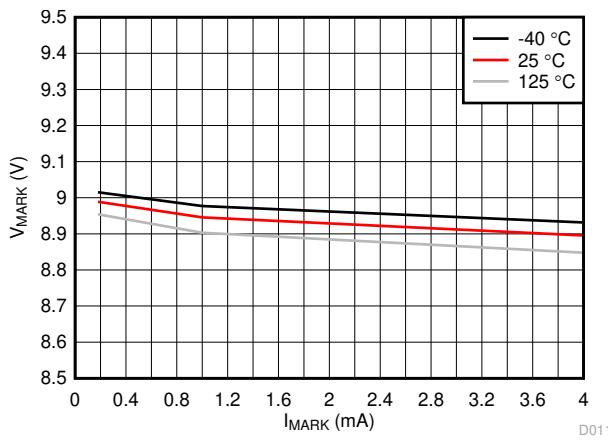

図 6-11. マーク電圧と  $I_{MARK}$  および温度との関係

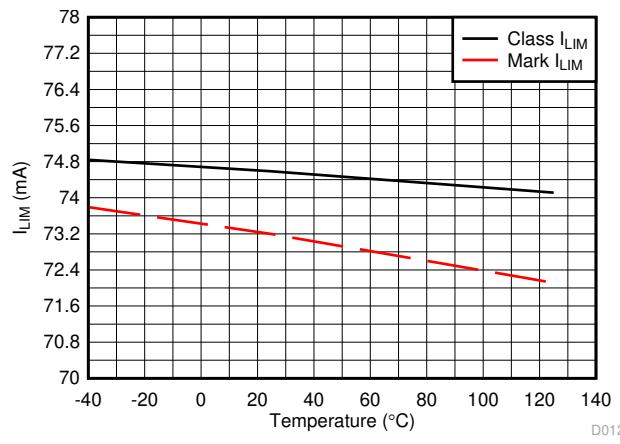

図 6-12. 分類およびマーク電流制限と温度との関係

## 6.6 代表的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、KSENSA、KSENSB、KSENCS、KSENSD を AGND に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_S = 0.200\Omega$ 、KSENSA (SEN1 または SEN2) との間、KSENSB (SEN3 または SEN4) との間、KSENCS (SEN5 または SEN6) または KSENSD (SEN7 または SEN8) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は AGND を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

図 6-13. パワー グッド スレッショルドと温度との関係

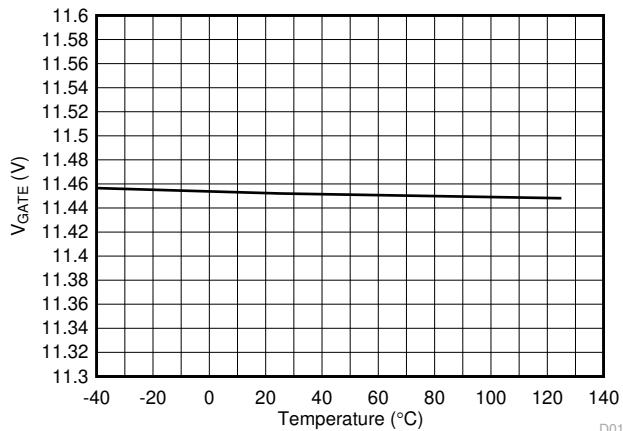

図 6-14. ゲート電圧 (ポートオン) と温度との関係

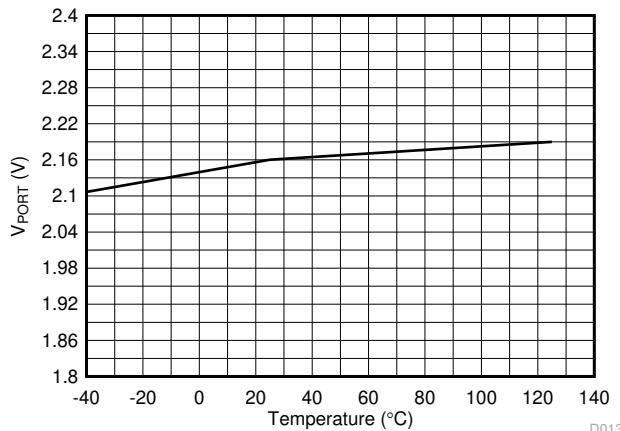

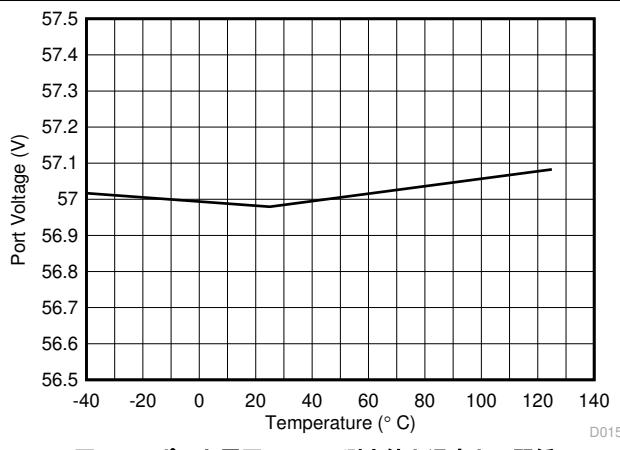

図 6-15. ポート電圧の ADC 測定値と温度との関係

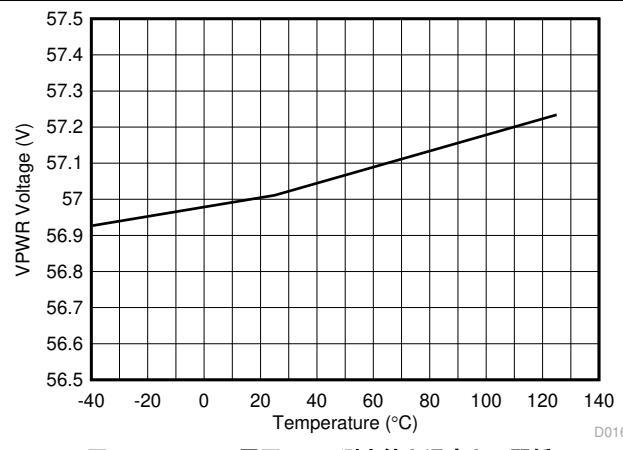

図 6-16. VPWR 電圧 ADC 測定値と温度との関係

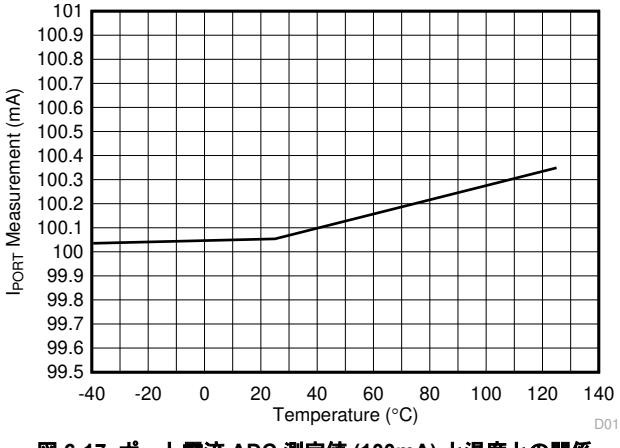

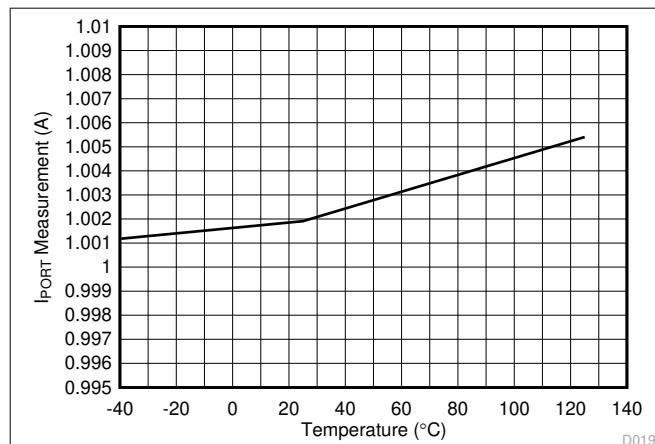

図 6-17. ポート電流 ADC 測定値 (100mA) と温度との関係

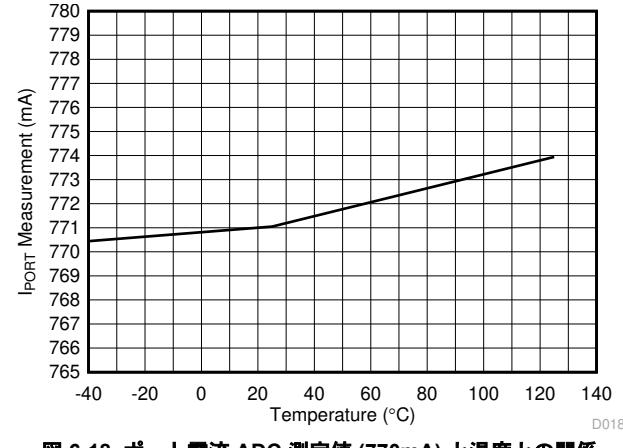

図 6-18. ポート電流 ADC 測定値 (770mA) と温度との関係

## 6.6 代表的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^{\circ}\text{C}$  です。 $V_{\text{VDD}} = 3.3\text{V}$ 、 $V_{\text{VPWR}} = 54\text{V}$ 、 $V_{\text{DGND}} = V_{\text{AGND}}$ 、 $\text{DGND}$ 、 $\text{KSENSA}$ 、 $\text{KSENSB}$ 、 $\text{KSENSC}$ 、 $\text{KSENSD}$  を  $\text{AGND}$  に接続。すべての出力は無負荷、 $2 \times \text{FBn} = 0$ 。正の電流はピンに流れます。 $R_S = 0.200\Omega$ 、 $\text{KSENSA}$  ( $\text{SEN1}$  または  $\text{SEN2}$ ) との間、 $\text{KSENSB}$  ( $\text{SEN3}$  または  $\text{SEN4}$ ) との間、 $\text{KSENSC}$  ( $\text{SEN5}$  または  $\text{SEN6}$ ) または  $\text{KSENSD}$  ( $\text{SEN7}$  または  $\text{SEN8}$ ) に接続。標準値は  $25^{\circ}\text{C}$  状態です。特に記述のない限り、すべての電圧は  $\text{AGND}$  を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

図 6-19. ポート電流 ADC 測定値 (1A) と温度との関係

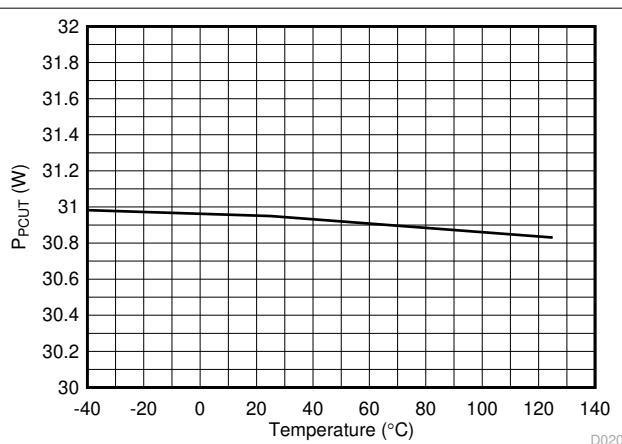

図 6-20. 2 ペア PCut スレッショルド (30W) と温度との関係

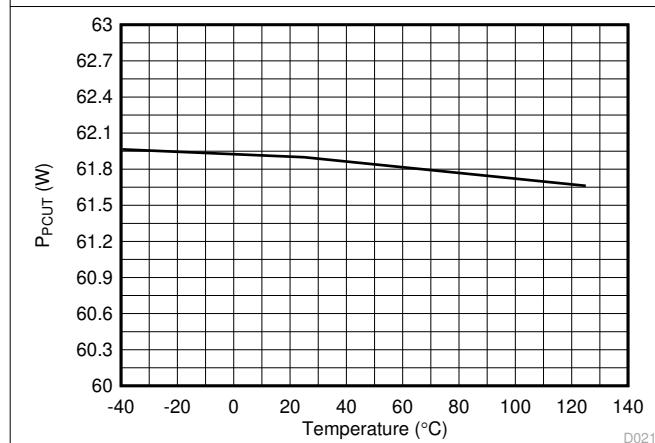

図 6-21. 4 ペア PCut スレッショルド (60W) と温度との関係

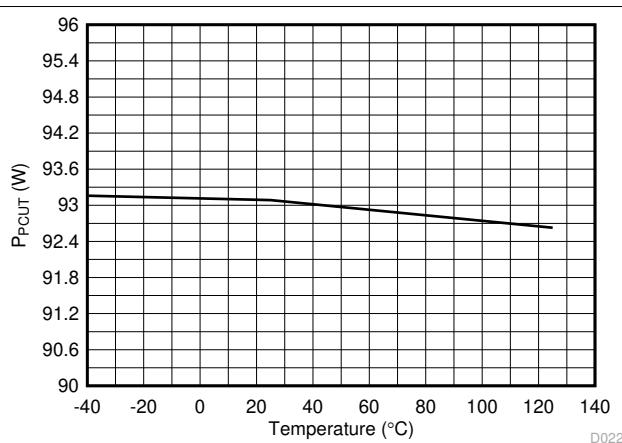

図 6-22. 4 ペア PCut スレッショルド (90W) と温度との関係

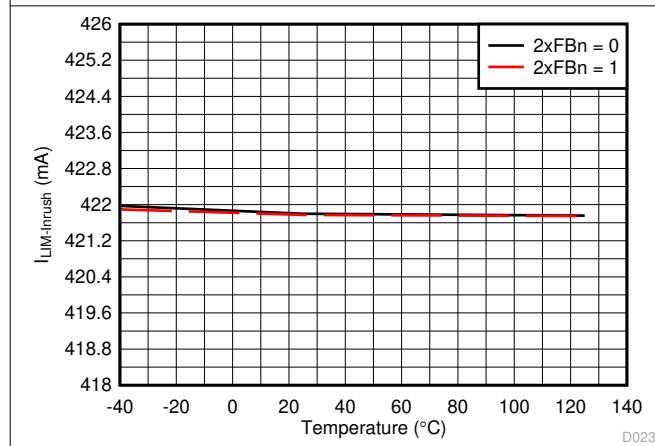

図 6-23. 突入電流制限と温度との関係

図 6-24. 1x モード (2xFBn = 0) の電流制限と温度との関係

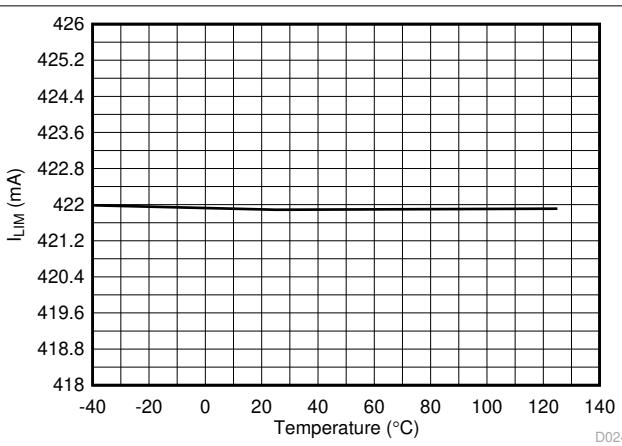

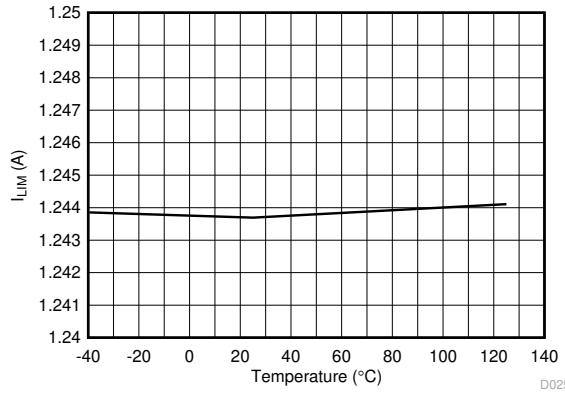

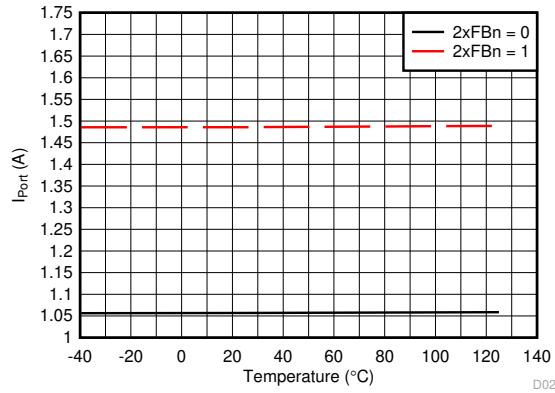

## 6.6 代表的特性 (続き)

特に記載がない限り、条件は  $-40 < T_J < 125^\circ\text{C}$  です。 $V_{VDD} = 3.3\text{V}$ 、 $V_{VPWR} = 54\text{V}$ 、 $V_{DGND} = V_{AGND}$ 、 $DGND$ 、 $KSENSA$ 、 $KSENSB$ 、 $KSENSC$ 、 $KSENSD$  を  $AGND$  に接続。すべての出力は無負荷、 $2 \times FBn = 0$ 。正の電流はピンに流れます。 $R_S = 0.200\Omega$ 、 $KSENSA$  ( $SEN1$  または  $SEN2$ ) との間、 $KSENSB$  ( $SEN3$  または  $SEN4$ ) との間、 $KSENSC$  ( $SEN5$  または  $SEN6$ ) または  $KSENSD$  ( $SEN7$  または  $SEN8$ ) に接続。標準値は  $25^\circ\text{C}$  状態です。特に記述のない限り、すべての電圧は  $AGND$  を基準とします。特に記述のない限り、動作レジスタにはデフォルト値が書き込まれます。

図 6-25. 2x モード ( $2xFBn = 1$ ) の電流制限と温度との関係

図 6-26.  $I_{SHORT}$  スレッショルドと温度との関係

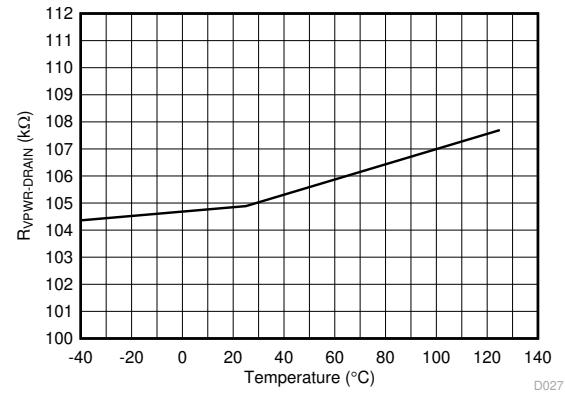

図 6-27.  $R_{OFF}$  ( $VPWR$  から  $DRAIN$  へ) と温度との関係

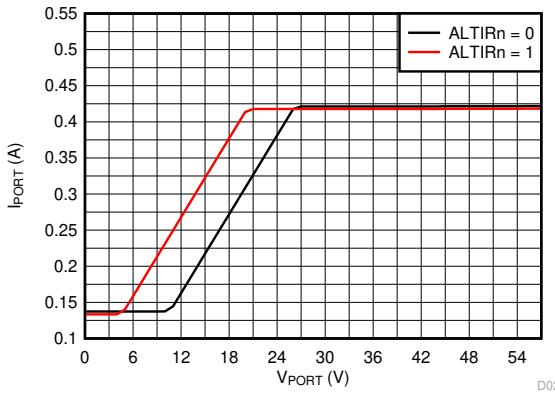

図 6-28. 突入電流フォールドバックとポート電圧との関係

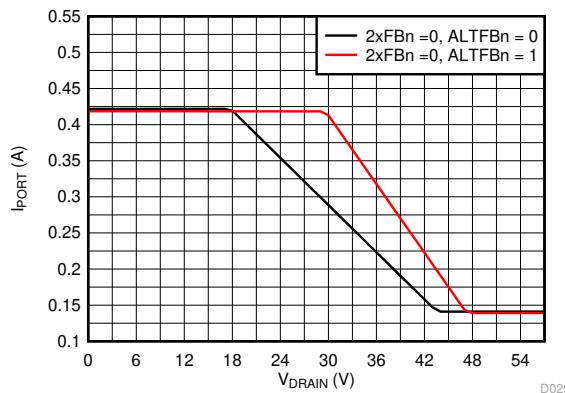

図 6-29. 1x モード ( $2xFBn = 0$ ) 電流フォールドバックとドレン電圧との関係

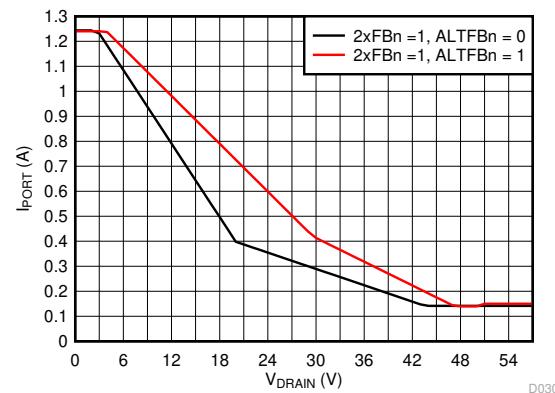

図 6-30. 2x モード ( $2xFBn = 1$ ) 電流フォールドバックとドレン電圧との関係

## 7 パラメータ測定情報

### 7.1 タイミング図

図 7-1. I<sup>2</sup>C タイミング

図 7-2. 過電流FAULT タイミング

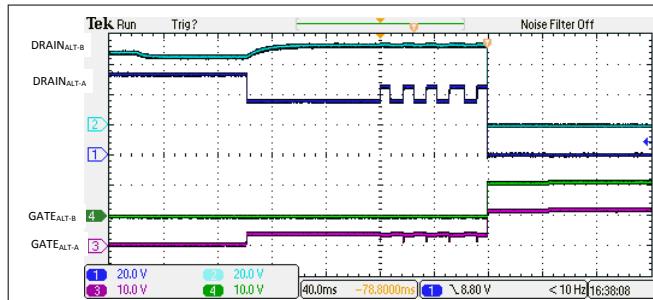

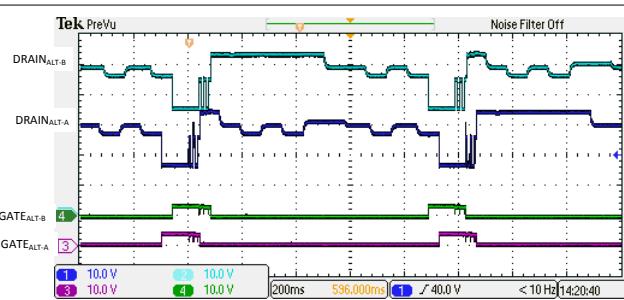

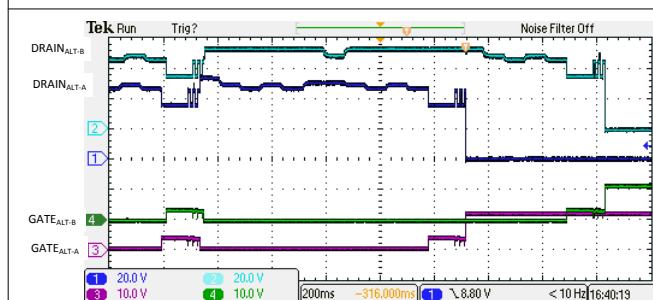

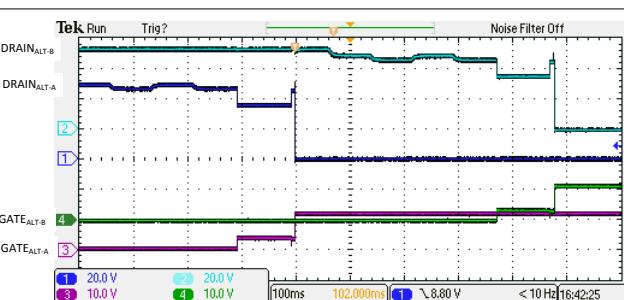

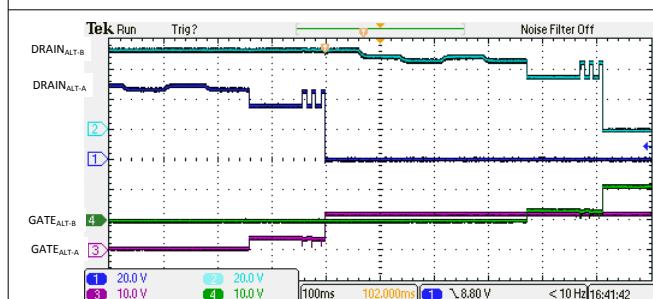

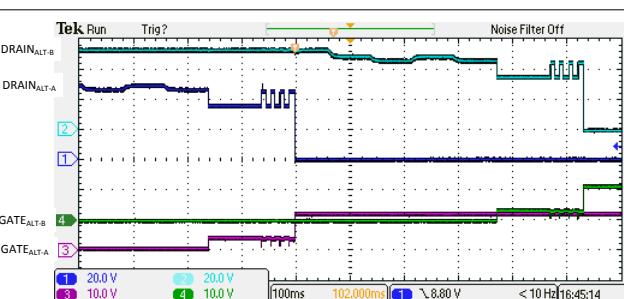

図 7-3. 2 ペア検出、1 イベント分類、ターンオン

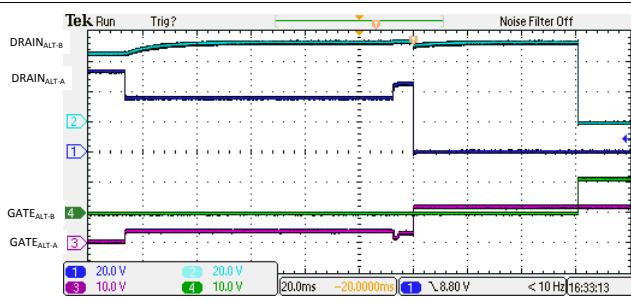

図 7-4. 2 ペア検出、3 イベント分類、ターンオン

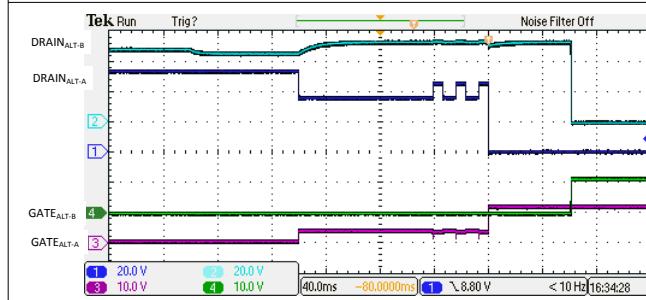

図 7-5.4 ペア シングル シグネチャ検出、3 イベント分類、およびターンオン

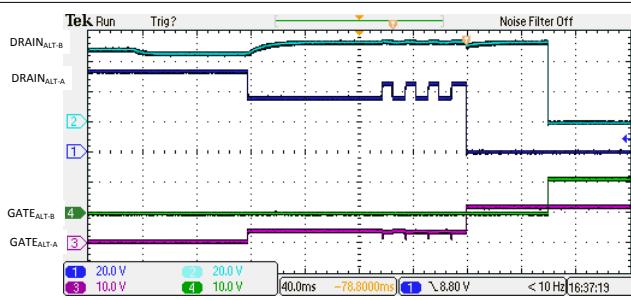

図 7-6.4 ペア シングル シグネチャ検出、5 イベント分類、およびターンオン

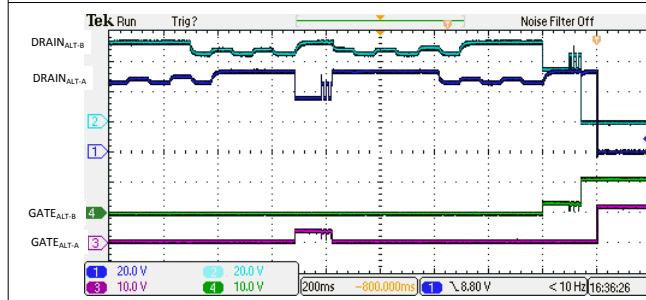

図 7-7.4 ペア デュアル シグネチャ検出、3 イベント分類、およびターンオン

## 8 詳細説明

### 8.1 概要

TPS23881B は、PoE (パワー オーバー イーサネット) アプリケーション用の 8 チャネル PSE です。8 つのチャネルのそれぞれに、IEEE 802.3bt 規格に準拠した検出、分類、保護、シャットダウンを提供します。

PoE の基本的な機能は次のとおりです。

- 高信頼性の 4 ポイント負荷検出を行います

- PoE 2 3/4 (3 本、4 本、5 本の指) を含め、最大クラス 8 の負荷に対応する相互識別分類を実行

- シングル シグニチャおよびデュアル シグニチャ PD を認識します

- 保護フォールドバック電流制限機能付き電力、および調整可能な  $P_{cut}$  スレッショルドを使用できます

- 過電流または出力短絡などのフォルト中にシャットダウンします

- 負荷が切断された際に電力が取り除かれるように、電力維持シグネチャ機能を実行します

- VPWR が  $V_{PUV\_F}$  (標準値 26.5V) を下回ると、低電圧誤動作防止が発生します。

強化された機能には、以下のものがあります。

- プログラム可能な SRAM メモリ

- ポートごとに専用の 14 ビット積算電流 ADC

- ポートの再マッピング機能

- 8 ビットと 16 ビットのアクセス モードを選択可能

- 1 ビットおよび 3 ビットのポート シャットダウン優先度

#### 8.1.1 動作モード

##### 8.1.1.1 車載

ポートは、検出と分類を継続的に実行します (有効な検出が発生した場合)。レジスタは、検出または分類が発生するたびに更新されます。ポートの電力は、有効な分類が測定された場合、レジスタ 0x29 の「電力配分」設定に基づいて自動的にオンになります。

##### 8.1.1.2 自律

この場合も、TPS23881B の動作を一連の I<sup>2</sup>C コマンドで初期化する必要がある自動モードとは異なり、デバイスが自律モードに構成されている場合、ホストや I<sup>2</sup>C 通信は必要ありません。

電源投入時、AUTO ピンの抵抗 ( $R_{AUTO}$ ) を測定し、表 8-16 に従ってデバイスが事前構成されます。ポートは、すべてのポートで検出と分類を継続的に実行します (有効な検出が発生した場合)。有効な分類が測定された場合、レジスタ 0x29 の「電力割り当て」設定に基づいてポートの電力は自動的にオンになります。

引き続きポートの遠隔測定が必要なアプリケーションでは、I<sup>2</sup>C 機能は自律モードでもサポートされています。

#### 注

自律モード選択で安定性を確保するため、 $R_{AUTO}$  と並列に 10nF のコンデンサが必要です。

自動ピン抵抗 ( $R_{AUTO}$ ) は、デバイスリセット後 ( $\overline{RESET}$  ピンまたはレジスタ 0x1A の RESAL ビットがアサートされた後) は測定されません。デバイスは、電源投入時 ( $V_{VPWR}$  および  $V_{VDD}$  がそれぞれの UVLO スレッショルド以上に上昇する) にのみ測定 ( $R_{AUTO}$ )、内部レジスタを事前構成します。

### 注

自律モードで最初に電源を投入した後に自律モードからデバイスを削除するアプリケーションをサポートするために、デバイスの SRAM をプログラムする必要があります。

自律モードで内部 ROM (プログラムされていない SRAM) から実行されるデバイスは、RESET ピン、I<sup>2</sup>C レジスタ 0x1A RESAL または RESPn ビット、またはモード オフ コマンドのアサート後に、有効な負荷の検出と電源投入を自動的に再開します。プログラムされた SRAM を備えた自律モードで実行されているデバイスはオフになり、ホストが I<sup>2</sup>C バス経由でポートを再度イネーブルにするまで、非アクティブのままになります。

#### 8.1.1.3 半自動

ポートは、検出と分類を継続的に実行します (有効な検出が発生した場合)。レジスタは、検出または分類が発生するたびに更新されます。ポートの電源が自動的にオンになることはありません。ポートをオンにするには、パワー イネーブル コマンドが必要です。

#### 8.1.1.4 手動および診断

このモードは、半自動または自動モードの IEEE 802.3bt 規格に従ってポートに電力を供給できない場合にのみ、システム診断目的を目的としています。

ポートはレジスタの設定に従って機能を実行します。自動的な状態変更はありません。命令されたときに特異検出および分類測定が実行されます。ポートは、パワー イネーブル コマンドの直後にオンになり、検出または分類の測定は行われません。複数の分類イベントが実行される場合でも、ポート電圧は最後の指の直後にリセットされ、PD がリセットされます。

#### 8.1.1.5 電源オフ

ポートの電源がオフになっており、検出、分類、または電源投入は実行されません。このモードでは、関連するポートのステータスビットとイネーブルビットがリセットされます。

#### 8.1.2 PoE 適合性の用語

IEEE 802.3bt 規格の発表に伴い、シングルまたはデュアル シグネチャ構成で、2 ペアまたは 4 ペアを介した給電をサポートする 4 種類の「タイプ」のデバイスが追加され、0 ~ 8 の分類が可能になりました。各メーカーは、時間の経過とともにさまざまな用語を使用して機器の機能を説明してきましたが、特定の機器を正しく分類してブランド化する方法を特定することが困難になる可能性があります。このため、PoE 機器およびデバイスの業界をリードするプロバイダーは、Ethernet Alliance (EA) と協力して、次の表 [表 8-1](#) に従って「PoE 1」および「PoE 2」バンドを使用することに同意しました。

表 8-1. PoE 準拠用語のまとめ表

| ブランド/頭字語 | IEEE 規格 | 条項  | 条項タイトル                 | タイプ | クラス                           | EA 認定ロゴ       |

|----------|---------|-----|------------------------|-----|-------------------------------|---------------|

| PoE 1    | 802.3af | 33  | 2 ペア経由のパワー オーバー イーサネット | 1   | 0 - 3                         | 第 1 世代クラス 1-4 |

|          | 802.3at |     |                        | 2   | 0 - 4                         |               |

| PoE 2    | 802.3bt | 145 | パワー オーバー イーサネット        | 3   | 1-6 または 1-4 DS <sup>(1)</sup> | 第 2 世代クラス 1-8 |

|          |         |     |                        | 4   | 7-8 または 5 DS <sup>(1)</sup>   |               |

(1) 「DS」は「デュアル シグネチャ」PD を指定するために使用されます。

### 注

設計上、PoE 2 PSE は既存の PoE 1 機器と完全に相互運用可能です。すべての機能が有効になるとは限りませんが、PoE 1 PSE に接続された PoE 2 PD は、PSE が提供する電力機能に対する消費を制限する必要があります。[電源の割り当てと電源の降格](#)を参照してください。

### 8.1.3 チャネルとポートの関係の用語

このドキュメント全体を通して、ポートと チャネルという用語は定期的に使用されていますが、これらの用語は互換性がありません。代わりに、「ポート」という用語は、最も一般的に RJ45 コネクタに関連する PSE PI (Power Interface) を指し、「チャネル」という用語は各ポートに関連付けられた個別のパワー パスまたはパスを指すために使用されます。

従来の PSE デバイスは一般にポートとして制御される出力の数を同一にしていました。各出力は RJ45 ジャック/イーサネット ポートの ALT-A または Alt-B ペア セットへの電力供給専用であるためです。ただし、ALT-A と ALT-B の両方のペア セットをパワーダウンする 4 ペア電源供給を採用することで、2 ペアと 4 ペアの PoE ポートを区別する必要が生じています。さらに、ペア セットごとに個別の電流制限を提供する必要があるため、任意の 4 ペア ポートでは 4 ペア ポートごとに 2 チャネルを使用して、各ペア セットを安全かつ確実にパワーダウンします。

TPS23881B は 8 チャネルの PSE コントローラであるため、最大 8 つの 2 ペア PoE ポートまたは 4 つの 4 ペア PoE ポート、あるいはそれらの組み合わせ (各 2 ペア ポートが 1 つのチャネルに対応し、各 4 ペア ポートは 2 チャネルに対応します) をサポートするように構成できます。

### 8.1.4 要求されたクラスと割り当てられたクラス

要求されたクラスは、PSE がターンオンする前に相互識別を行う際に測定する分類です。割り当てられたクラスは、レジスタ **0x29h** の電力割り当て設定に基づいてチャネルが給電された分類レベルです。ほとんどの場合、電力割り当てが要求されたクラスと等しいかそれを超えると、要求されたクラスと割り当てられたクラスは同じになります。ただし、電力低下の場合、これらの値は異なります。

次に例を示します。クラス 8 PD が 60W (クラス 6) 制限付き PSE ポートに接続されている場合、要求されたクラスは「クラス 8」、割り当てられたクラスは「クラス 6」をレポートします。

要求された分類結果は、レジスタ **0x0C-0F** で入手可能です。

割り当てられた分類結果は、レジスタ **0x4C ~ 4F** で参照できます。

#### 注

手動モードおよび診断モードからパワーアウトされたポートおよびチャネルに割り当てられたクラスはありません。

### 8.1.5 電源の割り当てと電源の降格

レジスタ **0x29** の電源割り当て設定は、A ポートがパワーオンする最大電力レベルを設定します。2 ペア 4W (クラス 1) から 4 ペア 90W (クラス 8) までの各クラス レベルの設定により、システム設計の柔軟性を最大限に高めることができます。

#### 注

レジスタ **0x29** の「電力割り当て」設定は、特定のポートの電力制限を設定しません。ポートおよびチャネルの電力制限は、2P (レジスタ **0x1E-x21**) および 4P (**0x2A-x2B**) ポリシング レジスタで設定されます。

ターンオンの試行中に、PD がポートの電力割り当て設定よりも高い分類レベルを提示した場合、TPS23881B は、レジスタ **0x29** の電力割り当て設定に基づいてオンになる前に、PD に表示される分類フィンガーの数を制限します (電源切断と呼ばれます)。電源切断は、PD が無効にできるまでに引き込むことができる最大電力レベルを設定する、PD に提示されるフィンガーの数です。

#### 注

IEEE 802.3 規格では、相互識別中に PSE が提示する指の数で設定されたタイプ/クラス レベル未満に総消費電力を制限するため、PSE が電力を降格する PD が必要です。

PSE から PD への唯一の通信方法は、電源をオンにする前の分類フィンガーの数であるため、ポートの電源切断はタイプ境界に制限されます。

- 1 フィンガー = 15.4W、3 フィンガー = 30W、4 フィンガー = 60W、5 フィンガー = 90W

**表 8-2. シングル シグネチャ PD 電源切断テーブル**

| 電力割り当て<br>レジスタ <b>0x29</b> | 割り当てられたクラス値 (ポートで接続されている PD に基づく) |            |            |            |            |            |

|----------------------------|-----------------------------------|------------|------------|------------|------------|------------|

|                            | クラス 3 の PD                        | クラス 4 の PD | クラス 5 の PD | クラス 6 の PD | クラス 7 の PD | クラス 8 の PD |

| 4 ペア 15W                   | クラス 3                             | クラス 3      | クラス 3      | クラス 3      | クラス 3      | クラス 3      |

| 4 ペア 30W                   | クラス 3                             | クラス 4      |

| 4 ペア 45W                   | クラス 3                             | クラス 4      | クラス 5      | クラス 4      | クラス 4      | クラス 4      |

| 4 ペア 60W                   | クラス 3                             | クラス 4      | クラス 5      | クラス 6      | クラス 6      | クラス 6      |

| 4 ペア 75W                   | クラス 3                             | クラス 4      | クラス 5      | クラス 6      | クラス 7      | クラス 6      |

| 4 ペア 90W                   | クラス 3                             | クラス 4      | クラス 5      | クラス 6      | クラス 7      | クラス 8      |

**表 8-3. デュアル シグネチャ PD 電源切断テーブル**

| 電力割り当て<br>レジスタ 0x29 | 割り当てられたクラス値 (ポートで接続されている PD に基づく) |                   |                   |                   |                   |                   |

|---------------------|-----------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

|                     | クラス 3D PD                         |                   | クラス 4D PD         |                   | クラス 5D PD         |                   |

|                     | 奇数チャネル (1 次<br>側)                 | 偶数チャネル (2 次<br>側) | 奇数チャネル (1 次<br>側) | 偶数チャネル (2 次<br>側) | 奇数チャネル (1 次<br>側) | 偶数チャネル (2 次<br>側) |

| 4 ペア 15W            | クラス 3                             | 電力不足              | クラス 3             | 電力不足              | クラス 3             | 電力不足              |

| 4 ペア 30W            | クラス 3                             | クラス 3             | クラス 4             | 電力不足              | クラス 4             | 電力不足              |

| 4 ペア 45W            | クラス 3                             | クラス 3             | クラス 4             | クラス 3             | クラス 4 (1)         | クラス 3 (1)         |

| 4 ペア 60W            | クラス 3                             | クラス 3             | クラス 4             | クラス 4             | クラス 4 (1)         | クラス 4 (1)         |

| 4 ペア 75W            | クラス 3                             | クラス 3             | クラス 4             | クラス 4             | クラス 5D            | クラス 4             |

| 4 ペア 90W            | クラス 3                             | クラス 3             | クラス 4             | クラス 4             | クラス 5D            | クラス 5D            |

- (1) IEEE 802.3bt に準拠するため、タイプ 3 の構成済み PSE は、どのペアにも 30W (クラス 4) を超える電力を割り当てるなどを許可されています。注: SRAM リリース v05 で、この要件に準拠するよう変更を加えました。

**注**

クラス「X-D」デュアル シグネチャ PD は、各変更ペアでクラス「X」として表示されます。例えば、「クラス 4D」の PD は、代替 A ペアと代替 B ペアの両方でクラス 4 として提示されます。

**8.1.6 プログラマブル SRAM**

TPS23881B デバイスは、IEEE 802.3bt 標準のリリースに伴って新しい機器が導入される際に発生する可能性のある相互運用性やコンプライアンスの問題をサポートするため、将来のファームウェア アップデートに対応できるようにプログラム可能な SRAM を内蔵しています。

**注**

最新バージョンのファームウェアおよび SRAM リリース ノートは、[TI mySecure Software Web](#) ページからアクセスできます。

SRAM リリース ノートおよび ROM アドバイザリ ドキュメントには、各ファームウェア リリースに関連する既知の問題や変更に関する詳細情報が記載されています。

TI では、電源投入時に、TPS23881B デバイスの SRAM を最新バージョンの SRAM コードで I<sup>2</sup>C 経由でプログラムし、適切な動作と IEEE 準拠のパフォーマンスを確保することを推奨しています。SRAM のプログラムに必要なコマンドを除くすべての I<sup>2</sup>C トランザクションは、SRAM のプログラミング シーケンスが完了するまで延期する必要があります。

複数の TPS23881B デバイスを含むシステムでは、0x7F「グローバル」ブロードキャスト I<sup>2</sup>C アドレスを使用して、すべてのデバイスを同時にプログラムできます。

SRAM のプログラミング手順の詳細な手順については、『[SRAM 制御レジスタ](#)』および『[TPS2388x SRAM と I<sup>2</sup>C を介したパリティコードのロード方法](#)』アプリケーション概要 (Ti.com) を参照してください。

## 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 ポートの再割り当て

TPS23881B は、論理ポートから物理チャネルおよびピンへのポートの再マッピング機能を備えています。

再マッピングは、4 ポートグループの任意のチャネル (1 ~ 4, 5 ~ 8) 間で行われます。

以下の例は、0x26 レジスタ = 00111001、00111001b に適用されます。

- 論理ポート 1 (5↔) 物理チャネル 2 (6)

- 論理ポート 2 (6↔) 物理チャネル 3 (7)

- 論理ポート 3 (7↔) 物理チャネル 4 (8)

- 論理ポート 4 (8↔) 物理チャネル 1 (5)

---

#### 注

4 つのポートすべてが OFF モードでない限り、デバイスはリマッピングコマンドを無視します。

---

TPS23881B が誤った構成を受信した場合、誤った構成を無視し、以前の構成を保持します。ACK は通常どおり通信終了時に送信されます。たとえば、複数のポートについて同じ再マッピング コードが受信された場合、再マッピング レジスタ (0x26) のリードバックが最後の有効な構成になります。

IC リセット コマンド (1Ah レジスタ) を受信した場合、ポートのリマッピング設定は変更されません。ただし、パワーオン リセットが存在する場合や、RESET ピンがアクティブになっている場合、再マッピング レジスタはデフォルト値に再初期化されます。

### 8.3.2 ポート電力の優先度

TPS23881B は、1 ビットおよび 3 ビットのシャットダウン優先度をサポートしており、汎用マスク レジスタ (0x17) の MbitPrty ビットで選択します。

1 ビットのシャットダウン優先度はポート電源優先度 (0x15) レジスタと連携して機能します。値が 1 の OSSN ビットは、対応するポートが低優先度として扱われ、値が 0 の場合は高優先度に対応します。OSS 入力が high になると、すぐに低優先度のポートがオフになります。

3 ビットのシャットダウン優先度は、優先度設定を保持するマルチビットパワー優先度 (0x27/28) レジスタと連動します。このレジスタの「000」コードを持つポートは、最も高い優先度を持ちます。3 ビットの値が大きくなると、ポートの優先度が低下し、最大 8 つの優先度レベルが設定されます。[図 8-1](#) を参照してください。

マルチビット ポートの優先順位の実装は、次のように定義されます。

- OSS コード≤優先度設定 (0x27/28 レジスタ): ポートはディセーブルです

- OSS コード>優先度設定 (0x27/28 レジスタ): ポートはアクティブのままです

図 8-1. マルチビット優先ポートのシャットダウン (低優先度ポートの場合)

#### 注

MbitPrty ビットを 0 から 1 に設定する前に、OSS ビットストリームとの同期が失われたことに関連してポートの誤動作を防止するため、OSS 入力が最小の 200 $\mu$ s の間アイドル (low) 状態になっていることを確認してください。

#### 注

OSS 入力には、1 $\mu$ s から 5 $\mu$ s へのグリッチ除去フィルタが内蔵されています。アイドル状態から、より長い期間のパルスは、有効なスタートビットとして解釈されます。OSS 信号がノイズフリーであることを確認します。

#### 注

OSS イベント中に 4 ペアポートの両方のチャネルが確実にディセーブルになるようにするには、0x15 または 0x27/28 レジスタの両方のチャネルの構成が同じであることを確認してください。

### 8.3.3 A/D コンバータ (ADC)

TPS23881B は、10 のマルチスロープ統合コンバータを搭載しています。最初に 8 個のコンバータはそれぞれ 1 つのチャネルの電流測定専用であり、独立して動作して分類時やチャネルの電源がオンになったときに測定を行います。チャネルに電力が供給されると、コンバータは電流 (平均 100ms) の監視、電力ポリシング、および DC 切断に使用されます。最後の 2 つのコンバータのそれぞれが、検出 (平均 16.6ms)、ポート電源電圧監視、パワー グッド ステータス、FET 短絡検出のための 4 つのチャネルからなるグループ内で共有されます。これらのコンバータは、入力電圧 (1ms) やダイ温度などの汎用の測定にも使用されます。

TPS23881B が使用している ADC タイプは、他の類似のコンバータとは異なり、入力信号が積分器によりサンプリングされている間、ADC が連続的に変換し、変換期間全体にわたって本質的にフィルタ処理を行うという点で異なります。電流コンバータの標準変換時間は 800 $\mu$ s であり、他のコンバータでは変換時間は 1ms です。受電側デバイス検出は、50Hz または 60Hz のライン周波数でのノイズの大幅な除去を実現する 16 の連続サンプルを平均化することによって実行されます。ポートに電力が供給されている間、デジタル平均化により、100ms の時間にわたって内蔵されたチャネル電流測定が行われます。電源電流監視用にアンチエイリアシング フィルタがあることに注意します。

#### 注

電力モードでは、電流変換が連続的に実行されます。また、電力モードでは、電流または電圧の ADC 変換を開始できるようになる前に、 $t_{START}$  タイマが満了しなければなりません。

### 8.3.4 I<sup>2</sup>C ウオッチドッグ

I<sup>2</sup>C ウオッチドッグ タイマは、TPS23881B デバイスで利用できます。タイマは、I<sup>2</sup>C、SCL ラインのクロック エッジを監視します。イネーブルにすると、ウォッチドoggのタイムアウトが発生すると、I<sup>2</sup>C インターフェイスとアクティブなポートがリセットされます。この機能により、ソフトウェアがハングした場合や、ターゲット デバイスによって I<sup>2</sup>C バスがハングアップした場合でも、保護が提供されます。後者の場合、コントローラがクロックの送信を停止したときに、ターゲットがデータビット 0 を送信しようとした場合、ターゲットは無期限にデータラインを low に駆動できます。データラインは low に駆動されるため、コントローラはストップを送信してバスをクリーンアップすることはできません。TPS23881B の I<sup>2</sup>C ウオッチドogg機能をアクティブ化すると、このデッドロック状態はクリアされます。2 秒のタイマが経過すると、ポートがラッチオフされ、WD ステータスビットがセットされます。ウォッチドoggがイネーブルではない場合でも WD ステータスが設定されることに注意してください。WD ステータスビットは、デバイスリセットまたは WDS ステータスビット位置に 0 の書き込みでのみクリアできます。4 ビットウォッチドogg ディセーブル フィールドでは、コード 1011b がロードされると、この機能がシャットダウンされます。TPS23881B の電源を最初に投入すると、このフィールドは 1011b にプリセットされます。詳細については、[I<sup>2</sup>C ウオッチドogg レジスタ](#)を参照してください。

### 8.3.5 電流フォールドバック保護

TPS23881B は、完全な MOSFET 保護のために 2 種類のフォールドバック メカニズムを備えています。

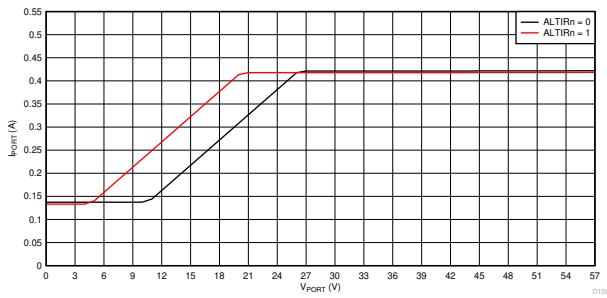

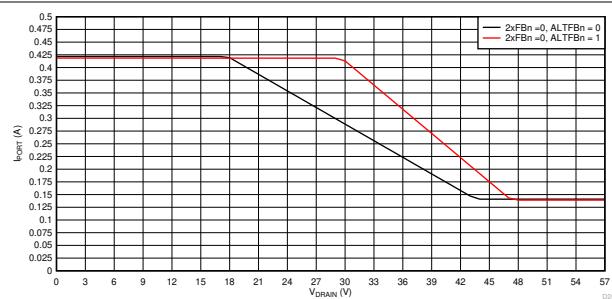

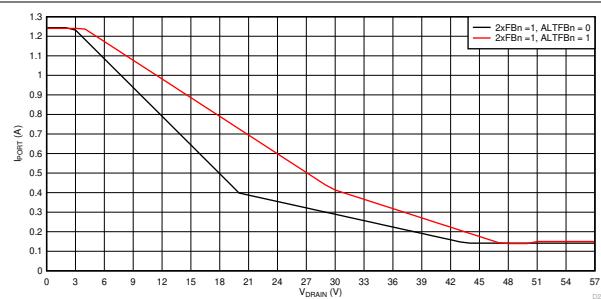

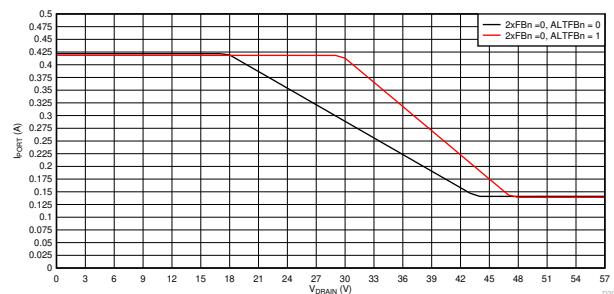

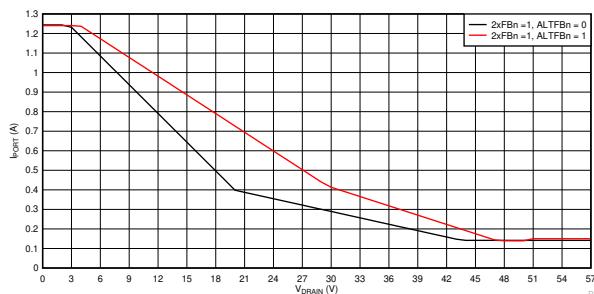

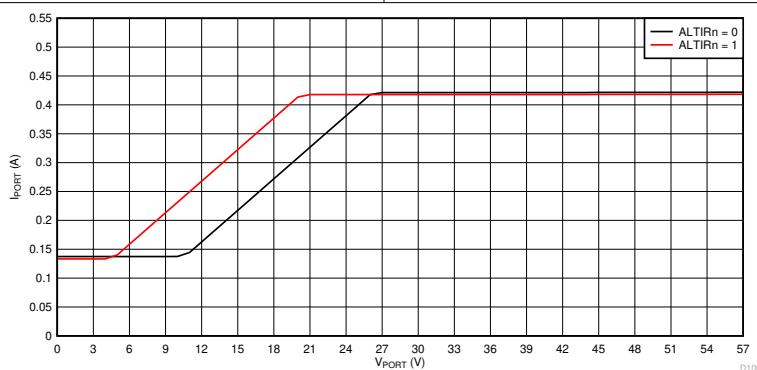

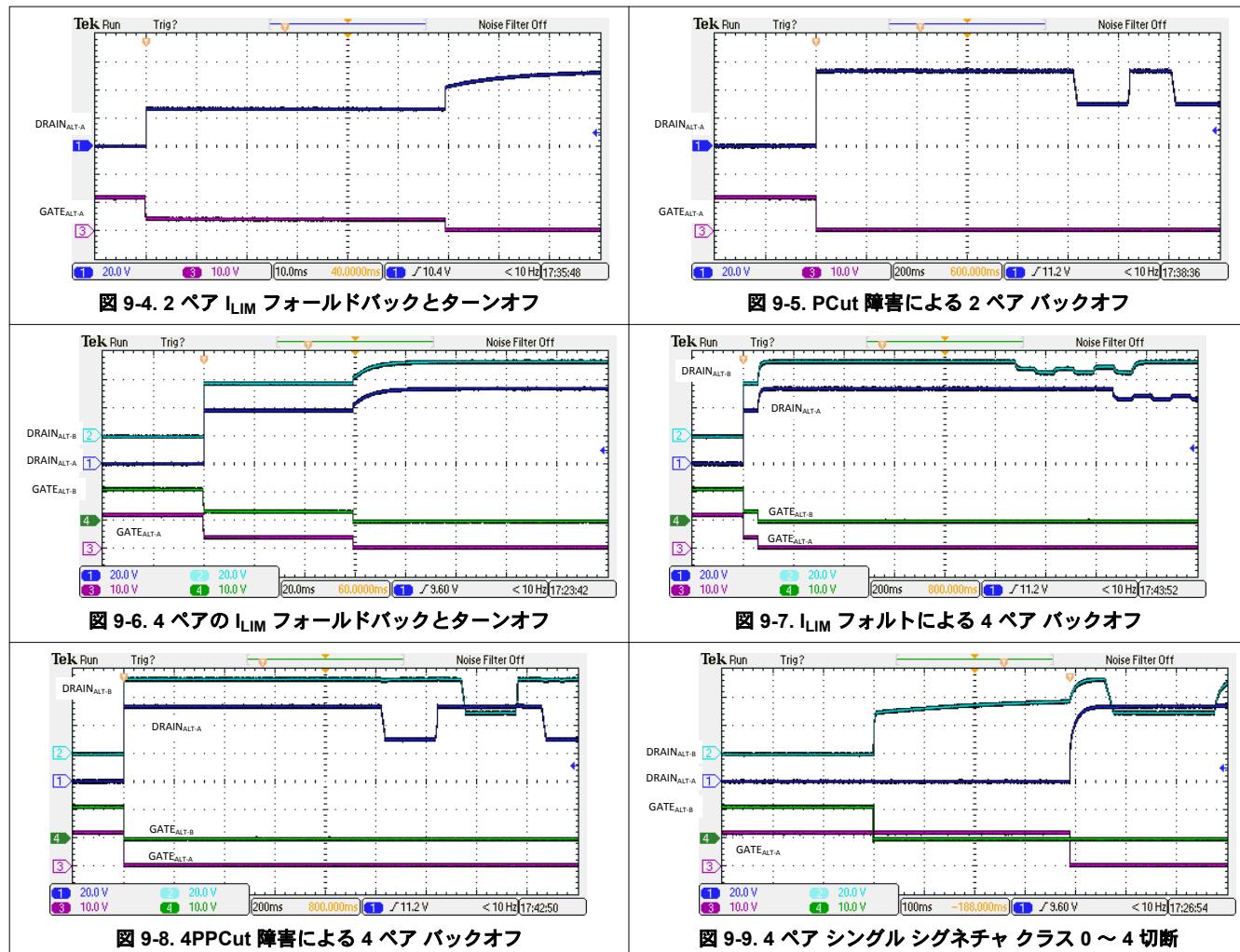

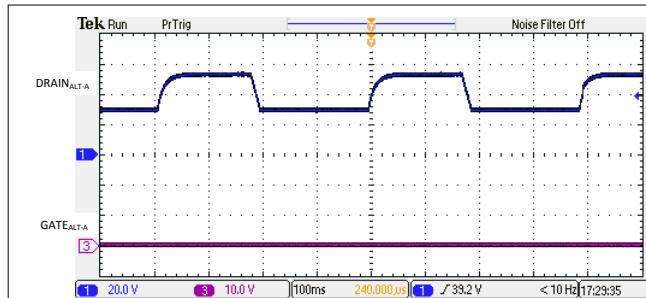

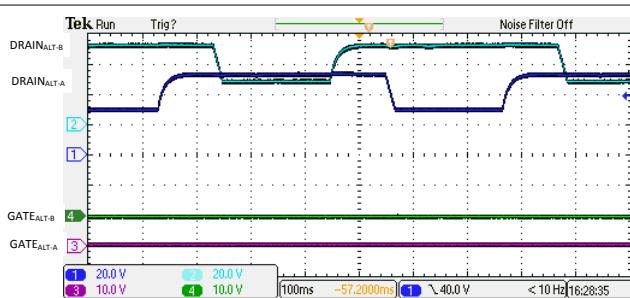

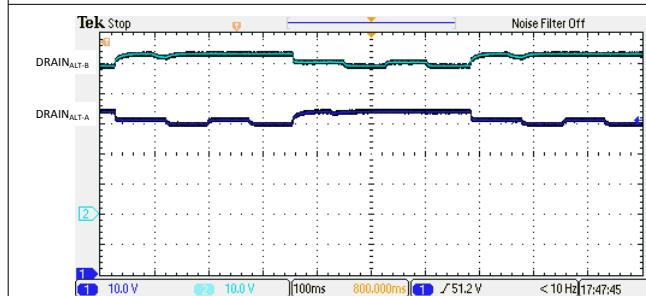

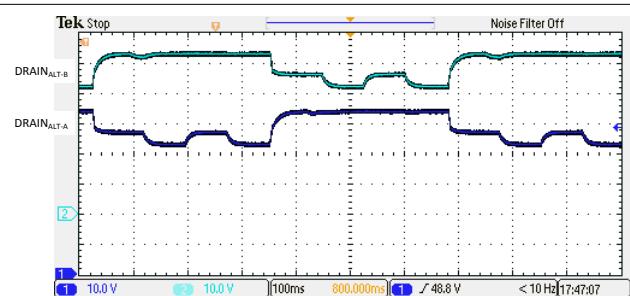

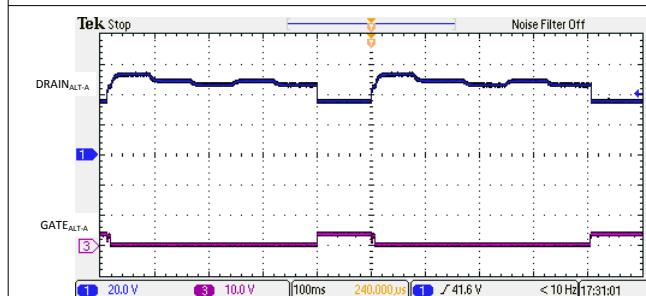

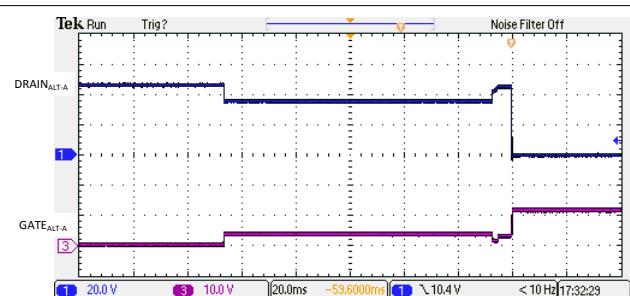

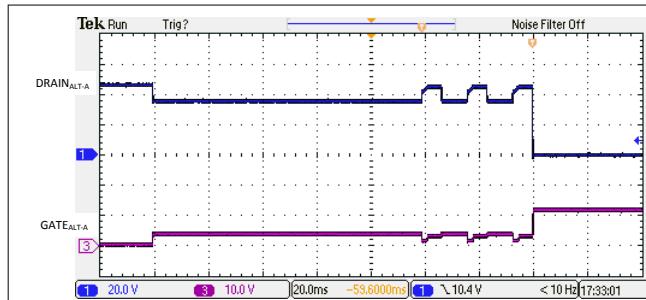

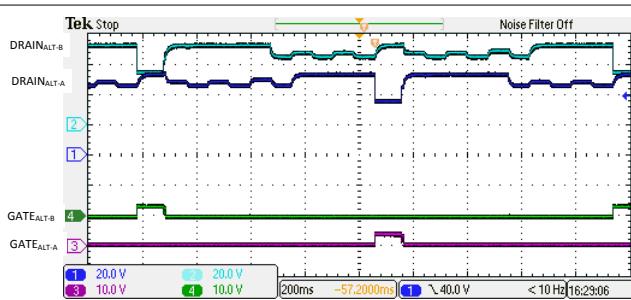

突入時、チャネル ターンオン時、フォールドバックはチャネル電圧に基づいて行われます (図 8-2 を参照)。レジスタ 0x40 の 2xFBn ビットの状態に関係なく、突入電流プロファイルは同じに維持されることに注意します。

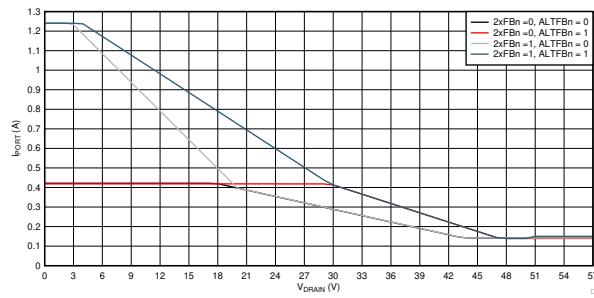

チャネルに電源が供給され、パワー グッドが有効な後、デュアル スロープ動作フォールドバックが使用され、ポート出力での部分的および合計短絡から保護されながら、PSE 入力電圧での通常の過渡現象において、PD 電力を維持できます。2xFBn ビットをセットすると、2x 曲線が選択され、クリアすると 1x 曲線が選択されることに注意してください。図 8-3 を参照してください。

デフォルトのフォールドバック曲線に加えて、TPS23881B は、突入と電源動作の両方について個別にイネーブルされた代替フォールドバック曲線を使用可能です。これらの曲線は、IEEE 規格に完全に準拠しておらず、電源をオンにするか電源を入れたままにする必要がある特定の負荷に対応するように設計されています。図 8-2 と 図 8-3 を参照してください。

#### 注

代替フォールドバック曲線 (ALTIRn または ALTFBn = 1) を使用する場合、設計者はこれらの条件のときに FET で発生する可能性のある追加の消費電力を考慮する必要があります。

図 8-2. 突入時のフォールドバック (ポート電源オン時) :  $I_{LIM}$  と  $V_{port}$  との関係

図 8-3. ポートがすでにオ n になっている場合のフォールドバック :  $I_{LIM}$  と  $V_{drain}$  との関係

## 8.4 デバイスの機能モード

### 8.4.1 検出

誤検出の可能性を排除するために、TPS23881B は TI 独自の 4 点検出法を採用して、PD デバイスのシグネチャ抵抗値を判定しています。ノイズの多い環境や負荷が高い容量性である場合、2 ポイント検出タイプの PSE で有効な 25kΩ シグネチャの誤検出が発生する可能性があります。

検出 1 と検出 2 は 1 つの検出機能に統合され、繰り返されます。検出 1 は I1 (160μA) をチャネルに適用し、約 60ms 待機してから、内蔵 ADC によるチャネル電圧 (V1) を測定します。次に検出 2 はチャネルに I2 (270μA) を印加し、約 60ms 待機した後、チャネル電圧 (V2) を再度測定します。その後、このプロセスを 2 回繰り返し、3 番目 (V3) と 4 番目 (V4) のチャネル電圧測定値をキャプチャします。非線形またはヒステリシス PD シグネチャの影響を排除するため、4 つの測定ポイントの組み合わせすべてに対して複数の比較と計算が実行されます。結果のチャネル シグネチャは、適切なカテゴリにソートされます。

#### 注

検出抵抗測定結果は、チャネル検出抵抗レジスタ (0x44 ~ 0x47) にもあります。

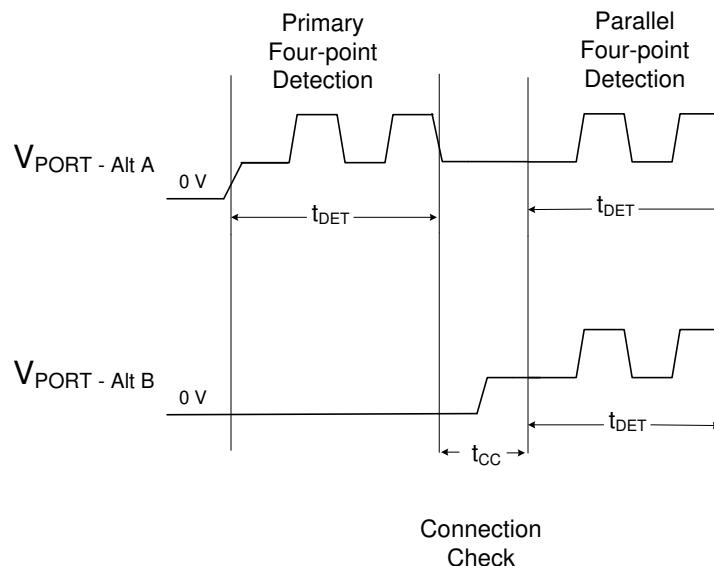

### 8.4.2 接続チェック

4ペア構成のポートの場合、は、いずれかのチャネルで有効な検出を測定した直後に接続チェックを実行します。接続チェック中に、両方のチャネルをプローブしてポートにシングル シグニチャまたはデュアル シグネチャ負荷が存在するかどうかを判定し、この測定結果はレジスタ 0x1C の下側ニブル (4 ビット) に示します。シングル シグニチャまたはデュアル シグニチャを正確に決定することは、ポートの PSE 管理にとって重要です。

図 8-4. シングル シグニチャ負荷における 4 ペア ポート、検出および接続チェック波形

図 8-5. デュアル シグネチャ負荷における 4 ペア ポート、検出および接続チェック波形

### 8.4.3 分類

ハードウェア分類 (クラス) は、電圧を供給し、結果の電流をサンプリングすることで実行されます。電源コントローラ チップで大電力の分類イベントが発生しないように、TPS23881B は、外部パワー FET を使用して分類を行います。

分類中、外部 MOSFET のゲート ノードの電圧はリニア制御ループの一部です。制御ループは、VPWR とドレインの間の差動電圧を 18.5V に維持するために適切な MOSFET ドライブを印加します。分類の間に、MOSFET のソースにある

センサ抵抗の両端の電圧を測定し、TPS23881B でクラス レベルに変換します。分類中に負荷の短絡が発生した場合、クラス イベントが発生している間、MOSFET のゲート電圧は線形制御された短絡の値に低下します。

分類結果は、I<sup>2</sup>C 検出イベントおよびチャネル n 検出レジスタから読み取られます。The TPS23881B は、パワー イネーブルとポート電源割り当てレジスタを使用して、クラス 0 ~ クラス 8 の範囲の PD について、1、3、4、5 の指分類にも対応しています。

#### 8.4.4 DC 接続解除

切断とは、ポートへの電源をオフにする自動プロセスです。ポートがアンロードされている場合、または最小負荷未満になっている場合は、ポートの電源をオフにして検出を再起動します。DC 切断では、検出抵抗の両端の電圧が測定されます。イネーブルにすると、DC 切断機能は電源ポートの検出抵抗電圧を監視して、ポートが少なくともアクティブ状態を維持するために必要な最小電流を消費していることを確認します。 $T_{DIS}$  タイマは、ポート電流が切断スレッショルド(ポートの設定に応じて 6.5mA または 4.5mA) を下回るとカウントアップします。タイムアウトが発生すると、ポートがシャットダウンされ、フォルト イベント レジスタの対応する切断ビットがセットされます。MPS (電力シグネチャを維持) 電流パルスを実装している PD の場合、電流が 3ms 以上にわたって切断スレッショルドより超え続けていくたびに、 $T_{DIS}$  カウンタがリセットされます。

$T_{DIS}$  の期間は、タイミング構成レジスタ (0x16) の  $T_{MPDO}$  ビットによって設定されます。

#### 注

クラス 4 以下の 4 ペア シングル シグネチャ PD が接続されている場合、TPS23881B ( $T_{MPDO}$  タイムアウトなし) すぐに 1 つのチャネルにパワーダウンします。その際、2 番目のチャネルに電力を供給したままにしている間、電流が切断スレッショルドを下回ってしまいます。残りのチャネルの電流が 75mA を超えると、このチャネルは再び給電されます。または、残りのチャネルの電流が、 $T_{MPDO}$  タイムアウトよりも長く切断スレッショルドを下回ると、そのポートがシャットダウンされ、故障イベント レジスタの対応する切断ビットが設定されます。

#### 注

4 ペア デュアル シグネチャ PD の両方のチャネルに電力が供給されている場合、電源オン後にレジスタ 0x2D の DCDTx ビットが自動的に設定され、IEEE 準拠の 4.5mA スレッショルドが使用されるようになります。

#### 注

4 ペアのシングル シグネチャ クラス 5-8 PD に電力を供給する場合、電源オン後にレジスタ 0x2D の DCDTx ビットが自動的に設定され、IEEE 準拠の 4.5mA スレッショルドが使用されるようになります。

## 8.5 I<sup>2</sup>C プログラミング

### 8.5.1 I<sup>2</sup>C シリアルインターフェイス

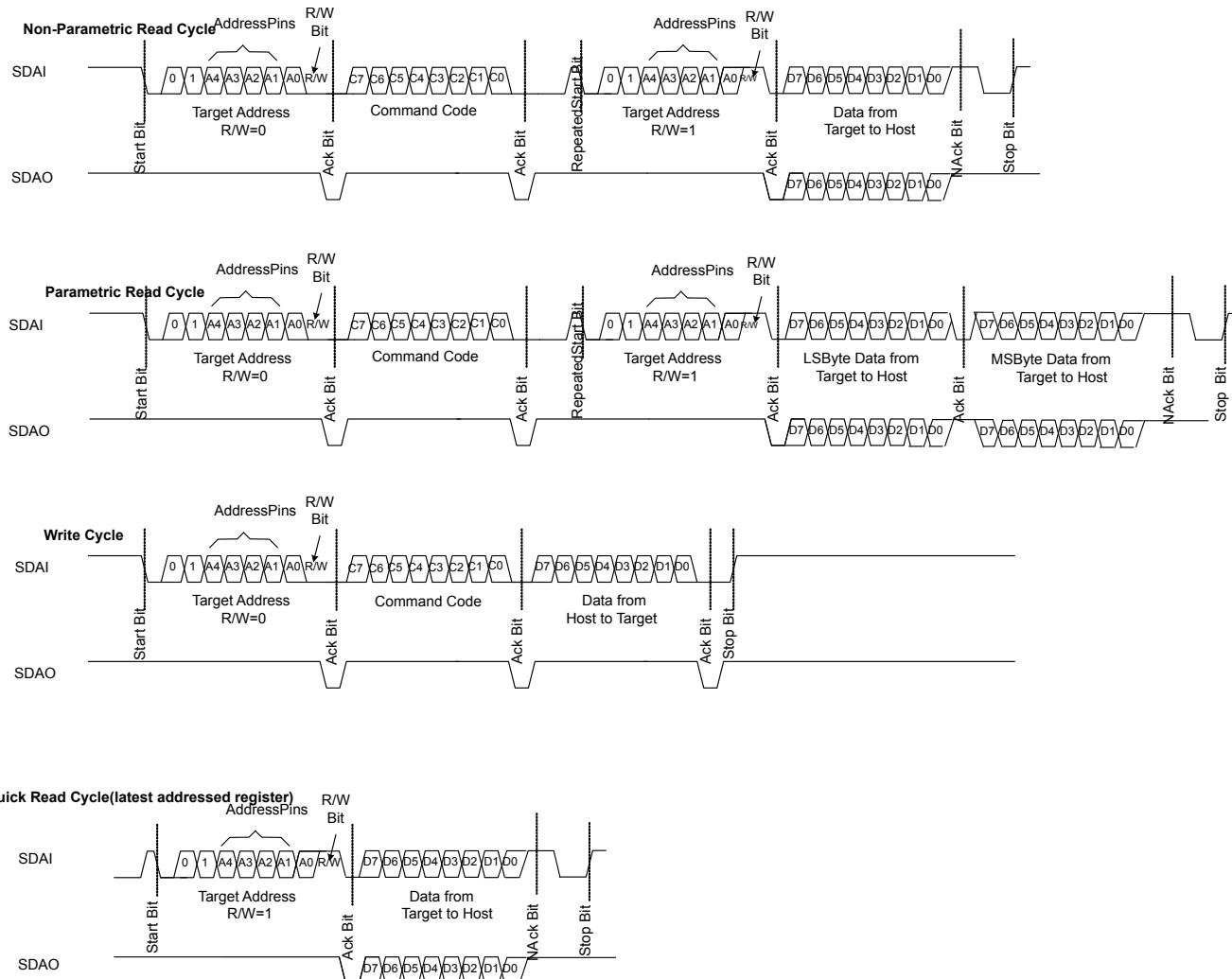

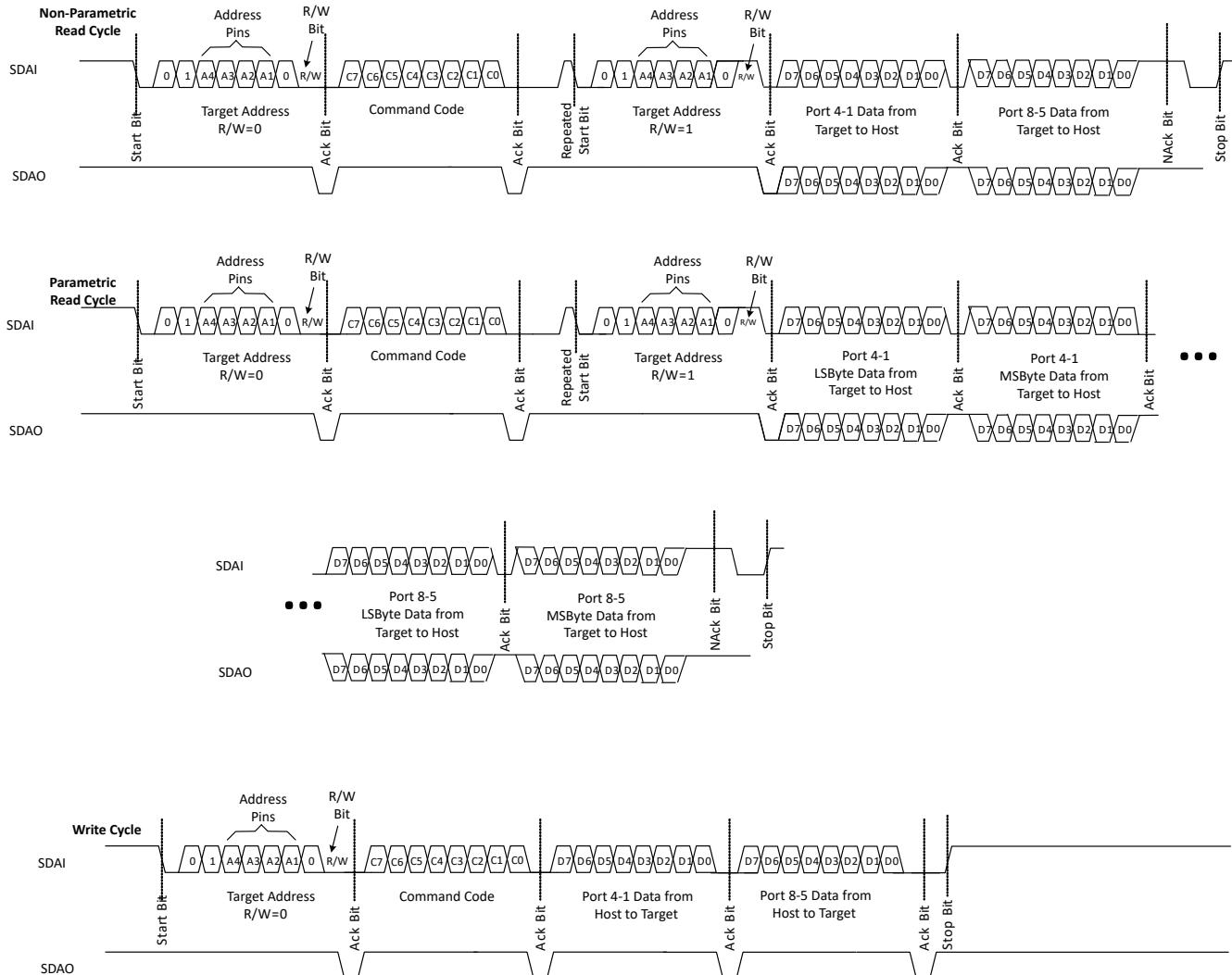

TPS23881B は、SDAI、SDAO、SCL を使用した 3 線式 I<sup>2</sup>C インターフェイスを備えています。各送信には、コントローラから送信された START 条件、R/W ビット付きのデバイス アドレス (7 ビット)、レジスタ アドレス バイト、1 つまたは 2 つのデータ バイト、STOP 条件が含まれます。受信者は、送信される各バイトの後にアノリッジ ビットを送信します。SDAI/SDAO は、START 条件または STOP 条件を除いて、SCL が high の間安定しています。

図 8-6 および図 8-7 に、構成 A または B を使用した I<sup>2</sup>C インターフェイスによる読み取りおよび書き込み動作を示します (詳細については、表 8-26 を参照)。パラメータ読み取り動作は、ADC 変換結果に適用できます。TPS23881B は、I<sup>2</sup>C バスを介して最新のアドレス指定レジスタにすばやくアクセスできます。ストップ ビットを受信したとき、レジスタ ポインタは自動的にリセットされません。

また、多くの TPS23881B デバイスに対して同時に書き込み操作を実行することもできます。PIN ステータス レジスタに示されているように、このブロードキャスト アクセス中のターゲット アドレスは 0x7F です。選択されている構成 (A または B) に応じて、グローバル書き込みは次のように処理されます。

- 構成 A: 両方の 4 ポートデバイス (1~4 および 5~8) が同時にアドレス指定されます。

- 構成 B: デバイス全体のアドレス指定が行われます。

図 8-6. I<sup>2</sup>C インターフェイス読み取り/書き込みプロトコル – 構成 A

図 8-7. I<sup>2</sup>C インターフェイス読み取り/書き込みプロトコル – 構成 B

## 8.6 レジスタ マップ

### 8.6.1 レジスタ セット全体

表 8-4. メイン レジスタ

| CMD コード | レジスタ コマンド名        | I <sup>2</sup> C R/W | データ パイト | RST 状態            | ビットの詳細           |            |         |            |                 |        |       |        |

|---------|-------------------|----------------------|---------|-------------------|------------------|------------|---------|------------|-----------------|--------|-------|--------|

| 割り込み    |                   |                      |         |                   |                  |            |         |            |                 |        |       |        |

| 00h     | 割り込み              | RO                   | 1       | 1000,0000b<br>(1) | SUPF             | STRTF      | FAULT   | CLASC      | DETC            | DISF   | PGC   | PEC    |

| 01h     | 割り込みマスク           | R/W                  | 1       | 1000,0000b        | SUMSK            | STMSK      | IFMSK   | CLMSK      | DEMSK           | DIMSK  | PGMSK | PEMSK  |

| EVENT   |                   |                      |         |                   |                  |            |         |            |                 |        |       |        |

| 02h     | パワー イベント          | RO                   | 1       | 0000, 0000b       | パワー グッド ステータスの変更 |            |         |            | 電源イネーブルのステータス変更 |        |       |        |

| 03h     |                   | CoR                  | 1       |                   | PGC4             | PGC3       | PGC2    | PGC1       | PEC4            | PEC3   | PEC2  | PEC1   |

| 04h     | 検出イベント            | RO                   | 1       | 0000, 0000b       | 分類               |            |         |            | 検出              |        |       |        |

| 05h     |                   | CoR                  | 1       |                   | CLSC4            | CLSC3      | CLSC2   | CLSC1      | DETC4           | DETC3  | DETC2 | DETC1  |

| 06h     | 故障イベント            | RO                   | 1       | 0000, 0000b       | 切断が発生しました        |            |         |            | PCUT 故障が発生しました  |        |       |        |

| 07h     |                   | CoR                  | 1       |                   | DISF4            | DISF3      | DISF2   | DISF1      | PCUT4           | PCUT3  | PCUT2 | PCUT1  |

| 08h     | 開始 / ILIM イベント    | RO                   | 1       | 0000, 0000b       | ILIM 故障が発生しました   |            |         |            | START 故障が発生しました |        |       |        |

| 09h     |                   | CoR                  | 1       |                   | ILIM4            | ILIM3      | ILIM2   | ILIM1      | STRT4           | STRT3  | STRT2 | STRT1  |

| 0Ah     | 電源供給/故障イベント       | RO                   | 1       | 0111,0000b<br>(2) | TSD              | VDUV       | VDWRN   | VPUV       | PCUT34          | PCUT12 | OSSE  | RAMFLT |

| 0Bh     |                   | CoR                  | 1       |                   | SLA4             | SLA3       | SLA2    | SLA1       | SLA0            | 予約済み   | 予約済み  | 予約済み   |

| STATUS  |                   |                      |         |                   |                  |            |         |            |                 |        |       |        |

| 0Ch     | チャネル 1 検出         | RO                   | 1       | 0000, 0000b       | 要求されたクラス チャネル 1  |            |         |            | チャネル 1 の検出      |        |       |        |

| 0Dh     | チャネル 2 検出         | RO                   | 1       | 0000, 0000b       | 要求されたクラス チャネル 2  |            |         |            | チャネル 2 の検出      |        |       |        |

| 0Eh     | チャネル 3 検出         | RO                   | 1       | 0000, 0000b       | 要求されたクラス チャネル 3  |            |         |            | チャネル 3 の検出      |        |       |        |

| 0Fh     | チャネル 4 検出         | RO                   | 1       | 0000, 0000b       | 要求されたクラス チャネル 4  |            |         |            | チャネル 4 の検出      |        |       |        |

| 10h     | 電源ステータス           | RO                   | 1       | 0000, 0000b       | PG4              | PG3        | PG2     | PG1        | PE4             | PE3    | PE2   | PE1    |