**TPS23880**

**INSTRUMENTS**

# TPS23880 タイプ 4、4 ペア、8 チャネル PoE 2 PSE コントローラ、プログラム可能な SRAM 内蔵

# 1 特長

- PoE 2 タイプ 3 またはタイプ 4 Power Over Ethernet アプリケーション用の IEEE 802.3bt PSE ソリューション

- 8つの独立した PSE チャネル

- プログラム可能な SRAM メモリ

- ±3% の精度で電力制限をプログラム可能

- 2ペアまたは4ペアのポート電力割り当てを選択 可能

- 15.4W、30W、45W、60W、75W、90W

- シングルおよびデュアル・シグネチャの PD 互換性

- ポートごとに専用の 14 ビット積算電流 ADC

- 固有フィルタ

- DC 分離用のノイズ耐性 MPS

- 2% の電流センシング精度

- 100ms でのポート電流のローリング平均化

- 1ビットまたは3ビットの高速ポート・シャットダ ウン入力

- 自動クラス検出および電力測定

- *「誤認なし」*の 4 ポイント検出

- 突入および動作フォールドバック保護

- 425mA と 1.25A の電流制限値を選択可能

- ポートの再マッピング

- 8 ビットまたは 16 ビットの I<sup>2</sup>C 通信

- 柔軟なプロセッサ制御の動作モード

- 自動、半自動、手動/診断

- ポートごとの電圧監視およびテレメトリ

- -40℃~+125℃の動作温度範囲

# 2 アプリケーション

- ビデオ・レコーダ (NVR、DVR など)

- 小規模企業向けスイッチ

- キャンパス / 分岐スイッチ

#### 3 概要

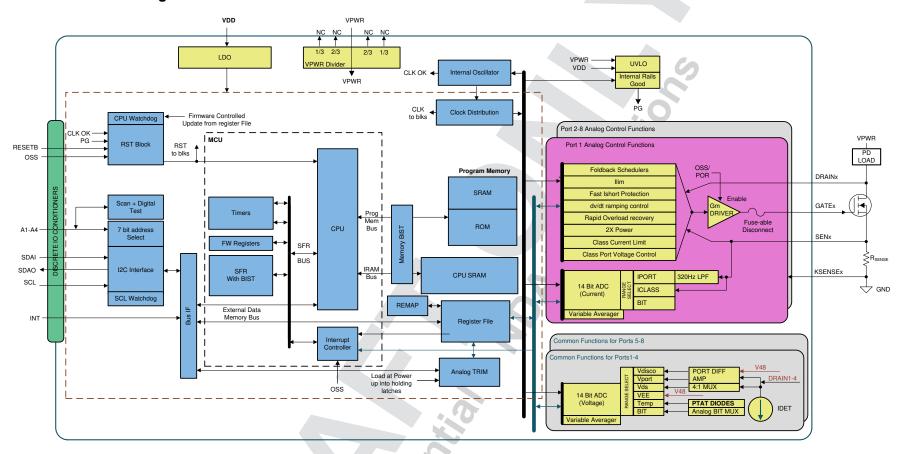

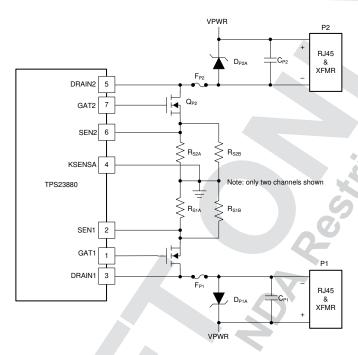

TPS23880 は、IEEE 802.3bt 規格に従ってイーサネッ ト・ケーブルに電力を重畳するための8チャネル給電 機器 (PSE) コントローラです。8 つの個別の電源チ ャネルは、2ペア (1 チャネル) または 4ペア (2 チャネ ル) の PoE ポートの任意の組み合わせに構成できま す。本 PSE コントローラは、有効なシグネチャを持 つ受電デバイス (PD) の検出、相互識別の完了、電力 の供給を行うことができます。

プログラム可能な SRAM により、I<sup>2</sup>C 経由で現場での ファームウェア・アップグレードが可能なため、IEEE 規格への準拠と最新の PoE 対応デバイスとの相互運 用性を確保できます。ポートごとに専用 ADC を備え ているため、ポート電流を連続的に監視でき、また分 類測定を同時に実行することでポートのターンオン時 間を短縮できます。±3% 精度のプログラム可能なポ ート電力制限により、最大電力を 90W 超に拡張でき ます (100W を超えることはありません)。また、シス テム・レベルの電力管理制御をより実装しやすく信頼 性の高いものにできます。 高速シャットダウン (OSS) 入力により、ポートごとに最大 8 レベルのシャ ットダウン優先度を設定でき、複数のポートをただち に無効にする必要のあるアプリケーションに対応でき ます。 255mΩ の電流センス抵抗と外部 FET を使う アーキテクチャにより、サイズ、効率、熱、ソリュー ション・コストの要件のバランスが取れた設計が可能

ポートの再マッピングと、TPS2388、TPS23881、 TPS23882 デバイスとのピン互換性により、前世代の PSE 設計から簡単に移行でき、交換可能な 2 層の PCB 設計により各種のシステム PoE 電源構成に適合 できます。

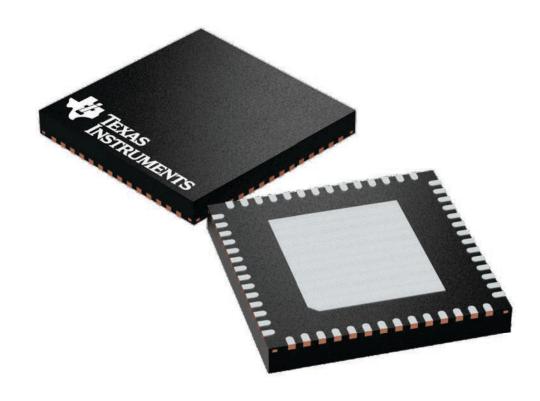

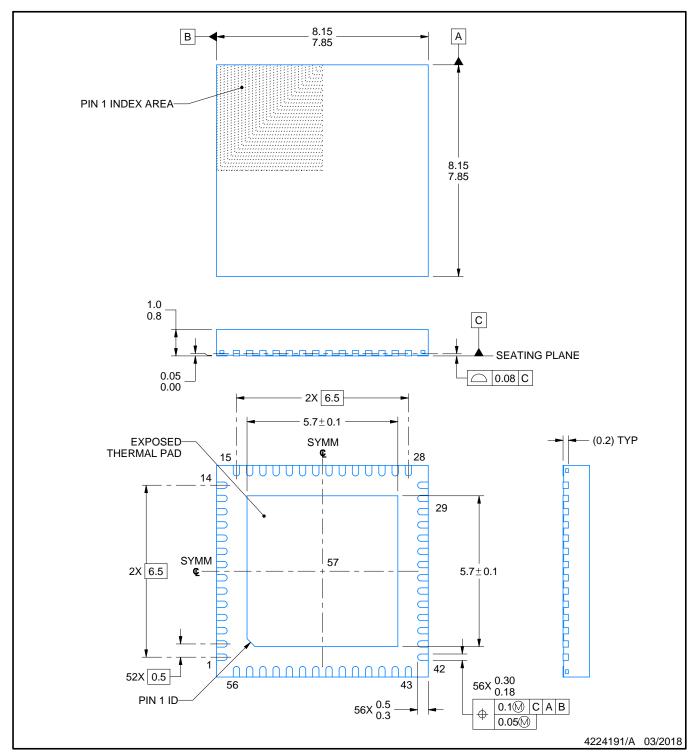

# 製品情報 (1) (1 ページ)

| 型番       | パッケージ     | 本体サイズ (公称)      |

|----------|-----------|-----------------|

| TPS23880 | VQFN (56) | 8.00mm × 8.00mm |

利用可能なすべてのパッケージについては、このデータシー トの末尾にある注文情報を参照してください。

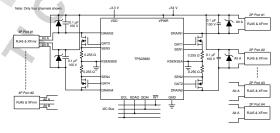

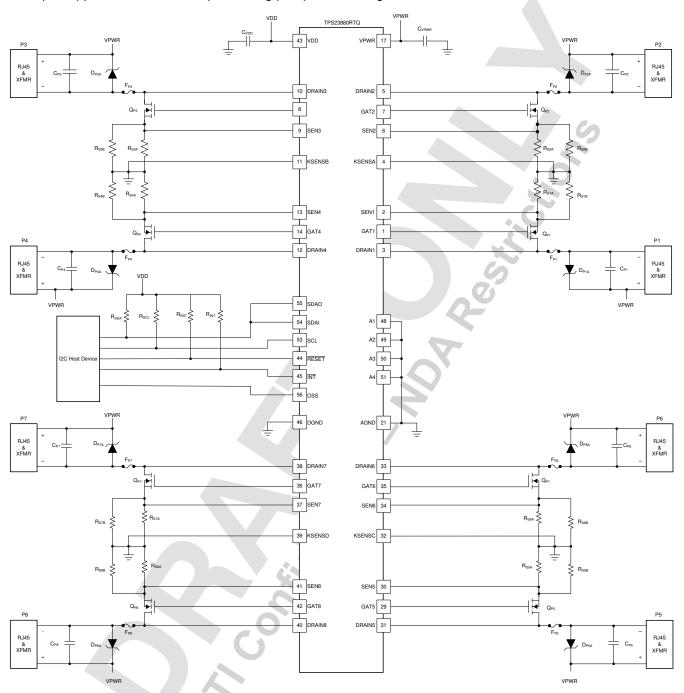

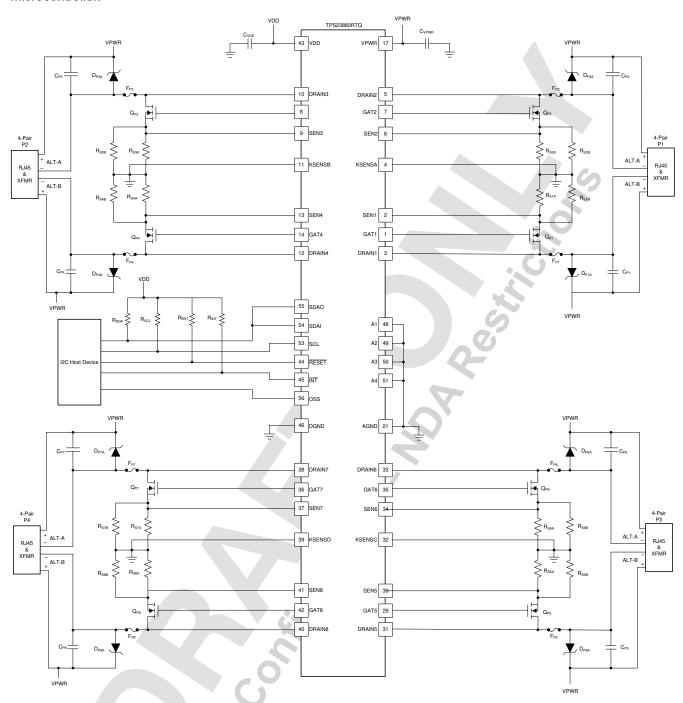

概略回路図

# **Table of Contents**

| 1 特長                                 | 1              | 9.5 I <sup>2</sup> C Programming                  | 33  |

|--------------------------------------|----------------|---------------------------------------------------|-----|

| 2 アプリケーション                           | 1              | 9.6 Register Maps                                 |     |

| 3 概要                                 | 1              | 10 Application and Implementation                 |     |

| 4 Revision History                   |                | 10.1 Application Information                      |     |

| 5 Device Comparison Table            |                | 10.2 Typical Application                          |     |

| 6 Pin Configuration and Functions    | 4              | 11 Power Supply Recommendations                   |     |

| 6.1 Detailed Pin Description         | 5              | 11.1 VDD                                          |     |

| 7 Specifications                     |                | 11.2 VPWR                                         | 124 |

| 7.1 Absolute Maximum Ratings         |                | 12 Layout                                         | 125 |

| 7.2 ESD Ratings                      |                | 12.1 Layout Guidelines                            | 125 |

| 7.3 Recommended Operating Conditions |                | 12.2 Layout Example                               | 126 |

| 7.4 Thermal Information              | <mark>7</mark> | 13 Device and Documentation Support               |     |

| 7.5 Electrical Characteristics       | 8              | 13.1 Documentation Support                        |     |

| 7.6 Typical Characteristics          | 15             | 13.2 Receiving Notification of Documentation Upon |     |

| 8 Parameter Measurement Information  |                | 13.3 Support Resources                            |     |

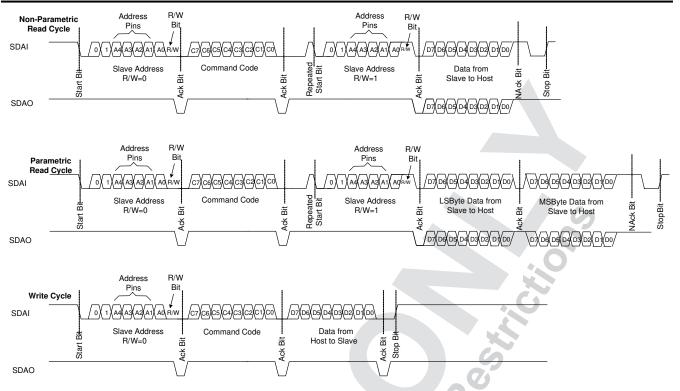

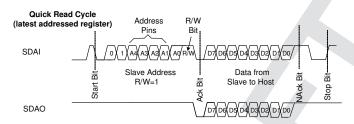

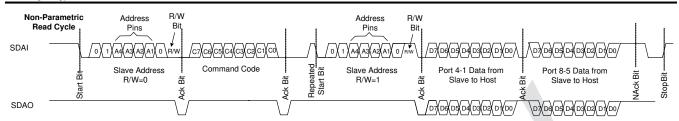

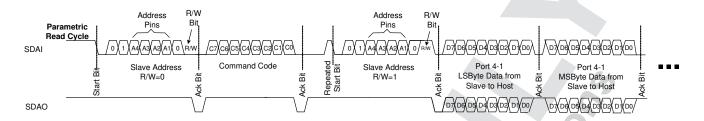

| 8.1 Timing Diagrams                  | 20             | 13.4 Trademarks                                   |     |

| 9 Detailed Description               |                | 13.5 Electrostatic Discharge Caution              |     |

| 9.1 Overview                         |                | 13.6 Glossary                                     | 127 |

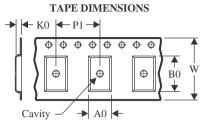

| 9.2 Functional Block Diagram         | 28             | 14 Mechanical, Packaging, and Orderable           |     |

| 9.3 Feature Description              |                | Information                                       | 127 |

| 9.4 Device Functional Modes          |                |                                                   |     |

|                                      |                |                                                   |     |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision F (May 2020) to Revision G (August 2020)                   | Page |

|----------------------------------------------------------------------------------|------|

| • 文書全体にわたって表、図、相互参照の採番方法を更新                                                      | 1    |

| Changes from Revision E (December 2019) to Revision F (May 2020)                 | Page |

| Deleted Autonomous operation description throughout data sheet for clarification | 4    |

| Changed Gate 1-8 voltage MAX value from 12 to 13 V in the Abs Max Ratings table  | 7    |

| Changes from Revision D (October 2019) to Revision E (December 2019)             | Page |

| • 最初のページのデバイス番号の誤字を修正                                                            | 1    |

| Changes from Revision C (July 2019) to Revision D (October 2019)                 | Page |

| Added TPS23882 to the Device Comparison Table.                                   | 3    |

| Changes from Revision B (October 2018) to Revision C (July 2019)                 | Page |

| Changed the MOSFET drawing in the application schematics                         | 115  |

| Changes from Revision A (May 2018) to Revision B (September 2018)                | Page |

| • 事前情報から量産データに変更                                                                 | 1    |

| Changes from Revision * (March 2018) to Revision A (May 2019)                    | Page |

| <ul><li>最初の公開リリース</li></ul>                                                      | 1    |

# **5 Device Comparison Table**

| KEY FEATURES                                 | TPS23880                                      | TPS23881                                      | TPS23882                         |

|----------------------------------------------|-----------------------------------------------|-----------------------------------------------|----------------------------------|

| Compatible with TI's FirmPSE system firmware | N/A                                           | Yes                                           | Yes                              |

| Pin to Pin compatible                        | Yes                                           | Yes                                           | Yes                              |

| Number of PSE Channels                       | 8                                             | 8                                             | 8                                |

| Supported IEEE 802.3 PSE Types               | PoE 2<br>802.3bt Type 3 or 4<br>(2 or 4 Pair) | PoE 2<br>802.3bt Type 3 or 4<br>(2 or 4 Pair) | PoE 2<br>802.3bt Type 3 (2-Pair) |

| R <sub>SENSE</sub>                           | 0.255 Ω                                       | 0.200 Ω                                       | 0.200 Ω                          |

| 2-Pair P <sub>CUT</sub> programable ranges   | 0.5 W to 54 W                                 | 2 W to 65 W                                   | 2 W to 65 W                      |

| 4-Pair P <sub>CUT</sub> programable ranges   | 0.5 W to 108 W                                | 4 W to 127 W                                  | N/A                              |

| 90+ W 4-pair P <sub>CUT</sub> accuracy       | ±3.0 %                                        | ±2.5 %                                        | N/A                              |

| Channel capacitance measurement range        | N/A                                           | 1 μF to 12 μF                                 | 1 μF to 12 μF                    |

| ULA Packaging                                | No                                            | Yes (TPS23881A)                               | N/A                              |

| I <sup>2</sup> C Programmable SRAM Memory    | 16 kB                                         | 16 kB                                         | 16 kB                            |

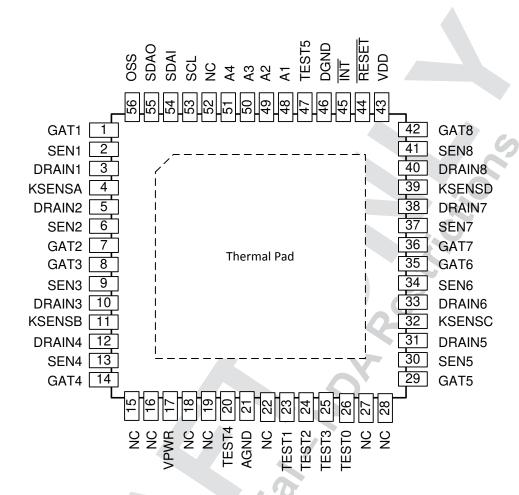

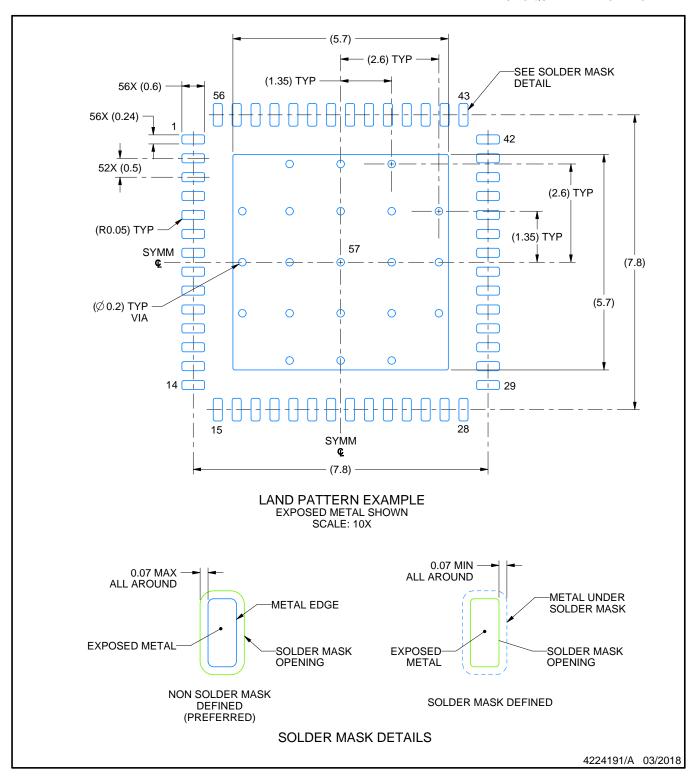

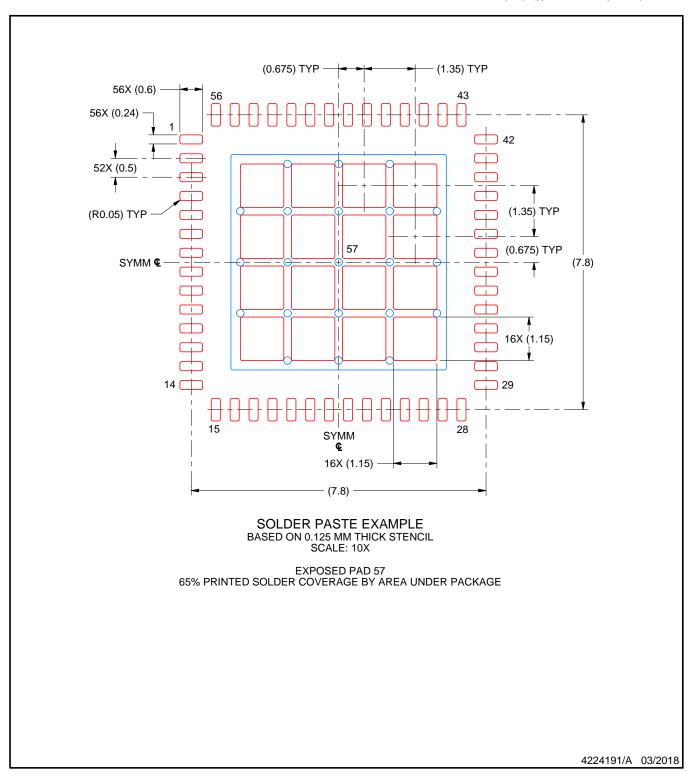

# **6 Pin Configuration and Functions**

図 6-1. RTQ Package With Exposed Thermal Pad 56-Pin VQFN Top View

#### **Pin Functions**

|             | PIN                             | I/O | DESCRIPTION                                                                                                                              |  |

|-------------|---------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.                             | 1/0 | DESCRIPTION                                                                                                                              |  |

| A1-4        | 48–51                           | ı   | I <sup>2</sup> C A1-A4 address lines. These pins are internally pulled up to VDD.                                                        |  |

| AGND        | 21                              | _   | Analog ground. Connect to GND plane and exposed thermal pad.                                                                             |  |

| DGND        | 46                              | _   | Digital ground. Connect to GND plane and exposed thermal pad.                                                                            |  |

| DRAIN1-8    | 3, 5, 10, 12, 31,<br>33, 38, 40 | I   | Channel 1-8 output voltage monitor.                                                                                                      |  |

| GAT1-8      | 1, 7, 8, 14, 29, 35,<br>36, 42  | 0   | Channel 1-8 gate drive output.                                                                                                           |  |

| INT         | 45                              | 0   | Interrupt output. This pin asserts low when a bit in the interrupt register is asserted. This output is open-drain.                      |  |

| KSENSA/B    | 4, 11                           | I   | Kelvin point connection for SEN1-4                                                                                                       |  |

| KSENSC/D    | 32, 39                          | I   | Kelvin point connection for SEN5-8                                                                                                       |  |

| NC          | 15, 16, 18, 19                  | 0   | No connect pins. These pins are internally biased at 1/3 and 2/3 of VPWR in order to control the voltage gradient from VPWR. Leave open. |  |

|             | 22, 27, 28, 52                  | _   | No connect pin. Leave open.                                                                                                              |  |

| OSS         | 56                              | I   | Channel 1-8 fast shutdown. This pin is internally pulled down to DGND.                                                                   |  |

| RESET       | 44                              | I   | Reset input. When asserted low, the TPS23880 is reset. This pin is internally pulled up to VDD.                                          |  |

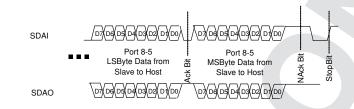

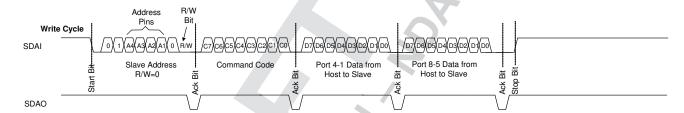

| SCL         | 53                              | I   | Serial clock input for I <sup>2</sup> C bus.                                                                                             |  |

| SDAI        | 54                              | I   | Serial data input for I <sup>2</sup> C bus. This pin can be connected to SDAO for non-isolated systems.                                  |  |

| SDAO        | 55                              | 0   | Serial data output for I <sup>2</sup> C bus. This pin can be connected to SDAI for non-isolated systems. This output is opendrain.       |  |

| SEN1-8      | 2, 6, 9, 13, 30, 34,<br>37, 41  | ı   | Channel 1-8 current sense input.                                                                                                         |  |

| TEST0-5     | 20, 23, 24, 25, 26,<br>47       | I/O | Used internally for test purposes only. Leave open.                                                                                      |  |

| Thermal pad | _                               | _   | The DGND and AGND terminals must be connected to the exposed thermal pad for proper operation.                                           |  |

| VDD         | 43                              | _   | Digital supply. Bypass with 0.1 μF to DGND pin.                                                                                          |  |

| VPWR        | 17                              | _   | Analog 54-V positive supply. Bypass with 0.1 µF to AGND pin.                                                                             |  |

### 6.1 Detailed Pin Description

The following descriptions refer to the pinout and the functional block diagram.

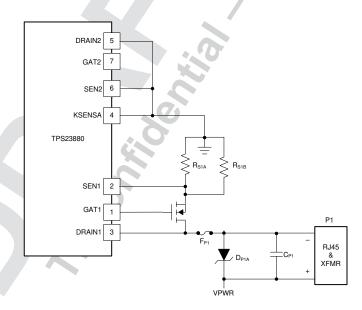

**DRAIN1-DRAIN8:** Channels 1-8 output voltage monitor and detect sense. Used to measure the port output voltage, for port voltage monitoring, port power good detection and foldback action. Detection probe currents also flow into this pin.

The TPS23880uses an innovative 4-point technique to provide reliable PD detection and avoids powering an invalid load. The discovery is performed by sinking two different current levels via the DRAINn pin, while the PD voltage is measured from VPWR to DRAINn. If prior to starting a new detection cycle the port voltage is >2.5 V, an internal  $100\text{-k}\Omega$  resistor is connected in parallel with the port and a 400-ms detect backoff period is applied to allow the port capacitor to be discharged before the detection cycle starts.

There is an internal resistor between each DRAINn pin and VPWR in any operating mode except during detection or while the port is ON. If the port n is not used, DRAINn can be left floating or tied to GND.

**GAT1-GAT8:** Channels 1-8 gate drive outputs are used for external N-channel MOSFET gate control. At port turn on, it is driven positive by a low current source to turn the MOSFET on. GATn is pulled low whenever any of the input supplies are low or if an overcurrent timeout has occurred. GATn is also pulled low if the port is turned off by use of manual shutdown inputs. Leave floating if unused.

For improved design robustness, the current foldback functions limit the power dissipation of the MOSFET during low resistance load or short-circuit events and during the inrush period at port turn on. There is also fast overload protection comparator for major faults like a direct short that forces the MOSFET to turn off in less than a microsecond.

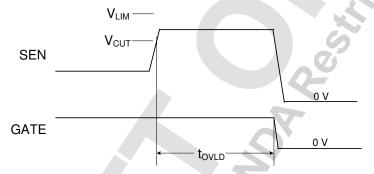

While a port is on and its  $P_{CUT}$  threshold is exceeded, a timer starts. During that time, linear current limiting ensures the current does not exceed  $I_{LIM}$  combined with current foldback action. When the timer reaches the  $t_{OVLD}$  (or  $t_{START}$  if at port turn on) limit, the port shuts off. When the port current goes below  $P_{CUT}$ , the counter counts down at a rate  $1/16^{th}$  of the increment rate and the counter must reach a count of 0 before the port can be turned on again.

The circuit leakage paths between the GATn pin and any nearby DRAINn pin, GND or Kelvin point connection must be minimized (< 250 nA), to ensure correct MOSFET control.

**INT:** This interrupt output pin asserts low when a bit in the interrupt register is asserted. This output is open-drain.

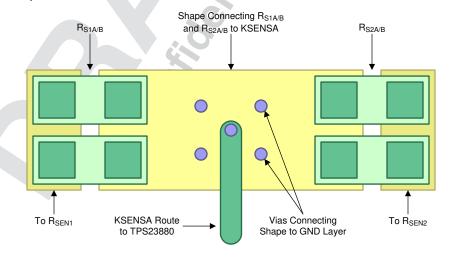

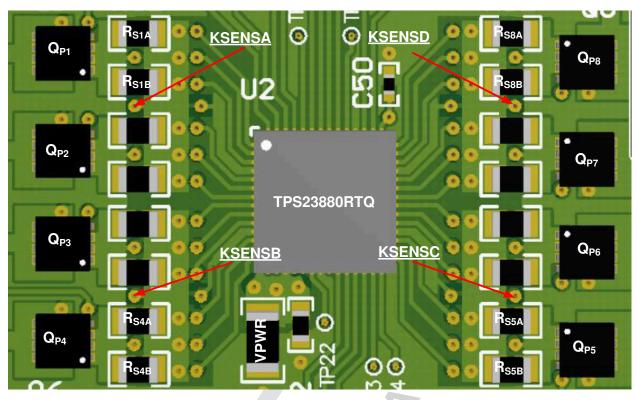

**KSENSA**, **KSENSB**, **KSENSC**, **KSENSD**: Kelvin point connection used to perform a differential voltage measurement across the associated current sense resistors.

Each KSENS is shared between two neighbor SEN pins as following: KSENSA with SEN1 and SEN2, KSENSB with SEN3 and SEN4, KSENSC with SEN5 and SEN6, KSENSD with SEN7 and SEN8. To optimize the measurement accuracy, ensure proper PCB layout practices are followed.

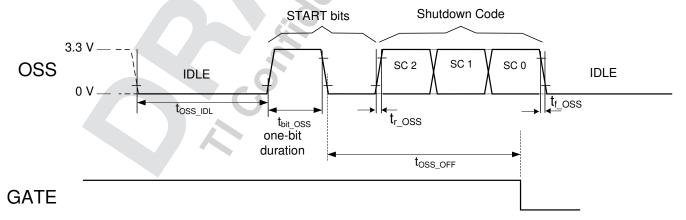

**OSS:** Fast shutdown, active high. This pin is internally pulled down to DGND, with an internal 1-µs to 5-µs deglitch filter.

The turn off procedure is similar to a port reset using Reset command (1Ah register). The 3-bit OSS function allows for a series of pulses on the OSS pin to turn off individual or multiple ports with up to 8 levels of priority.

**RESET:** Reset input, active low. When asserted, the TPS23880 resets, turning off all ports and forcing the registers to their power-up state. This pin is internally pulled up to VDD, with internal 1-µs to 5-µs deglitch filter. The designer can use an external RC network to delay the turn-on. There is also an internal power-on-reset which is independent of the RESET input.

**SCL:** Serial clock input for I<sup>2</sup>C bus.

**SDAI:** Serial data input for I<sup>2</sup>C bus. This pin can be connected to SDAO for non-isolated systems.

**SDAO:** Open-drain I<sup>2</sup>C bus output data line. Requires an external resistive pull-up. The TPS23880 uses separate SDAO and SDAI lines to allow optoisolated I<sup>2</sup>C interface. SDAO can be connected to SDAI for non-isolated systems.

**A4-A1:**  $I^2C$  bus address inputs. These pins are internally pulled up to VDD. See  $\pm 29.6.2.13$  for more details.

**SEN1-8:** Channel current sense input relative to KSENSn (see KSENSn description). A differential measurement is performed using KSENSA-D Kelvin point connection. Monitors the external MOSFET current by use of a  $0.255-\Omega$  current sense resistor connected to GND. Used by current foldback engine and also during classification. Can be used to perform load current monitoring via ADC conversion.

When the TPS23880 performs the classification measurements, the current flows through the external MOSFETs. This avoids heat concentration in the device and makes it possible for the TPS23880 to perform classification measurements on multiple ports at the same time. For the current limit with foldback function, there is an internal 2-µS analog filter on the SEN1-8 pins to provide glitch filtering. For measurements through an ADC, an anti-aliasing filter is present on the SEN1-8 pins. This includes the port-powered current monitoring, port policing, and DC disconnect.

If the port is not used, tie SENn to GND.

**VDD:** 3.3-V logic power supply input.

VPWR: High voltage power supply input. Nominally 54 V.

**AGND and DGND:** Ground references for internal analog and digital circuitry respectively. Not connected together internally. Both pins require a low resistance path to the system GND plane. If a robust GND plane is used to extract heat from the device's thermal pad, these pins may be connected together through the thermal pad connection on the pcb.

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                        | MIN  | MAX | UNIT |

|------------------|----------------------------------------|------|-----|------|

|                  | VPWR                                   | -0.3 | 70  | V    |

|                  | VDD                                    | -0.3 | 4   | V    |

|                  | OSS, RESET, A1-A4                      | -0.3 | 4   | V    |

|                  | SDAI, SDAO, SCL, INT                   | -0.3 | 4   | V    |

| Voltage          | SEN1-8, KSENSA, KSENSB, KSENSC, KSENSD | -0.3 | 3   | V    |

|                  | GATE1-8                                | -0.3 | 13  | V    |

|                  | DRAIN1-8                               | -0.3 | 70  | V    |

|                  | TEST0-3, ATST_DCPL0, DTST_DCPL1        | -0.3 | 4   | V    |

|                  | AGND                                   | -0.3 | 0.3 | V    |

| Sink Current     | INT, SDA                               |      | 20  | mA   |

| Lead Temperatur  | re 1/6mm from case for 10 seconds      |      | 260 | °C   |

| T <sub>stg</sub> | Storage temperature                    | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                           |                                                                                         | VALUE | UNIT |

|--------------------|---------------------------|-----------------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic discharge   | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, allpins <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Lieotrostatio disorialige | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ± 500 | •    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                           | MIN | NOM | MAX | UNIT |

|-------------------|---------------------------|-----|-----|-----|------|

| V <sub>VDD</sub>  |                           | 3   | 3.3 | 3.6 | V    |

| V <sub>VPWR</sub> |                           | 44  | 54  | 57  | V    |

|                   | Voltage Slew rate on VPWR |     |     | 1   | V/µs |

| f <sub>SCL</sub>  | SCL clock frequency       |     |     | 400 | kHz  |

| TJ                | Junction temperature      | -40 |     | 125 | °C   |

# 7.4 Thermal Information

|                       | Junction-to-case (top) thermal resistance    | TPS23880           |      |

|-----------------------|----------------------------------------------|--------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTQ Package (VQFN) | UNIT |

|                       |                                              | 56 PINS            |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 25.3               | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 9.7                | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 3.7                | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2                | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 3.7                | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.5                | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

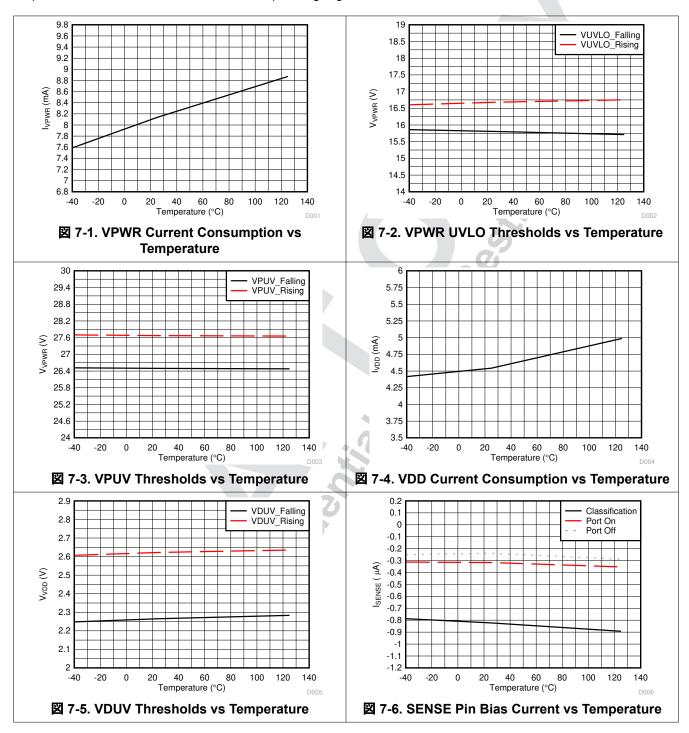

### 7.5 Electrical Characteristics

Conditions are  $-40 < T_J < 125$  °C unless otherwise noted.  $V_{VDD} = 3.3$  V,  $V_{VPWR} = 54$  V,  $V_{DGND} = V_{AGND}$ , DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn = 0. Positive currents are into pins.  $R_S = 0.255 \Omega$ , to KSENSA (SEN1 or SEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                           | PARAMETER                                          | TEST CONDITIONS                                                      | MIN       | TYP   | MAX   | UNIT   |

|---------------------------|----------------------------------------------------|----------------------------------------------------------------------|-----------|-------|-------|--------|

| INPUT SUPP                | LY VPWR                                            |                                                                      |           |       |       |        |

| I <sub>VPWR</sub>         | VPWR Current consumption                           | VVPWR = 54 V                                                         |           | 10    | 12.5  | mA     |

| V <sub>UVLOPW_F</sub>     | VPWR UVLO falling threshold                        | Check internal oscillator stops operating                            | 14.5      |       | 17.5  | V      |

| V <sub>UVLOPW_R</sub>     | VPWR UVLO rising threshold                         |                                                                      | 15.5      |       | 18.5  | V      |

| V <sub>PUV_F</sub>        | VPWR Undervoltage falling threshold                | VPUV threshold                                                       | 25        | 26.5  | 28    | V      |

| INPUT SUPP                | LY VDD                                             |                                                                      |           | -     |       |        |

| I <sub>VDD</sub>          | VDD Current consumption                            |                                                                      |           | 6     | 12    | mA     |

| $V_{UVDD\_F}$             | VDD UVLO falling threshold                         | For channel deassertion                                              | 2.1       | 2.25  | 2.4   | V      |

| V <sub>UVDD_R</sub>       | VDD UVLO rising threshold                          |                                                                      | 2.45      | 2.6   | 2.75  | V      |

| V <sub>UVDD_HYS</sub>     | Hysteresis VDD UVLO                                |                                                                      |           | 0.35  |       | V      |

| V <sub>UVW_F</sub>        | VDD UVLO warning threshold                         |                                                                      | 2.6       | 2.8   | 3     | V      |

| A/D CONVER                | RTERS                                              |                                                                      |           |       |       |        |

| T <sub>CONV_I</sub>       | Conversion time                                    | All ranges, each channel                                             | 0.64      | 0.8   | 0.96  | ms     |

| T <sub>CONV_V</sub>       | Conversiontime                                     | All ranges, each channel                                             | 0.82      | 1.03  | 1.2   | ms     |

| T <sub>INT_CUR</sub>      | Integration time, Current                          | Each channel, channel ON current                                     | 82        | 102   | 122   | ms     |

| T <sub>INT_DET</sub>      | Integration time, Detection                        |                                                                      | 13.1      | 16.6  | 20    | ms     |

| T <sub>INT_channelV</sub> | Integration time, Channel Voltage                  | channel powered                                                      | 3.25      | 4.12  | 4.9   | ms     |

| T <sub>INT_inV</sub>      | Integration time, Input Voltage                    |                                                                      | 3.25      | 4.12  | 4.9   | ms     |

|                           |                                                    |                                                                      | 15175     | 15565 | 15955 | Counts |

|                           | Input voltage conversion scale factor and accuracy | VVPWR = 57 V                                                         | 55.57     | 57    | 58.43 | V      |

|                           |                                                    | 10/DMB = 44 V                                                        | 11713     | 12015 | 12316 | Counts |

|                           |                                                    | VVPWR = 44 V                                                         | 42.89     | 44    | 45.10 | V      |

|                           |                                                    | WEWE VEELS ETV                                                       | 15175     | 15565 | 15955 | Counts |

|                           | Powered Channel voltage conversion                 | VVPWR - VDRAINn = 57 V                                               | 55.57     | 57    | 58.43 | V      |

|                           | scale factor and accuracy                          | VVPWR - VDRAINn = 44 V                                               | 11713     | 12015 | 12316 | Counts |

|                           |                                                    |                                                                      | 42.89     | 44    | 45.10 | V      |

| δV/V <sub>Channel</sub>   | Voltage reading accuracy                           | 70                                                                   | -2.5      |       | 2.5   | %      |

|                           |                                                    | 01.01                                                                | 10750     | 10970 | 11190 | Counts |

|                           | Powered Channel current conversion                 | Channel current = 770 mA                                             | 754.5     | 770   | 785.4 | mA     |

|                           | scale factor and accuracy                          | Channel Cument - 7.5 A                                               | 85        | 107   | 130   | Counts |

|                           |                                                    | Channel Current = 7.5 mA                                             | 5.966     | 7.5   | 9.125 | mA     |

| 21/1                      | Current reading accuracy                           | Channel Current =50 mA                                               | -3        |       | 3     | 0/     |

| δI/I <sub>Channel</sub>   | Current reading accuracy                           | Channel Current =770 mA                                              | -2        |       | 2     | %      |

|                           | Powered Channel current ful scale                  | Channel auments - 4.45 A                                             | 14959     | 15671 |       | Counts |

|                           | output                                             | Channel currents = 1.15 A                                            | 1.05      | 1.1   |       | Α      |

| σΙ                        | Current Reading Repeatability                      | Full Scale reading                                                   | -7.5      |       | 7.5   | mA     |

| δR/R <sub>Channel</sub>   | Resistance reading accuracy                        | 15 kΩ ≤ R <sub>Channel</sub> ≤ 33 kΩ, C <sub>Channel</sub> ≤ 0.25 μF | <b>-7</b> |       | 7     | %      |

| I <sub>bias</sub>         | Sense Pin bias current                             | Channel ON or during class                                           | -2.5      |       | 0     | μA     |

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Conditions are  $-40 < T_J < 125$  °C unless otherwise noted.  $V_{VDD} = 3.3$  V,  $V_{VPWR} = 54$  V,  $V_{DGND} = V_{AGND}$ , DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn = 0. Positive currents are into pins.  $R_S = 0.255 \Omega$ , to KSENSA (SEN1 or SEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                          | PARAMETER                                                                               | TEST CONDITIONS                                                                                              | MIN  | TYP  | MAX  | UNIT   |

|--------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| GATE 1-8                 |                                                                                         |                                                                                                              |      |      |      |        |

| V <sub>GOH</sub>         | Gate drive voltage                                                                      | V <sub>GATEn</sub> , I <sub>GATE</sub> = -1 μA                                                               | 10   |      | 12.5 | V      |

| I <sub>GO-</sub>         | Gate sinking current with Power-on<br>Reset, OSS detected or channel turnoff<br>command | V <sub>GATEn</sub> = 5 V                                                                                     | 60   | 100  | 190  | mA     |

| I <sub>GO short-</sub>   | Gate sinking current with channel short-circuit                                         | $V_{GATEn} = 5 \text{ V},$<br>$V_{SENn} \ge V_{short} \text{ (or } V_{short2X} \text{ if } 2X \text{ mode)}$ | 60   | 100  | 190  | mA     |

| I <sub>GO+</sub>         | Gate sourcing current                                                                   | V <sub>GATEn</sub> = 0 V, default selection                                                                  | 39   | 50   | 63   | μA     |

| t <sub>D_off_OSS</sub>   | Gate turnoff time from 1-bit OSS input                                                  | From OSS to VGATEn < 1 V,<br>VSENn = 0 V, MbitPrty = 0                                                       | 1    |      | 5    | μs     |

| t <sub>OSS_OFF</sub>     | Gate turnoff time from 3-bit OSS input                                                  | From Start bit falling edge to VGATEn < 1 V,<br>VSENn = 0 V, MbitPrty = 1                                    | 72   |      | 104  | μs     |

| t <sub>P_off_CMD</sub>   | Gate turnoff time from channel turnoff command                                          | From Channel off command to V <sub>GATEn</sub> < 1 V, V <sub>SENn</sub> = 0 V                                | 52   |      | 300  | μs     |

| t <sub>P_off_RST</sub>   | Gate turnoff time with /RESET                                                           | From /RESET low to V <sub>GATEn</sub> < 1 V,<br>V <sub>SENn</sub> = 0 V                                      | 1    |      | 5    | μs     |

| DRAIN 1-8                |                                                                                         |                                                                                                              |      |      | '    |        |

| V <sub>PGT</sub>         | Power-Good threshold                                                                    | Measured at V <sub>DRAINn</sub>                                                                              | 1    | 2.13 | 3    | V      |

| V <sub>SHT</sub>         | Shorted FET threshold                                                                   | Measured at V <sub>DRAINn</sub>                                                                              | 4    | 6    | 8    | V      |

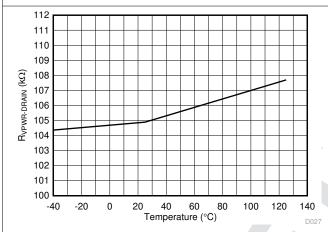

| R <sub>DRAIN</sub>       | Resistance from DRAINn to VPWR                                                          | Any operating mode except during detection or while the Channel is ON, including in device RESET state       | 80   | 100  | 190  | kΩ     |

| AUTOCLASS                |                                                                                         |                                                                                                              |      |      |      |        |

| t <sub>Class_ACS</sub>   | Start of Autoclass Detection                                                            | Measured from the start of Class                                                                             | 90   |      | 100  | ms     |

|                          |                                                                                         | Measured from the end of Inrush                                                                              | 1.4  |      | 1.6  | s      |

| t <sub>AUTO_PSE1</sub>   | Start of Autoclass Power Measurement                                                    | Measured from setting the MACx bit while channel is already powered                                          |      |      | 10   | ms     |

| t <sub>AUTO</sub>        | Duration of Autoclass Power<br>Measurement                                              | 7.6                                                                                                          | 1.7  | 1.8  | 1.9  | s      |

| t <sub>AUTO_window</sub> | Autoclass Power Measurement Sliding Window                                              | 0                                                                                                            | 0.15 |      | 0.3  | s      |

| D                        | Autoclass Channel Power conversion                                                      | VPWR = 52 V, VDRAINn = 0 V,<br>Channel current = 770 mA                                                      | 76   | 80   | 84   | Counts |

| P <sub>AC</sub>          | scale factor and accuracy                                                               | VPWR = 50 V, VDRAINn = 0 V,<br>Channel current = 100 mA                                                      | 9    | 10   | 11   |        |

Copyright © 2020 Texas Instruments Incorporated

Conditions are  $-40 < T_J < 125$  °C unless otherwise noted.  $V_{VDD} = 3.3$  V,  $V_{VPWR} = 54$  V,  $V_{DGND} = V_{AGND}$ , DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn = 0. Positive currents are into pins.  $R_S = 0.255 \Omega$ , to KSENSA (SEN1 or SEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                        | PARAMETER                                 | TEST CONDITIONS                                                      | MIN  | TYP  | MAX                                                                                                            | UNIT |

|------------------------|-------------------------------------------|----------------------------------------------------------------------|------|------|----------------------------------------------------------------------------------------------------------------|------|

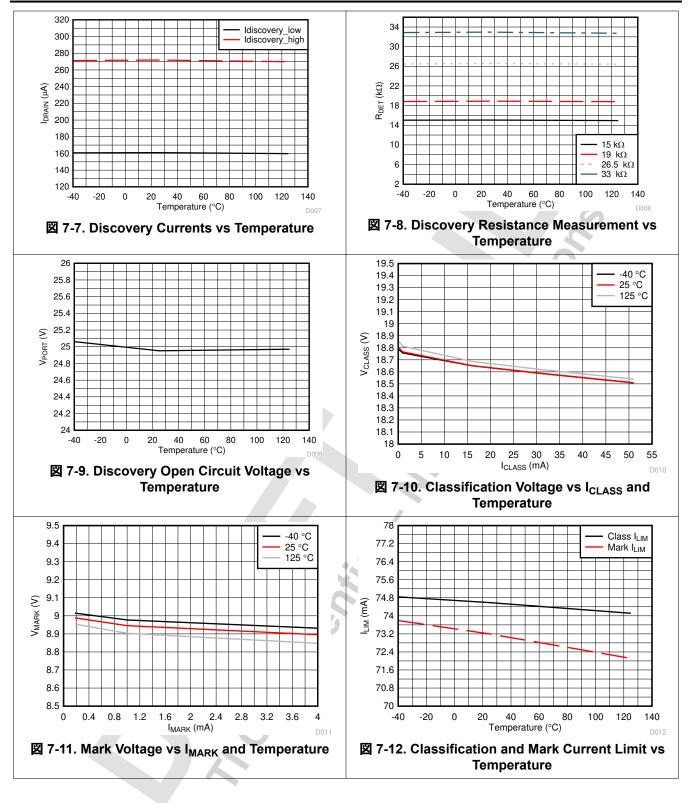

| DETECTION              | 1                                         |                                                                      |      | 77   |                                                                                                                |      |

| 1                      | Detection current                         | First and 3rd detection points VVPWR - VDRAINn = 0 V                 | 145  | 160  | 190                                                                                                            |      |

| I <sub>DISC</sub>      | Detection current                         | 2nd and 4th detection points VVPWR - VDRAINn = 0 V                   | 235  | 270  | 300                                                                                                            | μA   |

| ΔI <sub>DISC</sub>     | 2nd – 1st detection currents              | VVPWR - VDRAINn = 0 V                                                | 98   | 110  | 118                                                                                                            | μA   |

| V <sub>det_open</sub>  | Open circuit detection voltage            | Measured as VVPWR - VDRAINn                                          | 23.5 | 26   | 29                                                                                                             | V    |

| R <sub>REJ_LOW</sub>   | Rejected resistance low range             |                                                                      | 0.86 |      | 15                                                                                                             | kΩ   |

| R <sub>REJ_HI</sub>    | Rejected resistance high range            |                                                                      | 33   |      | 100                                                                                                            | kΩ   |

| R <sub>ACCEPT</sub>    | Accepted resistance range                 |                                                                      | 19   | 25   | 26.5                                                                                                           | kΩ   |

| R <sub>SHORT</sub>     | Shorted Channel threshold                 |                                                                      | 1    |      | 360                                                                                                            | Ω    |

| R <sub>OPEN</sub>      | Open Channel Threshold                    |                                                                      | 400  |      |                                                                                                                | kΩ   |

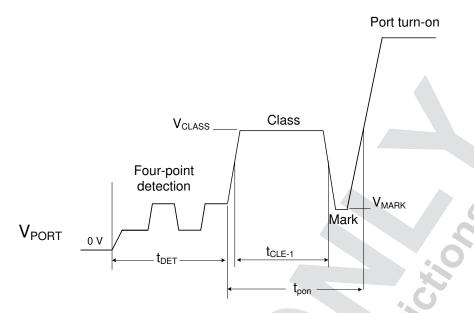

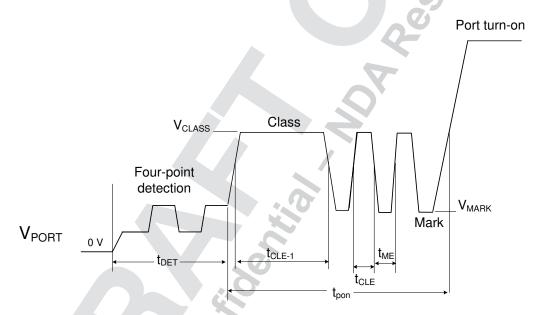

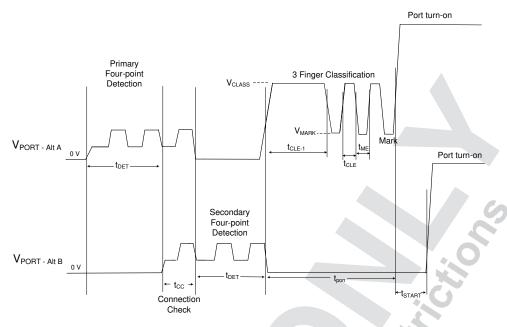

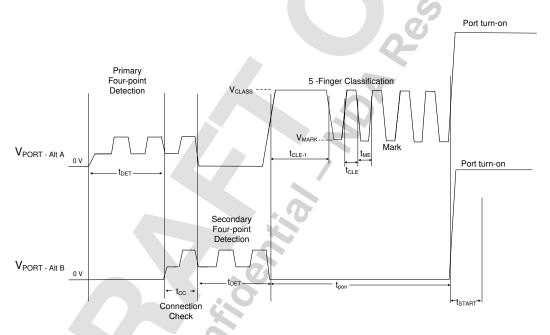

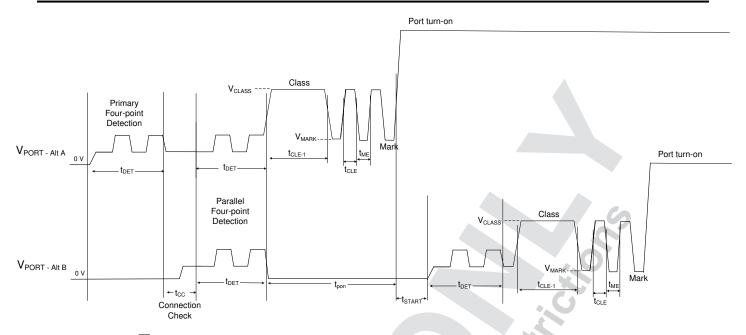

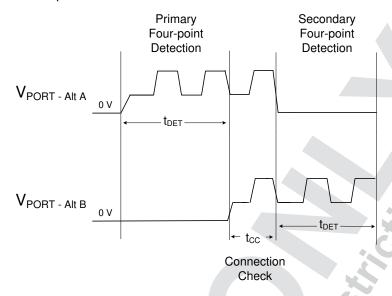

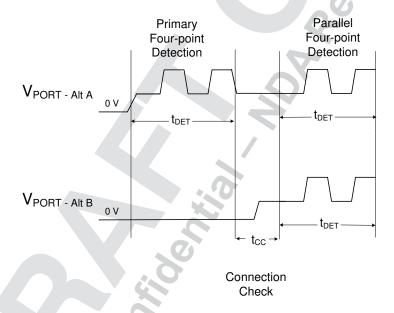

| t <sub>DET</sub>       | Detection Duration                        | Time to complete a detection, 4Pxx = 0                               | 275  | 350  | 425                                                                                                            | ms   |

| t <sub>CC</sub>        | Connection Check Duration                 | Time to complete connection check after a valid detection, 4Pxx = 1  |      | 150  | 400                                                                                                            | ms   |

| +                      | Detect backoff pause between              | VVPWR - VDRAINn > 2.5 V                                              | 300  | 400  | 500                                                                                                            | ms   |

| TDET_BOFF              | discovery attempts                        | VVPWR - VDRAINn < 2.5 V                                              | 20   |      | 100                                                                                                            | ms   |

| t <sub>DET_DLY</sub>   | Detection delay                           | From command or PD attachment to Channel detection complete 4Pxx = 0 |      |      | 590                                                                                                            | ms   |

| CLASSIFICA             | ATION                                     |                                                                      |      |      |                                                                                                                |      |

| V <sub>CLASS</sub>     | Classification Voltage                    | VVPWR - VDRAINn, VSENn ≥ 0 mV<br>I <sub>channel</sub> ≥ 180 μA       | 15.5 | 18.5 | 20.5                                                                                                           | V    |

| I <sub>CLASS_Lim</sub> | Classification Current Limit              | VVPWR - VDRAINn = 0 V                                                | 65   | 80   | 90                                                                                                             | mA   |

|                        |                                           | Class 0-1                                                            | 5    |      | 8                                                                                                              | mA   |

|                        |                                           | Class 1-2                                                            | 13   |      | 16                                                                                                             | mA   |

| I <sub>CLASS_TH</sub>  | Classification Threshold Current          | Class 2-3                                                            | 21   |      | 60 190 70 300 10 118 26 29 15 100 25 26.5 360 50 425 50 400 00 500 100 590 8.5 20.5 80 90 8 16 25 35 51 105 12 | mA   |

|                        |                                           | Class 3-4                                                            | 31   |      | 35                                                                                                             | mA   |

|                        |                                           | Class 4-Class overcurrent                                            | 45   |      | 51                                                                                                             | mA   |

| t <sub>LCE</sub>       | Classification Duration (1st Finger)      | From detection complete                                              | 95   |      | 105                                                                                                            | ms   |

| t <sub>CLE2-5</sub>    | Classification Duration (2nd- 5th Finger) | From Mark complete                                                   | 6.5  |      | 12                                                                                                             | ms   |

| MARK                   |                                           |                                                                      |      |      | '                                                                                                              |      |

| V <sub>MARK</sub>      | Mark Voltage                              | 4 mA ≥ IChannel ≥ 180 μA<br>VVPWR - VDRAINn                          | 7    |      | 10                                                                                                             | V    |

| I <sub>MARK_Lim</sub>  | Mark Sinking Current Limit                | VVPWR - VDRAINn = 0 V                                                | 10   | 70   | 90                                                                                                             | mA   |

| t <sub>ME</sub>        | Mark Duration                             |                                                                      | 6    |      | 12                                                                                                             | ms   |

Product Folder Links: TPS23880

Conditions are  $-40 < T_J < 125$  °C unless otherwise noted.  $V_{VDD} = 3.3$  V,  $V_{VPWR} = 54$  V,  $V_{DGND} = V_{AGND}$ , DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn = 0. Positive currents are into pins.  $R_S = 0.255 \Omega$ , to KSENSA (SEN1 or SEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                                     | PARAMETER                                      | TEST CONDITIONS                       | 1.02 1.6575 2.29  0.51 1.1475 1.78  320 40  75 10  150 20  600 80  2.5  1 0 3  50 7  25 3  100 14  200 28  1 1.025 1.05  V 25 38 5  0 V 102 114. | MAX             | UNIT  |                                          |

|-------------------------------------|------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|------------------------------------------|

| DC DISCON                           | NECT                                           |                                       |                                                                                                                                                                                         |                 |       |                                          |

| .,                                  | 50 11 111                                      | DCDTxx = 0                            | 1.02                                                                                                                                                                                    | 1.6575          | 2.295 | mV                                       |

| $V_{IMIN}$                          | DC disconnect threshold                        | DCDTxx = 1                            | 0.51                                                                                                                                                                                    | 1.1475          | 1.785 |                                          |

|                                     |                                                | TMPDO = 00                            | 320                                                                                                                                                                                     |                 | 400   | ms                                       |

|                                     | PD Maintain Power signature dropout            | TMPDO = 01                            | 75                                                                                                                                                                                      |                 | 100   | ms m |

| t <sub>MPDO</sub>                   | time limit                                     | TMPDO = 10                            | 150                                                                                                                                                                                     |                 | 200   |                                          |

|                                     |                                                | TMPDO = 11                            | 600                                                                                                                                                                                     |                 | 800   |                                          |

| t <sub>MPS</sub>                    | PD Maintain Power Signature time for validity  |                                       | 2.5 3 ms                                                                                                                                                                                |                 |       |                                          |

| PORT POWE                           | R POLICING                                     |                                       |                                                                                                                                                                                         |                 |       |                                          |

| ΣD /D                               | PCUT tolerance                                 | Policing settings < 15 W              | 0                                                                                                                                                                                       | 5               | 10    | 6 %<br>70 55 ms                          |

| δP <sub>CUT</sub> /P <sub>CUT</sub> | PCOT tolerance                                 | Policing settings ≥ 15 W              | 0                                                                                                                                                                                       | 3               | 6     | ms                                       |

|                                     |                                                | TOVLD = 00                            | 50                                                                                                                                                                                      |                 | 70    | -                                        |

| +                                   | PCUT time limit                                | TOVLD = 01                            | 25                                                                                                                                                                                      |                 | 35    |                                          |

| t <sub>OVLD</sub>                   |                                                | TOVLD = 10                            | 100                                                                                                                                                                                     |                 | 140   |                                          |

|                                     |                                                | TOVLD = 11                            | 200                                                                                                                                                                                     |                 | 280   |                                          |

| I <sub>CUT_MAX</sub>                | Internal ICUT Clamp                            | Measured per channel POL = 1111 1111b | 1                                                                                                                                                                                       | 1 1.025 1.050 A | Α     |                                          |

| PORT CURR                           | ENT INRUSH                                     |                                       |                                                                                                                                                                                         |                 |       |                                          |

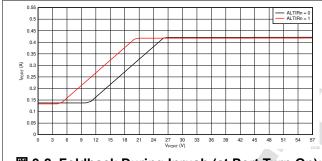

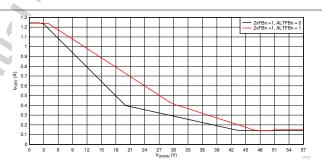

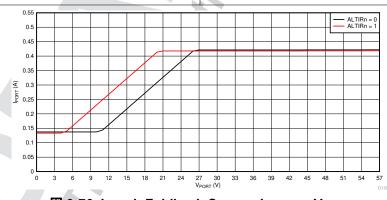

|                                     |                                                | VVPWR - VDRAINn = 1 V                 | 25                                                                                                                                                                                      | 38              | 51    |                                          |

|                                     |                                                | VVPWR - VDRAINn = 10 V                | 25                                                                                                                                                                                      | 38              | 51    |                                          |

|                                     | IInrush limit, ALTIRNn = 0                     | VVPWR - VDRAINn = 15 V                | 43                                                                                                                                                                                      | 56              | 69    |                                          |

|                                     |                                                | VVPWR - VDRAINn = 30 V                | 102                                                                                                                                                                                     |                 | 114.7 |                                          |

| \/                                  |                                                | VVPWR - VDRAINn = 55 V                | 102                                                                                                                                                                                     |                 | 114.7 | m\/                                      |

| $V_{Inrush}$                        |                                                | VVPWR - VDRAINn = 1 V                 | 25                                                                                                                                                                                      | 38              | 51    | mV                                       |

|                                     |                                                | VVPWR - VDRAINn = 10 V                | 47                                                                                                                                                                                      | 60              | 73    |                                          |

|                                     | IInrush limit, ALTIRNn = 1                     | VVPWR - VDRAINn = 15 V                | 69                                                                                                                                                                                      | 82              | 95    |                                          |

|                                     |                                                | VVPWR - VDRAINn = 30 V                | 102                                                                                                                                                                                     |                 | 114.7 |                                          |

|                                     |                                                | VVPWR - VDRAINn = 55 V                | 102                                                                                                                                                                                     |                 | 114.7 |                                          |

|                                     |                                                | TSTART = 00                           | 50                                                                                                                                                                                      |                 | 70    |                                          |

| t <sub>START</sub>                  | Maximum current limit duration in start-<br>up | TSTART = 01                           | 25                                                                                                                                                                                      |                 | 35    | ms                                       |

|                                     |                                                | TSTART = 10                           | 100                                                                                                                                                                                     |                 | 140   |                                          |

Copyright © 2020 Texas Instruments Incorporated

Conditions are  $-40 < T_J < 125$  °C unless otherwise noted.  $V_{VDD} = 3.3$  V,  $V_{VPWR} = 54$  V,  $V_{DGND} = V_{AGND}$ , DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn = 0. Positive currents are into pins.  $R_S = 0.255 \Omega$ , to KSENSA (SEN1 or SEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

| J 212.5                 | aded with default values unless otherwi<br>PARAMETER                                                            | TEST CONDITIONS                                                                    | MIN | TYP | MAX   | UNIT     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|-------|----------|

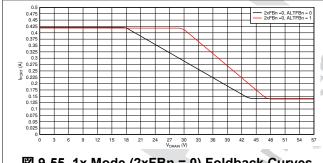

| PORT CURI               | RENT FOLDBACK                                                                                                   |                                                                                    |     |     |       |          |

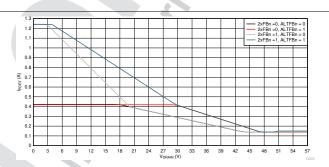

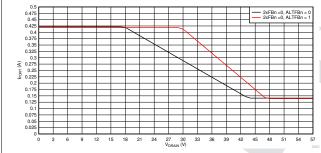

|                         |                                                                                                                 | VDRAINn = 1 V                                                                      | 102 |     | 114.7 |          |

|                         |                                                                                                                 | VDRAINn = 15 V                                                                     | 102 |     | 115   |          |

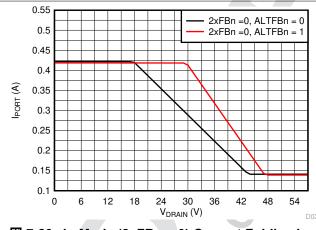

|                         | ILIM 1X limit, 2xFB = 0 and ALTFBn = 0                                                                          | VDRAINn = 30 V                                                                     | 66  | 74  | 81    | mV<br>ms |

| . ,                     |                                                                                                                 | VDRAINn = 50 V                                                                     | 30  | 38  | 46    | .,       |

| $V_{LIM}$               |                                                                                                                 | VDRAINn = 1 V                                                                      | 102 |     | 114.7 | mv       |

|                         | II IM 4X line is Out D. Out d. Al TED.                                                                          | VDRAINn = 30 V                                                                     | 99  |     | 114.7 |          |

|                         | ILIM 1X limit, 2xFB = 0 and ALTFBn = 1                                                                          | VDRAINn = 40 V                                                                     | 60  | 67  | 74    |          |

|                         |                                                                                                                 | VDRAINn = 50 V                                                                     | 30  | 38  | 46    |          |

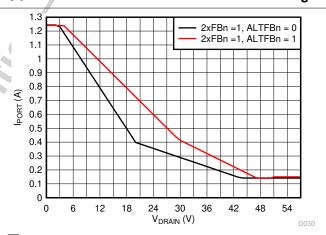

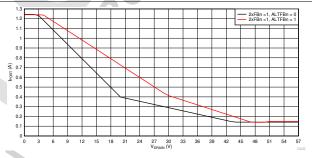

|                         |                                                                                                                 | VDRAINn = 1 V                                                                      | 310 | 320 | 330   |          |

|                         | ILIM 2X limit, 2xFB = 1 and ALTFBn = 0                                                                          | VDRAINn = 10 V                                                                     | 200 | 220 | 240   |          |

|                         | ILIM 2A IIIIII, 2XFB – 1 and ALTFBIT – 0                                                                        | VDRAINn = 30 V                                                                     | 66  | 74  | 81    |          |

| \                       |                                                                                                                 | VDRAINn = 50 V                                                                     | 30  | 38  | 46    | m\/      |

| $V_{LIM2X}$             |                                                                                                                 | VDRAINn = 1 V                                                                      | 310 | 320 | 330   | IIIV     |

|                         | ILIM 2X limit, 2xFB = 1 and ALTFBn = 1                                                                          | VDRAINn = 20 V                                                                     | 176 | 186 | 196   |          |

|                         | ILIW 2A IIIIII, 2XFB - 1 and ALTFBIT - 1                                                                        | VDRAINn = 40 V                                                                     | 60  | 67  | 74    |          |

|                         |                                                                                                                 | VDRAINn = 50 V                                                                     | 30  | 38  | 46    |          |

|                         | ILIM time limit                                                                                                 | 2xFBn = 0                                                                          | 55  | 60  | 65    |          |

|                         |                                                                                                                 | TLIM = 00                                                                          | 55  | 60  | 65    |          |

| t <sub>LIM</sub>        | 2xFBn = 1                                                                                                       | TLIM = 01                                                                          | 15  | 16  | 17    | ms       |

|                         | ZAF DII – I                                                                                                     | TLIM = 10                                                                          | 10  | 11  | 12    |          |

|                         |                                                                                                                 | TLIM = 11                                                                          | 6   | 6.5 | 7     |          |

| SHORT CIR               | CUIT DETECTION                                                                                                  |                                                                                    |     |     |       |          |

| $V_{short}$             | $I_{\mbox{\scriptsize SHORT}}$ threshold in 1X mode and during inrush                                           | 20                                                                                 | 234 |     | 306   | mV       |

| V <sub>short2X</sub>    | I <sub>SHORT</sub> threshold in 2X mode                                                                         |                                                                                    | 357 |     | 408   |          |

|                         | Cata turn off time from SEAIn input                                                                             | 2xFBn = 0, VDRAINn = 1 V<br>From VSENn pulsed to 0.425 V.                          |     |     | 0.9   |          |

| t <sub>D_off_</sub> SEN | Gate turnoff time from SENn input                                                                               | 2xFBn = 1, VDRAINn = 1 V<br>From VSENn pulsed to 0.62 V.                           |     |     | 0.9   | μs       |

| CURRENT F               | FAULT RECOVERY (BACKOFF) TIMING                                                                                 |                                                                                    |     |     |       |          |

| t <sub>ed</sub>         | Error delay timing. Delay before next attempt to power a channel following power removal due to error condition | P <sub>CUT</sub> , I <sub>LIM</sub> or I <sub>Inrush</sub> fault Semi-auto<br>mode | 0.8 | 1   | 1.2   | s        |

| δl <sub>fault</sub>     | Duty cycle of I <sub>channel</sub> with current fault                                                           |                                                                                    | 5.5 |     | 6.7   | %        |

|                         | SHUTDOWN                                                                                                        | 1                                                                                  | 1   |     |       |          |

|                         | Shutdown temperature                                                                                            | Temperature rising                                                                 | 135 | 146 |       | °C       |

|                         | Hysteresis                                                                                                      |                                                                                    |     | 7   |       | °C       |

Product Folder Links: TPS23880

Conditions are  $-40 < T_J < 125$  °C unless otherwise noted.  $V_{VDD} = 3.3$  V,  $V_{VPWR} = 54$  V,  $V_{DGND} = V_{AGND}$ , DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn = 0. Positive currents are into pins.  $R_S = 0.255 \Omega$ , to KSENSA (SEN1 or SEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typical values are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

| cyisicis iu           | aded with default values unless otherwi                                |                                                                               | B 415.1 | T\/2 | B4 6 37 |      |

|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------|------|---------|------|

|                       | PARAMETER                                                              | TEST CONDITIONS                                                               | MIN     | TYP  | MAX     | UNIT |

|                       | (SCL, SDAI, A1-A4, /RESET, OSS unless                                  | otherwise stated)                                                             |         |      |         |      |

| V <sub>IH</sub>       | Digital input High                                                     |                                                                               | 2.1     |      |         | V    |

| V <sub>IL</sub>       | Digital input Low                                                      |                                                                               |         |      | 0.9     | V    |

| V <sub>IT_HYS</sub>   | Input voltage hysteresis                                               |                                                                               | 0.17    |      |         | V    |

| V <sub>OL</sub>       | Digital output Low                                                     | SDAO at 9mA                                                                   |         | 9 6  | 0.4     | V    |

| VOL .                 | Digital output Low                                                     | /INT at 3mA                                                                   |         |      | 0.4     | V    |

| R <sub>pullup</sub>   | Pullup resistor to VDD                                                 | /RESET, A1-A4, TEST0                                                          | 30      | 50   | 80      | kΩ   |

| R <sub>pulldown</sub> | Pulldown resistor to DGND                                              | OSS, TEST1, TEST2                                                             | 30      | 50   | 80      | kΩ   |

| t <sub>FLT_INT</sub>  | Fault to /INT assertion                                                | Time to internally register an Interrupt fault, from Channel turn off         | 2       | 50   | 500     | μs   |

| T <sub>RESETmin</sub> | /RESET input minimum pulse width                                       |                                                                               |         |      | 5       | μs   |

| T <sub>bit_OSS</sub>  | 3-bit OSS bit period                                                   | MbitPrty = 1                                                                  | 24      | 25   | 26      | μs   |

| t <sub>oss_idL</sub>  | Idle time between consecutive shutdown code transmission in 3-bit mode | MbitPrty = 1                                                                  | 48      | 50   |         | μs   |

| t <sub>r_OSS</sub>    | Input rise time of OSS in 3-bit mode                                   | 0.8 V → 2.3 V, MbitPrty = 1                                                   | 1       | ,    | 300     | ns   |

| t <sub>f_OSS</sub>    | Input fall time of OSS in 3-bit mode                                   | 2.3 V → 0.8 V, MbitPrty = 1                                                   | 1 300   |      | 300     | ns   |

|                       | REQUIREMENTS                                                           |                                                                               |         |      |         |      |

| t <sub>POR</sub>      | Device power-on reset delay                                            |                                                                               |         |      | 20      | ms   |

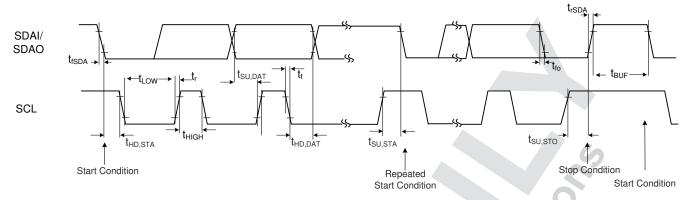

| f <sub>SCL</sub>      | SCL clock frequency                                                    |                                                                               | 10      |      | 400     | kHz  |

| t <sub>LOW</sub>      | LOW period of the clock                                                |                                                                               | 0.5     |      |         | μs   |

| t <sub>HIGH</sub>     | HIGH period of the clock                                               |                                                                               | 0.26    |      |         | μs   |

| t.                    | SDAO output fall time                                                  | SDAO, 2.3 V $\rightarrow$ 0.8 V, Cb = 10 pF, 10 k $\Omega$ pull-up to 3.3 V   | 10      |      | 50      | ns   |

| t <sub>fo</sub>       | SDAO output fail time                                                  | SDAO, 2.3 V $\rightarrow$ 0.8 V, Cb = 400 pF, 1.3 k $\Omega$ pull-up to 3.3 V | 10      |      | 50      | ns   |

| C <sub>I2C</sub>      | SCL capacitance                                                        |                                                                               |         |      | 10      | pF   |

| C <sub>I2C_SDA</sub>  | SDAI, SDAO capacitance                                                 |                                                                               |         |      | 6       | pF   |

| t <sub>SU,DATW</sub>  | Data setup tme (Write operation)                                       | 70                                                                            | 50      |      |         | ns   |

| t <sub>HD,DATW</sub>  | Data hold time (Write operation)                                       | A. C.                                                                         | 0       |      |         | ns   |

| t <sub>HD,DATR</sub>  | Data hold time (Read operation)                                        | SDAO, VDD/2 threshold, Cb = 10 pF, 1.3 k $\Omega$ pull-up to 3.3 V            | 150     |      | 400     | ns   |

| t <sub>fSDA</sub>     | Input fall times of SDAI                                               | 2.3 V → 0.8 V                                                                 | 20      |      | 120     | ns   |

| t <sub>rSDA</sub>     | Input rise times of SDAI                                               | 0.8 V → 2.3 V                                                                 | 20      |      | 120     | ns   |

| t <sub>r</sub>        | Input rise time of SCL                                                 | 0.8 V → 2.3 V                                                                 | 20      |      | 120     | ns   |

| t <sub>f</sub>        | Input fall time of SCL                                                 | 2.3 V → 0.8 V                                                                 | 20      |      | 120     | ns   |

| t <sub>BUF</sub>      | Bus free time between a STOP and START condition                       |                                                                               | 0.5     |      |         | μs   |

| t <sub>HD,STA</sub>   | Hold time After (Repeated) START condition                             |                                                                               | 0.26    |      |         | μs   |