## 統合100V IEEE 802.3af PDおよびDC/DCコントローラ

### 特 長

#### ● 完全な802.3af PoEインターフェイス

- TPS2375から機能を継承

- 100V、0.6Ωの内部パスMOSFET

- 標準および旧型対応のUVLOを選択可能

- 140mA固定の突入電流制限

#### ● 一次側DC/DCコンバータ制御

- 最小の外部部品数

- 電流モード制御

- 絶縁型および非絶縁型のトポロジ

- プログラミング可能な動作周波数

- 電流センスによるリーディング・エッジ・ブランギング

- 50%のデューティ・サイクル制限

- 電圧出力誤差増幅器

#### ● PoEおよびコンバータの内部シーケンシング

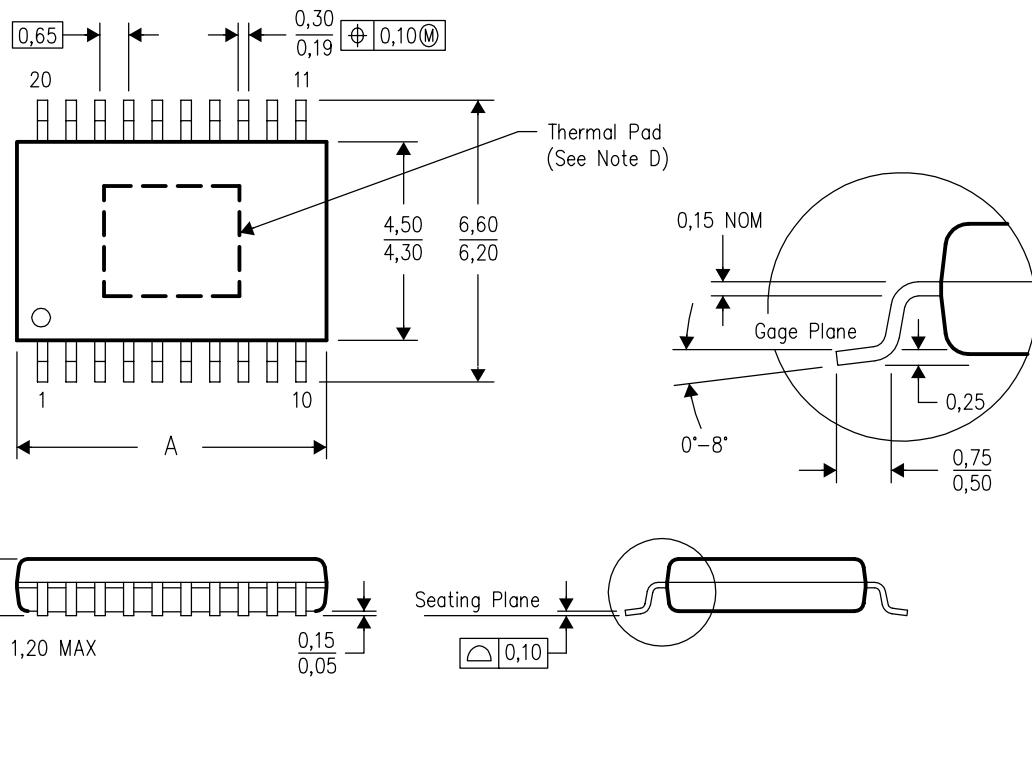

#### ● 業界標準の20リード・パッケージ

#### ● 業界標準温度範囲：-40°C～85°C

### ア プ リ ケ シ ョ ン

#### ● 以下を含むすべてのPoE PDデバイス

- 無線アクセス・ポイント

- VoIP電話

- セキュリティ・カメラ

### 概 要

TPS23750は、TPS2375の機能に一次側DC/DC PWMコントローラを統合した製品です。それにより設計者は、PoE-PDアプリケーションのフロントエンド・ソリューションを最小の外部部品数で実現することができます。TPS23770は、低電圧ロックアウトのオン電圧が旧型のシステムに対応した値となっていますが、それ以外の機能や特性はTPS23750と同じです。

PoEフロントエンドには、検出、分類、低電圧ロックアウト、突入電流制御をはじめ、必要なIEEE 802.3afの機能がすべて備えられています。PoE入力スイッチは、TPS23750内に組み込まれています。

DC/DCコントローラ部は、フライバック、フォワード、お

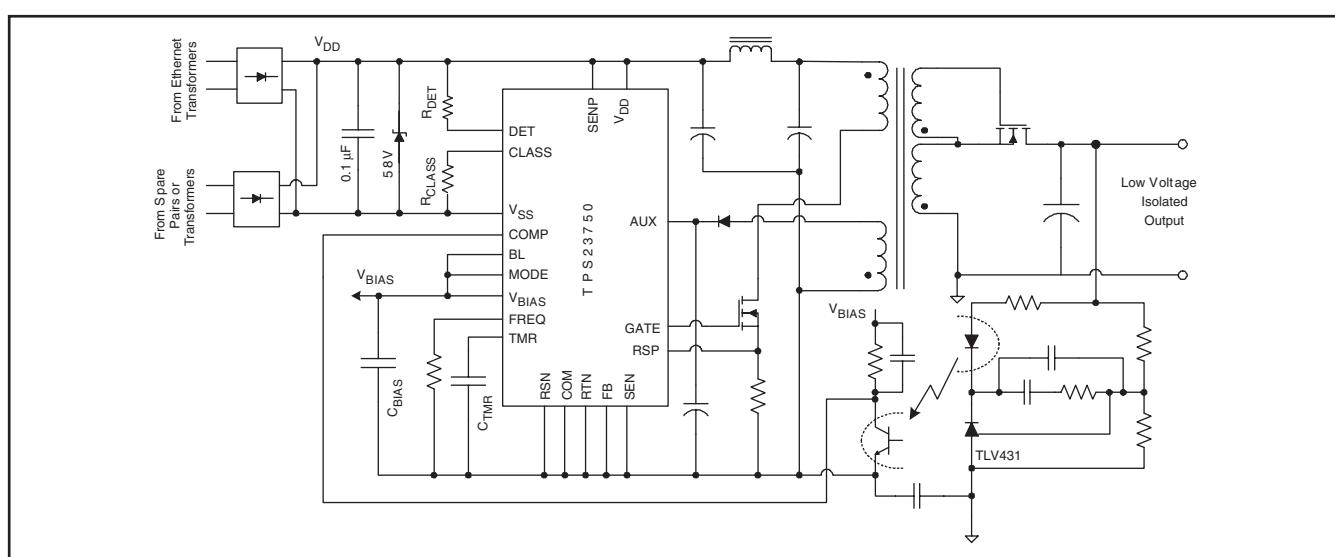

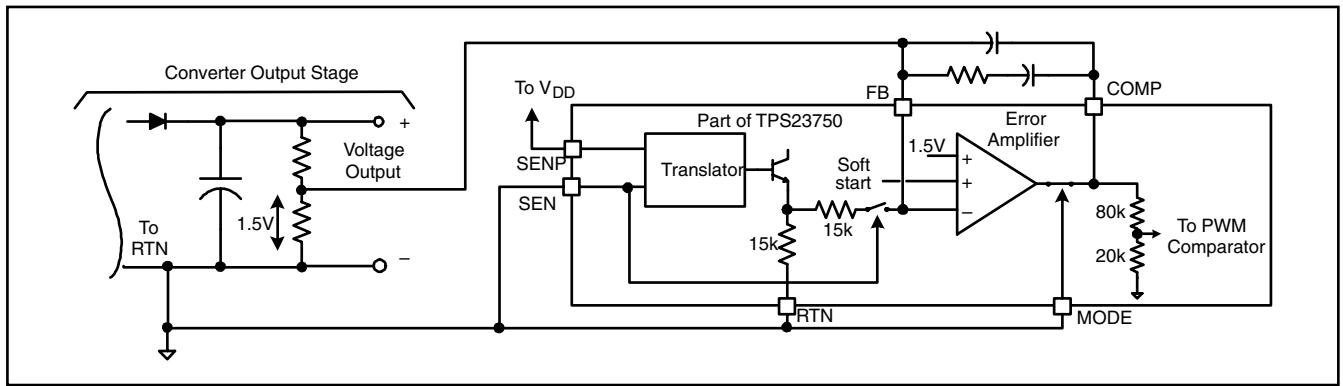

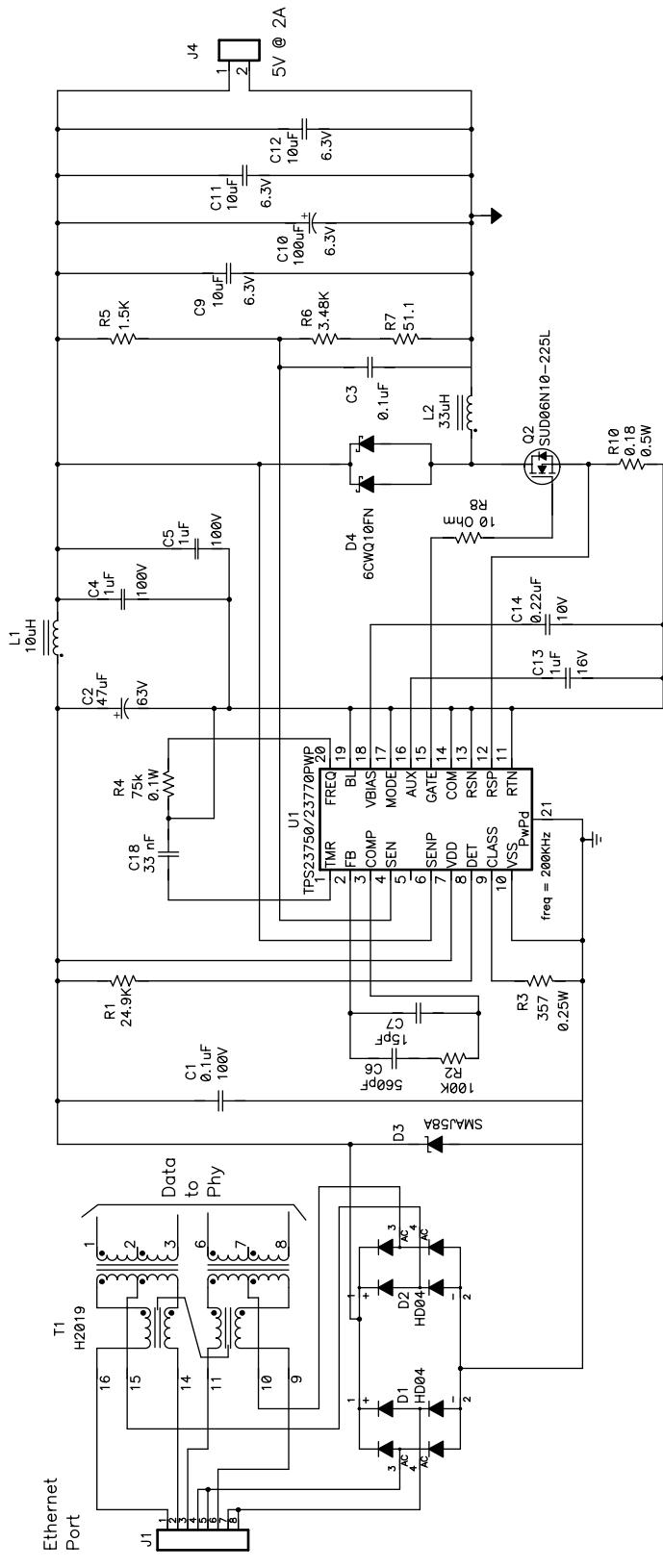

図 1. 標準ア プ リ ケ シ ョ ン

PowerPADは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

より非同期ローサイド・スイッチ降圧トポロジに対応した設計となっています。

外部のスイッチングMOSFETと電流センス抵抗により、トポロジ、電力レベル、および電流制限を柔軟に制御できます。このフル機能のDC/DCコントローラは、プログラミング可能なソフト・スタート、Hiccupタイプの障害制限、50%の最大デューティ・サイクル、プログラミング可能な一定スイッチング周波数、および真の電圧出力誤差増幅器を備えています。また、各種の保護機能により堅牢な設計となっています。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## ご発注の手引き<sup>(1)</sup>

| T <sub>A</sub> | UVLO THRESHOLDS |        |        | PACKAGE <sup>(2)</sup><br>TSSOP-20 PowerPAD™ | MARKING  |

|----------------|-----------------|--------|--------|----------------------------------------------|----------|

|                | TYPE            | LOW    | HIGH   |                                              |          |

| -40°C to 85°C  | Standard        | 30.5 V | 39.3 V | TPS23750PWP                                  | TPS23750 |

|                | Legacy          | 30.5 V | 35.1 V | TPS23770PWP                                  | TPS23770 |

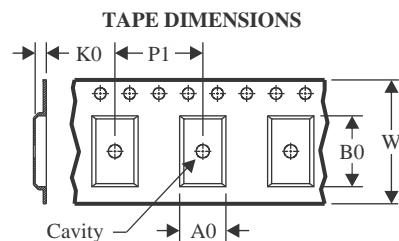

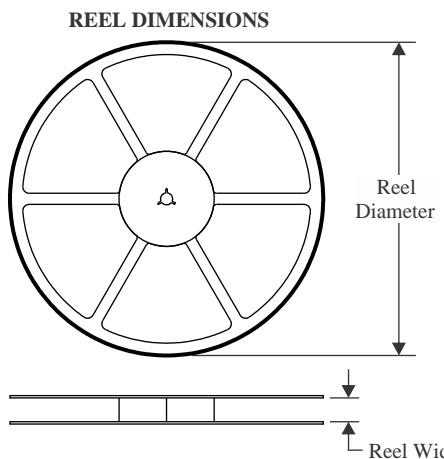

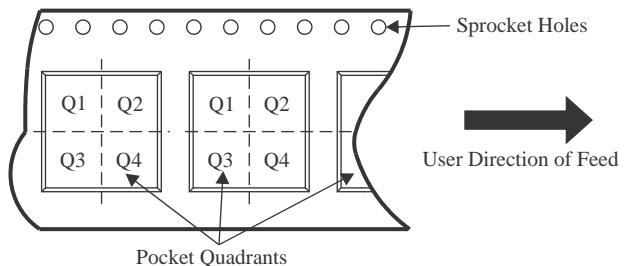

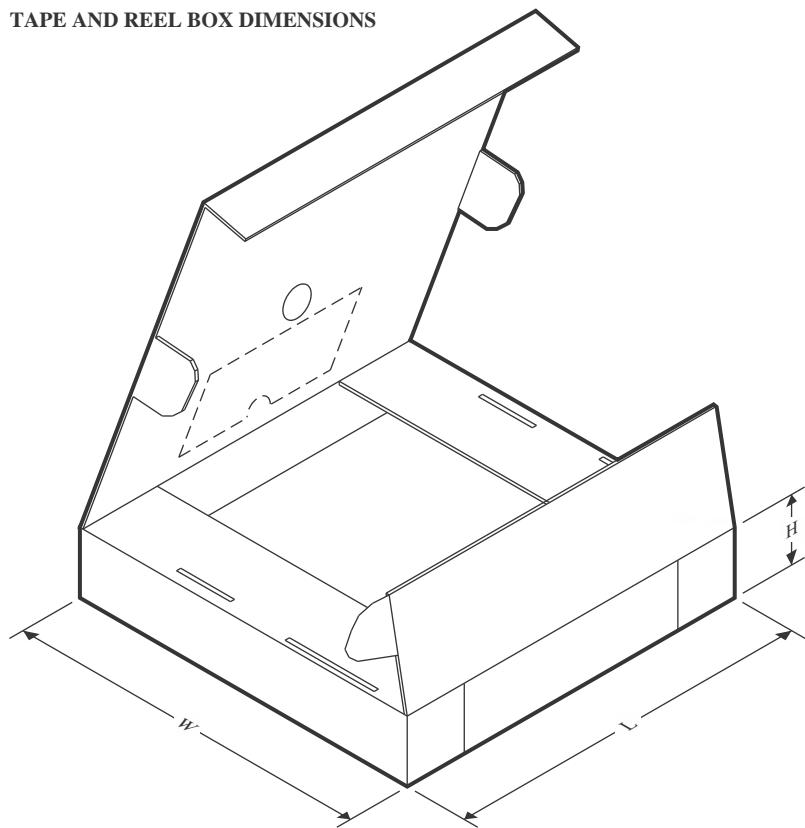

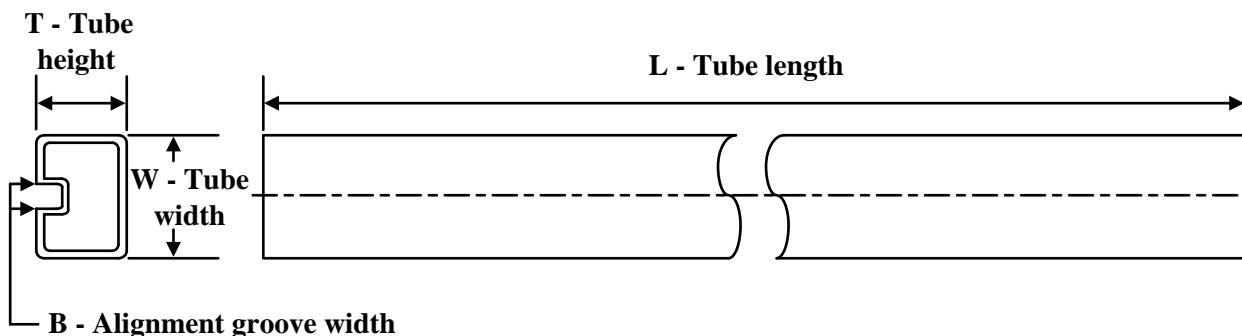

(1) テープ/リールの場合は、デバイス・タイプの末尾にRを付けてください。

(2) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録：パッケージ・オプション」を参照するか、またはTIのWebサイト (www.ti.com) をご覧ください。

## 絶対最大定格

V<sub>SS</sub>を基準、動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|                                                             |                                                                 | UNIT                         |

|-------------------------------------------------------------|-----------------------------------------------------------------|------------------------------|

| Input voltage range <sup>(2)</sup>                          | RSN, COM, RTN, SEN                                              | -0.7 V to 100 V              |

| Input voltage range                                         | AUX, VDD, DET, SENP                                             | -0.3 V to 100 V              |

| Input voltage range <sup>(3)</sup>                          | [V <sub>BIAS</sub> , BL, TMR, FB, COMP, FREQ, RSP, MODE] to RTN | -0.3 V to 6.5 V              |

| Input voltage range                                         | [GATE or AUX] to COM                                            | -0.3 V to 20 V               |

| Input voltage range                                         | [RSN to RTN] and [COM to RTN]                                   | -0.3 V to 0.3 V              |

|                                                             | SENP to SEN                                                     | -0.3 V to 100 V              |

| Input voltage range <sup>(3)</sup>                          | CLASS                                                           | -0.3 V to 12 V               |

| Sourcing current                                            | AUX                                                             | Internally limited           |

| V <sub>BIAS</sub>                                           | Sourcing current                                                | Internally limited           |

|                                                             | Sourcing or sinking current, COMP                               | Internally limited           |

| Average sourcing or sinking current, GATE                   |                                                                 | 25 mA <sub>rms</sub>         |

|                                                             |                                                                 | 2 kV                         |

| HBM ESD rating                                              |                                                                 | 8 kV / 15 kV                 |

|                                                             |                                                                 | See Dissipation Rating Table |

| T <sub>J</sub>                                              | Maximum operating junction temperature                          | Internally limited           |

|                                                             | Storage temperature range                                       | -65°C to 150°C               |

| Lead temperature 1.6mm (1/16-inch) from case for 10 seconds |                                                                 | 260°C                        |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) V<sub>RTN</sub> > 80VでI<sub>RTN</sub> = 0です。80Vで最大I<sub>RTN</sub> = 500mAです。

(3) CLASS、DET、GATE、FREQ、V<sub>BIAS</sub>、およびTMRには外部電圧源を接続しないでください。

(4) 図40のRJ-45に対して、RJ-45のピン間、およびピンと出力電圧レールの間に印加されるサージ電圧で、デバイスに障害の生じない上限値 (EN61000-4-2, 1999に準拠)。

## 推奨動作条件(1)(2)

特に指定のない限り、すべての電圧値はV<sub>SS</sub>を基準にしています。

|                 |                                      |                    | MIN  | NOM | MAX               | UNIT |

|-----------------|--------------------------------------|--------------------|------|-----|-------------------|------|

| V <sub>DD</sub> | Input voltage range <sup>(3)</sup>   | COM, SEN, SENP     | 0    | 67  |                   | V    |

|                 |                                      | FB, COMP, MODE, BL | 0    |     | V <sub>BIAS</sub> |      |

|                 | Input voltage range                  | AUX to COM         | 0    | 16  |                   | V    |

|                 |                                      | RSP to RSN         | 0    | 1   |                   |      |

|                 |                                      | AUX                | 0    | 2   |                   |      |

|                 | Sourcing current                     | V <sub>BIAS</sub>  | 0    | 2   |                   | mA   |

|                 |                                      | COMP               | 0    | 2   |                   |      |

| Q <sub>G</sub>  | GATE loading                         |                    |      | 20  |                   | nC   |

|                 | AUX load capacitance                 |                    | 0.8  | 25  |                   | μF   |

|                 | V <sub>BIAS</sub> load capacitance   |                    | 0.08 | 1.5 |                   | μF   |

|                 | R <sub>FREQ</sub>                    |                    | 30   | 300 |                   | kΩ   |

| T <sub>J</sub>  | Operating junction temperature range |                    | -40  | 125 |                   | °C   |

| T <sub>A</sub>  | Operating ambient temperature range  |                    | -40  | 85  |                   | °C   |

(1) RSN、COM、およびRTNは互いに接続する必要があります。バック回路構成時を除き、SENPはV<sub>DD</sub>に接続します。バック回路構成時は、正の出力レールに接続します。

(2) TMR、FREQ、CLASS、DET、V<sub>BIAS</sub>、およびGATEは、外部で駆動しないでください。

(3) 高バイアスの電力設計では、接合部温度が制約要素となる場合があります。

## 定格消費電力

| PACKAGE        | θ <sub>JP</sub><br>°C/W <sup>(1)</sup> | θ <sub>J<sub>C</sub></sub><br>°C/W | θ <sub>JA</sub><br>°C/W <sup>(2)</sup> | θ <sub>JA</sub><br>°C/W <sup>(3)</sup> | θ <sub>JA</sub><br>°C/W <sup>(4)</sup> | MAXIMUM POWER RATING<br>(W) <sup>(5)</sup> |

|----------------|----------------------------------------|------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--------------------------------------------|

| PWP (TSSOP-20) | 1.4                                    | 26.62                              | 32.6                                   | 151.9                                  | 73.8                                   | 1.2                                        |

(1) 接合部とパッド間の熱抵抗。

(2) 推奨レイアウトについては、TIのドキュメントSLMA002を参照してください。これはベスト・ケースの、空気流なしの数値です。

(3) 低k基板(2つの信号層)に対するJEDEC方式で、電源パッドは半田付けしていません(ワースト・ケース)。

(4) 高k基板(信号×2、プレーン×2の4層)に対するJEDEC方式で、電源パッドは半田付けしていません。

(5) TIの推奨レイアウトおよび周囲温度85°Cに基づいています。

## 電気的特性

$-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ 、 $V_{\text{DD}} - V_{\text{SS}} = 48\text{ V}$ 。特に記述のない限り、 $V_{\text{DD}}$ 、CLASS、DETは $V_{\text{SS}}$ を基準とし、他のすべてのピン電圧はRSN、COM、RTNを基準としています(RSN、COM、RTNは互いに接続)。特に記述のない限り、SEN = MODE = BL = RSP = RTN、FB =  $V_{\text{BIAS}}$ 、SENP =  $V_{\text{DD}}$ 、 $C_{\text{TMR}} = 1000\text{ pF}$ 、 $C_{\text{VBIAS}} = 0.1\text{ }\mu\text{F}$ 、 $C_{\text{VAUX}} = 0.1\text{ }\mu\text{F}$ 、 $R_{\text{FREQ}} = 150\text{ k}\Omega$ 、 $R_{\text{DET}} = 24.9\text{ k}\Omega$ 、 $R_{\text{CLASS}} = 255\text{ }\Omega$ 、GATEは無負荷、 $V_{\text{BIAS}}$ およびAUXに外部負荷なしです。

## DC/DCコントローラ部

この部分に限り、RTN =  $V_{\text{SS}}$ です。

| PARAMETER                             | TEST CONDITIONS                                                                                                                                                                     | MIN                                                                                                                                                                                                                                                  | TYP   | MAX   | UNIT          |                  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------|------------------|

| <b>BIAS SUPPLY (VBIAS)</b>            |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

| $V_{\text{BIAS}}$                     | Output voltage                                                                                                                                                                      | $0 \leq I_{\text{LOAD}} \leq 5\text{ mA}$                                                                                                                                                                                                            | 4.60  | 5.1   | 5.5           |                  |

| <b>AUX SUPPLY (AUX)</b>               |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

| $V_{\text{AUX}}$                      | Supply output voltage                                                                                                                                                               | $18\text{ V} \leq V_{\text{VDD} - \text{COM}} \leq 57\text{ V}$ , $0\text{ mA} \leq I_{\text{AUX}} \leq 10\text{ mA}$                                                                                                                                | 9     | 10    | 11            |                  |

|                                       | Current limit                                                                                                                                                                       | $V_{\text{AUX}} = 0\text{ V}$                                                                                                                                                                                                                        | 12    | 23.5  | 28            |                  |

| <b>OSCILLATOR (FREQ)</b>              |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

| $D_{\text{MAX}}$                      | Maximum duty cycle                                                                                                                                                                  | $R_{\text{FREQ}} = 30\text{ k}\Omega$ , $V_{\text{COMP}} = 3.9\text{ V}$ , MODE = $V_{\text{BIAS}}$ , Measure GATE voltage at 50% rising to 50% falling                                                                                              | 48.8  | 49.2  | 49.5          |                  |

| $f_{\text{OSC}}$                      | Oscillator frequency                                                                                                                                                                | MODE = $V_{\text{BIAS}}$ , $V_{\text{COMP}} = 3\text{ V}$ , Measure at GATE                                                                                                                                                                          |       |       | kHz           |                  |

|                                       |                                                                                                                                                                                     | $R_{\text{FREQ}} = 30\text{ k}\Omega$                                                                                                                                                                                                                | 435   | 487   |               |                  |

|                                       |                                                                                                                                                                                     | $R_{\text{FREQ}} = 150\text{ k}\Omega$                                                                                                                                                                                                               | 90    | 100   |               |                  |

| <b>ERROR AMPLIFIER (FB, COMP)</b>     |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

| COMP source current                   | $0 \leq V_{\text{COMP}} \leq 4\text{ V}$ , FB = RTN, $V_{\text{TMR}} = 2.5\text{ V}$                                                                                                | 2.5                                                                                                                                                                                                                                                  |       |       | mA            |                  |

| COMP sink current                     | $1.2\text{ V} \leq V_{\text{COMP}} \leq V_{\text{BIAS}}$ , $V_{\text{TMR}} = 2.5\text{ V}$                                                                                          | 2.4                                                                                                                                                                                                                                                  |       |       | mA            |                  |

| $V_{\text{REF}}$                      | FB regulation voltage                                                                                                                                                               | $V_{\text{COMP}} = 2.5\text{ V}$ , $V_{\text{TMR}} = 2.5\text{ V}$                                                                                                                                                                                   | 1.47  | 1.50  | 1.53          | V                |

|                                       | Open loop voltage gain                                                                                                                                                              | $1.2\text{ V} \leq V_{\text{COMP}} \leq 4\text{ V}$ , $V_{\text{TMR}} = 2.5\text{ V}$                                                                                                                                                                | 80    |       |               | dB               |

|                                       | Small signal unity gain bandwidth                                                                                                                                                   | $V_{\text{COMP}} = 2.5\text{ V}$ , $V_{\text{TMR}} = 2.5\text{ V}$                                                                                                                                                                                   | 1.5   | 2     |               | MHz              |

|                                       | COMP input resistance                                                                                                                                                               | MODE = $V_{\text{BIAS}}$ , $1.1 \leq V_{\text{COMP}} \leq 4.4$ , $V_{\text{TMR}} = 2.5\text{ V}$                                                                                                                                                     | 70    | 100   | 130           | $\text{k}\Omega$ |

|                                       | FB leakage (source or sink)                                                                                                                                                         | $0 \leq V_{\text{FB}} \leq V_{\text{BIAS}}$ , $V_{\text{TMR}} = 2.5\text{ V}$                                                                                                                                                                        |       |       | 1             | $\mu\text{A}$    |

| <b>SOFT START TIMER (TMR)</b>         |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

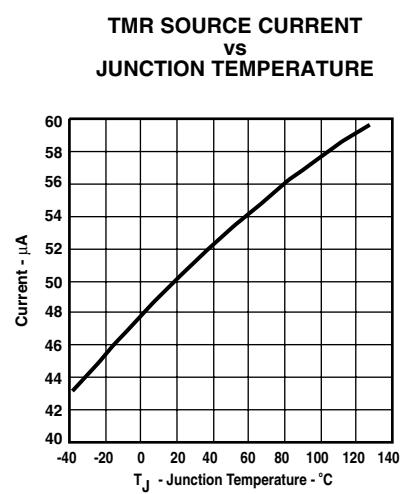

| Source current                        | TMR charging, $V_{\text{TMR}}$ between lower threshold and clamp                                                                                                                    | 38                                                                                                                                                                                                                                                   | 50    | 62    | $\mu\text{A}$ |                  |

| Ratio of source/sink current          |                                                                                                                                                                                     | 9                                                                                                                                                                                                                                                    | 10    | 11    | -             |                  |

| ON duty cycle                         | MODE = $V_{\text{BIAS}}$ , $V_{\text{COMP}} = 4.4\text{ V}$ , Second cycle and beyond                                                                                               | 8                                                                                                                                                                                                                                                    | 9.1   | 10    | %             |                  |

| <b>CURRENT SENSE (RSP, RSN, BL)</b>   |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

| Current limit threshold               | MODE = $V_{\text{BIAS}}$ , $V_{\text{COMP}} = 4.2\text{ V}$ , $V_{\text{TMR}} = 2.5\text{ V}$ , Increase $V_{\text{RSP-BSN}}$ until the duty cycle switches from 50% to the minimum | 0.46                                                                                                                                                                                                                                                 | 0.5   | 0.54  | V             |                  |

| Fault current threshold               | MODE = $V_{\text{BIAS}}$ , $V_{\text{COMP}} = 4.2\text{ V}$ , $V_{\text{TMR}} = 2.5\text{ V}$ , Increase $V_{\text{RSP-BSN}}$ until no gate pulses occur                            | 0.70                                                                                                                                                                                                                                                 | 0.765 | 0.83  | V             |                  |

| $t_{\text{BLNK}}$                     | Current limit delay                                                                                                                                                                 | $V_{\text{RSP-BSN}} = 0.6\text{ V}$ , $V_{\text{AUX}} = 12\text{ V}$ , MODE = $V_{\text{BIAS}}$ , $V_{\text{COMP}} = 4.2\text{ V}$ , $V_{\text{TMR}} = 2.5\text{ V}$ . Measure 50% of $V_{\text{GATE}} \uparrow$ to 50% $V_{\text{GATE}} \downarrow$ |       |       | ns            |                  |

|                                       |                                                                                                                                                                                     | Minimum propagation delay, BL floating                                                                                                                                                                                                               | 40    | 60    |               |                  |

|                                       |                                                                                                                                                                                     | Blanking period (pulse width above minimum), BL connected to RSN                                                                                                                                                                                     | 45    | 70    |               |                  |

|                                       |                                                                                                                                                                                     | Blanking period (pulse width above minimum), BL connected to $V_{\text{BIAS}}$                                                                                                                                                                       | 70    | 105   | 140           |                  |

|                                       | RSP current                                                                                                                                                                         | FREQ = $V_{\text{BIAS}}$ , MODE = $V_{\text{BIAS}}$ , $V_{\text{COMP}} = 4\text{ V}$ , $V_{\text{RSP-BSN}} = 0.4\text{ V}$ , $I_{\text{RSP}}$ sourcing                                                                                               | 2.5   | 4     | 8             |                  |

| <b>GATE DRIVER (GATE)</b>             |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

| Output voltage swing                  | 5 mA source, $V_{\text{AUX}} = 12\text{ V}$                                                                                                                                         | 11.9                                                                                                                                                                                                                                                 |       |       | V             |                  |

|                                       | 5 mA sink, $V_{\text{AUX}} = 12\text{ V}$                                                                                                                                           |                                                                                                                                                                                                                                                      |       | 0.05  |               |                  |

| Peak source current                   | $V_{\text{AUX}} = 12\text{ V}$ , pulse test                                                                                                                                         | 0.33                                                                                                                                                                                                                                                 | 0.58  | 0.8   | A             |                  |

| Peak sink current                     | $V_{\text{AUX}} = 12\text{ V}$ , AC test or pulse test with TMR = RSN                                                                                                               | 0.7                                                                                                                                                                                                                                                  | 1.0   | 1.3   | A             |                  |

| <b>VOLTAGE TRANSLATOR (SEN, SENP)</b> |                                                                                                                                                                                     |                                                                                                                                                                                                                                                      |       |       |               |                  |

| (SENP - SEN) regulation voltage       | $V_{\text{TMR}} = 2.5\text{ V}$ , Measure with servo loop that includes the error amplifier                                                                                         | 1.456                                                                                                                                                                                                                                                | 1.492 | 1.526 | V             |                  |

## DC/DCコントローラ部 (続き)

この部分に限り、RTN =  $V_{SS}$  です。

| PARAMETER                    | TEST CONDITIONS                                                                                                                                | MIN   | TYP  | MAX   | UNIT             |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|

| Translator output resistance | $V_{SEN\cdot SEN} = 1.5 \text{ V}$ , $TMR = RSN$ , $I_{FB} = 0 \mu\text{A}$ and $10 \mu\text{A}$ ,<br>$R_{FB} = \Delta V_{FB} / \Delta I_{FB}$ | 11.25 | 15   | 18.75 | $\text{k}\Omega$ |

| SEN sinking current          | $V_{SEN\cdot SEN} = 1.50 \text{ V}$ , $V_{TMR} = RSN$                                                                                          |       |      | 1     | $\mu\text{A}$    |

| SENP sinking current         | $V_{SEN\cdot SEN} = 1.50 \text{ V}$ , $V_{TMR} = RSN$                                                                                          | 17    | 22.5 | 28    | $\mu\text{A}$    |

## PoE部

| PARAMETER                        | TEST CONDITIONS                                                                                | MIN                                                                       | TYP  | MAX  | UNIT          |             |

|----------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|---------------|-------------|

| <b>DETECTION (DET)</b>           |                                                                                                |                                                                           |      |      |               |             |

| Offset current                   | DET open, $V_{DD} = V_{RTN} = 1.9 \text{ V}$ , Measure $I_{VDD} + I_{RTN} + I_{SEN\cdot SEN}$  | 0.45                                                                      | 4    |      | $\mu\text{A}$ |             |

| Sleep current                    | DET open, $V_{DD} = V_{RTN} = 10.1 \text{ V}$ , Measure $I_{VDD} + I_{RTN} + I_{SEN\cdot SEN}$ | 5.6                                                                       | 12   |      | $\mu\text{A}$ |             |

| DET leakage current              | $V_{DET} = V_{DD} = 57 \text{ V}$ , Measure $I_{DET}$                                          | 0.3                                                                       | 5    |      | $\mu\text{A}$ |             |

| Detection current                | $RTN = V_{DD}$ , Measure $I_{VDD} + I_{RTN} + I_{DET} + I_{SEN\cdot SEN}$                      | 51.5                                                                      | 55   | 58.7 |               |             |

|                                  | $V_{DD} = 1.4 \text{ V}$                                                                       | 395                                                                       | 411  | 417  | $\mu\text{A}$ |             |

| <b>CLASSIFICATION (CLASS)</b>    |                                                                                                |                                                                           |      |      |               |             |

| $I_{CLASS}$                      | Classification current                                                                         | $RTN = V_{DD}$ , Measure $I_{VDD} + I_{RTN} + I_{DET} + I_{SEN\cdot SEN}$ |      |      |               |             |

|                                  |                                                                                                | $R_{CLASS} = 4420 \Omega$ , $13 \leq V_{DD} \leq 21 \text{ V}$            | 2.2  | 2.5  | 2.8           |             |

|                                  |                                                                                                | $R_{CLASS} = 953 \Omega$ , $13 \leq V_{DD} \leq 21 \text{ V}$             | 10.3 | 10.6 | 11.3          |             |

|                                  |                                                                                                | $R_{CLASS} = 549 \Omega$ , $13 \leq V_{DD} \leq 21 \text{ V}$             | 17.7 | 18.3 | 19.5          |             |

|                                  |                                                                                                | $R_{CLASS} = 357 \Omega$ , $13 \leq V_{DD} \leq 21 \text{ V}$             | 27.1 | 28.0 | 29.5          |             |

|                                  |                                                                                                | $R_{CLASS} = 255 \Omega$ , $13 \leq V_{DD} \leq 21 \text{ V}$             | 38.0 | 39.4 | 41.2          |             |

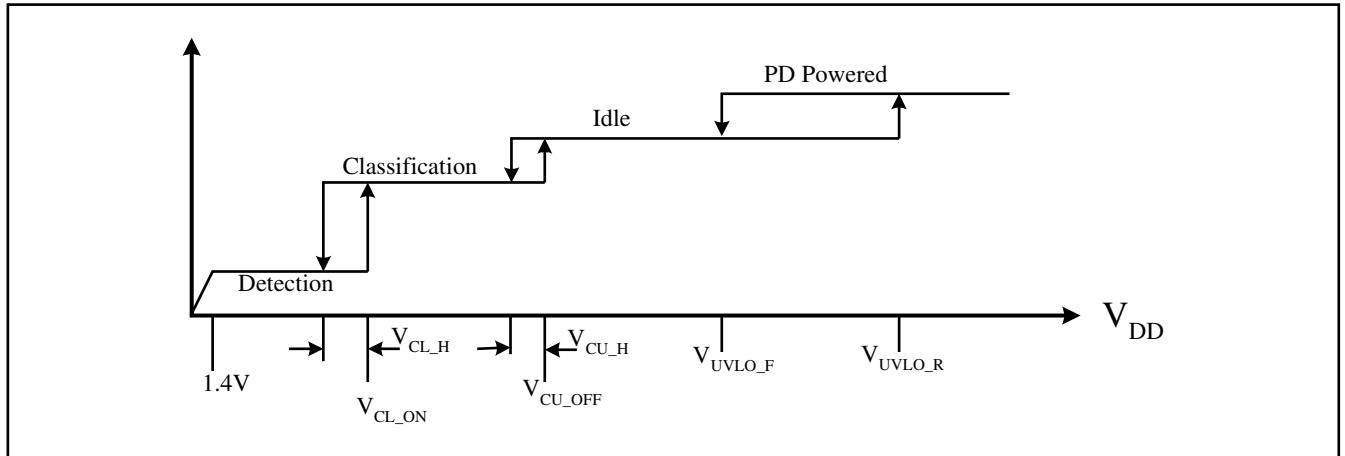

| $V_{CL\_ON}$                     | Classification lower threshold                                                                 | Regulator turns on, $V_{DD}$ rising                                       | 10.2 | 11.3 | 13.0          |             |

| $V_{CL\_H}$                      |                                                                                                | Hysteresis                                                                | 1    | 1.75 | 3             |             |

| $V_{CU\_OFF}$                    | Classification upper threshold                                                                 | Regulator turns off, $V_{DD}$ rising                                      | 21   | 21.9 | 23            |             |

| $V_{CU\_H}$                      |                                                                                                | Hysteresis                                                                | 0.5  | 0.83 | 1             |             |

| <b>PASS DEVICE (RTN)</b>         |                                                                                                |                                                                           |      |      |               |             |

| On resistance                    | $I_{RTN} = 300 \text{ mA}$                                                                     | 0.60                                                                      | 1    |      | $\Omega$      |             |

| Current limit                    | $V_{RTN} = 1 \text{ V}$                                                                        | 405                                                                       | 450  | 515  | $\text{mA}$   |             |

| $I_{INR}$                        | Inrush limit                                                                                   | $V_{RTN} = 1.6 \text{ V}$                                                 | 100  | 140  | 180           | $\text{mA}$ |

| <b>CONTROL</b>                   |                                                                                                |                                                                           |      |      |               |             |

| Inrush current state termination |                                                                                                | $I_{RTN}$ falling from $I_{INR}$ , $I_{RTN}/I_{INR}$                      | 0.85 | 1.00 |               |             |

| <b>UVLO</b>                      |                                                                                                |                                                                           |      |      |               |             |

| $V_{UVLO\_R}$                    | Standard UVLO threshold                                                                        | $V_{DD}$ rising, monitor $I_{RTN}$                                        | 38.4 | 39.3 | 40.4          |             |

| $V_{UVLO\_F}$                    |                                                                                                | $V_{DD}$ falling, monitor $I_{RTN}$                                       | 29.6 | 30.5 | 31.5          |             |

|                                  |                                                                                                | Hysteresis                                                                | 8.3  | 8.8  | 9.1           |             |

| $V_{UVLO\_R}$                    | Legacy UVLO threshold                                                                          | $V_{DD}$ rising, monitor $I_{RTN}$                                        | 34.1 | 35.1 | 36.0          |             |

| $V_{UVLO\_F}$                    |                                                                                                | $V_{DD}$ falling, monitor $I_{RTN}$                                       | 29.7 | 30.5 | 31.4          |             |

|                                  |                                                                                                | Hysteresis                                                                | 4.3  | 4.5  | 4.8           |             |

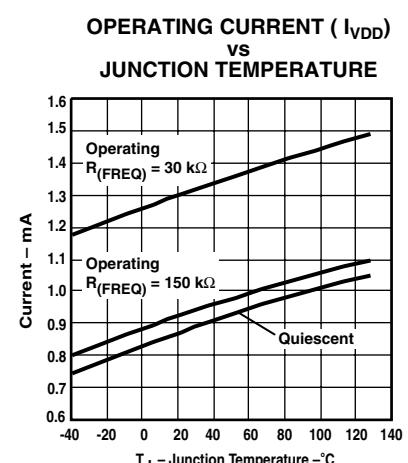

## 電気的特性- 全体

| PARAMETER               | TEST CONDITIONS                                     | MIN  | TYP | MAX  | UNIT |

|-------------------------|-----------------------------------------------------|------|-----|------|------|

| <b>BIAS CURRENT</b>     |                                                     |      |     |      |      |

| $I_{VDDQ}$              | Quiescent current                                   |      |     | 1    | 1.3  |

| Operational current     | COMP = FB                                           |      | 1.1 | 1.4  | mA   |

|                         | COMP = FB, $R_{FREQ} = 30\text{ k}\Omega$           |      | 1.3 | 1.75 |      |

| Off state current       | RTN = COM = RSN = $V_{DD}$ , $V_{DD} = 33\text{ V}$ | 0.18 | 0.5 |      | mA   |

| <b>THERMAL SHUTDOWN</b> |                                                     |      |     |      |      |

| Shutdown temperature    | Temperature rising                                  | 140  |     |      | °C   |

| Hysteresis              |                                                     | 17   |     |      | °C   |

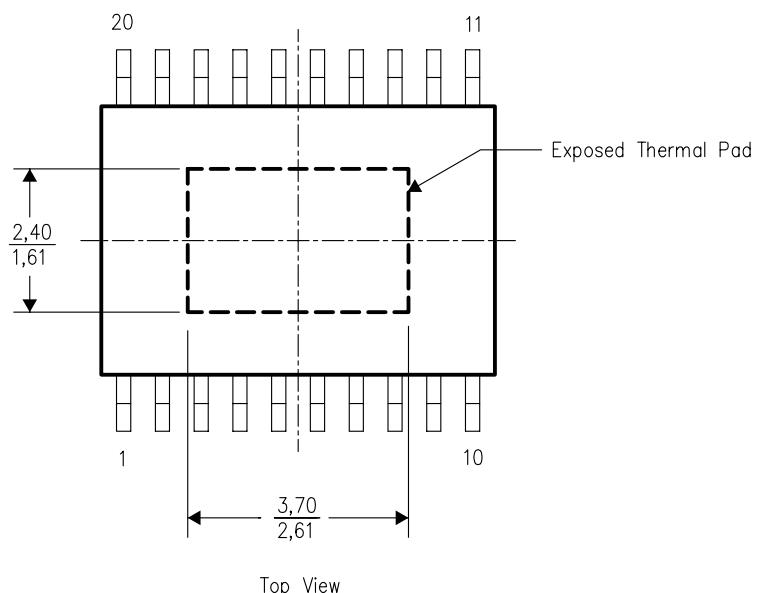

## デバイス情報

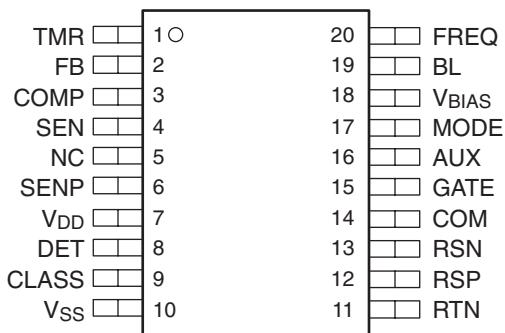

図 2. ピン配置

## 端子機能

| TERMINAL<br>NAME  | NO. | I/O | DESCRIPTION                                                                                                                    |

|-------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------|

| TMR               | 1   | O   | コンバータ・ソフト・スタートおよびHiccupタイマの兼用ピンです。RTNとの間のキャパシタにより、ソフトスタートとHiccupのタイミングが決定されます。                                                 |

| FB                | 2   | I   | コンバータ誤差増幅器反転入力。未使用時はRTNに接続します。                                                                                                 |

| COMP              | 3   | I/O | コンバータ誤差増幅器出力およびPWMブロック入力。COMPは、外部誤差増幅器およびオプトアイソレータによるループ補償またはPWM制御に使用します。                                                      |

| SEN               | 4   | I   | 電圧レベル・トランスレータのセンス入力およびイネーブル。ディスエーブル時は、RTNに接続します。トランスレータ使用時には、制御ループによってSENがSEMPより1.5V低い値に制限されます。通常、ローサイド・スイッチ・バック・コンバータで使用されます。 |

| NC                | 5   | -   | 接続なし。内部接続はありません。                                                                                                               |

| SENP              | 6   | I   | SENとともに使用される電圧レベル・トランスレータの正リファレンス電圧。トランスレータ使用時にはレギュレーション電圧の正側レールに接続し、それ以外の場合はV <sub>DD</sub> に接続します。                           |

| V <sub>DD</sub>   | 7   | PWR | 正電源入力。                                                                                                                         |

| DET               | 8   | O   | PoE検出ピン。V <sub>DD</sub> との間に24.9kΩの抵抗を接続することで、有効なシグネチャを確立します。検出中はV <sub>SS</sub> にプルダウンされます。                                   |

| CLASS             | 9   | O   | PoEの分類ピン。V <sub>SS</sub> との間に抵抗を接続して、PoEデバイス・クラスを設定します。検出中は10Vにプルアップされます。                                                      |

| V <sub>SS</sub>   | 10  | PWR | PoEフィードからの負電源入力(必要なORブリッジの後)。                                                                                                  |

| RTN               | 11  | I   | スイッチングされたPoE負出力。RTNは、コンバータの負の入力レールです。COMおよびRSNは、RTNに接続する必要があります。                                                               |

| RSP               | 12  | I   | コンバータのスイッチングMOSFET電流センス抵抗に接続します(電流センス抵抗の正端)。                                                                                   |

| RSN               | 13  | I   | コンバータのスイッチングMOSFET電流センス・リファレンス(電流センス抵抗の負端)および低雑音アナログ・リターン(グランド)。RTNに接続します。                                                     |

| COM               | 14  | I   | コンバータのMOSFETゲート・ドライバ回路のリターン。RTNに接続します。                                                                                         |

| GATE              | 15  | O   | コンバータのスイッチングMOSFETゲート・ドライブ。                                                                                                    |

| AUX               | 16  | I/O | コンバータのゲート・ドライバ電源。10Vを出力し、最大16Vを入力できます。COMとの間にバイパス・キャパシタを接続します。                                                                 |

| MODE              | 17  | I   | 誤差増幅器をディスエーブルする場合は、V <sub>BIAS</sub> に接続します。それ以外の場合は、RTNに接続します。                                                                |

| V <sub>BIAS</sub> | 18  | O   | コンバータの内部5Vバイアス電源出力。外部フォトカッピラのバイアスにも使用します。RTNとの間にバイパス・キャパシタが必要です。                                                               |

| BL                | 19  | I   | コンバータの電流センス・ブランкиング選択。ブランкиングを最小にする場合は、フローティングのままにします。短い期間の場合は、BLをRTNに接続します。長い期間の場合は、V <sub>BIAS</sub> に接続します。                 |

| FREQ              | 20  | I   | RTNとの間に抵抗を接続することで、スイッチング周波数が設定されます。                                                                                            |

| PowerPAD          | -   | PWR | 内部でV <sub>SS</sub> に接続されています。デバイスを基板上のトレースにヒートシンクするために使用します。V <sub>SS</sub> ピンに接続する必要があります。                                    |

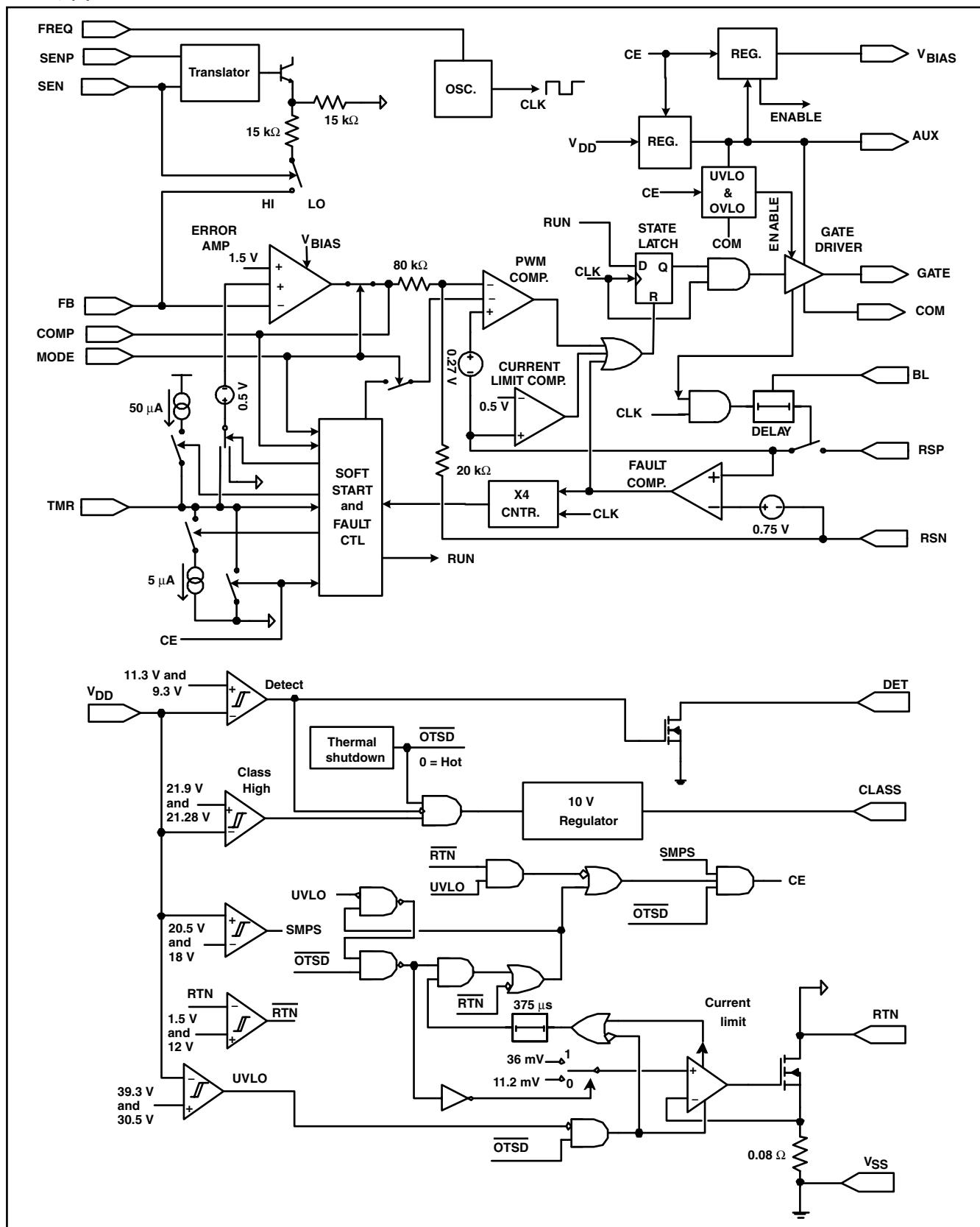

ブロック図

| BL CONNECTION | BLANKING OPERATION                      |

|---------------|-----------------------------------------|

| Open          | None (Minimum current-sense loop delay) |

| RSN           | Minimum plus 70 ns                      |

| $V_{BIAS}$    | Minimum plus 105 ns                     |

表 1. BLの接続

## 詳細説明

**AUX** — このピンは、内部の10Vコンバータ・バイアス・レギュレータ、ゲート・ドライブ電源、および残りのコンバータ制御回路に電源を供給する5Vレギュレータの接合点です。通常のコンバータ動作中にこのピンに電圧を印加することで、効率を高め、TPS23750の温度上昇を低減することができます。約8VのUVLOで $V_{AUX-COM}$ を監視することにより、不十分なバイアスでの動作を防ぎます。また、コンバータ過電圧ロックアウト機能により、バイアス巻線の使用時、 $V_{AUX}$ が17.5Vを超えて上昇した場合にICを保護します。

AUXとCOMの間に、0.8 $\mu$ F以上の低ESRバイパス・キャパシタを接続する必要があります。

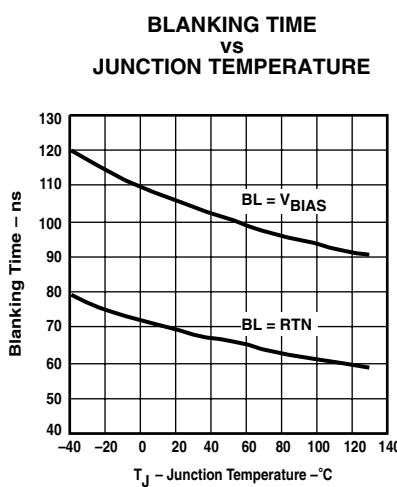

**BL** — このピンを使用して、希望のブランкиング動作を選択できます。ブランкиング機能は、GATEが“ハイ”になった後所定の時間の間、センスされたMOSFET電流によってPWMおよび電流制限コンパレータがトリップするのを防ぎます。これにより、ゲート駆動電流および外部電源整流器の回復電流によってコンパレータが誤ってトリガされるのを防ぐことができます。この回復電流は、トポロジ、デバイス選択、およびデバイスの寄生成分によって大きな影響を受けます。BLピンがオープンのときの最小遅延時間は、電流制限コンパレータ、ロジック、およびゲート・ドライバによって決まります。表1に示すように、2つの設定済み遅延時間を選択できます。BLをオープンにしてRCフィルタを使用することで、さらに短い遅延時間を得ることができます。

**CLASS** — CLASSと $V_{SS}$ の間に接続される外部抵抗 $R_{CLASS}$ により、PoEの分類機能が実行されます。入力電圧が13V～21Vの場合、電流は $R_{CLASS}$ を通して $V_{DD}$ から引き込まれます。分類機能により、PDは必要な平均電力要件をPSEに示すことができます。これを表2に示します。

CLASS抵抗には、最大75msの間、約10Vが印加されます。抵抗のワット数定格は、この過渡条件にのみ基づく必要があります。

CLASSピンをグランドに短絡してはなりません。推奨されるCLASS 0抵抗は、電源遮断後に、TPS23750の周囲に接続されている容量に対するブリーダとして機能します。

**COM** — スイッチング・レギュレータ・ゲート・ドライバのリターン。この信号は、ノイズ・カップリングを最小限に抑えるためにRTNおよびRSNから内部で分離されていますが、基板上では常にRSNおよびRTNと接続しておく必要があります。

**COMP** — TPS23750は、従来型の電流モード・コントローラです。COMPピンは、電圧制御ループの誤差増幅器出力と電流制御ループのリファレンス入力との間の接合点を表しています。この名前は、COMPとFBの間に接続される、ループ補償部品の従来型接続を示すものです。

COMPの機能は、MODEによって変更されます。MODEをRTNに接続すると、内部の誤差増幅器がイネーブルになります。MODEを $V_{BIAS}$ に接続すると、内部の増幅器がCOMPから切り離され、フォトカップラを直接PWMコンパレータ回路にフィードできます。このモードでは、COMPピンをRTNと $V_{BIAS}$ の間でのみ駆動してください。増幅器がディスエーブルのときは、FBをRTNに接続します。

電流モード制御範囲のCOMP電圧は、1.35V～4V未満です。1.35V未満のCOMP電圧に対しては、コンバータのスイッチングが禁止されます。COMP電圧が4.1Vを上回ると、TMR回路がHiccup動作を開始します。内部の誤差増幅器を使用している場合、Hiccupサイクルのオフ期間中はCOMPが強制的に“ロー”になります。

内部の誤差増幅器がアクティブなときは、COMP出力をオーバードライブしないでください。増幅器が大きな電流をソースおよびシンクして、消費電力が大きく上昇する可能性があります。内部の誤差増幅器を使用する場合、TMRを“ロー”にしてコンバータをオフにすることができます。クラスAB増幅器段の特性により、COMPがその飽和“ロー”電圧を下回ると、誤差増幅器は電流をソースします。

| CLASS | PD POWER (W) | $R_{CLASS}$ ( $\Omega$ ) | 802.3af CLASS CURRENT LIMITS (mA) | NOTE                 |

|-------|--------------|--------------------------|-----------------------------------|----------------------|

| 0     | 0.44 – 12.95 | $4420 \pm 1\%$           | 0 – 4                             | Default class        |

| 1     | 0.44 – 3.84  | $953 \pm 1\%$            | 9 – 12                            |                      |

| 2     | 3.84 – 6.49  | $549 \pm 1\%$            | 17 – 20                           |                      |

| 3     | 6.49 – 12.95 | $357 \pm 1\%$            | 26 – 30                           |                      |

| 4     | Reserved     | $255 \pm 1\%$            | 36 – 44                           | Treated like class 0 |

表 2. 分類

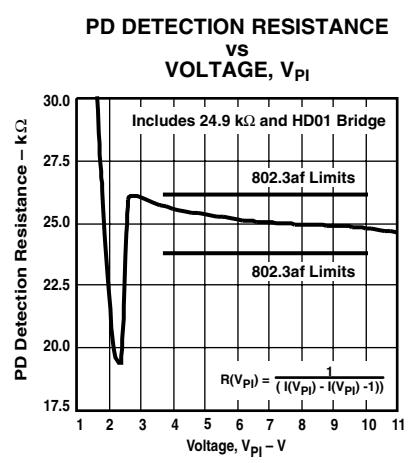

**DET** — DETとV<sub>DD</sub>の間には、 $24.9\text{k}\Omega \pm 1\%$ の抵抗(R<sub>DET</sub>)を接続します。V<sub>DD</sub>が1.4V～10.1Vの範囲のときに、R<sub>DET</sub>を入力ラインに接続します。電力節減のため、ライン電圧が12Vを超える場合にはR<sub>DET</sub>を切り離します。R<sub>DET</sub>を調整して入力ダイオード特性を補償することができます。

**FB** — 内部DC/DCコンバータ誤差増幅器の反転入力です。FBは、出力電圧帰還およびループ補償のために使用されます。帰還ループがレギュレーション範囲内の場合、FBは1.5Vになります。MODEを使用して誤差増幅器をディスエーブルする場合は、FBをRTNに接続する必要があります。SENを使用してイネーブルした場合、内部のレベル・トランスレータはこのピンを約15k $\Omega$ のソース・インピーダンスで駆動します。

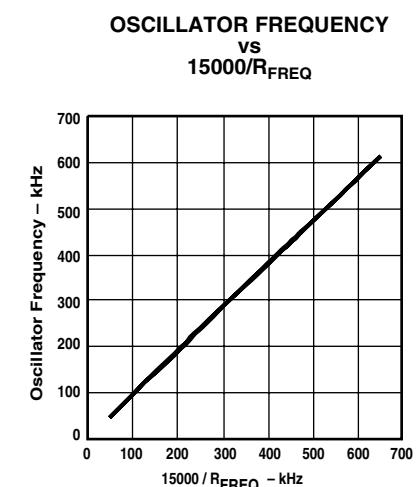

**FREQ** — FREQとRTNの間に接続した抵抗によって、コンバータのスイッチング周波数が設定されます。この機能により、磁気回路やフィルタリングの再設計なしに、既存の設計をTPS23750を使用した設計に簡単にアップグレードできます。発振回路の特性は100kHz～500kHzで規定されていますが、数kHzの周波数でも適切に動作します。

$$R_{\text{FREQ}} (\text{k}\Omega) = \frac{15000}{\text{switching\_frequency (kHz)}} \quad (1)$$

この式は十分に正確なですが、高い周波数領域では、周波数が予測値よりわずかに低くなります。

FREQは、グランドに短絡したり、電圧を印加したりしないでください。

**GATE** — DC/DCコンバータのスイッチングMOSFETドライバ出力です。このピンには内部プルダウンがあり、コンバータが非アクティブなときに外部スイッチングMOSFETをオフに保ちます。

**MODE** — このピンは、コンバータの誤差増幅器をディスエーブルして、フォトカップラがCOMPから直接PWMコンパレータを駆動できるようにします。MODEをRTNに接続すると誤差増幅器がイネーブルになり、V<sub>BIAS</sub>に接続するとディスエーブルになります。MODEは、フローティングにしないでください。

**RSN** — このピンは、電流センスおよび他の低レベル信号のための、電流モード・コントローラの低雑音“グランド”リファレンスです。RTN、RSN、およびCOMは互いに接続する必要があります。

**RSP** — このピンは、電流モード・コントローラの電流センス入力です。電流モード制御では、RSPとRSNの間の電圧としてセンスされる、スイッチングMOSFETのピーク電流を監視して、PWMデューティ・サイクルを設定します。ピーク電流制限は、最大センス電圧を約0.5Vに制限することで設定されます。

電源回路に短絡があると、ブランкиング期間中にMOSFET電流が高いレベルまで上昇する可能性があります。RSPピーク電

圧が連続4スイッチング・サイクルにわたって0.75Vを超えると、コンバータがオフになり、Hiccupサイクルが開始されます。

ブランкиングが十分で入力RCフィルタが必要ない場合は、このピンを直接センス抵抗に接続することができます。

**RTN** — このピンは、内部MOSFETによりVSSに接続されます。このMOSFETは、PoE部のUVLO、突入電流制限、電流制限、温度制限、および障害電圧制限によって制御されます。

ほとんどのアプリケーションでは、グランド・プレーンを通してRSNおよびCOMをRTNに接続します。

**SEN** — SENは、レベル・トランスレータの負入力です。これは、図40に示されるように、バック・コンバータで使用できます。トランスレータは、SENをV<sub>SS</sub>基準で1V以上に接続することにより、イネーブルになります。レベル・トランスレータは、15k $\Omega$ の内部抵抗を通してV<sub>SENP-SEN</sub>をFBピンに印加します。この機能により、RTNを超える帰還電圧センスが単純化されます。レベル・トランスレータを使用しない場合は、SENをRSNに接続してください。

**SENP** — SENPは、レベル・トランスレータの正入力です。これは、図40に示されるように、SENとともに使用します。このピンの存在により、フィルタ・インダクタをV<sub>DD</sub>と出力の間の正電源レールに配置できます。レベル・トランスレータがディスエーブルのときは、SENPをV<sub>DD</sub>に接続してください。SENPの電圧は、常にSENの電圧より高くなるようにしてください。

**TMR** — TMRとRTNの間にキャパシタを接続することで、ソフトスタートおよびHiccupタイマ機能をプログラミングできます。コンバータをディスエーブルするには、このピンをRTNにプルダウンします。

TMRは、ソフトスタート、過負荷タイムアウト、および過負荷時の自動再起動(Hiccup機能)を制御します。

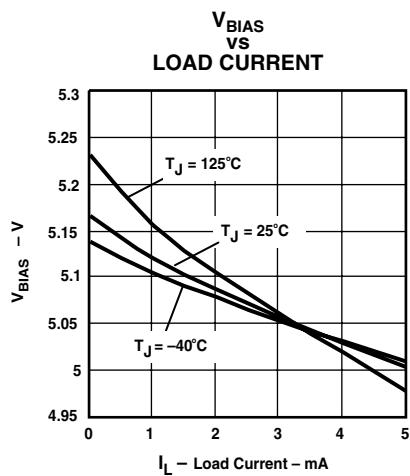

**V<sub>BIAS</sub>** — この5Vバイアス電源は、コンバータ機能の大部分に電源を供給します。V<sub>BIAS</sub>は、絶縁型アプリケーションで帰還フォトカップラへの電源供給に使用できます。過度の電力消費を避けるために、外部負荷は最小限にしてください。V<sub>BIAS</sub>は、出力が4.6V未満のときにコンバータの動作を禁止するUVLO機能を備えています。V<sub>BIAS</sub>は、0.08 $\mu\text{F}$ ～1.5 $\mu\text{F}$ のキャパシタでバイパスします。このピンには、外部バイアスを加えないでください。

**V<sub>DD</sub>** — ICの正電源ピンです。

**V<sub>SS</sub>** — 内部PoE回路の共通グランドです。このピンは、整流されたPoE電圧のローサイドに接続します。内部のパワーMOSFETにより、PoE部の制御下でRTNがV<sub>SS</sub>に接続されます。パッケージ下部のPowerPADは、内部でV<sub>SS</sub>に接続されています。PowerPADは、PCBを通してダイの熱を除去するために使用されます。

## 代表的特性

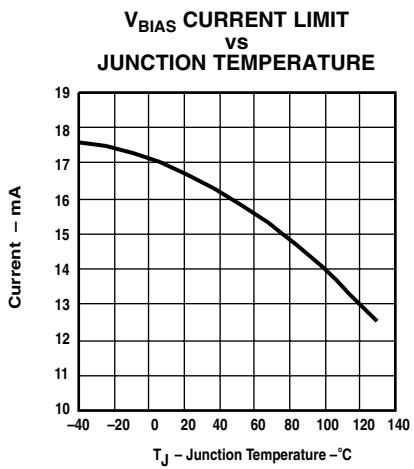

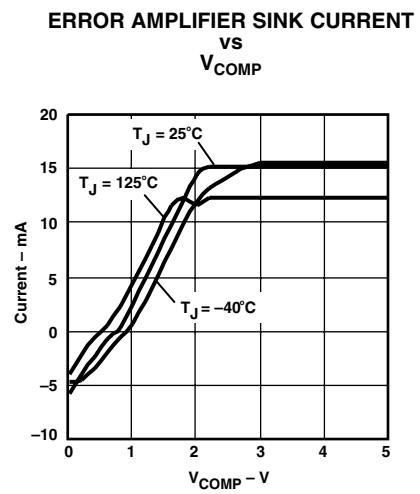

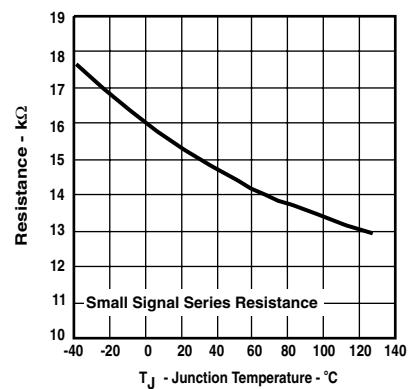

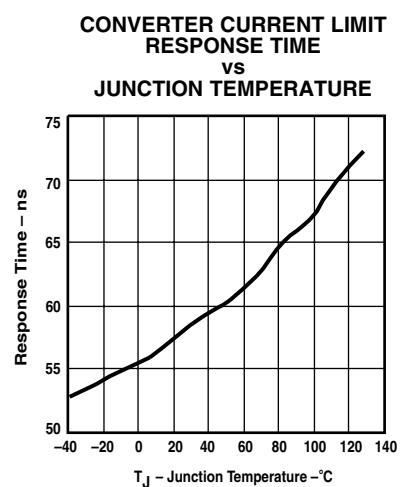

图 3

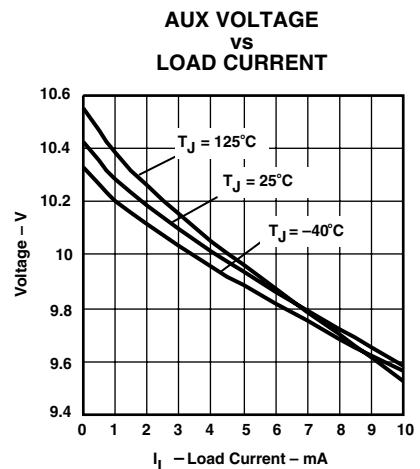

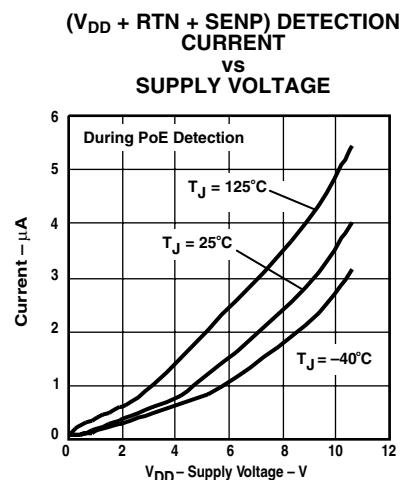

图 4

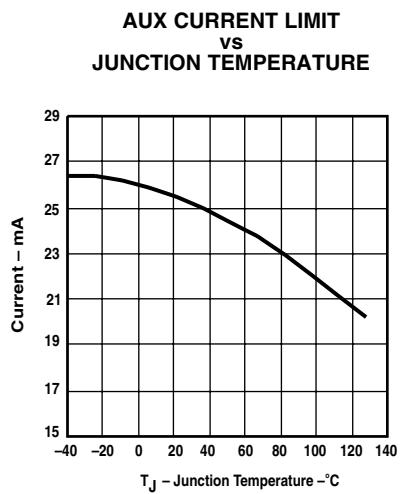

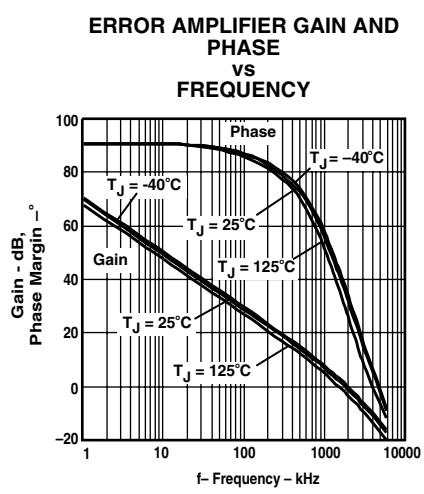

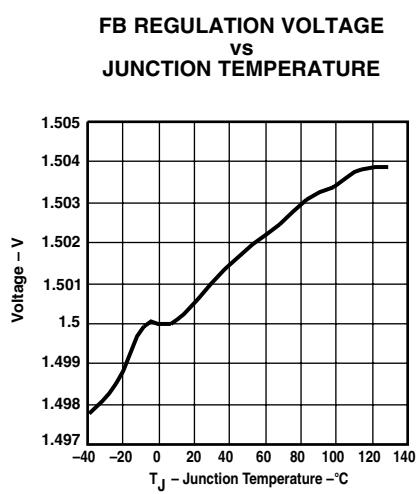

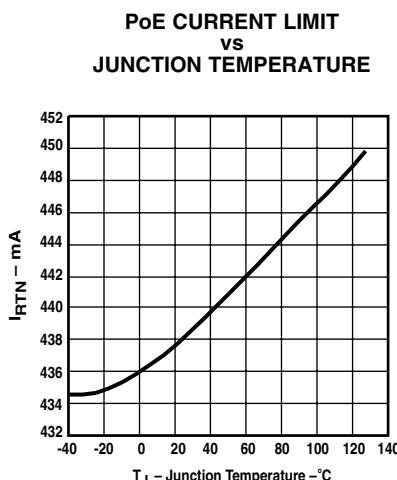

图 5

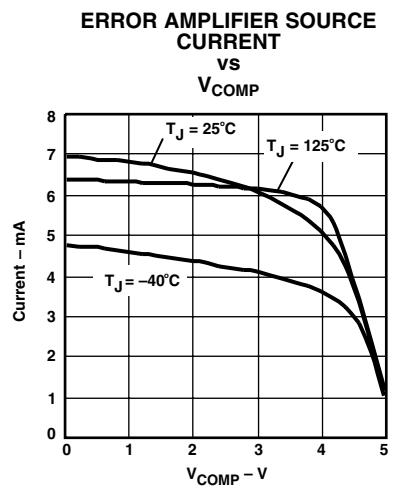

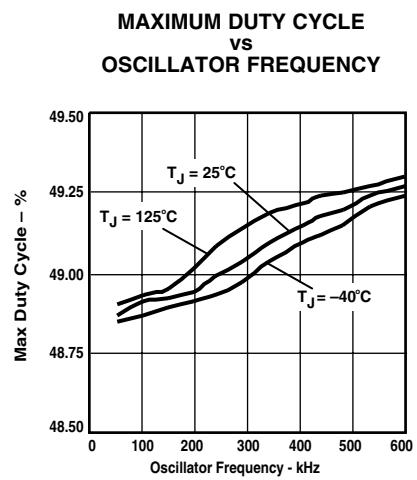

图 6

图 7

图 8

图 9

图 10

图 11

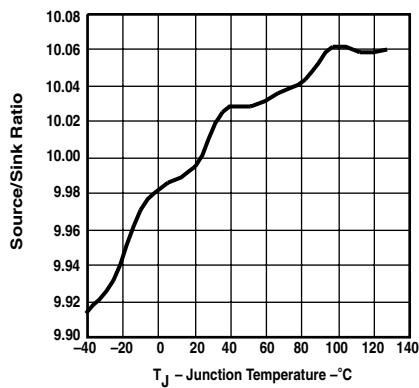

**TMR SOURCE/SINK CURRENT RATIO

vs

JUNCTION TEMPERATURE**

図 12

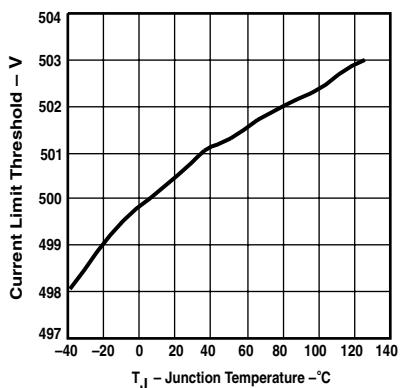

**CONVERTER CURRENT LIMIT THRESHOLD ( $V_{RSP}$ )

vs

JUNCTION TEMPERATURE**

図 13

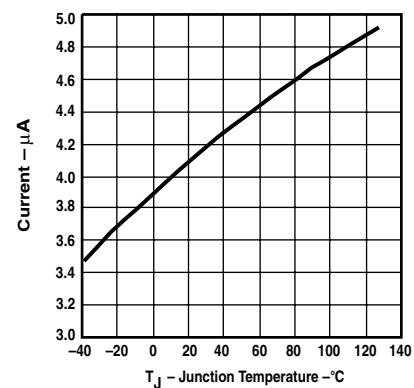

**RSP SOURCE CURRENT

vs

JUNCTION TEMPERATURE**

図 14

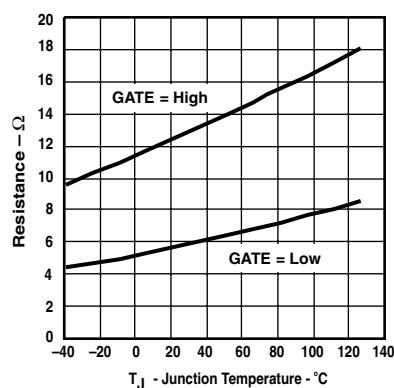

**GATE OUTPUT RESISTANCE

vs

JUNCTION TEMPERATURE**

図 15

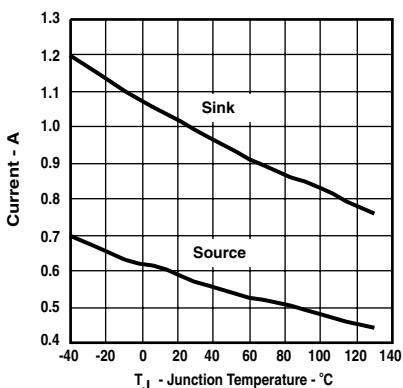

**GATE PEAK DRIVE CURRENT

vs

JUNCTION TEMPERATURE**

図 16

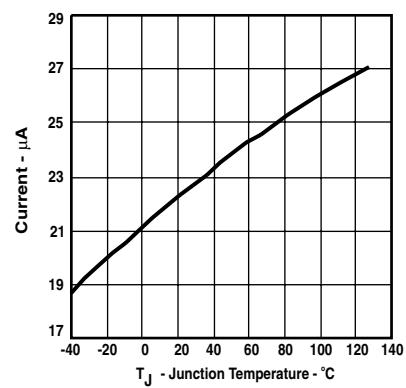

**SENP SINKING CURRENT

vs

JUNCTION TEMPERATURE**

図 17

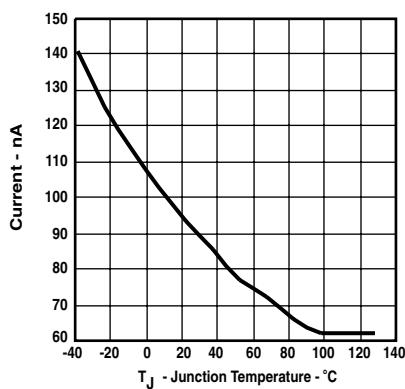

**SEN SINKING CURRENT

vs

JUNCTION TEMPERATURE**

図 18

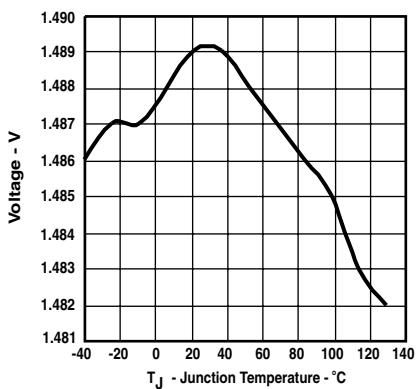

**(SENP - SEN) REGULATION VOLTAGE

vs

JUNCTION TEMPERATURE**

図 19

**TRANSLATOR OUTPUT RESISTANCE

vs

JUNCTION TEMPERATURE**

図 20

図 21

図 22

図 23

図 24

図 25

図 26

図 27

図 28

# アプリケーション情報

## PoEの概要

以下の説明は、TPS23750の動作を理解する助けとして意図されています。実際のIEEE 802.3af規格の代わりとなるものではありません。規格は変更される場合があり、設計上の決定を行う際には、常に実際の規格を参照してください。

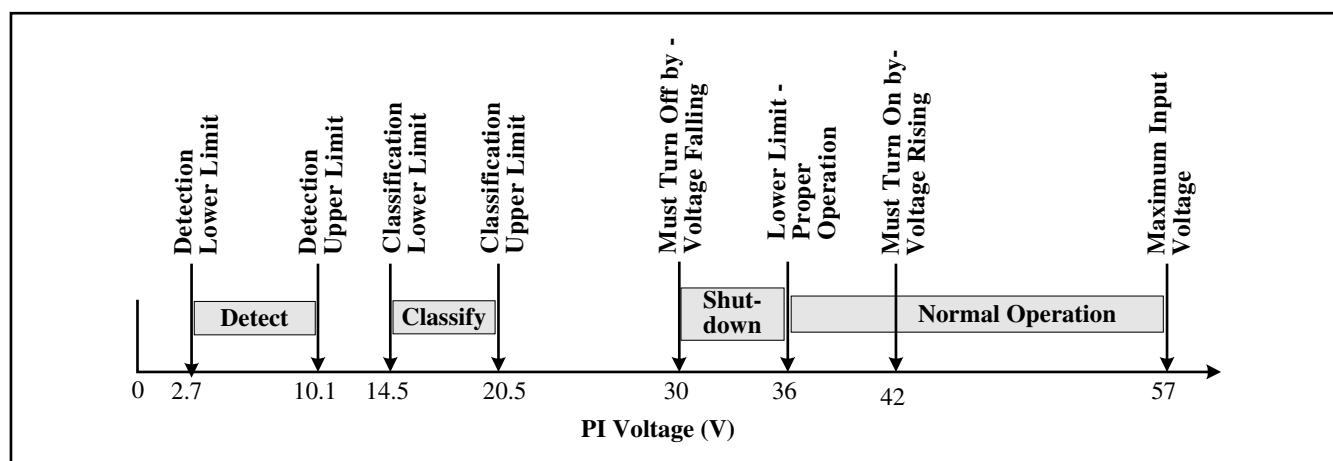

IEEE 802.3af規格は、ケーブルを介してPDに安全に電源を供給する方法、およびPDが取り外されたときに電力を遮断する方法を定義しています。このプロセスは、検出、分類、動作という3つの動作状態を経て進行します。PSEは、ケーブルに電力を供給しない状態で、何らかの機器が接続されたかどうかを定期的に監視しています。これを、検出と呼びます。検出時に使用される低い電力レベルは、PoE対応設計でないデバイスにも損傷を与えることはほとんどありません。有効なPDシグネチャが存在する場合、PSEはオプションとして、PDが必要とする電力について問い合わせることができます。これを分類と呼びます。PDは、デフォルトのフルパワー・シグネチャか、または他の4つの選択肢のいずれかを返します。次にPSEは、十分な容量がある場合には、PDに電源を供給します。いったん起動すると、PDは、電力保持シグネチャ(MPS)を示して、引き続き存在していることをPSEに知らせる必要があります。PSEは、有効なMPSが存在するかどうか出力を監視し、MPSが失われた場合にはポートをオフにします。MPSが失われると、

PSEは検出の初期状態に戻ります。図29に、各動作状態をPD入力電圧の関数として示しています。

PD入力は一般に8ピンのRJ-45コネクタであり、これは電源インターフェイス(PI)と呼ばれます。ケーブルでの電圧降下および動作余裕を考慮して、PDの入力要件は、PSEの出力要求と異なっています。仕様では、20Ωのケーブル抵抗を使用して、PSEの出力要件からPDでの電圧制限を導いています。規格ではPSE出力での出力電力を15.4Wと規定していますが、ケーブルでのワーストケースの電力損失により、PDの入力では12.95Wしか使用できません。

PSEは、RXとTXのペア間(ピン1-2および3-6)、または2つの予備ペア間(4-5および7-8)に電圧を印加できます。印加電圧は、いずれかの極性を使用し、一度に1組のペアにしか印加できません。PDは、入力ダイオード・ブリッジを使用して、可能なPSE構成のいずれかから電力を受け取ります。入力ブリッジに関連付けられた電圧降下により、PIでのIEEE 802.3af制限とTPS23750の仕様との間には違いがあります。

PSEは、通常動作時には平均350mA～400mAの電流制限を必要とし、この電流が75ms以上流れた場合には、PDを切断する必要があります。クラス0および3のPDには、最大400mAのピーク電流が流れます。PSEは、後述のように、PDの電力要求仕様に基づいて、より低い出力電流制限を設定することができます。

図 30. しきい値電圧

## PoE しきい値

TPS23750には、図29に示すような各種の状態間で安定した切り替えを行うために、ヒステリシスを有する内部コンパレータがいくつか内蔵されています。図30に、電気的特性のパラメータとPoE状態との関係を示します。分類状態と動作状態の間のIdle(アイドル)モードは、DET、CLASS、RTNの各ピンがすべてハイ・インピーダンスであることを表しています。

## 検出

IEEE 802.3afの検出機能は、48Vの印加を意図していないイーサネット・デバイスが損傷を受ける危険性を低減するものです。PIに2.7V~10.1Vの範囲の電圧が印加されている場合は、25kΩの差分抵抗により、PSEに対して、PDが電力を受け取ることが可能で、その準備ができていることが示されます。差分抵抗の測定は、2つ以上の異なる電圧をPIに印加して、流れる電流を測定することで行われます。この2つのテスト電圧は、指定された範囲内で、差が1V以上である必要があります。差分抵抗は、電圧の差を電流の差で割ったものに等しくなります。使用できる抵抗の範囲は、23.75kΩ~26.25kΩです。

電源電圧が分類の下限しきい値よりも低い場合、TPS23750は検出モードになります。この状態では、TPS23750には最小のバイアス電力が供給され、RTNはハイ・インピーダンスで、ほとんすべての内部回路はディスエーブルになります。検出中にはDETピンがグランドにプルダウンされるため、V<sub>DD</sub>とDETの間の24.9 kΩ/1%抵抗によって正しいシグネチャが示されます。R<sub>DET</sub>には約5mWのストレスしかかからないため、R<sub>DET</sub>は小さな低電力抵抗でかまいません。入力電圧が検出コンパレータの上限しきい値11.3Vを上回ると、電力節約のためにDETピンがオープンドレーン状態になります。

入力ダイオード・ブリッジの差分抵抗は、2.7VでPIに流れる非常に小さな電流において数百Ωです。ブリッジの抵抗はR<sub>DET</sub>と直列であり、PSEから見た全抵抗を増加させます。図29に見

られる検出シグネチャの非直線性は、ダイオード・ブリッジによるものです。これは設計者が選択するダイオードの種類によって異なり、通常はダイオードのデータ・シートには指定されていません。特定の種類のダイオードに対応するために、R<sub>DET</sub>の値は低く調整することができます。

## 分類

一端PDを検出すると、PSEはオプションでPDを分類することができます。分類によってPSEは、すべてのPDが15.4Wを必要とすると仮定する代わりに、PDの電力要求を個別に決定することができます。これにより、PSEは、その48V電源から最大数のPDに電源を供給できます。すべての受電ポートに最大電力を割り当てることができるPSEもあるので、このステップはオプションとなっています。

分類プロセスでは、PDの入力に14.5V~20.5Vの電圧が印加され、それにより、R<sub>CLASS</sub>で設定された固定電流が流れます。PSEは、PDの電流を測定することで、PDが5つの可能なクラス(表2を参照)のうちどれに属するかを決定します。分類中にPSEから流れる合計電流は、バイアス電流とR<sub>CLASS</sub>に流れる電流との和となります。過度の電力消費を避けるため、電圧が分類の範囲を上回る場合、TPS23750はR<sub>CLASS</sub>を切り離します(図29および図30を参照)。

R<sub>CLASS</sub>の値は、PDの平均電力要件に基づいて、表2に示される値の中から選択します。この抵抗の電力定格は、分類に必要な、10Vが印加される75msの期間内に、オーバーストレスにならないよう選択する必要があります。ベンチ・テスト条件下の場合、または分類範囲内の電圧の補助電源がPDのフロント・エンドに接続されている場合には、PDが長い時間分類状態になんでも許容できます。75msを超えると過熱保護が働いて分類がオフになる場合もありますが、抵抗の保護をこの機能に頼るような設計は行わないでください。

## 通常動作とPoE低電圧ロックアウト (UVLO)

TPS23750には、低電圧ロックアウト (UVLO) 回路が内蔵されています。この回路は、PoE入力電圧を監視して、コンバータに電力を供給するタイミングを決定することにより、PDのパワーアップと動作を制御します。IEEE 802.3afの仕様では、PDの最大オン電圧は42V、最小オフ電圧は30Vと規定されています(図30を参照)。IEEE 802.3af規格では、 $20\Omega$ の帰還抵抗と400mAの最大突入電流制限に基づいて、ケーブルでの電圧降下を8Vと仮定しています。PSEの最小出力電圧は44Vであるため、PDは最低36Vまでの入力電圧で適切に動作し続ける必要があります。TPS23750では、入力ダイオードで1.5Vの降下を許容し、その公称オン電圧を39.3V、オフ電圧を30.5Vに設定しています。TPS23770では、オン電圧、オフ電圧とも35Vです。

TPS23770のUVLO制限は、最小出力電圧が44V未満である旧型システムをサポートするために設計されています。これらのシステムでは、より低いオン電圧と小さなヒステリシスが要求されました。TPS23770も規格に準拠したPSEに対して動作しますが、PSEの出力電圧の上昇が遅い場合には、スタートアップが不安定になる可能性があります。規格に準拠したPSEに対しては、TPS23750を推奨します。

MPSは、PDが引き続き存在していることをPSEに対して示すための電気的シグネチャです。有効なMPSは、最小10mAのDC電流と、 $26.25k\Omega$ および $0.05\mu F$ の直列負荷よりも低いACインピーダンスから構成されます。通常は、このACインピーダンスよりも $5\mu F$ の最小容量要求が重要になります。

## PDのスタート・マシンおよびコンバータ動作

TPS23750には、突入電流および動作電流の制限状態を制御するスタート・マシンが内蔵されています。 $V_{DD}$ がUVLOの下限よりも低いと、パスMOSFETがオフになります。その結果、RTNピンはハイ・インピーダンスになり、出力キャパシタがコンバータによって放電されると、 $V_{DD}$ レベルになります。RTNが“ハイ”的状態で、 $V_{DD}$ が上昇してUVLOのオンしきい値を上回ると、TPS23750は電流制限を140mAに設定して内部パワーMOSFETをイネーブルします。出力キャパシタが充電され、 $V_{RTN}$ が $V_{DD}$ から $V_{SS}$ 付近まで低下する間、コンバータはディスエーブルになります。突入電流が設定された制限値を約10%下回ると、375μsの

遅延時間後に、電流制限が内部動作レベルの450mAに切り替わります。電流制限が切り替わると、コンバータ部がイネーブルになり、コンバータがソフトスタート・サイクルを開始します。入力電圧がUVLOの下限を下回った場合、PoE MOSFETはオフになりますが、コンバータは( $V_{VDD} - V_{SS}$ ) = 18Vでの動作が許可されます。

内部のパスMOSFETは、電流制限、および最大電流制限状態で動作しているときのフォールドバック機能により、出力障害から保護されています。過渡状態に対しては、PD MOSFETの保護をPSE出力に頼ることはできないため、PDは独自の出力保護が備わっています。高ストレス状況には、コンバータの出力短絡、 $V_{DD}$ とRTN間の短絡、入力ライン上の過渡状態などがあります。パスMOSFETへの過負荷は、電流制限を作動させ、結果として( $V_{RTN} - V_{SS}$ )が上昇します。 $V_{RTN}$ が12Vを上回ると、電流制限ステート・マシンが140mAの突入電流制限にリセットされ、コンバータがオフになります。「過熱保護」の項で後述するように、電流制限からの消費電力によってTPS23750が過熱した場合、デバイスを保護するためにサーマル・シャットダウンが働きます。RTNコンバータは、過負荷や入力過渡状態によってRTNがわずかな時間12Vを超えた場合でも、検出できます。過負荷の原因となった障害が除去されると、TPS23750は前述した通常のスタートアップ・サイクルを実行します。このような形の保護により、MOSFETのピーク消費電力が制限され、電流制限でのコンバータのロックアップを防ぎ、有害な電圧降下から負荷を保護し、問題が解消した場合は既知の状態から適切な回復が行えます。

TPS23750は、PoE電力が使用できない場合に、 $V_{DD}$ とRTNの間に接続された24V~48Vのアダプタで起動および動作が可能です。コンバータの動作は、次の場合にイネーブルになります。

- PoE部が突入状態でない。

- RTNが1.5V未満で $V_{DD} - V_{SS}$ がいったん20.5Vを超えている。

- $V_{DD} - V_{SS}$ が18Vを上回っている。

コンバータは実際には $V_{DD}$ からRTNの間で動作しますが、しきい値は $V_{DD} - V_{SS}$ で定義されています。内部のPoEパスMOSFETは、逆方向ダイオードを持ち、デバイスが出力側から電力供給されると、RTNより1つのダイオード降下分上回るレベルまで $V_{SS}$ をクランプします。

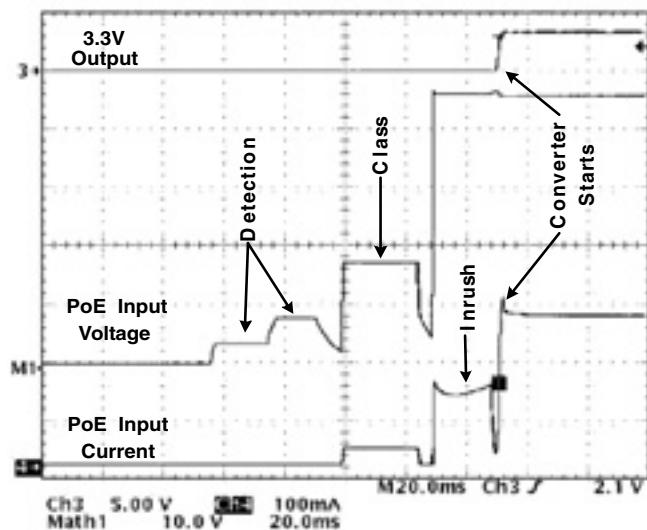

## PoEスタートアップ例

図31に、検出、分類、およびスタートアップの例を示します。PSEがPI上の電圧を制御し、PDが電流を制御します。図に示した波形は、PI電圧、PI電流、およびDC/DCコンバータ出力電圧です。IEEE 802.3af規格ではさまざまな使用を認めているため、異なるPSEでテストすると正確に同じ結果にはならない可能性があります。

最初のイベントは検出です。約4Vと8Vの2つの電圧レベルが見られますが、電流のスケールの関係で、検出電流レベルは見えません。2番目のイベントは分類です。PI電圧が約17VでPDに約28mAが流れ、クラス3デバイスであることが示されています。3番目のイベントはスタートアップです。PI電圧は約46Vまで上昇し、ダウンストリームのバルク・キャパシタが充電される間、PDには120mA～140mAの突入電流が流れます。バルク・キャパシタの充電が完了すると、PI電流は減少し、突入状態が終了してコンバータがイネーブルになります。最後のイベントは、 $1\Omega$ の固定負荷へのコンバータのスタートアップです。コンバータの出力電圧は3.3Vまで上昇し、対応するPI電流が流れます。PI電流は安定状態値の260mAまで増加し、出力キャパシタの充電時にわずかのオーバーシュートがあります。PDに電力が供給され、スタートアップが終了するとアプリケーション回路が動作可能になります。

## 過熱保護

ダイ温度が $140^{\circ}\text{C}$ を超えた場合、TPS23750は低電力モードに入ります。このとき、パスMOSFET、DC/DCコンバータ、AUXレギュレータ、およびCLASSレギュレータはオフになります。内部の電力消費源には、バイアス電流、パスMOSFET、およびAUX、 $V_{\text{BIAS}}$ 、CLASSの各レギュレータがあります。AUXレールが外部でバイアスされていない場合、主に寄与するのはAUXおよび $V_{\text{BIAS}}$ への負荷です。パスMOSFETが突入状態、コンバータがディスエーブル、およびTMRキャパシタが放電された状態で、ダイ温度が約 $17^{\circ}\text{C}$ まで下がると、TPS23750は自動的に再起動します。

TPS23750はPowerPADパッケージを使用して製造されているため、接合部と基板との間の熱抵抗が低くなっています。良好な熱特性を得るには、PowerPADを基板上の広い銅領域に半田付けする必要があります。

熱設計においては、PCBの局所的な温度上昇の原因となる他の要素も考慮してください。標準的な計算では、TPS23750がPCBの温度上昇に寄与する唯一の熱源と仮定されています。

図 31. 標準的なスタートアップ波形

## コンバータ制御回路の概要

TPS23750のDC/DC制御回路には、UC3844と同様な標準的な電流モード制御トポロジが実装されていますが、いくつかの点が強化されています。

入力FBと出力COMPの間には、1.5V固定リファレンスのクラスAB反転誤差増幅器が接続されています。この誤差増幅器は、ゲイン帯域幅積が1.5MHzであり、数mAの電流をソースまたはシンクできます。フォトカップラ帰還回路でPWM部を駆動する場合には、この増幅器をディスエーブルできます。

COMPは、電流モードPWM部の入力でもあります。COMP入力は、1/5デバイダでスケーリングされて電流コンバレータに入力されます。コンバレータに組み込まれたオフセットにより、デューティ・サイクルを0%まで駆動できます。RSPピン上で0.5Vの電流制限コンバレータしきい値が設定され、電流制限のレギュレーションが提供されます。RSP上のピーク電圧が0.75Vを上回ると、障害コンバレータによって暴走状態が検出されます。これは、変圧器の巻線の短絡、スイッチングMOSFETのドレインの短絡、バック・コンバータのインダクタの短絡などにより発生します。障害コンバレータが4回連続して作動すると、TPS23750は即座にシャットダウンし、TMRに基づくHiccupサイクルに入ります。

PoEで使用される標準的な回路に基づき、ディーティ・サイクルは50%に制限されています。これには、いくつかの利点があります。まず、安定化のための電流上昇の複雑さが解消されます。次に、磁気回路に対して十分なリセット時間が確保されます。また、1:1のリセット巻線を使用した多くのフォワード・コンバータでは、50%以下のデューティ・サイクルが要求されます。変圧器やバック・モード・コンバータを使用するほとんどのアプリケーションでは、そのような低いデューティ・サイクルが求められます。

ユーザがプログラミング可能な電流センス・ブランкиングにより、RCフィルタは必要ありません。出力整流器回復期間の短い高周波スイッチング回路のために、70nsのブランкиング期間が用意されています。また、大きなゲート駆動および回復要求を持つ中低周波回路のために、115nsのブランкиング期間も用意されています。最小のブランкиング・オプションを選択すると、短期間のRCフィルタを使用できます。

TMRピンは、誤差増幅器の使用時に閉ループ・ソフトスタート機能を提供します。内部誤差増幅器がディスエーブルのときは、開ループ・ソフトスタートが提供されます。また、TMRには、コンバータに障害が生じたときに平均消費電力を制限する、合成Hiccup機能(一時停止と再起動)が備えられています。障害状態中、コンバータは約9%の時間しか動作しないため、電力部品が冷却され、連鎖的な障害を防ぐことができます。Hiccup機能は、COMPピンが指定の時間“ハイ”になった場合にも動作します。これは、過負荷になった場合や、入力電圧が低すぎる場合に発生します。

内部のバイアス・レギュレータにより、外部のブートストラップ抵抗およびスタートアップ・レギュレータは不要になっています。この内部レギュレータによって、コンバータは突入状態の完了後ただちに起動して動作できます。これにより、起動の失敗や過度のスタートアップ遅延など、ブートストラップ起動トポロジに伴う問題を回避することができます。

一部のPD設計では、PoEが使用できないときに24VのACアダプタを使用できるようになっています。コンバータ制御により、V<sub>DD</sub>-RTN間に20.5V以上が印加された状態でスタートアップが許可され、最低約18Vまで動作が可能です。

## 誤差増幅器の接続

TPS23750では、多くの種類のコンバータと帰還方式が使用できます。レベル・トランスレータは単純なローサイド・スイッチ・バック・コンバータをサポートし、クラスAB電圧誤差増幅器は非絶縁型コンバータをサポートし、誤差増幅器ディスエーブルではフォトカップラ帰還をサポートしています。

PD設計者によっては、フライバックまたはフォワード・トポロジを使用した多出力電源を作成するかもしれません、PoEフロント・エンドとアプリケーション回路との間に金属絶縁は必要ありません。図32に、内部誤差増幅器をイネーブル、レベル・シフタをディスエーブルにした構成を示します。標準の出力電圧デバイダおよび補償方式で、FBおよびCOMPピンを使用しています。制御ループ設計により、誤差増幅器からPWMコンバレータへの減衰係数が0.2V/Vとなっています。TMRピンによって誤差増幅器へのリファレンス電圧が上昇し、閉ループ・ソフトスタートが提供されます。

図 32. 非絶縁型コンバータ構成

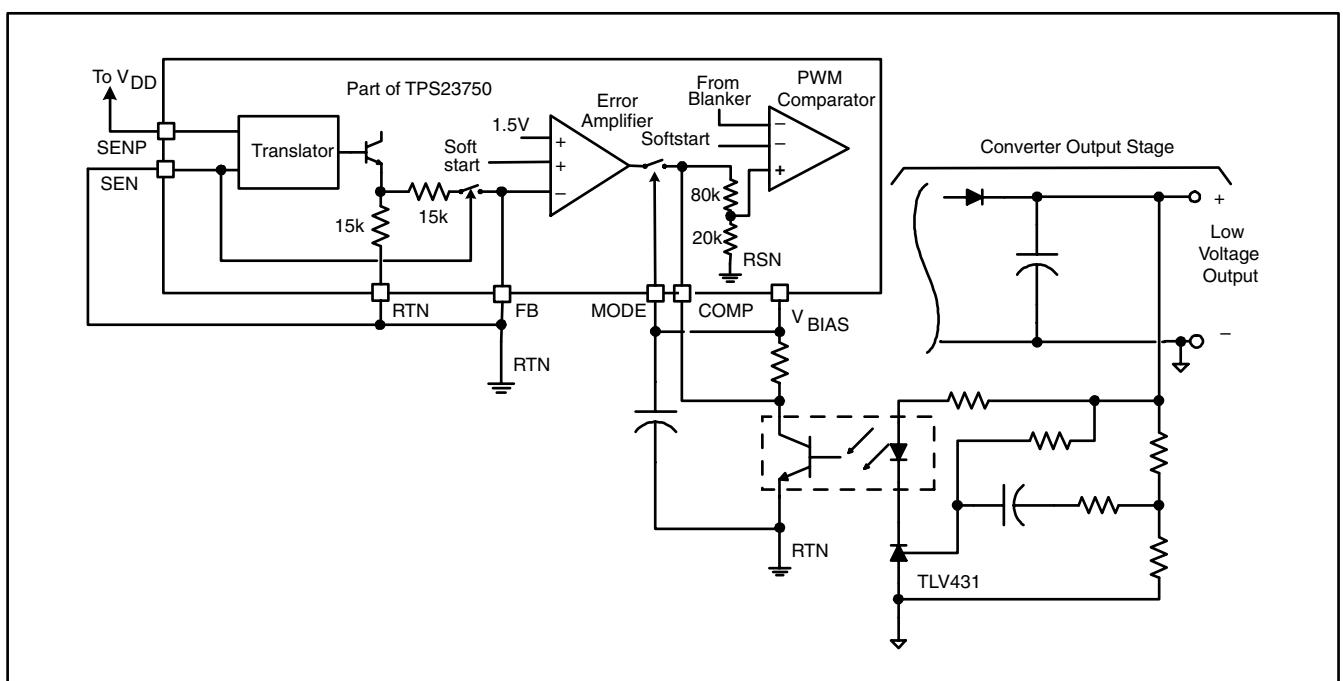

TL431ベースの回路のようなフォトカップラを使用する絶縁型PDコンバータでは、図33の構成を使用する必要があります。MODE接続によって内部誤差増幅器がディスエーブルになります。出力がハイ・インピーダンスになります。誤差増幅器がディスエーブルの場合、一次側のPWMソフトスタートが内部で使用されます。同じ0.2V/VのゲインがPWMコンパレータの前に現れます。この構成でHiccupを使用するために、COMPピンは引き続き監視されます。

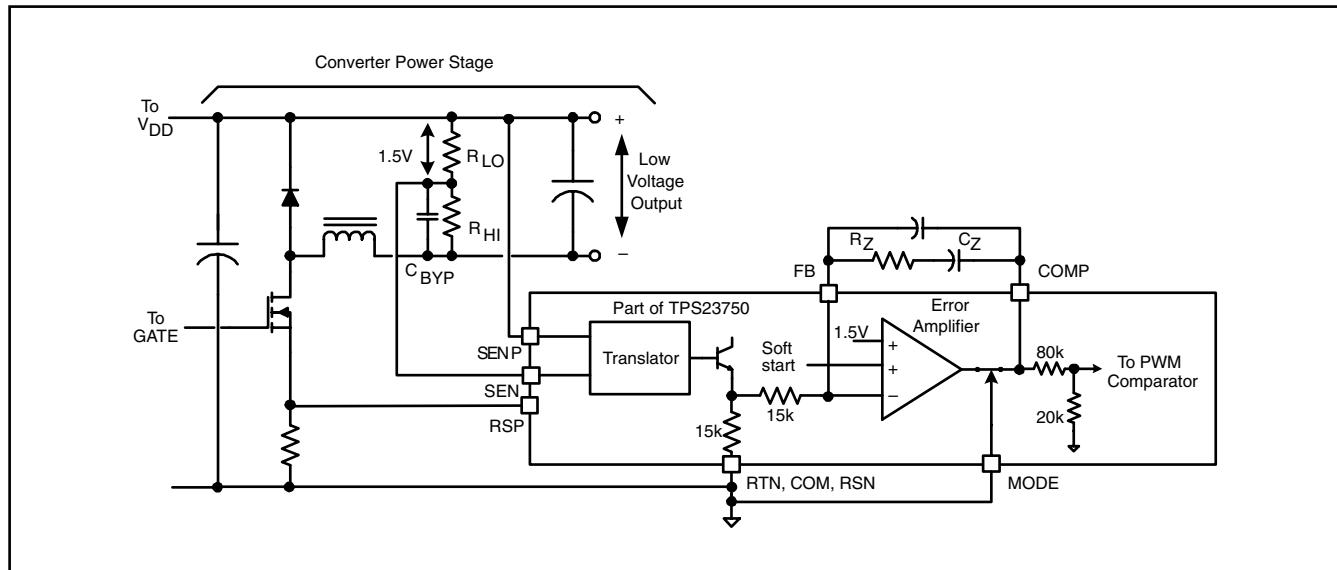

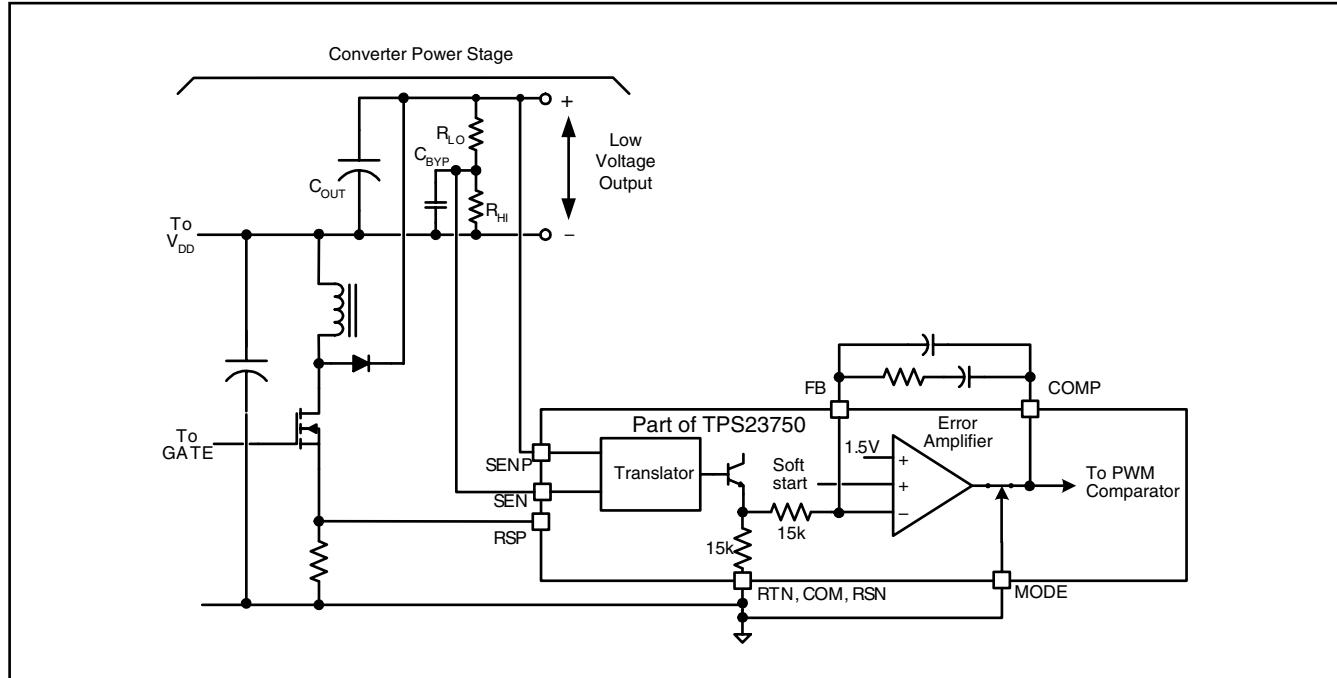

図34に、バック・コンバータ構成を示します。ループにより、 $R_{LO}$ にかかる電圧が1.5Vにレギュレーションされます。トランスレータ・トポロジにより、 $V_{SEN\text{P}}-SEN$ から15kΩの内部直列抵抗

へのゲインが1V/Vとなります。誤差増幅器ゲインの式は $(Z_{\text{COMP-FB}} / 15 \text{ k}\Omega)$ です。出力デバイダとトランスレータにより、図32の構成とは異なり、AC成分とDC成分の両方が減衰します。図32では、増幅器の入力での仮想的なグランドによって $R_{LO}$ の効果が相殺されるため、AC信号が分割されていません。 $R_{HI}$ と並列に $C_{\text{BYP}}$ を追加することで、AC信号の全体を誤差増幅器に入力しています。 $R_{HI}C_{\text{BYP}}$ コーナー周波数は、 $R_ZC_Z$ ゼロ周波数よりも1オクターブ以上低い必要があります。この方法により、標準的なループ設計手法に対して $C_{\text{BYP}}$ はほとんど影響しなくなります。

図 33. 絶縁型コンバータ構成

図 34. バック・コンバータ構成

## SENPおよびSENの他の使用法

レベル・トランシーバの入力であるSENPおよびSENの用途は、図34に示されるバック・アプリケーションに限られてはいません。V<sub>SS</sub>を基準とした推奨電圧範囲内であれば、V<sub>DD</sub>を超える電圧でも使用できます。SENPには約22.5 $\mu$ Aの電流が流れ、SENには1 $\mu$ A未満の電流が流れます。出力電圧デバイダのセンター・

タップに接続された場合、SENPに流れる電流により出力電圧に小さなオフセットが生じます。必要に応じて、このオフセットは最小化または補償することができます。次の例は、バッテリ・グランドを超える電圧を必要とする通信アプリケーションに対して、V<sub>DD</sub>を超える電圧を作成する方法を示しています。

図 35. バック/ブースト構成例

## バイアス電源

TPS23750には、AUX入出力およびV<sub>BIAS</sub>電源という2つのバイアス電源があり、それぞれに独自のUVLOがあります。

AUX電源は、電流制限10Vレギュレータであり、V<sub>DD</sub>から電流が供給されます。効率を向上させるために、より高い外部電圧をこのピンに印加してレギュレータを無効にすることもできます。ゲート・ドライバは、このレールから大きな電流パルスを受け取ります。そのため、低インピーダンスのバイパス・キャパシタ(1μFのセラミック・キャパシタなど)をTPS23750の隣りに低インピーダンス配線で接続する必要があります。電圧が8V未満の場合、UVLOによってゲート駆動が禁止されます。また、AUXには17.5Vの過電圧ロックアウト(OVLO)が備えられ、ゲート駆動の禁止時に図1のような開ループ・コンバータによってデバイスが損傷するのを防いでいます。V<sub>BIAS</sub>レギュレータには、AUXピンから電力が供給されます。

V<sub>BIAS</sub>レギュレータは、電流制限5.1Vレギュレータであり、その出力とRTNの間に0.08μF～1.5μFのキャパシタを必要とします。このレールから、フォトカップラに電源供給できます。V<sub>BIAS</sub>ピンからの電流が5mAを超えてはなりません。このレギュレータもUVLOを備え、4.6Vを下回るとコンバータがオフになります。

## ブランкиングの考慮事項およびRSP

プログラミング可能なブランкиングにより、一般にRSP入力で従来のようなRCフィルタを使用する必要がなくなります。ブランкиングによって、電流モードおよび電流制限コンパレータが、コンバータのスイッチングMOSFETがオンになるときに生じる電流スパイクに応答するのを防ぎます。この電流スパイクは、MOSFETゲート電流、寄生ドレイン容量電流、および出力整流器回復電流から構成されます。必要なブランкиング期間は、個々の設計に大きく依存します。ブランкиング期間が短すぎると、コンバータで電流が制限されたり、最大に満たない負荷で不規則に切り替わったりします。ブランкиング期間が長いと、サイクル・スキップを防ぐために必要な最小負荷が増加します。イーサネット・リンクを動作させるために必要な電力では、ほとんどのPDに対して、サイクル・スキップを防ぐのに十分な負荷が提供されるはずです。

BL設定のための最初の推奨事項は次のとおりです。

- 約150kHz未満で動作するか、または同期整流器を使用した、変圧器ベースの設計では、長いブランкиング期間を使用します。

- 150kHz以上で動作するか、またはショットキー出力ダイオードを使用した、変圧器ベースの設計では、短いブランкиング期間を使用します。

- バックまたはブースト・コンバータ・トポロジでは、短いブランкиング期間を使用します。

各ブランкиング期間を実現するためのBLピン接続を次に示します。

| BL CONNECTION     | BLANKING OPERATION                      |

|-------------------|-----------------------------------------|

| Open              | None (Minimum current-sense loop delay) |

| RSN               | Minimum plus 70 ns                      |

| V <sub>BIAS</sub> | Minimum plus 105 ns                     |

必要に応じて、RSPピンにRCフィルタを使用することができます。RSPピンからは、8μA未満のバイアス電流が流れます。

ブランкиング期間は、観察可能な最小ゲート・オン時間の増加として指定されます。観察可能な電流センス・ループ遅延に寄与する要素は、ブランкиング回路、電流制限またはPWMコンパレータ、制御ロジック、および負荷のかかったゲート・ドライバです。PWMおよび電流制限コンパレータは、20nsより短い信号には反応しないため、電流センス・ループ遅延測定において、本質的にある程度のブランкиングを提供しています。BLピンがオープンの場合、ブランкиング回路がループ遅延に与える要因はほとんど無視できます。ブランкиング期間は、BLがオープンのときに測定されたゲート・オン時間と、BLピンを“ハイ”または“ロー”に接続したときの時間との差として測定されます。表中のブランкиング期間には、コンパレータ遅延は含まれていません。

多くのコンバータ設計ではRSPに直列な抵抗は必要ありませんが、ピンを有害な電流から保護するために、それが必要な場合もあります。RSPピンの絶対最大電圧定格は-0.3Vですが、ESDクランプによって、100mA未満に制限されれば一時的な負電流パルスにも耐えることができます。図38の自己駆動同期整流回路など、いくつかの電源トポロジには、変圧器を通してエネルギーを戻す機能があります。これにより、RSPに負電圧が生じ、100mAを超える電流が流れる場合があります。RSPに小さな直列保護抵抗を接続することで、ショットキー・ダイオード・クランプなしでもデバイスを保護できます。

## コンバータのスタートアップ

コンバータの出力容量、コンバータの電流制限、入力バルク容量、およびソフトスタート時間の間の不均衡により、コンバータが起動時にHiccup状態になる場合があります。コンバータには、内部ホットスワップMOSFETまたはPSEのいずれかによって強制される固定入力電流制限があります。電流がこの制限を超えた場合、コンバータはバルク・キャパシタ上の電圧を取り込むことでエネルギー需要を満たします。キャパシタの電圧が下がると、内部MOSFETの両端の電圧が増加します。TPS23750のMOSFETの電圧が12Vに達すると、コンバータがオフになって、突入状態に戻り、再起動を試みます。

正常にスタートアップさせるためには、設計において出力容量と、コンバータの電流制限、入力バルク容量、およびソフトスタート時間をバランスさせる必要があります。出力容量とコンバータの電流制限は、できるだけ小さくしてください。次に、長いソフトスタート時間を使って、出力キャパシタの充電電流を制御します。最後に、このピーク需要に対応可能なエネルギーを蓄積できる大きな入力キャパシタを使用します。入力バルク・キャパシタの電圧降下は、一般に5Vを超えないようにします。

## TMRの動作

TMRは、ソフトスタートに加えて、Hiccupモードによる障害保護を提供します。Hiccup動作の各サイクルは、時間制限された過負荷状態、続いて強制的な無信号期間、そして自動再起動によって構成されます。Hiccup動作の利点には、障害時の平均熱ストレスの低減や、過渡状態でコンバータがシャットダウンした場合の自動的な再起動などがあります。

ソフトスタート中は、コンバータがイネーブルで、 $C_{TMR}$ は低電圧から3Vまで50 $\mu$ Aで充電されます。 $V_{TMR}$ が3Vに達したときに $V_{COMP}$ が4.2V未満の場合、 $C_{TMR}$ は引き続き3.5Vのクランプ・レベルまで充電され、コンバータはイネーブルのままでです。内部のスケーリングにより、4V未満の $V_{COMP}$ で最大のピーク電流制限が得られます。 $V_{COMP}$ が4.2V未満の場合、電圧ループがレギュレーション状態であることを示しています。 $V_{COMP}$ が高い場合は、何らかの問題があることを示し、最も可能性の高い問題は出力の過負荷です。 $V_{TMR}$ が3.0Vに達したときに $V_{COMP}$ が4.2Vを上回っている場合は、コンバータがディスエーブルになり、 $C_{TMR}$ が5 $\mu$ Aで放電されます。TMRが0.3Vになると、新たなソフトスタート・サイクルが開始されます。

コンバータが正常に動作しているときに、 $V_{COMP}$ が4.2Vを超えた場合、 $C_{TMR}$ は5 $\mu$ Aで3Vまで放電されます。TMRが3Vに達すると、コンバータはオフになり、Hiccupサイクルが開始されます。TMRが3Vになる前に $V_{COMP}$ が4.2Vを下回った場合は、 $C_{TMR}$ が50 $\mu$ Aで再充電され、コンバータの動作は中断なしで続行されます。 $C_{TMR}$ の値によって設定される固有のフィルタリングにより、短時間の過渡状態ではHiccup動作は行われません。

内部の誤差増幅器を使用しているかディスエーブルかにより、ソフトスタートの動作は異なります。誤差増幅器を使用している場合は、ソフトスタート中、FB上の電圧が(TMRの電圧)-0.5Vに等しくなるようレギュレーションされます。出力電圧はゆっくり上昇し、FBが1.5Vに等しいときにレギュレーション状態となります。誤差増幅器がディスエーブルの場合は、 $V_{TMR}$ が0.54Vから1.54Vに遷移するとともに、PWMコンパレータの作動点が0Vから0.5Vに上昇します。

コンバータがディスエーブルのとき、TMRは1k $\Omega$ のプルダウン抵抗によって放電されます。

その他、TMRに関係した条件には次のようなものがあります。

- PoE制御によってコンバータがディスエーブルになると、TMRは“ロー”になります。

- コンバータのUVLOが満足されていない場合、TMRは“ロー”になります。

- サーマル・シャットダウン時には、TMRは“ロー”になります。

- 障害コンパレータが4回連続して作動すると、TMRはHiccup動作を行います。Hiccupサイクルが発生する一方で、スイッチングはただちに停止されます。

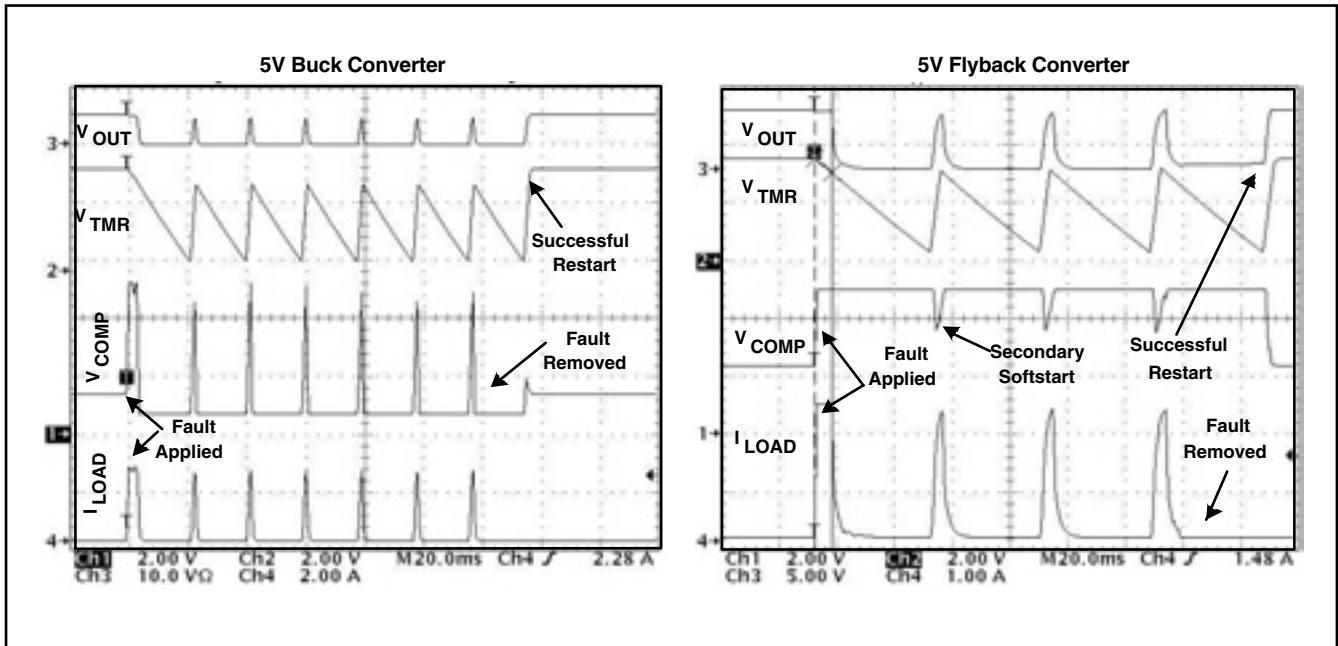

図36に、TMRピンの動作を示します。これらの波形は、図38および図40の回路を使用して得られたものです。バック・コンバータの例では、内部誤差増幅器を使用したソフトスタートが示され、フライバックの例ではフォトカップラ回路を使用したときの動作が示されています。フライバックの例では、内部誤差増幅器ではなく二次側ソフトスタートによるCOMP電圧の低下が見られます。

図 36. TMRピンの動作

### 補助電源のOR接続

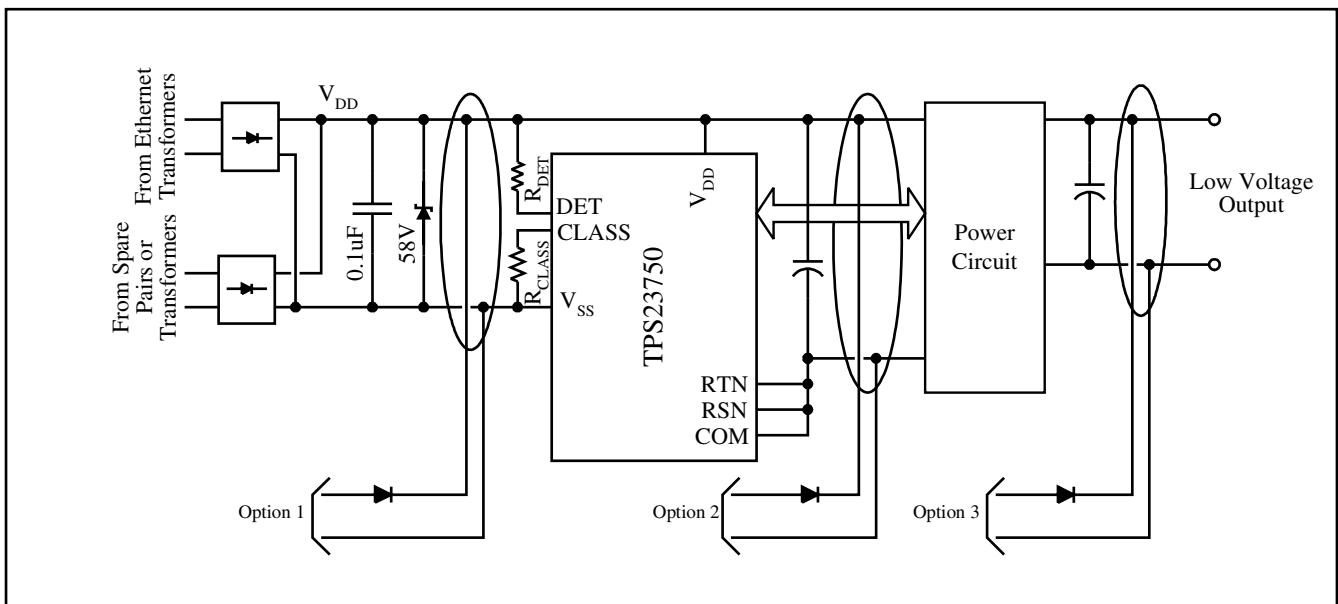

多くのPoE対応デバイスは、ACアダプタまたはPoE電源のいずれかで動作するように設計されています。ローカル電源ソリューションではコストや複雑さが増しますが、PoEが使用できるかどうかに関係なく製品を使用することができます。いずれか一方の入力を強制的に優先させることは、ソリューションの複雑化につながります。しかし、最も高電圧の電源で動作する設計であれば簡単です。ほとんどのアプリケーションでは、2つの電源が予測可能な状態で共存していることだけが要求されます。図37に、外部電源をPDにダイオードOR接続する3つのオプションを示します。オプション1は電源をTPS23750のPoE入力に供給し、オプション2はTPS23750のPoE部とコンバータ

の間に電源を挿入し、オプション3はPoE電源コンバータの出力側に電源を供給しています。これらの各オプションには、それぞれ長所と所があります。オプション1および2の場合、ACアダプタは、出力と他のすべての接続との間で最低AC1500Vの絶縁耐圧条件を満たす必要があります。オプション3の場合は、1500Vの絶縁(コンバータで提供されていない場合)だけが必要です。

すべてのオプションに対して、アダプタ入力のORダイオードが示されています。これにより、逆方向入力電圧や入力ピンでの短絡から回路を保護し、PoEと補助電圧の間に自然なOR接続が提供されます。オプション3では、MOSFETによってOR接続を実現する場合もあります。

図 37. 補助電源のOR接続

オプション1では、TPS23750の前に電源を挿入します。TPS23750のUVLOを満足する48Vのアダプタが必要です。アダプタ電源がPSEよりも前にPDに電源を供給すると、PSEがPDを検出できなくなります。これは、入力ブリッジが逆方向にバイアスされ、イーサネット電源パスがオープンに見えるためです。補助電源を接続した時点でPSEが既にPDに電源を供給している場合は、高い方の電源電圧が優先されます。

オプション2には、アダプタ電圧がPoE動作範囲より低くてもよい、という利点があります。TPS23750は、24Vのアダプタでも動作するように設計されています。V<sub>DD</sub>とRTNの間に接続されるバルク・キャパシタは、アダプタを接続したときに生じる過渡電圧を制御するのに十分な容量を持つ必要があります。通常は、最低数μF以上が必要です。PDにアダプタから電源が供給されると、PSEはPDの検出に失敗します。これは、内部MOSFETのボディ・ダイオードによって入力ブリッジに逆方向のバイアス電圧がかかるためです。PDにPSEから電源が供給されているときは、補助電源の電圧がPSE出力よりも高い場合にだけ、補助電源に切り替わります。

オプション1または2を使用するときには、一方の電源入力を他方よりも優先した方が望ましい場合もあります。これは、適切な電源パスにスイッチを設けて、一方の電源が他方の電源をオフにできるようにすることで、いくつかの構成に対して実現できます。これらのソリューションには、いくつかの追加部品が必要となります。PSEを切り離すためには、DC電流が5mAを下回り、ACインピーダンスが500Hzで2MΩを上回る必要があります。

オプション3では、PoEのDC/DCコンバータの出力に電源をOR接続しています。このオプションは、低電圧のACアダプタを使用する既存の設計にPoEを追加する場合に多く用いられます。比較的大きなPD出力容量により、アダプタの接続時に過渡電圧が生じる可能性は小さくなっています。PDに絶縁型コンバータが含まれる場合は、アダプタ出力を接地することができます。最も電圧の高い電源が優先されます。補助電源を強制的にオフにするPチャンネルMOSFETを使用した単純な回路も設計できます。帰還ノードをレギュレーション値よりも強制的に高くすることで、補助電源がTPS23750コンバータにスイッチングを停止させることも可能です。その結果、コンバータはシャットダウンされます。

## ESD

TPS23750は、図40に示す回路を使用し、EN61000-4-2に対してテストされています。使用したレベルは、8kVの接触放電と、15kVの気中放電です。RJ-45とDC EVM出力の間、および補助電源入力ジャックとDC出力の間にサージが印加され、障害は確認されていません。

TPS23750を組み込む装置のESD要求は、TIでのテストよりもずっと幅広い範囲と動作条件を含んでいます。装置レベルの要求は、TPS23750の堅牢性を検証するだけの基準設計テストとは別のものですので、注意してください。

## 部品の選択

### コンバータ部のバイパス・キャパシタ

コンバータ部のAUXおよびV<sub>BIAS</sub>ピンは、高品質のセラミック・キャパシタでバイパスする必要があります。V<sub>BIAS</sub>電源は、内部および外部回路に対して低雑音の電源を提供します。V<sub>BIAS</sub>レギュレータは、0.08μF～1.5μFの出力容量に対して安定しています。1μFのキャパシタを推奨します。また、実用上可能な限りTPS23750に近づけて配置してください。AUX電源は、GATE駆動電流パルスの電源となります。この電源には、0.8μF以上のセラミック・バイパス・キャパシタが必要です。AUXのキャパシタは、TPS23750にできるだけ近づけて配置する必要があります。AUXレギュレータは、これよりずっと大きな容量を負荷にできます。

### PoEデータ変圧器

ツイスト・ペア線で動作するイーサネット・インターフェイスは、長年使用されているIEEE 802.3要求に従って、一般に絶縁変圧器を使用します。変圧器は、メディア(ケーブル)側にセンター・タップを持ち、IEEE 802.3afのDC電流および不均衡を処理できる定格を持つ必要があります。

### 入力ダイオードまたはダイオード・ブリッジ

IEEE 802.3afでは、PDがどちらの入力ペアのどちらの極性でも電力を受け取ることを求めています。この要求は、図1に示すように、2つの全波入力ブリッジ整流器を使用することで満足されます。1Aまたは1.5A定格で耐圧100V以上のシリコンp-nダイオードを推奨します。検出時などの低電流動作状態では、ダイオードの動的抵抗が大きくなります。ダイオードの動作は、この状態でテストされる必要があります。ダイオードの順方向電圧降下は、最低の動作温度時に500μAで1.5V未満である必要があります。

## PoE入力キャパシタ

IEEE 802.3afでは、検出中のPD入力容量が0.05μF～0.12μFであることが求められています。このキャパシタは、図1に示されるように、TPS23750に隣接して配置する必要があります。100V/10%のX7Rセラミック・キャパシタは、幅広い温度範囲にわたってこの仕様を満足します。

## 入力過渡電圧抑制回路 (TVS)

図1に示すように、整流されたPoE電圧と並列にTVSを使用する必要があります。SMAJ58Aまたは同等以上の性能を持つ部品を推奨します。V<sub>DD</sub>-RTN間に補助電源を接続する場合は、入力ケーブル・インダクタンスが内部PD容量とリンクして過渡電圧が生じる可能性があります。適切な容量性フィルタリングまたはTVSによって、この電圧を絶対最大定格内に制限する必要があります。

## コンバータのバルク・キャパシタ

IEEE 802.3afでは、電源供給状態でPD入力容量が5μF以上である必要があります。一般に、CISPR22、またはIEEE 802.3afの33.3.4および33.3.5項で求められるような伝導性放射の条件を満たすには、さらに大きな容量が必要です。過渡状態の制御を助けるために、V<sub>DD</sub>とRTNの間に数μF以上が直接挿入される必要があります。

## TMRキャパシタ

C<sub>TMR</sub>は、内部誤差増幅器を使用するときのターンオン・プロファイルおよび入力電流の制御において主要な役割を果たします。このキャパシタの公称値は次の式で得られます。

$$C_{TMR} = 33 \times 10^{-6} \times t$$

ここで、tは必要なソフトスタート期間であり、C<sub>TMR</sub>の単位はファラッドです。TMR電流の変動およびキャパシタの公差により、ソフトスタート期間には50%の変動があります。キャパシタの容量もそれに合わせて多めに見積もる必要があります。標準的なソフトスタート期間は、数msのオーダーになります。出力障害からコンバータのシャットダウン (Hiccup開始) までの遅延時間は、次のようにになります。

$$t_{DELAY} = 95 \times 10^3 \times C_{TMR}$$

ここで、t<sub>DELAY</sub>の単位は秒、C<sub>TMR</sub>はファラッドです。

また、ソフトスタート・キャパシタは、ピーク入力電流の制限において内部誤差増幅器を使用しない絶縁型設計にも役立ちます。その場合も出力誤差増幅器はスタートアップ中に飽和からレギュレーションまでスイングする必要があるため、二次側ソフトスタートが必要な場合があります。

## 熱に関する考慮事項およびMOSFETのQ<sub>G</sub>

AUX内部レギュレータは、大量の熱を放散する可能性があります。これは、外部ソースよりもV<sub>DD</sub>レールから大きなAUXレール電流が流れる場合に起こります。AUXに外部電源を供給する場合は、内部の熱放散は低く保たれます。AUXは、スイッチングMOSFETやフォトカップラなどの外部負荷に加えて、内部バイアス電流を供給します。

変圧器結合回路を使用するアプリケーションでは、図38のような追加巻線によって、内部AUXレギュレータを無効にすることができます。出力短絡などの障害状態では、AUXレギュレータがアクティブになります。ゲート駆動負荷によって大きな瞬時電力が消費される可能性がありますが、フォトカップラはそのような場合に電力を取り込みません。TMRは、平均動作デューティ・サイクルを10%未満に制限します。それにより、内部消費電力が大きく低減されます。

内部AUXレギュレータを無効にしないアプリケーションでは、AUX上の負荷を最小限にする必要があります。主要な負荷源は、コンバータのスイッチングMOSFETのゲート容量です。Q<sub>G</sub>は、トランジスタをオンまたはオフにするために必要な電荷を定義する、MOSFETデータ・シートのパラメータです。スイッチングMOSFETは、r<sub>DS(on)</sub>に関連するMOSFETの損失と、必要なゲート駆動電流との間でバランスが取れるように選択してください。多くのアプリケーションに対しては、5nCの領域のQ<sub>G</sub>を持つ適切なデバイスが使用できます。20nCを超えるデバイスは推奨しません。ゲート駆動によって消費される内部電力は、次の式で概算されます。

$$P_{DISS\_GATE\_DRV} = [V_{DD} \times Q_G \times f].$$

PowerPADにより、熱を除去するための低熱抵抗パスが提供され、高消費電力が避けられないアプリケーションも設計可能になります。

| INTERNAL DISSIPATION MODEL                 |                                                                                                                                                                                      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Isolated converter with AUX override       | $P = \left[ \left( \frac{P_{IN}}{V_{DD}} \right)^2 \times R_{DSON} \right] + [V_{AUX} \times Q_G \times f] + [V_{AUX} \times I_{INTERNAL}] + [(V_{AUX} - V_{BIAS}) \times I_{OPTO}]$ |

| Isolated converter without AUX override    | $P = \left[ \left( \frac{P_{IN}}{V_{DD}} \right)^2 \times R_{DSON} \right] + [V_{DD} \times Q_G \times f] + [V_{DD} \times I_{INTERNAL}] + [(V_{DD} - V_{BIAS}) \times I_{OPTO}]$    |

| Nonisolated converter with AUX override    | $P = \left[ \left( \frac{P_{IN}}{V_{DD}} \right)^2 \times R_{DSON} \right] + [V_{AUX} \times Q_G \times f] + [V_{AUX} \times I_{INTERNAL}]$                                          |

| Nonisolated converter without AUX override | $P = \left[ \left( \frac{P_{IN}}{V_{DD}} \right)^2 \times R_{DSON} \right] + [V_{DD} \times Q_G \times f] + [V_{DD} \times I_{INTERNAL}]$                                            |

表3. 消費電力

内部の熱放散に寄与する主な要素は次の4つです。内部(ホットスワップ)MOSFETのI<sup>2</sup>R、ゲート駆動負荷、内部バイアス電力、およびフォトカップラの負荷です。この4つの要素により、表3に示すような一般的な構成での損失の概算式が導かれます。低入力電圧、中入力電圧、および高入力電圧での全損失をチェックしてください。I<sup>2</sup>Rが支配的な設計は低入力電圧で数値が悪く、AUX負荷損失が中心となる設計は高入力電圧で悪い傾向にあります。

- $I_{INTERNAL}$ は、電気的特性の表に記載された動作電流を表します。すべての電流がコントローラによるものであると近似しています。

- $P_{IN}$ は、コンバータの入力電力( $P_{OUT}$ /効率)です。PI上の電力ではありません。

- $f$ はコンバータのスイッチング周波数であり、 $I_{OPTO}$ はフォトカップラのバイアス電流です。

- $V_{DD}$ は次のように計算できます。

$$V_{DD} = \frac{(V_{PSE} - 2 \times V_D) + \sqrt{(V_{PSE} - 2V_D)^2 - 4 \times P_{IN} \times R_{LOOP}}}{2}$$

ここで、 $V_D$ は入力ダイオードの電圧降下(0.75V)、 $R_{LOOP}$ は0Ω～20Ω(+MOSFET抵抗)、および $P_{IN}$ は上記のとおりです。MOSFET損失が支配的な場合には、 $V_{PSE}$ は44Vです。

- $R_{DSON}$ は、内部パスMOSFET抵抗であり、標準0.6Ω、最大1Ωです。

- ワースト・ケースを決定するために、損失はいくつかの異なるPI電圧でチェックする必要があります(特に、AUXを無効にする機能を使用していない場合)。

接合部温度の単純な熱モデルは次のようにになります。

$$T_J = T_A + (P \times \theta_{JA})$$

ここで、 $T_J$ は接合部温度、 $T_A$ は周囲温度、 $P$ はTPS23750での合計消費電力、 $\theta_{JA}$ は接合部から周囲への熱抵抗です。 $\theta_{JA}$ には、ダイからパッケージを経由して直接空気中への熱パス、リードを経由して基板への熱パス、PowerPADから基板への熱パス、および基板から空気中への熱パスが含まれています。長期間の安定状態接合部温度は、125°C未満に保つ必要があります。

熱設計の事例として、次のようなバック・コンバータの例を考えます。

- 出力は1.5Aで5V、効率の見積もり値は85%。

- 選択されたスイッチングMOSFETの $Q_G$ は10nC、スイッチング周波数は200kHz。

- ワーストケースの内部MOSFET抵抗1Ωを使用。

- 周囲温度は65°Cと仮定。

- 热抵抗は45°C/Wと仮定(PowerPADが広い銅領域に接続されているが、正確にSLMA002の記載どおりではないため)。

- 表4に示される入力電圧とループ抵抗のワーストケースの組み合わせを使用。

$$P_{IN} = 5V \times 1.5A / 0.85 = 8.82W$$

$$V_{DD} = \frac{(44V - 2 \times 0.75V) + \sqrt{(44V - 2 \times 0.75V)^2 - 4 \times 8.82W \times 20\Omega}}{2} = 37.84V$$

$$P = \left[ \left( \frac{8.82W}{37.84V} \right)^2 \times 1\Omega \right] + [37.84V \times 10nC \times 200\text{kHz}] + [37.84V \times 2.2\text{mA}] = 0.213W$$

$$T_J = 65^\circ\text{C} + (0.213W \times 45^\circ\text{C}/W) = 74.6^\circ\text{C}$$

| V <sub>PSE</sub> | R <sub>LOOP</sub> (Ω) | V <sub>DD</sub> (V) | P (W) | T <sub>J</sub> (°C) |

|------------------|-----------------------|---------------------|-------|---------------------|

| 44               | 20                    | 37.84               | 0.213 | 74.6                |

| 50.5             | 10                    | 47.13               | 0.233 | 75.5                |

| 57               | 0                     | 55.5                | 0.258 | 76.6                |

表4. 温度上昇計算の一覧

3つの条件の計算により、どの場合に接合部温度がより高くなるかが決定されました。この例では、入力電圧に対するI<sup>2</sup>R損失とバイアス損失の変動はほとんど相殺されています。結果として得られた接合部温度は、かなり低くなっています。これは、適切な回路選択、適度な周囲温度、低い熱抵抗などによるものです。

## レイアウト

PoEフロント・エンドのレイアウトでは、電源およびEMI/ESDに関する適切な手法に従う必要があります。基本的な推奨事項を次に示します。

- 部品の配置は、ポイントごとの電力フローに沿って行う必要があります (RJ-45 → イーサネット変圧器 → ダイオード・ブリッジ → TVSおよび0.1μFキャパシタ → TPS23750 → バルク・キャパシタ → コンバータ入力、など)。

- 1つのフローから別のフローへの信号のクロスオーバーがないようにします。

- すべての電源リードは、できるだけ短くし、広い電源トレースを設け、信号とリターンをペアで配置してください。

- 48V入力電圧レールの間、および入力と絶縁型コンバータの出力との間には、IEC60950またはIPC2221Aなどの規格に準拠したスペースを確保してください。

- TPS23750は、PoE入力に対してはVSS基準、コンバータに対してはRTN基準の、分割されたローカル・グランド・プレーン上に配置してください。PoE側はグランド・プレーンなしでも動作可能ですが、コンバータ側には必ずグランド・プレーンが必要です。(特に消費電力が問題となる場合には) PowerPADをV<sub>SS</sub>プレーンまたはフィル領域に接続する必要があります。イーサネット入力またはコンバータの一次側の下にロジック・グランド層やロジック電源層が存在してはなりません。

- SMT電力消費デバイスには面積の大きな銅フィルおよびトレースを使用し、電源パスには幅広いトレースまたはオーバーレイ銅フィルを使用します。

- コンバータのレイアウトでは、次のような基本的な規則に従うことで良い結果が得られます。

- 信号をペアにすることで放射と雑音を低減します。特に、パワー半導体や磁気回路を通して高電流パルスを伝達するパスで重要です。

- 高電流パルスを伝達するすべてのトレースの長さをできるだけ短くします。

- 可能であれば、水平に並べるのではなく垂直に重ねてペアとします。

- 高電流および高電圧のスイッチング・トレースは、低レベルのアナログ回路(電源の外部の回路も含む)から離して配置します。FB、COMP、FREQ、およびTMRには特に注意してください。

- RSPへの電流センス・リードは、最も影響の大きい、雑音に敏感な信号です。このリードは、ゲート駆動信号に接触しないよう注意して、d項のように保護する必要があります。

- コンバータの高電圧部分の周囲には十分なスペースを確保します。

- 本製品に対しては、上記の原則に従った2つの評価モジュール(EVM)が用意されています。PCBレイアウトを含むドキュメントをオンラインで入手できます。

## 概念回路図

TPS23750は、従来のほとんどの回路で動作します。図38、図39、および図40に、TPS23750の応用例を示しています。図38は絶縁型同期フライバック、図39は非絶縁型フライバック、図40はバック・コンバータの一例です。これらの各回路は、単一の出力を提供します。二次側巻線を複数持つ変圧器や、リニア・レギュレータとスイッチング・レギュレータの組み合わせなどを用いて、複数の出力を得ることもできます。この3つの回路が、本製品に提供されている2つのEVMの基礎となっています。

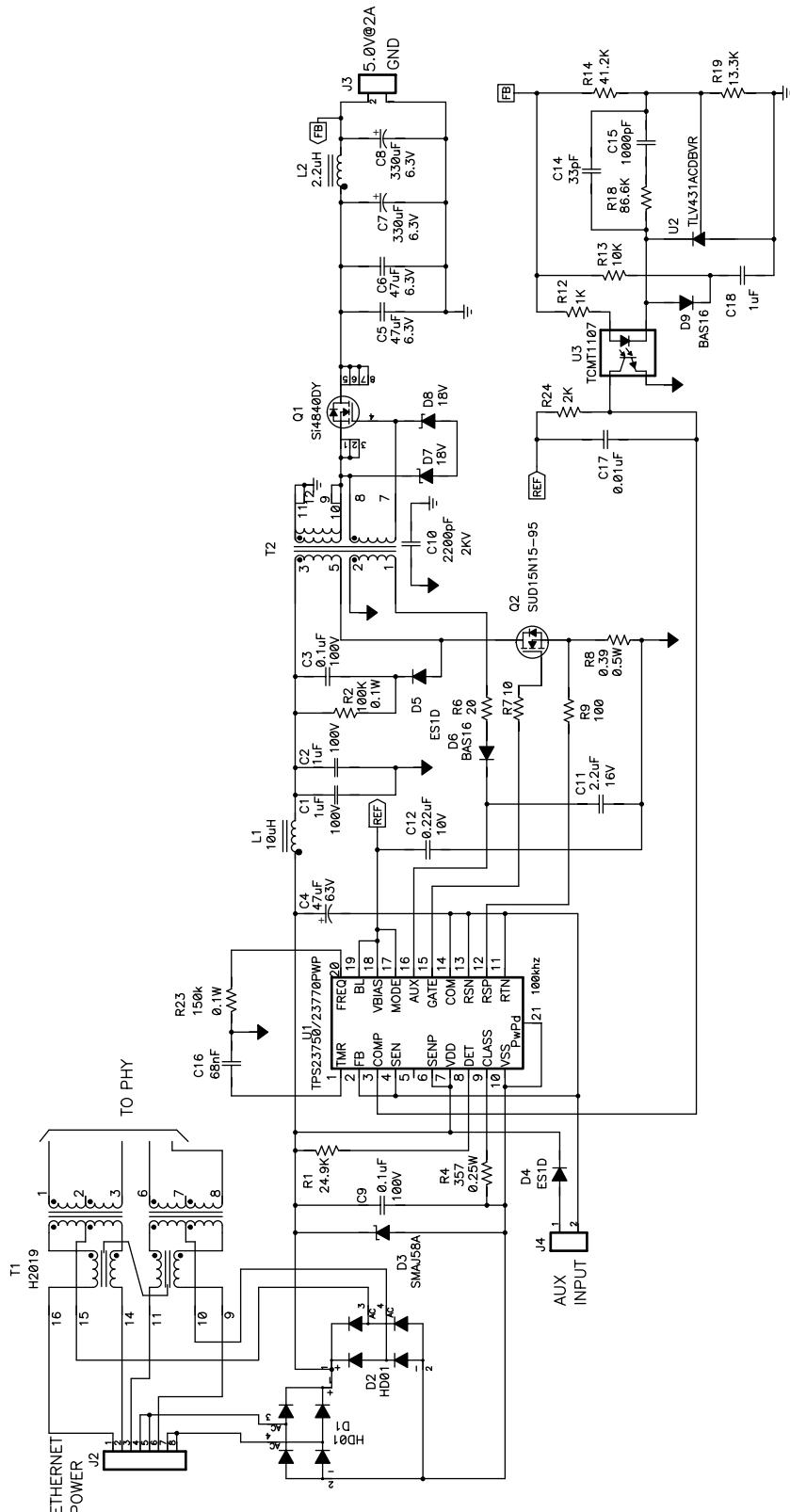

### 絶縁型フライバックの例

図38に示す絶縁型同期フライバックは、PDがRS-232やUSBなどの非絶縁型メタリック・インターフェイスを持つ場合、またはIEC60950の6.2項に従って1500Vの絶縁耐圧試験を満足できない場合などに適しています。このアプリケーションでは、フォワード・コンバータも使用できます。

この例では、外部のACアダプタで電圧をPoE出力後のコンバータ入力に直接印加できるようになっています。この例のコンバータは48Vで動作するように設計されていますが、24V~48V(公称)のアダプタ入力を接続でき、コンバータが起動します。PoE入力、アダプタ入力、およびコンバータ動作の間のシーケンシングは、内部で処理されます。

RJ-45コネクタから始まる標準的なPoEフロント・エンドには、ダイオード・ブリッジ、キャパシタ、およびTVSが含まれます。TPS23750は、制御回路の中核を成し、基本的なPoEおよびDC/DCコンバータ機能を実行します。R1は検出機能で使用されます。R4はPDをクラス3(フル・パワー)デバイスとして設定します。内部のMOSFETにより、障害状態で突入電流制限および電流制限を実施している間、PoE検出中および分類中にコンバータが入力から分離されます。入力エネルギーの蓄積およびEMIフィルタリングは、C4、L1、C1、C2で構成されるπフィルタによって実行されます。コンバータのスタートアップ・バイアスは、内部レギュレータによって処理されるため、いくつかの外部部品が不要となっています。

内部誤差増幅器およびバック・レギュレータ・センス回路は、MODEをV<sub>BIAS</sub>、SENをRTNに設定することでディスエーブルされます。内部誤差増幅器をディスエーブルすると、外部のフォトカッピラU3がCOMPをハイ・インピーダンス・ピンとして駆動できます。BLをV<sub>BIAS</sub>に接続することで長いブランкиング期間が選択され、出力同期整流器(Q1)の回復が可能になっています。C16はソフトスタートおよびHiccup期間を設定し、R23は100kHzのスイッチング周波数を設定します。この設計では、スイッチング損失を低減するために、スイッチング周波数が100kHz

に設定されています。C11およびC12は内部レギュレータのバイパスを提供し、D6およびR6は変圧器からのAUXバイアス電力を提供して効率を向上しています。D5、R2、およびC3は、スイッチングMOSFETのQ2をオフ時の電圧スパイクから保護するための電圧クランプを構成しています。電流センス抵抗R8は、RSPを通して電流モード制御コンパレータに接続され、電流制限を設定します。R9は、R8上の負電圧によって生じる過度の電流からRSPピンのESDクランプを保護するために使用されています。これは、この同期コンバータ・トポロジが出力に電圧の残った状態でスイッチングを停止した場合に生じる異常な状況であり、出力エネルギーが入力に再循環されます。

この5V出力の例では、変圧器の一次インダクタンスが150μHであり、巻線比はPRI:BIAS:OUTPUT:GATE = 5:2.22:1:1.56です。巻線7-8は、同期整流器Q1のゲート駆動を提供しています。この設計は、同期整流動作のため、無負荷までの連続導通で動作します。出力πフィルタは、C5、C6、C7、L2、C8によって構成されます。非常に低い出力リップルを提供するこのフィルタは、アプリケーションによっては単純化することができます。帰還は従来のTL431誤差増幅器U2によって駆動され、フォトカッピラU3を駆動しています。部品D9、C18、およびR13は、U2がレギュレーションのためにカソードを数ボルトにスイングする間、ターンオン時のオーバーシュートを制限するソフトスタートとして機能します。C17は、フォトカッピラを出力からバイアスすることで生じる内部の帰還ループを補償します。C10はEMI制御に使用され、規格で必要とされる1500Vの絶縁試験を満足するために高い電圧定格を持っています。

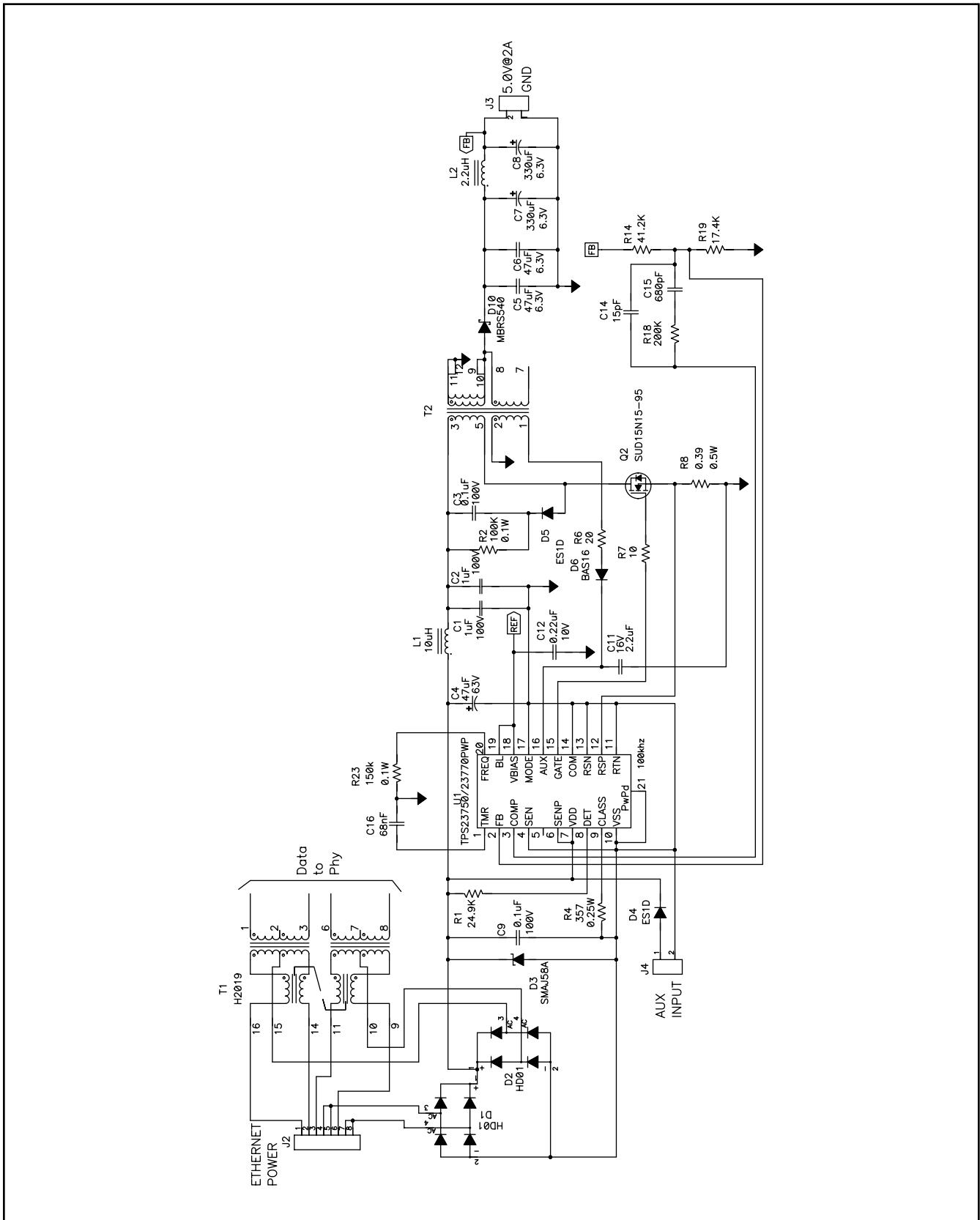

### 非絶縁型フライバックの例

図39の非絶縁型フライバックは、分離型フライバックと似ています。メタリック・インターフェイスを使用しておらず、PDが絶縁せずにIEEE802.3afの1500Vの絶縁耐圧を満足できるようなアプリケーションでは、このコンバータを使用して複数の出力を生成するために用いられます。複数の出力は、ダイオードおよびキャパシタとともにT2に二次巻線を追加することで実現できます。実例を示す目的上、同期整流器はダイオードで置き換えてあります。ダイオードの方が単純で安価ですが、同期整流器の方が電力損失が小さいため、低電圧、高電流出力に対しては効率が向上します。T2の巻線7-8は、実際の設計では必要ありません。TL431に基づく誤差増幅器とフォトカッピラは除去され、TPS23750の内部誤差増幅器はMODEをRTNに接続することでイネーブルになっています。制御および補償のために、FBとCOMPが標準的な誤差増幅器トポロジで使用されています。

## バック・コンバータの例