**TPS1HB35-Q1** JAJSHN5B - JUNE 2019 - REVISED FEBRUARY 2023

# TPS1HB35-Q1 40V、35mΩ のシングル・チャネル、車載用スマート・ハイサイ ド・スイッチ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証を取得

- 温度グレード 1:-40℃~125℃

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C4B

- 40V の負荷ダンプへの耐性

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可

- 35m $\Omega$  R<sub>ON</sub> (T<sub>J</sub> = 25°C) のシングル・チャネル、スマー ト・ハイサイド・スイッチ

- 可変電流制限によるシステム・レベルの信頼性の向上

- 電流制限を 2A~22A の範囲で設定可能

- 堅牢な出力保護機能を内蔵:

- 熱保護機能を内蔵

- グランド / バッテリへの短絡に対する保護

- 逆電圧による FET の自動スイッチ・オンを含むバッ テリ逆接続からの保護

- バッテリおよびグランドの喪失時に自動シャットオフ

- 誘導性負荷の逆起電圧の発生を防止する出力クラ ンプを内蔵

- フォルト処理を設定可能

- アナログ検出出力は、以下を正確に測定するよう設定 可能:

- 負荷電流

- デバイス温度

- SNS ピンによるフォルト表示を実現

- 開放負荷とバッテリ短絡の検出

## 2 アプリケーション

- 車載ディスプレイ・モジュール

- ADAS モジュール

- コンフォート・シート・モジュール

- トランスミッション制御ユニット

- HVAC (エアコン) 制御モジュール

- 車体制御モジュール

- 白熱光および LED ライティング

### 3 概要

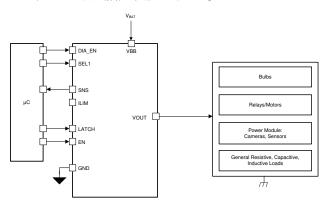

TPS1HB35-Q1 デバイスは、12V 車載システムでの使用 を目的としたスマート・ハイサイド・スイッチです。このデバ イスは、車載システムでの短絡など有害な事象の発生時 でも出力ポートを確実に保護できるよう、堅牢な保護およ び診断機能を内蔵しています。デバイスの種類に応じて 信頼性の高い電流制限を行い、障害から保護します。電 流制限は、2A~22A に設定可能です。 電流制限範囲を 小さくすると、大きなピーク電流を必要としない負荷で保護 を強化でき、電流制限範囲を大きくすると、大きな過渡電 流を必要とする負荷でも使用できます。このデバイスは、 広い範囲の負荷プロファイルを高い信頼性で駆動できま す。

TPS1HB35-Q1 は、負荷診断機能を強化できる高精度ア ナログ電流検出機能も備えています。負荷電流とデバイス 温度をシステムの MCU に報告することで、システムの寿 命を延ばす予知保全と負荷診断が可能です。

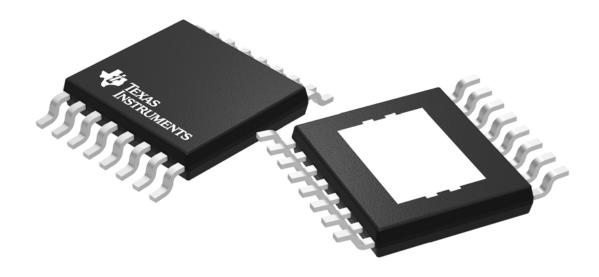

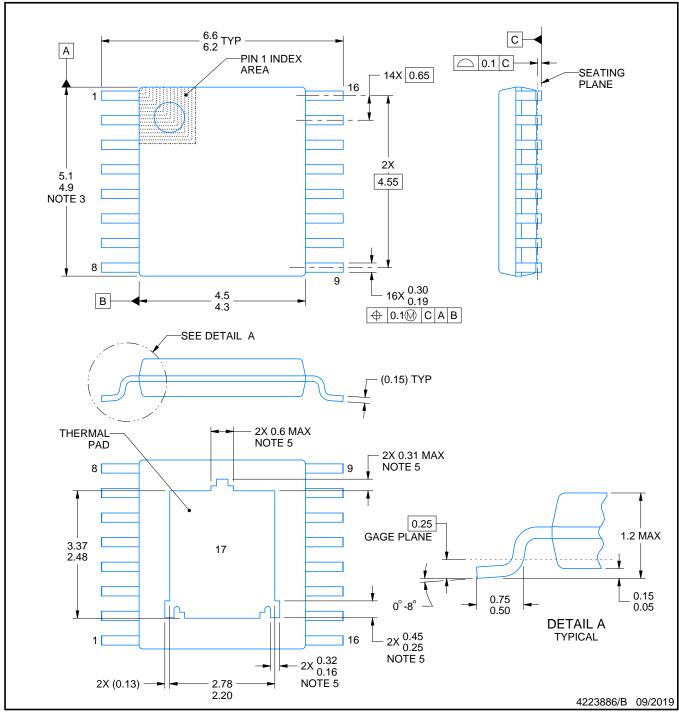

TPS1HB35-Q1 は、PCB の占有面積を減らすことができ る HTSSOP パッケージで供給されます。

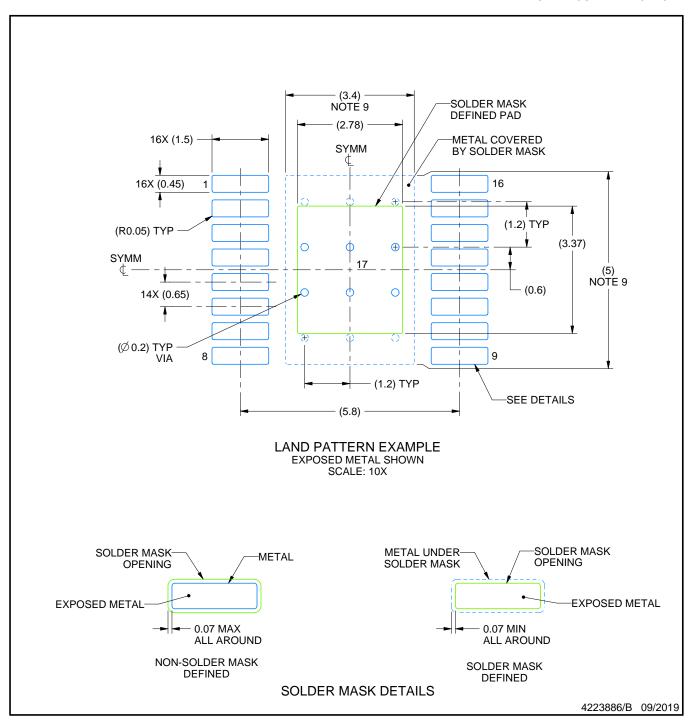

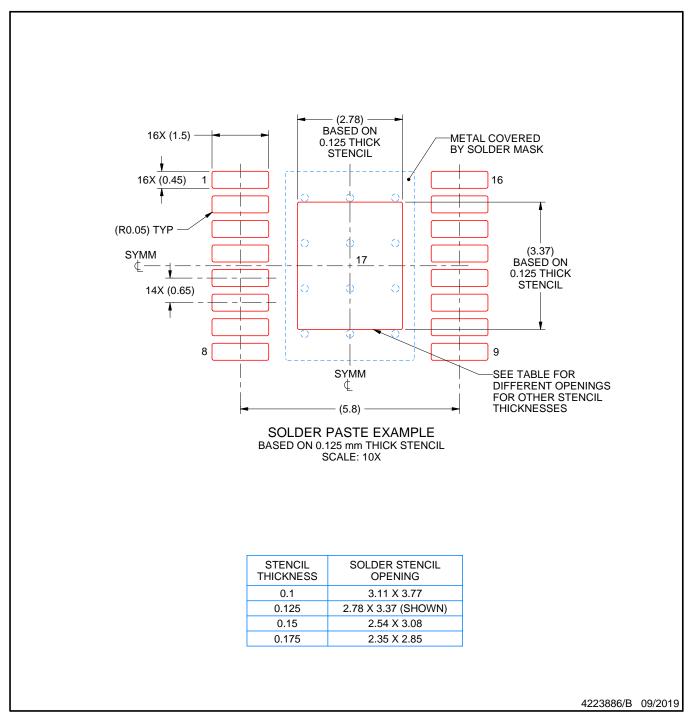

### パッケージ情報

| 部品番号(1)     | パッケージ       | 本体サイズ (公称)      |

|-------------|-------------|-----------------|

| TPS1HB35-Q1 | HTSSOP (16) | 5.00mm × 4.40mm |

利用可能なすべてのパッケージについては、このデータシートの (1) 末尾にある注文情報を参照してください。

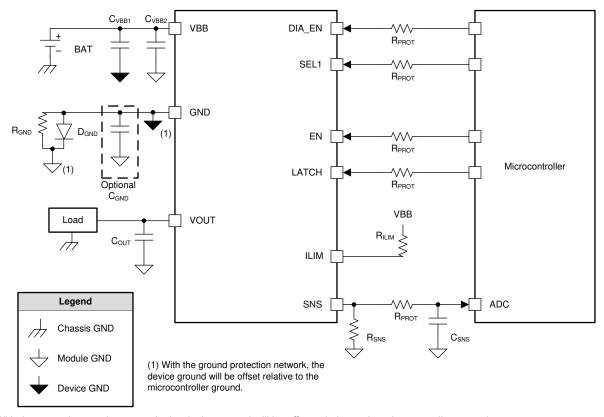

簡略回路図

## **Table of Contents**

| 1 特長 1                                       | 9.2 Functional Block Diagram            | 20 |

|----------------------------------------------|-----------------------------------------|----|

| 2 アプリケーション1                                  | 9.3 Feature Description                 |    |

| 3 概要                                         | 9.4 Device Functional Modes             |    |

| 4 Revision History2                          | 10 Application and Implementation       | 38 |

| 5 Device Comparison Table                    | 10.1 Application Information            | 38 |

| 6 Pin Configuration and Functions4           | 10.2 Typical Application                |    |

| 6.1 Recommended Connections for Unused Pins5 | 10.3 Typical Application                |    |

| 7 Specifications6                            | 10.4 Power Supply Recommendations       |    |

| 7.1 Recommended Operating Conditions6        | 10.5 Layout                             | 46 |

| 7.2 Electrical Characteristics               | 11 Device and Documentation Support     | 47 |

| 7.3 Absolute Maximum Ratings                 | 11.1 Documentation Support              | 47 |

| 7.4 ESD Ratings9                             | 11.2ドキュメントの更新通知を受け取る方法                  | 4  |

| 7.5 Thermal Information9                     | 11.3 サポート・リソース                          | 47 |

| 7.6 SNS Timing Characteristics               | 11.4 Trademarks                         |    |

| 7.7 Switching Characteristics                | 11.5 静電気放電に関する注意事項                      |    |

| 7.8 Typical Characteristics                  | 11.6 用語集                                |    |

| 8 Parameter Measurement Information17        | 12 Mechanical, Packaging, and Orderable |    |

| 9 Detailed Description19                     | Information                             | 47 |

| 9.1 Overview                                 |                                         |    |

|                                              |                                         |    |

|                                              |                                         |    |

## **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (October 2020) to Revision B (February 2023)                              | Page |

|---------------------------------------------------------------------------------------------------|------|

| Removed product preview note from device version C                                                | 3    |

| Updated device reference in Recommended Connections for Unused Pins section                       | 5    |

|                                                                                                   |      |

| Changes from Revision * (June 2019) to Revision A (October 2020)                                  | Page |

| Changes from Revision * (June 2019) to Revision A (October 2020)  ・ ドキュメント全体にわたって表、図、相互参照の採番方法を更新 |      |

# **5 Device Comparison Table**

| DEVICE<br>VERSION | PART NUMBER           | CURRENT LIMIT         | CURRENT LIMIT RANGE | OVERCURRENT BEHAVIOR                           |

|-------------------|-----------------------|-----------------------|---------------------|------------------------------------------------|

| Α                 | TPS1HB35 <b>A</b> -Q1 | Resistor Programmable | 2 A to 10 A         | Disable switch immediately                     |

| В                 | TPS1HB35 <b>B</b> -Q1 | Resistor Programmable | 4.4 A to 22 A       | Disable switch immediately                     |

| С                 | TPS1HB35 <b>C</b> -Q1 | Resistor Programmable | 2.5 A to 6 A        | Keep switch on until relative thermal shutdown |

| F                 | TPS1HB35 <b>F</b> -Q1 | Internally set        | 34 A                | Disable switch immediately                     |

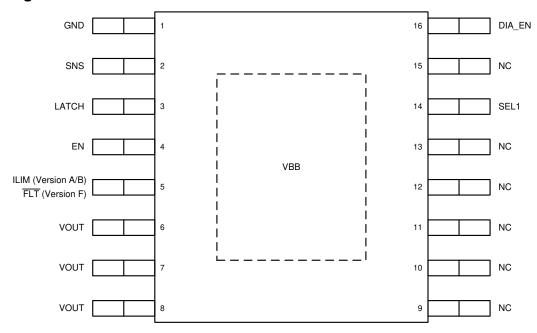

## **6 Pin Configuration and Functions**

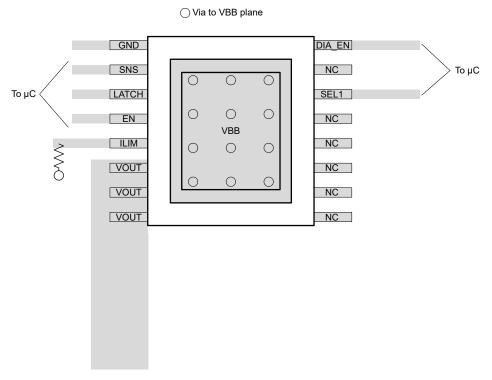

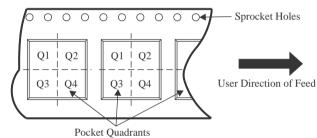

図 6-1. PWP Package 16-Pin HTSSOP Top View

表 6-1. Pin Functions

| P      | IN              |              |     |                                                                                                                |

|--------|-----------------|--------------|-----|----------------------------------------------------------------------------------------------------------------|

| NAME   | VERSION<br>A/BC | VERSION<br>F | I/O | DESCRIPTION                                                                                                    |

| GND    | 1               | 1            | _   | Device ground                                                                                                  |

| SNS    | 2               | 2            | 0   | Sense output                                                                                                   |

| LATCH  | 3               | 3            | I   | Sets fault handling behavior (latched or auto-retry)                                                           |

| EN     | 4               | 4            | I   | Control input, active high                                                                                     |

| ILIM   | 5               | -            | 0   | Connect resistor to set current-limit threshold                                                                |

| FLT    | -               | 5            | 0   | Open drain output with pulldown to signal fault.                                                               |

| VOUT   | 6 - 8           | 6 - 8        | 0   | Channel output                                                                                                 |

| NC     | 9 - 13, 15      | 9 - 13, 15   | I   | No Connect, leave floating                                                                                     |

| SEL1   | 14              | 14           | I   | Diagnostics select. No functionality on device version F; connect to IC GND through R <sub>PROT</sub> resistor |

| DIA_EN | 16              | 16           | I   | Diagnostic enable, active high                                                                                 |

| VBB    | Exposed pad     | Exposed pad  | I   | Power supply input                                                                                             |

## **6.1 Recommended Connections for Unused Pins**

The TPS1HB35-Q1 is designed to provide an enhanced set of diagnostic and protection features. However, if the system design only allows for a limited number of I/O connections, some pins can be considered as optional.

表 6-2. Connections For Optional Pins

| PIN NAME           | CONNECTION IF NOT USED                             | IMPACT IF NOT USED                                                                                                                                                                                                                            |

|--------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SNS                | Ground through 1-kΩ resistor                       | Analog sense is not available.                                                                                                                                                                                                                |

| LATCH              | Float or ground through R <sub>PROT</sub> resistor | With LATCH unused, the device auto-retries after a fault. If latched behavior is desired, but the system describes limited I/O, it is possible to use one microcontroller output to control the latch function of several high-side channels. |

| ILIM (Version A/B) | Float                                              | If the ILIM pin is left floating, the device is set to the default internal current-limit threshold.                                                                                                                                          |

| FAULT (Version F)  | Float                                              | Open drain FAULT signal is not able to be used                                                                                                                                                                                                |

| SEL1               | Ground through RPROT                               | SEL1 selects the TJ sensing feature. With SEL1 unused, only current sensing and open load detection are available. If unused, must be grounded through a resistor to engage FET turn-on during reverse battery.                               |

| DIA_EN             | Float or ground through R <sub>PROT</sub> resistor | With DIA_EN unused, the analog sense, open-load, and short-to-battery diagnostics are not available.                                                                                                                                          |

## 7 Specifications

## 7.1 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (1)

|                     |                                                 | MIN | MAX | UNIT |

|---------------------|-------------------------------------------------|-----|-----|------|

| V <sub>BB</sub>     | Nominal supply voltage <sup>(1)</sup>           | 6   | 18  | V    |

| V <sub>BB</sub>     | Extended lower supply voltage                   | 3   | 6   | V    |

| $V_{BB}$            | Extended higher supply voltage <sup>((2))</sup> | 18  | 28  | V    |

| V <sub>EN</sub>     | Enable voltage                                  | -1  | 5.5 | V    |

| V <sub>LATCH</sub>  | LATCH voltage                                   | -1  | 5.5 | V    |

| V <sub>DIA_EN</sub> | Diagnostic Enable voltage                       | -1  | 5.5 | V    |

| V <sub>SEL1</sub>   | Select voltage                                  | -1  | 5.5 | V    |

| V <sub>SNS</sub>    | Sense voltage                                   | -1  | 7   | V    |

<sup>(1)</sup> All operating voltage conditions are measured with respect to device GND

## 7.2 Electrical Characteristics

$V_{BB} = 6 \text{ V}$  to 18 V,  $T_{J} = -40 ^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$  (unless otherwise noted)

|                            | PARAMETER                                       | TEST CONDITIONS                                                                                                              | MIN | TYP  | MAX | UNIT |

|----------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| INPUT VOL                  | TAGE AND CURRENT                                |                                                                                                                              |     |      |     |      |

| V <sub>DSCLAMP</sub>       | V <sub>DS</sub> clamp voltage                   |                                                                                                                              | 40  |      | 46  | V    |

| V <sub>BBCLAMP</sub>       | V <sub>BB</sub> clamp voltage                   |                                                                                                                              | 58  |      | 76  | V    |

| V <sub>UVLOF</sub>         | V <sub>BB</sub> undervoltage lockout falling    | Measured with respect to the GND pin of the device                                                                           | 2.0 |      | 3   | V    |

| V <sub>UVLOR</sub>         | V <sub>BB</sub> undervoltage lockout rising     | Measured with respect to the GND pin of the device                                                                           | 2.2 |      | 3   | V    |

| 1                          | Standby current (total device leakage including | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 25°C<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V       |     |      | 0.1 | μΑ   |

| I <sub>SB</sub>            | MOSFET channel)                                 | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 85°C,<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V      |     |      | 0.5 | μΑ   |

| IL <sub>NOM</sub>          | Continuous load current                         | T <sub>AMB</sub> = 70°C                                                                                                      |     | 5    |     | Α    |

| 1                          | Output leakage current                          | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 25°C<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V       |     | 0.01 | 0.5 | μΑ   |

| I <sub>OUT</sub> (standby) | Output leakage current                          | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 125°C<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V      |     |      | 1.5 | μΑ   |

| I <sub>DIA</sub>           | Current consumption in diagnostic mode          | V <sub>BB</sub> = 13.5 V, I <sub>SNS</sub> = 0 mA<br>V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V, V <sub>OUT</sub> = 0V |     | 3    | 6   | mA   |

| IQ                         | Quiescent current                               | V <sub>BB</sub> = 13.5 V<br>V <sub>ENx</sub> = V <sub>DIA_EN</sub> = 5 V, I <sub>OUT</sub> = 0 A                             |     | 3    | 6   | mA   |

| t <sub>STBY</sub>          | Standby mode delay time                         | V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V to standby                                                                       | 12  | 17   | 22  | ms   |

| RON CHAR                   | ACTERISTICS                                     |                                                                                                                              |     |      | '   |      |

|                            | On-resistance                                   | $T_J = 25^{\circ}C, 6 \text{ V} \le V_{BB} \le 28 \text{ V}$                                                                 |     | 35   |     | mΩ   |

| R <sub>ON</sub>            | (Includes MOSFET and                            | T <sub>J</sub> = 150°C, 6 V ≤ V <sub>BB</sub> ≤ 28 V                                                                         |     | -    | 70  | mΩ   |

|                            | package)                                        | $T_J = 25^{\circ}C, 3 \text{ V} \le V_{BB} \le 6 \text{ V}$                                                                  |     |      | 55  | mΩ   |

| В                          | On-resistance during                            | $T_J = 25^{\circ}C$ , -18 V $\leq V_{BB} \leq$ -8 V                                                                          |     | 35   |     | mΩ   |

| $R_{ON(REV)}$              | reverse polarity                                | $T_J = 105^{\circ}C, -18 \text{ V} \le V_{BB} \le -8 \text{ V}$                                                              |     |      | 70  | mΩ   |

| CURRENT                    | SENSE CHARACTERISTIC                            | CS                                                                                                                           |     |      | 1   |      |

| K <sub>SNS</sub>           | Current sense ratio                             | I <sub>OUT</sub> = 1 A                                                                                                       |     | 2000 |     |      |

<sup>(2)</sup> All parameters specified are still valid, short circuit protection valide to value specified by V<sub>SC</sub> parameter

## 7.2 Electrical Characteristics (continued)

$V_{BB} = 6 \text{ V}$  to 18 V,  $T_{J} = -40^{\circ}\text{C}$  to 150°C (unless otherwise noted)

|                        | PARAMETER                                                                                                                                                         | TEST CO                                                           | ONDITIONS                                      | MIN    | TYP    | MAX                                                                                                                                                        | UNIT  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                        |                                                                                                                                                                   |                                                                   |                                                |        | 1.5    |                                                                                                                                                            | mA    |

|                        |                                                                                                                                                                   |                                                                   | I <sub>OUT</sub> = 3 A                         | -5     |        | 5                                                                                                                                                          | %     |

|                        |                                                                                                                                                                   |                                                                   |                                                |        | 0.5    |                                                                                                                                                            | mA    |

|                        |                                                                                                                                                                   |                                                                   | I <sub>OUT</sub> = 1 A                         | -5     |        |                                                                                                                                                            | %     |

|                        |                                                                                                                                                                   |                                                                   |                                                |        | 0.15   |                                                                                                                                                            | mA    |

|                        | Current sense current                                                                                                                                             | V <sub>EN</sub> = V <sub>DIA EN</sub> = 5 V,                      | I <sub>OUT</sub> = 300 mA                      | -6     |        |                                                                                                                                                            | %     |

| ISNSI                  | and accuracy                                                                                                                                                      | $V_{EN} = V_{DIA\_EN} = 5 \text{ V},$<br>$V_{SEL1} = 0 \text{ V}$ | 1. 400 4                                       |        | 0.05   |                                                                                                                                                            | mA    |

|                        |                                                                                                                                                                   |                                                                   | I <sub>OUT</sub> = 100 mA                      | -8.2   |        | 8.2                                                                                                                                                        | %     |

|                        |                                                                                                                                                                   |                                                                   | I = 50 m A                                     |        | 0.025  |                                                                                                                                                            | mA    |

|                        |                                                                                                                                                                   |                                                                   | I <sub>OUT</sub> = 50 mA                       | -13    |        | 13                                                                                                                                                         | %     |

|                        | $T_{J} = 125^{\circ}C$ $T_{J} = 150^{\circ}C$ $T_{J} = 150^{\circ}C$ S CHARACTERISTICS $T_{J} = 150^{\circ}C$ $V_{DIA\_EN} = 5 \text{ V, V}_{SEL1} = 0 \text{ V}$ | I = 20 m A                                                        |                                                | 0.0095 |        | mA                                                                                                                                                         |       |

|                        |                                                                                                                                                                   |                                                                   | I <sub>OUT</sub> – 20 IIIA                     | -40    |        | 35                                                                                                                                                         | %     |

| TJ SENSE               | CHARACTERISTICS                                                                                                                                                   |                                                                   |                                                |        |        |                                                                                                                                                            |       |

|                        |                                                                                                                                                                   |                                                                   | T <sub>J</sub> = -40°C                         | 0.01   | 0.12   | 0.38                                                                                                                                                       | mA    |

|                        |                                                                                                                                                                   |                                                                   | -                                              | 0.72   | 0.85   | 0.98                                                                                                                                                       | mA    |

| I <sub>SNST</sub>      | · ·                                                                                                                                                               | $V_{DIA\_EN} = 5 V, V_{SEL1} = 5 V$                               | T <sub>J</sub> = 85°C                          | 1.25   | 1.52   | 1.79                                                                                                                                                       | mA    |

|                        |                                                                                                                                                                   |                                                                   | T <sub>J</sub> = 125°C                         | 1.61   | 1.96   | 2.70                                                                                                                                                       | mA    |

|                        |                                                                                                                                                                   |                                                                   | T <sub>J</sub> = 150°C                         | 1.80   | 2.25   | 2.70                                                                                                                                                       | mA    |

| dI <sub>SNST</sub> /dT | Coefficient                                                                                                                                                       |                                                                   |                                                |        | 0.0112 |                                                                                                                                                            | mA/°C |

| SNS CHA                | RACTERISTICS                                                                                                                                                      |                                                                   |                                                |        |        |                                                                                                                                                            |       |

| I <sub>SNSFH</sub>     | I <sub>SNS</sub> fault high-level                                                                                                                                 | V <sub>DIA_EN</sub> = 5 V, V <sub>SEL1</sub> = 0 V                | /                                              | 4      | 4.5    | 5.3                                                                                                                                                        | mA    |

| I <sub>SNSleak</sub>   | I <sub>SNS</sub> leakage                                                                                                                                          | V <sub>DIA_EN</sub> = 0 V                                         |                                                |        |        | 1                                                                                                                                                          | μΑ    |

| CURRENT                | LIMIT CHARACTERISTIC                                                                                                                                              | S                                                                 |                                                |        |        | •                                                                                                                                                          |       |

|                        |                                                                                                                                                                   | Version A                                                         |                                                |        |        | 18                                                                                                                                                         | V     |

| V                      | Short Circuit Maximum                                                                                                                                             | Version B                                                         |                                                |        |        | 18                                                                                                                                                         | V     |

| CURRENT L              | Supply Voltage                                                                                                                                                    | Version C                                                         |                                                |        |        | 18                                                                                                                                                         | V     |

|                        |                                                                                                                                                                   | Version F                                                         |                                                |        |        | 18                                                                                                                                                         | V     |

|                        |                                                                                                                                                                   |                                                                   | R <sub>ILIM</sub> = 8.25 kΩ                    |        | 13     |                                                                                                                                                            | Α     |

|                        | Current Limit Maximum                                                                                                                                             | Device Version C, T <sub>J</sub> =                                | R <sub>ILIM</sub> = 10 kΩ                      |        | 12.5   |                                                                                                                                                            | Α     |

| <sup>1</sup> CL,max    | Current Limit Maximum                                                                                                                                             | -40°C to 150°C                                                    | R <sub>ILIM</sub> = 15 kΩ                      |        | 11.5   |                                                                                                                                                            | Α     |

|                        |                                                                                                                                                                   |                                                                   | $R_{ILIM} = 25 \text{ k}\Omega$                |        | 9      | 6   0.05   8.2   0.25   13   0.95   35   0.95   35   0.98   0.98   0.52   1.79   0.96   2.31   0.25   2.70   112   0.38   18   18   18   18   18   18   18 | Α     |

|                        |                                                                                                                                                                   | Device Version C, T <sub>J</sub> =                                | R <sub>ILIM</sub> = GND, open, or out of range |        | 14     |                                                                                                                                                            | Α     |

|                        |                                                                                                                                                                   | -40°C to 150°C                                                    | $R_{ILIM} = 8.25 \text{ k}\Omega$              | 4.4    | 6      | 8.4                                                                                                                                                        | Α     |

|                        |                                                                                                                                                                   |                                                                   | R <sub>ILIM</sub> = 25 kΩ                      | 1.52   | 2.5    | 3.48                                                                                                                                                       | Α     |

|                        |                                                                                                                                                                   | Device Version A, T <sub>J</sub> =                                | R <sub>ILIM</sub> = GND, open, or out of range |        | 14     |                                                                                                                                                            | Α     |

|                        |                                                                                                                                                                   | -40°C to 150°C                                                    | R <sub>ILIM</sub> = 5 kΩ                       | 8.2    | 10     | 12.7                                                                                                                                                       | Α     |

| I <sub>CL</sub>        | Current Limit Threshold                                                                                                                                           |                                                                   | R <sub>ILIM</sub> = 25 kΩ                      | 1.25   | 2      | 2.66                                                                                                                                                       | Α     |

| I <sub>CL</sub>        |                                                                                                                                                                   | Device Version B, T, =                                            | R <sub>ILIM</sub> = GND, open, or out of range |        | 33.3   |                                                                                                                                                            | Α     |

|                        |                                                                                                                                                                   | -40°C to 150°C                                                    | R <sub>ILIM</sub> = 5 kΩ                       | 18.24  | 22     | 27.9                                                                                                                                                       | Α     |

|                        |                                                                                                                                                                   |                                                                   | R <sub>ILIM</sub> = 25 kΩ                      | 3.15   | 4.4    | 5.65                                                                                                                                                       | Α     |

| I <sub>CL,max</sub>    |                                                                                                                                                                   | Doving Version F                                                  | T <sub>J</sub> = 25°C                          | 30.6   | 34     | 40.8                                                                                                                                                       | Α     |

|                        |                                                                                                                                                                   | Device Version F                                                  | T <sub>J</sub> = 150°C                         | 23.8   | 26.5   | 31.8                                                                                                                                                       | Α     |

## 7.2 Electrical Characteristics (continued)

$V_{BB} = 6 \text{ V}$  to 18 V,  $T_{J} = -40^{\circ}\text{C}$  to 150°C (unless otherwise noted)

|                              | PARAMETER                                         | TEST CONDITIONS                                                                                                                     | MIN | TYP | MAX | UNIT   |

|------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| IZ.                          | Commont Limit Datis                               | Version A/C                                                                                                                         |     | 50  |     | A * kΩ |

| K <sub>CL</sub>              | Current Limit Ratio                               | Version B                                                                                                                           |     | 110 |     | A * kΩ |

| FAULT CHA                    | ARACTERISTICS                                     |                                                                                                                                     |     |     | -   |        |

| V <sub>OL</sub>              | Open-load (OL) detection voltage                  | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V, V <sub>SEL1</sub> = 0 V                                                           | 2   | 3   | 4   | V      |

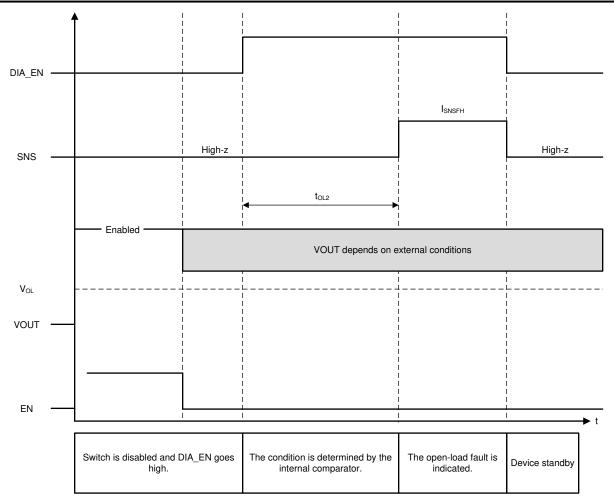

| t <sub>OL1</sub>             | OL and STB indication-<br>time from EN falling    | $V_{EN}$ = 5 V to 0 V, $V_{DIA\_EN}$ = 5 V, $V_{SEL1}$ = 0 V $I_{OUT}$ = 0 mA, $V_{OUT}$ = 4 V                                      | 300 | 500 | 700 | μs     |

| t <sub>OL2</sub>             | OL and STB indication-<br>time from DIA_EN rising | $V_{EN} = 0 \text{ V}, V_{DIA\_EN} = 0 \text{ V to 5 V}, V_{SEL1} = 0 \text{ V}$<br>$I_{OUT} = 0 \text{ mA}, V_{OUT} = 4 \text{ V}$ | 2   | 20  | 50  | μs     |

| t <sub>OL3</sub>             | OL and STB indication-<br>time from VOUT rising   | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V, V <sub>SEL1</sub> = 0 V<br>I <sub>OUT</sub> = 0 mA, V <sub>OUT</sub> = 0 V to 4 V | 2   | 20  | 50  | μs     |

| T <sub>ABS</sub>             | Thermal shutdown                                  |                                                                                                                                     | 150 |     |     | °C     |

| T <sub>REL</sub>             | Relative thermal shutdown                         |                                                                                                                                     |     | 60  |     | °C     |

| T <sub>HYS</sub>             | Thermal shutdown hysteresis                       |                                                                                                                                     | 20  | 25  | 30  | °C     |

| t <sub>FAULT</sub>           | Fault shutdown indication-time                    | V <sub>DIA_EN</sub> = 5 V<br>Time between switch shutdown and I <sub>SNS</sub> settling at<br>I <sub>SNSFH</sub>                    |     |     | 50  | μs     |

| t <sub>RETRY</sub>           | Retry time                                        | Time from fault shutdown until switch re-enable (thermal shutdown or current limit).                                                | 1   | 2   | 3   | ms     |

| EN PIN CH                    | ARACTERISTICS                                     |                                                                                                                                     |     |     |     |        |

| V <sub>IL, EN</sub>          | Input voltage low-level                           | No GND network diode                                                                                                                |     |     | 0.8 | V      |

| V <sub>IH, EN</sub>          | Input voltage high-level                          | No GND network diode                                                                                                                | 2.0 |     |     | V      |

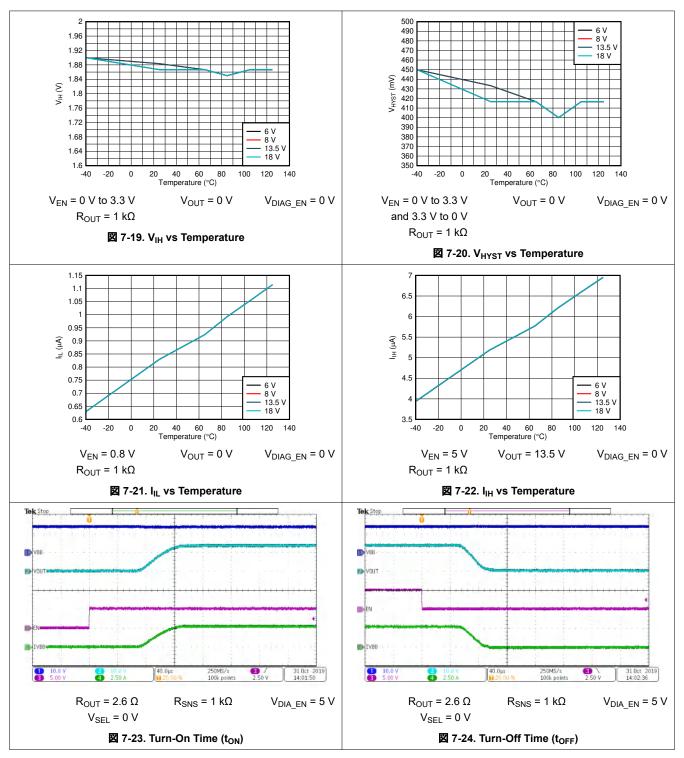

| V <sub>IHYS, EN</sub>        | Input voltage hysteresis                          |                                                                                                                                     |     | 350 |     | mV     |

| R <sub>EN</sub>              | Internal pulldown resistor                        |                                                                                                                                     | 0.5 | 1   | 2   | ΜΩ     |

| I <sub>IL, EN</sub>          | Input current low-level                           | V <sub>EN</sub> = 0.8 V                                                                                                             |     | 0.8 |     | μA     |

| I <sub>IH, EN</sub>          | Input current high-level                          | V <sub>EN</sub> = 5 V                                                                                                               |     | 5.0 |     | μA     |

| DIA_EN PI                    | CHARACTERISTICS                                   |                                                                                                                                     |     | -   |     |        |

| V <sub>IL, DIA_EN</sub>      | Input voltage low-level                           | No GND network diode                                                                                                                |     |     | 0.8 | V      |

| V <sub>IH, DIA_EN</sub>      | Input voltage high-level                          | No GND network diode                                                                                                                | 2.0 |     |     | V      |

| V <sub>IHYS,</sub><br>DIA_EN | Input voltage hysteresis                          |                                                                                                                                     |     | 350 |     | mV     |

| R <sub>DIA_EN</sub>          | Internal pulldown resistor                        |                                                                                                                                     | 0.5 | 1   | 2   | ΜΩ     |

| I <sub>IL, DIA_EN</sub>      | Input current low-level                           | $V_{DIA\_EN} = 0.8 \text{ V}$                                                                                                       |     | 0.8 |     | μA     |

| I <sub>IH, DIA_EN</sub>      | Input current high-level                          | V <sub>DIA_EN</sub> = 5 V                                                                                                           |     | 5.0 |     | μA     |

| SEL1 PIN C                   | HARACTERISTICS                                    |                                                                                                                                     |     |     | '   |        |

| V <sub>IL, SEL1</sub>        | Input voltage low-level                           | No GND network diode                                                                                                                |     |     | 8.0 | V      |

| V <sub>IH, SEL1</sub>        | Input voltage high-level                          | No GND network diode                                                                                                                | 2.0 |     |     | V      |

| V <sub>IHYS, SEL1</sub>      | Input voltage hysteresis                          |                                                                                                                                     |     | 350 |     | mV     |

| R <sub>SEL1</sub>            | Internal pulldown resistor                        |                                                                                                                                     | 0.5 | 1   | 2   | ΜΩ     |

| I <sub>IL, SEL1</sub>        | Input current low-level                           | V <sub>SEL1</sub> = 0.8 V                                                                                                           |     | 0.8 |     | μΑ     |

| I <sub>IH, SEL1</sub>        | Input current high-level                          | V <sub>SEL1</sub> = 5 V                                                                                                             | ,   | 5.0 |     | μΑ     |

| LATCH PIN                    | CHARACTERISTICS                                   |                                                                                                                                     |     |     | 1   |        |

| V <sub>IL, LATCH</sub>       | Input voltage low-level                           | No GND network diode                                                                                                                |     |     | 0.8 | V      |

| V <sub>IH, LATCH</sub>       | Input voltage high-level                          | No GND network diode                                                                                                                | 2.0 |     |     | V      |

## 7.2 Electrical Characteristics (continued)

$V_{BB}$  = 6 V to 18 V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

|                             | PARAMETER                  | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|-----------------------------|----------------------------|----------------------------|-----|-----|-----|------|

| V <sub>IHYS,</sub><br>LATCH | Input voltage hysteresis   |                            |     | 350 |     | mV   |

| R <sub>LATCH</sub>          | Internal pulldown resistor |                            | 0.5 | 1   | 2   | ΜΩ   |

| I <sub>IL, LATCH</sub>      | Input current low-level    | V <sub>LATCH</sub> = 0.8 V |     | 0.8 |     | μΑ   |

| I <sub>IH, LATCH</sub>      | Input current high-level   | V <sub>LATCH</sub> = 5 V   |     | 5.0 |     | μA   |

## 7.3 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                           | ,                                                                       | MIN | MAX               | UNIT |

|-----------------------------------------------------------|-------------------------------------------------------------------------|-----|-------------------|------|

| Maximum continuous supply voltage, V <sub>BB</sub>        |                                                                         |     | 36                | V    |

| Load dump voltage, V <sub>LD</sub>                        | ISO16750-2:2010(E)                                                      |     | 40                | V    |

| Reverse battery voltage, V <sub>Rev</sub> , t ≤ 3 minutes |                                                                         | -18 |                   | V    |

| Enable pin voltage, V <sub>EN</sub>                       |                                                                         | -1  | 7                 | V    |

| LATCH pin voltage, V <sub>LATCH</sub>                     |                                                                         | -1  | 7                 | V    |

| Diagnostic Enable pin voltage, V <sub>DIA_EN</sub>        |                                                                         | -1  | 7                 | V    |

| Sense pin voltage, V <sub>SNS</sub>                       |                                                                         | -1  | 18                | V    |

| Select pin voltage, V <sub>SEL1</sub>                     |                                                                         | -1  | 7                 | V    |

| Reverse ground current, I <sub>GND</sub>                  | V <sub>BB</sub> < 0 V                                                   |     | -50               | mA   |

| Energy dissipation during turnoff, E <sub>TOFF</sub>      | Single pulse, L <sub>OUT</sub> = 5 mH, T <sub>J,start</sub> = 125°C     |     | 26 <sup>(2)</sup> | mJ   |

| Energy dissipation during turnoff, E <sub>TOFF</sub>      | Repetitive pulse, L <sub>OUT</sub> = 5 mH, T <sub>J,start</sub> = 125°C |     | 12 <sup>(2)</sup> | mJ   |

| Maximum junction temperature, T <sub>J</sub>              |                                                                         |     | 150               | °C   |

| Storage temperature, T <sub>stg</sub>                     |                                                                         | -65 | 150               | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute maximum rated conditions for extended periods may affect device reliability

## 7.4 ESD Ratings

|                    |               |                                                         |                              |       | UNIT |

|--------------------|---------------|---------------------------------------------------------|------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | All pins except VBB and VOUT | ±2000 |      |

|                    | discharge     |                                                         | VBB and VOUT                 | ±4000 | V    |

|                    |               | Charged-device model (CDM), per AEC Q100-011            | All pins                     | ±750  |      |

<sup>(1)</sup> AEC-Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specifications.

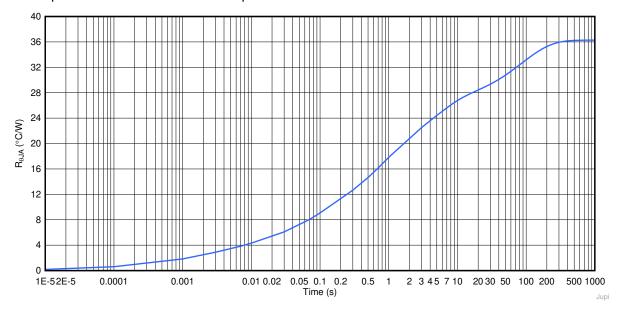

### 7.5 Thermal Information

| THERMAL METRIC (1) (2) |                                              | TPS1HB35-Q1 PWP (HTSSOP) 16 PINS | UNIT |

|------------------------|----------------------------------------------|----------------------------------|------|

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 36.0                             | °C/W |

| R <sub>0JC(top)</sub>  | Junction-to-case (top) thermal resistance    | 34.0                             | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 12.2                             | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 4.5                              | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 12.3                             | °C/W |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

<sup>(2)</sup> For further details, see the section regarding switch-off of an inductive load.

|                       |                                              | TPS1HB35-Q1  |      |  |

|-----------------------|----------------------------------------------|--------------|------|--|

|                       | THERMAL METRIC (1) (2)                       | PWP (HTSSOP) | UNIT |  |

|                       |                                              | 16 PINS      |      |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.9          | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.6 SNS Timing Characteristics

$V_{BB}$  = 6 V to 18 V,  $T_{J}$  = -40°C to +150°C (unless otherwise noted)

|                       | PARAMETER                                             | TEST CONDITIONS                                                                                                                                        | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SNS TIMII             | NG - CURRENT SENSE                                    |                                                                                                                                                        |     |     |     |      |

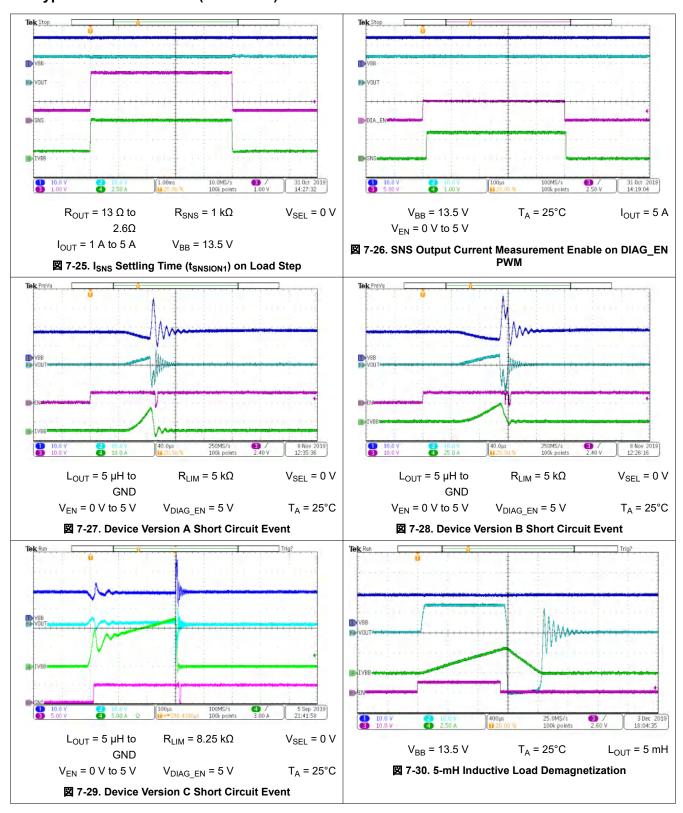

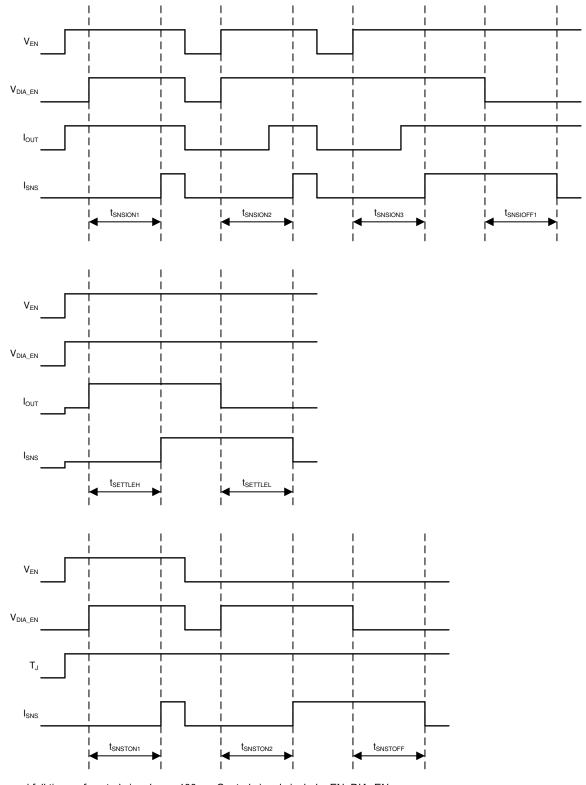

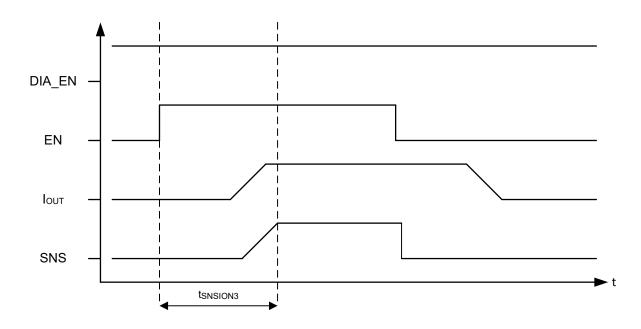

| t <sub>SNSION1</sub>  | Settling time from rising edge of DIA_EN              | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 0 V to 5 V<br>$R_{SNS}$ = 1 k $\Omega$ , $R_L$ ≤ 5 $\Omega$                                                            |     |     | 40  | μs   |

| t <sub>SNSION2</sub>  | Settling time from rising edge of EN and DIA_EN       | $V_{EN} = V_{DIA\_EN} = 0 \text{ V to 5 V}$<br>$R_{SNS} = 1 \text{ k}\Omega, R_L \le 5 \Omega$                                                         |     |     | 200 | μs   |

| t <sub>SNSION3</sub>  | Settling time from rising edge of EN                  | $V_{EN}$ = 0 V to 5 V, $V_{DIA\_EN}$ = 5 V $R_{SNS}$ = 1 k $\Omega$ , $R_L$ $\leq$ 5 $\Omega$                                                          |     |     | 165 | μs   |

| t <sub>SNSIOFF1</sub> | Settling time from falling edge of DIA_EN             | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 5 V to 0 V<br>$R_{SNS}$ = 1 k $\Omega$ , $R_L$ ≤ 5 $\Omega$                                                            |     |     | 20  | μs   |

| t <sub>SETTLEH</sub>  | Settling time from rising edge of load step           | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, I_{OUT} = 1 \text{ A to 5 A}$                                       |     |     | 20  | μs   |

| t <sub>SETTLEL</sub>  | Settling time from falling edge of load step          | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, I_{OUT} = 5 \text{ A to 1 A}$                                       |     |     | 20  | μs   |

| SNS TIMII             | NG - TEMPERATURE SENSE                                |                                                                                                                                                        |     |     | ·   |      |

| t <sub>SNSTON1</sub>  | Settling time from rising edge of DIA_EN              | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 0 V to 5 V $R_{SNS}$ = 1 k $\Omega$                                                                                    |     |     | 40  | μs   |

| t <sub>SNSTON2</sub>  | Settling time from rising edge of DIA_EN              | $V_{EN}$ = 0 V, $V_{DIA\_EN}$ = 0 V to 5 V $R_{SNS}$ = 1 k $\Omega$                                                                                    |     |     | 70  | μs   |

| t <sub>SNSTOFF</sub>  | Settling time from falling edge of DIA_EN             | $V_{EN} = X$ , $V_{DIA\_EN} = 5 V$ to 0 V<br>$R_{SNS} = 1 k\Omega$                                                                                     |     |     | 20  | μs   |

| SNS TIMII             | NG - MULTIPLEXER                                      |                                                                                                                                                        |     |     |     |      |

| <b>4</b>              | Settling time from temperature sense to current sense | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$V_{SEL1} = 5 \text{ V to 0 V}$<br>$R_{SNS} = 1 \text{ kΩ}, R_L \le 5 \Omega$                     |     |     | 60  | μs   |

| t <sub>MUX</sub>      | Settling time from current sense to temperature sense | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$V_{SEL1} = 0 \text{ V to } \overline{5} \text{ V}$<br>$R_{SNS} = 1 \text{ kΩ}, R_L \le 5 \Omega$ |     |     | 60  | μs   |

## 7.7 Switching Characteristics

$V_{BB} = 13.5 \text{ V}, T_{J} = -40 ^{\circ}\text{C} \text{ to } +150 ^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                 | - BB - 1010 1, 1, 1             |                                                                               |     |         |     |      |  |

|-----------------|---------------------------------|-------------------------------------------------------------------------------|-----|---------|-----|------|--|

| PARAMETER       |                                 | TEST CONDITIONS                                                               | MIN | TYP MAX |     | UNIT |  |

| t <sub>DR</sub> | Turnon delay time (from Active) | $V_{BB}$ = 13.5 V, $R_L \le 5 \Omega$ 50% EN rising to 10% $V_{OUT}$ rising   | 20  | 60      | 100 | μs   |  |

| t <sub>DF</sub> | Turnoff delay time              | $V_{BB}$ = 13.5 V, $R_L \le 5 \Omega$ 50% EN falling to 90% $V_{OUT}$ Falling | 20  | 60      | 100 | μs   |  |

| SR <sub>R</sub> | VOUT rising slew rate           | $V_{BB}$ = 13.5 V, 20% to 80% of $V_{OUT}$ rising, $R_L \le 5 \Omega$         | 0.1 | 0.4     | 0.7 | V/µs |  |

| SR <sub>F</sub> | VOUT falling slew rate          | $V_{BB}$ = 13.5 V, 80% to 20% of $V_{OUT}$ falling, $R_L \le 5 \Omega$        | 0.1 | 0.4     | 0.7 | V/µs |  |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

## 7.7 Switching Characteristics (continued)

$V_{BB}$  = 13.5 V,  $T_{J}$  = -40°C to +150°C (unless otherwise noted)

| PARAMETER                          |                                        | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |

|------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>ON</sub>                    | Turnon time (active)                   | $V_{BB}$ = 13.5 V, $R_{L} \le 5 \Omega$ , 50% EN rising to 80% $V_{OUT}$ rising | 39  | 94  | 235 | μs   |

| t <sub>OFF</sub>                   | Turnoff time                           | $V_{BB}$ = 13.5 V, $R_L \le 5 \Omega$ , 50% EN falling to 20% $V_{OUT}$ falling | 39  | 94  | 235 | μs   |

| $\Delta_{PWM}$                     | PWM accuracy - average load current    | 200-μs enable pulse, $V_S$ = 13.5 V, $R_L$ = 5 Ω                                | -25 | 0   | 25  | %    |

| t <sub>ON</sub> - t <sub>OFF</sub> | Turnon and turnoff matching            | 200-μs enable pulse, $R_L \le 5 Ω$                                              | -85 | 0   | 85  | μs   |

| E <sub>ON</sub>                    | Switching energy losses during turnon  | $V_{BB}$ = 13.5 V, $R_{L} \le 5 Ω$                                              |     | 0.7 |     | mJ   |

| E <sub>OFF</sub>                   | Switching energy losses during turnoff | $V_{BB}$ = 13.5 V, $R_{L} \le 5 Ω$                                              |     | 0.7 |     | mJ   |

## 7.8 Typical Characteristics

Product Folder Links: TPS1HB35-Q1

図 7-17. Fault High Output Current (I<sub>SNSFH</sub>) vs Temperature

図 7-18. V<sub>IL</sub> vs Temperature

## **8 Parameter Measurement Information**

図 8-1. Parameter Definitions

Rise and fall time of  $V_{\text{EN}}$  is 100 ns.

図 8-2. Switching Characteristics Definitions

Rise and fall times of control signals are 100 ns. Control signals include: EN, DIA\_EN.

**図** 8-3. SNS Timing Characteristics Definitions

## 9 Detailed Description

### 9.1 Overview

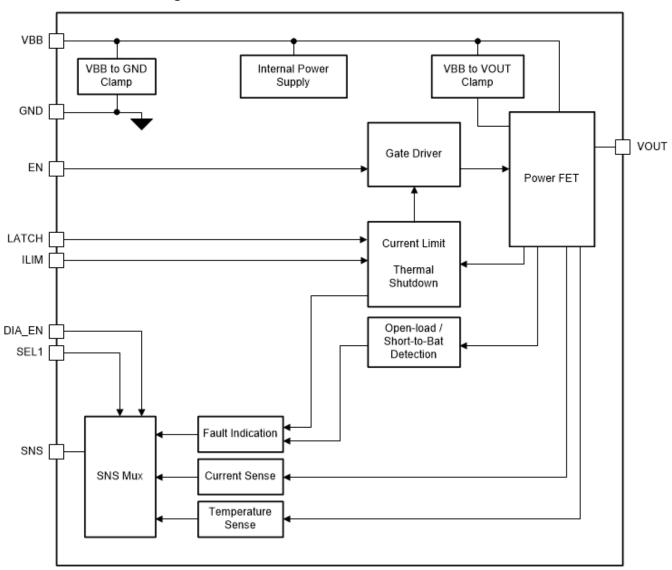

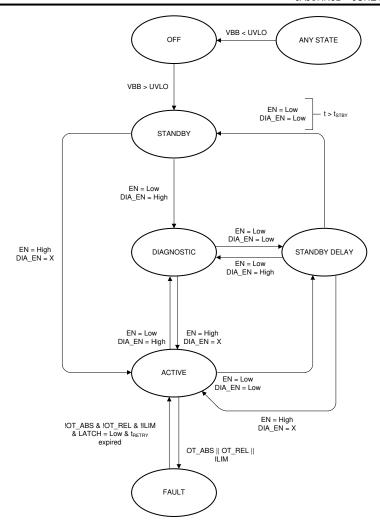

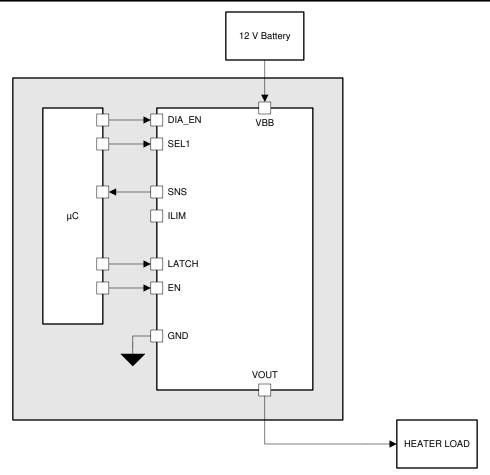

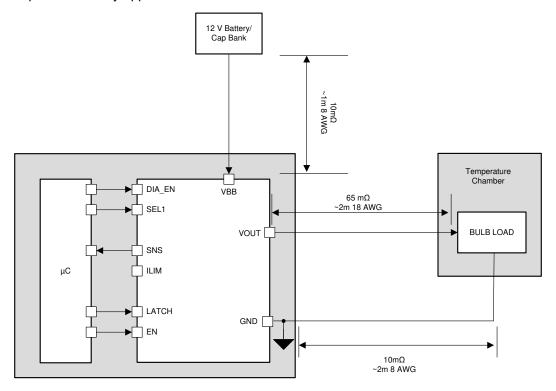

The TPS1HB35-Q1 device is a single-channel smart high-side switch intended for use with 12-V automotive batteries. Many protection and diagnostic features are integrated in the device.

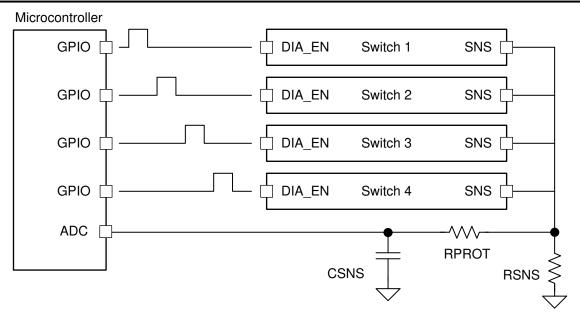

Diagnostics features include the analog SNS output that is capable of providing a signal that is proportional to load current or device temperature. The high-accuracy load current sense allows for diagnostics of complex loads.

This device includes protection through thermal shutdown, current limiting, transient withstand, and reverse battery operation. For more details on the protection features, refer to the *Feature Description* and *Application Information* sections of the document.

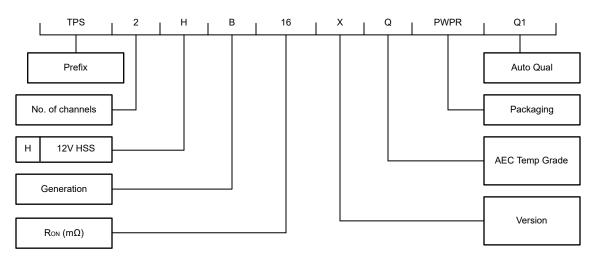

The TPS1HB35-Q1 is one device in a family of TI high side switches. For each device, the part number indicates elements of the device behavior.

■ 9-1 gives an example of the device nomenclature.

図 9-1. Naming Convention

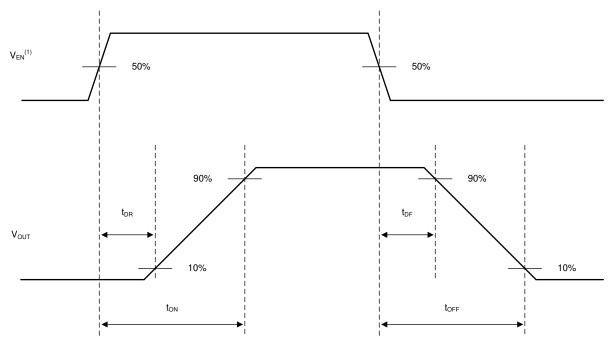

### 9.2 Functional Block Diagram

## 9.3 Feature Description

### 9.3.1 Protection Mechanisms

The TPS1HB35-Q1 is designed to operate in the automotive environment. The protection mechanisms allow the device to be robust against many system-level events such as load dump, reverse battery, short-to-ground, and

There are two protection features which, if triggered, will cause the switch to automatically disable:

- Thermal Shutdown

- **Current Limit**

When any of these protections are triggered, the device will enter the FAULT state. In the FAULT state, the fault indication will be available on the SNS pin (see the Diagnostic Mechanisms section of the data sheet for more details).

The switch is no longer held off and the fault indication is reset when all of the below conditions are met:

- LATCH pin is low

- t<sub>RETRY</sub> has expired

20

Copyright © 2023 Texas Instruments Incorporated

· All faults are cleared (thermal shutdown, current limit)

#### 9.3.1.1 Thermal Shutdown

The TPS1HB35-Q1 includes a temperature sensor on the power FET and also within the controller portion of the device. There are two cases that the device will consider to be a thermal shutdown fault:

- T<sub>J,FET</sub> > T<sub>ABS</sub>

- $(T_{J,FET} T_{J,controller}) > T_{REL}$

After the fault is detected, the switch will turn off. If  $T_{J,FET}$  passes  $T_{ABS}$ , the fault is cleared when the switch temperature decreases by the hysteresis value,  $T_{HYS}$ . If instead the  $T_{REL}$  threshold is exceeded, the fault is cleared after  $T_{RETRY}$  passes.

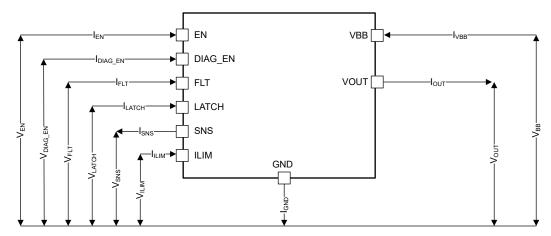

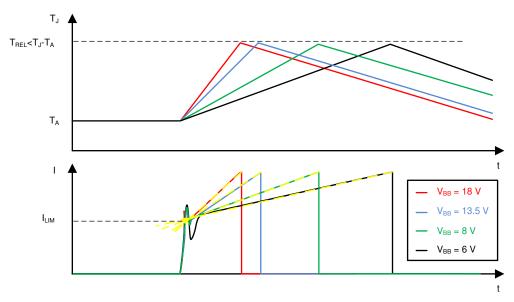

### 9.3.1.2 Current Limit

When  $I_{OUT}$  reaches the current limit threshold,  $I_{CL}$ , the channel will switch off immediately. The  $I_{CL}$  value will vary with slew rate and a fast current increase that occurs during a powered-on short circuit can temporarily go above the specified  $I_{CL}$  value. In the case that the device remains enabled and limits  $I_{OUT}$ , the thermal shutdown protection feature can be triggered due to the high amount of power dissipation in the device. When the switch is in the FAULT state, it will output an output current  $I_{SNSFH}$  on the SNS pin . In addition, fault indication will occur when the switch is actively limiting current (applicable to version C).

During a short-circuit event, the device will hit the  $I_{CL}$  value that is listed in the Electrical Characteristics table (for the given device version and  $R_{ILIM}$ ) and then turn the output off or regulate the output current to protect the device. The device will register a short-circuit event when the output current exceeds  $I_{CL}$ , however, the measured maximum current can exceed the  $I_{CL}$  value due to the TPS1HB35-Q1 deglitch filter and turn-off time. This deglitch time is defined at 3  $\mu$ s, so use the test setup described in the *AEC-Q100-012 Short Circuit Reliability* section, and take 3  $\mu$ s before the peak value as the  $I_{CL}$ . The device is assured to protect itself during a short-circuit event over the nominal supple voltage range (as defined in the Electrical Characteristics table) at 125°C.

The current threshold is defined for version C is different than version A or B. For version C, the current through the device continues to flow until the device hits relative thermal shutdown ( $T_{REL}$ ). For different  $V_{BB}$ s the slope of the current will change. Therefore, the intersection point of where each of the slopes for the different  $V_{BB}$  values is determined as the current threshold,  $I_{LIM}$ , as shown in  $\boxed{2}$  9-2. This behavior allows for the TPS1HB35**C**-Q1 to be able to charge up a 270- $\mu$ F capacitor without shutting off due to hitting the current limit as versions A and B would.

図 9-2. Version C Current Threshold Definition

#### 9.3.1.2.1 Current Limit Foldback

Version B of the TPS1HB35-Q1 implements a current limit foldback feature that is designed to protect the device in the case of a long-term fault condition. If the device undergoes fault shutdown events (either of thermal shutdown or current limit) seven consecutive times, the current limit will be reduced to half of the original value. The device will revert back to the original current limit threshold if either of the following occurs:

- · The device goes to standby mode.

- The switch turns on and turns off without any fault occurring.

Version A and C do not implement the current limit foldback due to the lower current limit causing less harm during repetitive long-term faults.

#### 9.3.1.2.2 Programmable Current Limit

All versions of the TPS1HB35-Q1 include an adjustable current limit. Some applications (for example, incandescent bulbs) will require a high current limit while other applications can benefit from a lower current limit threshold. In general, wherever possible a lower current limit is recommended due to allowing system advantages through:

- Reduced size and cost in current carrying components such as PCB traces and module connectors

- Less disturbance at the power supply (V<sub>BB</sub> pin) during a short-circuit event

- · Improved protection of the downstream load

To set the current limit threshold, connect a resistor from  $I_{LIM}$  to  $V_{BB}$ . The current limit threshold is determined by Equation 1 ( $R_{ILIM}$  in  $k\Omega$ ):

$$I_{CL} = K_{CL} / R_{ILIM}$$

(1)

The  $R_{ILIM}$  range is between 5 k $\Omega$  and 25 k $\Omega$ . An  $R_{ILIM}$  resistor is required, however in the fault case where the pin is floating, grounded, or outside of this range the current limit will default to an internal level that is defined in the *Specifications* section of this document. If  $R_{ILIM}$  is out of this range, the device cannot assure complete short-circuit protection.

注

Capacitance on the  $I_{LIM}$  pin can cause  $I_{LIM}$  to go out of range during short-circuit events. For accurate current limiting, place  $R_{ILIM}$  near to the device with short traces to ensure < 5-pF capacitance to GND on the  $I_{LIM}$  pin.

#### 9.3.1.2.3 Undervoltage Lockout (UVLO)

The device monitors the supply voltage  $V_{BB}$  to prevent unpredicted behaviors in the event that the supply voltage is too low. When the supply voltage falls down to  $V_{UVLOF}$ , the output stage is shut down automatically. When the supply rises up to  $V_{UVLOR}$ , the device turns back on.

During an initial ramp of  $V_{BB}$  from 0 V at a ramp rate slower than 1 V/ms,  $V_{EN}$  pin will have to be held low until  $V_{BB}$  is above UVLO threshold (with respect to board ground) and the supply voltage to the device has reliably reached above the UVLO condition. For best operation, ensure that  $V_{BB}$  has risen above UVLO before setting the  $V_{EN}$  pin to high.

## 9.3.1.2.4 V<sub>BB</sub> During Short-to-Ground

When  $V_{OUT}$  is shorted to ground, the module power supply ( $V_{BB}$ ) can have a transient decrease. This decrease is caused by the sudden increase in current flowing through the wiring harness cables. To achieve ideal system behavior, TI recommends that the module maintain  $V_{BB} > 3$  V (above the maximum  $V_{UVLOF}$ ) during  $V_{OUT}$  short-to-ground. This maintenance is typically accomplished by placing bulk capacitance on the power supply node.

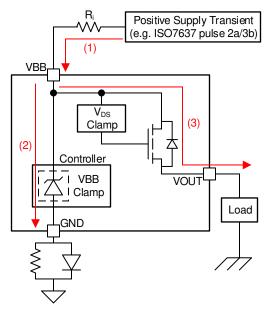

### 9.3.1.3 Voltage Transients

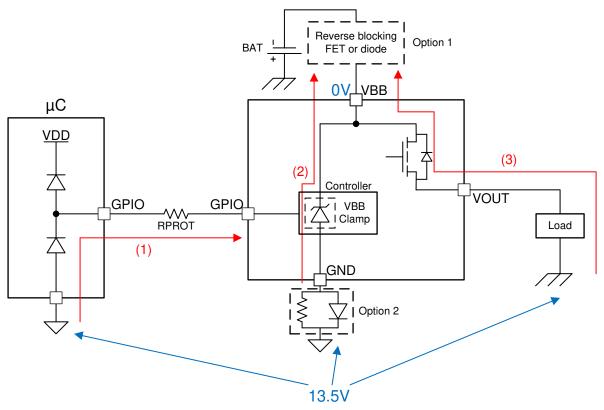

The TPS1HB35-Q1 device contains two types of voltage clamps which protect the FET against system-level voltage transients. The two different clamps are shown in  $\boxtimes$  9-3.

Product Folder Links: TPS1HB35-Q1

Copyright © 2023 Texas Instruments Incorporated

The clamp from  $V_{BB}$  to GND is primarily used to protect the controller from positive transients on the supply line (for example, ISO7637-2). The clamp from  $V_{BB}$  to  $V_{OUT}$  is primarily used to limit the voltage across the FET when switching off an inductive load. If the voltage potential from  $V_{BB}$  to GND exceeds the  $V_{BB}$  clamp level, the clamp will allow current to flow through the device from  $V_{BB}$  to GND (path 2). If the voltage potential from  $V_{BB}$  to  $V_{OUT}$  exceeds the clamping voltage, the power FET will allow current to flow from  $V_{BB}$  to  $V_{OUT}$  (path 3). Additional capacitance from  $V_{BB}$  to GND can increase the reliability of the system during ISO 7637 pulse 2-A testing.

図 9-3. Current Path During Supply Voltage Transient

#### 9.3.1.3.1 Load Dump

The TPS1HB35-Q1 device is tested according to ISO 16750-2:2010(E) suppressed load dump pulse. The device supports up to 40-V load dump transient and will maintain normal operation during the load dump pulse. If the switch is enabled, it will stay enabled and if the switch is disabled, it will stay disabled.

### 9.3.1.3.2 Driving Inductive Loads

When switching off an inductive load, the inductor can impose a negative voltage on the output of the switch. The TPS1HB35-Q1 includes a voltage clamp to limit voltage across the FET. The maximum acceptable load inductance is a function of the device robustness.

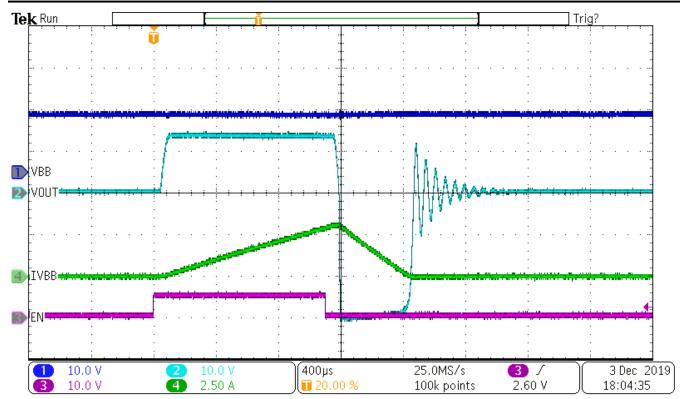

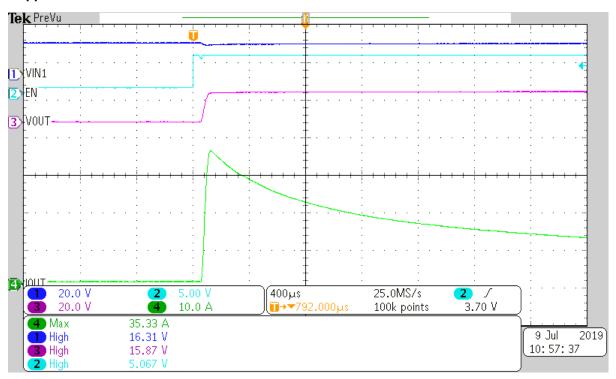

図 9-4. TPS1HB35-Q1 Inductive Discharge (5 mH)

For more information on driving inductive loads, refer to TI's *How To Drive Inductive, Capacitive, and Lighting Loads With Smart High Side Switches* application report.

### 9.3.1.4 Reverse Battery

In the reverse battery condition, the switch will automatically be enabled regardless of the state of EN to prevent excess power dissipation inside the MOSFET body diode. In many applications (for example, resistive loads), the full load current can be present during reverse battery. In order to activate the automatic switch on feature, SEL must have a path to ground from either from the MCU or it needs to be tied to ground through R<sub>PROT</sub> if unused.

There are two options for blocking reverse current in the system. The first option is to place a blocking device (FET or diode) in series with the battery supply, blocking all current paths. The second option is to place a blocking diode in series with the GND node of the high-side switch. This method will protect the controller portion of the switch (path 2), but it will not prevent current from flowing through the load (path 3). The diode used for the second option can be shared amongst multiple high-side switches.

Path 1 shown in 2 9-5 is blocked inside of the device.

**図 9-5. Current Path During Reverse Battery**

For more information on reverse battery protection, refer to TI's *Reverse Battery Protection for High Side Switches* application note.

## 9.3.1.5 Current Limit Behavior

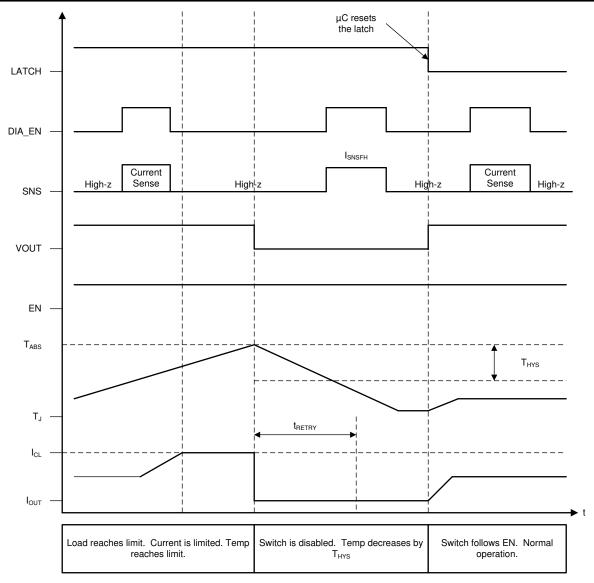

### 9.3.1.6 Fault Event - Timing Diagrams

注

All timing diagrams assume that the SEL1 pin is low.

The LATCH, DIA\_EN, and EN pins are controlled by the user. The timing diagrams represent a possible use-case.

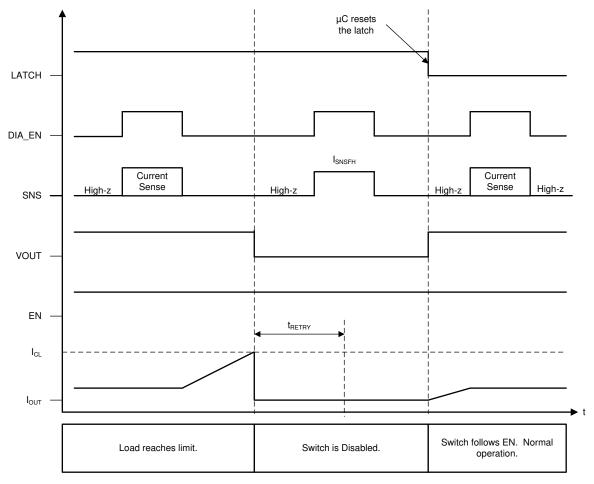

☑ 9-6 shows the immediate current limit switch off behavior. The diagram also illustrates the retry behavior. As shown, the switch will remain latched off until the LATCH pin is low.

図 9-6. Current Limit - Version A and B - Latched Behavior

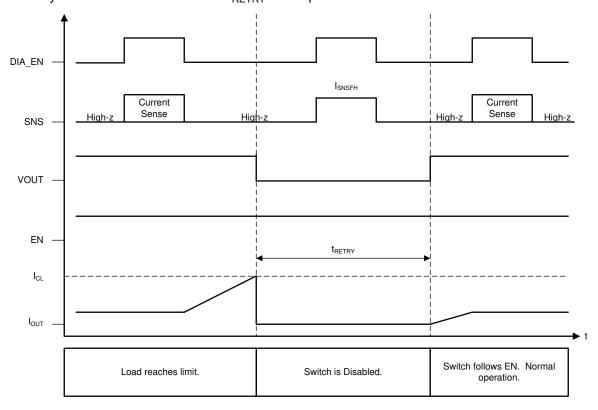

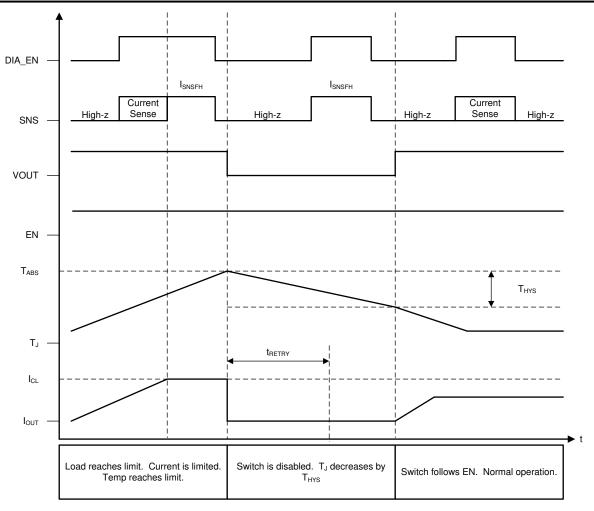

$\boxtimes$  9-7 shows the immediate current limit switch off behavior. In this example, LATCH is tied to GND; hence, the switch will retry after the fault is cleared and  $t_{RETRY}$  has expired.

図 9-7. Current Limit - Version A and B - LATCH = 0

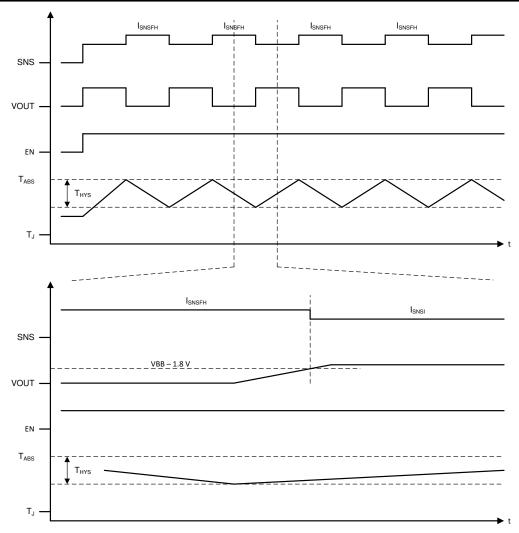

☑ 9-8 shows the active current behavior of version C. In version C, the switch will not shutdown until thermal shutdown is reached.

図 9-8. Current Limit - Version C - Latched Behavior

☑ 9-9 shows the active current behavior of version C. The switch will not shutdown until thermal shutdown is tripped. In this example, LATCH is tied to GND.

図 9-9. Current Limit - Version C - LATCH = 0

When the switch retries after a shutdown event, the SNS fault indication will remain until  $V_{OUT}$  has risen to  $V_{BB}$  – 1.8 V. After  $V_{OUT}$  has risen, the SNS fault indication is reset and current sensing is available. If there is a short-to-ground and  $V_{OUT}$  is not able to rise, the SNS fault indication will remain indefinitely.  $\boxtimes$  9-10 illustrates autoretry behavior and provides a zoomed-in view of the fault indication during retry.

注

LATCH = 0 V and DIA\_EN = 5 V

図 9-10. Fault Indication During Retry

### 9.3.2 Diagnostic Mechanisms

### 9.3.2.1 VOUT Short-to-Battery and Open-Load

The TPS1HB35-Q1 is capable of detecting short-to-battery and open-load events regardless of whether the switch is turned on or off, however the two conditions use different methods.

### 9.3.2.1.1 Detection With Switch Enabled

When the switch is enabled, the VOUT short-to-battery and open-load conditions can be detected by the current sense feature. In both cases, the load current will be measured through the SNS pin as below the expected value.

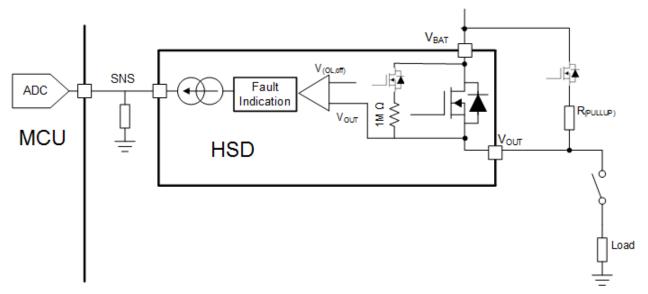

### 9.3.2.1.2 Detection With Switch Disabled

While the switch is disabled, if DIA\_EN is high, an internal comparator will detect the condition of  $V_{OUT}$ . If the load is disconnected (open load condition) or there is a short to battery the  $V_{OUT}$  voltage will be higher than the open load threshold ( $V_{OL,off}$ ) and a fault is indicated on the SNS pin. An internal pull-up of 1 M $\Omega$  is in series with an internal MOSFET switch, so no external component is required if a completely open load must be detected. However, if there is significant leakage or other current draw even when the load is disconnected, a lower value pull-up resistor and switch can be added externally to set the  $V_{OUT}$  voltage above the  $V_{OL,off}$  during open load conditions.

This figure assumes that the device ground and the load ground are at the same potential. In a real system, there can be a ground shift voltage of 1 V to 2 V.

### 図 9-11. Short to Battery and Open Load Detection