# TPS16890、9V~80V、3.65mΩ、20A、スタッカブル内蔵型ホットスワップ (eFuse)、PMBus® デジタル遠隔測定搭載

## 1 特長

- 動作入力電圧範囲: 9V ~ 80V

- 92V 絶対最大定格

- 出力側で最大 -5V の負の過渡電圧に耐える

- 低い ON 抵抗の FET を内蔵

- $R_{ON} = 3.65\text{m}\Omega$  (標準値)

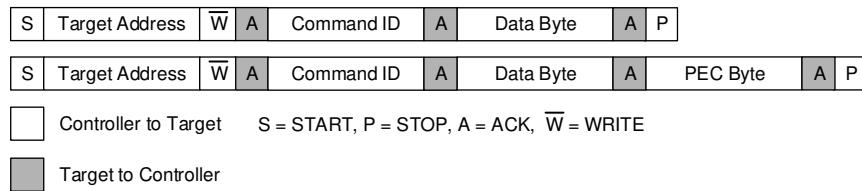

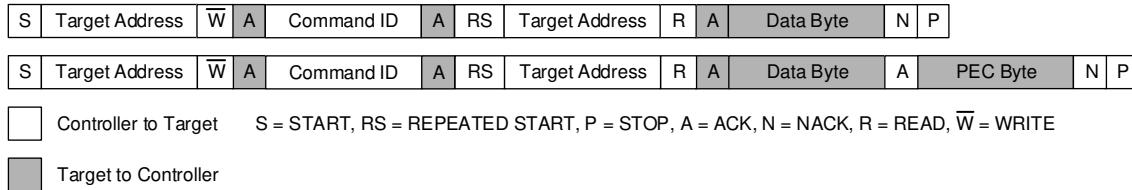

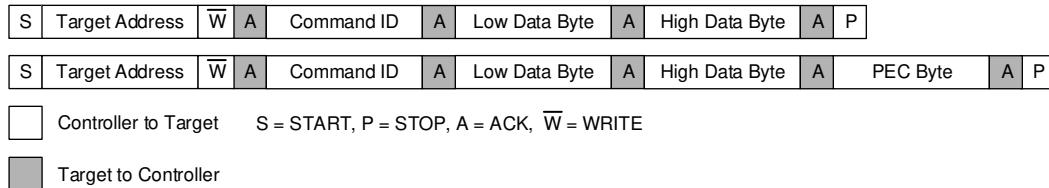

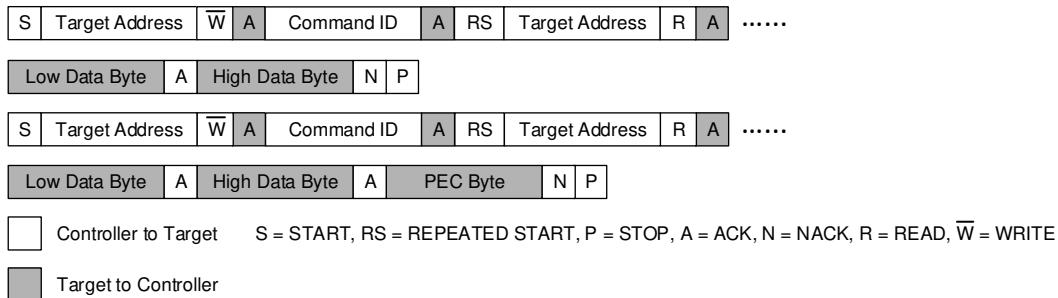

- 遠隔測定、制御、構成、デバッグ用の PMBus インターフェイス

- PIN/EIN/VIN/VOUT/IIN 温度と故障監視

- VIN/VOUT 監視精度:  $\pm 0.5\%$

- プログラム可能な過電流保護

- 調整可能な過電流スレッショルド: 2A ~ 20A

- プログラマブルな過渡過電流タイマ (OC\_TIMER)

- プログラマブルなスルーレート制御 (dvdt)

- プログラマブルなパワー グッド / 故障 / アラート表示

- プログラマブルな過熱保護

- 構成値用の不揮発性構成メモリ

- 外部 EEPROM への保存オプション付きのブラックボックス故障記録

- 重度の過電流(短絡)に対する高速トリップ応答

- 高精度アナログ負荷電流監視 (IMON)

- 誤差 3% 未満 (最大電流の 50% ~ 100% にわたり)

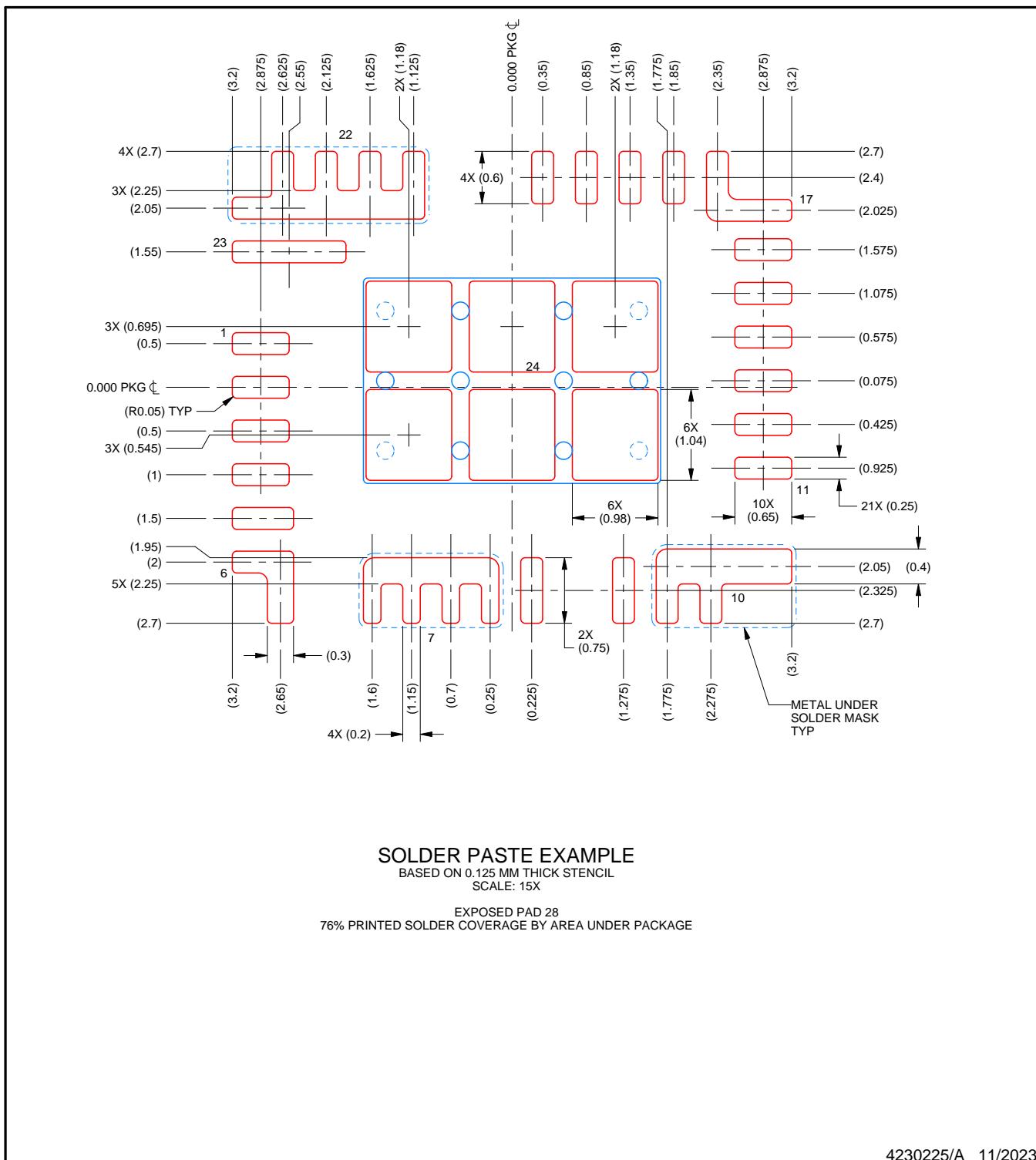

- 小さい占有面積: QFN 6mm × 5mm

- 60V 対応の IPC9592B クリアランス

## 2 アプリケーション

- サーバーおよび高性能コンピューティング

- ネットワークインターフェイスカード

- グラフィックスおよびハードウェアアクセラレータカード

- データセンター スイッチおよびルータ

- 入力ホットスワップおよびホットプラグ

- ファントレイ

## 3 概要

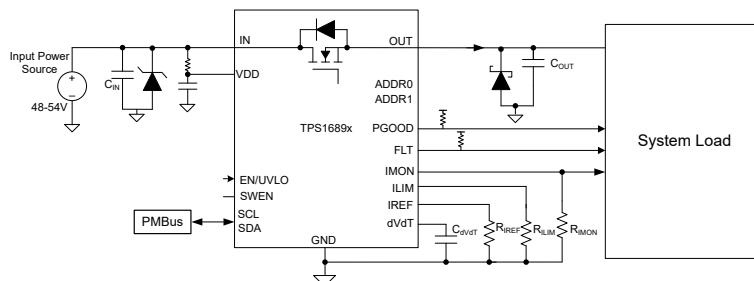

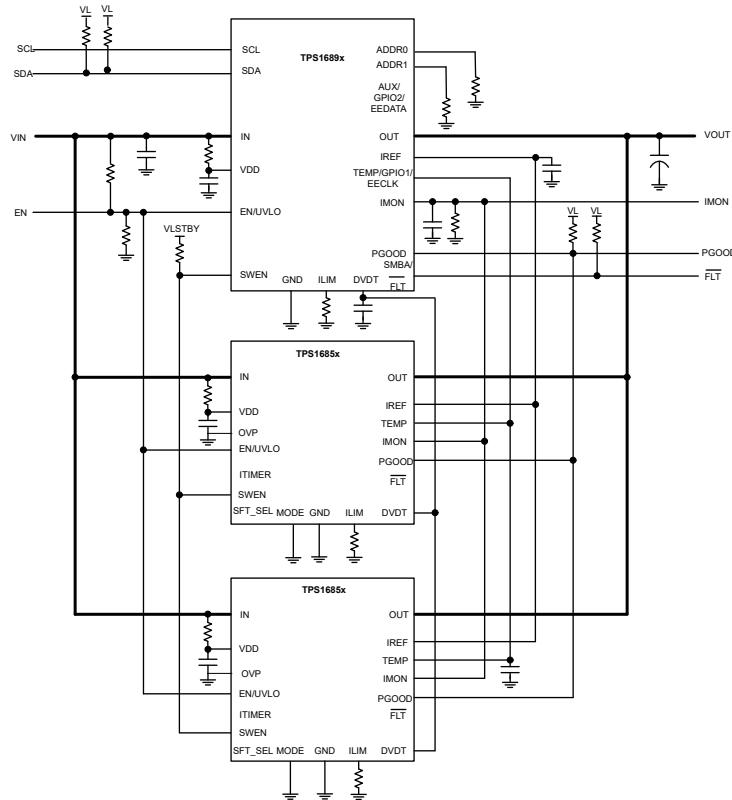

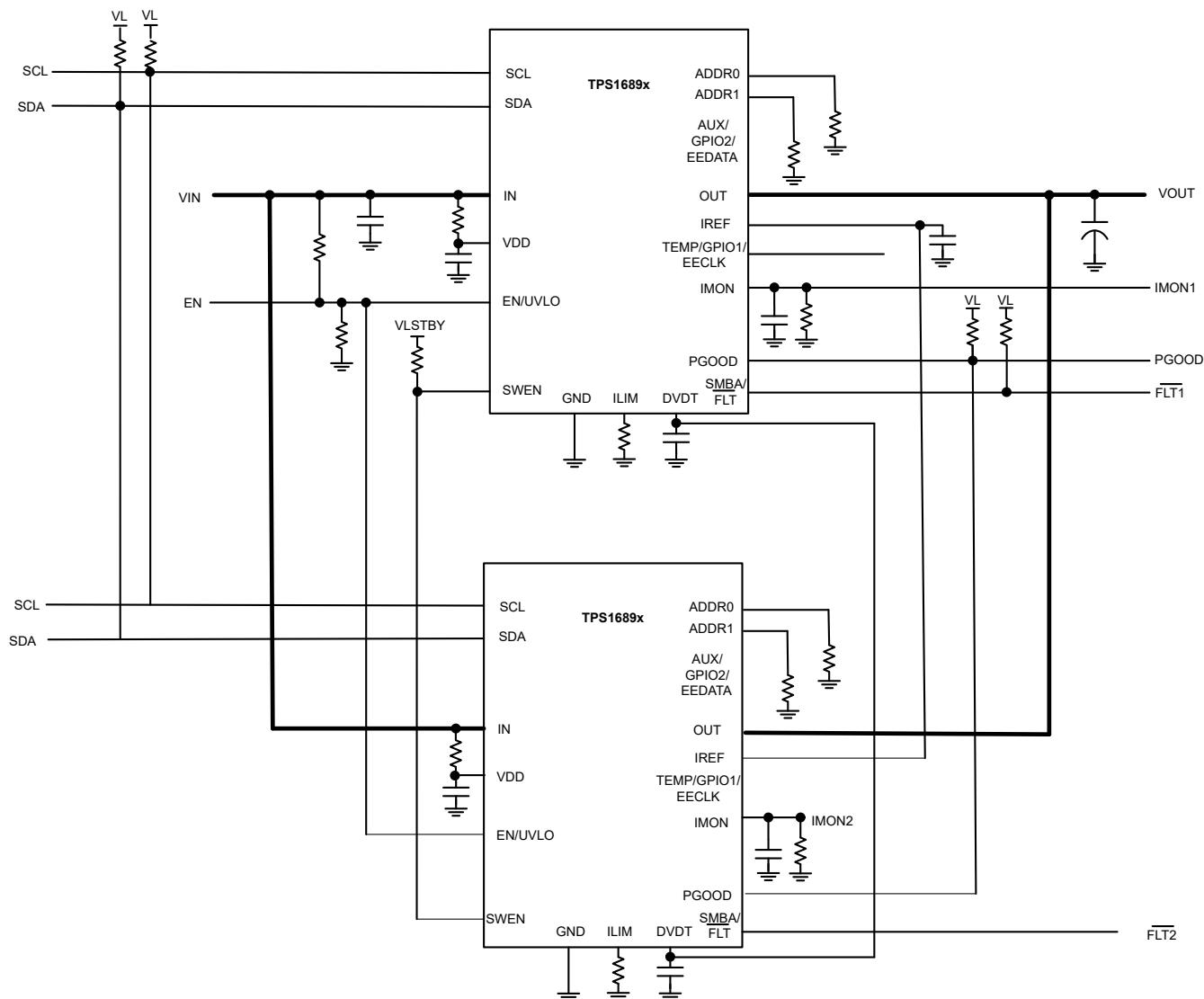

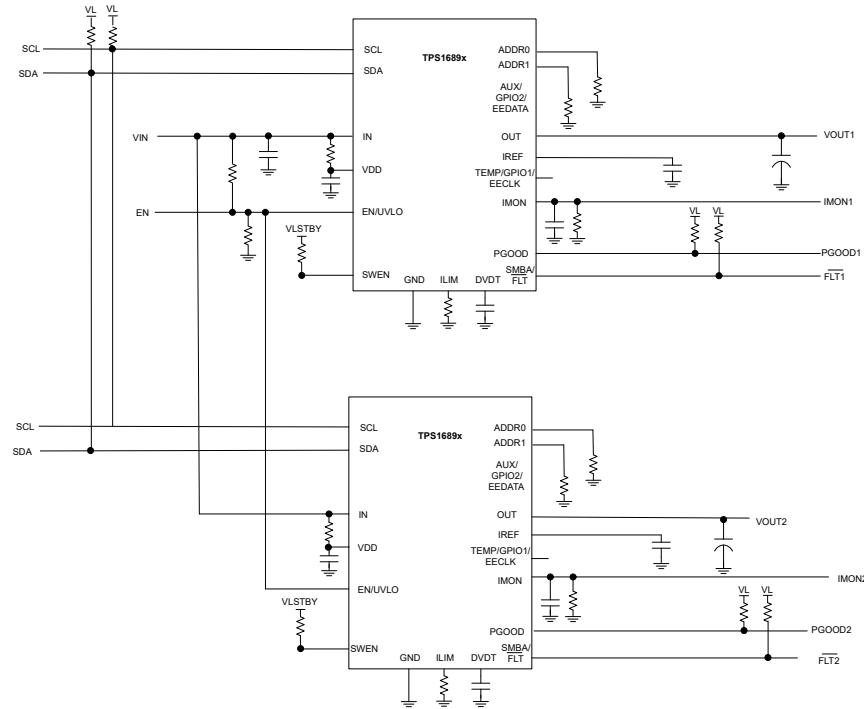

TPS1689x は統合型大電流回路保護およびパワー マネージメントソリューションであり、小型パッケージに封止されています。このデバイスは、非常に少数の外付け部品で複数の保護モードを提供し、過負荷、短絡、および過剰な突入電流に対して堅牢な保護を行います。内蔵 PMBus™ インターフェイスにより、ホストコントローラはシステムをリアルタイムで監視、制御、および構成できます。リモートテレメトリの場合、主なシステム パラメータを読み戻すことができます。各種の保護、警告スレッショルドおよび係数は、PMBus を使用して構成することも、不揮発性コンフィギュレーション メモリに保存することもできます。高速で高精度の検出を行う内蔵のアナログ負荷電流モニタにより、予知保全と高度な動的プラットフォーム電力管理 (Intel® PSYS、PROCHOT など) が容易になり、サーバーおよびデータセンターの性能を最適化します。ブラックボックスファルト記録機能は、フィールド障害のデバッグや返品時に役立ちます。より大きな電流をサポートするために、TPS1689x を TPS1685x と並列に接続できます。これらのデバイスは、-40°C ~ +125°C の接合部温度範囲で動作が規定されています。

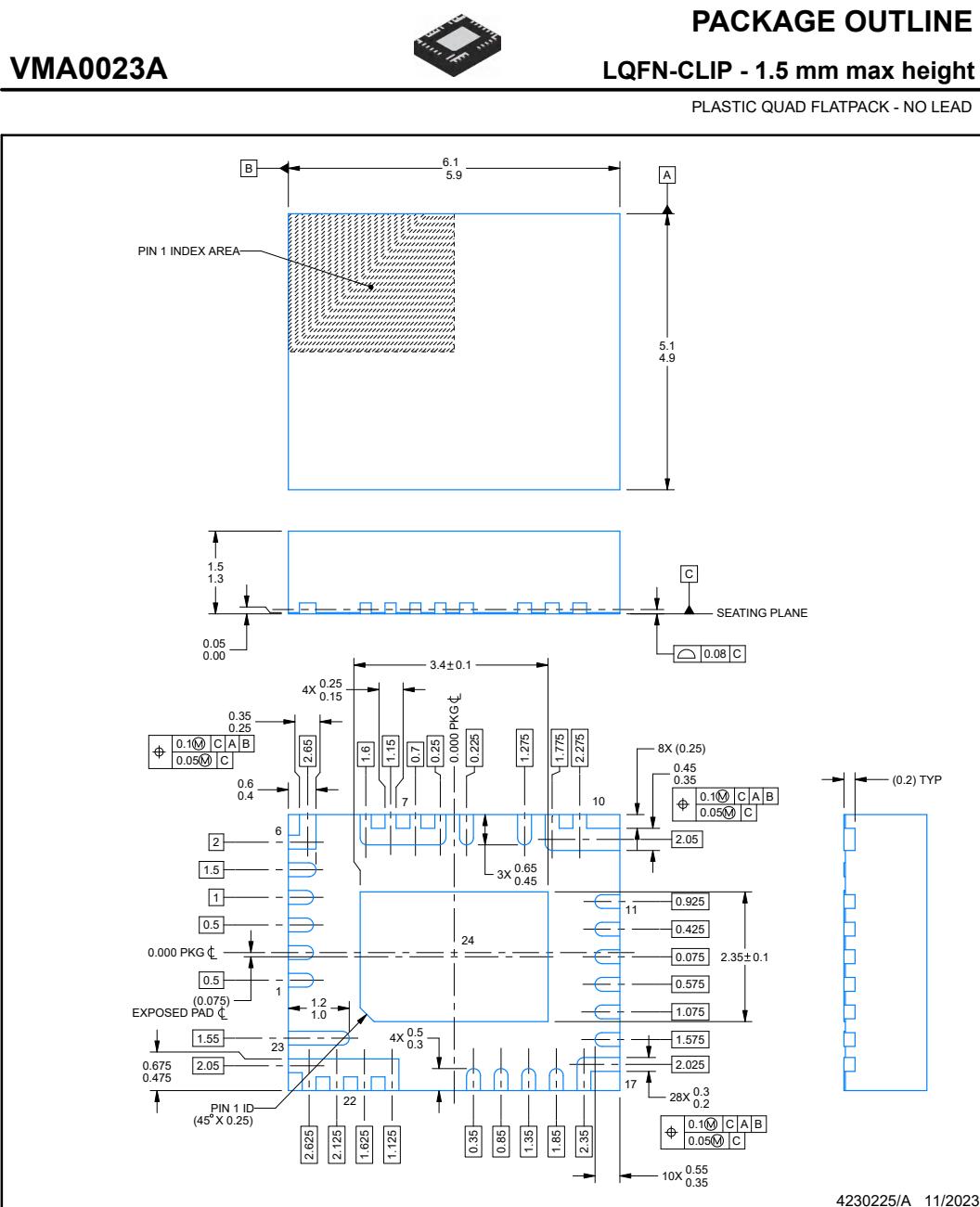

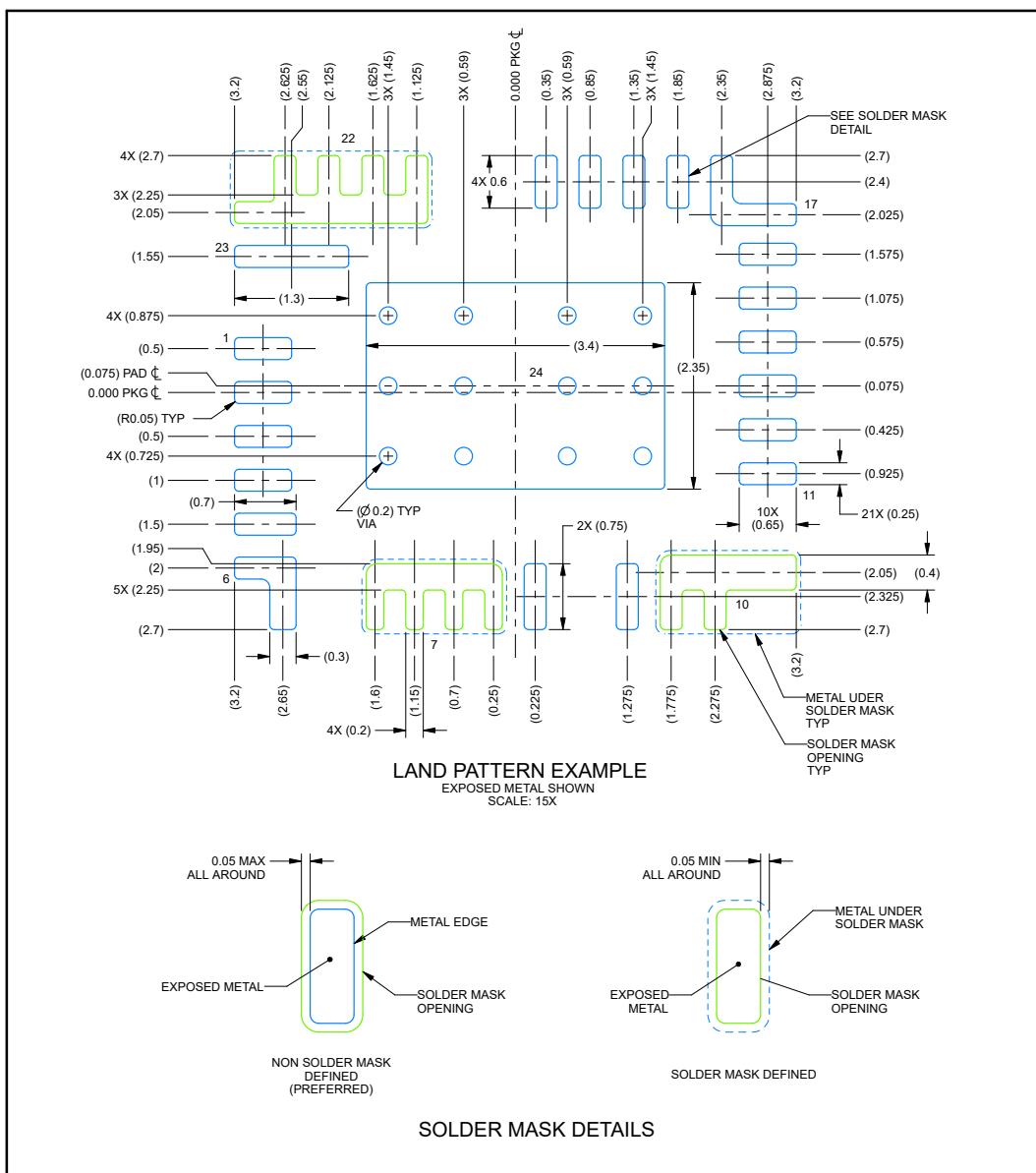

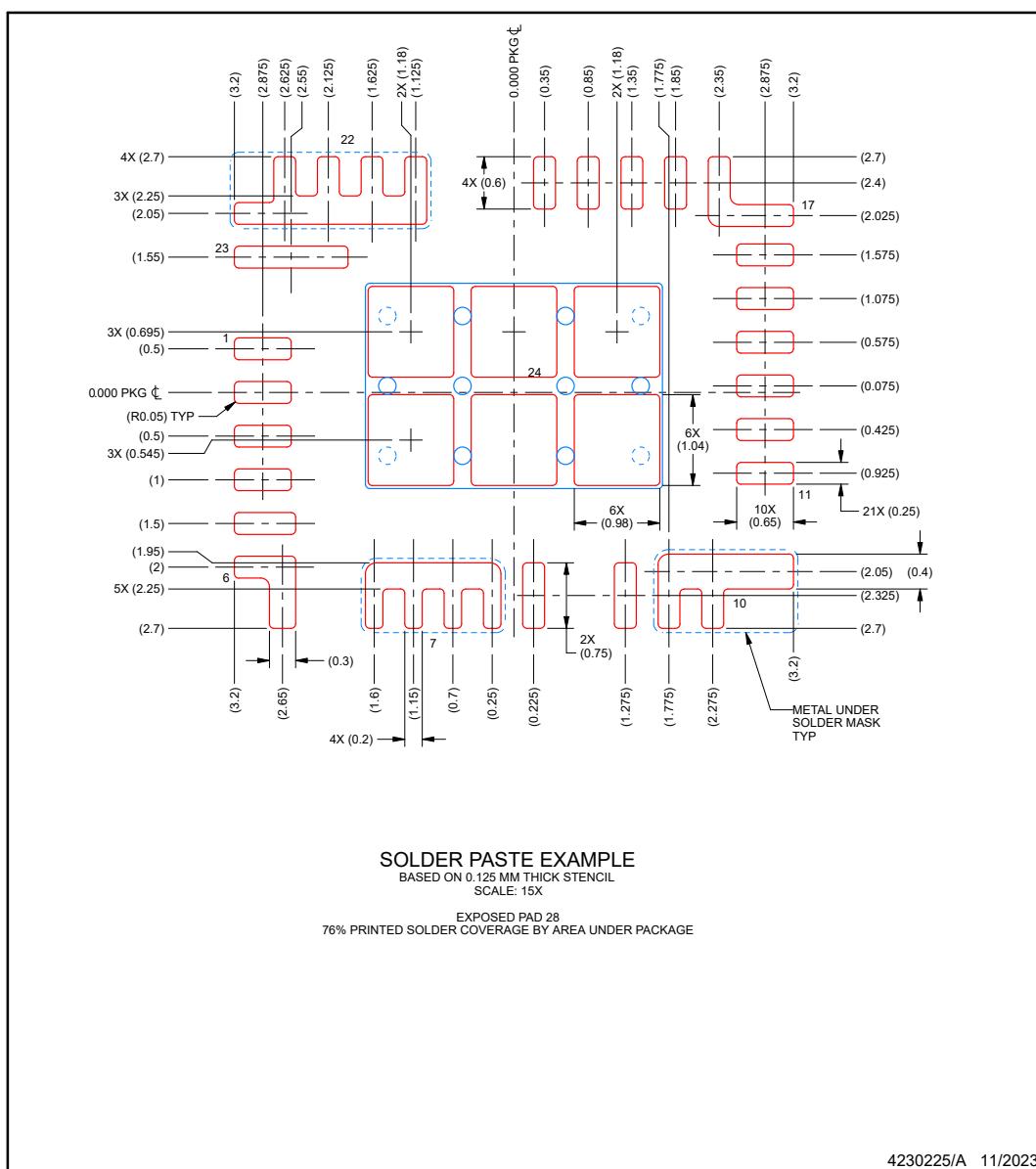

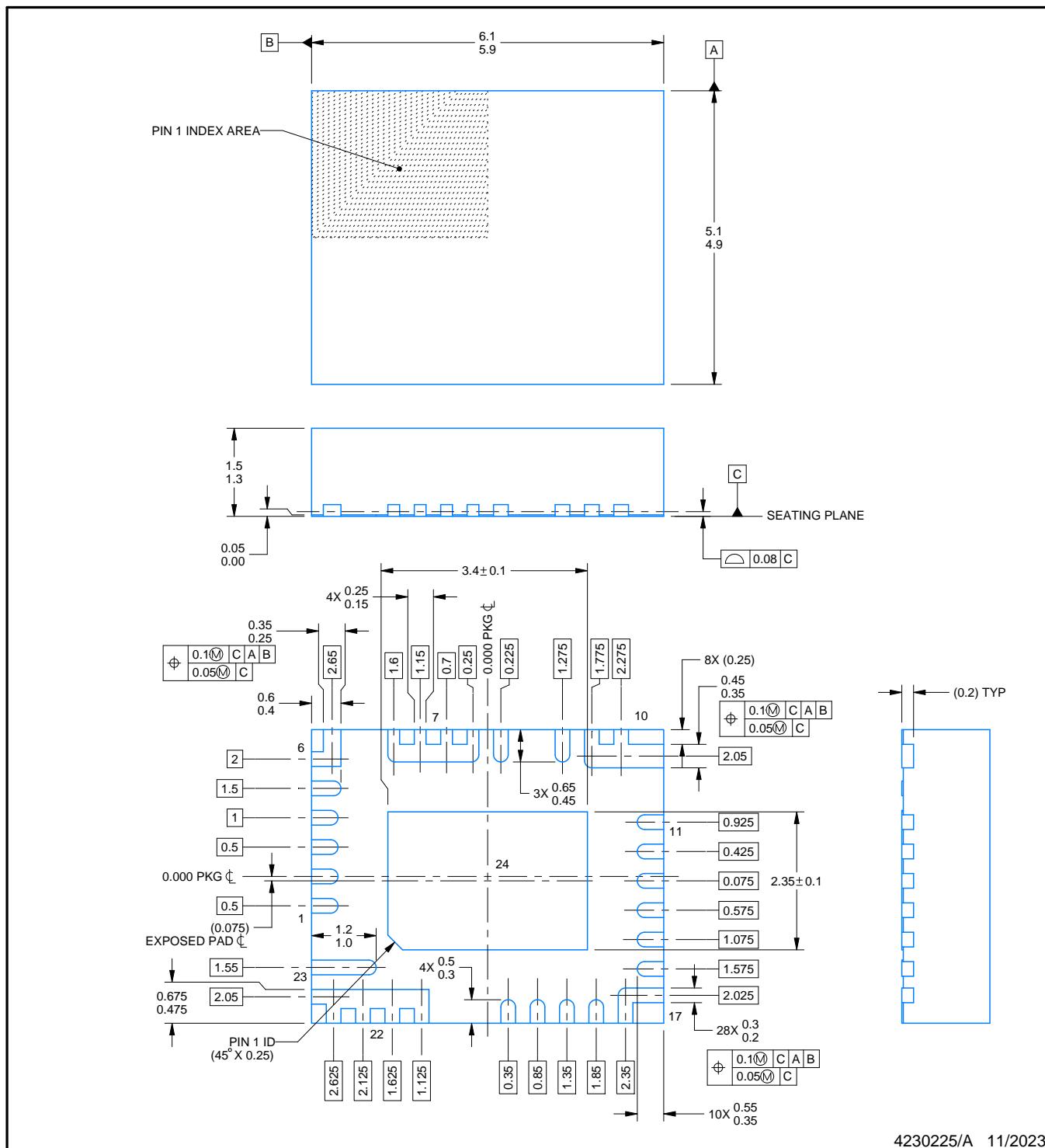

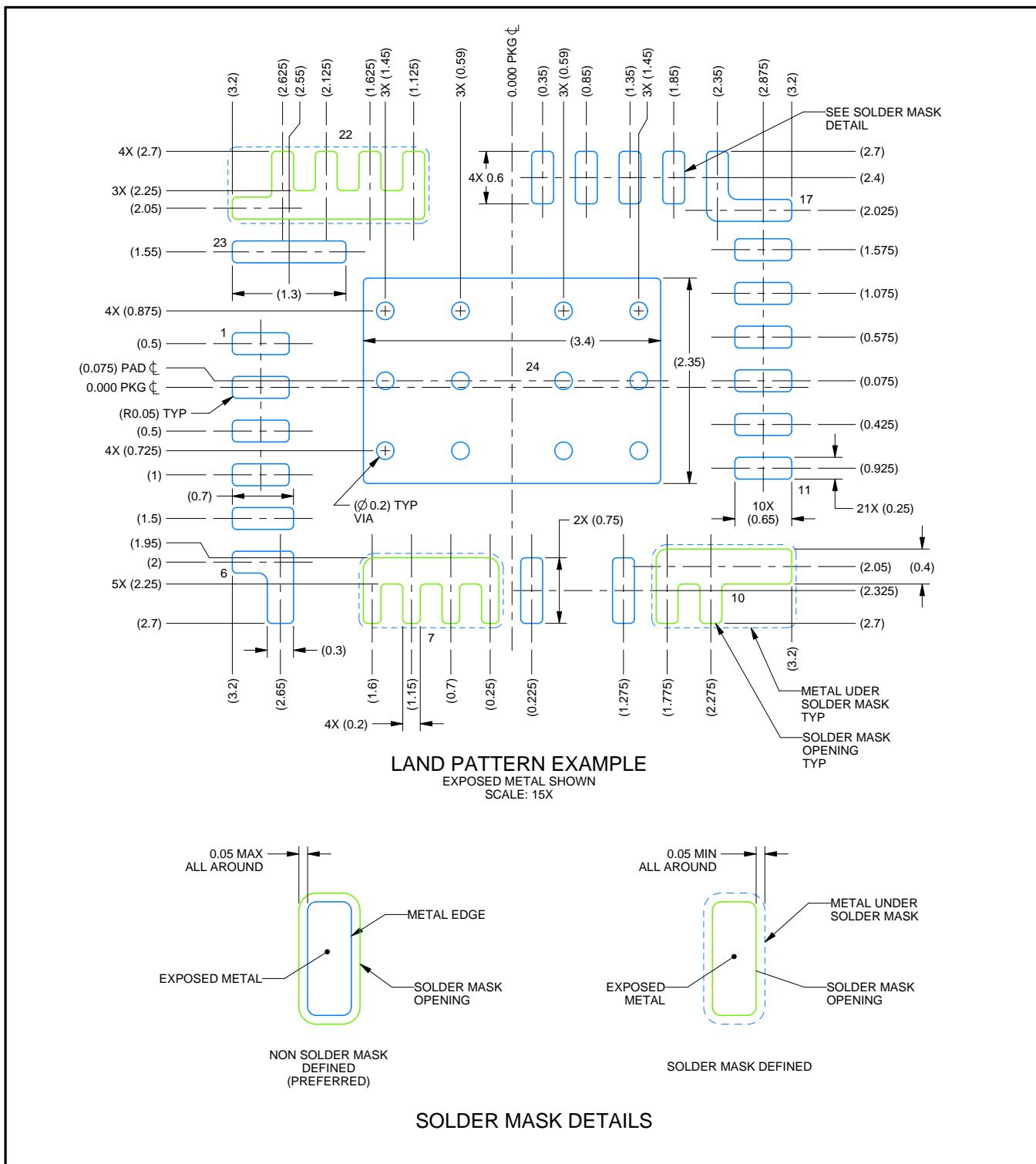

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| TPS16890 | VMA (LQFN, 23)       | 5mm × 6mm                |

(1) 供給されているすべてのパッケージについては、セクション 11 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

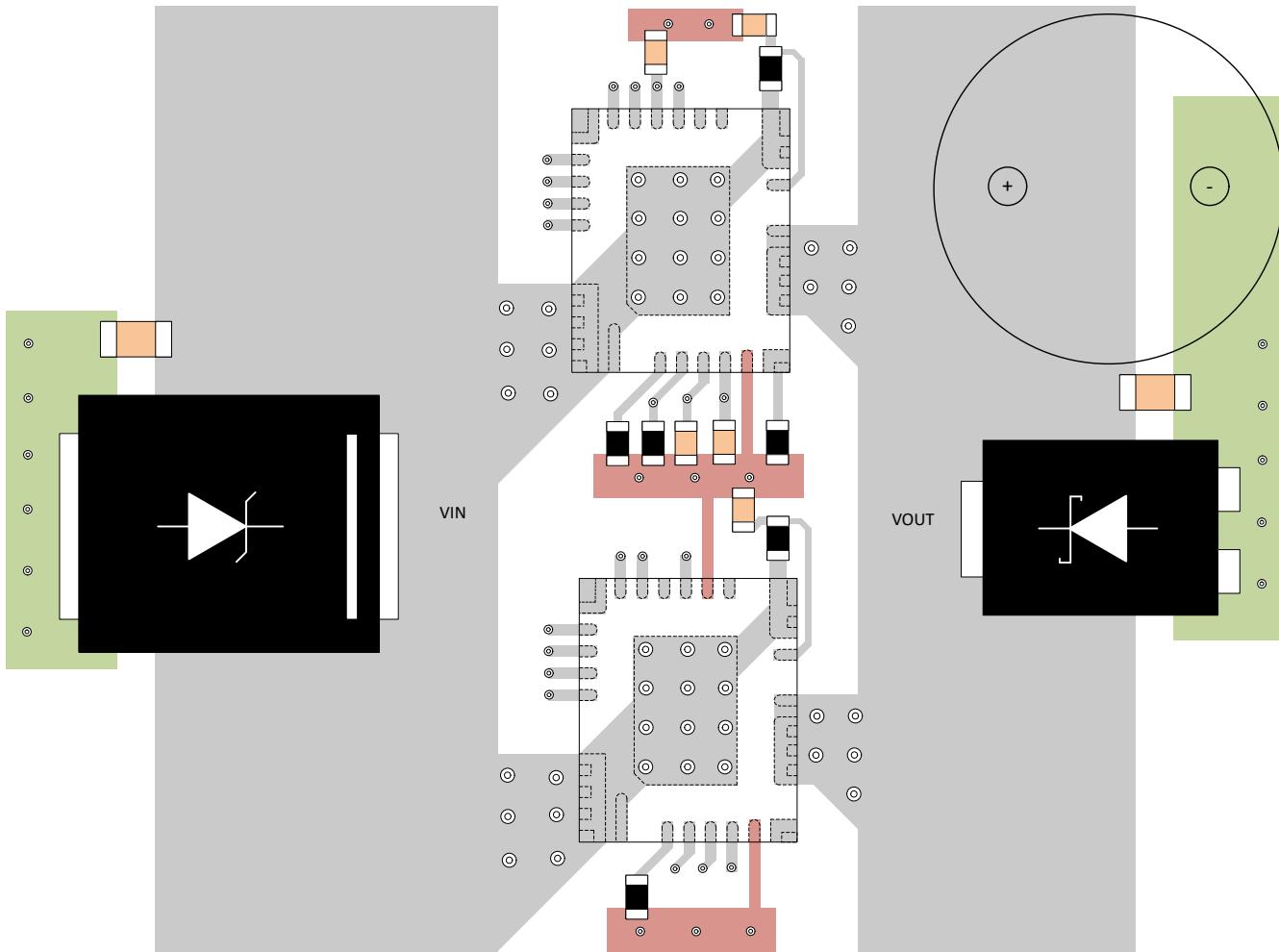

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSH01](#)

## 目次

|                                 |    |                                                                           |    |

|---------------------------------|----|---------------------------------------------------------------------------|----|

| 1 特長.....                       | 1  | 6.4 デバイスの機能モード.....                                                       | 46 |

| 2 アプリケーション.....                 | 1  | 7 アプリケーションと実装.....                                                        | 47 |

| 3 概要.....                       | 1  | 7.1 アプリケーション情報.....                                                       | 47 |

| 4 ピン構成および機能.....                | 3  | 7.2 代表的なアプリケーション: データセンター サーバーの PMBus® インターフェイスによる 54V、2kW パワー パスの保護..... | 53 |

| 5 仕様.....                       | 5  | 7.3 電源に関する推奨事項.....                                                       | 59 |

| 5.1 絶対最大定格.....                 | 5  | 7.4 レイアウト.....                                                            | 60 |

| 5.2 ESD 定格.....                 | 5  | 8 アプリケーションの制限とエラッタ.....                                                   | 63 |

| 5.3 推奨動作条件.....                 | 5  | 9 デバイスおよびドキュメントのサポート.....                                                 | 64 |

| 5.4 熱に関する情報.....                | 6  | 9.1 ドキュメントのサポート.....                                                      | 64 |

| 5.5 電気的特性.....                  | 6  | 9.2 ドキュメントの更新通知を受け取る方法.....                                               | 64 |

| 5.6 PMBus および GPIO の DC 特性..... | 9  | 9.3 サポート・リソース.....                                                        | 64 |

| 5.7 遠隔測定.....                   | 9  | 9.4 商標.....                                                               | 64 |

| 5.8 ロジック・インターフェイス.....          | 10 | 9.5 静電気放電に関する注意事項.....                                                    | 64 |

| 5.9 タイミング要件.....                | 10 | 9.6 用語集.....                                                              | 64 |

| 5.10 代表的特性.....                 | 12 | 10 改訂履歴.....                                                              | 64 |

| 6 詳細説明.....                     | 14 | 11 メカニカル、パッケージ、および注文情報.....                                               | 64 |

| 6.1 概要.....                     | 14 | 11.1 メカニカル データ.....                                                       | 65 |

| 6.2 機能ブロック図.....                | 15 |                                                                           |    |

| 6.3 機能説明.....                   | 15 |                                                                           |    |

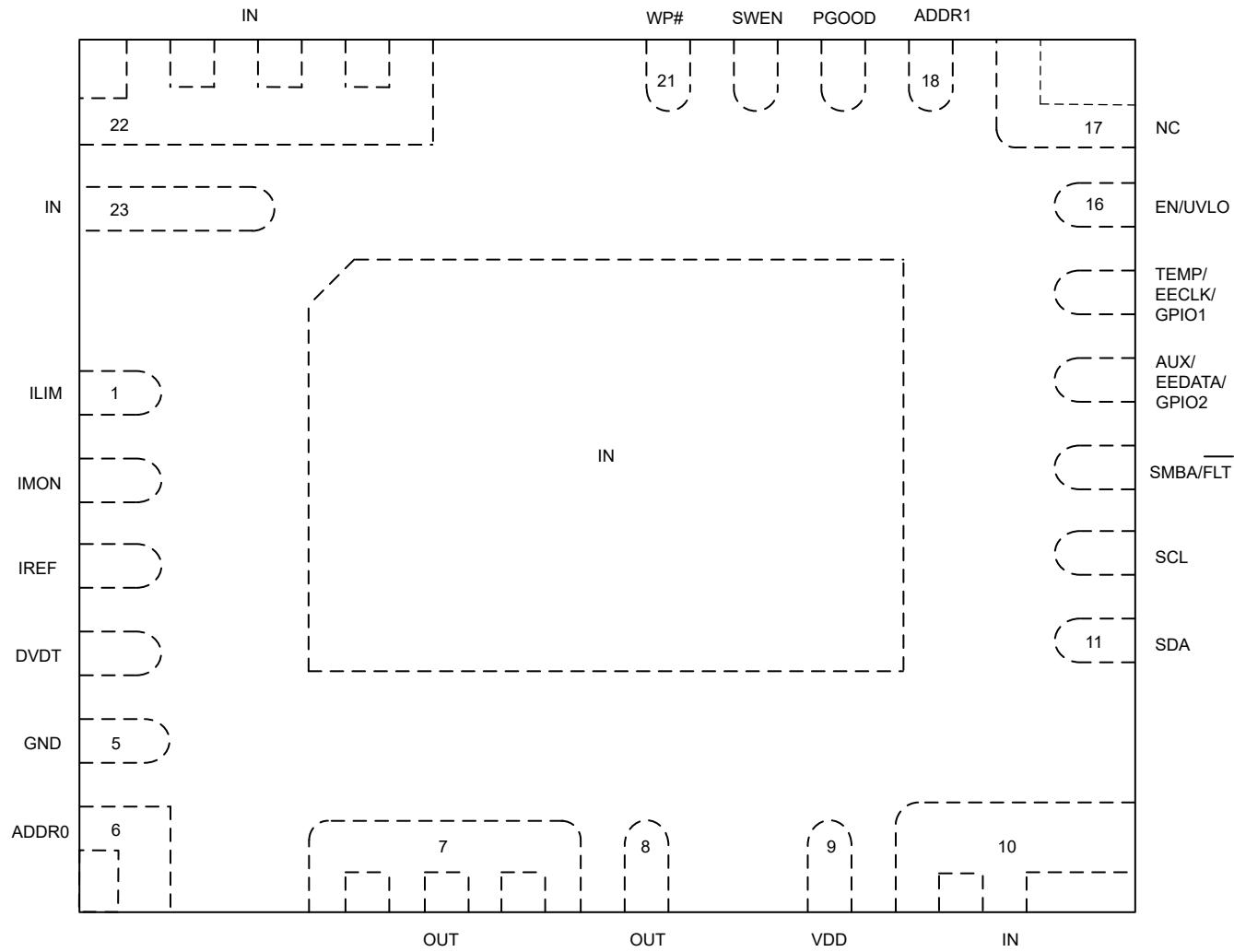

## 4 ピン構成および機能

図 4-1. TPS16890 VMA パッケージ、23 ピン LQFN 上面図

表 4-1. ピンの機能

| ピン   |    | タイプ | 説明                                                                                                                                                   |

|------|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号 |     |                                                                                                                                                      |

| ILIM | 1  | O   | このピンと GND との間に外付け抵抗を接続することで、定常状態時のアクティブ電流共有スレッショルドが設定されます。このピンは、定常状態時の個別の eFuse 電流モニタ出力としても機能します。 <b>フローティングのままにしないでください。</b>                        |

| IMON | 2  | O   | このピンと GND の間に外付け抵抗を接続することで、定常状態時の過電流/サーチキットブレーカ スレッショルドと高速トリップ スレッショルドが設定されます。このピンは、状態中の高速かつ高精度のアナログ出力負荷電流監視信号としても機能します。 <b>フローティングのままにしないでください。</b> |

| IREF | 3  | O   | 内部 DAC を使用して生成される、過電流保護ブロック用のプログラマブル リファレンス電圧。プライマリ / セカンダリ並列構成の他のセカンダリ デバイスのリファレンス電圧を駆動するために使用できます。                                                 |

| DVDT | 4  | O   | 起動時出力スルーレート制御ピン。これをオープンのままにすると、最速の起動が可能です。コンデンサをグランドと接続することで、スルーレートを低速にし、突入電流を管理します。                                                                 |

| GND  | 5  | G   | デバイスグランドリファレンスピン。システムグランドに接続します。                                                                                                                     |

表 4-1. ピンの機能 (続き)

| ピン               |                  | タイプ | 説明                                                                                                                             |

|------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| 名称               | 番号               |     |                                                                                                                                |

| ADDR0            | 6                | I   | I <sup>2</sup> C アドレス構成ピン。ピン ストラップをオープン / 接地短絡、または抵抗接地することで、各種アドレスの組み合わせを生成します。                                                |

| OUT              | 7, 8             | P   | 電力出力。適切な放熱のため、出力電源プレーンに均一に半田付けする必要があります。                                                                                       |

| VDD              | 9                | P   | コントローラ電源入力ピン。システムの過渡現象の影響を受けない、filtratingされた安定した電源で内部制御回路に電力を供給するために使用できます。<br>このピンを直列抵抗を介して VIN に接続し、デカップリングコンデンサを GND 追加します。 |

| IN               | 10, 22, 23、露出パッド | P   | 電源入力。適切な放熱を確保し、デバイスへの最適な電流分配を維持するため、入力電源プレーンに均一に半田付けする必要があります。                                                                 |

| SDA              | 11               | I/O | PMBus インターフェイス用の I <sup>2</sup> C データライン。外部プルアップ抵抗が必要です。                                                                       |

| SCL              | 12               | I   | PMBus インターフェイス用の I <sup>2</sup> C クロックライン。外部プルアップ抵抗が必要です。                                                                      |

| SMBA/FLT         | 13               | O   | FAULTB 出力。または SMBus アラート出力。外部プルアップ抵抗が必要です。                                                                                     |

| AUX/EEDATA/GPIO2 | 14               | I/O | ADC または外部 EEPROM データ IO または汎用デジタル IO 用の補助入力                                                                                    |

| TEMP/EECLK/GPIO1 | 15               | I/O | アナログ温度出力。複数のデバイスの TEMP 出力を並列構成で接続することで、チェーンのピーク温度を取得できます。または外部 EEPROM クロック出力、または汎用デジタル IO。                                     |

| EN/UVLO          | 16               | I   | アクティブ High イネーブル入力。入力電源から抵抗分器を接続して、低電圧ショルドを設定します。フローティングのままにしないでください。                                                          |

| NC               | 17               | -   | 内部接続なし。                                                                                                                        |

| ADDR1            | 18               | I   | I <sup>2</sup> C アドレス構成ピン。ピン ストラップをオープン / 接地短絡、または抵抗接地することで、各種アドレスの組み合わせを生成します。                                                |

| PGOOD            | 19               | O   | オープンドレインのアクティブ high パワーグッド出力。このピンには、内部電源電圧への弱いプルアップがあります。                                                                      |

| SWEN             | 20               | I/O | パワー スイッチのオン / オフ ステータスを示すオープンドレイン信号。これにより、並列チェーン内の複数のデバイスを簡単に同期できます。このピンには内部にプルアップ抵抗があります。                                     |

| WP#              | 21               | I   | 書き込み保護: このピンを GND に接続すると、デバイスへの PMBus 書き込みアクセスが完全に無効化されます。このピンがフローティングのとき、PMBuswrite アクセスは MFR_WRITE_PROTECT コマンドによって制御されます。   |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                          | ピン                                                                      | 最小値              | 最大値               | 単位                        |

|--------------------------------|-------------------------------------------------------------------------|------------------|-------------------|---------------------------|

| $V_{INMAX}, V_{DDMAX}$         | 最大入力および電源電圧 ( $-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ ) | IN, VDD          | -0.3              | 90                        |

| $V_{INMAX, 25}, V_{DDMAX, 25}$ | 最大入力および電源電圧 ( $25^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ )  | IN, VDD          | -0.3              | 92                        |

| $V_{OUTMAX}$                   | 最大出力電圧                                                                  | OUT              | -5 <sup>(2)</sup> | Min(92V, $V_{IN} + 0.3$ ) |

| $V_{IN} \sim V_{OUT}$          | IN と OUT の最大差                                                           | IN, OUT          | -0.3              | 90                        |

| $V_{ILIMMAX}$                  | ILIM ピンの最大電圧                                                            | ILIM             | -0.3              | 内部的に制限                    |

| $V_{IMONMAX}$                  | IMON ピンの最大電圧                                                            | IMON             | -0.3              | 内部的に制限                    |

| $V_{ADDRMAX}$                  | ADDR1, ADDR0 ピンの最大電圧                                                    | ADDR1, ADDR0     | -0.3              | 内部的に制限                    |

| $V_{I2CMAX}$                   | SCL, SDA ピンの最大電圧                                                        | SCL, SDA         | -0.3              | 6                         |

| $V_{IREFMAX}$                  | IREF ピンの最大電圧                                                            | IREF             | -0.3              | 6                         |

| $V_{DVDTMAX}$                  | DVDT ピンの最大電圧                                                            | DVDT             | -0.3              | 6                         |

| $V_{AUXMAX}$                   | AUX/EEDATA/GPIO2 ピンの最大電圧                                                | AUX/EEDATA/GPIO2 | -0.3              | 6                         |

| $V_{SWENMAX}$                  | SWEN ピンの最大電圧                                                            | SWEN             | -0.3              | 6                         |

| $I_{SWENMAX}$                  | SWEN ピンの最大シンク                                                           | SWEN             |                   | 10 mA                     |

| $V_{ENMAX}$                    | EN/UVLO ピンの最大電圧                                                         | EN/UVLO          | -0.3              | 6                         |

| $V_{FLTBMAX}$                  | SMBA/FLT ピンの最大電圧                                                        | SMBA/FLT         | -0.3              | 6                         |

| $I_{FLTBMAX}$                  | SMBA/FLT ピンの最大シンク電流                                                     | SMBA/FLT         |                   | 10 mA                     |

| $V_{PGOODMAX}$                 | PGOOD ピンの最大電圧                                                           | PGOOD            | -0.3              | 6                         |

| $I_{PGOODMAX}$                 | PGOOD ピンの最大シンク電流                                                        | PGOOD            |                   | 10 mA                     |

| $V_{TEMPMAX}$                  | TEMP/EECLK/GPIO1 ピンの最大電圧                                                | TEMP/EECLK/GPIO1 | -0.3              | 6                         |

| $I_{MAX}$                      | 最大連続スイッチ電流                                                              | IN から OUT        | 内部的に制限            | A                         |

| $T_{JMAX}$                     | 接合部温度                                                                   |                  | 内部的に制限            | °C                        |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) FET オフで最大 5μs の負の過渡状態。

### 5.2 ESD 定格

|             |      | 値                                                               | 単位         |

|-------------|------|-----------------------------------------------------------------|------------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン<br><sup>(1)</sup> | ±1500<br>V |

|             |      | デバイス帶電モデル (CDM)、JEDEC 規格 JESD22-C101 準拠、すべてのピン <sup>(2)</sup>   |            |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ    | ピン     | 最小値 | 最大値 | 単位 |

|----------|--------|-----|-----|----|

| $V_{IN}$ | 入力電圧範囲 | IN  | 9   | 80 |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                         |                                             | ピン                   | 最小値 | 最大値             | 単位   |

|-------------------------------|---------------------------------------------|----------------------|-----|-----------------|------|

| V <sub>DD</sub>               | 電源電圧範囲                                      | VDD                  | 9   | 80              | V    |

| V <sub>OUT</sub>              | 出力電圧範囲                                      | OUT                  |     | V <sub>IN</sub> | V    |

| V <sub>EN/UVLO</sub>          | イネーブルピン電圧範囲                                 | EN/UVLO              |     | 5               | V    |

| V <sub>dVdT</sub>             | dVdT ピン コンデンサ電圧定格                           | dVdT                 | 4   |                 | V    |

| V <sub>PGOOD</sub>            | PGOOD ピンのプルアップ電圧範囲                          | PG                   |     | 5               | V    |

| V <sub>I2C</sub>              | I <sup>2</sup> C プルアップ電圧範囲                  | SCL、SDA              | 1.8 | 5               | V    |

| C <sub>I2C</sub>              | I <sup>2</sup> C バスの容量                      | SCL、SDA              |     | 200             | pF   |

| V <sub>TEMP/EECLK/GPIO1</sub> | TEMP/EECLK/GPIO1 ピンの電圧範囲                    | TEMP/EECLK/<br>GPIO1 |     | 5               | V    |

| V <sub>SMBA/FLTb</sub>        | SMBA/FLT ピンのプルアップ電圧範囲                       | SMBA/FLT             |     | 5               | V    |

| V <sub>SWEN</sub>             | SWEN ピンのプルアップ電圧範囲                           | SWEN                 |     | 5               | V    |

| V <sub>AUX</sub>              | AUX ピンの電圧定格                                 | AUX                  |     | 1.2             | V    |

| V <sub>IREF</sub>             | IREF ピンの電圧範囲                                | IREF                 | 0.3 | 1.2             | V    |

| V <sub>ILIM</sub>             | ILIM ピンの電圧範囲                                | ILIM                 |     | 0.4             | V    |

| V <sub>IMON</sub>             | IMON ピンの電圧範囲                                | IMON                 |     | 1.2             | V    |

| C <sub>IN</sub>               | IN ピン上のコンデンサ                                | IN                   | 10  |                 | nF   |

| C <sub>OUT</sub>              | OUT ピン上のコンデンサ                               | OUT                  | 10  |                 | μF   |

| dV <sub>IN/dt</sub>           | IN ピンのスルーレート                                | IN                   |     | 500             | V/μs |

| I <sub>MAX</sub>              | 連続スイッチ電流                                    | IN から OUT            |     | 20              | A    |

| I <sub>MAX</sub> 、パルス         | 持続時間 ≤10 ms、T <sub>A</sub> ≤ 70 °C のピーク出力電流 | IN から OUT            |     | 27              | A    |

| T <sub>J</sub>                | 接合部温度                                       |                      | -40 | 125             | °C   |

## 5.4 热に関する情報

| 热評価基準            |                  | TPS1689x | 単位   |

|------------------|------------------|----------|------|

|                  |                  | LQFN     |      |

|                  |                  | ピン       |      |

| R <sub>θJA</sub> | 接合部から周囲への熱抵抗     | 22.8     | °C/W |

| Ψ <sub>JT</sub>  | 接合部から上面への特性パラメータ | 0.1      | °C/W |

| Ψ <sub>JB</sub>  | 接合部から基板への特性パラメータ | 10.7     | °C/W |

## 5.5 電気的特性

–40°C ≤ T<sub>J</sub> ≤ +125°C、VIN = V<sub>DD</sub> = 45 V ~ 60 V、OUT = Open、R<sub>ILIM</sub> = 931 Ω R<sub>IMON</sub> = 2.55 kΩ、V<sub>IREF</sub> = 1 V、FLT = 33 kΩ プルアップ (3.3 V)、PGOOD = 33 kΩ プルアップ (3.3 V)、C<sub>OUT</sub> = 10 μF、C<sub>IN</sub> = 10 nF、dVdT = Open、V<sub>EN/UVLO</sub> = 2 V、TEMP/EECLK/GPIO1 = Open、AUX/EEDATA/GPIO2 = Open、ADDR0 = Open、ADDR1 = Open、SCL = 330Ω プルアップ (3.3 V)、SDA = 330Ω プルアップ (3.3 V)。(特に記載がない限り、すべての電圧は GND を基準とする)

| パラメータ                 | テスト条件                             | 最小値                                                                                                             | 標準値             | 最大値  | 単位 |

|-----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|------|----|

| <b>入力電源 (VDD)</b>     |                                   |                                                                                                                 |                 |      |    |

| V <sub>IN</sub>       | 入力電圧範囲                            |                                                                                                                 | 9               | 80   | V  |

| V <sub>DD</sub>       | 入力電圧範囲                            |                                                                                                                 | V <sub>IN</sub> | 80   | V  |

| I <sub>QON(VDD)</sub> | V <sub>DD</sub> ON 状態静止電流         | V <sub>DD</sub> > V <sub>UVPR</sub> 、V <sub>EN</sub> ≥ V <sub>UVLOR</sub> 、V <sub>OVP</sub> < V <sub>OVPF</sub> |                 | 4.5  | mA |

| V <sub>UVPR</sub>     | V <sub>DD</sub> 低電圧保護スレッショルド立ち上がり | V <sub>DD</sub> 立ち上がり                                                                                           |                 | 8.5  | V  |

| V <sub>UVPF</sub>     | V <sub>DD</sub> 低電圧保護スレッショルド立ち下がり | V <sub>DD</sub> 立ち下がり                                                                                           |                 | 7.05 | V  |

$-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$ 、 $V_{IN} = V_{DD} = 45 \text{ V} \sim 60 \text{ V}$ 、 $OUT = \text{Open}$ 、 $R_{ILIM} = 931 \Omega$ 、 $R_{IMON} = 2.55 \text{ k}\Omega$ 、 $V_{IREF} = 1 \text{ V}$ 、 $\overline{FLT} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $PGOOD = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $C_{OUT} = 10 \mu\text{F}$ 、 $C_{IN} = 10 \text{ nF}$ 、 $dVdT = \text{Open}$ 、 $V_{EN/UVLO} = 2 \text{ V}$ 、 $\text{TEMP/EECLK/GPIO1} = \text{Open}$ 、 $\text{AUX/EEDATA/GPIO2} = \text{Open}$ 、 $\text{ADDR0} = \text{Open}$ 、 $\text{ADDR1} = \text{Open}$ 、 $SCL = 330\Omega$  プルアップ (3.3 V)、 $SDA = 330\Omega$  プルアップ (3.3 V)。(特に記載がない限り、すべての電圧は GND を基準とする)

| パラメータ                             |                                                           | テスト条件                                               | 最小値 | 標準値  | 最大値   | 単位               |

|-----------------------------------|-----------------------------------------------------------|-----------------------------------------------------|-----|------|-------|------------------|

| $V_{UVPHYS}$                      |                                                           | UVP ヒステリシス VDD                                      |     |      | 1.45  | V                |

| <b>入力電源 (IN)</b>                  |                                                           |                                                     |     |      |       |                  |

| $V_{UVLOR(VIN)}$                  | VIN 低電圧スレッショルド立ち上がり                                       | $V_{IN}$ 立ち上がり、 $VIN\_UV\_FLT = 0x71$               |     |      | 40.3  | V                |

| $V_{UVLOF(VIN)}$                  | VIN 低電圧スレッショルド立ち下がり                                       | $V_{IN}$ 立ち下がり、 $VIN\_UV\_FLT = 0x71$               |     |      | 38.7  | V                |

| $I_{QON(VIN)}$                    | $V_{IN}$ ON 状態静止電流                                        | $V_{EN} \geq V_{UVLOR}$                             |     |      | 1.38  | mA               |

| $I_{QOFF(VIN)}$                   | $V_{IN}$ OFF 状態電流                                         | $V_{SDR} < V_{EN} < V_{UVLO}$                       |     |      | 1.83  | mA               |

| $I_{SD(VIN)}$                     | $V_{IN}$ シャットダウン電流                                        | $V_{EN} < V_{SDF}$                                  |     |      | 1.81  | mA               |

| <b>イネーブル / 低電圧誤動作防止 (EN/UVLO)</b> |                                                           |                                                     |     |      |       |                  |

| $V_{UVLOR}$                       | オンにするための EN/UVLO ピン電圧スレッショルド、立ち上がり                        | EN/UVLO 立ち上がり                                       |     |      | 1.2   | V                |

| $V_{UVLOF}$                       | オフにして QOD を作動させるための EN/UVLO ピン電圧スレッショルド、立ち下がり (プライマリデバイス) | EN/UVLO 立ち下がり                                       |     |      | 1.12  | V                |

| $V_{UVLOHYS}$                     | UVLO ヒステリシス                                               |                                                     |     | 94   |       | mV               |

| $V_{SDF}$                         | シャットダウン スレッショルド                                           | EN/UVLO 立ち下がり                                       |     |      | 0.46  | V                |

| $V_{SDR}$                         | シャットダウン スレッショルド                                           | EN/UVLO 立ち上がり                                       |     |      | 0.51  | V                |

| <b>過電圧保護 (IN)</b>                 |                                                           |                                                     |     |      |       |                  |

| $V_{IN-OVPR}$                     | IN 過電圧保護スレッショルド (立ち上がり)                                   | $VIN\_OV\_FLT = 0xb1$                               |     |      | 60.1  | V                |

| $V_{IN-OVPF}$                     | IN 過電圧保護スレッショルド (立ち下がり)                                   | $VIN\_OV\_FLT = 0xb1$                               |     |      | 57    | V                |

| $V_{IN-OVPHYS}$                   | IN 過電圧保護スレッショルド (ヒステリシス)                                  | $VIN\_OV\_FLT = 0xb1$                               |     |      | 3     | V                |

| <b>オン抵抗 (IN - OUT)</b>            |                                                           |                                                     |     |      |       |                  |

| $R_{ON}$                          | オン状態抵抗                                                    | $I_{OUT} = 12\text{A}$                              |     |      | 3.65  | $\text{m}\Omega$ |

| <b>電流制限基準 (IREF)</b>              |                                                           |                                                     |     |      |       |                  |

| $V_{IREF}$                        | 電流制限リファレンス DAC 出力電圧                                       | $V_{IREF} = 0x32$ (デフォルト)                           |     |      | 1     | V                |

| $V_{IREF}$                        | 電流制限リファレンス DAC 出力電圧                                       | $V_{IREF} = 0x00$                                   |     |      | 0.3   | V                |

| $V_{IREF}$                        | 電流制限リファレンス DAC 出力電圧                                       | $V_{IREF} = 0x3F$                                   |     |      | 1.182 | V                |

| <b>電流制限 (ILIM)</b>                |                                                           |                                                     |     |      |       |                  |

| $G_{ILIM(LIN)}$                   | 電流モニタ ゲイン (ILIM:IOUT) 対 IOUT。                             | デバイスが定常状態 (PG アサート)、<br>$I_{OUT} = 12\text{A}$      |     |      | 18.26 | $\text{uA/A}$    |

| $I_{start-up}$                    | IOUT 起動電流制限レギュレーション スレッショルド                               | $V_{IN} - V_{OUT} = 350 \text{ mV}$                 |     |      | 0.47  | A                |

| $V_{FB}$                          | フォールドバック電圧                                                |                                                     |     | 2.11 |       | V                |

| <b>出力電流モニタと過電流保護 (IMON)</b>       |                                                           |                                                     |     |      |       |                  |

| $G_{IMON}$                        | 電流モニタ ゲイン (IMON:IOUT)                                     | デバイスが定常状態 (PG アサート)、<br>$I_{OUT} = 12\text{A}$      |     |      | 18.25 | $\text{uA/A}$    |

| $G_{IMON}$                        | 電流モニタ ゲイン (IMON:IOUT)                                     | デバイスが定常状態 (PG アサート)、<br>$I_{OUT} = 4\text{A}$       |     |      | 18.28 | $\text{uA/A}$    |

| $I_{TRIP}$                        | IOUT 電流制限トリップ (回路ブレーカ) スレッショルド                            | $R_{IMON} = 2.32 \Omega$ 、 $V_{IREF} = 1 \text{ V}$ |     |      | 21.52 | A                |

| <b>電流故障タイマ (ITIMER)</b>           |                                                           |                                                     |     |      |       |                  |

$-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$ 、 $V_{IN} = V_{DD} = 45 \text{ V} \sim 60 \text{ V}$ 、 $OUT = \text{Open}$ 、 $R_{ILIM} = 931 \Omega$ 、 $R_{IMON} = 2.55 \text{ k}\Omega$ 、 $V_{IREF} = 1 \text{ V}$ 、 $\overline{FLT} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $PGOOD = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $C_{OUT} = 10 \mu\text{F}$ 、 $C_{IN} = 10 \text{ nF}$ 、 $dVdT = \text{Open}$ 、 $V_{EN/UVLO} = 2 \text{ V}$ 、 $\text{TEMP/EECLK/GPIO1} = \text{Open}$ 、 $\text{AUX/EEDATA/GPIO2} = \text{Open}$ 、 $\text{ADDR0} = \text{Open}$ 、 $\text{ADDR1} = \text{Open}$ 、 $SCL = 330\Omega$  プルアップ (3.3 V)、 $SDA = 330\Omega$  プルアップ (3.3 V)。(特に記載がない限り、すべての電圧は GND を基準とする)

| パラメータ                       | テスト条件                                     | 最小値                                                                                 | 標準値 | 最大値   | 単位               |

|-----------------------------|-------------------------------------------|-------------------------------------------------------------------------------------|-----|-------|------------------|

| <b>短絡保護</b>                 |                                           |                                                                                     |     |       |                  |

| $I_{FFT}$                   | 定常状態における固定高速トリップ スレッショルド (プライマリ)          | PG を High にアサート (MODE = Open)                                                       |     | 87.27 | A                |

| $I_{SFT}$                   | スケーラブルな高速トリップ電流: $I_{TRIP}$ 比             | DEVICE_CONFIG[12:11] = 00                                                           |     | 40    | A                |

| $I_{SFT}$                   | スケーラブルな高速トリップ電流: $I_{TRIP}$ 比             | DEVICE_CONFIG[12:11] = 01                                                           |     | 2.5   | A/A              |

| $I_{SFT}$                   | スケーラブルな高速トリップ電流: $I_{TRIP}$ 比             | DEVICE_CONFIG[12:11] = 10                                                           |     | 2     | A/A              |

| $I_{SFT}$                   | スケーラブルな高速トリップ電流: $I_{TRIP}$ 比             | DEVICE_CONFIG[12:11] = 11                                                           |     | 1.5   | A/A              |

| <b>アクティブ電流共有</b>            |                                           |                                                                                     |     |       |                  |

| $R_{ON(ACS)}$               | アクティブ電流共有時の $R_{ON}$                      | $V_{ILIM} > 1.1 \times (1/3) \times V_{IREF}$                                       |     | 4.67  | $\text{m}\Omega$ |

| $G_{IMON(ACS)}$             | アクティブ電流制限時の IMON:IOUT 比                   | PG を High にアサート、 $V_{ILIM} > 1.1 \times V_{IREF}$                                   |     | 18.7  | $\text{uA/A}$    |

| $CL_{REF(ACS)}$             | アクティブ電流共有トリガ スレッショルドと定常状態回路ブレーカ スレッショルドの比 | PG は High にアサート                                                                     |     | 36.80 | %                |

| <b>突入電流保護 (DVDT)</b>        |                                           |                                                                                     |     |       |                  |

| $I_{DVDT}$                  | dVdt ピン充電電流 (プライマリ / スタンドアロン モード)         | DEVICE_CONFIG[10:9] = 11                                                            |     | 3.15  | $\mu\text{A}$    |

| $I_{DVDT}$                  | dVdt ピン充電電流 (プライマリ / スタンドアロン モード)         | DEVICE_CONFIG[10:9] = 10                                                            |     | 2.1   | $\mu\text{A}$    |

| $I_{DVDT}$                  | dVdt ピン充電電流 (プライマリ / スタンドアロン モード)         | DEVICE_CONFIG[10:9] = 01                                                            |     | 1.05  | $\mu\text{A}$    |

| $I_{DVDT}$                  | dVdt ピン充電電流 (プライマリ / スタンドアロン モード)         | DEVICE_CONFIG[10:9] = 00                                                            |     | 0.53  | $\mu\text{A}$    |

| $G_{DVDT}$                  | dVdt ゲイン                                  | $0.4 \text{ V} < V_{dVdt} < 2.4 \text{ V}$                                          |     | 24.9  | V/V              |

| $R_{DVDT}$                  | dVdt ピンから GND への放電抵抗                      |                                                                                     |     | 490   | $\Omega$         |

| <b>GHI</b>                  |                                           |                                                                                     |     |       |                  |

| $V_{GS(GHI)}$ 立ち上がり         | GHI/PG がアサートされている時の G-S スレッショルド           |                                                                                     |     | 7     | V                |

| $V_{GS(GHI)}$ 立ち下がり         | GHI/PG がデアサートされている時の G-S スレッショルド          |                                                                                     |     | 3.4   | V                |

| $R_{ON(GHI)}$               | GHI/PG がアサートされている時の Ron                   |                                                                                     |     | 3.9   | $\text{m}\Omega$ |

| <b>クイック出力放電 (QOD)</b>       |                                           |                                                                                     |     |       |                  |

| $I_{QOD}$                   | クイック出力放電プルダウン電流                           | $V_{SD(R)} < V_{EN} < V_{UVLO}, 0 < T_J < 125^\circ\text{C}, V_{IN} = 51 \text{ V}$ |     | 21    | $\text{mA}$      |

| <b>過熱保護 (OTP)</b>           |                                           |                                                                                     |     |       |                  |

| $TSD$                       | 絶対サーマル シャットダウン立ち上がりスレッショルド                | $T_J$ 立ち上がり、 $V_{IN} = 51 \text{ V}$                                                |     | 150   | $^\circ\text{C}$ |

| $TSD_{HYS}$                 | 絶対サーマル シャットダウンヒステリシス                      | $T_J$ 立ち下がり、 $V_{IN} = 51 \text{ V}$                                                |     | 13    | $^\circ\text{C}$ |

| <b>FET 正常性モニタ</b>           |                                           |                                                                                     |     |       |                  |

| $V_{DSFLT}$                 | FET D-S 故障スレッショルド                         | $SWEN = L, V_{IN} = 51 \text{ V}$                                                   |     | 0.5   | V                |

| <b>アドレス選択 (ADDR0/ADDR1)</b> |                                           |                                                                                     |     |       |                  |

| $I_{ADDRx}$                 | ADDR0 ピン プルアップ電流                          |                                                                                     |     | 5.05  | $\mu\text{A}$    |

|                             | ADDR1 ピン プルアップ電流                          |                                                                                     |     | 5.05  | $\mu\text{A}$    |

$-40^\circ\text{C} \leq T_J \leq +125^\circ\text{C}$ 、 $V_{IN} = V_{DD} = 45 \text{ V} \sim 60 \text{ V}$ 、 $OUT = \text{Open}$ 、 $R_{ILIM} = 931 \Omega$ 、 $R_{IMON} = 2.55 \text{ k}\Omega$ 、 $V_{IREF} = 1 \text{ V}$ 、 $\overline{FLT} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $PGOOD = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $C_{OUT} = 10 \mu\text{F}$ 、 $C_{IN} = 10 \text{ nF}$ 、 $dVdT = \text{Open}$ 、 $V_{EN/UVLO} = 2 \text{ V}$ 、 $\text{TEMP/EECLK/GPIO1} = \text{Open}$ 、 $\text{AUX/EEDATA/GPIO2} = \text{Open}$ 、 $\text{ADDR0} = \text{Open}$ 、 $\text{ADDR1} = \text{Open}$ 、 $SCL = 330\Omega$  プルアップ (3.3 V)、 $SDA = 330\Omega$  プルアップ (3.3 V)。(特に記載がない限り、すべての電圧は GND を基準とする)

| パラメータ         |                    | テスト条件         | 最小値 | 標準値 | 最大値 | 単位 |

|---------------|--------------------|---------------|-----|-----|-----|----|

| $I_{OC\_BKP}$ | バックアップ過電流保護スレッショルド | IMON はグランドへ短絡 |     | 39  |     | A  |

## 5.6 PMBus および GPIO の DC 特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                  |                   | テスト条件                                | 最小値  | 標準値   | 最大値 | 単位            |

|------------------------|-------------------|--------------------------------------|------|-------|-----|---------------|

| <b>GPIOx</b>           |                   |                                      |      |       |     |               |

| $V_{OL}$               | GPIOx 出力ロジック Low  | ピンは出力として構成され、Low にデアサー。シンク電流 = 20mA。 |      | 0.138 | 0.5 | V             |

| $V_{OH}$               | GPIOx 出力ロジック high | ピンは出力として構成され、high にアサー               | 4.8  | 4.9   |     | V             |

| $R_{GPIO}$             | GPIOx ピンのプルダウン抵抗  | ピンは出力として構成され、Low にデアサー               |      | 6.8   |     | $\Omega$      |

| $I_{GPIO}$             | GPIOx ピンのリーク電流    | ピンは出力として構成され、high にアサー               |      |       | 1   | $\mu\text{A}$ |

| $V_{IH}$               | GPIOx 入力ロジック high | ピンは入力として構成                           | 1.56 |       |     | V             |

| $V_{IL}$               | GPIOx 入力ロジック low  | ピンは入力として構成                           |      | 0.82  |     | V             |

| <b>PMBus (SCL/SDA)</b> |                   |                                      |      |       |     |               |

| $V_{IL\_PMBus}$        | SDA 入力ロジック low    |                                      |      | 0.85  |     | V             |

| $V_{IL\_PMBus}$        | SCL 入力ロジック low    |                                      |      | 0.85  |     | V             |

| $V_{IH\_PMBus}$        | SCL 入力ロジック high   |                                      | 1.35 |       |     | V             |

| $V_{IH\_PMBus}$        | SDA 入力ロジック high   |                                      | 1.35 |       |     | V             |

| $V_{OL\_PMBus}$        | Low レベル出力電圧 - SCL | $I_{OL} = -20\text{mA}$              |      | 0.4   |     | V             |

| $V_{OL\_PMBus}$        | Low レベル出力電圧 - SDA | $I_{OL} = -20\text{mA}$              |      | 0.4   |     | V             |

## 5.7 遠隔測定

$T_A = 25^\circ\text{C} \sim 85^\circ\text{C}$

| パラメータ       | テスト条件                                          | 最小値 | 標準値 | 最大値 | 単位  |

|-------------|------------------------------------------------|-----|-----|-----|-----|

| <b>遠隔測定</b> |                                                |     |     |     |     |

| ADC 分解能     |                                                | 10  |     |     | ビット |

| サンプリング レート  | ADC 高性能モード                                     | 150 |     |     | KHz |

| VAUX 絶対誤差   | ADC 高性能モード、VAUX = 1.95V (フルスケール)、1 サンプル        | 0.4 |     |     | %FS |

| VIN 絶対誤差    | ADC 高性能モード、VIN = 48V、1 サンプル                    | 0.4 |     |     | %FS |

| VOUT 絶対誤差   | ADC 高性能モード、VOUT = 48V、1 サンプル                   | 0.4 |     |     | %FS |

| VTEMP 絶対誤差  | ADC 高性能モード                                     | 5   |     |     | °C  |

| VIMON 絶対誤差  | ADC 高性能モード、VIMON = 0.8V、1 サンプル                 | 0.4 |     |     | %FS |

| PIN 絶対誤差    | ADC 高性能モード、VIN = 48V、VIMON = 0.8V、1 サンプル       | 1   |     |     | %FS |

| EIN 絶対誤差    | 5ms ウィンドウにおける累算エネルギー。VIN = 48V DC、VIMON = 0.8V | 1.5 |     |     | %   |

## 5.8 ロジック・インターフェイス

$-40^{\circ}\text{C} \leq T_J \leq +125^{\circ}\text{C}$ 、 $V_{\text{IN}} = V_{\text{DD}} = 45 \text{ V} \sim 60 \text{ V}$ 、 $\text{OUT} = \text{Open}$ 、 $R_{\text{ILIM}} = 931 \Omega$ 、 $R_{\text{IMON}} = 2.55 \text{ k}\Omega$ 、 $V_{\text{IREF}} = 1 \text{ V}$ 、 $\overline{\text{FLT}} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $\text{PGOOD} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $C_{\text{OUT}} = 10 \mu\text{F}$ 、 $C_{\text{IN}} = 10 \text{ nF}$ 、 $dVdT = \text{Open}$ 、 $V_{\text{EN/UVLO}} = 2 \text{ V}$ 、 $\text{TEMP/EECLK/GPIO1} = \text{Open}$ 、 $\text{AUX/EEDATA/GPIO2} = \text{Open}$ 、 $\text{ADDR0} = \text{Open}$ 、 $\text{ADDR1} = \text{Open}$ 、 $\text{SCL} = 330\Omega$  プルアップ (3.3 V)、 $\text{SDA} = 330\Omega$  プルアップ (3.3 V)。(特に記載がない限り、すべての電圧は GND を基準とする)

| パラメータ                 |                 | テスト条件                                      | 最小値 | 標準値 | 最大値 | 単位            |

|-----------------------|-----------------|--------------------------------------------|-----|-----|-----|---------------|

| <b>WPB</b>            |                 |                                            |     |     |     |               |

| $I_{\text{WPBLKG}}$   | WPB ピンのリーク電流    |                                            |     | 1   |     | $\mu\text{A}$ |

| $V_{\text{IH\_WPB}}$  | WPB 入力ロジック high |                                            | 2.5 |     |     | V             |

| $V_{\text{IL\_WPB}}$  | WPB 入力ロジック Low  |                                            |     | 0.5 |     | V             |

| <b>SWEN</b>           |                 |                                            |     |     |     |               |

| $R_{\text{SWEN}}$     | SWEN ピン プルダウン抵抗 | SWEN が Low にデアサー                           | 7   |     |     | $\Omega$      |

| $I_{\text{SWENLKG}}$  | SWEN ピンのリーク電流   | SWEN が high にアサー、10kohms 経由で 5V にプルアップ     |     | 2   |     | $\mu\text{A}$ |

| <b>故障表示 (FLTB)</b>    |                 |                                            |     |     |     |               |

| $R_{\text{FLTB}}$     | FLTB ピン プルダウン抵抗 | FLTB が Low にアサー                            | 7   |     |     | $\Omega$      |

| $I_{\text{FLTBLKG}}$  | FLTB ピンのリーク電流   | FLTB が High にデアサー、10k $\Omega$ で 5V にプルアップ |     | 2   |     | $\mu\text{A}$ |

| <b>パワー グッド表示 (PG)</b> |                 |                                            |     |     |     |               |

| $R_{\text{PG}}$       | PG ピン プルダウン抵抗   | PG が Low にデアサー                             | 7   |     |     | $\Omega$      |

| $I_{\text{PGKG}}$     | PG ピンのリーク電流     | PG が High にアサー、10kohms 経由で 5V にプルアップ       |     | 2   |     | $\mu\text{A}$ |

## 5.9 タイミング要件

$-40^{\circ}\text{C} \leq T_J \leq +125^{\circ}\text{C}$ 、 $V_{\text{IN}} = V_{\text{DD}} = 45 \text{ V} \sim 60 \text{ V}$ 、 $\text{OUT} = \text{Open}$ 、 $R_{\text{ILIM}} = 931 \Omega$ 、 $R_{\text{IMON}} = 2.55 \text{ k}\Omega$ 、 $V_{\text{IREF}} = 1 \text{ V}$ 、 $\overline{\text{FLT}} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $\text{PGOOD} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $C_{\text{OUT}} = 10 \mu\text{F}$ 、 $C_{\text{IN}} = 10 \text{ nF}$ 、 $dVdT = \text{Open}$ 、 $V_{\text{EN/UVLO}} = 2 \text{ V}$ 、 $\text{TEMP/EECLK/GPIO1} = \text{Open}$ 、 $\text{AUX/EEDATA/GPIO2} = \text{Open}$ 、 $\text{ADDR0} = \text{Open}$ 、 $\text{ADDR1} = \text{Open}$ 、 $\text{SCL} = 330\Omega$  プルアップ (3.3 V)、 $\text{SDA} = 330\Omega$  プルアップ (3.3 V)。(特に記載がない限り、すべての電圧は GND を基準とする)

| パラメータ                  |                                           | テスト条件                                                                                                                       | 最小値 | 標準値  | 最大値 | 単位            |

|------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------------|

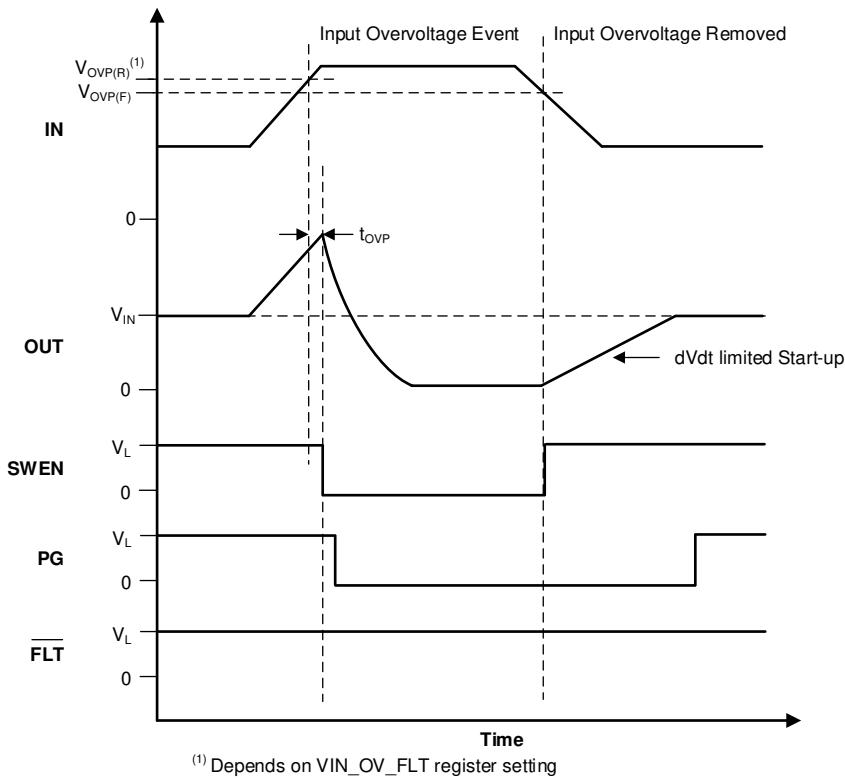

| $t_{\text{OVP}}$       | 過電圧保護応答時間                                 | $V_{\text{OVP}} > V_{\text{OVPR}}$ V から SWEN ↓                                                                              |     | 1.5  |     | $\mu\text{s}$ |

| $t_{\text{Insdly}}$    | 挿入遅延                                      | $\text{INS\_DLY} = 0x00$ 、 $V_{\text{EN/UVLO}} > V_{\text{UVLO(R)}}$ から SWEN ↑                                              |     | 10   |     | ms            |

|                        |                                           | $\text{INS\_DLY} = 0x07$ 、 $V_{\text{EN/UVLO}} > V_{\text{UVLO(R)}}$ から SWEN ↑                                              |     | 560  |     | ms            |

| $t_{\text{FFT}}$       | 固定高速トリップ応答時間ハード短絡                         | $V_{\text{DS}} > 1.5 \times V_{\text{DSCOMP}}$ から $I_{\text{OUT}} \downarrow$                                               |     | 200  |     | ns            |

| $t_{\text{SFT}}$       | スケーラブルな高速トリップ応答時間                         | $I_{\text{OUT}} > 3 \times I_{\text{TRIP}}$ から $I_{\text{OUT}} \downarrow$                                                  |     | 400  |     | ns            |

| $t_{\text{ITIMER}}$    | 過電流ブランкиング間隔                              | $I_{\text{OUT}} = 1.5 \times I_{\text{TRIP}}$ 、 $\text{OC\_TIMER} = 0x00$                                                   |     | 0    |     | ms            |

| $t_{\text{ITIMER}}$    | 過電流ブランкиング間隔                              | $I_{\text{OUT}} = 1.5 \times I_{\text{TRIP}}$ 、 $\text{OC\_TIMER} = 0x14$ (デフォルト)                                           |     | 2.1  |     | ms            |

| $t_{\text{ITIMER}}$    | 過電流ブランкиング間隔                              | $I_{\text{OUT}} = 1.5 \times I_{\text{TRIP}}$ 、 $\text{OC\_TIMER} = 0xFF$                                                   |     | 27.3 |     | ms            |

| $t_{\text{RST}}$       | 自動再試行間隔                                   | $\text{RETRY\_CONFIG}[2:0] = 100$                                                                                           |     | 800  |     | ms            |

| $t_{\text{EN(DG)}}$    | EN/UVLO デグリッチ時間                           |                                                                                                                             |     | 10   |     | $\mu\text{s}$ |

| $t_{\text{SU\_TMR}}$   | 起動タイムアウト間隔                                | SWEN ↑ から $\overline{\text{FLT}} \downarrow$                                                                                |     | 8    |     | s             |

| $t_{\text{Discharge}}$ | QOD 放電時間 ( $V_{\text{OUT}}$ の 90% から 10%) | $V_{\text{SD}} < V_{\text{EN/UVLO}} < V_{\text{UVLO}}$ 、 $C_{\text{OUT}} = 0.5 \text{ mF}$ 、 $V_{\text{IN}} = 51 \text{ V}$ |     | 1300 |     | ms            |

| $t_{\text{QOD}}$       | QOD イネーブル タイマ                             | $V_{\text{SD}} < V_{\text{EN/UVLO}} < V_{\text{UVLO}}$                                                                      |     | 5.9  |     | ms            |

$-40^{\circ}\text{C} \leq T_J \leq +125^{\circ}\text{C}$ 、 $V_{\text{IN}} = V_{\text{DD}} = 45 \text{ V} \sim 60 \text{ V}$ 、 $\text{OUT} = \text{Open}$ 、 $R_{\text{ILIM}} = 931 \Omega$ 、 $R_{\text{IMON}} = 2.55 \text{ k}\Omega$ 、 $V_{\text{IREF}} = 1 \text{ V}$ 、 $\overline{\text{FLT}} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $\text{PGOOD} = 33 \text{ k}\Omega$  プルアップ (3.3 V)、 $C_{\text{OUT}} = 10 \mu\text{F}$ 、 $C_{\text{IN}} = 10 \text{ nF}$ 、 $dVdT = \text{Open}$ 、 $V_{\text{EN/UVLO}} = 2 \text{ V}$ 、 $\text{TEMP/EECLK/GPIO1} = \text{Open}$ 、 $\text{AUX/EEDATA/GPIO2} = \text{Open}$ 、 $\text{ADDR0} = \text{Open}$ 、 $\text{ADDR1} = \text{Open}$ 、 $\text{SCL} = 330\Omega$  プルアップ (3.3 V)、 $\text{SDA} = 330\Omega$  プルアップ (3.3 V)。(特に記載がない限り、すべての電圧は GND を基準とする)

| パラメータ            |            | テスト条件                                                                                            | 最小値 | 標準値 | 最大値 | 単位            |

|------------------|------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $t_{\text{PGA}}$ | PG アサート遅延  | DEVICE_CONFIG[15] = 0、デバイスは定常状態、 $V_{\text{OUT}} > V_{\text{OUT\_PGTH}}$ から $\text{PG} \uparrow$ | 100 |     |     | $\mu\text{s}$ |

| $t_{\text{PGD}}$ | PG デアサート遅延 | デバイス定常状態、 $V_{\text{OUT}} < V_{\text{OUT\_PGTH}}$ から $\text{PG} \downarrow$                      | 3   |     |     | $\mu\text{s}$ |

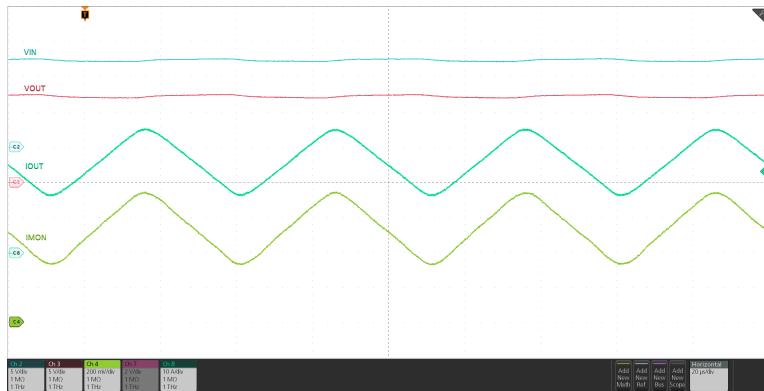

## 5.10 代表的特性

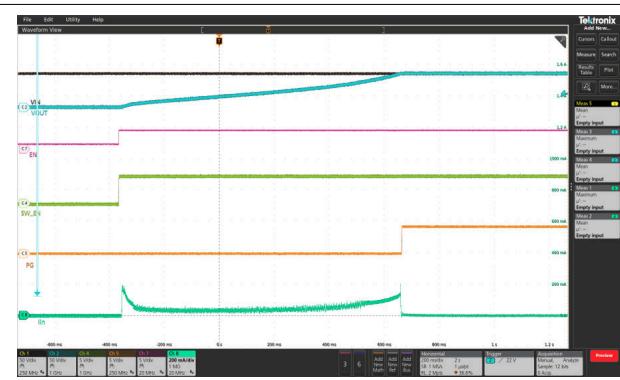

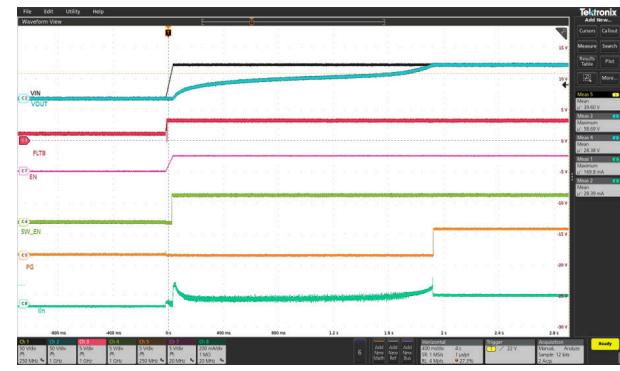

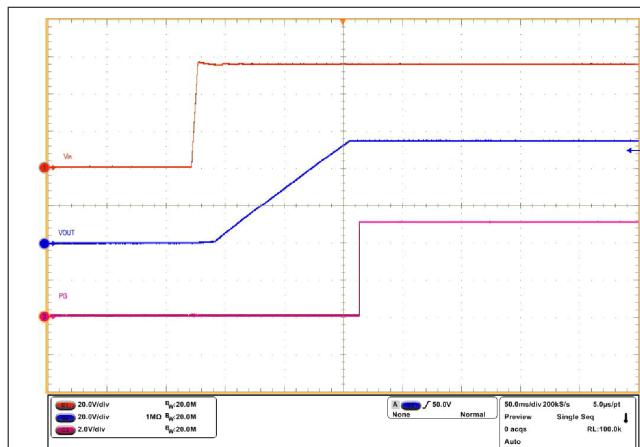

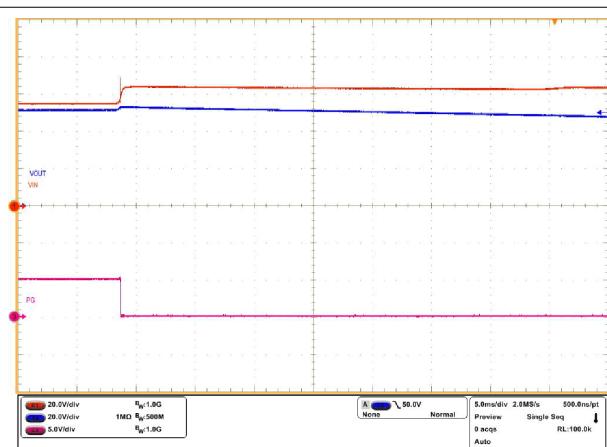

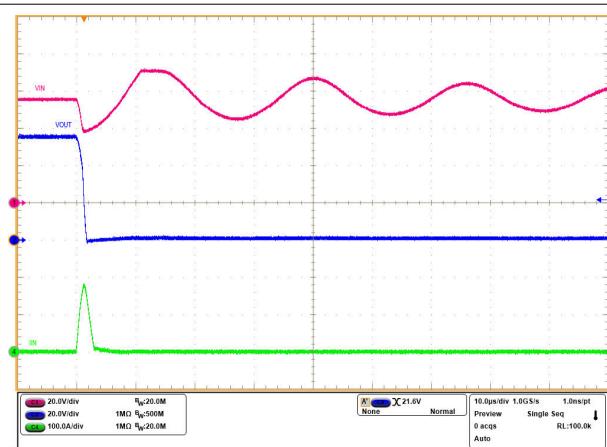

EN を high に保持し、IN 電源を 51V まで上昇。 $C_{OUT} = 1\text{mF}$ 、 $C_{dVdt} = 68\text{nF}$

図 5-1. 電源を使用したパワーアップ

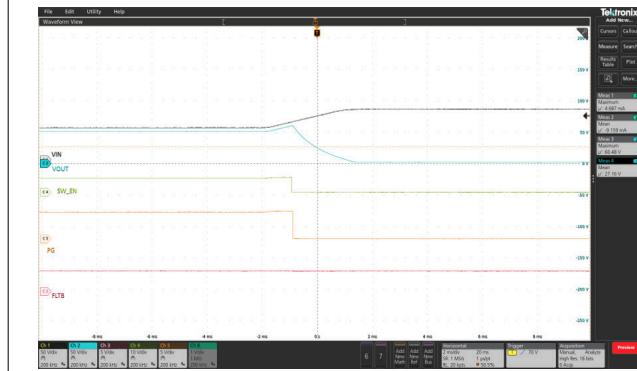

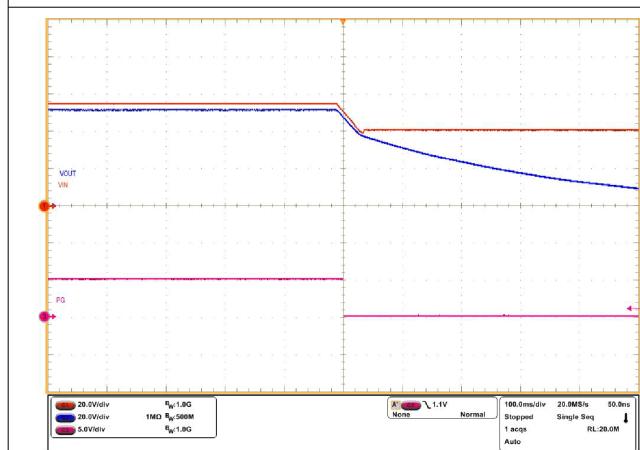

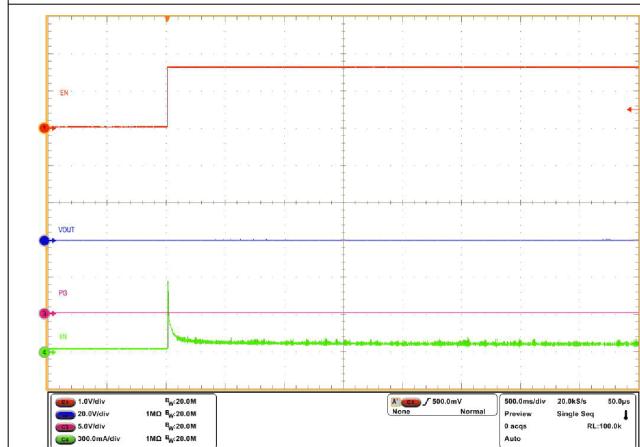

54V で安定している電源では、EN ピンを low から high に切り替え。 $C_{OUT} = 1\text{mF}$ 、 $C_{dVdt} = 68\text{nF}$

図 5-2. EN を使用したパワーアップ

VIN 過電圧立ち上がりスレッショルドは 60.47V にプログラム、EN は high に保持、電源電圧は 54V から 80V へと上昇、ランプレートは 10V/ms に設定。 $C_{OUT} = 1\text{mF}$ 、 $C_{dVdt} = 68\text{nF}$

図 5-3. 入力過電圧保護

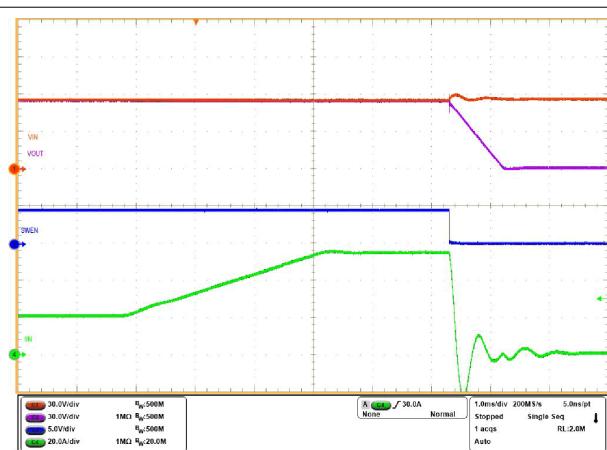

IN 電源は EN、 $C_{OUT} = 500\mu\text{F}$ 、 $C_{dVdt} = 68\text{nF}$ 、 $R_{OUT} = 820\Omega$  DVDT スケーリング 100% で 54V に上昇

図 5-4. R と C による突入

定常状態のデバイス、48A の負荷電流を 3ms にわたって印加した後、削除。過電流プランギング遅延を 3.2ms に設定。Vin = 54V

図 5-5. 過渡過電流プランギング

定常状態のデバイス、負荷電流は 3.2ms を超えて 48A まで上昇。過電流プランギング遅延を 3.2ms に設定

図 5-6. 過電流保護

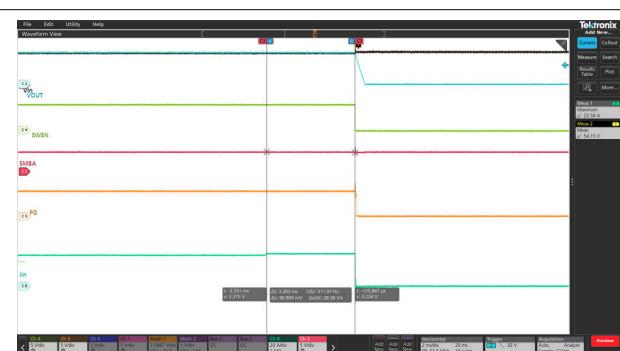

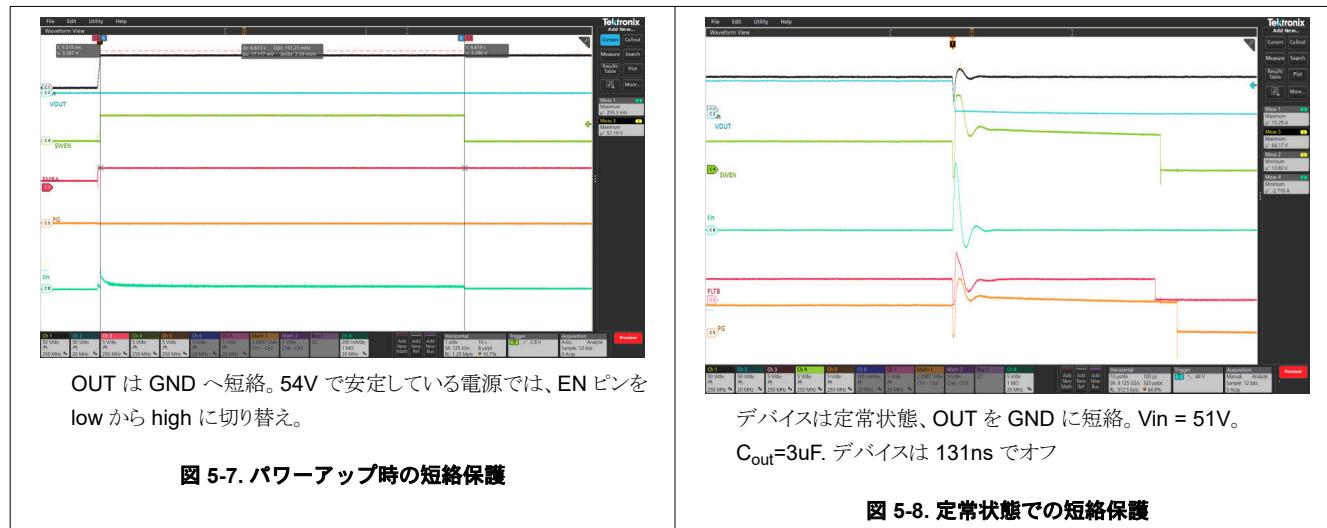

## 5.10 代表的特性 (続き)

OUT は GND へ短絡。54V で安定している電源では、EN ピンを low から high に切り替え。

デバイスは定常状態、OUT を GND に短絡。Vin = 51V。

$C_{out}=3\mu F$ 。デバイスは 131ns でオフ

## 6 詳細説明

### 6.1 概要

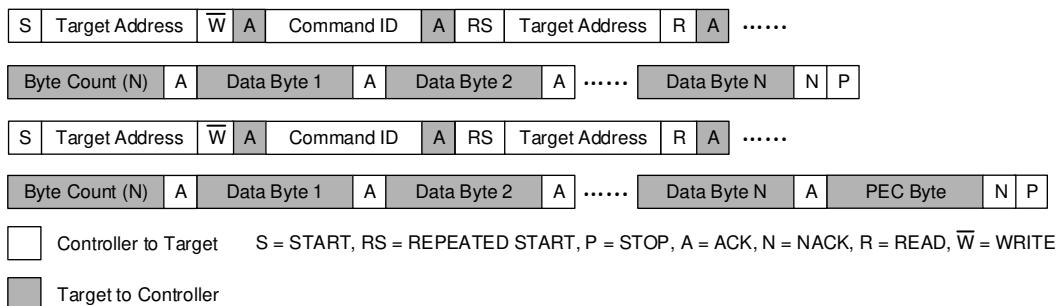

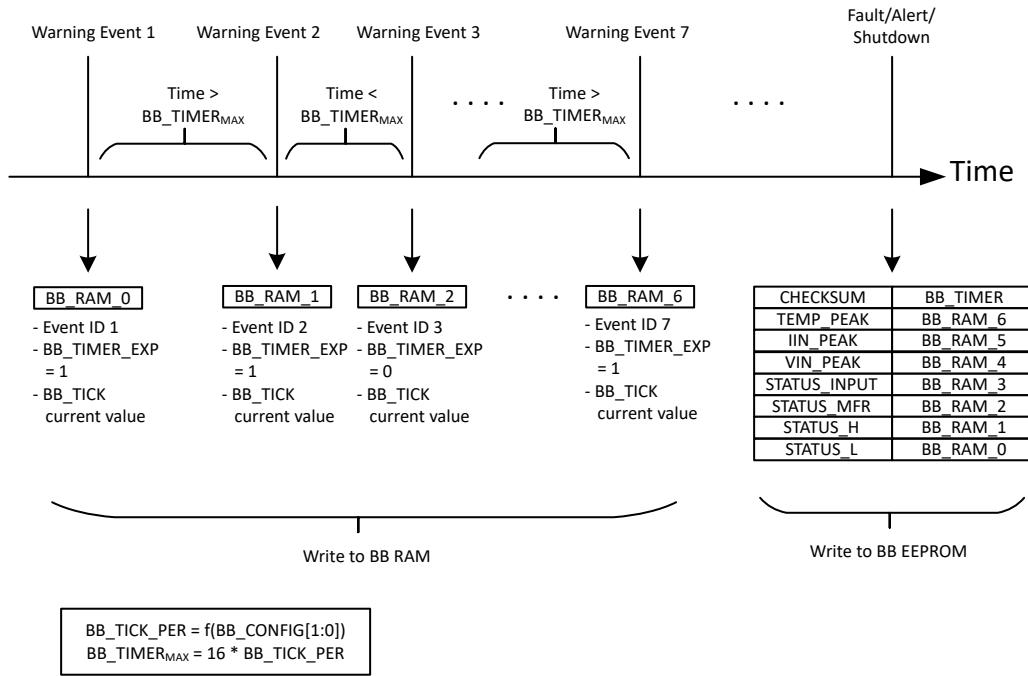

TPS1689x は、負荷電圧と負荷電流を管理するために使用されるパワー スイッチ内蔵 eFuse です。TPS1689x は、PMBus 互換のデジタル インターフェイスを備えており、ホストがデバイスの制御、構成、監視、デバッグを行うことが可能です。デバイスは、V<sub>DD</sub> と IN バスを監視して、動作を開始します。V<sub>DD</sub> および V<sub>IN</sub> がそれぞれの低電圧保護 (UVP) スレッショルドを超えた場合、デバイスは挿入遅延タイマ期間を待機して、起動前に電源が安定するようにします。次に、デバイスは EN/UVLO ピンをサンプリングします。EN/UVLO が Low に保持されている間は、内部 MOSFET とともに、内部制御/デジタル回路がオフになります。このピンが high レベルになると、内部制御回路が有効になり、ホストからコマンドを受信できるように PMBus エンジンが準備されます。

起動シーケンスが成功した後、TPS1689x デバイスは負荷電流と入力電圧をアクティブに監視し、内部 FET を制御して、プログラムされた過電流スレッショルド I<sub>TRIP</sub> を超過しておらず、過電圧スパイクがカットオフされていることを確認します。これにより、有害なレベルの電圧や電流からシステムを安全な状態に保つことができます。同時に、ユーザープログラマブル過電流ブランкиング タイマを使用すると、システムは eFuse をトリップせずに、負荷電流の過渡ピークに対応できます。これにより、過渡耐性のある実際の故障に対する堅牢な保護が維持されるため、システムの稼働時間を最大限に延ばすことができます。

デバイスには推奨動作条件の下でデバイスの安全性と信頼性を維持するため、保護回路が内蔵されています。サーマルシャットダウン メカニズムを使用して常に内部 FET が保護されています。この機能により、接合部温度 (T<sub>j</sub>) が過熱しすぎてデバイスの信頼性が高く動作できなくなると FET がオフになります。

TPS1689x には高精度で高帯域幅のアナログ負荷電流モニタが内蔵されているため、システムは定常状態と過渡時に負荷電流を正確に監視できます。これにより、高度な動的プラットフォーム パワー マネージメント手法を容易に実装でき、安全性や信頼性を損なうことなく、システムの電力使用率とスループットを最大化できます。

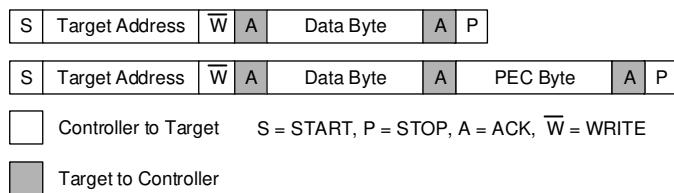

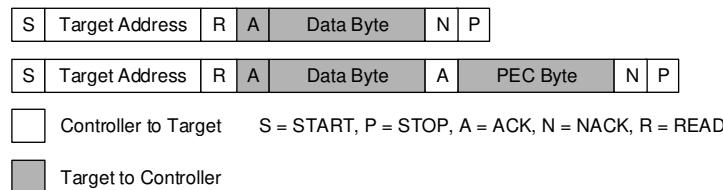

TPS1689x を使用すると、ホストは PMBus インターフェイス経由で各種のシステム パラメータとステータスを監視できます。また、PMBus 経由でデバイス構成を変更し、システムのニーズに応じてデバイスの動作を制御することもできます。これには、さまざまな警告/故障スレッショルド、タイマ、ピン機能が含まれます。構成値は、内部の不揮発性メモリに保存することもできるため、ホストの介入なしにデバイスを事前定義済みの構成で起動できます。

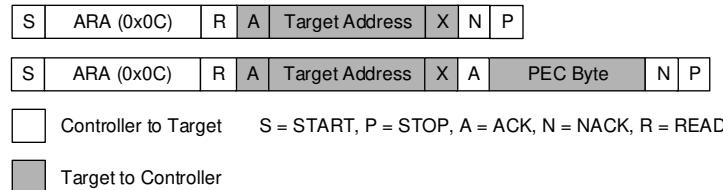

TPS1689x は、高速 ADC サンプル バッファリングやブラックボックス フォルト記録などの高度な遠隔測定機能も備えているため、システム設計とデバッグが容易になります。

より高い負荷電流のサポートを必要とするシステムの場合、TPS1689x を TPS1685x と並列に接続できます。TPS16890 はプライマリ コントローラとして動作し、PMBus 経由でチェーン全体の制御、遠隔測定、構成を可能にします。各デバイスは動作状態を同期し、適切な起動、シャットダウン、故障への応答を実現します。

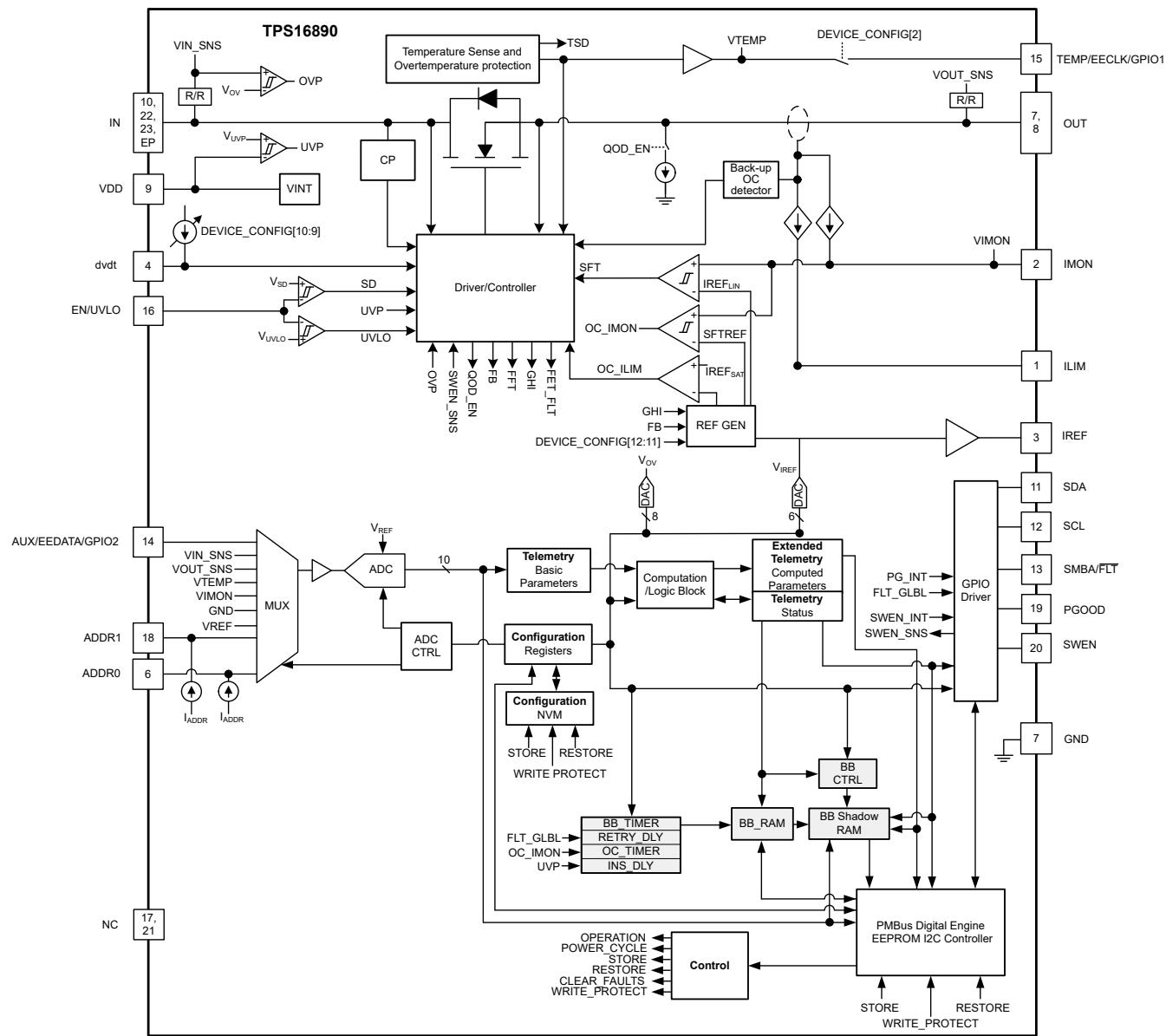

## 6.2 機能ブロック図

図 6-1. TPS16890 の機能ブロック図

## 6.3 機能説明

TPS1689 eFuse は、高集積かつ先進的な電力管理デバイスであり、システム故障発生時の監視、検出、保護、および報告を行います。

### 6.3.1 低電圧保護

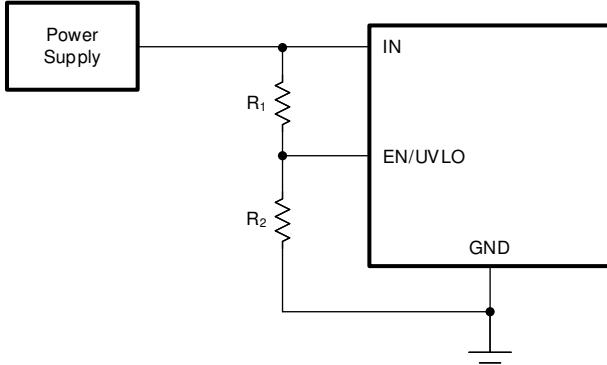

TPS1689 は、印加された電圧が低くなりすぎて、システムまたはデバイスが正常に動作できない場合に備えて、VDD および VIN に低電圧誤動作防止を実装しています。低電圧誤動作防止には、VDD にデフォルトの内部スレッショルド ( $V_{UVL}$ )、VIN にプログラム可能なスレッショルド ( $V_{UVLOIN}$ ) があります。また、EN/UVLO ピンに UVLO コンパレータを搭載しているため、外部から低電圧保護スレッショルドをユーザー一定義の値に調整することもできます。[図 6-2](#) および[式 1](#) に、抵抗デバイダを使用して、特定の電源電圧に対して UVLO 設定ポイントを設定する方法を示します。

図 6-2. 可変低電圧保護

$$V_{IN(UV)} = V_{UVLO(R)} \frac{R_1 + R_2}{R_2} \quad (1)$$

VIN UVLO 故障スレッショルドは、PMBus® 書き込みを使って VIN\_UV\_FLT レジスタにもプログラムできます。

EN/UVLO ピンには双方向のスレッショルドが実装されており、外部ホストからデバイスを制御するために使用できます。

1.  $V_{EN} > V_{UVLO(R)}$ : デバイスは完全にオンです。

2.  $V_{SD(F)} < V_{EN} < V_{UVLO(F)}$ : 一部の重要なバイアスとデジタル回路を除き、FET とほとんどのコントローラ回路がオフになります。EN/UVLO ピンをこの状態に  $t_{QOD}$  を超える時間保持すると、出力放電機能が起動します。

3.  $V_{EN} < V_{SD(F)}$ : 部品内のすべてのアクティブ回路がオフになり、デバイスはデジタル状態メモリを保持しません。また、ラッチされた故障、ステータス フラグ、および PMBus® 書き込みによりレジスタに書き込まれた構成値もリセットします。

### 6.3.2 挿入遅延

TPS1689 は、デバイスが負荷への電力をオンにしようとする前に、電源が安定したことを確認するため、スタートアップ時に挿入遅延を実装しています。これは、ホットスワップアプリケーションで、カードが稼働中のバックプレーンにホットプラグされ、カードがコネクタにしっかりと接続される前に接触バウンスが発生する可能性がある場合に役立ちます。デバイスは最初に、VDD 電源が  $V_{UVP}$  スレッショルドを上回り、すべての内部バイアス電圧が安定するまで待機します。その後、EN/UVLO ピンの状態に関係なく、 $t_{INSDLY}$  の追加遅延の間、デバイスはオフに維持されます。この操作により、カードがバックプレーンにしっかりと接続する前にデバイスが電源投入しようとした場合、または起動時に電源のリンクやノイズが発生した場合に、システムで予期しない動作が発生するのを防ぐことができます。

挿入遅延は、PMBus® を使用して不揮発性メモリ/EEPROM の INS\_DLY レジスタの値をプログラムすることで変更できます。

### 6.3.3 過電圧保護

TPS1689x は過電圧ロックアウト機能を実装しており、入力過電圧状態から負荷を保護します。IN の入力電圧が OVP 立ち上がりスレッショルドを超えると、 $t_{OVP}$  以内にパワー FET がオフになります。IN ピンの OVP コンパレータは、デフォルトの内部過電圧保護スレッショルドである  $V_{OVP(R)}$  を使用しています。このスレッショルドは、不揮発性構成メモリのプログラムにより、または PMBus® レジスタから VIN\_OV\_FLT レジスタへの書き込みにより動的に変更できます。OVP コンパレータには、ノイズ耐性を高めるためのヒステリシスが内蔵されています。IN の電圧が OVP 立ち下がりスレッショルド ( $V_{OVP(F)}$ ) を下回ると、FET は dVdt 制御された方法でオンになります。

図 6-3. 入力過電圧保護応答

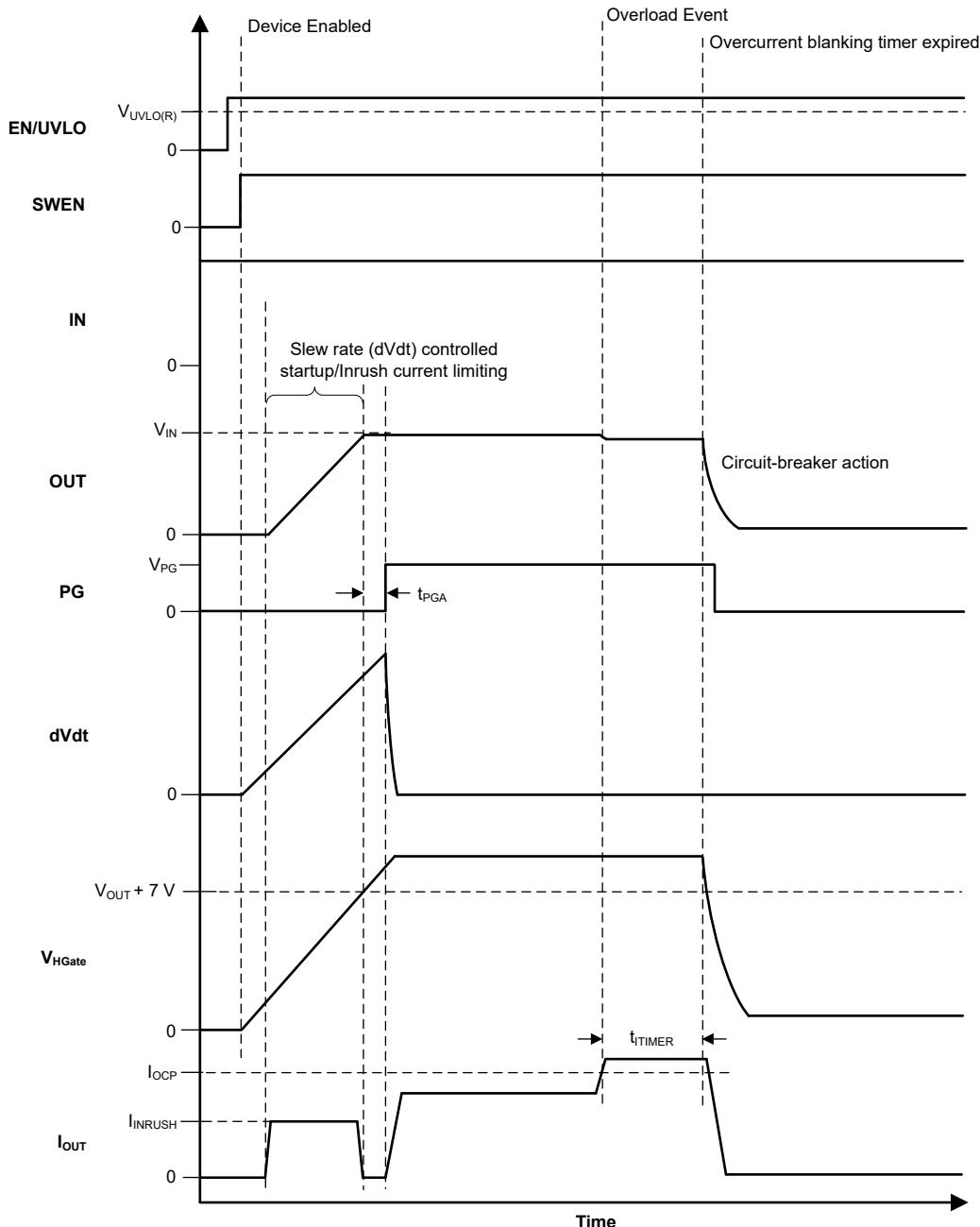

#### 6.3.4 突入電流、過電流、および短絡保護

TPS1689 には、過電流に対する 4 つのレベルの保護が組み込まれています。

1. 突入電流制御のための調整可能なスルーレート ( $dVdt$ )

2. 起動時の過電流保護のため、調整可能なスレッショルド ( $I_{LIM}$ ) を備えたアクティブ電流制限

3. 定常状態での過電流保護のため、調整可能なスレッショルド ( $I_{OCP}$ ) とランキングタイム ( $t_{OC\_TIMER}$ ) を備えた回路ブレーカ

4. あらゆる条件下での深刻な短絡から迅速に保護するためのプログラマブルなスレッショルド、および定常状態では固定スレッショルド ( $I_{FFT}$ ) を備えた、深刻な過電流故障に対する高速トリップ応答

##### 6.3.4.1 スルーレート ( $dVdt$ ) および突入電流制御

ホットプラグイベント時や大きな出力容量の充電中に、大きな突入電流が発生する可能性があります。突入電流を適切に管理しないと、システム電源に過剰なストレスが加わり、ドリープが発生したり、入力コネクタが損傷したりする可能性があります。この動作により、システム内の他の場所で予期しない再起動が発生する可能性があります。ターンオン時の突入電流は、負荷容量と立ち上がりスルーレートに正比例します。[式 2](#)を使用して、与えられた負荷容量 ( $C_{LOAD}$ ) について突入電流 ( $I_{INRUSH}$ ) を制限するのに必要なスルーレート (SR) を計算できます。

$$SR \left( \frac{V}{ms} \right) = \frac{I_{INRUSH} (mA)}{C_{OUT} (\mu F)} \quad (2)$$

DVDT ピンにコンデンサを追加することで、立ち上がりスルーレートを制御し、ターンオン時の突入電流を低減できます。これはまた  $dVdt$  レートのスケーリング係数の関数であり、DEVICE\_CONFIGregister への PMBus® 書き込みによってデジタル的にプログラムできます。特定のスルーレートを生成するために必要な  $C_{dVdt}$  容量は、[式 3](#)を使用して計算できます。

$$C_{dVdt} (pF) = \frac{50000 \times k}{SR \left( \frac{V}{ms} \right)} \quad (3)$$

ここで、 $k = 0.25$  (DEVICE\_CONFIG[10:9] = 00 の場合 (デフォルト))

$k = 0.5$  (DEVICE\_CONFIG[10:9] = 01 の場合)

$k = 1$  (DEVICE\_CONFIG[10:9] = 10 の場合)

$k = 1.5$  (DEVICE\_CONFIG[10:9] = 11 の場合)

dVdt ピンをオープンのままにし、DEVICE\_CONFIG[10:9] = 11 を設定すると、最も高速な出力スルーレートを実現できます。

スルーレートは、スタートアップ時に消費されるエネルギーの関数でもあります。DVDT によるスルーレート制御は、スタートアップ電流制限  $I_{Startup}$  のみを下回っています。dvdt ピンによるスタートアップ電流が  $I_{Startup}$  を超えると電流はクランプされ、スルーレートが遅くなります

#### 注

高いターンオン スルーレートと高い入力パワー パスのインダクタンスの組み合わせにより、起動時に発振が発生する場合があります。これは、次の 1 つまたは複数の手順を使用して軽減できます。

1. 入力インダクタンスを小さくする。

2. VIN ピンの容量を増やす。

3. DVDT ピンのコンデンサ値を増やすか、DEVICE\_CONFIG[10:9] レジスタビットを使用して DVDT スケーリング係数を変更することにより、スルーレートを低減したり、スタートアップ時間を長くしたりします。TI では最小スタートアップ時間は 30ms を推奨します。

#### 6.3.4.1.1 起動タイムアウト

スタートアップが完了しない場合、つまり、SWEN がアサートされた後、特定のタイムアウト間隔 ( $t_{SU\_TMR}$ ) 内に FET が完全にオンにならない場合、デバイスはそれを故障として登録します。故障ステータスは STATUS\_MFR\_SPECIFIC レジスタのビット[6] で報告されます。FLT は Low にアサートされ、デバイスは RETRY\_CONFIG レジスタ設定に応じてラッチオフまたは自動リトライモードに移行します。

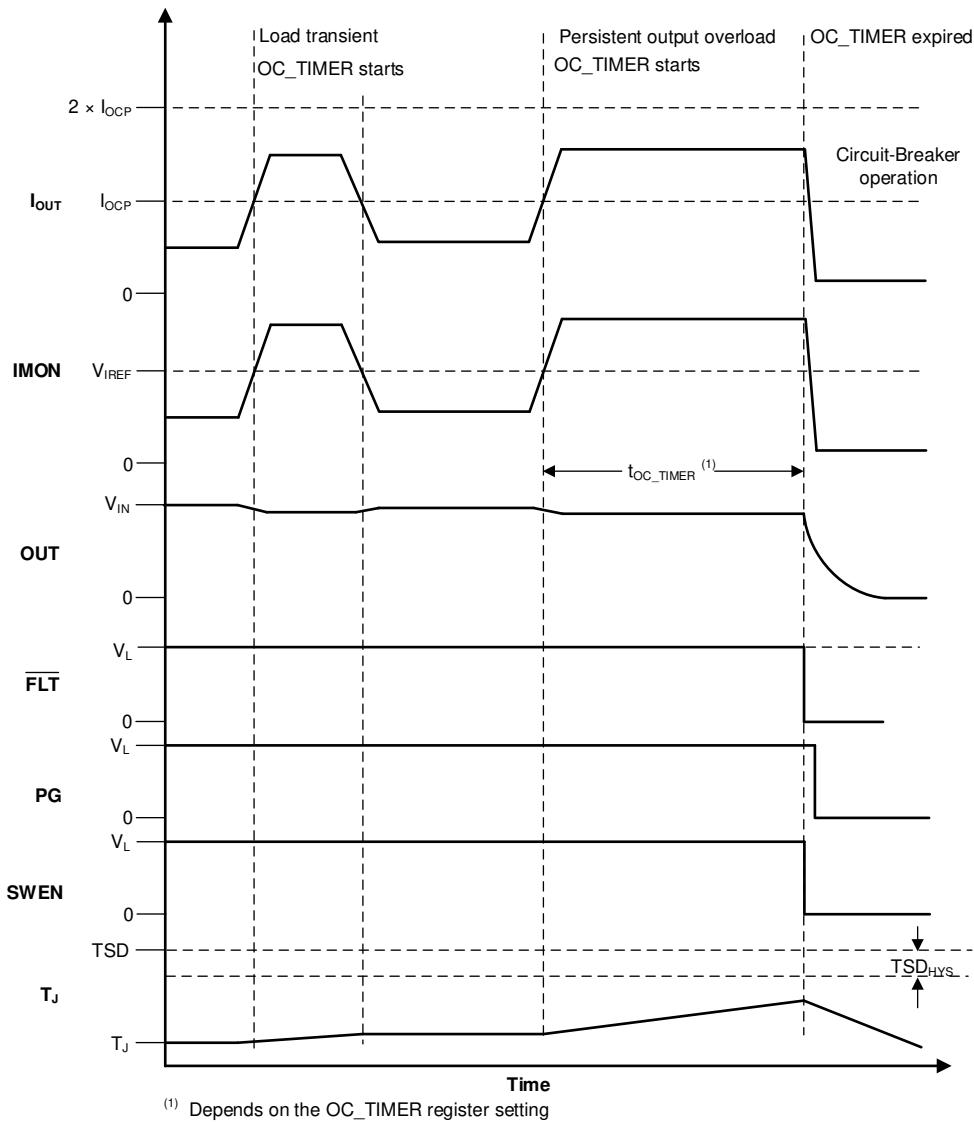

#### 6.3.4.2 定常状態の過電流保護 (サーチット ブレーカ)

TPS1689 は、定常状態時の出力過電流状態に応答して、ユーザーが調整可能な過渡故障ブランкиング間隔の後に回路ブレーカ動作を実行します。この動作により、デバイスは短いユーザー定義間隔でより高いピーク電流をサポートできるだけでなく、持続的な出力障害が発生した場合にも堅牢な保護を保証します。

このデバイスは出力負荷電流を継続的に検出し、負荷電流に比例するアナログ電流动出力 ( $I_{IMON}$ ) を IMON ピンに提供します。これにより、式 4 に従って IMON ピン抵抗 ( $R_{IMON}$ ) の両端に比例電圧 ( $V_{IMON}$ ) が生成されます。

$$V_{IMON} = I_{OUT} \times G_{IMON} \times R_{IMON} \quad (4)$$

ここで、 $G_{IMON}$  は電流モニタ ゲインです ( $I_{IMON}: I_{OUT}$ )

この電圧を基準となる IREF ピンの電圧と比較することで、過電流状態が検出されます。リファレンス電圧 ( $V_{IREF}$ ) は 2 つの方法で制御でき、それに応じて過電流保護スレッショルド ( $I_{OCP}$ ) を設定します。

- リファレンス電圧 ( $V_{IREF}$ ) は内部 DAC を使用して生成でき、不揮発性構成メモリをプログラムするか、VIREF レジスタへの PMBus® 書き込みにより動的に変更できます。

- また、外部の低インピーダンス高精度リファレンス電圧源から IREF ピンを駆動することも可能です。

定常状態 ( $I_{OCP}$ ) 時の過電流保護スレッショルドは、式 5 を使用して計算できます。

$$I_{OCP} = \frac{V_{IREF}}{G_{IMON} \times R_{IMON}} \quad (5)$$

### 注

TI は、ノイズ耐性を向上させるため、IREF ピンと GND の間に 1nF のコンデンサを追加することを推奨します。

過電流状態、つまり負荷電流がプログラムされた電流制限スレッショルド ( $I_{OCP}$ ) を上回るが、短絡スレッショルド ( $I_{SCP}$ ) を下回る状態が検出されると、デバイスは内部の過電流ブランкиング デジタル タイマ (OC\_TIMER) の実行を開始します。OC\_TIMER が期限切れになる前に負荷電流が電流制限スレッショルドを下回ると、回路ブレーカ動作は作動しません。この動作により、短い過負荷過渡パルスが回路をトリップせずにデバイスを通過できるようになります。同時に、OC\_TIMER はリセットされ、次の過電流イベントの前にデフォルト状態になります。これにより、すべての過電流イベントに対して、完全なブランкиング タイマ間隔が確保されます。

過電流状態が続く場合、OC\_TIMER は実行を継続し、期限が切れた後、回路ブレーカの動作により FET が直ちにオフになります。

式 6 を使用して、目的の過電流スレッショルドに対する  $R_{IMON}$  値を計算できます。

$$R_{IMON} = \frac{V_{IREF}}{G_{IMON} \times I_{OCP}} \quad (6)$$

過渡が許容される期間は、PMBus® 書き込みによる OC\_TIMER レジスタ設定を使用してプログラムできます。

図 6-4 に、TPS1689 eFuse の過電流応答を示します。回路ブレーカの故障により部品がシャットダウンした後、部品はラッチ オフ状態を維持するか、RETRY\_CONFIG レジスタの設定に基づいて自動的に再起動します。

図 6-4. 定常状態の過電流(回路ブレーカ)応答

過渡過電流状態(負荷電流がプログラムされた電流制限スレッショルドを超える、OC\_TIMERが満了しない)が検出された場合、デバイスは次のように動作します。

- STATUS\_MFR\_SPECIFIC\_2 レジスタの OC\_DET ビットをセットする

- ブラックボックス RAM レジスタの 1 つにイベント識別子を OC\_DET として書き込みを埋め(書き込み可能な場合)、相対タイムスタンプ情報として書き込みます

- BB\_TIMER レジスタのブラックボックス RAM アドレスポインタを、以前に 6 未満の場合は 1 増やし、それ以外の場合は 0 にリセットします。

## 注

VIN\_UV\_WARN、VIN\_OV\_WARN、VOUT\_UV\_WARN イベントは、ステップ負荷過渡のためにトリガされないと想定されます。

持続的な過電流状態(負荷電流がプログラムされた電流制限スレッショルドを超える、OC\_TIMERが満了)が検出された場合、デバイスは次のように動作します。

- STATUS\_BYTE レジスタの FET\_OFF ビットと NONE\_OF\_THE ABOVE/UNKNOWN ビットを設定します

- STATUS\_WORD レジスタの上位バイトの OUT\_STATUS、INPUT\_STATUS、PGOODB、NONE\_OF\_THE ABOVE/UNKNOWN ビットを設定します

- STATUS\_OUT レジスタの VOUT\_UV\_WARN ビットを設定します

- STATUS\_INPUT レジスタの OCFLT ビットを設定します

- STATUS\_MFR\_SPECIFIC\_2 レジスタの PGOODB ビットを設定します

- ALERT\_MASK レジスタの STATUS\_IN、PGOODB、STATUS\_OUT ビットがマスク設定されていない場合、SMBA をアサートしてホストに通知します。

- 外部 PG 信号をデアサートします。

- FAULT\_MASK レジスタの OCFLT ビットが high に設定されており、マスクされていない場合、FLT 信号をアサートします。

---

**注**

VIN\_UV\_WARN および VIN\_OV\_WARN イベントは、ステップ負荷過渡のためにトリガされないものと想定されます。

---

**6.3.4.3 起動時のアクティブ電流制限**

TPS1689 は、起動時に出力過電流状態に応答し、電流をアクティブに制限します。起動電流制限は、内部で  $I_{start-up}$  に固定されています。このデバイスはデバイス ( $I_{DEVICE}$ ) を流れる電流を継続的に検出し、ILIM ピンにアナログ電流输出 ( $I_{ILIM}$ ) を供給します。その結果、式 7 に従って ILIM ピン抵抗 ( $R_{ILIM}$ ) に比例した電圧 ( $V_{ILIM}$ ) を生成します。

$$V_{ILIM} = I_{DEVICE} \times G_{ILIM} \times R_{ILIM} \quad (7)$$

ここで、 $G_{ILIM}$  は電流モニタゲインです ( $I_{ILIM}: I_{DEVICE}$ )

電流レギュレーション中、出力電圧降下により FET 全体のデバイス消費電力が増加します。デバイスの内部温度 ( $T_J$ ) がサーマル シャットダウン スレッショルドを超えると、FET がオフになります。TSD 故障により部品がシャットダウンした後、本部品はラッチオフされたままになるか、RETRY\_CONFIG レジスタ設定に基づく遅延の後で自動的に再起動します。過熱に対するデバイスの応答の詳細については、「過熱保護」のセクションを参照してください。

---

**注**

アクティブ電流制限ブロックは、起動時に出力電圧 ( $V_{OUT}$ ) に基づくフォールドバック機構を採用します。 $V_{OUT}$  がフォールドバック スレッショルド ( $V_{FB}$ ) を下回ると、電流制限スレッショルドはさらに低下します。

---

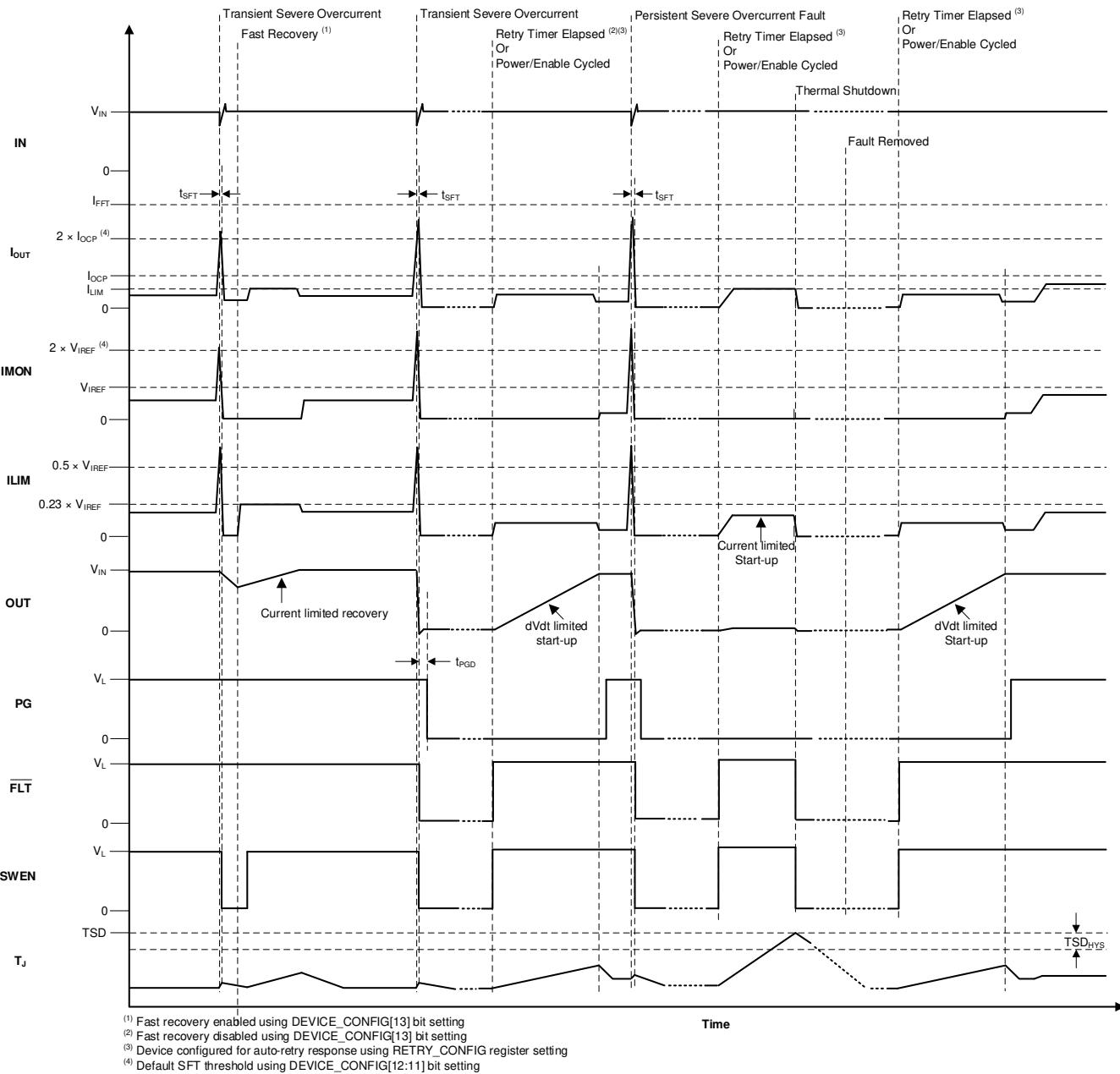

**6.3.4.4 短絡保護**

出力短絡発生中は、本デバイスを流れる電流が非常に急速に増加します。出力短絡が検出されると、内部高速トリップコンパレータは高速保護シーケンスをトリガし、電流がそれ以上蓄積して損傷や過剰な入力電源ドロープが発生するのを防止します。この操作により、ユーザーはすべてのシステムに適しているとは限らない高い固定スレッショルドを使用する代わりに、システム定格に従って高速トリップスレッショルドを調整できます。高速トリップコンパレータは、スケーラブルなスレッショルド ( $I_{SFT}$ ) を採用しています。これは、サーキットブレーカースレッショルド ( $I_{OCP}$ ) とデジタルでプログラム可能なスケーリング係数の関数です。デフォルトの高速トリップスレッショルドは、定常状態時は  $2 \times I_{OCP}$ 、突入時は  $2 \times I_{Startup}$  と等しくなります。定常状態の高速トリップスレッショルドのスケーリング係数は、DEVICE\_CONFIG[12:11] レジスタビットを使用して、異なる値にプログラムできます。 $1.5 \times$ 、 $2 \times$ 、 $2.5 \times$ 、 $8 \times$  のプログラミングオプションが利用可能です。電流が高速トリップスレッショルドを超えると、TPS1689 は  $t_{SFT}$  以内に FET をオフにします。

また、このデバイスは、より高い固定高速トリップスレッショルド ( $I_{FFT}$ ) を採用して、定常状態時 (リニア領域の FET) のハード短絡に対する高速保護を実現します。電流が  $I_{FFT}$  を超えると、FET は  $t_{FFT}$  内で完全にオフになります。

高速トリップイベント後のデバイスの応答は、PMBus® レジスタ書き込みまたは不揮発性構成メモリにより、DEVICE\_CONFIG レジスタの SC\_RETRY ビットを使用して設定できます。2 つのプログラミングオプションを利用可能です。

1. **SC\_RETRY = 0 (デフォルト設定):** デバイスは故障をラッチし、RETRY\_CONFIG レジスタ設定に従って、外部的にまたは内部の自動再試行メカニズムによって再起動がトリガされるまで、オフのまま維持されます。

DEVICE\_CONFIG レジスタが Low で、SC\_RETRY ビットで短絡故障が発生すると、デバイスは次のようになります。

- STATUS\_BYTE レジスタの FET\_OFF ビットと NONE\_OF\_THE ABOVE/UNKNOWN ビットを設定します

- STATUS\_WORD レジスタの上位バイト内の OUT\_STATUS、PGOODB、および NONE\_OF\_THE ABOVE/ UNKNOWN ビットを設定します

- STATUS\_OUT レジスタの VOUT\_UV\_WARN ビットを設定します

- STATUS\_MFR\_SPECIFIC\_2 レジスタの PGOODB および SC\_FLT ビットを設定します

- ALERT\_MASK レジスタの PGOODB ビットと STATUS\_OUT ビットを設定してマスクされていない場合、SMBA# をアサートしてホストに通知します。

- 外部 PG 信号をデアサートします。

- FAULT\_MASK レジスタの SC\_FLT ビットを high に設定してマスクされていない場合、FLT 信号をアサートします。

2. **SC\_RETRY = 1:** このデバイスは、短いデグリッチ期間 (30μs) の後で FET が完全にオンに戻るよう試みます。これにより、過渡過電流イベントが発生した後に FET は迅速に試行および回復し、出力電圧低下を最小化できます。ただし、障害が持続する場合、デバイスは電流制限に移行して接合部温度が上昇し、最終的にはサーマルシャットダウンに移行します。デバイスは故障をラッチし、RETRY\_CONFIG レジスタ設定に従って、外部的にまたは内部の自動再試行メカニズムによって再起動がトリガされるまで、オフのまま維持されます。過熱に対するデバイスの応答の詳細については、「[過熱保護](#)」セクションを参照してください。

DEVICE\_CONFIG レジスタの SC\_RETRY ビットで短絡フォルトが発生すると、デバイスは次のようになります。

- STATUS\_BYTE レジスタの FET\_OFF、STATUS\_TEMP、および NONE\_OF\_THE ABOVE/UNKNOWN ビットを設定します

- STATUS\_WORD レジスタの上位バイトの OUT\_STATUS、MFR\_STATUS、PGOODB、および NONE\_OF\_THE ABOVE/UNKNOWN ビットを設定します

- STATUS\_OUT レジスタの VOUT\_UV\_WARN ビットを設定します

- STATUS\_TEMP レジスタの OT\_FLT ビットを設定します

- STATUS\_MFR\_SPECIFIC レジスタの SOA\_FLT ビットを設定します

- STATUS\_MFR\_SPECIFIC\_2 レジスタの PGOODB ビットを設定します

- ALERT\_MASK レジスタの PGOODB、MFR\_STATUS、STATUS\_TEMP、および STATUS\_OUT ビットを設定してマスクされていない場合、SMBA# をアサートしてホストに通知します。

- 外部 PG 信号をデアサートします。

- FAULT\_MASK レジスタの SOA\_FLT ビットと TEMP\_FLT ビットを high に設定してマスクされていない場合、FLT 信号をアサートします。

図 6-5 に、TPS1689 eFuse の短絡応答を示します。

複数のホットプラグ可能ブレードまたは共通の電源バックプレーンに接続されたラインカードを搭載したブレードサーバー や通信機器などの一部のシステムでは、誘導バックプレーンを流れる大電流のスイッチングにより電源に過渡現象が発生する可能性があります。これによって、eFuse の高速トリップコンパレータをトリガするのに十分な大きさの、隣接カードの電流スパイクが発生する可能性があります。TPS1689 は独自のアルゴリズムを使用して、このような場合の不要なトリップを防止し、中断のないシステム動作を実現しています。

#### 注

- STATUS\_MFR\_SPECIFIC\_2 レジスタの VIN\_TRAN ステータス ビットが設定され、入力ライン過渡イベントが検出されてマスクされたかどうかを示します。

図 6-5. 短絡応答

### 6.3.5 アナログ負荷電流モニタ (IMON)

TPS1689 では、FET を流れる電流に比例したアナログ電流を IMON ピンに供給することで、システムが出力負荷電流を正確に監視できるようになります。電流出力の利点は、隣接するパターンからの電圧降下やノイズの結合による大きな誤差を発生させずに、信号を基板全体に配線できることです。この電流出力により、複数の eFuse デバイス (TPS1689 または TPS1685x) の IMON ピンを互いに接続して、並列構成で合計電流を得ることもできます。IMON 信号は、監視ポイントで抵抗を介して降下させることで電圧に変換できます。ユーザーは、 $R_{IMON}$  の全体で電圧 ( $V_{IMON}$ ) を検出し、式 8 を使用して出力負荷電流の測定値を取得できます。

$$I_{OUT} = \frac{V_{IMON}}{G_{IMON} \times R_{IMON}} \quad (8)$$

TPS1689 IMON 回路は、基板レイアウトやその他のシステム動作条件に関係なく、負荷や温度の条件にわたって高帯域と高精度を実現するように設計されています。この設計では、IMON 信号を Intel PSYS または PROCHOT などの高度な動的プラットフォーム パワー マネジメント手法に使用して、安全性や信頼性を犠牲にすることなく、システムの消費電力とプラットフォームのスループットを最大化できます。

図 6-6. アナログ負荷電流モニタ応答

### 注

1. IMON ピンは、定常状態時にのみ負荷電流監視情報を提供します。突入電流時、IMON ピンはゼロ負荷電流を報告します。

2. ILIM ピンは個別のデバイス負荷電流を常に報告するため、各デバイスのアナログ負荷電流モニタとしても使用できます。

3. TI は、ノイズ フィルタリングのため、IMON ピンと GND の間に 22 個の pF コンデンサを追加することを推奨します。

4. 起動時の過電流および短絡保護タイミングへの影響を避けるため、ILIM ピンの寄生容量を最小限に抑えるように注意する必要があります。

### 6.3.6 過熱保護

TPS1689 は、安全に動作するために、内部 FET が過熱した場合にデバイス自体を保護する、内部サーマル シャットダウン メカニズムを採用しています。TPS1689 が熱過負荷を検出すると、デバイスはシャットダウンします。その後、デバイスは、パワーサイクルされるか再度イネーブルになるまでラッチオフ状態にとどまります。またはデバイスの自動再試行構成に基づく遅延後に自動的に再起動されます。

過熱スレッショルドにはデフォルトのスレッショルド (TSD) があり、システムの必要性に応じて OT\_FLT レジスタを使用して低い値にデジタルでプログラムできます。

表 6-1. 過熱保護のまとめ

| 自動再試行構成 | TSD 開始                                            | TSD 終了                                                                                                                                                   |

|---------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ラッチオフ   | $V_{TEMP} \geq OT\_FLT$ スレッショルドまたは $T_J \geq TSD$ | $V_{TEMP} < OT\_FLT - OT_{Hys}$ または $T_J < TSD - TSD_{Hys}$<br>$VDD$ が 0V にサイクルされ、 $V_{UVP(R)}$ を上回る、または $EN/UVLO$ が $V_{SD(F)}$ より低くトグルされる              |

| 自動再試行   | $V_{TEMP} \geq OT\_FLT$ スレッショルドまたは $T_J \geq TSD$ | $V_{TEMP} < OT\_FLT - OT_{Hys}$ または $T_J < TSD - TSD_{Hys}$<br>再試行タイマが満了する、 $VDD$ が 0V にサイクルされ、 $V_{UVP(R)}$ を上回る、または $EN/UVLO$ が $V_{SD(F)}$ より低くトグルされる |

### 6.3.7 アナログ接合部温度モニタ (TEMP)

TPS1689 を使用すると、システムはダイの温度に比例するアナログ電圧を TEMP ピンに供給することで、接合部温度 ( $T_J$ ) を正確に監視できます。この電圧は、ADC 入力により検出され、デジタル遠隔測定用に READ\_TEMPERATURE\_1 PMBus® コマンドを使用して通知されます。TPS1689 と TPS1685x を含むマルチデバイス並列構成では、すべてのデバイスの TEMP 出力を相互接続できます。この構成では、チェーン内で最も高温のデバイスの温度が TEMP 信号により報告されます。

---

注

1. TEMP ピンの電圧は外部監視のみに使用され、純粋に内部温度監視に基づいている各個別デバイスの過熱保護方式には影響を与えません。

2. TI は、システム過渡時のグリッチをフィルタして除去するため、TEMP ピンに 22pF の容量を追加することを推奨します。

-

### 6.3.8 FET の正常性監視

TPS1689 は、パワー パス FET の故障を示す特定の条件を検出して報告できます。検出または報告されない場合、これらの状態は、負荷に正しく電力を供給しないか、必要なレベルの保護を提供しないかのいずれかにより、システム性能を低下させる可能性があります。FET 故障が検出されると、TPS1689 はゲートを Low に引き下げるにより内部 FET のオフを試み、FLT ピンをアサートします。指定の FET 故障タイプは、STATUS\_MFR\_SPECIFIC ステータス レジスタにも報告されます。

- **D-S 短絡:** D-S 短絡は、基板アセンブリの欠陥または内部 FET 故障のいずれかにより、ソースから負荷まで、制御されない一定の電力供給経路を形成する可能性があります。この状態は、FET がオンになる前に  $V_{IN-OUT} < V_{DSFLT}$  かどうかをチェックすることで、起動時に検出されます。もしそうであれば、デバイスは内部出力放電を作動させ、出力の放電を試みます。 $V_{OUT}$  が特定の許容間隔内に  $V_{FB}$  を下回るまで放電されない場合、デバイスは FLT ピンをアサートし、STATUS\_MFR\_SPECIFIC ステータス レジスタの FET\_FAULT\_DS ビットを設定します。

---

注

DEVICE\_CONFIG レジスタの DIS\_VDSFLT ビットを設定することで、D-S 故障検出をデジタル的に無効化するオプションがあります。これにより、デバイスは D-S 故障をトリガすることなく、事前に充電された出力で起動できます。

- **G-D 短絡:** TPS1689 は、内部制御ロジックが FET をオフ状態に保持しようとしても、ゲート電圧が  $V_{IN}$  に近いかどうかを常にチェックすることで、この種の FET 故障を常に検出します。この状態が検出されると、デバイスは FLT ピンをアサートし、STATUS\_MFR\_SPECIFIC ステータス レジスタの FET\_FAULT\_GD ビットを設定します。

- **G-S 短絡:** TPS1689 は、ゲートドライバがオンになった後、FET G-S 電圧が特定のタイムアウト期間 ( $t_{SU\_TMR}$ ) 内に必要なオーバードライブ電圧に達しないかどうかをチェックすることで、起動時にこの種の FET 故障を検出します。定常状態では、コントローラロジックがゲートドライバに FET をオフにするように信号を送信する前に G-S 電圧が Low になると、故障としてラッピングされます。この状態が検出されると、デバイスは FLT ピンをアサートし、STATUS\_MFR\_SPECIFIC ステータス レジスタの FET\_FAULT\_GS ビットを設定します。

### 6.3.9 シングル ポイント障害の軽減

TPS1689 は、あらゆる状況で過電流と短絡に対する保護を提供するため、IMON、ILIM、IREF ピンの適切な部品接続とバイアスを使用し、適切なスレッショルド デジタル構成を採用しています。安全対策の追加として、本デバイスは以下のメカニズムを使用して、これらのピンのいずれかがシステム内で正しく接続されなかった場合やフィールド内で関連部品に障害が発生した場合や、構成レジスタが正しくプログラムされていない場合でも、デバイスが何らかの過電流保護を実現するようにします。

### 6.3.9.1 IMON ピンのシングル ポイント障害

- IMON ピン オープン:**この場合、IMON ピン電圧が内部的に高電圧にプルアップされ、スレッショルド ( $V_{IREF}$ ) を超えてしまうため、デバイスに大きな電流が流れていらない場合でも、部品が回路ブレーカ動作を実行してしまいます。

- IMON ピンが直接または非常に低い抵抗を介して GND に短絡されている:**この場合、IMON ピンの電圧は低電圧に保持され、デバイスに大きな電流が流れる場合でもスレッショルド ( $V_{IREF}$ ) を超えることは許可されず、プライマリ過電流保護メカニズムは無効になります。このデバイスは、バックアップとして何らかの保護を提供するために、内部の過電流検出メカニズムに依存しています。デバイスがバックアップ電流センススレッショルド ( $I_{OC\_BKP}$ ) を超えたことを検出し、同時に IMON ピンのプライマリ過電流検出が失敗した場合、シングル ポイント障害検出がトリガされ、故障がラッチされます。FET はオフになり、 $\overline{FLT}$  ピンがアサートされます。同時に、STATUS\_MFR\_SPECIFIC\_2 レジスタの SPFAIL ステータスビットが設定され、SMBA# 信号がアサートされます。

### 6.3.9.2 IREF ピンのシングル ポイント障害

- IREF DAC の設定が不適切、または外部で強制的に高い電圧に設定されている:**この場合、IREF ピン ( $V_{IREF}$ ) は、推奨される  $I_{OCP}$  または  $I_{LIM}$  の計算に従って目標値よりも高い電圧に内部または外部でプルアップされ、デバイスに大電流が流れている場合でもプライマリ サーキットブレーカ、アクティブ電流制限、短絡保護がトリガされないようにしています。このデバイスは、内部過電流検出メカニズムに依存して、何らかの保護をバックアップとして実現します。デバイスが、負荷電流がバックアップ過電流スレッショルド ( $I_{OC\_BKP}$ ) を超えていることを検出したが、同時に ILIM または IMON ピンのプライマリ過電流または短絡検出に失敗する場合、シングル ポイント障害検出がトリガされ、故障がラッチされます。FET はオフになり、 $\overline{FLT}$  ピンがアサートされます。同時に、STATUS\_MFR\_SPECIFIC\_2 レジスタの SPFAIL ステータスビットが設定され、SMBA# 信号がアサートされます。

- IREF ピンは GND へ短絡:**この場合、 $V_{IREF}$  スレッショルドが OV に設定されたため、デバイスに大きな電流が流れない場合でも、部品はアクティブ電流制限またはサーキットブレーカ動作を実行します。

### 6.3.10 汎用デジタル入出力ピン

TPS1689 には、システムのニーズに応じて異なる機能に構成できる 2 つの汎用デジタル入出力ピンがあります。

- TEMP/EECLK/GPIO1 (汎用デジタル出力)

- Aux/EEDATA/GPIO2 (汎用デジタル出力)

これらのピンは、DEVICE\_CONFIG レジスタビットを使用して構成できます。

### 6.3.10.1 フォルト応答および表示 ( $\overline{FLT}$ )

表 6-2 は、各種故障条件に対するデバイスの応答をまとめたものです。

表 6-2. 故障のまとめ

| イベントまたは状態      | デバイスの応答 | 内部でラッチされた故障 | $\overline{FLT}$ ピンのステータス | ピン表示マスキングオプション | 遅延           |

|----------------|---------|-------------|---------------------------|----------------|--------------|

| 定常状態           | なし      | 該当なし        | H                         | 該当なし           |              |

| 突入電流           | なし      | 該当なし        | H                         | 該当なし           |              |

| 過熱             | シャットダウン | Y           | L                         | Y              |              |

| 低電圧 (EN/UVLO)  | シャットダウン | N           | H                         | 該当なし           |              |

| 低電圧 (VDD UVP)  | シャットダウン | N           | H                         | 該当なし           |              |

| 低電圧 (VIN UVP)  | シャットダウン | N           | H                         | 該当なし           |              |

| 過電圧 (VIN OVP)  | シャットダウン | N           | H                         | 該当なし           |              |

| 過渡過電流          | なし      | N           | H                         | 該当なし           |              |

| 持続的な過電流 (定常状態) | 回路ブレーカ  | Y           | L                         | Y              | $t_{ITIMER}$ |

| 持続的な過電流 (起動時)  | 電流制限    | N           | H                         | 該当なし           | TSD 後        |

| 出力短絡           | 高速トリップ  | Y           | L                         | Y              | $t_{FT}$     |

表 6-2. 故障のまとめ (続き)

| イベントまたは状態                                          | デバイスの応答                                | 内部でラッチされた故障 | FLT ピンのステータス | ピン表示マスキングオプション | 遅延            |

|----------------------------------------------------|----------------------------------------|-------------|--------------|----------------|---------------|

| 出力短絡 (高速回復構成)                                      | 高速トリップ後の電流制限付き起動                       | N           | H            | 該当なし           |               |

| IMON ピンオープン (定常状態)                                 | シャットダウン                                | Y           | L            | Y              |               |

| IMON ピン短絡 (定常状態)                                   | シャットダウン ( $I_{OUT} > I_{OC\_BKP}$ の場合) | Y           | L            | Y              | 45μs          |

| IREF ピンオープン (起動時)                                  | シャットダウン ( $I_{OUT} > I_{OC\_BKP}$ の場合) | Y           | L            | Y              |               |

| IREF ピンオープン (定常状態)                                 | シャットダウン ( $I_{OUT} > I_{OC\_BKP}$ の場合) | Y           | L            | Y              | $t_{ITIMER}$  |

| IREF ピン短絡 (定常状態)                                   | シャットダウン                                | Y           | L            | Y              |               |

| IREF ピン短絡 (起動時)                                    | シャットダウン                                | Y           | L            | Y              |               |

| 起動タイムアウト                                           | シャットダウン                                | Y           | L            | N              | $t_{SU\_TMR}$ |

| FET 正常性故障 (G-S)                                    | シャットダウン                                | Y           | L            | Y              | 10μs          |

| FET 正常性故障 (G-D)                                    | シャットダウン                                | Y           | L            | Y              |               |

| FET 正常性故障 (D-S)                                    | シャットダウン                                | N           | L            | Y              | $t_{SU\_TMR}$ |

| 外部故障 (デバイスが UV でも OV でもないときに SWEN が外部で Low にプルされる) | シャットダウン                                | Y           | L            | Y              |               |

故障後のデバイスの応答は、RETRY\_CONFIG レジスタ設定によって異なります。デバイスは、上記の表に従って故障をラッチし、その後、自動再試行またはラッチオフ応答を実行します。自動再試行構成では、ラッチされた故障は、FLT ピンを Low に維持しながら、自動再試行タイマの開始もトリガします。タイマ期間 ( $t_{RETRY}$ ) の満了時に、FLT ピンのプルダウンが解除され、デバイスは自動的に再起動する準備が整います。デバイスが再度オンになると、通常の DVDT 制限付き起動シーケンスに従います。

これに対する唯一の例外は、DEVICE\_CONFIG レジスタの SC\_RETRY ビットを使用して高速回復が構成されている場合の短絡故障時です。この場合、デバイスは迅速にオフになり、その後、電流制限された方法で自動的にオンに戻ります。これにより、システムは過渡的な障害からの迅速な回復を試みることができます。詳細については、「[短絡保護](#)」のセクションを参照してください。

内部でラッチされた故障の場合、部品の電源を入れ直すか、EN/UVLO ピンの電圧を  $V_{SD(F)}$  未満に引き下げることで故障がクリアされ、FLT ピンはデアサートされます。この動作により、自動再試行タイマもクリアされます。この状況では、EN/UVLO を UVLO スレッショルドよりもわずかに低くしても、デバイスに影響はありません。これは、ラッチオフ構成および自動再試行構成の場合にも当てはまります。

TPS1689 と TPS1685x を含む並列 eFuse 構成では、故障応答はプライマリ デバイスである TPS1689 によって決定されます。ただし、プライマリ デバイスが故障を登録できない場合、セカンダリ デバイスにはフェイルセーフ機構が備わっており、SWEN ピンを Low に引き下げてチェーン全体をオフにし、ラッチオフ状態に移行することで制御を取得します。その後、デバイスは VDD の電源を  $V_{UVF(F)}$  未満にして入れ直すか、EN/UVLO ピンを  $V_{SD(F)}$  未満してサイクルさせることによってのみ、再度オンになります。

### 6.3.10.2 パワー グッド表示 (PG)

パワー グッドは、デバイスが定常状態で最大電力を供給可能な場合に、high にアサートされるアクティブ high デジタル出力です。

**表 6-3. PG 表示のまとめ**

| イベントまたは状態                                                     | FET のステータス | PG ピン ステータス                                                        | PG 遅延                     |

|---------------------------------------------------------------|------------|--------------------------------------------------------------------|---------------------------|

| デバイス無効化 ( $V_{EN} < V_{UVLO}$ )                               | オフ         | L                                                                  | $t_{PGD}$                 |

| VIN 低電圧 ( $V_{IN} < V_{UVP}$ または $V_{IN} < V_{IN\_UV\_FLT}$ ) | オフ         | L                                                                  |                           |

| VDD 低電圧 ( $V_{DD} < V_{UVP}$ )                                | オフ         | L                                                                  |                           |

| VIN 過電圧 ( $V_{IN} > V_{IN\_OV\_FLT}$ )                        | オフ         | L                                                                  | $t_{PGD}$                 |

| 定常状態                                                          | オン         | H                                                                  | $t_{PGA}$                 |

| 突入電流                                                          | オン         | L                                                                  | $t_{PGA}$                 |

| 過渡過電流                                                         | オン         | H                                                                  | 該当なし                      |

| 回路ブレーカ (持続的な過電流後に OC_TIMER 満了)                                | オフ         | L                                                                  | $t_{OC\_TIMER} + t_{PGD}$ |

| 高速トリップ                                                        | オフ         | L ( $V_{OUT} < V_{OUT\_PGTH}$ )<br>H ( $V_{OUT} > V_{OUT\_PGTH}$ ) | $t_{PGD}$<br>該当なし         |

| 過熱                                                            | シャットダウン    | L                                                                  | $t_{PGD}$                 |

パワーアップ後、PG は初期状態で Low に引き下げられます。デバイスは突入シーケンスを開始し、ゲートドライバ回路が内部のチャージポンプからゲート容量の充電を開始します。FET ゲート電圧が最大オーバードライブに達し、突入シーケンスが完了し、デバイスが最大出力を供給できることを示すと、グリッチ除去時間 ( $t_{PGA}$ ) の後、PG ピンが high にアサートされます。PG のアサート遅延は、DEVICE\_CONFIG レジスタの PG\_DVDT\_DLY ビットを設定することで、オプションとして延長できます。

通常動作中に、いずれかの点で出力電圧がスレッショルドを下回ると、または、デバイスが故障 (短絡を除く) を検出すると、PG はデアサートされます。PG のデアサートスレッショルドは、VOUT\_PGTH レジスタによりデジタル的にプログラムできます。PG のデアサート時のグリッチ除去時間は  $t_{PGD}$  です。

図 6-7. TPS1689 PG タイミング図

PG はオープンドレインのピンであり、外部電源にプルアップする必要があります。

#### 注

デバイスに電源が供給されていない場合、PG ピンは Low のままであることが期待されています。ただし、この状態には、このピンを  $0V$  まで完全に駆動するためのアクティブプルダウンはありません。デバイスに電力が供給されていない場合でも、PG ピンが存在する独立した電源にプルアップされると、プルアップ電源電圧と抵抗の関数であるピンのシンク電流に応じて、このピンに小さな電圧が印加される可能性があります。シンク電流を最小化して、この状態で関連する外部回路によってロジック HIGH として検出されないよう、このピン電圧を十分に低く維持します。

### 6.3.10.3 並列デバイス同期 (SWEN)

SWEN ピンは、FET をオン状態に駆動する必要がある場合に high に駆動される信号です。このピンを Low (内部または外部) に駆動すると、ドライバ回路で FET が強制的にオフ状態に維持されます。並列 eFuse システムでは、TPS1689 プライマリ コントローラがこのピンを使用して他の eFuse を制御します。また、複数のデバイスを並列構成で使用して、オン / オフの遷移を同期させることもできます。

**表 6-4. SWEN のまとめ**

| デバイスの状態                                                       | FET ドライバ ステータス | SWEN                                                      |

|---------------------------------------------------------------|----------------|-----------------------------------------------------------|

| 定常状態                                                          | オン             | H                                                         |

| 突入電流                                                          | オン             | H                                                         |

| 過熱シャットダウン                                                     | オフ             | L                                                         |

| 自動再試行タイマが動作しています                                              | オフ             | L                                                         |

| デバイス無効化 ( $V_{EN} < V_{UVLO}$ )                               | オフ             | L                                                         |

| VIN 低電圧 ( $V_{IN} < V_{UVP}$ または $V_{IN} < V_{IN\_UV\_FLT}$ ) | オフ             | L                                                         |

| VDD 低電圧 ( $V_{DD} < V_{UVP}$ )                                | オフ             | L                                                         |

| 挿入遅延                                                          | オフ             | L                                                         |

| VIN 過電圧 ( $V_{IN} > V_{IN\_OV\_FLT}$ )                        | オフ             | L                                                         |

| 過渡過電流                                                         | オン             | H                                                         |

| 回路ブレーカ (持続的な過電流後に OC_TIMER 満了)                                | オフ             | L                                                         |

| 高速トリップ                                                        | オフ             | L                                                         |

| 高速トリップ応答、モノラルショット実行 (DEVICE_CONFIG[13]= 1)                    | オフ             | L                                                         |

| 高速トリップ応答モノラルショットの期限切れ (DEVICE_CONFIG[13]= 1)                  | オン             | H                                                         |

| FET 正常性故障                                                     | オフ             | L                                                         |

| 外部フォルト (並列チェーンでセカンダリ デバイスによって SWEN を Low にプル)                 | オフ             | L (しばらくした後でセカンダリ デバイスがプルダウンをリリースしても、TPS1689 によって Low に保持) |

| シングル ポイント障害 (IMON/IREF)                                       | オフ             | L                                                         |

SWEN はオープンドレインのピンであり、内部電源へのプルアップを備えています。

SWEN ピンには内部タイムアウト回路があります。SWEN が長時間 low (内部または外部) に保持されると (tSWENTO)、ロジックがリセットされ (FAST\_REC = 0)、SWEN が high になった後で次にデバイスが起動するように、通常の突入シーケンスに従います。それ以外の場合は、突入シーケンスをバイパスして電流制限の起動を実行し、高速で回復することもあります。

プライマリとセカンダリの並列構成では、SWEN ピンをプライマリ デバイスで使用して、セカンダリ デバイスのオン / オフ遷移を制御します。同時に、セカンダリ デバイスが障害やその他の状態を通信できるようになり、プライマリ デバイスがオンになるのを防ぐことができます。

これらのデバイスは、ステートマシンの同期を維持するために SWEN レベルの遷移とハンドシェイクのタイミングに依存します。これにより、すべてのデバイスが同期および同じ方法でオン / オフできます (dVdt 制御や電流制限によるスタートアップなど)。また、故障発生時にプライマリ デバイスが制御を取得できない場合でもチェーン全体が安全にオフになるようにする、フェイルセーフ メカニズムを SWEN 制御とハンドシェイク ロジックに備えています。

**注**

TI は、同期タイミングの問題を回避するため、SWEN ピンの寄生負荷を最小限に抑えることを推奨します。

### 6.3.11 複数の eFuse をスタックして無制限のスケーラビリティを実現

単一の TPS1689 でサポートされるよりも高電流を必要とするシステムの場合は、TPS1689 を並列に接続して、1 つまたは複数の TPS1685x デバイスに接続し、目的の合計システム電流を供給することができます。従来型の eFuse は、パス抵抗のミスマッチ（個別デバイスの  $R_{DSON}$  の部品間のバラツキや、PCB の寄生パターン抵抗を含む）により、定常状態時に電流を均等に共有しません。この事実は、システムの複数の問題につながる可能性があります。

1. 一部のデバイスは、他のデバイスより大きい電流を常に流します。この結果、故障が発生してシステムの動作寿命が全体的に短縮される可能性があります。

2. この結果、基板、デバイス、トレース、ビアにサーマル ホットスポットが形成され、大電流が流れ、PCB の信頼性の問題につながります。また、この問題により、熱モデル化と基板の熱管理は設計者にとって非常に困難になります。

3. より大きな電流を伝送するデバイスは、システムの合計負荷電流が全体のサーキットブレーカー レッショルドよりも低くなっている間に、より早く個別のサーキットブレーカー レッショルドに達する可能性があります。この動作により、通常動作中に eFuse チェーンの誤ったトリップが発生する可能性があります。これは並列チェーンの電流搬送能力を低下させてしまいます。言い換えると、並列 eFuse チェーンの電流定格は、個別の eFuse の電流定格の合計と比較してディレーティングする必要があります。このディレーティング係数は、パス抵抗のミスマッチ、並列接続されるデバイスの数、個別の eFuse サーキットブレーカーの精度の関数です。

ディレーティングの必要性は、システム設計に悪影響を及ぼします。設計者は、以下のいずれかのトレードオフを決定しなければなりません。