JAJSQ15B - SEPTEMBER 2024 - REVISED MAY 2025

TPS1685x、9V~80V、3.5mΩ、20A、スタッカブル内蔵型ホットスワップ (eFuse)、高 精度で高速な電流モニタ搭載

# 1 特長

- 動作入力電圧範囲:9V ~ 80V - 絶対最大電圧 92V

- 出力側で最大 -5V の負電圧に対応

- 低いオン抵抗の FET を内蔵: R<sub>ON</sub> = 3.5mΩ (標準 値)

- アクティブ HIGH のイネーブル入力、低電圧誤動作

防止 (UVLO) を設定可能

- 調整可能な過電圧保護機能

- 複数の eFuse の並列接続をサポートし、デバイス 状態の同期と電流共有を行います

- 突入電流からの保護のために出力スルーレート制御(dVdt)を調整可能

- 高精度な負荷電流監視機能

- 最大電流の 50~100% にわたって誤差 3% 未 満です

- 1MHz の帯域幅

- 堅牢な過電流保護機能

- サーキットブレーカ応答

- 可変スレッショルド:2A~20A

- 過電流保護の精度:±3%

- 可変の過渡過電流タイマ (ITIMER) によりピー ク電流をサポート

- 短絡イベントに対する高速トリップ応答

- アナログ ダイ温度監視出力 (TEMP) による過熱保 護 (OTP)

- FET SOA : 0.7W√s

- FET の健全性監視および報告機能

- フォルト表示ピン (FLT)

- パワー グッド表示ピン (PGOOD)

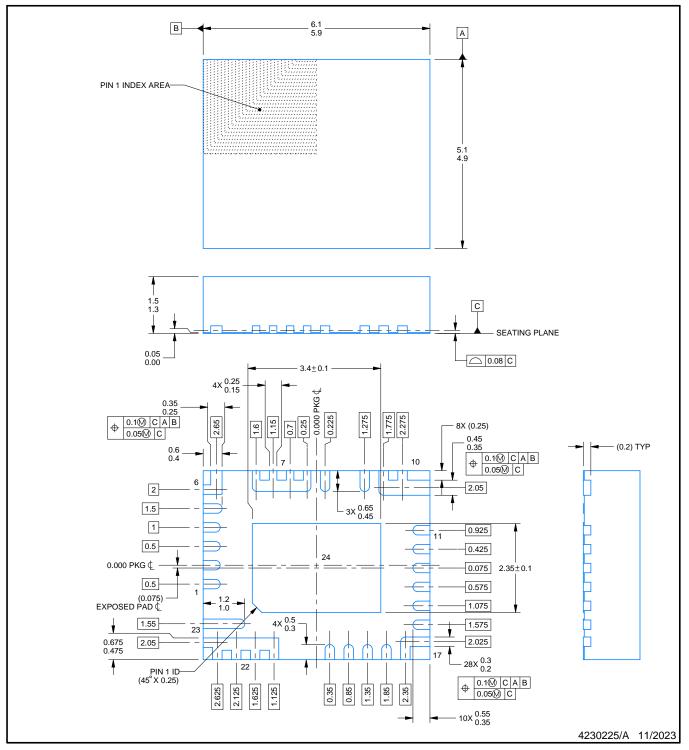

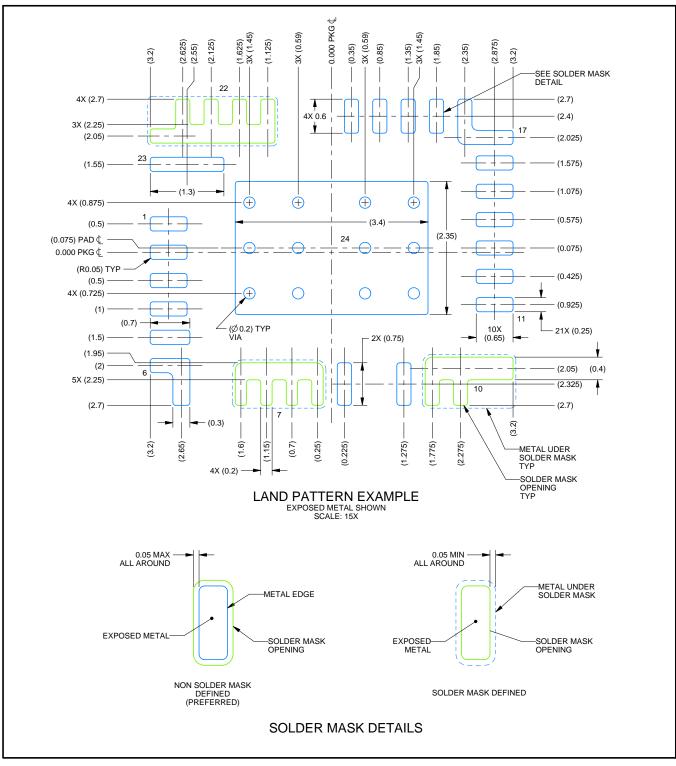

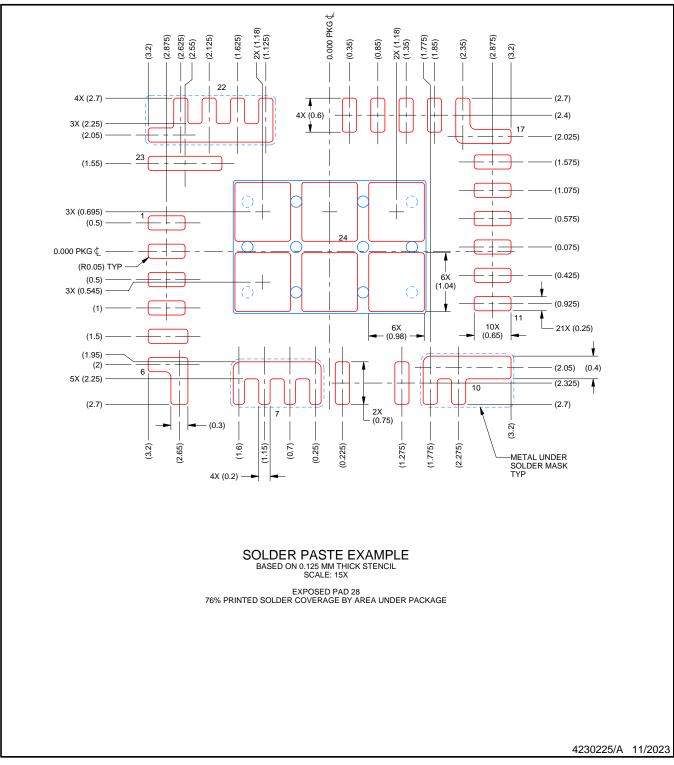

- 小さい占有面積:QFN 6mm × 5mm

- 60V 対応の IPC9592B クリアランス

# 2 アプリケーション

- 入力ホットスワップおよびホットプラグ

- サーバーおよび高性能コンピューティング

- ネットワーク インターフェイス カード

- グラフィックスおよびハードウェア アクセラレー タ カード

- データ センターのスイッチおよびルーター

- 火災警報制御パネル

### 3 説明

TPS1685x は統合型大電流回路保護およびパワーマ ネージメント デバイスです。このデバイスは、非常に 少数の外付け部品で複数の保護モードを提供し、過負 荷、短絡、および過剰な突入電流に対して堅牢な保護 を行います。特定の突入電流要件を持つアプリケーシ ョンでは、単一の外付けコンデンサにより出力スルー レートを設定できます。出力電流制限レベルは、シス テムの必要に応じてユーザーが設定できます。ユーザ ーが調整可能な過電流ブランキングタイマを使用す ると、システムは eFuse をトリップせずに、負荷電流 の過渡ピークに対応できます。高速で高精度の検出を 行う内蔵のアナログ負荷電流モニタにより、予知保全 と高度な動的プラットフォーム電力管理 (Intel® PSYS、PROCHOT# など)が容易になり、サーバーお よびデータセンターの性能を最適化します。

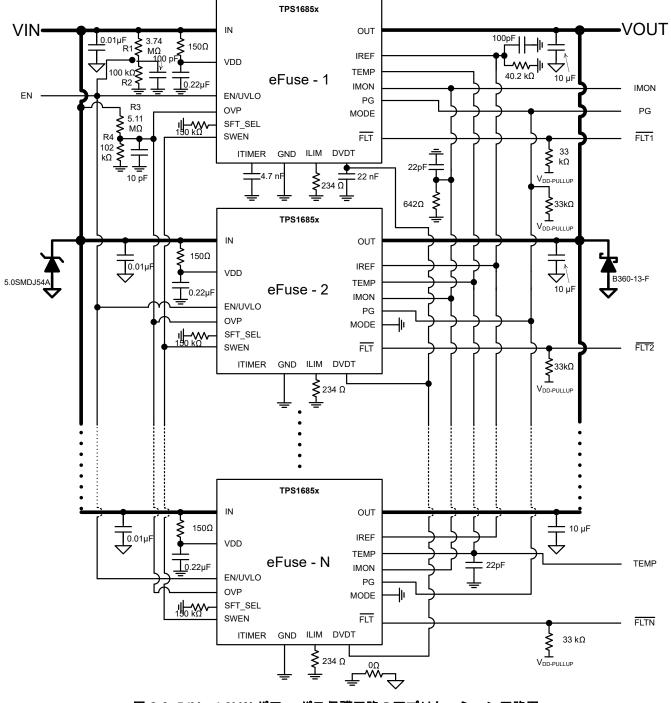

複数の TPS1685x デバイスを並列に接続して、大電力 システム用に合計電流容量を拡大できます。すべての デバイスが動作状態をアクティブに同期し、スタート アップ時や定常状態で電流を共有することで、一部の デバイスに過大なストレスがかかることを防ぎます。 このようなストレスは、並列チェーンの早期または部 分的なシャットダウンを引き起こす可能性がありま す。

これらのデバイスは、-40℃~+125℃の接合部温度範 囲で動作が規定されています。

#### パッケージ情報

| 部品番号                         | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------------------------|----------------------|--------------------------|

| TPS16850VMAR<br>TPS16851VMAR | VMA (LQFN, 23)       | 6.00mm × 5.00mm          |

- (1) 供給されているすべてのパッケージについては、セクション11 を参照してください。

- (2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合 はピンも含まれます。

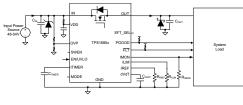

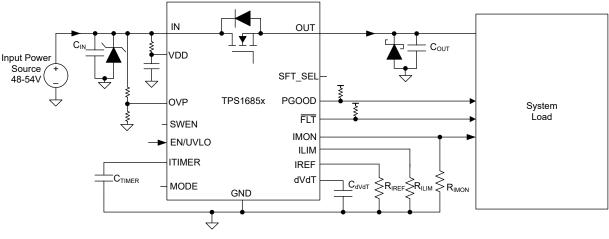

概略回路図

# 目次

| 1 | 特長                | . 1 |

|---|-------------------|-----|

| 2 | アプリケーション          | 1   |

|   | 説明                |     |

| 4 | デバイス比較表           | . 3 |

| 5 | ピン構成および機能         | .4  |

|   | <b>仕様</b>         |     |

|   | 6.1 絶対最大定格        |     |

|   | 6.2 ESD 定格        | . 6 |

|   | 6.3 推奨動作条件        |     |

|   | 6.4 熱に関する情報       | 7   |

|   | 6.5 電気的特性         | 8   |

|   | 6.6 ロジック・インターフェイス |     |

|   | 6.7 タイミング要件       |     |

|   | 6.8 スイッチング特性      |     |

|   | 6.9 代表的特性         | 13  |

| 7 | 詳細説明              |     |

|   | 7.1 概要            |     |

|   | 7.2 機能ブロック図       | 18  |

|   | 7.3 機能説明                    | 19   |

|---|-----------------------------|------|

|   | 7.4 デバイスの機能モード              |      |

| 8 | アプリケーションと実装                 |      |

|   | 8.1 アプリケーション情報              |      |

|   | 8.2 代表的なアプリケーション:データ センター サ |      |

|   | ーバーにおける 54V パワー パス保護        | 41   |

|   | 8.3 電源に関する推奨事項              | .47  |

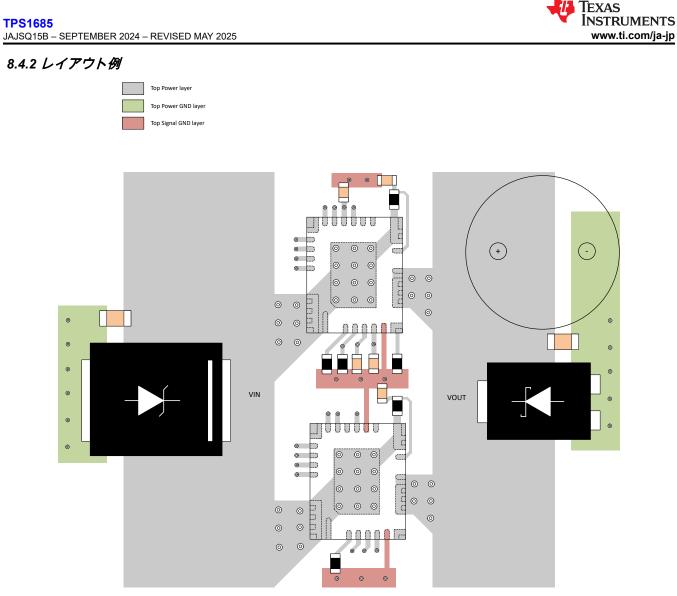

|   | 8.4 レイアウト                   | .49  |

| 9 | デバイスおよびドキュメントのサポート          | 51   |

|   | 9.1 ドキュメントのサポート             | . 51 |

|   | 9.2 ドキュメントの更新通知を受け取る方法      | . 51 |

|   | 9.3 サポート・リソース               | 51   |

|   | 9.4 商標                      | 51   |

|   | 9.5 静電気放電に関する注意事項           | . 51 |

|   | 9.6 用語集                     | . 51 |

| 1 | 0 改訂履歴                      |      |

|   | 1 メカニカル、パッケージ、および注文情報       |      |

|   |                             |      |

# 4 デバイス比較表

| 部品番号     | フォルト動作 |

|----------|--------|

| TPS16850 | 自動再試行  |

| TPS16851 | ラッチオフ  |

# 5ピン構成および機能

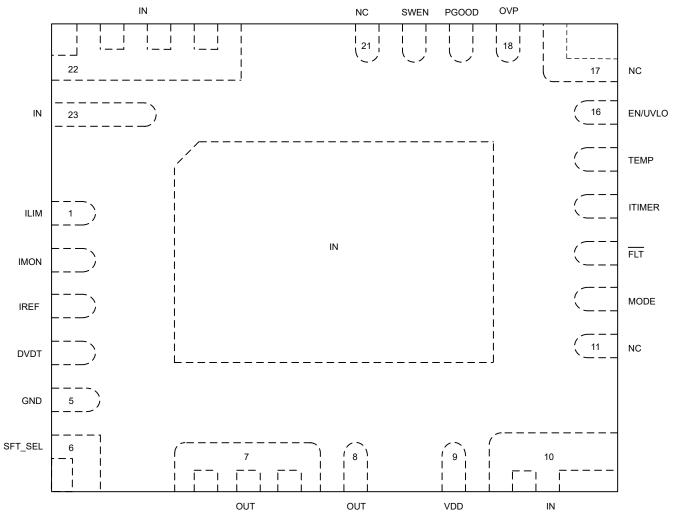

図 5-1. TPS1685x VMA パッケージ、QFN 23 ピン (上面図)

表 5-1. ピンの機能

| ۲<br>۲ | ン  | タイプ <sup>(1)</sup> | 説明                                                                                                                                                  |  |  |

|--------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 名称     | 番号 |                    | 8/6/73                                                                                                                                              |  |  |

| ILIM   | 1  | I/O                | このピンと GND との間に外付け抵抗を接続することで、定常状態時のアクティブ電流共有スレッショルドが設定されます。このピンは、定常状態時の個別の eFuse 電流モニタ出力としても機能します。フローティングのままにしないでください。                               |  |  |

| IMON   | 2  | I/O                | このピンと GND の間に外付け抵抗を接続することで、定常状態時の過電流 / 保<br>護スレッショルドと高速トリップ スレッショルドが設定されます。このピン<br>は、定常状態中の高速かつ高精度のアナログ出力負荷電流監視信号としても機<br>能します。フローティングのままにしないでください。 |  |  |

| IREF   | 3  | I/O                | このピンは、過電流、短絡保護とアクティブ電流共有ブロックに適したリファ<br>レンス電圧を設定します。リファレンス電圧は、このピンの内部電流源と抵抗<br>を使用して生成することも、外部電圧源から駆動することもできます。フロー<br>ティングのままにしないでください。              |  |  |

| dVdT   | 4  | I/O                | このピンを使用して、スタートアップ時の出力スルー レートを構成します。こ<br>のピンをオープンのままにすると、短時間で起動できます。コンデンサをグラ<br>ンドと接続することで、スルーレートを低速にし、突入電流を管理します。                                   |  |  |

| GND    | 5  | G                  | デバイス グランド リファレンス ピン。システム グランドに接続。                                                                                                                   |  |  |

4 資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

## 表 5-1. ピンの機能 (続き)

| ピン      |          | タイプ <sup>(1)</sup> | 84 69                                                                                                                                                                          |  |  |

|---------|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 名称      | 番号       | 2170               | 説明                                                                                                                                                                             |  |  |

| SFT_SEL | 6        | I/O                | このピンは、定常状態時のスケーラブルな高速トリップ スレッショルド逓倍器<br>を選択します。このピンと GND の間に抵抗を接続して、高速トリップ スレッ<br>ショルド逓倍器を選択します。                                                                               |  |  |

| Ουτ     | 7、8      | Р                  | 電力出力。適切な放熱のため、出力電源プレーンに均一に半田付けする必要が<br>あります。                                                                                                                                   |  |  |

| VDD     | 9        | Р                  | コントローラ電源入力ピン。システム過渡の影響を受けない、フィルタリング<br>され、安定した電源で内部制御回路に電力を供給することを目的としています。<br>このピンを直列抵抗を介して VIN に接続し、デカップリング コンデンサを<br>GND に追加します。                                            |  |  |

| IN      | 10、22、23 | Р                  | 電源入力.適切な放熱のため、入力電源プレーンに均一に半田付けする必要があ<br>ります。                                                                                                                                   |  |  |

| NC      | 11、17、21 | _                  | このピンに何も接続しないでください。                                                                                                                                                             |  |  |

| モード     | 12       | I                  | このピンは、スタンドアロン/1 次動作モードまたは 2 次動作モード用にデバイ<br>スを構成するために使用されます。このピンを GND に接続すると、デバイス<br>を 1 次側 eFuse/コントローラに対する 2 次デバイスとして構成できます。ス<br>タンドアロン/1 次動作モードの場合は、このピンをフローティングのままにし<br>ます。 |  |  |

| FLT     | 13       | 0                  | これは、オープン ドレインのアクティブ low ピンで、low にプルされることで<br>フォルトを示します。抵抗を使用して、このピンを外部電源電圧にプルアップ<br>します。                                                                                       |  |  |

| ITIMER  | 14       | I/O                | このピンと GND との間のコンデンサにより、デバイスの過電流応答が動作す<br>る前に、定常状態動作中に出力電流が過電流スレッショルド (ただし、高速トリ<br>ップ スレッショルドより低い) を一時的に超えることができる過電流ブランキ<br>ング間隔が設定されます。                                        |  |  |

| ТЕМР    | 15       | I/O                | 接合部温度のアナログ電圧出力。複数のデバイスの TEMP 出力を並列構成で<br>接続することで、並列チェーンのピーク温度を表示できます。                                                                                                          |  |  |

| EN/UVLO | 16       | I                  | アクティブ High イネーブル入力。入力電源から抵抗分割器を接続して、低電圧<br>スレッショルドを設定します。フローティングのままにしないでください。                                                                                                  |  |  |

| OVP     | 18       | I                  | このピンを使用して過電圧設定点を設定できます。VIN とこのピンとの間に抵<br>抗デバイダを接続します。フローティングのままにしないでください。                                                                                                      |  |  |

| PGOOD   | 19       | 0                  | これはオープン ドレインのアクティブ high パワー グッド ピンで、デバイスが<br>定常状態のときに high にアサートされます。このピンには、内部電源電圧への<br>弱いプルアップがあります。                                                                          |  |  |

| SWEN    | 20       | I/O                | これは、パワー スイッチのオン / オフ ステータスを示すオープン ドレイン信<br>号です。このピンにより、並列チェーン内の複数のデバイスを簡単にアクティ<br>ブに同期できます。このピンには、内部電源電圧への弱いプルアップがありま<br>す。                                                    |  |  |

| IN      | PowerPad | Р                  | 電源入力.適切な放熱のため、入力電源プレーンに均一に半田付けする必要があ<br>ります。                                                                                                                                   |  |  |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

# 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                              | パラメータ                                         | ピン           | 最小値  | 最大値                    | 単位 |

|----------------------------------------------|-----------------------------------------------|--------------|------|------------------------|----|

| V <sub>INMAX</sub> , V <sub>DDMAX</sub>      | 最大入力および電源電圧 (–40℃ ≤ T <sub>J</sub> ≤<br>125℃) | IN, VDD      | -0.3 | 90                     | V  |

| V <sub>INMAX、25</sub> 、V <sub>DDMAX、25</sub> | 最大入力および電源電圧 (25℃ ≤ T <sub>J</sub> ≤<br>125℃)  | IN、VDD       | -0.3 | 92                     | V  |

| V <sub>OUTMAX</sub>                          | 最大出力電圧                                        | OUT          |      | Min(92V、<br>/IN + 0.3) |    |

| V <sub>IN</sub> ~ V <sub>OUT</sub>           | IN と OUT の最大差                                 | IN、OUT       | -0.3 | 90                     | V  |

| V <sub>IILIMMAX</sub>                        | ILIM ピンの最大電圧                                  | ILIM         | -0.3 | 6                      | V  |

| VIMONMAX                                     | IMON ピンの最大電圧                                  | IMON         | -0.3 | 6                      | V  |

| V <sub>SFT_SELMAX</sub>                      | SFT_SEL ピンの最大電圧                               | SFT_SEL      | -0.3 | 6                      | V  |

| V <sub>OVP</sub>                             | OVP ピンの最大電圧                                   | OVP          | -0.3 | 6                      | V  |

| V <sub>ITIMER</sub>                          | ITIMER ピンの最大電圧                                | ITIMER       | -0.3 | 6                      | V  |

| V <sub>IREFMAX</sub>                         | IREF ピンの最大電圧                                  | IREF         | -0.3 | 6                      | V  |

| V <sub>DVDTMAX</sub>                         | DVDT ピンの最大電圧                                  | DVDT         | -0.3 | 6                      | V  |

| V <sub>MODEMAX</sub>                         | MODE ピンの最大電圧                                  | モード          | -0.3 | 6                      | V  |

| V <sub>SWENMAX</sub>                         | SWEN ピンの最大電圧                                  | SWEN         | -0.3 | 6                      | V  |

| ISWENMAX                                     | SWEN ピンの最大シンク                                 | SWEN         |      | 10                     | mA |

| V <sub>ENMAX</sub>                           | EN/UVLO ピンの最大電圧                               | EN/UVLO      | -0.3 | 6                      | V  |

| V <sub>FLTMAX</sub>                          | FLT ピンの最大電圧                                   | FLT          | -0.3 | 6                      | V  |

| I FLTMAX                                     | FLT ピンの最大シンク電流                                | FLT          |      | 10                     | mA |

| V <sub>PGOODMAX</sub>                        | PGOOD ピンの最大電圧                                 | PGOOD        | -0.3 | 6                      | V  |

| IPGOODMAX                                    | PGOOD ピンの最大シンク電流                              | PGOOD        |      | 10                     | mA |

| V <sub>TEMP</sub>                            | TEMP ピンの最大電圧                                  | TEMP         | -0.3 | 6                      | V  |

| I <sub>MAX</sub>                             | 最大連続スイッチ電流                                    | IN から<br>OUT | 内部的に | 制限                     | А  |

| T <sub>JMAX</sub>                            | 接合部温度                                         |              | 内部的に | 制限                     | °C |

(1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

(2) FET オフで負の過渡状態。

## 6.2 ESD 定格

|                    |                                                                          | 値     | 単位 |

|--------------------|--------------------------------------------------------------------------|-------|----|

| V                  |                                                                          | ±1500 | V  |

| V <sub>(ESD)</sub> | デモが電<br>デバイス帯電モデル (CDM)、JEDEC 規格<br>JESD22-C101 準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

# 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                      | パラメータ                                      | ピン           | 最小値 | 最大値             | 単位   |

|----------------------|--------------------------------------------|--------------|-----|-----------------|------|

| V <sub>IN</sub>      | 入力電圧範囲                                     | IN           | 9   | 80              | V    |

| V <sub>DD</sub>      | 電源電圧範囲                                     | VDD          | 9   | 80              | V    |

| V <sub>OUT</sub>     | 出力電圧範囲                                     | OUT          |     | V <sub>IN</sub> | V    |

| V <sub>EN/UVLO</sub> | イネーブル ピン電圧範囲                               | EN/<br>UVLO  |     | 5               | V    |

| dVdT                 | dVdT ピン コンデンサ電圧定格                          | dVdT         |     | 4               | V    |

| V <sub>PGOOD</sub>   | PGOOD ピンのプルアップ電圧範囲                         | PGOOD        |     | 5               | V    |

| V <sub>FLT</sub>     | FLTピンのプルアップ電圧範囲                            | FLT          |     | 5               | V    |

| V <sub>SWEN</sub>    | SWEN ピンのプルアップ電圧範囲                          | SWEN         |     | 5               | V    |

| V <sub>TEMP</sub>    | TEMP ピンの電圧定格                               | TEMP         |     | 5               | V    |

| V <sub>IREF</sub>    | IREF ピンの電圧範囲                               | IREF         | 0.3 | 1.2             | V    |

| VILIM                | ILIM ピンの電圧範囲                               | ILIM         |     | 0.4             | V    |

| V <sub>IMON</sub>    | IMON ピンの電圧範囲                               | IMON         |     | 1.2             | V    |

| C <sub>IN</sub>      | IN ピン上のコンデンサ                               | IN           | 10  |                 | nF   |

| C <sub>OUT</sub>     | OUT ピン上のコンデンサ                              | OUT          | 10  |                 | μF   |

| dV <sub>IN</sub> /dt | IN ピンのスルー レート                              | IN           |     | 500             | V/µs |

| I <sub>MAX</sub>     | RMS スイッチ電流 T」≤125℃                         | IN から<br>OUT |     | 20              | А    |

| I <sub>MAX、パルス</sub> | 持続時間 ≤10 ms、T <sub>A</sub> ≤ 70 ℃ のピーク出力電流 | IN から<br>OUT |     | 27              | А    |

| TJ                   | 接合部温度                                      |              | -40 | 125             | °C   |

### 6.4 熱に関する情報

|                  |                                 | TPS1685x |      |

|------------------|---------------------------------|----------|------|

|                  | <b>熱評価基準</b> <sup>(1) (2)</sup> | LQFN     | 単位   |

|                  |                                 | ピン       |      |

| R <sub>θJA</sub> | 接合部から周囲への熱抵抗                    | 22.1     | °C/W |

| $\Psi_{JT}$      | 接合部から上面への特性パラメータ                | 1.1      | °C/W |

| $\Psi_{JB}$      | 接合部から基板への特性パラメータ                | 9.4      | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照して ください。

(2) 3 x 4.5 インチ PCB (2s2p) に JESD51-7 として実装したデバイスで実施されたシミュレーションに基づく

# 6.5 電気的特性

-40°C ≤ T<sub>J</sub> ≤ +125°C、VIN = V<sub>DD</sub> = 50V、OUT = 開、R<sub>ILIM</sub> = 931Ω、R<sub>IMON</sub> = 2.55kΩ、V<sub>IREF</sub> = 1V、FLT = 3.3V への 33kΩ プ ルアップ、PGOOD = 3.3V への 33kΩ プルアップ、C<sub>OUT</sub> = 10µF、C<sub>IN</sub> = 10nF、dVdT = 開、ITIMER = Open、V<sub>EN/UVLO</sub> = 2V、TEMP = オープン、MODE = オープン。 (全電圧は GND 基準です、(特に記述のない限り))

|                        | パラメータ                                                             | テスト条件                                                         | 最小値             | 標準値  | 最大値      | 単位 |

|------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|-----------------|------|----------|----|

| 入力 <b>電源</b> (VDD)     |                                                                   |                                                               |                 |      | <u>.</u> |    |

| V <sub>IN</sub>        | 入力電圧範囲                                                            |                                                               | 9               |      | 80       | V  |

| V <sub>DD</sub>        | 入力電圧範囲                                                            |                                                               | V <sub>IN</sub> |      | 80       | V  |

| I <sub>QON(VDD)</sub>  | V <sub>DD</sub> ON 状態静止電流                                         | $V_{DD} > V_{UVPR}, V_{EN} \ge V_{UVLOR}, V_{OVP} < V_{OVPF}$ |                 | 0.6  | 4        | mA |

| V <sub>UVPR</sub>      | V <sub>DD</sub> 低電圧保護スレッショルド立ち上が<br>り                             | V <sub>DD</sub> 立ち上がり                                         |                 | 8.5  | 8.9      | V  |

| V <sub>UVPF</sub>      | V <sub>DD</sub> 低電圧保護スレッショルド立ち下が<br>り                             | V <sub>DD</sub> 立ち下がり                                         | 6.7             | 7.05 |          | V  |

| V <sub>UVPHYS</sub>    | UVP ヒステリシス VDD                                                    |                                                               |                 | 1.5  |          | V  |

| 入力 <b>電源</b> (IN)      |                                                                   |                                                               |                 |      |          |    |

| V <sub>UVPR(VIN)</sub> | VIN 低電圧保護スレッショルド                                                  | V <sub>IN</sub> 立ち上がり                                         |                 | 8.45 | 9        | V  |

| V <sub>UVPF(VIN)</sub> | VIN 低電圧保護スレッショルド                                                  | V <sub>IN</sub> 立ち下がり                                         | 6.5             | 7.05 |          | V  |

| I <sub>QON(VIN)</sub>  | V <sub>IN</sub> ON 状態静止電流                                         | V <sub>EN</sub> ≥ V <sub>UVLOR</sub>                          |                 | 1.69 |          | mA |

| I <sub>QOFF(VIN)</sub> | V <sub>IN</sub> OFF 状態電流                                          | V <sub>SDR</sub> < V <sub>EN</sub> < V <sub>UVLO</sub>        |                 | 47   |          | μA |

| I <sub>SD(VIN)</sub>   | V <sub>IN</sub> シャットダウン電流                                         | V <sub>EN</sub> < V <sub>SDF</sub>                            |                 | 46   |          | μA |

| イネーブル / 低              | 電圧誤動作防止 (EN/UVLO)                                                 |                                                               |                 |      |          |    |

| V <sub>UVLO(R)</sub>   | オンにするための EN/UVLO ピン電圧ス<br>レッショルド、立ち上がり                            | EN/UVLO 立ち上がり                                                 | 1.18            | 1.21 | 1.23     | V  |

| V <sub>UVLO(F)</sub>   | オフにして QOD を作動させるための<br>EN/UVLO ピン電圧スレッショルド、立ち<br>下がり (プライマリ デバイス) | EN/UVLO 立ち下がり                                                 | 1               | 1.12 | 1.14     | V  |

| V <sub>UVLOF</sub>     | オフにして QOD を作動させるための<br>EN/UVLO ピン電圧スレッショルド、立ち<br>下がり (セカンダリ デバイス) | EN/UVLO 立ち下がり                                                 |                 | 1    |          | V  |

| VUVLOHYS               | UVLO ヒステリシス                                                       |                                                               |                 | 89   |          | mV |

| V <sub>SDF</sub>       | シャットダウン スレッショルド                                                   | EN/UVLO 立ち下がり                                                 | 0.4             | 0.42 |          | V  |

| V <sub>SDR</sub>       | シャットダウン スレッショルド                                                   | EN/UVLO 立ち上がり                                                 |                 | 0.5  | 0.55     | V  |

| I <sub>ENLKG</sub>     | EN/UVLO ピンのリーク電流                                                  |                                                               | -100            |      | 100      | nA |

| 過電圧保護 (IN)             |                                                                   | I                                                             |                 |      | I        |    |

| V <sub>OVP(R)</sub>    | 過電圧保護スレッショルド (立ち上がり)                                              | OVP ピンの立ち上がり                                                  | 1.11            | 1.17 | 1.20     | V  |

| V <sub>OVP(F)</sub>    | 過電圧保護スレッショルド (立ち下がり)                                              | OVP ピンの立ち下がり                                                  | 1.08            | 1.12 | 1.15     | V  |

| V <sub>OVPHYS</sub>    | 過電圧保護スレッショルド (ヒステリシ<br>ス)                                         |                                                               |                 | 57   |          | mV |

| I <sub>OVPLKG</sub>    | OVP ピンのリーク電流                                                      | V <sub>OVP</sub> = 1.2V                                       | -100            |      | 100      | nA |

| V <sub>OVPR(IN)</sub>  | 内部過電圧保護スレッショルド (立ち上が<br>り)                                        | V <sub>IN</sub> 立ち上がり                                         | 84              | 90.8 | 95       | V  |

| V <sub>OVPF(IN)</sub>  | 内部過電圧保護スレッショルド (立ち下上<br>がり)                                       | V <sub>IN</sub> 立ち下がり                                         | 77              | 84.5 | 90       | V  |

| オン抵抗 (IN - C           | )<br>UT)                                                          | 1                                                             |                 |      |          |    |

| R <sub>ON</sub>        | オン状態抵抗                                                            | I <sub>OUT</sub> = 12A、T <sub>J</sub> = 25°C                  |                 | 3.5  | 5.55     | mΩ |

| R <sub>ON</sub>        | オン状態抵抗                                                            | I <sub>OUT</sub> = 12A、T <sub>J</sub> = −40°C ~<br>125°C      |                 |      | 6.1      | mΩ |

| 電流制限基準 (II             | REF)                                                              | 1                                                             |                 |      |          |    |

| V <sub>IREF</sub>      | IREF ピンの推奨電圧範囲                                                    |                                                               | 0.3             |      | 1.2      | V  |

# 6.5 電気的特性 (続き)

-40°C ≤ T<sub>J</sub> ≤ +125°C、VIN = V<sub>DD</sub> = 50V、OUT = 開、R<sub>ILIM</sub> = 931Ω、R<sub>IMON</sub> = 2.55kΩ、V<sub>IREF</sub> = 1V、FLT = 3.3V への 33kΩ プ ルアップ、PGOOD = 3.3V への 33kΩ プルアップ、C<sub>OUT</sub> = 10µF、C<sub>IN</sub> = 10nF、dVdT = 開、ITIMER = Open、V<sub>EN/UVLO</sub> = 2V、TEMP = オープン、MODE = オープン。 (全電圧は GND 基準です、(特に記述のない限り))

|                                       | パラメータ                                | テスト条件                                                                    | 最小値  | 標準値                        | 最大値   | 単位   |

|---------------------------------------|--------------------------------------|--------------------------------------------------------------------------|------|----------------------------|-------|------|

| I <sub>IREF</sub>                     | IREF ピン内部ソース電流                       | V <sub>IREF</sub> = 1V                                                   | 24.2 | 25                         | 25.8  | μA   |

| 電流制限 (ILIM)                           |                                      |                                                                          |      |                            |       |      |

| G <sub>ILIM(LIN)</sub>                | 電流モニタ ゲイン (ILIM:IOUT) 対 IOUT。        | デバイスが定常状態 (PG アサ<br>ート)、I <sub>OUT</sub> = 12A                           | 17   | 18                         | 20.6  | µA/A |

| start-up peak                         | 起動時のピーク電流 (Ipeak)                    | VOUT> VFB、GHI はデアサー<br>トされます。 VIN<=60V                                   |      | 0.5                        |       | А    |

| V <sub>FB</sub>                       | フォールドバック電圧                           |                                                                          |      | 2                          |       | V    |

| 出力電流モニタと                              | :過電流保護 (IMON)                        |                                                                          |      |                            |       |      |

| G <sub>IMON</sub>                     | 電流モニタ ゲイン (IMON:IOUT)                | デバイスが定常状態 (PG アサ<br>ート)、12A ≤ I <sub>OUT</sub> ≤ 20A の場合                 | 17.7 | 18.18                      | 18.49 | µA/A |

| G <sub>IMON</sub>                     | 電流モニタ ゲイン (IMON:IOUT)                | デバイスが定常状態 (PG アサ<br>ート)、I <sub>OUT</sub> = 4A                            | 17.4 | 18.31                      | 19.1  | µA/A |

| I <sub>OCP</sub>                      | IOUT 電流制限トリップ (回路ブレーカ)<br>スレッショルド    | $R_{IMON} = 2.55 k\Omega, V_{IREF} = 1V$                                 | 21.2 | 21.7                       | 22.3  | А    |

| 電流故障タイマ(                              | ITIMER)                              |                                                                          |      |                            |       |      |

| I <sub>ITMR</sub>                     | ITIMER ピンの内部放電電流                     | I <sub>OUT</sub> > I <sub>OCP</sub> 、ITIMER ↓                            | 1.77 | 2.2                        | 2.6   | μA   |

| R <sub>ITMR</sub>                     | ITIMER ピンの内部プルアップ抵抗                  |                                                                          | 7    | 12.3                       | 23    | kΩ   |

| V <sub>INT</sub>                      | ITIMER ピンの内部プルアップ電圧                  | I <sub>OUT</sub> < I <sub>OCP</sub>                                      | 4.4  | 5                          | 5.6   | V    |

| ΔV <sub>ITMR</sub>                    | ITIMER 放電電圧                          | I <sub>OUT</sub> > I <sub>TRIP</sub> 、ITIMER↓                            | 1.28 | 1.5                        | 1.8   | V    |

| ΔV <sub>ITMR</sub> /I <sub>ITMR</sub> | ITIMER 放電電圧と放電電流の比率                  | I <sub>OUT</sub> > I <sub>TRIP</sub> 、ITIMER↓                            | 0.49 | 0.72                       | 0.97  | V/µA |

| 短絡保護                                  |                                      |                                                                          |      |                            |       | -    |

| IFFT                                  | 定常状態における固定高速トリップ スレ<br>ッショルド (プライマリ) | PG を High にアサート<br>(MODE = Open)                                         |      | 73                         |       | А    |

| IFFT                                  | 定常状態における固定高速トリップ スレ<br>ッショルド (プライマリ) | PG を High にアサート<br>(MODE =開)、 <sub>T J</sub> = 25°C ~<br>125°C           | 55   |                            |       | A    |

| I <sub>FFT</sub>                      | 定常状態における固定高速トリップ スレ<br>ッショルド (セカンダリ) | PG を High にアサート<br>(MODE = GND)                                          |      | 95                         |       | А    |

| I <sub>SFT</sub>                      | スケーラブルな高速トリップ電流                      | R <sub>SFT_SEL</sub> < 95kΩ、PG を High<br>にアサート (MODE = オープ<br>ン)         |      | 38.3                       |       | A    |

| I <sub>SFT</sub>                      | スケーラブルな高速トリップ電流                      | 105kΩ < R <sub>SFT_SEL</sub> < 195kΩ、<br>PG を High にアサート(MODE<br>= オープン) |      | 2.5 ×<br>I <sub>OCP</sub>  |       | A    |

| SFT                                   | スケーラブルな高速トリップ電流                      | 105kΩ < R <sub>SFT_SEL</sub> < 195kΩ、<br>PG を High にアサート<br>(MODE = GND) |      | 2.8 ×<br>I <sub>OCP</sub>  |       | A    |

| SFT                                   | スケーラブルな高速トリップ電流                      | 205kΩ< R <sub>SFT_SEL</sub> <<br>295kΩ、 PG を High にアサー<br>ト(MODE = オープン) |      | 2 × I <sub>OCP</sub>       |       | A    |

| SFT                                   | スケーラブルな高速トリップ電流                      | 205kΩ < R <sub>SFT_SEL</sub> < 295kΩ、<br>PG を High にアサート<br>(MODE = GND) |      | 2.26 ×<br>I <sub>OCP</sub> |       | A    |

| I <sub>SFT</sub>                      | スケーラブルな高速トリップ電流                      | 305kΩ < R <sub>SFT_SEL、</sub> PG を High<br>にアサート (MODE =オープン)            |      | 1.5 ×<br>I <sub>OCP</sub>  |       | Α    |

| SFT                                   | スケーラブルな高速トリップ電流                      | 305kΩ < R <sub>SFT_SEL</sub> 、PG を High<br>にアサート (MODE = GND)            |      | 1.71 ×<br>I <sub>OCP</sub> |       | А    |

| I <sub>SFT(SAT)</sub>                 | スケーラブルな高速トリップ電流 (突入電<br>流)           | 電源投入時、PGOOD は Low                                                        |      | 2                          |       | А    |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信 9

# 6.5 電気的特性 (続き)

-40°C ≤ T<sub>J</sub> ≤ +125°C、VIN = V<sub>DD</sub> = 50V、OUT = 開、R<sub>ILIM</sub> = 931Ω、R<sub>IMON</sub> = 2.55kΩ、V<sub>IREF</sub> = 1V、FLT = 3.3V への 33kΩ プ ルアップ、PGOOD = 3.3V への 33kΩ プルアップ、C<sub>OUT</sub> = 10µF、C<sub>IN</sub> = 10nF、dVdT = 開、ITIMER = Open、V<sub>EN/UVLO</sub> = 2V、TEMP = オープン、MODE = オープン。 (全電圧は GND 基準です、(特に記述のない限り))

|                            | パラメータ                                             | テスト条件                                                                          | 最小値   | 標準値   | 最大値   | 単位    |

|----------------------------|---------------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|

| アクティブ電流共有                  |                                                   |                                                                                |       |       |       |       |

| R <sub>ON(ACS)</sub>       | アクティブ電流共有時の R <sub>ON</sub>                       | V <sub>ILIM</sub> > 1.1 x (1/3)xV <sub>IREF</sub>                              |       | 4.38  | 6.9   | mΩ    |

| G <sub>IMON(ACS)</sub>     | アクティブ電流制限時の IMON:IOUT 比                           | PG を High にアサート、V <sub>ILIM</sub><br>>1.1 x V <sub>IREF</sub>                  | 18.03 | 18.49 | 18.71 | µA/A  |

| CL <sub>REF(ACS)</sub>     | アクティブ電流共有トリガ スレッショル<br>ドと定常状態回路ブレーカ スレッショル<br>ドの比 | PG は High にアサート                                                                |       | 36.67 |       | %     |

| 突入電流保護 (DVD)               | r)                                                | 1                                                                              |       |       |       |       |

| I <sub>DVDT</sub>          | dVdt ピン充電電流 (プライマリ / スタン<br>ドアロン モード)             | MODE = オープン                                                                    | 1.5   | 2.0   | 3     | μA    |

| G <sub>DVDT</sub>          | dVdt ゲイン                                          | 0.4 V < V <sub>dVdt</sub> < 2.4 V                                              | 22    | 25    | 28    | V/V   |

| I <sub>DVDTLKG</sub>       | dVdt ピンのリーク電流 (2 次モード)                            | MODE = GND                                                                     | -100  |       | 100   | nA    |

| R <sub>DVDT</sub>          | dVdt ピンから GND への放電抵抗                              |                                                                                |       | 500   |       | Ω     |

| GHI                        |                                                   |                                                                                |       |       |       |       |

| V <sub>GS(GHI)</sub> 立ち上がり | GHI/PG がアサートされている時の G-S<br>スレッショルド                |                                                                                |       | 7     |       | V     |

| R <sub>ON(GHI)</sub>       | GHI/PG がアサートされている時の Ron                           |                                                                                |       | 3.6   |       | mΩ    |

| クイック出力放電 (0                | QOD)                                              | 1                                                                              |       |       | L     |       |

| I <sub>QOD</sub>           | クイック出力放電プルダウン電流                                   | V <sub>SD(R)</sub> < V <sub>EN</sub> < V <sub>UVLO</sub> , -40 < Tj<br>< 125°C | 17    | 22    | 25    | mA    |

| 温度センサ出力 (TE                | MP)                                               |                                                                                |       |       | I     |       |

| G <sub>TMP</sub>           | 温度センサ ゲイン                                         | V <sub>IN</sub> = 51V                                                          | 2.6   | 2.73  | 3.1   | mV/°C |

| V <sub>TMP</sub>           | TEMP ピン出力電圧                                       | T <sub>J</sub> = 25℃、V <sub>IN</sub> = 51V                                     | 670   | 678   | 690   | mV    |

| I <sub>TMPSRC</sub>        | TEMP ピン ソース電流                                     | V <sub>IN</sub> = 51V                                                          | 110   | 119   | 133   | μA    |

| ITMPSNK                    | TEMP ピン シンク電流                                     | V <sub>IN</sub> = 51V                                                          | 8     | 10    | 14    | μA    |

| 過熱保護 (OTP)                 |                                                   |                                                                                |       |       |       |       |

| TSD                        | 絶対サーマル シャットダウン立ち上がり<br>スレッショルド                    | T <sub>J</sub> 立ち上がり、V <sub>IN</sub> = 51V                                     |       | 150   |       | °C    |

| TSD <sub>HYS</sub>         | 絶対サーマル シャットダウン ヒステリシ<br>ス                         | T <sub>J</sub> 立ち下がり、V <sub>IN</sub> = 51V                                     |       | 13    |       | °C    |

| FET 正常性モニタ                 | 1                                                 | 1                                                                              |       |       |       |       |

| V <sub>DSFLT</sub>         | FET D-S 故障スレッショルド                                 | SWEN = L, V <sub>IN</sub> = 51V                                                |       | 0.5   |       | V     |

| V <sub>DSOK</sub>          | FET D-S 故障回復スレッショルド                               | SWEN = L、V <sub>IN</sub> = 51V                                                 |       | 0.64  |       | V     |

| シングル ポイント障                 | r害 (IMON、IREF、ITIMER)                             | · · · · · ·                                                                    |       |       |       |       |

| I <sub>OC_BKP</sub>        | バックアップ過電流保護スレッショルド                                | IMON はグランドへ短絡                                                                  |       | 38.3  |       | А     |

|                            | 1                                                 |                                                                                |       |       |       |       |

### 6.6 ロジック・インターフェイス

-40°C ≤ T<sub>J</sub> ≤ +125°C、V<sub>IN</sub> = V<sub>DD</sub> = 45V ~ 60V、OUT = オープン、R<sub>ILIM</sub> = 931Ω、R<sub>IMON</sub> = 2.55kΩ、V<sub>IREF</sub> = 1V、FLT = 3.3V への 33kΩ プルアップ、PGOOD = 3.3V への 33kΩ プルアップ、C<sub>OUT</sub> = 10µF、C<sub>IN</sub> = 10nF、dVdT = Open、ITIMER = オー プン、V<sub>EN/UVLO</sub> = 2V、TEMP = オープン、MODE = オープン。 (全電圧は GND 基準です、(特に記述のない限り))

|                      | パラメータ           | テスト条件             | 最小值 標準値 | 最大値 | 単位 |

|----------------------|-----------------|-------------------|---------|-----|----|

| SWEN                 |                 |                   |         |     |    |

| R <sub>SWEN</sub>    | SWEN ピン プルダウン抵抗 | SWEN が Low にデアサート | 6.8     |     | Ω  |

| フォルト通知               | 知 (FLT)         |                   | ÷.      |     |    |

| R <sub>FLTB</sub>    | FLT ピン プルダウン抵抗  | FLT を Low にアサート   | 6.6     |     | Ω  |

| I <sub>FLTBLKG</sub> | FLT ピンのリーク電流    | FLT が High にデアサート | -0.1    | 0.1 | μA |

| パワー グッ               | パワー グッド表示 (PG)  |                   |         |     |    |

| R <sub>PG</sub>      | PG ピン プルダウン抵抗   | PG が Low にデアサート   | 6.9     |     | Ω  |

| I <sub>PGKG</sub>    | PG ピンのリーク電流     | PG は High にアサート   | -1.5    | 1.5 | μΑ |

## 6.7 タイミング要件

-40°C ≤ T<sub>J</sub> ≤ +125°C、VIN = V<sub>DD</sub> = 45V ~ 60V、OUT = オープン、R<sub>ILIM</sub> = 931Ω R<sub>IMON</sub> = 2.55kΩ、V<sub>IREF</sub> = 1V、FLT = 3.3V への 33kΩ プルアップ、PGOOD = 3.3V への 33kΩ プルアップ、C<sub>OUT</sub> = 10µF、C<sub>IN</sub> = 10nF、dVdT = オープン、ITIMER = オ ープン。、V<sub>EN/UVLO</sub> = 2V、TEMP =オープン、MODE = オープン。 (全電圧は GND 基準です、(特に記述のない限り))

|                        | パラメータ                                    | テスト条件                                                                                                                     | 最小値 標準値 最大値 | 単位 |

|------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------|----|

| t <sub>OVP</sub>       | 過電圧保護応答時間                                | V <sub>OVP</sub> > V <sub>OVPR</sub> V から<br>SWEN↓                                                                        | 1.5         | μs |

| t <sub>Insdly</sub>    | 挿入遅延                                     | V <sub>EN/UVLO</sub> > V <sub>UVLO(R)</sub> から<br>SWEN↑                                                                   | 16          | ms |

| t <sub>FFT</sub>       | 固定高速トリップ応答時間ハード短絡                        | V <sub>DS</sub> > V <sub>DSCOMP</sub> から I <sub>OUT↓</sub>                                                                | 214         | ns |

| t <sub>SFT</sub>       | スケーラブルな高速トリップ応答時間                        | l <sub>OUT</sub> > 3 x l <sub>OCP</sub> から l <sub>OUT</sub> ↓                                                             | 600         | ns |

| t <sub>ITIMER</sub>    | 過電流ブランキング間隔                              | l <sub>OUT</sub> = 1.5 x l <sub>OCP</sub> 、C <sub>ITIMER</sub><br>= オープン                                                  | 0           | ms |

| t <sub>ITIMER</sub>    | 過電流ブランキング間隔                              | $I_{OUT} = 1.5 \times I_{OCP}, C_{ITIMER}$<br>= 4.7nF                                                                     | 3           | ms |

| t <sub>RST</sub>       | 自動再試行間隔                                  | 自動再試行バリアント、1<br>次モード (MODE = オープ<br>ン)                                                                                    | 680         | ms |

| t <sub>REC</sub>       | フォルト復帰時間                                 | 2 次モード (MODE =<br>GND)、SWEN↓ ~<br>SWEN ↑                                                                                  | 8.9         | μs |

| t <sub>EN(DG)</sub>    | EN/UVLO デグリッチ時間                          |                                                                                                                           | 12          | μs |

| t <sub>SWEN(TO)</sub>  | 高速回復を無効にするための SWEN Low 間隔                |                                                                                                                           | 35          | μs |

| t <sub>SU_TMR</sub>    | 起動タイムアウト間隔                               | SWEN↑ から FLT↓                                                                                                             | 6.6         | s  |

| t <sub>Discharge</sub> | QOD 放電時間 (V <sub>OUT</sub> の 90% から 10%) | $\label{eq:VSD} \begin{array}{l} V_{SD} < V_{EN/UVLO} < V_{UVLO}, \\ C_{OUT} = 0.5mF, \ V_{IN} = 51V_{\circ} \end{array}$ | 872         | ms |

| t <sub>QOD</sub>       | QOD イネーブル タイマ                            | V <sub>SD</sub> < V <sub>EN/UVLO</sub> < V <sub>UVLO</sub>                                                                | 6           | ms |

## 6.8 スイッチング特性

出力の立ち上がりスルーレートは内部的に制御され、動作電圧範囲の全体にわたって一定であるため、ターンオン タイミン グが負荷条件の影響を受けないようにしています。立ち上がりスルーレートは、dVdt ピンとグランドの間に容量を追加する ことで調整できます。C<sub>dVdt</sub> が大きくなると、立ち上がりスルーレート (SR) が低下します。詳細については、「スルーレー トおよび突入電流制御 (dVdt)」セクションを参照してください。ただし、ターンオフ遅延時間と立ち下がり時間は負荷容量 (C<sub>OUT</sub>) および負荷抵抗 (R<sub>L</sub>)の RC 時定数に依存します。スイッチング特性は、電源が定常状態で利用可能で、デバイスがイ ネーブルになる前に負荷電圧が完全に放電されているパワーアップ シーケンスに対してのみ有効です。標準値は T<sub>J</sub> = 25℃ 時に測定 (特に記述のない限り)。V<sub>IN</sub> = 12V、R<sub>OUT</sub> = 500Ω、C<sub>OUT</sub> = 1mF

|                    | パラメータ          | C <sub>dVdt</sub> = 22nF                 | C <sub>dVdt</sub> = 68nF | 単位  |

|--------------------|----------------|------------------------------------------|--------------------------|-----|

| SR <sub>ON</sub>   | 出力立ち上がりスルー レート | 87.1                                     | 80.9                     | V/s |

| t <sub>D,ON</sub>  | ターン オン遅延       | 23.5                                     | 26.7                     | ms  |

| t <sub>R</sub>     | 立ち上がり時間        | 467.7                                    | 503.2                    | ms  |

| t <sub>ON</sub>    | ターンオン時間        | 491.2                                    | 529.9                    | ms  |

| t <sub>D,OFF</sub> | ターンオフ遅延時間      | 1                                        | 1                        | μs  |

| t <sub>F</sub>     | 立ち下がり時間        | R <sub>OUT</sub> と C <sub>OUT</sub> に依存し |                          | μs  |

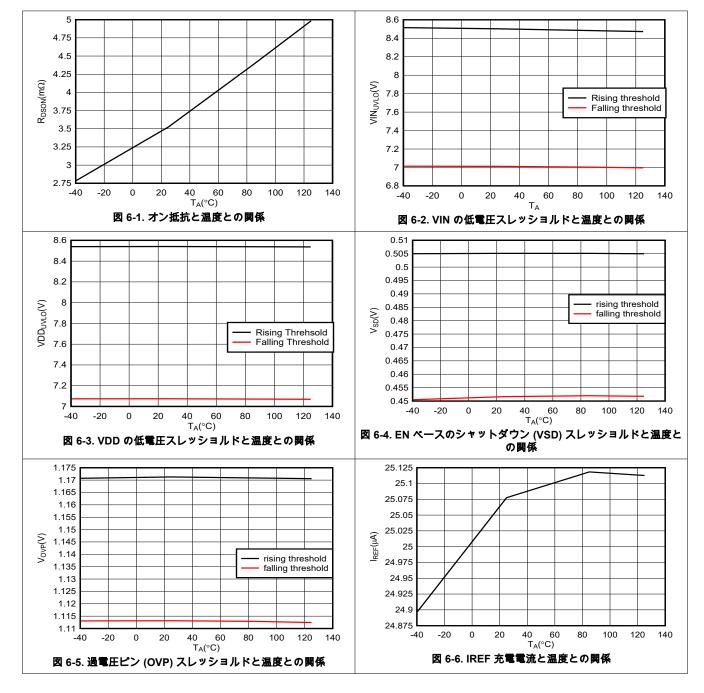

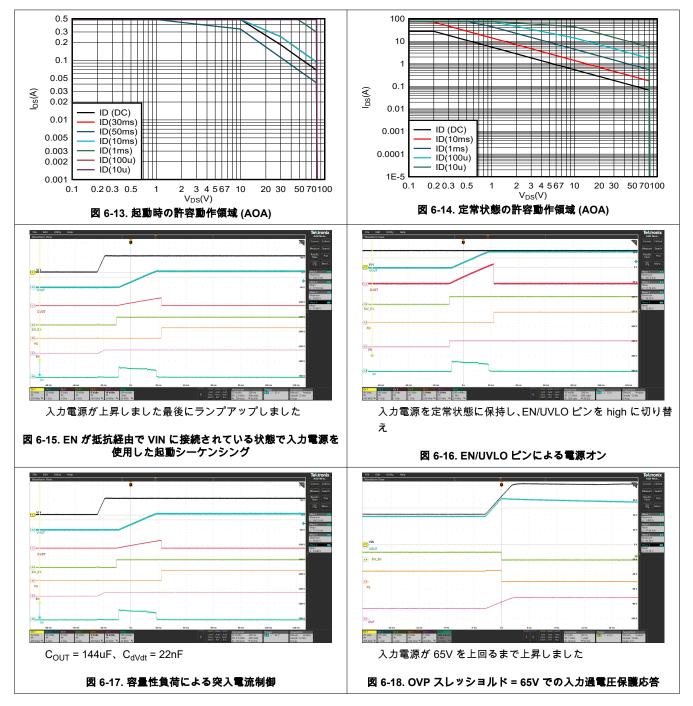

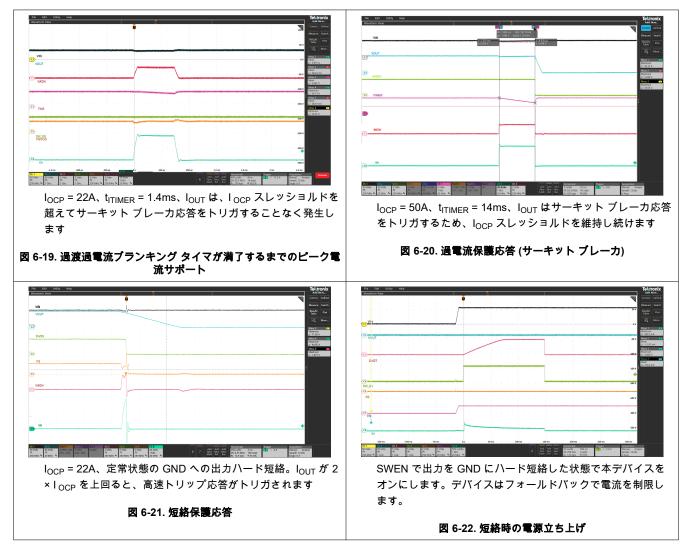

### 6.9 代表的特性

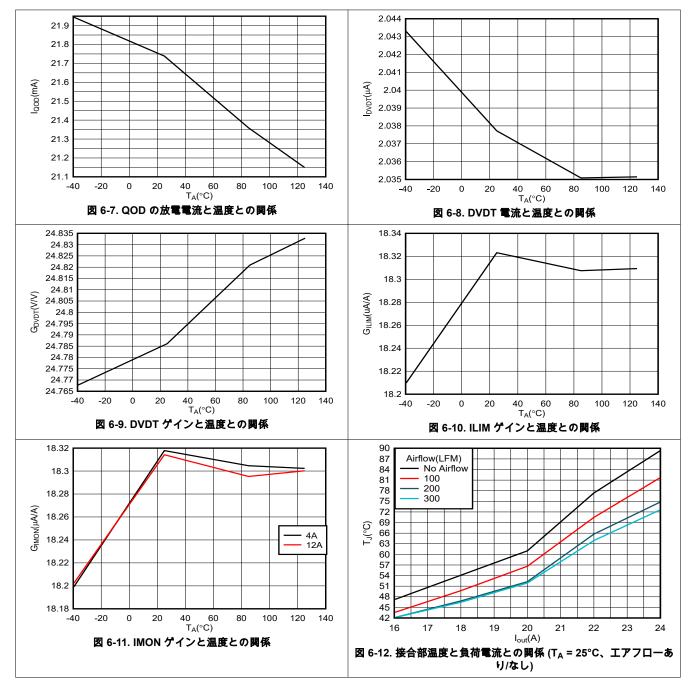

# 6.9 代表的特性 (続き)

# 6.9 代表的特性 (続き)

# 6.9 代表的特性 (続き)

### 7 詳細説明

### 7.1 概要

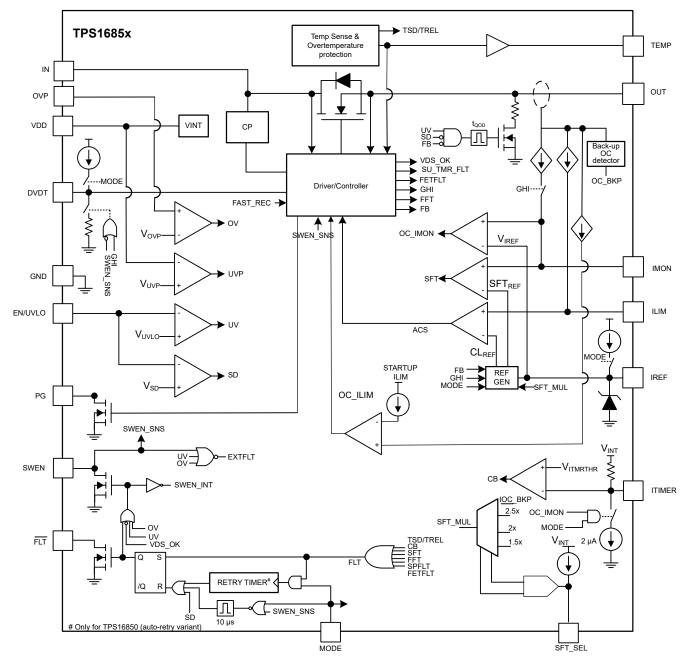

TPS1685x は、負荷電圧と負荷電流を管理するために使用されるパワー スイッチ内蔵 eFuse です。デバイスは、 VDD と IN バスを監視して、動作を開始します。V<sub>DD</sub> および V<sub>IN</sub> がそれぞれの低電圧保護 (UVP) スレッショルド を超えた場合、デバイスは挿入遅延タイマ期間を待機して、起動前に電源が安定するようにします。次に、デバ イスは EN/UVLO ピンをサンプリングします。このピンが High レベルになると、内部 MOSFET が導通し始め、 電流が IN から OUT に流れます。EN/UVLO が Low に保持されると、内部 MOSFET がオフになります。

起動シーケンスが成功した後、TPS1685x デバイスは負荷電流と入力電圧をアクティブに監視し、内部 FET を 制御して、ユーザーが調整可能な過電流スレッショルド制限 I<sub>LIM</sub> を超過しておらず、IN ピンの過電圧スパイクが カットオフされていることを確認します。これにより、有害なレベルの電圧や電流からシステムを安全な状態に 保つことができます。同時に、ユーザーが調整可能な過電流ブランキング タイマを使用すると、システムは eFuse をトリップせずに、負荷電流の過渡ピークに対応できます。同様に、電源ラインの電圧過渡は、不要なト リップを防止するためにインテリジェントにマスクされます。これにより、過渡耐性のある実際の故障に対する 堅牢な保護ソリューションが維持されるため、システムの稼働時間を最大限に延ばすことができます。

このデバイスには高精度で高帯域幅のアナログ負荷電流モニタが内蔵されているため、システムは定常状態と過 渡時に負荷電流を正確に監視できます。これにより、高度な動的プラットフォーム パワー マネージメント手法 を容易に実装でき、安全性や信頼性を損なうことなく、システムの電力使用率とスループットを最大化できま す。

より高い負荷電流への対応を必要とするシステムの場合、複数の TPS1685x eFuse を並列接続できます。すべて のデバイスがスタートアップ時と定常状態で電流を共有することで、一部のデバイスに他のデバイスより過大な ストレスがかかることを防ぎます。このようなストレスは、並列チェーンの早期または部分的なシャットダウン を引き起こす可能性があります。このデバイスは動作状態を同期し、適切な起動、シャットダウン、故障への応 答を実現します。

デバイスには推奨動作条件の下でデバイスの安全性と信頼性を確保するため、保護回路が内蔵されています。サ ーマル シャットダウン メカニズムを使用して常に内部 FET が保護されています。この機能により、接合部温度 (Tj) が過熱しすぎると FET がオフになります。

# 7.2 機能ブロック図

### 7.3 機能説明

TPS1685x eFuse は、小型で機能豊富高な電力管理デバイスであり、システム故障発生時の検出、保護、および 表示報告を行います。

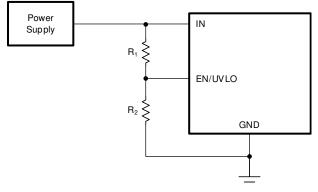

### 7.3.1 低電圧保護

TPS1685x は、印加された電圧が低くなりすぎて、システムまたはデバイスが正常に動作できない場合に備え て、VDD および VIN に低電圧誤動作防止を実装しています。低電圧誤動作防止には、VDD に対して内部的に V<sub>UVP</sub>、V<sub>IN</sub> に対して V<sub>UVPIN</sub> というデフォルトのロックアウト スレッショルドがあります。また、EN/UVLO ピ ンに UVLO コンパレータを搭載しているため、外部から低電圧保護スレッショルドをユーザー定義の値に調整す ることもできます。下記の図および式に、抵抗デバイダを使用して、特定の電源電圧に対して UVLO 設定ポイン トを設定する方法を示します。

図 7-1. 可変低電圧保護

$$V_{IN(UV)} = V_{UVLO(R)} \frac{R_1 + R_2}{R_2}$$

(1)

EN/UVLO ピンには 2 レベルのスレッショルドが実装されています。

- 1. V<sub>EN</sub> > V<sub>UVLO(R)</sub>: デバイスは完全にオンです。

- V<sub>SD(F)</sub> < V<sub>EN</sub> < V<sub>UVLO(F)</sub>: 一部の重要なバイアスとデジタル回路を除き、FET とほとんどのコントローラ回路 がオフになります。EN/UVLO ピンをこの状態に t<sub>QOD</sub> を超える時間保持すると、出力放電機能が起動しま す。

- V<sub>EN</sub> < V<sub>SD(F)</sub>: 部品内のすべてのアクティブ回路がオフになり、デジタル状態メモリを保持しません。また、 ラッチされたフォルトもリセットされます。この状態では、デバイスの静止時消費電流は最小限に抑えられ ます。

### 7.3.2 *挿入遅延*

TPS1685x は、デバイスがオンにしようとする前に、電源が安定したことを確認するため、スタートアップ時に 挿入遅延を実装しています。これは、カードがバックプレーンにしっかりと接触していないときにデバイスが電 源投入しようとした場合、または起動時に電源のリンギングや発振が発生した場合に、システムで予期しない動 作が発生するのを防ぐためです。

デバイスは最初に、VDD 電源が UVP スレッショルドを上回り、すべての内部バイアス電圧が安定するまで待機 します。その後、EN/UVLO ピンの状態に関係なく、T<sub>Insdly</sub> の追加遅延の間、デバイスはオフに維持されます。

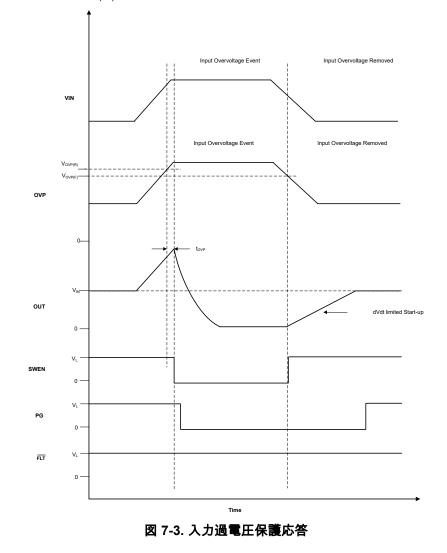

# 7.3.3 *過電圧保護*

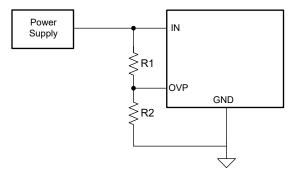

TPS1685x は過電圧ロックアウト機能を実装しており、入力過電圧状態から負荷を保護します。過電圧設定ポイントを外部で設定するには、OVP ピンに抵抗デバイダを接続する必要があります。

(2)

### 図 7-2. 調整可能な過電圧保護機能

$V_{IN(OVP)} = V_{OVP(R)} \frac{R1+R2}{R2}$

V<sub>IN</sub> がこの値を超えると、デバイスがオフになり、負荷を過電圧から保護します。 このデバイスは、IN ピンの V<sub>OVPR(IN)</sub> における固定の内部 OV 保護機能も備えています。

### 7.3.4 突入電流、過電流、および短絡保護

TPS1685xには、過電流に対する4つのレベルの保護が組み込まれています。

- 1. 突入電流制御のための調整可能なスルーレート (dVdt)

- 2. 起動時の過電流保護のための固定電流制限 (I<sub>start-up</sub>)

- 3. 定常状態での過電流保護のための、調整可能なスレッショルド (I<sub>OCP</sub>) とブランキング タイマ (t<sub>ITIMER</sub>)を備え た回路ブレーカ

#### 7.3.4.1 スルーレート (dVdt) および突入電流制御

ホットプラグ イベント時や大きな出力容量の充電中に、大きな突入電流が発生する可能性があります。突入電流 を適切に管理しないと、突入電流により入力コネクタが損傷し、システム電源が低下する可能性があります。こ の動作により、システム内の他の場所で予期しない再起動が発生する可能性があります。ターンオン時の突入電 流は、負荷容量と立ち上がりスルーレートに正比例します。式3を使用して、与えられた負荷容量 (C<sub>LOAD</sub>) につ いて突入電流 (I<sub>INRUSH</sub>)を制限するのに必要なスルーレート (SR) を計算できます。

$$SR(V/ms) = \frac{I_{INRUSH}(A)}{C_{LOAD}(mF)}$$

(3)

DVDT ピンにコンデンサを追加することで、立ち上がりスルーレートを制御し、ターンオン時の突入電流を低減 できます。特定のスルー レートを生成するために必要な CdVdt 容量は、式 4 を使用して計算できます。

$$C_{DVDT}(nF) = \frac{48}{SR(V/ms)}$$

(4)

dVdt ピンをオープンのままにし、最も高速な出力スルーレートを実現できます。

注

- 1. TI では最小 dvdt 抵抗 22nf を推奨します。

- 高い入力スルーレートと高い入力パワーパスのインダクタンスの組み合わせにより、起動時に発振が発生する場合があります。これは、次の1つまたは複数の手順を使用して軽減できます。

- a. 入力インダクタンスを小さくする。

- b. VIN ピンの容量を増やす。

- c. dVdt ピンの容量を増やして、スルー レートを下げたり、スタートアップ時間を長くしたりします。

#### 7.3.4.1.1 スタートアップ タイムアウト

スタートアップが完了しない場合、つまり、SWEN がアサートされた後、特定のタイムアウト間隔 (t<sub>SU\_TMR</sub>)内 に FET が完全にオンにならない場合、デバイスはそれを故障として登録します。FLT は Low にアサートされ、 デバイスはデバイス設定に応じてラッチオフまたは自動リトライモードに移行します。

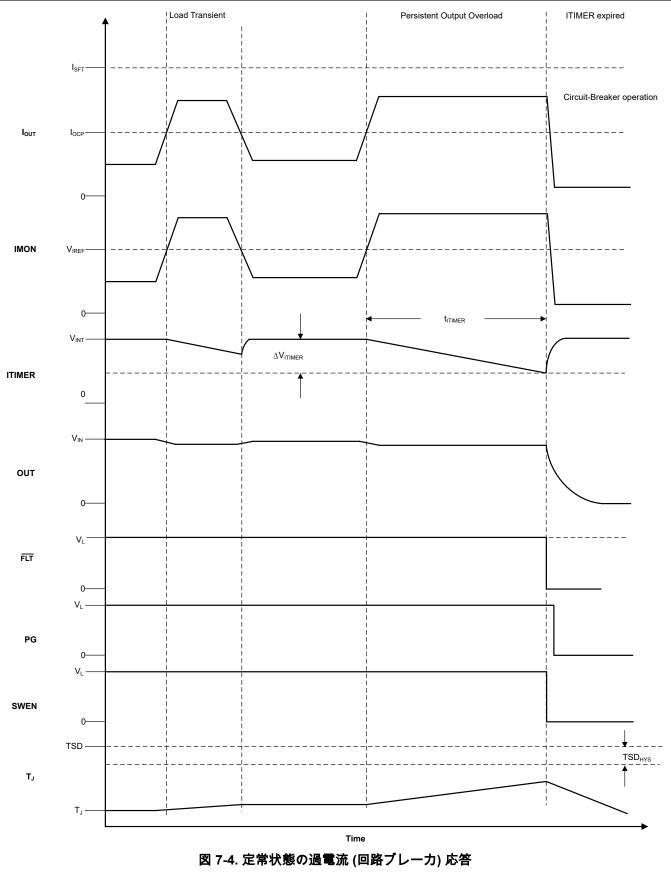

#### 7.3.4.2 定常状態の過電流保護 (サーキット ブレーカ)

TPS1685x は、定常状態時の出力過電流状態に応答して、ユーザーが調整可能な過渡故障ブランキング間隔の後 に回路ブレーカ動作を実行します。この動作により、デバイスは短いユーザー定義間隔でより高いピーク電流を サポートできるだけでなく、持続的な出力障害が発生した場合にも堅牢な保護を保証します。

このデバイスは出力負荷電流を継続的に検出し、負荷電流に比例するアナログ電流出力 (I<sub>IMON</sub>) を IMON ピンに 提供します。これにより、式 5 に従って IMON ピン抵抗 (R<sub>IMON</sub>) の両端に比例電圧 (V<sub>IMON</sub>) が生成されます。

$V_{IMON} = I_{OUT} \times G_{IMON} \times R_{IMON}$

(5)

ここで、G<sub>IMON</sub> は電流モニタ ゲインです (I<sub>IMON</sub>: I<sub>OUT</sub>)

この電圧を基準となる IREF ピンの電圧と比較することで、過電流状態が検出されます。リファレンス電圧 (V<sub>IREF</sub>) は 2 つの方法で制御でき、それに応じて過電流保護スレッショルド (I<sub>OCP</sub>) を設定します。

スタンドアロンまたは1次動作モードでは、内部電流源が外部のIREF ピン抵抗 (R<sub>IREF</sub>)と相互作用して、基準電圧を生成します。式6に示すように、低インピーダンスリファレンス電圧からIREF ピンを駆動することも可能です。

$V_{IREF} = I_{IREF} \times R_{IREF}$

(6)

1 次側と 2 次側の並列構成では、1 次側 eFuse またはコントローラが IREF ピンの電圧を駆動して、チェーン内のすべての 2 次側デバイスに外部リファレンス (V<sub>IREF</sub>)を供給します。

定常状態 (I<sub>OCP</sub>) 時の過電流保護スレッショルドは、式7を使用して計算できます。

$$I_{OCP} = \frac{V_{IREF}}{G_{IMON} \times R_{IMON}}$$

(7)

過電流状態、つまり負荷電流がユーザー調整可能な過電流制限スレッショルド (I<sub>OCP</sub>)を上回るが、短絡スレッシ ョルド (I<sub>SFT</sub>)を下回る状態が検出されると、デバイスは内部のプルダウン電流を使用して ITIMER ピン コンデン サの放電を開始します。ITIMER コンデンサが ΔV<sub>ITIMER</sub> によって放電される前に、負荷電流が電流制限スレッシ ョルドを下回ると、ITIMER は内部で V<sub>INT</sub> までプルアップされ、サーキット ブレーカ動作は開始されません。 この動作により、短い過負荷過渡パルスが回路をトリップせずにデバイスを通過できるようになります。過電流 状態が続く場合、ITIMER コンデンサは放電を継続し、ΔV<sub>ITIMER</sub> によって低下すると、サーキットブレーカの動 作により FET が直ちにオフになります。同時に、ITIMER コンデンサは再度 V<sub>INT</sub> まで充電されるため、次の過 電流イベントの前にデフォルト状態になります。このアクションれにより、すべての過電流イベントに対して、 完全なブランキング タイマ間隔が確保されます。式 8 を使用して、目的の過電流スレッショルドに対する R<sub>IMON</sub> 値を計算できます。

$$R_{IMON} = \frac{V_{IREF}}{G_{IMON} \times I_{OCP}}$$

(8)

過渡を許容する時間は、ITIMER ピンとグランドの間の適切なコンデンサ値を使用して調整できます。過渡過電 流ブランキング期間は、式9を使用して計算できます。

$t_{ITIMER}(ms) = \frac{C_{ITIMER}(nF) \times \Delta V_{ITIMER}(V)}{I_{ITIMER}(\mu A)}$

(9)

注

- ITIMER ピンをオープンのままにすると、本デバイスが最小限の遅延で回路を切断できるようになります。ただし、これにより、サーキット ブレーカの応答がノイズの影響を非常に受けやすくなり、負荷過渡時に誤トリップが発生する可能性があります。

- 2. ITIMER ピンをグランドに短絡すると、過電流応答遅延は最小になります (ITIMER ピンの開放状態 と同様)が、静止電流は増加します。ただし、推奨動作モードではありません。

- 3. ITIMER 容量値を増やすと、過電流ブランキング期間が延長されます。ただし、次の過電流イベン ト前に、ITIMER 容量が V<sub>INT</sub> まで再充電するのに必要な時間も延長されます。ITIMER コンデンサ が完全に再充電される前に次の過電流イベントが発生した場合、VITIMER スレッショルドまで放 電するのに要する時間が短いため、意図したよりも短いブランキング間隔が得られます。

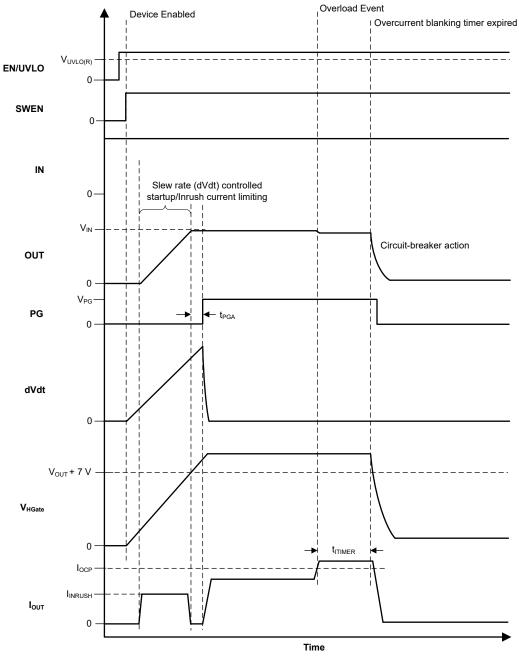

図 7-4 に、TPS1685x eFuse の過電流応答を示します。回路ブレーカの故障により部品がシャットダウンした 後、部品はラッチ オフ状態を維持するか (TPS16851 バリアント)、または固定遅延後に自動的に再起動します (TPS16850 バリアント)。

TPS1685 JAJSQ15B – SEPTEMBER 2024 – REVISED MAY 2025

資料に関するフィードバック(ご意見やお問い合わせ)を送信 23

#### 7.3.4.3 起動時のアクティブ電流制限

TPS1685x は、起動時に出力過電流状態に応答し、電流をアクティブに制限します。起動電流制限は、内部で I<sub>start-up</sub> に固定されています。

起動時に負荷電流が I<sub>Start-up</sub> を超えると、デバイスは I<sub>Start-up</sub> の負荷電流をレギュレートおよび保持しようとしま す。

電流レギュレーション中、出力電圧降下により FET 全体のデバイス消費電力が増加します。デバイスの内部温度(T」)がサーマル シャットダウン スレッショルド (TSD)を超えると、FET がオフになります。TSD の故障により部品がシャットダウンした後、部品はラッチ オフ状態を維持するか (TPS16851 バリアント)、または固定遅延後に自動的に再起動します (TPS16850 バリアント)。過熱に対するデバイスの応答の詳細については、「過熱保護」のセクションを参照してください。

注

アクティブ電流制限ブロックは、起動時に出力電圧 (V<sub>OUT</sub>) に基づくフォールドバック機構を採用しま す。V<sub>OUT</sub> がフォールドバック スレッショルド (V<sub>FB</sub>) を下回ると、電流制限スレッショルドはさらに低 下します。

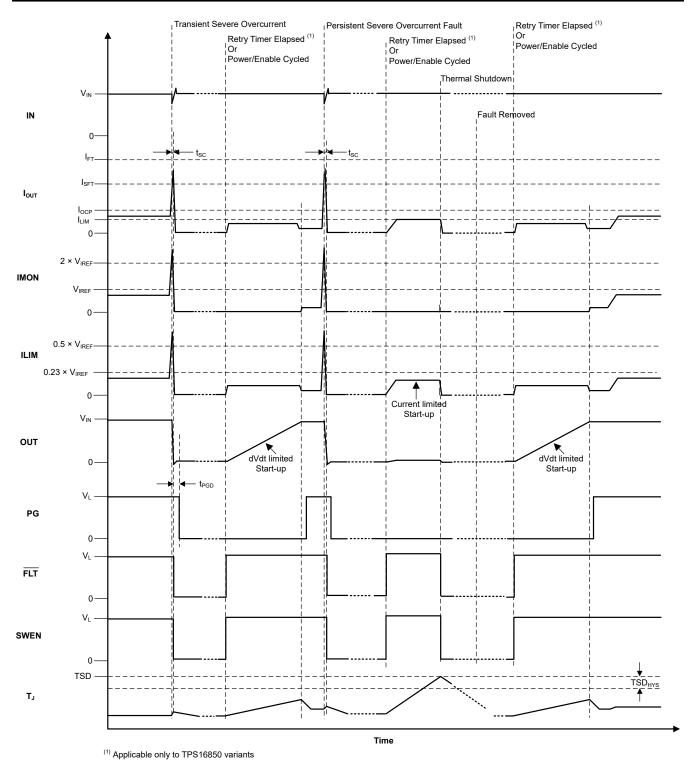

#### 7.3.4.4 短絡保護

出力短絡発生中は、本デバイスを流れる電流が非常に急速に増加します。出力短絡が検出されると、内部高速ト リップ コンパレータは高速保護シーケンスをトリガし、電流がそれ以上蓄積して損傷や過剰な入力電源ドループ が発生するのを防止します。高速トリップ コンパレータは、定常状態時にスケーラブルなスレッショルド (I<sub>SFT</sub>) を採用します。I<sub>SFT</sub> は SFT\_SEL ピンの抵抗によって選択できます。これにより、ユーザーはすべてのシステム に適しているとは限らない高い固定スレッショルドを使用する代わりに、システム定格に従って高速トリップ ス レッショルドを調整できます。電流が高速トリップ スレッショルドを超えると、TPS1685x は t<sub>SFT</sub> 以内に FET をオフにします。また、このデバイスは、より高い固定高速トリップ スレッショルド (I<sub>FFT</sub>) を採用して、定常状 態時 (リニア領域の FET) のハード短絡に対する高速保護を実現します。電流が I<sub>FFT</sub> を超えると、FET は t<sub>FFT</sub> 内 で完全にオフになります。

| ISFT_SEL                | SFT_SEL ピン                              | MODE ピン |

|-------------------------|-----------------------------------------|---------|

| Іос_вкр                 | R <sub>SFT_SEL</sub> <95kΩ              | オープン    |

| 2.5 × I <sub>OCP</sub>  | 105kΩ < R <sub>SFT_SEL</sub> < 195kΩ    | オープン    |

| 2.8 × I <sub>OCP</sub>  | 105kΩ < R <sub>SFT_SEL</sub> < 195kΩ    | Gnd     |

| 2 × I <sub>OCP</sub>    | $205k\Omega < R_{SFT_SEL} < 295k\Omega$ | オープン    |

| 2.26 × I <sub>OCP</sub> | $205k\Omega < R_{SFT_SEL} < 295k\Omega$ | Gnd     |

| 1.5 × I <sub>OCP</sub>  | 305kΩ < R <sub>SFT_SEL</sub>            | オープン    |

| 1.71 × I <sub>OCP</sub> | 305kΩ < R <sub>SFT_SEL</sub>            | Gnd     |

表 7-1. SFT\_SEL ピンの抵抗に基づくデバイスの機能モード

図 7-5 に、TPS1685x eFuse の短絡応答を示します。

### 図 7-5. 短絡応答

# 7.3.5 アナログ負荷電流モニタ (IMON)

TPS1685x では、FET を流れる電流に比例したアナログ電流を IMON ピンに供給することで、システムが出力負 荷電流を正確に監視できるようになります。電流出力の利点は、隣接するパターンからの電圧降下やノイズの結 合による大きな誤差を発生させずに、信号を基板全体に配線できることです。この電流出力により、複数の

Copyright © 2025 Texas Instruments Incorporated

TPS1685x の IMON ピンを互いに接続して、並列構成で合計電流を得ることもできます。IMON 信号は、監視ポイントで抵抗を介して降下させることで電圧に変換できます。ユーザーは、R<sub>IMON</sub> の全体で電圧 (V<sub>IMON</sub>) を検出し、式 10 を使用して出力負荷電流の測定値を取得できます。

$$I_{OUT} = \frac{V_{IMON}}{G_{IMON} \times R_{IMON}}$$

(10)

TPS1685x IMON 回路は、基板レイアウトやその他のシステム動作条件に関係なく、負荷や温度の条件にわたっ て高帯域と高精度を実現するように設計されています。この設計では、IMON 信号を Intel® PSYS または PROCHOT# などの高度な動的プラットフォーム パワー マネジメント手法に使用して、安全性や信頼性を犠牲 にすることなく、システムの消費電力とプラットフォームのスループットを最大化できます。

図 7-6. アナログ負荷電流モニタ応答

注

- 1. IMON ピンは、定常状態時にのみ負荷電流監視情報を提供します。突入電流時、IMON ピンはゼロ 負荷電流を報告します。

- 2. ILIM ピンは個別のデバイス負荷電流を常に報告するため、各デバイスのアナログ負荷電流モニタ としても使用できます。

- 3. 過電流および短絡保護タイミングへの影響を避けるため、IMON と ILIM の寄生容量を最小限に抑 えるように注意する必要があります。

### 7.3.6 モード選択 (MODE)

このピンは、2 次デバイスとして指定されている他の TPS1685x eFuse と同様に、チェーンの 1 次デバイスとし TPS1685x を構成できます。この機能により、TPS1685x の一部のピン機能を変更し、1 次側および 2 次側の並 列接続を支援できます。

このピンは、電源投入時にサンプリングされます。このピンをオープンにすると、プライマリまたはスタンドア ロン デバイスとして構成されます。このピンを GND に接続すると、セカンダリ デバイスとして構成されます。

2 次モードでは、以下の機能がディセーブルされ、デバイスはこの機能を実現するためにプライマリ デバイスに 依存します。

- 1. IREF 内部電流源

- 2. DVDT 内部電流源

- 3. サーキット ブレーカの応答の定常状態での過電流検出

- 4. 定常状態に達した後の PG デアサート (プルダウン)

- 5. フォルト後のラッチオフ

セカンダリ モードでは、次の機能が引き続き作動します。

- 1. 過熱保護

- 2. スタートアップ時の電流制限

TEXAS INSTRUMENTS www.ti.com/ja-jp

- 3. 突入時や、定常状態時のアクティブ電流共有

- 4. 定常状態のアナログ電流モニタ (IMON)

- 5. IMON に基づく定常状態の過電流検出これは、ITIMER ピンを内部で Low にプルすることで示されますが、 ITIMER 有効期限時にサーキット ブレーカ動作はトリガされません。代わりに、プライマリ デバイスが独自 の ITIMER を開始し、ITIMER 満了後に SWEN を Low にして、チェーン全体のサーキット ブレーカ動作を トリガする必要があります。ただし、1 次側デバイスが長時間にわたってサーキット ブレーカ操作の開始に 失敗した場合のバックアップとして 2 次側デバイスは内部過電流タイマを使用します。詳細については、 *「シングル ポイント障害の軽減」*セクションを参照してください。

- 6. 各デバイスには、デバイス自体を保護するために、個別のスケーラブルかつ固定の高速トリップスレッショ ルドが内蔵されています。個別の短絡保護スレッショルドは、2次モードではより高い値に設定されていま す。これにより、1次側デバイスがシステム全体でさらに降下させることができます。

- 7. 個別 OVP は 2 次デバイスの最大値に設定され、1 次側がシステム全体でさらに低下できるようになります。

- 8. 個別のデバイス フォルト検出に基づく FLT アサート (サーキット ブレーカを除く)。

- デバイスが定常状態に達した後の突入電流時の PG デアサート制御、およびアサート制御。ただし、定常状態であれば、障害発生時に2次側デバイスが PG のアサート解除を制御しなくなります。

- 10. 内部イベントに基づく SWEN のアサートまたはデアサート、および SWEN ピンのステータスに基づく FET のオン/オフ制御。

2 次モードでは、短絡および高速トリップ時のデバイス動作も変更されます。詳細については*、「短絡保護」*セク ションを参照してください。

#### 7.3.7 並列デバイス同期 (SWEN)

SWEN ピンは、FET をオンにする必要がある場合に high に駆動される信号です。SWEN ピンを low (内部また は外部) に駆動すると、ドライバ回路に FET をオフにするよう信号が送信されます。このピンは制御およびハン ドシェイク信号の両方として機能し、複数のデバイスを並列構成で使用して FET のオン/オフ遷移を同期するこ とができます。

| デバイスの状態                               | FET ドライバ ステータス | SWEN |

|---------------------------------------|----------------|------|

| 定常状態                                  | オン             | Н    |

| 突入電流                                  | オン             | Н    |

| 過熱シャットダウン                             | OFF            | L    |

| 自動再試行タイマが動作しています                      | OFF            | L    |

| 低電圧 (EN/UVLO)                         | OFF            | L    |

| 低電圧 (VDD UVP)                         | OFF            | L    |

| 低電圧 (VIN UVP)                         | OFF            | L    |

| 挿入遅延                                  | OFF            | L    |

| 過電圧誤動作防止 (VIN OVP)                    | OFF            | L    |

| 過渡過電流                                 | オン             | Н    |

| 回路ブレーカ (持続的な過電流後に ITIMER 満了)          | OFF            | L    |

| 高速トリップ                                | OFF            | L    |

| フォルト応答のモノラル ショット実行 (MODE = GND)       | OFF            | L    |

| フォルト応答のモノラル ショットの期限切れ (MODE =<br>GND) | オン             | н    |

| IMON ピン オープン (定常状態)                   | OFF            | L    |

| IMON ピン短絡 (定常状態)                      | OFF            | L    |

| FET 正常性故障                             | OFF            | L    |

表 7-2. SWEN のまとめ

スタンバイ レールの使用を推奨します。

#### 注

- SWEN ピンはオープン ドレインのピンですが、内部的に弱く V<sub>INT</sub> にプルアップされています。

SWEN は、外部電源にプルアップすることもできます。eFuse の入力から生成されたシステム・

- プライマリとセカンダリの並列構成では、SWEN ピンをプライマリ デバイスで使用して、セカンダリ デバイス のオン / オフ遷移を制御します。同時に、セカンダリ デバイスが障害やその他の状態を通信できるようになり、

のオン/オノ達移を制御します。同時に、セカノダリ テハイスが障害やその他の状態を通信できるようになり、 プライマリ デバイスがオンになるのを防ぐことができます。詳細については*、「フォルト応答および表示 (FLT*)」 を参照してください。

これらのデバイスは、ステートマシンの同期を維持するために SWEN レベルの遷移とハンドシェイクのタイミ ングに依存します。これにより、すべてのデバイスが同期および同じ方法でオン / オフできます (DVDT 制御や 電流制限によるスタートアップなど)。また、故障発生時にプライマリ デバイスが制御を取得できない場合でも チェーン全体が安全にオフになるようにする、フェイルセーフ メカニズムを SWEN 制御とハンドシェイク ロジ ックに備えています。

#### 注

TI は、同期タイミングの問題を回避するため、SWEN ピンの寄生負荷を最小限に抑えることを推奨し ます。

### 7.3.8 複数の eFuse をスタックして無制限のスケーラビリティを実現

単一の TPS1685x で対応するよりも高電流を必要とするシステムでは、複数の TPS1685x または TPS1689x デ バイスを並列に接続して、システム全体の電流を供給できます。従来型の eFuse は、パス抵抗のミスマッチ (個 別デバイスの R<sub>DSON</sub> の部品間のバラツキや、PCB の寄生パターン抵抗を含む) により、定常状態時に電流を均 等に共有しません。この事実は、システムの複数の問題につながる可能性があります。

- 1. 一部のデバイスは、他のデバイスより大きい電流を常に流します。この結果、故障が発生してシステムの動 作寿命が全体的に短縮される可能性があります。

- この結果、基板、デバイス、トレース、ビアにサーマルホットスポットが形成され、大電流が流れ、PCB の信頼性の問題につながります。また、この問題により、熱モデル化と基板の熱管理は設計者にとって非常 に困難になります。

- 3. より大きな電流を伝送するデバイスは、システムの合計負荷電流が全体のサーキット ブレーカ スレッショル ドよりも低くなっている間に、より早く個別のサーキット ブレーカ スレッショルドに達する可能性がありま す。この動作により、通常動作中に eFuse の誤ったトリップが発生する可能性があります。これは並列チェ ーンの電流搬送能力を低下させてしまいます。言い換えると、並列 eFuse チェーンの電流定格は、個別の eFuse の電流定格の合計と比較してディレーティングする必要があります。このディレーティング係数は、 パス抵抗のミスマッチ、並列接続されるデバイスの数、個別の eFuse サーキット ブレーカの精度の関数で す。

ディレーティングの必要性は、システム設計に悪影響を及ぼします。設計者は、以下のいずれかのトレードオフ を決定しなければなりません。

- システムの動作負荷電流が eFuse チェーンのディレーティング電流スレッショルドを下回るように制限し ます。基本的に、これは、電源 (PSU) でサポートされているプラットフォーム機能よりも低くなることを意 味します。

- 2. 全体のサーキット ブレーカ スレッショルドを高くして、必要なシステム負荷電流がトリップせずに通過でき るようにします。結果的に、サーキットブレーカ全体の精度の低下を考慮し、電源 (PSU) のサイズを大きく して、故障発生時により大きな電流を供給する必要があります。

いずれの場合も、システムの電源使用率が低下するため、システムのスループットが最適ではないか、設置コストと運用コストが増加するか、またはその両方が発生します。

TPS1685x は、これらの問題に対処するために独自の技術を採用しており、必要に応じて多数の eFuse を並列接 続することで、ソリューションの無制限の拡張性を実現します。これは、大きな電流共有や精度の低下を伴わず に組み込まれています。

この方式を正しく機能させるには、デバイスを次の方法で接続する必要があります。

- ・ すべてのデバイスの SWEN ピンを互いに接続します。

- すすべてのデバイスの IMON ピンを互いに接続する必要があります。結合した IMON ピンの R<sub>IMON</sub> 抵抗の 値は、式 11 を使用して計算できます。

$$R_{IMON} = \frac{V_{IREF}}{G_{IMON} \times I_{OCP(TOTAL)}}$$

(11)

• <u>式</u> 12 に基づいて個別の eFuse の R<sub>ILIM</sub> を選択する必要があります。

$$R_{ILIM} = \frac{1.1 \times N \times R_{IMON}}{3} \tag{12}$$

ここで、N は並列チェーン内のデバイス数です。

注

アクティブ電流共有方式は、定常状態にある間に任意の eFuse を流れる電流が、式 13 に基づいて R<sub>IIIM</sub> で設定された個別の電流共有スレッショルドを超えると、アクティブになります。

$R_{ILIM} = \frac{1.1 \times V_{IREF}}{3 \times G_{ILIM} \times I_{LIM}(ACS)}$

(13)

システムの合計電流がシステムの過電流 (サーキット ブレーカ) スレッショルド (I<sub>OCP(TOTAL)</sub>) を上回 ると、アクティブ電流共有方式は解除されます。

#### 7.3.8.1 起動中の電流バランスの維持

TPS1685x は、起動時に独自の電流バランシング機構を実装しており、並列に接続された 複数の TPS1685x デ バイスが突入電流を共有し、すべてのデバイスに熱ストレスを分散できるようにします。この機能は、すべての デバイスで正常な起動を完了し、一部の eFuse が早期にサーマル シャットダウンに至るシナリオを回避するの に役立ちます。これにより、並列チェーンの突入電流能力が実質的に向上します。突入電流性能の向上により、 突入時間やシステムの信頼性を損なうことなく、大電流プラットフォーム上で非常に大きな負荷コンデンサをサ ポートすることが可能になります。

#### 7.3.9 アナログ接合部温度モニタ (TEMP)

このデバイスを使用すると、システムはダイの温度に比例するアナログ電圧を TEMP ピンに供給することで、接 合部温度 (T」) を正確に監視できます。この電圧は、 デジタル遠隔測定 (テレメトリ) 機能を使用して、ホスト コ ントローラまたは eFuse の ADC 入力に接続できます。マルチデバイス並列構成では、すべてのデバイスの TEMP 出力を相互接続できます。この構成では、チェーン内で最も高温のデバイスの温度が TEMP 信号により 報告されます。

#### 7.3.10 過熱保護

TPS1685x は、安全に動作するために、内部 FET が過熱した場合にデバイス自体を保護する、内部サーマル シャットダウン メカニズムを採用しています。TPS16851 は熱的過負荷を検出すると、シャットダウンし、デバイスの電源をオフにして再サイクルするか再度イネーブルにするまで、ラッチオフ状態を維持します。TPS16850 が熱的過負荷を検出すると、温度が十分に下がるまでオフに維持されます。その後、デバイスは t<sub>RST</sub> の追加の遅延時間オフのまま維持され、その後デバイスがイネーブルのままなら、自動的にオンを試みます。

# 表 7-3. 過熱保護のまとめ

| デバイス             | TSD 開始               | TSD 終了                                                                                                                                                              |

|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS16851 (ラッチオフ) | T <sub>J</sub> ≥ TSD | T <sub>J</sub> < TSD – TSD <sub>HYS</sub><br>VDD が 0V にサイクルされ、V <sub>UVP(R)</sub> を上回<br>る、または EN/UVLO が V <sub>SD(F)</sub> より低くトグ<br>ルされる                          |

| TPS16850 (自動再試行) |                      | T <sub>J</sub> < TSD – TSD <sub>HYS</sub><br>t <sub>RST</sub> タイマが満了する、VDD が 0V にサイク<br>ルされ、V <sub>UVP(R)</sub> を上回る、または EN/UVLO<br>が V <sub>SD(F)</sub> より低くトグルされる |

# 7.3.11 フォルト応答および表示 (FLT)

表 7-4 は、各種故障条件に対するデバイスの応答をまとめたもので。

|                                                               |                                                                                                    | 表 7-4. 故障のまとめ |              |                     |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------|--------------|---------------------|

| イベントまたは状態                                                     | デバイスの応答                                                                                            | 内部でラッチされた故障   | FLT ピンのステータス | 遅延                  |

| 定常状態                                                          | なし                                                                                                 | 該当なし          | Н            |                     |

| 突入電流                                                          | なし                                                                                                 | 該当なし          | Н            |                     |

| 過熱                                                            | シャットダウン                                                                                            | Y             | L            |                     |

| 低電圧 (EN/UVLO)                                                 | シャットダウン                                                                                            | Ν             | н            |                     |

| 低電圧 (VDD UVP)                                                 | シャットダウン                                                                                            | Ν             | н            |                     |

| 低電圧 (VIN UVP)                                                 | シャットダウン                                                                                            | Ν             | н            |                     |

| 過電圧 (VIN OVP)                                                 | シャットダウン                                                                                            | Ν             | н            |                     |

| 過渡過電流                                                         | なし                                                                                                 | N             | Н            |                     |

| 持続的な過電流 (定常状態)                                                | 回路ブレーカ                                                                                             | Y             | L            | t <sub>ITIMER</sub> |

| 持続的な過電流 (起動時)                                                 | 電流制限                                                                                               | Ν             | L            |                     |

| 短絡 (プライマリ モード)                                                | <br>高速トリップ                                                                                         | Y             | L            | t <sub>FT</sub>     |

| 短絡 (セカンダリ モード)                                                | 高速トリップ後の電流制<br>限付き起動                                                                               | Ν             | Н            |                     |

| ILIM ピン オープン (定常状<br>態)                                       | アクティブ電流共有ルー<br>プは常にアクティブです                                                                         | N             | н            |                     |

| ILIM ピン短絡 (定常状態)                                              | アクティブ電流共有ルー<br>プが無効                                                                                | N             | н            |                     |

| IMON ピン オープン (定常<br>状態)                                       | シャットダウン                                                                                            | Y             | L            |                     |

| IMON ピン短絡 (定常状態)                                              | シャットダウン (I <sub>OUT</sub> ><br>I <sub>OC_BKP</sub> の場合)                                            | Y             | L            | 50µs                |

| IREF ピン オープン (定常状<br>態)                                       | シャットダウン (I <sub>OUT</sub> ><br>I <sub>OC_BKP</sub> の場合)                                            | Y             | L            | t <sub>ITIMER</sub> |

| IREF ピン短絡 (定常状態)                                              | シャットダウン                                                                                            | Y             | L            |                     |

| ITIMER ピンが強制的に高電<br>圧に移行                                      | シャットダウン (I <sub>OUT</sub> ><br>I <sub>OCP</sub> または I <sub>OUT</sub> ><br>I <sub>OC_BKP</sub> の場合) | Y             | L            | tspfail_tmr         |

| 起動タイムアウト                                                      | シャットダウン                                                                                            | Y             | L            | t <sub>SU_TMR</sub> |

| FET 正常性故障 (G-S)                                               | シャットダウン                                                                                            | Y             | L            | 10 µs               |

| FET 正常性故障 (G-D)                                               | シャットダウン                                                                                            | Y             | L            |                     |

| FET 正常性故障 (D-S)                                               | シャットダウン                                                                                            | Ν             | L            | t <sub>SU_TMR</sub> |

| 外部故障 (デバイスが UV で<br>も OV でもないときに<br>SWEN が外部で Low にプル<br>される) | シャットダウン                                                                                            | Y             | L            |                     |

# 表 7-4. 故障のまとめ

FLT はオープン ドレインのピンであり、外部電源にプルアップする必要があります。

故障後のデバイスの応答は、動作モードによって異なります。

- スタンドアロンまたはプライマリ動作モード (MODE = オープン)の間、デバイスはフォルトをラッチし、デバイスの選択に従って、自動再試行またはラッチオフ応答に従います。デバイスが再度オンになると、通常のDVDT 制限付き起動シーケンスに従います。

- 2、2次動作モード (MODE = GND) 中、デバイスがフォルトを検出すると、SWEN ピンが一時的に Low にプル されて、イベントが1次デバイスに通知されます。その後、1次側を利用してフォルト応答を制御します。 ただし、プライマリ デバイスが故障を登録できない場合、セカンダリ デバイスにはフェイルセーフ機構が備 わっており、チェーン全体をオフにし、ラッチオフ状態に移行します。その後、デバイスは VDD の電源を V<sub>UVP(F)</sub> 未満にして入れ直すか、EN/UVLO ピンを V<sub>SD(F)</sub> 未満してサイクルさせることによってのみ、再度オ ンにできます。

内部でラッチされた故障の場合、部品の電源を入れ直すか、EN/UVLO ピンの電圧を V<sub>SD(F)</sub> 未満に引き下げるこ とで故障がクリアされ、ピンはデアサートされます。この操作により、t<sub>RST</sub> タイマもクリアされます (自動再試 行バリアントのみ)。この状況では、EN/UVLO を UVLO スレッショルドよりもわずかに低くしても、デバイスに 影響はありません。これは、ラッチオフおよび自動再試行の両方のバリアントに当てはまります。

### 7.3.12 パワー グッド表示 (PG)

パワー グッド表示は、デバイスが定常状態で最大電力を供給可能な場合に、high にアサートされるアクティブ high 出力です。

| イベントまたは状態                                  | FET のステータス | PG ピン ステータス                  | PG 遅延                    |

|--------------------------------------------|------------|------------------------------|--------------------------|

| 低電圧 (V <sub>EN</sub> < V <sub>UVLO</sub> ) | OFF        | L                            | t <sub>PGD</sub>         |

| V <sub>IN</sub> < V <sub>UVP</sub>         | OFF        | L                            |                          |

| V <sub>DD</sub> < V <sub>UVP</sub>         | OFF        | L                            |                          |

| 過電圧 (V <sub>IN</sub> > V <sub>OVP</sub> )  | OFF        | L                            | t <sub>PGD</sub>         |

| 定常状態                                       | オン         | Н                            | t <sub>PGA</sub>         |

| 突入電流                                       | オン         | L                            | t <sub>PGA</sub>         |

| 過渡過電流                                      | オン         | Н                            | 該当なし                     |

| 回路ブレーカ (持続的な過電流後<br>に ITIMER 満了)           | OFF        | L (MODE = H)<br>H (MODE = L) | t <sub>PGD</sub><br>該当なし |

| 高速トリップ                                     | OFF        | L (MODE = H)<br>H (MODE = L) | t <sub>PGD</sub><br>該当なし |

| 過熱                                         | シャットダウン    | L (MODE = H)<br>H (MODE = L) | t <sub>PGD</sub><br>該当なし |

#### 表 7-5. PG 表示のまとめ

パワーアップ後、PG は初期状態で Low に引き下げられます。デバイスは突入シーケンスを開始し、ゲート ド ライバ回路が内部のチャージ ポンプからゲート容量の充電を開始します。FET ゲート電圧が最大オーバードラ イブに達し、突入シーケンスが完了し、デバイスが最大出力を供給できることを示すと、グリッチ除去時間 (t<sub>PGA</sub>) の後、PG ピンが HIGH にアサートされます。

通常動作中のいずれかの時点で FET がオフになると、PG はアサート解除されます。PG のデアサート時のグリッチ除去時間は t<sub>PGD</sub> です。

図 7-7. TPS1685x PG タイミング図

PG はオープン ドレインのピンであり、外部電源にプルアップする必要があります。

デバイスに電源が供給されていない場合、PG ピンは Low のままであることが期待されています。ただし、この 状態には、このピンを 0V まで完全に駆動するためのアクティブプルダウンはありません。デバイスに電力が供 給されていない場合でも、PG ピンが存在する独立した電源にプルアップされると、プルアップ電源電圧と抵抗 の関数であるピンのシンク電流に応じて、このピンに小さな電圧が印加される可能性があります。シンク電流を 最小化して、この状態で関連する外部回路によってロジック HIGH として検出されないよう、このピン電圧を十 分に低く維持します。

デバイスを 2 次モード (MODE = GND)で、別の TPS1685x デバイスと組み合わせて、並列チェーン内の 1 次デ バイスとして使用すると、起動時の PG のアサートを制御しますが、デバイスが定常状態に達した後は、PG の アサート解除を制御できなくなります。詳細については、*モデル選択 (MODE*)を参照してください。

### 7.3.13 出力放電

デバイスには出力放電機能が内蔵されており、GND への内部定電流 (I<sub>QOD</sub>)を使用して OUT ピンのコンデンサ を放電します。出力放電機能は、EN/UVLO が最小期間 (t<sub>QOD</sub>) にわたって Low (V<sub>SD(F)</sub> < V<sub>EN</sub> < V<sub>UVLO(F)</sub>) に保持 されているときにアクティブになります。出力放電機能により、大きな出力コンデンサに残っている残留電荷を すばやく除去し、バスが長時間にわたって特定の未定義電圧にとどまることを防止します。出力放電は、V<sub>OUT</sub> < V<sub>FB</sub> のとき、またはデバイスがフォルトを検出すると解除されます。

出力放電機能により、デバイス内部で過剰な電力消費が発生し、接合部温度 (T」) が上昇する可能性があります。 接合部温度 (T」) が TSD を超えると、出力放電は無効になり、部品の長期的な劣化を防ぎます。

注

TI は、プライマリおよびセカンダリの並列構成では、EN/UVLO 電圧をセカンダリデバイスの V<sub>UVLO(F)</sub> スレッショルドよりも低く保持して、チェーン内のすべてのデバイスの出力放電をアクティブにする ことを推奨します。

### 7.3.14 FET の正常性監視

TPS1685x は、パワー パス FET の故障を示す特定の条件を検出して報告できます。検出または報告されない場合、これらの状態は、負荷に正しく電力を供給しないか、必要なレベルの保護を提供しないかのいずれかにより、システム性能を低下させる可能性があります。FET 故障が検出されると、TPS1685x はゲートを Low に引き下げることにより内部 FET のオフを試み、FLT ピンをアサートします。

- D-S 短絡: D-S 短絡は、基板アセンブリの欠陥または内部 FET 故障のいずれかにより、ソースから負荷まで、 制御されない一定の電力供給経路を形成する可能性があります。この状態は、FET がオンになる前に V<sub>IN-OUT</sub>

V<sub>DSFLT</sub> かどうかをチェックすることで、起動時に検出されます。もしそうであれば、デバイスは内部出力 放電を作動させ、出力の放電を試みます。特定の許容期間内に V<sub>OUT</sub> が V<sub>FB</sub> を下回るまで放電されないデバ イスは FLT ピンをアサートします。

- G-D 短絡: TPS1685x は、内部制御ロジックが FET をオフ状態に保持しようとしていても、ゲート電圧が V<sub>IN</sub> に近いかどうかを常にチェックすることで、この種の FET 故障を常に検出します。

- G-S 短絡: TPS1685x は、ゲート ドライバがオンになった後、FET G-S 電圧が特定のタイムアウト期間 (t<sub>SU\_TMR</sub>)内に必要なオーバードライブ電圧に達しないかどうかをチェックすることで、起動時にこの種の FET 故障を検出します。定常状態では、コントローラ ロジックがゲート ドライバに FET をオフにするよう に信号を送信する前に G-S 電圧が Low になると、故障としてラッチされます。

#### 7.3.15 シングル ポイント障害の軽減

TPS1685x は、あらゆる状況で過電流と短絡に対する保護を提供するため、IMON、IREF、ITIMER ピンへの適 切な部品接続とバイアスを使用します。安全対策の追加として、本デバイスは以下のメカニズムを使用して、こ れらのピンのいずれかがシステム内で正しく接続されなかった場合やフィールド内で関連部品に障害が発生し た場合、デバイスが何らかの過電流保護を実現するようにします。

7.3.15.1 IMON ピンのシングル ポイント障害

- IMON ピンオープン:この場合、IMON ピン電圧が内部的に高電圧にプルアップされ、スレッショルド (V<sub>IREF</sub>) を超えてしまうため、デバイスに大きな電流が流れていない場合でも、部品が回路ブレーカ動作を実行して しまいます。

- ・ IMON ピンが直接または非常に低い抵抗を介して GND に短絡されている:この場合、IMON ピンの電圧は低電圧に保持され、デバイスに大きな電流が流れる場合でもスレッショルド (V<sub>IREF</sub>)を超えることは許可されず、プライマリ過電流保護メカニズムは無効になります。このデバイスは、バックアップとして何らかの保護を提供するために、内部の過電流検出メカニズムに依存しています。デバイスがバックアップ電流センススレッショルド (I<sub>OC\_BKP</sub>)を超えたことを検出し、同時に IMON ピンのプライマリ過電流検出が失敗した場合、シングルポイント障害検出がトリガされ、故障がラッチされます。FET はオフになり、FLT ピンがアサートされます。

TEXAS INSTRUMENTS www.ti.com/ja-jp

7.3.15.2 IREF ピンのシングル ポイント障害

- ・ IREF ピンガオープンまたは強制的に高電圧に設定:この場合、IREF ピン (V<sub>IREF</sub>)は、推奨される I<sub>OCP</sub> または I<sub>LIM</sub> の計算に従って目標値よりも高い電圧に内部または外部でプルアップされ、デバイスに大電流が流れている場合でも プライマリ サーキット ブレーカ、アクティブ電流制限、短絡保護がトリガされないようにしています。このデバイスは、内部過電流検出メカニズムに依存して、何らかの保護をバックアップとして実現します。デバイスが、バックアップ過電流スレッショルドを超えていることを検出したが、同時に IMON ピンのプライマリ過電流または短絡検出に失敗する場合、シングル ポイント障害検出がトリガされ、故障がラッチされます。FET はオフになり、FLT ピンがアサートされます。

- IREF ピンは GND へ短絡:この場合、V<sub>IREF</sub> スレッショルドが 0V に設定されるため、デバイスに大きな電流 が流れない場合でも、部品はアクティブ電流制限またはサーキット ブレーカ動作を実行します。

#### 7.3.15.3 ITIMER ピンのシングル ポイント障害

- ITIMER ピンの開放または GND への短絡:この場合、ITIMER ピンはすでに V<sub>ITIMERTHR</sub> を下回って放電されているため、過電流イベント後即座に過電流ブランキングタイマが満了し、遅延なしにサーキット ブレーカ動作がトリガされていることを示します。

- ITIMER ピンが強制的に V ITIMERTHR よりも高い電圧になります:この場合、ITIMER ピンは VITIMERTHR を下回るまで放電できないため、過電流ブランキング タイマの期限切れを示すことができないため、サーキットブレーカ メカニズムは無効になります。このデバイスは、バックアップとして何らかの保護を提供するために、バックアップの過電流タイマ メカニズムに依存しています。デバイスが IMON ピンとバックアップ過電流検出回路のどちらかで過電流イベントを検出すると、デバイスは内部バックアップ時間に入り、タイマが経過すると (t<sub>SPELTMR</sub>)、フォルトがラッチされます。FET はオフになり、FLT ピンがアサートされます。

# 7.4 デバイスの機能モード

デバイスの機能は、動作モードによって異なります。表 7-6 と表 7-7 は、デバイスの機能モードをまとめたものです。

# 表 7-6. EN/UVLO ピンに基づくデバイスの機能モード

| ピン:EN/UVLO                                      | デバイスの状態 | 出力放電   |

|-------------------------------------------------|---------|--------|

| > V <sub>UVLO(R)</sub>                          | 完全にオン   | ディセーブル |

| $> V_{SD(F)}$ , $< V_{UVLO(F)}$ ( $< t_{QOD}$ ) | FET オフ  | ディセーブル |

| $> V_{SD(F)}$ , $< V_{UVLO(F)}$ (> $t_{QOD}$ )  | FET オフ  | イネーブル  |

| < V <sub>SD(F)</sub>                            | シャットダウン | ディセーブル |

#### 表 7-7. MODE ピンに基づくデバイスの機能モード

| ピン:モード | デバイス設定          |

|--------|-----------------|

| オープン   | プライマリまたはスタンドアロン |

| GND    | セカンダリ           |

### 表 7-8. SFT\_SEL ピンの抵抗に基づくデバイスの機能モード

| I <sub>SFT_SEL</sub>    | SFT_SEL ピン                               | MODE ピン |

|-------------------------|------------------------------------------|---------|

| Іос_вкр                 | $R_{SFT\_SEL} < 95k\Omega$               | オープン    |

| $2.5 \times I_{OCP}$    | 105kΩ < R <sub>SFT_SEL</sub> < 195kΩ     | オープン    |

| 2.8 × I <sub>OCP</sub>  | $105k\Omega < R_{SFT\_SEL} < 195k\Omega$ | GND     |

| 2 × I <sub>OCP</sub>    | $205k\Omega < R_{SFT\_SEL} < 295k\Omega$ | オープン    |

| 2.26 × I <sub>OCP</sub> | $205k\Omega < R_{SFT\_SEL} < 295k\Omega$ | GND     |

| 1.5 × I <sub>OCP</sub>  | $305k\Omega < R_{SFT\_SEL}$              | オープン    |

| 1.71 × I <sub>OCP</sub> | 305kΩ < R <sub>SFT_SEL</sub>             | GND     |

# 8 アプリケーションと実装

注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、 テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の 適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実 装を検証しテストすることで、システムの機能を確認する必要があります。

# 8.1 アプリケーション情報

TPS1685x は、一般に電源レールの保護用途に使用される高電圧および大電流 eFuse です。このデバイスは 9V ~ 80V で動作し、入力過電圧保護と、可変低電圧保護を備えています。このデバイスは、突入電流を制御する機能を搭載しており、過電流や短絡の各状況に対する保護を提供します。このデバイスは、サーバーのマザーボード、アドオン カード、グラフィックス カード、アクセラレータ カード、エンタープライズ スイッチ、ルータなど、さまざまなシステムで使用できます。以降のセクションで説明する設計手順を使用すると、アプリケーションの要件に基づいてサポート部品の値を選択できます。さらに、スプレッドシート設計ツールである TPS1685x 設計カリキュレータを Web 製品フォルダで入手できます。

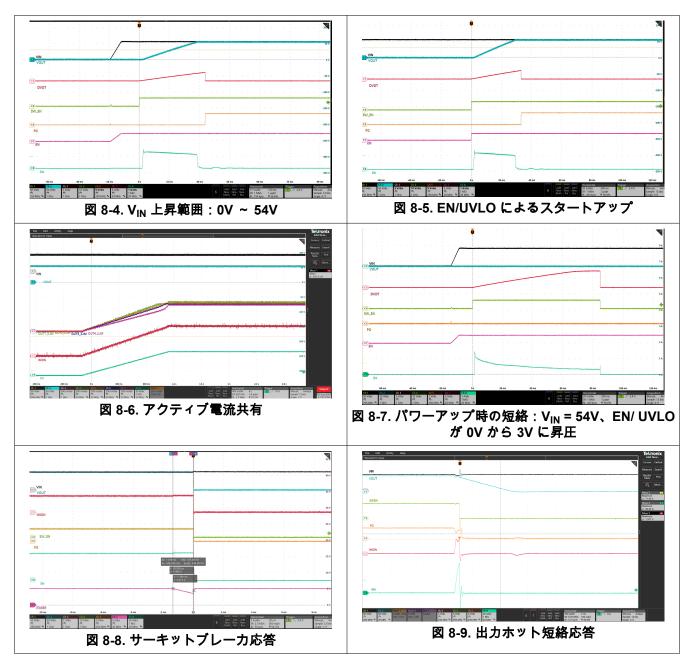

# 8.1.1 シングル デバイス、スタンドアロン動作

図 8-1. シングル デバイス、スタンドアロン動作

注

スタンドアロン動作用に構成するには、MODE ピンをオープンのままにします。

# その他のパリエーション:

- 1. IREF ピンは、外部リファレンス電圧ソースから駆動できます。

- ホスト MCU 制御システムでは、EN/UVLO を GPIO ピンに接続して、デバイスを制御できます。IMON ピン の電圧は、ADC を使用して監視できます。ホスト MCU は、DAC を使用して IREF を駆動し、電流制限スレ ッショルドを動的に変更できます。

- このデバイスは、ILIM ピンと IMON ピンを GND に接続して IREF ピンをオープンのままにすることで、調整可能な過電流保護または高速トリップ保護なしのシンプルな大電流ロード スイッチとして使用できます。この状況でも、突入電流保護、固定高速トリップ、内部固定過電流保護が引き続きアクティブになります。

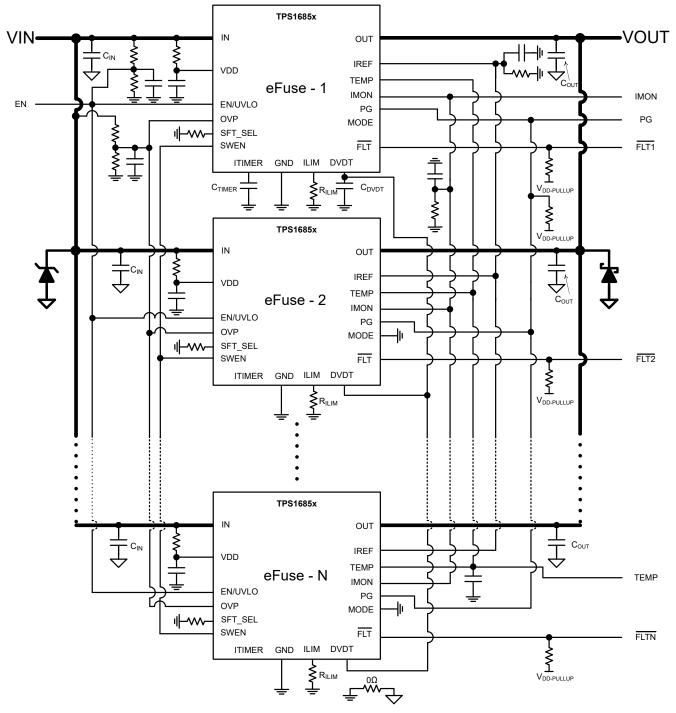

# 8.1.2 複数デバイス、並列接続

図 8-2. 大電流能力を実現するために並列接続されたデバイス

この構成では、1 つの TPS1685x デバイスがプライマリ デバイスとして動作し、チェーン内のセカンダリ デバ イスとして設計されている他の TPS1685x デバイスを制御します。この構成は、次のようにプライマリ デバイ スを接続することで実現されます。

- 1. VDD は、R-C フィルタを介して IN に接続します。

- 2. MODE ピンはオープンのままにします。

- 3. ITIMER は、コンデンサを介して GND に接続します。

- 4. DVDT は、コンデンサを介して GND に接続します。

- 5. IREF は抵抗を介して GND に接続します。

- 6. IMON は抵抗を介して GND に接続します。

- 7. ILIM は抵抗を介して GND に接続します。

- 8. SWEN は 3.3-V から 5-V へのスタンバイ レールにプルアップされます。このレールには、eFuse とは独立 して電源を投入する必要があります。

セカンダリ デバイスは、次の方法で接続する必要があります。

- 1. VDD は、R-C フィルタを介して IN に接続します。

- 2. MODE ピンは GND に接続します。

- 3. ITIMER ピンはオープンのままにします。

- 4. ILIM は抵抗を介して GND に接続します。

すべてのデバイスの以下のピンは互いに接続する必要があります。

- 1. IN

- 2. OUT

- 3. EN/UVLO

- 4. OVP

- 5. DVDT

- 6. SWEN

- 7. PG

- 8. IMON

- 9. IREF

この構成では、すべてのデバイスが同時に電源投入され、有効になります。

**パワーアップ**:パワーアップまたはイネーブル後、すべてのデバイスは最初は、内部ブロックが正しくバイアス され初期化されるまで、SWEN を low に保持します。その後、各デバイスは独自の SWEN をリリースします。 すべてのデバイスが SWEN をリリースすると、結合された SWEN が high になり、各デバイスはそれぞれの FET を同時にオンにする準備ができます。

**突入電流**: 突入時は、DVDT ピンが 1 つの DVDT コンデンサに接続されているため、すべてのデバイスが同じ スルー レート (SR) で出力をオンにします。以下の 式 14 と 式 15 に基づいて一般的な DVDT コンデンサ (C<sub>DVDT</sub>) を選択します。

| $SR(V/ms) = \frac{I_{INRUSH}(A)}{C_{LOAD}(mF)}$ | (14) |

|-------------------------------------------------|------|

| $C_{DVDT}(nF) = \frac{48}{SR(V/ms)}$            | (15) |

この状態で、内部のバランシング回路により、スタートアップ時に負荷電流がすべてのデバイスで共有されるこ とが保証されます。この動作により、一部のデバイスが他のデバイスよりも高速にオンになる状況や、他のデバ イスより大きな熱ストレスが発生する状況を防止できます。これにより、並列チェーンの早期または部分的なシ ャットダウン、またはデバイスの SOA 損傷が発生する可能性があります。電流バランシング方式により、並列 に接続されるデバイスの数に応じてチェーンスケールの突入電流能力が保証されるため、起動時のより大きな出 力キャパシタンスや高負荷でのスタートアップが確実に成功します。

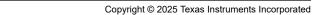

すべてのデバイスが、スタートアップ中はそれぞれの PG 信号を low に保持します。出力が完全に上昇して定常 状態に達すると、各デバイスは独自の PG プルダウンをリリースします。すべてのデバイスの DVDT ピンは互い に接続されているため、すべてのデバイスの内部ゲート high 検出が同期されます。デバイス間に何らかのスレ ッショルドまたはタイミングの不一致がある場合、PG は交互にアサートされます。ただし、すべてのデバイス の PG ピンは互いに接続されているため、結合された PG 信号は、すべてのデバイスが PG プルダウンをリリー スした後でのみ high になります。この信号がダウンストリーム負荷に送信され、電力を引き出せるようになり ます。