# TPS1212-Q1 低 I<sub>Q</sub> 車載ハイサイド スイッチ コントローラ (双方向 IMON、低消 費電カモード、負荷ウェークアップ、I2t、診断機能搭載)

### 1 特長

- AEC-Q100 車載グレード 1 温度認定済み

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可

- 3.5V~73V の入力範囲 (絶対最大定格 74V)

- 最低 –65V までの逆入出力保護

- 内蔵 12V チャージ ポンプ

- 低消費電力モードでの I<sub>O</sub> = 20μA (LPM = Low)

- 1µA の低シャットダウン電流 (EN/UVLO = Low)

- デュアル ゲートドライブ: GATE: ソース 0.5A / シンク 2A G:ソース 100µA / シンク 0.39A

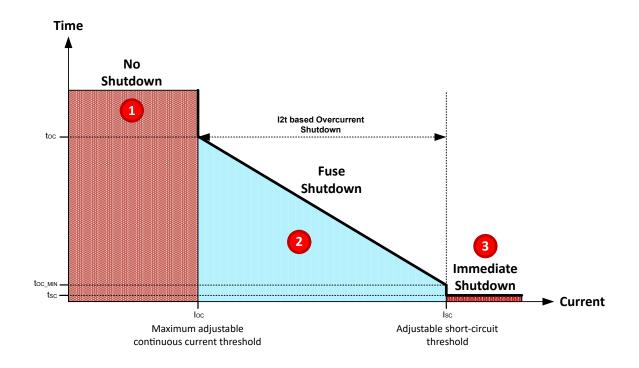

- 調整可能なサーキットブレーカタイマ (I2t) 付きの高 精度 I2t 過電流保護 (IOC)

- 高精度で高速 (5µs) の短絡保護機能

- 可変の負荷ウェークアップスレッショルド、または WAKE 通知付きの LPM トリガによる、低消費電力モ ードからアクティブ モードへの高速遷移 (5µs)

- 高精度アナログ双方向電流モニタ出力 (IMON、 I DIR):±2% (30mV V<sub>SNS</sub>)

- NTC ベースの過熱検出 (TMP) とモニタリング出力 (ITMPO)

- 短絡フォルト時のフォルト表示 (FLT)、12t、チャージ ポ ンプ UVLO、過熱

- TPS12120-Q1 (I2t イネーブル)、TPS12121-Q1 (I2t ディスエーブル)

- 高精度 (±2%) で調整可能な低電圧誤動作防止 (UVLO)

# 2 アプリケーション

- パワー ディストリビューション ボックス

- ボディコントロール モジュール

- DC/DC コンバータ

- バッテリマネージメントシステム

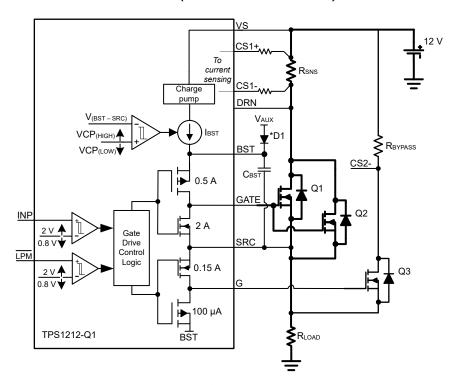

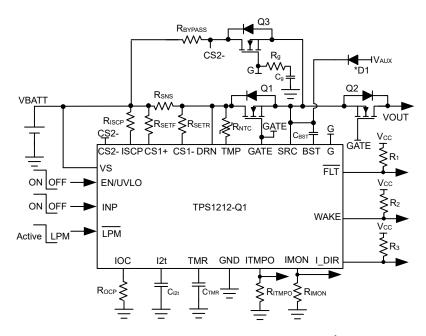

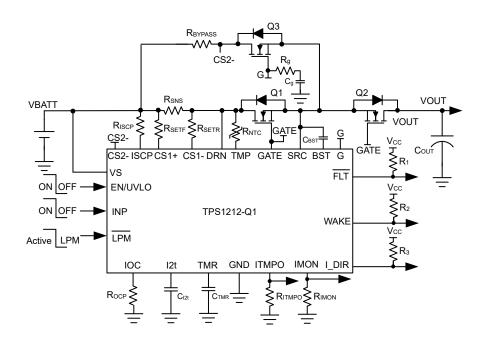

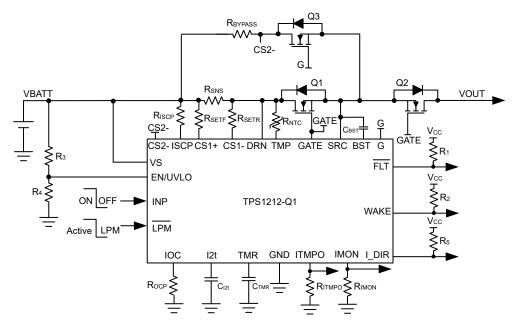

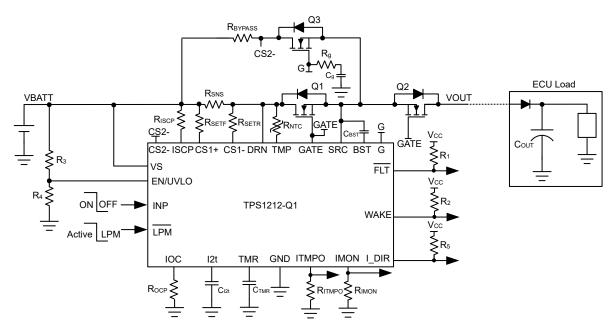

負荷ウェークアップ付き PAAT 負荷を駆動する TPS12120-Q1 アプリケーション回路

### 3 説明

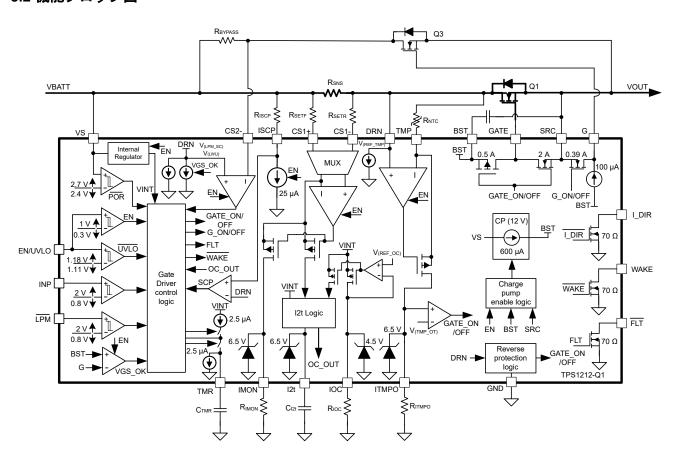

TPS1212-Q1 は、保護および診断機能を備えた 低 Io の スマート ハイサイド ドライバのファミリです。このデバイス は、3.5V ~ 73V の広い動作電圧範囲、74V の絶対最大 電圧を備えており、12V、24V、48V の車載用システム設 計に適しています。

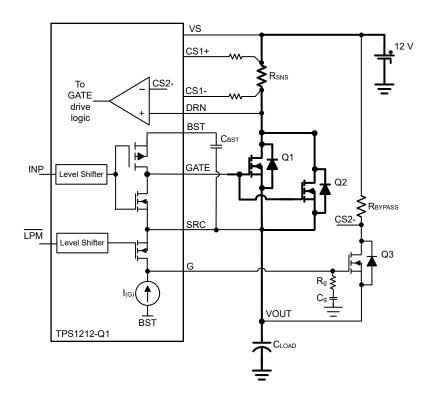

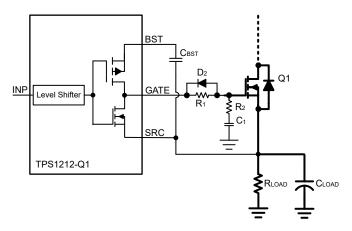

これらのデバイスには、0.5A/2A (GATE) および 100μA/ 0.39A (G) の 2 つのゲートドライブが内蔵されています。 LPM が Low のとき、低消費電力パスがオンに維持され、 メイン FET がオフになり、Io は 20µA (標準値) になりま す。DRN と CS2- の間に配置された RRYPASS 抵抗を使 用して、自動負荷ウェークアップのスレッショルドを調整で きます。EN/UVLO が Low のとき、IQ は 1µA (代表値) ま で減少します。

デバイスは、高精度の 双方向電流検出 (±2%) 出力 (IMON) を備えており、外部 R<sub>SNS</sub> 抵抗と FLT 通知を使 用して、可変の I2t ベースの過電流および短絡保護を実 現しています。 自動リトライおよびラッチオフ フォルト動作 は設定可能です。このデバイスは、外部 FET の過熱検出 用に、NTC ベースの温度センシング (TMP) およびモニタ リング監視出力 (ITMPO) も備えています。

TPS1212-Q1 は、23 ピン VQFN パッケージで供給され ます。

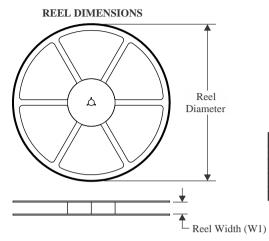

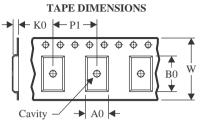

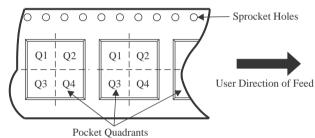

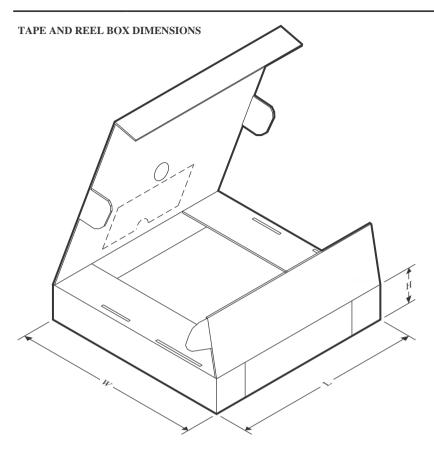

#### パッケージ情報

| 部品番号                        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------------------------|----------------------|--------------------------|

| TPS12120-Q1、<br>TPS12121-Q1 | RGE (VQFN, 23)       | 4mm × 4mm                |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

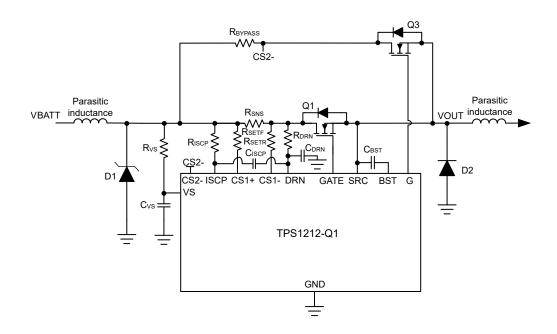

負荷ウェークアップおよびバルク コンデンサ充電付き で PAAT 負荷を駆動する TPS12120-Q1 アプリケーシ ョン回路

# 目次

| 1 特長              | 8.4 デバイスの機能モード                 | 34              |

|-------------------|--------------------------------|-----------------|

| 2アプリケーション1        | 9 アプリケーションと実装                  |                 |

| 3 説明1             | 9.1 アプリケーション情報                 | 40              |

| <b>4</b> デバイス比較表3 | 9.2 代表的なアプリケーション 1: 自動負荷ウェークアッ |                 |

| 5 ピン構成および機能4      | プによる常時オン (PAAT) 負荷の駆動          | 40              |

| 6 仕様7             | 9.3 代表的なアプリケーション 2: 自動負荷ウェークアッ |                 |

| 6.1 絶対最大定格7       | プおよび出力バルクコンデンサ充電による常時オン        |                 |

| 6.2 ESD 定格7       | (PAAT) 負荷の駆動                   | 46              |

| 6.3 推奨動作条件7       | 9.4 電源に関する推奨事項                 | 49              |

| 6.4 熱に関する情報8      | 9.5 レイアウト                      | 50              |

| 6.5 電気的特性8        | 10 デバイスおよびドキュメントのサポート          | 52              |

| 6.6 スイッチング特性11    | 10.1 ドキュメントの更新通知を受け取る方法        | <mark>52</mark> |

| 6.7 代表的特性12       | 10.2 サポート・リソース                 | <mark>52</mark> |

| 7 パラメータ測定情報14     | 10.3 商標                        | 52              |

| 8 詳細説明17          | 10.4 静電気放電に関する注意事項             | 52              |

| 8.1 概要17          | 10.5 用語集                       | 52              |

| 8.2 機能ブロック図18     | 11 改訂履歴                        | 52              |

| 8.3 機能説明19        | 12 メカニカル、パッケージ、および注文情報         | 52              |

|                   |                                |                 |

# 4 デバイス比較表

| デバイス名/機能 | TPS12120-Q1 | TPS12121-Q1 |  |  |

|----------|-------------|-------------|--|--|

| 12t 保護   | あり          | いいえ         |  |  |

3

Product Folder Links: TPS1212-Q1 English Data Sheet: SLUSFL9

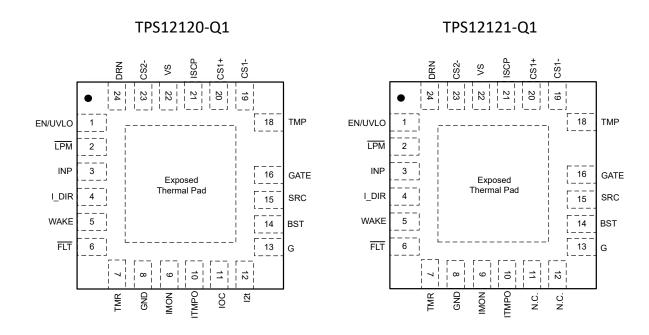

# 5 ピン構成および機能

図 5-1. RGE パッケージ、23 ピン VQFN (透過上面図)

表 5-1. ピンの機能

|           | 式 3-1. こ / V)放射と |                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                 |  |

|-----------|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | ピン               |                 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                 |  |

| 名称        | TPS12120-<br>Q1  | TPS12121-<br>Q1 | 種類(1)                                                                                                                                             | 説明                                                                                                                                                                                                                                                                                                                              |  |

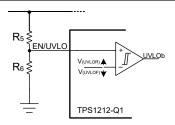

| EN/UVLO   | 1                | 1               | I                                                                                                                                                 | EN/UVLO 入力。 このピンの電圧が V <sub>(UVLOR)</sub> 1.2V を上回ると、通常動作が可能になります。EN/UVLO が V <sub>(UVLOF)</sub> を下回ると、ゲートドライブはオフになります。 このピンを V <sub>(ENF)</sub> 0.3V 未満に強制すると、デバイスがシャットダウンし、静止電流が約 1µA (標準値) に低下します。オプションで、抵抗デバイダ経由で入力電源に接続し、低電圧誤動作防止を設定します。 EN/UVLO がフローティングになっている場合、100nA の内部プルダウンにより、EN/UVLO が Low にプルされ、デバイスがオフ状態のままになります。 |  |

| LPM       | 2                | 2               | I                                                                                                                                                 | モード制御入力。 High に駆動すると、デバイスはアクティブ モードに遷移します。Low に駆動すると、デバイスは低消費電力モードに遷移します。 低消費電力モードが不要な場合は、LPM ピンを EN/UVLO ピンに接続できます。 LPM をフローティングのままにすると、100nA の内部プルダウンによって LPM が Low にプルされます。                                                                                                                                                  |  |

| INP 3 3 I |                  | I               | 外部 FET 制御のための入力信号。<br>GATE ピンの状態を設定する GND への CMOS 互換入力リファレンス。<br>INP は、INP がフローティングのままのときに GND がゲートを SRC にプルダウンする<br>ために、100nA の弱い内部プルダウンを備えています。 |                                                                                                                                                                                                                                                                                                                                 |  |

Copyright © 2025 Texas Instruments Incorporated

## 表 5-1. ピンの機能 (続き)

| L_DIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | ピン        |    |       | 5-1. こノの懐形 (続さ)                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 名称    | TPS12120- |    | 種類(1) | 説明                                                                                                                                                                                                                                                           |

| WAKE         5         5         0         デバイズがアクティブ モードに遷移するとき (LPM が High に駆動された場合または名のフェークアップ イベントが発生した場合) に、デバイズによってこのピンが Low にアナートされます。           オープン ドレイン フォルト出力。         オープン ドレイン フォルト出力。         ナイ・ジャン・フォルト出力。         ナイ・ジャン・フォルト出力。         ナイ・ジャン・ファルド 2V に達すると、このピンが、Low にアサートされます。このにつは、通路でオート・スレッショルド 2V に達すると、このピンが、ためにアサートされます。このにつは、通路でフォルト発生後の自動ルライ族間が経過するまで、FLT ピンはハイ インピータンス状態にはなりません。         通電波フォルト発生後の自動ルライ族間が正めにファナートされる CATと いこのはまたがます。         通電波大機と自動ルライ族間が正めにファナートされる CATと いこのもの・ファル・ファルトを持続することで、ルアイ期間の時間が設定されます。 ファナインでは、エーブンのよまにするのが最も速い変定です。 ファナインファルドを接続します。 ファナインファルドを接続します。 ファナインファルドを接続します。 フェンンと GND との間の抵抗は、電圧に比例する電流を変換します。 と見 Lat・このピンは、外部の電道とフォルカル・ファルドの表にといできます。 ファナイングのままにします。 通電液検型設定。         このピンは、外部の電道とファルティングのままにします。 通電液を関出設定。 IOC とのD の間に抵抗を接続することで、通電液・ファーティングのままにします。 は間流 他上記を 場合は、ファーティングのままにします。 は間流 WDL がます IOC とのD の間に抵抗を接続することで、通電液・ファーティングのままにします。 コロン と COD とのD の間に近れを接続することで、通電液(CoC) の時間を設定します。 スピック・ファース はどと CND の間にコンデンサを接続することで、通電液 (CoC) の時間を設定します。 ストロン 12 とりと CND の間にコンデンサを接続することで、通徳液 (CoC) の時間を設定します。 ストロン 13 13 0 1000 メール・ファース はは、最小様の 0.1 μF の外部コンデンサを接続できます。この との電圧スイングは 12V ~ (VIN + 12V) です。           BST         14         14         0 このピンと SRC との間に、最小様の 0.1 μF の外部コンデンサを接続できます。この につい 2 にとり CND で 1 には、最小様の 0.1 μF の外部コンデンサを接続できます。この 2 このとと SRC との間に、最小様の 0.1 μF の外部コンデンサを接続できます。 この 2 こととの 2 にとり CND で 1 には、最小様の 0.1 μF の外部コンデンサを接続できます。 この 2 ことの 2 にとり CND で 1 には、最小様の 0.1 μF の外部コンデンサを接続できます。 この 2 ことの 2 にとり CND で 1 に対します。 2 この 2 にとり CND で 1 には、最小様の 0.1 μF の外部コンデンサを接続できます。 この 2 ことの 2 にとり CND で 1 には、 最小様の 0.1 μF の外部コンデンサを接続できます。 この 2 にとり CND で 1 には、 最小様の 0.1 μF の外部コンデンサを接続できます。 2 にとり 2 にとり CND で 1 には、 最小様の 0.1 μF の外部コンデンサを接続できます。 2 にとり 2 により CND で 1 にはなが 1 に | I_DIR | 4         | 4  | I     |                                                                                                                                                                                                                                                              |

| FET 6 6 6 0 0 VILO、メイン FET SCP、 l2t タイマトリガ、NTC ベースの外部 FE 過剰フォルト財に、FET が Low に力ります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WAKE  | 5         | 5  | 0     | デバイスがアクティブ モードに遷移するとき (LPM が High に駆動された場合または負荷ウェークアップ イベントが発生した場合) に、デバイスによってこのピンが Low にアサ                                                                                                                                                                  |

| TMR ピンと GND の間にコンデンサを接続することで、リトライ期間の時間が設定され<br>す。オーブンのままにするのが最も連い設定です。<br>ラッチオフ機能を実現するには、TMR ピンから GND までの C <sub>TMR</sub> 間に抵抗を接続します。<br>GND 8 8 G GND をシステム グランドに接続します。<br>アナログ双方向電流モニタ出力。<br>このピンは、外部の電流センス抵抗 R <sub>SNS</sub> を介して、電流のスケールダウン比をソース<br>します。このピンと GND との間の抵抗は、電圧に比例する電流を変換します。<br>使用しない場合は、フローティングのままにするか、グランドに接続することができます。<br>アナログ電圧帰還は、サーミスタの温度に比例する電圧を供給します。<br>値電流検出設定。<br>IOC 11 ー I IOC を GND の間に抵抗を接続することで、過電流コンパレータ スレッショルドを設定<br>ます IOC と GND の間に抵抗を接続することで、過電流コンパレータ スレッショルドを設定<br>ます IOC と ビンは、MCU を使用して外部から駆動することもできます。<br>N.C. ー 11 ー 未接続。<br>I2t ゲンと GND の間にコンデンサを接続することで、過電流 (toc) の時間を設定しま<br>す。<br>N.C. ー 12 ー 未接続。<br>外部バイバス FET のゲート。<br>G 13 13 O 1004 ピークソースおよび 0.39A シンク容量。<br>外部バイバス FET のゲートに接続します。<br>ハイサイド ブートストラップ電源。<br>BST 14 14 O このピンと SRC との間には、最小値の 0.1µF の外部コンデンサを接続できます。この<br>ピンの電圧スイングは 12V ~ (VIN + 12V) です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FLT   | 6         | 6  | 0     | チャージ ポンプの UVLO、メイン FET SCP、I2t タイマトリガ、NTC ベースの外部 FET 過熱フォルト時に、FLT が Low になります。 I2t ピンの電圧がフォルト スレッショルド 2V に達すると、このピンが Low にアサートされます。このピンは、過負荷状態に起因してメイン FET がオフになりそうな状態を示すものです。このピンは、短絡時に Low にアサートされ、GATE がオフになります。過電流状態と自動リトライ時間が経過するまで、FLT ピンはハイインピーダンス状態に |

| IMON 9 9 0 ○                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TMR   | 7         | 7  | I     | TMR ピンと GND の間にコンデンサを接続することで、リトライ期間の時間が設定されます。オープンのままにするのが最も速い設定です。<br>ラッチオフ機能を実現するには、TMR ピンから GND までの C <sub>TMR</sub> 間に抵抗を接続し                                                                                                                             |

| IMON       9       O       このピンは、外部の電流センス抵抗 R <sub>SNS</sub> を介して、電流のスケールダウン比をソースします。このピンと GND との間の抵抗は、電圧に比例する電流を変換します。使用しない場合は、フローティングのままにするか、グランドに接続することができます。アナログ電圧帰還は、サーミスタの温度に比例する電圧を供給します。使用しない場合は、フローティングのままにします。         IOC       11       —       I 過電流検出設定。IOC と GND の間に抵抗を接続することで、過電流コンパレータ スレッショルドを設定します IOC ピンは、MCU を使用して外部から駆動することもできます。N.C.         I2t       1       —       未接続。I2t タイマ入力。I2t ピンと GND の間にコンデンサを接続することで、過電流 (toc) の時間を設定します。N.C.         N.C.       —       12       —       未接続。Aがボイパス FET のゲート。Aがバイパス FET のゲート。Aがバイパス FET のゲートに接続します。Aがボイパス FET のゲートに接続します。Aがイパス FET のゲートに接続します。Aがイパス FET のゲートに接続します。Aがイパイス FET のゲートに接続します。Aがイイパス FET のゲートに接続します。Aがイパス FET のゲートを使用します。Aがイパス FET のゲートを使用しまする。Aがイパス FET のがりまする。Aがイパス FET のゲートを使用しまする。Aがイパス FET のゲートを使用しまする。Aがイパス FET のがりまする。Aがイパス FET                 | GND   | 8         | 8  | G     | GND をシステム グランドに接続します。                                                                                                                                                                                                                                        |

| ITMPO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IMON  | 9         | 9  | 0     | このピンは、外部の電流センス抵抗 R <sub>SNS</sub> を介して、電流のスケールダウン比をソース                                                                                                                                                                                                       |

| IOC       11       —       IOC と GND の間に抵抗を接続することで、過電流コンパレータスレッショルドを設定します IOC ピンは、MCU を使用して外部から駆動することもできます。         N.C.       —       11       —       未接続。         I2t       9/4 マ入力。       12t ピンと GND の間にコンデンサを接続することで、過電流 (toc) の時間を設定します。         N.C.       —       12       一       未接続。         N.C.       —       12       一       未接続。         G       13       13       O       100uA ピークソースおよび 0.39A シンク容量。外部バイパス FET のゲートに接続します。         タキボイパス FET のゲートに接続します。       ハイサイド ブートストラップ電源。       このピンと SRC との間には、最小値の 0.1μF の外部コンデンサを接続できます。このピンの電圧スイングは 12V ~ (VIN + 12V) です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ITMPO | 10        | 10 | 0     | アナログ電圧帰還は、サーミスタの温度に比例する電圧を供給します。                                                                                                                                                                                                                             |

| 12t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IOC   | 11        | _  | I     | IOCとGND の間に抵抗を接続することで、過電流コンパレータ スレッショルドを設定し                                                                                                                                                                                                                  |

| I2t       12       -       O       I2t ピンと GND の間にコンデンサを接続することで、過電流 (toc) の時間を設定します。         N.C.       -       12       -       未接続。         G       13       13       O       100uA ピークソースおよび 0.39A シンク容量。<br>外部バイパス FET のゲートに接続します。         BST       14       O       ハイサイド ブートストラップ電源。<br>このピンと SRC との間には、最小値の 0.1μF の外部コンデンサを接続できます。このピンの電圧スイングは 12V ~ (VIN + 12V) です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N.C.  | _         | 11 | _     | 未接続。                                                                                                                                                                                                                                                         |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I2t   | 12        | _  | 0     | 12t ピンと GND の間にコンデンサを接続することで、過電流 (toc) の時間を設定しま                                                                                                                                                                                                              |

| G 13 13 0 100uA ピークソースおよび 0.39A シンク容量。<br>外部パイパス FET のゲートに接続します。<br>ハイサイド ブートストラップ電源。<br>Cのピンと SRC との間には、最小値の 0.1µF の外部コンデンサを接続できます。このピンの電圧スイングは 12V ~ (VIN + 12V) です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N.C.  | _         | 12 | _     | 未接続。                                                                                                                                                                                                                                                         |

| BST 14 14 O このピンと SRC との間には、最小値の 0.1μF の外部コンデンサを接続できます。このピンの電圧スイングは 12V ~ (VIN + 12V) です。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | G     | 13        | 13 | 0     | 100uA ピークソースおよび 0.39A シンク容量。                                                                                                                                                                                                                                 |

| SRC 15 0 外部 FET のソース接続。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BST   | 14        | 14 | 0     | このピンと SRC との間には、最小値の 0.1µF の外部コンデンサを接続できます。この                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SRC   | 15        | 15 | 0     | 外部 FET のソース接続。                                                                                                                                                                                                                                               |

English Data Sheet: SLUSFL9

## 表 5-1. ピンの機能 (続き)

|      | ピン              |                 |       | O I. C > O IMAGE (NOLC)                                                                                                                          |  |

|------|-----------------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 名称   | TPS12120-<br>Q1 | TPS12121-<br>Q1 | 種類(1) | 説明                                                                                                                                               |  |

| GATE | 16              | 16              | 0     | 大電流ゲートドライバのプルアップおよびプルダウン。 0.5A ピークソースおよび 2A シンク容量。 このピンは、ゲートを BST にプルアップし、SRC にプルダウンします。オン / オフを最速にするには、このピンをメイン パスの外部ハイサイド MOSFET のゲートに直接接続します。 |  |

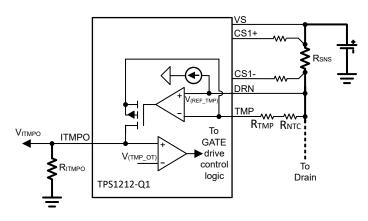

| TMP  | 18              | 18              | I     | 温度入力。<br>外部 NTC サーミスタへのアナログ接続。<br>この機能を使用しない場合は、TMP ピンを VS に直接接続します。                                                                             |  |

| CS1- | 19              | 19              | I     | メイン パス電流センスの負入力。<br>CS1-と外部電流センス抵抗の間に抵抗 (R <sub>SETR</sub> ) を接続して、IMON ゲインを逆方に設定します。                                                            |  |

| CS1+ | 20              | 20              | I     | メイン パス電流センスの正入力。<br>CS1+ と外部電流センス抵抗の間に抵抗 (R <sub>SETF</sub> ) を接続して、IMON ゲインを順方向<br>に設定します。<br>メイン FET 電流検出を使用しない場合は、CS1+ と CS1- を VBATT に接続します。 |  |

| ISCP | 21              | 21              | I     | メイン パス SCP 検出の正入力および短絡検出スレッショルドの設定。<br>短絡保護が不要な場合は、ISCP を CS1- に接続します。                                                                           |  |

| VS   | 22              | 22              | Р     | コントローラの電源ピン。                                                                                                                                     |  |

| CS2- | 23              | 23              | I     | バイパス パス電流センスの負入力。                                                                                                                                |  |

| DRN  | 24              | 24              | I     | メイン パス SCP 検出の負入力。<br>バイパス パスを使用しない場合は、DRN+ と CS2- を一緒に RSNS の後に VBATT<br>に接続します。                                                                |  |

| GND  | サーマル パッド        | _               | _     | 露出サーマル パッドを GND プレーンに接続します。                                                                                                                      |  |

<sup>(1)</sup> I =入力、O =出力、I/O =入力または出力、G =グランド、P =電源。

## 6 仕様

## 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)(1)

|                       |                                                                                     | 最小値               | 最大値                       | 単位 |

|-----------------------|-------------------------------------------------------------------------------------|-------------------|---------------------------|----|

| 入力ピン                  | VS, CS1+, CS1-, DRN, CS2-, ISCP, TMP $\sim$ GND                                     | -65               | 74                        | V  |

| 入力ピン                  | VS, CS1+, CS1-, DRN, CS2-, ISCP, TMP $\sim$ SRC                                     | -65               | 74                        | V  |

| 入力ピン                  | SRC ∼ GND                                                                           | -65               | 74                        | V  |

| 入力ピン                  | GATE, G, BST ∼ SRC                                                                  | -0.3              | 19                        | V  |

| 入力ピン                  | $TMR \sim GND$                                                                      | -0.3              | 5.5                       | V  |

| 入力ピン                  | IOC ~ GND、TPS12120-Q1 のみ                                                            | -1                | 5.5                       | V  |

| 入力ピン                  | EN/UVLO、INP、 LPM。 V <sub>(VS)</sub> > 0V                                            | -1                | 74                        | V  |

| 入力ピン                  | EN/UVLO、INP、 \(\overline{LPM}\), \(V(VS) \leq 0V\)                                  | V <sub>(VS)</sub> | (70 + V <sub>(VS)</sub> ) | V  |

| 入力ピン                  | CS1+ ~ CS1-                                                                         | -0.3              | 0.4                       | V  |

| 入力ピン                  | DRN ~ CS2-                                                                          | -5                | 100                       | V  |

| 出力ピン                  | $\overline{\text{FLT}}$ , I_DIR, WAKE $\sim$ GND                                    | -1                | 20                        | V  |

| 出力ピン                  | $IMON \sim GND$                                                                     | -1                | 5.5                       | V  |

| 出力ピン                  | I2t、ITMPO ~ GND、TPS12120-Q1 のみ                                                      | -1                | 7.5                       | V  |

| 出力ピン                  | ITMPO ~ GND、TPS12121-Q1 のみ                                                          | -1                | 7.5                       | V  |

| 出力ピン                  | GATE, G, BST $\sim$ GND                                                             | -65               | 88                        | V  |

| シンク電流                 | I <sub>(FLT)</sub> , I <sub>(I_DIR)</sub> , I <sub>(WAKE)</sub>                     |                   | 10                        | mA |

| シンク電流                 | $I_{(CS1+)} \sim I_{(CS1-)}$ , 1msec $_{\circ}$ $I_{(DRN)} \sim I_{(CS2-)}$ , 1msec |                   | 100                       | mA |

| 動作時の接合部温度、            | T <sub>j</sub> <sup>(2)</sup>                                                       | -40               | 150                       | °C |

| 保管温度、T <sub>stg</sub> |                                                                                     | -40               | 150                       | C  |

<sup>(1) 「</sup>絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |      |                            |         | 値     | 単位 |

|--------------------|------|----------------------------|---------|-------|----|

|                    |      | 人体モデル (HBM)、AEC Q100-002 / | こ準拠(1)  | ±2000 |    |

| V <sub>(ESD)</sub> | 静電放電 | 荷電デバイス モデル (CDM)、AEC       | コーナー ピン | ±750  | V  |

|                    |      | Q100-011 準拠                | その他のピン  | ±500  |    |

<sup>(1)</sup> AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)(1)

|      |                                                           | 最小値 | 公称值 | 最大値 | 単位 |

|------|-----------------------------------------------------------|-----|-----|-----|----|

| 入力ピン | VS, CS1+, CS1-, DRN, CS2-, ISCP, TMP $\sim$ GND           | -60 |     | 73  | V  |

| 入力ピン | EN/UVLO、INP、 LPM                                          | 0   |     | 73  | V  |

| 入力ピン | IOC, TMR $\sim$ GND, TPS12120-Q1 $\mathcal{O}\mathcal{P}$ | 0   |     | 5   | V  |

| 入力ピン | TMR $\sim$ GND、TPS12121-Q1 のみ                             | 0   |     | 5   | V  |

| 出力ピン | l2t、IMON、ITMPO $\sim$ GND、TPS12120-Q1 only                | 0   |     | 5   | V  |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

1

<sup>(2)</sup> 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125℃を超えると、動作寿命が短くなります。

# 6.3 推奨動作条件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り) (1)

|              |                                           | 最小値 | 公称値 最大値 | 単位 |

|--------------|-------------------------------------------|-----|---------|----|

| 出力ピン         | IMON、ITMPO ~ GND、TPS12121-Q1 のみ           | 0   | 5       | V  |

| 出力ピン         | $\overline{FLT}$ , WAKE, I_DIR $\sim$ GND | 0   | 15      | V  |

| 外付けコン<br>デンサ | VS, SRC ∼ GND                             | 22  |         | nF |

| 外付けコン<br>デンサ | $BST \sim SRC$                            | 0.1 |         | μF |

| 外付けコン<br>デンサ | l2t から GND へ                              | 10  |         | nF |

| 外付けコン<br>デンサ | TMR $\sim$ GND                            | 1   |         | nF |

| Tj           | 動作時接合部温度(2)                               | -40 | 150     | °C |

- (1) 推奨動作条件は、デバイスが機能すると想定されている条件を示します。仕様およびテスト条件については、「電気的特性」を参照してください。

- (2) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125℃を超えると、動作寿命が短くなります。

## 6.4 熱に関する情報

|                        |                     | TPS1212x-Q1 |      |

|------------------------|---------------------|-------------|------|

|                        | 熱評価基準(1)            | RGE (VQFN)  | 単位   |

|                        |                     | 23 ピン       |      |

| $R_{\theta JA}$        | 接合部から周囲への熱抵抗        | 43          | °C/W |

| R <sub>0</sub> JC(top) | 接合部からケース (上面) への熱抵抗 | 38.3        | °C/W |

| $R_{\theta JB}$        | 接合部から基板への熱抵抗        | 20.8        | °C/W |

| $\Psi_{JT}$            | 接合部から上面への特性パラメータ    | 0.8         | °C/W |

| $\Psi_{JB}$            | 接合部から基板への特性パラメータ    | 20.7        | °C/W |

<sup>(1)</sup> 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

### 6.5 電気的特性

$T_J = -40 \, ^{\circ}\text{C} \sim +125 \, ^{\circ}\text{C.V}_{(VS)} = 12 \, \text{V.V}_{(BST-SRC)} = 12 \, \text{V.V}_{(SRC)} = 0 \, \text{V}$

|                       | パラメータ                          | テスト条件                                                                             | 最小値  | 標準値  | 最大値   | 単位 |

|-----------------------|--------------------------------|-----------------------------------------------------------------------------------|------|------|-------|----|

| 電源電圧 (VS)             |                                |                                                                                   |      |      | '     |    |

| VS                    | 動作時入力電圧                        |                                                                                   | 3.5  |      | 73    | V  |

| V <sub>(S_PORR)</sub> | 入力電源 POR スレッショルド、立ち上がり         |                                                                                   | 2.06 | 2.6  | 3.12  | V  |

| V <sub>(S_PORF)</sub> | 入力電源 POR スレッショルド、立ち下がり         |                                                                                   | 2    | 2.5  | 3.01  | V  |

|                       | システム全体の静止電流、I <sub>(GND)</sub> | $V_{(EN/UVLO)} = V_{(LPM)} = 2V$                                                  |      | 430  | 525   | μA |

|                       | システム全体の静止電流、I(GND)             | V <sub>(EN/UVLO)</sub> = V <sub>(LPM)</sub> = 2V<br>TPS12121-Q1 のみ                |      | 370  | 470   | μΑ |

|                       | システム全体の静止電流、I(GND)             | $V_{(EN/UVLO)} = 2V \cdot V_{(EPM)} = 0V$                                         |      | 20   | 24    | μA |

| I <sub>(SHDN)</sub>   | SHDN 電流、I <sub>(GND)</sub>     | V <sub>(SRC)</sub> = 12V, V <sub>(EN/UVLO)</sub> = 0V, V <sub>(SRC)</sub><br>= 0V |      | 0.9  | 3.4   | μΑ |

| イネーブル、低               | 電圧誤動作防止 (EN/UVLO)、過電圧保護入力      | (OV)                                                                              |      |      | '     |    |

| V <sub>(UVLOR)</sub>  | UVLO スレッショルド電圧、立ち上がり           |                                                                                   | 1.16 | 1.2  | 1.245 | V  |

| V <sub>(UVLOF)</sub>  | UVLO スレッショルド電圧、立ち下がり           |                                                                                   | 1.09 | 1.11 | 1.16  | V  |

Product Folder Links: TPS1212-Q1

Copyright © 2025 Texas Instruments Incorporated

# 6.5 電気的特性 (続き)

$T_{J}$  = –40 °C  $\sim$  +125°C.V  $_{(VS)}$  = 12V  $_{\rm V}$  V  $_{(BST-SRC)}$  = 12V  $_{\rm V}$  V  $_{(SRC)}$  = 0V

|                           | パラメータ                                                                                   | テスト条件                                                          | 最小値   | 標準値  | 最大値  | 単位 |

|---------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|-------|------|------|----|

| V <sub>(ENR)</sub>        | 低 IQ シャットダウンのイネーブル スレッショルド電圧、立ち上がり                                                      |                                                                |       |      | 1    | V  |

| V <sub>(ENF)</sub>        | 低 lq シャットダウンのイネーブル スレッショルド電圧、立ち下がり                                                      |                                                                | 0.3   |      |      | V  |

| I <sub>(EN/UVLO)</sub>    | イネーブル入力リーク電流                                                                            | V <sub>(EN/UVLO)</sub> = 12V                                   |       |      | 500  | nA |

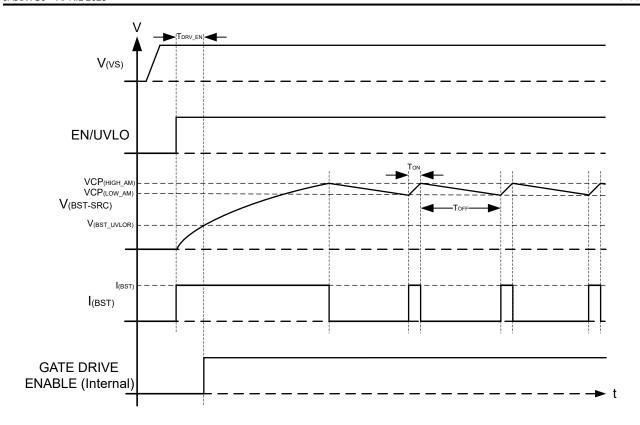

| チャージ ポンプ (E               | BST-SRC)                                                                                |                                                                |       |      |      |    |

| I <sub>(BST_LPM)</sub>    | LPM のチャージ ポンプ電源電流                                                                       | $V_{(BST-SRC)} = 10V, V_{(EN/UVLO)} = 2V,$<br>$V_{(LPM)} = 0V$ | 175   | 360  | 575  | μΑ |

| I <sub>(BST_AM)</sub>     | アクティブ モードでのチャージ ポンプ電<br>源電流                                                             | $V_{(BST-SRC)} = 12V, V_{(EN/UVLO)} = 2V,$<br>$V_{(LPM)} = 2V$ | 300   | 540  | 775  | μΑ |

|                           | V <sub>(BST - SRC)</sub> UVLO 電圧スレッショルド、<br>立ち上がり                                       | V <sub>(EN/UVLO)</sub> = 2V                                    | 7     | 7.6  | 8.4  | V  |

| V <sub>(BST UVLO)</sub>   | V <sub>(BST - SRC)</sub> UVLO 電圧スレッショルド、<br>立ち下がり                                       | V <sub>(EN/UVLO)</sub> = 2V                                    | 6     | 6.6  | 7.2  | V  |

| VCP <sub>(AM_LOW)</sub>   | アクティブ モードでのチャージ ポンプ タ<br>ーンオン電圧                                                         | $V_{(EN/UVLO)} = 2V \setminus V_{(\overline{LPM})} = 2V$       | 9.5   | 10.4 | 12.3 | V  |

| VCP <sub>(AM_HIGH)</sub>  | アクティブモードでのチャージ ポンプ タ<br>ーンオフ電圧                                                          | $V_{(EN/UVLO)} = 2V \setminus V_{(\overline{LPM})} = 2V$       | 10.42 | 11.3 | 13   | V  |

| VCP <sub>(LPM_LOW)</sub>  | 低消費電力モードでのチャージポンプ タ<br>ーンオン電圧                                                           | $V_{(EN/UVLO)} = 2V \cdot V_{(\overline{LPM})} = 0V$           | 8.3   | 9.3  | 10.6 | V  |

| VCP <sub>(LPM_HIGH)</sub> | 低消費電力モードでのチャージ ポンプ<br>ターンオフ電圧                                                           | $V_{(EN/UVLO)} = 2V \cdot V_{(\overline{LPM})} = 0V$           | 9.02  | 10.3 | 11.8 | V  |

| VCP <sub>(AM_VS_3V)</sub> | アクティブ モードでの V <sub>(VS)</sub> = 3V でのチャージ ポンプ電圧                                         | V <sub>(EN/UVLO)</sub> = 2V                                    | 8     |      |      | ٧  |

| V <sub>(G_GOOD)</sub>     | バイパス コンパレータのリファレンス電圧<br>が 2V から 200mV に変化したときの<br>BST を基準とした G ドライブ グッド立ち<br>上がりスレッショルド |                                                                |       | 2.3  |      | V  |

| I <sub>(SRC)</sub>        | SRC ピンのリーク電流                                                                            | $V_{(EN/UVLO)} = 2V \cdot V_{(INP)} = 0 \cdot V_{(LPM)} = 2V$  |       | 1    | 1.57 | μA |

| ゲートドライバ出力                 | 力 (GATE、G)                                                                              | 1                                                              |       |      |      |    |

| I <sub>(GATE)</sub>       | ピークソース電流                                                                                |                                                                |       | 0.5  |      | Α  |

| I <sub>(GATE)</sub>       | ピークシンク電流                                                                                |                                                                |       | 2    |      | Α  |

| I <sub>(G)</sub>          | ゲート電荷 (ソース) 電流、オン状態                                                                     |                                                                |       | 100  |      | μA |

| I <sub>(G)</sub>          | Gピークシンク電流                                                                               |                                                                |       | 390  |      | mA |

| 電流センスおよび                  | 電流モニタ (CS1+、CS1–、IMON、I_DIR)                                                            |                                                                |       |      | l    |    |

| V <sub>(OS_SET)</sub>     | 入力換算オフセット (V <sub>SNS</sub> から V <sub>(IMON)</sub><br>へのスケーリング)                         |                                                                | -140  |      | 140  | μV |

| V <sub>(GE_SET)</sub>     | ゲイン誤差 (V <sub>SNS</sub> から V <sub>(IMON)</sub> へのスケーリング)                                |                                                                | -1    |      | 1    | %  |

| V <sub>(IMON_Acc)</sub>   | IMON の精度                                                                                | V <sub>SNS</sub> = ±6mV                                        | -5    |      | 5    | %  |

| V <sub>(IMON_Acc)</sub>   | IMON の精度                                                                                | V <sub>SNS</sub> = ±10mV                                       | -5    |      | 5    | %  |

| V <sub>(IMON_Acc)</sub>   | IMON の精度                                                                                | V <sub>SNS</sub> = ±15mV                                       | -2    |      | 2    | %  |

| V <sub>(IMON Acc)</sub>   | IMON の精度                                                                                | V <sub>SNS</sub> = ±30mV                                       | -2    |      | 2    | %  |

| · - /                     | <br>び短絡保護 (IOC、I2t、ISCP、DRN)                                                            | 1                                                              | 1     |      |      |    |

| V <sub>(OCP)</sub>        | OCP スレッショルド精度                                                                           | 15mV ≤ V <sub>(OCP)</sub> ≤ 100mV                              | -7.5  |      | 7.5  | %  |

# 6.5 電気的特性 (続き)

T\_J = -40 °C  $\sim$  +125°C.V $_{(VS)}$  = 12V, V $_{(BST-SRC)}$  = 12V, V $_{(SRC)}$  = 0V

|                                                                                     | パラメータ                                                 | テスト条件                                                                                               | 最小値  | 標準値  | 最大値  | 単位 |

|-------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|----|

| I <sup>2</sup> (I2t_Acc)                                                            | <b>I2t</b> ピンの <b>I<sup>2</sup></b> 電流精度              | $15\text{mV} \le V_{(OCP)} \le 100\text{mV}$<br>$V_{SNS} = V_{(OCP)} + V_{(OCP)} \nearrow 50\%$     | -15  |      | 15   | %  |

| I <sup>2</sup> (I2t_Acc)                                                            | <b>I2t</b> ピンの <b>I<sup>2</sup></b> 電流精度              | $15\text{mV} \le V_{(OCP)} \le 100\text{mV}$ $V_{SNS} = V_{(OCP)} + V_{(OCP)} \mathcal{O} 100\%$    | -10  |      | 10   | %  |

| I <sup>2</sup> (I2t_Acc)                                                            | <b> 2t</b> ピンの   <sup>2</sup> 電流精度                    | $15\text{mV} \le V_{(OCP)} \le 100\text{mV}$<br>$V_{SNS} = V_{(OCP)} + V_{(OCP)} \varnothing 200\%$ | -10  |      | 10   | %  |

| V <sub>(I2t_OC)</sub>                                                               | 過電流シャットダウンの l2t ピン電圧スレッショルド                           |                                                                                                     | 1.93 | 2    | 2.09 | V  |

| I <sub>(I2t_Charge)</sub>                                                           | I2t ピンから V <sub>(I2t_OFFSET)</sub> への充電電流             |                                                                                                     |      | 5100 |      | μA |

| R <sub>(I2t_Discharge)</sub>                                                        | 内部スイッチの放電抵抗                                           |                                                                                                     |      | 1200 |      | Ω  |

| V <sub>(I2t_OFFSET)</sub>                                                           | <b>I2t</b> ピンのオフセット電圧                                 |                                                                                                     | 490  | 500  | 415  | mV |

| V <sub>(REF_OC)</sub>                                                               | IOC ピンのリファレンス電圧                                       |                                                                                                     | 190  | 200  | 205  | mV |

| V <sub>(SCP)</sub>                                                                  | SCP スレッショルド精度                                         | $V_{(SNS\_SCP)} = 10 \text{mV},$ $R_{(ISCP)} = 328\Omega$                                           |      | 10   |      | mV |

| V <sub>(SCP)</sub>                                                                  | SCP スレッショルド精度                                         | $V_{(SNS\_SCP)} = 20 \text{mV},$ $R_{(ISCP)} = 732 \Omega$                                          | 19   | 20   | 21   | mV |

| V <sub>(SCP)</sub>                                                                  | SCP スレッショルド精度                                         | $V_{(SNS\_SCP)} = 100 \text{mV},$ $R_{(ISCP)} = 3.92 \text{k}\Omega$                                | 95   | 100  | 105  | mV |

| I <sub>SCP</sub>                                                                    | SCP 入力バイアス電流                                          |                                                                                                     | 24.4 | 25   | 25.2 | μA |

| 負荷ウェークアップ                                                                           | プコンパレータ (CS2-、DRN)                                    |                                                                                                     |      |      | 1    |    |

| V <sub>(LPM_SCP)</sub>                                                              | LPM の短絡スレッショルド                                        |                                                                                                     | 1.72 | 2    | 2.17 | V  |

| V <sub>(LWU)</sub>                                                                  | 負荷ウェークアップ電流スレッショルド                                    |                                                                                                     | 177  | 200  | 218  | mV |

|                                                                                     | ラッチオフ タイマ (TMR)                                       |                                                                                                     |      |      | '    |    |

| I <sub>(TMR_SRC_FLT)</sub>                                                          | TMR ソース電流                                             |                                                                                                     | 2    | 2.5  | 3    | μA |

| I <sub>(TMR_SNK)</sub>                                                              | TMR シンク電流                                             |                                                                                                     | 2    | 2.5  | 3    | μA |

| V <sub>(TMR_HIGH)</sub>                                                             | AR カウンタ立ち上がりスレッショルドの<br>TMR ピンの電圧                     |                                                                                                     | 1.04 | 1.23 | 1.42 | V  |

| V <sub>(TMR_LOW)</sub>                                                              | AR カウンタ立ち下がりスレッショルドの<br>TMR ピンの電圧                     |                                                                                                     | 0.15 | 0.25 | 0.39 | V  |

| N <sub>(A-R Count)</sub>                                                            |                                                       |                                                                                                     |      | 32   |      |    |

| 温度モニタ (CS1-                                                                         | -、TMP、ITMPO)                                          |                                                                                                     |      |      | I    |    |

| V <sub>(REF_TMP)</sub>                                                              | 温度アンプの内部リファレンス電圧                                      |                                                                                                     | 475  | 500  | 525  | mV |

| V <sub>(ITMPO)</sub>                                                                | 150℃ での温度モニタ出力電圧<br>R <sub>(NTC)</sub> = 10kΩ (25℃)   | $R_{(TMP)} = 330\Omega$ ,<br>$R_{(NTC)} = 309\Omega$ (150°C),<br>$R_{(ITMPO)} = 2.55k\Omega$        | -6   |      | 6.64 | %  |

| $V_{(ITMPO)}$                                                                       | 150°C での温度モニタ出力電圧<br>R <sub>(NTC)</sub> = 47kΩ (25°C) | $R_{(TMP)} = 1k\Omega,$ $R_{(NTC)} = 520\Omega (150^{\circ}C),$ $R_{(ITMPO)} = 6.19k\Omega$         | -6   |      | 6.67 | %  |

| I <sub>(TMP)</sub>                                                                  | TMP のリーク電流                                            |                                                                                                     |      |      | 100  | nA |

| V <sub>(TMP_OT)</sub>                                                               | 過熱スレッショルド                                             |                                                                                                     | 1.9  | 2    | 2.06 | V  |

| 入力制御 (INP、II                                                                        | NP_G、LPM)、& フォルト フラグ (FLT)                            |                                                                                                     | '    |      | '    |    |

| $\begin{array}{c} R_{(\overline{FLT})} \ \ R_{(WAKE)}, \\ R_{(I\_DIR)} \end{array}$ | FLT、WAKE、I_DIR プルダウン抵抗                                |                                                                                                     |      | 70   |      | Ω  |

| I <sub>(FLT)</sub> , I <sub>(WAKE)</sub> ,<br>I <sub>(I_DIR)</sub>                  | FLT、WAKE、I_DIR リーク電流                                  | $0V \le V_{(FLT)} \le 20V$ ,<br>$0V \le V_{(WAKE)} \le 20V$ ,<br>$0V \le V_{(I\_DIR)} \le 20V$      |      |      | 400  | nA |

| $V_{(INP\_H)} \setminus V_{(\overline{LPM}\_H)}$                                    | 1)                                                    | ,                                                                                                   |      |      | 2    | V  |

Copyright © 2025 Texas Instruments Incorporated

English Data Sheet: SLUSFL9

# 6.5 電気的特性 (続き)

$T_{J}$  = –40 °C  $\sim$  +125°C.V  $_{(VS)}$  = 12V  $_{\rm V}$  V  $_{(BST-SRC)}$  = 12V  $_{\rm V}$  V  $_{(SRC)}$  = 0V

|                                                 | パラメータ          | テスト条件 | 最小値  | 標準値 | 最大値 | 単位 |

|-------------------------------------------------|----------------|-------|------|-----|-----|----|

| $V_{(INP\_L)} \ V_{(\overline{LPM}\_L)}$        |                |       | 0.72 |     |     | V  |

| $V_{(INP\_Hys)}$ , $V_{(\underline{LPM}\_Hys)}$ | INP、LPM ヒステリシス |       |      | 400 |     | mV |

| I <sub>(INP)</sub> , I <sub>(<u>LPM</u>)</sub>  | INP、LPM リーク電流  |       |      |     | 200 | nA |

# 6.6 スイッチング特性

$T_{J} = -40~^{\circ}\text{C} \sim +125 ^{\circ}\text{C.V}_{(VS)} = 12\text{V.V}_{(BST-SRC)} = 11\text{V.V}_{(SRC)} = 0\text{V}$

|                                              | パラメータ                                                                     | テスト条件                                                                                                                                                                           | 最小値 標準値 | 最大値 | 単位 |

|----------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|----|

| t <sub>GATE(INP_H)</sub>                     | INP ターンオン伝搬遅延                                                             | INP $\uparrow \sim$ GATE $\uparrow$ 、C <sub>L(GATE)</sub> = 47nF                                                                                                                | 1.2     | 2.5 | μs |

| t <sub>GATE(INP_L)</sub>                     | INP ターンオフ伝搬遅延                                                             | INP $\downarrow \sim$ GATE $\downarrow$ 、C <sub>L(GATE)</sub> = 47nF                                                                                                            | 0.35    | 1.5 | μs |

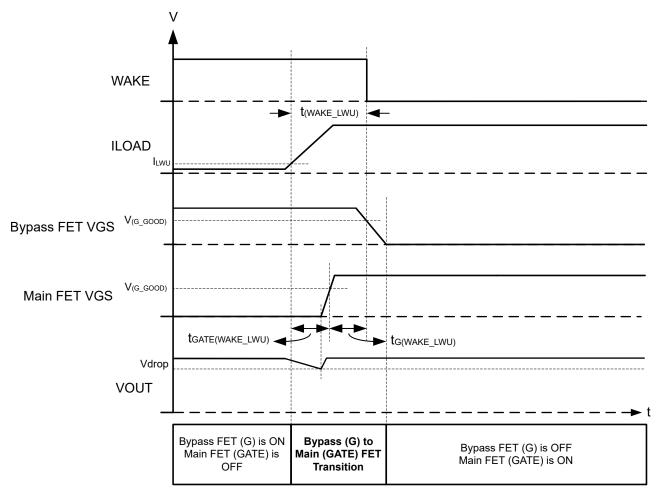

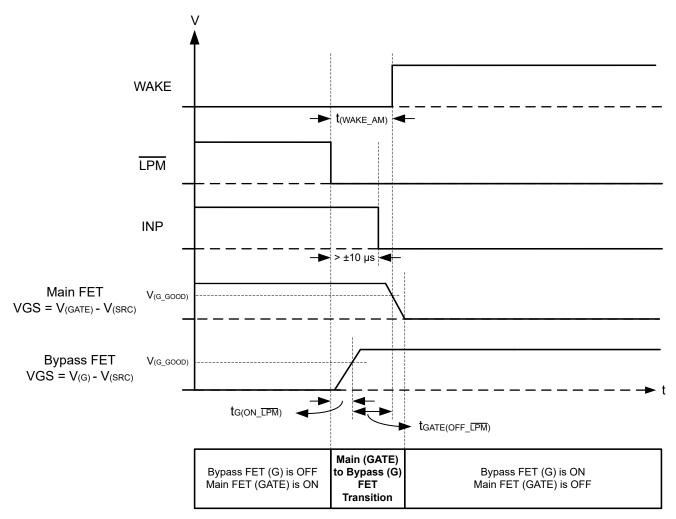

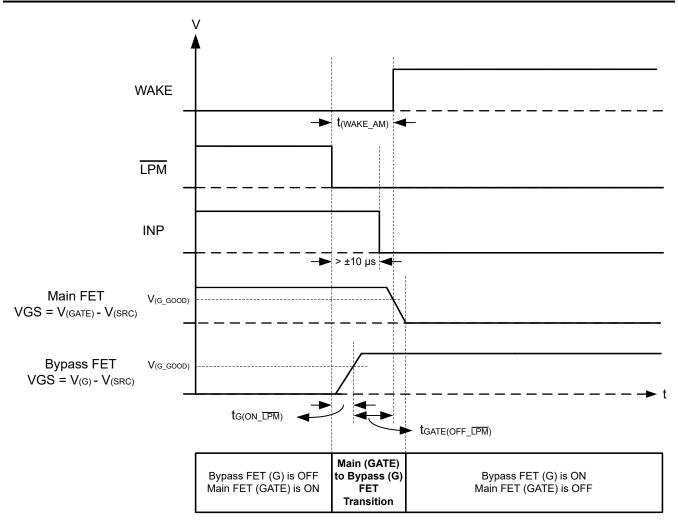

| t <sub>G_ON(EPM)</sub>                       | アクティブ モードから LPM モードへの遷<br>移遅延                                             | $\overline{	ext{LPM}} \downarrow \sim 	ext{G} \uparrow \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                    | 1.8     | 9   | μs |

| t <sub>GATE_OFF(LPM)</sub>                   | アクティブ モードから LPM モードへの遷<br>移遅延                                             | $\overline{\text{LPM}}$ ↓、G ↑ $(V_{(G\_GOOD)}$ 以上) $\sim$ GATE ↓、WAKE ↑ $(\text{Low} \sim \text{High Z})$ 、 $C_{L(GATE)}$ = 47nF                                                | 37      | 51  | μs |

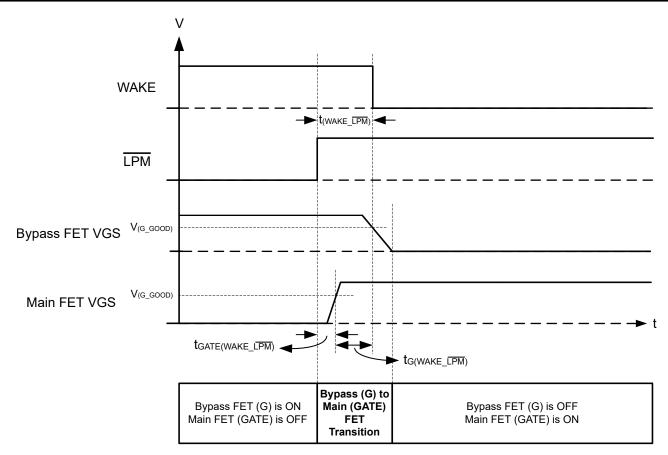

| t <sub>GATE(WAKE_LPM)</sub>                  | LPM トリガによる LPM モードからアクティブ モードへの遷移遅延                                       | $\overline{	ext{LPM}} \uparrow \sim 	ext{GATE} \uparrow \text{, } 	ext{C}_{	ext{L(GATE)}} 	ext{= 47nF}$                                                                         | 3.8     | 6   | μs |

| t <sub>G(WAKE_LPM)</sub>                     | LPM トリガによる LPM モードからアクティブ モードへの遷移遅延                                       | $\overline{\text{LPM}}$ ↑、GATE ↑ $(V_{(G\_GOOD)}$ 以上) $\sim$ G ↓、WAKE ↓、 $C_{L(G)}$ = 47nF、 $V_{(LPM)}$ = 0V                                                                    | 9       | 15  | μs |

| t <sub>GATE(WAKE_LWU)</sub>                  | 負荷ウェークアップ時の GATE ターンオン伝播遅延                                                | $V_{(DRN-CS2-)} \uparrow V_{(LWU)} \sim GATE \uparrow$ , $C_{L(GATE)} = 47nF$ , $V_{(\overline{LPM})} = 0V$                                                                     | 4       | 5.5 | μs |

| t <sub>G(WAKE_LWU)</sub>                     | 負荷ウェークアップ時の G ターンオフ伝<br>搬遅延                                               | $V_{(DRN-CS2-)} \uparrow V_{(LWU)}$ 、GATE $\uparrow$ $(V_{(G\_GOOD)}$ 以上) $\sim$ G $\downarrow$ 、WAKE $\downarrow$ 、 $C_{L(G)}$ = 47nF、 $V_{(LPM)}$ = 0V                        | 9       | 15  | μs |

| t <sub>GATE(EN_OFF)</sub>                    | EN ターンオフ伝搬遅延                                                              | $EN \downarrow \sim GATE \downarrow \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                       | 3.1     | 4.5 | μs |

| t <sub>GATE(UVLO_OFF)</sub>                  | UVLO ターンオフ伝搬遅延                                                            | $ \begin{array}{c} \text{UVLO} \ \downarrow \ \sim \text{GATE} \ \downarrow \ , \\ \text{C}_{\text{L(GATE)}} = \text{47nF}, \ \overline{\text{LPM}} = \text{High} \end{array} $ | 4       | 6.5 | μs |

| t <sub>GATE(UVLO_ON)</sub>                   | CBT プリバイアス > VPORF および INP<br>が High に維持された状態での UVLO<br>~ GATE ターンオン伝搬遅延  | $\begin{array}{c} EN/UVLO \ \uparrow \ \sim GATE \ \uparrow \ , \\ C_{L(GATE)} = 47nF, \ INP = 2V, \ \overline{LPM} = \\ High \end{array}$                                      | 8.5     | 25  | μs |

| t <sub>GATE(VS_OFF)</sub>                    | VS 立ち下がり < VPORF および INP、<br>EN/UVLO が High に維持された状態で<br>の GATE ターンオフ伝搬遅延 | VS ↓ (VPORF 超過) ~ GATE ↓、<br>C <sub>L(GATE)</sub> = 47nF、<br>INP = EN/UVLO = 2V、 LPM = High                                                                                     | 25      | 40  | μs |

| t <sub>sc</sub>                              | アクティブ モードでの短絡保護回路の伝搬遅延                                                    | $ \begin{array}{c} V_{(CS1+\_CS1-)} \uparrow V_{(SCP)} \sim \text{GATE} \downarrow , \\ C_{L(GATE)} = 47 \text{nF}, V_{(\overline{LPM})} = 2 V \end{array} $                    | 3.9     | 5   | μs |

| t <sub>LPM_SC</sub>                          | LPM での短絡保護回路の伝搬遅延 (短絡による LPM へのパワーアップ)                                    | $V_{(DRN-CS2-)} \uparrow V_{(LPM\_SCP)} \sim GATE \uparrow$ , $C_{L(GATE)} = 47nF$ , $V_{(LPM)} = 0V$                                                                           | 3.1     | 4.5 | μs |

| t <sub>GATE(FLT_ASSERT)</sub>                | 短絡中の FLT アサート遅延                                                           | $V_{(CS1+-CS1-)} \uparrow V_{(SCP)} \sim \overline{FLT} \downarrow$                                                                                                             | 15      | 21  | μs |

| t <sub>GATE(FLT_DE_ASSER</sub><br>T)         | 短絡中の FLT デアサート遅延                                                          | $V_{(CS1+-CS1-)} \downarrow V_{(SCP)} \sim \overline{FLT} \uparrow$                                                                                                             | 3.8     |     | μs |

| t <sub>GATE(FLT_ASSERT_B</sub><br>STUVLO)    | GATE ドライブ UVLO 中の FLT アサート<br>遅延                                          | $V_{(GATE-SRC)} \downarrow V_{(BSTUVLOR)} \sim \overline{FLT} \downarrow$                                                                                                       | 30      |     | μs |

| t <sub>GATE(FLT_DE_ASSER</sub><br>T_BSTUVLO) | GATE ドライブ UVLO 中の FLT デアサート遅延                                             | $V_{(GATE-SRC)} \uparrow V_{(BSTUVLOR)} \sim \overline{FLT} \uparrow$                                                                                                           | 15      |     | μs |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

11

## 6.6 スイッチング特性 (続き)

$T_{J} = -40~^{\circ}\text{C} \sim +125 ^{\circ}\text{C.V}_{(VS)} = 12\text{V. V}_{(BST-SRC)} = 11\text{V. V}_{(SRC)} = 0\text{V}$

|               | パラメータ              | テスト条件                                                                               | 最小値 | 標準値 | 最大値 | 単位 |

|---------------|--------------------|-------------------------------------------------------------------------------------|-----|-----|-----|----|

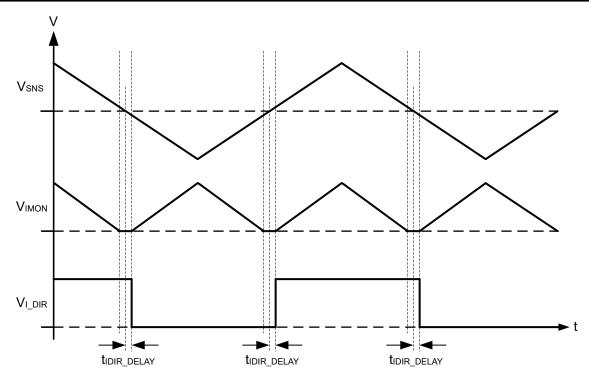

| t(IDIR_DELAY) | I_DIR ピンの電流方向表示の遅延 | $V_{(SNS)} \uparrow stat \downarrow \sim V_{(I\_DIR)} \uparrow stat$ は $\downarrow$ |     | 6.5 | 10  | μs |

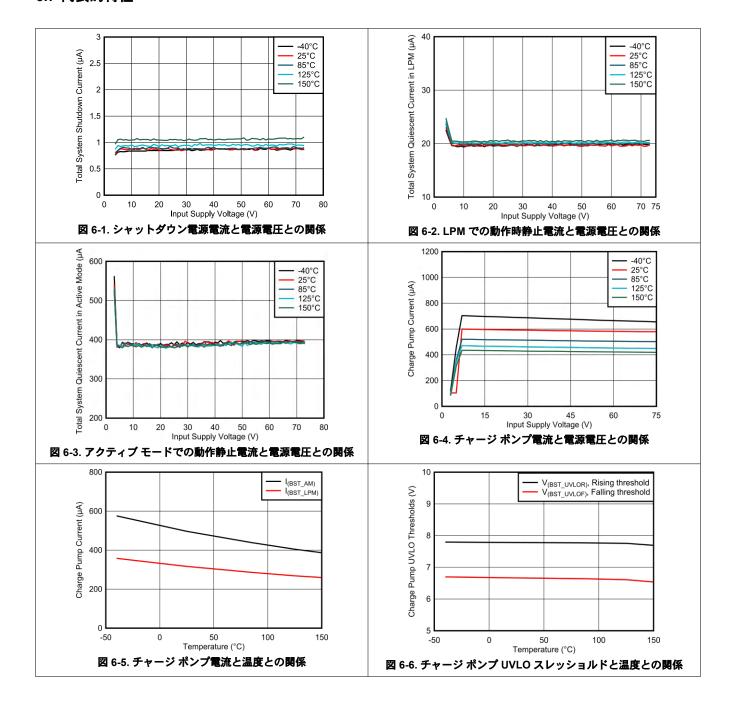

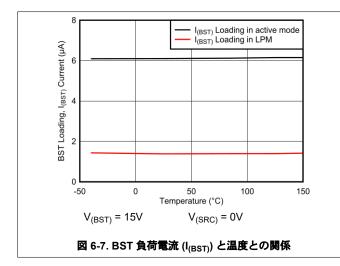

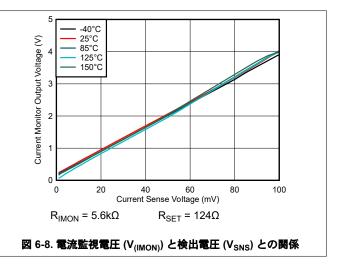

### 6.7 代表的特性

## 6.7 代表的特性 (続き)

13

# 7パラメータ測定情報

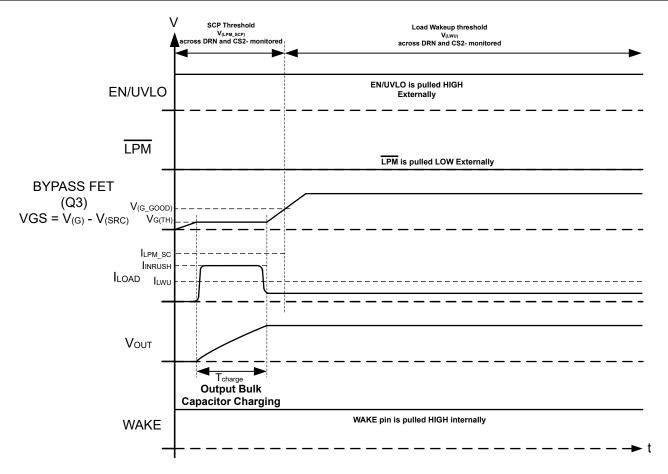

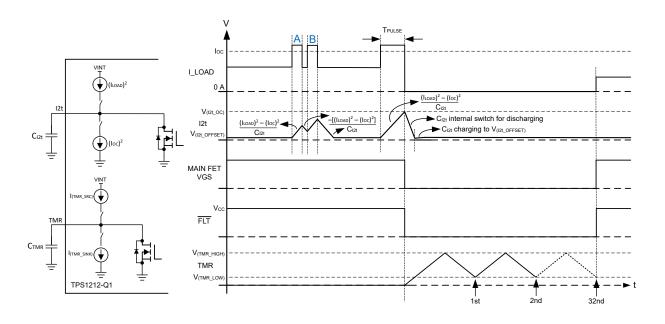

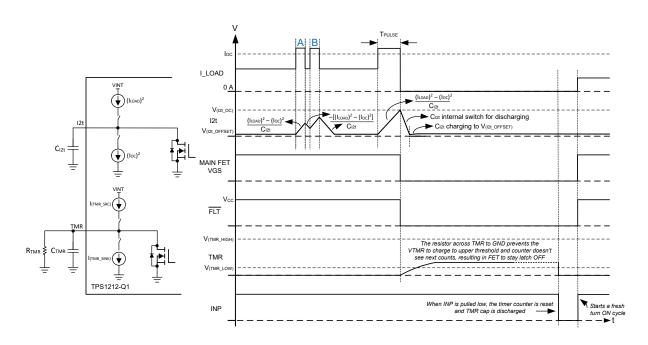

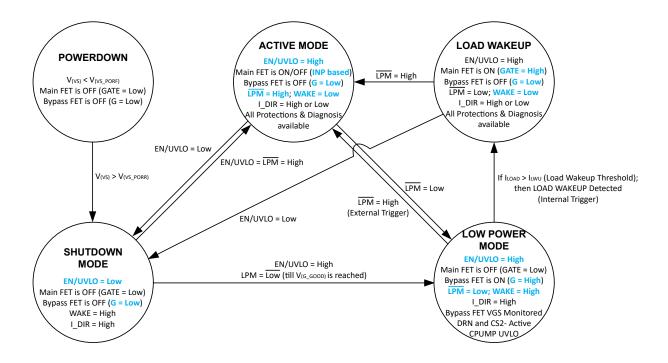

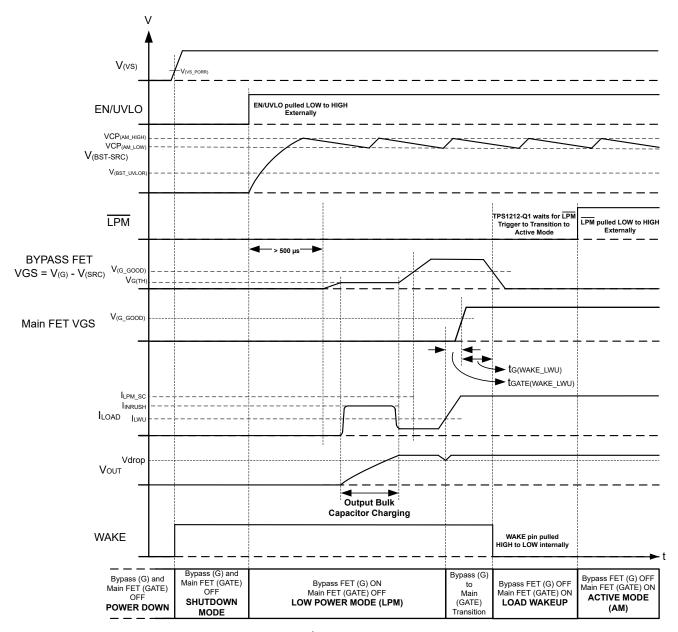

図 7-1. 負荷ウェークアップによるシステムの低消費電力モードからアクティブ モードへの遷移

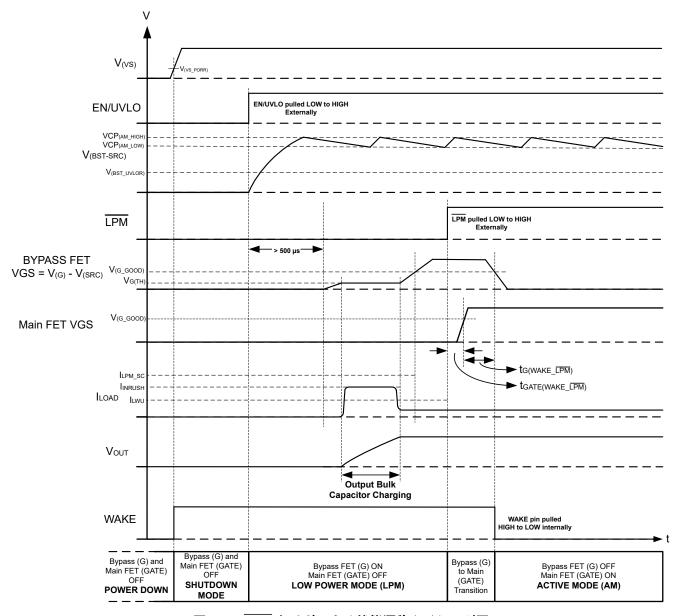

図 7-2. LPM 外部トリガによるシステムの低消費電力モードからアクティブ モードへの遷移

15