# TMUX1511 低静電容量、1:1 (SPST) 4 チャネル、電源オフ保護スイッチ、1.8V ロジック互換

## 1 特長

- 広い電源電圧範囲: 1.5V ~ 5.5V

- 小さいオン容量: 3.3pF

- 低オン抵抗: 2Ω

- 高帯域幅: 3GHz

- -40°C ~ +125°C の動作温度

- 1.8V ロジック互換

- 電源電圧を超える入力電圧に対応

- ロジックピンにプルダウン抵抗を内蔵

- 双方向の信号パス

- フェイルセーフ ロジック

- 最大 3.6V の 電源オフ保護

- SN74CBTLV3126 とピン配置互換

- SN74CBTLV3125 とピン配置互換(ロジックバリエーション)

## 2 アプリケーション

- サーバー

- 有線ネットワーク

- ワイヤレスインフラ

- データセンターのスイッチおよびルーター

- PC / ノートPC

- ビルオートメーション

- ePOS

- モータドライブ

- 家電製品

- バッテリ動作装置

- JTAG 絶縁

- SPI 絶縁

## 3 概要

TMUX1511 は、相補型金属酸化膜半導体 (CMOS) スイッチです。TMUX1511 は 4 チャネルの 1:1 SPST スイッチ構成を提供し、各チャネルは個別に制御されます。動作電圧範囲が 1.5V ~ 5.5V と広いため、サーバーや通信機器から産業用途まで、広範なアプリケーションに使用できます。このデバイスは、ソース (Sx) ピンとドレイン (Dx) ピンでの 双方向 アナログおよびデジタル信号をサポートしており、最大で  $V_{DD} \times 2$  (最大入出力電圧は 5.5V) の信号を通すことができます。

電源電圧が取り除かれたとき ( $V_{DD} = 0V$ )、TMUX1511 の信号パスに最大 3.6V を供給し、絶縁を行います。この保護機能がない場合、内部 ESD ダイオード経由でスイッチから電源レールに電流が逆流し、システムに損傷を引き起こすことがあります。

フェイルセーフ ロジック 回路により、電源ピンよりも前にロジック制御ピンに電圧が印加されるため、デバイスへの損傷の可能性が避けられます。すべてのロジック制御入力のスレッショルドは 1.8V ロジック互換 で、有効な電源電圧範囲で動作していれば、TTL と CMOS の両方のロジックと互換性が保証されます。

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)       |

|----------|----------------------|------------------|

| TMUX1511 | TSSOP (14)           | 5.00mm × 4.40mm  |

|          | QFN (16)             | 2.60 mm × 1.80mm |

|          | X2QFN (12)           | 1.60mm × 1.60 mm |

(1) 利用可能なパッケージについては、データシートの末尾にあるパッケージオプションについての付録を参照してください。

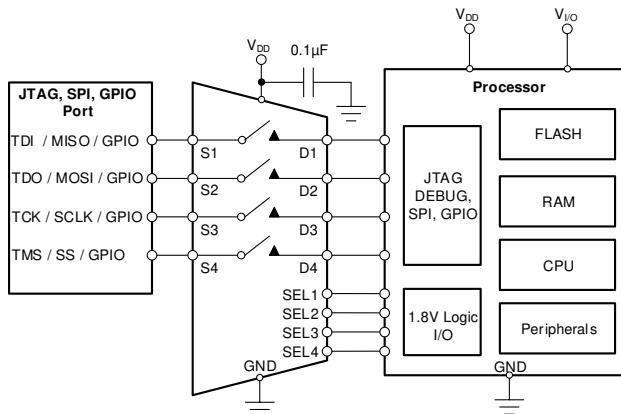

### アプリケーションの例

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                           |    |                         |    |

|-------------------------------------------|----|-------------------------|----|

| 1 特長                                      | 1  | 6.12 チャネル間クロストーク        | 19 |

| 2 アプリケーション                                | 1  | 6.13 帯域幅                | 20 |

| 3 概要                                      | 1  | 7 詳細説明                  | 21 |

| 4 ピン構成および機能                               | 3  | 7.1 概要                  | 21 |

| ピンの機能                                     | 3  | 7.2 機能ブロック図             | 21 |

| 5 仕様                                      | 4  | 7.3 機能説明                | 21 |

| 5.1 絶対最大定格                                | 4  | 7.4 デバイスの機能モード          | 22 |

| 5.2 ESD 定格                                | 4  | 7.5 真理値表                | 22 |

| 5.3 推奨動作条件                                | 4  | 8 アプリケーションと実装           | 23 |

| 5.4 熱に関する情報                               | 4  | 8.1 アプリケーション情報          | 23 |

| 5.5 電気的特性                                 | 6  | 8.2 代表的なアプリケーション        | 23 |

| 5.6 動的特性                                  | 7  | 9 電源に関する推奨事項            | 26 |

| 5.7 タイミング要件                               | 7  | 10 レイアウト                | 27 |

| 5.8 代表的特性                                 | 8  | 10.1 レイアウトのガイドライン       | 27 |

| 6 パラメータ測定情報                               | 14 | 10.2 レイアウト例             | 28 |

| 6.1 オン抵抗                                  | 14 | 11 デバイスおよびドキュメントのサポート   | 29 |

| 6.2 オフリーカ電流                               | 14 | 11.1 サード・パーティ製品に関する免責事項 | 29 |

| 6.3 オンリーク電流                               | 15 | 11.2 ドキュメントのサポート        | 29 |

| 6.4 IPOFF リーカ電流                           | 15 | 11.3 ドキュメントの更新通知を受け取る方法 | 29 |

| 6.5 遷移時間                                  | 16 | 11.4 サポート・リソース          | 29 |

| 6.6 $T_{ON}$ (VDD) および $T_{OFF}$ (VDD) 時間 | 16 | 11.5 商標                 | 29 |

| 6.7 伝搬遅延                                  | 17 | 11.6 静電気放電に関する注意事項      | 29 |

| 6.8 スキュー                                  | 17 | 11.7 用語集                | 29 |

| 6.9 チャージインジェクション                          | 18 | 12 改訂履歴                 | 30 |

| 6.10 容量                                   | 18 | 13 メカニカル、パッケージ、および注文情報  | 30 |

| 6.11 オフアイソレーション                           | 19 |                         |    |

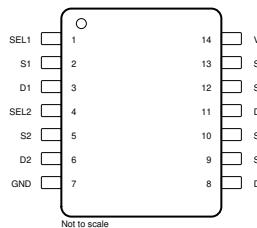

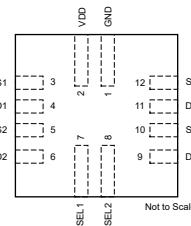

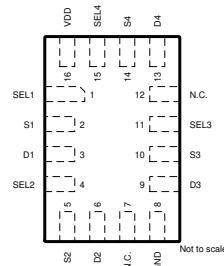

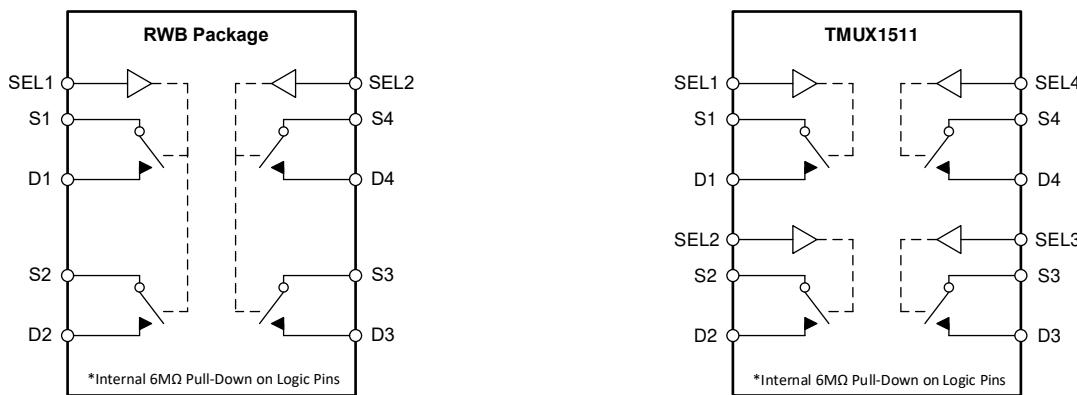

## 4 ピン構成および機能

図 4-1. PW パッケージ 14 ピン TSSOP 上面図

図 4-2. RWB パッケージ 12 ピン X2QFN (上面図)

図 4-3. RSV パッケージ 16 ピン QFN 上面図

## ピンの機能

| 名称   | ピン    |      |       | 種類 (1) | 説明                                                                                                          |

|------|-------|------|-------|--------|-------------------------------------------------------------------------------------------------------------|

|      | TSSOP | UQFN | X2QFN |        |                                                                                                             |

| SEL1 | 1     | 1    | 7     | I      | ピン 1 を選択: スイッチ #1 の状態を制御 (ロジック Low = OFF、ロジック High = ON)。GND を接続先とする内部 $6\text{M}\Omega$ ブルダウン。             |

| S1   | 2     | 2    | 3     | I/O    | ソースピン 1 入力または出力として使用が可能。                                                                                    |

| D1   | 3     | 3    | 4     | I/O    | ドレインピン 1。入力または出力として使用が可能。                                                                                   |

| SEL2 | 4     | 4    | 8     | I      | ピン 2 を選択: スイッチ #2 の状態を制御 (ロジック Low = OFF、ロジック High = ON)。GND を接続先とする内部 $6\text{M}\Omega$ ブルダウン。             |

| S2   | 5     | 5    | 5     | I/O    | ソースピン 2 入力または出力として使用が可能。                                                                                    |

| D2   | 6     | 6    | 6     | I/O    | ドレインピン 2。入力または出力として使用が可能。                                                                                   |

| N.C. | -     | 7    | -     | 接続なし   | 接続なし - GND に短絡するか、フローティングのままにすることができる                                                                       |

| GND  | 7     | 8    | 1     | P      | グランド (0V) リファレンス                                                                                            |

| D3   | 8     | 9    | 11    | I/O    | ドレインピン 3。入力または出力として使用が可能。                                                                                   |

| S3   | 9     | 10   | 12    | I/O    | ソースピン 3 入力または出力として使用が可能。                                                                                    |

| SEL3 | 10    | 11   | -     | I      | ピン 3 を選択: スイッチ #3 の状態を制御 (ロジック Low = OFF、ロジック High = ON)。GND を接続先とする内部 $6\text{M}\Omega$ ブルダウン。             |

| N.C. | -     | 12   | -     | 接続なし   | 接続なし - GND に短絡するか、フローティングのままにすることができる                                                                       |

| D4   | 11    | 13   | 9     | I/O    | ドレインピン 4。入力または出力として使用が可能。                                                                                   |

| S4   | 12    | 14   | 10    | I/O    | ソースピン 4 入力または出力として使用が可能。                                                                                    |

| SEL4 | 13    | 15   | -     | I      | ピン 4 を選択: スイッチ #4 の状態を制御 (ロジック Low = OFF、ロジック High = ON)。GND を接続先とする内部 $6\text{M}\Omega$ ブルダウン。             |

| VDD  | 14    | 16   | 2     | P      | 正電源。このピンは最も正の電源電位になる。確実な動作を保証するため、 $V_{DD}$ と GND の間に $0.1\mu\text{F} \sim 10\mu\text{F}$ のデカップリングコンデンサを接続。 |

(1) I = 入力、O = 出力、I/O = 入力および出力、P = 電源

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1) (2) (3)</sup>

|                                          |                                       | 最小値  | 最大値 | 単位 |

|------------------------------------------|---------------------------------------|------|-----|----|

| V <sub>DD</sub>                          | 電源電圧                                  | -0.5 | 6   | V  |

| V <sub>SEL</sub>                         | ロジック制御入力ピン電圧 (SEL1、SEL2、SEL3、SEL4)    | -0.5 | 6   | V  |

| I <sub>SEL</sub>                         | ロジック制御入力ピン電流 (SEL1、SEL2、SEL3、SEL4)    | -30  | 30  | mA |

| V <sub>S</sub> または V <sub>D</sub>        | ソースまたはドレインピンの電圧                       | -0.5 | 6   | V  |

| I <sub>S</sub> または I <sub>D</sub> (CONT) | ソースおよびドレインピンの連続電流: (S1 ~ S4, D1 ~ D4) | -25  | 25  | mA |

| T <sub>stg</sub>                         | 保存温度                                  | -65  | 150 | °C |

| T <sub>J</sub>                           | 接合部温度                                 |      | 150 | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗示するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 代数規約。これにより、最も大きな負の値は最小値になり、最も大きな正の値は最大値になります。

- (3) 特に指定のない限り、すべての電圧値はグランドを基準にしています。

### 5.2 ESD 定格

|                    |      |                                                         | 値     | 単位 |

|--------------------|------|---------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±750  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

|                                           |                                                                    | 最小値 | 最大値                 | 単位 |

|-------------------------------------------|--------------------------------------------------------------------|-----|---------------------|----|

| V <sub>DD</sub>                           | 電源電圧                                                               | 1.5 | 5.5                 | V  |

| V <sub>S</sub> または V <sub>D</sub>         | 信号バスにおける入出力電圧 (ソースまたはドレインピン)、V <sub>DD</sub> ≥ 1.5V <sup>(1)</sup> | 0   | V <sub>DD</sub> × 2 | V  |

| V <sub>S_off</sub> または V <sub>D_off</sub> | 信号バスにおける入出力電圧 (ソースまたはドレインピン)、V <sub>DD</sub> < 1.5V <sup>(2)</sup> | 0   | 3.6                 | V  |

| V <sub>SEL</sub>                          | ロジック制御入力電圧 (SELx)                                                  | 0   | 5.5                 | V  |

| T <sub>A</sub>                            | 周囲温度                                                               | -40 | 125                 | °C |

- (1) デバイスの入出力は、最大入出力電圧 5.5V で V<sub>DD</sub> × 2 (最大) で動作できます。

- (2) V<sub>S\_off</sub> および V<sub>D\_off</sub> は、電源が 1.5V 未満のときのソースピンまたはドレインピンの電圧を指します。

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | デバイス       | デバイス       | デバイス        | 単位   |

|-----------------------|---------------------|------------|------------|-------------|------|

|                       |                     | PW (TSSOP) | RSV (UQFN) | RWB (X2QFN) |      |

|                       |                     | 14 ピン      | 16 ピン      | 12 ピン       |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 129.4      | 141.5      | 166.1       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 58.8       | 77.9       | 59.5        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 72.4       | 67.6       | 103.6       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 11.6       | 5.1        | 1.0         | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 71.9       | 65.5       | 103.4       | °C/W |

| 熱評価基準 <sup>(1)</sup> | デバイス              | デバイス       | デバイス        | 単位   |      |

|----------------------|-------------------|------------|-------------|------|------|

|                      | PW (TSSOP)        | RSV (UQFN) | RWB (X2QFN) |      |      |

|                      | 14 ピン             | 16 ピン      | 12 ピン       |      |      |

| $R_{θJC(bot)}$       | 接合部からケース(底面)への熱抵抗 | 該当なし       | 該当なし        | 該当なし | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

$V_{DD} = 1.5V \sim 5.5V$ ,  $GND = 0V$ ,  $T_A = -40^\circ C \sim +125^\circ C$ ,

標準値は  $V_{DD} = 3.3V$ ,  $T_A = 25^\circ C$  (特に記述のない限り)

| パラメータ                        |                    | テスト条件                                                                                                                                           | 最小値  | 標準値     | 最大値 | 単位        |

|------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----|-----------|

| <b>電源</b>                    |                    |                                                                                                                                                 |      |         |     |           |

| $V_{DD}$                     | 電源電圧               |                                                                                                                                                 | 1.5  | 5.5     |     | V         |

| $I_{DD}$                     | 電源電流               | $V_{SEL} = 0V, 1.4V$ または $V_{DD}$<br>$V_S = 0V \sim 5.5V$                                                                                       | 37   | 70      |     | $\mu A$   |

| <b>DC 特性</b>                 |                    |                                                                                                                                                 |      |         |     |           |

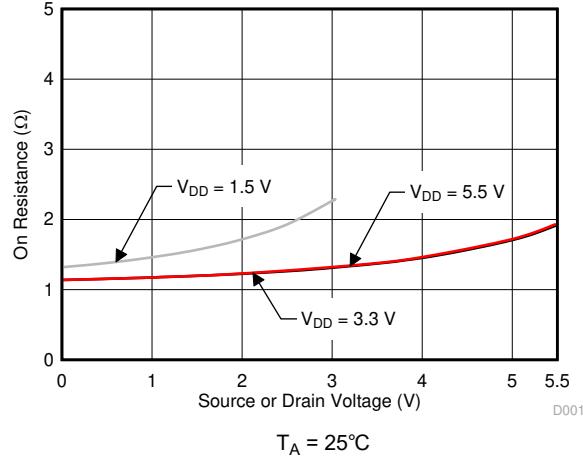

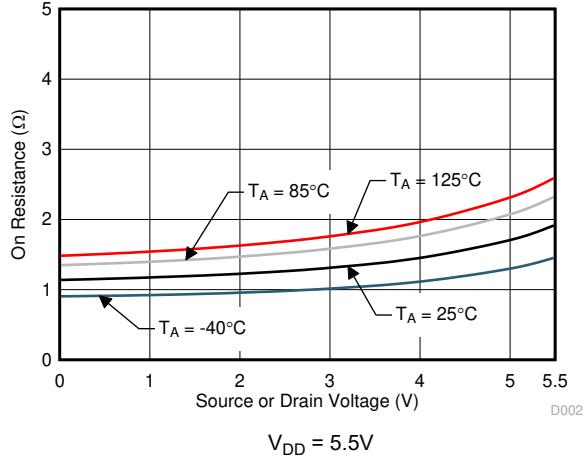

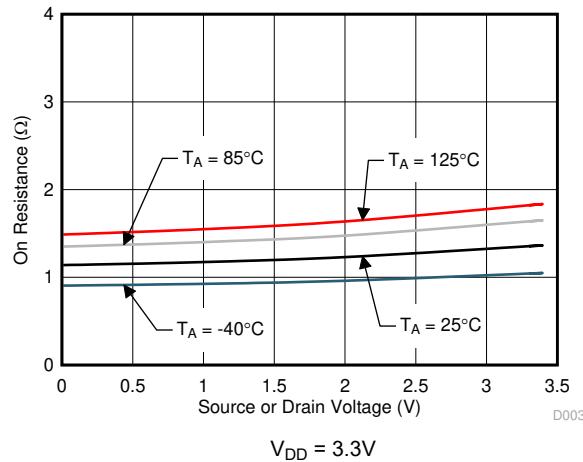

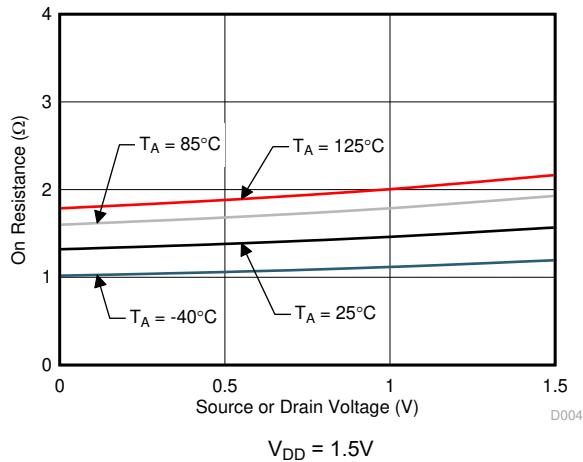

| $R_{ON}$                     | オン抵抗               | $V_S = 0V \sim V_{DD} * 2$<br>$V_{S(max)} = 5.5V$<br>$I_{SD} = 8mA$<br><a href="#">オン抵抗の図を参照</a>                                                | 2    | 4.5     |     | $\Omega$  |

| $\Delta R_{ON}$              | チャネル間のオン抵抗の整合      | $V_S = V_{DD}$<br>$I_{SD} = 8mA$<br><a href="#">オン抵抗の図を参照</a>                                                                                   | 0.07 | 0.28    |     | $\Omega$  |

| $R_{ON(FLAT)}$               | オン抵抗の平坦性           | $V_S = 0V \sim V_{DD}$<br>$I_{SD} = 8mA$<br><a href="#">オン抵抗の図を参照</a>                                                                           | 1    | 1.8     |     | $\Omega$  |

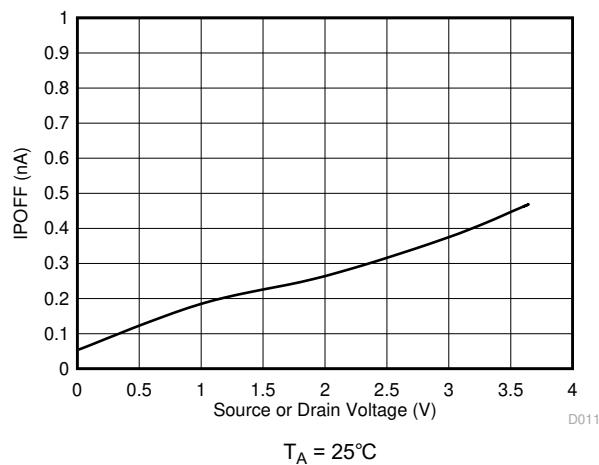

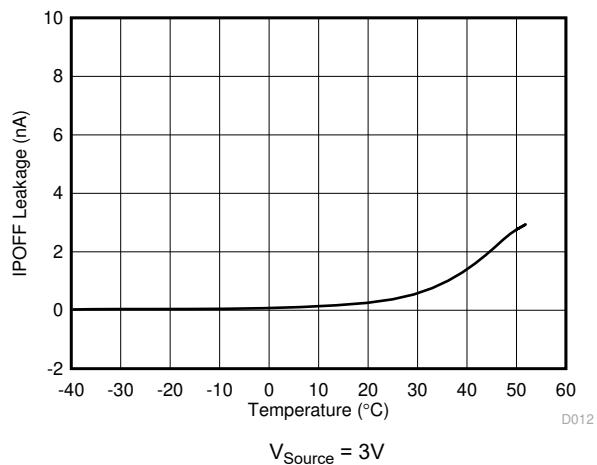

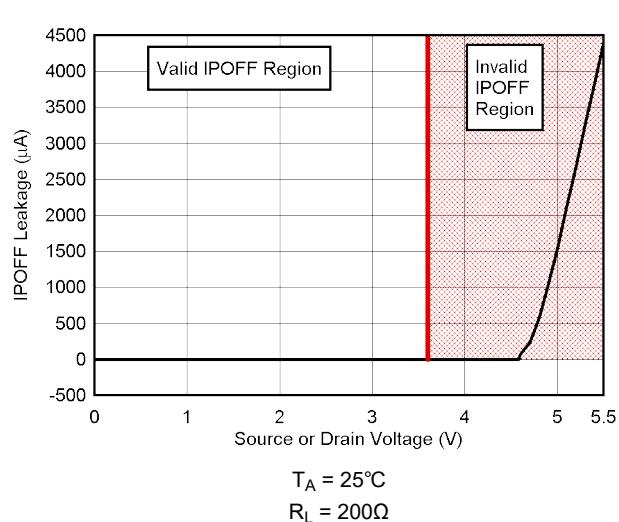

| $I_{POFF}$                   | 電源オフ I/O ピンのリーク電流  | $V_{DD} = 0V$<br>$V_S = 0V \sim 3V$<br>$V_D = 0V$<br>$T_A = 25^\circ C$<br><a href="#">Ipoff リーケージの図を参照</a>                                     | -10  | 0.01    | 10  | nA        |

| $I_{POFF}$                   | 電源オフ I/O ピンのリーク電流  | $V_{DD} = 0V$<br>$V_S = 0V \sim 3.6V$<br>$V_D = 0V$<br><a href="#">Ipoff リーケージの図を参照</a>                                                         | -2   | 0.01    | 2   | $\mu A$   |

| $I_{S(OFF)}$<br>$I_{D(OFF)}$ | OFF のリーク電流         | スイッチ オフ<br>$V_D = 0.8*V_{DD} / 0.2*V_{DD}$<br>$V_S = 0.2*V_{DD} / 0.8*V_{DD}$<br><a href="#">オフ リークの図を参照</a>                                    | -100 | 0.03    | 100 | nA        |

| $I_{D(ON)}$<br>$I_{S(ON)}$   | ON のリーク電流          | スイッチ オン<br>$V_D = 0.8*V_{DD} / 0.2*V_{DD}$ 、S ピン フローティング<br>または<br>$V_S = 0.8*V_{DD} / 0.2*V_{DD}$ 、D ピン フローティング<br><a href="#">オン リークの図を参照</a> | -50  | 0.01    | 50  | nA        |

| <b>ロジック入力</b>                |                    |                                                                                                                                                 |      |         |     |           |

| $V_{IH}$                     | 入力ロジック High        |                                                                                                                                                 | 1.2  | 5.5     |     | V         |

| $V_{IL}$                     | 入力ロジック Low         |                                                                                                                                                 | 0    | 0.45    |     | V         |

| $I_{IH}$                     | 入力 High リーク電流      | $V_{SEL} = 1.8V$ 、 $V_{DD}$                                                                                                                     | 1    | $\pm 2$ |     | $\mu A$   |

| $I_{IL}$                     | 入力 Low リーク電流       | $V_{SEL} = 0V$                                                                                                                                  | 0.2  | $\pm 2$ |     | $\mu A$   |

| $R_{PD}$                     | ロジック入力ピンの内部プルダウン抵抗 |                                                                                                                                                 | 6    |         |     | $M\Omega$ |

| $C_I$                        | ロジック入力容量           | $V_{SEL} = 0V, 1.8V$ 、または $V_{DD}$<br>$f = 1MHz$                                                                                                | 3    |         |     | pF        |

## 5.6 動的特性

$V_{DD} = 1.5V \sim 5.5V$ ,  $GND = 0V$ ,  $T_A = -40^\circ C \sim +125^\circ C$ ,

標準値は  $V_{DD} = 3.3V$ ,  $T_A = 25^\circ C$  (特に記述のない限り)

| パラメータ      |                 | テスト条件                                                                       |            | 最小値 | 標準値   | 最大値 | 単位  |

|------------|-----------------|-----------------------------------------------------------------------------|------------|-----|-------|-----|-----|

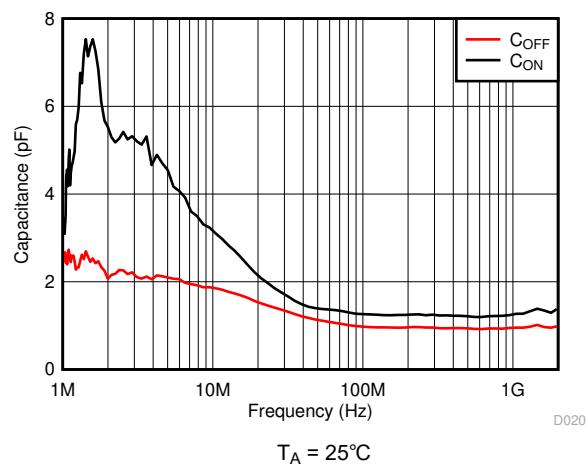

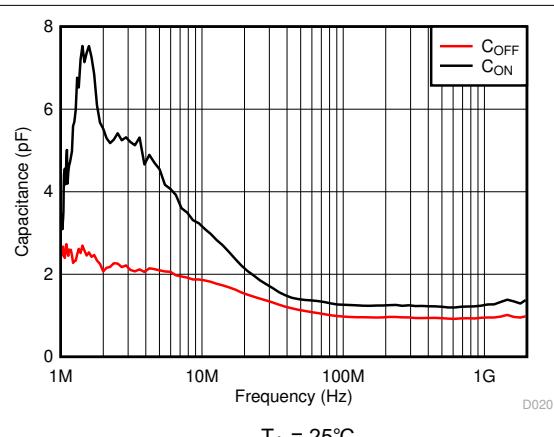

| $C_{OFF}$  | ソース容量とドレイン オフ容量 | $V_S = V_{DD} / 2$<br>$V_{SEL} = 0V$<br>$f = 1MHz$<br>容量の図を参照               | スイッチ<br>オフ |     | 2.5   | 4   | pF  |

| $C_{ON}$   | ソース容量とドレイン オン容量 | $V_S = V_{DD} / 2$<br>$V_{SEL} = V_{DD}$<br>$f = 1MHz$<br>容量の図を参照           | スイッチ<br>オン |     | 3.3   | 6   | pF  |

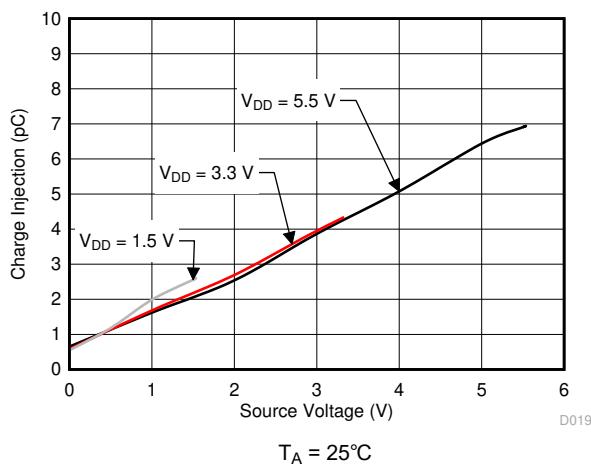

| $Q_C$      | チャージ インジェクション   | $V_S = V_{DD} / 2$<br>$R_S = 0\Omega$ , $C_L = 100pF$<br>チャージ インジェクションの図を参照 | スイッチ<br>オン |     | 2     |     | pC  |

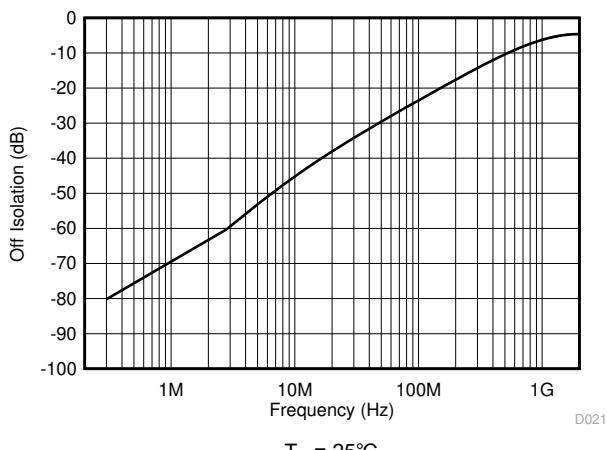

| $O_{ISO}$  | オフ アイソレーション     | $R_L = 50\Omega$<br>$f = 100kHz$<br>オフ絶縁の図を参照                               | スイッチ<br>オフ |     | -90   |     | dB  |

|            |                 | $R_L = 50\Omega$<br>$f = 1MHz$<br>オフ絶縁の図を参照                                 | スイッチ<br>オフ |     | -75   |     | dB  |

| $X_{TALK}$ | チャネル間クロストーク     | $R_L = 50\Omega$<br>$f = 100kHz$<br>クロストークの図を参照                             | スイッチ<br>オン |     | -90   |     | dB  |

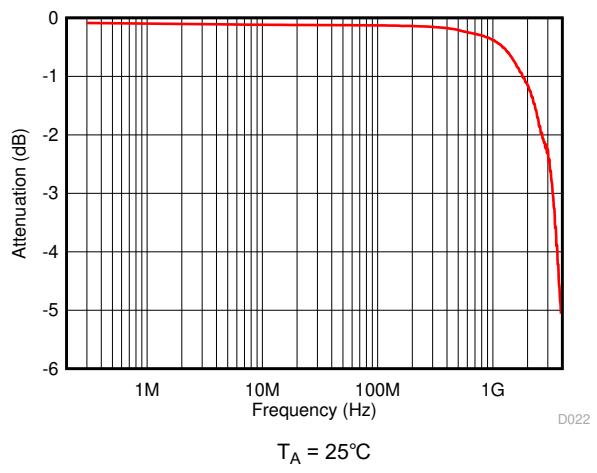

| $BW$       | 帯域幅             | $R_L = 50\Omega$<br>帯域幅の図を参照                                                | スイッチ<br>オン |     | 3     |     | GHz |

| $I_{LOSS}$ | 挿入損失            | $R_L = 50\Omega$<br>$f = 1MHz$<br>帯域幅の図を参照                                  | スイッチ<br>オン |     | -0.12 |     | dB  |

## 5.7 タイミング要件

$V_{DD} = 1.5V \sim 5.5V$ ,  $GND = 0V$ ,  $T_A = -40^\circ C \sim +125^\circ C$ ,

標準値は  $V_{DD} = 3.3V$ ,  $T_A = 25^\circ C$  (特に記述のない限り)

| パラメータ          |                               | テスト条件                                                                                                      |  | 最小値 | 標準値 | 最大値 | 単位 |

|----------------|-------------------------------|------------------------------------------------------------------------------------------------------------|--|-----|-----|-----|----|

| $t_{ON(VDD)}$  | デバイスのターンオン時間 ( $V_{DD}$ から出力) | $V_S = 3.6V$<br>$V_{DD}$ 立ち上がり時間 = 1us<br>$R_L = 200\Omega$ , $C_L = 15pF$<br>Ton(vdd) および Toff(vdd) の図を参照 |  |     | 20  | 60  | μs |

| $t_{OFF(VDD)}$ | デバイスのターンオフ時間 ( $V_{DD}$ から出力) | $V_S = 3.6V$<br>$V_{DD}$ 立ち下がり時間 = 1us<br>$R_L = 200\Omega$ , $C_L = 15pF$<br>Ton(vdd) および Toff(vdd) の図を参照 |  |     | 1.2 | 4   | μs |

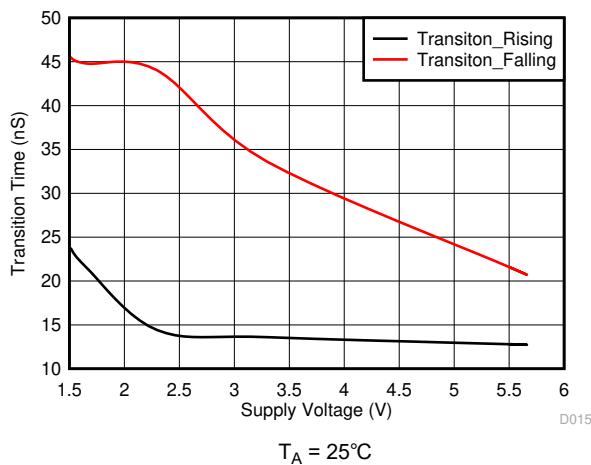

| $t_{TRAN}$     | 制御入力からの遷移時間                   | $V_{DD} = 2.5V \sim 5.5V$<br>$V_S = V_{DD}$<br>$R_L = 200\Omega$ , $C_L = 15pF$<br>遷移時間の図を参照               |  |     | 25  | 55  | ns |

| $t_{TRAN}$     | 制御入力からの遷移時間                   | $V_{DD} < 2.5V$<br>$V_S = V_{DD}$<br>$R_L = 200\Omega$ , $C_L = 15pF$<br>遷移時間の図を参照                         |  |     | 50  | 80  | ns |

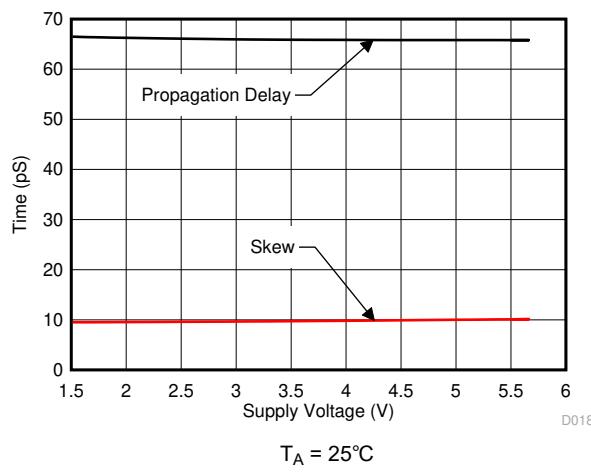

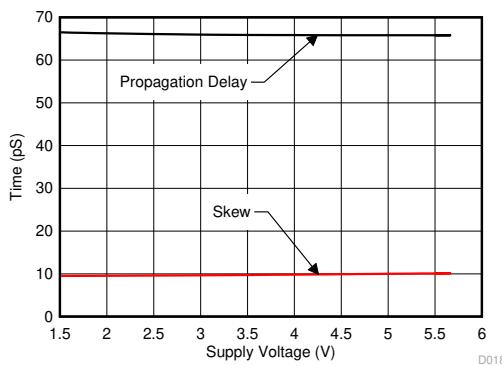

| $t_{SK(P)}$    | チャネル間スキュー                     | Tsk 図を参照                                                                                                   |  |     | 10  |     | ps |

| $t_{PD}$       | 伝搬遅延                          | Tpd 図を参照                                                                                                   |  |     | 67  |     | ps |

## 5.8 代表的特性

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$  (特に記述のない限り)

図 5-1. オン抵抗とソースまたはドレイン電圧との関係

図 5-2. オン抵抗とソースまたはドレイン電圧との関係

図 5-3. オン抵抗とソースまたはドレイン電圧との関係

図 5-4. オン抵抗とソースまたはドレイン電圧との関係

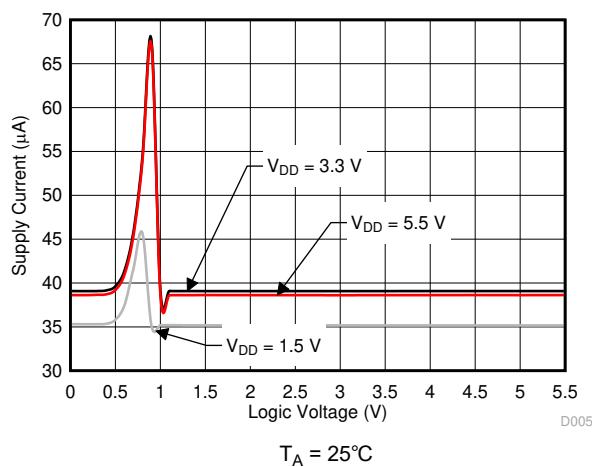

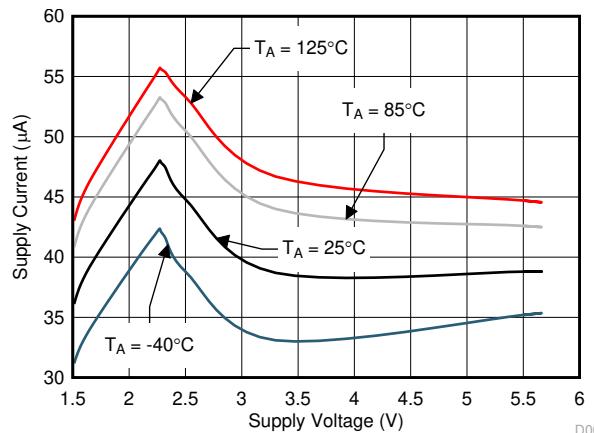

図 5-5. 電源電流とロジック電圧との関係

図 5-6. 電源電流と電源電圧との関係

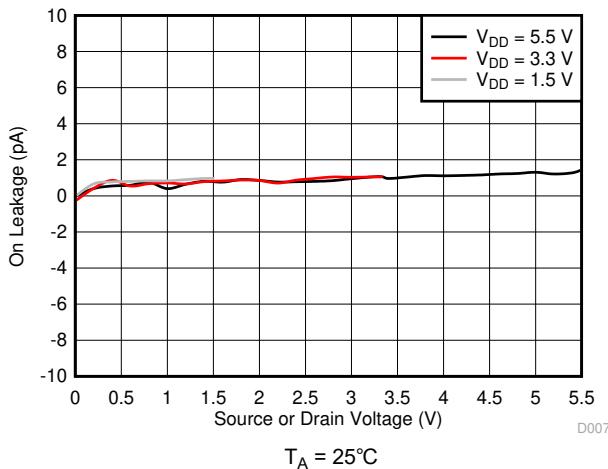

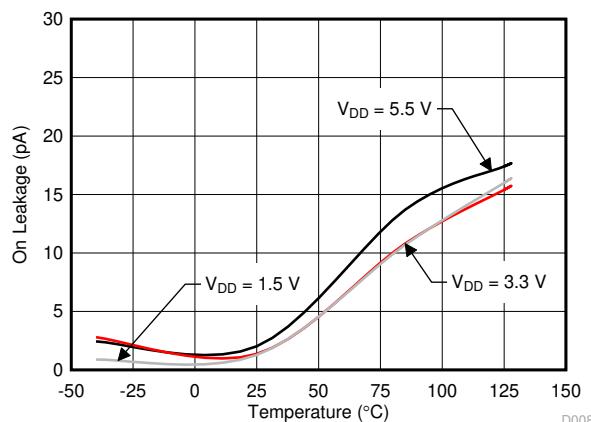

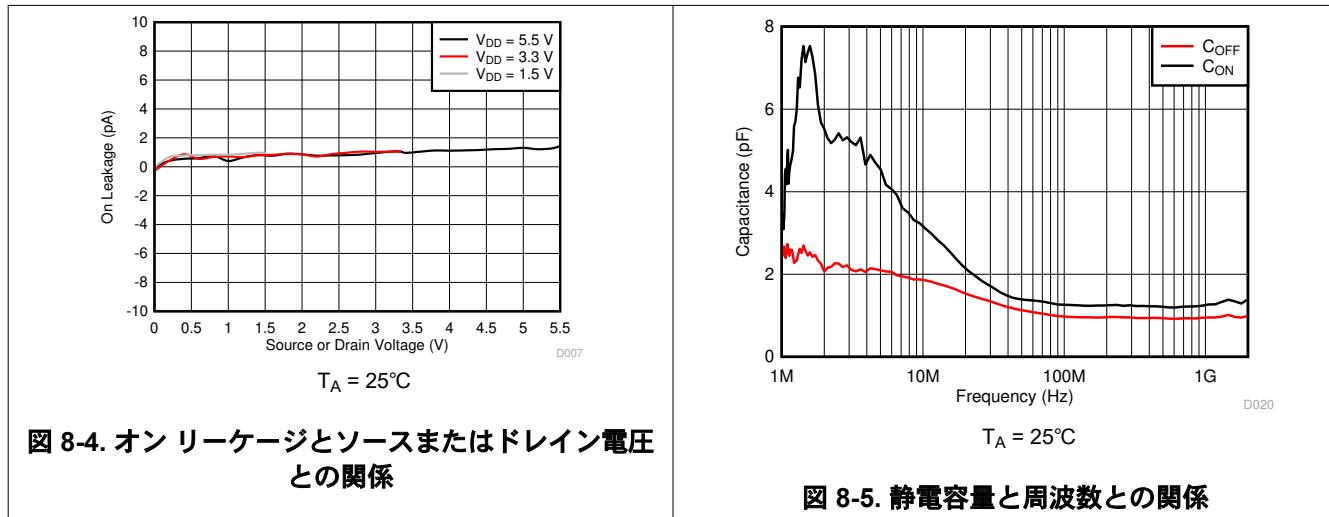

図 5-7. オン リーケージとソースまたはドレイン電圧との関係

図 5-8. オン リーケージと温度との関係

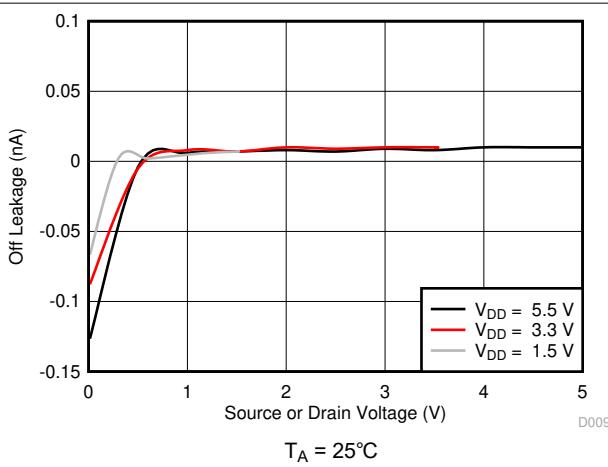

図 5-9. オフ リーケージとソースまたはドレイン電圧との関係

図 5-10. オフ リーケージと温度との関係

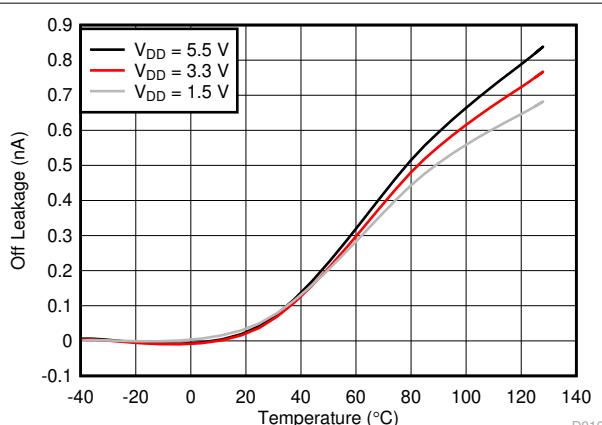

図 5-11. IPOFF リーケージとソースまたはドレイン電圧との関係

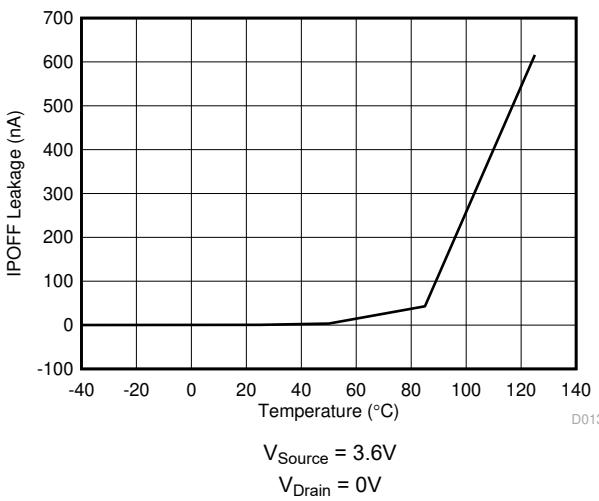

図 5-12. IPOFF ピンのリーク電流と温度との関係

図 5-13. IPOFF ピンのリーク電流と温度との関係

図 5-14. IPOFF リーケージとソースまたはドレイン電圧との関係

図 5-15.  $T_{TRANSITION}$  と電源電圧との関係

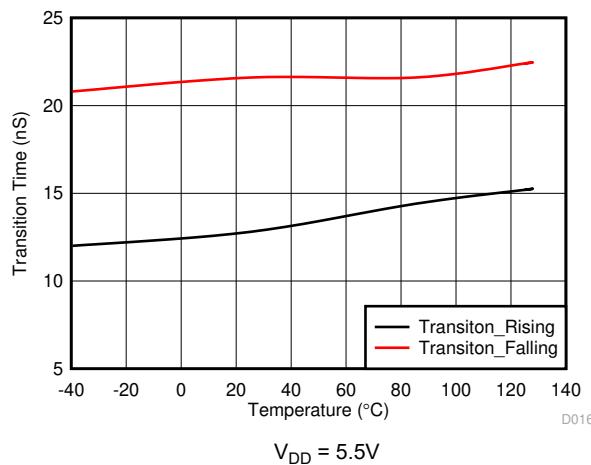

図 5-16.  $T_{TRANSITION}$  と温度との関係

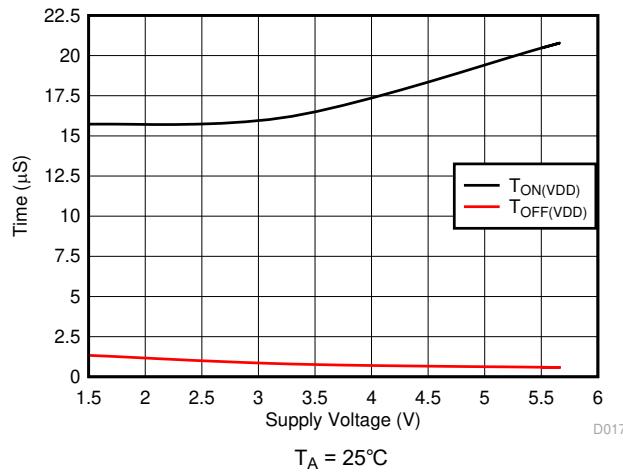

図 5-17.  $T_{ON}(VDD)$  および  $T_{OFF}(VDD)$  と電源電圧との関係

図 5-18. スキューおよび伝搬遅延と電源電圧との関係

図 5-19. チャージインジェクションとソースまたはドレイン電圧との関係

図 5-20. 静電容量と周波数との関係

図 5-21. オフ絶縁と周波数との関係

図 5-22. オン応答と周波数との関係

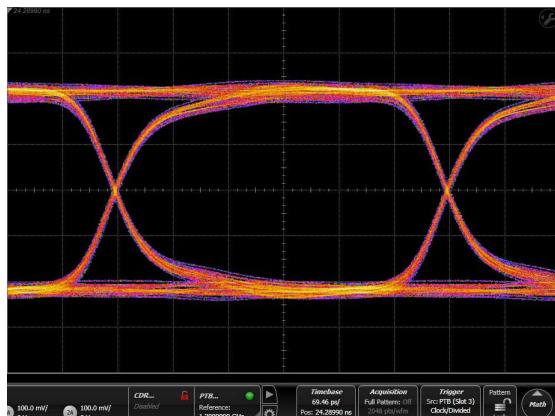

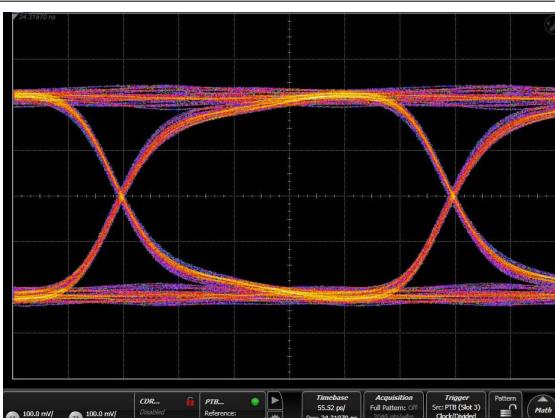

### 5.8.1 アイダイアグラム

$T_A = 25^\circ\text{C}$

バイアス = 1.5V

50Ω 終端

図 5-23. アイ パターン : 2.4Gbps

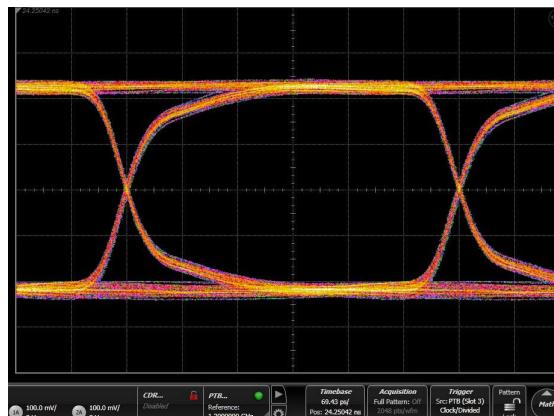

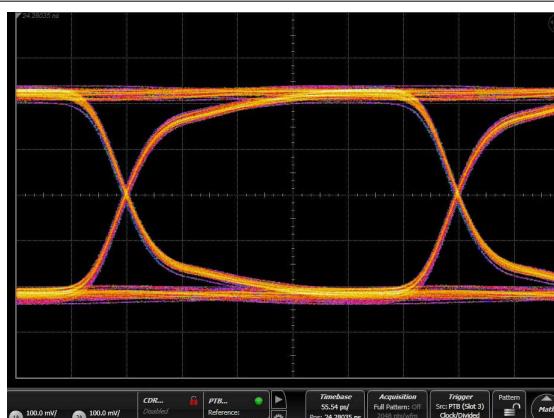

$T_A = 25^\circ\text{C}$

バイアス = 1.5V

50Ω 終端

図 5-24. アイ パターン : 2.4Gbps スルーパス

$T_A = 25^\circ\text{C}$

バイアス = 1.5V

50Ω 終端

図 5-25. アイ パターン : 3Gbps

$T_A = 25^\circ\text{C}$

バイアス = 1.5V

50Ω 終端

図 5-26. アイ パターン : 3Gbps スルーパス

## 6 パラメータ測定情報

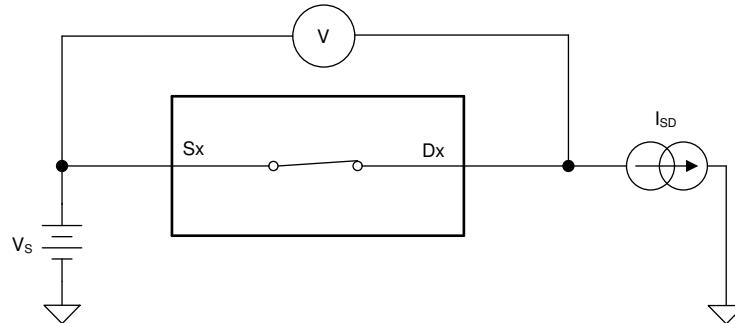

### 6.1 オン抵抗

デバイスのオン抵抗は、デバイスのソースピン ( $S_x$ ) とドレインピン ( $D_x$ ) の間の抵抗値 ( $\Omega$ ) です。オン抵抗は、入力電圧と電源電圧によって変化します。オン抵抗は、記号  $R_{ON}$  を使用して示されます。 $R_{ON}$  の測定時に使用する設定を 図 6-1 に示します。この設定を使用して電圧 ( $V$ ) と電流 ( $I_{SD}$ ) を測定し、 $R_{ON} = V / I_{SD}$  で計算します:

図 6-1. オン抵抗測定時の構成

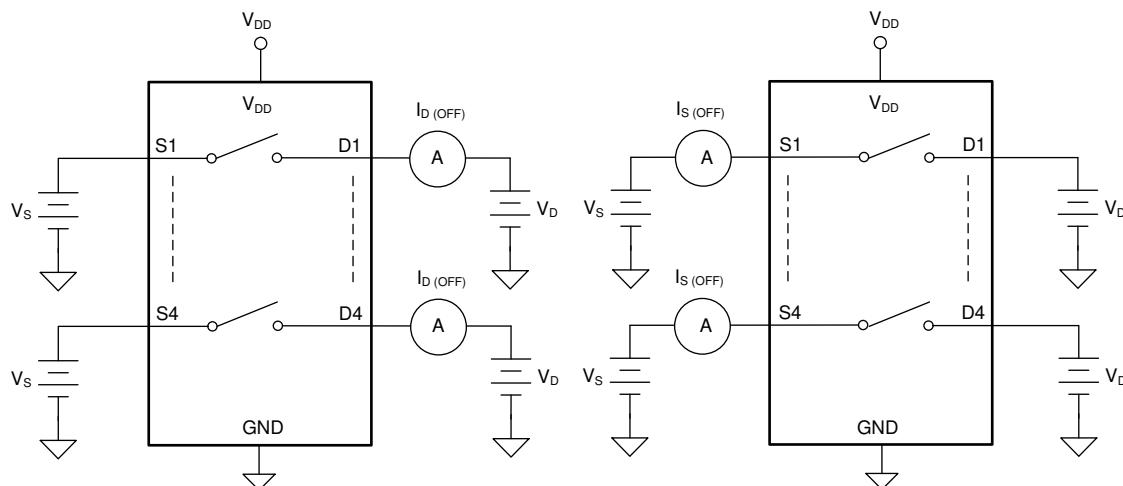

### 6.2 オフリーケ電流

ソース側オフリーケ電流は、スイッチがオフ状態にあるとき、ソースピンに流入する、または流出するリーケ電流と定義されます。この電流は、記号  $I_{S(OFF)}$  を使用して示されます。

ドレイン側オフリーケ電流は、スイッチがオフ状態にあるとき、ドレインピンに流入する、または流出するリーケ電流と定義されます。この電流は、記号  $I_{D(OFF)}$  を使用して示されます。

図 6-2 に、これら 2 種類のオフリーケ電流の測定に使用する設定を示します。

図 6-2. オフリーケ測定時の構成

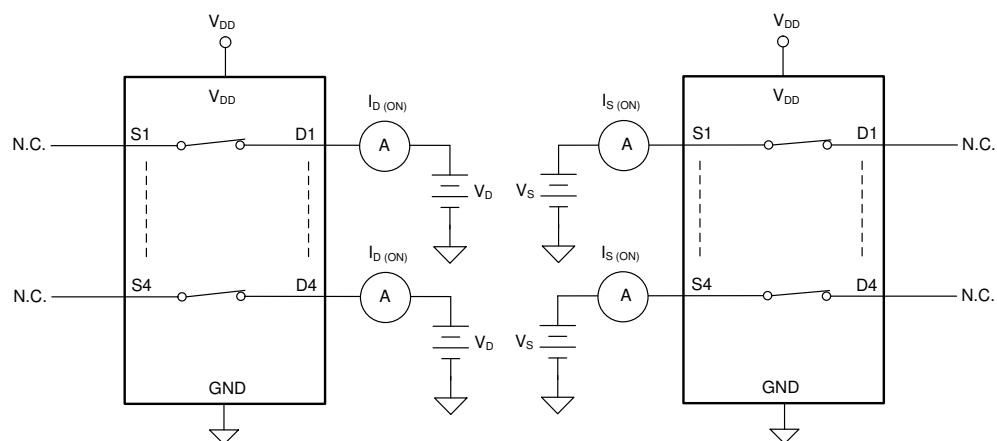

## 6.3 オン リーク電流

ソース側オンリーク電流は、スイッチがオン状態にあるとき、ソースピンに流入する、または流出するリーク電流と定義されます。この電流は、記号  $I_{S(ON)}$  を使用して示されます。

ドレイン側オンリーク電流は、スイッチがオン状態にあるとき、ドレインピンに流入する、または流出するリーク電流と定義されます。この電流は、記号  $I_{D(ON)}$  を使用して示されます。

測定中、ソースピンまたはドレインピンはフローティング状態を維持します。図 6-3 に、オンリーク電流 ( $I_{S(ON)}$  または  $I_{D(ON)}$ ) の測定時に使用される回路構成を示します。

図 6-3. オン リーク測定時の構成

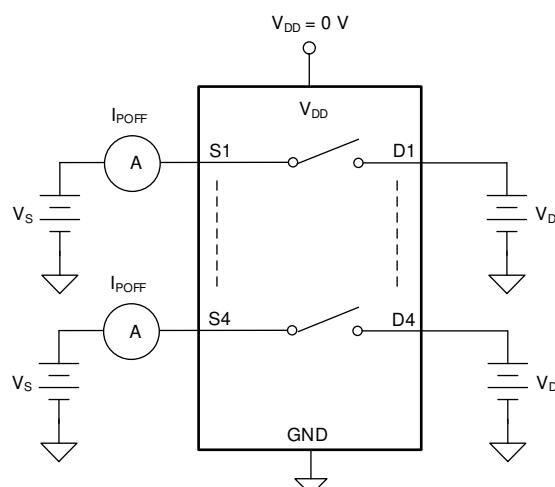

## 6.4 IPOFF リーク電流

IPOFF リーク電流は、デバイスが電源オフ状態にあるとき、ソースピンに流入する、または流出するリーク電流と定義されます。この電流は、記号  $I_{POFF}$  を使用して示されます。

両方の IPOFF リーク電流の測定時に使用する設定を 図 6-4 に示します。

図 6-4. IPOFF リーケージ測定時の設定

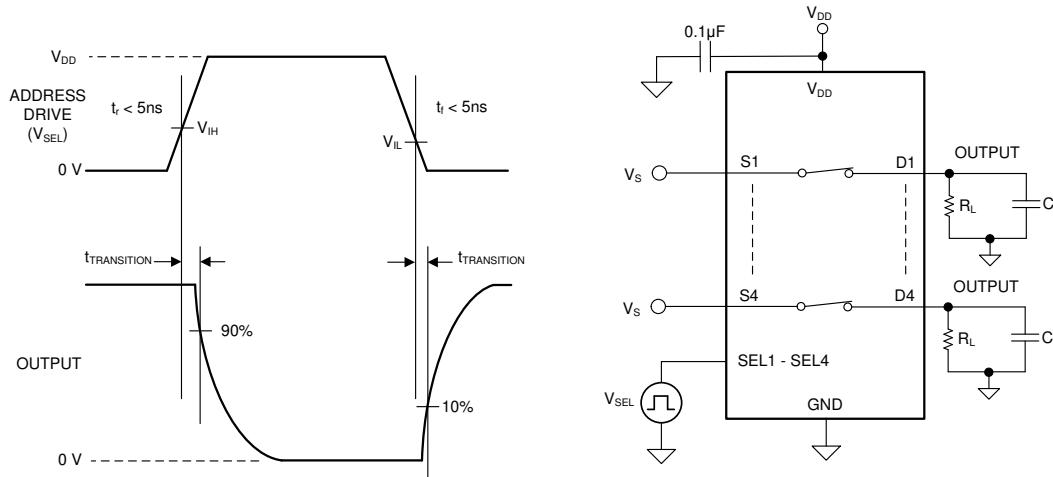

## 6.5 遷移時間

遷移時間は、制御選択信号がロジック スレッショルドを上回った、または下回った後に、デバイスの出力が 10% 上昇または降下するまでに要する時間として定義されます。デバイスのタイミングは、10% の遷移時間の測定値を使用します。負荷抵抗と負荷容量からの時定数を遷移時間に追加して、システム レベルのタイミングを計算できます。図 6-5 に、遷移時間 (記号  $t_{TRANSITION}$ ) の測定に使用する構成を示します。

図 6-5. 遷移時間測定時の構成

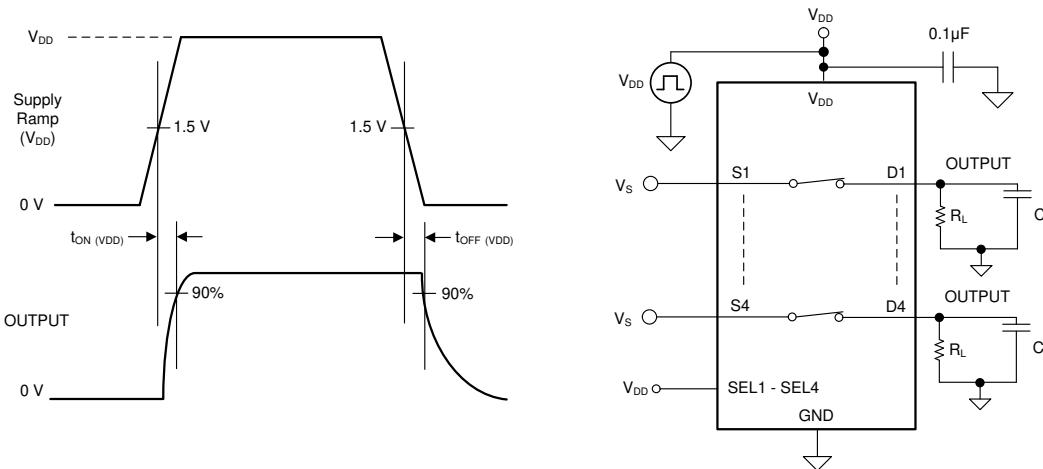

## 6.6 $T_{ON(VDD)}$ および $T_{OFF(VDD)}$ 時間

$T_{ON(VDD)}$  時間は、電源が電源スレッショルドを超えた後、デバイスの出力信号が 90% に上昇するまでの所要時間として定義されます。90% の測定値を使用して、システムでデバイスがオンになるタイミングを提供します。負荷抵抗と負荷容量からの時定数をターンオン VDD 時間に追加することで、システム レベルのタイミングを計算できます。図 6-6 に、遷移時間 (記号  $t_{ON(VDD)}$ ) の測定に使用する設定を示します。

$T_{OFF(VDD)}$  時間は、イネーブル信号が電源スレッショルドを下回った後、デバイスの出力信号が 90% に低下するまでの所要時間として定義されます。90% の測定値を使用して、システムでデバイスがオフになるタイミングを提供します。負荷抵抗と負荷容量からの時定数をターンオフ VDD 時間に追加することで、システム レベルのタイミングを計算できます。図 6-6 に、遷移時間 (記号  $t_{OFF(VDD)}$ ) の測定に使用する設定を示します。

図 6-6. ターンオン VDD およびターンオフ VDD 時間の測定に使用する設定

## 6.7 伝搬遅延

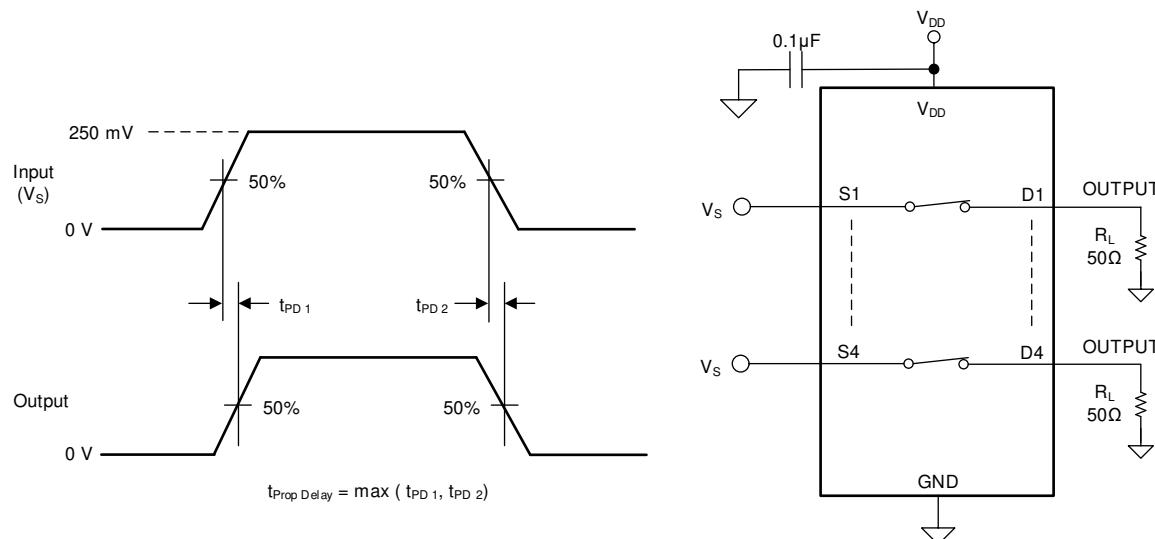

伝搬遅延は、入力信号が 50% のスレッショルドを上回った、または下回った後に、デバイスの出力が 50% に上昇または降下するまでに要する時間として定義されます。図 6-7 に、伝搬遅延 (記号  $t_{PD}$ ) の測定に使用する構成を示します。

図 6-7. 伝搬遅延測定時の構成

## 6.8 スキュー

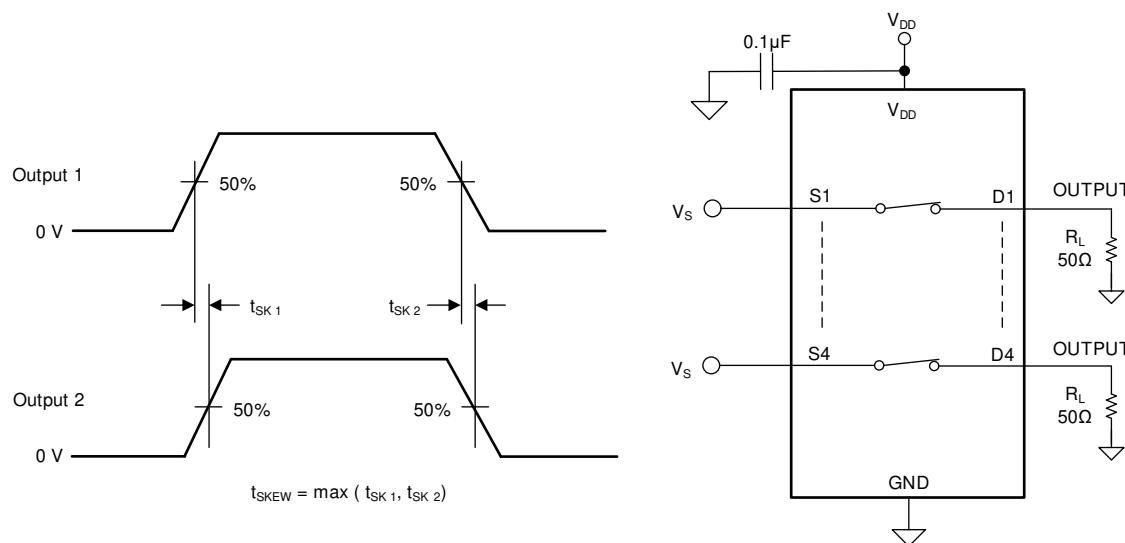

スキューは、同じデバイス内の任意の 2 つの出力の伝搬遅延の差として定義されます。スキュー測定は、入力信号が同時に切り替わるとき、1 つのチャネルの出力が立ち上がりまたは立ち下がりで 50% を通過してから、2 番目のチャネルの出力が立ち上がりまたは立ち下がりで 50% のスレッショルドを通過するまで行われます。図 6-8 に、スキュー (記号  $t_{SK}$ ) の測定に使用する設定を示します。

図 6-8. スキュー測定設定

## 6.9 チャージ インジェクション

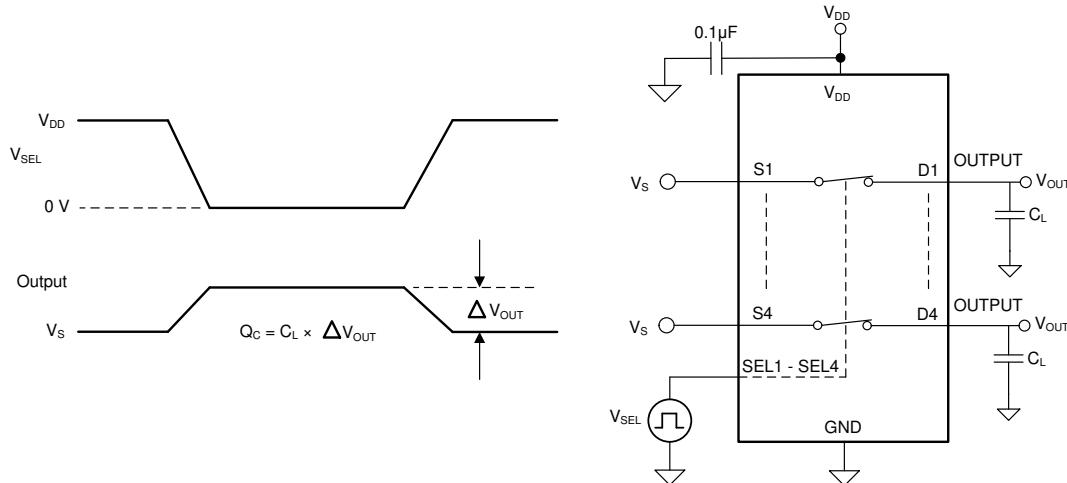

ゲート信号の立ち下がりエッジまたは立ち上がりエッジ中にデバイスのソースまたはドレインに注入される電荷の量をチャージ インジェクションと呼び、 $Q_C$  という記号で表します。図 6-9 に、ソース ( $S_x$ ) からドレイン ( $D_x$ ) に向けた電荷注入の測定に使用する設定を示します。

図 6-9. 電荷注入測定時の設定

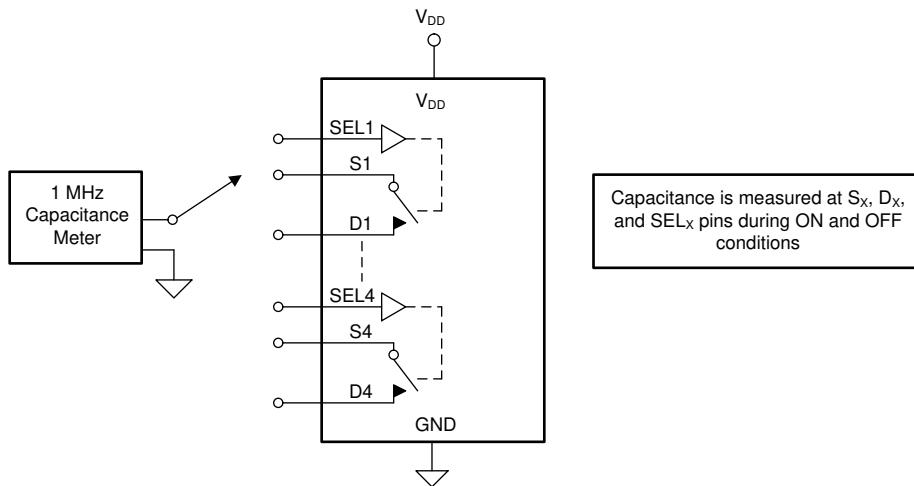

## 6.10 容量

本デバイスの寄生容量は、ソース ( $S_x$ )、ドレイン ( $D_x$ )、セレクト ( $SEL_x$ ) ピンでキャプチャします。容量は、オンとオフの両方の状態で測定され、記号  $C_{ON}$  および  $C_{OFF}$  によって示されます。図 6-10 に、静電容量を測定する際の設定を示します。

図 6-10. 静電容量測定時の設定

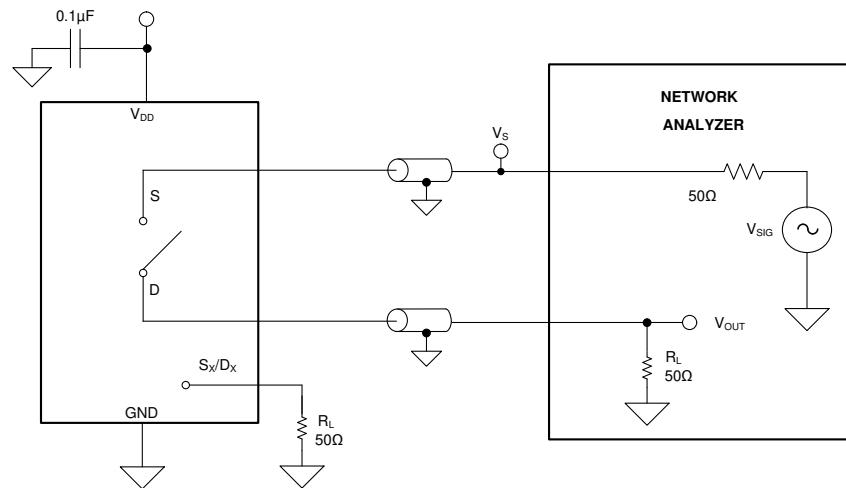

## 6.11 オフ アイソレーション

オフ絶縁は、オフチャネルのソースピン (**Sx**) に信号が印加された場合に、そのデバイスのドレインピン (**Dx**) に現れる信号の比率として定義されます。測定の特性インピーダンス  $Z_0$  は  $50\Omega$  です。[図 6-11](#) に、オフ絶縁の測定に使用する設定を示します。オフ絶縁の式を使用して、オフ絶縁を計算します。

図 6-11. オフ絶縁測定時の設定

$$\text{Off Isolation} = 20 \cdot \log\left(\frac{V_{OUT}}{V_S}\right) \quad (1)$$

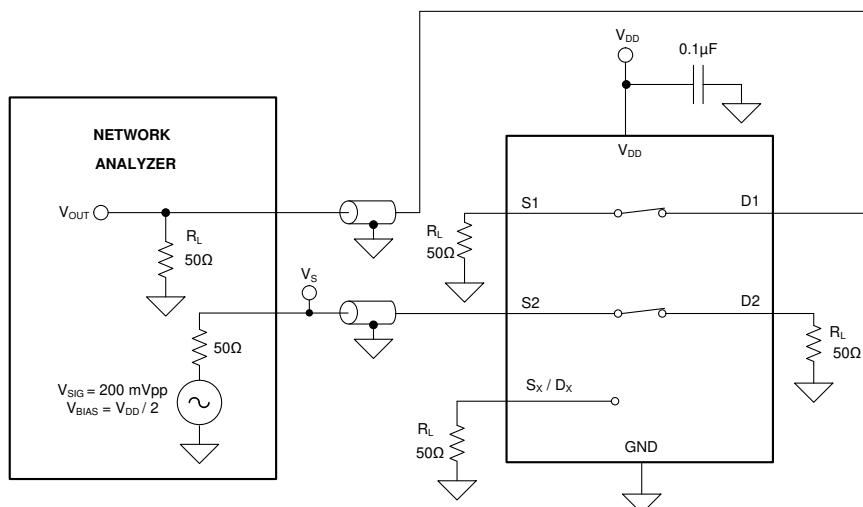

## 6.12 チャネル間クロストーク

クロストークは、オンチャネルのソースピン (**Sx**) に信号が印加された場合に、他のチャネルのドレインピン (**Dx**) に現れる信号の比率として定義されます。測定の特性インピーダンス  $Z_0$  は  $50\Omega$  です。[図 6-12](#) に、クロストークの測定を行う際の設定と、クロストークの計算に使用する式を示します。

図 6-12. チャネル間クロストーク測定時の設定

$$\text{Channel-to-Channel Crosstalk} = 20 \cdot \log\left(\frac{V_{\text{OUT}}}{V_s}\right) \quad (2)$$

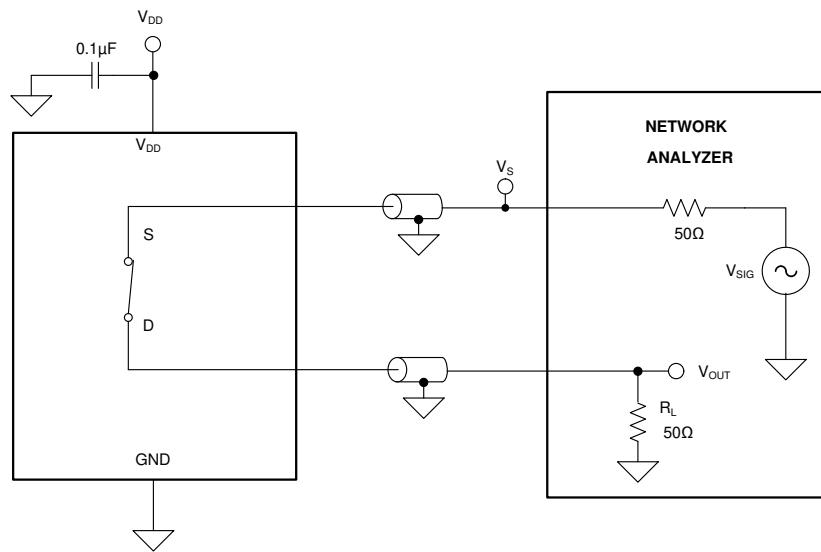

### 6.13 帯域幅

帯域幅は、入力をオンチャネルのソースピン ( $S_x$ ) に印加し、出力がデバイスのドレインピン ( $D_x$ ) で測定された場合に減衰量が 3dB 未満である周波数の範囲として定義されます。測定の特性インピーダンス  $Z_0$  は  $50\Omega$  です。図 6-13 に、帯域幅を測定する際の設定を示します。

図 6-13. 帯域幅測定時の設定

## 7 詳細説明

### 7.1 概要

TMUX1511 は、最大 3.6V の電源オフ保護機能を備えた高速 1:1 (SPST) 4 チャネル スイッチです。動作電圧範囲が 1.5V ~ 5.5V と広いため、サーバーや通信機器から産業用途まで、広範なアプリケーションに使用できます。このデバイスは、ソース (Sx) ピンとドレイン (Dx) ピンでの双方向アナログおよびデジタル信号をサポートしています。このスイッチは広帯域幅のため、出力での高速信号の減衰がわずかまたはまったく発生せず、エッジおよび位相の歪み、さらに伝搬遅延を最小限に抑えて通過できます。

選択 (SELx) ピンはアクティブ HIGH ロジック ピンで、デバイスのソース (Sx) ピンとドレイン (Dx) ピンの間の接続を制御します。TMUX1511 の各チャネルは、関連する選択ピンを使用して個別に制御できます。または、4 つの選択ピンをすべて互いに接続することで、すべてのチャネルを 1 つの GPIO で同時に制御できます。フェイルセーフ ロジック回路により、電源ピンよりも前にロジック制御ピンに電圧が印加されるため、デバイスへの損傷の可能性が避けられます。すべてのロジック制御入力のスレッショルドは 1.8V ロジック互換で、有効な電源電圧範囲で動作していれば、TTL と CMOS の両方のロジックと互換性が保証されます。

TMUX1511 の信号パスの最大 3.6V の電源オフ保護機能は、電源電圧が取り除かれたとき ( $V_{DD} = 0V$ ) に絶縁を行います。この保護機能がない場合、内部 ESD ダイオード経由でスイッチから電源レールに電流が逆流し、システムに損傷を引き起こすことがあります。

### 7.2 機能ブロック図

### 7.3 機能説明

#### 7.3.1 双方向動作

TMUX1511 は、ソース (Sx) からドレイン (Dx)、またはドレイン (Dx) からソース (Sx) への双方向で、良好な動作を提供します。各チャネルは両方向で非常に類似した特性を持ち、アナログ信号とデジタル信号の両方をサポートします。

#### 7.3.2 電源電圧範囲外での動作

TMUX1511 に 1.5V ~ 5.5V の電源を供給する場合、信号パスの有効な入出力電圧は、GND から  $V_{DD} \times 2$  の範囲で、最大入出力電圧は 5.5V です。

事例 1: TMUX1511 に 1.5V の電源を供給する場合、信号範囲は 0V ~ 3V です。

事例 2: TMUX1511 に 3V の電源を供給する場合、信号範囲は 0V ~ 5.5V です。

事例 3: TMUX1511 に 5.5V の電源を供給する場合、信号範囲は 0V ~ 5.5V です。

この例で言及していない他の電圧レベルは、電源電圧が推奨動作条件の 1.5V ~ 5.5V の範囲内である限り、電源電圧範囲外での動作をサポートします。

### 7.3.3 1.8V ロジック互換入力

TMUX1511 には 1.8V ロジック互換制御入力があります。 $V_{DD}$  電圧にかかわらず、制御入力スレッショルドは固定されたままとなり、外部変換器は必要なく 1.8V プロセッサ GPIO から TMUX1511 を制御できます。これにより、スペースと BOM コストの両方を削減できます。[『1.8V ロジックのマルチプレクサとスイッチを使用した設計の簡素化』](#)を参照してください。

### 7.3.4 電源オフ保護機能

TMUX1511 の信号バスの最大 3.6V の電源オフ保護機能は、電源電圧が取り除かれたとき ( $V_{DD} = 0V$ ) に絶縁を行います。TMUX1511 が電源オフのとき、デバイスの I/O はハイインピーダンス状態を維持します。電源オフ保護機能により、信号バスの電源シーケンスが不要になり、システムの複雑さが最小限に抑えられます。デバイスの性能は、「電気的仕様」に記載されているリーク性能の範囲内に維持されます。電源オフ保護機能の詳細については、[『電源オフ保護を備えた信号スイッチで電源シーケンスを不要に』](#)を参照してください。

### 7.3.5 フェイルセーフ ロジック

TMUX1511 は、制御入力ピン (SELx) でフェイルセーフ ロジックをサポートしているため、電源ピンの状態に関係なく、最大 5.5V での動作が可能です。この機能により、電源ピンよりも先に制御ピンに電圧が印加されるため、デバイスへの損傷の可能性が避けられます。フェイルセーフ ロジックにより、ロジック制御ピンの電源シーケンスが不要になり、システムの複雑さが最小限に抑えられます。たとえば、フェイルセーフ ロジック機能を使用すると、 $V_{DD} = 0V$  の間、TMUX1511 の選択ピンを 5.5V に上昇させることができます。また、この機能により TMUX1511 は  $V_{DD} = 1.5V$  での動作が可能になり、選択ピンは最大 5.5V で他のデバイスのロジック レベルと接続できます。

### 7.3.6 低静電容量

TMUX1511 は、ソース ピンとドレイン ピンのオンとオフの両方の状態で非常に小さい静電容量を実現しています。TMUX1511 は低静電容量の仕様のため、サンプルおよびホールド回路、オペアンプのフィードバック パスなどのアプリケーションで使用できます。静電容量が小さいので、スイッチを帰還回路に接続したときに、アンプ回路の大きなオーバーシュートとリングを低減できます。さらに、静電容量が小さいことで、オン抵抗とオン静電容量によって形成されるスイッチ時定数が短くなり、システムのセトリング タイムが短縮されます。低静電容量の利点について詳しくは、[『低  \$C\_{ON}\$  マルチプレクサにおける安定性の問題の改善』](#)を参照してください。

### 7.3.7 内蔵プルダウン抵抗

TMUX1511 では、内部の弱いプルダウン抵抗 ( $6M\Omega$ ) が GND に接続されており、ロジックピンがフローティングのままにならないようにしています。この機能は、最大 4 つの外部コンポーネントを統合し、システムのサイズとコストを節約します。

## 7.4 デバイスの機能モード

選択 (SELx) ピンはアクティブ HIGH ロジック ピンで、デバイスのソース (Sx) ピンとドレイン (Dx) ピンの間の接続を制御します。TMUX1511 には GND への弱いプルダウン抵抗 ( $6M\Omega$ ) が内蔵されているため、スイッチがディスエーブルされたときに電源オンになります。TMUX1511 の特定の選択ピンが High にプルされると、対応するスイッチはソースからドレインに導通します。選択ピンのいずれかが Low にプルされると、対応するスイッチは開放状態 (ハイインピーダンス) になります。TMUX1511 の各チャネルは、関連する選択ピンを使用して個別に制御できます。または、4 つの選択ピンをすべて互いに接続することで、すべてのチャネルを 1 つの GPIO で同時に制御できます。

## 7.5 真理値表

表 7-1 に、TMUX1511 の真理値表を示します。

表 7-1. TMUX1511 真理値表

| SELx | Sx / Dx: 状態     |

|------|-----------------|

| 0    | ハイインピーダンス (OFF) |

| 1    | 導通 (ON)         |

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TMUX15xx ファミリは、広い動作電源電圧 (1.5V ~ 5.5V) と動作温度 (-40°C ~ +125°C) の全域で高速なシステム性能を実現します。TMUX1511 は、[セクション 7.3.3、電源電圧を超える入力電圧、フェイルセーフ ロジック](#) など、システム性能を向上させる多数の機能に対応しています。上記の特長を持つ TMUX15xx ファミリは、マルチプレクサおよびスイッチとして多目的に使用でき、これによりシステムの複雑さ、基板サイズ、およびシステム全体でのコスト低減が行えます。

### 8.2 代表的なアプリケーション

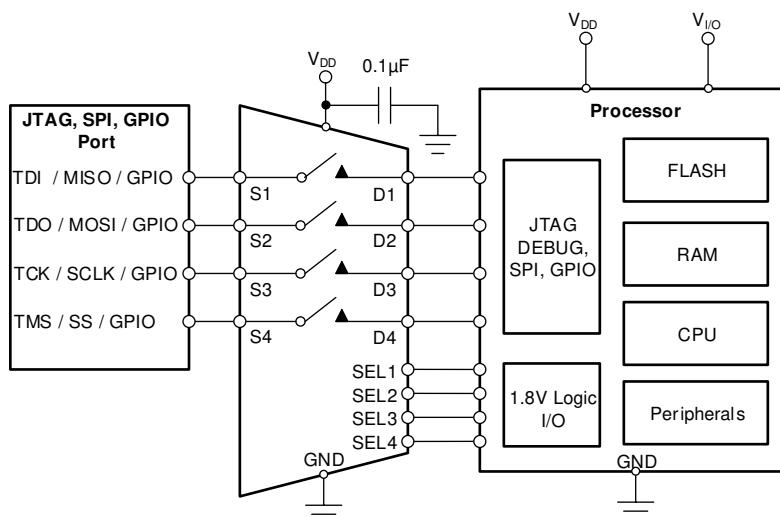

#### 8.2.1 プロトコル / 信号の絶縁

この TMUX1511 機能を利用するが有用なアプリケーションの 1 つは、**JTAG**、**SPI**、標準的な **GPIO** 信号など、既存のプロセッサまたはマイコンから各種プロトコルを絶縁することです。本デバイスは電源供給時に非常に優れた絶縁性能を発揮します。電源オフ保護のもう 1 つの利点は、ホットスワップや活線挿入アプリケーションで電源シーケンスを不要にして、システムの複雑さを最小化できることです。

図 8-1. JTAG、SPI、GPIO 信号の絶縁

##### 8.2.1.1 設計要件

この設計例では、表 2 に記載されているパラメータを使用します。

表 8-1. 設計パラメータ

| パラメータ             | 値         |

|-------------------|-----------|

| 電源電圧 ( $V_{DD}$ ) | 3.3V      |

| 入力 / 出力信号範囲       | 0V ~ 3.3V |

| 制御入力のロジック スレッショルド | 1.8V 互換   |

### 8.2.1.2 詳細な設計手順

TMUX1511 の動作には、電源デカップリング コンデンサを除き、一切の外部コンポーネントが不要です。このデバイスには GND への弱いプルダウン抵抗 ( $6\text{M}\Omega$ ) が内蔵されており、スイッチがディスエーブルされたときに電源オンになります。スイッチをパス スルーするすべての入力信号は、信号範囲や連続電流を含め、TMUX1511 の推奨動作条件内に収まっている必要があります。この設計例では、電源が  $3.3\text{V}$  の場合、デバイスに電力が供給されると信号範囲は  $0\text{V} \sim 3.3\text{V}$  になります。この例では、機能を活用することもでき、 $V_{DD} = 0\text{V}$  のとき、入力範囲は  $0\text{V} \sim 3.3\text{V}$  です。最大連続電流は  $25\text{mA}$  です。電圧範囲と高速能力を備えているため、この TMUX1511 サンプルは標準的なアプリケーションで  $100\text{MHz}$  の最大値を超える JTAG および SPI アプリケーションでの使用に適しています。

### 8.2.1.3 アプリケーション曲線

スイッチまたはマルチプレクサを使用して信号を渡すときの 2 つの重要な仕様は、デバイスの伝搬遅延とスキューです。

図 8-2. 伝搬遅延とスキュー測定

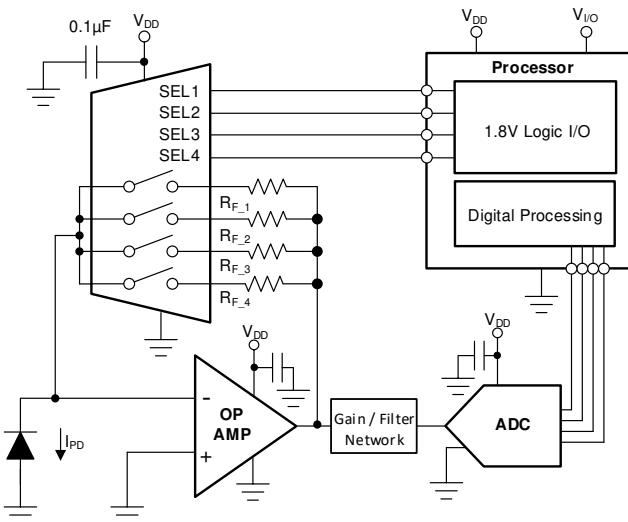

### 8.2.2 トランスインピーダンス アンプの帰還制御

スイッチとマルチプレクサは、構成可能なゲイン制御を実現するため、アンプ回路のフィードバック パスで一般的に使用されます。スイッチ パスごとにさまざまな抵抗値を使用することで、TMUX1511 のシステムは複数のゲインを設定できます。外部抵抗を使用するか、または 1 チャネルを常に閉じていることにより、アンプが開ループ構成で動作することを防止します。フォトダイオード用のトランスインピーダンス アンプ (TIA) は一般的な回路であり、マルチチャネル スイッチを使用したゲイン制御を必要とし、フォトダイオードの出力電流を、MCU またはプロセッサの電圧に変換します。TMUX1511 のリーク電流、静電容量、チャージ インジェクション性能は、ゲイン制御用のデバイスを選択するときに評価する重要な仕様です。

図 8-3. TIA 回路のマルチプレクシング ゲイン

#### 8.2.2.1 設計要件

この設計例では、表 3 に記載されているパラメータを使用します。

表 8-2. 設計パラメータ

| パラメータ             | 値        |

|-------------------|----------|

| 電源電圧 ( $V_{DD}$ ) | 5V       |

| 入力 / 出力信号範囲       | 0μA～10μA |

| 制御入力のロジック スレッショルド | 1.8V 互換  |

#### 8.2.2.2 詳細な設計手順

フォトダイオードは一般に、吸収する光の量に応じて数百 pA から数十 μA の範囲の電流を出力します。TMUX1511 の標準オンリーケ電流は 10pA 未満であり、フルスケール 10μA 信号の 1% 以内の精度を達成できます。TMUX1511 はオンおよびオフ容量が小さいため、アンプの出力の総容量が最小化され、システムの安定性が向上します。容量が小さいと、システムのオーバーシュートとリンギングが減少し、位相マージンが 45° 以上ない場合、アンプ回路が不安定になる可能性があります。位相マージンとオーバーシュート比率の計算の詳細については、『[低  \$C\_{ON}\$  マルチプレクサにおける安定性の問題の改善](#)』を参照してください。

### 8.2.2.3 アプリケーション曲線

## 9 電源に関する推奨事項

TMUX1511 は、1.5V~5.5V の広範囲な電源電圧で動作します。絶対最大定格を超えないようにしてください。記載されている定格を超えるストレスはデバイスに永続的な損傷を与える可能性があります。

電源のバイパスによって、ノイズ マージンが向上し、 $V_{DD}$  から他の部品へのスイッチング ノイズの伝搬を防止します。最適な性能を実現するには、良好な電源デカップリングが重要です。電源のノイズ耐性を向上させるため、 $V_{DD}$  からグランドに対し、 $0.1\mu F \sim 10\mu F$  の範囲の電源デカップリング コンデンサを使用してください。バイパスコンデンサは、デバイスの電源ピンのできるだけ近くに配置し、低インピーダンスで接続します。テキサス・インスツルメントでは、電源デカップリング用として、ESR (等価直列抵抗) および ESL (インダクタンス) が低い特性を持つ、積層セラミック チップ コンデンサ (MLCC) の使用を推奨しています。非常に敏感なシステムや、過酷なノイズ環境のシステムでは、コンデンサとデバイスのピン間の接続にビアの使用を避けることで、ノイズ耐性を改善できる場合があります。並列に複数のビアを使用すると、全体的なインダクタンスが低減でき、さらにグランド プレーンへの接続も改善されます。

## 10 レイアウト

### 10.1 レイアウトのガイドライン

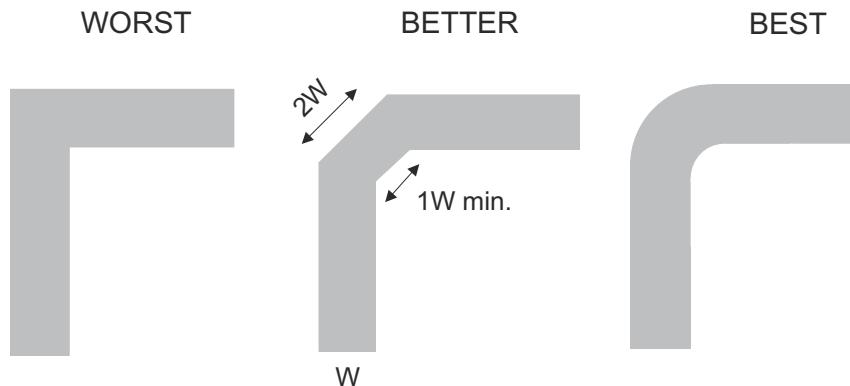

PCB パターンが  $90^\circ$  の角度でコーナーを曲がると、反射が発生する可能性があります。反射は主に、パターンの幅の変化が原因で発生します。曲がりの頂点では、パターン幅が幅の 1.414 倍に増加します。これにより、伝送ラインの特性のアップセットが向上します。特に、パターンの分散静電容量と自己インダクタンスが増加し、反射が発生します。すべての PCB トレースが直線的であるとは限らないため、一部のパターンはコーナーを曲がる必要があります。図 10-1 に、コーナーを丸める斬新で優れた方法を示します。最後の例 (BEST) のみが一定のパターン幅を維持し、反射を最小限に抑えます。

図 10-1. パターン例

高速信号は、ビア数とコーナー数を最小にして配線し、信号の反射とインピーダンスの変化を低減します。ビアを使用する必要がある場合は、周囲の空間距離を大きく確保することで、そこでの静電容量を最小化します。各ビアは、信号の伝送ラインにおいて連続性を損ない、また、ボードの他の層からの干渉を拾う可能性を高くしています。高周波信号向けのテストポイントを設計する際、スルーホール ピンの使用は推奨されません。

水晶振動子、発振器、クロック信号ジェネレータ、スイッチング レギュレータ、マウントホール、磁気デバイス、クロック信号を使用または複製する IC の下または近くに高速信号トレースを配線しないでください。

高速信号トレースでは、信号の反射を引き起こすため、スタブは使用しないでください。

すべての高速信号トレースは、中断なしに連続的な GND プレーン上に配線します。

通常、平面分割で見られるアンチエッティング上で交差しないようにします。

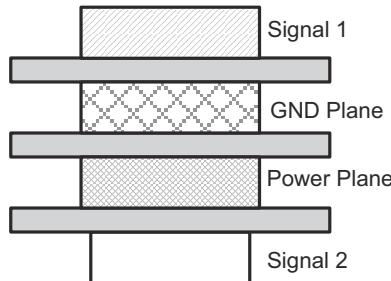

高周波で動作する場合は、4 層以上のプリント基板をお勧めします。図 10-2 に示すように、グランドと電源層で 2 つの信号層を分離しています。

図 10-2. レイアウト例

信号トレースの大部分は、単一の層、できれば信号 1 上に配線する必要があります。この層のすぐ隣には、切れ目がないソリッド GND プレーンを配置する必要があります。グランドまたは電源プレーンの分割をまたいで信号トレースを配線する

ことは避けてください。分割されたプレーンをまたぐ配線が避けられない場合は、十分なデカップリングを使用する必要があります。信号ビアの数を最小化すると、高周波でのインダクタンスを小さくし、EMI を低減できます。

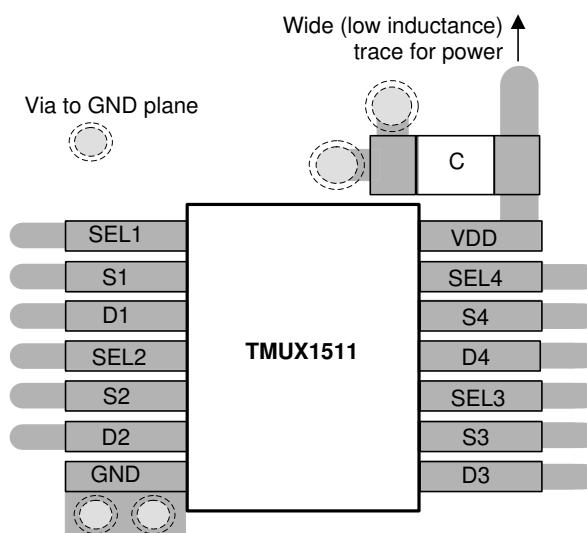

図 10-3 に、TMUX1511 向けの PCB レイアウト例を示します。主な検討事項は次のとおりです。

$V_{DD}$  ピンは、可能な限りそのピンの近くで  $0.1\mu F$  のコンデンサによるデカップリングを行います。電源電圧  $V_{DD}$  に対してコンデンサの電圧定格が十分であることを確認します。

高速スイッチには、最適性能を得るために、適切なレイアウトと設計手順が必要です。

入力への配線は可能な限り短くします。

平面状のグランドプレーンを使用し、電磁干渉 (EMI) ノイズのピックアップを低減します。

デジタルパターンと並行して敏感なアナログパターンを配線しないでください。可能な限り、デジタルパターンとアナログパターンの交差は避け、どうしても必要な場合には、必ず直角に交差させてください。

## 10.2 レイアウト例

図 10-3. レイアウト例

## 11 デバイスおよびドキュメントのサポート

### 11.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 11.2 ドキュメントのサポート

#### 11.2.1 関連資料

- テキサス・インスツルメンツ、『[低 CON マルチプレクサにおける安定性の問題の改善](#)』

- テキサス・インスツルメンツ、『[1.8V ロジックのマルチプレクサおよびスイッチにおける設計の単純化](#)』

- テキサス・インスツルメンツ、『[電源オフ保護を備えた信号スイッチで電源シーケンスを不要に](#)』

- テキサス・インスツルメンツ、『[高速インターフェイスのレイアウトガイドライン](#)』

- テキサス・インスツルメンツ、『[高速レイアウトガイドライン](#)』

- テキサス・インスツルメンツ、『[QFN/SON の PCB 実装](#)』

- テキサス・インスツルメンツ、『[クワッド フラットパックリード端子なしロジック パッケージ](#)』

### 11.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。右上の【アラートを受け取る】をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 11.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 11.7 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 12 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (December 2018) to Revision B (March 2025) | Page              |

|--------------------------------------------------------------------|-------------------|

| • RWB パッケージを追加.....                                                | <a href="#">4</a> |

| Changes from Revision * (September 2018) to Revision A (December 2018) | Page              |

|------------------------------------------------------------------------|-------------------|

| • データシートのステータスを次のように変更: 「事前情報」から「量産データ」に変更.....                        | <a href="#">1</a> |

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins   | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TMUX1511PWR           | Active        | Production           | TSSOP (PW)   14  | 2000   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 125   | MUX1511             |

| TMUX1511PWR.A         | Active        | Production           | TSSOP (PW)   14  | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | MUX1511             |

| TMUX1511PWRG4         | Active        | Production           | TSSOP (PW)   14  | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | MUX1511             |

| TMUX1511PWRG4.A       | Active        | Production           | TSSOP (PW)   14  | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | MUX1511             |

| TMUX1511RSVR          | Active        | Production           | UQFN (RSV)   16  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1511                |

| TMUX1511RSVR.A        | Active        | Production           | UQFN (RSV)   16  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1511                |

| TMUX1511RSVRG4.A      | Active        | Production           | UQFN (RSV)   16  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1511                |

| TMUX1511RWBR          | Active        | Production           | X2QFN (RWB)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | QZ                  |

| TMUX1511RWBR.A        | Active        | Production           | X2QFN (RWB)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | QZ                  |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

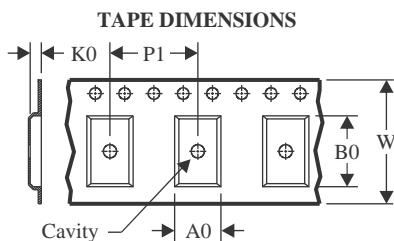

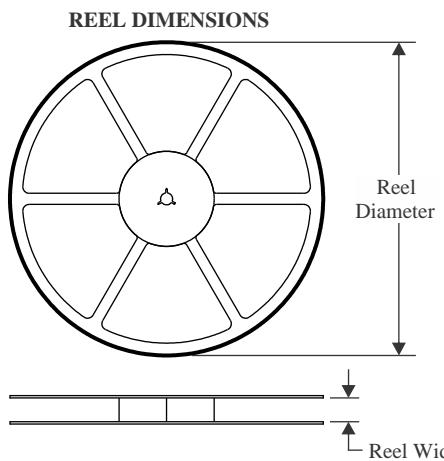

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

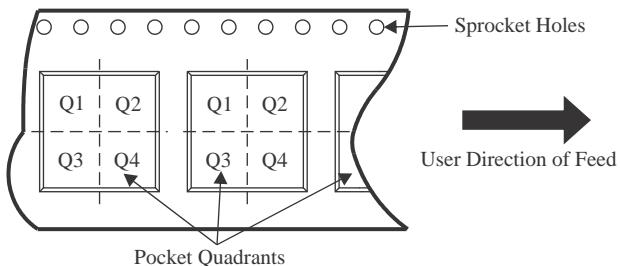

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TMUX1511PWR   | TSSOP        | PW              | 14   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

| TMUX1511PWRG4 | TSSOP        | PW              | 14   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

| TMUX1511RSVR  | UQFN         | RSV             | 16   | 3000 | 178.0              | 13.5               | 2.1     | 2.9     | 0.75    | 4.0     | 12.0   | Q1            |

| TMUX1511RWBR  | X2QFN        | RWB             | 12   | 3000 | 180.0              | 8.4                | 1.8     | 1.8     | 0.48    | 4.0     | 8.0    | Q2            |

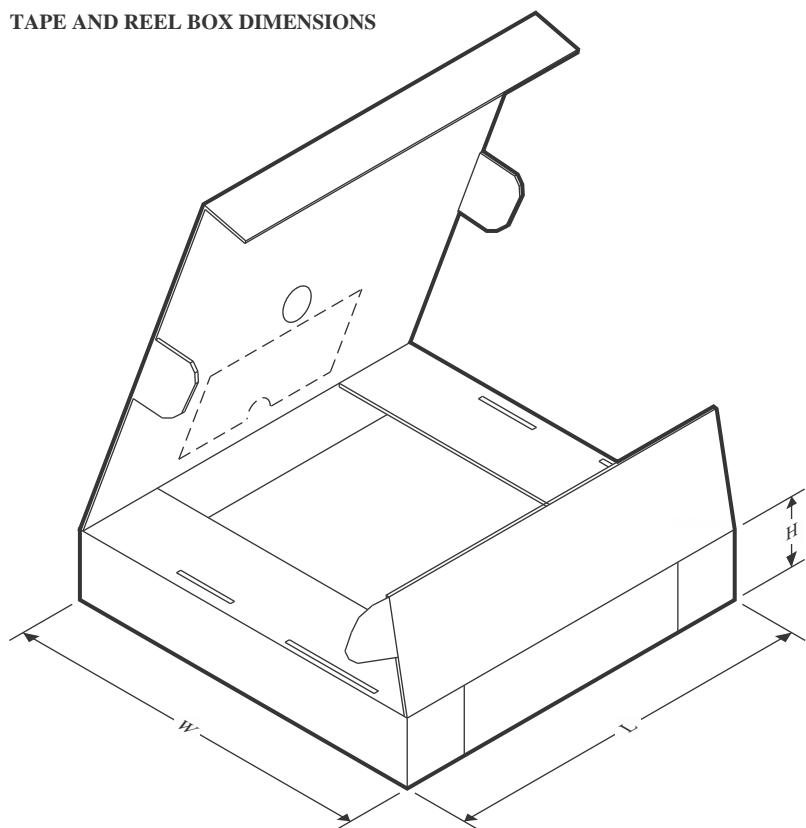

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TMUX1511PWR   | TSSOP        | PW              | 14   | 2000 | 356.0       | 356.0      | 35.0        |

| TMUX1511PWRG4 | TSSOP        | PW              | 14   | 2000 | 353.0       | 353.0      | 32.0        |

| TMUX1511RSVR  | UQFN         | RSV             | 16   | 3000 | 189.0       | 185.0      | 36.0        |

| TMUX1511RWBR  | X2QFN        | RWB             | 12   | 3000 | 210.0       | 185.0      | 35.0        |

## GENERIC PACKAGE VIEW

**RSV 16**

**UQFN - 0.55 mm max height**

**1.8 x 2.6, 0.4 mm pitch**

**ULTRA THIN QUAD FLATPACK - NO LEAD**

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4231225/A

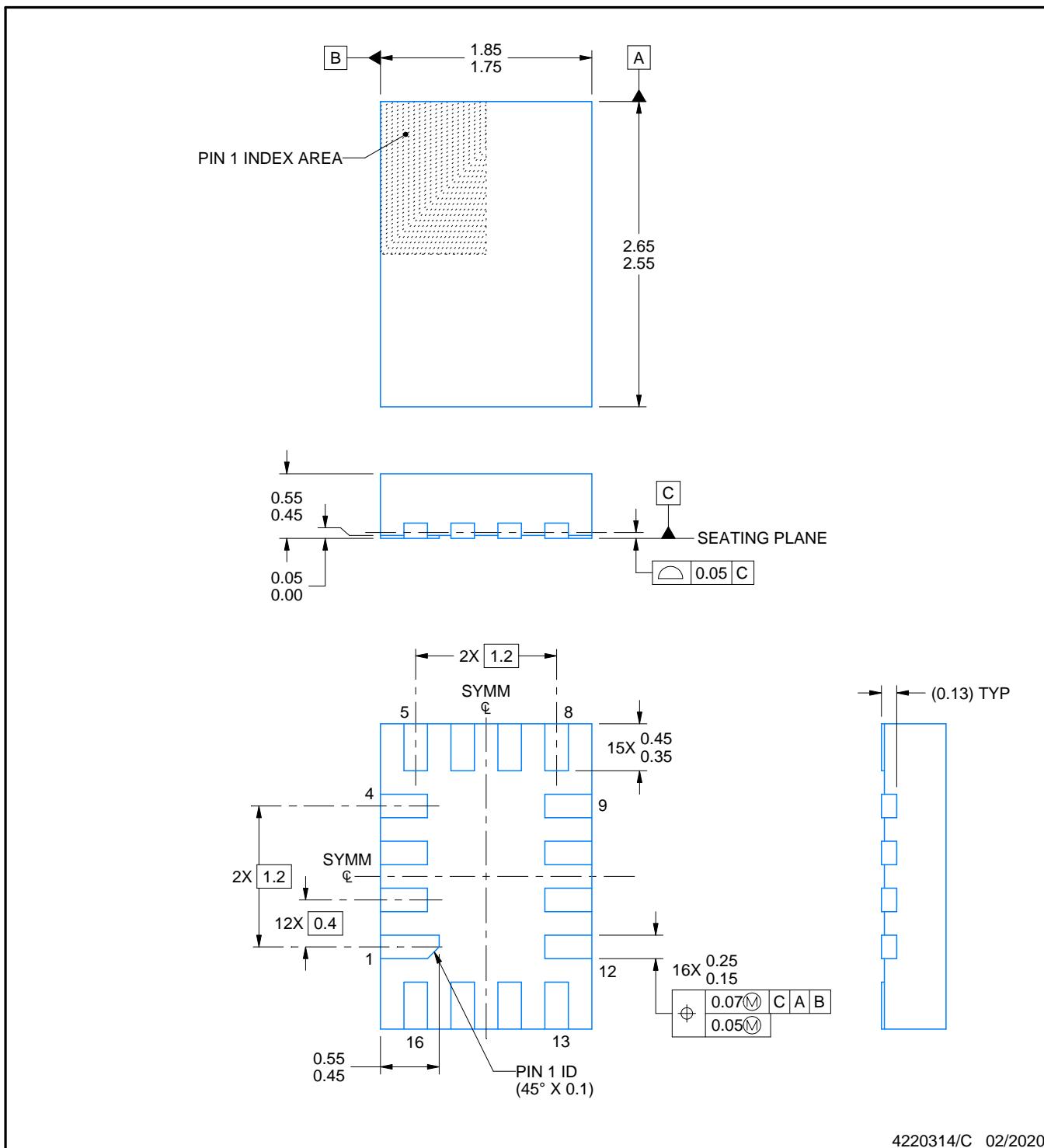

# PACKAGE OUTLINE

**RSV0016A**

**UQFN - 0.55 mm max height**

ULTRA THIN QUAD FLATPACK - NO LEAD

4220314/C 02/2020

**NOTES:**

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

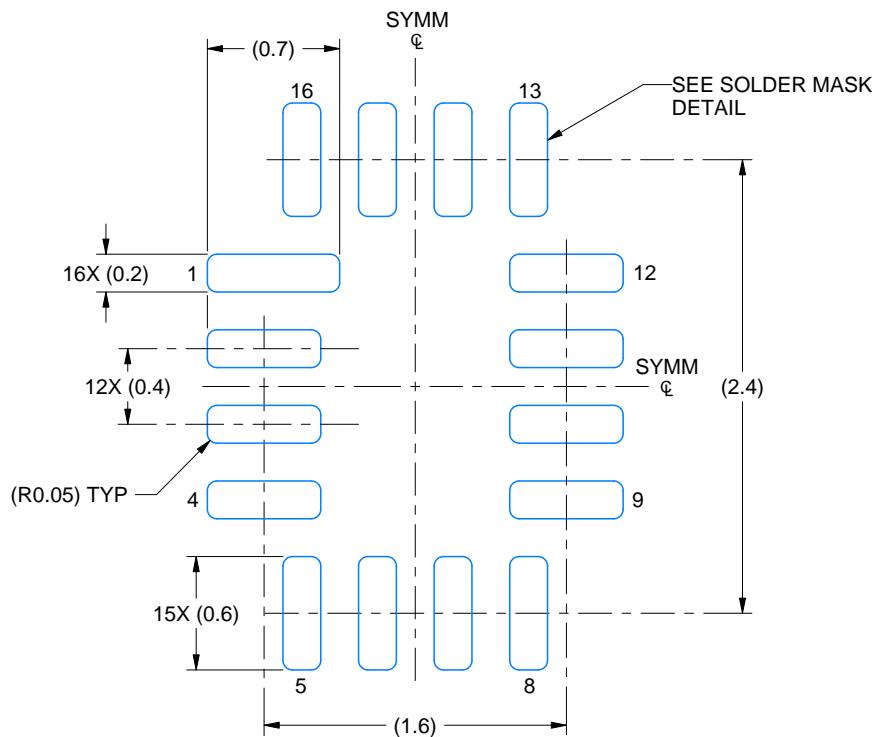

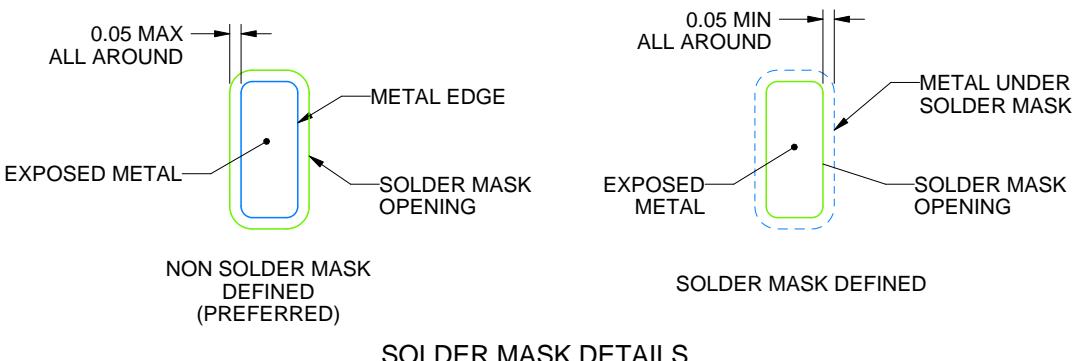

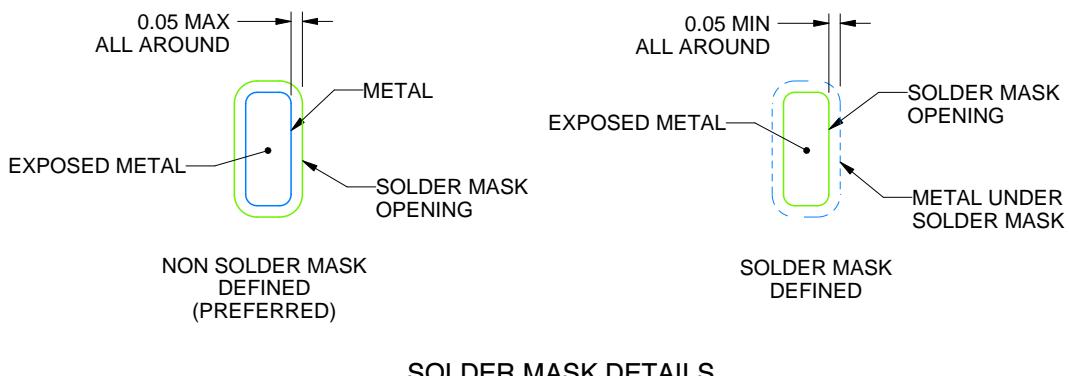

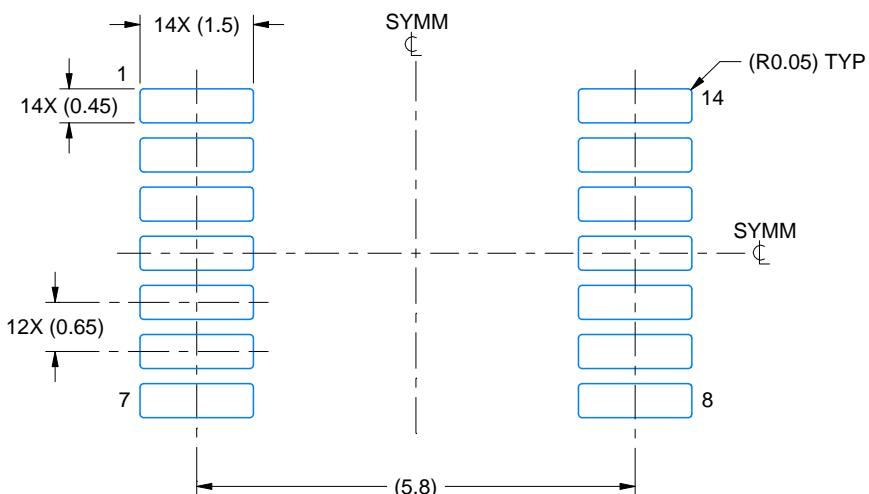

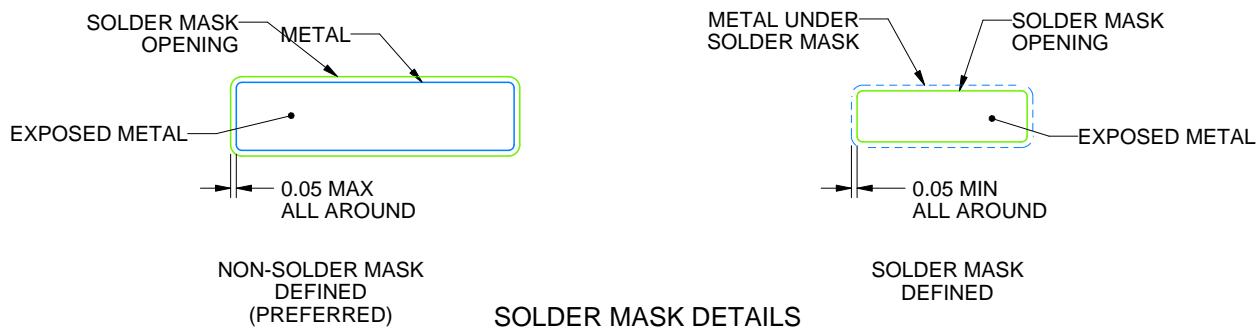

# EXAMPLE BOARD LAYOUT

RSV0016A

UQFN - 0.55 mm max height

ULTRA THIN QUAD FLATPACK - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 25X

SOLDER MASK DETAILS

4220314/C 02/2020

NOTES: (continued)

3. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

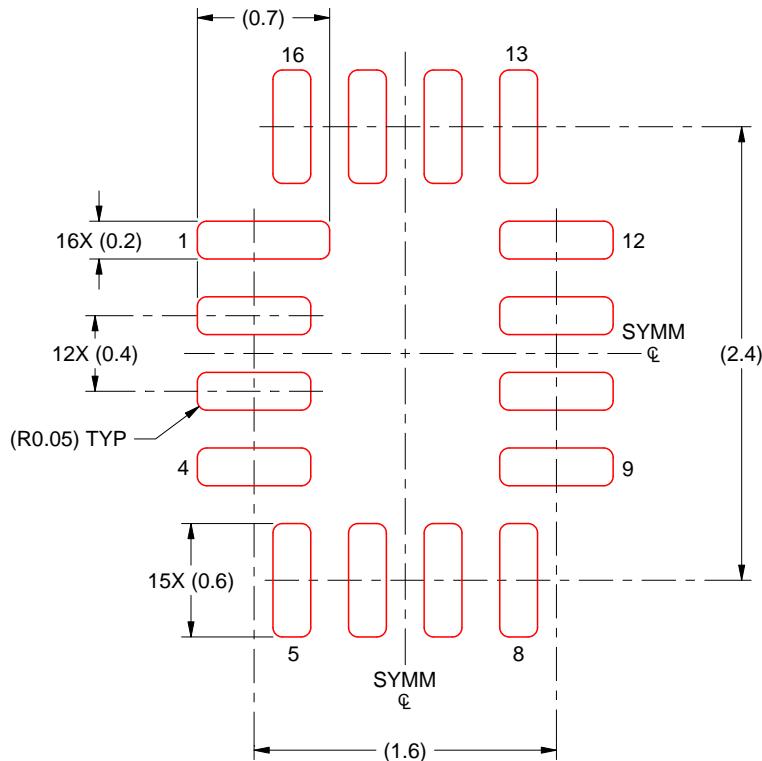

## EXAMPLE STENCIL DESIGN

RSV0016A

## **UQFN - 0.55 mm max height**

#### ULTRA THIN QUAD FLATPACK - NO LEAD

**SOLDER PASTE EXAMPLE

BASED ON 0.125 MM THICK STENCIL

SCALE: 25X**

4220314/C 02/2020

#### NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

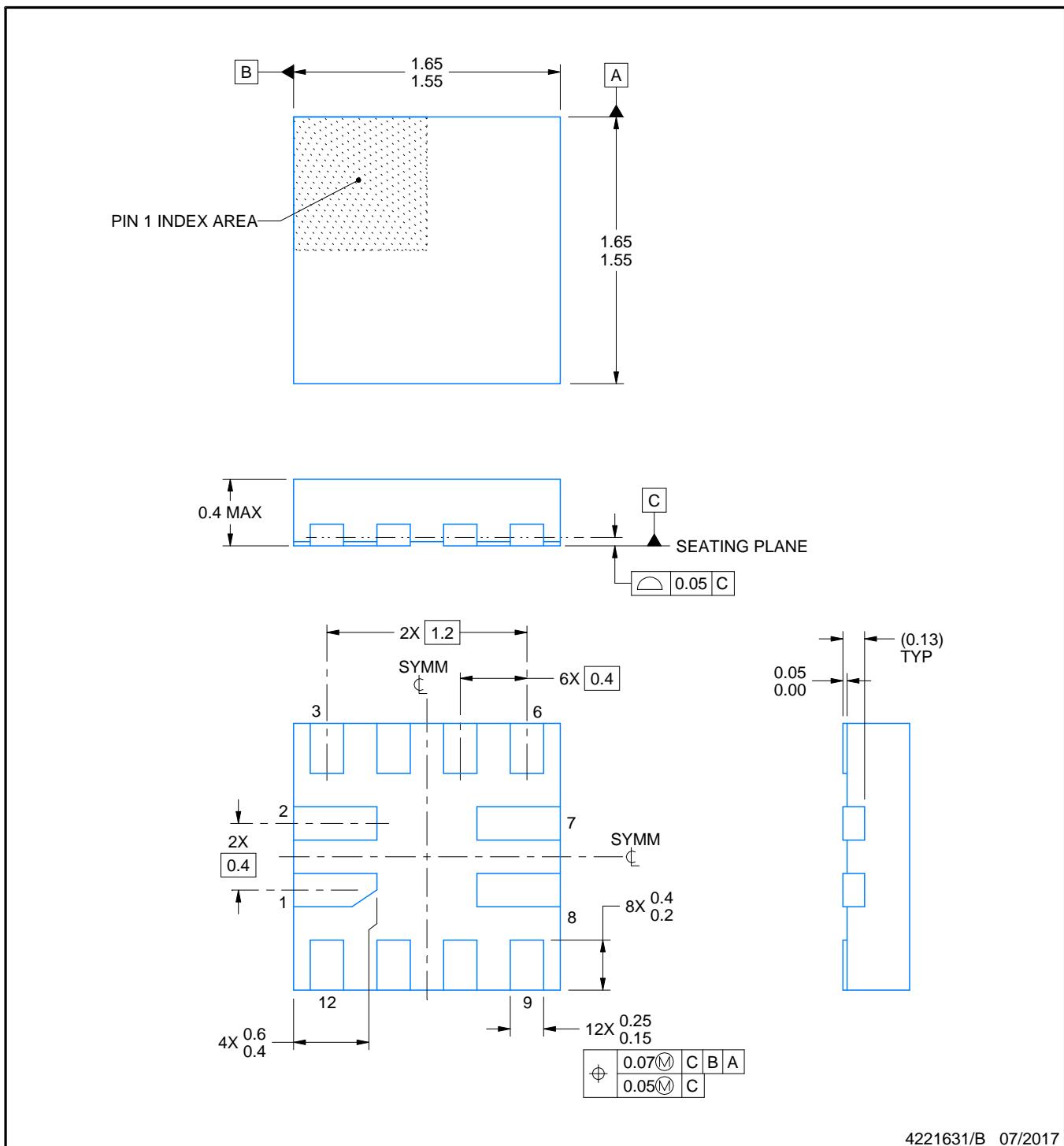

# PACKAGE OUTLINE

RWB0012A

X2QFN - 0.4 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

4221631/B 07/2017

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

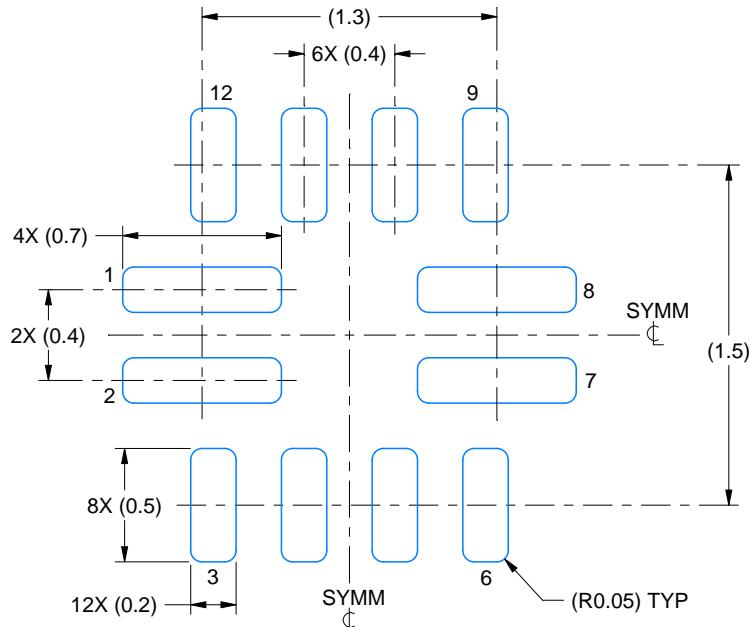

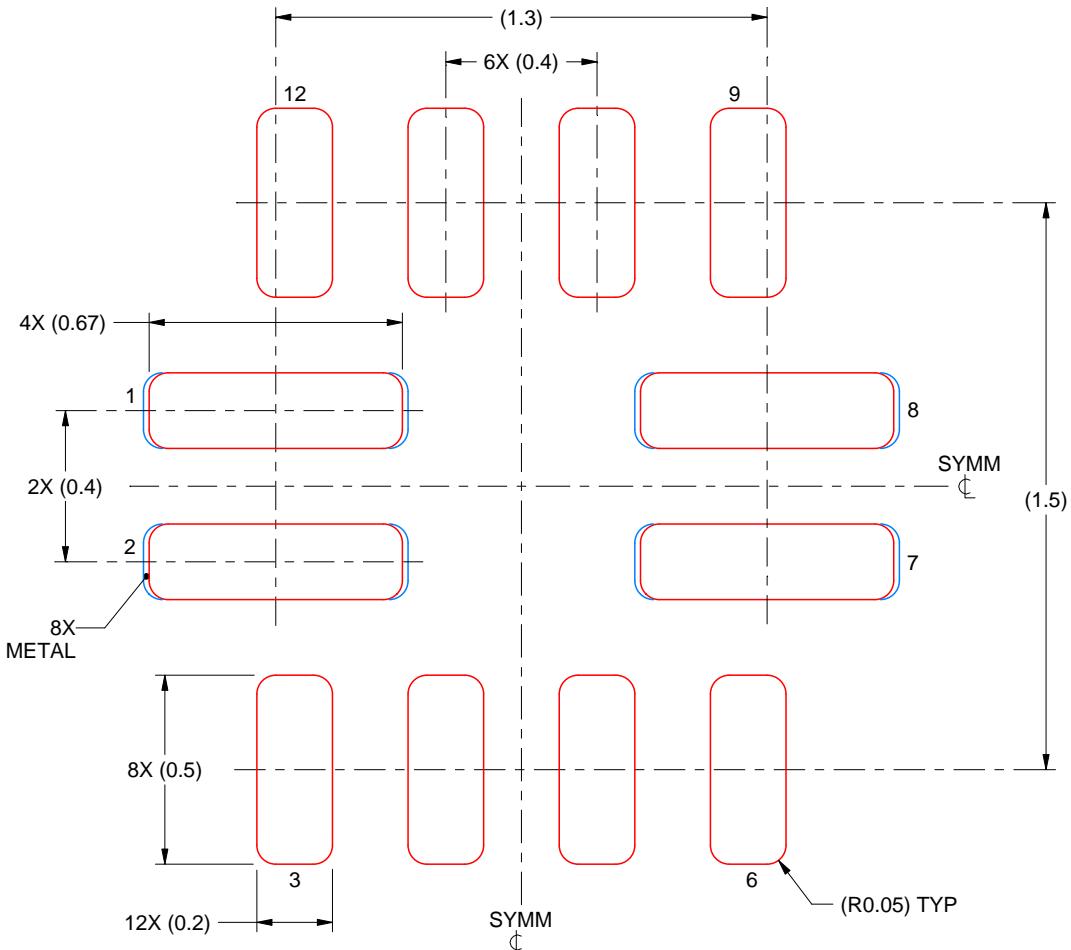

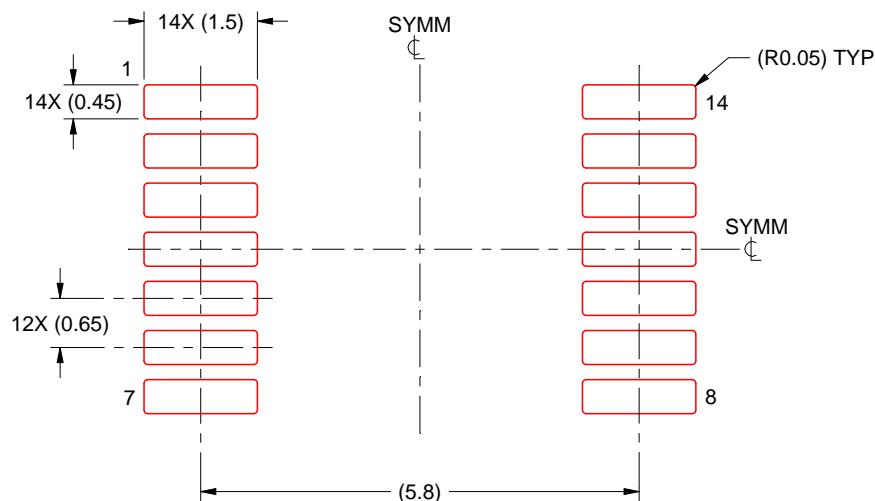

# EXAMPLE BOARD LAYOUT

RWB0012A

X2QFN - 0.4 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:30X

SOLDER MASK DETAILS

4221631/B 07/2017

NOTES: (continued)

3. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

# EXAMPLE STENCIL DESIGN

RWB0012A

X2QFN - 0.4 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

PADS 1,2,7 & 8

96% PRINTED SOLDER COVERAGE BY AREA

SCALE:50X

4221631/B 07/2017

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# PACKAGE OUTLINE

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- Reference JEDEC registration MO-153.

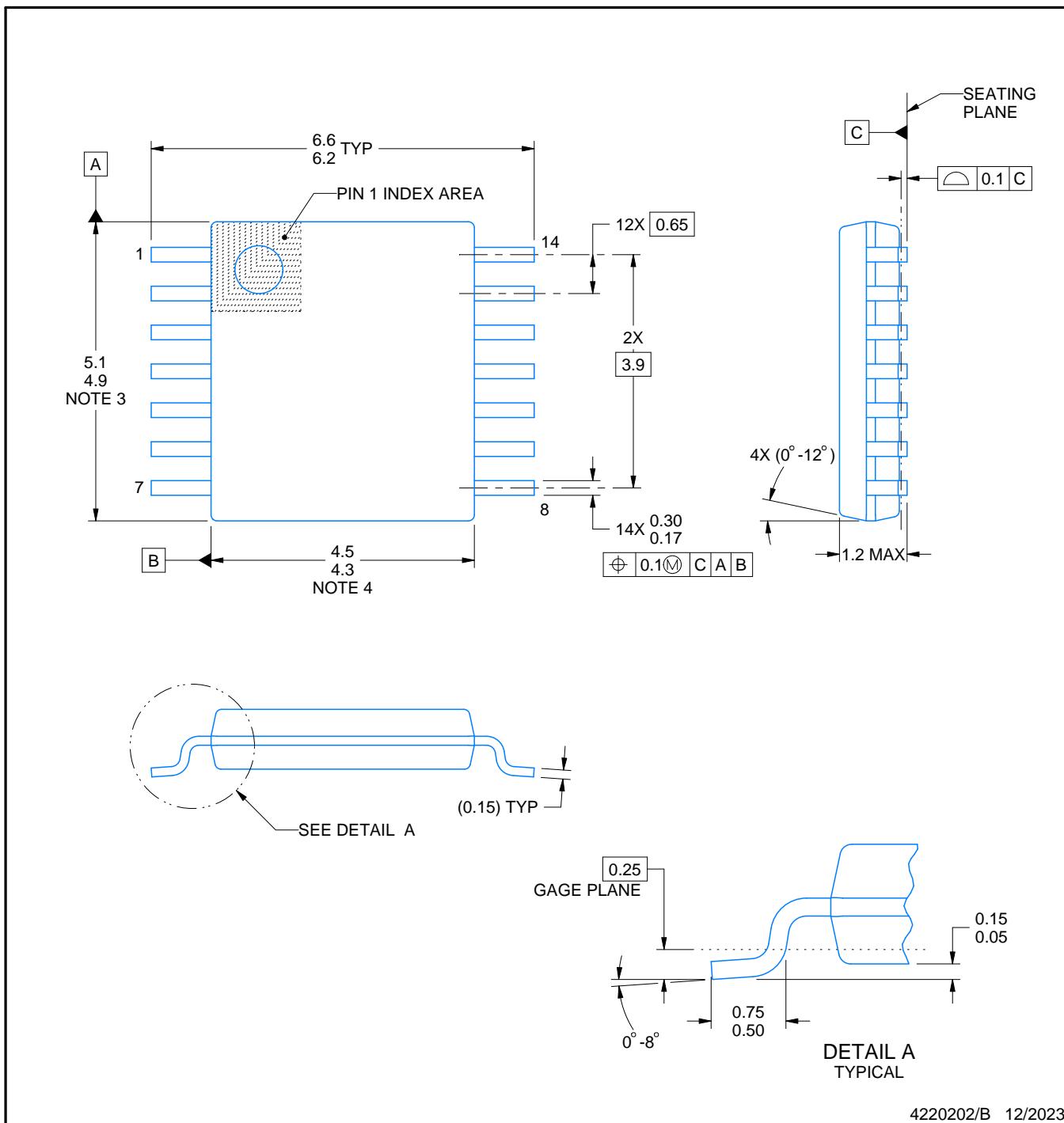

# EXAMPLE BOARD LAYOUT

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

4220202/B 12/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 10X

4220202/B 12/2023

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月