# TMS320F28P55x リアルタイムマイクロコントローラ

## 1 特長

- リアルタイム処理:

- 150MHz C28x 32ビット DSP CPU

- 300MHz Arm® Cortex®-M7 ベースのデバイスと同等のリアルタイム信号チェーン性能 (『C2000™ 制御 MCU の最適化された信号チェーンのリアルタイムベンチマーク』アプリケーションノートを参照)

- IEEE 754 単精度浮動小数点ユニット (FPU32)

- 三角関数演算ユニット (TMU)

- 非線形 PID (NLPID) 制御をサポート

- CRC エンジンおよび命令 (VCRC)

- プログラム可能な制御補償器アクセラレータ (CLA)

- 150MHz

- 200MHz Arm® Cortex®-M7 ベースのデバイスと同等のリアルタイム信号チェーン性能 (『C2000™ 制御 MCU の最適化された信号チェーンのリアルタイムベンチマーク』アプリケーションノートを参照)

- IEEE 754 単精度浮動小数点命令

- メイン CPU と独立にコードを実行

- オンチップメモリ

- 5つの独立したバンクで構成される 1088KB フラッシュ (ECC 保護)

- 4つの 256KB バンク

- LFU / ブートローダ / データに理想的な 1つの 64KB バンク

- 8KB の OTP (ワンタイムプログラマブルフラッシュメモリ)

- 133KB の RAM (ECC / パリティ保護)

- セキュリティ

- セキュアブート

- JTAG ロック

- AES (Advanced Encryption Standard) アクセラレータ

- 固有の識別 (UID) 番号

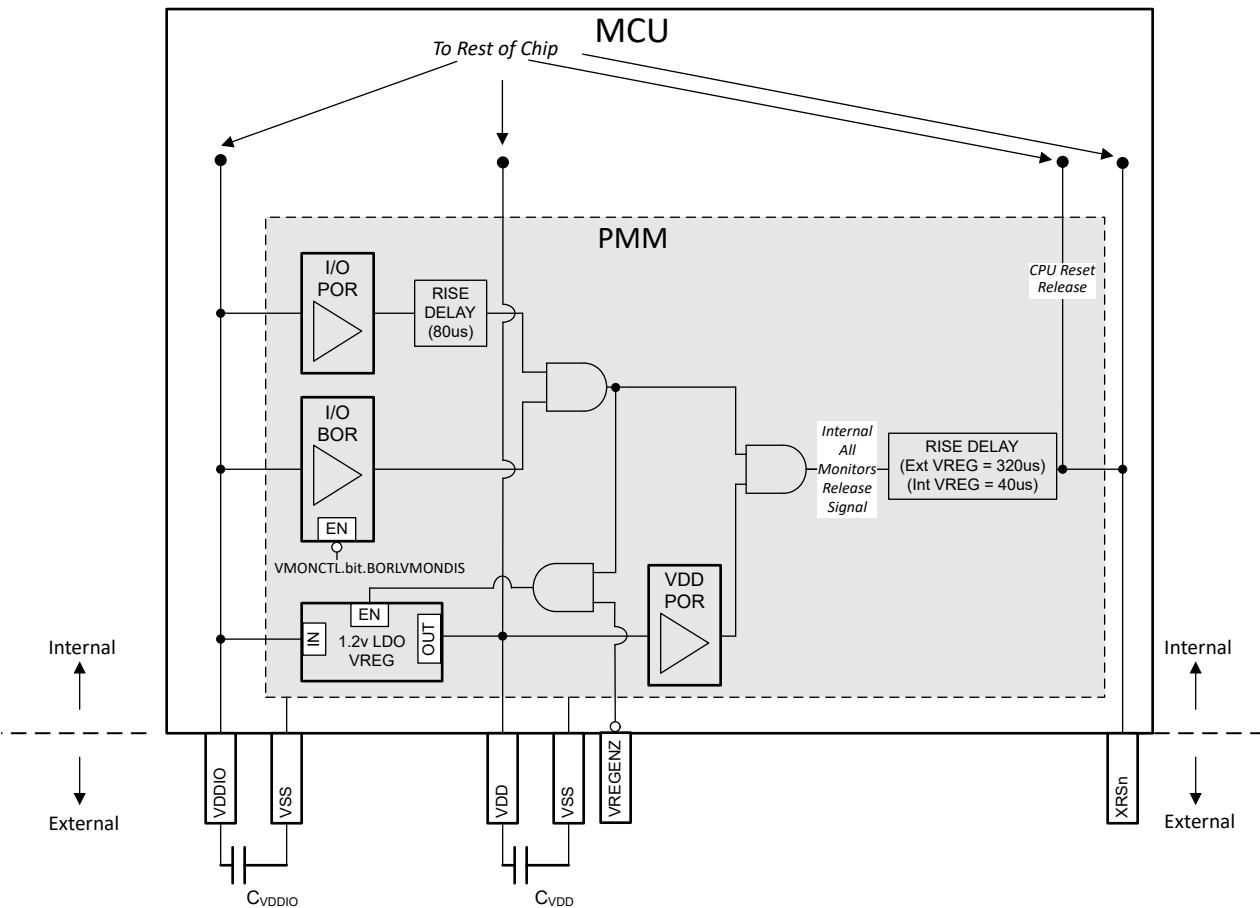

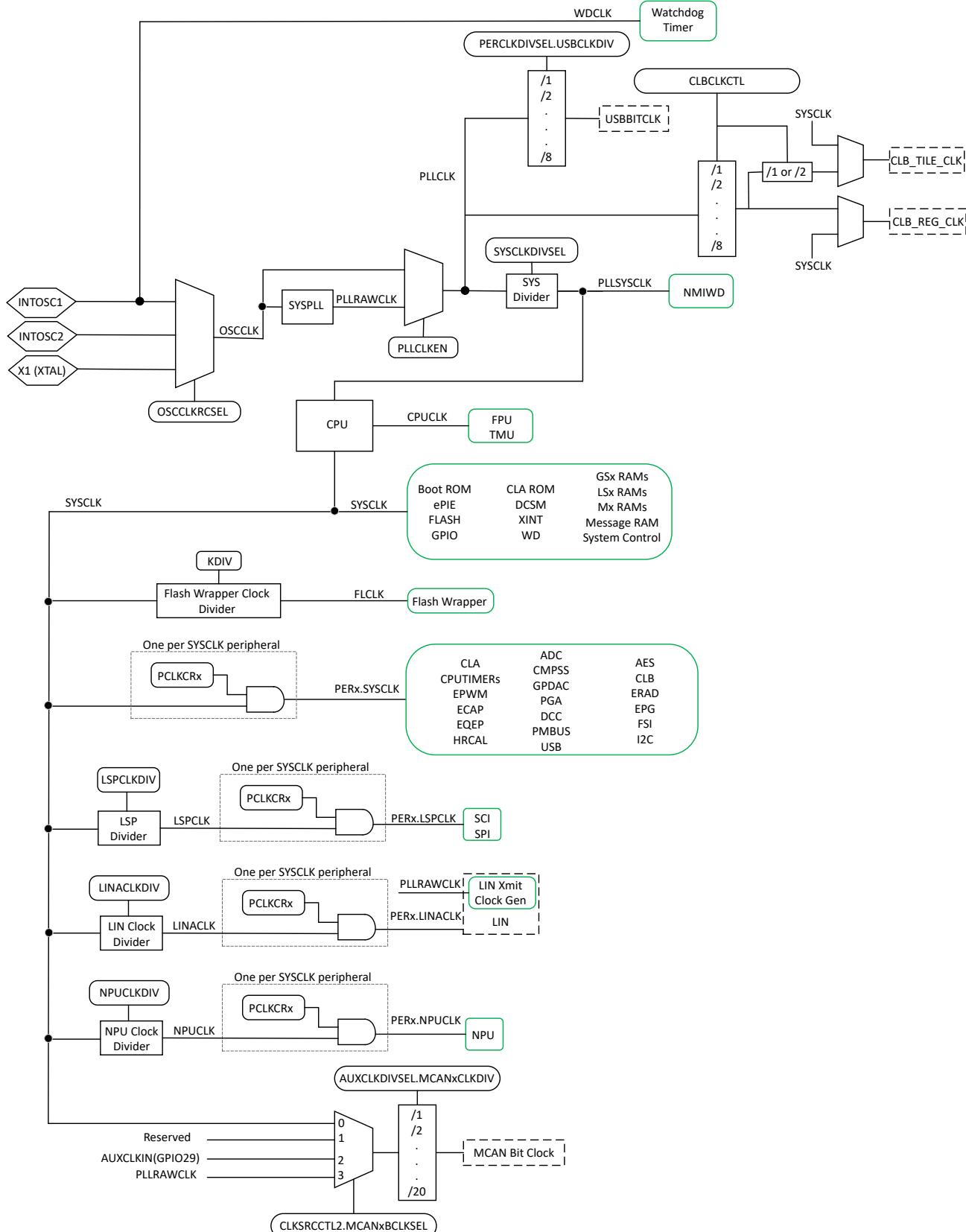

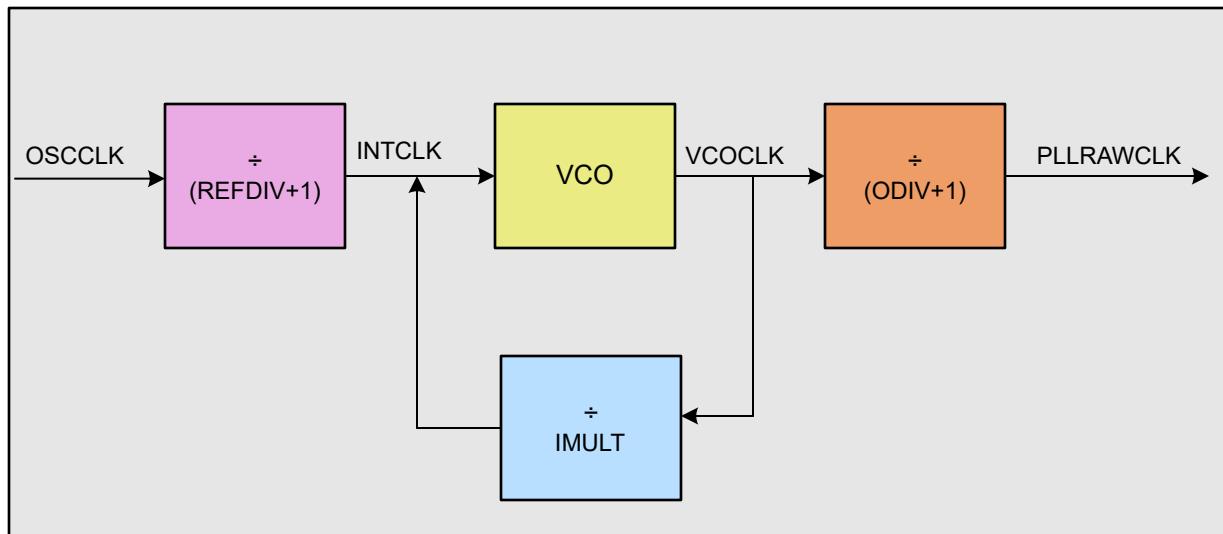

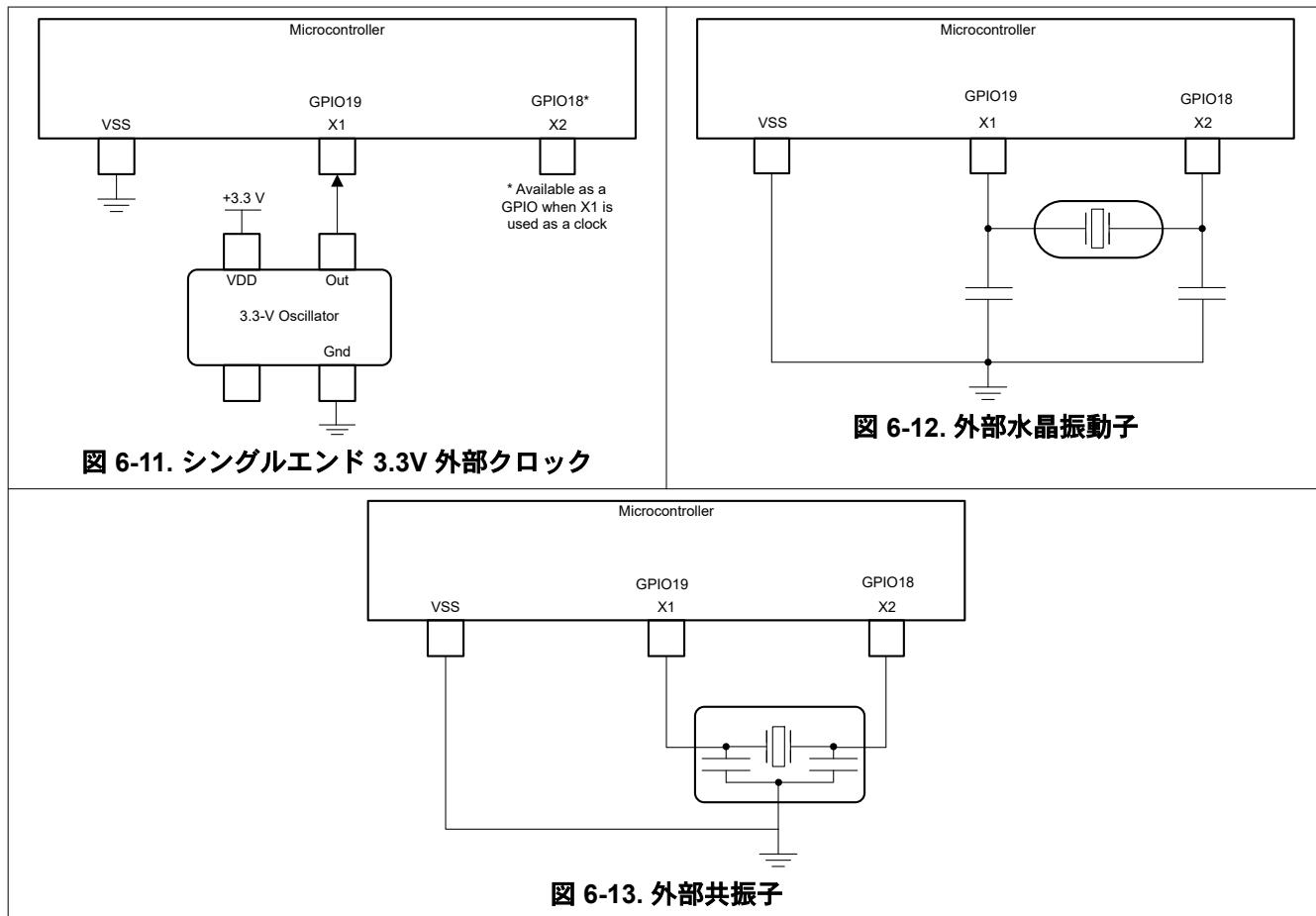

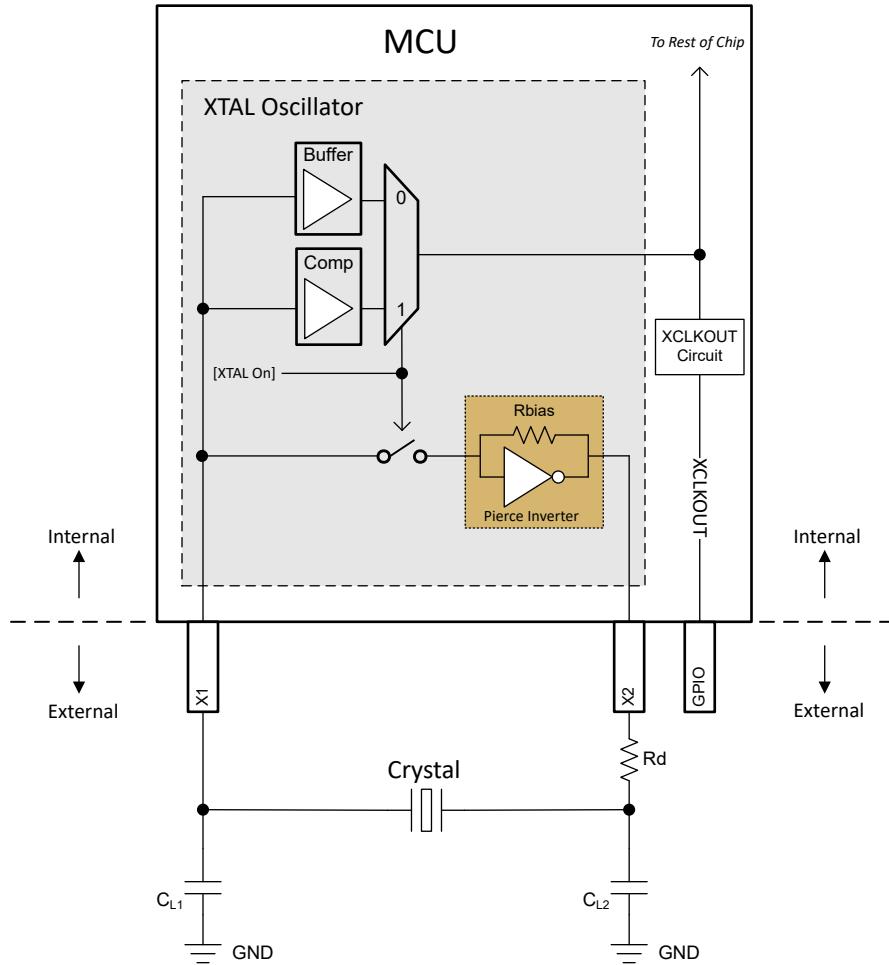

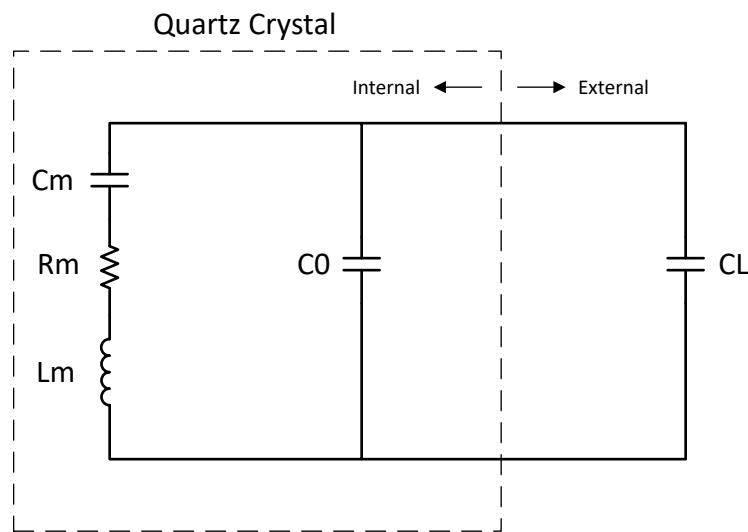

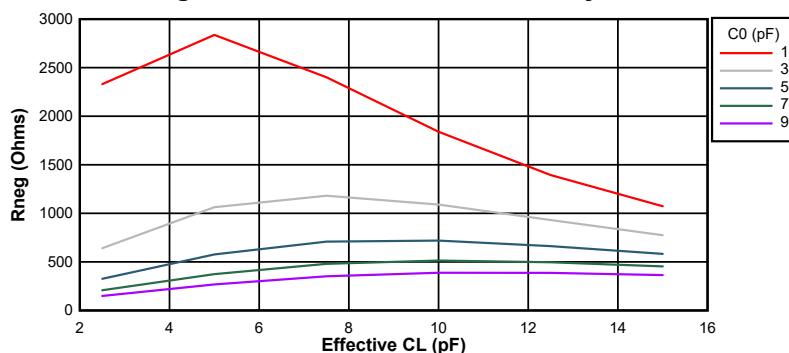

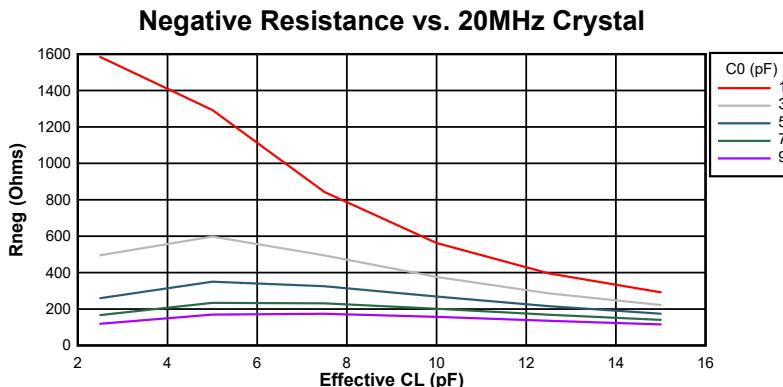

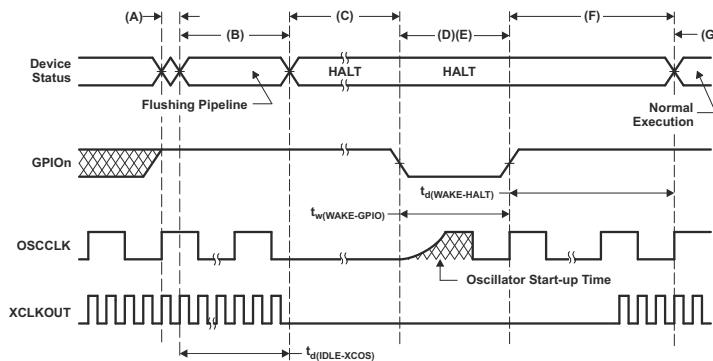

- クロックおよびシステム制御

- 2つの内部 10MHz 発振器

- 水晶発振器または外部クロック入力

- ウィンドウ付きウォッチドッグ タイマ モジュール

- クロック消失検出回路

- デュアルクロックコンパレータ (DCC)

- 3.3V I/O 設計

- 内部 VREG 生成により、単一電源設計が可能

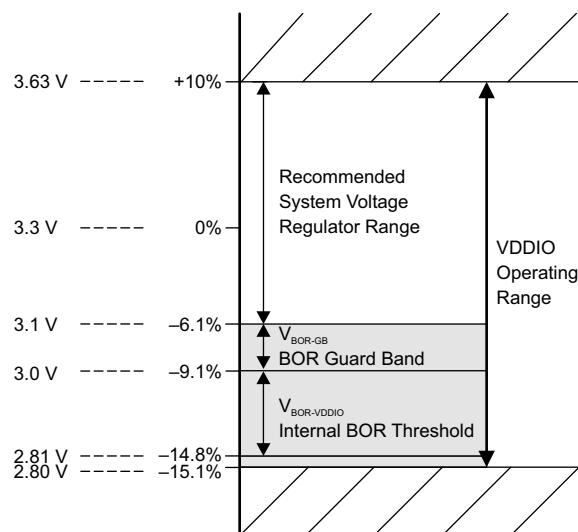

- ブラウンアウトリセット (BOR) 回路

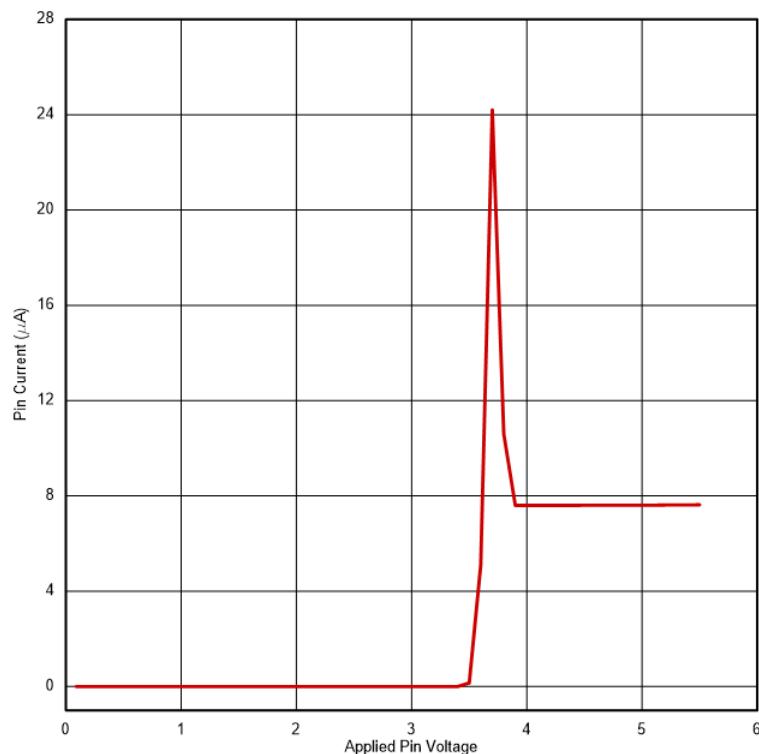

- PMBUS/I2C をサポートするために 4つの GPIO で 5V フェイルセーフ / 許容に対応

- 4つの GPIO で 1.35V の  $V_{IH}$  を設定可能

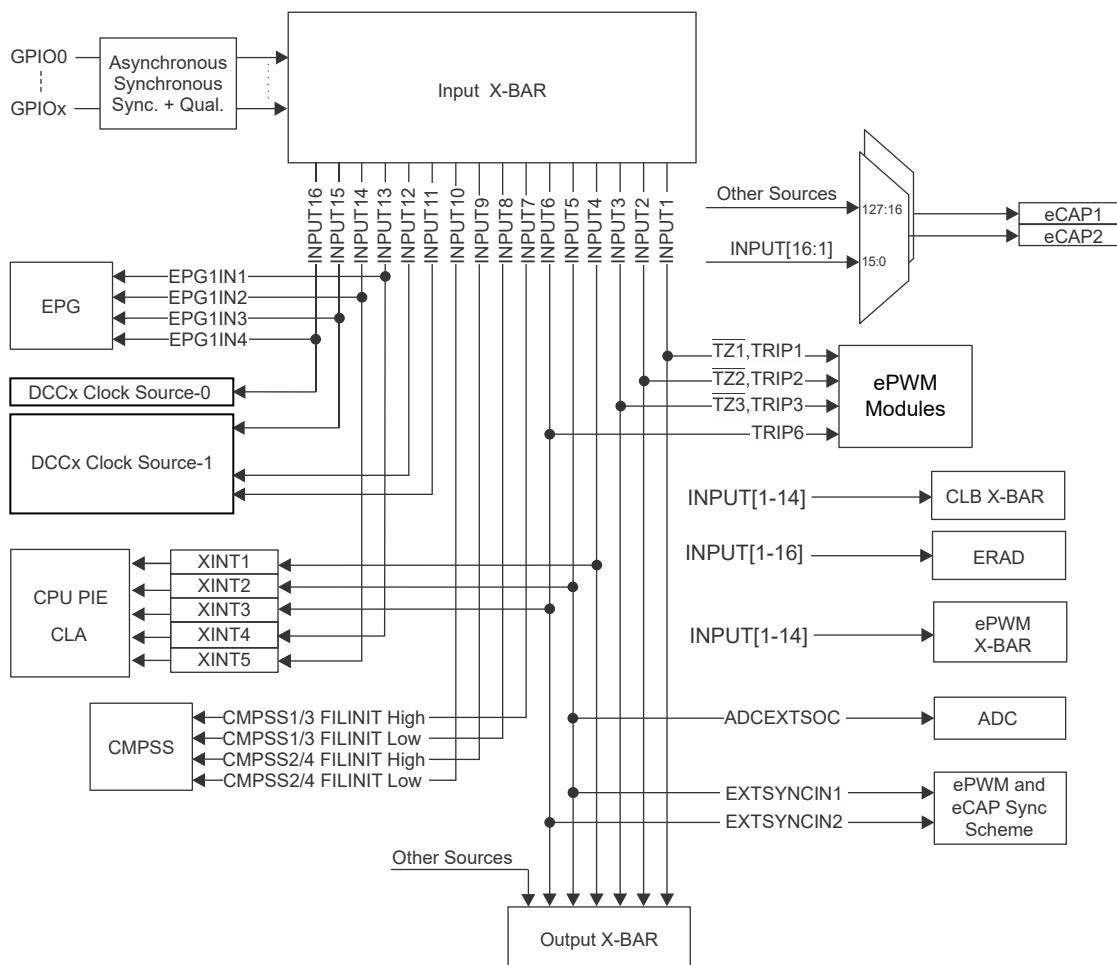

- システムペリフェラル

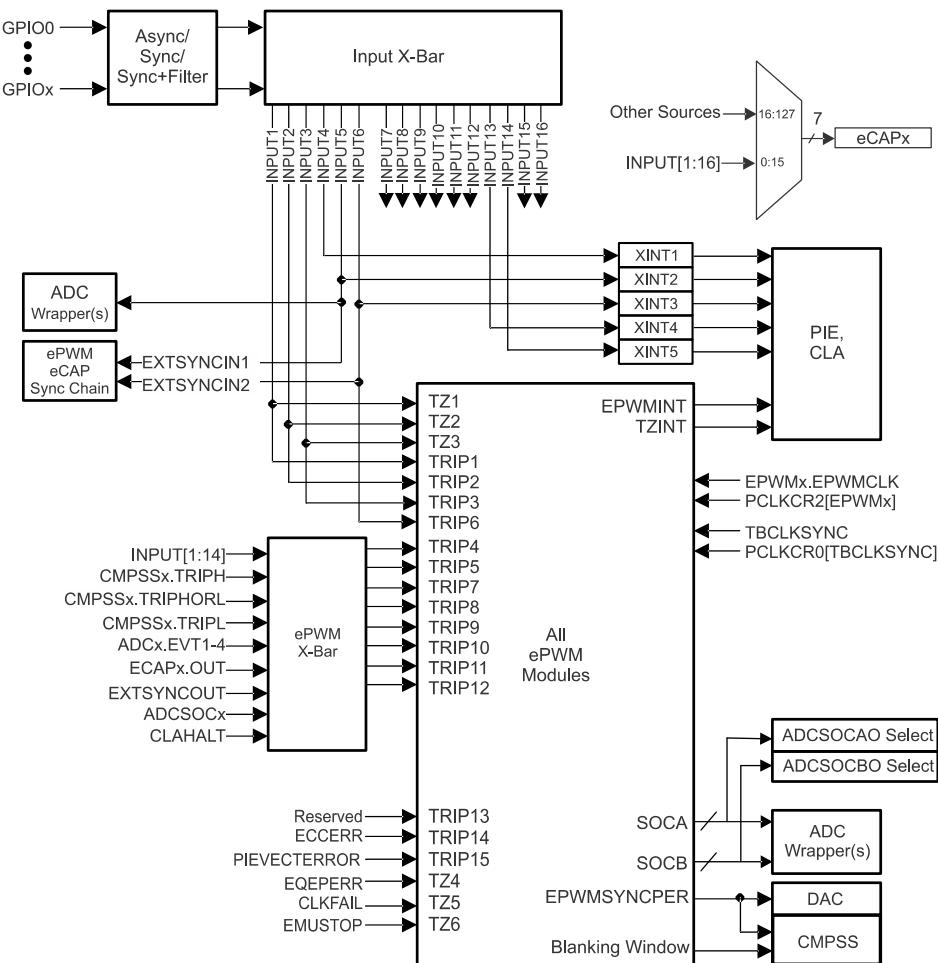

- 6チャネルのダイレクトメモリアクセス (DMA) コントローラ

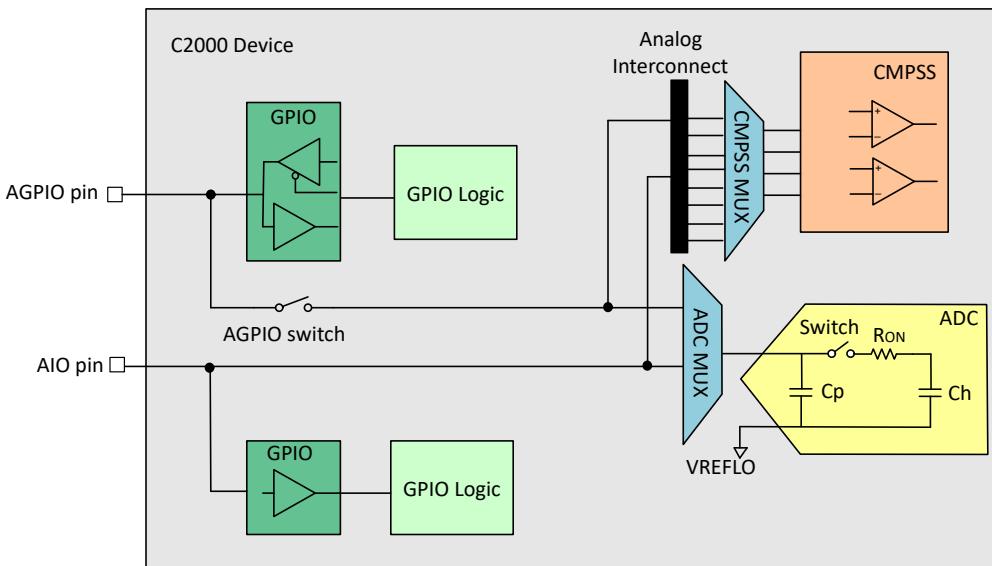

- 91本の個別にプログラム可能な多重化された汎用入出力 (GPIO) ピン (22本はアナログと共有)

- アナログピング上の 17のデジタル入力

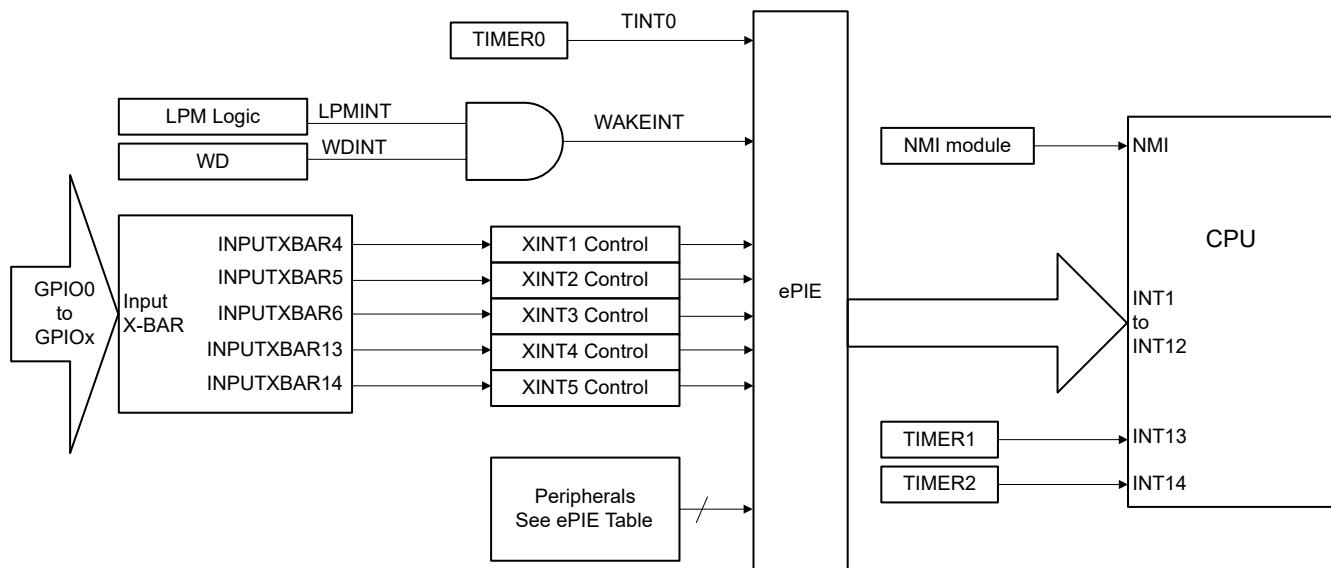

- 強化ペリフェラル割り込み拡張 (ePIE)

- 多様な低消費電力モード (LPM) のサポート

- 通信ペリフェラル

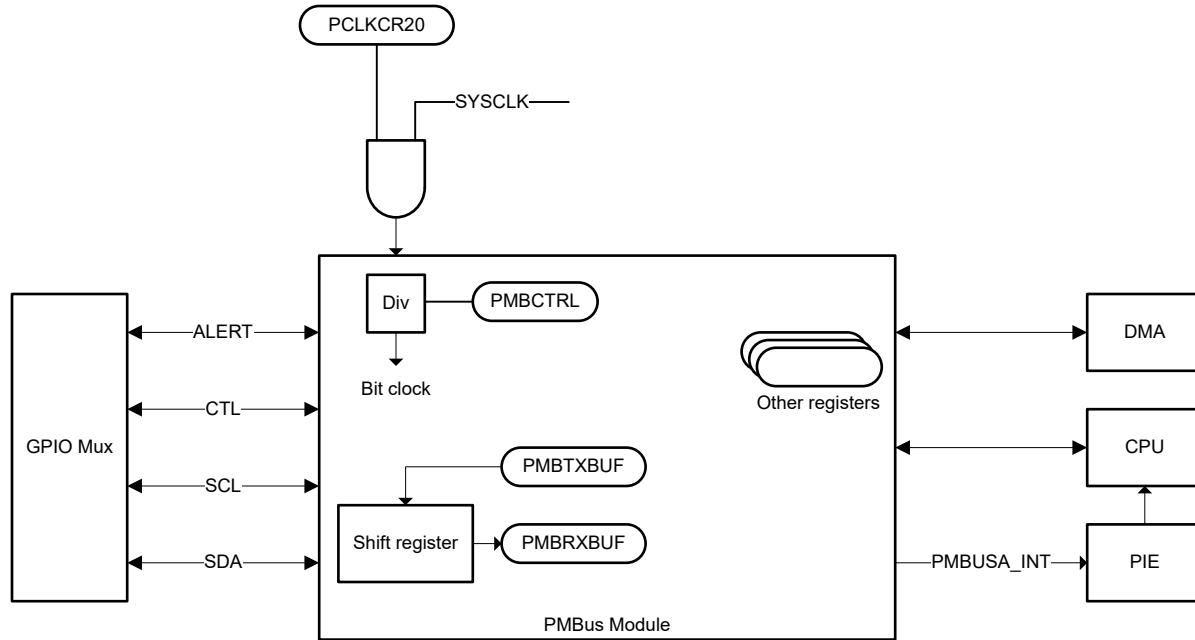

- 1つの電力管理バス (PMBus) インターフェイス

- ファストプラスモードのサポート - 1MHz SCL

- 一部のピンで 5V/3.3V/1.35V の  $V_{IH}$  をサポート

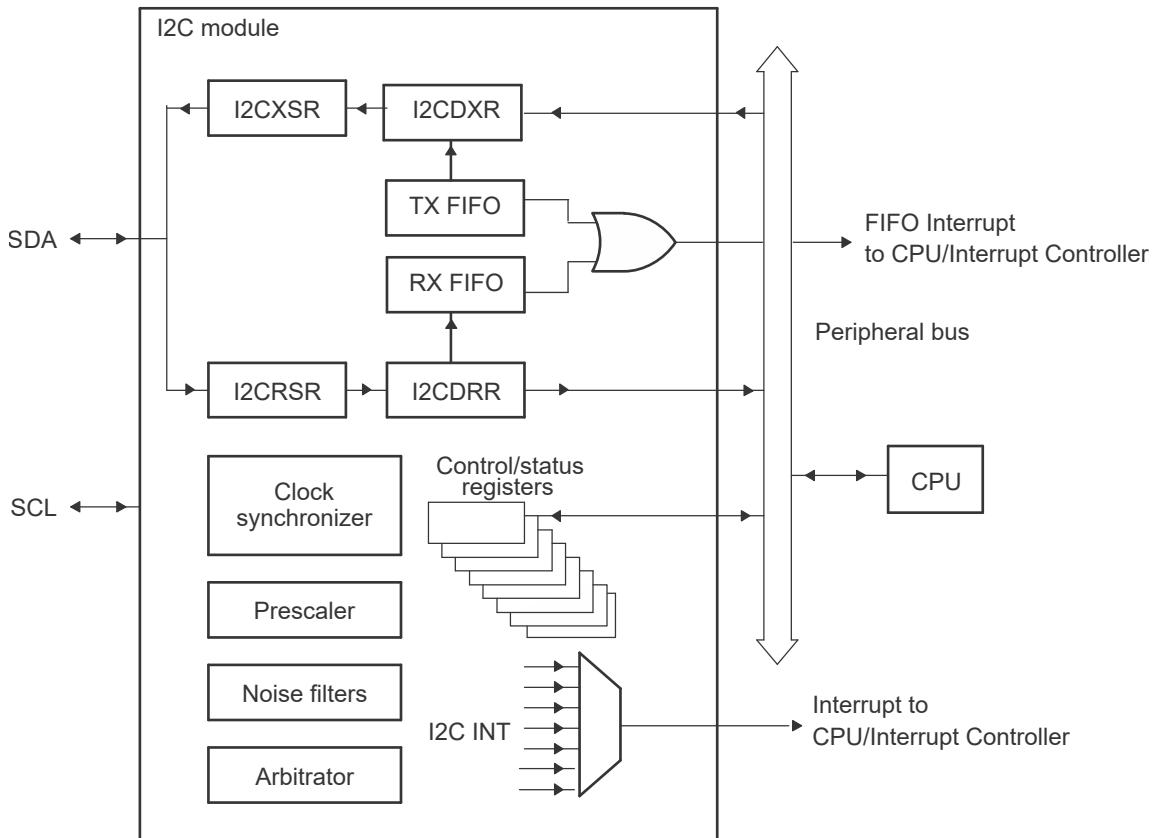

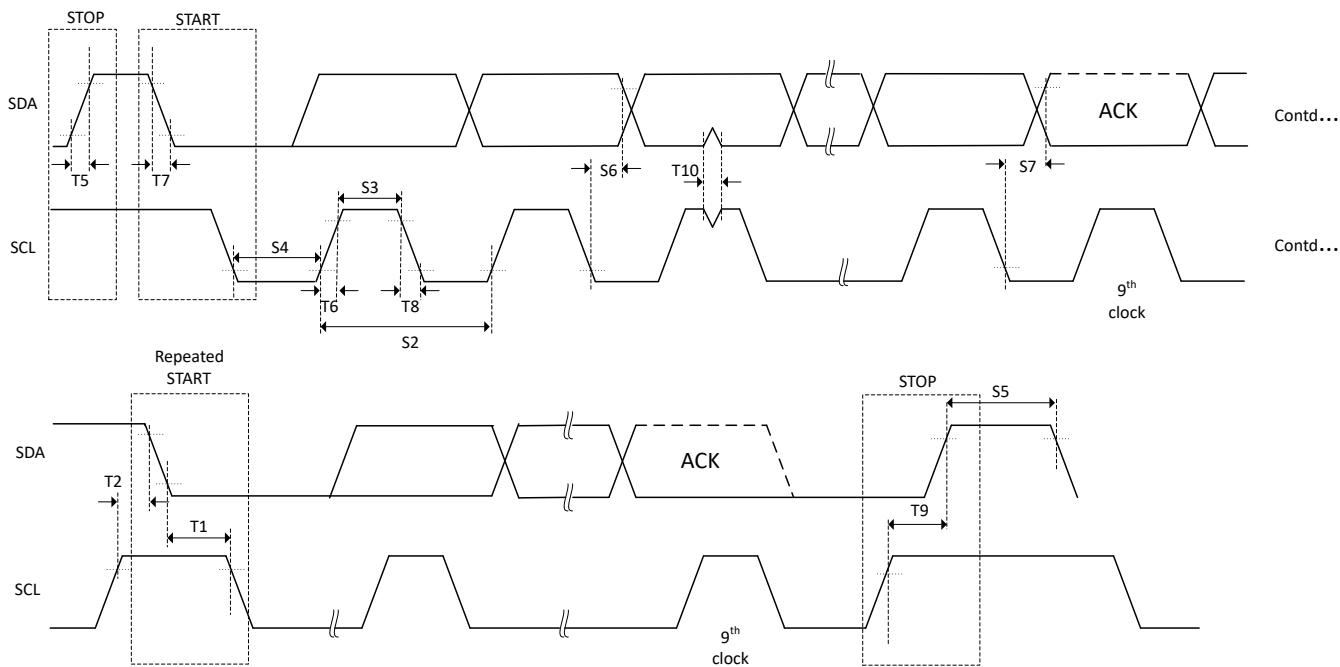

- 2つの I2C (Inter-integrated Circuit) インターフェイス

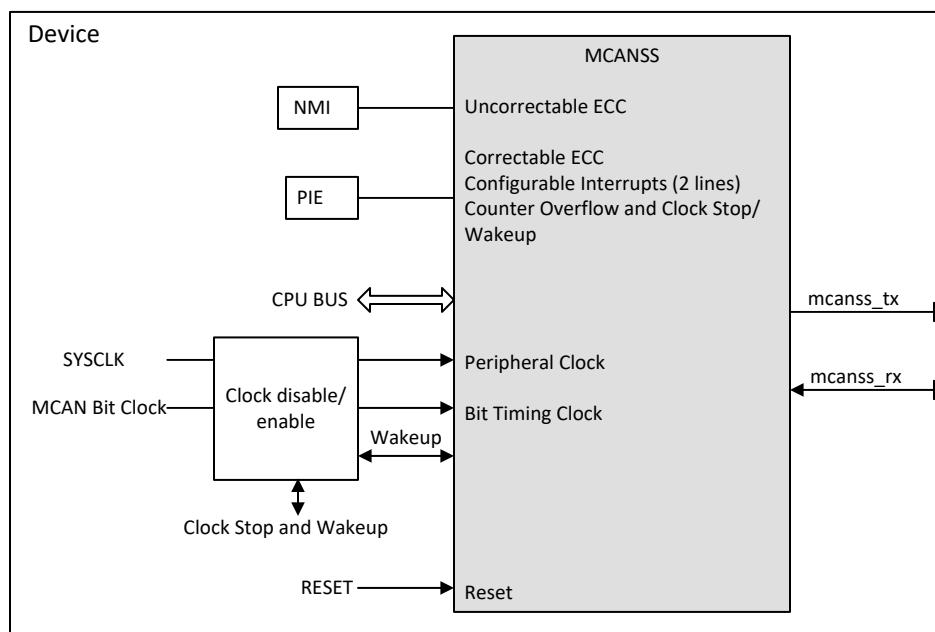

- 2つの CAN FD (Controller Area Network with Flexible Data-Rate) / MCAN バスポート

- MCAN モジュールごとに 4KB のメッセージ RAM (システムメモリとは無関係)

- CPU のデータ変数として RAM を再利用可能 (MCAN を使用しない場合)

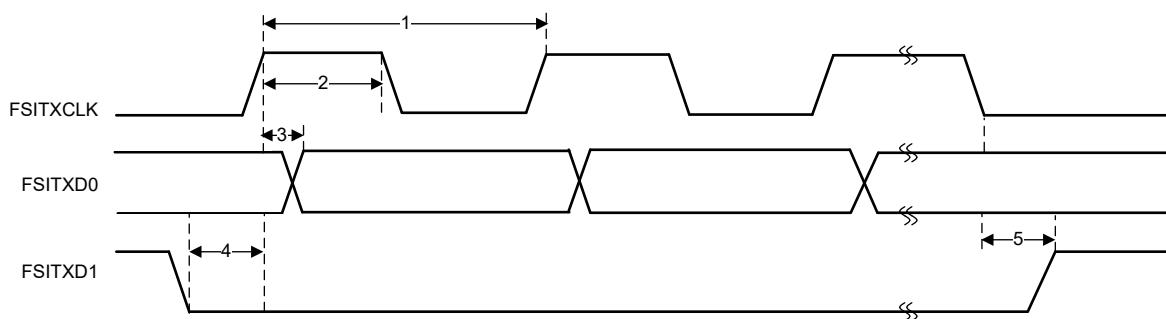

- 1つのユニバーサルシリアルバス (USB 2.0 MAC + PHY)

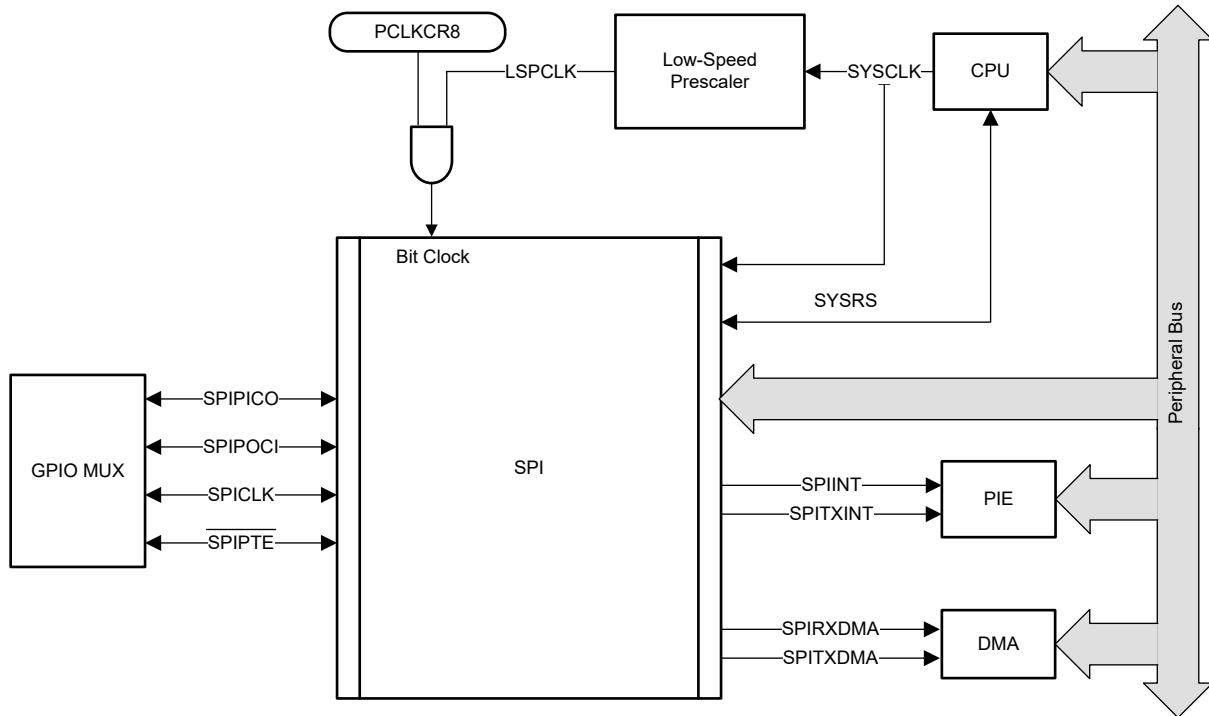

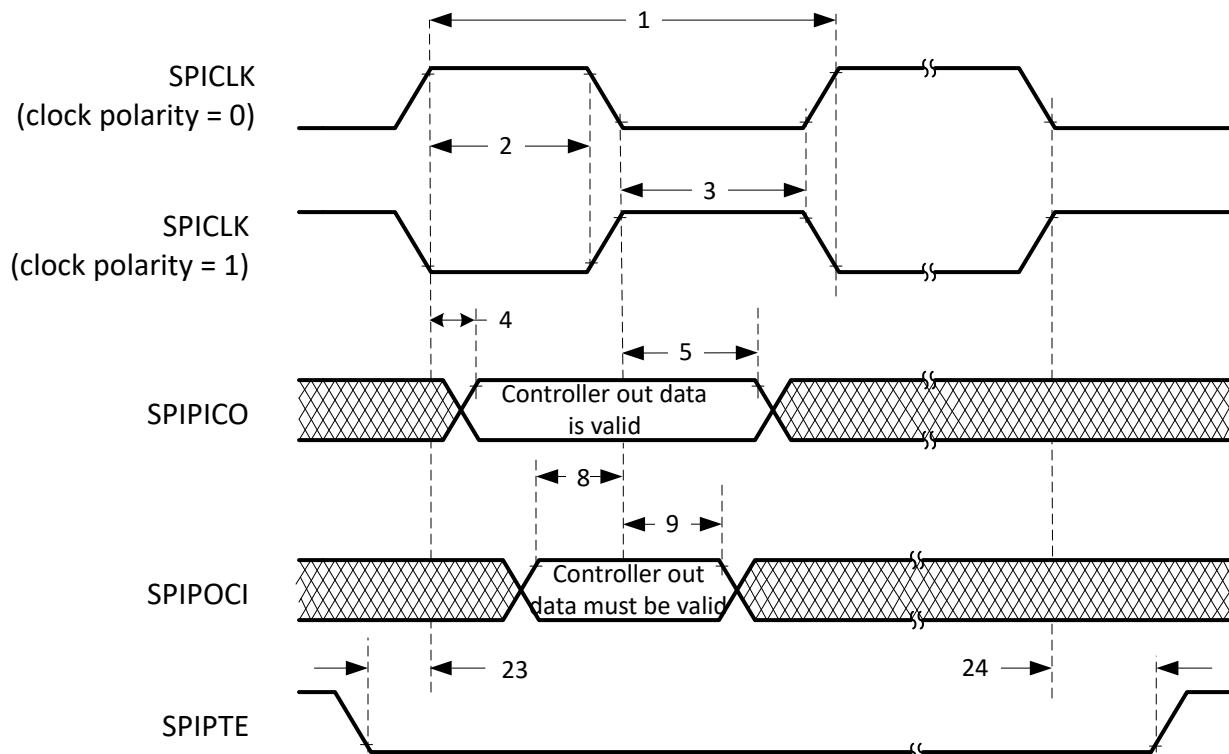

- 2つのシリアルペリフェラルインターフェイス (SPI) ポート

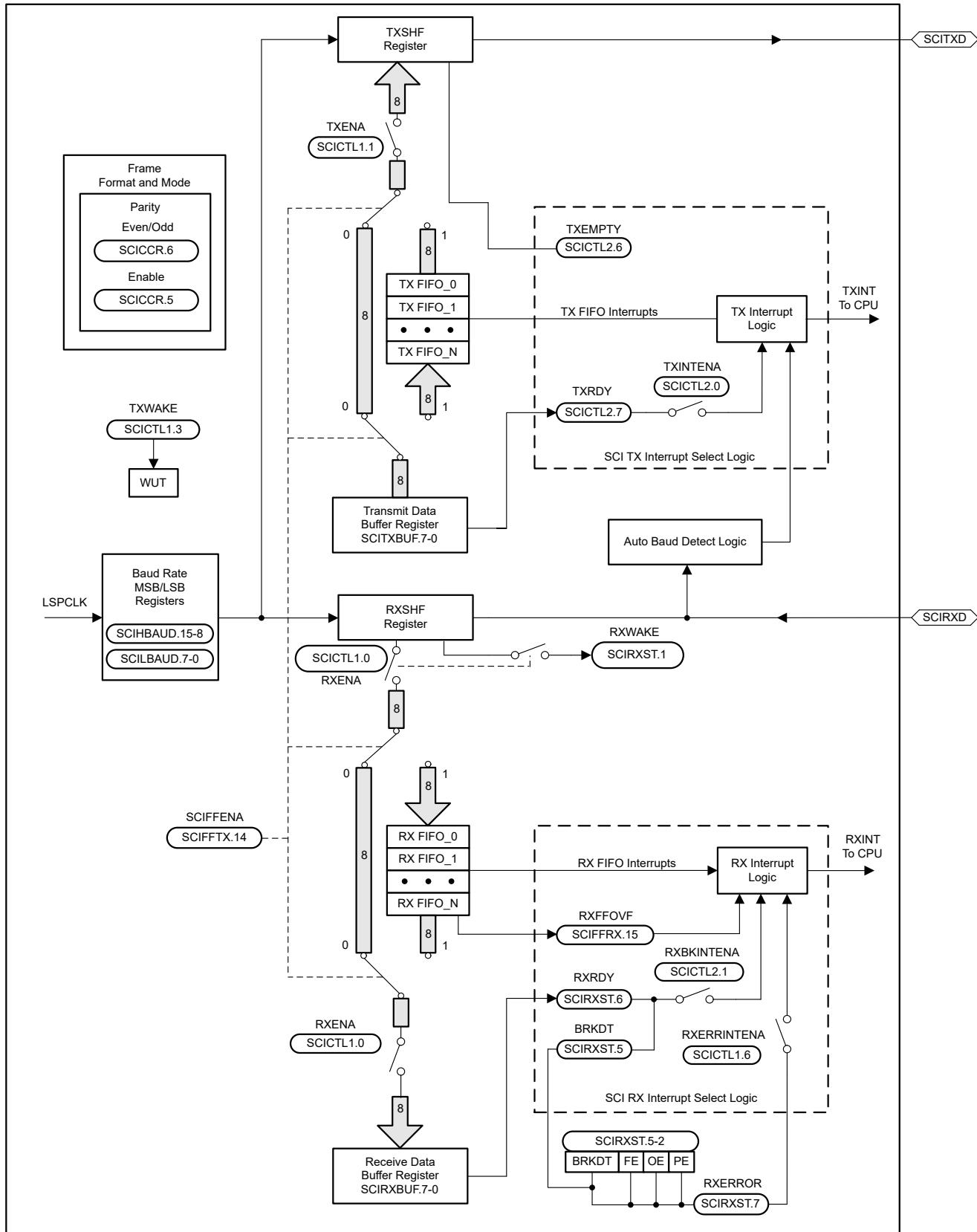

- 3つのUART 互換シリアル通信インターフェイス (SCI)

- 1つのUART 互換LIN (Local Interconnect Network) インターフェイス

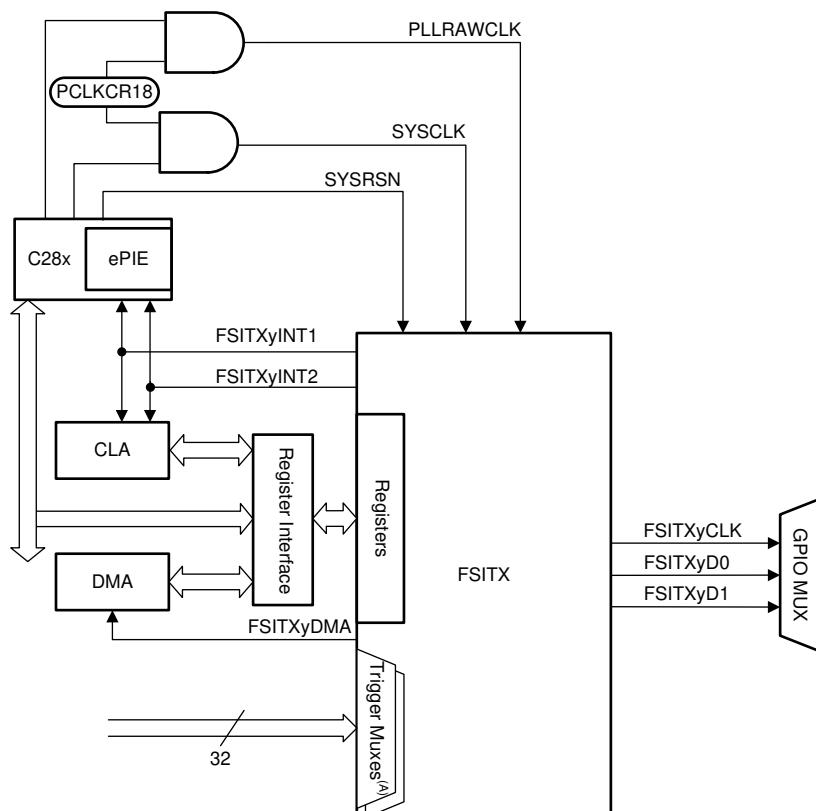

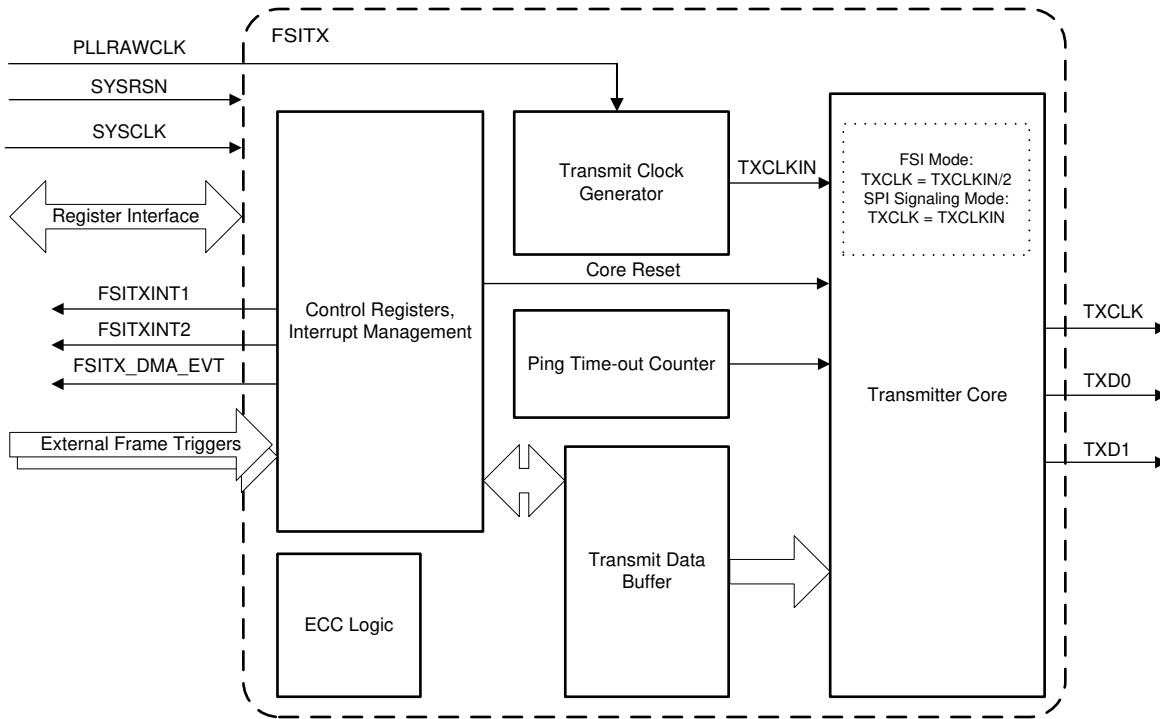

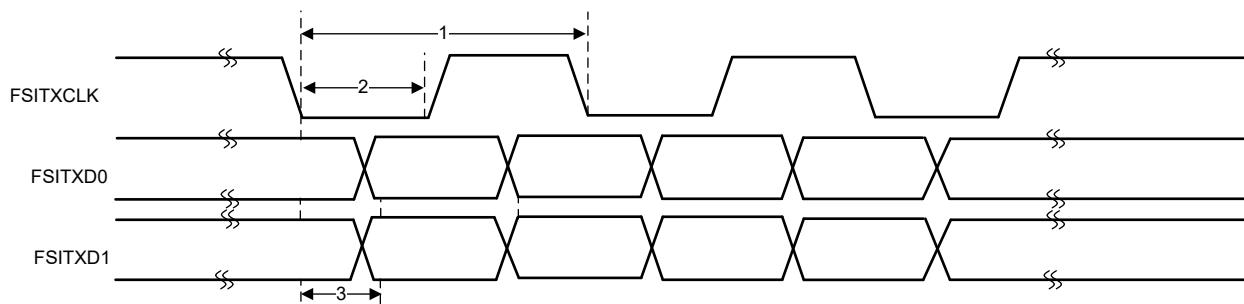

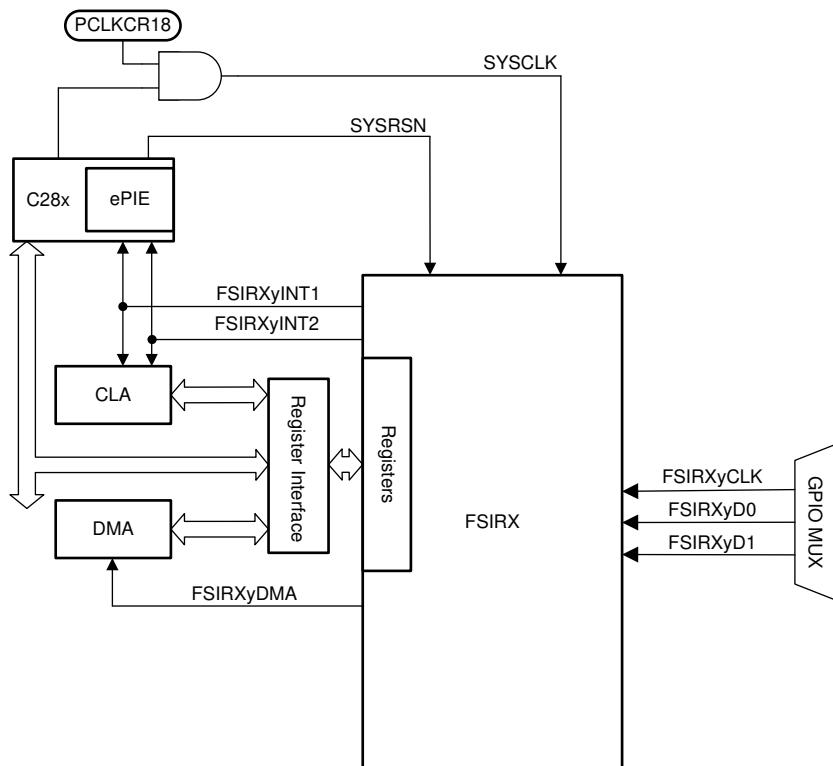

- 1つのトランスマッタおよび1つのレシーバを備えた最大 200Mbps の高速シリアルインターフェイス (FSI)

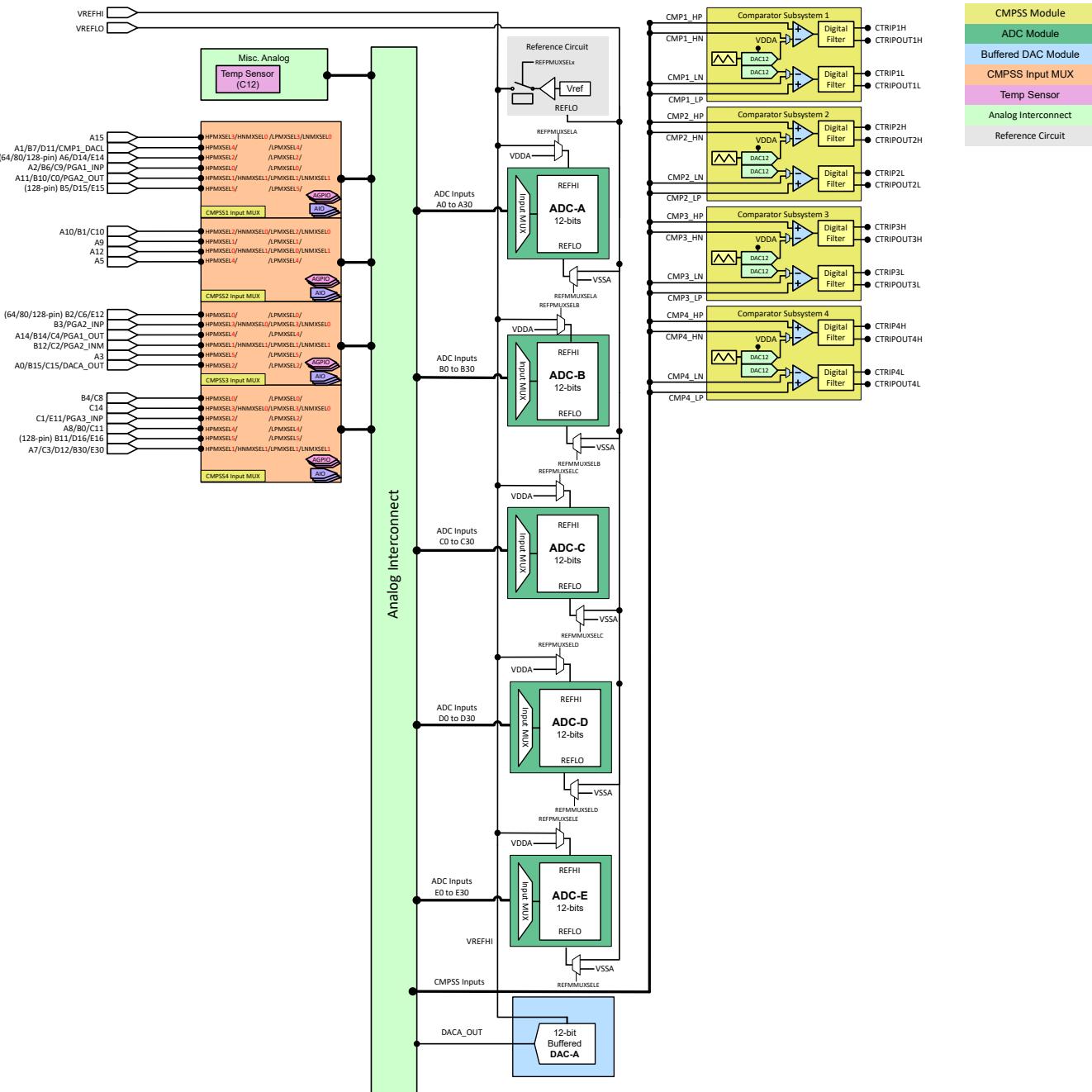

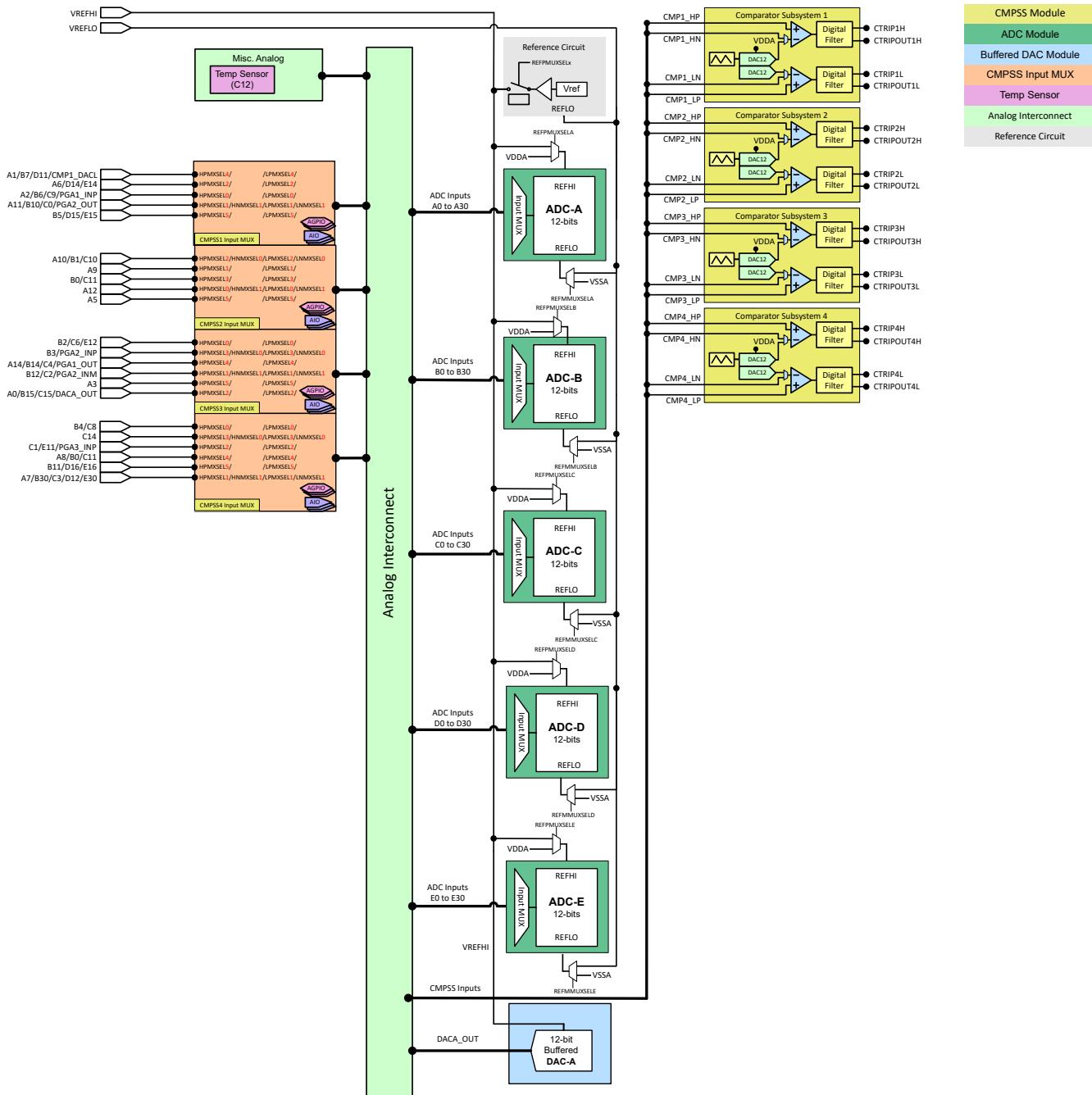

- アナログシステム

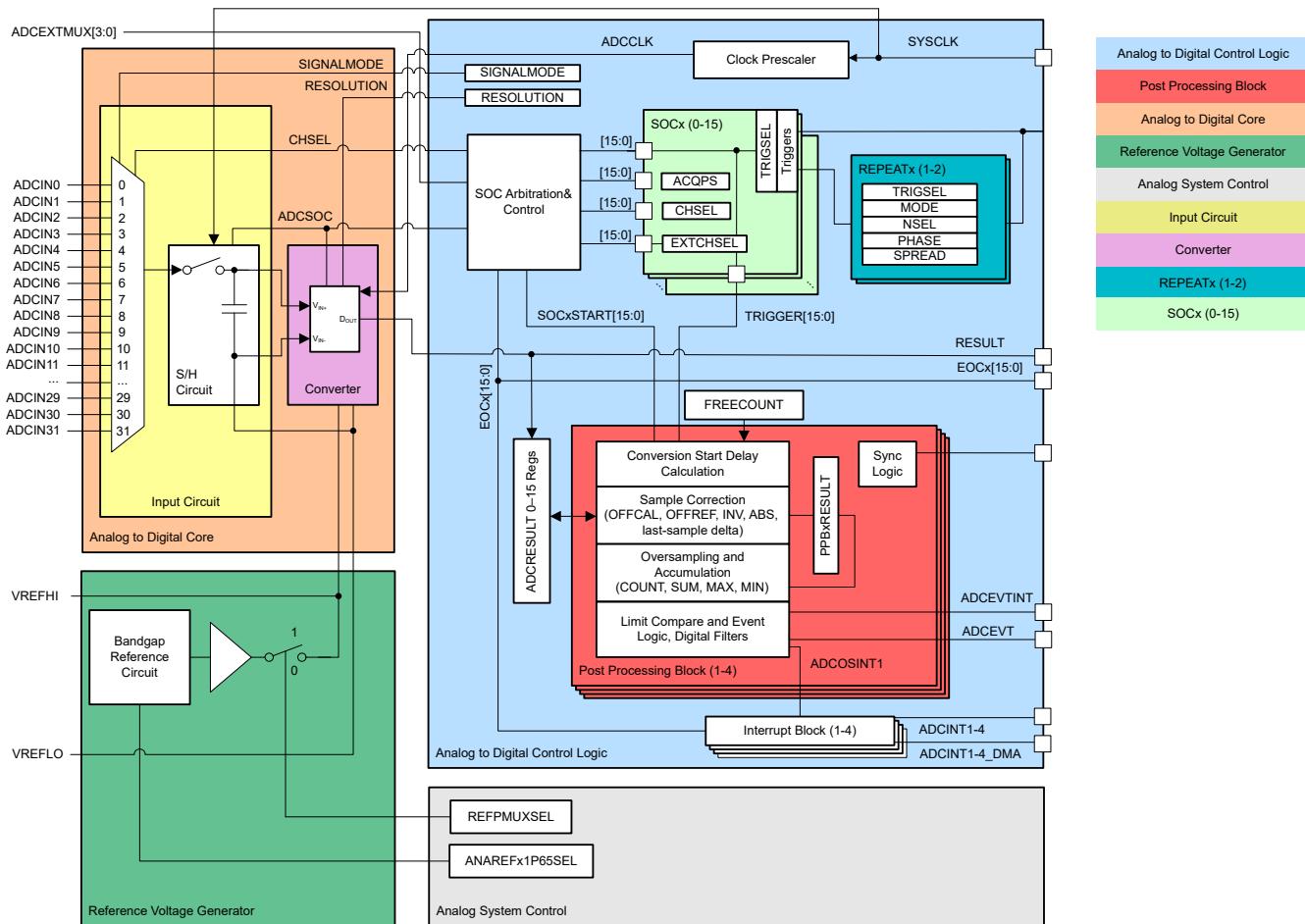

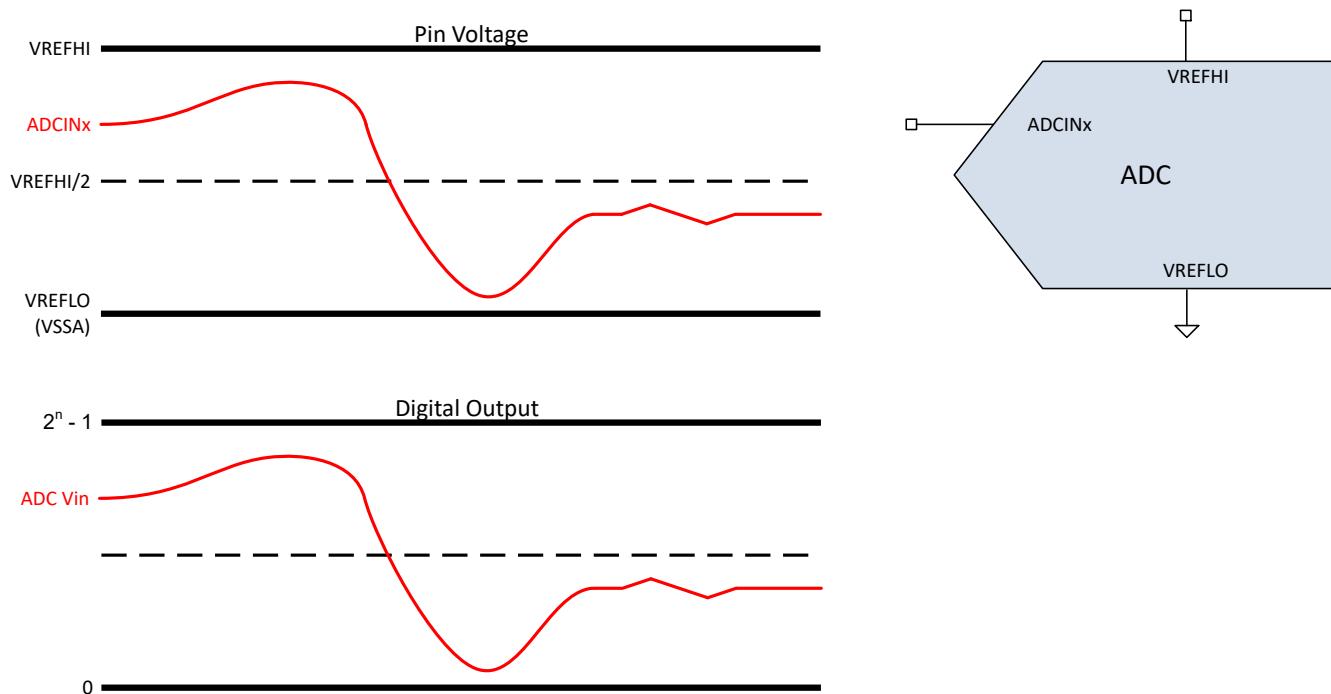

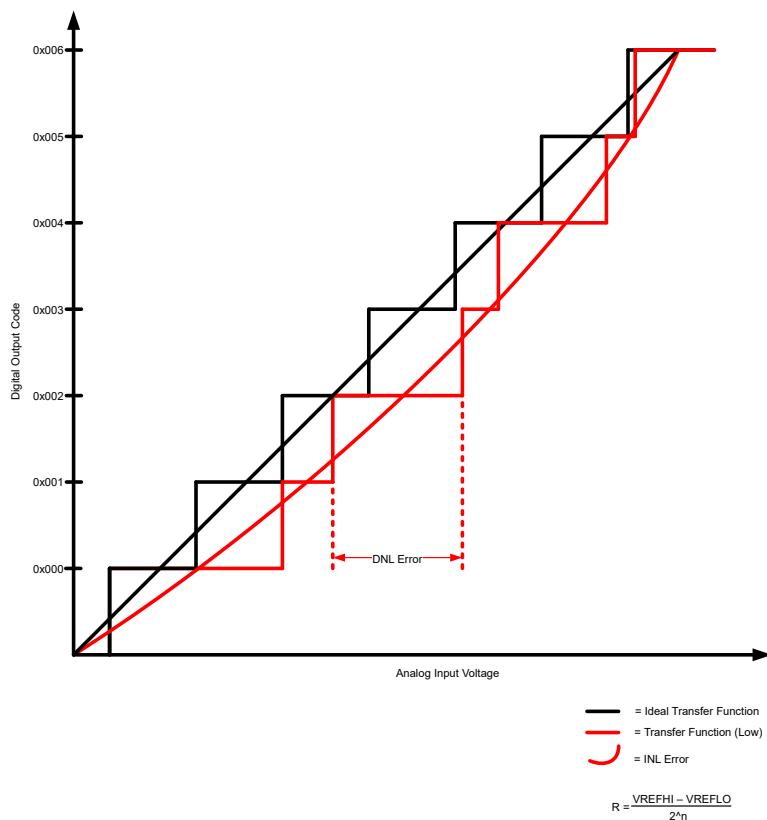

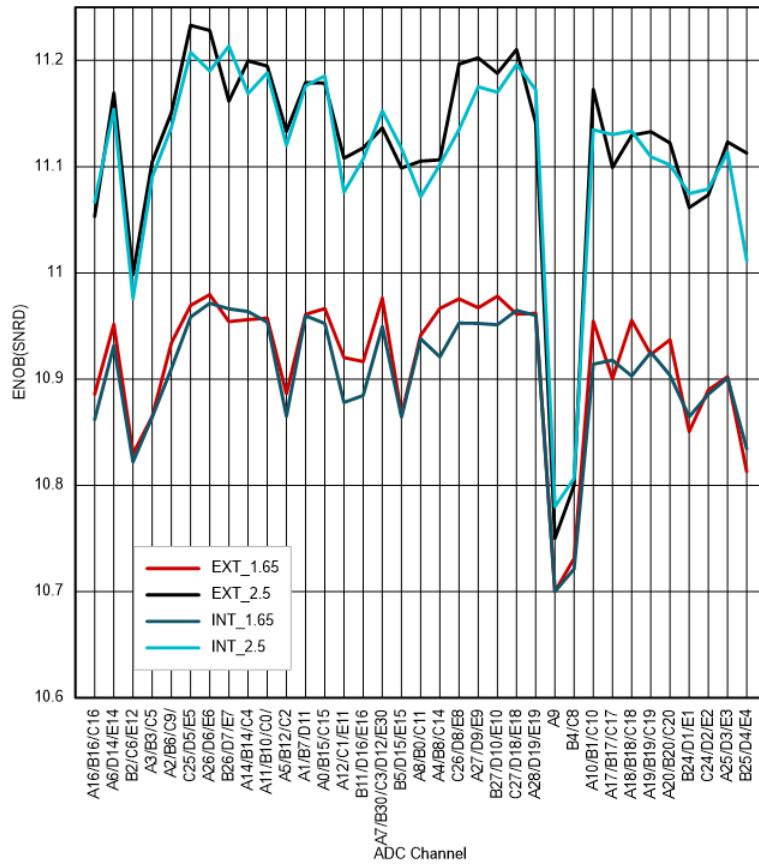

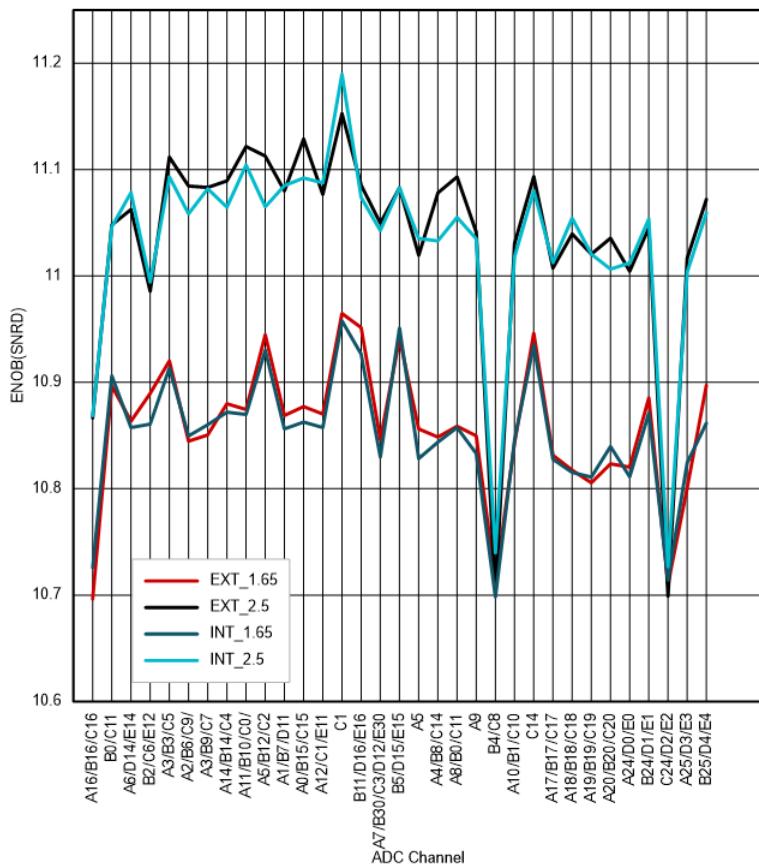

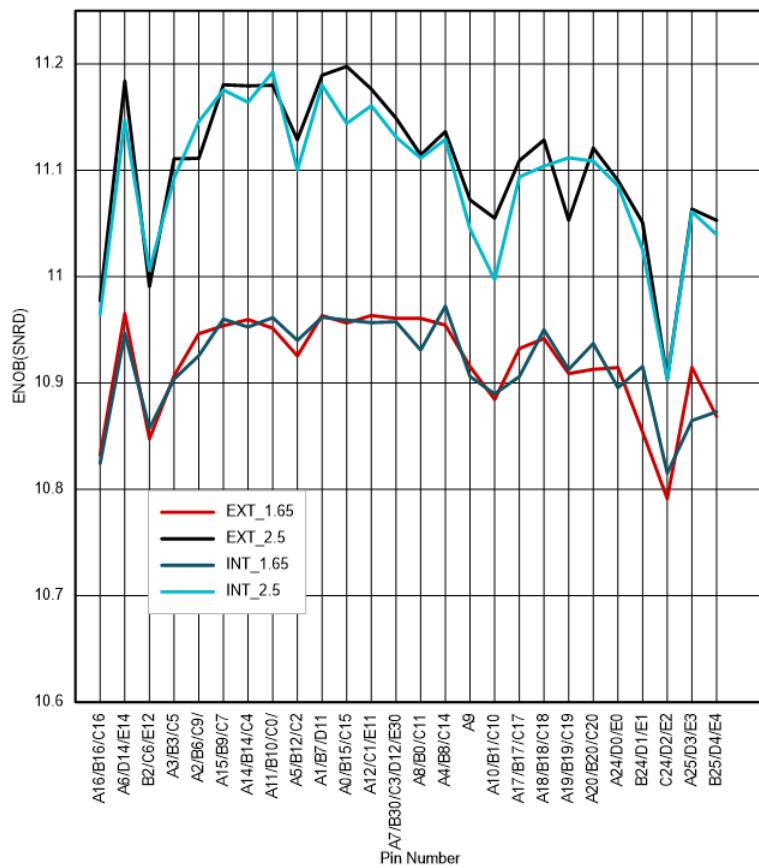

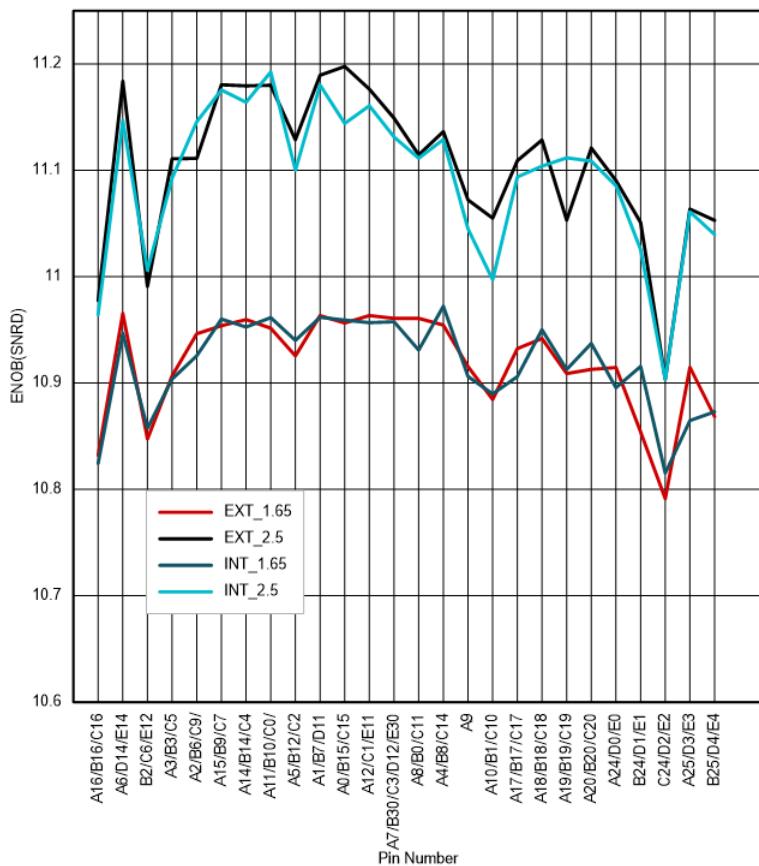

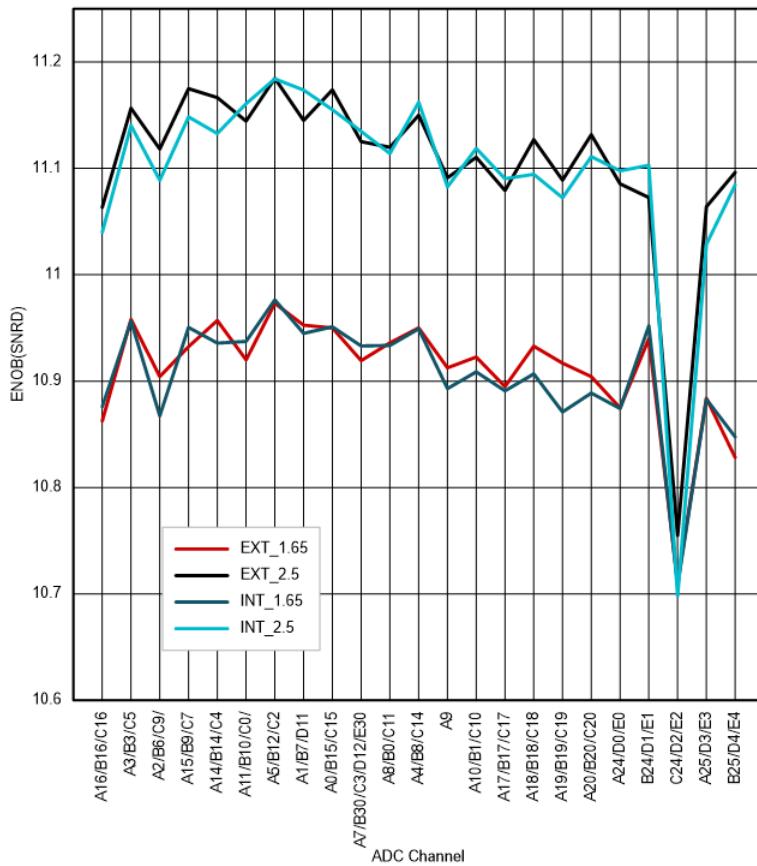

- 5つの3.9MSPS、12ビットのアナログ / デジタルコンバータ (ADC)

- 最大 39 の外部チャネル (1つの gpdac 出力を含む)

- ADC ごとに 4つの後処理ブロック (PPB) を内蔵

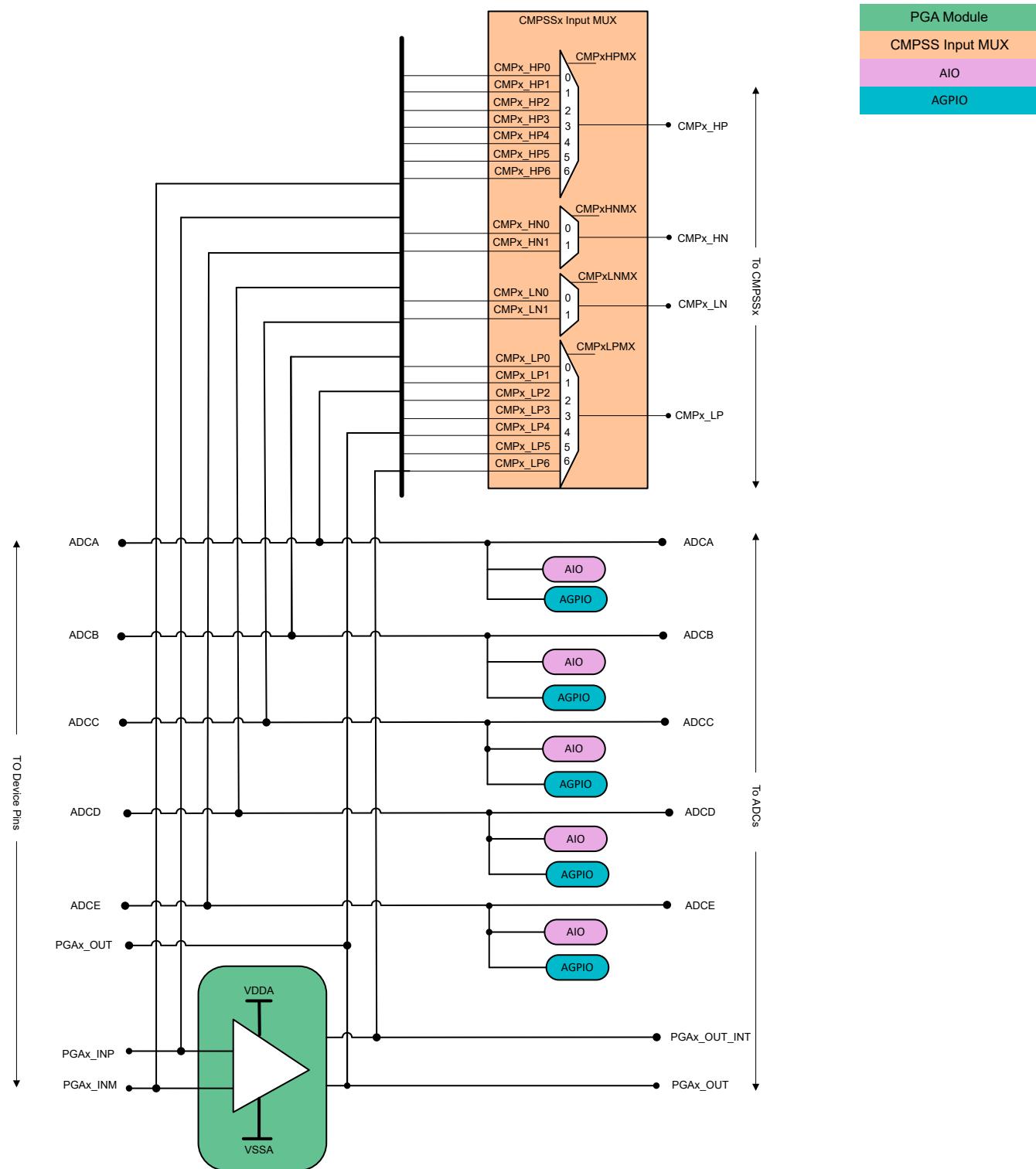

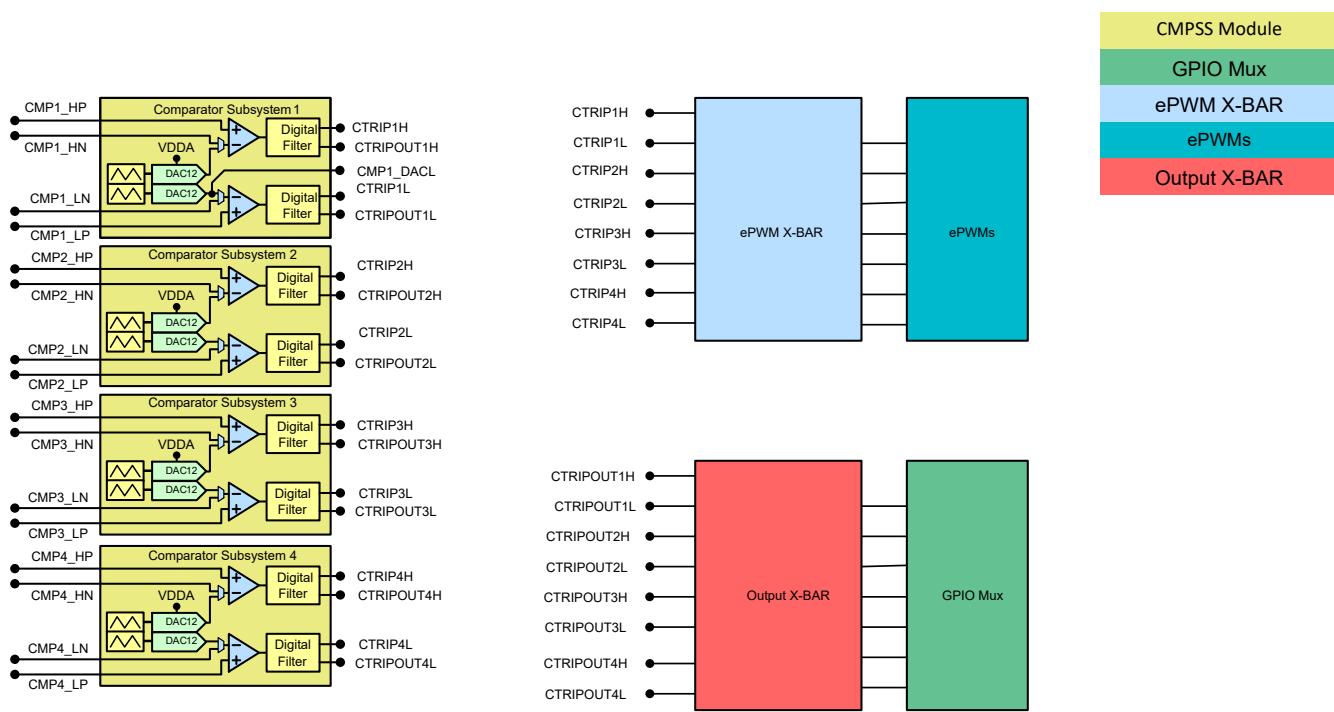

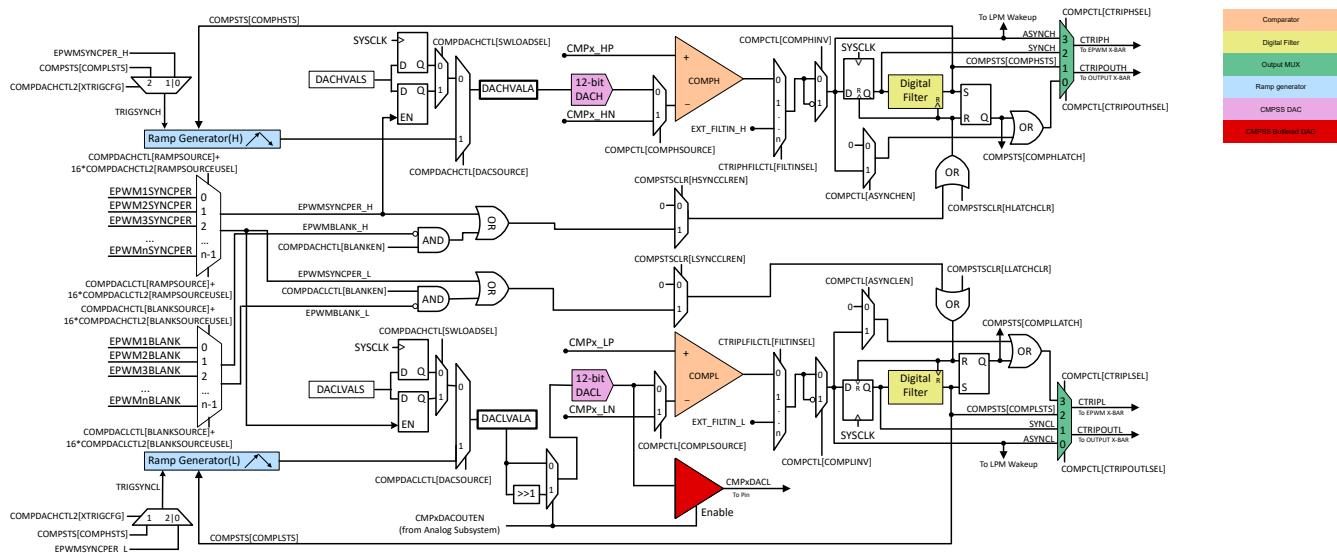

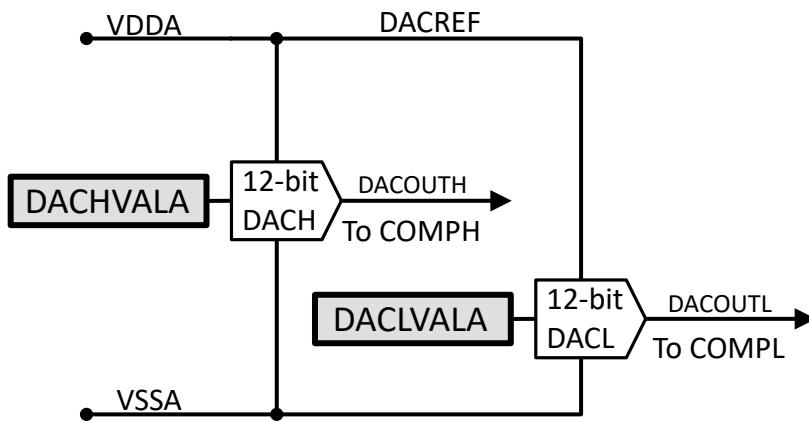

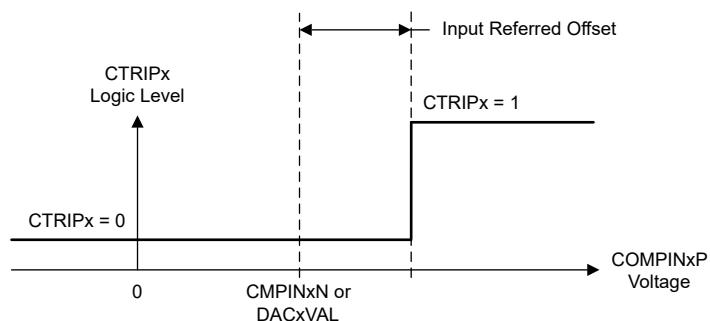

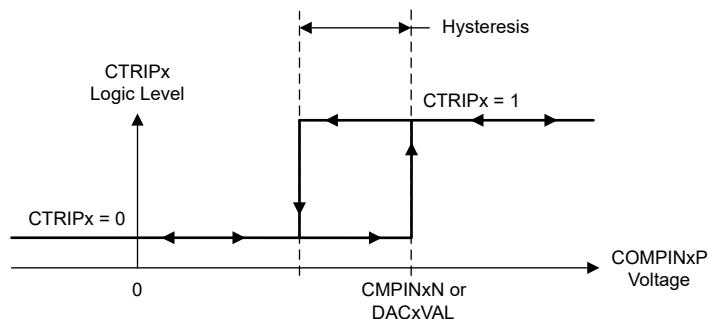

- 12ビットリファレンス D/A コンバータ (DAC) を備えた4つのウィンドウ付きコンパレータ (CMPSS)

- デジタルグリッチフィルタ

- ピンへの低 DAC 出力機能 (CMPSS1)

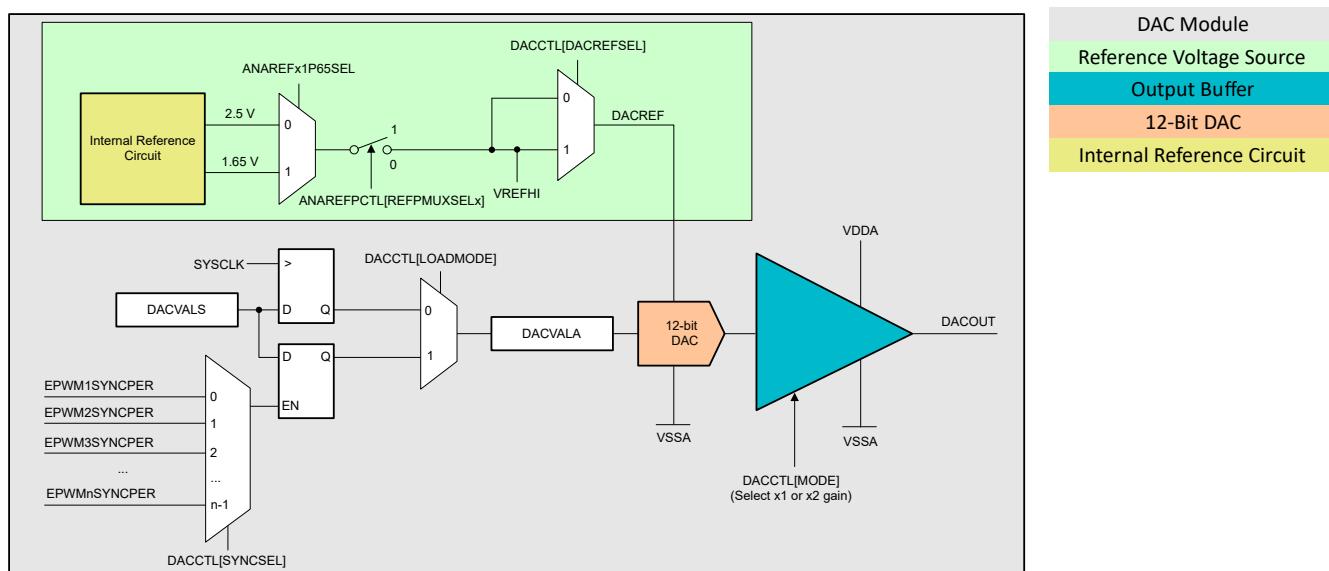

- 1つの12ビットDAC出力 (バッファ付き)

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

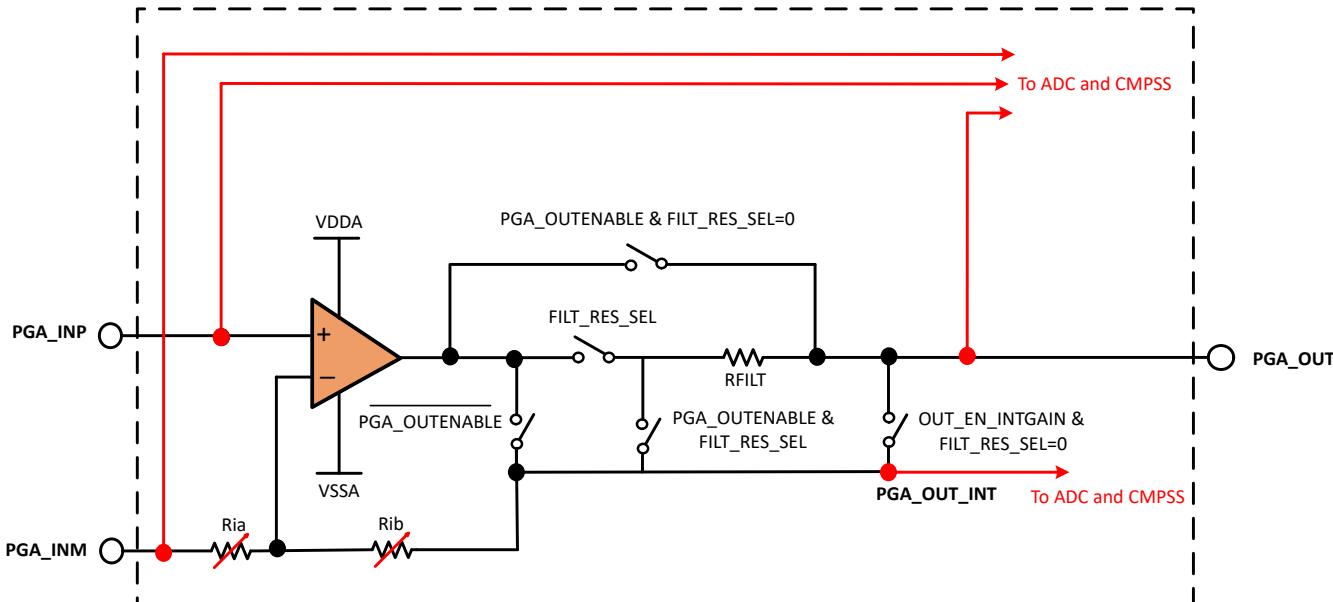

- 3つのプログラマブル ゲイン アンプ (PGA)

- ユニティ ゲインのサポート

- 反転および非反転ゲイン モードのサポート

- 出力フィルタ処理をプログラム可能

- 拡張制御ペリフェラル

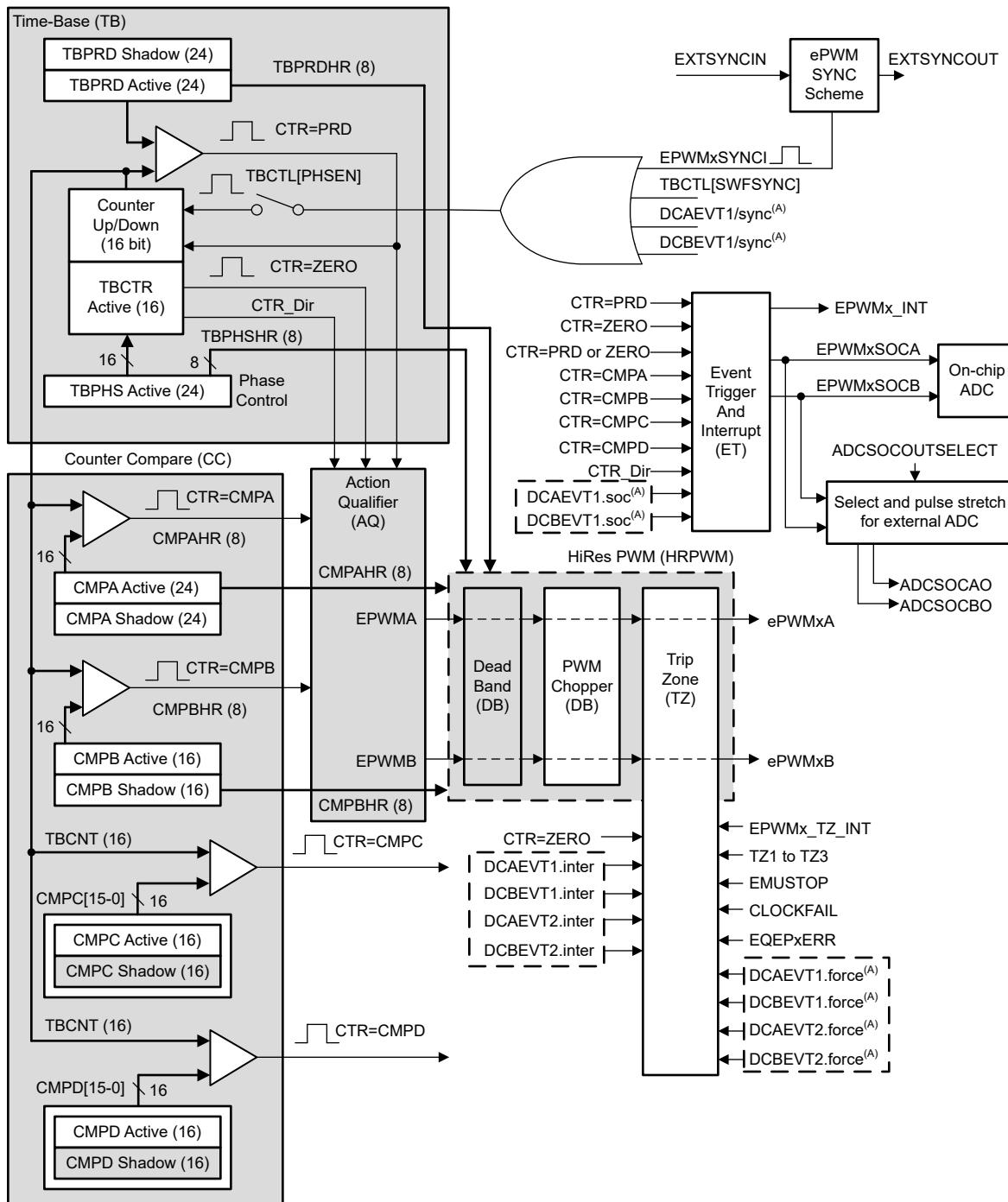

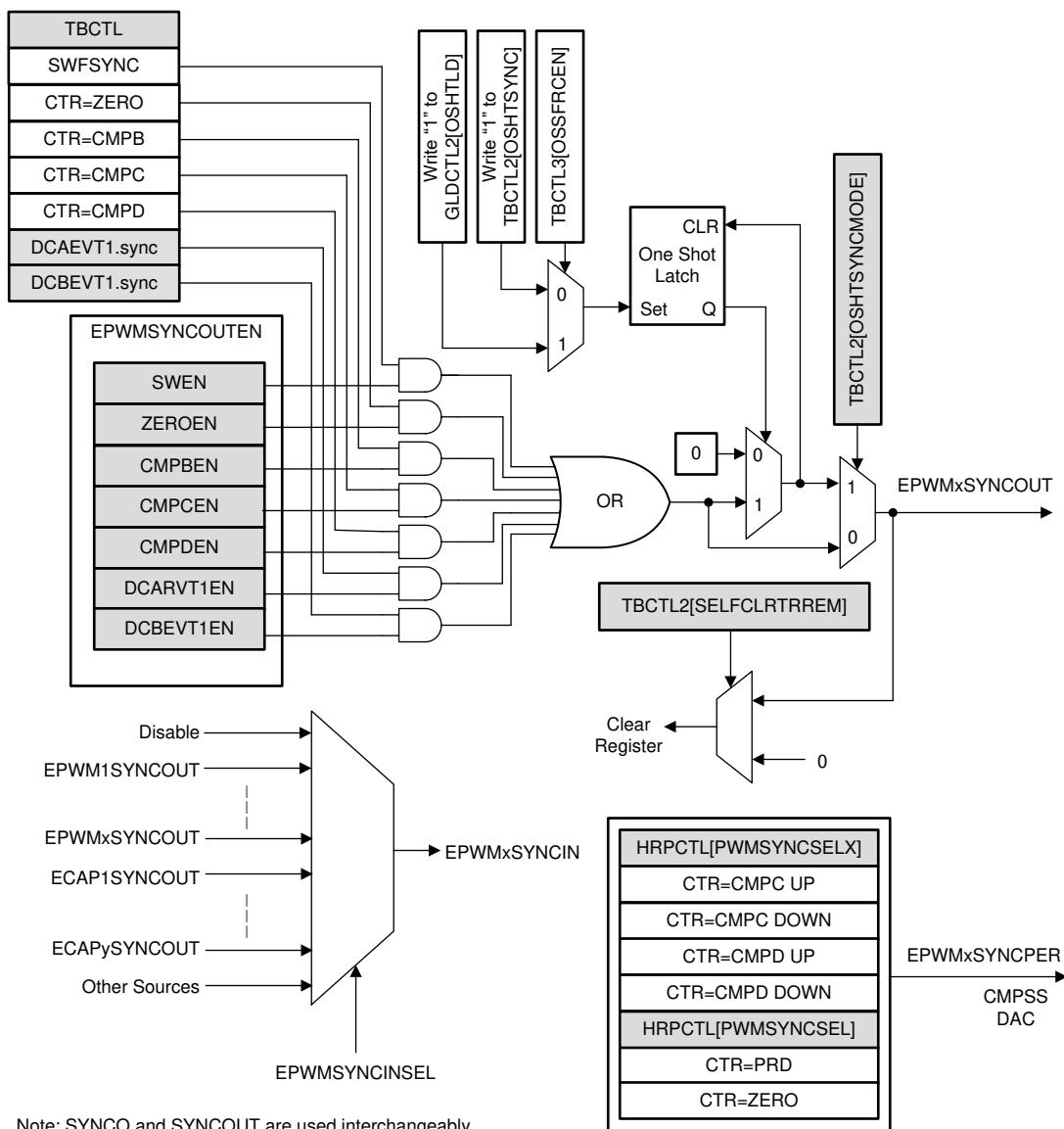

- 24 の ePWM チャネル、うち 12 チャネルが高分解能 (分解能 150ps)

- デッドバンド サポートを内蔵

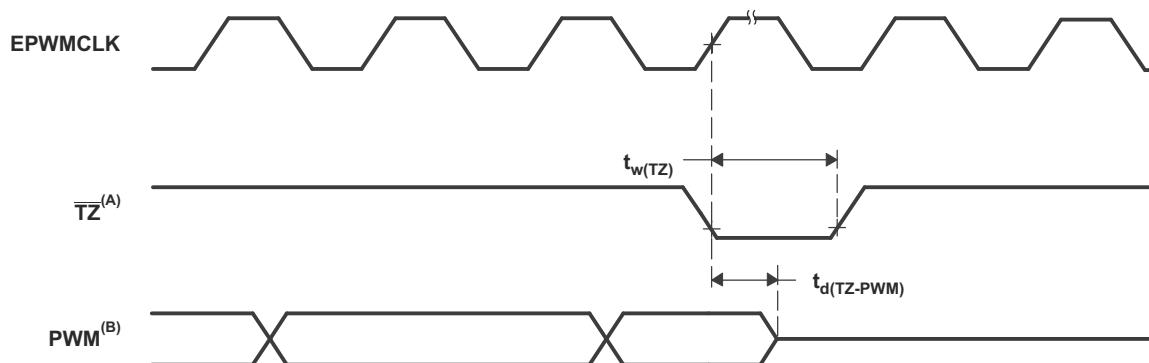

- ハードウェア トリップ ゾーン (TZ) を内蔵

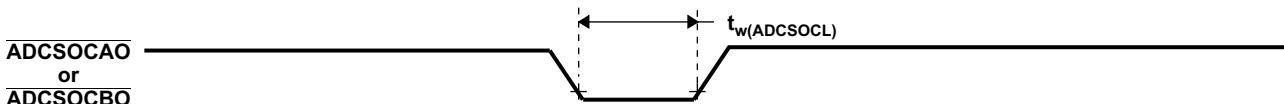

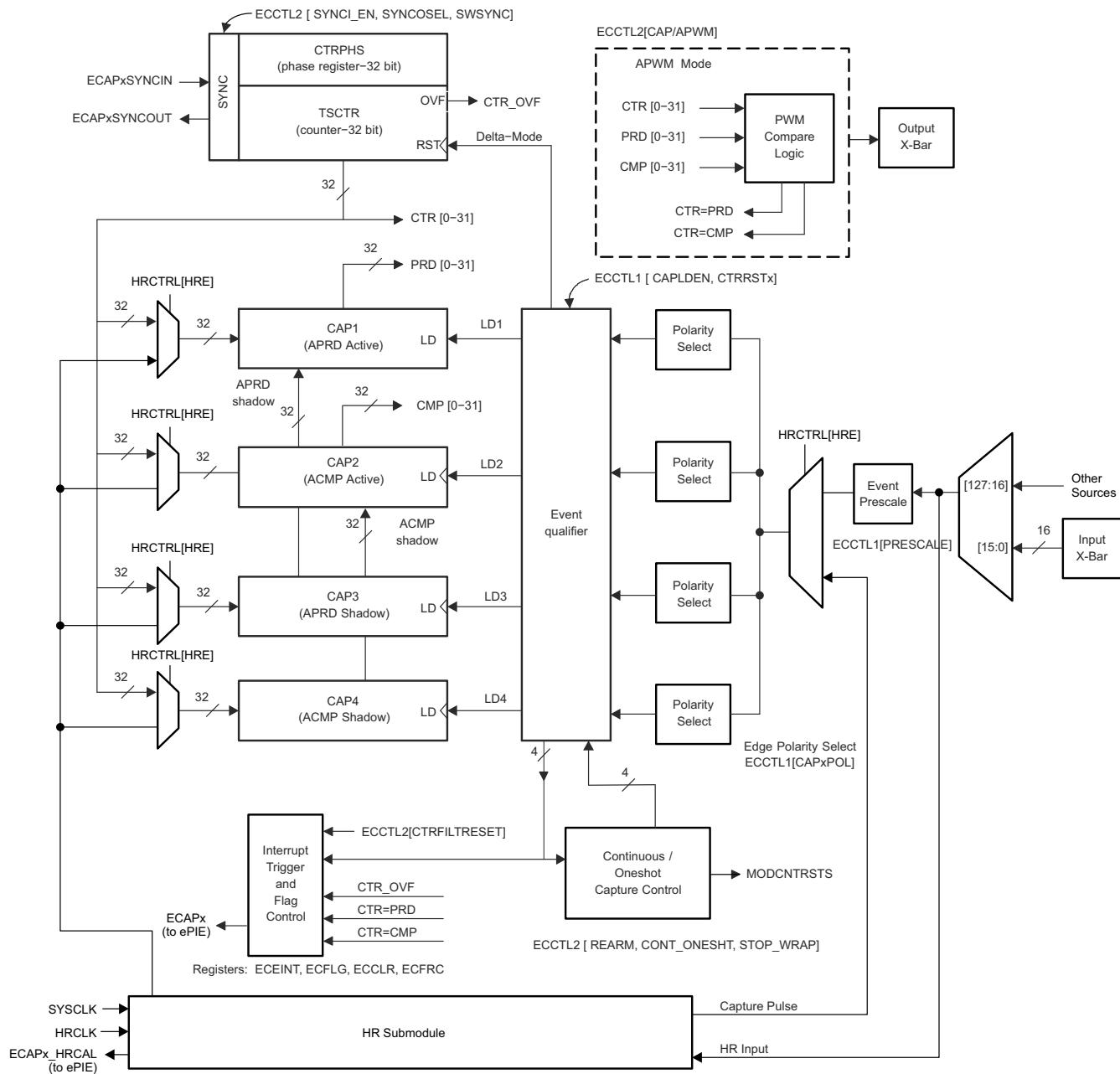

- 2 つの拡張キャプチャ (eCAP) モジュール

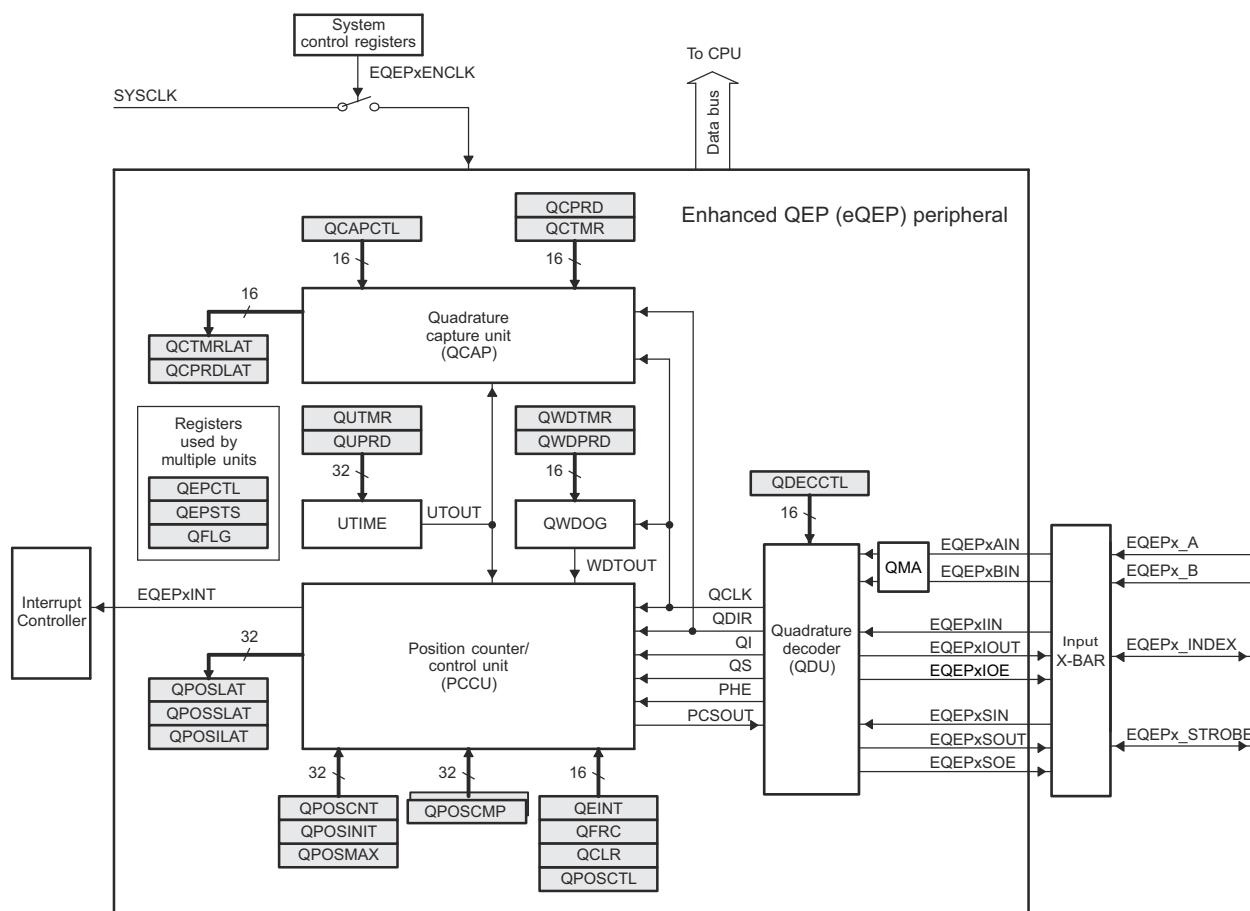

- 3 つの拡張直交エンコーダ パルス (eQEP) モジュール、CW/CCW 動作モードをサポート

- 組み込みパターン ジェネレータ (EPG)

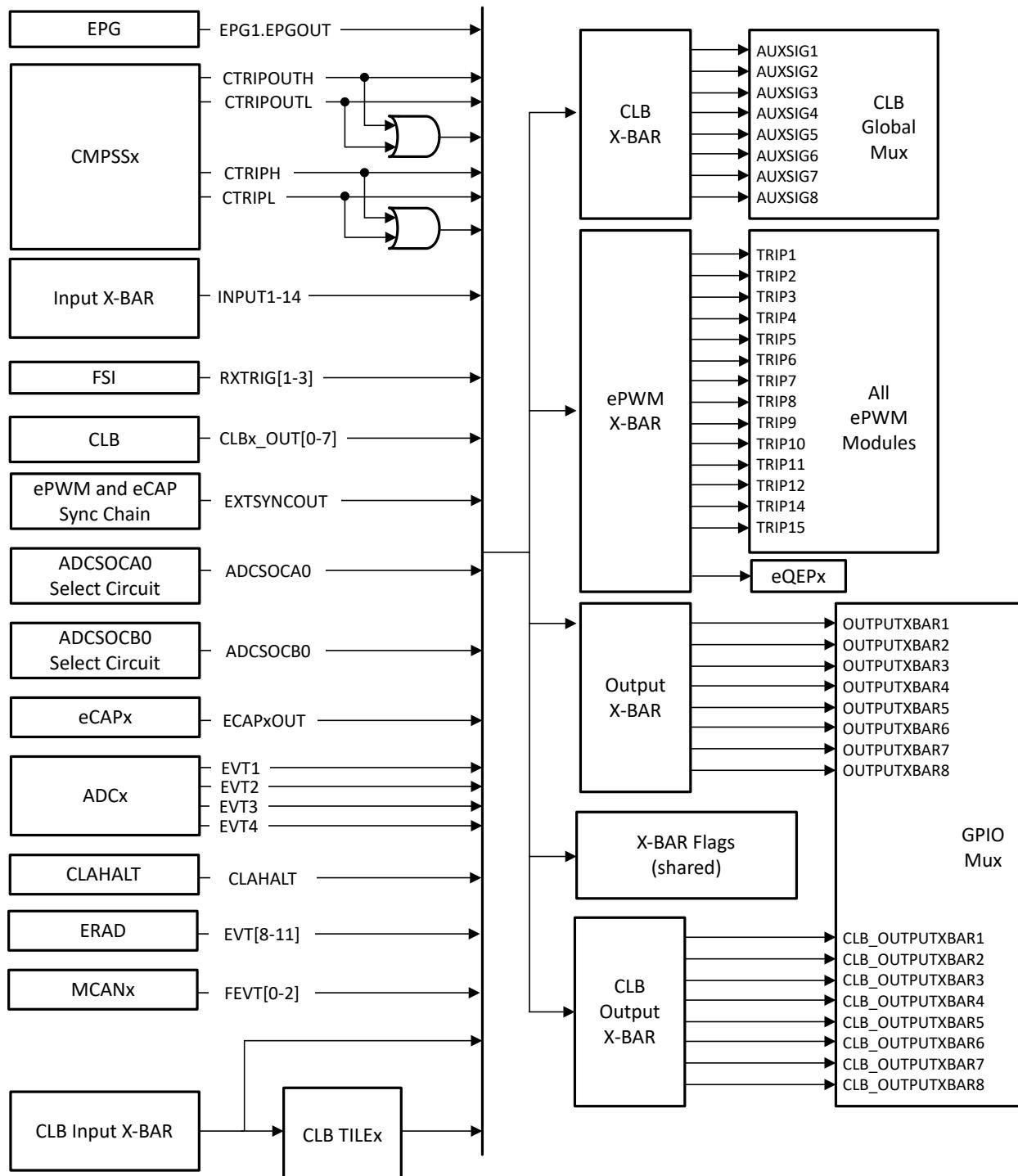

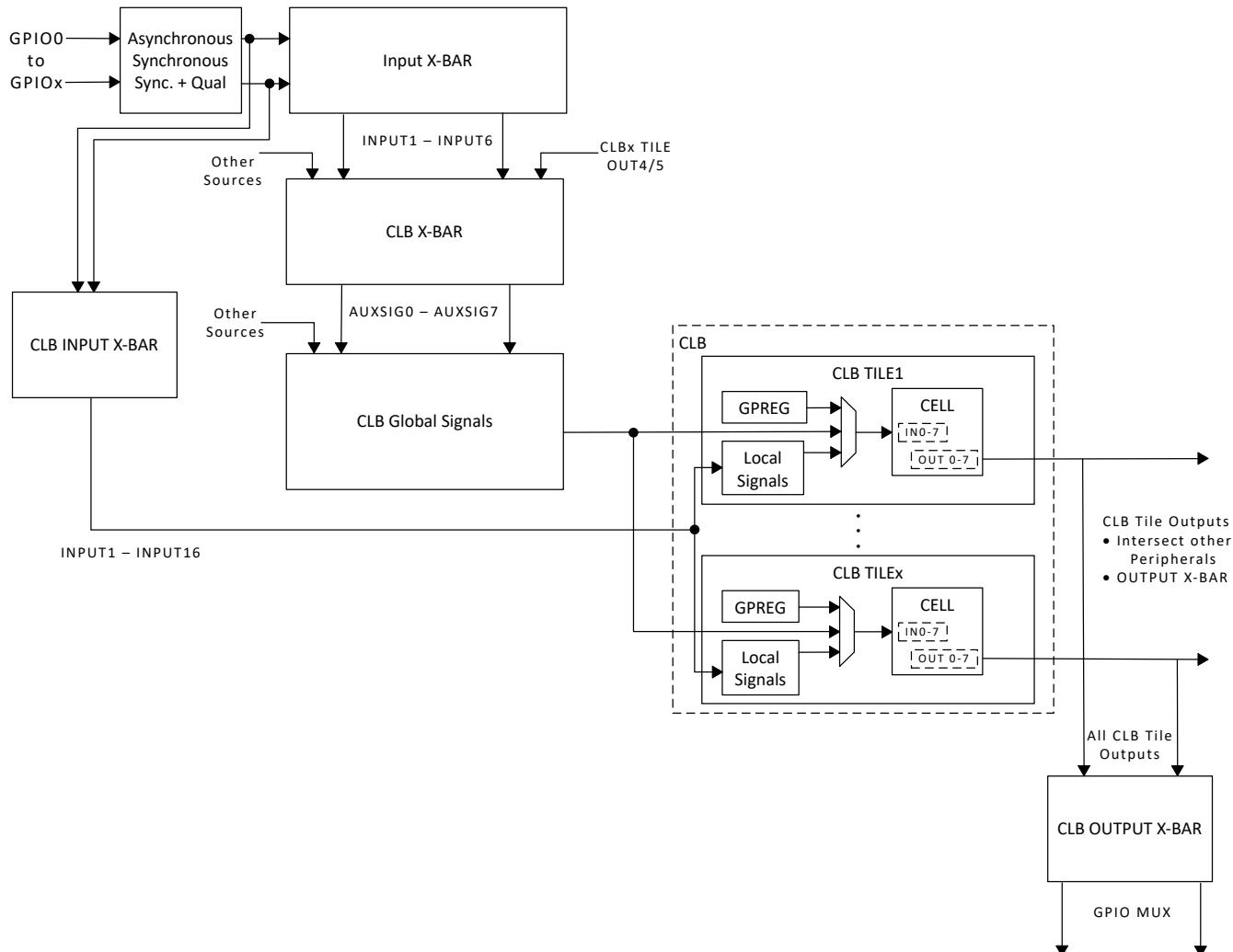

- 構成可能ロジック ブロック (CLB)

- 2 タイプ

- 既存のペリフェラル機能を強化

- ポジション マネージャ ソリューションをサポート

- ニューラル ネットワーク処理ユニット (NPU)

- ディープ畳み込みニューラル ネットワーク (CNN) 向けに高度に最適化

- 可変重みとデータ長

- 8 ビットと 4 ビットの重み

- 8 ビットと 4 ビットのデータ

- 8bWx8bD の 75MHz で 600MOPS (メガ オペレーション/秒)

- 4bWx8bD の 75MHz で 1200MOPS

- SW 手法と比較して NN 推論のパフォーマンスを最大 10 倍向上

- テキサス・インスツルメンツの AI ツールによって FW ライブラリが生成されるため、直接コーディングは不要

- リアルタイム制御に重点を置いたエッジ AI モデル

- ARC フォルトの例

- モーター フォルトの例

- ライブ ファームウェア アップデート (LFU)

- 診断機能

- メモリ パワー オン自己テスト (MPOST)

- 機能安全準拠<sup>1</sup>

- 機能安全アプリケーション向けに開発

- ISO 26262 および IEC 61508 システムの設計を支援するドキュメントを使用可能

- ASILD および SIL 3 までの決定論的能力

- ASIL B および SIL 2 までのハードウェア 安全度

- 安全関連の認証

- TÜV SÜD により ISO 26262 認証済み (ASIL B まで)

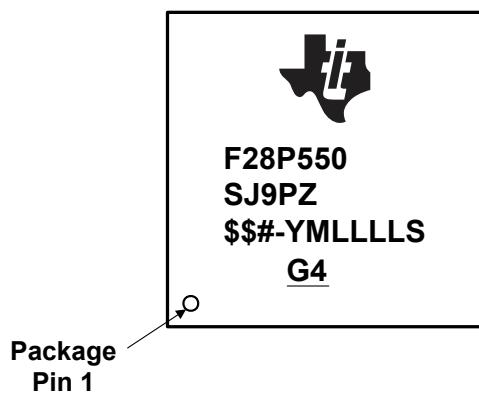

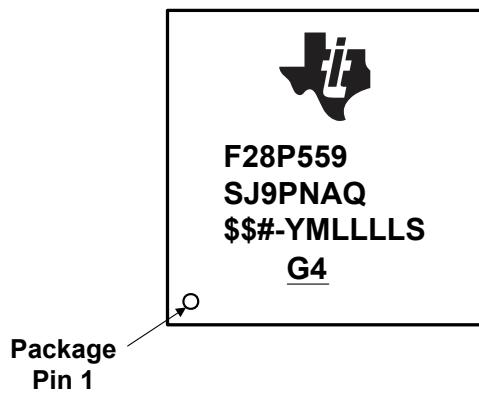

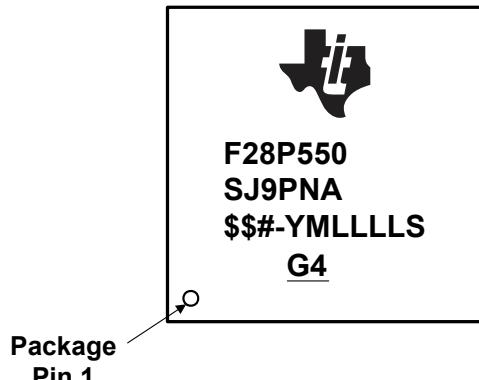

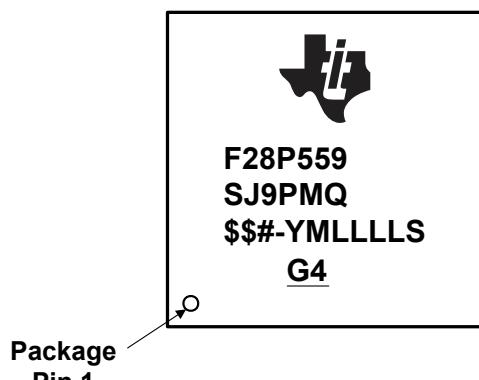

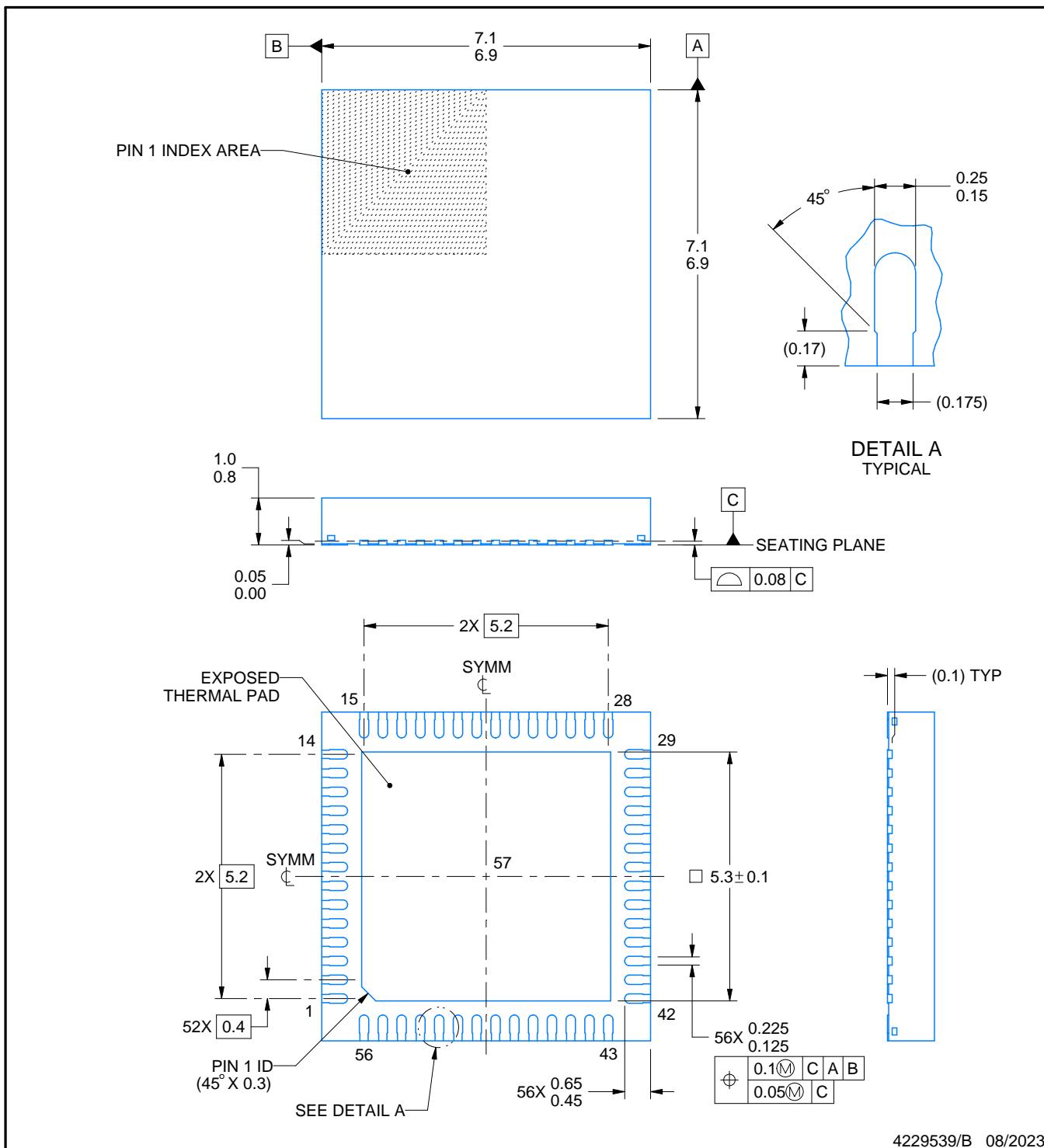

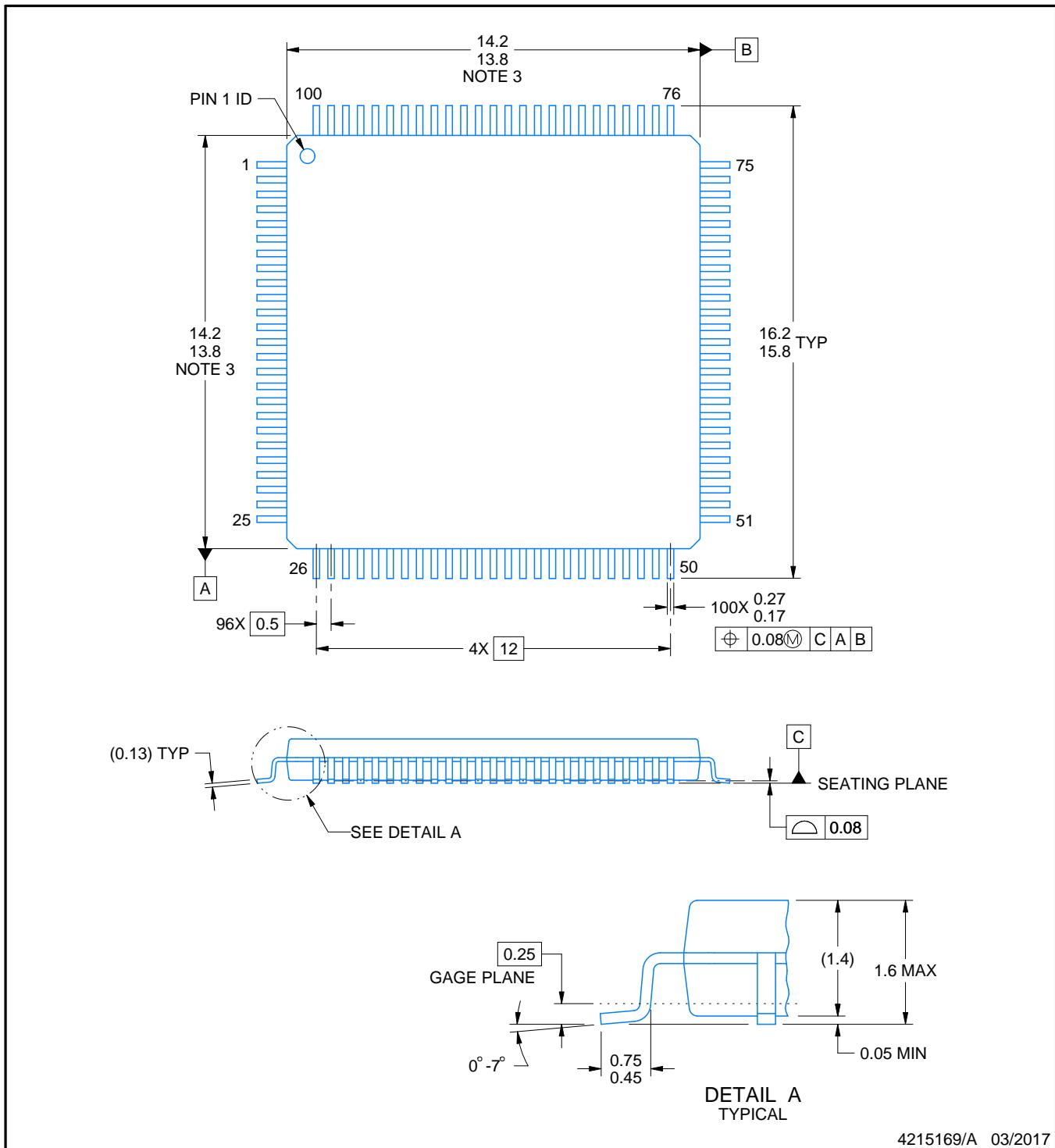

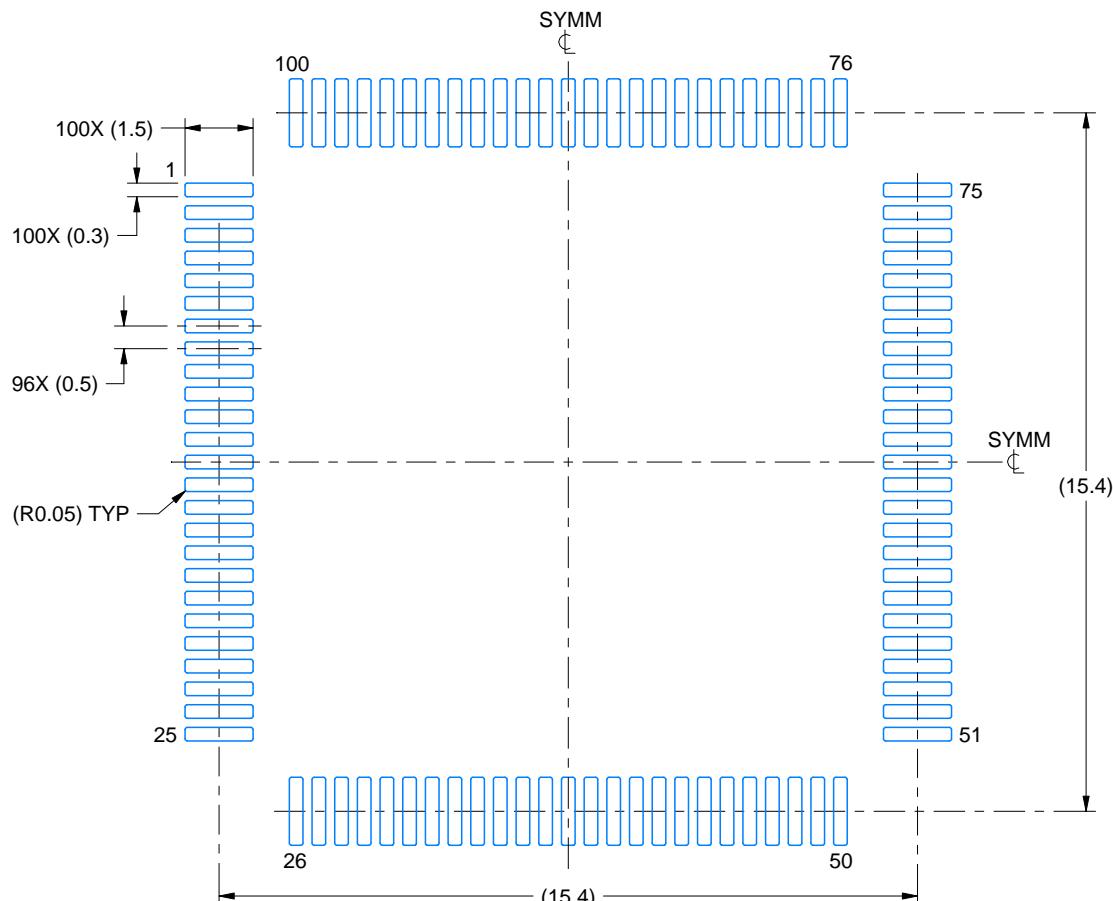

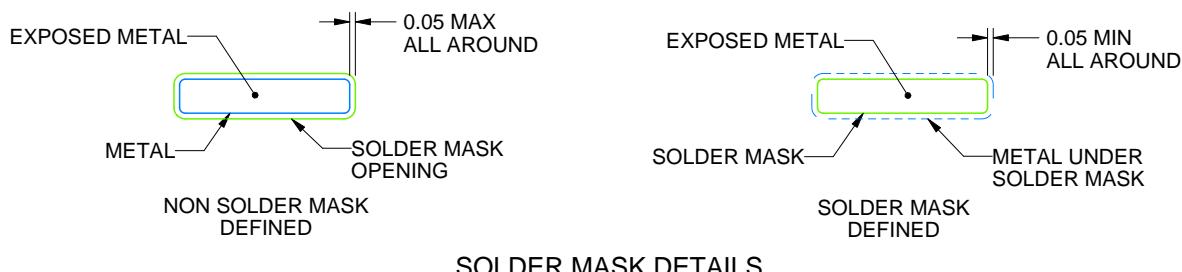

- パッケージ オプション:

- 128 ピンの薄型クワッド フラットパック (TQFP)

<sup>1</sup> 機能安全準拠または機能安全品質管理された正確な部品番号については、[TMS320F28P55x リアルタイム マイクロコントローラの機能安全マニュアル](#)および [TÜV 認証](#)を参照してください。

- [PDT サフィックス]

- 100 ピンの薄型クワッド フラットパック (LQFP)

- [PZ サフィックス]

- 80 ピンの TQFP [PNA サフィックス]

- 64 ピンの LQFP [PM サフィックス]

- 56 ピンの超薄型クワッド フラットパック リードなし (VQFN) [接尾辞 RSH]

- 温度オプション:

- 接合部温度 ( $T_J$ ): -40°C ~ 150°C

## 2 アプリケーション

- 家電製品

- エアコン 室外機

- ビル オートメーション

- ドア開閉装置 ドライブの制御

- 産業用機械と工作機械

- 自動仕分け機器

- 繊維機械

- AC インバータと VF ドライブ

- AC ドライブ 制御 モジュール

- AC ドライブ 位置 フィードバック

- AC ドライブ 電力段 モジュール

- リニア モーター 輸送用システム

- リニア モーター の 電力段

- 単軸と多軸のサーボ ドライブ

- サーボ ドライブ 位置 フィードバック

- サーボ ドライブ の 電力段 モジュール

- 速度制御 BLDC ドライブ

- AC 入力 BLDC モーター ドライブ

- DC 入力 BLDC モーター ドライブ

- ファクトリ オートメーション

- ロボット 向け サーボ ドライブ

- 移動型 ロボット の モーター 制御

- 位置センサ

- 産業用電源

- 産業用 AC-DC

- UPS

- 3 相 UPS

- 単相 オンライン UPS

- テレコムとサーバーの電源

- 商用 DC/DC

- 商用 ネットワーク および サーバー の PSU (電源)

- 商用 テレコム 整流器

- ハイブリッド、電動、パワートレイン システム

- DC/DC コンバータ

- インバータ および モーター 制御

- オンボード チャージャ (OBC) / ワイヤレス チャージャ

- パーチャル エンジン サウンド システム (VESS)

- エンジン ファン

- eTurbo / チャージャ

- ポンプ

- 電動パワー ステアリング (EPS)

- インフォテインメントおよびクラスタ

- ヘッドアップ ディスプレイ

- 車載用ヘッド ユニット

- 車載用外部アンプ

- ボディ エレクトロニクス / ライティング

- 車載用 HVAC (エアコン) コンプレッサ・モジュール

- DC/AC インバータ

- ヘッドライト

- ADAS

- 機械式スキャン LIDAR

- EV 充電インフラ

- AC 充電 (パイル) ステーション

- DC 充電 (パイル) ステーション

- EV 充電ステーション向け電源モジュール

- EV (電気自動車) ワイヤレス充電ステーション

- 再生可能エネルギー ストレージ

- エネルギー ストレージ電力変換システム (PCS)

- ポータブル電源

- ソーラー エネルギー

- セントラル インバータ

- マイクロ インバータ

- 太陽光発電オプティマイザ

- ソーラー アーク保護

- 緊急遮断機能

- ストリング インバータ

### 3 説明

TMS320F28P55x (F28P55x) は、電力密度の向上、スイッチング周波数の向上、GaN および SiC 技術の使用のサポートなど、パワー エレクトロニクスの効率を向上させるように設計された、スケーラブルできわめてレイテンシの低いデバイスである C2000™ リアルタイム マイクロコントローラ ファミリの製品です。

主なアプリケーションには以下が含まれます。

- モータードライブ

- 電化製品

- ハイブリッド、電気、パワートレイン システム

- ソーラーと EV (電気自動車) 充電

- デジタル電源

- ボディ エレクトロニクス / ライティング

- 試験 / 測定機器

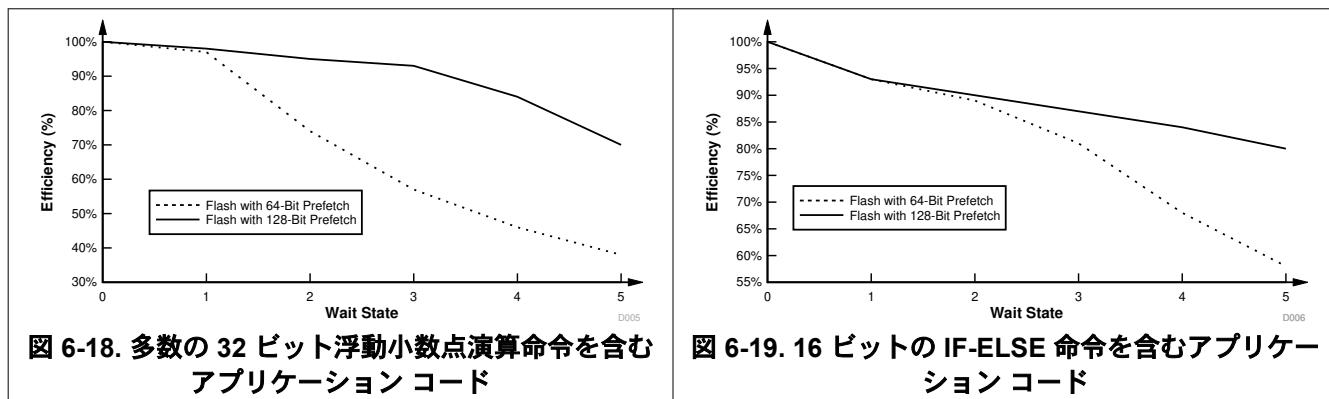

リアルタイム制御サブシステムは、テキサス・インスツルメンツの 32 ビット C28x DSP コアをベースにしており、オンチップ フラッシュまたは SRAM から実行される浮動小数点または固定小数点コードに対して 150MHz の信号処理性能を発揮します。C28x CPU は、浮動小数点演算ユニット (FPU)、三角関数演算ユニット (TMU) および VCRC (巡回冗長検査) 拡張命令セットによってさらに強化され、リアルタイム制御システムでよく使われる主要なアルゴリズムを高速化します。

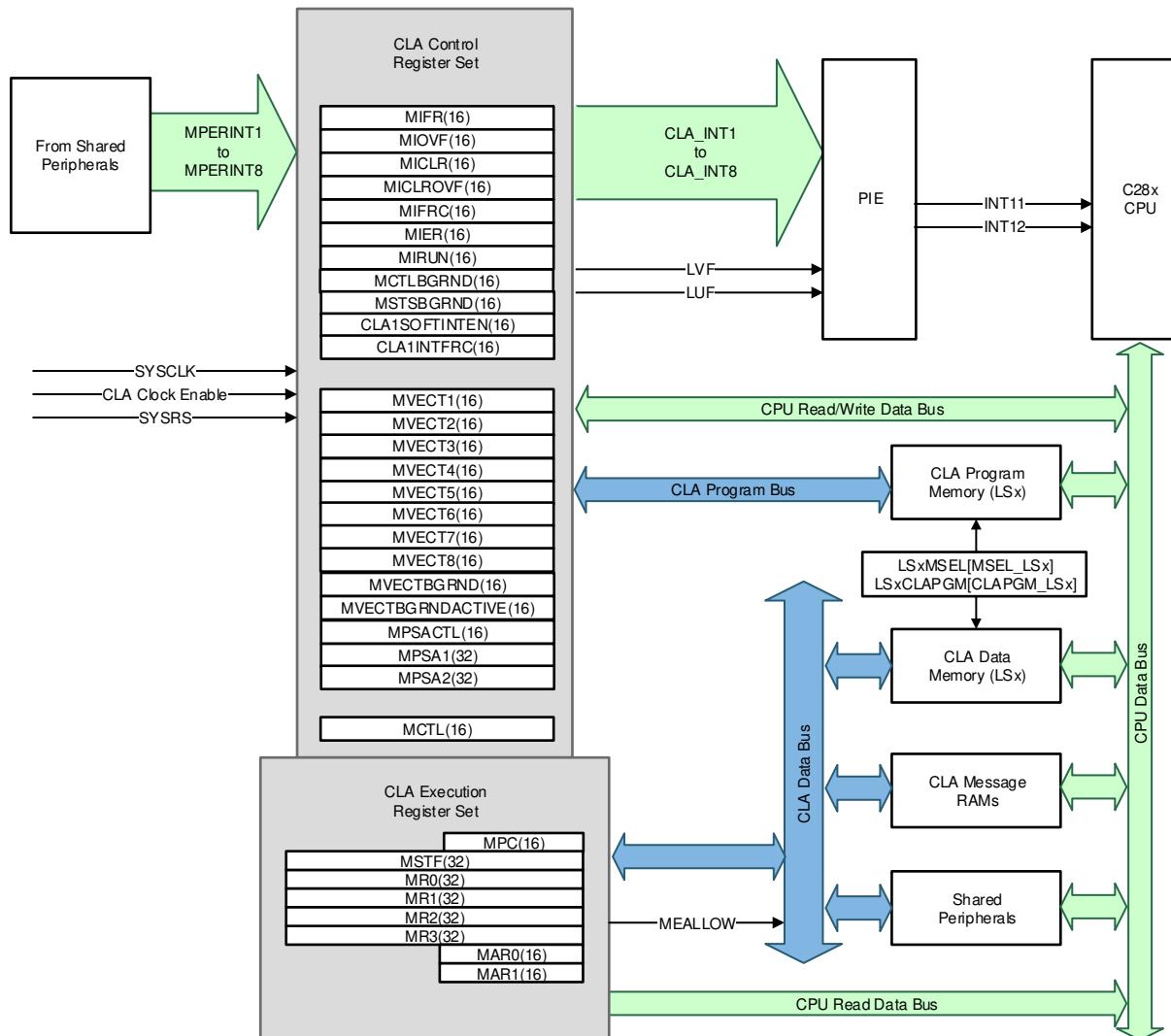

CLA により、一般的なタスクの負荷の多くをメインの C28x CPU から取り除くことができます。CLA は独立の 32 ビット浮動小数点演算アクセラレータであり、CPU と並列に実行されます。さらに、CLA には独自の専用メモリリソースがあり、一般的な制御システムで必要となる主要なペリフェラルに直接アクセスできます。ANSI C のサブセット、およびハードウェア ブレークポイントやハードウェアによるタスク切り替えなどの主要な機能が標準でサポートされています。

ニューラル ネットワーク処理ユニット (NPU) は、事前トレーニング済みのモデルを使用した機械学習推論をサポートできます。600~1200MOPS (メガ オペレーション/秒) の処理性能と、ARC フォルト検出またはモーター フォルト検出のモデル サポートを備えており、SW のみをベースとする実装と比べて NN 推論サイクルを最大 10 倍まで向上できます。TI の Edge AI Studio - Model Composer または Tiny ML Modelmaker でモデルをロードしてトレーニングすると、高度な機能セットを実現できます。C28x のソース コードはこれらのツールによって生成されるため、手動コーディングは必要ありません。お客様が独自の AI トレーニング フレームワークを採用している場合は、テキサス・インスツルメンツのニューラル ネットワーク コンパイラを使用することで、使用中の AI モデルを移植して多くの C28x ベースの MCU との互換性を確保できます。リファレンス ソリューションに关心をお持ちの場合は、テキサス・インスツルメンツのアーキ フォルト検出プロジェクト、またはモーター ベアリング フォルト検出プロジェクトにアクセスしてください。

F28P55x は、最大 1088KB のフラッシュ メモリをサポートしています。これらは 4 つの 256KB バンクと 1 つの 64KB バンクに分割されるため、1 つのバンクでプログラミングを行い、並行して別のバンクで実行を行えます。最大 133KB のオンチップ SRAM も利用でき、フラッシュ メモリを補完できます。

F28P55x のライブ ファームウェア アップデート ハードウェア拡張により、古いファームウェアから新しいファームウェアへのコンテキスト切り替えを高速化し、デバイス ファームウェアの更新時のアプリケーションのダウンタイムを最小限に抑えることができます。

F28P55x リアルタイム マイクロコントローラ (MCU) に内蔵された高性能アナログ ブロックは、リアルタイム シグナル チェーン性能を最適化するために、処理および PWM ユニットと密結合されています。24 個の PWM チャネルはすべて周波数に依存しない分解能モードをサポートしており、3 相インバータから、力率補正、高度なマルチレベル電源トポロジまで、さまざまな電力段を制御できます。

構成可能ロジック ブロック (CLB) を内蔵しているため、ユーザーはカスタム ロジックを追加し、[FPGA](#) に類似した機能を C2000 リアルタイム マイコンに統合できます。

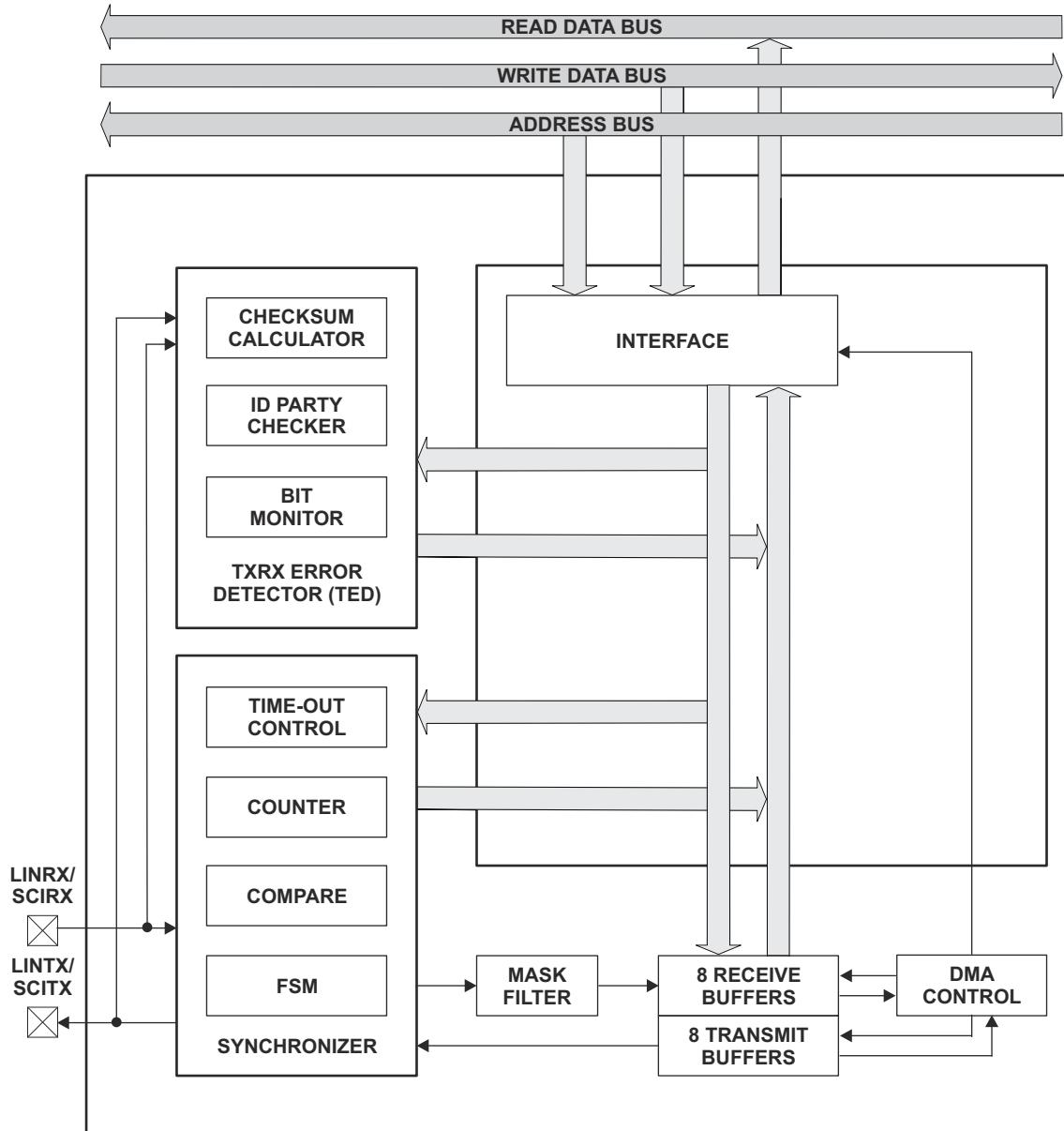

インターフェイスは、各種の業界標準通信ポート (SPI、SCI、I2C、PMBus、LIN、CAN FD など) によりサポートされており、最適な信号配置を行うための[複数のピン多重化方法](#)を備えています。

C2000 リアルタイム MCU は、お客様のリアルタイム制御システムに適した選択肢です。その機能について詳しく知るには、『[C2000™ リアルタイム マイクロコントローラを使った開発のための基本ガイド](#)』をご覧いただくとともに、[C2000™ リアルタイム マイコン](#)のページにアクセスしてください。

『[C2000™ リアルタイム制御マイコン \(MCU\) を使用した設計の開始』入門ガイド』は、C2000 デバイスを使用する開発について、ハードウェアからサポートリソースまで、あらゆる側面をカバーしています。主要な参考資料に加えて、各セクションには関連するリンクとリソースが掲載されており、さらに詳細な情報を知ることができます。](#)

設計を開始する際は、以下の資料をご確認ください。[TMDSCNCD28P55X](#) 評価ボードまたは [LAUNCHXL-F28P55X](#) 開発キットをご覧いただき、[C2000Ware](#) をダウンロードしてください。

### パッケージ情報

| 部品番号 <sup>(1)</sup> | パッケージ <sup>(2)</sup> | パッケージ サイズ <sup>(3)</sup> |

|---------------------|----------------------|--------------------------|

| TMS320F28P559SJ-Q1  | PDT (QFP、128)        | 16mm × 16mm              |

|                     | PZ (QFP、100)         | 16mm × 16mm              |

|                     | PNA (QFP、80)         | 12mm × 12mm              |

|                     | PM (QFP、64)          | 12mm × 12mm              |

| TMS320F28P550SJ     | PDT (QFP、128)        | 16mm × 16mm              |

|                     | PZ (QFP、100)         | 16mm × 16mm              |

|                     | PNA (QFP、80)         | 12mm × 12mm              |

|                     | PM (QFP、64)          | 12mm × 12mm              |

|                     | RSH (VQFN、56)        | 7mm × 7mm                |

| TMS320F28P559SG-Q1  | PDT (QFP、128)        | 16mm × 16mm              |

|                     | PZ (QFP、100)         | 16mm × 16mm              |

|                     | PNA (QFP、80)         | 12mm × 12mm              |

|                     | PM (QFP、64)          | 12mm × 12mm              |

| TMS320F28P550SG     | PDT (QFP、128)        | 16mm × 16mm              |

|                     | PZ (QFP、100)         | 16mm × 16mm              |

|                     | PNA (QFP、80)         | 12mm × 12mm              |

|                     | PM (QFP、64)          | 12mm × 12mm              |

|                     | RSH (VQFN、56)        | 7mm × 7mm                |

- (1) これらのデバイスの詳細については、「デバイスの比較」の表を参照してください。

(2) 詳細については、「メカニカル、パッケージ、および注文情報」セクションを参照してください。

(3) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

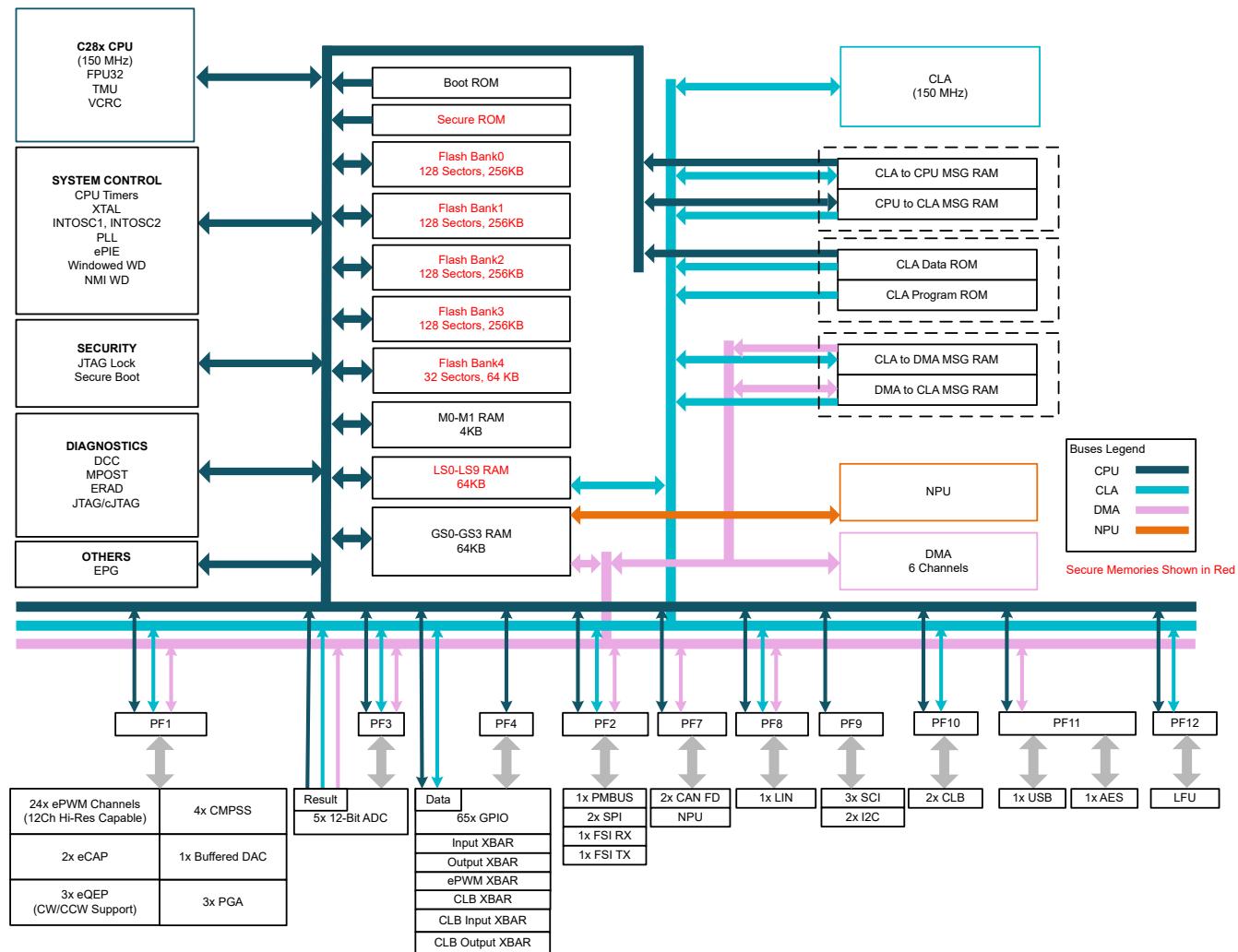

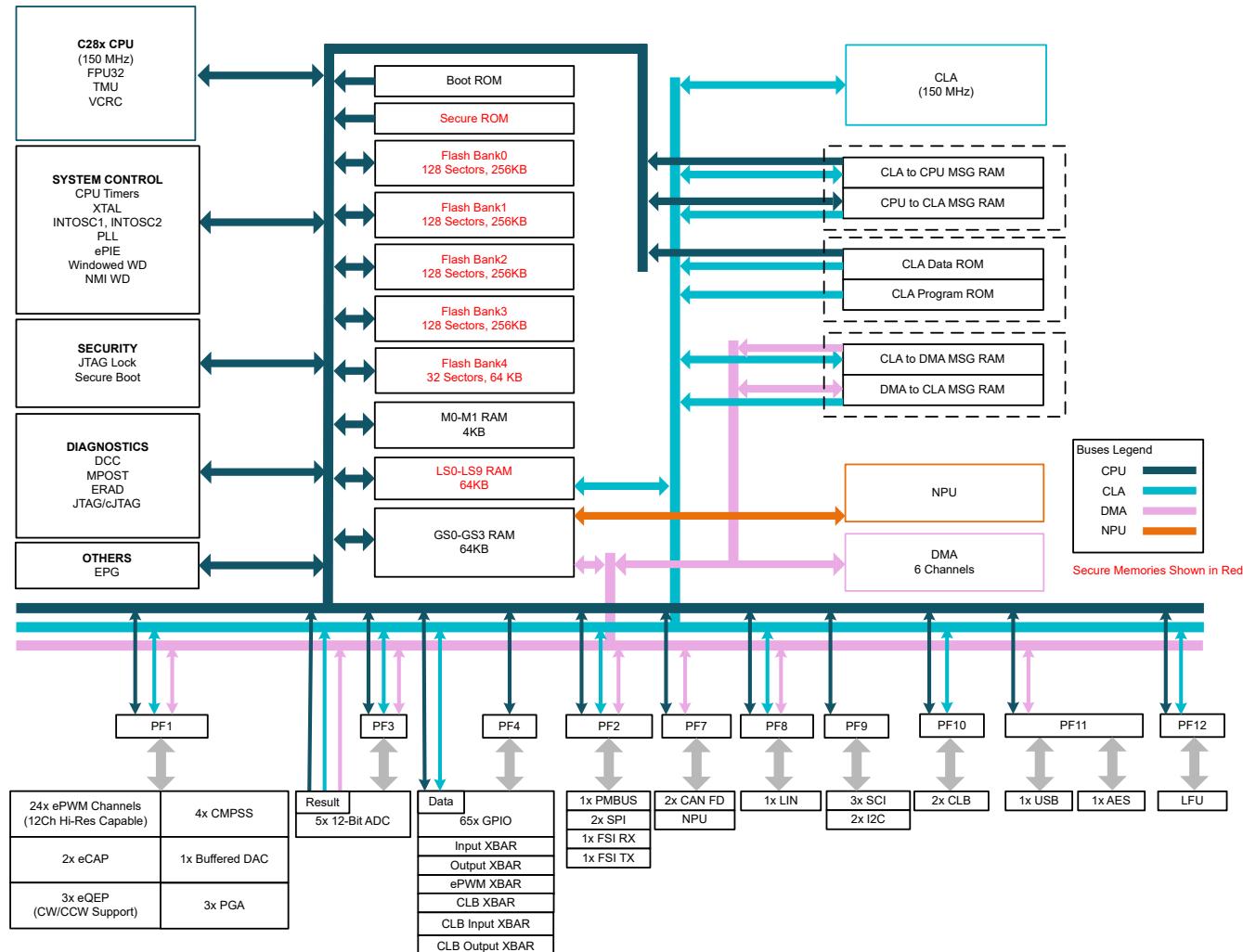

### 3.1 機能ブロック図

- CMPSS モジュールの 1 つに接続された内部 DAC は、出力 DAC として構成できます。

- LIN モジュールは SCI モジュールとしても使えます。

図 3-1. 機能ブロック図

## 目次

|                             |     |                                |     |

|-----------------------------|-----|--------------------------------|-----|

| <b>1 特長</b>                 | 1   | 6.17 通信ペリフェラル                  | 188 |

| <b>2 アプリケーション</b>           | 2   | <b>7 詳細説明</b>                  | 223 |

| <b>3 説明</b>                 | 3   | 7.1 概要                         | 223 |

| 3.1 機能ブロック図                 | 6   | 7.2 機能ブロック図                    | 224 |

| <b>4 デバイスの比較</b>            | 8   | 7.3 メモリ                        | 225 |

| 4.1 関連製品                    | 10  | 7.4 識別                         | 236 |

| <b>5 ピン構成および機能</b>          | 11  | 7.5 バスアーキテクチャ - ペリフェラルコネクティビティ | 237 |

| 5.1 ピン配置図                   | 11  | 7.6 C28x プロセッサ                 | 238 |

| 5.2 ピン属性                    | 16  | 7.7 制御補償器アクセラレータ (CLA)         | 240 |

| 5.3 信号の説明                   | 43  | 7.8 組み込みのリアルタイム解析および診断 (ERAD)  | 243 |

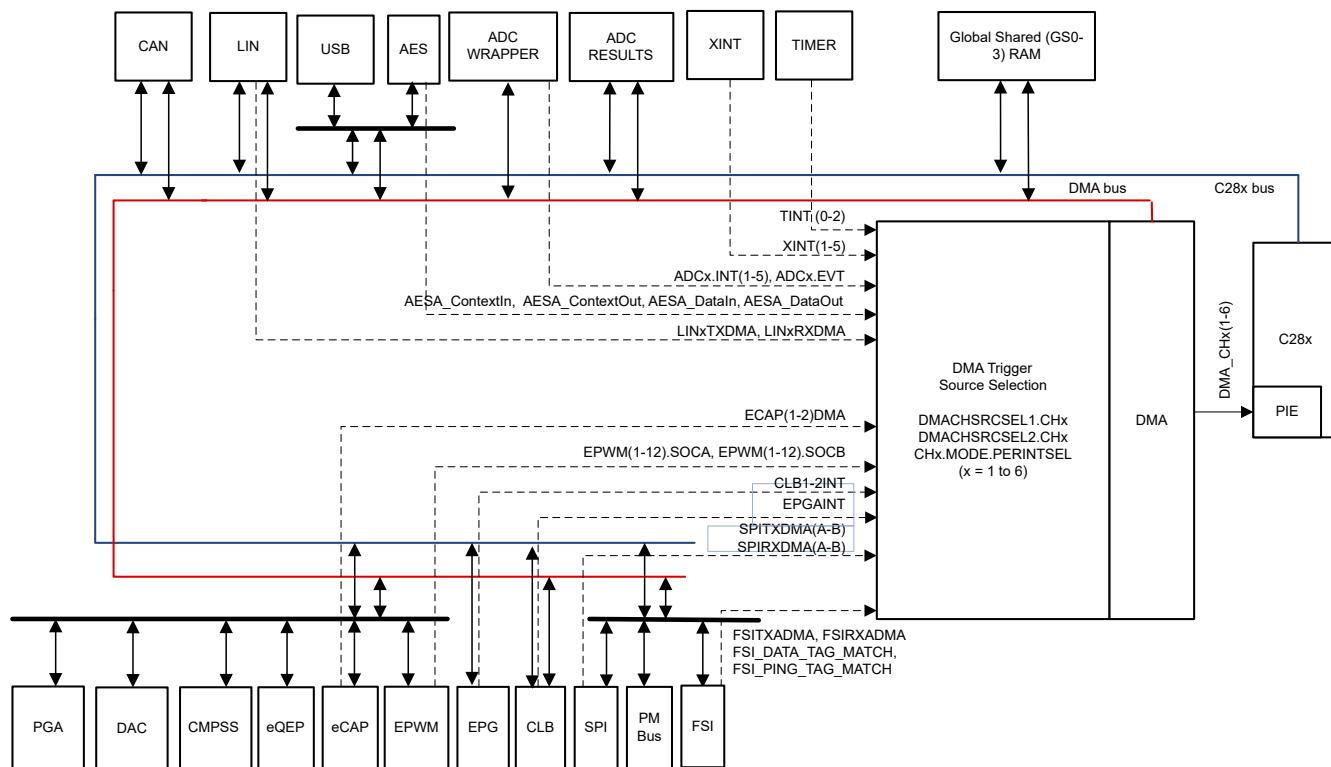

| 5.4 ピン多重化                   | 56  | 7.9 ダイレクトメモリアクセス (DMA)         | 244 |

| 5.5 内部プルアップおよびプルダウン付きのピン    | 68  | 7.10 デバイスブートモード                | 245 |

| 5.6 未使用ピンの接続                | 69  | 7.11 セキュリティ                    | 252 |

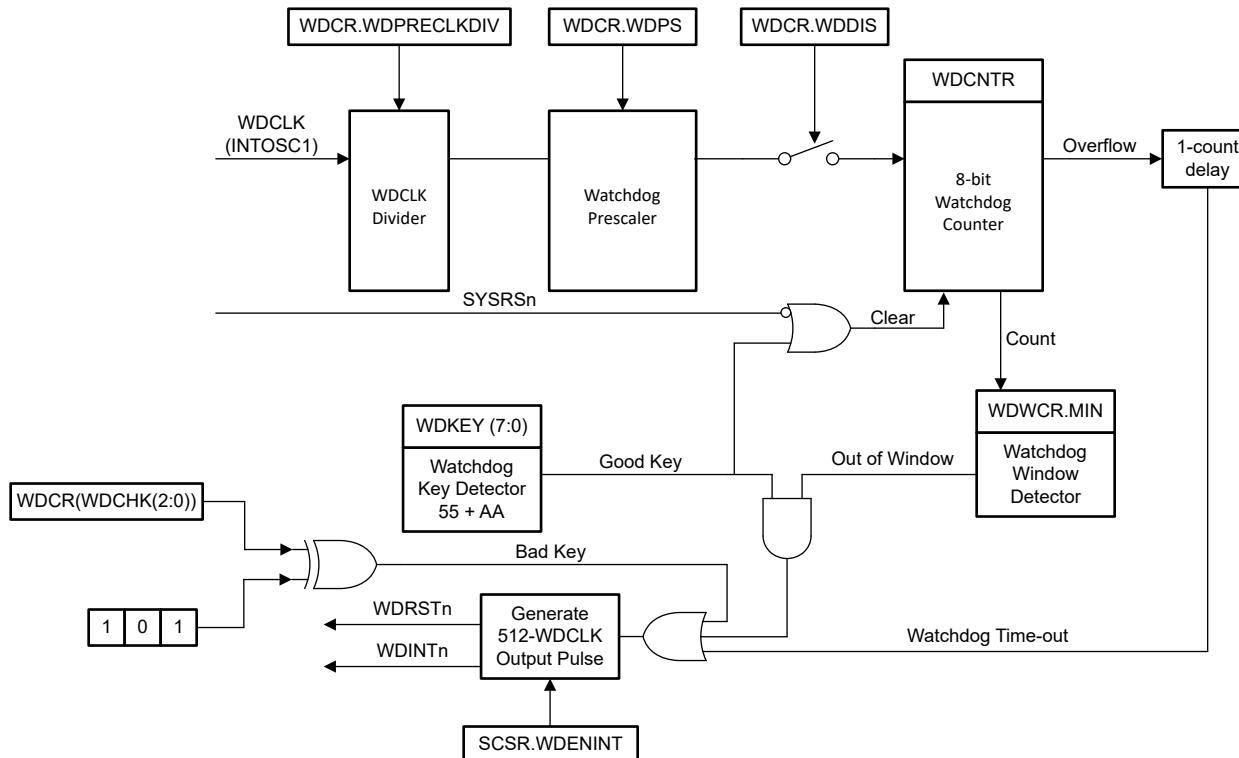

| <b>6 仕様</b>                 | 71  | 7.12 ウオッチドッグ                   | 253 |

| 6.1 絶対最大定格                  | 71  | 7.13 C28x タイマ                  | 254 |

| 6.2 ESD 定格 - 民生用            | 72  | 7.14 デュアル・クロック・コンパレータ (DCC)    | 255 |

| 6.3 ESD 定格 - 車載用            | 73  | 7.15 構成可能ロジック ブロック (CLB)       | 256 |

| 6.4 推奨動作条件                  | 74  | <b>8 リファレンス デザイン</b>           | 258 |

| 6.5 消費電力の概略                 | 75  | <b>9 デバイスおよびドキュメントのサポート</b>    | 260 |

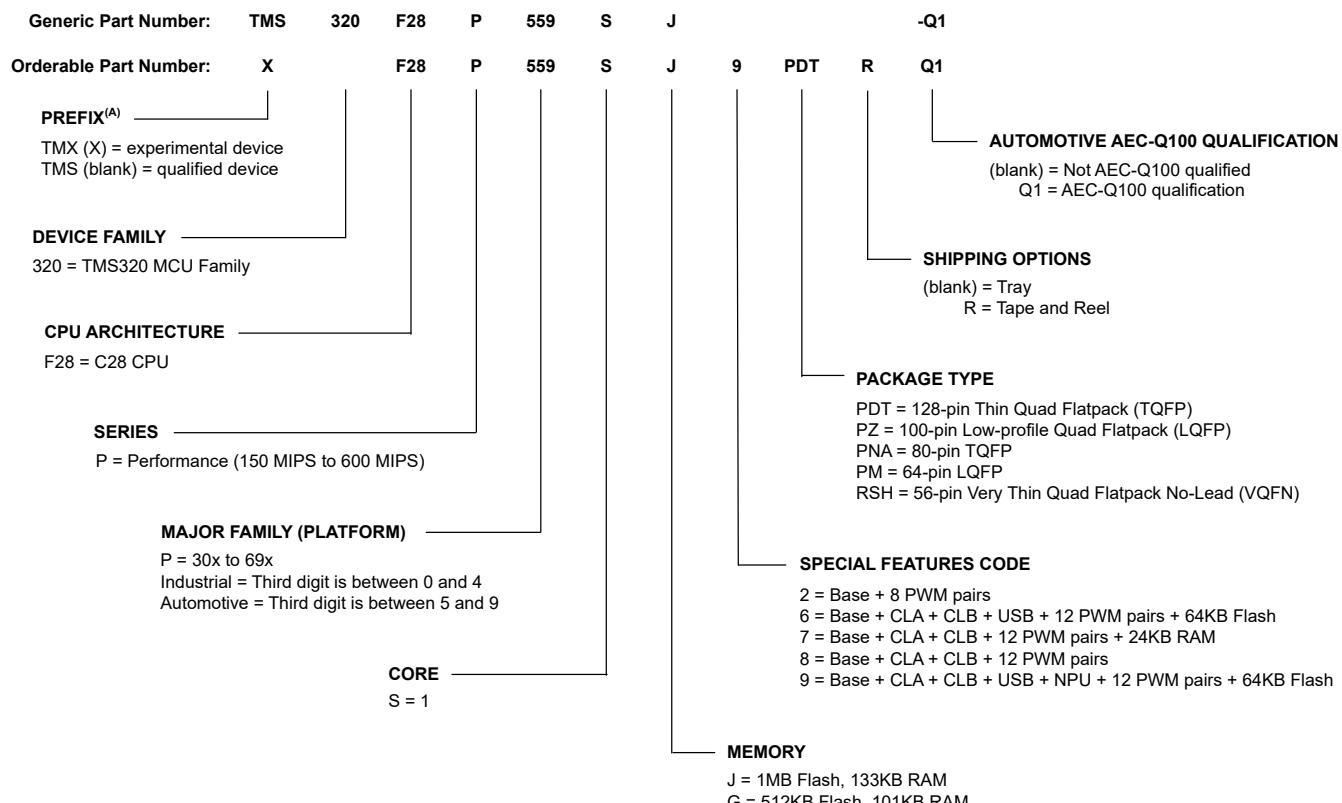

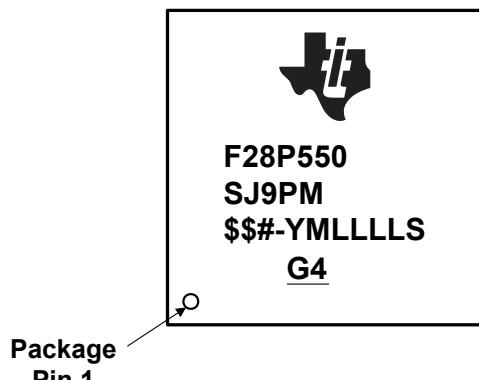

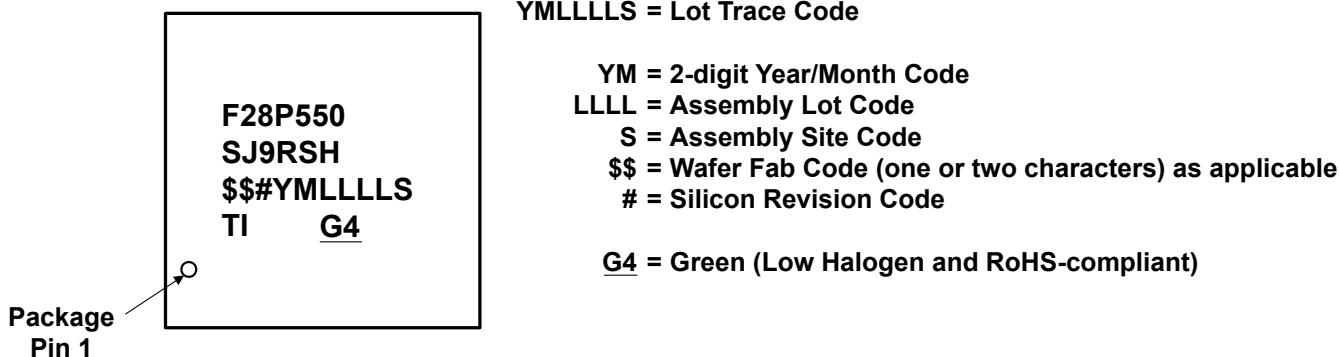

| 6.6 電気的特性                   | 82  | 9.1 デバイスの命名規則                  | 260 |

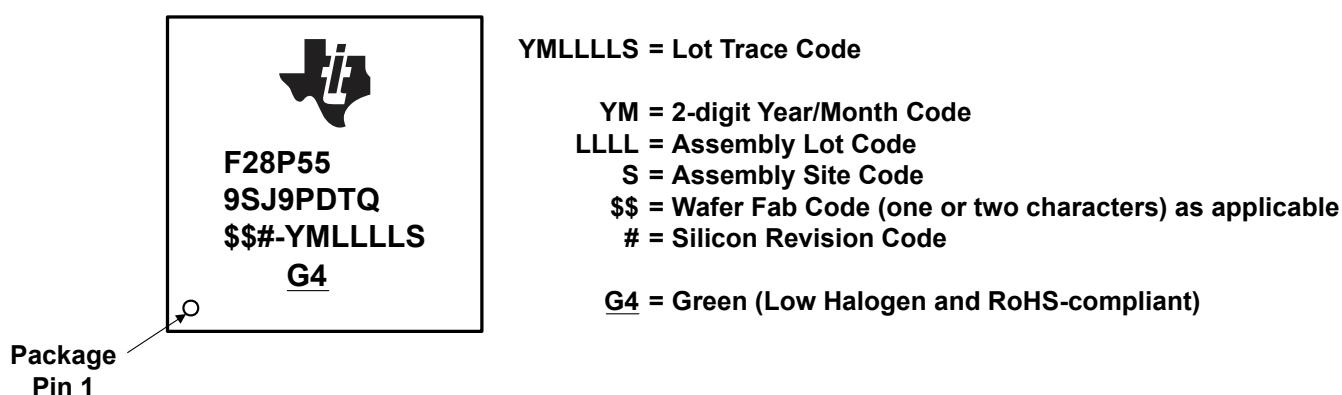

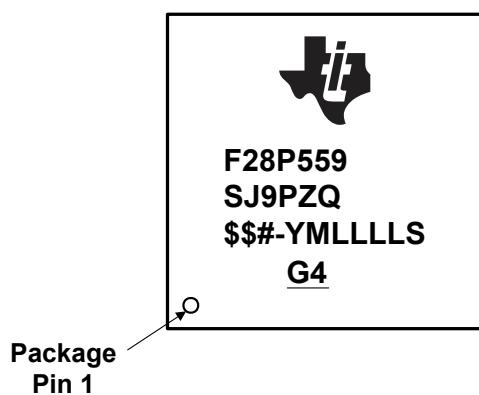

| 6.7 5V フェイルセーフピンに関する特別な考慮事項 | 84  | 9.2 マーキング                      | 261 |

| 6.8 PDT パッケージの熱抵抗特性         | 85  | 9.3 ツールとソフトウェア                 | 264 |

| 6.9 PZ パッケージの熱抵抗特性          | 85  | 9.4 ドキュメントのサポート                | 265 |

| 6.10 PNA パッケージの熱抵抗特性        | 85  | 9.5 サポート・リソース                  | 268 |

| 6.11 PM パッケージの熱抵抗特性         | 86  | 9.6 商標                         | 268 |

| 6.12 RSH パッケージの熱抵抗特性        | 86  | 9.7 静電気放電に関する注意事項              | 268 |

| 6.13 热設計の検討事項               | 86  | 9.8 用語集                        | 268 |

| 6.14 システム                   | 87  | <b>10 改訂履歴</b>                 | 269 |

| 6.15 アナログ ペリフェラル            | 131 | <b>11 メカニカル、パッケージ、および注文情報</b>  | 270 |

| 6.16 制御ペリフェラル               | 177 |                                |     |

## 4 デバイスの比較

表 4-1. デバイスの比較

| 機能 (1) (4)                                 | F28P559SJ-Q1 <sup>(3)</sup>                                                                                     | F28P550SJ                                                                      | F28P559SG-Q1 <sup>(3)</sup> | F28P550SG                                            |   |  |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------|---|--|--|--|--|

| C28x サブシステム                                |                                                                                                                 |                                                                                |                             |                                                      |   |  |  |  |  |

| 周波数 (MHz)                                  | 150                                                                                                             |                                                                                |                             |                                                      |   |  |  |  |  |

| C28x                                       | 32 ビット浮動小数点ユニット (FPU)                                                                                           | あり                                                                             |                             |                                                      |   |  |  |  |  |

|                                            | VCRC                                                                                                            | あり                                                                             |                             |                                                      |   |  |  |  |  |

|                                            | TMU - タイプ 1                                                                                                     | あり - タイプ 1 - NLPID 命令をサポート                                                     |                             |                                                      |   |  |  |  |  |

| CLA - タイプ 2                                | 個数                                                                                                              | 1:F28P559SJ9-Q1、<br>F28P559SJ6-Q1<br>0:F28P559SJ2-Q1                           | 1                           | 1:F28P559SG9-Q1、<br>F28P559SG8-Q1<br>0:F28P559SG2-Q1 | 1 |  |  |  |  |

|                                            | 周波数 (MHz)                                                                                                       | 150                                                                            |                             |                                                      |   |  |  |  |  |

| 6 チャネル DMA - タイプ 0                         | 1                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| 外部割り込み                                     | 5                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| MIPS                                       | 300 (CPU + CLA)                                                                                                 |                                                                                |                             |                                                      |   |  |  |  |  |

| メモリ                                        |                                                                                                                 |                                                                                |                             |                                                      |   |  |  |  |  |

| フラッシュ                                      | メイン アレイ                                                                                                         | 1MB (4 x 256KB バンク)                                                            | 512KB (2 x 256KB バンク)       |                                                      |   |  |  |  |  |

|                                            | 64KB バンク                                                                                                        | F28P559SJ9-Q1、F28P550SJ9、F28P559SJ6-Q1、F28P550SJ6、F28P559SG9-Q1、<br>F28P550SG9 |                             |                                                      |   |  |  |  |  |

|                                            | ユーザー OTP                                                                                                        | 8KB                                                                            | 2KB                         |                                                      |   |  |  |  |  |

| RAM                                        | 専用                                                                                                              | 4KB                                                                            |                             |                                                      |   |  |  |  |  |

|                                            | ローカル共有 RAM                                                                                                      | 64KB                                                                           |                             |                                                      |   |  |  |  |  |

|                                            | メッセージ                                                                                                           | 1KB                                                                            |                             |                                                      |   |  |  |  |  |

|                                            | グローバル共有 RAM                                                                                                     | 64KB                                                                           | 32KB                        |                                                      |   |  |  |  |  |

|                                            | RAM 合計                                                                                                          | 133KB                                                                          | 101KB                       |                                                      |   |  |  |  |  |

| メッセージ RAM のタイプ                             | C28x CPU および CLA                                                                                                | 512 バイト (方向ごとに 256 バイト)                                                        |                             |                                                      |   |  |  |  |  |

|                                            | DMA と CLA                                                                                                       | 512 バイト (方向ごとに 256 バイト)                                                        |                             |                                                      |   |  |  |  |  |

| ECC                                        | フラッシュ、Mx RAM                                                                                                    |                                                                                |                             |                                                      |   |  |  |  |  |

| パリティ                                       | ROM、CAN RAM、Message RAM、LSx RAM、GSx RAM                                                                         |                                                                                |                             |                                                      |   |  |  |  |  |

| システム                                       |                                                                                                                 |                                                                                |                             |                                                      |   |  |  |  |  |

| 構成可能ロジック ブロック (CLB)                        | 2 タイプ - F28P559SJ9-Q1、F28P559SJ6-Q1、F28P550SJ9、F28P550SJ6、F28P559SG9-Q1、<br>F28P550SG9、F28P559SG8-Q1、F28P550SG8 |                                                                                |                             |                                                      |   |  |  |  |  |

| ニューラル ネットワーク処理ユニット (NPU)                   | 1 - F28P559SJ9-Q1、F28P550SJ9、F28P559SG9-Q1、F28P550SG9                                                           |                                                                                |                             |                                                      |   |  |  |  |  |

| 組み込みパターン ジェネレータ (EPG)                      | 1                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| 32 ビット CPU タイマ                             | 3                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| AES (Advanced Encryption Standard) アクセラレータ | 1                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| ライブ フームウェア アップデート (LFU) サポート               | あり、拡張機能とフラッシュ バンク消去時間の改善によりサポート                                                                                 |                                                                                |                             |                                                      |   |  |  |  |  |

| オンチップ フラッシュおよび RAM のセキュリティ                 | あり                                                                                                              |                                                                                |                             |                                                      |   |  |  |  |  |

| ゼロピン ブート                                   | あり                                                                                                              |                                                                                |                             |                                                      |   |  |  |  |  |

| セキュアブート                                    | あり                                                                                                              |                                                                                |                             |                                                      |   |  |  |  |  |

| JTAG ロック                                   | あり                                                                                                              |                                                                                |                             |                                                      |   |  |  |  |  |

| MPOST                                      | あり                                                                                                              |                                                                                |                             |                                                      |   |  |  |  |  |

| 組み込みリアルタイム解析および診断 (ERAD) - タイプ 2           | 1                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| ノンマスカブル割り込みウォッチドッグ (NMWD) タイマー             | 1                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| ウォッチドッグ (WD) タイマー                          | 1                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| 水晶発振器 / 外部クロック入力                           | 1                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

| 内部発振器 (オプションの外付け高精度抵抗)                     | 2                                                                                                               |                                                                                |                             |                                                      |   |  |  |  |  |

**表 4-1. デバイスの比較 (続き)**

| 機能 (1) (4)                                                           | F28P559SJ-Q1(3)                                           | F28P550SJ                                                                    | F28P559SG-Q1(3)                | F28P550SG                                                                    |

|----------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------|

| デジタルおよびアナログ ピン数                                                      |                                                           |                                                                              |                                |                                                                              |

| GPIO                                                                 | 128 ピン PDT                                                | 65                                                                           | 65 - F28P559SG9-Q1, F28P550SG9 |                                                                              |

|                                                                      | 100 ピン PZ                                                 |                                                                              | 43                             |                                                                              |

|                                                                      | 80 ピン PNA                                                 |                                                                              | 32                             |                                                                              |

|                                                                      | 64 ピン PM                                                  |                                                                              | 17                             |                                                                              |

|                                                                      | 56 ピン RSH                                                 | -                                                                            | 15                             | -                                                                            |

|                                                                      | 追加 GPIO                                                   | 4 (cJTAG から 2 個、X1/X2 から 2 個)                                                |                                |                                                                              |

| AIO (デジタル入力付きアナログ)                                                   | 128 ピン PDT                                                | 17                                                                           | 17 - F28P559SG9-Q1, F28P550SG9 |                                                                              |

|                                                                      | 100 ピン PZ                                                 |                                                                              | 16                             |                                                                              |

|                                                                      | 80 ピン PNA                                                 |                                                                              | 12                             |                                                                              |

|                                                                      | 64 ピン PM                                                  |                                                                              | 12                             |                                                                              |

|                                                                      | 56 ピン RSH                                                 | -                                                                            | 12                             | -                                                                            |

| AGPIO (デジタル入力と出力付きアナログ)                                              | 128 ピン PDT                                                | 22                                                                           | 22 - F28P559SG9-Q1, F28P550SG9 |                                                                              |

|                                                                      | 100 ピン PZ                                                 |                                                                              | 19                             |                                                                              |

|                                                                      | 80 ピン PNA                                                 |                                                                              | 16                             |                                                                              |

|                                                                      | 64 ピン PM                                                  |                                                                              | 16                             |                                                                              |

|                                                                      | 56 ピン RSH                                                 | -                                                                            | 14                             | -                                                                            |

| C28x アナログ ベリフェラル(5)                                                  |                                                           |                                                                              |                                |                                                                              |

| A/D コンバータ (ADC) (12 ビット) - タイプ 6                                     | ADC の数                                                    |                                                                              | 5                              |                                                                              |

|                                                                      | MSPS                                                      |                                                                              | 3.9                            |                                                                              |

|                                                                      | 変換時間 (ns)(2)                                              |                                                                              | 187                            |                                                                              |

| ADC 入力チャネル (シングルエンド) (2 つの DAC 出力を含む)                                | 128 ピン PDT                                                | 39                                                                           | 39 - F28P559SG9-Q1, F28P550SG9 |                                                                              |

|                                                                      | 100 ピン PZ                                                 |                                                                              | 35                             |                                                                              |

|                                                                      | 80 ピン PNA                                                 |                                                                              | 28                             |                                                                              |

|                                                                      | 64 ピン PM                                                  |                                                                              | 28                             |                                                                              |

|                                                                      | 56 ピン RSH                                                 |                                                                              | 26                             | 26                                                                           |

| PGA - タイプ 2                                                          |                                                           |                                                                              | 3                              |                                                                              |

| 温度センサ                                                                |                                                           |                                                                              | 1                              |                                                                              |

| コンパレータ サブシステム (CMPSS) (各 CMPSS に 2 つのコンパレータと 2 つの内部 DAC を含む) - タイプ 6 |                                                           |                                                                              | 4                              |                                                                              |

| バッファ付き D/A コンバータ (DAC) - タイプ 2                                       |                                                           |                                                                              | 1                              |                                                                              |

| CMPSS からの DAC 出力                                                     |                                                           |                                                                              | 1                              |                                                                              |

| C28x 制御ペリフェラル (5)                                                    |                                                           |                                                                              |                                |                                                                              |

| eCAP - タイプ 2                                                         | 合計入力数                                                     |                                                                              | 2                              |                                                                              |

| ePWM/HRPWM - タイプ 4                                                   | 合計チャネル数                                                   | 24 - F28P559SJ9-Q1、<br>F28P559SJ6-Q1<br>16 - F28P559J2-Q1<br>(ePWM1-ePWM8)   | 24                             | 24 - F28P559SG9-Q1、<br>F28P559SG8-Q1<br>16 - F28P559SG2-Q1<br>(ePWM1-ePWM8)  |

|                                                                      | 高分解能チャネル                                                  | 12 - F28P559SJ9-Q1、<br>F28P559SJ6-Q1<br>8 - F28P559SJ2-Q1<br>(HRPWM1-HRPWM4) | 12                             | 12 - F28P559SG9-Q1、<br>F28P559SG8-Q1<br>8 - F28P559SG2-Q1<br>(HRPWM1-HRPWM4) |

| eQEP モジュール - タイプ 2                                                   |                                                           |                                                                              | 3                              |                                                                              |

| C28x 通信ペリフェラル (5)                                                    |                                                           |                                                                              |                                |                                                                              |

| CAN FD (CAN with Flexible Data-Rate) - タイプ 2                         |                                                           |                                                                              | 2                              |                                                                              |

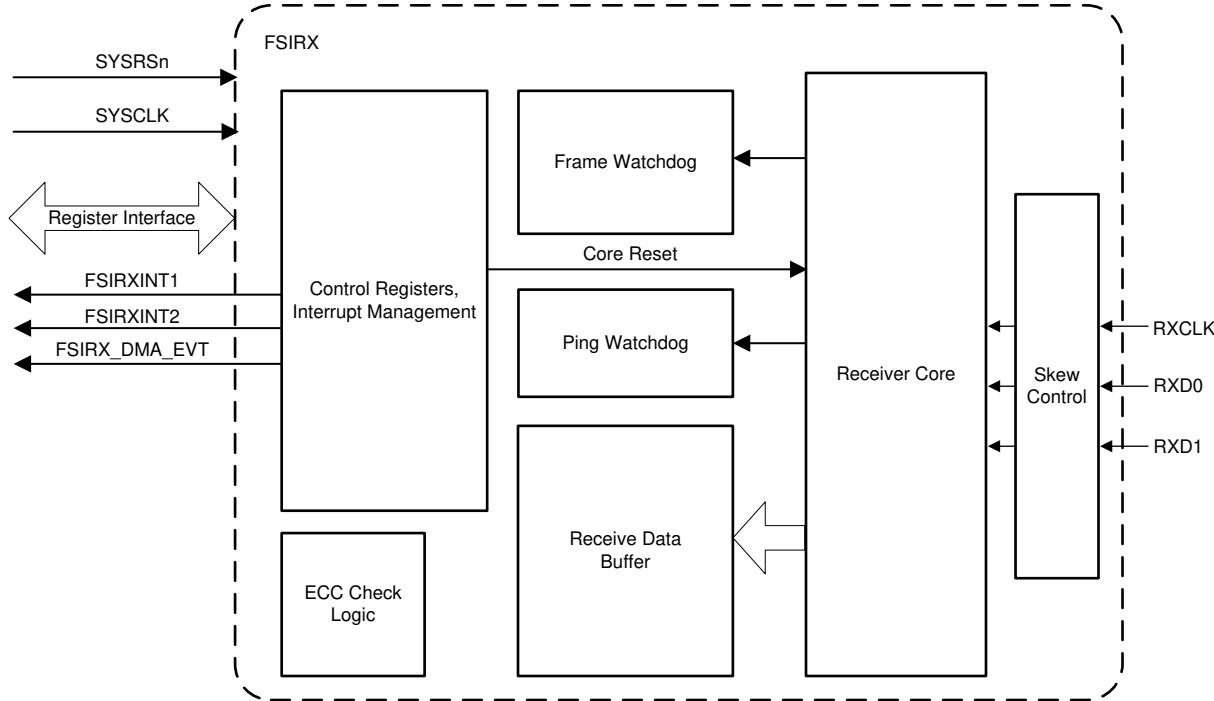

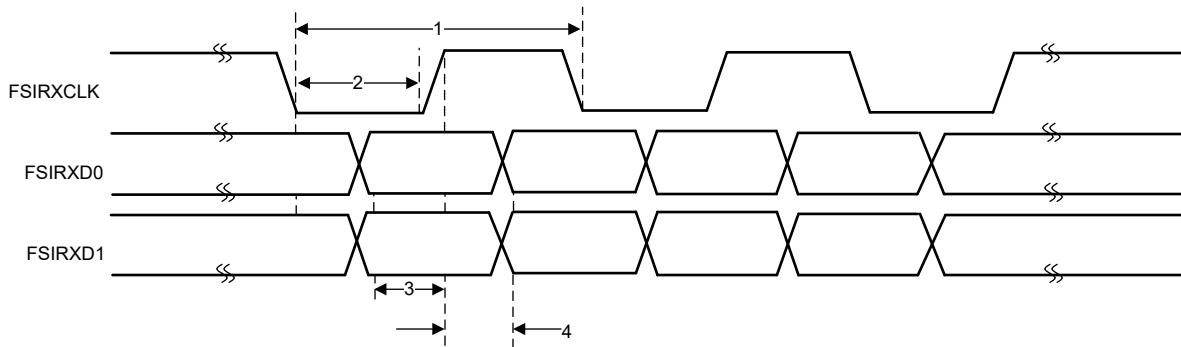

| 高速シリアル インターフェイス (FSI) RX - タイプ 2                                     |                                                           |                                                                              | 1                              |                                                                              |

| 高速シリアル インターフェイス (FSI) TX - タイプ 2                                     |                                                           |                                                                              | 1                              |                                                                              |

| I2C (Inter-Integrated Circuit) - タイプ 2                               |                                                           |                                                                              | 2                              |                                                                              |

| ローカル相互接続ネットワーク (LIN) - タイプ 1                                         |                                                           |                                                                              | 1                              |                                                                              |

| パワー マネージメント バス (PMBus) - タイプ 1                                       |                                                           |                                                                              | 1                              |                                                                              |

| シリアル通信インターフェイス (SCI) - タイプ 0 (UART 互換)                               |                                                           |                                                                              | 3                              |                                                                              |

| シリアル ベリフェラル インターフェイス (SPI) - タイプ 2                                   |                                                           |                                                                              | 2                              |                                                                              |

| ユニバーサル シリアル バス (USB) - タイプ 0                                         | 1 - F28P559SJ9-Q1、F28P550SJ9、<br>F28P559SJ6-Q1、F28P550SJ6 |                                                                              | 1 - F28P559SG9-Q1、F28P550SG9   |                                                                              |

**表 4-1. デバイスの比較 (続き)**

| 機能 <sup>(1) (4)</sup> | F28P559SJ-Q1 <sup>(3)</sup> | F28P550SJ                                                                                                                                | F28P559SG-Q1 <sup>(3)</sup> | F28P550SG |                        |

|-----------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|------------------------|

| 温度および認定               |                             |                                                                                                                                          |                             |           |                        |

| 接合部温度 ( $T_J$ )       | -40°C ~ 150°C               |                                                                                                                                          |                             |           |                        |

| 自由気流での周囲温度 ( $T_A$ )  | -40°C ~ 125°C               |                                                                                                                                          |                             |           |                        |

| パッケージ オプション           | 128 ピン PDT                  | F28P559SJ9-Q1, F28P559SJ6-Q1, F28P559SJ2-Q1, F28P550SJ9, F28P550SJ6, F28P559SG9-Q1, F28P550SG9                                           |                             |           |                        |

|                       | 100 ピン PZ                   | F28P559SJ9-Q1, F28P559SJ6-Q1, F28P559SJ2-Q1, F28P550SJ9, F28P550SJ6, F28P559SG9-Q1, F28P559SG8-Q1, F28P559SG2-Q1, F28P550SG9, F28P550SG8 |                             |           |                        |

|                       | 80 ピン PNA                   | F28P559SJ9-Q1, F28P559SJ6-Q1, F28P559SJ2-Q1, F28P550SJ9, F28P550SJ6, F28P559SG9-Q1, F28P559SG8-Q1, F28P559SG2-Q1, F28P550SG9, F28P550SG8 |                             |           |                        |

|                       | 64 ピン PM                    | F28P559SJ9-Q1, F28P559SJ6-Q1, F28P559SJ2-Q1, F28P550SJ9, F28P550SJ6, F28P559SG9-Q1, F28P559SG8-Q1, F28P559SG2-Q1, F28P550SG9, F28P550SG8 |                             |           |                        |

|                       | 56 ピン RSH                   | -                                                                                                                                        | F28P550SJ9, F28P550SJ6      | -         | F28P550SG9, F28P550SG8 |

- (1) タイプの違いは、ペリフェラル モジュールの機能上の主要な相違を表します。同じペリフェラル タイプのデバイス間でも、モジュールの基本的な機能には影響しないわずかな違いがあることがあります。詳細については、『[C2000 リアルタイム制御ペリフェラル リファレンス ガイド](#)』を参照してください。

- (2) サンプル アンド ホールド ウィンドウの開始から、次の変換のサンプル アンド ホールド ウィンドウの開始までの時間。

- (3) -Q1 という接尾辞は、車載アプリケーション向けの AEC Q100 認定を表します。

- (4) 機能に「-」が入力されているのは、対応するパッケージタイプが提供されていないことを示します。

- (5) 複数のパッケージで供給されるデバイスの場合、パッケージが小さいほどデバイスのピン数が少ないため、小型パッケージに記載されているペリフェラル数が減少します。デバイスに内部的に存在するペリフェラルの数は、その型番で提供される最大のパッケージに比べて減少しません。

## 4.1 関連製品

### [TMS320F280013x リアルタイム マイコン](#)

F280013x は、F28P55x デバイス シリーズと共に共通のピン配置を持っています。F28P55x シリーズでは、CPU クロック速度の高速化とメモリ サイズの拡大に加えて、CLA と DMA のサポートも行っています。また、F28P55x はプログラマブルゲインアンプ (PGA)、USB、CLB を内蔵しており、FW のライブ更新もサポートしています。

### [TMS320F280015x リアルタイム マイコン](#)

F280015x は、F28P55x デバイス シリーズと共に共通のピン配置を持っています。F28P55x シリーズでは、CPU クロック速度の高速化とメモリ サイズの拡大に加えて、CLA と DMA のサポートも行っています。また、F28P55x はプログラマブルゲインアンプ (PGA)、USB、CLB を内蔵しており、FW のライブ更新もサポートしています。F280015x シリーズは、安全関連システムのためのロックステップ C28x CPU を備えています。

### [TMS320F28003x リアルタイム マイコン](#)

F28003x は、F28P55x デバイス シリーズと共に共通のピン配置を持っています。F28P55x シリーズでは、プログラマブル ゲイン アンプ (PGA) と USB のサポートに加えて、CPU 全体のクロック速度の高速化とメモリ サイズの拡大も行っています。F28003x シリーズでは、BGCRC と HWBIST 行っています。

## 5 ピン構成および機能

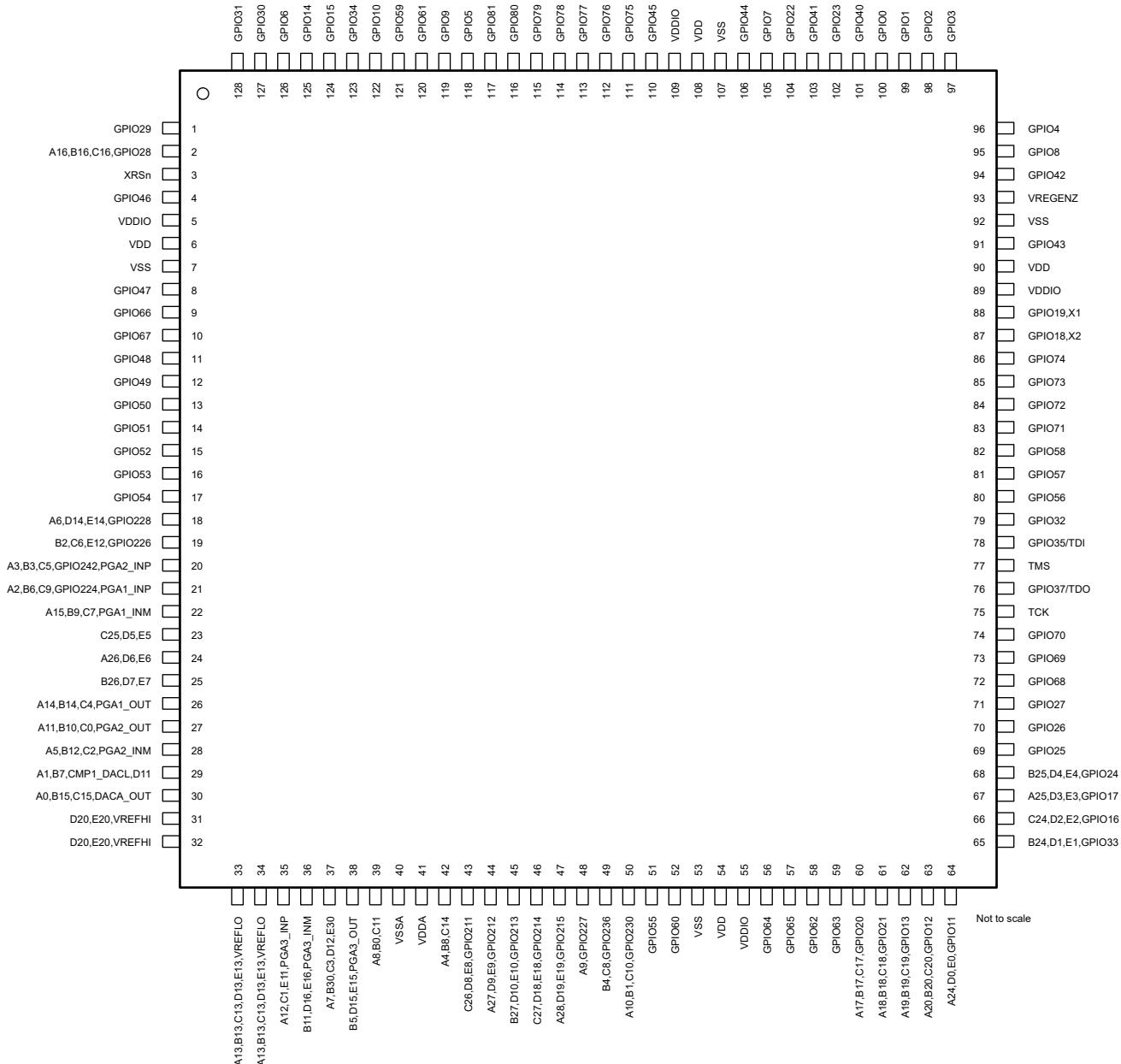

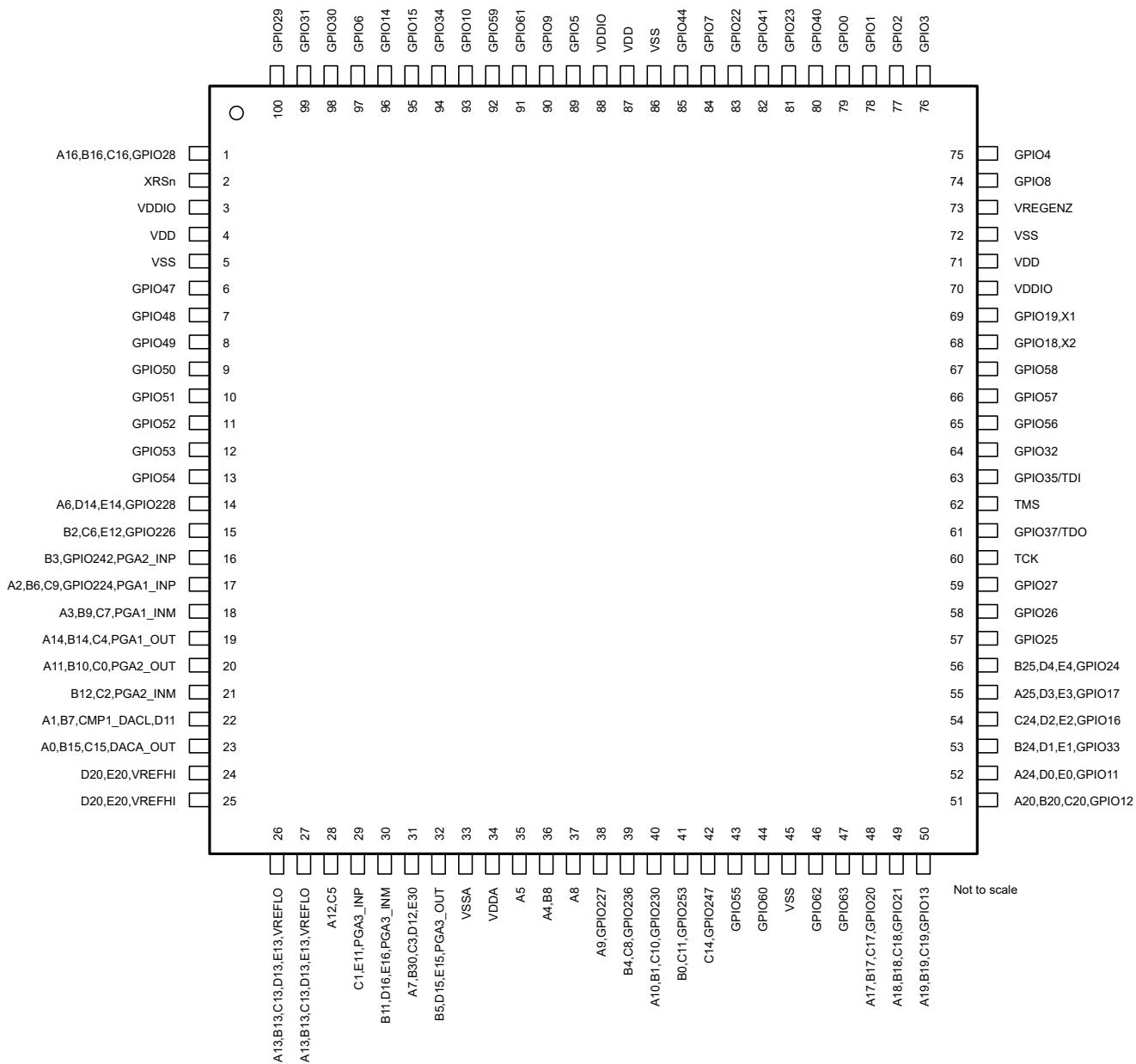

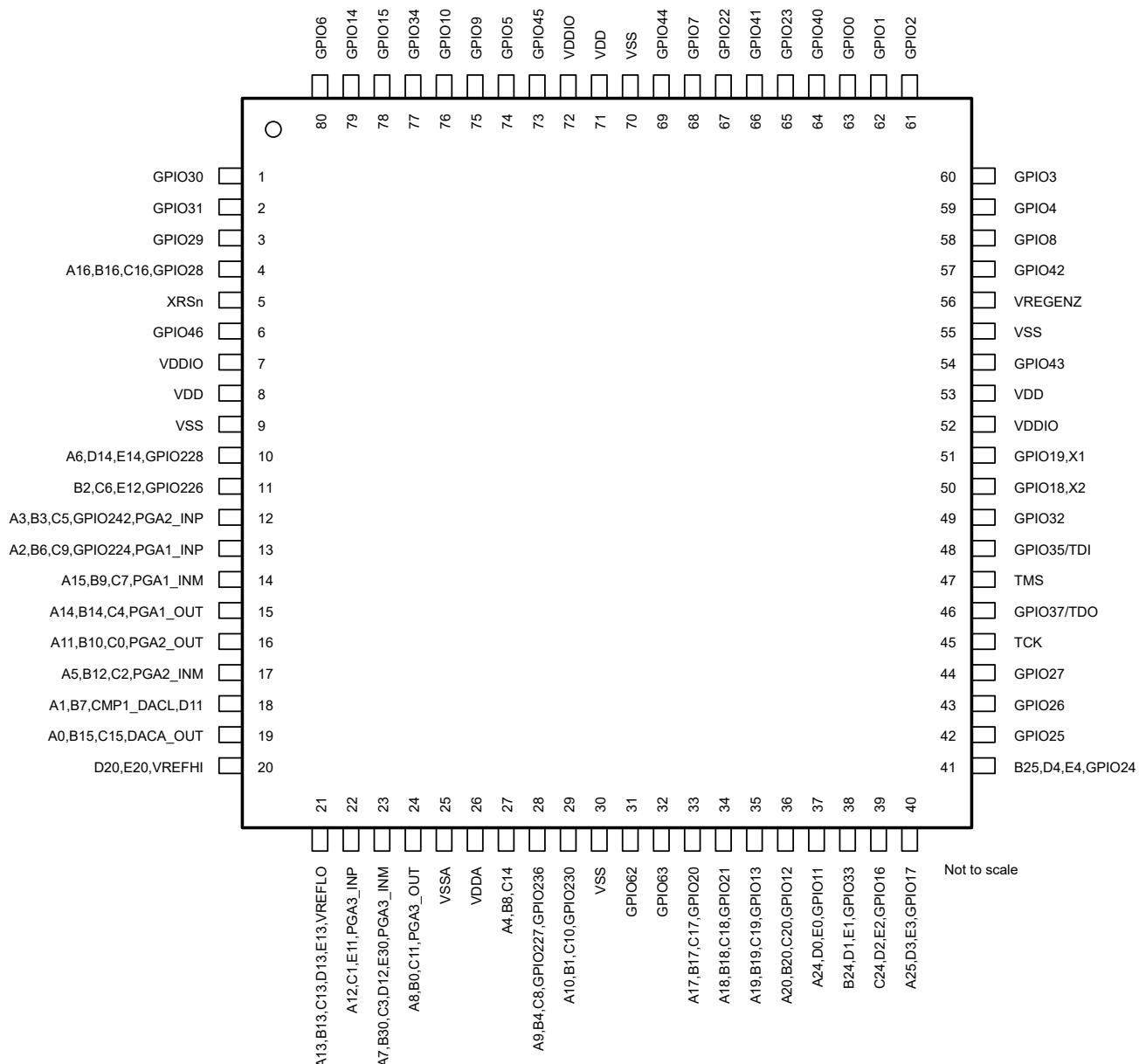

## 5.1 ピン配置図

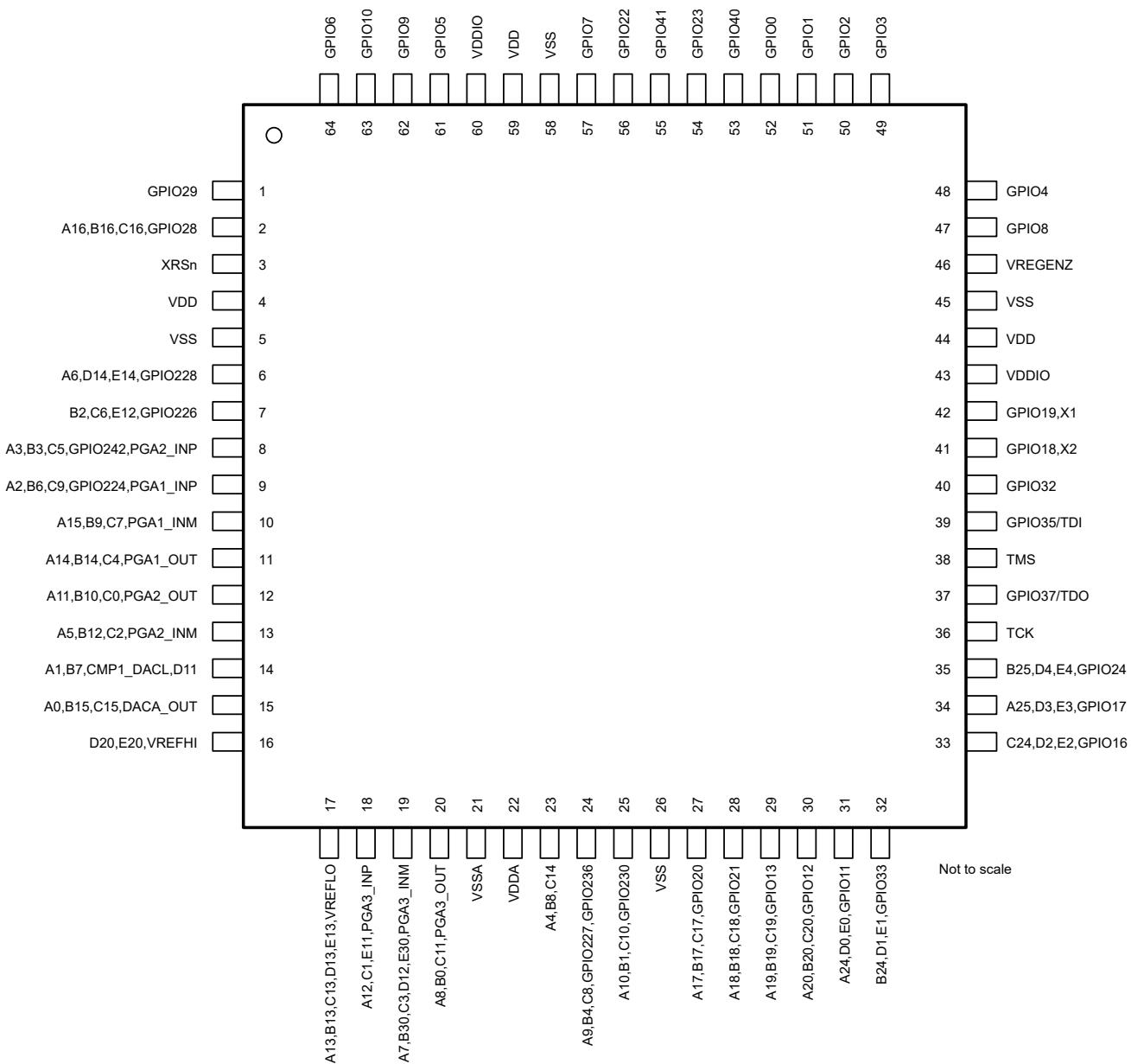

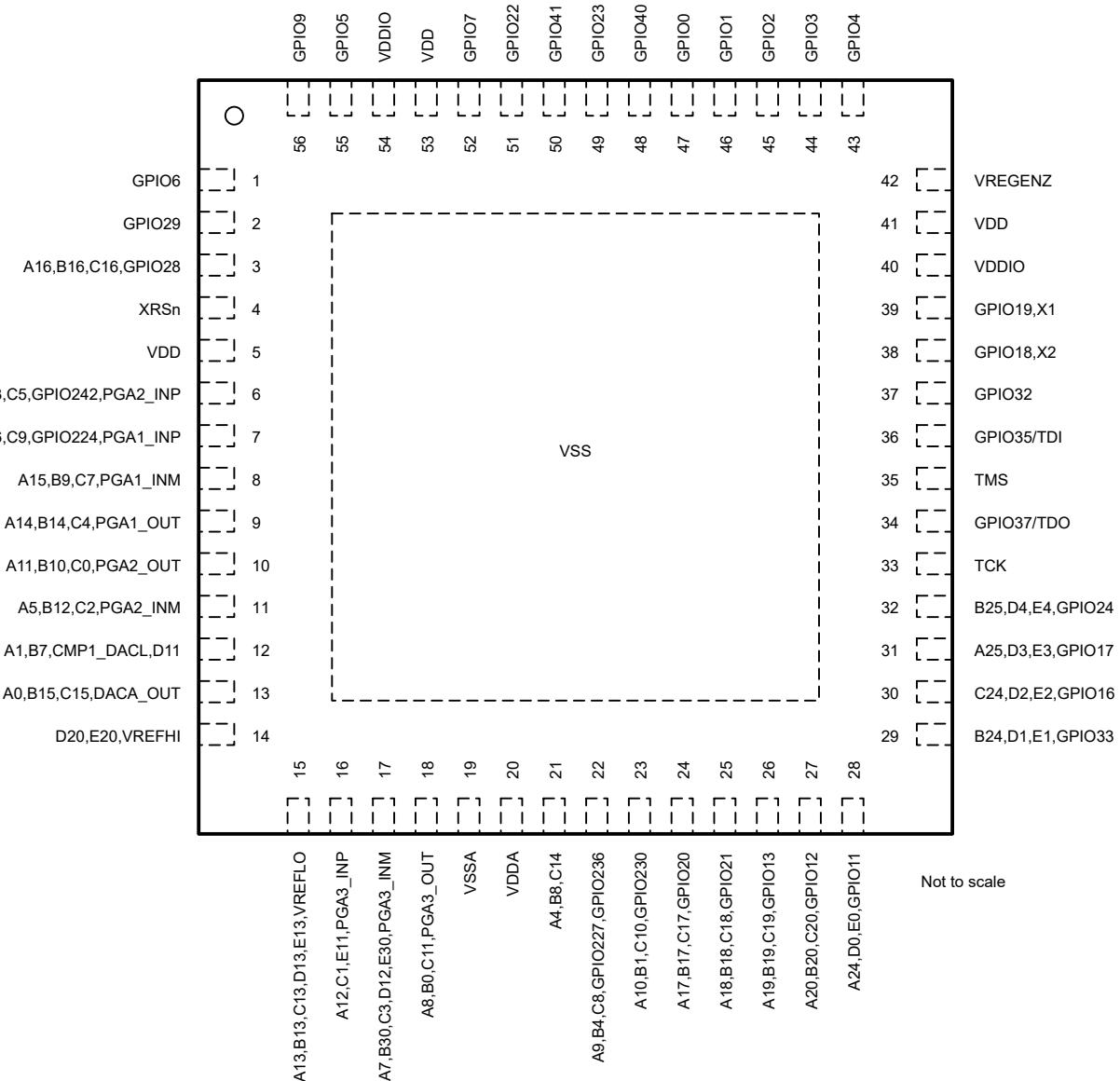

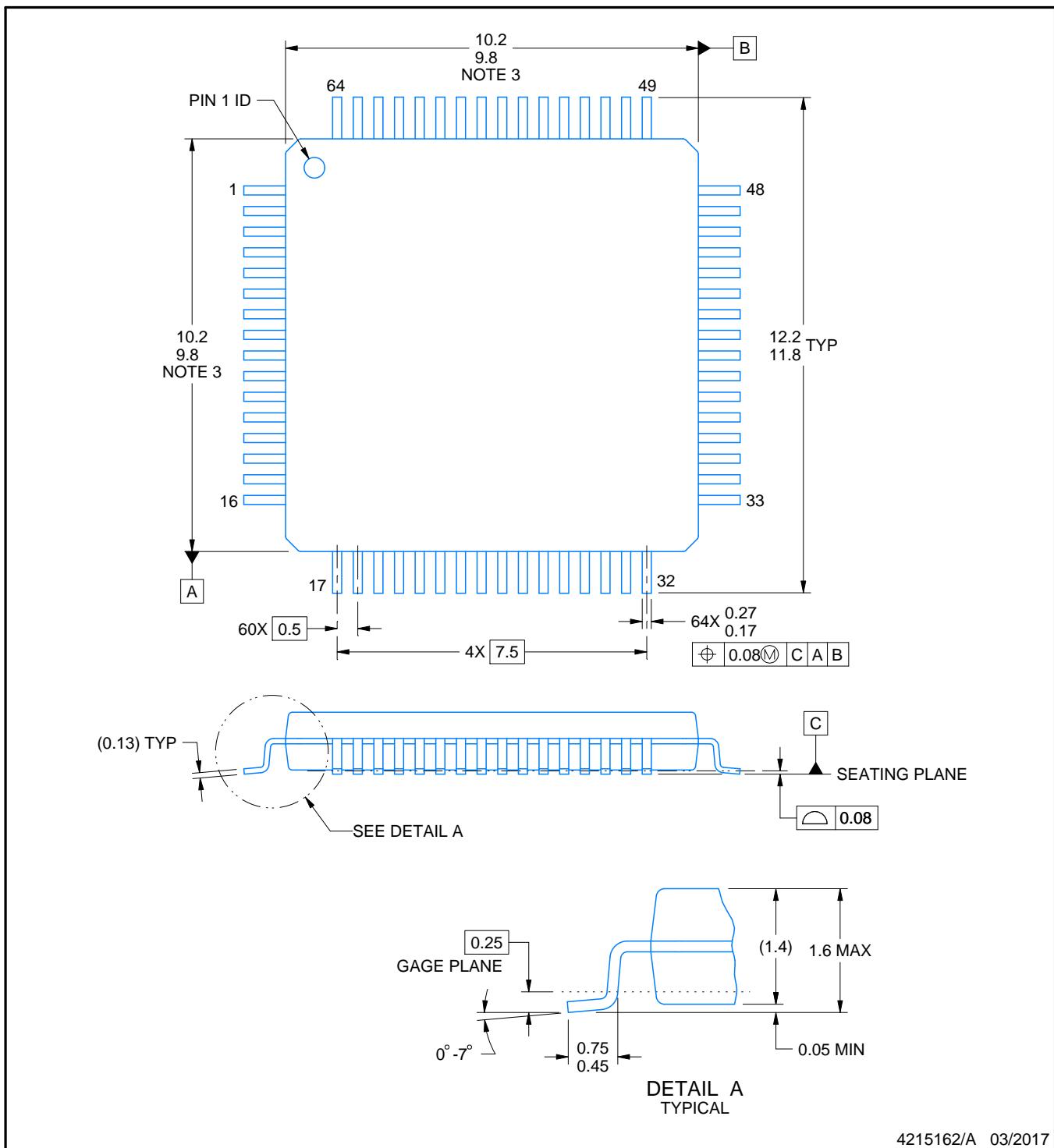

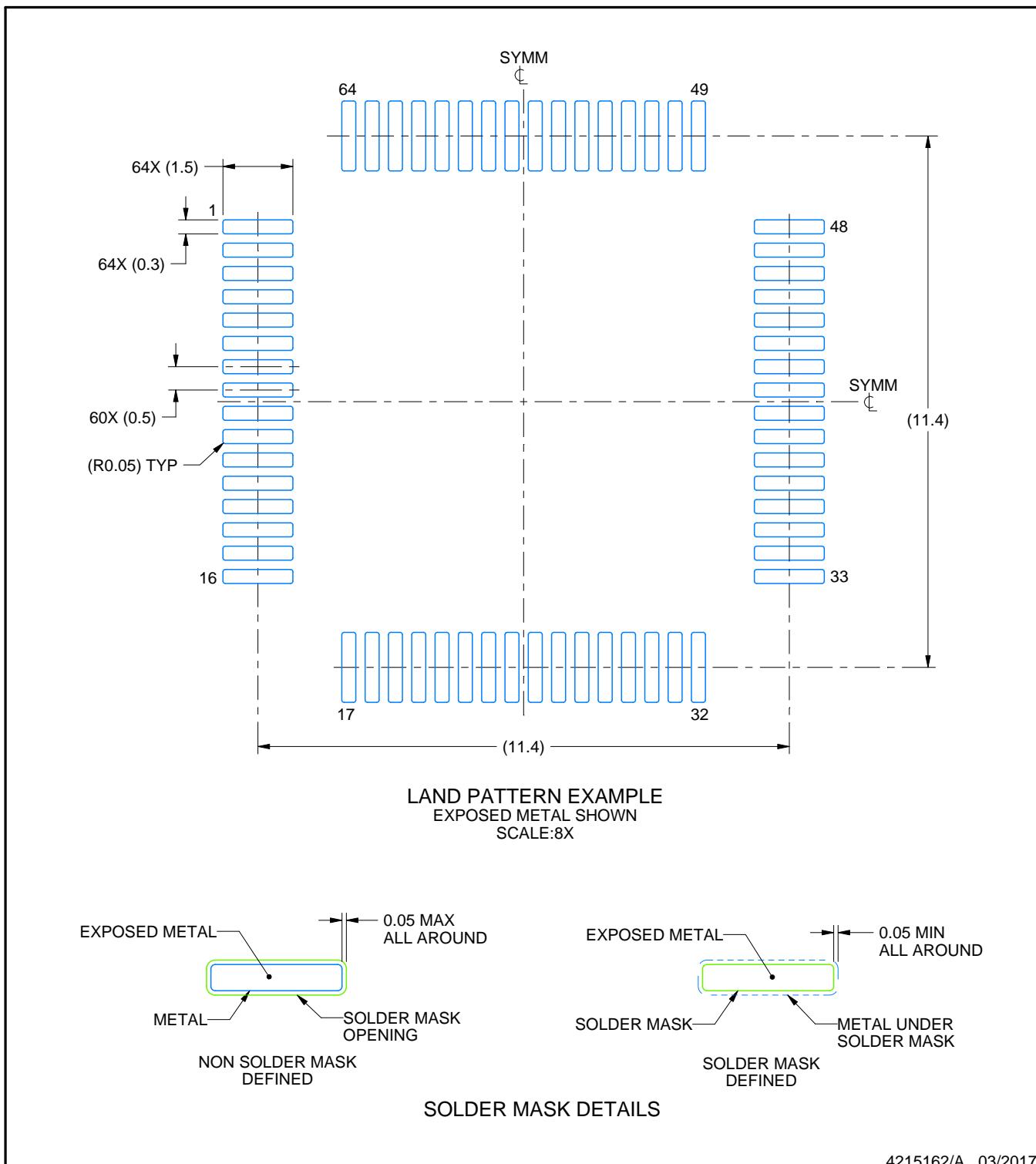

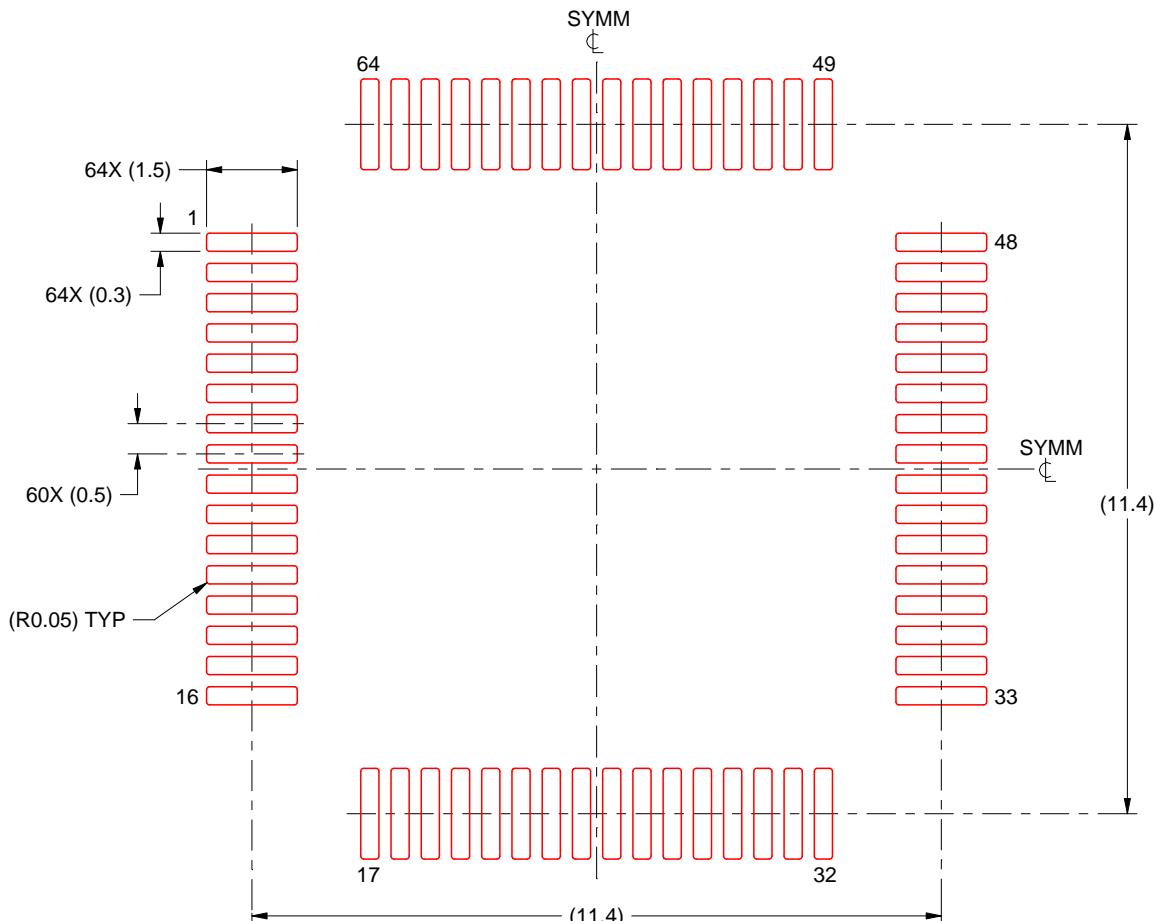

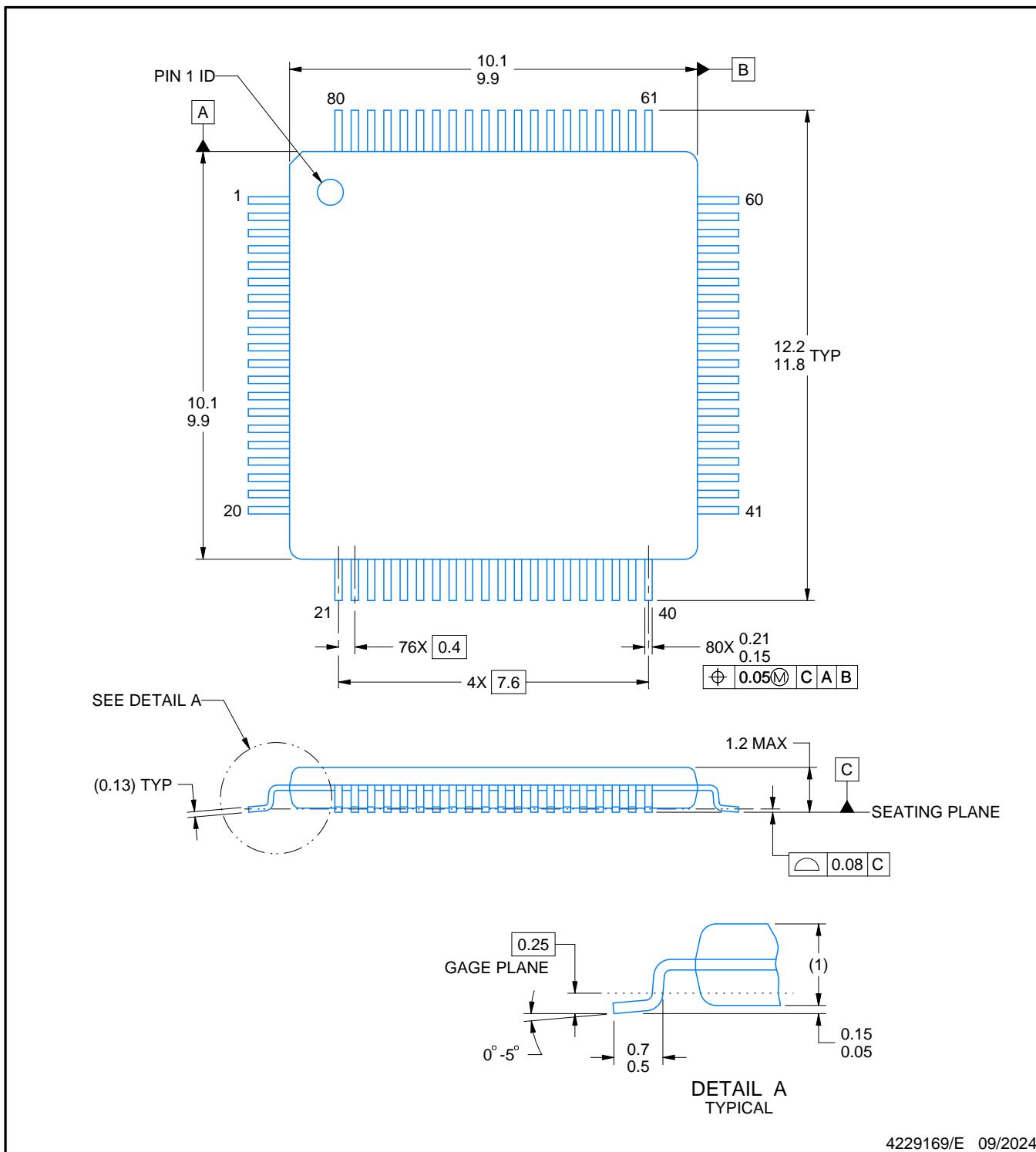

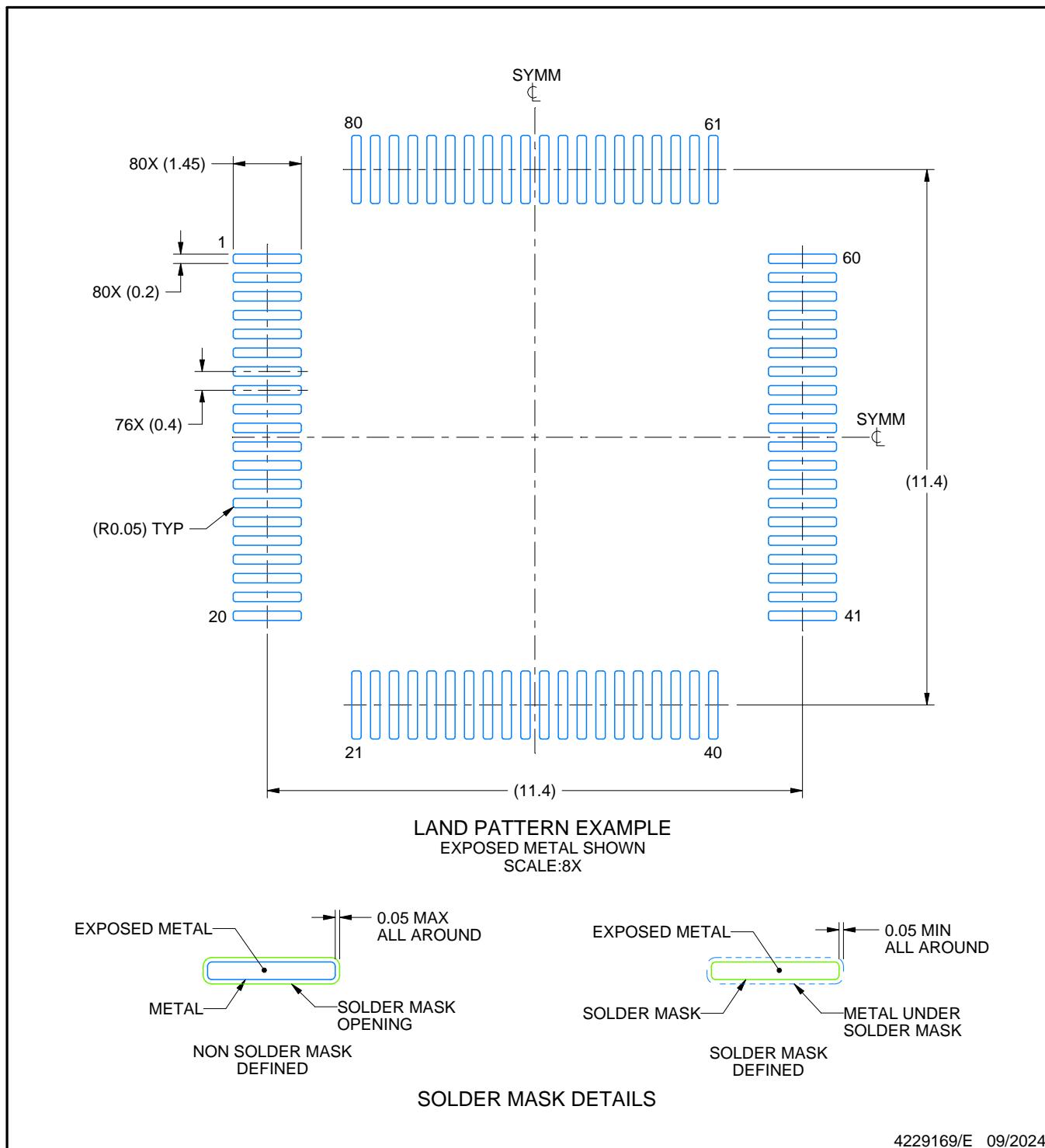

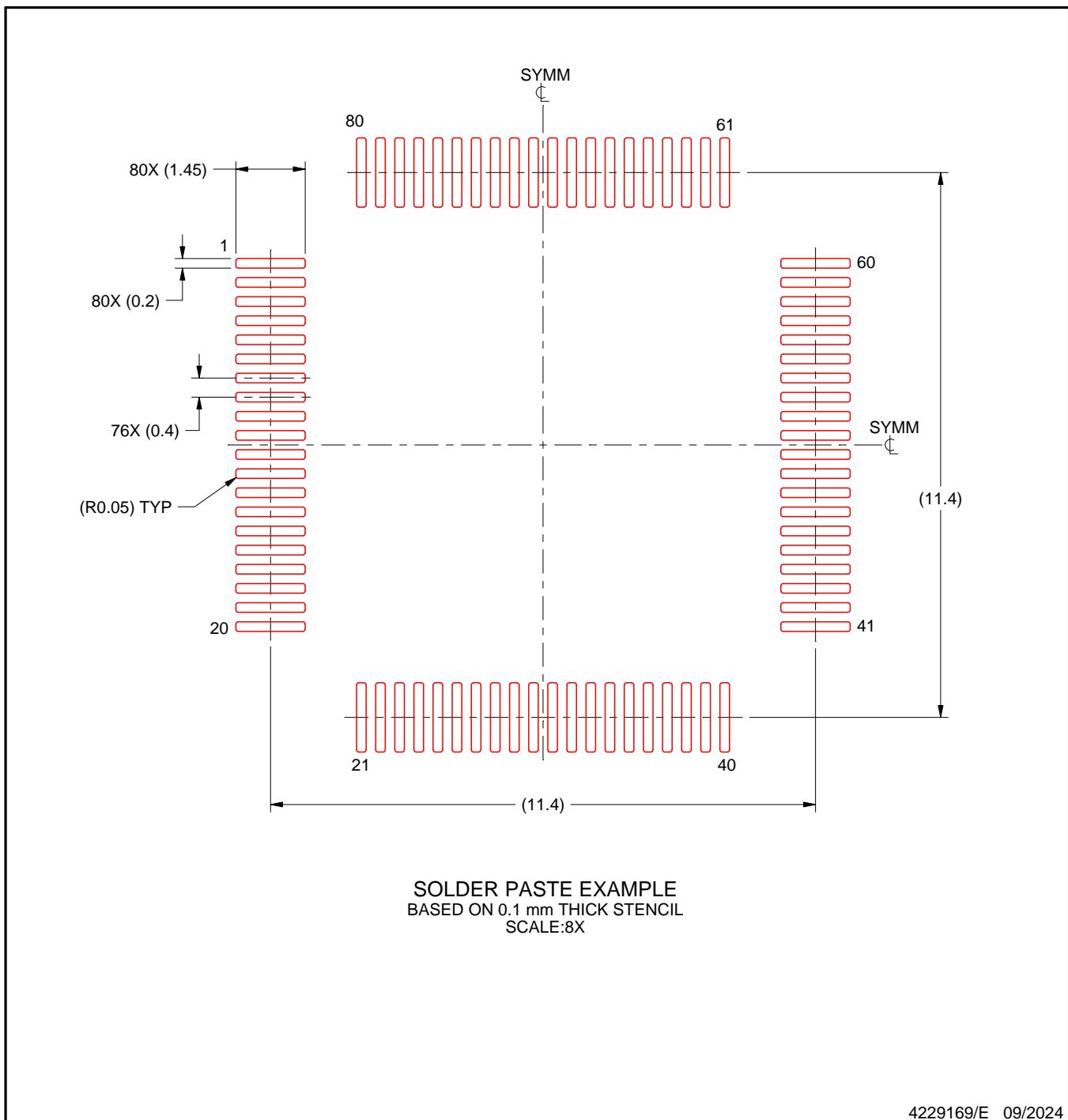

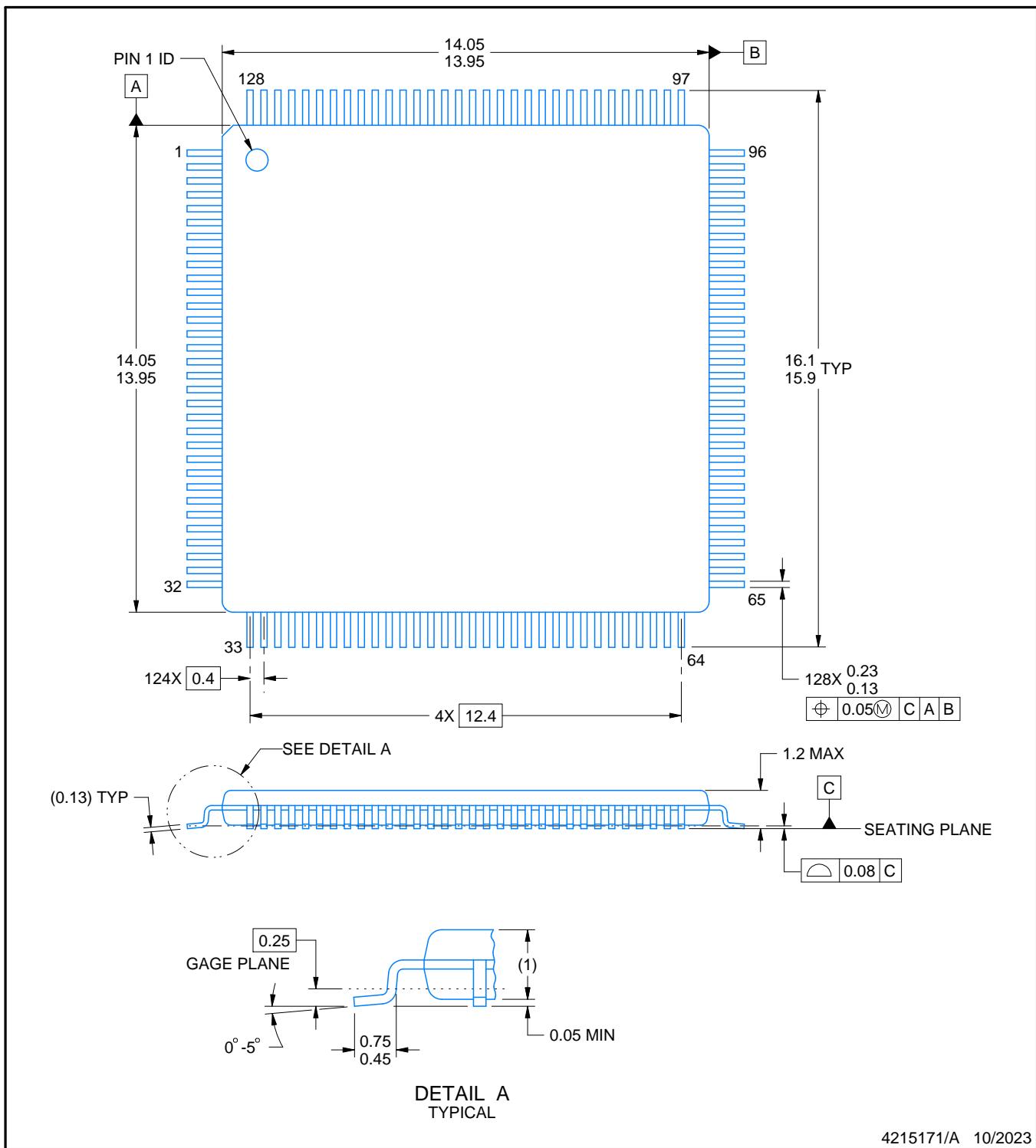

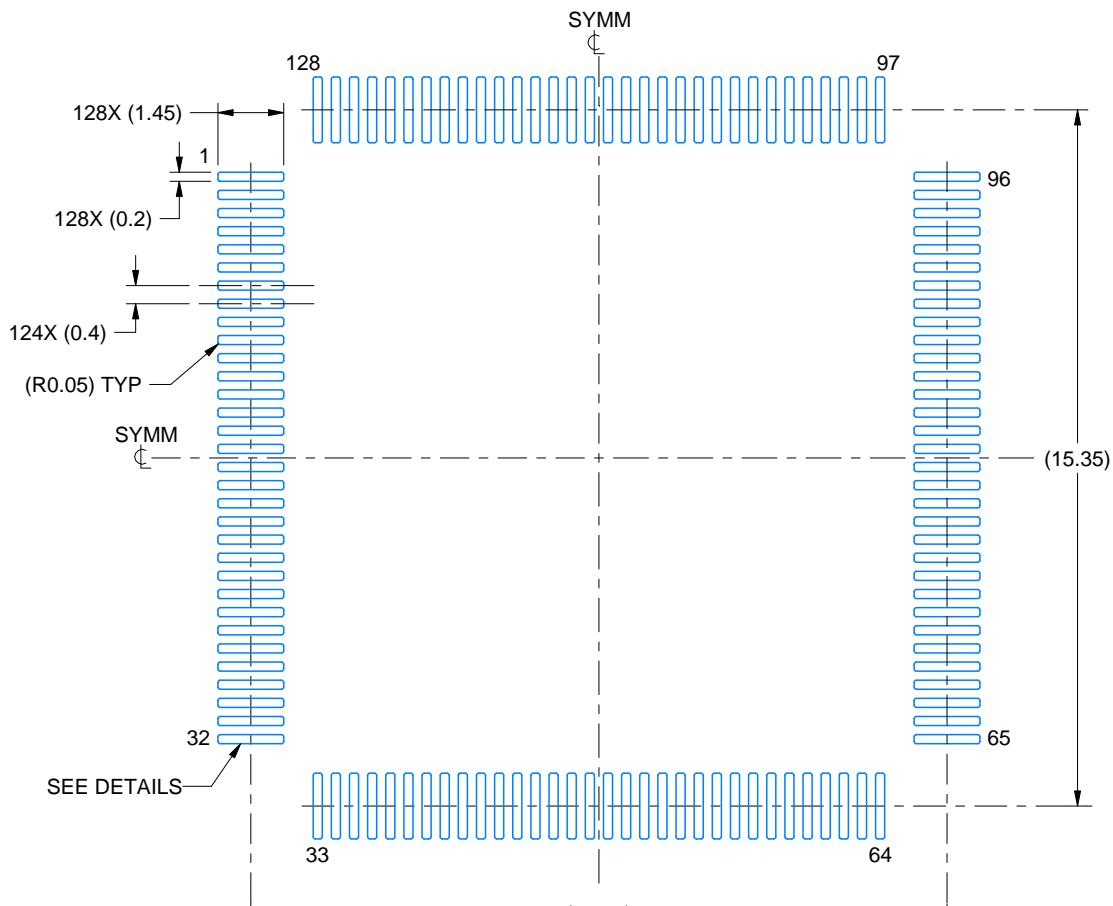

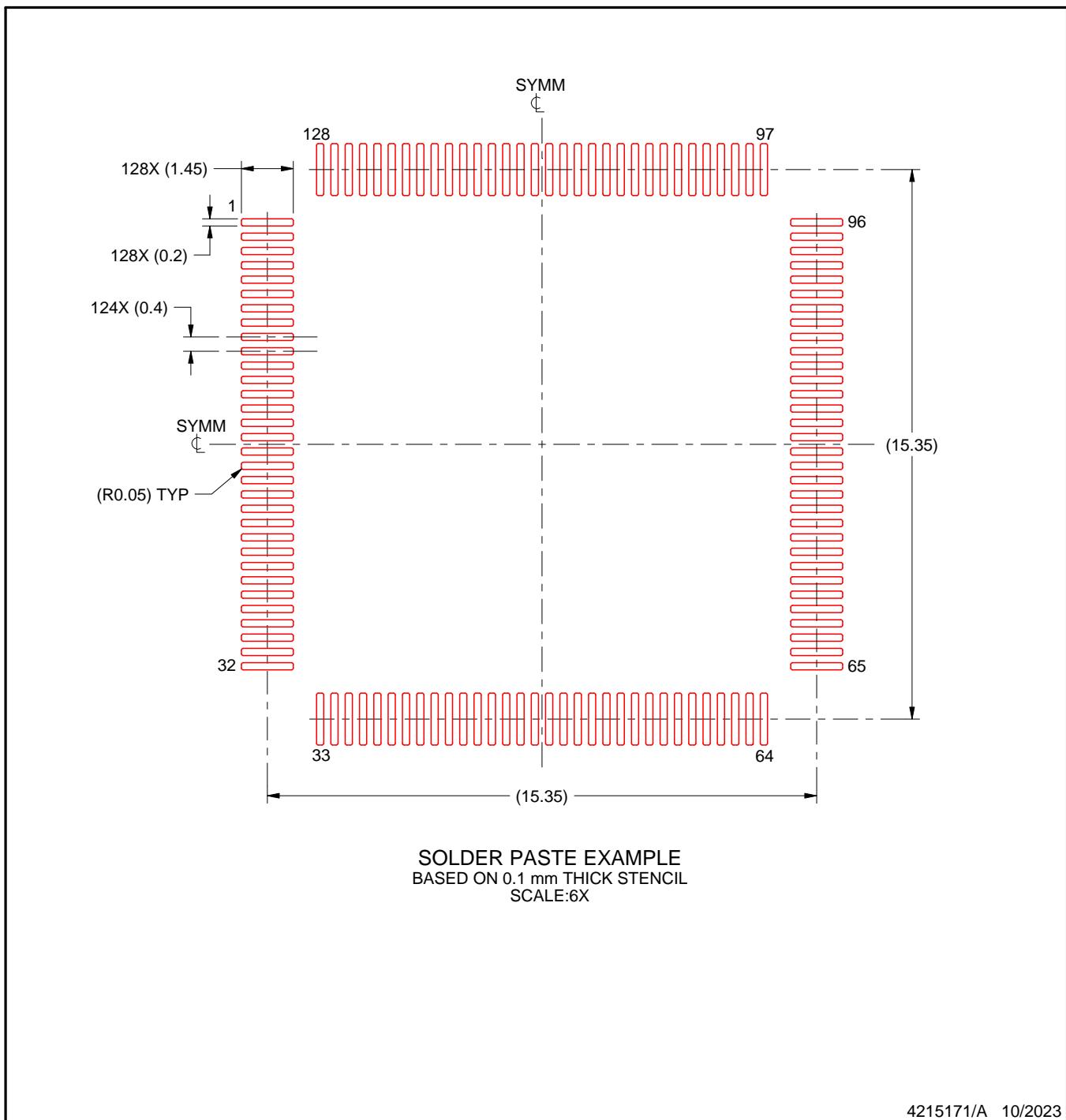

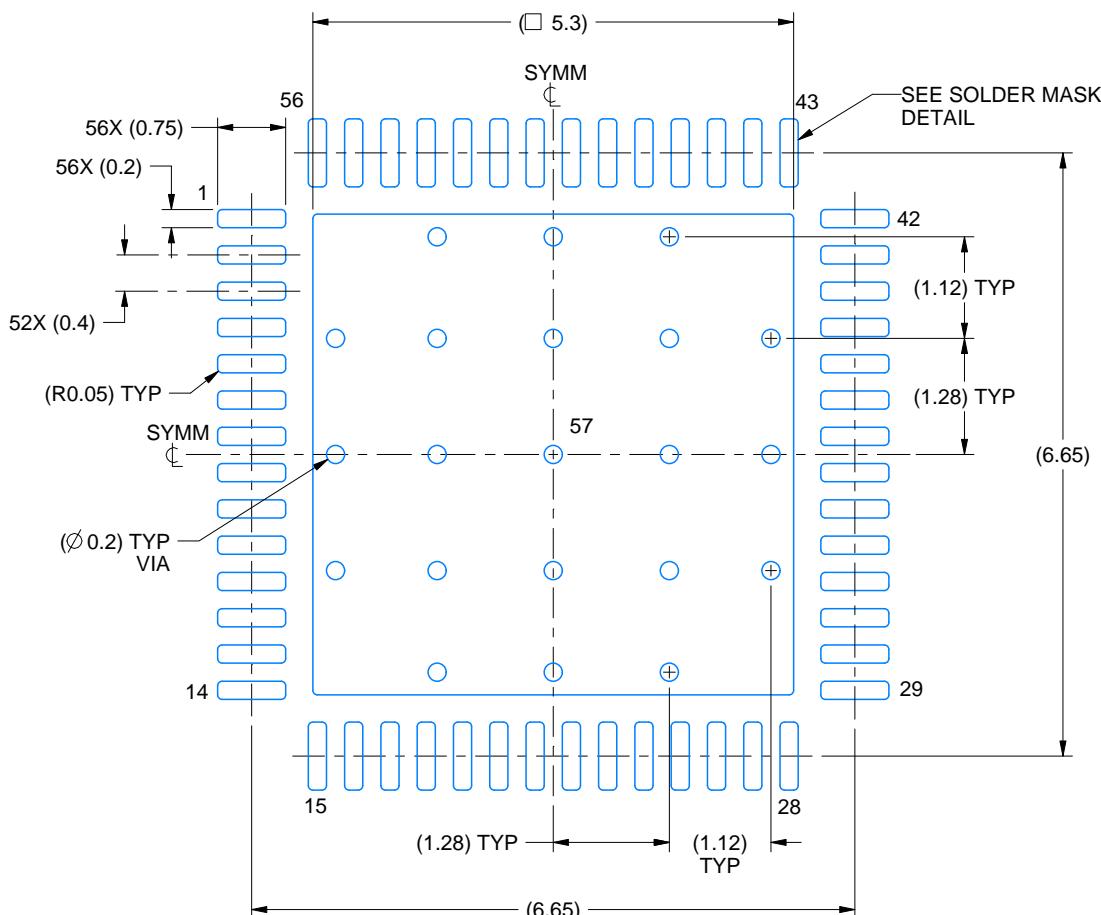

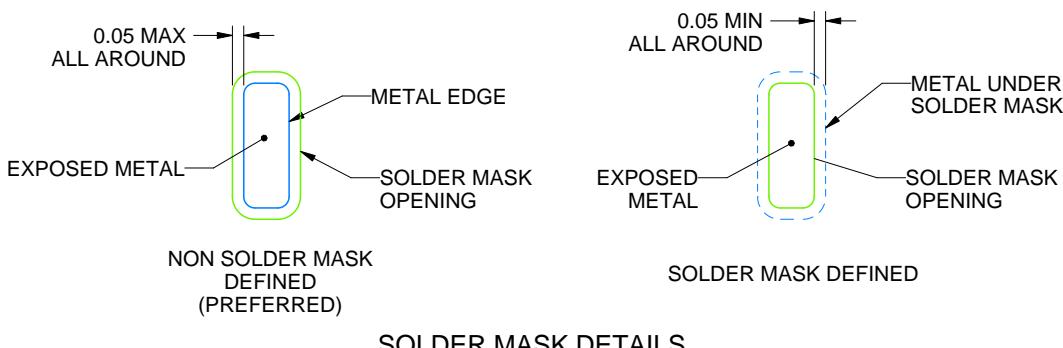

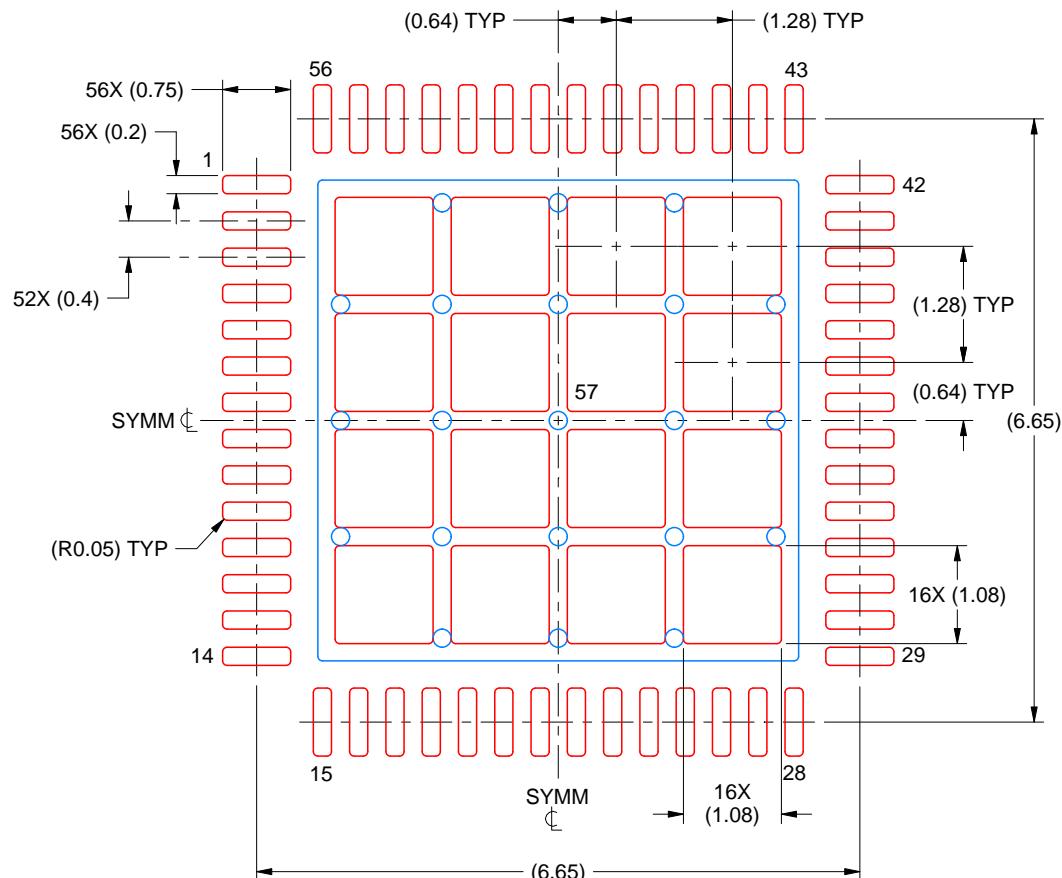

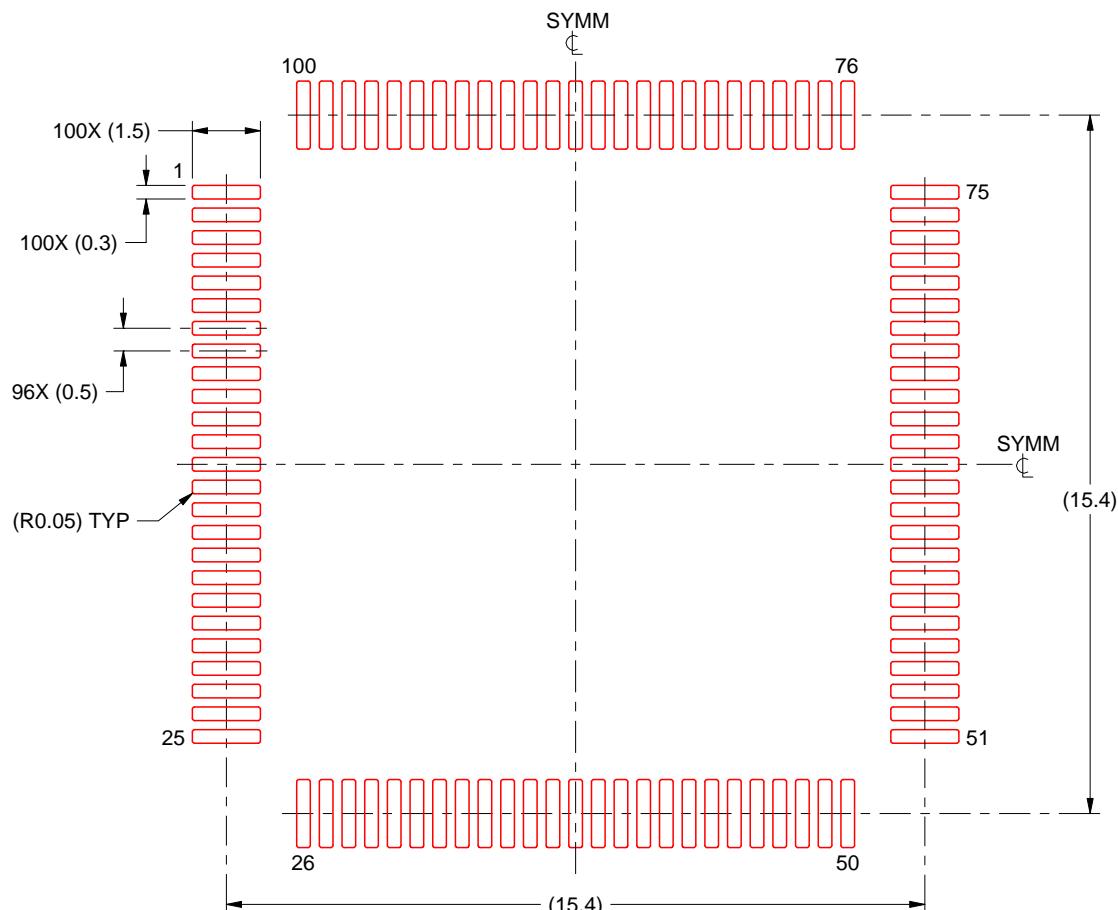

図 5-1 に、128 ピン PDT 薄型クワッド フラットパックのピン配置を示します。図 5-2 に、100 ピン PZ 薄型クワッド フラットパックのピン配置を示します。図 5-3 に、80 ピン PNA 薄型クワッド フラットパックのピン配置を示します。図 5-4 に、64 ピン PM 薄型クワッド フラットパックのピン配置を示します。図 5-5 に、56 ピン RSH 超薄型クワッド フラットパック リードなしのピン配置を示します。

A. GPIO ピンには GPIO 機能のみを表示しています。完全な多重化された信号名については、「ピン属性」表を参照してください。

図 5-1. 128 ピン PDT 薄型クワッド フラットパック (上面図)

A. GPIO ピンには GPIO 機能のみを表示しています。完全な多重化された信号名については、「ピン属性」表を参照してください。

図 5-2. 100 ピン PZ 薄型クワッド フラットパック (上面図)

A. GPIO ピンには GPIO 機能のみを表示しています。完全な多重化された信号名については、「ピン属性」表を参照してください。

図 5-3. 80 ピン PNA 薄型クワッド フラットパック (上面図)

A. GPIO ピンには GPIO 機能のみを表示しています。完全な多重化された信号名については、「ピン属性」表を参照してください。

図 5-4. 64 ピン PM 薄型クワッド フラットパック (上面図)

A. GPIO ピンには GPIO 機能のみを表示しています。完全な多重化された信号名については、「ピン属性」表を参照してください。

図 5-5. 56 ピン RSH 超薄型クワッド フラットパック、リードなし (上面図)

## 5.2 ピン属性

表 5-1. ピン属性

| 信号名       | 多重化位置       | 128 PDT | 100 PZ | 80 PNA | 64 PM | 56 RSH | ピンの種類 | 説明                                                         |

|-----------|-------------|---------|--------|--------|-------|--------|-------|------------------------------------------------------------|

| アナログ      |             |         |        |        |       |        |       |                                                            |

| A0        |             |         |        |        |       |        | I     | ADC-A 入力 0                                                 |

| B15       |             |         |        |        |       |        | I     | ADC-B 入力 15                                                |

| C15       |             |         |        |        |       |        | I     | ADC-C 入力 15                                                |

| CMP3_HP2  |             | 30      | 23     | 19     | 15    | 13     | I     | CMPSS-3 ハイコンバレータ正入力 2                                      |

| CMP3_LP2  |             |         |        |        |       |        | I     | CMPSS-3 ロー コンバレータ正入力 2                                     |

| DACA_OUT  |             |         |        |        |       |        | O     | バッファ付き DAC-A 出力。                                           |

| AIO231    | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 231 に使用されるアナログ ピン                                   |

| A1        |             |         |        |        |       |        | I     | ADC-A 入力 1                                                 |

| B7        |             |         |        |        |       |        | I     | ADC-B 入力 7                                                 |

| CMP1_DACL |             | 29      | 22     | 18     | 14    | 12     | I     | CMPSS-1 低 DAC 出力                                           |

| CMP1_HP4  |             |         |        |        |       |        | I     | CMPSS-1 ハイコンバレータ正入力 4                                      |

| CMP1_LP4  |             |         |        |        |       |        | I     | CMPSS-1 ロー コンバレータ正入力 4                                     |

| D11       |             |         |        |        |       |        | I     | ADC-D 入力 11                                                |

| AIO232    | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 232 に使用されるアナログ ピン                                   |

| A2        |             |         |        |        |       |        | I     | ADC-A 入力 2                                                 |

| B6        |             |         |        |        |       |        | I     | ADC-B 入力 6                                                 |

| C9        |             |         |        |        |       |        | I     | ADC-C 入力 9                                                 |

| CMP1_HP0  |             | 21      | 17     | 13     | 9     | 7      | I     | CMPSS-1 ハイコンバレータ正入力 0                                      |

| CMP1_LP0  |             |         |        |        |       |        | I     | CMPSS-1 ロー コンバレータ正入力 0                                     |

| GPIO224   |             |         |        |        |       |        | I/O   | 汎用入出力 224。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。 |

| PGA1_INP  |             |         |        |        |       |        | I     | PGA-1 正                                                    |

| A3        |             |         |        |        |       |        | I     | ADC-A 入力 3                                                 |

| CMP3_HP5  |             | 18      |        |        |       |        | I     | CMPSS-3 ハイコンバレータ正入力 5                                      |

| CMP3_LP5  |             |         |        |        |       |        | I     | CMPSS-3 ロー コンバレータ正入力 5                                     |

| AIO229    | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 229 に使用されるアナログ ピン                                   |

| A3        |             | 20      |        | 12     | 8     | 6      | I     | ADC-A 入力 3                                                 |

| CMP3_HP5  |             |         |        |        |       |        | I     | CMPSS-3 ハイコンバレータ正入力 5                                      |

| CMP3_LP5  |             |         |        |        |       |        | I     | CMPSS-3 ロー コンバレータ正入力 5                                     |

| A4        |             |         |        |        |       |        | I     | ADC-A 入力 4                                                 |

| B8        |             |         |        |        |       |        | I     | ADC-B 入力 8                                                 |

| CMP2_HP0  |             | 42      | 36     | 27     | 23    | 21     | I     | CMPSS-2 ハイコンバレータ正入力 0                                      |

| CMP2_LP0  |             |         |        |        |       |        | I     | CMPSS-2 ロー コンバレータ正入力 0                                     |

| AIO225    | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 225 に使用されるアナログ ピン                                   |

| A5        |             |         |        |        |       |        | I     | ADC-A 入力 5                                                 |

| CMP2_HP5  |             | 35      |        |        |       |        | I     | CMPSS-2 ハイコンバレータ正入力 5                                      |

| CMP2_LP5  |             |         |        |        |       |        | I     | CMPSS-2 ロー コンバレータ正入力 5                                     |

| AIO249    | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 249 に使用されるアナログ ピン                                   |

| A5        |             |         |        |        |       |        | I     | ADC-A 入力 5                                                 |

| CMP2_HP5  |             | 28      |        | 17     | 13    | 11     | I     | CMPSS-2 ハイコンバレータ正入力 5                                      |

| CMP2_LP5  |             |         |        |        |       |        | I     | CMPSS-2 ロー コンバレータ正入力 5                                     |

**表 5-1. ピン属性 (続き)**

| 信号名      | 多重化位置       | 128 PDT | 100 PZ | 80 PNA | 64 PM | 56 RSH | ピンの種類 | 説明                                                         |

|----------|-------------|---------|--------|--------|-------|--------|-------|------------------------------------------------------------|

| A6       |             |         |        |        |       |        | I     | ADC-A 入力 6                                                 |

| CMP1_HP2 |             |         |        |        |       |        | I     | CMPSS-1 ハイ コンバレータ正入力 2                                     |

| CMP1_LP2 |             |         |        |        |       |        | I     | CMPSS-1 ロー コンバレータ正入力 2                                     |

| D14      |             | 18      | 14     | 10     | 6     |        | I     | ADC-D 入力 14                                                |

| E14      |             |         |        |        |       |        | I     | ADC-E 入力 14                                                |

| GPIO228  |             |         |        |        |       |        | I/O   | 汎用入出力 228。このピンには、この表の GPIO セクションに記載されているデジタル マルチプレクサ機能もある。 |

| A7       |             |         |        |        |       |        | I     | ADC-A 入力 7                                                 |

| B30      |             |         |        |        |       |        | I     | ADC-B 入力 30                                                |

| C3       |             |         |        |        |       |        | I     | ADC-C 入力 3                                                 |

| CMP4_HN1 |             |         |        |        |       |        | I     | CMPSS-4 ハイ コンバレータ負入力 1                                     |

| CMP4_HP1 |             | 37      | 31     | 23     | 19    | 17     | I     | CMPSS-4 ハイ コンバレータ正入力 1                                     |

| CMP4_LN1 |             |         |        |        |       |        | I     | CMPSS-4 ロー コンバレータ負入力 1                                     |

| CMP4_LP1 |             |         |        |        |       |        | I     | CMPSS-4 ロー コンバレータ正入力 1                                     |

| D12      |             |         |        |        |       |        | I     | ADC-D 入力 12                                                |

| E30      |             |         |        |        |       |        | I     | ADC-E 入力 30                                                |

| AIO245   | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 245 に使用されるアナログ ピン                                   |

| A8       |             |         |        |        |       |        | I     | ADC-A 入力 8                                                 |

| CMP4_HP4 |             |         |        |        |       |        | I     | CMPSS-4 ハイ コンバレータ正入力 4                                     |

| CMP4_LP4 |             |         |        |        |       |        | I     | CMPSS-4 ロー コンバレータ正入力 4                                     |

| AIO240   | 0, 4, 8, 12 |         | 37     |        |       |        | I     | デジタル入力 240 に使用されるアナログ ピン                                   |

| A8       |             |         |        |        |       |        | I     | ADC-A 入力 8                                                 |

| B0       |             |         |        |        |       |        | I     | ADC-B 入力 0                                                 |

| C11      |             |         |        |        |       |        | I     | ADC-C 入力 11                                                |

| CMP4_HP4 |             | 39      |        | 24     | 20    | 18     | I     | CMPSS-4 ハイ コンバレータ正入力 4                                     |

| CMP4_LP4 |             |         |        |        |       |        | I     | CMPSS-4 ロー コンバレータ正入力 4                                     |

| AIO241   | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 241 に使用されるアナログ ピン                                   |

| A9       |             |         |        |        |       |        | I     | ADC-A 入力 9                                                 |

| CMP2_HP2 |             |         |        |        |       |        | I     | CMPSS-2 ハイ コンバレータ正入力 2                                     |

| CMP2_LP2 |             | 48      | 38     | 28     | 24    | 22     | I     | CMPSS-2 ロー コンバレータ正入力 2                                     |

| GPIO227  |             |         |        |        |       |        | I/O   | 汎用入出力 227。このピンには、この表の GPIO セクションに記載されているデジタル マルチプレクサ機能もある。 |

| A10      |             |         |        |        |       |        | I     | ADC-A 入力 10                                                |

| B1       |             |         |        |        |       |        | I     | ADC-B 入力 1                                                 |

| C10      |             |         |        |        |       |        | I     | ADC-C 入力 10                                                |

| CMP2_HN0 |             |         |        |        |       |        | I     | CMPSS-2 ハイ コンバレータ負入力 0                                     |

| CMP2_HP3 |             | 50      | 40     | 29     | 25    | 23     | I     | CMPSS-2 ハイ コンバレータ正入力 3                                     |

| CMP2_LN0 |             |         |        |        |       |        | I     | CMPSS-2 ロー コンバレータ負入力 0                                     |

| CMP2_LP3 |             |         |        |        |       |        | I     | CMPSS-2 ロー コンバレータ正入力 3                                     |

| GPIO230  |             |         |        |        |       |        | I/O   | 汎用入出力 230。このピンには、この表の GPIO セクションに記載されているデジタル マルチプレクサ機能もある。 |

表 5-1. ピン属性 (続き)

| 信号名                   | 多重化位置       | 128 PDT | 100 PZ | 80 PNA | 64 PM | 56 RSH | ピンの種類 | 説明                                                                                                |

|-----------------------|-------------|---------|--------|--------|-------|--------|-------|---------------------------------------------------------------------------------------------------|

| A11                   |             |         |        |        |       |        | I     | ADC-A 入力 11                                                                                       |

| B10                   |             |         |        |        |       |        | I     | ADC-B 入力 10                                                                                       |

| C0                    |             |         |        |        |       |        | I     | ADC-C 入力 0                                                                                        |

| CMP1_HN1              |             |         |        |        |       |        | I     | CMPSS-1 ハイ コンバレータ負入力 1                                                                            |

| CMP1_HP1              |             | 27      | 20     | 16     | 12    | 10     | I     | CMPSS-1 ハイ コンバレータ正入力 1                                                                            |

| CMP1_LN1              |             |         |        |        |       |        | I     | CMPSS-1 ロー コンバレータ負入力 1                                                                            |

| CMP1_LP1              |             |         |        |        |       |        | I     | CMPSS-1 ロー コンバレータ正入力 1                                                                            |

| PGA2_OUT              |             |         |        |        |       |        | O     | PGA-2 出力                                                                                          |

| AIO237                | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 237 に使用されるアナログ ピン                                                                          |

| A12                   |             |         |        |        |       |        | I     | ADC-A 入力 12                                                                                       |

| CMP2_HN1              |             |         |        |        |       |        | I     | CMPSS-2 ハイ コンバレータ負入力 1                                                                            |

| CMP2_HP1              |             | 35      | 28     | 22     | 18    | 16     | I     | CMPSS-2 ハイ コンバレータ正入力 1                                                                            |

| CMP2_LN1              |             |         |        |        |       |        | I     | CMPSS-2 ロー コンバレータ負入力 1                                                                            |

| CMP2_LP1              |             |         |        |        |       |        | I     | CMPSS-2 ロー コンバレータ正入力 1                                                                            |

| AIO238                | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 238 に使用されるアナログ ピン                                                                          |

| A13                   |             |         |        |        |       |        | I     | ADC-A 入力 13                                                                                       |

| B13                   |             |         |        |        |       |        | I     | ADC-B 入力 13                                                                                       |

| C13                   |             |         |        |        |       |        | I     | ADC-C 入力 13                                                                                       |

| D13                   |             |         |        |        |       |        | I     | ADC-D 入力 13                                                                                       |

| E13                   |             | 34      | 26     | 21     | 17    | 15     | I     | ADC-E 入力 13                                                                                       |

| VREFLO <sup>(1)</sup> |             |         |        |        |       |        | I     | すべての ADC が VSSA への内部接続を使用して低いリファレンス電圧を供給する場合、共有アナログ ピンで ADC チャネル A13/B13/C13/D13/E13 をサンプリングできます。 |

| AIO235                | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 235 に使用されるアナログ ピン                                                                          |

| A13                   |             |         |        |        |       |        | I     | ADC-A 入力 13                                                                                       |

| B13                   |             |         |        |        |       |        | I     | ADC-B 入力 13                                                                                       |

| C13                   |             |         |        |        |       |        | I     | ADC-C 入力 13                                                                                       |

| D13                   |             |         |        |        |       |        | I     | ADC-D 入力 13                                                                                       |

| E13                   |             | 33, 34  | 26, 27 | 21     | 17    | 15     | I     | ADC-E 入力 13                                                                                       |

| VREFLO <sup>(1)</sup> |             |         |        |        |       |        | I     | すべての ADC が VSSA への内部接続を使用して低いリファレンス電圧を供給する場合、共有アナログ ピンで ADC チャネル A13/B13/C13/D13/E13 をサンプリングできます。 |

| AIO235                | ALT         |         |        |        |       |        | I     | デジタル入力 235 に使用されるアナログ ピン                                                                          |

| A14                   |             |         |        |        |       |        | I     | ADC-A 入力 14                                                                                       |

| B14                   |             |         |        |        |       |        | I     | ADC-B 入力 14                                                                                       |

| C4                    |             |         |        |        |       |        | I     | ADC-C 入力 4                                                                                        |

| CMP3_HP4              |             | 26      | 19     | 15     | 11    | 9      | I     | CMPSS-3 ハイ コンバレータ正入力 4                                                                            |

| CMP3_LP4              |             |         |        |        |       |        | I     | CMPSS-3 ロー コンバレータ正入力 4                                                                            |

| PGA1_OUT              |             |         |        |        |       |        | O     | PGA-1 出力                                                                                          |

| AIO239                | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 239 に使用されるアナログ ピン                                                                          |

| A15                   |             |         |        |        |       |        | I     | ADC-A 入力 15                                                                                       |

| CMP1_HN0              |             |         |        |        |       |        | I     | CMPSS-1 ハイ コンバレータ負入力 0                                                                            |

| CMP1_HP3              |             | 22      |        | 14     | 10    | 8      | I     | CMPSS-1 ハイ コンバレータ正入力 3                                                                            |

| CMP1_LN0              |             |         |        |        |       |        | I     | CMPSS-1 ロー コンバレータ負入力 0                                                                            |

| CMP1_LP3              |             |         |        |        |       |        | I     | CMPSS-1 ロー コンバレータ正入力 3                                                                            |

| AIO233                | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 233 に使用されるアナログ ピン                                                                          |

**表 5-1. ピン属性 (続き)**

| 信号名     | 多重化位置       | 128 PDT | 100 PZ | 80 PNA | 64 PM | 56 RSH | ピンの種類 | 説明                                                         |

|---------|-------------|---------|--------|--------|-------|--------|-------|------------------------------------------------------------|

| A16     |             |         |        |        |       |        | I     | ADC-A 入力 16                                                |

| B16     |             |         |        |        |       |        | I     | ADC-B 入力 16                                                |

| C16     |             |         |        |        |       |        | I     | ADC-C 入力 16                                                |

| GPIO28  |             | 2       | 1      | 4      | 2     | 3      | I/O   | 汎用入出力 28。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。  |

| A17     |             |         |        |        |       |        | I     | ADC-A 入力 17                                                |

| B17     |             |         |        |        |       |        | I     | ADC-B 入力 17                                                |

| C17     |             | 60      | 48     | 33     | 27    | 24     | I     | ADC-C 入力 17                                                |

| GPIO20  |             |         |        |        |       |        | I/O   | 汎用入出力 20。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。  |

| A18     |             |         |        |        |       |        | I     | ADC-A 入力 18                                                |

| B18     |             |         |        |        |       |        | I     | ADC-B 入力 18                                                |

| C18     |             | 61      | 49     | 34     | 28    | 25     | I     | ADC-C 入力 18                                                |

| GPIO21  |             |         |        |        |       |        | I/O   | 汎用入出力 21。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。  |

| A19     |             |         |        |        |       |        | I     | ADC-A 入力 19                                                |

| B19     |             |         |        |        |       |        | I     | ADC-B 入力 19                                                |

| C19     |             | 62      | 50     | 35     | 29    | 26     | I     | ADC-C 入力 19                                                |

| GPIO13  |             |         |        |        |       |        | I/O   | 汎用入出力 13。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。  |

| A20     |             |         |        |        |       |        | I     | ADC-A 入力 20                                                |

| B20     |             |         |        |        |       |        | I     | ADC-B 入力 20                                                |

| C20     |             | 63      | 51     | 36     | 30    | 27     | I     | ADC-C 入力 20                                                |

| GPIO12  |             |         |        |        |       |        | I/O   | 汎用入出力 12。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。  |

| A24     |             |         |        |        |       |        | I     | ADC-A 入力 24                                                |

| D0      |             |         |        |        |       |        | I     | ADC-D 入力 0                                                 |

| E0      |             | 64      | 52     | 37     | 31    | 28     | I     | ADC-E 入力 0                                                 |

| GPIO11  |             |         |        |        |       |        | I/O   | 汎用入出力 11。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。  |

| A25     |             |         |        |        |       |        | I     | ADC-A 入力 25                                                |

| D3      |             |         |        |        |       |        | I     | ADC-D 入力 3                                                 |

| E3      |             | 67      | 55     | 40     | 34    | 31     | I     | ADC-E 入力 3                                                 |

| GPIO17  |             |         |        |        |       |        | I/O   | 汎用入出力 17。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。  |

| A26     |             |         |        |        |       |        | I     | ADC-A 入力 26                                                |

| D6      |             |         |        |        |       |        | I     | ADC-D 入力 6                                                 |

| E6      |             |         |        |        |       |        | I     | ADC-E 入力 6                                                 |

| AIO209  | 0, 4, 8, 12 | 24      |        |        |       |        | I     | デジタル入力 209 に使用されるアナログ ピン                                   |

| A27     |             |         |        |        |       |        | I     | ADC-A 入力 27                                                |

| D9      |             |         |        |        |       |        | I     | ADC-D 入力 9                                                 |

| E9      |             | 44      |        |        |       |        | I     | ADC-E 入力 9                                                 |

| GPIO212 |             |         |        |        |       |        | I/O   | 汎用入出力 212。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。 |

| A28     |             |         |        |        |       |        | I     | ADC-A 入力 28                                                |

| D19     |             |         |        |        |       |        | I     | ADC-D 入力 19                                                |

| E19     |             |         |        |        |       |        | I     | ADC-E 入力 19                                                |

| GPIO215 |             | 47      |        |        |       |        | I/O   | 汎用入出力 215。このピンには、この表の GPIO セクションに記載されているデジタル マルチブレクサ機能もある。 |

表 5-1. ピン属性 (続き)

| 信号名      | 多重化位置       | 128 PDT | 100 PZ | 80 PNA | 64 PM | 56 RSH | ピンの種類 | 説明                                                        |

|----------|-------------|---------|--------|--------|-------|--------|-------|-----------------------------------------------------------|

| B0       |             |         |        |        |       |        | I     | ADC-B 入力 0                                                |

| C11      |             |         |        |        |       |        | I     | ADC-C 入力 11                                               |

| CMP2_HP3 |             |         | 41     |        |       |        | I     | CMPSS-2 ハイコンバレータ正入力 3                                     |

| CMP2_LP3 |             |         |        |        |       |        | I     | CMPSS-2 ローコンバレータ正入力 3                                     |

| GPIO253  |             |         |        |        |       |        | I/O   | 汎用入出力 253。このピンには、この表の GPIO セクションに記載されているデジタルマルチプレクサ機能もある。 |

| B2       |             |         |        |        |       |        | I     | ADC-B 入力 2                                                |

| C6       |             |         |        |        |       |        | I     | ADC-C 入力 6                                                |

| CMP3_HP0 |             | 19      | 15     | 11     | 7     |        | I     | CMPSS-3 ハイコンバレータ正入力 0                                     |

| CMP3_LP0 |             |         |        |        |       |        | I     | CMPSS-3 ローコンバレータ正入力 0                                     |

| E12      |             |         |        |        |       |        | I     | ADC-E 入力 12                                               |

| GPIO226  |             |         |        |        |       |        | I/O   | 汎用入出力 226。このピンには、この表の GPIO セクションに記載されているデジタルマルチプレクサ機能もある。 |

| B3       |             |         |        |        |       |        | I     | ADC-B 入力 3                                                |

| CMP3_HN0 |             |         |        |        |       |        | I     | CMPSS-3 ハイコンバレータ負入力 0                                     |

| CMP3_HP3 |             | 20      | 16     | 12     | 8     | 6      | I     | CMPSS-3 ハイコンバレータ正入力 3                                     |

| CMP3_LN0 |             |         |        |        |       |        | I     | CMPSS-3 ローコンバレータ負入力 0                                     |

| CMP3_LP3 |             |         |        |        |       |        | I     | CMPSS-3 ローコンバレータ正入力 3                                     |

| GPIO242  |             |         |        |        |       |        | I/O   | 汎用入出力 242。このピンには、この表の GPIO セクションに記載されているデジタルマルチプレクサ機能もある。 |

| PGA2_INP |             |         |        |        |       |        | I     | PGA-2 正                                                   |

| B4       |             |         |        |        |       |        | I     | ADC-B 入力 4                                                |

| C8       |             |         |        |        |       |        | I     | ADC-C 入力 8                                                |

| CMP4_HP0 |             | 49      | 39     | 28     | 24    | 22     | I     | CMPSS-4 ハイコンバレータ正入力 0                                     |

| CMP4_LP0 |             |         |        |        |       |        | I     | CMPSS-4 ローコンバレータ正入力 0                                     |

| GPIO236  | 0, 4, 8, 12 |         |        |        |       |        | I/O   | 汎用入出力 236。このピンには、この表の GPIO セクションに記載されているデジタルマルチプレクサ機能もある。 |

| B5       |             |         |        |        |       |        | I     | ADC-B 入力 5                                                |

| CMP1_HP5 |             |         |        |        |       |        | I     | CMPSS-1 ハイコンバレータ正入力 5                                     |

| CMP1_LP5 |             | 38      | 32     |        |       |        | I     | CMPSS-1 ローコンバレータ正入力 5                                     |

| D15      |             |         |        |        |       |        | I     | ADC-D 入力 15                                               |

| E15      |             |         |        |        |       |        | I     | ADC-E 入力 15                                               |

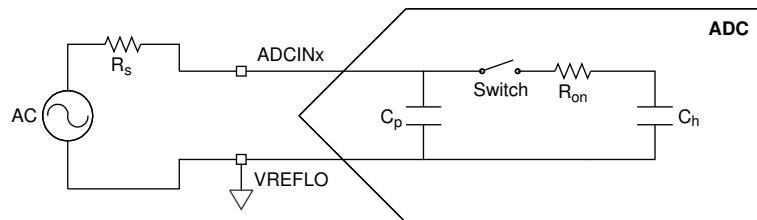

| AIO252   | 0, 4, 8, 12 |         |        |        |       |        | I     | デジタル入力 252 に使用されるアナログピン                                   |