## TMS320F2833x、TMS320F2823x リアルタイム・マイクロコントローラ

### 1 特長

- 高性能スタティック CMOS テクノロジ

- 最大 150MHz (サイクル・タイム 6.67ns)

- コア 1.9V/1.8V、I/O 3.3V の設計

- 高性能の 32 ビット CPU (TMS320C28x)

- IEEE 754 単精度浮動小数点ユニット (FPU) (F2833x のみ)

- 16 ビット × 16 ビットおよび 32 ビット × 32 ビットの MAC 演算

- 16 ビット × 16 ビットのデュアル MAC

- ハーバード・バス・アーキテクチャ

- 高速な割り込み応答とプロセッシング

- 統合メモリ・プログラミング・モデル

- 高いコード効率 (C/C++ およびアセンブリ)

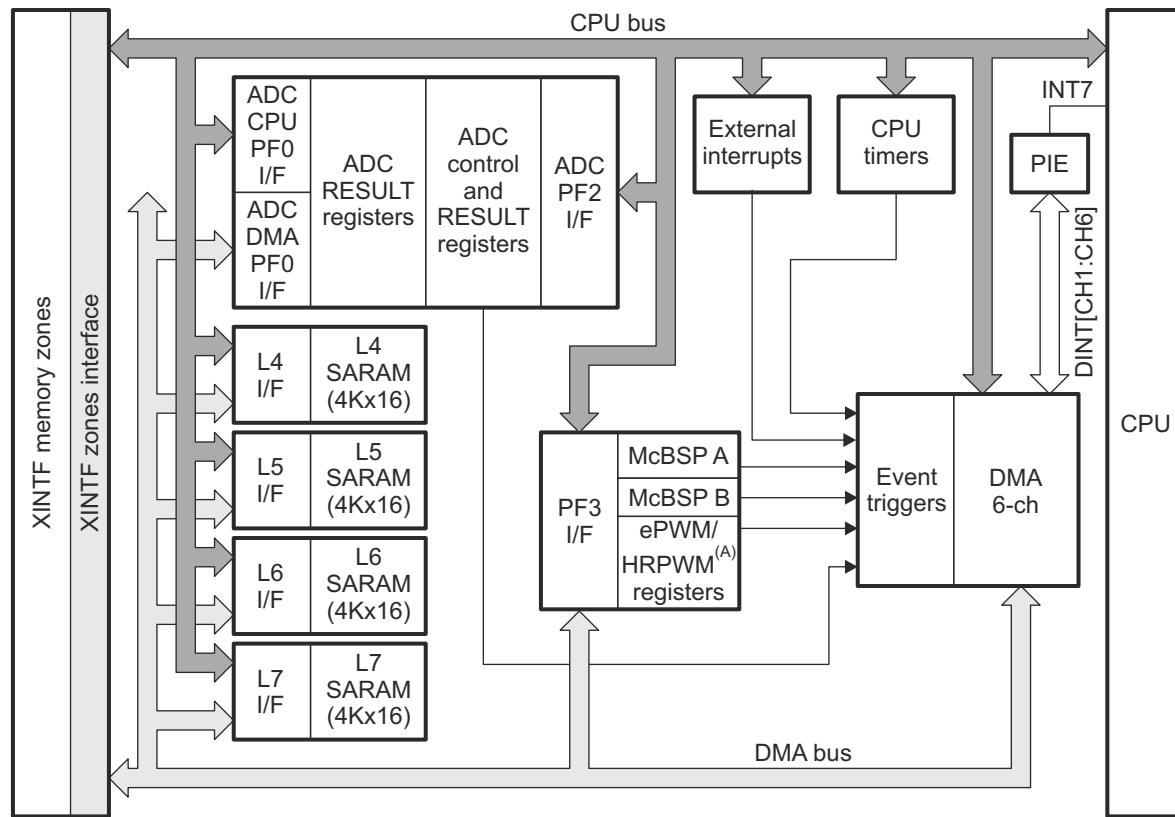

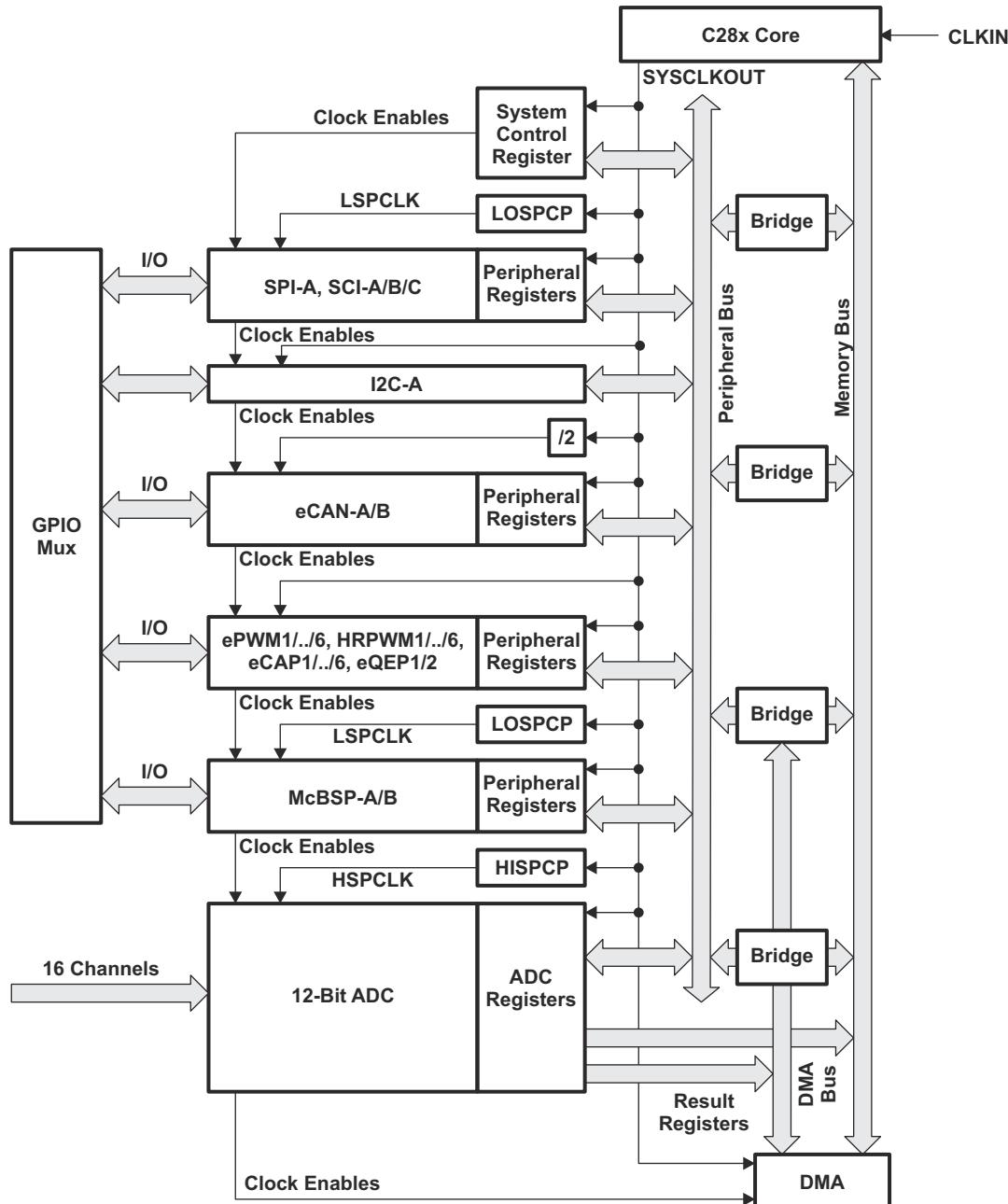

- 6 チャネル DMA コントローラ (ADC、 McBSP、ePWM、XINTF、SARAM 用)

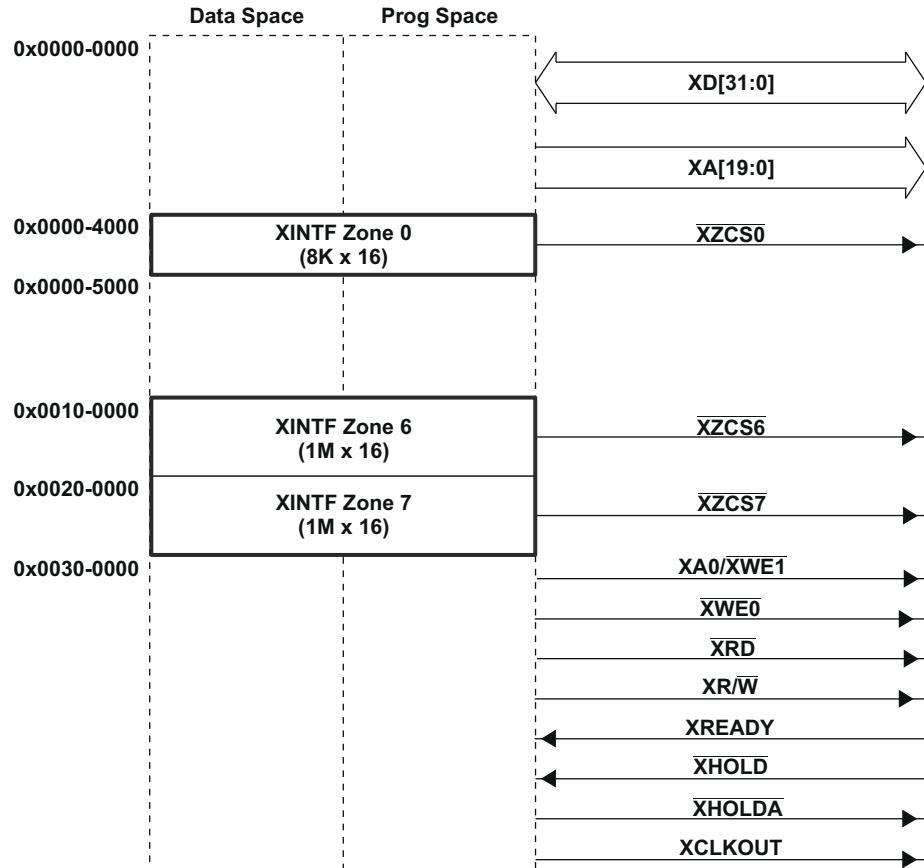

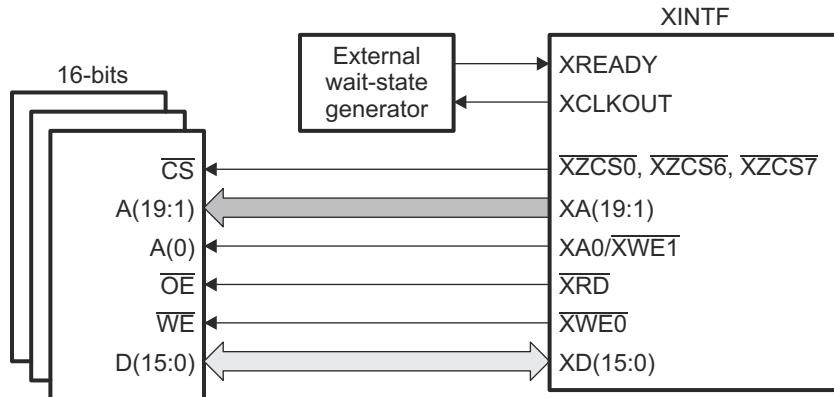

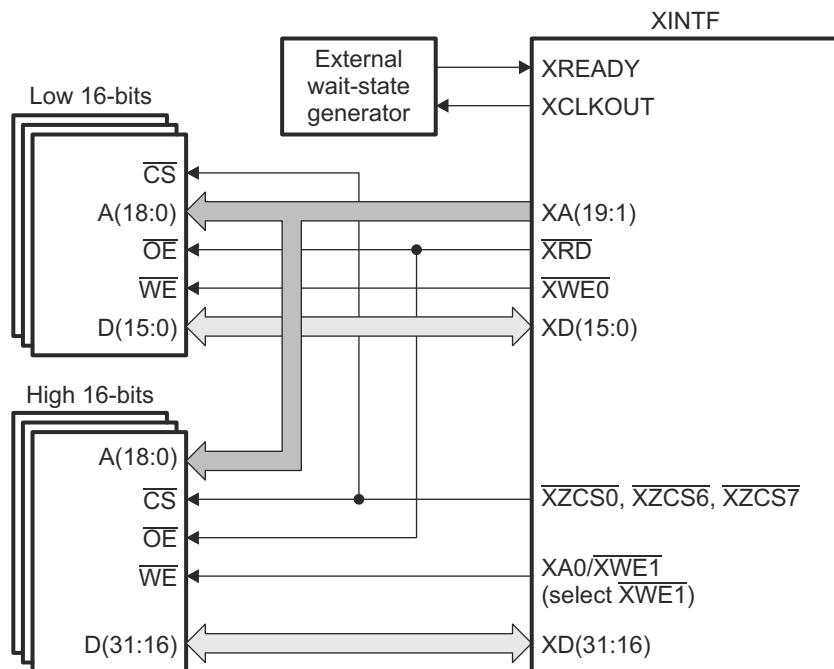

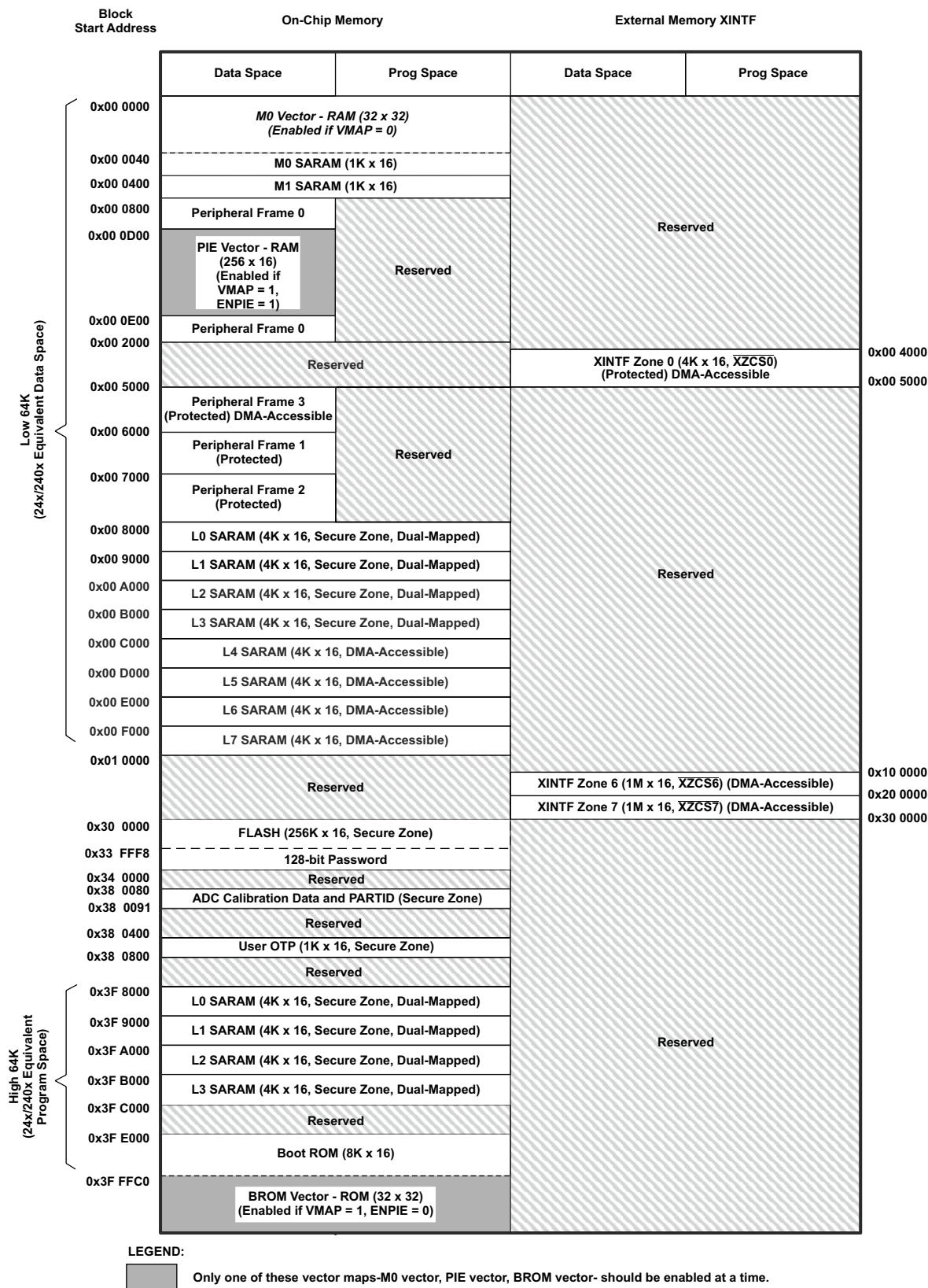

- 16 ビットまたは 32 ビットの外部インターフェイス (XINTF)

- 2M × 16 を超えるアドレスを使用可能

- オンチップ・メモリ

- F28335、F28333、F28235:

フラッシュ: 256K × 16、SARAM: 34K × 16

- F28334、F28234:

フラッシュ: 128K × 16、SARAM: 34K × 16

- F28332、F28232:

フラッシュ: 64K × 16、SARAM: 26K × 16

- OTP ROM: 1K × 16

- ブート ROM (8K × 16)

- ソフトウェア・ブート・モード搭載 (SCI、SPI、CAN、I2C、McBSP、XINTF、パラレル I/O 経由)

- 標準演算テーブル

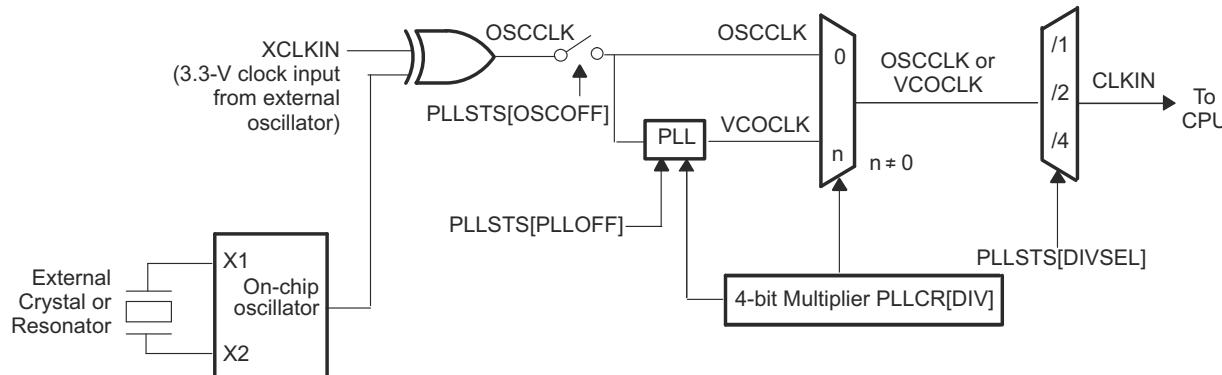

- クロックおよびシステム制御

- オンチップ発振器

- ウオッチドッグ・タイマ・モジュール

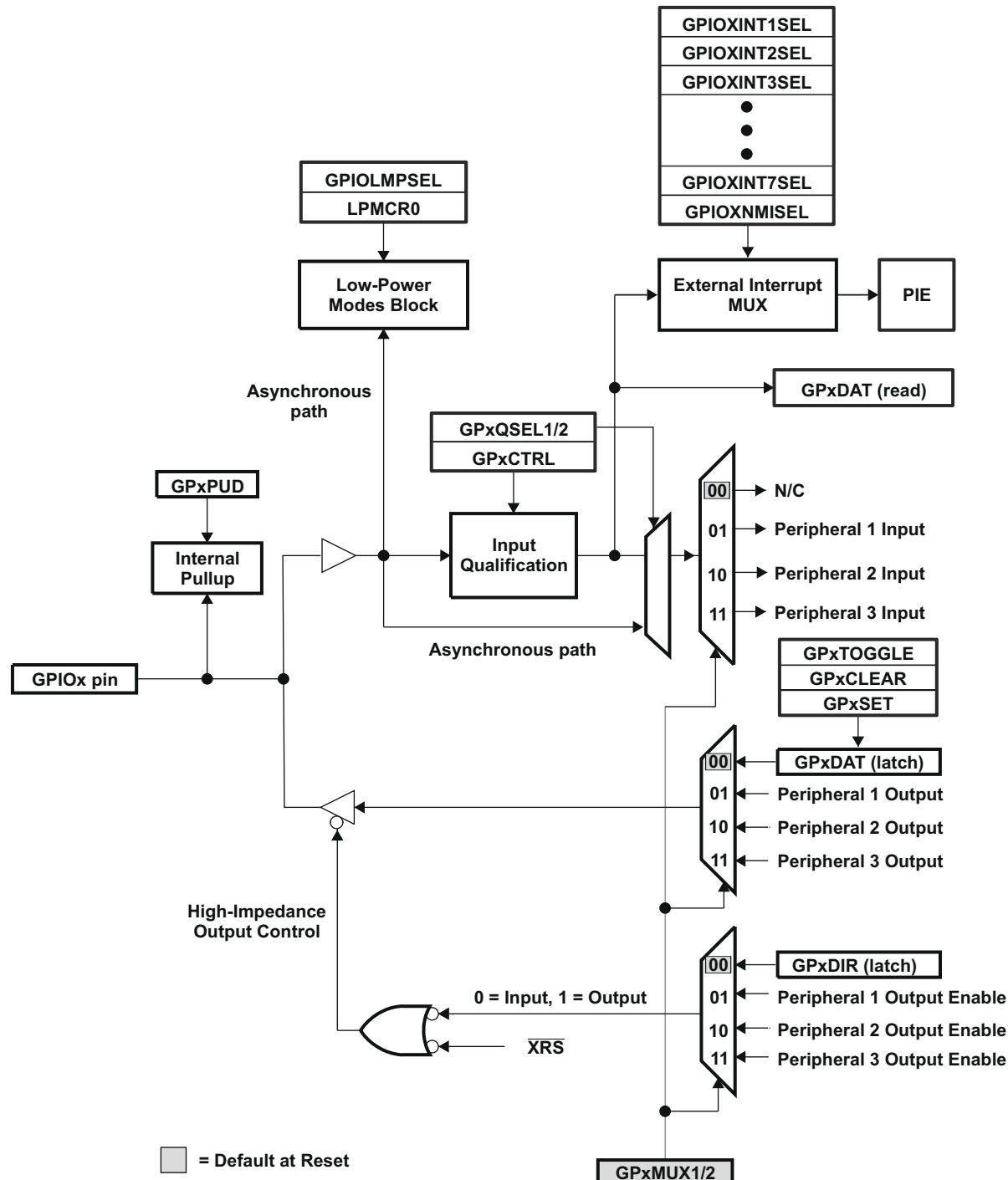

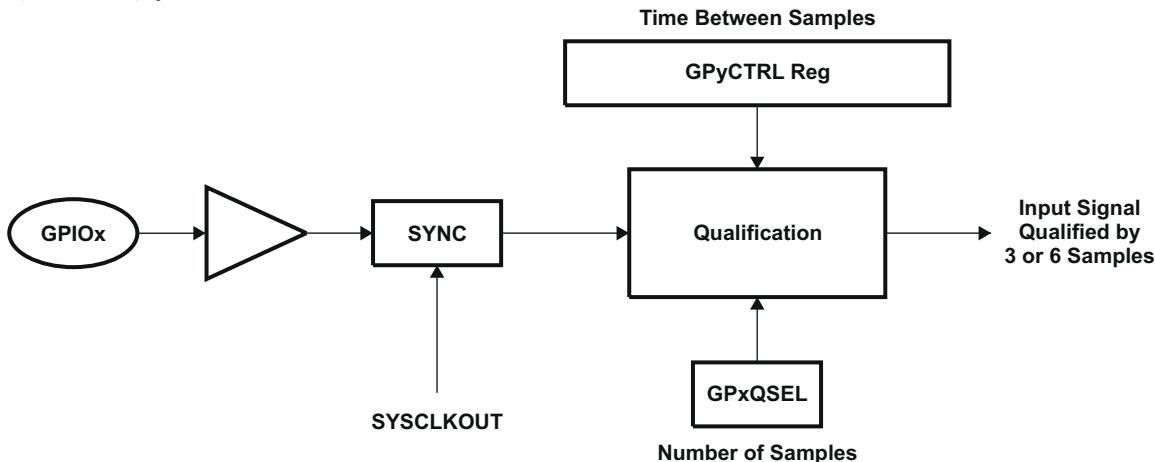

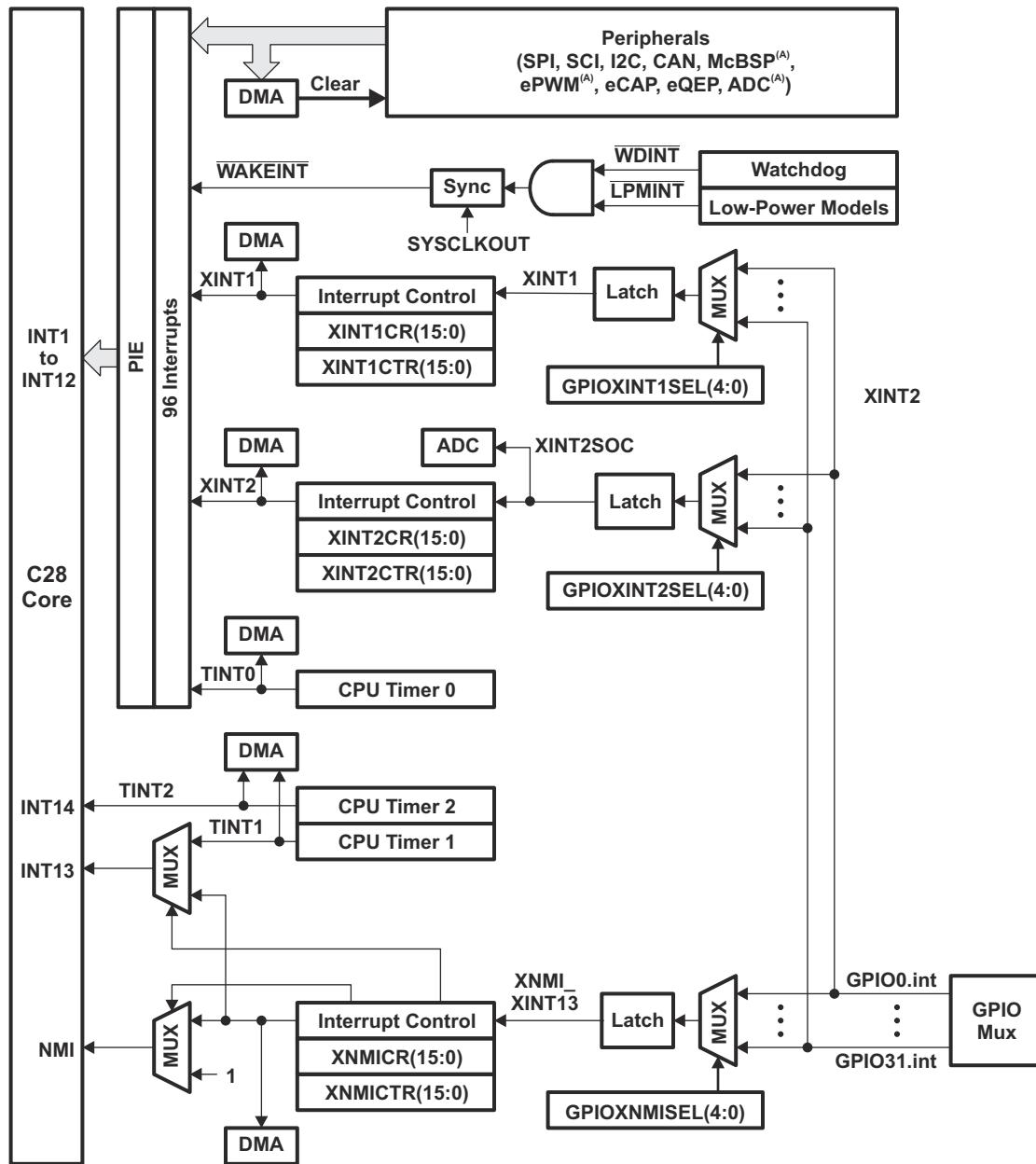

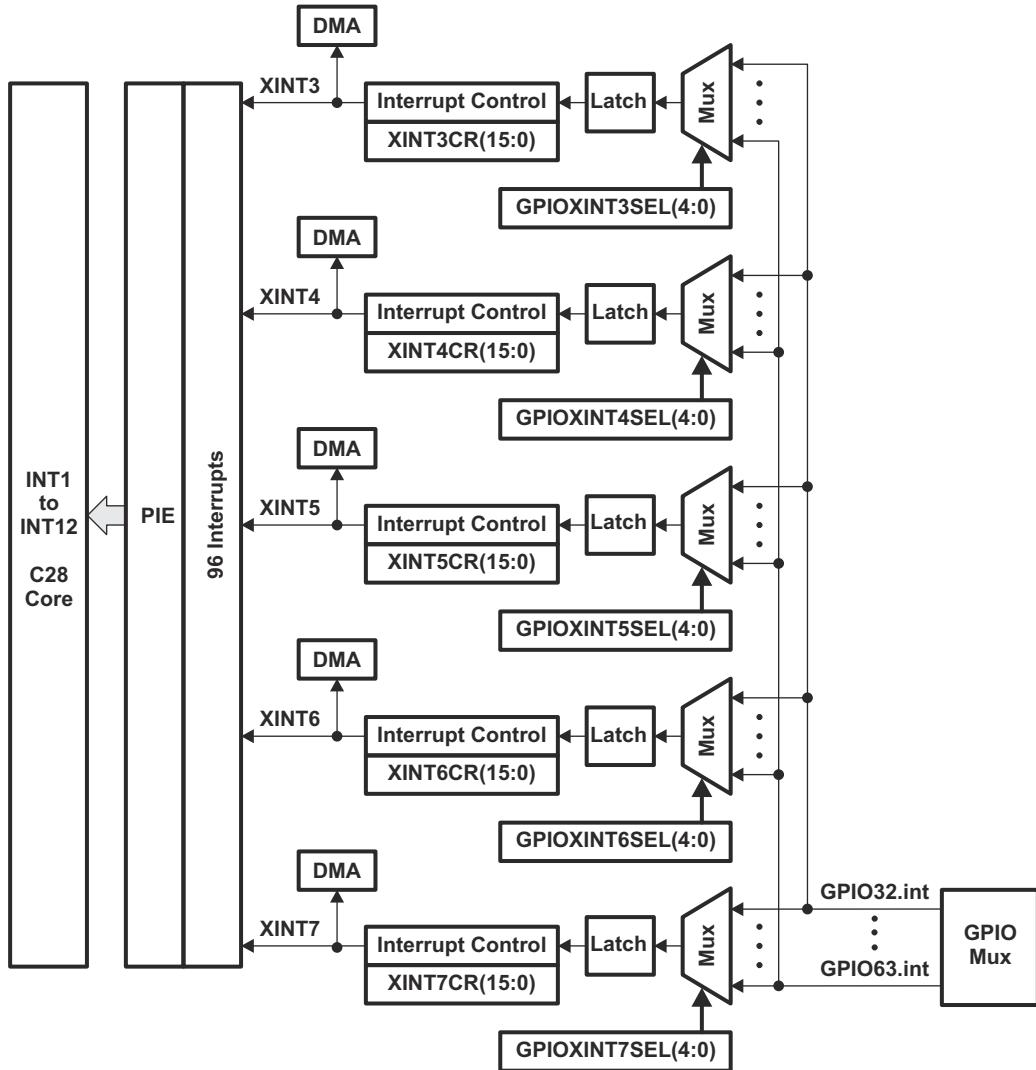

- GPIO0～GPIO63 ピンは、8 つの外部コア割り込みのいずれかに接続可能

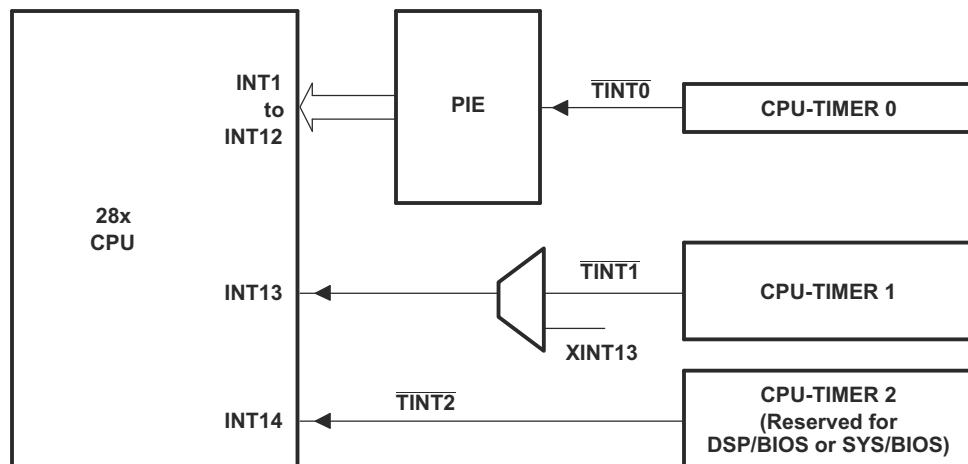

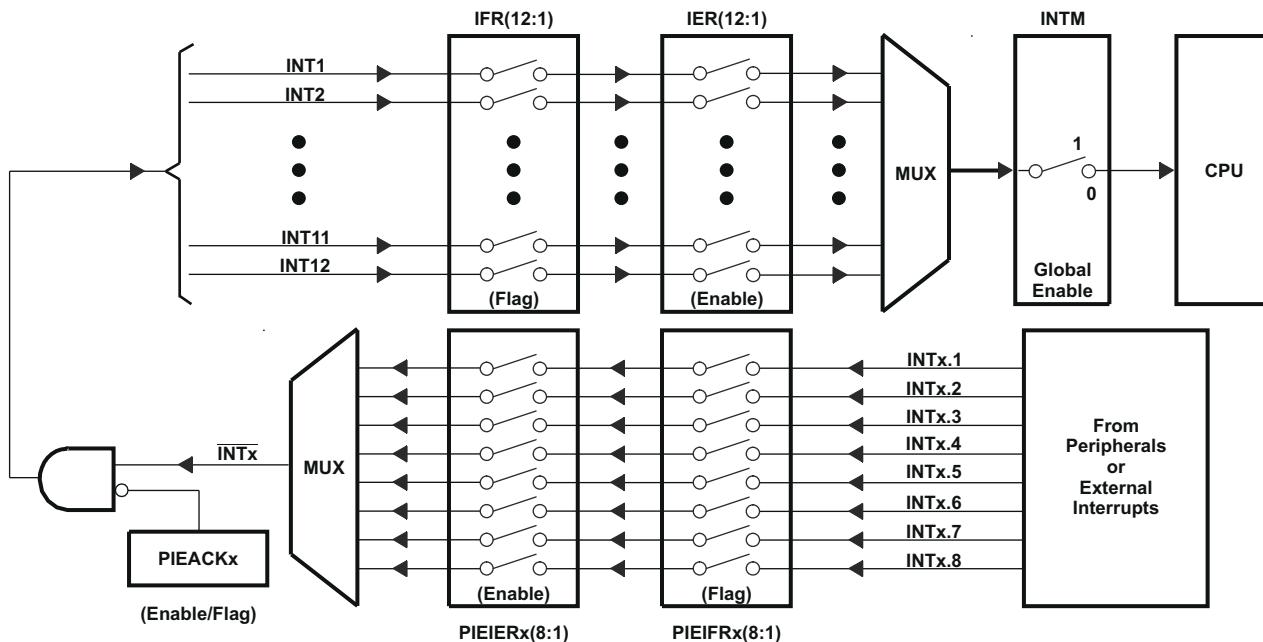

- 58 のペリフェラル割り込みすべてをサポートする、ペリフェラル割り込み拡張 (PIE) ブロック

- 128 ビットのセキュリティ・キー / ロック

- フラッシュ / OTP / RAM ブロックを保護

- ファームウェアのリバース・エンジニアリングを防止

- 拡張制御ペリフェラル

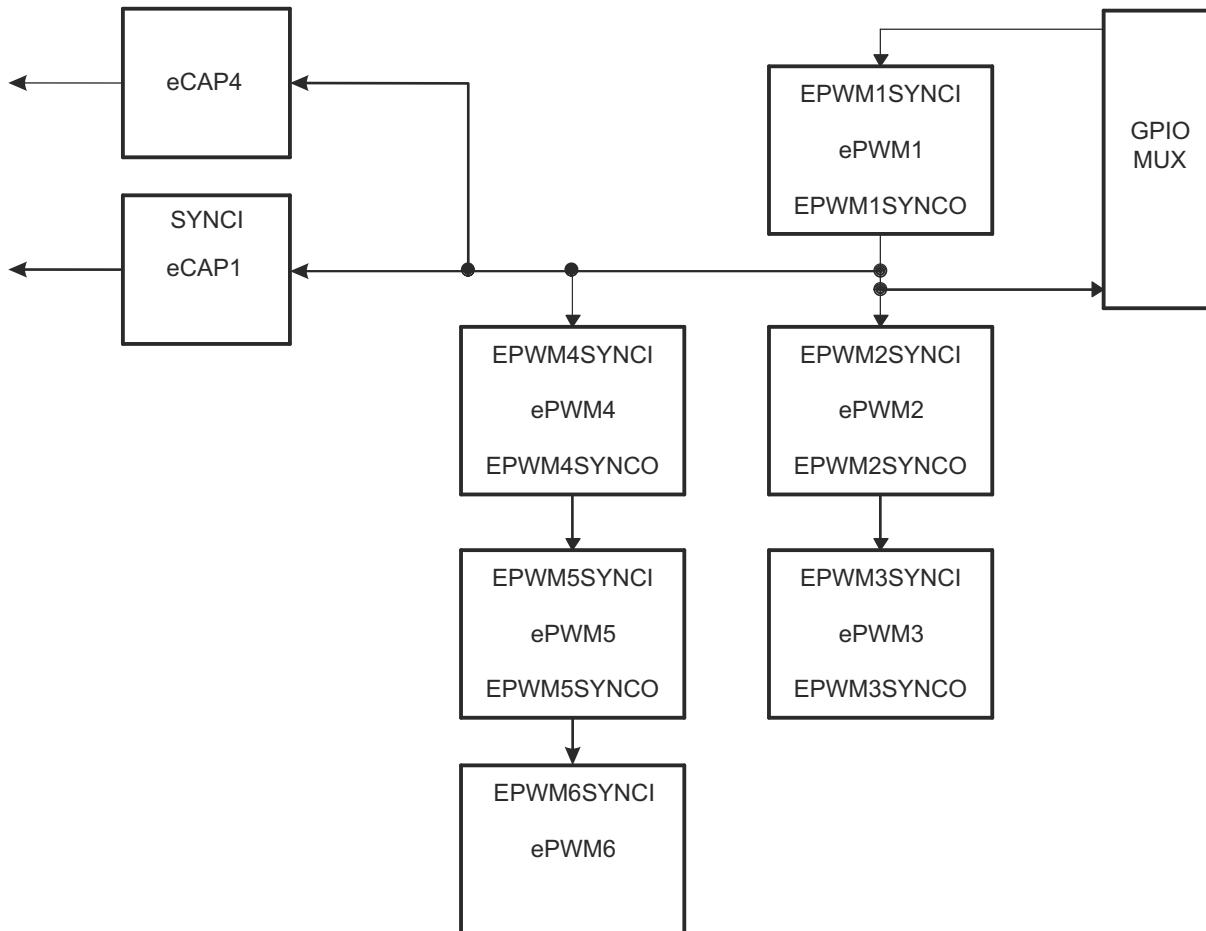

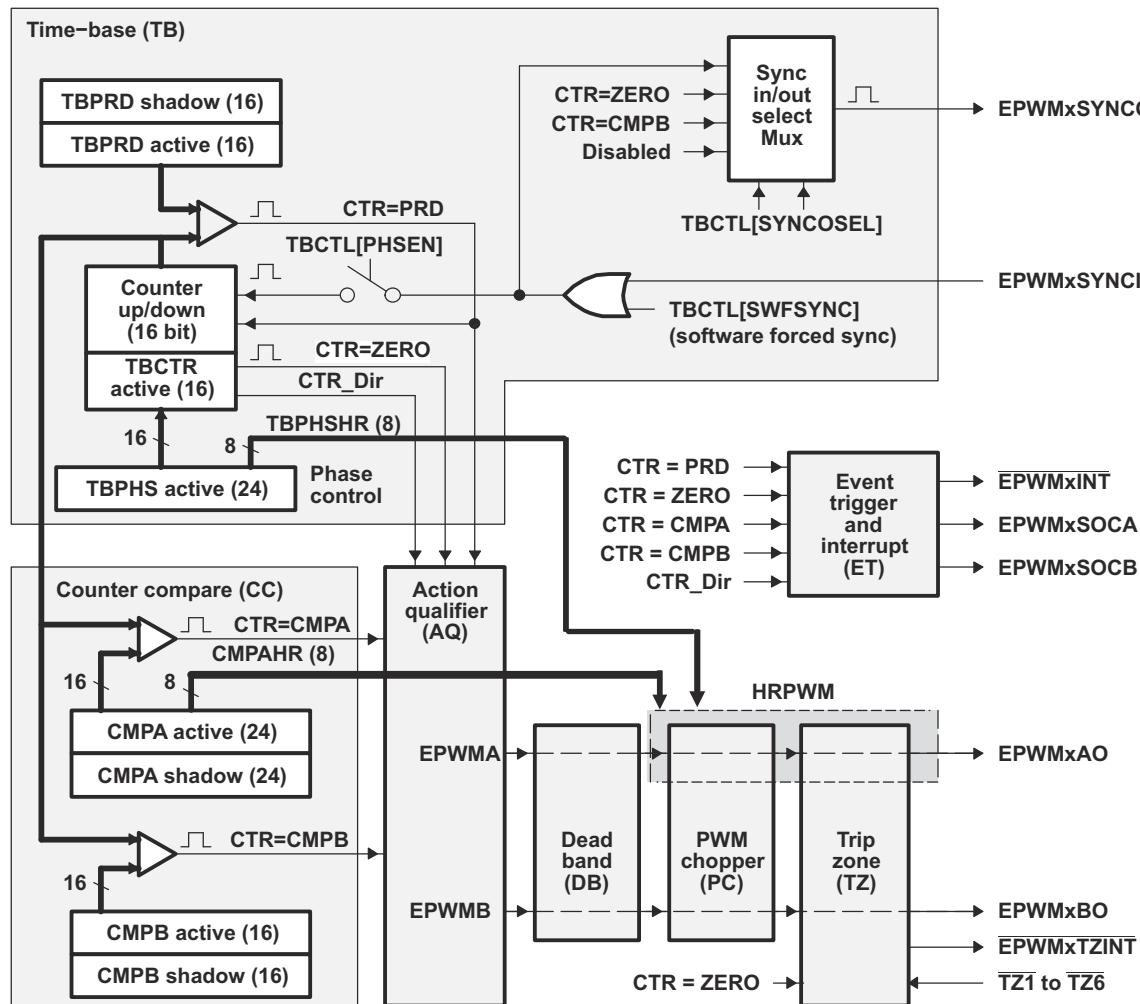

- 最大 18 の PWM 出力

- 150ps MEP 分解能を持つ、最大 6 つの HRPWM 出力

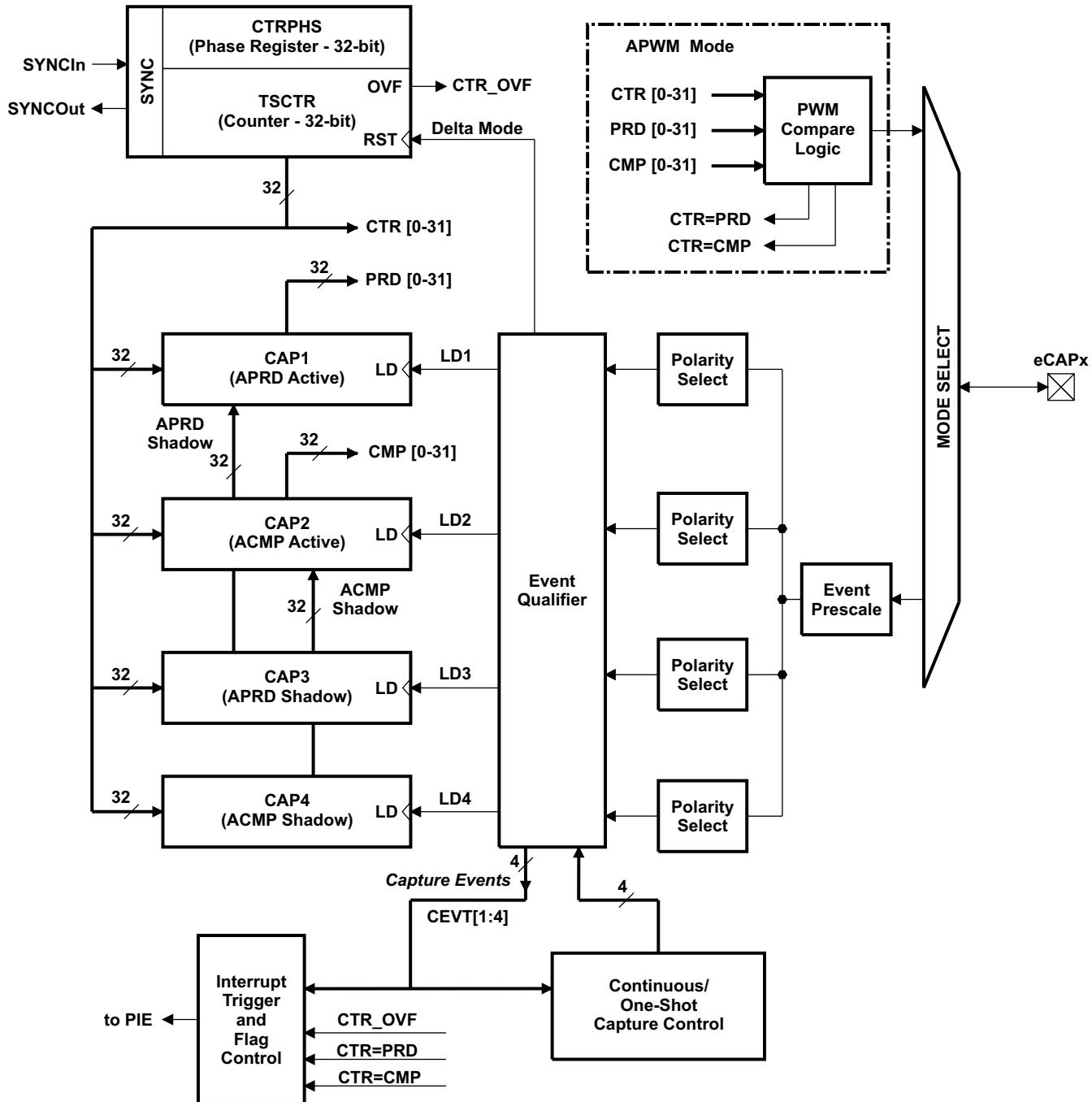

- 最大 6 つのイベント・キャプチャ入力

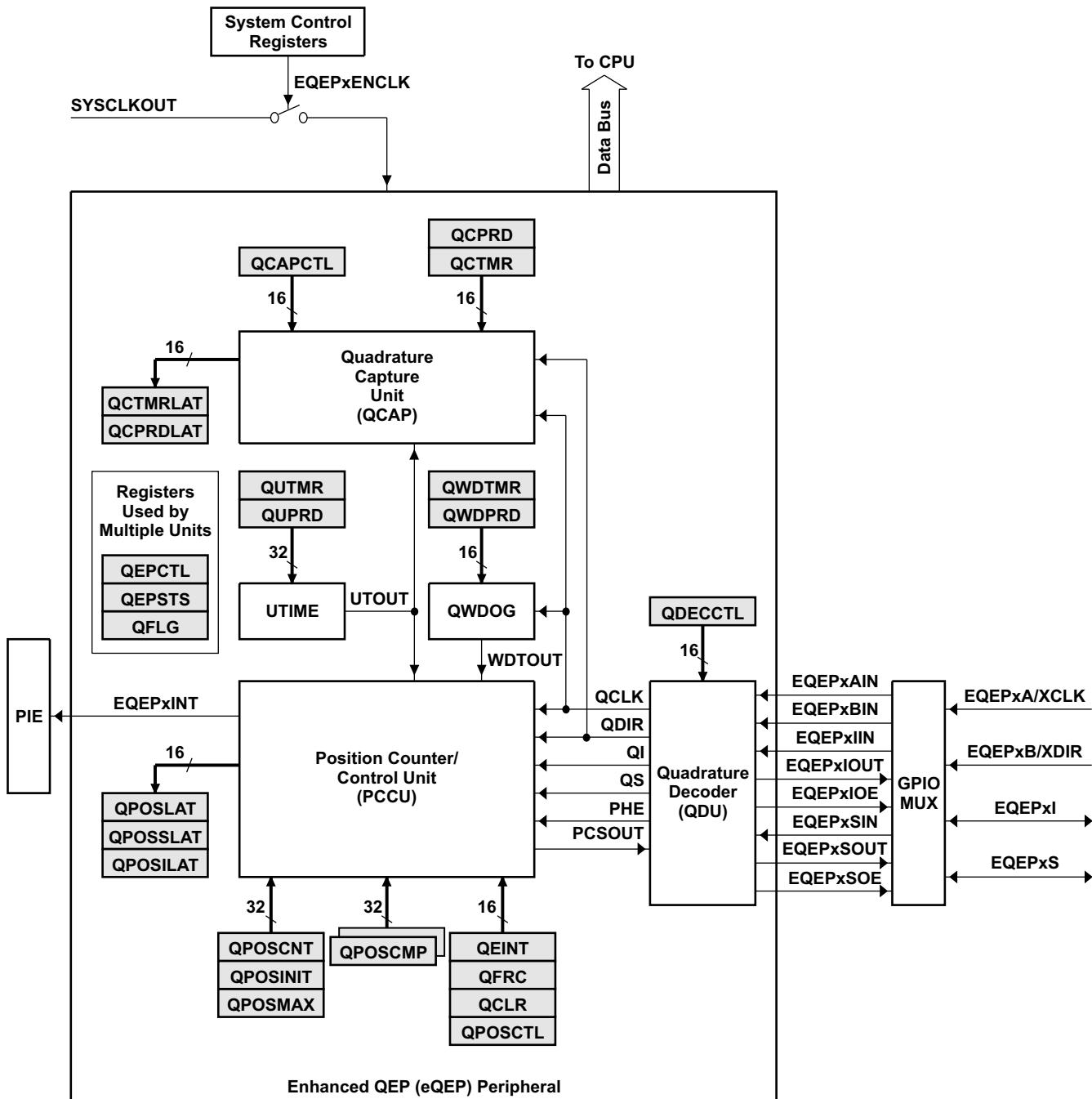

- 最大 2 つの直交エンコーダ・インターフェイス

- 最大 8 つの 32 ビット・タイマ (eCAP 用に 6 つ、eQEP 用に 2 つ)

- 最大 9 つの 16 ビット・タイマ (ePWM 用に 6 つ、XINTCTR 用に 3 つ)

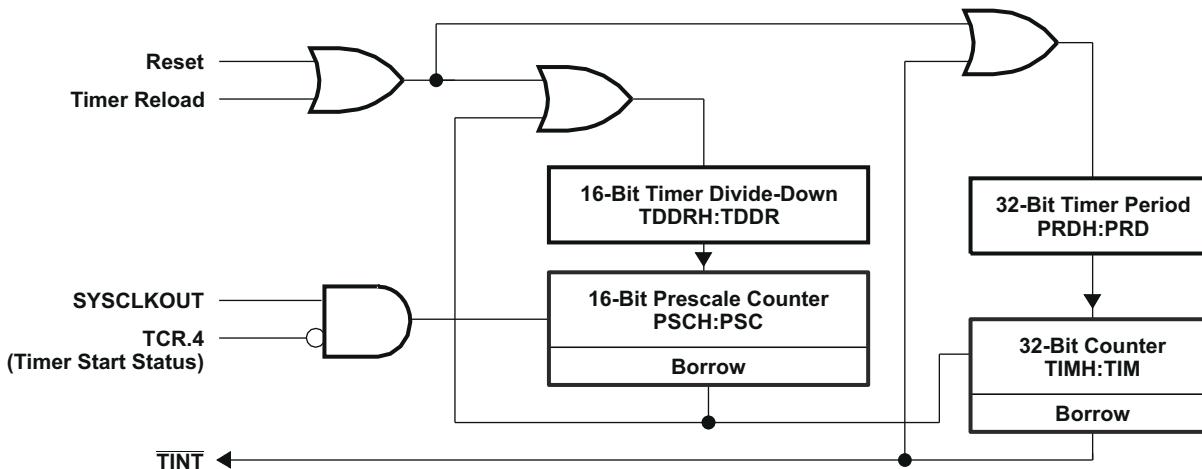

- 3 つの 32 ビット CPU タイマ

- シリアル・ポート・ペリフェラル

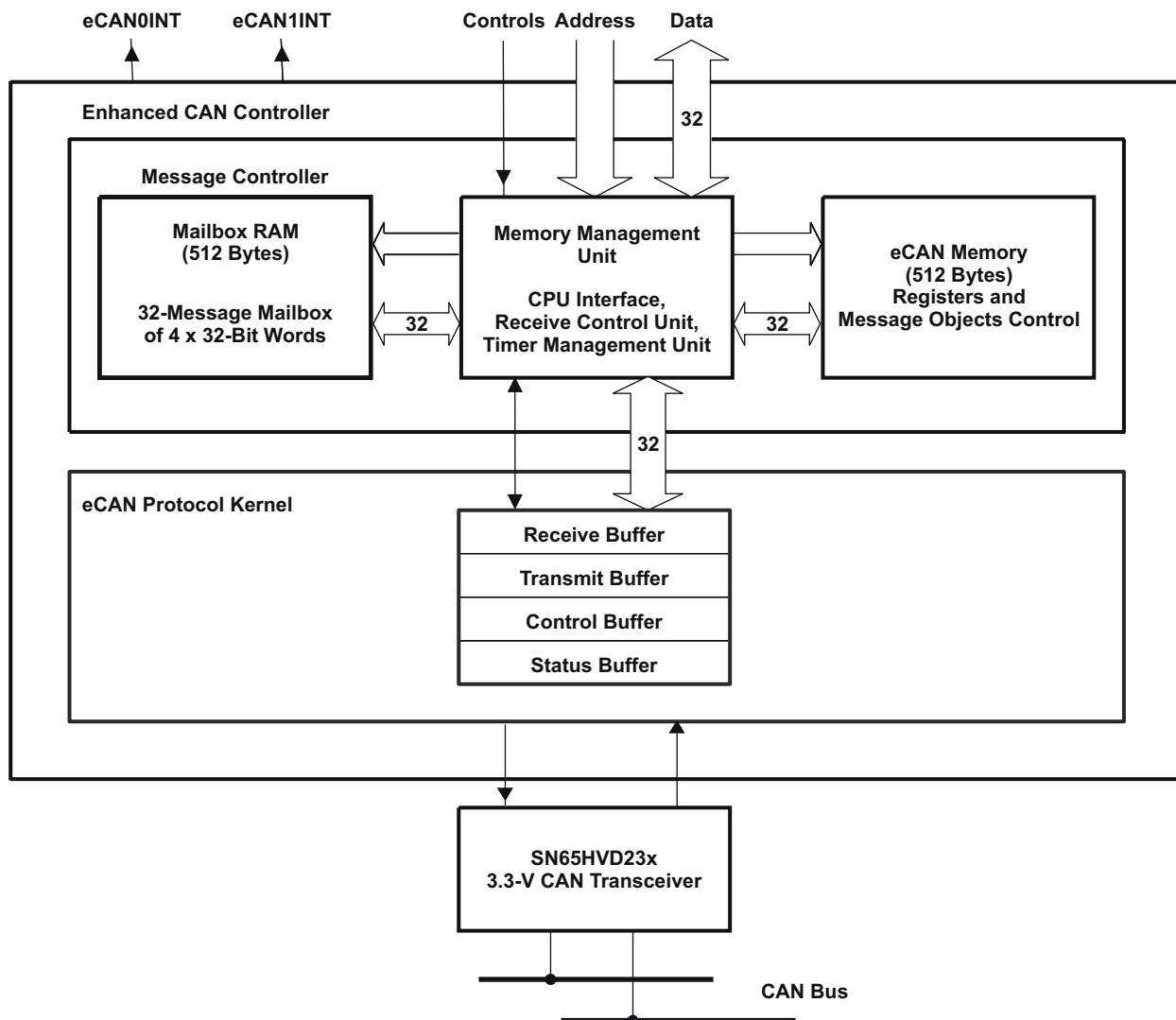

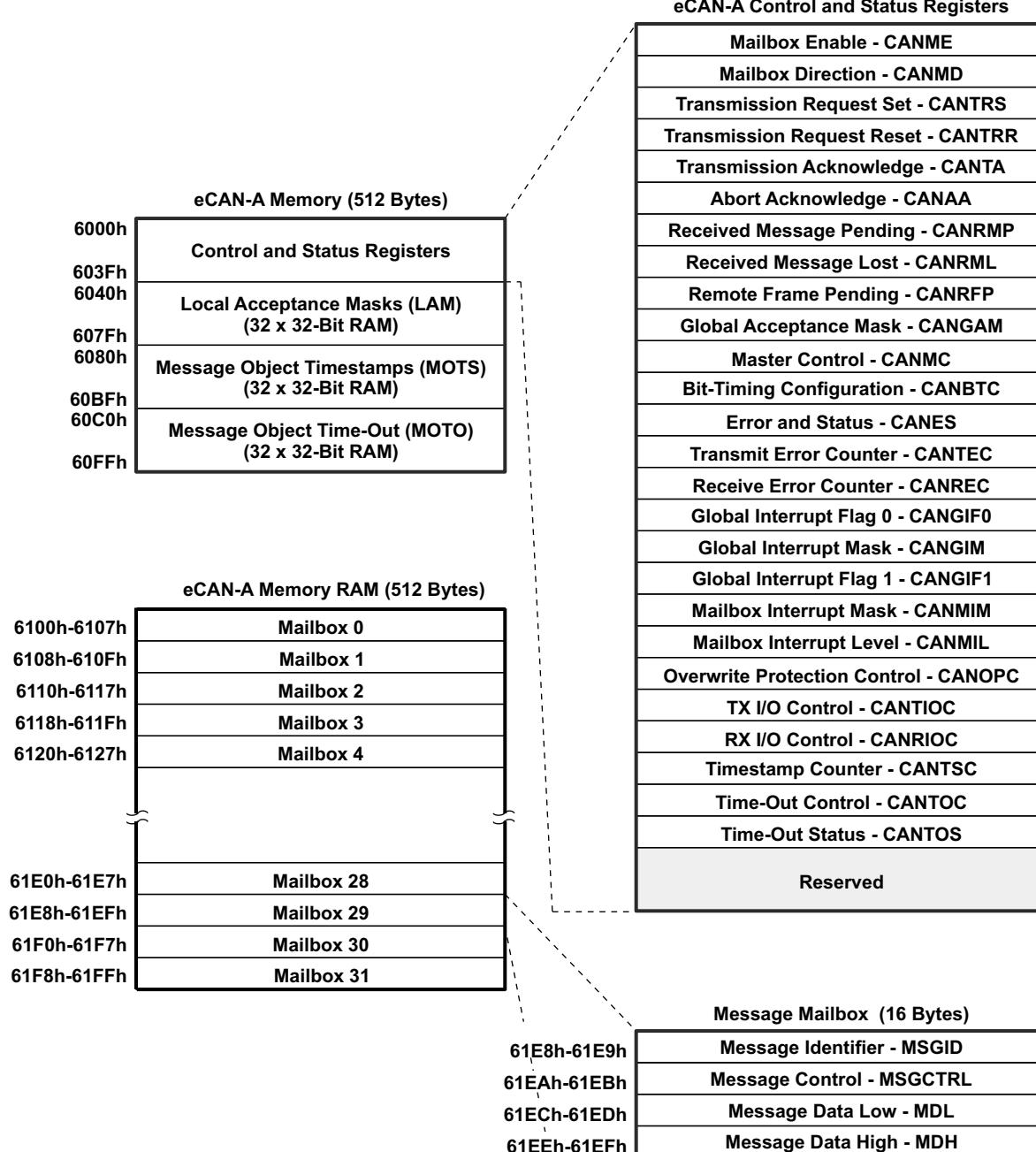

- 最大 2 つの CAN モジュール

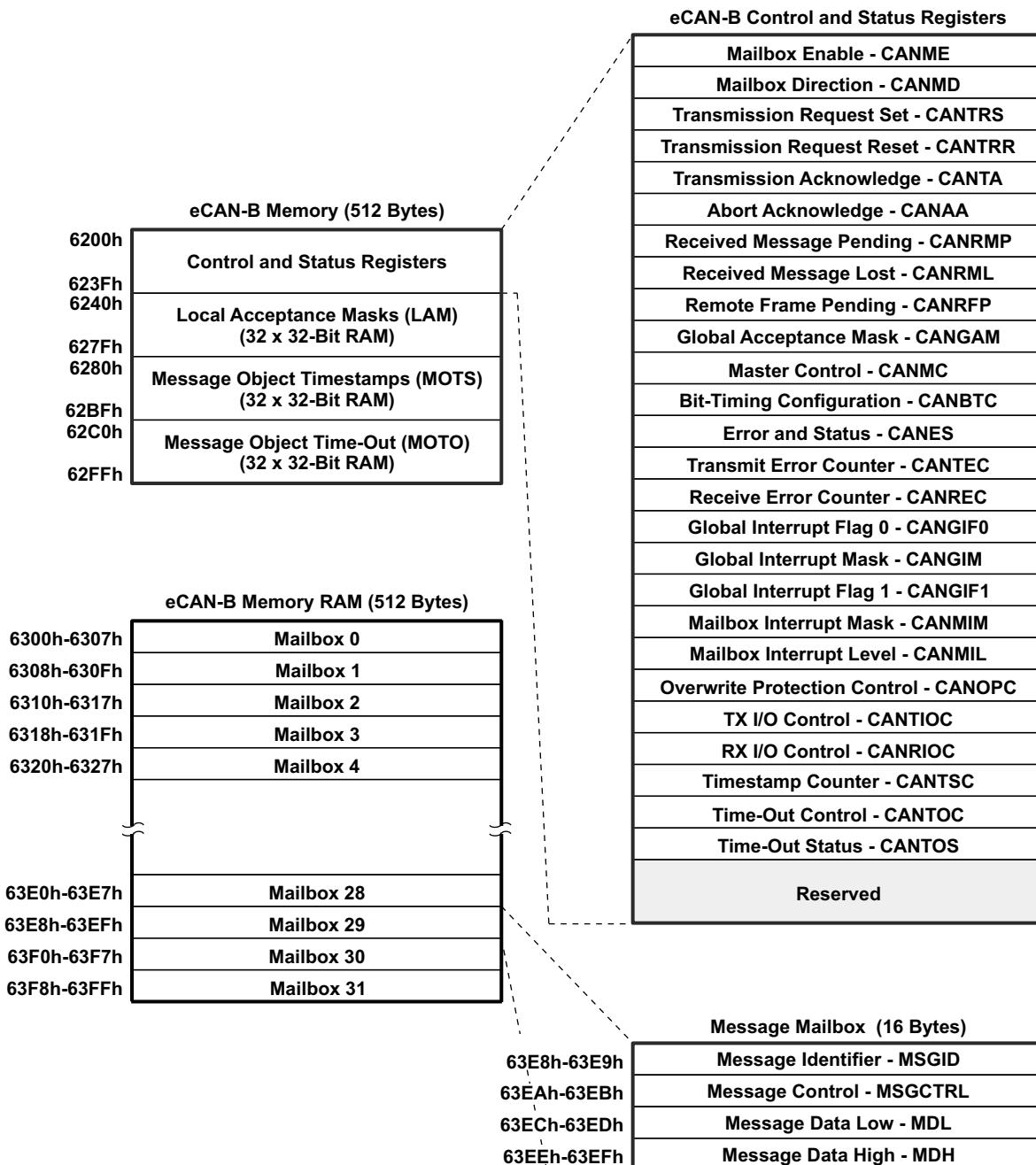

- 最大 3 つの SCI (UART) モジュール

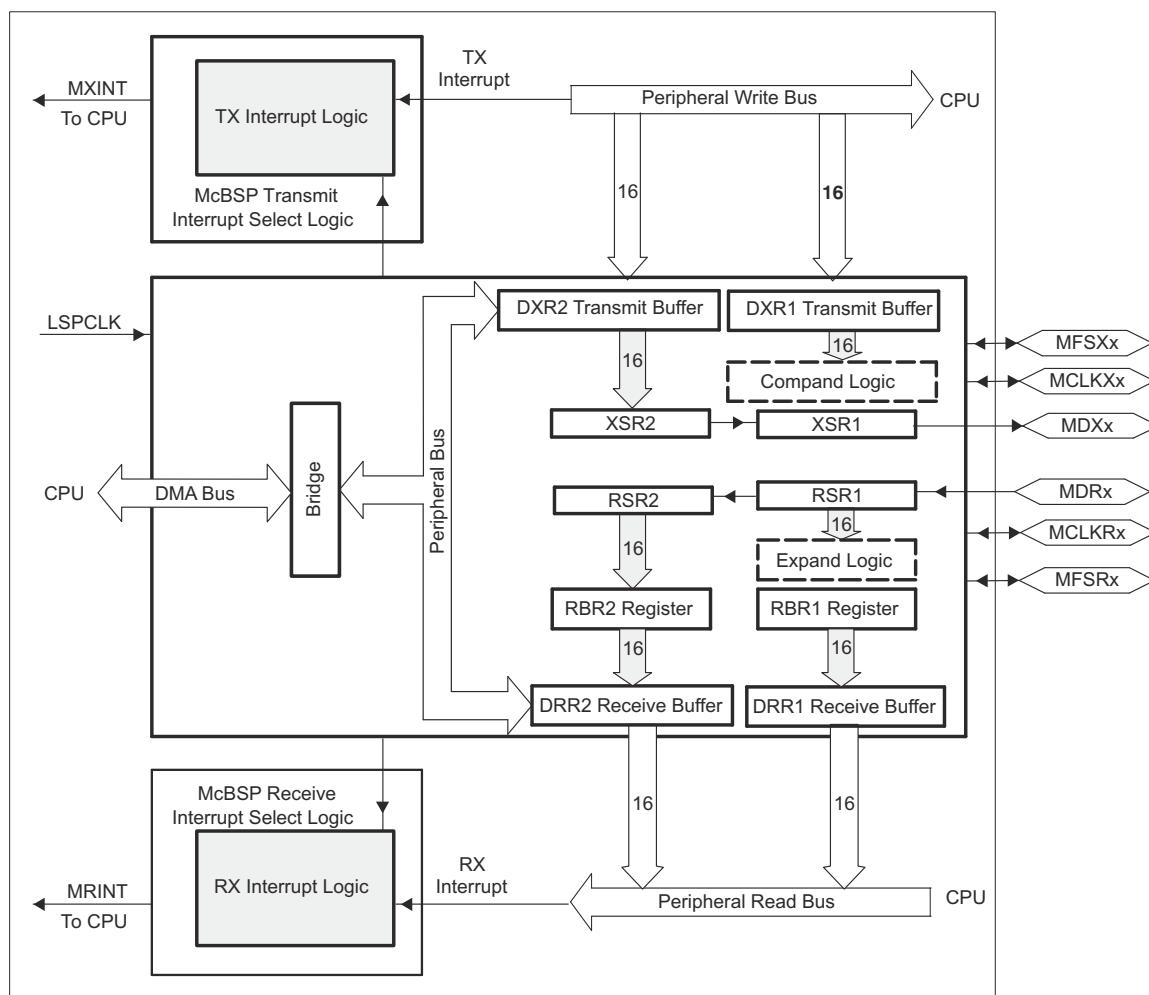

- 最大 2 つの McBSP モジュール (SPI として構成可能)

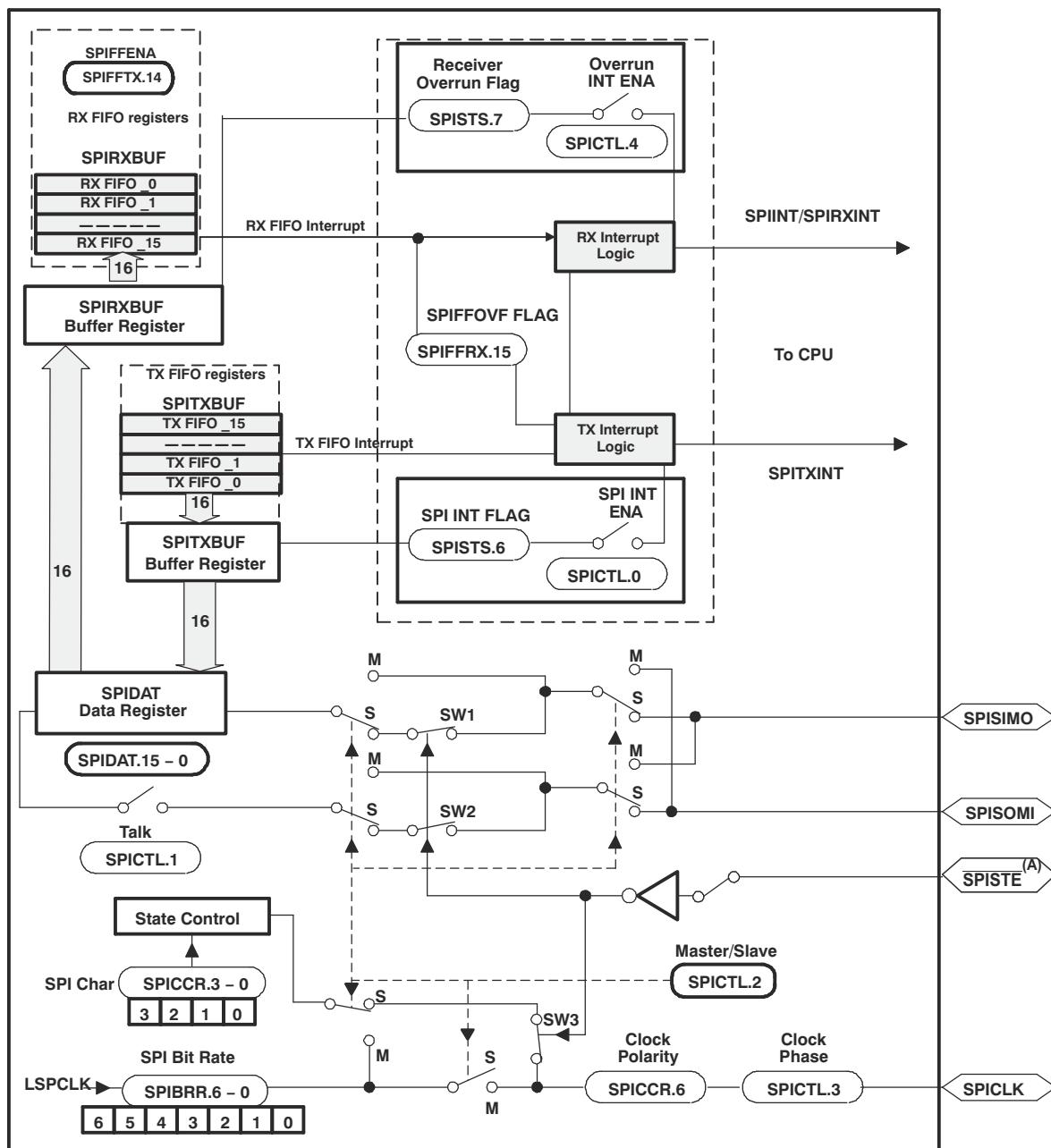

- 1 つの SPI モジュール

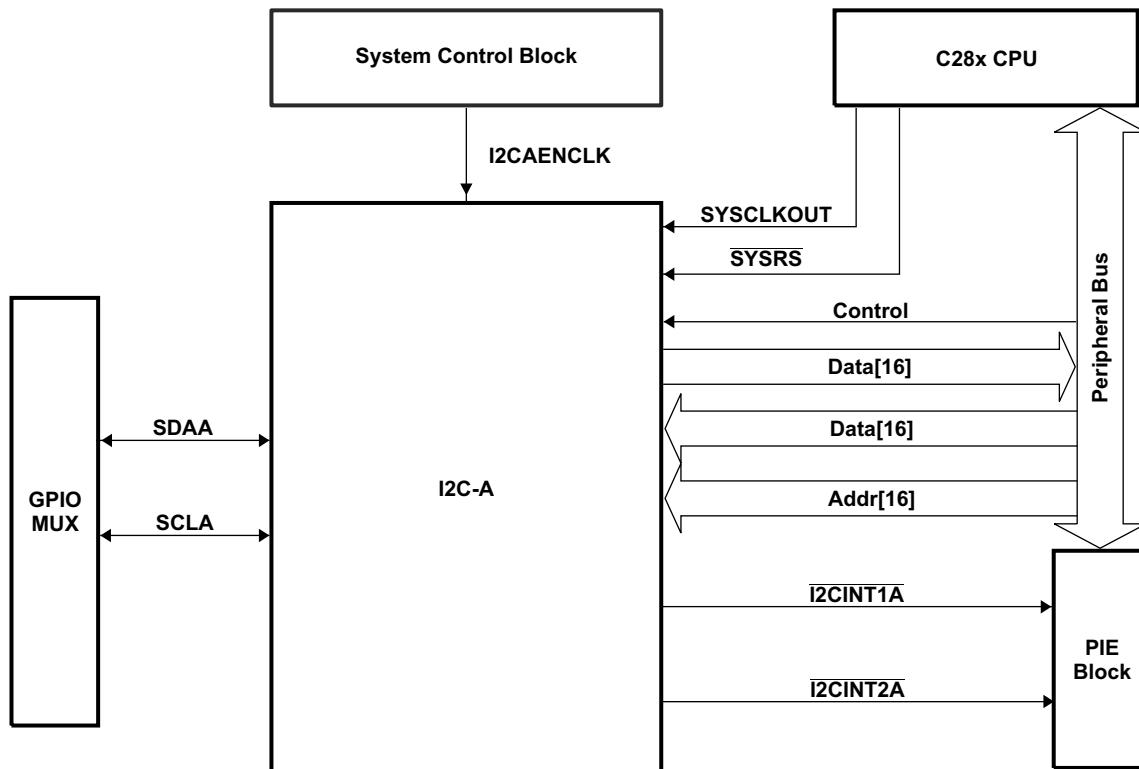

- 1 つの I2C (Inter-Integrated Circuit) バス

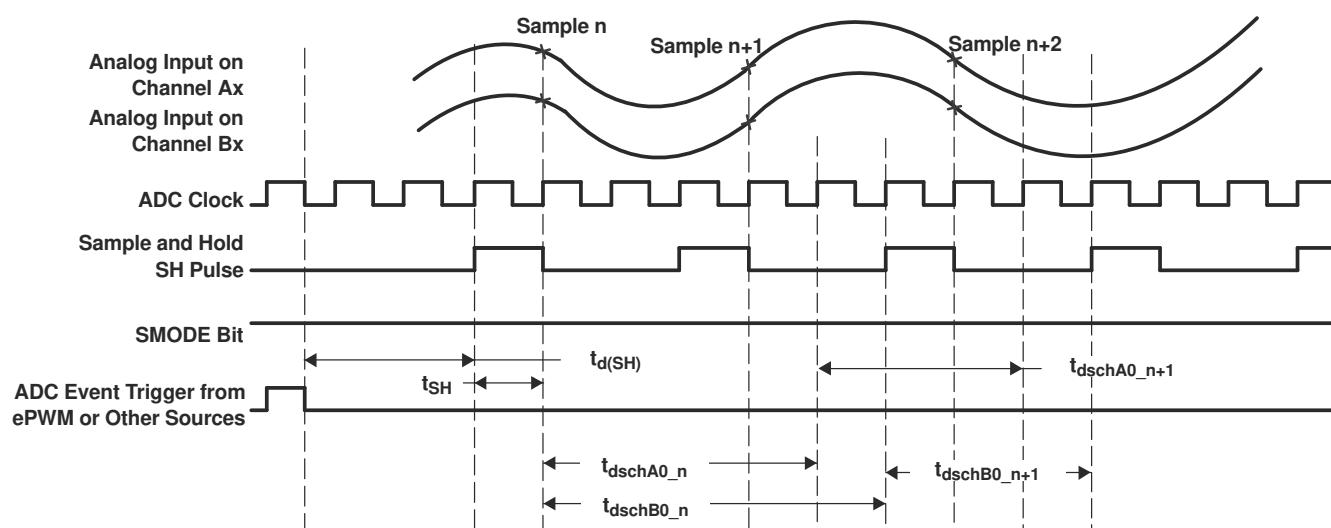

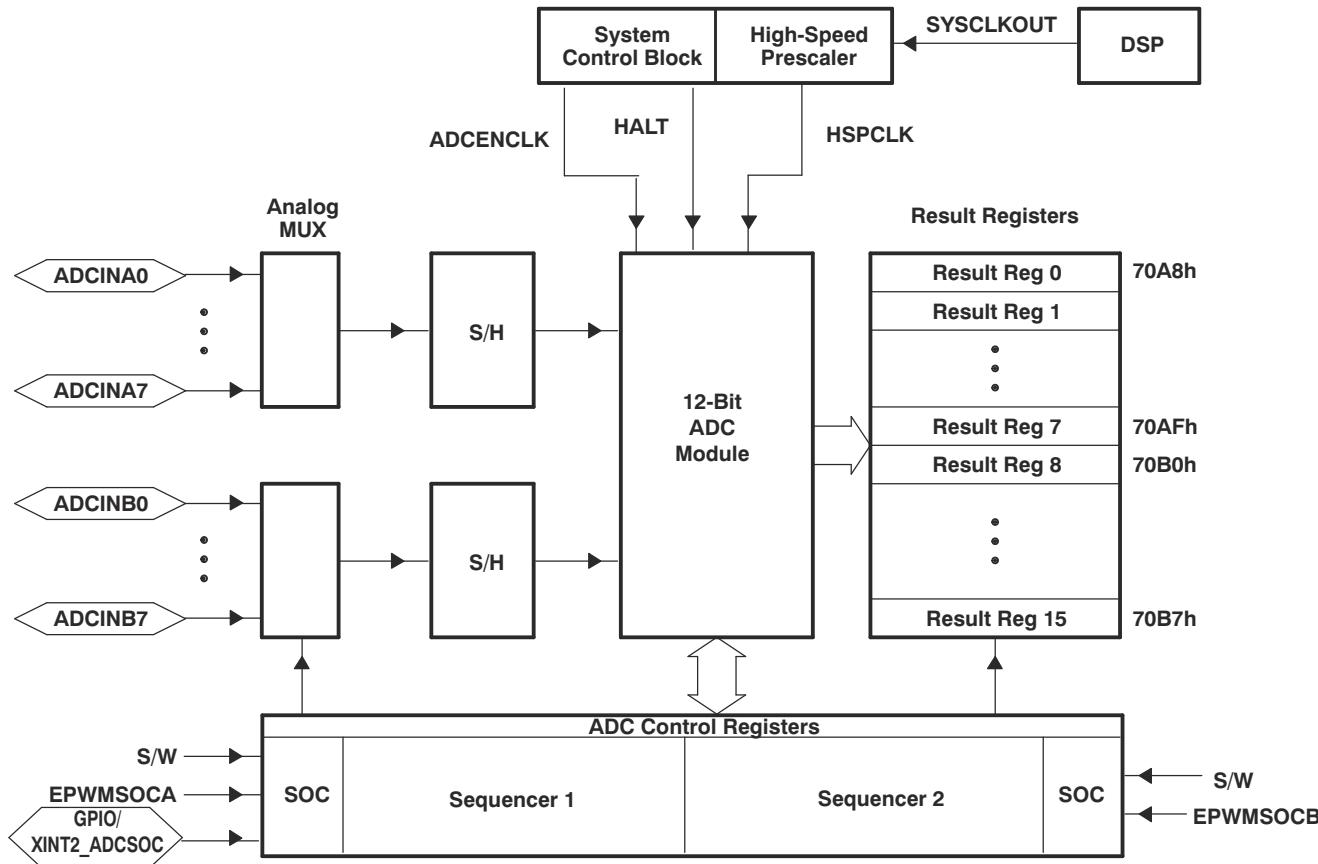

- 12 ビット ADC、16 チャネル

- 80ns の変換速度

- 2 × 8 チャネルの入力マルチプレクサ

- 2 つのサンプル・アンド・ホールド

- 単独 / 同時変換

- 内部または外部のリファレンス

- 最大 88 の個別にプログラム可能な、多重化された、入力フィルタリング付き GPIO ピン

- JTAG バウンダリ・スキャンをサポート

- IEEE 規格 1149.1-1990 標準テスト・アクセス・ポートおよびバウンダリ・スキャン・アーキテクチャ

- 高度なデバッグ機能

- 分析およびブレークポイント機能

- ハードウェアによるリアルタイム・デバッグ

- 開発サポート

- ANSI C/C++ コンパイラ / アセンブラー / リンカ

- Code Composer Studio™ IDE

- DSP/BIOS™ および SYS/BIOS

- デジタル・モータ制御およびデジタル電源のソフトウェア・ライブラリ

- 低消費電力モードとパワー・セービング

- アイドル、スタンバイ、ホールト・モードをサポート

- 個別のペリフェラル・クロックの無効化

- エンディアンネス: リトル・エンディアン

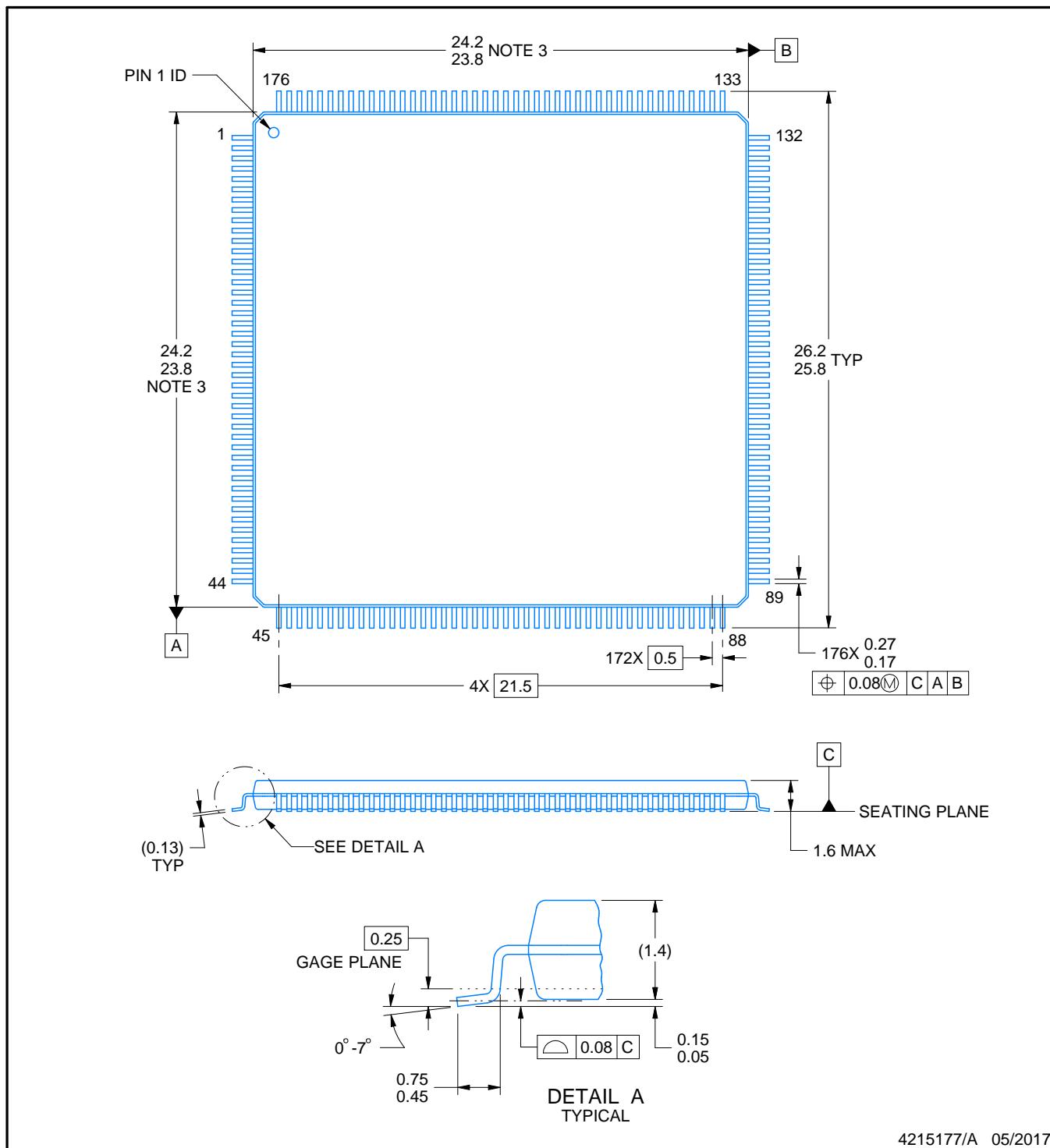

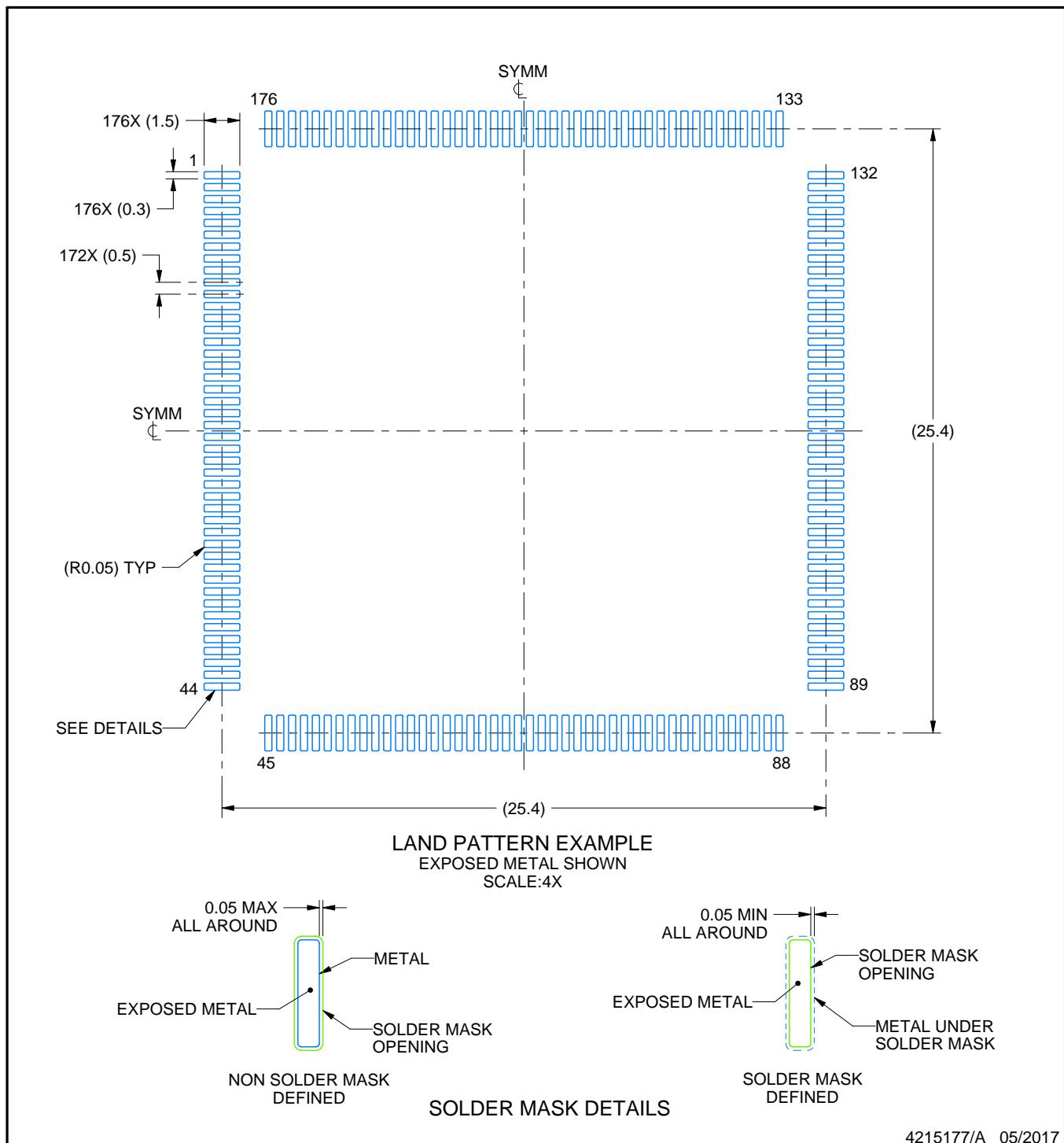

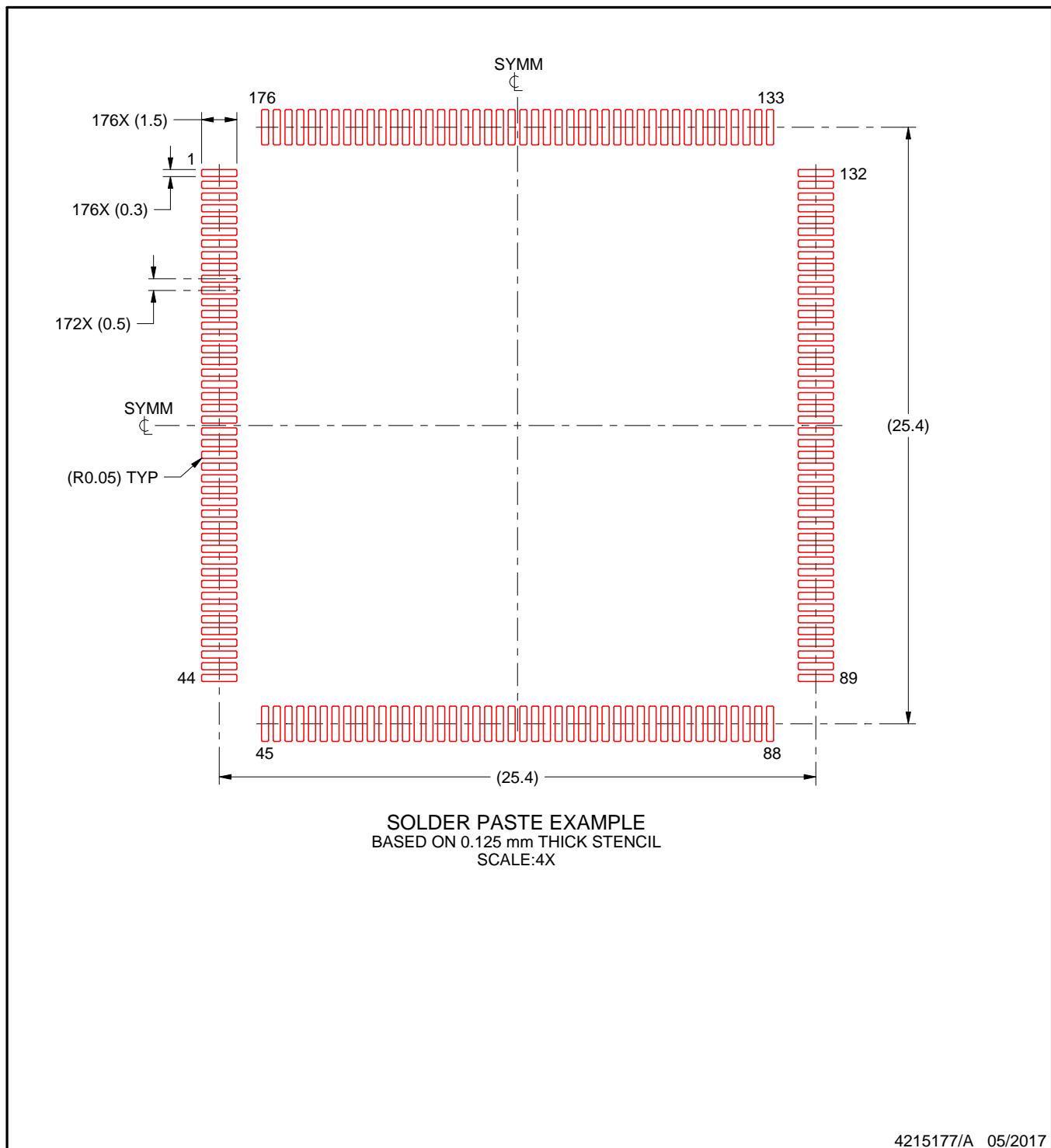

- パッケージ・オプション:

- 鉛フリー、グリーン・パッケージ

- 176 ポールのプラスチック・ボール・グリッド・アレイ (BGA) [ZJZ]

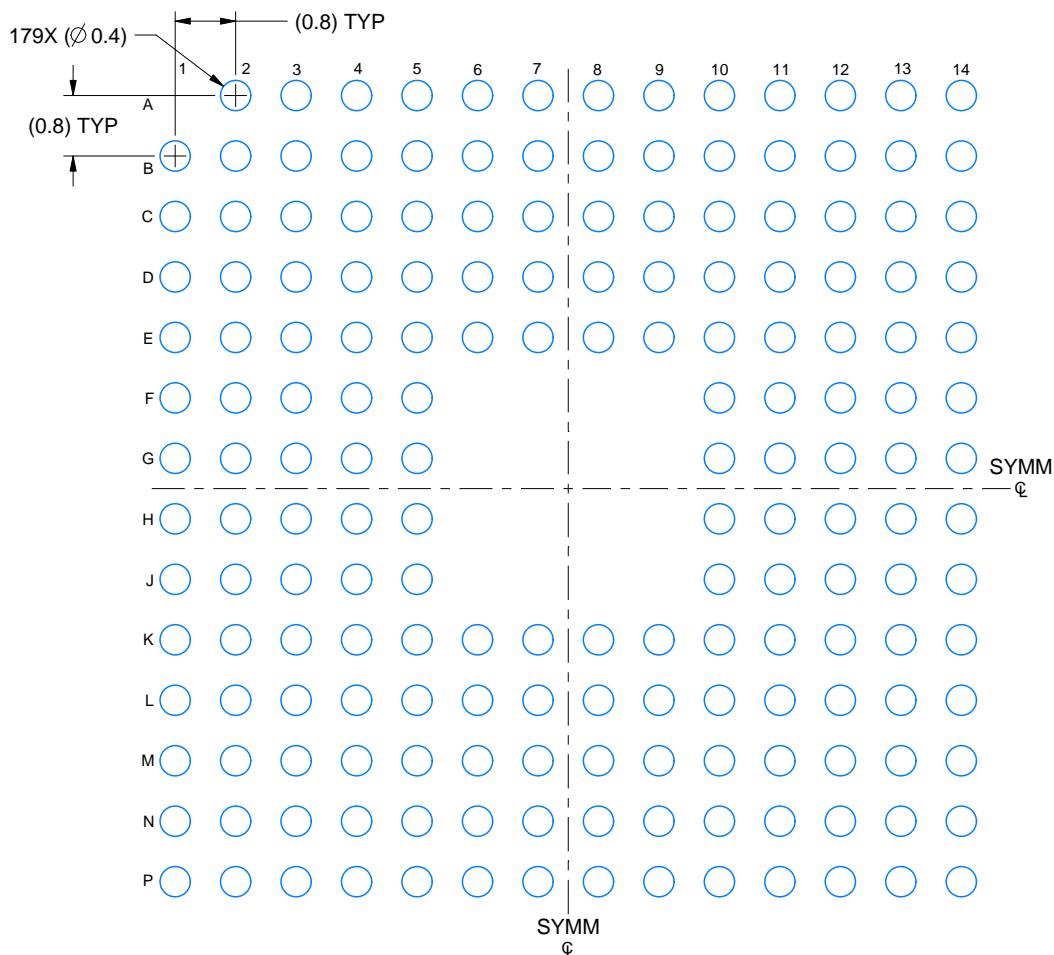

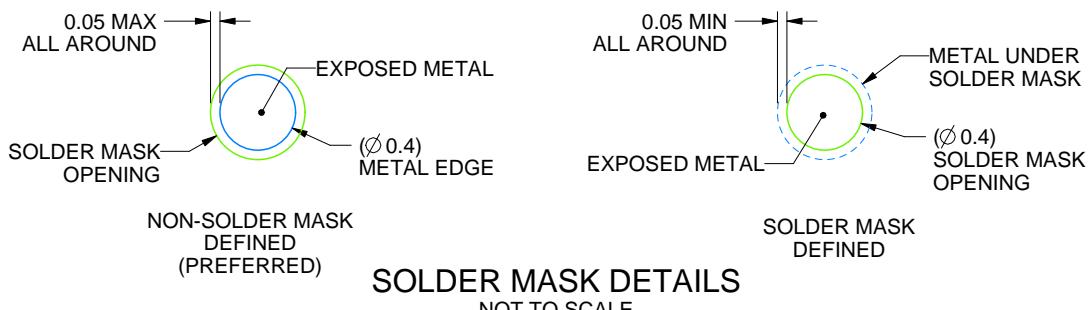

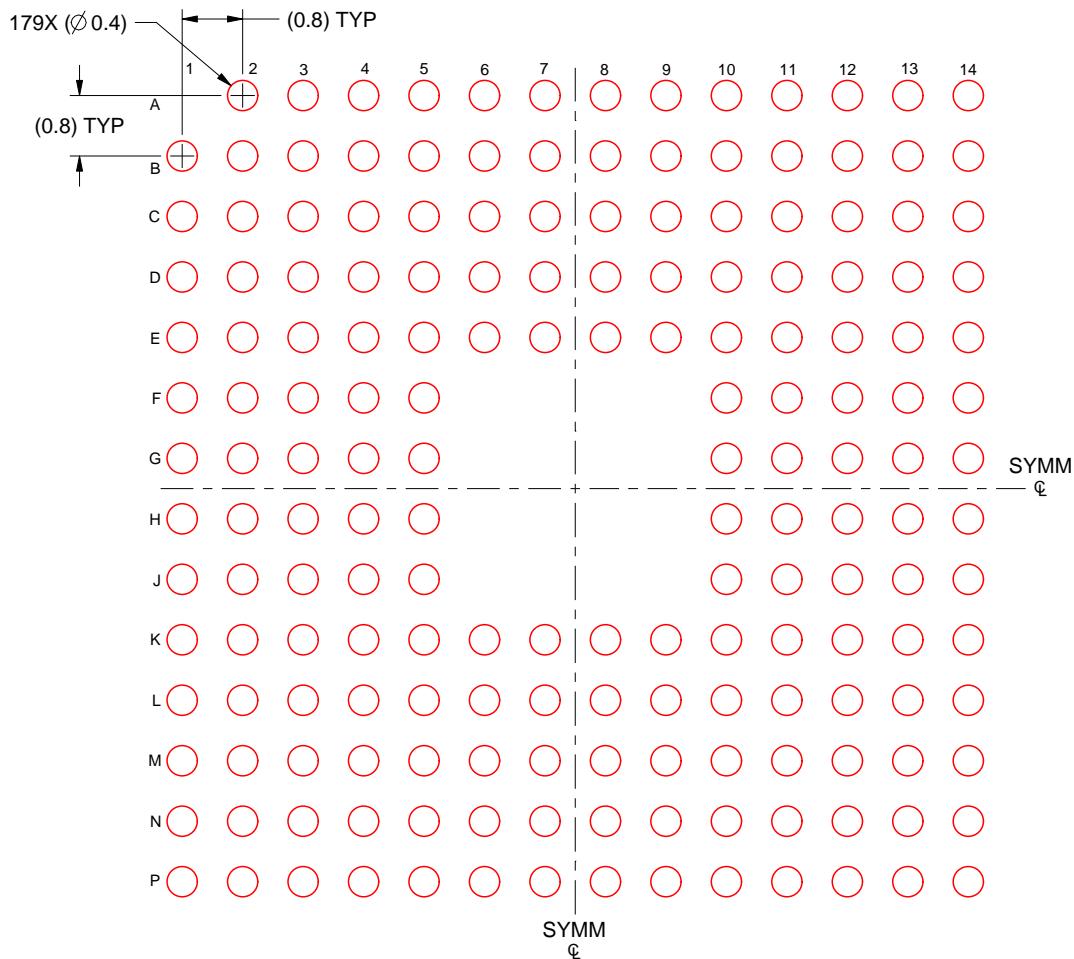

- 179 ポールの MicroStar BGA [ZHH]™

- 179 ポールの新ファイン・ピッチ・ボール・グリッド・アレイ (nFBGA) [ZAY]

- 176 ピンの薄型クワッド・フラットパック (LQFP) [PGF]

- 176 ピンの熱的に強化された薄型クワッド・フラットパック (HLQFP) [PTP]

- 温度オプション:

- A:-40°C~85°C (PGF、ZHH、ZAY、ZJZ)

- S:-40°C~125°C (PTP、ZJZ)

- Q:-40°C~125°C (PTP、ZJZ)

(車載アプリケーション向けに AEC Q100 認定)

## 2 アプリケーション

- 先進運転支援システム (ADAS)

- 中距離 / 短距離レーダー

- ビル・オートメーション

- HVAC (空調) モーター制御

- トラクション・インバータ・モーター制御

- ファクトリ・オートメーションおよび制御

- 自動仕分け機器

- CNC 制御

- グリッド・インフラ

- セントラル・インバータ

- ストリング・インバータ

- ハイブリッド、電動、パワートレイン・システム

- インバータおよびモーター制御

- オンボード・チャージャ (OBC) およびワイヤレス・チャージャ

- モータ・ドライブ

- AC 入力 BLDC モーター・ドライブ

- サーボ・ドライブ制御モジュール

- パワー・デリバリ

- 産業用 AC-DC

## 3 概要

C2000™ 32 ビット・マイクロコントローラは、処理、センシング、アクチュエーションに最適化されており、リアルタイム制御アプリケーション、たとえば産業用モーター・ドライブ、ソーラー・インバータおよびデジタル電源、電気自動車および輸送、モーター制御、センシングおよび信号処理などにおける閉ループ性能が向上しています。C2000 ラインには最高性能の MCU とエントリ性能の MCU があります。

TMS320F28335、TMS320F28334、TMS320F28333、TMS320F28332、TMS320F28235、TMS320F28234 および TMS320F28232 デバイスは、要求の厳しい制御アプリケーション向けの高集積、高性能ソリューションです。

このデータシート全体を通して、これらのデバイスは、それぞれ F28335、F28334、F28333、F28332、F28235、F28234、F28232 と略記されます。F2833x のデバイス比較 と F2823x のデバイス比較 には、各デバイスの機能の概要が記載されています。

「C2000™ リアルタイム制御マイクロコントローラ (MCU) 入門ガイド」は、C2000 デバイスを使用する開発について、ハードウェアからサポート・リソースまで、あらゆる侧面をカバーしています。主要な参考資料に加えて、各セクションには関連するリンクとリソースが掲載されており、さらに詳細な情報を知ることができます。

C2000 MCU の詳細については、C2000™ リアルタイム制御 MCU のページをご覧ください。

### パッケージ情報

| 部品番号 <sup>(1)</sup> | パッケージ               | 本体サイズ           |

|---------------------|---------------------|-----------------|

| TMS320F28335ZAY     | nFBGA (179)         | 12.0mm × 12.0mm |

| TMS320F28334ZAY     | nFBGA (179)         | 12.0mm × 12.0mm |

| TMS320F28234ZAY     | nFBGA (179)         | 12.0mm × 12.0mm |

| TMS320F28232ZAY     | nFBGA (179)         | 12.0mm × 12.0mm |

| TMS320F28335ZHH     | BGA MicroStar (179) | 12.0mm×12.0mm   |

| TMS320F28334ZHH     | BGA MicroStar (179) | 12.0mm×12.0mm   |

| TMS320F28332ZHH     | BGA MicroStar (179) | 12.0mm×12.0mm   |

| TMS320F28235ZHH     | BGA MicroStar (179) | 12.0mm×12.0mm   |

| TMS320F28234ZHH     | BGA MicroStar (179) | 12.0mm×12.0mm   |

**パッケージ情報 (continued)**

| 部品番号 <sup>(1)</sup> | パッケージ               | 本体サイズ         |

|---------------------|---------------------|---------------|

| TMS320F28232ZHH     | BGA MicroStar (179) | 12.0mm×12.0mm |

| TMS320F28335ZJZ     | BGA (176)           | 15.0mm×15.0mm |

| TMS320F28334ZJZ     | BGA (176)           | 15.0mm×15.0mm |

| TMS320F28332ZJZ     | BGA (176)           | 15.0mm×15.0mm |

| TMS320F28235ZJZ     | BGA (176)           | 15.0mm×15.0mm |

| TMS320F28234ZJZ     | BGA (176)           | 15.0mm×15.0mm |

| TMS320F28232ZJZ     | BGA (176)           | 15.0mm×15.0mm |

| TMS320F28335PGF     | LQFP (176)          | 24.0mm×24.0mm |

| TMS320F28334PGF     | LQFP (176)          | 24.0mm×24.0mm |

| TMS320F28333PGF     | LQFP (176)          | 24.0mm×24.0mm |

| TMS320F28332PGF     | LQFP (176)          | 24.0mm×24.0mm |

| TMS320F28235PGF     | LQFP (176)          | 24.0mm×24.0mm |

| TMS320F28234PGF     | LQFP (176)          | 24.0mm×24.0mm |

| TMS320F28232PGF     | LQFP (176)          | 24.0mm×24.0mm |

| TMS320F28335PTP     | HLQFP (176)         | 24.0mm×24.0mm |

| TMS320F28334PTP     | HLQFP (176)         | 24.0mm×24.0mm |

| TMS320F28332PTP     | HLQFP (176)         | 24.0mm×24.0mm |

| TMS320F28235PTP     | HLQFP (176)         | 24.0mm×24.0mm |

| TMS320F28234PTP     | HLQFP (176)         | 24.0mm×24.0mm |

| TMS320F28232PTP     | HLQFP (176)         | 24.0mm×24.0mm |

(1) これらのデバイスの詳細については、[メカニカル](#)、[パッケージ](#)、および[注文情報](#)を参照してください。

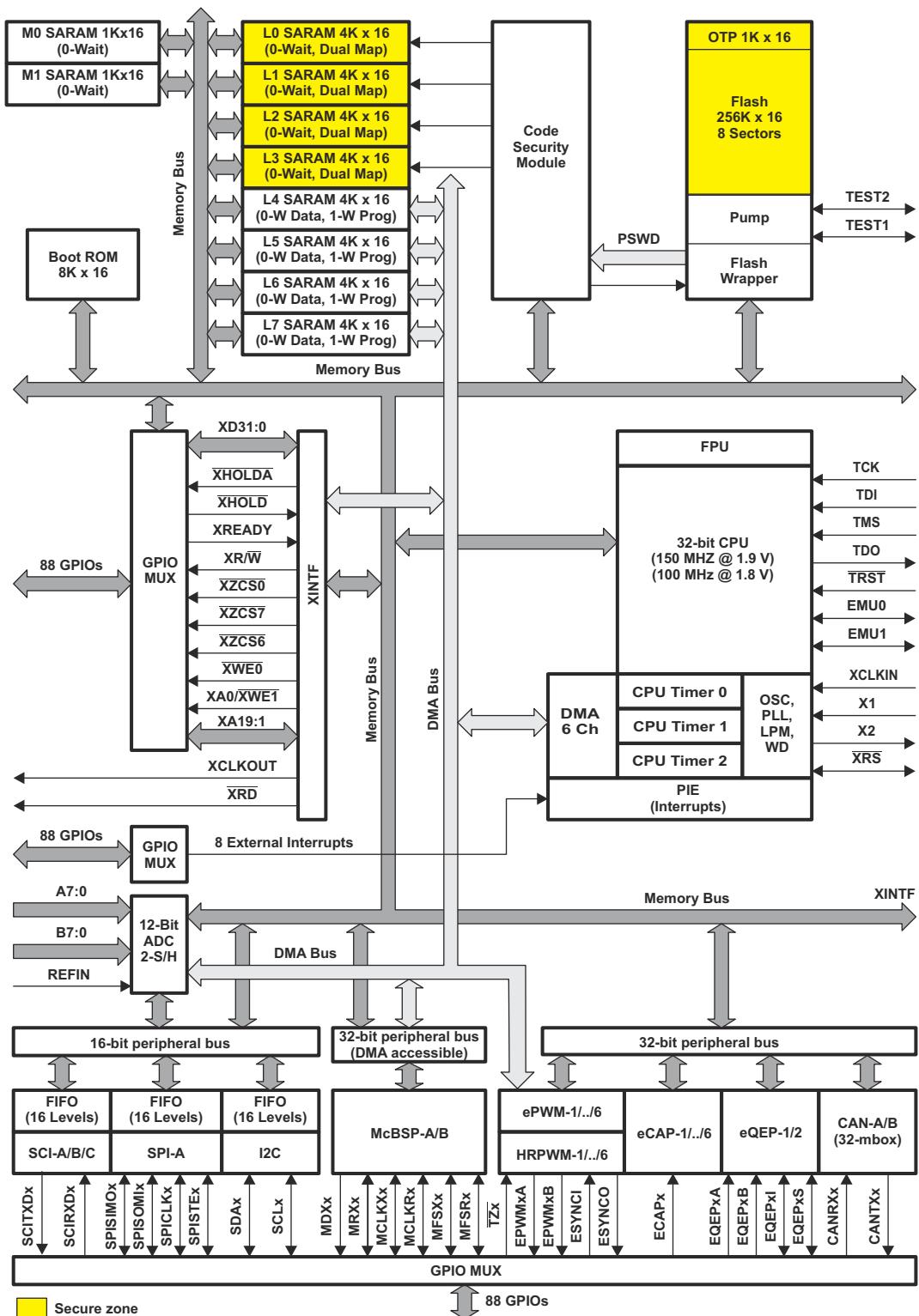

### 3.1 機能ブロック図

図 3-1. 機能ブロック図

## 目次

|                                        |     |                                           |     |

|----------------------------------------|-----|-------------------------------------------|-----|

| 1 特長.....                              | 1   | 8 詳細説明.....                               | 112 |

| 2 アプリケーション.....                        | 2   | 8.1 概要.....                               | 112 |

| 3 概要.....                              | 2   | 8.2 ペリフェラル.....                           | 120 |

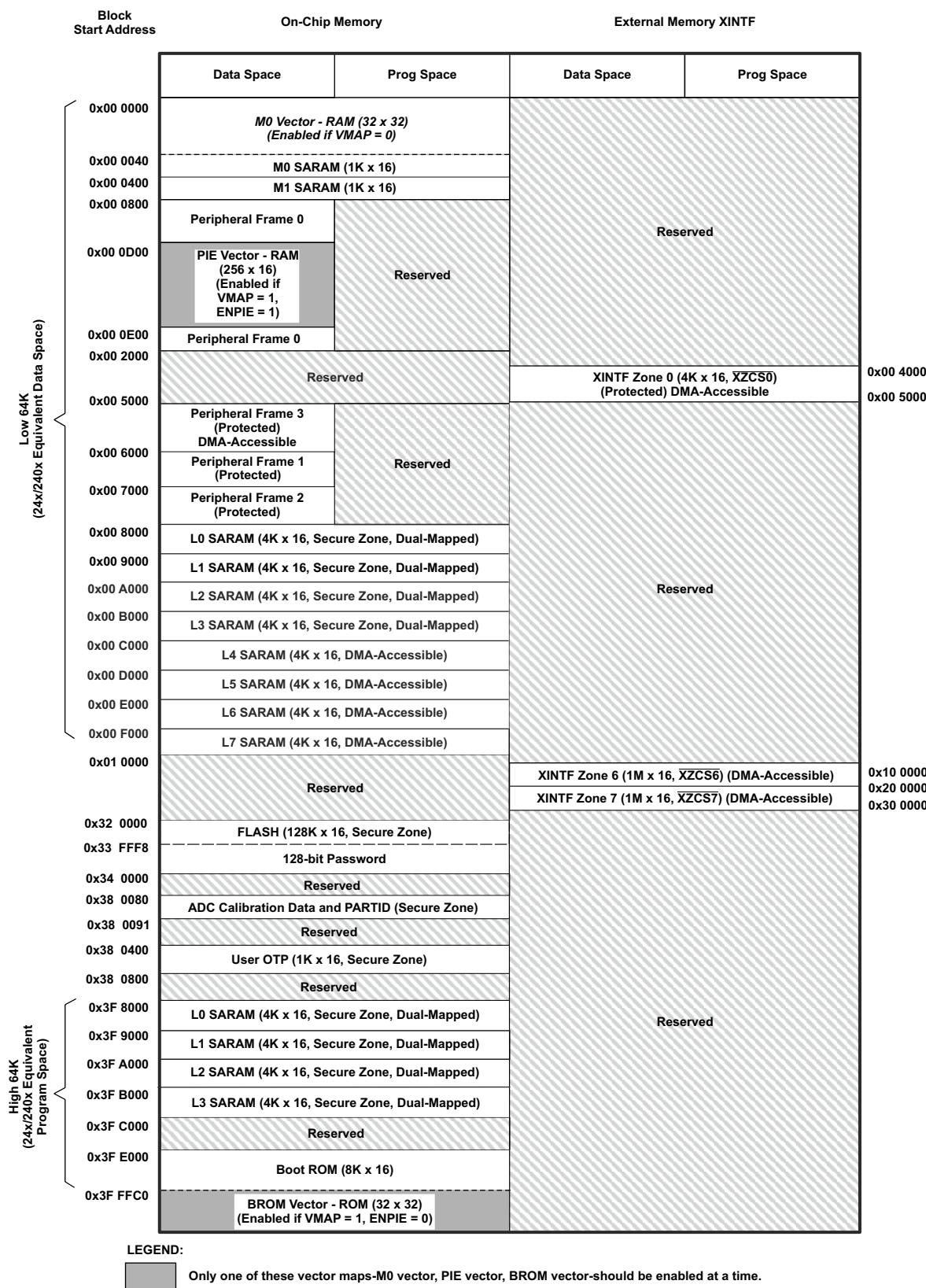

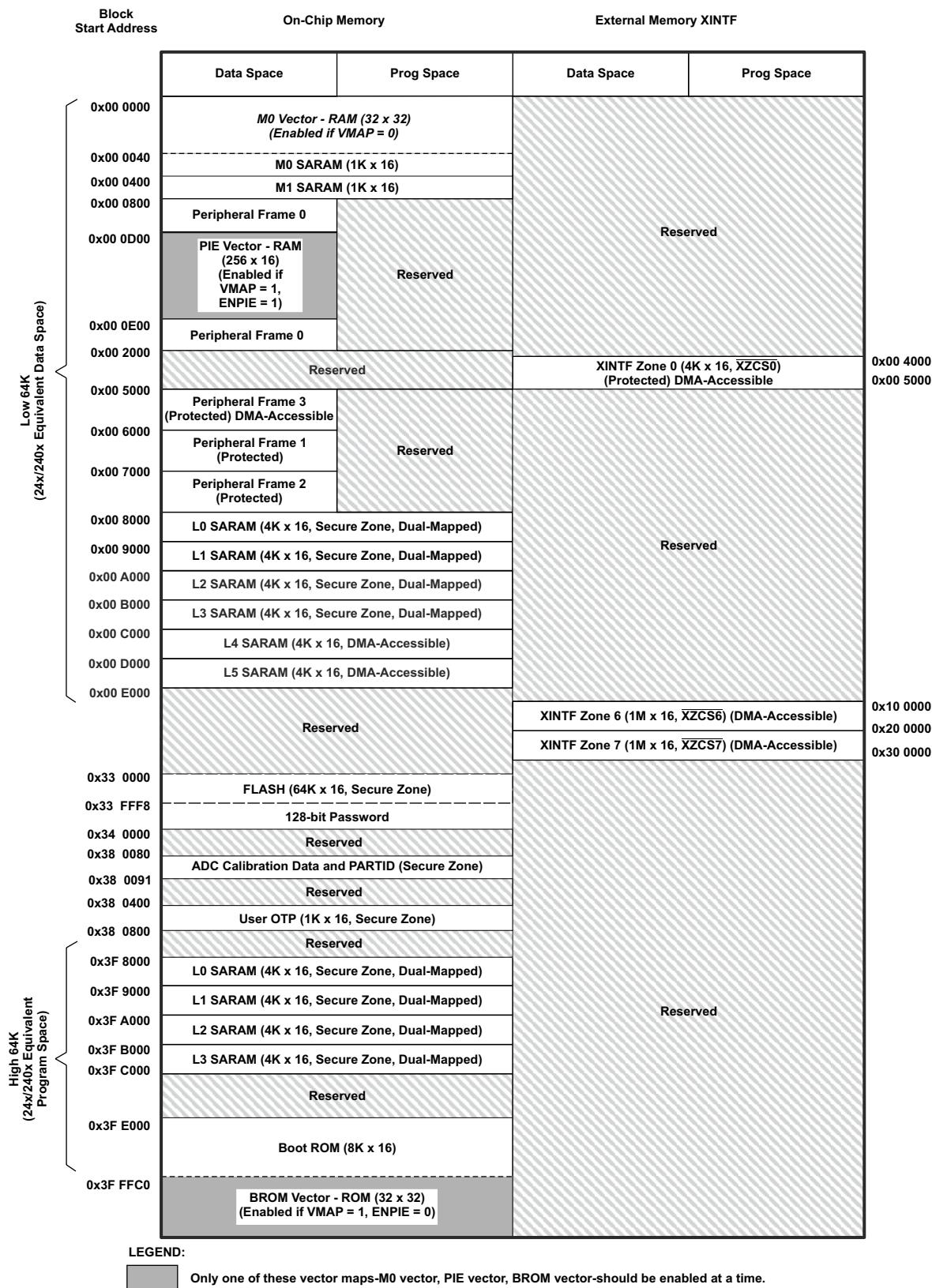

| 3.1 機能ブロック図.....                       | 4   | 8.3 メモリ・マップ.....                          | 167 |

| 4 改訂履歴.....                            | 6   | 8.4 レジスタ・マップ.....                         | 174 |

| 5 デバイスの比較.....                         | 8   | 8.5 割り込み.....                             | 178 |

| 5.1 関連製品.....                          | 11  | 8.6 システム制御.....                           | 183 |

| 6 端子構成および機能.....                       | 12  | 8.7 低消費電力モード・ブロック.....                    | 189 |

| 6.1 ピン配置図.....                         | 12  | 9 アプリケーション、実装、およびレイアウト.....               | 190 |

| 6.2 信号の説明.....                         | 22  | 9.1 TI リファレンス・デザイン.....                   | 190 |

| 7 仕様.....                              | 34  | 10 デバイスおよびドキュメントのサポート.....                | 191 |

| 7.1 絶対最大定格.....                        | 34  | 10.1 使い始めと次の手順.....                       | 191 |

| 7.2 ESD 定格 - 車載用.....                  | 35  | 10.2 デバイスおよび開発ツールの命名規則.....               | 191 |

| 7.3 ESD 定格 - 民生用.....                  | 35  | 10.3 ツールとソフトウェア.....                      | 193 |

| 7.4 推奨動作条件.....                        | 36  | 10.4 ドキュメントのサポート.....                     | 195 |

| 7.5 消費電力の概略.....                       | 37  | 10.5 サポート・リソース.....                       | 196 |

| 7.6 電気的特性.....                         | 43  | 10.6 商標.....                              | 197 |

| 7.7 熱抵抗特性.....                         | 44  | 10.7 Electrostatic Discharge Caution..... | 197 |

| 7.8 热設計の検討事項.....                      | 48  | 10.8 Glossary.....                        | 197 |

| 7.9 タイミングおよびスイッチング特性.....              | 49  | 11 メカニカル、パッケージ、および注文情報.....               | 198 |

| 7.10 オンチップ A/D コンバータ.....              | 104 | 11.1 パッケージ再設計の詳細.....                     | 198 |

| 7.11 F2833x デバイスと F2823x デバイス間の移行..... | 111 | 11.2 パッケージ情報.....                         | 198 |

## 4 改訂履歴

Changes from FEBRUARY 2, 2021 to AUGUST 8, 2022 (from Revision P (February 2021) to Revision Q (August 2022))

|                                                                                                                                                                                                        | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • グローバル:ドキュメントのタイトルを <i>TMS320F2833x, TMS320F2823x デジタル・シグナル・コントローラ (DSC)</i> から <i>TMS320F2833x, TMS320F2823x リアルタイム・マイクロコントローラ</i> に変更。.....                                                         | 1    |

| • グローバル:「デジタル・シグナル・コントローラ」を「リアルタイム・マイクロコントローラ」に変更。「DSC」を「MCU」に変更。.....                                                                                                                                 | 1    |

| • グローバル:サブストレート・サプライヤからの機器の寿命終了に関する通知により、一部の MicroStar BGA™ パッケージ・デバイスを段階的に廃止しています。これらのデバイスは、新ファイン・ピッチ・ボール・グリッド・アレイ (nFBGA) パッケージに変更されました。詳細については、「 <a href="#">パッケージの再設計の詳細</a> 」セクションを参照してください。..... | 1    |

| • グローバル:179 ボールの ZAY 新ファイン・ピッチ・ボール・グリッド・アレイ (nFBGA) を追加。.....                                                                                                                                          | 1    |

| • グローバル:エラッタのタイトルを『 <i>TMS320F2833x, TMS320F2823x DSC シリコン・エラッタ</i> 』から『 <i>TMS320F2833x, TMS320F2823x リアルタイム MCU シリコン・エラッタ</i> 』に変更。.....                                                             | 1    |

| • グローバル:ペリフェラル・リファレンス・ガイドへの参照を、『 <a href="#">TMS320x2833x, TMS320x2823x リアルタイム・マイクロコントローラ・テクニカル・リファレンス・マニュアル</a> 』への参照に更新。.....                                                                        | 1    |

| • グローバル:「エミュレータ」を「JTAG デバッグ・プローブ」に置き換え。.....                                                                                                                                                           | 1    |

| • セクション 1 (特長):「高度なエミュレーション機能」を「高度なデバッグ機能」に変更。.....                                                                                                                                                    | 1    |

| • セクション 1:「パッケージ・オプション」に「179 ボールの新ファイン・ピッチ・ボール・グリッド・アレイ (nFBGA) [ZAY]」を追加。.....                                                                                                                        | 1    |

| • セクション 1:温度オプション「A」に「ZAY」を追加。.....                                                                                                                                                                    | 1    |

| • セクション 2 (アプリケーション):セクションを更新。.....                                                                                                                                                                    | 2    |

| • セクション 3 (概要):セクションを更新。「製品情報」表を「パッケージ情報」表に変更。「パッケージ情報」表に ZAY nFBGA を追加。.....                                                                                                                          | 2    |

| • 表 5-1 (F2833x デバイスの比較):「シリアル通信インターフェイス (SCI)」に「(UART 互換)」を追加。.....                                                                                                                                   | 8    |

| • 表 5-1:「パッケージ」セクションに「179 ボール ZAY」を追加。「A」温度オプションに ZAY を追加。.....                                                                                                                                        | 8    |

| • 表 5-2 (F2823x デバイスの比較):「シリアル通信インターフェイス (SCI)」に「(UART 互換)」を追加。.....                                                                                                                                   | 8    |

| • 表 5-2:「パッケージ」セクションに「179 ボール ZAY」を追加。「A」温度オプションに ZAY を追加。.....                                                                                                                                        | 8    |

| • セクション 5.1 (関連製品):セクションを更新。.....                                                                                                                                                                      | 11   |

| • セクション 6.1 (ピン配置図):179 ボール ZAY 新しいファイン・ピッチ・ボール・グリッド・アレイ (nFBGA) を追加。....                                                                                                                              | 12   |

| • 表 6-1 (信号の説明):ZAY パッケージを追加。.....                                                                                                                                                                     | 22   |

| • 表 6-1:EMU0、EMU1、XRS の説明を更新。.....                                                                                                                                                                     | 22   |

| • セクション 7.3 (ESD 定格 - 民生用):ZAY パッケージのデータを追加。.....                                                                                                                                                      | 35   |

| • セクション 7.5.3 (消費電流の低減):消費電力を低減する方法の一覧を更新。.....                                                                                                                                                        | 40   |

| • セクション 7.7.4 (ZAY パッケージ):表を追加。.....                                                                                                                                                                   | 47   |

| • セクション 7.9.2 (電源シーケンス):「パワーアップおよびパワーダウン・シーケンスに...要件はありません」の段落を更新。.....                                                                                                                                | 51   |

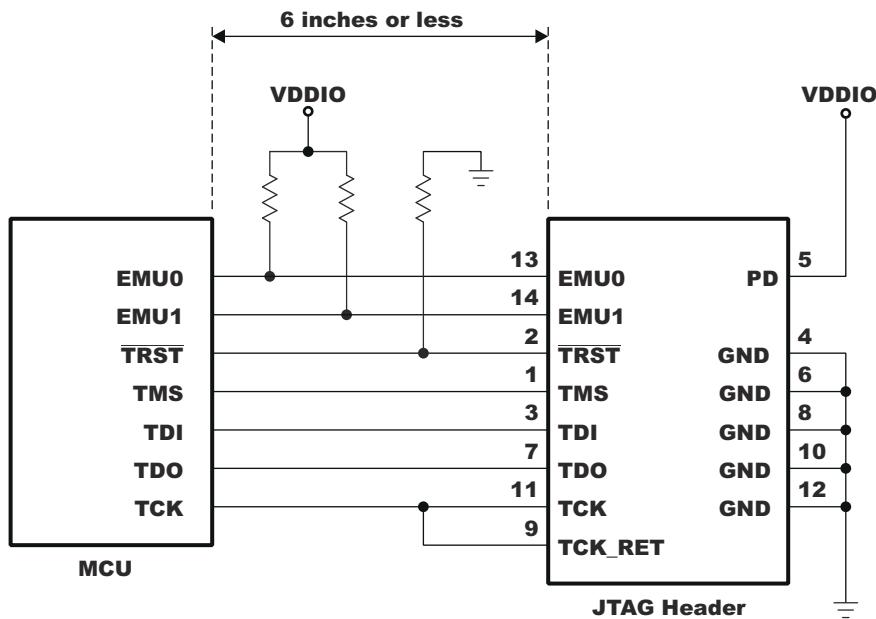

| • セクション 7.9.5:セクションのタイトルを「DSP へのエミュレータ接続 (信号バッファなし)」から「MCU への JTAG デバッグ・プローブ接続 (信号バッファなし)」に変更。.....                                                                                                    | 82   |

| • 図 7-27:図のタイトルを「DSP へのエミュレータ接続 (信号バッファなし)」から「MCU への JTAG デバッグ・プローブ接続 (信号バッファなし)」に変更。.....                                                                                                             | 82   |

| • 図 7-27 (MCU への JTAG デバッグ・プローブ接続 (信号バッファなし)):「DSC」を「MCU」に変更。.....                                                                                                                                     | 82   |

| • セクション 7.9.6.8.2 (同期 XREADY のタイミング要件 (書き込み時のレディ、1 つのウェイト状態)):脚注を復元。...                                                                                                                                | 95   |

| • 表 8-14 (SCI-C レジスタ):脚注を復元。.....                                                                                                                                                                      | 146  |

| • 図 8-15 (シリアル通信インターフェイス (SCI) モジュールのブロック図):図を更新。.....                                                                                                                                                 | 146  |

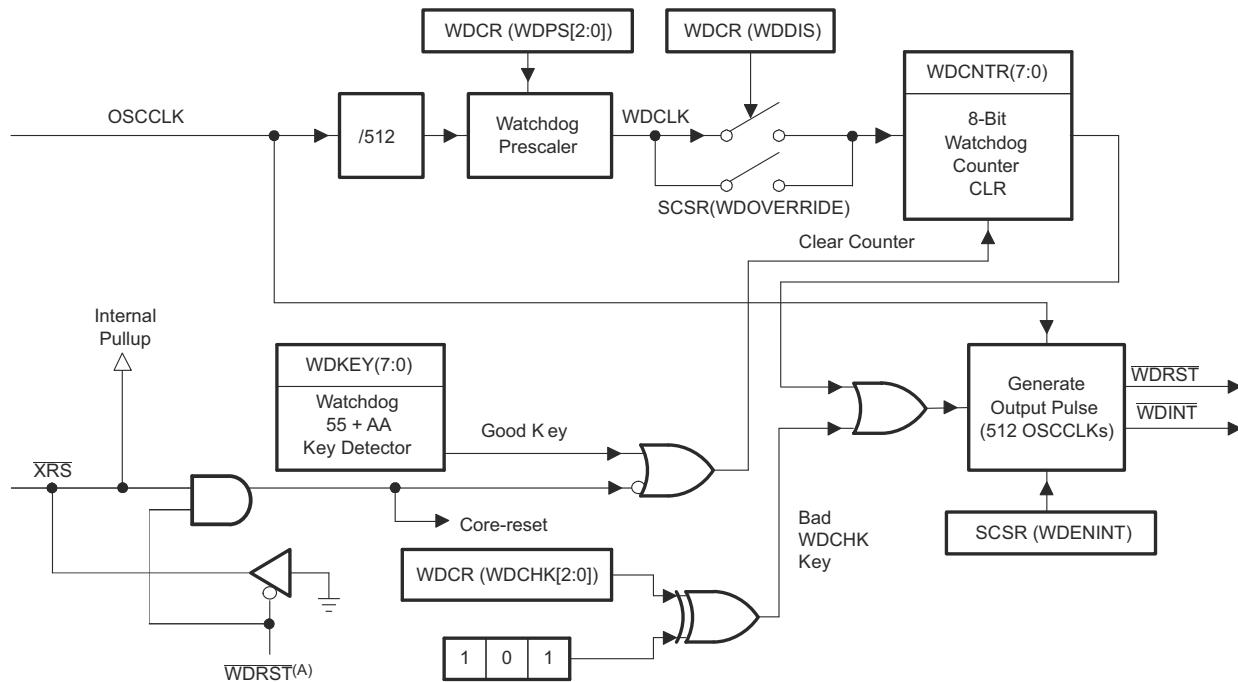

| • 図 8-34 (ウォッチドッグ・モジュール):図を更新。.....                                                                                                                                                                    | 188  |

| • セクション 9.1:タイトルを「TI デザインまたはリファレンス・デザイン」から「TI リファレンス・デザイン」に変更。.....                                                                                                                                    | 190  |

| • セクション 9.1 (TI リファレンス・デザイン):セクションを更新。.....                                                                                                                                                            | 190  |

| • セクション 10 (デバイスおよびドキュメントのサポート):セクションを更新。.....                                                                                                                                                         | 191  |

| • セクション 10.1:タイトルを「はじめに」から「使い始めと次の手順」に変更。セクションを更新。.....                                                                                                                                                | 191  |

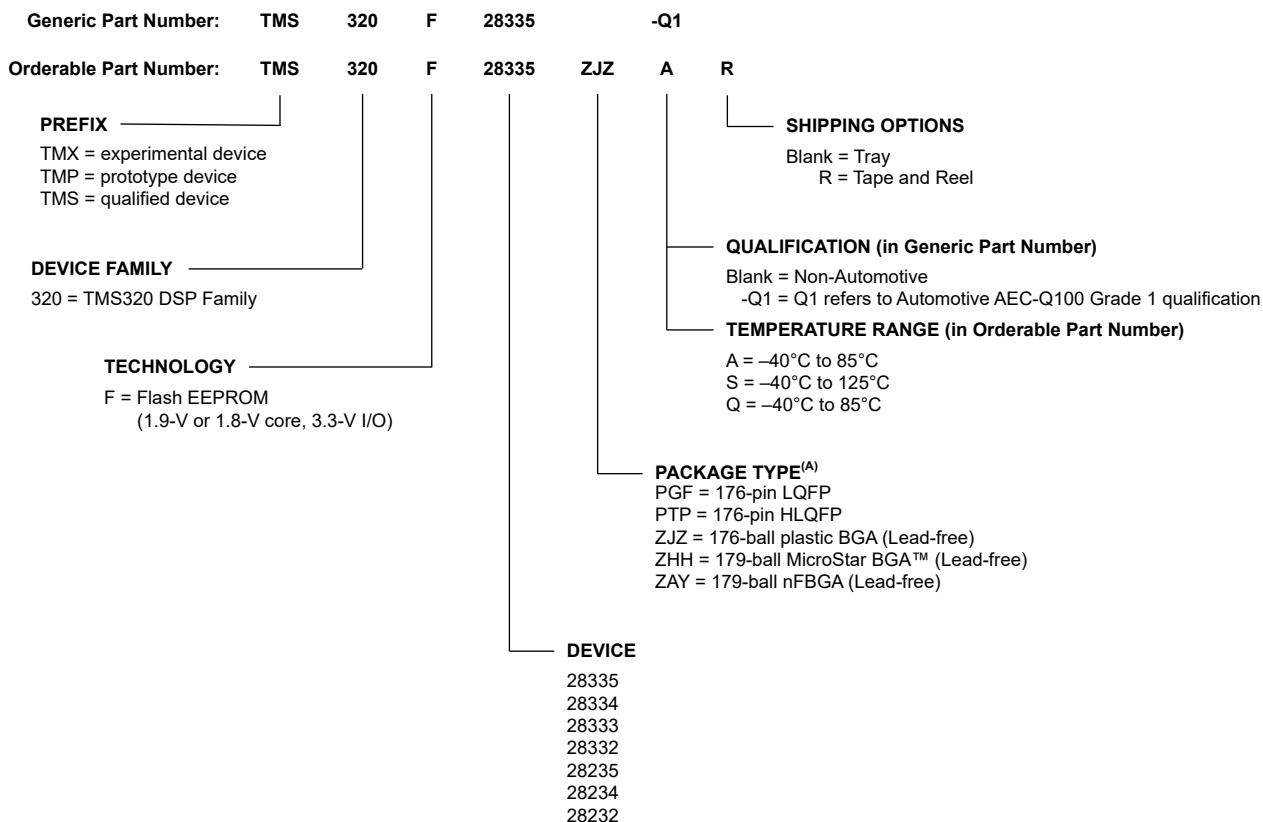

- [図 10-1 \(F2833x, F2823x デバイスの命名規則\): パッケージ・タイプに 179 ボール ZAY パッケージを追加。..... 191](#)

- [セクション 10.3 \(ツールとソフトウェア\): セクションを更新。「設計キットと評価モジュール」セクションを更新。「モデル」セクションを更新。「トレーニング」セクションを追加。..... 193](#)

- [セクション 10.4 \(ドキュメントのサポート\): \*nFBGA\* パッケージ・アプリケーション・レポートを追加。..... 195](#)

- [セクション 10.4: 「テクニカル・リファレンス・マニュアル」セクションを追加。ほとんどのペリフェラル・リファレンス・ガイドは、現在、\*『TMS320x2833x, TMS320x2823x リアルタイム・マイクロコントローラ・テクニカル・リファレンス・マニュアル』\*に置き換えられているため削除。..... 195](#)

- [セクション 11.1 \(パッケージ再設計の詳細\): セクションを追加。..... 198](#)

## 5 デバイスの比較

表 5-1. F2833x デバイスの比較

| 機能                                        | タイプ <sup>(1)</sup> | F28335<br>F28335-Q1<br>(150MHz) | F28334<br>(150MHz)        | F28333<br>(100MHz)        | F28332<br>(100MHz) |

|-------------------------------------------|--------------------|---------------------------------|---------------------------|---------------------------|--------------------|

| 命令サイクル                                    | –                  | 6.67ns                          | 6.67ns                    | 10ns                      | 10ns               |

| 浮動小数点ユニット                                 | –                  | あり                              | あり                        | あり                        | あり                 |

| 3.3V オンチップ・フラッシュ (16 ビット・ワード)             | –                  | 256K                            | 128K                      | 256K                      | 64K                |

| シングル・アクセス RAM (SARAM)<br>(16 ビット・ワード)     | –                  | 34K                             | 34K                       | 34K                       | 26K                |

| ワンタイム・プログラマブル (OTP) ROM<br>(16 ビット・ワード)   | –                  | 1K                              | 1K                        | 1K                        | 1K                 |

| オンチップ・フラッシュ / SARAM / OTP プログラムコード・セキュリティ | –                  | あり                              | あり                        | あり                        | あり                 |

| ブート ROM (8K × 16)                         | –                  | あり                              | あり                        | あり                        | あり                 |

| 16 ビットまたは 32 ビットの外部インターフェイス (XINTF)       | 1                  | あり                              | あり                        | あり                        | あり                 |

| 6 チャネルのダイレクト・メモリ・アクセス (DMA)               | 0                  | あり                              | あり                        | あり                        | あり                 |

| PWM チャネル                                  | 0                  | ePWM1/2/3/4/5/6                 | ePWM1/2/3/4/5/6           | ePWM1/2/3/4/5/6           | ePWM1/2/3/4/5/6    |

| HRPWM チャネル                                | 0                  | ePWM1A/2A/3A/4A/<br>5A/6A       | ePWM1A/2A/3A/4A/<br>5A/6A | ePWM1A/2A/3A/4A/<br>5A/6A | ePWM1A/2A/3A/4A    |

| 32 ビットのキャプチャ入力または補助 PWM 出力                | 0                  | eCAP1/2/3/4/5/6                 | eCAP1/2/3/4               | eCAP1/2/3/4/5/6           | eCAP1/2/3/4        |

| 32 ビット QEP チャネル (4 入力/チャネル)               | 0                  | eQEP1/2                         | eQEP1/2                   | eQEP1/2                   | eQEP1/2            |

| ウォッチドッグ・タイマ                               | –                  | あり                              | あり                        | あり                        | あり                 |

| 12 ビット ADC                                | チャネル数              | 16                              | 16                        | 16                        | 16                 |

|                                           | MSPS               | 12.5                            | 12.5                      | 12.5                      | 12.5               |

|                                           | 変換時間               | 80ns                            | 80ns                      | 80ns                      | 80ns               |

| 32 ビット CPU タイマ                            | –                  | 3                               | 3                         | 3                         | 3                  |

| マルチチャネルのバッファ付きシリアル・ポート (McBSP)/SPI        | 1                  | 2 (A/B)                         | 2 (A/B)                   | 2 (A/B)                   | 1 (A)              |

| シリアル・ペリフェラル・インターフェイス (SPI)                | 0                  | 1                               | 1                         | 1                         | 1                  |

| シリアル通信インターフェイス (SCI) (UART 互換)            | 0                  | 3 (A/B/C)                       | 3 (A/B/C)                 | 3 (A/B/C)                 | 2 (A/B)            |

| 拡張コントローラ・エリア・ネットワーク (eCAN)                | 0                  | 2 (A/B)                         | 2 (A/B)                   | 2 (A/B)                   | 2 (A/B)            |

| I2C (Inter-Integrated Circuit)            | 0                  | 1                               | 1                         | 1                         | 1                  |

| 汎用 I/O (GPIO) (共有)                        | –                  | 88                              | 88                        | 88                        | 88                 |

| 外部入力                                      | –                  | 8                               | 8                         | 8                         | 8                  |

| パッケージ                                     | 176 ピン PGF         | –                               | あり                        | あり                        | あり                 |

|                                           | 176 ピン PTP         | –                               | あり                        | あり                        | –                  |

|                                           | 179 ボール ZHH        | –                               | あり                        | あり                        | あり                 |

|                                           | 179 ボール ZAY        | –                               | あり                        | あり                        | –                  |

|                                           | 176 ボール ZJZ        | –                               | あり                        | あり                        | あり                 |

**表 5-1. F2833x デバイスの比較 (continued)**

| 機能      |                                | タイプ <sup>(1)</sup> | F28335<br>F28335-Q1<br>(150MHz) | F28334<br>(150MHz)    | F28333<br>(100MHz) | F28332<br>(100MHz) |

|---------|--------------------------------|--------------------|---------------------------------|-----------------------|--------------------|--------------------|

| 温度オプション | A:-40°C~85°C                   | –                  | PGF, ZHH, ZAY,<br>ZJZ           | PGF, ZHH, ZAY,<br>ZJZ | PGF                | PGF, ZHH, ZJZ      |

|         | S:-40°C~125°C                  | –                  | PTP, ZJZ                        | PTP, ZJZ              | –                  | PTP, ZJZ           |

|         | Q:-40°C~125°C<br>(AEC Q100 認定) | –                  | PTP, ZJZ                        | PTP, ZJZ              | –                  | PTP, ZJZ           |

- (1) タイプの違いは、ペリフェラル・モジュールの機能上の主要な相違を表します。同じペリフェラルのタイプの中でも、モジュールの基本的な機能に影響を与えない、わずかな相違がデバイス間に存在することがあります。これらのデバイス固有の相違点は、『[C2000 リアルタイム制御 MCU ペリフェラル・リファレンス・ガイド](#)』および『[TMS320x2833x, TMS320x2823x リアルタイム・マイクロコントローラ・テクニカル・リファレンス・マニュアル](#)』に記載されています。

表 5-2. F2823x デバイスの比較

| 機能                                       | タイプ <sup>(1)</sup>                | F28235<br>F28235-Q1<br>(150MHz) | F28234<br>F28234-Q1<br>(150MHz) | F28232<br>F28232-Q1<br>(100MHz) |

|------------------------------------------|-----------------------------------|---------------------------------|---------------------------------|---------------------------------|

| 命令サイクル                                   | –                                 | 6.67ns                          | 6.67ns                          | 10ns                            |

| 浮動小数点ユニット                                | –                                 | なし                              | なし                              | なし                              |

| 3.3V オンチップ・フラッシュ (16 ビット・ワード)            | –                                 | 256K                            | 128K                            | 64K                             |

| シングル・アクセス RAM (SARAM)<br>(16 ビット・ワード)    | –                                 | 34K                             | 34K                             | 26K                             |

| ワンタイム・プログラマブル (OTP) ROM<br>(16 ビット・ワード)  | –                                 | 1K                              | 1K                              | 1K                              |

| オンチップ・フラッシュ/ SARAM / OTP プロックのコード・セキュリティ | –                                 | あり                              | あり                              | あり                              |

| ブート ROM (8K × 16 ビット)                    | –                                 | あり                              | あり                              | あり                              |

| 16 ビットまたは 32 ビットの外部インターフェイス (XINTF)      | 1                                 | あり                              | あり                              | あり                              |

| 6 チャネルのダイレクト・メモリ・アクセス (DMA)              | 0                                 | あり                              | あり                              | あり                              |

| PWM チャネル                                 | 0                                 | ePWM1/2/3/4/5/6                 | ePWM1/2/3/4/5/6                 | ePWM1/2/3/4/5/6                 |

| HRPWM チャネル                               | 0                                 | ePWM1A/2A/3A/4A/5A/6A           | ePWM1A/2A/3A/4A/5A/6A           | ePWM1A/2A/3A/4A                 |

| 32 ビットのキャプチャ入力または補助 PWM 出力               | 0                                 | eCAP1/2/3/4/5/6                 | eCAP1/2/3/4                     | eCAP1/2/3/4                     |

| 32 ビット QEP チャネル (4 入力/チャネル)              | 0                                 | eQEP1/2                         | eQEP1/2                         | eQEP1/2                         |

| ウォッチドッグ・タイマー                             | –                                 | あり                              | あり                              | あり                              |

| 12 ビット ADC                               | チャネル数                             | 16                              | 16                              | 16                              |

|                                          | MSPS                              | 12.5                            | 12.5                            | 12.5                            |

|                                          | 変換時間                              | 80ns                            | 80ns                            | 80ns                            |

| 32 ビット CPU タイマー                          | –                                 | 3                               | 3                               | 3                               |

| マルチチャネルのバッファ付きシリアル・ポート (McBSP)/SPI       | 1                                 | 2 (A/B)                         | 2 (A/B)                         | 1 (A)                           |

| シリアル・ペリフェラル・インターフェイス (SPI)               | 0                                 | 1                               | 1                               | 1                               |

| シリアル通信インターフェイス (SCI) (UART 互換)           | 0                                 | 3 (A/B/C)                       | 3 (A/B/C)                       | 2 (A/B)                         |

| 拡張コントローラ・エリア・ネットワーク (eCAN)               | 0                                 | 2 (A/B)                         | 2 (A/B)                         | 2 (A/B)                         |

| I2C (Inter-Integrated Circuit)           | 0                                 | 1                               | 1                               | 1                               |

| 汎用 I/O (GPIO) (共有)                       | –                                 | 88                              | 88                              | 88                              |

| 外部入力                                     | –                                 | 8                               | 8                               | 8                               |

| パッケージ                                    | 176 ピン PGF                        | –                               | あり                              | あり                              |

|                                          | 176 ピン PTP                        | –                               | あり                              | あり                              |

|                                          | 179 ボール ZHH                       | –                               | あり                              | あり                              |

|                                          | 179 ボール ZAY                       | –                               | –                               | あり                              |

|                                          | 176 ボール ZJZ                       | –                               | あり                              | あり                              |

| 温度オプション                                  | A: -40°C ~ 85°C                   | –                               | PGF, ZHH, ZJZ                   | PGF, ZHH, ZAY, ZJZ              |

|                                          | S: -40°C ~ 125°C                  | –                               | PTP, ZJZ                        | PTP, ZJZ                        |

|                                          | Q: -40°C ~ 125°C<br>(AEC Q100 認定) | –                               | PTP, ZJZ                        | PTP, ZJZ                        |

- (1) タイプの違いは、ペリフェラル・モジュールの機能上の主要な相違を表します。同じペリフェラルのタイプの中でも、モジュールの基本的な機能に影響を与えない、わずかな相違がデバイス間に存在することがあります。これらのデバイス固有の相違点は、『[C2000 リアルタイム制御 MCU ペリフェラル・リファレンス・ガイド](#)』および『[TMS320x2833x, TMS320x2823x リアルタイム・マイクロコントローラ・テクニカル・リファレンス・マニュアル](#)』に記載されています。

## 5.1 関連製品

類似製品の詳細については、以下のリンクを参照してください。

### [TMS320F2833x リアルタイム・マイクロコントローラ](#)

F2833x シリーズは、浮動小数点ユニット (FPU) 付きで提供される初の C2000™ MCU です。第 1 世代の ePWM タイマを搭載しています。12.5MSPS、12 ビット ADC は、内蔵 A/D コンバータとして引き続きクラス最高の性能を発揮します。F2833x は、150MHz CPU および最大 512KB のオンチップ・フラッシュを搭載しています。176 ピン QFP または 179 ボール BGA パッケージで供給されます。

### [TMS320C2834x リアルタイム・マイクロコントローラ](#)

C2834x シリーズは、オンチップ・フラッシュ・メモリと内蔵 ADC を取り除いて、最高 300MHz の最速クロック速度を実現しています。179 ボールの nFBGA または 256 ボール BGA パッケージで供給されます。

### [TMS320F2837xD リアルタイム・マイクロコントローラ](#)

F2837xD シリーズは、デュアル・サブシステムの性能に関する新しい標準を確立します。各サブシステムは、C28x CPU および並列制御補償器アクセラレータ (CLA) で構成され、それぞれが 200MHz で動作します。性能を強化するものとして、TMU および VCU アクセラレータがあります。新しい機能としては、複数の 16 ビット / 12 ビット・モード ADC、DAC、デルタ・シグマ・フィルタ、USB、コンフィギュラブル・ロジック・ブロック (CLB)、オンチップ発振器、すべてのペリフェラルの拡張バージョンがあります。F2837xD は、最大 1MB のフラッシュを搭載しています。176 ピン QFP または 337 ピン BGA パッケージで供給されます。

### [TMS320F2837xS リアルタイム・マイクロコントローラ](#)

F2837xS シリーズは、F2837xD のピン互換バージョンですが、C28x-CPU-CLA サブシステムが 1 つのみ有効です。また、[TMS320F2807x](#) シリーズとの互換性を確保するために、100 ピン QFP も用意されています。

## 6 端子構成および機能

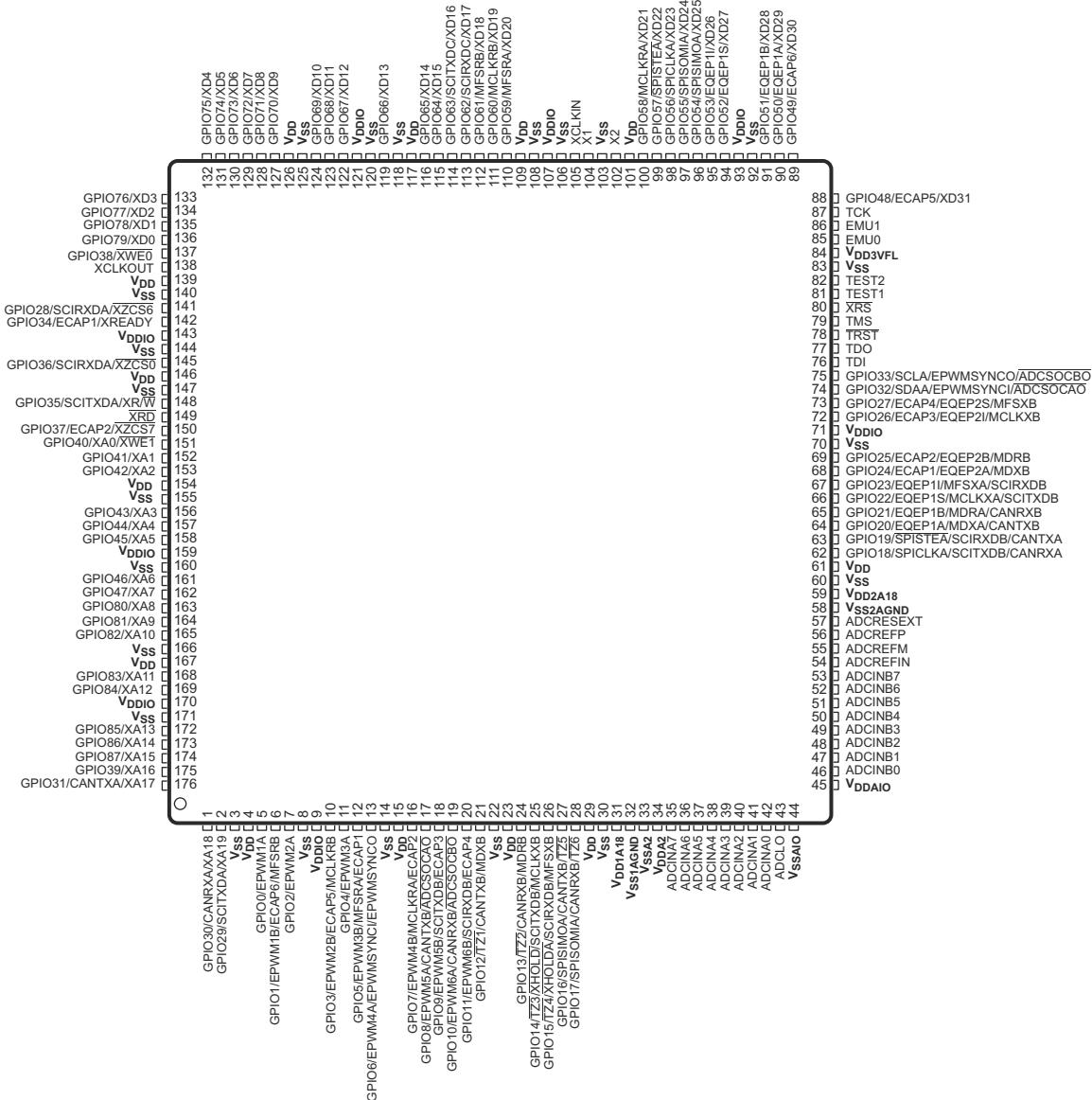

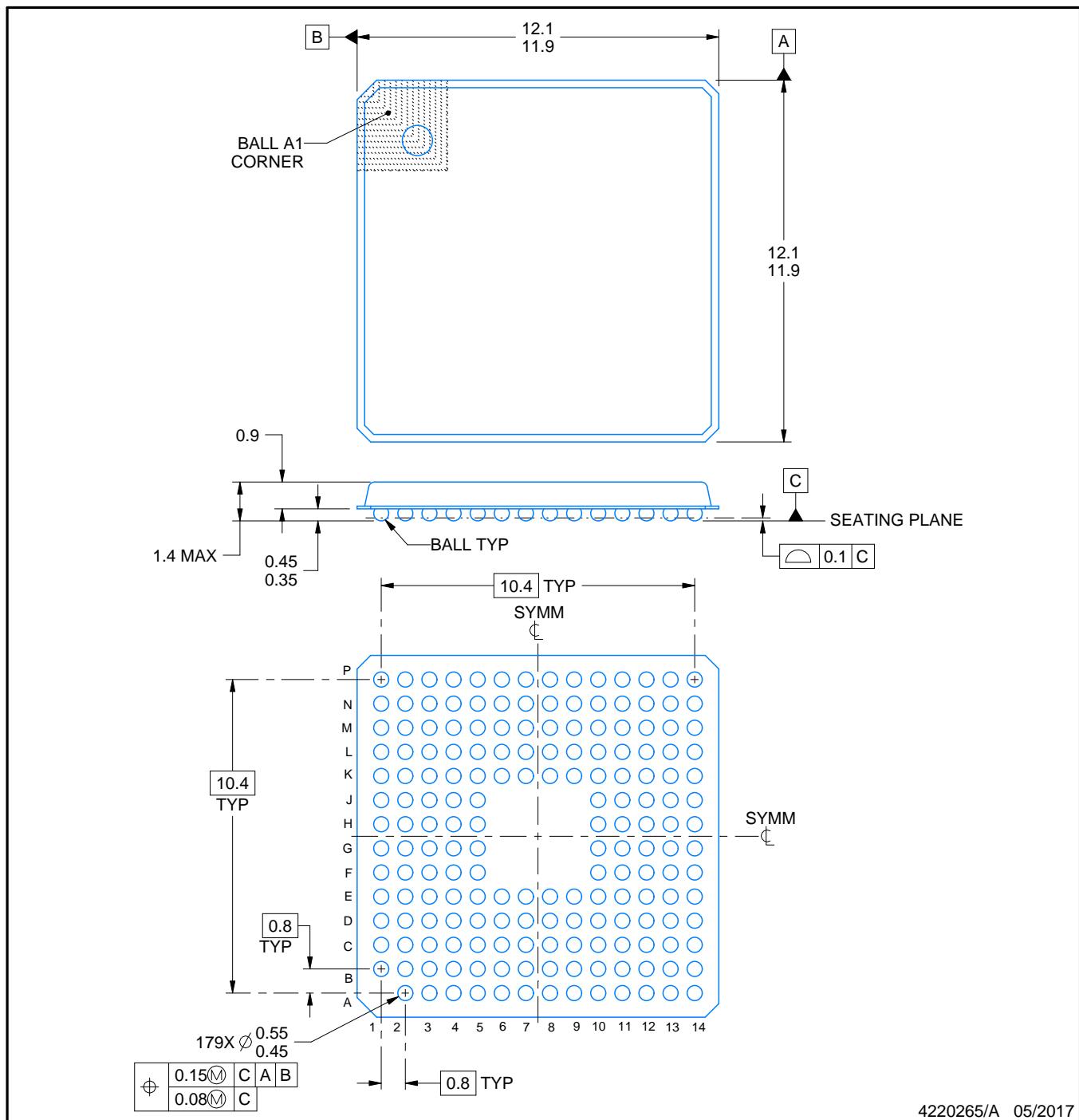

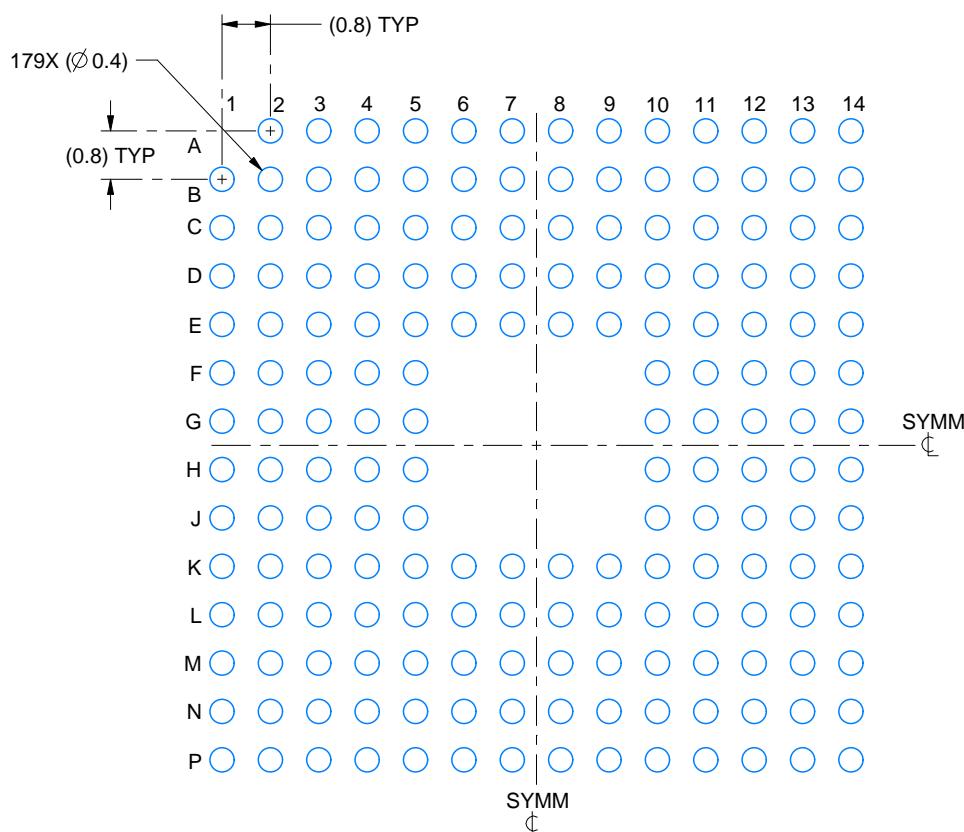

### 6.1 ピン配置図

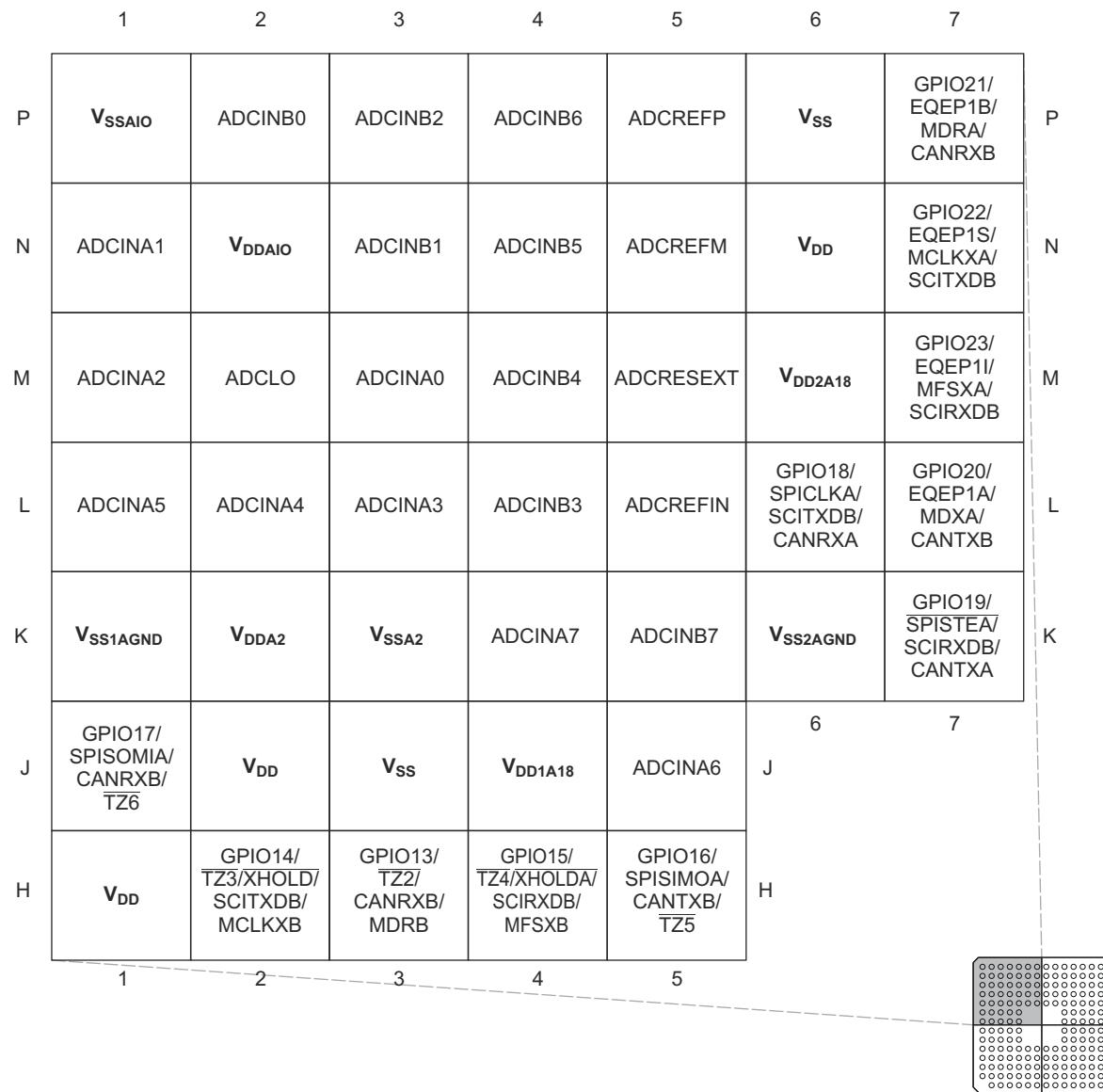

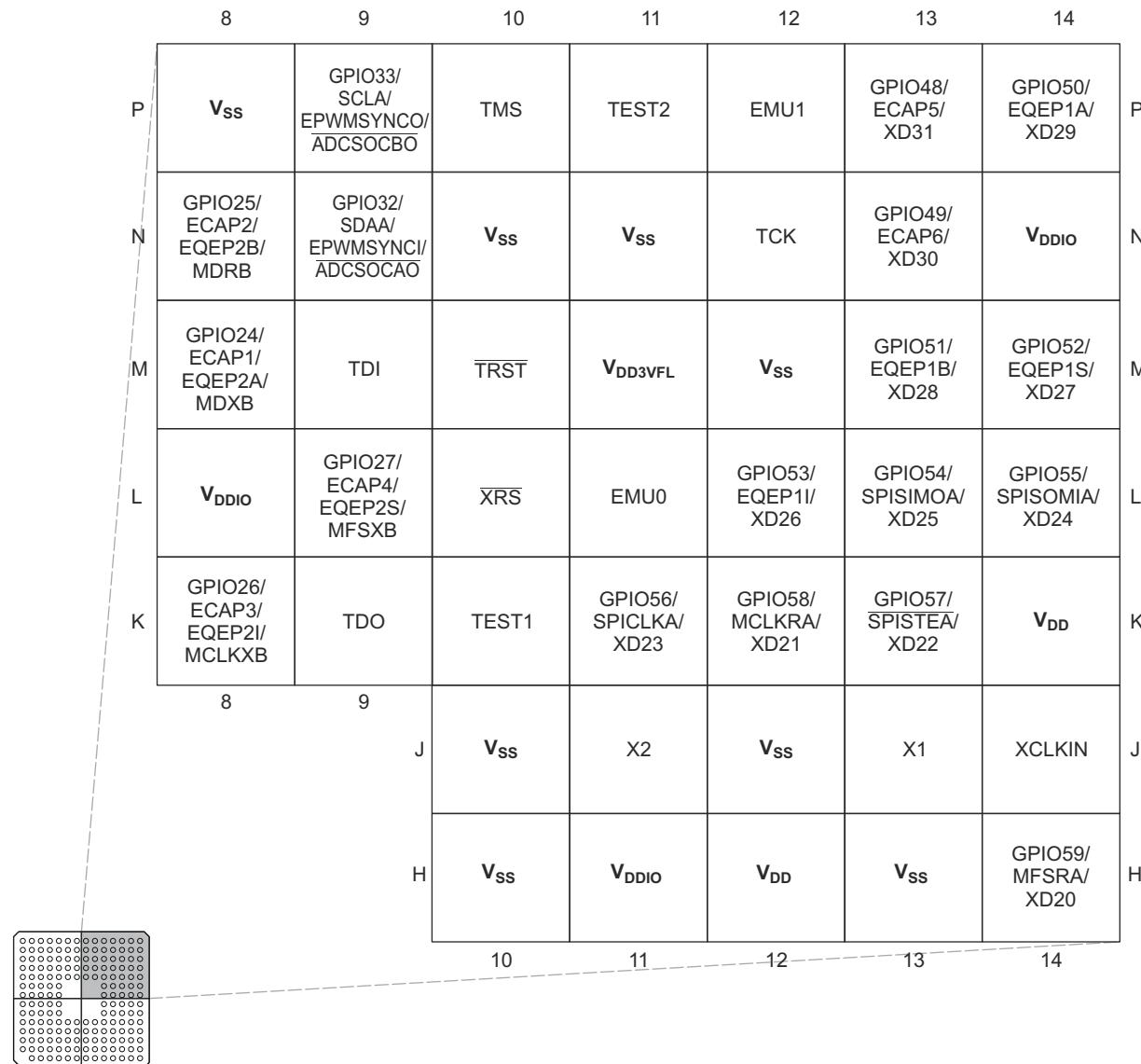

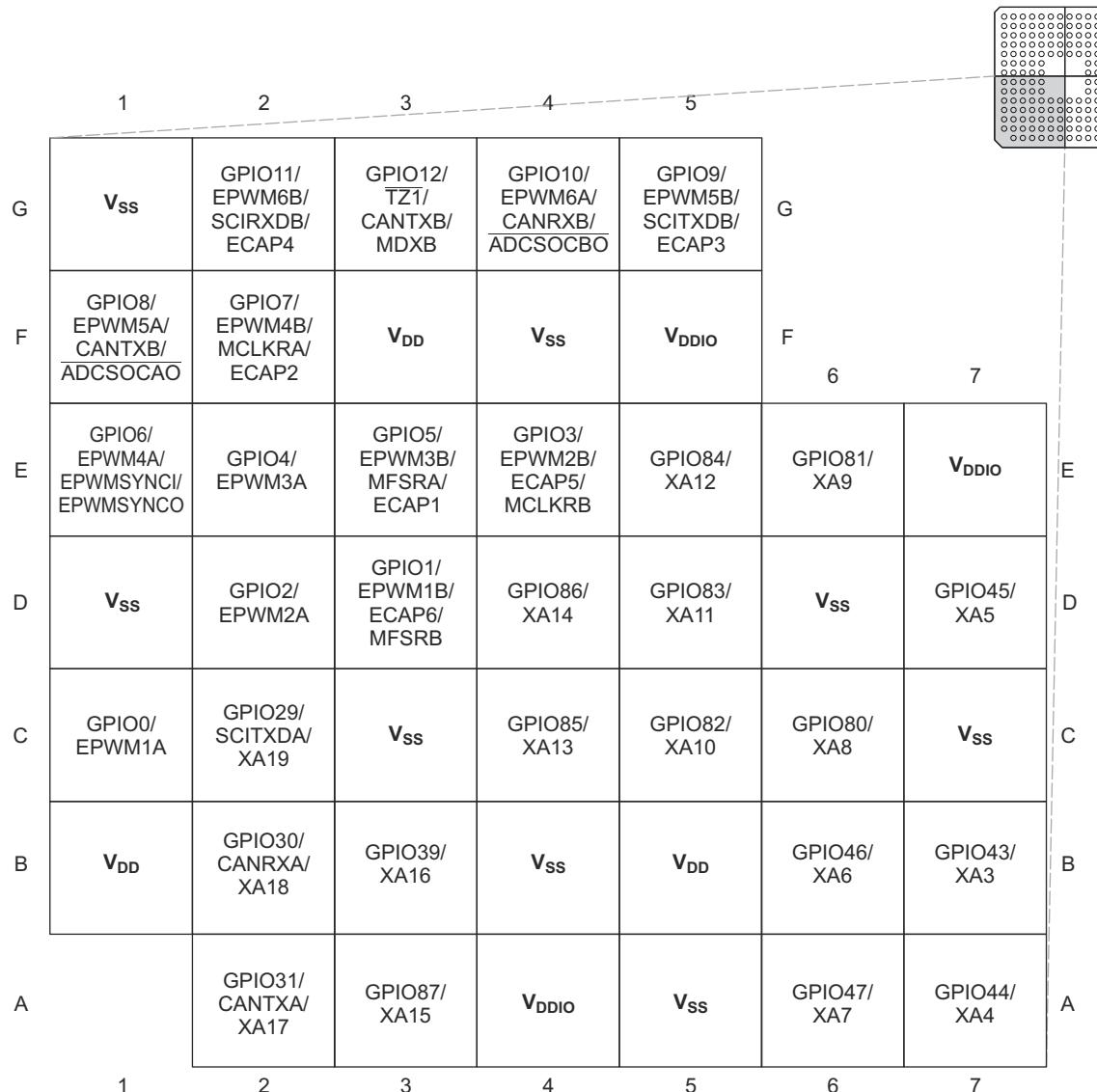

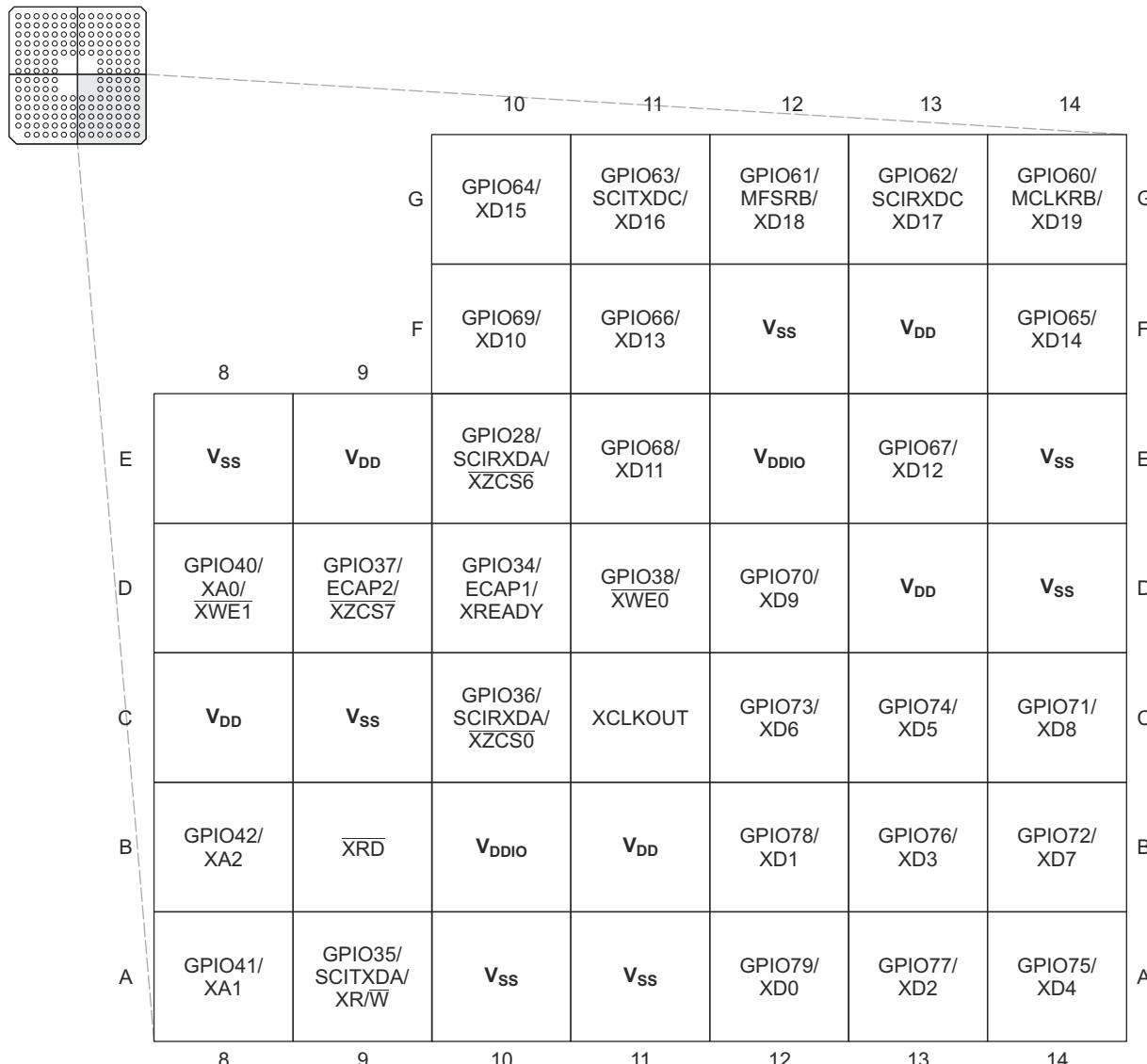

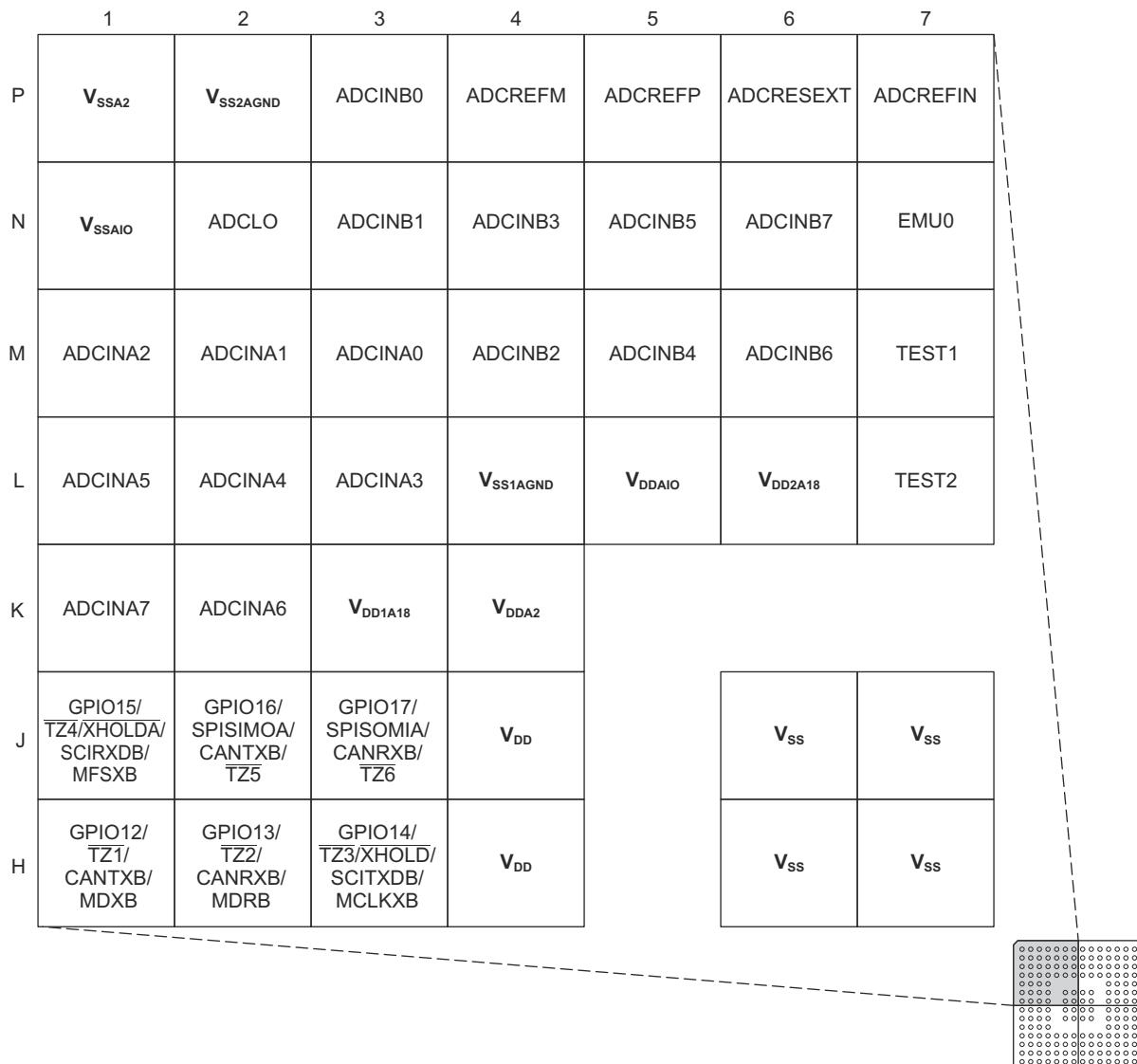

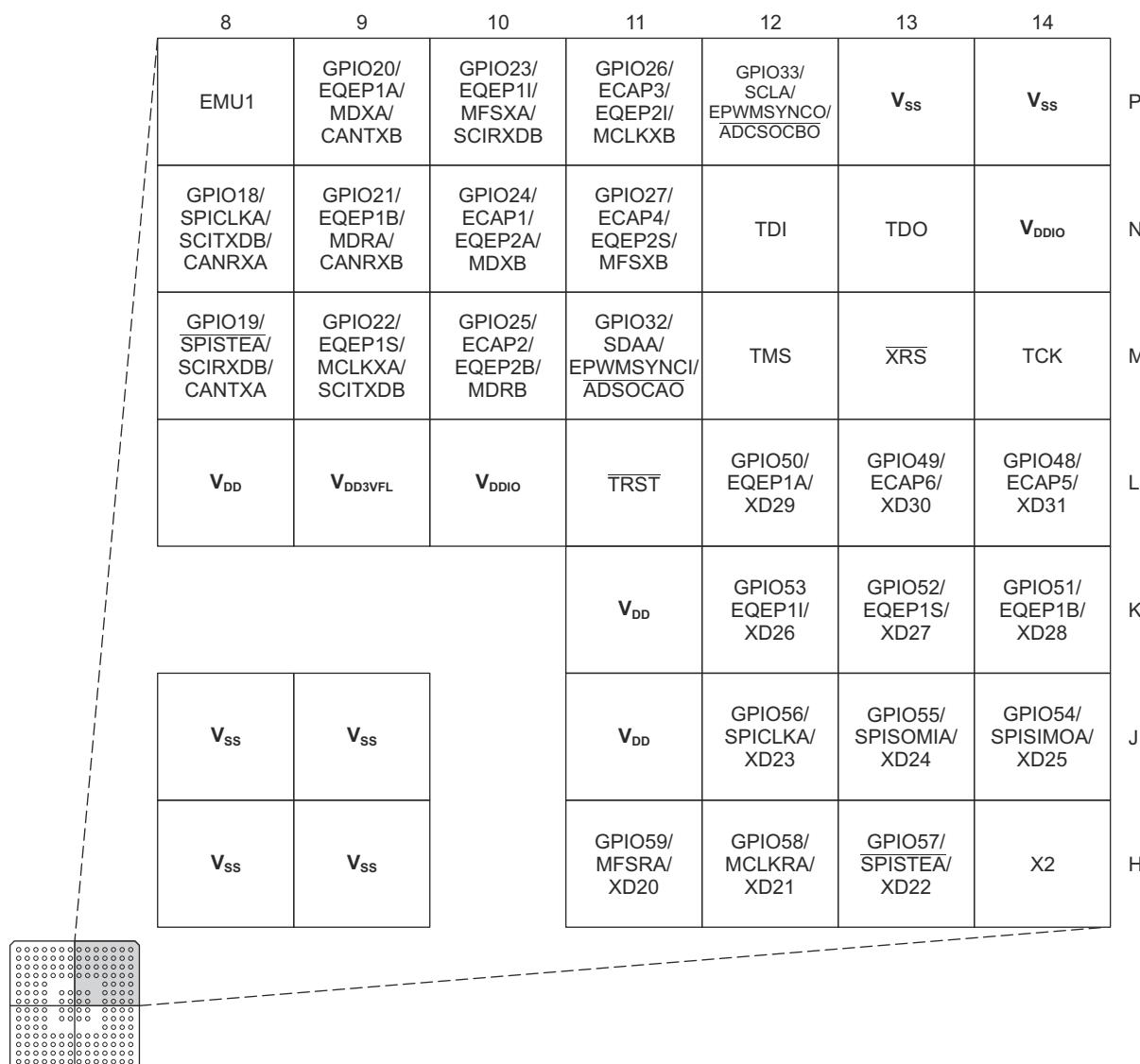

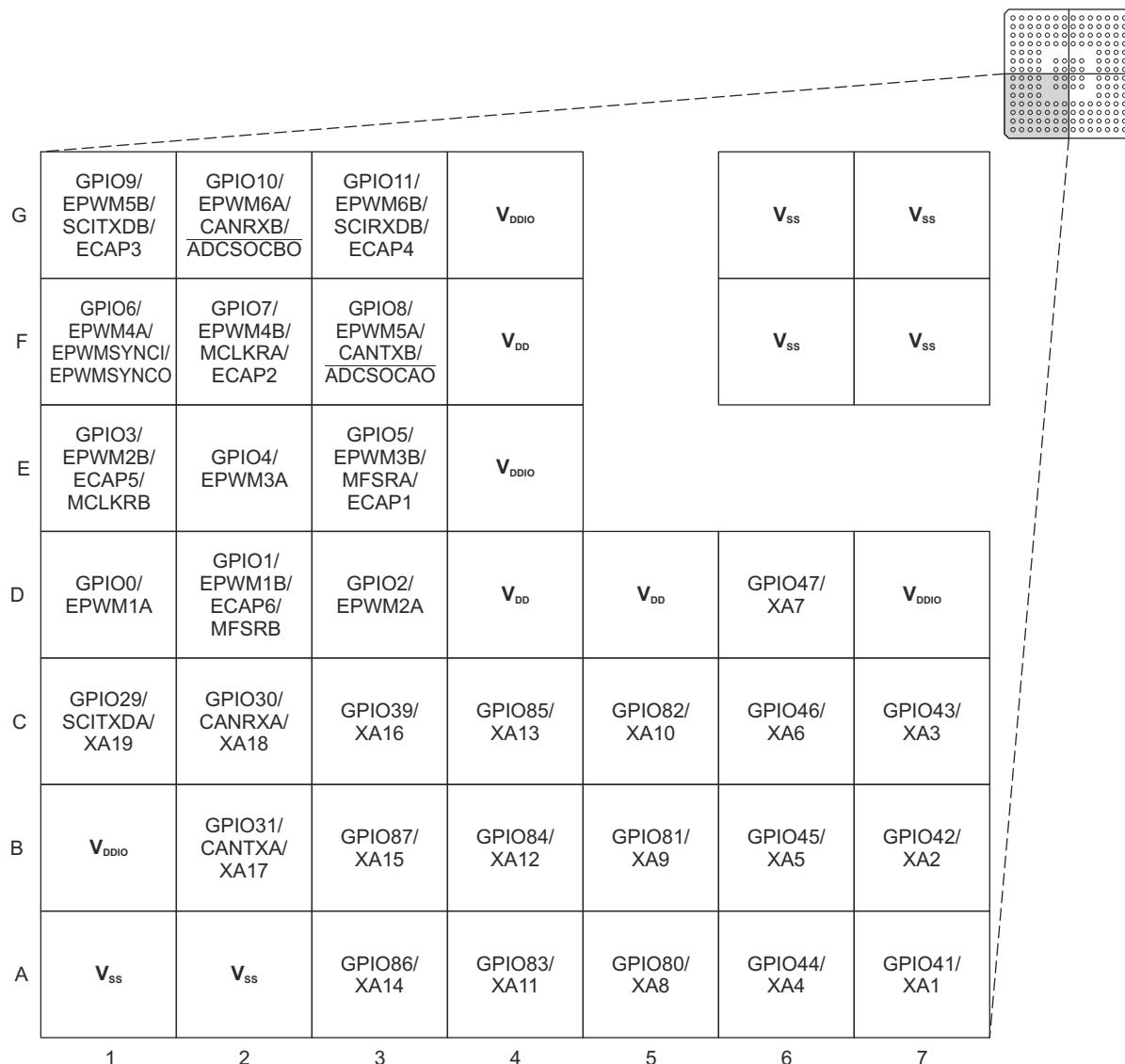

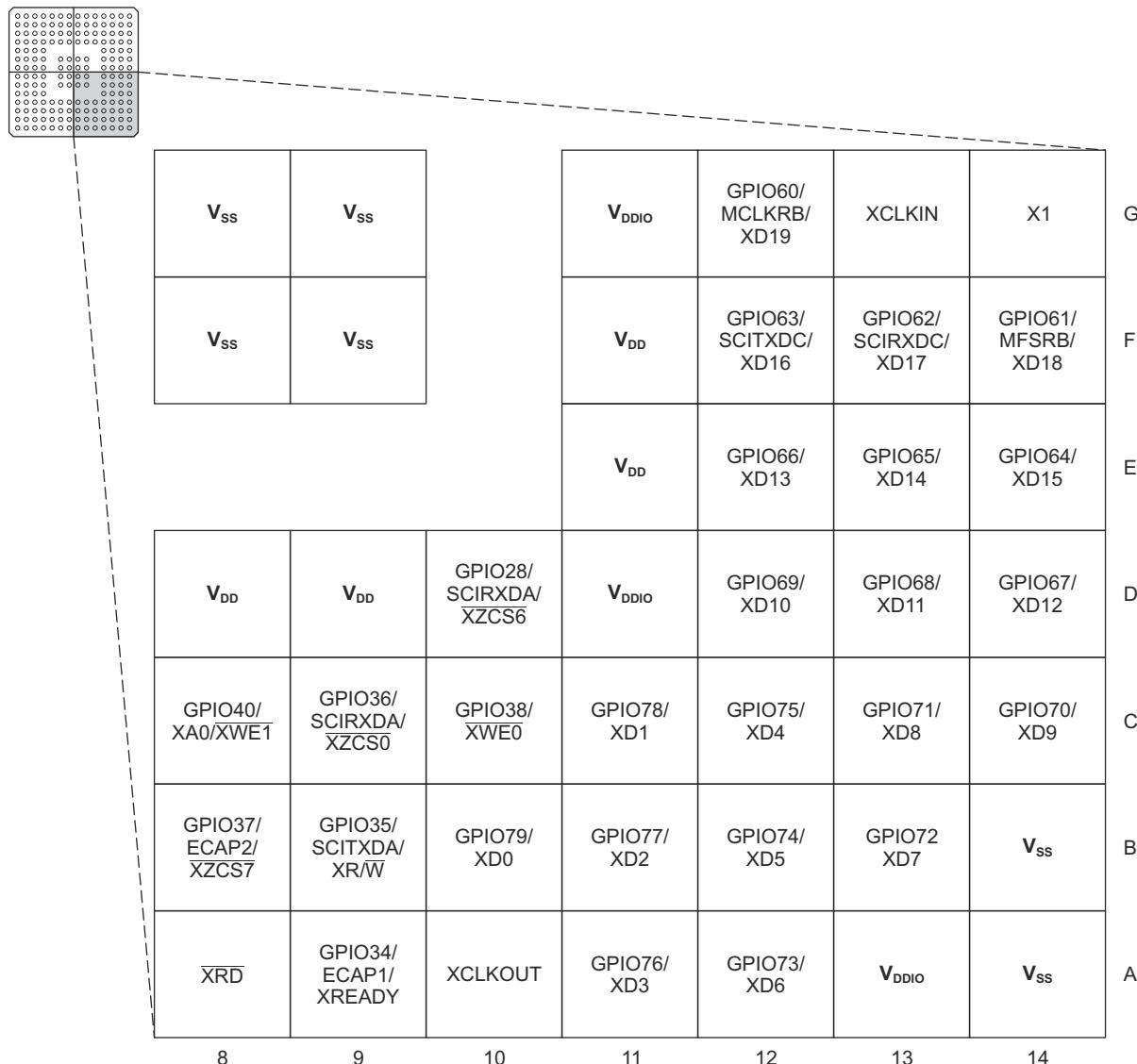

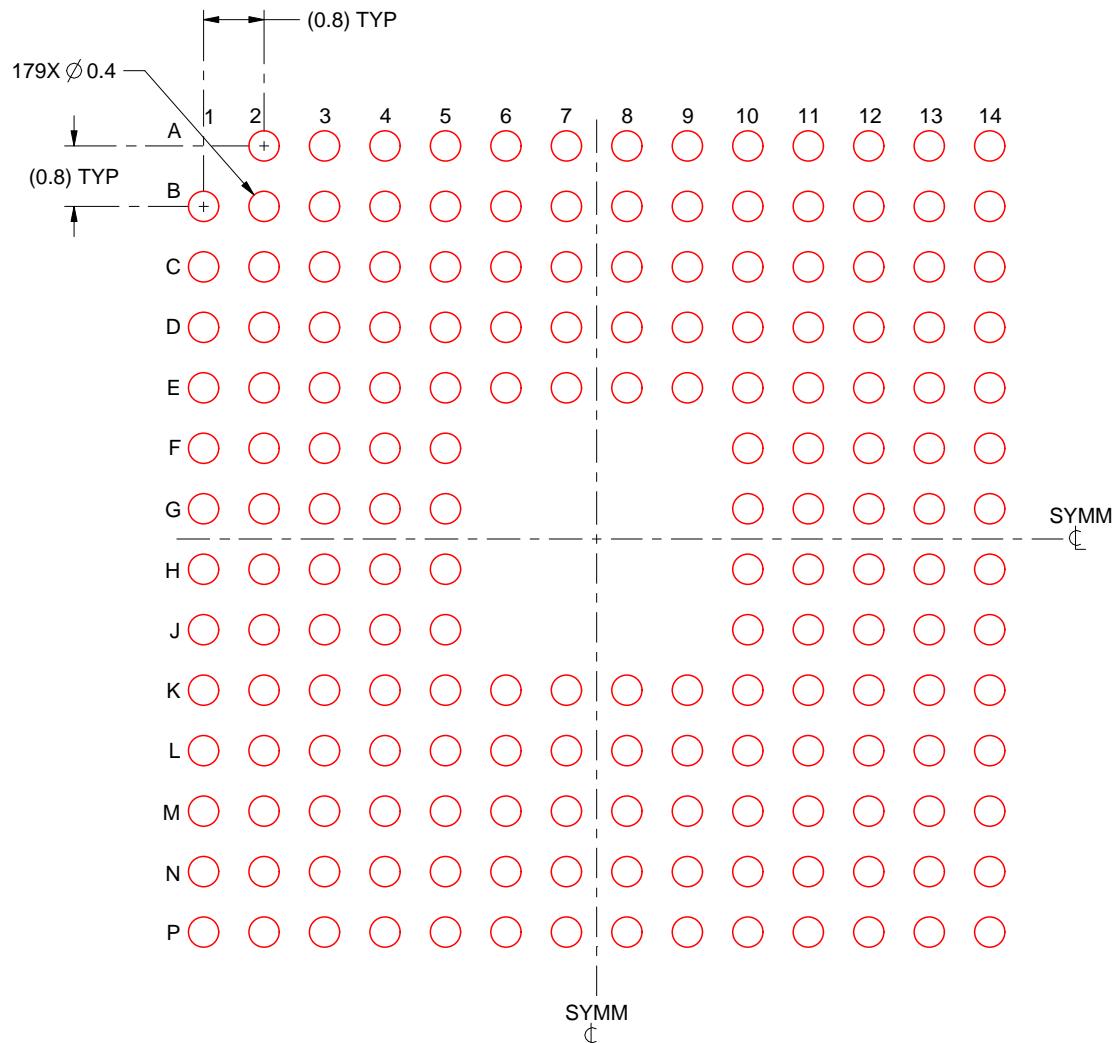

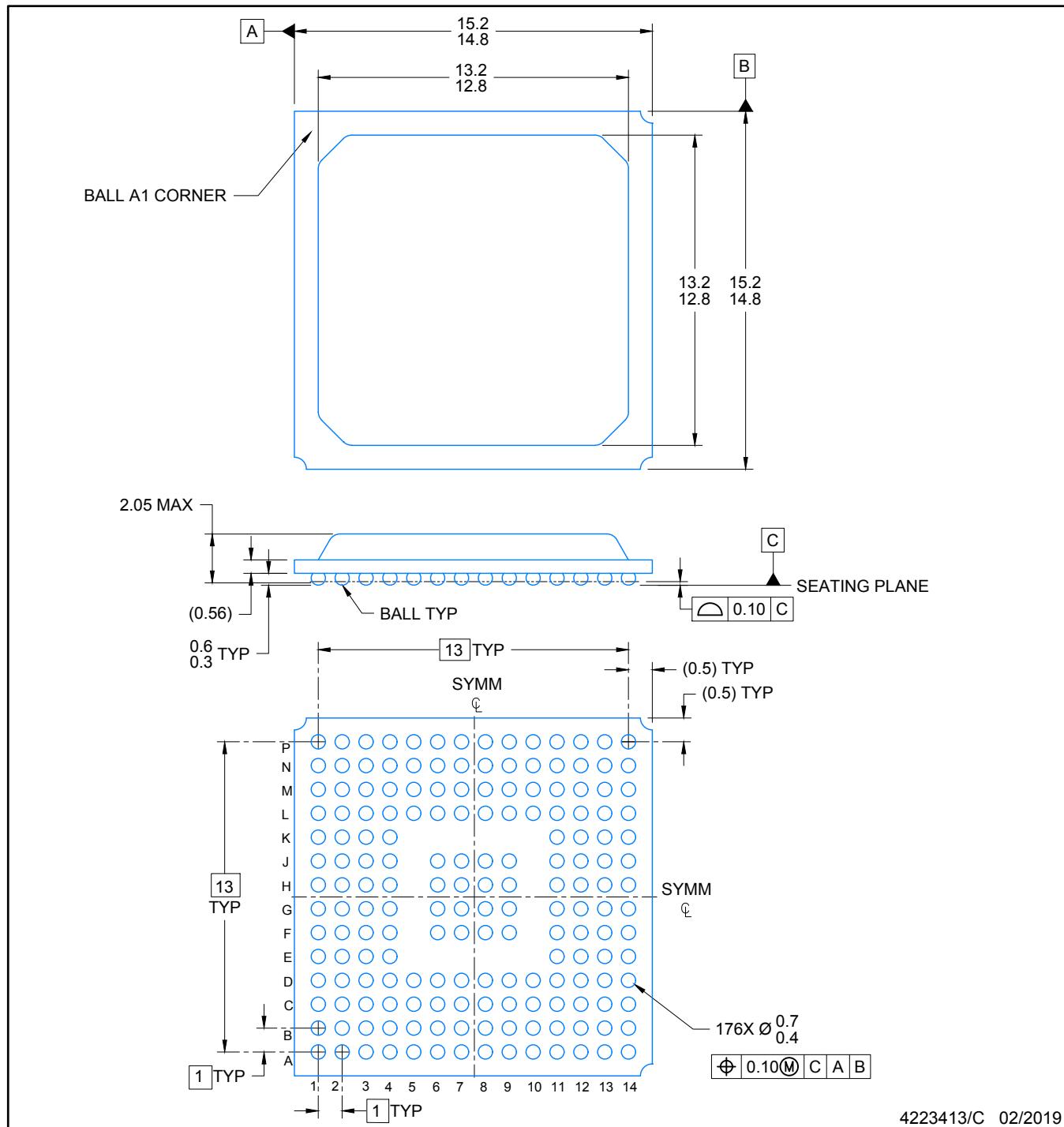

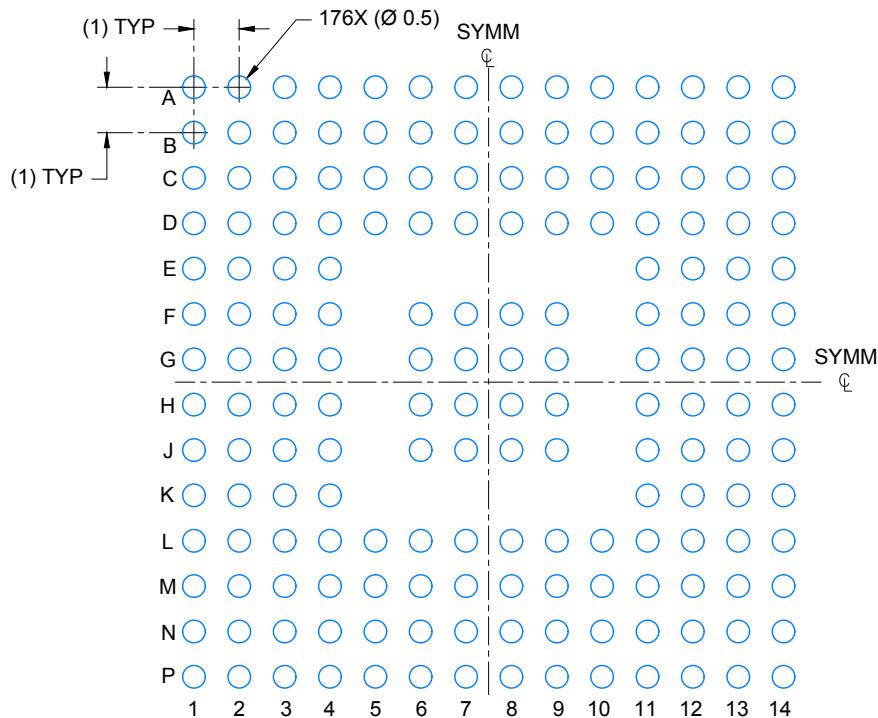

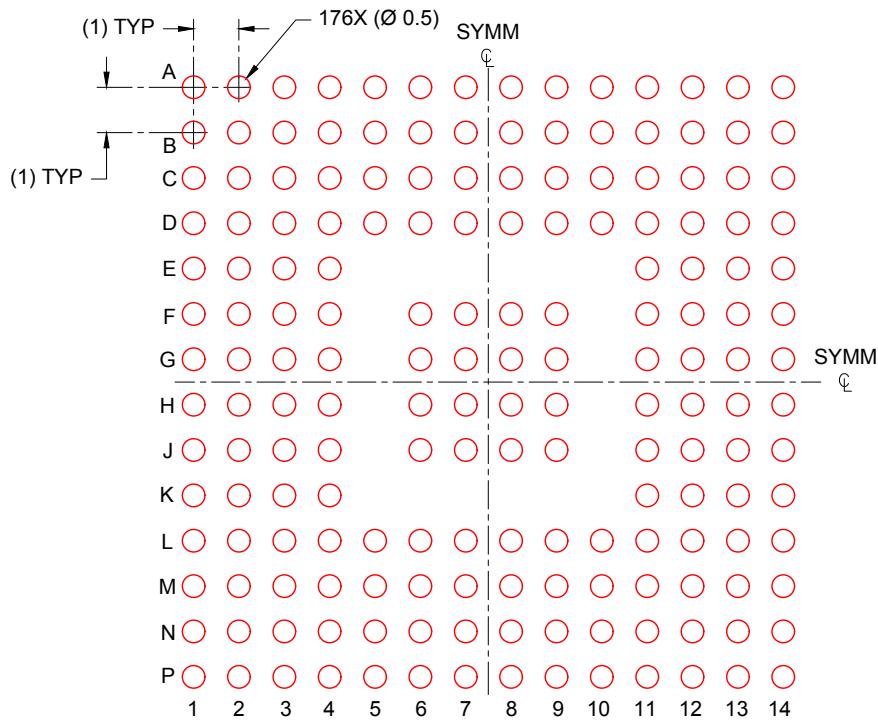

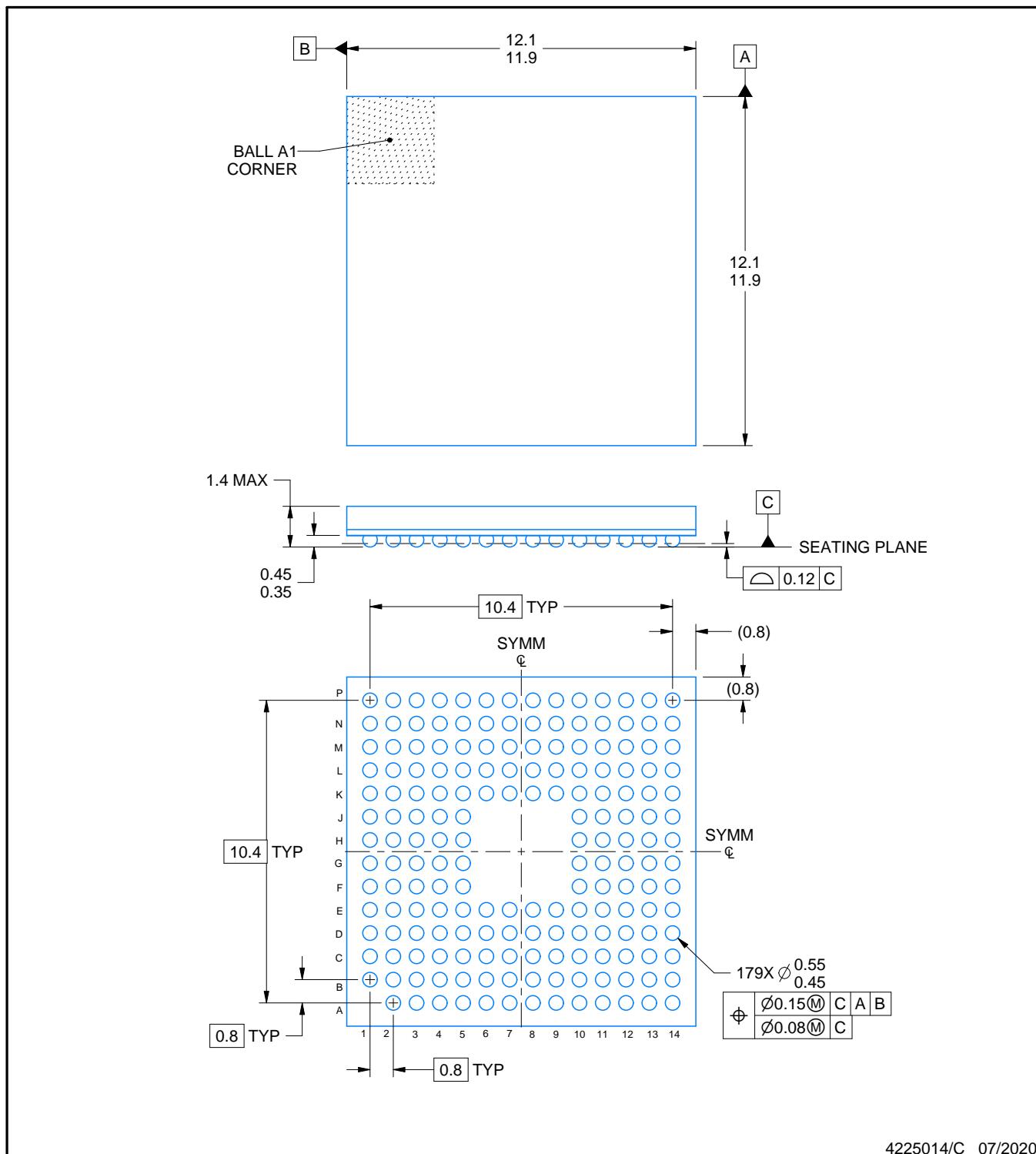

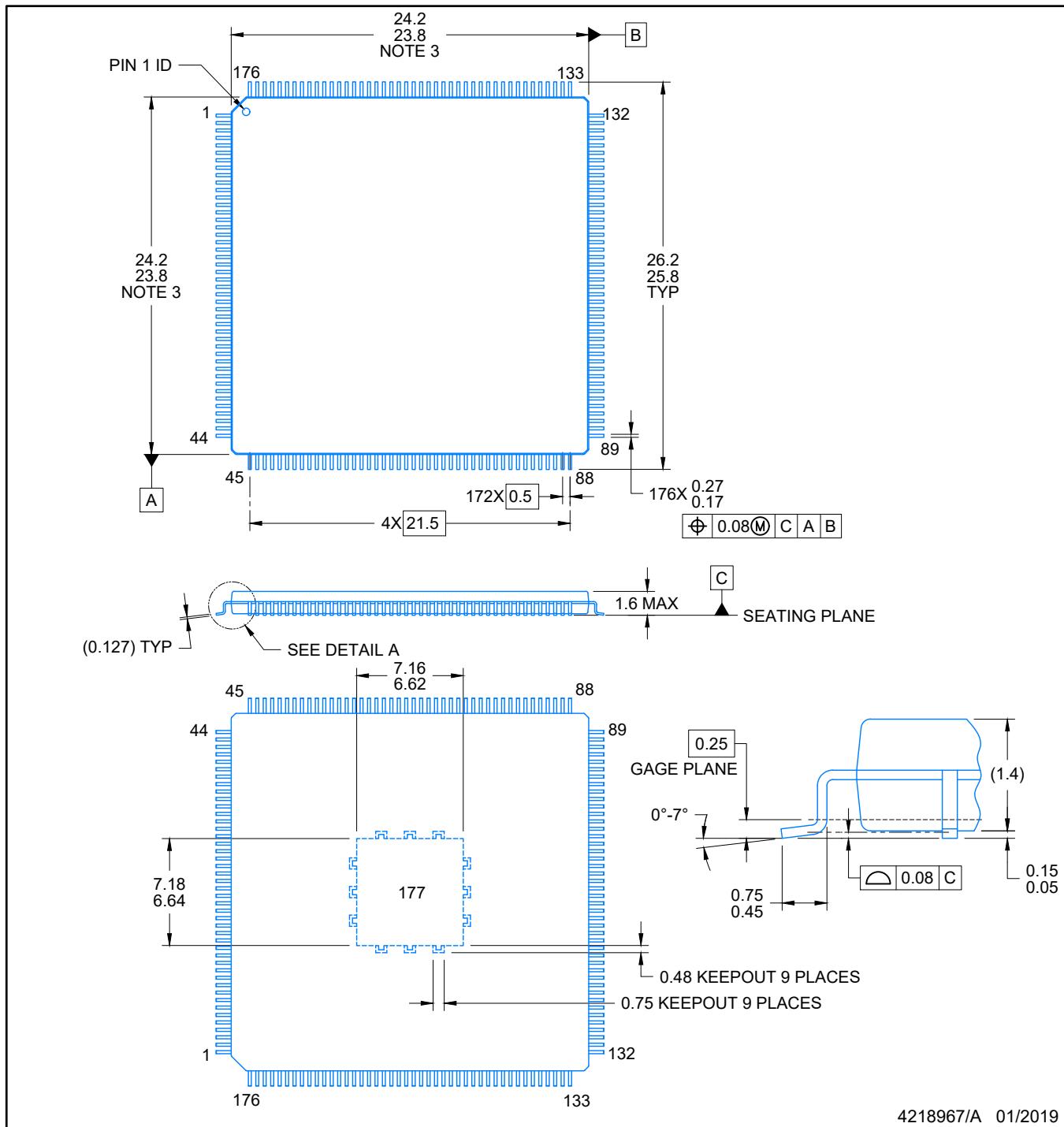

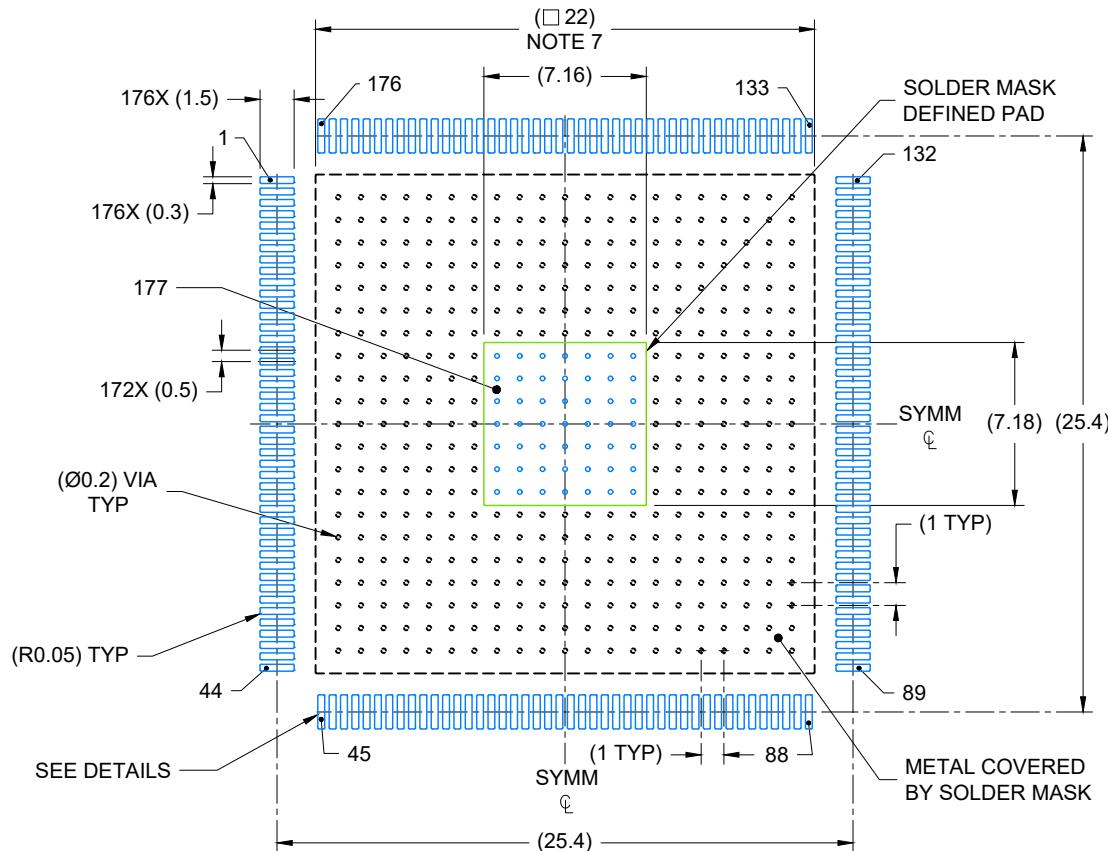

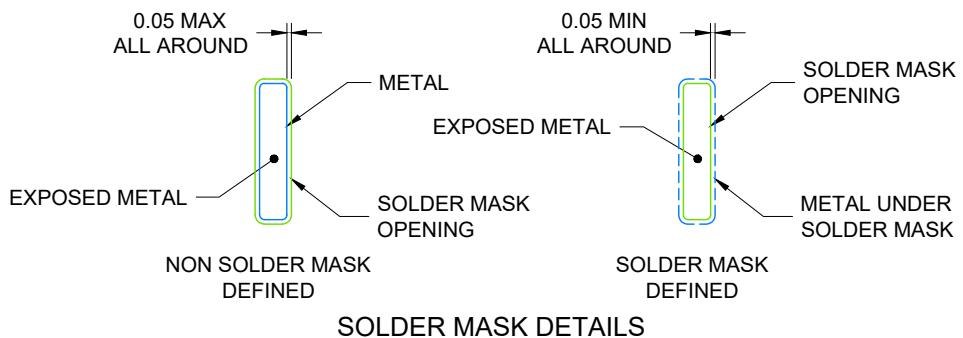

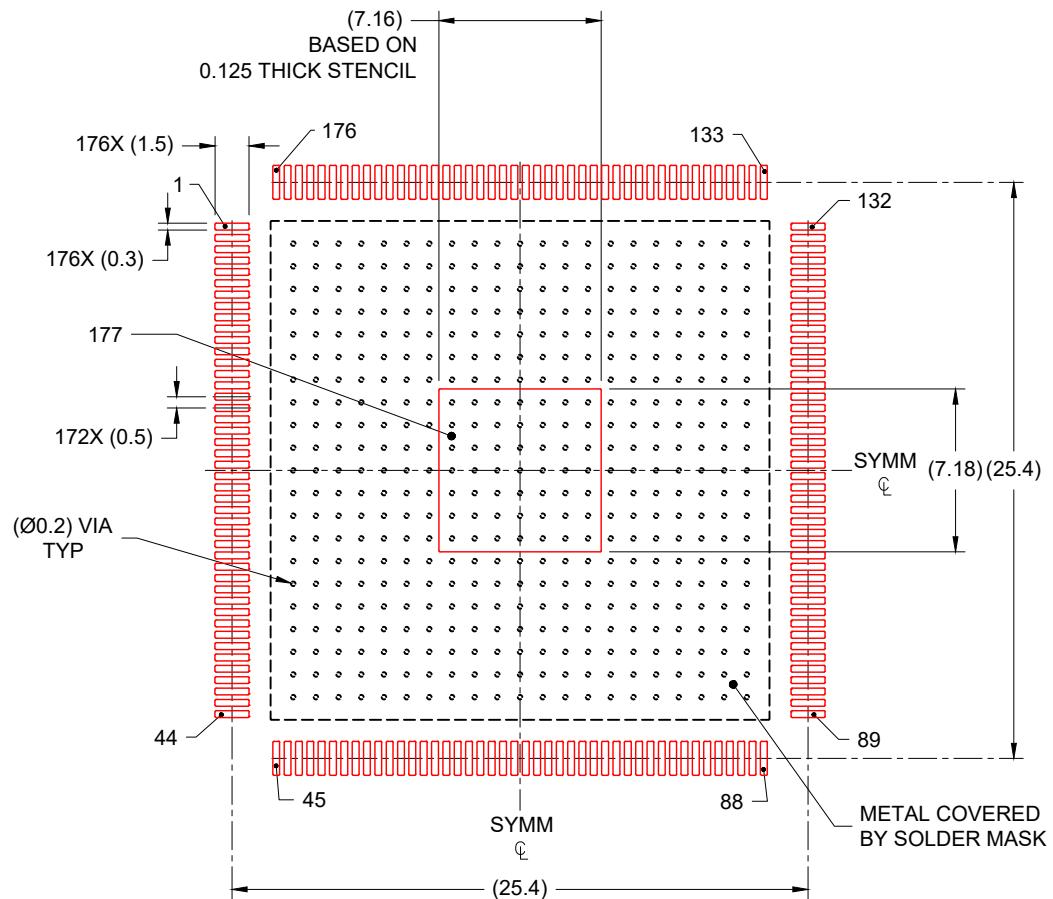

図 6-1 に、176 ピン PGF/PTP 薄型クワッド・フラットパック (LQFP) のピン配置を示します。図 6-2～図 6-5 に、179 ボール ZHH ボール・グリッド・アレイ (BGA) および 179 ボール ZAY 新しいファイン・ピッチ・ボール・グリッド・アレイ (nFBGA) の端子割り当てを示します。図 6-6～図 6-9 に、176 ボール ZJZ プラスチック BGA の端子割り当てを示します。表 6-1 に、各ピンの機能を示します。

図 6-1. F2833x, F2823x 176 ピン PGF/PTP LQFP (上面図)

---

### 注

サーマル・パッドは、最良の熱伝導パスを得るために、PCB のグランド (GND) プレーンに半田付けする必要があります。このデバイスでは、サーマル・パッドが内部ダイ  $V_{SS}$  に電気的に短絡していないので、サーマル・パッドは、PCB グランドへの電気的接続を提供しません。PowerPAD™ パッケージで設計された熱効率を最適に利用するには、このテクノロジーを考慮して PCB を設計する必要があります。PowerPAD 本体直下の PCB 表面に、サーマル・ランドが必要です。このサーマル・ランドは、サーマル・パッドに半田付けする必要があります。熱を放散するために、必要に応じてサーマル・ランドを大きくする必要があります。サーマル・パッドを基板の内層 GND プレーンに接続するには、複数のサーマル・ビアを使用する必要があります。PowerPAD パッケージの使用方法の詳細については、『[PowerPAD™ 热的に強化されたパッケージ](#)』を参照してください。

---

図 6-2. F2833x、F2823x 179 ポール ZHH MicroStar BGA および 179 ポール ZAY nFBGA (左上象限) (底面図)

図 6-3. F2833x、F2823x 179 ボール ZHH MicroStar BGA および 179 ボール ZAY nFBGA (右上象限) (底面図)

図 6-4. F2833x、F2823x 179 ポール ZHH MicroStar BGA および 179 ポール ZAY nFBGA (左下象限) (底面図)

図 6-5. F2833x、F2823x 179 ポール ZHH MicroStar BGA および 179 ポール ZAY nFBGA (右下象限) (底面図)

図 6-6. F2833x、F2823x 176 ポール ZJZ プラスチック BGA (左上象限) (底面図)

図 6-7. F2833x、F2823x 176 ポール ZJZ プラスチック BGA (右上象限) (底面図)

図 6-8. F2833x、F2823x 176 ポール ZJZ プラスチック BGA (左下象限) (底面図)

図 6-9. F2833x、F2823x 176 ボール ZJZ プラスチック BGA (右下象限) (底面図)

## 6.2 信号の説明

表 6-1 では、信号について説明します。GPIO 機能（斜体で表示）がリセット時のデフォルトです。その下に表示されているペリフェラル信号は、代替機能です。一部のペリフェラル機能は、すべてのデバイスで利用できるわけではありません。詳細は 表 5-1 および 表 5-2 を参照してください。入力は、5V 許容ではありません。XINTF 出力機能を生成できるすべてのピンの駆動能力は 8mA（標準値）です。これは、ピンが XINTF 機能用に設定されていない場合でも同様です。他のすべてのピンの駆動能力は、特に記述のない限り、4mA（標準値）です。すべての GPIO ピンは I/O であり、内部プルアップを備えており、ピンごとにイネーブルまたはディセーブルを選択できます。この機能は、GPIO ピンにのみ適用されます。GPIO0～GPIO11 ピンのプルアップは、リセット時にはイネーブルされません。GPIO12～GPIO87 のプルアップは、リセット時にイネーブルされます。

表 6-1. 信号の説明

| 名称                  | ピン番号                    |                          |                  | 説明 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|-------------------------|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | PGF、<br>PTP<br>ピン番<br>号 | ZHH、<br>ZAY<br>ボール番<br>号 | ZJZ<br>ボール番<br>号 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>JTAG</b>         |                         |                          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRST                | 78                      | M10                      | L11              | 内部プルダウン付きの JTAG テスト・リセット。 <u>TRST</u> を HIGH に駆動すると、スキャン・システムがデバイスの動作を制御するようになります。この信号が接続されていない場合、または LOW に駆動されている場合、デバイスは機能モードで動作し、テスト・リセット信号は無視されます。<br>注: <u>TRST</u> は、アクティブ HIGH のテスト・ピンであり、通常のデバイス動作中は常に LOW に維持する必要があります。このピンには外付けプルダウン抵抗が必要です。この抵抗の値は、設計に適用されるデバッガ・ポッドの駆動能力に基づいて決定する必要があります。一般的には、2.2kΩ の抵抗を使用すれば、適切な保護が得られます。この抵抗の値は、アプリケーションによって決まるので、デバッガおよびアプリケーションが適切に動作するように、各ターゲット・ボードを検証することを推奨します。(I, ↓)                                                          |

| TCK                 | 87                      | N12                      | M14              | 内部プルアップ付き JTAG テスト・クロック (I, ↑)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMS                 | 79                      | P10                      | M12              | 内部プルアップ付き JTAG テスト・モード選択 (TMS)。このシリアル制御入力は、TCK の立ち上がりエッジで、TAP コントローラにシフトインされます。(I, ↑)                                                                                                                                                                                                                                                                                                                                                                                              |

| TDI                 | 76                      | M9                       | N12              | 内部プルアップ付き JTAG テスト・データ入力 (TDI)。TDI は、TCK の立ち上がりエッジで、選択したレジスタ（命令またはデータ）にシフトインされます。(I, ↑)                                                                                                                                                                                                                                                                                                                                                                                            |

| TDO                 | 77                      | K9                       | N13              | JTAG スキャンアウト、テスト・データ出力 (TDO)。選択したレジスタ（命令またはデータ）の内容は、TCK の立ち下りエッジで、TDO からシフトアウトされます。(O/Z 8mA 駆動)                                                                                                                                                                                                                                                                                                                                                                                    |

| EMU0                | 85                      | L11                      | N7               | エミュレータ・ピン 0。 <u>TRST</u> が HIGH に駆動されているとき、このピンは、JTAG デバッグ・プローブ・システムに対する割り込み、または同システムからの割り込みとして使用され、JTAG スキャンによって入力または出力として定義されます。このピンは、デバイスをバウンダリ・スキャン・モードにするためにも使用されます。EMU0 ピンがロジック HIGH 状態、EMU1 ピンがロジック LOW 状態のとき、 <u>TRST</u> ピンの立ち上がりエッジによって、デバイスがバウンダリ・スキャン・モードにラッチされます。(I/O/Z, 8mA 駆動 ↑)<br>注: このピンには外付けプルアップ抵抗が必要です。この抵抗の値は、設計に適用されるデバッガ・ポッドの駆動能力に基づいて決定する必要があります。一般的には、2.2kΩ～4.7kΩ の抵抗が適切です。この抵抗の値は、アプリケーションによって決まるので、デバッガおよびアプリケーションが適切に動作するように、各ターゲット・ボードを検証することを推奨します。 |

| EMU1                | 86                      | P12                      | P8               | エミュレータ・ピン 1。 <u>TRST</u> が HIGH に駆動されているとき、このピンは、JTAG デバッグ・プローブ・システムに対する割り込み、または同システムからの割り込みとして使用され、JTAG スキャンによって入力または出力として定義されます。このピンは、デバイスをバウンダリ・スキャン・モードにするためにも使用されます。EMU0 ピンがロジック HIGH 状態、EMU1 ピンがロジック LOW 状態のとき、 <u>TRST</u> ピンの立ち上がりエッジによって、デバイスがバウンダリ・スキャン・モードにラッチされます。(I/O/Z, 8mA 駆動 ↑)<br>注: このピンには外付けプルアップ抵抗が必要です。この抵抗の値は、設計に適用されるデバッガ・ポッドの駆動能力に基づいて決定する必要があります。一般的には、2.2kΩ～4.7kΩ の抵抗が適切です。この抵抗の値は、アプリケーションによって決まるので、デバッガおよびアプリケーションが適切に動作するように、各ターゲット・ボードを検証することを推奨します。 |

| <b>フラッシュ</b>        |                         |                          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>DD3VFL</sub> | 84                      | M11                      | L9               | 3.3V フラッシュ・コア電源ピン。このピンは、常時 3.3V に接続する必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TEST1               | 81                      | K10                      | M7               | テスト・ピン。TI で使用のため予約済み。未接続のままにする必要があります。(I/O)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

**表 6-1. 信号の説明 (continued)**

| 名称    | ピン番号                    |                          |                  | 説明 <sup>(1)</sup>                           |

|-------|-------------------------|--------------------------|------------------|---------------------------------------------|

|       | PGF、<br>PTP<br>ピン番<br>号 | ZHH、<br>ZAY<br>ボール番<br>号 | ZJZ<br>ボール番<br>号 |                                             |

| TEST2 | 82                      | P11                      | L7               | テスト・ピン。TI で使用のため予約済み。未接続のままにする必要があります。(I/O) |

表 6-1. 信号の説明 (continued)

| 名称            | ピン番号                    |                          |                  | 説明 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-------------------------|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | PGF、<br>PTP<br>ピン番<br>号 | ZHH、<br>ZAY<br>ボール番<br>号 | ZJZ<br>ボール番<br>号 |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>クロック</b>   |                         |                          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

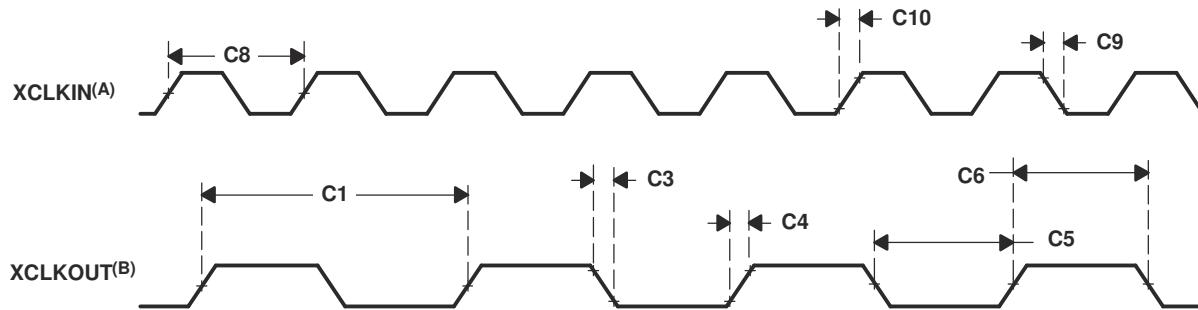

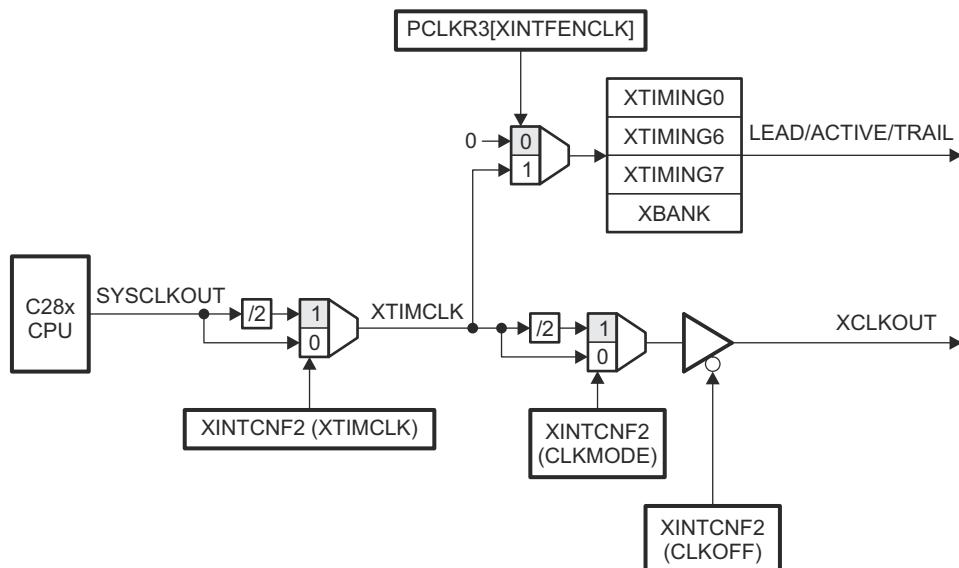

| XCLKOUT       | 138                     | C11                      | A10              | SYSCLKOUT から生成される出力クロック。XCLKOUT は、SYSCLKOUT と同じ周波数、1/2 の周波数、または 1/4 の周波数のいずれかです。これは、XINTCNF2 レジスタのビット 18:16 (XTIMCLK) およびビット 2 (CLKMODE) によって制御されます。リセット時は、XCLKOUT = SYSCLKOUT/4 です。XCLKOUT 信号は、XINTCNF2[CLKOFF] を 1 に設定するとオフにできます。他の GPIO ピンとは異なり、XCLKOUT ピンはリセット時に高インピーダンス状態になりません。(O/Z, 8mA 駆動)。                                                                                                                                      |

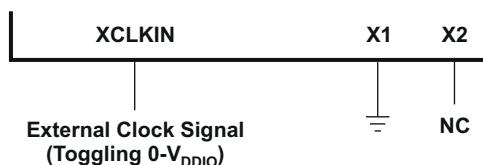

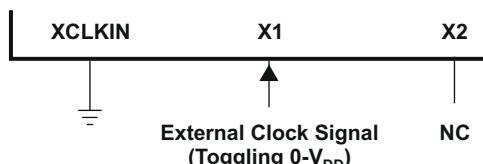

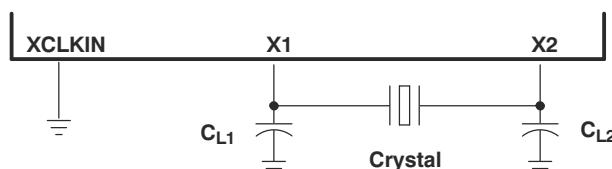

| XCLKIN        | 105                     | J14                      | G13              | 外部発振器入力。このピンは、外部 3.3V 発振器からクロックを供給するためのものです。この場合、X1 ピンを GND に接続する必要があります。水晶振動子 / 発振子を使用する場合（または、外付けの 1.9V 発振器を使用して X1 ピンにクロックを供給する場合）、このピンを GND に接続する必要があります。(I)                                                                                                                                                                                                                                                                         |

| X1            | 104                     | J13                      | G14              | 内部 / 外部発振器入力。内部発振器を使用するには、X1 と X2 の間に水晶振動子またはセラミック発振子を接続します。X1 ピンは、1.9V/1.8V コア・デジタル電源を基準としています。1.9V/1.8V の外部発振器を X1 ピンに接続することもできます。この場合、XCLKIN ピンをグランドに接続する必要があります。XCLKIN ピンで 3.3V の外部発振器を使用する場合は、X1 を GND に接続する必要があります。(I)                                                                                                                                                                                                             |

| X2            | 102                     | J11                      | H14              | 内蔵発振器出力。X1 と X2 の間に水晶振動子またはセラミック共振器を接続できます。X2 を使用しない場合は、未接続のままにする必要があります。(O)                                                                                                                                                                                                                                                                                                                                                             |

| <b>RESET</b>  |                         |                          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XRS           | 80                      | L10                      | M13              | デバイス・リセット (IN) およびウォッチドッグ・リセット (OUT)。<br>デバイス・リセット。XRS は、デバイスの実行を終了させます。PC は、0x3FFFC0 の位置にあるアドレスを指します。XRS を HIGH レベルに駆動すると、PC が指しているアドレスから実行が開始されます。ウォッチドッグ・リセットが発生すると、MCU によってこのピンが LOW に駆動されます。ウォッチドッグ・リセット中、ウォッチドッグ・リセット期間である 512 OSCCLK サイクルにわたって、XRS ピンが LOW に駆動されます。(I/OD, ↑)<br>このピンの出力バッファは、内部プルアップ付きのオープン・ドレインです。このピンが外部デバイスによって駆動される場合は、オープン・ドレイン・デバイスを使用して駆動する必要があります。パワードウン時のタイミング要件が満たされるようにするために、このピンに外部 R-C 回路を使うこともできます。 |

| <b>ADC 信号</b> |                         |                          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADCINA7       | 35                      | K4                       | K1               | ADC グループ A、チャネル 7 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINA6       | 36                      | J5                       | K2               | ADC グループ A、チャネル 6 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINA5       | 37                      | L1                       | L1               | ADC グループ A、チャネル 5 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINA4       | 38                      | L2                       | L2               | ADC グループ A、チャネル 4 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINA3       | 39                      | L3                       | L3               | ADC グループ A、チャネル 3 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINA2       | 40                      | M1                       | M1               | ADC グループ A、チャネル 2 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINA1       | 41                      | N1                       | M2               | ADC グループ A、チャネル 1 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINA0       | 42                      | M3                       | M3               | ADC グループ A、チャネル 0 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB7       | 53                      | K5                       | N6               | ADC グループ B、チャネル 7 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB6       | 52                      | P4                       | M6               | ADC グループ B、チャネル 6 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB5       | 51                      | N4                       | N5               | ADC グループ B、チャネル 5 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB4       | 50                      | M4                       | M5               | ADC グループ B、チャネル 4 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB3       | 49                      | L4                       | N4               | ADC グループ B、チャネル 3 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB2       | 48                      | P3                       | M4               | ADC グループ B、チャネル 2 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB1       | 47                      | N3                       | N3               | ADC グループ B、チャネル 1 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCINB0       | 46                      | P2                       | P3               | ADC グループ B、チャネル 0 入力 (I)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCLO         | 43                      | M2                       | N2               | 低い基準電圧 (アナログ・グランドに接続) (I)                                                                                                                                                                                                                                                                                                                                                                                                                |

表 6-1. 信号の説明 (continued)

| 名称        | ピン番号                    |                          |                  | 説明 <sup>(1)</sup>                        |

|-----------|-------------------------|--------------------------|------------------|------------------------------------------|

|           | PGF、<br>PTP<br>ピン番<br>号 | ZHH、<br>ZAY<br>ボール番<br>号 | ZJZ<br>ボール番<br>号 |                                          |

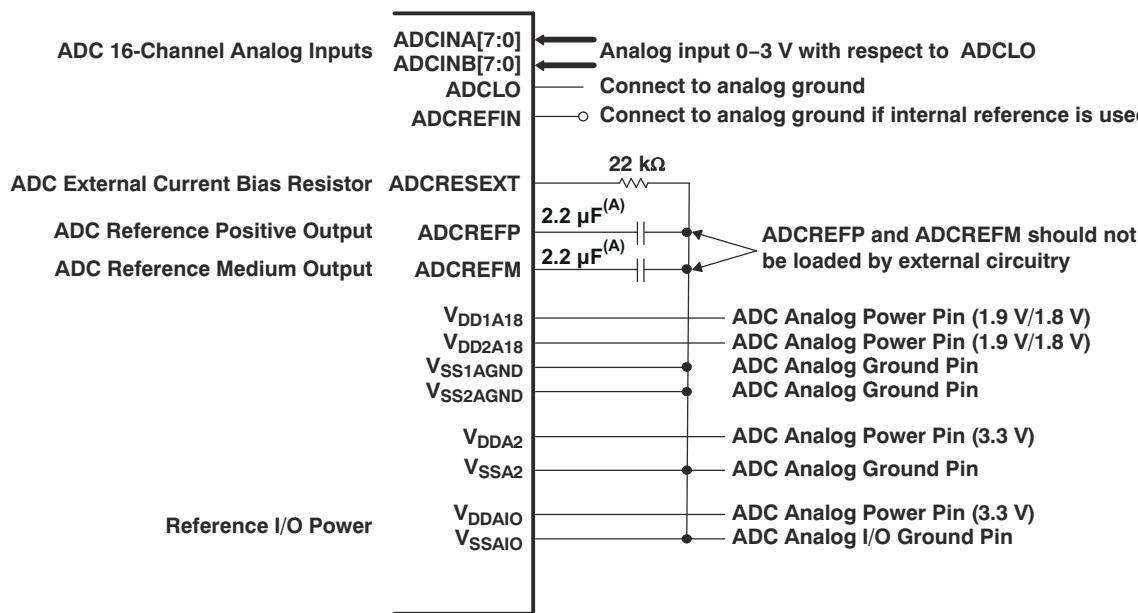

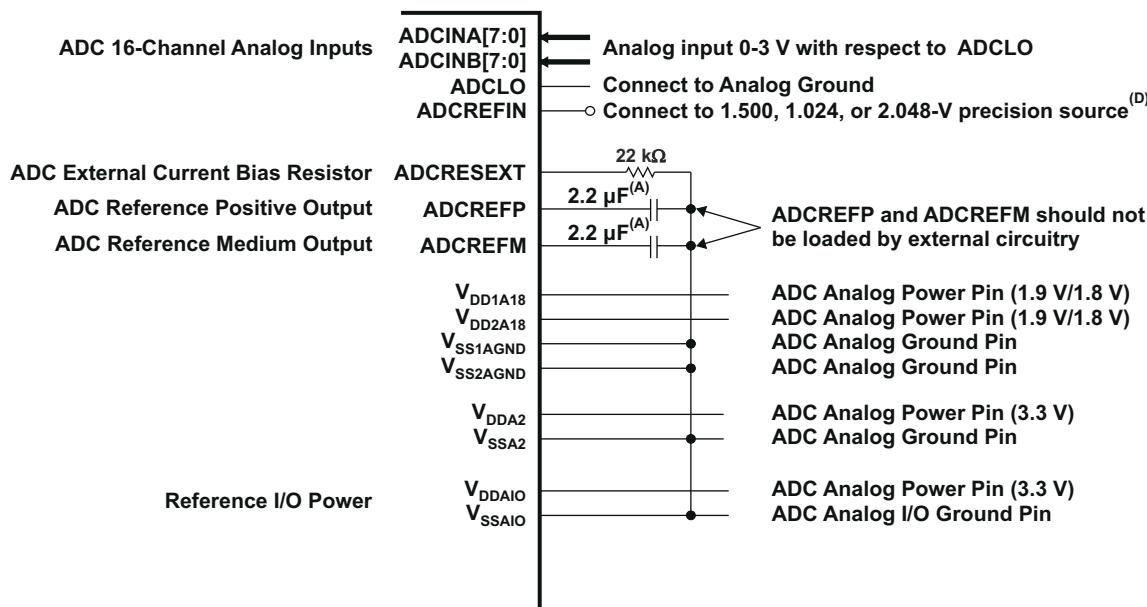

| ADCREFEXT | 57                      | M5                       | P6               | ADC 外部電流バイアス抵抗。22kΩ の抵抗をアナログ・グランドに接続します。 |

| ADCREFIN  | 54                      | L5                       | P7               | 外部基準電圧入力ピン (I)                           |

表 6-1. 信号の説明 (continued)

| 名称                       | ピン番号                    |                          |                  | 説明 <sup>(1)</sup>                                                                                                                        |

|--------------------------|-------------------------|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                          | PGF、<br>PTP<br>ピン番<br>号 | ZHH、<br>ZAY<br>ボール番<br>号 | ZJZ<br>ボール番<br>号 |                                                                                                                                          |

| ADCREFP                  | 56                      | P5                       | P5               | 内部基準電圧正出力。アナログ・グランドに対して、2.2μF の低 ESR (1.5Ω 未満) セラミック・バイパス・コンデンサが必要です。(O)<br>注:ADC クロック・レートを使って、システムで使用されているコンデンサのデータシートから ESR 仕様を導出します。  |

| ADCREFM                  | 55                      | N5                       | P4               | 内部基準電圧中間出力。アナログ・グランドに対して、2.2μF の低 ESR (1.5Ω 未満) セラミック・バイパス・コンデンサが必要です。(O)<br>注:ADC クロック・レートを使って、システムで使用されているコンデンサのデータシートから ESR 仕様を導出します。 |

| <b>CPU および I/O の電源ピン</b> |                         |                          |                  |                                                                                                                                          |

| V <sub>DDA2</sub>        | 34                      | K2                       | K4               | ADC アナログ電源ピン                                                                                                                             |

| V <sub>SSA2</sub>        | 33                      | K3                       | P1               | ADC アナログ・グランド・ピン                                                                                                                         |

| V <sub>DDAIO</sub>       | 45                      | N2                       | L5               | ADC アナログ I/O 電源ピン                                                                                                                        |

| V <sub>SSAIO</sub>       | 44                      | P1                       | N1               | ADC アナログ I/O グランド・ピン                                                                                                                     |

| V <sub>DD1A18</sub>      | 31                      | J4                       | K3               | ADC アナログ電源ピン                                                                                                                             |

| V <sub>SS1AGND</sub>     | 32                      | K1                       | L4               | ADC アナログ・グランド・ピン                                                                                                                         |

| V <sub>DD2A18</sub>      | 59                      | M6                       | L6               | ADC アナログ電源ピン                                                                                                                             |

| V <sub>SS2AGND</sub>     | 58                      | K6                       | P2               | ADC アナログ・グランド・ピン                                                                                                                         |

| V <sub>DD</sub>          | 4                       | B1                       | D4               | CPU およびロジックのデジタル電源ピン                                                                                                                     |

| V <sub>DD</sub>          | 15                      | B5                       | D5               |                                                                                                                                          |

| V <sub>DD</sub>          | 23                      | B11                      | D8               |                                                                                                                                          |

| V <sub>DD</sub>          | 29                      | C8                       | D9               |                                                                                                                                          |

| V <sub>DD</sub>          | 61                      | D13                      | E11              |                                                                                                                                          |

| V <sub>DD</sub>          | 101                     | E9                       | F4               |                                                                                                                                          |

| V <sub>DD</sub>          | 109                     | F3                       | F11              |                                                                                                                                          |

| V <sub>DD</sub>          | 117                     | F13                      | H4               |                                                                                                                                          |

| V <sub>DD</sub>          | 126                     | H1                       | J4               |                                                                                                                                          |

| V <sub>DD</sub>          | 139                     | H12                      | J11              |                                                                                                                                          |

| V <sub>DD</sub>          | 146                     | J2                       | K11              |                                                                                                                                          |

| V <sub>DD</sub>          | 154                     | K14                      | L8               |                                                                                                                                          |

| V <sub>DD</sub>          | 167                     | N6                       |                  |                                                                                                                                          |

| V <sub>DDIO</sub>        | 9                       | A4                       | A13              | デジタル I/O 電源ピン                                                                                                                            |

| V <sub>DDIO</sub>        | 71                      | B10                      | B1               |                                                                                                                                          |

| V <sub>DDIO</sub>        | 93                      | E7                       | D7               |                                                                                                                                          |

| V <sub>DDIO</sub>        | 107                     | E12                      | D11              |                                                                                                                                          |

| V <sub>DDIO</sub>        | 121                     | F5                       | E4               |                                                                                                                                          |

| V <sub>DDIO</sub>        | 143                     | L8                       | G4               |                                                                                                                                          |

| V <sub>DDIO</sub>        | 159                     | H11                      | G11              |                                                                                                                                          |

| V <sub>DDIO</sub>        | 170                     | N14                      | L10              |                                                                                                                                          |

| V <sub>DDIO</sub>        |                         |                          | N14              |                                                                                                                                          |

**表 6-1. 信号の説明 (continued)**

| 名称                                 | ピン番号                    |                          |                  | 説明 <sup>(1)</sup>                                                                     |

|------------------------------------|-------------------------|--------------------------|------------------|---------------------------------------------------------------------------------------|

|                                    | PGF、<br>PTP<br>ピン番<br>号 | ZHH、<br>ZAY<br>ボール番<br>号 | ZJZ<br>ボール番<br>号 |                                                                                       |

| V <sub>SS</sub>                    | 3                       | A5                       | A1               |                                                                                       |

| V <sub>SS</sub>                    | 8                       | A10                      | A2               |                                                                                       |

| V <sub>SS</sub>                    | 14                      | A11                      | A14              |                                                                                       |

| V <sub>SS</sub>                    | 22                      | B4                       | B14              |                                                                                       |

| V <sub>SS</sub>                    | 30                      | C3                       | F6               |                                                                                       |

| V <sub>SS</sub>                    | 60                      | C7                       | F7               |                                                                                       |

| V <sub>SS</sub>                    | 70                      | C9                       | F8               |                                                                                       |

| V <sub>SS</sub>                    | 83                      | D1                       | F9               |                                                                                       |

| V <sub>SS</sub>                    | 92                      | D6                       | G6               |                                                                                       |

| V <sub>SS</sub>                    | 103                     | D14                      | G7               |                                                                                       |

| V <sub>SS</sub>                    | 106                     | E8                       | G8               |                                                                                       |

| V <sub>SS</sub>                    | 108                     | E14                      | G9               |                                                                                       |

| V <sub>SS</sub>                    | 118                     | F4                       | H6               | デジタル・グランド・ピン                                                                          |

| V <sub>SS</sub>                    | 120                     | F12                      | H7               |                                                                                       |

| V <sub>SS</sub>                    | 125                     | G1                       | H8               |                                                                                       |

| V <sub>SS</sub>                    | 140                     | H10                      | H9               |                                                                                       |

| V <sub>SS</sub>                    | 144                     | H13                      | J6               |                                                                                       |

| V <sub>SS</sub>                    | 147                     | J3                       | J7               |                                                                                       |

| V <sub>SS</sub>                    | 155                     | J10                      | J8               |                                                                                       |

| V <sub>SS</sub>                    | 160                     | J12                      | J9               |                                                                                       |

| V <sub>SS</sub>                    | 166                     | M12                      | P13              |                                                                                       |

| V <sub>SS</sub>                    | 171                     | N10                      | P14              |                                                                                       |

| V <sub>SS</sub>                    |                         | N11                      |                  |                                                                                       |

| V <sub>SS</sub>                    |                         | P6                       |                  |                                                                                       |

| V <sub>SS</sub>                    |                         | P8                       |                  |                                                                                       |

| <b>GPIO およびペリフェラル信号</b>            |                         |                          |                  |                                                                                       |

| GPIO0<br>EPWM1A<br>-<br>-          | 5                       | C1                       | D1               | 汎用入出力 0 (I/O/Z)<br>拡張 PWM1 出力 A および HRPWM チャネル (O)<br>-<br>-                          |

| GPIO1<br>EPWM1B<br>ECAP6<br>MFSRB  | 6                       | D3                       | D2               | 汎用入出力 1 (I/O/Z)<br>拡張 PWM1 出力 B (O)<br>拡張キャプチャ 6 入出力 (I/O)<br>McBSP-B 受信フレーム 同期 (I/O) |

| GPIO2<br>EPWM2A<br>-<br>-          | 7                       | D2                       | D3               | 汎用入出力 2 (I/O/Z)<br>拡張 PWM2 出力 A および HRPWM チャネル (O)<br>-<br>-                          |

| GPIO3<br>EPWM2B<br>ECAP5<br>MCLKRB | 10                      | E4                       | E1               | 汎用入出力 3 (I/O/Z)<br>拡張 PWM2 出力 B (O)<br>拡張キャプチャ 5 入出力 (I/O)<br>McBSP-B 受信クロック (I/O)    |

| GPIO4<br>EPWM3A<br>-<br>-          | 11                      | E2                       | E2               | 汎用入出力 4 (I/O/Z)<br>拡張 PWM3 出力 A および HRPWM チャネル (O)<br>-<br>-                          |

表 6-1. 信号の説明 (continued)

| 名称                                                | ピン番号                    |                          |                  | 説明 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------|-------------------------|--------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | PGF、<br>PTP<br>ピン番<br>号 | ZHH、<br>ZAY<br>ボール番<br>号 | ZJZ<br>ボール番<br>号 |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GPIO5<br>EPWM3B<br>MFSRA<br>ECAP1                 | 12                      | E3                       | E3               | 汎用入出力 5 (I/O/Z)<br>拡張 PWM3 出力 B (O)<br>McBSP-A 受信フレーム同期 (I/O)<br>拡張キャプチャ入出力 1 (I/O)                                                                                                                                                                                                                                                                                                                                               |

| GPIO6<br>EPWM4A<br>EPWMSYNCI<br>EPWMSYNCO         | 13                      | E1                       | F1               | 汎用入出力 6 (I/O/Z)<br>拡張 PWM4 出力 A および HRPWM チャネル (O)<br>外部 ePWM 同期パルス入力 (I)<br>外部 ePWM 同期パルス出力 (O)                                                                                                                                                                                                                                                                                                                                  |

| GPIO7<br>EPWM4B<br>MCLKRA<br>ECAP2                | 16                      | F2                       | F2               | 汎用入出力 7 (I/O/Z)<br>拡張 PWM4 出力 B (O)<br>McBSP-A 受信クロック (I/O)<br>拡張キャプチャ入出力 2 (I/O)                                                                                                                                                                                                                                                                                                                                                 |

| GPIO8<br>EPWM5A<br>CANTXB<br>ADCSOCAO             | 17                      | F1                       | F3               | 汎用入出力 8 (I/O/Z)<br>拡張 PWM5 出力 A および HRPWM チャネル (O)<br>拡張 CAN-B 送信 (O)<br>ADC 変換開始 A (O)                                                                                                                                                                                                                                                                                                                                           |

| GPIO9<br>EPWM5B<br>SCITXDB<br>ECAP3               | 18                      | G5                       | G1               | 汎用入出力 9 (I/O/Z)<br>拡張 PWM5 出力 B (O)<br>SCI-B 送信データ (O)<br>拡張キャプチャ入出力 3 (I/O)                                                                                                                                                                                                                                                                                                                                                      |

| GPIO10<br>EPWM6A<br>CANRXB<br>ADCSOCBO            | 19                      | G4                       | G2               | 汎用入出力 10 (I/O/Z)<br>拡張 PWM6 出力 A および HRPWM チャネル (O)<br>拡張 CAN-B 受信 (I)<br>ADC 変換開始 B (O)                                                                                                                                                                                                                                                                                                                                          |

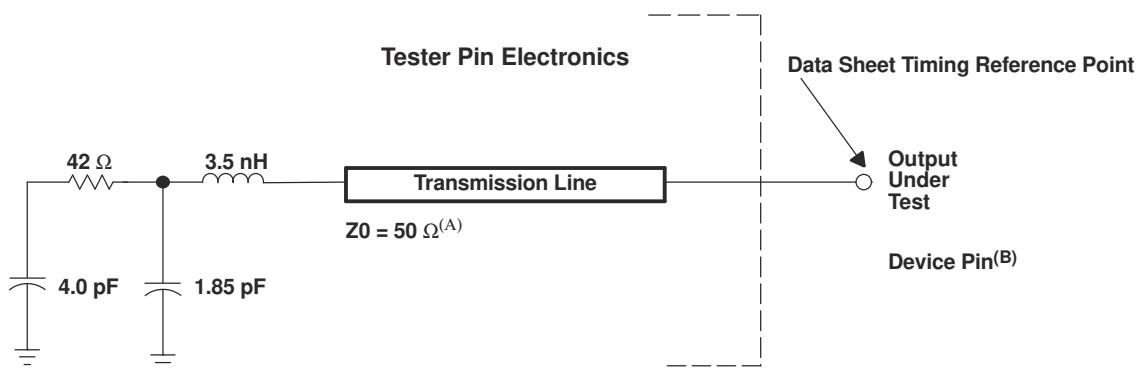

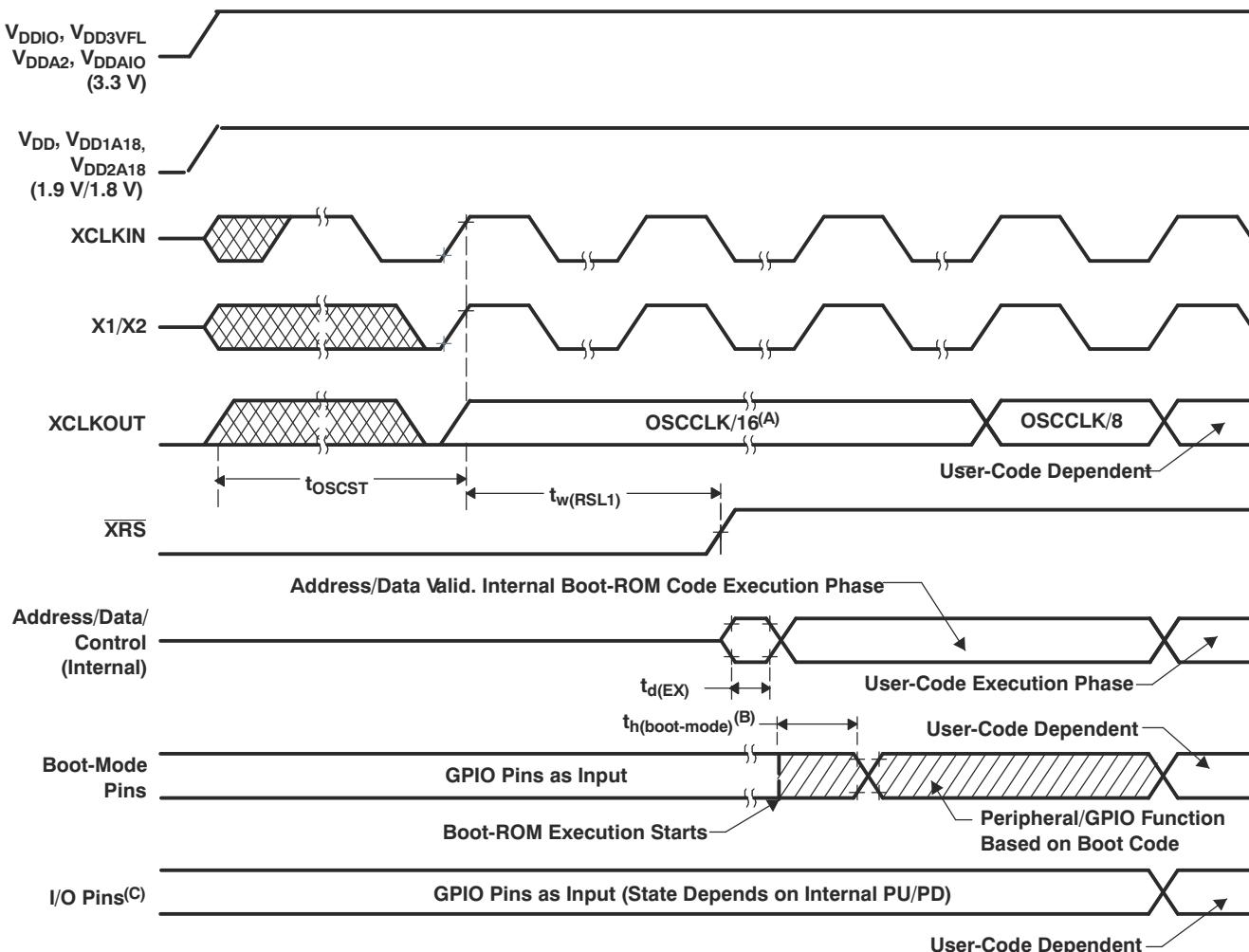

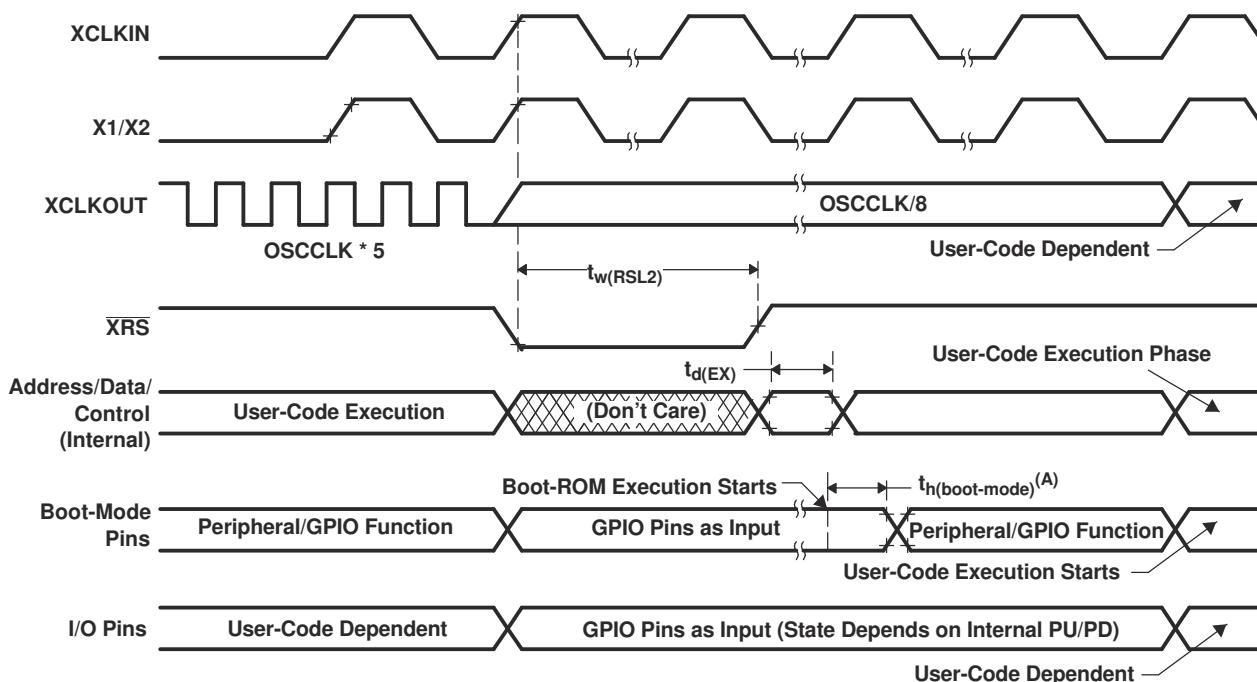

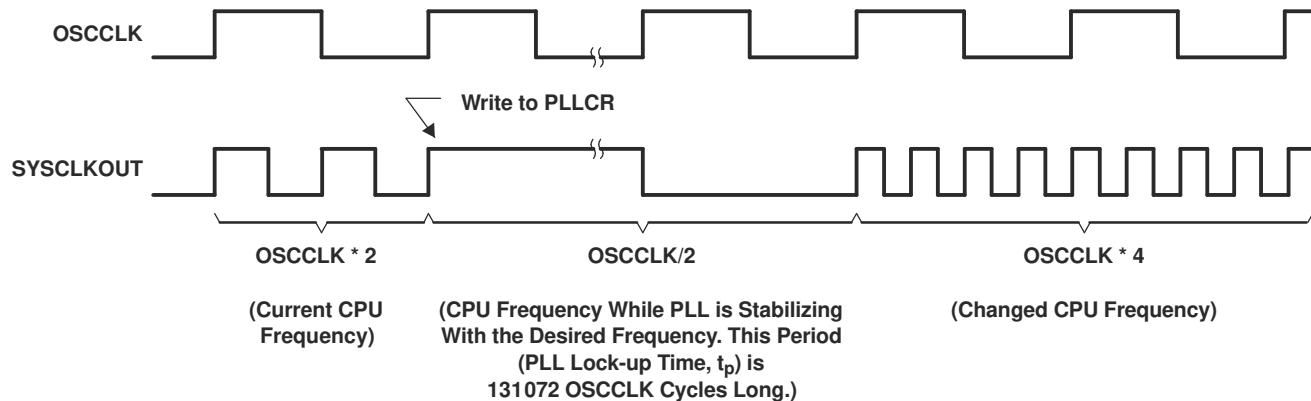

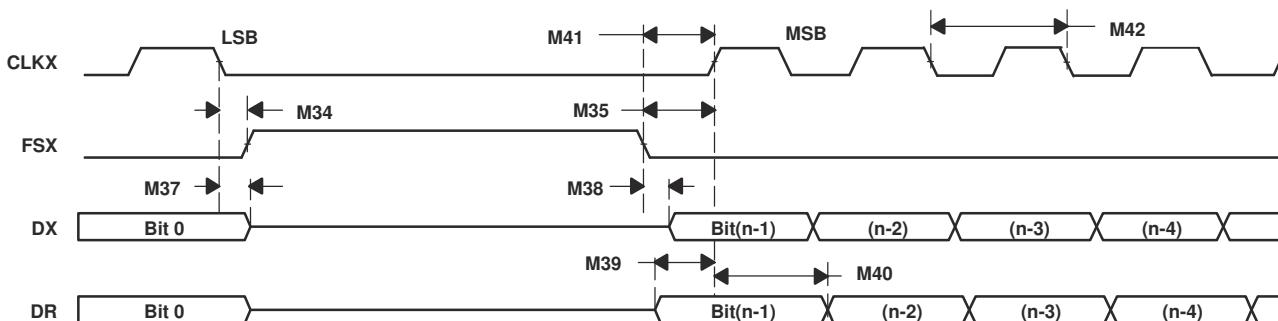

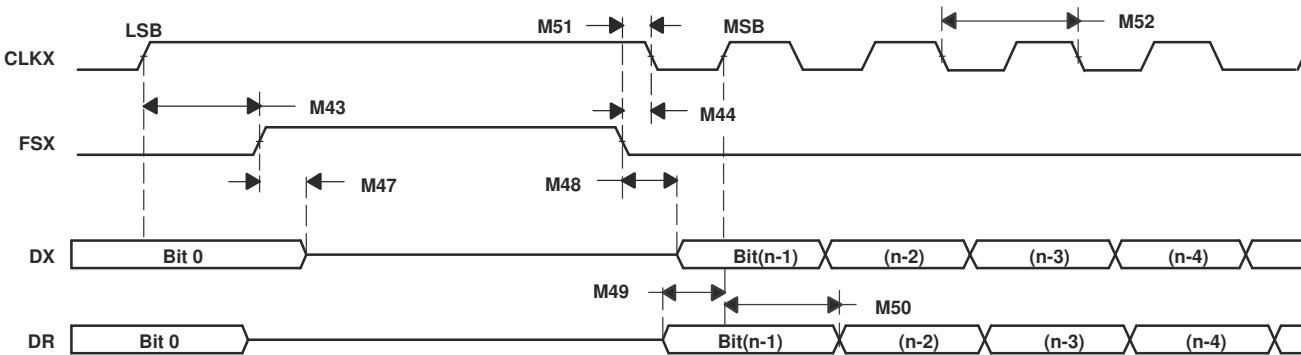

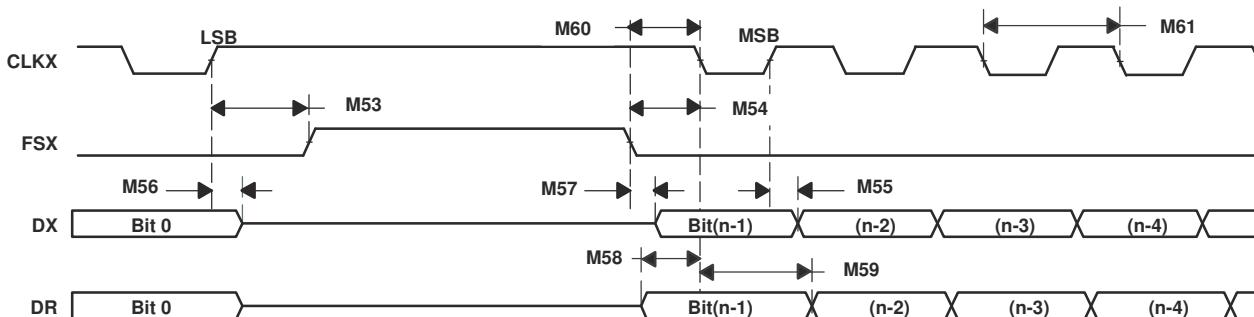

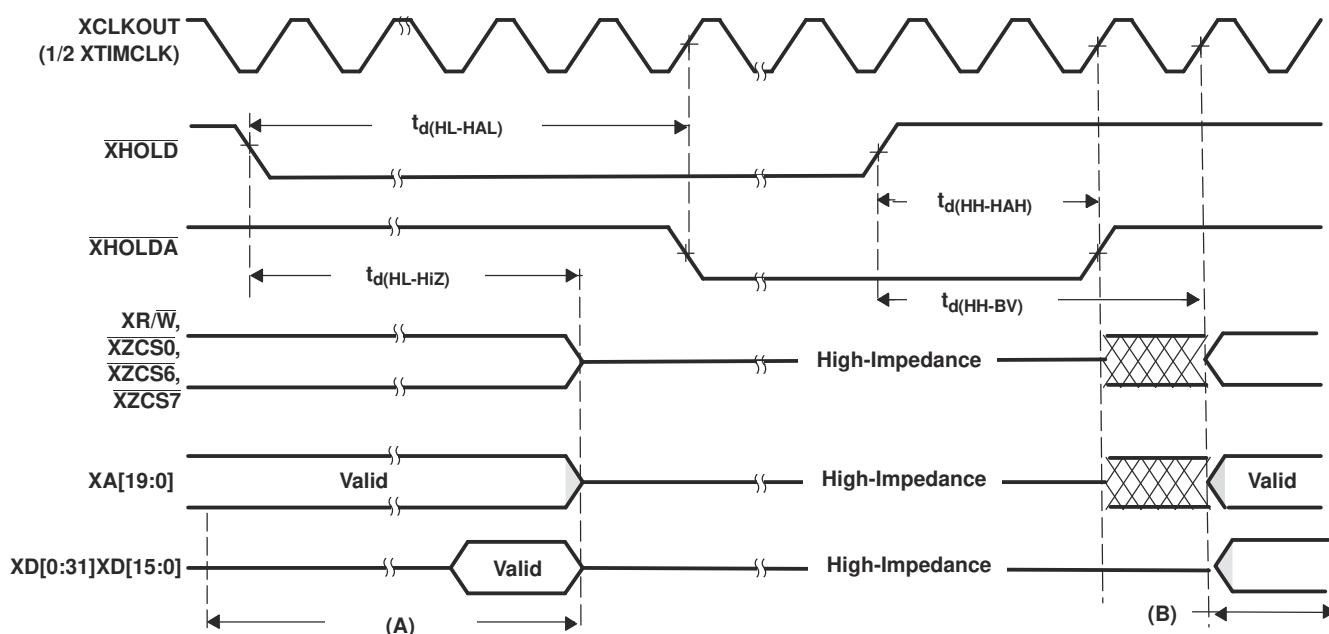

| GPIO11<br>EPWM6B<br>SCIRXDB<br>ECAP4              | 20                      | G2                       | G3               | 汎用入出力 11 (I/O/Z)<br>拡張 PWM6 出力 B (O)<br>SCI-B 受信データ (I)<br>拡張 CAP 入出力 4 (I/O)                                                                                                                                                                                                                                                                                                                                                     |