## TMF0064 64K ビットシリアル FRAM、SDQ インターフェイス搭載

### 1 特長

- 複数のページに分割された、ユーザー プログラマブルな構成データを保存するための 64768 ビットの FRAM

- 基板の配線を削減するシングルワイヤインターフェイス

- シングルワイヤプロトコルを使用した通信: 15.4kbps (標準速度) および 90Kbps (オーバードライブ速度)

- デバイス内蔵のスイッチポイントヒステリシスおよびフィルタリングにより、ノイズの存在下でも性能を向上

- IEC 61000-4-2 レベル 4 ESD 保護 (接触  $\pm 8\text{kV}$ 、気中  $\pm 15\text{kV}$ 、標準値)

- 工場出荷時設定の固有の 64 ビット ID 番号

- 動作温度範囲:  $-10^\circ\text{C} \sim 85^\circ\text{C}$

- 動作電圧範囲: 5V  $\pm 5\%$  (標準速度およびオーバードライブ速度)

- 動作電圧範囲: 3.3V  $\pm 5\%$  (標準速度のみ)

- TO-92 (LP) および VSON (DRS) パッケージで供給

### 2 アプリケーション

- 医療用ケーブルの識別

- アセットトラッカー (資産追跡機能)**

- ネットワーク接続の周辺機器とプリンタ

- 偽造ハードウェアの防止

### 3 説明

TMF0064 は、64K ビットのシリアル不揮発性メモリ (NVM) デバイスであり、工場出荷時にプログラムされる 48 ビットの識別番号と 8 ビットのファミリコードを内蔵しています。このメモリは FRAM ベースであり、他の NVM 技術と比較して耐久性が高くなっています ( $10^6 \text{ R/W サイクル}$ )。

このデバイスは、SDQ™ 1 線式インターフェイスで通信を行い、15.4kbps および 90Kbps の両方の速度をサポートしています。SDQ ピンは、デバイスの通信および電源ピンの両方として機能します。メモリは、ページあたり 256 ビットの 253 のメモリページで構成されています。データは、まず 32 バイトのスクラッチパットに書き込まれます。FRAM メモリにコピーする前に、データは検証されます。

このデバイスは、3.3V  $\pm 5\%$  および 5V  $\pm 5\%$  の 2 つの電源電圧範囲で動作し、 $-10^\circ\text{C}$  から  $85^\circ\text{C}$  までの範囲で仕様が規定されています。動作範囲はほとんどのアプリケーションに対応しており、低コストの開発においてピーク設計を可能にします。

#### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> | 本体サイズ(公称)        |

|---------|----------------------|-------------------------|------------------|

| TMF0064 | VSON (DRP)           | 3 mm × 3mm              | 3 mm × 3mm       |

|         | TO-92 (LP)           | 5.2 mm × 3.68mm         | 4.83 mm × 4.83mm |

(1) 詳細については、[メカニカル、パッケージ、および注文情報を参照してください。](#)

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンも含まれます。

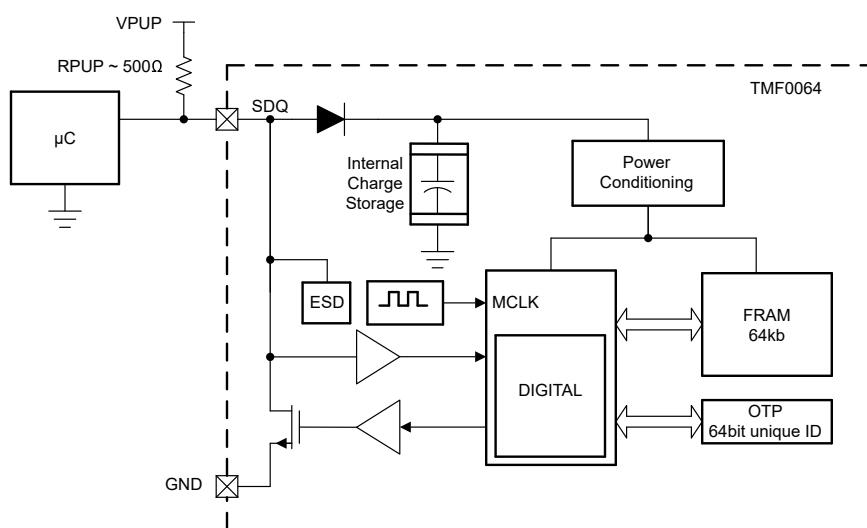

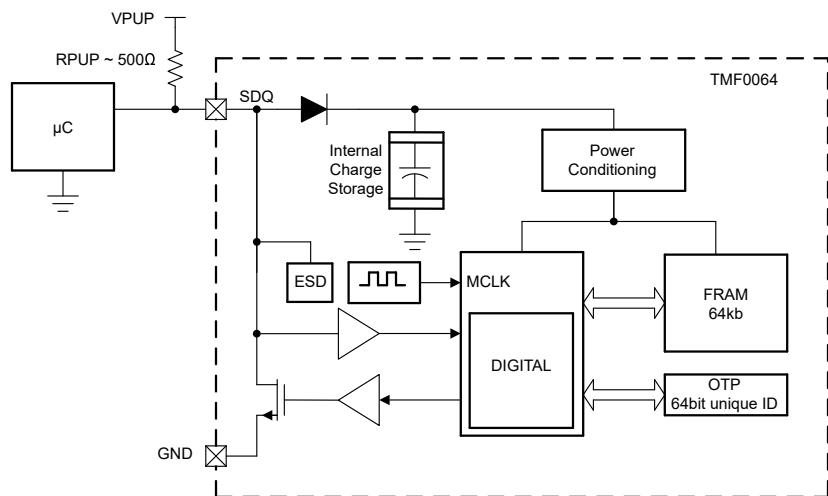

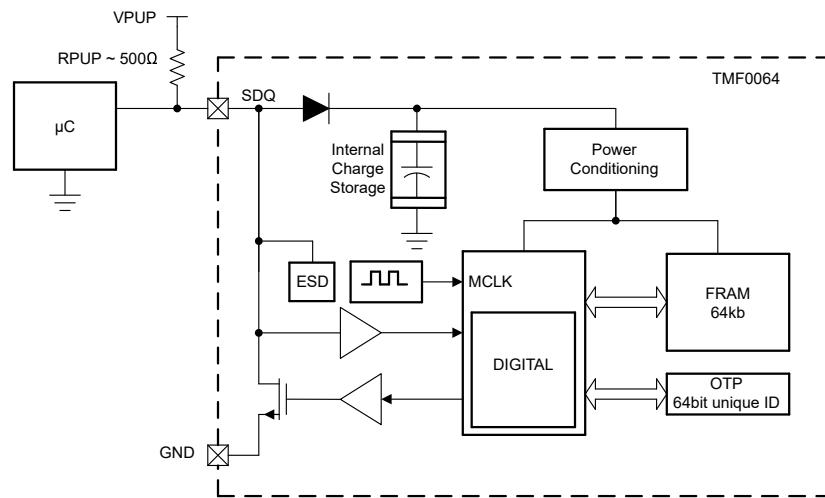

ブロック図

## 目次

|             |   |                        |    |

|-------------|---|------------------------|----|

| 1 特長        | 1 | 6.4 デバイスの機能モード         | 12 |

| 2 アプリケーション  | 1 | 6.5 プログラミング            | 12 |

| 3 説明        | 1 | 7 アプリケーションと実装          | 26 |

| 4 ピン構成および機能 | 3 | 7.1 アプリケーション情報         | 26 |

| 5 仕様        | 4 | 7.2 代表的なアプリケーション       | 26 |

| 5.1 絶対最大定格  | 4 | 7.3 電源に関する推奨事項         | 27 |

| 5.2 ESD 定格  | 4 | 7.4 レイアウト              | 28 |

| 5.3 推奨動作条件  | 4 | 8 デバイスおよびドキュメントのサポート   | 29 |

| 5.4 熱に関する情報 | 4 | 8.1 ドキュメントの更新通知を受け取る方法 | 29 |

| 5.5 電気的特性   | 5 | 8.2 サポート・リソース          | 29 |

| 5.6 タイミング要件 | 6 | 8.3 商標                 | 29 |

| 5.7 機能テスト   | 7 | 8.4 静電気放電に関する注意事項      | 29 |

| 5.8 代表的特性   | 7 | 8.5 用語集                | 29 |

| 6 詳細説明      | 8 | 9 改訂履歴                 | 29 |

| 6.1 概要      | 8 | 10 メカニカル、パッケージ、および注文情報 | 29 |

| 6.2 機能ブロック図 | 8 | 10.1 パッケージ情報           | 30 |

| 6.3 機能説明    | 8 | 10.2 テープおよびリール情報       | 31 |

## 4 ピン構成および機能

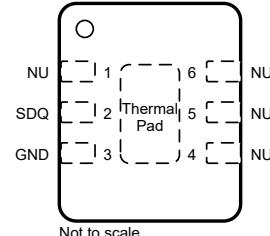

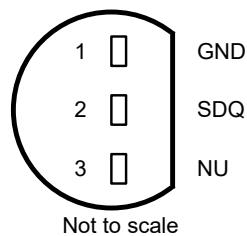

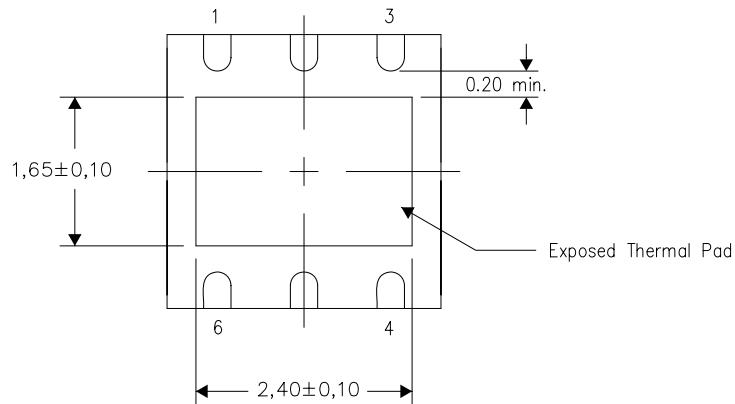

図 4-1. TMF0064 LP パッケージ、3 ピン TO-92 (底面 図 4-2. TMF0064 DRS パッケージ、6 ピン VSON (上面 図)

表 4-1. ピンの機能

| 名称  | ピン      |         | タイプ <sup>(1)</sup> | 説明                               |  |  |

|-----|---------|---------|--------------------|----------------------------------|--|--|

|     | TMF0064 |         |                    |                                  |  |  |

|     | TO-92   | VSON    |                    |                                  |  |  |

| EP  | —       | EP      | —                  | 露出したサーマル パッド。GND に接続。            |  |  |

| GND | 1       | 3       | GND                | グランド                             |  |  |

| NU  | 3       | 1、4、5、6 | —                  | 使用できない端末。接続しないでください。             |  |  |

| SDQ | 2       | 2       | I/O                | データ。オープンドレイン には外付けのプルアップ抵抗が必要です。 |  |  |

(1) GND = グランド、I/O = 双方向

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                 | 最小値  | 最大値 | 単位 |

|------------------|-----------------|------|-----|----|

| V <sub>PUP</sub> | データに印加される DC 電圧 | -0.3 | 5.5 | V  |

| I <sub>OL</sub>  | Low レベル出力電流     |      | 30  | mA |

| T <sub>STG</sub> | 保存温度            | -40  | 125 | °C |

- (1) 絶対最大定格外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内で、一時的に「推奨動作条件」の範囲を超えた動作をさせる場合、必ずしもデバイスが損傷を受けるものではありませんが、完全には機能しない可能性があります。この方法でデバイスを動作させると、デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります

### 5.2 ESD 定格

|                    |      | 値                                                        | 単位     |

|--------------------|------|----------------------------------------------------------|--------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | ±1000  |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±250   |

|                    |      | ESD IEC 61000-4-2 エア放電、SDQ および GND                       | ±15000 |

- (1) JEDEC ドキュメント JEP155 には、500VHBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250VCDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|                  |                        | 最小値  | 公称値 | 最大値  | 単位 |

|------------------|------------------------|------|-----|------|----|

| V <sub>PUP</sub> | 動作プルアップ電圧              | 3.13 |     | 5.25 | V  |

| R <sub>PUP</sub> | シリアル通信インターフェイスのプルアップ抵抗 |      | 500 |      | Ω  |

| T <sub>A</sub>   | 外気温度での動作時              | -10  |     | 85   | °C |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | DRP (VSON) | TO-92 (LP) | 単位   |

|-----------------------|---------------------|------------|------------|------|

|                       |                     | 6 ピン       | 3 ピン       |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 50.1       | 129.3      | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 54.3       | 93.6       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 21.8       | 99.3       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.9        | 23.7       | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 21.7       | 99.3       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 5.9        | -          | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

最小および最大仕様は、 $T_A = -10^\circ\text{C} \sim 85^\circ\text{C}$  の範囲に適用されます。標準仕様は、 $25^\circ\text{C}$ 、 $V_{PUP} = 3.3\text{V}$  および  $5\text{V}$  (特に記載がない限り) での値です。

| パラメータ               |                                          | テスト条件                                                  | 最小値  | 標準値  | 最大値  | 単位            |

|---------------------|------------------------------------------|--------------------------------------------------------|------|------|------|---------------|

| <b>I/O ピン:一般データ</b> |                                          |                                                        |      |      |      |               |

| $V_{PUP}$           | プルアップ電圧                                  | $\pm 5\%$ の誤差                                          | 3.13 | 3.3  | 3.46 | V             |

|                     |                                          |                                                        | 4.75 | 5    | 5.25 | V             |

| $R_{PUP}$           | プルアップ抵抗                                  | (1) (2) (3)                                            |      | 500  |      | $\Omega$      |

| $C_{CABLE}$         | ケーブル容量                                   | (4) (5)                                                |      |      | 1.7  | nF            |

| $C_{IO}$            | 入力容量                                     | (6) (4)                                                |      | 2000 |      | pF            |

| $I_L$               | 入力負荷電流                                   | (7)                                                    |      | 7    | 14   | $\mu\text{A}$ |

| $V_{IL}$            | 入力 Low 電圧                                | (8)                                                    |      |      | 0.5  | V             |

| $V_{OL}$            | 出力 LOW 電圧                                | $R_{PUP} = 500\Omega$ 、<br>$V_{PUP} = 3.3\text{V}$ で測定 |      | 0.4  | 0.5  | V             |

|                     |                                          | $R_{PUP} = 500\Omega$ 、<br>$V_{PUP} = 5\text{V}$ で測定   |      | 0.4  | 0.5  | V             |

| $V_{TL}$            | High から Low へのスイッチング スレッショルド(4) (3) (9)  | $V_{PUP} = 3.3\text{V}$                                | 0.84 |      | 1.72 | V             |

|                     |                                          | $V_{PUP} = 5\text{V}$                                  | 2    |      | 3    | V             |

| $V_{TH}$            | Low から High へのスイッチング スレッショルド(4) (3) (10) | $V_{PUP} = 3.3\text{V}$                                | 1.64 |      | 2.75 | V             |

|                     |                                          | $V_{PUP} = 5\text{V}$                                  | 3.2  |      | 4.3  | V             |

| $V_{HY}$            | スイッチング ヒステリシス(4) (3) (11)                | $V_{PUP} = 3.3\text{V}$                                | 0.44 |      | 1.1  | V             |

|                     |                                          | $V_{PUP} = 5\text{V}$                                  | 0.9  |      | 1.3  | V             |

- (1) 最大許容プルアップ抵抗は、接続されているデバイスの数と復帰時間によって異なります。規定値は、6 つのデバイスがシステム内で接続されていると仮定し、最小復帰時間です。

- (2) 抵抗の許容誤差の誤差は 1% 以下です。

- (3)  $V_{TL}$ 、 $V_{TH}$ 、 $V_{HY}$  は内部電源電圧の関数で、 $v_{pup}$ 、 $r_{pup}$ 、 $1_{pup}$ 、 $R_{PUP}$ 、1 線式タイミング、SDQ ピンの容量性負荷の関数です。 $V_{PUP}$  が低く、 $R_{PUP}$  が大きく、 $t_{REC}$  が短く、容量性負荷が大きいと、 $V_{TL}$ 、 $V_{TH}$ 、 $V_{HY}$  の値が小さくなります。

- (4) 設計、特性評価、シミュレーションによる規定のみ。実製品の検査は行っていません。

- (5) システム要件。

- (6) 最大容量値は、 $V_{PUP}$  が最初に印加されたときの内部寄生容量を表します。寄生電荷ストレージ容量が充電されると、通常のロジック遷移に影響はありません。

- (7) SDQ が HIGH ( $V_{PUP}$  時) で、デバイスがアイドル モード (デジタル アクティビティやメモリ アクセスなし) の場合に適用されます。数値は、スタンバイ消費電流を示しています。

- (8) ホストが SDQ をロジック 0 レベルに駆動しているときは、常に SDQ の電圧が  $V_{ILMAX}$  以下である必要があります。

- (9) その電圧を下回ると、SDQ の立ち下がりエッジで、ロジック 0 が検出されます。

- (10) その電圧を上回ると、SDQ の立ち上がりエッジで、ロジック 1 が検出されます。

- (11) SDQ ピンの立ち上がりエッジ中に  $V_{TH}$  を超えた後、SDQ の電圧は、ロジック 0 として検出されるには、少なくとも  $V_{HY}$  の分だけ低下する必要があります。

## 5.6 タイミング要件

最小および最大仕様は、 $T_A = -10^\circ\text{C} \sim 85^\circ\text{C}$  の範囲に適用されます。標準仕様は、 $25^\circ\text{C}$ 、 $V_{PUP} = 3.3\text{V}$  および  $5\text{V}$  (特に記載がない限り) での値です。

|                                 |                                    |                                                | 最小値 | 公称値               | 最大値           | 単位   |

|---------------------------------|------------------------------------|------------------------------------------------|-----|-------------------|---------------|------|

| <b>I/O ピン:一般データ</b>             |                                    |                                                |     |                   |               |      |

| $t_{STARTUP}$                   | 起動時間                               | デバイスがプレゼンス パルスで応答する前に、最小 SDQ が HIGH である必要があります |     | 10                |               | ms   |

| $t_{REC}$                       | 復帰時間                               | 標準速度 <sup>(1) (2)</sup>                        | 5   |                   |               | μs   |

|                                 |                                    | オーバードライブ速度 <sup>(1) (2)</sup>                  | 5   |                   |               | μs   |

| $t_{REH}$                       | 立ち上がりエッジ ホールドオフ時間                  | 標準速度 <sup>(1) (2)</sup>                        | 0.5 |                   | 5             | μs   |

| $t_{SLOT}$                      | タイム スロット期間                         | 標準速度 <sup>(3)</sup>                            | 65  |                   |               | μs   |

|                                 |                                    | オーバードライブ速度 <sup>(3)</sup>                      | 11  |                   |               | μs   |

| <b>I/O ピン:1 線式リセット、存在検出サイクル</b> |                                    |                                                |     |                   |               |      |

| $t_{RSTL}$                      | リセット Low 時間                        | 標準速度                                           | 480 |                   | 550           | μs   |

|                                 |                                    | オーバードライブ速度                                     | 48  |                   | 80            | μs   |

| $t_{PDH}$                       | 存在検出 High パルス                      | 標準速度                                           | 15  |                   | 60            | μs   |

|                                 |                                    | オーバードライブ速度                                     | 2   |                   | 6             | μs   |

| $t_{PDL}$                       | 存在検出 Low 時間                        | 標準速度                                           | 60  |                   | 240           | μs   |

|                                 |                                    | オーバードライブ速度                                     | 8   |                   | 24            | μs   |

| $t_{PDS}$                       | 存在検出サンプル時間 <sup>(4), (5)</sup>     | 標準速度                                           | 60  | 70                | 75            | μs   |

|                                 |                                    | オーバードライブ速度                                     | 6   | 8.7               | 10            | μs   |

| <b>IO ピン:1 線式書き込み</b>           |                                    |                                                |     |                   |               |      |

| $t_{WOL}$                       | Write-Zero Low 時間                  | 標準速度 <sup>(6)</sup>                            | 60  |                   | 120           | μs   |

|                                 |                                    | オーバードライブ速度 <sup>(6)</sup>                      | 5   |                   | 15.5          | μs   |

| $t_{W1L}$                       | Write-One Low 時間                   | 標準速度 <sup>(6)</sup>                            | 1   |                   | 15            | μs   |

|                                 |                                    | オーバードライブ速度 <sup>(6)</sup>                      | 1   |                   | 2             | μs   |

| <b>IO ピン:1 線式読み取り</b>           |                                    |                                                |     |                   |               |      |

| $t_{RL}$                        | 読み取り Low 時間                        | 標準速度 <sup>(2) (7)</sup>                        | 5   |                   | 15 - $t_{RC}$ | μs   |

|                                 |                                    | オーバードライブ速度 <sup>(2) (7)</sup>                  | 1   |                   | 2 - $t_{RC}$  | μs   |

| $t_{RDS}$                       | 読み取りサンプル時間 <sup>(8)</sup>          | 標準速度 <sup>(2) (7)</sup>                        |     | $t_{RL} + t_{RC}$ | 15            | μs   |

|                                 |                                    | オーバードライブ速度 <sup>(2) (7)</sup>                  |     | $t_{RL} + t_{RC}$ | 3             | μs   |

| <b>FRAM</b>                     |                                    |                                                |     |                   |               |      |

| NCY                             | 書き込み / 消去サイクル (耐久性) <sup>(2)</sup> |                                                |     |                   | 100 万         | サイクル |

| $t_{PROG}$                      | プログラミング時間 <sup>(2)</sup>           | 63.25Kb のすべてのメモリ用                              |     |                   | 1             | ms   |

| $t_{DR}$                        | データ保持期間 <sup>(9)</sup>             | 70°C で                                         |     | 10                |               | 年    |

- (1) ホストが SDQ をロジック 0 レベルに駆動しているときは、常に SDQ の電圧が  $V_{ILMAX}$  以下であることを確認してください。

- (2) 設計、特性評価、シミュレーションによる規定のみ。実製品の検査は行っていません。

- (3) 最大ピットレートを定義します。

- (4)  $t_{RSTL}$  後のインターバル。TMF0064 が存在する場合に、バス ホストが SDQ のロジック 0 を読み出すことができる期間。存在検出パルスはこの間隔外ですが、電源投入後 2ms 以内に完了します。この動作は、1 線式デバイスの電源が長時間オフ (バスが low) になったシナリオを示します。その後、バス電力が印加されます。このデバイスは誤動作が発生し、プレゼンス タイミング仕様に違反するプレゼンス パルスを生成します。しかし、通常は 10ms 以内に異常状態は解消されます。

- (5) システム要件。

- (6) 図 6-18 および図 6-19 の  $t_e$  は、プルアップ回路が SDQ ピンの電圧を  $V_{IL}$  から  $V_{TH}$  に上昇させるために必要な時間を表します。したがって、ホストがラインを low にプルする実際の最大期間は、それぞれ  $t_{W1LMAX} + t_F - t_e$  および  $t_{WOLMAX} + t_F - t_e$  です。

- (7) 図 6-20 の  $t_{RC}$  は、プルアップ回路によって SDQ ピンの電圧を  $V_{IL}$  からホスト デバイスの入力 high スレッショルドに上昇させるために必要な時間を表します。したがって、ホストがラインを low にプルする実際の最大期間は  $t_{RLMAX} + t_F$  です。

- (8) 前の立ち上がりエッジで  $V_{TH}$  に達した後、負のエッジが認識できる最小時間を表します。

- (9)  $T_A$  が増加すると、データ保持時間が低下します。高温での長期保存はお勧めできません。

## 5.7 機能テスト

動作自由気流での温度範囲内、 $V_{PUP} = 3.3V$  および  $5V$  (特に記述のない限り)

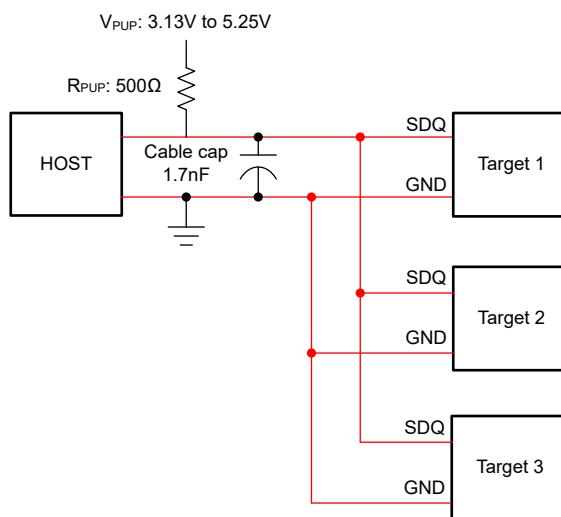

| パラメータ      | テスト条件                                                                                                    | 最小値 | 標準値 | 最大値 | 単位                   |

|------------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|----------------------|

| マルチターゲットバス | TMF0064 がネットワーク内で複数のターゲットデバイスと通信できる<br>ことを確認します。図 6-6 に、3つのターゲットデバイス (DUT を含む) の構成例を示します。 <sup>(1)</sup> | 0   |     |     | マルチターゲットバスに障害が発生しました |

(1) セクション 6.4.1 を参照してください。

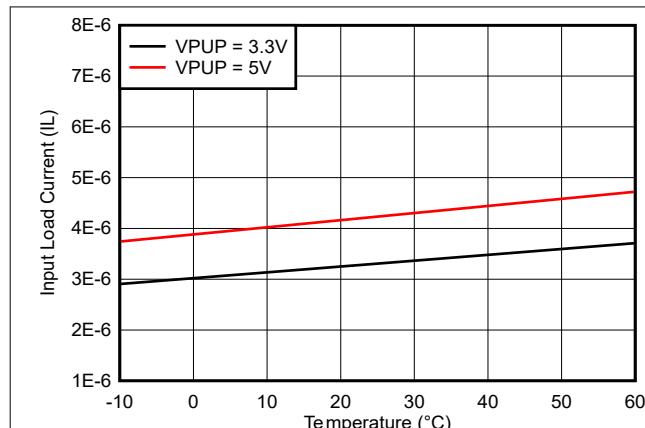

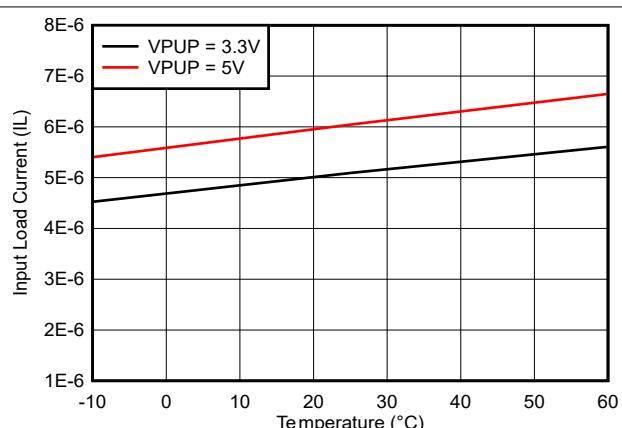

## 5.8 代表的特性

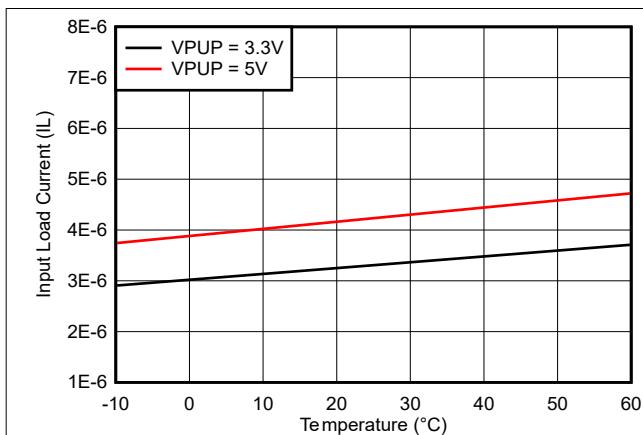

図 5-1. 入力負荷電流 ( $I_L$ ) と温度との関係 (標準速度)

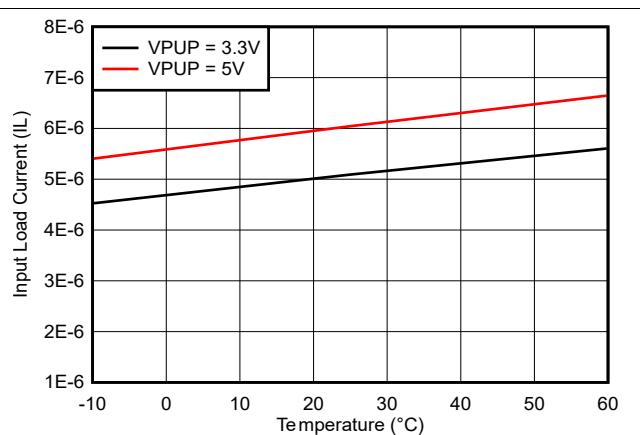

図 5-2. 入力負荷電流 ( $I_L$ ) と温度との関係 (オーバードライブ速度)

## 6 詳細説明

### 6.1 概要

**機能ブロック図**に、TMF0064 の主要な制御セクションとメモリ セクションの関係を示します。デバイスには、工場出荷時にプログラムされた 64 ビット ROM、8 ビット ファミリ コード、48 ビットの識別番号と 8 ビットの CRC 値、64768 ビットの FRAM という 3 つの主要データコンポーネントが含まれています。読み取り/書き込み動作用の電力は、SDQ ピンから生成されます。内部コンデンサは、信号ラインが high の間にエネルギーを蓄積し、SDQ ピンが high に戻ってコンデンサの電荷が補充されるまで、SDQ ピンが low の間にエネルギーを解放します。

### 6.2 機能ブロック図

図 6-1. 機能ブロック図

### 6.3 機能説明

#### 6.3.1 64768 ビット FRAM

表 6-1 は、TMF0064 デバイスの 64768 ビット FRAM セクションのメモリマップで、それぞれ 253 ページの 32 バイトとして構成されています。隣接する 8 つのページが 1 つの 256 バイト ブロックを形成します。FRAM メモリのプログラミング時は、32 バイトの揮発性スクラッチパッド バッファが使用されます。FRAM メモリへの書き込みプロセスには、2 つのステップがあります。データは、まずスクラッチパッド バッファに書き込まれます。次に、データが適切に受信されたことを確認するスクラッチパッド バッファを読み取ることでデータが検証されます。バッファの内容が正しい場合は、スクラッチパッド バッファを FRAM メモリにコピーするスクラッチパッド コピー コマンドが発行されます。このプロセスにより、メモリをプログラムするときにデータの整合性が検証されます。TMF0064 の 7680 ビット FRAM 部分のプログラミングと読み出しの詳細について、[セクション 6.5.4](#) を参照してください。

表 6-1. FRAM データ メモリ マップ

| アドレス範囲      | タイプ <sup>(1)</sup> | 説明                           | 保護コード (注記)            |

|-------------|--------------------|------------------------------|-----------------------|

| 0000h~00FFh | R/(W)              | データ メモリ ページ 0 ~ 7 (ブロック 0)   | (アドレス 1FA0h で制御される保護) |

| 0100h~01FFh | R/(W)              | データ メモリ ページ 8 ~ 15 (ブロック 1)  | (アドレス 1FA1h で制御される保護) |

| 0200h~02FFh | R/(W)              | データ メモリ ページ 16 ~ 23 (ブロック 2) | (アドレス 1FA2h で制御される保護) |

| 0300h~03FFh | R/(W)              | データ メモリ ページ 24 ~ 31 (ブロック 3) | (アドレス 1FA3h で制御される保護) |

| 0400h~04FFh | R/(W)              | データ メモリ ページ 32 ~ 39 (ブロック 4) | (アドレス 1FA4h で制御される保護) |

| 0500h~05FFh | R/(W)              | データ メモリ ページ 40 ~ 47 (ブロック 5) | (アドレス 1FA5h で制御される保護) |

| 0600h~06FFh | R/(W)              | データ メモリ ページ 48 ~ 55 (ブロック 6) | (アドレス 1FA6h で制御される保護) |

| 0700h~07FFh | R/(W)              | データ メモリ ページ 56 ~ 63 (ブロック 7) | (アドレス 1FA7h で制御される保護) |

| ...         | ...                | ...                          | ...                   |

**表 6-1. FRAM データ メモリ マップ (続き)**

| アドレス範囲      | タイプ <sup>(1)</sup> | 説明                            | 保護コード (注記)             |

|-------------|--------------------|-------------------------------|------------------------|

| 1D00h～1DFFh | R/(W)              | データ メモリ ページ 232～239 (ブロック 29) | (アドレス 1FBDh で制御される保護)  |

| 1E00h～1EFFh | R/(W)              | データ メモリ ページ 240～247 (ブロック 30) | (アドレス 1FB Eh で制御される保護) |

| 1F00h～1F9Fh | R/(W)              | データ メモリ ページ 248～252 (ブロック 31) | (アドレス 1FB Fh で制御される保護) |

(1) R = 読み取り、W = 書き込み

### 6.3.2 FRAM ステータス メモリ

表 6-1 に示すように、TMF0064 のデータ メモリは、32 つの連続する FRAM メモリ ブロックで構成されます。ブロック 0～30 はそれぞれ 256 バイトであり、8 つの隣接するメモリ ページによって形成されます。ブロック 31 は 160 バイトで、5 つの隣接するメモリ ページ (データ メモリ ページは 32 の隣接するメモリ バイト) によって形成されます。

TMF0064 は、データ メモリに加えて、アドレス 1FA0h から始まるステータス メモリで構成されます (表 6-2 を参照)。ステータス メモリのレジスタ ページは、32 つの保護制御 バイト、各 1 バイトで構成されており、メモリ ブロックとレジスタ ページをロックします。

32 つの保護制御 バイトとメモリ ブロック ロック バイトの組み合わせにより、32 つのデータ メモリ ブロックへのアクセスが制御されます。デフォルトでは、メモリ ブロックはオープン アクセスに設定されています。保護 バイト 値 55h を設定すると、対応するメモリ ブロックが書き込み保護 モードに設定され、保護 バイト 値 AAh を設定すると、対応するメモリ ブロックが EEPROM モードに設定されます。

メモリ ブロック ロック バイトが 55h または AAh にプログラムされている場合、書き込み保護されているすべてのデータ メモリ ブロックに対してコピー保護が設定されます (EEPROM モードのメモリ ブロックは影響を受けません)。同様に、レジスタ ページのロック バイトを 55h と AAh のどちらかにプログラムすると、レジスタ ページ全体に対してコピー保護が設定されます。

FRAM デバイスでは、デジタル情報は誘電体内の偏波として保存されます。分極は温度依存性の速度で失われる可能性があり、温度が高いほど脱分極率は高くなります。このルールは、「電気的特性」表のデータ保持を決定します。

メモリ位置を書き込み保護 モードに設定すると、コピー スクラッチ パッド 操作が可能になりますが、データの変更はできません。これにより、同じデータを使用してメモリを再プログラムでき、データ保持の耐用期間を確保するために、分極がリフレッシュされます。

書き込み保護と比較して、コピー 保護はスクラッチ パッド コピー 機能をブロックします。このコピー 保護機能は、書き込み保護されたすべてのブロックと関連する保護制御 バイトが最終値に設定された後にのみ使用します。コピー 保護では、デバイス間でのデータのコピーは禁止されることに注意してください。55H または AAh に設定すると、保護制御 レジスタ ロック バイトは自身を書き込み保護します。その他の設定では、無制限の書き込みアクセスが許可されます。

オプションのメーカー ID をプログラミングするためにアドレス 1FC3h および 1FC4h を使用できます。これらの値はホストを読み取ります。たとえば、エンドユーザー 製品を TMF0064 に関連付けることができます。アドレス 1FC2h には、TMF0064 にメーカー ID をロックするためのバイトが保存され、デフォルト値は 00h です。この位置に AAh または 55h を書き込んだ後、メーカー ID ロック バイトは永続的に書き込み保護されます。

**表 6-2. FRAM ステータス メモリ マップ**

| アドレス範囲 | タイプ <sup>(1)</sup> | 説明                | 保護コード (注記)                |

|--------|--------------------|-------------------|---------------------------|

| 1FA0h  | R/(W)              | 保護制御 バイト (ブロック 0) | 55h: 書き込み保護 ブロック 0        |

|        |                    |                   | AAh: EEPROM モード ブロック 0    |

|        |                    |                   | 55H または AAh: 書き込み保護 1FA0h |

| 1FA1h  | R/(W)              | 保護制御 バイト (ブロック 1) | 55h: 書き込み保護 ブロック 1        |

|        |                    |                   | AAh: EEPROM モード ブロック 1    |

|        |                    |                   | 55H または AAh: 書き込み保護 1FA1h |

**表 6-2. FRAM ステータス メモリ マップ (続き)**

| アドレス範囲 | タイプ <sup>(1)</sup> | 説明               | 保護コード(注記)                       |

|--------|--------------------|------------------|---------------------------------|

| 1FA2h  | R/(W)              | 保護制御バイト(ブロック 2)  | 55h:書き込み保護ブロック 2                |

|        |                    |                  | AAh: EPROM モード ブロック 2           |

|        |                    |                  | 55H または AAh:書き込み保護 1FA2h        |

| 1FA3h  | R/(W)              | 保護制御バイト(ブロック 3)  | 55h:書き込み保護ブロック 3                |

|        |                    |                  | AAh: EPROM モード ブロック 3           |

|        |                    |                  | 55H または AAh:書き込み保護 1FA3h        |

| 1FA4h  | R/(W)              | 保護制御バイト(ブロック 4)  | 55h:書き込み保護ブロック 4                |

|        |                    |                  | AAh: EPROM モード ブロック 4           |

|        |                    |                  | 55H または AAh:書き込み保護 1FA4h        |

| 1FA5h  | R/(W)              | 保護制御バイト(ブロック 5)  | 55h:書き込み保護ブロック 5                |

|        |                    |                  | AAh: EPROM モード ブロック 5           |

|        |                    |                  | 55H または AAh:書き込み保護 1FA5h        |

| 1FA6h  | R/(W)              | 保護制御バイト(ブロック 6)  | 55h:書き込み保護ブロック 6                |

|        |                    |                  | AAh: EPROM モード ブロック 6           |

|        |                    |                  | 55H または AAh:書き込み保護 1FA6h        |

| 1FA7h  | R/(W)              | 保護制御バイト(ブロック 7)  | 55h:書き込み保護ブロック 7                |

|        |                    |                  | AAh: EPROM モード ブロック 7           |

|        |                    |                  | 55H または AAh:書き込み保護 1FA7h        |

| ...    | ...                | ...              | ...                             |

| 1FB0h  | R/(W)              | 保護制御バイト(ブロック 29) | 55h:書き込み保護ブロック 29               |

|        |                    |                  | AAh: EPROM モード ブロック 29          |

|        |                    |                  | 55H または AAh:書き込み保護 1FB0h        |

| 1FB1h  | R/(W)              | 保護制御バイト(ブロック 30) | 55h:書き込み保護ブロック 30               |

|        |                    |                  | AAh: EPROM モード ブロック 30          |

|        |                    |                  | 55H または AAh:書き込み保護 1FB1h        |

| 1FB2h  | R/(W)              | 保護制御バイト(ブロック 31) | 55h:書き込み保護ブロック 31               |

|        |                    |                  | AAh: EPROM モード ブロック 31          |

|        |                    |                  | 55H または AAh:書き込み保護 1FB2h        |

| 1FC0h  | R/(W)              | メモリ ブロック ロック     | 55H または AAh:コピー保護               |

|        |                    |                  | 書き込み保護されたデータ メモリ ページ            |

|        |                    |                  | 55H または AAh:書き込み保護 1FC0h        |

| 1FC1h  | R/(W)              | レジスタ ページ ロック     | 55H または AAh:コピー保護 1FA0h-1FC1h   |

| 1FC2h  | R                  | 工場バイト            | 55h:有効なメーカー ID がありません           |

|        |                    |                  | AAh: 1FC3h-1FC4h は有効なメーカー ID です |

| 1FC3h  | R                  | メーカー ID          |                                 |

| 1FC4h  | R                  | メーカー ID          |                                 |

| 1FC5h  | R                  | 予約済み             |                                 |

(1) R = 読み取り、W = 書き込み

### 6.3.3 アドレス レジスタ転送ステータス

TMF0064 は、3 つのアドレス レジスタを使用します。TA1、TA2、および E/S (図 6-2、図 6-3、および 図 6-4)。

レジスタ TA1 および TA2 には、データが書き込まれ読み取りされるターゲット アドレスがロードされます。レジスタ E/S は、書き込みコマンドによってデータの整合性を検証するために使用される読み取り専用転送ステータスレジスタです。書き込みスクラッチパッド コマンドの実行中、E/S ビット E[4:0] には最初に着信 T[4:0] がロードされ、その後着信する各データ バイトごとに増分されます。したがって、E[4:0] は 32 バイトのスクラッチ パッド内の終了オフセット カウンタです。E/S レジスタの PF ビットは部分的バイト フラグであり、電力の喪失により受信バイトが部分的 (8 の整数倍でないデータ バイト) である場合、またはスクラッチパッドのデータが無効な場合に設定されます。

スクラッチパッドへの書き込みが成功すると、PF ビットはクリアされます。E/S レジスタの認証承認 (AA) ビットは、Copy Scratchpad コマンドの実行中に認証が一致した場合に設定されます。AA = 1かつ PF = 0 の場合、スクラッチパッドに保存されているデータがターゲット メモリにすでにコピーされていることを示します。データがスクラッチパッドに書き込まれると、AA フラグはクリアされます。AA フラグは、PF フラグが 0 の場合にのみ有効です。

図 6-2. ターゲット アドレス (TA1)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| T7 | T6 | T5 | T4 | T3 | T2 | T2 | T0 |

図 6-3. ターゲット アドレス (TA2)

| 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|-----|-----|-----|-----|-----|-----|----|----|

| T15 | T14 | T13 | T12 | T11 | T10 | T9 | T8 |

図 6-4. データ ステータス付き終了アドレス (E/S) (読み取り専用)

| 7  | 6 | 5  | 4  | 3  | 2  | 1  | 0  |

|----|---|----|----|----|----|----|----|

| AA | 0 | PF | E4 | E3 | E2 | E1 | E0 |

### 6.3.4 FRAM へのデータの書き込み

TMF0064 デバイスでは、ホストから FRAM メモリへの直接書き込みは許可されていません。ホストから FRAM メモリへの直接書き込みは、スクラッチパッドを中間リポジトリとして使用して行います。スクラッチパッドに書き込むには、ホストがまずスクラッチパッド書き込みコマンドを発行し、次に目的のターゲット アドレスと、スクラッチパッドに書き込むデータを送信します。スクラッチパッド書き込みコマンド セクションに記載されている条件に応じて、ホストはスクラッチパッド書き込みコマンド シーケンスの終了時に、スクラッチパッド書き込みシーケンス全体 (スクラッチパッド書き込みがコマンドされ、アドレス、データ) の反転 CRC16 を受信できます。

ホストが CRC16 値を受信した場合、ホストは受信した値を予測される計算値と比較できます。一致する場合、スクラッチパッド書き込み通信は成功し、ホストはスクラッチパッド コピー コマンドに進むかどうかを決定できます。

ホストが CRC16 値を受信しない場合、ホストはスクラッチパッド読み取りコマンドを使用して、スクラッチパッドに保存されているデータの整合性を検証できます。スクラッチパッド読み取りコマンドを受信した後、TMF0064 は最初にターゲット アドレス レジスタ (TA1、TA2) と E/S レジスタの内容を送信します。PF フラグがセットされている場合、または AA フラグがセットされていて、PF フラグがクリアされている場合、前の スクラッチパッド書き込みコマンドは成功しません。この場合、ホストはスクラッチパッド読み取りシーケンスを終了し、スクラッチパッドにデータを書き込む試みを再度開始できます。前のスクラッチパッド書き込みが成功すると、両方のフラグがクリアされ、読み取られる E[4:0] は、スクラッチパッドに最後に書き込まれたバイトのアドレスを示します。この場合、ホストは TMF0064 からの読み取りを続行し、すべてのデータ バイトを検証できます。一致がある場合、ホストはスクラッチパッド コピー コマンドとそれに続く、ホストがスクラッチパッドを読み取ることで取得したレジスタ TA1、TA2、E/S の正確なデータを送信できます。スクラッチパッド コピー シーケンスの最後に、認可パターンが一致している場合、TMF0064 はスクラッチパッド データの要求された場所へのコピーを開始します。コピー保護が設定されておらず、PF フラグがクリアされ、書き込みスクラッチパッド コマンドとコピースクラッチパッド コマンドの間に読み取りメモリまたは拡張読み取りメモリ コマンドが発行されていない場合です。

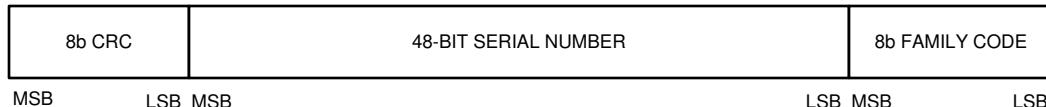

### 6.3.5 TMF0064 デバイス ID

64 ビット ID は、各 TMF0064 を識別します。48 ビットのシリアル番号は、テキサス インスツルメンツによってプログラムされます。

図 6-5. 64 ビットの工場出荷時にプログラミングされた EPROM

### 6.3.6 バス終端

TMF0064 の駆動出力はオープンドレインの N チャネル MOSFET です。正常に動作させるには、 $500\Omega$  の外付けプルアップ抵抗を SDQ バスに接続します (図 7-1 を参照)。

## 6.4 デバイスの機能モード

### 6.4.1 機能テストのテスト手順

機能テストセクションでは、データシートのセクションに記載されているパラメータを取得するために使用される具体的なテスト手順の概要を示します。

#### 6.4.1.1 複数ターゲット構成

このテストでは、マルチドロップの使用事例で TMF0064 の動作を検証します。ホストは、SDQ バス上で複数のデバイスと通信できることを確認します。他の DUT が存在する場合、選択した DUT との通信に影響を与えないことを確認します。

図 6-6. 複数ターゲット構成

通信が正常に行われると、次の一連の命令を失敗なく実行します。

- 標準速度でリセットを発行し、プレゼンスパルスを確認します。

- ROM サーチコマンドを発行して、SDQ バス上のターゲットの ID を識別します。

- 標準速度でリセットを発行し、プレゼンスパルスを確認します。

- ROM サーチコマンドで識別されたターゲットの特定の ID を指定して ROM サーチコマンドを発行し、ターゲットの 1 つを選択します。

- メモリコマンドを発行して、メモリをプログラムまたはメモリから読み取ります。

- SDQ バス上の他のターゲットデバイスについても、手順 3、4、5 を繰り返します。

## 6.5 プログラミング

### 6.5.1 シリアル通信

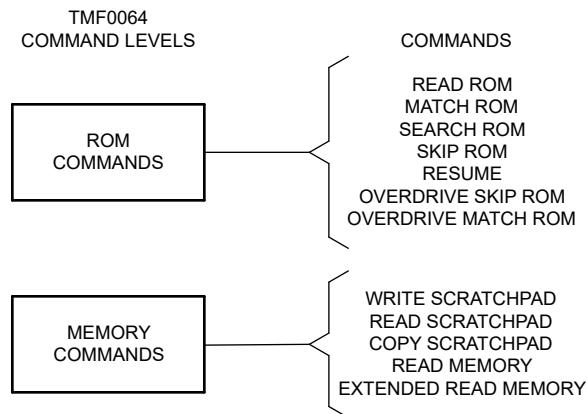

ホストは、図 6-7 に示すように、SDQ インターフェイスのコマンド構造を使用して TMF0064 のステータスを読み取り、プログラム、またはチェックします。コマンド構造には、ROM およびメモリコマンドが含まれます。

図 6-7. TMF0064 のコマンド構造

### 6.5.2 初期化

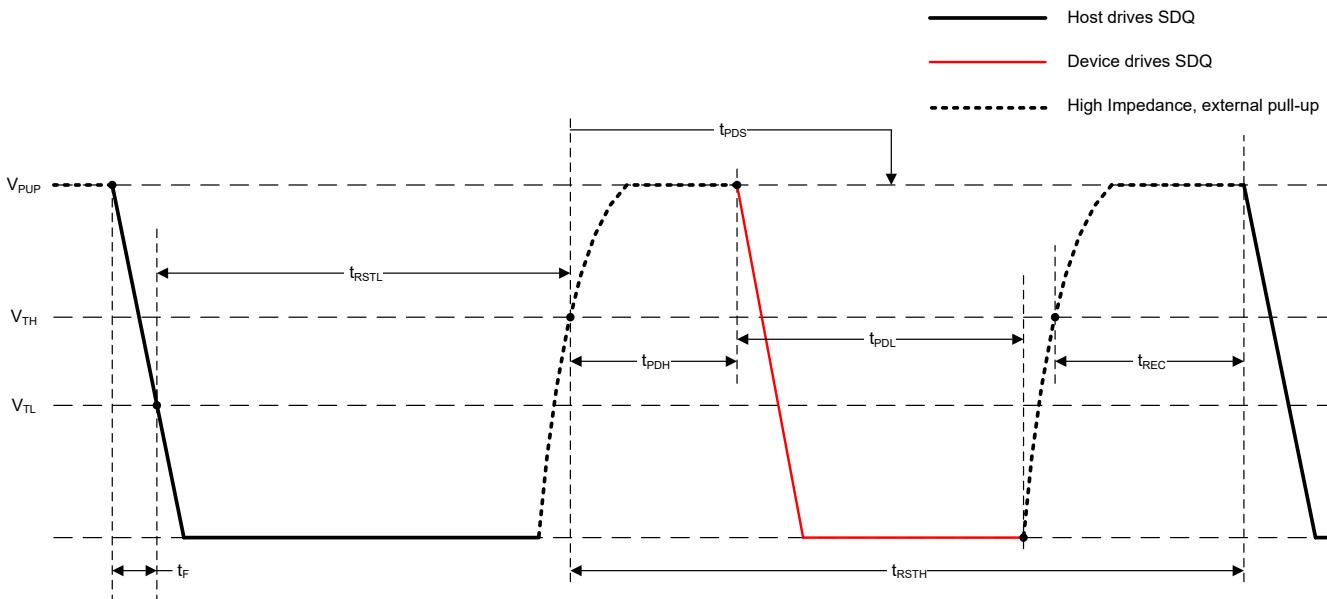

ホストは、常に初期化プロセスにより TMF0064 (ターゲット) とのトランザクションを開始します。初期化プロセスは、次の 2 つのパルスで構成されます。リセットおよび存在。ホストはリセットパルスを生成し、TMF0064 はプレゼンスパルスで応答します。ホストは、SDQ バスを 480 $\mu$ s 以上の間 low に駆動して TMF0064 をリセットします。プレゼンスパルスは、バス上に動作準備ができている 1 つまたは複数の TMF0064 デバイスがあることをホストに警告します。

### 6.5.3 ROM コマンド

ホストは、SDQ バス上に 1 つ以上のターゲットデバイスが存在することを検出すると、ユースケースのシナリオに応じて TMF0064 がサポートする 8 ビット ROM 機能コマンドの 1 つを送信できます。このセクションでは、各 ROM コマンドを発行できるシナリオについて説明します。これらのコマンドのリストについては、図 6-7 を参照してください。

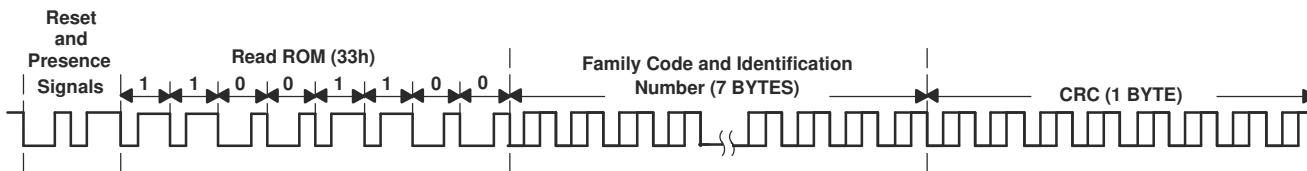

#### 6.5.3.1 ROM 読み取りコマンド [33h]

ROM 読み取りコマンド シーケンス (図 6-8 を参照) は、ホストが少なくとも 480 $\mu$ s の RESET パルスを生成することから開始します。デバイスは、プレゼンスパルスで応答します。次に、ホストは読み取り ROM コマンド 33h を発行し続け、56 ビットファミリコードとシリアル番号をリードバックし、その後、データフレーム中に読み取り信号を使用して 8 ビットの CRC を読み取ります (「読み取り/書き込み信号」セクションを参照)。ホストは、SDQ バス上に TMF0064 デバイスの 1 つだけある場合にのみ READ ROM コマンドを発行できます。SDQ バス上に 1 つ以上のターゲットデバイスがあるときにホストがこのコマンドを発行すると、すべてのターゲットデバイスがホストに応答しようとするため、データ衝突が発生します。ホストは、読み取り ROM シーケンスからの CRC を、計算された CRC と比較することでデータの不一致を識別できます。これにより、不一致が生じます。

図 6-8. ROM シーケンスの読み取り

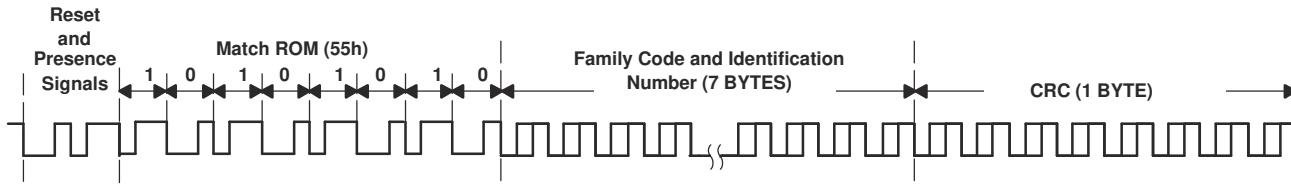

#### 6.5.3.2 MATCH ROM マッチコマンド [55h]

バス上に複数のターゲットがある場合、ホストは、ファミリコードと識別番号がわかっているときに Match ROM コマンド 55h を使用して特定のターゲットを選択します。ホストが ROM サーチコマンドを発行してから、ファミリコード、シリアル番号、CRC バイトを送信します。64 ビットのシリアル ID と一致するターゲットデバイスが選択され、以後のメモリ機能コマンドを実行するために使用されます。一致 ROM コマンドは、バス上の 1 つの TMF0064 でも使用できます。

図 6-9. MATCH ROM シーケンス

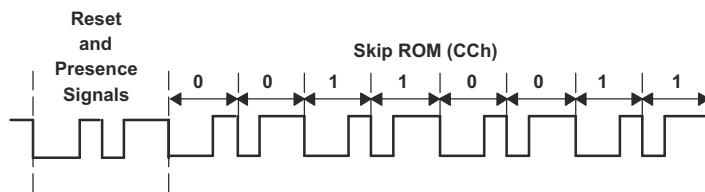

#### 6.5.3.3 ROM スキップ コマンド [CCh]

ROM スキップ コマンド シーケンス (図 6-10 を参照) は、ホストがターゲット デバイスとのトランザクションを開始できる最速のシーケンスです。Skip ROM コマンド CCh を使用すると、ホストは 64 ビットのシリアル ID を発行せずにメモリ機能にアクセスできます。メモリ機能コマンドは、Skip ROM コマンドの直後に実行されます。SDQ バス上に単一の TMF0064 が存在する場合、ホストのみが SKIP ROM コマンドを発行します。SDQ バス上に複数のターゲットがあるときに SKIP ROM コマンドを発行すると、すべてのターゲットが後続のメモリコマンドに応答し、バス上のデータ衝突が発生します。

図 6-10. ROM スキップ シーケンス

#### 6.5.3.4 ROM サーチ コマンド [F0h]

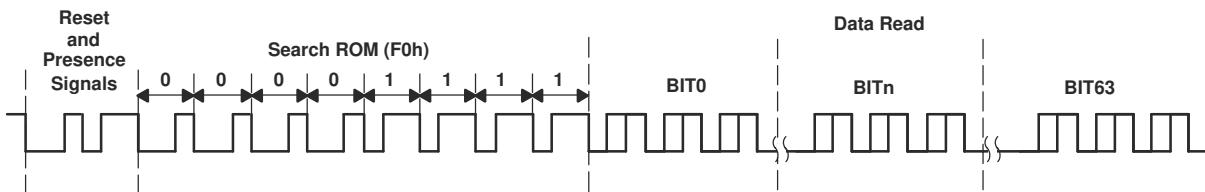

ROM サーチコマンドは、ホストが SDQ バス上のデバイス数を認識していないときに、最初のシステム起動時に、デバイス数と各デバイスの 64 ビットの固有 ID を識別するのに役立ちます。ROM サーチ コマンド シーケンスは、ホストが少なくとも 480μs のリセット パルスを生成することから開始されます。SDQ バス上のすべてのターゲット デバイスは、プレゼンス パルスで応答します。次に、ホストは ROM サーチコマンド F0h を発行して続行します。ROM サーチコマンドの後、図 6-11 に示すように、ホストは 64 ビットシリアル ID の各ビットに対して 3 つのタイム スロットを発行します。最初のタイム スロットで、ターゲット デバイスは、最下位ビットから始まる 64 個のシリアル ID ビットの送信を開始します。2 番目のタイム スロットでは、ターゲット デバイスはビットの補数を送信します。3 番目のタイム スロットでは、ホストが選択するビットを書き込みます。このプロセスは、64 ビットのシリアル ID が終了するまで継続されます。3 番目のタイム スロットでホストによって書き込まれたビットと一致しないターゲット デバイスはすべて、検索プロセスを終了します。ホストが最初の 2 つのタイム スロットでゼロを読み取ると、衝突状態が発生しています。ホストは SDQ バス上に複数のデバイスが存在することを認識します。書き込みするビット値を選択することで、ホストは分岐して、競合する 1 つまたは複数のターゲット デバイスを除去します。最初の実行シーケンスの最後に、ホストは単一のデバイスのシリアル ID を認識します。その後、このシーケンスが繰り返され、SDQ バス上の残りのデバイスのシリアル ID が識別されます。

図 6-11. ROM シーケンスを検索します

#### 6.5.3.5 レジューム コマンド [A5h]

SDQ バス上に複数のターゲット デバイスがある場合、レジューム コマンド A5h を使用すると、ターゲット デバイスの選択に必要なビット トランザクション数を減らすことで、データスループットを最大化できます。レジューム コマンドを発行する前に、ホストは最初に ROM マッチまたはオーバードライブ ROM マッチ コマンド シーケンスを発行してターゲット デバイ

スを選択する必要があります。これにより、ターゲット デバイスが選択されます。他のすべてのターゲットは、以後のメモリ機能コマンドやコマンド再開機能には応答しません。

#### 6.5.3.6 ROM オーバードライブ スキップ コマンド [3Ch]

TMF0064 は、オーバードライブ モードと呼ばれる高速モードをサポートしています。OVERDRIVE SKIP ROM コマンド シーケンスは、ホストが少なくとも  $480\mu\text{s}$  の RESET パルスを生成することから開始します。TMF0064 は、プレゼンス パルスで応答します。次に、ホストは標準速度で OVERDRIVE SKIP ROM コマンド 3Ch を発行し続けます。デバイスがオーバードライブ モードになります。ターゲット デバイスとのそれ以降のすべての通信がオーバードライブ速度であることを確認します。ホストは  $480\mu\text{s}$  以上のリセット パルスを発行することで、すべてのターゲット デバイスを標準速度に戻します。

SDQ バス上に複数のターゲットがあるときに、OVERDRIVE SKIP ROM コマンドが発行された場合。すべてのターゲット デバイスがオーバードライブ モードに移行します。後続のすべての通信が特定のデバイスをアドレス指定していることを確認します。これは、オーバードライブ速度でリセット パルスを発行し、続いて OVERDRIVE MATCH ROM または SEARCH ROM のコマンド シーケンスを発行することで開始します。これにより、検索プロセスの時間が短縮されます。SDQ バス上に複数のターゲットがあるときに OVERDRIVE SKIP ROM コマンドが発行された場合、すべてのターゲット が後続のメモリコマンドに応答を開始し、バスデータの衝突が発生します。

#### 6.5.3.7 ROM オーバードライブ マッチ コマンド [69h]

ROM オーバードライブ マッチ コマンドは、SDQ バス上に複数のターゲット デバイスがある場合に特定のターゲット デバイスを選択し、同時に選択されたターゲットをオーバードライブ モードに設定するために使用されます。ROM オーバードライブ マッチ コマンドは、バス上の 1 つのターゲット デバイスでも使用できます。64 ビットのシリアル ID と一致し、それ以降のメモリ機能コマンドをオーバードライブ速度で実行できるターゲット デバイスを選択します。すでにオーバードライブ モードになっている他のターゲット デバイスは、ホストが  $480\mu\text{s}$  以上のリセット パルスを発行してすべてのターゲット デバイスを標準速度に戻すまでオーバードライブ モードを続けます。

### 6.5.4 メモリ機能コマンド

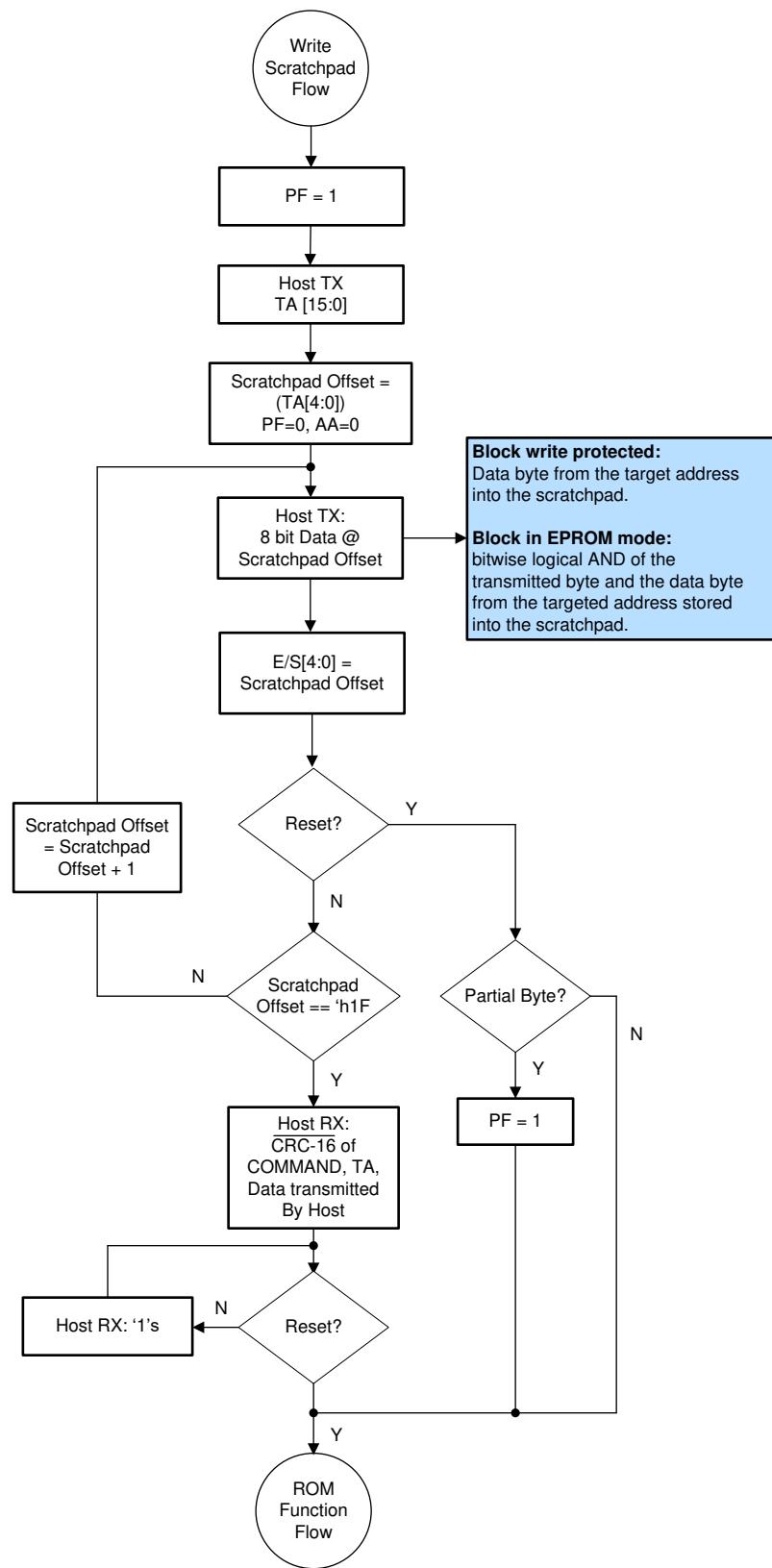

#### 6.5.4.1 スクラッチパッド書き込みコマンド [0Fh]

スクラッチパッド書き込みコマンド 0Fh は、スクラッチパッドに書き込みます。ROM コマンドを使用してターゲット TMF0064 を選択すると、ホストは 2 バイトのアドレスの後にデータを送信します。デバイスは、2 バイト アドレスの 5LSB ビットをスクラッチパッド オフセット アドレスとして設定します。また、E/S レジスタ (E[4:0]) の 5LSB ビットにもオフセット アドレスがロードされます。それ以降のデータ バイトごとに、スクラッチパッド オフセット アドレスと E/S ビット (E[4:0]) の両方がインクリメントされます。データ バイトが部分的である場合、そのデータ バイトは無視され、部分バイトフラグ (PF) と呼ばれるエラーフラグがセットされます。2 バイトのアドレス全体が受信されない場合にも、このフラグがセットされます。デバイスが完全な 2 バイト アドレスを受信すると、このフラグはクリアされます。

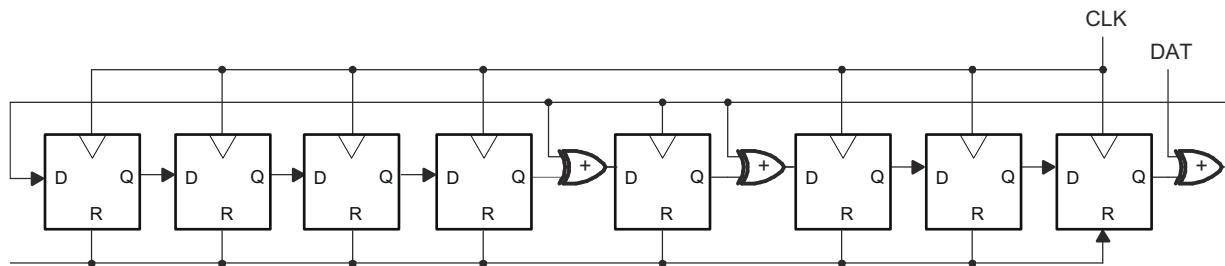

スクラッチパッド書き込みコマンドの実行中、内部 CRC ジェネレータが、スクラッチパッド書き込みコマンド (0Fh)、2 バイトアドレス、データ バイトを含むデータストリームに基づいて 16 ビット CRC を計算します。この CRC は、CRC ジェネレータを最初にクリアすることにより、CRC16 多項式 ( $X^{16} + X^{15} + X^2 + 1$ ) を使用して生成されます。ホストは、RESET コマンドを発行することにより、いつでも Write Scratchpad コマンド シーケンスを終了できます。ホストは、スクラッチパッド オフセット アドレスが 11111b に達すると、TMF0064 デバイスによって生成された 16 ビット CRC を読み取ることができます。

TMF0064 のメモリアドレス範囲は 0000h ~ 1FC5h なので、ホストがアドレス範囲を超えて書き込みを試みると、2 バイトアドレスが内部アドレス レジスタにシフトされるため、デバイスの内部回路によって上位 6 ビットのアドレス ビットが 0 に設定されます。この変更されたアドレスは、スクラッチパッド読み取りコマンドから読み取ることができます。ホストがスクラッチパッドを読み取り、アドレスとデータ バイトを検証せずにスクラッチパッド コピー コマンドを発行した場合、スクラッチパッドのメモリ内容はターゲット FRAM メモリにコピーされません。ホストが書き込み保護されているメモリ領域への書き込みを試みると、デバイスはホストによって書き込まれるデータ バイトではなく、FRAM メモリから 2 バイトのアドレスからスクラッチパッドにデータ バイトをコピーします。同様に、ホストが EEPROM で保護されているメモリ位置に書き込もうとすると、デバイ

スはホストによって書き込まれたデータ バイトと **FRAM** メモリの 2 バイト アドレスのデータ バイトのビット単位の論理 **AND** をスクラッチパッドにコピーします。

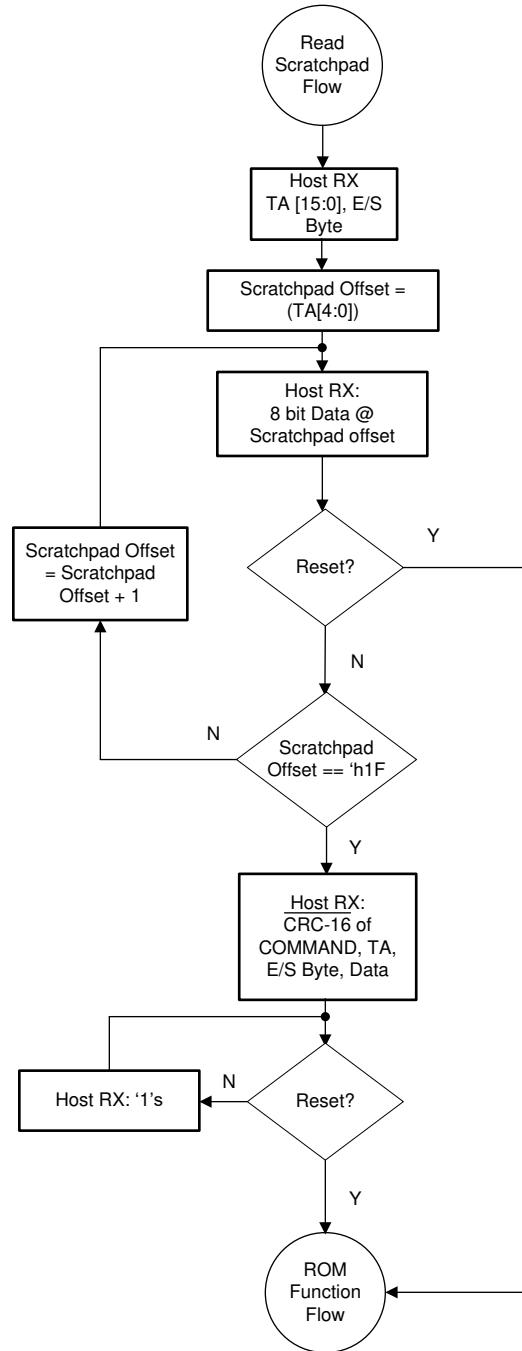

#### 6.5.4.2 スクラッチパッド読み出しコマンド [AAh]

スクラッチパッドを読み出すには、ホストが スクラッチパッド読み出しコマンド [AAh] を発行してから、2 バイトのアドレス、終了オフセット / データステータス バイト (E/S) を読み出し、最後にスクラッチパッドのオフセット アドレスから開始されるスクラッチパッドのデータを読み出します。ホストは、アドレス、E/S バイト、およびスクラッチパッド データが、スクラッチパッド書き込みコマンド中に送信された情報と一致していることを検証します。Read Scratchpad コマンドを使用して、2 バイトのアドレスとスクラッチパッドのデータを検証します。スクラッチパッドの終了に達すると、ホストは反転 CRC16 を読み取ることができます。2 CRC バイトを読み取った後もホストが引き続き読み出しを行う場合、ホストは 1 秒のみを受信します。

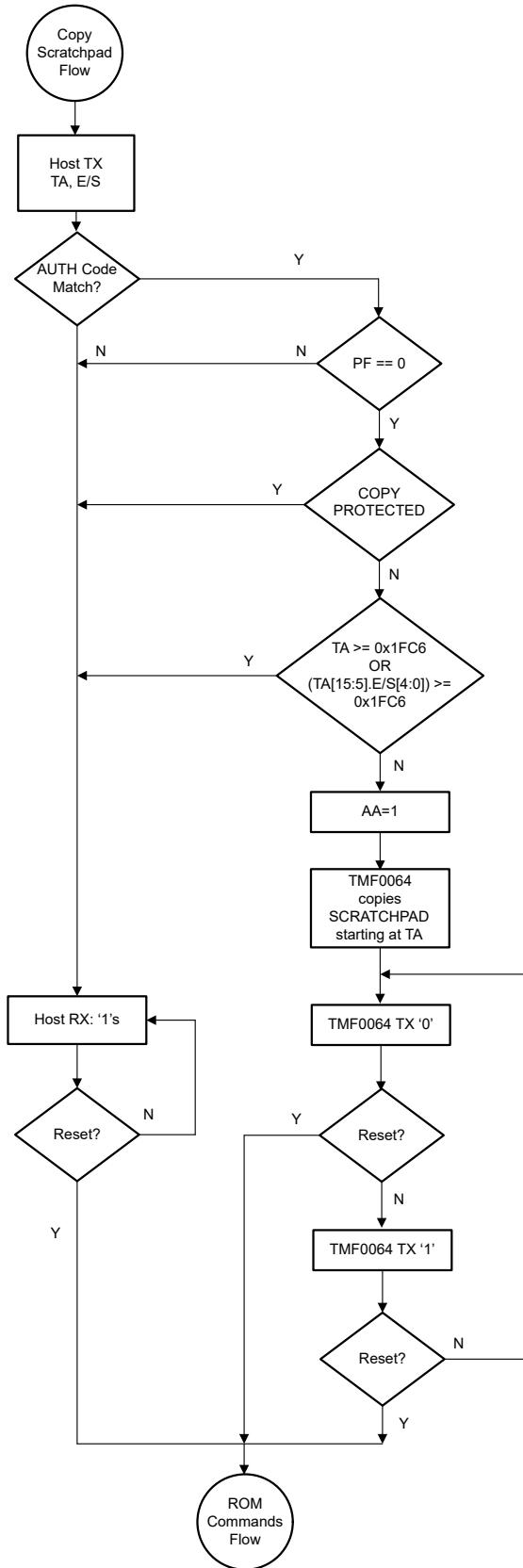

#### 6.5.4.3 スクラッチパッド コピー [55h]

スクラッチパッドから **FRAM** メモリにデータをコピーするには、ホストはスクラッチパッド コピー コマンド (55h) を発行し、その後にスクラッチパッドの読み取りコマンドから取得された 2 バイトのアドレスと E/S バイト (認証コードと呼ばれます) を発行します。デバイスは、ターゲット アドレスから始まり、ターゲット アドレスから末尾にターゲット アドレスに記載されたターゲット アドレスにスクラッチパッド オフセット アドレスを加算して E/S バイトに記載されたスクラッチパッド オフセット アドレスを加算した値にスクラッチパッドを **FRAM** メモリにコピーします。承認コードが E/S バイトと一致している場合、PF フラグは設定されず、ターゲット アドレスがアドレス可能範囲内である場合にのみです。ホストが読み取りを続行する場合、デバイスは 0 秒と 1 秒を交互に送信します。ホストは、 $t_{PROG}$  期間が経過した後にのみリセット パルスを発行することで、スクラッチパッド コピー コマンド シーケンスを終了できます。メモリ ページがコピー保護されているページである場合、または PF フラグがセットされている場合、TMF0064 では AA フラグをリセットすることでメモリ コピーを許可しません。この動作は、スクラッチパッド 読み取りコマンドで E/S バイトの AA フラグ ビットを読み取ることで確認できます。

#### 6.5.4.4 メモリ読み取り [F0h]

ホストは、メモリ読み取りコマンド (F0h) を発行し、その後に 2 バイトのアドレスを発行することで、**FRAM** メモリを読み取ります。ホストが 1FC5h より大きなアドレスを発行すると、デバイスは最上位 6 ビットを 0 に設定します。その後ホストは、アドレス 1FC5h に達するまで、アドレス範囲内のアドレスまたは変更されたアドレスからデータを読み取ります。ホストがそれ以上読み出しを続ける場合、TMF0064 は 1 を送信します。ホストがリセット パルスを発行して、メモリの読み取りコマンド シーケンスを終了します。

#### 6.5.4.5 メモリ拡張読み取り [A5h]

拡張読み取りメモリ コマンドは、各メモリ ページの末尾で送信される 2 バイトの CRC を除いて、メモリの読み取りコマンドと同様に機能します。ホストは、拡張読み出しメモリ コマンド (A5h) を発行し、その後に 2 バイトのアドレスを発行することで、**FRAM** メモリを読み取ります。ホストが 1FC5h より大きなアドレスを発行すると、デバイスは最上位 6 ビットを 0 に設定します。ホストは、アドレス範囲内のアドレスまたは変更されたアドレスから、32 バイト ページが終了するまでデータを読み取ります。メモリ ページの最後で、ホストは 2 バイトの反転 CRC を読み出します。ホストが読み取りを継続すると、ホストは次のページの先頭に対応するデータを受信し、その後、終了アドレス 1FC4h に達するまでこのデータが受信されます。ホストがそれ以上読み出しを続ける場合、TMF0064 は 1 を送信します。ホストは、リセット パルスを発行することでメモリの読み取りコマンド シーケンスを終了します。

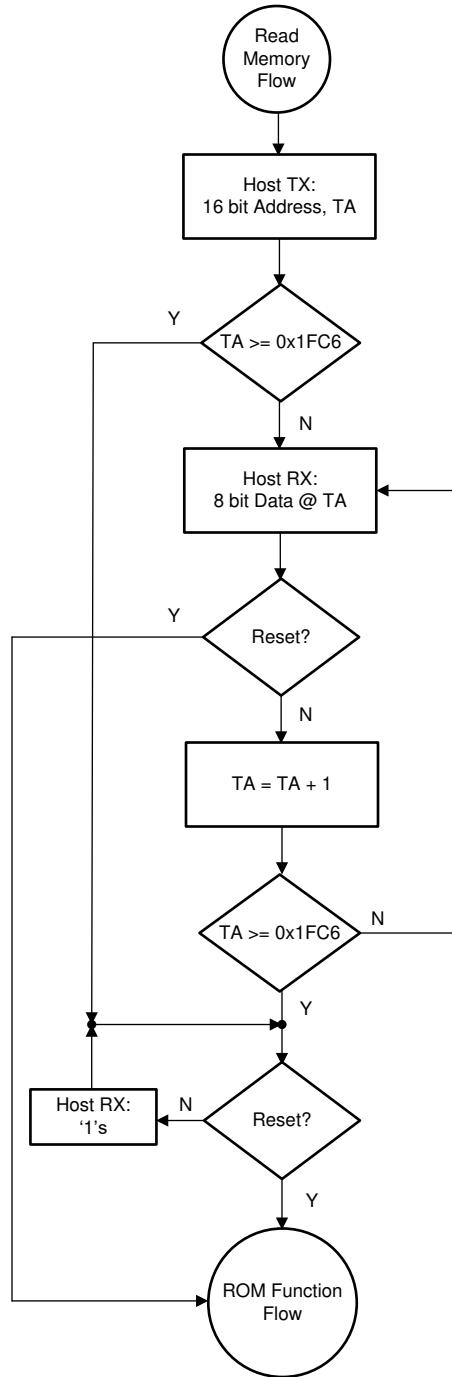

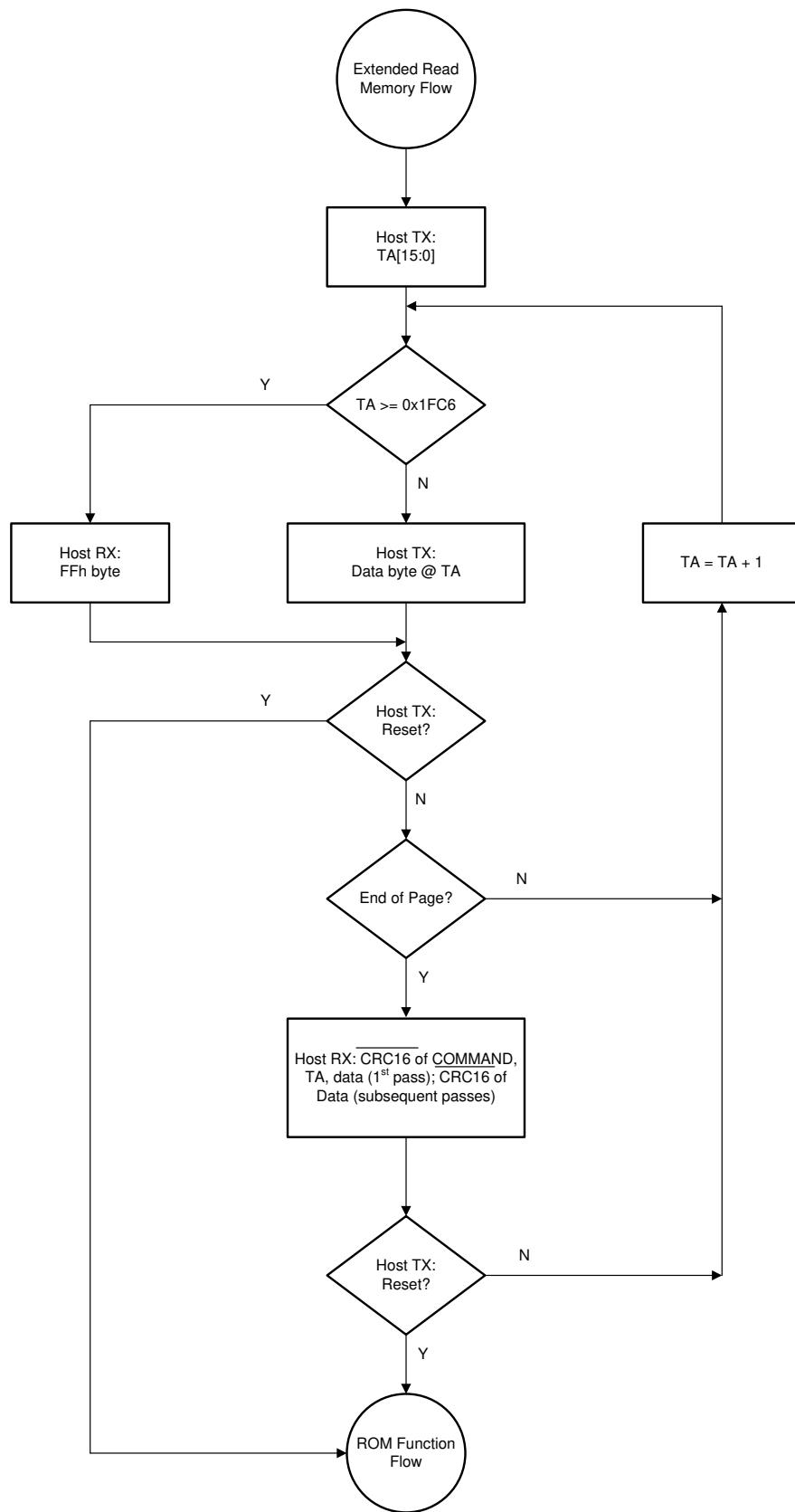

#### 6.5.4.6 メモリ コマンド フローチャート

図 6-12. スクラッチパッド書き込みフローチャート

図 6-13. スクラッチパッド読み取りフローチャート

図 6-14. スクラッチパッド コピー フローチャート

図 6-15. メモリ読み取りフローチャート

図 6-16. 拡張メモリ読み取りフローチャート

## 6.5.5 SDQ シグナリング

1 線式通信には基準クロックがなく、データの整合性を維持するために厳格なタイミング プロトコルに準拠するために重要です。タイミング プロトコルは、次の 4 種類のシグナリングで構成されています。

1. リセット パルスと存在パルスを使用するリセット シーケンス

2. Write-zero タイミング シーケンス

3. Write-one タイミング シーケンス

4. Read-data タイミング シーケンス

ホストは、SDQ バス上のターゲット デバイスにより開始されるプレゼンス パルスを除き、SDQ ラインを low にすることで通信を開始します。ターゲット デバイスは、標準とオーバードライブの 2 つの異なる速度で通信できます。ターゲット デバイスはデフォルトでは、デバイスがオーバードライブ モードに設定されていない限り、標準速度でのみ通信を行います。このモードでは、ターゲット デバイスはオーバードライブ タイミング（高速タイミング）で発行されたコマンドに応答します。以下のすべてのタイミング波形は、標準タイミングとオーバードライブ タイミングの両方に適用できます。

すべての SDQ 信号は、デバイスの初期化から開始し、その後、ホストがバスを low に駆動して 1 または 0 を書き込むか、またはビット読み取りの開始フレームを開始します。[リセット シーケンスのタイミング図](#)に初期化タイミングを示す一方、[Write-One タイミング図](#)、[Write-Zero タイミング図](#)、および [Read-Data タイミング図](#)に、開始期間  $t_{W1L}$  /  $t_{W0L}$  /  $t_{RL}$  の間 SDQ バスを low に駆動することで、ホストが各ビットを開始することを示します。ビットの開始後、ホストが書き込み中にバスの制御を継続するか、またはターゲット デバイスが読み取り中に 0 ビットを転送するようバスを制御します。

### 6.5.5.1 リセットおよび存在パルス

リセット シーケンスのとき、SDQ バスが  $120\mu s$  より長い間 low に駆動された場合、ターゲット デバイスはリセットできます。SDQ バスが  $480\mu s$  を超えて low に駆動されている場合、ターゲット デバイスはリセットされ、プレゼンス パルスにより応答することで、デバイスは通信準備ができたことを示します。TMF0064 がオーバードライブ モードで、ホストが  $480\mu s$  以上の  $t_{RSTL}$  持続時間を発行すると、デバイスはオーバードライブ モードを終了し、標準速度に戻ります。デバイスがオーバードライブ モードにあり、 $t_{RSTL}$  が  $80\mu s$  より長くならない場合、デバイスはオーバードライブ モードにとどまります。デバイスがオーバードライブ モードにあり、 $t_{RSTL}$  が  $80\mu s$  と  $480\mu s$  の間にある場合、デバイスはリセットされますが、通信速度は不定になります。

[リセット シーケンスのタイミング図](#)に、ホストによって開始されるリセット パルスと、TMF0064（ターゲット）から開始される応答存在パルスを示します。

図 6-17. リセット シーケンスのタイミング図

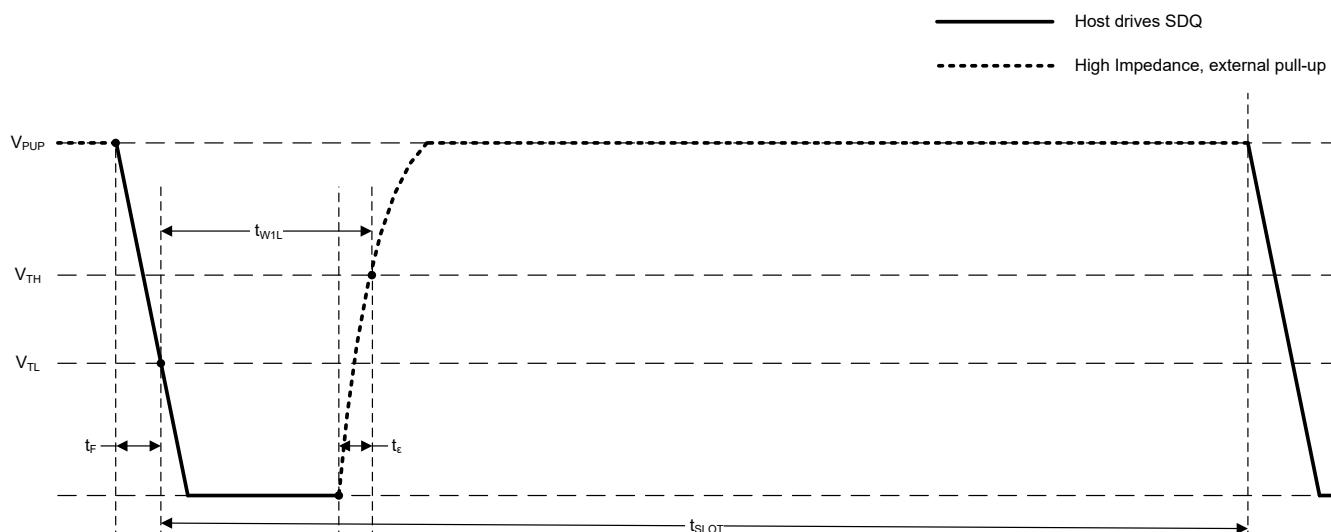

### 6.5.5.2 読み取り書き込みタイム スロット

1 線式インターフェイス通信には、基準クロックがありません。したがって、すべての通信は、固定時間スロット ( $t_{SLOT}$ ) と、ロジック 0 および 1 を示す可変パルス幅を使用して非同期に実行されます。アイドル状態のときは、外部プルアップ抵抗によってラインが High に保持されます。すべてのビット通信が書き込みであるか読み取りであるかに関係なく、どちらもホストによってデータ ラインを低く駆動することによって開始され、ビット値はデータ ラインが低く保持されている時間としてデコードされます。

通信は一度に 1 ビットずつ行われますが、ホストとデバイス間のデータの交換はバイト単位で実行されます。すべてのバイトは LSB ファーストで送信されます。不完全なバイトが送信された場合、デバイスの動作は検証されません。

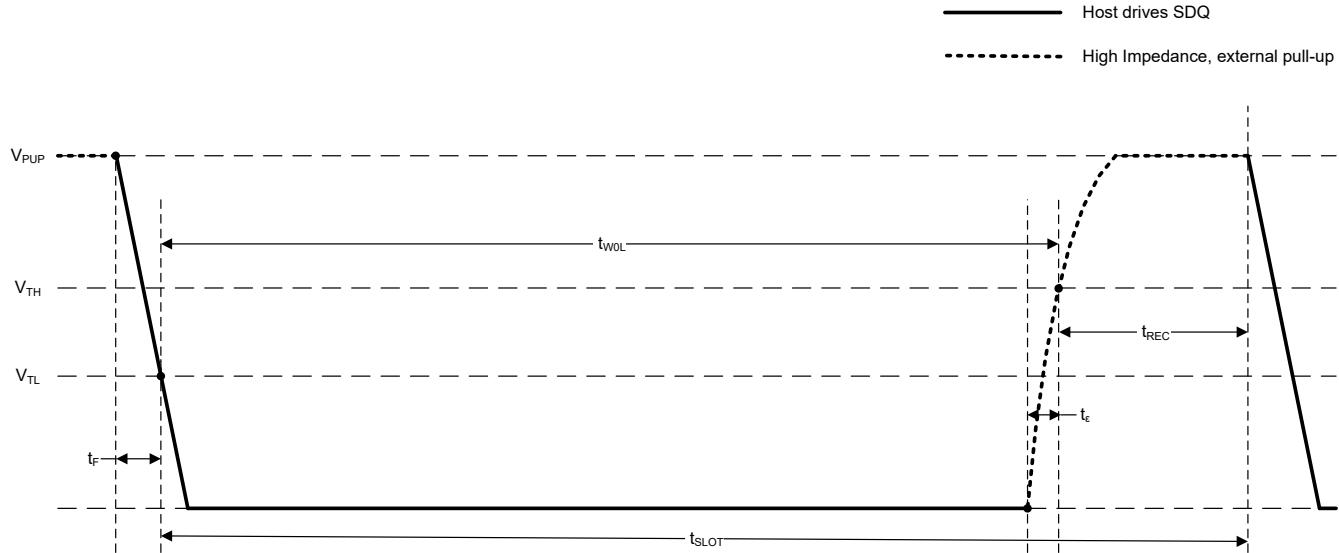

**Write-One タイミング図** 図中の Write-One タイミング図は、ホストが SDQ バスを  $t_F + t_{W1L} - t_e$  の間 low にプルダウンし、その後 SDQ バスを解放することで Write-One 転送を開始することを示しています。同様に、**Write-Zero タイミング図** 図中の Write-Zero タイミング図は、ホストが SDQ バスを  $t_F + t_{W0L} - t_e$  の間 low にプルダウンし、その後 SDQ バスを解放することで Write-Zero 転送を開始することを示しています。SDQ バスの電圧がスレッショルド  $V_{TL}$  を下回ると、デバイスは内部タイミング ジェネレータを起動し、書き込みタイム スロット中に SDQ ラインをサンプリングするタイミングを決定します。このタイミング ジェネレータは、ビットが 1 か 0 かを判定します。デバイスは、SDQ ラインを最大  $t_{W1L}$  期間から最小  $t_{W0L}$  期間までの一定の時間サンプリングします。

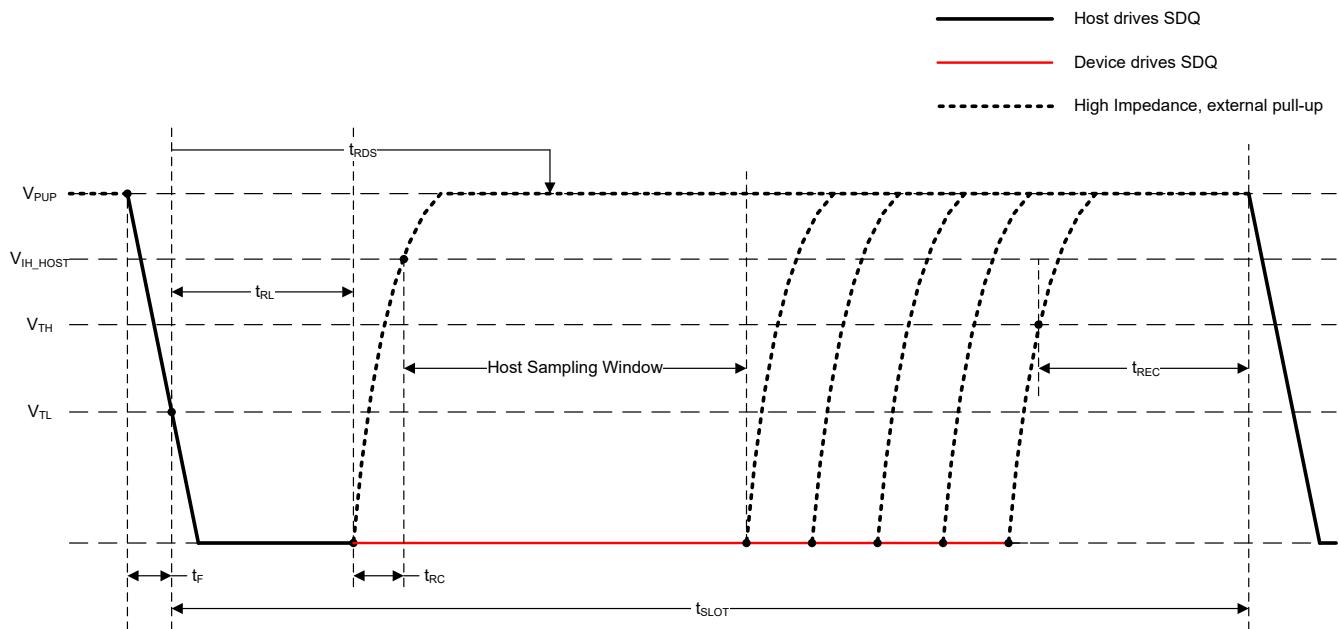

**Read-Data タイミング図** の読み取りデータのタイミング図に、ホストが  $t_F + t_{RL}$  期間の間 SDQ バスを low にすることで、このビットの送信を開始することを示しています。次にデバイスは、SDQ バスを low に駆動して読み出し 0 を送信するか、SDQ バスを解放して読み出し 1 を送信することにより応答します。ホストは、プルアップ抵抗とバス容量による立ち上がり時間を考慮して、デバイスから送信されたビットレベルをサンプリングするサンプリング ウィンドウ、または次の読み取りビット時間スロットを駆動するタイミングを決定する必要があります。

図 6-18. Write-One タイミング図

図 6-19. Write-Zero タイミング図

図 6-20. Read-Data タイミング図

### 6.5.6 IDLE

SDQ バスが high の場合、バスは IDLE 状態。SDQ バスを IDLE 状態のままにして、バストランザクションを中断します。バストランザクションは、IDLE 状態からいつでも再開できます。

### 6.5.7 CRC 生成

TMF0064 には、64 ビット ROM の最上位バイトに 8 ビット CRC が格納されています。バス ホストは、64 ビット ROM の最初の 56 ビットから CRC 値を計算し、CRC 値を TMF0064 に格納されている値と比較することで、ROM データがバス ホストによってエラー フリーで受信されたかどうかを判定できます。この CRC の等価多項式関数は次のとおりです。

$$X^8 + X^5 + X^4 + 1 \quad (1)$$

バス ホストは CRC 値の比較と、動作を続行するかどうかを完全に決定します。TMF0064 に回路がないと、CRC がで保存されている場合、または、デバイスによって計算された場合に、コマンド シーケンスの処理を続行できなくなります。バス ホストによって生成された値と一致しません。CRC を適切に使用すると、高いレベルの整合性を持つ通信チャネルが得られる可能性があります。

図 6-21. 8 ビット CRC ジェネレータ回路 ( $X^8 + X^5 + X^4 + 1$ )

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

代表的なアプリケーションは、マイクロ コントローラが SDQ 通信ホスト デバイスとして構成され、TMF0064 が SDQ ターゲット デバイスとして構成されます。ホストおよびターゲットにはオープンドレイン機能があり、プルアップ抵抗 (標準値 500Ω) が必要で、3.13V ~ 5.25V の範囲のプルアップ電圧に接続されています。

### 7.2 代表的なアプリケーション

SDQ バス上の追加容量は避けてください。 $C_{CABLE}$  より大きな容量は通信障害を引き起こす可能性があります。SDQ ラインにデカップリングやバイパスコンデンサを追加しないでください。

図 7-1. 代表的なアプリケーション回路

#### 7.2.1 設計要件

| 設計パラメータ   | 数値の例          |

|-----------|---------------|

| プルアップ電圧   | 3.13V ~ 5.25V |

| 外気温度での動作時 | -10°C ~ 85°C  |

| プルアップ抵抗   | 500 Ω         |

### 7.2.2 詳細な設計手順

GPIO 経由でビット バンギングを使用して SDQ ホストを実装することも可能です。この場合、TMF0064 のリセット ルーチンの追加エラー チェックを検討し、ターゲットがバス上で期待どおりに動作していることを確認します。

ホストがリセットを送信するたびに、ターゲット デバイスはプレゼンス パルスでリセットをアクノリッジします。プレゼンス パルスの前に、ホストはバスが解放されて高レベルに戻り、バスを予期せず低く保持するものがないことを示すことを確認する必要があります。最小  $t_{PDH}$  は  $15\mu s$  であるため、リセット後にバスを解放した後にホストがバス  $10\mu s$  のロジック high を確認すると、バスが解放されてターゲット デバイスがアクノリッジを返すのに十分です。

### 7.2.3 アプリケーション曲線

図 7-2. 入力負荷電流 ( $I_L$ ) と温度との関係 (標準速度)

図 7-3. 入力負荷電流 ( $I_L$ ) と温度との関係 (オーバードライブ速度)

### 7.3 電源に関する推奨事項

TMF0064 は低消費電力デバイスで、通信時にのみオンにする必要があります。デバイスの電源は、システム内のデジタル I/O に使用される電源電圧から供給されます。デバイスに専用の VCC ピンが存在しません。電源入力バイパスコンデンサは、必要ありません。デバイスは SDQ 通信入力から電力を受け取り、通常の通信動作中も持続できます。

電源が最初に印加されたときの SDQ 電圧のランプ時間は、ソースからの電流制限により遅くなる可能性があります。200μs よりも大きいランプ時間を超えると、POR 回路に望ましくないバウンスが発生し、デバイスが存在パルスを生成しない可能性があります。デバイスへのこの望ましくない影響を考慮するために、通信ホストのベストプラクティスは、SDQ ラインを 5ms を超える時間プルダウンし、その後、SDQ バスを解放することで、デバイスに「ハード」リセットを発行することです。これにより、約 480μs の長さのリセットパルスが発行されます。

図 7-4 に、最初の電源オンランプを処理するためのベスト プラクティスを示します。

図 7-4. 電源投入時のベスト プラクティス

- 最初の電源オンランプは持続時間が長くなる場合があります。

- ホストが 5ms を超える「ハード」リセットを発行し、これによりデバイスがリセットされます。

- TMF0064 は、プレゼンス パルスを発行することでハード リセットに応答します。

- 前のプレゼンス パルスの後に、約 480μs の「ソフト」リセットを適用します。

5. TMF0064 は、プレゼンス パルスを発行することでソフトリセットに応答します。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

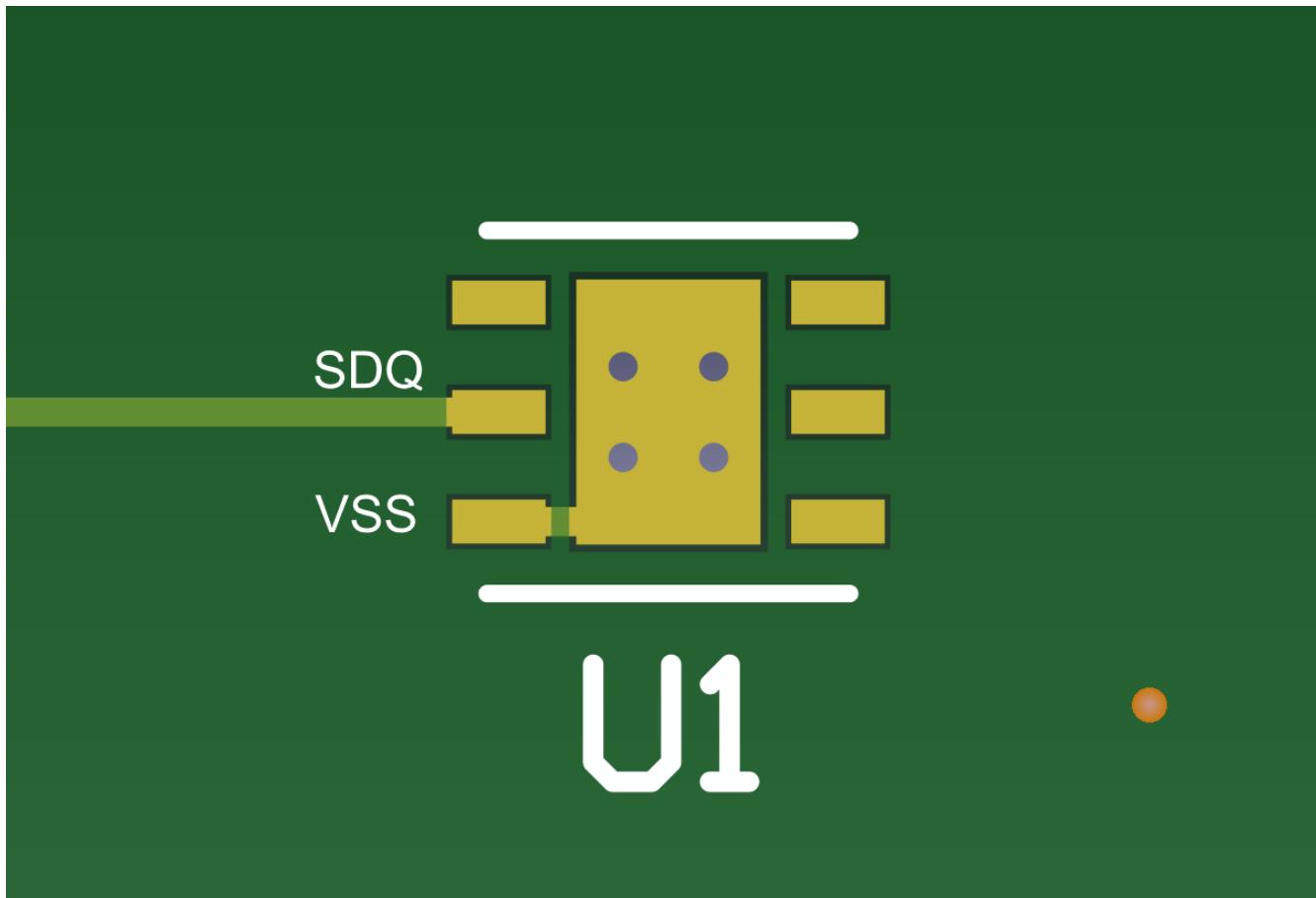

TMF0064 には 1 つの信号 (SDQ) しかありません。ベスト プラクティスとしては、デバイス の SDQ ピンからアプリケーション システムの外部コネクタ、またはホスト SDQ ホスト デバイスに信号トレースを直接配線することができます。図 7-5 に示すように、平行なグランド プレーンを使用して信号トレースを適切にシールドします。完全なグランド プレーンが利用できない場合は TMF0064 で、デバイスのほとんどを囲む大きなパターンで GND ピンを接続してみます。SDQ ピンに隣接する GND ピンから出るトレースを作成して、SDQ トレースに従い SDQ ホスト インターフェイス ピンに戻ります。

### 7.4.2 レイアウト例

図 7-5. ボード レイアウトの例

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.3 商標

SDQ™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.5 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付             | 改訂 | 注      |

|----------------|----|--------|

| September 2025 | *  | 初版リリース |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 10.1 パッケージ情報

| 発注可能なデバイス   | 供給状況 <sup>(1)</sup> | パッケージタイプ | パッケージ図 | ピン | パッケージの数量 | エコプラン <sup>(2)</sup>     | リード / ポール仕上げ <sup>(4)</sup> | MSL ピーク温度 <sup>(3)</sup> | 動作温度 (°C)    | デバイスマーキング <sup>(5) (6)</sup> |

|-------------|---------------------|----------|--------|----|----------|--------------------------|-----------------------------|--------------------------|--------------|------------------------------|

| TMF0064DRPR | アクティブ               | SON      | DRP    | 6  | 3000     | グリーン (RoHS 準拠、Sb/Br 非含有) | CU NIPDAU                   | レベル-2-260C-1 年           | -10°C ~ 85°C | TMF0064                      |

(1) マーケティングステータスの値は次のように定義されています。

**供給中:**新しい設計への使用が推奨される量産デバイス。

**最終受注中:**テキサス・インスツルメンツによりデバイスの生産中止予定が発表され、ライフトайム購入期間が有効です。

**非推奨品:**新規設計には推奨しません。デバイスは既存の顧客をサポートするために生産されていますが、テキサス・インスツルメンツでは新規設計にこの部品を使用することを推奨していません。

**量産開始前:**量産されていない、市販されていない、またはウェブで発表されていない未発表デバイスで、サンプルは提供されていません。

**プレビュー:**デバイスは発表済みですが、まだ生産は開始されていません。サンプルが提供される場合と提供されない場合があります。

**生産中止品:**テキサス・インスツルメンツはデバイスの生産を終了しました。

(2) エコプラン - 環境に配慮した計画的な分類:鉛フリー (RoHS)、鉛フリー (RoHS 適用除外)、またはグリーン (RoHS 準拠、Sb/Br 非含有) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent> でご確認ください。

**未定:**鉛フリー / グリーン転換プランが策定されていません。

**鉛フリー (RoHS):**テキサス・インスツルメンツにおける「Lead-Free」または「Pb-Free」(鉛フリー) は、6 つの物質すべてに対して現在の RoHS 要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が 0.1% を超えないという要件も含まれます。高温はんだに対応したテキサス・インスツルメンツ鉛フリー製品は、鉛フリー仕様プロセスでの使用に適しています。

**鉛フリー (RoHS 適用除外):**この部品は、1) ダイとパッケージとの間に鉛ベース フリップチップのはんだバンプ使用、または 2) ダイとリードフレームとの間に鉛ベースの接着剤を使用、のいずれかについて、RoHS が免除されています。この部品はそれ以外の点では、上記の定義の鉛フリー (RoHS 準拠) の条件を満たしています。

**グリーン (RoHS 準拠、Sb/Br 非含有):**テキサス・インスツルメンツにおけるグリーンは、鉛フリー (RoHS 互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質な材質中の Br または Sb 重量が 0.1% を超えない) ことを意味しています。

(3) MSL、ピーク温度-- JEDEC 業界標準分類に従った耐湿性レベル、およびピークはんだ温度です。

(4) リード / ポール仕上げ - 発注可能なデバイスには、複数の材料仕上げオプションが用意されていることがあります。複数の仕上げオプションは、縦罫線で区切られています。リード / ポール仕上げの値が最大列幅に収まらない場合は、2 行にまたがります。

(5) ロゴ、ロットトレースコード情報、または環境カテゴリに関する追加マークがデバイスに表示されることがあります

(6) 複数のデバイスマーキングが、括弧書きされています。カッコ内に複数のデバイスマーキングがあり、「～」で区切られている場合、その中の 1 つだけがデバイスに表示されます。行がインデントされている場合は、前行の続きということです。2 行合わせたものが、そのデバイスマーキング全体となります。

**重要なお知らせと免責事項:**このページに掲載されている情報は、発行日現在のテキサス・インスツルメンツの知識および見解を示すものです。テキサス・インスツルメンツの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。テキサス・インスツルメンツでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。テキサス・インスツルメンツおよびテキサス・インスツルメンツのサプライヤは、特定の情報を機密情報として扱っているため、CAS 番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じた TI の責任は、このドキュメント発行時点での TI 製品の価格に基づく TI からお客様への合計購入価格 (年次ベース) を超えることはありません。

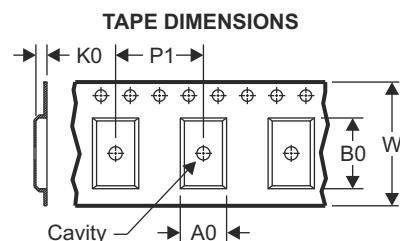

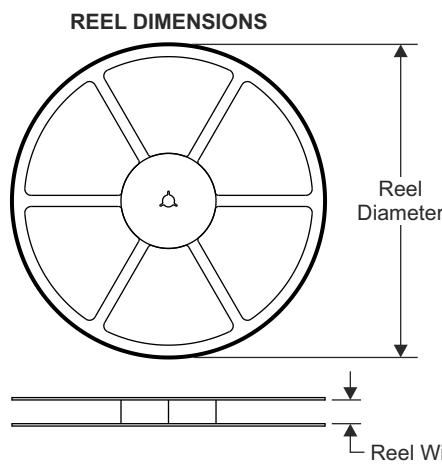

## 10.2 テープおよびリール情報

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

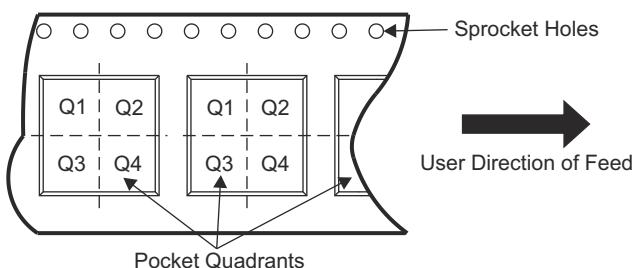

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス        | パッケージ<br>タイプ | パッケージ<br>図 | ピン | SPQ  | リール<br>直径 (mm) | リール<br>幅 W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | ピン 1 の<br>象限 |

|-------------|--------------|------------|----|------|----------------|------------------|------------|------------|------------|------------|-----------|--------------|

| TMF0064DRPR | SON          | DRP        | 6  | 3000 | 330.0          | 12.4             | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2           |

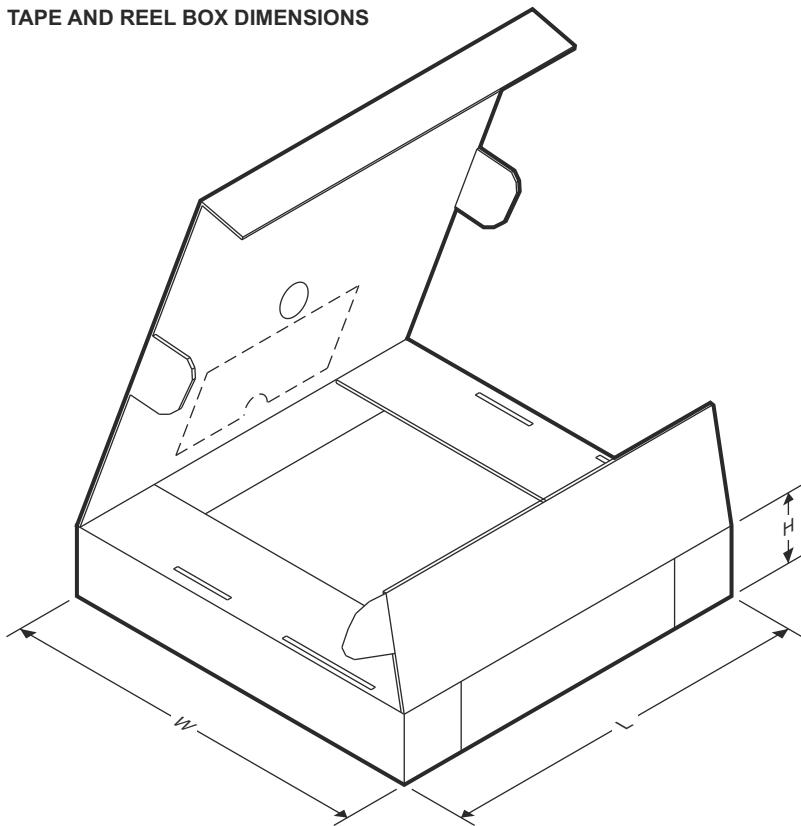

TAPE AND REEL BOX DIMENSIONS

| デバイス        | パッケージタイプ | パッケージ図 | ピン | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|-------------|----------|--------|----|------|---------|--------|---------|

| TMF0064DRPR | SON      | DRP    | 6  | 3000 | 367.0   | 367.0  | 35.0    |

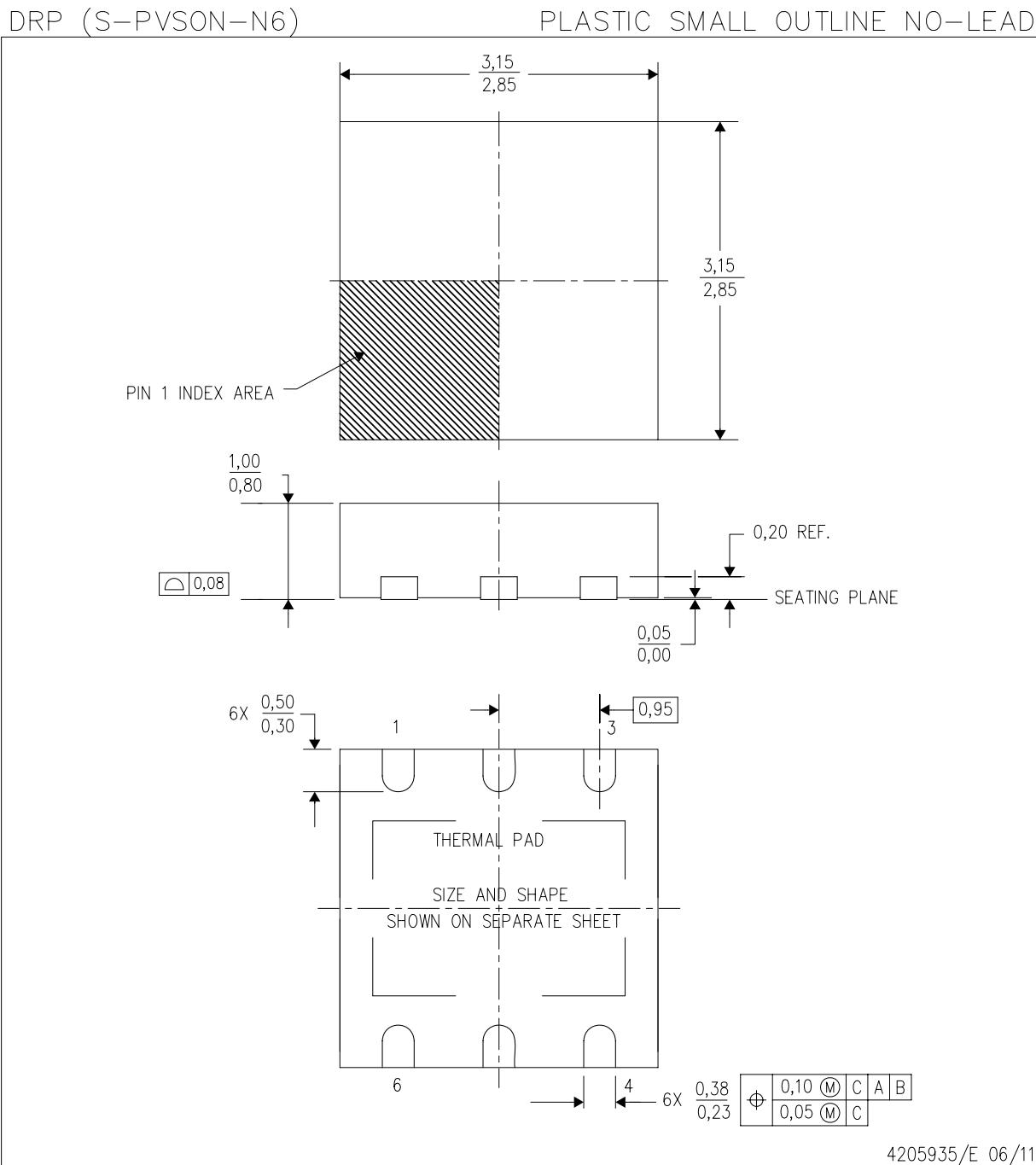

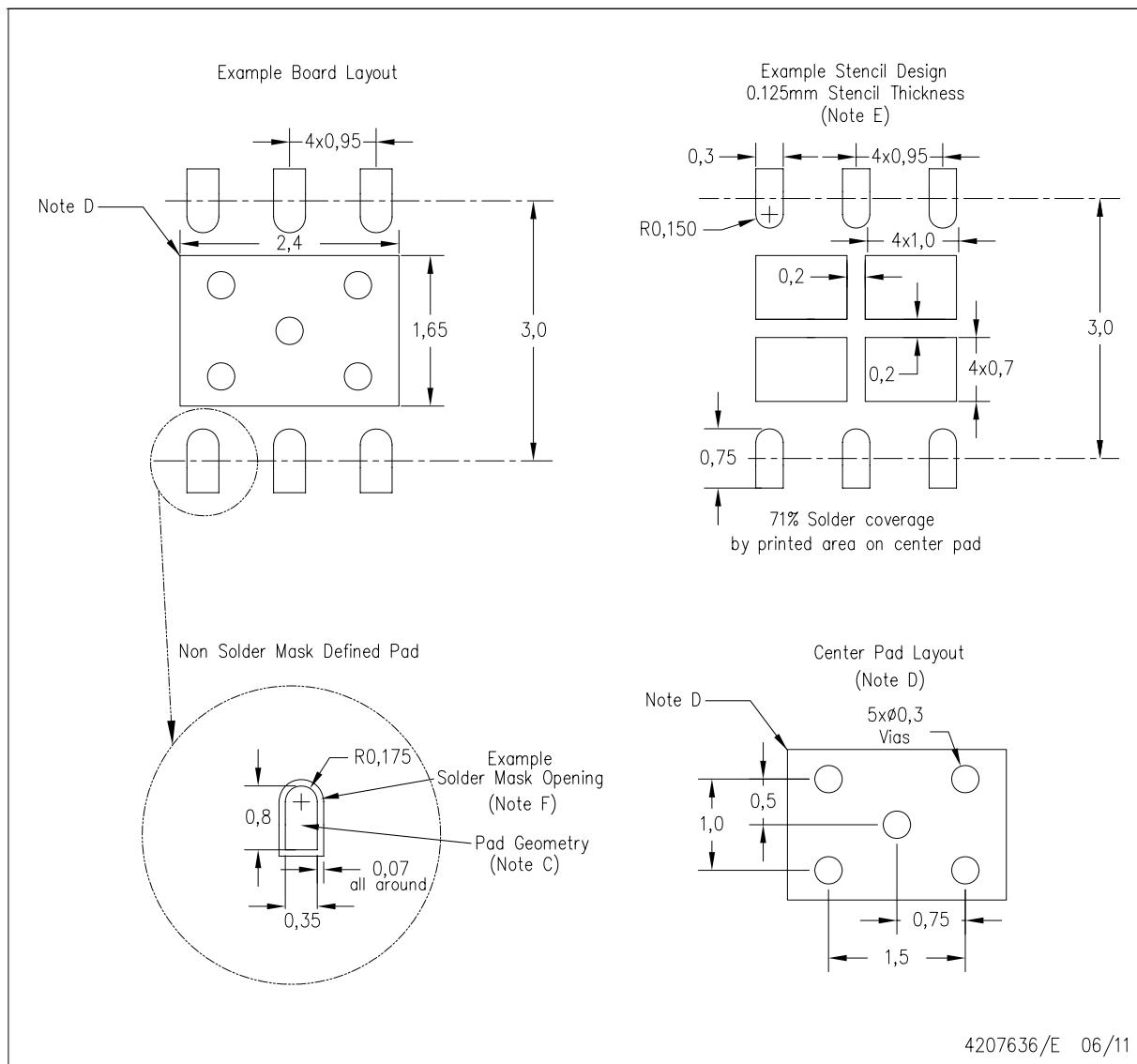

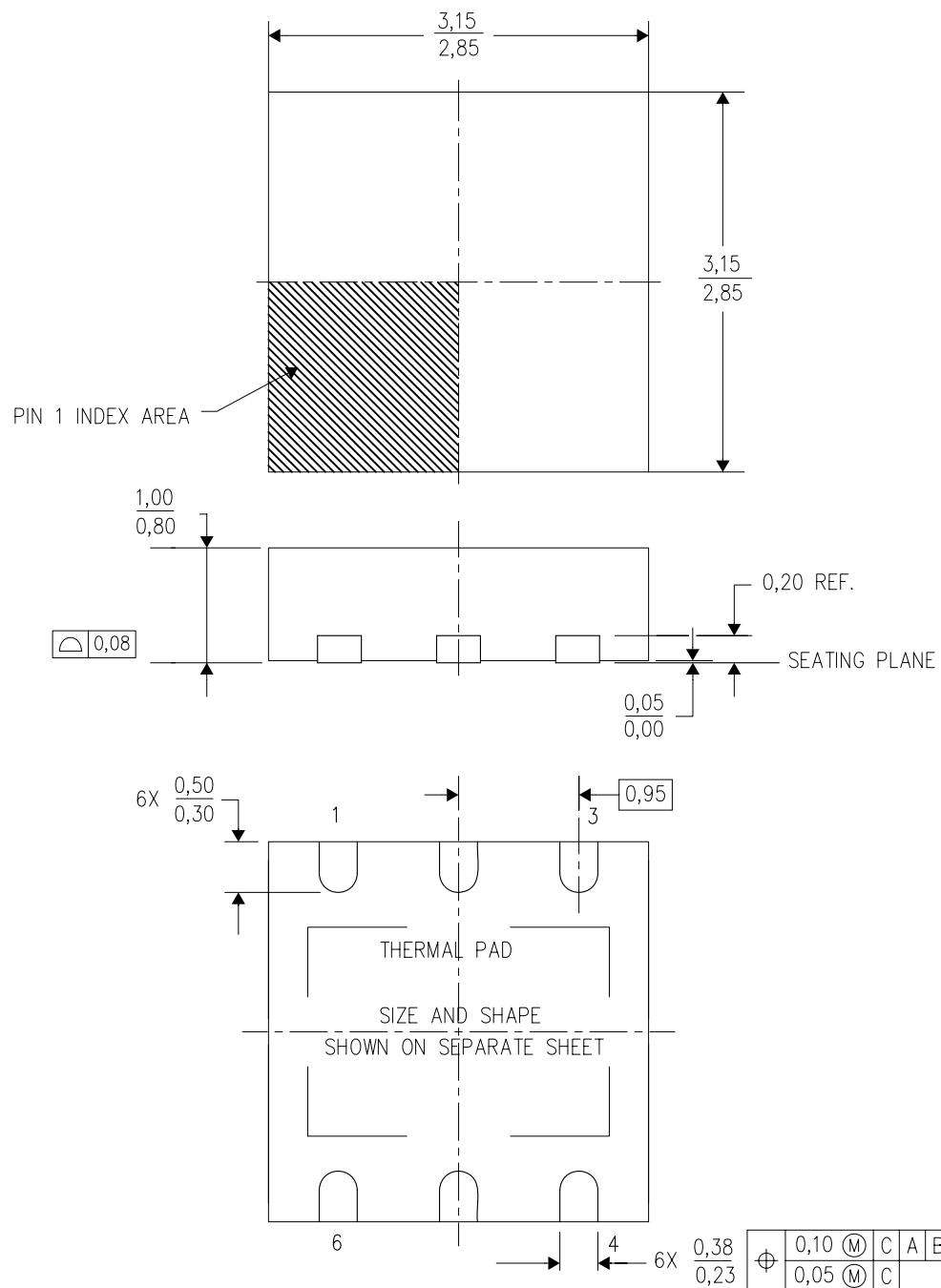

## MECHANICAL DATA

- NOTES:

- All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- This drawing is subject to change without notice.

- Small Outline No-Lead (SON) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance.

- See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

## THERMAL PAD MECHANICAL DATA

### DRP (S-PVSON-N6)

### PLASTIC SMALL OUTLINE NO-LEAD

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

Exposed Thermal Pad Dimensions

4207637/G 06/11

NOTE: All linear dimensions are in millimeters

## LAND PATTERN DATA

DRP (S-PVSON-N6)

PLASTIC SMALL OUTLINE NO-LEAD

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Publication IPC-7351 is recommended for alternate designs.

- This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- Customers should contact their board fabrication site for solder mask tolerances.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## MECHANICAL DATA

DRP (S-PVSON-N6)

PLASTIC SMALL OUTLINE NO-LEAD

4205935/E 06/11

- NOTES:

- All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- This drawing is subject to change without notice.

- Small Outline No-Lead (SON) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance.

- See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月