# TLVM13610 高密度、3V～36V 入力、1V～10V 出力、8A (10A ピーク) 同期整流式降圧 DC/DC パワー・モジュール、Enhanced HotRod™ QFN パッケージ

## 1 特長

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可能

- 用途の広い 36V<sub>IN</sub>、8A<sub>OUT</sub> 同期整流式降圧モジュール

- MOSFET、インダクタ、コントローラを内蔵

- 出力電圧を調整可能、1V～10V

- 6.5mm × 7.5mm × 4mm のオーバーモールド・パッケージ

- 40°C～125°C の接合部温度範囲

- 周波数を 200kHz～2.2MHz の範囲で変更可能

- 全負荷範囲にわたって極めて高い効率を実現

- 95% 以上のピーク効率

- 外部バイアス・オプションによる効率向上

- 露出パッドによる熱インピーダンスの低減 EVM θ<sub>JA</sub> = 18.2°C/W

- シャットダウン時静止電流: 0.6μA (標準値)

- 非常に小さい伝導および放射 EMI シグネチャ

- デュアル入力パスと内蔵コンデンサを備えた低ノイズ・パッケージにより、スイッチのリンクが減少

- 抵抗により調整可能なスイッチ・ノードのスルーレート

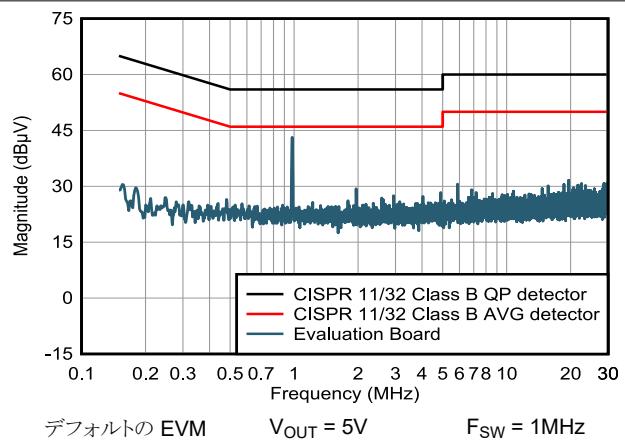

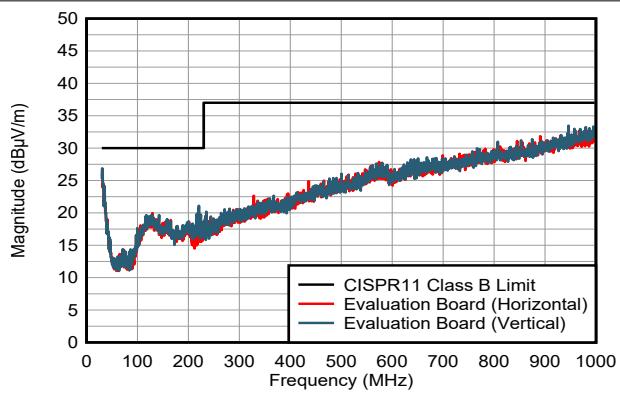

- CISPR 11 および 32 Class B の放射規格に準拠

- 堅牢な設計のための本質的な保護機能

- 高精度のイネーブル入力とオープン・ドレインの PGOOD インジケータによるシーケンシング、制御、V<sub>IN</sub> UVLO

- 過電流およびサーマル・シャットダウン保護機能

- WEBENCH® Power Designer により、TLVM13610 を使用するカスタム設計を作成

## 2 アプリケーション

- 試験および測定、航空宇宙および防衛

- ファクトリ・オートメーションおよび制御

- 降圧および反転型の昇降圧電源

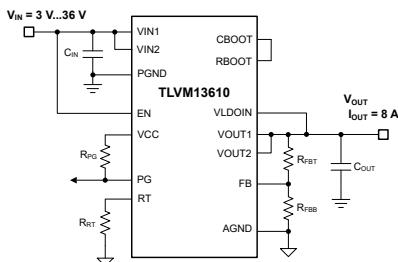

代表的な回路図

## 3 概要

TLVM13610 は、パワー MOSFET、シールド付きインダクタ、受動部品を Enhanced HotRod™ QFN パッケージに実装した、高集積 36V、8A DC/DC ソリューションです。このモジュールは、VIN および VOUT ピンをパッケージの角に配置し、入力および出力コンデンサの配置を最適化しています。モジュールの下面には大きな 4 つのサーマル・パッドがあるため、単純なレイアウトが可能で、製造時の扱いも容易です。

出力電圧が 1V～10V の TLVM13610 は、小さな PCB フットプリントで低 EMI の設計を迅速かつ容易に実装できるよう設計されています。このトータル・ソリューションを使用すると、外付け部品はわずか 4 個で済み、設計プロセスで磁気および補償のための部品選択も不要です。

TLVM13610 モジュールはスペースに制約のあるアプリケーション向けに小型でシンプルな設計となっていますが、調整可能な入力電圧 UVLO 用のヒステリシス付き高精度イネーブル、EMI 改善のための抵抗によりプログラム可能なスイッチ・ノードのスルーレートなど、堅牢な性能を実現するための多くの機能を備えています。また、VCC、ブートストラップ、入力コンデンサを内蔵しているため、信頼性と密度が向上します。このモジュールは、軽負荷時の効率を向上させるために、固定スイッチング周波数 (FPWM) または可変周波数 (PFM) の間で自動的に遷移します。シーケンシング、フォルト保護、出力電圧監視用の PGOOD インジケータも内蔵しています。

### パッケージ情報

| 部品番号      | パッケージ (1)       | 本体サイズ (公称)      |

|-----------|-----------------|-----------------|

| TLVM13610 | RDF (B3QFN, 22) | 6.50mm × 7.50mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

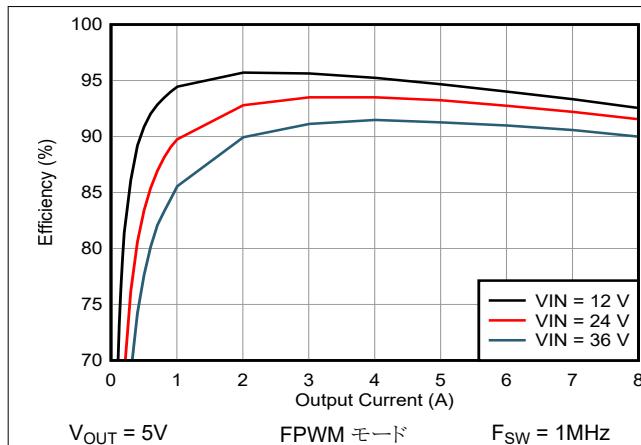

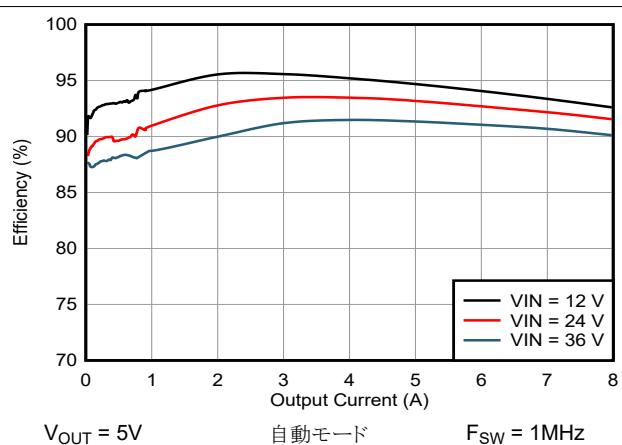

代表的な効率、V<sub>OUT</sub> = 5V、F<sub>SW</sub> = 1MHz

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参考ください。

## 目次

|             |    |                         |    |

|-------------|----|-------------------------|----|

| 1 特長        | 1  | 8.3 機能説明                | 13 |

| 2 アプリケーション  | 1  | 8.4 デバイスの機能モード          | 19 |

| 3 概要        | 1  | 9 アプリケーションと実装           | 20 |

| 4 改訂履歴      | 2  | 9.1 アプリケーション情報          | 20 |

| 5 デバイス比較表   | 3  | 9.2 代表的なアプリケーション        | 20 |

| 6 ピン構成および機能 | 3  | 9.3 電源に関する推奨事項          | 25 |

| 7 仕様        | 5  | 9.4 レイアウト               | 25 |

| 7.1 絶対最大定格  | 5  | 10 デバイスおよびドキュメントのサポート   | 28 |

| 7.2 ESD 定格  | 5  | 10.1 デバイスのサポート          | 28 |

| 7.3 推奨動作条件  | 5  | 10.2 ドキュメントのサポート        | 29 |

| 7.4 熱に関する情報 | 6  | 10.3 ドキュメントの更新通知を受け取る方法 | 29 |

| 7.5 電気的特性   | 6  | 10.4 サポート・リソース          | 29 |

| 7.6 システム特性  | 9  | 10.5 商標                 | 29 |

| 7.7 代表的な特性  | 10 | 10.6 静電気放電に関する注意事項      | 29 |

| 8 詳細説明      | 12 | 10.7 用語集                | 29 |

| 8.1 概要      | 12 | 11 メカニカル、パッケージ、および注文情報  | 30 |

| 8.2 機能ブロック図 | 13 |                         |    |

## 4 改訂履歴

| 日付      | リビジョン | 注  |

|---------|-------|----|

| 2023年2月 | *     | 初版 |

## 5 デバイス比較表

| デバイス      | 発注用製品型番       | 定格出力電流 | ピーク出力電流<br>(過渡条件) | 接合部温度範囲     |

|-----------|---------------|--------|-------------------|-------------|

| TLVM13610 | TLVM13610RDFR | 8A     | 10A               | -40°C~125°C |

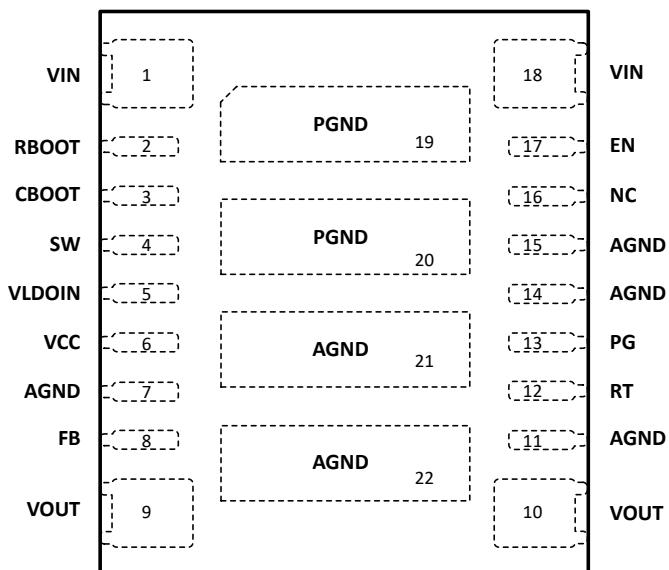

## 6 ピン構成および機能

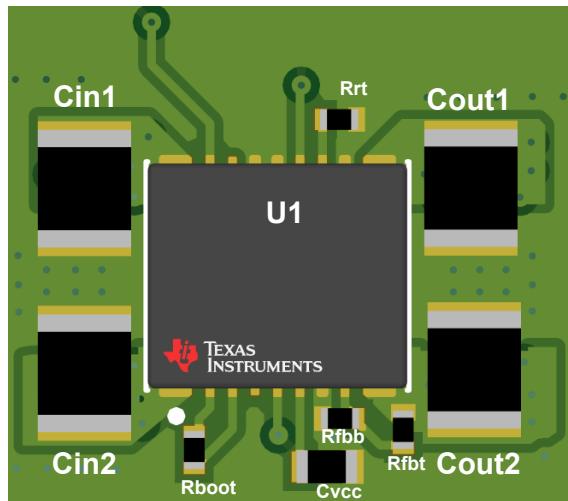

図 6-1.22 ピン B3QFN RDF パッケージ (上面図)

表 6-1. ピン機能

| 番号                             | ピン         | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                  |

|--------------------------------|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 18                          | VIN1, VIN2 | P                 | 入力電源電圧。入力電源をこれらのピンに接続します。入力コンデンサをこれらのピンと PGND の間で、デバイスの近くに接続します。                                                                                                                                                                                                    |

| 2                              | RBOOT      | I                 | 外部ブートストラップ抵抗の接続。内部の直列ブートストラップ抵抗の値を実質的に小さくしてスイッチ・ノードのスルーレートを調整するため、必要に応じて RBOOT を持ち出して CBOOT と組み合わせて使用します。RBOOT と CBOOT の間に 0~500Ω の抵抗を接続できます。抵抗が 0Ω の場合、スルーレートは最高速かつ最高効率です。100Ω の値を使用すると、効率と EMI の間で良好なバランスを実現できます。オープンのままにするとスルーレートが 20ns に設定され、自己発熱が増加するため推奨しません。 |

| 3                              | CBOOT      | O                 | 内部下限側ゲート・ドライバのブートストラップ・ピン。このピンからモジュール内の SW に 100nF のブートストラップ・コンデンサが内部で接続され、ブートストラップ電圧が供給されています。内部の直列ブートストラップ抵抗の値を実質的に小さくしてスイッチ・ノードのスルーレートを調整するため、必要に応じて CBOOT を持ち出して RBOOT と組み合わせて使用します。                                                                            |

| 4                              | SW         | O                 | スイッチ・ノード。このピンに外部部品を配置したり、信号に接続したりしないでください。ノイズや EMI の問題を防止するため、このピンに配置する銅の量は最小限に抑える必要があります。                                                                                                                                                                          |

| 5                              | VLDOIN     | P                 | 入力バイアス電圧。内部制御回路に電力を供給する内部 LDO への入力。効率を向上させるため、出力電圧点に接続します。ノイズ耐性を向上させるには、このピンとグランドとの間に高品質の 0.1μF~1μF コンデンサを任意で接続します。                                                                                                                                                 |

| 6                              | VCC        | P                 | 内部 LDO 出力。内部制御回路への電源として使用されます。いずれの外部負荷にも接続しないでください。1μF のコンデンサが内部で VCC から AGND に接続されています。                                                                                                                                                                            |

| 7, 11、<br>14, 15、<br>21、<br>22 | AGND       | G                 | アナログ・グランド。内部リファレンスおよびロジックのゼロ電圧リファレンスです。すべての電気的パラメータは、これらのピンを基準に測定されます。これらのピンは PGND に接続する必要があります。推奨レイアウトについては、「レイアウト例」を参照してください。                                                                                                                                     |

表 6-1. ピン機能 (continued)

| ピン     |                 | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                |

|--------|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号     | 名称              |                   |                                                                                                                                                                   |

| 8      | FB              | I                 | 帰還入力。帰還分圧抵抗の中点をこのピンに接続します。目的のレギュレーション・ポイントで、帰還分圧器の上側抵抗 ( $R_{FBT}$ ) を $V_{OUT}$ に接続します。帰還分圧器の下側抵抗 ( $R_{FBB}$ ) を AGND に接続します。オープン状態にすることも、グランドに接続することもしないでください。 |

| 9, 10  | VOUT1、<br>VOUT2 | P                 | 出力電圧。これらのピンは、内部の降圧インダクタに接続されています。これらのピンは出力負荷に接続し、PGND との間に外部出力コンデンサを接続します。                                                                                        |

| 12     | RT              | I                 | RT と AGND の間に外付け抵抗を配置することで、スイッチング周波数を 200kHz～2.2MHz の範囲に設定するために使用する周波数設定ピン。400kHz の場合は VCC に接続します。2.2MHz の場合はグランドに接続します。オープンの状態にしないでください。                         |

| 13     | PG              | O                 | FB 電圧が指定されたウインドウ・レッショルドを超えた場合に Low にアサートするオープン・ドレインのパワー・グッド・モニタ出力。適切な電圧に $10k\Omega$ ～ $100k\Omega$ のプルアップ抵抗が必要です。使用しない場合は、PG をオープンの状態にするか GND に接続できます。           |

| 16     | NC              | —                 | 接続なし。GND に接続するか、オープンの状態にします。                                                                                                                                      |

| 17     | EN              | I                 | レギュレータへの高精度イネーブル入力。High = オン、Low = オフ。VIN に接続できます。高精度イネーブルを使うと、このピンを調整可能な UVLO として使用できます。フローティングしないでください。                                                         |

| 19, 20 | PGND            | G                 | 電源グランド。これは、デバイスの電力段のリターン電流パスです。これらのパッドは、入力電源のリターン、負荷のリターン、VIN ピンと VOUT ピンに接続されたコンデンサに接続します。推奨レイアウトについては、「レイアウト例」を参照してください。                                        |

(1) P = 電源、G = グランド、I = 入力、O = 出力

## 7 仕様

### 7.1 絶対最大定格

接合部の動作時推奨温度範囲において<sup>(1)</sup>

| パラメータ     |                                         | 最小値  | 最大値            | 単位 |

|-----------|-----------------------------------------|------|----------------|----|

| 電圧        | 「AGND、PGND」に対する VIN (過渡) <sup>(2)</sup> | -0.3 | 42             | V  |

| 電圧        | 「AGND、PGND」に対する VIN (連続) <sup>(2)</sup> | -0.3 | 36             | V  |

| 電圧        | 「AGND、PGND」に対する SW                      | -0.3 | $V_{IN} + 0.3$ | V  |

| 電圧        | SW に対する CBOOT、RBOOT                     | -0.3 | 5.5            | V  |

| 電圧        | 「AGND、PGND」に対する EN (過渡) <sup>(2)</sup>  | -0.3 | 42             | V  |

| 電圧        | 「AGND、PGND」に対する EN (連続) <sup>(2)</sup>  | -0.3 | 36             | V  |

| 電圧        | 「AGND、PGND」に対する BIAS                    | -0.3 | 16             | V  |

| 電圧        | 「AGND、PGND」に対する FB: 可変バージョン             | -0.3 | 5.5            | V  |

| 電圧        | 「AGND、PGND」に対する RESET                   | 0    | 20             | V  |

| 電流        | RESET シンク電流 <sup>(4)</sup>              | 0    | 10             | mA |

| 電圧        | 「AGND、PGND」に対する RT                      | -0.3 | 5.5            | V  |

| 電圧        | 「AGND、PGND」に対する VCC                     | -0.3 | 5.5            | V  |

| 電圧        | AGND に対する PGND <sup>(3)</sup>           | -1   | 2              | V  |

| $T_{stg}$ | 保存温度                                    | -65  | 150            | °C |

- (1) 絶対最大定格の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の範囲内であっても推奨動作条件の範囲外で使用すると、デバイスが完全に機能しなくなる可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) このピンでは、0.01% 以下のデューティ・サイクルで 100ms 以下の間、最大 42V を持続させることができます。このデバイスの寿命にわたって 36V を維持できます。

- (3) この仕様は、100ns 以下の持続時間の電圧に適用されます。D.C. 電圧は、 $\pm 0.3V$  の範囲内である必要があります。

- (4) ピンの電圧定格を超えないようにしてください。

### 7.2 ESD 定格

|             |       | 値                                                        | 単位           |

|-------------|-------|----------------------------------------------------------|--------------|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | $\pm 2000$ V |

|             |       | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | $\pm 750$ V  |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

### 7.3 推奨動作条件

接合部の動作時推奨温度範囲である  $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ において (特に記述のない限り)<sup>(1)</sup>

|       |                                 | 最小値 | 最大値  | 単位  |

|-------|---------------------------------|-----|------|-----|

| 入力電圧  | 入力電圧範囲 <sup>(1)</sup>           | 3   | 36   | V   |

| 出力電圧  | 可変出力バージョンの出力調整範囲 <sup>(2)</sup> | 1   | 10   | V   |

| 周波数   | 周波数調整範囲                         | 200 | 2200 | kHz |

| 同期周波数 | 同期周波数範囲                         | 200 | 2200 | kHz |

| 出力電流  | $I_{out}$ 、TLVM13610            | 0   | 8    | A   |

| 温度    | 動作時の接合部温度、 $T_J$                | -40 | 125  | °C  |

- (1) VIN では起動に 3.7V が必要です。起動後は、3.0V までの拡張入力電圧範囲が可能です。起動条件については、「最小入力電圧」を参照してください。

(2) いかなる条件下でも、出力電圧は 0V を下回ることはできません。

## 7.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                                            | TLVM13610 | 単位   |

|----------------------|--------------------------------------------|-----------|------|

|                      |                                            | RDF       |      |

|                      |                                            | 22 ピン     |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗 (TLVM13610EVM) <sup>(3)</sup> | 18        | °C/W |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗 (JESD 51-7) <sup>(2)</sup>    | 25        | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗                        | 12.8      | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗                               | 7.4       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ                           | 0.7       | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ                           | 7.2       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗                        | 3.6       | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

(2) この表に示す  $R_{\theta JA}$  の値は他のパッケージとの比較にのみ有効であり、設計目的に使用することはできません。これらの値は JESD 51-7 に従つて計算されており、4 層 JEDEC 基板上でシミュレーションされています。これらは、実際のアプリケーションで得られた性能を表すものではありません。たとえば、EVM  $R_{\theta JA} = 21.6^{\circ}\text{C}/\text{W}$  です。設計情報については、「熱設計およびレイアウト」セクションを参照してください。

(3) 基板レイアウトと追加情報については、『EVM ユーザー・ガイド』を参照してください。熱設計の情報については、「熱設計とレイアウト」セクションを参照してください。

## 7.5 電気的特性

制限値は、接合部の動作時推奨温度範囲である  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ において適用されます (特に記述のない限り)。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 12$ 。 $VIN1$  が  $VIN2$  に短絡 =  $V_{IN}$ 。 $V_{OUT}$  は出力設定点です。

| パラメータ                  | テスト条件                              | 最小値                                   | 標準値 | 最大値   | 単位      |

|------------------------|------------------------------------|---------------------------------------|-----|-------|---------|

| <b>電源電圧 (VIN ピン)</b>   |                                    |                                       |     |       |         |

| $V_{IN}$               | 最小動作入力電圧                           | 起動するために必要な電圧                          | 3.7 |       | V       |

|                        |                                    | 動作開始後                                 | 3   |       | V       |

| <b>イネーブル (EN ピン)</b>   |                                    |                                       |     |       |         |

| $V_{EN}$               | 入力スレッショルド電圧 (立ち上がり) をイネーブル         | $V_{EN}$ の立ち上がり                       | 1.0 | 1.263 | $1.365$ |

| $V_{EN\_HYST}$         | スレッショルド・ヒステリシスをイネーブル               |                                       | 0.1 | 0.35  | 0.5     |

| $V_{EN\_WAKE}$         | ウェークアップ・スレッショルドをイネーブル              |                                       | 0.4 |       | V       |

| $I_{EN}$               | ピンの入力電流をイネーブル                      | $V_{IN} = V_{EN} = 12\text{V}$        | 1.5 | 50    | nA      |

| <b>内部 LDO (VCC ピン)</b> |                                    |                                       |     |       |         |

| $V_{CC}$               | 内部 VCC 電圧                          | $V_{BIAS} = 0\text{V}$                | 3.4 |       | V       |

|                        |                                    | $V_{BIAS} = 3.3\text{V}, 20\text{mA}$ | 3.2 |       |         |

| $V_{CC\_UVLO}$         | 内部 VCC 低電圧ロックアウトが解除される $V_{IN}$ 電圧 | $I_{VCC} = 0\text{A}$                 |     | 3.75  | V       |

| $V_{CC\_UVLO\_HYST}$   | 内部 VCC 低電圧ロックアウト・ヒステリシス            | $V_{CC\_UVLO}$ の下側のヒステリシス             |     | 1.2   | V       |

## 7.5 電気的特性 (continued)

制限値は、接合部の動作時推奨温度範囲である  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ において適用されます (特に記述のない限り)。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。  $V_{IN} = 12$ 。  $VIN1$  が  $VIN2$  に短絡 =  $V_{IN}$ 。 $V_{OUT}$  は出力設定点です。

| パラメータ                            | テスト条件                                                                                     | 最小値                                                                               | 標準値   | 最大値  | 単位       |

|----------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|----------|

| <b>電圧リファレンス (FB ピン)</b>          |                                                                                           |                                                                                   |       |      |          |

| $V_{FB}$                         | 可変 (1V FB) バージョンの初期リファレンス電圧精度                                                             | $V_{IN} = 3.0\text{V} \sim 36\text{V}$ 、FPWM モード                                  | 0.985 | 1    | 1.015    |

| $I_{FB}$                         | FB から AGND への入力電流                                                                         | 可変バージョンのみ、 $V_{FB} = 1\text{V}$                                                   |       | 50   | nA       |

| <b>電流制限</b>                      |                                                                                           |                                                                                   |       |      |          |

| $I_{SC}$                         | 短絡ハイサイド電流制限                                                                               | デューティ・サイクルを 0% に近付ける                                                              | 11.5  | 13.8 | 15.7     |

| $I_{LS-LIMIT}$                   | ローサイド電流制限                                                                                 |                                                                                   | 8     | 9.2  | 10.5     |

| $I_{PEAK-MIN}$                   | 最小ピーク・インダクタ電流                                                                             |                                                                                   | 1.9   |      | A        |

| $I_{L-NEG}$                      | 負の電流制限                                                                                    |                                                                                   | -6.4  | -5.3 | -3.9     |

| $I_{L-ZC}$                       | ゼロクロスの電流制限値。正の電流の方向は、SW ピンから流れ出す電流の方向です。                                                  | 自動モード、静的測定                                                                        | 70    |      | mA       |

| $V_{HICCUP}$                     | FB ピンのヒップ・スレッショルド                                                                         |                                                                                   | 0.36  | 0.4  | 0.44     |

| <b>POWER GOOD (/RESET ピン)</b>    |                                                                                           |                                                                                   |       |      |          |

| $V_{RESET-OV}$                   | RESET の上側スレッショルド - 立ち上がり                                                                  | % of FB voltage                                                                   | 109.5 | 112  | 114.5    |

| $V_{RESET-UV}$                   | RESET の下側スレッショルド - 立ち下がり                                                                  | % of FB voltage                                                                   | 93    | 95   | 97.5     |

| $V_{RESET GUARD}$                | 出力電圧と UV スレッショルド、立ち下がり、同じ $T_J$ と $V_{IN}$ で読み取った、定常状態の出力電圧のパーセンテージとしての RESET UV スレッショルド。 | 立ち下がり                                                                             |       | 97   | %        |

| $V_{RESET-HYS-FALLING}$          | RESET 立ち下がりスレッショルド・ヒステリシス                                                                 | % of FB voltage                                                                   |       | 1.3  | %        |

| $V_{RESET-HYS-RISING}$           | RESET 立ち上がりスレッショルド・ヒステリシス                                                                 | % of FB voltage                                                                   |       | 1.3  | %        |

| $V_{RESET_VALID}$                | 有効な RESET 機能の最小入力電圧                                                                       | 外部 5V ～ 10kΩ プルアップして $V_{RESET} < 0.4\text{V}$ のときに測定                             |       | 1.2  | V        |

| $V_{OL}$                         | RESET 低レベル機能の出力電圧                                                                         | RESET ピンに 46.0 $\mu\text{A}$ プルアップ、 $V_{IN} = 1.0\text{V}$ 、 $V_{EN} = 0\text{V}$ |       | 0.4  | V        |

|                                  |                                                                                           | RESET ピンに 1mA プルアップ、 $V_{IN} = 12\text{V}$ 、 $V_{EN} = 0\text{V}$                 |       | 0.4  |          |

|                                  |                                                                                           | RESET ピンに 2 mA プルアップ、 $V_{IN} = 12\text{V}$ 、 $V_{EN} = 3.3\text{V}$              |       | 0.4  |          |

| $R_{RESET}$                      | RESET ON 抵抗、                                                                              | $V_{EN} = 5\text{V}$ 、1mA のプルアップ電流                                                | 44    | 125  | $\Omega$ |

| $R_{RESET}$                      | RESET ON 抵抗、                                                                              | $V_{EN} = 0\text{V}$ 、1mA のプルアップ電流                                                | 18    | 40   | $\Omega$ |

| $t_{RESET\_FILTER}$              | RESET エッジ・グリッチ除去遅延                                                                        |                                                                                   | 10    | 26   | 45       |

| $t_{RESET\_ACT}$                 | RESET アクティブ時間                                                                             | RESET をリリースする前に、時間 FB が有効である必要がある。                                                | 1.2   | 2.1  | 3.75     |

| <b>OSCILLATOR (RT と SYNC ピン)</b> |                                                                                           |                                                                                   |       |      |          |

| $f_{OSC}$                        | 内部発振器の周波数                                                                                 | RT = GND                                                                          | 1.90  | 2.2  | 2.42     |

| $f_{OSC}$                        | 内部発振器の周波数                                                                                 | RT = VCC                                                                          | 320   | 400  | 450      |

| $f_{FIXED\_2.2MHz}$              | 2.2MHz を選択するために RT 抵抗の最大値を使用して測定された発振器の周波数                                                | RT = 6.81k $\Omega$                                                               | 1.95  | 2.2  | 2.42     |

## 7.5 電気的特性 (continued)

制限値は、接合部の動作時推奨温度範囲である  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ において適用されます (特に記述のない限り)。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 12$ 。 $VIN1$  が  $VIN2$  に短絡 =  $V_{IN}$ 。 $V_{OUT}$  は出力設定点です。

| パラメータ                        |                                             | テスト条件                                                                                         | 最小値  | 標準値 | 最大値 | 単位               |

|------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------|------|-----|-----|------------------|

| $f_{FIXED\_0.4\text{MHz}}$   | 0.4MHz を選択するために RT 抵抗の最小値を使用して測定された発振器の周波数  | $RT = 40.2\text{k}\Omega$                                                                     | 352  | 400 | 448 | kHz              |

| $f_{ADJ}$                    | センター・トリム発振器の周波数                             | $RT = 22.6\text{k}\Omega$                                                                     | 630  | 700 | 770 | kHz              |

| <b>ハイサイド・ドライブ (CBOOT ピン)</b> |                                             |                                                                                               |      |     |     |                  |

| $V_{CBOOT\_UVLO}$            | ハイサイド・スイッチがオフになる CBOOT ピンの電圧 (SW 基準)        |                                                                                               |      | 1.9 |     | V                |

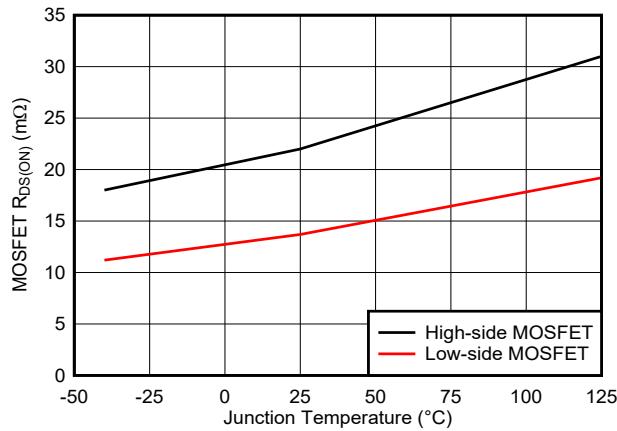

| <b>MOSFET</b>                |                                             |                                                                                               |      |     |     |                  |

| $R_{DS-ON-HS}$               | ハイサイド MOSFET オン抵抗                           | 負荷 = 1A、 $C_{BOOT-SW} = 3.2\text{V}$                                                          | 21   | 39  |     | $\text{m}\Omega$ |

| $R_{DS-ON-LS}$               | ローサイド MOSFET オン抵抗                           | 負荷 = 1A、 $C_{BOOT-SW} = 3.2\text{V}$                                                          | 13   | 25  |     | $\text{m}\Omega$ |

| <b>PWM 制限値 (SW ピン)</b>       |                                             |                                                                                               |      |     |     |                  |

| $t_{ON-MIN}$                 | HS スイッチの最小オン時間                              | $V_{IN} = 18\text{V}$ 、 $I_{OUT} = 2\text{A}$ 、 $R_{BOOT} = 0\Omega$                          | 62   | 81  |     | ns               |

| $t_{OFF-MIN}$                | HS スイッチの最小オフ時間                              | $V_{IN} = 5\text{V}$                                                                          | 70   | 103 |     | ns               |

| $t_{ON-MAX}$                 | 最大スイッチ・オン時間                                 | ドロップアウト時の HS タイムアウト                                                                           | 6.9  | 8.9 | 11  | $\mu\text{s}$    |

| $D_{MAX}$                    | 最大スイッチ・デューティ・サイクル                           | 周波数フォールドバック中                                                                                  | 98   |     |     | %                |

|                              |                                             | $f_{sw} = 1.85\text{MHz}$                                                                     |      | 87  |     |                  |

| <b>今すぐ開始</b>                 |                                             |                                                                                               |      |     |     |                  |

| $t_{EN}$                     | ターンオン遅延                                     | $V_{IN} = 12\text{V}$ 、 $C_{VCC} = 1\mu\text{F}$ 、EN High から最初の SW パルスまでの時間 (出力が 0V から開始する場合) | 0.82 | 1.2 |     | ms               |

| $t_{SS}$                     | 最初の SW パルスから $V_{REF}$ が設定点の 90% に達するまでの時間。 |                                                                                               | 1.6  | 2.2 | 2.7 | ms               |

| $t_W$                        | 短絡待機時間 (「ヒップ」時間)                            |                                                                                               | 40   |     |     | ms               |

## 7.6 システム特性

以下の仕様は、標準的なアプリケーション回路にのみ適用され、コンポーネントの公称値が設定されています。「代表値 (TYP)」列の仕様は、 $T_J = 25^\circ\text{C}$  にのみ適用されます。これらの仕様は、製造試験では保証されていません。

| パラメータ             |                  | テスト条件                                                                                                                                                | 最小値  | 標準値 | 最大値 | 単位            |

|-------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|---------------|

| <b>電源</b>         |                  |                                                                                                                                                      |      |     |     |               |

| $I_{IN}$          | レギュレーション時の入力電源電流 | $V_{IN} = V_{EN/SYNC} = 24\text{V}$ , $V_{OUT} = V_{VLDOIN} = 3.3\text{V}$ , $V_{MODE} = 0\text{V}$ , $F_{SW} = 1\text{MHz}$ , $I_{OUT} = 0\text{A}$ | 8    |     |     | $\mu\text{A}$ |

| <b>出力電圧</b>       |                  |                                                                                                                                                      |      |     |     |               |

| $\Delta V_{OUT1}$ | 負荷レギュレーション       | $V_{OUT} = 3.3\text{V}$ , $V_{IN} = 24\text{V}$ , $I_{OUT} = 0.1\text{A} \sim 8\text{A}$                                                             | 4    |     |     | $\text{mV}$   |

| $\Delta V_{OUT2}$ | ライン・レギュレーション     | $V_{OUT} = 3.3\text{V}$ , $V_{IN} = 4\text{V} \sim 36\text{V}$ , $I_{OUT} = 8\text{A}$                                                               | 1    |     |     | $\text{mV}$   |

| $\Delta V_{OUT3}$ | 負荷過渡応答           | $V_{OUT} = 5\text{V}$ , $V_{IN} = 24\text{V}$ , $I_{OUT} = 0\text{A} \sim 4\text{A}$ , $1\text{A}/\mu\text{s}$ , $C_{OUT(derated)} = 100\mu\text{F}$ | 150  |     |     | $\text{mV}$   |

| <b>効率</b>         |                  |                                                                                                                                                      |      |     |     |               |

| $\eta$            | 効率               | $V_{IN} = 12\text{V}$ , $V_{OUT} = V_{VLDOIN} = 3.3\text{V}$ , $I_{OUT} = 4\text{A}$ , $F_{SW} = 1\text{MHz}$                                        | 92.1 |     |     | %             |

| $\eta$            | 効率               | $V_{IN} = 24\text{V}$ , $V_{OUT} = V_{VLDOIN} = 3.3\text{V}$ , $I_{OUT} = 4\text{A}$ , $F_{SW} = 1\text{MHz}$                                        | 91   |     |     | %             |

| $\eta$            | 効率               | $V_{IN} = 12\text{V}$ , $V_{OUT} = V_{VLDOIN} = 5\text{V}$ , $I_{OUT} = 4\text{A}$ , $F_{SW} = 1\text{MHz}$                                          | 94.3 |     |     | %             |

| $\eta$            | 効率               | $V_{IN} = 24\text{V}$ , $V_{OUT} = V_{VLDOIN} = 5\text{V}$ , $I_{OUT} = 4\text{A}$ , $F_{SW} = 1\text{MHz}$                                          | 93   |     |     | %             |

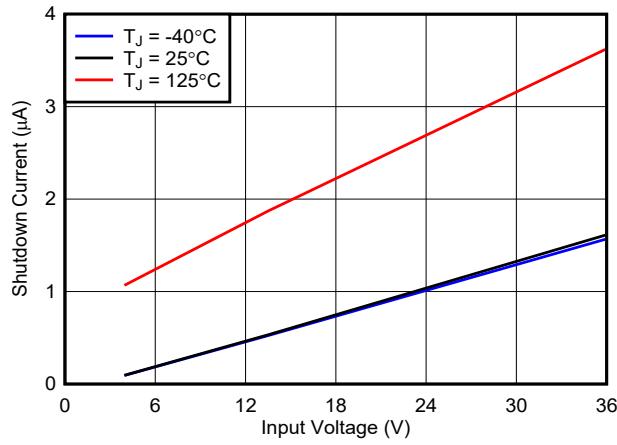

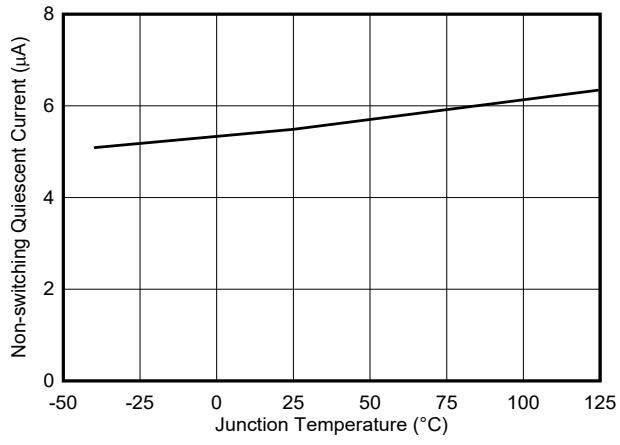

## 7.7 代表的な特性

$V_{IN} = 12V$  (特に記述のない限り)

図 7-1. シャットダウン時の電源電流

図 7-2. 非スイッチング時の入力電源電流

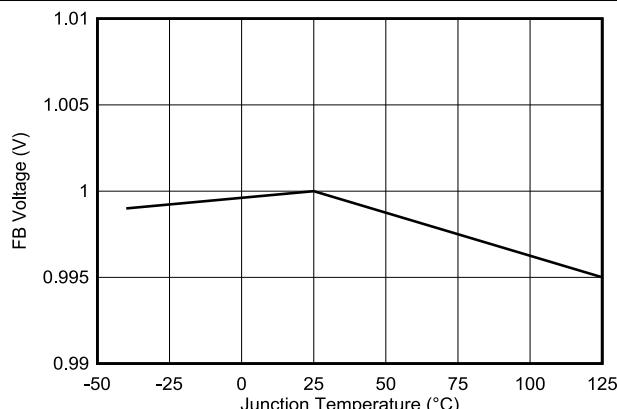

図 7-3. 帰還電圧

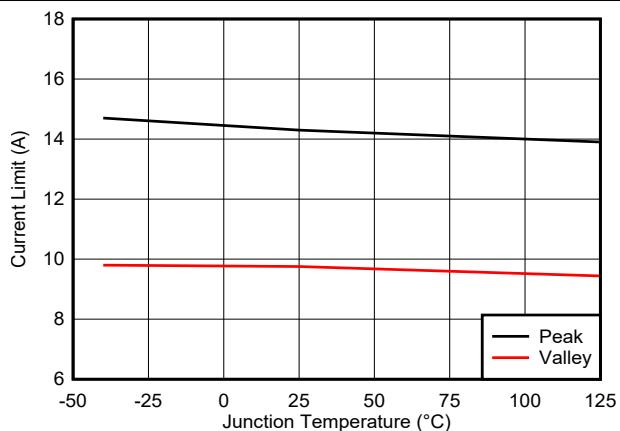

図 7-4. 下限側(ピーク)および上限側(バレー)の電流制限

図 7-5. 下限側および上限側 MOSFET  $R_{DS(on)}$

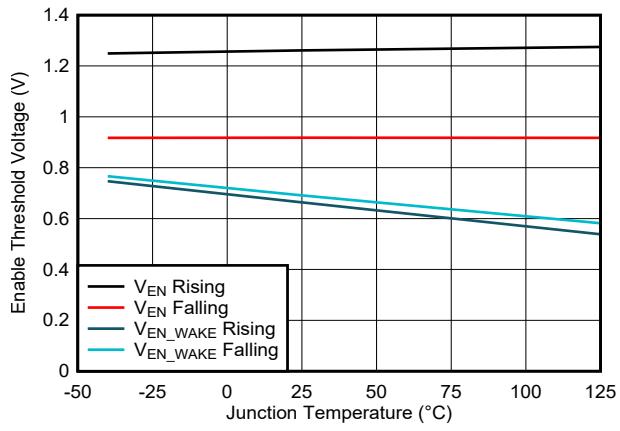

図 7-6. イネーブル・スレッショルド

## 7.7 代表的な特性 (continued)

$V_{IN} = 12V$  (特に記述のない限り)

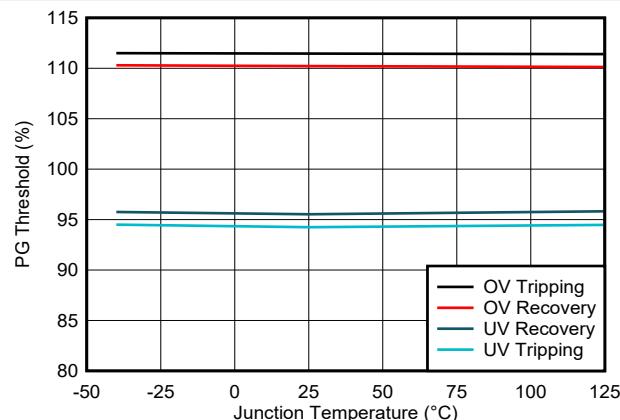

図 7-7. パワー・グッド (PG) スレッショルド

図 7-8. RT 抵抗により設定されるスイッチング周波数

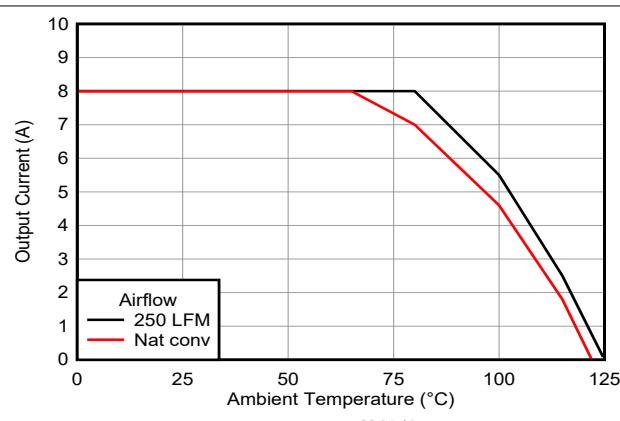

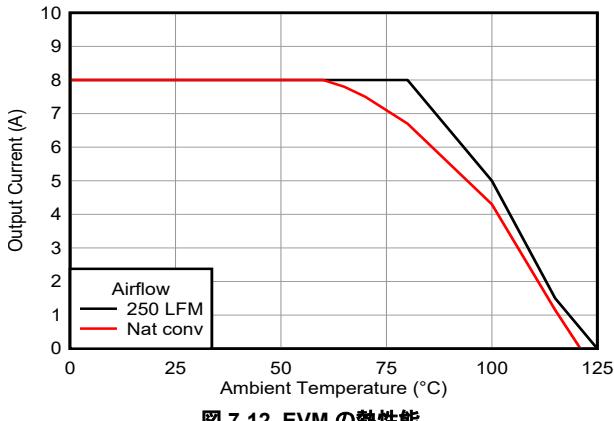

図 7-9. EVM の熱性能

( $V_{IN} = 12V$ 、 $V_{OUT} = 5V$ 、 $F_{SW} = 1MHz$ )

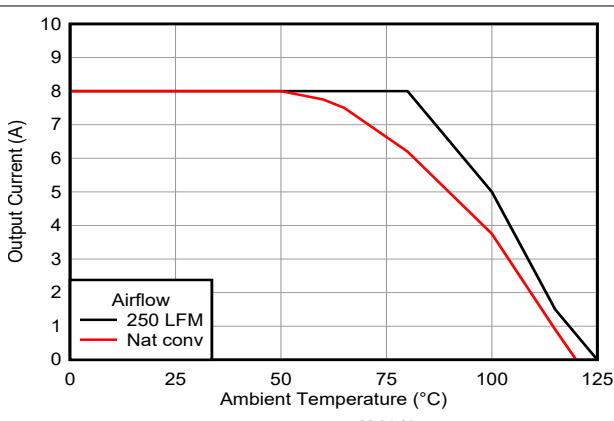

図 7-10. EVM の熱性能

( $V_{IN} = 24V$ 、 $V_{OUT} = 5V$ 、 $F_{SW} = 1MHz$ )

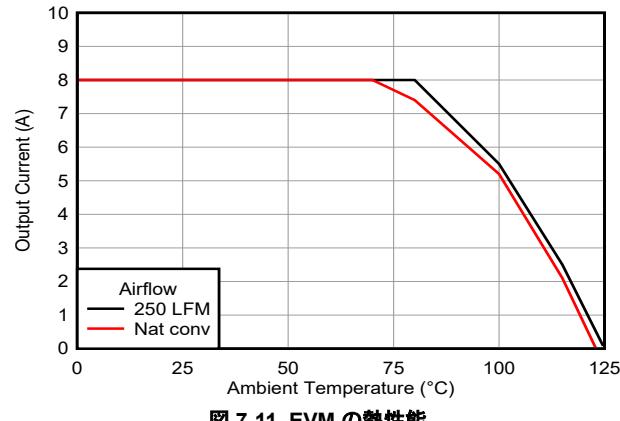

図 7-11. EVM の熱性能

( $V_{IN} = 12V$ 、 $V_{OUT} = 3.3V$ 、 $F_{SW} = 700kHz$ )

図 7-12. EVM の熱性能

( $V_{IN} = 24V$ 、 $V_{OUT} = 3.3V$ 、 $F_{SW} = 700kHz$ )

## 8 詳細説明

### 8.1 概要

TLVM13610 は使いやすい同期整流降圧 DC/DC 電源モジュールで、信頼性、小型ソリューション・サイズ、低 EMI 特性が非常に重要なさまざまなアプリケーション向けに設計されています。パワー MOSFET、降圧インダクタ、また PWM コントローラを内蔵した TLVM13610 は、3V~36V の入力電圧範囲で動作し、最大 42V の過渡電圧に対応します。このモジュールは、変換効率が高く、超低入力静止電流を非常に小さなソリューションの専有面積で実現し、最大 8A (10A ピーク) の DC 負荷電流を供給します。制御ループ補償は不要で、設計時間が短縮し、外部部品点数が減ります。

TLVM13610 は、RT ピンまたは外部クロック信号を使用して 200kHz~2.2MHz のプログラム可能なスイッチング周波数を備えており、ノイズに影響されるアプリケーションで EMI 性能を向上させる特定の機能を内蔵しています。

- ・ パッケージとピン配置を最適化した設計により、放射 EMI を低減するシールド付きスイッチ・ノードのレイアウトが可能になる

- ・ 対称型のコンデンサ・レイアウトを採用した並列入出力パスにより、寄生インダクタンス、スイッチ電圧リンクギング、放射フィールド・カップリングを最小限に抑える

- ・ 抵抗によりプログラム可能なスイッチ・ノードのスルーレート

- ・ 強化型ゲート・ドライブ制御を備えたパワー MOSFET を内蔵しているため、低ノイズの PWM スイッチングが可能

これらの機能を組み合わせることで、EMI フィルタリング要件を大幅に低減すると同時に、伝導型および放射型の電磁波に関する CISPR 11 および CISPR 32 クラス B EMI の制限を満たすことができます。

TLVM13610 モジュールには、堅牢なシステム要件に対応する固有の保護機能も内蔵されています。

- ・ 電源レールのシーケンシングと障害報告用のオープン・ドレイン PGOOD インジケータ

- ・ ヒステリシス付きの高精度イネーブル入力により以下を実現する

- プログラム可能なライン低電圧誤動作防止 (UVLO)

- リモート・オン / オフ特性

- ・ プリバイアス負荷への単調起動を備えた内部固定出力電圧ソフト・スタート

- ・ サイクル単位のピーク電流制限とバレー電流制限によるヒップ・モード過電流保護

- ・ 自動回復機能付きサーマル・シャットダウン。

TLVM13610 は、外付け部品をわずかしか必要としないシンプルなレイアウト向けに設計されたピン配置を活用して、最大接合部温度 125°C での動作が規定されています。特定の周囲環境における適合性を推定するには、[代表的性能曲線](#)を参照してください。

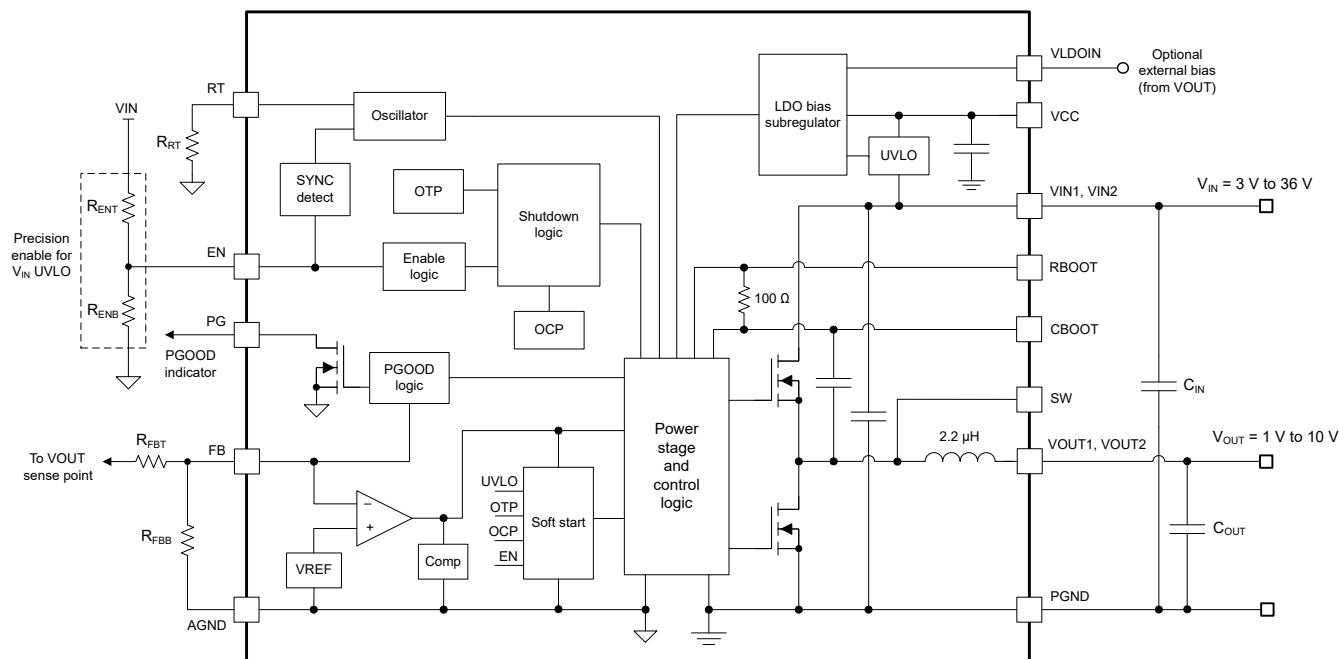

## 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 入力電圧範囲 (VIN1、VIN2)

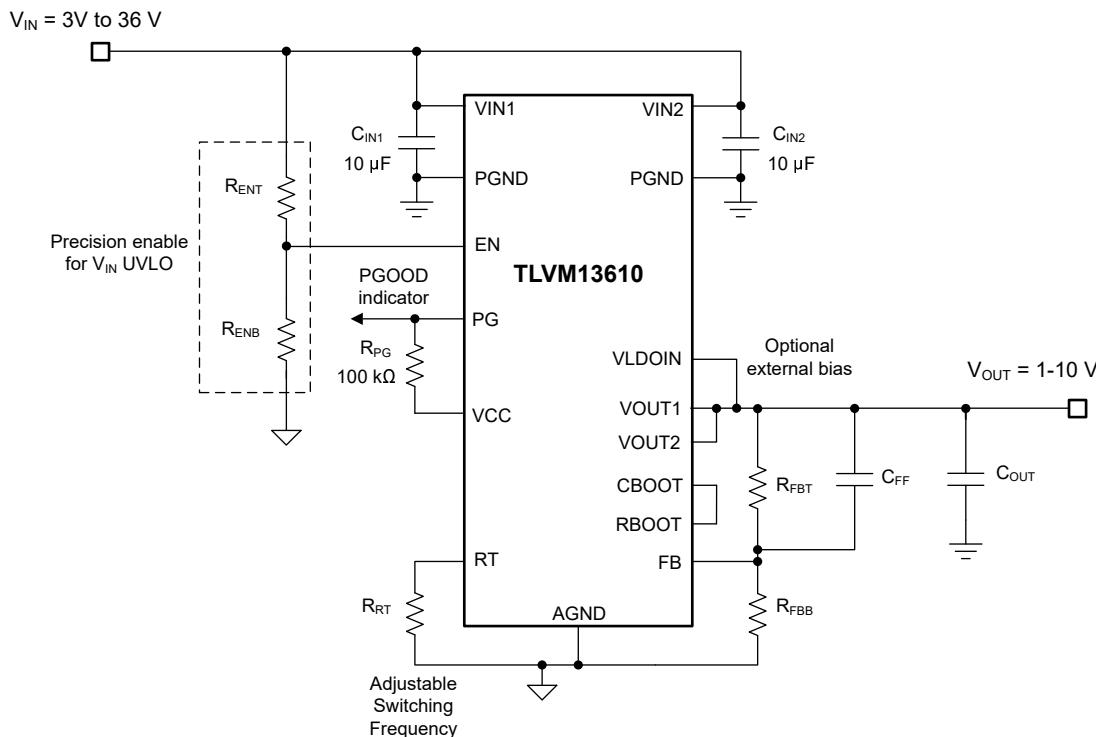

TLVM13610 モジュールは、3V～36V の定常状態入力電圧範囲に対応しており、標準的な 12V、24V、28V の入力電源レールからの降圧変換を目的としています。図 8-1 の回路図に、単一の入力電源を使用して TLVM13610 ベースの降圧レギュレータを実装するために必要なすべての部品を示します。

図 8-1. 入力電圧動作範囲が 3V～36V の場合の TLVM13610 の回路図

起動に必要な最小入力電圧は 3.7V です。モジュールの VIN ピン (VIN1 および VIN2) の電圧が、ラインまたは負荷過渡事象中に絶対最大電圧定格 42V を超えないように十分注意してください。絶対最大定格を超える VIN ピンでの電圧リンクは、IC に損傷を与える可能性があります。

### 8.3.2 可変出力電圧 (FB)

TLVM13610 の可変出力電圧範囲は、1V から最大 20V まで、またはわずかに  $V_{IN}$  未満、のどちらか小さい方になります。出力電圧を設定するには、図 8-1 の  $R_{FBT}$  および  $R_{FBB}$  として指定された 2 つの帰還抵抗が必要です。FB ピンの基準電圧は 1V に設定され、 $\pm 1\%$  の接合部温度範囲にわたってフィードバック・システムの精度が得られます。デバイスの接合部温度範囲は  $-40^{\circ}\text{C}$ ~ $125^{\circ}\text{C}$  です。

$R_{FBT}$  の推奨値 100k $\Omega$  に基づいて、式 1 を使用して  $R_{FBB}$  の値を計算します。

$$R_{FBB}(\text{k}\Omega) = \frac{R_{FBT}(\text{k}\Omega)}{\frac{V_{OUT}}{1} - 1} \quad (1)$$

表 8-1 に、いくつかの出力電圧の標準抵抗値と、適切なピーク・ツー・ピーク・インダクタ・リップル電流を維持するための推奨スイッチング周波数範囲を示します。この表には、安定性を維持するために各出力電圧設定に必要な最小出力容量も記載されています。以下に示す容量は、DC バイアス電圧および温度に対してディレーティングされたセラミック・コンデンサの実効値を表します。さらに、フィードフォワード・コンデンサ  $C_{FF}$  を  $R_{FBT}$  と並列に配置し、出力容量が最小推奨値に近いときに位相マージンを増やします。

**表 8-1. 標準  $R_{FBT}$  値、推奨  $F_{SW}$  範囲、最小  $C_{OUT}$**

| $V_{OUT}$ (V) | $R_{FBT}$ (k $\Omega$ ) <sup>(1)</sup> | 推奨する $F_{SW}$ 範囲 (kHz) | $C_{OUT(min)}$ ( $\mu$ F) (実効値) | BOM <sup>(2)</sup>         | $C_{FF}$ (pF) |

|---------------|----------------------------------------|------------------------|---------------------------------|----------------------------|---------------|

| 1             | オープン                                   | 200~750                | 400                             | $4 \times 100\mu$ F (6.3V) | —             |

| 1.8           | 125                                    | 300~900                | 350                             | $4 \times 100\mu$ F (6.3V) | 100           |

| 3.3           | 43.4                                   | 400~1100               | 100                             | $4 \times 47\mu$ F (10V)   | 47            |

| 5             | 25                                     | 500~1400               | 75                              | $3 \times 47\mu$ F (10V)   | 22            |

| 9             | 12.5                                   | 0.75~1.5               | 66                              | $4 \times 47\mu$ F (16V)   | —             |

(1)  $R_{FBT} = 100\text{k}\Omega$ 。

(2) 出力コンデンサのリストについては、[表 8-3](#) を参照してください。

帰還抵抗が大きいほど、DC 電流の消費が小さくなることに注意してください。ただし、 $R_{FBT}$  上限抵抗値が  $1\text{M}\Omega$  を超えると、フィードバック・パスはノイズの影響を受けやすくなります。一般に、帰還抵抗が大きいほど、フィードバック・パスのレイアウトをより慎重に行う必要があります。帰還抵抗は、FB ピンおよび AGND ピンの近くに配置し、帰還パターンをできるだけ短く（また、PCB のノイズの多い領域から遠ざけるように）してください。詳細については、「[レイアウト例](#)」を参照してください。

### 8.3.3 入力コンデンサ

入力コンデンサは、スイッチング周波数の AC 電流により、モジュールへの入力リップル電圧を制限する必要があります。テキサス・インスツルメンツは、幅広い温度範囲で低インピーダンスと高い RMS 電流定格を実現するセラミック・コンデンサの使用を推奨しています。[式 2](#) に入力コンデンサの RMS 電流を示します。入力コンデンサの RMS 電流の最大値は  $D = 0.5$  のときに発生します。この時点で、コンデンサの RMS 電流定格は出力電流の半分を超えていました。

$$I_{CIN, rms} = \sqrt{D \times \left( I_{OUT}^2 \times (1 - D) + \frac{\Delta i_L^2}{12} \right)} \quad (2)$$

ここで

- $D = V_{OUT} / V_{IN}$  はモジュールのデューティ・サイクルです。

理想的には、降圧段への入力電流の DC 成分と AC 成分は、それぞれ入力電圧源と入力コンデンサによって供給されます。インダクタ・リップル電流を無視すると、入力コンデンサは、 $D$  間隔の間に振幅 ( $I_{OUT} - I_{IN}$ ) の電流をソースし、 $1 - D$  間隔の間に  $I_{IN}$  をシンクします。そのため、入力コンデンサは、出力電流に等しいピーク・ツー・ピーク振幅の方形波電流を導通します。この結果、AC リップル電圧の合成容量成分は三角波になります。[ESR](#) 関連のリップル成分だけでなく、[式 3](#) にピーク・ツー・ピーク・リップル電圧の振幅を示します。

$$\Delta V_{IN} = \left( \frac{I_{OUT} \times D \times (1 - D)}{F_{SW} \times C_{IN}} + I_{OUT} \times R_{ESR} \right) \quad (3)$$

[式 4](#) に、特定の負荷電流に必要な入力容量を示します。

$$C_{IN} \geq \left( \frac{I_{OUT} \times D \times (1 - D)}{F_{SW} \times (\Delta V_{IN} - I_{OUT} \times R_{ESR})} \right) \quad (4)$$

ここで

- $\Delta V_{IN}$  は、入力電圧リップルの仕様です。

TLVM13610 は、 $10\mu$ F のセラミック入力コンデンサが 2 個以上必要です。X7R または X7S 誘電体の使用と、占有面積は 1206 または 1210 を推奨します。CISPR 11 や CISPR 32 などの伝導型 EMI 仕様を満たすアプリケーションでは、追加の容量が必要になる場合があります。

[表 8-2](#) に、メーカー毎に推奨されるコンデンサのリストを示します。スイッチング・ループの寄生インダクタンスを最小限に抑えるため、セラミック入力コンデンサを  $VIN1$  ピンと  $VIN2$  ピンの近くに対称的のレイアウトで配置し、モジュールの下にある銅のグランド・プレーンを使用してコンデンサのリターン端子を  $PGND$  ピンに接続します。

表 8-2. 推奨セラミック入力コンデンサ

| メーカー <sup>(1)</sup> | 誘電  | 部品番号                | ケース・サイズ | 容量(μF) <sup>(2)</sup> | 定格電圧(V) |

|---------------------|-----|---------------------|---------|-----------------------|---------|

| TDK                 | X7R | C3216X7R1H106K160AC | 1206    | 10                    | 50      |

| Murata              | X7S | GCM32EC71H106KA03K  | 1210    | 10                    | 50      |

| AVX                 | X7R | 12105C106MAT2A      | 1210    | 10                    | 50      |

| Murata              | X7R | GRM32ER71H106KA12L  | 1210    | 10                    | 50      |

(1) この表に記載されているコンデンサの入手可能性、材料組成、RoHS および鉛フリーのステータス、製造プロセスの要件については、コンデンサのサプライヤにお問い合わせください。「[サード・パーティー製品に関する免責事項](#)」をご覧ください。

(2) 銘板の容量値(実効値は、印加された DC 電圧および温度に基づいて低いです)。

「[電源に関する推奨事項](#)」で説明したように、電解バルク容量(68μF~100μF)は低周波数フィルタリングと並列ダンピングを実現し、低 ESR の高 Q セラミック入力コンデンサでの入力寄生インダクタンスの共振の影響を緩和します。

### 8.3.4 出力コンデンサ

表 8-1 に、TLVM13610 に必要な最小出力容量を示します。セラミック・コンデンサを使用する場合は、DC バイアスと温度変動の影響を考慮する必要があります。特にセラミック・コンデンサの場合、パッケージ・サイズ、電圧定格、誘電体材料は、標準定格値と容量の実際の実効値の差に寄与します。

$C_{OUT(min)}$  を超える追加容量を含める場合、容量にはセラミック・タイプ、低 ESR ポリマー・タイプ、またはこれら 2 つの組み合わせを使用できます。メーカーごとに推奨される出力コンデンサのリストについては、表 8-3 を参照してください。

表 8-3. 推奨セラミック出力コンデンサ

| メーカー <sup>(1)</sup> | 誘電  | 部品番号                | ケース・サイズ | 容量(μF) <sup>(2)</sup> | 電圧(V) |

|---------------------|-----|---------------------|---------|-----------------------|-------|

| Murata              | X7R | GRM31CZ71C226ME15L  | 1206    | 22                    | 16    |

| TDK                 | X7R | C3225X7R1C226M250AC | 1210    | 22                    | 16    |

| Murata              | X7R | GRM32ER71C226KEA8K  | 1210    | 22                    | 16    |

| TDK                 | X6S | C3216X6S1E226M160AC | 1206    | 22                    | 25    |

| AVX                 | X7R | 12103C226KAT4A      | 1210    | 22                    | 25    |

| Murata              | X7R | GRM32ER71E226ME15L  | 1210    | 22                    | 25    |

| AVX                 | X7R | 1210ZC476MAT2A      | 1210    | 47                    | 10    |

| Murata              | X7R | GRM32ER71A476ME15L  | 1210    | 47                    | 10    |

| Murata              | X6S | GRM32EC81C476ME15L  | 1210    | 47                    | 16    |

| TDK                 | X6S | C3216X6S0G107M160AC | 1206    | 100                   | 4     |

| Murata              | X6T | GRM31CD80J107MEA8L  | 1206    | 100                   | 6.3   |

| Murata              | X7S | GRM32EC70J107ME15L  | 1210    | 100                   | 6.3   |

(1) 表に記載されているコンデンサの入手可能性、材料組成、RoHS および鉛フリーのステータス、製造プロセスの要件については、コンデンサのサプライヤにお問い合わせください。「[サード・パーティー製品に関する免責事項](#)」をご覧ください。

(2) 銘板の容量値(実効値は、印加された DC 電圧および温度に基づいて低いです)。

### 8.3.5 スイッチング周波数 (RT)

図 8-1 で RT と AGND の間に  $R_{RT}$  と指定された抵抗を接続し、スイッチング周波数を 200kHz~2.2MHz の範囲内に設定します。目的の周波数について  $R_{RT}$  を計算するには、式 5 を参照してください。

$$R_{RT}(k\Omega) = \frac{16.4}{F_{SW} [\text{MHz}]} - 0.633 \quad (5)$$

表 8-1 を参照するか、式 5 の簡略化された式を使用して、公称入力電圧でインダクタ・リップル電流を 8A モジュール電流定格の 25%~40% に設定するスイッチング周波数を求めます。

### 8.3.6 高精度のイネーブルおよび入力電圧 UVLO (EN)

EN ピンは、TLVM13610 の高精度オン / オフ制御を行います。EN ピンの電圧が立ち上がりスレッショルドを超えると、 $V_{IN}$  が最小ターンオン・スレッショルドを上回った後、デバイスは動作を開始します。TLVM13610 をイネーブルにする最も簡単な方法は、EN を  $V_{IN}$  に直接接続することです。この動作により、 $V_{IN}$  が有効な動作範囲内にあるときに TLVM13610 を

起動できます。しかし多くのアプリケーションでは、図 8-1 に示すようにイネーブル分圧回路を採用することの恩恵を受けます。これにより、高精度の入力低電圧誤動作防止 (UVLO) を実現できるためです。この機能はシーケンシング、長い入力ケーブルと併用した場合のデバイスの再トリガの防止、またはバッテリ電源の過放電の発生頻度低減に使用できます。外部ロジック信号を使用してイネーブル入力を駆動し、出力のオン / オフを切り替え、システムのシーケンシングや保護を行うこともできます。

式 6 を使用して  $R_{ENB}$  を計算します。

$$R_{ENB}[\text{k}\Omega] = R_{ENT}[\text{k}\Omega] \times \left( \frac{V_{EN\_RISE}[\text{V}]}{V_{IN(on)}[\text{V}] - V_{EN\_RISE}[\text{V}]} \right) \quad (6)$$

ここで

- $R_{ENT}$  の標準値は  $100\text{k}\Omega$  です。

- $V_{EN\_RISE}$  は、 $1.263\text{V}$  (標準値) の立ち上がりスレッショルド電圧をイネーブルします。

- $V_{IN(on)}$  は目的の起動入力電圧です。

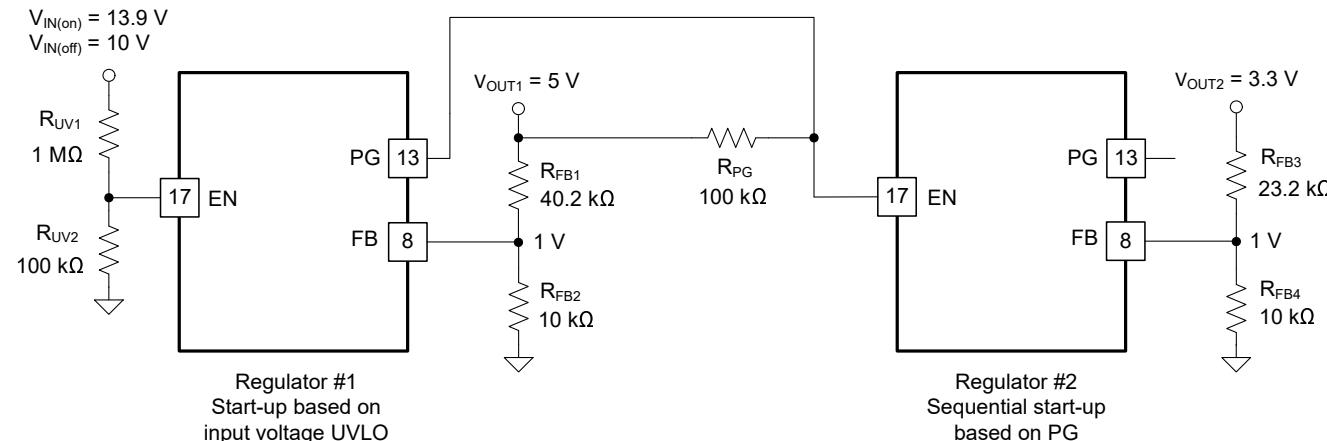

### 8.3.7 パワー・グッド・モニタ (PG)

TLVM13610 は、出力電圧が  $94\% \sim 112\%$  のレギュレーション範囲内にあることを示すパワー・グッド・ステータス信号を提供します。帰還 (FB) 電圧が、規定された PGOOD スレッショルドの範囲外になると、PG 電圧は Low に遷移します (図 7-7 参照)。この動作は、電流制限中、サーマル・シャットダウン中、ディセーブル中、また起動中に発生する可能性があります。

PG はオープン・ドレイン出力であり、VCC や  $V_{OUT}$  などの DC 電源への外部プルアップ抵抗が必要です。VCC から供給される電流を制限するため、推奨されるプルアップ抵抗の範囲は  $20\text{k}\Omega \sim 100\text{k}\Omega$  です。 $26\mu\text{s}$  のデグリッチ・フィルタは、出力電圧の短時間の変動 (ラインおよび負荷過渡時など) に対するフラグの誤動作を防止します。EN を Low にすると、PG は強制的に Low になり、入力電圧が  $1\text{V}$  (標準値) を上回っている限り有効なままになります。図 8-2 に示すように、ダウンストリーム・レギュレータの起動シーケンシングには、また、フォルト保護および出力監視には PG 信号を使用します。

図 8-2. PG および EN を使用した TLVM13610 シーケンシングの実装

### 8.3.8 可変スイッチ・ノード・スルーレート (RBOOT、CBOOT)

スイッチ・ノードの電圧立ち上がり時間を遅くし、高周波での EMI 性能を改善するよう TLVM13610 のスイッチ・ノード・スルーレートを調整します。ただし、立ち上がり時間を遅くすると効率が低下します。改善された EMI と効率低下のバランスを取るために注意が必要です。

RBOOT と CBOOT の間に抵抗を配置し、内部抵抗を調整して EMI と効率の性能のバランスを確保します。EMI を改善する必要がない場合は、RBOOT を CBOOT に接続して内部抵抗を短絡し、最高の効率を実現します。より低い EMI が

必要な場合は、 $100\Omega$ ~ $500\Omega$  の抵抗を接続します。 $R_{BOOT}$  ピンをフローティングすると立ち上がり時間は 20ns になりますが、負荷電流が大きくなると電力損失が大きくなるため、推奨しません。

### 8.3.9 バイアス電源レギュレータ (VCC、VLDOIN)

VCC は、TLV13610 の制御回路に電力を供給するために使用される内部 LDO サブレギュレータの出力です。公称 VCC 電圧は 3.3V です。VLDOIN ピンは内部 LDO への入力です。入力電源電流をできるだけ小さくするため、この入力を  $V_{OUT}$  に接続します。VLDOIN 電圧が 3.1V 未満の場合、VIN1 と VIN2 は内部 LDO に直接電力を供給します。

不適切な動作を防止するため、VCC には、内部電圧が低すぎる場合にスイッチングを止める UVLO 保護機能が備わっています。「電気的特性」の  $V_{CC\_UVLO}$  および  $V_{CC\_UVLO\_HYS}$  を参照してください。

VCC は外部回路への電力供給に使用しないでください。VCC をロードしたり、グランドに短絡したりしないでください。VLDOIN は、内部 LDO へのオプション入力です。ノイズ耐性を向上させるには、オプションの高品質  $0.1\mu F$ ~ $1\mu F$  コンデンサを VLDOIN から AGND に接続します。

LDO は、次の 2 つの入力のいずれかから VCC 電圧を供給します。 $V_{IN}$  または VLDOIN。VLDOIN をグランドまたは 3.1V 未満に接続すると、LDO は  $V_{IN}$  から電力を引き出します。VLDOIN が 3.1V を超える電圧に接続されている場合、LDO 入力は VLDOIN になります。VLDOIN 電圧は  $V_{IN}$  と 12V の両方を超えないようにしてください。

式 7 に、LDO の電力損失の低減を次のように規定します。

$$P_{LDO-LOSS} = I_{LDO} \times (V_{IN-LDO} - V_{VCC}) \quad (7)$$

VLDOIN 入力には、 $V_{IN}$  より低い電圧で LDO に電力を供給するオプションがあり、VCC を基準とする LDO 入力電圧を最小化し、電力損失を低減できます。たとえば、 $V_{IN} = 24V$ 、 $V_{OUT} = 5V$  で、1MHz で LDO 電流が 10mA の場合、グランドに接続された VLDOIN での LDO 電力損失は  $10mA \times (24V - 3.3V) = 207mW$  になります。一方 VLDOIN を  $V_{OUT}$  に接続した場合の損失は、 $10mA \times (5V - 3.3V) = 17mW$  と等しくなり 190mW 減少しています。

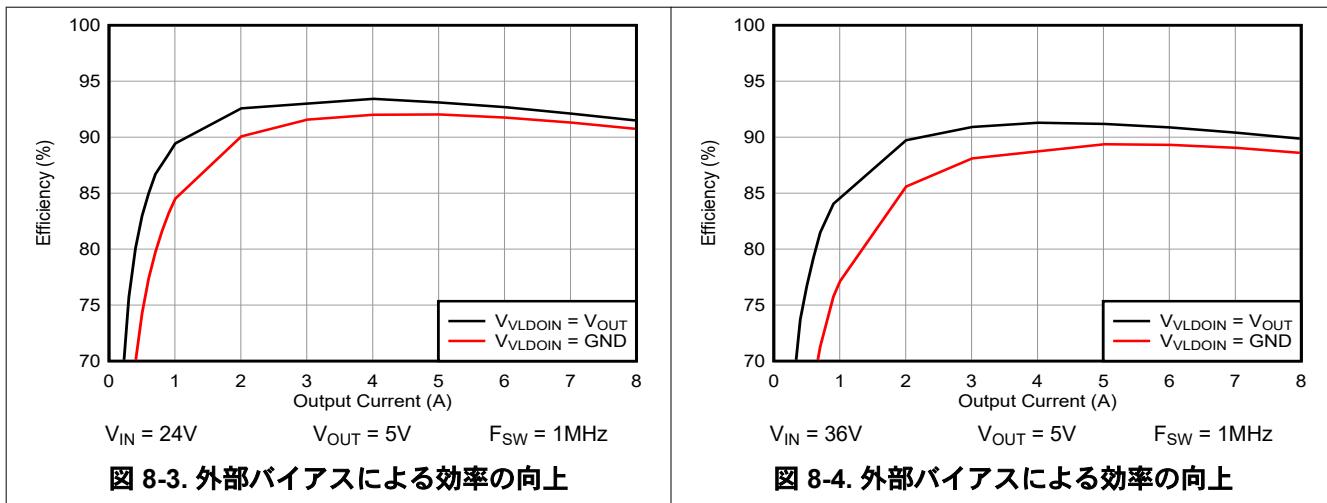

図 8-3 および図 8-4 に、VLDOIN を  $V_{OUT}$  に接続した場合と接続しない場合の代表的な効率プロットを示します。

### 8.3.10 過電流保護 (OCP)

TLV13610 は、ピーク・インダクタ電流のサイクルごとの電流制限を使用して、過電流状態から保護されています。電流は、スイッチング・サイクルごとに電流制限スレッショルドと比較されます。過電流状態の間、出力電圧は低下します。

TLV13610 は、極端な過負荷が発生した場合にヒップアップ過電流保護を採用しています。ヒップアップ・モードでは、TLV13610 モジュールがシャットダウンされ、再起動しようとする前に 40ms (標準値) オフに保持されます。それでも過電流または短絡によるフォルト状態が続く場合は、フォルト状態が解消されるまでヒップアップが繰り返されます。ヒップアップ・モードは、重度の過電流状態での消費電力を低減し、過熱やデバイスが損傷する可能性を防止します。障害が解消されると、モジュールは自動的に回復し、通常動作に戻ります。

### 8.3.11 サーマル・シャットダウン

サーマル・シャットダウンは、接合部温度を制限し、過熱に起因する損傷を防止するために使用される内蔵自己保護機能です。接合部温度が  $168^{\circ}\text{C}$  (標準値) を超えると、サーマル・シャットダウンによってデバイスがオフになり、それ以上の電力消費および温度上昇を防ぎます。シャットダウン後に接合部温度が低下し、TLVM13610 は接合部温度が  $159^{\circ}\text{C}$  (標準値) まで低下したときに再起動を試みます。

## 8.4 デバイスの機能モード

### 8.4.1 シャットダウン・モード

EN ピンは、TLVM13610 のオン / オフを制御します。 $V_{\text{EN}}$  が約  $0.4\text{V}$  を下回ると、デバイスはシャットダウン・モードになります。内部 LDO とスイッチング・レギュレータの両方がオフになります。シャットダウン・モードでの静止電流は、 $0.6\mu\text{A}$  (標準値) まで減少します。TLVM13610 は低電圧保護機能も内蔵しています。入力電圧がその UV スレッショルドを下回ると、レギュレータはオフのままになります。

### 8.4.2 スタンバイ・モード

VCC バイアス電源用の内部 LDO は、レギュレータ自体よりも低いイネーブル・スレッショルドを備えています。 $V_{\text{EN}}$  が  $1.1\text{V}$  (最大値) を超え、高精度イネーブル・スレッショルドの  $1.263\text{V}$  (標準値) を下回ると、内部 LDO がオンになり、レギュレーションが行われます。内部  $V_{\text{CC}}$  がその UVLO スレッショルドを上回ると、高精度イネーブル回路がオンになります。スイッチング動作および電圧レギュレーションは、 $V_{\text{EN}}$  が高精度イネーブル・スレッショルドを上回るまでイネーブルなりません。

### 8.4.3 アクティブ・モード

TLVM13610 は、 $V_{\text{VCC}}$  および  $V_{\text{EN}}$  が関連するスレッショルドを超えると、フォルト条件が存在しない場合、アクティブ・モードになります。この動作を可能にする最も簡単な方法は、EN を  $V_{\text{IN}}$  に接続することです。これにより、印加された入力電圧が最小起動電圧を超えると自動的に起動できます。

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性について

は、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

TLVM13610 同期整流降圧モジュールは、幅広い電源電圧を最大 8A の出力電流で固定出力電圧に変換するために外付け部品をわずか数個しか必要としません。TLVM13610 ベースのレギュレータの設計プロセスを迅速化および合理化するため、包括的な TLVM13610 クイックスタート・カリキュレータ・ツールをダウンロードして、システム設計者が特定のアプリケーションのコンポーネントを選択するのに使用できます。

### 9.2 代表的なアプリケーション

TLVM13610 を使用した実装の回路図、部品表、PCB レイアウト・ファイル、テスト結果については、TLVM13610EVM を参照してください。

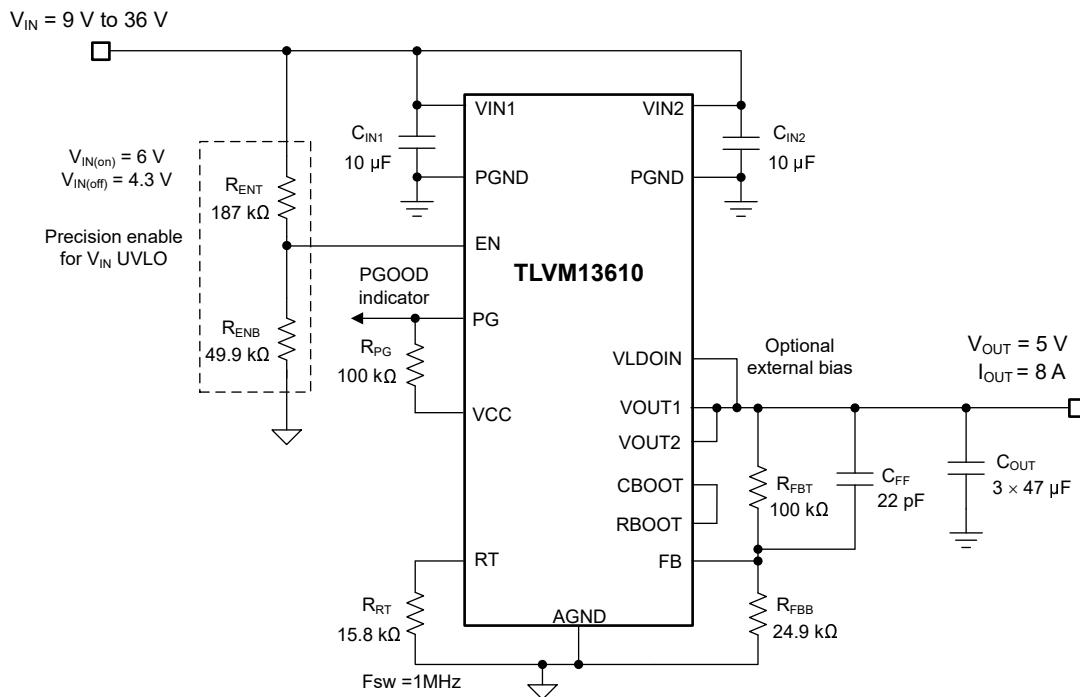

#### 9.2.1 設計 1 – 産業用アプリケーション向け高効率 8A (10A ピーク) 同期整流降圧レギュレータ

次の図に、1MHz のスイッチング周波数を使用する 5V、8A の降圧レギュレータの回路図を示します。この例では、9V から 36V の範囲内の公称入力電圧 24V に基づき、半負荷効率と全負荷効率の目標はそれぞれ、93.4% と 91.5% です。抵抗  $R_{RT}$  を 15.8k $\Omega$  にするとフリーランニング・スイッチング周波数が 1MHz に設定されます。

図 9-1. 回路図

#### 9.2.1.1 設計要件

表 9-1 に、この車載用アプリケーションの対象となる入力、出力、性能の各パラメータを示します。入力電圧が約 6V を下回ると、レギュレータは 5V の設定ポイントを下回る出力電圧で、ドロップアウトで動作することに注意してください。

**表 9-1. 設計パラメータ**

| 設計パラメータ          | 値       |

|------------------|---------|

| 入力電圧範囲           | 9V~36V  |

| 入力電圧 UVLO がオン、オフ | 6V、4.3V |

| 出力電圧             | 5V      |

| 最大出力電流           | 8A      |

| スイッチング周波数        | 1MHz    |

| 出力電圧レギュレーション     | ±1%     |

| モジュール・シャットダウン電流  | 1µA 未満  |

表 9-2 により、選択した降圧モジュールの電力段部品を複数のベンダから入手できるようになります。このデザインでは、完全セラミック出力コンデンサを実装しています。

**表 9-2. アプリケーション回路 1 の部品表**

| リファレンス指定子                                               | 数量 | 仕様                           | メーカー <sup>(1)</sup> | 部品番号               |

|---------------------------------------------------------|----|------------------------------|---------------------|--------------------|

| C <sub>IN1</sub> 、C <sub>IN2</sub>                      | 2  | 10µF、50V、X7R、1210、セラミック      | Taiyo Yuden         | UMJ325KB7106KMHT   |

|                                                         |    |                              | TDK                 | CNA6P1X7R1H106K    |

|                                                         | 3  | 10µF、50V、X7S、1210、セラミック      | Murata              | GCM32EC71H106KA03  |

|                                                         |    |                              | TDK                 | CGA6P3X7S1H106M    |

| C <sub>OUT1</sub> 、C <sub>OUT2</sub> 、C <sub>OUT3</sub> | 3  | 47µF、6.3V、X7R、1210、セラミック     | Murata              | GRM32ER70J476ME20K |

|                                                         |    |                              | AVX                 | 12106C476MAT2A     |

|                                                         | 3  | 47µF、10V、X7R、1210、セラミック      | Murata              | GRM32ER71A476ME15L |

|                                                         |    |                              | AVX                 | 1210ZC476MAT2A     |

|                                                         | 1  | 100µF、6.3V、X7S、1210、セラミック    | Murata              | GRM32EC70J107ME15L |

| U <sub>1</sub>                                          | 1  | TLVM13610 36V、8A 同期整流降圧モジュール | テキサス・インスツルメンツ       | TLVM13610RDLR      |

(1) 「サード・パーティ製品に関する免責事項」をご覧ください。

一般的に TLVM13610 モジュールは、幅広い外付け部品とシステム・パラメータで機能するように設計されています。しかし内部ループ補償は、特定の範囲の出力容量に対して最適化されています。

### 9.2.1.2 詳細な設計手順

#### 9.2.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer を搭載した TLVM13610 モジュールを使用してカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する考えられる他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを一般的な CAD フォーマットにエクスポートする。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

WEBENCH ツールの詳細は、[www.tij.co.jp/WEBENCH](http://www.tij.co.jp/WEBENCH) でご覧になれます。

### 9.2.1.2.2 出力電圧の設定ポイント

TLV13610 モジュールの出力電圧は、分圧抵抗を使用して外部で調整可能です。 $R_{FBT}$  の推奨値である  $100\text{k}\Omega$  は  $1\text{M}\Omega$  に比べてノイズ耐性が向上しており、より小さい抵抗値に比べて消費電流が低減しています。以下の式を使用して  $R_{FBB}$  を計算します。

$$R_{FBB} = \frac{R_{FBT} \times V_{REF}}{V_{OUT} - V_{REF}} \quad (8)$$

$R_{FBB}$  に最も近い標準値である  $24.9\text{k}\Omega$  を選択します。

### 9.2.1.2.3 スイッチング周波数の選択

RT と AGND の間に  $15.8\text{k}\Omega$  の抵抗を接続し、スイッチング周波数を  $1\text{MHz}$  に設定します。このスイッチング周波数は、公称入力電圧  $24\text{V}$  で  $8\text{A}$  定格出力電流の  $20\% \sim 40\%$  の範囲でインダクタのピーク・ツー・ピーク・リップル電流を確立するため  $5\text{V}$  の出力用に設計されています。

### 9.2.1.2.4 入力コンデンサの選択

TLV13610 には、最低入力容量が  $2 \times 10\mu\text{F}$  のセラミックが必要で、X7R 誘電体の使用を推奨します。入力コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。この設計では、VIN1 および VIN2 から PGND へモジュールのできるだけ近くに接続された  $10\mu\text{F}$ 、X7R、 $50\text{V}$ 、1210 ケース・サイズのセラミック・コンデンサを 2 個選択します。推奨レイアウトの配置については、図 9-13 を参照してください。

### 9.2.1.2.5 出力コンデンサの選択

表 8-1 から TLV13610 では  $2.2\text{MHz}$  で  $5\text{V}$  の出力電圧で適切に動作させるには、 $25\mu\text{F}$  以上の実効出力容量が必要です。電圧と温度の定格な十分な高品質のセラミック・タイプ・コンデンサを使用します。必要に応じて、追加の出力容量を接続してリップル電圧を低減するか、特定の負荷過渡要件を持つアプリケーションに接続します。

この設計例では、VOUT1 ピンと VOUT2 ピンから PGND へモジュールの近くに接続された  $47\mu\text{F}$ 、 $6.3\text{V}$  または  $10\text{V}$ 、X7R、1210 のセラミック・コンデンサを 2 個使用します。 $5\text{V}$  での総実効容量は、 $25^\circ\text{C}$  で約  $52\mu\text{F}$ 、 $-40^\circ\text{C}$  で  $38\mu\text{F}$  です。

### 9.2.1.2.6 その他の接続

最高の効率を得るには、RBOOT を CBOOT に短絡し、VLDOIN を  $5\text{V}$  出力に接続します。表 8-1 の最小値に近い出力容量を使用するときに位相マージンを増やすには、 $C_{FF}$  として指定されたフィードフォワード・コンデンサを上側の帰還抵抗の両端に配置できます。 $C_{FF}$  と  $R_{FBT}$  によって生成されるゼロは、スイッチングの  $1/5$  よりも高く設定します。これにより、位相が増加しますが、クロスオーバー周波数が大幅に増加することはありません。この  $C_{FF}$  コンデンサは、回路の出力から IC の FB ノードに直接ノイズを導く可能性があるため、 $4.99\text{k}\Omega$  の抵抗 ( $R_{FF}$ ) を  $C_{FF}$  と直列に配置する必要があります。出力コンデンサの ESR ゼロが  $200\text{kHz}$  未満である場合、CFF を使用しないでください。

### 9.2.1.3 アプリケーション曲線

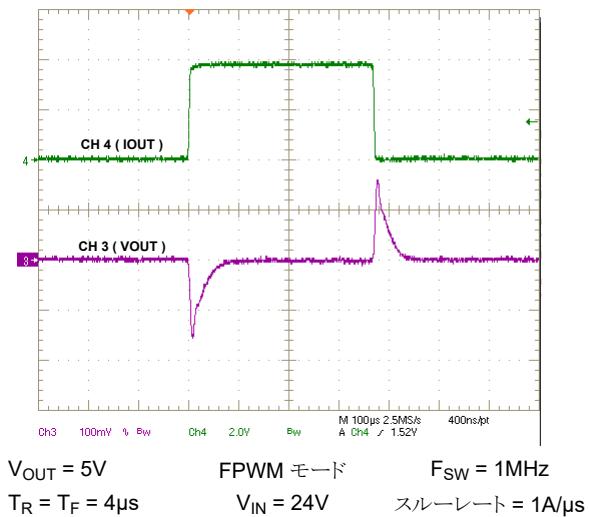

特に記述のない限り、 $V_{IN} = 24V$ 、 $V_{OUT} = 5V$ 、 $I_{OUT} = 8A$ 、および  $F_{SW} = 1MHz$  です。

図 9-2.  $V_{OUT} = 5V$  での効率

図 9-3.  $V_{OUT} = 5V$  での効率

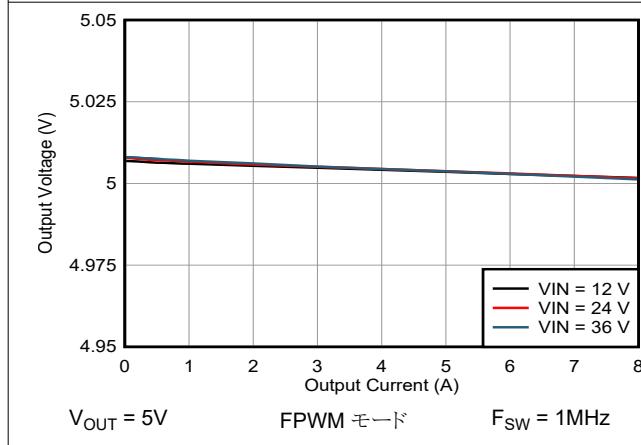

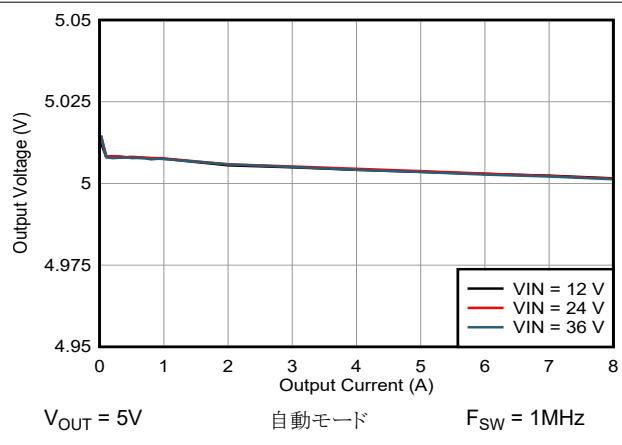

図 9-4.  $V_{OUT} = 5V$  の負荷レギュレーション

図 9-5.  $V_{OUT} = 5V$  の負荷レギュレーション

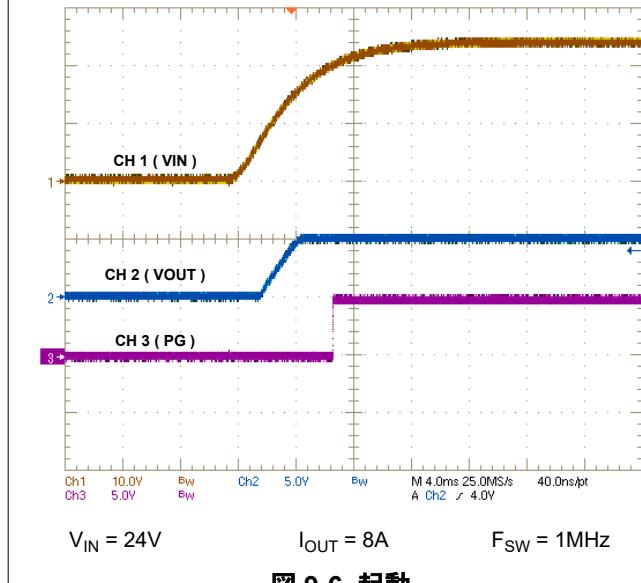

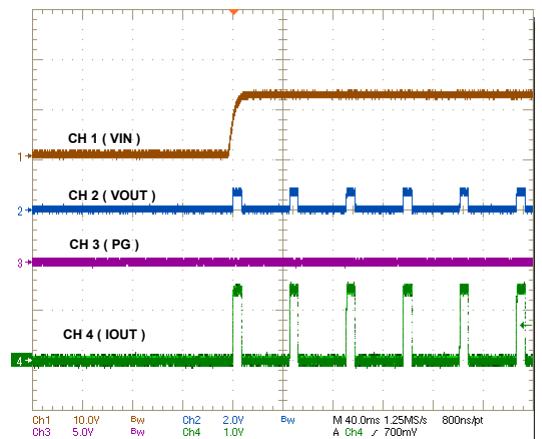

図 9-6. 起動

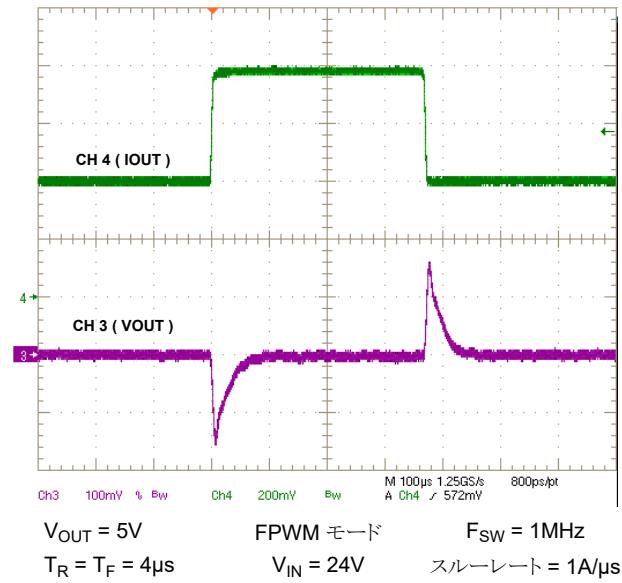

図 9-7. 負荷過渡、4A～8A、1A/μs

図 9-8. 負荷過渡、0A～4A、 $1A/\mu s$

図 9-9. 短絡への起動

図 9-10. CISPR 11/32 クラス B 伝導性放射： $V_{IN} = 24V$

図 9-11. CISPR 11 クラス B 伝導性放射： $V_{IN} = 24V$

## 9.3 電源に関する推奨事項

TLVM13610 降圧モジュールは、3V~36V の幅広い入力電圧範囲で動作するように設計されています。入力電源の特性は、このデータシートの [絶対最大定格](#) および [推奨動作条件](#) と互換性がある必要があります。また、入力電源は、負荷時レギュレータ回路に必要な入力電流を供給できる必要があります。[式 9](#) を使用して平均入力電流を推定します。

$$I_{IN} = \left( \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta} \right) \quad (9)$$

ここで

- $\eta$  は効率です。

モジュールが高インピーダンスを持つ長い配線や PCB パターンを経由して入力電源に接続されている場合は、安定した性能を実現するために特に注意が必要です。入力ケーブルの寄生インダクタンスと抵抗は、モジュールの動作に悪影響を及ぼすおそれがあります。具体的には、寄生インダクタンスと低 ESR のセラミック入力コンデンサの組み合わせにより、低減衰共振回路が形成され、入力電源のオン / オフが繰り返されるたびに不安定または電圧過渡が発生する可能性があります。寄生抵抗により、負荷過渡中に入力電圧が低下する場合があります。モジュールが最小入力電圧に近い値で動作している場合、この低下によって UVLO が誤って起動され、システムがリセットされる可能性があります。

こうした問題を解決する最善策は、入力電源からモジュールまでの距離を短くして、電解入力コンデンサをセラミックと並列に使用することです。中程度の ESR を持つ電解コンデンサは、入力共振回路の振動を減衰させ、入力のすべてのオーバーシュートまたはアンダーシュートを低減するのに役立ちます。通常、47 $\mu$ F~100 $\mu$ F の容量は入力並列ダンピングに十分であり、大きな負荷過渡中も入力電圧を安定した状態に保持できます。代表的な ESR は 0.1 $\Omega$ ~0.4 $\Omega$  であり、ほとんどの入力回路構成で十分な減衰を実現します。

## 9.4 レイアウト

信頼性の高いデバイス動作と設計の堅牢性を実現するために、大電流、(高い内部電圧および電流スルーレートの) 高速スイッチング・モジュール回路では、適切な PCB 設計とレイアウトが重要です。さらに、モジュールの EMI 性能は、PCB レイアウトによって大きく異なります。

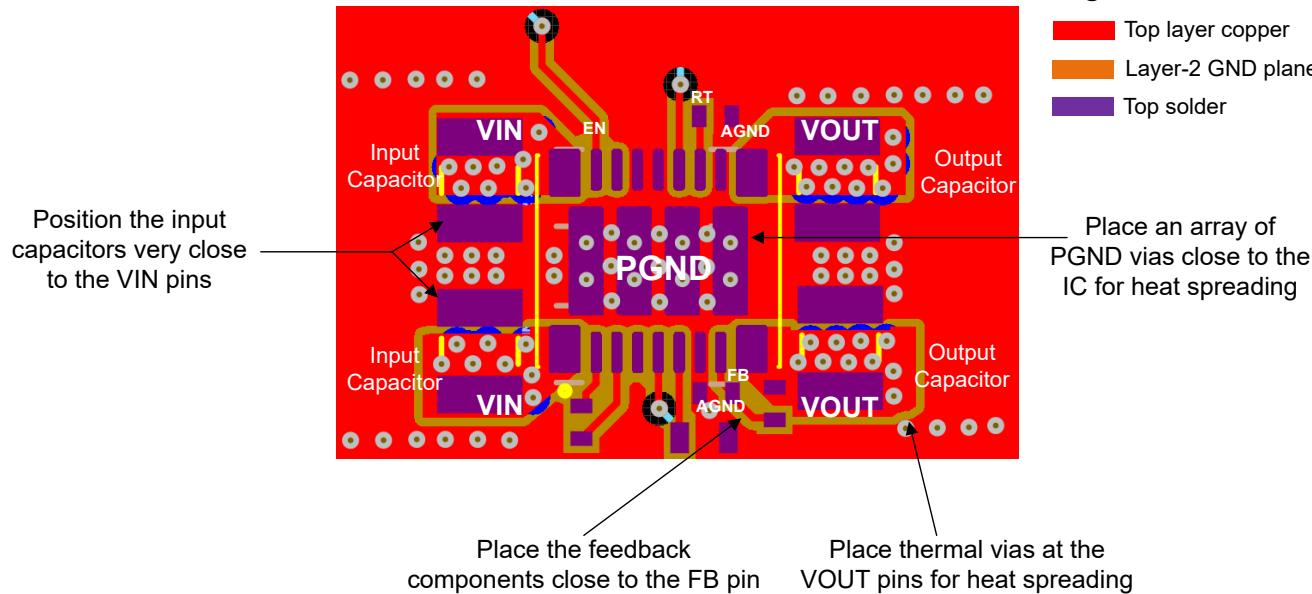

### 9.4.1 レイアウトのガイドライン

次のリストに、PCB レイアウトと部品の配置に関する重要なガイドラインを要約し、熱や EMI 特性を含めて DC/DC モジュールの性能を最適化します。[図 9-12](#) および [図 9-13](#) に、TLVM13610 の推奨 PCB レイアウトと、最適化された電力段および小信号部品の配置および配線を示します。

- 入力コンデンサは、**VIN** ピンにできる限り近づけて配置してください。モジュール・パッケージの各側に配置されている **VIN1** ピンと **VIN2** ピンに基づいて、入力コンデンサのデュアル配置と対称配置に注意してください。高周波電流は 2 つに分割され、関連する磁界の寄与が互いに打ち消し合うように効果的に逆方向に流れ、EMI 性能が向上します。

- **X7R** または **X7S** 誘電体とともに、低 ESR の **1206** または **1210** セラミック・コンデンサを使用します。このモジュールには、高周波バイパス用のデュアル **0402** 入力コンデンサが内蔵されています。

- 入力コンデンサのグランド・リターン・パスは、モジュールの下にある **PGND** パッドに接続する局所的な上面プレーンで構成されている必要があります。

- **VIN** ピンは内部で接続されていますが、下側の PCB 層で広いポリゴン・プレーンを使用して、これらのピンを相互に接続し、入力電源に接続します。

- 出力コンデンサは、**VOUT** ピンにできる限り近づけて配置してください。出力コンデンサのデュアル配置と対称配置が類似しているため、磁界の打ち消しと EMI の低減が可能です。

- 出力コンデンサのグランド・リターン・パスは、モジュールの下にある **PGND** パッドに接続する局所的な上面プレーンで構成されている必要があります。

- **VOUT** ピンは内部で接続されていますが、下側の PCB 層で広いポリゴン・プレーンを使用して、これらのピンを相互に接続し、負荷に接続することで、導通損失と熱ストレスを低減します。

- 帰還抵抗を **FB** ピンの近くに配置することで、**FB** パターンをできるだけ短くします。分圧抵抗を負荷ではなく **FB** ピン近くに配置することで、出力電圧帰還パスのノイズの影響を小さくします。**FB** は電圧ループ・エラー・アンプへの入力

であり、ノイズの影響を受けやすい高インピーダンス・ノードを表します。上側の帰還抵抗から必要な出力電圧レギュレーション・ポイントまでパターンを配線します。

- モジュールの上層の直下にある **PCB** 層のソリッド・グランド・プレーンを使用します。このプレーンは、スイッチング・ループ内の電流に関連する磁界を最小化することで、ノイズ・シールドとして機能します。AGND ピン 6 と 11 をモジュールの下にある PGND ピン 19 に直接接続します。

- 適切なヒートシンクのために十分な **PCB** 面積を確保します。十分な銅面積を使用して、最大負荷電流および周囲温度条件に対応する低熱インピーダンスを実現します。接合部温度を 150°C 未満に維持するために、TLVM13610 には十分なヒートシンクを用意してください。全定格負荷で動作する場合、上面のグランド・プレーンは重要な放熱面積になります。一連のヒートシンク・ビアを使用して、パッケージの露出したパッド (PGND) を PCB グランド・プレーンに接続します。PCB に複数の銅層がある場合は、これらのサーマル・ビアを内部層のグランド・プレーンに接続します。PCB 層の上部と下部は 2 オンスの銅厚 (最低でも 1 オンス以上) を推奨します。

#### 9.4.1.1 熱設計およびレイアウト

DC/DC モジュールを特定の温度範囲で使用できるようにするには、パッケージは接合部温度を定格制限内に維持しながら、発生する熱を効率的に除去する必要があります。TLVM13610 モジュールは、豊富なアプリケーション要件に対応する小型の 6.5mm × 7.55mm 22 ピン QFN (RDL) パッケージで供給されます。熱に関する情報の表には、このパッケージの熱指標と、『半導体および IC パッケージの熱指標アプリケーション・レポート』に記載された関連する詳細情報が要約されています。

22 ピン QFN パッケージでは、パッケージの底面にある露出した熱パッドを介して熱が除去されます。これによってヒートシンクが大幅に改善されますが、熱除去サブシステムを完成させるには PCB の設計にサーマル・ランド、サーマル・ビア、1 つ以上のグランド・プレーンを入れることが必須となります。TLVM13610 の露出したパッドは、PCB 上でデバイスのパッケージの真下にある、グランドに接続された銅ランドにはんだ付けされているため、熱抵抗を非常に小さい値まで低減します。

すべての層に 2oz の銅厚の 4 層基板を使用して、低インピーダンス、適切なシールド、低い熱抵抗を実現することを推奨します。サーマル・ランドから内部とはんだ側のグランド・プレーンに接続された直径 0.3mm の大量のビアは、伝熱に不可欠です。PCB を複数層に積み上げる場合、通常は電力段部品下の PCB 層にソリッド・グランド・プレーンを配置します。このプレーンの配置には、電力段の電流を流すためだけでなく、熱を生成するデバイスから熱伝導経路を離す役割もあります。

#### 9.4.2 レイアウト例

図 9-12. 標準レイアウト

Legend

- Top layer copper

- Layer-2 GND plane

- Top solder

図 9-13. 標準上層部の設計

## 10 デバイスおよびドキュメントのサポート

### 10.1 デバイスのサポート

#### 10.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 10.1.2 開発サポート

TLVM13610 同期整流降圧電源モジュールは、3V～36V の入力動作電圧と最大 10A の定格出力電流を実現し、多様なアプリケーションに対応できる柔軟性、スケーラビリティ、最適化されたソリューション・サイズを実現します。これらのモジュールを使用すると、高密度、低 EMI で高い柔軟性を持つ DC/DC ソリューションを実現できます。利用可能な EMI 低減機能には、RBOOT 構成のスイッチ・ノード・スルーレート制御機能と、内蔵の入力バイパス・コンデンサが含まれます。

表 10-1. 同期整流降圧 DC/DC 電源モジュール・ファミリ

| DC/DC モジュール | 定格 $I_{OUT}$ | パッケージ      | 寸法              | 特長                                      | EMI 軽減                             |

|-------------|--------------|------------|-----------------|-----------------------------------------|------------------------------------|

| TLVM13610   | 8A           | B3QFN (22) | 6.5 × 7.5 × 4mm | RT 可変 $F_{SW}$ 、外部同期、モード調整可能 (PFM/FPWM) | DRSS、RBOOT、内蔵入力、VCC および BOOT コンデンサ |

開発サポートについては、以下を参照してください。

- テキサス・インスツルメンツのリファレンス・デザイン・ライブラリについては、[テキサス・インスツルメンツ・リファレンス・デザイン・ライブラリ](#)をご覧ください。

- テキサス・インスツルメンツの **WEBENCH** 設計環境については、[WEBENCH® 設計センター](#)をご覧ください。

- 低 EMI の電源を設計するには、テキサス・インスツルメンツの包括的な [EMI トレーニング・シリーズ](#)をご覧ください。

- 反転昇降圧 (IBB) レギュレータを設計するには、[DC/DC 反転昇降圧モジュール](#)をご覧ください。

- テキサス・インスツルメンツ・リファレンス・デザイン

- 『Kintex 7 アプリケーション向け複数出力電源ソリューション』

- 『Arria V 向けの電源リファレンス・デザイン』

- 『Altera 製 Cyclone V SoC 向けの電源リファレンス・デザイン』

- 『BOM (部品表) 点数が最小で、スペースを最適化した DC/DC 反転型電源モジュールのリファレンス・デザイン』

- 『小型の低ノイズ・システム用の  $V_{IN} = 3\text{~}11.5\text{V}$ 、 $V_{OUT} = -5\text{V}$ 、1.5A の反転電源モジュールのリファレンス・デザイン』

- 寄稿記事:

- 『DC/DC 降圧コンバータを使用した医療用画像処理アプリケーションへの電力供給』

- 『How To Create A Programmable Output Inverting Buck-boost Regulator (英語)』

- この製品の関連デバイスを参照するには、[『LM61495 36V、10A 同期整流降圧コンバータ』](#)を参照してください。

#### 10.1.2.1 WEBENCH® ツールによるカスタム設計

[ここをクリック](#)すると、WEBENCH® Power Designer を搭載した TLVM13610 モジュールを使用してカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する考えられる他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを一般的な CAD フォーマットにエクスポートする。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

WEBENCH ツールの詳細は、[www.tij.co.jp/WEBENCH](http://www.tij.co.jp/WEBENCH) でご覧になれます。

## 10.2 ドキュメントのサポート

### 10.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『テキサス・インスツルメンツ降圧スイッチング DC/DC アプリケーション・ノートのクイック・リファレンス・ガイド』

- テキサス・インスツルメンツ、『革新的な DC/DC 電源モジュール』セレクション・ガイド

- テキサス・インスツルメンツ、『Enhanced HotRod™ QFN パッケージ・テクノロジーによる小型で低発熱の静音電源モジュールの実現』ホワイト・ペーパー

- テキサス・インスツルメンツ、『電源モジュール・パッケージの各種オプションの利点とトレードオフ』ホワイト・ペーパー

- テキサス・インスツルメンツ、『電源モジュールによる低 EMI 設計の簡素化』ホワイト・ペーパー

- テキサス・インスツルメンツ、『ラボ計測用電源モジュール』ホワイト・ペーパー

- テキサス・インスツルメンツ、『DC/DC レギュレータの EMI エンジニア・ガイド』e-book

- テキサス・インスツルメンツ、『電源モジュールの半田付けに関する考慮事項』アプリケーション・レポート

- テキサス・インスツルメンツ、『DC/DC 電源モジュールを使った実用的な熱設計』アプリケーション・レポート

- テキサス・インスツルメンツ、『新しい熱評価基準の解説』アプリケーション・レポート

- テキサス・インスツルメンツ、『AN-2020 Thermal Design By Insight, Not Hindsight』アプリケーション・レポート (英語)

- テキサス・インスツルメンツ、『負出力反転昇降圧アプリケーションに TPSM53602/3/4 を使用する方法』アプリケーション・レポート

## 10.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 10.4 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

## 10.5 商標

HotRod™ and TI E2E™ are trademarks of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 10.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 10.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

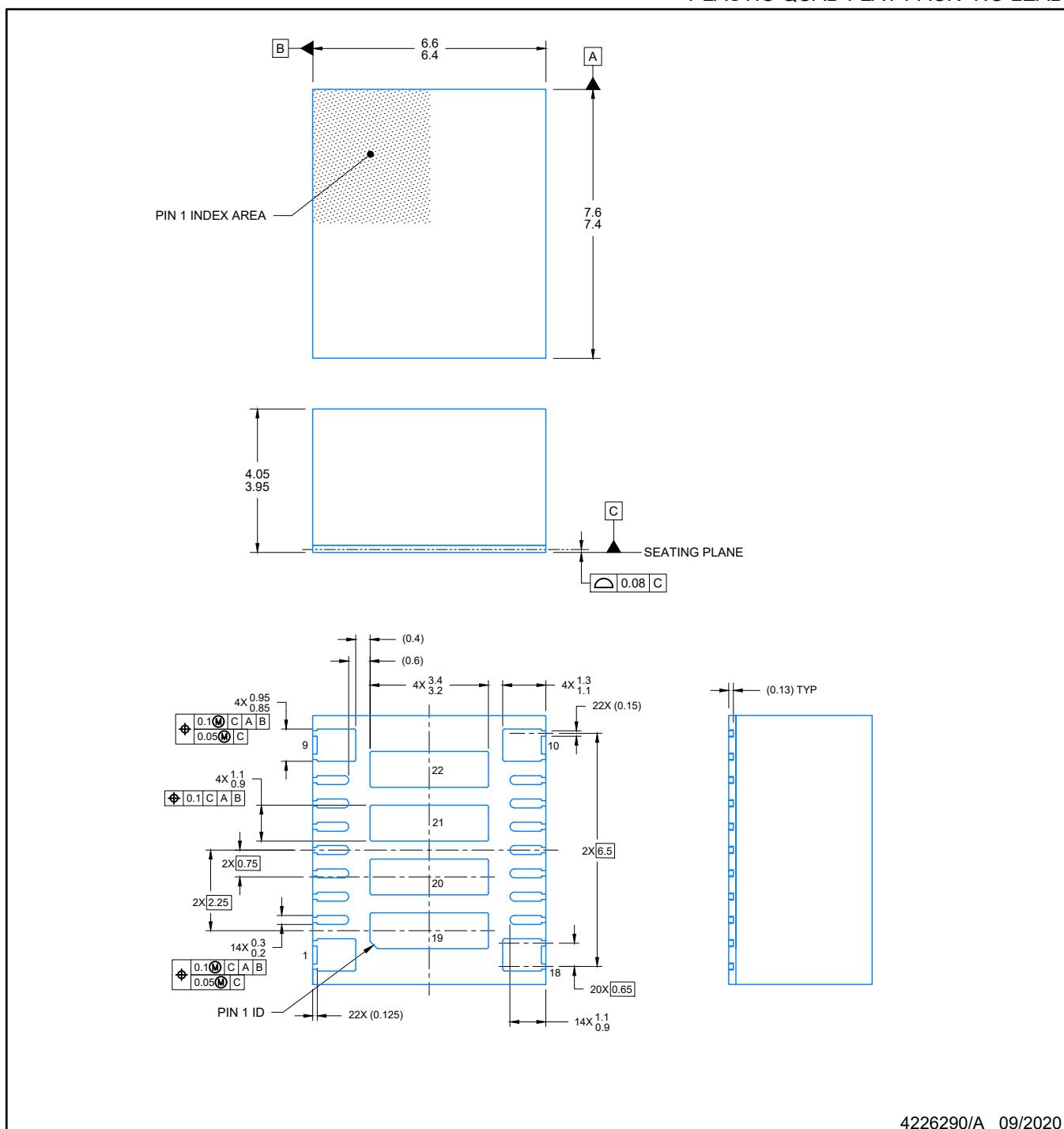

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins   | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TLVM13610RDFR         | Active        | Production           | B3QFN (RDF)   22 | 1000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-250C-168 HR               | -40 to 125   | 13610               |

| TLVM13610RDFR.A       | Active        | Production           | B3QFN (RDF)   22 | 1000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-250C-168 HR               | -40 to 125   | 13610               |

| TLVM13610RDFR.B       | Active        | Production           | B3QFN (RDF)   22 | 1000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

RDF0022A

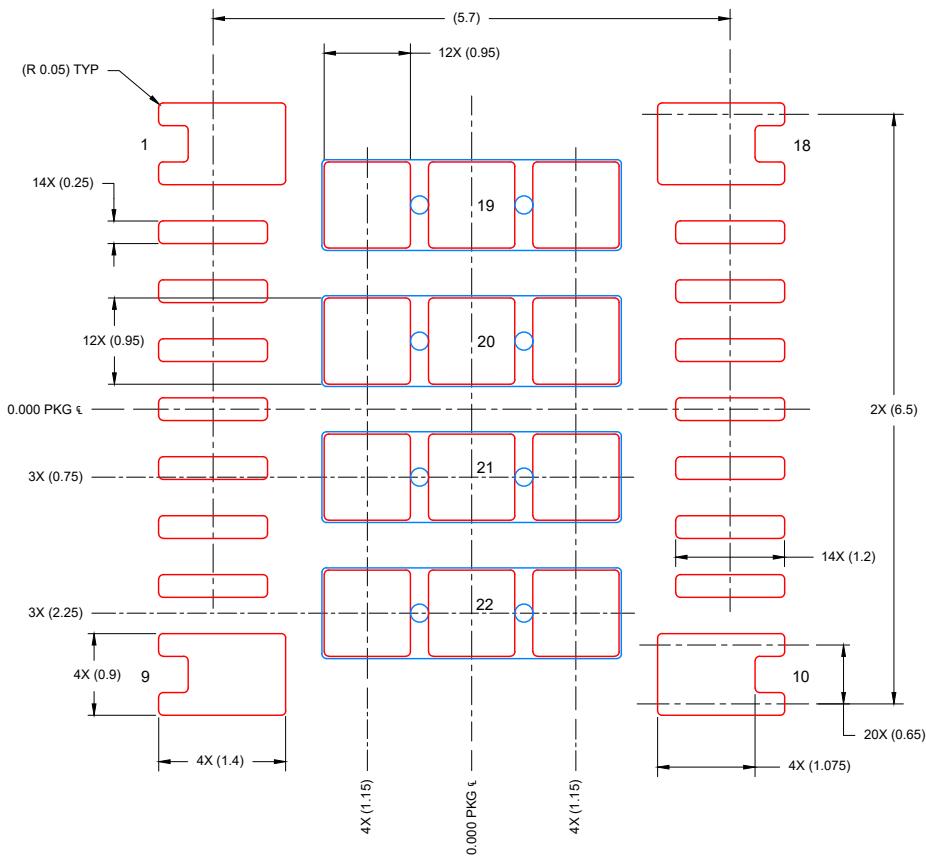

# PACKAGE OUTLINE

## B3QFN - 4.05 mm max height

## PLASTIC QUAD FLAT PACK- NO LEAD

4226290/A 09/2020

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

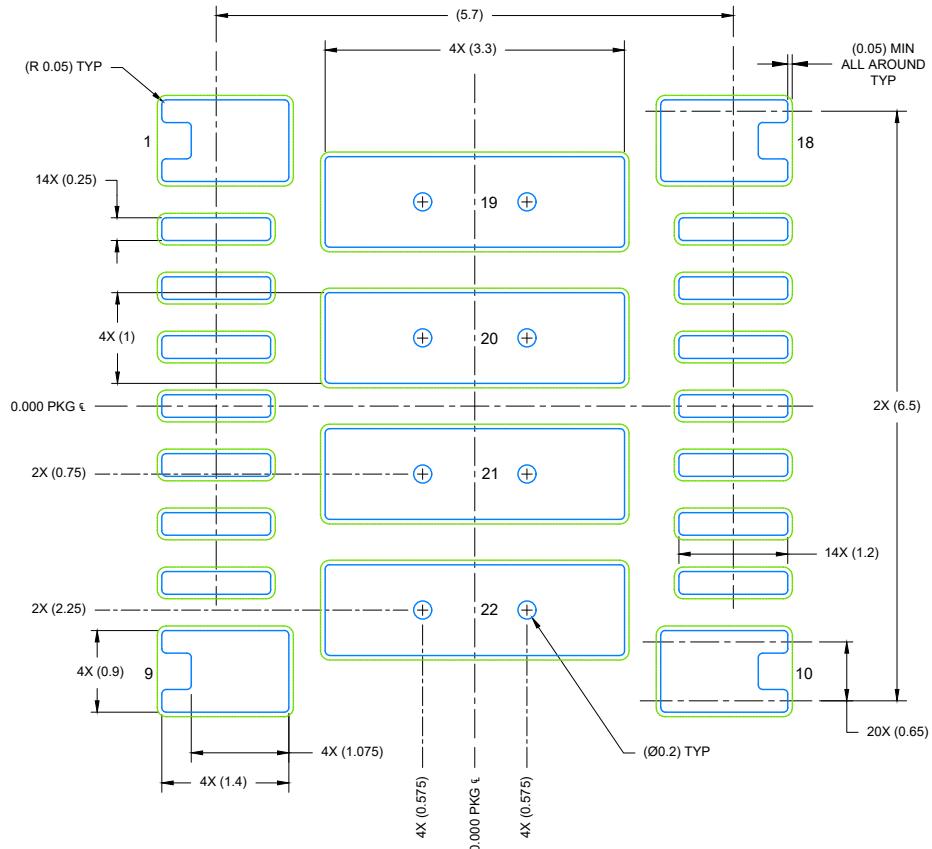

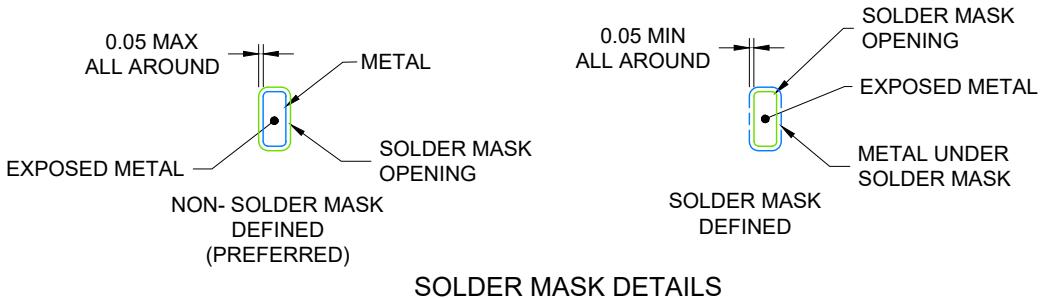

## EXAMPLE BOARD LAYOUT

RDF0022A

## **B3QFN - 4.05 mm max height**

## PLASTIC QUAD FLAT PACK- NO LEAD

## LAND PATTERN EXAMPLE EXPOSED METAL SHOWN

EXPOSED METAL SHOWN

SCALE: 12X

SCALE: 12X

4226290/A 09/2020

#### NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

## B3QFN - 4.05 mm max height

RDF0022A

PLASTIC QUAD FLAT PACK- NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

SOLDER COVERAGE:

PIN 19 TO 22 : 82%

SCALE: 12X

4226290/A 09/2020

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月