# TLV902xL および TLV903xL 高精度、自己ラッチ コンパレータ ファミリ

### 1 特長

- 立ち下がりエッジトリガクリア機能付き出力ラッチ

- 既知のスタートアップ条件でのパワーオンリセット (POR)

- 起動状態を選択可能:

- 電源投入時にラッチなし(「L1」オプション) - 電源投入時にラッチあり(「L2」 オプション)

- ・ 電源電圧範囲:1.65V~5.5V

- 精密入力オフセット電圧: 300µV

- フォルトトレランス付きレールツーレール入力

- 伝搬遅延時間:110ns (代表値)

- 低い静止電流:チャネルあたり 22µA

- 低い入力バイアス電流:5pA

- ・ オープンドレイン出力オプション (TLV902xL)

- ・ プッシュプル出力オプション (TLV903xL)

- 全温度範囲 (-40℃~+125℃)

- ESD 保護:2kV

### 2 アプリケーション

- 家電製品向けパワーモジュール

- ACドライブ制御

- 電力変換システム

- バッテリバックアップユニット

- バッテリテスト機器

### 3 説明

TLV902xL および TLV903xL は、のシングルおよびデュ アル チャネル ラッチ コンパレータのファミリです。また、こ のファミリは低い入力オフセット電圧、パワーオン リセット (POR)、フォルトトレラントのレール ツー レール入力も備 えています。これらのデバイスは速度と消費電力の組み合 わせが非常に優れており、伝搬遅延は 110ns、チャネル あたりの静止時電流はわずか 22µA です。

TLV90xxL の独自の特長は出力ラッチ機能です。出力は 最初のスレッショルド超過時にラッチされるため、システム コントローラの完全な注意を必要とせずにイベントやエラ ー状態をキャプチャできます。これにより、起動時にシステ

ムコントローラが初期化中、または他のタスクでビジー状 態になっているときに、イベントをキャプチャできます。立 ち下がりエッジトリガのクリア入力により、システムコントロ ーラは必要なタスクを実行した後にラッチをリセットし、安 全重視の要件を満たすことができます。「L1」および「L2」 オプションは、パワーアップラッチ動作を定義します。

これらのコンパレータは、出力位相反転なし、損傷なしで 最大 6V まで印加可能なフォルトトレラント入力も備えて います。このことにより、このファミリのコンパレータは、過酷 でノイズの多い環境での高精度電圧監視向けの設計にな っています。

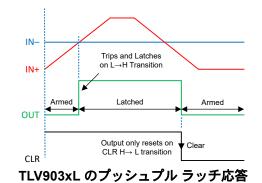

TLV902xL は、電源電圧以下またはそれ以上にプルアッ プ可能なオープンドレイン出力を備え、複数の出力の OR 接続やレベル変換用に設計されています。High から Low への出力遷移時にラッチが発生します。

TLV903xL は、MOSFET ゲートなどの容量性負荷を駆動 するために、最大 85mA のシンクおよびソース可能なプッ シュプル出力段を備えています。Low から High への出 力遷移時にラッチが発生します。

このファミリは 産業用 温度範囲 -40℃ から +125℃ で動 作が規定されており、標準のリード付きおよびリードレスパ ッケージで供給されます。

|                              | 製品情報                   |                           |  |  |  |  |  |  |  |

|------------------------------|------------------------|---------------------------|--|--|--|--|--|--|--|

| 部品番号                         | パッケージ <sup>(1)</sup>   | 本体サイズ (公称) <sup>(2)</sup> |  |  |  |  |  |  |  |

| TLV9020Lx (プレビ               | SC-70 (6) (プレビュー)      | 1.25mm × 2.00mm           |  |  |  |  |  |  |  |

| ュー)、<br> TLV9030Lx (プレビ      | SOT-23 (6) (プレビュー)     | 1.60 mm × 2.90mm          |  |  |  |  |  |  |  |

| ユー)、<br>(シングル)               | WSON (6) (プレビュー)       | 1.50mm × 1.50mm           |  |  |  |  |  |  |  |

| TLV9022Lx、<br>TLV9032Lx (プレビ | VSSOP (10) (プレビュ<br>ー) | 3.00mm × 3.00mm           |  |  |  |  |  |  |  |

| ュー)<br>(デュアル)                | X2QFN (10)             | 2.00mm × 1.50mm           |  |  |  |  |  |  |  |

利用可能なすべてのパッケージについては、データシートの末尾 (1) にある注文情報を参照してください。

パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ (2) ンも含まれます。

# 目次

| 1 特長1                             |

|-----------------------------------|

| <b>2</b> アプリケーション1                |

| 3 説明1                             |

| 4ピン構成および機能4                       |

| ピンの機能:TLV9020L および TLV9030L シングル4 |

| ピン構成: TLV9022L および TLV9032L デュアル5 |

| 5 仕様6                             |

| 5.1 絶対最大定格6                       |

| 5.2 ESD 定格6                       |

| 5.3 推奨動作条件6                       |

| 5.4 熱に関する情報 - シングル7               |

| 5.5 熱に関する情報 - デュアル7               |

| 5.6 電気的特性8                        |

| 5.7 スイッチング特性9                     |

| 5.8 代表的特性10                       |

| 6 詳細説明16                          |

| 6.1 概要16                          |

|   | 6.2 機能ブロック図                          | 16 |

|---|--------------------------------------|----|

|   | 6.3 機能説明                             |    |

|   | 6.4 デバイスの機能モード                       |    |

| 7 | アプリケーションと実装                          |    |

|   | 7.1 アプリケーション情報                       |    |

|   | 7.2 代表的なアプリケーション                     |    |

|   | 7.3 電源に関する推奨事項                       |    |

|   | 7.4 レイアウト                            |    |

| 8 | デバイスおよびドキュメントのサポート                   |    |

|   | 8.1ドキュメントのサポート                       |    |

|   | 8.2ドキュメントの更新通知を受け取る方法                |    |

|   |                                      |    |

|   | 8.4 商標                               |    |

|   | 8.5 静電気放電に関する注意事項                    |    |

|   | 8.6 用語集                              |    |

| 9 | 改訂履歴                                 |    |

|   | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |    |

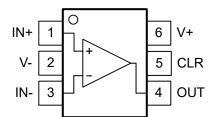

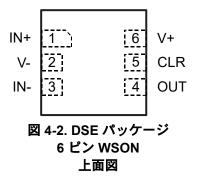

## 4 ピン構成および機能

ピンの機能: TLV9020L および TLV9030L シングル

図 4-1. DCK および DBV パッケージ クリア ピン機能付き標準「南東」ピン配置 6 ピン SC-70 および SOT-23 上面図

|     | TL    | V9020L 、TLV903 | 30L  |     |                                   |

|-----|-------|----------------|------|-----|-----------------------------------|

| 名称  | ピン    | ピン             | ピン   | I/O | 説明                                |

|     | SC-70 | SOT-23         | WSON |     |                                   |

| IN+ | 1     | 1              | 1    | I   | 非反転 (+) 入力                        |

| V-  | 2     | 2              | 2    | -   | 負電源電圧                             |

| IN- | 3     | 3              | 3    | I   | 反転 (-) 入力                         |

| OUT | 4     | 4              | 4    | 0   | 出力                                |

| CLR | 5     | 5              | 5    | I   | 入力をクリア - パルス High (>1.2V) で出力をクリア |

| V+  | 6     | 6              | 6    | -   | 正電源電圧                             |

#### 表 4-1. ピンの機能: TLV9020L および TLV9030L

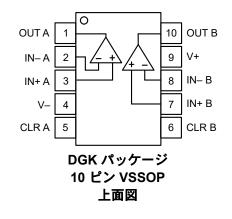

### ピン構成: TLV9022L および TLV9032L デュアル

### 表 4-2. ピンの機能: TLV9022L および TLV9032L

|       | TLV9022L、<br>TLV9032L |       |     |                                |

|-------|-----------------------|-------|-----|--------------------------------|

| 名称    | ピン                    | ピン    | I/O | 説明                             |

|       | VSSOP                 | X2QFN | 1   |                                |

| OUT A | 1                     | 8     | 0   | コンパレータ A の出力                   |

| IN– A | 2                     | 9     | I   | コンパレータAの反転 (-)入力               |

| IN+ A | 3                     | 10    | I   | コンパレータAの非反転 (+) 入力             |

| V-    | 4                     | 1     | -   | 負電源電圧                          |

| CLR A | 5                     | 2     | I   | コンパレータAのクリア入力 - 立ち下がりエッジでクリア   |

| CLR B | 6                     | 3     | I   | コンパレータ B のクリア入力 - 立ち下がりエッジでクリア |

| IN+ B | 7                     | 4     | I   | コンパレータBの非反転 (+) 入力             |

| IN– B | 8                     | 5     | I   | コンパレータ B の反転 (-) 入力            |

| V+    | 9                     | 6     | -   | 正電源電圧                          |

| OUT B | 10                    | 7     | 0   | コンパレータ B の出力                   |

### 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内(特に記述のない限り)(1)

|                                         | 最小値  | 最大値        | 単位 |

|-----------------------------------------|------|------------|----|

| 電源電圧:V <sub>S</sub> = (V+) - (V-)       | -0.3 | 6          | V  |

| (V-)から入力ピン (IN+、IN-、CLR) <sup>(2)</sup> | -0.3 | 6          | V  |

| 入力ピンへの電流 (IN+、IN-、CLR)                  | -10  | 10         | mA |

| (V-) から出力 (OUT) <sup>(3)</sup>          | -0.3 | 6          | V  |

| (V-) から出力 (OUT) (オープンドレイン)              | -0.3 | (V+) + 0.3 | V  |

| 出力短絡時間 <sup>(4)</sup>                   |      | 10         | s  |

| 接合部温度、T」                                |      | 150        | C° |

| 保管温度、T <sub>stg</sub>                   | -65  | 150        | C° |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、 推奨動作条件に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態に長時間置くと、デバイスの信頼性に影響を及ぼす場合があります。

(2) 入力端子は (V-) に対してダイオード クランプされています。(V-) を超えて 0.3V 以上スイングする入力信号は、電流を 10mA 以下に抑える必要 があります。また、入力 (IN+、IN-、CLR) は、電圧が -0.3V から 6V の範囲内である限り、V+ および OUT を超えることができます。

(3) オープンドレインの出力 (OUT) は、(V+) を超えることができます。

(4) (V-)または (V+) への短絡。

### 5.2 ESD 定格

|                    |      |                                                         | 値     | 単位 |

|--------------------|------|---------------------------------------------------------|-------|----|

| V                  | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2000 | V  |

| V <sub>(ESD)</sub> | 靜电放电 | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±1000 | v  |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内(特に記述のない限り)

|                                    | 最小値   | 最大値        | 単位 |

|------------------------------------|-------|------------|----|

| 電源電圧: V <sub>S</sub> = (V+) - (V-) | 1.65  | 5.5        | V  |

| 入力電圧範囲 (V-) から (IN+、IN-、CLR)       | -0.2  | 5.5        | V  |

| 入力共通モード同相電圧範囲 (V-) から (IN+、IN-)    | - 0.2 | (V+) + 0.2 | V  |

| 出力電圧範囲、オープンドレイン出力、(V-)から           | 0     | 5.5        | V  |

| 出力電圧範囲、プッシュプル出力                    | (V-)  | (V+)       | V  |

| 周囲温度、TA                            | -40   | 125        | C° |

### 5.4 熱に関する情報 - シングル

|                       | 熱評価基準 <sup>(1)</sup> |     | TLV9020L、TLV9030L |               |      |  |

|-----------------------|----------------------|-----|-------------------|---------------|------|--|

|                       |                      |     | DCK<br>(SC-70)    | DSE<br>(WSON) | 単位   |  |

|                       |                      | 6ピン | 6ピン               | 6ピン           |      |  |

| R <sub>qJA</sub>      | 接合部から周囲への熱抵抗         | -   | 210.5             | -             | °C/W |  |

| R <sub>qJC(top)</sub> | 接合部からケース (上面) への熱抵抗  | -   | 143.9             | -             | °C/W |  |

| R <sub>qJB</sub>      | 接合部から基板への熱抵抗         | -   | 64.7              | -             | °C/W |  |

| Ујт                   | 接合部から上面への特性パラメータ     | -   | 46.1              | -             | °C/W |  |

| У <sub>ЈВ</sub>       | 接合部から基板への特性パラメータ     | -   | 64.5              | -             | °C/W |  |

| R <sub>qJC(bot)</sub> | 接合部からケース(底面)への熱抵抗    | -   | -                 | -             | °C/W |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』レポートを参照してください。

### 5.5 熱に関する情報 - デュアル

|                       | т                   |                |                |      |

|-----------------------|---------------------|----------------|----------------|------|

|                       | 熱評価基準(1)            | DGK<br>(VSSOP) | RUG<br>(X2QFN) | 単位   |

|                       |                     | 10 ピン          | 10 ピン          |      |

| R <sub>qJA</sub>      | 接合部から周囲への熱抵抗        | -              | 222.8          | °C/W |

| R <sub>qJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | -              | 94.2           | °C/W |

| R <sub>qJB</sub>      | 接合部から基板への熱抵抗        | -              | 147.1          | °C/W |

| Ујт                   | 接合部から上面への特性パラメータ    | -              | 3.4            | °C/W |

| Ујв                   | 接合部から基板への特性パラメータ    | -              | 146.4          | °C/W |

| R <sub>qJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | -              | -              | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』レポートを参照してください。

### 5.6 電気的特性

V<sub>S</sub> (合計電源電圧) = (V+) – (V-) = 5V、V<sub>CM</sub> = (V-) (T<sub>A</sub> = 25℃時) (特に記述のない限り)

|                               | パラメータ                     | テスト条件                                                                                            | 最小値        | 標準値  | 最大値        | 単位   |

|-------------------------------|---------------------------|--------------------------------------------------------------------------------------------------|------------|------|------------|------|

| オフセット電                        | t庄                        | · · · · · · · · · · · · · · · · · · ·                                                            |            |      |            |      |

| V <sub>T</sub>                | 入力スレッショルド電圧               | V <sub>S</sub> = 1.8V および 5V                                                                     | -1.75      | ±0.3 | 1.75       |      |

| V <sub>T</sub>                | 入力スレッショルド電圧               | V <sub>S</sub> = 1.8V および 5V、T <sub>A</sub> = -40℃~+125℃                                         | -2.25      |      | 2.25       | mV   |

| dV <sub>T</sub> /dT           | 入力スレッショルド電圧ドリ<br>フト       | V <sub>S</sub> = 1.8V および 5V、T <sub>A</sub> = -40°C~+125°C                                       |            | ±0.5 |            | µV/℃ |

| 電源                            | 1                         |                                                                                                  |            |      |            |      |

| Ι <sub>Q</sub>                | 静止電流 (コンパレータ1<br>個あたり)    | V <sub>S</sub> = 1.8V および 5V、無負荷、出力 Low                                                          |            | 22   | 30         |      |

| l <sub>Q</sub>                | 静止電流 (コンパレータ1<br>個あたり)    | V <sub>S</sub> = 1.8V および 5V、無負荷、出力 Low、T <sub>A</sub> =<br>-40℃~+125℃                           |            |      | 42         | μA   |

| V <sub>POR</sub><br>(postive) | パワーオンリセット電圧               |                                                                                                  |            | 1.25 |            | V    |

| PSRR                          | 電源除去比                     | V <sub>S</sub> = 1.8V~5V、T <sub>A</sub> = -40℃~+125℃、(プッシュ<br>プルのみ)                              | 75         | 95   |            | dB   |

| PSRR                          | 電源除去比                     | V <sub>S</sub> = 1.8V~5V、T <sub>A</sub> = -40℃~+125℃ (オープン<br>ドレインのみ)                            | 80         | 95   |            | dB   |

| 入力バイアン                        | 」<br>ス電流                  |                                                                                                  |            |      |            |      |

| IB                            | 入力バイアス電流                  | $V_{CM} = V_S/2$                                                                                 |            | 5    |            | pА   |

| I <sub>OS</sub>               | 入力オフセット電流                 | $V_{CM} = V_S/2$                                                                                 |            | 1    |            | pА   |

| 入力容量                          |                           |                                                                                                  |            |      |            |      |

| C <sub>ID</sub>               | 入力容量、差動                   | $V_{CM} = V_S/2$                                                                                 |            | 2    |            | pF   |

| C <sub>IC</sub>               | 入力容量、同相                   | $V_{CM} = V_S/2$                                                                                 |            | 3    |            | pF   |

| 入力電圧範                         | i<br>ت                    | · · · · ·                                                                                        |            |      | ŀ          |      |

| V <sub>IH_CLR</sub>           | CLR 電圧入力 High スレ<br>ッショルド |                                                                                                  | 1.2        |      |            | V    |

| V <sub>IL_CLR</sub>           | CLR 電圧入力 Low スレ<br>ッショルド  |                                                                                                  |            |      | 0.6        | V    |

| V <sub>CM-Range</sub>         | 同相電圧範囲                    | V <sub>S</sub> = 1.8V および 5V、T <sub>A</sub> = -40°C~+125°C                                       | (V-) - 0.2 |      | (V+) + 0.2 | V    |

| CMRR                          | 同相除去比                     | $V_{S} = 5V_{(V-)} - 0.2V < V_{CM} < (V+) + 0.2V_{TA} = -40^{\circ}C^{+}+125^{\circ}C$           | 60         | 70   |            | dB   |

| CMRR                          | 同相除去比                     | $V_{S} = 1.8V_{,}$ (V-) - 0.2V < $V_{CM}$ < (V+) + 0.2V_{,} T_{A} = -40^{\circ}C^{+125^{\circ}C} | 50         | 60   |            | dB   |

| 出力                            |                           |                                                                                                  |            |      |            |      |

| V <sub>OL</sub>               | (V-) からの電圧スイング            | I <sub>SINK</sub> = 4mA、T <sub>A</sub> = 25°C                                                    |            | 75   | 125        | mV   |

| V <sub>OL</sub>               | (V-) からの電圧スイング            | I <sub>SINK</sub> = 4mA, T <sub>A</sub> = -40°C~+125°C                                           |            |      | 175        | mV   |

| V <sub>OH</sub>               | (V+) からの電圧スイング            | I <sub>SOURCE</sub> = 4mA、T <sub>A</sub> = 25°C (プッシュプルのみ)                                       |            | 75   | 125        | mV   |

| V <sub>OH</sub>               | (V+) からの電圧スイング            | I <sub>SOURCE</sub> = 4mA、T <sub>A</sub> = -40°C~+125℃ (プッシュプ<br>ルのみ)                            |            |      | 175        | mV   |

| I <sub>LKG</sub>              | オープンドレイン出力リー<br>ク電流       | V <sub>PULLUP</sub> = (V+), T <sub>A</sub> = 25°C                                                |            | 100  |            | pА   |

| I <sub>SC</sub>               | 短絡電流                      | V <sub>S</sub> = 5V、シンク                                                                          | 75         | 85   |            | mA   |

| I <sub>SC</sub>               | 短絡電流                      | V <sub>S</sub> = 5V、ソース (プッシュプルのみ)                                                               | 75         | 85   |            | mA   |

### 5.7 スイッチング特性

V<sub>S</sub> = 5V、CLR = 5V<sub>PP</sub>、V<sub>L</sub> = 0V、V<sub>H</sub> = 5V、2.5V DC オフセット、V<sub>CM</sub> = V<sub>S</sub>/2、C<sub>L</sub> = 15pF (T<sub>A</sub> = 25°C 時) (特に記述のない限り)

|                       | パラメータ テスト条件                                        |                                                                                       | 最小値 | 標準値 | 最大值 | 単位 |

|-----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|-----|----|

| 出力                    |                                                    |                                                                                       |     |     | ·   |    |

| T <sub>PD-HL</sub>    | 伝搬遅延時間、High から Low、<br>オープンドレインのみ                  | V <sub>ID</sub> = -100mV、CLR = 0V、入力の中間点か<br>ら出力の中間点までの遅延、R <sub>P</sub> = 2.5KΩ      |     | 110 |     | ns |

| T <sub>PD-LH</sub>    | 伝搬遅延時間、Low から High、<br>プッシュプルのみ                    | V <sub>ID</sub> = +100mV、CLR = 0V、入力の中間点から出力の中間点まで                                    |     | 125 |     | ns |

| T <sub>PD-CLR-F</sub> | クリア立ち下がりからラッチ リセット<br>までの伝搬遅延時間                    | CLR = 1.8V から 5V、<br>CLR の立ち下がりエッジ信号からラッチされて<br>いない出力状態までの遅延                          |     | 25  | 70  | ns |

| CLR_Min               | レジスタ ラッチ ディセーブルおよ<br>び遷移出力状態までの最小クリア<br>ホールド パルス時間 | CLR = 1.8V から 5V、<br>CLR 立ち下がりエッジで状態変更 (ラッチ リセ<br>ット) をレジスタするために必要な最小 CLR パ<br>ルス サイズ | 10  |     |     | ns |

| T <sub>FALL</sub>     | 5Vの出力立ち下がり時間、80%<br>から20%                          | V <sub>ID</sub> = -100mV                                                              |     | 3   |     | ns |

| T <sub>RISE</sub>     | 5V の出力立ち上がり時間、20%<br>から 80%                        | V <sub>ID</sub> = +100mV、プッシュプルのみ                                                     |     | 3   |     | ns |

| パワーオン                 | 時間                                                 |                                                                                       |     |     | ·   |    |

| P <sub>ON</sub>       | パワーオン時間                                            |                                                                                       |     | 35  |     | μs |

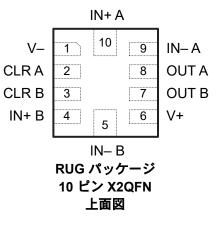

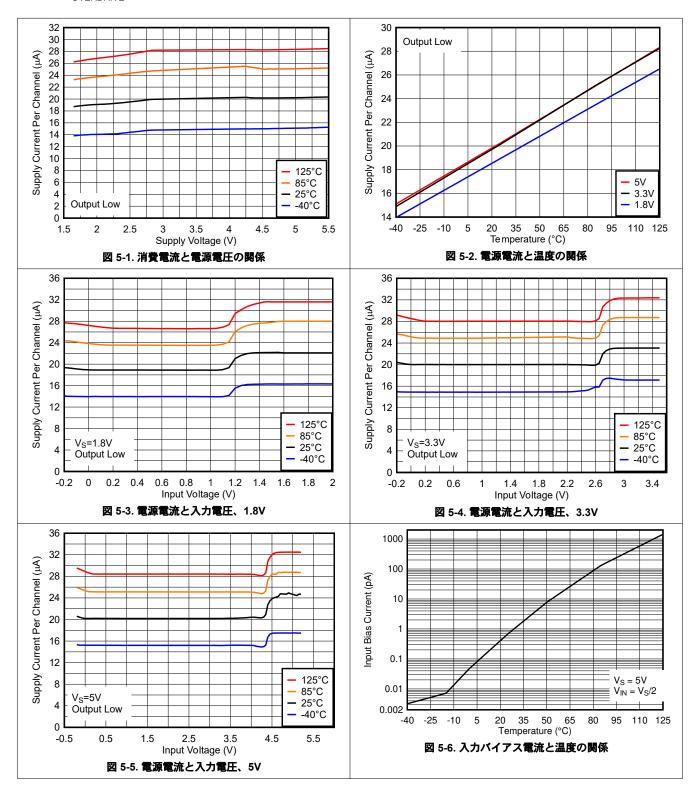

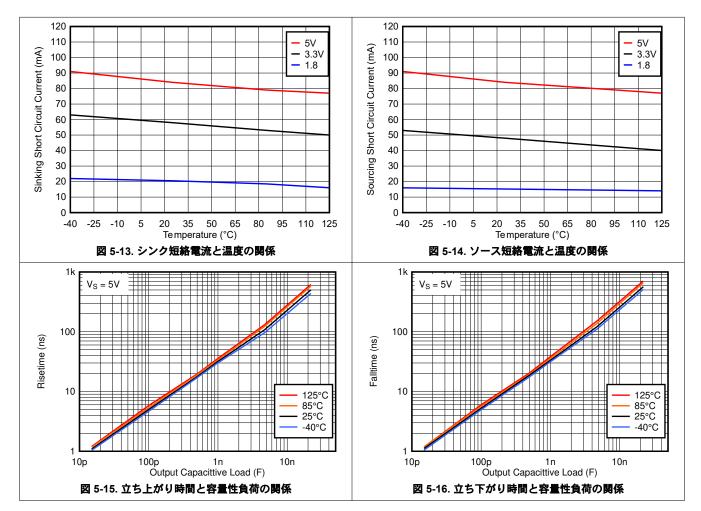

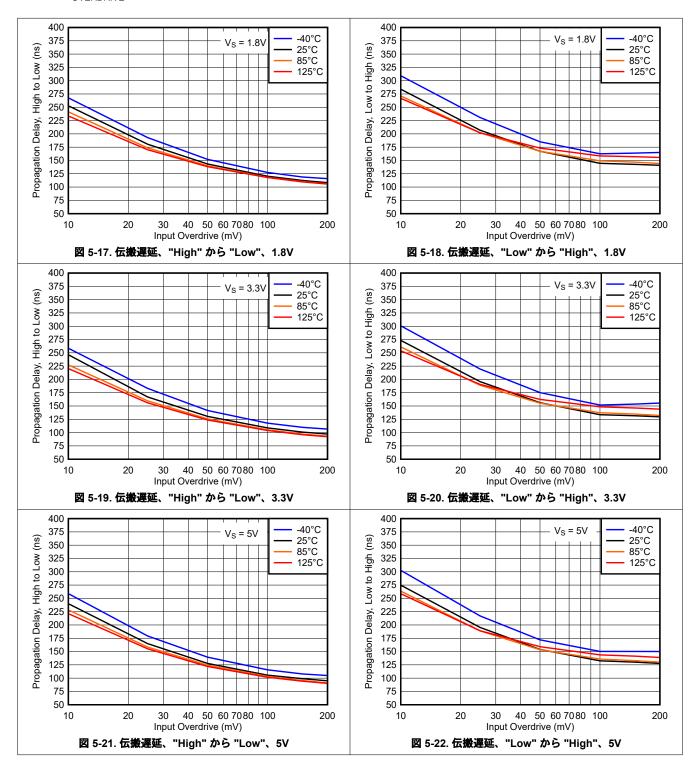

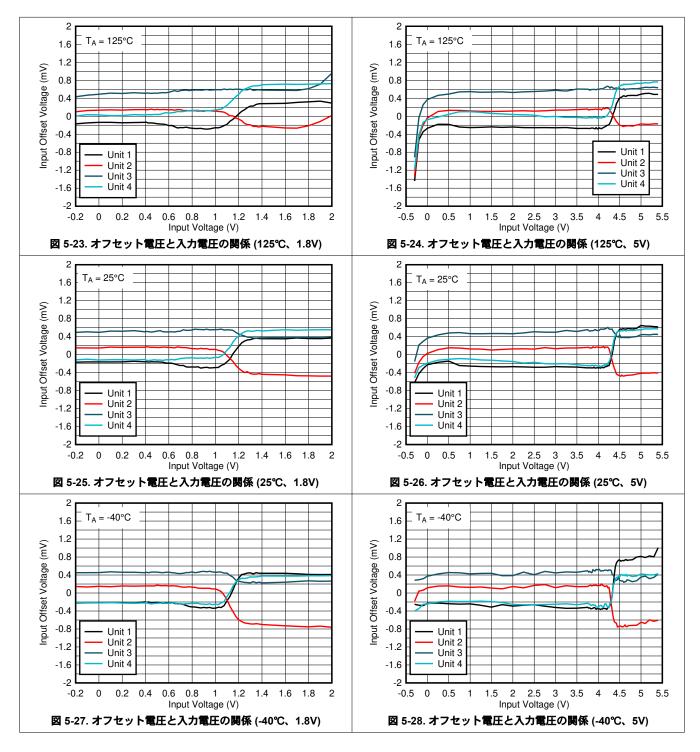

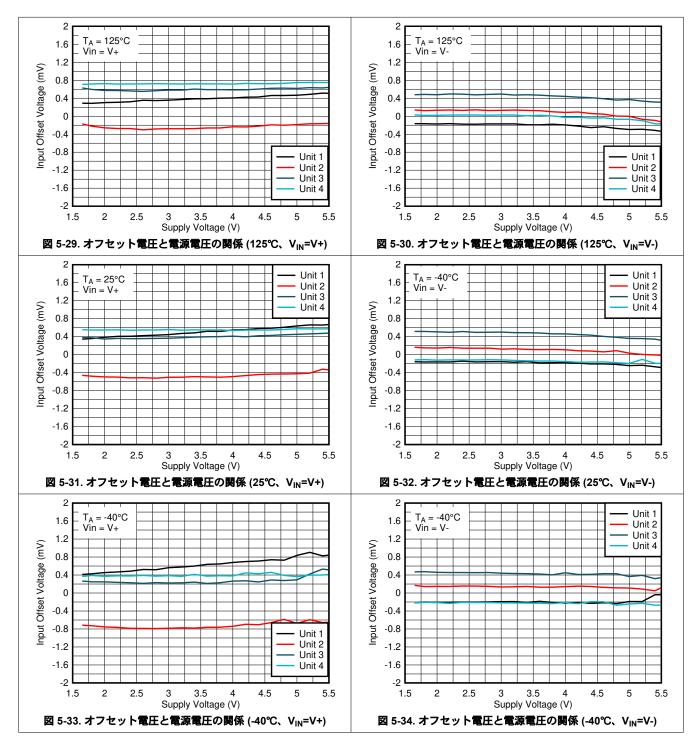

### 5.8 代表的特性

特に記述のない限り、 $T_A = 25^{\circ}C$ 、 $V_S = 5V$ 、 $R_{PULLUP} = 5.1k$ から 5V (プッシュプルのみ)、 $C_L = 15pF$ 、 $V_{CM} = 0V$ 、 $V_{UNDERDRIVE} = 100mV$ 、 $V_{OVERDRIVE} = 100mV$ 。

Copyright © 2025 Texas Instruments Incorporated

特に記述のない限り、T<sub>A</sub> = 25°C、V<sub>S</sub> = 5V、R<sub>PULLUP</sub> = 5.1k から 5V (プッシュプルのみ)、C<sub>L</sub> = 15pF、V<sub>CM</sub> = 0V、V<sub>UNDERDRIVE</sub> = 100mV、V<sub>OVERDRIVE</sub> = 100mV。

### 6 詳細説明

### 6.1 概要

TLV902xL および TLV903xL は、シングルおよびデュアル チャネル ラッチ コンパレータのファミリです。このファミリは、 低い入力オフセット電圧、パワー オン リセット(POR)、フォルトトレラント入力、および優れた速度と電力の組み合わせ (110ns の伝搬遅延時間とチャネルあたり 22µA の静止消費電流)を実現しています。

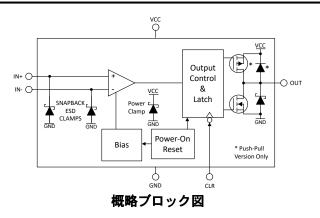

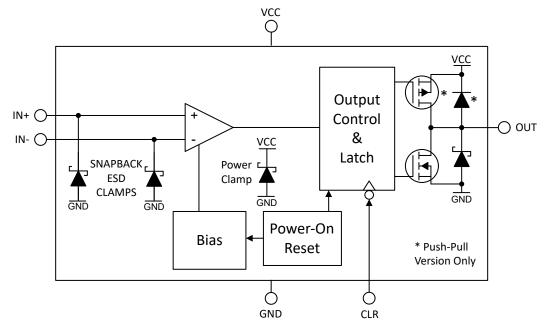

### 6.2 機能ブロック図

### 6.3 機能説明

TLV902xL および TLV903xL の独自の特長は出力ラッチ機能です。出力は最初のスレッショルド超過時にラッチされる ため、システム コントローラの完全な注意を必要とせずにイベントやエラー状態をキャプチャできます。これにより、起動時 にシステム コントローラが初期化中でも、イベントをキャプチャできます。システム コントローラは、必要なタスクを実行した 後でラッチをリセットできます。ユーザーは、電源オン時に出力がラッチされない(「L1」オプション)と、パワーアップ時にラ ッチされる(「L2」オプション)のどちらかを選択できます。

これらのコンパレータは、出力位相反転なし、損傷なしで最大 6V まで印加可能なフォルトトレラント入力も備えています。このことにより、このファミリのコンパレータは、過酷でノイズの多い環境での高精度電圧監視向けの設計になっています。

#### 6.4 デバイスの機能モード

#### 6.4.1 出力

#### 6.4.1.1 TLV902xL オープン ドレイン出力

TLV902xL はオープンドレイン (オープン コレクタとも呼ばれる) シンクのみの出力段を備えているため、コンパレータの 電源電圧 (V<sub>S</sub>) にかかわらず、出力ロジックレベルを最大 5.5V の電圧にプルアップできます。オープンドレイン出力に より、複数のオープンドレイン出力の論理 OR 接続とロジックレベルの変換も可能になります。

プルアップ抵抗電流は 100µA~1mA の範囲で設定することを TI では推奨しています。プルアップ抵抗の値を小さくす ると、立ち上がりエッジの立ち上がり時間を短縮しやすくなりますが、V<sub>OL</sub> が高くなり、消費電力が大きくなります。立ち上 がり時間は、総プルアップ抵抗と総負荷容量の時定数によって決定されます。プルアップ抵抗の値が大きいと (>1MΩ)、 RC 時定数が原因で指数関数的な立ち上がりエッジが発生し、立ち上がり時間が長くなります。

使用しないオープンドレイン出力はフローティングのままにすることができます。フローティングピンが許されない場合は、 V-ピンに接続できます。

オープンドレイン出力保護は、出力と V-の間に ESD クランプを配置し、プルアップ電圧が V<sub>S</sub> を超えた場合でも、出力を最大 5.5V までの任意の電圧に引き下げることができるように構成されています。

#### 6.4.1.2 TLV903xL プッシュプル出力

TLV903xL にはプッシュプル出力段があり、シンク電流とソース電流の両方を供給できます。このため、LED や MOSFET ゲートなどの負荷を駆動することができ、外付けプルアップ抵抗で電力を浪費する必要もなく、容量性負荷に依存しない 対称的なエッジ レートを実現します。

プッシュプル出力は、絶対に他の出力に接続しないでください。出力を逆の電源へ直接短絡すると、熱暴走が発生し、最終的にデバイスが破壊される可能性があります。出力が短絡する可能性がある場合は、消費電力を制限するために直列の電流制限抵抗を使用することを推奨します。

使用しないプッシュプル出力はフローティングのままにします。電源、グランド、または他の出力に接続してはなりません。

出力保護は、出力と V- 間、および出力と V+ 間に ESD クランプで構成されており、出力はどちらの電源レールも超えてはなりません。

### 6.4.2 パワーオン リセット (POR)

TLV90xxL には内部パワー オン リセット (POR) 回路があり、既知のスタートアップまたはパワーダウン状態を維持しま す。電源電圧 (V<sub>s</sub>)の上昇または下降中に、電源電圧の最小スレッショルドの V<sub>POR</sub> (通常 1.25V)を超えた後、最大 60µs (過熱時)の間、または電源電圧が V<sub>POR</sub> 未満に低下した直後に、POR 回路がアクティブになります。POR 期間中 は、入力状態は無視されます。電源電圧が最小電源電圧以上であれば、遅延時間が経過した時点で、コンパレータの出 力は差動入力の状態 (「L1」オプション)または初期ラッチ状態 (「L2」オプション)を反映します。

早期ラッチを防止するため、POR 期間の終了前に入力レベルをセトリングする必要があります。入力上のフィルタリング部 品または RC 部品 (基準電圧、分圧器、バイパスコンデンサなど)の時定数に注意を払う必要があります。

オープンドレインおよびプッシュプル出力タイプは、POR およびラッチ動作が異なります。次のセクションでは、これらの違いについて説明します。

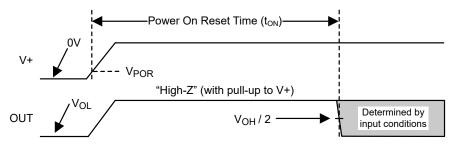

### 6.4.2.1 TLV902xL オープン ドレイン出力 POR 動作

TLV902xL1 オープンドレイン出力の場合、POR 回路は POR 期間 (t<sub>on</sub>) 中出力を **High**、または High インピーダンス (「HI-Z」) に維持します。

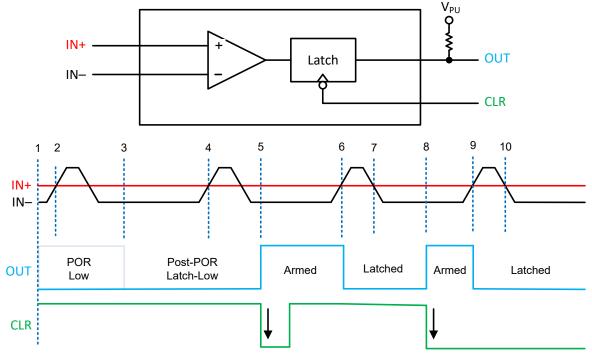

図 6-1. TLV902xL1 パワーオン リセットのタイミング図の例

オープンコレクタ出力の性質上、POR 期間中にプルアップ電圧とともに出力が上昇します。

TLV902xL2 オプションは、POR を通じて出力を Low から開始し、POR 後はクリアされるまで Low にラッチされたまま になります。

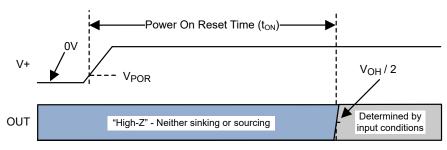

### 6.4.2.2 TLV903xL プッシュプル出力 POR 動作

TLV903xL1 プッシュプル出力の場合、POR 回路はソース電流もシンク電流もどちらも出力を High-Z に維持します。出力は、POR 期間 (ton) 中に V+ と V- の間でランダムに「フローティング」になります。小さい値のプルアップ抵抗 (V+ まで) またはプルダウン抵抗 (V- まで) を使用して、出力状態をプリバイアスし、出力がフローティングになることを防止できます。

図 6-2. TLV903xL1 パワーオン リセットのタイミング図の例

TLV903xL2 オプションは、POR を通じて出力を High (ソース) から開始し、POR 後はクリアされるまで High にラッチされます。

### 6.4.3 *出カラッチ*

TLV90xxL には、作動可能時に、最初の入力遷移が入力スレッショルドを通過したときにラッチされる出力があります。 CLR ピンの立ち下がりエッジまで出力はラッチされたまま維持されます。

ユーザーは、**電源オン時に出力がラッチされない (「L1**」オプション) と、**電源オン時にラッチされる (「L2**」オプション) のどちらかを選択できます。

ラッチの動作は、オープンドレイン出力タイプとプッシュプル出力タイプでは異なります。動作については、以下のセクションで説明します。

### 6.4.3.1 「L1」および「L2」のパワーオン オプション

TLV90xxL は、2 つのパワーオン オプションで利用できます。

「L1」オプションは POR から出力され、出力は ラッチされていない 状態で、次のラッチ イベントで有効になります。

「L2」オプションは、出力を ラッチ 状態に保持するときに POR から出力されますが、CLR ピンが High から Low に遷移 して、次のラッチ イベントのためにコンパレータが作動可能になるためにはクリアする必要があります。

次の関数の概要表に、動作の概要を示します。

| デバイス      | 出力タイプ    | POR 時の         POR 後の           出力状態         出力状態 |           | 作動可能出力<br>ラッチ オン: | 出力ラッチ状態 |  |  |  |  |  |  |

|-----------|----------|---------------------------------------------------|-----------|-------------------|---------|--|--|--|--|--|--|

| TLV902xL1 | オープンドレイン | High                                              | 作動可能      | $H \rightarrow L$ | Low     |  |  |  |  |  |  |

| TLV902xL2 | オープンドレイン | Low                                               | Low にラッチ  | $H \rightarrow L$ | Low     |  |  |  |  |  |  |

| TLV903xL1 | プッシュプル   | ハイ インピーダンス                                        | 作動可能      | $L \rightarrow H$ | High    |  |  |  |  |  |  |

| TLV903xL2 | プッシュプル   | High                                              | High にラッチ | $L \rightarrow H$ | High    |  |  |  |  |  |  |

表 6-1. 機能の概要

以下のセクションでは、各種の出力タイプのラッチ状態の動作について詳細に説明します。

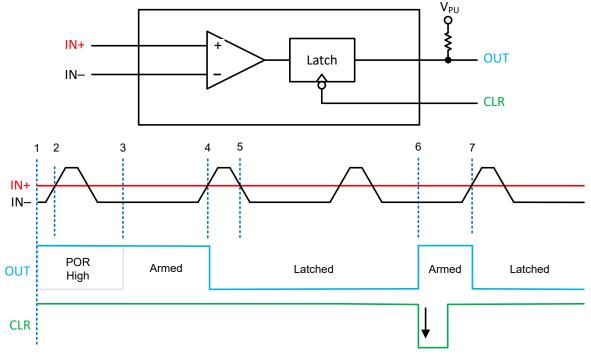

#### 6.4.3.2 TLV902xL1 オープンドレイン ラッチ動作

TLV902xL1 のオープンドレイン出力は、POR 期間中 は High になります。POR 期間の後、ラッチは作動し、最初の High から Low への 出力遷移時に Low にラッチされます。以下に、ラッチ動作の概要を示します。

### 図 6-3. オープン ドレイン ラッチのタイミング例 (「L1」オプション)

- 1. 最初の電源投入時の POR 期間中は出力が High になります。

- 2. POR 期間中、入力遷移は無視されます。

- 3. POR 期間後、コンパレータが作動可能になり、入力を監視します。

- 4. IN- が IN+ より高くなり、出力 Low、 ラッチ High に設定します。

- 5. IN+ は IN- より高くなりますが、出力は依然として Low (ラッチ)のままです。

- 6. CLR の立ち下がりエッジで次の遷移のラッチがリセットされます。IN+ > IN- では、出力は High に維持され、次の入力遷移のために作動可能です。

- 7. IN->IN+では、出力を Low にして再びラッチします。IN+>IN-でも出力はラッチされたままです。

#### 6.4.3.3 TLV902xL2 オープンドレイン ラッチ動作

TLV902xL2 のオープンドレイン出力は、POR 期間中は High にラッチします。POR 期間の後、出力は Low にラッチ され、CLR ピンの High から Low への 遷移によってクリアされる必要があります。以下に、ラッチ動作の概要を示します。

図 6-4. オープン ドレイン ラッチのタイミング例 (「L2」オプション)

ラッチの動作の概要を以下に示します。

- 1. 最初の電源オン後の POR 期間中、出力は Low になります。

- 2. POR 期間中は入力遷移は無視されます。

- 3. POR 期間の後、OUT は Low にラッチされたままです。

- 4. IN-は IN+を通過しますが、ラッチ中は遷移は無視されます。

- 5. CLR の立ち下がりエッジがリセットされ、次の遷移を待つラッチが作動可能になります。

- 6. IN- > IN+ では、OUT が Low になり、ラッチします。

- 7. IN+ > IN- でも、OUT は Low にラッチされたままです。

- 8. CLR の立ち下がりエッジがリセットされ、次の遷移に向けてラッチが作動可能になります。

- 9. IN- が IN+ を超えると、出力は Low になり、再びラッチします。

- 10. IN+ > IN- でも出力は Low にラッチされたままです。

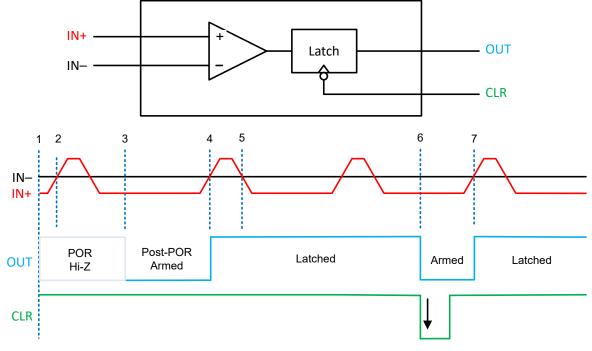

#### 6.4.3.4 TLV903xL1 のプッシュプル ラッチ動作

TLV903xL1 のプッシュプル出力は、POR 期間中 は High-Z (ディザリング シンクまたはソース電流) です。POR 期間の 後、ラッチが作動し、最初の Low から High への 出力遷移時に High にラッチされます。

図 6-5. プッシュプル ラッチのタイミング例 (「L1」オプション)

ラッチの動作の概要を以下に示します。

- 1. 最初の電源投入時の POR 期間中は出力が Hi-Z になります。

- 2. POR 期間中、入力遷移は無視されます。

- 3. POR 期間後、コンパレータが作動可能になり、入力を監視します。

- 4. IN+ が IN- より高くなり、出力 High とラッチ High に設定します。

- 5. IN-は IN+より高くなりますが、出力は依然として High (ラッチ)のままです。

- 6. CLR の立ち下がりエッジで次の遷移のラッチがリセットされます。IN->IN+では、出力は Low に維持され、次の入力遷移のために作動可能です。

- 7. IN+ > IN- では、出力を High にして再びラッチします。 IN- > IN+ でも出力はラッチされたままです。

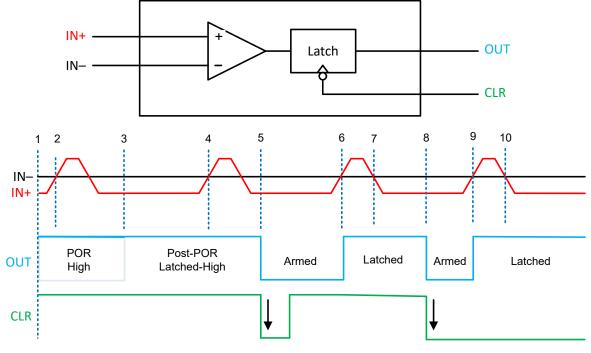

### 6.4.3.5 TLV903xL2 のプッシュプル ラッチ動作

TLV903xL2 のプッシュプル出力は、POR 期間中は High (ソース電流) にラッチします。POR 期間の後、出力は High にラッチ され、CLR ピンの High から Low への遷移によりクリアされる必要があります。

図 6-6. プッシュプル ラッチのタイミング例 (「L2」オプション)

ラッチの動作の概要を以下に示します。

- 1. 最初の電源オン後の POR 期間中、出力は High になります。

- 2. POR 期間中は入力遷移は無視されます。

- 3. POR 期間の後、OUT は High にラッチされます。

- 4. IN+ は IN- を通過しますが、ラッチ中は遷移は無視されます。

- 5. CLR の立ち下がりエッジがリセットされ、次の遷移を待つラッチが作動可能になります。

- 6. IN+ > IN- では、OUT が High になり、ラッチします。

- 7. IN- > IN+ でも、OUT は High にラッチされたままです。

- 8. CLR の立ち下がりエッジがリセットされ、次の遷移に向けてラッチが作動可能になります。

- 9. IN+ が IN- を超えると、出力は High になり、再びラッチします。

- 10. IN- > IN+ でも出力は High にラッチされたままです。

#### 6.4.3.6 クリア (CLR) 入力

CLR が High または Low で、コンパレータがラッチ状態でない場合、コンパレータはアクティブ (「作動可能」) で、入力状態に応答することで、次の認定状態をラッチできるようになります。

**CLR 入力は、CLR 入力の High から Low (立ち下がり) エッジの出力ラッチをクリアします。**コンパレータはクリアの後、 次のラッチ状態イベントまでアクティブ (作動可能)になります。

立ち下がりエッジを使用してリセットをトリガすることで、CLR ピンを安定した High または Low にできます。これにより、ハードウェアまたはソフトウェアの障害によってコンパレータがロックアップされるのを防ぎ、安全性の高い設計要件を満たすことができます。

コンパレータの出力遷移と同時に CLR ピンが遷移 (立ち下がり)している場合、セットアップ時間の競合が発生する可能 性があります。 CLR の立ち下がりエッジ時間中は、出力の状態は不定です。 この競合に対応できるよう、 CLR 立ち下がり エッジはできるだけ高速にすること (立ち下がり時間 100ns 未満)を推奨します。

CLR ピンにはフェイルセーフ (または「5V 互換」) 入力が搭載されており、コンパレータの電源電圧に関係なく、最大 5V のロジック High レベルに対応できます。ロジック High (VOH) スレッショルドは 1.2V です。

また、CLR 入力にはわずか 200nA のアクティブ プルダウン電流があり、起動時に CLR ピンが Low になり、コンパレー タがアクティブであることを保証します。このプルダウンを使用した場合でも、CLR 入力をフローティングにすることは推奨 されません。

### 6.4.4 入力

#### 6.4.4.1 レール ツー レール入力

TLV90xxL の入力電圧範囲は、V-より 200mV 低い電圧から V+より 200mV 高い電圧までです。差動入力電圧 (V<sub>ID</sub>) は、これらの制限値の範囲内で自由に設定できます。入力ピンの電圧が V+ または V- を超えても、コンパレータ出力の 位相反転は発生しません。

#### 6.4.4.2 フェイルセーフ入力

TLV90xxL の入力は、Vs の影響を受けず、最高 5.5V までフォルトトレラントです。フォルトトレラントとは、Vs が電源供給されていないとき、または推奨動作範囲内にあるときに、同じ高い入力インピーダンスを維持することと定義されます。

フォルトトレラント入力には、V<sub>S</sub>が0またはランプアップ/ダウン中を含めて、0V~5.5Vの範囲で任意の値を使用できます。この機能により、入力電圧範囲と電源電圧が規定の最大範囲内にある限り、電源シーケンスの問題が回避されます。 これが可能なのは、入力がV+にクランプされていないため、入力に高電圧が印加されても入力電流のHigh インピーダンスが維持されるためです。

いずれかの入力ピンが有効な入力範囲内にあり、電源電圧が有効で POR ではない限り、出力状態は正常です。

入力電圧異常とその結果の概要を以下に示します:

1. IN+とIN-の両方が規定の入力電圧範囲内の場合:

- a. IN- が IN+ およびオフセット電圧より高い場合、出力は Low になります。

- b. IN-が IN+ およびオフセット電圧より低い場合、出力は High になります。

- 2. IN- が規定の入力電圧範囲より高く、IN+ が規定の電圧範囲内にある場合、出力は Low になります。

- 3. IN+ が規定の入力電圧範囲より高く、IN- が規定の入力電圧範囲内に入る場合、出力は High になります。

- 4. IN-とIN+の両方が規定の入力電圧範囲から外れている場合、出力は不定(ランダム)になります。この範囲の値で は使用しないでください。出力はランダムに反転できます。

耐故障性機能があるものの、TIでは、データシートの仕様を維持するため、通常のシステム動作時に入力を規定の入力 電圧範囲内に維持することを強く推奨します。指定された入力範囲外で動作すると、伝搬遅延時間や入力バイアス電流 などの仕様が変化し、それにより予測不能な動作の原因となる可能性があります。

#### 6.4.4.3 入力保護

TLV90xxL ファミリには、すべてのピンに内部 ESD 保護回路が組み込まれています。入力には、各ピンから V- への独自の「スナップバック」型 ESD クランプが使用されています。V+ への「上側」ESD クランプはありません。これにより、入力ピンが電源電圧 (V+) を超えられます。ESD イベントの間、スナップバック ダイオードは「短絡」し、V- への Low インピーダンスになります (SCR など)。

電源やバッファ付きリファレンスラインなど、低インピーダンスのソースに入力を接続する場合は、過渡によりクランプが導通した場合に過渡電流を制限するため、入力と直列に電流制限抵抗を追加することを TI では推奨しています。電流は 10mA 以下に制限する必要があります。この直列抵抗は、任意の抵抗入力分圧器またはネットワークの一部として使用できます。

ESD ダイオードは、高電圧にクランプできません。ESD クランプは、ツェナー ダイオードのような固定最大電圧で「ホールド」しません。入力を 5.5V を超える可能性がある電源に接続する場合は、最大入力電圧を超えないように外部クランプが 必要です。

入力バイアス電流は、通常は V+ と V- の間の入力電圧に対して 5pA です。入力バイアス電流は、通常は温度が 10℃ 上昇するごとに 2 倍になります。

#### 6.4.4.4 内部ヒステリシス

TLV90xxL にはヒステリシスが内蔵されていません。ラッチ機能により、最初の出力遷移時に出力がラッチされるため、ヒス テリシスが不要になります。基準レベルは目的のスレッショルドレベルに設定し、入力信号は早期トリガを引き起こす可能 性のあるノイズや過渡電圧を除去するために適切にフィルタリングする必要があります。

#### 6.4.4.5 未使用入力

チャネルを使用しない場合、入力を互いに接続しないでください。等価帯域幅が広く、オフセット電圧が低いため、入力を 互いに直接接続すると、デバイスが内部広帯域ノイズでトリガされ、高周波の発振が発生することがあります。使用しない 入力は、規定の入力電圧範囲内で使用可能な任意の電圧に接続し、50mV以上の差動電圧を確保する必要がありま す。たとえば、一方の入力を接地し、もう一方の入力を基準電圧または (V+)に接続できます。

### 7アプリケーションと実装

注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・イン スツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お 客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システム の機能を確認する必要があります。

### 7.1 アプリケーション情報

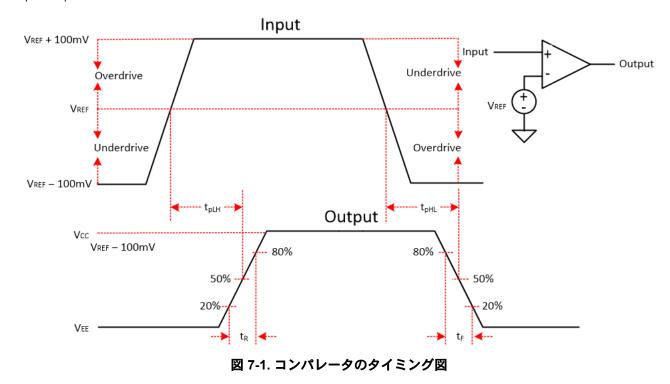

### 7.1.1 基本的なコンパレータの定義

#### 7.1.1.1 動作

基本コンパレータは、一方の入力の入力電圧 ( $V_{IN}$ )を、もう一方の入力の基準電圧 ( $V_{REF}$ )と比較します。以下の 図 7-1 の例で、 $V_{IN}$ が  $V_{REF}$ より低くなると、出力電圧 ( $V_O$ ) はロジック "Low" ( $V_{OL}$ ) になります。 $V_{IN}$ が  $V_{REF}$ より高くなると、出力電圧 ( $V_O$ ) は論理 "High" ( $V_{OH}$ ) になります。表 7-1 に、出力の条件のまとめを示します。入力ピンを入れ替えることにより、出力ロジックを反転できます。

| 表 7-1. 出力条件表 7-1. 出力条件表 7-1. 出力条件 |                           |  |  |  |  |  |  |

|-----------------------------------|---------------------------|--|--|--|--|--|--|

| 入力の条件                             | 出力                        |  |  |  |  |  |  |

| IN+ > IN-                         | "High" (V <sub>OH</sub> ) |  |  |  |  |  |  |

| IN+ = IN-                         | 不定                        |  |  |  |  |  |  |

| IN+ < IN-                         | "Low" (V <sub>OL</sub> )  |  |  |  |  |  |  |

#### 7.1.1.2 伝搬遅延

入力が基準電圧を超えてから出力が応答するまでの間には、遅延があります。これを伝搬遅延と呼びます。伝搬遅延は、"High" から "Low" への入力遷移と "Low" から "High" への入力遷移で異なることがあります。図 7-1 では、伝搬遅延を t<sub>oLH</sub> と t<sub>oHL</sub> として示し、入力の中間点から出力の中間点までで測定しています。

#### 7.1.1.3 オーバードライブ電圧

オーバードライブ電圧 (V<sub>OD</sub>) は、基準電圧を超える入力電圧の大きさです。入力ピークツー ピーク電圧の合計ではありません。図 7-1 の例に示したオーバードライブ電圧は 100mV です。オーバードライブ電圧は、伝搬遅延 (t<sub>p</sub>) に影響を与える可能性があります。オーバードライブ電圧が小さいほど、特に 100mV 未満の場合、伝搬遅延時間が長くなります。高速で応答させたい場合は、できる限り大きなオーバードライブ電圧を印加します。

立ち上がり時間 (t<sub>r</sub>) は出力波形の 20% から 80% のポイントまでの時間、立ち下がり時間 (t<sub>r</sub>) は 80% から 20% のポイントまでの時間です。

#### 7.2 代表的なアプリケーション

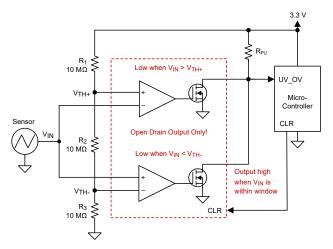

### 7.2.1 ウィンドウ コンパレータ

ウインドウ コンパレータは、一般的に低電圧および過電圧状態を検出するために使用されます。図 7-2 に、簡単なウィンドウ コンパレータ回路を示します。出力を互いに直接接続する場合、ウィンドウ コンパレータにはオープンドレイン出力 (TLV902xL1)を使用する必要があります。

図 7-2. TLV9022L1 を使用するウィンドウ コンパレータ

#### 7.2.1.1 設計要件

この設計については、以下の設計要件に従ってください。

- 入力信号が 1.1V を下回る場合のラッチ (論理 "Low" 出力)

- 入力信号が 2.2V を超える場合のラッチ (論理 "Low" 出力)

- 3.3V 電源で動作

#### 7.2.1.2 詳細な設計手順

図 7-2 に示されているように、回路を構成します。R1、R2、R3 をそれぞれ 10MΩ 抵抗にします。これらの 3 つの抵抗を 使用して、ウィンドウ コンパレータの正と負のスレッショルド (V<sub>TH+</sub> と V<sub>TH-</sub>)を作成します。

各抵抗が等しい場合、V<sub>TH+</sub> は 2.2V、V<sub>TH-</sub> は 1.1V です。消費電力を最小限に抑えるため、10MΩ などの大きな抵抗値 を使用します。抵抗値を再計算して、目的のトリップ ポイント値を得ることができます。

センサの出力電圧は、2 つのコンパレータの反転入力と非反転入力に印加されます。2 つのオープンドレイン出力コンパレータを使用すると、2 つのコンパレータ出力を OR 接続できます。

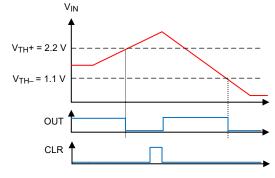

センサが 1.1V 未満または 2.2V 超の場合、それぞれのコンパレータ出力は Low にラッチします。図 7-3 に示すように、 センサが 1.1V~2.2V の範囲内 (「ウィンドウ」内) の場合、それぞれのコンパレータ出力は High になります。

出力をリセットし、コンパレータを作動可能にするには、CLR ピンを High から Low に切り替える必要があります。

#### 7.2.1.3 アプリケーション曲線

### 図 7-3. ウィンドウ コンパレータの結果

詳細については、アプリケーション ノート SBOA221 「ウィンドウ コンパレータ回路」を参照してください。

### 7.3 電源に関する推奨事項

出力エッジが高速であるため、電源リンギングおよび誤トリガーや発振を防ぐために、電源ピンのバイパスコンデンサが重要です。(V+) ピンとグランド ピンの間に低 ESR の 0.1µF セラミック バイパス コンデンサを直接接続し、それぞれのデバイスで電源を直接バイパスします。出力遷移時間中に、特にプッシュプル出力デバイスの場合、狭いピーク電流が流れる場合があります。これらの狭いパルスにより、バイパスされない電源ラインや品質の低いグランドにリンギングが発生する可能性があり、これが入力電圧範囲に影響を与えて、不正確な比較や発振を引き起こす場合があります。

デバイスには、「分割」電源 ((V+) および (V-))、または「単一」電源 ((V+) および GND) から電力を供給できます ((V-) ピンに GND を印加)。いずれのタイプについても、入力信号を推奨の入力範囲内に維持する必要があります。「分割」電源では、出力は GND ではなく (V-) の電位まで「Low」 (V<sub>OL</sub>) になることに注意してください。

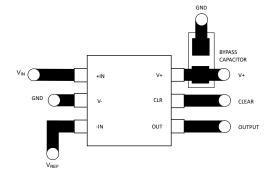

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

高精度のコンパレータアプリケーションには、ノイズやグリッチを最小限に抑えた安定した電源が必要です。出力の立ち上がり時間と立ち下がり時間は数十ナノ秒であり、高速ロジックデバイスとして扱う必要があります。バイパスコンデンサは電源ピンにできる限り近づけて配置し、必要に応じてベタのグランドプレーンに接続します。また、できれば (V+) ピンとGND ピンの間に直接接続します。

出力の発振を防ぐため、出力と入力間のカップリングを最小限に抑えてください。カップリングを低減するために、出力間 に (V+) または GND のパターンが存在する場合を除いて、出力パターンと入力パターンを並列に配置しないでくださ い。入力に直列抵抗を追加する場合、デバイスの近くに抵抗を配置します。出力と直列に小さい値 (<100Ω)の抵抗を追 加して、制御された長い非インピーダンストレース上のリンギングや反射を減衰させることもできます。エッジの形状を最適 化するには、長距離の配線にはバック終端を持つ制御されたインピーダンストレースを使用する必要があります。

### 7.4.2 *レイアウト例*

### 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントのサポート

### 8.1.1 **関連資料**

『アナログ エンジニア向け回路設計ヒント集: アンプ(コンパレータのセクションを参照)、SLYY137

『Precision Design、ヒステリシス付きコンパレータのリファレンス デザイン』、TIDU020

『ウィンドウ コンパレータ回路』、SBOA221

『リファレンス デザイン、ウィンドウ コンパレータのリファレンス デザイン』、TIPD178

『ヒステリシス回路付き/なしのコンパレータ』、SBOA219

『ヒステリシスを持つ反転コンパレータ回路』、SNOA997

『ヒステリシスを持つ非反転コンパレータ回路』、SBOA313

『独立して動作する 4 つのコンパレータ』、SNOA654

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jpのデバイス製品フォルダを開いてください。[通知]をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツ ルメンツの使用条件を参照してください。

#### 8.4 商標

テキサス・インスツルメンツ E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

#### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずか に変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

### 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付                       | 改訂 | 注      |

|--------------------------|----|--------|

| <b>2025</b> 年 <b>5</b> 月 | *  | 初版リリース |

### 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本 データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンスデザインを含みます)、アプリケーショ ンや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性 および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否しま す。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種 規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated

### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type | Package   Pins   | Package qty   Carrier | <b>RoHS</b><br>(3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|---------------|------------------|-----------------------|--------------------|-------------------------------|----------------------------|--------------|---------------------|

|                       |               |               |                  |                       |                    | (4)                           | (5)                        |              |                     |

| TLV9022L1RUGR         | Active        | Production    | X2QFN (RUG)   10 | 3000   LARGE T&R      | Yes                | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 1WD                 |

| TLV9032L1RUGR         | Active        | Production    | X2QFN (RUG)   10 | 3000   LARGE T&R      | Yes                | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 1WE                 |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

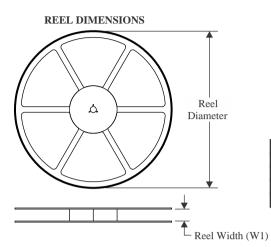

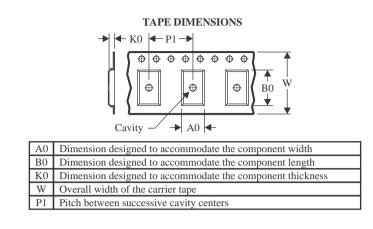

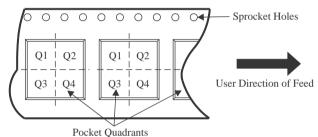

### TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TLV9022L1RUGR               | X2QFN           | RUG                | 10 | 3000 | 180.0                    | 8.4                      | 1.75       | 2.25       | 0.55       | 4.0        | 8.0       | Q1               |

| TLV9032L1RUGR               | X2QFN           | RUG                | 10 | 3000 | 180.0                    | 8.4                      | 1.75       | 2.25       | 0.55       | 4.0        | 8.0       | Q1               |

www.ti.com

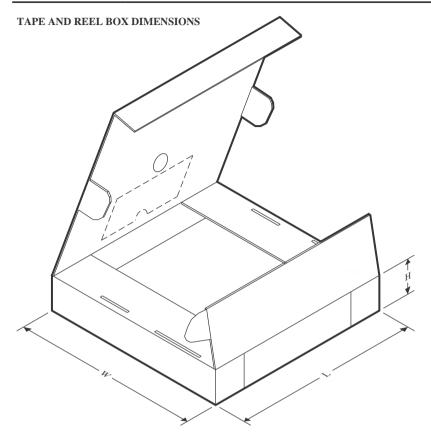

# PACKAGE MATERIALS INFORMATION

11-Jul-2025

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV9022L1RUGR | X2QFN        | RUG             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| TLV9032L1RUGR | X2QFN        | RUG             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

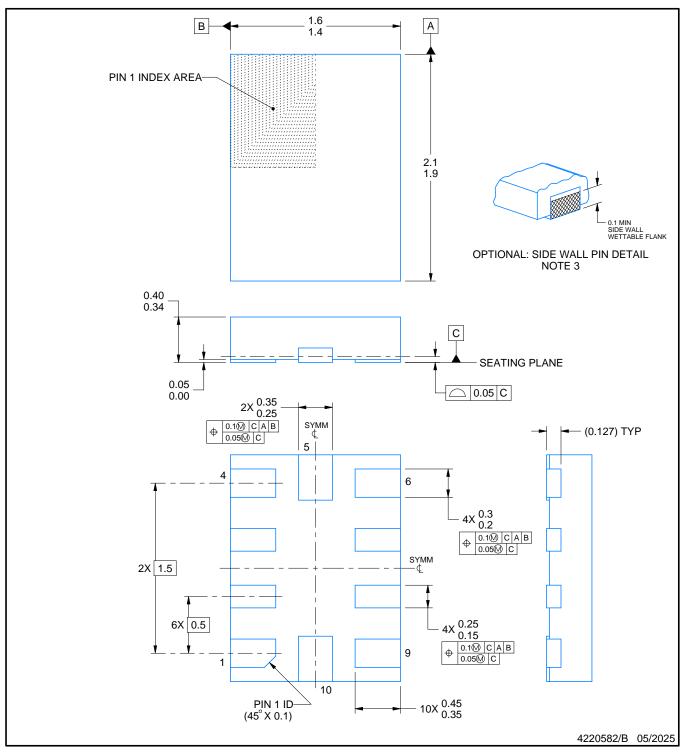

# **RUG0010B**

# **PACKAGE OUTLINE**

### X2QFN - 0.4 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. Minimum 0.1 mm solder wetting on pin side wall. Available for wettable flank version only.

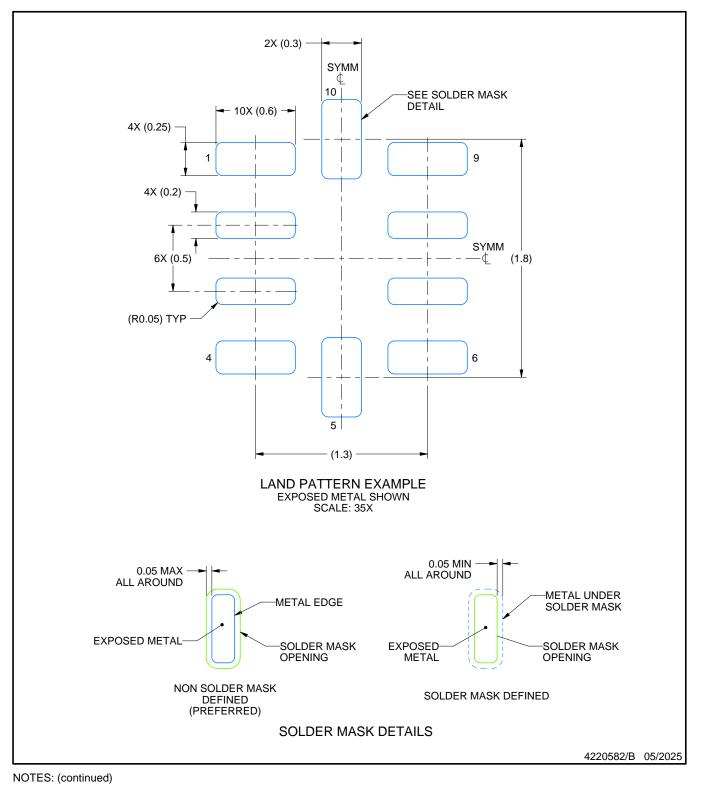

# **RUG0010B**

# **EXAMPLE BOARD LAYOUT**

### X2QFN - 0.4 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

4. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

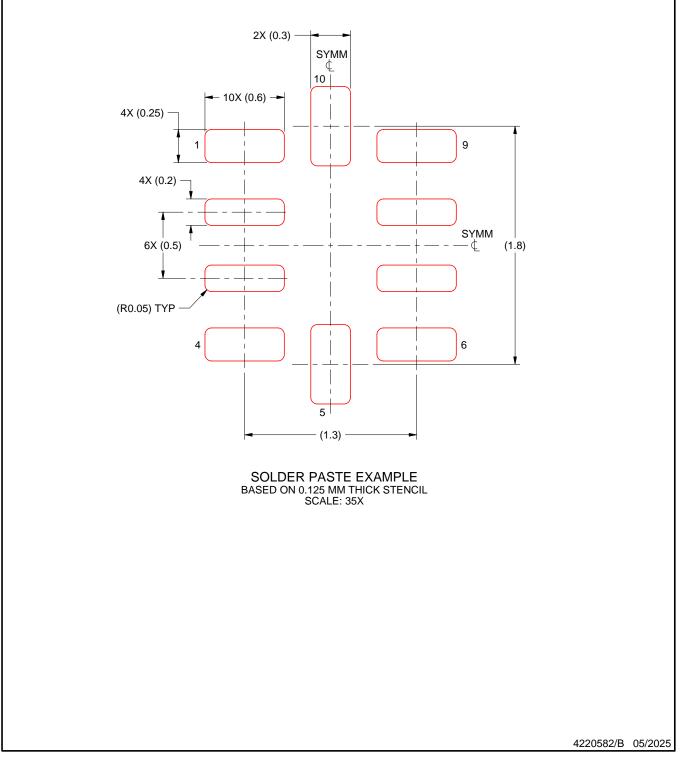

# **RUG0010B**

# **EXAMPLE STENCIL DESIGN**

### X2QFN - 0.4 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みま す)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある 「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証 も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様 のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様の アプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任 を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツル メンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらの リソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権の ライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、 費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは 一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 <del>テキサス・インスツルメンツの販売条件</del>、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ ースを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありませ ん。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated