# TLV6741、TLV6742、TLV6744 10MHz、低い広帯域ノイズ、RRO、オペアンプ

## 1 特長

- 低い広帯域ノイズ:  $3.5\text{nV}/\sqrt{\text{Hz}}$

- ゲイン帯域幅: 10MHz

- 低い入力バイアス電流:  $\pm 3\text{pA}$

- 低いオフセット電圧: 0.15mV

- 低い入力オフセット電圧ドリフト:  $\pm 0.2\mu\text{V}/^\circ\text{C}$

- レール・ツー・レール出力

- ユニティ・ゲイン安定

- 低い  $I_Q$ :

- TLV6741: 890 $\mu\text{A}/\text{Ch}$

- TLV6742/4: 990 $\mu\text{A}/\text{Ch}$

- 広い電源電圧範囲:

- TLV6741: 2.25V ~ 5.5V

- TLV6742/4: 1.7V ~ 5.5V

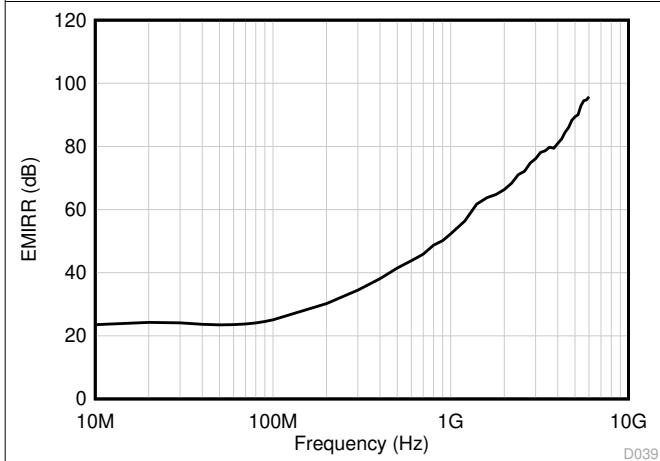

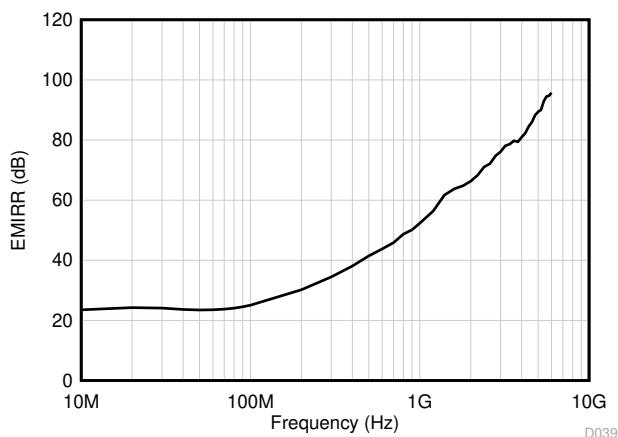

- 堅牢な EMIRR 性能: 2.4GHz 時に 71dB

## 2 アプリケーション

- ソリッド・ステート・ドライブ (SSD)

- ウェアラブル (医療以外)

- 業務用オーディオ・アンプ (ラック・マウント)

- トランシスインピーダンス・アンプ回路

- 試験および測定機器

- モーター・ドライブ

- 圧力トランスマッタ

- 実験室およびフィールド計測

- ブリッジ・アンプ回路

- ゲーム・アプリケーション

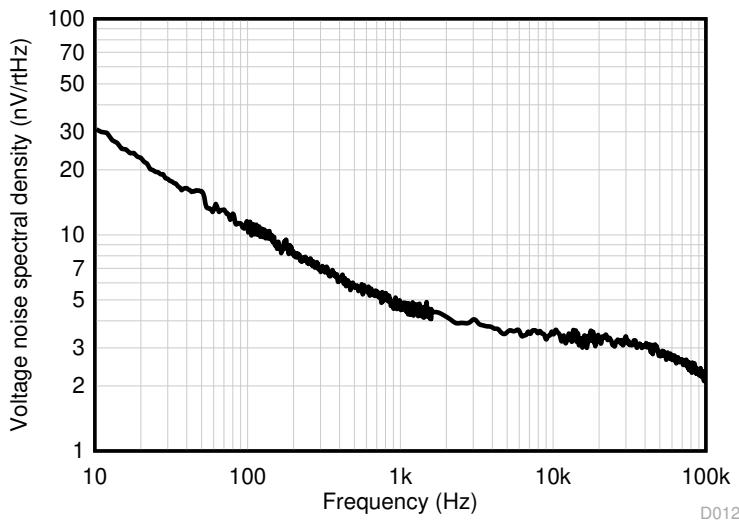

D012

ノイズのスペクトル密度と周波数の関係

## 3 概要

TLV674x ファミリには、 $3.5\text{nV}/\sqrt{\text{Hz}}$  の低いノイズ指数と 10MHz の広い帯域幅を備えた、シングル (TLV6741)、デュアル (TLV6742)、クワッド・チャネルの汎用 CMOS オペアンプ があります。低いノイズと広い帯域幅を特長とする TLV674x ファミリのデバイスは、コストと性能のバランスが求められる各種の高精度アプリケーションにおいて魅力的な製品です。また、TLV674x ファミリの入力バイアス電流は、ソース・インピーダンスが高いアプリケーションにも対応します。

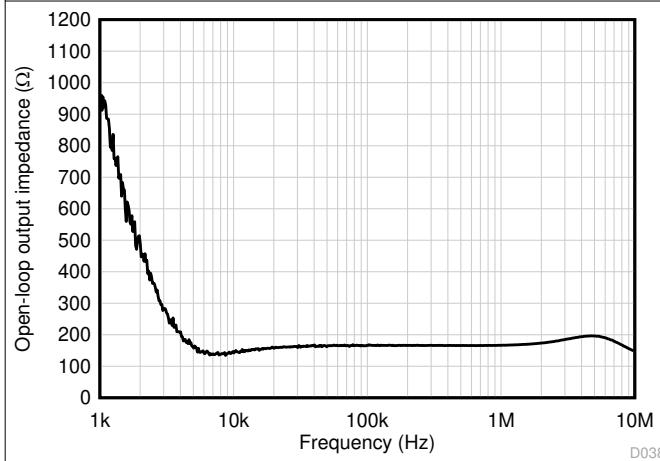

TLV674x ファミリは堅牢に設計されており、ユニティ・ゲイン安定性、RFI/EMI 除去フィルタ内蔵、オーバードライブ条件で位相反転が発生しない、高い静電放電 (ESD) 保護 (2kV HBM) という特長があるため回路設計が容易です。さらに、オープン・ループ出力インピーダンスが抵抗性であるため、非常に大きな容量性負荷でも簡単に安定化できます。

このオペアンプ・ファミリは、TLV6741 では最低 2.25V ( $\pm 1.125\text{ V}$ )、TLV6742 と TLV6744 では最低 1.7V ( $\pm 0.85\text{ V}$ ) の低電圧動作に最適化されています。すべてのデバイスは最高 5.5V ( $\pm 2.75\text{ V}$ ) で動作し、-40°C ~ 125°C の温度範囲で動作が規定されています。

シングル・チャネルの TLV6741 は、小型の SC70-5 パッケージで供給されます。デュアル・チャネルの TLV6742 は、小型の 1.5mm × 2.0mm X2QFN パッケージを含む複数のパッケージ・オプションで供給されます。

### 製品情報

| 部品番号 <sup>(1)</sup> | パッケージ      | 本体サイズ (公称)      |

|---------------------|------------|-----------------|

| TLV6741             | SC70 (5)   | 1.25mm × 2.00mm |

| TLV6742             | SOIC (8)   | 3.91mm × 4.90mm |

|                     | TSSOP (8)  | 3.00mm × 4.40mm |

|                     | VSSOP (8)  | 3.00mm × 3.00mm |

|                     | SOT-23 (8) | 1.60mm × 2.90mm |

|                     | WSON (8)   | 2.00mm × 2.00mm |

| TLV6742S            | X2QFN (10) | 1.50mm × 2.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                       |    |                                                      |    |

|-----------------------|----|------------------------------------------------------|----|

| 1 特長                  | 1  | 8.3 機能説明                                             | 26 |

| 2 アプリケーション            | 1  | 8.4 デバイスの機能モード                                       | 30 |

| 3 概要                  | 1  | 9 アプリケーションと実装                                        | 31 |

| 4 改訂履歴                | 2  | 9.1 アプリケーション情報                                       | 31 |

| 5 デバイス比較表             | 4  | 9.2 音声フィルタ付き単一電源エレクトレット・マイク・プリ                       |    |

| 6 ピン構成および機能           | 5  | アンプ                                                  | 31 |

| 7 仕様                  | 7  | 10 電源に関する推奨事項                                        | 34 |

| 7.1 絶対最大定格            | 7  | 11 レイアウト                                             | 35 |

| 7.2 ESD 定格            | 7  | 11.1 レイアウトのガイドライン                                    | 35 |

| 7.3 推奨動作条件            | 7  | 11.2 レイアウト例                                          | 36 |

| 7.4 シングル・チャネルの熱に関する情報 | 7  | 12 デバイスおよびドキュメントのサポート                                | 38 |

| 7.5 デュアル・チャネルの熱に関する情報 | 8  | 12.1 ドキュメントのサポート                                     | 38 |

| 7.6 電気的特性             | 9  | 12.2 Receiving Notification of Documentation Updates | 38 |

| 7.7 TLV6741: 代表的特性    | 12 | 12.3 サポート・リソース                                       | 38 |

| 7.8 TLV6742: 代表的特性    | 19 | 12.4 商標                                              | 38 |

| 8 詳細説明                | 26 | 12.5 Electrostatic Discharge Caution                 | 38 |

| 8.1 概要                | 26 | 12.6 Glossary                                        | 38 |

| 8.2 機能ブロック図           | 26 | 13 メカニカル、パッケージ、および注文情報                               | 39 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from Revision H (February 2021) to Revision I (August 2021)

|                                            | Page |

|--------------------------------------------|------|

| • 「製品情報」セクションで TLV6742 VSSOP からレビュー・タグを削除  | 1    |

| • 「デバイス比較表」セクションの VSSOP (DGK) へのレビュー・タグを削除 | 4    |

### Changes from Revision G (April 2020) to Revision H (February 2021)

|                                                  | Page |

|--------------------------------------------------|------|

| • 文書全体にわたって表、図、相互参照の採番方法を更新                      | 1    |

| • 「製品情報」セクションで TLV6742S X2QFN のレビュー・タグを削除        | 1    |

| • 「ピン構成および機能」セクションの TLV6742S の X2QFN からレビューの注を削除 | 5    |

| • 「仕様」セクションから TLV6741 のグラフの表と TLV6742 のグラフの表を削除  | 12   |

| • 「デバイスおよびドキュメントのサポート」セクションから「関連リンク」セクションを削除     | 38   |

### Changes from Revision F (January 2020) to Revision G (April 2020)

|                                                        | Page |

|--------------------------------------------------------|------|

| • 「アプリケーション」セクションに最終機器のリンクを追加                          | 1    |

| • 「製品情報」セクションで、TSSOP、SOT-23、WSO、X2QFN パッケージのレビュー・タグを削除 | 1    |

| • 「製品情報」セクションで VSSOP (8) パッケージを削除                      | 1    |

| • 「製品情報」セクションで TLV6742S X2QFN にレビュー・タグを追加              | 1    |

| • 「デバイス比較表」セクションの VSSOP (DGK) を削除                      | 4    |

| • 「デバイス比較表」セクションの X2QFN (RUG) へのレビュー・タグを追加             | 4    |

| • 「ピン構成および機能」セクションの TLV6742 パッケージのピン配置図の DGK パッケージを削除  | 5    |

| • 「デュアル・チャネルの熱に関する情報」セクションの DGK VSSOP を削除              | 7    |

| • シャットダウンの電気的特性の情報を追加                                  | 9    |

| • 「レイアウト例」セクションの VSSOP-8 (DGK) パッケージのレイアウト例を削除         | 36   |

### Changes from Revision E (December 2019) to Revision F (January 2020)

|                                           | Page |

|-------------------------------------------|------|

| • データシートのページ・ヘッダから TLV6744 製品フォルダへのリンクを削除 | 1    |

| <b>Changes from Revision D (January 2019) to Revision E (December 2019)</b> | <b>Page</b> |

|-----------------------------------------------------------------------------|-------------|

| • TLV6742 と TLV744 の $I_Q$ の定義を「特長」セクションに追加.....                            | 1           |

| • 「特長」セクションに EMIRR、電源電圧範囲、 $I_Q$ 、オフセット電圧ドリフトを追加.....                       | 1           |

| • 先頭ページのノイズのスペクトル密度と周波数の関係のプロットを TLV6742 および TLV6744 のノイズ・プロットに変更.....      | 1           |

| • TLV6742 および TLV6744 デバイスのリリースを反映して「概要」セクションの表現を変更.....                    | 1           |

| • 「製品情報」で TLV6742 のパッケージを変更.....                                            | 1           |

| • 「デバイス比較表」セクションを追加.....                                                    | 4           |

| • 「ピンの機能:TLV6741」の表に单一電源動作に関する注を追加.....                                     | 5           |

| • 「ピン構成および機能」セクションの TLV6742 パッケージのピン配置図を追加.....                             | 5           |

| • TLV6742 パッケージのピン機能を追加.....                                                | 5           |

| • 「ピン構成および機能」セクションの TLV6742S の X2QFN パッケージ図およびピン機能を追加.....                  | 5           |

| • 「仕様」セクションの TLV6742 の代表的特性のグラフを追加.....                                     | 12          |

| • TLV6742 および TLV6744 デバイスの追加を含むように「詳細説明」セクションの表現を変更.....                   | 26          |

| • 「詳細説明」セクションに「EMI 除去」セクションと説明を追加.....                                      | 27          |

| • 「詳細説明」セクションに電気的オーバーストレスのセクションと図を追加.....                                   | 28          |

| • 「詳細説明」セクションに「代表的な仕様と分布」セクションを追加.....                                      | 29          |

| • 「詳細説明」セクションに、「シャットダウン機能」セクションと TLV6742S の説明を追加.....                       | 30          |

| • 「詳細説明」セクションに「露出サーマル・パッド付きパッケージ」セクションを追加.....                              | 30          |

| • 「アプリケーションと実装」セクションの文言を、TLV6742 と TLV6744 の追加を含めるように変更.....                | 31          |

| • 「電源に関する推奨事項」セクションに TLV6742 と TLV6744 の情報を追加.....                          | 34          |

| • 「レイアウト」セクションのデュアル・チャネルのレイアウトの例を追加.....                                    | 36          |

| <b>Changes from Revision C (October 2017) to Revision D (January 2019)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • 「絶対最大定格」の動作温度を 125 から 150 に変更 .....                                      | 7           |

| • 「絶対最大定格」に接合部温度仕様を追加.....                                                 | 7           |

| <b>Changes from Revision B (October 2017) to Revision C (October 2017)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • 「電気的特性」表の入力オフセット電圧パラメータにテスト条件を追加.....                                    | 9           |

| • 入力電流ノイズ密度の値 (標準値) を $2fA/\sqrt{Hz}$ から $23fA/\sqrt{Hz}$ に変更.....         | 9           |

| • 「電気的特性」の条件文の総電源電圧を 5V から 5.5V に変更.....                                   | 9           |

| • 「電気的特性」の同相信号除去比パラメータの「 $V_s = 2.25V \sim 5.5V$ 」のテスト条件を削除 .....          | 9           |

| • 図 7-25 と 図 7-26、図 7-27 と 図 7-28 から「 $C_L = 0$ 」のテスト条件を削除.....            | 12          |

| • 図 7-32 の電圧ステップを 5V から 2V に変更.....                                        | 12          |

| <b>Changes from Revision A (September 2017) to Revision B (October 2017)</b>                      | <b>Page</b> |

|---------------------------------------------------------------------------------------------------|-------------|

| • 人体モデル (HBM) の値を $\pm 1000$ から $\pm 3000$ に、デバイス帶電モデル (CDM) の値を $\pm 250$ から $\pm 1000$ に変更..... | 7           |

| <b>Changes from Revision * (June 2017) to Revision A (September 2017)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • ドキュメントのステータスを事前情報から量産データに変更.....                                        | 1           |

## 5 デバイス比較表

| デバイス     | チャネル数 | パッケージのリード本数 |              |              |             |             |               |              |

|----------|-------|-------------|--------------|--------------|-------------|-------------|---------------|--------------|

|          |       | SOIC<br>D   | SC-70<br>DCK | VSSOP<br>DGK | WSON<br>DSG | TSSOP<br>PW | SOT-23<br>DDF | X2QFN<br>RUG |

| TLV6741  | 1     | —           | 5            | —            | —           | —           | —             | —            |

| TLV6742  | 2     | 8           | —            | 8            | 8           | 8           | 8             | —            |

| TLV6742S |       | —           | —            | —            | —           | —           | —             | 10           |

## 6 ピン構成および機能

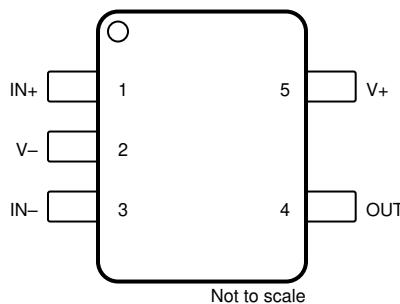

図 6-1. TLV6741 DCK パッケージ

5 ピン SC70

上面図

表 6-1. ピンの機能 : TLV6741

| ピン  |    | I/O | 説明                        |

|-----|----|-----|---------------------------|

| 名称  | 番号 |     |                           |

| IN+ | 1  | I   | 非反転入力                     |

| IN- | 3  | I   | 反転入力                      |

| OUT | 4  | O   | 出力                        |

| V+  | 5  | —   | 正(最高)電源                   |

| V-  | 2  | —   | 負(最低)電源またはグランド(単一電源動作の場合) |

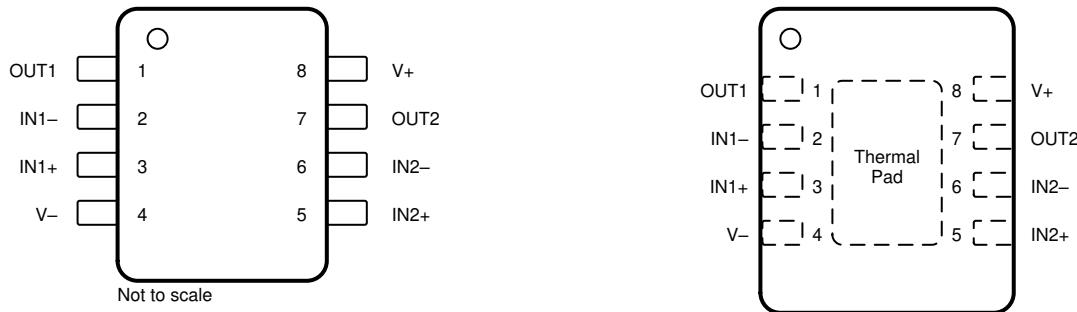

図 6-2. TLV6742 D, DGK, PW, DDF パッケージ

8 ピン SOIC、VSSOP、TSSOP、SOT-23

上面図

サーマル・パッドを V- に接続します。詳細については、「[セクション 8.3.8](#)」を参照してください。

図 6-3. TLV6742 DSG パッケージ

8 ピン WSON (露出サーマル・パッド付き)

上面図

表 6-2. ピンの機能 : TLV6742

| ピン   |    | I/O | 説明           |

|------|----|-----|--------------|

| 名称   | 番号 |     |              |

| IN1- | 2  | I   | 反転入力、チャネル 1  |

| IN1+ | 3  | I   | 非反転入力、チャネル 1 |

| IN2- | 6  | I   | 反転入力、チャネル 2  |

| IN2+ | 5  | I   | 非反転入力、チャネル 2 |

| OUT1 | 1  | O   | 出力、チャネル 1    |

表 6-2. ピンの機能 : TLV6742 (continued)

| ピン   |    | I/O | 説明                        |

|------|----|-----|---------------------------|

| 名称   | 番号 |     |                           |

| OUT2 | 7  | ○   | 出力、チャネル 2                 |

| V-   | 4  | —   | 負(最低)電源またはグランド(单一電源動作の場合) |

| V+   | 8  | —   | 正(最高)電源                   |

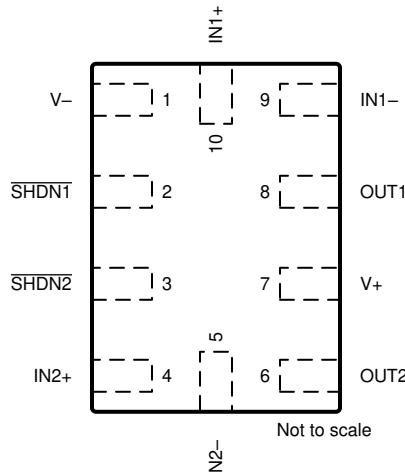

図 6-4. TLV6742S RUG パッケージ

10 ピン X2QFN

上面図

表 6-3. ピンの機能 : TLV6742S

| ピン    |    | I/O     | 説明                                                                                            |

|-------|----|---------|-----------------------------------------------------------------------------------------------|

| 名称    | 番号 |         |                                                                                               |

| IN1-  | 9  | I       | 反転入力、チャネル 1                                                                                   |

| IN1+  | 10 | I       | 非反転入力、チャネル 1                                                                                  |

| IN2-  | 5  | I       | 反転入力、チャネル 2                                                                                   |

| IN2+  | 4  | I       | 非反転入力、チャネル 2                                                                                  |

| OUT1  | 8  | O       | 出力、チャネル 1                                                                                     |

| OUT2  | 6  | O       | 出力、チャネル 2                                                                                     |

| SHDN1 | 2  | I       | シャットダウン:Low = アンプを無効化、High = アンプを有効化。チャネル 1。詳細については、「 <a href="#">セクション 8.3.7</a> 」を参照してください。 |

| SHDN2 | 3  | I       | シャットダウン:Low = アンプを無効化、High = アンプを有効化。チャネル 2。詳細については、「 <a href="#">セクション 8.3.7</a> 」を参照してください。 |

| V-    | 1  | I または — | 負 (最低) 電源またはグランド (単一電源動作の場合)                                                                  |

| V+    | 7  | I       | 正 (最高) 電源                                                                                     |

## 7 仕様

### 7.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                           |                         | 最小値          | 最大値          | 単位 |

|---------------------------|-------------------------|--------------|--------------|----|

| 電源電圧、 $V_S = (V+) - (V-)$ |                         | 0            | 6            | V  |

| 信号入力ピン                    | 同相電圧 <sup>(3)</sup>     | $(V-) - 0.5$ | $(V+) + 0.5$ | V  |

|                           | 差動電圧 <sup>(3) (4)</sup> |              | $V_S + 0.2$  | V  |

|                           | 電流 <sup>(3)</sup>       | -10          | 10           | mA |

| 出力短絡 <sup>(2)</sup>       |                         |              | 連続           |    |

| 動作時の周囲温度、 $T_A$           |                         | -55          | 150          | °C |

| 接合部温度、 $T_J$              |                         |              | 150          | °C |

| 保存温度、 $T_{stg}$           |                         | -65          | 150          | °C |

- (1) 「絶対最大定格」に示す定格を超えて本デバイスを動作させた場合、デバイスに永続的な損傷が発生します。これらはプロセスと設計の制約に基づくストレス定格に過ぎず、「推奨動作条件」に示された以外の条件で動作するようにはこのデバイスは設計されていません。絶対最大定格条件を含め、推奨動作条件以外のいかなる条件にも長時間さらすと、デバイスの信頼性と性能に影響を及ぼす可能性があります。

- (2) グランドへの短絡、1 パッケージ当たり 1 アンプ。

- (3) 入力ピンは、電源レールに対してダイオード・クランプされています。入力信号のスイングが 0.5V より大きく電源レールを超える可能性がある場合は、電流を 10mA 以下に制限する必要があります。

- (4) 0.25V を超える差動入力電圧を連続的に印加すると、入力オフセット電圧がこのパラメータの最大仕様を上回る可能性があります。この影響の大きさは、動作時の周囲温度が上がるにつれて大きくなります。

### 7.2 ESD 定格

|             |       |                                                                      | 値     | 単位 |

|-------------|-------|----------------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電気放電 | <b>TLV6741:</b> 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> | ±3000 | V  |

|             |       | <b>TLV6742:</b> 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> | ±2000 |    |

|             |       | すべてのデバイス: デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup>     | ±1500 |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

### 7.3 推奨動作条件

動作時周囲温度範囲内 (特に記述のない限り)

|       |                                            | 最小値                 | 最大値 | 単位 |

|-------|--------------------------------------------|---------------------|-----|----|

| $V_S$ | 電源電圧、 $(V+) - (V-)$ 、TLV6742 と TLV6744 の場合 | 1.7 <sup>(1)</sup>  | 5.5 | V  |

| $V_S$ | 電源電圧、 $(V+) - (V-)$ 、TLV6741 の場合のみ         | 2.25                | 5.5 | V  |

| $V_I$ | 入力電圧範囲                                     | $(V-) - (V+) - 1.2$ |     | V  |

| $T_A$ | 仕様温度範囲                                     | -40                 | 125 | °C |

- (1) 1.7V と 1.8V の間の動作は、 $T_A = 0 \sim 85^\circ\text{C}$  でのみ推奨されます。

### 7.4 シングル・チャネルの熱に関する情報

|                             | 熱評価基準 <sup>(1)</sup> | TLV6741 | 単位   |

|-----------------------------|----------------------|---------|------|

|                             | DCK (SC70)           |         |      |

|                             | 5 ピン                 |         |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗         | 240.9   | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗  | 151.7   | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗         | 64      | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への熱特性パラメータ    | 34.8    | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への熱特性パラメータ    | 63.3    | °C/W |

## 7.4 シングル・チャネルの熱に関する情報 (continued)

| 熱評価基準 <sup>(1)</sup>  |                   | TLV6741       | 単位   |

|-----------------------|-------------------|---------------|------|

|                       |                   | DCK<br>(SC70) |      |

|                       |                   | 5 ピン          |      |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | n/a           | °C/W |

- (1) 従来および新しい熱特性の詳細については、アプリケーション・レポート『半導体および IC パッケージの熱測定値』、[SPRA953C](#) を参照してください。

## 7.5 デュアル・チャネルの熱に関する情報

| 熱評価基準 <sup>(1)</sup>  | TLV6742, TLV6742S |                   |               |               |                |                | 単位    |      |

|-----------------------|-------------------|-------------------|---------------|---------------|----------------|----------------|-------|------|

|                       | D<br>(SOIC)       | DDF<br>(SOT-23-8) | DSG<br>(WSON) | PW<br>(TSSOP) | DGK<br>(VSSOP) | RUG<br>(X2QFN) |       |      |

|                       | 8 ピン              | 8 ピン              | 8 ピン          | 8 ピン          | 8 ピン           | 10 ピン          |       |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 131.1             | 153.8         | 78.2          | 185.6          | 177.0          | 140.3 | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 73.2              | 80.2          | 97.5          | 74.5           | 68.6           | 52.6  | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 74.5              | 73.1          | 44.6          | 116.3          | 98.7           | 69.7  | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性パラメータ | 24.4              | 6.6           | 4.7           | 12.6           | 12.4           | 1.0   | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性パラメータ | 73.3              | 72.7          | 44.6          | 114.6          | 97.1           | 67.5  | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | n/a               | n/a           | 19.8          | n/a            | n/a            | n/a   | °C/W |

- (1) 従来および新しい熱特性の詳細については、アプリケーション・レポート『半導体および IC パッケージの熱測定値』、[SPRA953C](#) を参照してください。

## 7.6 電気的特性

**TLV6742/4 の仕様:**  $V_S = (V+) - (V-) = 1.8V \sim 5.5V$  ( $\pm 0.9V \sim \pm 2.75V$ )、 $T_A = 25^\circ C$ 、 $R_L = 10k\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)。

**DC 仕様:**  $V_S = (V+) - (V-) = 5.5V$ 、 $T_A = 25^\circ C$ 、 $R_L = 10k\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)。

| パラメータ           |                  | テスト条件                                                                               |                                      | 最小値              | 標準値              | 最大値       | 単位                     |  |

|-----------------|------------------|-------------------------------------------------------------------------------------|--------------------------------------|------------------|------------------|-----------|------------------------|--|

| <b>オフセット電圧</b>  |                  |                                                                                     |                                      |                  |                  |           |                        |  |

| $V_{OS}$        | 入力オフセット電圧        | $V_S = 5.0V$                                                                        | $T_A = -40^\circ C \sim 125^\circ C$ | TLV6742/4 (3)    | $\pm 0.15$       | $\pm 1.0$ | mV                     |  |

|                 |                  |                                                                                     |                                      | TLV6741 (2)      | $\pm 1.2$        |           |                        |  |

| $dV_{OS}/dT$    | 入力オフセット電圧ドリフト    |                                                                                     | $T_A = -40^\circ C \sim 125^\circ C$ | TLV6741 (2)      | $\pm 0.35$       |           | $\mu V/^\circ C$       |  |

|                 |                  |                                                                                     |                                      | TLV6742/4 (3)    | $\pm 0.2$        |           |                        |  |

| PSRR            | 入力オフセット電圧と電源との関係 | $V_{CM} = V_-$                                                                      |                                      | TLV6741 (2)      | $\pm 0.32$       | $\pm 6.3$ | $\mu V/V$              |  |

|                 |                  | $V_{CM} = V_-$                                                                      |                                      | TLV6742/4 (3)    | $\pm 0.7$        | $\pm 5.8$ |                        |  |

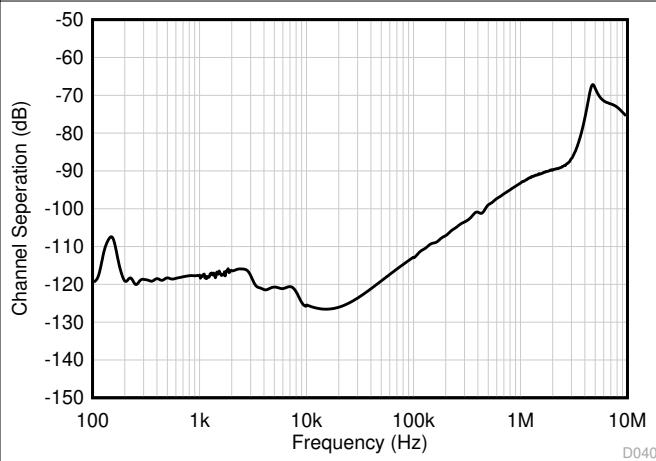

| チャネル・セパレーション    |                  | $f = 20kHz$                                                                         |                                      |                  | 130              |           | dB                     |  |

| <b>入力バイアス電流</b> |                  |                                                                                     |                                      |                  |                  |           |                        |  |

| $I_B$           | 入力バイアス電流         |                                                                                     | TLV6741 (2)                          | $\pm 10$         |                  |           | pA                     |  |

|                 |                  |                                                                                     | TLV6742/4 (3)                        | $\pm 3$          |                  |           |                        |  |

| $I_{OS}$        | 入力オフセット電流        |                                                                                     | TLV6741 (2)                          | $\pm 10$         |                  |           | pA                     |  |

|                 |                  |                                                                                     | TLV6742/4 (3)                        | $\pm 0.5$        |                  |           |                        |  |

| <b>ノイズ</b>      |                  |                                                                                     |                                      |                  |                  |           |                        |  |

| $E_N$           | 入力電圧ノイズ          | $f = 0.1 \sim 10Hz$                                                                 |                                      |                  | 1.2              |           | $\mu V_{PP}$           |  |

|                 |                  |                                                                                     |                                      |                  | 0.227            |           | $\mu V_{RMS}$          |  |

| $e_n$           | 入力電圧ノイズ密度        | $f = 10Hz$                                                                          | TLV6742/4 (3)                        | 30               |                  |           | $nV/\sqrt{Hz}$         |  |

|                 |                  | $f = 1kHz$                                                                          | TLV6741 (2)                          | 5.0              |                  |           |                        |  |

|                 |                  |                                                                                     | TLV6742/4 (3)                        | 4.6              |                  |           |                        |  |

|                 |                  | $f = 10kHz$                                                                         | TLV6741 (2)                          | 3.7              |                  |           |                        |  |

|                 |                  |                                                                                     | TLV6742/4 (3)                        | 3.5              |                  |           |                        |  |

| $i_N$           | 入力電流ノイズ          | $f = 1kHz$                                                                          |                                      |                  | 23               |           | $fA/\sqrt{Hz}$         |  |

| <b>入力電圧範囲</b>   |                  |                                                                                     |                                      |                  |                  |           |                        |  |

| $V_{CM}$        | 同相電圧範囲           |                                                                                     |                                      | $(V-) \sim (V+)$ | $(V+) - 1.2V$    |           | V                      |  |

| CMRR            | 同相信号除去比          | $(V-) < V_{CM} < (V+) - 1.2V$                                                       | TLV6741 (2)                          | 95               | 120              |           | dB                     |  |

|                 |                  | $V_S = 1.8V$ 、 $(V-) < V_{CM} < (V+) - 1.2V$                                        | TLV6742/4 (3)                        | 87               | 100              |           |                        |  |

|                 |                  | $V_S = 5.5V$ 、 $(V-) < V_{CM} < (V+) - 1.2V$                                        |                                      | 94               | 110              |           |                        |  |

| <b>入力容量</b>     |                  |                                                                                     |                                      |                  |                  |           |                        |  |

| $Z_{ID}$        | 差動               |                                                                                     |                                      |                  | 10 $\parallel$ 6 |           | $M\Omega \parallel pF$ |  |

| $Z_{ICM}$       | 同相               |                                                                                     |                                      |                  | 10 $\parallel$ 6 |           | $G\Omega \parallel pF$ |  |

| <b>開ループ・ゲイン</b> |                  |                                                                                     |                                      |                  |                  |           |                        |  |

| $A_{OL}$        | 開ループ電圧ゲイン        | $(V-) + 40mV < V_O < (V+) - 40mV$ 、 $R_L = 10k\Omega$ を $V_S/2$ に接続                 | TLV6741 (2)                          |                  | 125              |           | dB                     |  |

|                 |                  | $(V-) + 150mV < V_O < (V+) - 150mV$ 、 $R_L = 2k\Omega$ を $V_S/2$ に接続                |                                      |                  | 110              | 130       |                        |  |

|                 |                  | $V_S = 1.8V$ 、 $(V-) + 150mV < V_O < (V+) - 150mV$ 、 $R_L = 2k\Omega$ を $V_S/2$ に接続 | TLV6742/4 (3)                        |                  | 107              | 120       |                        |  |

|                 |                  | $V_S = 5.5V$ 、 $(V-) + 150mV < V_O < (V+) - 150mV$ 、 $R_L = 2k\Omega$ を $V_S/2$ に接続 |                                      |                  |                  | 140       |                        |  |

|                 |                  | $V_S = 1.8V$ 、 $(V-) + 40mV < V_O < (V+) - 40mV$ 、 $R_L = 10k\Omega$ を $V_S/2$ に接続  |                                      |                  | 110              | 120       |                        |  |

|                 |                  | $V_S = 5.5V$ 、 $(V-) + 40mV < V_O < (V+) - 40mV$ 、 $R_L = 10k\Omega$ を $V_S/2$ に接続  |                                      |                  |                  | 140       |                        |  |

## 7.6 電気的特性 (continued)

**TLV6742/4 の仕様:**  $V_S = (V+) - (V-) = 1.8V \sim 5.5V$  ( $\pm 0.9V \sim \pm 2.75V$ )、 $T_A = 25^\circ C$ 、 $R_L = 10k\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)。

**DC 仕様:**  $V_S = (V+) - (V-) = 5.5V$ 、 $T_A = 25^\circ C$ 、 $R_L = 10k\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)。

| パラメータ            | テスト条件           | 最小値                                                                                           | 標準値           | 最大値        | 単位         |    |

|------------------|-----------------|-----------------------------------------------------------------------------------------------|---------------|------------|------------|----|

| <b>周波数特性</b>     |                 |                                                                                               |               |            |            |    |

| GBW              | ゲイン帯域幅積         |                                                                                               |               | 10         | MHz        |    |

| SR               | スルーレート          | $V_S = 5.5V$ 、 $G = +1$ 、 $C_L = 20pF$                                                        |               | 4.5        | V/ $\mu$ s |    |

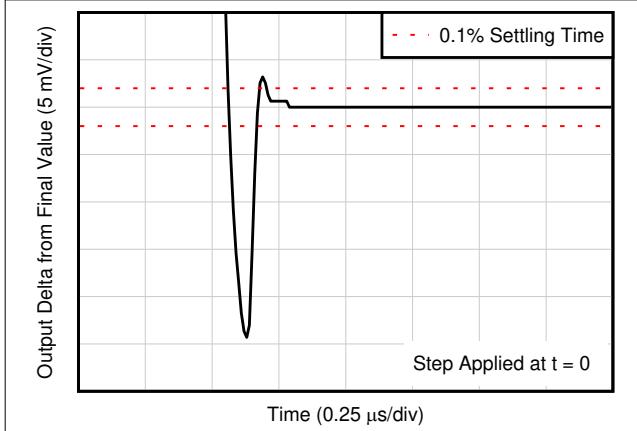

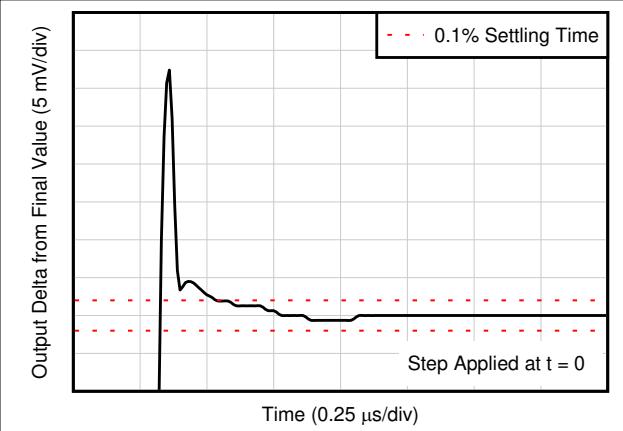

| $t_S$            | セトリング・タイム       | 0.1% まで、 $V_S = 5.5V$ 、 $V_{STEP} = 2V$ 、 $G = +1$ 、 $CL = 20pF$                              |               | 0.65       | $\mu$ s    |    |

|                  |                 | 0.01% まで、 $V_S = 5.5V$ 、 $V_{STEP} = 2V$ 、 $G = +1$ 、 $CL = 20pF$                             |               | 1.2        |            |    |

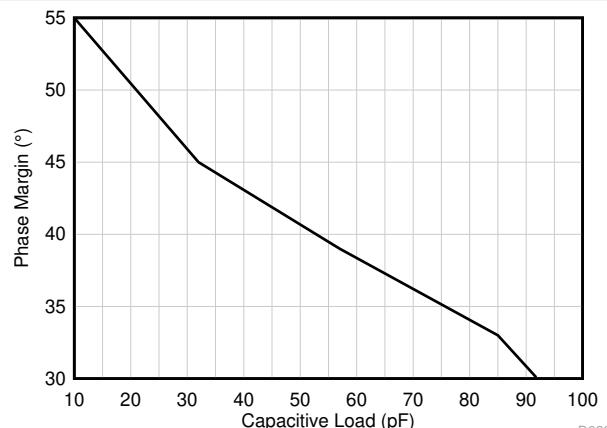

|                  | 位相マージン          | $G = +1$ 、 $R_L = 10k\Omega$ 、 $C_L = 20pF$                                                   |               | 55         | °          |    |

|                  | 過負荷復帰時間         | $V_{IN} \times \text{ゲイン} > V_S$                                                              |               | 0.2        | $\mu$ s    |    |

| THD+N            | 全高調波歪 + ノイズ     | $V_S = 5.5V$ 、 $V_{CM} = 2.5V$ 、 $V_O = 1V_{RMS}$ 、 $G = +1$ 、 $f = 1kHz$ 、 $R_L = 10k\Omega$ | TLV6741 (2)   | 0.00035%   |            |    |

|                  |                 |                                                                                               | TLV6742/4 (3) | 0.00015%   |            |    |

| EMIRR            | 電磁干渉除去比 (EMIRR) | $f = 1GHz$                                                                                    | TLV6742/4 (3) | 51         | dB         |    |

| <b>出力</b>        |                 |                                                                                               |               |            |            |    |

| レールからの電圧出力スイッチング | 正 / 負レールのヘッドルーム | $V_S = 5.5V$ 、 $R_L = 10k$                                                                    | TLV6741 (2)   | 8          | 10         | mV |

|                  |                 | $V_S = 5.5V$ 、 $R_L = \text{無負荷}$                                                             |               |            | 7          |    |

|                  |                 | $V_S = 5.5V$ 、 $R_L = 2k\Omega$                                                               |               |            | 35         |    |

|                  |                 | $V_S = 5.5V$ 、 $R_L = 10k\Omega$                                                              |               | 5          | 14         |    |

|                  |                 | $V_S = 5.5V$ 、 $R_L = \text{無負荷}$                                                             |               |            | 7          |    |

|                  |                 | $V_S = 5.5V$ 、 $R_L = 2k\Omega$                                                               |               |            | 35         |    |

|                  |                 | $V_S = 5.5V$ 、 $R_L = 10k\Omega$                                                              |               | 5          | 14         |    |

|                  |                 |                                                                                               |               |            |            |    |

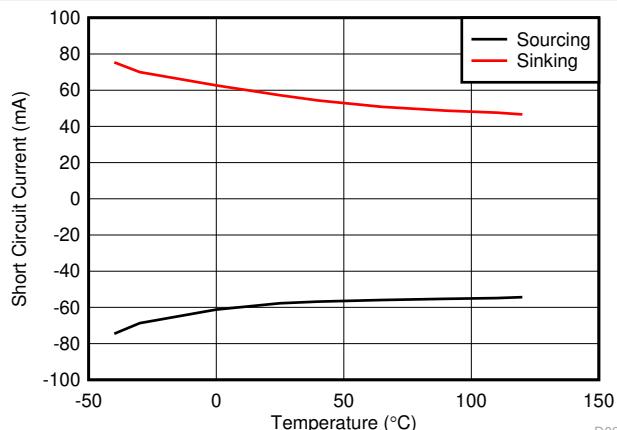

| $I_{SC}$         | 短絡電流            |                                                                                               | TLV6742/4 (3) | $\pm 68$   | mA         |    |

| $C_{LOAD}$       | 容量性負荷ドライブ       |                                                                                               |               | 図 7-58 を参照 |            |    |

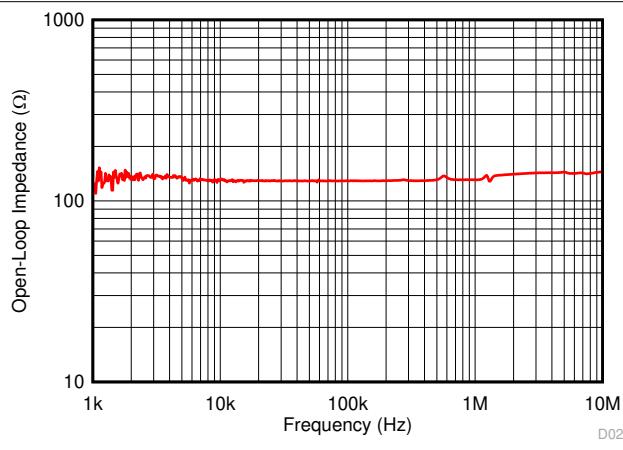

| $Z_O$            | 開ループ出力インピーダンス   | $f = 10MHz$ 、 $I_O = 0A$                                                                      | TLV6741 (2)   | 160        | $\Omega$   |    |

|                  |                 | $f = 2MHz$ 、 $I_O = 0A$                                                                       | TLV6742/4 (3) | 165        |            |    |

| <b>電源</b>        |                 |                                                                                               |               |            |            |    |

| $I_Q$            | アンプごとの静止電流      | $V_S = 5.5V$ 、 $I_O = 0A$                                                                     | TLV6741 (2)   | 890        | $\mu$ A    |    |

|                  |                 |                                                                                               |               | 1100       |            |    |

|                  |                 | $T_A = -40^\circ C \sim 125^\circ C$                                                          | TLV6742/4 (3) | 990        |            |    |

|                  |                 |                                                                                               |               | 1200       |            |    |

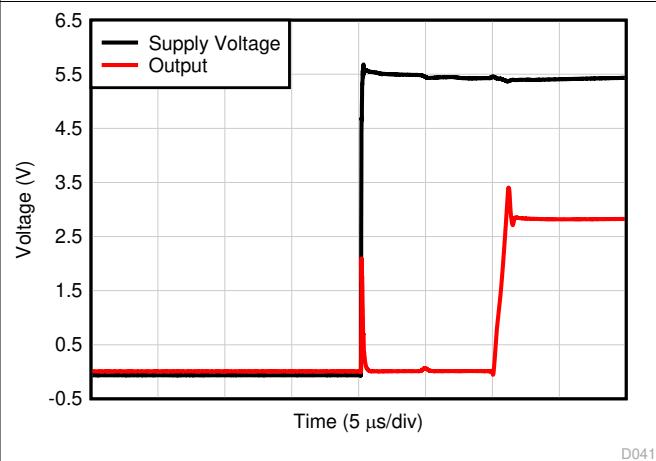

|                  | ターンオン時間         | $T_A = 25^\circ C$ 、 $V_S = 5.5V$ 、 $V_S \text{ ランプ・レート} > 0.3V/\mu s$                        | TLV6742/4 (3) | 1250       |            |    |

|                  |                 |                                                                                               |               | 10         | $\mu$ s    |    |

## 7.6 電気的特性 (continued)

**TLV6742/4 の仕様:**  $V_S = (V+) - (V-) = 1.8V \sim 5.5V$  ( $\pm 0.9V \sim \pm 2.75V$ )、 $T_A = 25^\circ C$ 、 $R_L = 10k\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)。

**DC 仕様:**  $V_S = (V+) - (V-) = 5.5V$ 、 $T_A = 25^\circ C$ 、 $R_L = 10k\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)。

| パラメータ          | テスト条件                                   | 最小値                                           | 標準値 | 最大値              | 単位                     |

|----------------|-----------------------------------------|-----------------------------------------------|-----|------------------|------------------------|

| <b>シャットダウン</b> |                                         |                                               |     |                  |                        |

| $I_{QSD}$      | 静止電流 (アンプ 1 個あたり)                       | すべてのアンプを無効化、 $\overline{SHDN} = V-$           |     | 1                | $3.5 \mu A$            |

| $Z_{SHDN}$     | シャットダウン時の出力インピーダンス                      | アンプを無効化                                       |     | $10 \parallel 6$ | $G\Omega \parallel pF$ |

| $V_{IH}$       | ロジック High スレッショルド電圧 (アンプがイネーブル)         |                                               |     | $(V-) + 1.1V$    | $V$                    |

| $V_{IL}$       | ロジック Low スレッショルド電圧 (アンプがディスエーブル)        |                                               |     | $(V-) + 0.2V$    |                        |

| $t_{ON}$       | アンプのイネーブル時間 (フル・シャットダウン) <sup>(1)</sup> | $G = +1, V_{CM} = V-, V_O = 0.1 \times V_S/2$ |     | 15               | $\mu s$                |

|                | アンプのイネーブル時間 (部分的シャットダウン) <sup>(1)</sup> | $G = +1, V_{CM} = V-, V_O = 0.1 \times V_S/2$ |     | 8                |                        |

| $t_{OFF}$      | アンプのディスエーブル時間 <sup>(1)</sup>            | $V_{CM} = V-, V_O = V_S/2$                    |     | 3                |                        |

|                | SHDN ピンの入力バイアス電流 (ピンごとの)                | $(V+) \geq \overline{SHDN} \geq (V-) + 0.9V$  |     | 0.4              | $\mu A$                |

|                |                                         | $(V-) \leq \overline{SHDN} \leq (V-) + 0.7V$  |     | 0.25             |                        |

(1) ディスエーブル時間 ( $t_{OFF}$ ) とイネーブル時間 ( $t_{ON}$ ) は、 $\overline{SHDN}$  ピンに印加される信号の 50% ポイントと、出力電圧が 10% (ディスエーブル) または 90% (イネーブル) レベルに達する時点との時間間隔として定義されます。

(2) この電気的特性は、シングル・チャネルの TLV6741 にのみ適用されます。

(3) この電気的特性は、デュアル・チャネルの TLV6742 とクワッド・チャネルの TLV6744 にのみ適用されます。

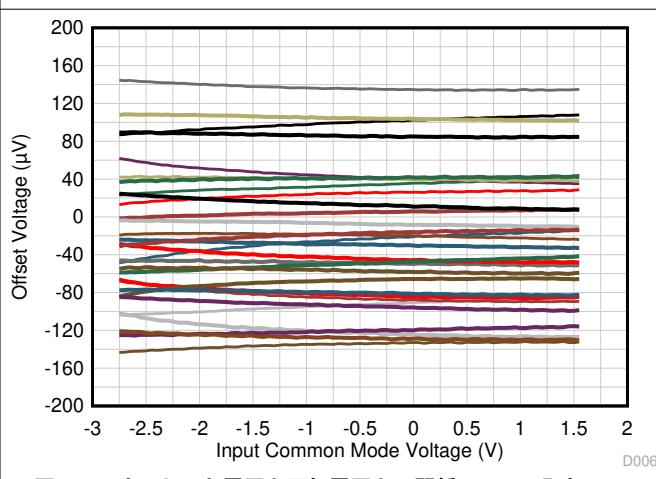

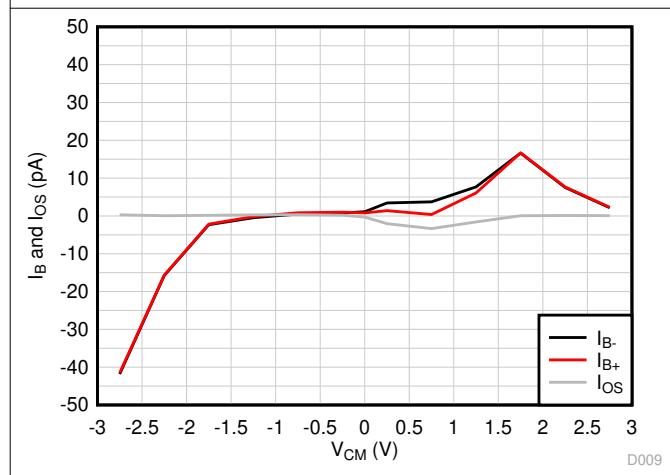

## 7.7 TLV6741 : 代表的特性

$T_A = 25^\circ\text{C}$ 、 $V_S = 5.5\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

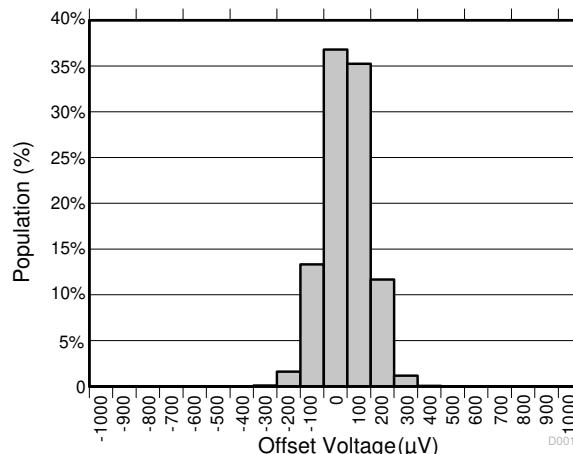

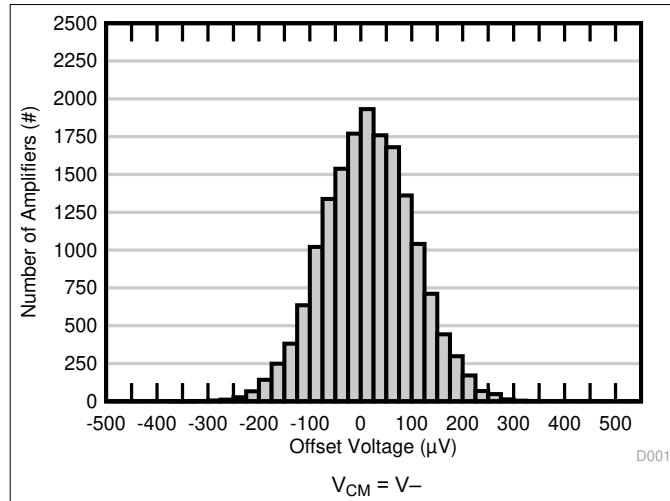

図 7-1. オフセット電圧の製品分布

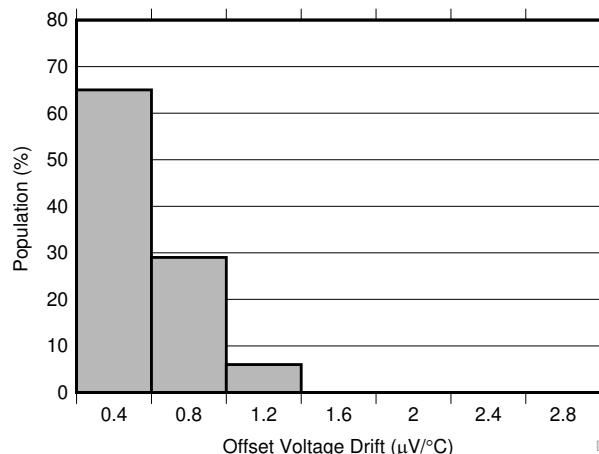

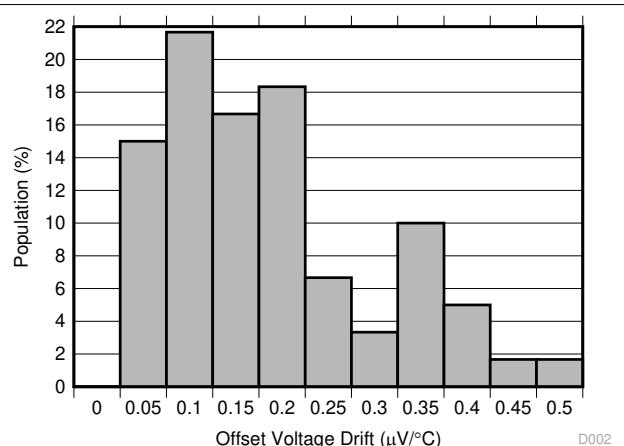

図 7-2. オフセット電圧ドリフトの分布

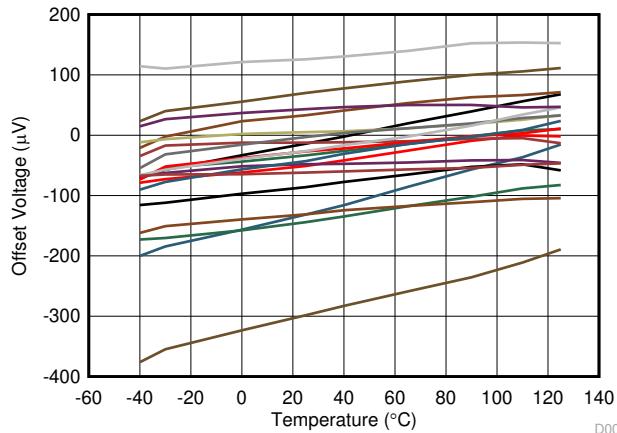

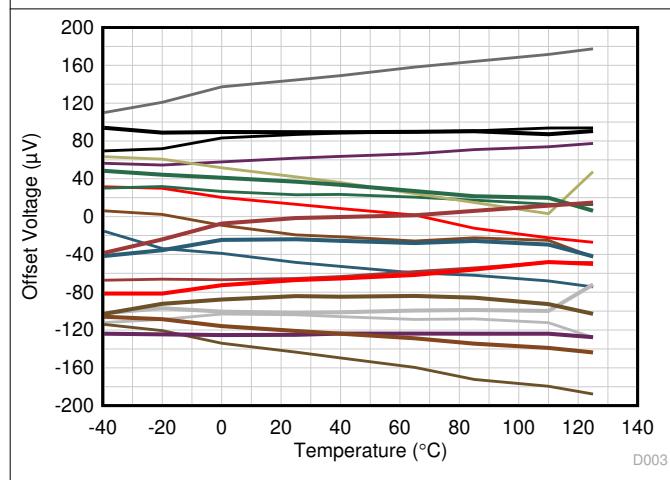

図 7-3. オフセット電圧と温度との関係

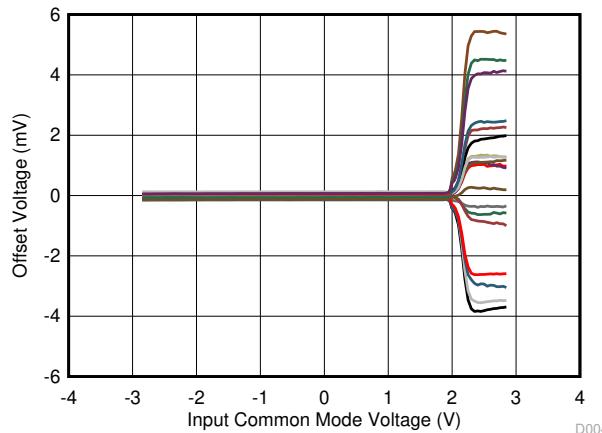

図 7-4. オフセット電圧と同相電圧との関係

図 7-5. オフセット電圧と同相電圧との関係

図 7-6. オフセット電圧と電源電圧との関係

## 7.7 TLV6741 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = 5.5\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

図 7-7.  $I_B$  および  $I_{OS}$  と同相電圧との関係

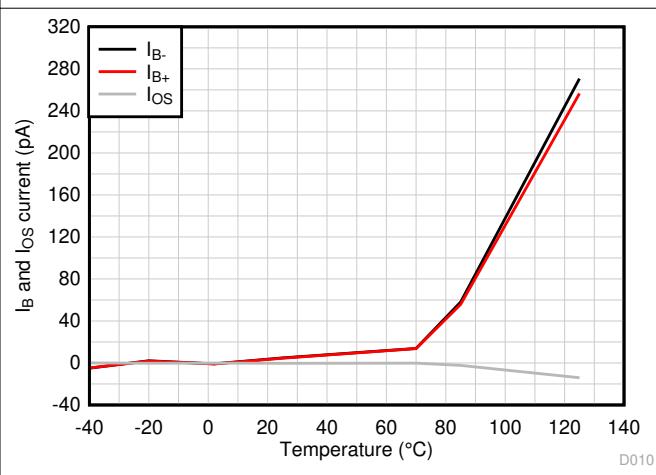

図 7-8.  $I_B$  および  $I_{OS}$  と温度との関係

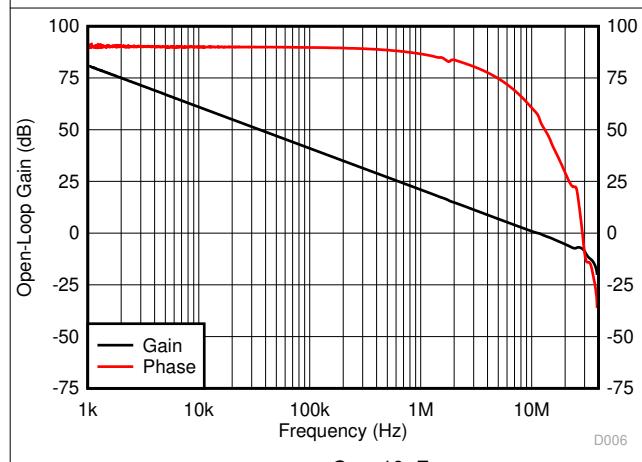

図 7-9. 開ループのゲインおよび位相と周波数との関係

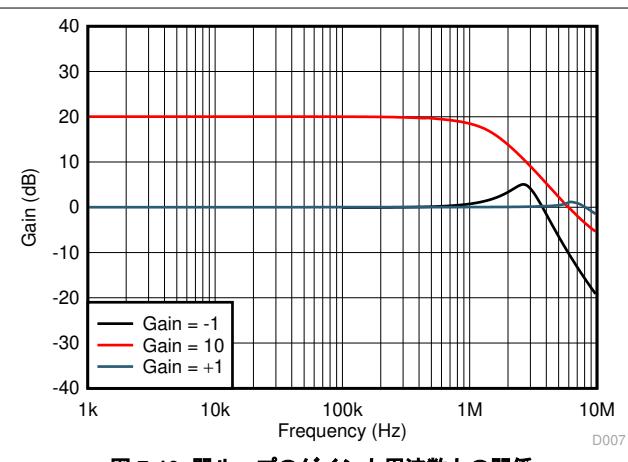

図 7-10. 閉ループのゲインと周波数との関係

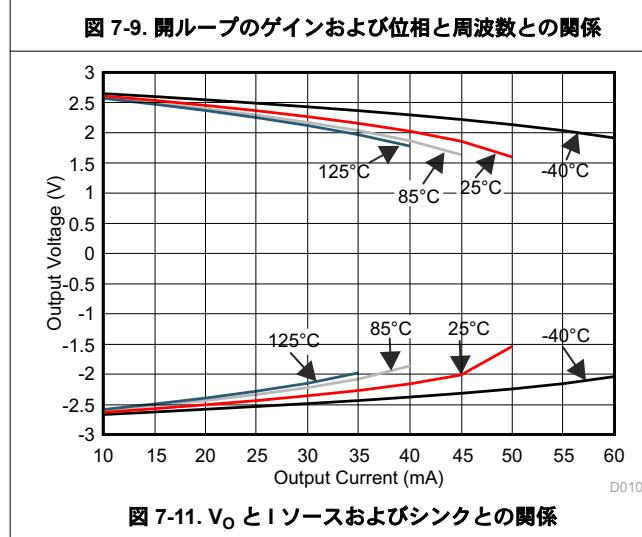

図 7-11.  $V_0$  と  $I_{SOURCE}$  および  $I_{SINK}$  との関係

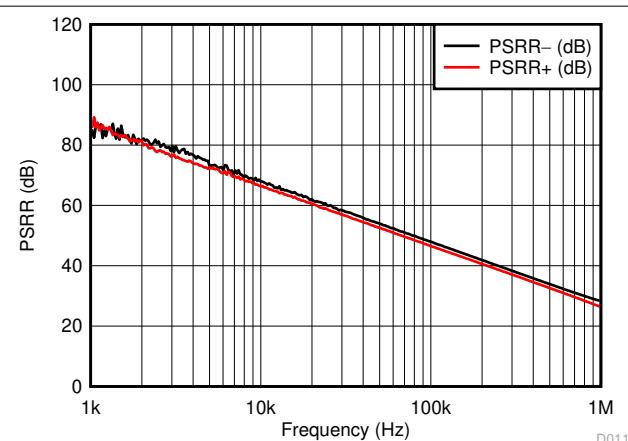

図 7-12. PSRR と周波数との関係 (入力基準)

## 7.7 TLV6741 : 代表的特性 (continued)

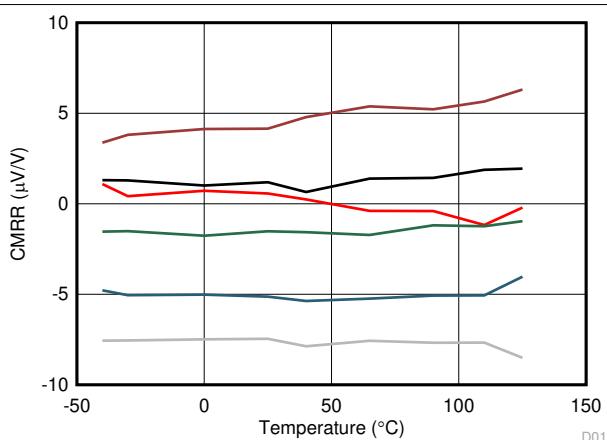

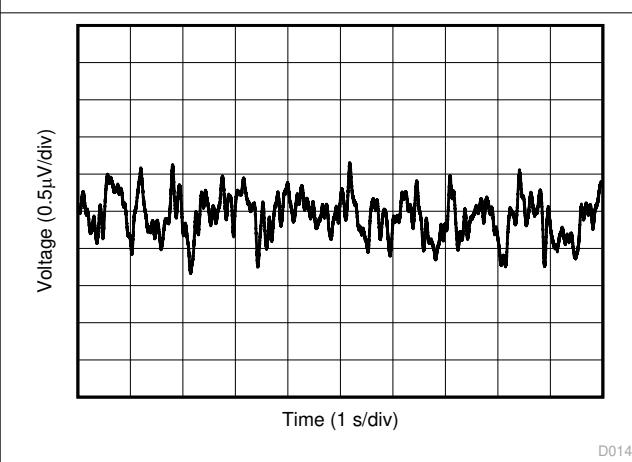

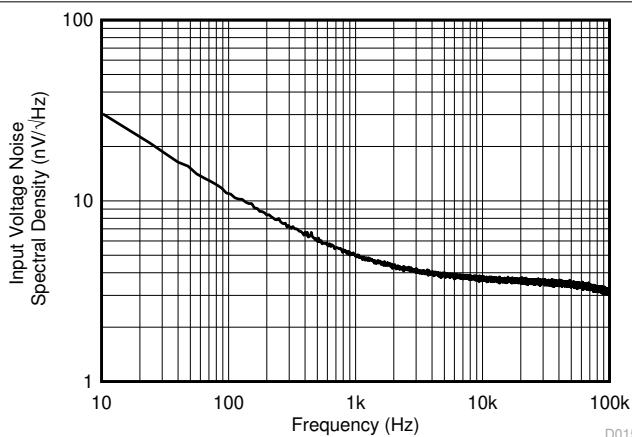

$T_A = 25^\circ\text{C}$ 、 $V_S = 5.5\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

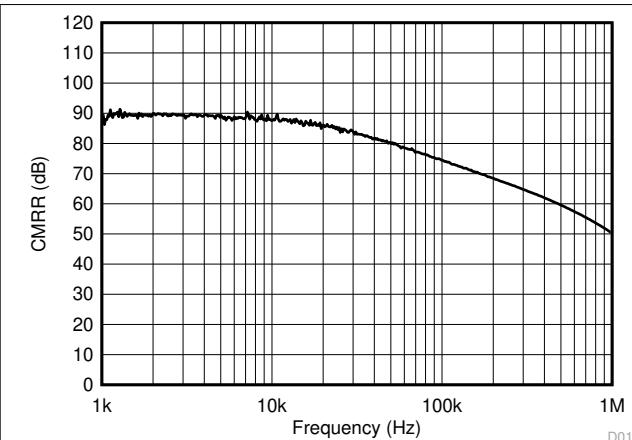

図 7-13. CMRR と周波数との関係 (入力基準)

図 7-14. CMRR と温度との関係

図 7-15. 0.1Hz~10Hz のフリッカ・ノイズ

図 7-16. 入力電圧ノイズのスペクトル密度と周波数との関係

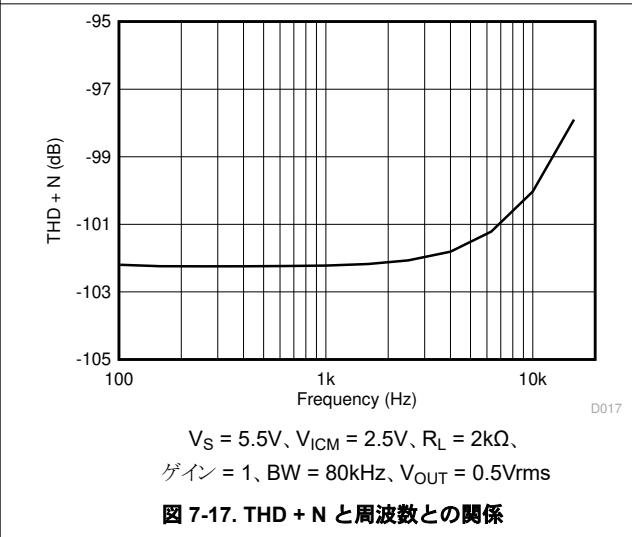

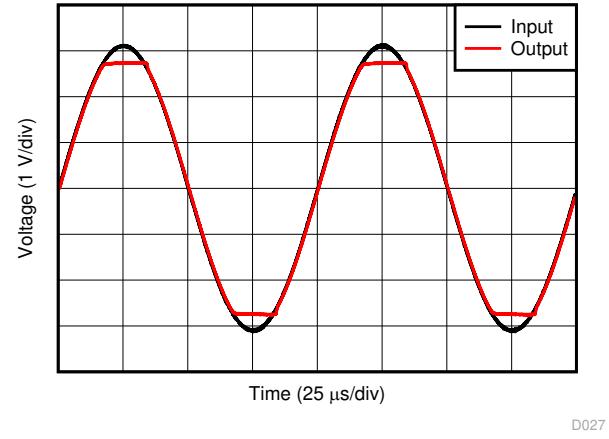

$V_S = 5.5\text{V}$ 、 $V_{ICM} = 2.5\text{V}$ 、 $R_L = 2\text{k}\Omega$ 、

ゲイン = 1、BW = 80kHz、 $V_{OUT} = 0.5\text{Vrms}$

図 7-17. THD + N と周波数との関係

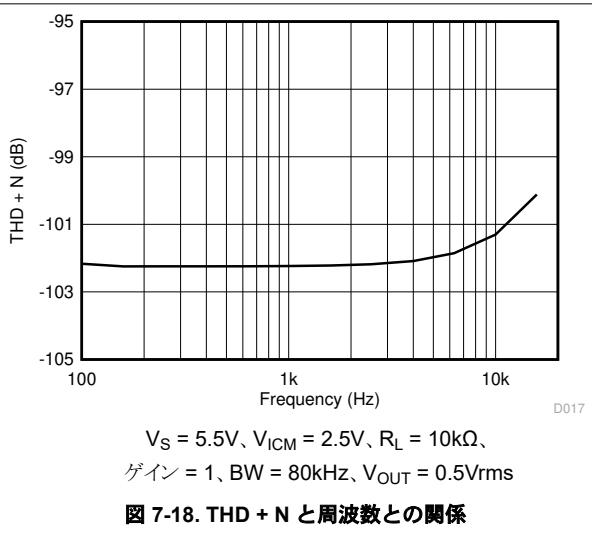

$V_S = 5.5\text{V}$ 、 $V_{ICM} = 2.5\text{V}$ 、 $R_L = 10\text{k}\Omega$ 、

ゲイン = 1、BW = 80kHz、 $V_{OUT} = 0.5\text{Vrms}$

図 7-18. THD + N と周波数との関係

## 7.7 TLV6741 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = 5.5\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

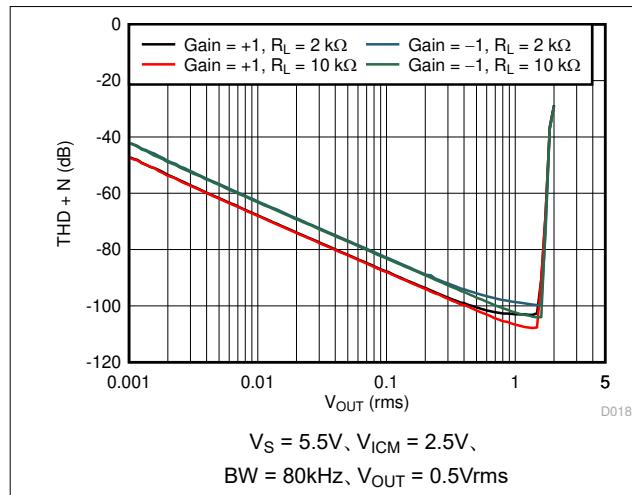

図 7-19. THD + N と振幅との関係

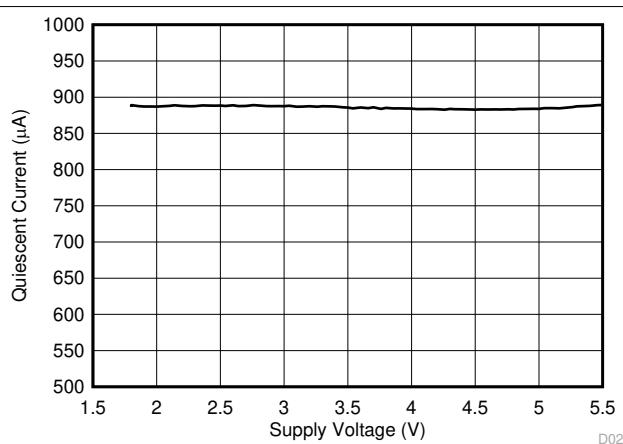

図 7-20. 静止電流と電源電圧との関係

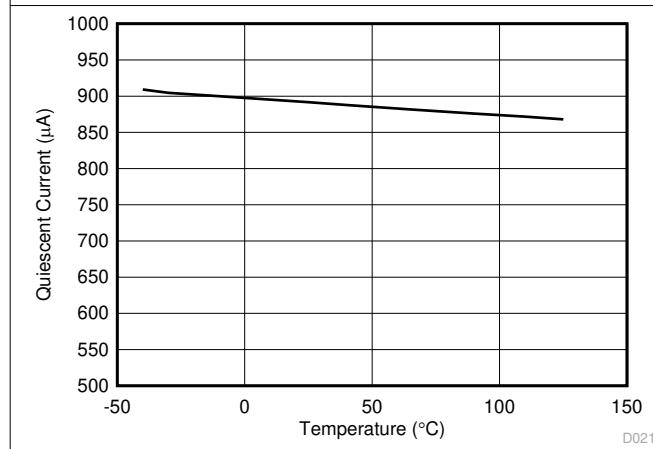

図 7-21. 静止電流と温度との関係

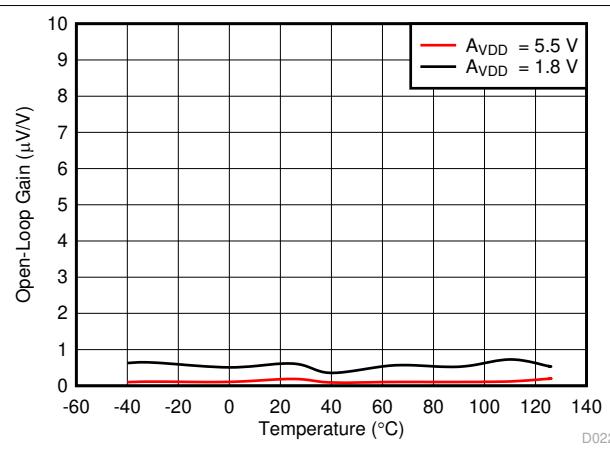

図 7-22. 開ループのゲインと温度との関係

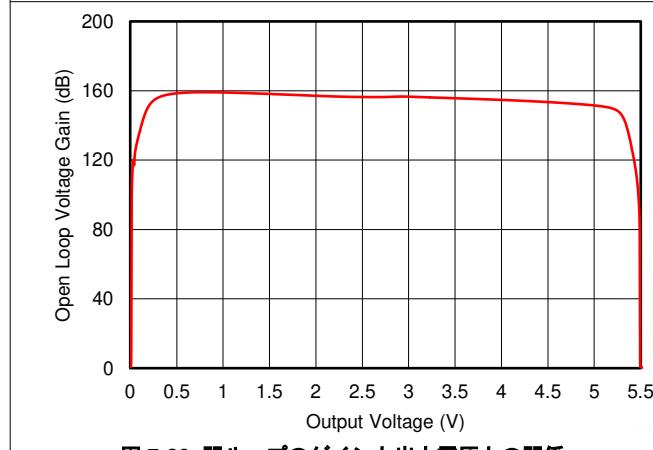

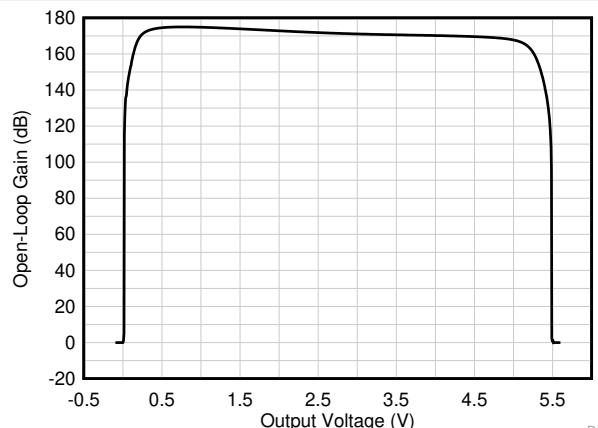

図 7-23. 開ループのゲインと出力電圧との関係

図 7-24. 開ループの出力インピーダンスと周波数との関係

## 7.7 TLV6741 : 代表的特性 (continued)

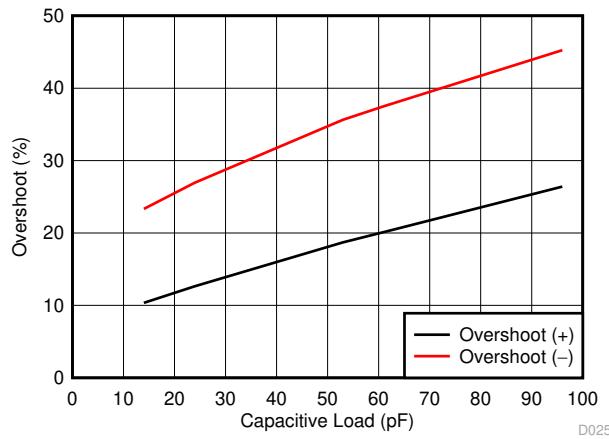

$T_A = 25^\circ\text{C}$ 、 $V_S = 5.5\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

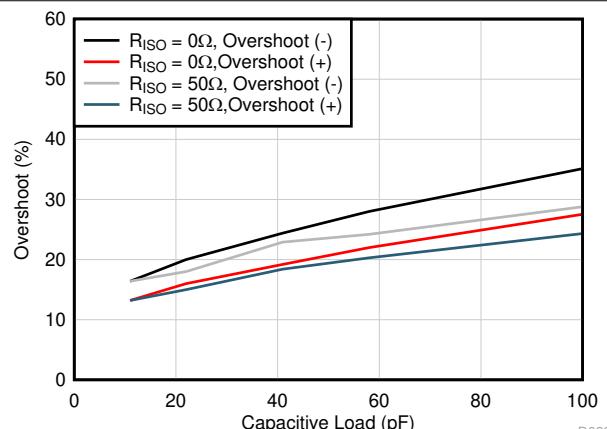

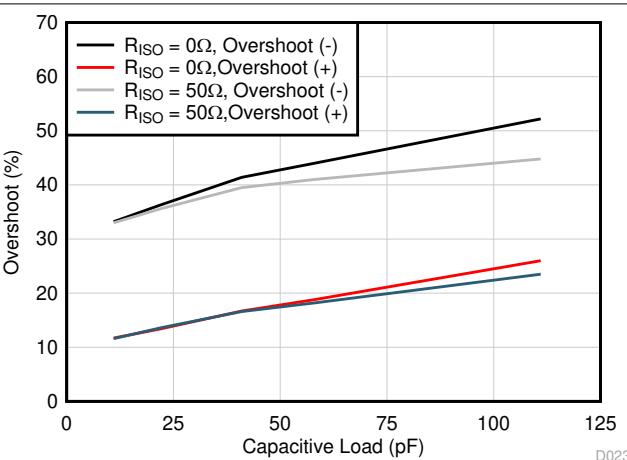

$V_S = 5.5\text{V}$ 、 $V_{ICM} = 2.75\text{V}$ 、

$V_{OCM} = 2.75\text{V}$ 、 $G = 1$ 、 $100\text{mV}$  の出力ステップ

図 7-25. 小信号のオーバーシュートと負荷容量との関係

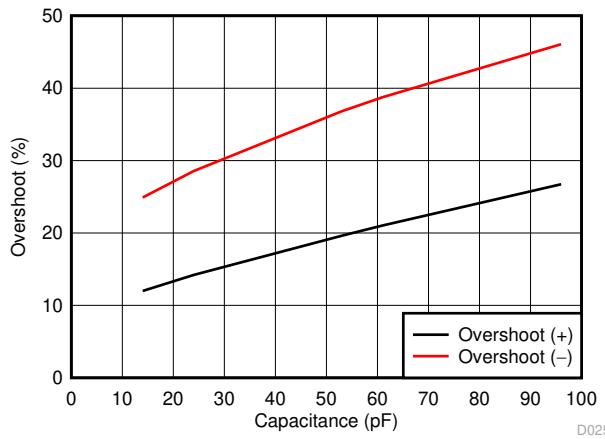

$V_S = 1.8\text{V}$ 、 $V_{ICM} = 0.9\text{V}$

$V_{OCM} = 0.9\text{V}$ 、 $G = 1$ 、 $100\text{mV}$  出力ステップ

図 7-26. 小信号のオーバーシュートと負荷容量との関係

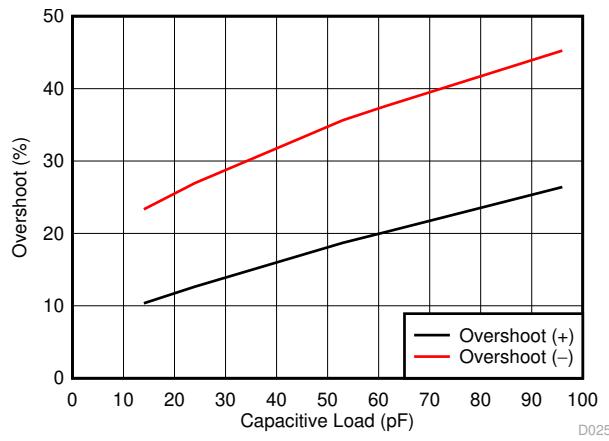

$V_S = 5.5\text{V}$ 、 $V_{ICM} = 2.75\text{V}$ 、

$V_{OCM} = 2.75\text{V}$ 、ゲイン = -1、 $100\text{mV}$  の出力ステップ

図 7-27. 小信号のオーバーシュートと負荷容量との関係

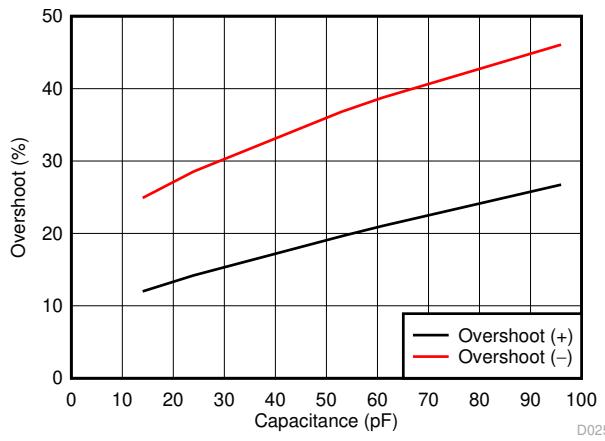

$V_S = 1.8\text{V}$ 、 $V_{ICM} = 0.9\text{V}$

$V_{OCM} = 0.9\text{V}$ 、ゲイン = -1、 $100\text{mV}$  の出力ステップ

図 7-28. 小信号のオーバーシュートと負荷容量との関係

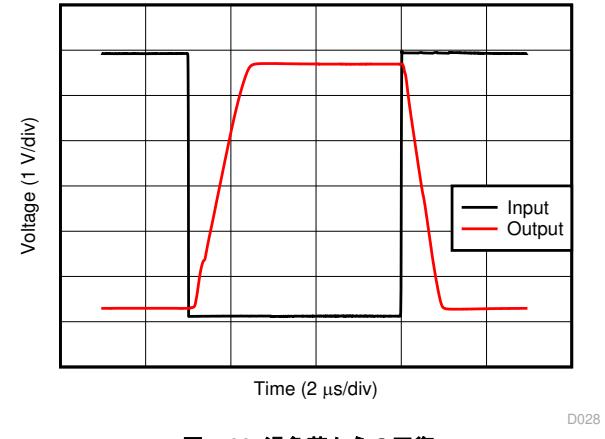

図 7-29. 位相反転なし

図 7-30. 過負荷からの回復

## 7.7 TLV6741 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = 5.5\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

## 7.7 TLV6741 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = 5.5\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{\text{CM}} = V_S/2$ 、 $V_{\text{OUT}} = V_S/2$  (特に記述のない限り)

図 7-35. 短絡電流と温度との関係

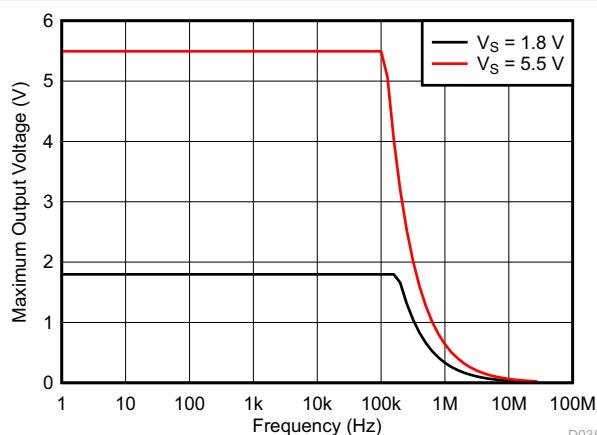

$V_{\text{ICM}} = V_S/2$ 、 $V_{\text{OCM}} = V_S/2$ 、

$C_L = 10\text{pF}$ 、ゲイン = 1

図 7-36. 最大出力電圧と周波数との関係

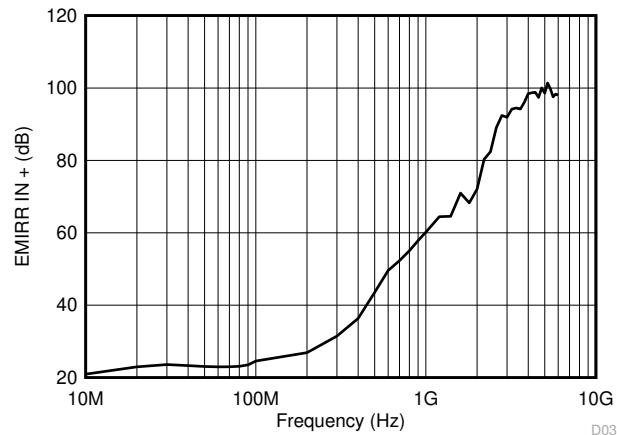

図 7-37. 非反転入力を基準とする電磁干渉除去比 (EMIRR+) と周波数との関係

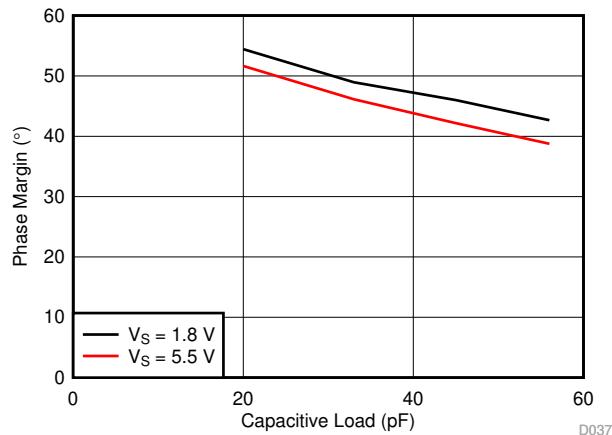

$V_{\text{ICM}} = V_{\text{OCM}} = V_S/2$

図 7-38. 位相マージンと容量性負荷との関係

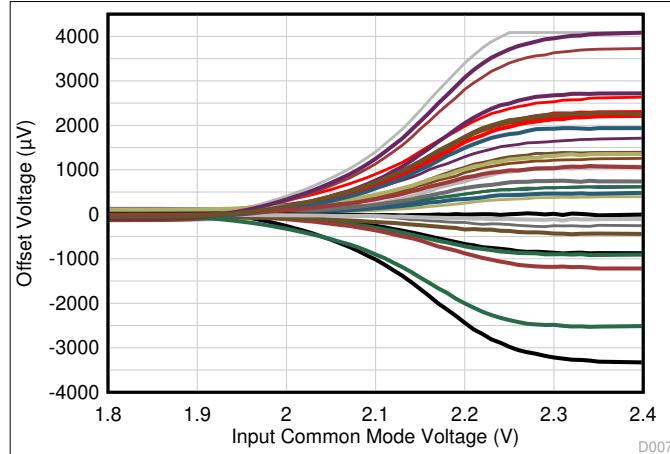

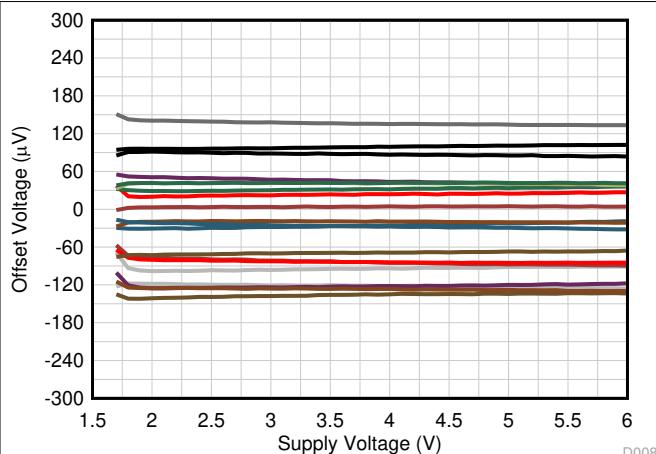

## 7.8 TLV6742 : 代表的特性

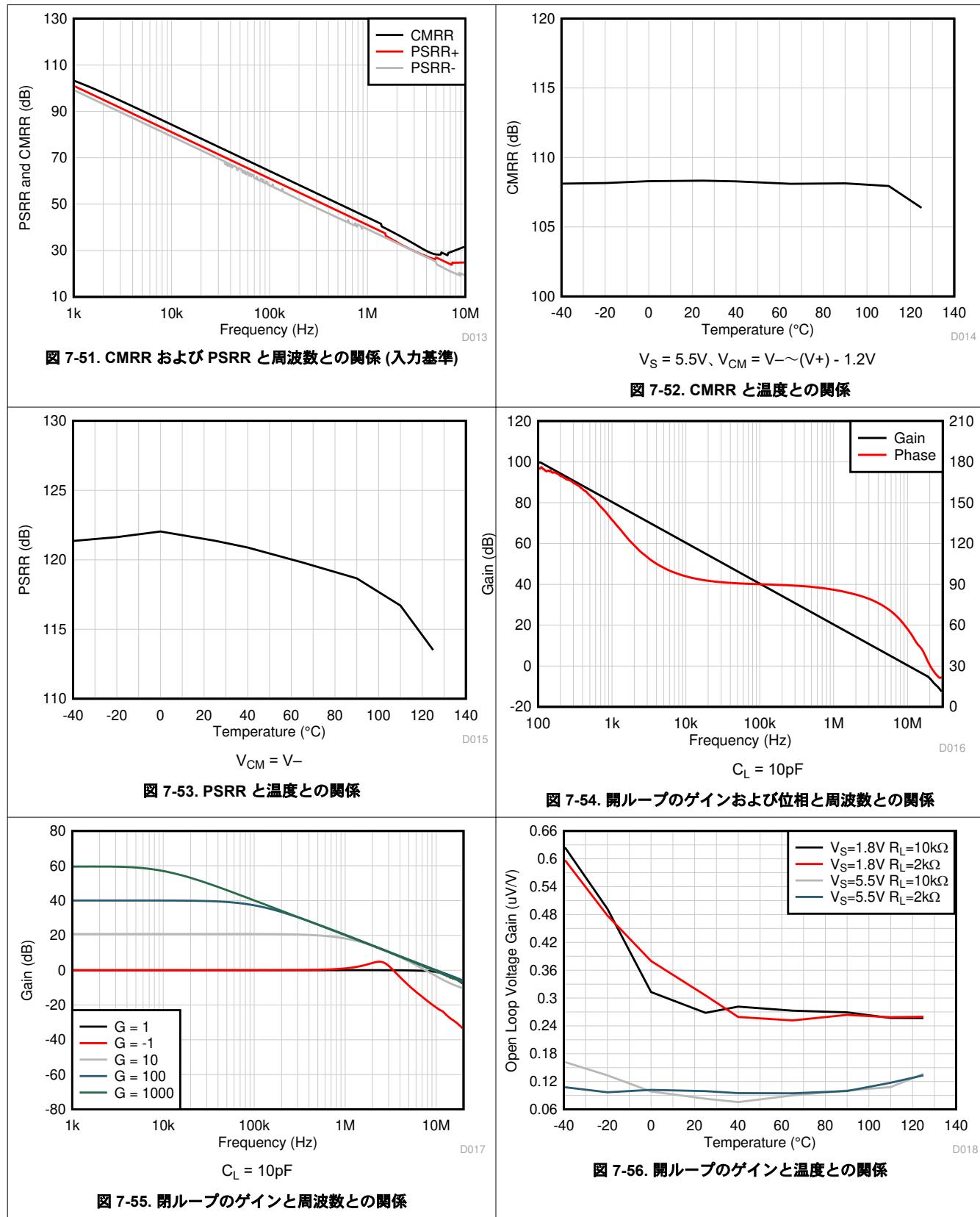

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 2.75\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

図 7-39. オフセット電圧の製品分布

図 7-40. オフセット電圧ドリフトの分布

図 7-41. オフセット電圧と温度との関係 (PMOS 入力ペア)

図 7-42. オフセット電圧と温度との関係 (NMOS 入力ペア)

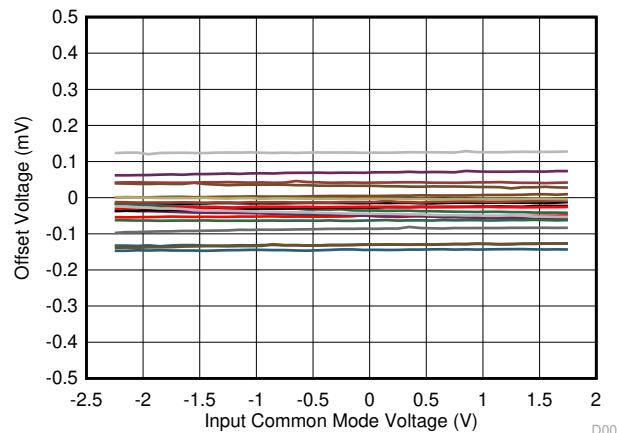

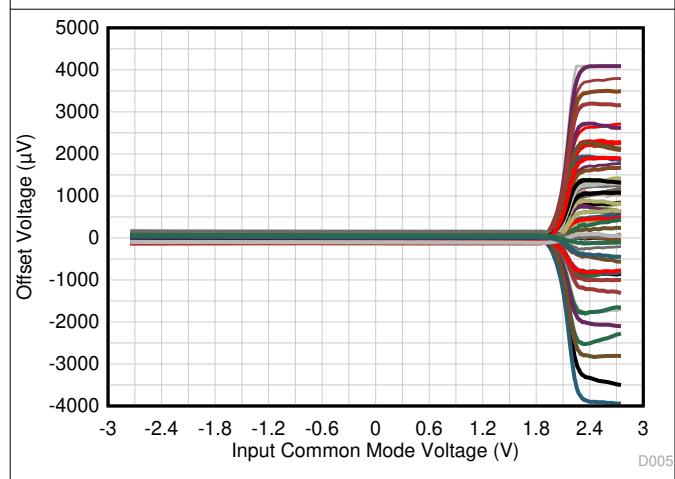

図 7-43. オフセット電圧と同相電圧との関係 (全範囲)

図 7-44. オフセット電圧と同相電圧との関係 (PMOS 入力ペア)

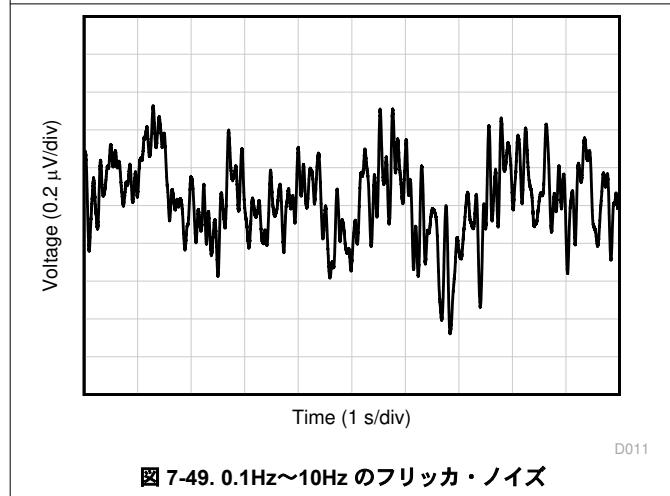

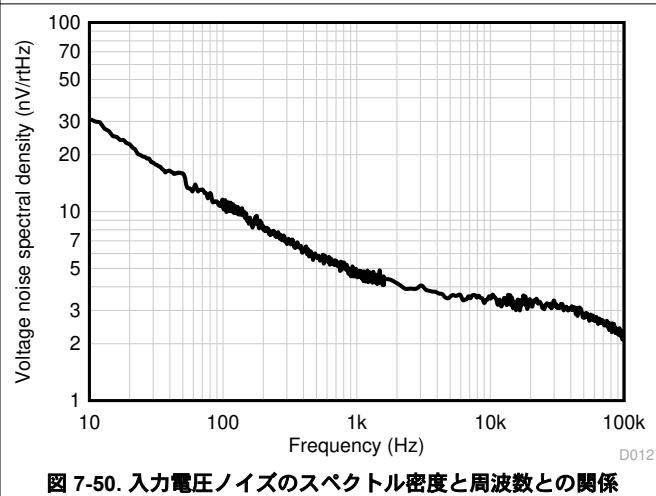

## 7.8 TLV6742 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 2.75\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

図 7-45. オフセット電圧と同相電圧との関係 (遷移領域)

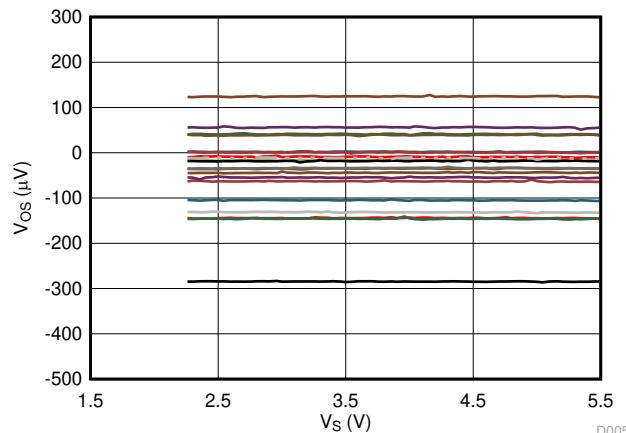

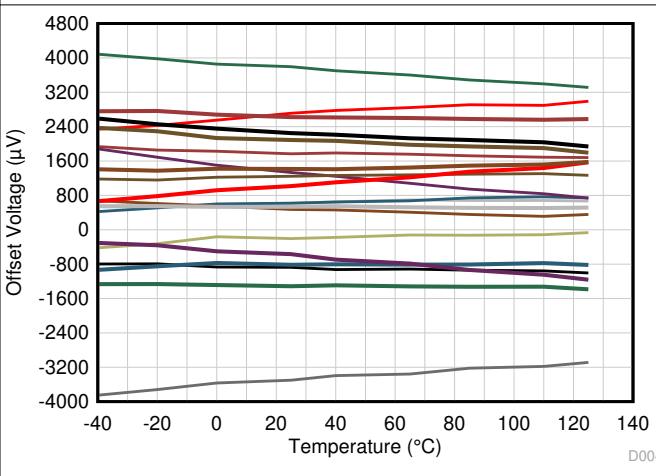

図 7-46. オフセット電圧と電源電圧との関係

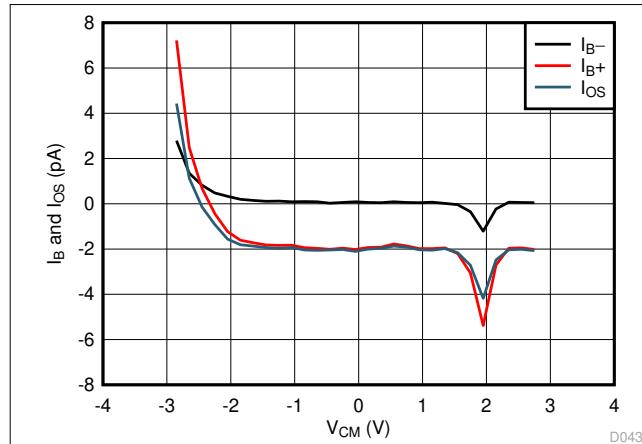

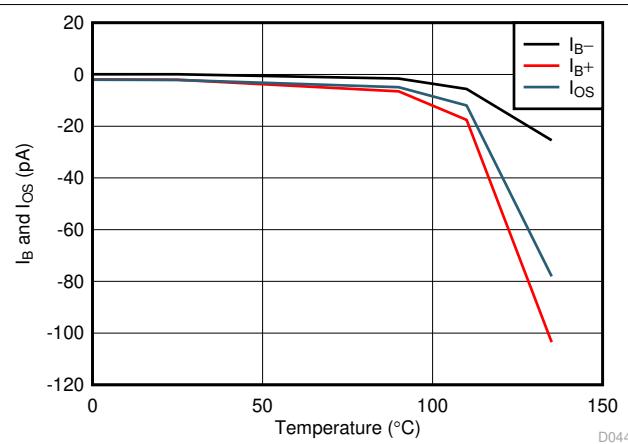

図 7-47.  $I_B$  および  $I_{OS}$  と同相電圧との関係

図 7-48.  $I_B$  および  $I_{OS}$  と温度との関係

図 7-49. 0.1Hz~10Hz のフリッカ・ノイズ

図 7-50. 入力電圧ノイズのスペクトル密度と周波数との関係

## 7.8 TLV6742 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 2.75\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

## 7.8 TLV6742 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 2.75\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

図 7-57. 開ループのゲインと出力電圧との関係

図 7-58. 位相マージンと容量性負荷との関係

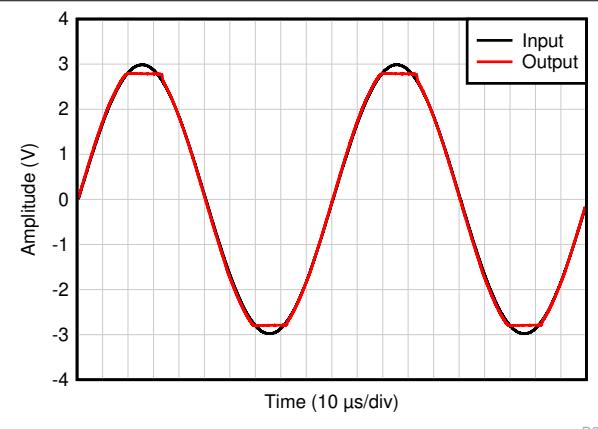

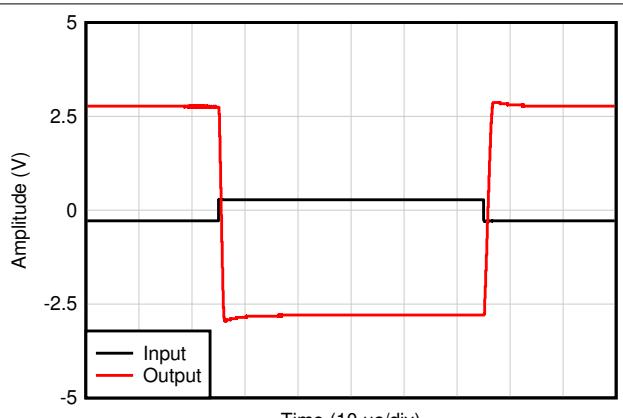

図 7-59. 位相反転なし

図 7-60. 小信号のオーバーシュートと負荷容量との関係

図 7-61. 小信号のオーバーシュートと負荷容量との関係

$V_{IN} = 0.6\text{Vpp}$ 、 $G = -10$ 、 $V_{IN} \times \text{ゲイン} > V_S$

図 7-62. 過負荷からの回復

## 7.8 TLV6742 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 2.75\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

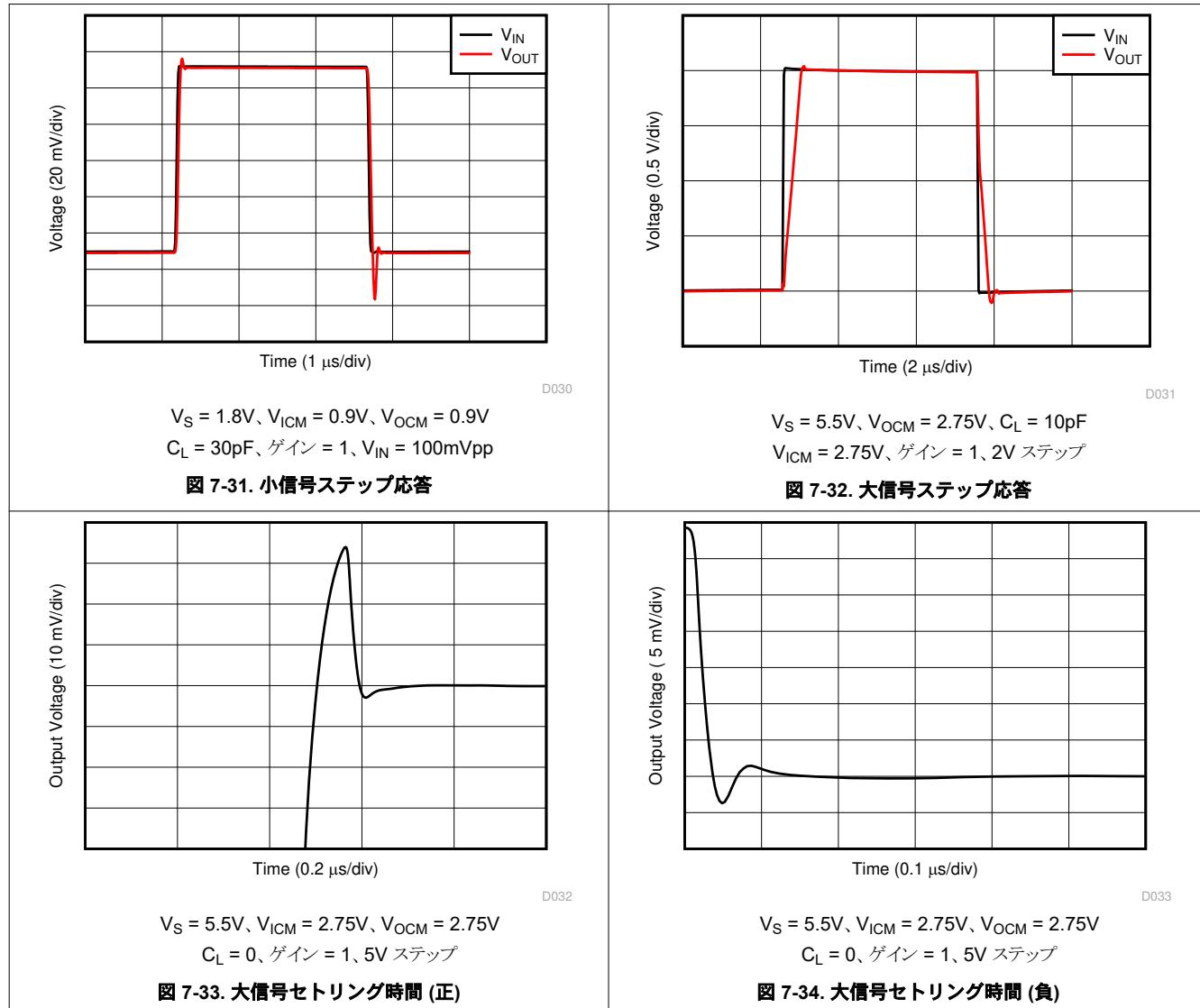

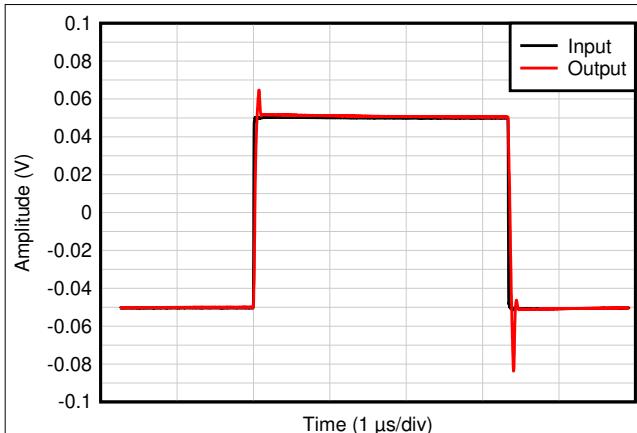

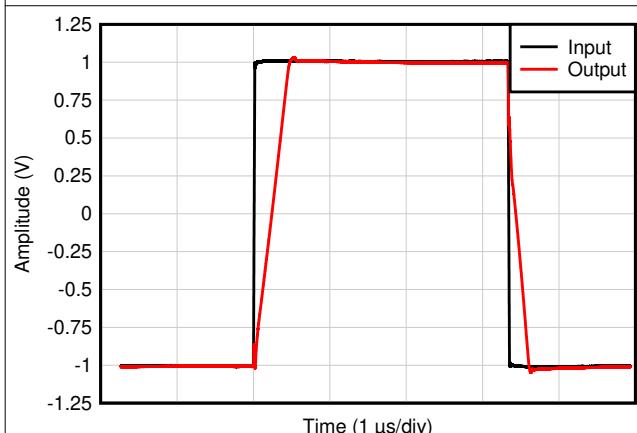

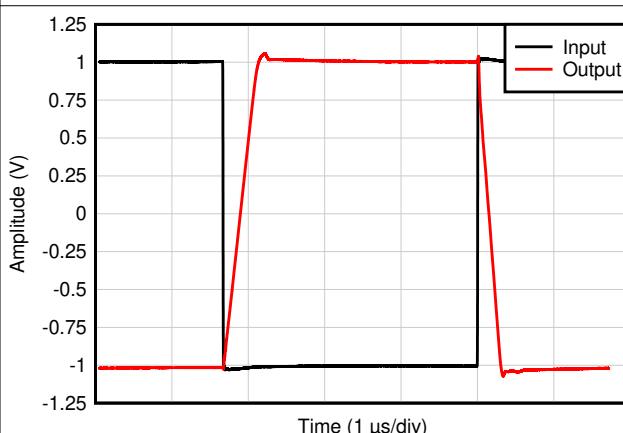

図 7-63. 小信号ステップ応答

図 7-64. 小信号ステップ応答

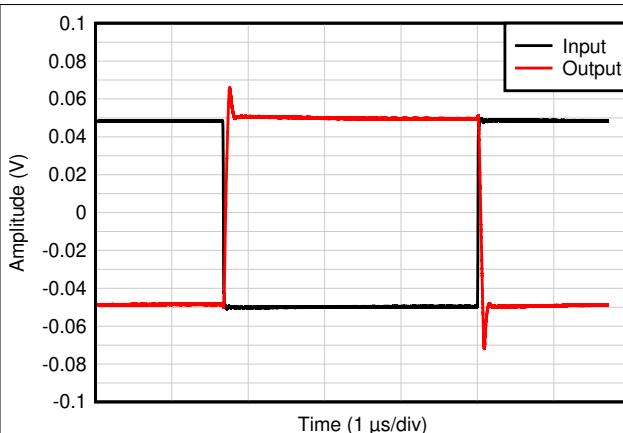

図 7-65. 大信号ステップ応答

図 7-66. 大信号ステップ応答

図 7-67. 大信号セトリング時間 (正)

図 7-68. 大信号セトリング時間 (負)

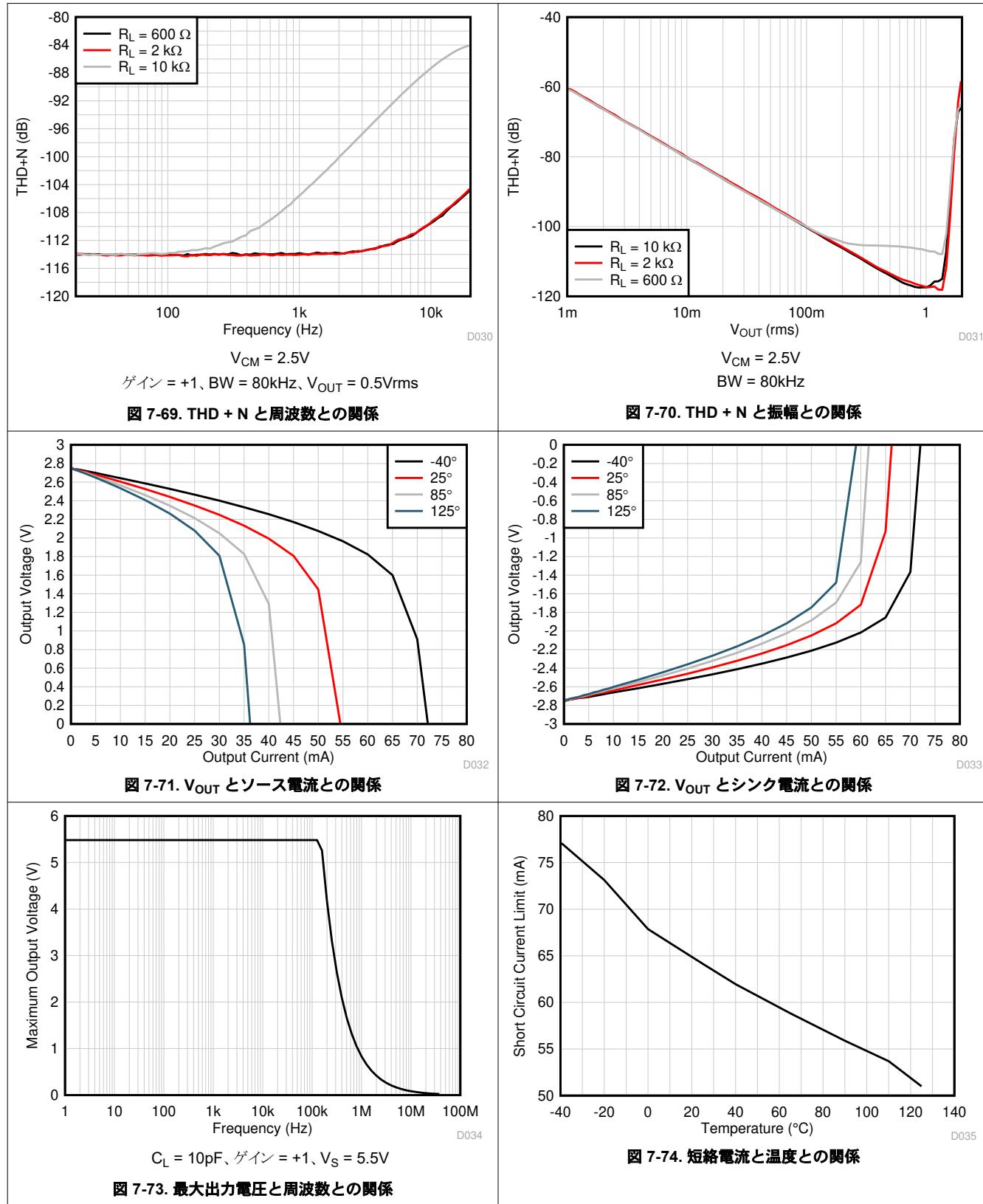

## 7.8 TLV6742 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 2.75\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

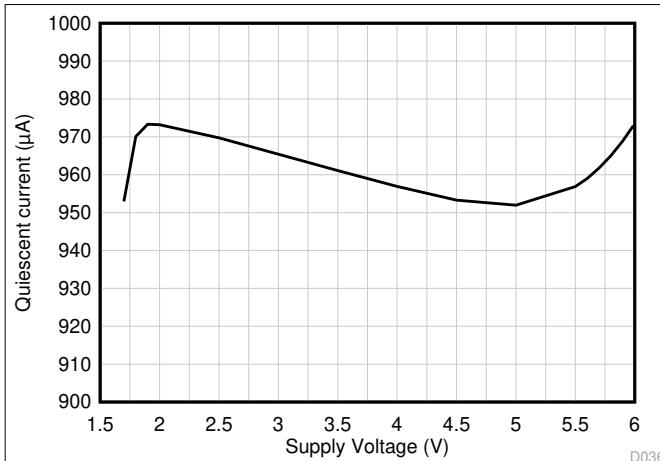

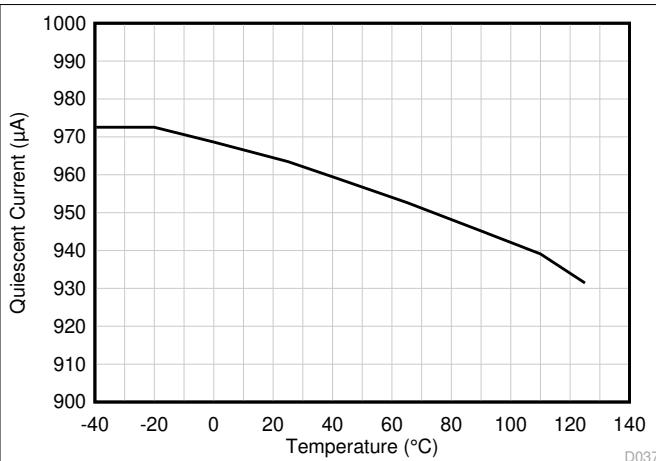

## 7.8 TLV6742 : 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 2.75\text{V}$ 、 $R_L = 10\text{k}\Omega$  を  $V_S/2$  に接続、 $V_{CM} = V_S/2$ 、 $V_{OUT} = V_S/2$  (特に記述のない限り)

図 7-75. 静止電流と電源電圧との関係

図 7-76. 静止電流と温度との関係

図 7-77. 開ループの出力インピーダンスと周波数との関係

$A_{VDD} = 5.5\text{V}$ 、 $V_{ICM} = V_{OCM} = 2.75\text{V}$

図 7-78. チャネル・セパレーションと周波数との関係

図 7-79. 非反転入力を基準とする電磁干渉除去比 (EMIRR+) と周波数との関係

$V_S = 0 \sim 5.5\text{V}$ 、 $V_{OUT} = 0 \sim 2.75\text{V}$

図 7-80. ターンオン時間

## 8 詳細説明

### 8.1 概要

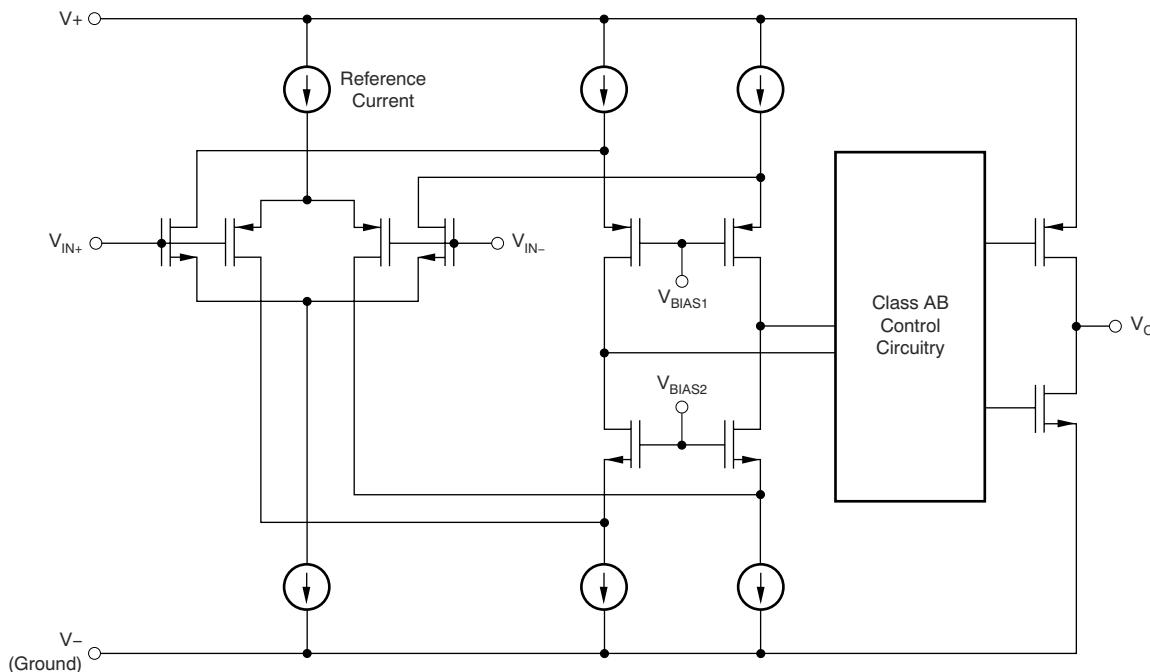

TLV674x ファミリは超低ノイズのレール・ツー・レール出力オペアンプ・ファミリです。これらのデバイスは 2.25V~5.5V (TLV6741) と 1.7V~5.5V (LV6742, TLV6744) の電源電圧で動作し、ユニティ・ゲインで安定しており、幅広い汎用アプリケーションに適しています。入力同相電圧範囲に負レールが含まれるため、TLV674x オペアンプ・ファミリはほとんどの単一電源アプリケーションで使用できます。レール・ツー・レール出力スイングにより、特に電源電圧が低いアプリケーションでダイナミック・レンジを大きく広げることができます。サンプリング A/D コンバータ (ADC) の駆動だけでなく多くのオーディオ・アプリケーションに本ファミリは適しています。

### 8.2 機能ブロック図

### 8.3 機能説明

#### 8.3.1 THD+ノイズ性能

TLV674x オペアンプ・ファミリは、優れた歪み特性を備えています。TLV6742 と TLV6744 の THD + ノイズは、20Hz~20kHz のオーディオ周波数範囲全体で 0.00015% 未満です ( $G = +1$ 、 $V_O = 1V_{RMS}$ 、 $V_{CM} = 1.8V$ 、 $V_S = 5.5V$ 、 $10k\Omega$  負荷時)。TLV6741 の THD + ノイズは、20Hz~20kHz のオーディオ周波数範囲全体で 0.00035% 未満です ( $G = +1$ 、 $V_O = 1V_{RMS}$ 、 $V_{CM} = 2.5V$ 、 $V_S = 5.5V$ 、 $10k\Omega$  負荷時)。10MHz 汎用アンプの広帯域ノイズは  $3.5nV/\sqrt{Hz}$  (TLV6742/4) と  $3.7nV/\sqrt{Hz}$  (TLV6741) であり、非常に低い値です。

#### 8.3.2 動作電圧

TLV674x オペアンプ・ファミリは、1.7V~5.5V (TLV6742/4) と 2.25V~5.5V (TLV6741) で動作することが規定および保証されています。また、仕様の多くは  $-40^{\circ}C$ ~ $125^{\circ}C$  で適用されます。電源ピンは、 $0.1\mu F$  のセラミック・コンデンサでバイパスする必要があります。

#### 8.3.3 レール・ツー・レール出力

低消費電力、低電圧のオペアンプとして設計された TLV674x デバイスは強力な出力駆動能力を備えています。共通ソース・トランジスタを使用した Class AB 出力段により、完全レール・ツー・レール出力スイング能力を実現しています。 $10k\Omega$  の抵抗性負荷の場合、印加された電源電圧にかかわらず、どちらの電源レールからも数 mV 以内まで出力がスイングします。負荷条件が変わると、レール近くでのアンプのスイング能力も変わります (図 7-11 を参照)。

### 8.3.4 EMI 除去

TLV674x は、統合型の電磁干渉 (EMI) フィルタリングを使用して、ワイヤレス通信や、アナログ信号チェーンとデジタル・コンポーネントを組み合わせた高密度実装のボードなどから発生する EMI の影響を低減します。EMI 耐性は、回路設計手法により改善可能です。TLV674x は、このような設計の改善を活用しています。テキサス・インスツルメンツは、10MHz から 6GHz までの幅広い周波数スペクトルにわたって、オペアンプの耐性を正確に測定および数量化する機能を開発しました。TLV674x でこのテストを行った結果を、図 8-1 に示します。実際のアプリケーションで一般的に発生する特定の周波数における TLV674x の EMIRR IN+ 値を、表 8-1 に示します。「オペアンプの EMI 除去率」アプリケーション・レポートには、オペアンプに関連する EMIRR 性能の詳細情報が記載されており、[www.ti.com](http://www.ti.com) からダウンロードできます。

図 8-1. EMIRR テスト

表 8-1. 対象周波数における TLV674x の EMIRR IN+

| 周波数    | アプリケーションまたは割り当て                                                                                         | EMIRR IN+ |

|--------|---------------------------------------------------------------------------------------------------------|-----------|

| 400MHz | モバイル無線、モバイル衛星、宇宙での運用、気象、レーダー、極超短波 (UHF) アプリケーション                                                        | 59.5dB    |

| 900MHz | GSM (モバイル通信) アプリケーション向けのグローバル・システム、無線通信、ナビゲーション、GPS (最高 1.6GHz まで)、GSM、航空モバイル、UHF アプリケーション              | 68.9dB    |

| 1.8GHz | GSM アプリケーション、モバイル・パーソナル通信、ブロードバンド、衛星、L バンド (1GHz~2GHz)                                                  | 77.8dB    |

| 2.4GHz | 802.11b、802.11g、802.11n、Bluetooth®、モバイル・パーソナル通信、産業用、科学用および医療用 (ISM) 無線帯域、アマチュア無線および衛星、S バンド (2GHz~4GHz) | 78.0dB    |

| 3.6GHz | 無線測位、航空通信およびナビゲーション、衛星、モバイル、S バンド                                                                       | 88.8dB    |

| 5GHz   | 802.11a、802.11n、航空通信とナビゲーション、モバイル通信、宇宙と衛星の運用、C バンド (4GHz~8GHz)                                          | 87.6dB    |

### 8.3.5 電気的オーバーストレス

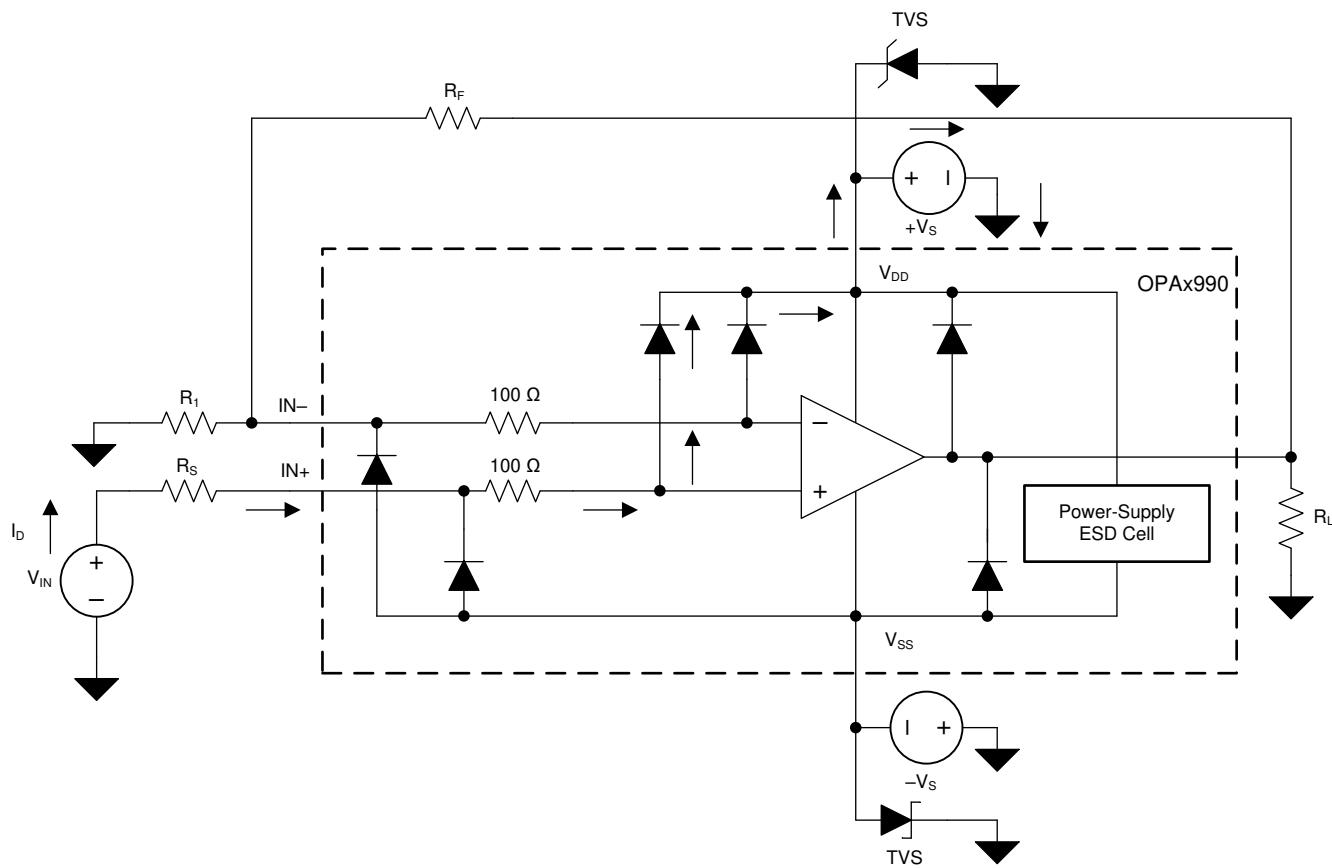

設計者は多くの場合、オペアンプが電気的オーバーストレス (EOS) にどの程度耐えられるのかという質問をします。これらの質問は、主にデバイスの入力に関するものですが、電源電圧ピンや、さらに出力ピンにも関係する場合があります。これらの各ピンの機能には、特定の半導体製造プロセスの電圧ブレーカダウン特性と、ピンに接続された特定の回路とで決まる電気的ストレスの制限値があります。また、これらの回路には内部静電気放電 (ESD) 保護機能が組み込まれており、製品の組み立て前と組み立て中の両方で、偶発的な ESD イベントから保護します。

この基本的な ESD 回路と、電気的オーバーストレス・イベントとの関連性を十分に理解しておくと役に立ちます。TLV674x に含まれる ESD 回路の図を、図 8-2 に示します (破線で囲まれている部分)。ESD 保護回路には、いくつかの電流ステアリング・ダイオードが含まれており、これらは入力ピンや出力ピンから接続され、内部の電源ラインに戻るようルーティングされます。これらのダイオードは、オペアンプ内部の吸収デバイスや電源 ESD セルで接続されます。この保護回路は、通常の回路動作中は非アクティブに保たれるよう設計されます。

図 8-2. 代表的な回路アプリケーションと比較して等価な内部 ESD 回路

ESD イベントは持続時間が非常に短く、電圧が非常に高い (例: 1kV, 100ns) のに対して、EOS イベントは持続時間が長く、電圧も低くなります (例: 50V, 100ms)。ESD ダイオードは、回路外の ESD 保護 (つまり、PCB に半田付けする前にデバイスの組み立て、テスト、保管を行うとき) を目的として設計されています。ESD イベントの間、ESD 信号は ESD ステアリング・ダイオードを通過して吸収回路 (「ESD 電源回路」とラベル付けされています) に渡されます。ESD 吸收回路は、電源を安全なレベルにクランプします。

この動作は回路外保護のためには必要なものですが、回路内でこの動作をアクティブにすると、過大な電流と損傷が発生します。過渡電圧サプレッサ (TVS) を使用すると、回路内の ESD イベント発生時に ESD 吸收回路がオンになることで生じる損傷を防止できます。適切な電流制限抵抗と TVS ダイオードを使うと、デバイスの ESD ダイオードを使って EOS イベントから保護できます。

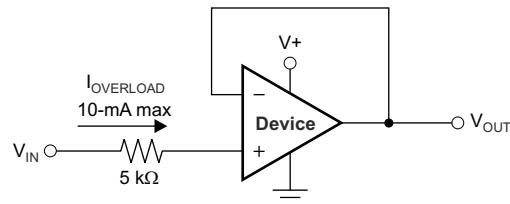

TLV674x ファミリは、上記のように、すべてのピンに内部静電気放電 (ESD) 保護回路を内蔵しています。これらの ESD 保護ダイオードは、セクション 7.1 に示すように電流が 10mA に制限されている限り、回路内の入力オーバードライブ保

護の役割も果たします。図 8-3 に、入力電流を制限するために駆動入力に直列入力抵抗を追加する方法を示します。追加された抵抗はアンプ入力での熱ノイズに寄与するため、ノイズに敏感なアプリケーションではその値を最小限に抑える必要があります。

図 8-3. 入力電流保護

### 8.3.6 代表的な仕様と分布

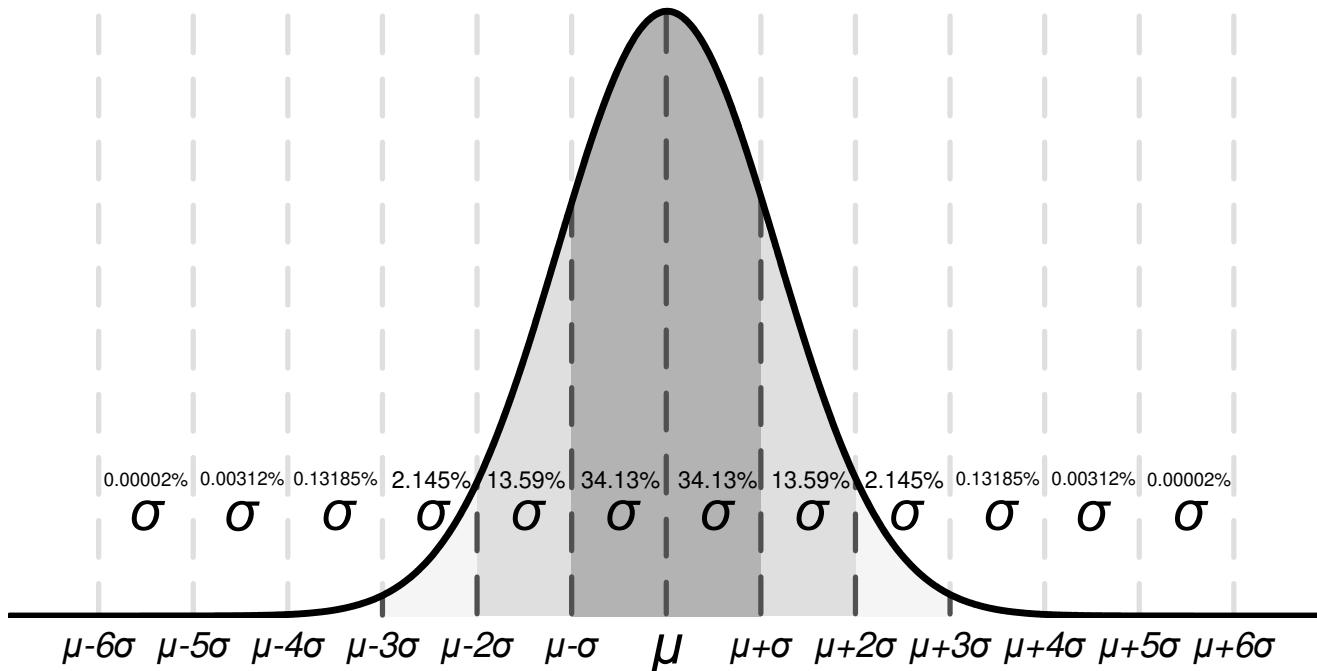

設計者は多くの場合、より堅牢な回路を設計するため、アンプの標準仕様についての疑問を抱きます。プロセス・テクノロジーや製造手順には自然に差異が発生するため、アンプのすべての仕様は、アンプの入力オフセット電圧など、理想的な値からある程度の偏差が生じます。これらの偏差は多くの場合、ガウス分布（「ベル曲線」）または正規分布に従います。回路設計者は、セクション 7.6 に最小値または最大値の仕様がない場合でも、この情報を活用してシステムの最低限の品質を確保できます。

図 8-4. 理想的なガウス分布

分布の例を、図 8-4 に示します。ここで、 $\mu$ （ミュー）は分布の平均値、 $\sigma$ （シグマ）はシステムの標準偏差です。このような分布を示す仕様では、すべてのユニットの約 2/3 (68.26%) が平均値から 1 標準偏差（シグマ）以内 ( $\mu - \sigma$  から  $\mu + \sigma$  まで) に存在していると予想できます。

セクション 7.6 の「標準値」列に記載されている値は、仕様に応じてさまざまな方法で表現されます。一般的な目安として、仕様の性質上平均値が 0 以外の場合（ゲイン帯域幅など）、標準値は平均値 ( $\mu$ ) と等しくなります。ただし、入力オフセット電圧のように、その性質上仕様の平均値が 0 に近い場合、最も正確に標準値を表すため、標準値は平均値に 1 標準偏差を加えた値 ( $\mu + \sigma$ ) と等しくなります。

このグラフを使用して、ユニット内の仕様のおおよその確率を計算できます。たとえば TLV6742 の場合、入力電圧オフセットの標準値は  $150\mu\text{V}$  なので、すべての TLV6742 デバイスのうち 68.2% は  $-150\mu\text{V} \sim 150\mu\text{V}$  のオフセットを持つと予想されます。

仕様の最小値または最大値の列に値が記載されているものはテキサス・インスツルメンツによって保証されており、これらの制限値を超えたユニットは生産から除去されます。たとえば、TLV6742 デバイスの最大オフセット電圧は  $25^\circ\text{C}$ において  $1.0\text{mV}$  で、これは  $5\sigma$  (約 170 万ユニットのうち 1 つ) に相当し、確率としては非常に低いです。テキサス・インスツルメンツは、オフセット電圧が  $1.0\text{mV}$  を超えるユニットを生産品から除去することを保証しています。

最小値または最大値の列に値が記載されていない仕様については、アプリケーションに十分な余裕のあるシグマ値を選択し、この値を使用してワーストケース条件を設計することを検討してください。たとえば、 $6\sigma$  の値は約 5 億個のうちの 1 個に相当します。これは非常に小さい確率であり、システム全体を設計するための広いガードバンドとしてこの値を選択できます。この場合、TLV6742 にはオフセット電圧ドリフトの最大値または最小値はありませんが、図 7-40 とセクション 7.6 の標準値である  $0.2\mu\text{V}/^\circ\text{C}$ に基づいて、オフセット電圧ドリフトの  $6\sigma$  値は約  $1.0\mu\text{V}/^\circ\text{C}$ と計算できます。ワーストケースのシステム条件を設計する場合、この値を使用すると、実際の最小値または最大値を使用せずに、温度範囲全体で可能性があるワーストケースのオフセットを推定できます。

ただし、時間の経過に伴うプロセスの変動と調整によって、標準偏差と平均値の標準値が変動する可能性があるため、仕様の最小値または最大値の列に値が記載されていないものについて、テキサス・インスツルメンツはデバイスの性能を保証できません。この情報は、デバイスの性能を推定する目的でのみ使用する必要があります。

### 8.3.7 シャットダウン機能

TLV674xS デバイスは、オペアンプを無効化して低消費電力のスタンバイ・モードに移行する SHDN ピンを備えています。このモードでは、オペアンプの消費電流は通常  $1\mu\text{A}$  未満です。SHDN ピンはアクティブ Low なので、SHDN ピンへの入力が有効なロジック Low のとき、シャットダウン・モードがイネーブルになります。

SHDN ピンは、オペアンプの負電源電圧を基準としています。シャットダウン機能のスレッショルドは、負レールより約  $800\text{mV}$  (標準値) 大きい値です。スムーズなスイッチング特性を確保するため、スイッチング・スレッショルドにはヒステリシスが含まれています。最適なシャットダウン動作を確保するため、SHDN ピンは有効なロジック信号で駆動する必要があります。有効なロジック Low は、 $V_-$  と  $V_- + 0.2\text{V}$  の間の電圧と定義され、有効なロジック High は、 $V_- + 1.2\text{V}$  と  $V_+$  の間の電圧と定義されます。シャットダウン・ピンは、オープンのままにしないで、有効な High 電圧と Low 電圧のどちらかに接続または駆動する必要があります。アンプを有効化するための内部プルアップは備わっていません。

SHDN ピンは高インピーダンスの CMOS 入力です。デュアル・オペアンプ・バージョンは独立して制御され、クワッド・オペアンプ・バージョンはロジック入力と対になって制御されます。バッテリ駆動のアプリケーションでは、この機能を使用することによって平均電流を大幅に低下させ、バッテリ駆動時間を延長することができます。全チャネル・フル・シャットダウンのイネーブル時間は  $15\mu\text{s}$ 、ディスエーブル時間は  $3\mu\text{s}$  です。ディスエーブル状態のとき、出力は高インピーダンス状態です。このアーキテクチャにより、TLV674xS をゲートで開閉可能なアンプとして動作させること (または本デバイスの出力を 1 つのコモン・アナログ出力バスにマルチプレクスすること) ができます。シャットダウン時間 ( $t_{OFF}$ ) は負荷条件に依存し、負荷抵抗が増加すると増加します。特定のシャットダウン時間内にシャットダウン (ディスエーブル) を確実に実行するには、指定された  $10\text{k}\Omega$  負荷を中間電源 ( $V_s/2$ ) に接続する必要があります。TLV674xS を負荷なしで使用すると、結果的にターンオフ時間が大幅に増加します。

### 8.3.8 露出サーマル・パッド付きパッケージ

TLV674x ファミリは、露出サーマル・パッドを備えた WSON-8 (DSG) などのパッケージで供給されます。パッケージ内で、ダイは導電性コンパウンドを使用して、このサーマル・パッドに取り付けられます。このため、露出サーマル・パッド付きのパッケージを使用する場合、サーマル・パッドは  $V_-$  に接続するか、フローティングのままにする必要があります。 $V_-$  以外の電位にサーマル・パッドを取り付けることは許可されず、これを行った場合にデバイスの性能は保証されません。

## 8.4 デバイスの機能モード

TLV674x ファミリは 1 つの機能モードを持っています。電源電圧が  $1.7\text{V}$  ( $\pm 0.85\text{V}$ ) と  $5.5\text{V}$  ( $\pm 2.75\text{V}$ ) の間にある限り、TLV6742 と TLV6744 は機能します。電源電圧が  $2.25\text{V}$  ( $\pm 1.125\text{V}$ ) と  $5.5\text{V}$  ( $\pm 2.75\text{V}$ ) の間にある限り、TLV6741 は機能します。

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

TLV674x ファミリは、10MHz の帯域幅、4.5V/μs のスルーレート、チャネルあたりわずか 890μA (TLV6741)、990μA (TLV6742/4) の消費電流を特長としており、非常に少ない消費電力で優れた AC 性能を実現します。DC アプリケーションには、3.5nV/vHz (TLV6742/4)、3.7nV/vHz (TLV6741) の非常に小さい入力ノイズ電圧 (10kHz 時)、小さい入力バイアス電流、0.15mV (標準値) の入力オフセット電圧が役に立ちます。

### 9.2 音声フィルタ付き単一電源エレクトレット・マイク・プリアンプ

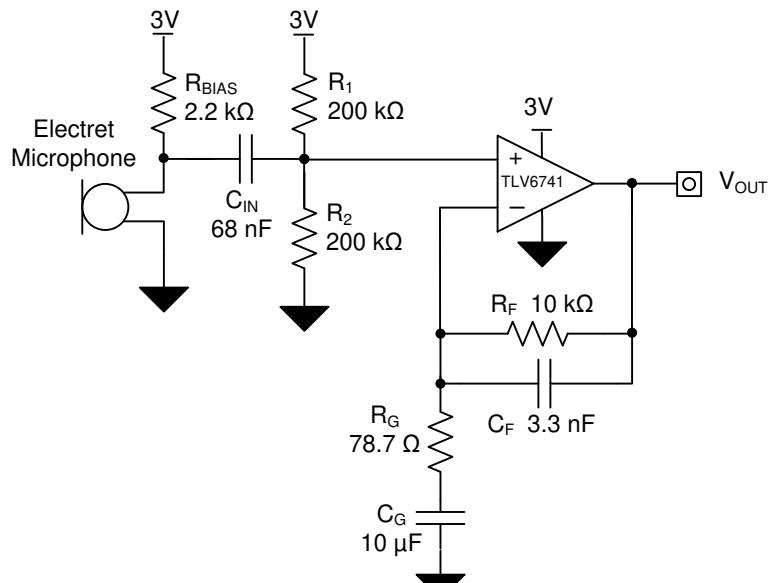

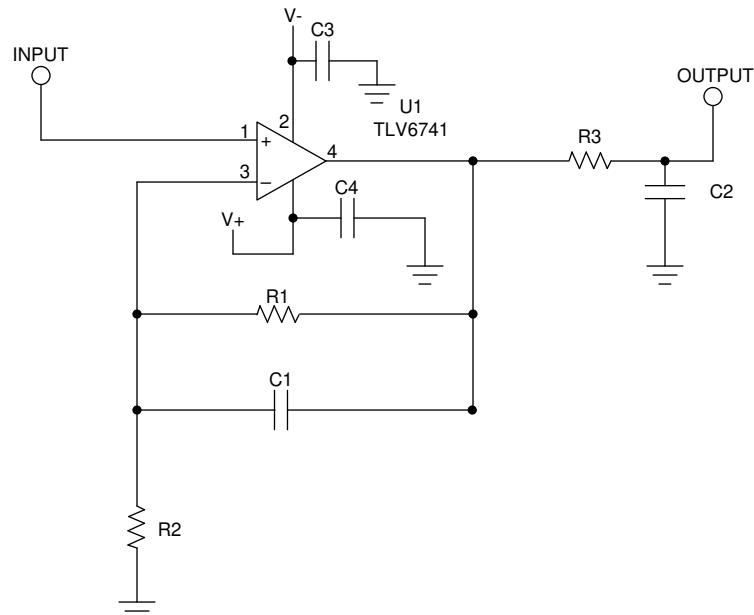

エレクトレット・マイクは、サイズが小さく、低コストであり、信号対雑音比 (SNR) が比較的優れているため、ポータブル電子機器で広く使われています。TLV674x ファミリの小さいパッケージ・サイズ、低い動作電圧、優れた AC 性能は、エレクトレット・マイク用のプリアンプ回路に最適です。図 9-1 に示す回路は、TLV6741 デバイスを使ったエレクトレット・マイク用単一電源プリアンプ回路です。

Copyright © 2017, Texas Instruments Incorporated

図 9-1. マイク・プリアンプ

#### 9.2.1 設計要件

設計要件は次のとおりです。

- 電源電圧: 3V

- 入力: 7.93mV<sub>RMS</sub> (0.63Pa, -38dB SPL のマイクを使用)

- 出力: 1V<sub>RMS</sub>

- 帯域幅: 300Hz～3kHz

#### 9.2.2 詳細な設計手順

式 1 に、V<sub>OUT</sub> と AC 入力信号の関係を定義する伝達関数を示します。

$$V_{OUT} = V_{IN\_AC} \times \left( 1 + \frac{R_F}{R_G} \right) \quad (1)$$

必要なゲインは、入力信号レベル期待値と目的の出力レベルに基づいて計算できます (式 2 を参照)。

$$G_{OPA} = \frac{V_{OUT}}{V_{IN\_AC}} = \frac{1V_{RMS}}{7.93mV_{RMS}} = 126 \frac{V}{V} \quad (2)$$

標準の  $10k\Omega$  の帰還抵抗を選択し、 $R_G$  を計算します。

$$R_G = \frac{R_F}{G_{OPA} - 1} = \frac{10k\Omega}{126 - 1} = 80\Omega \rightarrow 78.7\Omega \text{ (closest standard value)} \quad (3)$$

300Hz～3kHz の必要通過帯域での減衰を最小化するため、次のようにカットオフ周波数の上限 ( $f_H$ ) と下限 ( $f_L$ ) を必要帯域幅の外に設定します。

$$f_L = 200\text{Hz} \quad (4)$$

と

$$f_H = 5\text{kHz} \quad (5)$$

$f_L$  カットオフ周波数を設定するため、式 6 を使って  $C_G$  を選択します。

$$C_G = \frac{1}{2 \times \pi \times R_G \times f_L} = \frac{1}{2 \times \pi \times 78.7\Omega \times 200\text{Hz}} = 10.11\mu F \rightarrow 10\mu F \quad (6)$$

$f_H$  カットオフ周波数を設定するため、式 7 を使って  $C_F$  を選択します。

$$C_F = \frac{1}{2 \times \pi \times R_F \times f_H} = \frac{1}{2 \times \pi \times 10k\Omega \times 5\text{kHz}} = 3.18nF \rightarrow 3.3nF \text{ (Standard Value)} \quad (7)$$

低周波数の音波でも通過するように、入力信号のカットオフ周波数は十分に低く設定する必要があります。したがって、30Hz のカットオフ周波数 ( $f_{IN}$ ) を実現するため、式 8 を使って  $C_{IN}$  を選択します。

$$C_{IN} = \frac{1}{2 \times \pi \times (R_1 \parallel R_2) \times f_{IN}} = \frac{1}{2 \times \pi \times 100k\Omega \times 30\text{Hz}} = 53nF \rightarrow 68nF \text{ (Standard Value)} \quad (8)$$

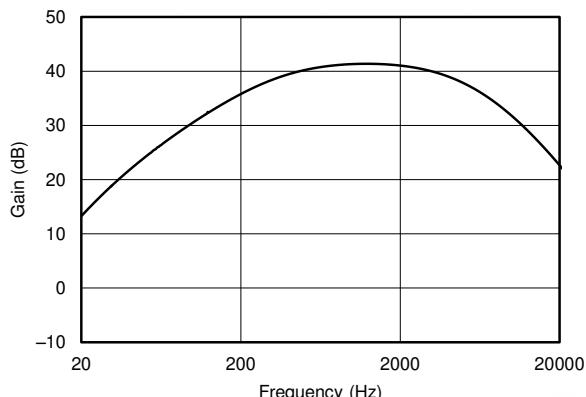

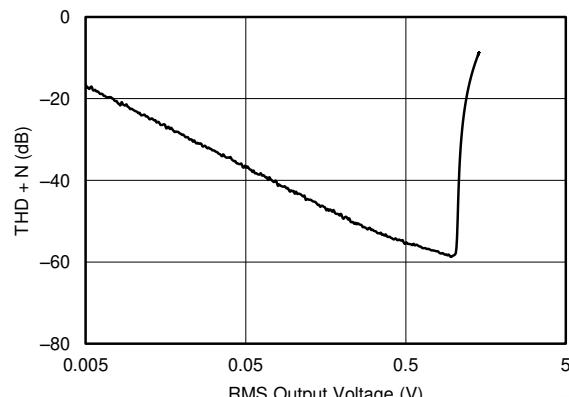

マイク・プリアンプ回路の伝達関数の測定値を図 9-2 に示し、マイク・プリアンプ回路の THD+N 性能の測定値を図 9-3 に示します。

### 9.2.3 アプリケーション曲線

図 9-2. ゲインと周波数との関係

図 9-3. THD + N と RMS 出力電圧との関係

## 10 電源に関する推奨事項

TLV6742 および TLV6744 デバイスは、1.7V～5.5V ( $\pm 0.85V \sim \pm 2.75V$ ) で動作することが規定されています。TLV6741 デバイスは、2.25V～5.5V ( $\pm 1.125V \sim \pm 2.75V$ ) で動作することが規定されています。TLV674x ファミリの仕様の多くは -40°C～125°C で適用されます

### 注意

7V を超える電源電圧を印加すると、デバイスに永続的な損傷を与える可能性があります ([セクション 7.1](#) を参照)。

電源ピンの近くに  $0.1\mu F$  のバイパス・コンデンサを配置すると、ノイズの多い電源や高インピーダンスの電源からの誤差を低減できます。バイパス・コンデンサの配置の詳細については、[セクション 11.1](#) を参照してください。

## 11 レイアウト

### 11.1 レイアウトのガイドライン

デバイスで最高の動作性能を実現するため、以下のような優れた PCB レイアウト手法を使用してください。

- ノイズが回路全体とオペアンプの電源ピンを経由して、アナログ回路に伝播することがあります。バイパス・コンデンサは、アナログ回路に対してローカルに低インピーダンスの電源を供給し、結合ノイズを低減するために使用されます。

- 各電源ピンとグランドとの間に、低 ESR の  $0.1\mu\text{F}$  セラミック・バイパス・コンデンサを接続し、可能な限りデバイスの近くに配置します。単一電源アプリケーションの場合は、V+ からグランドに対して単一のバイパス・コンデンサを接続します。

- 回路のアナログ部分とデジタル部分のグランドを分離することは、ノイズを抑制する最も簡単かつ効果的な方法の 1 つです。通常、多層 PCB のうち 1 つ以上の層はグランド・プレーン専用です。グランド・プレーンは熱の分散に役立ち、EMI ノイズを拾いにくくなります。グランド電流の流れに注意しながら、デジタル・グランドとアナログ・グランドを物理的に分離してください。

- 寄生カップリングを低減するには、入力配線を電源配線または出力配線からできるだけ離して配置します。これらの配線を離しておけない場合、敏感な配線をノイズの多い配線と平行に配線するのではなく、90 度で交差させる方がはるかに良い結果が得られます。

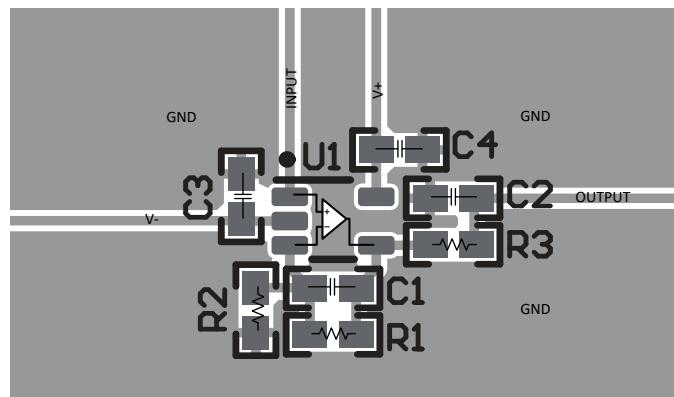

- 外付け部品は、可能な限りデバイスに近く配置します。図 11-1 に示すように、RF と RG を反転入力に近づけて配置すると、寄生容量が最小化されます。

- 入力の配線はできる限り短くします。入力配線は回路の最も敏感な部分であることに常に注意してください。

- 重要な配線の周囲に、駆動される低インピーダンスのガード・リングを配置することを検討します。ガード・リングを使用すると、付近に存在する、さまざまな電位の配線からのリーク電流を大幅に低減できます。

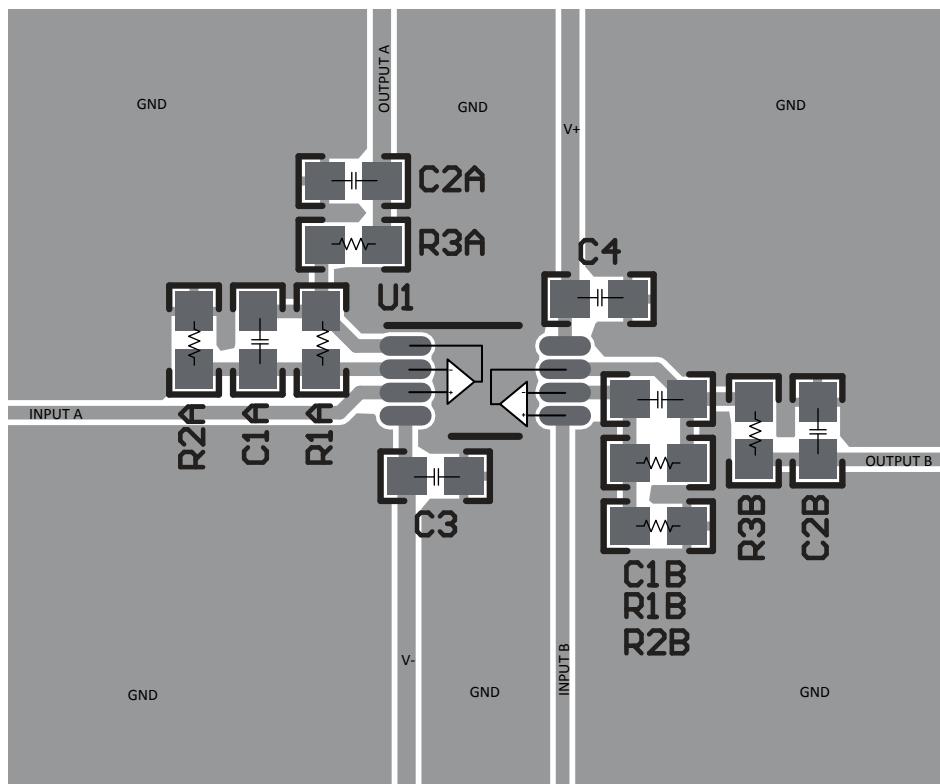

## 11.2 レイアウト例

図 11-1. 非反転構成のオペアンプ基板のレイアウト

Copyright © 2017, Texas Instruments Incorporated

図 11-2. レイアウト例の回路図

図 11-3. VSSOP-8 (DGK) パッケージのレイアウト例

## 12 デバイスおよびドキュメントのサポート

### 12.1 ドキュメントのサポート

#### 12.1.1 関連資料

関連資料については、以下を参照してください。

- 『QFN/SON の PCB 実装』

- 『クワッド・フラットパック・リード端子なしロジック・パッケージ』

- 『オペアンプの EMI 除去率』

### 12.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on [ti.com](http://ti.com). Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 12.3 サポート・リソース

**TI E2E™ サポート・フォーラム**は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

### 12.4 商標

TI E2E™ is a trademark of Texas Instruments.

Bluetooth® is a registered trademark of Bluetooth SIG, Inc.

すべての商標は、それぞれの所有者に帰属します。

### 12.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 12.6 Glossary

#### [TI Glossary](#)

This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number          | Status<br>(1) | Material type<br>(2) | Package   Pins        | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|--------------------------------|---------------|----------------------|-----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">TLV6741DCKR</a>    | Active        | Production           | SC70 (DCK)   5        | 3000   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | 18E                 |

| TLV6741DCKR.A                  | Active        | Production           | SC70 (DCK)   5        | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 18E                 |

| <a href="#">TLV6741DCKRG4</a>  | Active        | Production           | SC70 (DCK)   5        | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 18E                 |

| TLV6741DCKRG4.A                | Active        | Production           | SC70 (DCK)   5        | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 18E                 |

| <a href="#">TLV6741DCKT</a>    | Active        | Production           | SC70 (DCK)   5        | 250   SMALL T&R       | Yes         | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | 18E                 |

| TLV6741DCKT.A                  | Active        | Production           | SC70 (DCK)   5        | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 18E                 |

| <a href="#">TLV6742IDDFR</a>   | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | T42D                |

| TLV6742IDDFR.A                 | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | T42D                |

| <a href="#">TLV6742IDGKR</a>   | Active        | Production           | VSSOP (DGK)   8       | 2500   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 125   | 2H8T                |

| TLV6742IDGKR.A                 | Active        | Production           | VSSOP (DGK)   8       | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 2H8T                |

| <a href="#">TLV6742IDR</a>     | Active        | Production           | SOIC (D)   8          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | T6742D              |

| TLV6742IDR.A                   | Active        | Production           | SOIC (D)   8          | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | T6742D              |

| <a href="#">TLV6742IDSGR</a>   | Active        | Production           | WSON (DSG)   8        | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | D42S                |

| TLV6742IDSGR.A                 | Active        | Production           | WSON (DSG)   8        | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | D42S                |

| <a href="#">TLV6742IDSGRG4</a> | Active        | Production           | WSON (DSG)   8        | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | D42S                |

| TLV6742IDSGRG4.A               | Active        | Production           | WSON (DSG)   8        | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | D42S                |

| <a href="#">TLV6742IPWR</a>    | Active        | Production           | TSSOP (PW)   8        | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | T6742P              |

| TLV6742IPWR.A                  | Active        | Production           | TSSOP (PW)   8        | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | T6742P              |

| <a href="#">TLV6742SIRUGR</a>  | Active        | Production           | X2QFN (RUG)   10      | 3000   LARGE T&R      | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | -40 to 125   | HHF                 |

| TLV6742SIRUGR.A                | Active        | Production           | X2QFN (RUG)   10      | 3000   LARGE T&R      | Yes         | NIPDAUAG                             | Level-2-260C-1 YEAR               | -40 to 125   | HHF                 |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

**(4) Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**(5) MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

**(6) Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

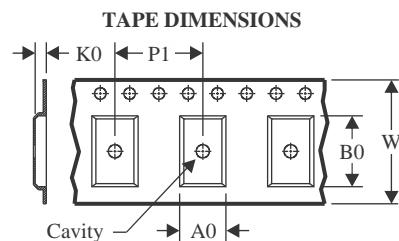

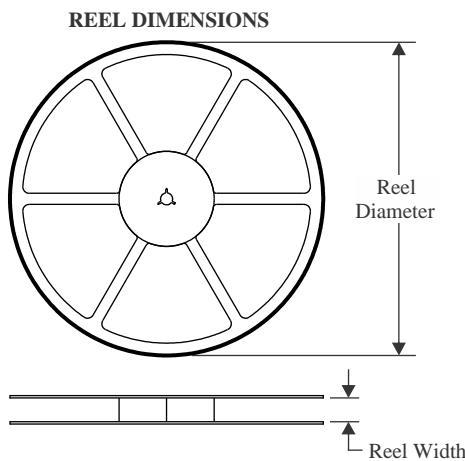

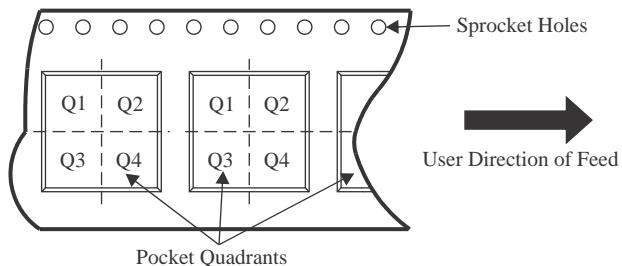

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TLV6741DCKR    | SC70         | DCK             | 5    | 3000 | 180.0              | 8.4                | 2.3     | 2.5     | 1.2     | 4.0     | 8.0    | Q3            |

| TLV6741DCKRG4  | SC70         | DCK             | 5    | 3000 | 178.0              | 9.0                | 2.4     | 2.5     | 1.2     | 4.0     | 8.0    | Q3            |

| TLV6741DCKT    | SC70         | DCK             | 5    | 250  | 180.0              | 8.4                | 2.3     | 2.5     | 1.2     | 4.0     | 8.0    | Q3            |

| TLV6741DCKT    | SC70         | DCK             | 5    | 250  | 178.0              | 9.0                | 2.4     | 2.5     | 1.2     | 4.0     | 8.0    | Q3            |

| TLV6742IDDFR   | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TLV6742IDGKR   | VSSOP        | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| TLV6742IDR     | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| TLV6742IDSGR   | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TLV6742IDSGRG4 | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

| TLV6742IPWR    | TSSOP        | PW              | 8    | 2000 | 330.0              | 12.4               | 7.0     | 3.6     | 1.6     | 8.0     | 12.0   | Q1            |

| TLV6742SIRUGR  | X2QFN        | RUG             | 10   | 3000 | 178.0              | 8.4                | 1.75    | 2.25    | 0.56    | 4.0     | 8.0    | Q1            |

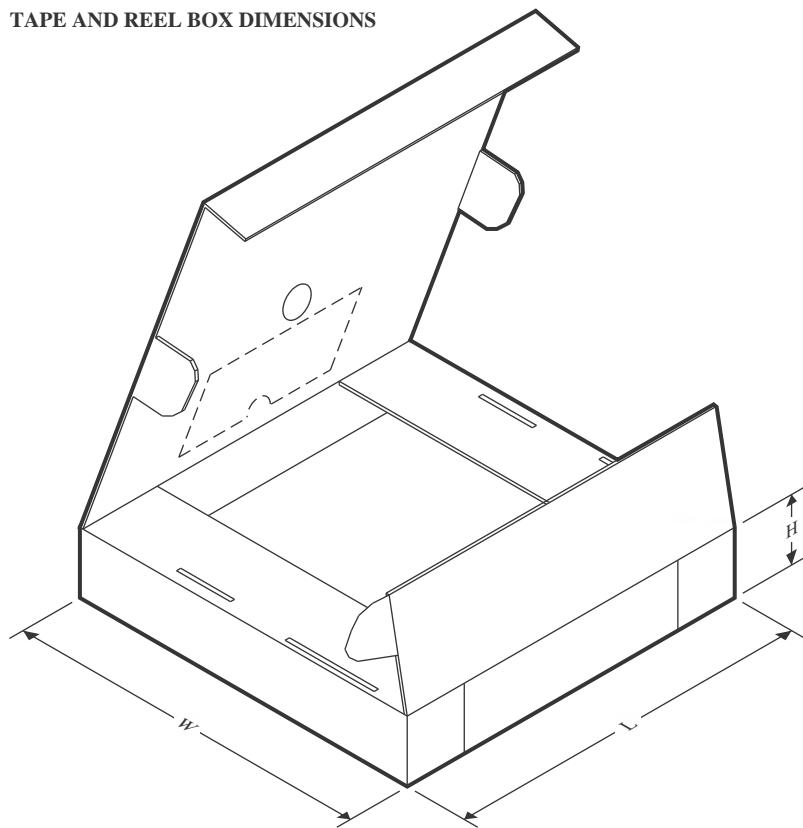

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV6741DCKR    | SC70         | DCK             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV6741DCKRG4  | SC70         | DCK             | 5    | 3000 | 190.0       | 190.0      | 30.0        |

| TLV6741DCKT    | SC70         | DCK             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| TLV6741DCKT    | SC70         | DCK             | 5    | 250  | 190.0       | 190.0      | 30.0        |

| TLV6742IDDFR   | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV6742IDGKR   | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| TLV6742IDR     | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| TLV6742IDSGR   | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV6742IDSGRG4 | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV6742IPWR    | TSSOP        | PW              | 8    | 2000 | 353.0       | 353.0      | 32.0        |

| TLV6742SIRUGR  | X2QFN        | RUG             | 10   | 3000 | 205.0       | 200.0      | 33.0        |

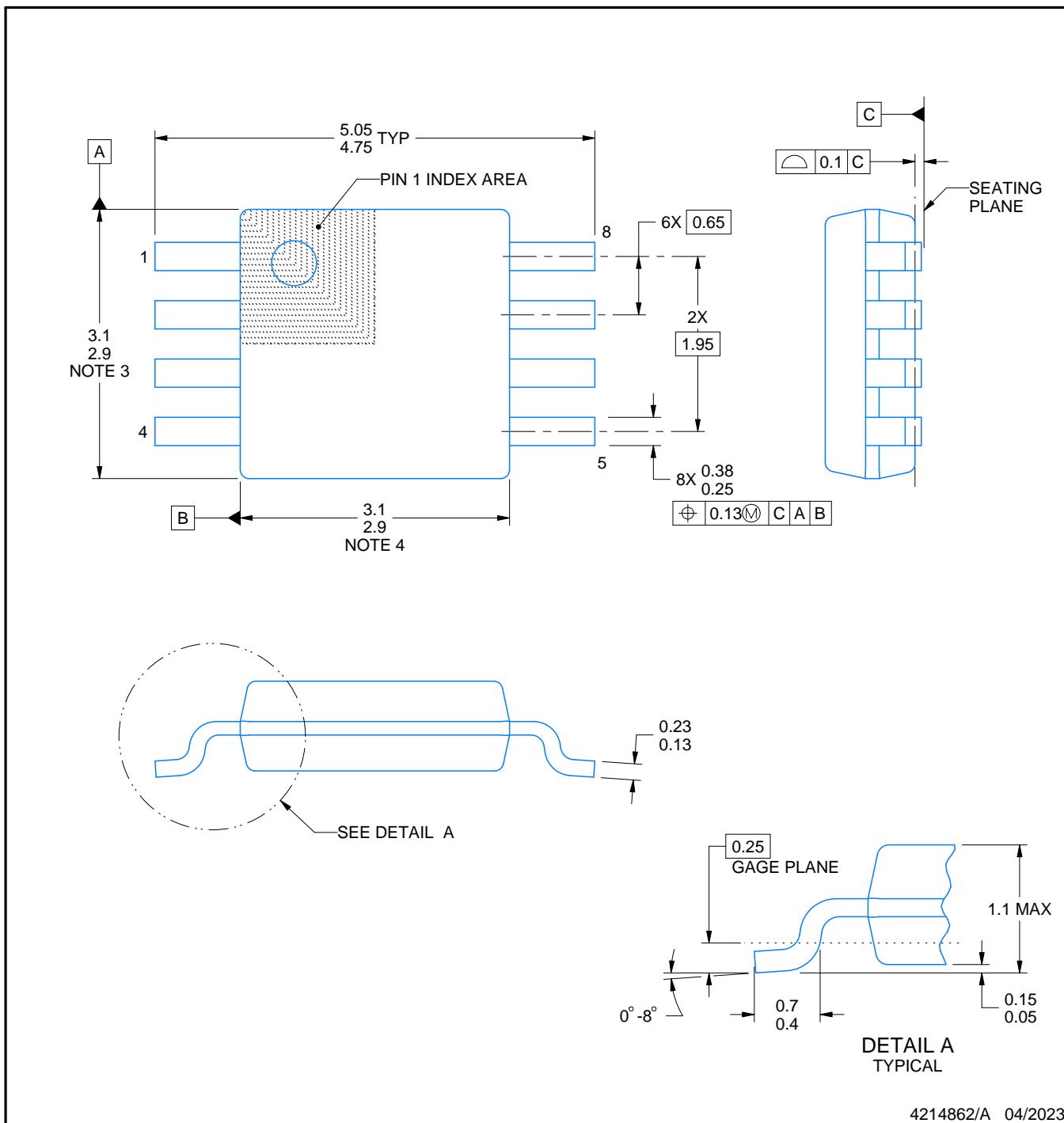

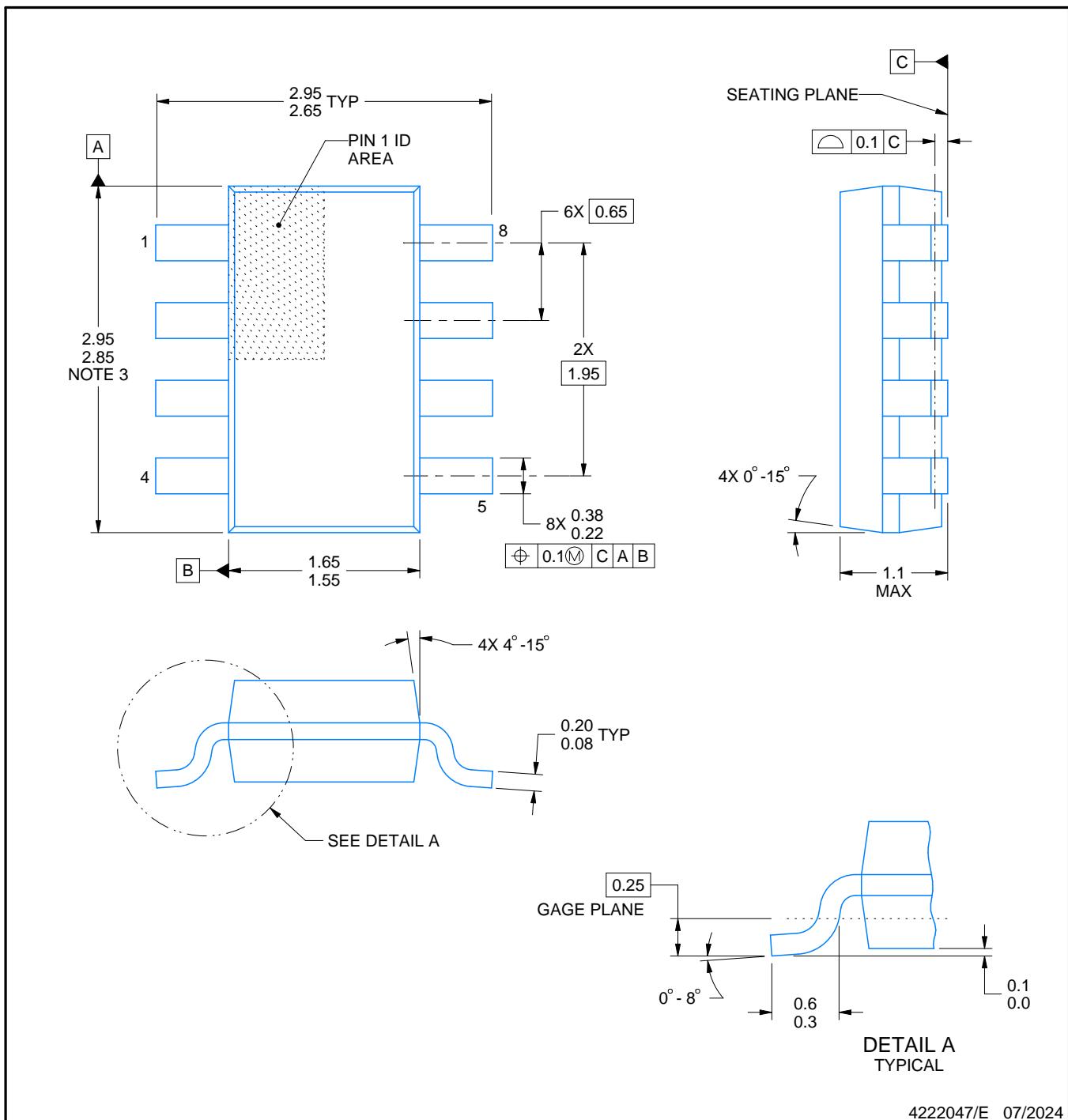

# PACKAGE OUTLINE

DGK0008A

VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MO-187.

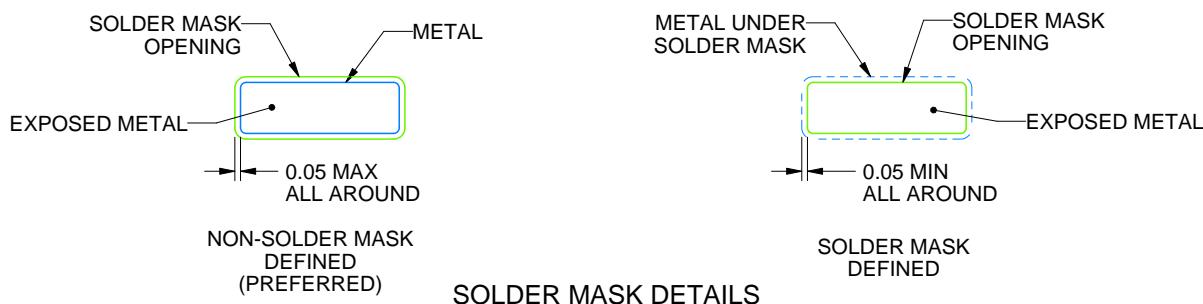

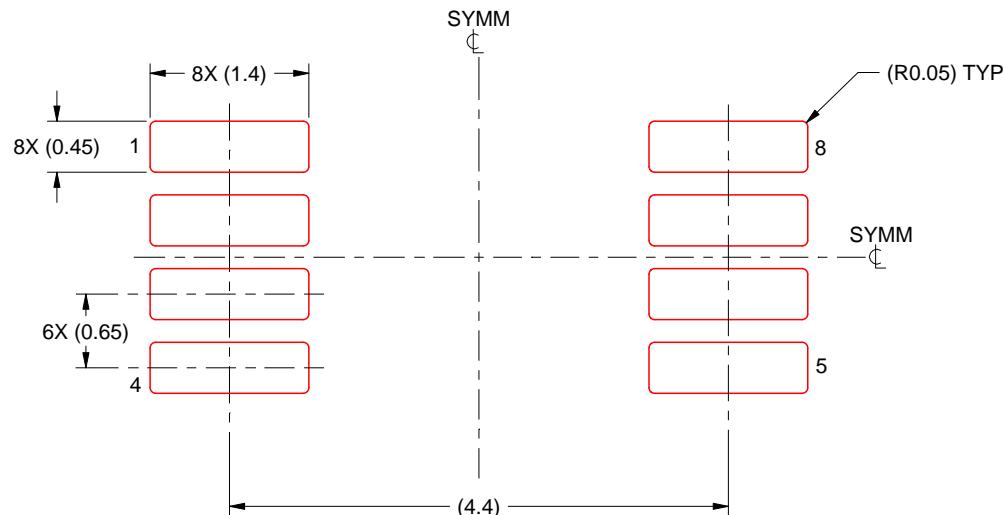

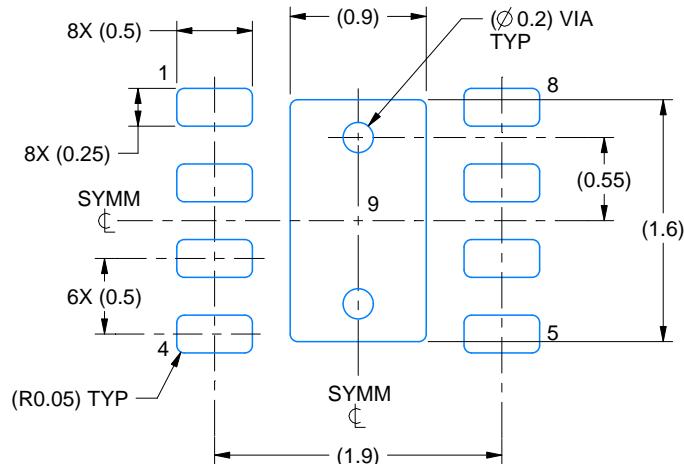

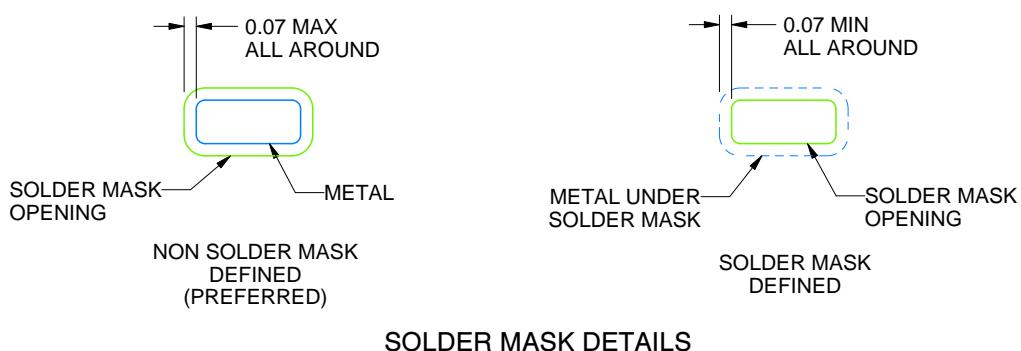

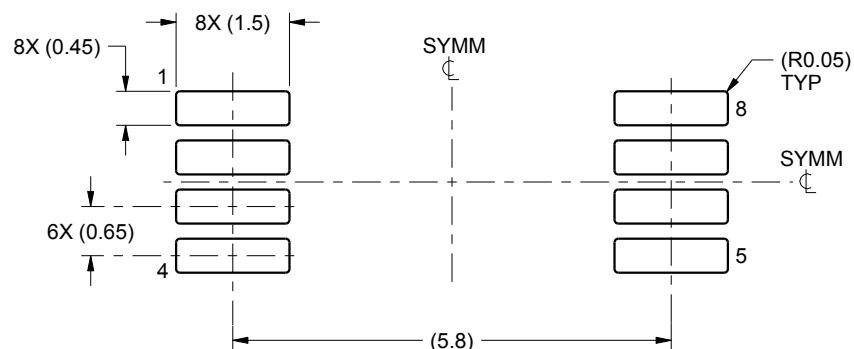

# EXAMPLE BOARD LAYOUT

DGK0008A

™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

4214862/A 04/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

9. Size of metal pad may vary due to creepage requirement.

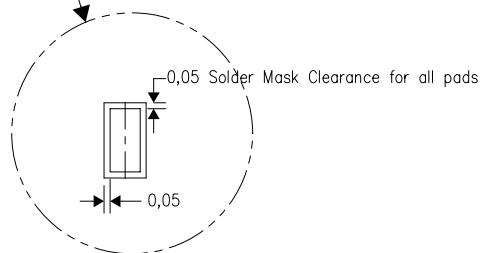

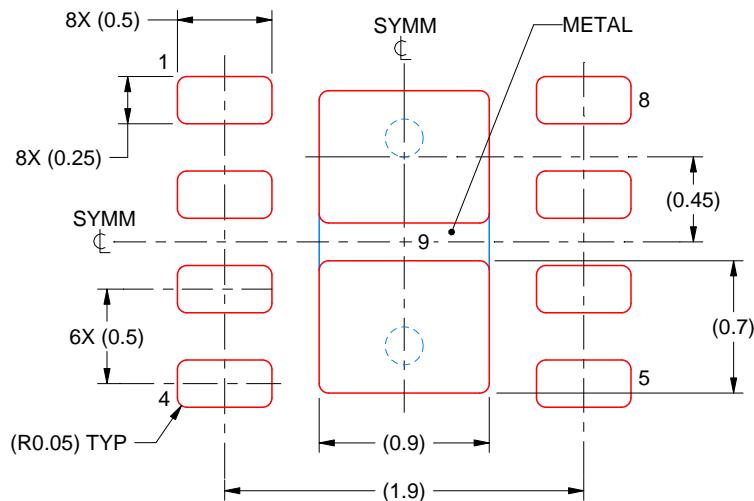

# EXAMPLE STENCIL DESIGN

DGK0008A

<sup>TM</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

SCALE: 15X

4214862/A 04/2023

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

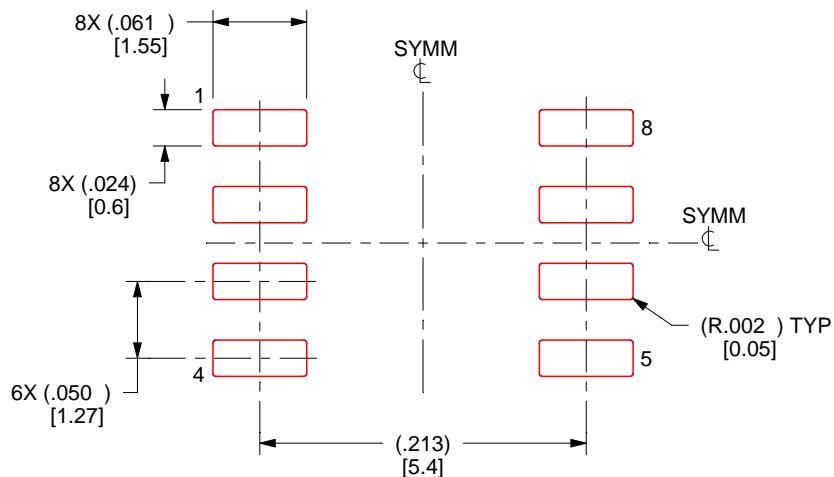

## GENERIC PACKAGE VIEW

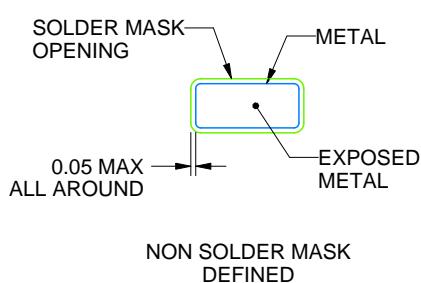

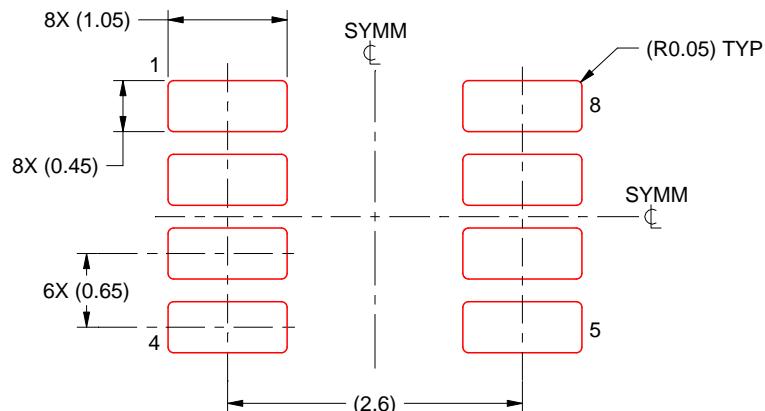

### RUG 10

1.5 x 2, 0.5 mm pitch

X2QFN - 0.4 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4231768/A

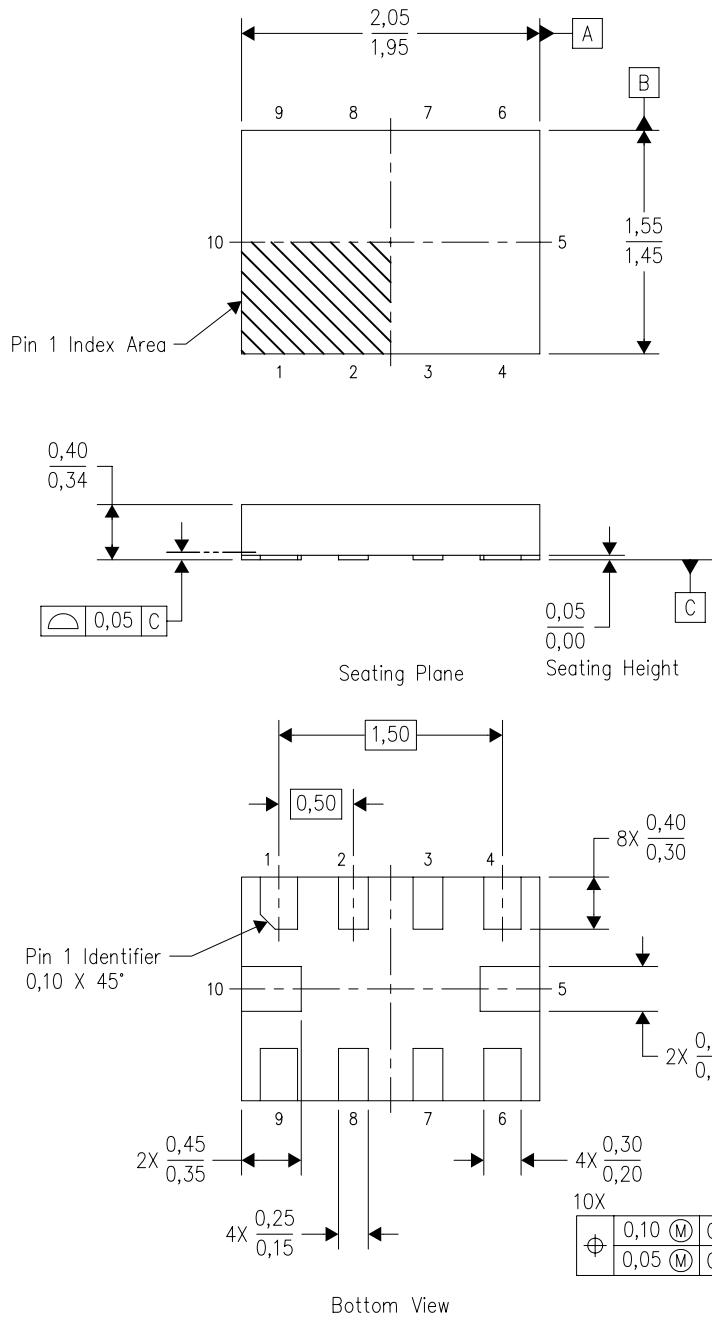

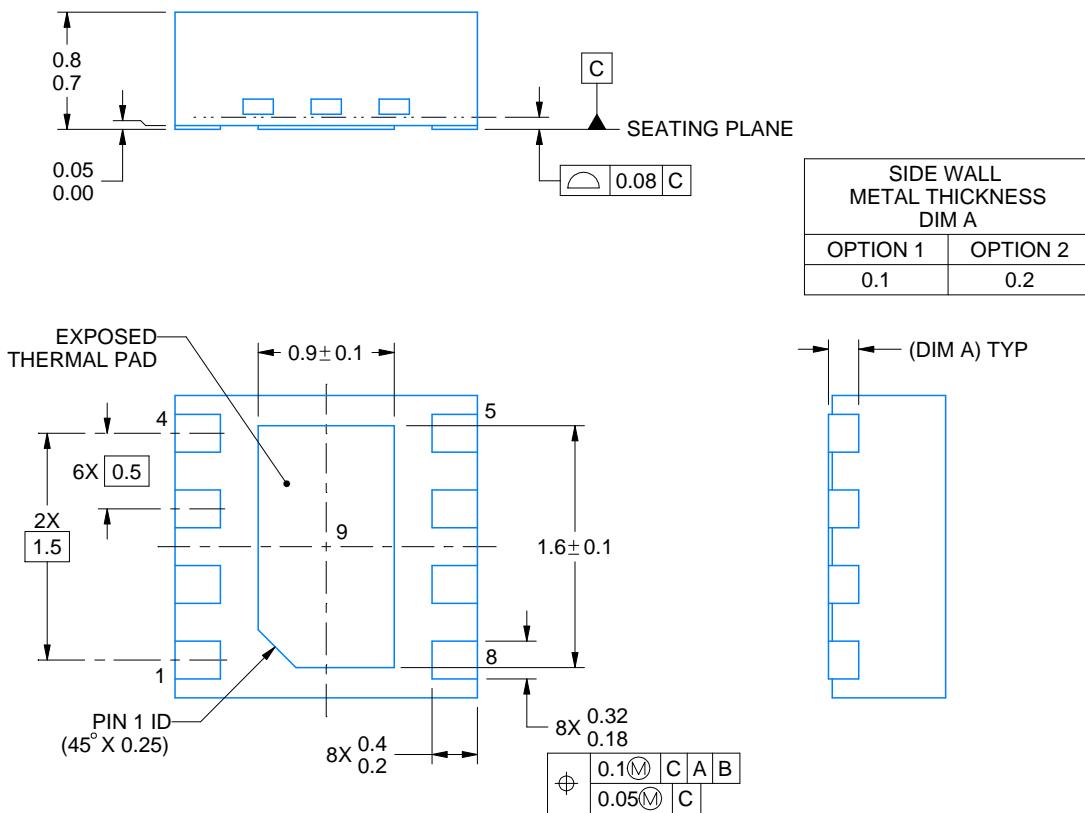

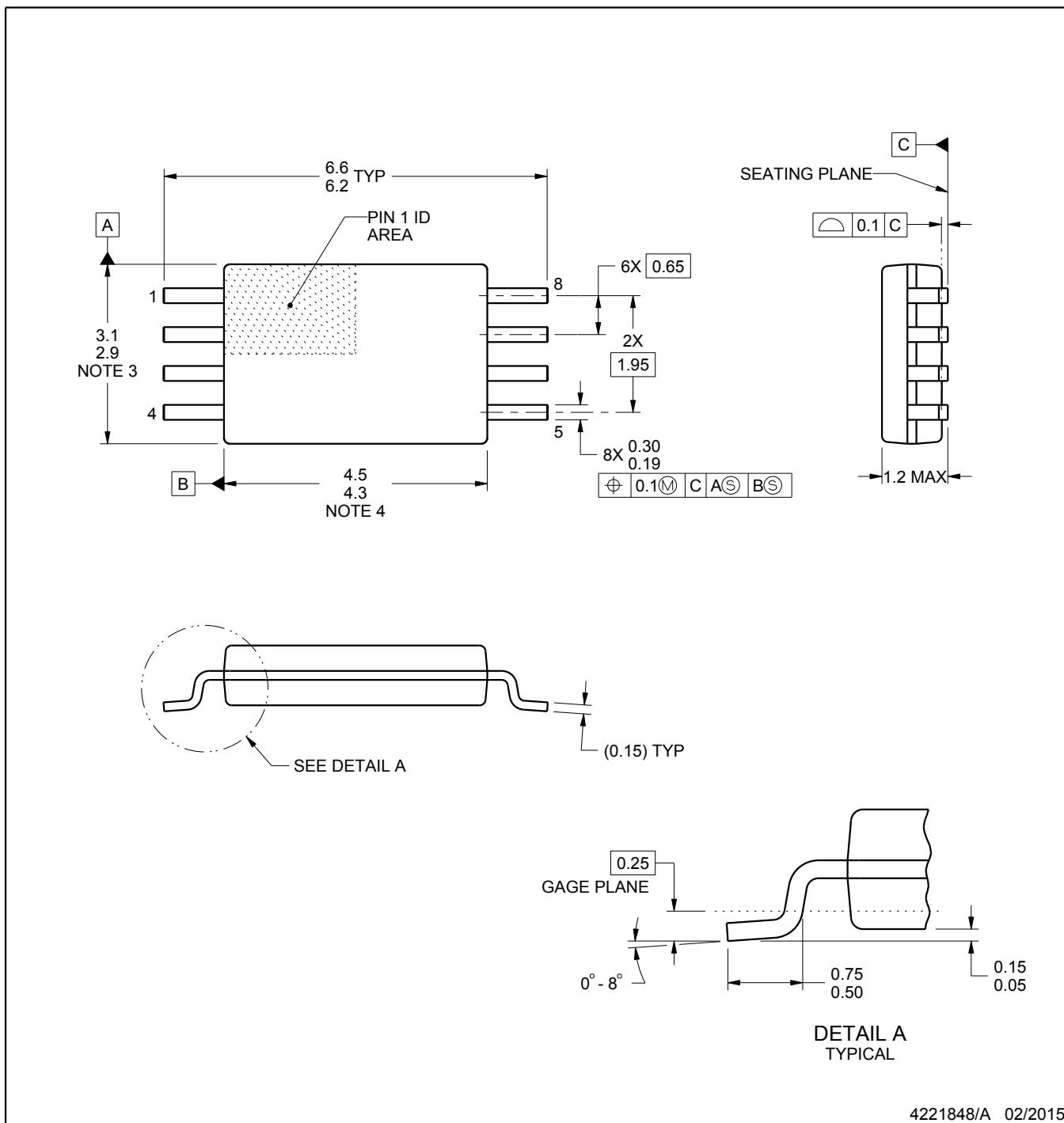

## MECHANICAL DATA

RUG (R-PQFP-N10)

PLASTIC QUAD FLATPACK

4208528-3/B 04/2008

- NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) package configuration.

- D. This package complies to JEDEC MO-288 variation X2EFD.

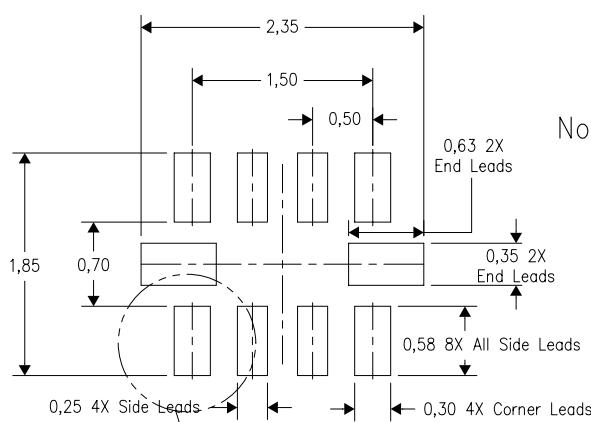

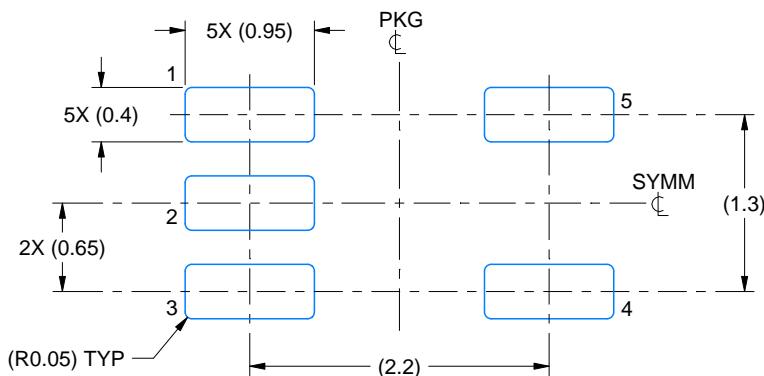

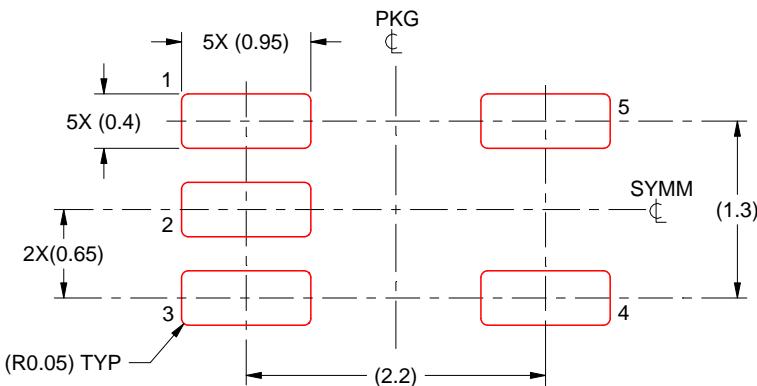

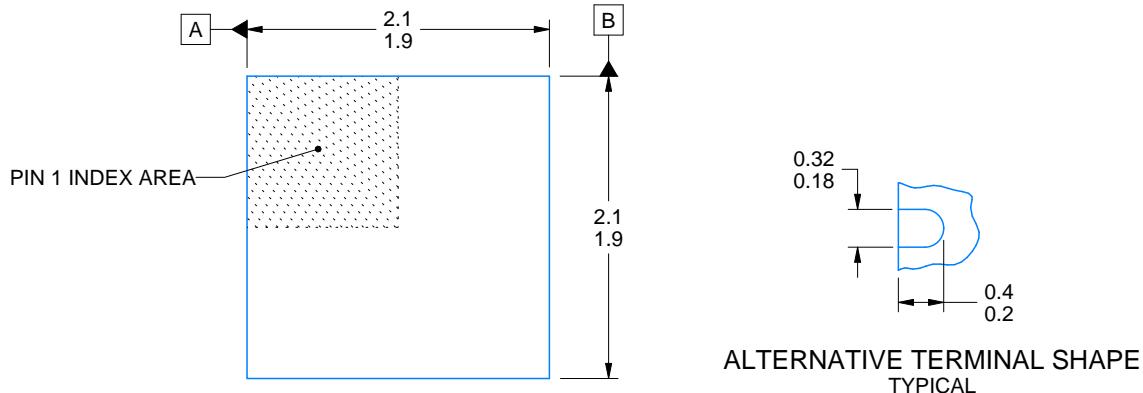

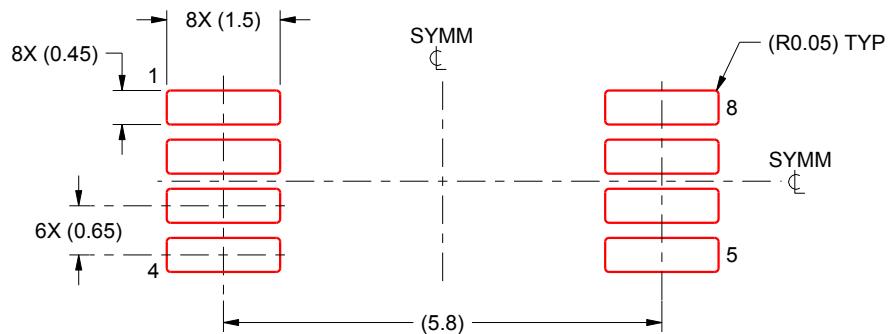

RUG (R-PQFP-N10)

Example Board Layout

Example Stencil Design

(Note E)

4210299-3/A 06/09

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Publication IPC-7351 is recommended for alternate designs.

- Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

- Maximum stencil thickness 0,127 mm (5 mils). All linear dimensions are in millimeters.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- Side aperture dimensions over-print land for acceptable area ratio  $> 0.66$ . Customer may reduce side aperture dimensions if stencil manufacturing process allows for sufficient release at smaller opening.

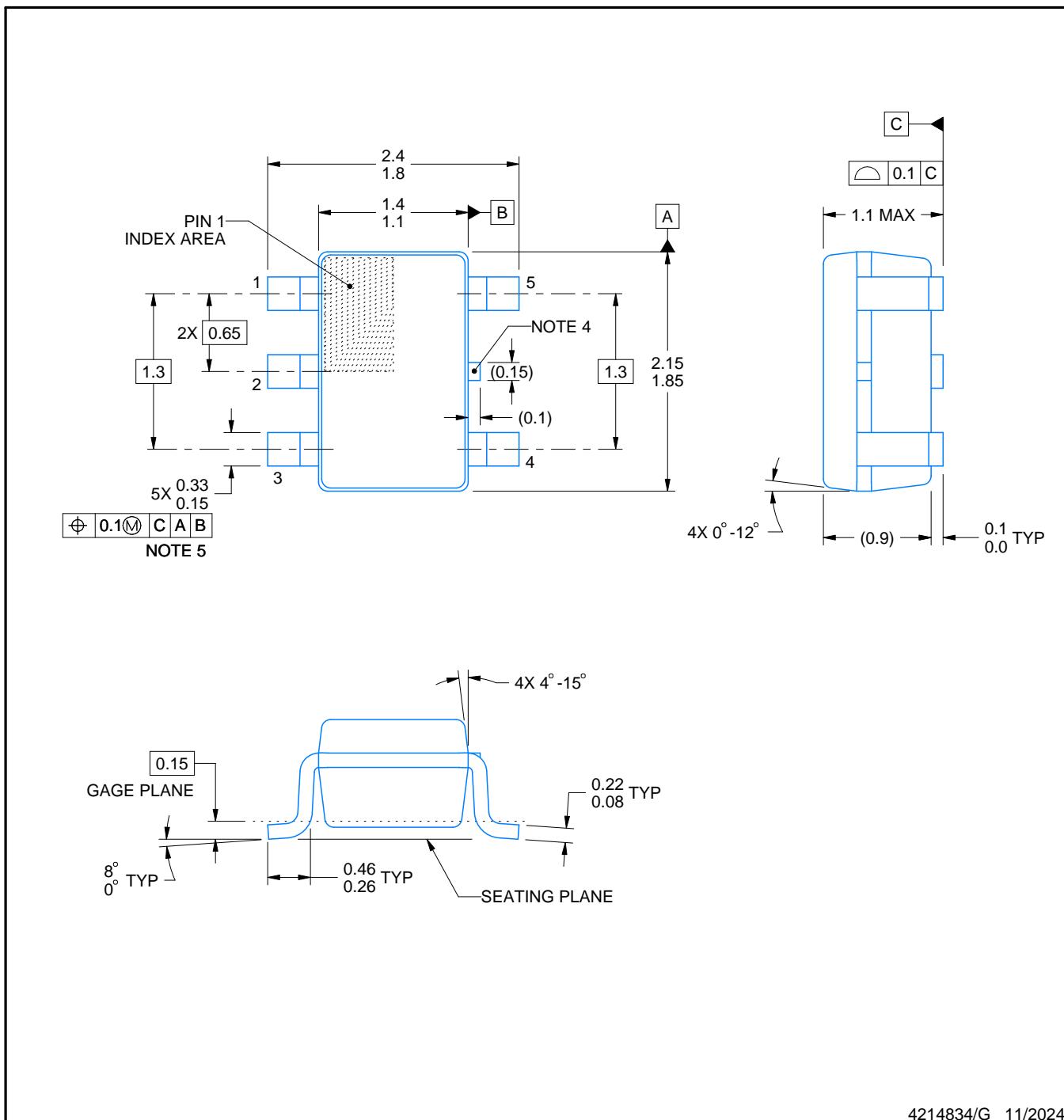

# PACKAGE OUTLINE

DCK0005A

SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-203.

4. Support pin may differ or may not be present.

5. Lead width does not comply with JEDEC.

6. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25mm per side

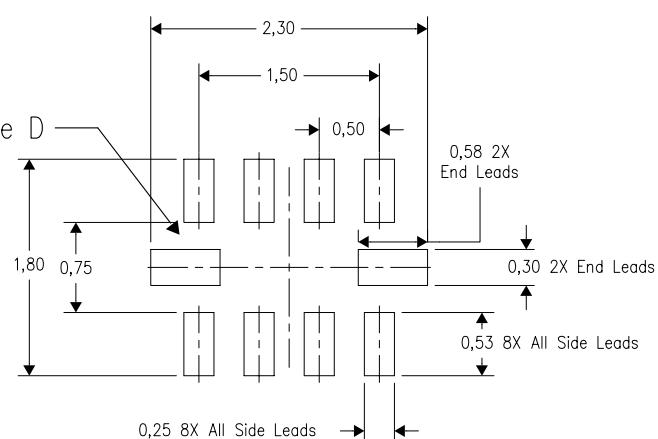

# EXAMPLE BOARD LAYOUT

DCK0005A

SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:18X

4214834/G 11/2024

NOTES: (continued)

7. Publication IPC-7351 may have alternate designs.

8. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

DCK0005A

SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

SOLDER PASTE EXAMPLE

BASED ON 0.125 THICK STENCIL

SCALE:18X

4214834/G 11/2024

NOTES: (continued)

9. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

10. Board assembly site may have different recommendations for stencil design.

# PACKAGE OUTLINE

DDF0008A

SOT-23-THIN - 1.1 mm max height

PLASTIC SMALL OUTLINE

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

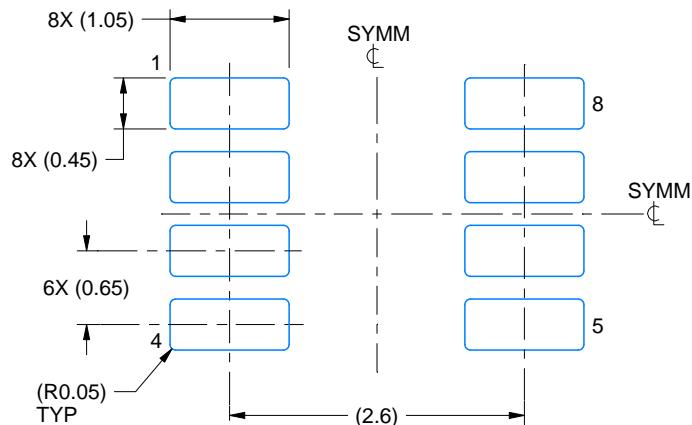

## EXAMPLE BOARD LAYOUT

**DDF0008A**

## **SOT-23-THIN - 1.1 mm max height**

## PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:15X

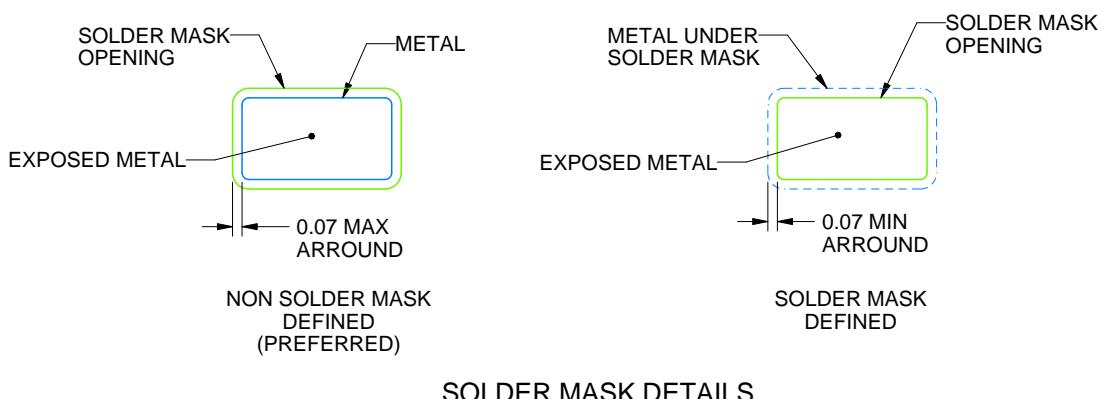

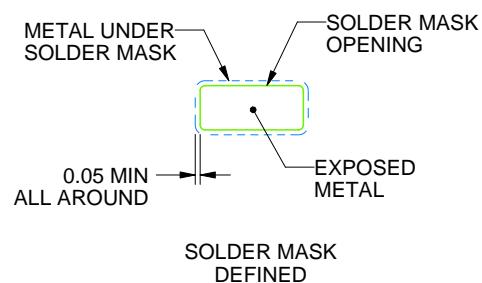

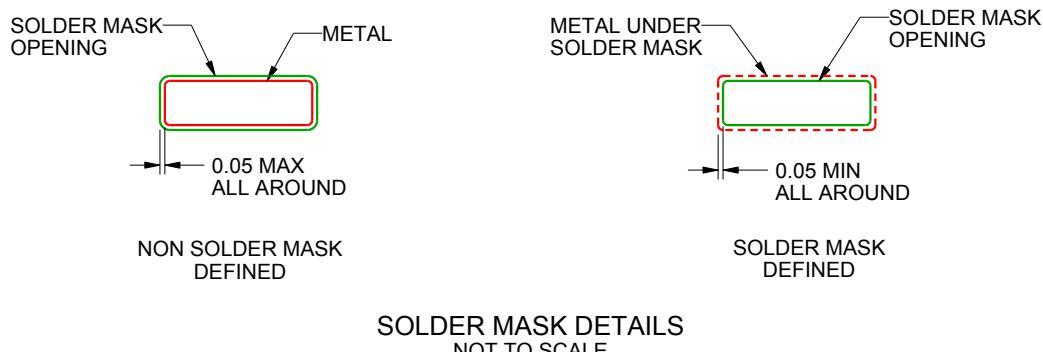

## SOLDER MASK DETAILS

4222047/E 07/2024

#### NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

DDF0008A

SOT-23-THIN - 1.1 mm max height

PLASTIC SMALL OUTLINE

4222047/E 07/2024

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

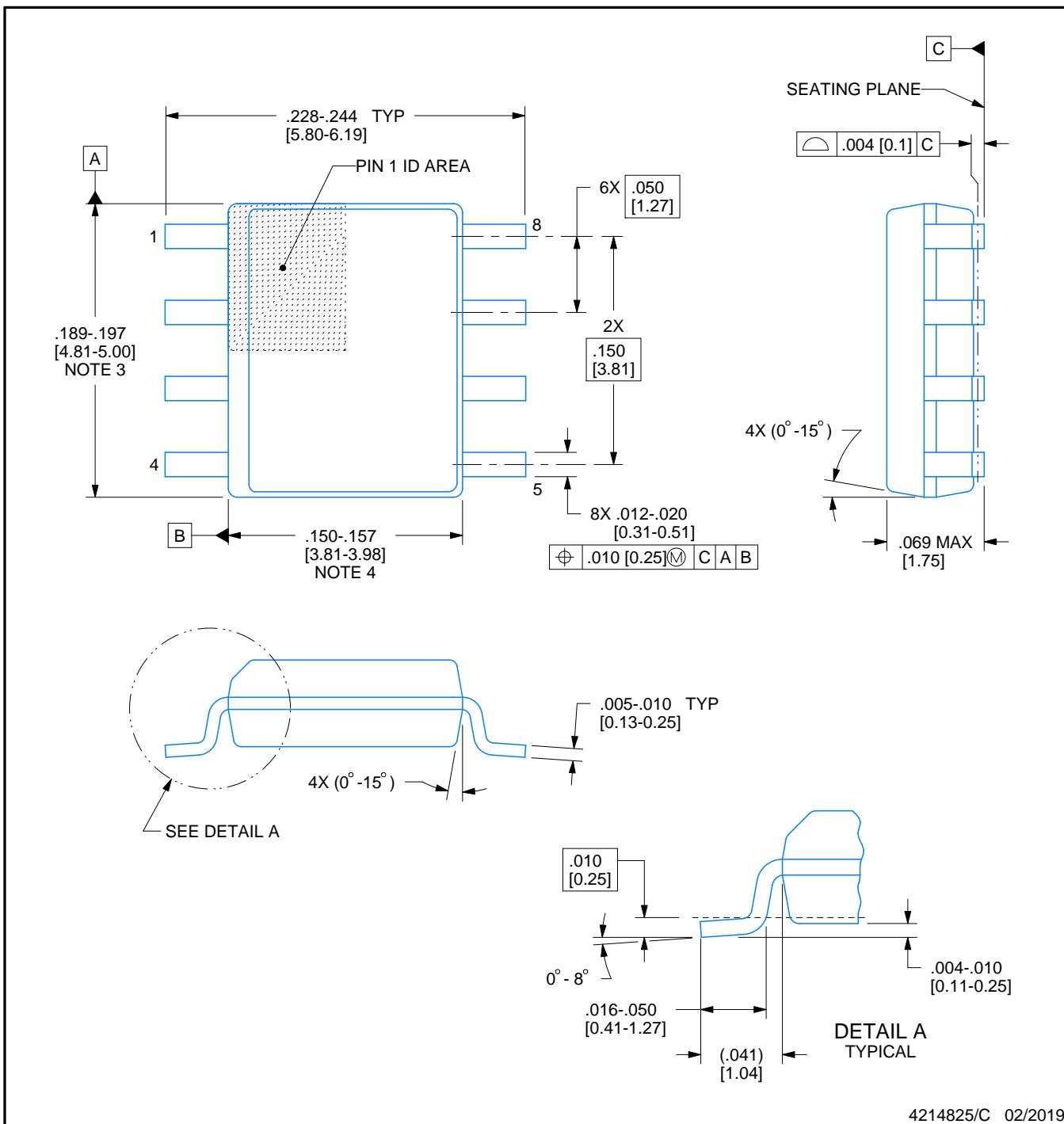

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

4. This dimension does not include interlead flash.

5. Reference JEDEC registration MS-012, variation AA.

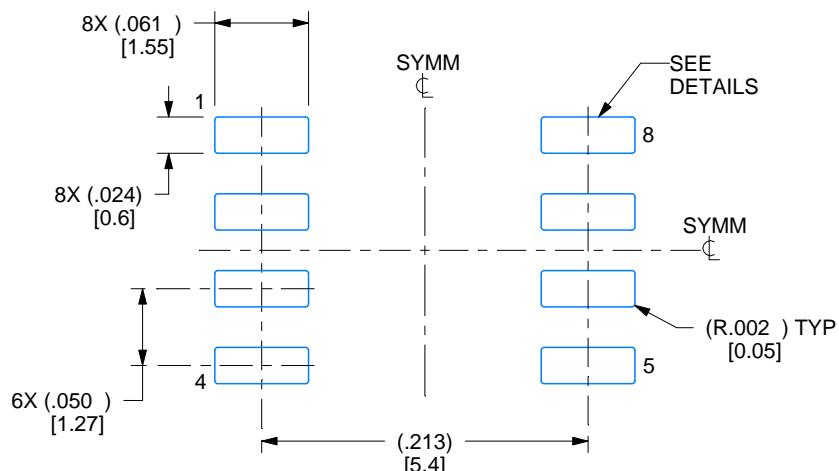

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

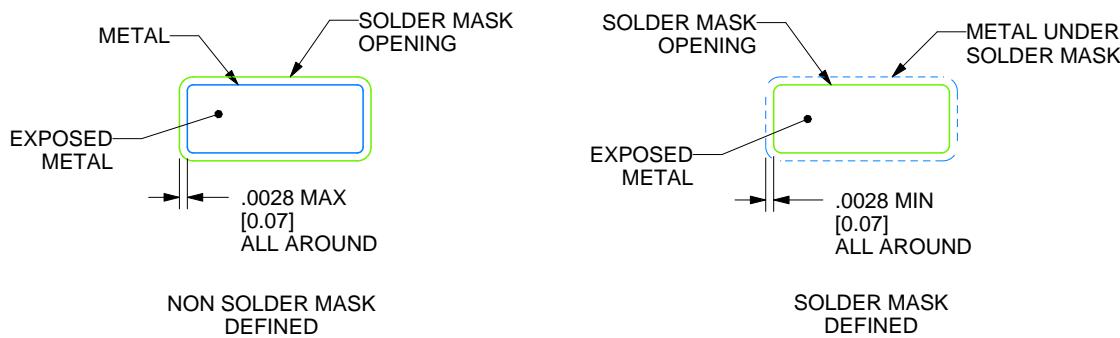

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.