#### features

- Fast Throughput Rate: 1.25 MSPS at 5 V, 625 KSPS at 3 V

- Wide Analog Channel Input: 0 V to AV<sub>DD</sub>

- Eight Analog Input Channels

- Channel Auto-Scan

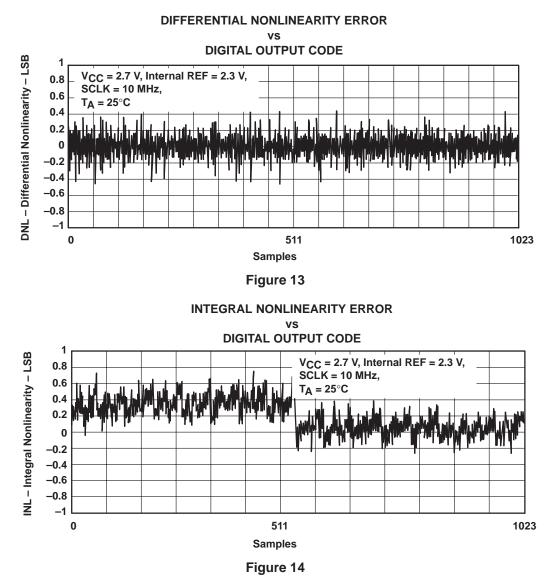

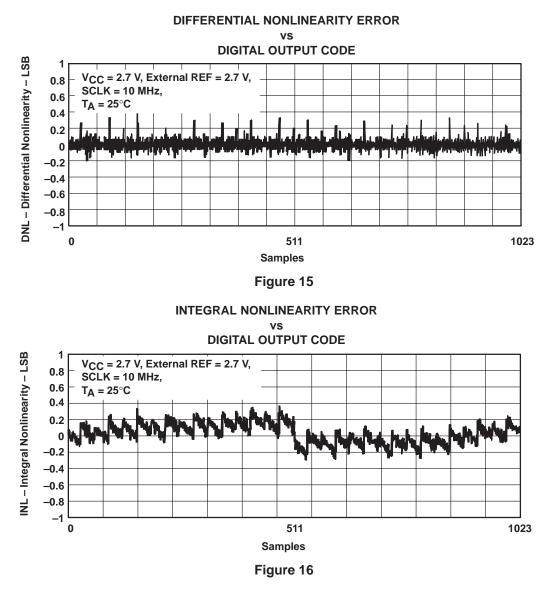

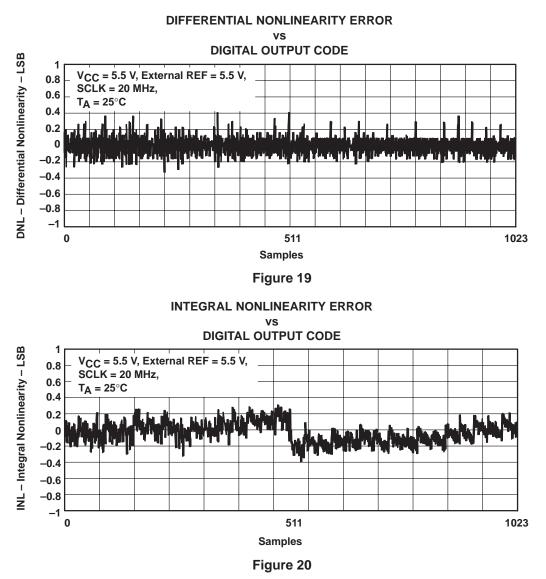

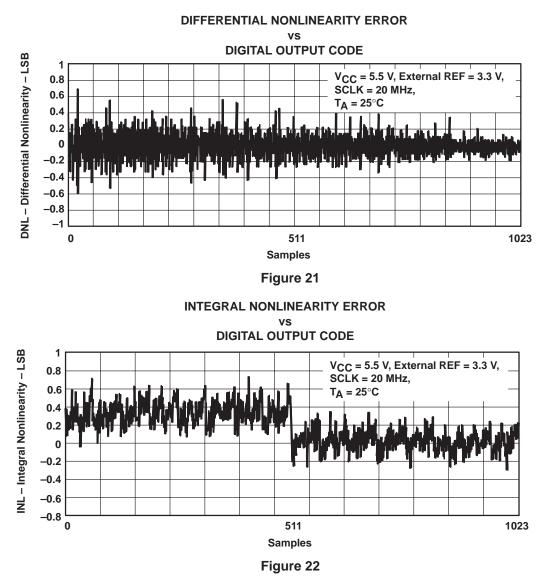

- Differential Nonlinearity Error: < ±1 LSB

- Integral Nonlinearity Error: < ±1 LSB

- Signal-to-Noise and Distortion Ratio: 57 dB

- Single 2.7-V to 5.5-V Supply Operation

- Very Low Power: 40 mW at 5.5 V, 8 mW at 2.7 V

- Autopower-Down: 300 μA Max

- Software Power Down: 10 μA Max

- Glueless Serial Interface to TMS320 DSPs and (Q)SPI Compatible Microcontrollers

- Programmable Internal Reference Voltage: 3.8-V Reference for 5-V Operation, 2.3-V Reference for 3-V Operation

#### applications

- Mass Storage and Hard Disk Drive

- Automotive

- Digital Servos

- Process Control

- General-Purpose DSP

- Image Sensor Processing

| DW OR PW PACKAGE<br>(TOP VIEW)                                            |                                                   |                                                          |                                                                                          |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| CH4 H<br>CH3 H<br>CH2 CH1 CH0<br>DV DD CH0<br>DGND H<br>FS SCLK<br>SDIN H | 1 O<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | 20<br>19<br>18<br>17<br>16<br>15<br>14<br>13<br>12<br>11 | AIN<br>MO<br>CH5<br>CH6<br>CH7<br>AV <sub>DD</sub><br>AGND<br>AGND<br>REF<br>CS<br>SDOUT |  |  |  |

#### description

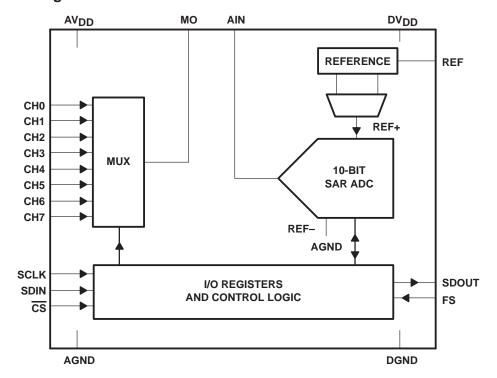

The TLV1570 is a 10-bit data acquisition system that combines an 8-channel input multiplexer (MUX), a high-speed 10-bit ADC, an on-chip reference, and a high-speed serial interface. The device contains an on-chip control register allowing control of channel selection, conversion start, reference voltage levels, and power down via the serial port. The MUX is independently accessible, which allows the user to insert a signal conditioning circuit such as an antialiasing filter or an amplifier, if required, between the MUX and the ADC. Therefore one signal conditioning circuit can be used for all eight channels.

The TLV1570 operates from a single 2.7-V to 5.5-V power supply. The device accepts an analog input range from 0 V to AV<sub>DD</sub> and digitizes the input at a maximum 1.25 MSPS throughput rate. Power dissipation is only 8 mW with a 2.7-V supply or 40 mW with a 5.5-V supply. The device features an autopower-down mode that automatically powers down to 300  $\mu$ A, 10 ns after a conversion is performed. With software power down enabled, the device is further powered down to only 10  $\mu$ A.

The TLV1570 communicates with digital microprocessors via a simple 4- or 5-wire serial port that interfaces directly to Texas Instruments TMS320 DSPs, and SPI<sup>™</sup> and QSPI<sup>™</sup> compatible microcontrollers without using additional glue logic.

A very high throughput rate, a simple serial interface, and low power consumption make the TLV1570 an ideal choice for high-speed digital signal processing requiring multiple analog inputs.

| AVAILABLE OPTIONS |                       |                       |  |  |  |

|-------------------|-----------------------|-----------------------|--|--|--|

|                   | PACKAGED DEVICES      |                       |  |  |  |

| TA                | SMALL OUTLINE<br>(DW) | SMALL OUTLINE<br>(PW) |  |  |  |

| 0°C to 70°C       | TLV1570CDW            | TLV1570CPW            |  |  |  |

| -40°C to 85°C     | TLV1570IDW            | TLV1570IPW            |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI and QSPI are trademarks of Motorola, Inc.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright  $\ensuremath{\textcircled{}}$  2000, Texas Instruments Incorporated

## functional block diagram

### **Terminal Functions**

| TERM      | INAL                   |     |                                                                                                                                                                                                                                                            |

|-----------|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.                    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                |

| AGND      | 14                     |     | Analog ground                                                                                                                                                                                                                                              |

| AIN       | 20                     | Ι   | ADC analog input                                                                                                                                                                                                                                           |

| AVDD      | 15                     |     | Analog supply voltage, 2.7 V to 5.5 V                                                                                                                                                                                                                      |

| CH0 – CH7 | 5,4,3,2,1,<br>18,17,16 | I   | Analog input channels 0 – 7                                                                                                                                                                                                                                |

| CS        | 12                     | I   | Chip select. A low level signal on $\overline{CS}$ enables the TLV1570. A high level signal on $\overline{CS}$ disables the device and disconnects power to the TLV1570.                                                                                   |

| DGND      | 7                      |     | Digital ground                                                                                                                                                                                                                                             |

| DVDD      | 6                      |     | Digital supply voltage, 2.7 V to 5.5 V                                                                                                                                                                                                                     |

| FS        | 8                      | I   | Frame sync. The falling edge of the frame sync pulse from a DSP indicates the start of a serial data frame shifted out of the TLV1570. FS is pulled high when interfaced to a microcontroller.                                                             |

| МО        | 19                     | 0   | On-chip MUX analog output                                                                                                                                                                                                                                  |

| REF       | 13                     | I   | Reference voltage input. The voltage applied to REF defines the input span of the TLV1570. In external reference mode, a 0.1 $\mu$ F decoupling capacitor must be placed between the reference and AGND. This is not required for internal reference mode. |

| SCLK      | 9                      | I   | Serial clock input. SCLK synchronizes the serial data transfer and is also used for internal data conversion.                                                                                                                                              |

| SDIN      | 10                     | Ι   | Serial data input used to configure the internal control register.                                                                                                                                                                                         |

| SDOUT     | 11                     | 0   | Serial data output. A/D conversion results are output at SDOUT.                                                                                                                                                                                            |

### detailed description

#### analog-to-digital converter

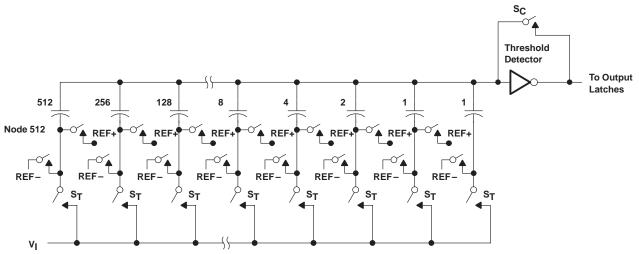

The TLV1570 ADC uses the SAR architecture described in this section. The CMOS threshold detector in the successive-approximation conversion system determines the value of each bit by examining the charge on a series of binary-weighted capacitors (see Figure 1). In the first phase of the conversion process, the analog input is sampled by closing the  $S_C$  switch and all  $S_T$  switches simultaneously. This action charges all of the capacitors to the input voltage.

NOTE: REF- is tied to AGND

Figure 1. Simplified Model of the Successive-Approximation System

In the next phase of the conversion process, all  $S_T$  and  $S_C$  switches are opened and the threshold detector begins identifying bits by identifying the charge (voltage) on each capacitor relative to the reference (REF–) voltage (REF– is tied to AGND). In the switching sequence, ten capacitors are examined separately until all ten bits are identified and then the charge-convert sequence is repeated. In the first step of the conversion phase, the threshold detector looks at the first capacitor (weight = 512). Node 512 of this capacitor is switched to the REF+ voltage, and the equivalent nodes of all the other capacitors on the ladder are switched to REF–. If the voltage at the summing node is greater than the trip point of the threshold detector (approximately one-half  $V_{CC}$ ), a bit 0 is placed in the output register and the 512-weight capacitor is switched to REF–. If the voltage at the summing node is less than the trip point of the threshold detector, a bit 1 is placed in the register and the 512-weight capacitor, a bit 1 is placed in the register and the 512-weight capacitor, a bit 1 is placed in the register and the 152-weight capacitor, a bit 1 is placed in the register and the 512-weight capacitor, a bit 1 is placed in the register and the 512-weight capacitor, a bit 1 is placed in the register and the 1512-weight capacitor, a bit 1 is placed in the register and the 512-weight capacitor, a bit 1 is placed in the register and the 512-weight capacitor, and so forth down the line until all bits are counted.

With each step of the successive-approximation process, the initial charge is redistributed among the capacitors. The conversion process relies on charge redistribution to count and weigh the bits from MSB to LSB.

In the case of the TLV1570, REF- is tied to ground and REF+ is connected to the REF input.

The TLV1570 can be programmed to use the on-chip internal reference (DI6=1). The user can select between two values of internal reference, 2.3 V or 3.8 V, using the control bit DI5.

During internal reference mode, the reference voltage is not output on the REF pin. Therefore it cannot be decoupled to analog ground (AGND), which acts as the negative reference for the ADC, using an external capacitor. Hence this mode requires the ground noise to be very low. The REF pin can be left open in this mode.

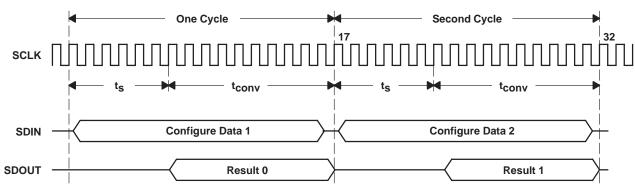

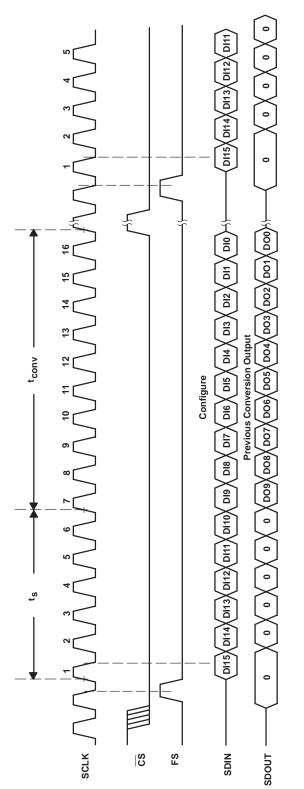

sampling frequency, fs

The TLV1570 requires 16 SCLKs for each sampling and conversion, therefore the equivalent maximum sampling frequency achievable with a given SCLK frequency is:

$f_{S(MAX)} = (1/16)f_{SCLK}$

#### power down

The TLV1570 offers two different power-down options. With autopower-down mode enabled, (DI4=0) the ADC proceeds to power down if FS is not detected on the 17th falling SCLK edge of a cycle (a cycle starts with FS being detected on a falling edge of SCLK) in DSP mode and after 16 SCLKs in  $\mu$ C mode. The TLV1570 will recover from auto power down when FS goes high in DSP mode or when the next SCLK comes in  $\mu$ C mode. In the case of software power down, the ADC goes to the software power-down state one cycle after CR.DI15 is set to 1. Unlike autopower down which recovers in 1 SCLK, software power down takes 16 SCLKs to recover.

|                              | DESCRIPTION                  | AUTOPOWER DOWN                                             | SOFTWARE<br>POWERDOWN<br>CS = DV <sub>DD</sub> |

|------------------------------|------------------------------|------------------------------------------------------------|------------------------------------------------|

| Maximum pov                  | ver down dissipation current | 300 μΑ                                                     | 10 μΑ                                          |

| Comparator                   |                              | Power down                                                 | Powerdown                                      |

| Clock buffer <sup>†</sup>    |                              | Power down                                                 | Powerdown                                      |

| Reference                    |                              | Active                                                     | Powerdown                                      |

| Register                     |                              | Not saved                                                  | Not saved                                      |

| Minimum pow                  | er down time                 | 1 SCLK                                                     | 1 μs                                           |

| Minimum resu                 | ime time                     | 1 SCLK                                                     | 800 ns                                         |

| Power down                   | DSP mode                     | No FS present one SCLK after previous conversion completed | CR.DI15 set to 1                               |

| Microprocessor mode (FS = 1) |                              | SCLK stopped after previous conversion completed           | CR.DI15 set to 1                               |

| Doworup                      | DSP mode                     | FS present                                                 | CR.DI15 set to 1                               |

| Power up                     | Microprocessor mode (FS = 1) | SCLK present                                               | CR.DI15 set to 1                               |

<sup>†</sup>Only in DSP mode is input buffer of clock in power-down mode.

<sup>‡</sup> The software power down enable/disable bit is not acted until the start of the next cycle (see section *configuring the TLV1570 for more information*.

### configuring the TLV1570

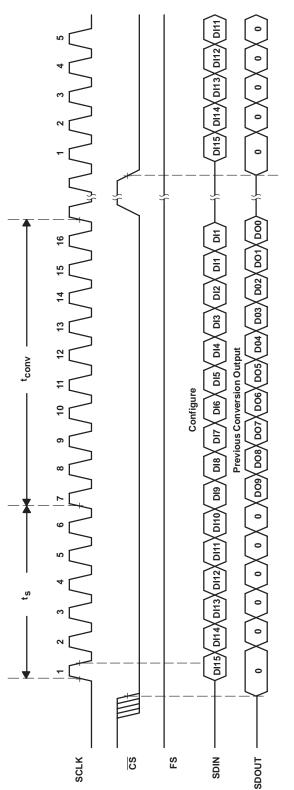

The TLV1570 is to be configured by writing the control bits to SDIN. The configuration will not take affect until the next cycle. A new configuration is needed for each conversion. Once the channel input and other options are selected, the conversion takes place in the next cycle. Conversion results are shifted out as conversion progresses (see Figure 2).

Figure 2. TLV1570 Configuration Cycle Timing

| BIT           | DESCR                                                                                         | IPTION                                                                                            | 5 V | 3 V      |  |

|---------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|----------|--|

|               | Software power down:                                                                          |                                                                                                   | Х   | Х        |  |

| DI15          | 0: Normal                                                                                     |                                                                                                   | x   | X        |  |

|               | 1: Power down enabled                                                                         |                                                                                                   |     |          |  |

| DI14          | Reads out values of the internal register, 1 - read. On                                       | ,                                                                                                 | Х   | Х        |  |

|               | These two bits select the self-test voltage to be applie                                      | ed to the ADC input during next clock cycle:                                                      | X   | X        |  |

|               | 00: Allow AIN to come in normally                                                             |                                                                                                   |     |          |  |

| DI13, DI12    | 01: Apply AGND to AIN                                                                         |                                                                                                   |     |          |  |

|               | 10: Apply VREF/2 to AIN                                                                       |                                                                                                   |     |          |  |

|               | 11: N/A                                                                                       |                                                                                                   |     | ┣──      |  |

|               | Choose speed application                                                                      |                                                                                                   | X   | X        |  |

| DI11          | 0: High speed (higher power consumption)                                                      |                                                                                                   |     |          |  |

|               | 1: Low speed (lower power consumption)                                                        |                                                                                                   |     | $\vdash$ |  |

| Ditto         | This bit enables channel auto-scan function.                                                  | This bit enables channel auto-scan function.                                                      |     |          |  |

| DI10          | 0: Autoscan disabled<br>1: Autoscan enabled                                                   |                                                                                                   |     |          |  |

|               | DI9 - DI7 These three bits select which of the eight channels is to be used (if $DI10 = 0$ ). | DI9, DI8 These two bits select the channel swept sequence used by auto scan mode (if $DI10 = 1$ ) | х   | х        |  |

|               | 000: Channel 0 selected as input                                                              | 00: Analog inputs CH0, CH1, CH2,, CH7 sequentially selected                                       |     |          |  |

|               | 001: Channel 1 selected as input                                                              | 01: Analog inputs CH1, CH3, CH5, CH7 sequentially selected                                        |     |          |  |

| DI9, DI8, DI7 | 010: Channel 2 selected as input                                                              | 10: Analog inputs CH0, CH2, CH4, CH6 sequentially selected                                        |     |          |  |

|               | 011: Channel 3 selected as input                                                              | 11: Analog inputs CH7, CH6, CH5,, CH0 sequentially selected                                       |     |          |  |

|               | 100: Channel 4 selected as input                                                              | DI7 Auto-scan reset                                                                               | ]   |          |  |

|               | 101: Channel 5 selected as input                                                              | 0: No reset                                                                                       | ]   |          |  |

|               | 110: Channel 6 selected as input                                                              | 1: Reset autoscan sequence                                                                        |     |          |  |

|               | 111: Channel 7 selected as input                                                              |                                                                                                   |     |          |  |

|               | Selects Internal or external reference voltage:                                               | -                                                                                                 | Х   | Х        |  |

| DI6           | 0: External<br>1: Internal                                                                    |                                                                                                   |     |          |  |

|               | Selects internal reference voltage value to be applied                                        | to the ADC during next conversion cycle.                                                          |     |          |  |

| DI5           | 0: 2.3 V                                                                                      |                                                                                                   |     | X        |  |

|               | 1: 3.8 V                                                                                      |                                                                                                   | Х   |          |  |

|               | Enables/disables autopower-down function:                                                     |                                                                                                   | Х   | Х        |  |

| DI4           | 1: Enable                                                                                     |                                                                                                   |     |          |  |

|               | 0: Disable                                                                                    |                                                                                                   |     |          |  |

|               | Performance optimizer – linearity                                                             |                                                                                                   |     |          |  |

| DI3           | 0: AV <sub>DD</sub> = 5.5 V to 3.6 V<br>1: AV <sub>DD</sub> = 3.5 V to 2.7 V                  |                                                                                                   | X   | X        |  |

| DI2           | Always write 0 (reserved bit)                                                                 |                                                                                                   | X   | X        |  |

| DI1           | Always write 0 (reserved bit)                                                                 |                                                                                                   | X   | X        |  |

|               |                                                                                               |                                                                                                   |     | 1        |  |

### configuration register (CR) definition

### initialization-software sequence

This sequence shows the default settings, unless otherwise specified. The ADC requires that the user write to it every cycle. There is a cycle delay before control bits are implemented.

| -           |                  | -                  |                                                                                                      |                                                           |

|-------------|------------------|--------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| CYCLE       | WRITE TO<br>SDIN | CHANNEL<br>SAMPLED | OUTPUT FROM<br>SDOUT                                                                                 | COMMENT                                                   |

| 1st         | 0040h            | N/A                | Invalid                                                                                              | No analog input channel sampled                           |

| 2nd         | 01C0h            | N/A                | Invalid                                                                                              | No analog input channel sampled                           |

| 3rd         | 0040h            | 3                  | From Channel 3                                                                                       |                                                           |

| 4th         | 8040h            | 0                  | From Channel 0                                                                                       | Software power down enabled                               |

| 5th         | 0040h            | N/A                | Invalid                                                                                              | Software power-down mode, no analog input channel sampled |

| Wait 800 ns |                  | -                  | Recovery time, no analog input channel sampled (16 SCLKs if $AV_{DD} = 5 V$ and $f_{CLK} = 20 MHz$ ) |                                                           |

| 6th         | 0140h            | N/A                | Invalid                                                                                              | Recovery time, no analog input channel sampled            |

| 7th         | 0040h            | 2                  | From Channel 2                                                                                       |                                                           |

#### **Example 1. Normal Sample Mode With Internal Reference**

#### Example 2. Auto Scan Mode

| CYCLE | WRITE TO<br>SDIN | CHANNEL<br>SAMPLED | OUTPUT FROM<br>SDOUT | COMMENT                                                 |

|-------|------------------|--------------------|----------------------|---------------------------------------------------------|

| 1st   | 0480h            | N/A                | Invalid              | Autoscan reset enabled, no analog input channel sampled |

| 2nd   | 0480h            | N/A                | Invalid              | No analog input channel sampled                         |

| 3rd   | 0400h            | 0                  | From Channel 0       |                                                         |

| 4th   | 0400h            | 1                  | From Channel 1       |                                                         |

| 5th   | 0400h            | 2                  | From Channel 2       |                                                         |

| 6th   | 0400h            | 3                  | From Channel 3       |                                                         |

| 7th   | 0400h            | 4                  | From Channel 4       |                                                         |

| 8th   | 0400h            | 5                  | From Channel 5       |                                                         |

| 9th   | 0400h            | 6                  | From Channel 6       |                                                         |

| 10th  | 0400h            | 7                  | From Channel 7       |                                                         |

| 11th  | 0400h            | 0                  | From Channel 0       |                                                         |

NOTE: If software power down is enabled during auto-scan mode, the next channel in the sequence is skipped.

### initialization-software sequence (continued)

#### Example 3. Auto-Scan Mode

This example shows a change in sequence in the middle of the current sequence. The following shows that after the initial autoscan reset, a reset is not necessary again when switching channel sequences.

| CYCLE | WRITE TO<br>SDIN | CHANNEL<br>SAMPLED | OUTPUT FROM<br>SDOUT | COMMENT                                                 |

|-------|------------------|--------------------|----------------------|---------------------------------------------------------|

| 1st   | 0480h            | N/A                | N/A                  | No analog input channel sampled                         |

| 2nd   | 0480h            | N/A                | N/A                  | Autoscan reset enabled, no analog input channel sampled |

| 3rd   | 0400h            | 0                  | From Channel 0       | Start of sequence 0                                     |

| 4th   | 0700h            | 1                  | From Channel 1       | Enable channel sequence 3 (no auto-scan reset required) |

| 5th   | 0700h            | 7                  | From Channel 7       | Start of sequence 3                                     |

| 6th   | 0700h            | 6                  | From Channel 6       |                                                         |

| 7th   | 0700h            | 5                  | From Channel 5       |                                                         |

| 8th   | 0700h            | 4                  | From Channel 4       |                                                         |

| 9th   | 0700h            | 3                  | From Channel 3       |                                                         |

| 10th  | 0700h            | 2                  | From Channel 2       |                                                         |

| 11th  | 0700h            | 1                  | From Channel 1       |                                                         |

| 12th  | 0700h            | 0                  | From Channel 0       |                                                         |

#### Example 4. Auto-Scan Mode

This example shows a switch in sequence in the course of a sequence. The following shows that a particular sequence does not have to be continued if remaining channels do not need to be sampled (i.e., only channel 1 through channel 5 sampled, not channels 6, 7, 8)

| CYCLE | WRITE TO<br>SDIN | CHANNEL<br>SAMPLED | OUTPUT FROM<br>SDOUT | COMMENT                                                 |

|-------|------------------|--------------------|----------------------|---------------------------------------------------------|

| 1st   | 0480h            | N/A                | N/A                  | No analog input channel sampled                         |

| 2nd   | 0480h            | N/A                | N/A                  | Autoscan reset enabled, no analog input channel sampled |

| 3rd   | 0400h            | 0                  | From Channel 0       |                                                         |

| 4th   | 0400h            | 1                  | From Channel 1       |                                                         |

| 5th   | 0400h            | 2                  | From Channel 2       |                                                         |

| 6th   | 0400h            | 3                  | From Channel 3       |                                                         |

| 7th   | 0400h            | 4                  | From Channel 4       |                                                         |

| 8th   | 0480h            | 5                  | From Channel 5       | Autoscan reset enabled                                  |

| 9th   | 0400h            | 0                  | From Channel 0       | Sequence is reset to channel 0                          |

| 10th  | 0400h            | 1                  | From Channel 1       |                                                         |

| 11th  | 0400h            | 2                  | From Channel 2       |                                                         |

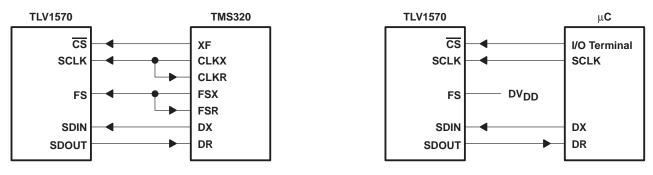

The TLV1570 is a 800-ns 10-bit 8-analog input channel analog-to-digital converter with a throughput of up to 1.25 MSPS at 5 V and up to 625 KSPS at 3 V respectively. To run at its fastest conversion rate, it must be clocked at 20 MHz at 5-V or 10 MHz at 3-V. The TLV1570 can be easily interfaced to microcontrollers, ASICs, DSPs, or shift registers. The TLV1570 serial interface is designed to be fully compatible with serial peripheral interface (SPI) and TMS320 DSP serial ports. No additional hardware is required to interface between the TLV1570 and a microcontroller ( $\mu$ Cs) with a SPI serial port or a TMS320 DSP. However, the speed is limited by the SCLK rate of the  $\mu$ C or the DSP.

initialization-software sequence (continued)

The TLV1570 interfaces to a DSP over five lines:  $\overline{CS}$ , SCLK, SDOUT, SDIN, and FS, and interfaces to a  $\mu$ C over four lines:  $\overline{CS}$ , SCLK, SDOUT, and SDIN. The FS input should be pulled high in  $\mu$ C mode. The device is in 3-state and power-down mode when  $\overline{CS}$  is high. After  $\overline{CS}$  falls, the TLV1570 checks the FS input at the  $\overline{CS}$  falling edge to determine the operation mode. If FS is low, DSP mode is set, otherwise  $\mu$ C mode is set.

Figure 3. DSP to TLV1570 Interface

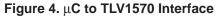

### grounding and decoupling considerations

General practices should apply to the PCB design to limit high frequency transients and noise that are fed back into the supply and reference lines (see Figure 5). This requires that the supply and reference pins be sufficiently bypassed. In most cases 0.1  $\mu$ F ceramic chip capacitors are adequate to keep the impedance low over a wide frequency range. Since their effectiveness depends largely on the proximity to the individual supply pin. They should be placed as close to the supply pins as possible.

To reduce high frequency and noise coupling, it is highly recommended that digital and analog ground be shorted immediately outside the package. This can be accomplished by running a low impedance line between DGND and AGND, under the package.

**Figure 5. Placement of Decoupling Capacitors**

### power supply ground layout

Printed-circuit boards that use separate analog and digital ground planes offer the best system performance. Wire-wrap boards do not perform well and should not be used. The two ground planes should be connected together at the low-impedance power-supply source. The best ground connection may be achieved by connecting the ADC AGND terminal to the system analog ground plane making sure that analog ground currents are well managed.

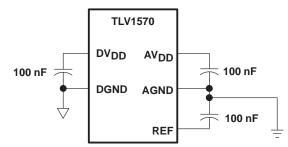

#### simplified analog input analysis

Using the equivalent circuit in Figure 6, the time required to charge the analog input capacitance from 0 to  $V_S$  within 1/2 LSB,  $t_{ch}(1/2 \text{ LSB})$ , can be derived as follows:

The capacitance charging voltage is given by:

$$V_{C(t)} = V_{S} \left( 1 - e^{-t} ch^{/R} t^{C} i \right)$$

$$R_{t} = R_{s} + R_{i}$$

$$R_{i} = R_{i(ADC)} + R_{i(MUX)}$$

(1)

t<sub>ch</sub> = Charge time

The input impedance R<sub>i</sub> is 718  $\Omega$  at 5 V, and is higher (~1.25 k $\Omega$ ) at 2.7 V. The final voltage to 1/2 LSB is given by:

$$V_{\rm C} (1/2 \text{ LSB}) = V_{\rm S} - (V_{\rm S}/2048)$$

(2)

Equating equation 1 to equation 2 and solving for cycle time t<sub>c</sub> gives:

$$V_{S} - \left(V_{S}/2048\right) = V_{S}\left(1 - e^{-t}ch^{/R}t^{C}i\right)$$

and time to change to 1/2 LSB (minimum sampling time) is:

$$t_{ch} (1/2 \text{ LSB}) = R_t \times C_j \times \ln(2048)$$

Where:

Where:

ln(2048) = 7.625

Therefore, with the values given, the time for the analog input signal to settle is:

$$t_{ch} (1/2 LSB) = (R_s + 718 \Omega) \times 15 \, pF \times ln(2048)$$

(4)

This time must be less than the converter sample time shown in the timing diagrams. Which is 6x SCLK.

$$t_{ch} (1/2 \text{ LSB}) \le 6x \ 1/f_{(SCLK)}$$

(5)

Therefore the maximum SCLK frequency is:

$$Max(f_{(SCLK)}) = 6/t_{ch}(1/2 LSB) = 6/(ln(2048) \times R_t \times C_j)$$

(6)

<sup>†</sup> Driving source requirements:

• Noise and distortion for the source must be equivalent to the resolution of the converter.

• R<sub>S</sub> must be real at the input frequency.

(3)

### definitions of specifications and terminology

#### integral nonlinearity (INL)

Integral nonlinearity refers to the deviation of each individual code from a line drawn from zero through full scale. The point used as zero occurs 1/2 LSB before the first code transition. The full scale point is defined as level 1/2 LSB beyond the last code transition. The deviation is measured from the center of each particular code to the true straight line between these two points.

#### differential nonlinearity (DNL)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. A differential nonlinearity error of less than  $\pm$ 1 LSB ensures no missing codes.

#### zero offset

The major carry transition should occur when the analog input is at zero volts. Zero error is defined as the deviation of the actual transition from that point.

#### gain error

The first code transition should occur at an analog value 1/2 LSB above negative full scale. The last transition should occur at an analog value 1 1/2 LSB below the nominal full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.

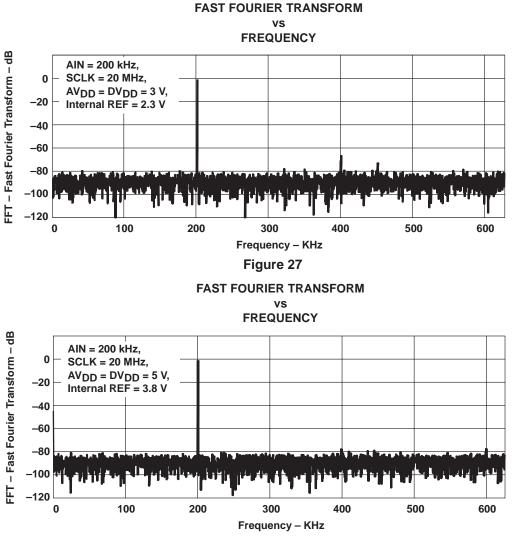

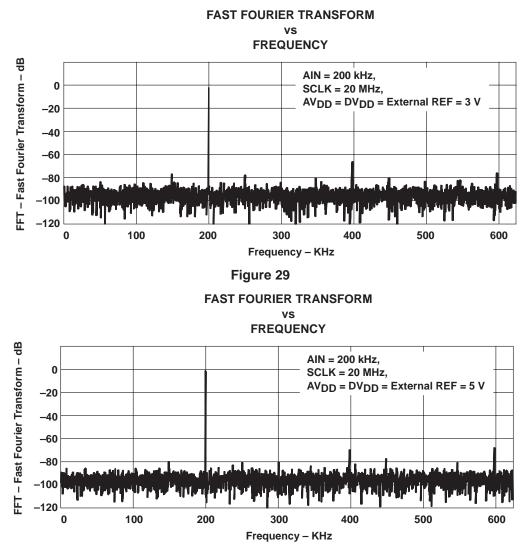

#### signal-to-noise ratio + distortion (SINAD)

SINAD is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for SINAD is expressed in decibels.

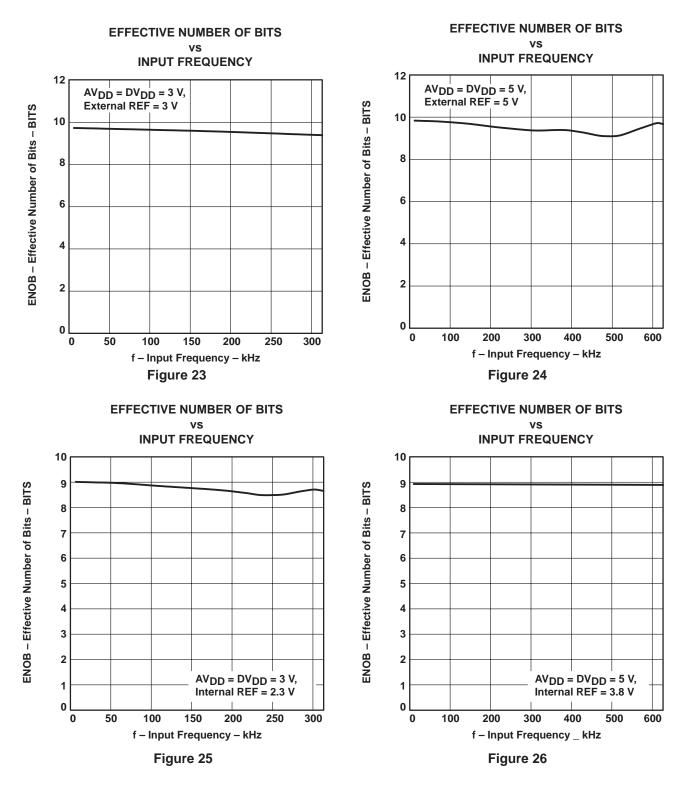

#### effective number of bits (ENOB)

For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula,

N = (SINAD - 1.76)/6.02

It is possible to get a measure of performance expressed as N, the effective number of bits. Thus, effective number of bits for a device for sine wave inputs at a given input frequency can be calculated directly from its measured SINAD.

#### total harmonic distortion (THD)

Total harmonic distortion is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is expressed as a percentage or in decibels.

#### spurious free dynamic range (SFDR)

Spurious free dynamic range is the difference in dB between the rms amplitude of the input signal and the peak spurious signal.

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage range, AGND to AV <sub>DD</sub> , DGND to DV <sub>DD</sub>                                   |                   |

|-------------------------------------------------------------------------------------------------------------|-------------------|

| Reference input voltage                                                                                     |                   |

| Digital input voltage range                                                                                 |                   |

| Operating virtual junction temperature range, T <sub>J</sub>                                                | –40°C to 150°C    |

| Operating free-air temperature range, T <sub>A</sub> : TLV1570C                                             | 0°C to 70°C       |

| TLV1570I                                                                                                    | –40°C to 85°C     |

| Storage temperature range, T <sub>stg</sub><br>Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 65°C to 150°C<br> |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

#### power supplies

|                                                       | MIN | TYP MAX | UNIT |

|-------------------------------------------------------|-----|---------|------|

| Analog supply voltage, AV <sub>DD</sub> (see Note 1)  | 2.7 | 5.5     | V    |

| Digital supply voltage, DV <sub>DD</sub> (see Note 1) | 2.7 | 5.5     | V    |

NOTE 1: Abs  $(AV_{DD} - DV_{DD}) < 0.5 V$

#### analog inputs

|                              |                                   | MIN                  | TYP MAX | UNIT |

|------------------------------|-----------------------------------|----------------------|---------|------|

| Analog input voltage, AIN    |                                   | AGND                 | VREF    | V    |

| Reference input voltage, REF | DV <sub>DD</sub> = 3.3 V to 2.7 V | 55% AV <sub>DD</sub> | AVDD    |      |

|                              | DV <sub>DD</sub> = 5.5 V to 4.5 V | 60% AV <sub>DD</sub> | AVDD    | ] `  |

#### digital inputs

|                                                 |                                                     | MIN | TYP | MAX | UNIT   |

|-------------------------------------------------|-----------------------------------------------------|-----|-----|-----|--------|

| High-level input voltage, VIH                   | $DV_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$         | 2.1 |     |     | V      |

| Low-level input voltage, V <sub>IL</sub>        | $DV_{DD} = 2.7 \text{ V} \text{ to } 5.5 \text{ V}$ |     |     | 0.8 | V      |

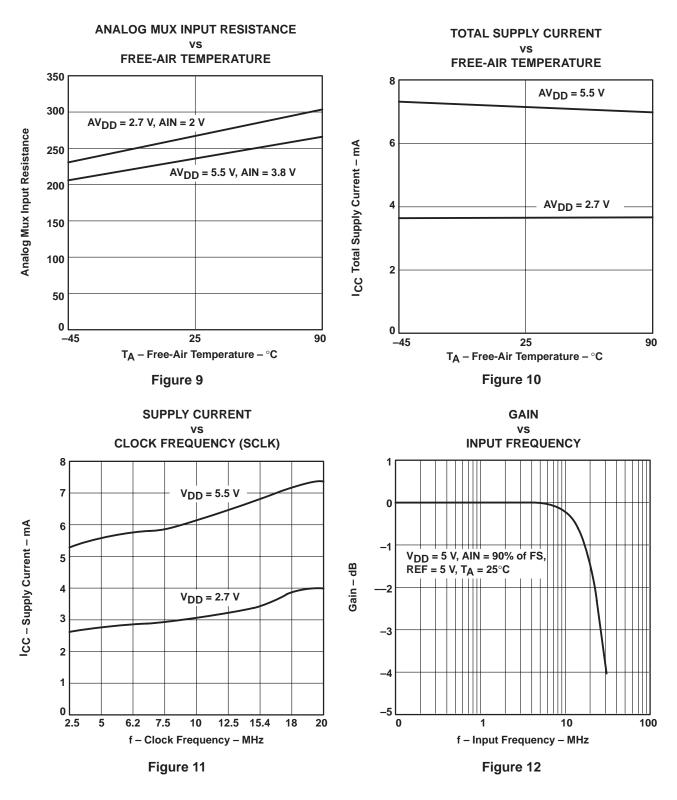

| Input SCLK frequency                            | $DV_{DD} = 5.5 \text{ V} \text{ to } 4.5 \text{ V}$ |     |     | 20  | MHz    |

| Input SCER frequency                            | DV <sub>DD</sub> = 3.6 V to 2.7 V 1                 |     |     | 10  | IVITIZ |

| CCI K pulse duration alook high to a surviv     | $DV_{DD} = 5.5 \text{ V} \text{ to } 4.5 \text{ V}$ | 23  |     |     |        |

| SCLK pulse duration, clock high, $t_{W}(SCLKH)$ | $DV_{DD} = 3.6 \text{ V to } 2.7 \text{ V}$         | 46  |     |     | ns     |

|                                                 | $DV_{DD} = 5.5 \text{ V to } 4.5 \text{ V}$         | 23  |     |     |        |

| SCLK pulse duration, clock low, $t_W(SCLKL)$    | DV <sub>DD</sub> = 3.6 V to 2.7 V                   | 46  |     |     | ns     |

### electrical characteristics, over recommended operating free-air temperature range, supply voltages, and reference voltages (unless otherwise noted)

#### digital specifications (SDOUT at 25 pF)

|       | PARAMETER                | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |  |  |  |  |

|-------|--------------------------|-----------------------------------|-----|-----|-----|------|--|--|--|--|

| Logic | inputs                   |                                   |     |     |     |      |  |  |  |  |

| Iн    | High-level input current | $DV_{DD} = 5 V$ , $V_{I} = 5 V$   |     |     | 1   | μΑ   |  |  |  |  |

| IIL   | Low-level input current  | $DV_{DD} = 5 V, \qquad V_I = 0 V$ |     |     | -1  | μΑ   |  |  |  |  |

| Cl    | Input capacitance        | Control inputs                    |     | 5   | 15  | pF   |  |  |  |  |

| Logic | Logic outputs            |                                   |     |     |     |      |  |  |  |  |

| ∨он              | High-level output voltage           | $I_{OH} = 50 \ \mu A - 0.5 \ m A$ | DV <sub>DD</sub> -0.4 | V  |

|------------------|-------------------------------------|-----------------------------------|-----------------------|----|

| VOL              | Low-level output voltage            | $I_{OL} = 50 \ \mu A - 0.5 \ m A$ | 0.4                   | V  |

| IOZH             | High-impedance-state output current |                                   | 1                     | μΑ |

| I <sub>OZL</sub> | Low-impedance-state output current  |                                   | -1                    | μΑ |

| CO               | Output capacitance                  |                                   | 5                     | pF |

### electrical characteristics, over recommended operating free-air temperature range, supply voltages, and reference voltages (unless otherwise noted) (continued)

#### dc specifications

|                     | PARAMETER                 |                                         |                                   | TEST CONDIT                                | IONS                                    | MIN  | TYP   | MAX   | UNIT   |  |                       |  |   |    |  |

|---------------------|---------------------------|-----------------------------------------|-----------------------------------|--------------------------------------------|-----------------------------------------|------|-------|-------|--------|--|-----------------------|--|---|----|--|

|                     | Resolution                |                                         |                                   |                                            |                                         |      | 10    |       | Bits   |  |                       |  |   |    |  |

| Accuracy            |                           |                                         | -                                 |                                            |                                         |      |       |       |        |  |                       |  |   |    |  |

|                     | Integral nonlinearity, II | ۱L                                      | Best fit                          |                                            |                                         |      | ±0.6  | ±1    | LSB    |  |                       |  |   |    |  |

|                     | Differential nonlinearit  | y, DNL                                  |                                   |                                            |                                         |      | ±0.65 | ±1    | LSB    |  |                       |  |   |    |  |

| EO                  | Offset error              |                                         |                                   |                                            |                                         |      | ±0.1  | ±0.15 | %FSR   |  |                       |  |   |    |  |

| EG                  | Gain error                |                                         |                                   |                                            |                                         |      | ±0.1  | ±0.2  | %FSR   |  |                       |  |   |    |  |

| Analog inpu         | ıt                        |                                         |                                   |                                            |                                         |      |       |       |        |  |                       |  |   |    |  |

| Ci                  | Input capacitance         |                                         |                                   |                                            |                                         |      | 15    | 20    | pF     |  |                       |  |   |    |  |

| l <sub>lkg</sub>    | Input leakage current     |                                         | V <sub>AIN</sub> = 0 V to A       | V <sub>AIN</sub> = 0 V to AV <sub>DD</sub> |                                         |      |       | ±1    | μΑ     |  |                       |  |   |    |  |

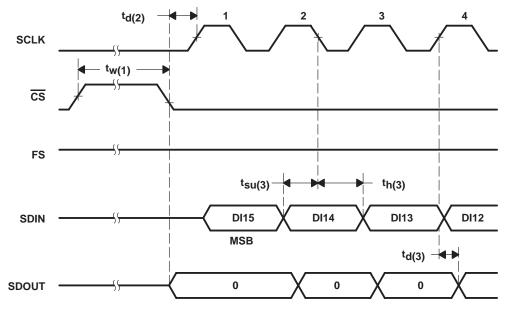

|                     |                           |                                         | $DV_{DD} = 3 V$ , $AV_{DD} = 3 V$ |                                            |                                         |      | 265   | 780   | Ω      |  |                       |  |   |    |  |

| R <sub>i(MUX)</sub> | Input MUX ON resista      | nce                                     | $DV_{DD} = 5 V$ , $AV_{DD} = 5 V$ |                                            |                                         |      | 235   | 450   | Ω      |  |                       |  |   |    |  |

| D                   |                           | ~~~                                     | DV <sub>DD</sub> = 3 V,           | $AV_{DD} = 3 V$                            |                                         |      | 158   | 465   | Ω      |  |                       |  |   |    |  |

| R <sub>i(ADC)</sub> | Input MUX ON resista      | nce                                     | DV <sub>DD</sub> = 5 V,           | $AV_{DD} = 5 V$                            |                                         |      | 140   | 268   | Ω      |  |                       |  |   |    |  |

| Voltage refe        | erence                    |                                         |                                   |                                            |                                         |      |       |       |        |  |                       |  |   |    |  |

| REF                 | Internal reference volt   | Internal reference mode, $V_{DD} = 3 V$ |                                   |                                            | 2.08                                    | 2.26 | 2.48  | V     |        |  |                       |  |   |    |  |

| KEF                 | Internal reference volt   | aye                                     | Internal referen                  | ce mode, V <sub>DD</sub> =                 | 5 V                                     | 3.48 | 3.82  | 4.15  | V      |  |                       |  |   |    |  |

|                     | Temperature coefficier    | nt                                      |                                   |                                            |                                         |      | 100   |       | ppm/°C |  |                       |  |   |    |  |

| r <sub>i</sub>      | Input resistance          |                                         | External referer                  | nce mode                                   |                                         | 3    |       |       | kΩ     |  |                       |  |   |    |  |

| C <sub>i(VR)</sub>  | Input capacitance         |                                         | External referer                  | nce mode                                   |                                         |      | 300   |       | pF     |  |                       |  |   |    |  |

| Power supp          | oly                       |                                         | _                                 |                                            |                                         |      |       |       |        |  |                       |  |   |    |  |

|                     | Operating oursely ours    |                                         | AV <sub>DD</sub> = 2.7 V,         | DV <sub>DD</sub> = 2.7 V,                  | <sup>f</sup> SCLK = 10 MHz <sup>†</sup> |      | 3     | 5     | mA     |  |                       |  |   |    |  |

| IDD + IREF          | Operating supply curre    | ent                                     | AV <sub>DD</sub> = 5.5 V,         | DV <sub>DD</sub> = 5.5 V,                  | fSCLK = 20 MHz‡                         |      | 7.2   | 8.5   | mA     |  |                       |  |   |    |  |

| PD                  | Power dissipation         |                                         | AV <sub>DD</sub> = 2.7 V,         | $DV_{DD} = 2.7 V$                          |                                         |      | 8     | 13    | mW     |  |                       |  |   |    |  |

| ۲D                  | Fower dissipation         |                                         | AV <sub>DD</sub> = 5.5 V,         | DV <sub>DD</sub> = 5.5 V                   |                                         |      | 40    | 47    | mW     |  |                       |  |   |    |  |

|                     | -                         |                                         |                                   |                                            | CS = AV <sub>DD</sub>                   |      | 3     | 10    |        |  |                       |  |   |    |  |

|                     |                           | Cothuran                                |                                   | AVDD = 2.7 V                               | CS = AGND                               |      | 500   |       | μA     |  |                       |  |   |    |  |

|                     | Supply current in         | Software                                |                                   |                                            |                                         |      | 1 1   |       |        |  | CS = AV <sub>DD</sub> |  | 3 | 10 |  |

|                     | power down                |                                         |                                   | AVDD = 5.5 V                               | CS = AGND                               |      | 2000  |       | μA     |  |                       |  |   |    |  |

|                     |                           | Auto                                    |                                   | AVDD = 2.7V                                |                                         |      | 175   | 275   | μΑ     |  |                       |  |   |    |  |

|                     |                           | Auto                                    | IDD + IREF                        | AVDD = 5.5V                                |                                         |      | 200   | 300   | μΑ     |  |                       |  |   |    |  |

$^{\dagger}$  I<sub>REF</sub> = 0.7 mA typ.  $^{\ddagger}$  I<sub>REF</sub> = 1.5 mA typ.

electrical characteristics, over recommended operating free-air temperature range, supply voltages, and reference voltages (unless otherwise noted) (continued)

#### ac specifications

|       | PARAMETER                          |                                                                                                                      | TEST CONDITION              | ONS                | MIN | TYP | MAX | UNIT     |  |  |  |  |  |  |                            |                    |  |     |  |  |

|-------|------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|-----|-----|-----|----------|--|--|--|--|--|--|----------------------------|--------------------|--|-----|--|--|

|       |                                    |                                                                                                                      | f <sub>s</sub> = 1.25 MSPS, | External reference | 58  | 61  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 100 kHz,                                                                                            | $AV_{DD} = 5 V$             | Internal reference | 53  | 56  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 70% of FS                                                                                                            | f <sub>S</sub> = 625 KSPS,  | External reference | 56  | 61  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

| CNID  | Signal to paigo ratio              |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference | 53  | 55  |     | dD       |  |  |  |  |  |  |                            |                    |  |     |  |  |

| SNR   | Signal-to-noise ratio              |                                                                                                                      | f <sub>S</sub> = 1.25 MSPS, | External reference |     | 61  |     | dB       |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 50 kHz,                                                                                             | $AV_{DD} = 5 V$             | Internal reference |     | 56  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 90% of FS                                                                                                            | f <sub>s</sub> = 625 KSPS,  | External reference |     | 61  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference |     | 55  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | f <sub>S</sub> = 1.25 MSPS, | External reference | 55  | 58  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 100 kHz,                                                                                            | $AV_{DD} = 5 V$             | Internal reference | 53  | 55  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 70% of FS                                                                                                            | f <sub>S</sub> = 625 KSPS,  | External reference | 53  | 58  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference | 52  | 54  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

| SINAD | Signal-to-noise ratio + distortion |                                                                                                                      | f <sub>s</sub> = 1.25 MSPS, | External reference |     | 59  |     | dB       |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 50 kHz,                                                                                             | $AV_{DD} = 5 V$             | Internal reference |     | 55  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 90% of FS                                                                                                            | f <sub>S</sub> = 625 KSPS,  | External reference |     | 60  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference |     | 55  |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | f <sub>s</sub> = 1.25 MSPS, | External reference |     | -60 | -55 |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 100 kHz,                                                                                            | $AV_{DD} = 5 V$             | Internal reference |     | -70 | -58 |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 70% of FS                                                                                                            | f <sub>S</sub> = 625 KSPS,  | External reference |     | -60 | -55 |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       | Total bases a facilitate effect    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference |     | -66 | -58 |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

| THD   | Total harmonic distortion          |                                                                                                                      | f <sub>S</sub> = 1.25 MSPS, | External reference |     | -64 |     | dB       |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 50 kHz                                                                                              | $AV_{DD} = 5 V$             | Internal reference |     | -72 |     | ]        |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 90% of FS                                                                                                            |                             |                    |     |     |     |          |  |  |  |  |  |  | f <sub>S</sub> = 625 KSPS, | External reference |  | -63 |  |  |

|       |                                    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference |     | -68 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | f <sub>s</sub> = 1.25 MSPS, | External reference |     | -63 | -57 | <u> </u> |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 100 kHz,                                                                                            | $AV_{DD} = 5 V$             | Internal reference |     | -73 | -59 |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 70% of FS                                                                                                            | f <sub>S</sub> = 625 KSPS,  | External reference |     | -61 | -57 |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference |     | -68 | -60 |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

| SFDR  | Spurious-free dynamic range        |                                                                                                                      | f <sub>s</sub> = 1.25 MSPS, | External reference |     | -66 |     | dB       |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 50 kHz,                                                                                             | $AV_{DD} = 5 V$             | Internal reference |     | -75 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 90% of FS                                                                                                            | f <sub>S</sub> = 625 KSPS,  | External reference |     | -65 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference |     | -70 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | f <sub>S</sub> = 1.25 MSPS, | External reference | 8.8 | 9.3 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | f <sub>i</sub> = 100 kHz,                                                                                            | $AV_{DD} = 5 V$             | Internal reference | 8.6 | 8.9 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | 70% of FS                                                                                                            | f <sub>S</sub> = 625 KSPS,  | External reference | 8.6 | 9.3 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       | Effective events of this           |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference | 8.4 | 8.8 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

| ENOB  | Effective number of bits           |                                                                                                                      | f <sub>s</sub> = 1.25 MSPS, | External reference |     | 9.5 |     | dB       |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    | $\begin{array}{c} f_{i} = 50 \text{ kHz}, \\ 90\% \text{ of FS} \end{array} \begin{array}{c} A \\ f_{s} \end{array}$ | $AV_{DD} = 5 V$             | Internal reference |     | 8.9 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | ( TO                        | External reference |     | 9.5 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

|       |                                    |                                                                                                                      | $AV_{DD} = 3 V$             | Internal reference |     | 8.9 |     |          |  |  |  |  |  |  |                            |                    |  |     |  |  |

#### PARAMETER **TEST CONDITIONS** MIN TYP MAX UNIT Analog Input Channel-to-channel crosstalk -75 dB MHz -1 dB full-scale input sine wave 12 15 BW Full-power bandwidth -3 dB full-scale input sine wave MHz 25 –1 dB 15 20 MHz ВW Small-signal bandwidth –3 dB 35 MHz $AV_{DD} = 5 V$ 0.0625 1.25 Sampling rate MSPS f<sub>S</sub> $AV_{DD} = 3 V$ 0.625 0.0625

#### ac specifications (continued)

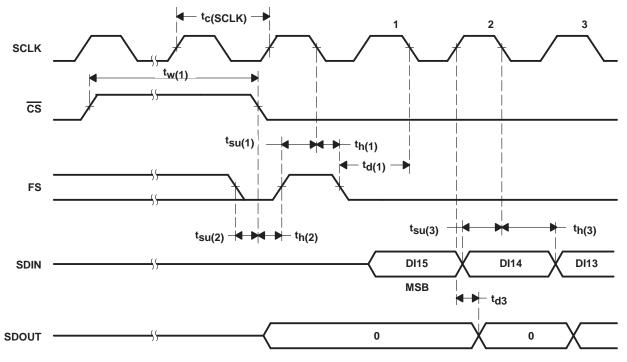

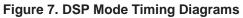

### timing requirements<sup>†</sup>

|                      | PARAMETER                                                                                    | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT           |

|----------------------|----------------------------------------------------------------------------------------------|-----------------------------------|-----|-----|-----|----------------|

|                      |                                                                                              | DV <sub>DD</sub> = 5.5 V to 4.5 V | 50  |     |     | ns             |

| <sup>t</sup> c(SCLK) | SCLK cycle time                                                                              | DV <sub>DD</sub> = 3.6 V to 2.7 V | 100 |     |     |                |

| <sup>t</sup> w(1)    | Pulse duration, chip select                                                                  |                                   | 100 |     |     | ns             |

| <sup>t</sup> (s)     | Sampling period                                                                              |                                   |     | 6   |     | SLCK<br>cycles |

| <sup>t</sup> (conv)  | Conversion period                                                                            |                                   |     | 10  |     | SLCK<br>cycles |

| <sup>t</sup> su(1)   | Setup time, FS to SCLK falling edge in DSP mode                                              |                                   | 5   |     |     | ns             |

| <sup>t</sup> h(1)    | Hold time, FS to SCLK falling edge in DSP mode                                               |                                   | 2   |     |     | ns             |

| t <sub>su(2)</sub>   | Setup time, FS to $\overline{\text{CS}}$ falling edge in DSP mode                            |                                   | 5.5 |     |     | ns             |

| <sup>t</sup> h(2)    | Hold time, FS to $\overline{\text{CS}}$ falling edge in DSP mode                             |                                   | 9   |     |     | ns             |

| <sup>t</sup> d(1)    | Delay time, FS falling edge to next SCLK falling edge in DSP mode                            |                                   | 6   |     |     | ns             |

| <sup>t</sup> d(2)    | Delay time, SCLK rising edge after $\overline{\text{CS}}$ falling edge in $\mu\text{C}$ mode |                                   | 4   |     |     | ns             |

| <sup>t</sup> d(3)    | Delay time, output after SCLK rising edge in $\mu\text{C}$ mode and DSP mode                 |                                   |     | 10  | 20  | ns             |

| t <sub>su(3)</sub>   | Setup time, serial input data to SCLK falling edge                                           |                                   | 10  |     |     | ns             |

| <sup>t</sup> h(3)    | Hold time, serial input data to SCLK falling edge                                            |                                   | 4   |     |     | ns             |

| tr                   | Rise time                                                                                    |                                   | 3   |     | 200 | ns             |

<sup>†</sup> Specifications subject to change without notice.

### PARAMETER MEASUREMENT INFORMATION

Figure 8. µC Mode Timing Diagrams

0.4 0.2 0 -0.2 -0.4 -0.6 -0.8 0

#### DIFFERENTIAL NONLINEARITY ERROR vs **DIGITAL OUTPUT CODE** DNL – Differential Nonlinearity – LSB 1 V<sub>CC</sub> = 5.5 V, Internal REF = 3.8 V, 0.8 SCLK = 20 MHz, 0.6 T<sub>A</sub> = 25°C 0.4 0.2 0 -0.2 -0.4 -0.6 -0.8 -1 511 1023 0 Samples Figure 17 INTEGRAL NONLINEARITY ERROR vs **DIGITAL OUTPUT CODE** INL – Integral Nonlinearity – LSB 1 $V_{CC} = 5.5 \text{ V}$ , Internal REF = 3.8 V, SCLK = 20 MHz, 0.8 T<sub>A</sub> = 25°C 0.6

#### **TYPICAL CHARACTERISTICS**

511

Samples Figure 18 1023

Figure 31. Typical Timing Diagram for DSP Application

Figure 32. Typical Timing Diagram for  $\mu\text{C}$  Application

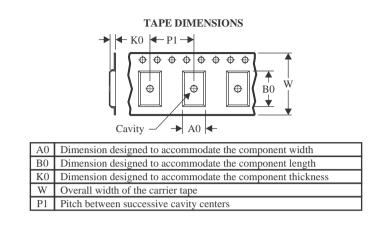

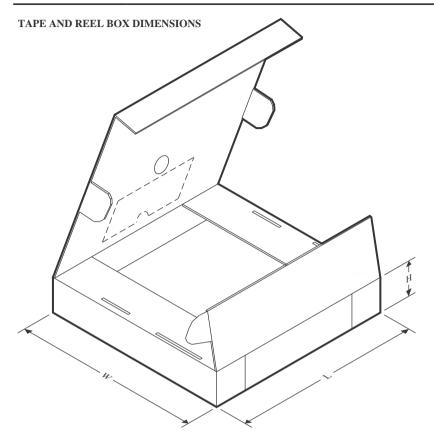

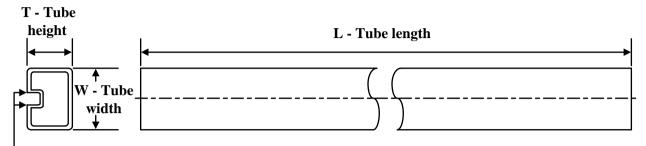

### PACKAGING INFORMATION

| Orderable part number | Status | Material type (2) | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|-------------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)               |                 |                       | (3)             | (4)                           | (5)                        |              | (0)          |

| TLV1570CDW            | Active | Production        | SOIC (DW)   20  | 25   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TLV1570C     |

| TLV1570CDW.A          | Active | Production        | SOIC (DW)   20  | 25   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TLV1570C     |

| TLV1570CDWR           | Active | Production        | SOIC (DW)   20  | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TLV1570C     |

| TLV1570CDWR.A         | Active | Production        | SOIC (DW)   20  | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TLV1570C     |

| TLV1570CPW            | Active | Production        | TSSOP (PW)   20 | 70   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TV1570       |

| TLV1570CPW.A          | Active | Production        | TSSOP (PW)   20 | 70   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TV1570       |

| TLV1570CPWG4          | Active | Production        | TSSOP (PW)   20 | 70   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TV1570       |

| TLV1570CPWR           | Active | Production        | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TV1570       |

| TLV1570CPWR.A         | Active | Production        | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TV1570       |

| TLV1570CPWRG4         | Active | Production        | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | TV1570       |

| TLV1570IDW            | Active | Production        | SOIC (DW)   20  | 25   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | TLV1570I     |

| TLV1570IDW.A          | Active | Production        | SOIC (DW)   20  | 25   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | TLV1570I     |

| TLV1570IPW            | Active | Production        | TSSOP (PW)   20 | 70   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | TY1570       |

| TLV1570IPW.A          | Active | Production        | TSSOP (PW)   20 | 70   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | TY1570       |

| TLV1570IPWG4          | Active | Production        | TSSOP (PW)   20 | 70   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | TY1570       |