# TLIN2029-Q1 ドミナント状態タイムアウト機能を備えた、故障保護 LIN (Local Interconnect Network) トランシーバ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認定済み

- 温度グレード 1:  $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$   $T_A$

- デバイス HBM 認定レベル:  $\pm 8\text{kV}$

- デバイス CDM 認定レベル:  $\pm 1.5\text{kV}$

- LIN 2.0、LIN 2.1、LIN 2.2、LIN 2.2 A、および ISO/DIS 17987-4.2 に準拠（「[SLLA490](#)」を参照）

- LIN 用の SAE J2602 推奨プラクティスに準拠（[SLLA490](#) を参照）

- ISO 9141 (K ライン) をサポート

- 12V アプリケーションをサポート

- 最高 20kbps の LIN 送信データレート

- 広い動作範囲

- 電源電圧:  $4\text{V} \sim 36\text{V}$

- LIN バスのフォルト保護:  $\pm 45\text{V}$

- スリープ モード: 超低消費電流で、次のウェイクアップ イベントに対応

- LIN バス

- EN 経由のローカル ウェイクアップ

- 電源オンおよびオフ時のグリッチ フリー動作

- 保護機能:

- $V_{\text{SUP}}$  の低電圧保護

- TXD ドミナント タイムアウト保護 (DTO)

- サーマル シャットダウン保護機能

- 電源なしノードまたはグランド切断に対するシステム レベルのフェイルセーフ

- SOIC (8) パッケージと自動光学検査 (AOI) 性能を向上させたリードレス VSON (8) パッケージで供給

## 2 アプリケーション

- ボディ エレクトロニクスおよび照明

- インフォテインメントおよびクラスター

- ハイブリッド電気自動車およびパワートレイン システム

- パッシブ型安全運転支援システム

- 電化製品

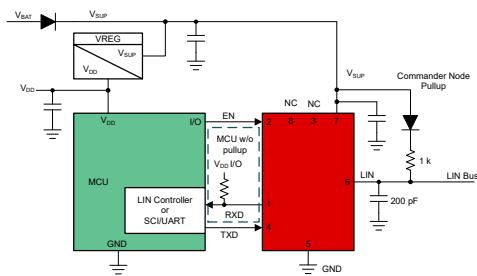

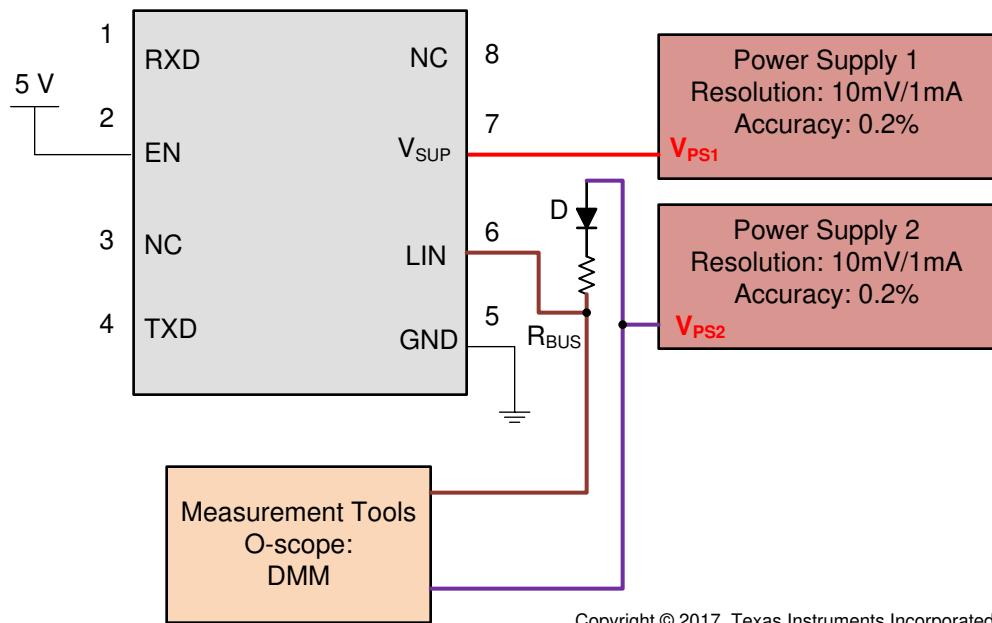

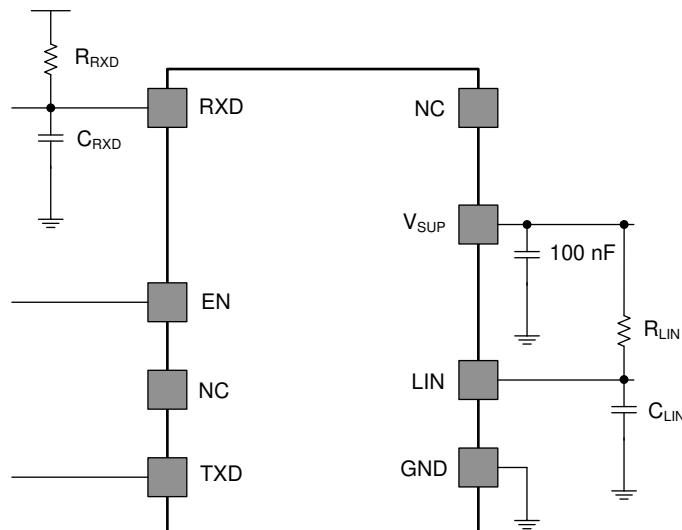

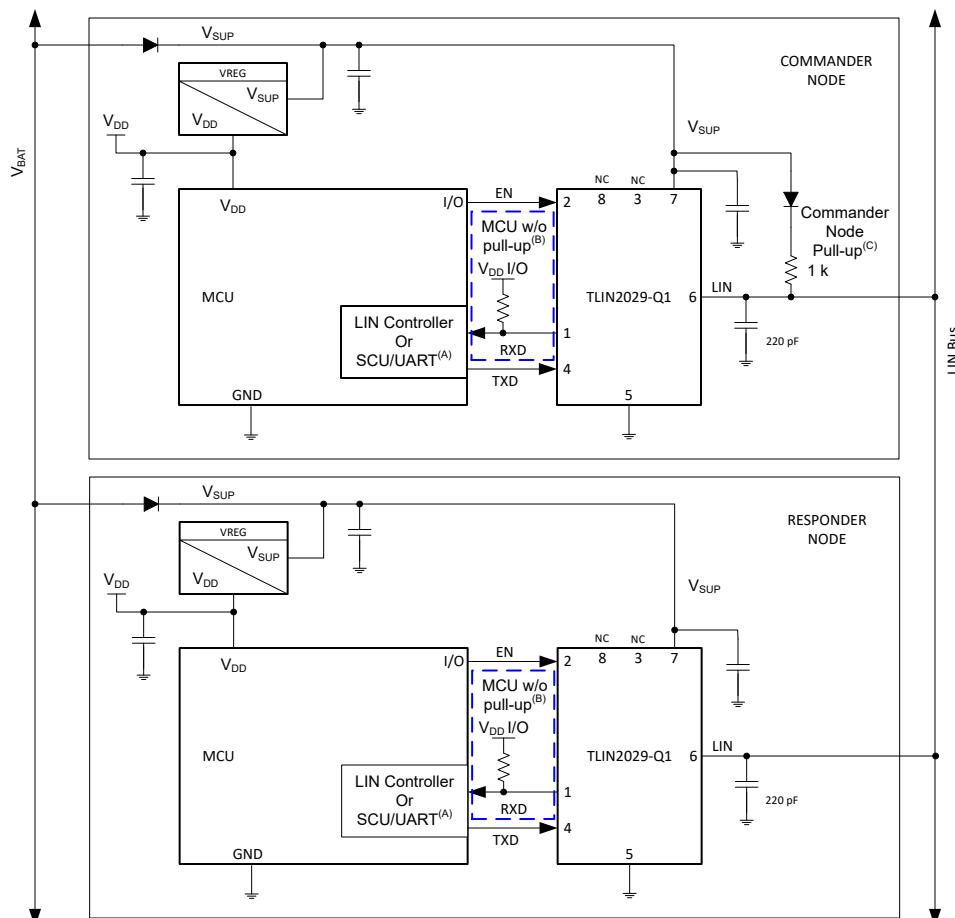

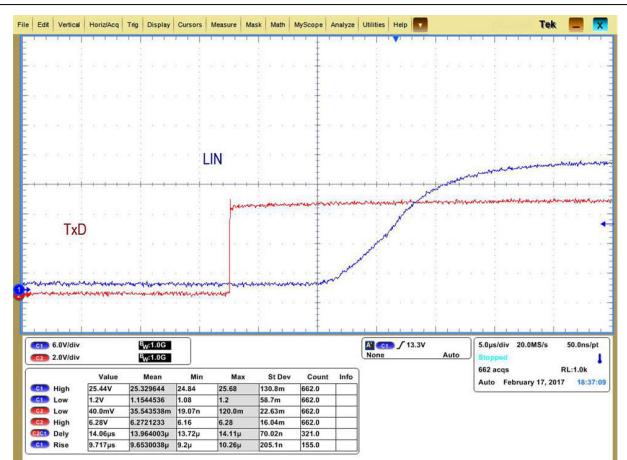

概略回路図、コマンダ モード

## 3 概要

TLIN2029-Q1 は、ウェークアップおよび保護機能を内蔵し、LIN 2.0、LIN 2.1、LIN 2.2、LIN 2.2A、および ISO/DIS 17987-4.2 標準に準拠したローカル相互接続ネットワーク (LIN) 物理層トランシーバです。LIN は、データレートが最高 20kbps の車載ネットワークで一般に使用されている単線式双方向バスです。TLIN2029-Q1 は、幅広い動作電圧に対応し、かつ追加のバス フォルト保護機能を備えた 12V アプリケーションをサポートするように設計されています。

LIN レシーバは、高速インライン プログラミング用に最大 100kbps のデータ レートをサポートしています。TLIN2029-Q1 は、電磁放射 (EME) を低減する電流制限波形整形ドライバを使用して、TXD 入力のデータストリームを LIN バス信号に変換します。本レシーバは、データストリームを論理レベル信号に変換し、オープンドレインの RXD ピンを経由してマイクロプロセッサに送信します。スリープ モードから LIN バスや EN ピンによるウェイクアップが可能なため、非常に低い消費電流を実現できます。

抵抗、静電放電 (ESD) 保護、フォルト保護機能を内蔵しているため、アプリケーションの基板面積を削減できます。

## パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| TLIN2029-Q1 | SOIC (D) (8)         | 4.9mm × 6mm              |

|             | VSON (DRB) (8)       | 3mm × 3mm                |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

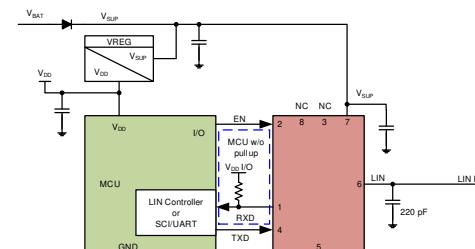

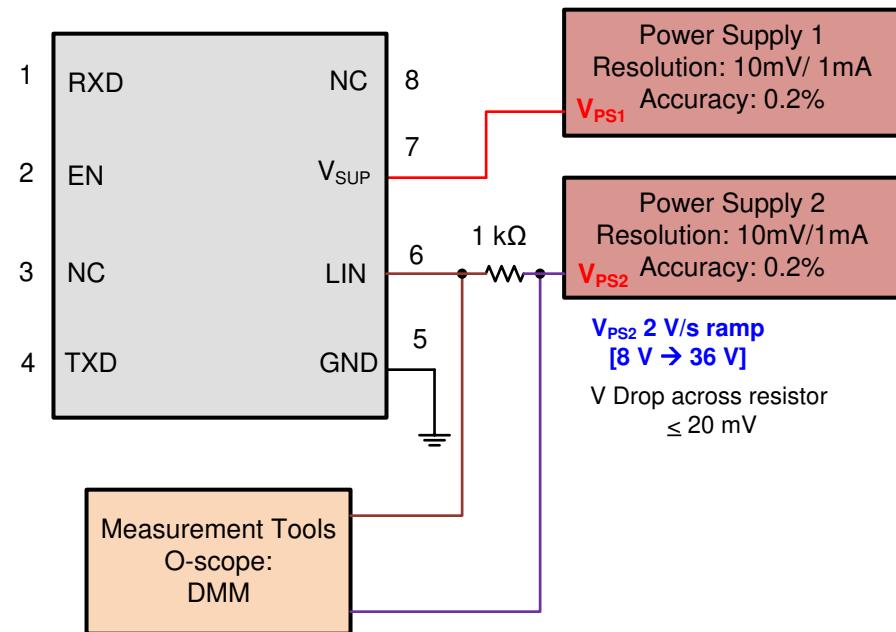

概略回路図、レスポンダ モード

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                  |    |                        |    |

|------------------|----|------------------------|----|

| 1 特長             | 1  | 7.3 機能説明               | 19 |

| 2 アプリケーション       | 1  | 7.4 デバイスの機能モード         | 23 |

| 3 概要             | 1  | 8 アプリケーションと実装          | 25 |

| 4 ピン構成および機能      | 3  | 8.1 アプリケーション情報         | 25 |

| 5 仕様             | 4  | 8.2 代表的なアプリケーション       | 25 |

| 5.1 絶対最大定格       | 4  | 8.3 電源に関する推奨事項         | 26 |

| 5.2 ESD 定格       | 4  | 8.4 レイアウト              | 27 |

| 5.3 ESD 定格 - IEC | 4  | 9 デバイスおよびドキュメントのサポート   | 29 |

| 5.4 熱に関する情報      | 4  | 9.1 ドキュメントのサポート        | 29 |

| 5.5 推奨動作条件       | 5  | 9.2 ドキュメントの更新通知を受け取る方法 | 29 |

| 5.6 電気的特性        | 5  | 9.3 サポート・リソース          | 29 |

| 5.7 スイッチング特性     | 7  | 9.4 商標                 | 29 |

| 5.8 タイミング要件      | 9  | 9.5 静電気放電に関する注意事項      | 30 |

| 6 パラメータ測定情報      | 10 | 9.6 用語集                | 30 |

| 7 詳細説明           | 19 | 10 改訂履歴                | 30 |

| 7.1 概要           | 19 | 11 メカニカル、パッケージ、および注文情報 | 31 |

| 7.2 機能ブロック図      | 19 |                        |    |

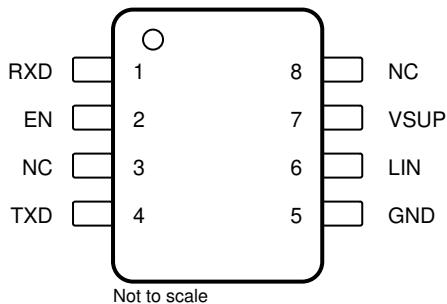

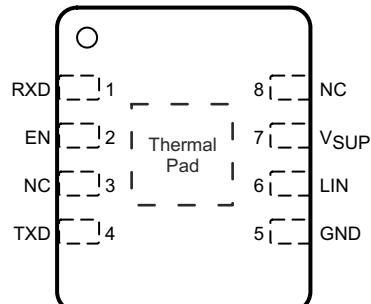

## 4 ピン構成および機能

図 4-1. D パッケージ、8 ピン (SOIC)

(上面図)

図 4-2. DRB パッケージ、8 ピン (VSON)

(上面図)

表 4-1. ピンの機能

| ピン               |    | タイプ     | 説明                                                       |

|------------------|----|---------|----------------------------------------------------------|

| 名称               | 番号 |         |                                                          |

| RXD              | 1  | DO      | LIN バス電圧の状態を報告する RXD 出力 (オープンドレイン) インターフェイス              |

| EN               | 2  | DI      | イネーブル入力 - High は本デバイスを通常動作モードにし、Low は本デバイスをスリープ モードにします。 |

| NC               | 3  | -       | 未接続                                                      |

| TXD              | 4  | DI      | LIN 出力の状態を制御する TXD 入力インターフェイス - 内部的にグランドにプルされています。       |

| GND              | 5  | GND     | グランド                                                     |

| LIN              | 6  | HV I/O  | LIN バスの単線式トランスマッタおよびレシーバ                                 |

| V <sub>SUP</sub> | 7  | HV サプライ | デバイス電源電圧 (外付けの逆方向ブロッキング ダイオードと直列にバッテリに接続します。)            |

| NC               | 8  | -       | 未接続                                                      |

| サーマル パッド         |    | -       | 電気的に接続されていません。熱的結合を改善するため PCB に接続可能 (DRB パッケージのみ)        |

## 5 仕様

### 5.1 絶対最大定格

パラメータは  $-40^{\circ}\text{C} \leq T_A \leq 125^{\circ}\text{C}$  で有効 (特に記述のない限り) <sup>(1)</sup>

| 記号                 | パラメータ                               | 最小値  | 最大値 | 単位 |

|--------------------|-------------------------------------|------|-----|----|

| $V_{\text{SUP}}$   | 電源電圧範囲 (ISO/DIS 17987 Param 10)     | -0.3 | 60  | V  |

| $V_{\text{LIN}}$   | LIN バス入力電圧 (ISO/DIS 17987 Param 82) | -60  | 60  | V  |

| $V_{\text{LOGIC}}$ | ロジック ピン電圧 (RXD、TXD、EN)              | -0.3 | 6   | V  |

| $T_A$              | 周囲温度範囲                              | -40  | 125 | °C |

| $T_J$              | 接合部温度範囲                             | -55  | 150 | °C |

(1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみに関するものであり、絶対最大定格において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格

| ESD 定格             |      |                                                                        | 値      | 単位 |

|--------------------|------|------------------------------------------------------------------------|--------|----|

| $V_{(\text{ESD})}$ | 静電放電 | 人体モデル (HBM)、TXD、RXD、EN ピン、AEC Q100-002 準拠 <sup>(1)</sup>               | ±4000  | V  |

|                    |      | 人体モデル (HBM)、LIN および $V_{\text{SUP}}$ ピン、AEC Q100-002 準拠 <sup>(2)</sup> | ±8000  |    |

|                    |      | 荷電デバイス モデル (CDM)、AEC Q100-011 準拠                                       | すべての端子 |    |

|                    |      |                                                                        | ±1500  |    |

(1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) LIN バスには、GND を基準としたストレスが印加されます。

### 5.3 ESD 定格 - IEC

| ESD およびサージ保護定格                                                                                     |                                            |                                 | 値      | 単位 |

|----------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------|--------|----|

| $V_{(\text{ESD})}$                                                                                 | 静電放電                                       | ISO 10605 接触放電 (IEC 62228-3 準拠) | ±8000  | V  |

| $V_{(\text{ESD})}$                                                                                 | 電源供給時の ESD 性能、SAEJ2962-1 準拠 <sup>(1)</sup> | 接触放電                            | ±8000  | V  |

|                                                                                                    |                                            | エアギャップ放電                        | ±25000 |    |

| IBEE LIN EMC テスト仕様に準拠した ISO 7637-2 および IEC 62215-3 過渡応答 <sup>(2)</sup> (LIN および $V_{\text{SUP}}$ ) | パルス 1                                      | -100                            | V      |    |

|                                                                                                    | パルス 2                                      | 75                              | V      |    |

|                                                                                                    | パルス 3a                                     | -150                            | V      |    |

|                                                                                                    | パルス 3b                                     | 100                             | V      |    |

(1) SAEJ2962-1 テストは、サード パーティーの EMC テスト施設で実施しました。ご要望に応じてテスト レポートを提供します。

(2) ISO 7637 はシステム レベルの過渡テストです。異なるシステム レベル構成を使用すると、結果も異なる可能性があります。

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | TLIN2029D | TLIN2029DRB | 単位   |

|-----------------------|---------------------|-----------|-------------|------|

|                       |                     | D (SOIC)  | DRB (VSON)  |      |

|                       |                     | 8-PINS    | 8-PINS      |      |

| $R_{\text{QJA}}$      | 接合部から周囲への熱抵抗        | 115.5     | 48.5        | °C/W |

| $R_{\text{QJC(top)}}$ | 接合部からケース (上面) への熱抵抗 | 58.7      | 55.5        | °C/W |

| $R_{\text{QJB}}$      | 接合部から基板への熱抵抗        | 58.9      | 22.2        | °C/W |

| $\Psi_{\text{JT}}$    | 接合部から上面への特性パラメータ    | 14.1      | 1.2         | °C/W |

| $\Psi_{\text{JB}}$    | 接合部から基板への特性パラメータ    | 58.2      | 22.2        | °C/W |

## 5.4 热に関する情報 (続き)

| 热評価基準 <sup>(1)</sup> |                     | TLIN2029D | TLIN2029DRB | 単位   |

|----------------------|---------------------|-----------|-------------|------|

|                      |                     | D (SOIC)  | DRB (VSON)  |      |

|                      |                     | 8-PINS    | 8-PINS      |      |

| $R_{θJC(bot)}$       | 接合部からケース (底面) への热抵抗 | -         | 4.8         | °C/W |

(1) 従来および新しい热評価基準の詳細については、アプリケーションレポート『半導体およびIC パッケージの热評価基準』、SPRA953 を参照してください。

## 5.5 推奨動作条件

パラメータは  $-40°C \leq T_A \leq 125°C$  で有効 (特に記述のない限り)

| パラメータ - 定義    |                         | 最小値 | 公称値  | 最大値  | 単位 |

|---------------|-------------------------|-----|------|------|----|

| $V_{SUP}$     | 電源電圧                    | 4   | 48   | 48   | V  |

| $V_{LIN}$     | LIN バス入力電圧              | 0   | 48   | 48   | V  |

| $V_{LOGIC}$   | ロジックピン電圧 (RXD, TXD, EN) | 0   | 5.25 | 5.25 | V  |

| TSD           | サーマル シャットダウン温度          | 165 |      |      | °C |

| $TSD_{(HYS)}$ | サーマル シャットダウン ヒステリシス     |     | 15   |      | °C |

## 5.6 電気的特性

パラメータは  $-40°C \leq T_A \leq 125°C$  で有効 (特に記述のない限り)

| パラメータ      |                                     | テスト条件                                                                                                                                       | 最小値 | 代表値  | 最大値  | 単位 |

|------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|----|

| <b>電源</b>  |                                     |                                                                                                                                             |     |      |      |    |

| $V_{SUP}$  | 動作電源電圧 (ISO/DIS 17987 Param 10, 53) | 本デバイスは、LIN で定義された公称電源電圧範囲外でも動作可能です。 <a href="#">図 1-1</a> および <a href="#">図 1-1</a> を参照。                                                    | 4   | 48   | 48   | V  |

| $V_{SUP}$  | 公称電源電圧 (ISO/DIS 17987 Param 10, 53) | 通常モードおよびスタンバイモード: LIN 信号として 50% デューティサイクル、36V 振幅の 10kHz 方形波を印加しながら、 $V_{SUP}$ を立ち上げます。 <a href="#">図 1-1</a> および <a href="#">図 1-1</a> を参照。 | 4   | 48   | 48   | V  |

| $V_{SUP}$  |                                     | スリープモード                                                                                                                                     | 4   | 48   | 48   | V  |

| $UV_{SUP}$ | $V_{SUP}$ 低電圧スレッショルド                | 最小値は立ち下がりエッジ、最大値は立ち上がりエッジ                                                                                                                   | 2.9 | 3.85 | 3.85 | V  |

| $UV_{HYS}$ | $V_{SUP}$ 低電圧スレッショルドのヒステリシス電圧差      |                                                                                                                                             |     | 0.2  |      | V  |

| $I_{SUP}$  | 消費電流                                | 通常モード: EN = High、バスドミナント: $R_{LIN} > 500\Omega$ かつ $C_{LIN} < 10nF$ での総バス負荷 ( <a href="#">図 1-1</a> を参照)                                    | 1.2 | 5    | 5    | mA |

|            |                                     | スタンバイモード: EN = Low、バスドミナント: $R_{LIN} > 500\Omega$ かつ $C_{LIN} < 10nF$ での総バス負荷 ( <a href="#">図 1-1</a> を参照)                                  | 1   | 2.1  | 2.1  | mA |

## 5.6 電気的特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_A \leq 125^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ                      |                                                                 | テスト条件                                                                                                                                        | 最小値  | 代表値 | 最大値 | 単位               |

|----------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------------------|

| I <sub>SUP</sub>           | 消費電流                                                            | 通常モード: EN = High、バスリセッショ (LIN = V <sub>SUP</sub> )                                                                                           |      | 400 | 700 | μA               |

|                            |                                                                 | スタンバイ モード: EN = Low、バスリセッショ (LIN = V <sub>SUP</sub> )                                                                                        |      | 20  | 35  | μA               |

|                            |                                                                 | スリープ モード: $4.0\text{V} < V_{\text{SUP}} \leq 27\text{V}$ 、LIN = VSUP、EN = 0V、TXD と RXD はフローティング                                              |      | 9   | 15  | μA               |

|                            |                                                                 | スリープ モード: $27\text{V} < V_{\text{SUP}} \leq 48\text{V}$ 、LIN = VSUP、EN = 0V、TXD と RXD はフローティング                                               |      | 30  |     | μA               |

| TSD                        | サーマル シャットダウン                                                    |                                                                                                                                              | 165  |     |     | °C               |

| TSD(HYS)                   | サーマル シャットダウンヒステリシス                                              |                                                                                                                                              |      | 15  |     | °C               |

| <b>RXD 出力ピン (オープンドレイン)</b> |                                                                 |                                                                                                                                              |      |     |     |                  |

| V <sub>OL</sub>            | 出力 LOW 電圧                                                       | R <sub>PU</sub> = 2.4kΩ                                                                                                                      |      | 0.6 |     | V                |

| I <sub>OL</sub>            | Low レベル出力電流、オープンドレイン                                            | LIN = 0V、RXD = 0.4V                                                                                                                          | 1.5  |     |     | mA               |

| I <sub>ILG</sub>           | リーコ電流、High レベル                                                  | LIN = V <sub>SUP</sub> 、RXD = 5V                                                                                                             | -5   | 0   | 5   | μA               |

| <b>TXD 入力ピン</b>            |                                                                 |                                                                                                                                              |      |     |     |                  |

| V <sub>IL</sub>            | Low レベル入力電圧                                                     |                                                                                                                                              | -0.3 | 0.8 |     | V                |

| V <sub>IH</sub>            | High レベル入力電圧                                                    |                                                                                                                                              | 2    | 5.5 |     | V                |

| I <sub>ILG</sub>           | Low レベル入力リーコ電流                                                  | TXD = Low                                                                                                                                    | -5   | 0   | 5   | μA               |

| R <sub>TXD</sub>           | 内部プルダウン抵抗値                                                      |                                                                                                                                              | 125  | 350 | 800 | kΩ               |

| <b>LIN ピン</b>              |                                                                 |                                                                                                                                              |      |     |     |                  |

| V <sub>OH</sub>            | High レベル出力電圧                                                    | LIN リセッショ、TXD = High、I <sub>O</sub> = 0mA、V <sub>SUP</sub> = 7V~48V <sup>(1)</sup>                                                           | 0.85 |     |     | V <sub>SUP</sub> |

|                            |                                                                 | LIN リセッショ、TXD = High、I <sub>O</sub> = 0mA、V <sub>SUP</sub> = 4V ≤ V <sub>SUP</sub> < 7V <sup>(1)</sup>                                       | 3    |     |     | V                |

| V <sub>OL</sub>            | Low レベル出力電圧                                                     | LIN ドミナント、TXD = Low、V <sub>SUP</sub> = 7V~48V <sup>(1)</sup>                                                                                 |      | 0.2 |     | V <sub>SUP</sub> |

|                            |                                                                 | LIN ドミナント、TXD = Low、V <sub>SUP</sub> = 4V ≤ V <sub>SUP</sub> < 7V <sup>(1)</sup>                                                             |      | 1.2 |     | V                |

| V <sub>SUP_NON_OP</sub>    | リセッショの LIN バスの影響が < 5% の場合の VSUP (ISO/DIS 17987 Param 11、54/56) | TXD & RXD オープン、LIN = 4V~58V                                                                                                                  | -0.3 | 58  |     | V                |

| I <sub>BUS_LIM</sub>       | 制限電流 (ISO/DIS 17987 Param 57)                                   | TXD = 0V、V <sub>LIN</sub> = 36V、R <sub>MEAS</sub> = 440Ω、V <sub>SUP</sub> = 36V、V <sub>BUSdom</sub> < 4.518V <a href="#">図 1-1</a> を参照してください | 75   | 120 | 300 | mA               |

| I <sub>BUS_PAS_DOM</sub>   | レシーバのリーコ電流、ドミナント (ISO/DIS 17987 Param 13, 58)                   | LIN = 0V、V <sub>SUP</sub> = 24V、ドライバオフ / リセッショ、 <a href="#">図 1-1</a>                                                                        | -1   |     |     | mA               |

| I <sub>BUS_PAS_rec1</sub>  | レシーバのリーコ電流、リセッショ (ISO/DIS 17987 Param 14, 59)                   | LIN > V <sub>SUP</sub> 、4V ≤ V <sub>SUP</sub> ≤ 45V、ドライバオフ、 <a href="#">図 1-1</a>                                                            |      | 20  |     | μA               |

| I <sub>BUS_PAS_rec2</sub>  | レシーバのリーコ電流、リセッショ (ISO/DIS 17987 Param 14, 59)                   | LIN = V <sub>SUP</sub> 、ドライバオフ、 <a href="#">図 1-1</a>                                                                                        | -5   | 5   |     | μA               |

| I <sub>BUS_NO_GND</sub>    | リーコ電流、グランド喪失 (ISO/DIS 17987 Param 15, 60)                       | GND = V <sub>SUP</sub> 、V <sub>SUP</sub> = 27V、LIN = 0V、 <a href="#">図 1-1</a>                                                               | -1   | 1   |     | mA               |

| I <sub>BUS_NO_GND</sub>    | リーコ電流、グランド喪失 (ISO/DIS 17987 Param 15, 60)                       | GND = V <sub>SUP</sub> 、V <sub>SUP</sub> ≥ 36V、LIN = 0V、 <a href="#">図 1-1</a>                                                               | -1.5 | 1.5 |     | mA               |

| I <sub>BUS_NO_BAT</sub>    | リーコ電流、電源喪失 (ISO/DIS 17987 Param 16, 61)                         | LIN = 48V、V <sub>SUP</sub> = GND、 <a href="#">図 1-1</a>                                                                                      |      | 5   |     | μA               |

## 5.6 電気的特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_A \leq 125^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ                      | テスト条件                                          | 最小値                                                                        | 代表値   | 最大値   | 単位               |

|----------------------------|------------------------------------------------|----------------------------------------------------------------------------|-------|-------|------------------|

| $V_{\text{BUSdom}}$        | Low レベル入力電圧 (ISO/DIS 17987 Param 17, 62)       |                                                                            |       | 0.4   | $V_{\text{SUP}}$ |

| $V_{\text{BUSrec}}$        | High レベル入力電圧 (ISO/DIS 17987 Param 18, 63)      |                                                                            | 0.6   |       | $V_{\text{SUP}}$ |

| $V_{\text{BUS_CNT}}$       | レシーバのセンター スレッショルド (ISO/DIS 17987 Param 19, 64) | $V_{\text{BUS_CNT}} = (V_{\text{IL}} + V_{\text{IH}})/2$ 、図 1-1 と図 1-1 を参照 | 0.475 | 0.5   | 0.525            |

| $V_{\text{HYS}}$           | ヒステリシス電圧 (ISO/DIS 17987 Param 20, 65)          | $V_{\text{HYS}} = (V_{\text{IL}} - V_{\text{IH}})$ 、図 1-1 と図 1-1 を参照       |       | 0.175 | $V_{\text{SUP}}$ |

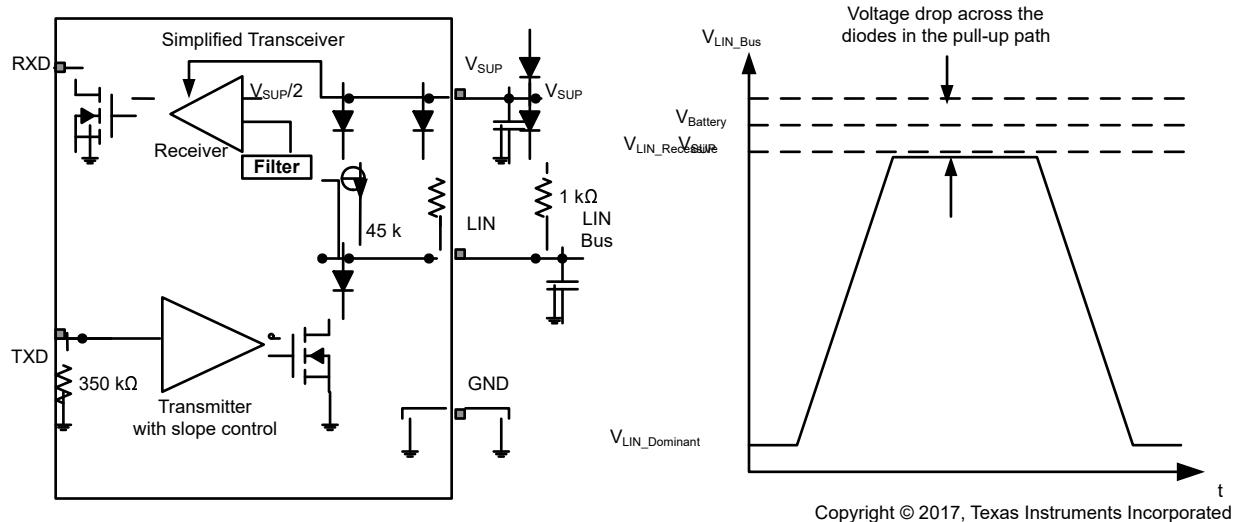

| $V_{\text{SERIAL\_DIODE}}$ | 直列ダイオードの LIN 端子プルアップ経路                         | 設計と特性評価による。                                                                | 0.4   | 0.7   | 1                |

| $R_{\text{PU-LIN}}$        | $V_{\text{SUP}}$ に接続された内部プルアップ抵抗               | 通常モードとスタンバイモード                                                             | 20    | 45    | 60               |

| $I_{\text{RSLEEP}}$        | $V_{\text{SUP}}$ に接続されたプルアップ電流源                | スリープモード、 $V_{\text{SUP}} = 27\text{ V}$ 、LIN = GND                         | -2    | -20   | $\mu\text{A}$    |

| $C_{\text{LINPIN}}$        | LIN ピンの容量                                      | $V_{\text{SUP}} = 14\text{ V}$                                             |       | 25    | $\text{pF}$      |

| <b>EN 入力ピン</b>             |                                                |                                                                            |       |       |                  |

| $V_{\text{IL}}$            | Low レベル入力電圧                                    |                                                                            | -0.3  | 0.8   | $\text{V}$       |

| $V_{\text{IH}}$            | High レベル入力電圧                                   |                                                                            | 2     | 5.5   | $\text{V}$       |

| $V_{\text{IT}}$            | ヒステリシス電圧                                       | 設計と特性評価による。                                                                | 50    | 500   | $\text{mV}$      |

| $I_{\text{ILG}}$           | Low レベル入力電流                                    | EN = Low                                                                   | -5    | 0     | $\mu\text{A}$    |

| $R_{\text{EN}}$            | 内部プルダウン抵抗                                      |                                                                            | 125   | 350   | 800              |

(1) LIN ドライバのバス負荷条件 ( $C_{\text{LIN}}$ ,  $R_{\text{LIN}}$ ): 外部負荷なし

## 5.7 スイッチング特性

パラメータは  $-40^{\circ}\text{C} \leq T_A \leq 125^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ      | テスト条件                                               | 最小値                                                                                                                                                                                                                                                                                                                 | 代表値   | 最大値   | 単位 |

|------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|----|

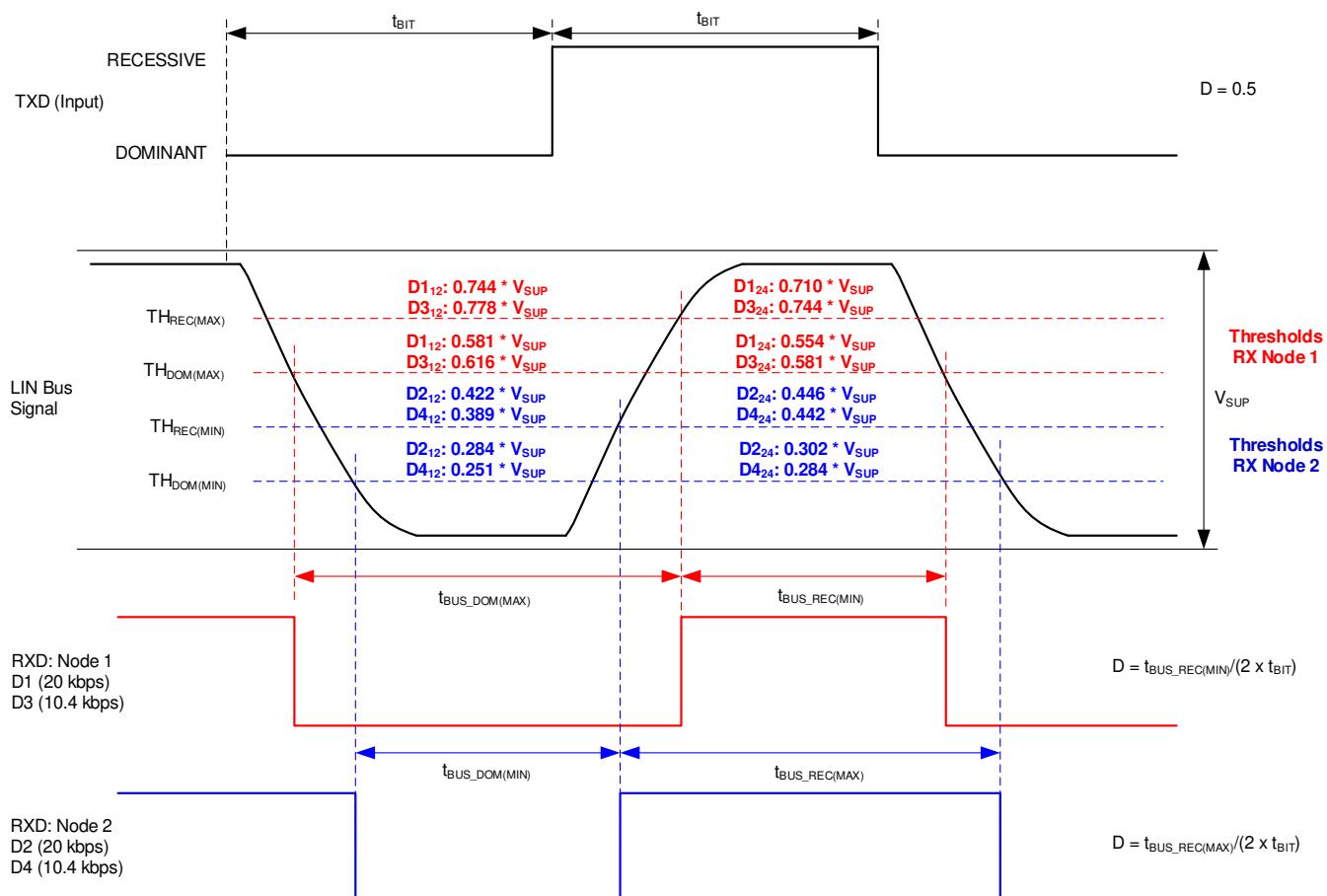

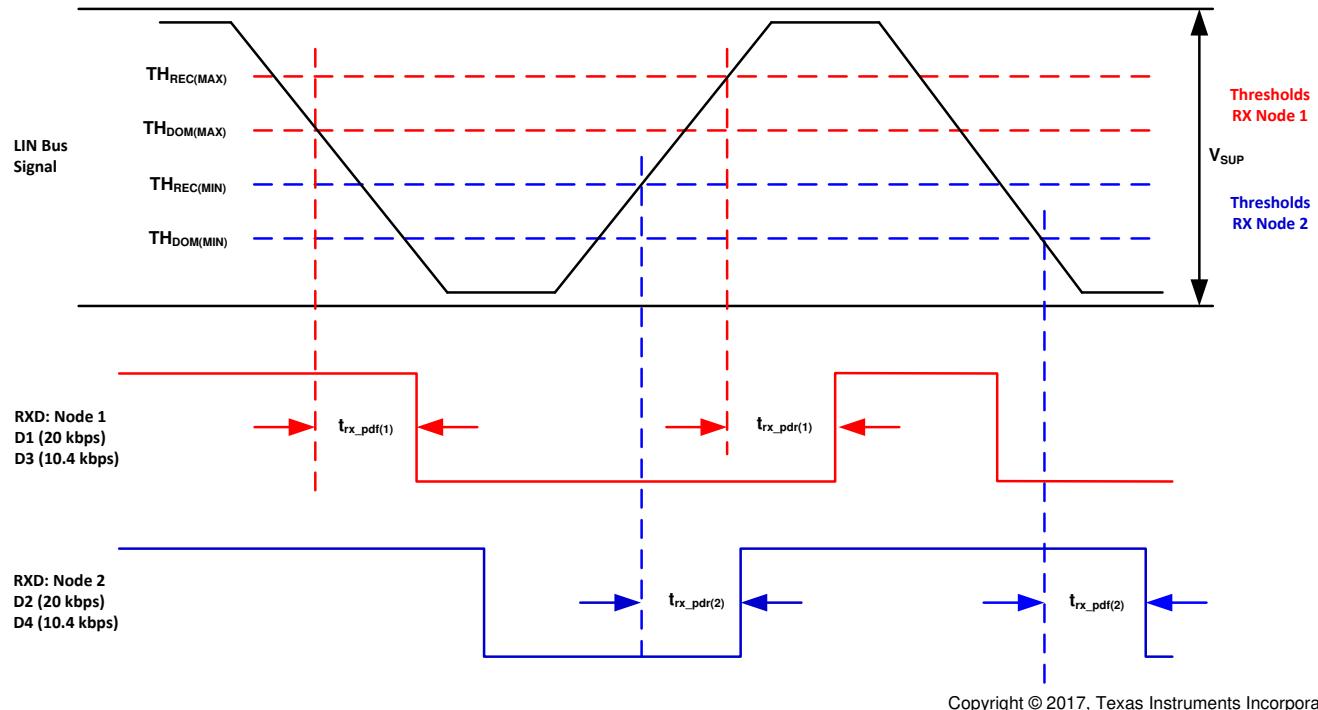

| $D1_{12V}$ | デューティサイクル 1 (ISO/DIS 17987 Param 27) <sup>(1)</sup> | $TH_{\text{REC}(\text{MAX})} = 0.744 \times V_{\text{SUP}}$ 、<br>$TH_{\text{DOM}(\text{MAX})} = 0.581 \times V_{\text{SUP}}$ 、 $V_{\text{SUP}} = 4\text{ V}$<br>$\sim 7.4\text{ V}$ 、 $t_{\text{BIT}} = 50\mu\text{s}$ (20kbps)、 $D1 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照) | 0.396 |       |    |

| $D1_{12V}$ | デューティサイクル 1 <sup>(2)</sup>                          | $TH_{\text{REC}(\text{MAX})} = 0.625 \times V_{\text{SUP}}$ 、<br>$TH_{\text{DOM}(\text{MAX})} = 0.581 \times V_{\text{SUP}}$ 、 $V_{\text{SUP}} = 7.4\text{ V} \sim 9.4\text{ V}$ 、 $t_{\text{BIT}} = 50\mu\text{s}$ (20kbps)、 $D1 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)    | 0.368 |       |    |

| $D1_{12V}$ | デューティサイクル 1 (ISO/DIS 17987 Param 27)                | $TH_{\text{REC}(\text{MAX})} = 0.744 \times V_{\text{SUP}}$ 、<br>$TH_{\text{DOM}(\text{MAX})} = 0.581 \times V_{\text{SUP}}$ 、 $V_{\text{SUP}} = 9.4\text{ V} \sim 18\text{ V}$ 、 $t_{\text{BIT}} = 50\mu\text{s}$ (20kbps)、 $D1 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)     | 0.396 |       |    |

| $D2_{12V}$ | デューティサイクル 2 (ISO/DIS 17987 Param 28)                | $TH_{\text{REC}(\text{MIN})} = 0.422 \times V_{\text{SUP}}$ 、 $TH_{\text{DOM}(\text{MIN})} = 0.284 \times V_{\text{SUP}}$ 、 $V_{\text{SUP}} = 4\text{ V} \sim 7.4\text{ V}$ 、 $t_{\text{BIT}} = 50\mu\text{s}$ (20kbps)、 $D2 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)         |       | 0.581 |    |

| $D2_{12V}$ | デューティサイクル 2 <sup>(2)</sup>                          | $TH_{\text{REC}(\text{MIN})} = 0.422 \times V_{\text{SUP}}$ 、 $TH_{\text{DOM}(\text{MIN})} = 0.284 \times V_{\text{SUP}}$ 、 $V_{\text{SUP}} = 7.4\text{ V} \sim 9.4\text{ V}$ 、 $t_{\text{BIT}} = 50\mu\text{s}$ (20kbps)、 $D2 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)       |       | 0.67  |    |

## 5.7 スイッチング特性 (続き)

パラメータは  $-40^{\circ}\text{C} \leq T_A \leq 125^{\circ}\text{C}$  で有効 (特に記述のない限り)

| パラメータ             |                                                      | テスト条件                                                                                                                                                                                                                                                                                                     | 最小値   | 代表値   | 最大値 | 単位 |

|-------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----|----|

| D2 <sub>12V</sub> | デューティ サイクル 2 (ISO/DIS 17987 Param 28)                | $TH_{\text{REC}(\text{MIN})} = 0.422 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MIN})} = 0.284 \times V_{\text{SUP}}, V_{\text{SUP}} = 9.4\text{V} \sim 18\text{V}, t_{\text{BIT}} = 50\mu\text{s} (20\text{kbps}), D2 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)    |       | 0.581 |     |    |

| D3 <sub>12V</sub> | デューティ サイクル 3 (ISO/DIS 17987 Param 29)                | $TH_{\text{REC}(\text{MAX})} = 0.778 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MAX})} = 0.616 \times V_{\text{SUP}}, V_{\text{SUP}} = 7\text{V} \sim 18\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D3 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)    | 0.417 |       |     |    |

| D3 <sub>12V</sub> | デューティ サイクル 3                                         | $TH_{\text{REC}(\text{MAX})} = 0.645 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MAX})} = 0.616 \times V_{\text{SUP}}, V_{\text{SUP}} = 4\text{V} \sim 7\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D3 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)     | 0.417 |       |     |    |

| D4 <sub>12V</sub> | デューティ サイクル 4 (ISO/DIS 17987 Param 30)                | $TH_{\text{REC}(\text{MIN})} = 0.389 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MIN})} = 0.251 \times V_{\text{SUP}}, V_{\text{SUP}} = 4.6\text{V} \sim 7.4\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D4 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照) |       | 0.59  |     |    |

| D4 <sub>12V</sub> | デューティ サイクル 4 <sup>(2)</sup>                          | $TH_{\text{REC}(\text{MIN})} = 0.389 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MIN})} = 0.251 \times V_{\text{SUP}}, V_{\text{SUP}} = 7.4\text{V} \sim 9.4\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D4 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照) |       | 0.6   |     |    |

| D4 <sub>12V</sub> | デューティ サイクル 4 (ISO/DIS 17987 Param 30)                | $TH_{\text{REC}(\text{MIN})} = 0.389 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MIN})} = 0.251 \times V_{\text{SUP}}, V_{\text{SUP}} = 7.4\text{V} \sim 18\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D4 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)  |       | 0.59  |     |    |

| D1 <sub>24V</sub> | デューティ サイクル 1 (ISO/DIS 17987 Param 72) <sup>(1)</sup> | $TH_{\text{REC}(\text{MAX})} = 0.710 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MAX})} = 0.544 \times V_{\text{SUP}}, V_{\text{SUP}} = 15\text{V} \sim 36\text{V}, t_{\text{BIT}} = 50\mu\text{s} (20\text{kbps}), D1 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)     | 0.33  |       |     |    |

| D2 <sub>24V</sub> | デューティ サイクル 2 (ISO/DIS 17987 Param 73)                | $TH_{\text{REC}(\text{MIN})} = 0.446 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MIN})} = 0.302 \times V_{\text{SUP}}, V_{\text{SUP}} = 15.6\text{V} \sim 36\text{V}, t_{\text{BIT}} = 50\mu\text{s} (20\text{kbps}), D2 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)   |       | 0.642 |     |    |

| D3 <sub>24V</sub> | デューティ サイクル 3 (ISO/DIS 17987 Param 74)                | $TH_{\text{REC}(\text{MAX})} = 0.744 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MAX})} = 0.581 \times V_{\text{SUP}}, V_{\text{SUP}} = 7\text{V} \sim 36\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D3 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)    | 0.386 |       |     |    |

| D3 <sub>24V</sub> | デューティ サイクル                                           | $TH_{\text{REC}(\text{MAX})} = 0.645 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MAX})} = 0.581 \times V_{\text{SUP}}, V_{\text{SUP}} = 4\text{V} \sim 7\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D3 = t_{\text{BUS\_rec}(\text{min})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)     |       | 0.386 |     |    |

| D4 <sub>24V</sub> | デューティ サイクル 4 (ISO/DIS 17987 Param 75)                | $TH_{\text{REC}(\text{MIN})} = 0.422 \times V_{\text{SUP}}, TH_{\text{DOM}(\text{MIN})} = 0.284 \times V_{\text{SUP}}, V_{\text{SUP}} = 4.6\text{V} \sim 36\text{V}, t_{\text{BIT}} = 96\mu\text{s} (10.4\text{kbps}), D4 = t_{\text{BUS\_rec}(\text{MAX})}/(2 \times t_{\text{BIT}})$ (図 1-1、図 1-1 を参照)  |       | 0.591 |     |    |

(1) デューティ サイクル: LIN ドライババスの負荷条件 ( $C_{\text{LIN}}, R_{\text{LIN}}$ ): 負荷 1 =  $1\text{nF}$ 、 $1\text{k}\Omega$ 、負荷 2 =  $10\text{nF}$ 、 $500\Omega$ 、負荷 3 =  $6.8\text{nF}$ 、 $660\Omega$ 。

10.4kbps 動作のために、デューティ サイクル 3 および 4 が定義されています。TLIN2029 は、デューティ サイクル 1 および 2 で規定された高速 20kbps 動作に対応していると同時に、これらの低データレート要件も満たしています。SAEJ2602 は、LIN 2.0 のデューティ サイクルの定義から伝搬遅延の式を導出しています。詳細については、SAEJ2602 の仕様を参照してください。

(2) 正誤表『TLIN1029-Q1 および TLIN2029-Q1 のデューティ サイクルと  $V_{\text{SUP}}$  との関係』を参照してください。

## 5.8 タイミング要件

| 記号、シンボル                       | 説明                                                                                                       | テスト条件                                                                                                                                 | 最小値 | 公称値 | 最大値 | 単位      |

|-------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| $t_{rx\_pdf}$ 、 $t_{rx\_pd़}$ | レシーバの立ち上がりおよび立ち下がり伝搬遅延時間 (ISO/DIS 17987 Param 31、76)                                                     | $R_{RXD} = 2.4k\Omega$ 、 $C_{RXD} = 20pF$ (図 1-1 と図 1-1 を参照)                                                                          |     |     | 6   | $\mu s$ |

| $t_{rx\_sym}$                 | レシーバの伝搬遅延時間の対称性                                                                                          | 立ち下がり伝搬遅延時間と立ち上がり伝搬遅延時間の差、( $t_{rx\_sym} = t_{rx\_pd़} - t_{rx\_pdf}$ )、 $R_{RXD} = 2.4k\Omega$ 、 $C_{RXD} = 20pF$ (図 1-1 と図 1-1 を参照) |     | -2  | 2   | $\mu s$ |

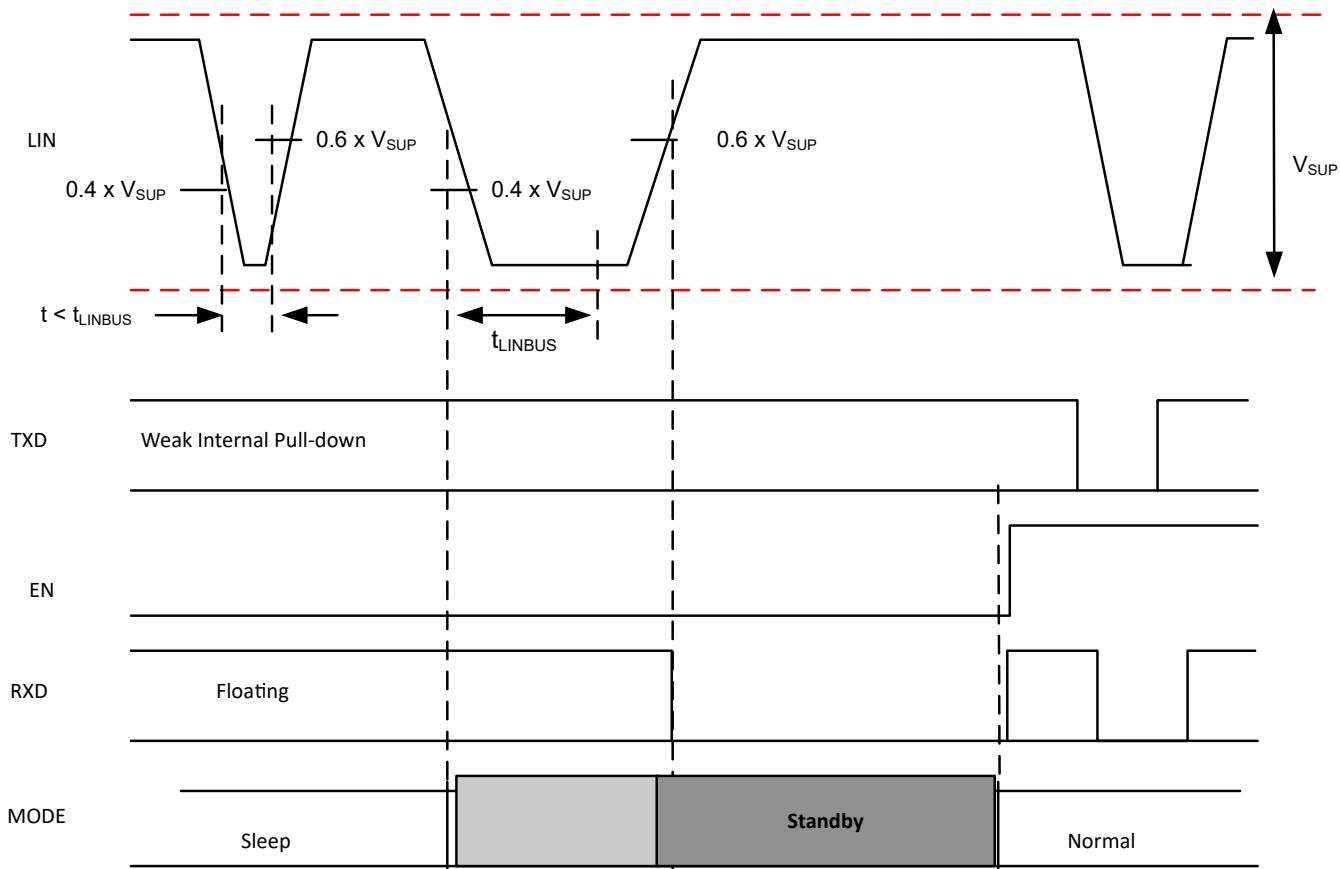

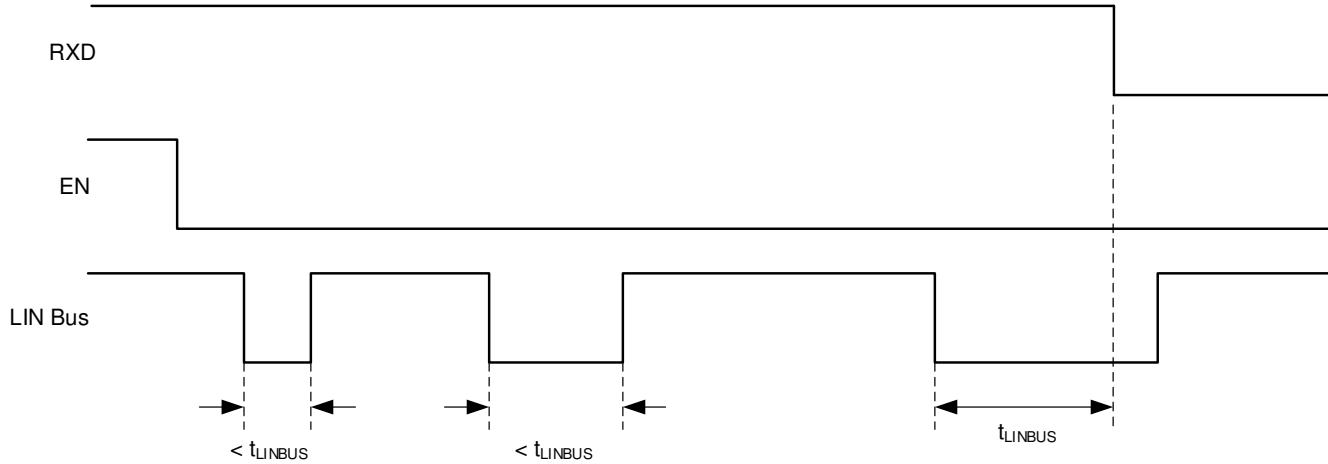

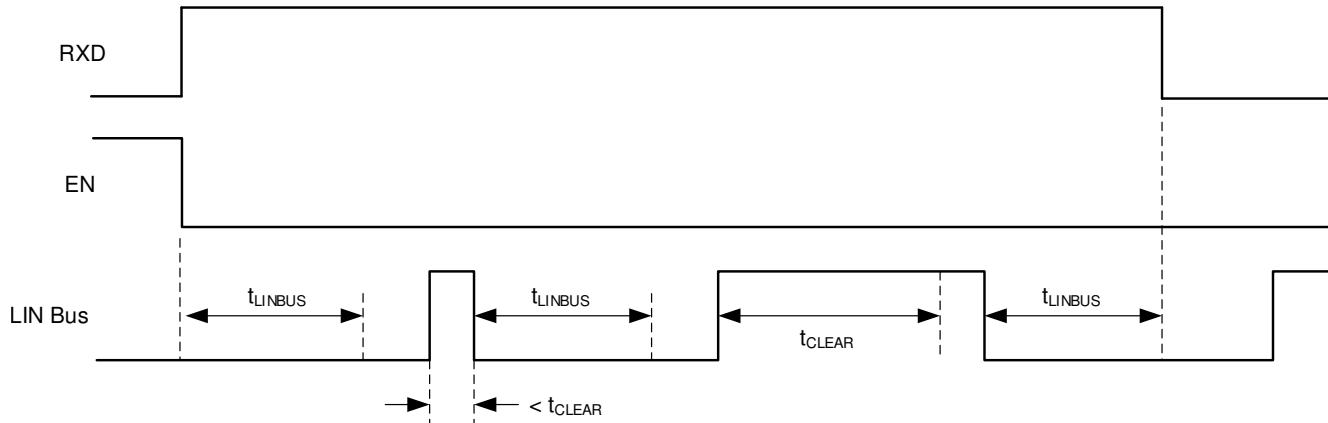

| $t_{LINBUS}$                  | LIN ウエークアップ時間 (ウェークアップのための LIN バスの最小ドミナント時間)                                                             | 図 1-1 と図 1-1 を参照                                                                                                                      | 25  | 65  | 150 | $\mu s$ |

| $t_{CLEAR}$                   | LIN バスにバス スタック ドミナント フォルトが発生した際に、誤ウェークアップ防止ロジックをクリアするための時間 (バス スタック ドミナント フォルトをクリアするための LIN バスのリセッショブ時間) | 図 1-1 を参照してください                                                                                                                       | 8   | 25  | 50  | $\mu s$ |

| $t_{DST}$                     | ドミナント状態タイムアウト                                                                                            |                                                                                                                                       | 20  | 45  | 80  | ms      |

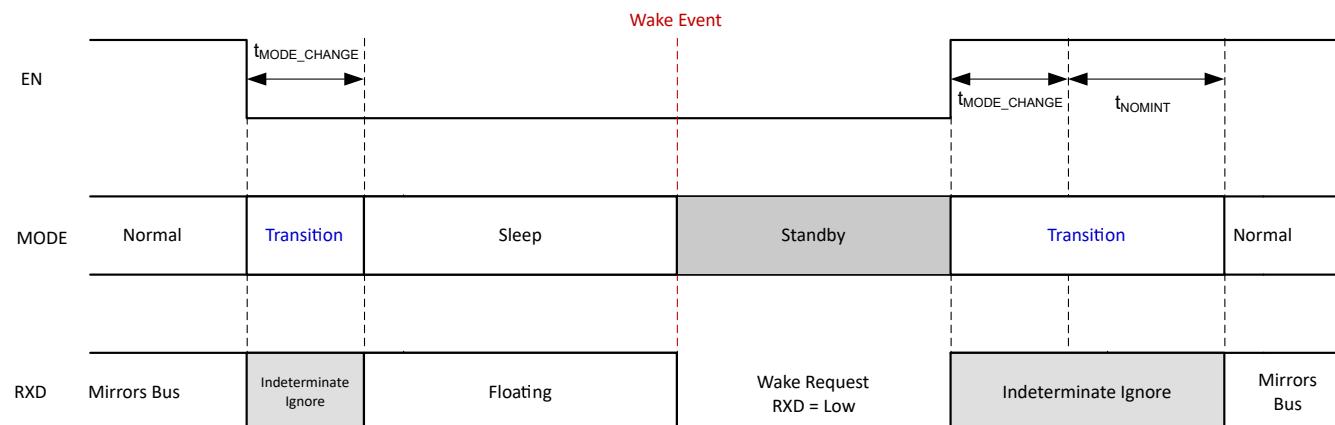

| $t_{MODE\_CHANGE}$            | モード変化遅延時間                                                                                                | EN ピンによってスタンバイ モードから通常 モード、または通常 モードからスリープ モードに変化するための時間 (図 1-1 および 図 1-1 を参照)                                                        | 2   |     | 15  | $\mu s$ |

| $t_{NOMINT}$                  | 通常モードの初期化時間                                                                                              | 通常モードが初期化され、RXD ピンのデータが有効になるまでの時間 (図 1-1 を参照)                                                                                         |     |     | 35  | $\mu s$ |

| $t_{PWR}$                     | パワーアップ時間                                                                                                 | 電源オン時に RXD 上のデータが有効になるまでの時間                                                                                                           |     |     | 1.5 | ms      |

## 6 パラメータ測定情報

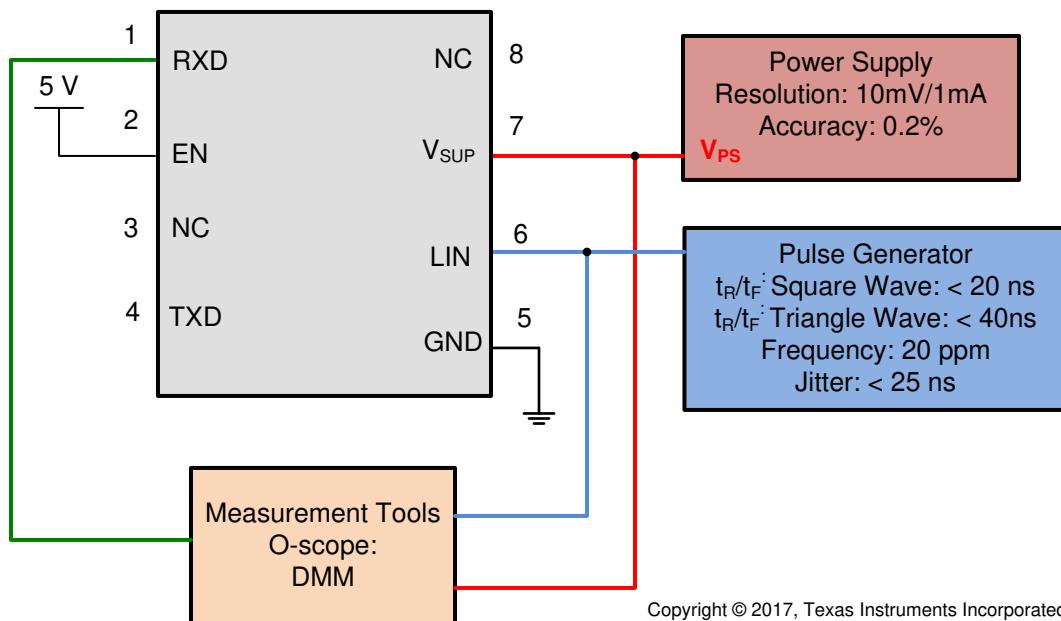

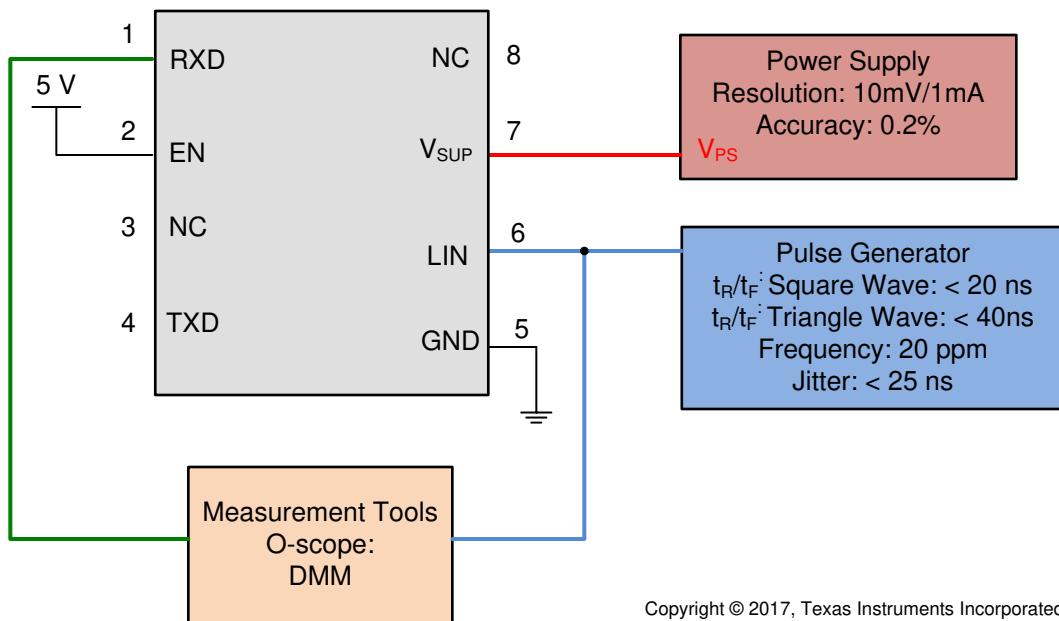

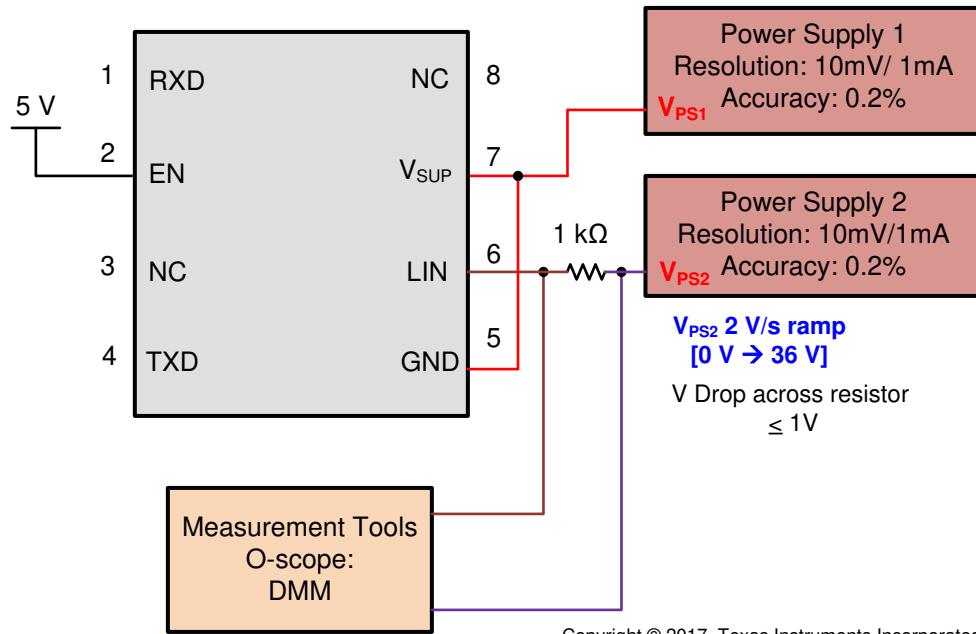

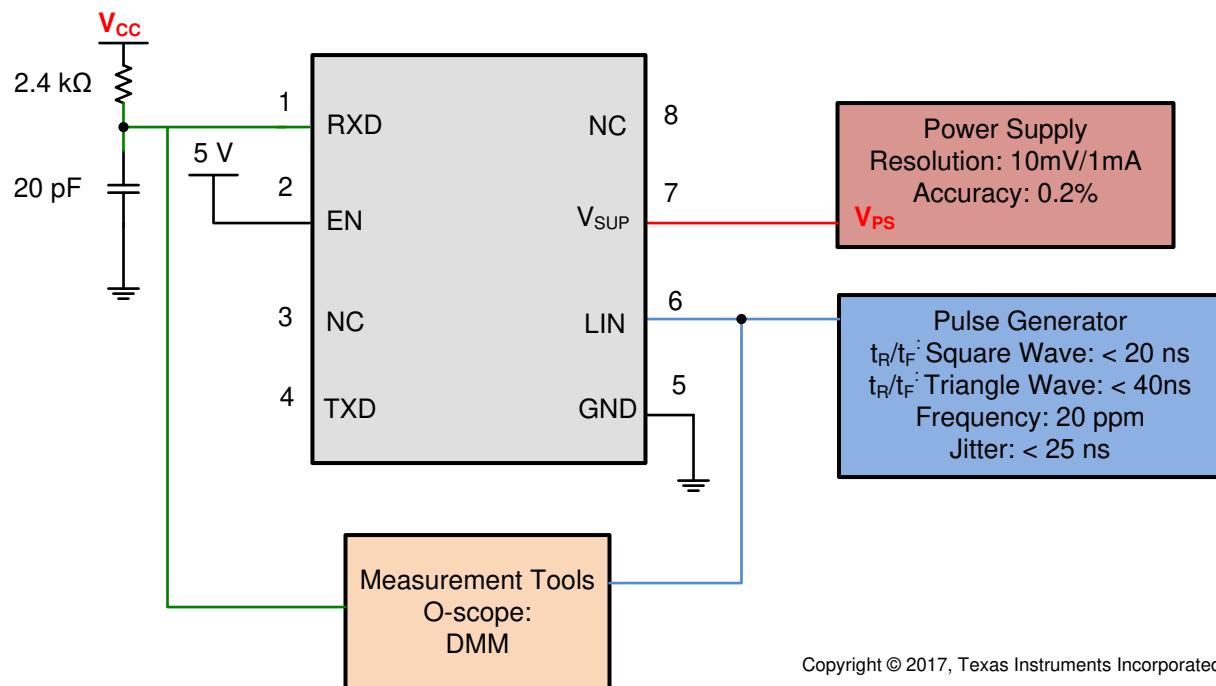

図 6-1. テストシステム：RX および TX アクセスによる動作電圧範囲：パラメータ 9、10

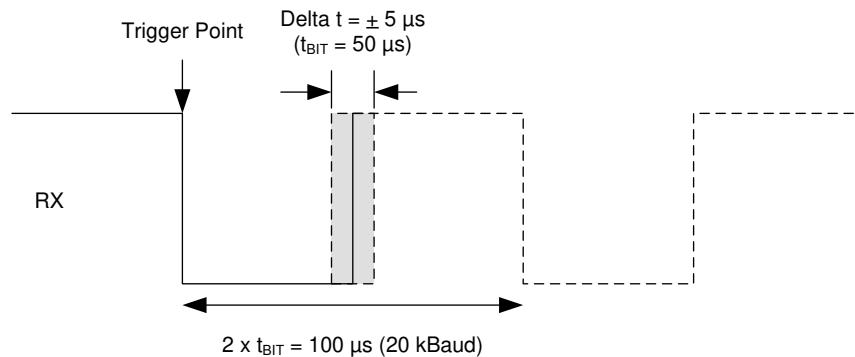

図 6-2. RX 応答：動作電圧範囲

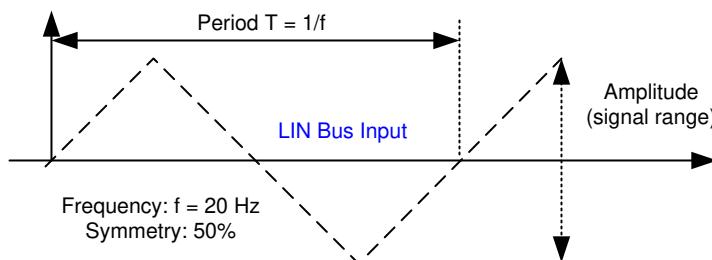

図 6-3. LIN バス入力信号

Copyright © 2017, Texas Instruments Incorporated

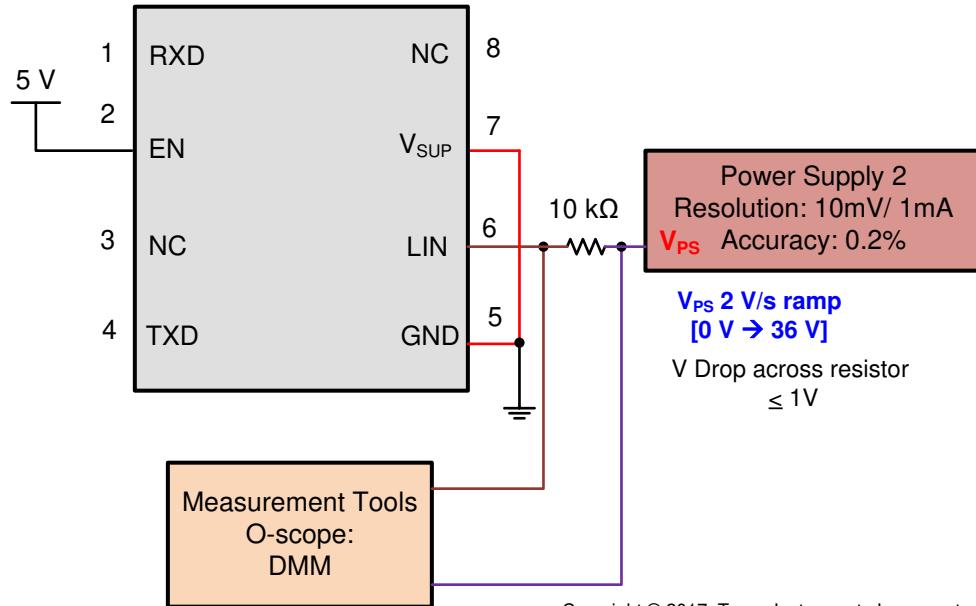

図 6-4. RX アクセスによる LIN レシーバ テスト：パラメータ 17、18、19、20

Copyright © 2017, Texas Instruments Incorporated

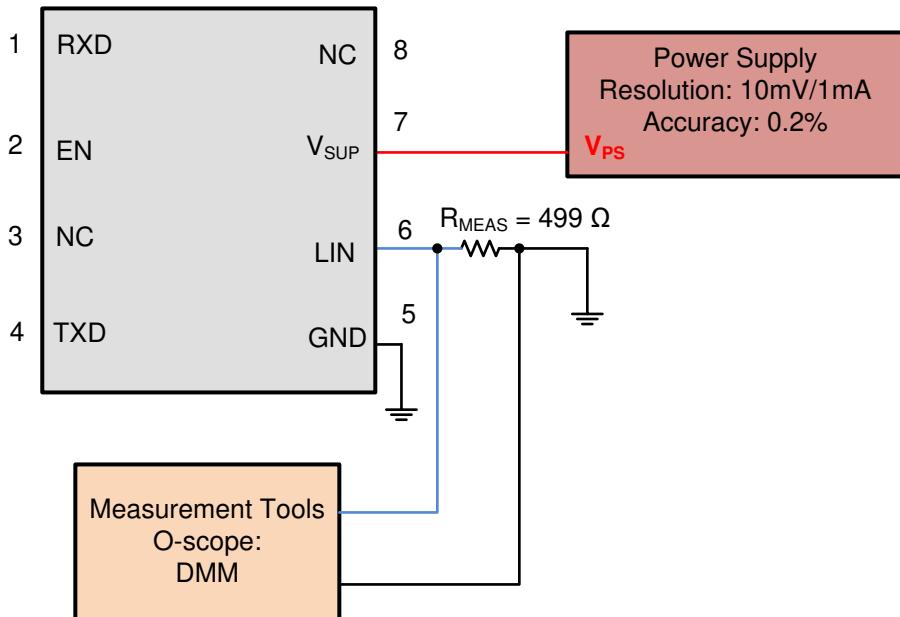

図 6-5. VSUP\_NON\_OP : パラメータ 11 54/56

Copyright © 2017, Texas Instruments Incorporated

図 6-6.  $I_{BUS\_LIM}$  のテスト回路：ドミナント状態（ドライバオン）、パラメータ 12

Copyright © 2017, Texas Instruments Incorporated

図 6-7.  $I_{BUS\_PAS\_DOM}$  のテスト回路：TXD = リセッシブ状態、 $V_{BUS} = 0V$ 、パラメータ 13

Copyright © 2017, Texas Instruments Incorporated

図 6-8.  $I_{BUS\_PAS\_rec}$  のテスト回路：パラメータ 14

Copyright © 2017, Texas Instruments Incorporated

図 6-9.  $I_{BUS\_NO\_GND}$  のテスト回路：GND 喪失

Copyright © 2017, Texas Instruments Incorporated

図 6-10.  $I_{BUS\_NO\_BAT}$  のテスト回路：バッテリ喪失

Copyright © 2017, Texas Instruments Incorporated

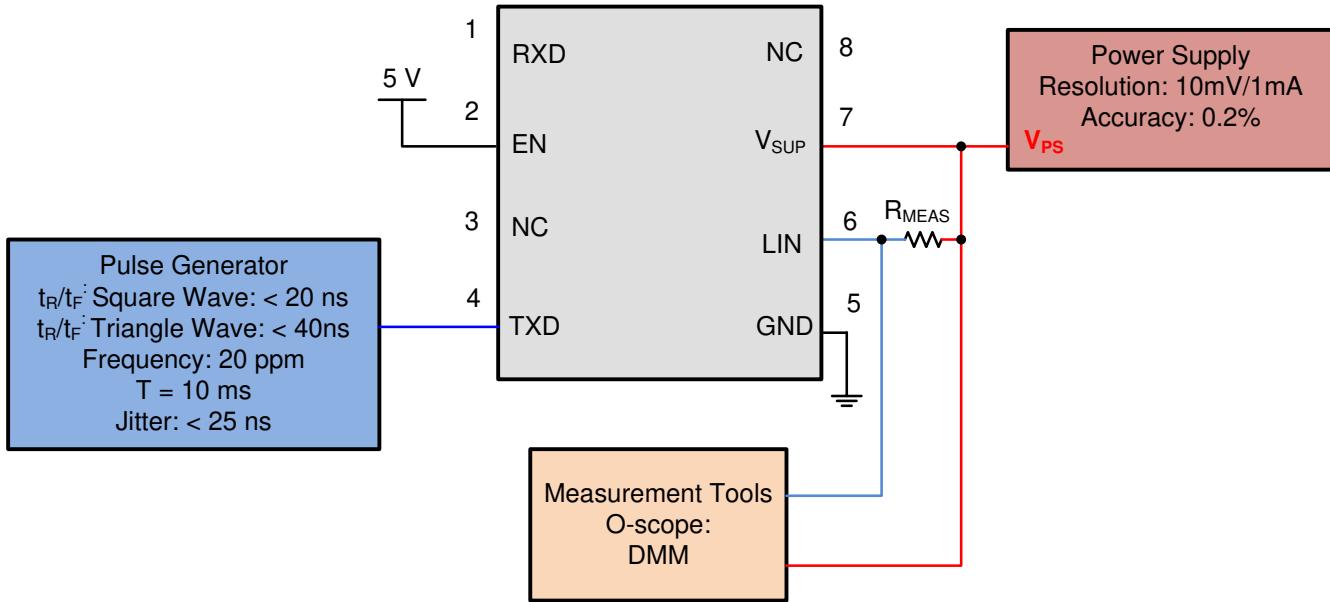

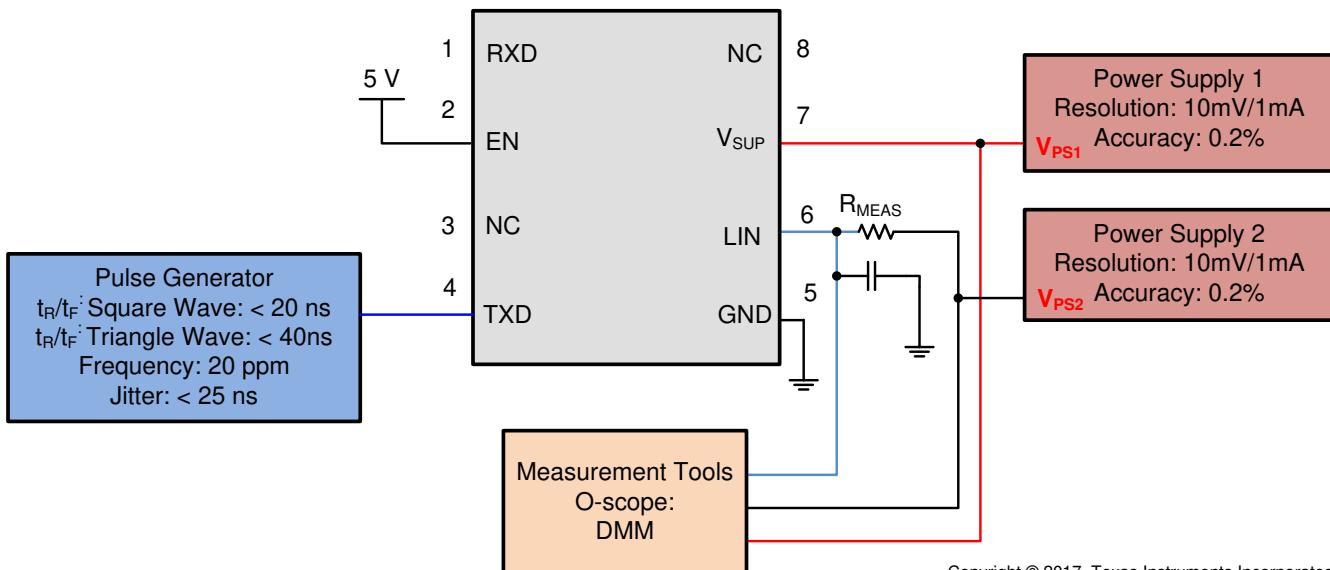

図 6-11. スロープ制御とデューティ サイクルのテスト回路：パラメータ 27、28、29、30、72、73、74、75

図 6-12. バスタイミングパラメータの定義

図 6-13. 伝搬遅延テスト回路: パラメータ 31、32

図 6-14. 伝搬遅延

図 6-15. モード遷移

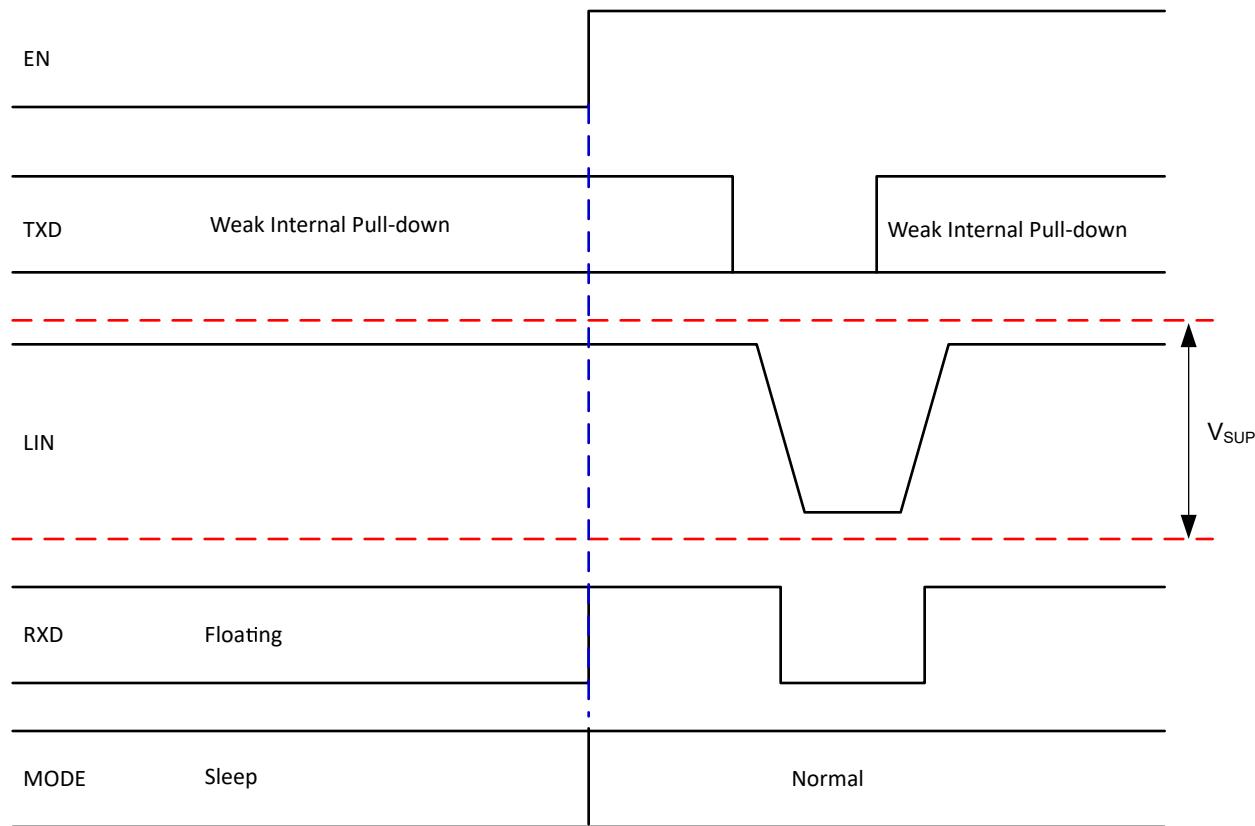

図 6-16. EN によるウェークアップ

図 6-17. LIN によるウェークアップ

Copyright © 2017, Texas Instruments Incorporated

図 6-18. AC 特性のテスト回路

## 7 詳細説明

### 7.1 概要

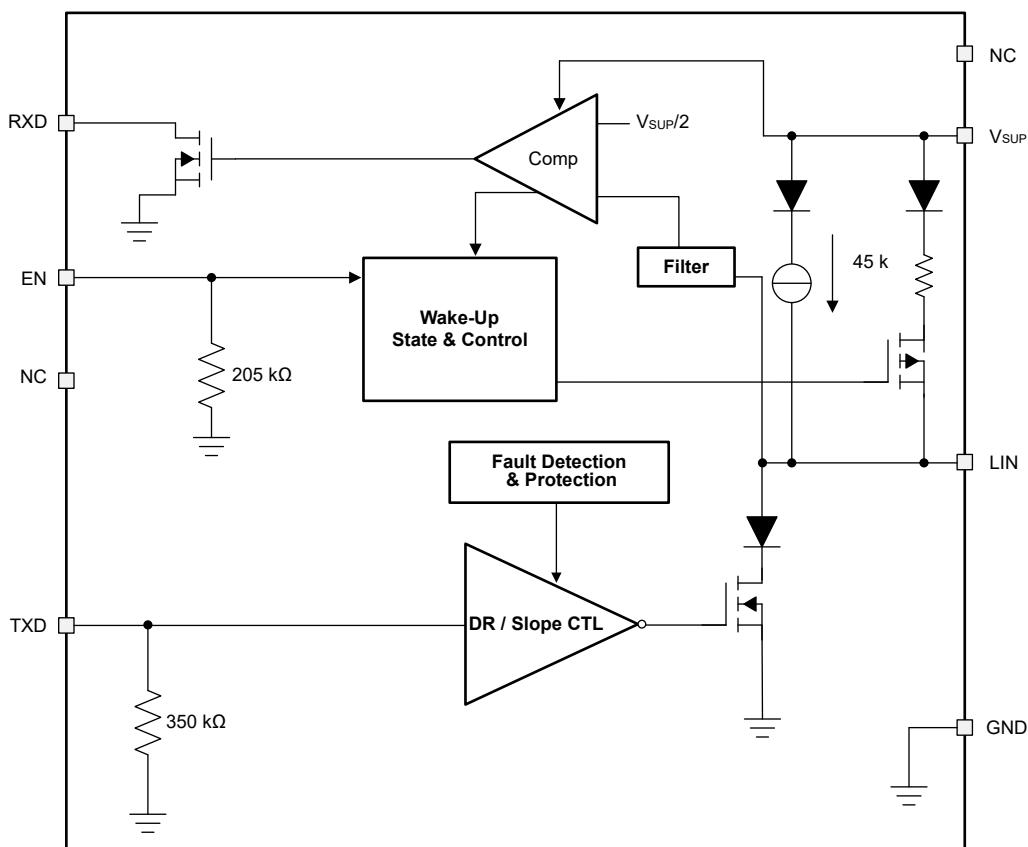

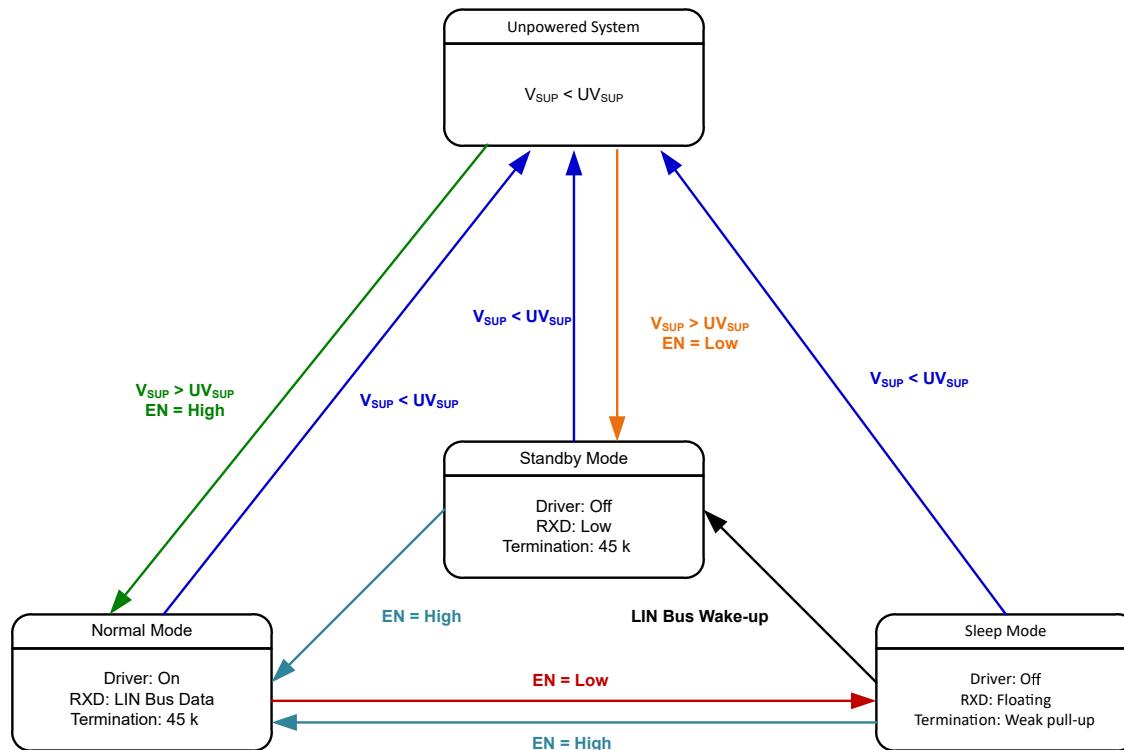

TLIN2029-Q1 は、ウェークアップおよび保護機能を内蔵し、LIN 2.0、LIN 2.1、LIN 2.2、LIN 2.2A、ISO/DIS 17987-4 標準に準拠したローカル相互接続ネットワーク (LIN) 物理層トランシーバです。LIN バスとは、2.4kbps~20kbps のデータレートを使った低速車載ネットワークで一般に使用されている単線式双方向バスです。TLIN2029-Q1 の LIN レシーバは最大 100kbps で動作し、インライン プログラミングをサポートしています。LIN 物理層仕様で規定されているように、TXD 入力上の LIN プロトコル データストリームは、TLIN2029-Q1 によって電流制限波形整形ドライバを使って LIN バス信号に変換されます。本レシーバは、データストリームを論理レベル信号に変換し、オープンドレインの RXD ピンを経由してマイクロプロセッサに送信します。LIN バスには、ドミナント状態 (グランドに近い電圧) とリセシティブ状態 (バッテリに近い電圧) という 2 つの状態があります。リセシティブ状態では、内蔵プルアップ抵抗 (45kΩ) および直列ダイオードにより、LIN バスが High になります。レスポンダ モード用途では、外付けプルアップ部品は不要です。コマンダ モード用途では、LIN 仕様に従って外付けプルアップ抵抗 (1kΩ) と直列ダイオードが必要です。TLIN2029-Q1 は、ESD 耐性や高いバススタンドオフ電圧など、多くの保護機能を備えています。また、このデバイスは次の 2 つの方法でウェークアップすることができます。それは、EN ピンによる方法と LIN バスからの信号による方法です。

### 7.2 機能ブロック図

### 7.3 機能説明

#### 7.3.1 LIN (Local Interconnect Network) バス

この高電圧入出力ピンは、単線式 LIN バストランシッタおよびレシーバです。LIN ピンは最大 60V の過渡電圧に耐えられます。グランドシフトまたは電源 (VSUP) 喪失が発生しても、ブロッキング ダイオードにより、LIN から電源 (VSUP) への逆電流を最小限に抑えます。

### 7.3.1.1 LIN トランシッタの特性

トランシッタは、LIN 仕様に準拠したスレッショルドと AC パラメータを持っています。トランシッタは、電流制限機能とサーマル シャットダウン機能を内蔵したローサイド トランジスタです。サーマル シャットダウン状態の間、本デバイスを保護するため、トランシッタは無効化されます。 $V_{SUP}$  に対して接続された直列ダイオード付きプルアップ抵抗が内蔵されているため、LIN レスポンダ モード用途では外付けプルアップ部品は不要です。本デバイスをコマンダ モード用途で使用する場合、 $V_{SUP}$  に対して接続された直列ダイオード付き外部プルアップ抵抗を追加する必要があります。

### 7.3.1.2 LIN レシーバの特性

レシーバ特性のスレッショルドは、LIN 仕様に従って、本デバイスの電源ピンの電圧に比例します。

レシーバは、LIN または SAEJ2602 仕様でサポートされているデータレートよりも高いデータレート ( $> 100\text{ kbps}$ ) で受信できます。そのため、最終工程またはその他のアプリケーションでの高速ダウンロードに TLIN2029-Q1 を使用できます。実現可能な実際のデータレートは、システムの時定数 (バス容量とプルアップ抵抗) と、そのシステムで使用されるドライバの特性で決まります。

#### 7.3.1.2.1 終端

$V_{SUP}$  に対して接続された直列ダイオード付きプルアップ抵抗が内蔵されているため、LIN レスponsa モード用途では外付けプルアップ部品は不要です。本デバイスを、LIN 仕様に従ってコマンダ モード用途で使用する場合、 $V_{SUP}$  に対して接続された直列ダイオード付き外部プルアップ抵抗 ( $1\text{ k}\Omega$ ) を追加する必要があります。

図 1-1 に、コマンダ ノードの構成と、電圧レベルの定義方法を示します。

図 7-1. コマンダ ノードの構成と電圧レベル

### 7.3.2 TXD (送信入力および出力)

TXD は、MCU の LIN プロトコル コントローラとのインターフェイス (SCI および UART) であり、LIN 出力の状態を制御するために使用されます。TXD を Low にすると、LIN 出力はドミナント (ほぼグランド) になります。TXD を High にすると、LIN 出力はリセッショブ (ほぼ  $V_{Battery}$ ) になります。図 1-1 を参照してください。TXD の入力構造は、3.3V および 5V I/O を備えたマイクロコントローラと互換性があります。TXD は内部プルダウン抵抗を備えています。LIN バスは、TXD が Low に駆動されるというシステム障害によってドミナント状態に張り付くことがないように、ドミナント状態タイムアウト タイマによって保護されています。

### 7.3.3 RXD (受信出力)

RXD は、MCU の LIN プロトコル コントローラとのインターフェイス (SCI および UART) であり、LIN バス電圧の状態を報告します。LIN リセッショブ (ほぼ  $V_{Battery}$ ) は RXD の High レベルによって表され、LIN ドミナント (ほぼグランド) は RXD

ピンの **Low** レベルによって表されます。RXD 出力の構造はオープンドレイン出力段です。そのため、本デバイスは 3.3V および 5V I/O のマイクロコントローラと組み合わせて使用できます。マイクロコントローラの RXD ピンがプルアップを内蔵していない場合、マイクロコントローラの I/O 電源電圧に接続された外部プルアップ抵抗が必要です。スタンバイモードでは、LIN バスからのウェークアップ要求を示すため、RXD ピンは **Low** に駆動されます。

### 7.3.4 $V_{SUP}$ (電源電圧)

$V_{SUP}$  は電源ピンです。 $V_{SUP}$  は、外付けの逆方向ブロッキングダイオードを経由してバッテリに接続されます (図 1-1)。ECU レベルで電力が失われても、本デバイスの LIN ピンによるリーク電流は非常に小さいため、バスの負荷となってバス電圧を低下させることはできません。これは、一部のノード (イグニッション電源) には電力が供給されないが、ネットワークの残りの部分 (バッテリ電源) には電力が供給される LIN システムに最適です。

### 7.3.5 $GND$ (グランド)

$GND$  は本デバイスのグランド接続です。グランドシフトによって  $V_{SUP}$  が最小動作電圧を下回らない限り、本デバイスはグランドシフトを使って動作できます。入力および出力電圧がそれぞれの適切なスレッショルドの範囲内に確実に入るようになります。本デバイスの LIN ピンからのリーク電流は非常に小さいため、ECU レベルでグランドが失われても、本デバイスはバスの電位を引き下げません。これは、ネットワークの一部のノード (イグニッション電源) には電力が供給されないが、残りの部分 (バッテリ電源) には電力が供給される LIN システムに最適です。

### 7.3.6 $EN$ (イネーブル入力)

$EN$  は、本デバイスの動作モードを制御します。 $EN$  を **High** にすると、本デバイスは通常動作モードになり、TXD から LIN、さらに LIN から RXD への伝送バスが利用可能になります。 $EN$  を **Low** にすると、本デバイスはスリープモードに移行し、伝送バスは利用できなくなります。本デバイスが通常モードに移行できるのは、ウェークアップした後のみです。 $EN$  がフローティングになっても本デバイスが確実に低消費電力モードにとどまるように、 $EN$  には内部プルダウン抵抗が備わっています。

### 7.3.7 保護機能

TLIN2029-Q1 は、以下に説明するように、複数の保護機能を備えています。

### 7.3.8 TXD ドミナントタイムアウト (DTO)

通常モードの間に、ハードウェアまたはソフトウェア アプリケーションの障害によって TXD が意図せず永続的に **Low** に駆動された場合、LIN バスはドミナント状態タイムアウトタイマによって保護されます。このタイマは TXD ピンの立ち上がりエッジによってトリガれます。 $t_{DST}$  よりも長い間 TXD が **Low** に維持されると、トランスマッタは無効化され、LIN バスはリセッショップ状態に戻り、バス上で通信を再開できます。TXD の立ち上がりエッジで保護はクリアされ、 $t_{DST}$  タイマはリセットされます。TXD が切り離された場合に、本デバイスが機能しなくなても必ず既知の状態になるように、TXD ピンは内部プルダウンを備えています。このフォルト中、トランシーバは ( $EN$  での状態変化要求がないものと仮定して) 通常モードに維持され、トランスマッタは無効化され、RXD ピンは LIN バスを反映し、LIN バスのプルアップ終端はオンのまま維持されます。

### 7.3.9 バスがドミナント状態で固着するシステム フォルト：偽のウェークアップ誤動作防止

TLIN2029-Q1 には、バス スタック ドミナント システム フォルトを検出するロジックが内蔵されており、システム フォルト時に本デバイスが誤ってウェークアップするのを防止しています。スリープモードに移行すると、本デバイスは LIN バスの状態を検出します。バスがドミナントの場合、バスがドミナントに固着した状態をバスの有効なりセッショップが「クリア」するまで、ウェークアップ ロジックは作動せず、過剰な電流消費を防止します。図 1-1 と図 1-1 に、この保護機能の動作を示します。

図 7-2. バス フォルトなし：バス リセッショップ条件とウェークアップによるスリープ モードへの移行

図 7-3. バス フォルト：バス スタック ドミナント フォルト、クリア、ウェークアップによるスリープ モードへの移行

### 7.3.10 サーマル シャットダウン

LIN トランシッタは電流制限回路によって保護されていますが、本デバイスの接合部温度がサーマル シャットダウン スレッショルドを超えると、本デバイスは LIN トランシッタをリセッショップ状態にします。過熱フォルト状態が解消され、接合部温度がヒステリシス温度よりも低くなると、本デバイスは通常動作モードにとどまっていると仮定して、トランシッタを再び有効化します。このフォルト中、トランシーバは (EN の状態変化要求がないと仮定して) 通常モードに維持され、トランシッタはリセッショップ状態になり、RXD ピンは LIN バスを反映し、LIN バスのプルアップ終端はオンに維持されます。

### 7.3.11 $V_{SUP}$ の低電圧保護

TLIN2029-Q1 は、低電圧状態 ( $V_{SUP}$  が  $UV_{SUP}$  未満) での誤ったバス メッセージを防止するため、パワーオン リセット回路を備えています。

### 7.3.12 電源なレデバイスと LIN バス

車載アプリケーションでは、システム内的一部の LIN ノードにバッテリで電力を供給したまま、ネットワーク内のその他の LIN ノードへの電力供給を停止すること (イグニッション電源) があります。TLIN2029-Q1 は、電源オフ時にバスから流れ込むリーク電流が非常に小さいため、電力が供給されていないノードがネットワークに影響を与える (ネットワークの負荷となってバス電圧を低下させる) ことはありません。

## 7.4 デバイスの機能モード

TLIN2029-Q1 には 3 つの動作モード (通常、スリープ、スタンバイ) があります。次のセクションでは、これらのモードと、本デバイスが各モード間をどのように移動するかについて説明します。図 1-1 にその関係を図示し、表 7-1 にピンの状態を示します。

表 7-1. 動作モード

| モード   | EN   | RXD       | LIN バスの終端  | トランシミッタ | 備考                                    |

|-------|------|-----------|------------|---------|---------------------------------------|

| スリープ  | Low  | フローティング   | 弱電流プルアップ   | オフ      |                                       |

| スタンバイ | Low  | Low       | 45kΩ (標準値) | オフ      | ウェークアップ イベントを検出済み、MCU が EN をセットするのを待機 |

| 通常    | High | LIN バスデータ | 45kΩ (標準値) | オン      | 最大 20kbps の LIN 転送                    |

Copyright © 2017, Texas Instruments Incorporated

図 7-4. 動作の状態図

### 7.4.1 通常モード

電源投入時に EN ピンが High の場合、本デバイスは通常モードで起動します。EN ピンが Low の場合、本デバイスはスタンバイモードで起動します。EN ピンは本デバイスのモードを制御します。通常動作モードでは、レシーバとトランシミッタは作動しています。LIN 仕様の最大値である 20kbps の LIN 伝送がサポートされています。本レシーバは LIN バス上のデータストリームを検出し、それを RXD で LIN コントローラに出力します。LIN バスのリセッショナル信号はロジック High であり、LIN バスのドミナント信号はロジック Low です。ドライバは入力データを TXD から LIN バスに送信します。> ( $t_{MODE\_CHANGE} + t_{NOMINT}$ ) の期間にわたって TLIN2029-Q1 がスリープモードまたはスタンバイモードにある間に、EN が High に遷移すると、通常モードに移行します。

## 7.4.2 スリープモード

スリープモードは、TLIN2029-Q1 の省電力モードです。EN ピンが Low になったときに、かつ通常モードからのみ、スリープモードに移行します。このモードの非常に小さい消費電流でも、ウェークアップ信号によって LIN バスから、または EN が  $t_{MODE\_CHANGE}$  より長い間 High に設定された場合、TLIN2029-Q1 はウェークアップできます。誤ウェークアップイベントを防止するため、LIN バスはフィルタ処理されます。ウェークアップイベントは、それぞれの期間 ( $t_{LINBUS}$ ) にわたってアクティブである必要があります。

EN を  $t_{MODE\_CHANGE}$  より長い間 Low に設定すると、スリープモードに移行します。

本デバイスがスリープモードに入っている間、次の条件が成立しています。

- LIN バスドライバは無効化され、内部 LIN バス終端はオフになります (LIN がグランドに短絡した場合の電力損失を最小化するため)。ただし、LIN バスへの外部接続が失われた際に誤ってウェークアップイベントが発生しないように、弱電流プルアップが機能しています。

- 通常のレシーバは無効化されています。

- EN 入力と LIN ウェークアップ レシーバは機能しています。

## 7.4.3 スタンバイモード

本デバイスがスリープモードに入っている間に、LIN バスによってウェークアップイベントが発生すると、常にこのモードに移行します。スタンバイモードに入ると、LIN バスレスポンダモードの終端回路がターンオンされます。スタンバイモードは、RXD の Low レベルによって通知されます。アプリケーションの詳細については、[セクション 8.2.2.2](#) を参照してください。

本デバイスがスタンバイモードに入っている間に、 $t_{MODE\_CHANGE}$  よりも長い時間 EN が High に設定されると、本デバイスは通常モードに戻ります。TXD から LIN バスへ、そして LIN バスから RXD への通常の伝送パスが有効化されます。

## 7.4.4 ウェークアップイベント

スリープモードからウェークアップするには次の 2 つの方法があります。

- リモートウェークアップ: LIN バスのリセッショップ (High) 状態からドミナント (Low) 状態への遷移の立ち下がりエッジで開始されます。ここで、このドミナント状態は、 $t_{LINBUS}$  フィルタ時間にわたって保持される必要があります。この  $t_{LINBUS}$  フィルタ時間が経過した後、LIN バスのドミナント状態からリセッショップ状態への遷移の立ち上がりエッジでリモートウェークアップイベントが開始されるため、LIN バス電圧の変動またはバスのグランドとの短絡による誤ったウェークアップを防止できます。

- ローカルウェークアップ: EN が  $t_{MODE\_CHANGE}$  より長い間 High に設定されることで開始されます。

### 7.4.4.1 ウェークアップ要求 (RXD)

TLIN2029-Q1 が LIN バスからウェークアップイベントを検出すると、RXD が Low になり、本デバイスはスタンバイモードに遷移します。その後、EN が High に再アサートされると、本デバイスは通常モードに移行します。本デバイスが通常モードに移行すると、RXD ピンはウェークアップ要求信号を解放した後、LIN バスからのレシーバ出力を反映します。

### 7.4.4.2 モード遷移

TLIN2029-Q1 が通常モードからスリープモードまたはスタンバイモードに遷移する際に、EN ピンの変化が本デバイスの中を完全に伝搬して新しい状態に変わるために、本デバイスは  $t_{MODE\_CHANGE}$  の時間を必要とします。スリープモードまたはスタンバイモードから通常モードに遷移する際に、本デバイスは  $t_{MODE\_CHANGE} + t_{NOMINT}$  の時間を必要とします。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

TLIN2029-Q1 は、LIN ネットワーク内でレスポンダ ノード デバイスとコマンダ ノード デバイスの両方として使用できます。本デバイスは、リモート ウェークアップ要求とローカル ウェークアップ要求の両方をサポートする機能を備えています。

### 8.2 代表的なアプリケーション

このデバイスは、レスポンダ ノード用に  $45\text{k}\Omega$  プルアップ抵抗と直列ダイオードを内蔵しています。コマンダ用途の場合、外付けの  $1\text{k}\Omega$  プルアップ抵抗と直列ブロッキング ダイオードを使用できます。図 1-1 に、コマンダ モードとレスポンダ モードの両方の用途に本デバイスを使用している例を示します。

- A. LIN レスポンダ ノードの MCU の RXD に内部プルアップがある場合、外部プルアップ抵抗は不要です。

- B. LIN レスポンダ ノードの MCU の RXD に内部プルアップがない場合、外付けプルアップ抵抗が必要です。

- C. コマンダ ノード用途では、外付けの  $1\text{k}\Omega$  プルアップ抵抗と直列ダイオードが必要です。

- D. デカップリング コンデンサの値はシステムによって異なりますが、通常は  $100\text{nF}$ 、 $1\mu\text{F}$ 、 $10\mu\text{F}$  以上です。

図 8-1. 代表的な LIN バス

## 8.2.1 設計要件

RXD 出力の構造はオープンドレイン出力段です。そのため、TLIN2029-Q1 は 3.3V および 5V I/O のプロセッサと組み合わせて使用できます。プロセッサの RXD ピンがプルアップを内蔵していない場合、プロセッサの I/O 電源電圧に接続された外部プルアップ抵抗が必要です。外部プルアップ抵抗の値は、使用する電源に応じて  $1\text{k}\Omega$ ~ $10\text{k}\Omega$  の範囲で選択する必要があります (電気的特性の  $I_{OL}$  を参照)。本デバイスの  $V_{SUP}$  ピンは、本デバイスの電源ピンにできる限り近づけて配置した  $100\text{nF}$  のコンデンサでデカップリングする必要があります。

## 8.2.2 設計手順の詳細

### 8.2.2.1 通常モードのアプリケーションノート

RXD ピンを監視してウェークアップ要求を検出するシステムで TLIN2029-Q1 を使用する場合、モード遷移に特に注意を払う必要があります。RXD ピンの出力は、レシーバが交代している最中は不定です。アプリケーション ソフトウェアは、 $t_{MODE\_CHANGE}$  が経過するまで、ウェークアップ要求を示すエッジを RXD ピンで検出しないようにする必要があります。これは、図 1-1 に示すとおりです。

### 8.2.2.2 スタンバイ モードのアプリケーションノート

TLIN2029-Q1 が  $V_{SUP}$  の低電圧を検出すると、RXD ピンが Low に変化し、TLIN2029-Q1 がスタンバイ モードに入ったことをソフトウェアに通知します。消費電力が最小の状態にするには、本デバイスをスリープ モードに戻す必要があります。

#### 8.2.2.2.1 TXD ドミナント状態タイムアウトのアプリケーションノート

TXD ドミナント状態タイムアウトで許容される最大ドミナント TXD 時間により、本デバイスの最小データ レートが制限されます。LIN プロトコルは、コマンダ ノード用途とレスポンダ ノード用途で制約が異なるため、それぞれの用途の場合で連続ドミナント ビット数の最大値が異なり、データ レートの最小値も異なります。

## 8.2.3 アプリケーション曲線

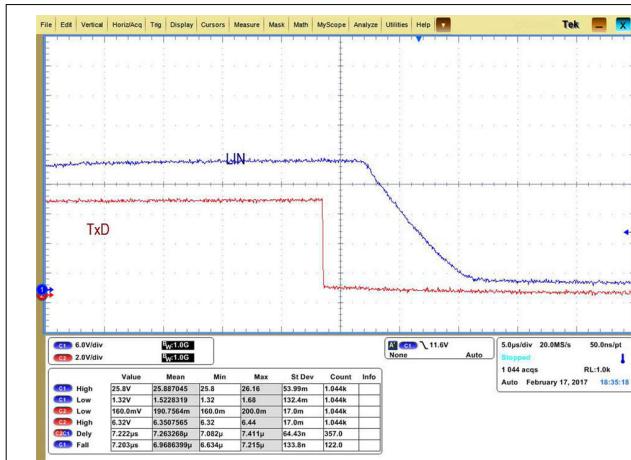

以下の図は、軽負荷条件での、「ドミナントからリセッショブ」と「リセッショブからドミナント」の両方の、TXD ピンから LIN ピンまでの伝搬遅延を示しています。

図 8-2. リセッショブからドミナントまでの伝搬遅延

図 8-3. ドミナントからリセッショブまでの伝搬遅延

## 8.3 電源に関する推奨事項

TLIN2029-Q1 は、自動車のバッテリ、または 4V~45V のその他の DC 電源で直接動作するように設計されています。100nF のデカップリング コンデンサは、本デバイスの  $V_{SUP}$  ピンのできるだけ近くに配置する必要があります。ノイズの多い電源を使用するアプリケーションでは、 $1\mu\text{F}$ ~ $10\mu\text{F}$  のデカップリング コンデンサを使うことを推奨します。

## 8.4 レイアウト

PCB を適切に設計するには、保護およびフィルタ回路の設計から始めます。ESD 過渡はおよそ 3MHz～3GHz という広い周波数帯域幅を持つため、PCB 設計で高周波レイアウト手法を適用する必要があります。デバイスをコネクタにできるだけ近づけて配置することで、これらのノイズの多いイベントが PCB とシステムの中に伝播するのを防止します。

### 8.4.1 レイアウトのガイドライン

- **ピン 1 (RXD):**このピンはオープンドレイン出力であり、適切に機能させるには、 $1\text{k}\Omega$  から  $10\text{k}\Omega$  までの範囲の外付けプルアップ抵抗が必要です。その最小値は、使用する IO 電源電圧によって決まることに注意します。電気的仕様の  $I_{OL}$  を参照してください。トランシーバと組み合わせるマイクロプロセッサにプルアップが内蔵されていない場合、RXD とマイクロプロセッサの安定化電源電圧との間に外付け抵抗を配置する必要があります。

- **ピン 2 (EN):**EN は、本デバイスを低消費電力スリープ モードに移行させるために使用される入力ピンです。この機能を使用しない場合、 $1\text{k}\Omega$ ～ $10\text{k}\Omega$  の直列抵抗でマイクロプロセッサの安定化電源電圧にこのピンをプルアップする必要があります。また、過電圧フォルト時のデジタル ラインの電流を制限するため、このピンに直列抵抗を配置することもできます。

- **ピン 3 (NC):**接続なし。

- **ピン 4 (TXD):**TXD ピンは、マイクロコントローラからの入力信号を送信するために使用されます。このピンに過電圧が発生した場合の本デバイスへの入力電流を制限するため、直列抵抗を配置できます。本デバイスの入力ピンに近付けて、グランドとの間にコンデンサを配置することで、ノイズをフィルタできます。

- **ピン 5 (GND):**これは、本デバイスのグランド接続です。総リターン インダクタンスを制限するため、2 つのビアを使って短いパターンでこのピンをグランド プレーンに接続する必要があります。

- **ピン 6 (LIN):**このピンは、LIN バスに接続されます。レスポンダ モード用途の場合、グランドとの間に  $220\text{pF}$  のコンデンサを実装します。コマンダ モード用途の場合、LIN ピンと  $V_{SUP}$  ピンの間に直列抵抗とブロッキング ダイオードを追加します。[図 1-1](#) を参照してください。

- **ピン 7 (VSUP):**本デバイスの電源ピンです。 $100\text{nF}$  デカップリング コンデンサは、本デバイスにできるだけ近付けて配置してください。

- **ピン 8 (NC):**接続なし。

#### 注

すべてのグランドおよび電源接続はできるだけ短くし、総ループ インダクタンスを最小化するため、2 つ以上のビアを使います。

#### 8.4.2 レイアウト例

図 8-4. レイアウト例

## 9 デバイスおよびドキュメントのサポート

### 9.1 ドキュメントのサポート

#### 9.1.1 関連資料

##### TLIN1029-Q1 および TLIN2029-Q1 のデューティサイクルと $V_{SUP}$ との関係

関連資料については、以下を参照してください。

- LIN 標準

- ISO/DIS 17987-1:道路車両 -- ローカル相互接続ネットワーク (LIN) -- 第 1 部:一般情報とユースケースの定義

- ISO/DIS 17987-4:道路車両 -- ローカル相互接続ネットワーク (LIN) -- 第 4 部:電気物理層 (EPL) 仕様 12V/24V

- SAEJ2602-1:車載アプリケーション用の LIN ネットワーク

- LIN 仕様 LIN 2.0、LIN 2.1、LIN 2.2、LIN 2.2A

- EMC 要件

- SAEJ2962-1:通信トランシーバ認定要件 - LIN

- ISO 10605:道路車両 - 静電放電による電気的障害のテスト手法

- ISO 11452-4:2011:道路車両 - ナローバンド放射の電磁気エネルギーによる電気的障害のコンポーネント テスト手法 - 第 4 部:ハーネス励起方法

- ISO 7637-1:2015:道路車両 - 伝導および結合による電気的障害 - 第 1 部:定義および一般的な考慮事項

- ISO 7637-3:道路車両 - 伝導および結合による電気的障害 - 第 3 部:供給ライン以外のラインを介した容量性および誘導性結合による電気的過渡伝達

- IEC 62132-4:2006:集積回路 - 150kHz~1GHz の電磁気耐性の測定 - 第 4 部:直接 RF 電力注入手法

- IEC 61000-4-2

- IEC 61967-4

- CISPR25

- 準拠テストの要件

- ISO/DIS 17987-7.2:道路車両 -- ローカル相互接続ネットワーク (LIN) -- 第 7 部:電気物理層 (EPL) 適合性テスト仕様

- SAEJ2602-2:車載アプリケーション用 LIN ネットワークの準拠テスト

-

### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。右上の [アラートを受け取る] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの [使用条件](#) を参照してください。

### 9.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.6 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision F (May 2022) to Revision G (February 2024) | Page |

|------------------------------------------------------------------|------|

| • 「製品情報」表を「パッケージ情報」表に変更.....                                     | 1    |

| • 「電気的特性」表の $I_{BUS\_LIM}$ の値を更新 .....                           | 5    |

| Changes from Revision E (May 2020) to Revision F (May 2022) | Page |

|-------------------------------------------------------------|------|

| • 旧式の用語を使っている場合、すべてコマンダおよびレスポンダに変更.....                     | 1    |

| Changes from Revision D (April 2020) to Revision E (May 2020)                   | Page |

|---------------------------------------------------------------------------------|------|

| • 「特長」のリストに「SLLA490 を参照」を追加.....                                                | 1    |

| • 追加: 正誤表『TLIN1029-Q1 および TLIN2029-Q1 のデューティサイクルと $V_{SUP}$ との関係』を参照してください。.... | 7    |

| Changes from Revision C (July 2019) to Revision D (April 2020)                          | Page |

|-----------------------------------------------------------------------------------------|------|

| • 「特長」を「 $\pm 58V$ の LIN バス フオルト保護」を「 $\pm 60V$ の LIN バス フオルト保護」に変更.....                | 1    |

| • 概略回路図 (レスポンダ モード) の $200pF$ のコンデンサを $220pF$ に変更.....                                  | 1    |

| • 概略回路図 (レスポンダ モード) の $200pF$ のコンデンサを $220pF$ に変更.....                                  | 1    |

| • 絶対最大定格の $V_{LIN}$ を「最小値 = -58、最大値 = 58」から「最小値 = -60、最大値 = 60」に変更.....                 | 4    |

| • 電気的特性の $C_{LINPIN}$ を最大値 = $45pF$ から最大値 = $25pF$ に変更し、テスト条件に $V_{SUP} = 14V$ を追加..... | 5    |

| • 「レイアウトのガイドライン」のピン 6 (LIN) の説明文の「 $200pF$ のコンデンサ」を「 $220pF$ のコンデンサ」に変更 .....           | 27   |

| Changes from Revision B (February 2018) to Revision C (July 2019)                    | Page |

|--------------------------------------------------------------------------------------|------|

| • 製品情報の SOIC パッケージの本体サイズを $4.90mm \times 6.00mm$ から $4.90mm \times 3.91mm$ に変更 ..... | 1    |

| • 概略回路図 (レスポンダ モード) の $220pF$ のコンデンサを $200pF$ に変更.....                               | 1    |

| • 概略回路図 (レスポンダ モード) の $220pF$ のコンデンサを $200pF$ に変更.....                               | 1    |

| • $V_{LOGIC}$ の絶対最大定格の最大値を $5.5V$ から $6V$ に変更.....                                   | 4    |

| • 図 8-2 のタイトルをリセッスピからドミナントまでの伝搬遅延に変更.....                                            | 26   |

| • 図 8-3 のタイトルをドミナントからリセッスピまでの伝搬遅延に変更.....                                            | 26   |

| • 「レイアウトのガイドライン」のピン 6 (LIN) の説明文の「 $220pF$ のコンデンサ」を「 $200pF$ のコンデンサ」に変更 .....        | 27   |

---

| Changes from Revision A (December 2017) to Revision B (February 2018)                        | Page |

|----------------------------------------------------------------------------------------------|------|

| • 以下のように変更:「Complaint to LIN 2.0」から「Compliant to LIN 2.0 (LIN 2.0 に準拠)」に、「特長」および「概要」で変更..... | 1    |

| • 以下のように変更:「概要」セクションの「complaint to LIN 2.0...」を「compliant to LIN 2.0... (LIN 2.0 に準拠 ...)」   | 19   |

---

| Changes from Revision * (October 2017) to Revision A (December 2017) | Page |

|----------------------------------------------------------------------|------|

| • デバイス ステータスを「事前情報」から「量産データ」に変更.....                                 | 1    |

---

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側のナビゲーションリンクを参照してください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TLIN2029DQ1           | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU   NIPDAUAG                    | Level-1-260C-UNLIM                | -40 to 125   | TL029               |

| TLIN2029DQ1.A         | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | TL029               |

| TLIN2029DRBRQ1        | Active        | Production           | SON (DRB)   8  | 3000   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | TL029               |

| TLIN2029DRBRQ1.A      | Active        | Production           | SON (DRB)   8  | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TL029               |

| TLIN2029DRBTQ1        | Active        | Production           | SON (DRB)   8  | 250   SMALL T&R       | Yes         | NIPDAU   SN                          | Level-2-260C-1 YEAR               | -40 to 125   | TL029               |

| TLIN2029DRBTQ1.A      | Active        | Production           | SON (DRB)   8  | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TL029               |

| TLIN2029DRQ1          | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG                    | Level-1-260C-UNLIM                | -40 to 125   | TL029               |

| TLIN2029DRQ1.A        | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | TL029               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

---

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

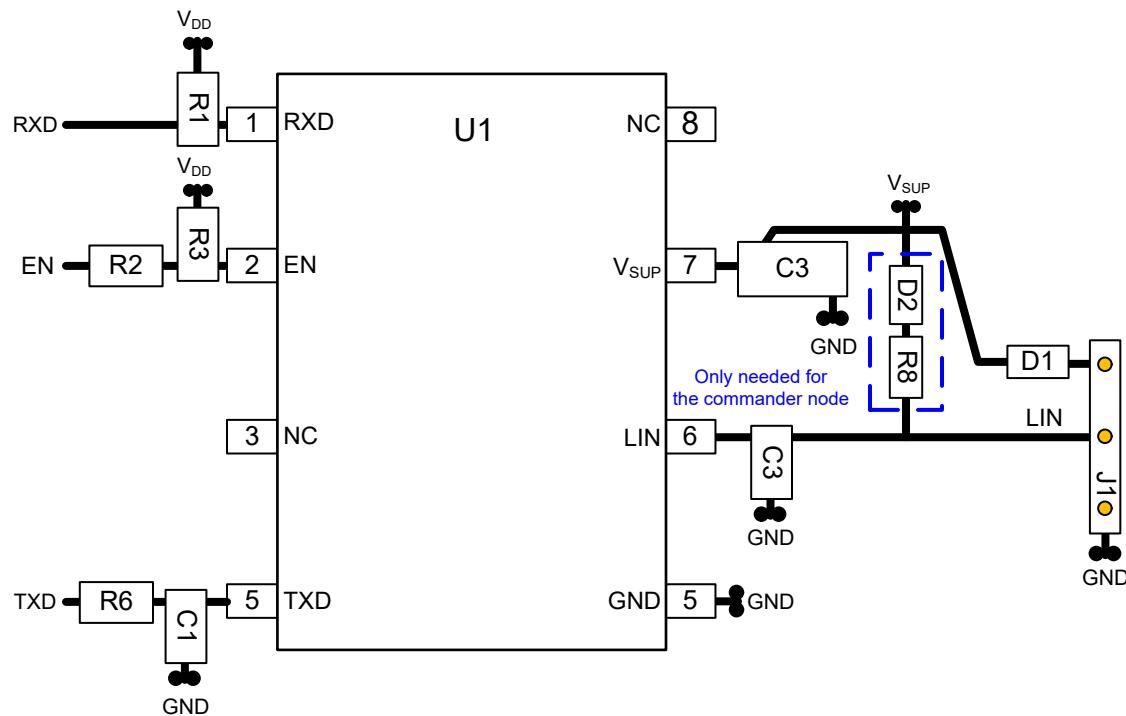

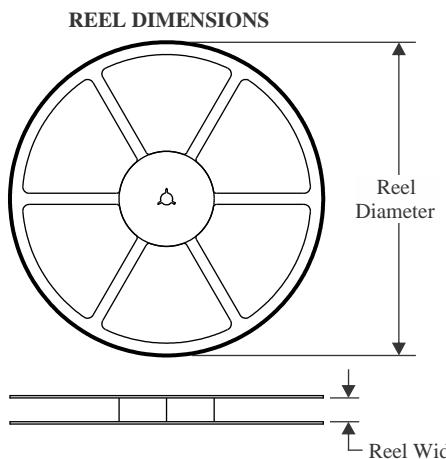

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

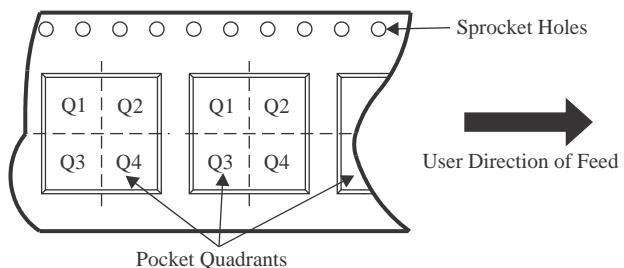

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TLIN2029DRBRQ1 | SON          | DRB             | 8    | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TLIN2029DRBRQ1 | SON          | DRB             | 8    | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.0     | 8.0     | 12.0   | Q2            |

| TLIN2029DRBTQ1 | SON          | DRB             | 8    | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.0     | 8.0     | 12.0   | Q2            |

| TLIN2029DRBTQ1 | SON          | DRB             | 8    | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| TLIN2029DRQ1   | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

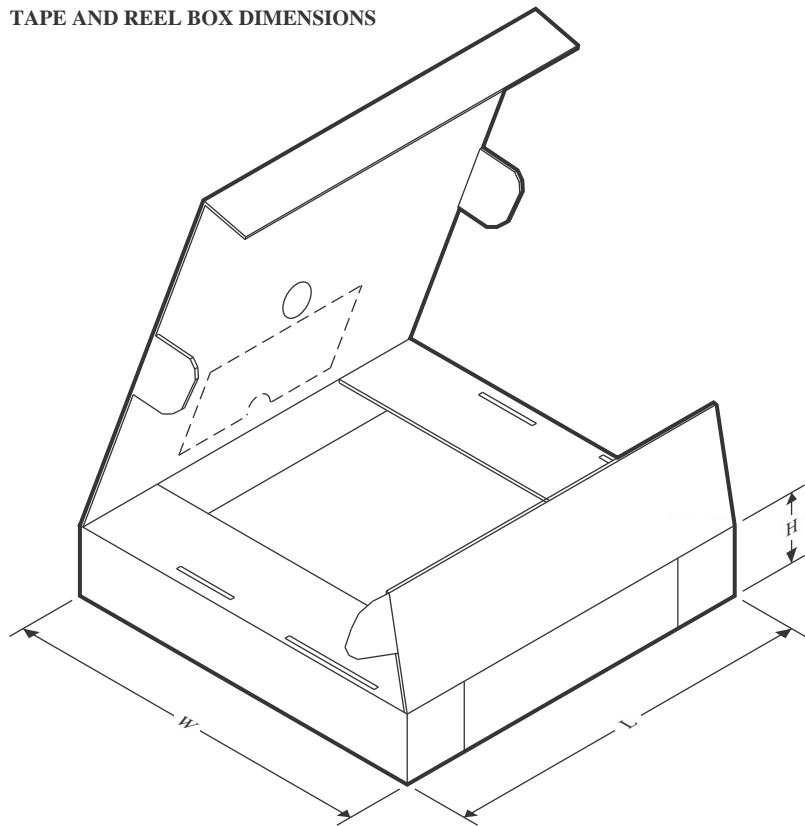

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLIN2029DRBRQ1 | SON          | DRB             | 8    | 3000 | 367.0       | 367.0      | 35.0        |

| TLIN2029DRBRQ1 | SON          | DRB             | 8    | 3000 | 367.0       | 367.0      | 38.0        |

| TLIN2029DRBTQ1 | SON          | DRB             | 8    | 250  | 213.0       | 191.0      | 35.0        |

| TLIN2029DRBTQ1 | SON          | DRB             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| TLIN2029DRQ1   | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

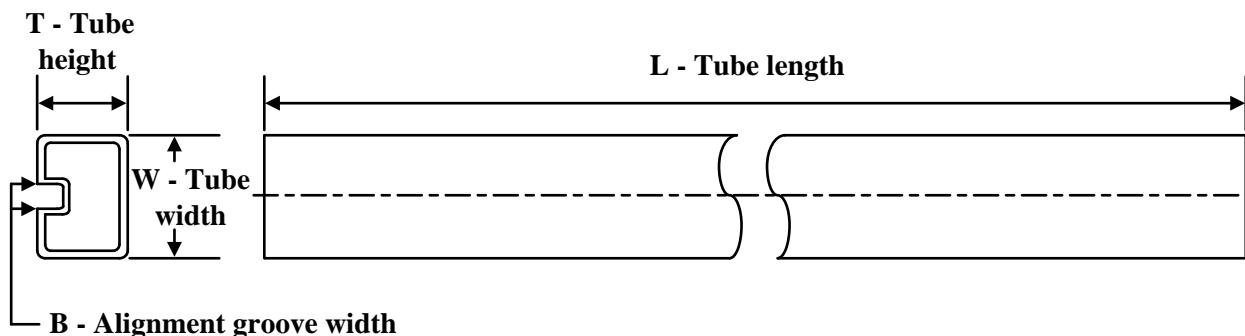

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (μm) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TLIN2029DQ1   | D            | SOIC         | 8    | 75  | 517    | 7.87   | 635    | 4.25   |

| TLIN2029DQ1   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLIN2029DQ1   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLIN2029DQ1.A | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLIN2029DQ1.A | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLIN2029DQ1.A | D            | SOIC         | 8    | 75  | 517    | 7.87   | 635    | 4.25   |

## GENERIC PACKAGE VIEW

**DRB 8**

**VSON - 1 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4203482/L

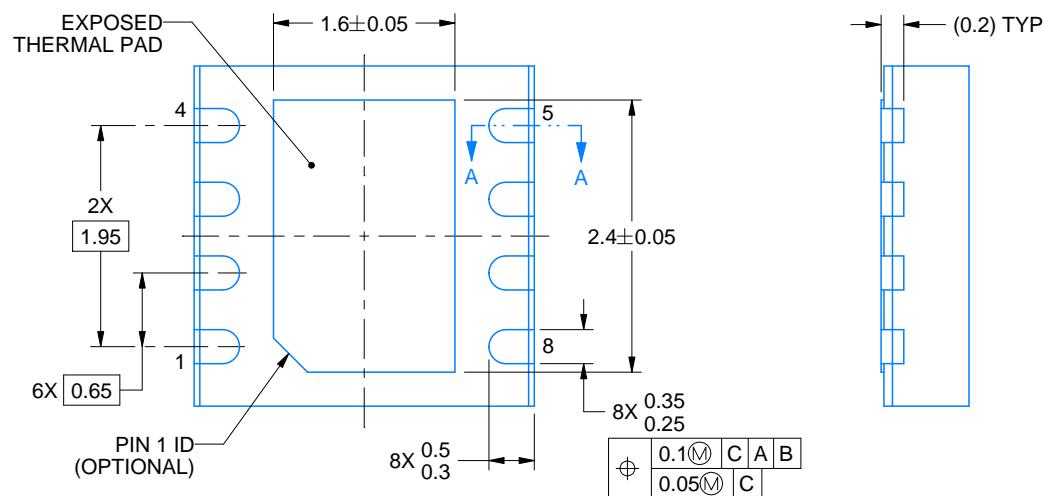

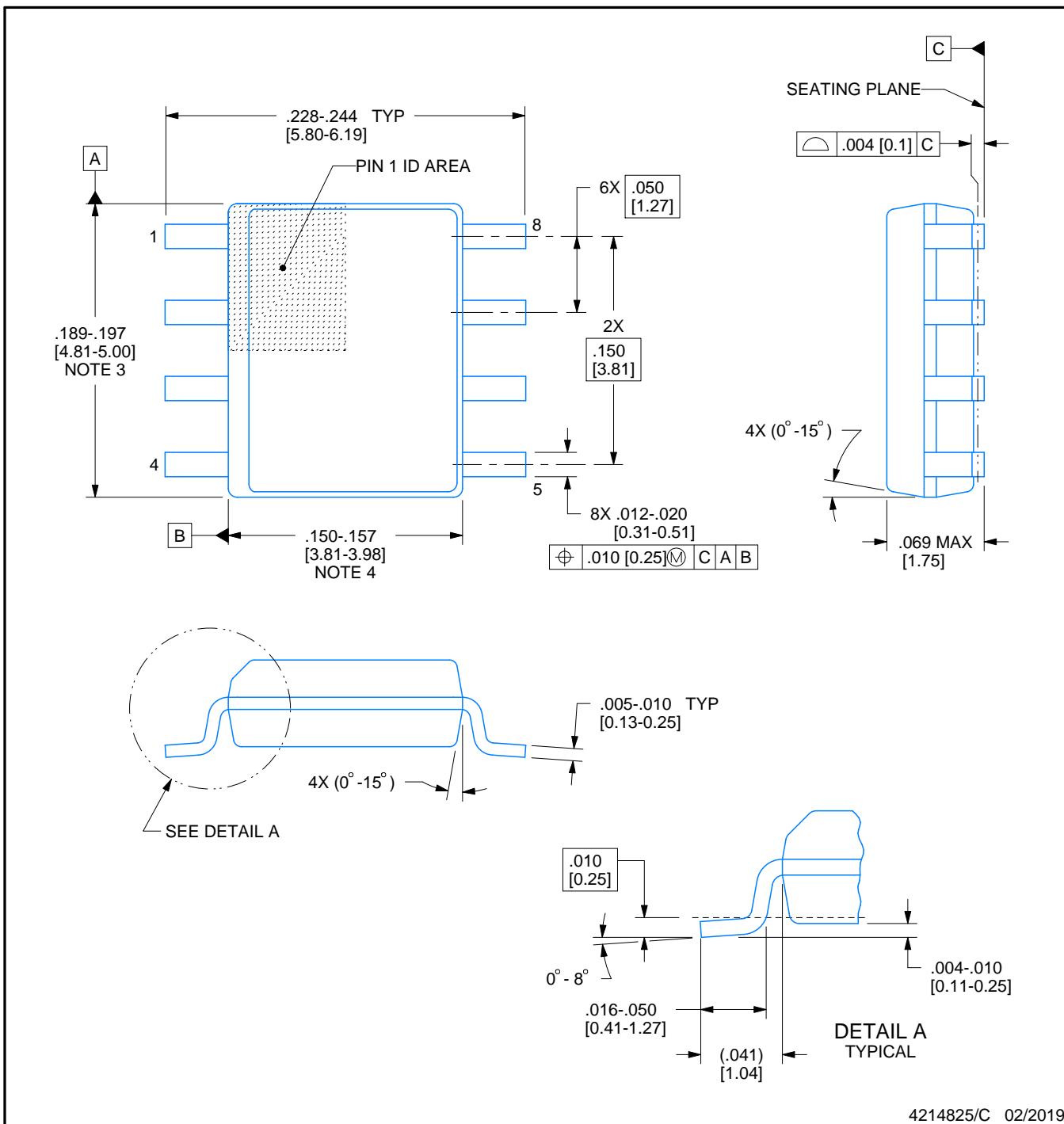

# PACKAGE OUTLINE

**DRB0008F**

**VSON - 1 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

4222121/C 10/2016

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

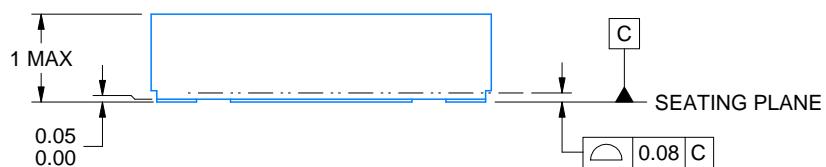

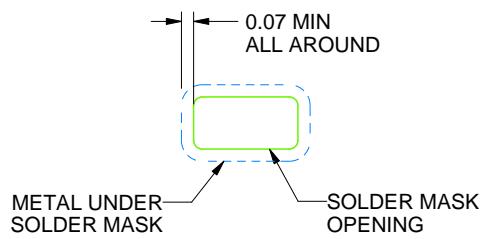

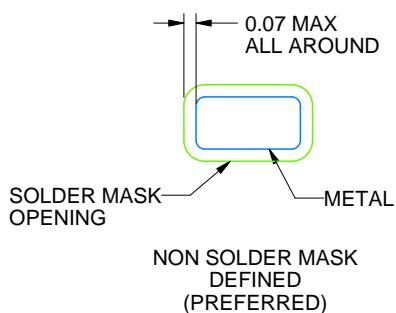

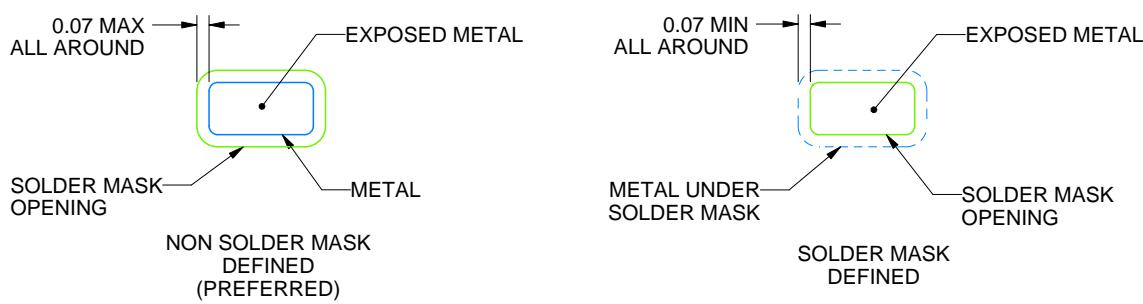

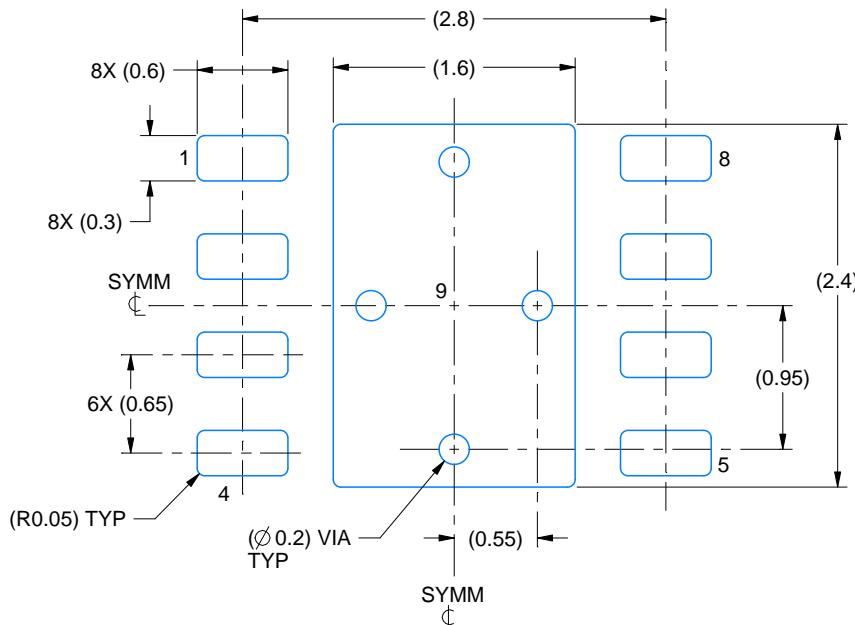

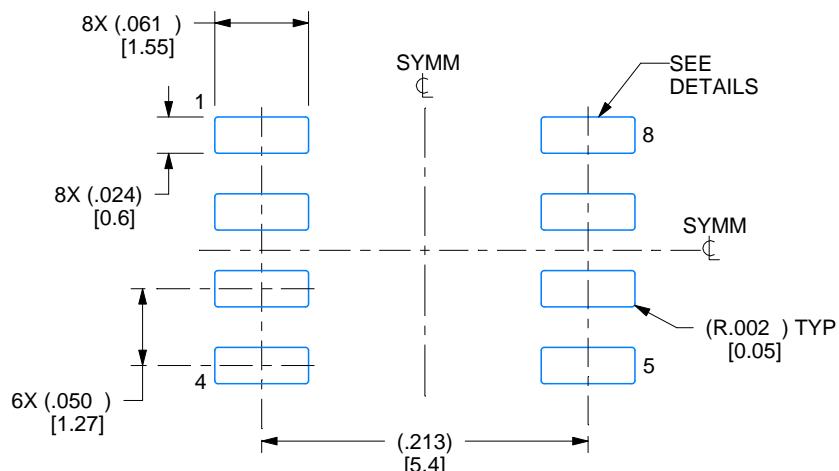

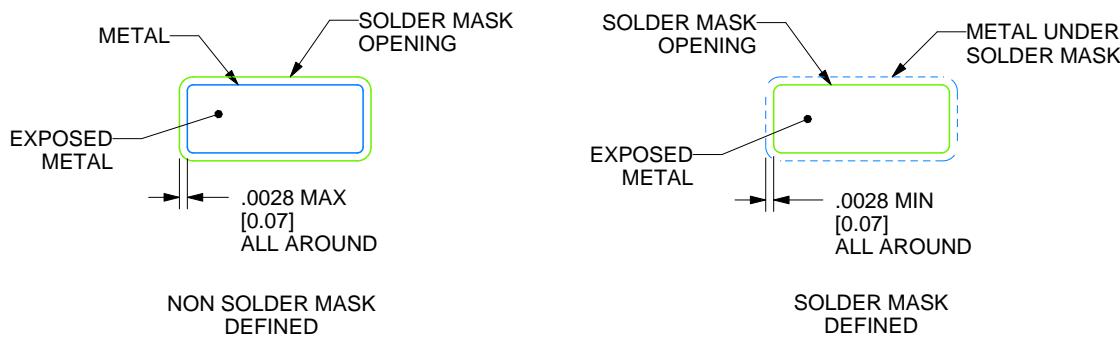

## EXAMPLE BOARD LAYOUT

**DRB0008F**

## VSON - 1 mm max height

## PLASTIC SMALL OUTLINE - NO LEAD

## LAND PATTERN EXAMPLE

SCALE:20X

## SOLDER MASK DETAILS

4222121/C 10/2016

#### NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

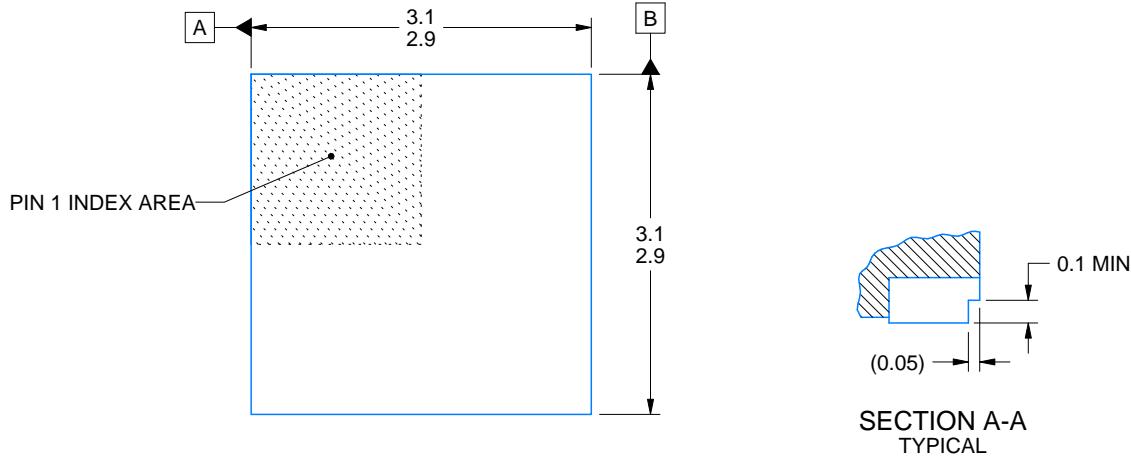

# EXAMPLE STENCIL DESIGN

DRB0008F

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD

82% PRINTED SOLDER COVERAGE BY AREA

SCALE:25X

4222121/C 10/2016

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

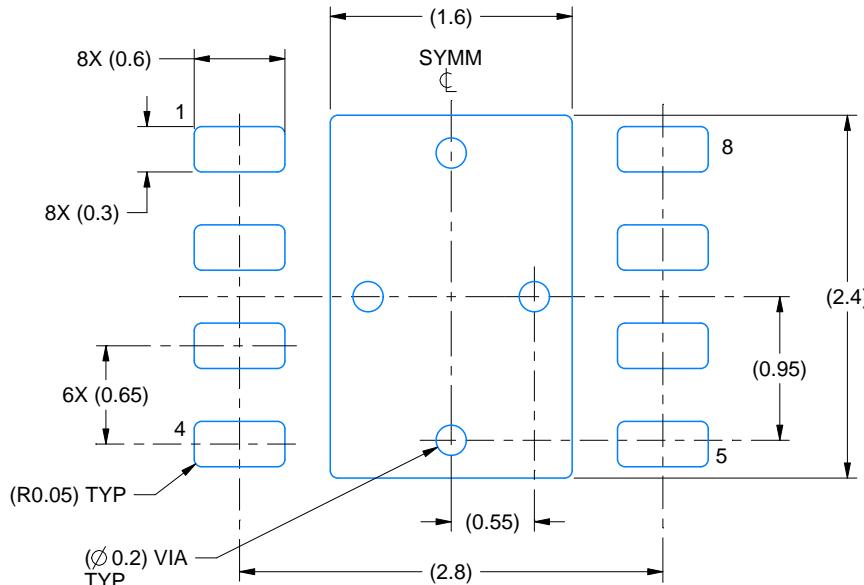

DRB0008K

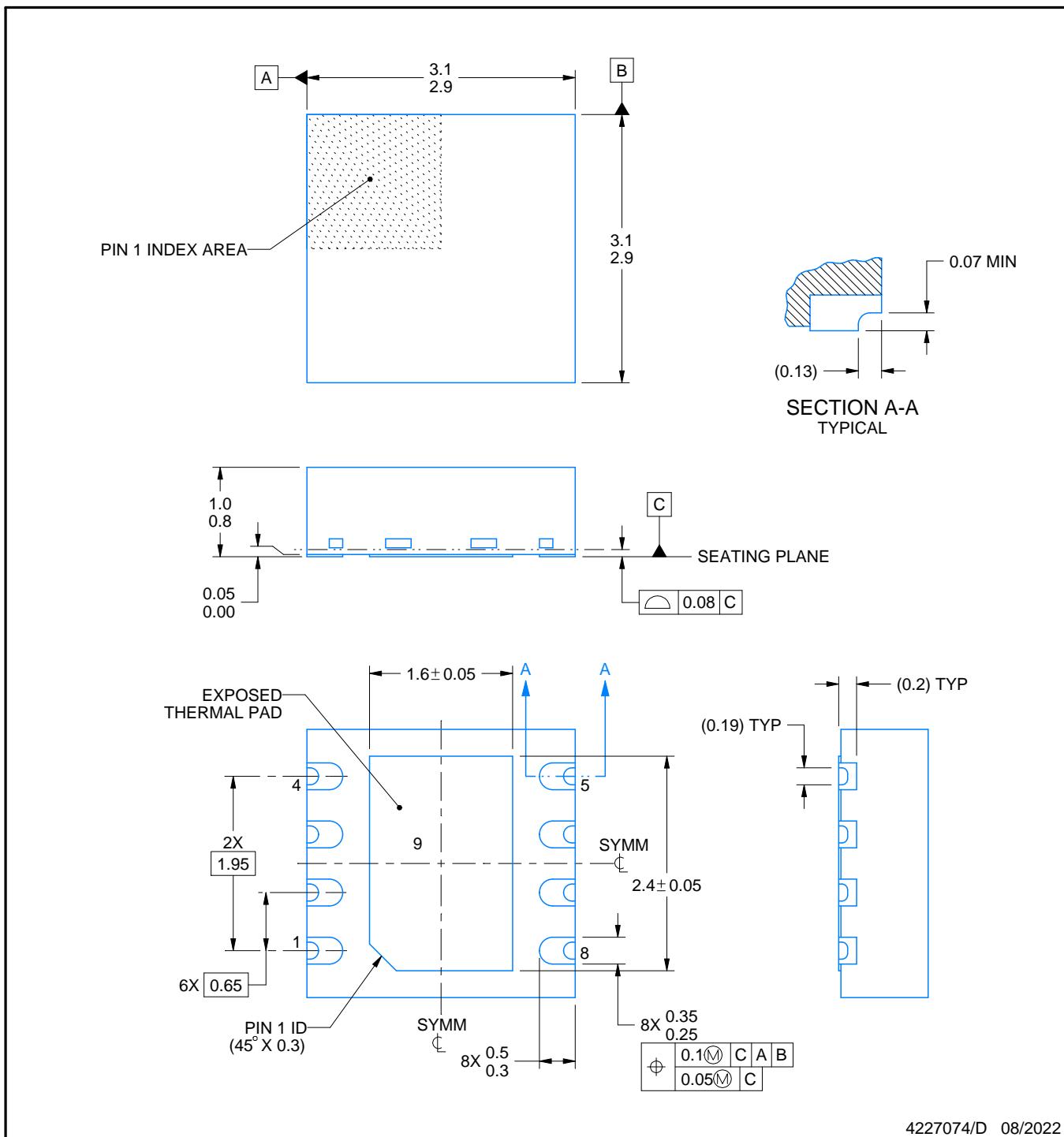

# PACKAGE OUTLINE

## VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

4227074/D 08/2022

### NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

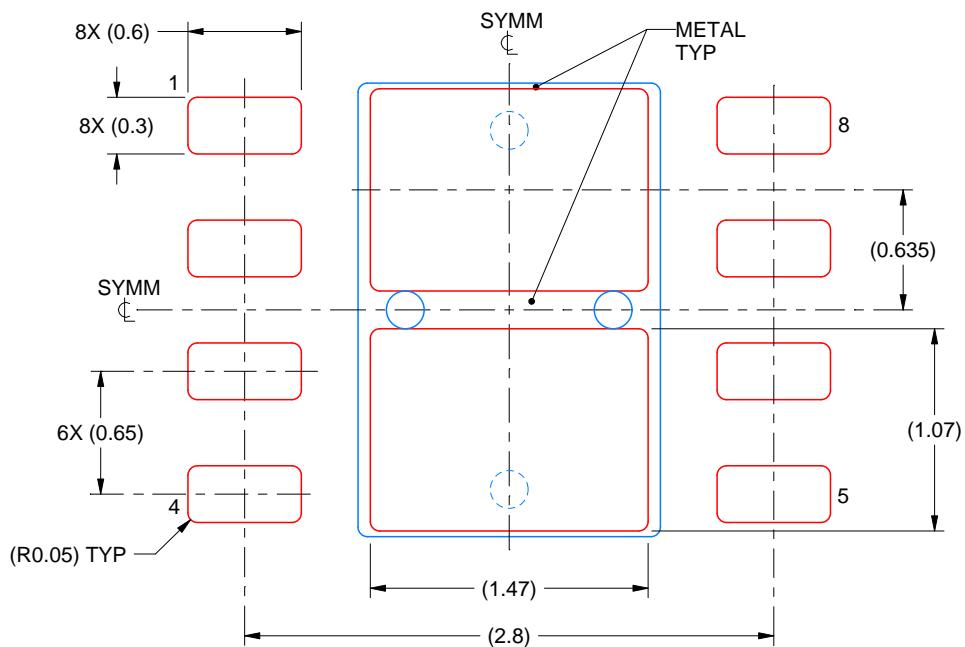

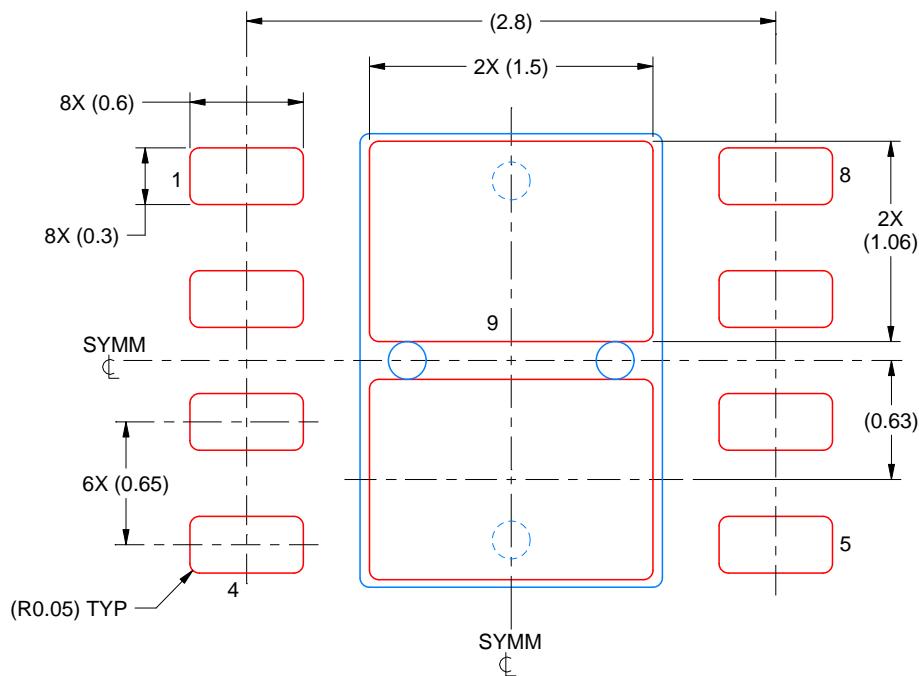

# EXAMPLE BOARD LAYOUT

DRB0008K

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER MASK DETAILS

4227074/D 08/2022

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

## EXAMPLE STENCIL DESIGN

**DRB0008K**

## VSON - 1 mm max height

## PLASTIC SMALL OUTLINE - NO LEAD

## SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD 9:

80% PRINTED SOLDER COVERAGE BY AREA

SCALE:25X

4227074/D 08/2022

#### NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

4. This dimension does not include interlead flash.

5. Reference JEDEC registration MS-012, variation AA.

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

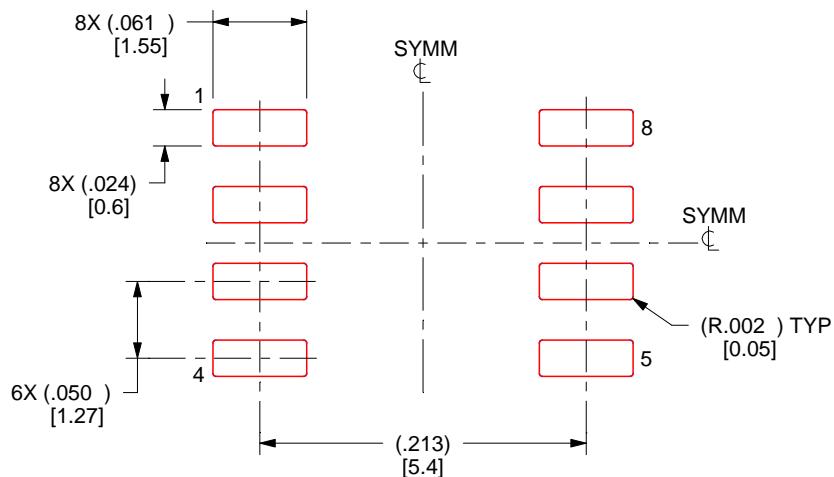

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月