## TDP142-Q1 DisplayPort™、8.1Gbps のリニアリドライバ

### 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度:-40°C~105°C,  $T_A$

- DisplayPort™ 1.4 で最大 8.1Gbps (HBR3)

- 超低消費電力アーキテクチャ

- 4.05GHz で最大 12dB のイコライゼーション付きのリニアリドライバ

- DisplayPort™ リンクトレーニングに対して透過的

- GPIO または I<sup>2</sup>C により設定可能

- ホットプラグ対応

- DisplayPort™ のデュアルモード標準バージョン 1.1 をサポート (AC 結合 HDMI®)

- 7mm × 5mm、0.5mm ピッチの VQFN パッケージで供給

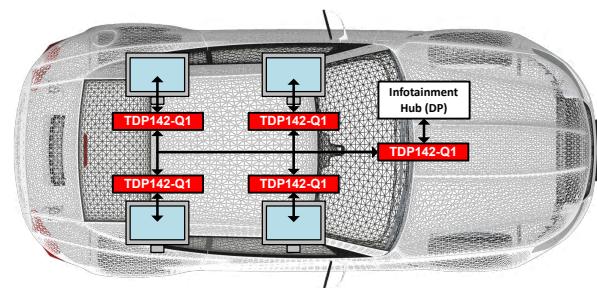

### 2 アプリケーション

- 後部座席用エンターテインメント

- 車載用ヘッドユニット

- 車載用インフォテインメントおよびクラスター

- アクティブケーブル

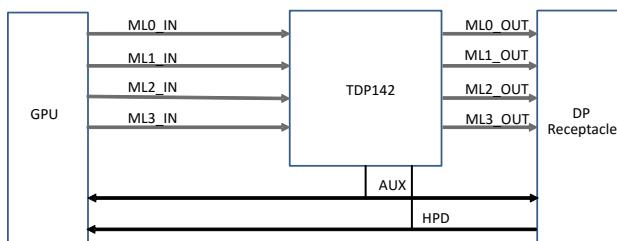

**概略回路図**

### 3 概要

TDP142-Q1 は DisplayPort™ (DP) リニアリドライバで、AUX および HPD 信号をスヌープできます。このデバイスは VESA® DisplayPort™ 標準バージョン 1.4 に準拠し、1~4 レーンのメインリンク インターフェイス信号処理で HBR3 (レーンごとに 8.1Gbps) までをサポートします。さらに、このデバイスは位置に依存せず動作します。TDP142-Q1 はソース、ケーブル、シンクの中に配置でき、リンク バジェット全体に対して実質的に負の損失コンポーネントとして機能します。

TDP142-Q1 は、符号間干渉 (ISI) によるケーブルや基板配線での損失を補償するため、いくつかのレベルで受信リニアイコライゼーションを行えます。TDP142-Q1 は単一の 3.3V 電源で動作し、車載グレード 2 の温度範囲に対応しています。

#### パッケージ情報

| 部品番号      | パッケージ (1)      | パッケージ サイズ(2) |

|-----------|----------------|--------------|

| TDP142-Q1 | RGF (VQFN, 40) | 7mm × 5mm    |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

**アプリケーション使用事例**

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                      |    |                        |    |

|----------------------|----|------------------------|----|

| 1 特長                 | 1  | 6.4 デバイスの機能モード         | 14 |

| 2 アプリケーション           | 1  | 6.5 プログラミング            | 16 |

| 3 概要                 | 1  | 7 レジスタ マップ             | 18 |

| 4 ピン構成および機能          | 3  | 7.1 TDP142-Q1 レジスタ     | 18 |

| 5 仕様                 | 5  | 8 アプリケーションと実装          | 23 |

| 5.1 絶対最大定格           | 5  | 8.1 アプリケーション情報         | 23 |

| 5.2 ESD 定格           | 5  | 8.2 代表的なアプリケーション       | 25 |

| 5.3 推奨動作条件           | 5  | 8.3 電源に関する推奨事項         | 28 |

| 5.4 熱に関する情報          | 5  | 8.4 レイアウト              | 29 |

| 5.5 電源特性             | 6  | 9 デバイスおよびドキュメントのサポート   | 31 |

| 5.6 制御 I/O DC の電気的特性 | 6  | 9.1 ドキュメントの更新通知を受け取る方法 | 31 |

| 5.7 DP の電気的特性        | 7  | 9.2 サポート・リソース          | 31 |

| 5.8 スイッチング特性         | 8  | 9.3 商標                 | 31 |

| 5.9 代表的特性            | 9  | 9.4 静電気放電に関する注意事項      | 31 |

| 6 詳細説明               | 12 | 9.5 用語集                | 31 |

| 6.1 概要               | 12 | 10 改訂履歴                | 31 |

| 6.2 機能ブロック図          | 12 | 11 メカニカル、パッケージ、および注文情報 | 31 |

| 6.3 機能説明             | 13 |                        |    |

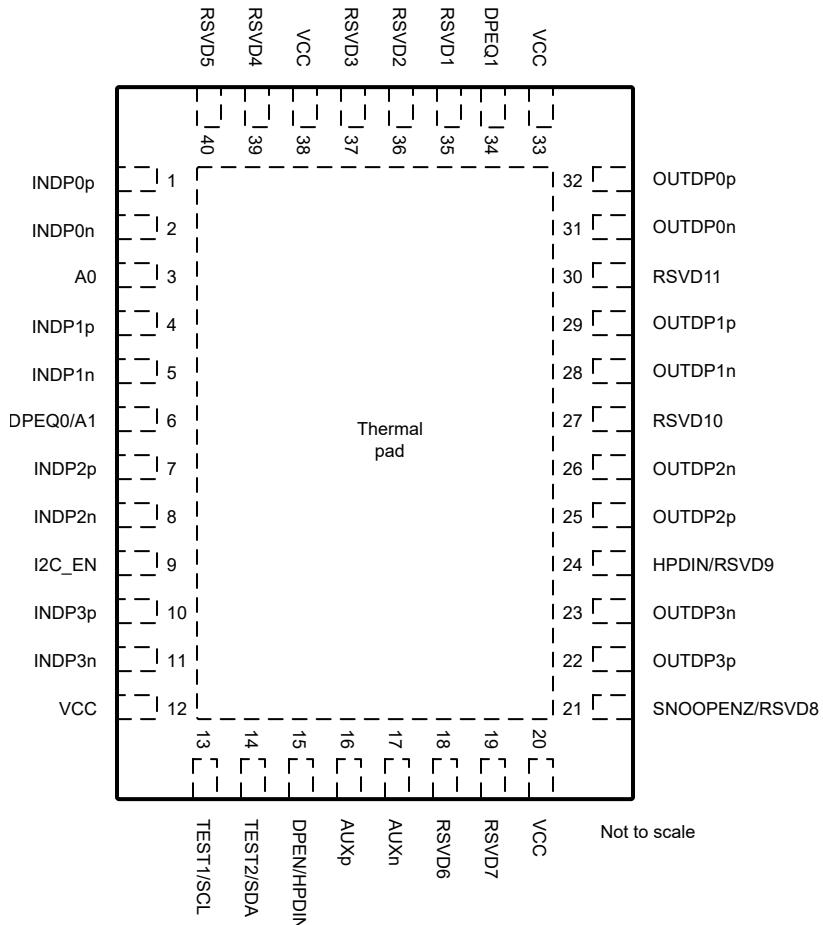

## 4 ピン構成および機能

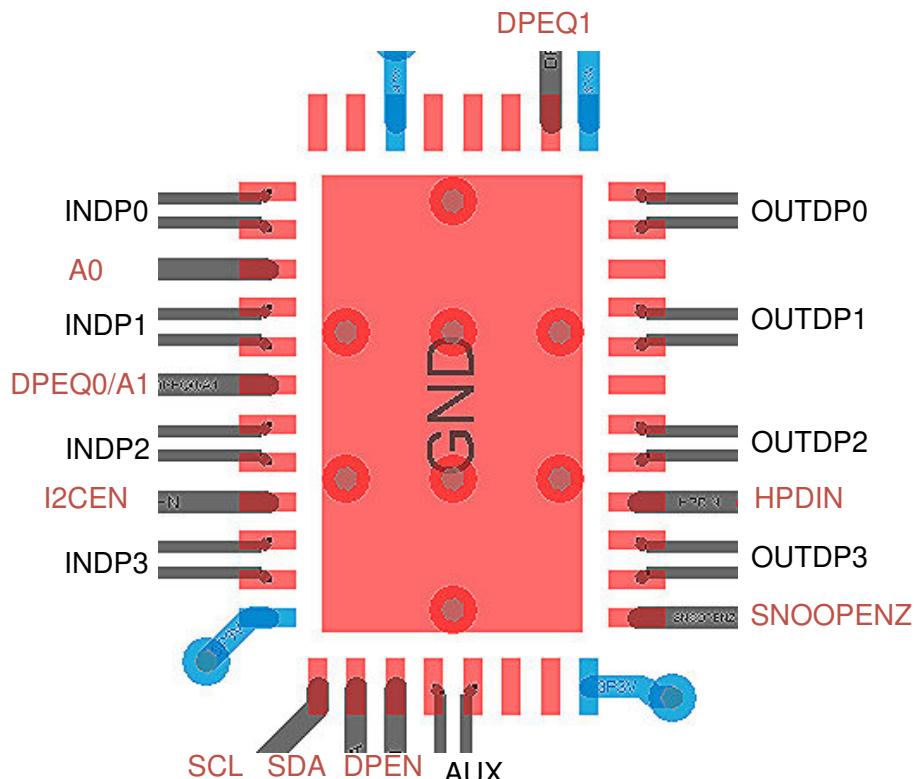

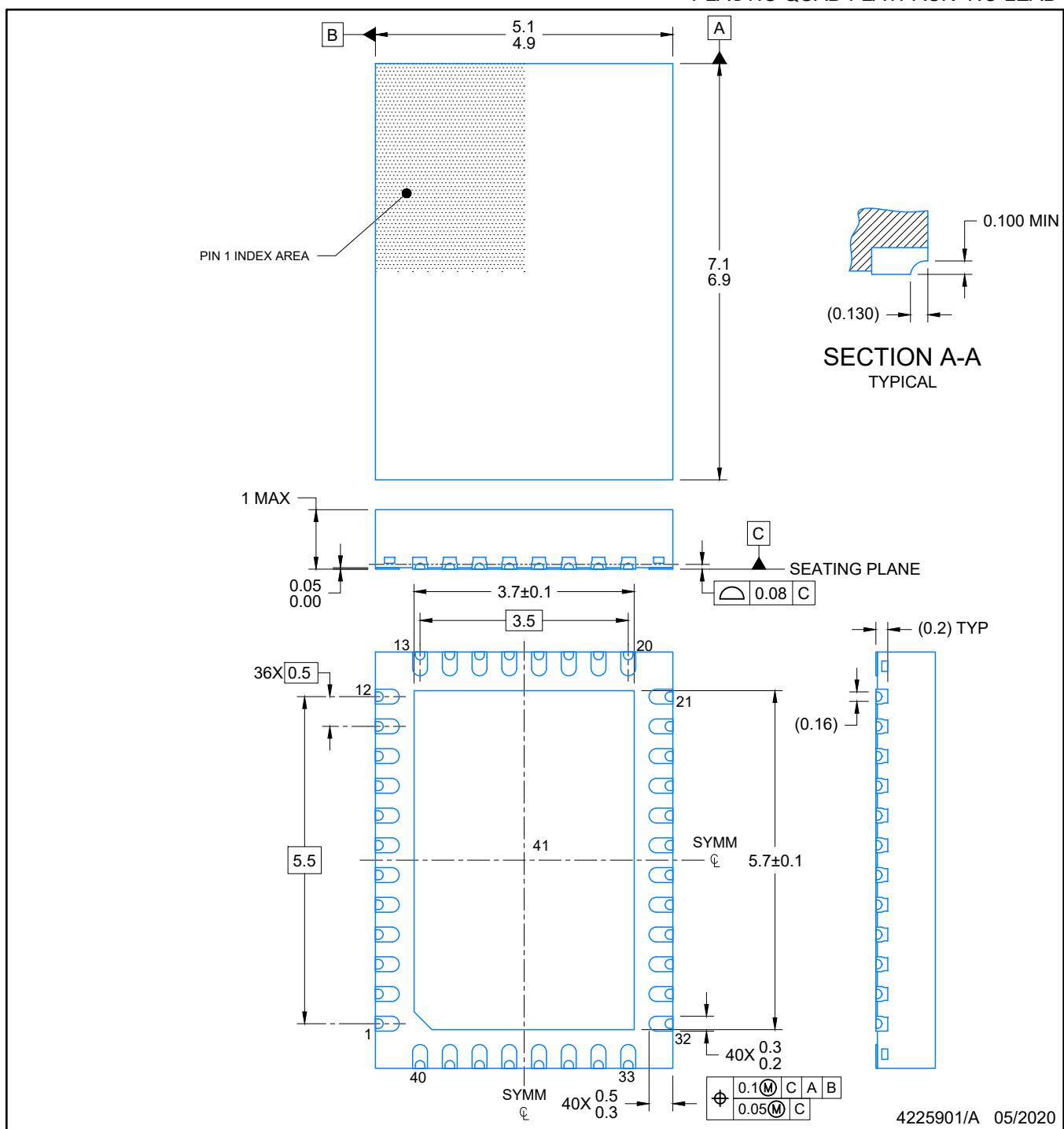

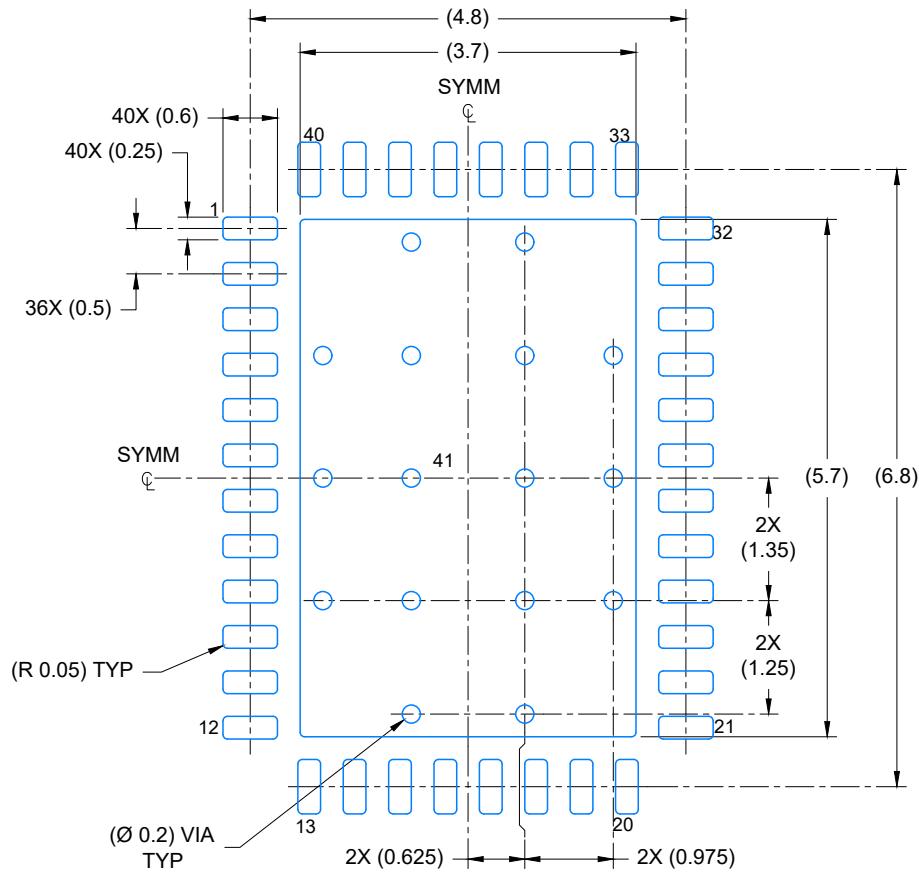

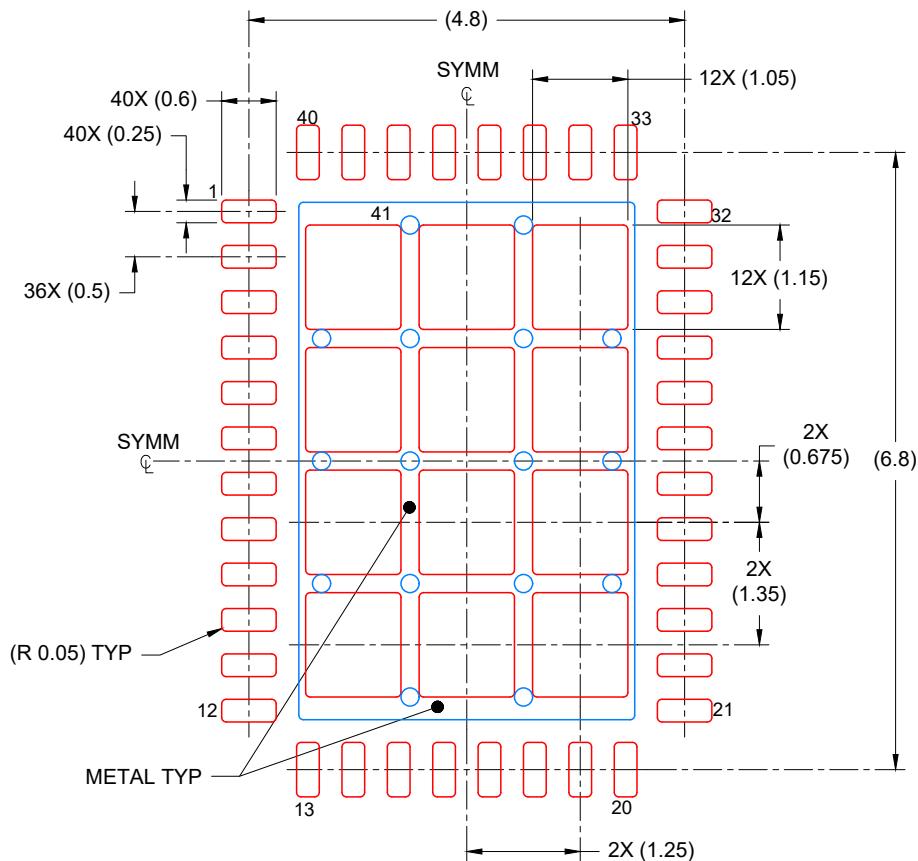

図 4-1. RGF パッケージ 40 ピン (VQFN) 上面図

表 4-1. ピンの機能

| 名称                  | 番号 | I/O     | 説明                                                                                                                                                                                                                                                                     |

|---------------------|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INDP0p              | 1  | I       | DisplayPort レーン 0 の DP 差動正入力。                                                                                                                                                                                                                                          |

| INDP0n              | 2  | I       | DisplayPort レーン 0 の DP 差動負入力。                                                                                                                                                                                                                                          |

| A0                  | 3  | 4 レベル I | I <sup>2</sup> C_EN = 0 の場合、ピンを未接続のままにします。<br>I <sup>2</sup> C_EN が「0」でない場合、このピンは TDP142-Q1 I <sup>2</sup> C アドレスも設定します。<br>表 6-4 を参照してください。<br>I <sup>2</sup> C_EN = 'F' の場合、このピンを 'F' または '0' に設定する必要があります。                                                          |

| INDP1p              | 4  | 差動 I    | DisplayPort レーン 1 の DP 差動正入力。                                                                                                                                                                                                                                          |

| INDP1n              | 5  | 差動 I    | DisplayPort レーン 1 の DP 差動負入力。                                                                                                                                                                                                                                          |

| DPEQ0/A1            | 6  | 4 レベル I | DisplayPort レシーバ EQ 制御。これと DPEQ1 は、DisplayPort レシーバのイコライゼーションゲインを選択します。イコライゼーション設定については、表 6-2 を参照してください。<br>I <sup>2</sup> C_EN が '0' でない場合、このピンは TDP142-Q1 I <sup>2</sup> C アドレスも設定します。<br>表 6-4 を参照してください。                                                           |

| INDP2p              | 7  | 差動 I    | DisplayPort レーン 2 の DP 差動正入力。                                                                                                                                                                                                                                          |

| INDP2n              | 8  | 差動 I    | DisplayPort レーン 2 の DP 差動負入力。                                                                                                                                                                                                                                          |

| I <sup>2</sup> C_EN | 9  | 4 レベル I | I <sup>2</sup> C プログラミングモードまたは GPIO プログラミング選択。<br>0 = GPIOモード(I <sup>2</sup> C無効化)<br>R = TIテストモード(I <sup>2</sup> Cは3.3Vで有効)<br>RSVD11 = '0'かつRSVD10 = '0'のとき、F = I <sup>2</sup> Cは1.8Vで有効になります。それ以外の場合、GPIOモード(I <sup>2</sup> C無効化)1 = I <sup>2</sup> Cは3.3Vで有効になります。 |

表 4-1. ピンの機能(続き)

| ピン             |                   | I/O                          | 説明                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|-------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称             | 番号                |                              |                                                                                                                                                                                                                                                                                                                                                                                                     |

| INDP3p         | 10                | 差動 I                         | DisplayPort レーン 3 の DP 差動正入力。                                                                                                                                                                                                                                                                                                                                                                       |

| INDP3n         | 11                | 差動 I                         | DisplayPort レーン 3 の DP 差動負入力。                                                                                                                                                                                                                                                                                                                                                                       |

| VCC            | 12, 20, 33, 38    | P                            | 3.3V 電源。                                                                                                                                                                                                                                                                                                                                                                                            |

| TEST1/SCL      | 13                | 2 レベル I                      | I <sub>2</sub> C_EN =「0」のときは、10k でプルダウンするか、グランドに直接接続します。それ以外の場合、このピンは I <sub>2</sub> C クロックです。I <sub>2</sub> C クロックに使用する場合は、このピンを I <sub>2</sub> C コントローラの VCC I <sub>2</sub> C 電源にプルアップします。                                                                                                                                                                                                        |

| TEST2/SDA      | 14                | 2 レベル I                      | I <sub>2</sub> C_EN =「0」のときは、10k でプルダウンするか、グランドに直接接続します。それ以外の場合、このピンは I <sub>2</sub> C データです。I <sub>2</sub> C データに使用する場合は、このピンを I <sub>2</sub> C コントローラの VCC I <sub>2</sub> C 電源にプルアップします。                                                                                                                                                                                                          |

| DPEN/HPDIN     | 15                | 2 レベル I<br>(フェイルセーフ)<br>(PD) | DP イネーブルピン。I <sub>2</sub> C_EN =「0」のとき、このピンは DisplayPort 機能を有効または無効化します。それ以外の場合、I <sub>2</sub> C_EN が「0」でない場合、DisplayPort 機能は I <sub>2</sub> C レジスタにより有効化および無効化されます。<br>L = DisplayPort 無効化。(10k 抵抗によるプルダウン)<br>H = DisplayPort 有効化。(10k 抵抗によるプルアップ)<br>I <sub>2</sub> C_EN が「0」でない場合、このピンは DisplayPort シンクから受信されたホット プラグ検出 (HPD) の入力です。この HPDIN が 2ms を超える間 Low になると、すべての DisplayPort レーンが無効化されます。 |

| AUXp           | 16                | I/O, CMOS                    | このピンと AUXn は、TDP142-Q1 によって AUX スヌーピングに使用されます。詳細については、「 <a href="#">アプリケーションと実装</a> 」セクションを参照してください。                                                                                                                                                                                                                                                                                                |

| AUXn           | 17                | I/O, CMOS                    | このピンと AUXp は、TDP142-Q1 によって AUX スヌーピングに使用されます。詳細については、「 <a href="#">アプリケーションと実装</a> 」セクションを参照してください。                                                                                                                                                                                                                                                                                                |

| RSVD6          | 18                | I/O, CMOS                    | 予約済み。 <a href="#">(1)</a>                                                                                                                                                                                                                                                                                                                                                                           |

| RSVD7          | 19                | I/O, CMOS                    | 予約済み。 <a href="#">(1)</a>                                                                                                                                                                                                                                                                                                                                                                           |

| SNOOPENZ/RSVD8 | 21 <sup>(2)</sup> | I/O<br>(PD)                  | I <sub>2</sub> C_EN ! = 0 の場合、このピンは予約済みです。I <sub>2</sub> C_EN = 0 の場合、このピンは SNOOPENZ です (L = AUX スヌープは有効化、H = AUX スヌープはすべてのレーンが無効化)。                                                                                                                                                                                                                                                                |

| OUTDP3p        | 22                | 差動 O                         | DisplayPort レーン 3 の DP 差動正出力。                                                                                                                                                                                                                                                                                                                                                                       |

| OUTDP3n        | 23                | 差動 O                         | DisplayPort レーン 3 の DP 差動負出力。                                                                                                                                                                                                                                                                                                                                                                       |

| HPDIN/RSVD9    | 24 <sup>(2)</sup> | I/O<br>(PD)                  | I <sub>2</sub> C_EN ! = 0 の場合、このピンは予約済みです。I <sub>2</sub> C_EN = 0 の場合、このピンは DisplayPort シンクから受信したホット プラグ検出の入力です。HPDIN が 2ms を超える間 Low になると、すべての DisplayPort レーンが無効化されます。                                                                                                                                                                                                                            |

| OUTDP2p        | 25                | 差動 O                         | DisplayPort レーン 2 の DP 差動正出力。                                                                                                                                                                                                                                                                                                                                                                       |

| OUTDP2n        | 26                | 差動 O                         | DisplayPort レーン 2 の DP 差動負出力。                                                                                                                                                                                                                                                                                                                                                                       |

| RSVD10         | 27                | I                            | 予約済み。1.8V I <sub>2</sub> C を使用する場合は GND に接続します。それ以外の場合は、ピンはフローティングのままにします。                                                                                                                                                                                                                                                                                                                          |

| OUTDP1n        | 28                | 差動 O                         | DisplayPort レーン 1 の DP 差動負出力。                                                                                                                                                                                                                                                                                                                                                                       |

| OUTDP1p        | 29                | 差動 O                         | DisplayPort レーン 1 の DP 差動正出力。                                                                                                                                                                                                                                                                                                                                                                       |

| RSVD11         | 30                | I                            | 予約済み。1.8V I <sub>2</sub> C を使用する場合は GND に接続します。それ以外の場合は、ピンはフローティングのままにします。                                                                                                                                                                                                                                                                                                                          |

| OUTDP0n        | 31                | 差動 O                         | DisplayPort レーン 0 の DP 差動負出力。                                                                                                                                                                                                                                                                                                                                                                       |

| OUTDP0p        | 32                | 差動 O                         | DisplayPort レーン 0 の DP 差動正出力。                                                                                                                                                                                                                                                                                                                                                                       |

| DPEQ1          | 34                | 4 レベル I                      | DisplayPort レシーバ EQ 制御。これと DPEQ0 は、DisplayPort レシーバのイコライゼーション ゲインを選択します。イコライゼーション設定については、 <a href="#">表 6-2</a> を参照してください。                                                                                                                                                                                                                                                                          |

| RSVD1          | 35                | I                            | 予約済み。 <a href="#">(1)</a>                                                                                                                                                                                                                                                                                                                                                                           |

| RSVD2          | 36                | O                            | 予約済み。 <a href="#">(1)</a>                                                                                                                                                                                                                                                                                                                                                                           |

| RSVD3          | 37                | O                            | 予約済み。 <a href="#">(1)</a>                                                                                                                                                                                                                                                                                                                                                                           |

| RSVD4          | 39                | I                            | 予約済み。 <a href="#">(1)</a>                                                                                                                                                                                                                                                                                                                                                                           |

| RSVD5          | 40                | I                            | 予約済み。 <a href="#">(1)</a>                                                                                                                                                                                                                                                                                                                                                                           |

(1) PCB 上では未接続のままにします。

(2) フェイルセーフ I/O ではない。VCC が除去された状態でピンを積極的に High に駆動すると、VCC ピンにリーク電圧が発生します。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                        |                 | 最小値  | 最大値 | 単位 |

|------------------------|-----------------|------|-----|----|

| 電源電圧範囲                 | V <sub>CC</sub> | -0.3 | 4   | V  |

| 任意の入力または出力ピンの電圧範囲      | 正入力と負入力との間の差動電圧 | -2.5 | 2.5 | V  |

|                        | 差動入力での電圧        | -0.5 | 4   | V  |

|                        | CMOS 入力         | -0.5 | 4   | V  |

| 最大接合部温度、T <sub>J</sub> |                 | -40  | 125 | °C |

| 保管温度、T <sub>stg</sub>  |                 | -65  | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      | 値                                                  | 単位    |

|--------------------|------|----------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup> に準拠、すべてのピン | ±2000 |

|                    |      | デバイス帶電モデル (CDM)、AEQ Q100-011 に準拠、すべてのピン            | ±1500 |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならぬと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |                                    | 最小値 | 公称値 | 最大値 | 単位 |

|--------------------|------------------------------------|-----|-----|-----|----|

| V <sub>CC</sub>    | メイン電源                              | 3.0 | 3.3 | 3.6 | V  |

|                    | メイン電源ランプ要件                         | 0.1 |     | 50  | ms |

| V <sub>(I2C)</sub> | SDA と SCL に外部抵抗をプルアップする電源          | 1.7 |     | 3.6 | V  |

| V <sub>(PSN)</sub> | V <sub>CC</sub> ピンの電源ノイズ (4MHz 未満) |     |     | 100 | mV |

| T <sub>A</sub>     | 自由空気での動作温度                         | -40 |     | 105 | °C |

| T <sub>PCB</sub>   | PCB 温度 (デバイスから 1mm 離れた場所)          | -40 |     | 112 | °C |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | デバイス       | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | RGF (VQFN) |      |

|                       |                     | 40 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 29.4       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 18.9       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 11.0       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.3        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 10.9       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 3.6        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電源特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                         | テスト条件                           | 最小値                                                          | 標準値   | 最大値 | 単位 |

|-------------------------------|---------------------------------|--------------------------------------------------------------|-------|-----|----|

| P <sub>CC(ACTIVE-4DP)</sub>   | 平均アクティブ電力<br>(4 レーン DP のみ)      | 8.1Gbps で動作時の 4 つのアクティブな DP レーン、PRBS7 パターン、DPEN = H、LINR_L3、 | 500   |     | mW |

| P <sub>CC(HPDLOW-4DP)</sub>   | HPDIN = L の場合の 4 レーン DP のみの電力   | DPEN = H, HPDIN = L,                                         | 0.475 |     | mW |

| P <sub>CC(DISABLED-I2C)</sub> | I <sup>2</sup> C モードでのデバイスの無効電力 | I2C_EN ! = 0, HPDIN = L, CTLSEL = 0x0,                       | 0.122 |     | mW |

| P <sub>CC(DISABLED)</sub>     | デバイスの無効電力                       | DPEN = L, I2C_EN = 0, HPDIN = L,                             | 0.110 |     | mW |

## 5.6 制御 I/O DC の電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                 | テスト条件                                            | 最小値                                            | 標準値  | 最大値  | 単位   |    |

|---------------------------------------|--------------------------------------------------|------------------------------------------------|------|------|------|----|

| <b>4 レベル入力</b>                        |                                                  |                                                |      |      |      |    |

| I <sub>IH</sub>                       | High レベル入力電流                                     | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 3.6V | 20   | 60   | μA   |    |

| I <sub>IL</sub>                       | Low レベル入力電流                                      | V <sub>CC</sub> = 3.6V, V <sub>IN</sub> = 0V   | -100 | -40  | μA   |    |

| 4 レベル V <sub>TH</sub>                 | スレッショルド 0/R                                      | V <sub>CC</sub> = 3.3V                         | 0.55 |      | V    |    |

| 4 レベル V <sub>TH</sub>                 | スレッショルド R/Float                                  | V <sub>CC</sub> = 3.3V                         | 1.65 |      | V    |    |

| 4 レベル V <sub>TH</sub>                 | スレッショルド Float/1                                  | V <sub>CC</sub> = 3.3V                         | 2.7  |      | V    |    |

| R <sub>PU</sub>                       | 内部プルアップ抵抗                                        |                                                | 48   |      | kΩ   |    |

| R <sub>PD</sub>                       | 内部プルダウン抵抗                                        |                                                | 98   |      | kΩ   |    |

| <b>2 ステート CMOS 入力</b>                 |                                                  |                                                |      |      |      |    |

| V <sub>IH</sub>                       | High レベル入力電圧                                     | V <sub>CC</sub> = 3.0 V                        | 2    | 3.6  | V    |    |

| V <sub>IL</sub>                       | Low レベル入力電圧                                      | V <sub>CC</sub> = 3.6 V                        | 0    | 0.8  | V    |    |

| R <sub>PD</sub>                       | HPDIN, CADSNK の内部プルダウン抵抗                         |                                                | 300  | 500  | 600  | kΩ |

| R <sub>PD</sub>                       | DPEN の内部プルダウン抵抗                                  |                                                | 300  | 500  | 600  | kΩ |

| I <sub>IH_DPEN</sub>                  | DPEN の High レベル入力電流                              | V <sub>IN</sub> = 3.6V                         | -12  | 12   | μA   |    |

| I <sub>IL_DPEN</sub>                  | DPEN の Low レベル入力電流                               | V <sub>IN</sub> = GND, V <sub>CC</sub> = 3.6V  | -1   | 1    | μA   |    |

| I <sub>IH_HPD_CAD</sub>               | HPDIN, CADSNK の High レベル入力電流                     | V <sub>IN</sub> = 3.6V                         | -11  | 11   | μA   |    |

| I <sub>IL_HPD_CAD</sub>               | HPDIN, CADSNK の Low レベル入力電流                      | V <sub>IN</sub> = GND, V <sub>CC</sub> = 3.6V  | -1   | 1    | μA   |    |

| <b>I<sup>2</sup>C 制御ピン (SCL, SDA)</b> |                                                  |                                                |      |      |      |    |

| V <sub>IH_3p3V</sub>                  | 3.3V の I <sup>2</sup> C レベルに構成したときの High レベル入力電圧 | I2C_EN = 1                                     | 2.0  | 3.6  | V    |    |

| V <sub>IL_3p3V</sub>                  | 3.3V の I <sup>2</sup> C レベルに構成したときの Low レベル入力電圧  | I2C_EN = 1                                     | 0    | 0.8  | V    |    |

| V <sub>IH_1p8V</sub>                  | 1.8V の I <sup>2</sup> C レベルに構成したときの High レベル入力電圧 | I2C_EN = F                                     | 1.2  |      | V    |    |

| V <sub>IL_1p8V</sub>                  | 1.8V の I <sup>2</sup> C レベルに構成したときの Low レベル入力電圧  | I2C_EN = F                                     | 0    | 0.6  | V    |    |

| V <sub>OL</sub>                       | Low レベル出力電圧                                      | I2C_EN = 0, I <sub>OL</sub> = 6mA              | 0    | 0.4  | V    |    |

| I <sub>OL</sub>                       | Low レベル出力電流                                      | I2C_EN = 0, V <sub>OL</sub> = 0.4V             | 20   |      | mA   |    |

| I <sub>(I2C)</sub>                    | 入力電流                                             | 0.1 × V <sub>(I2C)</sub> < 入力電圧 < 3.3V         | -1   | 1    | μA   |    |

| C <sub>(I2C)</sub>                    | 入力容量                                             |                                                |      | 10   | pF   |    |

| C <sub>(I2C_FM+, BUS)</sub>           | FM+(1MHz) での I <sup>2</sup> C バス容量               |                                                |      | 150  | pF   |    |

| C <sub>(I2C_FM_BUS)</sub>             | FM (400kHz) での I <sup>2</sup> C バス容量             |                                                |      | 150  | pF   |    |

| R <sub>(EXT_I2C_FM+)</sub>            | FM+(1MHz) で動作時の SDA と SCL の両方の外付け抵抗              | C <sub>(I2C_FM+, BUS)</sub> = 150pF            | 620  | 820  | 910  | Ω  |

| R <sub>(EXT_I2C_FM)</sub>             | FM+(400kHz) で動作時の SDA と SCL の両方の外付け抵抗            | C <sub>(I2C_FM_BUS)</sub> = 150pF              | 620  | 1500 | 2200 | Ω  |

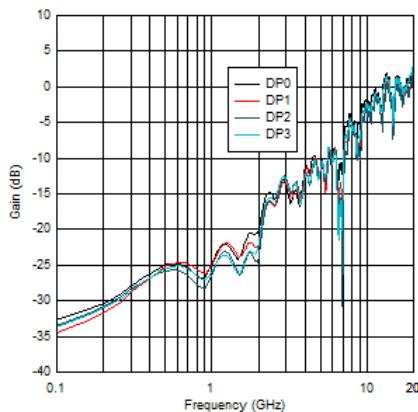

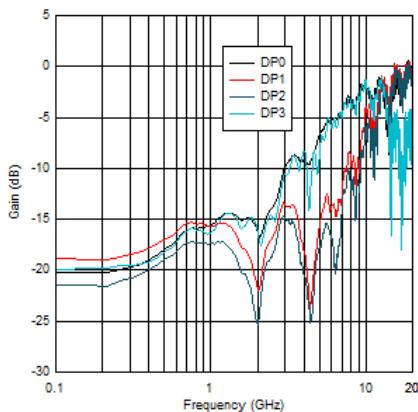

## 5.7 DP の電気的特性

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ                      | テスト条件                                                                                          | 最小値                                                                                                                                   | 標準値   | 最大値  | 単位    |

|----------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|

| <b>AC の特性</b>              |                                                                                                |                                                                                                                                       |       |      |       |

| CP <sub>LF-LINRL0</sub>    | LINR_L0 設定時の低周波数における -1dB 圧縮ポイント。                                                              | 100MHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                  |       | 750  | mVppd |

| CP <sub>HF-LINRL0</sub>    | LINR_L0 設定時の高周波数における -1dB 圧縮ポイント。                                                              | 5GHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                    |       | 675  | mVppd |

| CP <sub>LF-LINRL1</sub>    | LINR_L1 設定時の低周波数における -1dB 圧縮ポイント。                                                              | 100MHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                  |       | 850  | mVppd |

| CP <sub>HF-LINRL1</sub>    | LINR_L1 設定時の高周波数における -1dB 圧縮ポイント。                                                              | 5GHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                    |       | 740  | mVppd |

| CP <sub>LF-LINRL2</sub>    | LINR_L2 設定時の低周波数における -1dB 圧縮ポイント。                                                              | 100MHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                  |       | 975  | mVppd |

| CP <sub>HF-LINRL2</sub>    | LINR_L2 設定時の高周波数における -1dB 圧縮ポイント。                                                              | 5GHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                    |       | 800  | mVppd |

| CP <sub>LF-LINRL3</sub>    | LINR_L3 設定時の低周波数における -1dB 圧縮ポイント。                                                              | 100MHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                  |       | 1050 | mVppd |

| CP <sub>HF-LINRL3</sub>    | LINR_L3 設定時の高周波数における -1dB 圧縮ポイント。                                                              | 5GHz, 200mVpp < V <sub>ID</sub> < 1200mVpp, EQ = 0                                                                                    |       | 775  | mVppd |

| t <sub>TX_DJ</sub>         | TX 出力の確定的残留ジッタ                                                                                 | V <sub>ID</sub> = 0.8Vppd、最適な EQ 設定、12 インチ ブリチャネル (5GHz で SDD21 = -8.2dB)、1.6 インチ ポスト チャネル (5GHz で SDD21 = -1.8dB)、PRBS7、8.1Gbps で DP |       | 0.06 | UI    |

| <b>DisplayPort レシーバ</b>    |                                                                                                |                                                                                                                                       |       |      |       |

| V <sub>ID(PP)</sub>        | ピークツー ピークの入力差動ダイナミック 電圧範囲                                                                      |                                                                                                                                       |       | 1400 | V     |

| V <sub>IC</sub>            | 入力同相電圧                                                                                         |                                                                                                                                       | 0.8   | 1.75 | 2     |

| V <sub>RX_CM-INST</sub>    | 次の動作状態での最大瞬時 RX DC 同相 電圧変化: オフからオン、ディスエーブル から 4DP 低電力、4DP アクティブからディ スエーブル。 <a href="#">(1)</a> | 200kΩ 負荷を使用して、AC 結合コンデンサのリドライバ以外の側でシングル エンドを測定。                                                                                       | -1200 | 1000 | mV    |

| V <sub>RX_CM-INST</sub>    | 次の動作状態での最大瞬時 RX DC 同相 電圧変化: ディスエーブルから 4DP アク ティブ (D0)、D0 から D3、D3 から D0。                       | 50Ω 負荷を使用して、AC 結合コンデンサのリドライバ以外の側でシングル エンドを測定。                                                                                         | -500  | 1000 | mV    |

| d <sub>R</sub>             | データレート                                                                                         |                                                                                                                                       |       | 8.1  | Gbps  |

| R <sub>(t)</sub>           | 入力終端抵抗                                                                                         |                                                                                                                                       | 72    | 90   | 110   |

| C <sub>(AC)</sub>          | 必須の外付け AC カップリング コンデンサ                                                                         |                                                                                                                                       | 75    | 265  | nF    |

| E <sub>Q_DP0</sub>         | 100MHz での DP0 レシーバ イコライゼー ション                                                                  | DP0EQ_SEL = 0、                                                                                                                        |       | -0.2 | dB    |

| E <sub>Q_DP15</sub>        | 100MHz での DP0 レシーバ イコライゼー ション                                                                  | DP0EQ_SEL = 15                                                                                                                        |       | 2.3  | dB    |

| E <sub>Q_DP0</sub>         | 4.05GHz での DP0 レシーバ イコライゼー ション                                                                 | DP0EQ_SEL = 0、                                                                                                                        |       | 0.6  | dB    |

| E <sub>Q_DP15</sub>        | 4.05GHz での DP0 レシーバ イコライゼー ション                                                                 | DP0EQ_SEL = 15                                                                                                                        |       | 14.5 | dB    |

| <b>DisplayPort トランスマッタ</b> |                                                                                                |                                                                                                                                       |       |      |       |

| V <sub>TX-CM-INST</sub>    | 次の動作状態での最大瞬時 TX DC 同相 電圧変化: ディスエーブルから 4DP アクテ ィブ (D0)、D0 から D3、D3 から D0。                       | 50Ω 負荷を使用して、AC 結合コンデンサのリドライバ以外の側で測定。                                                                                                  | -500  | 1000 | mV    |

| V <sub>TX-CM-INST</sub>    | 次の動作状態での最大瞬時 TX DC 同相 電圧変化: ディスエーブルから 4DP 低電 力、4DP アクティブからディスエーブル                              | 200kΩ 負荷を使用して、AC 結合コンデンサのリドライバ以外の側で測定。                                                                                                | -1000 | 1000 | mV    |

| V <sub>TX(DC-CM)</sub>     | トランスマッタの同相電圧バイアス (DC)                                                                          |                                                                                                                                       | 0.6   | 1    | V     |

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ          | テスト条件          | 最小値 | 標準値 | 最大値 | 単位       |

|----------------|----------------|-----|-----|-----|----------|

| $R_{TX(DIFF)}$ | ドライバの差動インピーダンス | 72  | 90  | 120 | $\Omega$ |

(1) DPTX 終端を無効にする前にリドライバを無効にすることで、GPU (DPTX) が観測する瞬間的な同相変位を最小化できます。

## 5.8 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                 | テスト条件                                                 | 最小値             | 標準値   | 最大値 | 単位      |

|-----------------------|-------------------------------------------------------|-----------------|-------|-----|---------|

| <b>HPDIN</b>          |                                                       |                 |       |     |         |

| $t_{HPDIN\_DEBOUNCE}$ | H から L に遷移するときの DOPEN および HPDIN デバウンス時間。              |                 | 2     | 10  | ms      |

| <b>I<sup>2</sup>C</b> |                                                       |                 |       |     |         |

| $f_{SCL}$             | I <sup>2</sup> C クロック周波数                              |                 | 1     |     | MHz     |

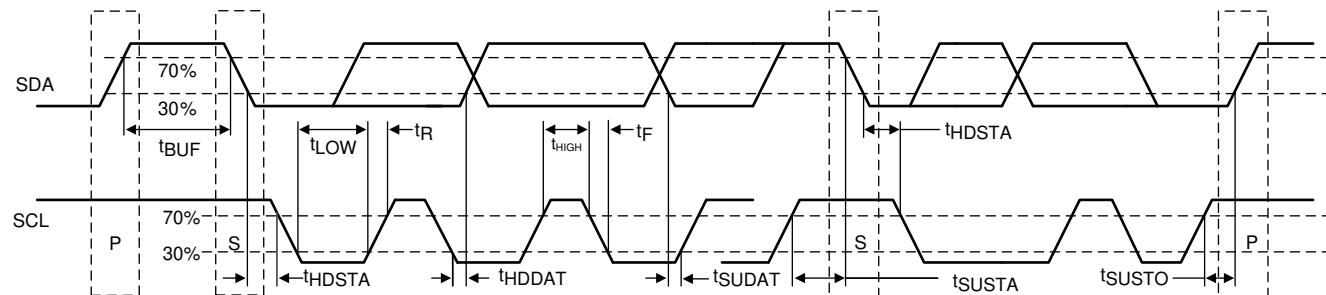

| $t_{BUF}$             | START 条件と STOP 条件の間でのバス開放時間                           | 図 6-1 を参照してください | 0.5   |     | $\mu s$ |

| $t_{HDSTA}$           | リピートスタートコンディションの後のホールド時間。この時間が経過すると、最初のクロックパルスが生成されます | 図 6-1 を参照してください | 0.26  |     | $\mu s$ |

| $t_{LOW}$             | I <sup>2</sup> C クロックの Low 期間                         | 図 6-1 を参照してください | 0.5   |     | $\mu s$ |

| $t_{HIGH}$            | I <sup>2</sup> C クロックの High 期間                        | 図 6-1 を参照してください | 0.26  |     | $\mu s$ |

| $t_{SUSTA}$           | 反復開始条件のセットアップ時間                                       | 図 6-1 を参照してください | 0.26  |     | $\mu s$ |

| $t_{HDDAT}$           | データホールド時間                                             | 図 6-1 を参照してください | 0.008 |     | $\mu s$ |

| $t_{SUDAT}$           | データセットアップ時間                                           | 図 6-1 を参照してください | 50    |     | ns      |

| $t_R$                 | SDA 信号と SCL 信号の立ち上がり時間                                | 図 6-1 を参照してください |       | 120 | ns      |

| $t_F$                 | SDA 信号と SCL 信号の立ち下がり時間                                | 図 6-1 を参照してください | 1.2   | 120 | ns      |

| $t_{SUSTO}$           | 停止条件のセットアップ時間                                         | 図 6-1 を参照してください | 0.26  |     | $\mu s$ |

| $C_b$                 | 各バスラインの容量性負荷                                          |                 |       | 150 | pF      |

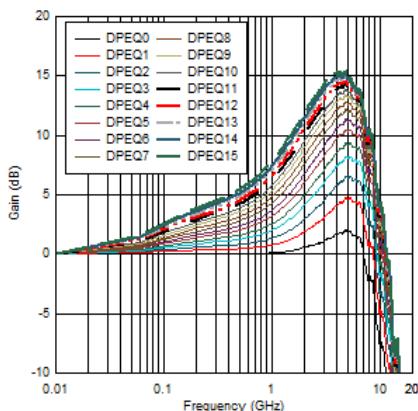

## 5.9 代表的特性

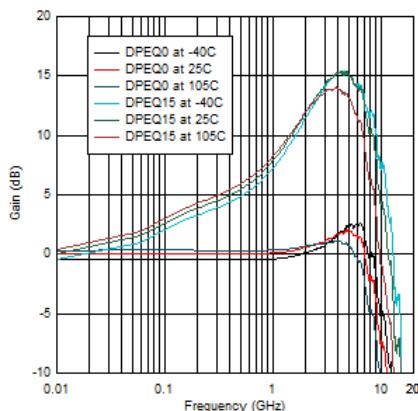

図 5-1. DisplayPort EQ 設定曲線

図 5-2. 温度範囲全体にわたる DisplayPort EQ 設定曲線

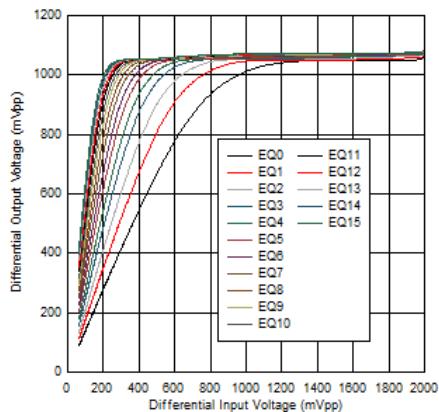

図 5-3. 4.05GHz の DisplayPort 直線性曲線

図 5-4. DisplayPort 入力のリターンロス性能

図 5-5. DisplayPort 出力のリターンロス性能

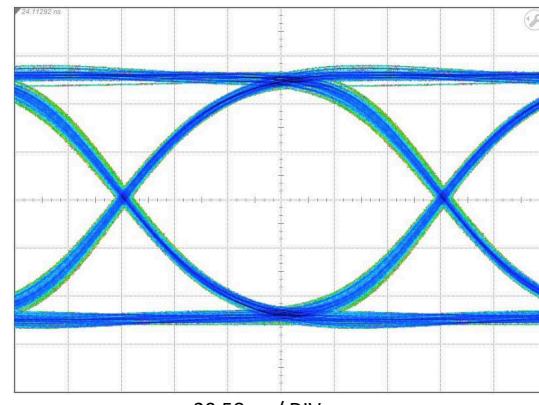

図 5-6. 8.1Gbps での 12 インチ入力 PCB トレースによる DisplayPort HBR3 のアイパターン性能

## 5.9 代表的特性 (続き)

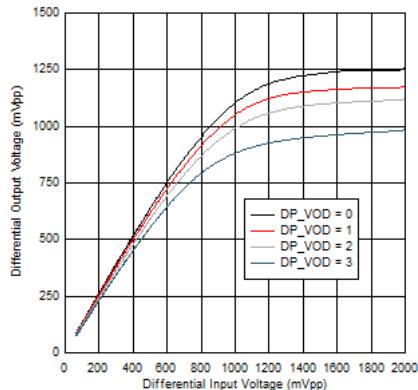

図 5-7. 100MHz での DP VOD 直線性設定

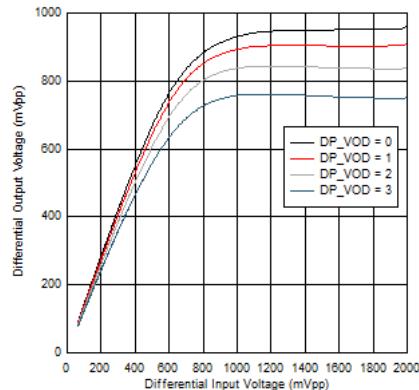

図 5-8. 5GHz での DP VOD 直線性設定

## パラメータ測定情報

図 6-1. I<sup>2</sup>C のタイミング図の定義

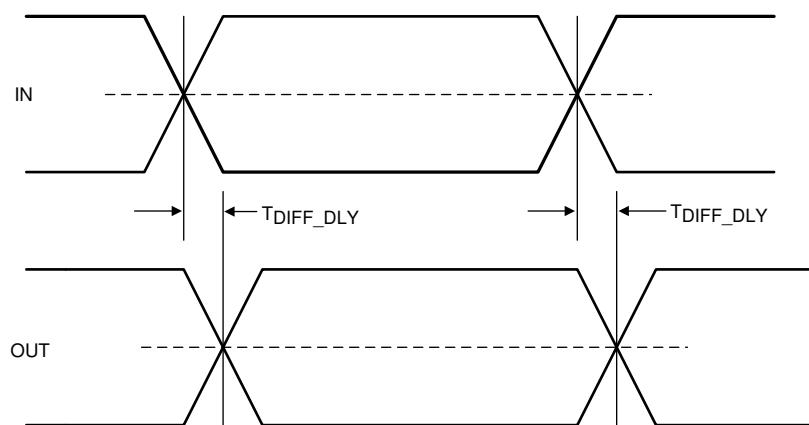

図 6-2. 伝搬遅延

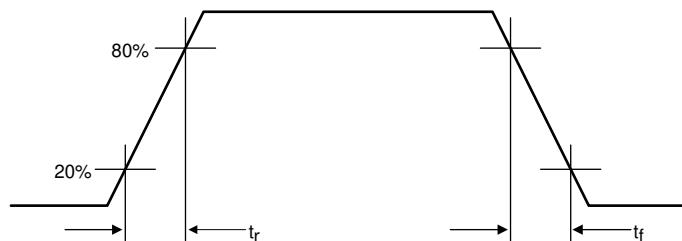

図 6-3. 出力の立ち上がりおよび立ち下がり時間

## 6 詳細説明

### 6.1 概要

TDP142-Q1 は、各レーンで最大 8.1Gbps をサポートする DisplayPort リニアリドライバです。また、デバイスの DP リンクトレーニングへの透過性により、TDP142-Q1 はソース / シンクまたはケーブルアプリケーション用に設計された位置に依存しないデバイスとなります。

TDP142-Q1 は、システムが DisplayPort バージョン 1.4 HBR3 のトランスマッタとレシーバの両方の準拠に合格するために役立ちます。リドライバは、チャネル損失を補償するイコライゼーションを適用して入力データを回復し、高い差動電圧で信号を駆動します。各チャネルにはレシーバイコライザがあり、ゲイン設定を選択可能です。TDP142-Q1 レシーバ前の挿入損失量に基づいてイコライゼーションを設定します。イコライゼーション制御は、DPEQ[1:0] ピンまたは I<sup>2</sup>C レジスタで制御できます。

このデバイスの超低消費電力アーキテクチャは、3.3V の電源で動作し、性能向上を実現しています。また、TDP142-Q1 には商業用温度範囲と工業用温度範囲があります。

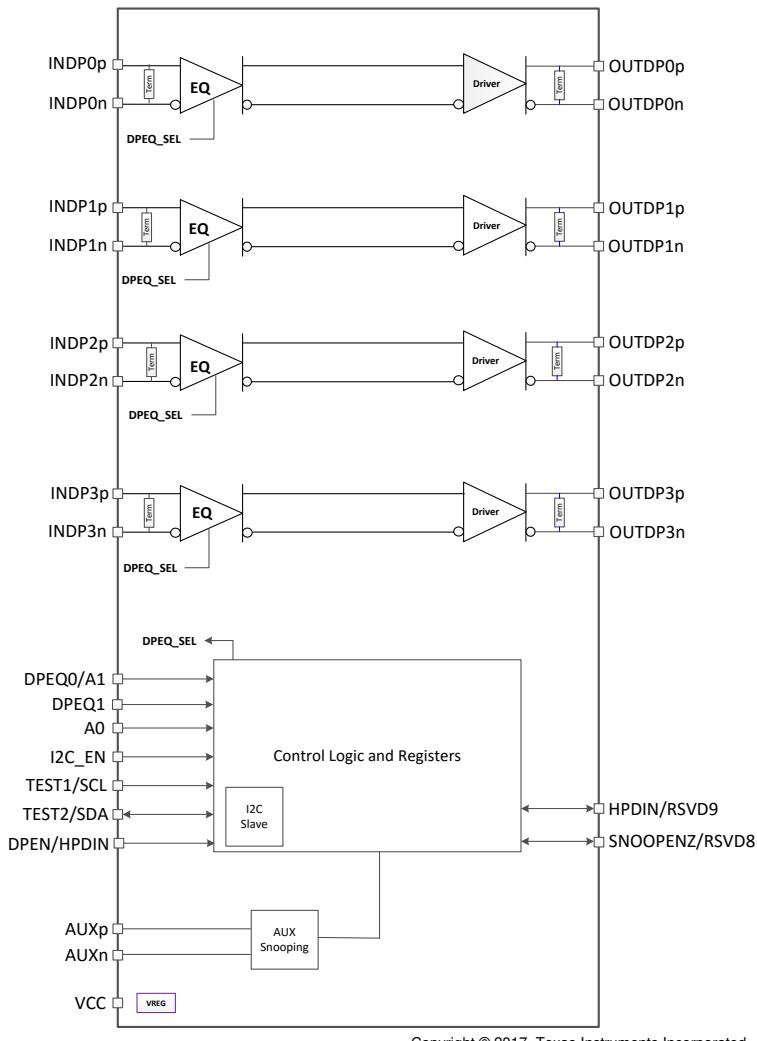

### 6.2 機能ブロック図

Copyright © 2017, Texas Instruments Incorporated

## 6.3 機能説明

### 6.3.1 DisplayPort

TDP142-Q1 は、最高 8.1 Gbps (HBR3) のデータ速度で最大 4 つの DisplayPort レーンをサポートします。TDP142-Q1 は、デバイスが DisplayPort ソースと DisplayPort シンクの間を通過するときに、ネイティブ AUX トラフィックを監視します。消費電力を低減するために、TDP142-Q1 は AUX トランザクションの内容に基づいてアクティブな DisplayPort レーン数を管理します。TDP142-Q1 は、DisplayPort シンクの DPCD レジスタ 0x00101 (LANE\_COUNT\_SET) および 0x00600 (SET\_POWER\_STATE) へのネイティブ AUX 書き込みをスヌープします。TDP142-Q1 は、LANE\_COUNT\_SET に書き込まれた値に基づいてレーンを無効化または有効化します。SET\_POWER\_STATE が D3 のとき、TDP142-Q1 はすべてのレーンを無効化します。それ以外の場合、アクティブなレーンは LANE\_COUNT\_SET の値に基づいています。

DisplayPort AUX スヌーピングは、デフォルトで有効になっていますが、AUX\_SNOOP\_DISABLE レジスタを変更することで無効化することもできます。AUX スヌープが無効化されている場合、TDP142-Q1 DisplayPort レーンは各種の構成レジスタで制御されます。TDP142-Q1 が GPIO モード ( $I2C\_EN = '0'$ ) で有効にされているとき、SNOOPENZ ピンを使用して AUX スヌーピングを無効化することができます。SNOOPENZ ピンが High のとき、AUX スヌーピング機能が無効化され、4 つの DisplayPort レーンすべてがアクティブになります。

### 6.3.2 構成ジャンパレベル

TDP142-Q1 評価基板は、4 レベル入力ピン ( $I2C\_EN$ 、 $A0$ 、 $DPEQ[1:0]$ ) を備えており、これはイコライゼーション ゲインを制御し、TDP142-Q1 をさまざまな動作モードに設定するために使用できます。これらの 4 レベル入力は、4 つの有効なレベルを設定するために抵抗デバイダを使用しており、制御設定範囲を広げることができます。内部プルアップおよびプルダウン抵抗があり、外付け抵抗の接続と組み合わせることで目的の電圧レベルを達成できます

**表 6-1. 4 レベル構成のジャンパ設定**

| レベル  | 設定                               |

|------|----------------------------------|

| Low  | $1k\Omega$ 5% を GND に接続します。      |

| R    | $20k\Omega$ 5% を GND に接続します。     |

| F    | フロート (ピンはオープンのままにする)             |

| High | $1k\Omega$ 5% を $V_{CC}$ に接続します。 |

---

### 注

すべての 4 レベル入力は、内部リセットの立ち上がりエッジでラッチされます。 $t_{CFG\_HD}$  の後、消費電力を削減するため、内部プルアップおよびプルダウン抵抗を絶縁します。

### 6.3.3 レシーバのリニアイコライゼーション

レシーバのイコライゼーションは、TDP142-Q1 の入力前にシステムでのチャネル挿入損失とシンボル間干渉を補償することを目的としています。レシーバは、高周波成分を基準として信号の低周波数成分を減衰させることで、これらの損失を克服します。TDP142-Q1 レシーバの入力前のチャネル挿入損失に対応するように、適切なゲイン設定を選択します。2 本の 4 レベル入力ピンにより、最大 16 件のイコライゼーション設定が可能です。また、TDP142-Q1 は、I<sup>2</sup>C レジスタを介して設定を柔軟に調整できます。

## 6.4 デバイスの機能モード

### 6.4.1 GPIO モードでのデバイス構成

TDP142-Q1 は、I<sub>2</sub>C\_EN =「0」のとき、GPIO 構成です。DPEN ピンは DisplayPort を有効にするかどうかを制御し、SNOOPENZ ピンは AUX スヌープ モードを有効にするかどうかを制御します。

### 6.4.2 I<sup>2</sup>C モードでのデバイス構成

TDP142-Q1 は I<sub>2</sub>C\_EN が「0」と等しくない場合、I<sup>2</sup>C モードになります。GPIO モードで定義されているのと同じ構成が、I<sup>2</sup>C モードでも使用できます。TDP142-Q1 DisplayPort の構成は、[プログラミング](#)セクションに基づいてプログラムされます。

### 6.4.3 リニア EQ の構成

レシーバのイコライゼーション ゲイン値は、I<sup>2</sup>C レジスタまたは GPIO のどちらかにより制御可能です。TDP142-Q1 が GPIO モードの場合、利用可能な各組み合わせのゲイン値の詳細を表 6-2 に示します。I<sup>2</sup>C モードでは、レジスタ DP0EQ\_SEL、DP1EQ\_SEL、DP2EQ\_SEL、DP3EQ\_SEL を更新することにより、同じオプションまたは個別のレーン EQ 設定を行うこともできます。

**表 6-2. TDP142-Q1 レシーバのイコライゼーション制御**

| レジスタ (S):DP0EQ_SEL、DP1EQ_SEL、<br>DP2EQ_SEL、DP3EQ_SEL<br>イコライゼーション設定 # | DPEQ1 ピンレベル | DPEQ0 ピンレベル | 2.7/4.05/5GHz での EQ ゲイン 100MHz での<br>負のゲイン<br>(dB) |

|-----------------------------------------------------------------------|-------------|-------------|----------------------------------------------------|

| 0                                                                     | 0           | 0           | 0.4/0.8/0.83                                       |

| 1                                                                     | 0           | R           | 2.0/3.1/3.4                                        |

| 2                                                                     | 0           | F           | 3.0/4.6/5.0                                        |

| 3                                                                     | 0           | 1           | 4.2/6.0/6.5                                        |

| 4                                                                     | R           | 0           | 5.0/7.0/7.5                                        |

| 5                                                                     | R           | R           | 6.0/8.0/8.4                                        |

| 6                                                                     | R           | F           | 6.5/8.7/9.1                                        |

| 7                                                                     | R           | 1           | 7.2/9.4/9.8                                        |

| 8                                                                     | F           | 0           | 7.8/10.0/10.3                                      |

| 9                                                                     | F           | R           | 8.3/10.4/10.7                                      |

| 10                                                                    | F           | F           | 8.7/10.7/10.9                                      |

| 11                                                                    | F           | 1           | 9.1/11.1/11.2                                      |

| 12                                                                    | 1           | 0           | 9.4/11.3/11.3                                      |

| 13                                                                    | 1           | R           | 9.7/11.5/11.5                                      |

| 14                                                                    | 1           | F           | 10.0/11.7/11.6                                     |

| 15                                                                    | 1           | 1           | 10.2/11.8/11.7                                     |

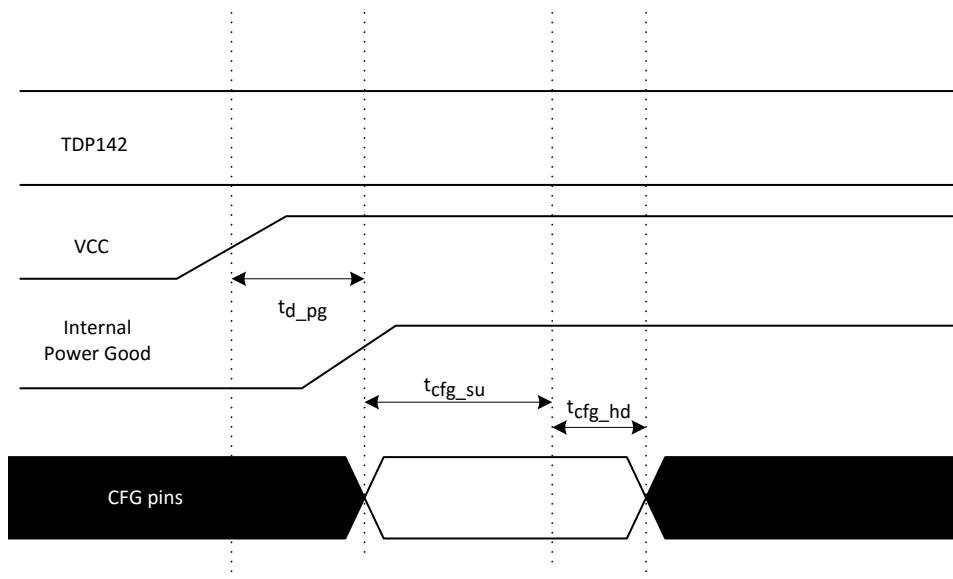

#### 6.4.4 動作タイミング – パワーアップ

図 6-1. パワーアップのタイミング

表 6-3. パワーアップのタイミング (1) (2)

| パラメータ           |                                             | 最小値 | 最大値 | 単位      |

|-----------------|---------------------------------------------|-----|-----|---------|

| $t_{d\_pg}$     | $V_{CC}$ (最小値) から内部パワー グッドが High にアサートされるまで |     | 500 | $\mu s$ |

| $t_{cfg\_su}$   | CFG <sup>(1)</sup> ピンの設定 <sup>(2)</sup>     | 50  |     | $\mu s$ |

| $t_{cfg\_hd}$   | CFG <sup>(1)</sup> ピン ホールド                  | 10  |     | $\mu s$ |

| $t_{VCC\_RAMP}$ | VCC 電源ランプ要件                                 |     | 100 | ms      |

(1) 以下のピンは CFG ピンで構成されます。I2C\_EN、DPEQ[1:0]。

(2) 推奨される CFG ピンは、 $V_{CC}$  が最小のとき安定するようにしてください。

## 6.5 プログラミング

さらにプログラマビリティを高めるため、I<sup>2</sup>C を使用して TDP142-Q1 を制御できます。I<sup>2</sup>C\_EN != 0 の場合、SCL ピンと SDA ピンは、それぞれ I<sup>2</sup>C クロックと I<sup>2</sup>C データに使用されます。

表 6-4. TDP142-Q1 の I<sup>2</sup>C ターゲットアドレス

| DPEQ0/A1<br>ピンレベル | A0<br>ピンレベル | ピット 7 (MSB) | ピット 6 | ピット 5 | ピット 4 | ピット 3 | ピット 2 | ピット 1 | ピット 0 (W/R) |

|-------------------|-------------|-------------|-------|-------|-------|-------|-------|-------|-------------|

| 0                 | 0           | 1           | 0     | 0     | 0     | 1     | 0     | 0     | 0/1         |

| 0                 | R           | 1           | 0     | 0     | 0     | 1     | 0     | 1     | 0/1         |

| 0                 | F           | 1           | 0     | 0     | 0     | 1     | 1     | 0     | 0/1         |

| 0                 | 1           | 1           | 0     | 0     | 0     | 1     | 1     | 1     | 0/1         |

| R                 | 0           | 0           | 1     | 0     | 0     | 0     | 0     | 0     | 0/1         |

| R                 | R           | 0           | 1     | 0     | 0     | 0     | 0     | 1     | 0/1         |

| R                 | F           | 0           | 1     | 0     | 0     | 0     | 1     | 0     | 0/1         |

| R                 | 1           | 0           | 1     | 0     | 0     | 0     | 1     | 1     | 0/1         |

| F                 | 0           | 0           | 0     | 1     | 0     | 0     | 0     | 0     | 0/1         |

| F                 | R           | 0           | 0     | 1     | 0     | 0     | 0     | 1     | 0/1         |

| F                 | F           | 0           | 0     | 1     | 0     | 0     | 1     | 0     | 0/1         |

| F                 | 1           | 0           | 0     | 1     | 0     | 0     | 1     | 1     | 0/1         |

| 1                 | 0           | 0           | 0     | 0     | 1     | 1     | 0     | 0     | 0/1         |

| 1                 | R           | 0           | 0     | 0     | 1     | 1     | 0     | 1     | 0/1         |

| 1                 | F           | 0           | 0     | 0     | 1     | 1     | 1     | 0     | 0/1         |

| 1                 | 1           | 0           | 0     | 0     | 1     | 1     | 1     | 1     | 0/1         |

TDP142-Q1 I<sup>2</sup>C レジスタに書き込むには、次の手順を使用します。

1. コントローラが START 条件 (S) を生成して書き込み動作を開始し、TDP142-Q1 の 7 ビット アドレスと 0 値「W/R」ビットを送信して書き込みサイクルを示します。

2. TDP142-Q1 が、アドレス サイクルをアクノリッジ (受信確認) します。

3. コントローラが 1 バイトのデータ (MSB ファースト) で構成された書き込むサブアドレス (TDP142-Q1 内の I<sup>2</sup>C レジスタ) を送信します。

4. TDP142-Q1 が、サブアドレス サイクルをアクノリッジ (受信確認) します。

5. コントローラが I<sup>2</sup>C レジスタに書き込むデータの最初のバイトを送信します。

6. TDP142-Q1 が、バイト転送をアクノリッジします。

7. コントローラが書き込むデータの追加のバイトを送信し続けます。各バイト転送は、TDP142-Q1 からのアクノリッジで完了します。

8. コントローラが STOP 条件 (P) を生成して書き込み動作を終了します。

TDP142-Q1 I<sup>2</sup>C レジスタを読み出すには、次の手順を使用します。

1. コントローラが開始条件 (S) を生成して読み出し動作を開始し、TDP142-Q1 の 7 ビット アドレスと 1 値「」ビットを送信して読み出しサイクルを示します。

2. TDP142-Q1 が、アドレス サイクルをアクノリッジ (受信確認) します。

3. TDP142-Q1 は、レジスタ 00h または最後の読み出しサブアドレス + 1 から、メモリ レジスタの内容を MSB ファーストで送信します。読み出しの前に TI I<sup>2</sup>C レジスタへの書き込みが発生した場合、TDP142-Q1 は書き込みで指定されたサブアドレスから開始します。

4. TDP142-Q1 は、各バイト転送の後、コントローラからのアクノリッジ (ACK) または非アクノリッジ (NACK) を待ちます。I<sup>2</sup>C コントローラは、各データ バイト転送の受信をアクノリッジします。

5. TDP142-Q1 は、ACK を受信するとデータの次のバイトを送信します。

6. コントローラが STOP 条件 (P) を生成して読み出し動作を終了します。

I<sup>2</sup>C 読み出しの開始サブアドレスを設定するには、次の手順を使用します。

1. コントローラが START 条件 (S) を生成して書き込み動作を開始し、TDP142-Q1 の 7 ビット アドレスと 0 値「W/R」ビットを送信して書き込みサイクルを示します。

2. TDP142-Q1 が、アドレス サイクルをアクノリッジ (受信確認) します。

3. コントローラが 1 バイトのデータ (MSB ファースト) で構成された書き込むサブアドレス (TDP142-Q1 内の I<sup>2</sup>C レジスタ) を送信します。

4. TDP142-Q1 が、サブアドレス サイクルをアクノリッジ (受信確認) します。

5. コントローラが STOP 条件 (P) を生成して書き込み動作を終了します。

#### 注

読み出し手順にサブアドレス指定が含まれていない場合、読み出しへはレジスタ オフセット 00h から開始し、I<sup>2</sup>C コントローラが読み出し動作を終了するまでレジスタの内容をバイト単位で送信します。読み出しの前に I<sup>2</sup>C レジスタへの書き込みが発生した場合、読み出しへはアドレス書き込みで指定されたサブアドレスから開始します。

**表 6-5. レジスタ凡例**

| アクセスタグ | 名称     | 意味                                                  |

|--------|--------|-----------------------------------------------------|

| R      | 読み出し   | このフィールドは、ソフトウェアで読み出すことができます                         |

| W      | 書き込み   | このフィールドは、ソフトウェアで書き込むことができます                         |

| S      | 設定     | このフィールドは、1 を書き込むことで設定できます。フィールドにゼロを書き込んでも影響はありません。  |

| C      | わかりやすい | このフィールドは、1 を書き込むことでクリアできます。フィールドにゼロを書き込んでも影響はありません。 |

| U      | 更新     | ハードウェアはこのフィールドを自律的に更新できます。                          |

| 該当なし   | アクセスなし | アクセス不可または該当なし                                       |

## 7 レジスタ マップ

### 7.1 TDP142-Q1 レジスタ

表 7-1 に、TDP142-Q1 レジスタの一覧を示します。表 7-1 にないレジスタ オフセット アドレスはすべて予約済みと見なして、レジスタの内容は変更しないでください。

表 7-1. TDP142-Q1 レジスタ

| オフセット | 略称            | レジスタ名                         | セクション |

|-------|---------------|-------------------------------|-------|

| 0xA   | General_1     | 汎用レジスタ                        | 表示    |

| 0x10  | DP01EQ_SEL    | DisplayPort レーン 0 および 1 EQ 制御 | 表示    |

| 0x11  | DP23EQ_SEL    | DisplayPort レーン 2 および 3 EQ 制御 | 表示    |

| 0x12  | DisplayPort_1 | AUX スヌープ ステータス                | 表示    |

| 0x13  | DisplayPort_2 | DP レーン有効化 / 無効化制御             | 表示    |

| 0x32  | VOD_CTRL      | VOD の直線性                      | 表示    |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 7-2 に、このセクションでアクセス タイプに使用しているコードを示します。

表 7-2. TDP142-Q1 のアクセス タイプ コード

| アクセス タイプ      | 表記      | 概要                              |

|---------------|---------|---------------------------------|

| 読み取りタイプ       |         |                                 |

| R             | R       | 読み出し                            |

| RH            | R<br>H  | ハードウェアによってセットまたはクリアされる<br>の読み取り |

| 書き込みタイプ       |         |                                 |

| W             | W       | 書き込み                            |

| W1S           | W<br>1S | 1 を書き込むことで<br>セット               |

| WS            | W       | 書き込み                            |

| リセットまたはデフォルト値 |         |                                 |

| -n            |         | リセット後の値またはデフォルト値                |

#### 7.1.1 General\_1 レジスタ (オフセット = 0xA) [リセット = 0x1]

General\_1 を表 7-3 に示します。

概略表に戻ります。

このレジスタは、無効化モードと DisplayPort モードのどちらかを選択するために使用します。ソフトウェアは EQ\_OVERRIDE ビットを設定し、ピンの代わりに EQ レジスタを使用することができます。

表 7-3. General\_1 レジスタのフィールドの説明

| ビット | フィールド    | タイプ | リセット | 概要   |

|-----|----------|-----|------|------|

| 7   | RESERVED | R/W | 0x0  | 予約済み |

| 6   | RESERVED | R   | 0x0  | 予約済み |

**表 7-3. General\_1 レジスタのフィールドの説明 (続き)**

| ピット | フィールド          | タイプ | リセット | 概要                                                                                                                                                                                                                                           |

|-----|----------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | SWAP_HPDIN     | R/W | 0x0  | HPDIN がどのピンから派生するかを制御します。<br>0x0 = HPDIN はデフォルト位置にあります<br>0x1 = HPDIN 位置が交換されます (ピン 23 からピン 32 へ、またはピン 32 からピン 23 へ)。                                                                                                                        |

| 4   | EQ_OVERRIDE    | R/W | 0x0  | このフィールドを設定すると、ソフトウェアはピンからサンプリングされた値ではなく、レジスタからの EQ 設定を使用できます。<br>0x0 = EQ ピンのサンプリングされた状態に基づく EQ 設定。<br>0x1 = 各 EQ レジスタにプログラムされた値に基づく EQ 設定。                                                                                                  |

| 3   | HPDIN_OVERRIDE | R/W | 0x0  | HPDIN ピンの状態をオーバーライドします。<br>0x0 = HPD_IN ピンに基づく HPD_IN<br>0x1 = HPD_IN High。                                                                                                                                                                  |

| 2   | RESERVED       | R/W | 0x0  | RESERVED                                                                                                                                                                                                                                     |

| 1-0 | CTLSEL         | R/W | 0x1  | 電源オン時、ソフトウェアは 0x2 を書き込んで DisplayPort 機能を有効にする必要があります。DisplayPort 機能が不要な場合、ソフトウェアは 0x0 を書き込んで DisplayPort を無効化する必要があります<br>0x0 = ディセーブル。DP がディスエーブルで、最小消費電力状態<br>0x1 = DP はディスエーブルだが、最小消費電力状態ではない。<br>0x2 = DisplayPort はイネーブル。<br>0x3 = 予約済み |

### 7.1.2 DP01EQ\_SEL レジスタ (オフセット = 0x10) [リセット = 0x0]

DP01EQ\_SEL を表 7-4 に示します。

概略表に戻ります。

このレジスタは、DisplayPort レシーバ 0 および 1 のレシーバ イコライゼーション設定を制御します。

**表 7-4. DP01EQ\_SEL レジスタのフィールドの説明**

| ピット | フィールド     | タイプ  | リセット | 概要                                                                                                                                                                   |

|-----|-----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | DP1EQ_SEL | RH/W | 0x0  | フィールドは DP レーン 1 ピンの EQ を選択します。EQ_OVERRIDE = 0b の場合、このフィールドは DPEQ[1:0] ピンのサンプリングされた状態を反映します。EQ_OVERRIDE = 1b のとき、ソフトウェアはこのフィールドに書き込まれた値に基づいて DP レーン 1 の EQ 設定を変更できます。 |

| 3-0 | DP0EQ_SEL | RH/W | 0x0  | フィールドは DP レーン 0 ピンの EQ を選択します。EQ_OVERRIDE = 0b の場合、このフィールドは DPEQ[1:0] ピンのサンプリングされた状態を反映します。EQ_OVERRIDE = 1b のとき、ソフトウェアはこのフィールドに書き込まれた値に基づいて DP レーン 0 の EQ 設定を変更できます。 |

### 7.1.3 DP23EQ\_SEL レジスタ (オフセット = 0x11) [リセット = 0x0]

DP23EQ\_SEL を表 7-5 に示します。

[概略表](#)に戻ります。

このレジスタは、DisplayPort レシーバ 2 および 3 のレシーバ イコライゼーション設定を制御します。

**表 7-5. DP23EQ\_SEL レジスタのフィールドの説明**

| ピット | フィールド     | タイプ  | リセット | 概要                                                                                                                                                                   |

|-----|-----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | DP3EQ_SEL | RH/W | 0x0  | フィールドは DP レーン 3 ピンの EQ を選択します。EQ_OVERRIDE = 0b の場合、このフィールドは DPEQ[1:0] ピンのサンプリングされた状態を反映します。EQ_OVERRIDE = 1b のとき、ソフトウェアはこのフィールドに書き込まれた値に基づいて DP レーン 3 の EQ 設定を変更できます。 |

| 3-0 | DP2EQ_SEL | RH/W | 0x0  | フィールドは DP レーン 2 ピンの EQ を選択します。EQ_OVERRIDE = 0b の場合、このフィールドは DPEQ[1:0] ピンのサンプリングされた状態を反映します。EQ_OVERRIDE = 1b のとき、ソフトウェアはこのフィールドに書き込まれた値に基づいて DP レーン 2 の EQ 設定を変更できます。 |

#### 7.1.4 DisplayPort\_1 レジスタ (オフセット = 0x12) [リセット = 0x0]

DisplayPort\_1 を表 7-6 に示します。

[概略表](#)に戻ります。

このレジスタは、AUX スヌーピングを有効にするときの AUX スヌーピングのステータスを示します。

**表 7-6. DisplayPort\_1 レジスタのフィールドの説明**

| ピット | フィールド           | タイプ | リセット | 概要                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RESERVED        | R   | 0x0  | 予約済み                                                                                                                                                                                                                                                                                                                             |

| 6-5 | SET_POWER_STATE | RH  | 0x0  | このフィールドは、DPCD アドレス 0x00600 への AUX 書き込みのスヌーピング値を表します。AUX_SNOOP_DISABLE = 0b のとき、スヌーピング値に基づいて DP レーンをイネーブルまたはディスエーブルにします。AUX_SNOOP_DISABLE = 1b の場合、DP レーンのイネーブル / ディスエーブルは DP <sub>x</sub> _DISABLE レジスタの状態によって決定されます。ここで、x = 0, 1, 2、または 3 です。CTLSEL1 が 1b から 0b に変化すると、このフィールドはハードウェアによって 0h にリセットされます。                         |

| 4-0 | LANE_COUNT_SET  | RH  | 0x0  | このフィールドは、DPCD アドレス 0x00101 レジスタへの AUX 書き込みのスヌーピング値を表します。AUX_SNOOP_DISABLE = 0b のとき、スヌープ値で指定された DP レーンをイネーブルにします。未使用の DP レーンは、電力を節約するためディスエーブルされます。AUX_SNOOP_DISABLE = 1b の場合、DP レーンのイネーブル / ディスエーブルは DP <sub>x</sub> _DISABLE レジスタによって決定されます。ここで、x = 0, 1, 2、または 3 です。CTLSEL1 が 1b から 0b に変化すると、このフィールドはハードウェアによって 0h にリセットされます。 |

#### 7.1.5 DisplayPort\_2 レジスタ (オフセット = 0x13) [リセット = 0x0]

DisplayPort\_2 を表 7-7 に示します。

[概略表](#)に戻ります。

このレジスタを使用すると、AUX スヌーピングと個別の DP レーンのイネーブルとディスエーブルを制御できます。

**表 7-7. DisplayPort\_2 レジスタのフィールドの説明**

| ビット | フィールド             | タイプ | リセット | 概要                                                                                                                                                                                    |

|-----|-------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUX_SNOOP_DISABLE | R/W | 0x0  | AUX スヌーピング値またはレジスタに基づいて DP レーンを有効にするかどうかを制御します。<br><br>0x0 = AUX スヌープは有効です。<br><br>0x1 = AUX スヌープは無効化されます。DP レーンはレジスタによって制御されます。                                                      |

| 6   | RESERVED          | R   | 0x0  | 予約済み                                                                                                                                                                                  |

| 5-4 | RESERVED          | R/W | 0x0  | 予約済み                                                                                                                                                                                  |

| 3   | DP3_DISABLE       | R/W | 0x0  | AUX_SNOP_DISABLE = 1b の場合に、このフィールドを使用して DP レーン 3 を有効または無効化できます。AUX_SNOP_DISABLE = 0b の場合、このフィールドを変更してもレーン 3 の機能には影響しません。<br><br>0x0 = DP レーン 3 は有効です。<br><br>0x1 = DP レーン 3 は無効化されます。 |

| 2   | DP2_DISABLE       | R/W | 0x0  | AUX_SNOP_DISABLE = 1b の場合に、このフィールドを使用して DP レーン 2 を有効または無効化できます。AUX_SNOP_DISABLE = 0b の場合、このフィールドを変更してもレーン 2 の機能には影響しません。<br><br>0x0 = DP レーン 2 は有効です。<br><br>0x1 = DP レーン 2 は無効化されます。 |

| 1   | DP1_DISABLE       | R/W | 0x0  | AUX_SNOP_DISABLE = 1b の場合に、このフィールドを使用して DP レーン 1 を有効または無効化できます。AUX_SNOP_DISABLE = 0b の場合、このフィールドを変更してもレーン 1 の機能には影響しません。<br><br>0x0 = DP レーン 1 は有効です。<br><br>0x1 = DP レーン 1 は無効化されます。 |

| 0   | DP0_DISABLE       | R/W | 0x0  | AUX_SNOP_DISABLE = 1b の場合に、このフィールドを使用して DP レーン 0 を有効または無効化できます。AUX_SNOP_DISABLE = 0b の場合、このフィールドを変更してもレーン 0 の機能には影響しません。<br><br>0x0 = DP レーン 0 は有効です。<br><br>0x1 = DP レーン 0 は無効化されます。 |

### 7.1.6 VOD\_CTRL レジスタ (オフセット = 0x32) [リセット = 0x40]

VOD\_CTRL を表 7-8 に示します。

概略表に戻ります。

このレジスタは、トランスマッタの出力直線性範囲を制御します。

**表 7-8. VOD\_CTRL レジスタ フィールドの説明**

| ビット | フィールド | タイプ | リセット | 概要   |

|-----|-------|-----|------|------|

| 7-6 | 予約済み  | R/W | 0x1  | 予約済み |

**表 7-8. VOD\_CTRL レジスタ フィールドの説明 (続き)**

| ピット | フィールド  | タイプ | リセット | 概要                                                                                              |

|-----|--------|-----|------|-------------------------------------------------------------------------------------------------|

| 5-4 | DP_VOD | R/W | 0x0  | DP パスの VOD 直線性制御。<br>0x0 = LINR_L3 (最高)<br>0x1 = LINR_L2<br>0x2 = LINR_L1<br>0x3 = LINR_L0 (最低) |

| 3-0 | 予約済み   | R/W | 0x0  | 予約済み                                                                                            |

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

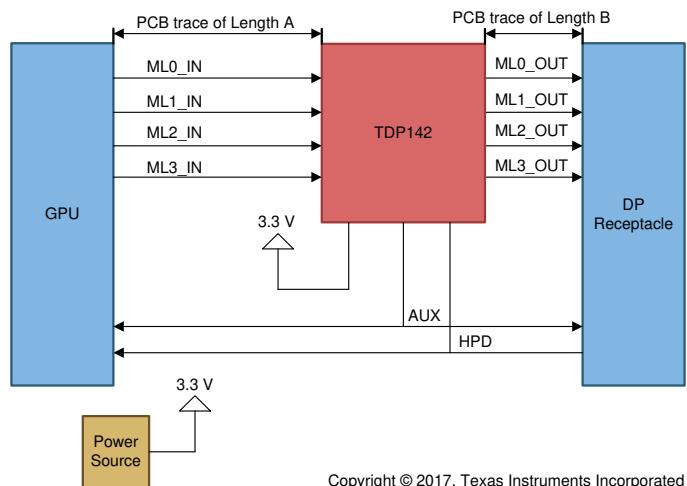

TDP142-Q1 は、PCB パターンやケーブルなどの受動媒体を介した信号の減衰によって発生するシンボル間干渉 (ISI) ジッタを補償するように特別に設計されたリニア リドライバです。本デバイスは、ソース、シンク、ケーブル アプリケーションで使用でき、デバイスはリンクトレーニングに対して透過的です。説明のため、このセクションではソース アプリケーションとシンク アプリケーションの実装を示します。図 8-1 および図 8-2 は、それぞれ DisplayPort ソース側アプリケーションと DisplayPort シンク側アプリケーションの大まかなブロック図であり、TDP142-Q1 は AUX 信号と HPD 信号の両方のチャネルをスヌーピングします。

図 8-1. TDP142-Q1 のソース アプリケーション

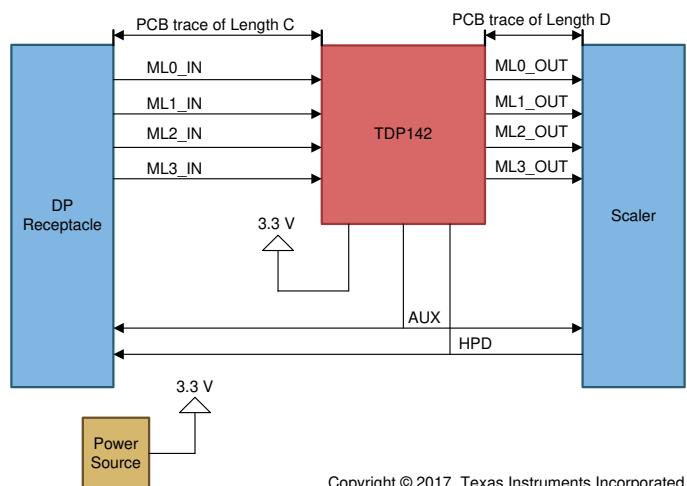

図 8-2. TDP142-Q1 のシンク アプリケーション

### 8.1.1 ESD 保護

TDP142-Q1 を静電放電 (ESD) から保護するために、ESD 部品を内蔵する必要がある場合があります。TI は、表 8-1 に示す ESD 保護に関する推奨事項に従うことを推奨します。クランプ電圧が表 8-1 に規定されている値よりも大きい場合、各差動ピンに  $R_{ESD}$  を接続する必要がある場合があります。ESD 部品を USB コネクタの近くに配置してください。

表 8-1. ESD ダイオードの推奨特性

| パラメータ                                         | 推奨事項                                           |

|-----------------------------------------------|------------------------------------------------|

| ブレークダウン電圧                                     | DP 入力ピン用 $\geq 3.5V$<br>DP 以外入力ピン用 $\geq 1.5V$ |

| I/O ライン容量                                     | 最大 5Gbps のデータレート: $\leq 0.50\text{pF}$         |

|                                               | 5Gbps を超えるデータレート: $\leq 0.35\text{pF}$         |

| P および N の I/O ピン間での容量の差                       | $\leq 0.07\text{pF}$                           |

| 8A $I_{PP}$ IO から GND へのクランプ電圧 <sup>(1)</sup> | $\leq 4.5V$                                    |

| 標準的な動的抵抗                                      | $\leq 30\text{m}\Omega$                        |

(1) IEC 61000-4-5 に準拠 (8/20μs 電流波形)

表 8-2. 推奨 ESD 保護部品

| メーカー          | 部品番号           | IEC 61000-4-2 搾触 $\pm 8\text{kV}$ をサポートする $R_{ESD}$ |

|---------------|----------------|-----------------------------------------------------|

| Nexperia      | PUSB3FR4       | 1 Ω                                                 |

| Nexperia      | PESD2V8Y1BSF   | 1 Ω                                                 |

| テキサス・インスツルメンツ | TPD1E04U04DPLR | 2 Ω                                                 |

| テキサス・インスツルメンツ | TPD4E02B04DQAR | 2 Ω                                                 |

## 8.2 代表的なアプリケーション

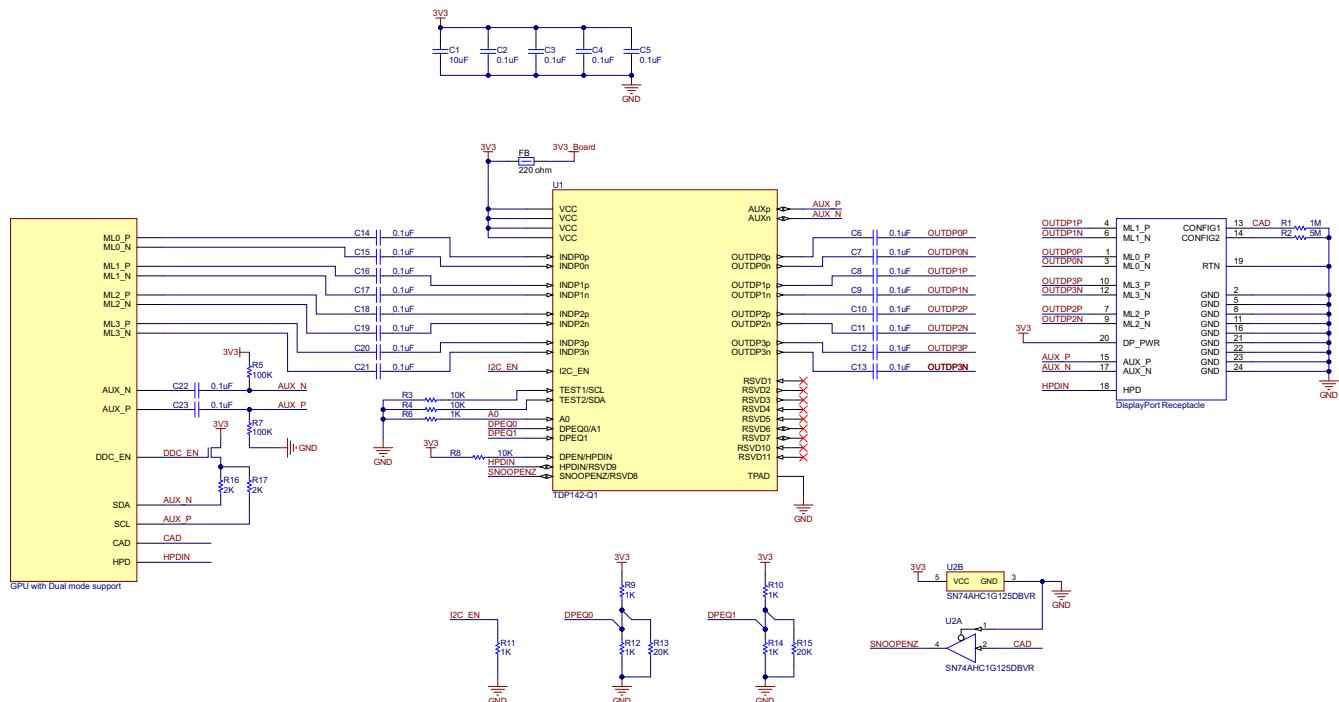

### 8.2.1 ソース アプリケーションの実装

図 8-3 に、ソース側アプリケーションの回路図を示します。TDP142-Q1 は、DisplayPort グラフィックス プロセッsing ユニット (GPU) と DisplayPort レセプタクルとの間に配置されます。SNOOPENZ が Low のとき、TDP142-Q1 はパワーマネージメントのために AUX トライフィックを監視します。

図 8-3. DisplayPort ソース アプリケーションのブロック図

#### 8.2.1.1 設計要件

TDP142-Q1 は多くの種類のアプリケーションに設計できます。すべてのアプリケーションには、システムが正常に動作するための特定の要件があります。たとえば、ソース アプリケーションは、シンク アプリケーションとは異なるハードウェア構成を HPD チャンネルおよび AUX チャンネルで使用します。このデバイスは I<sup>2</sup>C を使用して構成可能です。ただし、I<sup>2</sup>C として GPIO 構成が提供されている場合は、必ずしも利用できるわけではありません。さらに、ソースの命名規則が異なる場合があるため、ソースとレセプタクル間のリンクが TDP142-Q1 を介して正しくマッピングされていることを確認してください。

表 8-3. 設計パラメータ

| パラメータ                                   | 値                                           |

|-----------------------------------------|---------------------------------------------|

| 最大動作データレート<br>(RBR、HBR、HBR2、HBR3)       | HBR3 (8.1Gbps)                              |

| 電源電圧                                    | 3.3 V                                       |

| A のパターン長と幅                              | 12 インチと幅 6 mil                              |

| B のパターン長と幅                              | 2 インチと幅 6 mil                               |

| メイン リンク AC デカッピング コンデンサ<br>(75nF~265nF) | 100nF を推奨                                   |

| 制御モード (I <sup>2</sup> C または GPIO)       | GPIO (I2C_EN = 0)                           |

| デュアル モード DisplayPort のサポート(はい / いいえ)    | はい。SNOOPENZ は、バッファ経由で CONFIG1 に接続する必要があります。 |

### 8.2.1.2 詳細な設計手順

TDP142-Q1 を使用して設計を行うには、以下の要件が必要です。

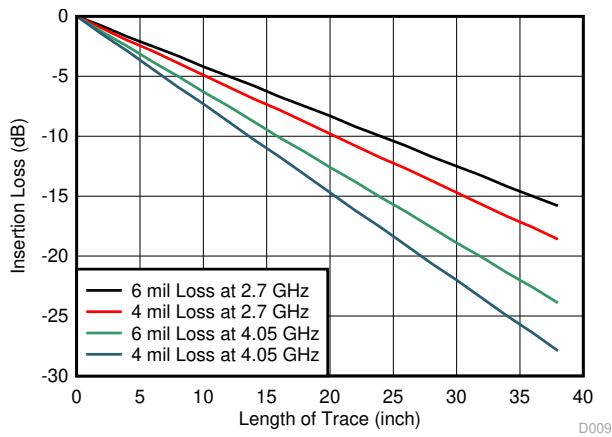

- DisplayPort 入力 (A) および出力 (B) チャネルの損失プロファイルを決定します。6mil パターン挿入損失については、[図 8-5](#) を参照してください。

- 損失プロファイルに基づいて、TDP142-Q1 が電気的規格に準拠するために最適な構成を決定します。DPEQ[1:0] は適切な値に設定する必要があります。この場合、12 インチの FR4 パターンは、4.05GHz で約 8dB の損失に相当します。そのため、DPEQ1 20kΩ をグランドに、DPEQ0 1kΩ をグランドに接続します。

- AC カップリングコンデンサ、制御ピン抵抗、および推奨のデカッピングコンデンサを VCC ピンからグランドに使用するソースアプリケーションの詳細については、[図 8-3](#) を参照してください。

- AUX:AUXP に 100kΩ プルダウン抵抗、AUXN に 100kΩ プルアップ抵抗があることを確認します。これらの 100kΩ 抵抗は、100nF コンデンサの TDP142-Q1 側に配置する必要があります。

- HPDIN は、省電力のために DisplayPort 機能を有効または無効にするために使用されます。GPIO/I<sup>2</sup>C モードに基づいて、HPD 信号をピン 23 またはピン 32 に配線します。

**表 8-4. HPD GPIO/I<sup>2</sup>C の選択**

| モード                                         | HPD   |

|---------------------------------------------|-------|

| GPIO (I <sup>2</sup> C_EN = 0)              | ピン 32 |

| I <sup>2</sup> C (I <sup>2</sup> C_EN != 0) | ピン 23 |

- デュアル モード DisplayPort をサポートするアプリケーションの場合:SNOOPENZ ピンは、SN74AHC125 などのバッファを介して、DisplayPort レセプタクルの CONFIG1 に接続する必要があります。デュアル モードアダプタが DisplayPort レセプタクルに接続されている場合、SNOOPENZ ピンの内部プルダウンが強すぎて有効な VIH を登録できないため、バッファが必要です。

- GPIO 端子または I<sup>2</sup>C インターフェイスを使用して TDP142-Q1 を構成します。

- GPIO - 端子 DPEQ0 および DPEQ1 を使用。

- I<sup>2</sup>C – 詳細な構成手順については、[I<sup>2</sup>C レジスタマップとプログラミングセクション](#)を参照してください。

- サーマル パッドはグランドに接続する必要があります。

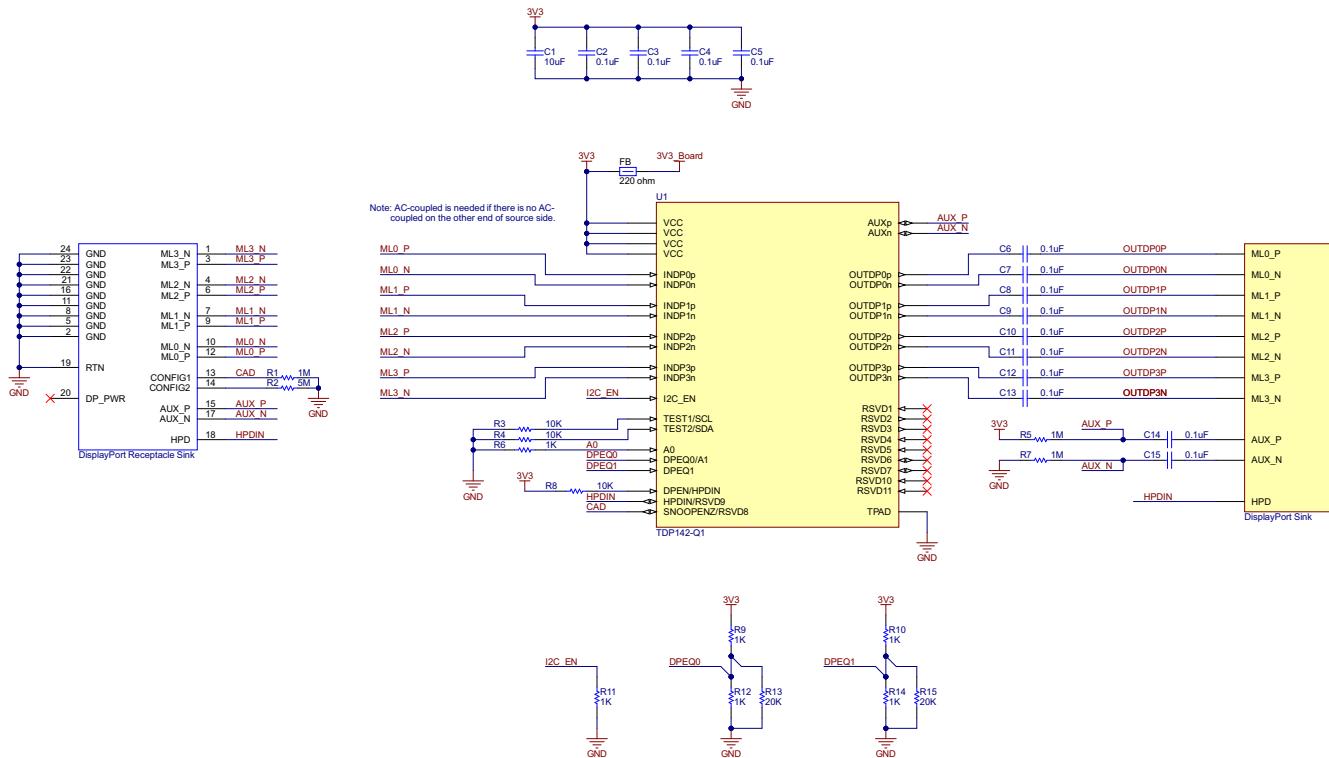

## 8.2.2 シンク アプリケーションの実装

図 8-4 は、シンク アプリケーションの回路図です。TDP142-Q1 の左側は DisplayPort レセプタクルに接続され、TDP142-Q1 の右側は Scaler または DisplayPort シンクに接続されています。

図 8-4. DisplayPort シンク アプリケーションのブロック図

### 8.2.2.1 設計要件

この設計例では、表 8-5 に記載されているパラメータを使用します。

表 8-5. 設計パラメータ

| パラメータ                                  | 値                              |

|----------------------------------------|--------------------------------|

| 最大動作データレート<br>(RBR、HBR、HBR2、HBR3)      | HBR3 (8.1Gbps)                 |

| 電源電圧                                   | 3.3 V                          |

| C のパターン長と幅                             | 12 inch/6 mil                  |

| D のパターン長と幅                             | 2 inch/6 mil                   |

| メインリンク AC デカッピング コンデンサ<br>(75nF~265nF) | 100nF を推奨                      |

| 制御モード (I <sup>2</sup> C または GPIO)      | GPIO (I <sup>2</sup> C_EN = 0) |

### 8.2.2.2 詳細な設計手順

シンク アプリケーションの設計手順を以下に示します。

- DP 入力 (C) と出力 (D) のチャネルとケーブルの損失プロファイルを決定します。6mil パターン挿入損失については、[図 8-5](#) を参照してください。

- 損失プロファイルに基づいて、TDP142 が電気的規格に準拠するために最適な構成を決定します。

- AC カップリング コンデンサ、制御ピン抵抗、および推奨のデカッピング コンデンサを VCC ピンからグランドに使用するソース アプリケーションの詳細については、[図 8-4](#) を参照してください。

- AUX:AUXP に  $1\text{M}\Omega$  プルアップ抵抗、AUXN に  $1\text{M}\Omega$  プルダウン抵抗があることを確認します。 $1\text{M}\Omega$  抵抗は、 $100\text{nF}$  コンデンサの TDP142-Q1 側に配置する必要があります。

- HPDIN:GPIO/I2C モードに基づいて、HPD 信号をピン 23 またはピン 32 に配線します。このセットアップにより、TDP142-Q1 はソースが接続されていないときに電力を節約できます。

**表 8-6. HPD GPIO/I2C の選択**

| モード                                                      | HPD   |

|----------------------------------------------------------|-------|

| GPIO ( $\text{I}^2\text{C\_EN} = 0$ )                    | ピン 32 |

| $\text{I}^2\text{C}$ ( $\text{I}^2\text{C\_EN} \neq 0$ ) | ピン 23 |

- GPIO 端子または  $\text{I}^2\text{C}$  インターフェイスを使用して TDP142-Q1 を構成します。

- GPIO - 端子 DPEQ0 および DPEQ1 を使用。

- まず、 $13\text{dB}$  や  $15\text{dB}$  などの高いイコライゼーション値を開始し、必要に応じて値を調整することを推奨します。

- $\text{I}^2\text{C}$  - 詳細な構成手順については、[I2C レジスタ マップ](#)と[プログラミングセクション](#)を参照してください。

- サーマル パッドはグランドに接続する必要があります。

### 8.2.3 アプリケーション曲線

**図 8-5. FR4 PCB パターンの挿入損失**

## 8.3 電源に関する推奨事項

TDP142-Q1 は、 $3.3\text{V}$  電源で動作するように設計されています。[絶対最大定格](#) 表に記載されているレベルより上のレベルは使用しないでください。アプリケーションに高電圧のシステム電源が使用される場合は、電圧レギュレータを使用して  $3.3\text{V}$  に降圧してください。ノイズを低減し、電源の整合性を向上させるためにデカッピング コンデンサを使用します。各電源ピンに  $0.1\mu\text{F}$  コンデンサを使用します。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

1. INDP[3:0]P/N and OUTDP[3:0]P/N のペアは、制御された  $100\Omega$  の差動インピーダンス ( $\pm 10\%$ ) で配線します。

2. その他の高速信号から遠ざけます。

3. ペア内の配線を 5mil 以内に抑えます。

4. [DisplayPort 設計ガイド](#)に従って、ペア間スキューを 2 UI 以内に抑えます

5. 配線長を一致させるための調整は、配線長の不一致が発生している場所の近くで行います。

6. 各ペアは、信号配線幅の 3 倍以上離す必要があります。

7. 差動配線での曲げの使用は最小限に抑えます。曲げを使用する場合、左右の曲げの数は可能な限り等しくし、曲げの角度は 135 度以上としてください。この設定により、曲げに起因する長さの不一致が最小限に抑えられ、その結果、曲げが EMI に及ぼす影響が最小限に抑えられます。

8. すべての差動ペアは同じ層に配線します。

9. ビアの数を最小限に抑えます。ビアの数を 2 以下にすることを推奨します。

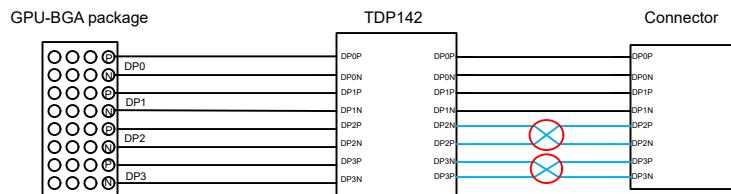

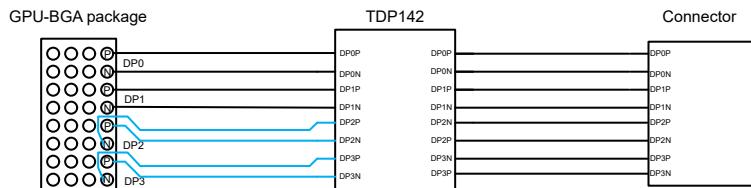

10. デバイスの出力ピンとコネクタとの間の順序が一致していないため、レイアウトでは OUTDP2 と OUTDP3 で信号が交差する可能性があります (図 8-7 を参照)。オプションの 1 つは、GPU が BGA パッケージである場合にデバイスの入力で極性をスワップし、使用するビアの数を最小限に抑えることです。

11. グランドプレーンに隣接する層に配線を配置します。

12. 差動ペアは、プレーンの割れ目の上には配線しないようにします。

13. なお、テストポイントを追加することは、インピーダンスの非連続性をもたらすため、信号性能に悪影響を及ぼします。テストポイントを使用する場合、テストポイントを連續的かつ対称的に配置します。差動ペアにスタブを形成するような方法で、テストポイントを配置するべきではありません。

### 8.4.2 レイアウト例

図 8-6. レイアウト例

以下の図は、BGA パッケージを使用して、デバイスの出力とソースの DisplayPort コネクタとの間の不一致順序を調整する方法を示しています。図 8-7 に、TDP142-Q1 とコネクタとの間の交差セクションを示します。通常、交差を避けるためにビアを使用しますが、ビアを使用するとシグナルインテグリティが減衰する可能性があります。したがって、TDP142-Q1 の入力に極性スワップを実装できます。図 8-8 に、TDP142-Q1 とコネクタとの間に交差セクションがなくなることを示しています。このため、使用するビアの数を最小限に抑えることができます。このオプションは、BGA パッケージを使用しているソースにのみ有用であることに注意してください。

図 8-7. レイアウト例：出力側での信号交差

図 8-8. レイアウト例：INDP2 と INDP3 の極性スワップ

## 9 デバイスおよびドキュメントのサポート

### 9.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 9.3 商標

DisplayPort™ is a trademark of VESA.

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

HDMI® is a registered trademark of HDMI Licensing LLC.

VESA® is a registered trademark of Video Electronics Standards Association.

すべての商標は、それぞれの所有者に帰属します。

### 9.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.5 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (November 2024) to Revision A (February 2025) | Page              |

|-----------------------------------------------------------------------|-------------------|

| • データシートのステータスを「事前情報」から「量産データ」.....                                   | <a href="#">1</a> |

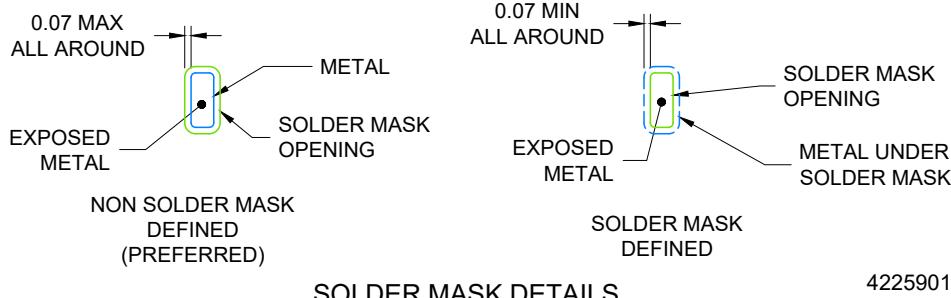

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのプラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

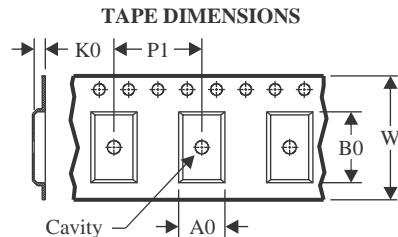

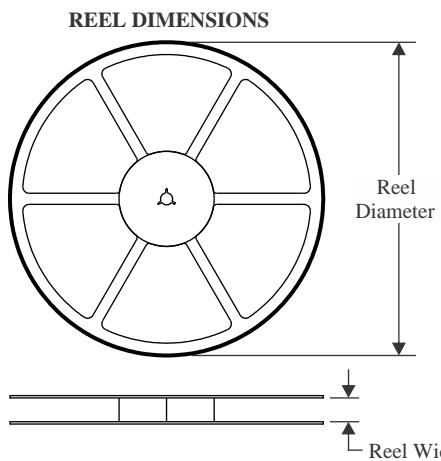

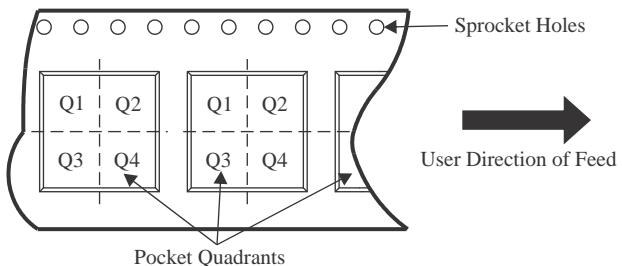

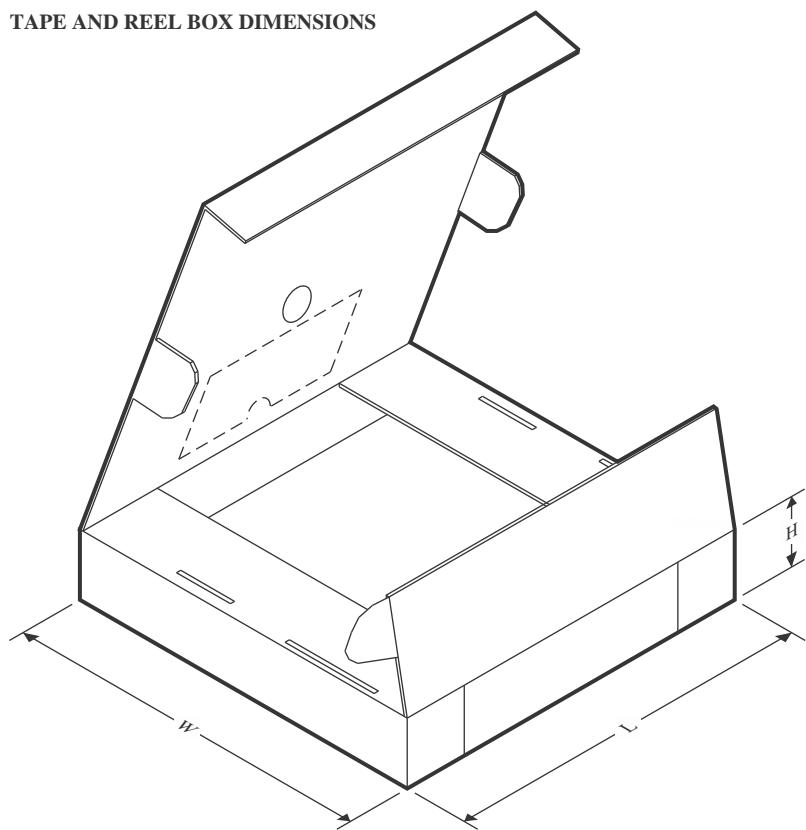

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TDP142RGFRQ1          | Active        | Production           | VQFN (RGF)   40 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | TDB461              |

| TDP142RGFRQ1.B        | Active        | Production           | VQFN (RGF)   40 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | TDB461              |

| TDP142RGFTQ1          | Active        | Production           | VQFN (RGF)   40 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | TDB461              |

| TDP142RGFTQ1.B        | Active        | Production           | VQFN (RGF)   40 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 105   | TDB461              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.