**TDC7201**

JAJSC78-MAY 2016

### TDC7201 LIDAR、距離測定機、およびADASの タイム・オブ・フライト・アプリケーション用タイム-デジタル・コン バータ

#### 1 特長

分解能: 55ps標準偏差: 35ps

• 測定範囲:

個別モード1: 12ns~2000ns 個別モード2: 250ns~8ms 結合動作: 0.25ns~8ms

• アクティブ時の低消費電力: 2.7mA

• 最大10個のSTOP信号をサポート

• 自律的なマルチサイクル平均化モードによる低消費電力

• 電源電圧: 2V~3.6V

動作温度: -40°C~+85°C

• レジスタ・アクセス用SPIインターフェイス

#### 2 アプリケーション

- 距離測定器

- LIDAR

- ドローンおよびロボット工学

- 先進運転支援システム (ADAS)

- 衝突検出システム

- 流量計

#### 3 概要

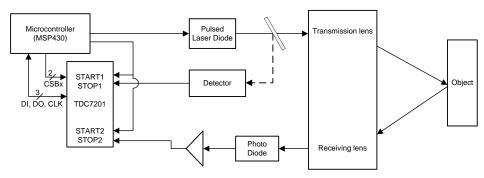

TDC7201は、タイム・オブ・フライト技法を使用する超音波、レーザー、レーダーの距離測定機器で使用するよう設計されています。TDC7201には2つのタイム-デジタル・コンバータ(TDC)が内蔵され、単純なアーキテクチャで4cmから数kmまでの距離を測定でき、高価なFPGAやプロセッサを必要としません。

各TDCはストップウォッチの機能を果たし、STARTパルスから、最大5つのSTOPパルスまでの経過時間(タイム・オブ・フライト、TOF)を測定します。2つの内蔵TDCを使用して、STARTおよびSTOPピンの2つのペアを同時に、かつ個別に測定できるため、時間測定について非常に柔軟な設計が可能になります。

このデバイスには内部的に自己較正された時間ベースが搭載されており、時間や温度によるドリフトを補償します。自己較正により、ピコ秒単位の精度で時間-デジタル変換が可能になります。この精度のため、TDC7201は距離測定アプリケーションに理想的です。

自律的なマルチサイクル平均化モードに設定したとき、TDC7201デバイスはシステムの消費電力が低くなるよう最適化可能で、バッテリ駆動の流量計に理想的です。このモードでは、ホストはスリープ・モードに移行して電力を節約し、測定シーケンスが完了した時点でTDCから割り込みを受けてウェークアップできます。

#### 製品情報<sup>(1)</sup>

| 型番      | パッケージ      | 本体サイズ(公称)     |

|---------|------------|---------------|

| TDC7201 | nFBGA (25) | 4.00mm×4.00mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

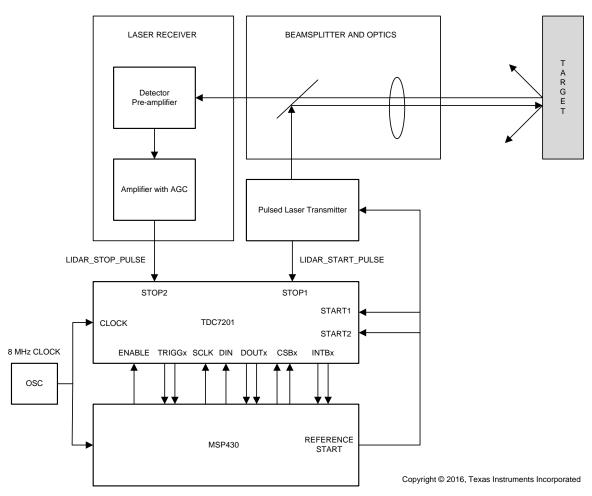

#### 単純化したLIDARアプリケーションのブロック図

Copyright © 2016, Texas Instruments Incorporated

### 目次

| 1 | 特長1                                  | 7.4 Device Functional Modes      | 13 |

|---|--------------------------------------|----------------------------------|----|

| 2 | アプリケーション1                            | 7.5 Programming                  | 21 |

| 3 | 概要1                                  | 7.6 Register Maps                |    |

| 4 | 改訂履歴2                                | 8 Application and Implementation | 35 |

| 5 | Pin Configuration and Functions      | 8.1 Application Information      | 35 |

| 6 | Specifications4                      | 8.2 Typical Application          | 35 |

| 0 | 6.1 Absolute Maximum Ratings         | 8.3 CLOCK Recommendations        | 38 |

|   | 6.2 ESD Ratings                      | 9 Power Supply Recommendations   | 40 |

|   | 6.3 Recommended Operating Conditions | 10 Layout                        | 40 |

|   | 6.4 Thermal Information              | 10.1 Layout Guidelines           |    |

|   | 6.5 Electrical Characteristics 6     | 10.2 Layout Example              | 41 |

|   | 6.6 Timing Requirements              | 11 デバイスおよびドキュメントのサポート            | 42 |

|   | 6.7 Switching Characteristics        | 11.1 ドキュメントのサポート                 | 42 |

|   | 6.8 Typical Characteristics8         | 11.2 コミュニティ・リソース                 | 42 |

| 7 | Detailed Description 11              | 11.3 商標                          | 42 |

| • | 7.1 Overview                         | 11.4 静電気放電に関する注意事項               | 42 |

|   | 7.2 Functional Block Diagram         | 11.5 Glossary                    | 42 |

|   | 7.3 Feature Description              | 12 メカニカル、パッケージ、および注文情報           | 42 |

|   | •                                    |                                  |    |

### 4 改訂履歴

| 日付      | 改訂内容 | 注  |

|---------|------|----|

| 2016年5月 | *    | 初版 |

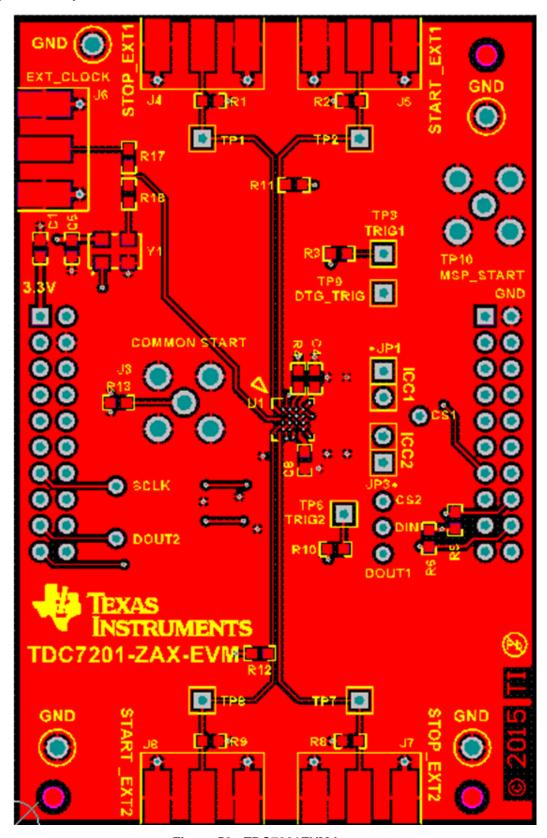

### **5 Pin Configuration and Functions**

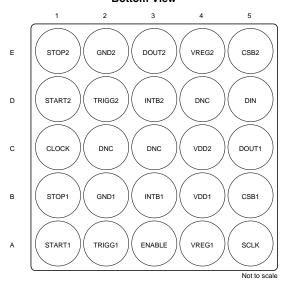

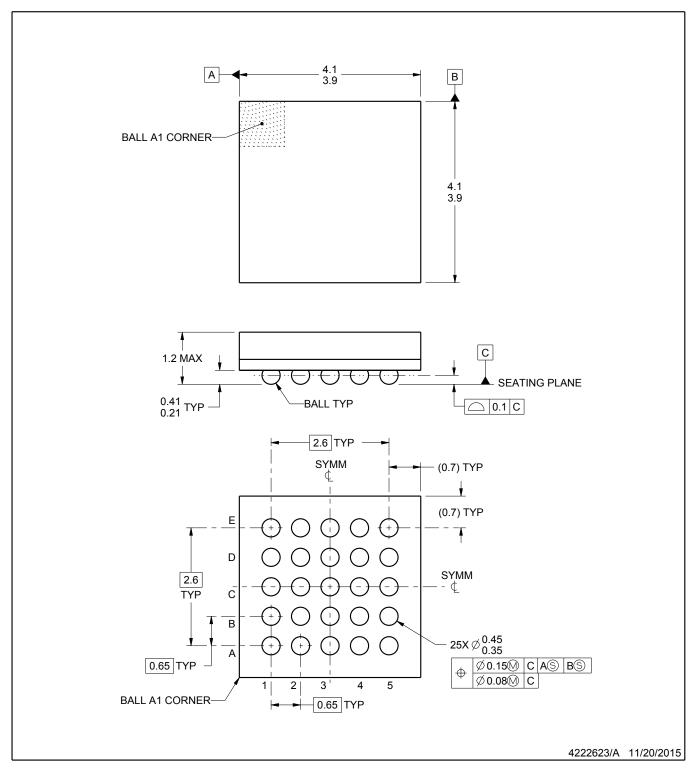

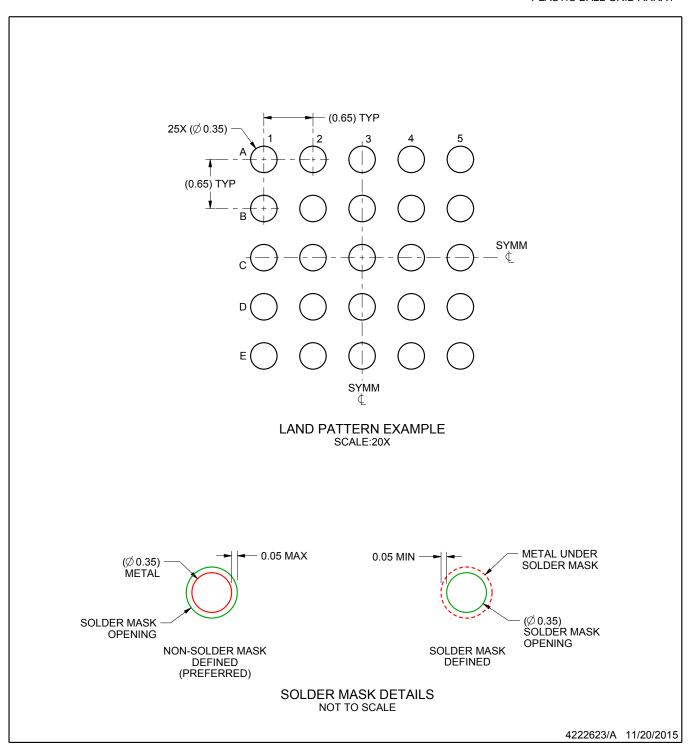

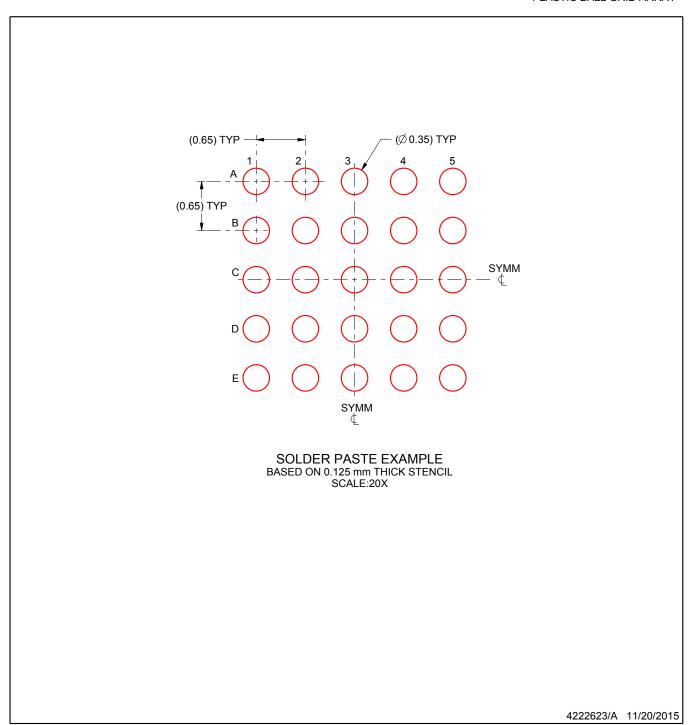

#### ZAX Package 25-Pin nFBGA Bottom View

#### **Pin Functions**

|     | PIN    | TVDE   | DECODINE                                           |

|-----|--------|--------|----------------------------------------------------|

| NO. | NAME   | TYPE   | DESCRIPTION                                        |

| A1  | START1 | Input  | START signal for TDC1                              |

| A2  | TRIGG1 | Output | Trigger output signal for TDC1                     |

| A3  | ENABLE | Input  | Enable signal to TDC                               |

| A4  | VREG1  | Output | LDO output terminal for external decoupling cap    |

| A5  | SCLK   | Input  | SPI clock                                          |

| B1  | STOP1  | Input  | STOP signal for TDC1                               |

| B2  | GND1   | Ground | Ground                                             |

| В3  | INTB1  | Output | Interrupt to MCU for TDC1, active low (open drain) |

| B4  | VDD1   | Power  | Supply input                                       |

| B5  | CSB1   | Input  | SPI chip select for TDC1, active low               |

| C1  | CLOCK  | Input  | Clock input to TDC                                 |

| C2  | DNC    | _      | Do not connect                                     |

| C3  | DNC    | _      | Do not connect                                     |

| C4  | VDD2   | Power  | Supply input                                       |

| C5  | DOUT1  | Output | SPI data output for TDC1                           |

| D1  | START2 | Input  | START signal for TDC2                              |

| D2  | TRIGG2 | Output | Trigger output signal for TDC2                     |

| D3  | INTB2  | Output | Interrupt to MCU for TDC2, active low (open drain) |

| D4  | DNC    | _      | Do not connect                                     |

| D5  | DIN    | Input  | SPI data input                                     |

| E1  | STOP2  | Input  | STOP signal for TDC2                               |

| E2  | GND2   | Ground | Ground                                             |

| E3  | DOUT2  | Output | SPI data output for TDC2                           |

| E4  | VREG2  | Output | LDO output terminal for external decoupling cap    |

| E5  | CSB2   | Input  | SPI chip select for TDC2, active low               |

JAJSC78 – MAY 2016 www.ti.com

# TEXAS INSTRUMENTS

#### 6 Specifications

#### 6.1 Absolute Maximum Ratings

at  $T_A = 25$ °C , VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V (unless otherwise noted). (1)(2)(3)(4)(5)

|                    |                                                                 | MIN         | MAX            | UNIT |

|--------------------|-----------------------------------------------------------------|-------------|----------------|------|

| $V_{DD}$           | Supply voltage                                                  | -0.3        | 3.9            | V    |

| V                  | Voltage on VREG1, VREG2 pins                                    | -0.3        | 1.65           | V    |

| V <sub>I</sub>     | Terminal input voltage on any other pin                         | -0.3        | $V_{DD} + 0.3$ |      |

| $V_{DIFF\_IN}$     | Voltage differential  between any two input terminals           |             | 3.9            | V    |

| $V_{IN\_GND\_VDD}$ | Voltage differential  between any input terminal and GND or VDD |             | 3.9            | V    |

| I                  | Input current at any pin                                        | -5          | 5              | mA   |

| T <sub>A</sub>     | Ambient temperature                                             | -40         | 125            | °C   |

| T <sub>stg</sub>   | Storage temperature                                             | <b>–</b> 55 | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum

- (3) All voltages are with respect to ground, unless otherwise specified.

- (4) Pins VDD1 and VDD2 must be tied together at the board level and supplied from the same source.

- (5) When the terminal input voltage (V<sub>I</sub>) at any pin exceeds power supplies (V<sub>I</sub> < GND or V<sub>I</sub> > VDD), the current at that pin must not exceed 5 mA (source or sink), and the voltage (V<sub>I</sub>) at the pin must not exceed 3.9 V.

#### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| .,                 | Floatrootatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

At  $T_A = 25$ °C, VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V (unless otherwise noted).

|                             |                                                 | MIN                    | NOM  | MAX                           | UNIT |

|-----------------------------|-------------------------------------------------|------------------------|------|-------------------------------|------|

| V <sub>DD</sub>             | Supply voltage                                  | 2                      |      | 3.6                           | V    |

| VI                          | Terminal voltage                                | 0                      |      | VDD                           | V    |

| V <sub>IH</sub>             | Voltage input high                              | 0.7 × VDD              |      | 3.6                           | V    |

| V <sub>IL</sub>             | Voltage input low                               | 0                      |      | 0.3 × VDD                     | V    |

| F <sub>CALIB_CLK</sub>      | Frequency (reference or calibration clock)      | 1 (1)                  | 8    | 16                            | MHz  |

| t <sub>CLOCK</sub>          | Time period (reference or calibration clock)    | 62.5                   | 125  | 1000                          | ns   |

| DUTY <sub>CLOCK</sub>       | Input clock duty cycle                          |                        | 50%  |                               |      |

| TIMING REQUIREM             | IENTS: Measurement Mode 1 (1)(2)(3)             |                        |      |                               |      |

| T1 <sub>Min_STARTSTOP</sub> | Minimum time between start and stop signal      | 12                     |      |                               | ns   |

| T1 <sub>Max_STARTSTOP</sub> | Maximum time between start and stop signal      |                        | 2000 |                               | ns   |

| T1 <sub>Min_STOPSTOP</sub>  | Minimum time between 2 stop signals             | 67                     |      |                               | ns   |

| T1 <sub>Max_LASTSTOP</sub>  | Maximum time between start and last stop signal |                        | 2000 |                               | ns   |

| TIMING REQUIREM             | IENTS: Measurement Mode 2 <sup>(1)(2)(3)</sup>  |                        |      |                               |      |

| T2 <sub>Min_STARTSTOP</sub> | Minimum time between start and stop signal      | 2 × t <sub>CLOCK</sub> |      |                               | S    |

| T2 <sub>Max_STARTSTOP</sub> | Maximum time between start and stop signal      |                        |      | $(2^{16}-2) \times t_{CLOCK}$ | S    |

| T2 <sub>Min_STOPSTOP</sub>  | Minimum time between 2 stop signals             | 2 × t <sub>CLOCK</sub> |      |                               | S    |

| T2 <sub>Max_LASTSTOP</sub>  | Maximum time between start and last stop signal |                        |      | $(2^{16}-2) \times t_{CLOCK}$ | S    |

- (1) Specified by design.

- (2) Applies to both pairs of START1, STOP1 and START2, STOP2 pins.

- 3) Minimum time between 2 stop signals applies to 2 stop signals on the same TDC.

www.ti.com

#### **Recommended Operating Conditions (continued)**

At  $T_A = 25^{\circ}\text{C}$ , VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V (unless otherwise noted).

| ,                                       | ,                                                            | MIN | NOM      | MAX      | UNIT |

|-----------------------------------------|--------------------------------------------------------------|-----|----------|----------|------|

| TIMING REQUIREME                        | NTS: ENABLE INPUT                                            |     |          |          |      |

| T <sub>REN</sub>                        | Rise time for enable signal (20% to 80%)                     |     | 1 to 100 |          | ns   |

| T <sub>FEN</sub>                        | Fall time for enable signal (20% to 80%)                     |     | 1 to 100 |          | ns   |

| TIMING REQUIREME                        | NTS: START1, STOP1, CLOCK, START2, STOP2                     |     |          | <u> </u> |      |

| T <sub>RST</sub> , T <sub>FST</sub>     | Maximum rise, fall time for START, STOP signals (20% to 80%) |     | 1        |          | ns   |

| T <sub>RXCLK</sub> , T <sub>FXCLK</sub> | Maximum rise, fall time for external CLOCK (20% to 80%)      |     | 1        |          | ns   |

| TIMING REQUIREME                        | NTS: TRIGG1, TRIGG2                                          |     |          |          |      |

| T <sub>TRIG1START1</sub>                | Time from TRIG1 to START1                                    | 5   |          |          | ns   |

| T <sub>TRIG2START2</sub>                | Time from TRIG2 to START2                                    | 5   |          |          | ns   |

| TIMING REQUIREME                        | NTS: Measurement Mode 1 Combined Operation (4)               |     |          |          |      |

| T1 <sub>STARTSTOP_Comb_Min</sub>        | Minimum time between START and STOP signal combined          |     | 0.25     |          | ns   |

| TEMPERATURE                             |                                                              |     |          |          |      |

| T <sub>A</sub>                          | Ambient temperature                                          | -40 |          | 85       | °C   |

| T <sub>J</sub>                          | Junction temperature                                         | -40 |          | 85       | °C   |

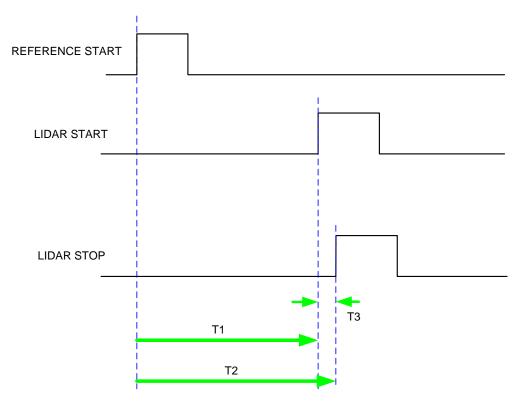

<sup>(4)</sup> TDC7201 device in combined measurement mode where START1 and START2 are connected together:

#### 6.4 Thermal Information

|                      |                                              | TDC7201     |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | ZAX (nFBGA) | UNIT |

|                      |                                              | 25 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 155.1       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 109.5       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 114.1       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 20.8        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 110.6       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

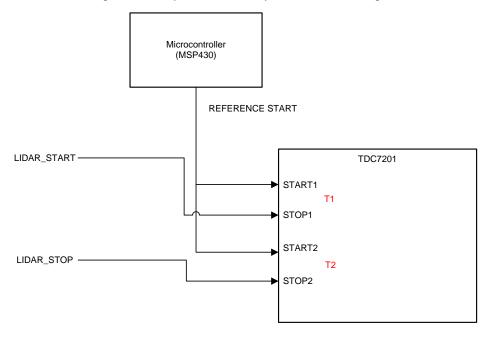

<sup>(</sup>a) A common REFERENCE\_START signal is applied to START1 and START2 at least 12 ns before occurrence of actual START and STOP signals in Mode 1 (and at least 2 × t<sub>CLOCK</sub> before occurrence of actual Start and Stop signals in Mode 2).

<sup>(</sup>b) Start signal is connected to STOP1

<sup>(</sup>c) Stop signal is connected to STOP2

<sup>(</sup>d) Two time periods T1 (REFERENCE\_START to Start) and T2 (REFERENCE\_START to Stop) are measured and their difference (T2-T1) is the time between Start to Stop

# NSTRUMENTS

#### 6.5 Electrical Characteristics

$T_A = 25^{\circ}C$ , VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V (unless otherwise noted).

|                    | PARAMETER                                              | TEST CONDITIONS                                          | MIN  | TYP  | MAX  | UNIT |

|--------------------|--------------------------------------------------------|----------------------------------------------------------|------|------|------|------|

| TDC CH             | IARACTERISTICS                                         |                                                          |      |      |      |      |

| LSB                | Resolution                                             | Single shot measurement                                  |      | 55   |      | ps   |

| T <sub>ACC-2</sub> | Accuracy (Mode 2) <sup>(1)</sup>                       | CLOCK = 8 MHz, Jitter (RMS) < 1 ps,<br>Stability < 5 ppm |      | 28   |      | ps   |

| _                  | Standard Deviation (Mode 2)                            | Measured time = 100 μs                                   |      | 50   |      | ps   |

| T <sub>STD-2</sub> | Standard Deviation (widde 2)                           | Measured time = 1 μs                                     |      | 35   |      | ps   |

| OUTPU              | T CHARACTERISTICS: TRIGG1, TRIGG2                      | , INTB1, INTB2, DOUT1, DOUT2                             |      |      |      |      |

| $V_{OH}$           | Output voltage high                                    | Isource = -2 mA                                          | 2.31 | 2.95 |      | V    |

| $V_{OL}$           | Output voltage low                                     | Isink = 2 mA                                             |      | 0.35 | 0.99 | V    |

| INPUT              | CHARACTERISTICS: START1, STOP1, S                      | TART2, STOP2, CSB1, CSB2                                 |      |      |      |      |

| C <sub>in</sub>    | Input capacitance (2)                                  |                                                          |      | 4    |      | pF   |

| INPUT              | CHARACTERISTICS: ENABLE, CLOCK, I                      | DIN, SCLK                                                |      |      |      |      |

| C <sub>in</sub>    | Input capacitance (2)                                  |                                                          |      | 8    |      | pF   |

| POWER              | R CONSUMPTION <sup>(3)</sup> (see <i>Measurement N</i> | lode 1 and Measurement Mode 2)                           |      |      |      |      |

| I <sub>sh</sub>    | Shutdown current                                       | EN = LOW                                                 |      | 0.6  |      | μΑ   |

| $I_{QA}$           | Quiescent Current A                                    | EN = HIGH; TDC running                                   |      | 2.7  |      | mA   |

| $I_{QB}$           | Quiescent Current B                                    | EN = HIGH; TDC OFF, Clock Counter running                |      | 140  |      | μΑ   |

| I <sub>QC</sub>    | Quiescent Current C                                    | EN = HIGH; measurement stopped, SPI communication only   |      | 175  |      | μΑ   |

| $I_{QD}$           | Quiescent Current D                                    | EN = HIGH, TDC OFF, counter stopped, no communication    |      | 100  |      | μΑ   |

<sup>(1)</sup> Accuracy is defined as the systematic error in the output signal; the error of the device excluding noise.

#### 6.6 Timing Requirements

| nimir o.o           | ig Requirements                                                                                        | 1   |       |     |      |

|---------------------|--------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

|                     |                                                                                                        | MIN | NOM I | MAX | UNIT |

| TIMING REQ          | UIREMENTS: START1, STOP1, START2, STOP2, CLOCK                                                         |     |       |     |      |

| PW <sub>START</sub> | Pulse width for Start Signal                                                                           | 10  |       |     | ns   |

| PW <sub>STOP</sub>  | Pulse width for Stop Signal                                                                            | 10  |       |     | ns   |

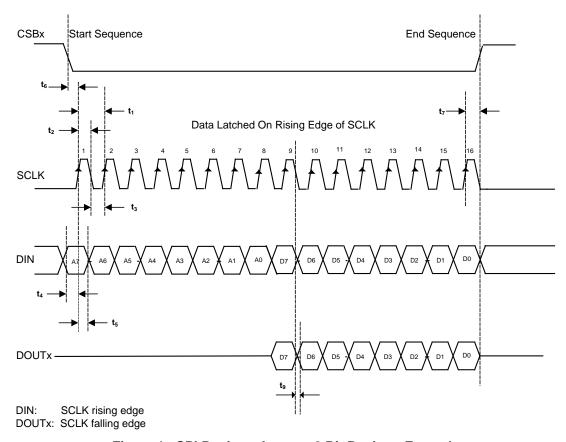

| SERIAL INTE         | RFACE TIMING CHARACTERISTICS (VDD = $3.3 \text{ V}$ , $f_{\text{SCLK}} = 25 \text{ MHz}$ ) (See Figure | 1)  |       |     |      |

| f <sub>SCLK</sub>   | SCLK frequency                                                                                         |     |       | 25  | MHz  |

| t <sub>1</sub>      | SCLK period                                                                                            | 40  |       |     | ns   |

| SERIAL INTE         | RFACE TIMING CHARACTERISTICS (VDD = $3.3 \text{ V}$ , $f_{\text{SCLK}} = 20 \text{ MHz}$ ) (See Figure | 1)  |       |     |      |

| t <sub>1</sub>      | SCLK period                                                                                            | 50  |       |     | ns   |

| t <sub>2</sub>      | SCLK High Time                                                                                         | 16  |       |     | ns   |

| t <sub>3</sub>      | SCLK Low Time                                                                                          | 16  |       |     | ns   |

| t <sub>4</sub>      | DIN setup time                                                                                         | 5   |       |     | ns   |

| t <sub>5</sub>      | DIN hold time                                                                                          | 5   |       |     | ns   |

| t <sub>6</sub>      | CSB1 or CSB2 fall to SCLK rise                                                                         | 6   |       |     | ns   |

| t <sub>7</sub>      | Last SCLK rising edge to CSB1 or CSB2 rising edge                                                      | 6   |       |     | ns   |

| t <sub>8</sub>      | Minimum pause time (CSB high)                                                                          | 40  |       |     | ns   |

| t <sub>9</sub>      | Clk fall to DOUT1 or DOUT2 bus transition                                                              |     |       | 12  | ns   |

Specified by design.

Sum of TDC1 and TDC2 values

www.ti.com

### 6.7 Switching Characteristics

$T_A = 25^{\circ}C$  , VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V (unless otherwise noted).

| PARAMETER                  |                                  | TEST CONDITIONS                  | MIN | TYP | MAX | UNIT |

|----------------------------|----------------------------------|----------------------------------|-----|-----|-----|------|

| WAKE UP TIME               |                                  |                                  |     |     |     |      |

| T <sub>WAKEUP_PERIOD</sub> | Time to be ready for measurement | LSB within 0.3% of settled value |     | 300 |     | μs   |

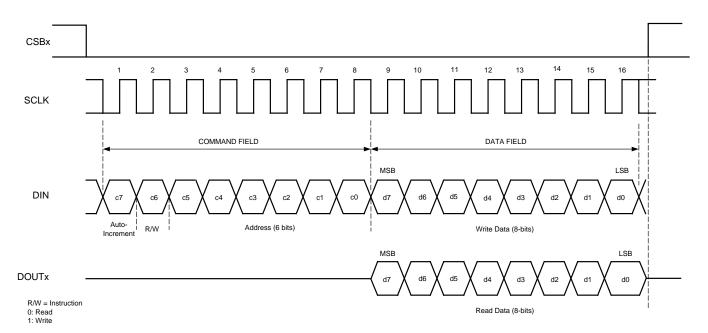

Figure 1. SPI Register Access: 8 Bit Register Example

# TEXAS INSTRUMENTS

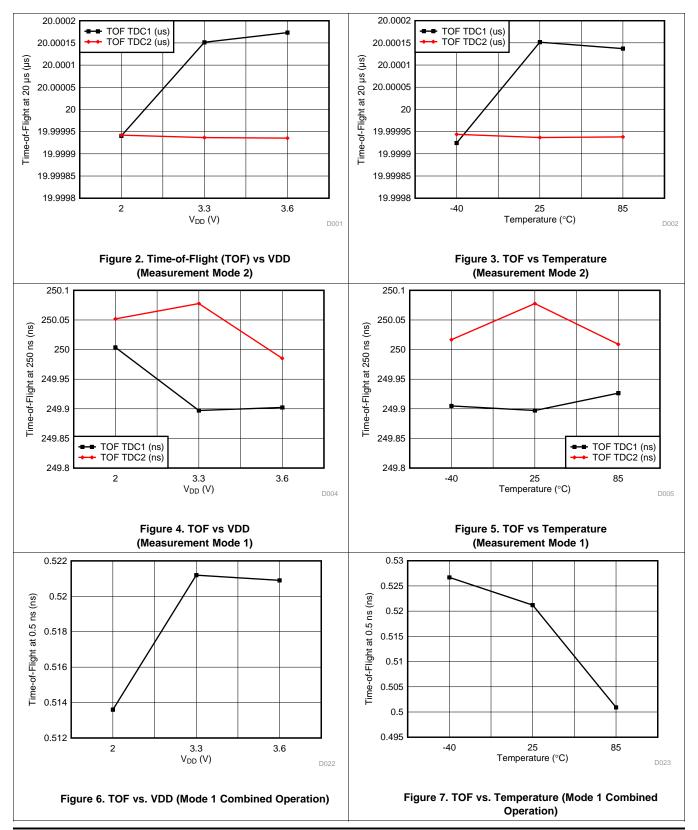

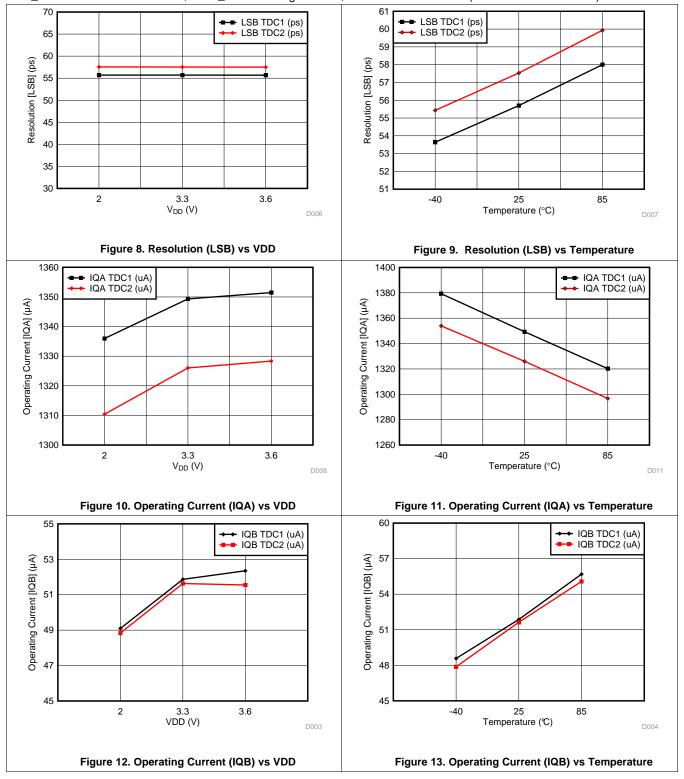

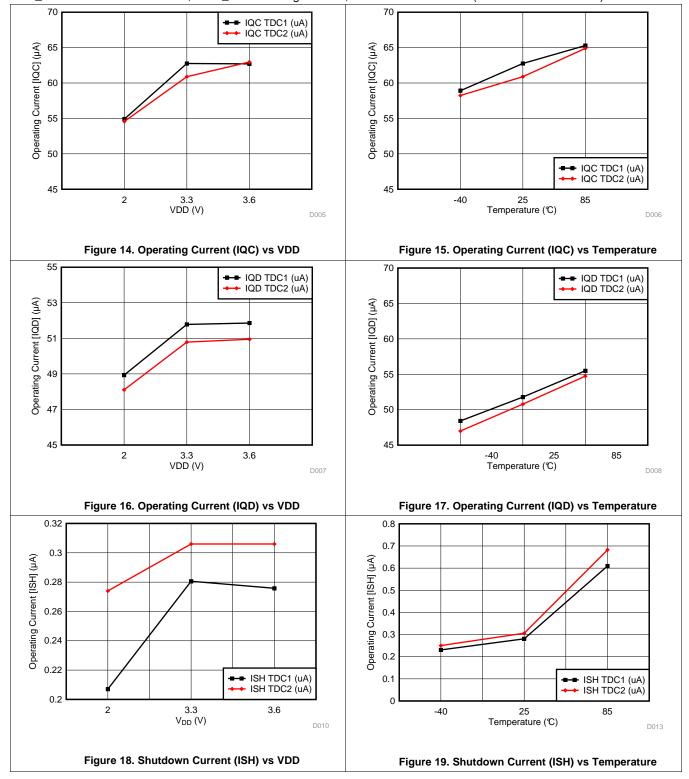

#### 6.8 Typical Characteristics

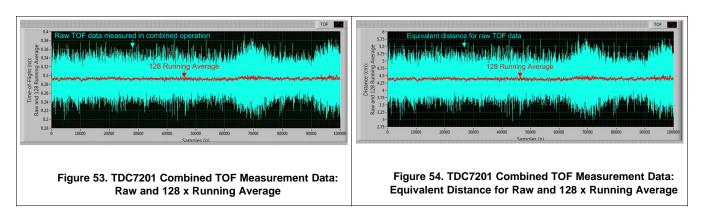

At  $T_A = 25^{\circ}\text{C}$ , VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V, CLOCK = 8 MHz,  $CALIBRATION2\_PERIODS = 10$ ,  $AVG\_CYCLES = 1$  Measurement,  $NUM\_STOP = Single STOP$ , Measurement Mode 2 (unless otherwise noted).

www.ti.com

#### **Typical Characteristics (continued)**

At  $T_A = 25^{\circ}\text{C}$ , VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V, CLOCK = 8 MHz,  $CALIBRATION2\_PERIODS = 10$ ,  $AVG\_CYCLES = 1$  Measurement,  $NUM\_STOP = Single STOP$ , Measurement Mode 2 (unless otherwise noted).

#### TEXAS INSTRUMENTS

#### **Typical Characteristics (continued)**

At  $T_A = 25^{\circ}\text{C}$ , VDD1 = VDD2 = 3.3 V, GND1 = GND2 = 0 V, CLOCK = 8 MHz, CALIBRATION2\_PERIODS = 10, AVG\_CYCLES = 1 Measurement, NUM\_STOP = Single STOP, Measurement Mode 2 (unless otherwise noted).

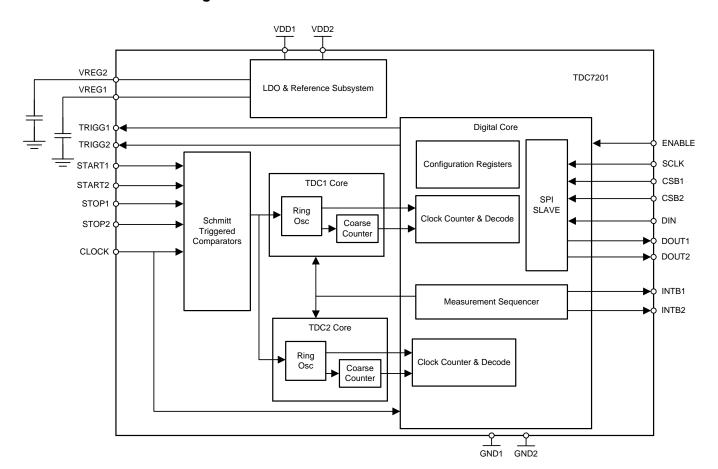

7 Detailed Description

### 7.1 Overview

www.ti.com

The TDC7201 has two built-in TDCs with the capability to simultaneously and individually measure time delay on two pairs of START and STOP pins. Each TDC is a stopwatch that measures time between a single event (edge on START pin) and multiple subsequent events (edge on STOP pin). An event from a START pulse to a STOP pulse is also known as time-of-flight, or TOF for short. The TDC has an internal time base that is used to measure time with accuracy in the order of picoseconds. This accuracy makes the TDC7201 ideal for applications such as drones and range finders, which require high accuracy in the picoseconds range.

#### **NOTE**

In rest of the documentation, we use TDCx to refer each TDC of the TDC7201, where x = 1, 2. Also, the prefix TDCx is used in register names to identify the TDC the register belongs to. Further the associated START, STOP, TRIGG, CSB, DOUT, and INTB pins of TDCx are represented as STARTx, STOPx, TRIGGx, CSBx, DOUTx, and INTBx.

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

**NOTE**

Do not tie together VREG1 and VREG2.

## TEXAS INSTRUMENTS

#### 7.3 Feature Description

#### 7.3.1 LDO

The LDO (low-dropout) is an internal supply voltage regulator for the TDC7201. Each of the two TDC cores of the TDC7201 has its own dedicated LDO. No external circuitry needs to be connected to the output of this regulator other than the mandatory external decoupling capacitor on VREG1 and VREG2.

Recommendations for the decoupling capacitor parameters:

- Type: ceramic

- Capacitance: 0.4 μF to 2.7 μF (1 μF typical). If using a capacitor value outside the recommended range, the part may malfunction and can be damaged.

- ESR: 100 mΩ (maximum)

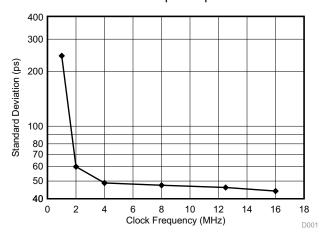

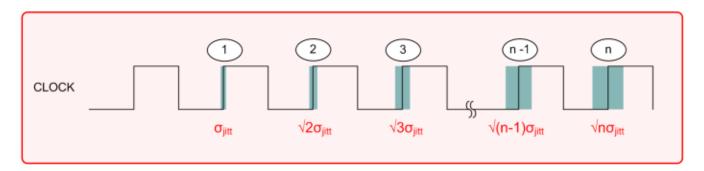

#### 7.3.2 CLOCK

The TDC7201 needs an external reference clock connected to the CLOCK pin. This external clock input serves as the reference clock for both TDCs of the TDC7201. The external CLOCK is used to calibrate the internal time base accurately and therefore, the measurement accuracy is heavily dependent on the external CLOCK accuracy. This reference clock is also used by all digital circuits inside the device; thus, CLOCK has to be available and stable at all times when the device is enabled (ENABLE = HIGH).

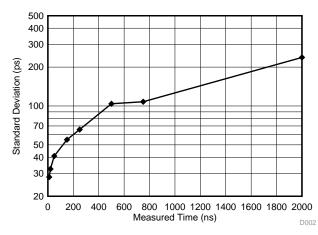

Figure 20 shows the typical effect of the external CLOCK frequency on the measurement uncertainty. With a reference clock of 1 MHz, the standard deviation of a set of measurement results is approximately 243 ps. As the reference clock frequency is increased, the standard deviation (or measurement uncertainty) reduces. Therefore, using a reference clock of 16 MHz is recommended for optimal performance.

Figure 20. Standard Deviation vs CLOCK

#### 7.3.3 Counters

#### 7.3.3.1 Coarse and Clock Counters Description

Time measurements by each TDCx of the TDC7201 rely on two counters: the Coarse Counter and the Clock Counter. The Coarse Counter counts the number of times the ring oscillator (the TDCx's core time measurement mechanism) wraps, which is used to generate the results in the TDCx\_TIME1 to TDCx\_TIME6 registers.

The Clock Counter counts the number of integer clock cycles between START and STOP events and is used in *Measurement Mode 2* only. The results for the Clock Counter are displayed in the TDCx\_CLOCK\_COUNT1 to TDCx\_CLOCK\_COUNT5 registers.

#### 7.3.3.2 Coarse and Clock Counters Overflow

Once the coarse counter value has reached the corresponding value of the Coarse Counter Overflow registers, then its interrupt bit will be set to 1. In other words, if  $(TDCx\_TIMEn / 63) \ge COARSE\_CNTR\_OVF$ , then  $COARSE\_CNTR\_OVF\_INT = 1$  (this interrupt bit is located in the  $TDCx\_INT\_STATUS$  register).

www.ti.com

### **Feature Description (continued)**

TDCx\_COARSE\_CNTR\_OVF = (TDCx\_COARSE\_CNTR\_OVF\_H x 2<sup>8</sup> + TDCx\_COARSE\_CNTR\_OVF\_L), where TDCx\_TIMEn refers to the TDCx\_TIME1 to TDCx\_TIME6 registers.

Similarly, once the clock counter value has reached the corresponding value of the Clock Counter Overflow registers, then its interrupt bit will be set to 1. In other words, if TDCx\_CLOCK\_COUNTn > TDCx\_CLOCK\_CNTR\_OVF, then CLOCK\_CNTR\_OVF\_INT = 1 (this interrupt bit is located in the INT\_STATUS register).

TDCx\_CLOCK\_CNTR\_OVF = (TDCx\_CLOCK\_CNTR\_OVF\_H × 2<sup>8</sup> + TDCx\_CLOCK\_CNTR\_OVF\_L), where TDCx\_CLOCK\_COUNTn refers to the TDCx\_CLOCK\_COUNT1 to TDCx\_CLOCK\_COUNT5 registers.

As soon as there is an overflow detected, the running measurement will be terminated immediately.

#### 7.3.3.3 Clock Counter STOP Mask

The values in the Clock Counter STOP Mask registers define the end of the mask window. The Clock Counter STOP Mask value will be referred to as TDCx\_CLOCK\_CNTR\_STOP\_MASK = (TDCx\_CLOCK\_CNTR\_STOP\_MASK\_H x 28 + TDCx\_CLOCK\_CNTR\_STOP\_MASK\_L).

The Clock Counter is started by the first rising edge of the external CLOCK after the START signal (see Figure 23). All STOP signals occurring before the value set by the TDCx\_CLOCK\_CNTR\_STOP\_MASK registers will be ignored. This feature can be used to help suppress wrong or unwanted STOP trigger signals.

For example, assume the following values:

- The first time-of-flight (TOF1), which is defined as the time measurement from the START to the 1<sup>st</sup> STOP = 19 μs.

- The second time-of-flight (TOF2), which is defined as the time measurement from the START to the  $2^{nd}$  STOP = 119  $\mu$ s.

- CLOCK = 8 MHz

In this example, the TDC7201 will provide a TDCx\_CLOCK\_COUNT1 of approximately 152 (19  $\mu$ s /  $t_{CLOCK}$ ), and TDCx\_CLOCK\_COUNT2 of approximately 952 (119  $\mu$ s /  $t_{CLOCK}$ ). If the user sets TDCx\_CLOCK\_CNTR\_STOP\_MASK anywhere between 152 and 952, then the 1<sup>st</sup> STOP will be ignored and 2<sup>nd</sup> STOP will be measured.

The Clock Counter Overflow value (TDCx\_CLOCK\_CNTR\_OVF\_H  $\times$  28 + TDCx\_CLOCK\_CNTR\_OVF\_L) should always be higher than the Clock Counter STOP Mask value (TDCx\_CLOCK\_CNTR\_STOP\_MASK\_H  $\times$  28 + TDCx\_CLOCK\_CNTR\_STOP\_MASK\_L). Otherwise, the Clock Counter Overflow Interrupt will be set before the STOP mask time expires, and the measurement will be halted.

#### 7.3.3.4 ENABLE

The ENABLE pin is used as a reset to all digital circuits in the TDC7201. Therefore, it is essential that the ENABLE pin sees a positive edge after the device has powered up. It is also important to ensure that there are no transients (such as glitches) on the ENABLE pin; such glitches could cause the device to reset

#### 7.4 Device Functional Modes

#### 7.4.1 Calibration

The time measurements performed by each TDCx of the TDC7201 are based on an internal time base which is represented as the LSB value of the TDCx\_TIME1 to TDCx\_TIME6 results registers. The typical LSB value can be seen in *Electrical Characteristics*. However, the actual value of the LSB can vary depending on environmental variables (temperature, systematic noise, and so forth). This variation can introduce significant error into the measurement result. There is also an offset error in the measurement due to certain internal delays in the device.

In order to compensate for these errors and to calculate the actual LSB value, calibration needs to be performed. The TDCx calibration consists of two measurement cycles of the external CLOCK. The first is a measurement of a single clock cycle period of the external clock; the second measurement is for the number of external CLOCK periods set by the CALIBRATION2\_PERIODS in the TDCx\_CONFIG2 register. The results from the calibration measurements are stored in the TDCx\_CALIBRATION1 and TDCx\_CALIBRATION2 registers.

#### **Device Functional Modes (continued)**

The two-point calibration is used to determine the actual LSB in real time in order to convert the TDCx\_TIME1 to TDCx\_TIME6 results from number of delays to a real TOF number. Calibration is automatic and performed every time after a measurement and before measurement completion interrupt is sent to the MCU through INTBx pin. Only if a measurement is interrupted (for example, due to counter overflow or missing STOP signal), calibration is not performed. As discussed in the next sections, the calibrations will be used for calculating TOF in measurement modes 1 and 2.

#### 7.4.2 Measurement Modes

#### 7.4.2.1 Measurement Mode 1

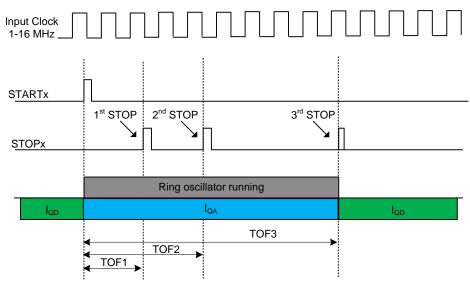

In measurement mode 1, as shown in Figure 21, each TDCx of the TDC7201 performs the entire counting from START to the last STOP using its internal ring oscillator plus coarse counter. This method is recommended for measuring shorter time durations of < 2000 ns. TI does not recommend using measurement mode 1 for measuring time > 2000 ns because this decreases accuracy of the measurement (as shown in Figure 22).

Figure 21. Measurement Mode 1

Figure 22. Measurement Mode 1 Standard Deviation vs Measured Time-of-Flight

www.ti.com JAJSC78 – MAY 2016

#### **Device Functional Modes (continued)**

#### 7.4.2.1.1 Calculating Time-of-Flight (Measurement Mode 1)

For measurement mode 1, the TOF between the START to the n<sup>th</sup> STOP can be calculated using Equation 1:

$$\begin{split} & \text{TOF}_{n} = \big(\text{TIME}_{n}\big) \big(\text{normLSB}\big) \\ & \text{normLSB} = \frac{\big(\text{CLOCKperiod}\big)}{\big(\text{calCount}\big)} \\ & \text{calCount} = \frac{\text{CALIBRATION2} - \text{CALIBRATION1}}{\big(\text{CALIBRATION2} - \text{PERIODS}\big) - 1} \end{split}$$

#### where

- TOF<sub>n</sub> [sec] = time-of-flight measurement from the START to the n<sup>th</sup> STOP

- TIME<sub>n</sub> = n<sup>th</sup> TIME measurement given by the TIME1 to TIME6 registers

- normLSB [sec] = normalized LSB value from calibration

- CLOCKperiod [sec] = external CLOCK period

- CALIBRATION1 = TDCx CALIBRATION1 register value = TDC count for first calibration cycle

- CALIBRATION2 = TDCx CALIBRATION2 register value = TDC count for second calibration cycle

- CALIBRATION2\_PERIODS = setting for the second calibration cycle; located in register TDCx\_CONFIG2 (1)

For example, assume the time-of-flight between the START to the 1<sup>st</sup> STOP is desired, and the following readouts were obtained:

- TDCx CALIBRATION2 = 21121 (decimal)

- TDCx CALIBRATION1 = 2110 (decimal)

- CALIBRATION2 PERIODS = 10

- CLOCK = 8 MHz

- TDCx TIME1 = 4175 (decimal)

Therefore, the calculation for time-of-flight is:

- calCount = (21121 2110) / (10 1) = 2112.33

- normLSB = (1/8MHz) / (2112.33) = 59.17 ps

- TOF1 =  $(4175)(5.917 \times 10^{-11}) = 247.061 \text{ ns}$

#### 7.4.2.2 Measurement Mode 2

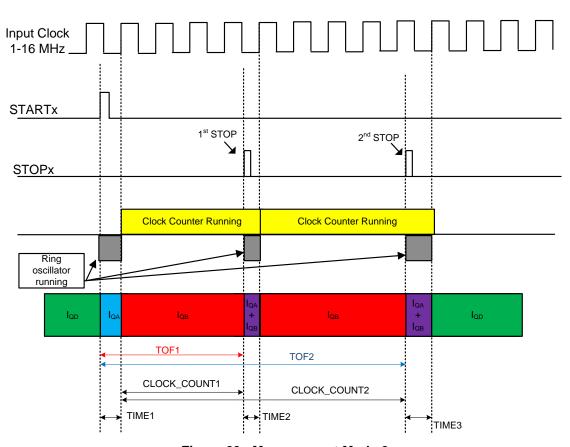

In measurement mode 2, the internal ring oscillator of each TDCx of the TDC7201 is used only to count fractional parts of the total measured time. As shown in Figure 23, the internal ring oscillator starts counting from when it receives the START signal until the first rising edge of the CLOCK. Then, the internal ring oscillator switches off, and the Clock counter starts counting the clock cycles of the external CLOCK input until a STOP pulse is received. The internal ring oscillator again starts counting from the STOP signal until the next rising edge of the CLOCK.

### **Device Functional Modes (continued)**

Figure 23. Measurement Mode 2

JAJSC78-MAY 2016

#### **Device Functional Modes (continued)**

#### 7.4.2.2.1 Calculating Time-of-Flight (TOF) (Measurement Mode 2)

The TOF between the START to the nth STOP can be calculated using Equation 2:

$$\begin{split} & \text{TOF}_{n} = \text{normLSB}\big(\text{TIME1-TIME}_{n+1}\big) + \big(\text{CLOCK\_COUNT}_{n}\big)\big(\text{CLOCKperiod}\big) \\ & \text{normLSB} = \frac{\big(\text{CLOCKperiod}\big)}{\big(\text{calCount}\big)} \\ & \text{calCount} = \frac{\text{CALIBRATION2-CALIBRATION1}}{\big(\text{CALIBRATION2\_PERIODS}\big) - 1} \end{split}$$

#### where

- TOF<sub>n</sub> [sec] = time-of-flight measurement from the START to the n<sup>th</sup> STOP

- TIME1 = TDCx\_TIME1 register value = time 1 measurement given by the TDC7201 register address 0x10

- $TIME_{(n+1)} = TDCx\_TIME_{(n+1)}$  register value = (n+1) time measurement, where n = 1 to 5 (TDCx\\_TIME2 to TDCx\_TIME6 registers)

- normLSB [sec] = normalized LSB value from calibration

- CLOCK COUNT<sub>n</sub> = nth clock count, where n = 1 to 5 (TDCx CLOCK COUNT1 to TDCx CLOCK COUNT5)

- CLOCKperiod [sec] = external CLOCK period

- CALIBRATION1 = TDCx\_CALIBRATION1 register value = TDC count for first calibration cycle

- CALIBRATION2 = TDCx\_CALIBRATION2 register value = TDC count for second calibration cycle

- CALIBRATION2 PERIODS = setting for the second calibration; located in register TDCx CONFIG2 (2)

For example, assume the time-of-flight between the START to the 1<sup>st</sup> STOP is desired, and the following readouts were obtained:

- CALIBRATION2 = 23133 (decimal)

- CALIBRATION1 = 2315 (decimal)

- CALIBRATION2 PERIODS = 10

- CLOCK = 8 MHz

- TIME1 = 2147 (decimal)

- TIME2 = 201 (decimal)

- CLOCK\_COUNT1 = 318 (decimal)

Therefore, the calculation for time-of-flight is:

$$calCount = \frac{CALIBRATION2 - CALIBRATION1}{(CALIBRATION2\_PERIODS) - 1} = \frac{(23133 - 2315)}{(10 - 1)} = 2313.11$$

$$normLSB = \frac{(CLOCKperiod)}{(calCount)} = \frac{(1/8MHz)}{2313.11} = 54 \text{ ps}$$

$$TOF1 = (TIME1)(normLSB) + (CLOCK\_COUNT1)(CLOCKperiod) - (TIME2)(normLSB)$$

$$TOF1 = (2147) \left(5.40*10^{-11}\right) + (318)(1/8MHz) - (201)(5.40*10^{-11})$$

$$TOF1 = 39.855 \mu s$$

(3)

#### **Device Functional Modes (continued)**

#### 7.4.3 Timeout

For one STOP, each TDCx of the TDC7201 performs the measurement by counting from the START signal to the STOP signal. If no STOP signal is received, either the Clock Counter or Coarse Counter will overflow and will generate an interrupt (see *Coarse and Clock Counters Overflow*). If no START signal is received, the timer waits indefinitely for a START signal to arrive.

For multiple STOPs, each TDCx performs the measurement by counting from the START signal to the last STOP signal. All earlier STOP signals are captured and stored into the corresponding Measurement Results registers (TDCx\_TIME1 to TDCx\_TIME6, TDCx\_CLOCK\_COUNT1 to TDCx\_CLOCK\_COUNT5, TDCx\_CALIBRATION1, TDCx\_CALIBRATION2). The minimum time required between two consecutive STOP signals is defined in the *Recommended Operating Conditions* table. The device can be programmed to measure up to 5 STOP signals by setting the NUM STOP bits in the TDCx\_CONFIG2 register.

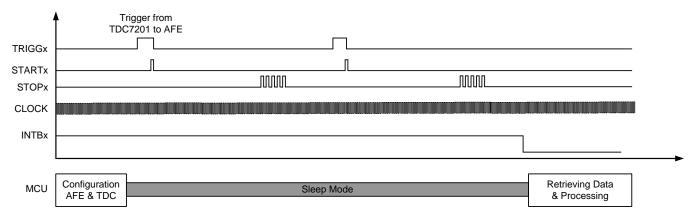

#### 7.4.4 Multi-Cycle Averaging

In the Multi-Cycle Averaging Mode, the TDC7201 will perform a series of measurements on its own and will only send an interrupt to the MCU (for example, MSP430, C2000, and so forth) for wake up after the series has been completed. While waiting, the MCU can remain in sleep mode during the whole cycle (as shown in Figure 24).

Multi-Cycle Averaging Mode Setup and Conditions:

- The number of averaging cycles should be selected (1 to 128). This is done by programming the AVG CYCLES bit in the TDCx CONFIG2 register.

- The results of all measurements are reported in the Measurement Results registers (TDCx\_TIME1 to TDCx\_TIME6, TDCx\_CLOCK\_COUNT1 to TDCx\_CLOCK\_COUNT5, TDCx\_CALIBRATION1, TDCx\_CALIBRATION2 registers). The CLOCK\_COUNTn registers should be right shifted by the log2(AVG\_CYCLES) before calculating the TOF. For example, if using the multi-cycle averaging mode, Equation 2 should be rewritten as: TOFn = normLSB [TDCx\_TIME1 TDCx\_TIME(n+1)] + [TDCx\_CLOCK\_COUNTn >> log 2 (AVG\_CYCLES)] x [CLOCKperiod]

- Following each average cycle, the TDCx generates either a trigger event on the TRIGGx pin after the

calibration measurement to commence a new measurement or an interrupt on the INTBx pin, indicating that

the averaging sequence has completed.

This mode allows multiple measurements without MCU interaction, thus optimizing power consumption for the overall system.

Figure 24. Multi-Cycle Averaging Mode Example with 2 Averaging Cycles and 5 STOP Signals

#### 7.4.5 START and STOP Edge Polarity

In order to achieve the highest measurement accuracy, having the same edge polarity for the START and STOP input signals is highly recommended. Otherwise, slightly different propagation delays due to symmetry shift between the rising and falling edge configuration will impact the measurement accuracy.

JAJSC78-MAY 2016

#### **Device Functional Modes (continued)**

For highest measurement accuracy in measurement mode 2, TI recommends to choose for the START and STOP signal the rising edge. This is done by setting the START\_EDGE and STOP\_EDGE bits in the TDCx\_CONFIG1 register to 0.

#### 7.4.6 Measurement Sequence

The TDC7201 has two built-in TDCs with the capability to simultaneously and individually measure time delay on two pairs of START and STOP pins. Each TDCx is a stopwatch that measures time between a single event (edge on STARTx pin) and multiple subsequent events (edge on STOPx pin). The measurement sequence for each TDCx is as follows:

1. After powering up the device, the ENABLE pin needs to be low. There is one low to high transition required while VDD is supplied for correct initialization of the device.

#### NOTE

Pins VDD1 and VDD2 must be tied together at the board level and supplied from the same source.

- 2. MCU software requests new TDCx measurements to be initiated through the SPI™ interface.

- 3. After the start new measurement bit START\_MEAS has been set in the TDCx\_CONFIG1 register, the TDCx generates a trigger signal on the TRIGGx pin, which is typically used by the corresponding ultrasonic analogfront-end (such as the TDC1000) as start trigger for a measurement (for example, transmit signal for the

- 4. Immediately after sending the trigger, the TDCx enables the STARTx pin and waits to receive the START pulse edge.

- 5. After receiving a START, the TDCx resets the TRIGGx pin.

- 6. The Clock counter is started after the next rising edge of the external clock signal (Measurement Mode 2). **STOP** (TDCx CLOCK CNTR STOP MASK H Clock Counter Mask registers TDCx\_CLOCK\_CNTR\_STOP\_MASK\_L) determine the length of the STOP mask window.

- 7. After reaching the Clock Counter STOP Mask value, the STOPx pin waits to receive a single or multiple STOP trigger signal from the analog-front-end (for example, detected echo signal of the ultrasonic burst signal).

- 8. After the last STOP trigger has been received, the TDCx will signal to the MCU through interrupt (INTBx pin) that there are new measurement results waiting in the registers. STARTx, STOPx and TRIGGx pins are disabled (in Multi-Cycle Averaging Mode, the TDCx will start the next cycle automatically by generating a new TRIGG signal). INTBx goes back to high whenever a new measurement is initiated through SPI or when the TDCx INT STATUS register bit NEW MEAS INT is cleared by writing a 1 to it.

#### NOTE

INTBx must be utilized to determine TDCx measurement completion; polling the register to determine TDCx INT STATUS measurement completion recommended as it will interfere with the TDCx measurement.

- 9. After the results are retrieved, the MCU can then start a new measurement with the same register settings. This is done by just setting the START MEAS bit through SPI. It is not required to drive the ENABLE pin low between measurements.

- 10. The ENABLE pin can be taken low, if the time duration between measurements is long, and it is desired to put the TDC7201 in its lowest power state. However, upon taking ENABLE high again, the device will come up with its default register settings and will need to be configured through SPI.

The two TDCs of TDC7201 can be used independently to measure TOF. When used independently, the TDCx operation is as explained in the measurement sequence steps above. In this case, each TDCx has dedicated START, STOP inputs and measures their STARTx to STOPx time individually when the START MEAS bit in the TDCx CONFIG1 register is set. The MCU has to set up, control, and read the results from the two TDCs individually through the master SPI interface. To set up the registers and read back measurement results of TDCx, MCU needs to perform SPI read and write transactions with corresponding CSBx asserted.

# TEXAS INSTRUMENTS

#### **Device Functional Modes (continued)**

#### **NOTE**

START1, STOP1 and START2, STOP2 inputs can be separate from different sources or can be identical with START1 connected to START2 and STOP1 connected to STOP2. In the latter case, when the TDCx inputs are connected together and the TDCx register setup is identical, then both the TDCs measure the same input in parallel and this can be used to achieve finer resolution. By measuring the same time with both TDCs and taking the average, the LSB resolution is halved.

#### 7.4.7 Wait Times for TDC7201 Startup

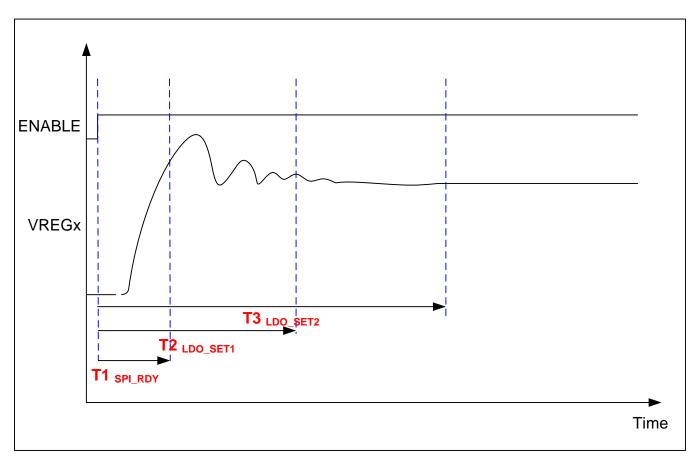

The required wait time following the rising edge of the ENABLE pin of the TDC7201 is defined by three key times, as shown in Figure 25. All three times relate to the startup of the TDCx's internal dedicated LDO, which is power gated when the device is disabled for optimal power consumption. The first parameter, T1<sub>SPI\_RDY</sub>, is the time after which the SPI interface is accessible. The second (T2<sub>LDO\_SET1</sub>) parameter and third (T3<sub>LDO\_SET2</sub>) parameter are related to the performance of a measurement made while the internal LDO is settling. The LDO supplies the TDC7201's time measurement device, and a change in voltage on its supply during a measurement translates directly to an inaccuracy. It is therefore recommended to wait until the LDO is settled before time measurement begins.

The first time period relating to the measurement accuracy is  $T2_{LDO\_SET1}$ , the LDO settling time 1. This is the time after which the LDO has settled to within 0.3% of its final value. A 0.3% error translates to a worst case time error (due to the LDO settling) of 0.3% ×  $t_{CLOCK}$ , which is 375 ps in the case of an 8-MHz reference clock, or 187.5 ps if a 16-MHz clock is used. Finally, the time  $T3_{LDO\_SET2}$  is the time after which the LDO has settled to its final value. For best performance, TI recommends that a time measurement is not started before  $T3_{LDO\_SET2}$  to allow the LDO to fully settle. Typical times for these parameters are:  $T1_{SPI\_RDY}$  is 100  $\mu$ s, for  $T2_{LDO\_SET1}$  is 300  $\mu$ s, and for  $T3_{LDO\_SET2}$  is 1.5 ms.

#### **Device Functional Modes (continued)**

Figure 25. VREGx Startup Time

#### 7.5 Programming

#### 7.5.1 Serial Peripheral Interface (SPI)

The serial interface consists of data input (DIN), data output (DOUTx), serial interface clock (SCLK), and chip select bar (CSBx). The serial interface is used to configure the TDC7201 parameters available in various configuration registers.

The two TDCs of TDC7201 share the serial interface DIN and SCLK pins but support dedicated CSB and DOUT pins. Registers of the TDCx are selected for read/write access when their corresponding dedicated CSBx pin is asserted. By connecting together DOUT1 and DOUT2, a single SPI master interface of the MCU can be used to access both the TDC register sets by asserting the corresponding CSBx. Alternatively, by keeping DOUT1 and DOUT2 separate, data can be read out of the TDCs in parallel using their dedicated DOUTx pins. This doubles the data readout throughput but requires a second dedicated SPI interface of the MCU.

The communication on the SPI bus supports write and read transactions. A write transaction consists of a single write command byte, followed by single data byte. A read transaction consists of a single read command byte followed by 8 or 24 SCLK cycles. The write and read command bytes consist of a 1-bit auto-increment bit, a 1-bit read or write instruction, and a 6-bit register address. Figure 26 shows the SPI protocol for a transaction involving one byte of data (read or write).

JAJSC78 – MAY 2016 www.ti.com

# TEXAS INSTRUMENTS

#### **Programming (continued)**

Figure 26. SPI Protocol

#### 7.5.1.1 CSBx

CSBx is an active-low signal and needs to be low throughout a transaction. That is, CSBx should not pulse between the command byte and the data byte of a single transaction.

De-asserting CSBx always terminates an ongoing transaction, even if it is not yet complete. Re-asserting CSBx will always bring the device into a state ready for the next transaction, regardless of the termination status of a previous transaction.

Registers of the TDCx are selected for read/write access when their corresponding dedicated CSBx pin is asserted.

#### 7.5.1.2 SCLK

SPI clock can idle high or low. TI recommends to keep SCLK as clean as possible to prevent glitches from corrupting the SPI frame.

#### 7.5.1.3 DIN

Data In (DIN) is driven by the SPI master by sending the command and the data byte to configure the TDC7201.

#### 7.5.1.4 DOUTX

Data Out (DOUTx) is driven by the TDC7201 when the SPI master initiates a read transaction with CSBx asserted. When the TDC7201 is not being read out, the DOUT pin is in high impedance mode and is undriven.

Registers of the TDCx are selected for read/write access when their corresponding dedicated CSBx pin is asserted. By connecting together DOUT1 and DOUT2, a single SPI master interface of the MCU can be used to access both the TDC register sets by asserting the corresponding CSBx. Alternatively, by keeping DOUT1 and DOUT2 separate, data can be read out of the TDCs in parallel using their dedicated DOUTx pins. This doubles the data readout throughput but requires a second dedicated SPI interface of the MCU.

#### 7.5.1.5 Register Read/Write

Access to the TDCx internal registers can be done through the serial interface formed by pins CSBx (Chip Select - active low), SCLK (serial interface clock), DIN (data input), and DOUTx (data out).

www.ti.com

### Programming (continued)

Serial shift of bits into the TDCx is enabled when CSBx is low. Serial data DIN is latched (MSB received first, LSB received last) at every rising edge of SCLK when CSBx is active (low). The serial data is loaded into the register with the last data bit SCLK rising edge when CSBx is low. In the case that the word length exceeds the register size, the excess bits are ignored. The interface can work with SCLK frequency from 25 MHz down to very low speeds (a few Hertz) and even with a non-50% duty-cycle SCLK.

The SPI transaction is divided in two main portions:

- Address and Control as shown in Table 1: Auto Increment Mode selection bit, Read/Write bit, Address 6 bits

- Data: 8 bit or 24 bit

When writing to a register with unused bits, these should be set to 0.

Table 1. Address and Control Byte of SPI transaction

|                   | Address and Control (A7 - A0) |    |                |     |               |    |    |  |

|-------------------|-------------------------------|----|----------------|-----|---------------|----|----|--|

| A7                | A6                            | A5 | A4             | А3  | A2            | A1 | A0 |  |

| Auto<br>Increment | RW                            |    |                | Reg | ister Address |    |    |  |

| 0: OFF<br>1: ON   | Read = 0<br>Write = 1         |    | 00 h up to 3Fh |     |               |    |    |  |

#### 7.5.1.6 Auto Increment Mode

When the Auto Increment Mode is OFF, only the register indicated by the Register Address will be accessed, all cycles beyond the register length will be ignored. When the Auto Increment is ON, the register of the Register Address is accessed first, then without interruption, subsequent registers are accessed.

The Auto Increment Mode can be either used to access the configuration (TDCx\_CONFIG1 and TDCx\_CONFIG2) and status (TDCx\_INT\_STATUS) registers, or for the Measurement Results registers (TDCx\_TIME1 to TDCx\_TIME6, TDCx\_CLOCK\_COUNT1 to TDCx\_CLOCK\_COUNT5, TDCx\_CALIBRATION1, TDCx\_CALIBRATION2). As both register block use registers with different length, it is not possible to access all registers of the device within one single access cycle.

# TEXAS INSTRUMENTS

#### 7.6 Register Maps

#### 7.6.1 Register Initialization

After power up (VDD supplied, ENABLE Pin low to high transition) the internal registers are initialized with the default value. Disabling the part by pulling ENABLE pin to GND will set the device into total shutdown. As the internal LDO is turned off settings in the register will be lost. The device initializes the registers with default values with the next enable (ENABLE pin to VDD).

Table 2. TDCx\_ Register Summary(1)

| REGISTER ADDRESS | REGISTER NAME               | REGISTER DESCRIPTION                    | SIZE (BITS) | RESET<br>VALUE |

|------------------|-----------------------------|-----------------------------------------|-------------|----------------|

| 00h              | TDCx_CONFIG1                | Configuration Register 1                | 8           | 00h            |

| 01h              | TDCx_CONFIG2                | Configuration Register 2                | 8           | 40h            |

| 02h              | TDCx_INT_STATUS             | Interrupt Status Register               | 8           | 00h            |

| 03h              | TDCx_INT_MASK               | Interrupt Mask Register                 | 8           | 07h            |

| 04h              | TDCx_COARSE_CNTR_OVF_H      | Coarse Counter Overflow Value High      | 8           | FFh            |

| 05h              | TDCx_COARSE_CNTR_OVF_L      | Coarse Counter Overflow Value Low       | 8           | FFh            |

| 06h              | TDCx_CLOCK_CNTR_OVF_H       | CLOCK Counter Overflow Value High       | 8           | FFh            |

| 07h              | TDCx_CLOCK_CNTR_OVF_L       | CLOCK Counter Overflow Value Low        | 8           | FFh            |

| 08h              | TDCx_CLOCK_CNTR_STOP_MASK_H | CLOCK Counter STOP Mask High            | 8           | 00h            |

| 09h              | TDCx_CLOCK_CNTR_STOP_MASK_L | CLOCK Counter STOP Mask Low             | 8           | 00h            |

| 10h              | TDCx_TIME1                  | Measured Time 1                         | 24          | 00_000h        |

| 11h              | TDCx_CLOCK_COUNT1           | CLOCK Counter Value                     | 24          | 00_000h        |

| 12h              | TDCx_TIME2                  | Measured Time 2                         | 24          | 00_000h        |

| 13h              | TDCx_CLOCK_COUNT2           | CLOCK Counter Value                     | 24          | 00_000h        |

| 14h              | TDCx_TIME3                  | Measured Time 3                         | 24          | 00_000h        |

| 15h              | TDCx_CLOCK_COUNT3           | CLOCK Counter Value                     | 24          | 00_000h        |

| 16h              | TDCx_TIME4                  | Measured Time 4                         | 24          | 00_000h        |

| 17h              | TDCx_CLOCK_COUNT4           | CLOCK Counter Value                     | 24          | 00_0000h       |

| 18h              | TDCx_TIME5                  | Measured Time 5                         | 24          | 00_0000h       |

| 19h              | TDCx_CLOCK_COUNT5           | CLOCK Counter Value                     | 24          | 00_000h        |

| 1Ah              | TDCx_TIME6                  | Measured Time 6                         | 24          | 00_000h        |

| 1Bh              | TDCx_CALIBRATION1           | Calibration 1, 1 CLOCK Period           | 24          | 00_000h        |

| 1Ch              | TDCx_CALIBRATION2           | Calibration 2, 2/10/20/40 CLOCK Periods | 24          | 00_000h        |

<sup>(1)</sup> Registers of the TDCx are selected for read/write access when their corresponding dedicated CSBx pin is asserted.

www.ti.com

# 7.6.2 TDCx\_CONFIG1: TDCx Configuration Register 1 R/W (address = 00h, CSBx asserted) [reset = 0h] Figure 27. TDCx\_CONFIG1 Register

| 7         | 6         | 5          | 4         | 3          | 2     | 1     | 0          |

|-----------|-----------|------------|-----------|------------|-------|-------|------------|

| FORCE_CAL | PARITY_EN | TRIGG_EDGE | STOP_EDGE | START_EDGE | MEAS_ | MODE  | START_MEAS |

| R/W-0     | R/W-0     | R/W-0      | R/W-0     | R/W-0      | R/W-0 | R/W-0 | R/W-0      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 3. TDCx\_CONFIG1 Register Field Descriptions

| Bit   | Field             | Туре          | Reset | Description                                                                                                                                                                                                                                                                                                                        |

|-------|-------------------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | FORCE_CAL         | R/W           | 0     | Calibration is automatic and performed every time after a measurement.     Only if a measurement is interrupted (for example, due to counter overflow or missing STOP signal), calibration is not performed.                                                                                                                       |

|       |                   |               |       | 1: Calibration is always performed at the end (for example, after a counter overflow) even if a measurement is interrupted.                                                                                                                                                                                                        |

| 6     | 6 PARITY_EN R/W 0 |               | 0     | 0: Parity bit for Measurement Result Registers* disabled (Parity Bit always 0)                                                                                                                                                                                                                                                     |

|       |                   |               |       | 1: Parity bit for Measurement Result Registers enabled (Even Parity)                                                                                                                                                                                                                                                               |

|       |                   |               |       | *The Measurement Results registers are the TDCx_TIME1 to TDCx_TIME6, TDCx_CLOCK_COUNT1 to TDCx_CLOCK_COUNT5, TDCx_CALIBRATION1, TDCx_CALIBRATION2 registers.                                                                                                                                                                       |

| 5     | TRIGG_EDGE        | RIGG_EDGE R/W |       | 0: TRIGG is output as a Rising edge signal                                                                                                                                                                                                                                                                                         |

|       |                   |               |       | 1: TRIGG is output as a Falling edge signal                                                                                                                                                                                                                                                                                        |

| 4     | STOP_EDGE         | R/W           | 0     | 0: Measurement is stopped on Rising edge of STOP signal                                                                                                                                                                                                                                                                            |

|       |                   |               |       | 1: Measurement is stopped on Falling edge of STOP signal                                                                                                                                                                                                                                                                           |

| 3     | START_EDGE        | R/W           | 0     | 0: Measurement is started on Rising edge of START signal                                                                                                                                                                                                                                                                           |

|       |                   |               |       | 1: Measurement is started on Falling edge of START signal                                                                                                                                                                                                                                                                          |

| [2:1] | MEAS_MODE         | R/W           | b00   | 00: Measurement Mode 1 (for expected time-of-flight < 2000 ns).                                                                                                                                                                                                                                                                    |

|       |                   |               |       | 01: Measurement Mode 2 (recommended)                                                                                                                                                                                                                                                                                               |

|       |                   |               |       | 10, 11: Reserved for future functionality                                                                                                                                                                                                                                                                                          |

| 0     | START_MEAS        | R/W           | 0     | Start New Measurement:                                                                                                                                                                                                                                                                                                             |

|       |                   |               |       | This bit is cleared when Measurement is Completed.                                                                                                                                                                                                                                                                                 |

|       |                   |               |       | 0: No effect                                                                                                                                                                                                                                                                                                                       |

|       |                   |               |       | 1: Start New Measurement. Writing a 1 will clear all bits in the Interrupt Status Register and Start the measurement (by generating a TRIGG signal) and will reset the content of all Measurement Results registers (TDCx_TIME1 to TDCx_TIME6, TDCx_CLOCK_COUNT1 to TDCx_CLOCK_COUNT5, TDCx_CALIBRATION1, TDCx_CALIBRATION2) to 0. |

# 7.6.3 TDCx\_CONFIG2: TDCx Configuration Register 2 R/W (address = 01h, CSBx asserted) [reset = 40h] Figure 28. TDCx\_CONFIG2 Register

| 7          | 6          | 5     | 4          | 3     | 2     | 1        | 0     |

|------------|------------|-------|------------|-------|-------|----------|-------|

| CALIBRATIO | N2_PERIODS |       | AVG_CYCLES |       |       | NUM_STOP |       |

| R/W-0      | R/W-1      | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0    | R/W-0 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 4. TDCx\_CONFIG2 Register Field Descriptions

| Bit   | Field                | Туре | Reset | Description                                                                                                                                                                                                                                              |

|-------|----------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | CALIBRATION2_PERIODS | R/W  | b01   | 00: Calibration 2 - measuring 2 CLOCK periods 01: Calibration 2 - measuring 10 CLOCK periods 10: Calibration 2 - measuring 20 CLOCK periods 11: Calibration 2 - measuring 40 CLOCK periods                                                               |

| [5:3] | AVG_CYCLES           | R/W  | b000  | 000: 1 Measurement Cycle only (no Multi-Cycle Averaging Mode) 001: 2 Measurement Cycles 010: 4 Measurement Cycles 011: 8 Measurement Cycles 100: 16 Measurement Cycles 101: 32 Measurement Cycles 110: 64 Measurement Cycles 111: 128 Measurement Cycles |

| [2:0] | NUM_STOP             | R/W  | b000  | 000: Single Stop 001: Two Stops 010: Three Stops 011: Four Stops 100: Five Stops 101, 110, 111: No Effect. Single Stop                                                                                                                                   |

www.ti.com

# 7.6.4 TDCx\_INT\_STATUS: Interrupt Status Register (address = 02h, CSBx asserted) [reset = 00h] Figure 29. TDCx\_INT\_STATUS Register

# 4 3 2 1

| 7     | 7 6 5 4  |       | 5 4 3 2                    |                       | 2                          | 1                       | 0                |  |

|-------|----------|-------|----------------------------|-----------------------|----------------------------|-------------------------|------------------|--|

|       | Reserved |       | MEAS_<br>COMPLETE_<br>FLAG | MEAS_STARTED_<br>FLAG | CLOCK_<br>CNTR_<br>OVF_INT | COARSE_CNTR_<br>OVF_INT | NEW_MEAS_<br>INT |  |

| R/W-0 | R/W-0    | R/W-0 | R/W-0                      | R/W-0                 | R/W-0                      | R/W-0                   | R/W-0            |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 5. TDCx\_INT\_STATUS Register Field Descriptions

| Bit   | Field               | Туре | Reset | Description                                                                                                                                         |

|-------|---------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 - 5 | Reserved            | R/W  | b000  |                                                                                                                                                     |

| 4     | MEAS_COMPLETE_FLAG  | R/W  | 0     | Writing a 1 will clear the status 0: Measurement has not completed 1: Measurement has completed (same information as NEW_MEAS_INT)                  |

| 3     | MEAS_STARTED_FLAG   | R/W  | 0     | Writing a 1 will clear the status 0: Measurement has not started 1: Measurement has started (START signal received)                                 |

| 2     | CLOCK_CNTR_OVF_INT  | R/W  | 0     | Requires writing a 1 to clear interrupt status 0: No overflow detected 1: Clock overflow detected, running measurement will be stopped immediately  |

| 1     | COARSE_CNTR_OVF_INT | R/W  | 0     | Requires writing a 1 to clear interrupt status 0: No overflow detected 1: Coarse overflow detected, running measurement will be stopped immediately |

| 0     | NEW_MEAS_INT        | R/W  | 0     | Requires writing a 1 to clear interrupt status 0: Interrupt not detected 1: Interrupt detected – New Measurement has been completed                 |

# 7.6.5 TDCx\_INT\_MASK: TDCx Interrupt Mask Register R/W (address = 03h, CSBx asserted) [reset = 07h] Figure 30. TDCx\_INT\_MASK Register

| 7     | 6     | 5        | 4     | 3     | 2                       | 1                        | 0                 |

|-------|-------|----------|-------|-------|-------------------------|--------------------------|-------------------|

|       |       | Reserved |       |       | CLOCK_CNTR<br>_OVF_MASK | COARSE_CNTR<br>_OVF_MASK | NEW_MEAS<br>_MASK |

| R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-1h                  | R/W-1h                   | R/W-1h            |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 6. TDCx\_INT\_MASK Register Field Descriptions

| Bit   | Field                | Туре | Reset   | Description                                                                              |

|-------|----------------------|------|---------|------------------------------------------------------------------------------------------|

| 7 - 3 | Reserved             | R/W  | p0,0000 |                                                                                          |

| 2     | CLOCK_CNTR_OVF_MASK  | R/W  | 1       | CLOCK Counter Overflow Interrupt disabled     CLOCK Counter Overflow Interrupt enabled   |

| 1     | COARSE_CNTR_OVF_MASK | R/W  | 1       | Coarse Counter Overflow Interrupt disabled     Coarse Counter Overflow Interrupt enabled |

| 0     | NEW_MEAS_MASK        | R/W  | 1       | New Measurement Interrupt disabled     New Measurement Interrupt enabled                 |

A disabled interrupt will no longer be visible on the device pin (INTB). The interrupt bit in the TDCx\_INT\_STATUS register will still be active.

## 7.6.6 TDCx\_COARSE\_CNTR\_OVF\_H: Coarse Counter Overflow High Value Register (address = 04h, CSBx asserted) [reset = FFh]

Figure 31. TDCx\_COARSE\_CNTR\_OVF\_H Register

| 7                 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------------|-------|-------|-------|-------|-------|-------|-------|

| COARSE_CNTR_OVF_H |       |       |       |       |       |       |       |

| R/W-1             | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 7. TDCx\_COARSE\_CNTR\_OVF\_H Register Field Descriptions

| Bit | Field             | Туре | Reset | Description                                |

|-----|-------------------|------|-------|--------------------------------------------|

| 7-0 | COARSE_CNTR_OVF_H | R/W  | FFh   | Coarse Counter Overflow Value, upper 8 Bit |

www.ti.com JAJSC78 – MAY 2016

## 7.6.7 TDCx\_COARSE\_CNTR\_OVF\_L: TDCx Coarse Counter Overflow Low Value Register (address = 05h, CSBx asserted) [reset = FFh ]

#### Figure 32. TDCx\_COARSE\_CNTR\_OVF\_L Register

| 7     | 6     | 5     | 4        | 3         | 2     | 1     | 0     |

|-------|-------|-------|----------|-----------|-------|-------|-------|

|       |       |       | COARSE_C | NTR_OVF_L |       |       |       |

| R/W-1 | R/W-1 | R/W-1 | R/W-1    | R/W-1     | R/W-1 | R/W-1 | R/W-1 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 8. TDCx\_COARSE\_CNTR\_OVF\_L Register Field Descriptions

| Bit | Field             | Туре | Reset | Description                                |

|-----|-------------------|------|-------|--------------------------------------------|

| 7-0 | COARSE_CNTR_OVF_L | R/W  | FFh   | Coarse Counter Overflow Value, lower 8 Bit |

|     |                   |      |       | Note: Do not set COARSE_CNTR_OVF_L to 1.   |

## 7.6.8 TDCx\_CLOCK\_CNTR\_OVF\_H: Clock Counter Overflow High Register (address = 06h, CSBx asserted) [reset = FFh]

#### Figure 33. TDCx\_CLOCK\_CNTR\_OVF\_H Register

| 7     | 6     | 5     | 4        | 3         | 2     | 1     | 0     |

|-------|-------|-------|----------|-----------|-------|-------|-------|

|       |       |       | CLOCK_CN | ITR_OVF_H |       |       |       |

| R/W-1 | R/W-1 | R/W-1 | R/W-1    | R/W-1     | R/W-1 | R/W-1 | R/W-1 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 9. TDCx\_CLOCK\_CNTR\_OVF\_H Register Field Descriptions

| Bit | Field            | Туре | Reset | Description                               |

|-----|------------------|------|-------|-------------------------------------------|

| 7-0 | CLOCK_CNTR_OVF_H | R/W  | FFh   | CLOCK Counter Overflow Value, upper 8 Bit |

## 7.6.9 TDCx\_CLOCK\_CNTR\_OVF\_L: Clock Counter Overflow Low Register (address = 07h, CSBx asserted) [reset = FFh]

#### Figure 34. TDCx\_CLOCK\_CNTR\_OVF\_L Register

| 7     | 6     | 5     | 4        | 3         | 2     | 1     | 0     |

|-------|-------|-------|----------|-----------|-------|-------|-------|

|       |       |       | CLOCK_CN | NTR_OVF_L |       |       |       |

| R/W-1 | R/W-1 | R/W-1 | R/W-1    | R/W-1     | R/W-1 | R/W-1 | R/W-1 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 10. TDCx\_CLOCK\_CNTR\_OVF\_L Register Field Descriptions

| Bit | Field            | Туре | Reset | Description                               |

|-----|------------------|------|-------|-------------------------------------------|

| 7-0 | CLOCK_CNTR_OVF_L | R/W  | FFh   | CLOCK Counter Overflow Value, lower 8 Bit |

JAJSC78 – MAY 2016 www.ti.com

# TEXAS INSTRUMENTS

### 7.6.10 TDCx\_CLOCK\_CNTR\_STOP\_MASK\_H: CLOCK Counter STOP Mask High Value Register (address = 08h, CSBx asserted) [reset = 00h]

#### Figure 35. TDCx\_CLOCK\_CNTR\_STOP\_MASK\_H Register

| 7     | 6     | 5     | 4           | 3           | 2     | 1     | 0     |

|-------|-------|-------|-------------|-------------|-------|-------|-------|

|       |       |       | CLOCK_CNTR_ | STOP_MASK_H |       |       |       |

| R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 11. TDCx CLOCK CNTR STOP MASK H Register Field Descriptions

| Bit | Field                  | Туре | Reset | Description                          |

|-----|------------------------|------|-------|--------------------------------------|

| 7-0 | CLOCK_CNTR_STOP_MASK_H | R/W  | 00h   | CLOCK Counter STOP Mask, upper 8 Bit |

### 7.6.11 TDCx\_CLOCK\_CNTR\_STOP\_MASK\_L: CLOCK Counter STOP Mask Low Value Register (address = 09h, CSBx asserted) [reset = 00h]

#### Figure 36. TDCx\_CLOCK\_CNTR\_STOP\_MASK\_L Register

| 7     | 6     | 5     | 4           | 3           | 2     | 1     | 0     |

|-------|-------|-------|-------------|-------------|-------|-------|-------|

|       |       |       | CLOCK_CNTR_ | STOP_MASK_L |       |       |       |

| R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 12. TDCx CLOCK CNTR STOP MASK L Register Field Descriptions

| Bit | Field                  | Туре | Reset | Description                          |

|-----|------------------------|------|-------|--------------------------------------|

| 7-0 | CLOCK_CNTR_STOP_MASK_L | R/W  | 00h   | CLOCK Counter STOP Mask, lower 8 Bit |

#### 7.6.12 TDCx\_TIME1: Time 1 Register (address: 10h, CSBx asserted) [reset = 00\_0000h]

#### Figure 37. TDCx\_TIME1 Register

| 23         | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15    | 14     | 13      | 12     | 11      | 10      | 9   | 8       | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-------|--------|---------|--------|---------|---------|-----|---------|-------|-----|-----|-----|-----|-----|-----|-----|

| Parity Bit |     |     |     |     |     |     | 7   | ГІМЕ1 | : 23 b | it inte | ger va | alue (l | 3it 22: | MSB | , Bit 0 | : LSB | )   |     |     |     |     |     |     |