# TCAN245x-Q1 車載用、降圧レギュレータおよびウォッチドッグ内蔵、信号改善対応 CAN FD システムベースチップ (SBC)

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- CAN-FD および CAN-FD 信号改善機能 (SIC) に関する ISO 11898-2:2024 の要件に適合

- 機能安全品質管理**

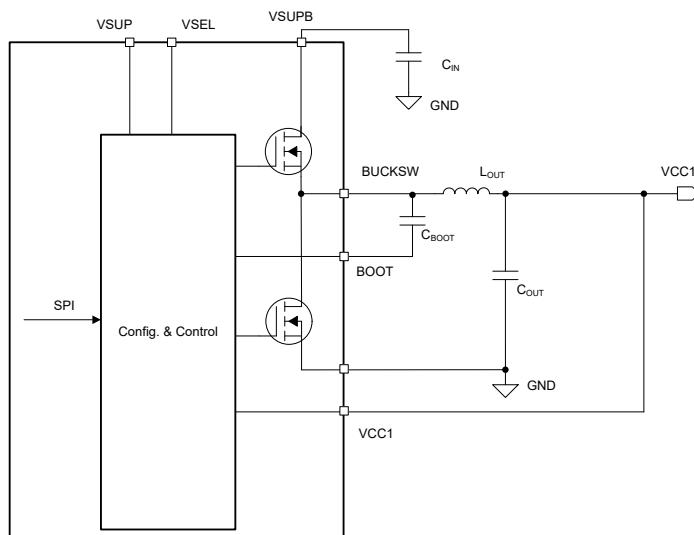

- 1A を出力可能な 3.3V または 5V 降圧レギュレータ (VCC1) を内蔵

- VSEL ピン接続に基づいて出力 (3.3V または 5V) をピンで選択可能

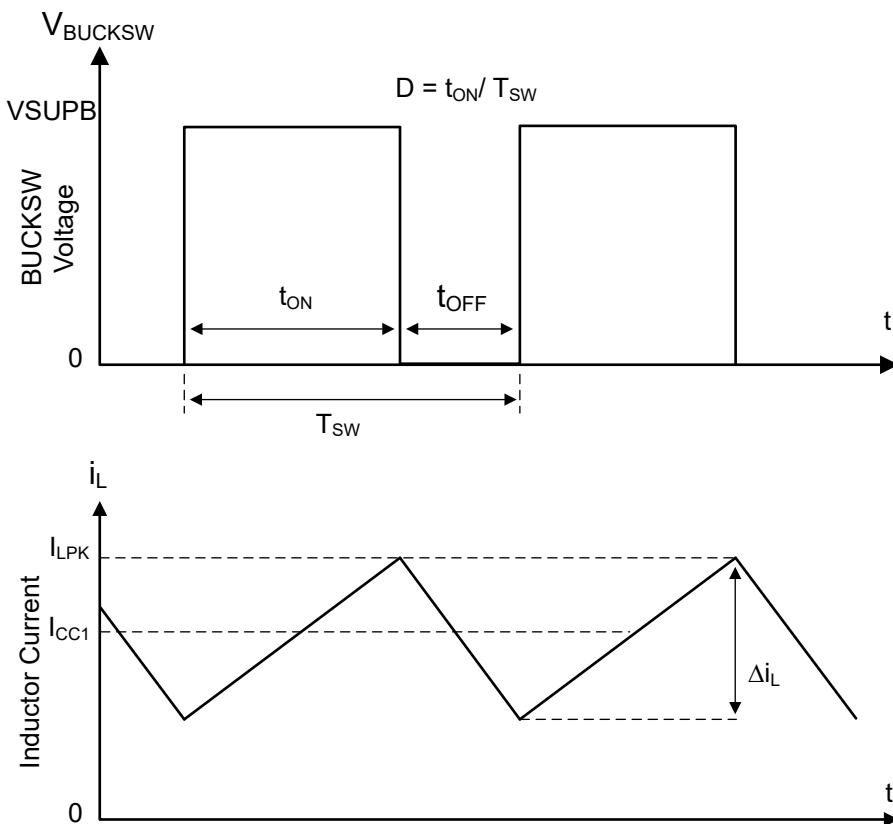

- 1.8MHz ~ 2.4MHz のスイッチング周波数オプションにより、オンボード インダクタの小型化が可能

- EMC 性能を向上させるスペクトラム拡散変調機能を内蔵

- 最大 200mA をサポートする 5V LDO レギュレータ (VCC2)、オフボード機能とバッテリ短絡保護機能付き

- スリープ モードから複数の方法でウェークアップ可能

- CAN バスのウェークアップ パターン (WUP)

- WAKE ピンによるローカル ウェークアップ (LWU)

- ハイサイド スイッチ (HSS4) を使用した周期的 センシング ウェークアップ

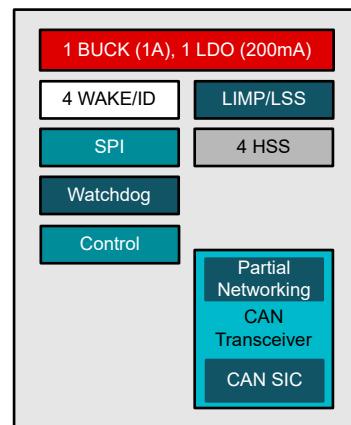

- 選択的ウェイク (部分的ネットワーキング機能)、TCAN2451-Q1 のみ

- SW ピンによるデジタル ウェイクアップ

- WAKE ピンを車両内の ECU 位置を識別する ID ピンとして構成可能

- 4 個のハイサイド スイッチにより複数の負荷をサポートし、周期的センシングによるウェークアップが可能

- フェイルセーフ出力ピン (LIMP)

- ローサイド スイッチとして使用することも可能

- ±58V のバス フォルト保護

- 高度な CAN バス障害診断

- タイムアウト、ウンドウ、Q&A ウォッチドッグをサポート

- EEPROM へのアクセスによりデバイス構成を保存

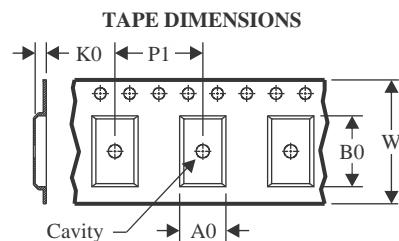

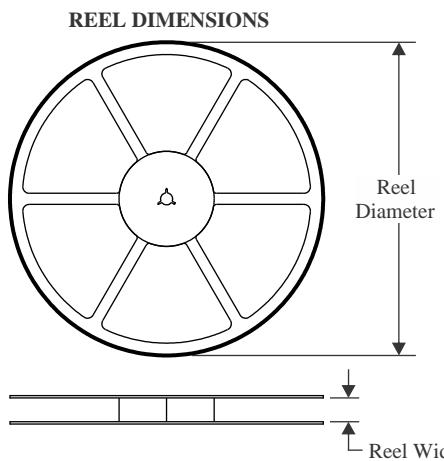

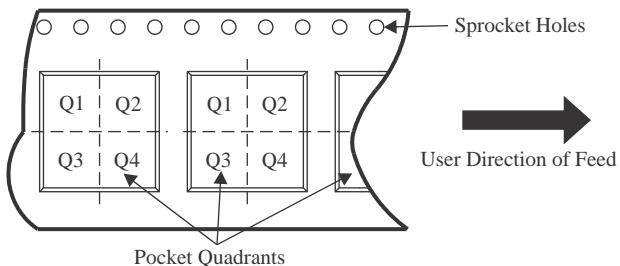

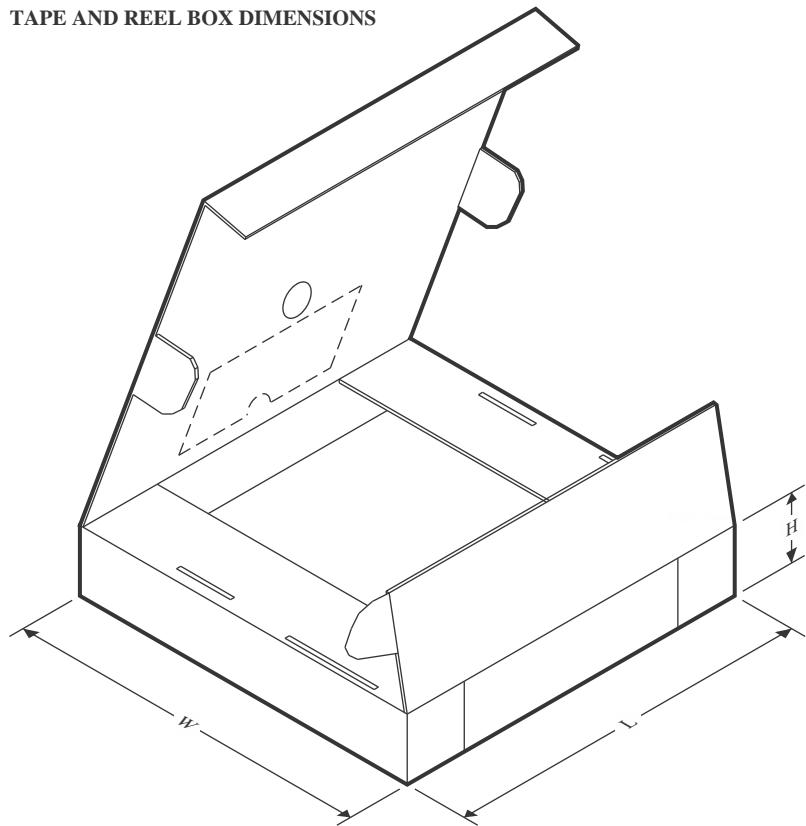

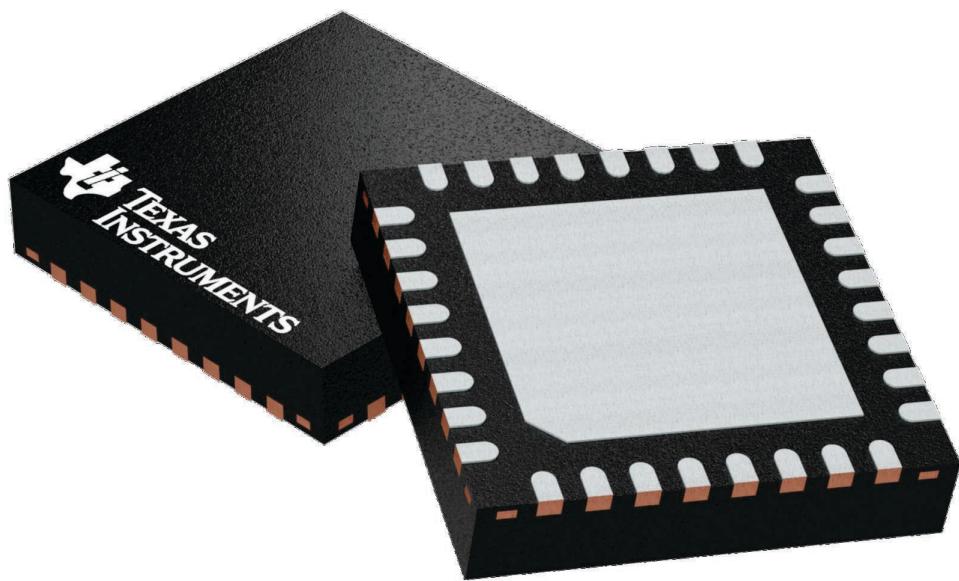

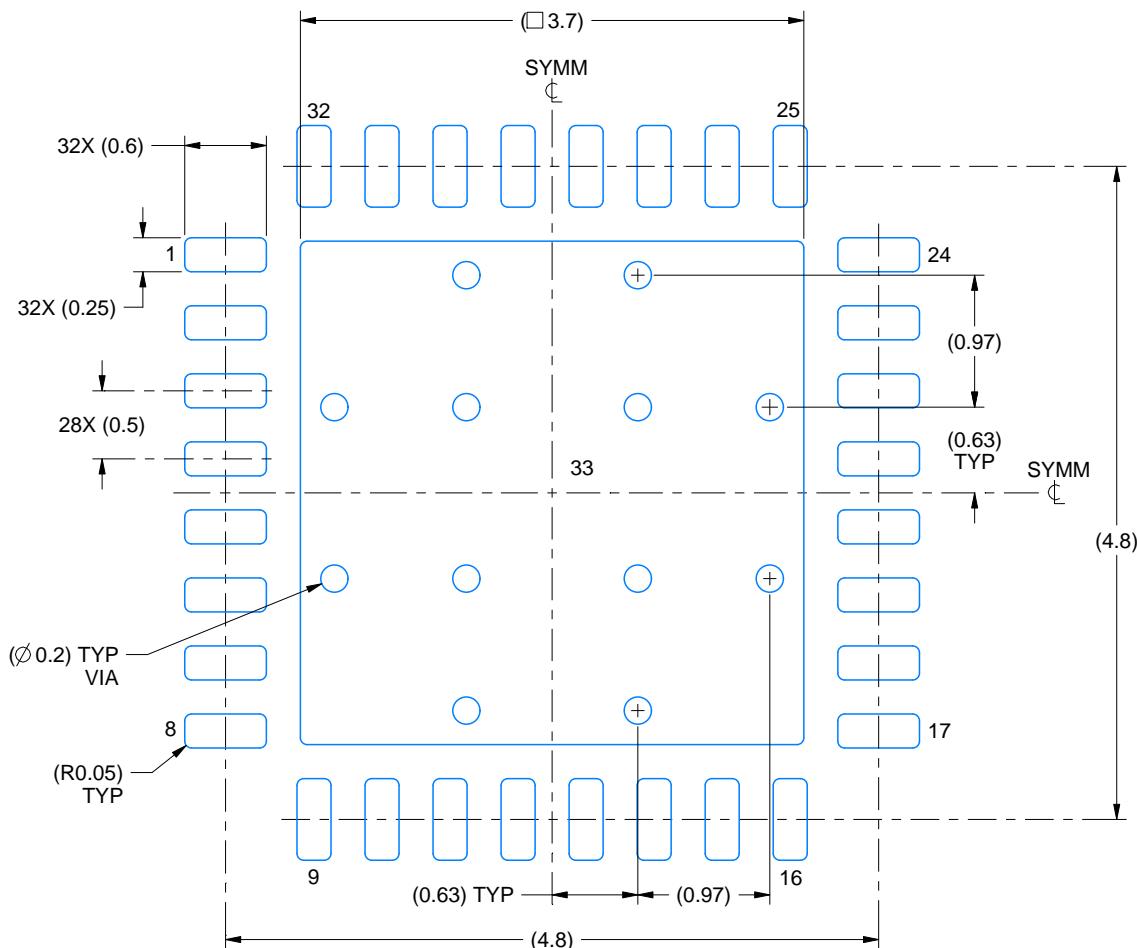

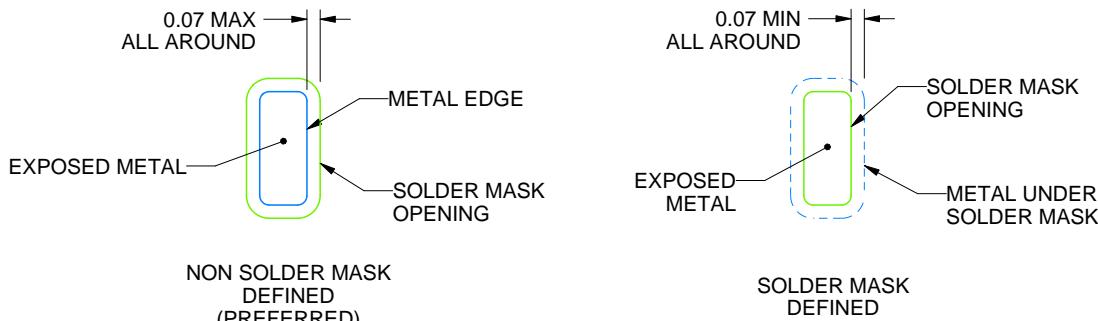

- 自動光学検査 (AOI) 機能を向上させるためウェッタブル フランク付き 32 ピンリードレス パッケージで供給

## 2 アプリケーション

- ボディ エレクトロニクスおよび照明

- カー アクセスとセキュリティ

- ハイブリッド、電動、パワートレイン システム

- 産業用輸送システム

## 3 説明

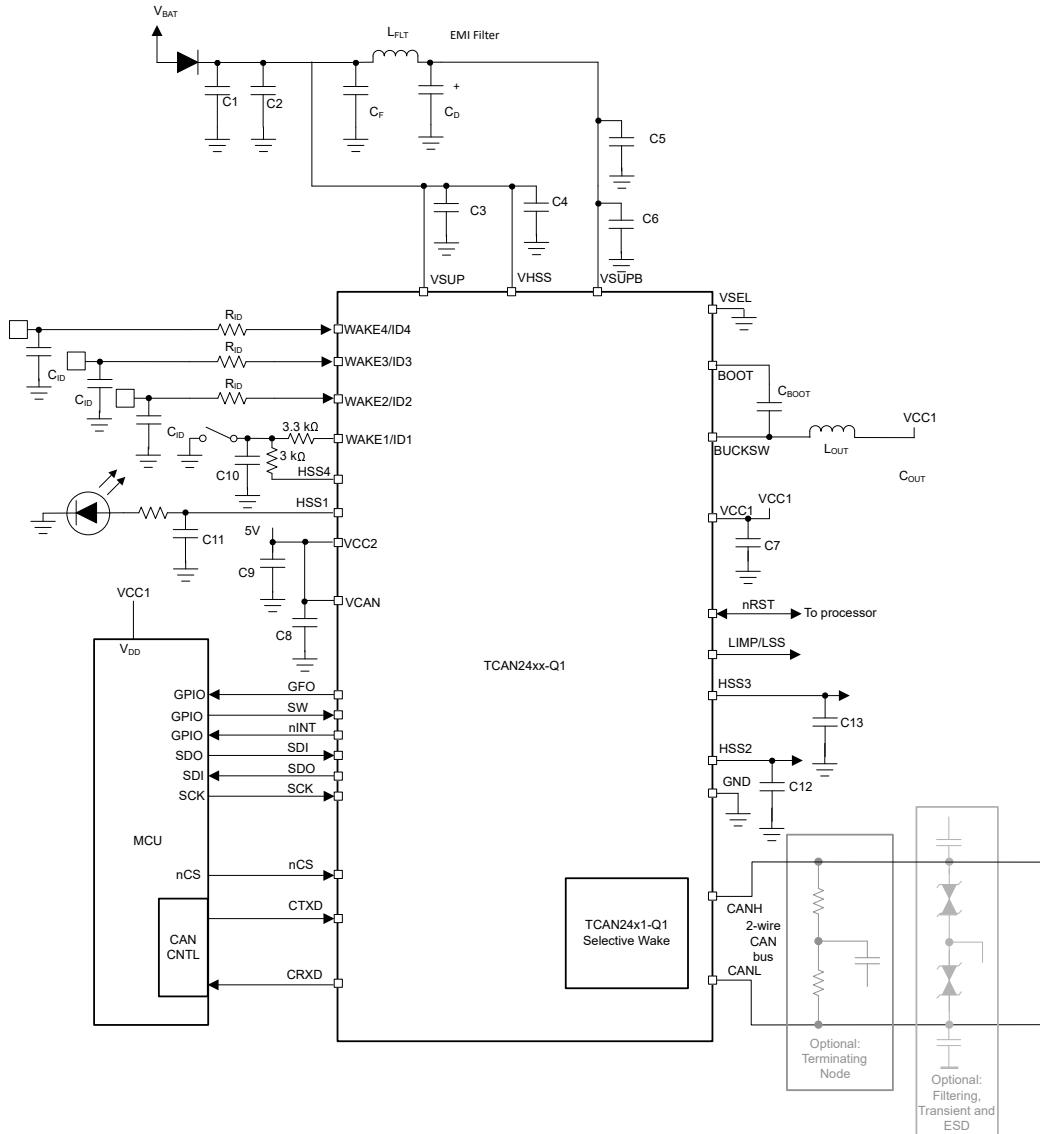

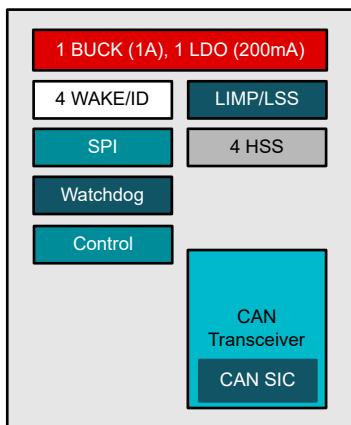

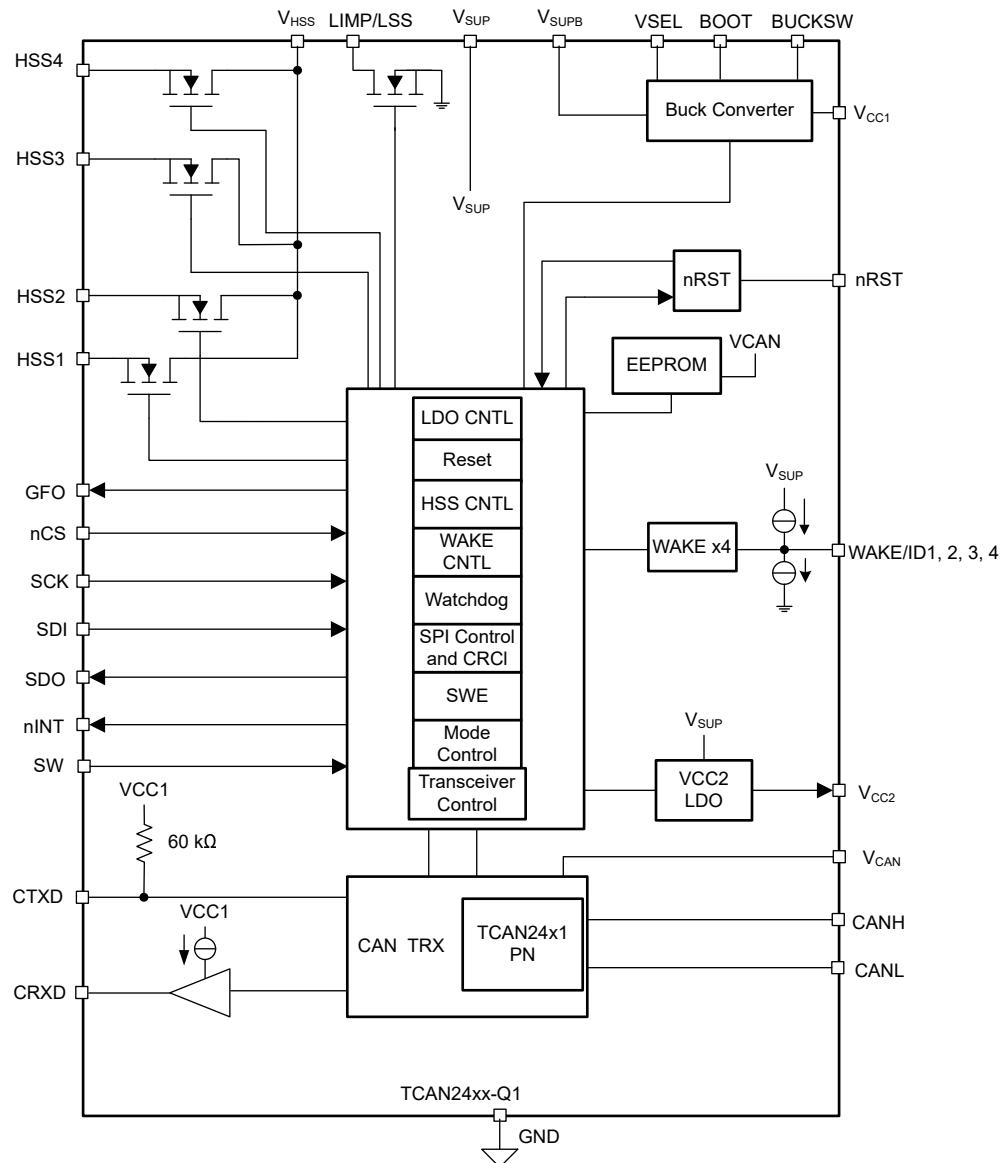

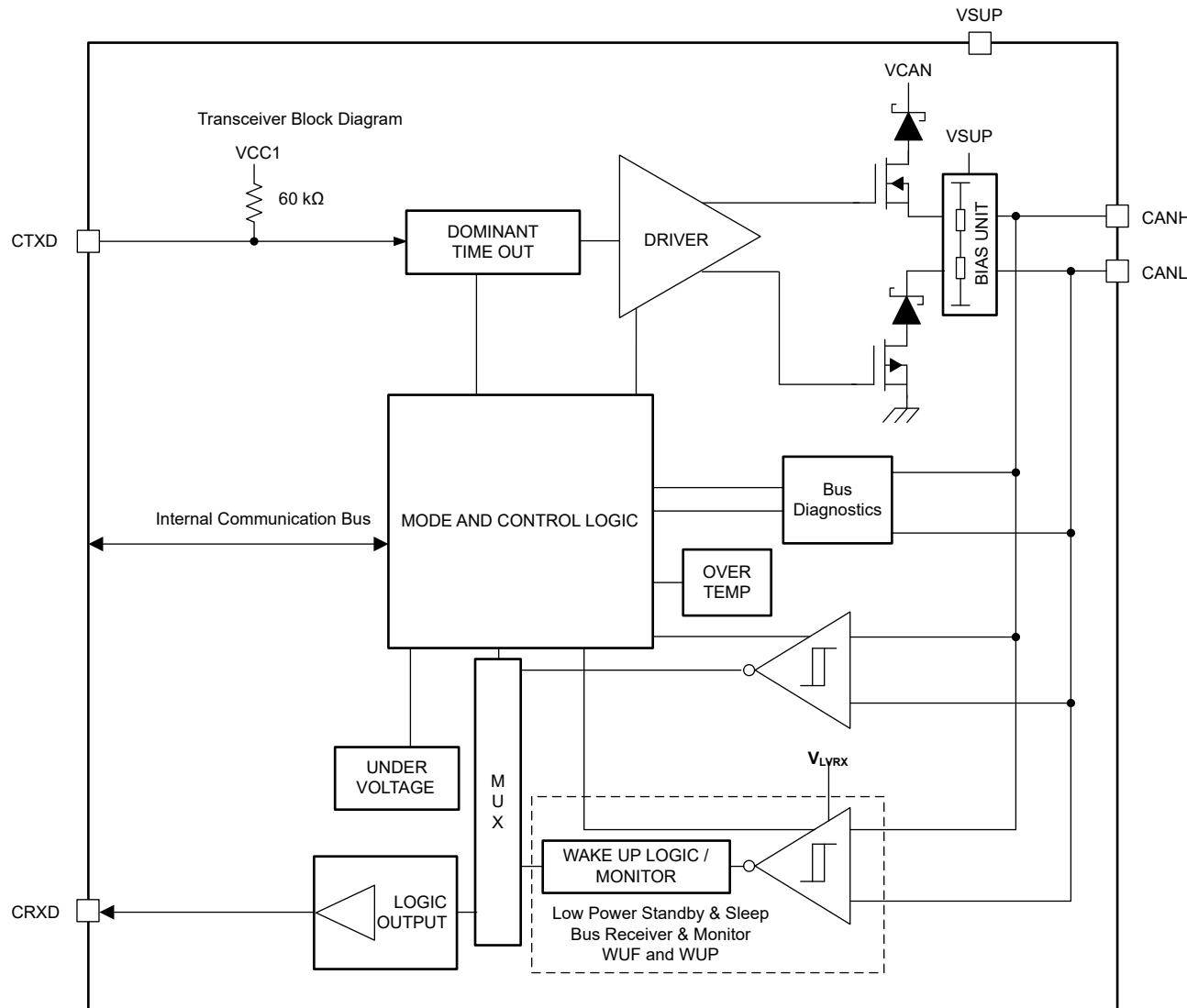

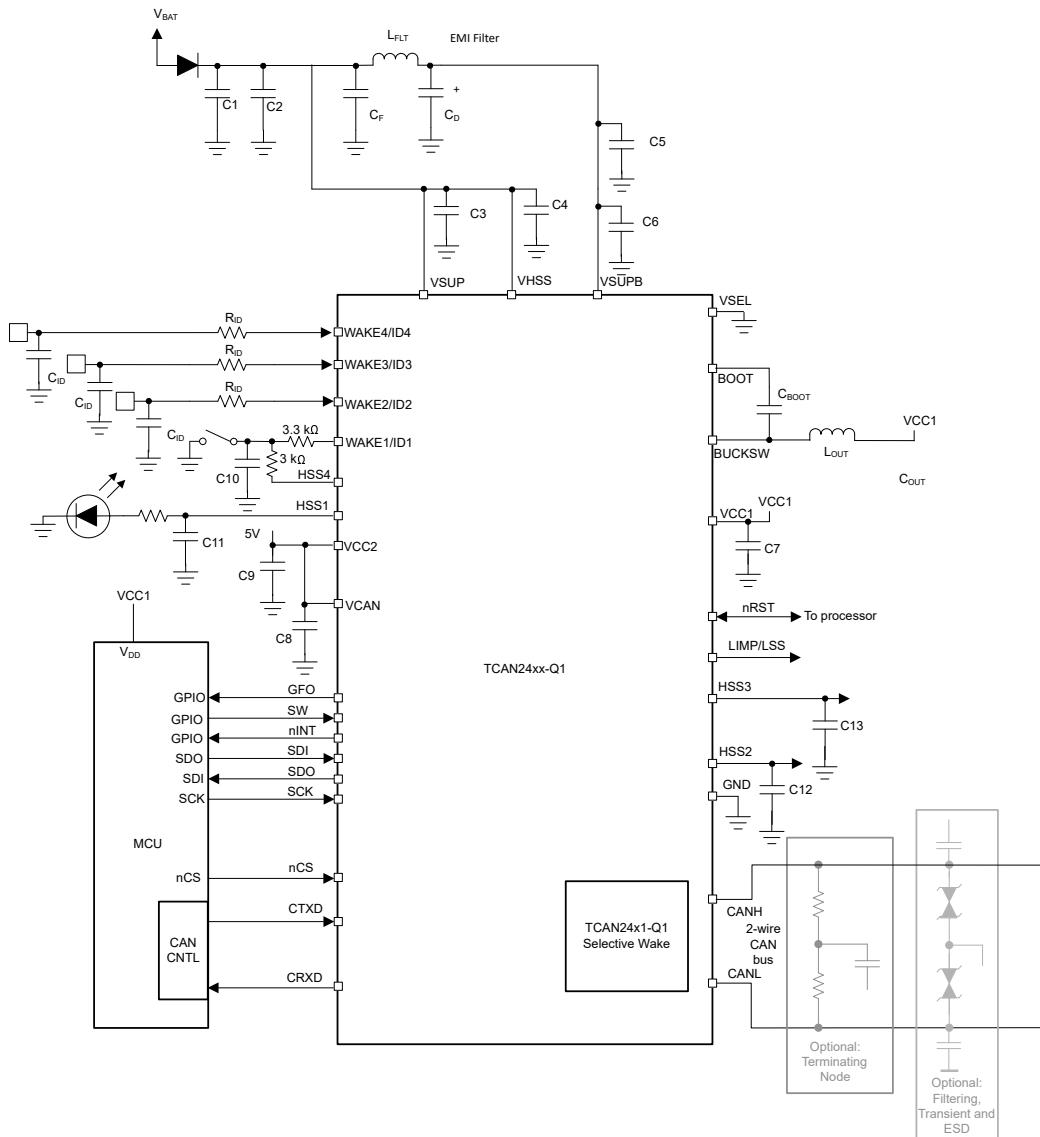

TCAN245x-Q1 は、SIC 仕様を含む ISO-11898-2:2024 の物理層要件を満たす CAN FD (コントローラ エリア ネットワーク フレキシブル データ レート) 対応トランシーバを提供するシステム ベース チップ (SBC) ファミリです。CAN FD トランシーバは、最高 8Mbps のデータ レートをサポートします。TCAN245x-Q1 は、3.3V または 5V を出力でき、最大 1A の出力電流を供給できる降圧レギュレータ (VCC1) を内蔵しています。降圧レギュレータには、EMC 性能を向上させるためのスペクトラム拡散変調が内蔵されています。VCC2 LDO は、最大 200mA の負荷に対して 5V の出力を供給します。TCAN2451-Q1 は、選択的ウェイクアップ フレーム (WUF) を認識することにより、部分的ネットワーク機能をサポートしています。

TCAN245x-Q1 には、LIMP、4 つのローカル ウェイク入力、4 つのハイサイド スイッチなどの機能が搭載されています。ハイサイド スイッチは、オン / オフ、10 ビット PWM、またはタイマ制御が可能です。GFO ピンを使用して、外部 CAN FD、LIN トランシーバ、CAN SBC、または LIN SBC の制御が可能です。WAKE ピンは、ウェークアップ用に静的センシング、周期的センシング (HSS4 ピンを使用)、パルス ベースに構成できます。これらのデバイスは、特定のデバイス構成情報を保存するための EEPROM を備えているので、電源変動後の大がかりな再プログラミングを回避できます。

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| TCAN2450-Q1 | VQFN (32)            | 5mm × 5mm                |

| TCAN2451-Q1 |                      |                          |

(1) 詳細については、[セクション 13](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

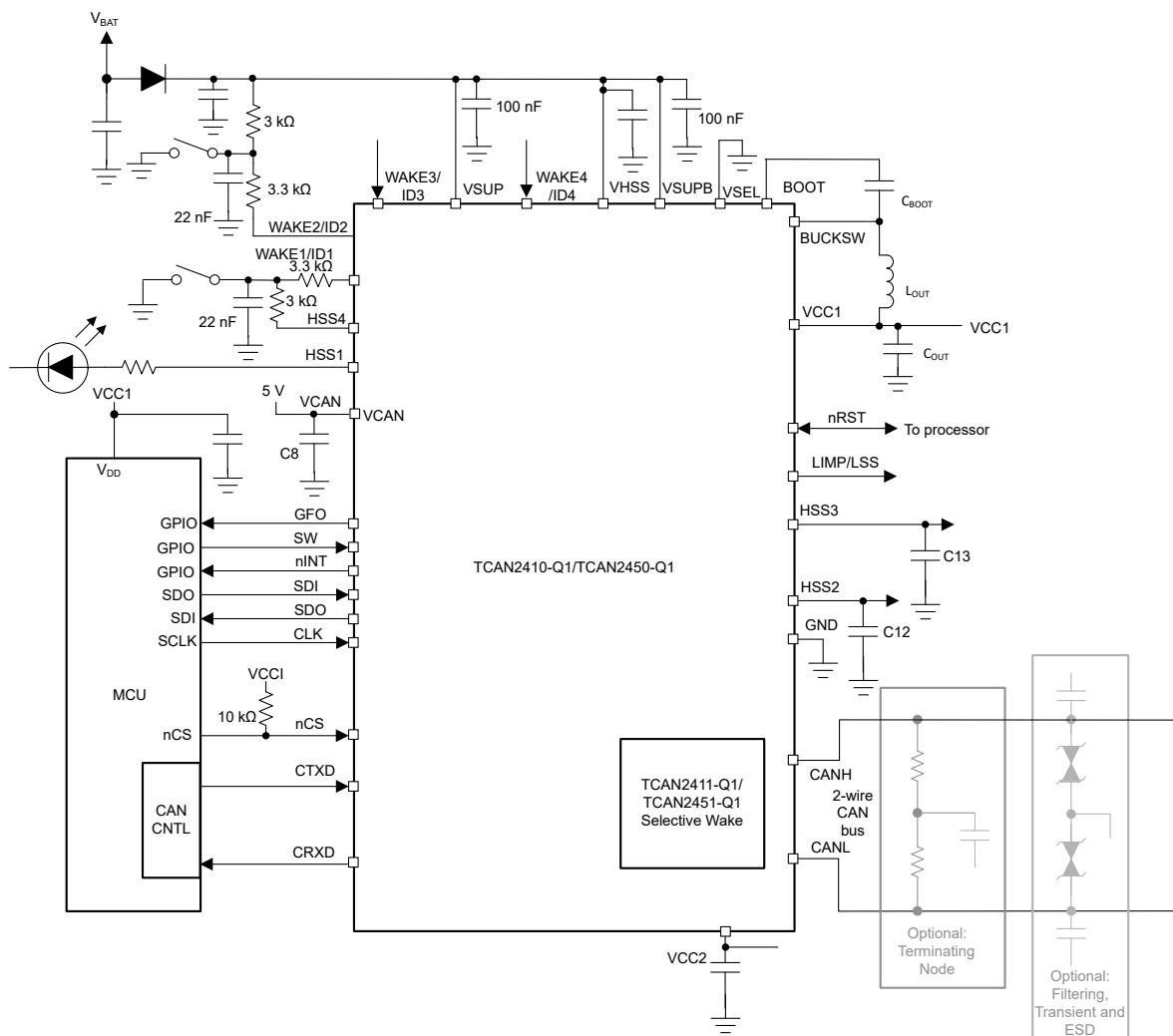

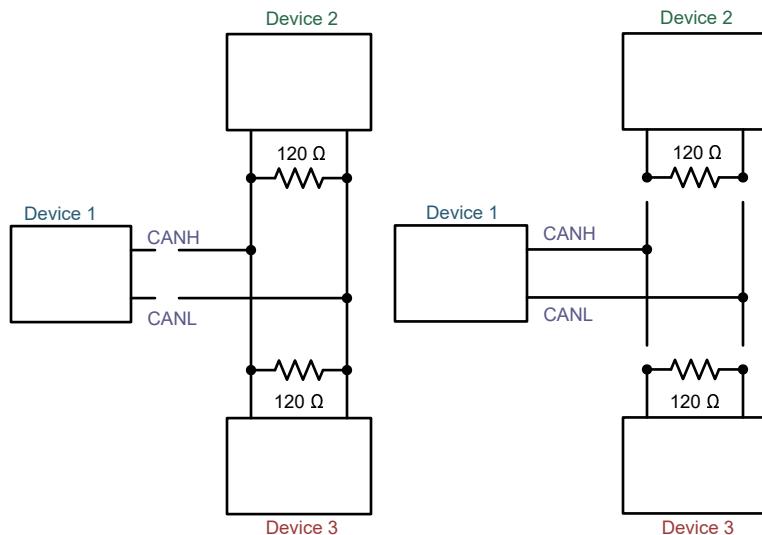

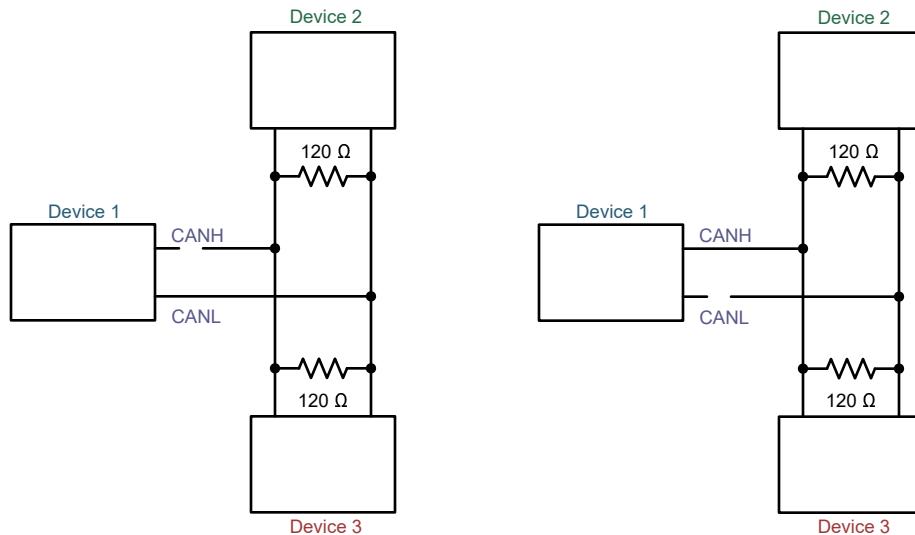

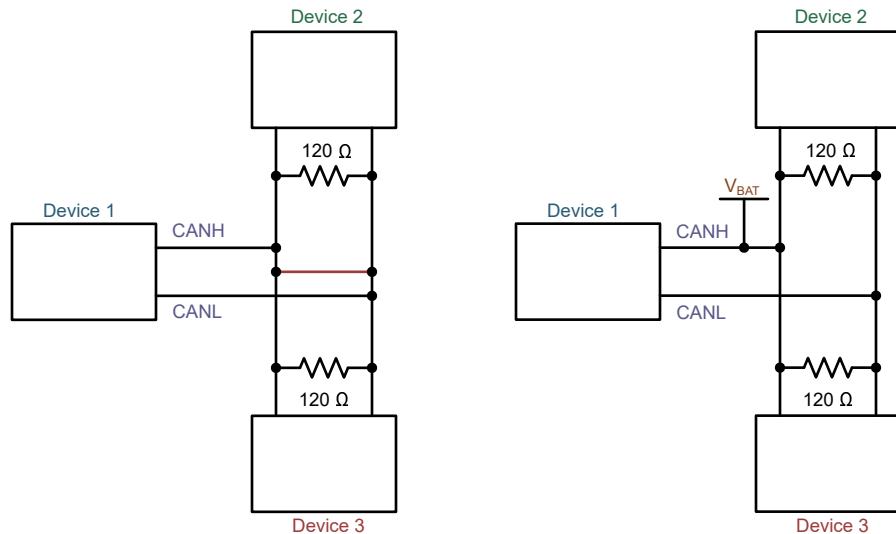

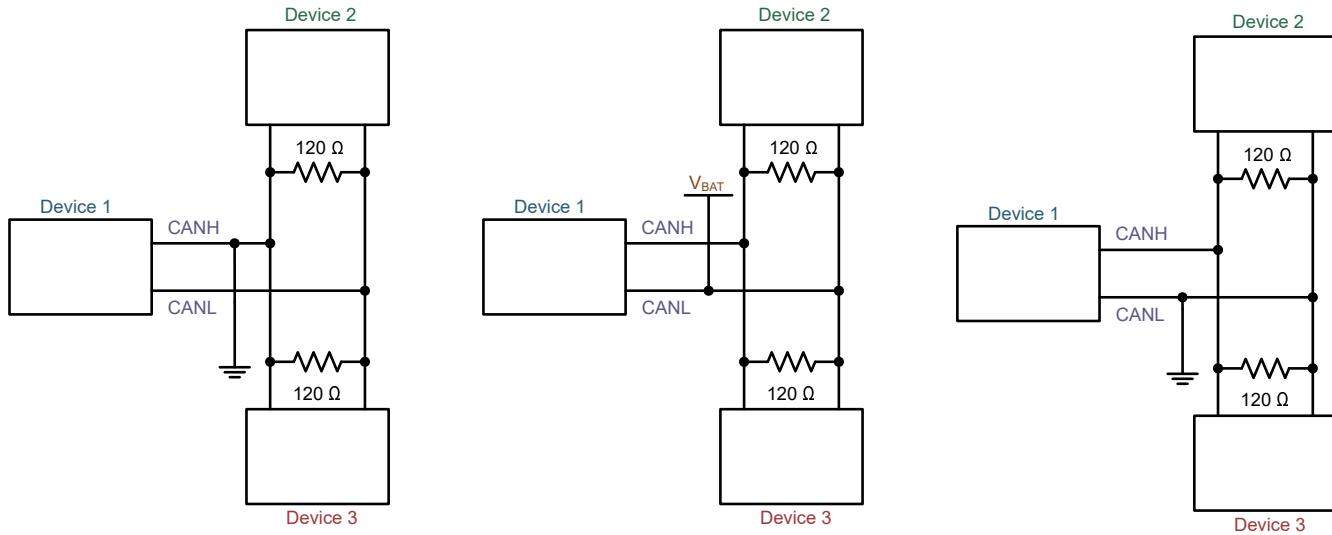

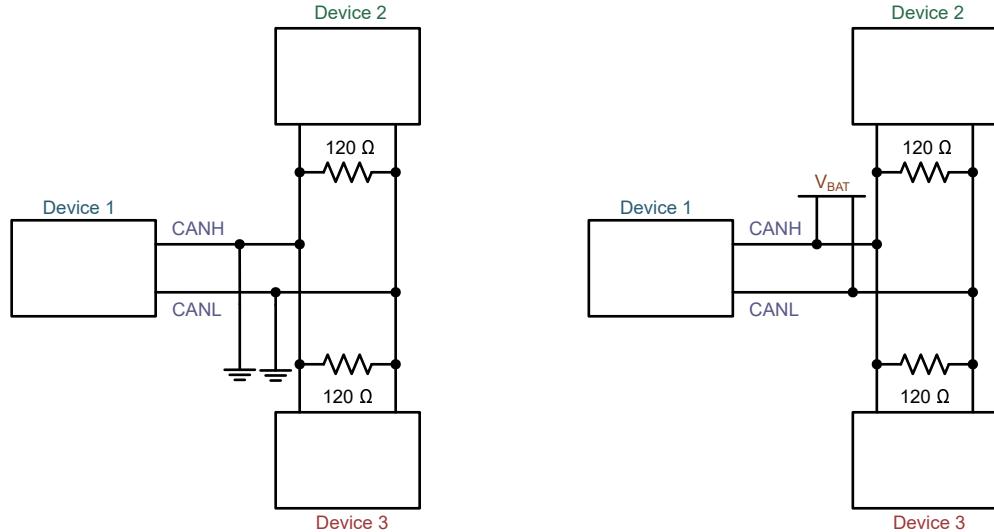

代表的なアプリケーションの図

TCAN2450-Q1 の図

TCAN2451-Q1 の図

## 目次

|                |    |                         |     |

|----------------|----|-------------------------|-----|

| 1 特長           | 1  | 8.2 機能ブロック図             | 36  |

| 2 アプリケーション     | 1  | 8.3 機能説明                | 38  |

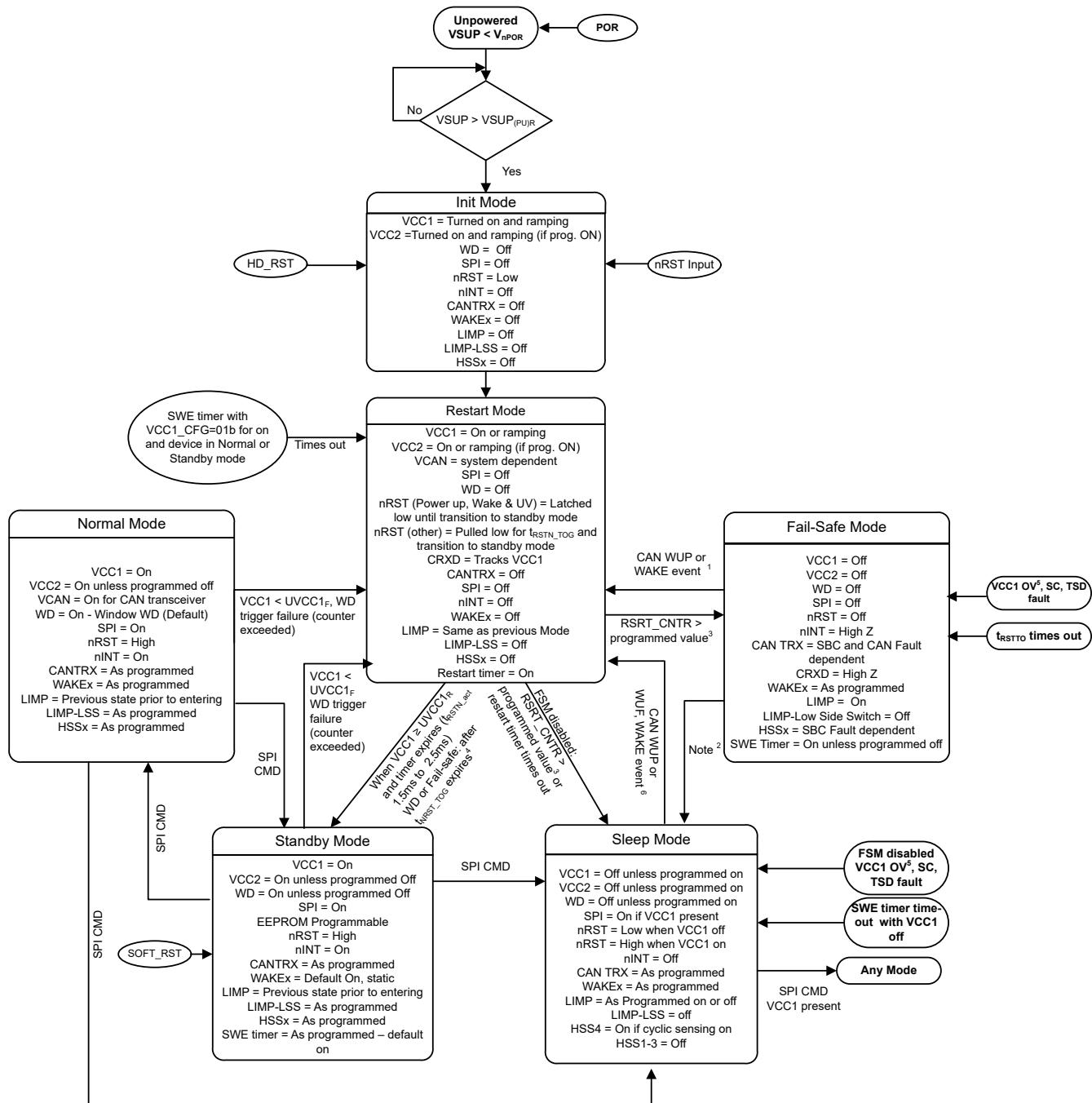

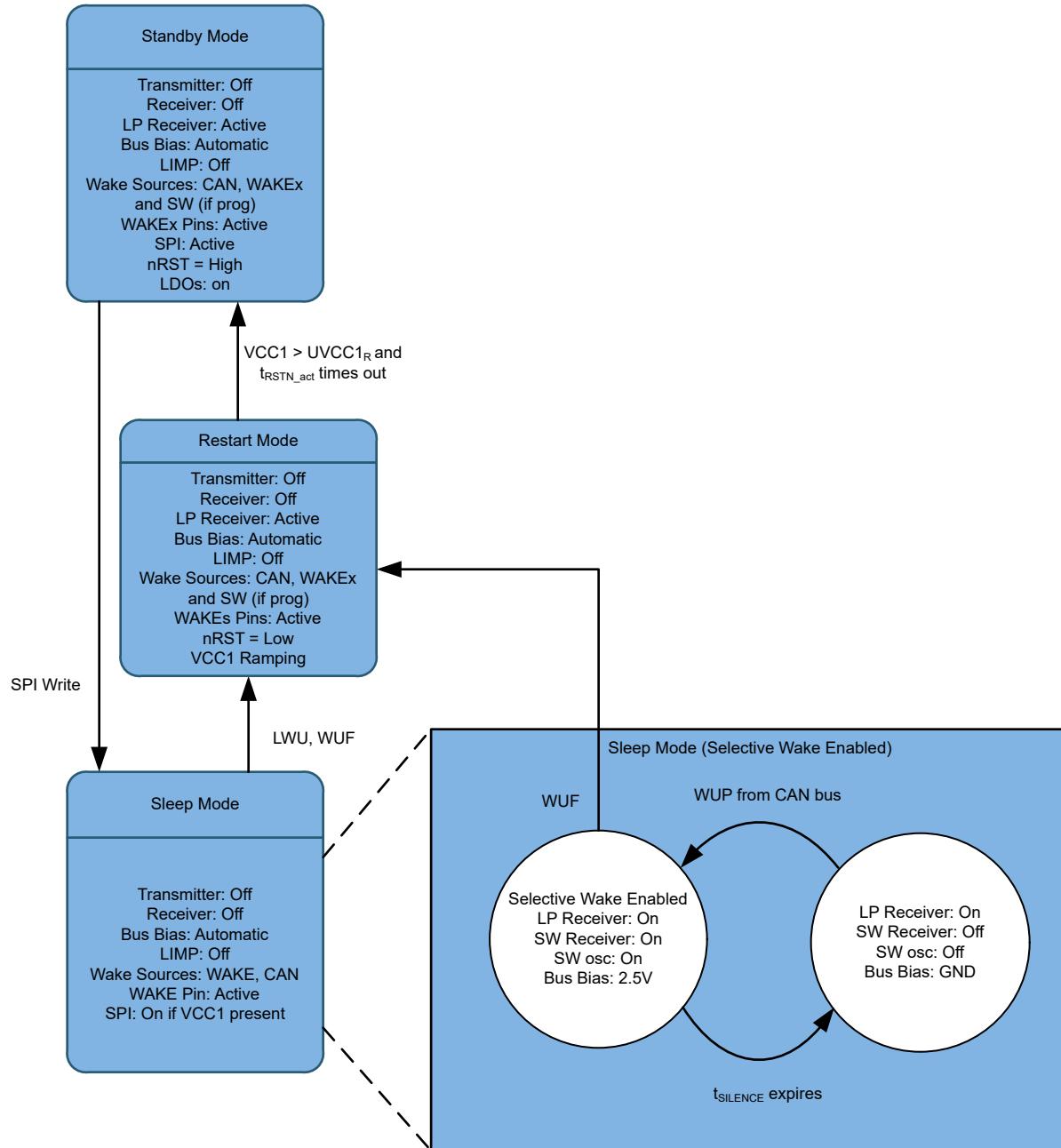

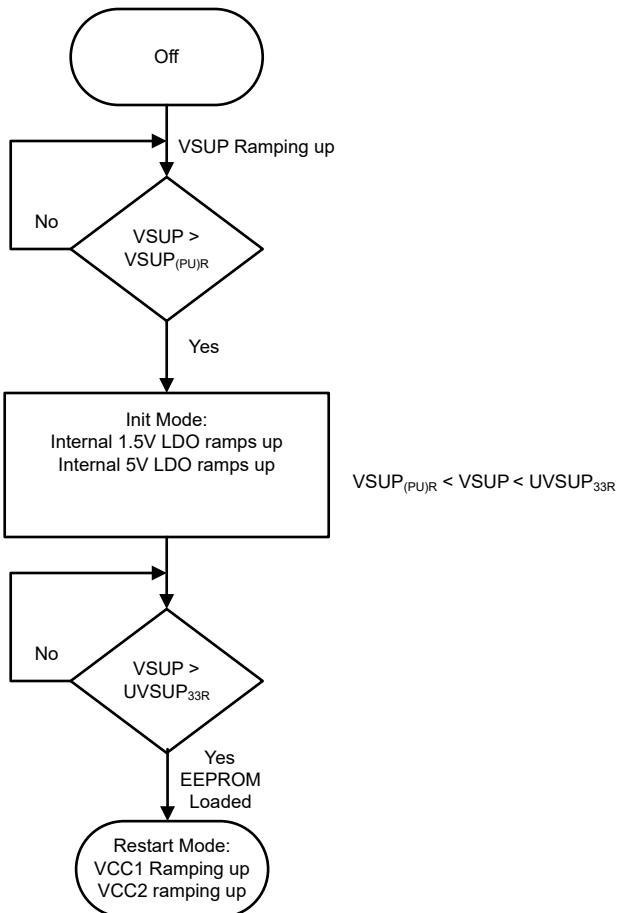

| 3 説明           | 1  | 8.4 デバイスの機能モード          | 104 |

| 4 デバイス比較表      | 4  | 9 デバイスレジスタ表             | 116 |

| 5 ピン構成および機能    | 5  | 9.1 デバイスのレジスタ           | 116 |

| 6 仕様           | 7  | 10 アプリケーションと実装          | 201 |

| 6.1 絶対最大定格     | 7  | 10.1 アプリケーション情報         | 201 |

| 6.2 ESD 定格     | 7  | 10.2 代表的なアプリケーション       | 206 |

| 6.3 IEC ESD 定格 | 8  | 10.3 電源に関する推奨事項         | 209 |

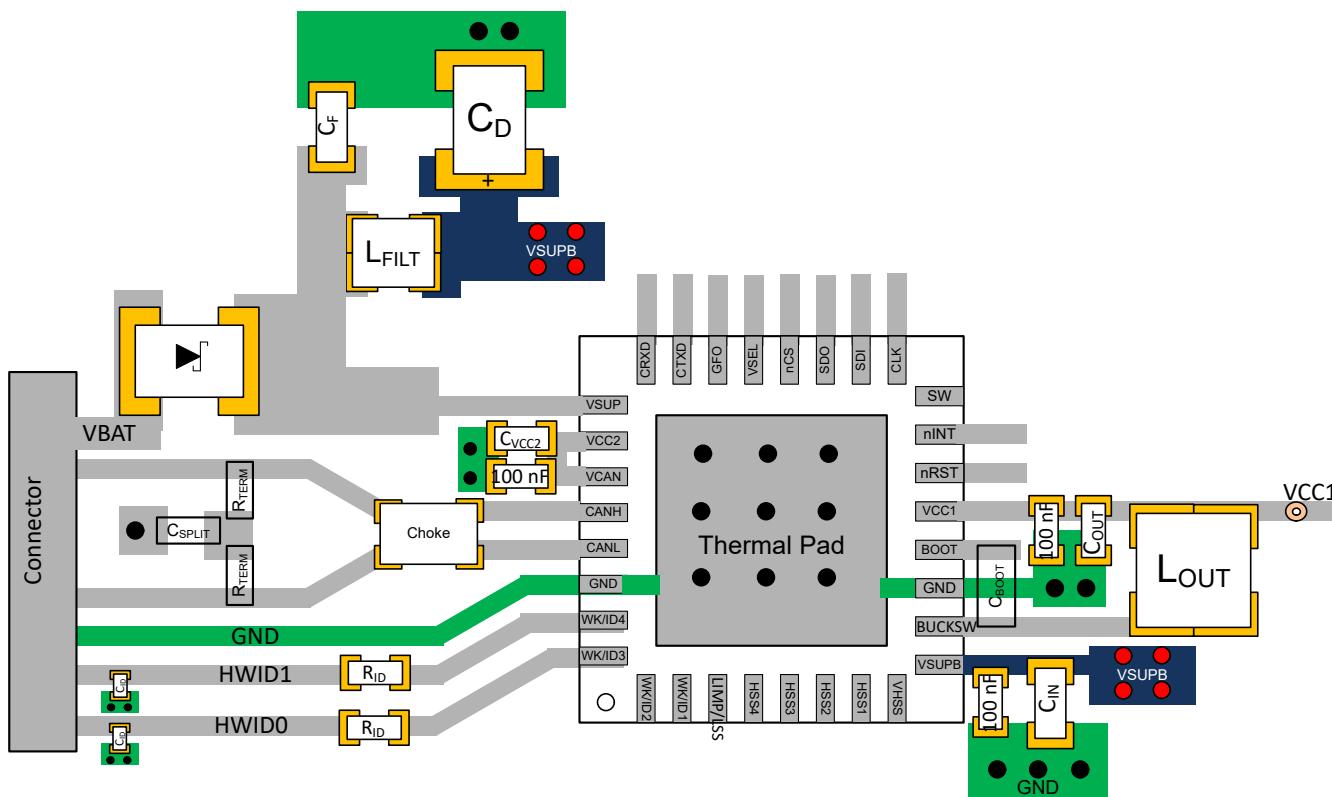

| 6.4 推奨動作条件     | 8  | 10.4 レイアウト              | 209 |

| 6.5 熱に関する情報    | 9  | 11 デバイスおよびドキュメントのサポート   | 212 |

| 6.6 電源の特性      | 9  | 11.1 ドキュメントのサポート        | 212 |

| 6.7 電気的特性      | 15 | 11.2 ドキュメントの更新通知を受け取る方法 | 212 |

| 6.8 タイミング要件    | 20 | 11.3 サポート・リソース          | 212 |

| 6.9 スイッチング特性   | 24 | 11.4 商標                 | 213 |

| 6.10 代表的特性     | 27 | 11.5 静電気放電に関する注意事項      | 213 |

| 7 パラメータ測定情報    | 28 | 11.6 用語集                | 213 |

| 8 詳細説明         | 35 | 12 改訂履歴                 | 213 |

| 8.1 概要         | 35 | 13 メカニカル、パッケージ、および注文情報  | 213 |

#### 4 デバイス比較表

| デバイス番号      | 選択式ウェークアップ機能 | 発注用型番           | REV_ID |

|-------------|--------------|-----------------|--------|

| TCAN2450-Q1 |              | TCAN2450RHBRQ1  | 20h    |

|             |              | TCAN2450MRHBRQ1 | 21h    |

| TCAN2451-Q1 | X            | TCAN2451RHBRQ1  | 20h    |

|             |              | TCAN2451MRHBRQ1 | 21h    |

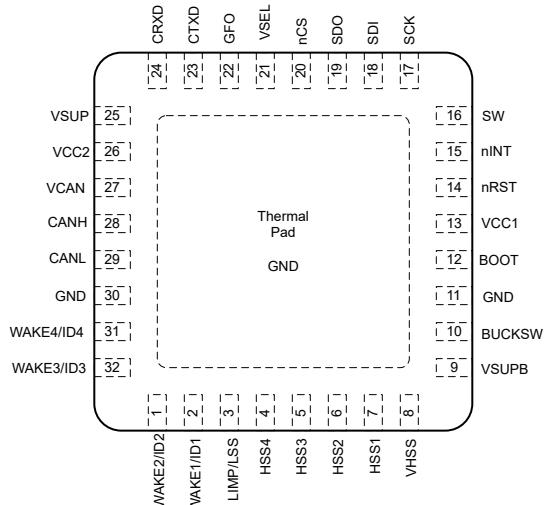

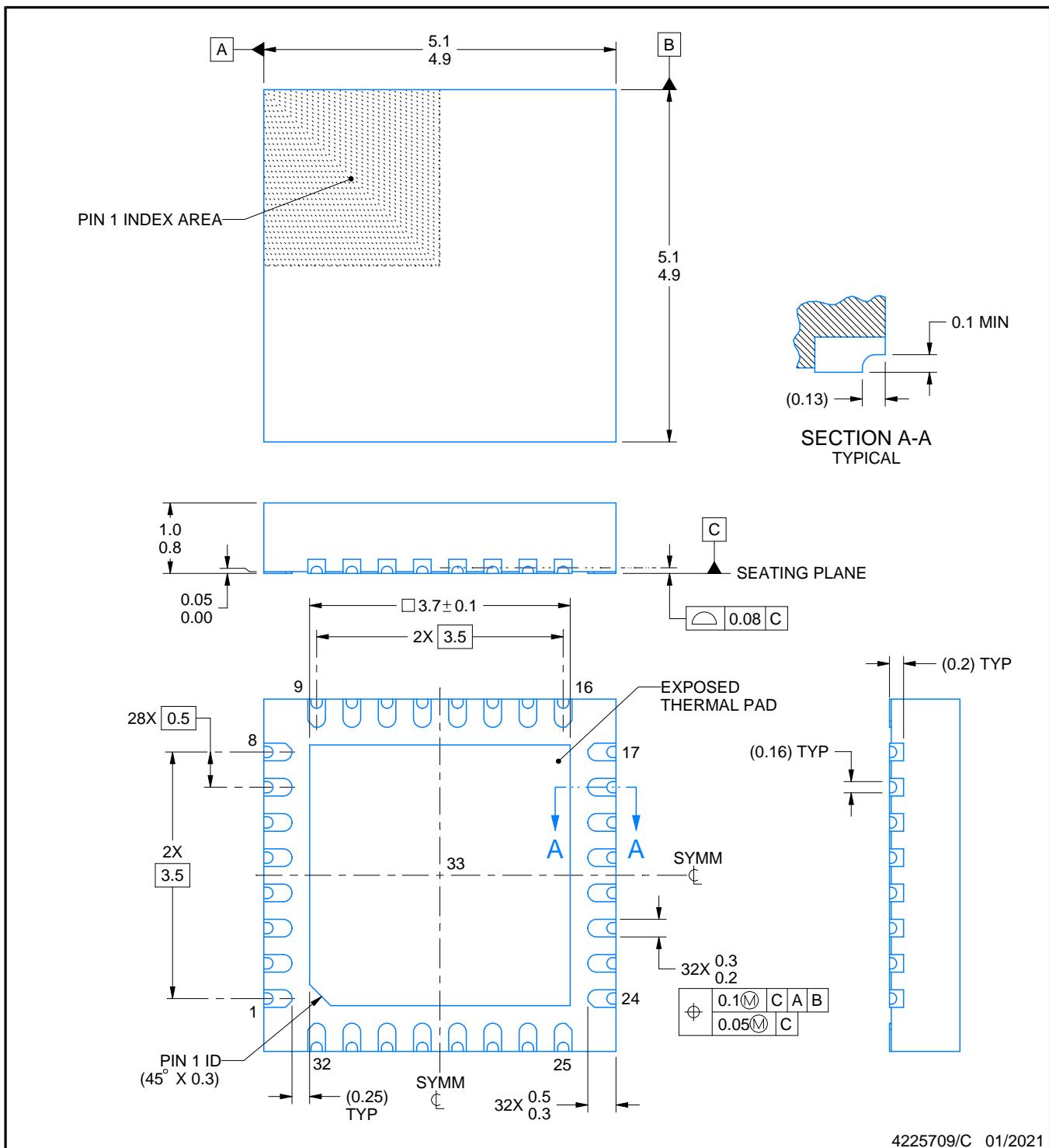

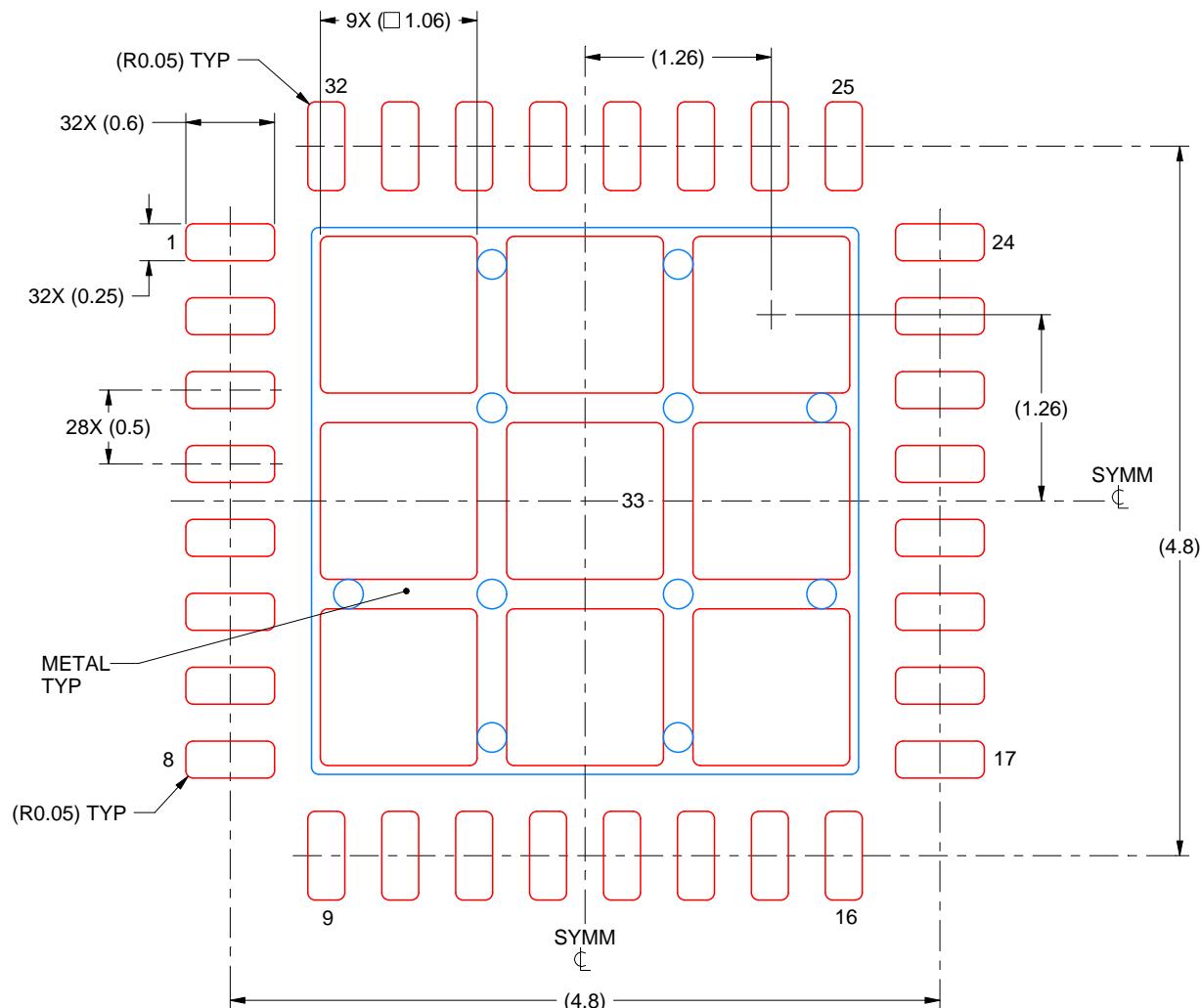

## 5 ピン構成および機能

図 5-1. RHB パッケージ、32 ピン (VQFN)

(上面図)

表 5-1. ピンの機能

| 名称       | ピン番号     | タイプ <sup>(1)</sup> | 説明                                                                           |

|----------|----------|--------------------|------------------------------------------------------------------------------|

|          | RHB      |                    |                                                                              |

| BOOT     | 12       | P                  | HV。内部ハイサイド ドライバのブートストラップ電源電圧。このピンと BUCKSW ピンとの間に高品質の 100nF コンデンサを接続します。      |

| BUCKSW   | 10       | P                  | HV。降圧レギュレータのスイッチング ノード。パワー インダクタに接続します。                                      |

| CANH     | 28       | I/O                | HV 対応。High レベル CAN バス I/O ライン                                                |

| CANL     | 29       | I/O                | HV 対応。Low レベル CAN バス I/O ライン                                                 |

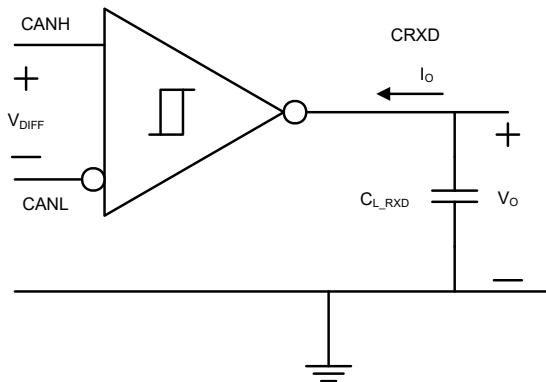

| CRXD     | 24       | O                  | LV デジタル。CAN 受信データ出力 (ドミナント バス状態の場合は Low、リセッショブ バス状態の場合は High)、トライステート        |

| CTXD     | 23       | I                  | LV デジタル。CAN 送信データ入力 (ドミナント バス状態の場合は Low、リセッショブ バス状態の場合は High)、60kΩ の内部プルアップ。 |

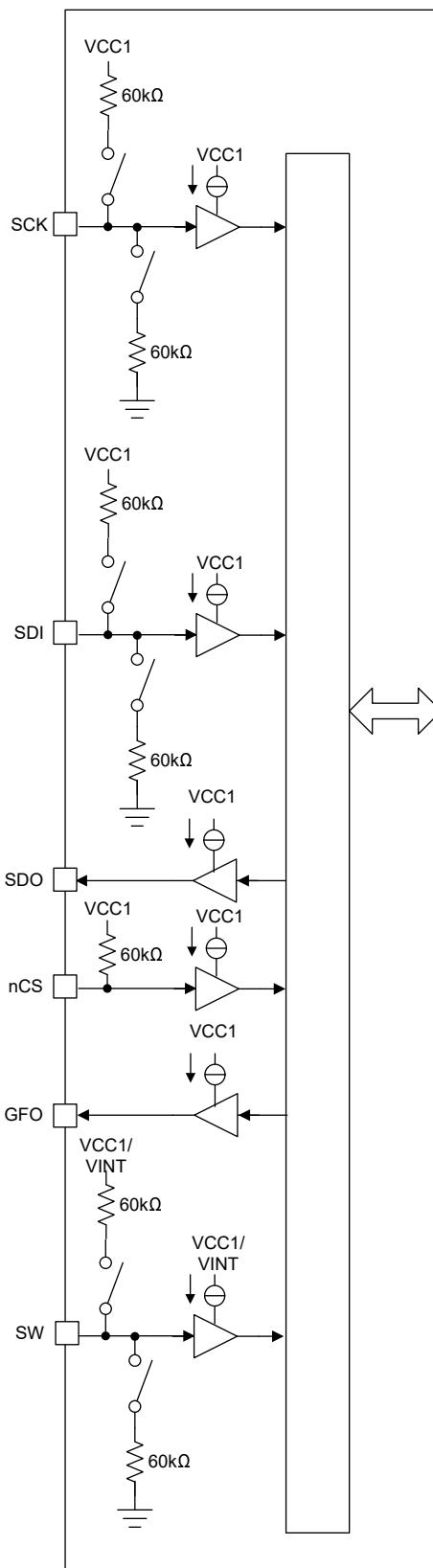

| GFO      | 22       | O                  | LV デジタル。汎用出力ピン (SPI 構成可能)、ブッシュホール                                            |

| GND      | 11       | G                  | グラウンド                                                                        |

| GND      | 30       | G                  | グラウンド接続: グラウンドに接続する必要があります。                                                  |

| GND      | サーマル パッド | G                  | グラウンド接続: グラウンドに接続する必要があります。                                                  |

| HSS1     | 7        | O                  | HV。ハイサイド スイッチ 1 出力                                                           |

| HSS2     | 6        | O                  | HV。ハイサイド スイッチ 2 出力                                                           |

| HSS3     | 5        | O                  | HV。ハイサイド スイッチ 3 出力                                                           |

| HSS4     | 4        | O                  | HV。ハイサイド スイッチ 4 出力                                                           |

| LIMP/LSS | 3        | O                  | HV 対応。リンプ ホーム出力 (アクティブ Low、オープンドレイン出力)                                       |

| NC       | -        | NC                 | 内部未接続。                                                                       |

| nCS      | 20       | I                  | LV デジタル。チップ セレクト入力 (アクティブ Low)、60kΩ の内部プルアップ                                 |

| nINT     | 15       | O                  | LV デジタル。割り込み出力 (アクティブ Low)                                                   |

表 5-1. ピンの機能 (続き)

| 名称        | ピン番号 | タイプ <sup>(1)</sup> | 説明                                                                                                                        |

|-----------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

|           | RHB  |                    |                                                                                                                           |

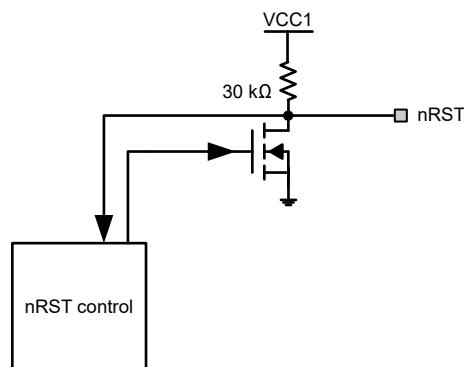

| nRST      | 14   | I/O                | 低電圧 (LV) デジタル。VCC1 低電圧モニタ出力ピン (アクティブ Low) およびデバイスリセット入力                                                                   |

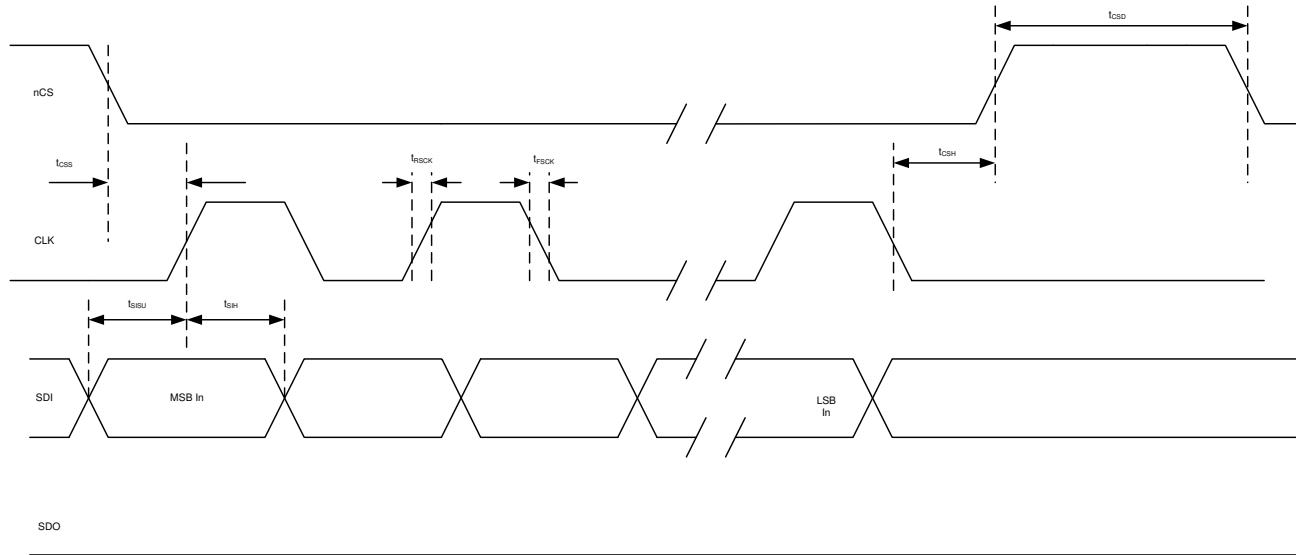

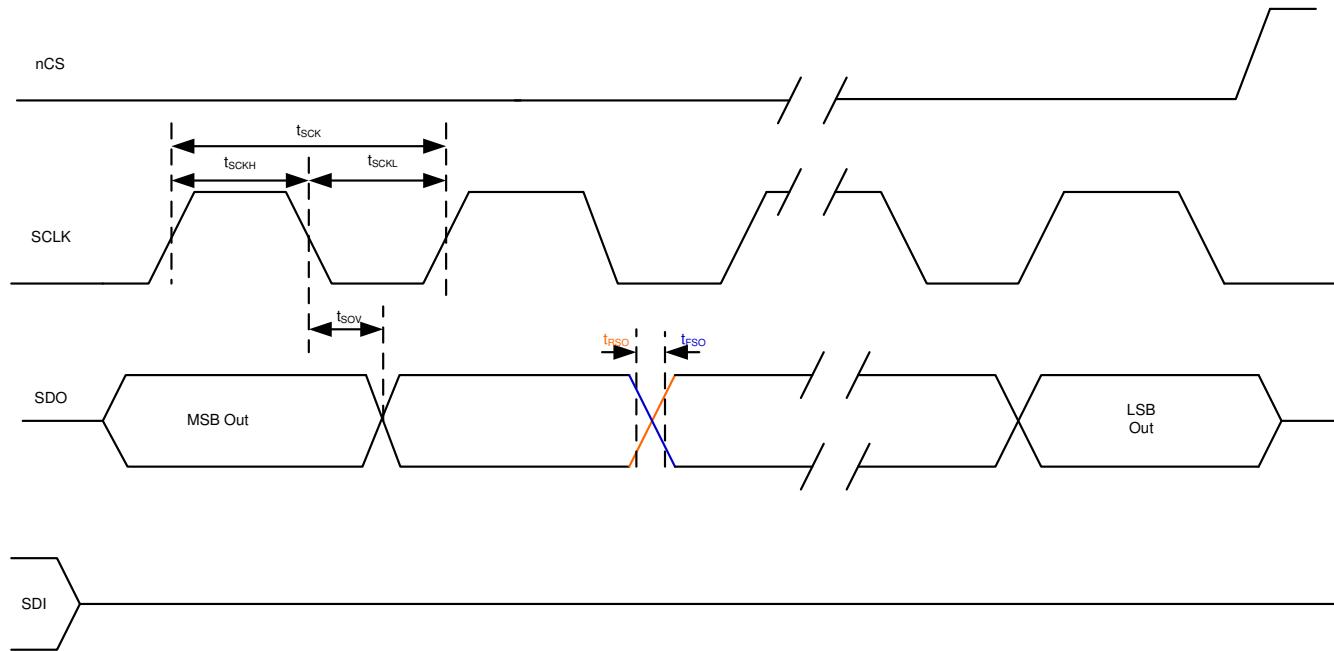

| SCK       | 17   | I                  | LV デジタル。SPI クロック入力。                                                                                                       |

| SDI       | 18   | I                  | LV デジタル。SPI データ入力。<br>60kΩ の内部プルアップ                                                                                       |

| SDO       | 19   | O                  | LV デジタル。SPI データ出力。                                                                                                        |

| SW        | 16   | I                  | LV デジタル。プログラミング モード入力ピン (SPI で構成可能、アクティブ High またはアクティブ Low)。<br>60kΩ の内部プルアップ (アクティブ Low 構成) またはプルダウン (アクティブ High 構成)     |

| VCAN      | 27   | P                  | CAN FD トランシーバ用の 5V 電源入力                                                                                                   |

| VCC1      | 13   | P                  | 降圧レギュレータ出力 3.3V または 5V。高品質のコンデンサを GND との間に接続します。                                                                          |

| VCC2      | 26   | P                  | 5V LDO 出力。バッテリ短絡保護付き。                                                                                                     |

| VHSS      | 8    | P                  | HV。ハイサイド スイッチ用の個別の入力電源。通常はバッテリに接続しますが、個別に電力を供給することもできます。                                                                  |

| VSEL      | 21   | I                  | LV デジタル。<br>VCC1 出力電圧セレクタ ピン。<br>1. GND に接続: VCC1 = 5 V<br>2. フローティング: VCC1 = 3.3V。<br>30kΩ の内部プルアップ                      |

| VSUP      | 25   | P                  | HV。入力電源ピン。通常はバッテリに接続します。                                                                                                  |

| VSUPB     | 9    | P                  | HV。降圧レギュレータのバッテリからの入力電源。<br>VSUPB と VSUP は、同じバッテリ電源に接続する必要がありますが、VSUP ピンの伝導 EMI を低減するため、アプリケーション回路図に示すように、EMI フィルタで分離します。 |

| WAKE1/ID1 | 2    | I                  | HV 対応。ローカル WAKE 入力端子。ID ピンとして構成可能                                                                                         |

| WAKE2/ID2 | 1    | I                  | 高電圧 (HV) 対応。ローカル WAKE 入力端子。<br>ID ピンとして構成可能                                                                               |

| WAKE3/ID3 | 32   | I                  | HV。ローカル WAKE 入力端子。ID ピンとして構成可能                                                                                            |

| WAKE4/ID4 | 31   | I                  | HV 対応。ローカル WAKE 入力端子。ID ピンとして構成可能                                                                                         |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源、NC = 未接続

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                 |                                     | 最小値  | 最大値                             | 単位 |

|-----------------|-------------------------------------|------|---------------------------------|----|

| $V_{SUP}$       | 電源電圧 <sup>(2)</sup>                 | -0.3 | 40                              | V  |

| $V_{SUPB}$      | 降圧レギュレータの入力電源電圧 <sup>(2)</sup>      | -0.3 | 40                              | V  |

| $V_{SW}$        | 降圧スイッチング ノード電圧 <sup>(2)</sup>       | -1   | $V_{SUPB} + 0.3$                | V  |

| $V_{BOOT_SW}$   | BOOT から SW への電圧                     | -0.3 | 6                               | V  |

| $V_{HSS}$       | ハイサイドスイッチの電源電圧 <sup>(2)</sup>       | -0.3 | 40                              | V  |

| $V_{CC1}$       | 3.3V と 5V の安定化出力電圧                  | -0.3 | 6                               | V  |

| $V_{nRST}$      | リセット出力電圧                            | -0.3 | $V_{CC1} + 0.3$                 | V  |

| $V_{CAN}$       | CAN トランシーバ電源電圧                      | -0.3 | 6                               | V  |

| $V_{CC2}$       | 5V CAN トランシーバと外部 LDO <sup>(2)</sup> | -0.3 | 40 および $V_O \leq V_{SUP} + 0.3$ | V  |

| $V_{BUSCAN}$    | CAN バス I/O 電圧 (CANH, CANL)          | -58  | 58                              | V  |

| $V_{WAKE/ID}$   | WAKE 入力電圧 <sup>(2)</sup>            | -0.3 | 40 および $V_O \leq V_{SUP} + 0.3$ | V  |

| $V_{HSSx}$      | ハイサイドスイッチピンの出力電圧範囲 <sup>(2)</sup>   | -0.3 | 40 および $V_O \leq V_{HSS} + 0.3$ | V  |

| $V_{LIMP}$      | LIMP ピン出力電圧範囲 <sup>(2)</sup>        | -0.3 | 40 および $V_O \leq V_{SUP} + 0.3$ | V  |

| $V_{LOGIC_IN}$  | ロジックピン入力電圧範囲                        | -0.3 | 6                               | V  |

| $V_{LOGIC_OUT}$ | ロジック ピン出力電圧範囲                       | -0.5 | 6                               | V  |

| $I_{O(LOGIC)}$  | ロジック ピン出力電流                         |      | 8                               | mA |

| $I_{(WAKE/ID)}$ | WAKE ピンの入力電流                        | -55  | 55                              | mA |

| $I_{(LIMP)}$    | LIMP ピンの入力電流                        |      | 40                              | mA |

| $I_{O(nRST)}$   | リセット出力電流                            | -5   | 5                               | mA |

| $T_J$           | 接合部温度                               | -55  | 165                             | °C |

| $T_{stg}$       | 保存温度                                | -65  | 150                             | °C |

(1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

(2) 300ms 間最大 40V のロード ダンプに耐えることが可能

### 6.2 ESD 定格

|             |      |                                              | 値                                                    | 単位         |

|-------------|------|----------------------------------------------|------------------------------------------------------|------------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup>  | $V_{SUP}, V_{SUPB}, V_{HSS}, CANL/H, WAKEx と GND の間$ | $\pm 8000$ |

|             |      | 人体モデル (HBM)、AEC - Q100-002 準拠 <sup>(1)</sup> | その他のすべてのピン                                           | $\pm 4000$ |

|             |      | デバイス帯電モデル (CDM)、AEC Q100-011 準拠              |                                                      | $\pm 750$  |

|             |      |                                              |                                                      | $\pm 750$  |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 6.3 IEC ESD 定格

|                                                                   |                                                       |                                     | 値           | 単位 |

|-------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------|-------------|----|

| $V_{(ESD)}$                                                       | IEC 62228-3 準拠の静電放電 <sup>(1)</sup>                    | 接触放電、CANH、CANL、VSUP、VSUPB、VHSS、WAKE | $\pm 8000$  | V  |

| $V_{(ESD)}$                                                       | ISO 10605 に準拠した SAE J2962-2 電動接触放電                    | 接触放電 (CANH、CANL)                    | $\pm 8000$  | V  |

| $V_{(ESD)}$                                                       | ISO 10605 に準拠した SAE J2962-2 動力空中放電                    | 空隙放電 (CANH、CANL)                    | $\pm 15000$ |    |

| ISO7637-2 および IEC 62215-3 過渡、CANH/L、VSUP、VHSS、WAKE <sup>(2)</sup> | パルス 1                                                 | -100                                | V           |    |

|                                                                   | パルス 2                                                 | 75                                  |             |    |

|                                                                   | パルス 3a                                                | -150                                |             |    |

|                                                                   | パルス 3b                                                | 100                                 |             |    |

| IS07637-3 低速過渡パルス: CAN バス端子から GND への印加 <sup>(3)</sup>             | 100nF のカッピング コンデンサを備えた容量結合コンデンサ「スロートランジエントパルス」 - 電源供給 | $\pm 30$                            | V           |    |

- (1) IBEE Zwickau が実施した IEC 62228-3 ESD。システムレベルの構成が異なると、結果も異なる可能性があります。VSUP、VSUPB、VHSS は、推奨アプリケーション図に従ってバッテリ電源に接続されます

- (2) IEC 62228-2 と IEC 62228-3 に基づく ISO 7637-2 は、システムレベルの過渡テストです。システムレベルの構成が異なると、結果も異なる可能性があります。

- (3) ISO 7637-3 はシステムレベルの過渡テストです。システムレベルの構成が異なると、結果も異なる可能性があります。

## 6.4 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                              |                                        | 最小値   | 公称値  | 最大値  | 単位 |

|------------------------------|----------------------------------------|-------|------|------|----|

| $V_{SUP}$ 、 $V_{SUPB}$       | 電源電圧範囲                                 | 5.5   | 28   | V    |    |

| $V_{SUP}$ 、 $V_{SUPB}$       | VCC1 = 3.3V 構成の電源電圧範囲 <sup>(1)</sup>   | 4.5   | 28   | V    |    |

| $V_{HSS}$                    | ハイサイドスイッチの電源電圧                         | 5     | 28   | V    |    |

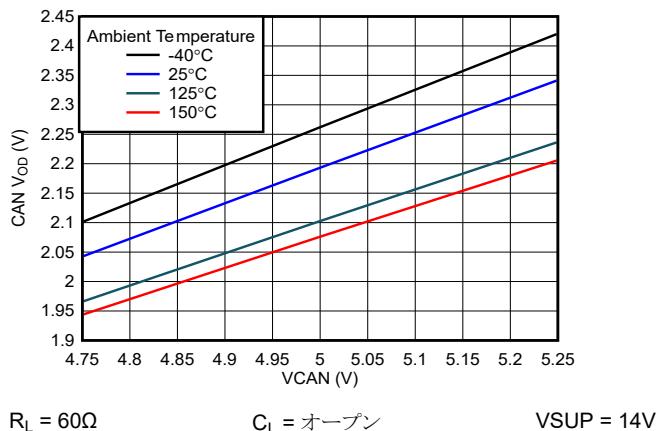

| $V_{CAN}$                    | CAN トランシーバ電源電圧                         | 4.75  | 5    | 5.25 | V  |

| $I_{OH(DO)}$                 | デジタル出力 High レベル電流                      | -2    |      |      | mA |

| $I_{OL(DO)}$                 | デジタル出力 Low レベル電流                       |       | 2    |      | mA |

| $I_{O(LIMP)}$                | LIMP として構成時の LIMP/LSS ピン電流             |       | 6    |      | mA |

| $I_{O(LSS)}$                 | ローサイド スイッチとして構成されている場合の LIMP/LSS ピンの電流 |       | 25   |      | mA |

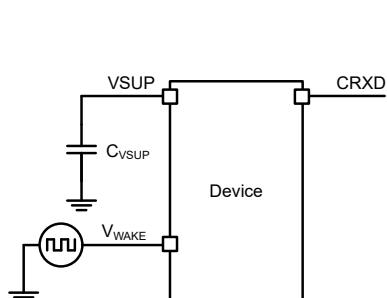

| $C_{(VSUP)}$ 、 $C_{(VSUPB)}$ | $V_{SUP}$ 、 $V_{SUPB}$ の電源容量           | 100   |      |      | nF |

| $C_{(VCC2)}$                 | VCC2 電源実効容量                            | 1     |      |      | μF |

| $ESR_{CO}$                   | VCC2 出力コンデンサの ESR 要件                   | 0.001 | 1    |      | Ω  |

| TSDWR                        | サーマルシャットダウン警告                          | 140   | 165  |      | °C |

| TSDWF                        | サーマルシャットダウン警告解除                        | 130   | 155  |      | °C |

| TSDWHYS                      | サーマルシャットダウン警告ヒステリシス                    |       | 10.0 |      | °C |

| TSDR                         | サーマルシャットダウン                            | 165   | 200  |      | °C |

| TSDF                         | サーマルシャットダウン解除                          | 155   | 190  |      | °C |

| TSDHYS                       | サーマルシャットダウンヒステリシス                      |       | 10.0 |      | °C |

| $T_J$                        | 動作ジャンクション温度範囲                          | -40   | 150  |      | °C |

- (1) VCC1 が 3.3V 出力の場合、VCC1 は 4.5V の VSUP で動作しますが、他の LDO はパススルーモードとなり、出力電圧は調整値になりません。すべての LDO がレギュレーションになるには、VSUP は 5.5V 以上である必要があります。

## 6.5 热に関する情報

| 热評価基準 <sup>(1)</sup> |                   | RHB (VQFN) | 単位   |

|----------------------|-------------------|------------|------|

|                      |                   | 32-PINS    |      |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗      | 31.8       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗      | 11.8       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への热抵抗 | 21.4       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への热抵抗 | 2.8        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 0.3        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 11.8       | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体およびICパッケージの热評価基準』アプリケーションノートを参照してください。

## 6.6 電源の特性

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ C$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                                    | テスト条件                                                                            | 最小値                                                                                                                                                                                                                                   | 標準値 | 最大値 | 単位 |

|------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

| <b>バッテリ消費電流 (VSUP および VSUPB を含む)</b>     |                                                                                  |                                                                                                                                                                                                                                       |     |     |    |

| ISUP <sub>NORMAL-150C</sub>              | 通常モード: バッテリ供給電流                                                                  | 通常モードでの SBC、CAN トランシーバがオフ、VCC1 = オン (FPWM モード)、無負荷、VCC2 = オフ、 $V_{SUP} = 5.5V \sim 28V$                                                                                                                                               | 8   | 11  | mA |

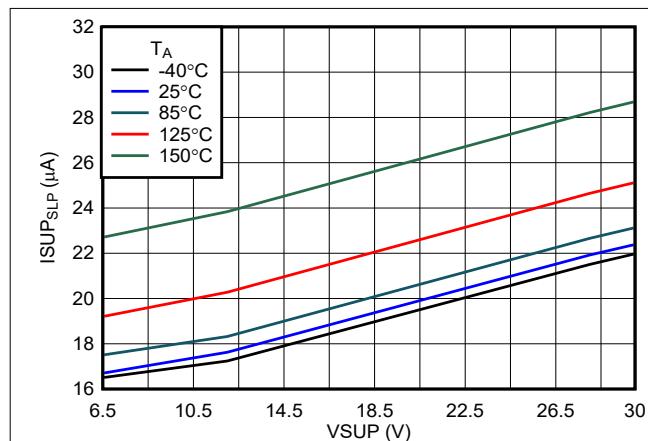

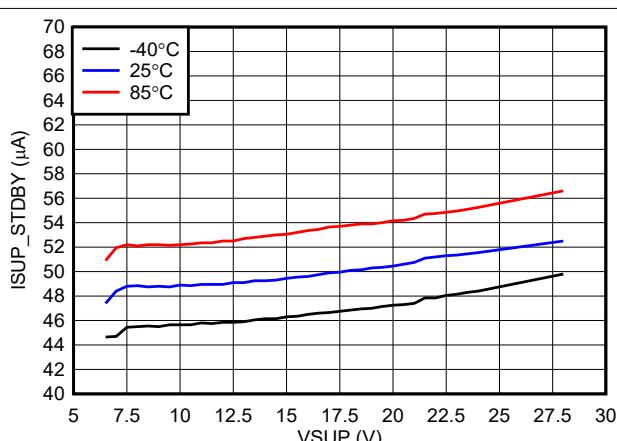

| ISUP <sub>STDBY-85C</sub>                | スタンバイ モード: バッテリ電源電流 (最大 85°Cまで)                                                  | VCC1 = オン (負荷なし)、拡散スペクトラム変調 = 無効、VCC2 = オフ、すべての HSS = オフ、VCC1 シンク = 無効、CAN トランシーバ = オフ、ウェークビン = オフ、選択的ウェーク = オフ、周期的センシング = オフ、周期的ウェーク = オフ、WD = オフ、ロング ウィンドウは期限切れ<br>$VSUP, VSUPB = 6.5V \sim 12V, T_J : -40^\circ C \sim 85^\circ C$ | 60  | 70  | μA |

| ISUP <sub>SLP-85C</sub>                  | スリープ モード: 最大 85°C のバッテリ電源電流                                                      | スリープモード、選択的ウェークオフ、VCC1 および VCC2 = オフ、 $6.5V \leq VSUP \leq 12V$ 、トランシーバがオフ、すべての HSS がオフ、1 つの WAKE ピンがアクティブ、周期的センシング / ウェークオフ、VCC1 と VCC2 がオフ、 $T_J \leq 85^\circ C$                                                                   | 18  | 31  | μA |

| ISUP <sub>SLP-150C</sub>                 | スリープ モード: 最大 150°C のバッテリ電源電流                                                     | スリープ モード、VCC1 および VCC2 = オフ、1 つの wake ピンがアクティブ、CAN トランシーバ = オフ、周期的センシング ウェーク = オフ、周期的ウェーク = オフ<br>$VSUP, VSUPB = 6.5V \sim 28V, T_J : -40^\circ C \sim 150^\circ C$                                                                   | 18  | 50  | μA |

| <b>機能ごとの追加電流消費量 (VSUP および VSUPB を含む)</b> |                                                                                  |                                                                                                                                                                                                                                       |     |     |    |

| ISUP <sub>STDBY-CS-WK-85C</sub>          | スタンバイまたはスリープ モードで、WAKE1、WAKE2、WAKE3 ピンに対して周期センシング ウェークが有効な場合の追加電流 <sup>(1)</sup> | スリープ モード、周期的センシング ウェークがイネーブル、 $VSUP = 14V, T_J \leq 85^\circ C, \text{TIMERx}$ (オン幅 = 1ms、周期 = 100ms)                                                                                                                                 | 2.5 | 8   | μA |

| ISUP <sub>STDBY-CS-WK4-85C</sub>         | WAKE4 ピンのスタンバイ モードまたはスリープ モードで、周期的センシング ウェークがイネーブルになっている場合の追加の電流 <sup>(1)</sup>  | スリープ モード、周期的センシング ウェークがイネーブル、 $VSUP = 14V, T_J \leq 85^\circ C, \text{TIMERx}$ (オン幅 = 1ms、周期 = 100ms)                                                                                                                                 | 45  | 50  | μA |

## 6.6 電源の特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                            | テスト条件                                           | 最小値                                                                                                                | 標準値 | 最大値 | 単位 |

|----------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|-----|----|

| ISUP <sub>STDBY-HSS-NOLOAD</sub> | スタンバイ モード:各 HSS を有効にしたときの追加の電源電流消費              |                                                                                                                    | 35  | 60  | μA |

| ISUP <sub>SLP-VCC2-85C</sub>     | スリープ モード:VCC2 を有効にしたときの追加電源電流                   |                                                                                                                    | 25  | 35  | μA |

| ISUP <sub>SLP-VCC1-85C</sub>     | スリープ モード:VCC1 降圧レギュレータがイネーブルのときの追加の電源電流         | VCC1= オン (無負荷)、VCC1 シンク = オフ、拡散スペクトラム変調 = オフ、VSUP = 6.5V ~ 12V、 $T_J : -40^\circ\text{C} \sim 85^\circ\text{C}$    | 30  | 39  | μA |

| ISUP <sub>SLP-swk</sub>          | 選択的ウェークがオンで、CAN バスで WUP が発生し、バスがアクティブな場合の追加電流   | 選択的ウェークが有効で、バスがアクティブな場合の追加スリープ電流、VCC1 と VCC2 = オフ                                                                  | 480 | 550 | μA |

| ISUP <sub>SLP-CANWK-85C</sub>    | スリープ モード:CAN トランシーバがウェイク機能を持つ場合の追加電源電流          | スリープ モード:CAN トランシーバがウェイク機能を持つ場合の追加電源電流、VSUP = 6.5V ~ 12V、 $T_J : -40^\circ\text{C} \sim 85^\circ\text{C}$          | 7   | 10  | μA |

| ISUP <sub>SLP-wake-85C</sub>     | スリープ モード:WAKE ピンによる追加の電源電流消費                    | スリープ モード:ウェーク機能が有効で、WAKE ピンがフローティングまたはグランド接続の場合に、各 WAKE ピンから生じる追加電流。                                               | 0.5 | 1   | μA |

| ISUP <sub>WD-T0-85C</sub>        | スタンバイまたはスリープ モード:WD タイプがタイムアウトに設定されている場合の追加供給電流 | スタンバイまたはスリープ モード:WD タイプがタイムアウトに設定されている場合の追加供給電流。VSUP = 6.5V ~ 12V、 $T_J : -40^\circ\text{C} \sim 85^\circ\text{C}$ | 2   | 2.5 | μA |

| ISUP <sub>WD-85C</sub>           | スタンバイ モード:WD がウインドウまたはQ/A タイプに設定されているときの追加の電源電流 | スタンバイ モード:WD がウインドウまたはQ/A に設定されているときの追加の電源電流。VSUP = 6.5V ~ 12V、 $T_J : -40^\circ\text{C} \sim 85^\circ\text{C}$    | 40  | 50  | μA |

### VSUP 電源監視

|                             |                                            |                                 |      |     |      |    |

|-----------------------------|--------------------------------------------|---------------------------------|------|-----|------|----|

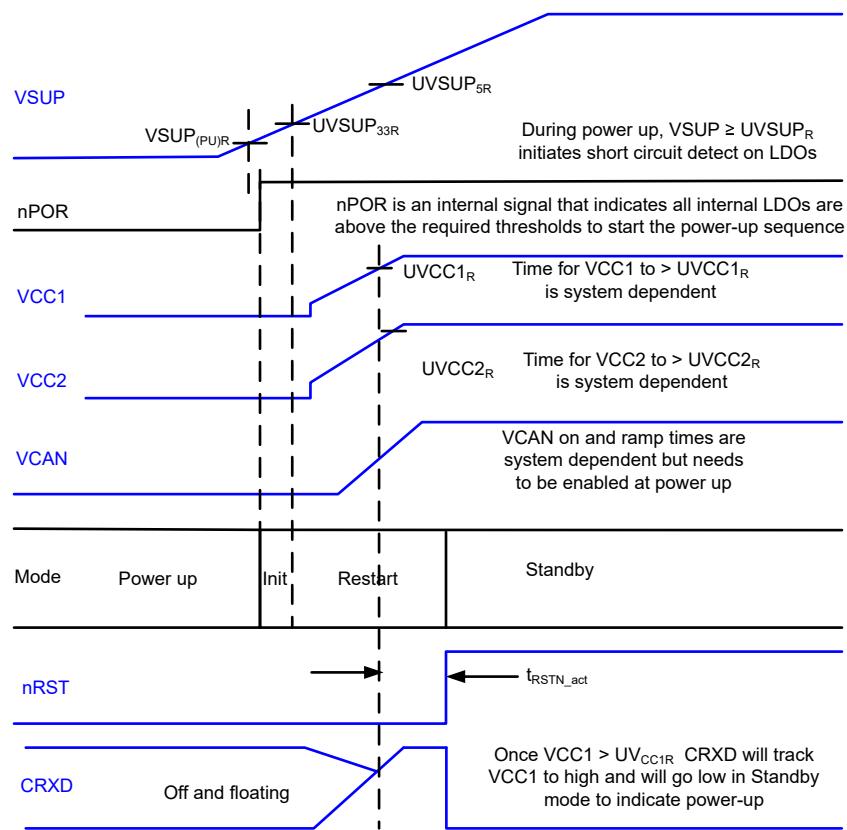

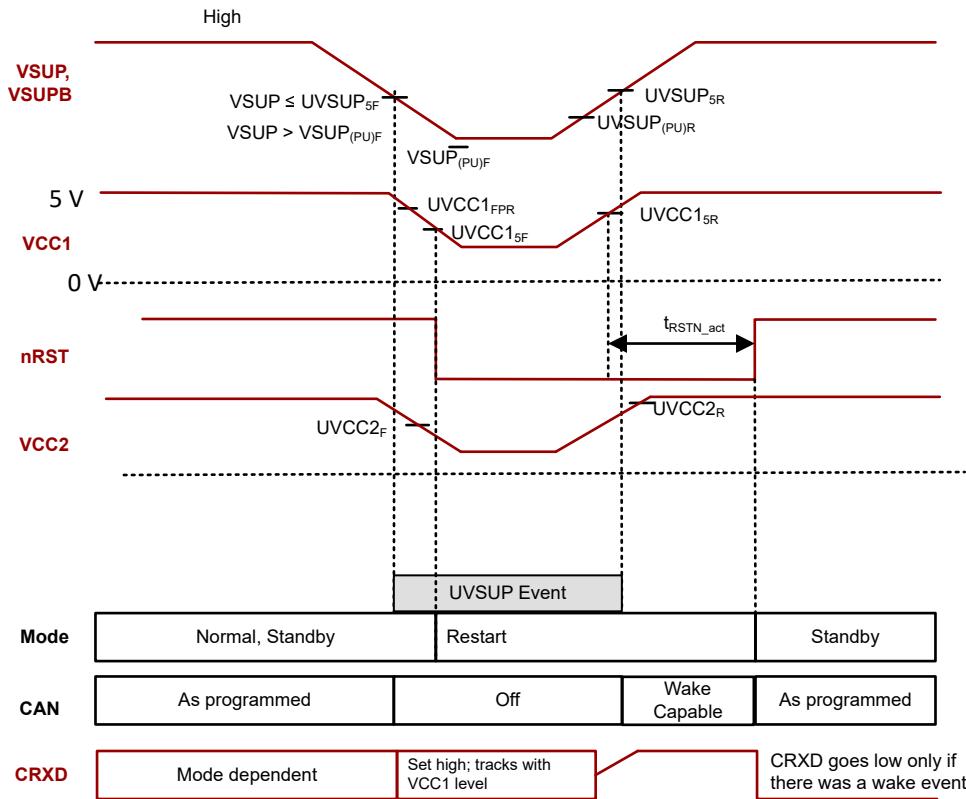

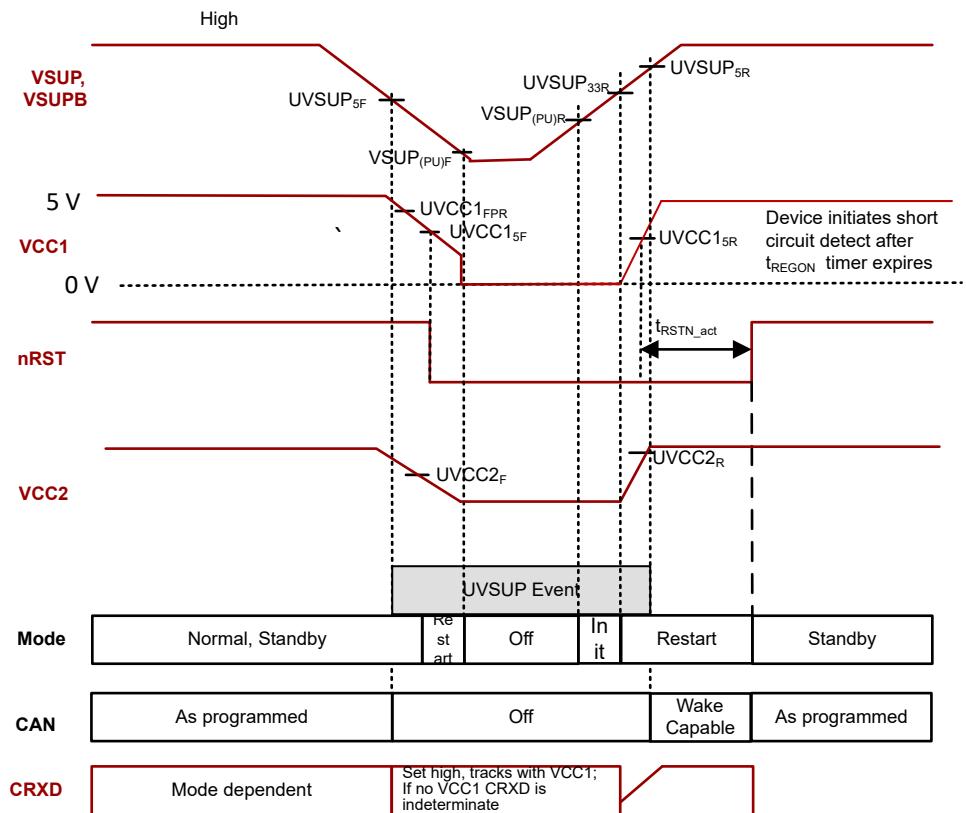

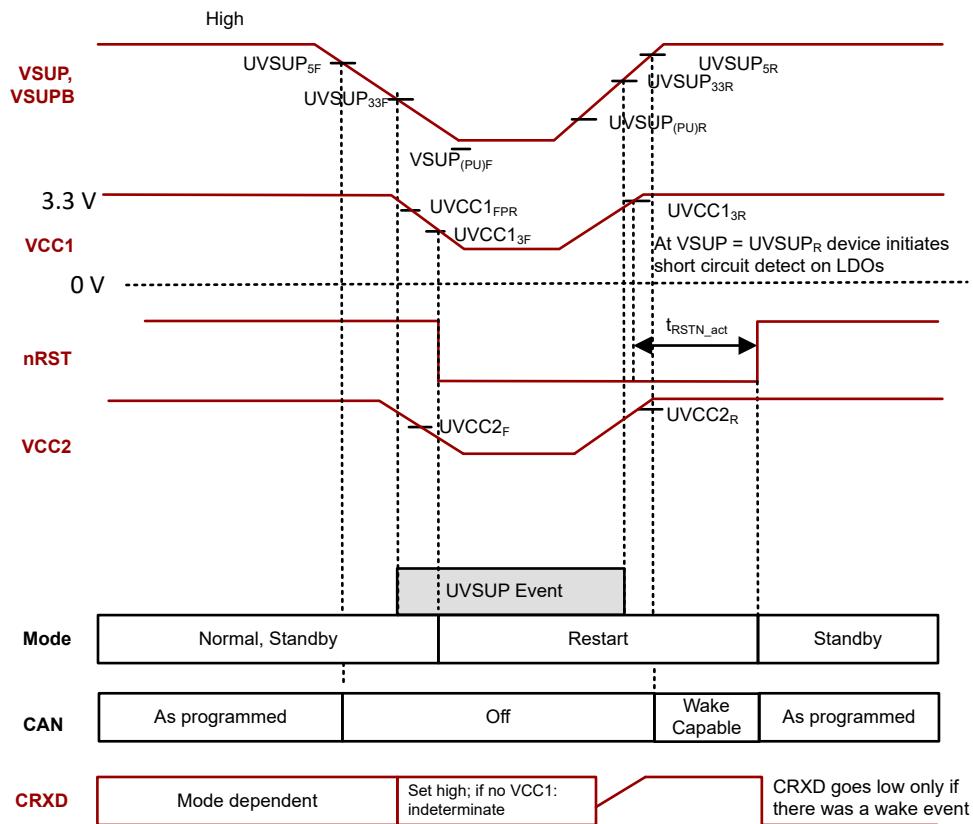

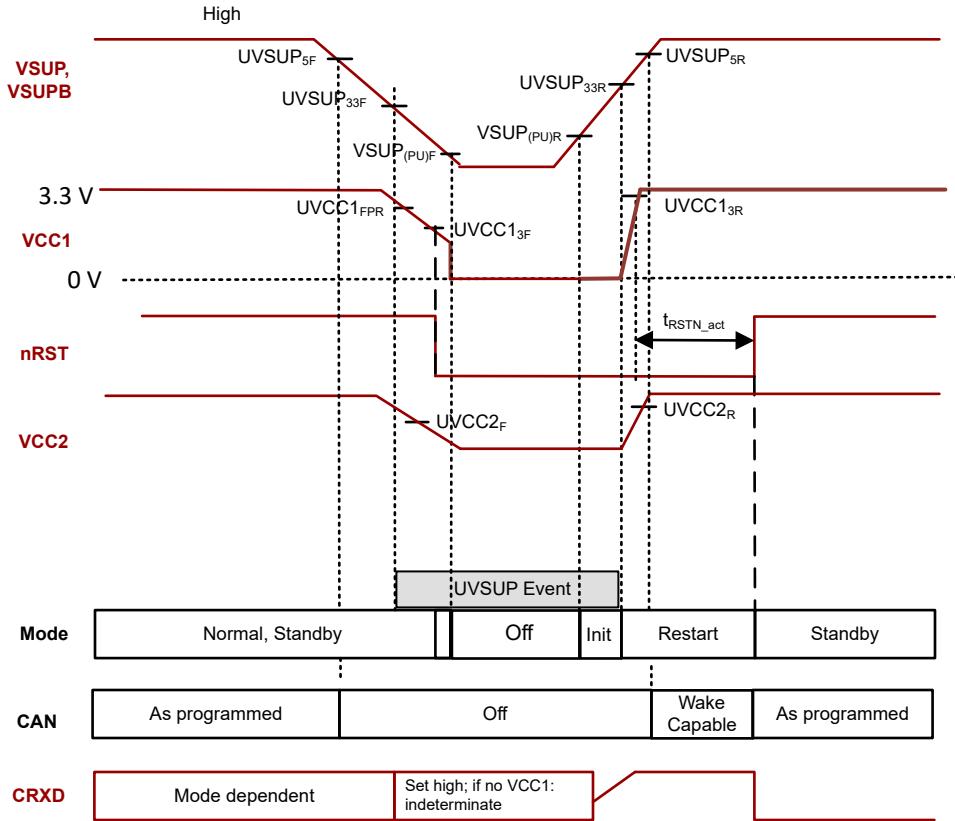

| VSUP <sub>(PU)R</sub>       | 電源オン検出                                     | VSUP 立ち上がり、図 10-6 および図 10-4 を参照 | 3.1  | 3.4 | 3.7  | V  |

| VSUP <sub>(PU)F</sub>       | 電源オフ検出                                     | VSUP 立ち下がり、図 10-6 および図 10-4 を参照 | 2.7  | 3   | 3.3  | V  |

| VSUP <sub>(PU)HYS</sub>     | 電源オフ検出ヒステリシス                               |                                 | 50   | 150 | 550  | mV |

| UVSUP <sub>5R</sub>         | 電源低電圧回復                                    | VSUP 立ち上がり、図 10-3 および図 10-4 を参照 | 4.9  |     | 5.5  | V  |

| UVSUP <sub>5F</sub>         | 電源低電圧検出                                    | VSUP 立ち下がり、図 10-3 および図 10-4 を参照 | 4.5  |     | 5.1  | V  |

| UVSUP <sub>5HYS</sub>       | 電源低電圧検出ヒステリシス                              |                                 | 400  |     |      | mV |

| UVSUP <sub>33R</sub>        | 電源低電圧回復                                    | VSUP 立ち上がり、図 10-5 および図 10-6 を参照 | 3.7  |     | 4.4  | V  |

| UVSUP <sub>33F</sub>        | 電源低電圧検出                                    | VSUP 立ち下がり、図 10-5 および図 10-6 を参照 | 3.55 |     | 4.25 | V  |

| UVSUP <sub>33HYS</sub>      | 電源低電圧検出ヒステリシス                              |                                 | 150  |     |      | mV |

| VSUP <sub>UVLOVCC1(F)</sub> | VCC1 レギュレータがオフになる、VSUP の低電圧ロックアウト下降スレッショルド | 立ち下がり VSUP、VSUP_UVLO_SEL = 0b   | 3.1  |     | 3.3  | V  |

## 6.6 電源の特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                         | テスト条件                                                                    | 最小値                                                                              | 標準値  | 最大値  | 単位   |   |

|-------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|---|

| VSUP <sub>UVLOVCC1(R)</sub>   | 立ち上がり VSUP、VSUP_UVLO_SEL = 0b                                            | 3.3                                                                              | 3.5  | 3.5  | V    |   |

| VSUP <sub>UVLOVCC1(F)</sub>   | 立ち下がり VSUP、VSUP_UVLO_SEL = 1b                                            | 4.9                                                                              | 5.1  | 5.1  | V    |   |

| VSUP <sub>UVLOVCC1(R)</sub>   | 立ち上がり VSUP、VSUP_UVLO_SEL = 1b                                            | 5.1                                                                              | 5.3  | 5.3  | V    |   |

| <b>VSUPB - 降圧レギュレータ入力電源</b>   |                                                                          |                                                                                  |      |      |      |   |

| ISUPB <sub>VCC1-OFF-85c</sub> | 降圧がディスエーブルのときの VSUPB 電源電流                                                | スリープ モード、VCC1 ディスエーブル、VSUPB = 12V、 $T_J \leq 85^\circ\text{C}$                   | 1    | 3    | μA   |   |

| ISUPB <sub>VCC1-ON-85c</sub>  | 降圧がイネーブルだが負荷電流がないときの VSUPB 電源電流、VCC1 = 5V                                | VCC1 イネーブル、無負荷、VCC1 シンク ディスエーブル、自動モード、VSUPB = 12V、 $T_J \leq 85^\circ\text{C}$   | 3    | 8    | μA   |   |

| ISUPB <sub>VCC1-ON-85c</sub>  | 降圧が有効で負荷電流がない場合の VSUPB 電源電流、VCC1 = 3.3V                                  | VCC1 イネーブル、無負荷、VCC1 シンク ディスエーブル、自動モード、VSUPB = 12V、 $T_J \leq 85^\circ\text{C}$   | 2.5  | 5    | μA   |   |

| <b>VHSS - ハイサイドスイッチ電源入力</b>   |                                                                          |                                                                                  |      |      |      |   |

| IVHSS <sub>SLP</sub>          | スリープモードでのハイサイドスイッチ電源 (VHSS) の消費電流                                        | スリープモード、サイクリックセンシングウェーク = オフ、 $-40^\circ\text{C} \leq T_J \leq 85^\circ\text{C}$ | 1    | 2    | μA   |   |

| IHSS <sub>NOLOAD</sub>        | 各 HSS がオンの場合、さらに電流が引き込まれます                                               | 各 HSS がオンの場合、HSS 出力に負荷なし                                                         | 100  | 140  | μA   |   |

| UVHSS <sub>R</sub>            | ハイサイドスイッチ電源の低電圧回復                                                        | VHSS 立ち上がり                                                                       | 4.6  | 4.9  | V    |   |

| UVHSS <sub>F</sub>            | ハイサイドスイッチ電源の低電圧検出                                                        | VHSS 立ち下がり                                                                       | 4.4  | 4.7  | V    |   |

| UVHSS <sub>HYS</sub>          | ハイサイドスイッチ電源の低電圧検出ヒステリシス                                                  |                                                                                  | 100  |      | mV   |   |

| OVHSS <sub>F</sub>            | VHSS 過電圧立ち下がりスレッショルド。ハイサイドスイッチを再度イネーブルにするには VHSS をこのスレッショルドより低くする必要があります | VHSS 立ち下がり                                                                       | 18.8 | 21.2 | V    |   |

| OVHSS <sub>R</sub>            | VHSS 過電圧立ち上がりスレッショルド。HSS_OV_DIS = 0b の場合ハイサイドスイッチはオフ                     | VHSS 立ち上がり                                                                       | 20   | 22   | V    |   |

| OVHSS <sub>HYS</sub>          | VHSS 過電圧スレッショルドヒステリシス                                                    |                                                                                  | 800  | 1200 | mV   |   |

| <b>VCC1 - 降圧レギュレータ出力</b>      |                                                                          |                                                                                  |      |      |      |   |

| VCC1 <sub>5</sub>             | レギュレートされた出力範囲、5V バージョン                                                   | VSUPB = 6V ~ 28V、ICC1 = 0 ~ 1A、PWM モード                                           | 4.9  | 5    | 5.1  | V |

| VCC1 <sub>5</sub>             | レギュレートされた出力範囲、5V バージョン                                                   | VSUPB = 6V ~ 28V、ICC1 = 0 ~ 1A、PFM モード                                           | 4.85 | 5    | 5.15 | V |

| VCC1 <sub>33</sub>            | レギュレートされた出力範囲、3.3V バージョン                                                 | VSUPB = 4.5V ~ 28V、ICC1 = 0 ~ 1A、PWM モード                                         | 3.23 | 3.3  | 3.37 | V |

| VCC1 <sub>33</sub>            | レギュレートされた出力範囲、3.3V バージョン                                                 | VSUPB = 4.5V ~ 28V、ICC1 = 0 ~ 1A、PFM モード                                         | 3.20 | 3.3  | 3.40 | V |

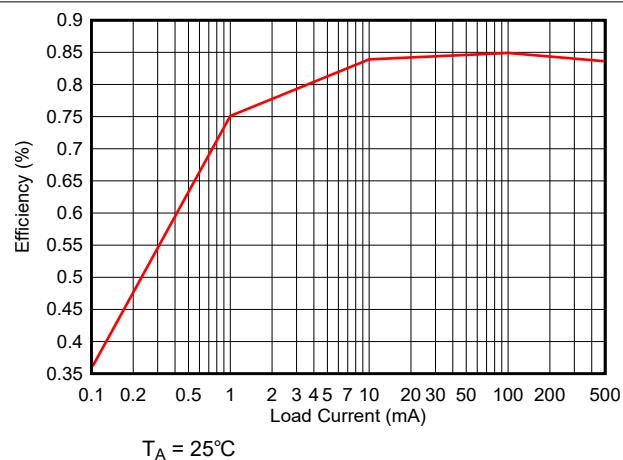

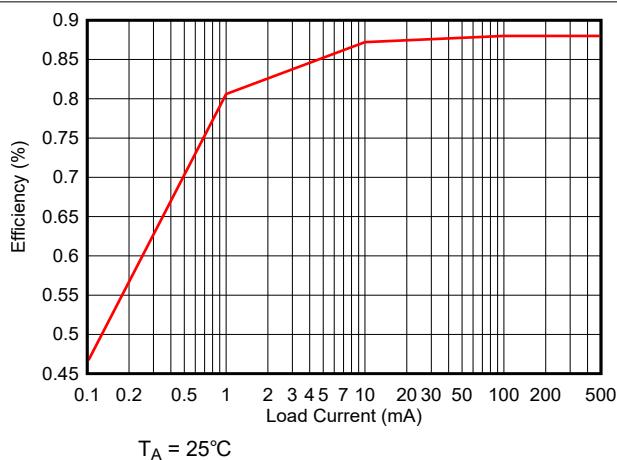

| VCC1 <sub>EFF</sub>           | 降圧コンバータの効率                                                               | ICC1 = 500mA、VCC1 電流シンクがディスエーブル。VCC1 = 3.3V、VSUPB = 12V、PWM モード                  |      | 0.85 |      |   |

## 6.6 電源の特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                | テスト条件                                                           | 最小値                                              | 標準値  | 最大値   | 単位               |

|----------------------|-----------------------------------------------------------------|--------------------------------------------------|------|-------|------------------|

| $V_{CC1_{EFF}}$      | ICC1 = 100mA、VCC1 電流シンクがディスエーブル。VCC1 = 3.3V、VSUPB = 12V、PFM モード |                                                  | 0.80 |       |                  |

|                      | ICC1 = 10mA、VCC1 電流シンクがディスエーブル。VCC1 = 3.3V、VSUPB = 12V、PFM モード  |                                                  | 0.8  |       |                  |

|                      | ICC1 = 1mA、VCC1 電流シンクがディスエーブル。VCC1 = 3.3V、VSUPB = 12V、PFM モード   |                                                  | 0.7  |       |                  |

|                      | ICC1 = 0.1mA、VCC1 電流シンクがディスエーブル。VCC1 = 3.3V、VSUPB = 12V、PFM モード |                                                  | 0.4  |       |                  |

| $R_{DS-ON-LS}$       | ローサイド MOSFET オン抵抗                                               | ICC1 = 0.3A、VSUPB = 12V                          | 0.24 |       | $\Omega$         |

| $R_{DS-ON-HS}$       | ハイサイド MOSFET オン抵抗                                               | ICC1 = 0.3A、VSUPB = 12V                          | 0.45 |       | $\Omega$         |

| ICC1                 | VCC1 出力電流                                                       | レギュレーション時の VCC1、VSUPB = 12V                      | 0    | 1     | A                |

| ICC1 <sub>SINK</sub> | VCC1 がオンのときの VCC1 電流シンク能力 (イネーブルの場合)                            | VSUPB = 12V、レジスタ 8'h0C[4]= 0b および 8'h0D[3]= 0b   |      | -10   | $\mu\text{A}$    |

|                      |                                                                 | VSUPB = 12V、レジスタ 8'h0C[4]= 0b および 8'h0D[3]= 1b   |      | -1000 | $\mu\text{A}$    |

| $R_{QOD-VCC1}$       | VCC1 がディスエーブルのときの VCC1 の出力放電抵抗                                  | VCC1 が無効で、外部から VCC1 = 100mV (3.3V VCC1 オプションの場合) | 0.9  |       | $\text{k}\Omega$ |

| $R_{QOD-VCC1}$       | VCC1 がディスエーブルのときの VCC1 の出力放電抵抗                                  | VCC1 が無効で、外部から VCC1 = 100mV (5V VCC1 オプションの場合)   | 0.9  |       | $\text{k}\Omega$ |

| ICC1 <sub>SC</sub>   | 降圧ハイサイド電流制限                                                     | レジスタ 8'h65[0] = 0                                | 1.2  | 1.6   | 1.95             |

| ICC1 <sub>SC</sub>   | 降圧ハイサイド電流制限                                                     | レジスタ 8'h65[0]=1                                  | 0.6  | 0.8   | 1                |

| ICC1 <sub>LS</sub>   | 降圧ローサイド電流制限                                                     | レジスタ 8'h65[0] = 0                                | 0.9  | 1.1   | 1.3              |

| ICC1 <sub>LS</sub>   | 降圧ローサイド電流制限                                                     | レジスタ 8'h65[0]=1                                  | 0.45 | 0.55  | 0.65             |

| UVCC15FPR            | VCC1 低電圧回復スレッショルドの事前警告                                          | VCC1 の立ち上がり                                      | 4.65 | 4.78  | V                |

|                      | VCC1 低電圧検出スレッショルドの事前警告                                          | VCC1 の立ち下がり                                      | 4.55 | 4.67  | V                |

| UVCC15R1             | VCC1 低電圧回復スレッショルド 1                                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 00b                 | 4.60 | 4.72  | V                |

| UVCC15F1             | VCC1 低電圧検出スレッショルド 1                                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 00b                 | 4.50 | 4.62  | V                |

| UVCC15R2             | VCC1 低電圧回復スレッショルド 2                                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 01b                 | 3.85 | 4.00  | V                |

| UVCC15F2             | VCC1 低電圧検出スレッショルド 2                                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 01b                 | 3.75 | 3.90  | V                |

| UVCC15R3             | VCC1 低電圧回復スレッショルド 3                                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 10b                 | 3.25 | 3.40  | V                |

| UVCC15F3             | VCC1 低電圧検出スレッショルド 3                                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 10b                 | 3.15 | 3.30  | V                |

| UVCC15R4             | VCC1 低電圧回復スレッショルド 4                                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 11b                 | 4.60 | 4.72  | V                |

## 6.6 電源の特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                   |                                                 | テスト条件                                                                            | 最小値   | 標準値    | 最大値  | 単位 |

|-------------------------|-------------------------------------------------|----------------------------------------------------------------------------------|-------|--------|------|----|

| UVCC1 <sub>5F4</sub>    | VCC1 低電圧検出スレッショルド 4                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 11b                                                 | 3.45  | 3.6    | 3.75 | V  |

| UVCC1 <sub>5HYS</sub>   | 低電圧検出 5V ヒステリシス、VCC1 は 5V に設定                   | レジスタ 8'h0E[4:3] = 00b, 01b または 10b                                               | 50.00 | 150.00 | mV   |    |

| UVCC1 <sub>5HYS4</sub>  | 低電圧検出 5V ヒステリシス、VCC1 は 5V に設定                   | レジスタ 8'h0E[4:3] = 11b                                                            |       | 1200   |      | mV |

| UVCC1 <sub>33RPR</sub>  | VCC1 低電圧回復スレッショルドの事前警告                          | VCC1 の立ち上がり                                                                      | 3.1   | 3.2    | 3.28 | V  |

| UVCC1 <sub>33FPR</sub>  | VCC1 低電圧検出スレッショルドの事前警告                          | VCC1 の立ち下がり                                                                      | 3     | 3.1    | 3.2  | V  |

| UVCC1 <sub>33R1</sub>   | VCC1 低電圧回復スレッショルド 1                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 00b                                                 | 3     | 3.1    | 3.2  | V  |

| UVCC1 <sub>33F1</sub>   | VCC1 低電圧検出スレッショルド 1                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 00b                                                 | 2.95  | 3.05   | 3.15 | V  |

| UVCC1 <sub>33R2</sub>   | VCC1 低電圧回復スレッショルド 2                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 01b                                                 | 2.55  | 2.65   | 2.75 | V  |

| UVCC1 <sub>33F2</sub>   | VCC1 低電圧検出スレッショルド 2                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 01b                                                 | 2.5   | 2.6    | 2.7  | V  |

| UVCC1 <sub>33R3</sub>   | VCC1 低電圧回復スレッショルド 3                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 10b                                                 | 2.25  | 2.35   | 2.45 | V  |

| UVCC1 <sub>33F3</sub>   | VCC1 低電圧検出スレッショルド 3                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 10b                                                 | 2.2   | 2.3    | 2.4  | V  |

| UVCC1 <sub>33R4</sub>   | VCC1 低電圧回復スレッショルド 4                             | VCC1 立ち上がり、レジスタ 8'h0E[4:3] = 11b                                                 | 3     | 3.1    | 3.2  | V  |

| UVCC1 <sub>33F4</sub>   | VCC1 低電圧検出スレッショルド 4                             | VCC1 立ち下がり、レジスタ 8'h0E[4:3] = 11b                                                 | 2.2   | 2.3    | 2.4  | V  |

| UVCC1 <sub>33HYS</sub>  | 低電圧検出ヒステリシス、VCC1 は 3.3V に設定されています               | レジスタ 8'h0E[4:3] = 00b, 01b または 10b                                               | 30    | 140    | mV   |    |

| UVCC1 <sub>33HYS4</sub> | 低電圧検出ヒステリシス、VCC1 は 3.3V に設定されています               | レジスタ 8'h0E[4:3] = 11b                                                            |       | 800    |      | mV |

| VDROP-OUT-33            | ドロップアウト電圧。VCC1 を 3.3V に設定します                    | VSUPB = 3.5V, ICC1 = 0.5A, F <sub>SW</sub> = 2.2MHz, L <sub>OUT-ESR</sub> = 50mΩ |       | 0.35   |      | V  |

| VDROP-OUT-33            | ドロップアウト電圧。VCC1 を 3.3V に設定します                    | VSUPB = 3.5V, ICC1 = 1A, F <sub>SW</sub> = 2.2MHz, L <sub>OUT-ESR</sub> = 50mΩ   |       | 0.7    |      | V  |

| VDROP-OUT-5             | ドロップアウト電圧。VCC1 を 5V に設定します                      | VSUPB = 5V, ICC1 = 0.5A, F <sub>SW</sub> = 2.2MHz, L <sub>OUT-ESR</sub> = 50mΩ   |       | 0.35   |      | V  |

| VDROP-OUT-5             | ドロップアウト電圧。VCC1 を 5V に設定します                      | VSUPB = 5V, ICC1 = 1A, F <sub>SW</sub> = 2.2MHz, L <sub>OUT-ESR</sub> = 50mΩ     |       | 0.7    |      | V  |

| OVCC1 <sub>5R1</sub>    | スリープモードまたはフェイルセーフモードに移行するための過電圧 5V VCC1 スレッショルド | ランプアップ、レジスタ 8'h0C[7] = 0b                                                        | 5.3   | 5.45   | 5.6  | V  |

| OVCC1 <sub>5F1</sub>    | 過電圧 5V VCC1 スレッショルド                             | ランプダウン、レジスタ 8'h0C[7] = 0b                                                        | 5.2   | 5.35   | 5.5  | V  |

| OVCC1 <sub>5R2</sub>    | スリープモードまたはフェイルセーフモードに移行するための過電圧 5V VCC1 スレッショルド | ランプアップ、レジスタ 8'h0C[7] = 1b                                                        | 5.47  | 5.6    | 5.73 | V  |

| OVCC1 <sub>5F2</sub>    | 過電圧 5V VCC1 スレッショルド                             | ランプダウン、レジスタ 8'h0C[7] = 1b                                                        | 5.37  | 5.5    | 5.63 | V  |

| OVCC1 <sub>5HYS</sub>   | 過電圧 5V VCC1 スレッショルドのヒステリシス                      |                                                                                  |       | 100    |      | mV |

## 6.6 電源の特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                   | テスト条件                                                    | 最小値                        | 標準値  | 最大値  | 単位 |

|-------------------------|----------------------------------------------------------|----------------------------|------|------|----|

| OVCC1 <sub>33R1</sub>   | スリープモードまたはフェイルセーフモードに移行するための過電圧 3.3V VCC スレッショルド         | ランプアップ、レジスタ 8'h0C [7] = 0b | 3.5  | 3.6  | V  |

| OVCC1 <sub>33F1</sub>   | 過電圧 3.3V VCC スレッショルド                                     | ランプダウン、レジスタ 8'h0C[7] = 0b  | 3.4  | 3.5  | V  |

| OVCC1 <sub>33R2</sub>   | スリープモードまたはフェイルセーフモードに移行するための過電圧 3.3V VCC スレッショルド         | ランプアップ、レジスタ 8'h0C [7] = 1b | 3.6  | 3.7  | V  |

| OVCC1 <sub>33F2</sub>   | 過電圧 3.3V VCC スレッショルド                                     | ランプダウン、レジスタ 8'h0C[7] = 1b  | 3.55 | 3.65 | V  |

| OVCC1 <sub>33HYS1</sub> | 過電圧 3.3V VCC スレッショルドのヒステリシス                              | レジスタ 8'h0C[7] = 0b         |      | 100  | mV |

| OVCC1 <sub>33HYS2</sub> | 過電圧 3.3V VCC スレッショルドのヒステリシス                              | レジスタ 8'h0C[7] = 1b         |      | 50   | mV |

| VCC1 <sub>5SC</sub>     | 5V バージョンにおいてスリープ モードまたはフェイルセーフ モードに移行する VCC1 短絡スレッショルド   |                            | 1.7  | 2    | V  |

| VCC1 <sub>33SC</sub>    | 3.3V バージョンにおいてスリープ モードまたはフェイルセーフ モードに移行する VCC1 短絡スレッショルド |                            | 1.12 | 1.22 | V  |

### VCC2 - LDO レギュレータ出力

|                      |                                     |                                                                                     |      |      |      |    |

|----------------------|-------------------------------------|-------------------------------------------------------------------------------------|------|------|------|----|

| VCC2nom              | 負荷レギュレーションを含む安定化出力電圧                | VSUP = 14V、ICC2 = 5 ~ 200mA                                                         | 4.9  | 5    | 5.1  | V  |

| VCC2reg              | 負荷レギュレーションおよびライン レギュレーションを含む安定化出力電圧 | VSUP = 8V ~ 18V、ICC2 = 10µA ~ 200mA                                                 | 4.85 | 5    | 5.15 | V  |

| VCC2red              | 負荷範囲が縮小された場合の安定化出力電圧                | VSUP = 8V ~ 18V、ICC2 = 10µA ~ 5mA、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ | 4.95 | 5    | 5.05 | V  |

| ICC2 <sub>LIM</sub>  | VCC2 出力電流制限                         | VCC2 = 2.5 V                                                                        | 250  | 650  | mA   |    |

| UVCC2 <sub>R</sub>   | 低電圧回復 VCC2                          | VCC2 の立ち上がり                                                                         | 4.6  | 4.9  | V    |    |

| UVCC2 <sub>F</sub>   | 低電圧検出 VCC2                          | VCC2 の立ち下がり                                                                         | 4.5  | 4.75 | V    |    |

| UVCC2 <sub>HYS</sub> | 低電圧検出 VCC2 ヒステリシス                   |                                                                                     | 70   | 125  | 175  | mV |

| OVCC2 <sub>R</sub>   | 過電圧 CAN LDO スレッショルド                 | をランプアップ                                                                             | 5.37 | 5.5  | 5.63 | V  |

| OVCC2 <sub>F</sub>   | 過電圧 CAN LDO スレッショルド                 | をランプダウン                                                                             | 5.25 | 5.38 | 5.5  | V  |

| OVCC2 <sub>HYS</sub> | 過電圧 CAN LDO スレッショルドのヒステリシス          |                                                                                     |      | 125  |      | mV |

| VCC2 <sub>SC</sub>   | VCC2 LDO 短絡スレッショルド                  | VSUP ≥ UVSP                                                                         | 1.7  | 2.3  | V    |    |

| $V_{5DROP2}$         | ドロップアウト電圧 (5V LDO 出力 VCC2)          | VSUP = 5V、ICC2 = 100mA                                                              |      | 750  |      | mV |

### VCAN - CAN 電源入力

|                             |                       |                                                                                                  |   |     |    |

|-----------------------------|-----------------------|--------------------------------------------------------------------------------------------------|---|-----|----|

| I <sub>CAN-NORMAL-REC</sub> | 通常モード:CAN FD バスリセッショブ | 通常モード:リセッショブ、 $V_{TXD} = VCC1$ 、 $VCC1$ 、 $VCC2$ = 無負荷                                           | 3 | 5   | mA |

| I <sub>CAN-NORMAL-DOM</sub> | 通常モード:CAN FD バスドミナント  | 通常モード:ドミナント、 $V_{TXD} = 0V$ 、 $R_L = 60\Omega$ 、 $C_L$ = 開放、標準バス負荷、 $VCC1$ 、 $VCC2$ = 無負荷        |   | 60  | mA |

|                             |                       | 通常モード:ドミナント、 $V_{TXD} = 0V$ 、 $R_L = 50\Omega$ and $C_L$ = 開放、高バス負荷、 $VCC1$ および $VCC2$ = 無負荷     |   | 65  | mA |

|                             |                       | 通常モード:バス故障のドミナント、 $V_{TXD} = 0V$ 、 $CANH = -25V$ 、 $R_L$ および $C_L$ = 開放、 $VCC1$ および $VCC2$ = 無負荷 |   | 100 | mA |

## 6.6 電源の特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                | テスト条件              | 最小値        | 標準値 | 最大値  | 単位 |

|----------------------|--------------------|------------|-----|------|----|

| UVCAN <sub>R</sub>   | 電源低電圧回復            | VCAN 立ち上がり | 4.6 | 4.85 | V  |

| UVCAN <sub>F</sub>   | 電源低電圧検出            | VCAN 立ち下がり | 4.5 | 4.75 | V  |

| UVCAN <sub>HYS</sub> | VCAN 電源低電圧検出ヒステリシス |            | 100 |      | mV |

- (1) WAKE1、WAKE2、WAKE3 ピンの周期センシングは、電流消費を減らすために低消費電力の 10kHz 内部クロックを使用します。WAKE4 ピンの周期センシングは 1MHz の内部クロックを使用し、10kHz クロックより多くの電流を消費します。消費電流を低減するため、周期的センシングを行う場合、WAKE1-3 ピンを使用することを推奨します。

## 6.7 電気的特性

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                                        | テスト条件                                                                                                       | 最小値                                                                                                                                                                  | 標準値  | 最大値  | 単位  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|

| <b>CAN ドライバ</b>                              |                                                                                                             |                                                                                                                                                                      |      |      |     |

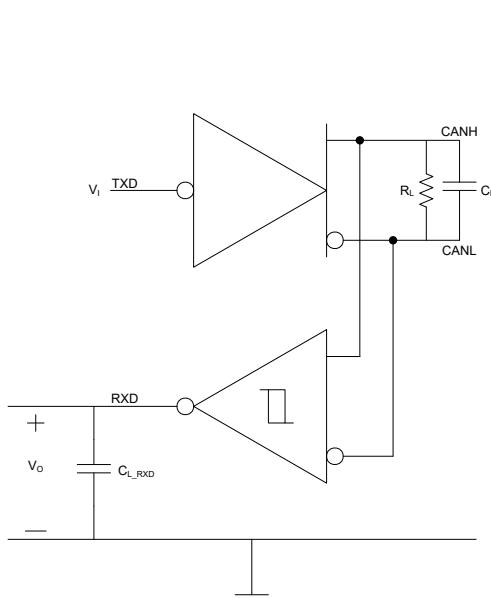

| V <sub>CANH(D)</sub>                         | バス出力電圧 (ドミナント) CANH                                                                                         | 図 7-4 を参照、 $V_{CTXD} = 0V$ 、 $R_L = 45\Omega \sim 65\Omega$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$                                                               | 3    | 4.26 | V   |

| V <sub>CANL(D)</sub>                         | バス出力電圧 (ドミナント) CANL                                                                                         |                                                                                                                                                                      | 0.75 | 2.01 | V   |

| V <sub>CANH(R)</sub><br>V <sub>CANL(R)</sub> | バス出力電圧 (リセシブ)                                                                                               | 図 7-1 と 図 7-4 を参照、 $V_{CTXD} = VCC1$ 、 $R_L = \text{開放 (負荷なし)}$ 、 $R_{CM} = \text{開放}$                                                                               | 2    | 2.5  | V   |

| V <sub>(DIFF)</sub>                          | 最大差動電圧定格                                                                                                    |                                                                                                                                                                      | -42  | 42   | V   |

| V <sub>DIFF(D)</sub>                         | 差動出力電圧 (ドミナント)                                                                                              | 図 7-1 および 図 7-4 を参照、 $V_{CTXD} = 0V$ 、 $45\Omega \leq R_L \leq 65\Omega$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$                                                  | 1.5  | 3    | V   |

|                                              |                                                                                                             | 図 7-1 と 図 7-4 を参照、 $V_{CTXD} = 0V$ 、 $45\Omega \leq R_L \leq 70\Omega$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$                                                    | 1.5  | 3.3  | V   |

|                                              |                                                                                                             | 図 7-1 と 図 7-4 を参照、 $V_{CTXD} = 0V$ 、 $R_L = 2.24k\Omega$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$                                                                  | 1.5  | 5    | V   |

| V <sub>DIFF(R)</sub>                         | 差動出力電圧 (リセシブ)                                                                                               | 図 7-1 と 図 7-4 を参照、 $V_{CTXD} = VCC1$ 、 $R_L = 60\Omega$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$                                                                   | -120 | 12   | mV  |

|                                              |                                                                                                             | 図 7-1 と 図 7-4 を参照、 $V_{CTXD} = VCC1$ 、 $R_L = \text{開放 (負荷なし)}$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$                                                           | -50  | 50   | mV  |

| V <sub>CANH(INACT)</sub>                     | バスバイアス無効 (STBY) 時の CANH バス出力電圧                                                                              |                                                                                                                                                                      | -0.1 | 0.1  | V   |

| V <sub>CANL(INACT)</sub>                     | バスバイアス無効 (STBY) 時の CANL バス出力電圧                                                                              | 図 7-1 と 図 7-4 を参照、 $V_{CTXD} = VCC1$ 、 $R_L = \text{開放}$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$                                                                  | -0.1 | 0.1  | V   |

| V <sub>DIFF(INACT)</sub>                     | バスバイアス無効 (STBY) 時の CANH - CANL (リセシブ) のバス出力電圧                                                               |                                                                                                                                                                      | -0.2 | 0.2  | V   |

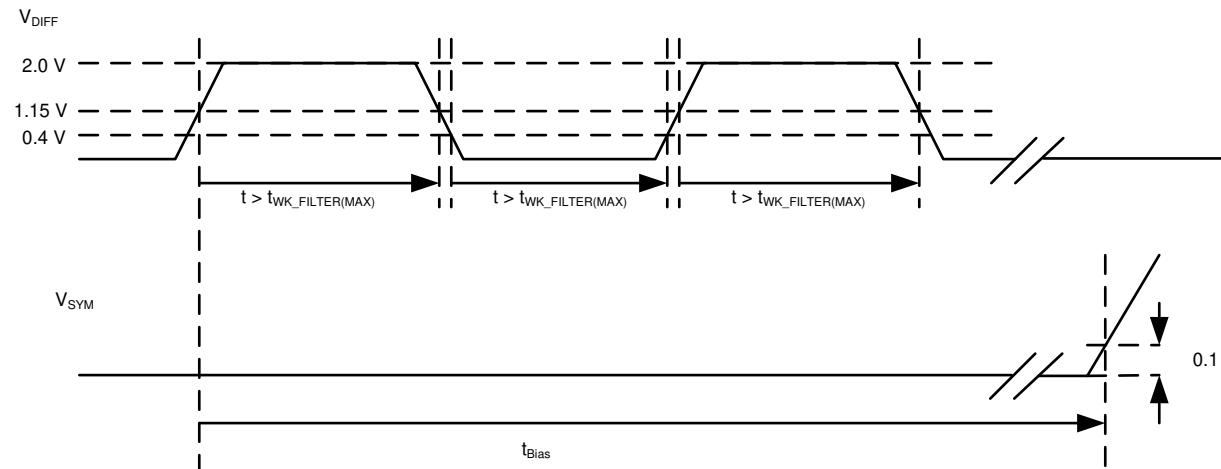

| V <sub>SYM</sub>                             | 出力対称 (ドミナントまたはリセシブ) ( $V_O(CANH) + V_O(CANL)$ ) / $V_{REC}$ 。<br>ここで、 $V_{REC} = V_{CANH(R)} + V_{CANL(R)}$ | 図 7-1 と 図 7-4 を参照、 $45\Omega \leq R_L \leq 65\Omega$ 、 $C_L = \text{開放}$ 、 $R_{CM} = \text{開放}$ 、 $C_1 = 4.7nF$ 、 $CTXD = 250\text{kHz}, 1\text{MHz}, 2.5\text{MHz}$ | 0.95 | 1.05 | V/V |

| V <sub>SYM_DC</sub>                          | DC 出力対称 ( $V_{CAN} - V_O(CANH) - V_O(CANL)$ )                                                               | 図 7-1 および 図 7-4 を参照、 $45\Omega \leq R_L \leq 65\Omega$ 、 $C_L = \text{オープン}$ 、 $R_{CM} = \text{オープン}$ 、 $C_1 = 4.7nF$                                                | -300 | 300  | mV  |

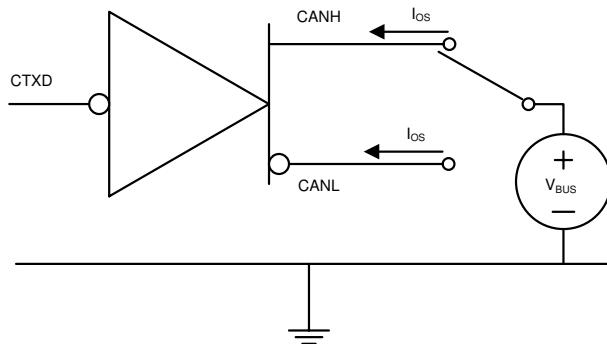

| I <sub>CANH(OS)</sub>                        | 短絡時の定常状態出力電流、図 7-1 と 図 7-8 を参照                                                                              | $-3.0V \leq V_{CANH} \leq +18.0V$ 、CANL = 開放、 $V_{CTXD} = 0V$                                                                                                        | -100 |      | mA  |

| I <sub>CANL(OS)</sub>                        |                                                                                                             | $-3.0V \leq V_{CANL} \leq +18.0V$ 、CANH = 開放、 $V_{CTXD} = 0V$                                                                                                        |      | 100  | mA  |

## 6.7 電気的特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                                 |                                                                                             | テスト条件                                                                                                                                    | 最小値  | 標準値  | 最大値 | 単位 |

|---------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|----|

| $I_{OS\_REC}$                         | 短絡時の定常状態出力電流、リセッショブ、 <a href="#">図 7-1</a> と <a href="#">図 7-8</a> を参照                      | $-42V \leq V_{BUS} \leq +42V, V_{BUS} = CANH = CANL$                                                                                     | -5   |      | 5   | mA |

| <b>CAN レシーバ</b>                       |                                                                                             |                                                                                                                                          |      |      |     |    |

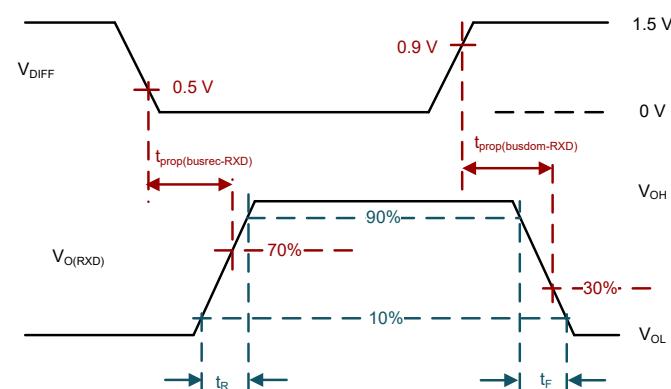

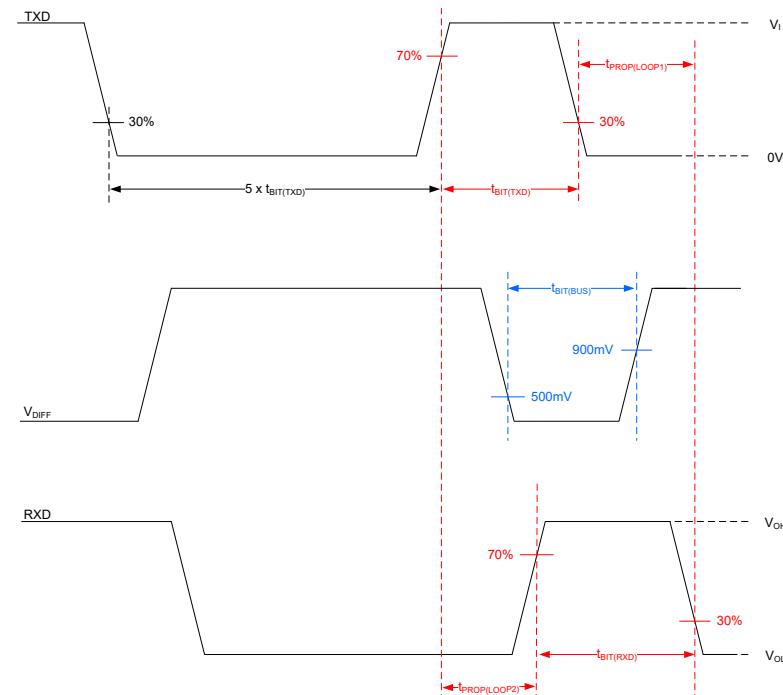

| $V_{DIFF\_RX(D)}$                     | レシーバがドミナント状態の差動入力電圧範囲、バスバイアスがアクティブ                                                          | $-12.0V \leq V_{CANL} \leq +12.0V$<br>$-12.0V \leq V_{CANH} \leq +12.0V, \text{図 7-5 と 表 8-3 を参照}$                                       | 0.9  | 8    |     | V  |

| $V_{DIFF\_RX(R)}$                     | レシーバリセッショブ状態の差動入力電圧範囲、バスバイアスがアクティブ                                                          |                                                                                                                                          | -3   | 0.5  |     | V  |

| $V_{HYS}$                             | 入力スレッショルド、通常、選択性ウェークモードのヒステリシス電圧                                                            |                                                                                                                                          |      | 135  |     | mV |

| $V_{DIFF\_RX(D\_INA\_CT)}$            | レシーバドミナント状態の差動入力電圧範囲、バスバイアスがアクティブ時                                                          | $-12.0V \leq V_{CANL} \leq +12.0V$<br>$-12.0V \leq V_{CANH} \leq +12.0V, \text{図 7-5 と 表 8-3 を参照}$                                       | 1.15 | 8    |     | V  |

| $V_{DIFF\_RX(R\_INA\_CT)}$            | レシーバリセッショブ状態の差動入力電圧範囲、バスバイアスがアクティブ中                                                         |                                                                                                                                          | -3   | 0.4  |     | V  |

| $V_{CM\_NORM}$                        | 同相モード範囲: 通常                                                                                 |                                                                                                                                          | -12  | 12   |     | V  |

| $V_{CM\_STBY}$                        | 同相モード範囲: スタンバイモード                                                                           |                                                                                                                                          | -12  | 12   |     | V  |

| $I_{LKG(OFF)}$                        | パワーオフ (電源オフ) バス入力リーク電流                                                                      | $CANH = CANL = 5V, VCAN = VSUP = 0$                                                                                                      |      |      | 5   | μA |

| $C_I$                                 | グランドに対する入力容量 (CANH または CANL)                                                                |                                                                                                                                          |      |      | 30  | pF |

| $C_{ID}$                              | 差動入力容量                                                                                      |                                                                                                                                          |      |      | 15  | pF |

| $R_{SE\_CANH/L}$                      | シングル エンド入力抵抗 (CANH または CANL)                                                                | $-2.0V \leq V_{CANH} \leq +7.0V$<br>$-2.0V \leq V_{CANL} \leq +7.0V$                                                                     | 6    | 50   |     | kΩ |

| $R_{DIFF\_PAS\_REC}$                  | パッシブ・リセッショブ期間中の差動入力抵抗                                                                       | $V_{TXD} = V_{IO}$ 、通常モード。 $-2.0V \leq V_{CANH} \leq +7.0V$<br>$-2.0V \leq V_{CANL} \leq +7.0V$                                          | 12   | 100  |     | kΩ |

| $R_{IN(M)}$                           | 入力抵抗マッチング: $[2x (R_{IN(CANH)} - R_{IN(CANL)}) / (R_{CANH} + R_{IN(CANL)})] \times 100 (\%)$ | $V_{CANH} = V_{CANL} = 5.0V$                                                                                                             | -1   | 1    |     | %  |

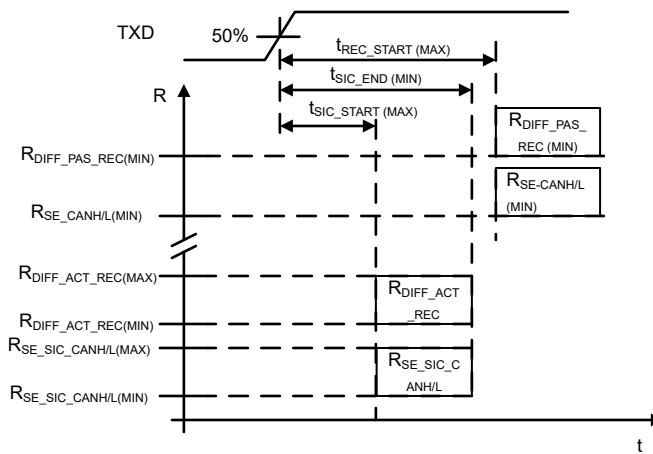

| <b>CAN 信号改善機能</b>                     |                                                                                             |                                                                                                                                          |      |      |     |    |

| $R_{SE\_ACT\_REC}$                    | アクティブ リセッショブ駆動位相時のシングル エンド SIC インピーダンス (CANH から 同相バイアス、CANL から 同相バイアス)                      | $2V \leq V_{CANH}, CANL \leq V_{CAN} - 2V$<br>TXD の立ち上がりエッジから、アクティブ リセッショブ期間が経過するまでの時間 ( $t_{SIC\_END}$ ).<br><a href="#">See 図 7-17</a> | 37.5 | 66.5 |     | Ω  |

| $R_{DIFF\_ACT\_REC}$                  | アクティブ リセッショブ駆動位相の差動入力抵抗 (CANH から CANL)                                                      | $2V \leq V_{CANH}, CANL \leq V_{CAN} - 2V$<br>TXD の立ち上がりエッジから、アクティブ リセッショブ期間が経過するまでの時間 ( $t_{SIC\_END}$ ).<br><a href="#">See 図 7-17</a> | 75   | 133  |     | Ω  |

| <b>LIMP 出力 (オープンドレイン)</b>             |                                                                                             |                                                                                                                                          |      |      |     |    |

| $V_{OL}$                              | オープンドレイン出力電圧 (アクティブ Low)                                                                    | $4.5V < V < 28V, I_{LIMP} = -6mA$                                                                                                        | 0.5  | 1    |     | V  |

| $I_{LKG(LIMP)}$                       | 出力電流 (非アクティブ)                                                                               | $V_{LIMP} = 0V \sim 28V$                                                                                                                 | -2   | 2    |     | μA |

| $V_{OL-LSS1}$                         | ローサイド出力電圧 (ローサイド スイッチとして構成されている場合)                                                          | $5V < VSUP < 28V, I_{LSS} = -20mA$                                                                                                       |      |      | 1   | V  |

| $V_{OL-LSS2}$                         | ローサイド出力電圧 (ローサイド スイッチとして構成されている場合)                                                          | $5V < VSUP < 28V, I_{LSS} = -100\mu A$                                                                                                   |      |      | 5   | mV |

| $I_{LSS}$                             | ローサイド スイッチ電流制限値                                                                             | $5V < VSUP < 28V$                                                                                                                        | 22   | 30   | 38  | mA |

| <b>HSS1, HSS2, HSS3, HSS4 (高電圧出力)</b> |                                                                                             |                                                                                                                                          |      |      |     |    |

## 6.7 電気的特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ            | テスト条件                                                    | 最小値                                                                                                                                    | 標準値  | 最大値  | 単位                     |             |

|------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|------|------------------------|-------------|

| $R_{dson}$       | HSS 出力のドレイン-ソース間オン抵抗                                     | $I_O = -60\text{mA}$                                                                                                                   |      | 7    | $\Omega$               |             |

| $I_{OC(HSS)}$    | HSS 過電流検出制限                                              | $VHSS = 14\text{V}$                                                                                                                    | 150  | 300  | $\text{mA}$            |             |

| $I_{OL(HSS)}$    | HSS のオーブン負荷検出電流スレッショルド、立ち下がり                             | $VHSS = 14\text{V}$                                                                                                                    | 0.4  | 3.0  | $\text{mA}$            |             |

| $I_{OLHYS(HSS)}$ | HSS 開放負荷検出電流ヒステリシス                                       | $VHSS = 14\text{V}$                                                                                                                    | 0.05 | 0.45 | 1                      | $\text{mA}$ |

| $I_{Ikg}$        | リーコ電流                                                    | $HSSx = 0\text{V}$ 、スリープ モード                                                                                                           | -1   | 1    | $\mu\text{A}$          |             |

| $SR_{R/F}$       | 出力の立ち上がりおよび立ち下がりスルーレート (HSS1-4)                          | $5\text{V} \leq VHSS \leq 18\text{V}$ , $R_L = 220\Omega$ , $V_{O(HSSx)} = 20\% \sim 80\%$ ( $t_R$ の場合), $80\% \sim 20\%$ ( $t_F$ の場合) | 0.45 | 2.5  | $\text{V}/\mu\text{s}$ |             |

| $t_{HSS\_on}$    | $nCS = \text{HIGH}$ から $VHSS$ の 80% に達するまでの $HSSx$ のオン遅延 | $VHSS = 14\text{V}$ , $R_L = 220\Omega$ , $V_{OUT} = VHSS$ の 80%                                                                       | 30   | 90   | $\mu\text{s}$          |             |

| $t_{HSS\_off}$   | $nCS = \text{HIGH}$ から $VHSS$ の 20% に達するまでの $HSSx$ のオフ遅延 | $VHSS = 14\text{V}$ , $R_L = 220\Omega$ , $V_{OUT} = VHSS$ の 20%                                                                       | 30   | 90   | $\mu\text{s}$          |             |

| $t_{OCFLTR}$     | 過電流割り込み故障を設定するための HSS の過電流フィルタ時間                         | $VHSS = 14\text{V}$                                                                                                                    |      | 16   | $\mu\text{s}$          |             |

| $t_{OLFLTR}$     | HSS 開放負荷フィルタ時間                                           | $VHSS = 14\text{V}$                                                                                                                    |      | 64   | $\mu\text{s}$          |             |

| $t_{OCOFF}$      | HSS 過電流シャットオフ時間。過電流状態がこの時間継続すると、HSS はオフになります             | $I_{O(HSS)} > I_{OC(HSS)}$                                                                                                             | 200  | 350  | $\mu\text{s}$          |             |

### WAKE1/ID1、WAKE2/ID2、WAKE3/ID3、WAKE4/ID4 入力端子 (高電圧入力)

|                     |                                                                                           |                                       |                 |                 |               |

|---------------------|-------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-----------------|---------------|

| $V_{IH}$            | High レベル入力電圧: WAKE ピンがイネーブルまたはスリープ状態、選択的ウェーケアップまたはスタンバイ モード、ID 機能がイネーブルの場合 <sup>(1)</sup> | レジスタ設定 00b VCC1 ベース                   | 0.7 x $V_{CC1}$ |                 | V             |

|                     |                                                                                           | レジスタ設定 01b                            | 2.7             | 2.8             | 2.9           |

|                     |                                                                                           | レジスタ設定 10b                            | 4.0             | 4.1             | 4.2           |

|                     |                                                                                           | レジスタ設定 10b (TCAN245 xMRHBRQ1 バリアントのみ) | 3.9             | 4.1             | 4.3           |

|                     |                                                                                           | レジスタ設定 11b                            | 6.4             | 6.6             | 6.8           |

|                     |                                                                                           |                                       |                 |                 | V             |

| $V_{IL}$            | Low レベル入力電圧: スリープ、選択的ウェーケアップまたはスタンバイ モードで WAKE ピンがイネーブル、ID 機能がイネーブルの場合 <sup>(1)</sup>     | レジスタ設定 00b VCC1 ベース                   |                 | 0.3 x $V_{CC1}$ | V             |

|                     |                                                                                           | レジスタ設定 01b                            | 2.1             | 2.2             | 2.4           |

|                     |                                                                                           | レジスタ設定 10b                            | 3.2             | 3.35            | 3.5           |

|                     |                                                                                           | レジスタ設定 11b                            | 5.3             | 5.45            | 5.6           |

|                     |                                                                                           | レジスタ設定 11b (TCAN245 xMRHBRQ1 バリアントのみ) | 5.2             | 5.45            | 5.6           |

| $I_{IH}$            | High レベル入力電流、WAKE ピンがイネーブル                                                                | WAKE = 12V                            |                 | 10              | $\mu\text{A}$ |

| $I_{IL}$            | Low レベル入力電流、WAKE ピンがイネーブル                                                                 | WAKE = 1V                             |                 | 1               | $\mu\text{A}$ |

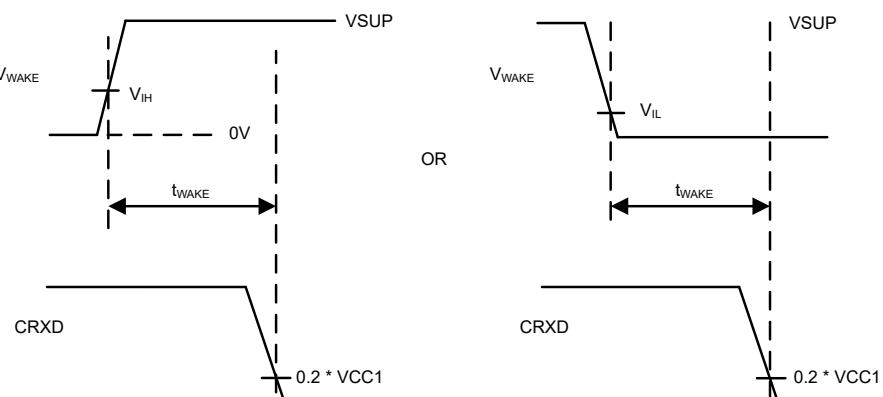

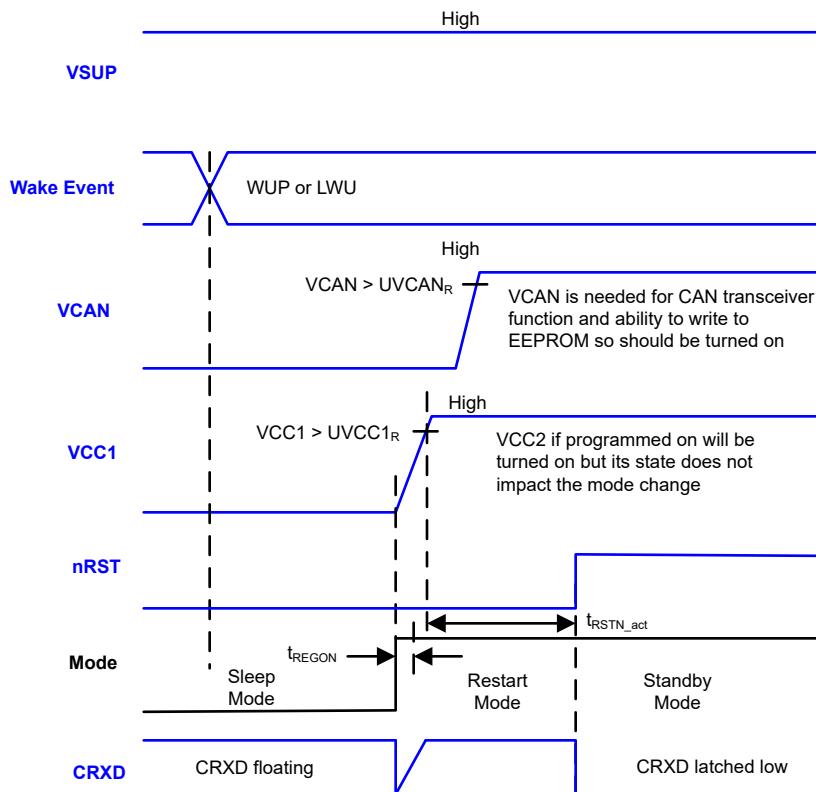

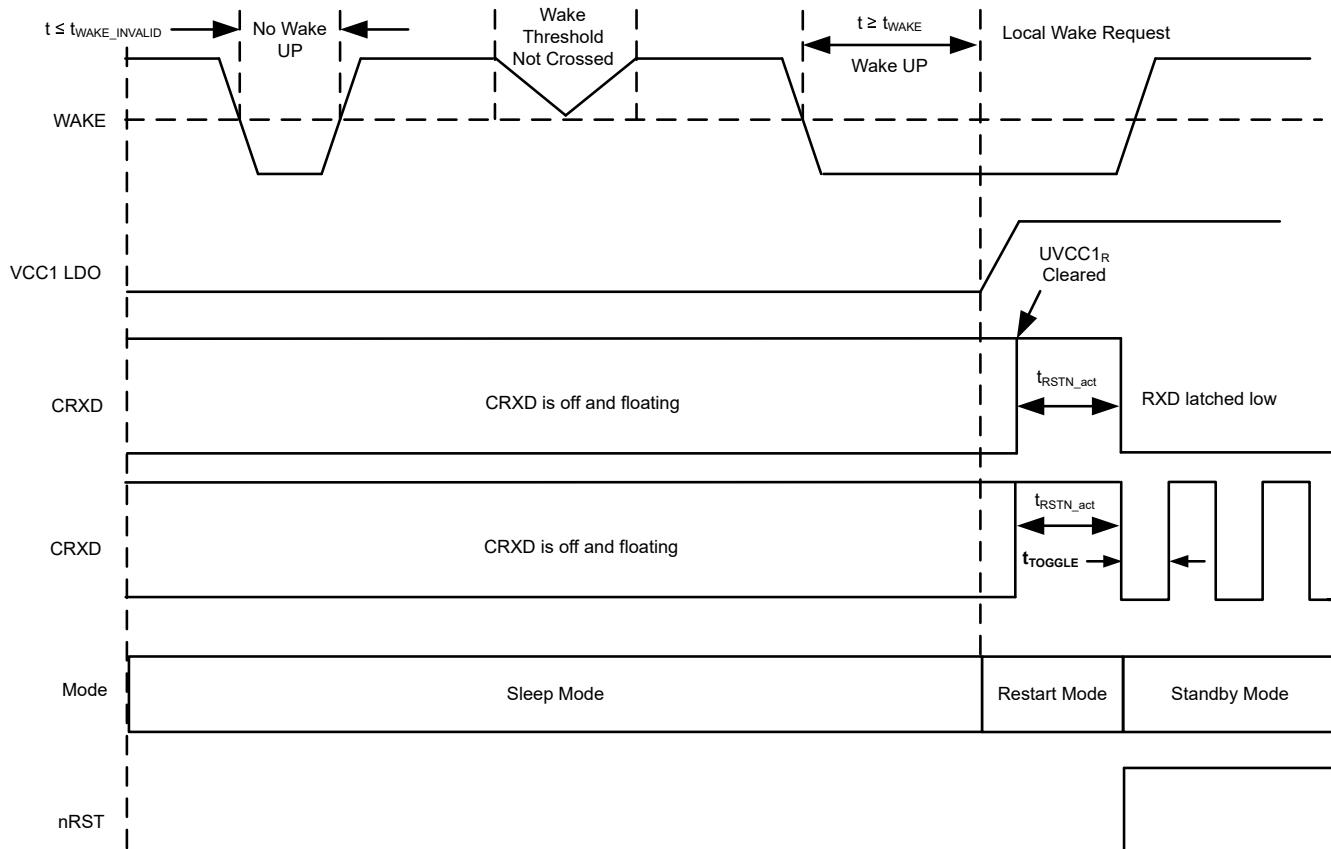

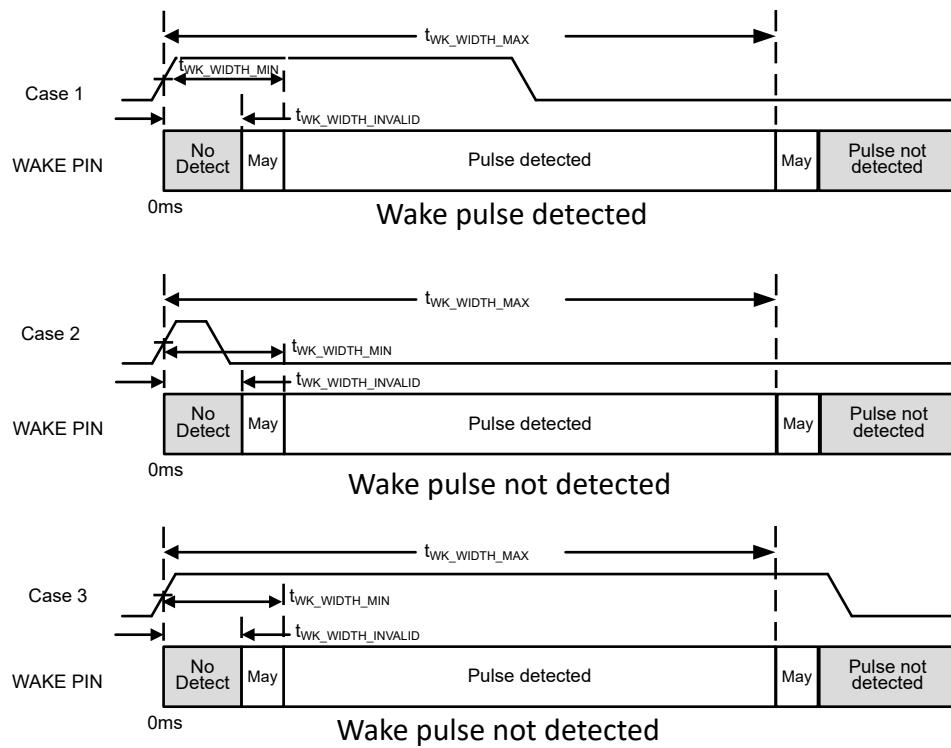

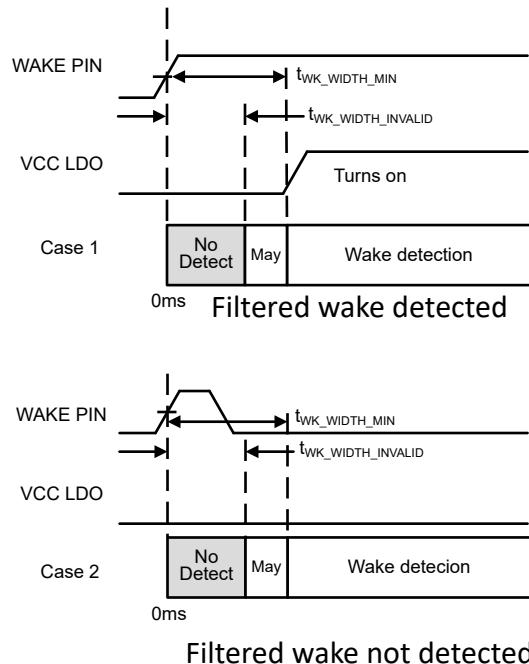

| $t_{WAKE}$          | スタンバイまたはスリープ モードで静的センシングを行う場合、WAKE の (立ち上がりまたは立ち下がり) エッジからのウェーケアップ保持時間。                   | 図 8-18 および図 8-19 を参照。                 | 140             |                 | $\mu\text{s}$ |

| $t_{WAKE\_INVALID}$ | これよりも短い WAKE ピンパルスは、スタンバイで、または静的センシングのスリープ モードでフィルタ処理されます。                                | 図 8-18 および図 8-19 を参照。                 |                 | 10              | $\mu\text{s}$ |

## 6.7 電気的特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                 |                                                  | テスト条件                                                                                           | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| ID <sub>Pu</sub>      | プルアップ電流                                          | IDx ピン イネーブル (レジスタビット IDX_EN = 1b)、VSUP = 5.5V ~ 18V、WAKE_ID_PU_PD = 10b                        | -2  | -1  |     | mA |

| ID <sub>Pd</sub>      | プルダウン電流 (TCAN245 x MRHBRQ1 パリアント)                | IDx ピン イネーブル (レジスタビット IDX_EN = 1b)、VSUP = 5.5V ~ 18V、WAKE_IDx_PU_PD = 01b、IDX_PD_VALUE = 0b     | 3   | 5   |     | mA |

| ID <sub>Pd</sub>      | プルダウン電流                                          | IDx ピン イネーブル (レジスタビット IDX_EN = 1b)、VSUP = 5.5V ~ 18V、WAKE_IDx_PU_PD = 01b、IDX_PD_VALUE = 0b     | 3   | 5.5 |     | mA |

| ID <sub>Pd</sub>      | プルダウン電流                                          | IDx ピン イネーブル (レジスタビット IDX_EN = 1b)、VSUP = 5.5V ~ 18V、WAKE_IDx_PU_PD = 01b、IDX_PD_VALUE = 1b     | 9   | 18  |     | mA |

| t <sub>d_IDSTAT</sub> | SPI 経由のコマンドと、IDX_STAT レジスタ内の ID ピンのステータス更新との間の遅延 | IDx ピンが有効 (レジスタビット IDX_EN = 1b で自動検出の場合)、または WAKE_IDx_PU_PD ビット値が 00b/ 01b/ 10b から 11b に変更された場合 | 20  | 30  |     | ms |

| t <sub>dcs</sub>      | SPI 経由のコマンドと電流源のアクティブ化との間の遅延                     | IDx ピンがイネーブル (レジスタビット IDX_EN = 1b)。WAKE_IDx_PU_PD ビットの値が 00b から 10b または 01b に変更されました            | 0.5 | 50  |     | μs |

### SW 入力端子

|                         |                                                        |                                                                               |      |      |    |

|-------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------|------|------|----|

| V <sub>IL</sub>         | Low レベル入力電圧: SW (VCC1 が存在する場合)                         |                                                                               | 0.3  | VCC1 |    |

| V <sub>IH</sub>         | High レベル入力電圧: SW (VCC1 が存在する場合)                        |                                                                               | 0.7  | VCC1 |    |

| V <sub>IHSWINT</sub>    | スリープまたはフェイルセーフモードで VCC1 が喪失しているときの SW ピンの High レベル入力電圧 | レジスタ 8'h0E[1] = 1 および / または 8'h0E[2] = 1 で、スリープまたはフェールセーフ モード中に VCC1 が存在しない場合 | 1.2  | V    |    |

| V <sub>ILSWINT</sub>    | スリープまたはフェイルセーフモードで VCC1 が喪失しているときの SW Low レベル入力電圧      | レジスタ 8'h0E[1] = 1 および / または 8'h0E[2] = 1 で、スリープまたはフェールセーフ モード中に VCC1 が存在しない場合 | 0.4  | V    |    |

| I <sub>IHSWINT-PD</sub> | VCC1 がオフのときの SW ピンの High レベル入力リーク電流 (アクティブ High)       | VCC1 オフ、内部プルダウン イネーブル、(SW_POL_SEL = 1b)、V <sub>SW</sub> = 5V                  | -2.5 | 125  | μA |

| I <sub>ILSWINT-PD</sub> | VCC1 がオフのときの SW ピンの Low レベル入力リーク電流 (アクティブ High)        | VCC1 オフ、内部プルダウン イネーブル、(SW_POL_SEL = 1b)、V <sub>SW</sub> = 0V                  | -1   | 1    | μA |

| I <sub>IHSWINT-PU</sub> | VCC1 がオフのときの SW ピンの High レベル入力リーク電流 (アクティブ Low)        | VCC1 オフ、内部プルアップ イネーブル、(SW_POL_SEL = 0b)、V <sub>SW</sub> = 5V                  | -1   | 1    | μA |

| I <sub>ILSWINT-PU</sub> | VCC1 がオフのときの SW ピンの Low レベル入力リーク電流 (アクティブ Low)         | VCC1 オフ、内部プルアップ イネーブル、(SW_POL_SEL = 0b)、V <sub>SW</sub> = 0V                  | -125 | -2   | μA |

| I <sub>IHSW</sub>       | VCC1 がオンのときの SW ピンの高レベル入力リーク電流                         | VCC1 オン、内部プルダウン イネーブル、V <sub>SW</sub> = VCC1                                  | -2   | 125  | μA |

## 6.7 電気的特性 (続き)

特記がない限り、VSUP/VSUPB/VHSS = 5.5V~28V の推奨動作条件を超える場合。特に記述がない限り、すべての代表値は  $T_J = 25^\circ\text{C}$ 、VSUP/VSUPB/VHSS = 12V、VCAN = 5V、 $R_L = 60\Omega$  で規定

| パラメータ                         |                                                                                                        | テスト条件                                                         | 最小値  | 標準値 | 最大値 | 単位               |

|-------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|-----|-----|------------------|

| $I_{ILSW}$                    | VCC1 がオンのときの SW ピンの低レベル入力リーケ電流                                                                         | VCC1 オン、内部プルアップ イネーブル、 $V_{SW} = 0\text{V}$                   | -125 |     | -2  | $\mu\text{A}$    |

| $R_{pd}$                      | SW ピン プルダウン抵抗                                                                                          |                                                               | 40   | 60  | 80  | $\text{k}\Omega$ |

| $R_{pu}$                      | SW ピン プルアップ抵抗                                                                                          |                                                               | 40   | 60  | 80  | $\text{k}\Omega$ |

| $I_{LKG(OFF)}$                | 電源がない場合のリーケ電流です                                                                                        | 入力 = 5.5V、VCC1 = VSUP = 0V、 $T_J = -40 \sim 85^\circ\text{C}$ | -1   | 0   | 1   | $\mu\text{A}$    |

| $C_{IN}$                      | 入力容量                                                                                                   |                                                               |      |     | 10  | $\text{pF}$      |

| <b>VSEL 入力端子</b>              |                                                                                                        |                                                               |      |     |     |                  |

| $R_{VSEL-SHORT}$              | 短絡として検出された VSEL ピンと GND との間の最大外部抵抗 (VCC1 が 5V に設定)                                                     |                                                               |      |     | 10  | $\text{k}\Omega$ |

| $R_{VSEL-OPEN}$               | VSEL ピンと GND の間がオープンと判定される最小外部抵抗値 (VCC1 が 3.3V に設定されている場合)                                             |                                                               | 35   |     |     | $\text{k}\Omega$ |

| <b>CTXD、SDI、CLK、nCS の入力端子</b> |                                                                                                        |                                                               |      |     |     |                  |

| $I_{LKG(OFF)}$                | 電源がない場合のリーケ電流です                                                                                        | 入力 = 5.5V、VCC1 = VSUP = 0V、 $T_J = -40 \sim 85^\circ\text{C}$ | -1   | 0   | 1   | $\mu\text{A}$    |

| $C_{IN}$                      | 入力容量                                                                                                   |                                                               | 2    | 10  |     | $\text{pF}$      |

| $I_{IH}$                      | High レベル入力リーケ電流                                                                                        | VCC1 $\pm 2\%$                                                | -1   |     | 1   | $\mu\text{A}$    |

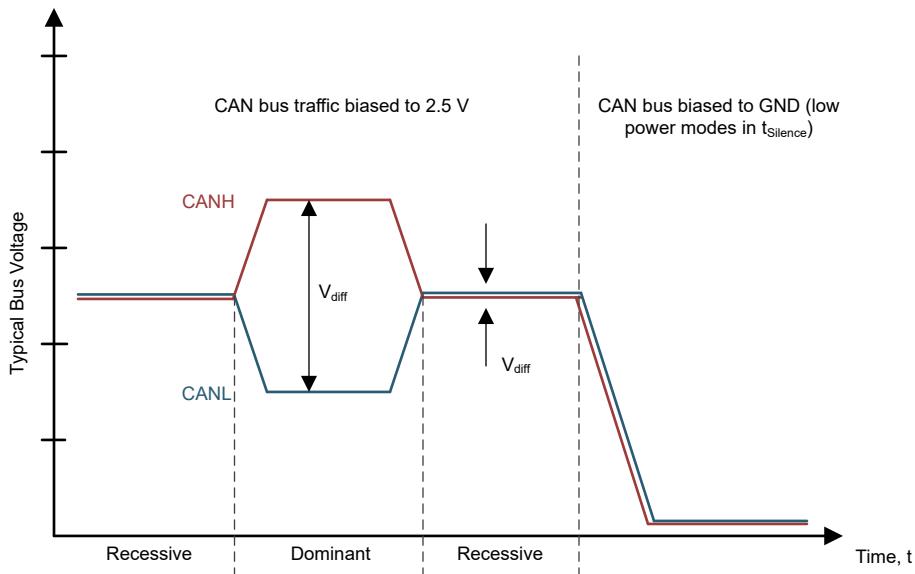

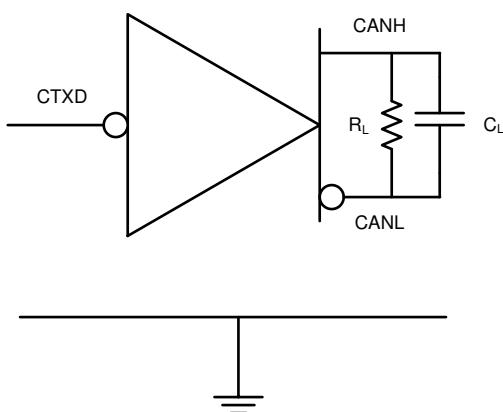

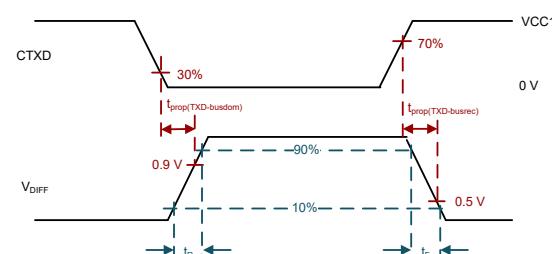

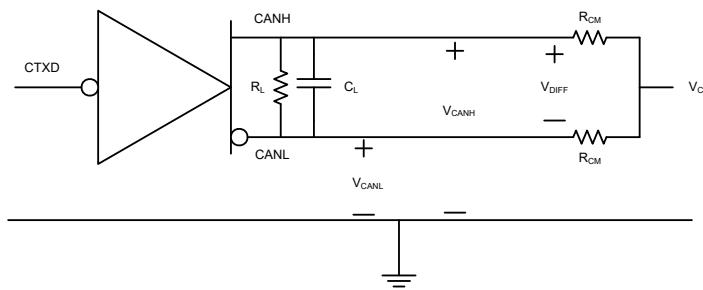

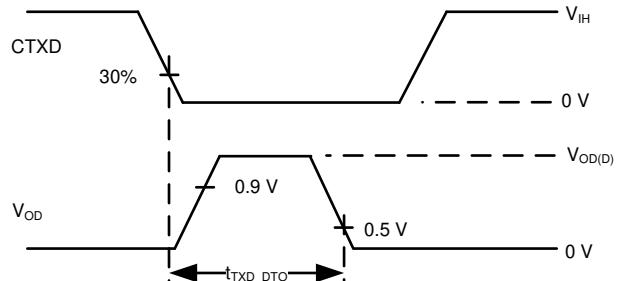

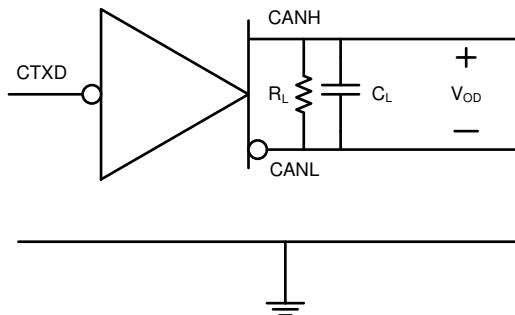

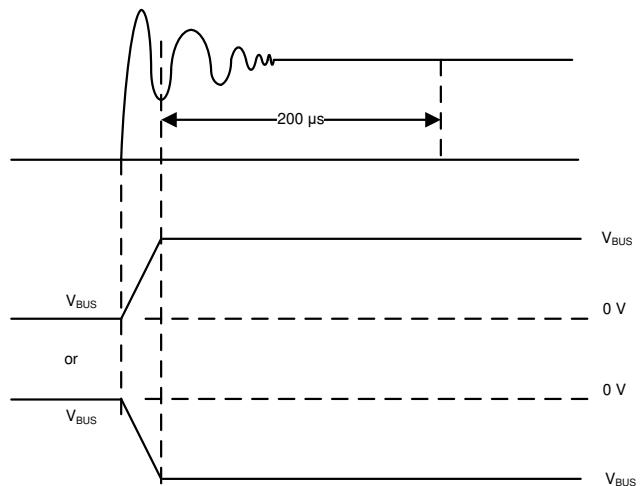

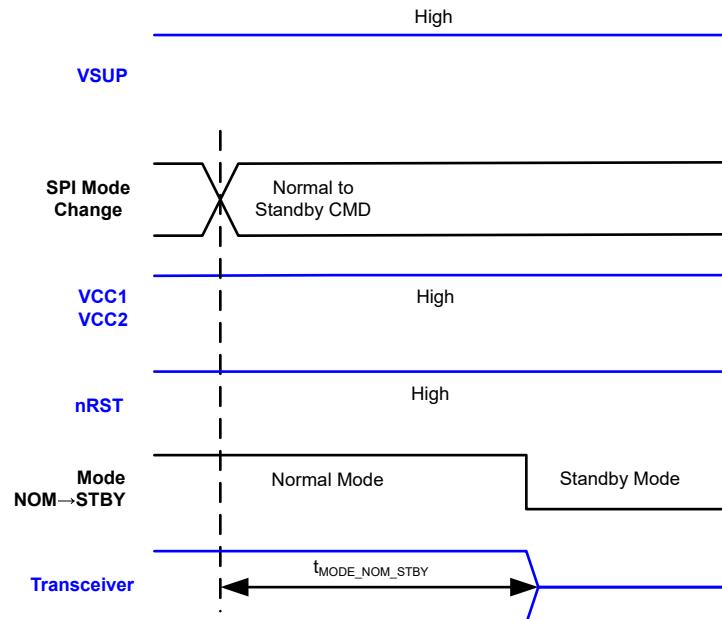

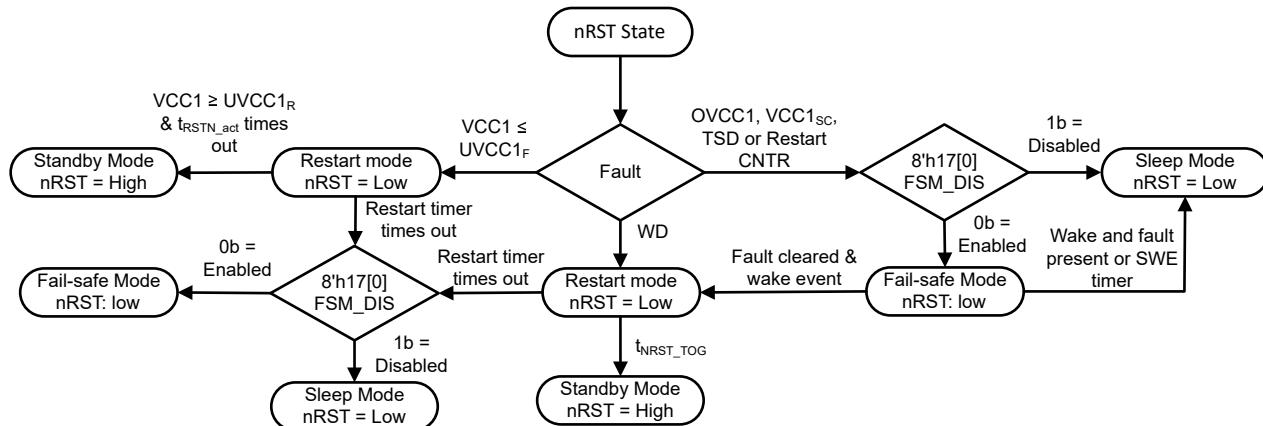

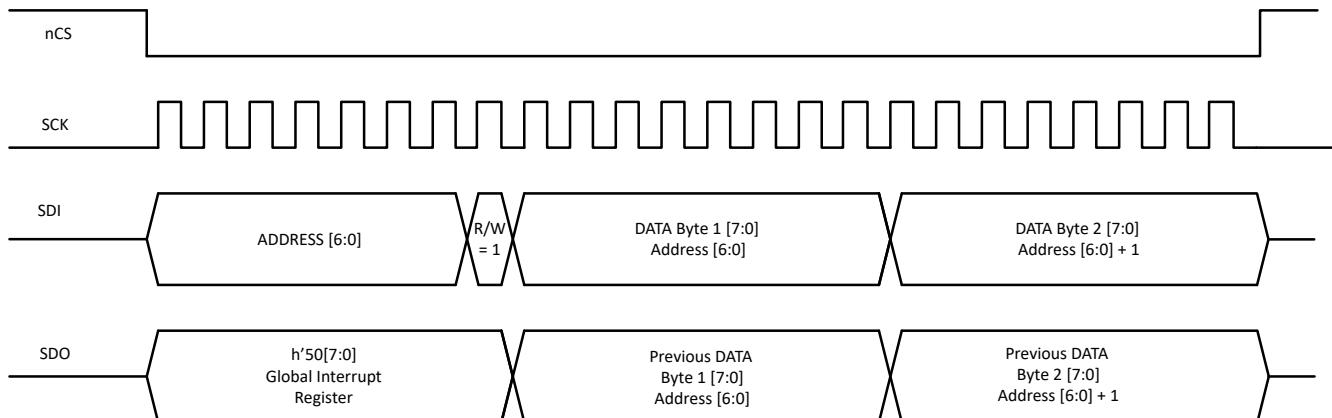

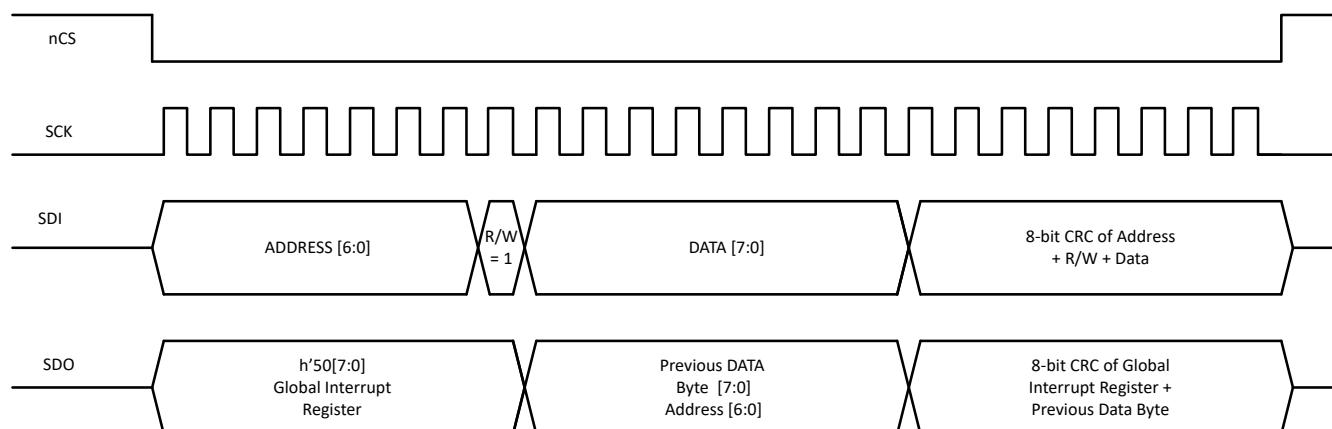

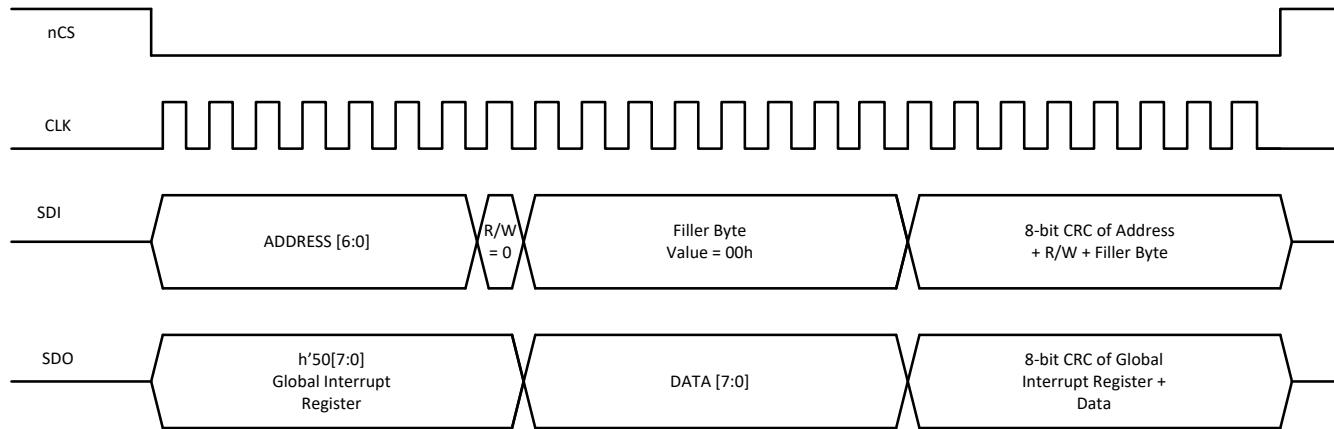

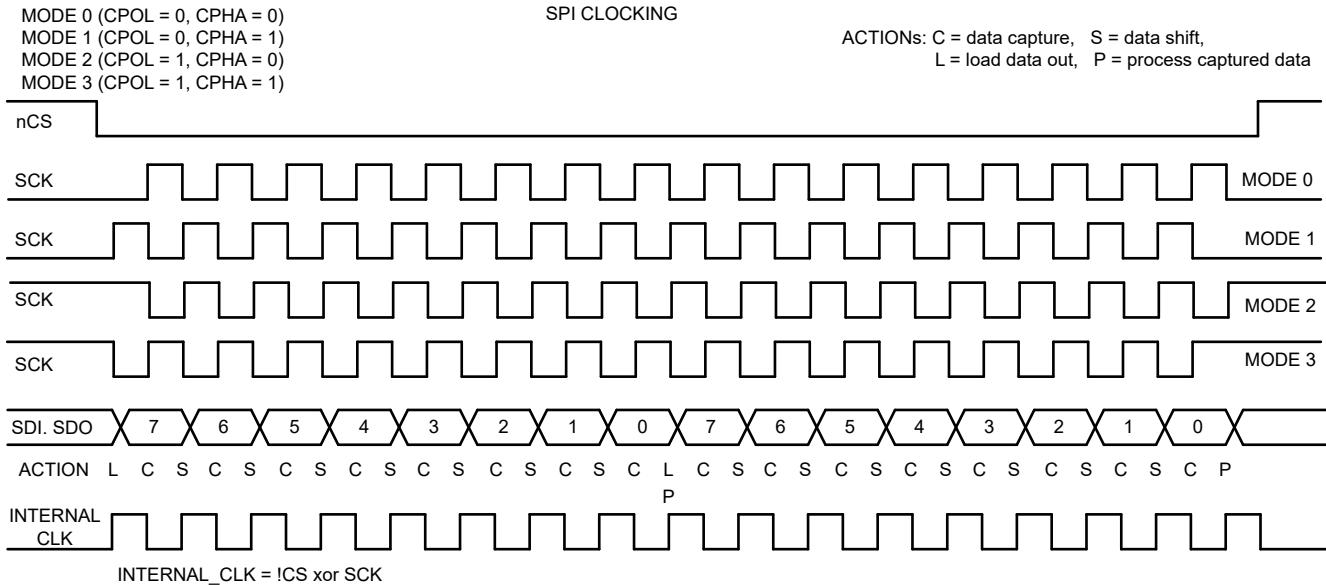

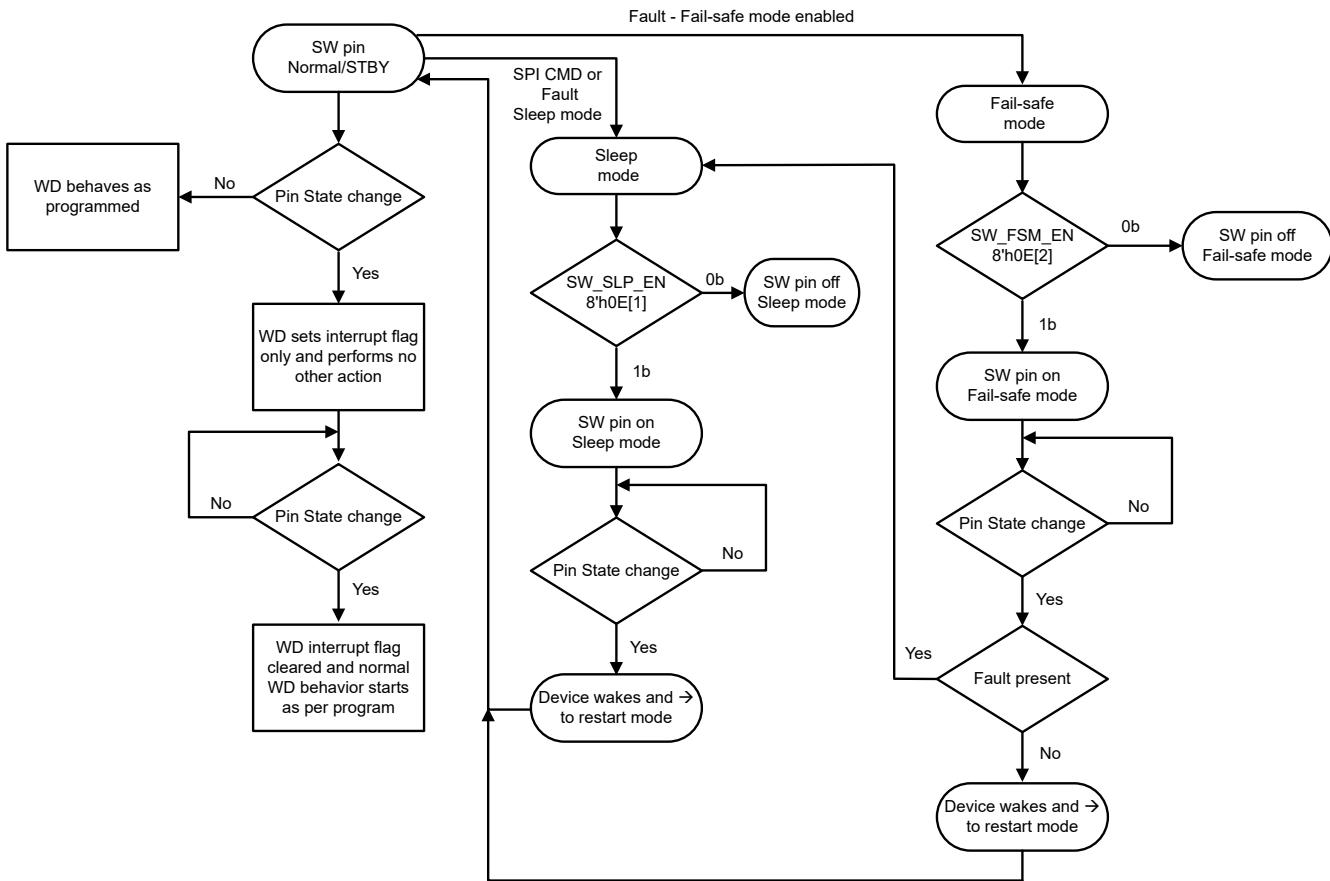

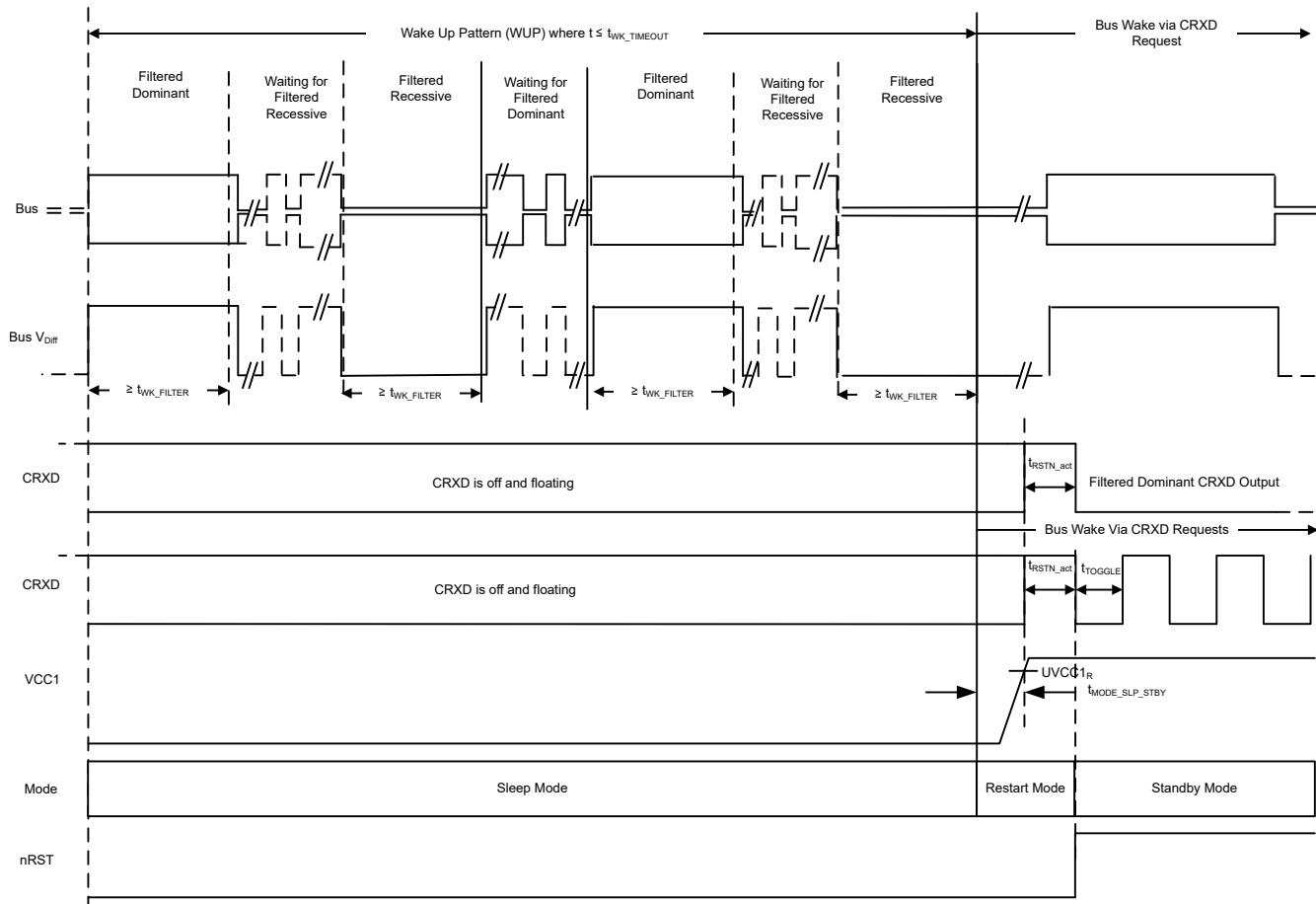

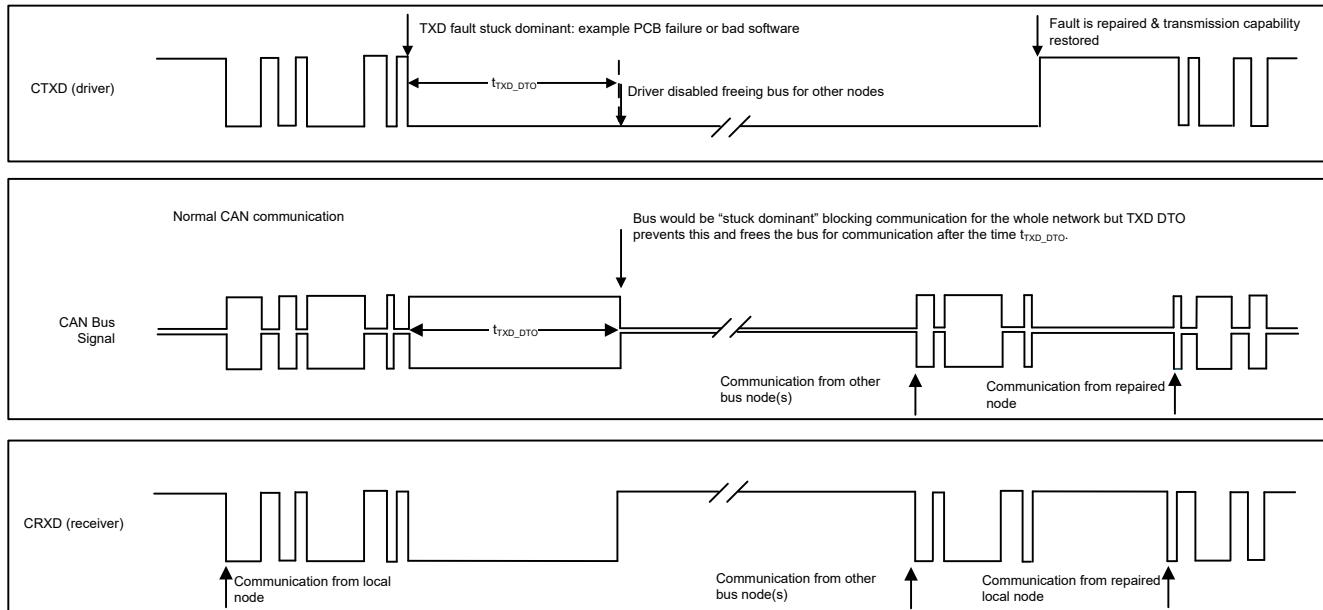

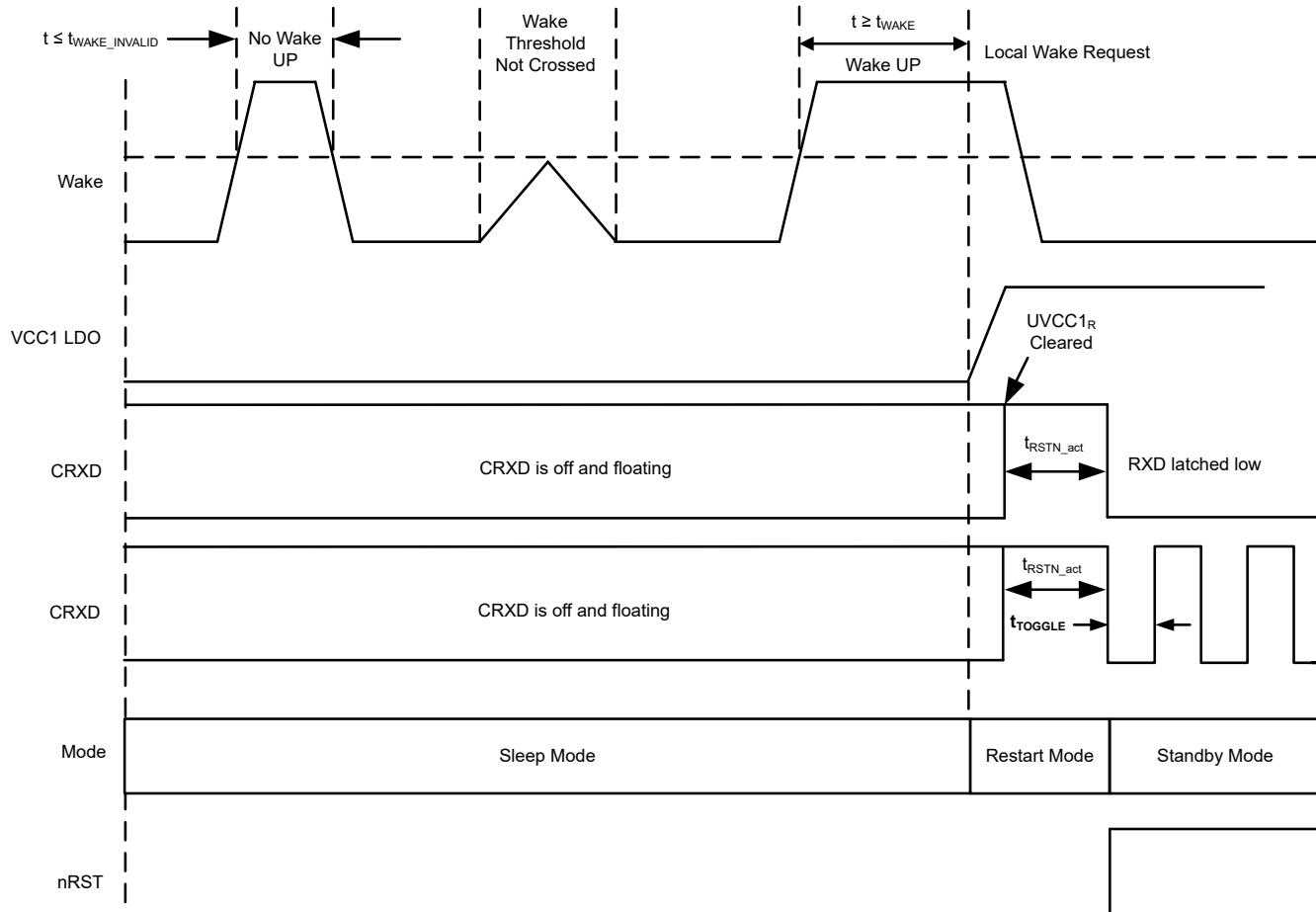

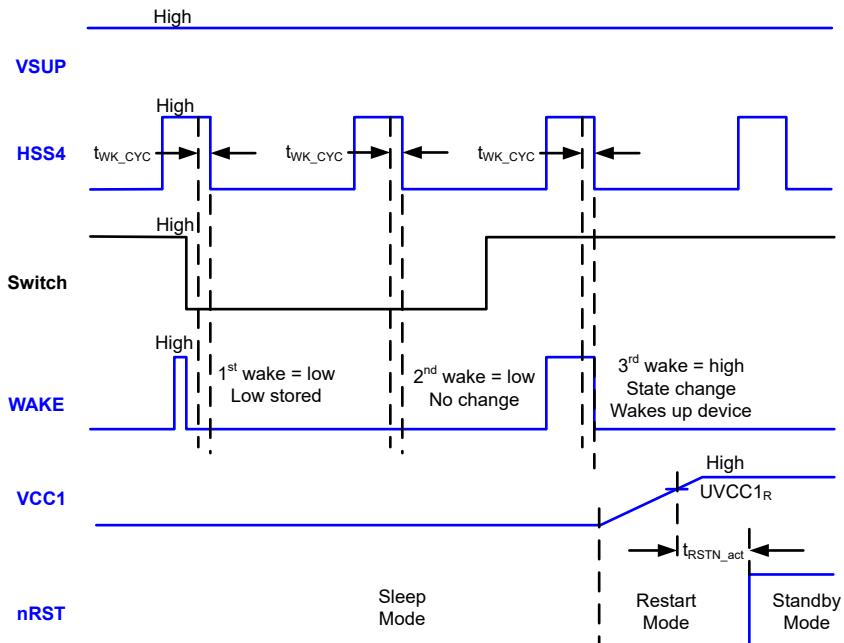

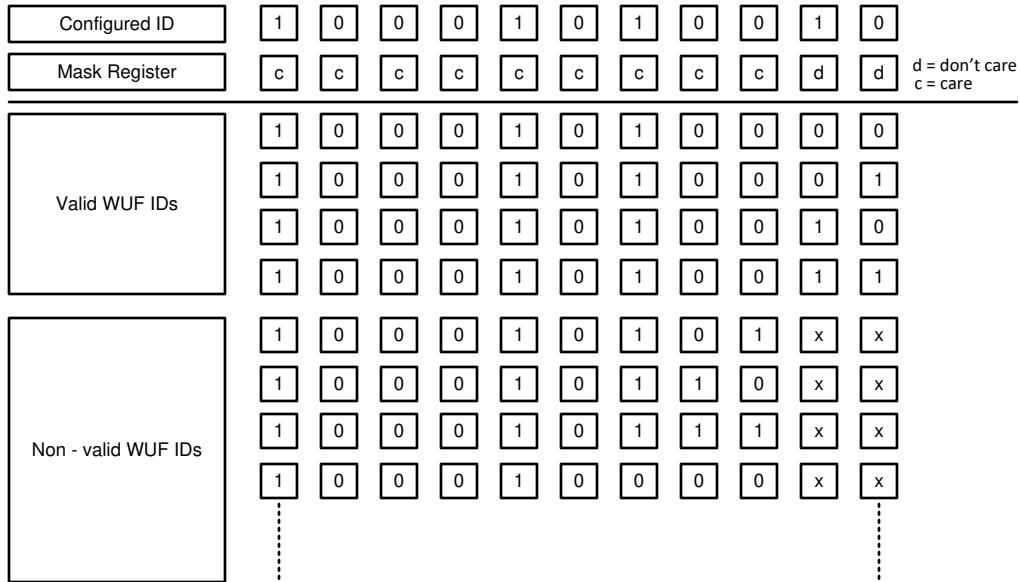

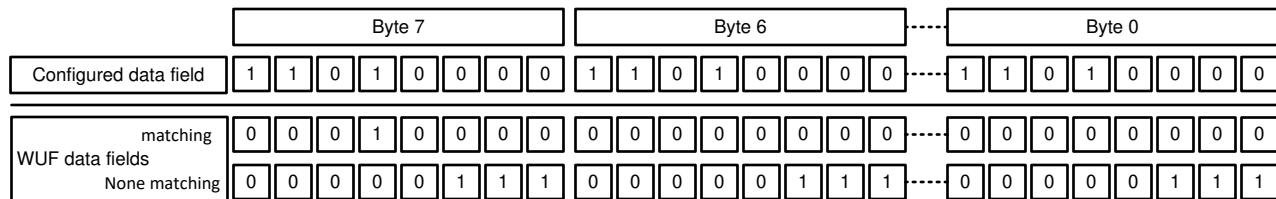

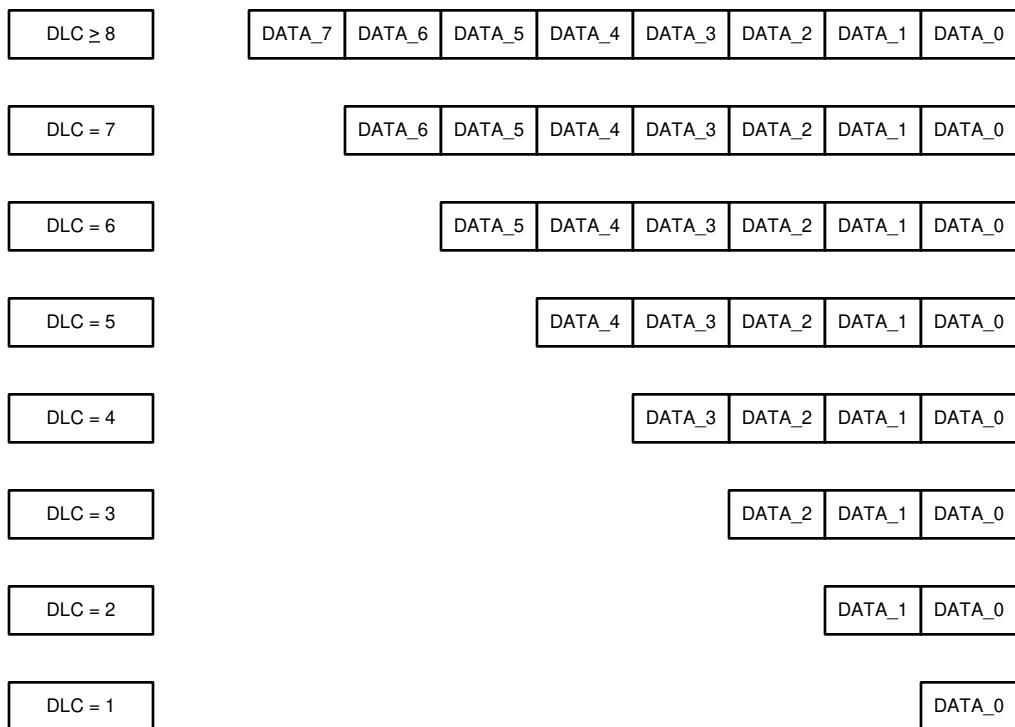

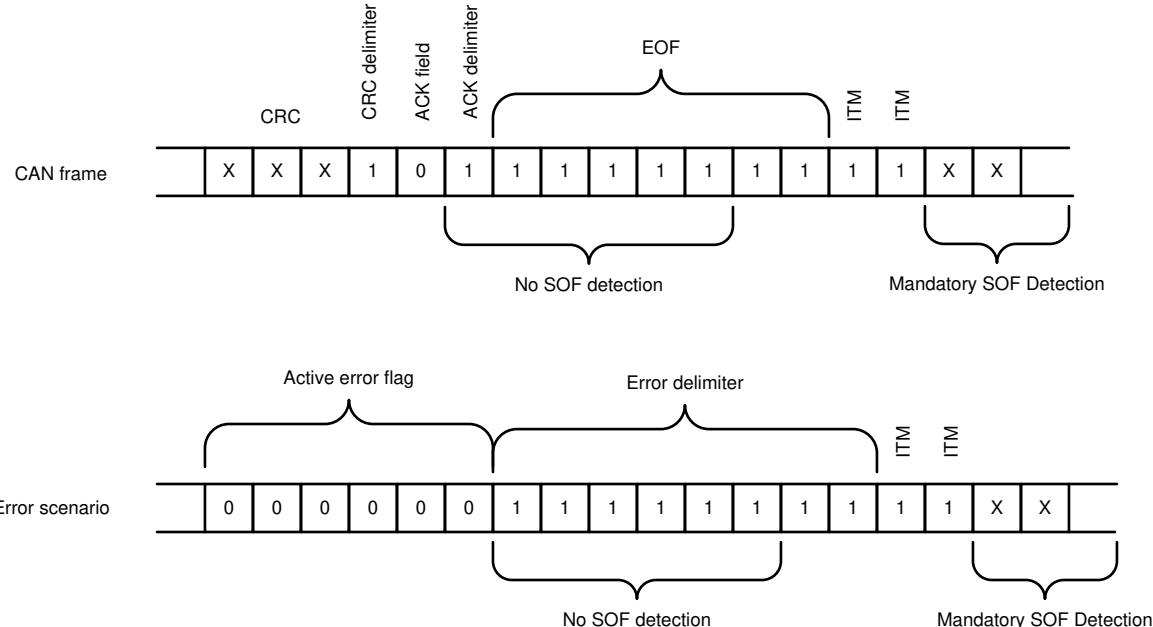

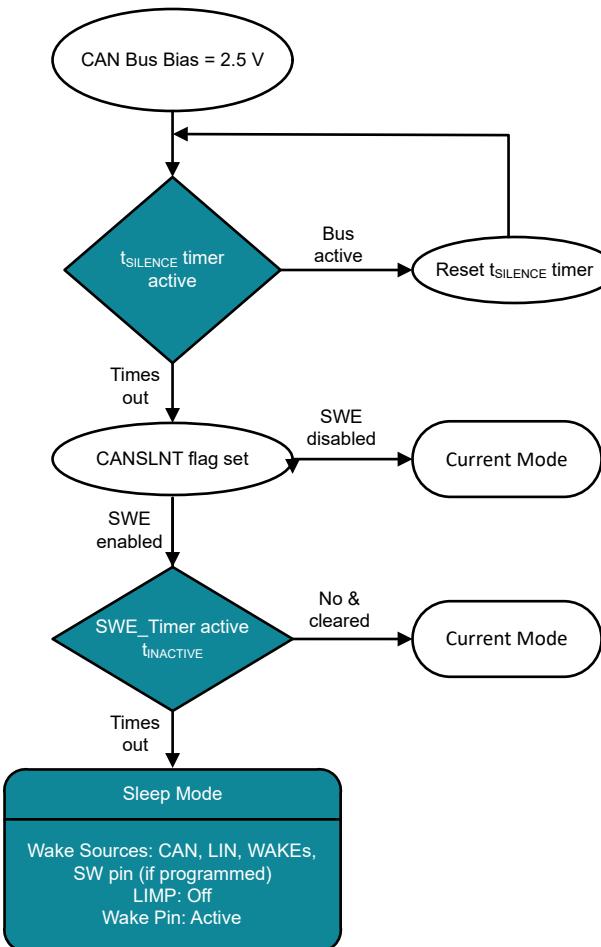

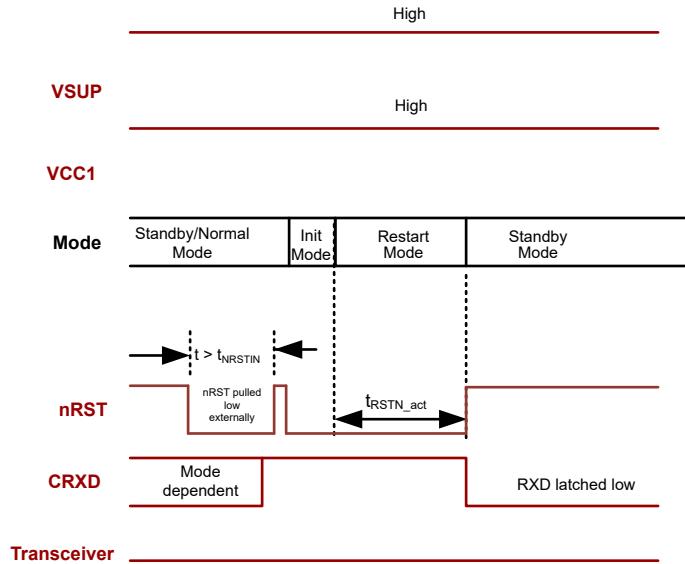

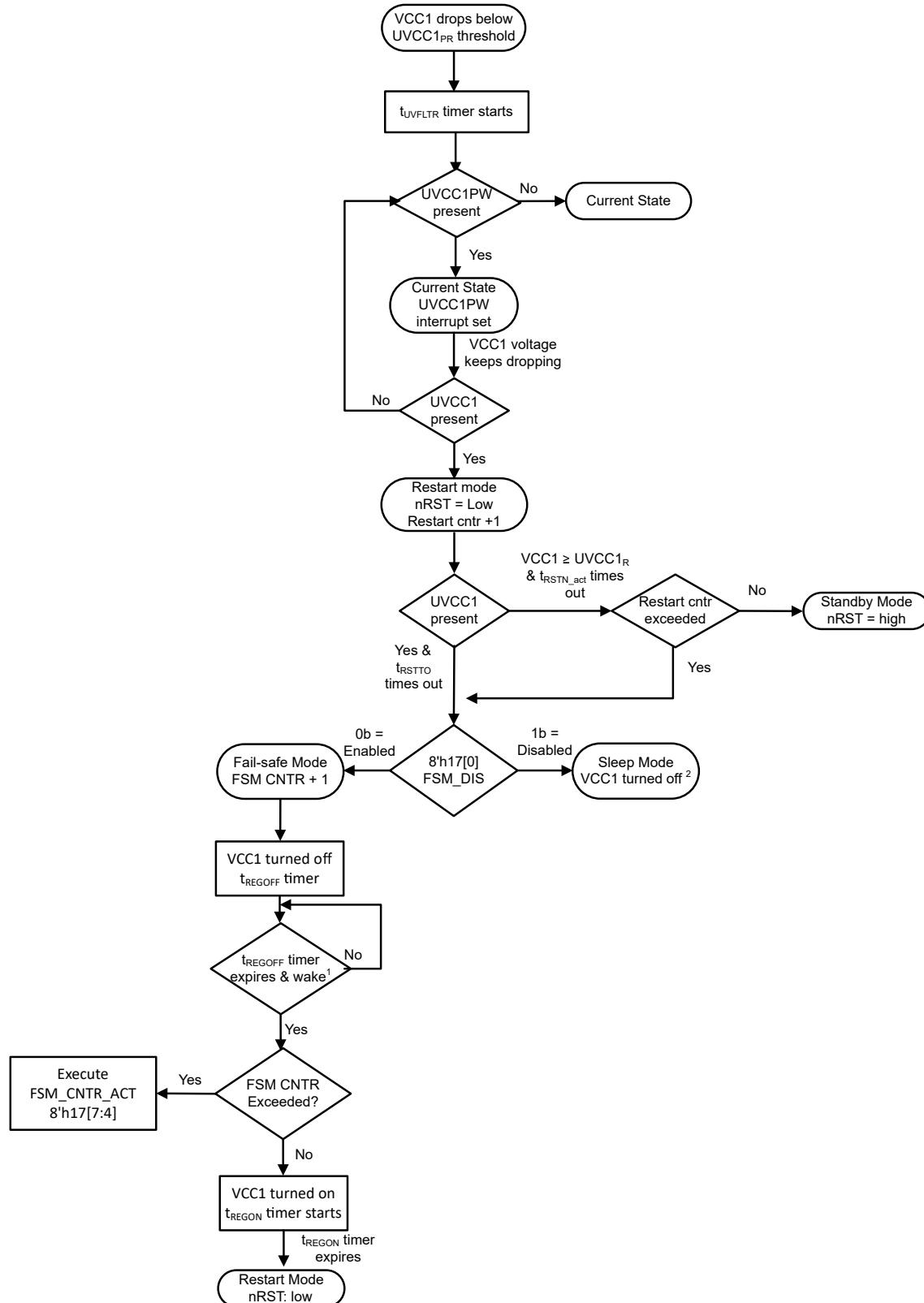

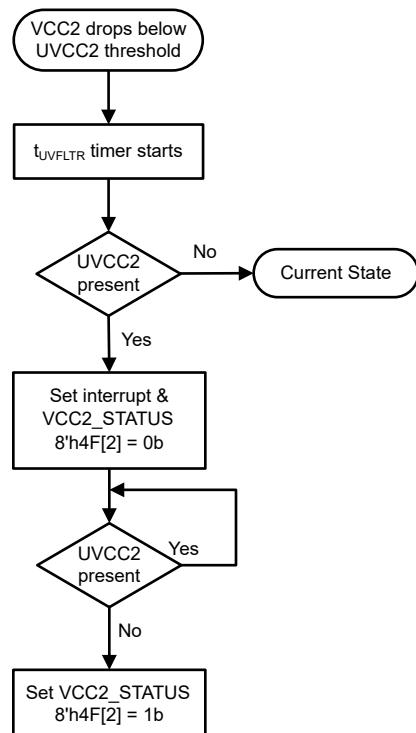

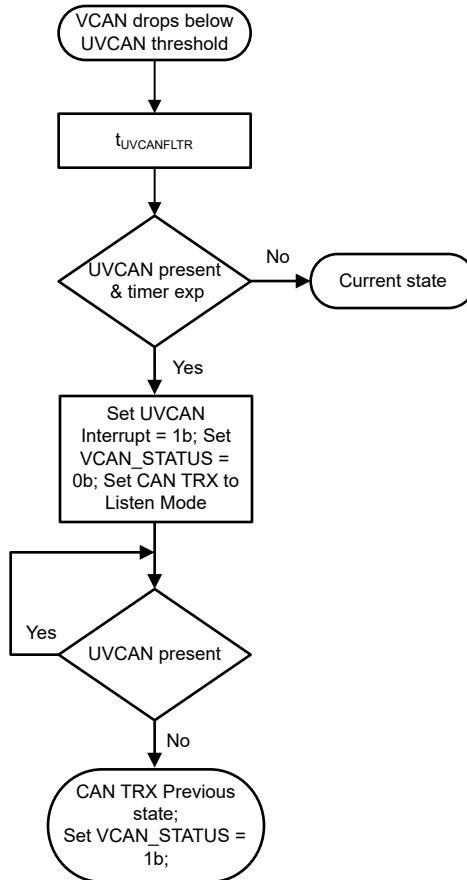

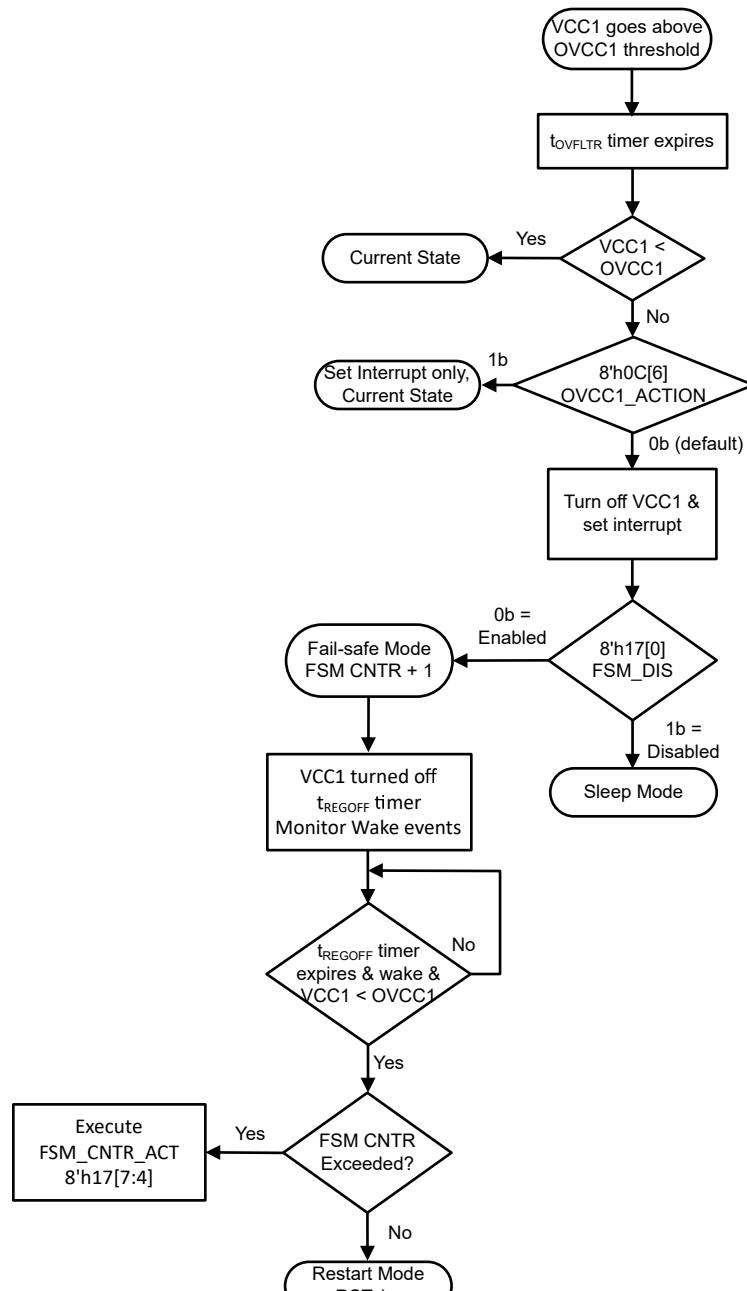

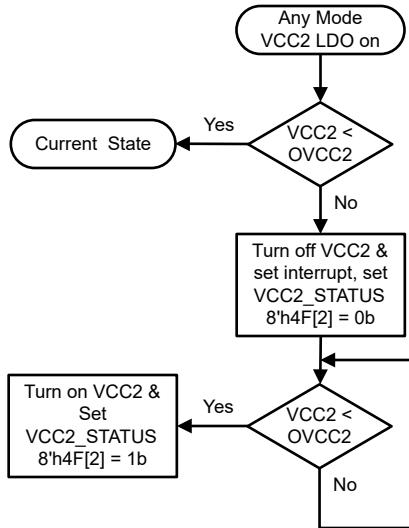

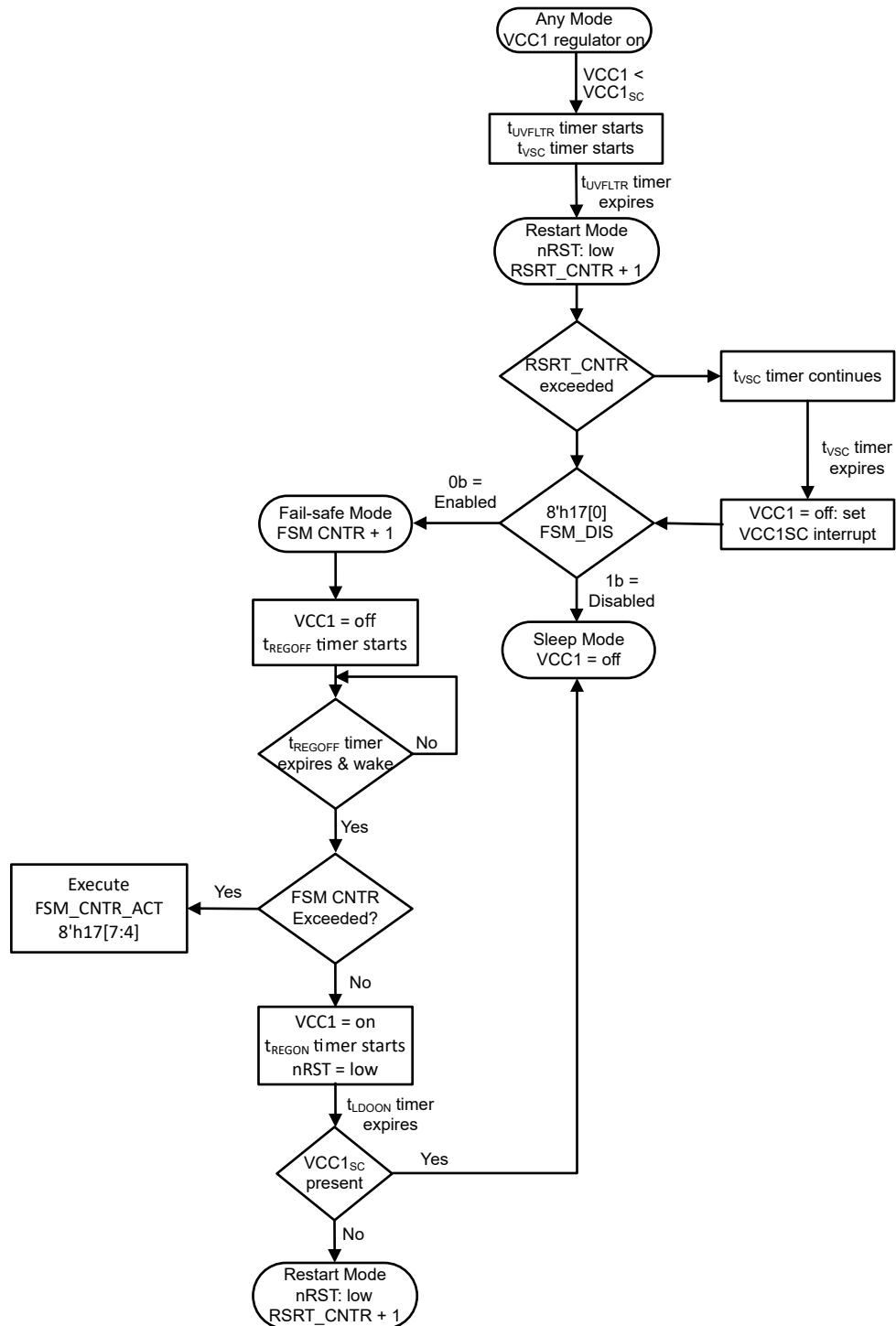

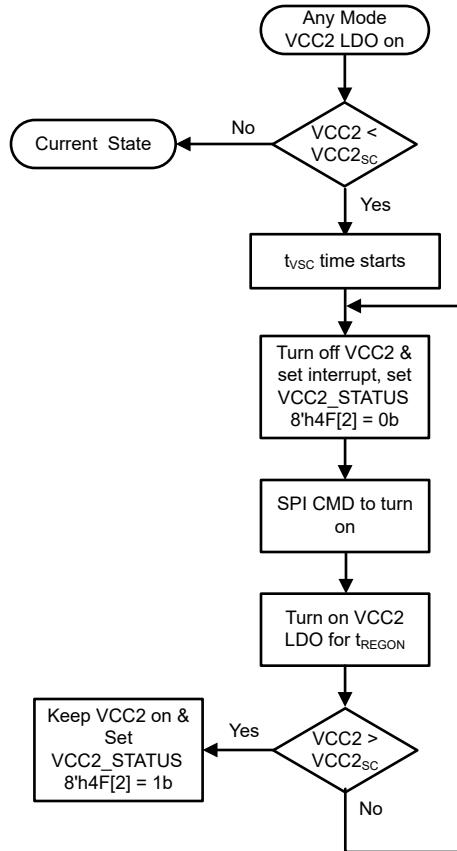

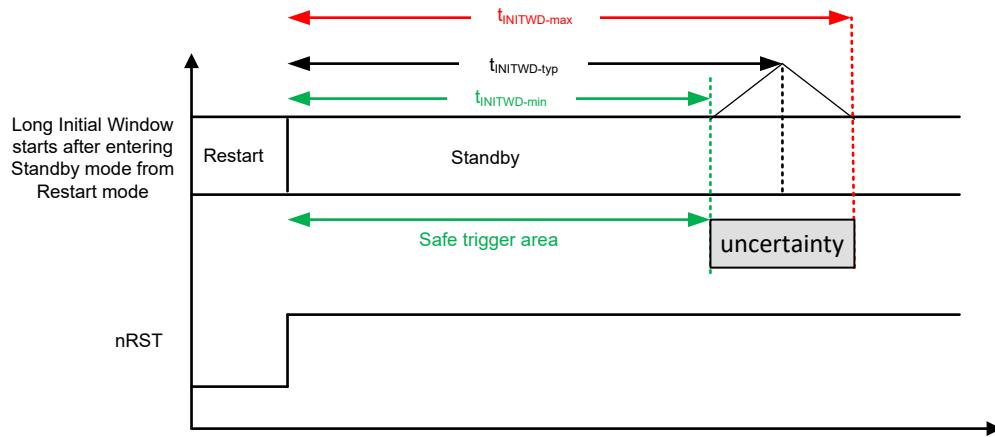

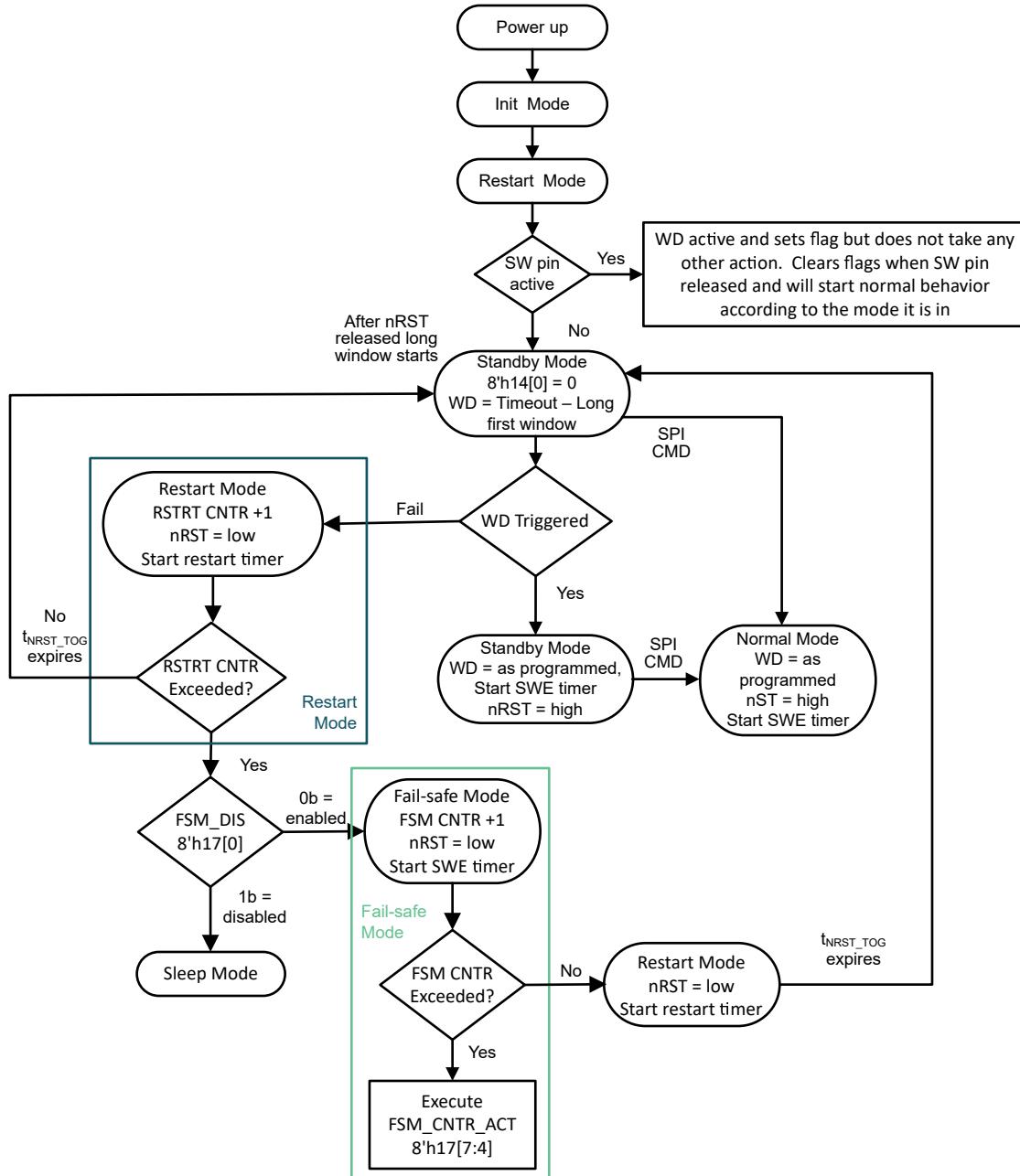

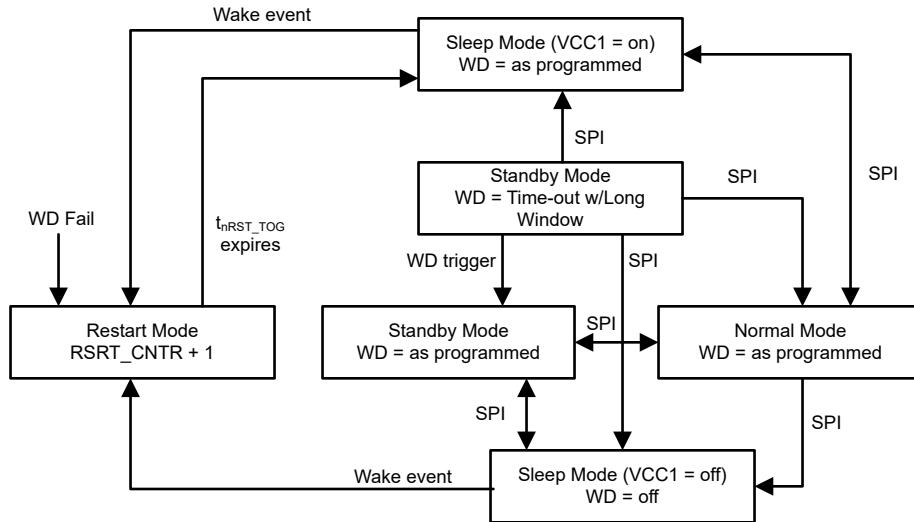

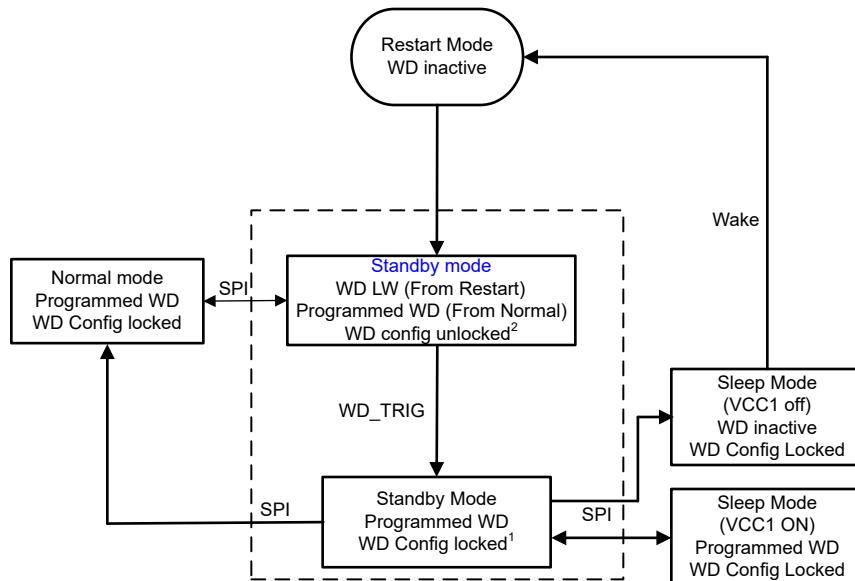

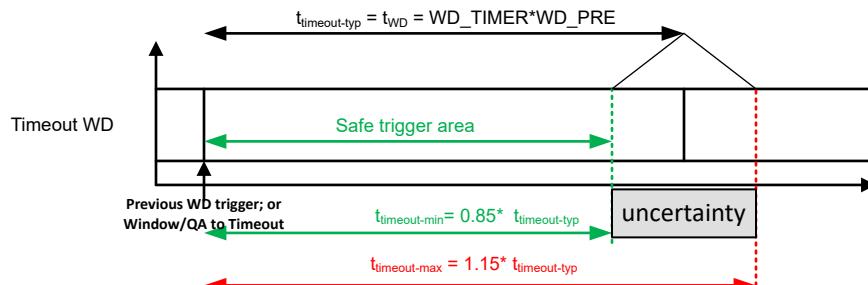

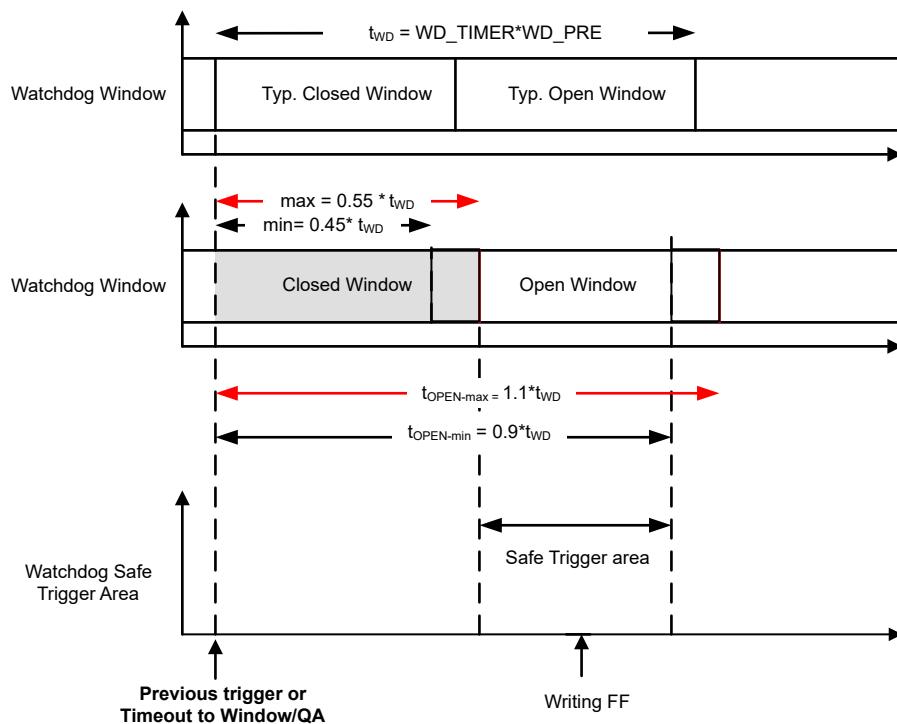

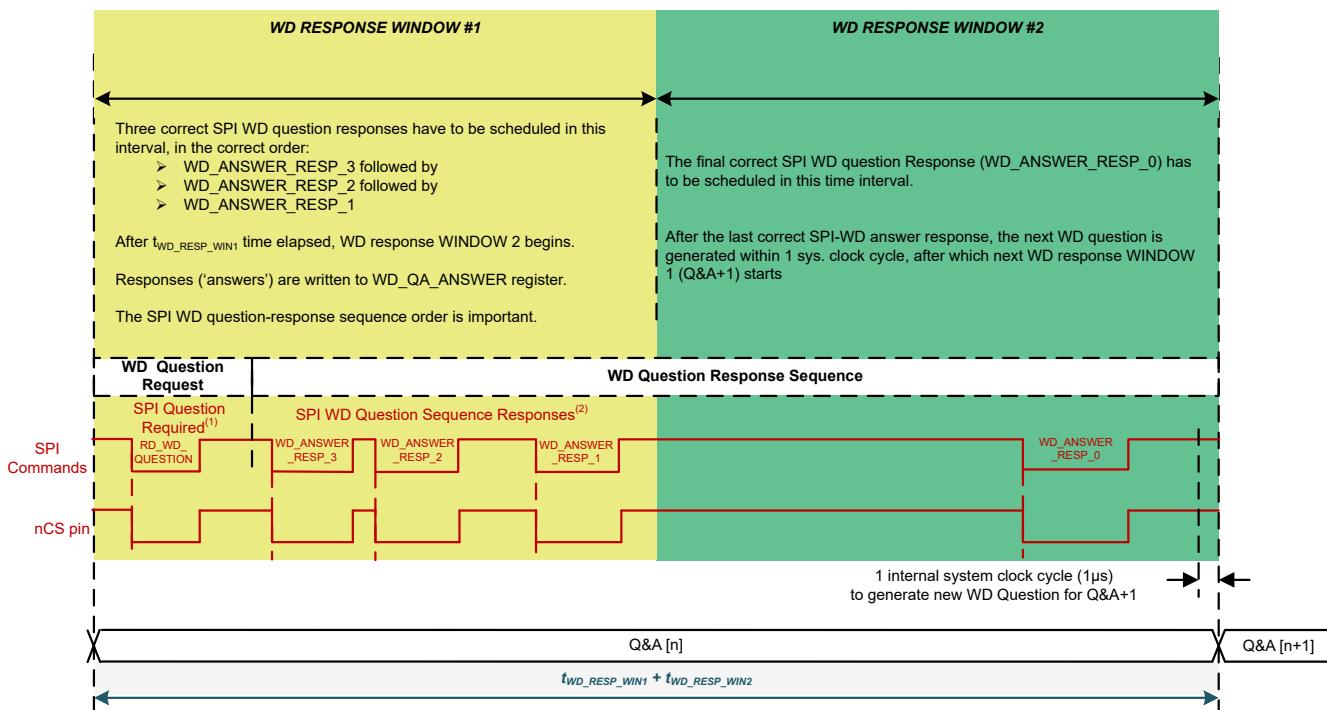

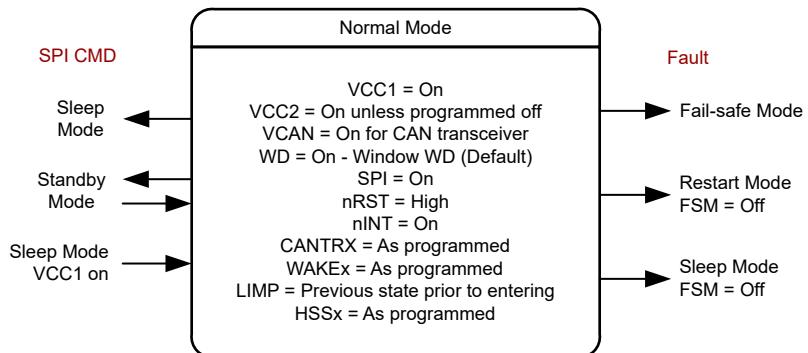

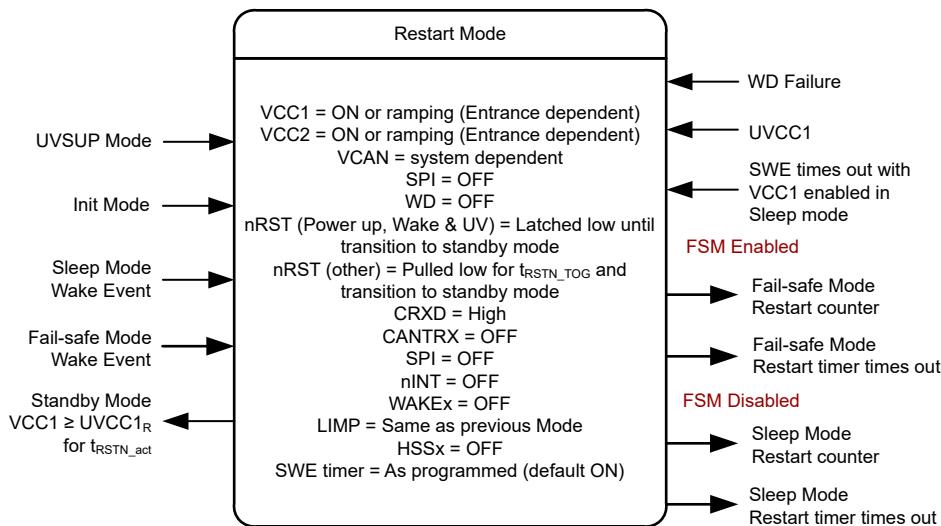

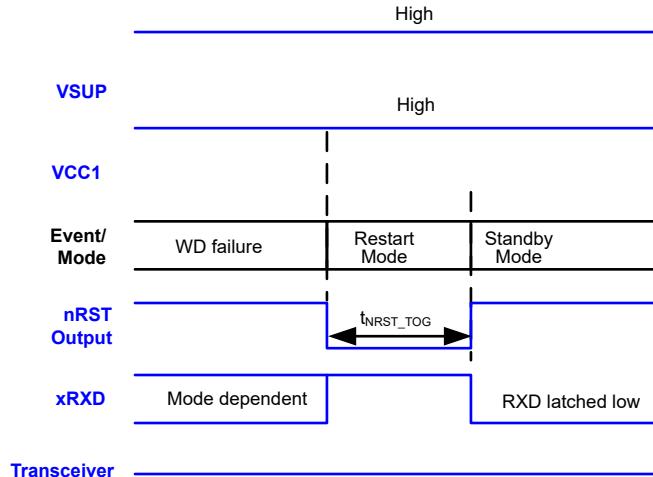

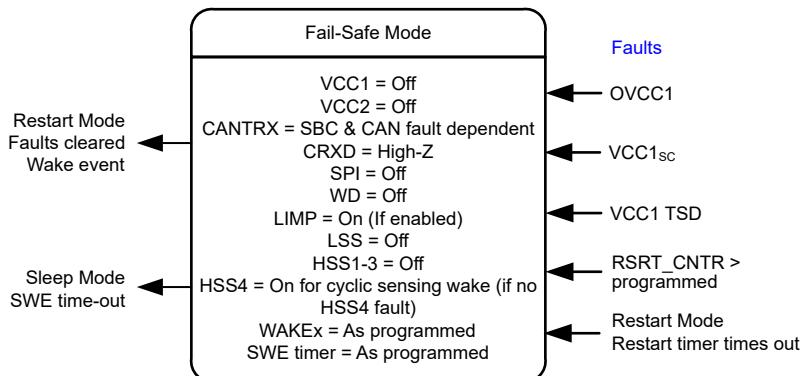

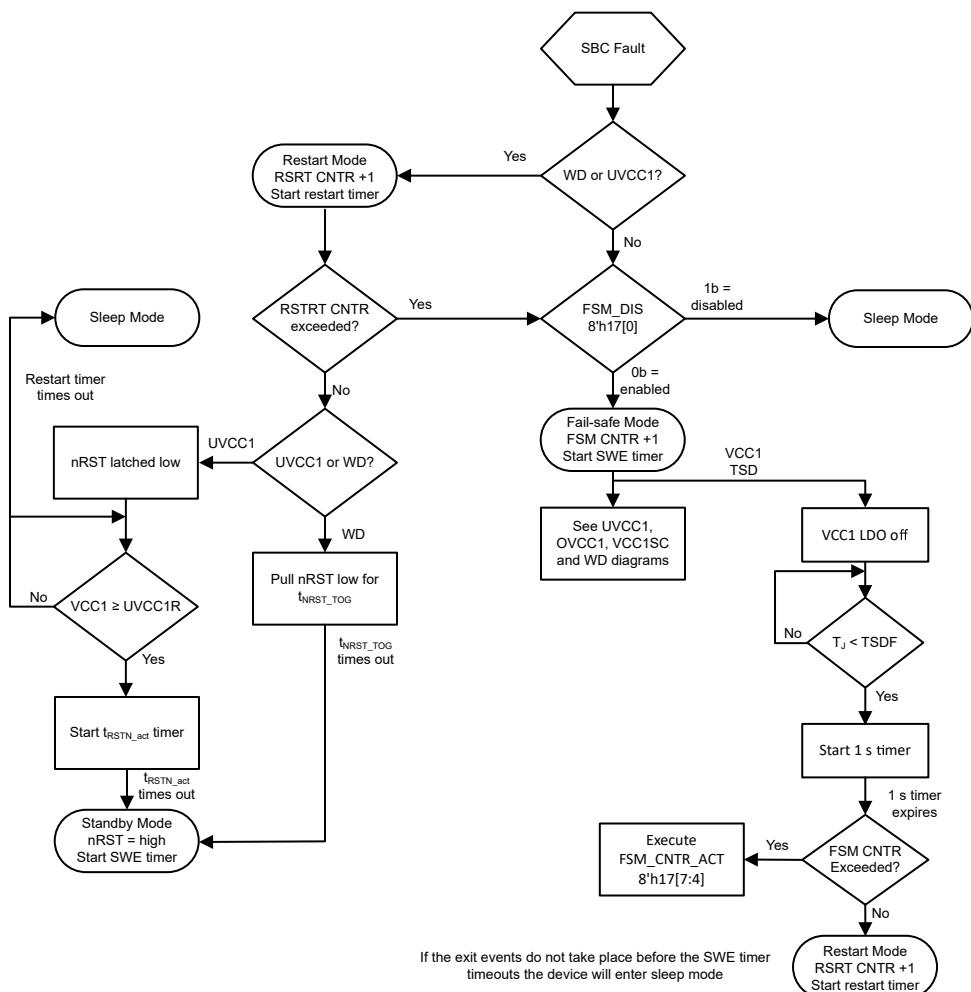

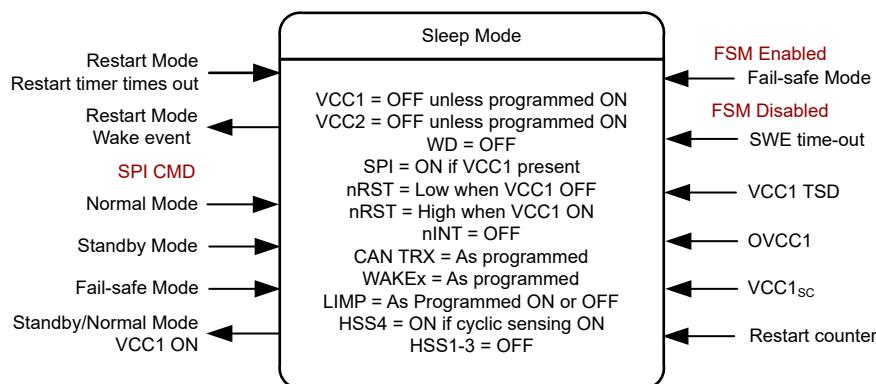

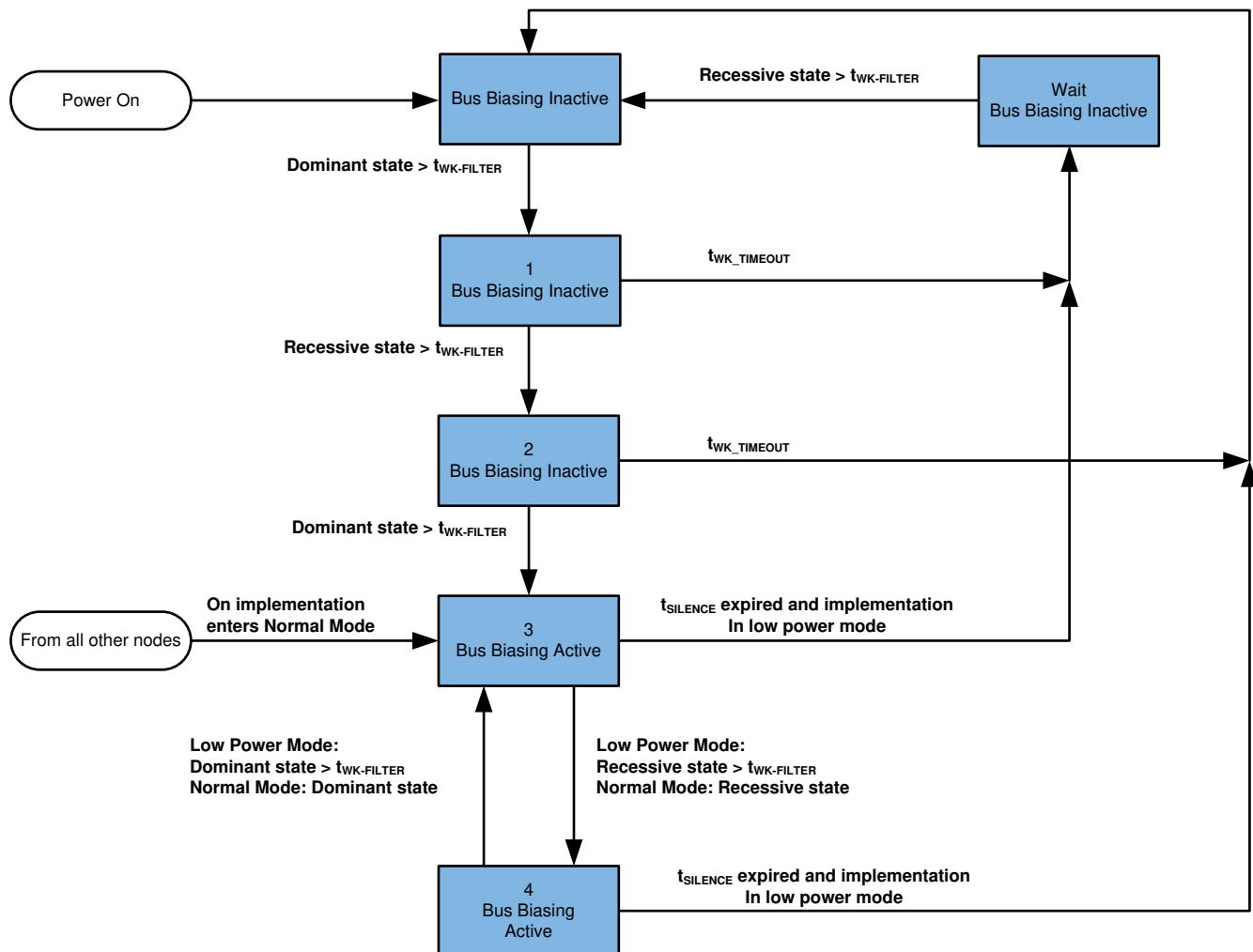

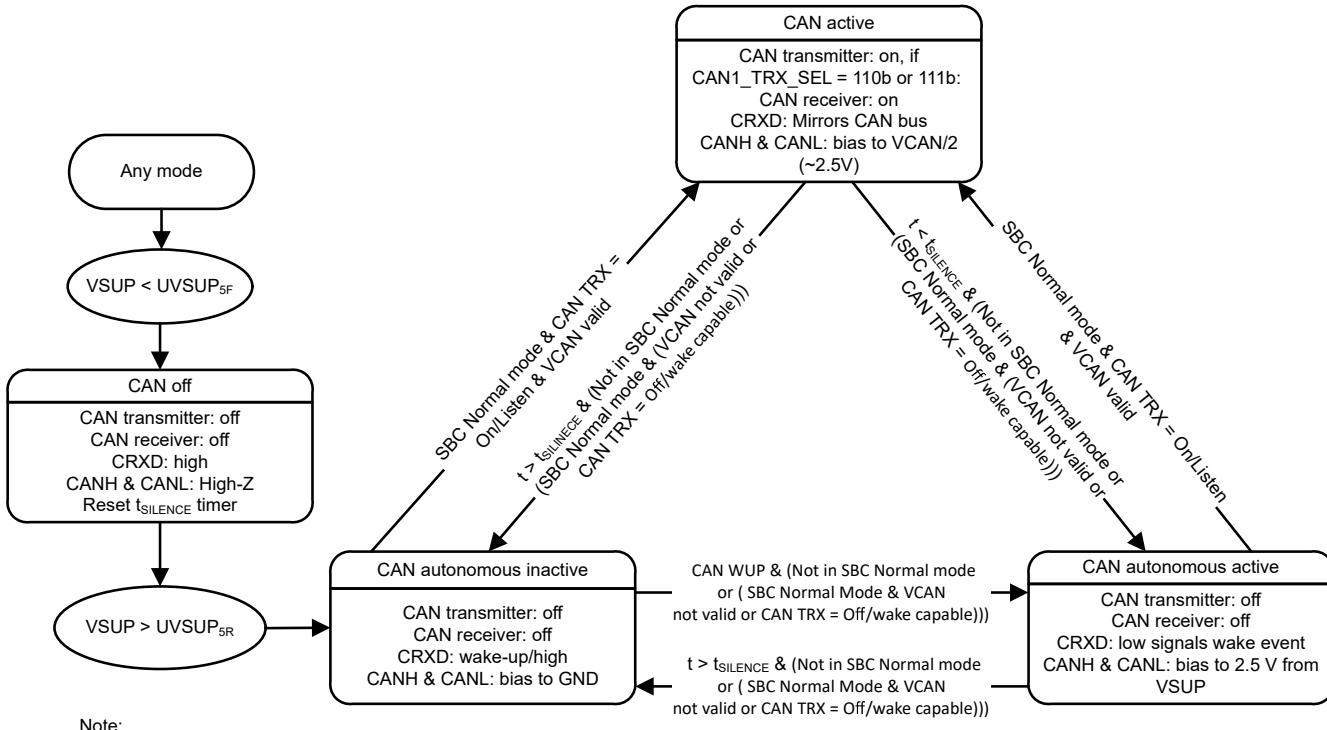

| $I_{IL}$                      | Low レベル入力リーケ電流                                                                                         | 入力 = 0V、VCC1 $\pm 2\%$                                        | -125 |     | -2  | $\mu\text{A}$    |