TCAN1164-Q1

JAJSNI0 - DECEMBER 2021

# TCAN1164-Q1 車載用 CAN FD システム・ベース・チップ、LDO 出力およびウォッチ ドッグ付き

# 1 特長

- 車載アプリケーション用に AEC Q100 (グレード 1) 認定済み

- ISO 11898-2:2016 の要件に適合

- 機能安全品質管理

- 機能安全システムの設計に役立つ資料を利用可

- 広い動作入力電圧範囲

- CAN トランシーバ電源用 LDO を内蔵

- 出力電流容量 100mA の 5V LDO

- Classic CAN および 最大 8Mbps の CAN FD (TCAN1164-Q1)

- 各種モードをサポートするウォッチドッグ・タ イマ

- タイムアウト

- ウィンドウ

- Q&A ウォッチドッグ

- 最大速度 5Mbps (TCAN1164T-Q1)

- 動作モードは SPI からプログラム可能

- 通常モード

- サイレント・モード

- スタンバイ・モード

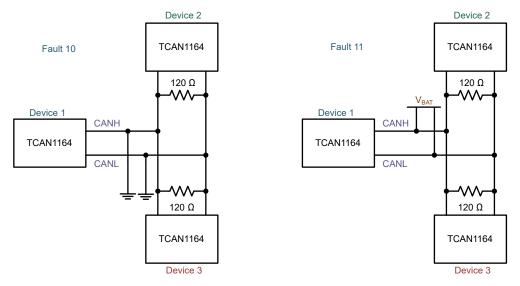

- 高度な CAN バス・フォルト検出をサポート

- 電源非接続時の規定された挙動

- バスおよび入出力端子は高インピーダンス (動 作中のバスまたはアプリケーションに対して無 負荷)

- 保護機能:

- ±58V の CAN バス・フォルト耐性

- V<sub>SUP</sub> でのロード・ダンプのサポート

- IEC ESD 保護

- 低電圧保護、過電圧保護

- サーマル・シャットダウン保護

- TXD ドミナント状態タイムアウト (TXD DTO)

- きわめて広い接合部温度に対応

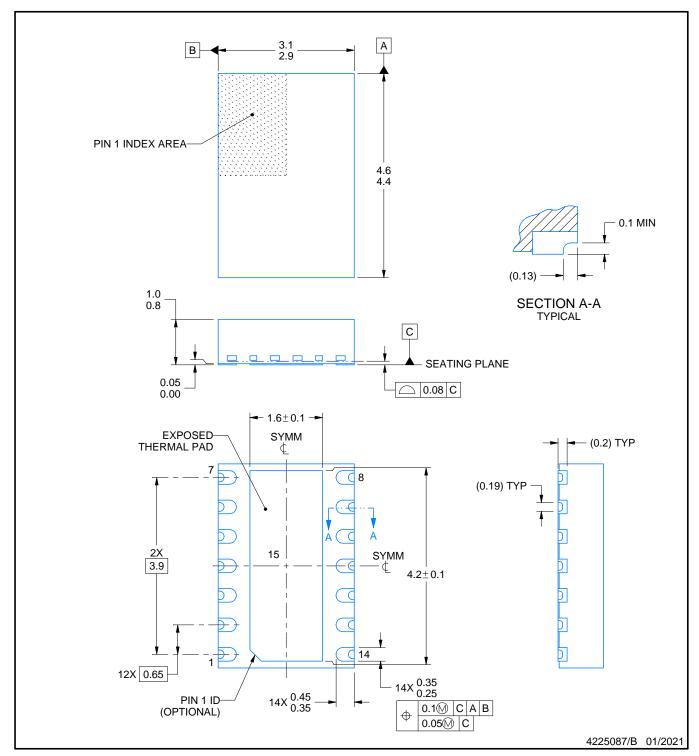

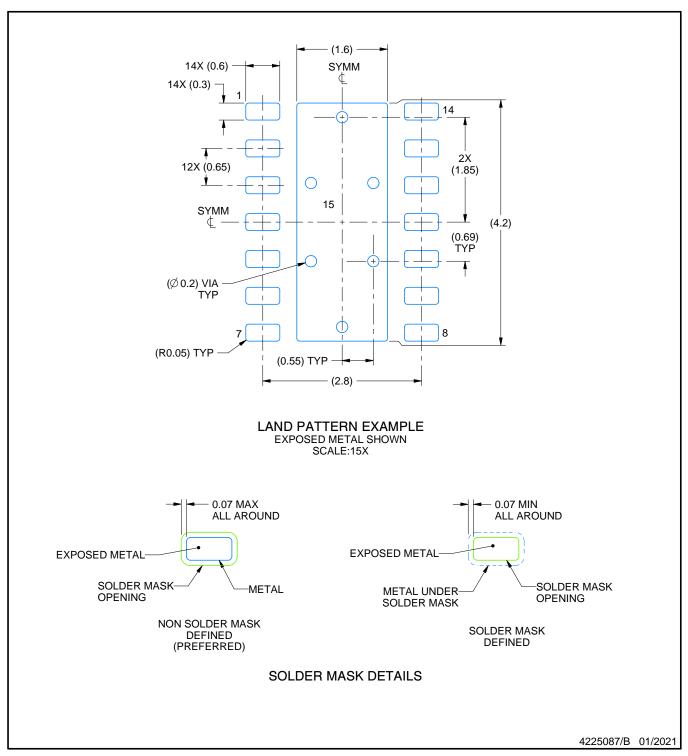

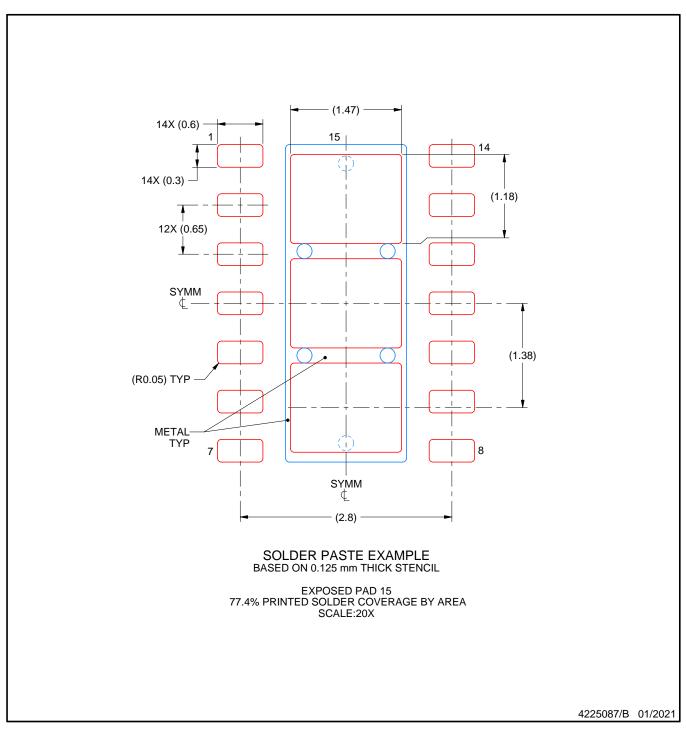

- 自動光学検査 (AOI) 性能を向上させたウェッタブ ル・フランク付きリードレス VSON (14) パッケー ジで供給

# 2 アプリケーション

- 先進運転支援システム (ADAS)

- ボディ・エレクトロニクス / 照明

- 車載用インフォテインメントおよびクラスタ

- ハイブリッド、電動、パワートレイン・システム

# 3 概要

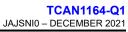

TCAN1164-Q1 は、ISO 11898-2:2016 高速 CAN (Controller Area Network) 仕様の物理層要件を満たす 高速 CAN SBC (システム・ベーシス・チップ) です。 このトランシーバは、Classical CAN ネットワークと 最高 8 メガビット/秒 (Mbps) (TCAN1164-Q1) または 5Mbps (TCAN1164T-Q1) の CAN FD ネットワークの 両方に対応しています。

TCAN1164-Q1 は、広い入力電源電圧範囲に対応し、 5V LDO 出力を内蔵しています。5V LDO 出力 (V<sub>CCOUT</sub>) は、CAN トランシーバ電圧を内部的に供給 し、さらに外部にも電流を供給できます。

#### 製品情報

| 部品番号         | パッケージ <sup>(1)</sup> | 本体サイズ (公称)     |

|--------------|----------------------|----------------|

| TCAN1164-Q1  | VSON (14)            | 4.5mm × 3.00mm |

| TCAN1164T-Q1 | VSON (14)            | 4.5mm × 3.00mm |

利用可能なすべてのパッケージについては、このデータシー トの末尾にある注文情報を参照してください。

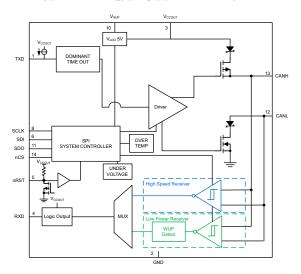

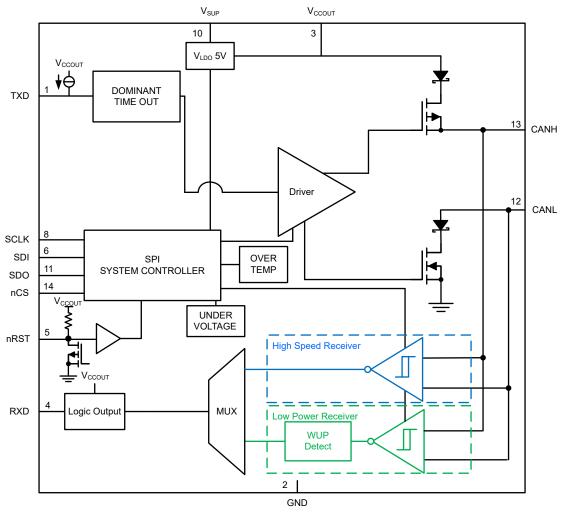

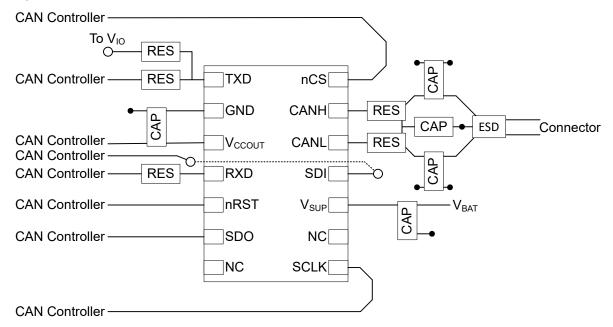

機能ブロック図

# **Table of Contents**

| 1 特長                                | 1  | 10.3 Feature Description                             | 19 |

|-------------------------------------|----|------------------------------------------------------|----|

| 2 アプリケーション                          |    | 10.4 Device Functional Modes                         |    |

| 3 概要                                | 1  | 10.5 Programming                                     | 42 |

| 4 Revision History                  | 2  | 11 Application Information Disclaimer                |    |

| 5 概要 (続き)                           |    | 11.1 Application Information                         |    |

| 6 Device Comparison Table           | 4  | 11.2 Typical Application                             |    |

| 7 Pin Configurations and Functions  | 5  | 11.3 Application Curves                              |    |

| 8 Specifications                    | 6  | 12 Power Supply Requirements                         |    |

| 8.1 Absolute Maximum Ratings        | 6  | 13 Layout                                            |    |

| 8.2 ESD Ratings                     | 6  | 13.1 Layout Guidelines                               |    |

| 8.3 ESD Ratings IEC Specification   | 6  | 13.2 Layout Example                                  | 62 |

| 8.4 Recomended Operating Conditions | 6  | 14 Device and Documentation Support                  | 63 |

| 8.5 Thermal Information             | 7  | 14.1 Documentation Support                           | 63 |

| 8.6 Power Supply Characteristics    | 7  | 14.2 Receiving Notification of Documentation Updates | 63 |

| 8.7 Electrical Characteristics      | 8  | 14.3 サポート・リソース                                       | 63 |

| 8.8 Switching Characteristics       | 10 | 14.4 Trademarks                                      | 63 |

| 8.9 Typical Characteristics         | 13 | 14.5 Electrostatic Discharge Caution                 | 63 |

| 9 Parameter Measurement Information | 14 | 14.6 Glossary                                        | 63 |

| 10 Detailed Description             |    | 15 Mechanical, Packaging, and Orderable              |    |

| 10.1 Overview                       | 18 | Information                                          | 63 |

| 10.2 Functional Block Diagram       | 18 |                                                      |    |

|                                     |    |                                                      |    |

# **4 Revision History**

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| December 2021 | *        | Initial Revision |

# 5 概要 (続き)

TCAN1164-Q1 は、CAN バス・ラインの短絡検出、サーマル・シャットダウン (TSD)、ドライバ・ドミナント・タイムアウト (TXD DTO)、最大  $\pm 58$ V のバス・フォルト保護を含む多くの保護および診断機能を備えています。

TCAN1164-Q1 はウォッチドッグ機能をサポートしているため、一定期間内にウォッチドッグ・タイマをリセットすることをプロセッサに要求して、システムが正常であることを確認できます。

# **6 Device Comparison Table**

| DEVICE NUMBER | Description                                                      | MAXIMUM DATA RATE | VeLIO <sup>(1)</sup> |

|---------------|------------------------------------------------------------------|-------------------|----------------------|

| TCAN1164-Q1   | CAN FD SBC with SPI Mode Control,<br>Reset, Watchdog and 5 V LDO | 8 Mbps            | No                   |

| TCAN1164T-Q1  | CAN FD SBC with SPI Mode Control,<br>Reset, Watchdog and 5 V LDO | 5 Mbps            | Yes                  |

1. Certified according to latest VeLIO (Vehicle LAN Interopability and Optimization) test requirements

Product Folder Links: TCAN1164-Q1

# 7 Pin Configurations and Functions

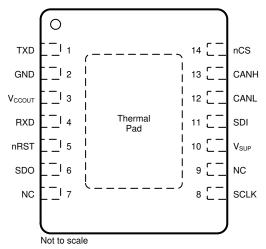

図 7-1. DMT package, 14 Pin (VSON), Top View

表 7-1. Pin Functions

| PIN                |     | TYPE    | Description                                 |

|--------------------|-----|---------|---------------------------------------------|

| NAME               | NO. | ITPE    | Description                                 |

| TXD                | 1   | Digital | CAN transmit data input, integrated pull-up |

| GND                | 2   | GND     | Ground connection                           |

| V <sub>CCOUT</sub> | 3   | Supply  | 5-V LDO regulated output voltage            |

| RXD                | 4   | Digital | CAN receive data output                     |

| nRST               | 5   | Digital | Reset input/output                          |

| SDO                | 6   | Digital | SPI data output                             |

| NC                 | 7   | _       | No connect (not internally connected)       |

| SCLK               | 8   | Digital | SPI clock input                             |

| NC                 | 9   | _       | No connect (not internally connected)       |

| V <sub>SUP</sub>   | 10  | Supply  | Reverse-blocked battery supply input        |

| SDI                | 11  | Digital | SPI data input                              |

| CANL               | 12  | Bus IO  | Low-level CAN bus input/output line         |

| CANH               | 13  | Bus IO  | High-level CAN bus input/output line        |

| nCS                | 14  | Digital | SPI chip select (active low)                |

# 8 Specifications

# 8.1 Absolute Maximum Ratings

over operating virtual junction temperature range (unless otherwise noted)(1)

|                             |                                              | MIN  | MAX | UNIT |

|-----------------------------|----------------------------------------------|------|-----|------|

| V <sub>SUP</sub>            | Supply voltage range                         | -0.3 | 42  | V    |

| V <sub>CCOUT</sub>          | 5 V regulated output                         | -0.3 | 6   | V    |

| V <sub>BUS</sub>            | CAN bus IO voltage range (CANH, CANL)        | -58  | 58  | V    |

| V <sub>(Logic_Input)</sub>  | Logic input terminal voltage range           | -0.3 | 6   | V    |

| V <sub>(Logic_Output)</sub> | Logic output terminal voltage range          | -0.3 | 6   | V    |

| I <sub>O(LOGIC)</sub>       | Logic output current                         |      | 8   | mA   |

| TJ                          | Operating virtual junction temperature range | -40  | 150 | °C   |

| T <sub>STG</sub>            | Storage temperature                          | -65  | 165 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 8.2 ESD Ratings

|                    |                         |                                                                                       |                                                         | VALUE  | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------|--------|------|

|                    |                         |                                                                                       | HBM classification level 3A for all pin                 | ±4000  |      |

| V                  | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup>                               | HBM classification level 3A for V <sub>SUP</sub> ,      | ±8000  | V    |

| V <sub>(ESD)</sub> | Electrostatic discrarge |                                                                                       | HBM classification level 3B for global pins CANH & CANL | ±10000 | V    |

|                    |                         | Charged-device model (CDM), per AEC Q100-011 CDM classification level C5 for all pins |                                                         | ±750   |      |

<sup>(1)</sup> AEC-Q100-002 indicates that HBM stresses shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 8.3 ESD Ratings IEC Specification

|                                                                             |                                              |                                        |                                                            | VALUE | UNIT |

|-----------------------------------------------------------------------------|----------------------------------------------|----------------------------------------|------------------------------------------------------------|-------|------|

| V <sub>ESD</sub> System level electro-static discharge (ESD) <sup>(1)</sup> |                                              | CAN bus terminals (CANH & CANL) to GND | IEC 61000-4-2 (150pF, 330Ω)<br>unpowered contact discharge | ±8000 |      |

|                                                                             | V <sub>SUP</sub>                             | unpowered contact discharge            | ±8000                                                      |       |      |

|                                                                             |                                              | CAN bue terminals (CANH & CANI ) to    | Pulse 1                                                    | -100  |      |

|                                                                             | ISO 7637 ISO pulse transients <sup>(2)</sup> |                                        | Pulse 2                                                    | 75    | V    |

| $V_{TRAN}$                                                                  |                                              |                                        | Pulse 3a                                                   | -150  |      |

|                                                                             |                                              | Pulse 3b                               | 100                                                        |       |      |

|                                                                             | ISO 7637-3 transient <sup>(3)</sup>          |                                        | DCC slow transient pulse                                   | ±30   |      |

- (1) Tested according to IEC 62228-3 CAN Transceiver, Section 6.4; DIN EN 61000-4-2

- (2) Tested according to IEC 62228-3 CAN Transceiver, Section 6.3; standard pulse parameters defined in ISO 7637-2

- (3) Tested according to ISO 7637-3; electrical transient transmission by capacitive and inductive coupling via lines other than supply line

# 8.4 Recomended Operating Conditions

|                     |                                                   | MIN | NOM | MAX | UNIT |

|---------------------|---------------------------------------------------|-----|-----|-----|------|

| V <sub>SUP</sub>    | Supply voltage range                              | 5.5 |     | 28  | V    |

| I <sub>OH(DO)</sub> | Digital output terminal high level output current | -2  |     |     | mA   |

| I <sub>OL(DO)</sub> | Digital output terminal low level output current  |     |     | 2   | mA   |

| C <sub>VSUP</sub>   | V <sub>SUP</sub> pin capacitance                  |     | 0.1 |     | μF   |

| C <sub>VCCOUT</sub> | V <sub>CCOUT</sub> pin capacitance                | 10  |     |     | μF   |

| T <sub>SDR</sub>    | Thermal shutdown rising                           | 175 | 180 |     | °C   |

| T <sub>SDF</sub>    | Thermal shutdown falling                          |     | 165 | 170 | °C   |

|                  |                             | MIN | NOM MA | X UNIT |

|------------------|-----------------------------|-----|--------|--------|

| T <sub>SDW</sub> | Thermal shutdown warning    | 150 |        | °C     |

| T <sub>HYS</sub> | Thermal shutdown hysterisis |     | 15     | °C     |

# 8.5 Thermal Information

|                       | THERMAL METRIC(1)                            | DMT (VSON) | UNIT |

|-----------------------|----------------------------------------------|------------|------|

|                       | I DERMAL METRIC                              | 14 PINS    | UNII |

| R <sub>⊙JA</sub>      | Junction-to-ambient thermal resistance       | 37.7       | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 37.9       | °C/W |

| R <sub>⊝JB</sub>      | Junction-to-board thermal resistance         | 14.2       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.7        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 14.2       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.9        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

# 8.6 Power Supply Characteristics

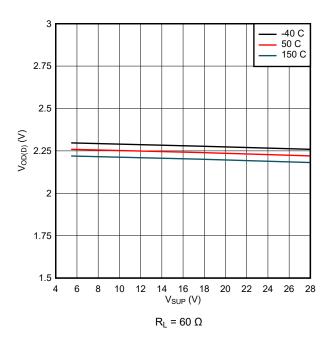

Over recomended operating conditions with  $T_J$  = -40°C to 150°C, unless otherwise noted. All typical values are taken at 25°C,  $V_{SUP}$  = 12 V, and  $R_L$  = 60  $\Omega$

|                                  | PARAMETER                                                       | TEST CONDITIONS                                                                                       | MIN  | TYP  | MAX      | UNIT |

|----------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|----------|------|

| Supply Voltage an                | d Current                                                       |                                                                                                       |      |      | <u> </u> |      |

|                                  | Supply current                                                  | TXD = 0 V, R <sub>L</sub> = 60 Ω, C <sub>L</sub> = open<br>See $\boxtimes$ 9-2                        |      |      | 60       | mA   |

| I <sub>SUP</sub>                 | Bus biasing active: dominant                                    | TXD = 0 V, R <sub>L</sub> = 50 Ω, C <sub>L</sub> = open<br>See $\boxtimes$ 9-2                        |      |      | 70       | mA   |

|                                  | Supply current Bus biasing active: recessive                    | TXD = V <sub>CCOUT</sub> , R <sub>L</sub> = 50 Ω, C <sub>L</sub> = open<br>See $\boxtimes$ 9-2        |      |      | 3        | mA   |

| I <sub>SUP(STB)</sub>            | Supply current<br>Standby mode<br>Bus bias autonomous: inactive | 5.5 V < V <sub>SUP</sub> ≤ 19 V<br>See ☑ 9-2                                                          |      |      | 230      | μA   |

| I <sub>SUP(BIAS)</sub>           | Supply current Bus bias autonomous: active <sup>(1)</sup>       | 5.5 V < V <sub>SUP</sub> ≤ 28 V<br>See 図 9-2                                                          |      |      | 60       | μΑ   |

| UV <sub>SUPR</sub>               | Under voltage V <sub>SUP</sub> threshold rising                 | Ramp Up                                                                                               | 4.05 |      | 4.42     | V    |

| UV <sub>SUPF</sub>               | Under voltage V <sub>SUP</sub> threshold falling                | Ramp Down                                                                                             | 3.9  |      | 4.25     | V    |

| V <sub>CCOUT</sub> Characteri    | stics                                                           |                                                                                                       |      |      |          |      |

| V <sub>CCOUT</sub>               | 5 V regulated output                                            | V <sub>SUP</sub> = 5.5 to 18 V<br>I <sub>L</sub> = 0 to 100 mA<br>TXD = V <sub>CCOUT</sub>            | 4.9  | 5    | 5.1      | ٧    |

| V <sub>CCOUT</sub>               | 5 V regulated output                                            | V <sub>SUP</sub> = 5.65 to 18 V<br>I <sub>L</sub> = 0 to 100 mA<br>TXD = 0 V; V <sub>CANH</sub> = 0 V | 4.9  | 5    | 5.1      | V    |

| V <sub>CCOUT_DROP</sub>          | Dropout voltage                                                 | 5 V LDO, V <sub>SUP</sub> – V <sub>CCOUT</sub> , I <sub>L</sub> = 125 mA                              |      | 300  | 650      | mV   |

| $\Delta V_{CCOUT(\Delta VSUP)}$  | Line regulation                                                 | $V_{SUP}$ = 5.5 to 28 V, $I_L$ = 10 mA, $\Delta V_{CCOUT}$                                            |      |      | 50       | mV   |

| $\Delta V_{CCOUT(\Delta VSUPL)}$ | Load regulation                                                 | $I_L$ = 1 to 125 mA, $V_{SUP}$ = 14 V, $\Delta V_{CCOUT}$                                             |      |      | 50       | mV   |

| UV <sub>VCCOUTR</sub>            | Under voltage V <sub>CCOUT</sub> threshold rising               | Ramp Up                                                                                               | 4.25 | 4.6  | 4.75     | V    |

| UV <sub>VCCOUTF</sub>            | Under voltage V <sub>CCOUT</sub> threshold falling              | Ramp Down                                                                                             | 4.2  | 4.45 | 4.7      | V    |

| OV <sub>CCOUTR</sub>             | Over voltage V <sub>CCOUT</sub> threshold rising                | Ramp Up                                                                                               |      | 5.7  | 6.15     | V    |

| OV <sub>CCOUTF</sub>             | Over voltage V <sub>CCOUT</sub> threshold falling               | Ramp Down                                                                                             | 5.47 | 5.65 |          | V    |

| I <sub>L_VCCOUT</sub>            | Output current limit                                            | V <sub>CCOUT</sub> short to ground                                                                    | 175  |      | 275      | mA   |

| PSRR <sub>VCCOUT</sub>           | Power supply rejection ripple rejection                         | $V_{RIP} = 0.5 V_{PP}$ , Load = 10 mA, $f = 100 Hz$ , $C_{O} = 10 \mu F$                              | 60   |      |          | dB   |

<sup>(1)</sup> After a valid wake-up the total  $I_{SUP}$  current is the sum of  $I_{SUP(STB)}$  and  $I_{SUP(BIAS)}$  ( $I_{SUP} = I_{SUP(STB)} + I_{SUP(BIAS)}$ )

# 8.7 Electrical Characteristics

Over recommended operating conditions with  $T_J$  =  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise noted. All typical values are taken at  $25^{\circ}$ C,  $V_{SUP}$  = 12 V, and  $R_L$  = 60  $\Omega$

|                        | PARAMETER                                                                                                                                                               |                   | TEST CONDITIONS                                                                                                              | MIN        | TYP MAX | UNIT |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|------------|---------|------|

| CAN Driver             | Electrical Characteristics                                                                                                                                              |                   |                                                                                                                              |            |         |      |

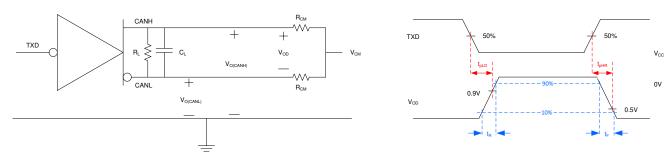

| ,                      | Dominant output voltage<br>Bus biasing active                                                                                                                           | CANH              | TXD = 0 V, 50 ≤ $R_L$ ≤ 65 Ω, $C_L$ = open, $R_{CM}$ =                                                                       | 2.75       | 4.5     | V    |

| $I_{O(D)}$             | Dominant output voltage<br>Bus biasing active                                                                                                                           | CANL              | ─ open<br>See 図 9-2                                                                                                          | 0.5        | 2.25    | V    |

| / <sub>O(R)</sub>      | Recessive output voltage<br>Bus biasing active                                                                                                                          |                   | TXD = V <sub>CCOUT</sub> , R <sub>L</sub> = open (no load), R <sub>CM</sub> = open See ⊠ 9-2                                 | 2          | 3       | V    |

| / <sub>SYM</sub>       | Driver symmetry Bus biasing active (V <sub>O(CANH)</sub> + V <sub>O(CANL)</sub> ) / V <sub>CC</sub>                                                                     | OUT               | $R_L$ = 60 $\Omega$ , $C_{SPLIT}$ = 4.7 nF, $C_L$ = Open, $R_{CM}$ = Open, TXD = 250 kHz, 1 Mhz, 2.5 MHz See $\boxed{2}$ 9-2 | 0.9        | 1.1     | V/V  |

| / <sub>SYM_DC</sub>    | DC Driver symmetry Bus biasing active VCCOUT - VO(CANH) - VO(CAN                                                                                                        | NL)               | R <sub>L</sub> = 60 Ω, C <sub>L</sub> = open<br>See ⊠ 9-2                                                                    | -400       | 400     | mV   |

|                        | Differential output voltage<br>Bus biasing active<br>Dominant                                                                                                           | CANH - CANL       | TXD = 0 V, 50 $\Omega$ ≤ R <sub>L</sub> ≤ 65 $\Omega$ , C <sub>L</sub> = open See $\square$ 9-2                              | 1.5        | 3       | V    |

| / <sub>OD(DOM)</sub>   | Differential output voltage<br>Bus biasing active<br>Dominant                                                                                                           | CANH - CANL       | TXD = 0 V, 45 $\Omega$ ≤ R <sub>L</sub> ≤ 70 $\Omega$ , CL = open See $\square$ 9-2                                          | 1.4        | 3.3     | V    |

|                        | Differential output voltage<br>Bus biasing active<br>Dominant                                                                                                           | CANH - CANL       | TXD = 0 V, R <sub>L</sub> = 2240 Ω, C <sub>L</sub> = open<br>See ⊠ 9-2                                                       | 1.5        | 5       | V    |

| / <sub>OD(REC)</sub>   | Differential output voltage<br>Bus biasing active<br>Bus biasing inactive<br>Recessive                                                                                  | CANH - CANL       | TXD = $V_{CCOUT}$ , $R_L$ = open $Ω$ , $C_L$ = open See $29-2$                                                               | -50        | 50      | mV   |

|                        | Pin output voltage<br>Bus biasing inactive                                                                                                                              | CANH              | TXD = V <sub>CCOUT</sub><br>R <sub>L</sub> = open (no load), C <sub>L</sub> = open<br>See ⊠ 9-2                              | -0.1       | 0.1     | V    |

| V <sub>O(INACT)</sub>  |                                                                                                                                                                         | CANL              | $TXD = V_{CCOUT}$<br>$R_L = \text{open (no load)}, C_L = \text{open}$<br>See $\boxed{3}$ 9-2                                 | -0.1       | 0.1     | V    |

| / <sub>OD(STB)</sub>   | Differential output voltage<br>Bus biasing inactive                                                                                                                     | CANH - CANL       | TXD = V <sub>CCOUT</sub> R <sub>L</sub> = open (no load), C <sub>L</sub> = open See ⊠ 9-2                                    | -0.2       | 0.2     | V    |

|                        | Short-circuit steady-state output current Bus biasing active Dominant  Short-circuit steady-state output current Bus biasing active Dominant                            |                   | TXD = 0 V<br>-15 V ≤ V <sub>(CANH)</sub> ≤ 40 V<br>See ⊠ 9-2 and ⊠ 9-8                                                       | <b>-75</b> |         | mA   |

| OS(DOM)                |                                                                                                                                                                         |                   | TXD = 0 V<br>-15 V ≤ V <sub>(CANL)</sub> ≤ 40 V<br>See ☑ 9-2 and ☑ 9-8                                                       |            | 75      | mA   |

| OS(REC)                | Short-circuit steady-state or<br>Bus biasing active<br>Recessive                                                                                                        | tput current      | V <sub>BUS</sub> = CANH = CANL<br>-27 V ≤ V <sub>BUS</sub> ≤ 42 V<br>See ဩ 9-2 and ဩ 9-8                                     | -3         | 3       | mA   |

| AN Receiv              | ver Electrical Characteristics                                                                                                                                          | <b>i</b>          |                                                                                                                              |            |         |      |

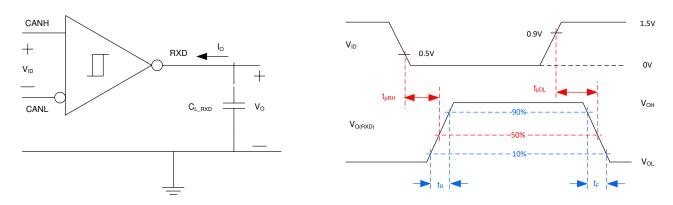

| IT(DOM)                | Receiver dominant state inp<br>Bus biasing active                                                                                                                       | out voltage range | -12 V ≤ V <sub>CM</sub> ≤ 12 V                                                                                               | 0.9        | 8       | V    |

| / <sub>IT(REC)</sub>   | Receiver recessive state inp<br>Bus biasing active                                                                                                                      |                   | See 図 9-3 and 表 10-14                                                                                                        | -3         | 0.5     | V    |

| / <sub>HYS</sub>       | Hysteresis voltage for input threshold Bus biasing active                                                                                                               |                   | See 図 9-3 and 表 10-14                                                                                                        | 80         | 140     | mV   |

| / <sub>DIFF(MAX)</sub> | Maximum rating of V <sub>DIFF</sub> Receiver dominant state input voltage range Bus biasing inactive  Receiver recessive state input voltage range Bus biasing inactive |                   |                                                                                                                              | -5         | 10      | V    |

| / <sub>DIFF(DOM)</sub> |                                                                                                                                                                         |                   | -12 V ≤ V <sub>CM</sub> ≤ 12 V                                                                                               | 1.150      | 8       | V    |

| J <sub>DIFF(REC)</sub> |                                                                                                                                                                         |                   | See 図 9-3 and 表 10-14                                                                                                        | -3         | 0.4     | V    |

| V <sub>CM</sub>        | Common mode range                                                                                                                                                       |                   | See 図 9-3 and 表 10-14                                                                                                        | -12        | 12      | V    |

| OFF(LKG)               | Power-off (unpowered) bus input leakage current                                                                                                                         |                   | V <sub>SUP</sub> = 0 V, CANH = CANL = 5 V                                                                                    |            | 2.5     | μA   |

Over recommended operating conditions with  $T_J$  = -40°C to 150°C, unless otherwise noted. All typical values are taken at 25°C,  $V_{SUP}$  = 12 V, and  $R_L$  = 60  $\Omega$

|                                    | PARAMETER                                                                                 |      | TEST CONDITIONS                                                                        | MIN  | TYP | MAX | UNIT               |

|------------------------------------|-------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|------|-----|-----|--------------------|

| Cı                                 | Input capacitance to ground (CANH or C                                                    | ANL) | $TXD = V_{CCOUT}$                                                                      |      |     | 20  | pF                 |

| C <sub>ID</sub>                    | Differential input capacitance <sup>(1)</sup>                                             |      | TXD = V <sub>CCOUT</sub>                                                               |      |     | 10  | pF                 |

| R <sub>ID</sub>                    | Differential input resistance                                                             |      | TXD = V <sub>CCOUT</sub>                                                               | 50   |     | 100 | kΩ                 |

| R <sub>IN</sub>                    | Input resistance (CANH or CANL)                                                           |      | -12 V ≤ V <sub>CM</sub> ≤ 12 V                                                         | 25   |     | 50  | kΩ                 |

| R <sub>IN(M)</sub>                 | Input resistance matching:<br>[1 – R <sub>IN(CANH)</sub> / R <sub>IN(CANL)</sub> ] × 100% |      | $V_{(CANH)} = V_{(CANL)} = 5 V$                                                        | -1   |     | 1   | %                  |

| TXD Input                          | Characteristics                                                                           |      |                                                                                        |      |     |     |                    |

| V <sub>IH</sub>                    | High level input voltage                                                                  |      |                                                                                        | 0.7  |     |     | V <sub>CCOUT</sub> |

| V <sub>IL</sub>                    | Low level input voltage                                                                   |      |                                                                                        |      |     | 0.3 |                    |

| I <sub>IH</sub>                    | High level input leakage current                                                          |      | TXD = V <sub>CCOUT</sub>                                                               | -1   | 0   | 1   | μA                 |

| I <sub>IL</sub>                    | Low level input leakage current                                                           |      | TXD = 0 V                                                                              | -130 |     | -15 | μA                 |

| R <sub>PU</sub>                    | Pull-up resistance                                                                        |      |                                                                                        | 40   | 60  | 80  | kΩ                 |

| I <sub>LKG(OFF)</sub>              | Unpowered leakage current                                                                 |      | TXD = 5.5 V, V <sub>SUP</sub> = 0 V                                                    | -1   | 0   | 1   | μA                 |

| Cı                                 | Input Capacitance                                                                         |      | $V_{IN} = 0.4 \times \sin(2 \times \pi \times 2 \times 10^6 \times t) + 2.5 \text{ V}$ |      | 5   |     | pF                 |

| RXD Outpu                          | ut Characteristics                                                                        |      |                                                                                        |      |     |     |                    |

| V <sub>OH</sub>                    | High level output voltage                                                                 |      | $I_{O} = -2 \text{ mA}.$                                                               | 0.8  |     |     | V <sub>CCOUT</sub> |

| V <sub>OL</sub>                    | Low level output voltage                                                                  |      | I <sub>O</sub> = 2 mA.                                                                 |      |     | 0.2 |                    |

| R <sub>PU</sub>                    | Pull-up resistance                                                                        |      |                                                                                        | 40   | 60  | 80  | kΩ                 |

| I <sub>LKG(OFF)</sub>              | Unpowered leakage curret                                                                  |      | RXD = 5.5 V, V <sub>SUP</sub> = 0 V                                                    | -5   |     | 5   | μA                 |

|                                    | rectional Characteristics                                                                 |      |                                                                                        |      |     |     |                    |

| V <sub>IH</sub>                    | High level input voltage                                                                  |      |                                                                                        | 0.8  |     |     | V <sub>CCOUT</sub> |

| V <sub>IL</sub>                    | Low level input voltage                                                                   |      |                                                                                        |      |     | 0.2 | V <sub>CCOUT</sub> |

| V <sub>OL</sub>                    | Low level output voltage                                                                  |      | I <sub>O</sub> = 2 mA.                                                                 |      |     | 0.2 |                    |

| I <sub>IH</sub>                    | High level input leakage current                                                          |      | nRST = V <sub>CCOUT</sub>                                                              | -1   |     | 1   | μА                 |

| R <sub>PU</sub>                    | Pull-up resistance to V <sub>CCOUT</sub>                                                  |      |                                                                                        | 160  | 240 | 320 | kΩ                 |

|                                    | Characteristics                                                                           |      |                                                                                        |      |     |     |                    |

| V <sub>IH</sub>                    | High level input voltage                                                                  |      |                                                                                        | 0.8  |     |     | V <sub>CCOUT</sub> |

| V <sub>IL</sub>                    | Low level input voltage                                                                   |      |                                                                                        |      |     | 0.2 |                    |

| I <sub>IH</sub>                    | High level input leakage current                                                          |      | SDI = V <sub>CCOUT</sub> (2)                                                           | -1   |     | 1   | μA                 |

| I <sub>IL</sub>                    | Low level input leakage current                                                           |      | SDI = 0 V                                                                              | -130 |     | -50 | μA                 |

| R <sub>PU</sub>                    | Pull-up resistance                                                                        |      |                                                                                        | 40   | 60  | 80  | kΩ                 |

| I <sub>LKG(OFF)</sub>              | Unpowered leakage current                                                                 |      | SDI = 5.5 V, V <sub>SUP</sub> = 0 V                                                    | -1   |     | 1   | μA                 |

| C <sub>IN</sub>                    | Input capacitance                                                                         |      | 20 MHz                                                                                 | 4    |     | 10  | pF                 |

|                                    | It Characteristics                                                                        |      |                                                                                        |      |     |     | '                  |

| V <sub>IH</sub>                    | High level input voltage                                                                  |      |                                                                                        | 0.7  |     |     | V <sub>CCOUT</sub> |

| V <sub>IL</sub>                    | Low level input voltage                                                                   |      |                                                                                        |      |     | 0.3 | V <sub>CCOUT</sub> |

| I <sub>IH</sub>                    | High level input leakage current                                                          |      | SCLK = V <sub>CCOUT</sub> (2)                                                          | 50   |     | 130 | μΑ                 |

| I <sub>IL</sub>                    | Low level input leakage current                                                           |      | SCLK = 0 V                                                                             | -1   |     | 1   | μA                 |

| R <sub>PD</sub>                    | Pull-down resistance                                                                      |      | <u> </u>                                                                               | 40   | 60  | 80  | kΩ                 |

| I <sub>LKG(OFF)</sub>              | Unpowered leakage current                                                                 |      | SCLK = 5.5 V, V <sub>SUP</sub> = 0 V                                                   | -1   |     | 1   |                    |

| C <sub>IN</sub>                    | Input capacitance                                                                         |      | 20 MHz                                                                                 | 4    |     | 10  | pF                 |

|                                    | Characteristics                                                                           |      | I                                                                                      |      |     |     | F *                |

| V <sub>IH</sub>                    | High level input voltage High level i voltage                                             | nput | High level input voltage                                                               | 0.7  |     |     | V <sub>CCOUT</sub> |

| V <sub>IL</sub>                    | Low level input voltage Low level in voltage                                              | nput | Low level input voltage                                                                |      |     | 0.3 | V <sub>CCOUT</sub> |

|                                    | High level input leakage current                                                          |      | nCS = V <sub>CCOUT</sub>                                                               | -1   |     | 1   | μA                 |

| liu                                |                                                                                           |      | ··· *GGOOT                                                                             |      |     |     | ۱ ۳٬               |

| I <sub>IH</sub><br>I <sub>IL</sub> | Low level input leakage current                                                           |      | nCS = 0 V                                                                              | -130 | -   | -50 | μA                 |

Over recommended operating conditions with  $T_J$  =  $-40^{\circ}C$  to 150°C, unless otherwise noted. All typical values are taken at 25°C,  $V_{SUP}$  = 12 V, and  $R_L$  = 60  $\Omega$

|                       | PARAMETER                 | TEST CONDITIONS                     | MIN | TYP MAX | UNIT               |

|-----------------------|---------------------------|-------------------------------------|-----|---------|--------------------|

| I <sub>LKG(OFF)</sub> | Unpowered leakage current | nCS = 5.5 V, V <sub>SUP</sub> = 0 V | -1  | 1       | μA                 |

| C <sub>IN</sub>       | Input capacitance         | 20 MHz                              | 4   | 10      | pF                 |

| SDO Outpu             | ut Characteristics        |                                     |     |         | •                  |

| V <sub>OH</sub>       | High-level output voltage | I <sub>OH</sub> = -2 mA             | 0.8 |         | V <sub>CCOUT</sub> |

| V <sub>OL</sub>       | Low-level output voltage  | I <sub>OL</sub> = 2 mA              |     | 0.2     | V <sub>CCOUT</sub> |

| I <sub>LKG(OFF)</sub> | Unpowered leakage current | V <sub>nCS</sub> = 5.5 V            | -1  | 1       | μA                 |

<sup>(1)</sup> Test according to ISO 11898-2:2003

# 8.8 Switching Characteristics

Over recomended operating conditions with  $T_J$  = -40°C to 150°C, unless otherwise noted. All typical values are taken at 25°C,  $V_{SUP}$  = 12 V and  $R_L$  = 60  $\Omega$

|                             | PARAMETER                                                                                   |                   | TEST CONDITIONS                                                                          | MIN | TYP | MAX | UNIT |

|-----------------------------|---------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Supply Switch               | ing Characteristics                                                                         |                   |                                                                                          |     |     |     |      |

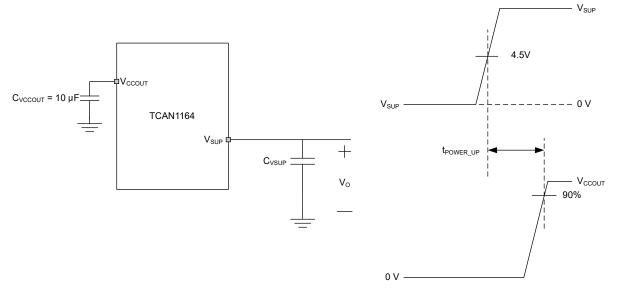

| t <sub>POWER_UP</sub>       | CAN supply power up time                                                                    |                   | C <sub>VCCOUT</sub> = 10 μF<br>See 図 9-9                                                 |     | 1.8 | 4   | ms   |

| t <sub>UV(SUP)</sub>        | V <sub>SUP</sub> filter time (rising and falling)                                           |                   |                                                                                          | 4   |     | 25  | μs   |

| t <sub>UV(VCCOUT)</sub>     | V <sub>CCOUT</sub> filter time (rising and falling)                                         |                   | Time for device to enter sleep state reset state once UV <sub>CCOUT</sub> is reached     |     | 30  |     | μs   |

| Device Switch               | ing Characteristics                                                                         |                   |                                                                                          |     |     | ·   |      |

| t <sub>UV(nRST)</sub>       | Undervoltage detection delay time nRST low                                                  |                   |                                                                                          |     | 10  | 50  | μs   |

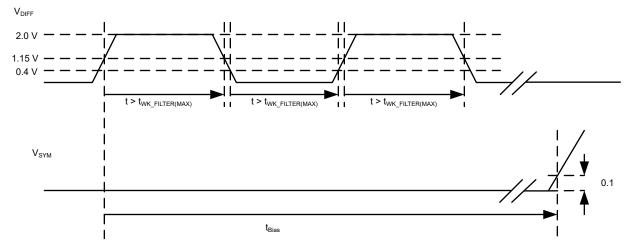

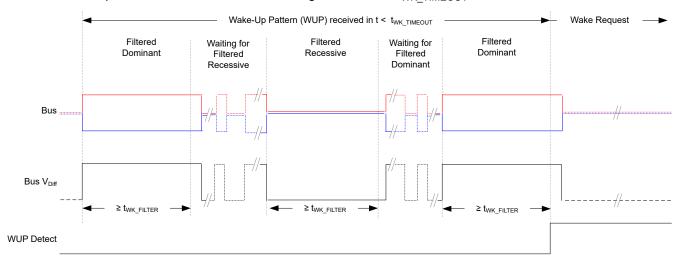

| t <sub>WK_FILTER</sub>      | Bus time to meet filtered bus requirments for waken                                         | ceup request      | See 図 10-15                                                                              | 0.5 |     | 1.8 | μs   |

| t <sub>WK_TIMEOUT</sub>     | Bus wakeup timeout value                                                                    |                   | See 🛭 10-15                                                                              | 0.8 |     | 2   | ms   |

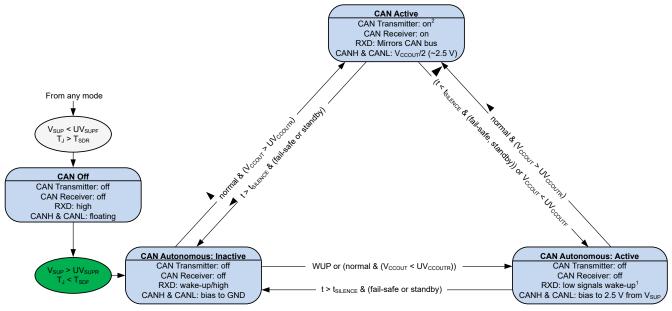

| t <sub>SILENCE</sub>        | Time out for bus inactivity                                                                 |                   |                                                                                          |     | 0.9 | 1.2 | s    |

| t <sub>INACTIVE</sub>       | Hardware timer for failsafe and power up inactivity                                         | ty <sup>(1)</sup> |                                                                                          | 3   | 4   | 5   | min  |

| t <sub>BIAS</sub>           | Time from the start of a dominant-recessive-dom until Vsym ≥ 0.1                            | inant sequence    | Each phase: 6 μs<br>See 🗵 9-10                                                           |     |     | 250 | μs   |

| t <sub>CAN(ACTIVE)</sub>    | Time from switching to CAN active mode to transtransmit                                     | ceiver ready to   | V <sub>CCOUT</sub> > UV <sub>VCCOUT(R)</sub>                                             |     |     | 25  | us   |

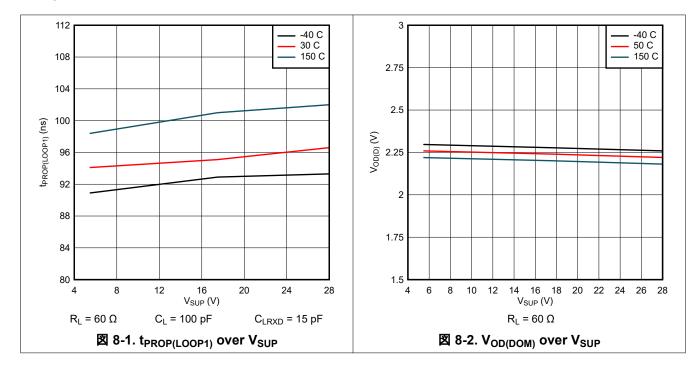

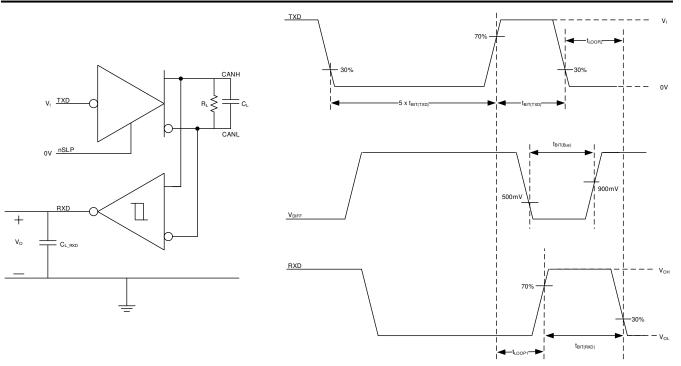

| t <sub>PROP(LOOP1)</sub>    | Total loop delay, driver input (TXD) to receiver ou<br>Recessive to dominant                | itput (RXD)       | R <sub>L</sub> = 60 Ω, C <sub>L</sub> = 100 pF, C <sub>L(RXD)</sub> = 15 pF<br>See 🗵 9-6 |     | 100 | 160 | ns   |

| t <sub>PROP(LOOP2)</sub>    | Total loop delay, driver input (TXD) to receiver ou<br>Dominant to recessive - TCAN1164-Q1  | itput (RXD)       | R <sub>L</sub> = 60 Ω, C <sub>L</sub> = 100 pF, C <sub>L(RXD)</sub> = 15 pF<br>See 🗵 9-6 |     | 120 | 175 | ns   |

| t <sub>PROP(LOOP2)</sub>    | Total loop delay, driver input (TXD) to receiver ou<br>Dominant to recessive - TCAN1164T-Q1 | itput (RXD)       | R <sub>L</sub> = 60 Ω, C <sub>L</sub> = 100 pF, C <sub>L(RXD)</sub> = 15 pF<br>See 🗵 9-6 |     | 130 | 195 | ns   |

| t <sub>mode_slp_reset</sub> | WUP or LWU event to INH asserted high, see                                                  |                   |                                                                                          |     |     | 50  | μs   |

| Driver Switchi              | ng Characteristics                                                                          |                   | '                                                                                        |     |     |     |      |

| t <sub>pHR</sub>            | Propagation delay time, high TXD to driver recessive                                        |                   |                                                                                          | 65  | 82  | 130 | ns   |

| t <sub>pLD</sub>            | Propagation delay time, low TXD to driver dominant                                          | TCAN1164T-Q1      | $R_L = 60 \Omega, C_L = 100 \text{ pF}, R_{CM} = 0$                                      | 25  | 50  | 110 | ns   |

| t <sub>sk(p)</sub>          | Pulse skew ( t <sub>pHR</sub> - t <sub>pLD</sub>  )                                         | 13/11/1041/01     | See 図 9-2                                                                                |     | 25  | 50  | ns   |

| t <sub>R</sub>              | Differential output signal rise time                                                        | 1                 |                                                                                          |     | 40  |     | ns   |

| t <sub>F</sub>              | Differential output signal fall time                                                        | 1                 |                                                                                          |     | 95  |     | ns   |

Product Folder Links: TCAN1164-Q1

<sup>(2)</sup> Note that there is an internal pull-up resistor to V<sub>CCOUT</sub>. If externally driven to a higher or lower voltage, the pin leakage measurement will be increased.

Over recomended operating conditions with  $T_J$  = -40°C to 150°C, unless otherwise noted. All typical values are taken at 25°C,  $V_{SUP}$  = 12 V and  $R_L$  = 60  $\Omega$

| 301                     | $p = 12 \text{ V and } R_L = 60 \Omega$ PARAMETER                   |               | TEST CONDITIONS                                                                | MIN | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>pHR</sub>        | Propagation delay time, high TXD to driver recessive                |               |                                                                                | 20  | 35  | 70  | ns   |

| t <sub>pLD</sub>        | Propagation delay time, low TXD to driver dominant                  | TCAN1164-Q1   | $R_L$ = 60 Ω, $C_L$ = 100 pF, $R_{CM}$ = open                                  | 15  | 40  | 70  | ns   |

| t <sub>sk(p)</sub>      | Pulse skew ( t <sub>pHR</sub> - t <sub>pLD</sub>  )                 | TCANTIO4-QT   | See ⊠ 9-2                                                                      |     | 10  | 20  | ns   |

| t <sub>R</sub>          | Differential output signal rise time                                |               |                                                                                |     | 40  |     | ns   |

| t <sub>F</sub>          | Differential output signal fall time                                |               |                                                                                |     | 45  |     | ns   |

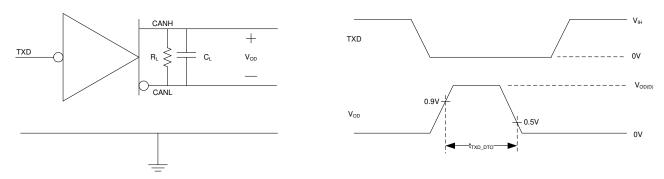

| t <sub>TXD_DTO</sub>    | Dominant timeout                                                    |               | $R_L = 60 \Omega$ , $C_L = open$<br>See $\boxtimes 9-7$ , TXD = 0 V            | 1.2 |     | 3.8 | ms   |

| Receiver Sw             | vitching Characteristics                                            |               |                                                                                |     |     |     |      |

| t <sub>pRH</sub>        | Propagation delay time, bus recessive input to high RXD             | TCAN1164T-Q1  | C <sub>L(RXD)</sub> = 15 pF<br>See ☑ 9-3                                       | 25  | 65  | 140 | ns   |

| t <sub>pRH</sub>        | Propagation delay time, bus recessive input to high RXD             | TCAN1164-Q1   | C <sub>L(RXD)</sub> = 15 pF<br>See 図 9-3                                       | 25  | 80  | 140 | ns   |

| t <sub>pDL</sub>        | Propagation delay time, bus dominant input to R                     | XD low output | C <sub>L(RXD)</sub> = 15 pF<br>See 図 9-3                                       | 20  | 50  | 110 | ns   |

| t <sub>R</sub>          | Output signal rise time (RXD)                                       |               | C <sub>L(RXD)</sub> = 15 pF<br>See ☑ 9-3                                       |     | 8   |     | ns   |

| t <sub>F</sub>          | Output signal fall time (RXD)                                       |               | C <sub>L(RXD)</sub> = 15 pF<br>See ☑ 9-3                                       |     | 5   |     | ns   |

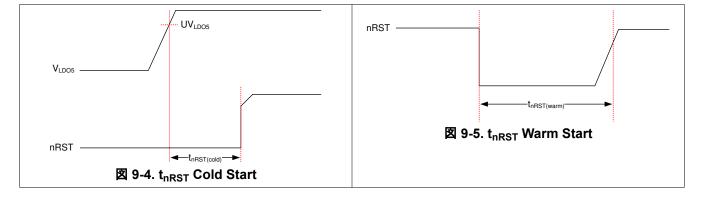

| nRST Chara              | cteristics                                                          |               |                                                                                |     |     |     |      |

| t <sub>nRST</sub>       | Minimum low time for reset                                          |               | Input pulse width                                                              | 15  |     |     | μs   |

| $t_{nRST(cold)}$        | Output pulse width                                                  |               | Cold crank                                                                     | 20  |     | 27  | ms   |

| t <sub>nRST(warm)</sub> | Output pulse width                                                  |               | Warm crank 1                                                                   |     |     | 1.5 | ms   |

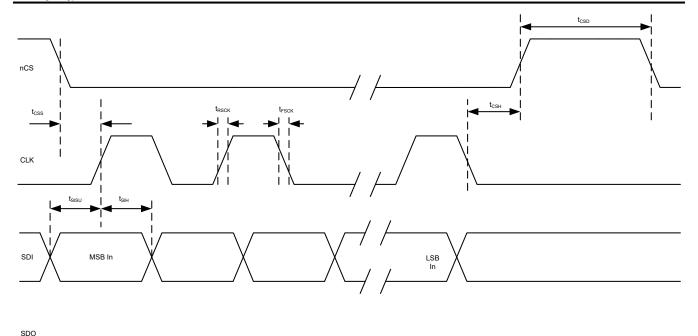

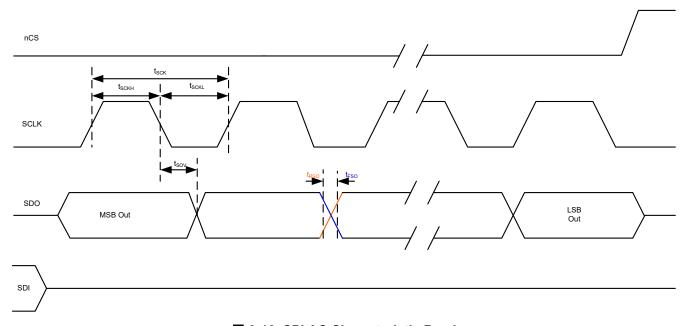

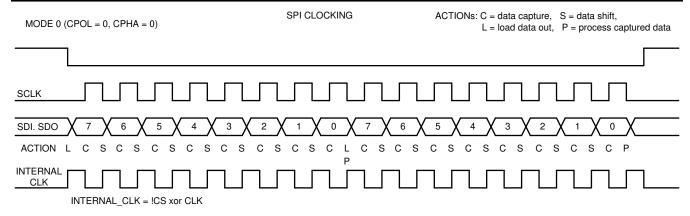

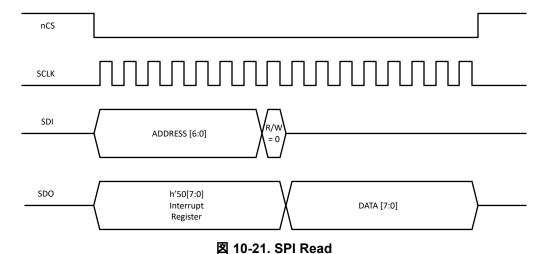

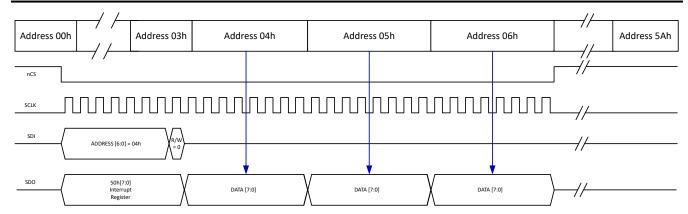

| SPI Switchin            | ng Characteristics                                                  |               |                                                                                |     |     |     |      |

| f <sub>SCK</sub>        | SCK, SPI clock frequency                                            |               | Normal, standby, and silent modes                                              |     |     | 4   | MHz  |

| t <sub>SCK</sub>        | SCK, SPI clock period                                               |               | Normal, standby, and silent modes; See ⊠ 9-12                                  | 250 |     |     | ns   |

| t <sub>RSCK</sub>       | SCK rise time                                                       |               | See 図 9-11                                                                     |     |     | 40  | ns   |

| t <sub>FSCK</sub>       | SCK fall time                                                       |               | See 図 9-11                                                                     |     |     | 40  | ns   |

| t <sub>SCKH</sub>       | SCK, SPI clock high                                                 |               | Normal, standby, and silent modes; See ⊠ 9-12                                  | 125 |     |     | ns   |

| t <sub>SCKL</sub>       | SCK, SPI clock low                                                  |               | Normal, standby, and silent modes; See ⊠ 9-12                                  | 125 |     |     | ns   |

| t <sub>ACC</sub>        | First read access time from chip select                             |               |                                                                                | 50  |     |     | ns   |

| t <sub>CSS</sub>        | Chip select setup time                                              |               | See 図 9-11                                                                     | 100 |     |     | ns   |

| t <sub>CSH</sub>        | Chip select hold time                                               |               | See 図 9-11                                                                     | 100 |     |     | ns   |

| t <sub>CSD</sub>        | Chip select disable time                                            |               | See 図 9-11                                                                     | 50  |     |     | ns   |

| t <sub>SISU</sub>       | Data in setup time                                                  |               | Normal, standby, and silent modes; See 図 9-11                                  | 50  |     |     | ns   |

| t <sub>SIH</sub>        | Data in hold time                                                   |               | Normal, standby, and silent modes; See ⊠ 9-11                                  | 50  |     |     | ns   |

| t <sub>SOV</sub>        | Data out valid                                                      |               | Normal, standby, and silent modes; See ⊠ 9-12                                  |     |     | 80  | ns   |

| t <sub>RSO</sub>        | SO rise time                                                        |               | See 図 9-12                                                                     |     |     | 40  | ns   |

| t <sub>FSO</sub>        | SO fall time                                                        |               | See 図 9-12                                                                     |     |     | 40  | ns   |

| CAN FD Tim              | ing Characteristics                                                 |               | 1                                                                              |     |     |     |      |

|                         | Bit time on CAN bus output pins with $t_{BIT(TXD)}$ = 500 ns        |               | R <sub>L</sub> = 60 Ω, C <sub>L</sub> = 100 pF                                 | 435 |     | 530 | ns   |

| t <sub>BIT(BUS)</sub>   | Bit time on CAN bus output pins with $t_{BIT(TXD)}$ = 200 ns        | TCAN1164-Q1   | $C_{L(RXD)} = 15 \text{ pF}$<br>$\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)}$ | 155 |     | 210 | ns   |

|                         | Bit time on CAN bus output pins with t <sub>BIT(TXD)</sub> = 125 ns |               | See 🗵 9-6                                                                      | 80  |     | 140 | ns   |

Over recomended operating conditions with  $T_J$  = -40°C to 150°C, unless otherwise noted. All typical values are taken at 25°C,  $V_{SUP}$  = 12 V and  $R_L$  = 60  $\Omega$

|                       | PARAMETER                                                       |                                                         | TEST CONDITIONS                                                                                                           | MIN | TYP MAX | UNIT |

|-----------------------|-----------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|---------|------|

| t <sub>BIT(BUS)</sub> | Bit time on CAN bus output pins with $t_{BIT(TXD)}$ = 500 ns    | TCAN1164T-Q1                                            | $R_L = 60 \Omega, C_L = 100 pF$<br>$C_{L(RXD)} = 15 pF$                                                                   | 450 | 530     | ns   |

|                       | Bit time on CAN bus output pins with $t_{BIT(TXD)}$ = 200 ns    | TCANTIO41-Q1                                            | $\begin{array}{c} \Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)} \\ \text{See} \ \ \boxed{\ \ \ } \ 9\text{-}6 \end{array}$ | 155 | 210     | ns   |

|                       | Bit time on RXD output pins with t <sub>BIT(TXD)</sub> = 500 r  | $R_L = 60 \Omega, C_L = 100 pF$<br>$C_{L(RXD)} = 15 pF$ | 400                                                                                                                       | 550 | ns      |      |

| t <sub>BIT(RXD)</sub> | Bit time on RXD output pins with $t_{BIT(TXD)} = 200 \text{ n}$ |                                                         | 120                                                                                                                       | 220 | ns      |      |

| -BIT(KAD)             | Bit time on RXD output pins with $t_{BIT(TXD)} = 125$ ns        | TCAN1164-Q1                                             | At <sub>REC</sub> = t <sub>BIT(RXD)</sub> - t <sub>BIT(BUS)</sub><br>See ⊠ 9-6                                            | 80  | 135     | ns   |

|                       | Receiver timing symmetry with t <sub>BIT(TXD)</sub> = 500 ns    |                                                         | R <sub>L</sub> = 60 Ω, C <sub>L</sub> = 100 pF                                                                            | -50 | 20      | ns   |

| $\Delta t_{REC}$      | Receiver timing symmetry with t <sub>BIT(TXD)</sub> = 200 ns    |                                                         | $C_{L(RXD)} = 15 \text{ pF}$<br>$\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)}$                                            | -45 | 15      | ns   |

|                       | Receiver timing symetry with t <sub>BIT(TXD)</sub> = 125 ns     | TCAN1164-Q1                                             | See 2 9-6                                                                                                                 | -40 | 10      | ns   |

<sup>(1)</sup> Timer is reset when the CAN bus changes states.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 8.9 Typical Characteristics

# **9 Parameter Measurement Information**

☑ 9-1. I<sub>SUP</sub> Test Circuit

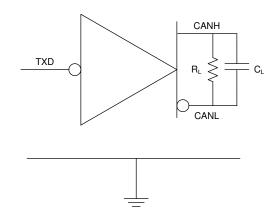

**図 9-2. Driver Test Circuit and Measurement**

図 9-3. Receiver Test Circuit and Measurement

図 9-6. Transmitter and Receiver Timing Behavior Test Circuit and Measurement

図 9-7. TXD Dominant Timeout Test Circuit and Measurement

図 9-8. Driver Short-Circuit Current Test and Measurement

**図 9-9.** t<sub>POWER UP</sub> Timing Measurement

図 9-10. Test Signal Definition for Bias Reaction Time Measurement

図 9-11. SPI AC Characteristic Write

図 9-12. SPI AC Characteristic Read

# 10 Detailed Description

# 10.1 Overview

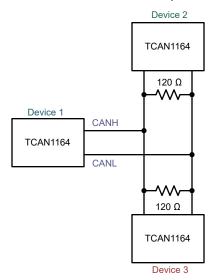

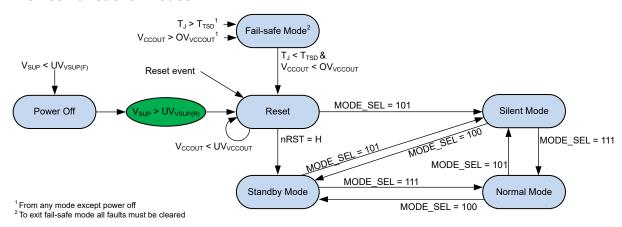

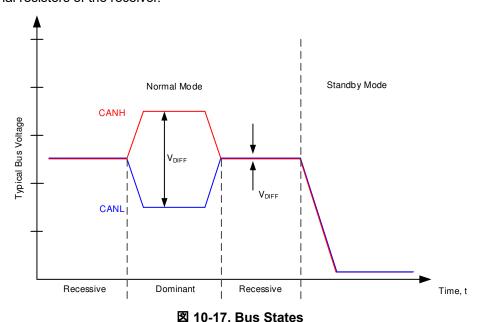

The TCAN1164-Q1 is a high speed Controller Area Network (CAN) system basis chip (SBC) that meets the physical layer requirements of the ISO 11898-2:2016 high speed CAN specification. The transceiver supports both classical CAN and CAN FD networks up to 8 megabits per second (Mbps) (TCAN1164-Q1) or 5-Mbps (TCAN1164T-Q1).

The TCAN1164-Q1 supports a wide input supply range and integrates a 5-V LDO output. The 5-V LDO output  $(V_{CCOUT})$  supplies the CAN transceiver voltage internally as well as additional current externally.

# 10.2 Functional Block Diagram

図 10-1. TCAN1164-Q1

# 10.3 Feature Description

#### 10.3.1 V<sub>SUP</sub> Pin

This pin is connected to the battery supply. It provides the supply to the internal regulators that support the digital core, the CAN transceiver, and the low power CAN receiver.

#### 10.3.2 V<sub>CCOUT</sub> Pin

An internal LDO provides power for the integrated CAN transceiver and the  $V_{CCOUT}$  output pin. The amount of current that can be delivered externally is dependent upon the CAN transceiver requirements during normal operation as well as the ambient operating temperature. When a CAN bus fault takes place that requires additional current from the LDO, the total available current to external load components may be degraded. This pin requires a 10  $\mu$ F external capacitor as close to the pin as possible.

#### 10.3.3 Digital Inputs and Outputs

The TCAN1164-Q1 has a  $V_{CCOUT}$  supply that is used to set the digital input thresholds. The input thresholds are ratio metric to the  $V_{CCOUT}$  supply using CMOS input levels. The TXD input is biased to the  $V_{CCOUT}$  level to force a recessive input in case the pin floats. The high level output voltage for the RXD and output pins is driven to the  $V_{CCOUT}$  level as logic-high outputs.

#### 10.3.3.1 TXD Pin

TXD is a digital signal, referenced to V<sub>CCOUT</sub>, from a CAN controller to the TCAN1164-Q1.

#### 10.3.3.2 RXD Pin

RXD is a digital signal, referenced to V<sub>CCOUT</sub>, from the TCAN1164-Q1 to a CAN controller.

When a wake event occurs, this pin is pulled low to signal that a wake event has taken place.

#### 10.3.4 GND

GND is the ground pin and it must be connected to the PCB ground.

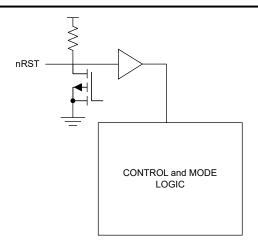

#### 10.3.5 nRST Pin

The nRST is an bidirectional open drain low side driver with an integrated pull-up resistor to  $V_{CCOUT}$ . It can be pulled low by the device when placed in fail-safe mode.

During initial power-up of the device, a fail-safe mode to reset transition, or an undervoltage event will be recognized as a cold crank reset condition. The nRST pin will be held low for  $t_{nRST(cold)}$  allowing the MCU and peripheral devices to power-up correctly before data transmission begins.

To enter reset mode from normal mode, or standby mode the nRST must be pulled low for a minimum of time of  $t_{nRST}$ . The TCAN1164-Q1 recognizes this and a watchdog error as a warm crank reset condition and holds the nRST pin low for  $t_{nRST(warm)}$ .

図 10-2. nRST Circuit

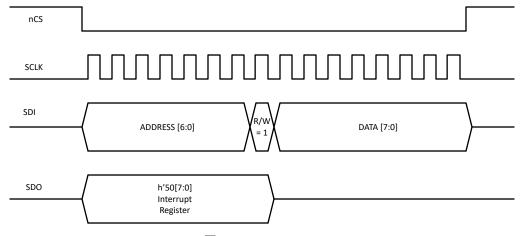

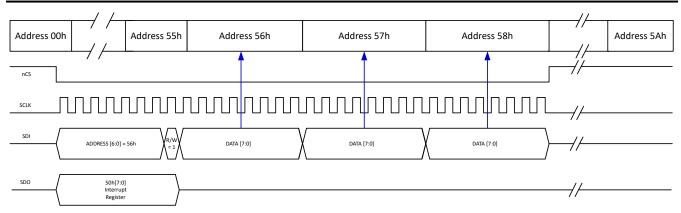

#### 10.3.6 SDO

When nCS is low this pin is the SPI serial data output pin. When nCS is high, the pin will be tri-stated.

#### 10.3.7 nCS Pin

The nCS pin is the SPI chip select pin. When pulled low and a clock is present the device can be written to or read from.

#### 10.3.8 SCLK

The SCLK pin is the SPI clock. The clock rate should not exceed the max f<sub>SCK</sub> value.

#### 10.3.9 SDI

When nCS is low this pin is the SPI serial data input pin used for programming the device or requesting data.

#### 10.3.10 CAN Bus Pins

These are the CAN high and CAN low, CANH and CANL, differential bus pins. These pins are connected to the CAN transceiver.

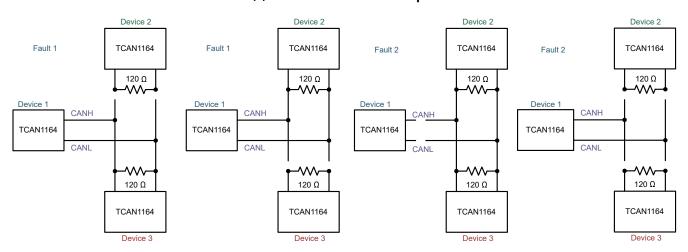

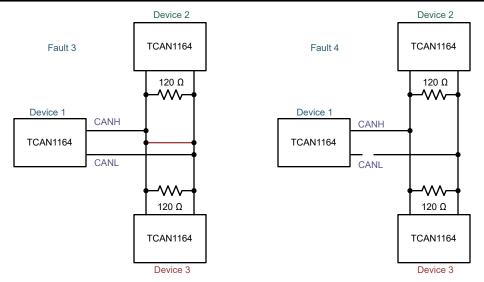

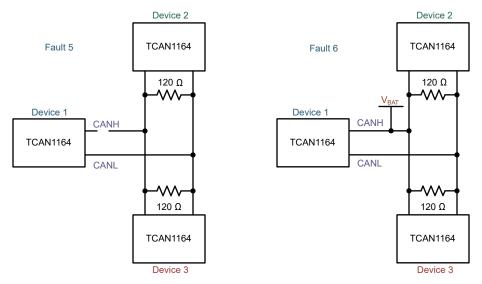

#### 10.3.11 Local Faults

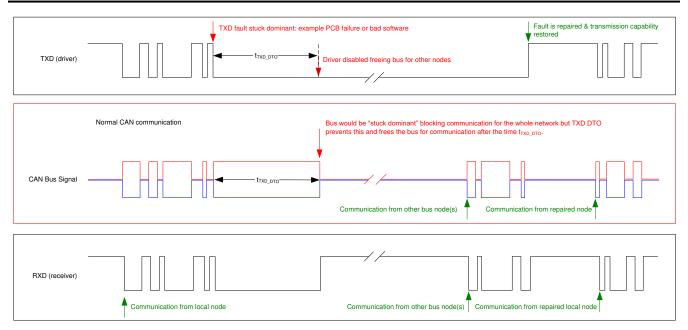

### 10.3.11.1 TXD Dominant Timeout (TXD DTO)

While the CAN driver is in active mode a TXD DTO circuit prevents the local node from blocking network communication in event of a hardware or software failure where TXD is held dominant longer than the time out period  $t_{TXD\_DTO}$ . The TXD DTO circuit is triggered by a falling edge on TXD. If no rising edge is seen before the time out constant of the circuit,  $t_{TXD\_DTO}$ , expires the CAN driver is disabled releasing the bus lines to the recessive level. This keeps the bus free for communication between other nodes on the network. The CAN driver is re-activated on the next dominant to recessive transition on the TXD terminal, thus clearing the dominant time out. The high-speed receiver and RXD terminal will reflect what is on the CAN bus during a TXD DTO fault. The TS terminal in driven low during a TXD DTO fault.

図 10-3. Timing Diagram for TXD DTO

The minimum dominant TXD time allowed by the TXD DTO circuit limits the minimum possible transmitted data rate of the device. The CAN protocol allows a maximum of eleven successive dominant bits (on TXD) for the worst case, where five successive dominant bits are followed immediately by an error frame. The minimum transmitted data rate may be calculated using the minimum  $t_{TXD\_DTO}$  time and the maximum number of successive dominant bits (11 bits).

Minimum Data Rate = 11 bits /

$$t_{TXD}$$

DTO = 11 bits / 1.2 ms = 9.2 kbps (1)

# 10.3.11.2 Thermal Shutdown (TSD)

If the junction temperature of the TCAN1164-Q1 exceeds the thermal shutdown threshold,  $T_J > T_{SDR}$ , the device transitions into fail-safe mode and disables the transceiver's transmitter and receiver blocking transmission to and from the CAN bus. The TSD fault condition is cleared when the device junction temperature falls below the thermal shutdown temperature threshold,  $T_J < T_{SDF}$ . If the fault condition that caused the TSD fault is still present, the temperature may rise again and the device will enter thermal shutdown again. Prolonged operation with a TSD fault conditions may affect device reliability.

### 10.3.11.3 Under/Over Voltage Lockout

The supply terminals implement undervoltage and over voltage detection circuitry. If an undervoltage is detected the TCAN1164-Q1 transitions into reset mode. The SBC will remain in reset mode until the undervoltage event clears.

If the over voltage fault is detected the TCAN1164-Q1 transitions into fail-safe mode. These mode changes place the device in a known state which protect the system from unintended behavior. See 表 10-1

Fault

Mode

UV<sub>CCOUT</sub>

Reset

OV<sub>CCOUT</sub>

Fail-safe

表 10-1. Undervoltage / Over Voltage Lockout

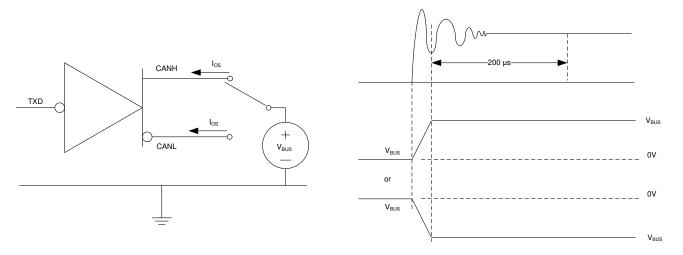

#### 10.3.11.4 Unpowered Devices

The device is designed to be an ideal passive or no load to the CAN bus if it is unpowered. The CANH and CANL pins have low leakage currents when the device is un-powered so they present no load to the bus. This is critical if some nodes of the network are unpowered while the rest of the of network remains in operation.

The logic terminals also have low leakage currents when the device is un-powered so they do not load down other circuits which may remain powered.

### 10.3.11.5 Floating Terminals

The TCAN1164-Q1 has internal pull-ups and pull-downs on critical pins to ensure a known operating behavior if the pins are left floating.

The TXD pin is pulled up to  $V_{CCOUT}$  which forces a recessive level if the pin floats. This internal bias should not be relied upon by design but rather a fall-safe option. Special care needs to be taken when the devive is used with a CAN controller that has open drain outputs. The device implements a weak internal pull-up resistor on the TXD pin. The CAN bit timing for CAN FD data rates will require special consideration and the pull-up strength should be considered carfully when using open drain outputs. An adequate external pull-up resistor must be used to ensure that the TXD output of the CAN controller maintains adequate bit timing input to the CAN device.

表 10-2. Terminal Fail-Safe Biasing

| TERMINAL PULL-UP or PULL-DOWN |           | COMMENT                                                                         |  |  |

|-------------------------------|-----------|---------------------------------------------------------------------------------|--|--|

| TXD                           | Pull-up   | Weakly biases TXD toward recessive to prevent bus blockage or TX DTO triggering |  |  |

| nCS                           | Pull-up   | Weakly biases nCS high to prevent un-intended SPI communication                 |  |  |

| SCLK                          | Pull-down | Weakly biased to ground                                                         |  |  |

### 10.3.11.6 CAN Bus Short Circuit Current Limiting

The TCAN1164-Q1 has several protection features that limit the short circuit current during dominant and recessive when a CAN bus line is shorted. The device has TXD dominant state timeout which prevents permanently having a higher short circuit current during a dominant state fault.

During CAN communication the bus switches between the dominant and recessive states, thus the short circuit current may be viewed either as the current during each bus state or as a DC average current. The average short circuit current should be used when considering system power for the termination resistors and common mode choke. The percentage dominant is limited by the TXD dominant state timeout and CAN protocol which has forced state changes and recessive bits such as bit stuffing, control fields, and interframe space. These ensure that there is a minimum recessive time on the bus even if the data field contains a high percentage of dominant bits.

The short circuit current of the bus depends on the ratio of recessive to dominant bits and their respective short circuit currents. The average short circuit current may be calculated using  $\pm 2$ .

$$I_{OS(AVG)}$$

= %Transmit × [(%REC\_Bits ×  $I_{OS(SS)}$  REC) + (%DOM\_Bits ×  $I_{OS(SS)}$  DOM)] + [%Receive ×  $I_{OS(SS)}$  REC] (2)

#### Where:

- I<sub>OS(AVG)</sub> is the average short circuit current

- %Transmit is the percentage the node is transmitting CAN messages

- %Receive is the percentage the node is receiving CAN messages

- %REC Bits is the percentage of recessive bits in the transmitted CAN messages

- %DOM Bits is the percentage of dominant bits in the transmitted CAN messages

- I<sub>OS(SS)</sub> REC is the recessive steady state short circuit current

- I<sub>OS(SS)</sub> DOM is the dominant steady state short circuit current

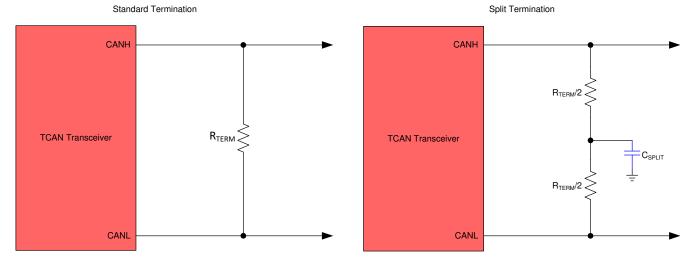

The short circuit current and possible fault cases of the network should be taken into consideration when sizing the power ratings of the termination resistance and other network components.

#### 10.3.11.7 Sleep Wake Error Timer

The sleep wake error (SWE) timer, t<sub>INACTIVE</sub>, is a timer used to determine if specific external and internal functions are working. The SWE timer starts when the device enters standby mode and only runs in standby mode. A mode transistion stops the timer. If the timer times out while the device is in standby mode the WKERR

Product Folder Links: TCAN1164-Q1

interrupt bit in the INT\_1 register will be set, register 8'h51[4], and the RXD pin will be pulled low to indicate an interrupt. The TCAN1164-Q1 will stay in standby mode.

#### 10.3.12 Watchdog

The TCAN1164-Q1 has an integrated watchdog function. The TCAN1164-Q1 provides a window based watchdog as well as selectable autonomous, time-out or question and answer (Q&A) watchdog using SPI programming. This function is default disabled. When enabled, the watchdog timer treats a mode transition as the first watchdog trigger event.

All four versions of the watchdog, autonomous, time-out, window and Q&A are avilable in normal and silent modes. When in standby mode the device will automactically transistion to a time-out watchdog. If autonomous has been selected the transistion to standby will keep the autonomous configuration.

#### 10.3.12.1 Watchdog Error Counter

The TCAN1164-Q1 has a watchdog error counter. This counter is an up down counter that increments for every missed window or incorrect input watchdog trigger event. For every correct input trigger, the counter decrements but does not drop below zero. The default trigger for this counter is set to trigger a watchdog error event. This counter can be changed to the fifth or ninth error. The error counter can be read at register 8'h13[3:2].

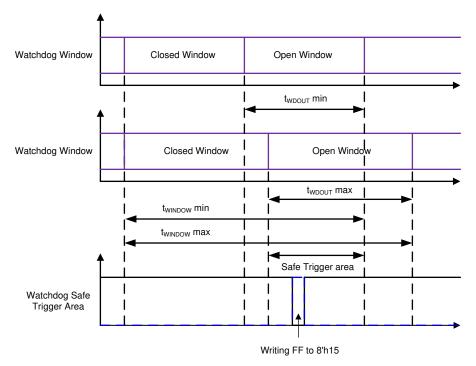

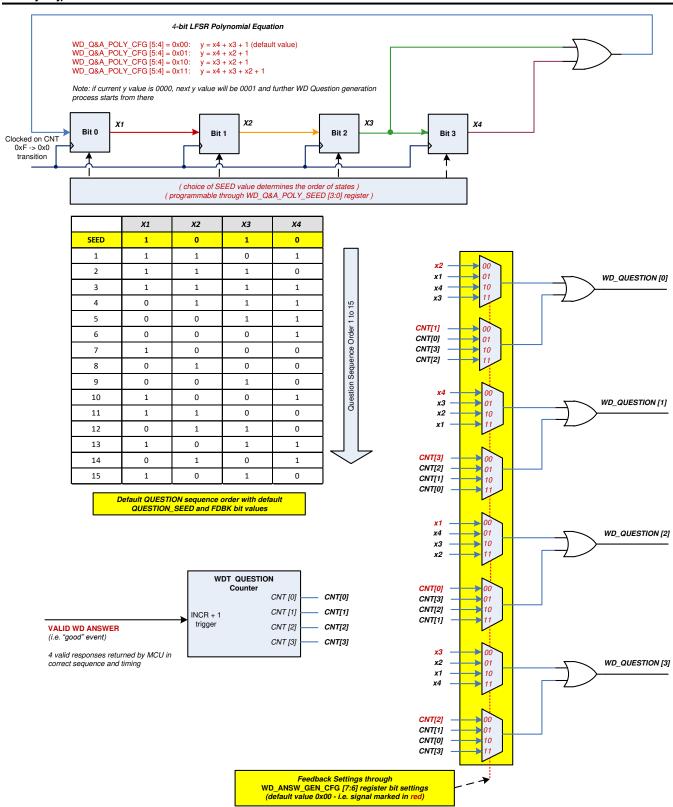

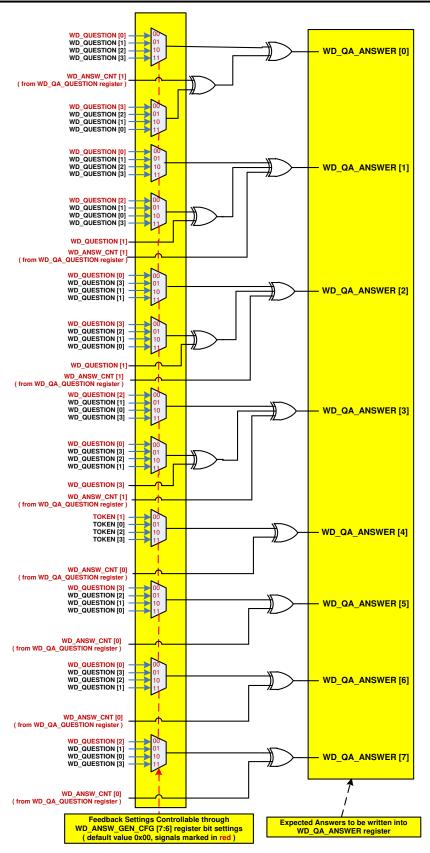

### 10.3.12.2 Watchdog SPI Control Programming

The watchdog is configured and controlled using registers 8'h13 through 8'h15. These registers are provided in table 表 10-3. The TCAN1164-Q1 watchdog can be set as autonomous, time-out, window or question and answer (Q&A) watchdog by setting 8'h13[7:6] to the method of choice. The time-out and window watchdog timer is based upon registers 8'h13[5:4] WD prescaler and 8'h14[7:5] WD timer and is in ms. See 表 10-3 for the achievable times. If using smaller time windows it is suggested to use the time-out version of the watchdog. This is for times between 4 ms and 64 ms.

| WD_TIMER (ms) | 8'h13[5:4] WD_PRE |       |      |      |  |  |

|---------------|-------------------|-------|------|------|--|--|

| 8'h14[7:5]    | 00                | 01    | 10   | 11   |  |  |

| 000           | 4                 | 8     | 12   | 16   |  |  |

| 001           | 32                | 64    | 96   | 128  |  |  |

| 010           | 128               | 256   | 384  | 512  |  |  |

| 011           | 256               | 384   | 512  | 768  |  |  |

| 100           | 512               | 1024  | 1536 | 2048 |  |  |

| 101           | 2048              | 4096  | 6144 | 8192 |  |  |