# TCAL9539-Q1 車載用、低電圧、16 ビット I<sup>2</sup>C バス / SMBus I/O エクスパンダ、割り込み出力、リセット、構成レジスタ付き

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:-40°C~+125°C, T<sub>A</sub>

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可能

- 1.08V~3.6V の動作電源電圧範囲

- 低いスタンバイ消費電流: 1μA (標準値、1.8V 時)

- 1MHz のファスト・モード・プラス I<sup>2</sup>C バス

- ハードウェア・アドレス・ピンにより、同じ I<sup>2</sup>C/SMBus バス上に 2 つのデバイスを接続可能

- アクティブ Low のリセット入力 (RESET)

- オープン・ドレインのアクティブ Low 割り込み出力 (INT)

- 入力 / 出力構成レジスタ

- 極性反転レジスタ

- 構成可能な I/O 駆動強度レジスタ

- プルアップおよびプルダウン抵抗構成レジスタ

- パワーオン・リセット内蔵

- SCL または SDA 入力のノイズ・フィルタ

- 大電流の最大駆動能力を持つラッチ付き出力により LED を直接駆動

- AEC Q100-004 準拠で 100mA 超のラッチアップ性能

- AEC - Q100 要件を上回る ESD 保護

- 人体モデルで 4000V (AEC - Q100-002)

- デバイス帶電モデルで 1000V (AEC - Q100-011)

## 2 アプリケーション

- 車載インフォテインメントおよびクラスター

- ボディ・エレクトロニクス / 照明

- ハイブリッド、電動、パワートレイン・システム

- 産業用輸送

- GPIO が制限されたプロセッサを使用する製品

## 3 概要

TCAL9539-Q1 デバイスは、2 ライン双方向 I<sup>2</sup>C バス (または SMBus) プロトコル用の汎用パラレル入出力 (I/O) 拡張機能を備えており、1.08V~3.6V の V<sub>CC</sub> で動作するように設計されています。

このデバイスは、100kHz (スタンダード・モード)、400kHz (ファスト・モード)、1MHz (ファスト・モード・プラス) の I<sup>2</sup>C クロック周波数をサポートしています。TCAL9539-Q1 をはじめとする I/O エクスパンダは、スイッチ、センサ、プッシュ・ボタン、LED、ファンなどに I/O を追加する必要がある場合に、簡単なソリューションとして使用できます。

TCAL9539-Q1 には、速度、消費電力、EMI に関して I/O 性能を向上させる追加機能を備えた Agile I/O ポートがあります。追加機能として、プログラム可能な出力駆動強度、プログラム可能なプルアップおよびプルダウン抵抗、ラッチ可能な入力、マスク可能な割り込み、割り込みステータス・レジスタ、プログラム可能なオープン・ドレインまたはプッシュ・プル出力があります。

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ・サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| TCAL9539-Q1 | WQFN (24)            | 4mm × 4mm                |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ・サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

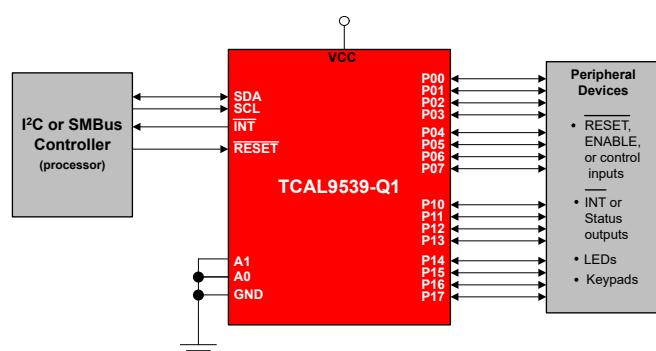

概略回路図

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照ください。

## 目次

|                                 |           |                               |           |

|---------------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>                     | <b>1</b>  | 8.2 機能ブロック図                   | <b>19</b> |

| <b>2 アプリケーション</b>               | <b>1</b>  | 8.3 機能説明                      | <b>20</b> |

| <b>3 概要</b>                     | <b>1</b>  | 8.4 デバイスの機能モード                | <b>22</b> |

| <b>4 改訂履歴</b>                   | <b>2</b>  | 8.5 プログラミング                   | <b>22</b> |

| <b>5 ピン構成および機能</b>              | <b>3</b>  | 8.6 レジスタ・マップ                  | <b>24</b> |

| <b>6 仕様</b>                     | <b>5</b>  | <b>9 アプリケーションと実装</b>          | <b>33</b> |

| 6.1 絶対最大定格                      | 5         | 9.1 アプリケーション情報                | 33        |

| 6.2 ESD 定格                      | 5         | 9.2 代表的なアプリケーション              | 33        |

| 6.3 推奨動作条件                      | 5         | 9.3 電源に関する推奨事項                | 36        |

| 6.4 熱に関する情報                     | 6         | 9.4 レイアウト                     | 39        |

| 6.5 電気的特性                       | 7         | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>40</b> |

| 6.6 タイミング要件                     | 8         | 10.1 ドキュメントの更新通知を受け取る方法       | 40        |

| 6.7 I <sup>2</sup> C バス・タイミング要件 | 8         | 10.2 サポート・リソース                | 40        |

| 6.8 スイッチング特性                    | 10        | 10.3 商標                       | 40        |

| 6.9 代表的特性                       | 11        | 10.4 静電気放電に関する注意事項            | 40        |

| <b>7 パラメータ測定情報</b>              | <b>15</b> | 10.5 用語集                      | 40        |

| <b>8 詳細説明</b>                   | <b>19</b> | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>40</b> |

| 8.1 概要                          | 19        |                               |           |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision * (November 2022) to Revision A (August 2023)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • データシートのステータスを「事前情報」から「量産データ」に変更                                          | 1           |

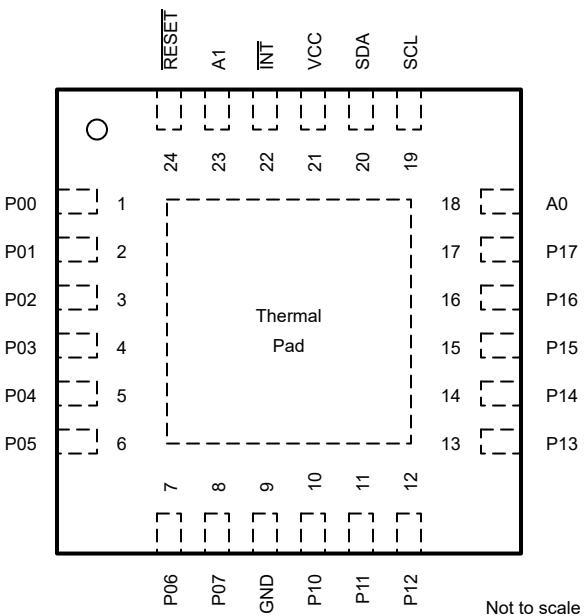

## 5 ピン構成および機能

図 5-1. RTW (WQFN) パッケージ、24 ピン

(上面図)

表 5-1. ピンの機能

| ピン    |    | 種類 <sup>(1)</sup> | 説明                                                                         |

|-------|----|-------------------|----------------------------------------------------------------------------|

| 名称    | 番号 |                   |                                                                            |

| A0    | 18 | I                 | アドレス入力。V <sub>CC</sub> またはグランドに直接接続します                                     |

| A1    | 23 | I                 | アドレス入力。V <sub>CC</sub> またはグランドに直接接続します                                     |

| GND   | 9  | G                 | グランド                                                                       |

| INT   | 22 | O                 | 割り込み出力。プルアップ抵抗を経由して V <sub>CC</sub> に接続します                                 |

| RESET | 24 | I                 | アクティブ Low のリセット入力。アクティブな接続が使用されていない場合は、プルアップ抵抗を経由して V <sub>CC</sub> に接続します |

| P00   | 1  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P00 は入力として構成されます                         |

| P01   | 2  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P01 は入力として構成されます                         |

| P02   | 3  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P02 は入力として構成されます                         |

| P03   | 4  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P03 は入力として構成されます                         |

| P04   | 5  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P04 は入力として構成されます                         |

| P05   | 6  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P05 は入力として構成されます                         |

| P06   | 7  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P06 は入力として構成されます                         |

| P07   | 8  | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P07 は入力として構成されます                         |

| P10   | 10 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P10 は入力として構成されます                         |

| P11   | 11 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P11 は入力として構成されます                         |

| P12   | 12 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P12 は入力として構成されます                         |

| P13   | 13 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P13 は入力として構成されます                         |

| P14   | 14 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P14 は入力として構成されます                         |

| P15   | 15 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P15 は入力として構成されます                         |

| P16   | 16 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P16 は入力として構成されます                         |

**表 5-1. ピンの機能 (continued)**

| ピン  |    | 種類 <sup>(1)</sup> | 説明                                                 |

|-----|----|-------------------|----------------------------------------------------|

| 名称  | 番号 |                   |                                                    |

| P17 | 17 | I/O               | P ポート入力 / 出力 (プッシュプルの設計構造)。電源投入時に、P17 は入力として構成されます |

| SCL | 19 | I                 | シリアル・クロック・バス。プルアップ抵抗を経由して V <sub>CC</sub> に接続します   |

| SDA | 20 | I/O               | シリアル・データ・バス。プルアップ抵抗を経由して V <sub>CC</sub> に接続します    |

| VCC | 21 | —                 | 電源電圧                                               |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                     |                    | 最小値  | 最大値  | 単位 |

|------------------|---------------------|--------------------|------|------|----|

| V <sub>CC</sub>  | 電源電圧                |                    | -0.5 | 4    | V  |

| V <sub>I</sub>   | 入力電圧 <sup>(2)</sup> |                    | -0.5 | 4    | V  |

| V <sub>O</sub>   | 出力電圧 <sup>(2)</sup> |                    | -0.5 | 4    | V  |

| I <sub>IK</sub>  | 入力クランプ電流            | V <sub>I</sub> < 0 |      | -20  | mA |

| I <sub>OK</sub>  | 出力クランプ電流            | V <sub>O</sub> < 0 |      | -20  | mA |

| I <sub>CC</sub>  | GND を流れる連続電流        |                    |      | -200 | mA |

| T <sub>J</sub>   | 接合部温度               |                    |      | 130  | °C |

| T <sub>stg</sub> | 保管温度                |                    | -65  | 150  | °C |

- (1) 絶対最大定格の範囲外の動作は、デバイスの恒久的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。絶対最大定格の範囲内であっても推奨動作条件の範囲外で使用すると、デバイスが完全に機能しなくなる可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 入力および出力の電流定格が遵守されているなら、入力の負電圧や出力電圧定格を超えてかまいません。

### 6.2 ESD 定格

|                    |       |                                                    | 値     | 単位 |

|--------------------|-------|----------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、AEC Q100-002 に準拠、すべてのピン <sup>(1)</sup> | ±4000 | V  |

|                    |       | デバイス帶電モデル (CDM)、AEC Q100-011 に準拠、すべてのピン            | ±1000 |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                 |              |  | 最小値  | 最大値 | 単位 |

|-----------------|--------------|--|------|-----|----|

|                 | 電源電圧         |  | 1.08 | 3.6 | V  |

| I <sub>OH</sub> | High レベル出力電流 |  |      | -10 | mA |

| I <sub>OL</sub> | Low レベル出力電流  |  |      | 25  | mA |

| T <sub>A</sub>  | 周囲温度         |  | -40  | 125 | °C |

| T <sub>J</sub>  | 接合部温度        |  |      | 125 | °C |

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                   | パッケージ      | 単位   |

|----------------------|-------------------|------------|------|

|                      |                   | RTW (WQFN) |      |

|                      |                   | 24 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 47.1       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗 | 41.2       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗      | 26.6       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 2.2        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 26.5       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 15.8       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.5 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ      |                                   | テスト条件                                                                                                                                                                        |                                     | 最小値          | 標準値  | 最大値  | 単位 |  |

|------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|------|------|----|--|

| $V_{IK}$   | 入力ダイオード・クランプ電圧                    | $I_I = -18\text{mA}$                                                                                                                                                         | $1.08\text{V} \sim 3.6\text{V}$     | -1.2         |      |      | V  |  |

| $V_{PORR}$ | パワーON・リセット電圧、 $V_{CC}$ 立ち上がり      | $V_I = V_{CC}$ または GND, $I_O = 0$                                                                                                                                            |                                     |              | 0.85 | 1.0  | V  |  |

| $V_{PORF}$ | パワーON・リセット電圧、 $V_{CC}$ 立ち下がり      | $V_I = V_{CC}$ または GND, $I_O = 0$                                                                                                                                            |                                     | 0.6          | 0.75 |      | V  |  |

| $V_{OH}$   | P ポート High レベル出力電圧 <sup>(1)</sup> | $I_{OH} = -8\text{mA}$ , CC-XX = 11b                                                                                                                                         | 1.08V                               | 0.8          |      |      | V  |  |

|            |                                   |                                                                                                                                                                              | 1.65V                               | 1.4          |      |      |    |  |

|            |                                   |                                                                                                                                                                              | 2.3V                                | 2.1          |      |      |    |  |

|            |                                   |                                                                                                                                                                              | 3V                                  | 2.8          |      |      |    |  |

|            |                                   | $I_{OH} = -2.5\text{mA}$ および CC-XX = 00b、<br>$I_{OH} = -5\text{mA}$ および CC-XX = 01b、<br>$I_{OH} = -7.5\text{mA}$ および CC-XX = 10b、<br>$I_{OH} = -10\text{mA}$ および CC-XX = 11b | 1.08V                               | 0.75         |      | V    |    |  |

|            |                                   |                                                                                                                                                                              | 1.65V                               | 1.4          |      |      |    |  |

|            |                                   |                                                                                                                                                                              | 2.3V                                | 2.1          |      |      |    |  |

|            |                                   |                                                                                                                                                                              | 3V                                  | 2.8          |      |      |    |  |

|            |                                   |                                                                                                                                                                              | 1.08V                               |              | 0.2  |      | V  |  |

|            |                                   |                                                                                                                                                                              | 1.65V                               |              | 0.15 |      |    |  |

| $V_{OL}$   | Low レベル出力電圧                       | P ポート                                                                                                                                                                        | $I_{OL} = 8\text{mA}$ , CC-XX = 11b | 2.3V         | 0.1  |      | V  |  |

|            |                                   |                                                                                                                                                                              |                                     | 3.0V         | 0.1  |      |    |  |

|            |                                   | P ポート                                                                                                                                                                        |                                     | 1.08V        |      | 0.25 | V  |  |

|            |                                   |                                                                                                                                                                              |                                     | 1.65V        |      | 0.15 |    |  |

| $I_{OL}$   | Low レベル出力電流                       | SDA                                                                                                                                                                          | $V_{OL} = 0.4\text{V}$              | 2.3V         |      | 0.1  | μA |  |

|            |                                   |                                                                                                                                                                              |                                     | 3.0V         |      | 0.1  |    |  |

|            |                                   | INT                                                                                                                                                                          | $V_{OL} = 0.4\text{V}$              | 1.08V ~ 3.6V | 20   |      |    |  |

|            |                                   |                                                                                                                                                                              |                                     |              | 4    |      |    |  |

| $I_I$      | 入力リーク電流                           | P ポート                                                                                                                                                                        | $V_I = V_{CC}$ または GND              | 1.08V ~ 3.6V |      | ±1   | μA |  |

|            |                                   |                                                                                                                                                                              | $V_I = 3.6\text{V}$                 | 0V           |      | ±1   |    |  |

| $I_I$      | 入力リーク電流                           | SCL, SDA, RESET                                                                                                                                                              | $V_I = V_{CC}$ または GND              | 1.08V ~ 3.6V |      | ±1   |    |  |

| $I_I$      | 入力リーク電流                           |                                                                                                                                                                              | $V_I = V_{CC}$ または GND              | 1.08V ~ 3.6V |      | ±1   | μA |  |

## 6.5 電気的特性 (continued)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ         |              | テスト条件                                                                                                                                                                            |                                                                                                                                                                | 最小値        | 標準値 | 最大値 | 単位            |            |

|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|---------------|------------|

| $I_{CC}$      | 静止時電流        | 動作モード<br>(400kHz)                                                                                                                                                                | SDA, $\overline{RESET} = V_{CC}$ , P ポート、<br>ADDR = $V_{CC}$ または GND,<br>I/O = 入力, $f_{SCL} = 400\text{kHz}$ , $-40^\circ\text{C} < T_A \leq 85^\circ\text{C}$ | 3.6V       | 11  | 15  | $\mu\text{A}$ |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 2.7V       | 8   | 11  |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.95V      | 5   | 8   |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.32V      | 2   | 6   |               |            |

|               |              | 動作モード<br>(1MHz)                                                                                                                                                                  | SDA, $\overline{RESET} = V_{CC}$ , P ポート、<br>ADDR = $V_{CC}$ または GND,<br>I/O = 入力, $f_{SCL} = 400\text{kHz}$ , $85^\circ\text{C} < T_A \leq 125^\circ\text{C}$ | 3.6V       | 7   | 24  | $\mu\text{A}$ |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 2.7V       | 5   | 18  |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.95V      | 4   | 14  |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.32V      | 2   | 11  |               |            |

|               | スタンバイ・モード    | SCL, SDA, $\overline{RESET} = V_{CC}$ , P ポート、<br>ADDR = $V_{CC}$ または GND,<br>I/O = 入力, $I_O = 0$ , $f_{SCL} = 0\text{kHz}$ ,<br>$-40^\circ\text{C} < T_A \leq 85^\circ\text{C}$ | 3.6V                                                                                                                                                           | 34         |     |     | $\mu\text{A}$ |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 2.7V       | 24  |     |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.95V      | 18  |     |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.32V      | 12  |     |               |            |

|               |              | SCL, SDA, $\overline{RESET} = V_{CC}$ , P ポート、<br>ADDR = $V_{CC}$ または GND,<br>I/O = 入力, $I_O = 0$ , $f_{SCL} = 0\text{kHz}$ ,<br>$85^\circ\text{C} < T_A \leq 125^\circ\text{C}$ | 3.6V                                                                                                                                                           | 42         |     |     | $\mu\text{A}$ |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 2.7V       | 30  |     |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.95V      | 22  |     |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                | 1.32V      | 16  |     |               |            |

| $R_{pu(int)}$ | 内部プルアップ抵抗    | P ポート                                                                                                                                                                            |                                                                                                                                                                | 3.6V       | 1   | 3   | $\mu\text{A}$ |            |

| $R_{pd(int)}$ | 内部プルダウン抵抗    |                                                                                                                                                                                  |                                                                                                                                                                | 2.7V       | 0.8 | 2.0 |               |            |

| $C_I$         | 入力ピン容量       | SCL                                                                                                                                                                              | $V_I = V_{CC}$ または GND                                                                                                                                         | 1.08V~3.6V | 2.5 | 5   | pF            |            |

| $C_{IO}$      | 入力 / 出力ピンの容量 | SDA                                                                                                                                                                              | $V_{IO} = V_{CC}$ または GND                                                                                                                                      | 1.08V~3.6V | 6   | 8   | pF            |            |

|               |              | P ポート                                                                                                                                                                            | $V_{IO} = V_{CC}$ または GND                                                                                                                                      | 1.08V~3.6V | 6   | 8.5 |               |            |

|               |              |                                                                                                                                                                                  |                                                                                                                                                                |            | 70  | 100 | 140           | k $\Omega$ |

(1) 各 I/O は外部で最大 25mA に制限する必要があります。CC-XX は出力駆動強度レジスタの設定を指します。

## 6.6 タイミング要件

自由気流での動作温度範囲内 (特に記述のない限り)

|          |                         | 最小値 | 最大値 | 単位 |

|----------|-------------------------|-----|-----|----|

| P ポート    |                         |     |     |    |

| $t_{PH}$ | 割り込みを発生させる P ポートの最小パルス幅 | 30  |     | ns |

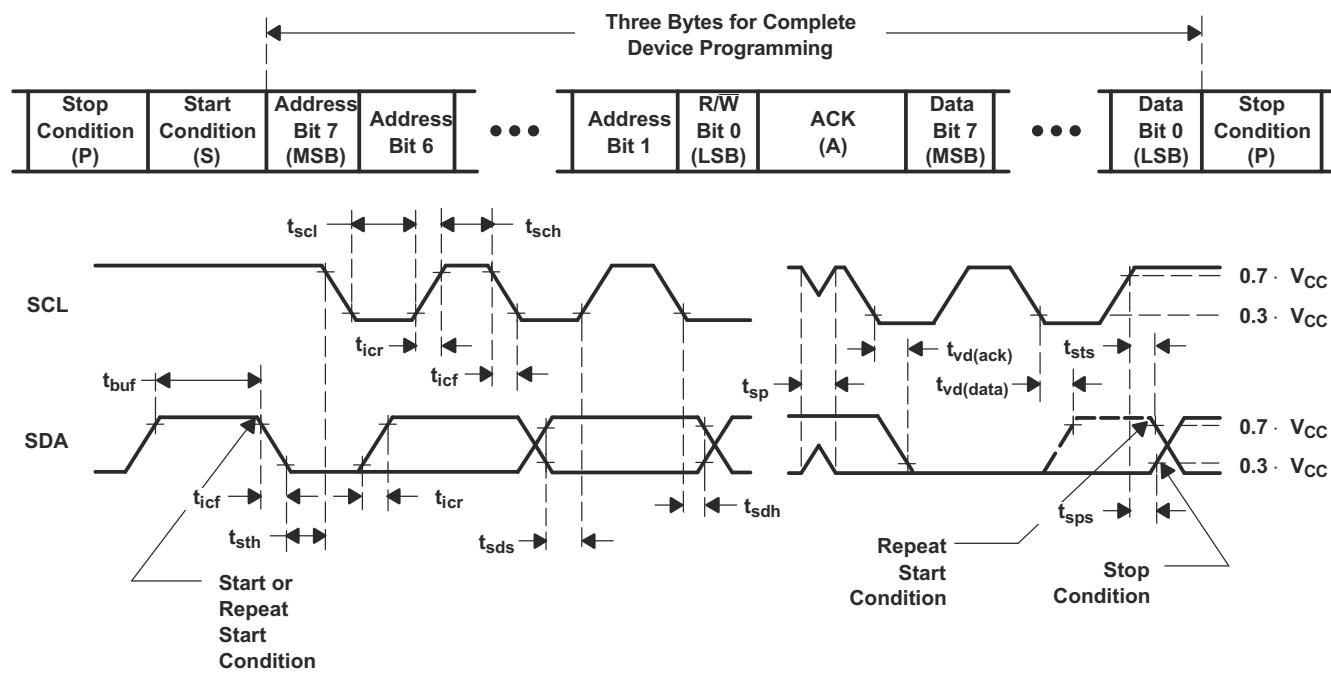

## 6.7 I<sup>2</sup>C バス・タイミング要件

自由気流での動作温度範囲内 (特に記述のない限り)

|                                  | 最小値 | 最大値 | 単位 |

|----------------------------------|-----|-----|----|

| I <sup>2</sup> C バス - スタンダード・モード |     |     |    |

## 6.7 I<sup>2</sup>C バス・タイミング要件 (continued)

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                                           |                                   | 最小値 | 最大値  | 単位  |

|----------------|-------------------------------------------|-----------------------------------|-----|------|-----|

| $f_{scl}$      | I <sup>2</sup> C クロック周波数                  |                                   | 0   | 100  | kHz |

| $t_{sch}$      | I <sup>2</sup> C クロックの High 時間            |                                   | 4   |      | μs  |

| $t_{scl}$      | I <sup>2</sup> C クロックの Low 時間             |                                   | 4.7 |      | μs  |

| $t_{sp}$       | I <sup>2</sup> C スパイク時間                   |                                   |     | 50   | ns  |

| $t_{sds}$      | I <sup>2</sup> C シリアル・データ・セットアップ時間        |                                   | 250 |      | ns  |

| $t_{sdh}$      | I <sup>2</sup> C シリアル・データ・ホールド時間          |                                   | 0   |      | ns  |

| $t_{icr}$      | I <sup>2</sup> C 入力の立ち上がり時間               |                                   |     | 1000 | ns  |

| $t_{icf}$      | I <sup>2</sup> C 入力の立ち下がり時間               |                                   |     | 300  | ns  |

| $t_{ocf}$      | I <sup>2</sup> C 出力の立ち下がり時間               | 10pF~400pF バス                     |     | 300  | ns  |

| $t_{buf}$      | STOP と START 間の I <sup>2</sup> C バスのフリー時間 |                                   | 4.7 |      | μs  |

| $t_{sts}$      | I <sup>2</sup> C START または反復 START 条件の設定  |                                   | 4.7 |      | μs  |

| $t_{sth}$      | I <sup>2</sup> C START または反復 START 条件ホールド |                                   | 4   |      | μs  |

| $t_{sps}$      | I <sup>2</sup> C STOP 条件の設定               |                                   | 4   |      | μs  |

| $t_{vd(data)}$ | 有効データ時間                                   | SCL Low から SDA 出力有効まで             |     | 3.45 | μs  |

| $t_{vd(ack)}$  | ACK 条件の有効データ時間                            | SCL Low から SDA (出力) Low への ACK 信号 |     | 3.45 | μs  |

| $C_b$          | I <sup>2</sup> C バスの容量性負荷                 |                                   |     | 400  | pF  |

### I<sup>2</sup>C バス - ファスト・モード

|                |                                           |                                   |                               |     |     |

|----------------|-------------------------------------------|-----------------------------------|-------------------------------|-----|-----|

| $f_{scl}$      | I <sup>2</sup> C クロック周波数                  |                                   | 0                             | 400 | kHz |

| $t_{sch}$      | I <sup>2</sup> C クロックの High 時間            |                                   | 0.6                           |     | μs  |

| $t_{scl}$      | I <sup>2</sup> C クロックの Low 時間             |                                   | 1.3                           |     | μs  |

| $t_{sp}$       | I <sup>2</sup> C スパイク時間                   |                                   |                               | 50  | ns  |

| $t_{sds}$      | I <sup>2</sup> C シリアル・データ・セットアップ時間        |                                   | 100                           |     | ns  |

| $t_{sdh}$      | I <sup>2</sup> C シリアル・データ・ホールド時間          |                                   | 0                             |     | ns  |

| $t_{icr}$      | I <sup>2</sup> C 入力の立ち上がり時間               |                                   | 20                            | 300 | ns  |

| $t_{icf}$      | I <sup>2</sup> C 入力の立ち下がり時間               |                                   | 20 × (V <sub>CC</sub> / 5.5V) | 300 | ns  |

| $t_{ocf}$      | I <sup>2</sup> C 出力の立ち下がり時間               | 10pF~400pF バス                     | 20 × (V <sub>CC</sub> / 5.5V) | 300 | ns  |

| $t_{buf}$      | STOP と START 間の I <sup>2</sup> C バスのフリー時間 |                                   | 1.3                           |     | μs  |

| $t_{sts}$      | I <sup>2</sup> C START または反復 START 条件の設定  |                                   | 0.6                           |     | μs  |

| $t_{sth}$      | I <sup>2</sup> C START または反復 START 条件ホールド |                                   | 0.6                           |     | μs  |

| $t_{sps}$      | I <sup>2</sup> C STOP 条件の設定               |                                   | 0.6                           |     | μs  |

| $t_{vd(data)}$ | 有効データ時間                                   | SCL Low から SDA 出力有効まで             |                               | 0.9 | μs  |

| $t_{vd(ack)}$  | ACK 条件の有効データ時間                            | SCL Low から SDA (出力) Low への ACK 信号 |                               | 0.9 | μs  |

| $C_b$          | I <sup>2</sup> C バスの容量性負荷                 |                                   |                               | 400 | pF  |

### I<sup>2</sup>C バス - ファスト・モード・プラス

|           |                                |  |      |      |     |

|-----------|--------------------------------|--|------|------|-----|

| $f_{scl}$ | I <sup>2</sup> C クロック周波数       |  | 0    | 1000 | kHz |

| $t_{sch}$ | I <sup>2</sup> C クロックの High 時間 |  | 0.26 |      | μs  |

| $t_{scl}$ | I <sup>2</sup> C クロックの Low 時間  |  | 0.5  |      | μs  |

## 6.7 I<sup>2</sup>C バス・タイミング要件 (continued)

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                                           |                                   | 最小値                           | 最大値  | 単位 |

|----------------|-------------------------------------------|-----------------------------------|-------------------------------|------|----|

| $t_{sp}$       | I <sup>2</sup> C スパイク時間                   |                                   |                               | 50   | ns |

| $t_{sds}$      | I <sup>2</sup> C シリアル・データ・セットアップ時間        |                                   | 50                            |      | ns |

| $t_{sdh}$      | I <sup>2</sup> C シリアル・データ・ホールド時間          |                                   | 0                             |      | ns |

| $t_{icr}$      | I <sup>2</sup> C 入力の立ち上がり時間               |                                   |                               | 120  | ns |

| $t_{icf}$      | I <sup>2</sup> C 入力の立ち下がり時間               |                                   | 20 × (V <sub>CC</sub> / 5.5V) | 120  | ns |

| $t_{ocf}$      | I <sup>2</sup> C 出力の立ち下がり時間               | 10pF～550pF バス                     | 20 × (V <sub>CC</sub> / 5.5V) | 120  | ns |

| $t_{buf}$      | STOP と START 間の I <sup>2</sup> C バスのフリー時間 |                                   | 0.5                           |      | μs |

| $t_{sts}$      | I <sup>2</sup> C START または反復 START 条件の設定  |                                   | 0.26                          |      | μs |

| $t_{sth}$      | I <sup>2</sup> C START または反復 START 条件ホールド |                                   | 0.26                          |      | μs |

| $t_{sps}$      | I <sup>2</sup> C STOP 条件の設定               |                                   | 0.26                          |      | μs |

| $t_{vd(data)}$ | 有効データ時間                                   | SCL Low から SDA 出力有効まで             |                               | 0.45 | μs |

| $t_{vd(ack)}$  | ACK 条件の有効データ時間                            | SCL Low から SDA (出力) Low への ACK 信号 |                               | 0.45 | μs |

| $C_b$          | I <sup>2</sup> C バスの容量性負荷                 |                                   |                               | 550  | pF |

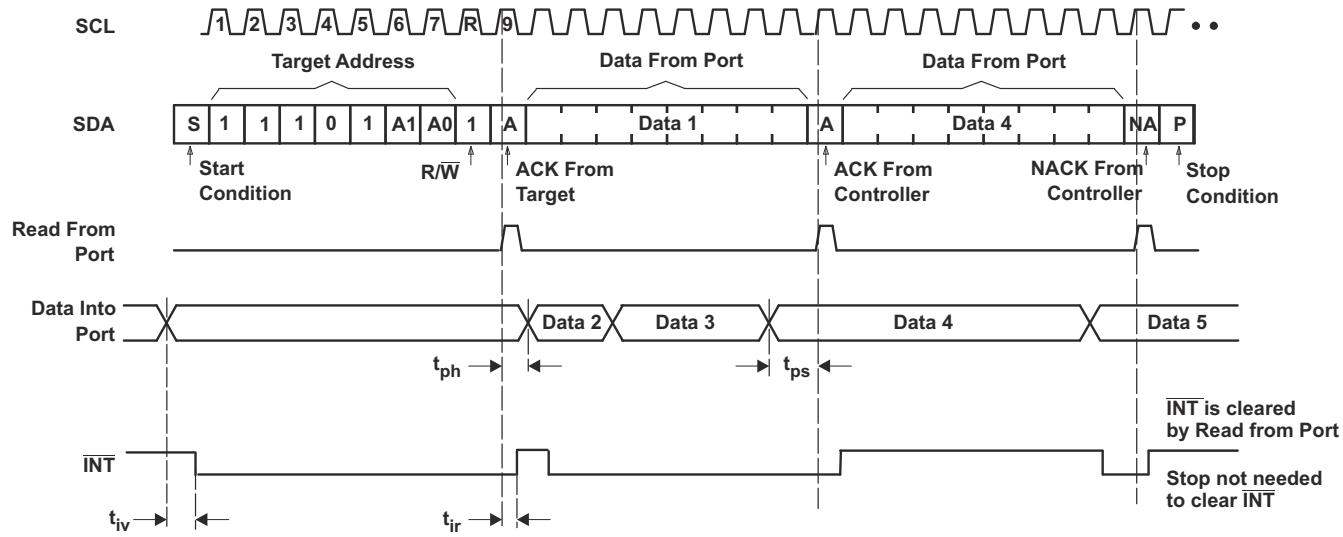

## 6.8 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ    |                | 始点 (入力) | 終点 (出力) | 最小値 | 標準値 | 最大値 | 単位 |

|----------|----------------|---------|---------|-----|-----|-----|----|

| $t_{lv}$ | 割り込み有効時間       | P ポート   | INT     |     | 1   |     | μs |

| $t_{lr}$ | 割り込みリセット遅延時間   | SCL     | INT     |     | 1   |     | μs |

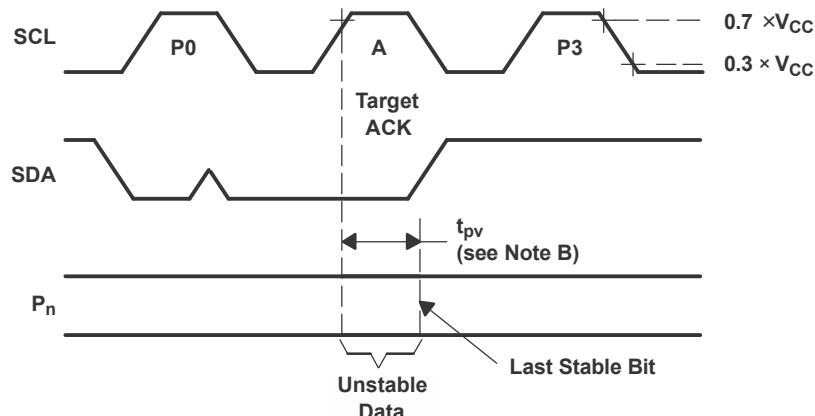

| $t_{pv}$ | 出力データ有効時間      | SCL     | P ポート   |     | 400 |     | ns |

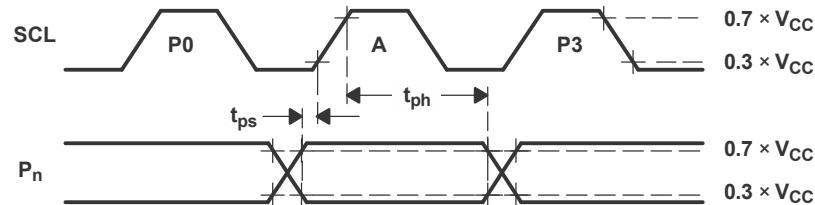

| $t_{ps}$ | 入力データ・セットアップ時間 | P ポート   | SCL     | 0   |     |     | ns |

| $t_{ph}$ | 入力データ・ホールド時間   | P ポート   | SCL     | 300 |     |     | ns |

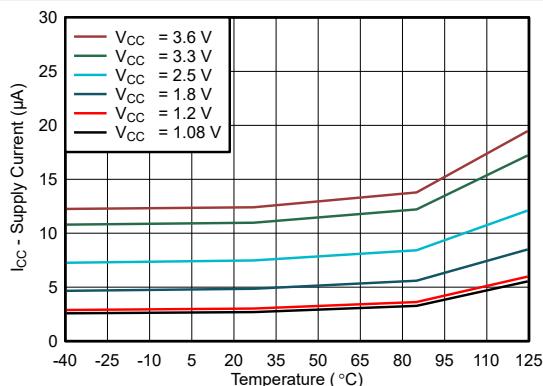

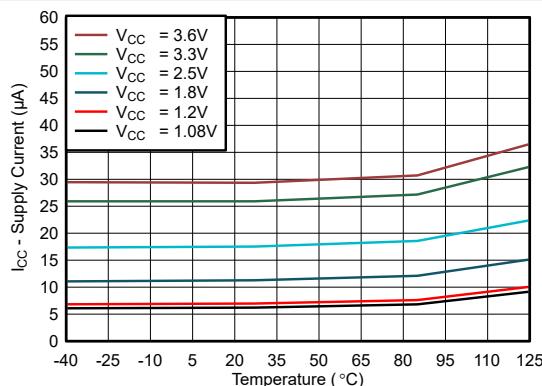

## 6.9 代表的特性

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

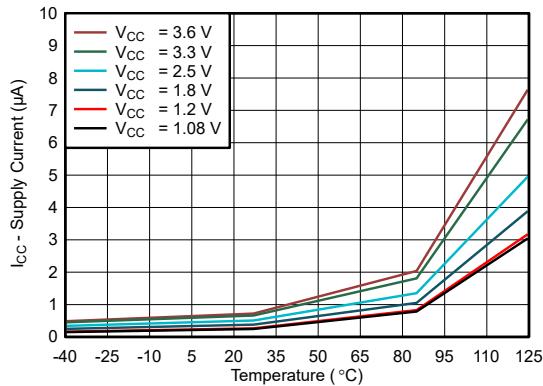

図 6-1. 消費電流と温度との関係 - FM モード

図 6-2. 消費電流と温度との関係 - FM+ モード

図 6-3. スタンバイ消費電流と温度との関係

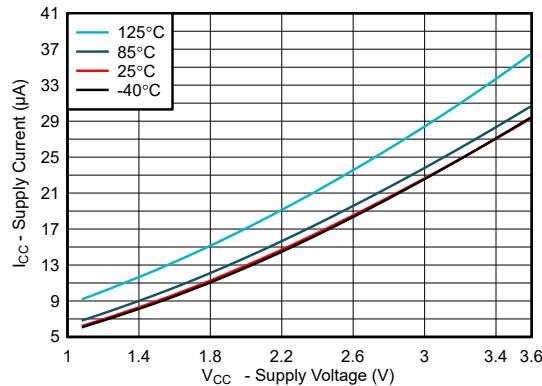

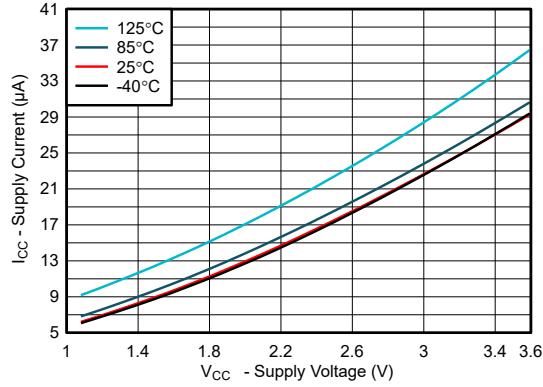

図 6-4. 消費電流と電源電圧との関係 - FM モード

図 6-5. 消費電流と電源電圧との関係 - FM+ モード

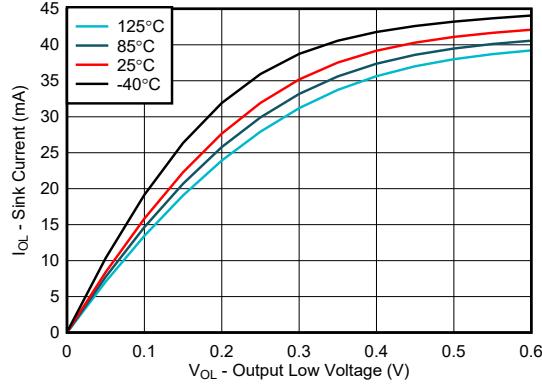

図 6-6. I/O シンク電流と出力 Low 電圧との関係、 $V_{CC} = 1.08V$

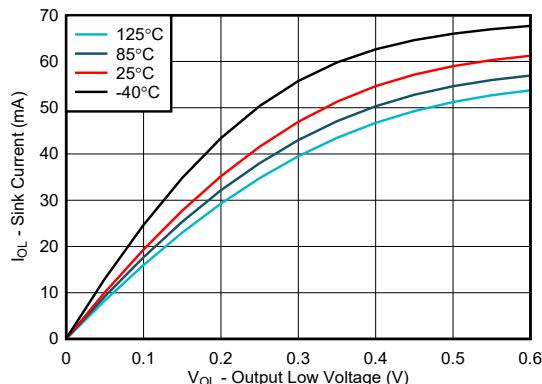

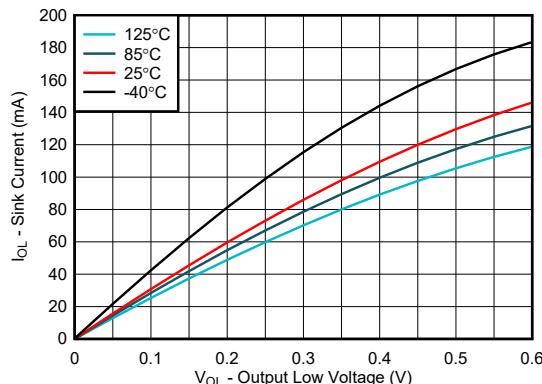

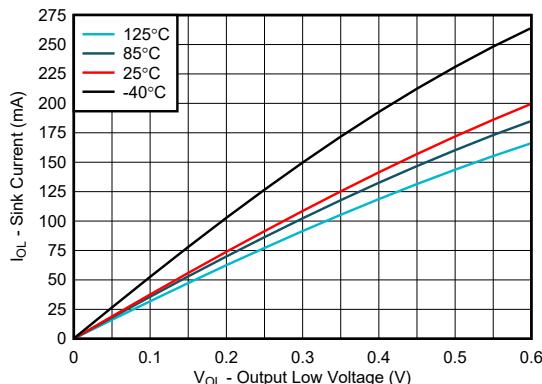

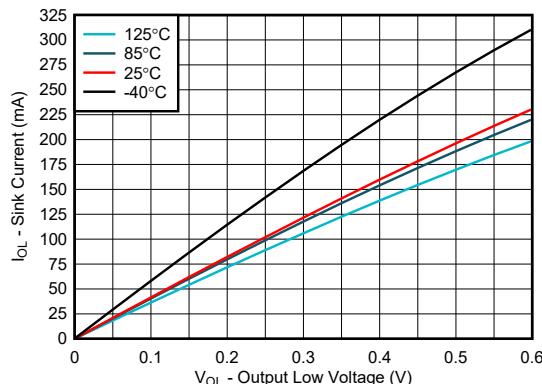

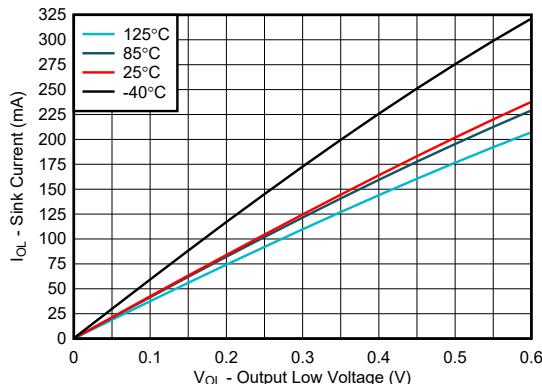

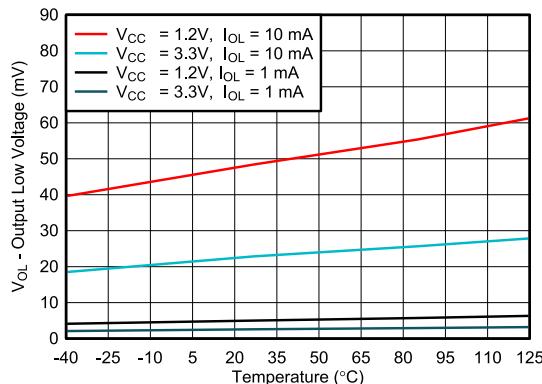

## 6.9 代表的特性 (continued)

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

図 6-7. I/O シンク電流と出力 Low 電圧との関係、 $V_{CC} = 1.2\text{V}$

図 6-8. I/O シンク電流と出力 Low 電圧との関係、 $V_{CC} = 1.8\text{V}$

図 6-9. I/O シンク電流と出力 Low 電圧との関係、 $V_{CC} = 2.5\text{V}$

図 6-10. I/O シンク電流と出力 Low 電圧との関係、 $V_{CC} = 3.3\text{V}$

図 6-11. I/O シンク電流と出力 Low 電圧との関係、 $V_{CC} = 3.6\text{V}$

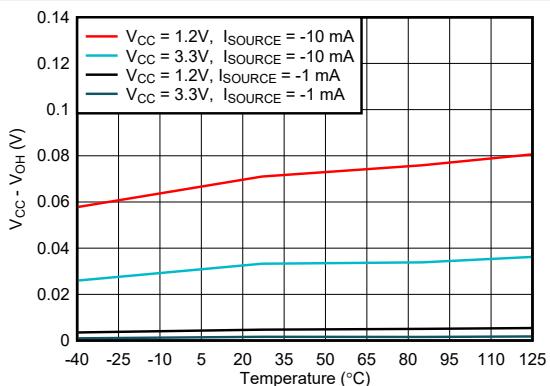

図 6-12. I/O Low 電圧と温度との関係

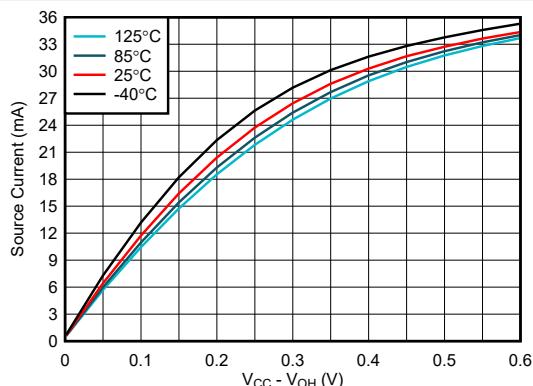

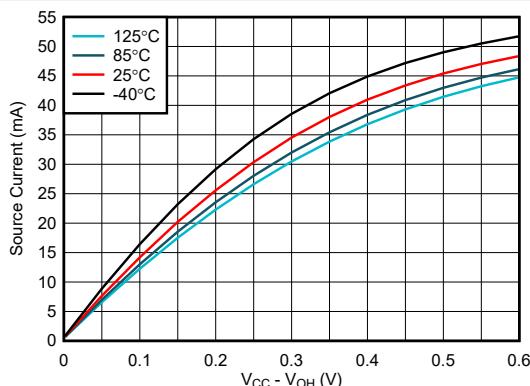

## 6.9 代表的特性 (continued)

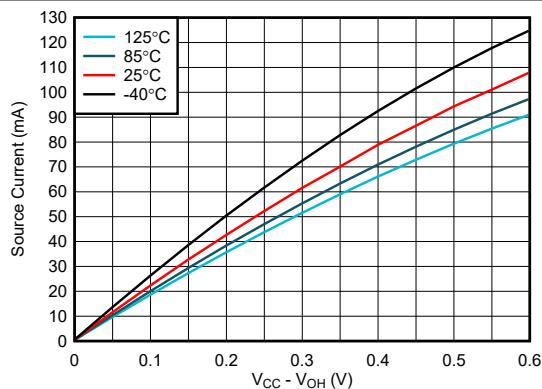

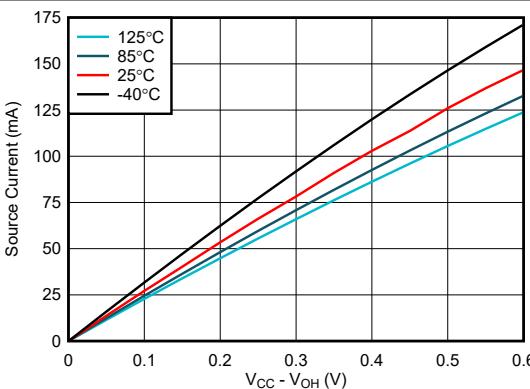

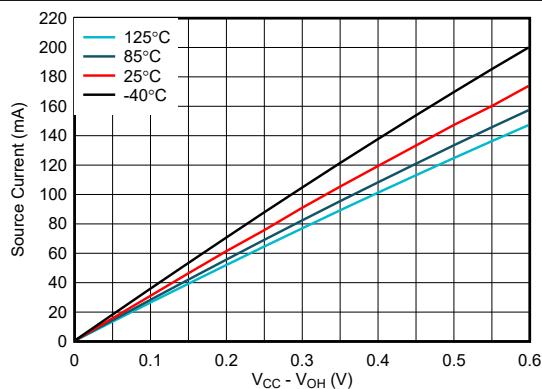

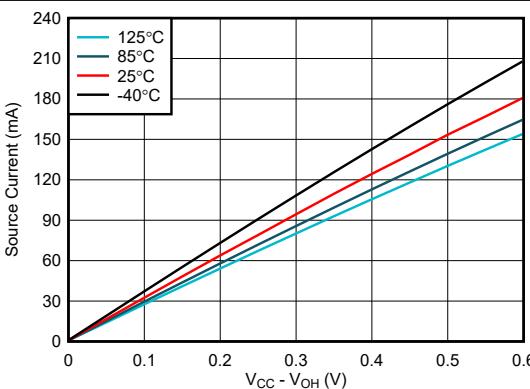

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

図 6-13. I/O ソース電流と出力 High 電圧との関係、

$V_{CC} = 1.08\text{V}$

図 6-14. I/O ソース電流と出力 High 電圧との関係、

$V_{CC} = 1.2\text{V}$

図 6-15. I/O ソース電流と出力 High 電圧との関係、

$V_{CC} = 1.8\text{V}$

図 6-16. I/O ソース電流と出力 High 電圧との関係、

$V_{CC} = 2.5\text{V}$

図 6-17. I/O ソース電流と出力 High 電圧との関係、

$V_{CC} = 3.3\text{V}$

図 6-18. I/O ソース電流と出力 High 電圧との関係、

$V_{CC} = 3.6\text{V}$

## 6.9 代表的特性 (continued)

$T_A = 25^\circ\text{C}$  (特に記述のない限り)

図 6-19. I/O High 電圧と温度との関係

## 7 パラメータ測定情報

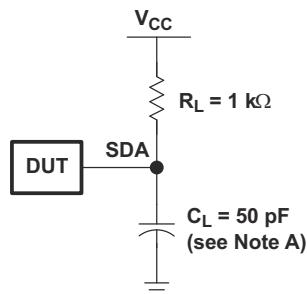

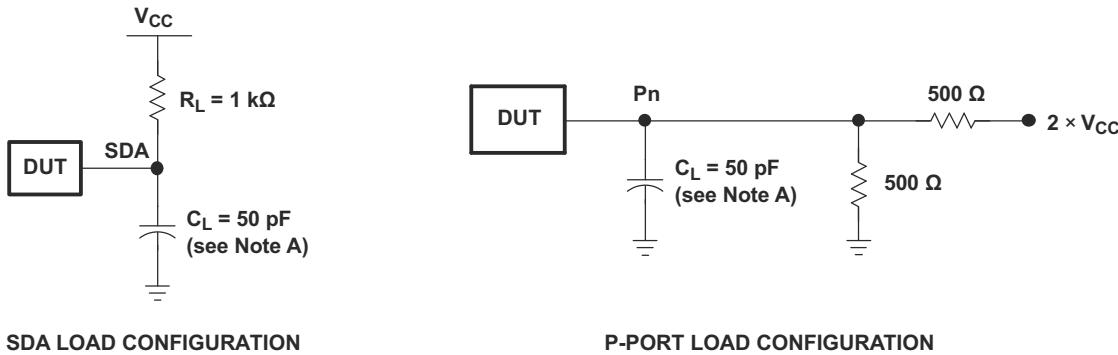

SDA LOAD CONFIGURATION

VOLTAGE WAVEFORMS

| BYTE | DESCRIPTION              |

|------|--------------------------|

| 1    | I <sup>2</sup> C address |

| 2, 3 | P-port data              |

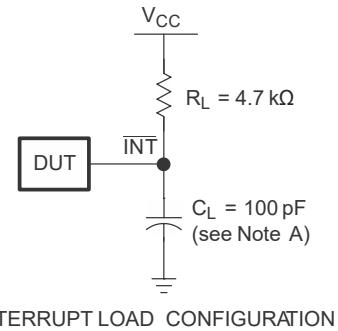

- A.  $C_L$  にはプローブと治具の容量が含まれます。 $t_{ocf}$  は、10pF または 400pF の  $C_L$  で測定されます。

- B. すべての入力は、以下の特性を持つジェネレータから供給されます: PRR ≤ 10MHz,  $Z_0 = 50\Omega$ ,  $t_p/t_f \leq 30\text{ns}$ 。

- C. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 7-1. I<sup>2</sup>C インターフェイスの負荷回路と電圧波形

- $C_L$  にはプローブと治具の容量が含まれます。

- すべての入力は、以下の特性を持つジェネレータから供給されます:  $PRR \leq 10\text{MHz}$ ,  $Z_O = 50\Omega$ ,  $t_f/t_r \leq 30\text{ns}$ 。

- すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

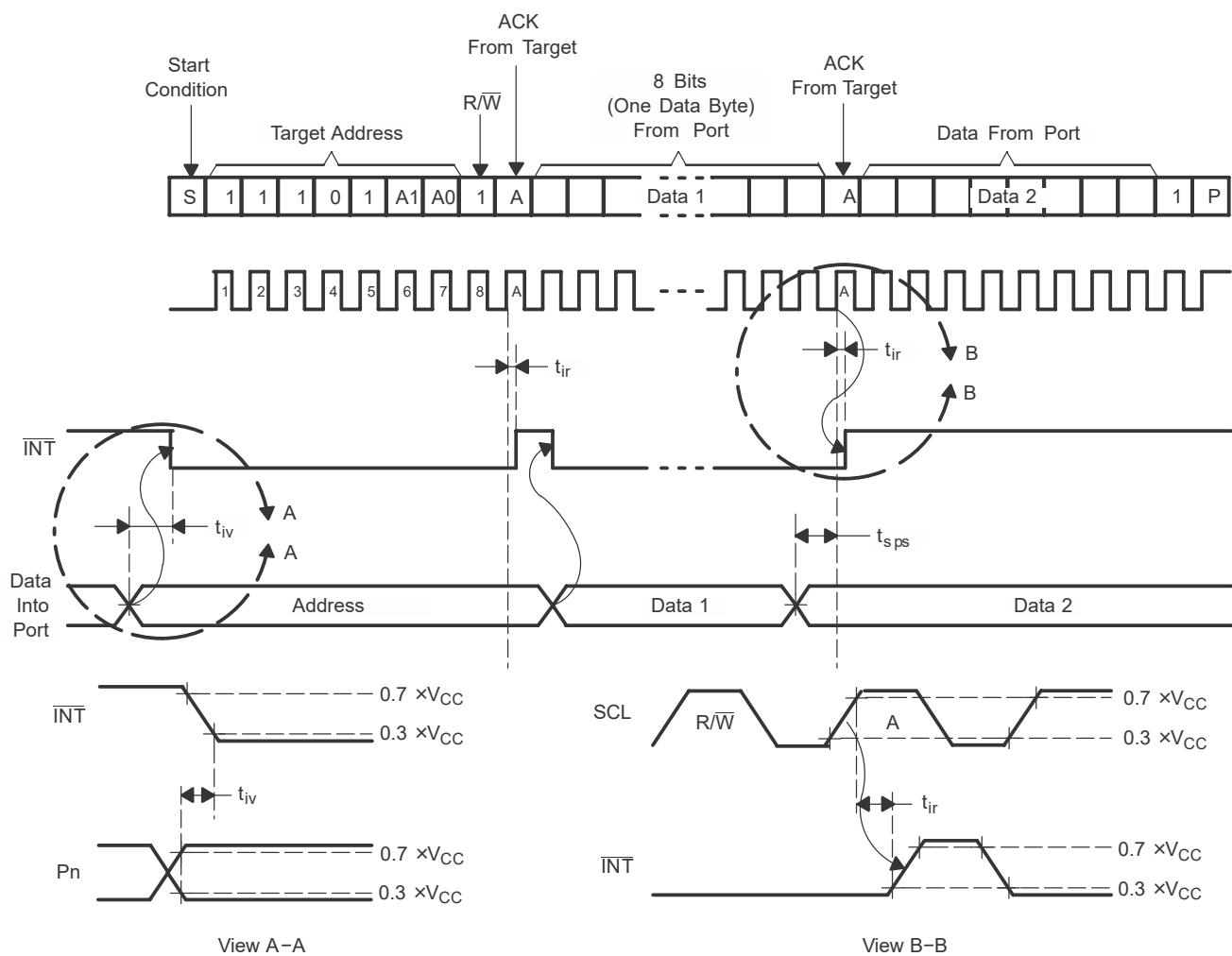

図 7-2. 割り込み負荷回路および電圧波形

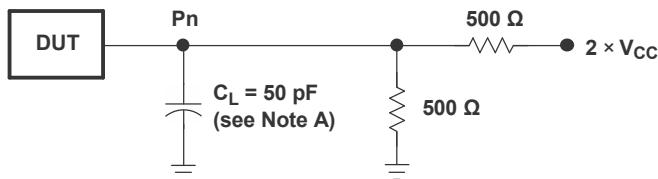

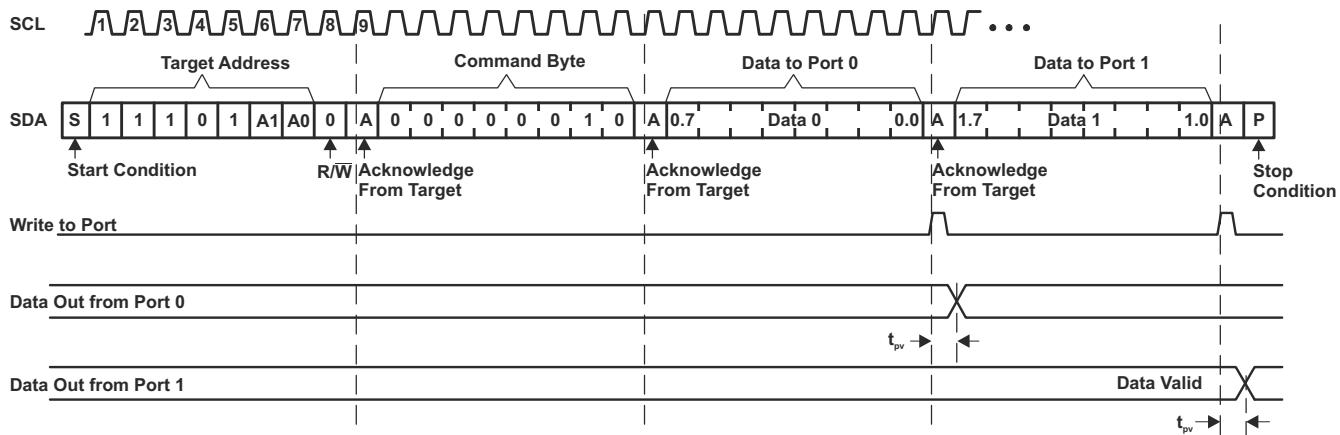

P-PORT LOAD CONFIGURATION

WRITE MODE ( $R/W = 0$ )

READ MODE ( $R/W = 1$ )

- A.  $C_L$  にはプローブと治具の容量が含まれます。

- B.  $t_{pv}$  は、SCL で  $0.7 \times V_{CC}$  から 50% の I/O (On) 出力まで測定されます。

- C. すべての入力は、以下の特性を持つジェネレータから供給されます:  $PRR \leq 10\text{MHz}$ ,  $Z_0 = 50\Omega$ ,  $t_r/t_f \leq 30\text{ns}$ 。

- D. 出力は一度に 1 つずつ測定され、測定するたびに 1 回遷移します。

- E. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 7-3. P ポートの負荷回路およびタイミング波形

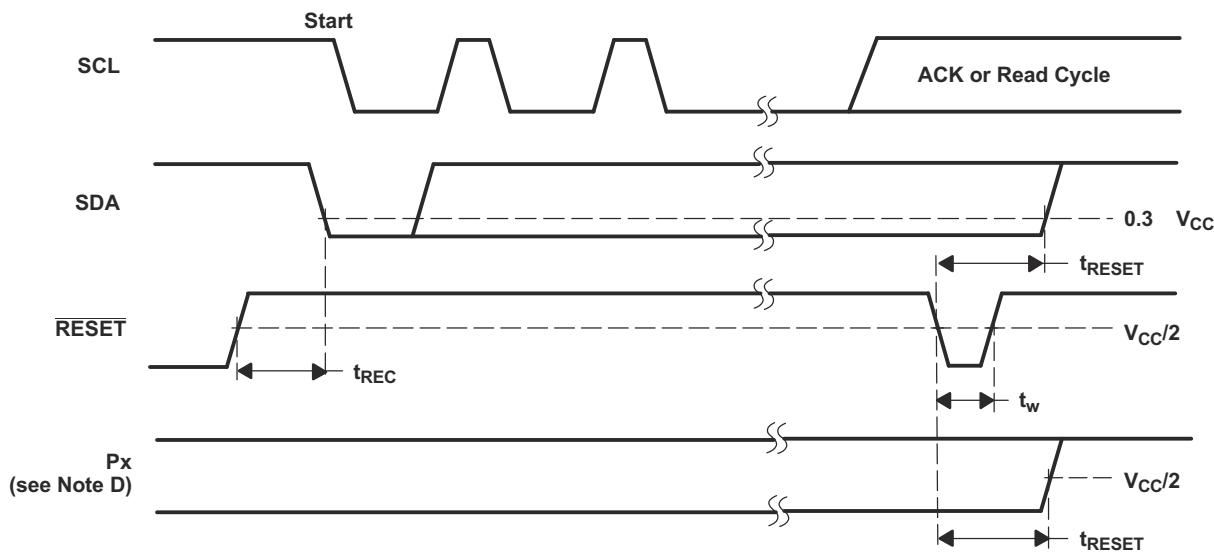

SDA LOAD CONFIGURATION

P-PORT LOAD CONFIGURATION

- A.  $C_L$  にはプローブと治具の容量が含まれます。

- B. すべての入力は、以下の特性を持つジェネレータから供給されます: PRR  $\leq 10\text{MHz}$ ,  $Z_0 = 50\Omega$ ,  $t_r/t_f \leq 30\text{ns}$ 。

- C. 出力は一度に 1 つずつ測定され、測定するたびに 1 回遷移します。

- D. I/O は入力として構成されます。

- E. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 7-4. リセット負荷回路および電圧波形

## 8 詳細説明

### 8.1 概要

TCAL9539-Q1 のデジタル・コアは 8 ビットのデータ・レジスタで構成されており、ユーザーは I/O ポートの特性を構成することができます。電源オン時、またはリセット後に、I/O は入力として構成されます。ただし、構成レジスタに書き込むことにより、システム・コントローラは I/O を入力または出力のどちらにも構成することができます。各入力または出力のデータは、対応する入力ポート・レジスタまたは出力ポート・レジスタに保持されます。入力ポート・レジスタの極性は、極性反転レジスタで反転できます。すべてのレジスタは、システム・コントローラで読み出すことができます。さらに、TCAL9539-Q1 には、I/O ポートの強化に特化した Agile I/O 機能が搭載されています。Agile I/O 機能とレジスタには、プログラム可能な出力駆動強度、プログラム可能なプルアップ抵抗とプルダウン抵抗、ラッチ可能な入力、マスク可能な割り込み、割り込みステータス・レジスタ、プログラム可能なオープン・ドレインまたはプッシュプル出力が含まれています。これらの構成レジスタにより柔軟性が向上するため、I/O は強化され、ユーザーは消費電力、スピード、EMI などの設計を最適化できるようになります。

デバイスの他の機能には、入力ポートの状態が変化するたびに **INT** ピンで発生する割り込みがあります。デバイスをデフォルトの状態にリセットするには、**RESET** ピンに Low 論理レベルを印加するか、ソフトウェア・リセット・コマンドを送信するか、またはデバイスの電源を一度切ってパワーオン・リセットを行います。

TCAL9539-Q1 のオープン・ドレイン割り込み (**INT**) 出力は、いずれかの入力状態が対応する入力ポート・レジスタの状態と異なる場合にアクティブになって、入力状態が変化したことをシステム・コントローラに示すために使用されます。**INT** ピンは、プロセッサの割り込み入力に接続することができます。このラインで割り込み信号を送信することにより、デバイスは I<sup>2</sup>C バスで通信しなくとも、リモート I/O ポートに受信データがあるかどうかをプロセッサに通知することができます。そのため、シンプルなターゲット・デバイスとして機能できます。

システム・コントローラは、タイムアウト時、またはその他の不正な動作時に、**RESET** 入力ピンに Low をアサートするか、または **V<sub>CC</sub>** ピンへの電源を一度切ってパワーオン・リセット (POR) することにより、リセットすることができます。リセットにより、レジスタはデフォルト状態になり、I<sup>2</sup>C/SMBus ステート・マシンは初期化されます。**RESET** 機能でも POR でも、同じようにリセット / 初期化を行えますが、**RESET** 機能はデバイスの電源をオフにする必要がありません。

2 本のハードウェア・ピン (A0 と A1) を使用すると、固定 I<sup>2</sup>C アドレスをプログラムして変更することができ、複数のデバイスで同じ I<sup>2</sup>C バスや SMBus を共有することができます。

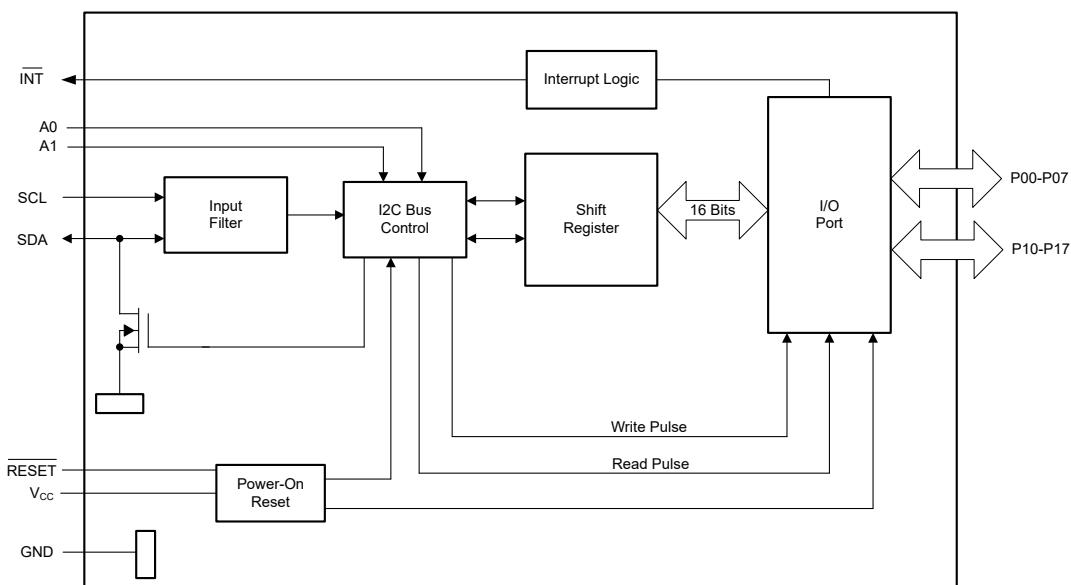

### 8.2 機能ブロック図

A. すべての I/O は、リセット時に入力に設定されます。

図 8-1. 論理図 (正論理)

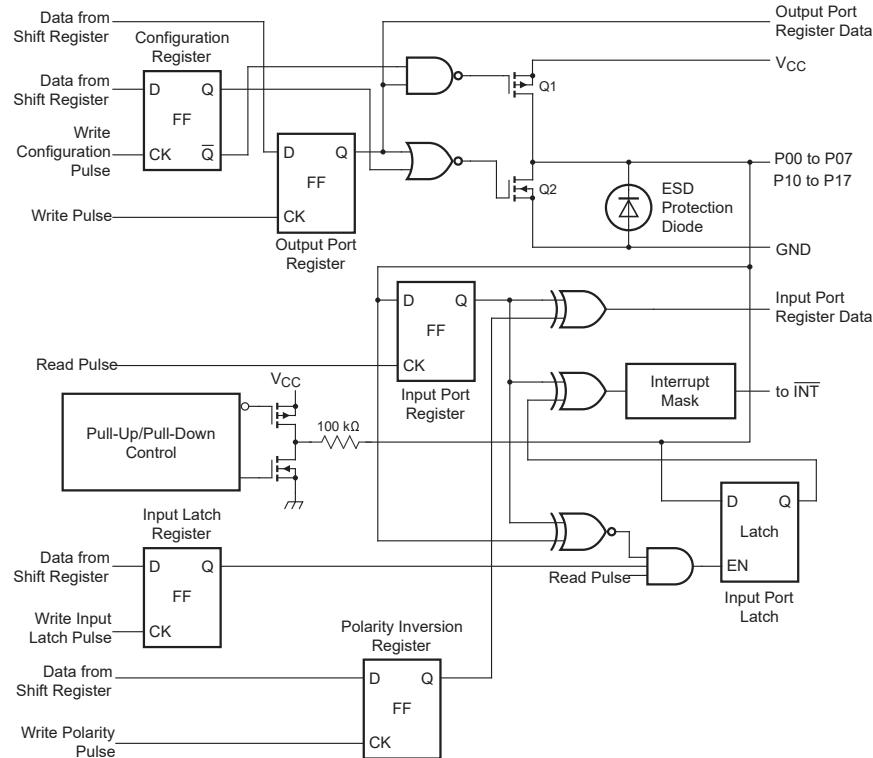

A. 電源オンまたはリセット時に、すべてのレジスタがデフォルト値に戻ります。

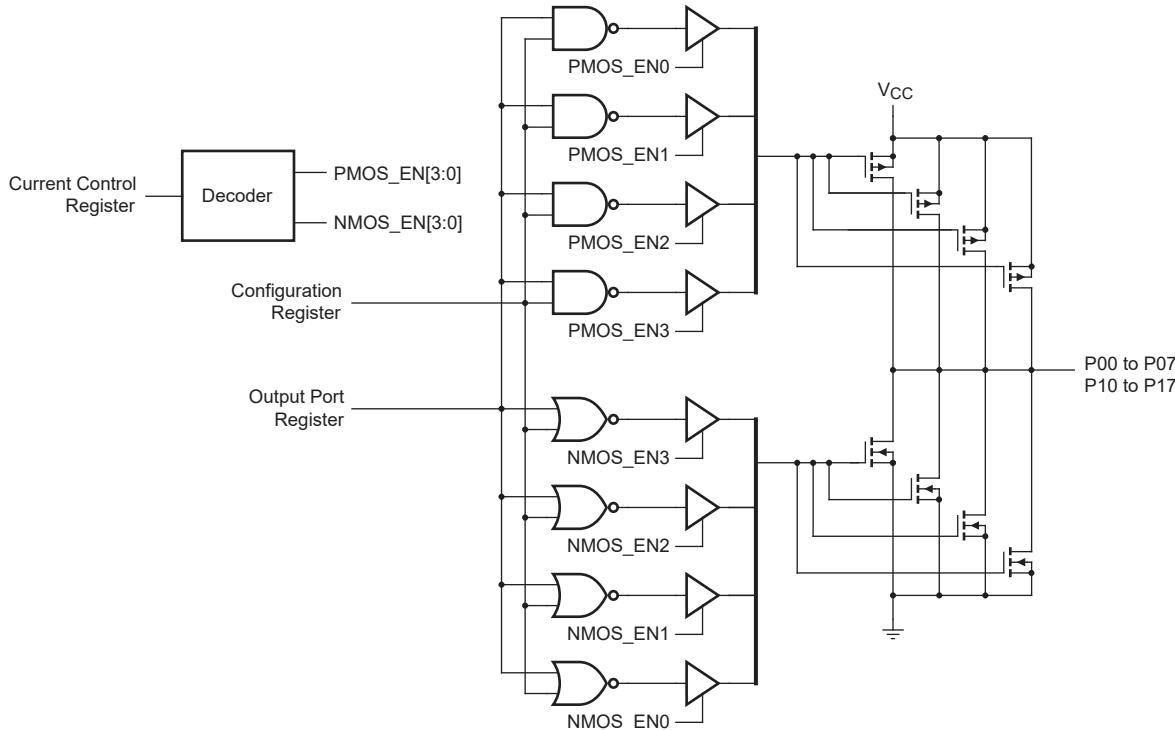

図 8-2. P00 から P17 の概略回路図

## 8.3 機能説明

### 8.3.1 I/O ポート

I/O が入力として構成されている場合、FET Q1 と Q2 はオフになり (図 8-2 を参照)、高インピーダンス入力が生成されます。入力電圧は、電源電圧より高い、最大 3.6V まで上昇させることができます。

I/O が出力として構成されている場合、Q1 または Q2 は出力ポート・レジスタの状態に応じてイネーブルになります。この場合、I/O ピンと電源または GND の間に低インピーダンスのパスがあります。この I/O ピンに印加される外部電圧は、適切に動作させるために推奨レベルを超えないようにする必要があります。

### 8.3.2 調整可能な出力駆動強度

出力駆動強度レジスタを使用すると、GPIO の駆動レベルを制御することができます。各 GPIO は、4 種類の電流レベルのいずれか 1 つに個別に構成できます。これらのビットをプログラムすることにより、ユーザーはトランジスタ・ペアの数か I/O パッドを駆動する「フィンガー」数を変更します。図 8-3 に、簡略化した出力段を示します。パッドの動作は、構成レジスタ、出力ポートのデータ、電流制御レジスタの影響を受けます。電流制御レジスタ・ビットを 01b にプログラムすると、2 つのフィンガーのみアクティブになり、電流駆動能力は 50% 低下します。

図 8-3. 簡単な出力段

システム・ノイズを低減するために電流駆動能力を低下させることをお勧めします。出力が切り替わると、出力駆動の選択によってピーク電流が発生します。このピーク電流は電源と GND パッケージのインダクタンスを経由して流れ、ノイズ（一部は放射されますが、多くは影響の大きな同時スイッチング・ノイズ (SSN)）を生成します。つまり、同時に多くの出力を切り替えるとグランド・ノイズと電源ノイズが発生します。出力駆動強度を出力駆動強度レジスタで制御することにより、ユーザーは外部の部品を追加することなく、SSN の問題を低減することができます。

### 8.3.3 割り込み出力 (INT)

割り込み機能がマスクされていない場合、入力モードでのポート入力の立ち上がりエッジまたは立ち下がりエッジによって割り込みが生成されます。 $t_{IV}$  時間が経過すると、INT 信号は有効になります。割り込み回路は、ポート上のデータが元の設定に戻されたとき、または割り込みを生成したポートからデータが読み取られたときにリセットされます。リセットは、読み取りモード時に SCL 信号の立ち上がりエッジの後のアクリッジ (ACK) ビットで発生します。ACK クロック・パルス中に発生する割り込みは、このパルス中に割り込みがリセットされるため、失われる（または非常に短くなる）ことがあります。リセット後に I/O の各変化が検出され、INT として送信されます。

他のデバイスとの間での読み取りや書き込みは、割り込み回路に影響しません。また、出力として構成されたピンが割り込みを発生させることはできません。I/O を出力から入力に変更すると、ピンの状態が入力ポート・レジスタの内容と一致しない場合、誤って割り込みが発生する可能性があります。

INT 出力にはオープン・ドレイン構造があり、割り込み機能が必要な場合は  $V_{CC}$  への外部プルアップ抵抗が必要です。そうしないと、フローティングのままになる可能性があります。

### 8.3.4 リセット入力 (RESET)

RESET 入力をアサートして、 $V_{CC}$  電源を動作レベルに保持しながら、システムを初期化することができます。リセットを行うには、 $t_W$  の最小時間の間、RESET ピンを Low に保持します。TCAL9539-Q1 のレジスタと I<sup>2</sup>C/SMBus のステート・マシンは、RESET が Low (0) になると、デフォルト状態に変更されます。RESET が High (1) になると、P ポートの I/O レベルは外部から、またはコントローラを使用して変更できます。アクティブ接続が使用されない場合、この入力には  $V_{CC}$  へのプルアップ抵抗が必要です。RESET がトグル切り替えされると、Input Port レジスタは GPIO ピンの状態を反映して更新されます。

### 8.3.5 ソフトウェア・リセット呼び出し

ソフトウェア・リセット呼び出しは、 $I^2C$  バス上のコントローラから送信されるコマンドで、このコマンドに対応しているすべてのデバイスに対して電源オンのデフォルト状態にリセットするよう指示を出します。想定どおりに機能させるためには、 $I^2C$  バスの機能を有効にして、このバスにデバイスが接続されていない状態にする必要があります。

ソフトウェア・リセット呼び出しは、以下の手順で定義します。

1.  $I^2C$  バスのコントローラから **START** 条件を送信します。

2. 使用するアドレスは、予約済みのジェネラル・コールの  $I^2C$  バス・アドレスで、R/W ビットを 0 にセットした「0000 0000」です。送信されるバイトは、0x00 です。

3. ジェネラル・コール機能をサポートしているすべてのデバイスは、ACK を送信します。R/W ビットが 1 (読み出し) にセットされると、デバイスは NACK を送信します。

4. ジェネラル・コール・アドレスの送信が確認されると、コントローラは 0x06 に相当するデータの 1 バイトのみを送信します。データ・バイトが他の値の場合、デバイスは応答を送信しないか、またはリセットを行います。1 バイト以上が送信された場合、これ以上のバイトに応答は送信されず、デバイスは無効と判断して  $I^2C$  メッセージを無視します。

5. データ (0x06) の 1 バイトが送信されると、コントローラはソフトウェア・リセット・シーケンスを終了させるために **STOP** 条件を送信します。**START** 条件が繰り返し送信されてもデバイスは無視し、リセットは実行されません。

上記の手順がすべて成功すると、デバイスはリセットを実行します。これにより、すべてのレジスタ値はクリアされ、電源オン時のデフォルト値に戻ります。

## 8.4 デバイスの機能モード

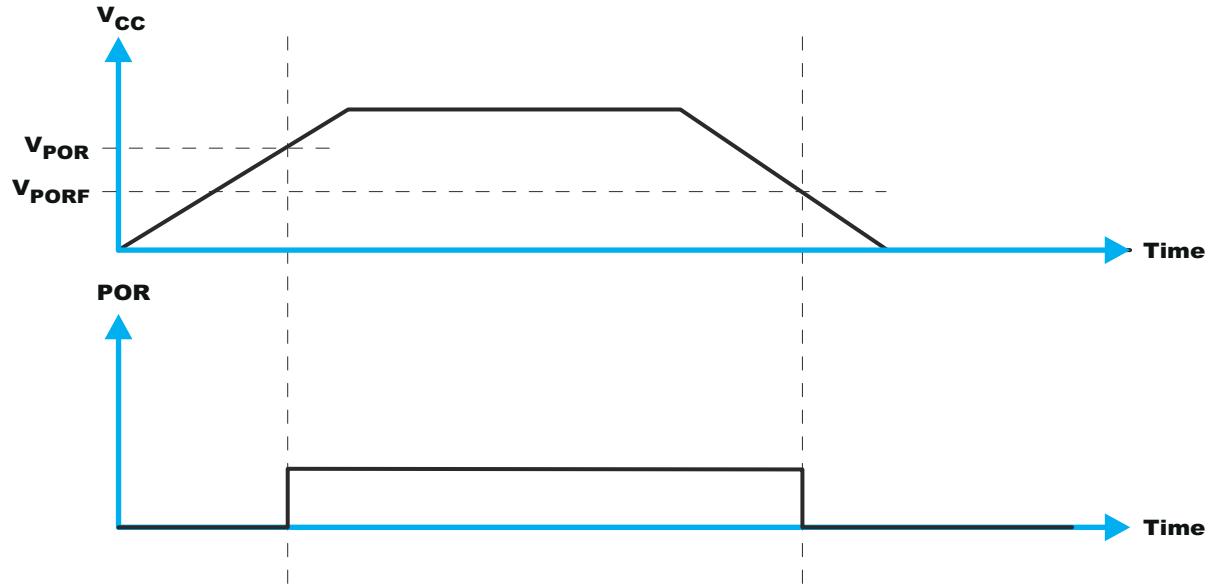

### 8.4.1 パワーオン・リセット

$V_{CC}$  に電力 (0V~) を印加すると、内部のパワーオン・リセットにより電源供給が  $V_{POR}$  に到達するまで TCAL9539-Q1 はリセット状態に保持されます。このとき、リセット状態は解除され、TCAL9539-Q1 のレジスタと  $I^2C/SMBus$  のステート・マシンはそれぞれのデフォルト状態に初期化されます。その後、 $V_{CC}$  を  $V_{PORF}$  未満に下げて、再びパワーリセット・サイクルの動作電圧まで戻す必要があります。

## 8.5 プログラミング

### 8.5.1 $I^2C$ インターフェイス

双方向  $I^2C$  バスは、シリアル・クロック (SCL) ラインとシリアル・データ (SDA) ラインで構成されます。デバイスの出力段に接続するときは、両方のラインをプルアップ抵抗経由で正の電源に接続する必要があります。データ転送は、バスがビギー状態でないときにのみ開始できます。

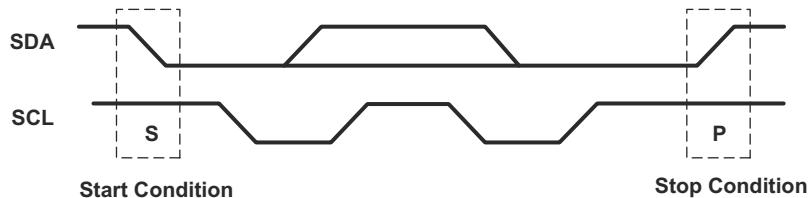

このデバイスとの  $I^2C$  通信は、**START** 条件を送信するコントローラによって開始されます。**START** 条件は、SCL 入力が High のときに、SDA 入力 / 出力が High から Low に遷移することです (図 8-4 を参照)。START 条件の後、デバイスのアドレス・バイトが送信されます。最初は、データ方向ビット (R/W) を含む最上位ビット (MSB) が送信されます。

有効なアドレス・バイトを受信すると、このデバイスは、ACK 関連のクロック・パルスが High のときに SDA 入力 / 出力を Low にするアクノリッジ (ACK) で応答します。ターゲット・デバイスのアドレス入力を **START** 条件と **STOP** 条件の間で変更することはできません。

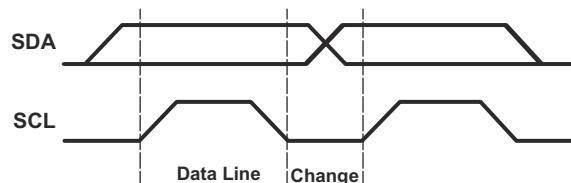

$I^2C$  バスでは、各クロック・パルスの間に 1 つのデータ・ビットのみが転送されます。SDA ラインのデータは、クロック周期の High パルス中は安定している必要があります。この時点でデータ・ラインが変化すると、制御コマンド (**START** または **STOP**) として解釈されるためです (図 8-5 を参照)。

**STOP** 条件は、SCL 入力が High のときに SDA 入力 / 出力が Low から High に遷移することで、コントローラから送信されます (図 8-4 を参照)。

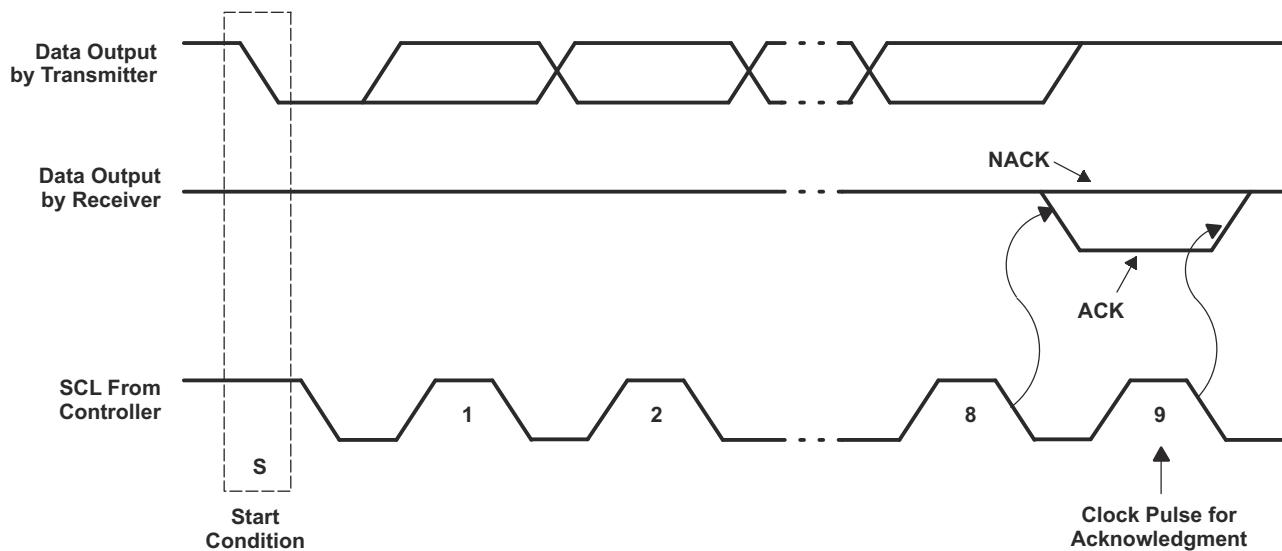

**START** 条件と **STOP** 条件の間に、トランスマッタからレシーバへ任意の数のデータ・バイトを転送できます。8 ビットの各バイトの後に 1 つの ACK ビットが続きます。レシーバが ACK ビットを送信する前に、トランスマッタは SDA ラインを解放する必要があります。アクノリッジを行うデバイスは、ACK 関連のクロック周期が High パルスのときは SDA ラインが安定して Low を維持できるように、ACK クロック・パルスの間は SDA ラインをプルダウンする必要があります (図 8-6 を参照)。ターゲットのレシーバがアドレス指定されている場合、各バイトを受信した後に ACK を生成する必要があります。同様に、

コントローラはターゲットのトランシミッタから受信した各バイトの後に ACK を生成する必要があります。適切な動作のためには、セットアップ時間とホールド時間の条件を満たす必要があります。

コントローラのレシーバは、最後のバイトがターゲットからクロック出力された後、アクノリッジ (NACK) を生成せずに、データの終了をターゲットのトランシミッタに通知します。これは、コントローラのレシーバで SDA ラインを High に保持することにより行われます。この場合、コントローラが STOP 条件を生成できるように、トランシミッタはデータ・ラインを解放する必要があります。

図 8-4. START 条件と STOP 条件の定義

図 8-5. ピット転送

図 8-6. I<sup>2</sup>C バスのアクノリッジ

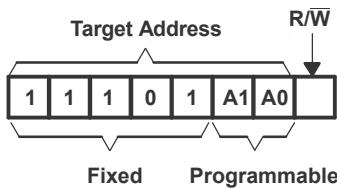

表 8-1. インターフェイスの定義

| バイト                         | ビット     |     |     |     |     |     |     |         |

|-----------------------------|---------|-----|-----|-----|-----|-----|-----|---------|

|                             | 7 (MSB) | 6   | 5   | 4   | 3   | 2   | 1   | 0 (LSB) |

| デバイスの I <sup>2</sup> C アドレス | H       | H   | H   | L   | H   | A1  | A0  | R/W     |

| I/O データ・バス                  | P07     | P06 | P05 | P04 | P03 | P02 | P01 | P00     |

|                             | P17     | P16 | P15 | P14 | P13 | P12 | P11 | P10     |

## 8.6 レジスタ・マップ

### 8.6.1 デバイス・アドレス

TCAL9539-Q1 のアドレスを 図 8-7 に示します。

図 8-7. TCAL9539-Q1 のアドレス

表 8-2. アドレス参照

| 入力 |    | I <sup>2</sup> C バスのターゲットのアドレス |

|----|----|--------------------------------|

| A1 | A0 |                                |

| L  | L  | 116 (10 進)、74 (16 進)           |

| L  | H  | 117 (10 進)、75 (16 進)           |

| H  | L  | 118 (10 進)、76 (16 進)           |

| H  | H  | 119 (10 進)、77 (16 進)           |

ターゲットのアドレスの最後のビットにより、実行する動作 (読み取りまたは書き込み) が定義されます。High (1) を選択すると読み取り動作、Low (0) を選択すると書き込み動作となります。

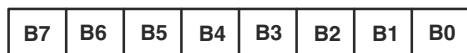

## 8.6.2 制御レジスタとコマンド・バイト

アドレス・バイトのアクノリッジが成功すると、バス・コントローラはコマンド・バイトを送信します。このバイトは TCAL9539-Q1 の制御レジスタに保存されます。このデータ・バイトの下位 ビットは、影響を受ける内部レジスタ（入力、出力、極性反転、または構成）を反映しています。ビット 6 とコマンド・バイトの下位 3 ビットを組み合わせて使用し、デバイスの拡張機能（Agile IO）を示します。コマンド・バイトは、書き込み転送中にのみ送信されます。

新しいコマンドが送信されると、アドレス指定されたレジスタは、新しいコマンド・バイトが送信されるまで、読み取りによってアクセスが継続されます。電源投入時、ハードウェア・リセット時、またはソフトウェア・リセット時に、制御レジスタはデフォルトで 00h に設定されます。

図 8-8. 制御レジスタ・ビット

表 8-3. コマンド・バイト

| 制御レジスタ・ビット |    |    |    |    |    |    |    | コマンド・バイト<br>(16 進) | レジスタ                       | プロトコル          | 電源オン<br>のデフォルト |

|------------|----|----|----|----|----|----|----|--------------------|----------------------------|----------------|----------------|

| B7         | B6 | B5 | B4 | B3 | B2 | B1 | B0 |                    |                            |                |                |

| 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00                 | 入力ポート 0                    | 読み取りバイト        | xxxx xxxx      |

| 0          | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 01                 | 入力ポート 1                    | 読み取りバイト        | xxxx xxxx      |

| 0          | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 02                 | 出力ポート 0                    | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03                 | 出力ポート 1                    | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 04                 | 極性反転 0                     | 読み取り / 書き込みバイト | 0000 0000      |

| 0          | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 05                 | 極性反転 1                     | 読み取り / 書き込みバイト | 0000 0000      |

| 0          | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 06                 | 構成 0                       | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 07                 | 構成 1                       | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 40                 | 出力駆動強度 0                   | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 41                 | 出力駆動強度 0                   | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 42                 | 出力駆動強度 1                   | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 43                 | 出力駆動強度レジスタ 1               | 読み取り / 書き込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 44                 | 入力ラッチ・レジスタ 0               | 読み取り / 書き込みバイト | 0000 0000      |

| 0          | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 45                 | 入力ラッチ・レジスタ 1               | 読み取り / 書き込みバイト | 0000 0000      |

| 0          | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 46                 | プルアップ / プルダウン・イネーブル・レジスタ 0 | 読み取り / 書き込みバイト | 0000 0000      |

| 0          | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 47                 | プルアップ / プルダウン・イネーブル・レジスタ 1 | 読み取り / 書き込みバイト | 0000 0000      |

| 0          | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 48                 | プルアップ / プルダウン選択レジスタ 0      | 読み取り / 書き込みバイト | 1111 1111      |

**表 8-3. コマンド・バイト (continued)**

| 制御レジスタ・ビット |    |    |    |    |    |    |    | コマンド・バイト<br>(16 進) | レジスタ                      | プロトコル              | 電源オン<br>のデフォルト |

|------------|----|----|----|----|----|----|----|--------------------|---------------------------|--------------------|----------------|

| B7         | B6 | B5 | B4 | B3 | B2 | B1 | B0 |                    |                           |                    |                |

| 0          | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 49                 | プルアップ / プルダウン選択<br>レジスタ 1 | 読み取り / 書き<br>込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 4A                 | 割り込みマスク・レジスタ 0            | 読み取り / 書き<br>込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 4B                 | 割り込みマスク・レジスタ 1            | 読み取り / 書き<br>込みバイト | 1111 1111      |

| 0          | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 4C                 | 割り込みステータス・レジスタ<br>0       | 読み取りバイト            | 0000 0000      |

| 0          | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 4D                 | 割り込みステータス・レジスタ<br>1       | 読み取りバイト            | 0000 0000      |

| 0          | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 4F                 | 出力ポート構成レジスタ               | 読み取り / 書き<br>込みバイト | 0000 0000      |

### 8.6.3 レジスタの説明

入力ポート・レジスタ (レジスタ 0 および 1) には、ピンが構成レジスタによって入力と出力のどちらに定義されているかに関係なく、ピンに入ってくるロジック・レベルが反映されます。入力ポート・レジスタは、読み取り専用です。これらのレジスタに書き込みを行っても、影響はありません。デフォルト値 (X) は、外部で印加されるロジック・レベルによって決まります。読み取り動作の前に、書き込み転送が送信され、それと同時に、次に入力ポート・レジスタがアクセスされることを I<sup>2</sup>C デバイスに通知するコマンド・バイトも送信されます。

**表 8-4. レジスタ 0 および 1 (入力ポート・レジスタ)**

| ビット   | I-07 | I-06 | I-05 | I-04 | I-03 | I-02 | I-01 | I-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | X    | X    | X    | X    | X    | X    | X    | X    |

| ビット   | I-17 | I-16 | I-15 | I-14 | I-13 | I-12 | I-11 | I-10 |

| デフォルト | X    | X    | X    | X    | X    | X    | X    | X    |

出力ポート・レジスタ (レジスタ 2 および 3) には、構成レジスタで出力として定義されているピンから出していくロジック・レベルが示されます。これらのレジスタのビット値は、入力として定義されたピンには影響しません。そして、これらのレジスタから読み出した値は、実際のピンの値ではなく、出力選択を制御しているフリップ・フロップの値に反映されます。

**表 8-5. レジスタ 2 および 3 (出力ポート・レジスタ)**

| ビット   | O-07 | O-06 | O-05 | O-04 | O-03 | O-02 | O-01 | O-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| ビット   | O-17 | O-16 | O-15 | O-14 | O-13 | O-12 | O-11 | O-10 |

| デフォルト | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

極性反転レジスタ (レジスタ 4 および 5) は、構成レジスタで入力として定義されたピンの極性を反転することができます。これらのレジスタのビットが設定されると (1 で書き込む)、対応するポート・ピンの極性は反転します。これらのレジスタのビットがクリアされると (0 で書き込む)、対応するポート・ピンの元の極性が保持されます。

**表 8-6. レジスタ 4 および 5 (極性反転レジスタ)**

| ビット   | P-07 | P-06 | P-05 | P-04 | P-03 | P-02 | P-01 | P-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ビット   | P-17 | P-16 | P-15 | P-14 | P-13 | P-12 | P-11 | P-10 |

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

構成レジスタ (レジスタ 6 および 7) は、I/O ピンの方向を構成します。これらのレジスタのビットを 1 に設定すると、対応するポート・ピンは高インピーダンス出力ドライバを持つ入力としてイネーブルになります。これらのレジスタのビットを 0 にクリアすると、対応するポート・ピンは出力としてイネーブルになります。ポートの構成を入力から出力に変更すると、クリアされたポートに関連する割り込みが発生します。

**表 8-7. レジスタ 6 および 7 (構成レジスタ)**

| ビット   | C-07        | C-06        | C-05        | C-04        | C-03        | C-02        | C-01        | C-00        |

|-------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| デフォルト | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

| ビット   | <b>C-17</b> | <b>C-16</b> | <b>C-15</b> | <b>C-14</b> | <b>C-13</b> | <b>C-12</b> | <b>C-11</b> | <b>C-10</b> |

| デフォルト | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

出力駆動強度レジスタは、P ポートの GPIO バッファの出力駆動レベルを制御します。各 GPIO は、2 つのレジスタの制御ビットを使用して、目標の出力電流レベルに個別に構成することができます。たとえば、ポート P07 はレジスタ 41 (ビット 7 および 6) で制御され、ポート P06 はレジスタ 41 (ビット 5 および 4) で制御され、以下も同様です。GPIO の出力駆動レベルは、00b = 0.25x の駆動強度、01b = 0.5x の駆動強度、10b = 0.75x の駆動強度、11b = 完全駆動強度の能力を持つ 1x にプログラムされます。詳細については、セクション 9.2 を参照してください。

**表 8-8. レジスタ 40、41、42、43(出力駆動強度レジスタ)**

| ビット   | CC-03 | CC-03 | CC-02 | CC-02 | CC-01 | CC-01 | CC-00 | CC-00 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| ビット   | CC-07 | CC-07 | CC-06 | CC-06 | CC-05 | CC-05 | CC-04 | CC-04 |

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| ビット   | CC-13 | CC-13 | CC-12 | CC-12 | CC-11 | CC-11 | CC-10 | CC-10 |

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| ビット   | CC-17 | CC-17 | CC-16 | CC-16 | CC-15 | CC-15 | CC-14 | CC-14 |

| デフォルト | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

入力ラッチ・レジスタは、P ポートの GPIO ピンの入力ラッチ機能をイネーブル / ディセーブルにします。これらのレジスタは、このピンが入力ポートとして構成されている場合にのみ有効です。入力ラッチ・レジスタ・ビットが 0 のとき、対応する入力ピンの状態はラッチされません。対応する入力ピンの状態が変化すると、割り込みが発生します。入力レジスタの読み出しを行うと、割り込みはクリアされます。入力が最初のロジック状態に戻ってから、入力ポート・レジスタを読み出すと、割り込みはクリアされます。

入力ラッチ・レジスタ・ビットが 1 にセットされると、対応する入力ピンの状態がラッチされます。入力状態が変化すると、割り込みが発生し、入力ロジック値が入力ポート・レジスタ (レジスタ 0 および 1) の対応ビットにロードされます。入力ポート・レジスタを読み出すと、割り込みはクリアされます。ただし、入力ポート・レジスタを読み出す前に、入力ピンが元のロジック状態に戻ると、割り込みはクリアされず、入力ポート・レジスタの対応するビットには割り込みが開始されたロジック値が保持されます。

たとえば、P04 入力がロジック 0 状態にあり、それからロジック 1 状態に遷移して、再びロジック 0 状態に戻ると、入力ポート 0 レジスタはこの変化を捉えて、割り込みが生成されます (マスクされていない場合)。入力ポート 0 レジスタで読み取りが実行されると、割り込みはクリアされ、それ以降で変化した入力はなかったとみなされ、入力ポート 0 レジスタのビット 4 は「1」を読み出します。入力ポート・レジスタのビット 4 の次の読み出し値は、この時点で「0」になります。

ラッチされていない入力とラッチされた入力の状態が同時に切り替わり、それから元の状態に戻ると、割り込みはアクティブのままとなります。入力レジスタを読み出すと、ラッチされた入力の状態変化のみが反映され、割り込みもクリアされます。入力ラッチ・レジスタがラッチされた構成からラッチされていない構成に変わると、入力のロジック値が元の状態に戻るタイミングで、割り込みはクリアされます。

入力ピンがラッチされた入力からラッチされていない入力に変わると、入力ポート・レジスタからの読み出しには、現在のポート・ロジック・レベルが反映されます。入力ピンがラッチされていない入力からラッチされた入力に変わると、入力レジスタからの読み出しにはラッチされたロジック・レベルが反映されます。

**表 8-9. レジスタ 44 および 45(入力ラッチ・レジスタ)**

| ビット   | L-07 | L-06 | L-05 | L-04 | L-03 | L-02 | L-01 | L-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ビット   | L-17 | L-16 | L-15 | L-14 | L-13 | L-12 | L-11 | L-10 |

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

プルアップ / プルダウン・イネーブル・レジスタを使用すると、GPIO ピンのプルアップ / プルダウン抵抗をイネーブル / ディセーブルにすることができます。ビットをロジック 1 にセットすると、プルアップ / プルダウン抵抗を選択することができます。ビットをロジック 0 にセットすると、GPIO ピンからプルアップ / プルダウン抵抗が切断されます。GPIO ピンを出力として構成すると、抵抗はディセーブルになります。プルアップ / プルダウン選択レジスタを使用すると、プルアップ抵抗またはプルダウン抵抗のいずれかを選択することができます。

**表 8-10. レジスタ 46 および 47 (プルアップ / プルダウン・イネーブル・レジスタ)**

| ビット   | PE-07 | PE-06 | PE-05 | PE-04 | PE-03 | PE-02 | PE-01 | PE-00 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| デフォルト | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| ビット   | PE-17 | PE-16 | PE-15 | PE-14 | PE-13 | PE-12 | PE-11 | PE-10 |

| デフォルト | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

プルアップ / プルダウン選択レジスタを使用すると、それぞれのレジスタ・ビットをプログラムすることにより、各 GPIO のプルアップ抵抗やプルダウン抵抗を構成することができます。ビットをロジック 1 にセットすると、その GPIO ピンに対して 100kΩ のプルアップ抵抗が選択されます。ビットをロジック 0 にセットすると、その GPIO ピンに対して 100kΩ のプルダウン抵抗が選択されます。レジスタ 46 と 47 を使用してプルアップ / プルダウン機能をディセーブルにすると、これらのレジスタに書き込みを行っても GPIO ピンに影響はありません。

**表 8-11. レジスタ 48 および 49 (プルアップ / プルダウン選択レジスタ)**

| ビット   | PUD-07 | PUD-06 | PUD-05 | PUD-04 | PUD-03 | PUD-02 | PUD-01 | PUD-00 |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| デフォルト | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

| ビット   | PUD-17 | PUD-16 | PUD-15 | PUD-14 | PUD-13 | PUD-12 | PUD-11 | PUD-10 |

| デフォルト | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

電源オン時には、割り込みマスク・レジスタはデフォルトのロジック 1 にセットされ、システムの起動時は割り込みはディセーブルになります。割り込みをイネーブルにするには、対応するマスク・ビットをロジック 0 にセットします。

入力状態が変化し、割り込みマスク・レジスタの対応ビットが 1 にセットされると、割り込みはマスクされ、割り込みピンはアサートされません。割り込みマスク・レジスタの対応ビットが 0 にセットされると、割り込みピンがアサートされます。

入力状態が変化し、その結果として割り込みがマスクされると、割り込みマスク・レジスタ・ビットを 0 にセットすることにより、割り込みピンがアサートされます。現時点ですでに割り込みのソースになっている入力の割り込みマスク・ビットが 1 にセットされると、割り込みピンのアサートは解除されます。

**表 8-12. レジスタ 4A および 4B (割り込みマスク・レジスタ)**

| ビット   | M-07 | M-06 | M-05 | M-04 | M-03 | M-02 | M-01 | M-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| ビット   | M-17 | M-16 | M-15 | M-14 | M-13 | M-12 | M-11 | M-10 |

| デフォルト | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

割り込みステータス・レジスタは、割り込みのソースを識別するために使用する読み取り専用レジスタです。読み取り値がロジック 1 の場合、対応する入力ピンは割り込みのソースだったことを示しています。ロジック 0 の場合、入力ピンは割り込みのソースではないことを示しています。割り込みマスク・レジスタの対応ビットが 1 にセットされると (マスクされる)、割り込みステータス・ビットはロジック 0 に戻ります。

**表 8-13. レジスタ 4C および 4D (割り込みステータス・レジスタ)**

| ビット   | S-07 | S-06 | S-05 | S-04 | S-03 | S-02 | S-01 | S-00 |

|-------|------|------|------|------|------|------|------|------|

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ビット   | S-17 | S-16 | S-15 | S-14 | S-13 | S-12 | S-11 | S-10 |

| デフォルト | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

出力ポート構成レジスタは、ポート単位でプッシュプルかオープン・ドレイン入出力段かを選択できます。ロジック 0 にセットすると、I/O をプッシュプルとして構成します (Q1 および Q2 はアクティブになります。図 8-2 を参照)。ロジック 1 にセットすると、I/O をオープン・ドレインとして構成します (Q1 はディセーブル、Q2 はアクティブ)。また、推奨コマンド・シーケンスは、構成レジスタ (06 および 07) でポート・ピンを出力としてセットする前に、このレジスタ (4F) をプログラムすることです。

ODEN0 はポート 0X を構成し、ODEN1 はポート 1X を構成します。

**表 8-14. レジスタ 4F (出力ポート構成レジスタ)**

| ビット   | 予約済み |   |   |   |   |   | ODEN-1 | ODEN-0 |

|-------|------|---|---|---|---|---|--------|--------|

| デフォルト | 0    | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

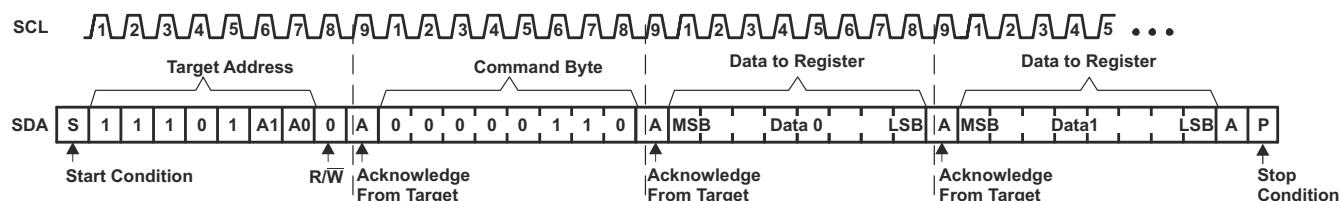

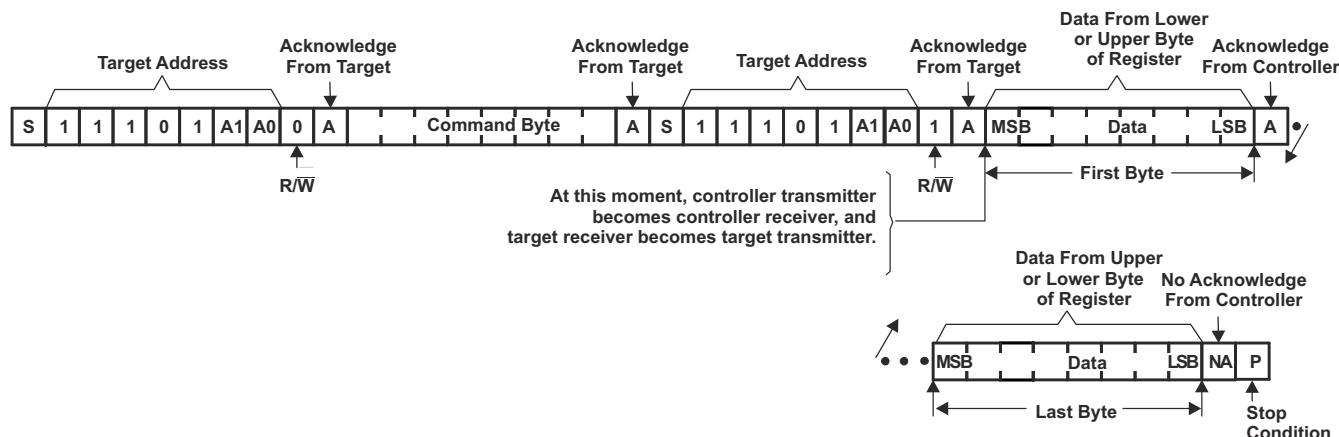

#### 8.6.4 バス・トランザクション

データは、書き込みおよび読み取りコマンドを使用して、コントローラと TCAL9539-Q1 の間で交換されます。

##### 8.6.4.1 書き込み

TCAL9539-Q1 にデータを送信するには、デバイス・アドレスを送信して、最下位ビット (LSB) をロジック 0 にセットします (デバイス・アドレスについては、図 8-7 を参照)。アドレスの後にコマンド・バイトが送信され、コマンド・バイトの後ろのデータを受信するレジスタを指定します。1 回の書き込みで送信されるデータ・バイト数に制限はありません。

TCAL9539-Q1 に内蔵された 22 個のレジスタは、11 組のレジスタ・ペアとして動作するように構成されています。11 組のペアはそれぞれ、Input Port、Output Port、Polarity Inversion、Configuration、Output Drive Strength (2 個の 16 ビット・レジスタ)、Input Latch、Pull-Up/Pull-Down Enable、Pull-Up/Pulldown Selection、Interrupt Mask、Interrupt Status レジスタです。1 つのレジスタにデータが送信されると、その次のデータ・バイトはペアになっているもう片方のレジスタに送信されます (図 8-9 および 図 8-10 を参照)。たとえば、最初のバイトが出力ポート 1 (レジスタ 3) に送信されると、次のバイトは出力ポート 0 (レジスタ 2) に格納されます。

1 回の書き込みで送信されるデータ・バイト数に制限はありません。このように、8 ビットの各レジスタ・ペアは、互いに独立して更新することができます。

**図 8-9. Output Port レジスタへの書き込み**

図 8-10. Configuration レジスタまたは Polarity Inversion レジスタへの書き込み

#### 8.6.4.2 読み取り

バス・コントローラは最初に、ロジック 0 にセットした LSB を付加した TCAL9539-Q1 のアドレスを送信する必要があります (デバイスのアドレスについては 図 8-7 を参照)。アドレスの後に、コマンド・バイトを送信して、アクセスするレジスタを決定します。

再起動後、デバイスのアドレスを再送信しますが、ここでは最下位ビットをロジック 1 にセットします。コマンド・バイトで定義されたレジスタからのデータを TCAL9539-Q1 により送信します (図 8-11 および 図 8-12 を参照)。データは、ACK クロック・パルスの立ち上がりエッジでレジスタに書き込まれます。最初のバイトが読み出された後に、他のバイトを読み出すこともできますが、この時点でデータにはペアになっているもう片方のレジスタの情報が反映されています。たとえば、入力ポート 1 が読み出されると、次に読み出されるバイトは入力ポート 0 になります。1 回の読み出し転送で受信するデータ・バイト数に制限はありませんが、バス・コントローラは最後に受信したバイトのデータに応答確認を返しません。続いて、再起動した後に、コマンド・バイトにペアで読み出す次のレジスタの値を入れます。たとえば、再起動の前に最後に入力ポート 1 を読み出した場合、再起動後に読み出されるレジスタは入力ポート 0 になります。

図 8-11. レジスタからの読み取り

- A. データの転送は、STOP 条件によりいつでも停止できます。このとき、最新のアノリッジ・フェーズに存在するデータが有効になります(出力モード)。これは、コマンド・バイトがここまで時点での 00(入力ポート・レジスタの読み取り)に設定されているものと想定しています。

- B. この図では、コマンド・バイト転送、再起動、および最初のターゲット・アドレス呼び出しと P ポートから転送される実データとの間のターゲット・アドレス呼び出しが除去されています(図 8-11 を参照)。

図 8-12. 入力ポート・レジスタの読み取り

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

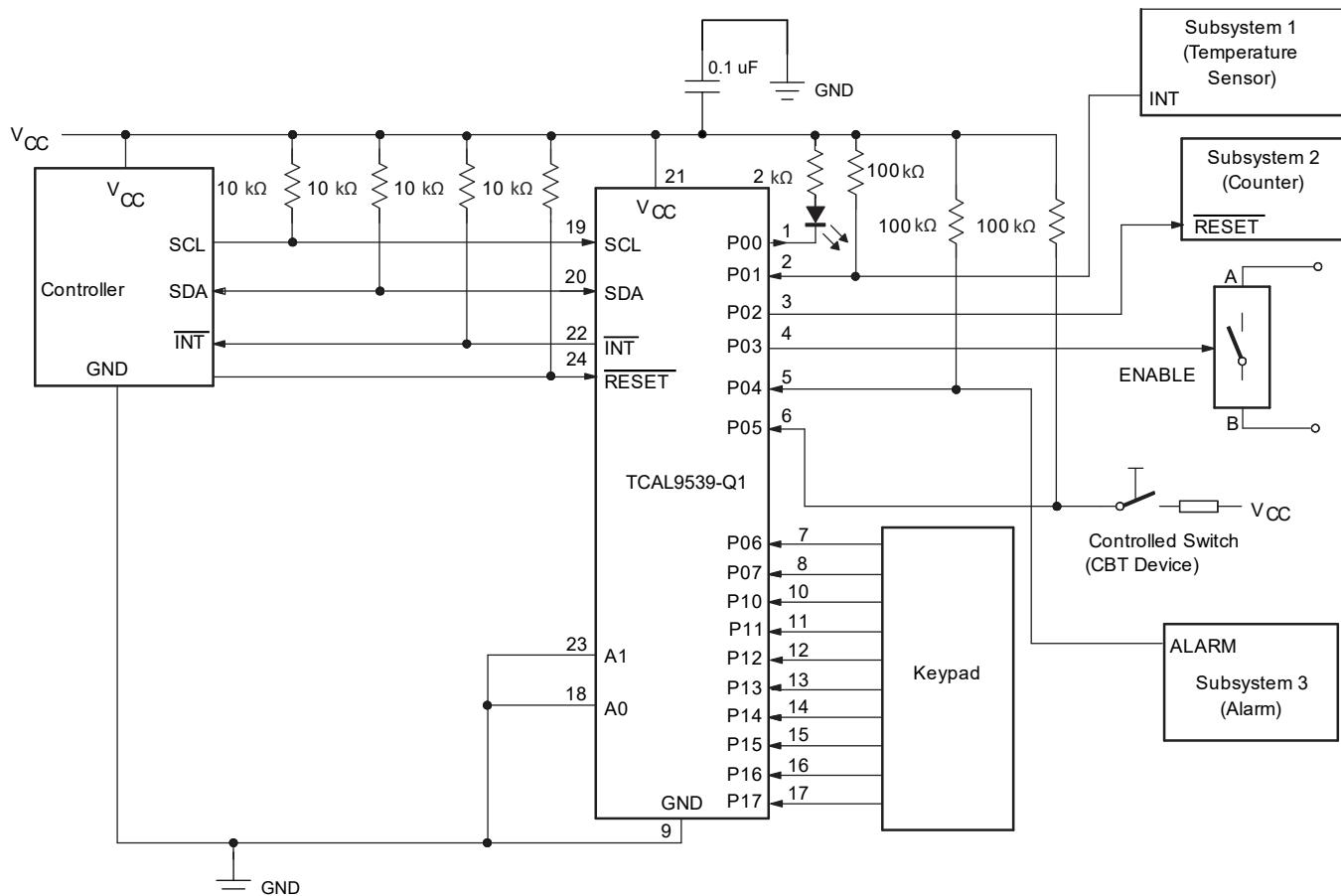

### 9.1 アプリケーション情報

TCAL9539-Q1 のアプリケーションでは、このデバイスを I<sup>2</sup>C コントローラ（プロセッサ）のターゲットとして接続し、I<sup>2</sup>C バスには他の任意の数のターゲット・デバイスを含めることができます。TCAL9539-Q1 はコントローラから離れた場所で、コントローラが監視または制御する必要のある GPIO の近くに配置されます。

### 9.2 代表的なアプリケーション

図 9-1 に、TCAL9539-Q1 を使用可能なアプリケーションを示します。

- A. この例では、デバイス・アドレスを 1110100 に設定しています。

- B. P00、P02、P03 は出力として構成されています。

- C. P01 および P04～P017 は入力として構成されています。

- D. フローティングになる可能性のある (P ポート上の) 入力には抵抗が必要です。ドライバにより入力がフローティングにならないのであれば、抵抗は不要です。出力 (P ポート内) にプルアップ抵抗は不要です。

図 9-1. 代表的なアプリケーション回路図

## 9.2.1 設計要件

表 9-1. 設計パラメータ

| 設計パラメータ                       | 値の例  |

|-------------------------------|------|

| 電源電圧 ( $V_{CC}$ )             | 1.8V |

| 出力電流定格、P ポート・シンク ( $I_{OL}$ ) | 25mA |

| 出力電流定格、P ポート・ソース ( $I_{OH}$ ) | 10mA |

| $I^2C$ バス・クロック (SCL) 速度       | 1MHz |

## 9.2.2 詳細な設計手順

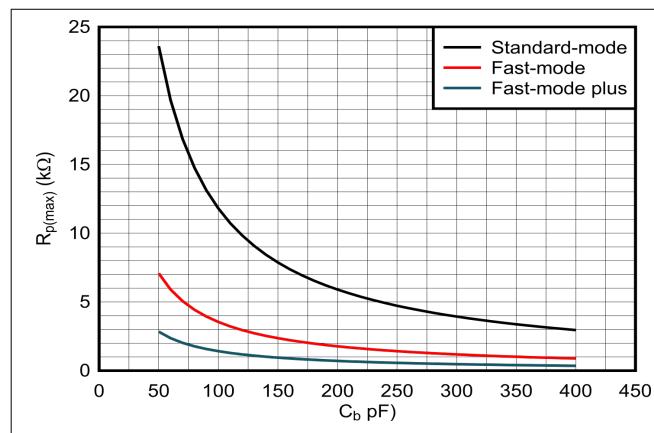

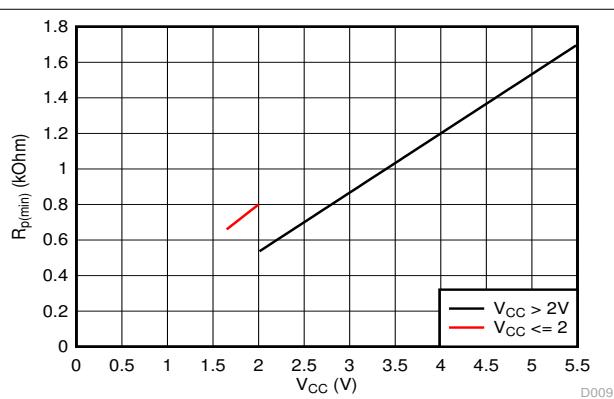

SCL および SDA ラインのプルアップ抵抗  $R_P$  は、 $I^2C$  バス上のすべてのターゲットの合計容量を考慮して、適切に選択する必要があります。最小プルアップ抵抗は、次のように  $V_{CC}$ 、 $V_{OL(max)}$ 、 $I_{OL}$  の関数です。

$$R_{P(min)} = \frac{V_{CC} - V_{OL(max)}}{I_{OL}} \quad (1)$$

最大プルアップ抵抗は、次のように最大立ち上がり時間  $t_r$  (ファスト・モード・プラス動作時は 120ns、 $f_{SCL} = 1\text{MHz}$ ) とバス容量  $C_b$  の関数です。

$$R_{P(max)} = \frac{t_r}{0.8473 \times C_b} \quad (2)$$

$I^2C$  バスの最大バス容量は、スタンダード・モードまたはファスト・モード動作で 400pF、またはファスト・モード・プラスで 550pF を超えないようにする必要があります。バス容量は、TCAL9539-Q1 の容量、SCL 用の  $C_i$  または SDA 用の  $C_{io}$ 、配線 / 接続 / パターンの容量、バス上の追加ターゲットの容量を追加することで近似値を求めることができます。

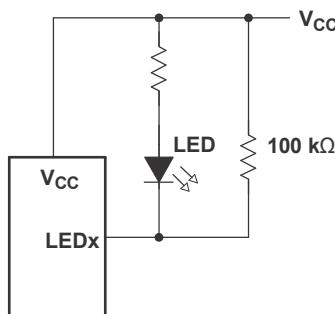

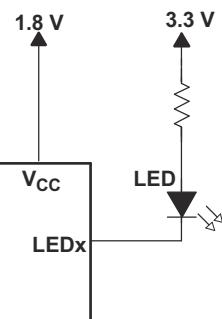

### 9.2.2.1 I/O で LED を制御する場合の $I_{CC}$ 最小化

I/O を使用して LED を制御する場合、通常は 図 9-2 に示すように抵抗を介して  $V_{CC}$  に接続します。P ポートが入力として構成されている場合、 $V_I$  が  $V_{CC}$  より小さくなるにつれて消費電流は大きくなります。LED はスレッショルド電圧  $V_T$  のダイオードです。P ポートが入力として構成されている場合、LED はオフになりますが、 $V_I$  は  $V_{CC}$  以下に降下する  $V_T$  です。

バッテリ駆動のアプリケーションでは、P ポートが入力として構成され消費電流が最小限に抑えられている場合、LED を制御する P ポートの電圧は  $V_{CC}$  と同じかそれ以上にする必要があります。図 9-2 に、LED と並列に設置した値の大きな抵抗を示します。図 9-3 に、少なくとも  $V_T$  によって、LED 供給電圧より小さくなる  $V_{CC}$  を示します。この方法はどちらも、I/O の  $V_I$  を  $V_{CC}$  と同じかそれ以上に維持するため、P ポートが入力として構成され LED がオフになった場合でも、消費電流の増加を防ぎます。

図 9-2. LED と並列に設置した値の大きな抵抗

図 9-3. 低電圧で供給されるデバイス

### 9.2.3 アプリケーション曲線

標準モード:  $f_{SCL} = 100\text{kHz}$ ,  $t_r = 1\mu\text{s}$

高速モード:  $f_{SCL} = 400\text{kHz}$ ,  $t_r = 300\text{ns}$

図 9-4. 最大プルアップ抵抗 ( $R_{p(\max)}$ ) とバス容量 ( $C_b$ ) との関係

$V_{OL} = 0.2 \times V_{CC}$ ,  $I_{OL} = 2\text{mA}$  ( $V_{CC} \leq 2\text{V}$  の場合)

$V_{OL} = 0.4\text{V}$ ,  $I_{OL} = 3\text{mA}$  ( $V_{CC} > 2\text{V}$ )

図 9-5. 最小プルアップ抵抗 ( $R_{p(\min)}$ ) とプルアップ基準電圧 ( $V_{CC}$ )

## 9.3 電源に関する推奨事項

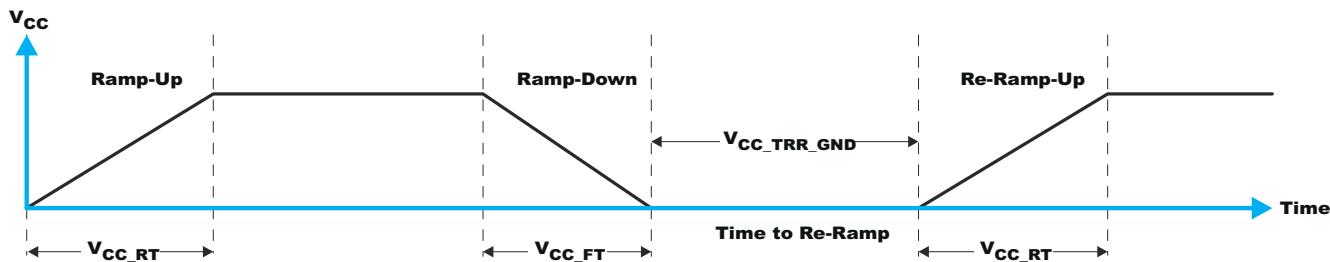

### 9.3.1 パワーオン・リセットの要件

グリッチやデータ破損が発生した場合、パワーオン・リセット機能を使用して TCAL9539-Q1 をデフォルト状態にリセットできます。パワーオン・リセットを実行するには、デバイスを完全にリセットするためにパワー・サイクルを完了させる必要があります。このリセットは、アプリケーションでデバイスの電源を初めてオンにしたときにも発生します。

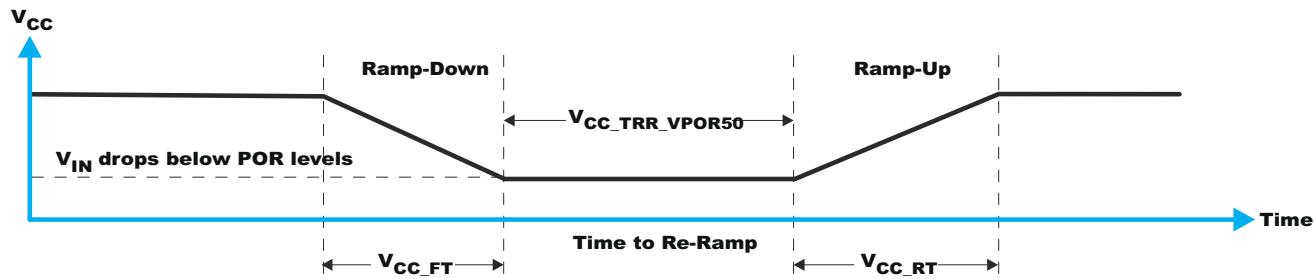

図 9-6 および 図 9-7 に、2 種類のパワーオン・リセットを示します。

図 9-6.  $V$  は 0.2V を下回るまで低下するか、または 0V になり、その後増加します

図 9-7.  $V$  は POR スレッショルドを下回るまで低下し、その後上昇して戻ります

表 9-2 に、両方のタイプのパワーオン・リセットについて、TCAL9539-Q1 のパワーオン・リセット機能の性能を規定します。

**表 9-2. 推奨される電源シーケンシングとランプ・レート**

| パラメータ <sup>(1) (2)</sup> |                                                     | 最小値       | 標準値 | 最大値  | 単位 |

|--------------------------|-----------------------------------------------------|-----------|-----|------|----|

| $t_{FT}$                 | 立ち下がりレート                                            | 図 9-6 を参照 | 0.1 | 2000 | ms |

| $t_{RT}$                 | 立ち上がりレート                                            | 図 9-6 を参照 | 0.1 | 2000 | ms |

| $t_{TRR\_GND}$           | 再ランプ時間 ( $V_{CC}$ が GND まで低下する場合)                   | 図 9-6 を参照 | 1   |      | μs |

| $t_{TRR\_POR50}$         | 再ランプ時間 ( $V_{CC}$ が $V_{POR\_MIN} - 50mV$ まで低下する場合) | 図 9-7 を参照 | 1   |      | μs |

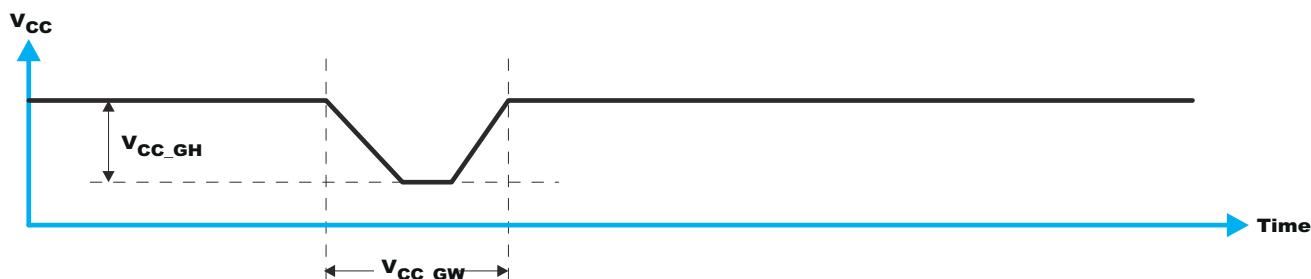

| $V_{CC\_GH}$             | $V$ にグリッチが発生することはあるが、 $V = 1\mu s$ のときに機能が途絶しないレベル  | 図 9-8 を参照 |     | 1.0  | V  |

| $t_{GW}$                 | $V = 0.5 \times V_{CCx}$ のときに、機能が途絶しないグリッチ幅         | 図 9-8 を参照 |     | 10   | μs |

| $V_{PORF}$               | $V_{CC}$ 立ち下がり時の POR の電圧トリップ・ポイント                   |           | 0.6 |      | V  |

| $V_{PORR}$               | $V_{CC}$ 立ち上がり時の POR の電圧トリップ・ポイント                   |           |     | 1.0  | V  |

(1)  $T_A = 25^\circ C$  (特に記述のない限り)。

(2) 未テスト。設計により規定されています。

電源のグリッチは、このデバイスのパワーオン・リセット性能にも影響を及ぼす可能性があります。グリッチ幅 ( $V_{CC\_GW}$ ) と高さ ( $V_{CC\_GH}$ ) は互いに依存します。バイパス容量、ソース・インピーダンス、デバイス・インピーダンスは、パワーオン・リセット性能に影響を及ぼす要因です。これらの仕様を測定する方法の詳細については、図 9-8 と 表 9-2 を参照してください。

**図 9-8. グリッチ幅とグリッチ高さ**

$V_{POR}$  は、パワーオン・リセットに不可欠です。 $V_{POR}$  は、リセット条件が解放され、すべてのレジスタと I<sup>2</sup>C/SMBus ステータス・マシンがデフォルト状態に初期化される電圧レベルです。 $V_{POR}$  の値は、0 に低下するか、または 0 から低下した  $V$  に応じて変わります。図 9-9 と 表 9-2 で、この仕様の詳細について説明します。

图 9-9.  $V_{POR}$

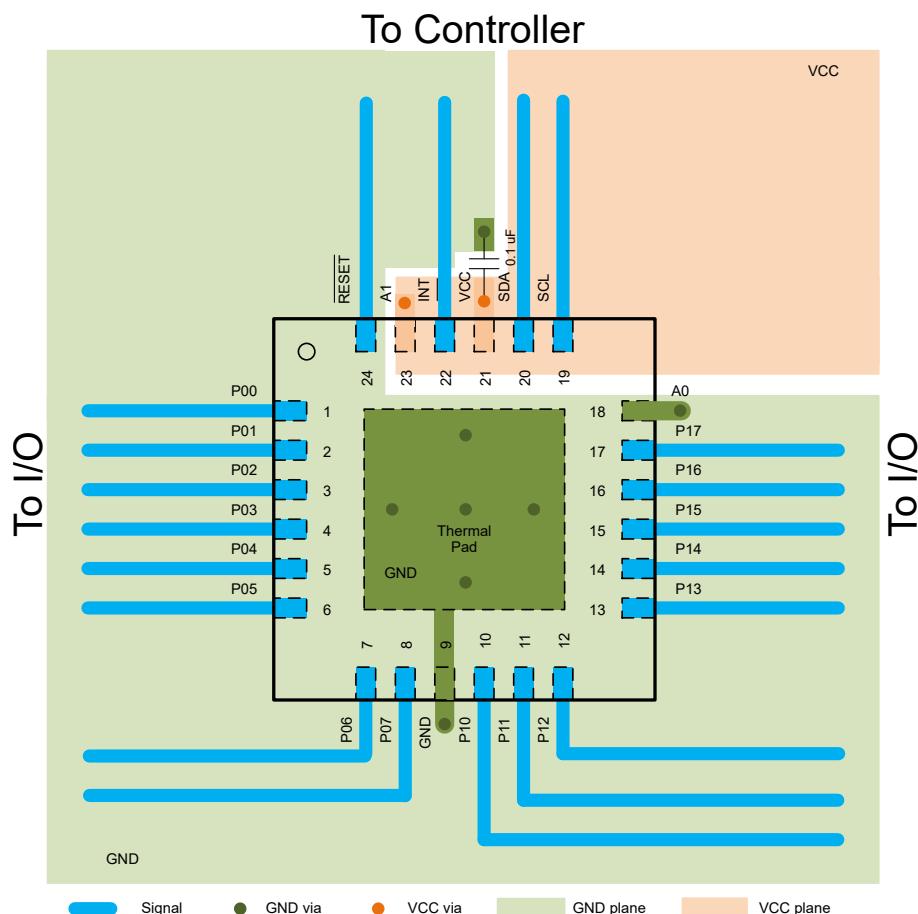

## 9.4 レイアウト

### 9.4.1 レイアウトのガイドライン

TCAL9539-Q1 のプリント回路基板 (PCB) レイアウトでは、一般的な PCB レイアウトの慣例に従う必要がありますが、適合したインピーダンスや差動ペアなどの高速データ転送は、I<sup>2</sup>C 信号速度では大きな問題にはなりません。

すべての PCB レイアウトにおける最善策は、信号トレースで適切な角度を回避すること、集積回路 (IC) の近接部を離れるときに信号トレースが互いに離れていくように配置すること、トレース幅を太くして電源とグランドのトレースを通常時に大容量の電流が流れるようにすることです。バイパス・コンデンサとデカップリング・コンデンサは、一般的に電源ピンの電圧の制御に使用されます。大容量コンデンサを使用すると、電源グリッチの短絡時に追加電力を供給し、容量の小さいコンデンサは高周波リップルの除去を行うことができます。これらのコンデンサは、できる限り TCAL9539-Q1 の近くに配置してください。理想的な配置を [セクション 9.4.2](#) に示します。

[セクション 9.4.2](#) に示すレイアウト例では、信号配線に最上層を使用し、電源とグランド (GND) に分割プレーンとして最下層を使用することで、2 層のみの PCB を製造することができます。ただし、信号配線密度の高い基板では、4 層基板が推奨されます。一般的に 4 層 PCB では、信号を最上層と最下層に配線し、内部の 1 層をグランド・プレーン専用にして、もう 1 つの内部層を電源プレーン専用にします。電源とグランドにプレーンまたは分割プレーンを使用する基板レイアウトの場合は、電源または GND に接続する必要がある表面実装部品パッドのすぐ隣にビアを配置し、ビアを内部層または基板の反対側に電気的に接続します。ビアは、信号パターンを基板の反対側に配線する必要がある場合にも使用されますが、この方法は [セクション 9.4.2](#) には示されていません。

### 9.4.2 レイアウト例

図 9-10. TCAL9539-Q1 のレイアウト

## 10 デバイスおよびドキュメントのサポート

### 10.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.2 サポート・リソース

[TI E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。[TI の使用条件](#)を参照してください。

### 10.3 商標

[TI E2E™ is a trademark of Texas Instruments.](#)

すべての商標は、それぞれの所有者に帰属します。

### 10.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.5 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TCAL9539RTWRQ1        | Active        | Production           | WQFN (RTW)   24 | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TCAL<br>9539Q1      |

| TCAL9539RTWRQ1.A      | Active        | Production           | WQFN (RTW)   24 | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TCAL<br>9539Q1      |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TCAL9539-Q1 :**

- Catalog : [TCAL9539](#)

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月