**TCA6408A** JAJSPM2E - APRIL 2009 - REVISED JANUARY 2023

# TCA6408A 割り込み出力、リセット、構成レジスタ内蔵の低電圧 8 ビット I<sup>2</sup>C/ SMBus I/O エクスパンダ

## 1 特長

- I2C からパラレル・ポートへのエクスパンダ

- 1.65V~5.5V の動作電源電圧範囲

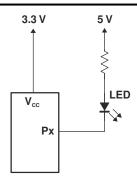

- 双方向電圧レベル変換と、1.8V、2.5V、3.3V、5V の I<sup>2</sup>C バスおよび P ポート間での GPIO 拡張が可能

- 低いスタンバイ消費電流:1µA

- 5V 許容の I/O ポート

- 400kHz の高速 I<sup>2</sup>C バス

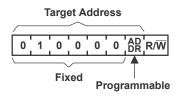

- ハードウェア・アドレス・ピンにより、同じ I<sup>2</sup>C/SMBus バ ス上に 2 つの TCA6408A デバイスを接続可能

- アクティブ LOW のリセット (RESET) 入力

- オープンドレインのアクティブ LOW 割り込み (INT) 出

- 入力 / 出力構成レジスタ

- 極性反転レジスタ

- パワーオン・リセット内蔵

- 電源投入時はすべてのチャネルが入力に構成された 状態

- 電源オン時のグリッチなし

- SCL/SDA 入力のノイズ・フィルタ

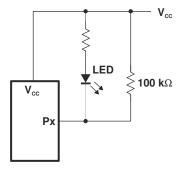

- 大電流の最大駆動能力を持つラッチ付き出力により LED を直接駆動

- JESD 78、Class II 準拠で 100mA 超のラッチアップ

- シュミット・トリガ動作により低速入力遷移が実現され、 SCL および SDA 入力でのスイッチング・ノイズ耐性が 向上

- JESD 22 を超える ESD 保護

- 2000V、人体モデル (A114-A)

- 1000V、デバイス帯電モデル (C101)

## 2 アプリケーション

- サーバー

- ルーター (テレコム・スイッチング機器)

- パーソナル・コンピュータ

- パーソナル・エレクトロニクス (ゲーム機)

- 産業用オートメーション

- GPIO が制限されたプロセッサを使用する製品

## 3 概要

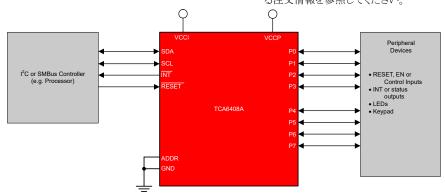

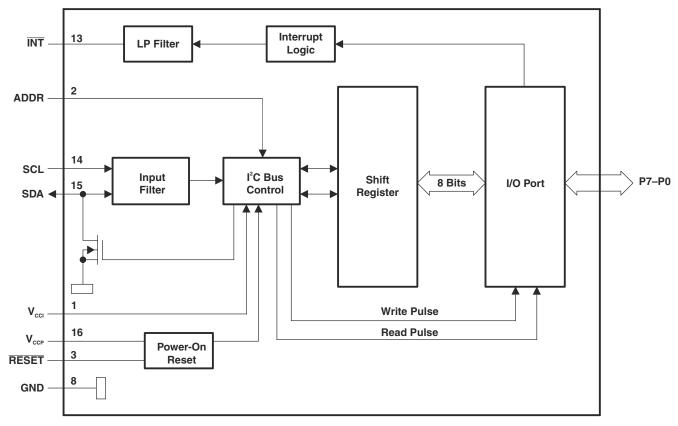

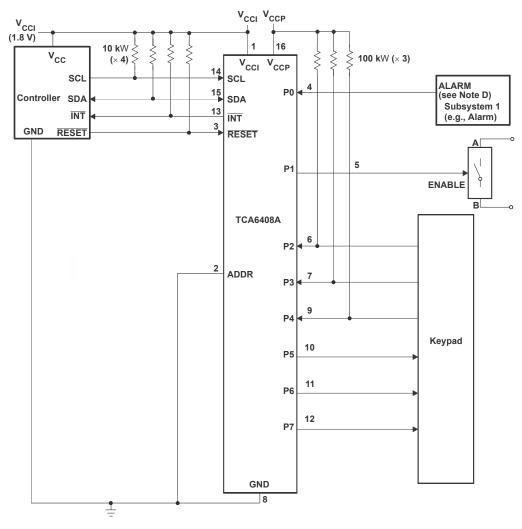

TCA6408A は 16 ピン・デバイスで、2 ライン双方向 I<sup>2</sup>C バス (または SMBus) プロトコル用に 8 ビットの汎用パラ レル入出力 (I/O) 拡張機能を提供します。このデバイス は、I<sup>2</sup>C バス側 (V<sub>CCI</sub>) と P ポート側 (V<sub>CCP</sub>) の両方とも 1.65V~5.5V の電源電圧で動作できます。このため、 TCA6408A は SDA/SCL 側で、消費電力削減のため電 源電圧レベルが引き下げられる次世代のマイクロプロセッ サおよびマイクロコントローラと接続できます。マイクロプロ セッサおよびマイクロコントローラの電源供給は低下します が、LED など PCB の部品には引き続き 5V の電源が供 給されます。

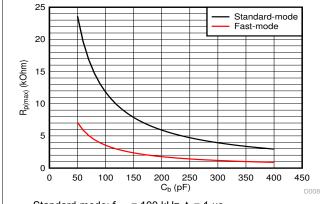

このデバイスは、100kHz (標準モード) と 400kHz (高速 モード)の両方のクロック周波数をサポートしています。 TCA6408A をはじめとする I/O エクスパンダは、スイッチ、 センサ、押しボタン、LED、ファンなどに I/O を追加する必 要がある場合の簡単なソリューションとなります。

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|----------|----------------------|-----------------|

|          | TSSOP (16)           | 5.00mm × 4.40mm |

| TCA6408A | VQFN (16)            | 3.00mm × 3.00mm |

|          | UQFN (16)            | 2.60mm × 1.80mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

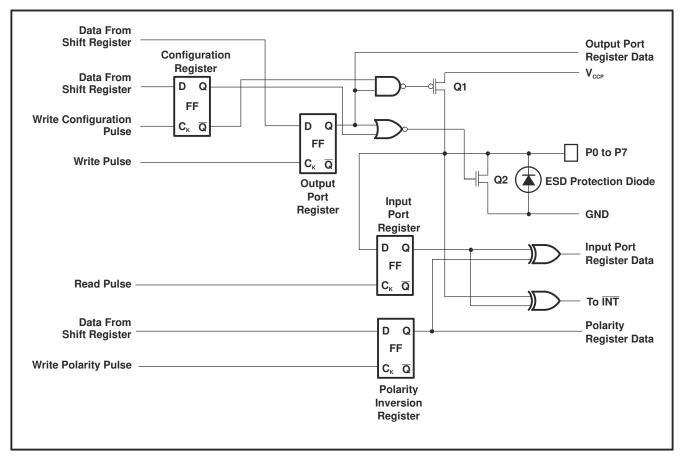

簡略回路図

### **Table of Contents**

|                                                                                      | CCP" to Power-On Reset Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Changes from Revision D (July 2015) to Revie  • I <sup>2</sup> C に言及している場合、すべての旧式の用語 | Sion E (January 2023)<br>をコントローラおよびターゲットに変更                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page<br>1 |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Dage      |

| 資料番号末尾の英字は改訂を表しています。その改                                                              | <b>女訂履歴は英語版に準じています。</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

| 4 Revision History                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 8.2 Functional Block Diagrams                                                        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

| 8.1 Overview                                                                         | 1 <b>2.0</b> / 13 pt = <b>12.0</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34        |

| 8 Detailed Description                                                               | M = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 100 = 10 | 34        |

| 7 Parameter Measurement Information                                                  | 13   12.3 商標                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34        |

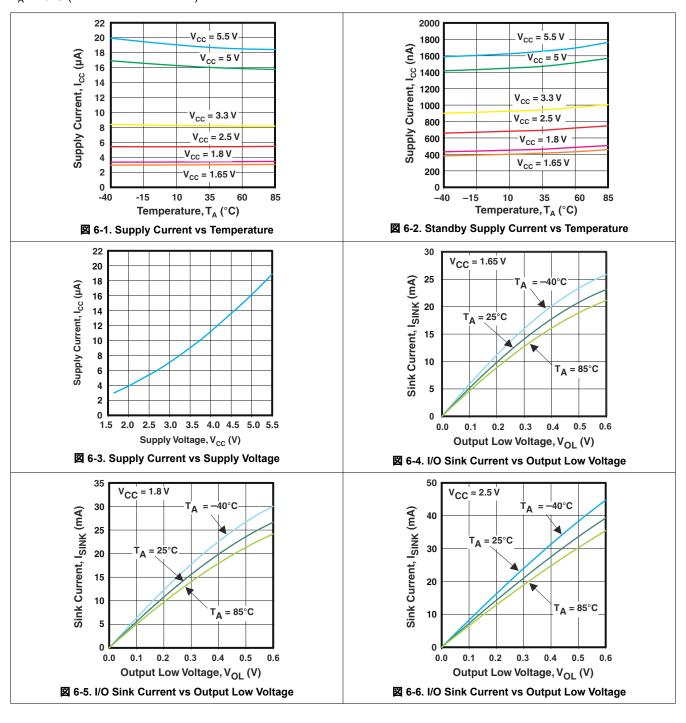

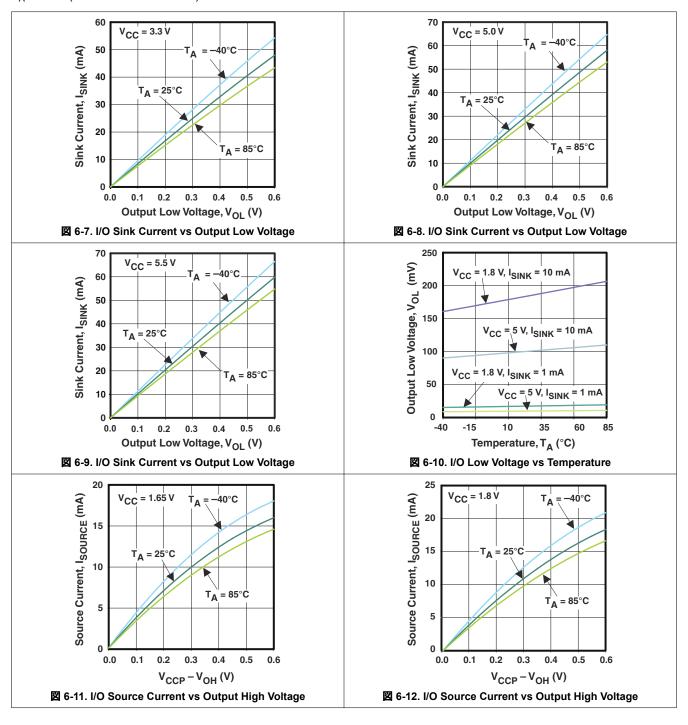

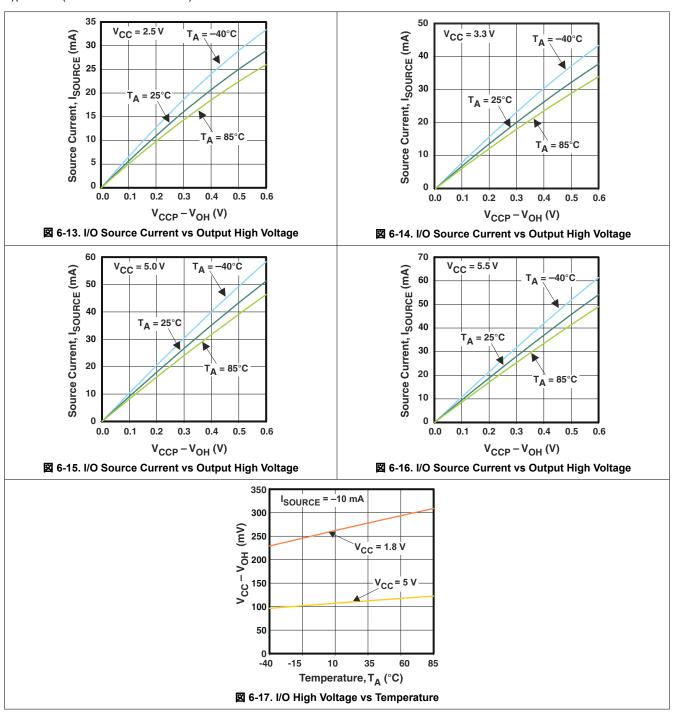

| 6.9 Typical Characteristics                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34        |

| 6.8 Switching Characteristics                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 6.6 I <sup>2</sup> C Interface Timing Requirements                                   | 400 1 10 441 0 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34        |

| 6.5 Electrical Characteristics                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33        |

| 6.4 Thermal Information                                                              | 44 4 1 1 0 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33        |

| 6.3 Recommended Operating Conditions                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 6.2 ESD Ratings                                                                      | 5 10 Power Supply Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

| 6.1 Absolute Maximum Ratings                                                         | 5 9.2 Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| 6 Specifications                                                                     | 9.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27        |

| 5 Pin Configuration and Functions                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 3 概要4 Revision History                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 2 アプリケーション                                                                           | 0.5 D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

| 1 特長                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

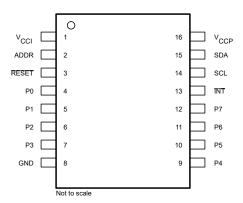

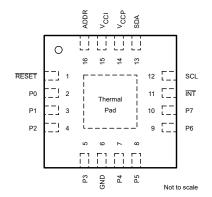

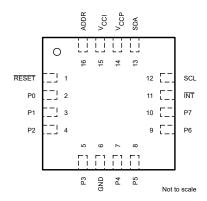

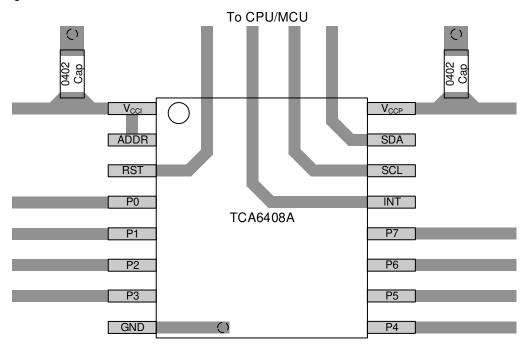

# **5 Pin Configuration and Functions**

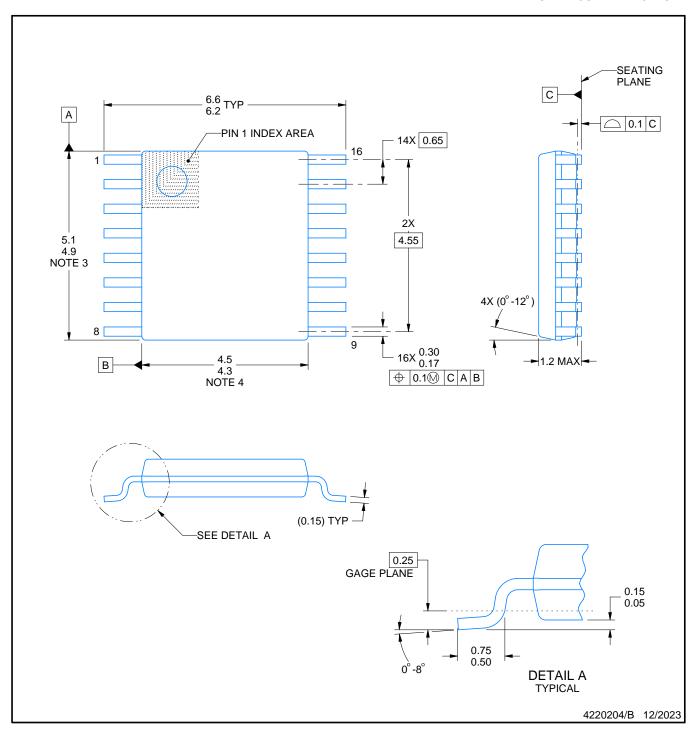

図 5-1. PW Package, 16-Pin TSSOP (Top View)

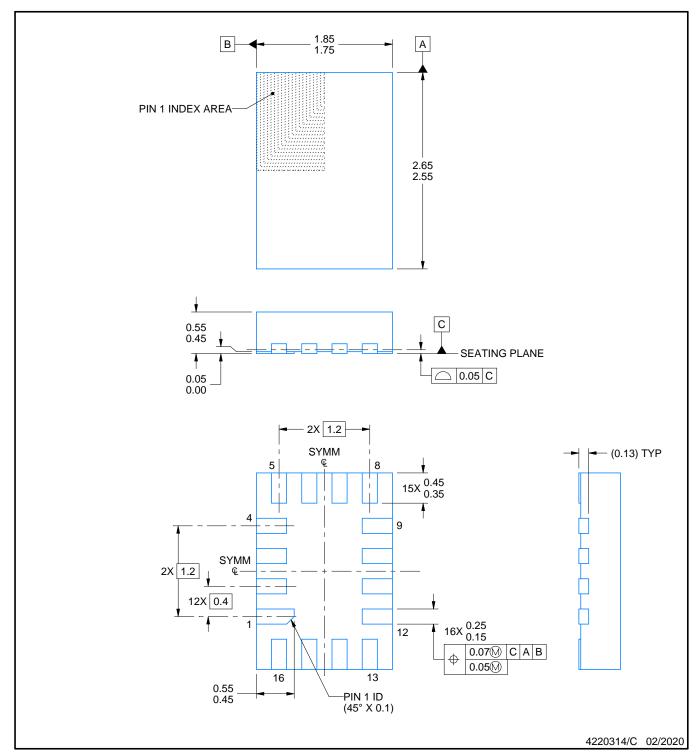

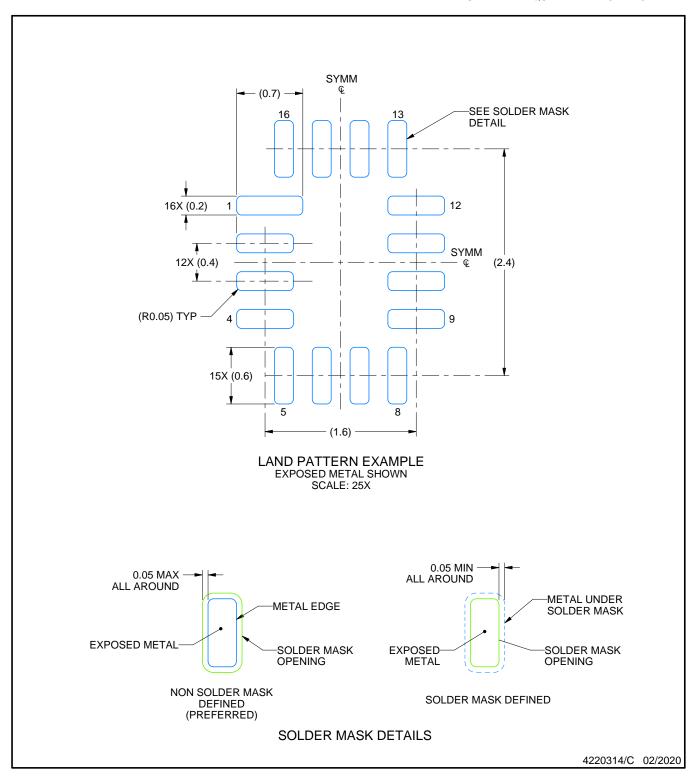

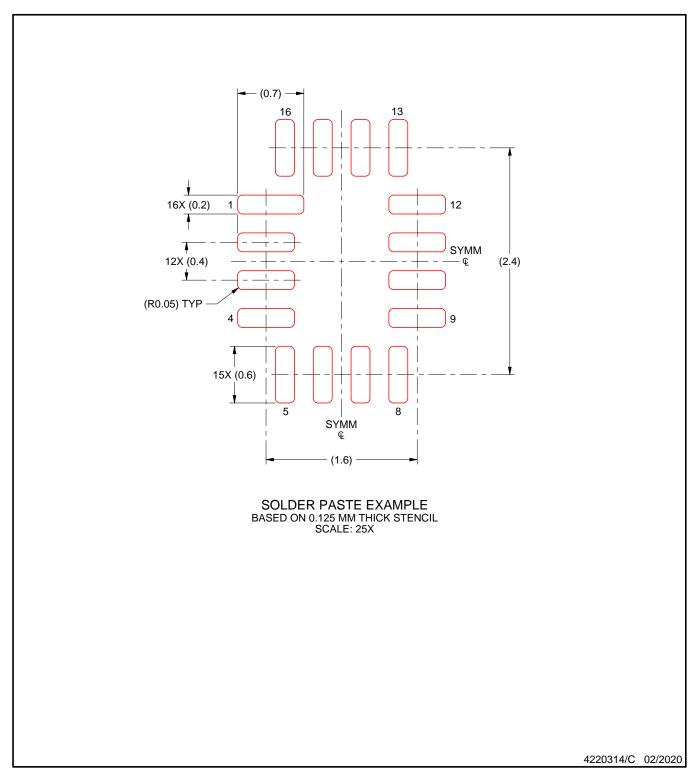

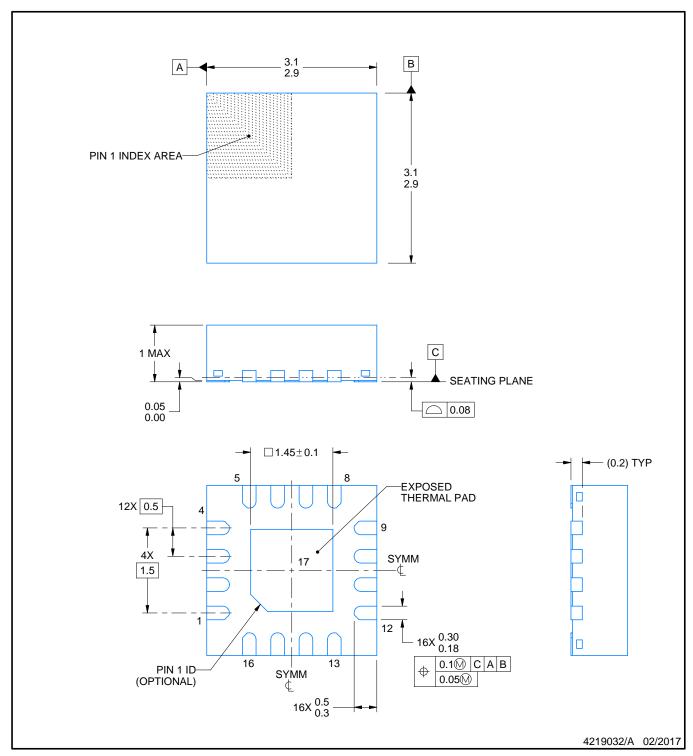

図 5-2. RGT Package, 16-Pin VQFN (Top View)

図 5-3. RSV Package, 16-Pin UQFN (Top View)

表 5-1. Pin Functions

|      | PIN   |            | DESCRIPTION                                                                                     |

|------|-------|------------|-------------------------------------------------------------------------------------------------|

| NAME | TSSOP | UQFN, VQFN | DESCRIPTION                                                                                     |

| ADDR | 2     | 16         | Address input. Connect directly to V <sub>CCP</sub> or ground.                                  |

| GND  | 8     | 6          | Ground                                                                                          |

| INT  | 13    | 11         | Interrupt output. Connect to V <sub>CCI</sub> through a pull-up resistor.                       |

| P0   | 4     | 2          | P-port input/output (push-pull design structure). At power on, P0 is configured as an input.    |

| P1   | 5     | 3          | P-port input/output (push-pull design structure). At power on, P1 is configured as an input.    |

| P2   | 6     | 4          | P-port input/output (push-pull design structure). At power on, P2 is configured as an input.    |

| P3   | 7     | 5          | P-port input/output (push-pull design structure). At power on, P3 is configured as an input.    |

| P4   | 9     | 7          | P-port input/output (push-pull design structure).<br>At power on, P4 is configured as an input. |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# 表 5-1. Pin Functions (continued)

|                  | PIN   |            | DESCRIPTION                                                                                                                           |  |  |  |

|------------------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME             | TSSOP | UQFN, VQFN | DESCRIPTION                                                                                                                           |  |  |  |

| P5               | 10    | 8          | P-port input/output (push-pull design structure). At power on, P5 is configured as an input.                                          |  |  |  |

| P6               | 11    | 9          | P-port input/output (push-pull design structure). At power on, P6 is configured as an input.                                          |  |  |  |

| P7               | 12    | 10         | P-port input/output (push-pull design structure). At power on, P7 is configured as an input.                                          |  |  |  |

| RESET            | 3     | 1          | Active-low reset input. Connect to V <sub>CCI</sub> through a pull-up resistor, if no active connection is used.                      |  |  |  |

| SCL              | 14    | 12         | Serial clock bus. Connect to V <sub>CCI</sub> through a pull-up resistor.                                                             |  |  |  |

| SDA              | 15    | 13         | Serial data bus. Connect to V <sub>CCI</sub> through a pull-up resistor.                                                              |  |  |  |

| V <sub>CCI</sub> | 1     | 15         | Supply voltage of $I^2C$ bus. Connect directly to the $V_{CC}$ of the external $I^2C$ controller. Provides voltage level translation. |  |  |  |

| V <sub>CCP</sub> | 16    | 14         | Supply voltage of TCA6408A for P-ports                                                                                                |  |  |  |

# **6 Specifications**

### **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (see (1))

|                  |                                             | ·                             |                              | MIN  | MAX | UNIT |

|------------------|---------------------------------------------|-------------------------------|------------------------------|------|-----|------|

| V <sub>CCI</sub> | Supply voltage for I <sup>2</sup> C pins    |                               |                              | -0.5 | 6.5 | V    |

| V <sub>CCP</sub> | Supply voltage for P-ports                  | pply voltage for P-ports      |                              |      |     | V    |

| VI               | Input voltage <sup>(2)</sup>                |                               |                              | -0.5 | 6.5 | V    |

| Vo               | Output voltage <sup>(2)</sup>               | Output voltage <sup>(2)</sup> |                              |      |     | V    |

| I <sub>IK</sub>  | Input clamp current                         | ADDR, RESET, SCL              | V <sub>I</sub> < 0           |      | ±20 | mA   |

| I <sub>OK</sub>  | Output clamp current                        | INT                           | V <sub>O</sub> < 0           |      | ±20 | mA   |

| ı                | Input/output alama aurrant                  | P-port                        | $V_O < 0$ or $V_O > V_{CCP}$ |      | ±20 | mA   |

| I <sub>IOK</sub> | Input/output clamp current                  | SDA                           | $V_O < 0$ or $V_O > V_{CCI}$ |      | ±20 | IIIA |

|                  | Continuous output low current               | P-port                        | $V_O = 0$ to $V_{CCP}$       |      | 50  | A    |

| I <sub>OL</sub>  | Continuous output low current               | SDA, ĪNT                      | $V_O = 0$ to $V_{CCI}$       |      | 25  | mA   |

| I <sub>OH</sub>  | Continuous output high current              | P-port                        | $V_O = 0$ to $V_{CCP}$       |      | 50  | mA   |

|                  | Continuous current through GND              |                               |                              |      | 200 |      |

| I <sub>CC</sub>  | Continuous current through V <sub>CCP</sub> |                               |                              |      | 160 | mA   |

|                  | Continuous current through V <sub>CCI</sub> |                               | 10                           |      |     |      |

| T <sub>stg</sub> | Storage temperature                         |                               |                              | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under セクション 6.3. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                                                                   |                                                                                | VALUE | UNIT |

|--------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

|                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                                          |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                           | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

|                  |                                          |                 | MIN                    | MAX                    | UNIT |

|------------------|------------------------------------------|-----------------|------------------------|------------------------|------|

| V <sub>CCI</sub> | Supply voltage for I <sup>2</sup> C pins |                 | 1.65                   | 5.5                    | V    |

| V <sub>CCP</sub> | Supply voltage for P-ports               |                 | 1.65                   | 5.5                    |      |

|                  |                                          | SCL, SDA        | 0.7 × V <sub>CCI</sub> | V <sub>CCI</sub>       |      |

| V <sub>IH</sub>  | High-level input voltage                 | RESET           | 0.7 × V <sub>CCI</sub> | 5.5                    | V    |

|                  |                                          | ADDR, P7-P0     | 0.7 × V <sub>CCP</sub> | 5.5                    |      |

|                  | Law level input valtage                  | SCL, SDA, RESET | -0.5                   | 0.3 × V <sub>CCI</sub> | V    |

| V <sub>IL</sub>  | Low-level input voltage                  | ADDR, P7-P0     | -0.5                   | 0.3 × V <sub>CCP</sub> | V    |

| I <sub>OH</sub>  | High-level output current                | P7-P0           |                        | 10                     | mA   |

| I <sub>OL</sub>  | Low-level output current                 | P7-P0           |                        | 25                     | mA   |

| T <sub>A</sub>   | Operating free-air temperature           |                 | -40                    | 85                     | °C   |

<sup>(2)</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.4 Thermal Information**

|                        |                                              |            | TCA6408A   |            |      |  |  |

|------------------------|----------------------------------------------|------------|------------|------------|------|--|--|

|                        | THERMAL METRIC(1)                            | PW (TSSOP) | RGT (VQFN) | RSV (UQFN) | UNIT |  |  |

|                        |                                              | 16 PINS    | 16 PINS    | 16 PINS    |      |  |  |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 122        | 65.5       | 127.7      | °C/W |  |  |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 56.4       | 92.1       | 62.3       | °C/W |  |  |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 67.1       | 40.0       | 48.4       | °C/W |  |  |

| ΨЈТ                    | Junction-to-top characterization parameter   | 10.8       | 6.9        | 2.5        | °C/W |  |  |

| ΨЈВ                    | Junction-to-board characterization parameter | 66.5       | 21.3       | 48.6       | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

over recommended operating free-air temperature range, V<sub>CCI</sub> = 1.65 V to 5.5 V (unless otherwise noted)

|                                                           | PARAMETER                  |                            | TEST CONDITIONS                                                                   | V <sub>CCP</sub>  | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|-----------------------------------------------------------|----------------------------|----------------------------|-----------------------------------------------------------------------------------|-------------------|------|--------------------|------|------|

| V <sub>IK</sub>                                           | Input diode c              | lamp voltage               | I <sub>I</sub> = -18 mA                                                           | 1.65 V to 5.5 V   | -1.2 |                    |      | V    |

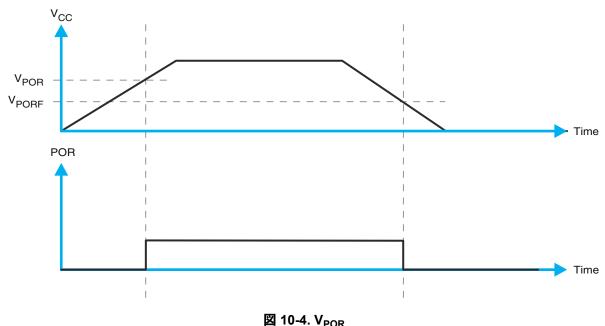

| V <sub>POR</sub>                                          | Power-on res               | set voltage <sup>(2)</sup> | V <sub>I</sub> = V <sub>CCP</sub> or GND, I <sub>O</sub> = 0                      | 1.65 V to 5.5 V   |      | 1                  | 1.4  | V    |

|                                                           |                            |                            |                                                                                   | 1.65 V            | 1.2  |                    |      |      |

|                                                           |                            |                            |                                                                                   | 2.3 V             | 1.8  |                    |      |      |

| Vou                                                       |                            |                            | $I_{OH} = -8 \text{ mA}$                                                          | 3 V               | 2.6  |                    |      |      |

|                                                           | P-port high-le             | evel output                |                                                                                   | 4.5 V             | 4.1  |                    |      | .,   |

| $V_{OH}$                                                  | voltage                    | ·                          |                                                                                   | 1.65 V            | 1.1  |                    |      | V    |

|                                                           |                            |                            | 10 1                                                                              | 2.3 V             | 1.7  |                    |      |      |

|                                                           |                            |                            | I <sub>OH</sub> = -10 mA                                                          | 3 V               | 2.5  |                    |      |      |

|                                                           |                            |                            |                                                                                   | 4.5 V             | 4.0  |                    |      |      |

|                                                           |                            |                            |                                                                                   | 1.65 V            | -    |                    | 0.45 |      |

|                                                           |                            |                            |                                                                                   | 2.3 V             |      |                    | 0.25 |      |

|                                                           |                            |                            | I <sub>OL</sub> = 8 mA                                                            | 3 V               |      |                    | 0.25 |      |

|                                                           | P-port low-le              | vel output                 |                                                                                   | 4.5 V             | -    |                    | 0.2  | .,   |

| V <sub>OL</sub>                                           | voltage                    | •                          |                                                                                   | 1.65 V            |      |                    | 0.6  | V    |

|                                                           |                            |                            | 40 4                                                                              | 2.3 V             |      |                    | 0.3  |      |

|                                                           |                            |                            | I <sub>OL</sub> = 10 mA                                                           | 3 V               |      |                    | 0.25 |      |

|                                                           |                            |                            |                                                                                   | 4.5 V             |      |                    | 0.2  |      |

|                                                           | SDA                        |                            | V = 0.4 V                                                                         | 1 GE V to E E V   | 3    |                    |      | A    |

| I <sub>OL</sub>                                           | INT                        |                            | $V_{OL} = 0.4 \text{ V}$                                                          | 1.65 V to 5.5 V   | 3    | 15                 |      | mA   |

|                                                           | SCL, SDA, R                | RESET                      | V <sub>I</sub> = V <sub>CCI</sub> or GND                                          | - 1.65 V to 5.5 V |      |                    | ±0.1 |      |

| I <sub>1</sub>                                            | ADDR                       |                            | V <sub>I</sub> = V <sub>CCP</sub> or GND                                          | 1.05 V 10 5.5 V   |      |                    | ±0.1 | μA   |

| I <sub>IH</sub>                                           | P-port                     |                            | V <sub>I</sub> = V <sub>CCP</sub>                                                 | - 1.65 V to 5.5 V |      |                    | 1    | μA   |

| I <sub>IL</sub>                                           | P-port                     |                            | V <sub>I</sub> = GND                                                              | 1.03 V to 3.3 V   |      |                    | 1    | μA   |

|                                                           |                            | SDA,                       | V <sub>I</sub> on SDA and RESET= V <sub>CCI</sub> or GND,                         | 3.6 V to 5.5 V    |      | 10                 | 20   |      |

|                                                           | Operating mode             | P-port,<br>ADDR,           | $V_I$ on P-port and ADDR = $V_{CCP}$ or GND,<br>$I_O = 0$ , I/O = inputs,         | 2.3 V to 3.6 V    |      | 6.5                | 15   |      |

|                                                           |                            | RESET                      | f <sub>SCL</sub> = 400 kHz                                                        | 1.65 V to 2.3 V   | -    | 4                  | 9    |      |

| I <sub>CC</sub><br>(I <sub>CCI</sub> + I <sub>CCP</sub> ) |                            | SCL, SDA,                  | V <sub>I</sub> on SCL, SDA and RESET = V <sub>CCI</sub> or                        | 3.6 V to 5.5 V    |      | 1.5                | 7    | μA   |

|                                                           | Standby                    | P-port,                    | GND,<br>V <sub>I</sub> on P-Port and ADDR = V <sub>CCP</sub> or GND,              | 2.3 V to 3.6 V    |      | 1                  | 3.2  |      |

|                                                           | mode                       | ADDR,<br>RESET             | $I_O = 0$ , $I/O = inputs$ , $f_{SCL} = 0$                                        | 1.65 V to 2.3 V   |      | 0.5                | 1.7  |      |

| ΔI <sub>CCI</sub>                                         | Additional sCL, SDA, RESET |                            | One input at V <sub>CCI</sub> – 0.6 V,<br>Other inputs at V <sub>CCI</sub> or GND | 1.65 V to 5.5 V   |      |                    | 25   | μΑ   |

| ΔI <sub>CCP</sub>                                         | standby<br>mode            | P-port,<br>ADDR            | One input at V <sub>CCP</sub> – 0.6 V,<br>Other inputs at V <sub>CCP</sub> or GND | 1.65 V to 5.5 V   |      |                    | 80   | μΑ   |

| C <sub>i</sub>                                            | SCL                        |                            | V <sub>I</sub> = V <sub>CCI</sub> or GND                                          | 1.65 V to 5.5 V   |      | 6                  | 7    | pF   |

| C                                                         | SDA                        |                            | V <sub>IO</sub> = V <sub>CCI</sub> or GND                                         | - 1.65 V to 5.5 V |      | 7                  | 8    | nΕ   |

| C <sub>io</sub>                                           | P-port                     |                            | V <sub>IO</sub> = V <sub>CCP</sub> or GND                                         | 1.00 / 10 3.5 /   |      | 7.5                | 8.5  | pF   |

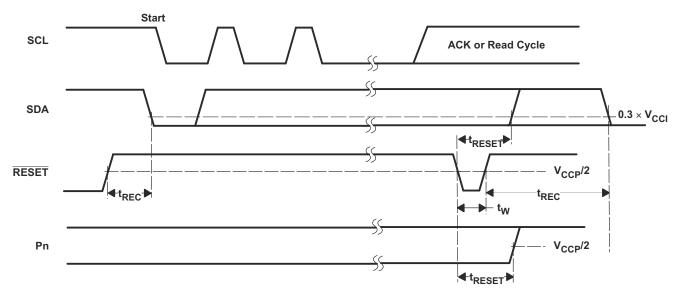

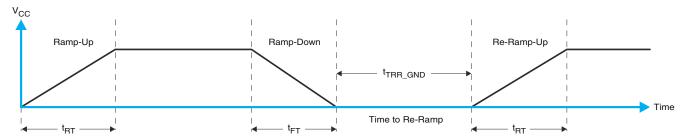

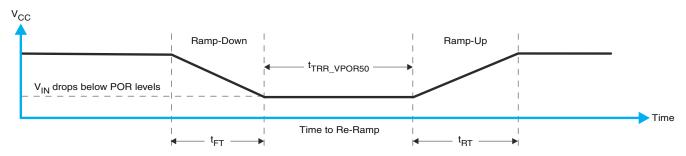

All typical values are at nominal supply voltage (1.8-V, 2.5-V, 3.3-V, or 5-V  $V_{CC}$ ) and  $T_A$  = 25°C. When power (from 0 V) is applied to  $V_{CCP}$ , an internal power-on reset holds the TCA6408A in a reset condition until  $V_{CCP}$  has reached  $V_{POR}$ . At that time, the reset condition is released, and the TCA6408A registers and  $I^2C/SMBus$  state machine initialize to their default states. After that, V<sub>CCP</sub> must be lowered to below 0.2 V and back up to the operating voltage for a power-reset cycle.

# 6.6 I<sup>2</sup>C Interface Timing Requirements

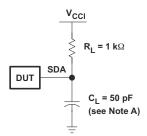

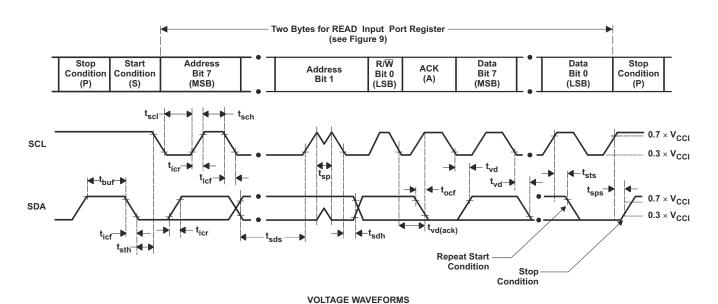

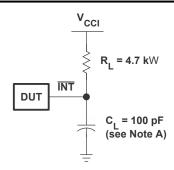

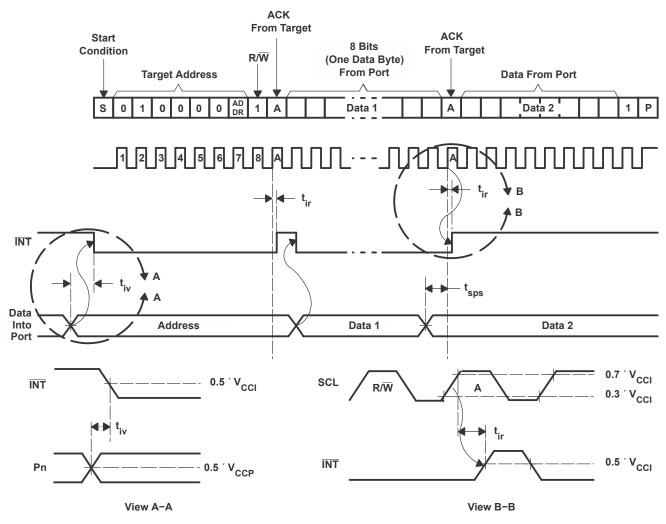

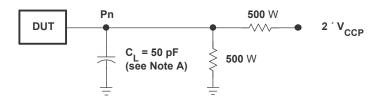

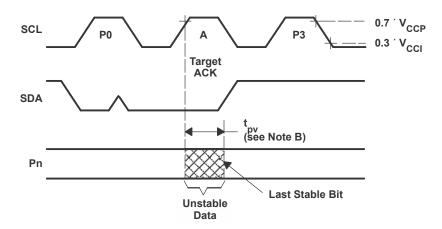

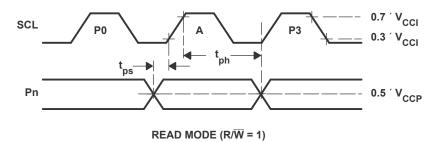

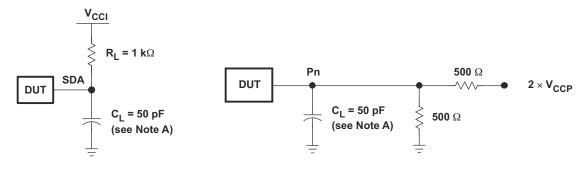

over recommended operating free-air temperature range (unless otherwise noted) (see 🗵 7-1)

|                       |                                                                            | STANDARI<br>I <sup>2</sup> C B | -    | FAST MODE<br>I <sup>2</sup> C BUS | FAST MODE<br>I <sup>2</sup> C BUS<br>MIN MAX |     |

|-----------------------|----------------------------------------------------------------------------|--------------------------------|------|-----------------------------------|----------------------------------------------|-----|

|                       |                                                                            | MIN                            | MAX  | MIN                               |                                              |     |

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                                           | 0                              | 100  | 0                                 | 400                                          | kHz |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time                                           | 4                              |      | 0.6                               |                                              | μs  |

| t <sub>scl</sub>      | I <sup>2</sup> C clock low time                                            | 4.7                            |      | 1.3                               |                                              | μs  |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                                                | 0                              | 50   | 0                                 | 50                                           | ns  |

| t <sub>sds</sub>      | I <sup>2</sup> C serial data setup time                                    | 250                            |      | 100                               |                                              | ns  |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial data hold time                                     | 0                              |      | 0                                 |                                              | ns  |

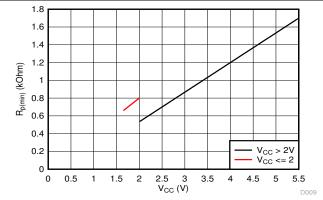

| t <sub>icr</sub>      | I <sup>2</sup> C input rise time                                           |                                | 1000 | 20 + 0.1C <sub>b</sub>            | 300                                          | ns  |

| t <sub>icf</sub>      | I <sup>2</sup> C input fall time                                           |                                | 300  | 20 + 0.1C <sub>b</sub>            | 300                                          | ns  |

| t <sub>ocf</sub>      | I <sup>2</sup> C output fall time, 10-pF to 400-pF bus                     |                                | 300  | 20 + 0.1C <sub>b</sub>            | 300                                          | μs  |

| t <sub>buf</sub>      | I <sup>2</sup> C bus free time between Stop and Start                      | 4.7                            |      | 1.3                               |                                              | μs  |

| t <sub>sts</sub>      | I <sup>2</sup> C Start or repeater Start condition setup time              | 4.7                            |      | 0.6                               |                                              | μs  |

| t <sub>sth</sub>      | I <sup>2</sup> C Start or repeater Start condition hold time               | 4                              |      | 0.6                               |                                              | μs  |

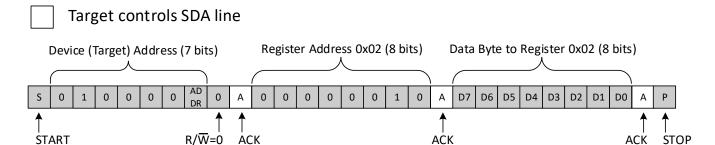

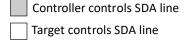

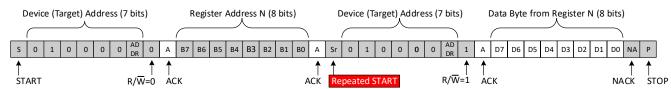

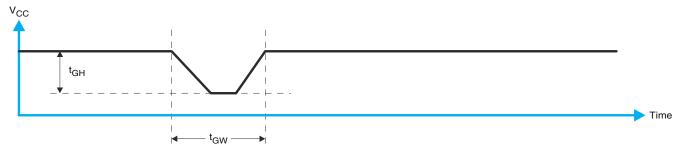

| t <sub>sps</sub>      | I <sup>2</sup> C Stop condition setup time                                 | 4                              |      | 0.6                               |                                              | μs  |