# TAS6754-Q1 1L 変調、2MHz デジタル入力の 4 チャネル車載用 Class-D オーディオアンプ、電流センス機能およびリアルタイム負荷診断機能を搭載

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1: -40°C ~ +125°C,  $T_A$

- 一般的な動作

- 4.5V ~ 19V の電源電圧、40V の負荷ダンプ

- 低レイテンシ・パスにより、48kHz 時にグループ遅延を 70% 以上低減

- 1.8V および 3.3V I/O をサポート

- 8 つのアドレスオプションを持つ I<sup>2</sup>C 制御

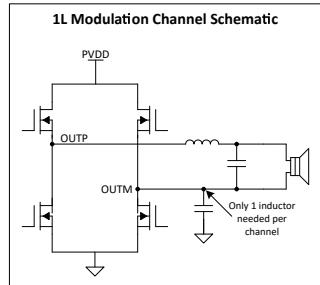

- 1L 変調

- 必要なのは、チャネルごとに 1 つのインダクタのみ。これにより、従来の設計に比べ 4 つのインダクタを節約できます

- インダクタのシステム部品コストを低減できます

- PCB フットプリントの小型化

- オーディオ性能

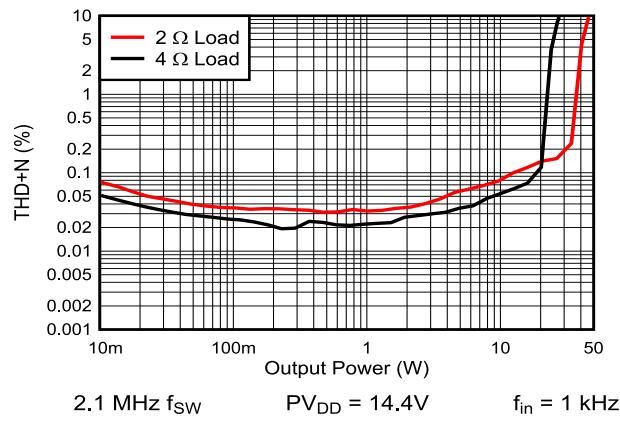

- THD+N 0.03% 未満 (4Ω, 1W, 1kHz)

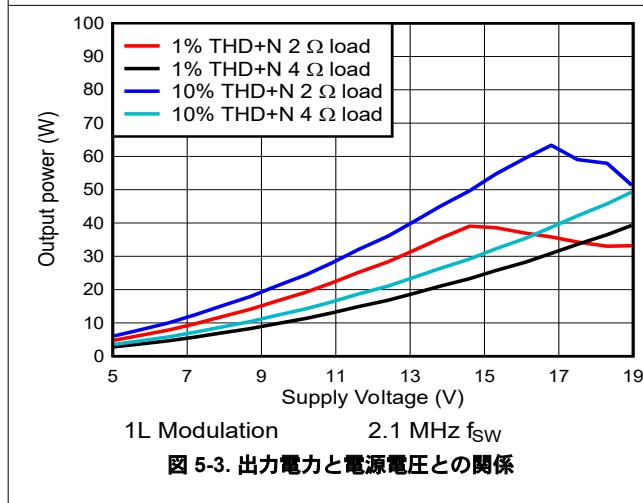

- 出力ノイズ: 14.4V で 35μV<sub>RMS</sub>, A 特性

- 効率 > 87% @ 4×25W, 4Ω, 14.4V

- I<sup>2</sup>S または TDM により、チャネルごとの出力電流検出

- 外付け回路は不要です

- リアルタイムの負荷診断

- オーディオ再生中に出力状態を監視

- 開放負荷および短絡負荷の検出

- DC および AC スタンバイ負荷の診断

- オーディオ入力

- 2-4 チャネルの I<sup>2</sup>S 入力または 4-16 チャネルの TDM 入力

- 入力サンプルレート: 44.1, 48, 96, 192kHz

- オーディオ出力

- 4 チャネルのプリッジ接続負荷 (BTL)

- 2MHz の出力スイッチング周波数

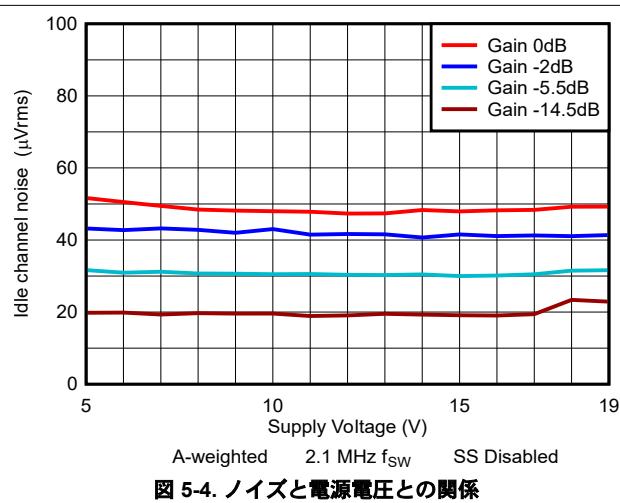

- 4×30W (4Ω, 14.4V, 1kHz, 10% THD+N)

- 4×50W (2Ω, 14.4V, 1kHz, 10% THD+N)

- 高度なスペクトラム拡散機能と選択可能な位相オフセット

- 保護および監視

- サイクル単位の電流制限

- 出力短絡保護

- 設定可能なスレッショルド付きのクリップ検出

- サーマル フォールドバックと PVDD フォールドバック

- I<sup>2</sup>C による温度と電源電圧の読み出し

- 過熱警告と個別チャネルのシャットダウンを設定可能

– DC オフセット、低電圧、過電圧

## 2 アプリケーション

- 車載用ヘッドユニット

- 車載用外部アンプ

- 車両接近通報装置 (AVAS)

## 3 概要

TAS6754-Q1 は、4 チャネルのデジタル入力 Class-D オーディオアンプで、BTL チャネルごとにインダクタが 1 個のみ必要な 1L 変調を実装し、従来のソリューションに比べてインダクタを 4 個減らし、システム サイズとコストを削減します。さらに、従来の Class-D 変調方式に比べて、1L 変調はスイッチング損失を低減します。

TAS6754-Q1 は、DC および AC 負荷の診断機能を内蔵しており、接続されている負荷の状態を判定できます。オーディオの再生中、電流センスによってこの状態を監視できます。これは各チャネルに対して利用可能で、TDM により最小限の遅延で測定値をホスト プロセッサに報告します。このデバイスは、ホストおよびオーディオ入力から独立したリアルタイム負荷診断機能によって、オーディオ再生中に出力負荷状態を監視します。

TAS6754-Q1 デバイスには各チャネルに追加の低レイテンシの信号パスがあり、48kHz での信号処理を最大 70% 高速化できるので、時間に制約のあるアクティブ ノイズ キャンセル (ANC)、ロード ノイズ キャンセル (RNC) アプリケーションを実現できます。

このデバイスは、I<sup>2</sup>C 読み出しにより、全体的な温度、チャネル温度、PVDD の値をサポートしているため、システム レベルの熱管理を簡単にします。

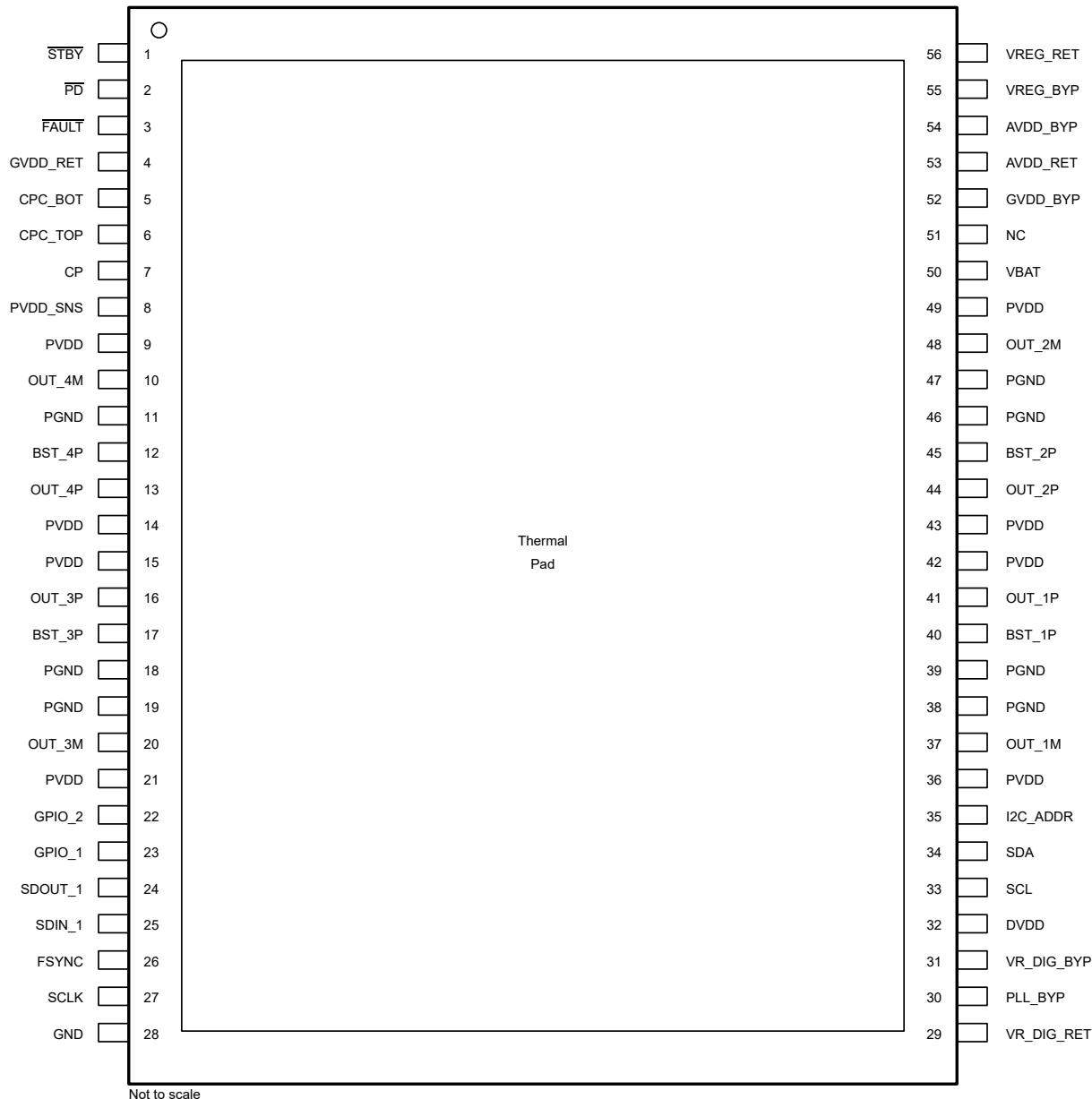

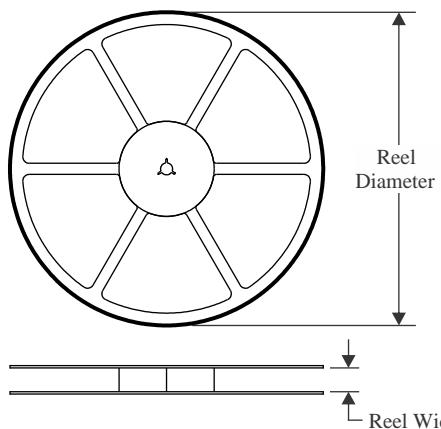

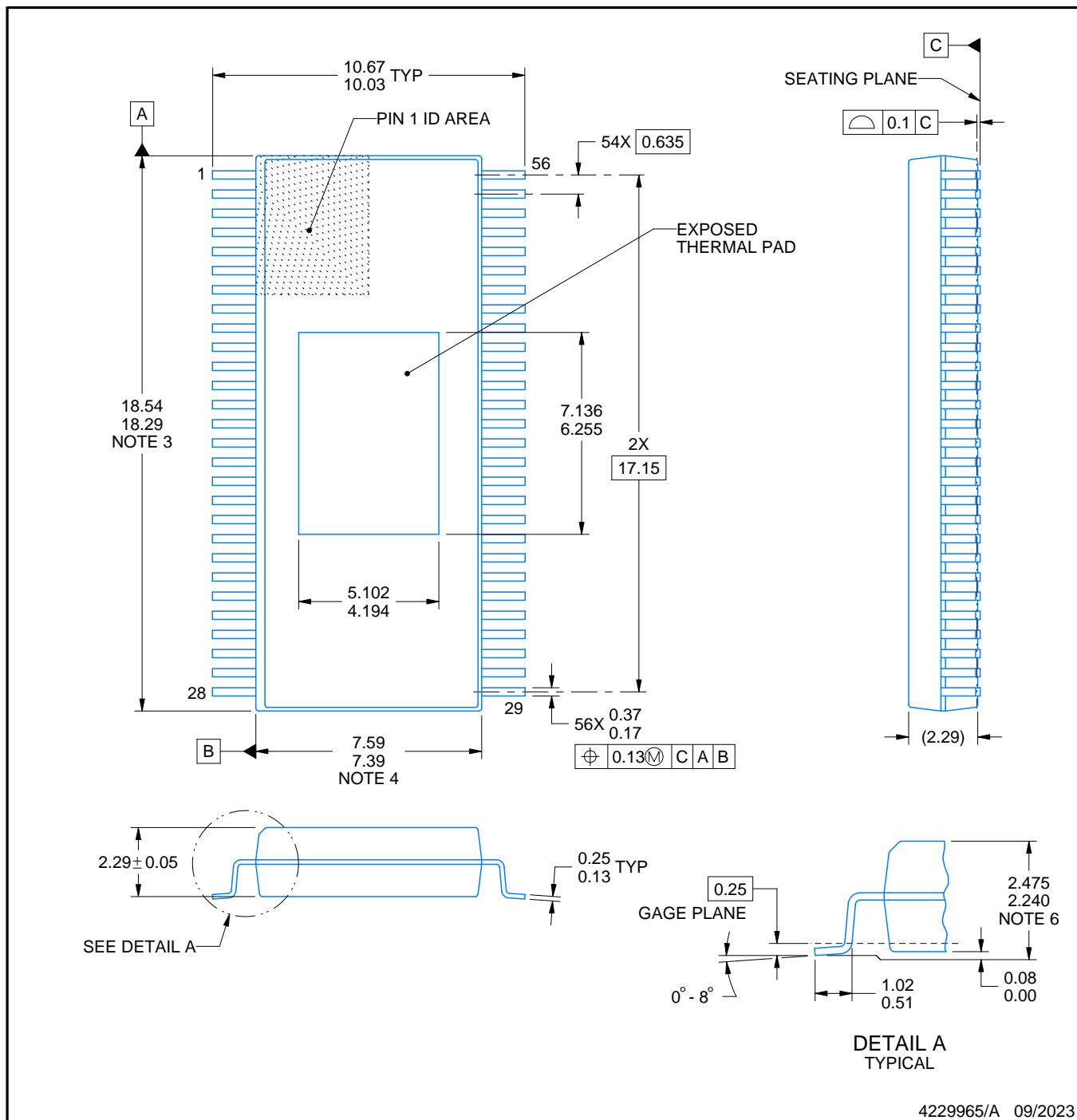

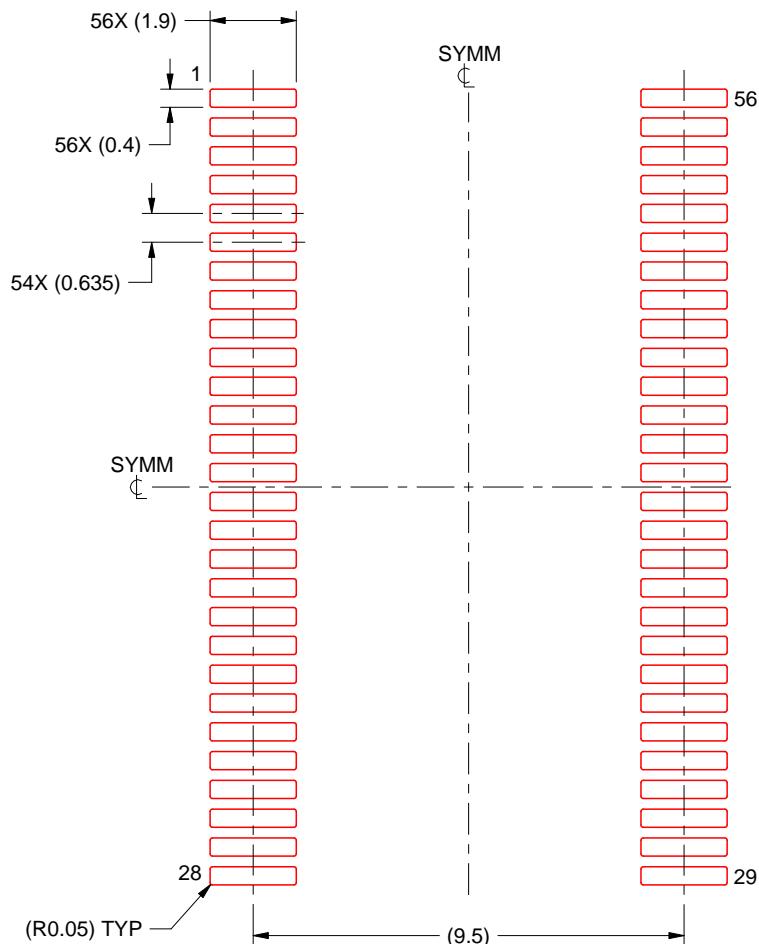

このデバイスは、サーマル パッドが上面に露出した 56 ピン HSSOP パッケージで供給されます。

## 製品情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| TAS6754-Q1 | HSSOP (56)           | 18.42mm × 10.35mm        |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

簡素化されたチャネル回路図

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | 7.4 デバイスの機能モード                | <b>38</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | 7.5 プログラミング                   | <b>42</b> |

| <b>3 概要</b>        | <b>1</b>  | <b>8 アプリケーション情報に関する免責事項</b>   | <b>46</b> |

| <b>4 ピン構成および機能</b> | <b>4</b>  | 8.1 アプリケーション情報                | <b>46</b> |

| <b>5 仕様</b>        | <b>6</b>  | 8.2 代表的なアプリケーション              | <b>47</b> |

| 5.1 絶対最大定格         | <b>6</b>  | 8.3 レイアウト                     | <b>49</b> |

| 5.2 推奨動作条件         | <b>7</b>  | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>52</b> |

| 5.3 ESD 定格         | <b>7</b>  | 9.1 ドキュメントのサポート               | <b>52</b> |

| 5.4 熱に関する情報        | <b>7</b>  | 9.2 ドキュメントの更新通知を受け取る方法        | <b>52</b> |

| 5.5 電気的特性          | <b>8</b>  | 9.3 サポート・リソース                 | <b>52</b> |

| 5.6 代表的特性          | <b>11</b> | 9.4 商標                        | <b>52</b> |

| <b>6 パラメータ測定情報</b> | <b>16</b> | 9.5 静電気放電に関する注意事項             | <b>52</b> |

| <b>7 詳細説明</b>      | <b>17</b> | 9.6 用語集                       | <b>52</b> |

| 7.1 概要             | <b>17</b> | <b>10 改訂履歴</b>                | <b>52</b> |

| 7.2 機能ブロック図        | <b>18</b> | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>53</b> |

| 7.3 機能説明           | <b>19</b> |                               |           |

## 4 ピン構成および機能

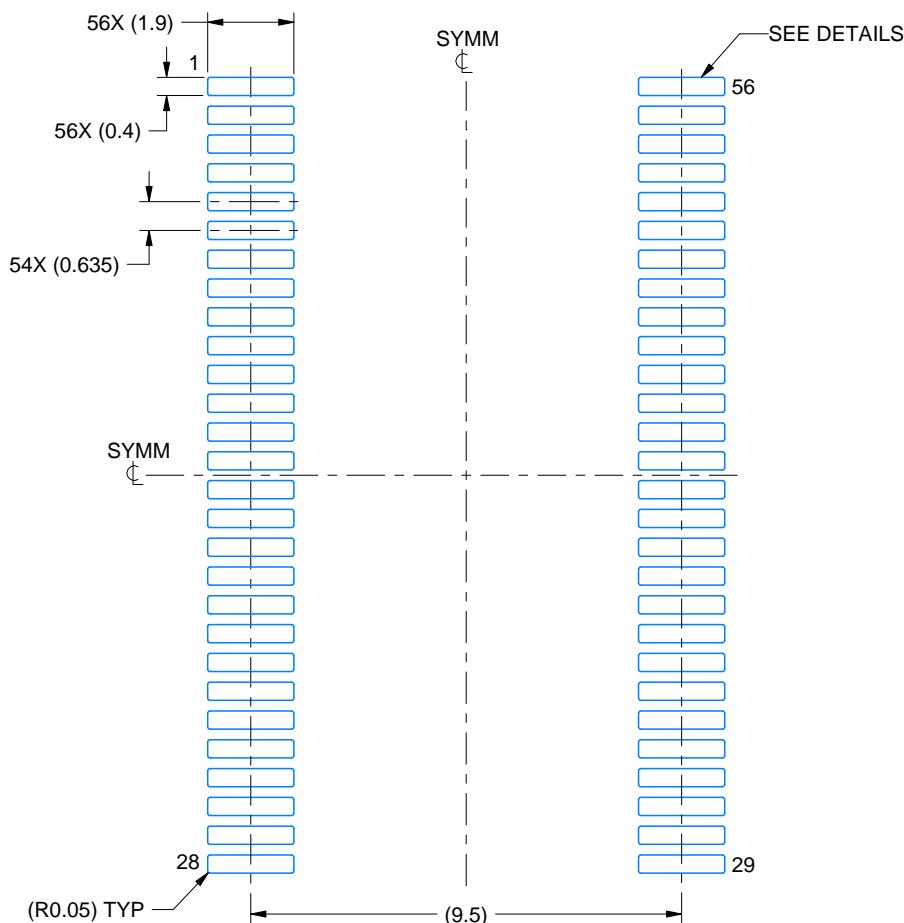

図 4-1. DKQ パッケージ 56 ピン HSSOP 露出サーマル パッド付き 上面図

表 4-1. ピンの機能

| ピン       |    | I/O <sup>(1)</sup> | 説明                                                   |

|----------|----|--------------------|------------------------------------------------------|

| 名称       | 番号 |                    |                                                      |

| AVDD_BYP | 54 | PWR                | 電圧レギュレータのバイパス。1μF コンデンサを AVDD_BYP から AVDD_RET に接続します |

| AVDD_RET | 53 | PWR                | AVDD バイパスコンデンサのリターン                                  |

| BST_1P   | 40 | PWR                | ハイサイド ゲートドライバ用ブートストラップ コンデンサ接続ピン                     |

| BST_2P   | 45 | PWR                | ハイサイド ゲートドライバ用ブートストラップ コンデンサ接続ピン                     |

| BST_3P   | 17 | PWR                | ハイサイド ゲートドライバ用ブートストラップ コンデンサ接続ピン                     |

| BST_4P   | 12 | PWR                | ハイサイド ゲートドライバ用ブートストラップ コンデンサ接続ピン                     |

| CP       | 7  | PWR                | チャージポンプ用メインストレージコンデンサの上部。330nF のコンデンサをピンから PVDD に接続  |

**表 4-1. ピンの機能 (続き)**

| ピン         |                        | I/O <sup>(1)</sup> | 説明                                                      |

|------------|------------------------|--------------------|---------------------------------------------------------|

| 名称         | 番号                     |                    |                                                         |

| CPC_BOT    | 5                      | PWR                | チャージポンプ用フライングコンデンサの下部。100nF のコンデンサをピンから CPC_TOP ピンに接続   |

| CPC_TOP    | 6                      | PWR                | チャージポンプ用フライングコンデンサの上部 100nF のコンデンサをピンから CPC_BOT ピンに接続   |

| DVDD       | 32                     | PWR                | DVDD 電源入力                                               |

| FAULT      | 3                      | DO                 | フォルト(アクティブ LOW、オープンドレイン)を通知、100kΩ 内部プルアップ抵抗             |

| FSYNC      | 26                     | DI                 | オーディオフレームクロック入力                                         |

| GND        | 28                     | GND                | グランド                                                    |

| GPIO_1     | 23                     | DI/O               | 汎用 IO、レジスタプログラミングにより機能を設定                               |

| GPIO_2     | 22                     | DI/O               | 汎用 IO、レジスタプログラミングにより機能を設定                               |

| GVDD_BYP   | 52                     | PWR                | VBAT 入力ピンから導かれるゲート駆動電圧レギュレータ。2.2μF コンデンサを GVDD_RET に接続  |

| GVDD_RET   | 4                      | PWR                | GVDD バイパスコンデンサのリターン                                     |

| I2C_ADDR   | 35                     | DI                 | I <sup>2</sup> C アドレスピン                                 |

| NC         | 51                     | NC                 | 内部接続なし未接続のままにするか、グランドに接続。                               |

| OUT_1M     | 37                     | PWR                | チャネルの負の出力                                               |

| OUT_1P     | 41                     | PWR                | チャネルの正の出力                                               |

| OUT_2M     | 48                     | PWR                | チャネルの負の出力                                               |

| OUT_2P     | 44                     | PWR                | チャネルの正の出力                                               |

| OUT_3M     | 20                     | PWR                | チャネルの負の出力                                               |

| OUT_3P     | 16                     | PWR                | チャネルの正の出力                                               |

| OUT_4M     | 10                     | PWR                | チャネルの負の出力                                               |

| OUT_4P     | 13                     | PWR                | チャネルの正の出力                                               |

| PD         | 2                      | DI                 | 消費電力最小化用デバイスのシャットダウン(アクティブ LOW)、110kΩ 内部プルダウン抵抗         |

| PGND       | 11,18,19,38,39,46,47   | GND                | グランド                                                    |

| PLL_BYP    | 30                     | PWR                | DVDD 入力由来の PLL 電源バイパス                                   |

| PVDD       | 9,14,15,21,36,42,43,49 | PWR                | PVDD 電圧入力(バッテリに接続可能)                                    |

| PVDD_SNS   | 8                      | PWR                | センシティブな内部回路用の PVDD 入力。PVDD と同じ電圧レベルに維持                  |

| SCL        | 33                     | DI                 | I <sup>2</sup> C クロック入力                                 |

| SCLK       | 27                     | DI                 | オーディオ入力シリアルクロック                                         |

| SDA        | 34                     | DI/O               | I <sup>2</sup> C データ入出力                                 |

| SDIN_1     | 25                     | DI                 | チャネル 1 および 2 の TDM データ入力およびオーディオ I <sup>2</sup> S データ入力 |

| SDOUT_1    | 24                     | DO                 | I <sup>2</sup> S / TDM データ出力                            |

| STBY       | 1                      | DI                 | 低消費電力 DEEP SLEEP 状態(アクティブ Low)の有効化、110kΩ 内部プルダウン抵抗      |

| VBAT       | 50                     | PWR                | バッテリ電圧入力                                                |

| VR_DIG_BYP | 31                     | PWR                | DSP コレギュレータ出力。1uF を GND に接続                             |

| VR_DIG_RET | 29                     | PWR                | VR_DIG バイパスコンデンサのリターン                                   |

| VREG_BYP   | 55                     | PWR                | 5V 内部電圧レギュレータ                                           |

| VREG_RET   | 56                     | PWR                | VREG バイパスコンデンサのリターン                                     |

| サーマル パッド   | -                      | GND                | デバイスの電気的および熱的接続を提供。ヒートシンクは GND に接続する必要があります。            |

(1) DI = デジタル入力、DO = デジタル出力、DI/O = デジタル入力/出力、GND = グランド、NC = 接続なし、NO = 負の出力、PO = 正の出力、PWR = 電源

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                         |                                          |               | 最小値  | 最大値        | 単位   |

|-------------------------|------------------------------------------|---------------|------|------------|------|

| PVDD、VBAT               | GND に対する DC 電源電圧範囲                       |               | -0.3 | 30         | V    |

| V <sub>MAX</sub>        | 過渡電源電圧 - PVDD、VBAT                       | t ≤ 400ms の曝露 | -1   | 40         | V    |

| V <sub>RAMP</sub>       | 電源電圧ランプレート - PVDD、VBAT                   |               |      | 75         | V/ms |

| DVDD                    | GND に対する DC 電源電圧範囲                       |               | -0.3 | 3.9        | V    |

| I <sub>MAX</sub>        | ピンあたりの最大電流 - PVDD、VBAT、GND、OUT_xP、OUT_xM |               |      | ±9         | A    |

| I <sub>MAX_PULSED</sub> | PVDD ピンあたりのパルス電源電流 (1 ショット)              | t < 100ms     |      | ±12        | A    |

| I <sub>MAX_Peak</sub>   | ピン OUT_xP、OUT_xM あたりの最大ピーク電流             | t < 100ms     |      | ±12        | A    |

| V <sub>LOGIC</sub>      | ロジックピンの入力電圧 - SCL、SDA、FAULT、STBY、GPIOx   |               | -0.3 | DVDD + 0.5 | V    |

| V <sub>GND</sub>        | GND ピン間の最大電圧                             |               |      | ±0.3       |      |

| T <sub>J</sub>          | 最大動作時の接合部温度範囲                            |               | -55  | 175        | °C   |

| T <sub>stg</sub>        | 保管温度範囲                                   |               | -55  | 150        |      |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

## 5.2 推奨動作条件

|                     |                                          |                                                           | 最小値  | 標準値  | 最大値 | 単位 |

|---------------------|------------------------------------------|-----------------------------------------------------------|------|------|-----|----|

| PVDD                | FET 出力 電源電圧範囲                            | GND に対する相対値                                               | 4.5  | 14.4 | 19  | V  |

| VBAT                | バッテリ電源電圧入力                               | GND に対する相対値                                               | 4.5  | 14.4 | 19  | V  |

| DVDD                | DC ロジック電源                                | GND に対する相対値                                               | 1.62 |      | 3.6 | V  |

| T <sub>A</sub>      | 周囲温度                                     |                                                           | -40  | 125  |     | °C |

| T <sub>J</sub>      | 接合部温度                                    | 適切な熱設計が必要                                                 | -40  | 175  |     |    |

| R <sub>L</sub>      | スピーカの公称負荷インピーダンス                         | BTL モード                                                   | 2    | 4    |     | Ω  |

| R <sub>PU_I2C</sub> | SDA および SCL ピンの I <sup>2</sup> C ブルアップ抵抗 |                                                           | 1    | 4.7  | 10  | kΩ |

| C <sub>Bypass</sub> | バイパスピンの外部容量                              | ピン 30, 31, 32, 54, 55                                     |      | 1    |     | μF |

| C <sub>GVDD</sub>   | GVDD ピンの外部容量                             | ピン 52                                                     |      | 2.2  |     | μF |

| L <sub>O</sub>      | OUTP 出力フィルタのインダクタンス - I <sub>SD</sub>    | I <sub>SD</sub> 電流レベルでの最小出力フィルタのインダクタンス。グランド短絡または電源保護に適用。 | 1    |      |     | μH |

## 5.3 ESD 定格

|                    |      |                                            | 値      | 単位 |

|--------------------|------|--------------------------------------------|--------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | ±3500  | V  |

|                    |      | デバイス帶電モデル (CDM)、AEC Q100-011 準拠            | すべてのピン |    |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | TAS6754-Q1 <sup>(2)</sup> | 単位   |

|-----------------------|---------------------|---------------------------|------|

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 38.9                      | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 0.3                       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 17.1                      | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.2                       | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 16.6                      | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | -                         | °C/W |

(1) 従来および最新の熱評価基準の詳細については、[半導体および IC パッケージの熱評価基準](#) アプリケーション レポートを参照してください。

(2) JEDEC 規格 4 層 PCB

## 5.5 電気的特性

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $PVDD = 14.4\text{V}$ 、 $VBAT = 14.4\text{V}$ 、 $DVDD = 1.8\text{V}$ 、 $R_L = 4\Omega$ 、

$P_{out} = 1\text{W/ch}$ 、 $f_{out} = 1\text{kHz}$ 、 $F_{sw} = 2.048\text{MHz}$ 、AES17 フィルタ、再構成フィルタ インダクタを使用:  $3.3\mu\text{H}$ -VCMT053T-3R3MN5 および  $1\mu\text{F}$ 、デフォルトの  $\text{I}^2\text{C}$  設定+起動スクリプト、アプリケーション図を参照

| パラメータ                                            |                     | テスト条件                                                                                                                   | 最小値  | 標準値 | 最大値 | 単位            |

|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|------|-----|-----|---------------|

| <b>動作電流</b>                                      |                     |                                                                                                                         |      |     |     |               |

| $I_{DVDD}$                                       | DVDD 電源電流           | 再生中の全チャンネル、-60dB 信号                                                                                                     | 22   | 28  |     | mA            |

|                                                  |                     | 再生中の全チャネル、-60dB 信号、 $DVDD = 3.3\text{V}$                                                                                | 22   |     |     |               |

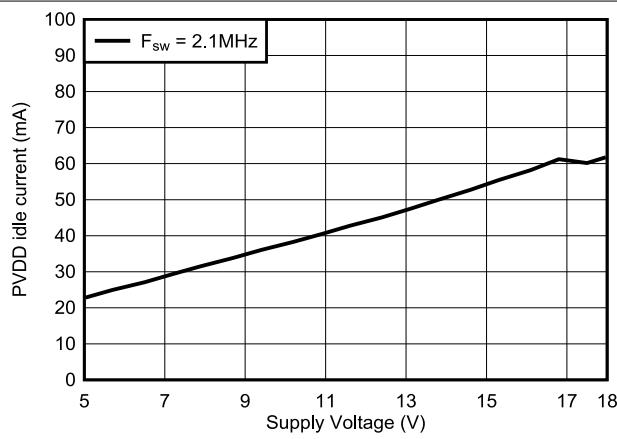

| $I_{PVDD\_IDLE}$                                 | PVDD アイドル電流         | 再生中の全チャネル、オーディオ入力なし、 $F_{sw} = 2.048\text{MHz}$                                                                         | 47   | 60  |     | mA            |

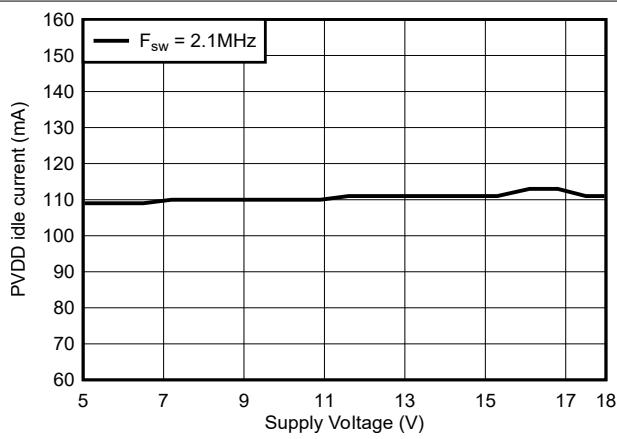

| $I_{VBAT\_IDLE}$                                 | VBAT アイドル電流         | 再生中の全チャネル、オーディオ入力なし、 $F_{sw} = 2.048\text{MHz}$                                                                         | 115  | 130 |     | mA            |

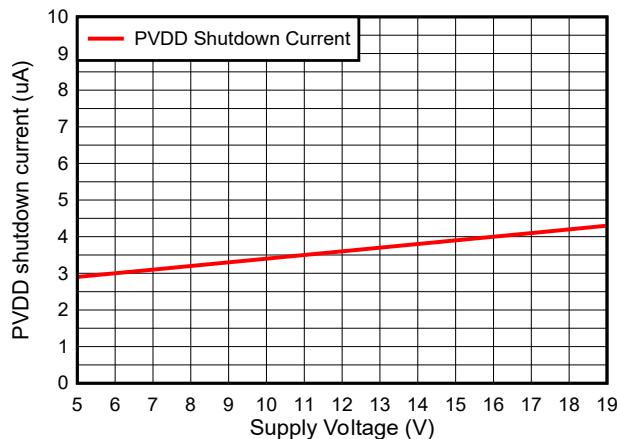

| $I_{PVDD\_Shutdown}$                             | PVDD シャットダウン電流      | PD アクティブ、 $DVDD = 0\text{V}$                                                                                            | 4    | 5   |     | $\mu\text{A}$ |

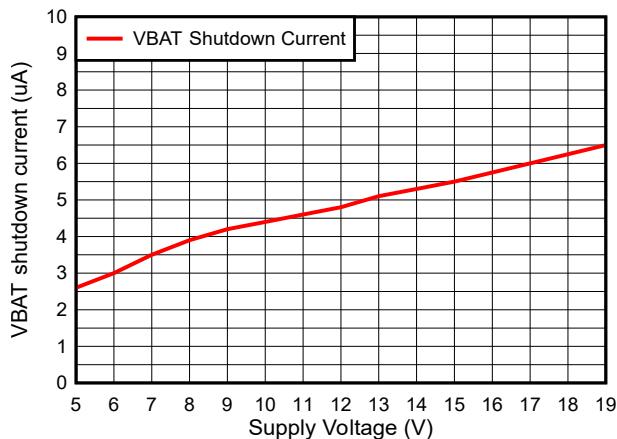

| $I_{VBAT\_Shutdown}$                             | VBAT シャットダウン電流      | PD アクティブ、 $DVDD = 0\text{V}$                                                                                            | 5    | 7   |     | $\mu\text{A}$ |

| $I_{TOTAL\_Shutdown}$                            | PVDD+VBAT シャットダウン電流 | PD アクティブ、 $DVDD = 0\text{V}$                                                                                            |      | 12  |     | $\mu\text{A}$ |

| $I_{DVDD\_Shutdown}$                             | DVDD シャットダウン電流      | PD アクティブ、 $DVDD = 1.8\text{V}$                                                                                          | 1    | 3   |     | $\mu\text{A}$ |

|                                                  |                     | PD アクティブ、 $DVDD = 3.3\text{V}$                                                                                          | 1    | 3   |     |               |

| <b>出力電力</b>                                      |                     |                                                                                                                         |      |     |     |               |

| $P_{O\_BTL}$                                     | チャネルあたりの出力電力、BTL    | 4Ω、 $PVDD=14.4\text{V}$ 、 $\text{THD+N} = 1\%$ 、 $T_C = 75^\circ\text{C}$                                               | 21   | 23  |     | W             |

|                                                  |                     | 4Ω、 $PVDD=14.4\text{V}$ 、 $\text{THD+N} = 10\%$ 、 $T_C = 75^\circ\text{C}$                                              | 26   | 30  |     |               |

|                                                  |                     | 4Ω、 $PVDD=18\text{V}$ 、 $\text{THD+N} = 1\%$ 、 $T_C = 75^\circ\text{C}$                                                 | 33   | 37  |     |               |

|                                                  |                     | 4Ω、 $PVDD=18\text{V}$ 、 $\text{THD+N} = 10\%$ 、 $T_C = 75^\circ\text{C}$                                                | 41   | 46  |     |               |

|                                                  |                     | 2Ω、 $PVDD = 14.4\text{V}$ 、 $\text{THD+N} = 1\%$ 、 $T_C = 75^\circ\text{C}$                                             | 37   | 40  |     |               |

|                                                  |                     | 2Ω、 $PVDD = 14.4\text{V}$ 、 $\text{THD+N} = 10\%$ 、 $T_C = 75^\circ\text{C}$                                            | 44   | 50  |     |               |

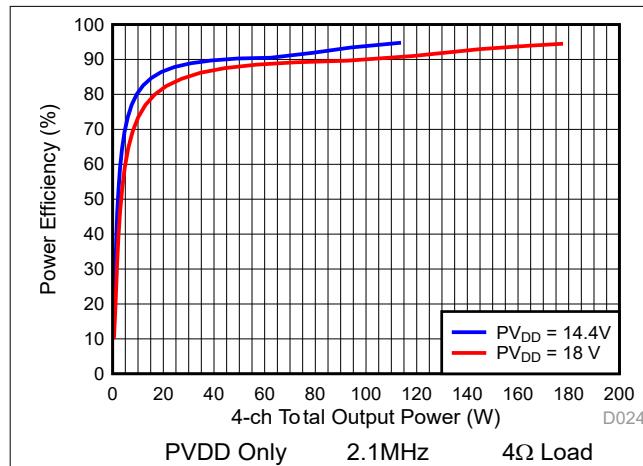

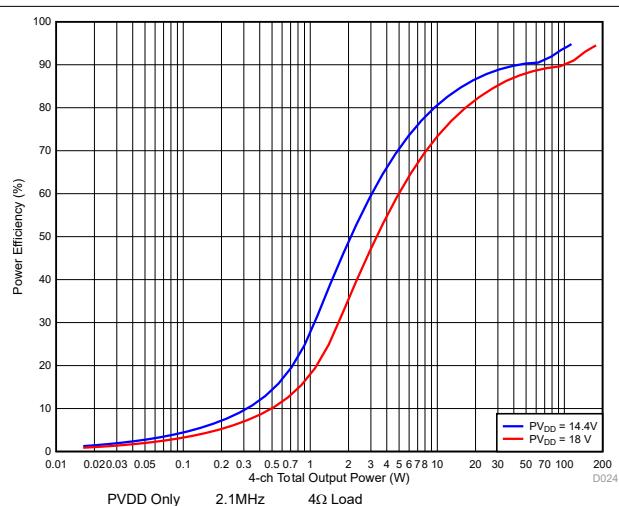

| $EFF_p$                                          | 高い電力効率              | 4 チャネルの動作、チャネルあたり $25\text{W}$ の出力電力、 $R_L = 4\Omega$ 、 $PVDD = 14.4\text{V}$ 、 $T_C = 25^\circ\text{C}$ (出力フィルタの損失を含む) |      | 87  |     | %             |

| <b>オーディオ性能</b>                                   |                     |                                                                                                                         |      |     |     |               |

| $V_n$                                            | 出力ノイズ電圧             | ゼロ入力、A-重み付け、 $14.4\text{V}$ の PVDD に合わせてゲイン = -5dB                                                                      | 35   |     |     | $\mu\text{V}$ |

| $G$                                              | ゲイン                 | フルスケールデジタル入力時のピーク出力電圧                                                                                                   | 28   |     |     | V/FS          |

| THD+N                                            | 全高調波歪み + ノイズ        |                                                                                                                         | 0.03 |     |     | %             |

|                                                  |                     | 20Hz ~ 20kHz                                                                                                            | 0.08 |     |     | %             |

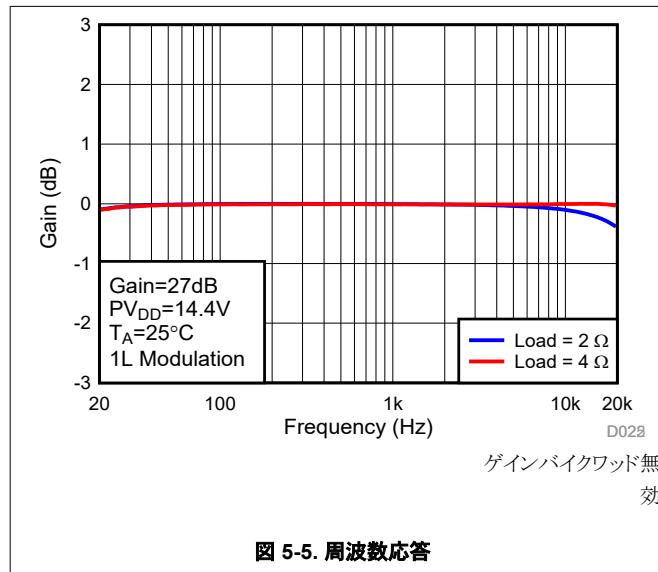

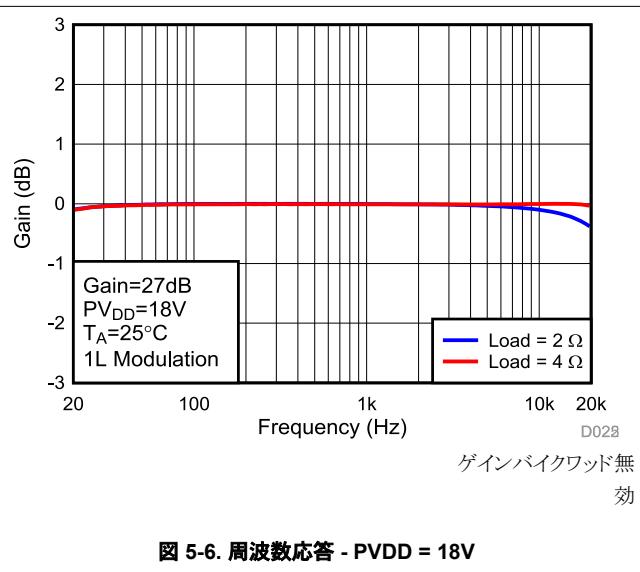

| $F_{BW}$                                         | 周波数応答               | 20Hz ~ 20kHz、LC フィルタの影響または統合補償なし                                                                                        | 0.5  |     |     | dB            |

| $G_{MUTE}$                                       | 出力減衰                | MUTE をアサートし、 $4\Omega$ で $1\text{W}$ オーディオを再生するアンプと比較                                                                   | 100  |     |     | dB            |

| クロストーク                                           | チャネルクロストーク          | $PVDD = 14.4\text{Vdc}$ 、 $f = 1\text{kHz}$                                                                             | -90  | -80 |     | dB            |

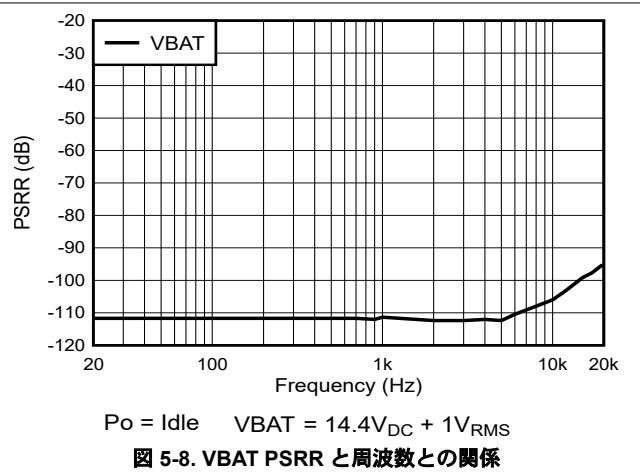

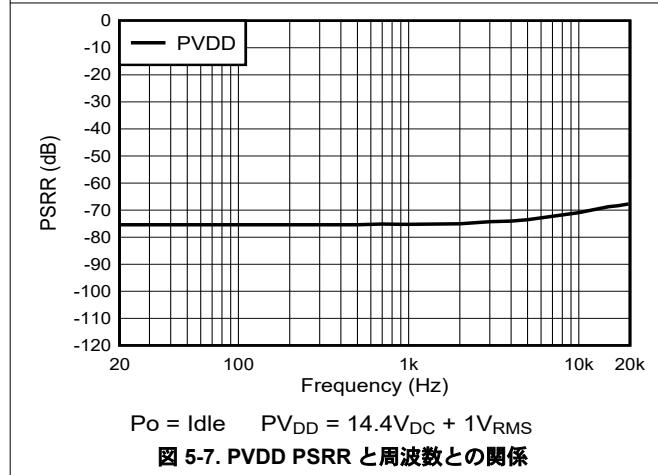

| PSRR                                             | 電源除去比               | $PVDD = 14.4\text{Vdc} + 1V_{RMS}$ 、 $f = 1\text{kHz}$                                                                  | -75  |     |     | dB            |

| <b>デジタル入力ピン</b>                                  |                     |                                                                                                                         |      |     |     |               |

| $V_{IH}$                                         | 入力ロジックレベル High      |                                                                                                                         | 70   |     |     | %DVDD         |

| $V_{IL}$                                         | 入力ロジックレベル Low       |                                                                                                                         |      | 30  |     |               |

| $I_{IH}$                                         | 入力ロジック電流            | $V_i = DVDD$                                                                                                            |      | 15  |     | $\mu\text{A}$ |

|                                                  |                     | $V_i = 0$                                                                                                               |      | -15 |     |               |

| <b>デジタル出力ピン</b>                                  |                     |                                                                                                                         |      |     |     |               |

| $V_{OH}$                                         | ロジックレベル High の出力電圧  | $I = \pm 1\text{mA}$                                                                                                    | 90   |     |     | %DVDD         |

| $V_{OL}$                                         | ロジックレベル Low の出力電圧   |                                                                                                                         |      | 10  |     |               |

| $V_{OH}$                                         | ロジックレベル High の出力電圧  | $DVDD = 3.3\text{V}$ 、 $I = \pm 2\text{mA}$                                                                             | 90   |     |     | %DVDD         |

| $V_{OL}$                                         | ロジックレベル Low の出力電圧   | $DVDD = 3.3\text{V}$ 、 $I = \pm 2\text{mA}$                                                                             |      | 10  |     | %DVDD         |

| <b>バイパス電圧</b>                                    |                     |                                                                                                                         |      |     |     |               |

| $V_{GVDD}$                                       | ゲートドライブ バイパスピン電圧    |                                                                                                                         | 5    |     |     | V             |

| $V_{AVDD\_BYP}$ 、 $V_{VREG\_BYP}$                | アナログバイパスピン電圧        |                                                                                                                         | 5    |     |     | V             |

| $V_{DVDD\_BYP}$ 、 $V_{PLL\_BYP}$ 、 $V_{VR\_DIG}$ | デジタル レギュレータ ピン電圧    |                                                                                                                         | 1.5  |     |     | V             |

| <b>過電圧保護 (OV)</b>                                |                     |                                                                                                                         |      |     |     |               |

| $PVDD_{OV\_SET}$                                 | PVDD 過電圧シャットダウン設定   |                                                                                                                         | 19.1 | 20  | 21  | V             |

| $PVDD_{OV\_HYS}$                                 | PVDD 過電圧回復ヒステリシス    |                                                                                                                         |      | 0.5 |     | V             |

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $\text{VBAT} = 14.4\text{V}$ 、 $\text{DVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega$ 、

$\text{P}_{\text{out}} = 1\text{W}/\text{ch}$ 、 $f_{\text{out}} = 1\text{kHz}$ 、 $F_{\text{sw}} = 2.048\text{MHz}$ 、AES17 フィルタ、再構成フィルタ インダクタを使用: 3.3 $\mu\text{H}$ -VCMT053T-3R3MN5 および 1 $\mu\text{F}$ 、デフォルトの I<sup>2</sup>C 設定+起動スクリプト、アプリケーション図を参照

| パラメータ                            |                                  | テスト条件                                                            | 最小値  | 標準値   | 最大値  | 単位  |

|----------------------------------|----------------------------------|------------------------------------------------------------------|------|-------|------|-----|

| VBAT <sub>OV_SET</sub>           | VBAT 過電圧シャットダウン設定                |                                                                  | 19.1 | 20    | 22   | V   |

| VBAT <sub>OV_HYS</sub>           | VBAT 過電圧回復ヒステリシス                 |                                                                  |      | 0.5   |      | V   |

| <b>低電圧(UV)保護</b>                 |                                  |                                                                  |      |       |      |     |

| PVDD <sub>UV_SET</sub>           | PVDD 低電圧シャットダウン設定                |                                                                  | 3.5  | 4     | 4.5  | V   |

| PVDD <sub>UV_HYS</sub>           | PVDD 低電圧ヒステリシス                   |                                                                  |      | 0.5   |      | V   |

| VBAT <sub>UV_SET</sub>           | VBAT 低電圧シャットダウン設定                |                                                                  | 3.5  | 4     | 4.5  | V   |

| VBAT <sub>UV_HYS</sub>           | VBAT 低電圧回復ヒステリシス                 |                                                                  |      | 0.5   |      | V   |

| DVDD <sub>UV_SET</sub>           | DVDD 低電圧シャットダウン設定                |                                                                  | 1.4  |       | 1.59 | V   |

| <b>パワーオンリセット (POR)</b>           |                                  |                                                                  |      |       |      |     |

| V <sub>POR_SET</sub>             | DVDD パワーオンリセット設定                 | DVDD の増加                                                         | 0.9  |       | 1.51 | V   |

| V <sub>POR_HYS</sub>             | DVDD パワーオンリセット回復ヒステリシス           |                                                                  |      | 0.2   |      | V   |

| V <sub>POR_OFF</sub>             | DVDD 電源オフしきい値                    | DVDD の減少                                                         | 0.5  |       | 1.3  | V   |

| <b>過熱(OT)保護と温度センシング</b>          |                                  |                                                                  |      |       |      |     |

| OTSD(I)                          | チャネルごとの過熱シャットダウン                 |                                                                  |      | 175   |      | °C  |

| OTW                              | グローバル接合部過熱警告                     |                                                                  |      | 135   |      | °C  |

| TOTSD                            | グローバル接合部過熱シャットダウン                |                                                                  |      | 155   |      | °C  |

| OT <sub>HYS_Global</sub>         | 過熱回復ヒステリシス                       |                                                                  |      | 15    |      | °C  |

| OT <sub>HYS_Local</sub>          | 過熱回復ヒステリシス                       |                                                                  |      | 15    |      | °C  |

| <b>負荷過電流保護</b>                   |                                  |                                                                  |      |       |      |     |

| I <sub>LIM</sub>                 | サイクルごとの過電流制限                     | OC レベル 1                                                         | 2.5  | 3.5   |      | A   |

|                                  |                                  | OC レベル 2                                                         | 3.3  | 4.3   |      |     |

|                                  |                                  | OC レベル 3                                                         | 4.6  | 5.6   |      |     |

|                                  |                                  | OC レベル 4                                                         | 6.3  | 6.7   |      |     |

| I <sub>SD</sub>                  | 過電流シャットダウン                       | OC レベル 1、電源、グランド、その他のチャネルへの短絡                                    |      | 5     |      | A   |

|                                  |                                  | OC レベル 2、電源、グランド、その他のチャネルへの短絡                                    |      | 6     |      |     |

|                                  |                                  | OC レベル 3、電源、グランド、その他のチャネルへの短絡                                    |      | 8     |      |     |

|                                  |                                  | OC レベル 4、電源、グランド、その他のチャネルへの短絡                                    |      | 9     |      |     |

| <b>クリックおよびポップ</b>                |                                  |                                                                  |      |       |      |     |

| V <sub>CP_Multi</sub>            | 出力クリックおよびポップ電圧                   | ITU-R 2k フィルタ、Hi-Z ~ PLAY、PLAY ~ Hi-Z、マルチステップ ターンオン、PVDD = 14.4V |      | 5     |      | mV  |

| <b>DC オフセット</b>                  |                                  |                                                                  |      |       |      |     |

| V <sub>OFFSET</sub>              | 出力オフセット電圧                        | T <sub>C</sub> = 50°C                                            |      | 2     | 5    | mV  |

| <b>DC 検出</b>                     |                                  |                                                                  |      |       |      |     |

| DC <sub>FAULT</sub>              | DC 出力オフセット保護                     |                                                                  | 1.4  | 2     | 2.5  | V   |

| <b>負荷診断</b>                      |                                  |                                                                  |      |       |      |     |

| S2P                              | OUT ピンから PVDD への短絡を検出するための最大抵抗   |                                                                  |      | 2000  |      | Ω   |

| S2G                              | OUT ピンからグランドへの短絡を検出するための最大抵抗     |                                                                  |      | 200   |      | Ω   |

| SL                               | 短絡負荷検出の許容誤差                      | Hi-Z の他のチャネル                                                     |      | ±0.5  |      | Ω   |

| OL                               | 開放負荷(OL) 検出しきい値                  | Hi-Z の他のチャネル                                                     |      | 40    |      | Ω   |

| AC <sub>IMP</sub>                | AC インピーダンス精度                     | f = 18.75kHz、R <sub>L</sub> = 4Ω、出力ピンでのインピーダンス                   |      | ±0.75 |      | Ω   |

| f <sub>AC</sub>                  | AC 診断テストの周波数                     | デフォルト                                                            |      | 18.75 |      | kHz |

| <b>I<sup>2</sup>C アドレスピン LSB</b> |                                  |                                                                  |      |       |      |     |

| t <sub>I2C_ADDR</sub>            | I <sup>2</sup> C アドレスの設定に必要な時間遅延 |                                                                  |      | 300   |      | μs  |

| <b>I<sup>2</sup>C 制御ポート</b>      |                                  |                                                                  |      |       |      |     |

| t <sub>bus</sub>                 | 開始条件と停止条件間のバス開放時間                |                                                                  |      | 1.3   |      | μs  |

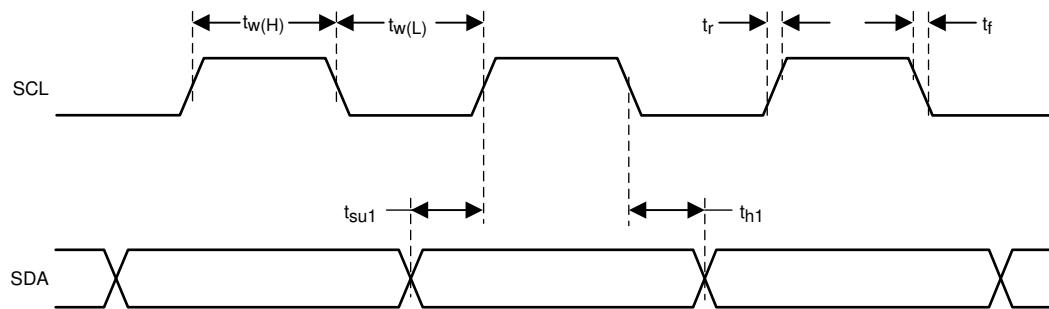

| t <sub>h1</sub>                  | ホールド時間、SCL から SDA                |                                                                  |      | 0     |      | ns  |

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $\text{VBAT} = 14.4\text{V}$ 、 $\text{DVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega$ 、

$P_{\text{out}} = 1\text{W/ch}$ 、 $f_{\text{out}} = 1\text{kHz}$ 、 $F_{\text{sw}} = 2.048\text{MHz}$ 、AES17 フィルタ、再構成フィルタ インダクタを使用: 3.3 $\mu\text{H}$ -VCMT053T-3R3MN5 および 1 $\mu\text{F}$ 、デフォルトの I<sup>2</sup>C 設定+起動スクリプト、アプリケーション図を参照

| パラメータ                  |                                          | テスト条件                     | 最小値  | 標準値    | 最大値 | 単位            |

|------------------------|------------------------------------------|---------------------------|------|--------|-----|---------------|

| $t_{\text{h2}}$        | ホールド時間、開始条件から SCL                        |                           | 0.6  |        |     | $\mu\text{s}$ |

| $t_{\text{START}}$     | DVDD パワーオン リセット後の I <sup>2</sup> C 起動時間  |                           |      | 12     |     | ms            |

| $t_{\text{RISE}}$      | SCL および SDA の立ち上がり時間                     |                           |      | 300    |     | ns            |

| $t_{\text{FALL}}$      | SCL および SDA の立ち下がり時間                     |                           |      | 300    |     | ns            |

| $t_{\text{SU1}}$       | セットアップ、SDA から SCL                        |                           | 100  |        |     | ns            |

| $t_{\text{SU2}}$       | セットアップ、SCL から開始条件                        |                           | 0.6  |        |     | $\mu\text{s}$ |

| $t_{\text{SU3}}$       | セットアップ、SCL から停止条件                        |                           | 0.6  |        |     | $\mu\text{s}$ |

| $t_{\text{W(H)}}$      | 必要なパルス持続期間 SCL 「High」                    |                           | 0.6  |        |     | $\mu\text{s}$ |

| $t_{\text{W(L)}}$      | 必要なパルス持続時間 SCL 「Low」                     |                           | 1.3  |        |     | $\mu\text{s}$ |

| シリアル オーディオ ポート         |                                          |                           |      |        |     |               |

| $D_{\text{SCLK}}$      | 許容入力クロックデューティ サイクル                       |                           | 45%  | 50%    | 55% |               |

| $f_S$                  | サポートしている入力サンプルレート                        |                           | 44.1 |        | 192 | kHz           |

| $f_{\text{SCLK}}$      | サポートしている SCLK 周波数                        |                           | 32   | 512    |     | xFS           |

| $f_{\text{SCLK\_Max}}$ | 最大周波数                                    |                           |      | 24.576 |     | MHz           |

| $t_{\text{SCY}}$       | SCLK パルスサイクル時間                           |                           | 40   |        |     | ns            |

| $t_{\text{SCL}}$       | SCLK パルス LOW                             |                           | 16   |        |     | ns            |

| $t_{\text{SCH}}$       | SCLK パルス-HIGH                            |                           | 16   |        |     | ns            |

| $t_{\text{SF}}$        | SCLK 立ち上がりエッジから FSYNC エッジ                |                           | 8    |        |     | ns            |

| $t_{\text{FS}}$        | FSYNC エッジから SCLK 立ち上がりエッジ                |                           | 8    |        |     | ns            |

| $t_{\text{DS}}$        | DATA のセットアップ時間                           |                           | 8    |        |     | ns            |

| $C_I$                  | 入力容量、ピン SCLK、FSYNC、SDIN_1、SDOUT_1、GPIO_x |                           |      | 10     |     | pF            |

| $t_{\text{DH}}$        | DATA のホールド時間                             |                           | 8    |        |     | ns            |

| $T_{\text{AudioLA}}$   | FSYNC サンプル数で測定した入力から出力までのオーディオバス遅延       | FSYNC = 44.1kHz または 48kHz |      | 22     |     | サンプル          |

|                        |                                          | FSYNC = 96kHz             |      | 23     |     |               |

|                        |                                          | FSYNC = 192kHz            |      | 24     |     |               |

| $T_{\text{LLP LA}}$    | FSYNC サンプル数で測定した入力から出力への低遅延バスの遅延         | FSYNC = 44.1kHz または 48kHz |      | 6      |     | サンプル          |

|                        |                                          | FSYNC = 96kHz             |      | 7      |     |               |

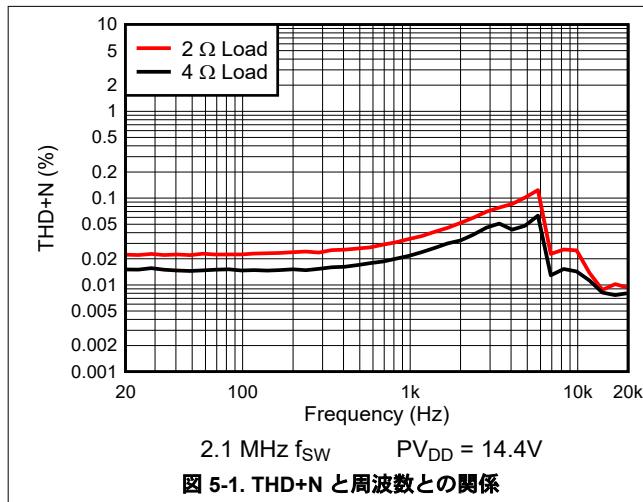

## 5.6 代表的特性

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $\text{VBAT} = 14.4\text{V}$ 、 $\text{DVDD} = 1.8\text{V}$ 、 $\text{R}_L = 4\Omega$ 、 $\text{P}_{\text{out}} = 1\text{W/ch}$ 、 $f_{\text{out}} = 1\text{kHz}$ 、 $f_{\text{sw}} = 2.048\text{MHz}$ 、AES17 フィルタ、パラメータ測定情報、デフォルト I<sup>2</sup>C 設定+スタートアップスクリプトで説明されている再構成フィルタ、アプリケーション図を参照してください。

## 5.6 代表的特性 (続き)

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $\text{VBAT} = 14.4\text{V}$ 、 $\text{DVDD} = 1.8\text{V}$ 、 $\text{R}_L = 4\Omega$ 、 $\text{P}_{\text{out}} = 1\text{W/ch}$ 、 $f_{\text{out}} = 1\text{kHz}$ 、 $F_{\text{sw}} = 2.048\text{MHz}$ 、AES17 フィルタ、パラメータ測定情報、デフォルト I<sup>2</sup>C 設定+スタートアップスクリプトで説明されている再構成フィルタ、アプリケーション図を参照してください。

図 5-5. 周波数応答

図 5-6. 周波数応答 - PVDD = 18V

## 5.6 代表的特性 (続き)

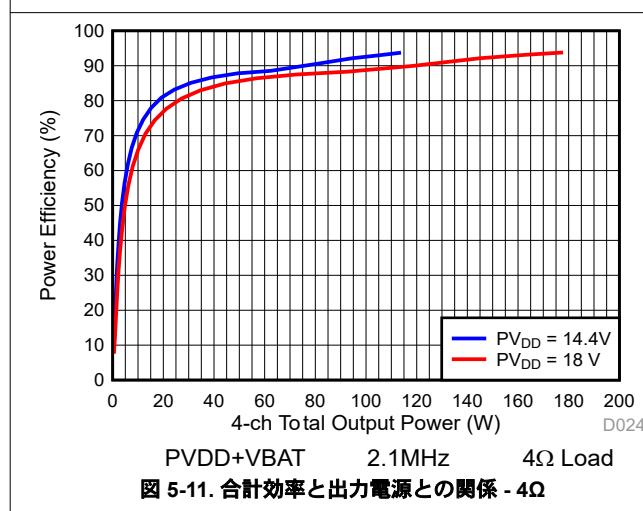

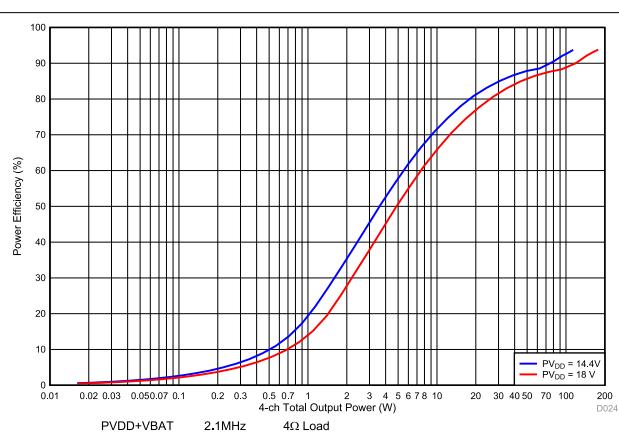

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $P_{VDD} = 14.4\text{V}$ 、 $V_{BAT} = 14.4\text{V}$ 、 $DVDD = 1.8\text{V}$ 、 $R_L = 4\Omega$ 、 $P_{out} = 1\text{W/ch}$ 、 $f_{out} = 1\text{kHz}$ 、 $F_{sw} = 2.048\text{MHz}$ 、AES17 フィルタ、パラメータ測定情報、デフォルト I<sup>2</sup>C 設定+スタートアップスクリプトで説明されている再構成フィルタ、アプリケーション図を参照してください。

図 5-9. 効率と出力電源との関係 - 4Ω, PVDD

図 5-10. 効率と出力電源との関係 - 4Ω、PVDD (拡大)

図 5-11. 合計効率と出力電源との関係 - 4Ω

図 5-12. 合計効率と出力電源との関係 - 4Ω (拡大)

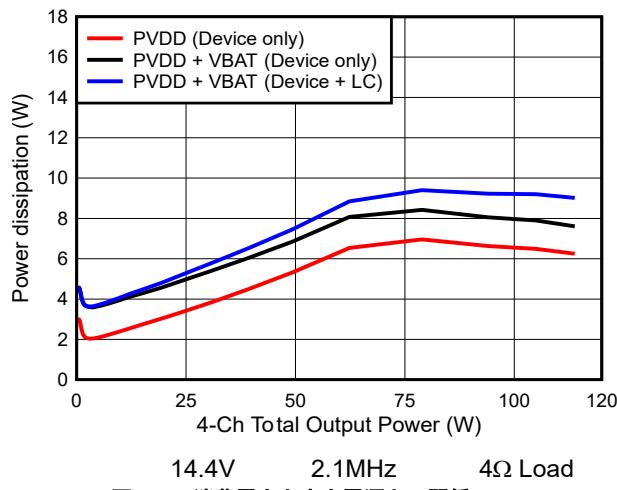

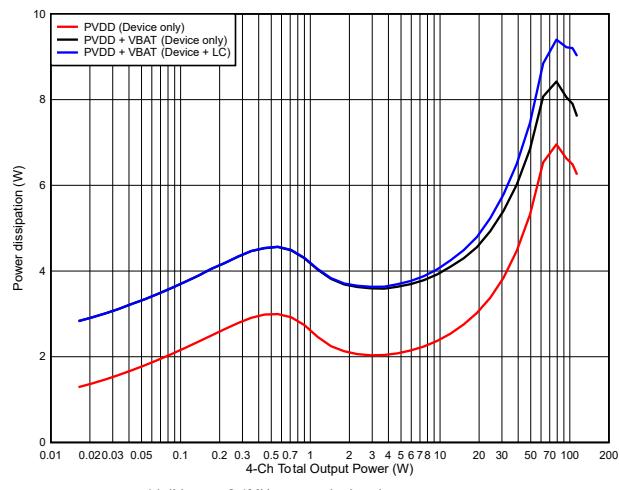

## 5.6 代表的特性 (続き)

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $\text{VBAT} = 14.4\text{V}$ 、 $\text{DVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega$ 、 $P_{\text{out}} = 1\text{W/ch}$ 、 $f_{\text{out}} = 1\text{kHz}$ 、 $F_{\text{sw}} = 2.048\text{MHz}$ 、AES17 フィルタ、パラメータ測定情報、デフォルト  $\text{I}^2\text{C}$  設定+スタートアップスクリプトで説明されている再構成フィルタ、アプリケーション図を参照してください。

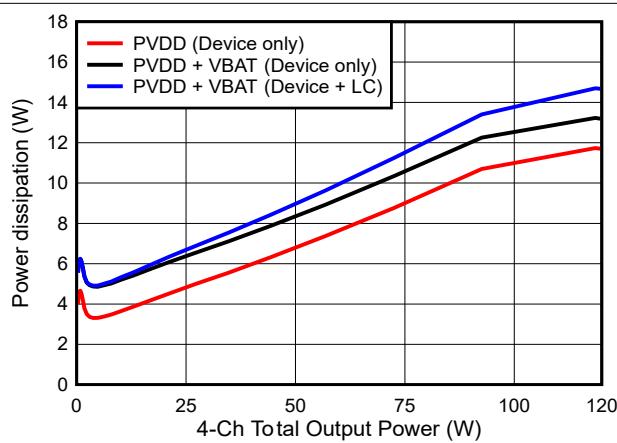

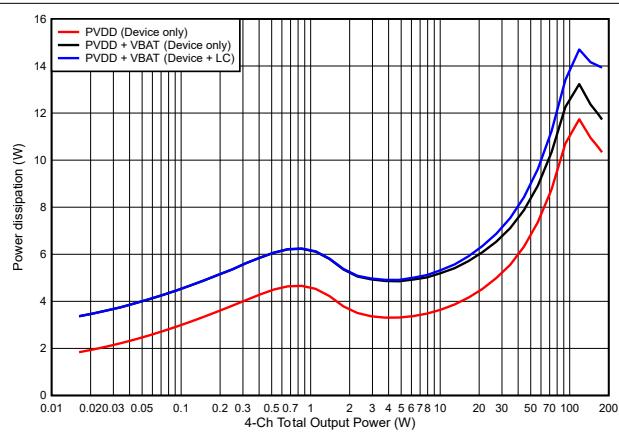

14.4V 2.1MHz 4Ω Load

図 5-13. 消費電力と出力電源との関係 - 4Ω

14.4V 2.1MHz 4Ω Load

図 5-14. 消費電力と出力電源との関係 - 4Ω (拡大)

18V 2.1MHz 4Ω Load

図 5-15. 消費電力と出力電源との関係 - 4Ω、 $\text{PVDD} = 18\text{V}$

18V 2.1MHz 4Ω Load

図 5-16. 消費電力と出力電源との関係 - 4Ω、 $\text{PVDD} = 18\text{V}$  (拡大)

## 5.6 代表的特性 (続き)

試験条件(特に注記のない限り):  $T_C = 25^\circ\text{C}$ 、 $\text{PVDD} = 14.4\text{V}$ 、 $\text{VBAT} = 14.4\text{V}$ 、 $\text{DVDD} = 1.8\text{V}$ 、 $\text{R}_L = 4\Omega$ 、 $\text{P}_{\text{out}} = 1\text{W/ch}$ 、 $f_{\text{out}} = 1\text{kHz}$ 、 $F_{\text{sw}} = 2.048\text{MHz}$ 、AES17 フィルタ、パラメータ測定情報、デフォルト  $\text{I}^2\text{C}$  設定+スタートアップスクリプトで説明されている再構成フィルタ、アプリケーション図を参照してください。

図 5-17. シャットダウン電流と電源電圧との関係, PVDD

図 5-18. シャットダウン電流と電源電圧との関係, VBAT

図 5-19. PVDD のアイドル電流と電圧との関係

図 5-20. VBAT のアイドル電流と電圧との関係

## 6 パラメータ測定情報

測定には、LC 再構成フィルタ Cyntec VCMT053T-3R3MN5 3.3 $\mu$ H インダクタ + 1 $\mu$ F コンデンサを使用します。

内蔵バイロットトーンでリアルタイム負荷診断を有効化するときは、誤った値の測定結果を避けるため、アナログ平衡化入力フィルタを使用する必要があります。カットオフ周波数が 20Hz の APx500 シリーズが提供する楕円型ハイパスフィルタと、AES17 (20kHz) などのローパスフィルタを推奨します。試験装置がこのフィルタタイプをサポートしていない場合は、正確な性能測定を行うために、TI ではリアルタイム負荷診断をオフにすることをお勧めします。

## 7 詳細説明

### 7.1 概要

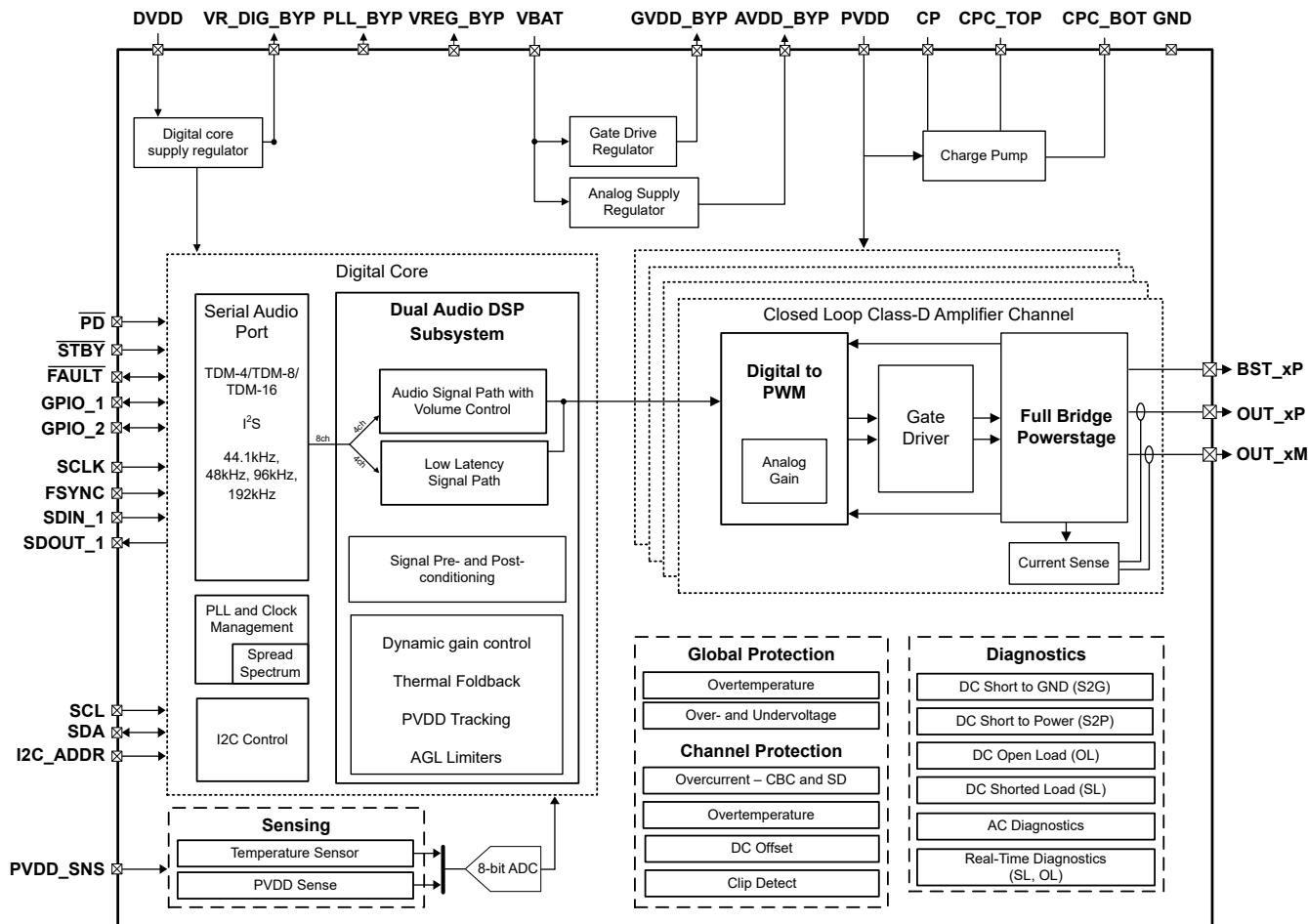

TAS6754-Q1 は、自動車業界向けに特別に設計された 4 チャネル デジタル入力 Class-D オーディオ アンプです。このデバイスは、19 の最大 V まで車両バッテリで動作し、最大 40V のロードダンプに対応するよう設計されています。高度な 1L 変調を用いた超高効率 Class-D テクノロジーにより、スイッチング損失を低減し、PCB 面積を小さくすることができます。このデバイスは、小型かつ軽量で、高度な機能を備えた高忠実度 (ハイファイ) オーディオ サウンド システムを実現します。

コア設計ブロックは次のとおりです。

- シリアル オーディオ ポート

- PLL およびクロック管理

- デュアルコアオーディオ DSP サブシステム

- 出力段フィードバック付きのパルス幅変調器 (PWM)

- ゲートドライブ

- パワー FET

- 電流センス

- リアルタイム負荷診断を含む診断

- 保護

- 電源

- I<sup>2</sup>C シリアル通信バス

- センシング

## 7.2 機能ブロック図

図 7-1. 機能ブロック図

## 7.3 機能説明

### 7.3.1 電源

このデバイスの 3 つの電源入力 (DVDD、VBAT、PVDD) があり、以下に説明します。

**DVDD** これは DVDD ピンに接続された 1.8V または 3.3V の電源で、デジタル回路に電力を供給します。

**VBAT** このピンは、推奨制限範囲内で、車両バッテリまたは調節用の昇圧システムの電圧レールに接続できる、高圧電源です。最善の性能を得るには、このレールは 10V 以上です。最大電源電圧については、[推奨動作条件](#) の表を参照してください。この電源レールは高電圧のアナログ回路に使用されますが、出力 FET には使用しません。

**PVDD** このピンは、車両バッテリまたは昇圧システム内の別の電圧レールに接続できる高電流電源です。PVDD ピンは出力 FET に電力を供給します。これは、VBAT 電源電圧を下回っていても [推奨動作条件](#) 内に収まるため、動的な電圧システムを実現できます。

内部回路に必要な電圧を生成する、複数のオンチップ レギュレータが内蔵されています。外部ピンは、電源をフィルタリングするためのバイパスコンデンサにのみ使用でき、他の回路への電力供給には使用できません。

このデバイスは、デバイスの絶対最大定格内の偶発的なオープングランドおよび電力条件に耐えられます。通常、スピーカーの配線がグランドに短絡し、意図しないオープングランドが発生した場合、出力 FET のボディダイオードを経由する 2 番目のグランドパスが利用できます。

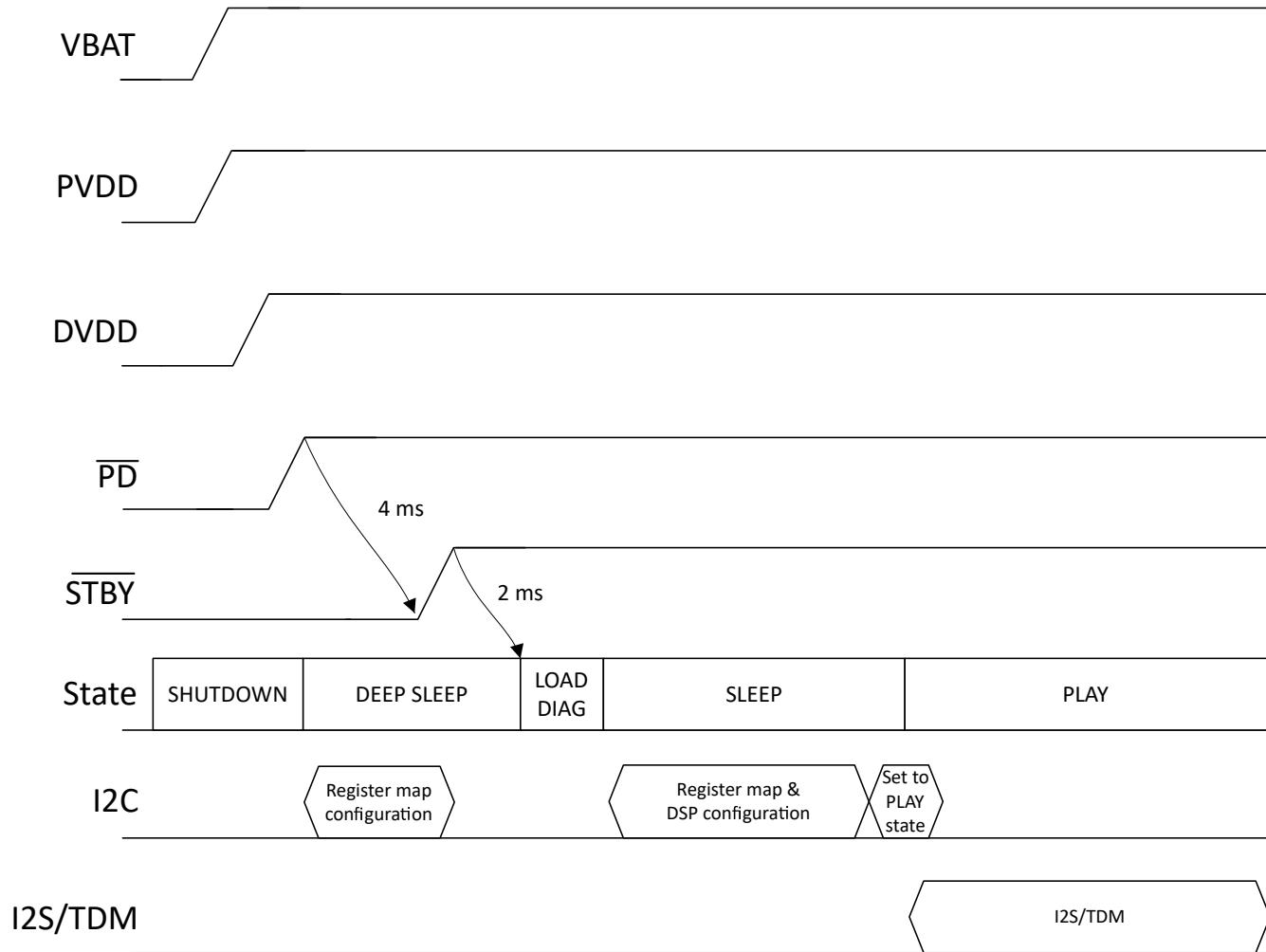

#### 7.3.1.1 電源シーケンス

標準的なシステムでは、VBAT と PVDD の両方の電源は車両のバッテリに接続され、同時に電源投入されます。

##### 7.3.1.1.1 パワーアップシーケンス

電源投入時には、3 つの電源レール (VBAT、PVDD、DVDD) すべてが [推奨動作条件](#) 内になるまで  $\overline{PD}$  ピンを LOW に維持することを推奨します。

すべての電源レールが印加され準備ができた時点で、 $\overline{PD}$  ピンを解放すると、内部デジタル回路に電源が投入されます。 $\overline{PD}$  ピンを解放した後、 $\overline{STBY}$  ピンを解放する前に、最低 4ms の待機時間が推奨されます。 $\overline{STBY}$  ピンを解放すると、内部アナログ回路が起動します。このシーケンスが不可能で、 $\overline{PD}$  と  $\overline{STBY}$  を同時に解放する必要がある場合、次の状態遷移に最大 6ms かかる場合があります。このとき、デバイスはアナログ回路を起動し、適切な内部ブート手順を維持します。

アナログ回路の電源投入後 (VBAT Ready および  $\overline{STBY}$  が解放された後) に電源故障が発生すると、必ず TAS6754-Q1 は PLAY またはその他の状態を終了して、電源故障が解消されるまで [自動復帰 \(AUTOREC\) 状態](#) に戻ります。

Applying DVDD before VBAT will lead to a reported “VBAT Undervoltage Fault” which needs to be cleared

図 7-2. TAS6754-Q1 のパワーアップ シーケンス

### 7.3.1.1.2 電源オフ シーケンス

デバイスの電源をオフにするには、まず STBY ピンまたは PD ピンを 10ms 以上 低く設定してから、PVDD、VBAT、または DVDD を取り外します。10ms 後に、電源を取り外すことができます。DVDD 電源を取り外す前に、まず PVDD と VBAT を取り外すことを推奨します。

### 7.3.1.2 デバイスの初期化とパワーオン リセット (POR)

デバイスは、システムの電源投入時、PD ピンを HIGH にするか、DVDD 電圧が POR しきい値を下回った後、通常状態に復帰すると初期化されます。

デバイスが初期化されると、すべての I<sup>2</sup>C レジスタはデフォルト値に設定されます。

I<sup>2</sup>C のデバイスアドレスは、I2C\_ADDR ピンによって決定されます。詳細については、[I<sup>2</sup>C アドレスの選択](#) を参照してください。

### 7.3.2 シリアルオーディオポート

シリアルオーディオのインターフェイスは、左揃えの I<sup>2</sup>S または DSP モードのフォーマットでデータを受信できます。さらに、時分割多重(TDM)を実装して、最大 TDM16 をサポートするマルチチャネル動作を実現できます。

SDIN\_1 ピンと SDOUT\_1 ピンはデータ転送に利用できますが、必要に応じて、GPIO ピンのいずれかを SDIN\_2 および SDOUT\_2 に割り当てるすることができます。詳細については、[GPIO ピン](#) を参照してください。

### 7.3.2.1 左詰めタイミング

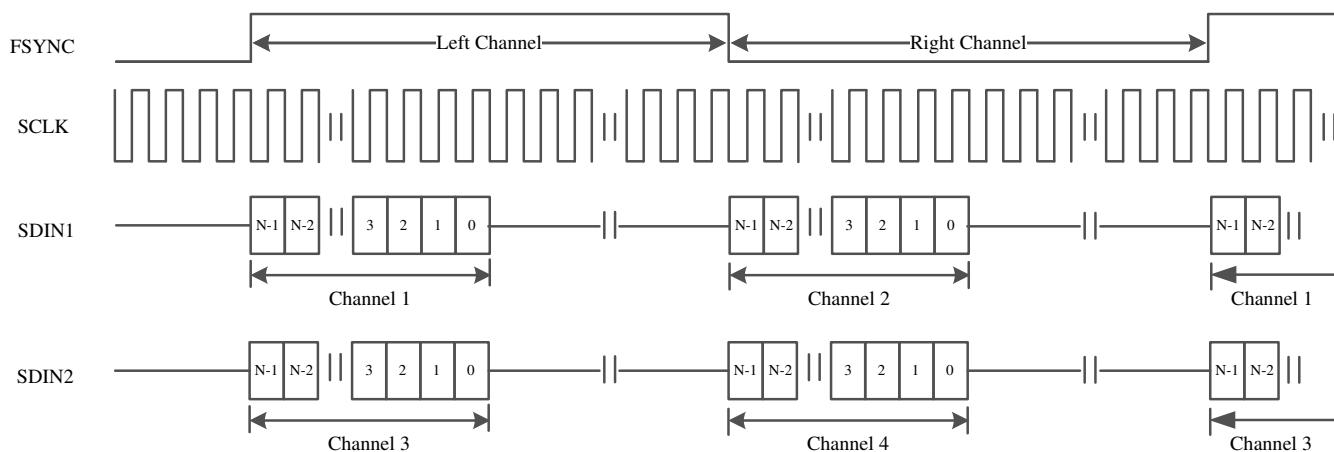

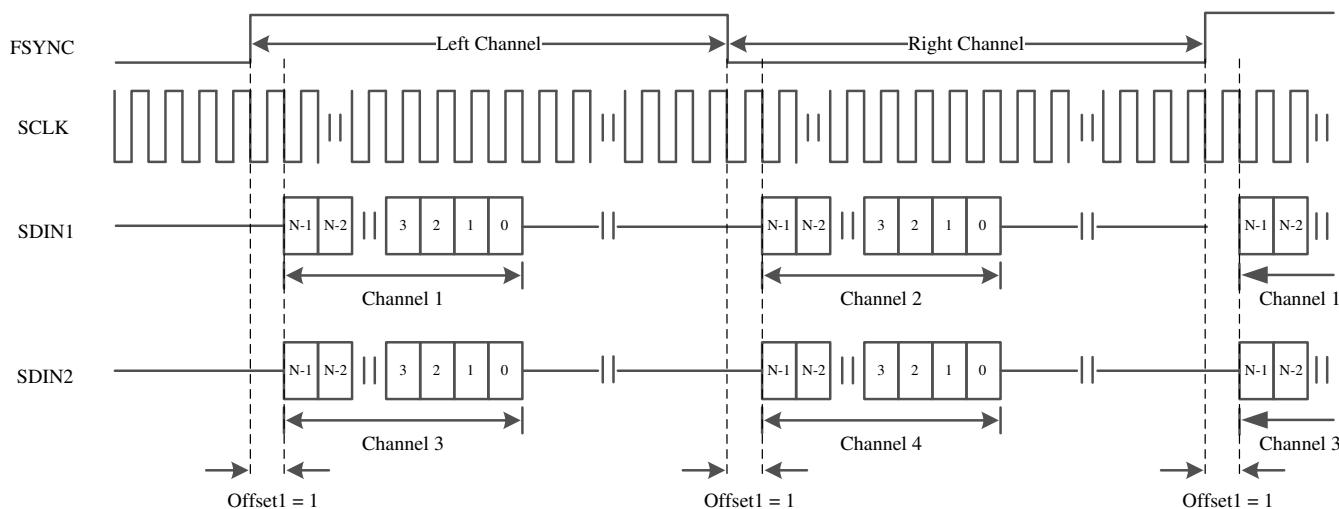

左詰めタイミングでは、FSYNC ピンを使用して、左チャネルまたは右チャネルのデータが送信されるタイミングを定義します。左チャネルの MSB は、オーディオフレームクロック(FSYNC)の立ち上がりエッジに続くシリアルクロック(SCLK)の立ち上がりエッジで有効です。同様に、右チャネルの MSB は、FSYNC の立ち下がりエッジに続く SCLK クロックの立ち上がりエッジで有効です。チャネルのオフセットは設定可能で、すべてのチャネルで同一です。

図 7-3. 左詰めタイミングのタイミング図

図 7-4. オフセット 1 = 1 による左詰めタイミングのタイミング図

### 7.3.2.2 I<sup>2</sup>S モード

I<sup>2</sup>S モードでは、FSYNC ピンを使用して、左チャネルのデータを送信するタイミング、右チャネルのデータを送信するタイミングを定義します。I<sup>2</sup>S モードでは、左チャネルの MSB は、オーディオフレームクロック(FSYNC)の立ち下がりエッジ後のシリアルクロック(SCLK)の 2 番目の立ち上がりエッジで有効になります。同様に、右チャネルの MSB は、FSYNC の立ち上がりエッジ後の SCLK の 2 番目の立ち上がりエッジで有効です。チャネルのオフセットは設定可能で、チャネル間で同一です。

図 7-5. I2S モードのタイミング図

図 7-6. オフセット = 1 による I2S モードのタイミング図

### 7.3.2.3 DSP モード

DSP モードでは、FSYNC ピンを使用してオーディオデータの開始を定義しますが、チャネルを区別することはできません。オーディオフレームクロック(FSYNC)の立ち上がりエッジで、左チャネルデータを最初に使用してデータ転送を開始し、その後直ちに右チャネルデータが続きます。各データビットは、シリアルクロック(SCLK)の立ち上がりエッジで有効となります。10 ビットのチャネルオフセットは設定可能ですが、すべてのチャネルで同一です。

図 7-7. DSP モードのタイミング図

図 7-8. オフセット = 1 による DSP モードのタイミング図

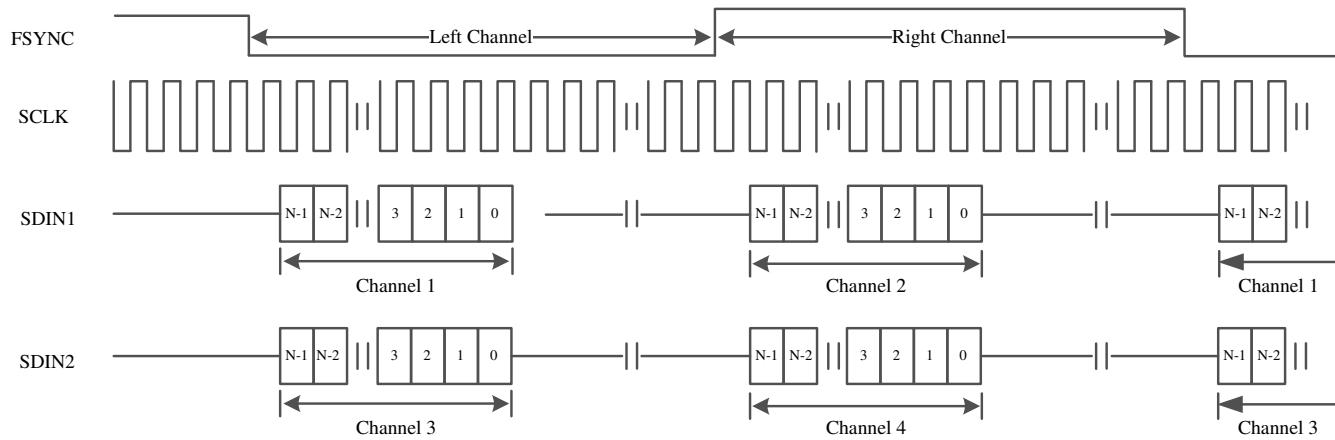

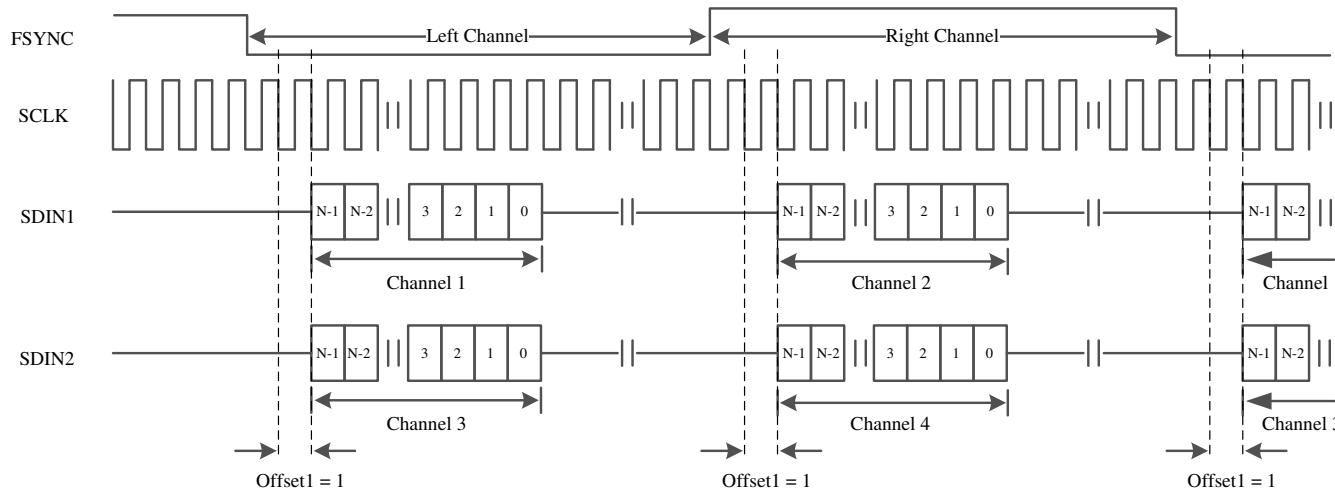

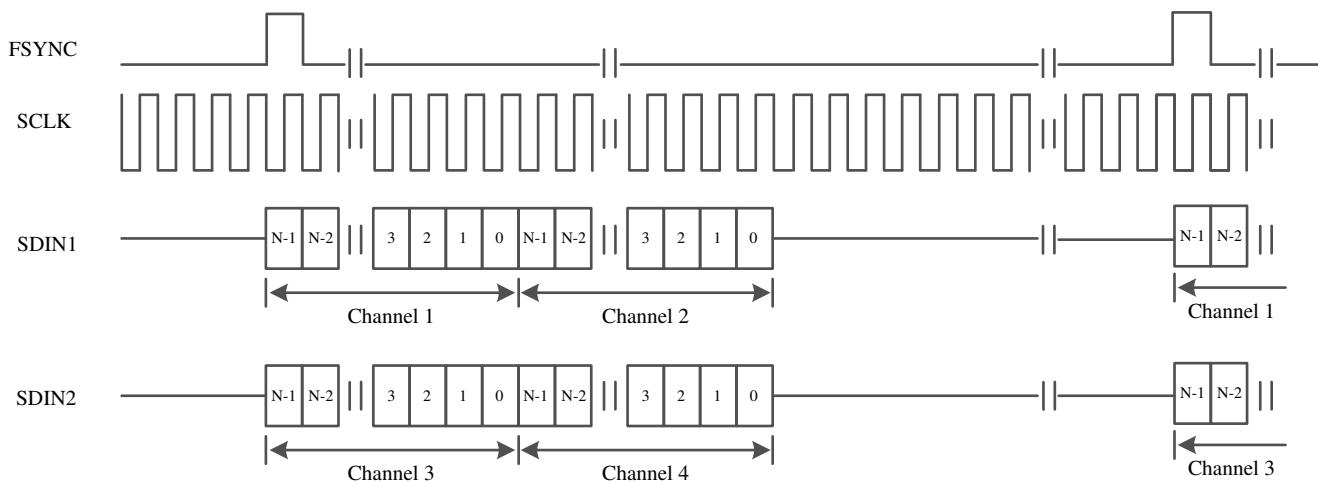

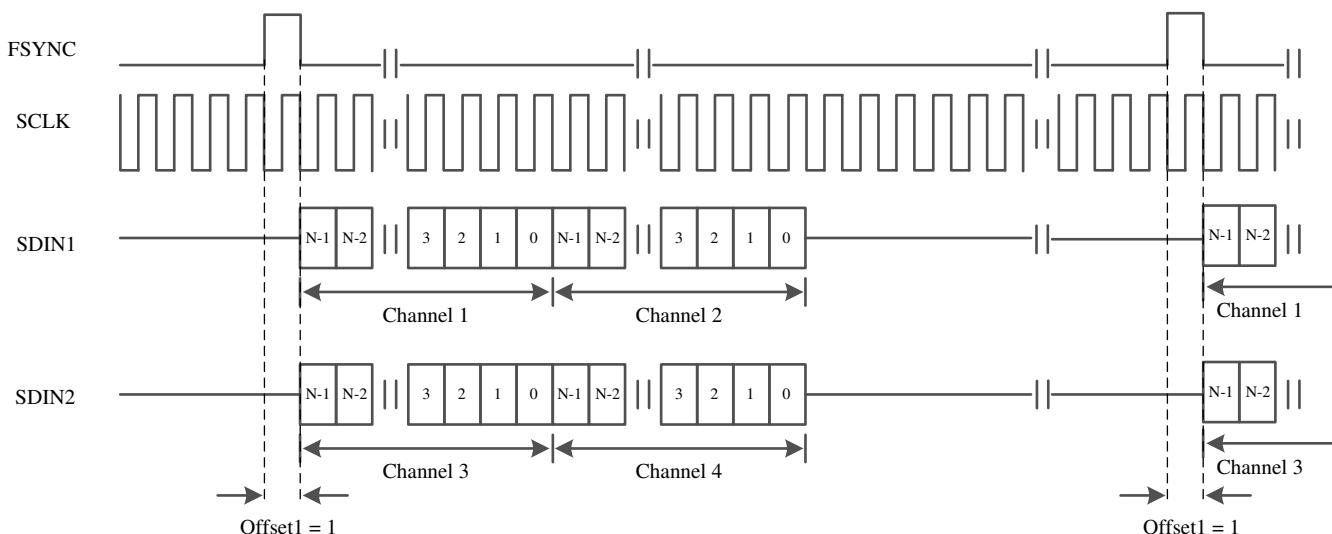

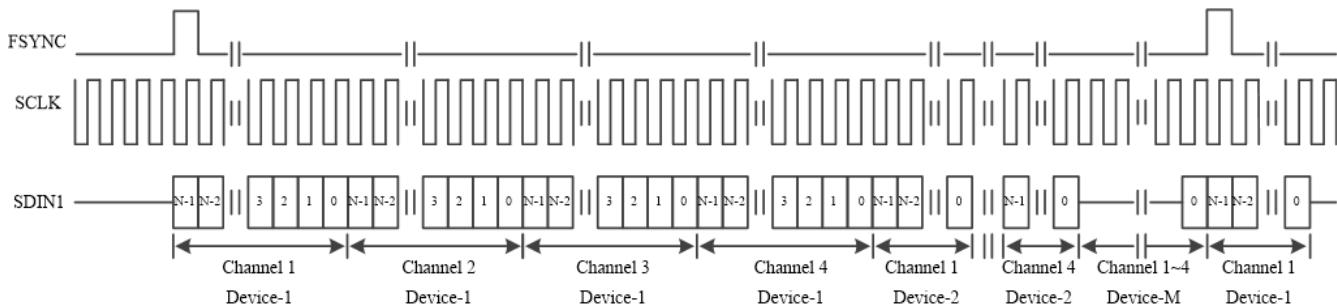

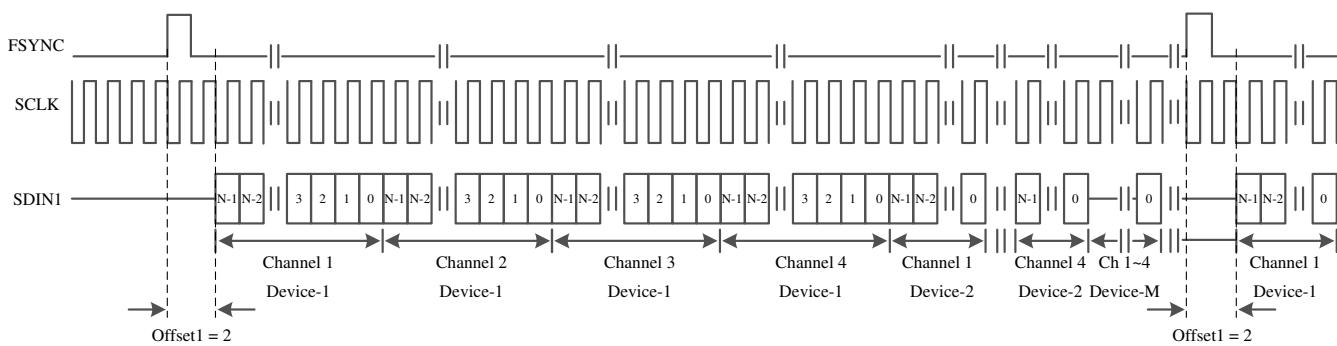

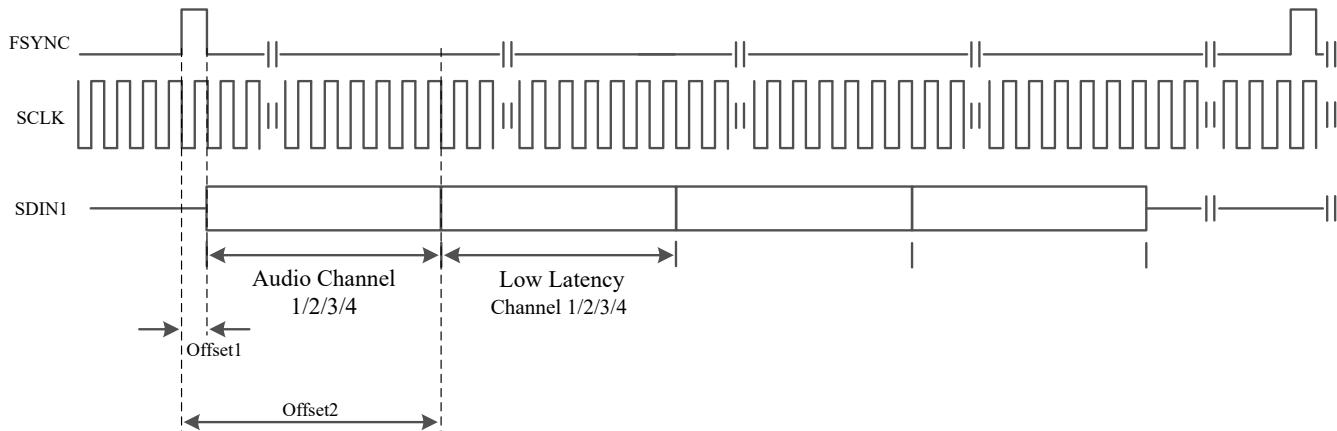

### 7.3.2.4 TDM モード

TDM モードは SDIN 経由で 4、8、または 16 チャンネルのオーディオデータをサポートしています。このデータは单一のビンで受信することも、SDIN\_1 と SDIN\_2 に分割して受信することもできます。データフォーマットは、**DSP モード** に準拠します。

図 7-9. TDM モードのタイミング図

図 7-10. TDM モードのタイミング図（オーディオチャネルがオフセット 1 = 2 の場合）

図 7-11. オーディオチャネルオフセット 1、低遅延チャネルオフセット 2 による TDM モードのタイミング図

### 7.3.2.5 SDOUT - データ出力

TAS6754-Q1 は、I<sup>2</sup>S モードと TDM モードのどちらかで、選択したデータを送信します。オーディオ入力のシリアルクロック (SCLK) とオーディオフレームクロック (FSYNC) は再利用され、出力データにはオーディオ入力信号と同じサンプリング周波数と最大オーディオフレームサイズがあります。

### 7.3.2.6 デバイスクロッキング

TAS6754-Q1 は柔軟なクロッキングシステムを搭載しています。内部的には、デバイスを正しく機能させるために、主に関連するクロックレートで、いくつかの追加クロックが必要です。これらのクロックは、すべてシリアルオーディオインターフェイスから入手できます。

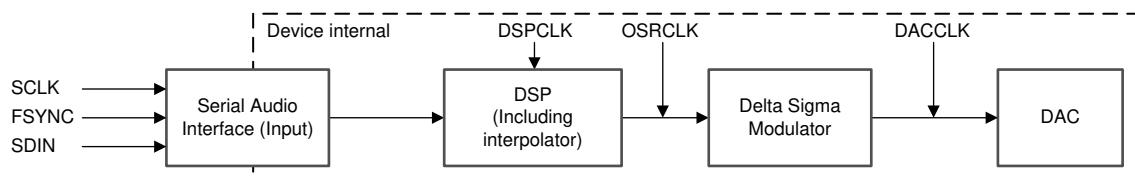

図 7-12 に、基本的なデータフローとクロックディストリビューションを示します。

図 7-12. 各クロックのオーディオフロー

シリアルオーディオインターフェイスには、通常、以下の 3 つの接続ピンがあります。

- SCLK (オーディオシリアルクロック)

- FSYNC (TDM または I<sup>2</sup>S の左/右におけるフレーム同期)

- SDIN (入力データ)。TDM モードでは、単一の SDIN を使用しますが、I<sup>2</sup>S では 4 チャネルのオーディオデータを提供するために 2 つの SDIN ピンが必要です

- オプション: 発信データ転送用 SDOUT。最大 2 つの SDOUT ピンを設定可能

このデバイスには内部 PLL が搭載されており、SCLK をリファレンスクロックとして使用し、DSP および DAC クロックに必要なより高速なクロックを生成します。

TAS6754-Q1 には、オーディオサンプリングレート検出回路が搭載されており、サンプリング周波数を自動検出します。44.1kHz ~ 48kHz、88.2kHz ~ 96kHz、192kHz の一般的なオーディオ・サンプリング周波数に対応しています。サンプリング周波数検出器は、DAC と DSP のクロックを自動的に設定します。

#### 7.3.2.6.1 クロックレート

シリアルオーディオインターフェイスポートは、信号 SCLK、FSYNC、SDIN\_1 と、I<sup>2</sup>S モードのオプションである SDIN\_2 を持つ 3 線式シリアルポートです。

SCLK は、SDIN\_x にあるシリアルデータをオーディオインターフェイスのシリアルシフトレジスタにクロック供給するためには、シリアルオーディオビットクロックです。シリアルデータは、SCLK によって TAS6754-Q1 デバイスにクロック入力されます。

FSYNC ピンは、デバイスが TDM モードで動作している場合、シリアルオーディオの左/右ワードクロックまたはフレーム同期です。

SDIN\_1 は TDM データ入力です。I<sup>2</sup>S モードでは、SDIN\_1 はチャネル 1 と 2 のデータ入力であり、チャネル 3 と 4 のデータ入力を受信するには、GPIO ピンを SDIN\_2 として設定する必要があります。

表 7-1. オーディオデータの形式、ピット深度、クロックレート

| フォーマット                | データピット         | FSYNC 最大周波数 (kHz) | SCLK レート (f <sub>s</sub> ) |

|-----------------------|----------------|-------------------|----------------------------|

| I <sup>2</sup> S / LJ | 32, 24, 20, 16 | 44.1 ~ 192        | x64, x32                   |

| TDM                   | 32, 24, 20, 16 | 44.1 / 48         | x128, x256, x512           |

|                       |                | 96                | x128, x256                 |

|                       |                | 192               | x128                       |

### 7.3.2.6.2 クロック HALT 自動回復

オーディオが再生中でない場合、特定のホストプロセッサにより、オーディオクロックを停止されます。クロックが停止すると、デバイスはすべてのチャネルを Hi-Z 状態に移行して、ラッチャエラー通知を発行します。Hi-Z への遷移は、オーディオインターフェイスから最後に受信したサンプルを保持し、音量を下げることでスムーズに行われます。この動作は、ビット 7 で変更できます。ラッチャエラー通知は、読み取ると消去されます。オーディオクロックが復旧すると、デバイスは自動的に以前の状態に戻ります。

### 7.3.2.6.3 サンプル レートの即時変更

TAS6754-Q1 は、FSYNC レートの即時変更をサポートしています。例えば 48kHz から 96kHz に FSYNC を変更する場合、ホストプロセッサは新しいサンプルレートに変更する前に少なくとも 30ms の間、FSYNC/SCLK を停止状態にする必要があります。この HALT 状態中に、クロックエラーが通知されます。詳細については、[クロック HALT 自動回復](#) セクションを参照してください。

### 7.3.2.7 クロック エラー処理

パワーオン リセット(POR) の後、デバイスはクロックエラーが存在することを想定しますが、クロックエラー検出結果が有効になるまでクロックエラーフラグをアサートしません。

入力クロックの変化が検出されると、自動検出システムは、オーディオインターフェイスから最後に受信したサンプルを保持することで、ただちにミュートするようデバイスに要求します。一方、自動検出は引き続き監視を続け、新しく安定した状態を識別します。

### 7.3.3 デジタル オーディオ処理

TAS6754-Q1 は、次のような先進のデジタルオーディオ処理機能を提供します：

- High フィルタ / DC ブロッキング

- デジタル ボリューム制御

- PVDD フォールドバック / AGL

- サーマル フォールドバック

- ゲイン補償バイクワッド

- リアルタイム負荷診断

- クリップ検出

- 低遅延の信号パス

特定の機能が利用できるかどうかは、選択したサンプリング周波数によって異なります。サンプリング周波数を高くすると、内蔵 DSP 処理時間が短縮され、並列動作できる機能が制限されます。有効化した機能の合計処理要件が、すべてのサンプリング周波数で利用可能な処理時間を超えないようご注意ください。

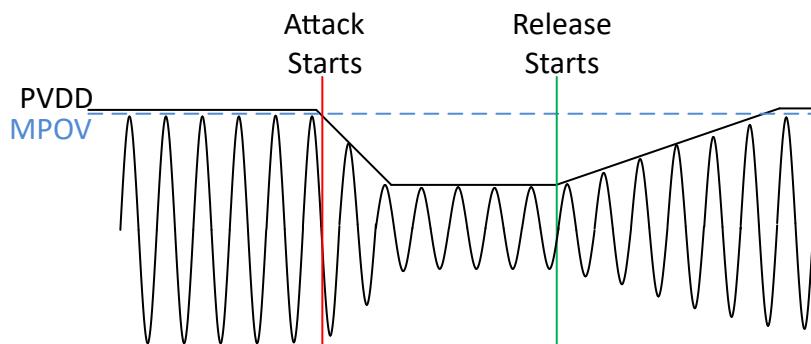

#### 7.3.3.1 PVDD フォールドバック

PVDD フォールドバックは、電源電圧 (PVDD) が変化しても一貫したダイナミックレンジを維持するため、オーディオ信号にスムーズな圧縮をかけます。この機能は、オーディオ信号が電源のヘッドルームを超えているシステムで、予期しない出力クリッピングや歪みを防止するのに役立ちます。自動ゲインリミッタ (AGL) と呼ぶこともあります。

図 7-13. PVDD フォールドバックの例

### 7.3.3.2 ハイパス フィルタ

TAS6754-Q1 に接続されているスピーカを保護するため、オーディオ処理パスに DC ブロッキングハイパスフィルタが内蔵されています。

### 7.3.3.3 アナログ ゲイン

TAS6754-Q1 では、ユーザーが各チャネルペアのアナログゲインを 0.5dB 単位で設定できます。

ゲイン設定の 0dB は、フルスケールデジタル入力における 28V/FS のピーク出力電圧に対応します。出力ノイズとダイナミックレンジ性能を最適化するため、TI では予想される PVDD による動作に対して可能な限り低いゲインを選択することを推奨しています

アナログゲイン設定を変更できるのは、影響を受けるチャネルが **DEEP SLEEP** または **SLEEP** 状態のときのみです。

デバイスが **PLAY 状態** に移行すると、デバイスはアナログゲインを 0.5dB 単位で徐々に目的の値まで上昇させます。

### 7.3.3.4 デジタル ボリューム制御

出力チャネルには、0.5dB 刻みで、-103dB ~ 0dB の範囲でデジタルボリューム制御機能があります。

#### 7.3.3.4.1 自動ミュート

オーディオ入力でゼロサンプルの連続したストリームを検出すると、デバイスはチャネルを自動的にミュートに設定できます。このモードでは、デバイスは入力信号を監視し続け、設定に応じて、有効なゼロ以外の信号が届けられると、個別のチャネルまたはすべてのチャネルのいずれかのミュートを同時に解除します。

#### 7.3.3.5 ゲイン補償バイクワッド

Class-D アンプの変調器と出力 LC フィルタは、周波数応答の直線性に望ましくない影響を及ぼし、周波数ドロップ/ピークを引き起こす可能性があります。この効果を補償し、フラットな応答を実現できるように、TAS6754-Q1 には統合型およびチャネルベースのゲイン補償バイクワッド機能が搭載されています。

バイクワッドは、チャネルごとに設定可能ですが、デフォルトでは無効になっています。希望の調整を有効にするには、それぞれの係数を DSP メモリに書き込む必要があります。

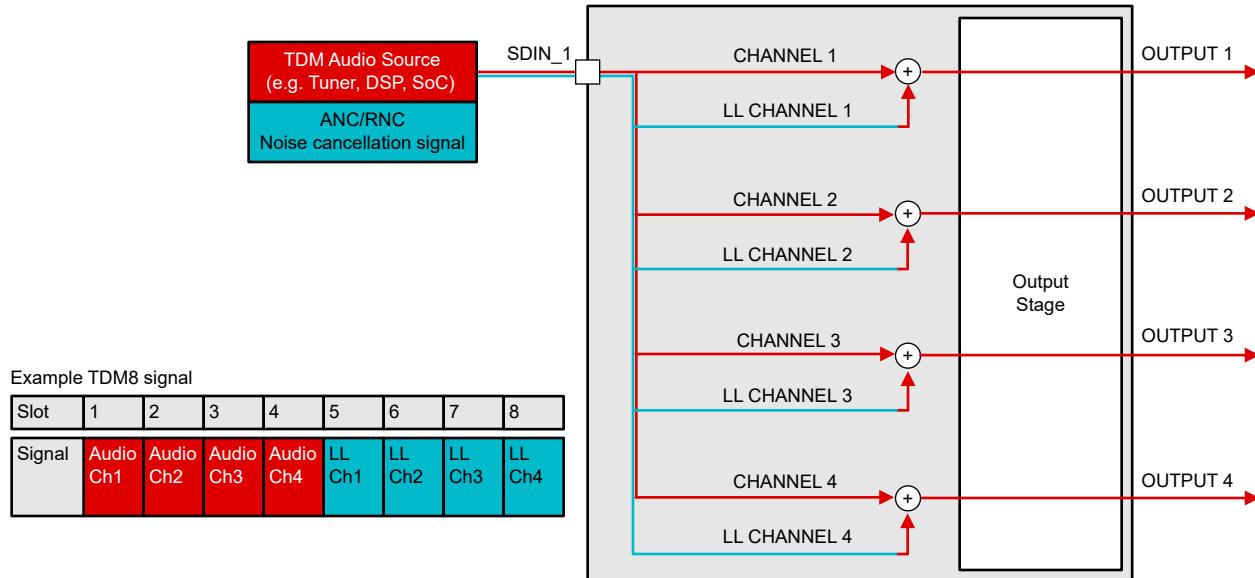

#### 7.3.3.6 低レイテンシの信号バス

アクティブノイズキャンセリング (ANC) やロードノイズキャンセレーション (RNC) など、最小の処理遅延時間が必要なオーディオ信号に対して、TAS6754-Q1 は低遅延の信号バスを提供します。サンプリング周波数が 48kHz の場合、このバスは内部信号処理を最小化することにより、アンプの入力と出力間の信号遅延を 70% 以上短縮します。

低遅延の信号バスは、通常のオーディオ信号バスと並列に確立されます。両方の信号バスに入力データが供給されると、各チャネルの 2 つの信号 (オーディオおよび低遅延) は、チャネルの出力増幅段の直前に内部で混合されます。両信号は加算され、合計信号振幅は、歪みを避けるために、利用可能なゲインレンジと電圧ヘッドルームを超えないようにしてください。低遅延の信号は、通常のオーディオバス信号よりも短い遅延でデバイスを通過しますのでご注意ください。

低遅延の信号バスは、サンプリング周波数が 48kHz または 96kHz の場合にのみ利用できます。

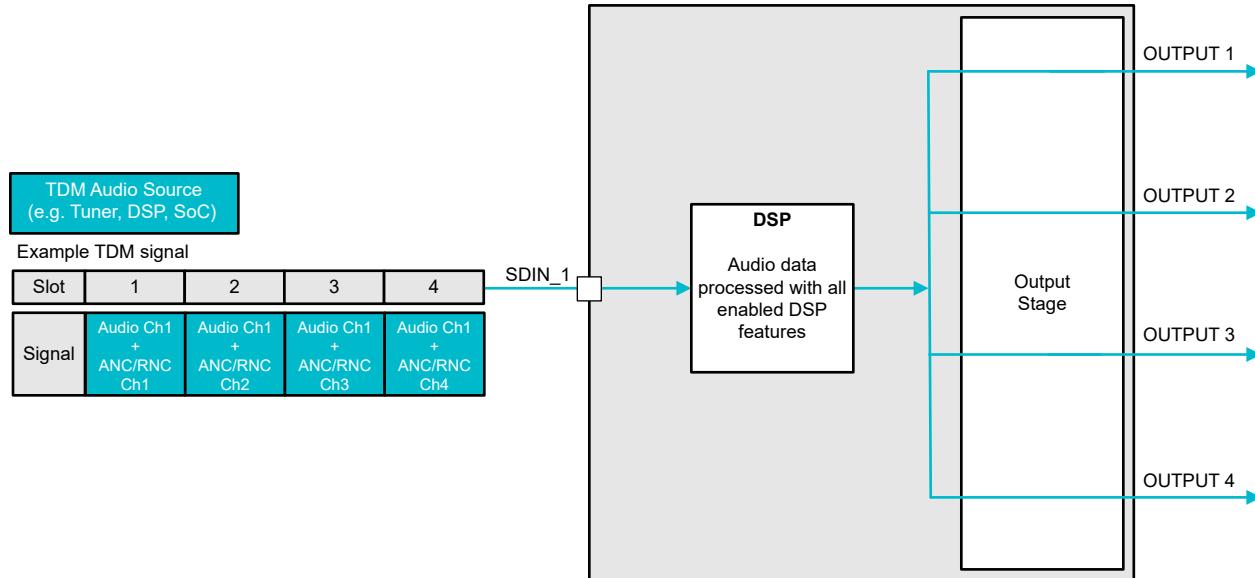

図 7-14. 低遅延とオーディオ信号バス

### 7.3.3.7 フル機能の低遅延パス

低遅延信号バスに加えて、TAS6754-Q1 にはフル機能の低遅延バスが内蔵されています。フル機能の低遅延バスを使用するアクティブノイズキャンセル(ANC)や走行ノイズキャンセル(RNC)など、時間に制約のあるオーディオ信号をプリミックスできるので、時間に制約のないオーディオデータと分離する必要はありません。プリミックスされたオーディオデータは、DSP を介して処理され、出力段で増幅されることで、グループ遅延をより小さくします。

図 7-15. フル機能による低遅延バスとオーディオ信号バス

### 7.3.4 Class-D 動作とスペクトラム拡散制御

#### 7.3.4.1 1L 変調

TAS6754-Q1 は、1L 変調をサポートしています。1L 変調により、OUT\_xP 側は 0V から、スイッチング周波数(Fsw)の電源電圧に切り替わります。OUT\_xM 側は、0V からオーディオ周波数の電源電圧に切り替わります。チャネルの OUT\_xM 側はより低い周波数でスイッチングするため、BTL チャネルの OUT\_xM 側にはインダクタは必要ありません。

#### 7.3.4.2 高周波パルス幅変調器 (PWM)

PWM 変調器は、入力オーディオデータを、デューティサイクルが変動するスイッチング信号に変換します。PWM 変調器は、高帯域幅、低ノイズ、低歪み、優れた安定性を備えた高度な設計です。

TAS6754-Q1 は、伝導型と放射型の電磁波を管理する設定可能な出力 PWM 位相制御機能を搭載しています。この機能により、チャネル出力の PWM 位相オフセットを、他のチャネルに合わせて変更できます。

#### 7.3.4.3 スペクトラム拡散制御

TAS6754-Q1 はスペクトラム拡散制御を変調器のクロック信号に適用します。クロック信号のスペクトルを制御すると、EMI 試験中に表示される高周波数の信号部品の動作が最適化されます。スペクトラム拡散変調は、PWM 変調技術であり、出力 PWM 周波数を変化させることで EMI 測定値のピークを引き下げます。スペクトルは広くなりますが、その結果、EMI ノイズはより低いレベルになります。

#### 7.3.4.4 ゲート ドライバ

ゲートドライバは低電圧 PWM 信号を受け入れ、レベルシフトを行い、大電流、フルブリッジのパワー FET 段を駆動します。

このデバイスは、独自の手法を使用して、EMI とオーディオ性能を最適化します。ゲートドライバの電源電圧 GVDD は内部で生成されるため、デカップリングコンデンサを接続する必要があります。

フル H ブリッジ出力段では、NMOS トランジスタのみを使用します。そのため、OUT-xP 側のハイサイド NMOS トランジスタを適切に作動させるためには、ブートストラップコンデンサが必要です。印加電圧(負荷ダンプ電圧を含む)に適した定格を持つ、品質 X7R 以上の  $1\mu\text{F}$  セラミックコンデンサを、各出力に対応するブートストラップ入力に接続しなければなりません。BST ピンと対応する出力との間に接続されたブートストラップコンデンサは、ハイサイド N チャネル パワー MOSFET ゲート駆動回路用のフローティング電源として機能します。各ハイサイドスイッチングサイクルの間、ブートストラップコンデンサはゲートソース間電圧を High に保持し、ハイサイド MOSFET をオンに保ちます。

OUT\_xM 側のハイサイド FET ゲートドライバには、4 つのチャネルすべてにチャージポンプ (CP) 電源が供給されます。印加電圧(負荷ダンプ電圧を含む)に適した定格を持つ、品質 X7R 以上の  $330\text{nF}$  セラミックコンデンサを、CP ピンと PVDD の間に接続しなければなりません。さらに、同様の定格で  $100\text{nF}$  のセラミックコンデンサを CPC\_TOP ピンから CPC\_BOT ピンに接続しなければなりません。

#### 7.3.4.5 パワー FET

BTL 出力チャネルは、高効率と負荷に最大限の電力供給を実現する 4 個の N-チャネル FET で構成されています。これらの FET は、[推奨動作条件](#) 内での動作時に高速なスイッチング周波数や大きな電圧過渡に対応できるよう設計されています。

#### 7.3.5 負荷診断

このデバイスには、DC および AC 負荷診断機能が内蔵されており、負荷のステータスを判定するために使用されます。DC 診断は、デフォルトではオンになっています。

##### 7.3.5.1 DC 負荷診断

DC 負荷診断機能は、負荷が適切に接続されているかどうかを検証するために使用されます。

ファストタイムオーディオに関するシステムレベルの起動要件をサポートすると:

- デバイスが DEEP SLEEP モードを終了し、電源が推奨動作範囲内になると、すぐに診断機能が利用可能になります。

- 診断機能は、外部オーディオ入力信号、利用可能なクロック周波数や同期周波数に依存しません。

DC 診断は正常に完了し、次のテストに合格した場合、チャネルが MUTE モードまたは PLAY モードに移行することができます。

- グランドへの短絡 なし

- 電源への短絡 なし

- 負荷短絡 なし

- 開放負荷 なし

#### 7.3.5.1.1 デバイス初期化時の自動 DC 負荷診断

TAS6754-Q1 は、デバイス起動時に自動的、自律的な DC 負荷診断をサポートしています。DEEP SLEEP 状態を終了し、すべての電源が推奨動作範囲内にあるという条件下では、デバイスは SLEEP 状態に移行し、4 つのチャネルすべてで DC 負荷診断を自動的に開始します。

TAS6754-Q1 では、デフォルト設定に基づいて電源への短絡(S2P)、グランドへの短絡(S2G)、開放負荷(OL)、短絡負荷(SL)の試験を実施する場合、I<sup>2</sup>C 設定もオーディオ信号も必要ありません。システムは、オーディオチェーンのデジタル部分を起動しながら負荷診断を実施できるため、この自律的な動作を活用できます。

#### 7.3.5.1.2 Hi-Z または PLAY 中の自動 DC 負荷診断

チャネルが Hi-Z または PLAY 状態のときに故障が発生した場合、デバイスはそのチャネルを FAULT 状態または自動復帰状態のいずれかに設定します。故障が解消されると、デバイスは影響を受けたチャネルで自動的に DC 負荷診断を実行し、I<sup>2</sup>C、以前の Hi-Z、再生状態にそれぞれ回復します。

#### 7.3.5.1.3 DC 負荷診断の手動による開始

手動 DC 負荷診断は、すべての電源が推奨動作範囲内にあり、かつデバイスが初めて SLEEP 状態に移行した後であれば、どのような状態でも有効にできます。DC 診断は、I<sup>2</sup>C 制御状態レジスタを設定し、一切のチャネルで LOAD DIAG 状態を実行することにより、手動で有効化できます。STBY ピンまたは GPIO ピンのどちらかの機能がデバイスを SLEEP または DEEP SLEEP 状態に設定している場合、手動の DC 負荷診断は実行できません。このことは、I<sup>2</sup>C 制御によってデバイスが SLEEP 状態または DEEP SLEEP 状態に設定されている場合には適用されません。この場合、手動の DC 負荷診断を利用できます。

#### 7.3.5.1.4 グランド短絡

グランド短絡(S2G)試験では、試験対象チャネル(I)の出力ピン OUT\_(I)M または OUT\_(I)P から GND までの導電性パスがあり、電気的特性セクションに規定されているインピーダンスより低い場合に、フォルト条件がトリガされます。

#### 7.3.5.1.5 電源への短絡

電源への短絡(S2P)テストでは、テストしたチャネル(I)の出力ピン OUT\_(I)M または OUT\_(I)P から、電気的特性セクションに規定されているインピーダンス以下の電源レールまでの導電性パスがある場合、フォルト条件がトリガされます。

#### 7.3.5.1.6 短絡負荷と開放負荷

短絡負荷(SL)テストでは、テスト対象のチャネル(I)の OUT\_(i)M ピンと OUT\_(i)P ピンの間の導電性パスがしきい値設定を下回った場合、FAULT 条件がトリガされます。SL テストでは、接続する予定の負荷に応じてしきい値を設定できます。各チャネルに接続されているスピーカーとケーブルのインピーダンスは異なるため、各チャネルに固有のしきい値を割り当てるできます。

開放負荷(OL)テストでは、テストしたチャネル(I)の OUT\_(i)M ピンと OUT\_(i)P ピンの間の導電性パスのインピーダンスが、電気的特性セクションに指定されたインピーダンスよりも高い場合にフォルト条件がトリガされます。

|            |                                          |                                           |

|------------|------------------------------------------|-------------------------------------------|

| OL Maximum | Open Load                                | Open Load Detected                        |

| OL Minimum | Open Load (OL)<br>Detection Threshold    | Normal or Open Load<br>May Be Detected    |

| SL Maximum | Normal Load                              | Play Mode                                 |

| SL Minimum | Shorted Load (SL)<br>Detection Threshold | Normal or Shorted Load<br>May Be Detected |

|            | Shorted Load                             | Shorted Load Detected                     |

図 7-16. DC 負荷診断を通知するしきい値

### 7.3.5.2 ライン出力診断

このデバイスは、ライン出力負荷(LO)を検出するためのオプションとして試験機能も搭載しています。ライン出力負荷が、開放負荷(OL)しきい値を上回る高インピーダンス負荷になると、DC 負荷診断によって OL 状態が通知されます。DC 診断試験中に OL 状態が検出されると、ライン出力検出ビットが High に設定されている場合、ライン出力負荷が存在するかどうかシステムがテストします。

### 7.3.5.3 AC 負荷診断

AC 負荷診断は、パッシブクロスオーバーで使用される場合、容量性カッピングスピーカやツイータの適切な接続を判定するために使用されます。AC 負荷診断は、I<sup>2</sup>C を通じてコントロールされます。TAS6754-Q1 は、AC インピーダンスを判定し、ツイータ検出結果を I<sup>2</sup>C レジスタに通知するために必要な信号ソースを提供します。I<sup>2</sup>C で選択したテスト周波数により、適切に検出できるように、目的のスピーカに電流が流れます。AC 負荷診断は、TDM/I<sup>2</sup>S クロックが存在しなくても動作できます。

#### 注

AC 診断中にフォルトが発生すると、AC 診断は停止します。AC 診断は、DC 診断が実行されるまで再度実行することはできません。これは、AC 診断中の障害に潜在的な危険性がないことを確認するためです。

### 7.3.5.3.1 動作原理

TAS6754-Q1 の AC 負荷診断回路は、負荷に対して内部で生成されたステイミュラスを提供し、負荷応答をキャプチャします。キャプチャされた複素負荷インピーダンスの実数部分と虚数部分を提供し、振幅推定機能とツイータ検出コンパレータを提供します。

### 7.3.5.3.2 刺激信号

このデバイスは、負荷を通して低レベルの 10mA 出力電流を駆動します。これにより、スピーカから大きな音圧レベルが生じることはありません。

### 7.3.5.3.3 負荷インピーダンス

デバイスから見た負荷インピーダンスは、単に出力ピンにかかる電圧と負荷を流れる電流の比を表したものです。

通常、負荷には周波数に依存した大きさがあり、電流と電圧に位相シフトを引き起します。TAS6754-Q1 は、負荷インピーダンスを実数部と虚数部からなる複素値として内部的に取り込みます。負荷インピーダンスを大きさと位相、または実数部と虚数部で表現することは、数学的に等価です。両方の形式は、情報を失うことなく互いに変換することができます。AC 負荷診断が完了すると、複素数インピーダンスの実数部分と虚数部はチャネルで利用でき、I<sup>2</sup>C レジスタから入手することができます。

### 7.3.5.3.4 ツイーター検出

ほとんどの場合、TAS6754-Q1 内蔵の振幅推定機能とツイーター検出レポートを使用すれば、希望のツイータ検出テストを実行するのに十分です。システムにツイーターが正しく接続されている場合、負荷インピーダンスの大きさはスピーカの公称インピーダンス(たとえば  $4\Omega$  など)に近くなります。

### 7.3.5.4 リアルタイム負荷診断

リアルタイム負荷診断(RTLDG)により、アンプのオーディオ動作中に負荷の短絡(SL)と開放負荷(OL)状態を検出できます。再生状態中に負荷インピーダンスを監視するため、TAS6754-Q1 はデバイスに内蔵された電流センス機能を使用してチャネルごとの出力インピーダンスを測定し、その結果設定可能なしきい値と比較します。内部で生成されるパイロット・トーンにより、外部オーディオ入力信号が存在するかどうかにかかわらず、出力インピーダンスを連続的に検出し続けます。

### 7.3.5.5 DC 抵抗の測定

TAS6754-Q1 は、各チャネルに接続した負荷の DC 抵抗測定をサポートしており、これらの負荷は I<sup>2</sup>C 経由でシステムプロセッサヘリードバックすることができます。各チャネルに接続している負荷の DC 抵抗を読み取るには、DC 負荷診断を完了する必要があります。

## 7.3.6 保護および監視

### 7.3.6.1 過電流制限(サイクルバイサイクル)

通常動作時に、高レベルの音楽再生中に、動的負荷電流がデバイスの最大負荷電流  $I_{LIM}$  を超える場合があります。このような場合、デバイスは負荷に流入する電流を動的に制限し、動作を中断することなく継続し、過渡的な音楽イベントで望ましくないシャットダウンを防止します。

### 7.3.6.2 過電流シャットダウン

出力負荷電流が  $I_{SD}$ (出力から GND への短絡時など)に達すると、過電流シャットダウン(OCSD)イベントが発生し、ピーク電流が制限され、影響を受けるチャネルがシャットダウンされます。チャネルをシャットダウンする時間は、短絡状態の重大度によって異なります。

チャネルが **FAULT 状態** になると、出力段は Hi-Z になります。

設定に基づき **Fault** 信号が生成されますが、デフォルトでは **FAULT** ピンにアクティブ LOW 信号が生成されます。

### 7.3.6.3 電流センス

TAS6754-Q1 は、各チャネルの出力電流を同時に測定できます。この機能は完全に統合されており、外付け部品は必要ありません。

チャネル出力電流の測定は、サンプリング周波数  $F_s$  のレートで行われます。電流振幅の測定値は、**SDOUT** によって提供されます。データ送信設定の詳細については、**SDOUT** を参照してください。電流測定とデータ送信は 2 つの別個の機能であり、どちらもデータを利用するようにするために適切な設定が必要です。

### 7.3.6.4 DC 検出

この回路は、通常動作中、アンプの DC オフセットを連続的に検出します。DC オフセットが **DC<sub>FAULT</sub>** のしきい値を超えると、DC フォルトイベントがトリガーされて **FAULT 状態** になり、出力段は高インピーダンスに設定されます。

設定に基づいてフォルト信号が生成され、デフォルトでは **FAULT** ピンにアクティブ LOW 信号が生成されます。

過剰な DC バイアス出力によるスピーカの損傷を防止するため、TI では常に DC 検出を有効にしておくことを推奨しています。

### 7.3.6.5 デジタルクリップ検出

DSP は各チャネルのオーディオ信号を個別に監視し、入力でのオーディオ信号の振幅を補間フィルタと、設定可能なしきい値と比較します。オーディオ信号がしきい値を超えると、**クリップ検出警告イベント** がトリガされます。

TAS6754-Q1 は、疑似アナログクリップ検出 (PACD) をサポートしています。PACD では、DSP 处理が、出力を設定したクリッピングしきい値に対してクリッピングしているかどうかを判断するときに、アナログゲインと電源電圧を考慮して、アナログクリップ検出アプローチを模倣します。

### 7.3.6.6 チャージポンプ

TAS6754-Q1 には、チャージポンプのピン (CP, CPC\_TOP, CPC\_BOT) に保護機能が組み込まれています。デバイスがチャージピンで障害状態を検出すると、チャージポンプはクロックサイクルをスキップします。これは、1 回の故障サイクルとみなされます。デバイスは、次の受信クロックサイクルで再試行します。2 回連続してまたは合計で 3 回の故障条件を検出すると、チャージポンプは受信クロックを無視し始め、出力段が Hi-Z になり、チャージポンプがシャットダウンする [チャージポンプ障害](#) の状態になります。

設定に基づき Fault 信号が生成されますが、デフォルトでは [FAULT](#) ピンにアクティブ LOW 信号が生成されます。

### 7.3.6.7 温度保護および監視

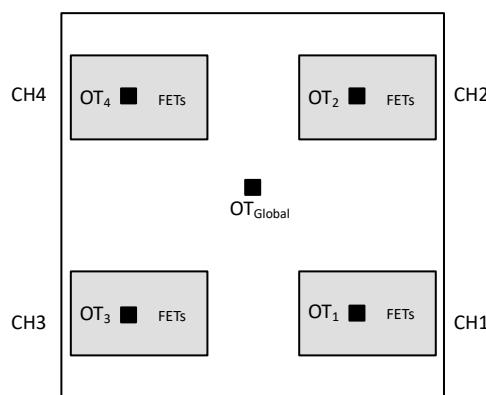

このデバイスは、5 つの温度センサを使用して温度を監視します。出力チャネルには、出力チャネル出力段の中央付近に温度センサがあり、各チャネルの温度を個別に監視します。追加の温度センサはダイ上のグローバルポジションに配置されています。これは、実際のダイ接合部温度を適切に表しています。これらのセンサに基づいて、警告信号やフォルト信号が生成されます。[サーマルゲインフォールドバック](#) 方式が利用可能で、オーディオゲインを自律的に調整し、結果的にダイ温度を制限します。

図 7-17. デバイス内の温度センサ位置の概要

#### 7.3.6.7.1 過熱シャットダウン

グローバル OTSD と出力チャネルによって生成される過熱シャットダウンのしきい値温度は、OTSD (i) で固定した値に設定します。公称温度および回復ヒステリシスの値については、[セクション 5.5](#) を参照してください。

**グローバル OTSD:** グローバル接合部温度が OTSD しきい値を上回ると、すべてのチャネルが保護シャットダウン状態になり、[過熱シャットダウン \(OTSD\) イベント](#) が生成されます。

**チャネル固有の OTSD:** チャネルの接合部温度が OTSD しきい値を上回ると、影響を受けるチャネルは保護状態になり、[過熱シャットダウン \(OTSD\) イベント](#) が生成されます。

警告レベルと OTSD の温度の許容誤差は互いに追従します。

デフォルトでは、OTSD イベントが発生すると、フォルト信号により [FAULT](#) ピンにアクティブ LOW 信号が生成されます。

#### 7.3.6.7.2 過熱警告

グローバル過熱警告 (OTW) のしきい値温度は、[電気的特性](#) に示されているレベルに固定されています。各出力チャネルには独立した温度センサがあります。

動作中に、デバイスが過熱してしきい値を超えると、グローバル [過熱警告イベント](#) が生成されます。同様に、チャネルの温度がしきい値を上回ると、そのチャネルの過熱警告イベントが生成されます。デバイスが動作を続けている間、OTW 情報によって高度なソフトウェアが熱システムの性能を最適化する決定を下すことができます。

[過熱警告イベント](#) で説明されているように、このレポートは、I<sup>2</sup>C レジスタによってポーリングするか、または警告信号用の GPIO ピンを割り当て、OTW レポートルーティングをイネーブルにすることでハードウェア信号を生成することができます。

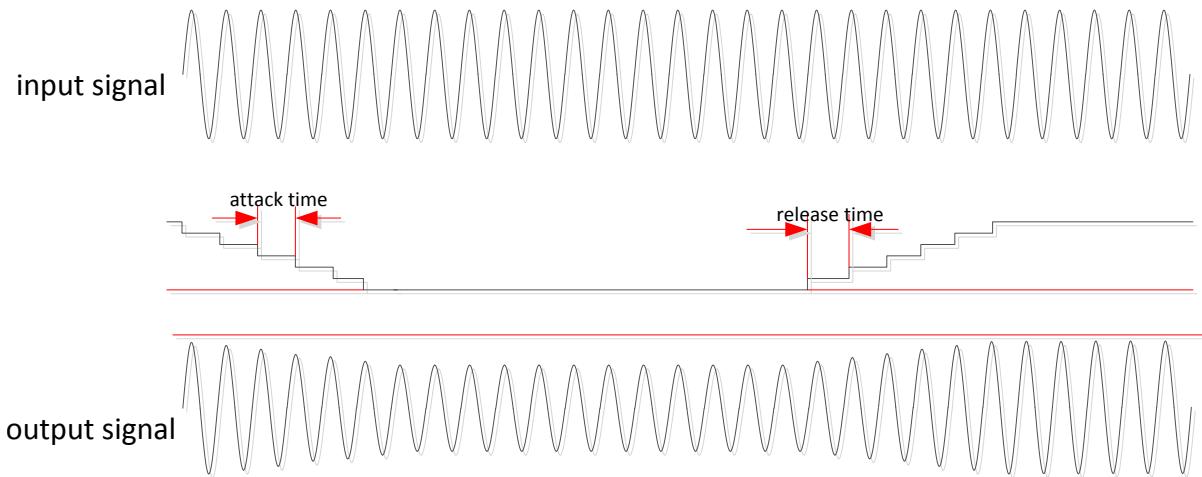

### 7.3.6.7.3 サーマルゲイン フォールドバック

サーマルゲインフォールドバック(TGFB)は、オーディオ出力を維持しながら TAS6754-Q1 を過剰なダイ温度から保護するための電力制限機能です。

フォールドバック電力制限の主な目的は、予期しない [過熱シャットダウン](#) を回避するために、出力段を安全な消費電力制限内に維持することです。この機能により、スムーズなオーディオ応答が得られ、温度制限を超えた場合でも、中断なく音楽を再生できます。つまり、TAS6754-Q1 は、単純にシャットダウンするのではなく、OTSD のトリガを避けながら、相当程度の音楽出力パワーで動作を継続します。

TAS6754-Q1 の DSP は、安全な動作のためにダイ温度をリアルタイムで継続的に監視します。ダイの温度が OTW 制限に近づいてくると、デバイスはホストに警告を発します。TAS6754-Q1 は、温度が OTSD しきい値に達するまで機能しますが、その時点で個別のチャネルまたはアンプがシャットダウンされます。

チャネルのダイ温度が設定したフォールドバックレベルを上回ると、最初はサーマルゲインフォールドバック回路がアクティブになります。デバイスは、サンプルごとに 0.25dB ずつゲインを減らし、これによって出力電力の低減を開始します。このアタックレートを設定できます。設定された最大減衰はレベルごとに異なり、レベル間で累積されません。

温度がフォールドバックレベルより以下の場合、減衰は設定可能なサンプル数を保持します。その後、サンプルあたり 0.1dB のゲインステップレートで減衰の解放を始めます。TGFB によるリリース率はプログラム可能です。

図 7-18. サーマルフォールドバックアタックおよびリリース

### 7.3.6.8 電源障害

電源 VBAT、PVDD、DVDD、チャージポンプは、[電源フォルトイイベント](#) に記載されているように、低電圧および過電圧イベントを監視しています。これにより自動的にシャットダウンが開始され、デバイスが保護されます。VBAT および PVDD の安全動作電圧範囲については、[推奨動作条件](#) の表をご確認ください。

DVDD 電源が V<sub>POR\_OFF</sub> を下回ると、デバイスはシャットダウンします。DVDD POR フォルトイイベントについては、[DVDD パワーオンリセット](#) で説明します。

## 7.3.7 ハードウェア制御ピン

### 7.3.7.1 FAULT ピン

デフォルトでは、FAULT ピンはフォルトイベントを通知し、以下のいずれかの条件でアクティブ Low になります。

- 過熱シャットダウン(OTSD) - ラッチングとラッチングなし

- 過電流制限およびシャットダウンイベント - ラッチ

- DC 検出 - ラッチング

レジスタビットは、フォルトイベントを FAULT ピンへの通知からマスクすることができます。これらのビットはピンの設定をマスクするだけで、デバイスのレジスタレポートまたは保護には影響しません。追加のフォルトイベントを FAULT ピンによるレポートに割り当てることができます。以下のものが該当します。

- 電源フォルト - ラッチングとラッチングなし

- DC 負荷診断エラー

- リアルタイム負荷診断レポート - ラッチングおよび

- クロックエラー - ラッチング

- チャージポンプの故障 - ラッチングとラッチングなし

- 警告イベント

このピンは内部の  $110\text{k}\Omega$  プルアップ抵抗を介して DVDD に接続されているオープンドレイン出力です。

### 7.3.7.2 PD ピン

PD ピンは、アクティブ Low です。アサートされると、デバイスはシャットダウンを開始し、消費電流が最小値に制限されます。シャットダウン時には、すべての内部ブロック電源がオフになり、次の起動時にレジスタはデフォルト値に初期化されます。

このピンには、 $110\text{k}\Omega$  の内部プルダウン抵抗があります。

### 7.3.7.3 STBY ピン

STBY ピンは、アクティブ Low です。アサートされると、STBY ピンはデバイスを DEEP SLEEP 状態に設定します。このモードでは、出力ピンが Hi-Z 状態になっている間、デバイスの電流が減少します。内部のアナログバイアスはすべて無効になっています。DEEP SLEEP 状態で、DVDD が存在するとき、I<sup>2</sup>C バスと内部レジスタが有効になります。

このピンには、内部に DGND への  $110\text{k}\Omega$  プルダウン抵抗があります。

### 7.3.7.4 GPIO ピン

TAS6754-Q1 には、設定可能な 2 つの GPIO ピンがあります。これらの GPIO は、入力または出力として設定できます。デバイス初期化およびパワーオンリセット(POR)後で、動作させる前に、これらのピンを I<sup>2</sup>C を通じて設定する必要があります。

#### 7.3.7.4.1 汎用入力

汎用入力(GPI)ピンは、関連するレジスタの I<sup>2</sup>C を使用してピンに機能を割り当てることで設定できます。

#### 7.3.7.4.2 汎用出力

汎用出力(GPO)ピンは、目的の出力機能の値を I<sup>2</sup>C を介して GPO ピンの設定レジスタに書き込むことでできます。すべての GPIO ピンの GPO 設定レジスタアドレスをリストアップします。

### 7.3.7.5 高度な GPIO 機能

#### 7.3.7.5.1 クロックの同期

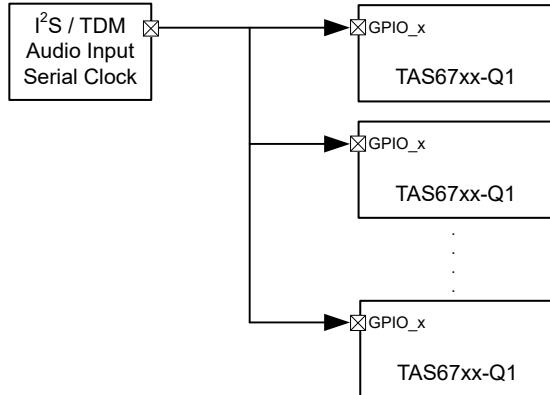

TAS6754-Q1 は、システムの EMI 振動向上と電源ピーク電流条件の制御のため、クロック同期のため複数のオプションをサポートしています。

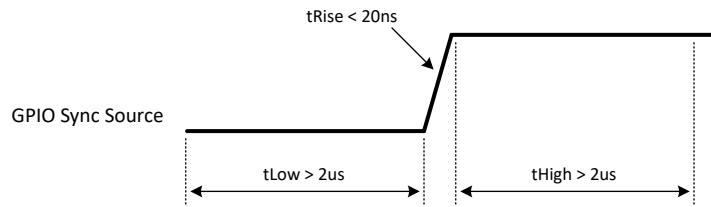

##### 7.3.7.5.1.1 外部同期信号 (GPIO sync)

複数の TAS6754-Q1 は、外部から供給される SYNC 信号を使用して、クロックを同期します。

図 7-19. 外部同期信号のアーキテクチャ

図 7-20. GPIO 同期ソース信号

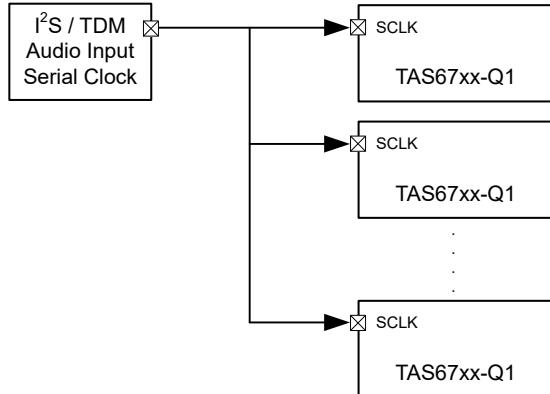

#### 7.3.7.5.1.2 オーディオシリアルクロック (SCLK) による同期

複数の TAS6754-Q1 は、オーディオシリアルクロック (SCLK) を経由してクロックを同期します。

図 7-21. オーディオシリアルクロック (SCLK) の同期アーキテクチャ

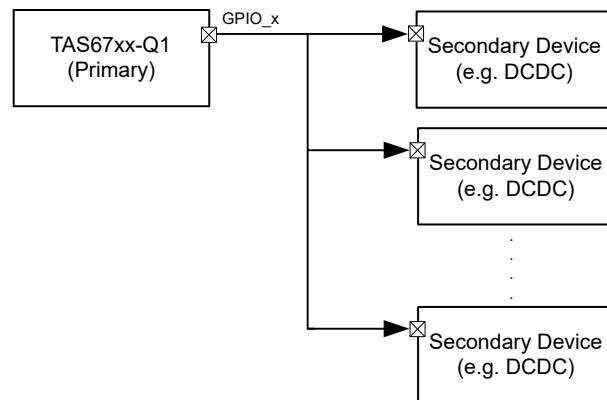

#### 7.3.7.5.1.3 外部デバイス用のクロックソースとしての TAS6754-Q1

この同期オプションを使用すると、TAS6754-Q1 はデバイスのクロックを、DC-DC レギュレータなどの外部システムコンポーネントと共有できます。このモードでは、デバイスは選択した GPIO ピンを通じて内部ランプクロックを共有します。スペクトラム拡散が有効化されている場合、クロック出力は影響を受け、接続部品と拡散信号周波数を共有します。クロック同期の正しいシーケンスを維持し、予期しないシステム動作を回避するには、接続しているシステムコンポーネントの技術資料を参照してください。

図 7-22. 外部デバイス アーキテクチャ用のクロックソース

## 7.4 デバイスの機能モード

### 7.4.1 内部報告信号

ソフトウェアドライバの開発をサポートするため、TAS6754-Q1 によって内部のフォルト信号および警告信号を柔軟に設定できます。これらの信号は、該当する場合、現在のデバイスステータスレジスタまたはメモリレジスタに保存されているイベントに基づいて設定できます。これらの信号は、信号伝達の目的で、使用可能な GPIO ピンに設定およびルーティングできます。

#### 7.4.1.1 フォルト信号

車載システムでは、予期しない状況が発生した場合、デバイス情報の収集に対して厳しく要求します。TAS6754-Q1 のなどのレジスタでは、上位レベルのシステムソフトウェアがシステムを効果的に制御するのに必要なフォルト情報を柔軟に設定できます。

Fault(異常検知)信号は、以下の [フォルトイベント](#) に応答してアクティブになるよう設定できます：

- 電源の故障(ラッチ付きまたはラッチなし)

- 過熱シャットダウン(ラッチまたはラッチなし)

- DC 負荷診断イベント

- 過電流制限およびシャットダウン(ラッチ)

- DC 検出(ラッチ)

- FAULT 状態のチャネル

- リアルタイム負荷診断フォルト(ラッチ)

- クロックエラー(ラッチ)

- チャージポンプフォルト(ラッチ)

デフォルトでは、Fault(異常検知)信号は [FAULT](#) にルーティングされ、HW 信号を生成します。Fault(異常検知)信号は、オプションで追加の [GPIO ピン](#) に配線することもできます。

FAULT 信号には、次の 2 つのレポートビットがあります。

- グローバルフォルト - フォルト信号の設定にかかわらず、デバイス内の 任意 のアクティブなフォルトを通知します

- FAULT 信号 - フォルト信号設定レジスタで適切に設定されたアクティブな FAULT 信号を報告します

#### 7.4.1.2 警告信号

警告信号は、次の [警告イベント](#) に応答するように有効化設定ができます：

- 電源の故障(ラッチ付きまたはラッチなし)

- 過熱シャットダウン(ラッチまたはラッチなし)

- 過熱警告(ラッチ付きまたはラッチなし)

- DC 負荷診断イベント

- 過電流制限(ラッチ付きまたはラッチなし)

- クリップ検出(ラッチ付きまたはラッチなし)

- リアルタイム負荷診断フォルト(ラッチ)

- クロックエラー(ラッチ)

警告信号は、デフォルトではピンにルーティングされていません。TAS6754-Q1 では、警告信号を [GPIO ピン](#) にルーティングして HW 信号を生成するように設定することができます。

- グローバル警告 - クロックフォルトイベントを除く警告信号の設定にかかわらず、デバイス内のアクティブな警告を通知します。

- 警告信号 - アクティブな警告信号を通知します。この信号は、警告信号設定レジスタに応じて設定されます

## 7.4.2 デバイスの状態とフラグ

### 7.4.2.1 オーディオ チャネルの状態

すべてのオーディオチャネルには音源から負荷までのオーディオパスのセットアップとシャットダウンの手順を入念に制御する一連のステータスがあります。これらの状態を [表 7-2](#) に示します。

**表 7-2. オーディオ チャネルの状態**

| 状態名       | 出力 FETS        | DSP   | 発振器   | I <sup>2</sup> C | レベル  |

|-----------|----------------|-------|-------|------------------|------|

| シャットダウン   | ハイインピーダンス      | 停止中   | 停止中   | 高インピーダンス         | デバイス |

| ディープ スリープ | ハイインピーダンス      | 停止中   | アクティブ | アクティブ            | デバイス |

| 負荷 DIAG   | ハイインピーダンス      | 停止中   | アクティブ | アクティブ            | チャネル |

| SLEEP     | ハイインピーダンス      | 停止中   | アクティブ | アクティブ            | チャネル |

| ハイインピーダンス | ハイインピーダンス      | アクティブ | アクティブ | アクティブ            | チャネル |

| PLAY      | オーディオによるスイッチング | アクティブ | アクティブ | アクティブ            | チャネル |

| フォルト      | ハイインピーダンス      | 停止中   | アクティブ | アクティブ            | チャネル |

| AUTOREC   | ハイインピーダンス      | 停止中   | アクティブ | アクティブ            | チャネル |

#### 7.4.2.1.1 シャットダウン状態

[PD](#) ピンが [Low](#) になると、デバイスは、シャットダウン状態を維持したままになります。消費電力を最小限に抑えるため、内部のレギュレータはすべて無効化されています。

[PD](#) ピンを解放するとデバイスが起動し、すべてのレジスタがデフォルト値にリセットされます。[SHUTDOWN](#) により、個々のチャネルは逸脱することなく、デバイスレベルで維持されます。

#### 7.4.2.1.2 DEEP SLEEP 状態

DEEP SLEEP では、デバイスはスタンバイ状態になります。DEEP SLEEP 時には、I<sup>2</sup>C 通信とレジスタ、デジタルコア用の 1.5V LDO がアクティブになります。他のすべてのレギュレータは、エネルギーを節約するために無効のままであります。

DEEP SLEEP では、電源投入前に I<sup>2</sup>C を使用したデバイスの設定に適した状態になっています。シャットダウン状態とは異なり、DEEP SLEEP 状態に移行したり終了したりしても、レジスタマップと DSP メモリは維持されます。

**注**

DSP は DEEP SLEEP 時に非アクティブになります。

#### 7.4.2.1.3 負荷診断の状態

診断モードでは、DC 診断回路を作動させ、出力電力ステージを作動させることなく、電源への短絡、グランドへの短絡、負荷短絡、負荷開放のテストを行います。出力 FET をアクティブにするには、その前にこれらのテストを異常なく終える必要があります。詳細については、[DC 負荷診断](#) を参照してください。

DC 診断は、デバイスの電源が [推奨動作条件](#) の範囲内であれば、すぐに利用できます。DC 診断機能は、外部のオーディオ入力信号、クロック周波数および同期周波数が利用可能である必要はありません。

Load DIAG は、チャネルレベルで設定できます。診断テストにパスすると、チャネルは [SLEEP 状態](#) モードに遷移します。

#### 7.4.2.1.4 SLEEP 状態

SLEEP 状態は、DEEP SLEEP 状態と比較して、アナログ回路やゲートドライバ用の内部 LDO を含む、さらなる機能ブロックをアクティブにします。デジタルから PWM への変換の電源は非アクティブのままであります。

SLEEP はチャネルレベルで設定できます。クロック エラーが存在しない状態で、状態制御レジスタを Hi-Z または PLAY のいずれかに設定することにより、各チャネルは [Hi-Z 状態](#) に遷移します。

#### 7.4.2.1.5 Hi-Z 状態

Hi-Z 状態では、出力ドライバが ハイインピーダンス状態に設定され、他のすべてのブロックは完全に機能します。

ステートコントロールレジスタを **PLAY** に設定することにより、チャネルは **PLAY 状態** に移行します。

#### 7.4.2.1.6 PLAY 状態

PLAY 状態では、デバイスは完全に動作可能です。出力段はアクティブであり、入力信号をスイッチングして増幅します。

**リアルタイム負荷診断** をアクティブにすると、接続されている負荷の短絡や開放状態を監視できます。

#### 7.4.2.1.7 FAULT 状態

故障状態は、デバイス内部で生成されるモードで、ユーザーが手動で設定することはできません。

デバイスの 1 つまたは複数のチャネルが **PLAY** 状態になって故障が発生した場合、デバイスは保護動作を行い、1 つまたは複数のオーディオチャネルをシャットダウンする必要があります。影響を受けるチャネルに限って出力 **FET** はオフになり、出力ピンは高インピーダンスになります。影響を受けるチャネルの状態が「故障」であることが通知されます。

各チャネルがこの状態に移行する理由として、次のことが考えられます：

- 過電流シャットダウン

- 負荷電流 故障

- DC 診断不具合

- リアルタイム負荷診断 故障

- チャネル過熱シャットダウン(自動回復なしに設定されている場合)

すべてのチャネルがこの状態に移行する理由として、以下が考えられます：

- 自動回復を行わないように設定されている場合、グローバル過熱シャットダウン

- チャージポンプ 故障

#### 7.4.2.1.8 自動復旧(AUTOREC) 状態

AUTOREC はデバイス内部で生成される状態のことで、ユーザーが手動で設定することはできません。

デバイスの 1 つまたは複数のチャネルが **PLAY** 状態になって故障が発生した場合、デバイスは保護動作を行い、1 つまたは複数のオーディオチャネルをシャットダウンする必要があります。影響を受けるチャネルの出力 **FET** はオフになり、出力ピンは高インピーダンスになります。保護シャットダウンの原因が解消されると、デバイスは自動的に復旧し、**PLAY** に戻ります。影響を受けたチャネルの通知済の状態が「AUTOREC」です。

各チャネルがこの状態に移行する理由としては、次のことが考えられます：

- チャネル過熱シャットダウン、OTSD(I)、(自動復旧に設定されている場合)

すべてのチャネルがこの状態に移行する理由としては、次のことが考えられます。

- 電源障害

- クロック エラー

- グローバル過熱シャットダウン、OTSD(自動復旧に設定されている場合)

### 7.4.3 フォルトイベント

#### 7.4.3.1 電源フォルトイベント

電源フォルトイベントは、デフォルトではピン通知からマスクされています。これは有効化できます。詳細については、**FAULT** をご覧ください。

##### 7.4.3.1.1 DVDD パワーオン リセット (POR)

DVDD が  $V_{POR\_OFF}$  を下回ると、デバイスはシャットダウンします。すべてのチャネルが **SLEEP** 状態に設定され、DSP が無効化され、 $I^2C$  通信が終了します。DVDD が  $V_{POR\_SET}$  を上回るか、デバイスに最初に電力が供給されたときに、

DVDD が  $V_{POR\_SET}$  を上回っていると、デバイスはパワーオンリセットルーチンを開始します。このルーチン中は、すべてのレジスタとデバイスの状態がデフォルト値に設定されます。

#### 7.4.3.1.2 DVDD 低電圧フォルト

DVDD 低電圧 (UV) 保護機能は、DVDD ピンの低電圧を検出します。UV 条件が発生した場合、デバイスはすべてのチャネルを PLAY/Hi-Z (ハイインピーダンス) から **自動復帰 (AUTOREC)** 状態に移行し、DSP を無効化して、I<sup>2</sup>C レポートレジスタを更新します。

#### 7.4.3.1.3 VBAT 過電圧フォルト

VBAT 電源レールが公称範囲を上回ると、VBAT 過電圧フォルトイベントが生成され、デバイスは **自動回復 (AUTOREC) 状態** になります。VBAT が公称範囲内に戻ると、フォルトイベントがクリアされます。

#### 7.4.3.1.4 VBAT 低電圧フォルト

VBAT 電源レールが公称範囲を下回ると、VBAT 低電圧フォルトイベントが発生し、デバイスは **自動回復 (AUTOREC) 状態** になります。VBAT が公称範囲まで戻ると、フォルトイベントはクリアされます。

#### 7.4.3.1.5 PVDD 過電圧フォルト

PVDD 電源レールが公称範囲を上回ると、PVDD 過電圧フォルトイベントが生成され、デバイスは **自動回復 (AUTOREC) 状態** になります。PVDD が公称範囲内に戻ると、フォルトイベントはクリアされます。

#### 7.4.3.1.6 PVDD 低電圧フォルト

PVDD 電源レールが公称範囲を下回ると、PVDD 低電圧フォルトイベントが生成され、デバイスは **自動回復 (AUTOREC) 状態** に移行します。PVDD が公称範囲まで戻ると、フォルトイベントはクリアされます。

#### 7.4.3.2 過熱シャットダウン (OTSD) イベント

**「過電流制限 (サイクル毎)」** セクションでは、デバイスが OTSD イベントを発生させる状況と設定可能な回復動作について説明します。これは、限られた時間だけ続く一時的なイベントです。

#### 7.4.3.4 過電流シャットダウン イベント

**過電流保護** のセクションでは、デバイスが OCSD イベントを生成する状況についてご説明します。

過電流シャットダウン (OCSD) イベントは過渡イベントであり、ステータスレジスタには通知されません。ラッチされた OCSD イベントは、チャネル過電流および DC 検出フォルトメモリレジスタに通知されます。影響を受けているチャネルは **FAULT 状態** になります。

#### 7.4.3.5 DC フォルトイベント

**DC 検出** セクションでは、デバイスが DC フォルトイベントを生成する状況についてご説明します。

DC フォルトイベントは過渡イベントであり、ステータスレジスタでは通知されません。ラッチされた DC フォルトイベントは、チャネル過電流および DC 検出フォルトメモリレジスタに通知されます。影響を受けているチャネルは **FAULT 状態** になります。

#### 7.4.3.6 クロック エラー イベント

**クロックレート** セクションでは、サポートしているオーディオデータ形式、ビット深度、クロックレートについて解説します。これらの条件に違反した場合やクロックが停止した場合、デバイスはクロック Error Fault イベントを通知し、徐々に **AUTOREC 状態** に遷移します。オーディオクロックの回復後、デバイスは自動的に以前の状態に戻ります。

クロックエラーイベントは過渡イベントであり、ステータスレジスタでは通知されません。

#### 7.4.3.7 チャージポンプの故障事象

チャージポンプ のセクションでは、デバイスがチャージポンプの故障事象を発生させる状況とそのリカバリ動作について説明します。

#### 7.4.4 警告イベント

##### 7.4.4.1 過熱警告イベント

過熱警告 セクションでは、デバイスが過熱警告イベントを発生させる状況について説明します。

##### 7.4.4.2 過電流制限警告イベント

過電流制限(サイクル毎) セクションでは、デバイスが過電流制限警告イベントを生成する状況について説明します。これは、限られた時間だけ続く一時的なイベントです。

##### 7.4.4.3 クリップ検出警告イベント

クリップ検出 セクションでは、デバイスがクリップ検出警告イベントを発生させる状況について説明します。

### 7.5 プログラミング

#### 7.5.1 I<sup>2</sup>C シリアル通信バス

このデバイスは、I<sup>2</sup>C シリアル通信バスを介して I<sup>2</sup>C ターゲット専用デバイスとしてシステムプロセッサと通信し、100kHz および 400kHz のデータ転送レートをサポートして、ランダムおよびシーケンシャルの書き込みおよび読み取り動作をサポートしています。プロセッサは I<sup>2</sup>C を介してデバイスをポーリングし、動作ステータスの判定、設定の構成、診断の実行を行うことができます。

TAS6754-Q1 のレジスタマップと DSP メモリは、複数のページとブックにまたがっています。ユーザーは、個別のレジスタや DSP メモリに書き込む前に、ページからページへの変更を行います。ページからページへの変更は、各ページのレジスタ 0 を介して行われます。このレジスタ値は、ページアドレスを 0 ~ 255 の範囲で選択します。TAS6754-Q1 データシートに記載されているすべてのレジスタは、ページ 0 に属します。

すべての I<sup>2</sup>C 制御の完全な一覧と説明については、レジスタマップのセクションを参照してください。

#### 7.5.2 I<sup>2</sup>C アドレスの選択

TAS6754-Q1 は、8 つの I<sup>2</sup>C アドレスをサポートしているため、バス切り替えハードウェアを追加しなくても、最大 8 つのデバイスを 1 つのシステム使用できます。

デバイスの I<sup>2</sup>C\_ADDR ピンと DVDD レール(プルアップ)または GND(プルダウン)の間に接続されているプルアップまたはプルダウン抵抗によって、電源投入時の I<sup>2</sup>C アドレスが決まります。I<sup>2</sup>C アドレスは POR イベントの後にラッチされ、次の POR イベントまでロックされます。

表 7-3. I<sup>2</sup>C アドレス

| I <sup>2</sup> C_ADDR ピン、プルアッ<br>ップ抵抗 | I <sup>2</sup> C_ADDR ピン、プルダウン抵抗 | I <sup>2</sup> C 書き込み | I <sup>2</sup> C 読み出し |

|---------------------------------------|----------------------------------|-----------------------|-----------------------|

| -                                     | 0                                | 0xE0                  | 0xE1                  |

| -                                     | 1kΩ                              | 0xE2                  | 0xE3                  |

| -                                     | 4.7kΩ                            | 0xE4                  | 0xE5                  |

| -                                     | 24kΩ                             | 0xE6                  | 0xE7                  |

| 24kΩ                                  | -                                | 0xE8                  | 0xE9                  |

| 4.7kΩ                                 | -                                | 0xEA                  | 0xEB                  |

| 1kΩ                                   | -                                | 0xEC                  | 0xED                  |

| 0                                     | -                                | 0xEE                  | 0xEF                  |

### 7.5.3 I<sup>2</sup>C バス プロトコル

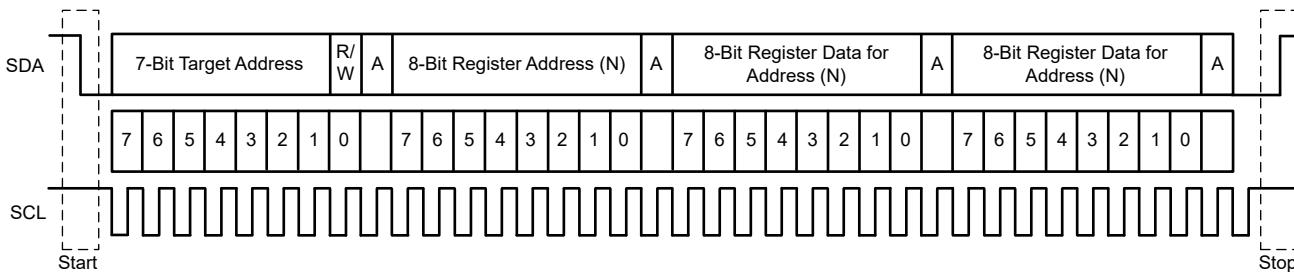

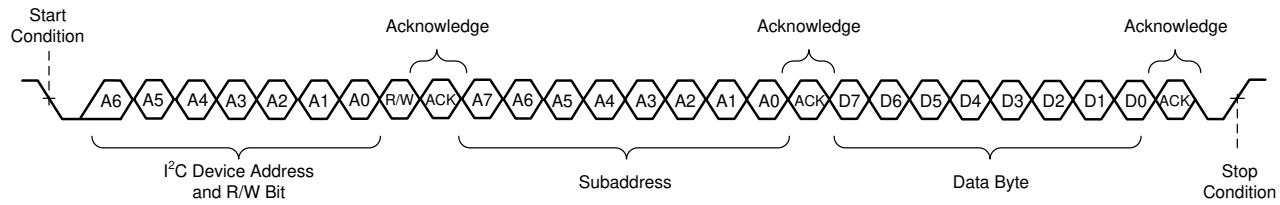

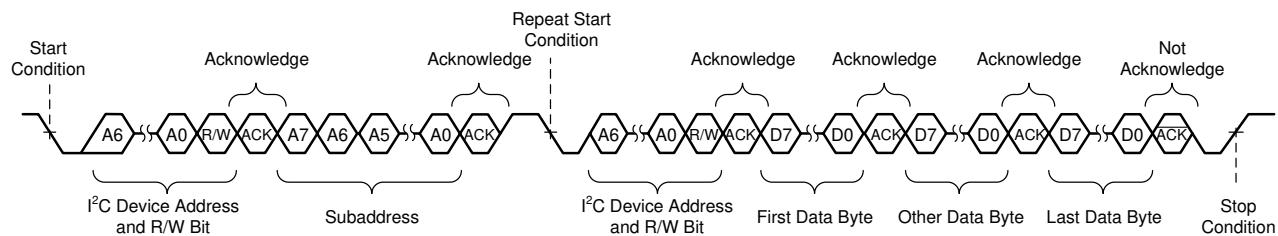

I<sup>2</sup>C バスは、SDA(データ)と SCL(クロック)の 2 つの信号を使用して、シリアル データ伝送によりシステム内の集積回路間で通信を行います。データはバス上に 1 ビットずつシリアルに送信されます。アドレスとデータはバイト(8 ビット)形式で転送され、最上位ビット(MSB)から送信されます。さらに、バス上で転送される各バイトは、受信デバイスによってアクノリッジ ビットで確認されます。各転送操作は、コントローラ デバイスがバス上にスタート コンディションを生成することで開始し、ストップ コンディションを生成することで終了します。バスは、クロックが HIGH のときに、データピン(SDA)の遷移を使用して、開始条件および停止条件を示します。SDA ラインでの HIGH から LOW への遷移は開始条件を示し、LOW から HIGH への遷移は停止条件を示します。通常のデータビット遷移は、クロック(SCL)が LOW のときです。コントローラは、7 ビットのターゲット アドレスを生成し、読み取り / 書き込み(R/W)ビットを送信して他のデバイスとの通信を開始し、次にアクノレッジ(ACK)条件を待ちます。デバイスは、アクノレッジ クロック期間に SDA LOW を保持し、アクノレッジを示します。この状態になると、コントローラ デバイスはシーケンスの次のバイトを送信します。各デバイスは、固有の 7 ビットのターゲット アドレスと R/W ビット(1 バイト)によってアドレス指定されます。すべての互換デバイスは、ワイヤード-AND 接続を使用した双方向バスを介して、同じ信号を共有します。外部プルアップ抵抗により SDA 信号と SCL 信号の両方にバスの HIGH レベルを設定する必要があります。開始条件と停止条件の間で送信できるバイト数は無制限です。最後のワードが転送されると、コントローラはバスを解放するために停止条件を生成します。

図 7-23. 代表的な I<sup>2</sup>C シーケンス

図 7-24. SCL と SDA のタイミング

### 7.5.4 ランダム書き込み

図 7-25 に示す通り、シングル バイトのデータ書き込み転送では、最初にマスター デバイスが開始条件を送信し、次に I<sup>2</sup>C デバイス アドレスと R/W ビットがこれに続きます。データ転送方向は、R/W ビットによって決定されます。書き込みデータ転送する場合、R/W ビットは 0 です。正しい I<sup>2</sup>C デバイス アドレスと R/W ビットを受信すると、デバイスはアクノリッジ ビットを返します。次に、コントローラは、アドレスバイトまたはアクセスしている内部メモリ アドレスに対応するバイトを送信します。デバイスは、レジスタ バイトを受信すると、再度アクノリッジ ビットを返信します。次に、コントローラ デバイスはアクセスしているメモリ アドレスに書き込まれたデータバイトを送信します。デバイスは、レジスタ バイトを受信すると、再度アクノリッジ ビットを返信します。最後に、コントローラ デバイスが停止条件を送信すると、シングル バイト データの書き込み転送が完了します。

図 7-25. ランダム書き込み転送

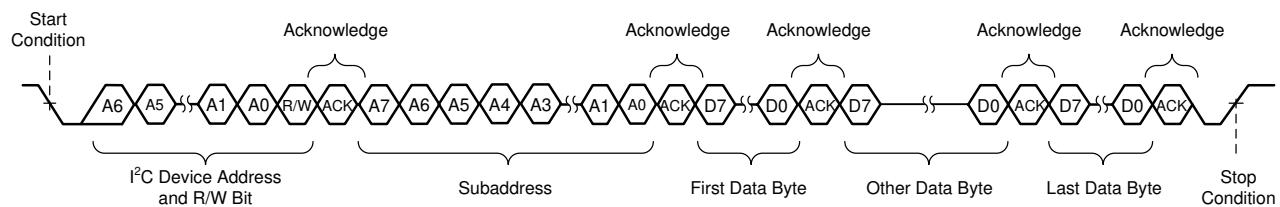

### 7.5.5 シーケンシャル書き込み

シーケンシャルデータの書き込み転送は、図 7-26 に示すように、複数のデータ バイトがコントローラからデバイスに送信される点を除き、シングル バイトデータの書き込み転送と同じです。各データバイトを受信すると、デバイスはアクノリッジ ビットで応答し、I<sup>2</sup>C サブアドレスが自動的に 1 つずつ増加します。

図 7-26. シーケンシャル書き込み転送

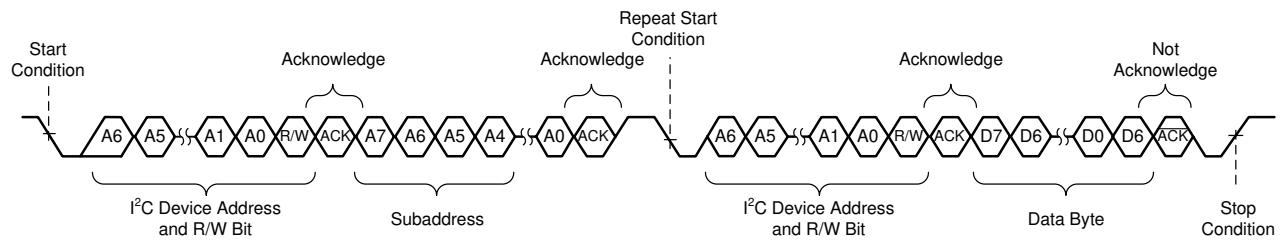

### 7.5.6 ランダム読み出し

図 7-27 に示すように、シングル バイトのデータ読み取り転送では、コントローラ デバイスが開始条件を送信し、次に I<sup>2</sup>C デバイス アドレスと R/W ビットを送信することで開始されます。データ読み取り転送の場合、書き込みとその次の読み取りの両方が行われれます。最初に、内部メモリ アドレスの読み取りに必要なアドレス バイトを転送するために、書き込みが実行されます。その結果、R/W ビットは 0 になります。このデバイスは、アドレスと読み取り / 書き込み ビットを受信すると、アクノリッジ ビットで応答します。さらに、内部メモリアドレス バイトを送信後、コントローラ デバイスは別の開始条件に続いて、アドレス、R/W ビットを送信します。このとき、R/W ビットは 1 に設定され、読み取り転送が実行されたことを示します。デバイスは、アドレスと R/W ビットを受信すると、再度アクノリッジ ビットで応答します。次に、デバイスは読み取り中のメモリアドレスからデータ バイトを送信します。データ バイトを受信すると、コントローラ デバイスは非応答 (not-acknowledge) を送信し、その後、停止条件を出して、シングル バイトデータ読み取り転送が完了します

図 7-27. ランダム読み取り転送

### 7.5.7 シーケンシャル読み出し

シーケンシャルデータの読み取り転送はシングル バイトのデータ読み取り転送と同じですが、図 7-28 に示すように、複数のデータ バイトがデバイス によってコントローラデバイスに送信されます。コントローラデバイスは、最後のデータバイトを除いて、各データバイトを受信すると肯定応答ビットで応答し、I<sup>2</sup>C サブアドレスを自動的に 1 ずつインクリメントします。最後のデータバイトを受信した後、コントローラデバイスは、転送を完了するために非応答(NACK)を送信し、その後に停止条件を送信します。

図 7-28. シーケンシャルリード転送

## 8 アプリケーション情報に関する免責事項

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 8.1 アプリケーション情報

TAS6754-Q1 は、車載用ヘッドユニットや外部アンプモジュールで使用するための 4 チャネルのデジタル入力 Class-D オーディオアンプの設計で、リアルタイム電流フィードバックと DSP が内蔵されています。TAS6754-Q1 は、厳しい条件が要求される車載用 OEM アプリケーションで機能するために必要な機能を搭載しています。

### 8.1.1 再構成フィルタ設計

アンプ出力は、H-ブリッジ設定の高電流 LDMOS ランジスタによって駆動されます。OUTP ランジスタは完全にオフになっているか、完全にオンになっています。その結果、オーディオ信号の振幅に比例するデューティサイクルの方形波出力信号が生成されます。オーディオ信号の復元には、LC 復調フィルタを使用します。このフィルタは、オーディオ帯域外の出力信号の高周波成分を減衰させます。復調フィルタの設計は、パワーアンプのオーディオ性能に大きな影響を及ぼします。したがって、システムの THD+N 要件を満たすためには、出力フィルタで使用するインダクタを、慎重に検討した上で、選定する必要があります。

## 8.2 代表的なアプリケーション

### 8.2.1 BTL アプリケーション

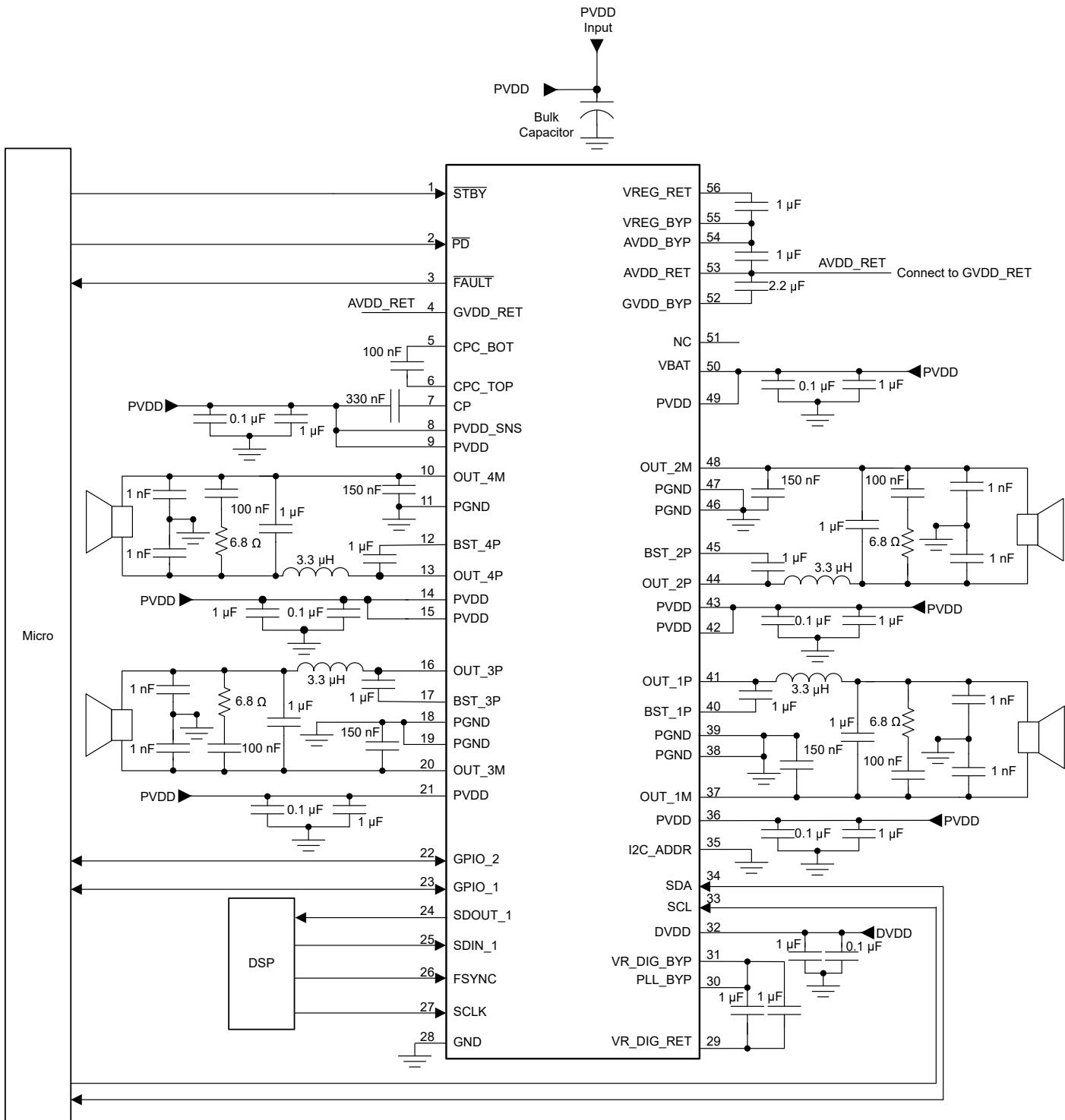

図 8-1 に、代表的な 4 チャネルアプリケーションの回路図を示しています。

## 8.2.2 電源に関する推奨事項

TAS6754-Q1 には、3 つの電源が必要です。PVDD 電源は、推奨電源範囲内の高電流電源です。VBAT 電源は、推奨電源電圧範囲内の低電流電源です。PVDD ピンと VBAT ピンは同じ電源に接続できます。より高い電圧を使用する場合、TI では VBAT に車載用バッテリ電圧を使用して効率を向上させることを推奨しています。DVDD 電源は 1.8Vdc または 3.3Vdc のロジック電源であり、デバイスデータシートの「推奨動作条件」に示されている許容誤差を守る必要があります。

## 8.2.3 電源のデカップリング

電源のデカップリングには複数の機能があります。大容量電解コンデンサーは、オーディオ周波数による PVDD 電圧リップルを低減するために使用されます。PVDD ピンの各グループの  $1\mu\text{F}$  MLCC は、PWM スイッチング周波数での PVDD 電圧リップルを低減するためのもので、 $100\text{nF}$  は EMI を低減するためのものです。大きな電解コンデンサの容量は、使用する昇圧コンバータのレギュレーション能力によって異なります。バッテリで長いワイヤを使用する場合、出力電力要件を満たすようにオーディオ帯域の電圧リップルを低減するには、より大きな容量が必要です。

## 8.3 レイアウト

### 8.3.1 レイアウトのガイドライン

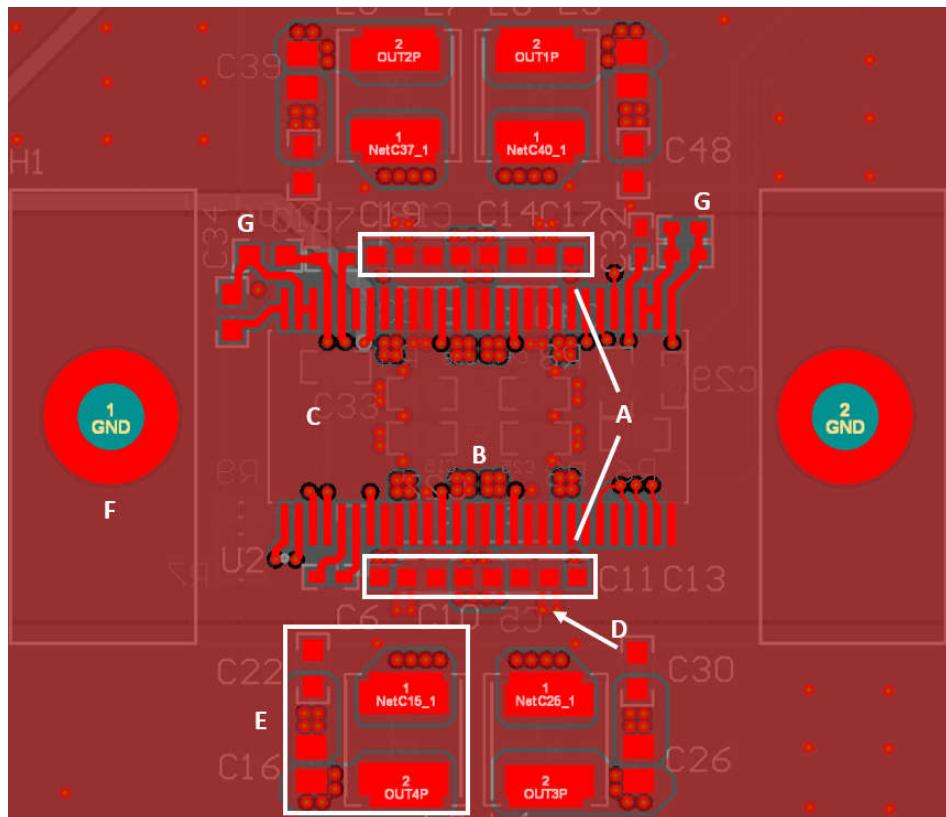

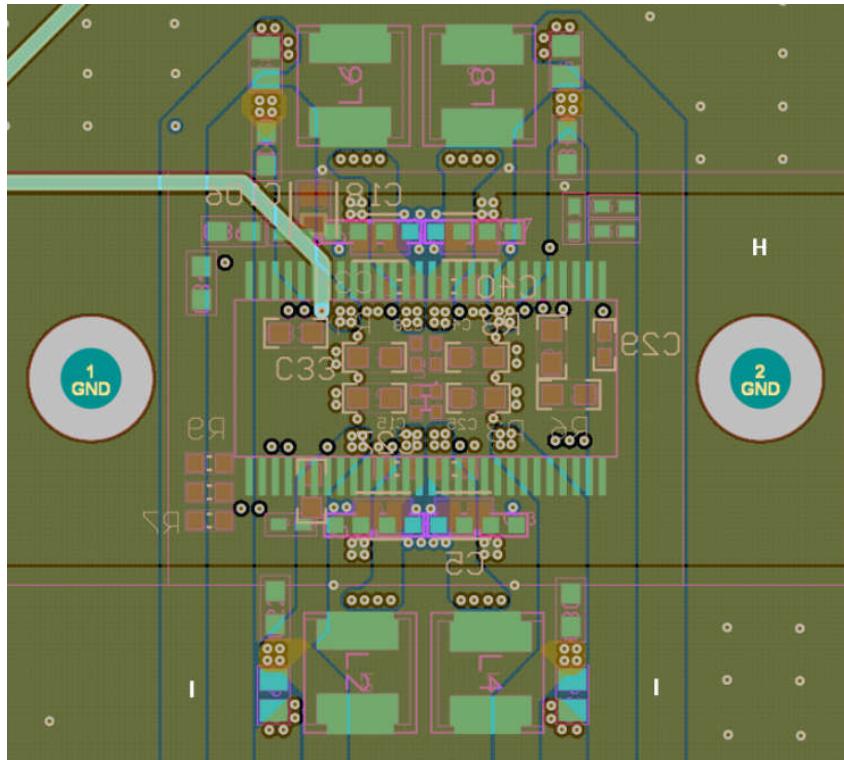

TAS6754-Q1 には、デバイスの両側に 2 つの出力チャネルがあり、最高の熱性能を実現しています。代表的なアプリケーション回路図については、[代表的なアプリケーション](#) を参照してください。図 8-2 に、低 EMI の参考レイアウトを示します。

#### 8.3.1.1 サーマルパッドとヒートシンクの電気的接続

DKQ パッケージの場合、デバイスのサーマルパッドに接続されたヒートシンクを GND に接続します。ヒートスラグは、他の電気ノードに接続しないでください。

#### 8.3.1.2 EMI に関する考慮事項

車載レベルの EMI 特性は、慎重な IC 設計と適切なシステムレベル設計の双方に依存しています。電磁干渉(EMI)の発生源を制御することは、設計のあらゆる面で主な検討事項になっていました。この設計では、パッケージ上のリードが短いため、寄生インダクタンスが最小限に抑えられています。これにより、ダイからシステム PCB に電流が流れることによる EMI を低減できます。また、チャネルごとに異なる位相で動作します。この設計には、EMI を引き起こす出力遷移を最適化する回路も内蔵されています。

EMI の最適化には、ソリッドなグランドレイヤープレーンを推奨します。TAS6754-Q1 の EVM レイアウトは適切な出発点ですが、EVM レイアウトは EMC 試験には推奨されません。EMI 要件にパスし続けるには、基板レベルのさらなる最適化が推奨されます。図 8-2 で、最初の参考資料をご覧ください。

#### 8.3.1.3 一般ガイドライン