# TAS5830 65W ステレオ、デジタル入力、クラス H アルゴリズム搭載の高効率クローズドループクラス D アンプ

## 1 特長

- 複数の出力構成をサポート

- 2 × 80W、BTL モード ( $4\Omega$ 、26V、THD + N = 10%)

- 2 × 65W、BTL モード ( $4\Omega$ 、26V、THD + N = 1%)

- 2 × 74W、BTL モード ( $6\Omega$ 、30V、THD + N = 10%)

- 2 × 63W、BTL モード ( $6\Omega$ 、30V、THD + N = 1%)

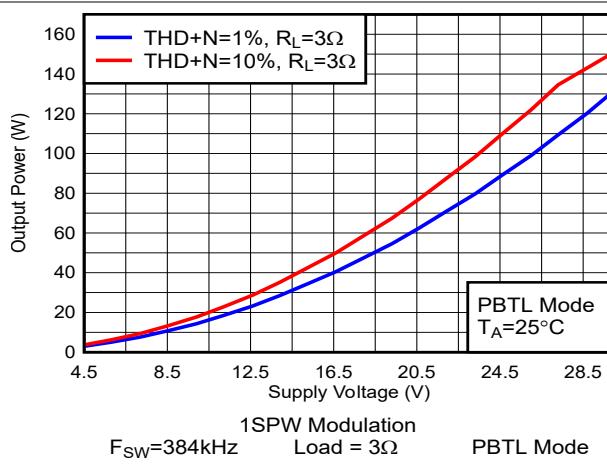

- 1 × 151W、PBTL モード ( $3\Omega$ 、30V、THD + N = 10%)

- 1 × 131W、PBTL モード ( $3\Omega$ 、30V、THD + N = 1%)

- 柔軟なオーディオ I/O:

- 32、44.1、48、88.2、96、192kHz のサンプルレートをサポート

- I<sup>2</sup>S、LJ、RJ、4~16 チャネル TDM 入力

- SDOUT によるオーディオ モニタ、サブチャネル、エコー キャンセル

- 3 線式のデジタル オーディオ インターフェイスをサポート (MCLK 不要)

- 高効率 Class-D 変調

- 90% を超える電力効率、 $70m\Omega$  の  $R_{DS}$  オン

- 優れたオーディオ性能:

- THD+N  $\leq 0.03\%$  (1W、1kHz、PVDD = 12V)

- SNR  $\geq 110\text{dB}$  (A-weighted)、ICN  $\leq 40\mu\text{Vrms}$

- フレキシブルな処理機能

- 3 バンドの高度な DRC + 2 EQ + AGL + 2 EQ

- チャネルごとに 15 の BQ、レベル メーター

- 96kHz、192kHz のプロセッサ サンプリング

- ミキサ、ボリューム、動的 EQ、出力クロスバー

- PVDD センシングと Class-H アルゴリズム オーディオ信号トラッキング

- ラトル抑制、周波数リミッタ

- 柔軟な電源構成

- PVDD: 4.5V ~ 30V

- DVDD および I/O: 1.8V または 3.3V

- 優れた自己保護機能を内蔵:

- 過電流エラー (OCE)

- サイクルごとの電流制限は、4 つの選択可能な OC レベルをサポート

- 過熱警告 (OTW)

- 過熱エラー (OTE)

- 低電圧 / 過電圧誤動作防止 (UVLO/OVLO)

- PVDD 電圧降下検出

- システム統合が簡単

- I<sup>2</sup>C ソフトウェア制御 (TAS5830 は、高速モードと高速モード プラスの両方をサポート) または **ハードウェア モード**

- 開ループ デバイスと比べて少ない受動部品数

## 2 アプリケーション

- バッテリ駆動スピーカー

- ワイヤレス Bluetooth スピーカー

- サウンドバーとサブウーファー

- スマート スピーカー

## 3 説明

TAS5830 は高性能のステレオ、閉ループの Class-D アンプで、オーディオ プロセッサと最高 192kHz のオーディオ サポートが内蔵されています。

ソフトウェア制御モードで起動すると、TAS5830 は従来の BQ、3 バンド DRC、AGL だけでなく、独自のオーディオ エンベロープトラッキング Class-H 制御アルゴリズムも実装しています。Class-H アルゴリズムは、必要なオーディオ 電力の需要を検出し、GPIO ピンにより DC-DC コンバータに PWM 形式の制御信号を出力します。TAS5830 は、BTL モードで最大 5ms、PBTL モードで最大 10ms の遅延バッファをサポートしており、Class-H 制御はシステム効率の向上に大きく役立ちます。

デバイスをハードウェア制御モードに設定する場合、TAS5830 は、ピン設定によるスイッチング周波数、アナログ ゲイン、BTL/PBTL モード、サイクル単位の電流制限スレッショルドの選択をサポートしています。このモードは、エンド システムのソフトウェア ドライバの統合に手間がかかるないように設計されています。

また TAS5830 には、ラトル抑制や周波数リミッタという DSP 機能も搭載されています。ラトル抑制は、スピーカ筐体との相互作用によるラトル音の原因となる周波数での信号のゲインを低減し、音質を向上させます。周波数リミッタ プロセスは入力レベルを感知し、EQ のゲインを動的に制限して、位相を変化させない SPL を実現します。

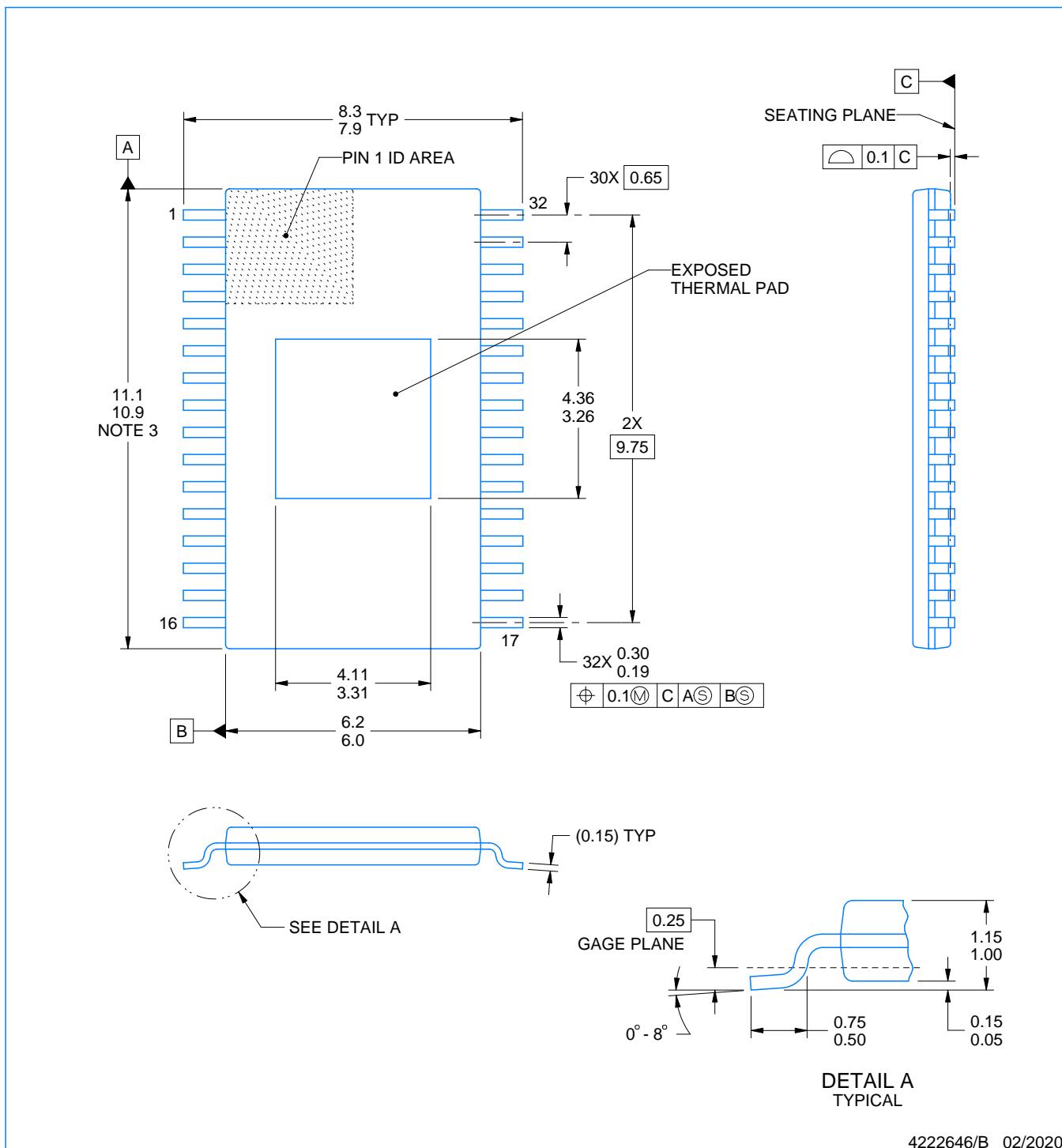

### 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ (公称)       |

|---------|----------------------|------------------|

| TAS5830 | TSSOP (32) DAD       | 11.00mm × 6.20mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                        |     |

|-------------|----|------------------------|-----|

| 1 特長        | 1  | 6.4 デバイスの機能モード         | 35  |

| 2 アプリケーション  | 1  | 7 レジスタ マップ             | 49  |

| 3 説明        | 1  | 7.1 REG_MAP レジスタ       | 49  |

| 4 ピン構成および機能 | 3  | 8 アプリケーションと実装          | 98  |

| 5 仕様        | 7  | 8.1 代表的なアプリケーション       | 99  |

| 5.1 絶対最大定格  | 7  | 8.2 電源に関する推奨事項         | 100 |

| 5.2 ESD 定格  | 7  | 8.3 レイアウト              | 102 |

| 5.3 推奨動作条件  | 7  | 9 デバイスおよびドキュメントのサポート   | 108 |

| 5.4 熱に関する情報 | 7  | 9.1 デバイス サポート          | 108 |

| 5.5 電気的特性   | 8  | 9.2 ドキュメントの更新通知を受け取る方法 | 108 |

| 5.6 タイミング要件 | 13 | 9.3 サポート・リソース          | 108 |

| 5.7 代表的特性   | 14 | 9.4 商標                 | 109 |

| 6 詳細説明      | 29 | 9.5 静電気放電に関する注意事項      | 109 |

| 6.1 概要      | 29 | 9.6 用語集                | 109 |

| 6.2 機能ブロック図 | 30 | 10 改訂履歴                | 109 |

| 6.3 機能説明    | 31 |                        |     |

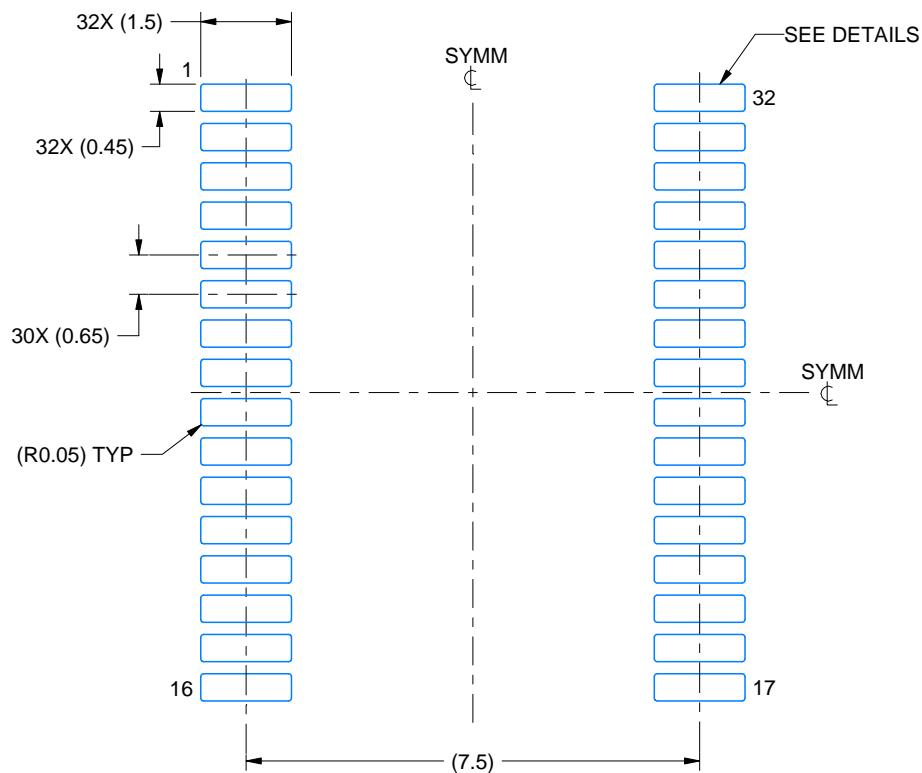

## 4 ピン構成および機能

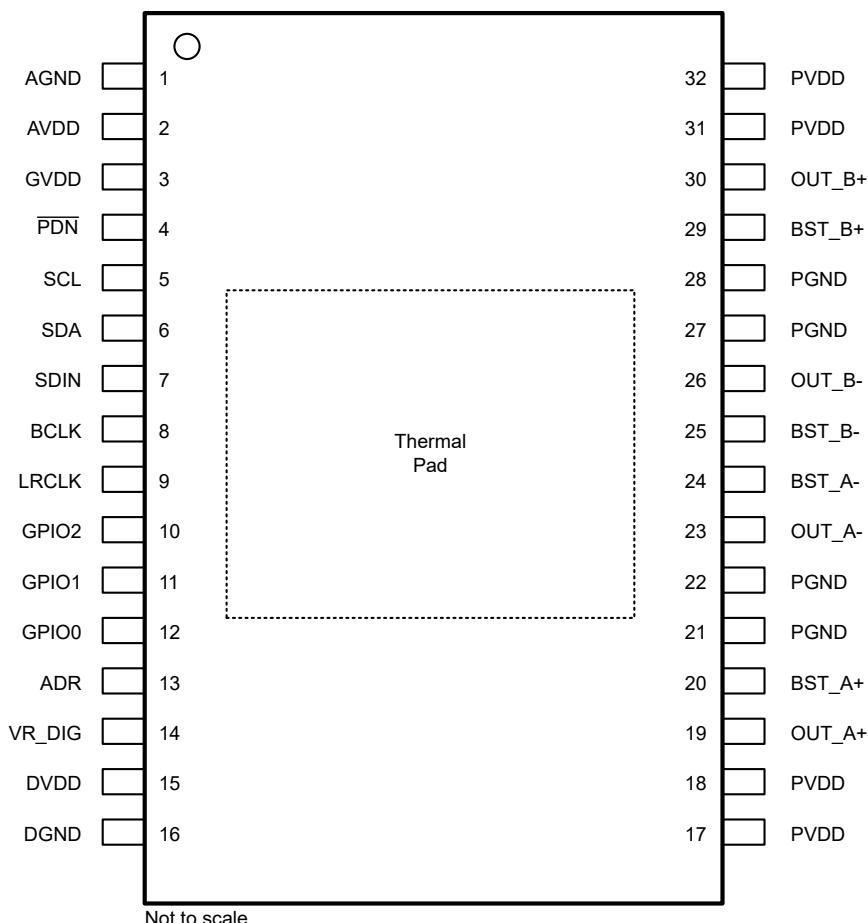

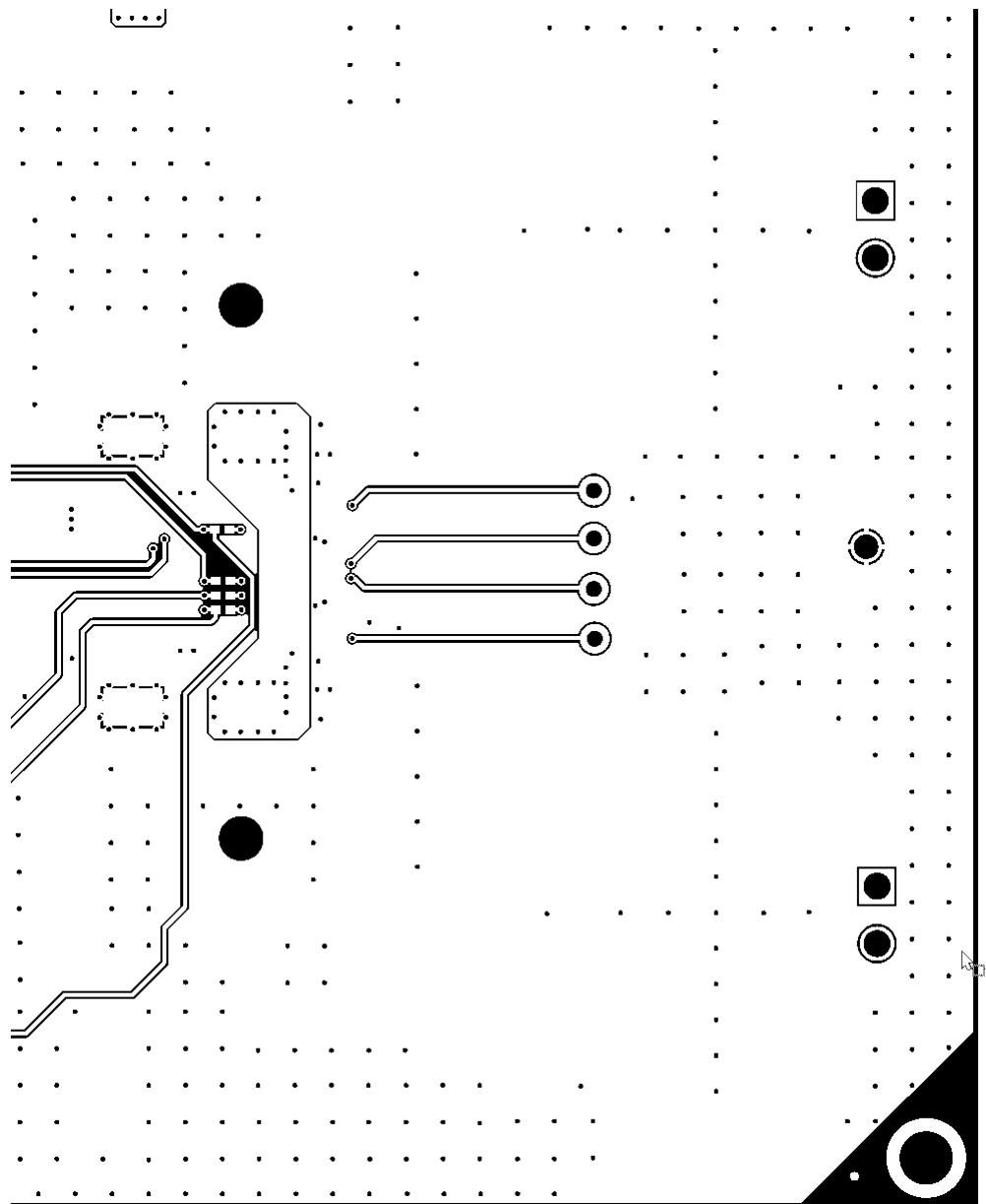

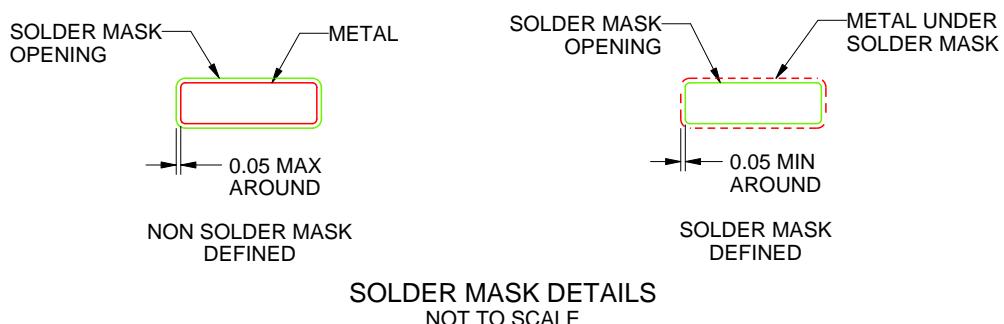

図 4-1. DAD (TSSOP) パッケージ、32 ピン PadUp、ソフトウェア モード、上面図

表 4-1. ピン機能 - ソフトウェア モード

| ピン                     |    | タイプ <sup>(1)</sup> | 説明                                                                                                                             |

|------------------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 名称                     | 番号 |                    |                                                                                                                                |

| AGND                   | 1  | G                  | アナログ グランド。                                                                                                                     |

| AVDD                   | 2  | P                  | 内部的に調整された 5V アナログ電源電圧。このピンを外部デバイスの駆動に使用しないでください。                                                                               |

| GVDD                   | 3  | P                  | ゲート駆動内部レギュレータ出力。このピンを外部デバイスの駆動に使用しないでください。                                                                                     |

| PDN                    | 4  | DI                 | パワーダウン、アクティブ low。PDN アンプをシャットダウンにし、すべての内蔵レギュレータをオフにします。                                                                        |

| SCL                    | 5  | DI                 | I <sup>2</sup> Cシリアル制御クロック入力                                                                                                   |

| SDA                    | 6  | DI/O               | I <sup>2</sup> Cシリアル制御データインターフェース入出力。                                                                                          |

| SDIN                   | 7  | DI                 | シリアル データ ポートへのデータ ライン。                                                                                                         |

| BCLK                   | 8  | DI                 | シリアル データ ポートの入力データ ラインでアクティブなデジタル信号のビット クロック。                                                                                  |

| LRCLK                  | 9  | DI                 | シリアル ポートの入力データ ラインでアクティブなデジタル信号のワード セレクト クロック。I <sup>2</sup> S、LJ、RJ では、これは左チャネルと右チャネルの境界に対応しています。TDM モードでは、これはフレーム同期境界に対応します。 |

| GPIO2                  | 10 | DI/O               | 汎用入出力。このピンの機能は、レジスタ (レジスタ アドレス 0x60h および 0x62h) によってプログラムできます。オープン ドレイン出力またはプッシュプル出力に構成可能。                                     |

| GPIO1                  | 11 | DI/O               | 汎用入出力。このピンの機能は、レジスタ (レジスタ アドレス 0x60h および 0x61h) によってプログラムできます。オープン ドレイン出力またはプッシュプル出力に構成可能。                                     |

| GPIO0                  | 12 | DI/O               | 汎用入出力。このピンの機能は、レジスタ (レジスタ アドレス 0x60h および 0x63h) によってプログラムできます。オープン ドレイン出力またはプッシュプル出力に構成可能。                                     |

| ADR                    | 13 | AI                 | 抵抗値の表 (GND にプルダウン) により、デバイスの I <sup>2</sup> C アドレスが決定されます。セクション 6.4.7.3 を参照してください。                                             |

| VR_DIG                 | 14 | P                  | 内部で安定化された 1.5V デジタル電源電圧。このピンを外部デバイスの駆動に使用しないでください。                                                                             |

| DVDD                   | 15 | P                  | 3.3V または 1.8V デジタル電源。                                                                                                          |

| DGND                   | 16 | G                  | デジタル グランド。                                                                                                                     |

| PVDD                   | 17 | P                  | PVDD 電圧入力。                                                                                                                     |

|                        | 18 | P                  |                                                                                                                                |

|                        | 31 | P                  |                                                                                                                                |

|                        | 32 | P                  |                                                                                                                                |

| PGND                   | 21 | G                  | 電源デバイス回路用のグランド リファレンス。このピンはシステム グランドに接続します。                                                                                    |

|                        | 22 | G                  |                                                                                                                                |

|                        | 27 | G                  |                                                                                                                                |

|                        | 28 | G                  |                                                                                                                                |

| OUT_A+                 | 19 | O                  | 差動スピーカ アンプ出力 A の正ピン                                                                                                            |

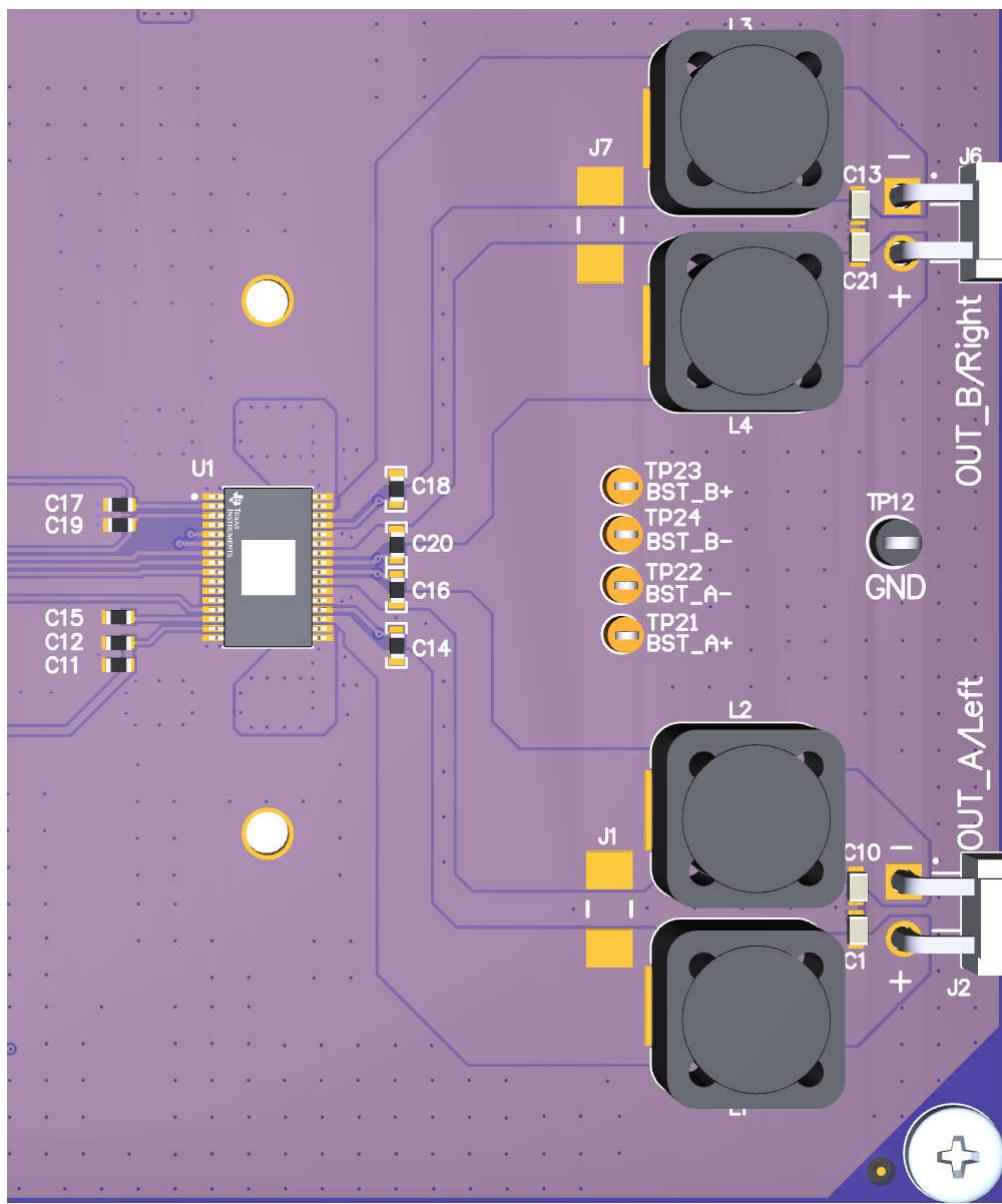

| BST_A+                 | 20 | P                  | OUT_A+ ブートストラップ コンデンサの接続点。これを使って、OUT_A+ の 1 次側ゲート駆動用の電源を作成します。                                                                 |

| OUT_A-                 | 23 | O                  | 差動スピーカ アンプ出力 A の負ピン                                                                                                            |

| BST_A-                 | 24 | P                  | OUT_A- ブートストラップ コンデンサの接続点。これを使って、OUT_A- の 1 次側ゲート駆動用の電源を作成します。                                                                 |

| BST_B-                 | 25 | P                  | OUT_B- ブートストラップ コンデンサの接続点。これを使用して、OUT_B- の 1 次側ゲート駆動用の電源を生成します。                                                                |

| OUT_B-                 | 26 | O                  | 差動スピーカ アンプ出力 B の負ピン                                                                                                            |

| BST_B+                 | 29 | P                  | OUT_B+ ブートストラップ コンデンサの接続点。これを使用して、OUT_B+ の 1 次側ゲート駆動用の電源を生成します。                                                                |

| OUT_B+                 | 30 | O                  | 差動スピーカ アンプ出力 B の正ピン                                                                                                            |

| PowerPAD <sup>TM</sup> |    | P                  | 最高のシステム性能を得るために、グランド接続されたヒートシンクに接続してください。                                                                                      |

(1) AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、DI/O = デジタル双方向 (入力および出力)、PO = 正出力、NO = 負出力、P = 電源、G = グランド (0V)

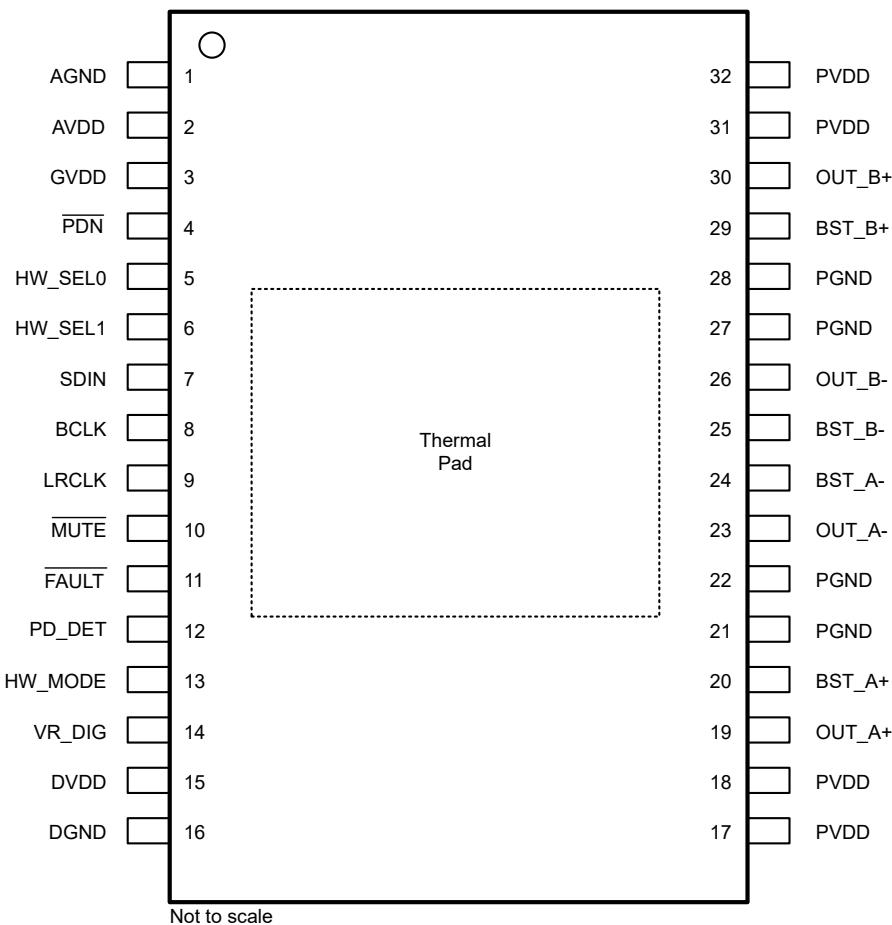

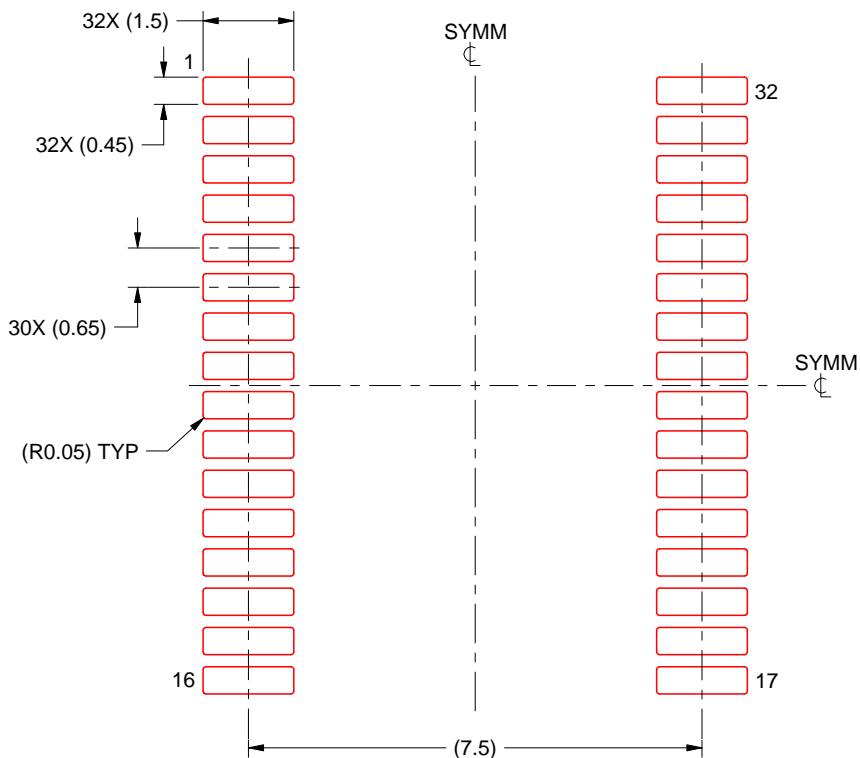

図 4-2. DAD (TSSOP) パッケージ、32 ピン PadUp、ハードウェア モード、上面図

表 4-2. ピン機能 - ハードウェア モード

| ピン      |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                      |

|---------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号 |                    |                                                                                                                                         |

| AGND    | 1  | G                  | アナログ グランド。                                                                                                                              |

| AVDD    | 2  | P                  | 内部的に調整された 5V アナログ電源電圧。このピンを外部デバイスの駆動に使用しないでください。                                                                                        |

| GVDD    | 3  | P                  | ゲート駆動内部レギュレータ出力。このピンを外部デバイスの駆動に使用しないでください。                                                                                              |

| PDN     | 4  | DI                 | パワーダウン、アクティブ low。PDN アンプをシャットダウンにし、すべての内蔵レギュレータをオフにします。                                                                                 |

| HW_SEL0 | 5  | DI                 | ハードウェア モードでのアナログ ゲインおよび BTL/PBTL モードの選択。それぞれの抵抗を使用して DVDD にプルアップするか、グランドにプルダウンします。 <a href="#">セクション 6.4.7.2</a> を参照してください。             |

| HW_SEL1 | 6  | DI                 | ハードウェア モードでの PWM スイッチング周波数と拡散スペクトラムのイネーブル/ディセーブルの選択。それぞれの抵抗を使用して DVDD にプルアップするか、グランドにプルダウンします。 <a href="#">セクション 6.4.7.2</a> を参照してください。 |

| SDIN    | 7  | DI                 | シリアル データ ポートへのデータライン。                                                                                                                   |

| BCLK    | 8  | DI                 | シリアル データ ポートの入力データ ラインでアクティブなデジタル信号のビットクロック。                                                                                            |

| LRCLK   | 9  | DI                 | シリアル ポートの入力データ ラインでアクティブなデジタル信号のワード セレクト クロック。I <sup>2</sup> S、LJ、RJ では、これは左チャネルと右チャネルの境界に対応しています。TDM モードでは、これはフレーム同期境界に対応します。          |

| MUTE    | 10 | DI                 | スピーカー アンプ ミュート/ミュート状態を終了するには、これを low にプル (DGND に接続) し、high (DVDD に接続) にプルアップする必要があります。ミュート状態では、デバイスの出力は Hi-Z 状態を維持します。                  |

| 障害      | 11 | DO                 | フォルト端子。内部フォルトが発生すると low にプルされます。                                                                                                        |

| PD_DET  | 12 | DO                 | PVDD 電圧降下検出。PVDD 電圧が 8V 未満に低下すると Low になります。                                                                                             |

| HW_MODE | 13 | AI                 | DVDD に直接接続して、デバイスがハードウェア制御モードに移行することを確認します。                                                                                             |

| VR_DIG  | 14 | P                  | 内部で安定化された 1.5V デジタル電源電圧。このピンを外部デバイスの駆動に使用しないでください。                                                                                      |

| DVDD    | 15 | P                  | 3.3V または 1.8V デジタル電源。                                                                                                                   |

表 4-2. ピン機能 - ハードウェア モード (続き)

| ピン        |    | タイプ <sup>(1)</sup> | 説明                                                              |

|-----------|----|--------------------|-----------------------------------------------------------------|

| 名称        | 番号 |                    |                                                                 |

| DGND      | 16 | G                  | デジタル グランド。                                                      |

| PVDD      | 17 | P                  | PVDD 電圧入力。                                                      |

|           | 18 | P                  |                                                                 |

|           | 31 | P                  |                                                                 |

|           | 32 | P                  |                                                                 |

|           | 21 | G                  |                                                                 |

| PGND      | 22 | G                  | 電源デバイス回路用のグランド リファレンス。このピンはシステム グランドに接続します。                     |

|           | 27 | G                  |                                                                 |

|           | 28 | G                  |                                                                 |

|           | 19 | O                  | 差動スピーカ アンプ出力 A の正ピン                                             |

| BST_A+    | 20 | P                  | OUT_A+ ブートストラップ コンデンサの接続点。これを使って、OUT_A+ の 1 次側ゲート駆動用の電源を作成します。  |

| OUT_A-    | 23 | O                  | 差動スピーカ アンプ出力 A の負ピン                                             |

| BST_A-    | 24 | P                  | OUT_A- ブートストラップ コンデンサの接続点。これを使って、OUT_A- の 1 次側ゲート駆動用の電源を作成します。  |

| BST_B-    | 25 | P                  | OUT_B- ブートストラップ コンデンサの接続点。これを使用して、OUT_B- の 1 次側ゲート駆動用の電源を生成します。 |

| OUT_B-    | 26 | O                  | 差動スピーカ アンプ出力 B の負ピン                                             |

| BST_B+    | 29 | P                  | OUT_B+ ブートストラップ コンデンサの接続点。これを使用して、OUT_B+ の 1 次側ゲート駆動用の電源を生成します。 |

| OUT_B+    | 30 | O                  | 差動スピーカ アンプ出力 B の正ピン                                             |

| PowerPAD™ |    | P                  | 最高のシステム性能を得るために、グランド接続されたヒートシンクに接続してください。                       |

(1) AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力、DI/O = デジタル双方向 (入力および出力)、PO = 正出力、NO = 負出力、P = 電源、G = グランド (0V)

## 5 仕様

### 5.1 絶対最大定格

自由気流での室温 25°C (特に記述のない限り)<sup>(1)</sup>

|                     |                               | 最小値  | 最大値              | 単位 |

|---------------------|-------------------------------|------|------------------|----|

| DVDD                | 低電圧デジタル電源                     | -0.3 | 3.9              | V  |

| PVDD                | PVDD 電源                       | -0.3 | 35               | V  |

| $V_{I(DigIn)}$      | DVDD 基準のデジタル入力 <sup>(2)</sup> | -0.5 | $V_{DVDD} + 0.5$ | V  |

| $V_{I(SPK\_OUTxx)}$ | スピーカー出力ピンの電圧                  | -0.3 | 32               | V  |

| $T_A$               | 動作時周囲温度                       | -40  | 85               | °C |

| $T_J$               | 動作時接合部温度                      | -40  | 150              | °C |

| $T_{stg}$           | 保存温度                          | -40  | 125              | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

(2) DVDD 基準のデジタルピンには以下が含まれます ADR/FAULT、LRCLK、SCLK、SDIN、SDOUT、SCL、SDA、PDN

### 5.2 ESD 定格

|             |                                                          | 値          | 単位 |

|-------------|----------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電                                                     | $\pm 2000$ | V  |

|             | 荷電デバイスモデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | $\pm 500$  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                 |                           | 最小値                         | 公称値                   | 最大値  | 単位 |

|-----------------|---------------------------|-----------------------------|-----------------------|------|----|

| $V_{(POWER)}$   | 電源入力                      | PVDD                        | 4.5                   | 30   | V  |

|                 |                           | DVDD                        | 1.62                  | 3.63 | V  |

| $R_{SPK}$       | スピーカーの最小負荷                | PVDD 範囲 4.5V ~ 30V、BTL モード  | 3.2                   |      | Ω  |

|                 |                           | PVDD 範囲 4.5V ~ 30V、PBTL モード | 1.6                   |      | Ω  |

| $V_{IH(DigIn)}$ | DVDD 参照デジタル入力の入力ロジック high | $0.9 \times V_{DVDD}$       |                       | DVDD | V  |

| $V_{IL(DigIn)}$ | DVDD 参照デジタル入力の入力ロジック low  |                             | $0.1 \times V_{DVDD}$ |      | V  |

| $L_{OUT}$       | 短絡状態での LC フィルタの最小インダクタ値   |                             | 1                     |      | μH |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | TAS5830-TSSOP32 (DAD) — 32 ピン | 単位   |

|----------------------|---------------------|-------------------------------|------|

|                      |                     | JEDEC 規格 4-LAYER PCB          |      |

| $R_{\theta JA(top)}$ | 接合部から周囲への熱抵抗        | 60.2                          | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 1.2                           | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 28.1                          | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.7                           | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 27.7                          | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 該当なし                          | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

自由気流での室温 25°C、1SPW モード、LC フィルタ = 10uH + 0.68μF、Fsw = 384kHz、Class-D 帯域幅 = 80kHz (特に記述のない限り)

| パラメータ                        |                                              | テスト条件                                                                                               | 最小値  | 標準値    | 最大値 | 単位         |

|------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------|------|--------|-----|------------|

| <b>デジタル I/O</b>              |                                              |                                                                                                     |      |        |     |            |

| I H                          | DVDD<br>参照デジタル入力ピンの<br>入力ロジック high 電流レベル     | $V_{IN(DigIn)} = V_{DVDD}$                                                                          |      | 10     |     | μA         |

| I L                          | DVDD<br>参照デジタル入力ピンの<br>入力ロジック low 電流レベル      | $V_{IN(DigIn)} = 0 \text{ V}$                                                                       |      | -10    |     | μA         |

| $V_{IH(Digin)}$              | DVDD<br>参照デジタル入力の<br>入力ロジック high しきい値        |                                                                                                     | 70%  |        |     | $V_{DVDD}$ |

| $V_{IL(Digin)}$              | DVDD<br>参照デジタル<br>入力の入力ロジック low しきい値         |                                                                                                     |      | 30%    |     | $V_{DVDD}$ |

| $V_{OH(Digin)}$              | ロジック high 出力電圧<br>レベル                        | $I_{OH} = 4 \text{ mA}$                                                                             | 80%  |        |     | $V_{DVDD}$ |

| $V_{OL(Digin)}$              | 出力ロジック low 電圧レベル                             | $I_{OH} = -4 \text{ mA}$                                                                            |      | 20%    |     | $V_{DVDD}$ |

| <b>I<sup>2</sup>C 制御ポート</b>  |                                              |                                                                                                     |      |        |     |            |

| $C_{L(I2C)}$                 | 各 I <sup>2</sup> C ラインで許容される負荷<br>容量         |                                                                                                     |      | 400    |     | pF         |

| $f_{SCL(fast)}$              | SCL 周波数をサポート                                 | ウェイトなし、高速モード                                                                                        | 400  | 1000   |     | kHz        |

| $f_{SCL(slow)}$              | SCL 周波数をサポート                                 | ウェイトなし、スロー モード                                                                                      |      | 100    |     | kHz        |

| <b>シリアル オーディオ ポート</b>        |                                              |                                                                                                     |      |        |     |            |

| $t_{DLY}$                    | 必要な LRCLK/SCLK から $f_S$<br>までの<br>立ち上がりエッジ遅延 |                                                                                                     | 5    |        |     | ns         |

| $D_{SCLK}$                   | 許容される SCLK デューティサイクル                         |                                                                                                     | 40%  | 60%    |     |            |

| $f_S$                        | サポートしている入力サンプルレート                            |                                                                                                     | 32   | 192    |     | kHz        |

| $f_{SCLK}$                   | サポートしている SCLK 周波数                            |                                                                                                     | 32   | 64     |     | $f_S$      |

| $f_{SCLK}$                   | SCLK 周波数                                     |                                                                                                     |      | 24.576 |     | MHz        |

| <b>アンプの動作モードと DC パラメータです</b> |                                              |                                                                                                     |      |        |     |            |

| $t_{off}$                    | ターンオフ時間                                      | シャットダウン、HiZ、スリープ、またはディープ スリープに再生します。ボリューム ランプを除外します。                                                | 4.35 |        |     | ms         |

| $t_{wake}$                   | ウェークアップ時間                                    | ディープ スリープから再生へ。ボリューム ランプを除外します。                                                                     | 2.4  |        |     | ms         |

| $t_{wake}$                   | ウェークアップ時間                                    | スリープから再生へ。ボリューム ランプを除外します。                                                                          | 2.3  |        |     | ms         |

| $t_{wake}$                   | ウェークアップ時間                                    | Hi-Z から再生へ。ボリューム ランプを除外します。                                                                         | 70   |        |     | μs         |

| $I_{cc}$                     | DVDD の静止電源電流                                 | $PDN = 2V, DVDD = 3.3V$ 、再生モード、一般的なオーディオ プロセス フロー。DSP が完全に動作している場合                                  | 24   |        |     | mA         |

| $I_{cc}$                     | DVDD の静止電源電流                                 | $PDN = 2V, DVDD = 3.3V$ 、スリープ モード                                                                   | 1    |        |     | mA         |

| $I_{cc}$                     | DVDD の静止電源電流                                 | $PDN = 2V, DVDD = 3.3V$ 、ディープ スリープ モード                                                              | 1    |        |     | mA         |

| $I_{cc}$                     | DVDD の静止電源電流                                 | $PDN = 0.8V, DVDD = 3.3V$ 、シャットダウン モード                                                              | 18   |        |     | μA         |

| $I_{cc}$                     | PVDD の静止電源電流                                 | $PDN = 2V, PVDD = 24V$ 、無負荷、LC フィルタ = $10\mu\text{H} + 0.68\mu\text{F}$ 、Fsw = 384kHz、1SPW 変調、再生モード | 35   |        |     | mA         |

| $I_{cc}$                     | PVDD の静止電源電流                                 | $PDN = 2V, PVDD = 24V$ 、無負荷、LC フィルタ = $10\mu\text{H} + 0.68\mu\text{F}$ 、Fsw = 384kHz、出力 HiZ モード    | 11   |        |     | mA         |

| $I_{cc}$                     | PVDD の静止電源電流                                 | $PDN = 2V, PVDD = 24V$ 、無負荷、LC フィルタ = $10\mu\text{H} + 0.68\mu\text{F}$ 、Fsw = 384kHz、スリープ モード      | 7.5  |        |     | mA         |

自由気流での室温 25°C、1SPW モード、LC フィルタ = 10uH + 0.68μF、Fsw = 384kHz、Class-D 帯域幅 = 80kHz (特に記述のない限り)

| パラメータ                    |                             | テスト条件                                                                                         | 最小値  | 標準値  | 最大値 | 単位  |

|--------------------------|-----------------------------|-----------------------------------------------------------------------------------------------|------|------|-----|-----|

| I <sub>CC</sub>          | PVDD の静止電源電流                | PDN = 2V、PVDD = 24V、無負荷、LC フィルタ = 10μH + 0.68μF、FSW = 384kHz、ディープスリープモード                      |      | 10   |     | μA  |

| I <sub>CC</sub>          | PVDD の静止電源電流                | PDN = 2V、PVDD = 24V、無負荷、LC フィルタ = 10 μH + 0.68 μF、FSW = 384kHz、シャットダウンモード                     |      | 10   |     | μA  |

| A <sub>V(SPK_AMP)</sub>  | プログラマブル ゲイン                 | 値は、0dB 入力 (1FS) で測定された低い PVDD によるクリッピングを無視した「ピーク電圧」を表します                                      | 14.9 | 30.4 |     | dBV |

| ΔA <sub>V(SPK_AMP)</sub> | アンプのゲイン誤差                   | ゲイン = 30.4dBV                                                                                 |      | 0.5  |     | dB  |

| f <sub>SPK_AMP</sub>     | スピーカ アンプのスイッチング周波数。         | ソフトウェア モード                                                                                    |      | 384  |     | kHz |

| f <sub>SPK_AMP</sub>     | スピーカ アンプのスイッチング周波数。         | ソフトウェア モード                                                                                    |      | 480  |     | kHz |

| f <sub>SPK_AMP</sub>     | スピーカ アンプのスイッチング周波数。         | ソフトウェア モード                                                                                    |      | 576  |     | kHz |

| f <sub>SPK_AMP</sub>     | スピーカ アンプのスイッチング周波数。         | ソフトウェア モード                                                                                    |      | 768  |     | kHz |

| f <sub>SPK_AMP</sub>     | スピーカ アンプのスイッチング周波数。         | ハードウェア モード                                                                                    |      | 480  |     | kHz |

| f <sub>SPK_AMP</sub>     | スピーカ アンプのスイッチング周波数。         | ハードウェア モード                                                                                    |      | 768  |     | kHz |

| R <sub>DS(on)</sub>      | 個別の出力 MOSFET のドレイン-ソース間オン抵抗 | FET + メタライゼーション。V <sub>PVDD</sub> = 24V、I <sub>(OUT)</sub> = 500mA、T <sub>J</sub> = 25°C      |      | 70   |     | mΩ  |

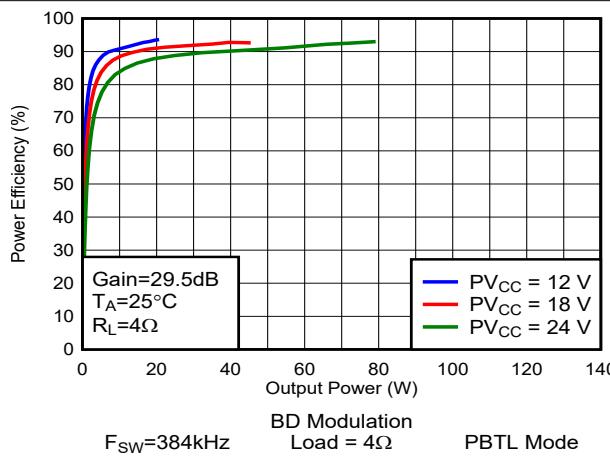

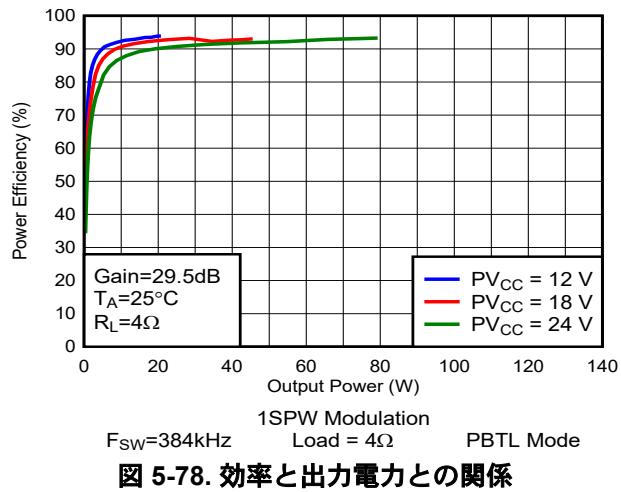

| 効率 (BTL)                 | 低消費電力再生の効率 (電力段の効率)         | PVDD = 24V、LC フィルタ = 10μH + 0.68μF、F <sub>sw</sub> = 384kHz、1SPW 変調、負荷 = 4Ω、各チャネルで 1W 出力電力を再生 |      | 53   |     | %   |

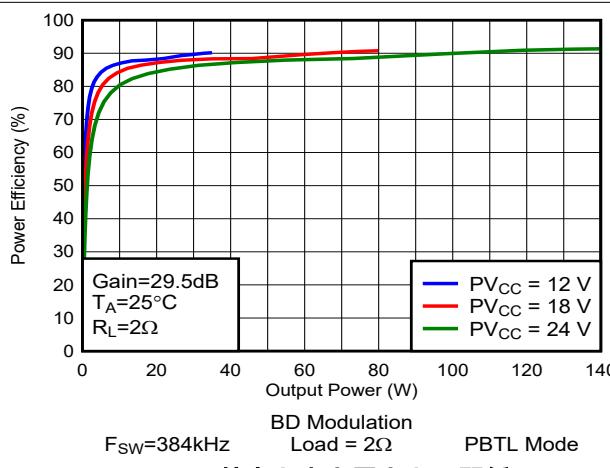

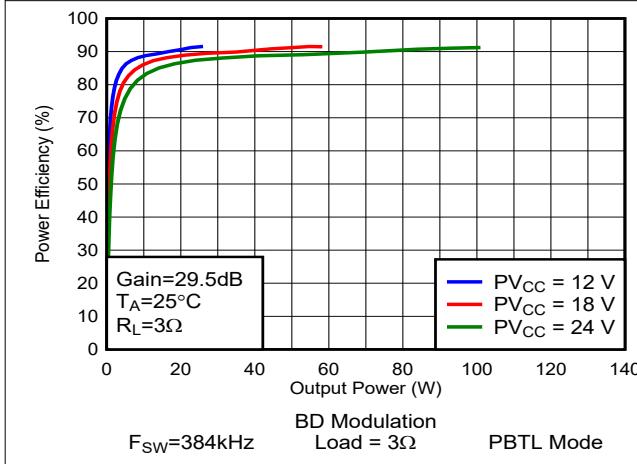

| 効率 (PBTL)                | より大きなパワー再生の効率 (出力段の効率)      | PVDD = 24V、LC フィルタ = 10μH + 0.68μF、F <sub>sw</sub> = 384kHz、1SPW 変調、負荷 = 3Ω、120W の出力電力を再生     |      | 92   |     | %   |

#### PROTECTION

|                            |                          |                                                            |      |     |      |    |

|----------------------------|--------------------------|------------------------------------------------------------|------|-----|------|----|

| OCE <sub>THRES</sub>       | 過電流エラー スレッショルド (スピーカー電流) | スピーカ出力電流 (LC フィルタ後)、スピーカ電流、LC フィルタ = 10uH + 0.68μF、BTL モード | 7.5  | 8   | 8.5  | A  |

| UVE <sub>THRES(PVDD)</sub> | PVDD 低電圧誤差 スレッショルド       |                                                            |      | 4   | 4.25 | V  |

| OVE <sub>THRES(PVDD)</sub> | PVDD 過電圧誤差 スレッショルド       |                                                            | 30.5 | 32  |      | V  |

| DCE <sub>THRES</sub>       | 出力 DC 誤差保護 スレッショルド       | Class-D アンプの出力 DC 電圧クロススピーカ負荷により、出力 DC フォルト保護をトリガ          |      | 3.2 |      | V  |

| T <sub>DCDET</sub>         | 出力 DC 検出時間               | Class-D アンプの出力は DCE <sub>THRES</sub> 以上のままで                | 640  |     |      | ms |

| OTE <sub>THRES</sub>       | 過熱エラー スレッショルド            |                                                            |      | 179 |      | °C |

| OTE <sub>Hystersis</sub>   | 過熱エラー ヒステリシス             |                                                            |      | 11  |      | °C |

| OTW <sub>THRES</sub>       | 過熱警告 レベル                 | レジスタ 0x73 のビット 0 を読み出します                                   |      | 106 |      | °C |

| OTW <sub>THRES</sub>       | 過熱警告 レベル                 | レジスタ 0x73 のビット 1 を読み出します                                   |      | 130 |      | °C |

| OTW <sub>THRES</sub>       | 過熱警告 レベル                 | レジスタ 0x73 のビット 2 を読み出します                                   |      | 143 |      | °C |

自由気流での室温 25°C、1SPW モード、LC フィルタ = 10uH + 0.68μF、Fsw = 384kHz、Class-D 帯域幅 = 80kHz (特に記述のない限り)

| パラメータ                | テスト条件       | 最小値                      | 標準値 | 最大値 | 単位 |

|----------------------|-------------|--------------------------|-----|-----|----|

| OTW <sub>THRES</sub> | 過熱警告<br>レベル | レジスタ 0x73 のビット 3 を読み出します | 156 |     | °C |

自由気流での室温 25°C、1SPW モード、LC フィルタ = 10uH + 0.68μF、Fsw = 384kHz、Class-D 帯域幅 = 80kHz (特に記述のない限り)

| パラメータ                               | テスト条件                                        | 最小値                                                                                            | 標準値   | 最大値 | 単位    |

|-------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------|-------|-----|-------|

| <b>オーディオ PERFORMANCE (ステレオ BTL)</b> |                                              |                                                                                                |       |     |       |

| Vos                                 | アンプのオフセット電圧                                  | 入力データがゼロで差動測定、30.4dBV<br>アナログ ゲインで<br>プログラム可能なゲイン構成、V <sub>PVDD</sub> 範囲: 12V ~ 30V            | -5    | 5   | mV    |

| THD+N <sub>SPK</sub>                | 全高調波歪みおよびノイズ (P <sub>O</sub> = 1W, f = 1kHz) | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、負荷 = 4Ω                                        | 0.015 |     | %     |

|                                     |                                              | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、負荷 = 8Ω                                        | 0.015 |     | %     |

| P <sub>O(SPK)</sub>                 | チャネルあたりの出力電力                                 | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、R <sub>SPK</sub> = 4Ω, f = 1kHz, THD + N = 10% | 80    |     | W     |

| P <sub>O(SPK)</sub>                 | チャネルあたりの出力電力                                 | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、R <sub>SPK</sub> = 4Ω, f = 1kHz, THD + N = 1%  | 65    |     | W     |

| P <sub>O(SPK)</sub>                 | チャネルあたりの出力電力                                 | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、R <sub>SPK</sub> = 8Ω, f = 1kHz, THD + N = 10% | 41    |     | W     |

| P <sub>O(SPK)</sub>                 | チャネルあたりの出力電力                                 | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、R <sub>SPK</sub> = 8Ω, f = 1kHz, THD + N = 1%  | 33    |     | W     |

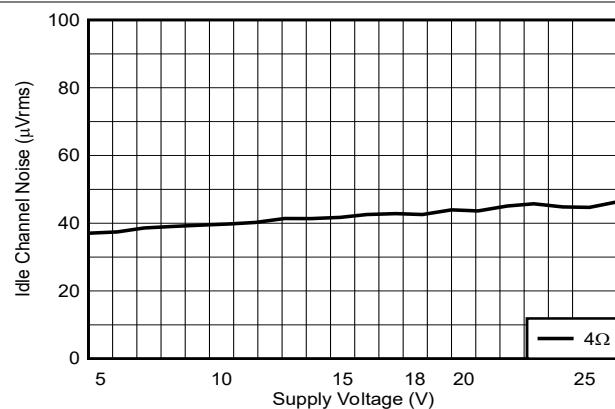

| ICN <sub>(SPK)</sub>                | アイドル チャネル ノイズ (重み付け、AES17)                   | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、負荷 = 4Ω, Fsw = 576kHz, BD 変調                   | 40    |     | μVrms |

|                                     |                                              | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、負荷 = 4Ω, Fsw = 384kHz, 1SPW 変調                 | 37    |     | μVrms |

|                                     |                                              | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、負荷 = 8Ω, Fsw = 576kHz, BD 変調                   | 42    |     | μVrms |

|                                     |                                              | V <sub>PVDD</sub> = 26V、LC フィルタ = 10uH + 0.68μF、負荷 = 8Ω, Fsw = 384kHz, 1SPW 変調                 | 40    |     | μVrms |

| DR                                  | ダイナミック レンジ                                   | A-Weighted、-60 dBFS 方式。V <sub>PVDD</sub> = 24V、負荷 = 6Ω アナログ ゲイン = 30.4dBV                      | 111   |     | dB    |

| SNR                                 | 信号対雑音比                                       | A-Weighted、1% THD+N 出力レベルを基準、V <sub>PVDD</sub> = 24V、負荷 = 6Ω                                   | 111   |     | dB    |

|                                     |                                              | A-Weighted、1% THD+N 出力レベルを基準、V <sub>PVDD</sub> = 18V、負荷 = 4Ω                                   | 108   |     | dB    |

| PSRR                                | 電源除去比                                        | 注入ノイズ = 1kHz, 1Vrms、V <sub>PVDD</sub> = 26V、入力オーディオ信号 = デジタル ゼロ                                | 73    |     | dB    |

| X-talk <sub>SPK</sub>               | クロストーク (左から右への結合と右から左への結合の間の最悪のケース)          | f = 1kHz、muRata のインダクタ (DFEG7030D-4R7) に基づく                                                    | 100   |     | dB    |

自由気流での室温 25°C、1SPW モード、LC フィルタ = 10uH + 0.68μF、Fsw = 384kHz、Class-D 帯域幅 = 80kHz (特に記述のない限り)

| パラメータ                      |                                                     | テスト条件                                                                                             | 最小値  | 標準値 | 最大値 | 単位 |

|----------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------|------|-----|-----|----|

| <b>オーディオ性能 (モノラル PBTL)</b> |                                                     |                                                                                                   |      |     |     |    |

| Vos                        | アンプのオフセット電圧                                         | ゼロ入力データで差動測定、<br>プログラマブル ゲインは 30.4dBV<br>アナログゲインに設定、V <sub>PVDD</sub> = 12V ~ 30V 範囲、<br>1SPW モード | -5   | 5   |     | mV |

| P <sub>O(SPK)</sub>        | 出力電力                                                | V <sub>PVDD</sub> = 29V、R <sub>SPK</sub> = 3Ω、f = 1kHz、THD+N = 1%                                 | 123  |     |     | W  |

|                            |                                                     | V <sub>PVDD</sub> = 29V、R <sub>SPK</sub> = 3Ω、f = 1kHz、THD+N = 10%                                | 148  |     |     | W  |

|                            |                                                     | V <sub>PVDD</sub> = 24V、R <sub>SPK</sub> = 2Ω、f = 1kHz、THD+N = 1%                                 | 119  |     |     | W  |

|                            |                                                     | V <sub>PVDD</sub> = 24V、R <sub>SPK</sub> = 2Ω、f = 1kHz、THD+N = 10%                                | 141  |     |     | W  |

| THD+N <sub>SPK</sub>       | 全高調波歪みおよび<br>ノイズ<br>(P <sub>O</sub> = 1W, f = 1kHz) | V <sub>PVDD</sub> = 24V、LC フィルタ = 10uH + 0.68uF、R <sub>SPK</sub> = 2Ω                             | 0.05 |     |     | %  |

|                            |                                                     | V <sub>PVDD</sub> = 29V、LC フィルタ = 10uH + 0.68uF、R <sub>SPK</sub> = 3Ω                             | 0.07 |     |     | %  |

| DR                         | ダイナミック レンジ                                          | A-Weighted、-60dBFS 方法、V <sub>PVDD</sub> = 29V、R <sub>SPK</sub> = 3Ω                               | 109  |     |     | dB |

| SNR                        | 信号対雑音比                                              | A-Weighted、1% THD+N 出力レベルを基準<br>、V <sub>PVDD</sub> = 29V、R <sub>SPK</sub> = 3Ω                    | 109  |     |     | dB |

|                            |                                                     | A-Weighted、1% THD+N 出力レベルを基準<br>、V <sub>PVDD</sub> = 24V、R <sub>SPK</sub> = 2Ω                    | 108  |     |     | dB |

| PSRR                       | 電源除去比                                               | 注入ノイズ = 1kHz、1Vrms、V <sub>PVDD</sub> = 18V、<br>入力オーディオ信号 = デジタル ゼロ                                | 70   |     |     | dB |

## 5.6 タイミング要件

|                                          |                                              | 最小値 | 公称値                    | 最大値  | 単位  |

|------------------------------------------|----------------------------------------------|-----|------------------------|------|-----|

| <b>シリアル オーディオ ポートのタイミング - ターゲット モード</b>  |                                              |     |                        |      |     |

| $t_{SCLK}$                               | SCLK 周波数                                     |     | 1.024                  |      | MHz |

| $t_{SCLK}$                               | SCLK 周期                                      |     | 40                     |      | ns  |

| $t_{SCLKL}$                              | SCLK パルス幅、low                                |     | 16                     |      | ns  |

| $t_{SCLKH}$                              | SCLK パルス幅、high                               |     | 16                     |      | ns  |

| $t_{SL}$                                 | SCLK の立ち上がりから LRCLK/FS エッジまで                 |     | 8                      |      | ns  |

| $t_{LS}$                                 | LRCK/FS エッジから SCLK 立ち上がりエッジまで                |     | 8                      |      | ns  |

| $t_{SU}$                                 | データ セットアップ時間、SCLK 立ち上がりエッジ前                  |     | 8                      |      | ns  |

| $t_{DH}$                                 | データ ホールド時間、SCLK 立ち上がりエッジ後                    |     | 8                      |      | ns  |

| $t_{DFS}$                                | SCLK 立ち下がりエッジからのデータ遅延時間                      |     |                        | 15   | ns  |

| <b>I<sup>2</sup>C バスタイミング - ファスト モード</b> |                                              |     |                        |      |     |

| $f_{SCL}$                                | SCL クロック周波数                                  |     |                        | 1000 | kHz |

| $t_{BUF}$                                | STOP 条件と START 条件の間のバス フリー時間                 |     | 0.5                    |      | μs  |

| $t_{LOW}$                                | SCL クロックの Low 期間                             |     | 0.5                    |      | μs  |

| $t_{HI}$                                 | SCL クロックの High 期間                            |     | 0.26                   |      | μs  |

| $t_{RS-SU}$                              | (反復) 開始条件のセットアップ時間                           |     | 0.26                   |      | μs  |

| $t_{S-HD}$                               | (反復) 開始条件のホールド時間                             |     | 0.26                   |      | μs  |

| $t_{D-SU}$                               | データ セットアップ時間                                 |     | 50                     |      | ns  |

| $t_{D-HD}$                               | データ ホールド時間                                   |     | 0                      |      | ns  |

| $t_{SCL-R}$                              | SCL 信号の立ち上がり時間                               |     | 20 + 0.1C <sub>B</sub> | 120  | ns  |

| $t_{SCL-R1}$                             | START 条件の繰り返し、およびアクノリッジ ビット後の SCL 信号の立ち上がり時間 |     | 20 + 0.1C <sub>B</sub> | 120  | ns  |

| $t_{SCL-F}$                              | SCL 信号の立ち下がり時間                               |     | 20 + 0.1C <sub>B</sub> | 120  | ns  |

| $t_{SDA-R}$                              | SDA 信号の立ち上がり時間                               |     | 20 + 0.1C <sub>B</sub> | 120  | ns  |

| $t_{SDA-F}$                              | SDA 信号の立ち下がり時間                               |     | 20 + 0.1C <sub>B</sub> | 120  | ns  |

| $t_{P-SU}$                               | 停止条件のセットアップ時間                                |     | 0.26                   |      | μs  |

| $C_b$                                    | 各バス ラインの容量性負荷                                |     |                        | 400  | pf  |

| <b>I<sup>2</sup>C バスタイミング - ファスト</b>     |                                              |     |                        |      |     |

| $f_{SCL}$                                | SCL クロック周波数                                  |     |                        | 400  | kHz |

| $t_{BUF}$                                | STOP 条件と START 条件の間のバス フリー時間                 |     | 1.3                    |      | μs  |

| $t_{LOW}$                                | SCL クロックの Low 期間                             |     | 1.3                    |      | μs  |

| $t_{HI}$                                 | SCL クロックの High 期間                            |     | 600                    |      | ns  |

| $t_{RS-SU}$                              | (反復) 開始条件のセットアップ時間                           |     | 600                    |      | ns  |

| $t_{RS-HD}$                              | (反復) 開始条件のホールド時間                             |     | 600                    |      | ns  |

| $t_{D-SU}$                               | データ セットアップ時間                                 |     | 100                    |      | ns  |

| $t_{D-HD}$                               | データ ホールド時間                                   |     | 0                      | 900  | ns  |

| $t_{SCL-R}$                              | SCL 信号の立ち上がり時間                               |     | 20 + 0.1C <sub>B</sub> | 300  | ns  |

| $t_{SCL-R1}$                             | START 条件の繰り返し、およびアクノリッジ ビット後の SCL 信号の立ち上がり時間 |     | 20 + 0.1C <sub>B</sub> | 300  | ns  |

| $t_{SCL-F}$                              | SCL 信号の立ち下がり時間                               |     | 20 + 0.1C <sub>B</sub> | 300  | ns  |

| $t_{SDA-R}$                              | SDA 信号の立ち上がり時間                               |     | 20 + 0.1C <sub>B</sub> | 300  | ns  |

| $t_{SDA-F}$                              | SDA 信号の立ち下がり時間                               |     | 20 + 0.1C <sub>B</sub> | 300  | ns  |

| $t_{P-SU}$                               | 停止条件のセットアップ時間                                |     | 600                    |      | ns  |

| $t_{SP}$                                 | 抑制されたスパイクのパルス幅                               |     |                        | 50   | ns  |

| $C_b$                                    | 各バス ラインの容量性負荷                                |     |                        | 400  | pf  |

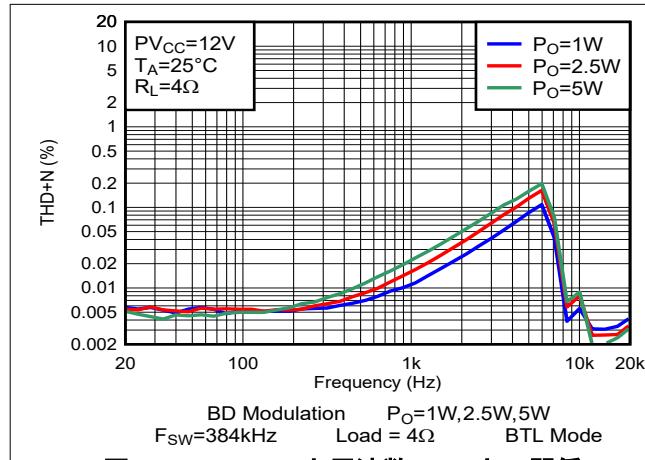

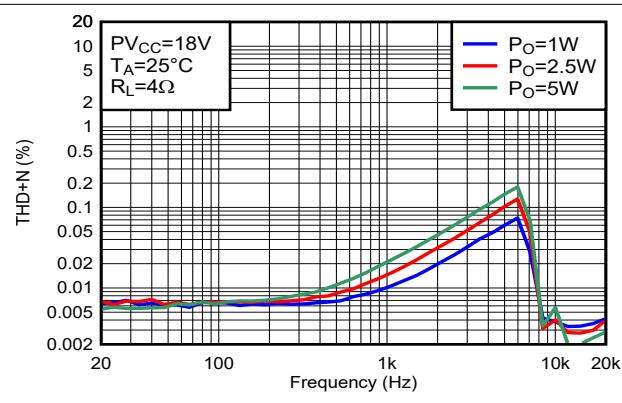

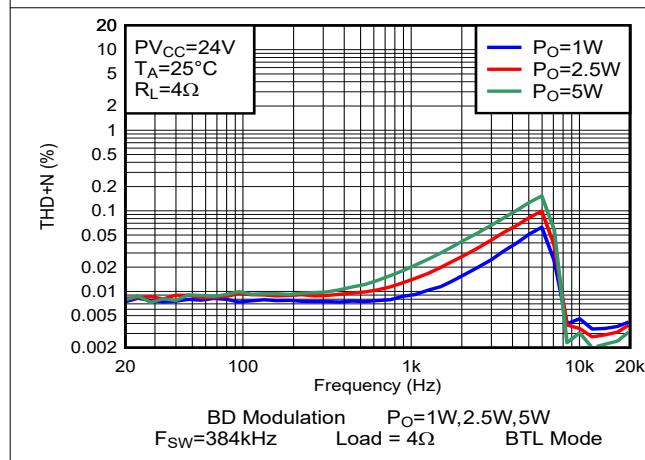

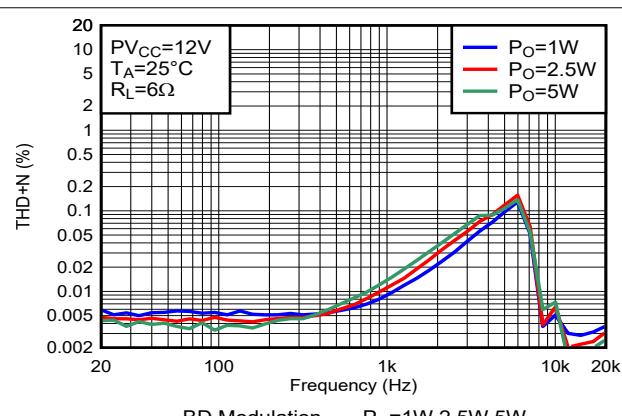

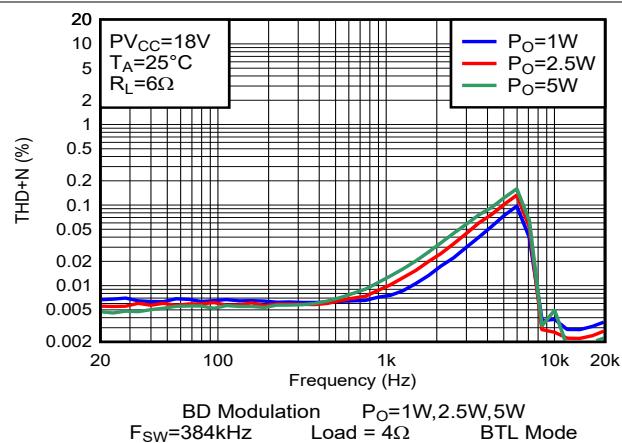

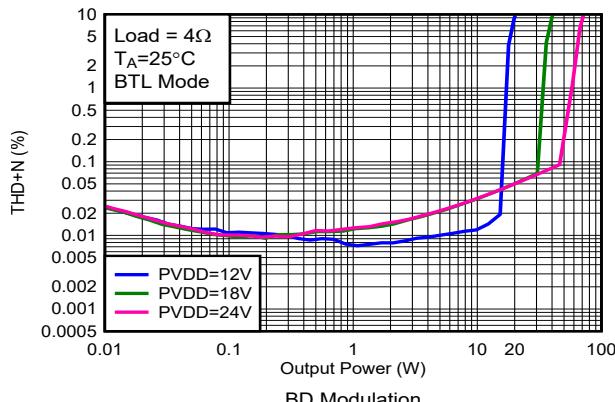

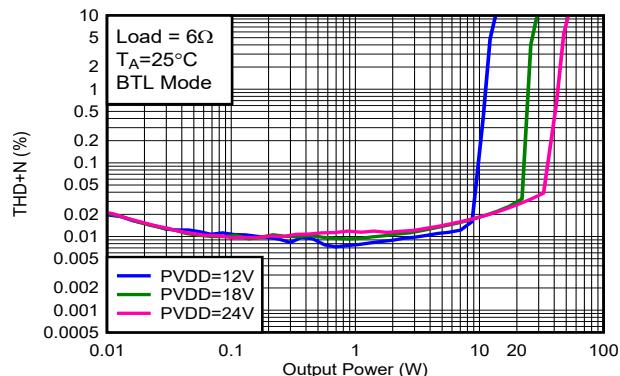

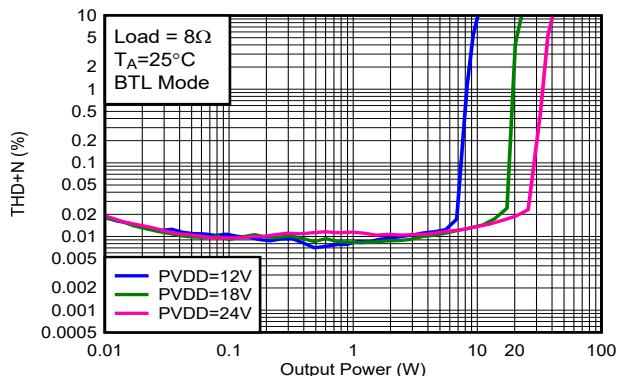

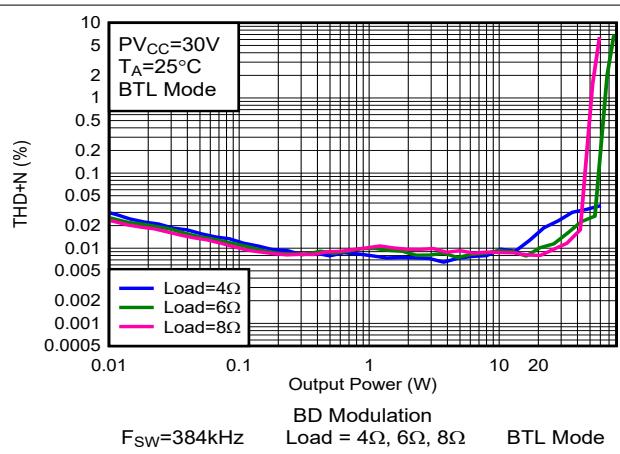

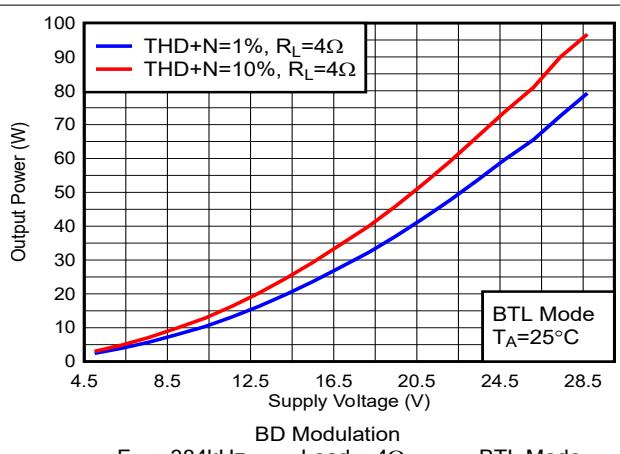

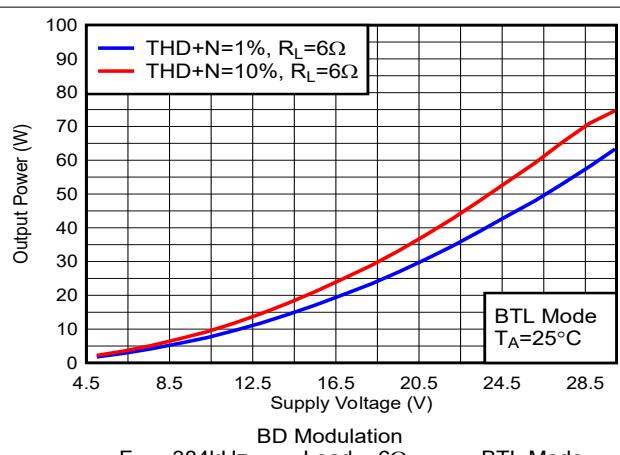

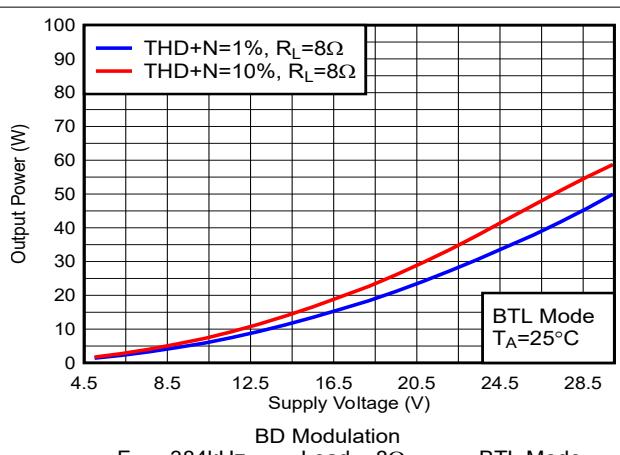

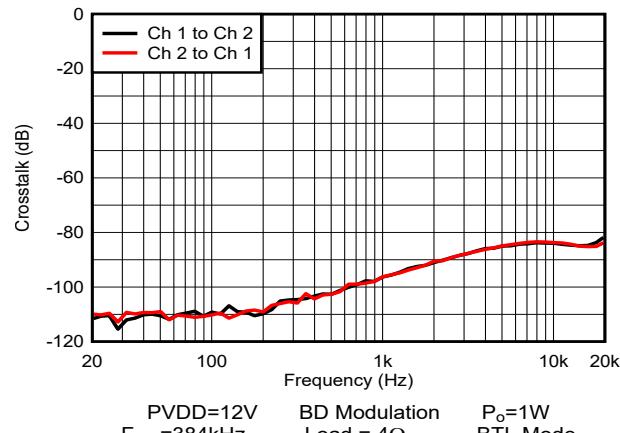

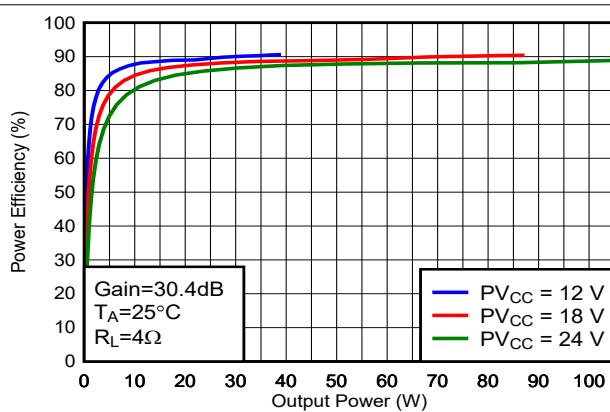

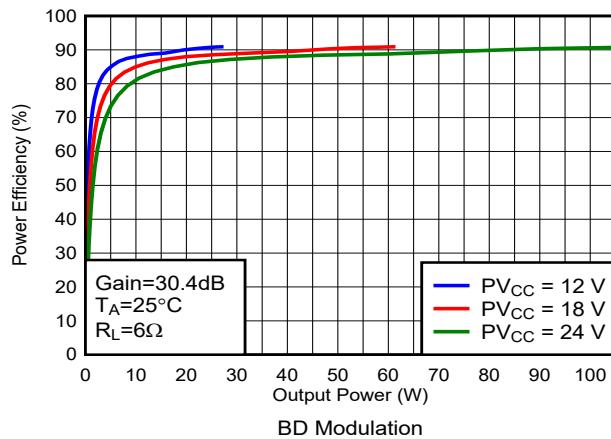

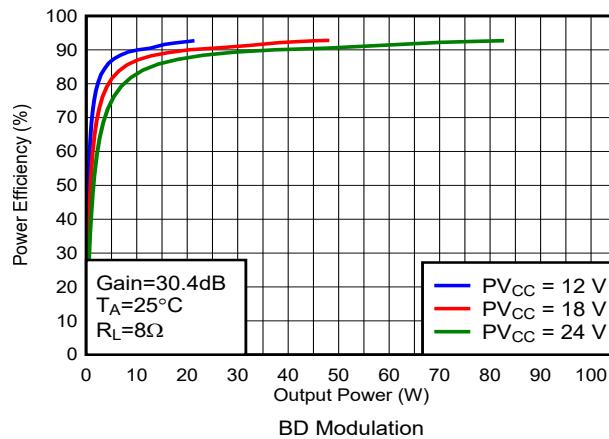

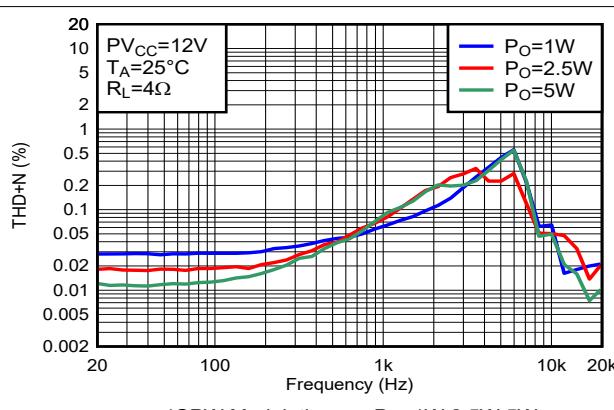

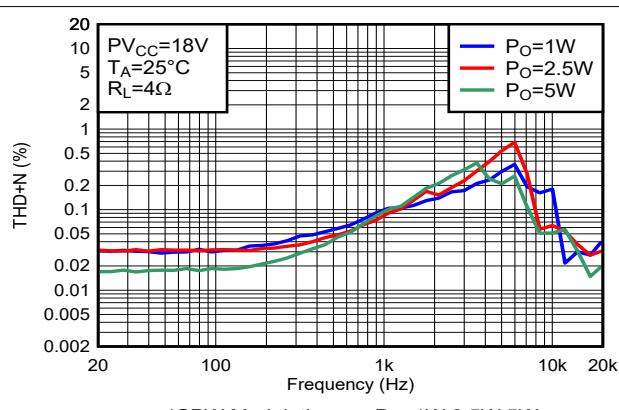

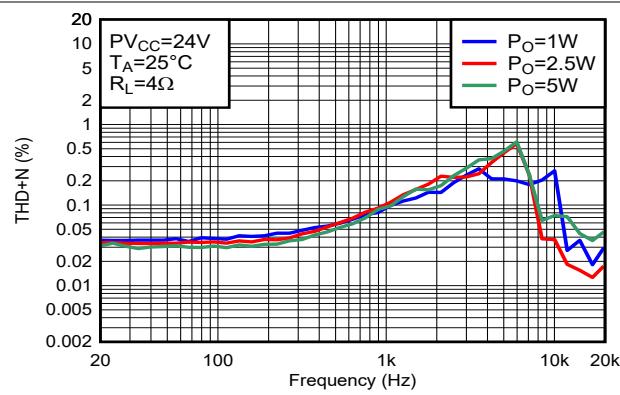

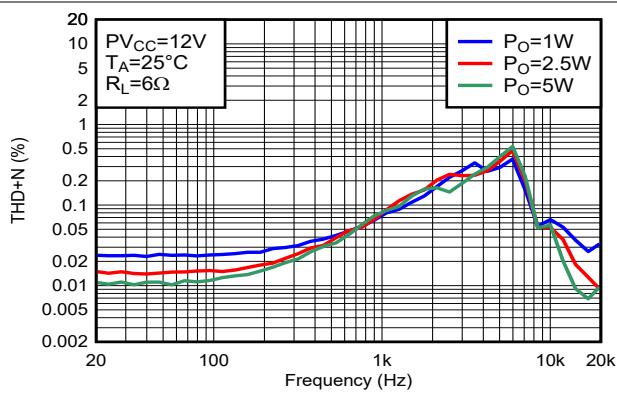

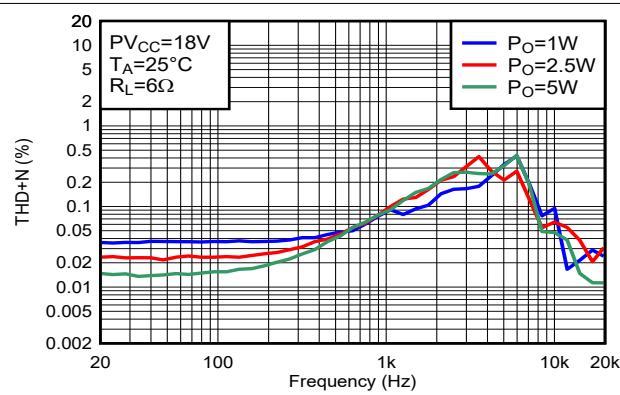

## 5.7 代表的特性

### 5.7.1 BD 変調によるブリッジ接続負荷 (BTL) 構成曲線

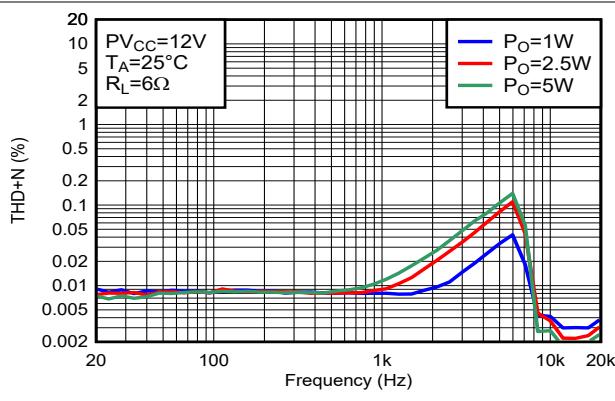

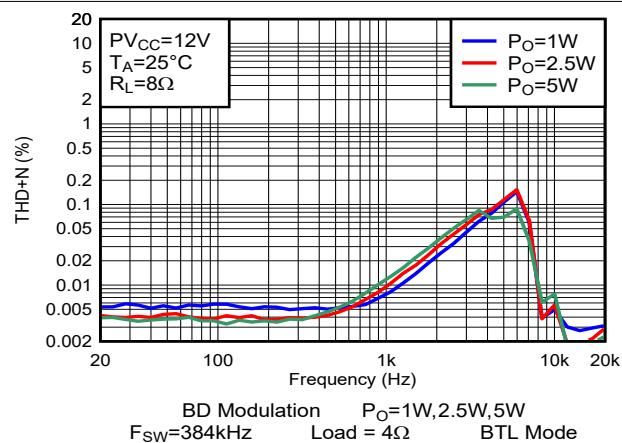

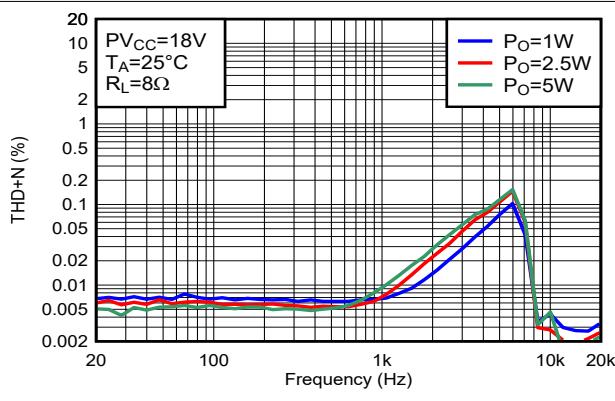

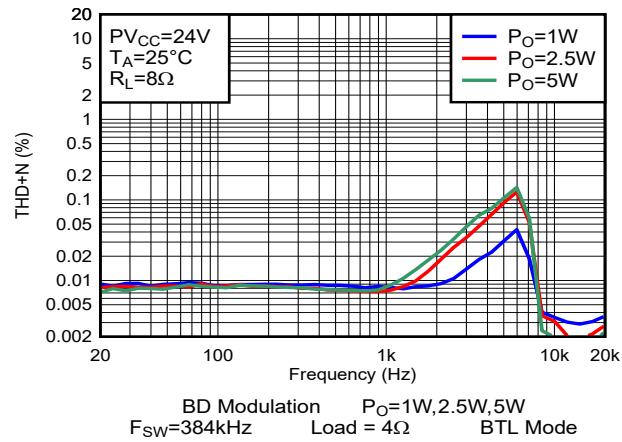

自由気流での室温 25°C (特に記述のない限り)。測定には、Audio Precision System 2722 を使用し、アナログ アナライザ フィルタを 20kHz のブリックウォール フィルタに設定しました。特に記述のない限り、すべての測定は、オーディオ周波数を 1kHz、デバイスの PWM 周波数を 384kHz、80kHz の Class-D アンプループ 帯域幅、10μH/0.68μF 付き LC フィルタに設定して行われます。

図 5-1. THD + N と周波数 BTL との関係

図 5-2. THD + N と周波数 BTL との関係

図 5-3. THD + N と周波数 BTL との関係

図 5-4. THD + N と周波数 BTL との関係

図 5-5. THD + N と周波数 BTL との関係

図 5-6. THD + N と周波数 BTL との関係

図 5-7. THD + N と周波数 BTL との関係

図 5-8. THD + N と周波数 BTL との関係

図 5-9. THD + N と周波数 BTL との関係

図 5-10. THD+N と出力電力 BTL との関係

図 5-11. THD+N と出力電力 BTL との関係

図 5-12. THD+N と出力電力 BTL との関係

図 5-13. THD+N と電源 BTL との関係

図 5-14. 出力電力と電源電圧との関係

図 5-15. 出力電力と電源電圧との関係

図 5-16. 出力電力と電源電圧との関係

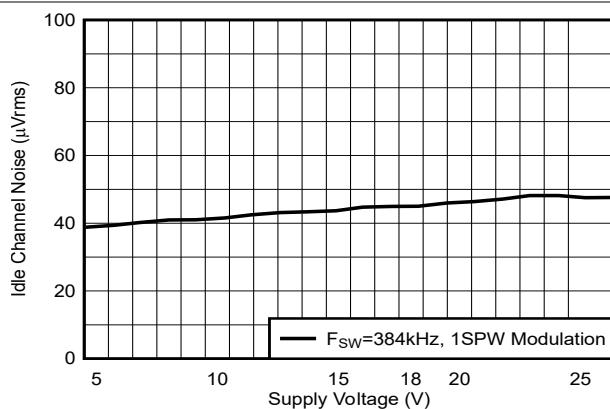

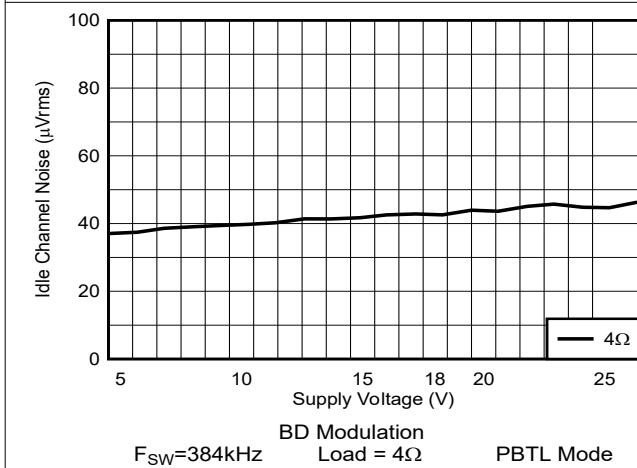

図 5-17. アイドルチャネルノイズと電源電圧との関係

図 5-18. アイドルチャネルノイズと電源電圧との関係

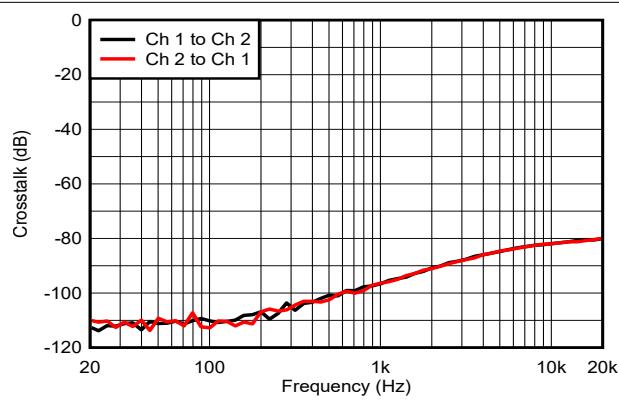

図 5-19. クロストーク

図 5-20. クロストーク

図 5-21. クロストーク

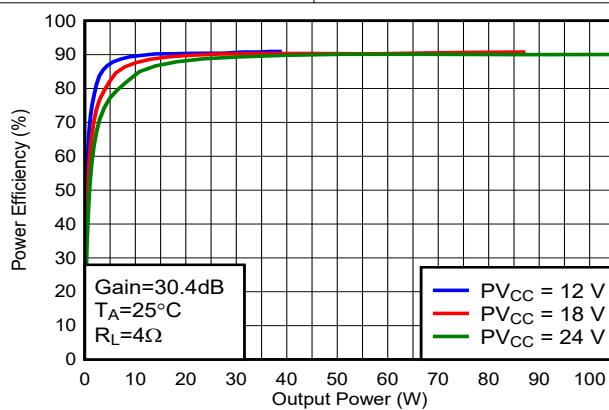

図 5-22. 効率と出力電力との関係

図 5-23. 効率と出力電力との関係

図 5-24. 効率と出力電力との関係

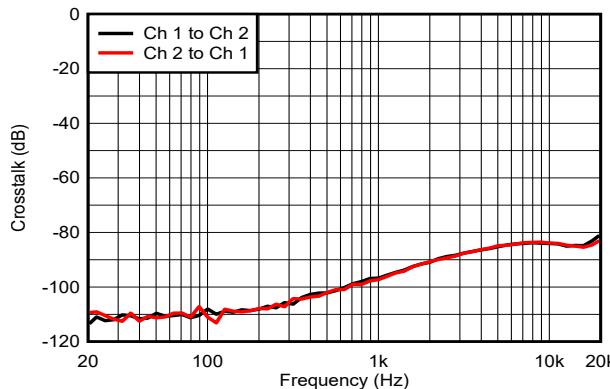

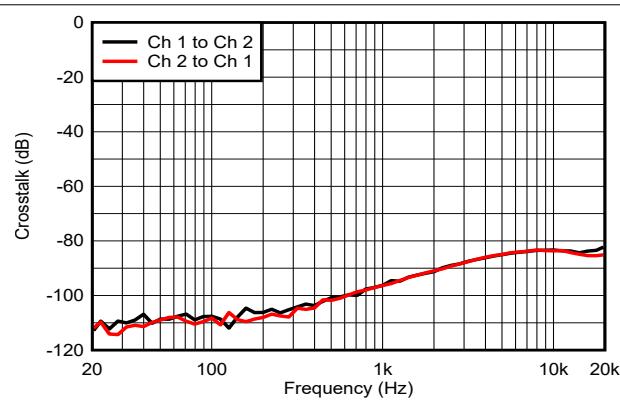

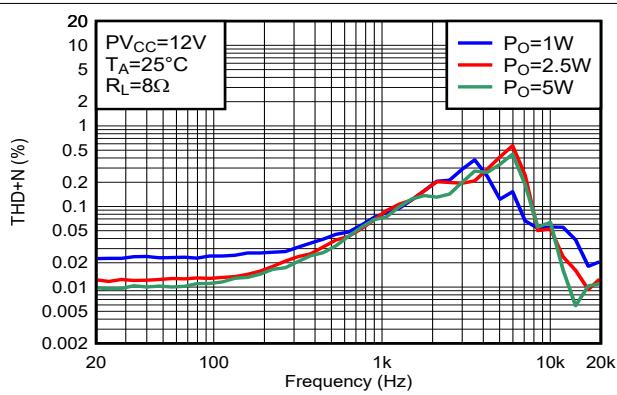

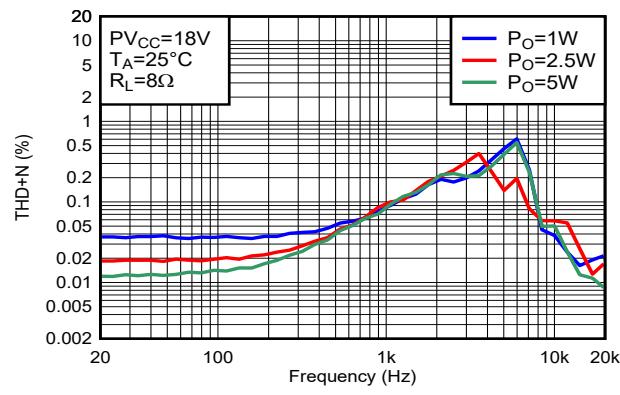

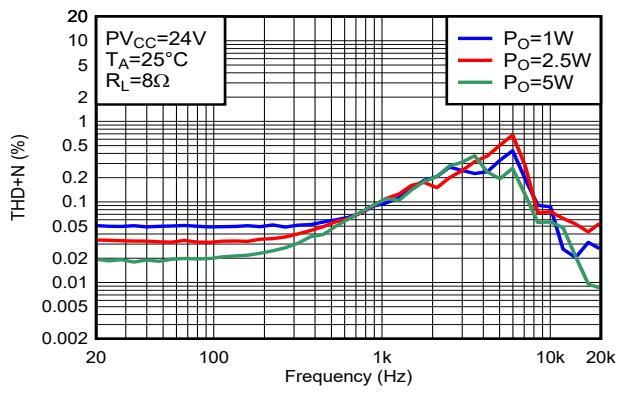

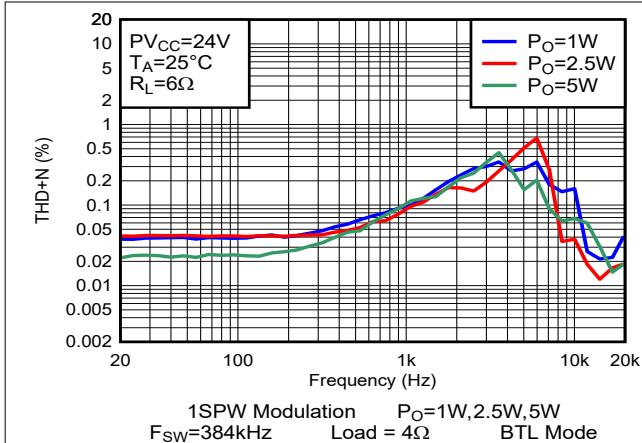

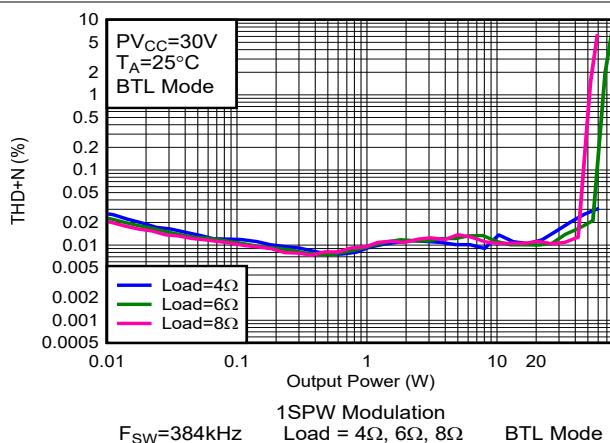

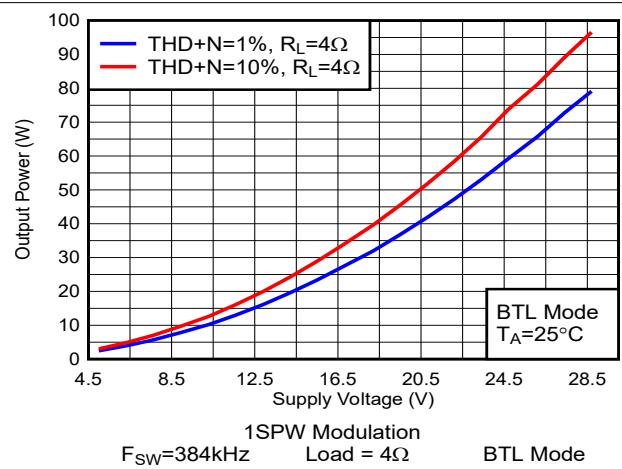

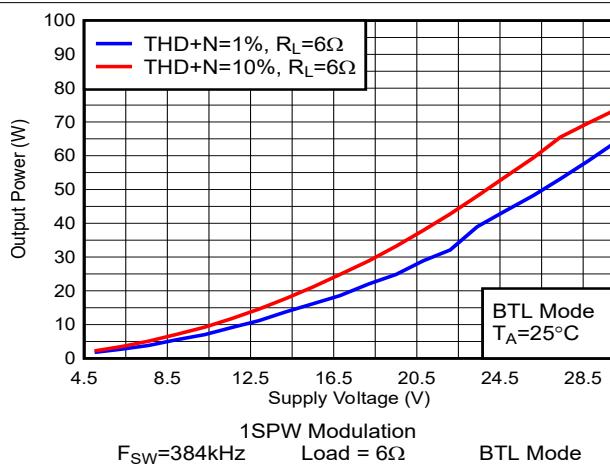

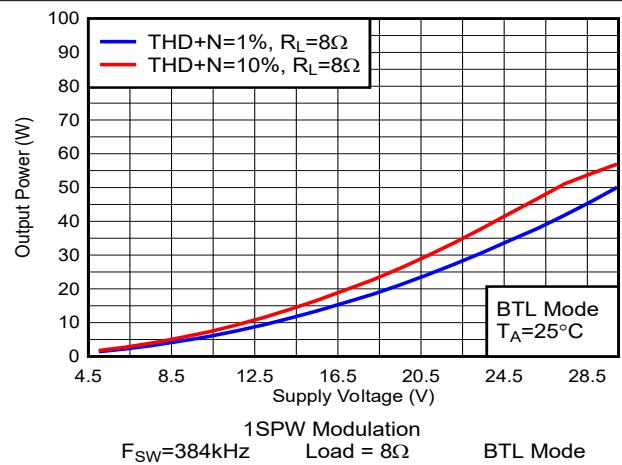

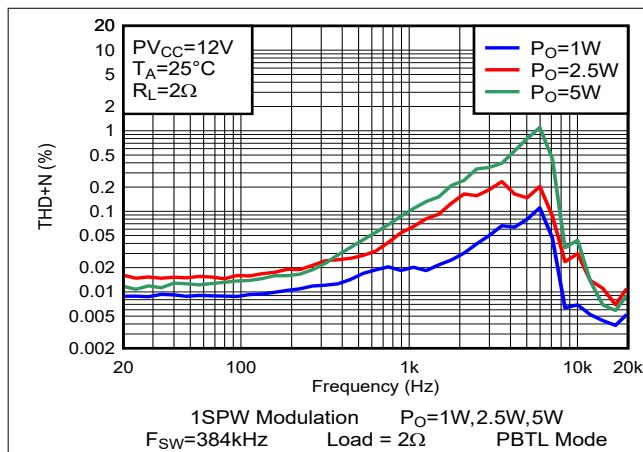

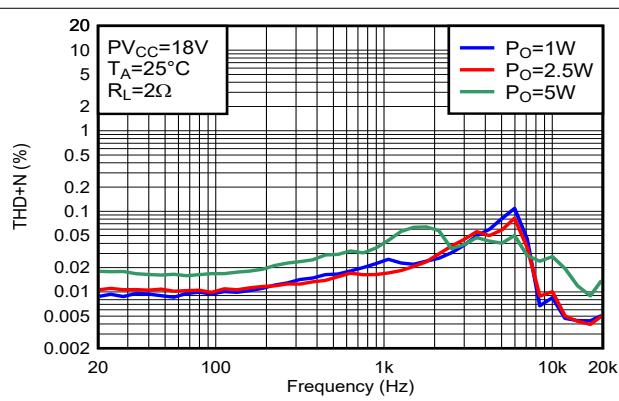

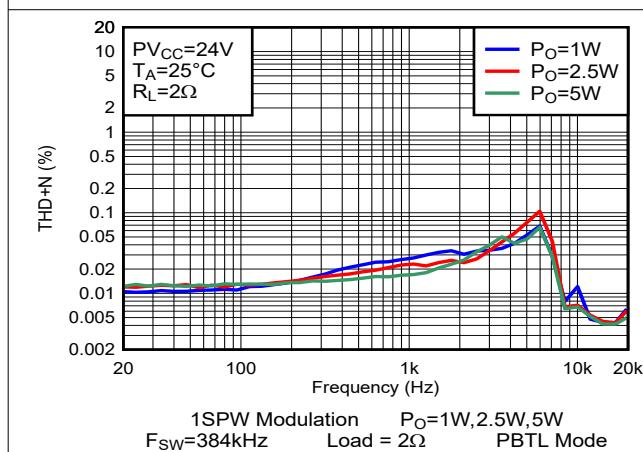

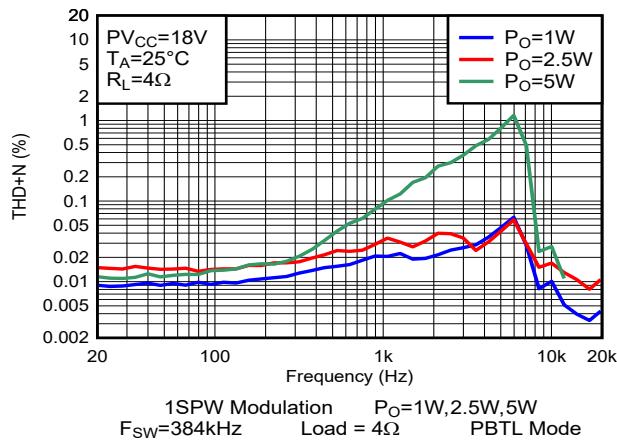

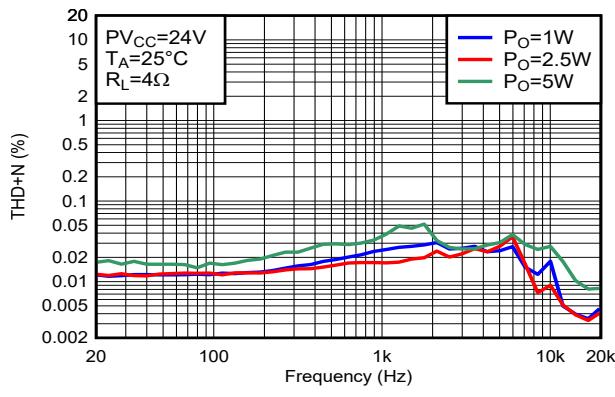

### 5.7.2 1SPW 変調によるブリッジ接続負荷 (BTL) 構成曲線

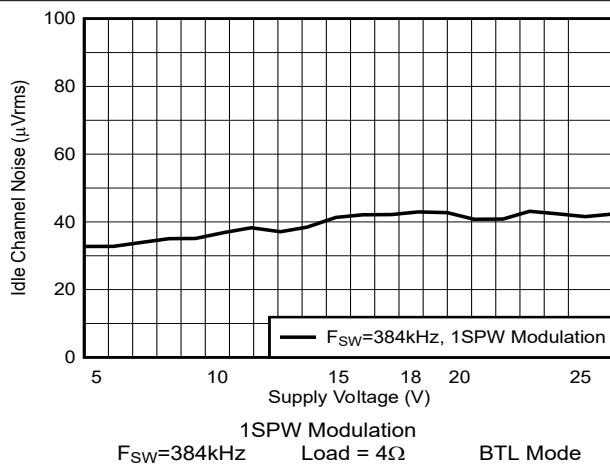

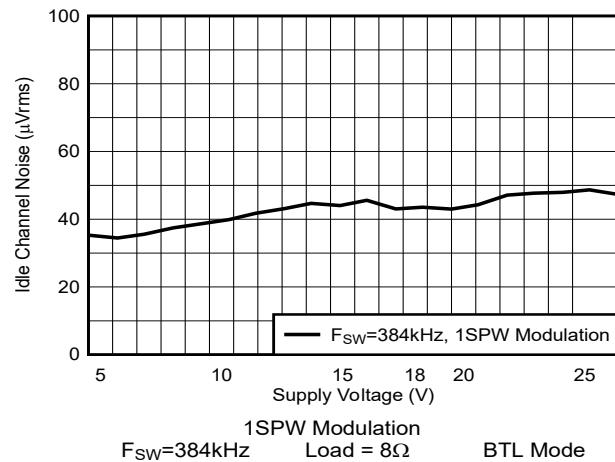

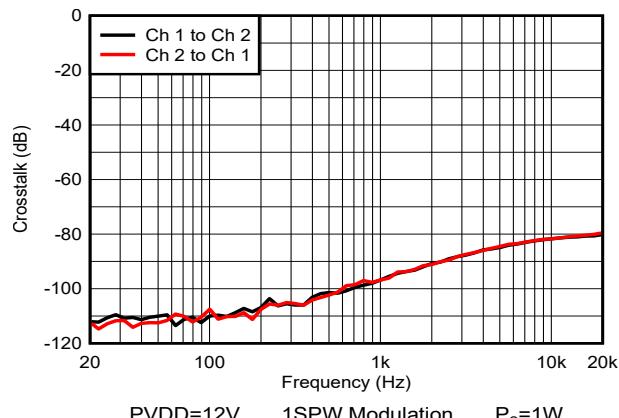

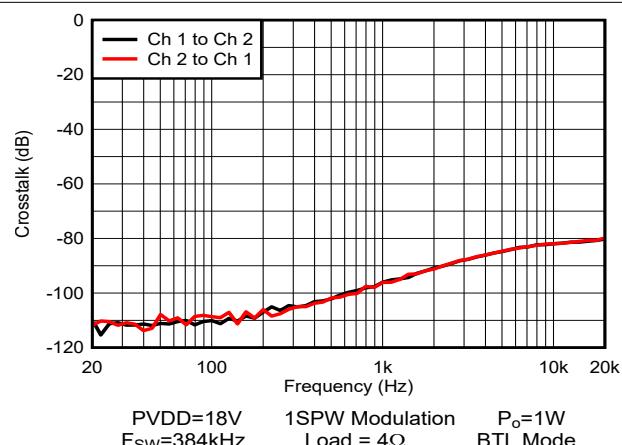

自由気流での室温 25°C (特に記述のない限り)。測定には、Audio Precision System 2722 を使用し、アナログ アナライザ フィルタを 20kHz のブリックウォール フィルタに設定しました。特に記述のない限り、すべての測定はオーディオ周波数を 1kHz、デバイスの PWM 周波数を 384kHz、80kHz の Class-D ループ帯域幅に設定した状態で行われます。ただし、LC フィルタの使用場所は 10μH/0.68μF でした。

図 5-25. THD + N と周波数 BTL との関係

図 5-26. THD + N と周波数 BTL との関係

図 5-27. THD + N と周波数 BTL との関係

1SPW Modulation  $P_o=1W, 2.5W, 5W$

$F_{sw}=384kHz$  Load =  $4\Omega$  BTL Mode

図 5-28. THD + N と周波数 BTL との関係

1SPW Modulation  $P_o=1W, 2.5W, 5W$

$F_{sw}=384kHz$  Load =  $4\Omega$  BTL Mode

図 5-29. THD + N と周波数 BTL との関係

1SPW Modulation  $P_o=1W, 2.5W, 5W$

$F_{sw}=384kHz$  Load =  $4\Omega$  BTL Mode

図 5-30. THD + N と周波数 BTL との関係

1SPW Modulation  $P_o=1W, 2.5W, 5W$

$F_{sw}=384kHz$  Load =  $4\Omega$  BTL Mode

図 5-31. THD + N と周波数 BTL との関係

1SPW Modulation  $P_o=1W, 2.5W, 5W$

$F_{sw}=384kHz$  Load =  $4\Omega$  BTL Mode

図 5-32. THD + N と周波数 BTL との関係

1SPW Modulation  $P_o=1W, 2.5W, 5W$

$F_{sw}=384kHz$  Load =  $4\Omega$  BTL Mode

図 5-33. THD+N と周波数 BTL との関係

図 5-34. THD+N と電源 BTL との関係

図 5-35. 出力電力と電源電圧との関係

図 5-36. 出力電力と電源電圧との関係

図 5-37. 出力電力と電源電圧との関係

図 5-38. アイドルチャネルノイズと電源電圧との関係

図 5-39. アイドルチャネルノイズと電源電圧との関係

図 5-40. クロストーク

図 5-41. クロストーク

図 5-42. クロストーク

図 5-43. 効率と出力電力との関係

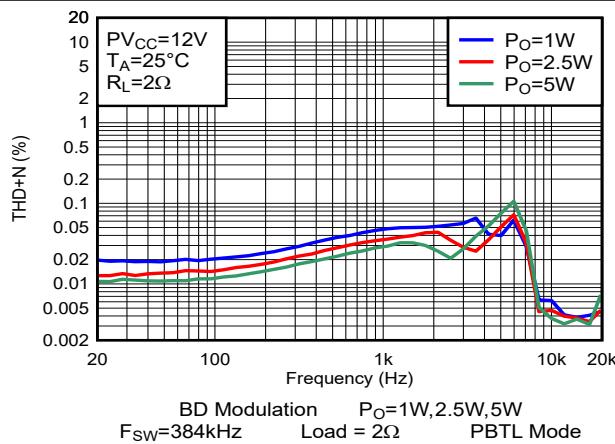

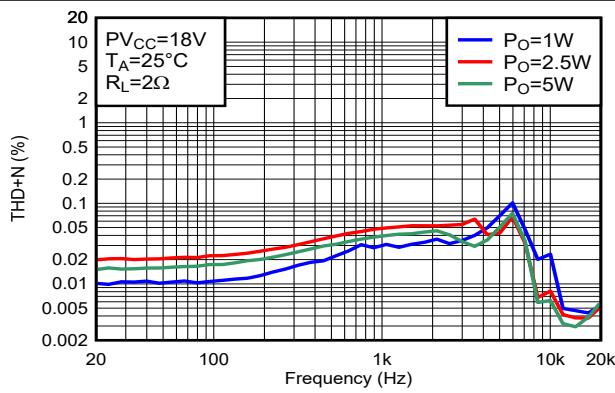

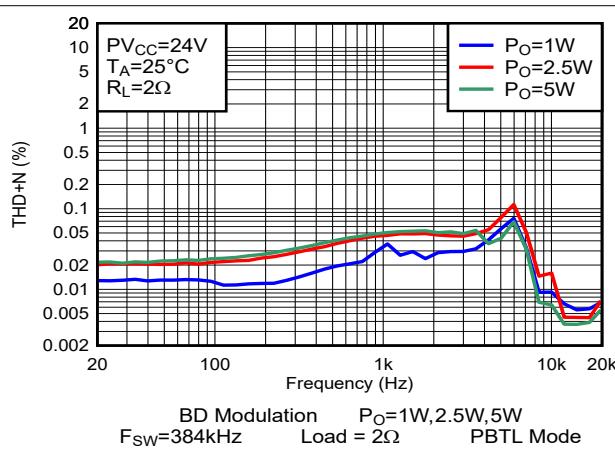

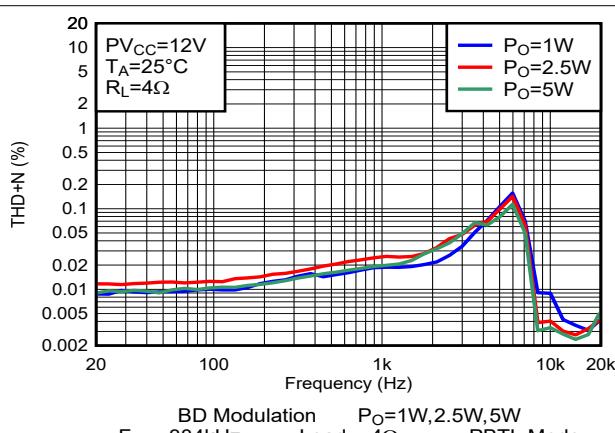

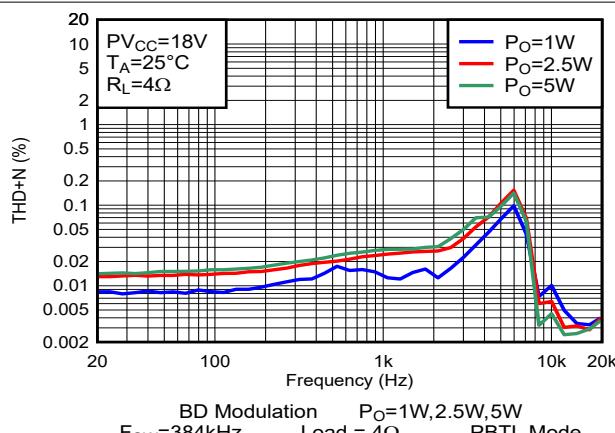

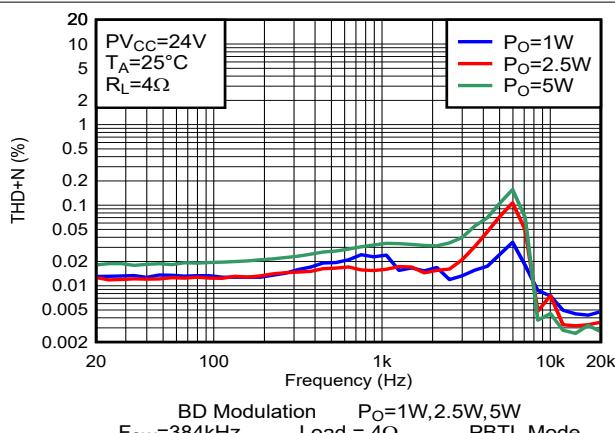

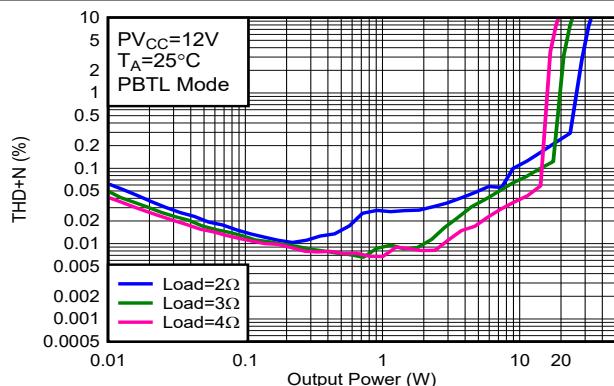

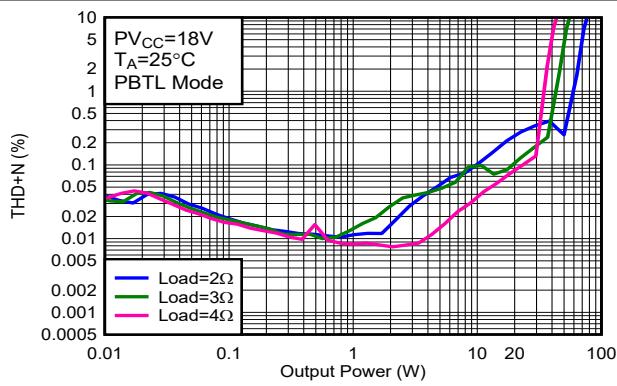

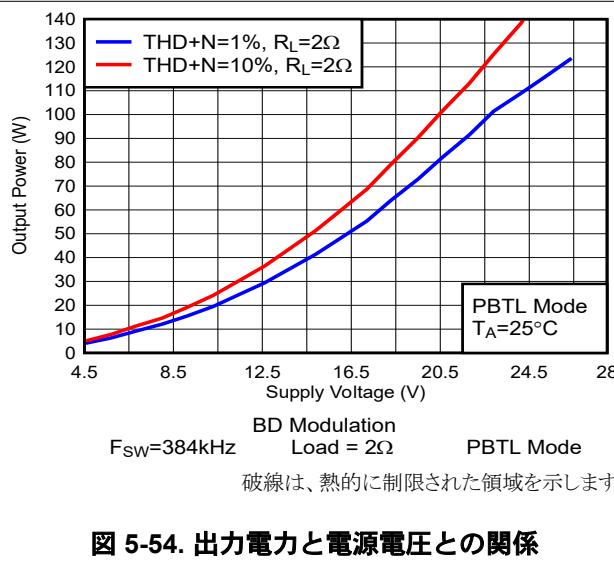

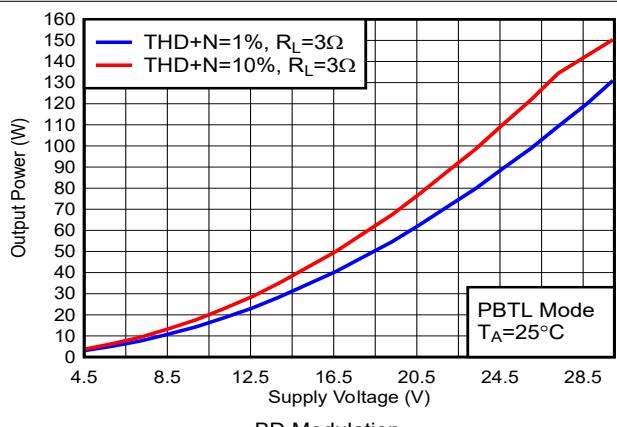

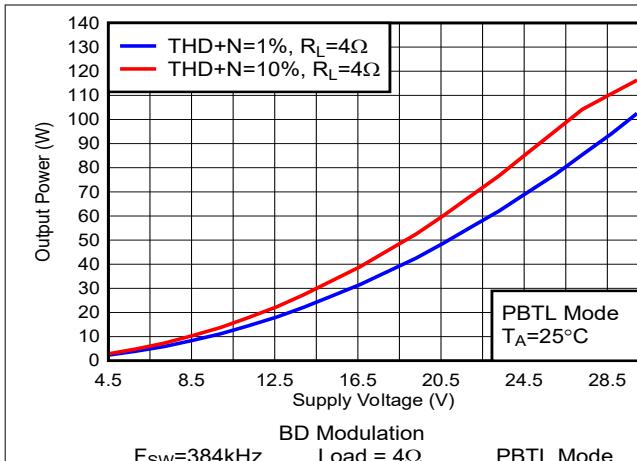

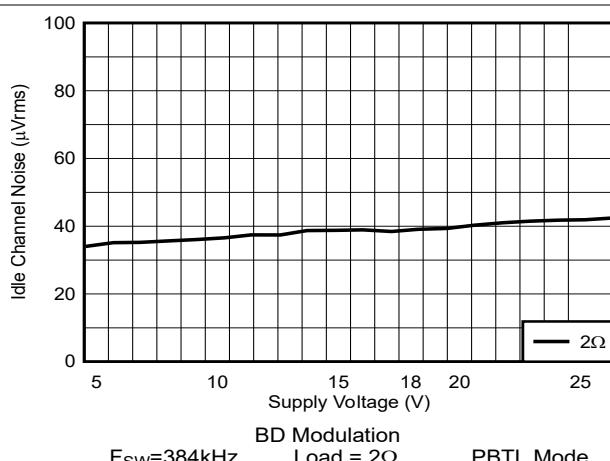

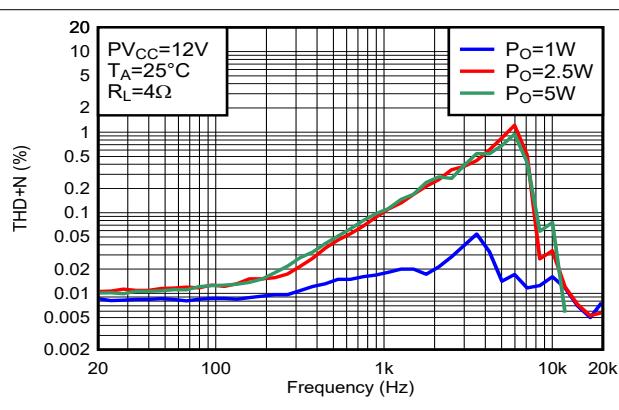

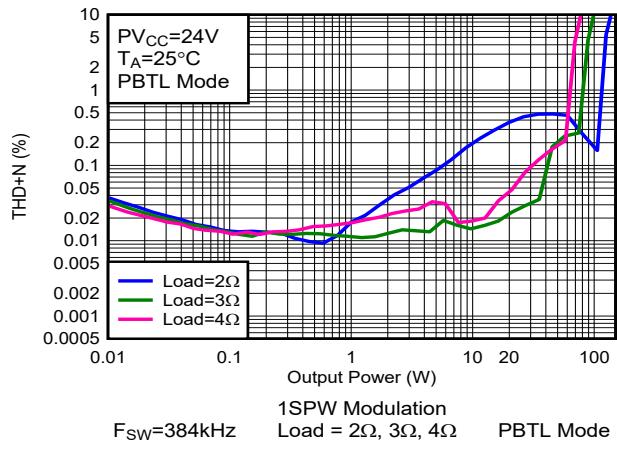

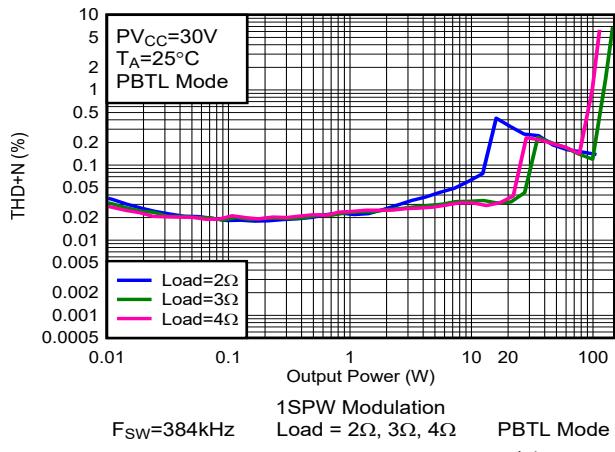

### 5.7.3 BD 変調による並列ブリッジ接続負荷 (PBTL) 構成

自由気流での室温 25°C (特に記述のない限り)。測定には、Audio Precision System 2722 を使用し、アナログ アナライザ フィルタを 20kHz のブリックウォール フィルタに設定しました。すべての測定は、オーディオ周波数を 1kHz、デバイスの PWM 周波数を 384kHz、クラス D アンプのループ帯域幅を 80kHz に設定して行いました。特に明記されていない限り、LC フィルターは 10µH / 0.68µF (ポストフィルター PBTL、出力フィルターのインダクタ部分の後の 2 つの出力チャネルの結合、セクション 8.1.2 の詳細を参照) を使用しました。

図 5-44. THD + N と周波数 PBTL との関係

図 5-45. THD + N と周波数 PBTL との関係

図 5-46. THD + N と周波数 PBTL との関係

図 5-47. THD + N と周波数 PBTL との関係

図 5-48. THD + N と周波数 PBTL との関係

図 5-49. THD + N と周波数 PBTL との関係

図 5-50. THD+N と出力電力 PBTL との関係

図 5-51. THD+N と出力電力 PBTL との関係

図 5-52. THD+N と出力電力 PBTL との関係

図 5-53. THD+N と電源 PBTL との関係

破線は、熱的に制限された領域を示します。

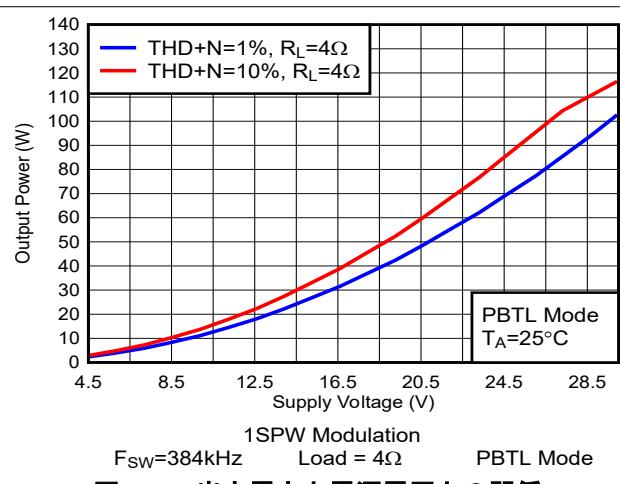

図 5-54. 出力電力と電源電圧との関係

図 5-55. 出力電力と電源電圧との関係

図 5-56. 出力電力と電源電圧との関係

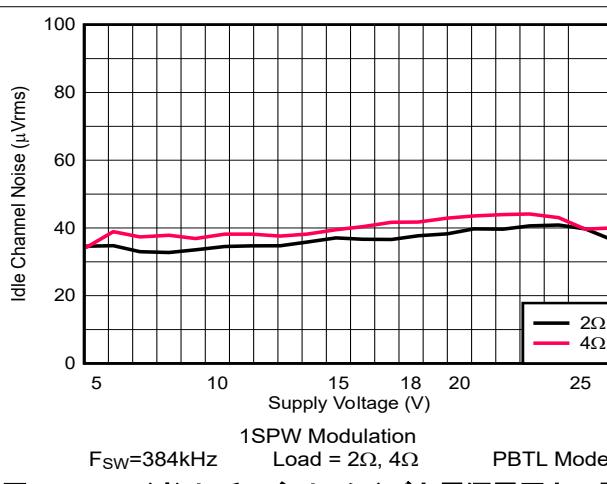

図 5-57. アイドルチャネルノイズと電源電圧との関係

図 5-58. アイドルチャネルノイズと電源電圧との関係

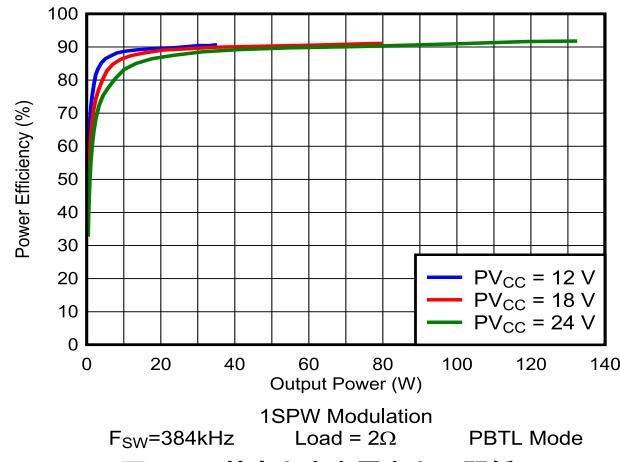

図 5-59. 効率と出力電力との関係

図 5-60. 効率と出力電力との関係

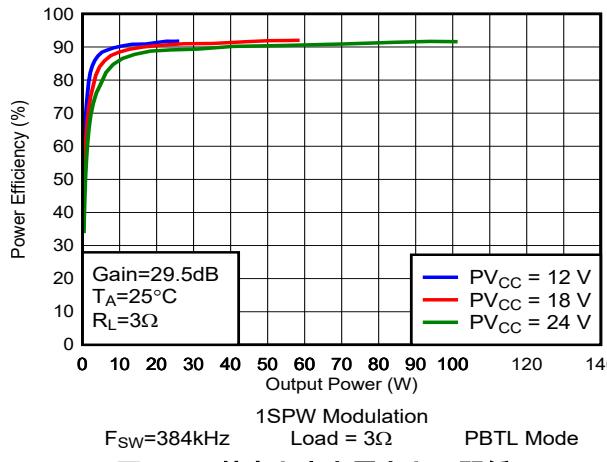

図 5-61. 効率と出力電力との関係

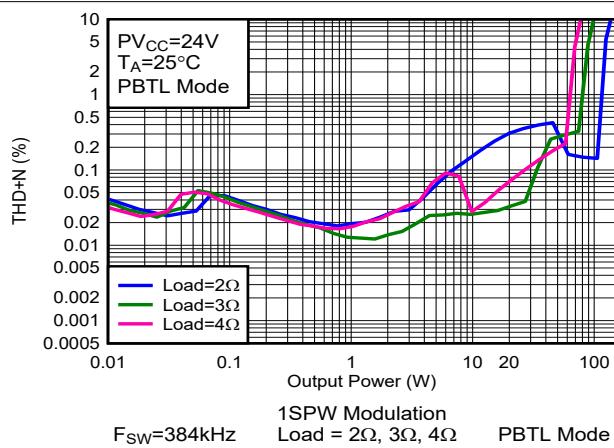

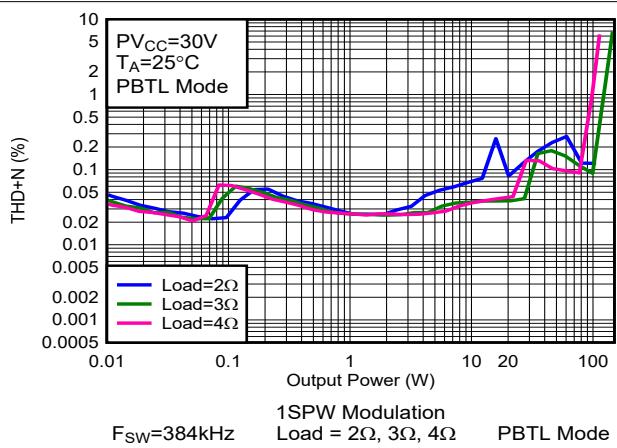

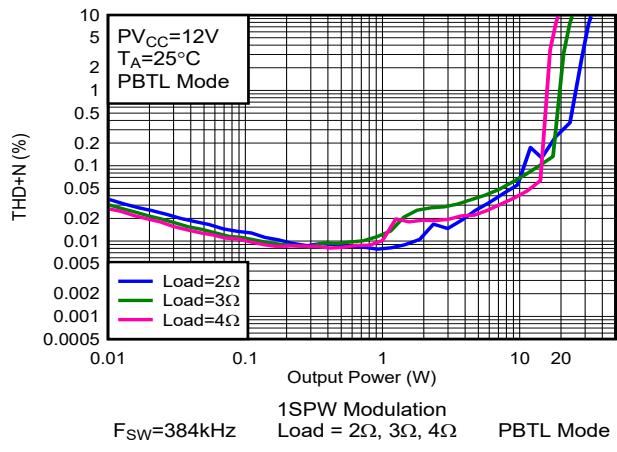

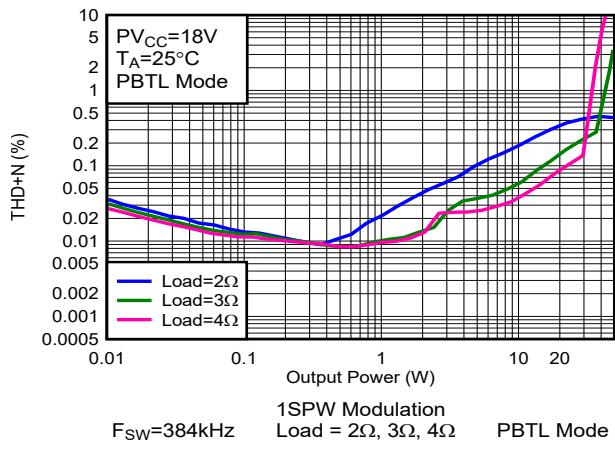

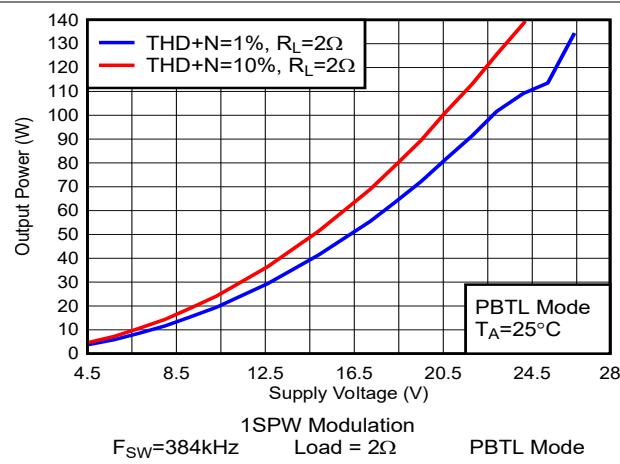

### 5.7.4 1SPW 変調による並列プリッジ接続負荷 (PBTL) 構成

自由気流での室温 25°C (特に記述のない限り)。測定には、Audio Precision System 2722 を使用し、アナログ アナライザ フィルタを 20kHz のブリックウォール フィルタに設定しました。すべての測定は、オーディオ周波数を 1kHz、デバイスの PWM 周波数を 384kHz、クラス D アンプのループ帯域幅を 80kHz に設定して行いました。特に明記されていない限り、LC フィルターは 10μH / 0.68μF (ポストフィルター PBTL、出力フィルターのインダクタ部分の後の 2 つの出力チャネルの結合、[セクション 8.1.2](#) の接続方法を参照)を使用しました。

図 5-62. THD + N と周波数 PBTL との関係

図 5-63. THD + N と周波数 PBTL との関係

図 5-64. THD + N と周波数 PBTL との関係

図 5-65. THD + N と周波数 PBTL との関係

図 5-66. THD + N と周波数 PBTL との関係

図 5-67. THD + N と周波数 PBTL との関係

図 5-68. THD+N と出力電力 PBTL との関係

図 5-69. THD+N と出力電力 PBTL との関係

図 5-70. THD+N と出力電力 PBTL との関係

図 5-71. THD+N と電源 BTL との関係

図 5-72. 出力電力と電源電圧との関係

図 5-73. 出力電力と電源電圧との関係

図 5-74. 出力電力と電源電圧との関係

図 5-75. アイドルチャネルノイズと電源電圧との関係

図 5-76. 効率と出力電力との関係

図 5-77. 効率と出力電力との関係

図 5-78. 効率と出力電力との関係

## 6 詳細説明

### 6.1 概要

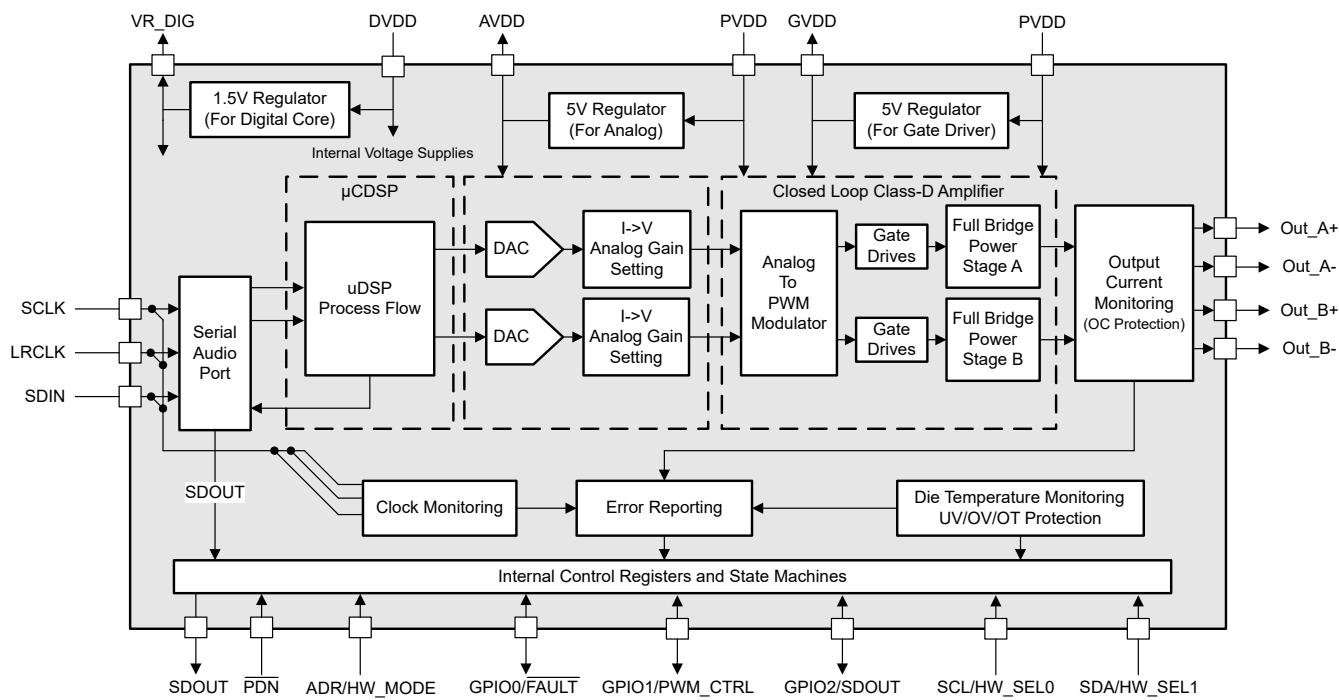

TAS5830 デバイスは、4 つの主要なビルディング ブロックを一つの集積デバイスに統合し、音質、柔軟性、使いやすさを最大限に高めています。4 つの主要なビルディング ブロックを以下に示します。

- ステレオ デジタルから PWM への変調器、その後 PWM 変調器を使用して出力段に変換します。

- オーディオ DSP サブシステム。

- フレキシブルな閉ループ アンプは、ステレオまたはモノラルで動作し、複数の異なるスイッチング周波数で動作し、さまざまな出力電圧および負荷に対応しています。

- デバイスとの通信用の I<sup>2</sup>C 制御ポート

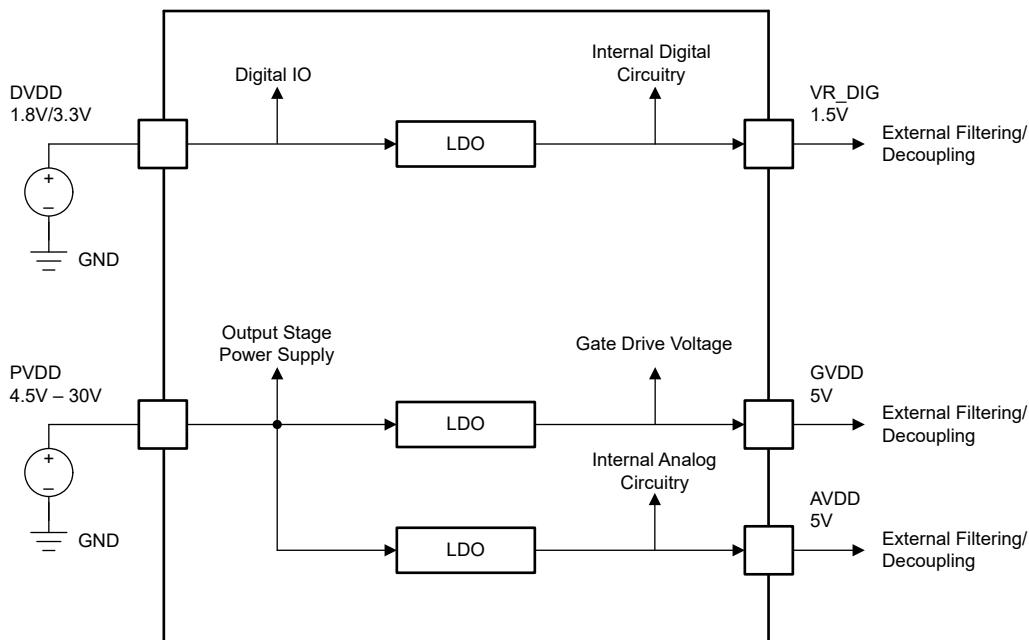

このデバイスが適切に動作するために必要な電源は 2 つだけです。低電圧デジタル回路に電力を供給するには DVDD 電源が必要です。オーディオ アンプの出力段に電力を供給するには、PVDD と呼ばれるもう 1 つの電源が必要です。2 つの内部 LDO は、GVDD と AVDD のために PVDD を 5V に変換し、1 つの内部 LDO は DVDD を VR\_DIG のため 1.5V に変換します。

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 電源

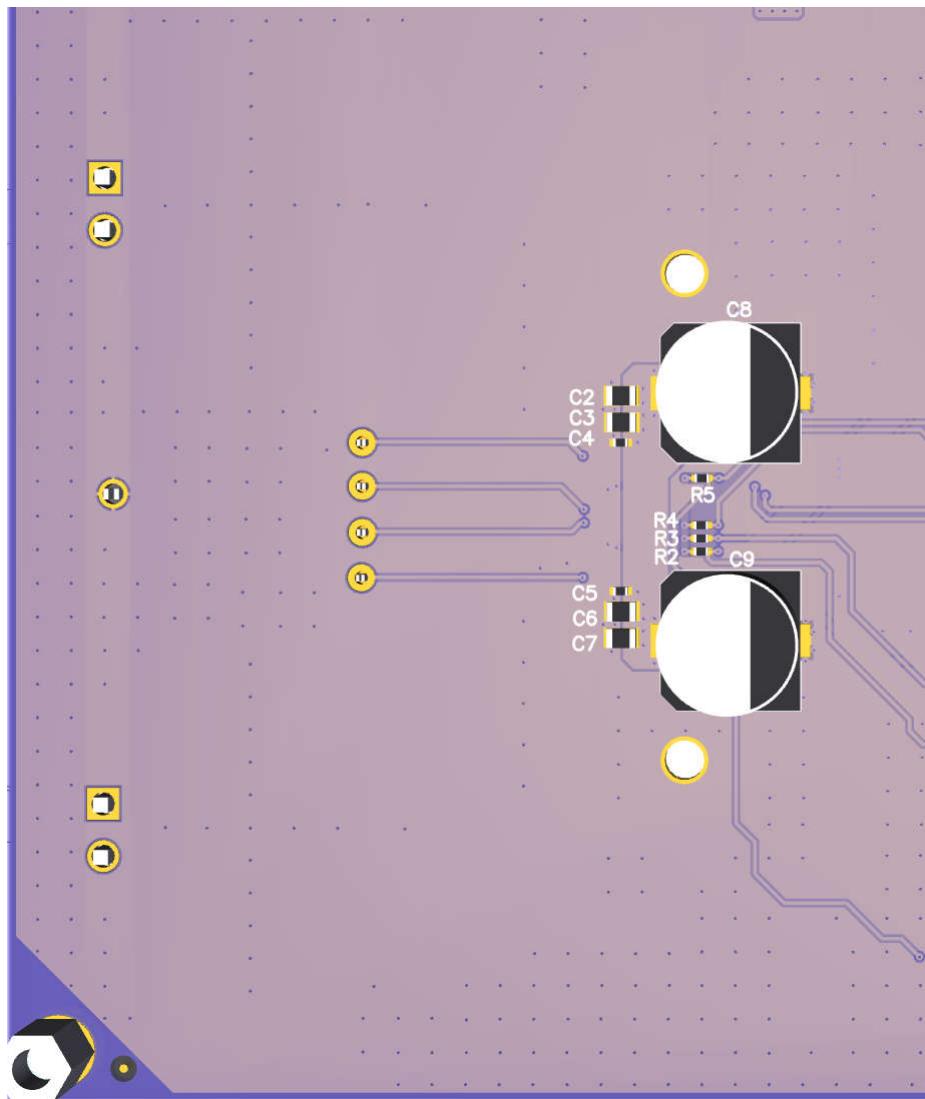

システム設計では、TAS5830 には(標準的な)12V または24V 電力段の電源に加えて、3.3V または1.8V の電源が必要です。2つの内部電圧レギュレータにより、ゲート駆動回路と内部回路に適した電圧レベルが提供されます。外部ピンは、電源をフィルタリングするためのオフチップバイパスコンデンサの接続ポイントとしてのみ提供されます。外部回路をこれらのレギュレータ出力に接続すると、性能が低下し、デバイスが損傷する可能性があります。また、フローティング電圧電源(ハイサイドゲートドライブ)を必要とするすべての回路は、数個の外付けコンデンサのみを必要とするブートストラップ回路を内蔵しています。優れた電気的特性と音響特性を得るために、出力段の PWM 信号路は同じ独立したハーフブリッジとして設計されています。このため、各ハーフブリッジには個別のブートストラップピン(BST\_X)があります。ゲート駆動電圧(GVDD)は PVDD 電圧から生成されます。すべてのデカップリングコンデンサは、関連するピンのできるだけ近くに配置するように、特に注意を払う必要があります。一般に、電源ピンとデカップリングコンデンサの間のインダクタンスを防ぐ必要があります。ブートストラップ回路を適切に機能させるには、各ブートストラップピン(BST\_X)と電力段出力ピン(OUT\_X)の間に小さなセラミックコンデンサを接続する必要があります。電力段の出力が low のとき、ゲート駆動レギュレータ出力ピン(GVDD)とブートストラップピンの間に接続された内部ダイオードを介してブートストラップコンデンサが充電されます。電力段の出力が high になると、ブートストラップコンデンサの電位が出力電位よりもシフトされるため、ハイサイドゲートドライバに適切な電圧電源が供給されます。

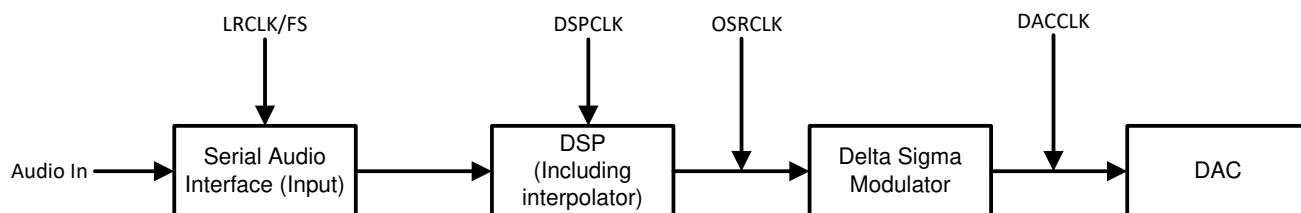

### 6.3.2 デバイスクロッキング

TAS5830 デバイスは、柔軟なクロック供給システムを備えています。内部的には、デバイスを正しく機能させるために、主に関連するクロックレートで、いくつかのクロックが必要です。これらのクロックは、すべてシリアルオーディオインターフェイスから入手できます。

図 6-2. 各クロックのオーディオフロー

図 6-2 に、基本的なデータフローとクロックディストリビューションを示します。

シリアルオーディオインターフェイスには、通常、以下の 3 つの接続ピンがあります。

- SCLK(ビットクロック)

- FS(左/右ワードクロックまたはフレーム同期)

- SDIN(入力データ)。

このデバイスには、SCLK を取得して DSP と DAC クロックに必要な高速クロックを作成するために使用される内部 PLL があります。

TAS5830 デバイスには、サンプリングレートがどの周波数で動作しているかを自動的に検知するオーディオサンプリングレート検出回路が搭載されています。32kHz、44.1kHz ~ 48kHz、88.2kHz ~ 96kHz、176.4kHz ~ 192kHz の一般的なオーディオサンプリング周波数に対応しています。サンプリング周波数検出器は、DAC と DSP のクロックを自動的に設定します。

音楽の再生中に入力 LRCLK/SCLK が停止した場合、TAS5830 はスリープ状態に切り替わり、クロック回復(Class-D 出力が自動的に Hi-Z に切り替わります)を待つ。LRCLK/SCLK が回復すると、TAS5830 は自動的に再生モードに戻ります。DSP コードを再ロードする必要はありません。

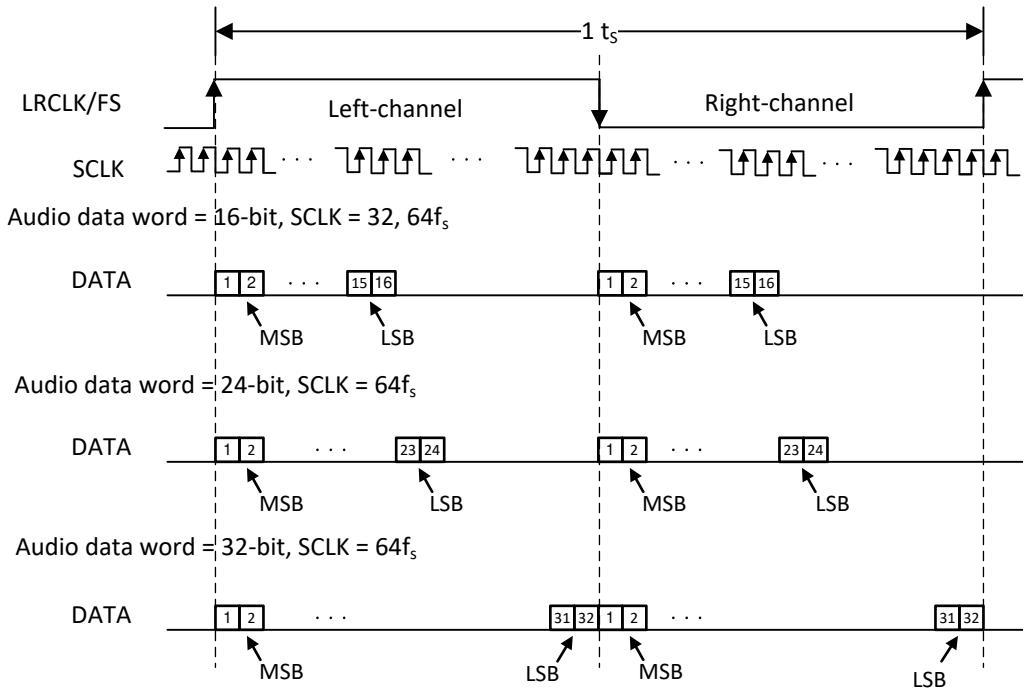

### 6.3.3 シリアルオーディオポートークロック速度

シリアルオーディオインターフェイスポートは、LRCLK/SCLK、FSおよびSDIN信号を持つ3線式シリアルポートです。SCLKは、SDINにあるシリアルデータをオーディオインターフェイスのシリアルシフトレジスタにクロック供給するために使用されるシリアルオーディオビットクロックです。シリアルデータは、SCLKによってTAS5830デバイスにクロック入力されます。LRCLK/FSピンは、デバイスがTDMモードで動作している場合、シリアルオーディオの左/右ワードクロックまたはフレーム同期です。

表 6-1. オーディオデータの形式、ピット深度、クロックレート

| フォーマット                 | データビット         | FS の最大周波数 (kHz) | SCLK レート (f <sub>s</sub> ) |

|------------------------|----------------|-----------------|----------------------------|

| I <sup>2</sup> S/LJ/RJ | 32, 24, 20, 16 | 32~192          | 64, 32                     |

|                        |                | 32              | 128                        |

|                        |                | 44.1, 48        | 128, 256, 512              |

|                        |                |                 | 96                         |

|                        |                |                 | 192                        |

クロック停止、サポートされていないSCLK対LRCLK(FS)比率が検出されると、デバイスはレジスタ113(レジスタアドレス0x71)にクロックエラーを報告します。

### 6.3.4 クロック HALT 自動回復

一部のホストプロセッサは、オーディオが再生されていないときにI<sup>2</sup>Sクロックを停止します。クロックが停止すると、デバイスはすべてのチャネルをHi-Z状態に移行して、レジスタGLOBAL\_FAULT1レジスタ(オフセット=71h)[リセット=00h]-D[2]でラッチクロックエラーを発行します。オーディオクロックの回復後、デバイスは自動的に以前の状態に戻ります。

### 6.3.5 サンプルレートの即時変更

TAS5830は、LRCLK(FS)レートの即時変更をサポートしています。例えば48kHzから96kHzにLRCLK(FS)を変更する場合、ホストプロセッサは新しいサンプルレートに変更する前に少なくとも100usの間、LRCLK(FS)/SCLKを停止状態にする必要があります。

### 6.3.6 シリアルオーディオポートーデータ形式とピット深度

このデバイスは、標準のI<sup>2</sup>S、左揃え、右揃え、TDM/DSPデータを含む、業界標準のオーディオデータフォーマットをサポートしています。データ形式はレジスタ(SAP\_CTRL1レジスタ(オフセット=33h)[リセット=02h]-D[5:4])により選択します。TDM/DSPモードでのLRCLK/SCK FSのhigh幅が8サイクル未満の場合、レジスタSAP\_CTRL1レジスタ(オフセット=33h)[リセット=02h](-D[3:2])を01に設定する必要があります。すべての形式には、バイナリの2の補数、MSBファーストのオーディオデータが必要です。最大32ビットのオーディオデータを受け付けます。このデバイスでサポートされているすべてのデータフォーマット、ワード長、クロックレートを表1に示します。データ形式については、図6-3から図6-7で詳しく説明します。ワード長はレジスタ(SAP\_CTRL1レジスタ(オフセット=33h)[リセット=02h]-D[1:0])によって選択されます。データのオフセットは、レジスタ(SAP\_CTRL2レジスタ(オフセット=34h)[リセット=00h]-D[7:0])とレジスタ(SAP\_CTRL1レジスタ(オフセット=33h)[リセット=02h]-D[7:0])により選択されます。デフォルト設定はI<sup>2</sup>Sと24ビットのワード長です。

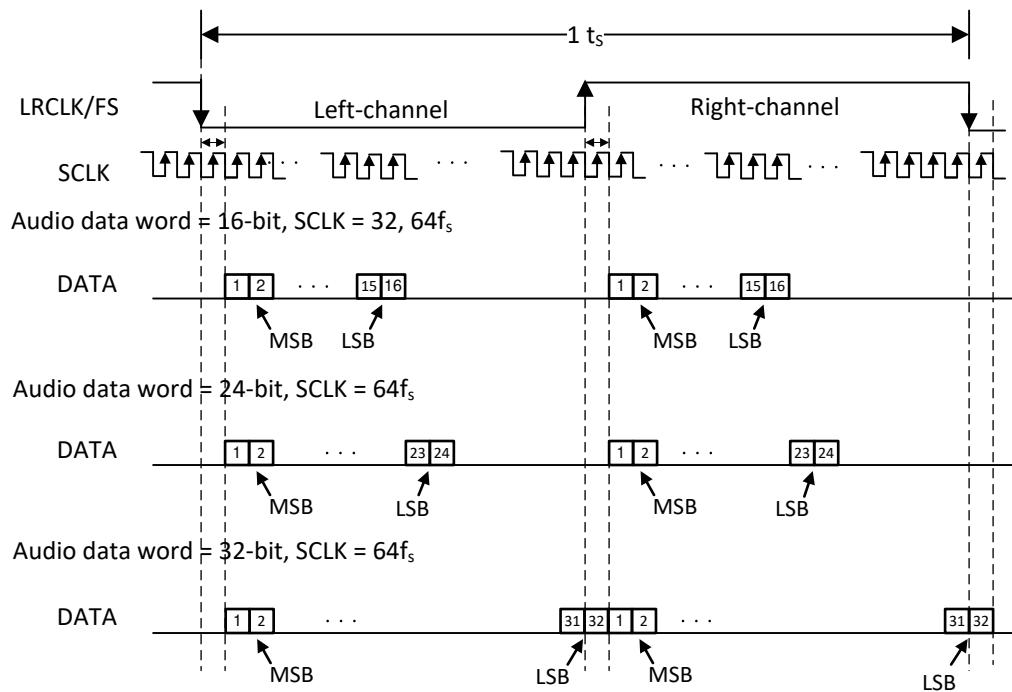

図 6-3. 左揃えのオーディオデータ形式

I<sup>2</sup>S Data Format; L-channel = LOW, R-channel = HIGH

I<sup>2</sup>S データフォーマット、L チャネル = LOW、R チャネル = HIGH

図 6-4. I<sup>2</sup>S オーディオデータ形式

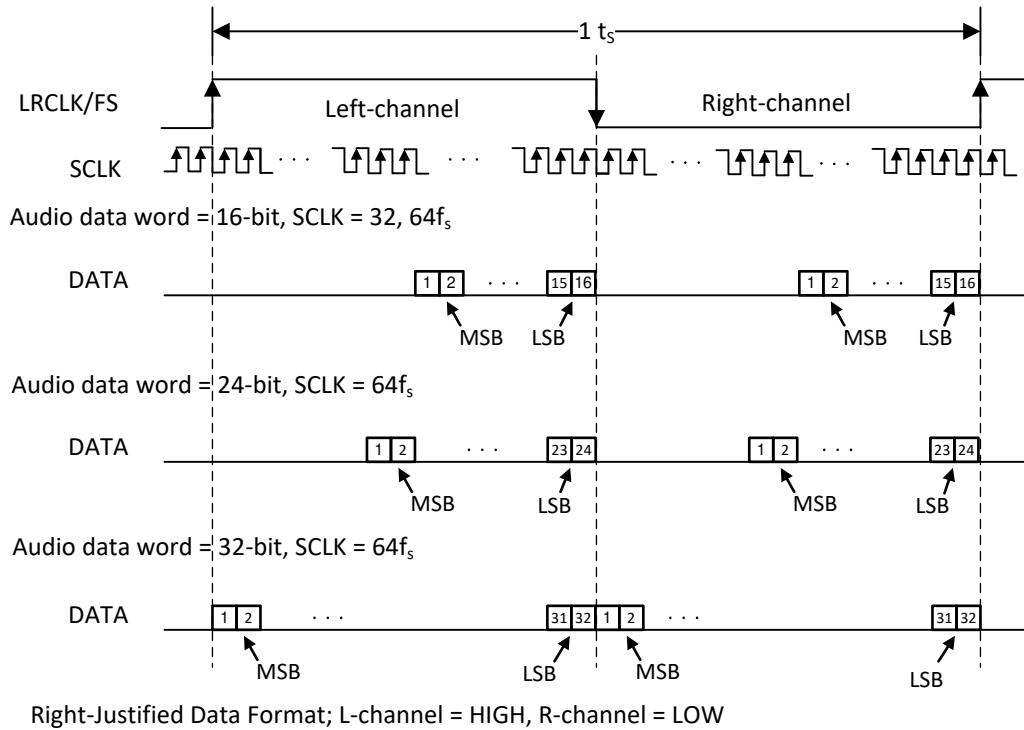

右揃えデータ形式、L チャネル = HIGH、R チャネル = LOW

図 6-5. 右揃えオーディオ データ形式

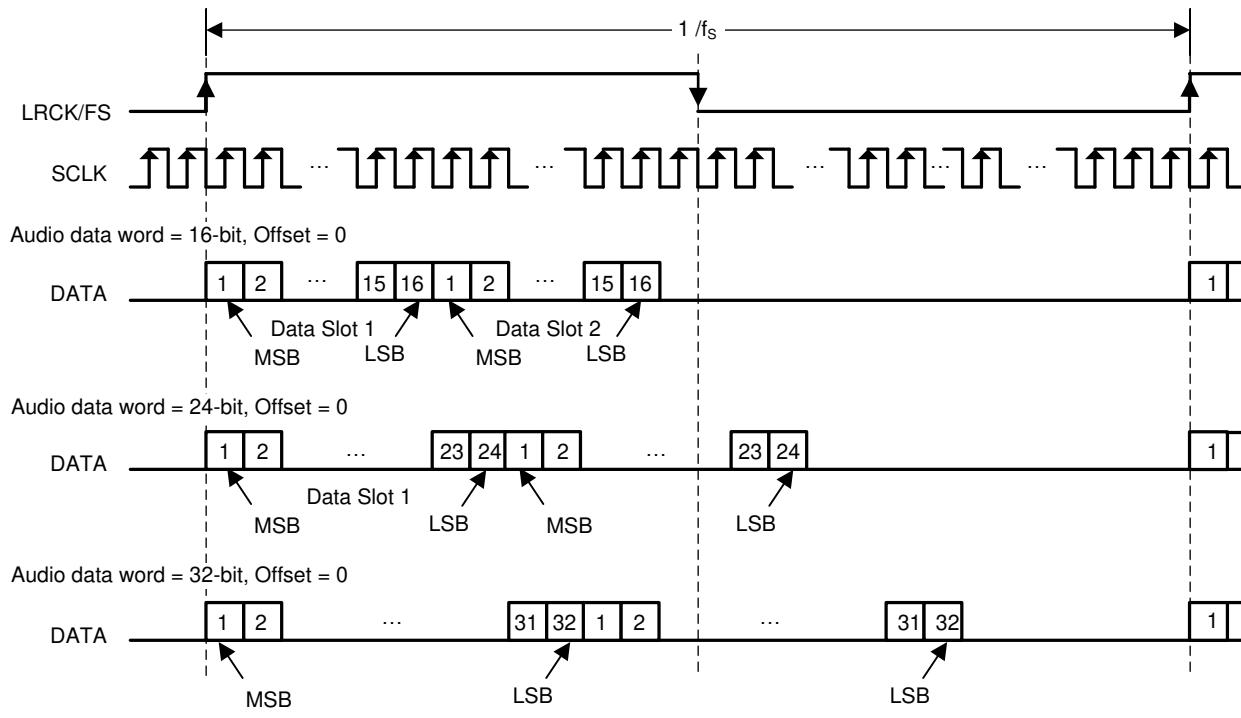

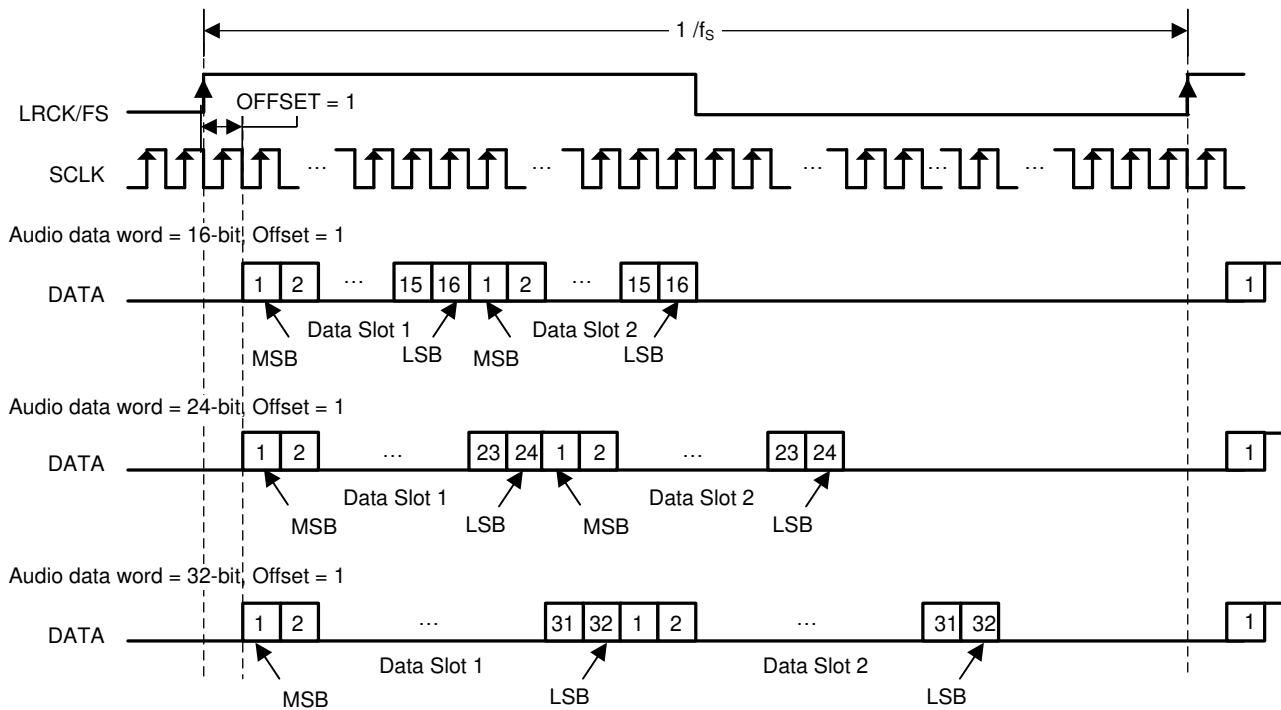

TDM モードでは、LRCK/FS のデューティサイクルは少なくとも 1x SCLK にする必要があります。立ち上がりエッジはフレームスタートと見なされます。

図 6-6. TDM 1 オーディオデータ形式

オフセット = 1 の TDM データ形式

TDM モードでは、LRCK/FS のデューティサイクルは少なくとも 1x SCLK にする必要があります。立ち上がりエッジはフレームスタートと見なされます。

図 6-7. TDM 2 オーディオデータ形式

## 6.4 デバイスの機能モード

### 6.4.1 ソフトウェアコントローラ

TAS5830 デバイスは、I<sup>2</sup>C 通信ポートを介して構成されます。

I<sup>2</sup>C 通信プロトコルについては、「[I<sup>2</sup>C 通信ポート](#)」セクションを参照してください。I<sup>2</sup>C のタイミング要件は、[セクション 5.6](#) に説明されています。

### 6.4.2 スピーカアンプの動作モード

TAS5830 デバイスは、レジスタ [DEVICE\\_CTRL1](#) レジスタ (オフセット = 2h) [リセット = 00h]-D[2] を使用して、2 種類のアンプ構成として構成することもできます。

- BTL モード

- PBTL モード

#### 6.4.2.1 BTL モード

BTL モードでは、TAS5830 はステレオ信号の左右の成分を表す 2 つの独立した信号を増幅します。左の増幅された信号は、OUT\_A+ と OUT\_A- として示された差動出力ペアに渡され、増幅された右の信号は、差動出力ペアに OUT\_B+ と OUT\_B- として示されます。

#### 6.4.2.2 PBTL モード

PBTL 動作モードは、デバイスの 2 つの出力を互いに並列に配置して、デバイスの電力供給能力を向上させる動作を表すために使用されます。TAS5830 デバイスの出力側では、事前フィルタ並列ブリッジ接続負荷 (PBTL) と呼ばれる構成で、フィルタの前にデバイスの合計を行うことができます。ただし、出力フィルタのインダクタ部分の後で 2 つの出力をマージする必要がある場合があります。これにより 2 つのインダクタが追加されますが電流が 2 つのインダクタで分割されるため、小型で低成本のインダクタを使用できます。このプロセスはポストフィルタ PBTL と呼ばれます。TAS5830 デバイスの入力側では、PBTL アンプへの入力信号は I<sup>2</sup>S または TDM データの左フレームです。

#### 6.4.3 低 EMI モード

TAS5830 には、オーディオ再生中に EMI を最小化するために複数のモードが備えられており、これらのモードは、さまざまなアプリケーションに基づいて使用できます。

##### 6.4.3.1 スペクトラム拡散

スペクトラム拡散変調は、PWM 変調技術であり、出力 PWM 周波数を変化させることで EMI 測定値のピークを引き下げます。スペクトルは広くありますが、その結果、EMI ノイズはより低いレベルになります。TAS5830 は、三角波モードとランダムモードの両方の拡散スペクトラムをサポートしています。

ユーザーは、三角波モードを有効にし、スペクトラム拡散を有効にするようにレジスタ **RAMP\_SS\_CTRL0** レジスタ (オフセット = 6Bh) [リセット = 00h] を構成し、拡散スペクトラム周波数と範囲を **RAMP\_SS\_CTRL1** レジスタ (オフセット = 6Ch) [リセット = 00h] と共に選択する必要があります。DEVICE\_CTRL1 レジスタ (オフセット = 2h) [リセット = 00h] で設定される 768kHz F<sub>sw</sub> の場合、拡散スペクトル周波数と範囲は [表 6-2](#) に記載されています。

**表 6-2. 三角波モードのスペクトラム拡散周波数および範囲選択**

| SS_TRI_CTRL[3:0] | 0  | 1   | 2   | 3   | 4  | 5   | 6   | 7   |

|------------------|----|-----|-----|-----|----|-----|-----|-----|

| 三角波周波数           |    |     | 24k |     |    |     | 48k |     |

| スペクトラム拡散範囲       | 5% | 10% | 20% | 25% | 5% | 10% | 20% | 25% |

ユーザー アプリケーションの例: 中心スイッチング周波数は 768kHz、三角波周波数は 48kHz。

レジスタ 0x02 = 0x41//768kHz F<sub>sw</sub>、BTL モード、1SPW モード。

レジスタ 0x6b = 0x03//スペクトラム拡散をイネーブルする

レジスタ 0x6c = 0x03// SS\_CTRL[3:0] = 0011、三角波周波数 = 48kHz、スペクトラム拡散範囲は 10% (729kHz ~ 807kHz) である必要があります

##### 6.4.3.2 チャネル間位相シフト

このデバイスは、チャネル間 180 度の PWM 位相シフトをサポートしており、EMI を最小限に抑えます。ANA\_CTRL レジスタ (オフセット = 53h) [リセット = 00h] のビット 0 を使用して、位相シフトをディセーブルまたはイネーブルにできます。

##### 6.4.3.3 マルチデバイスの PWM 位相同期

TAS5830 はマルチデバイス アプリケーションシステム用に最大 4 フェーズの選択をサポートしています。たとえば、システムが 4 個の TAS5830 デバイスを内蔵している場合、ユーザーはレジスタ **RAMP\_PHASE\_CTRL** レジスタ (オフセット = 6Ah) [リセット = 00h] を設定して各デバイスの位相 0/1/2/3 を選択することができます。これは、EMI を最小化するために、各デバイス間に 45 度の位相シフトが発生することを意味します。

マルチデバイスの PWM 位相同期には、2 つの方法があります。I<sup>2</sup>S クロックによる位相同期 (スタートアップ位相)、または GPIO による位相同期。

###### 6.4.3.3.1 起動フェーズでの I<sup>2</sup>S クロックとの位相同期

1. ステップ 1、I<sup>2</sup>S クロックを停止。

2. ステップ 2、各デバイスの位相選択を構成し、位相同期を有効にします。次に例を示します。デバイス 0 のレジスタ **RAMP\_PHASE\_CTRL** レジスタ (オフセット = 6Ah) [リセット = 00h] = 0x03、デバイス 1 のレジスタ

**RAMP\_PHASE\_CTRL** レジスタ (オフセット = 6Ah) [リセット = 00h] = 0x07、デバイス 2 のレジスタ

**RAMP\_PHASE\_CTRL** レジスタ (オフセット = 6Ah) [リセット = 00h] = 0x0B、デバイス 3 のレジスタ

**RAMP\_PHASE\_CTRL** レジスタ (オフセット = 6Ah) [リセット = 00h] = 0x0F。

3. ステップ 3、各デバイスを HIZ モードに構成します。

4. ステップ 4、各デバイスに I<sup>2</sup>S を入力します。4 つすべてのデバイスに対する位相同期は内部シーケンスによって自動的に行われます。

5. ステップ 5、DSP コードを初期化します (位相同期のみを実行する場合は、このステップをスキップできます)。

6. ステップ 6、デバイスからデバイスへの PWM 位相シフトは 45 度で固定される必要があります。

#### 6.4.3.3.2 GPIO との位相同期

1. ステップ 1、各デバイスの GPIOx ピンを PCB の SOC GPIO ピンに接続します。

2. ステップ 2、各デバイスの GPIOx を、レジスタ **GPIO\_CTRL** レジスタ (オフセット = 60h) [リセット = 00h] および **GPIO\_INPUT\_SEL** レジスタ (オフセット = 64h) [リセット = 00h] による位相同期入力使用として構成します。

3. ステップ 3、各デバイスで異なる位相を選択し、レジスタ **RAMP\_PHASE\_CTRL** レジスタ (オフセット = 6Ah) [リセット = 00h] で位相同期を有効にします。

4. ステップ 4、レジスタ **DEVICE\_CTRL1** レジスタ (オフセット = 2h) [リセット = 00h] を設定し、デバイスが HIZ 状態に変わるまで **POWER\_STATE** レジスタ (オフセット = 68h) [リセット = 00h] を監視することで、各デバイスを PLAY モードに設定します。

5. ステップ 5、SOC GPIO で 0 から 1 にトグルします。その後、4 つのデバイスすべてが PLAY モードに移行し、デバイス間の PWM 位相シフトを 45 度に固定する必要があります。

6. ステップ 6:位相同期が完了しました。GPIOx ピンを、アプリケーションに応じて別の機能に構成します。

#### 6.4.4 サーマル フォールドバック

サーマル フォールドバック (TFB) は、デバイスが推奨される温度/電力制限を超えて動作している場合や、熱システムの設計が推奨値よりも弱い場合に、ダイ温度の過度な上昇から TAS5830 を保護するように設計されています。TFB を使うと、予期しないサーマル シャットダウンをトリガすることなく、TAS5830 は可能な限り大きな音量で再生できます。TAS5830 には 4 つの過熱警告 (OTW) スレッショルドがあり、各スレッショルドは I<sup>2</sup>C レジスタ 0x73 のビット 0, 1, 2, 3 に表示されます。OTW 値がレベル 1 (最低 OTW 温度) からレベル 4 (最高 OTW 温度) まで上昇すると、内部の自動ゲイン リミッタ (AGL) により、デジタル ゲインが徐々に減衰します。適用されるゲイン減衰は OTW レベルに比例し、OTW レベルが低い場合は減衰が小さくなり、OTW レベルが高くなることで減衰が大きくなります。ダイの温度が低下して OTW レベルが低下すると、温度が OTW レベルを下回り、デジタル ゲインが元のレベルに復元されるまで、デジタル信号ゲインは徐々に増加します。減衰ゲインと調整可能レートの両方をプログラム可能です。TFB のゲイン レギュレーション速度 (アタック レートとリリース レート) の設定は通常の AGL と同じです。この AGL は PurePath™ Console3 の TAS5830 App を使用して構成することもできます。

#### 6.4.5 デバイスの状態制御

シャットダウン モード以外では、TAS5830 には他の 4 つの状態があり、消費電力は異なります。ディープ スリープ、スリープ、HiZ、および再生モード。各モードの電力レベルは [電気的特性](#) に記載されています。

- レジスタ 0x03[1:0] = 00 を書き込むと、デバイスはディープ スリープ モードに移行します。このモードでは、I<sup>2</sup>C がアクティブです。このモードを使用することにより、一部の携帯用スピーカー アプリケーションのバッテリ駆動時間を延長できます。ホスト プロセッサがオーディオの再生を停止すると、TAS5830 をディープ スリープ モードに設定して、ホスト プロセッサがオーディオの再生を再開するまで消費電力を最小限に抑えることができます。レジスタ 0x03 [1:0] を 11 に設定すると、デバイスは再生モードに戻ることができます。シャットダウン モード (PDN を low にプル) と比較して、ディープ スリープ モードは DSP と I<sup>2</sup>C をアクティブに維持します。

- レジスタ 0x03[1:0] = 01 を書き込むと、デバイスはスリープ モードに移行します。このモードでは、I<sup>2</sup>C ブロック、デジタル コア、DSP メモリ、5V アナログ LDO がアクティブになります。

- レジスタ 0x03[1:0] = 10 を書き込むと、デバイスは HiZ モードになります。このモードでは、ドライバ出力が HiZ ステートに設定され、他のすべてのブロックは通常動作します。

- レジスタ 0x03[1:0] = 11 を書き込むと、デバイスは再生モードになり、出力パスがイネーブルになります。

#### 6.4.6 デバイス変調

TAS5830 には次の 3 つの変調方式があります。BD 変調、1SPW 変調、ハイブリッド変調です。レジスタ **DEVICE\_CTRL1** レジスタ (オフセット = 2h) [リセット = 00h]D[1:0]-DAMP\_MOD を使用して TAS5830 の変調方式を選択します。

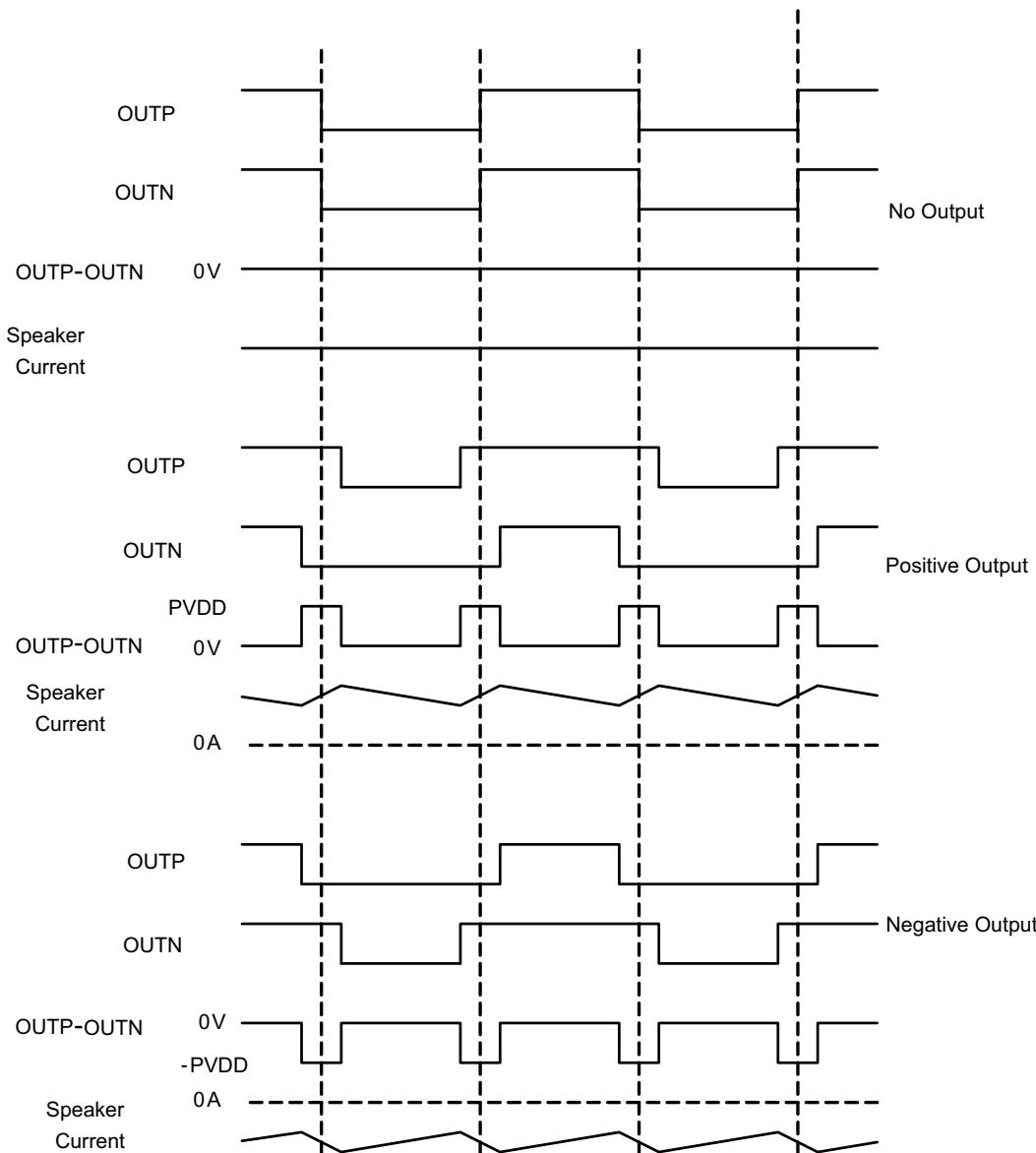

##### 6.4.6.1 BD 変調

これは変調方式で、アンプが短いスピーカ配線で誘導性負荷を駆動している場合に、従来の LC 再構成フィルタを使用しないで動作できるようにしています。各出力は、0V から電源電圧に切り替えられます。OUTPx と OUTNx は入力がない状態では互いに同位相なので、スピーカーには電流はほとんどまたはまったく流れません。正の出力電圧に対して、OUTPx のデューティサイクルは 50% より大きく、OUTNx は 50% 未満です。負の出力電圧に対して、OUTPx のデューティサイクルは 50% 未満、OUTNx は 50% を超えます。負荷にかかる電圧は、多くのスイッチング期間にわたって 0V となるためスイッチング電流が減少し、負荷での  $I^2R$  の損失が減少します。

図 6-8. BD モード変調

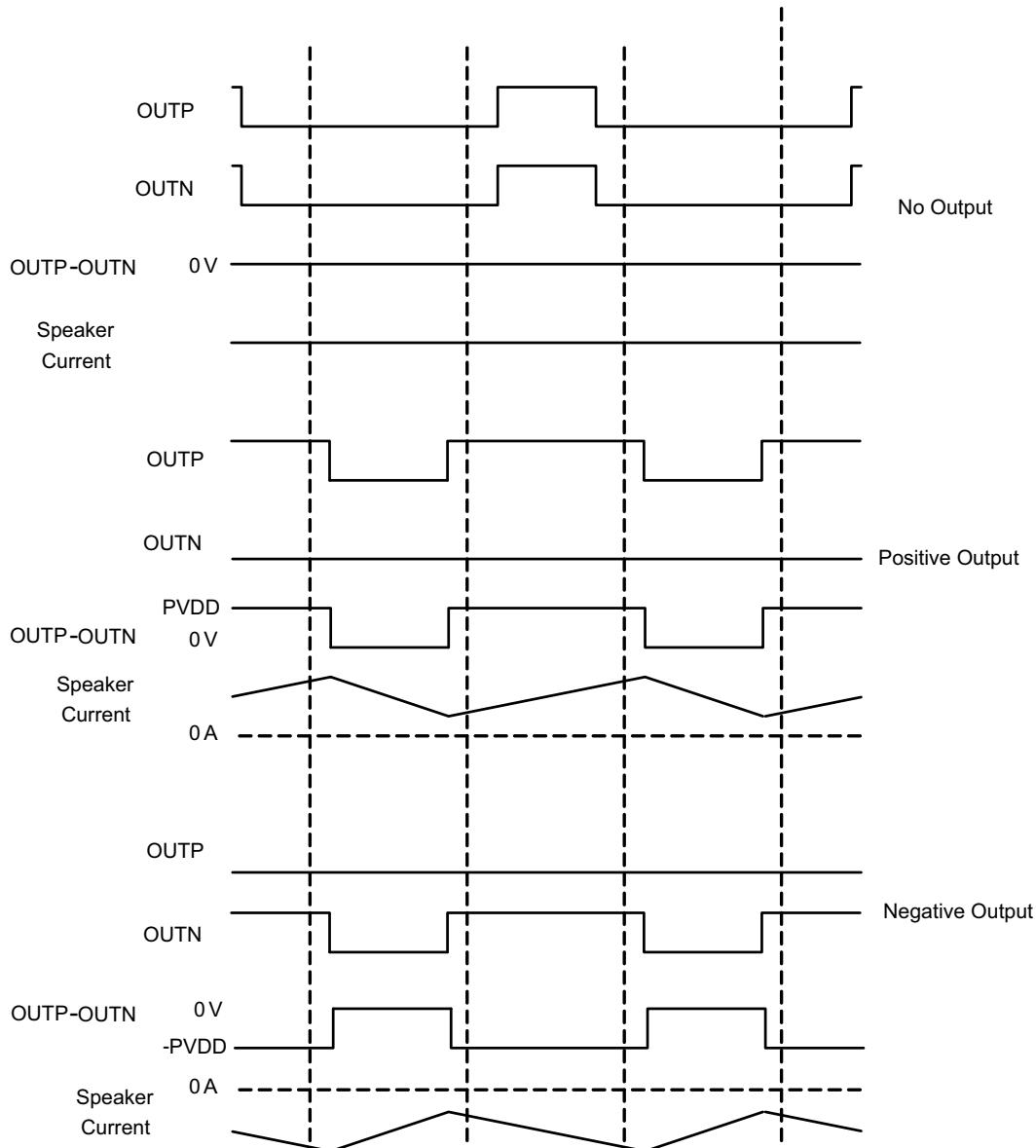

#### 6.4.6.2 1SPW 変調

1SPW モードでは、標準的な変調方式が変更されて、THD の劣化に関してわずかな欠点で、効率が向上し、出力フィルタの選択に多くの注意が必要になります。低アイドル電流モードでは、出力はアイドル条件で約 17% の変調で動作します。オーディオ信号を印加すると、1 つの出力が減少し、1 つが増加します。出力信号は減少して GND に送られます。この時点で、すべてのオーディオ変調は立ち上がり出力で行われます。その結果、オーディオ サイクルの大部分の間、1 つの出力だけがスイッチングします。このモードでは、スイッチング損失が減少するため、効率が向上します。

図 6-9. 1SPW モード変調

#### 6.4.6.3 ハイブリッド変調

ハイブリッド変調は、THD + N の性能を損なうことなく電力損失を最小限に抑えるように設計されており、バッテリ駆動アプリケーションに最適です。ハイブリッド変調により、TAS5830 は入力信号レベルを検出し、PVDD に基づいて PWM デューティサイクルを動的に調整します。ハイブリッド変調は、超低アイドル電流を実現し、BD 変調と同じオーディオ性能レベルを維持します。

## 注

ハイブリッド変調では、入力信号レベルを検出して PWM デューティ サイクルを動的に調整するために、内部 DSP が必要です。ハイブリッド変調を使用するには、TAS5830 PPC3 アプリでハイブリッド変調をサポートするプロセス フローを選択する必要があります TAS5830 のフレキシブルなオーディオ プロセス フローの詳細については TAS5830 PPC3 アプリをご覧ください。

### 6.4.7 プログラミングと制御

#### 6.4.7.1 I<sup>2</sup>C シリアル通信バス

このデバイスは双方向のシリアル制御インターフェイスを備え、I<sup>2</sup>C バスのプロトコルと互換性があり、標準モード、ファーストモード (FM)、ファースト モード プラス (FM+) データ転送レートをサポートしており、ターゲット デバイスとしてランダムおよびシーケンシャル書き込みおよび読み取り動作を実現します。TAS5830 レジスタ マップと DSP メモリは複数のページとブックにまたがるため、ユーザーはブックからブックに最初に変更し、その後ページごとにページを移動してから、個別のレジスタや DSP メモリに書き込みます。ページからページへの変更は、各ページのレジスタ 0 を介して行われます。このレジスタ値は、ページアドレスを 0 ~ 255 の範囲で選択します。TAS5830 データシートに記載されているすべてのレジスタは、ページ 0 に属します。

#### 6.4.7.2 ハードウェア制御モード

I<sup>2</sup>C レジスタ制御の高度な柔軟性を必要としないシステムや、I<sup>2</sup>C ホスト コントローラを利用できないシステムでは、TAS5830 をハードウェア制御モードで使用できます。その後で本デバイスはハードウェアモードのデフォルト構成で動作し、ハードウェア制御ピンによって変更が行われます。同じ構成でハードウェア制御モードとソフトウェア制御モードの間のオーディオ性能は同じですが、ソフトウェア制御モードでレジスタからより多くの機能を利用できます。

目的のスタートアップ設定として、回路図設計時に TAS5830 の複数の I/O を考慮する必要があります。ハードウェア制御モードに移行する方法は、HW\_MODE ピン 8 を DVDD にプルアップすることです。

TAS5830 のデフォルトのハードウェア構成は、BTL モード、768kHz のスイッチング周波数、1SPW モード、175kHz の Class-D アンプ ループ帯域幅、29.5Vp/FS のアナログ ゲイン、CBC スレッショルド、OCP スレッショルドの 80% です。このドライバでは、HW\_SEL0 ピン 16 および HW\_SEL1 ピン 15 が GND に直接接続されている必要があります。

表 6-3. ハードウェア制御 – HW\_SEL0 ピン 16

| ピン構成             | アナログ ゲイン               | H ブリッジ出力構成 |

|------------------|------------------------|------------|

| 0Ω を GND との間に接続  | 33.1V <sub>P</sub> /FS | BTL        |

| 1kΩ から GND へ     | 23.4V <sub>P</sub> /FS | BTL        |

| 4.7kΩ から GND へ   | 16.6V <sub>P</sub> /FS | BTL        |

| 15kΩ から GND へ    | 8.3V <sub>P</sub> /FS  | BTL        |

| 33kΩ から DVDD へ   | 8.3V <sub>P</sub> /FS  | PBTL       |

| 6.8kΩ から DVDD へ  | 16.6V <sub>P</sub> /FS | PBTL       |

| 1.5kΩ から DVDD へ  | 23.4V <sub>P</sub> /FS | PBTL       |

| 0Ω を DVDD との間に接続 | 33.1V <sub>P</sub> /FS | PBTL       |

表 6-4. ハードウェア制御 - HW\_SEL1 ピン 15

| ピン構成            | F <sub>sw</sub> と Class-D のループ帯域幅 | サイクル単位の電流制限スレッショルド       | スペクトラム拡散 | 変調   |

|-----------------|-----------------------------------|--------------------------|----------|------|

| 0Ω を GND との間に接続 | 768kHz F <sub>sw</sub> 、175kHz BW | CBC スレッショルド = 80%<br>OCP | 無効       | 1SPW |

| 1kΩ から GND へ    | 768kHz F <sub>sw</sub> 、175kHz BW | CBC ディスエーブル              | 無効       | 1SPW |

| 4.7kΩ から GND へ  | 768kHz F <sub>sw</sub> 、175kHz BW | CBC スレッショルド = 40%<br>OCP | 無効       | 1SPW |

| 15kΩ から GND へ   | 768kHz F <sub>sw</sub> 、175kHz BW | CBC スレッショルド = 60%<br>OCP | 無効       | 1SPW |

表 6-4. ハードウェア制御 - HW\_SEL1 ピン 15 (続き)

| ピン構成                     | $F_{sw}$ と Class-D のループ帯域幅 | サイクル単位の電流制限スレッショルド    | スペクトラム拡散 | 変調 |

|--------------------------|----------------------------|-----------------------|----------|----|

| 33k $\Omega$ から DVDD へ   | 480kHz $F_{sw}$ 、100kHz BW | CBC ディスエーブル           | イネーブル    | BD |

| 6.8k $\Omega$ から DVDD へ  | 480kHz $F_{sw}$ 、100kHz BW | CBC スレッショルド = 80% OCP | イネーブル    | BD |

| 1.5k $\Omega$ から DVDD へ  | 480kHz $F_{sw}$ 、100kHz BW | CBC スレッショルド = 40% OCP | イネーブル    | BD |

| 0 $\Omega$ を DVDD との間に接続 | 480kHz $F_{sw}$ 、100kHz BW | CBC スレッショルド = 60% OCP | イネーブル    | BD |

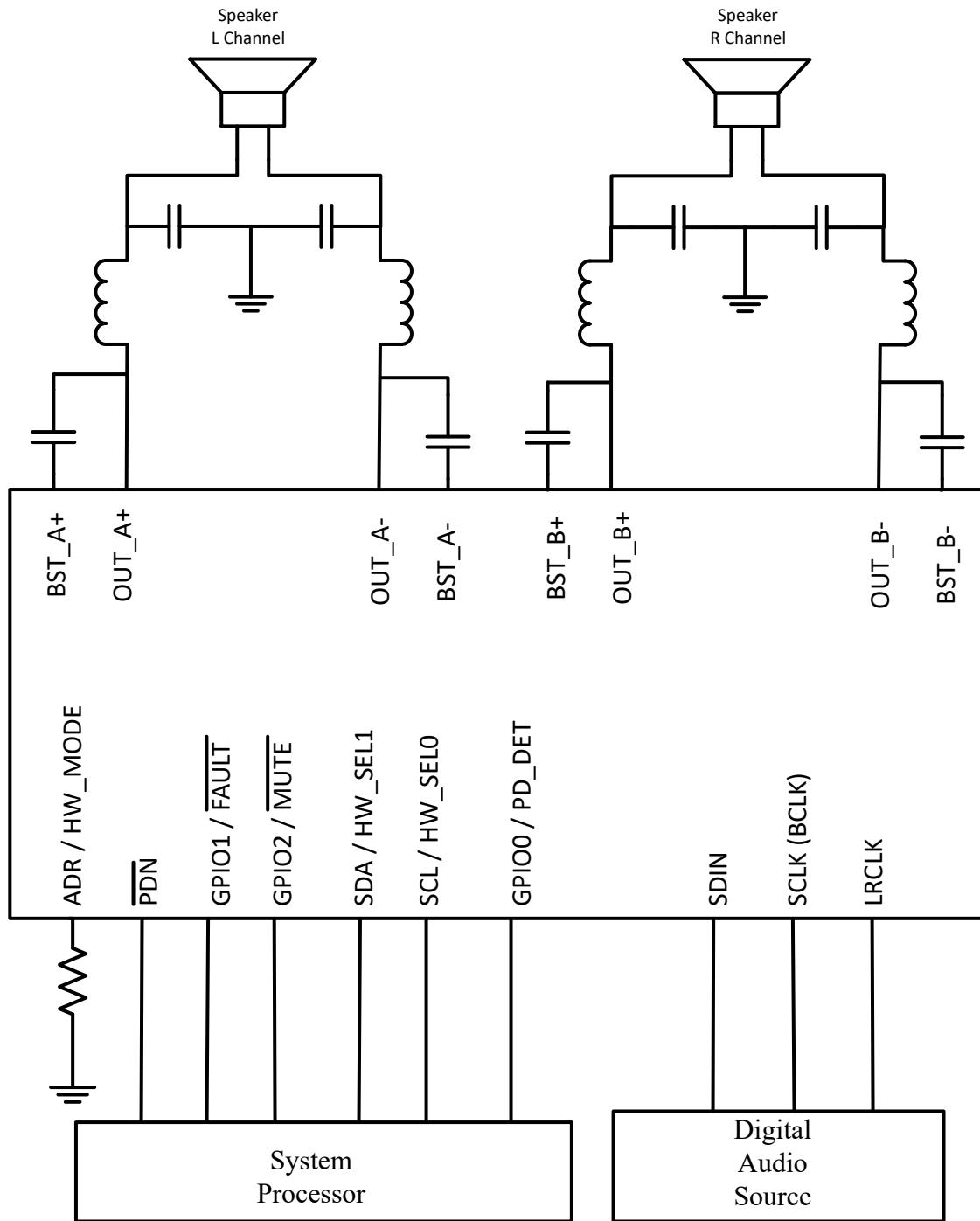

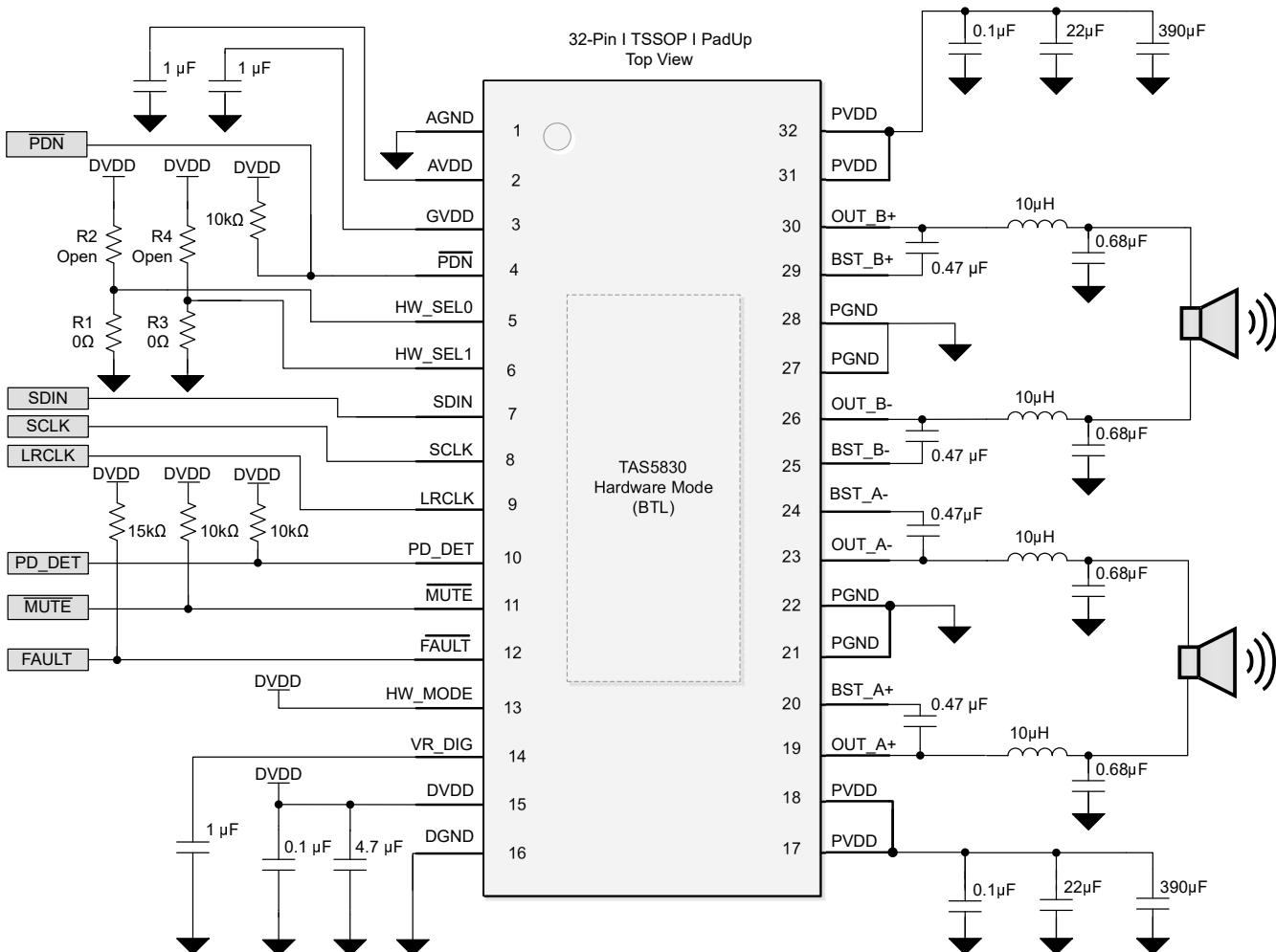

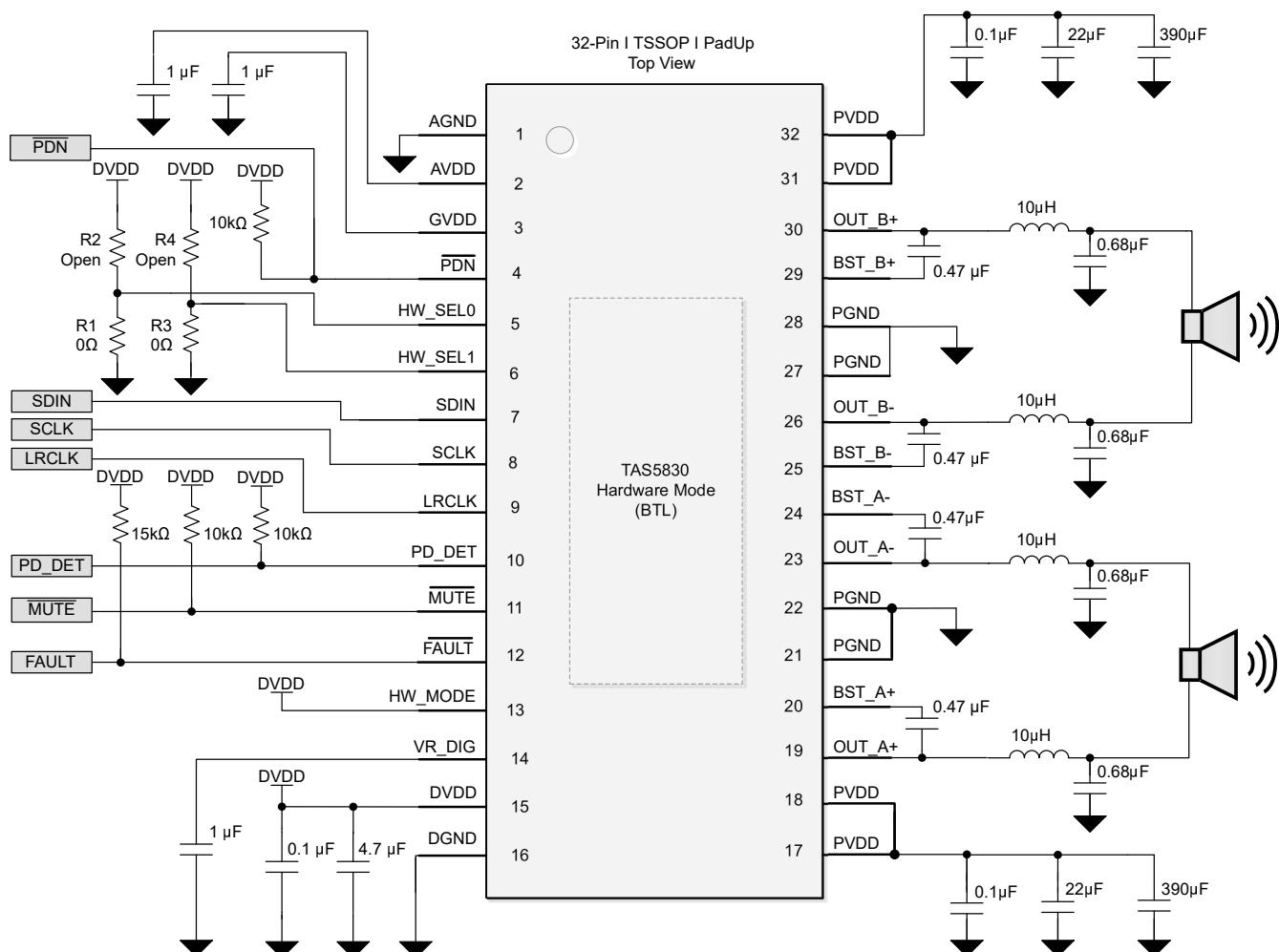

事例 1 :

BTL モード、 $F_{sw}$  = 768kHz、1SPW 変調、175kHz ループ帯域幅、CBC スレッショルド = 80% OCP、アナログ ゲイン = 29.5V<sub>P</sub>/FS、スペクトラム拡散はディセーブル。

図 6-10. 標準的なハードウェア制御モード アプリケーションの回路図 - BTL モード

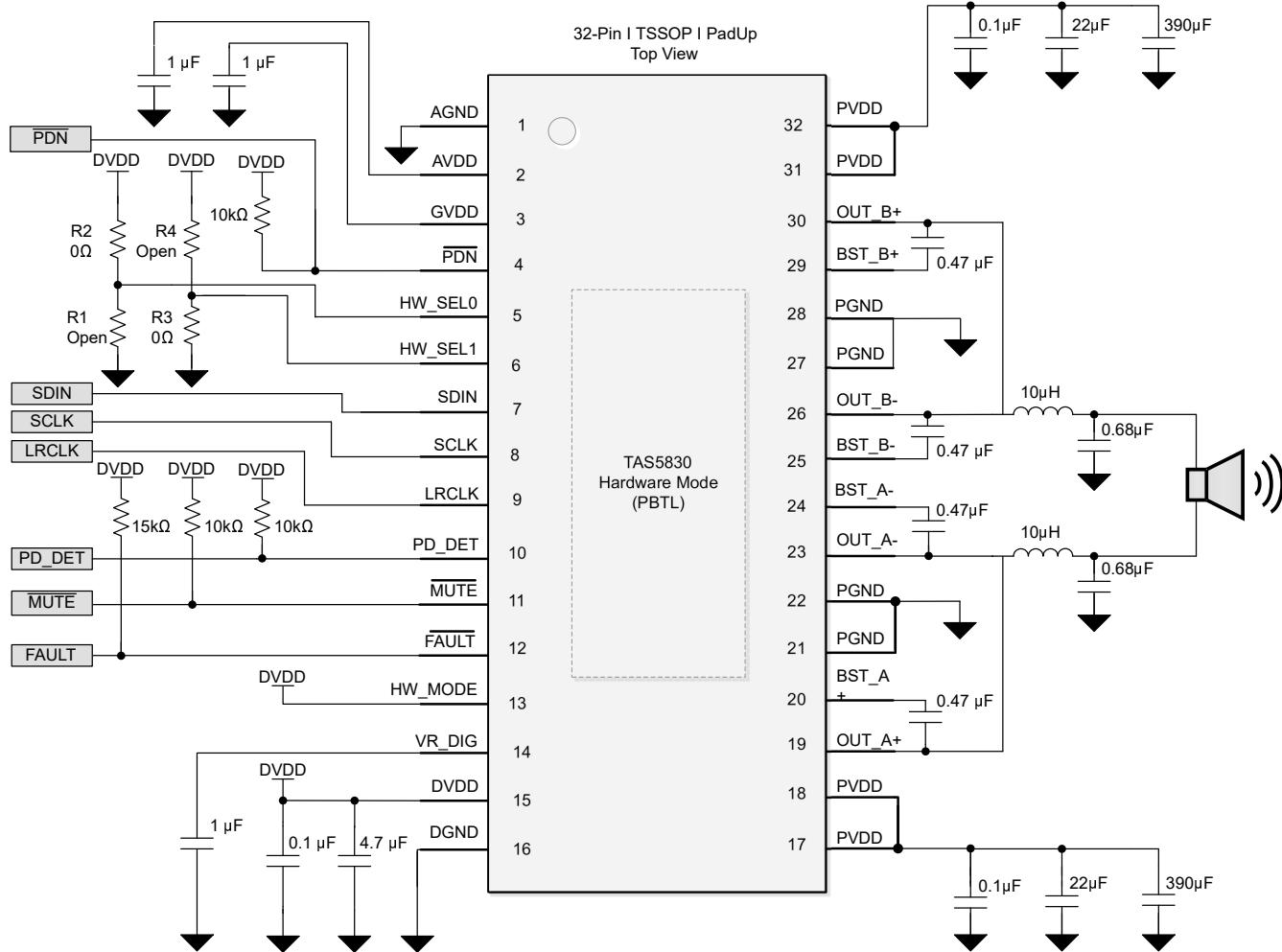

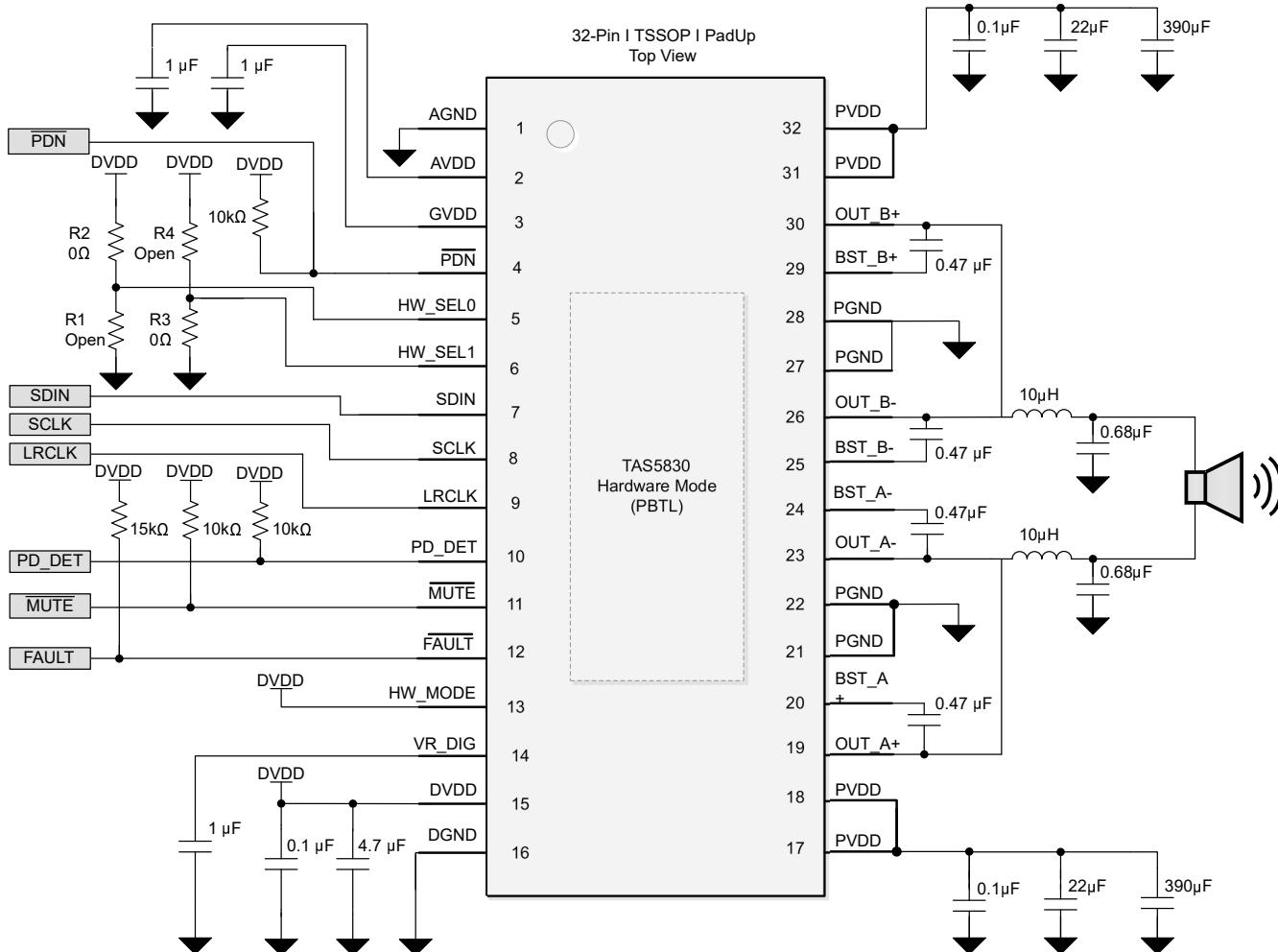

事例 2 :

PBTL モード、FSW = 768kHz、1 SPW 変調、175kHz ループ帯域幅、CBC スレッショルド = 80% OCP、アナログ ゲイン = 29.5V<sub>P</sub>/FS、スペクトラム拡散はディセーブル。

図 6-11. 標準的なハードウェア制御モード アプリケーションの回路図 - PBTL モード

6.4.7.3 I<sup>2</sup>C ターゲット アドレス

TAS5830 デバイスには、ターゲット アドレス用の 7 ビットがあります。表 6-5 に、ADR ピンによるユーザー定義アドレスを示します。

表 6-5. I<sup>2</sup>C ターゲット アドレス構成

| ADR ピンの構成       | MSB |   |   |   | ユーザー定義 |   |   | LSB |

|-----------------|-----|---|---|---|--------|---|---|-----|

| 0Ω から GND へ     | 1   | 1 | 0 | 0 | 0      | 0 | 0 | R/W |

| 1kΩ から GND へ    | 1   | 1 | 0 | 0 | 0      | 0 | 1 | R/W |

| 4.7kΩ から GND へ  | 1   | 1 | 0 | 0 | 0      | 1 | 0 | R/W |

| 15kΩ から GND へ   | 1   | 1 | 0 | 0 | 0      | 1 | 1 | R/W |

| 33kΩ から DVDD へ  | 1   | 1 | 0 | 0 | 1      | 0 | 0 | R/W |

| 6.8kΩ から DVDD へ | 1   | 1 | 0 | 0 | 1      | 0 | 1 | R/W |

#### 6.4.7.3.1 ランダム書き込み

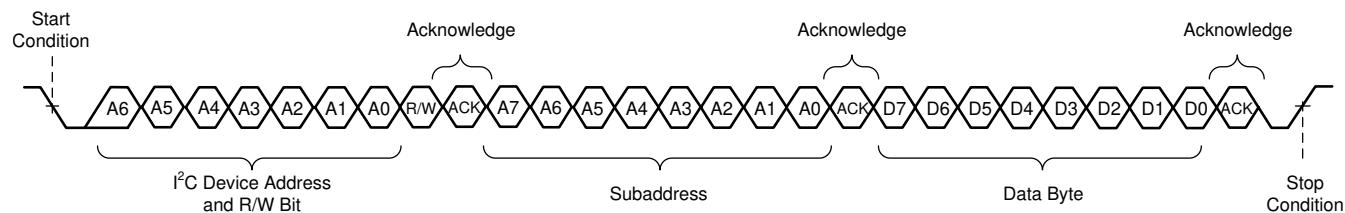

図 6-12 にあるように、シングル バイトのデータ書き込み転送では、最初にマスター デバイスが開始条件を送信し、次に I<sup>2</sup>C デバイス アドレスと読み取り / 書き込みビットが続きます。データ転送方向は、R/W ビットによって決定されます。書き込みデータ転送する場合、R/W ビットは 0 です。正しい I<sup>2</sup>C デバイス アドレスと R/W ビットを受信すると、デバイスはアクノリッジ ビットを返します。次に、コントローラは、アドレス バイトまたはアクセスしている内部メモリ アドレスに対応するアドレス バイトを送信します。デバイスは、レジスタ バイトを受信すると、再度アクノリッジ ビットを返信します。次に、コントローラ デバイスはアクセスしているメモリアドレスに書き込まれたデータ バイトを送信します。デバイスは、データ バイトを受信すると、再度アクノリッジ ビットを返信します。最後に、コントローラ デバイスが停止条件を送信すると、シングル バイト データの書き込み転送が完了します。

図 6-12. ランダム書き込み転送

#### 6.4.7.3.2 シーケンシャル書き込み

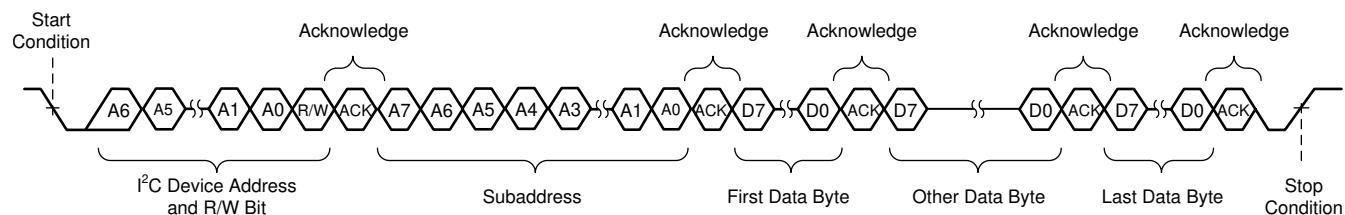

シーケンシャル データの書き込み転送は、図 6-13 に示すように、複数のデータ バイトがコントローラからデバイスに送信される点を除き、シングル バイト データの書き込み転送と同じです。各データ バイトを受信すると、デバイスはアクノリッジ ビットで応答し、I<sup>2</sup>C サブアドレスが自動的に 1 つずつ増加します。

図 6-13. シーケンシャル書き込み転送

#### 6.4.7.3.3 ランダム読み出し

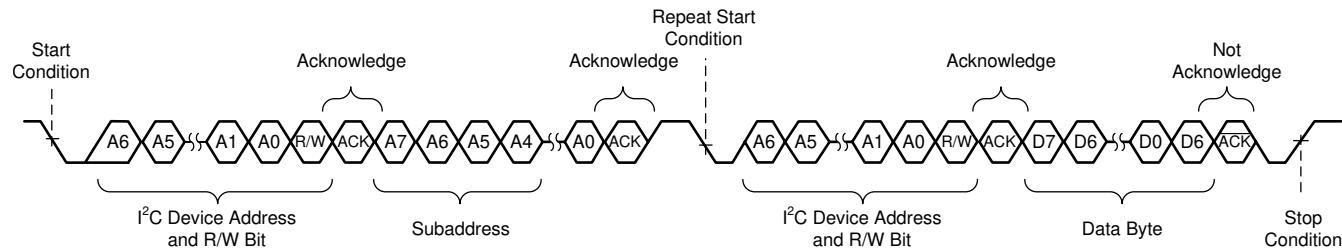

図 6-14 に示すように、シングル バイトのデータ読み取り転送では、コントローラ デバイスが開始条件を送信し、次に I<sup>2</sup>C デバイス アドレスと R/W ビットを送信することで開始されます。データ読み取り転送の場合、実際には書き込みとその次の読み取りの両方が行われます。最初に、内部メモリ アドレスの読み取りに必要なアドレス バイトを転送するために、書き込みが実行されます。その結果、R/W ビットは 0 になります。このデバイスは、アドレスと 読み取り / 書き込み ビットを受信すると、アクノリッジ ビットで応答します。さらに、内部メモリアドレスを送信後、コントローラ デバイスは別の開始条件に続いて、アドレス、R/W ビットを送信します。このとき、R/W ビットは 1 に設定され、読み取り転送が実行されたことを示します。デバイスは、アドレスと R/W ビットを受信すると、再度アクノリッジ ビットで応答します。次に、デバイスは読み取り中のメモリ アドレスからデータ バイトを送信します。データ バイトを受信すると、コントローラ デバイスは非応答 (not-acknowledge) を送信し、その後、停止条件を出して、シングル バイト データ読み取り転送が完了します。

図 6-14. ランダム読み取り転送

#### 6.4.7.3.4 シーケンシャル読み出し

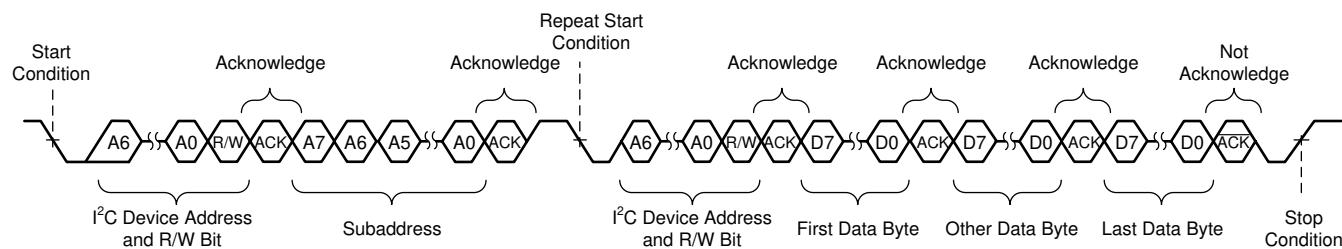

シーケンシャルデータの読み取り転送はシングルバイトのデータ読み取り転送と同じですが、図 6-15 に示すように、複数のデータバイトがデバイスによってコントローラデバイスに送信されます。コントローラデバイスは、最後のデータバイトを除いて、各データバイトを受信すると肯定応答ビットで応答し、I<sup>2</sup>C サブアドレスを自動的に 1 ずつインクリメントします。最後のデータバイトを受信した後、コントローラデバイスは、転送を完了するために非応答(NACK)を送信し、その後に停止条件を送信します。

図 6-15. シーケンシャルリード転送

#### 6.4.7.3.5 DSP メモリブック、ページおよびBQ を更新

各ブックのページ 0x00 で、ブックを変更するためにレジスタ 0x7f を使用します。各ページのレジスタ 0x00 は、ページを変更するために使用されます。ページを変更するには、まず、レジスタ 0x00 をレジスタ 0x00 に書き込んで、ページ 0 に切り換えるようにして、ページ 0 のレジスタ 0x7f にブック番号を書き込みます。ブック内のページを切り替えるには、レジスタ 0x00 にページ番号を書き込むだけです。

すべてのバイクワッドフィルタ係数は、ブック 0xAA でアドレス指定されています。すべてのバイクワッドフィルタの 5 つの係数は、すべて、最小アドレスから最高アドレスまで順に書き込まれます。すべてのバイクワッドフィルタのアドレスは、レジスタマップに記載されています

すべての DSP/オーディオプロセスフローに関連するレジスタは、アプリケーションノート『TAS5830 のプロセスフロー』に記載されています

#### 6.4.7.3.6 チェックサム

このデバイスは、巡回冗長性検査 (CRC) チェックサムと排他的 (XOR) チェックサムという 2 種類のチェックサム方式をサポートしています。レジスタの読み出しへはチェックサムは変更されませんが、存在しないレジスタに書き込みを行うと、チェックサムが変更されます。両方のチェックサムは 8 ビットのチェックサムであり、両方とも同時に利用できます。チェックサムは、開始値(例: 0x 00 00 00 00)をそれぞれの 4 バイトのレジスタ位置に追加します。

##### 6.4.7.3.6.1 巡回冗長性検査 (CRC) チェックサム

使用される 8 ビット CRC チェックサムは 0x7 多項式 (CRC-8-CCITT I.432.1、ATM HEC、ISDN HEC、およびセルの描画 ( $1 + x1 + x2 + x8$ )) である。CRC チェックサムの主な利点は、チェックサムが入力順序に敏感であることです。CRC は、ブックとページの切り替えを除く、すべての I<sup>2</sup>C トランザクションをサポートします。CRC チェックサムは、任意のブック (B\_x, Page\_0, Reg\_126) のレジスタ 0x7E から読み出されます。CRC チェックサムは、CRC チェックサムが有効なものであるのと同じレジスタ位置に 0x00 を書き込むことでリセットできます。

#### 6.4.7.3.6.2 排他 または (XOR) チェックサム

XOR チェックサムは、より単純なチェックサム方式である。チェックサムは、前の 8 ビット チェックサム レジスタ値とともに、各レジスタ バイト書き込みに対して順次 XOR を実行します。XOR は、ブック 0x8C のみをサポートしており、ブック 0x8C のページ 0x00 にあるすべてのレジスタは除外されます。XOR チェックサムは、ブック 0x8C (B\_140, Page\_0, Reg\_125) の 0x00 の位置レジスタ 0x7D から読み出されます。XOR チェックサムは、チェックサムが読み出されるのと同じレジスタ位置に 0x00 を書き込むことでリセットできます。

#### 6.4.7.4 ソフトウェアによる制御

- 起動手順

- シャットダウン手順

##### 6.4.7.4.1 起動手順

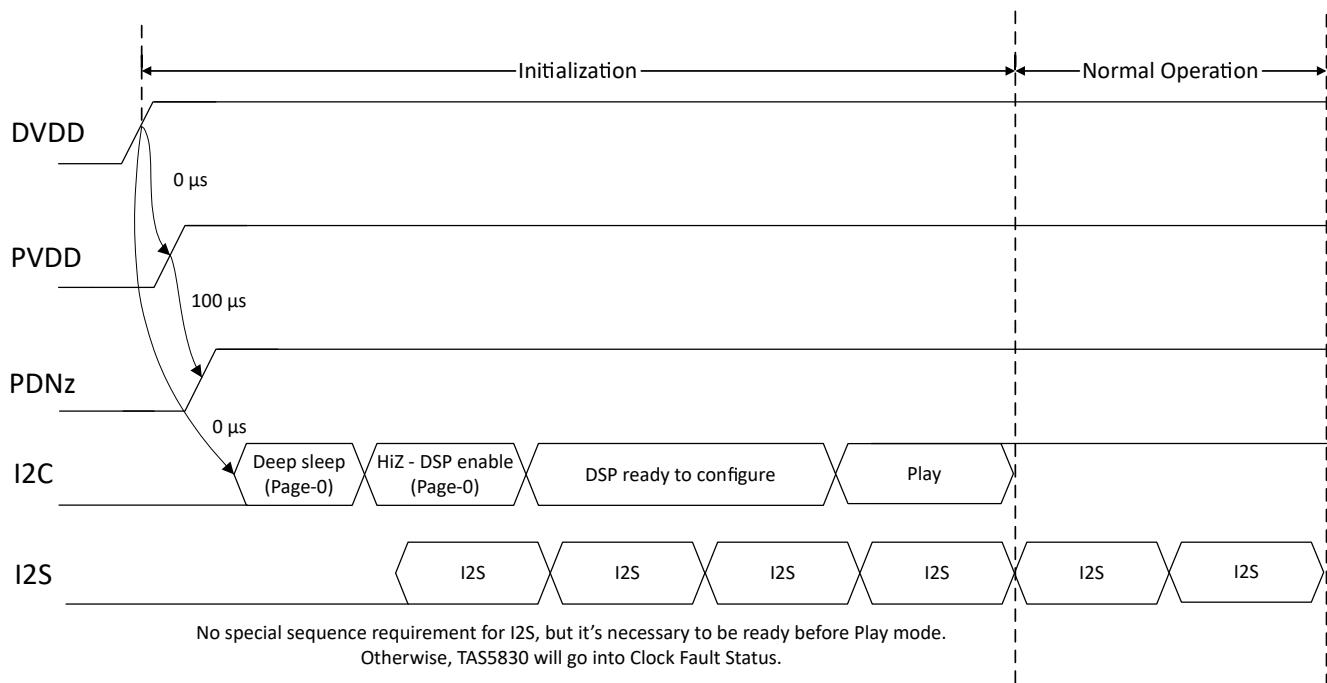

1. ADR ピンは、I<sup>2</sup>C デバイス アドレスまたはハードウェア モードの適切な設定で、HW\_SEL0 および HW\_SEL1 設定を行います。

2. 電源を起動します (PVDD と DVDD のどちらが先に起動するかは問題ではありません)。

3. 電源が安定した後、少なくとも 100μs を待ち、PDN<sub>z</sub> を High にして内部 LDO をイネーブルにします。

4. 目的の設定を構成するための I<sup>2</sup>C 制御ポート。このプロセスには、ディープ スリープから Hi-Z への変換、レジスタ マップ構成、DSP 係数、および Play モードに設定されます。ハードウェア モードでは、このステップ I<sup>2</sup>C 書き込みは必要ありません。

5. I<sup>2</sup>S クロックが安定すると、TAS5830 は通常動作の音楽再生に移行します。

図 6-16. TAS5830 の起動シーケンス

#### 6.4.7.4.2 シャットダウン手順

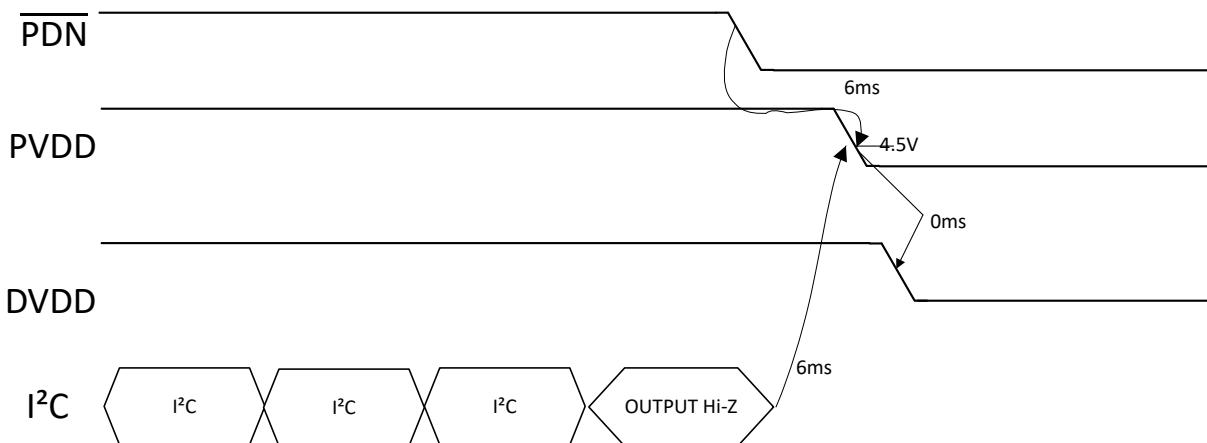

- デバイスは正常に動作しています。

- I<sup>2</sup>C 制御ポートを使用してレジスタ **DEVICE\_CTRL2** レジスタ (オフセット = 3h) [リセット = 10h]-D[1:0] = 10 (Hi-Z) を設定するか、**PDN** を low にプルします。

- 少なくとも 6ms 待ちます (この時間は、LRCLK レート、デジタル ボリューム、およびデジタル ボリュームのランプダウンレートに依存します)。

- 電源をオフにします。

- これでデバイス完全にシャットダウンし、電源がオフになりました。

Before PVDD/DVDD power down, Class D Output driver needs to be disabled by PDN or by I<sup>2</sup>C.

At least 6ms delay needed based on LRCLK(Fs) = 48kHz, digital volume ramp down update every sample period, decreased by 0.5dB for each update, digital volume = 24dB. Change the value of register 0x4C and 0x4E or change LRCLK rate, the delay changes.

図 6-17. 電源オフ シーケンス

#### 6.4.7.5 保護および監視

##### 6.4.7.5.1 過電流制限 (サイクルバイサイクル)

直接過電流シャットダウンによってオーディオ出力をミュートする代わりに、TAS5830 には CBC 電流制限保護もあります。目的は、PWM スイッチングにパルスを挿入することで過電流シャットダウンレベルよりも前に出力電流を減らすことで

す。スレッショルド (セクション 5.5 のリスト) はレジスタ **CBC\_CONTROL** レジスタ (オフセット = 77h) [リセット = 00h]-D[4:3] **Reg\_CBC\_Level\_Sel** で設定できます。

オーディオに対する全体的な影響は、過負荷の除去を中断することなく連続的な音楽再生を維持するために音楽信号のピーク電力を一時的に制限する電圧クリッピングに非常に似ています。

#### 6.4.7.5.2 過電流シャットダウン(OCSD)

出力が PVDD またはグランドに短絡するなどの重大な短絡イベントが発生した場合、TAS5830 はピーク電流検出器が過電流スレッショルド (セクション 5.5 のリスト) を超えると 100ns 以内にシャットダウン プロセスを開始します。シャットダウン速度は、短絡のインピーダンス、電源電圧、スイッチング周波数など、いくつかの要因に依存します。

OCSD イベントが発生すると、障害 GPIO が低く引き下げられ、I<sup>2</sup>C 障害レジスタの障害ステータス (**CHAN\_FAULT** レジスタ (オフセット = 70h) [リセット = 00h]-D[1:0]) が報告され、出力が高インピーダンス Hi-Z 状態に遷移して障害を示します。これはラッチエラーなので、ユーザーは **FAULT\_CLEAR** レジスタ (オフセット = 78h) [リセット = 00h]-D[0] = 1 を設定して I<sup>2</sup>C の障害クリア操作を介して出力を再開する必要があります。

#### 6.4.7.5.3 DC 検出エラー

TAS5830 が、出力電圧クロス スピーカの DC エラー保護スレッショルド DCR<sub>THRES</sub> の DC オフセットを検出し、このステータス期間が T<sub>DCDET</sub> (セクション 5.5 の一覧) を超えている場合、FAULTZ ラインが low にプルされ、OUT<sub>xx</sub> 出力が高インピーダンスに遷移してフォルトが通知されます。このラッチ付き DC 保護エラーでは、オーディオ出力を再開するには、**FAULT\_CLEAR** レジスタ (オフセット = 78h) [リセット = 00h]-D[0] = 1 に設定して、I<sup>2</sup>C のクリア フォルト動作が必要です。

#### 6.4.7.5.4 過熱シャットダウン(OTSD)

TAS5830 デバイスはダイ温度の監視を継続して、温度がセクション 5.5 に規定された過熱スレッショルドを超えないようにします。OTE イベントが発生すると、フォルト GPIO は low にプルされ、I<sup>2</sup>C フォルトステータス (**GLOBAL\_FAULT2** レジスタ (オフセット = 72h) [リセット = 00h]-D[0]) が通知されると、オーディオ出力は高インピーダンスの Hi-Z モードに移行して、フォルトが通知されます。これはラッチ エラーであり、オーディオ再生を再開するには、I<sup>2</sup>C のフォルト動作を **FAULT\_CLEAR** レジスタ (オフセット = 78h) [リセット = 00h]-D[0] = 1 に設定することでクリアする必要があります。

#### 6.4.7.5.5 PVDD 過電圧および低電圧誤差

PVDD 電源に供給される電圧が OVE<sub>THRES(PVDD)</sub> を超えるか、セクション 5.5 に記載されている UV<sub>E THRES(PVDD)</sub> を下回ると、障害 GPIO が低く引き下げられ、I<sup>2</sup>C 障害ステータス (**GLOBAL\_FAULT1** レジスタ (オフセット = 71h) [リセット = 00h]-D[1:0]) が報告され、オーディオ出力は高インピーダンス Hi-Z モードに移行します。これらは自己クリア エラーであるため、PVDD レベルが通常動作に戻ると、デバイスはオーディオ再生を再開します。

#### 6.4.7.5.6 PVDD 降下検出

TAS5830 は PVDD 低電圧シャットダウン保護だけでなく、オプションの PVDD 電圧降下検出も備えています。内部 PVDD のリアルタイム検出電圧に基づいて、TAS5830 は予測される動作に構成できます。この動作により、ピン 10 PD\_DET を high から low に切り替えることで、PVDD が特定のレベル (デフォルト 8V) を下回ったことを示し、また TAS5830 が自動的に Hi-Z モードに移行してオーディオ出力をシャットダウンするかどうかを示すことができます。

目的は、GPIO を経由してユーザー製品の制御システムに PVDD 電圧降下情報をフィードバックすることで、柔軟な保護戦略を実装できます。例えば、PD\_DET ピンが低すぎると、SOC によって、オーディオ ボリューム フェードアウト プロセスが開始される場合があります。このプロセスにより、効果的なポップクリック音なしで制御シャットダウンを実現できます。

#### 6.4.7.5.7 クロック障害

入力データ クロックでクロック誤差が検出されると、TAS5830 デバイスは内部発振器に切り替わり、DAC の駆動を続行します。これにより、最後に既知の値からデータは減衰します。このプロセスが完了すると、DAC 出力はグランドにハードミュートされ、オーディオ出力は停止します。このラッチされていないクロック フォルトステータスは I<sup>2</sup>C フォルトステータス (**GLOBAL\_FAULT1** レジスタ (オフセット = 71h) [リセット = 00h]-D[2]) で通知され、正しいクロックが戻ると本デバイスは自動的に再生モードに戻ります。

## 7 レジスタ マップ

### 7.1 REG\_MAP レジスタ

表 7-1 に、reg\_map レジスタに対してメモリマップされたレジスタを示します。表 7-1 に記載されていないすべてのレジスタ オフセット アドレスは予約領域とみなされ、レジスタの内容は変更しないでください。

**表 7-1. REG\_MAP レジスタ**

| オフセット | 略称                | レジスタ名                          | セクション |

|-------|-------------------|--------------------------------|-------|

| 1h    | RESET_CTRL        | リセット制御                         | 表示    |

| 2h    | DEVICE_CTRL1      | デバイス制御 1                       | 表示    |

| 3h    | DEVICE_CTRL2      | デバイス制御 2                       | 表示    |

| 4h    | PVDD_UV_CONTROL   | PVDD UV 制御                     | 表示    |

| Fh    | I2C_PAGE_AUTO_INC | I2C DSP メモリ アクセス ページの自動インクリメント | 表示    |

| 28h   | SIG_CH_CTRL       | シグナル チェーン制御                    | 表示    |

| 29h   | CLOCK_DET_CTRL    | クロック検出制御                       | 表示    |

| 30h   | SDOUT_SEL         | SDOUT の選択                      | 表示    |

| 31h   | I2S_CTRL          | I2S 制御 0                       | 表示    |

| 33h   | SAP_CTRL1         | I2S 制御 1                       | 表示    |

| 34h   | SAP_CTRL2         | I2S 制御 2                       | 表示    |

| 35h   | SAP_CTRL3         | I2S 制御 3                       | 表示    |

| 37h   | FS_MON            | FS モニタ                         | 表示    |

| 38h   | BCLK_MON          | BCLK モニタ                       | 表示    |

| 39h   | CLKDET_STATUS     | クロック検出ステータス                    | 表示    |

| 40h   | DSP_PGM_MODE      | DSP プログラム モード                  | 表示    |

| 46h   | DSP_CTRL          | DSP 制御                         | 表示    |

| 4Ch   | DIG_VOL           | デジタル ボリューム                     | 表示    |

| 4Eh   | DIG_VOL_CTRL2     | デジタル ボリューム制御 2                 | 表示    |

| 4Fh   | DIG_VOL_CTRL3     | デジタル ボリューム制御 3                 | 表示    |

| 50h   | AUTO_MUTE_CTRL    | 自動ミュート 制御                      | 表示    |

| 51h   | AUTO_MUTE_TIME    | 自動ミュート時間                       | 表示    |

| 53h   | ANA_CTRL          | アナログ コントローラ                    | 表示    |

| 54h   | AGAIN             | アナログ ゲイン                       | 表示    |

| 5Eh   | ADC_RPT           | ADC (PVDD 電圧) レポート             | 表示    |

| 60h   | GPIO_CTRL         | GPIO 制御                        | 表示    |

| 61h   | GPIO1_SEL         | GPIO1 出力の選択                    | 表示    |

| 62h   | GPIO2_SEL         | GPIO2 出力の選択                    | 表示    |

| 63h   | GPIO0_SEL         | GPIO0 出力の選択                    | 表示    |

| 64h   | GPIO_INPUT_SEL    | GPIO 入力の選択                     | 表示    |

| 65h   | MISC_CTRL1        | misc 制御 1                      | 表示    |

| 66h   | MISC_CTRL2        | misc 制御 2                      | 表示    |

| 67h   | DIE_ID            | DIE ID                         | 表示    |

| 68h   | POWER_STATE       | 電源の状態                          | 表示    |

| 69h   | AUTOMUTE_STATE    | 自動ミュート状態                       | 表示    |

| 6Ah   | RAMP_PHASE_CTRL   | スイッチング クロックの位相制御               | 表示    |

| 6Bh   | RAMP_SS_CTRL0     | スペクトラム拡散制御 0                   | 表示    |

| 6Ch   | RAMP_SS_CTRL1     | スペクトラム拡散制御 1                   | 表示    |

表 7-1. REG\_MAP レジスタ (続き)

| オフセット | 略称            | レジスタ名        | セクション |

|-------|---------------|--------------|-------|

| 70h   | CHAN_FAULT    | チャネル障害       | 表示    |

| 71h   | GLOBAL_FAULT1 | グローバル フォルト 1 | 表示    |

| 72h   | GLOBAL_FAULT2 | グローバル フォルト 2 | 表示    |

| 73h   | WARNING       | 警告           | 表示    |

| 74h   | PIN_CONTROL1  | ピン制御 1       | 表示    |

| 75h   | PIN_CONTROL2  | ピン制御 2       | 表示    |

| 76h   | MISC_CONTROL3 | その他の制御 3     | 表示    |

| 77h   | CBC_CONTROL   | CBC 制御       | 表示    |

| 78h   | FAULT_CLEAR   | フォルト クリア     | 表示    |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 7-2 に、このセクションでアクセス タイプに使用しているコードを示します。

表 7-2. reg\_map アクセス タイプ コード

| アクセス タイプ      | コード | 説明               |

|---------------|-----|------------------|

| 読み取りタイプ       |     |                  |

| R             | R   | 読み出し             |

| 書き込みタイプ       |     |                  |

| W             | W   | 書き込み             |

| リセットまたはデフォルト値 |     |                  |

| -n            |     | リセット後の値またはデフォルト値 |

### 7.1.1 RESET\_CTRL Register (オフセット = 1h) [リセット = 00h]

概略表に戻ります。

リセット制御

図 7-1. RESET\_CTRL レジスタ

| 7    | 6 | 5       | 4 | 3    | 2 | 1       | 0 |

|------|---|---------|---|------|---|---------|---|

| 予約済み |   | RST_MOD |   | 予約済み |   | RST_REG |   |

| W-0h |   | W-0h    |   | W-0h |   | W-0h    |   |

表 7-3. RESET\_CTRL レジスタのフィールドの説明

| ビット | フィールド   | タイプ | リセット | 説明                                                                                                                                                                                                                           |

|-----|---------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | 予約済み    | W   | 0h   |                                                                                                                                                                                                                              |

| 4   | RST_MOD | W   | 0h   | 書き込みクリア ビット リセット モジュールこのビットは、補間フィルタと <b>DAC</b> モジュールをリセットします。DSP もリセットされるので、 <b>RAM</b> 係数の内容も DSP によってクリアされます。このビットは自動にクリアされ、 <b>Hi-Z</b> モードでのみ設定できます。<br><b>0: 通常</b><br>1: リセット モジュール                                   |