# TAS3251175W ステレオ、350W モノラル ウルトラ HD デジタル入力 クラス・D アンプ(高度な DSP 处理搭載)

## 1 特長

- フレキシブルなオーディオ入力

- I<sup>2</sup>S、TDM、左揃え、右揃え

- 32kHz、44.1kHz、48kHz、96kHz

- 3 線式デジタル入力 (MCLK なし) をサポート

- 10% THD+N 時の合計出力電力

- BTL 構成で 4Ω 負荷に対してステレオ 175W 出力

- BTL 構成で 3Ω 負荷に対してステレオ 220W 出力

- PBTL 構成で 2Ω 負荷に対して 350W モノラル出力

- 1% THD+N 時の合計出力電力

- BTL 構成で 4Ω 負荷に対してステレオ 140W 出力

- BTL 構成で 3Ω 負荷に対してステレオ 175W 出力

- PBTL 構成で 2Ω 負荷に対して 285W モノラル出力

- 高度な統合型閉ループ設計

- 4Ω 負荷において 1W 出力時、超低歪み 0.01% THD+N

- クリッピングまで <0.01% THD+N

- PSRR 60dB (BTL、入力信号なしの場合)

- <95μV 出力ノイズ (A 特性)

- SNR: 108dB 超 (A ウェイト)

- 固定機能の処理機能

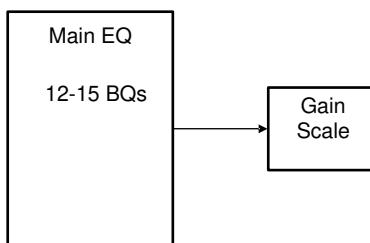

- SmartEQ (チャネルあたり最大 15 倍の BiQuads)

- クロスオーバー EQ (2x 5 バイクワッド)

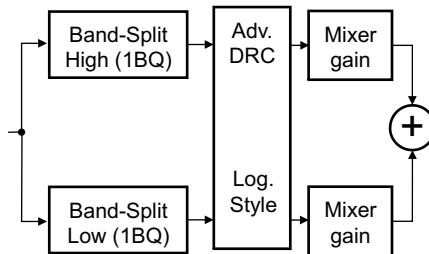

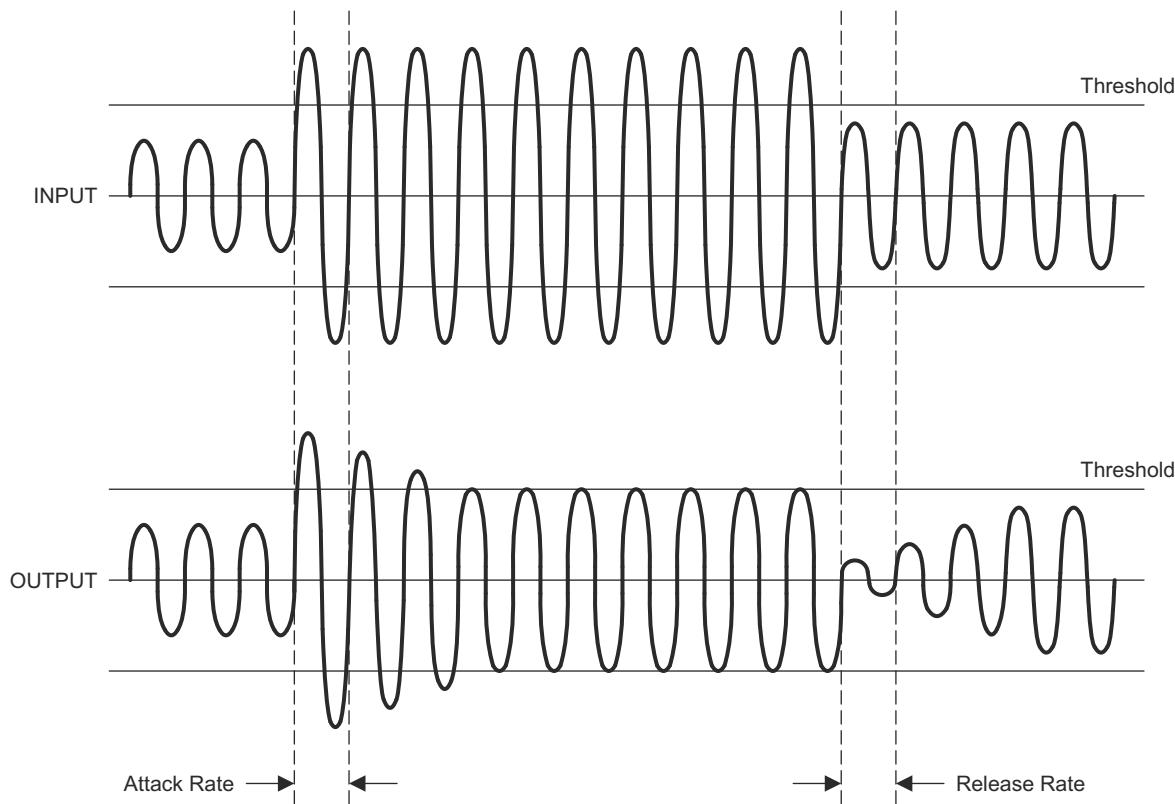

- 3 バンドの高度な DRC および AGL

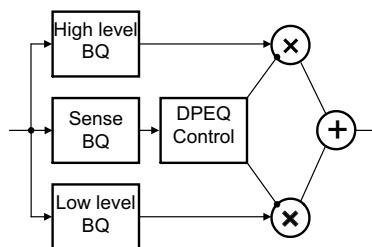

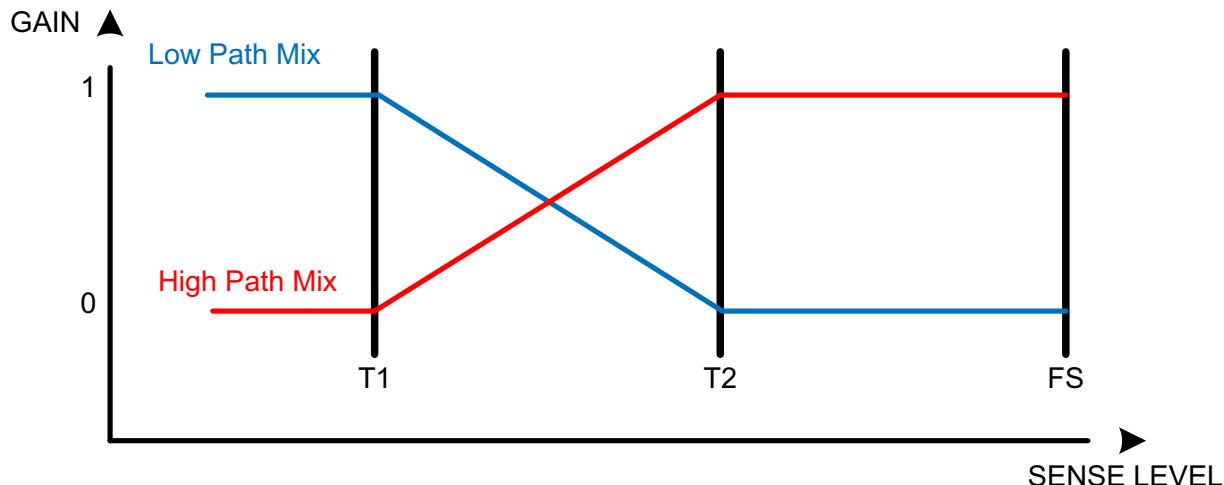

- ダイナミック EQ と SmartBass

- サンプル レート変換

- 制御機能

- I<sup>2</sup>C ソフトウェア モード制御

- アドレス選択ピン

- 90% 効率の Class-D 動作 (4Ω)

- 広い動作電源電圧範囲 (12V ~ 36V)

- エラー報告付き統合保護機能: 低電圧、サイクルごとの電流制限、短絡、クリッピング検出、過温度警告およびシャットダウン、DC スピーカ保護

## 2 アプリケーション

- Bluetooth および WiFi スピーカ

- サウンドバー

- サブウーファー

- ブックシェルフ型ステレオシステム

- 業務用および公共拡声音響システム (PA) 用スピーカー

- アクティブ クロスオーバーおよび 2 ウェイスピーカー

## 3 説明

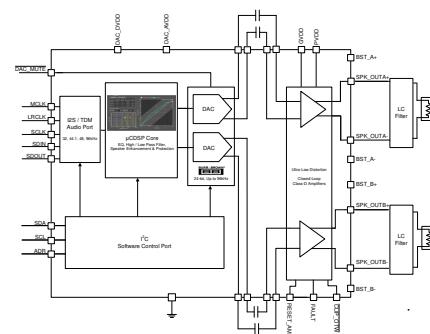

TAS3251 はデジタル入力の高性能、Class-D オーディオアンプで、最高のサウンド品質を Class-D の効率で実現します。このデジタル フロント エンドは、高性能の Burr-Brown™ DAC を採用したほか、DSP を内蔵しており、SmartAmp や SmartEQ を含め、先進的なオーディオ処理に役立ちます。この初めての大電力シングルチップ ソリューションにより、システム ソリューション全体のサイズとコストを削減できます。DSP は TI の PurePath™ Console グラフィカル チューニング ソフトウェアのサポート対象であり、スピーカのチューニングと制御を迅速かつ簡単に実施できます。この Class-D 電力段は、先進的なフィードバック機能を内蔵したほか、自社独自の高速ゲート ドライブ誤り訂正機能を搭載しており、オーディオ帯域全体で超低歪みと超低ノイズの実現に貢献します。このデバイスは AD モードで動作し、4Ω 負荷使用時に最大 2 x 175W、3Ω 負荷使用時に最大 2 x 220W を出力します。

### 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| TAS3251 | HSSOP (56)           | 18.42mm x 10.35mm        |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージサイズ (長さ x 幅) は公称値であり、該当する場合はピントを含みます。

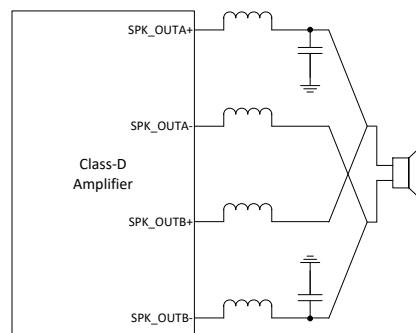

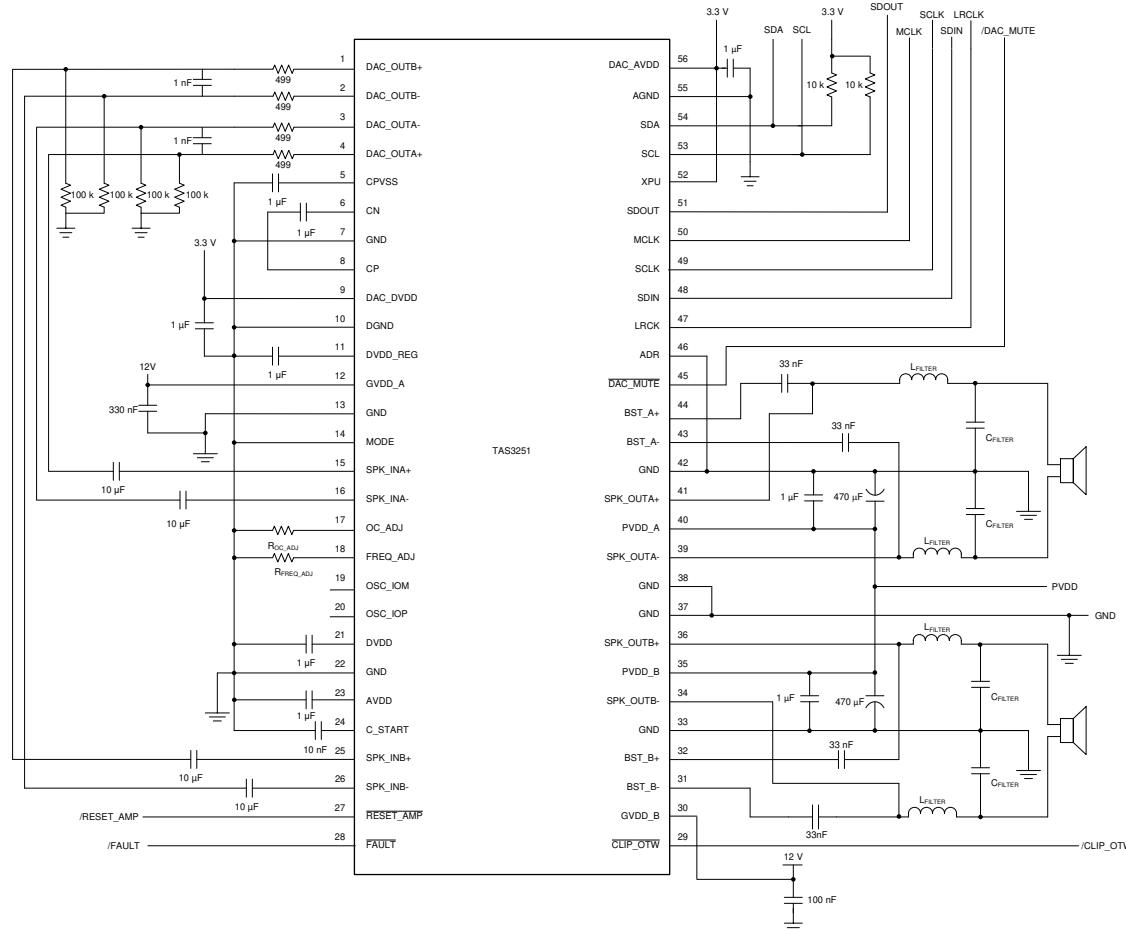

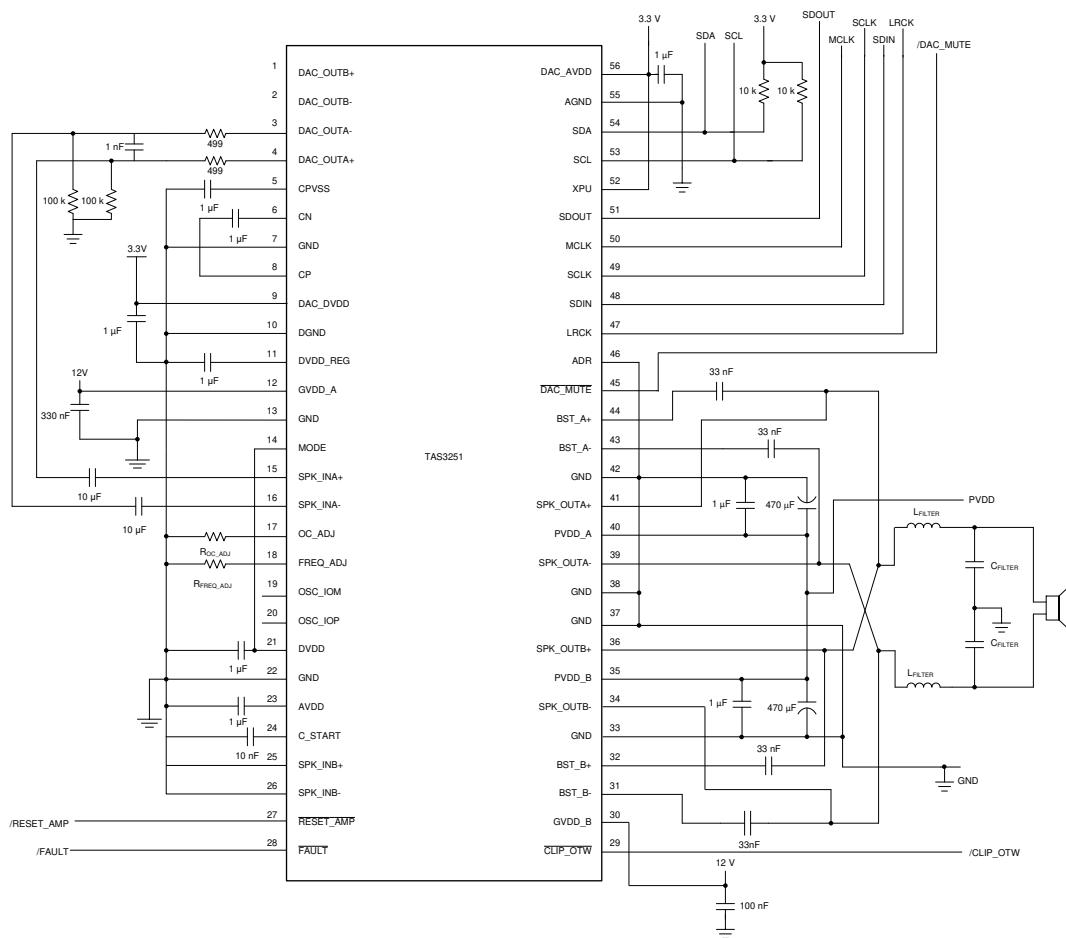

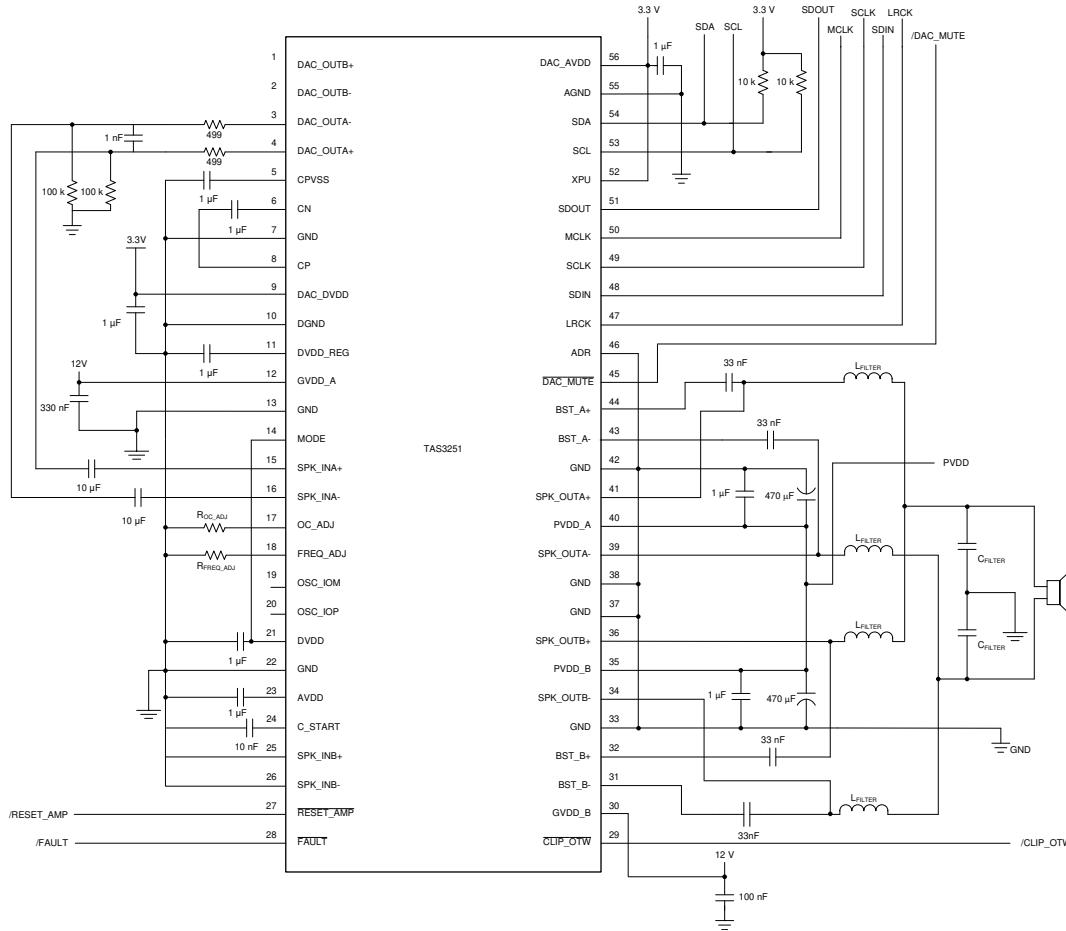

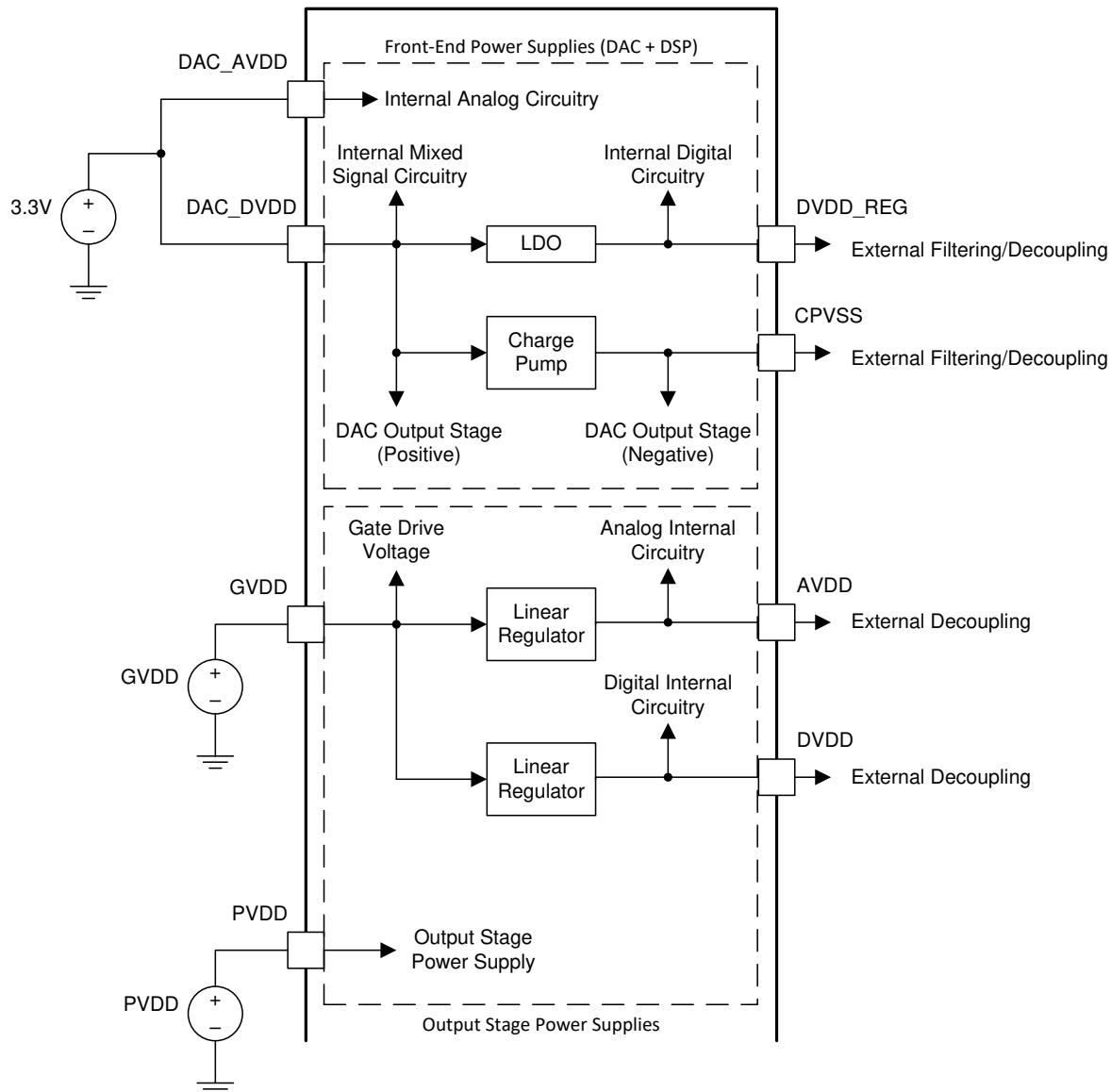

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                            |          |                               |            |

|--------------------------------------------|----------|-------------------------------|------------|

| <b>1 特長</b>                                | <b>1</b> | 6.15 代表的特性                    | <b>18</b>  |

| <b>2 アプリケーション</b>                          | <b>1</b> | <b>7 詳細説明</b>                 | <b>22</b>  |

| <b>3 説明</b>                                | <b>1</b> | 7.1 概要                        | <b>22</b>  |

| <b>4 デバイス比較表</b>                           | <b>3</b> | 7.2 機能ブロック図                   | <b>22</b>  |

| <b>5 ピン構成および機能</b>                         | <b>4</b> | 7.3 機能説明                      | <b>23</b>  |

| <b>6 仕様</b>                                | <b>8</b> | 7.4 デバイスの機能モード                | <b>54</b>  |

| 6.1 絶対最大定格                                 | 8        | 7.5 プログラミング                   | <b>56</b>  |

| 6.2 ESD 定格                                 | 8        | 7.6 レジスタ マップ                  | <b>67</b>  |

| 6.3 推奨動作条件                                 | 9        | <b>8 アプリケーションと実装</b>          | <b>107</b> |

| 6.4 熱に関する情報                                | 9        | 8.1 代表的なアプリケーション              | <b>107</b> |

| 6.5 アンプの電気的特性                              | 10       | 8.2 電源に関する推奨事項                | <b>113</b> |

| 6.6 DAC の電気的特性                             | 12       | 8.3 レイアウト                     | <b>117</b> |

| 6.7 オーディオ特性 (BTL)                          | 13       | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>121</b> |

| 6.8 オーディオ特性 (PBTL)                         | 13       | 9.1 デバイス サポート                 | <b>121</b> |

| 6.9 MCLK のタイミング                            | 14       | 9.2 ドキュメントの更新通知を受け取る方法        | <b>121</b> |

| 6.10 シリアル オーディオ ポートのタイミング - ターゲット<br>モード   | 14       | 9.3 サポート・リソース                 | <b>122</b> |

| 6.11 シリアル オーディオ ポートのタイミング - コントロー<br>ラ モード | 14       | 9.4 商標                        | <b>122</b> |

| 6.12 I <sup>2</sup> C バスタイミング - スタンダード     | 15       | 9.5 静電気放電に関する注意事項             | <b>122</b> |

| 6.13 I <sup>2</sup> C バスタイミング - フアスト       | 15       | 9.6 用語集                       | <b>122</b> |

| 6.14 タイミング図                                | 16       | <b>10 改訂履歴</b>                | <b>122</b> |

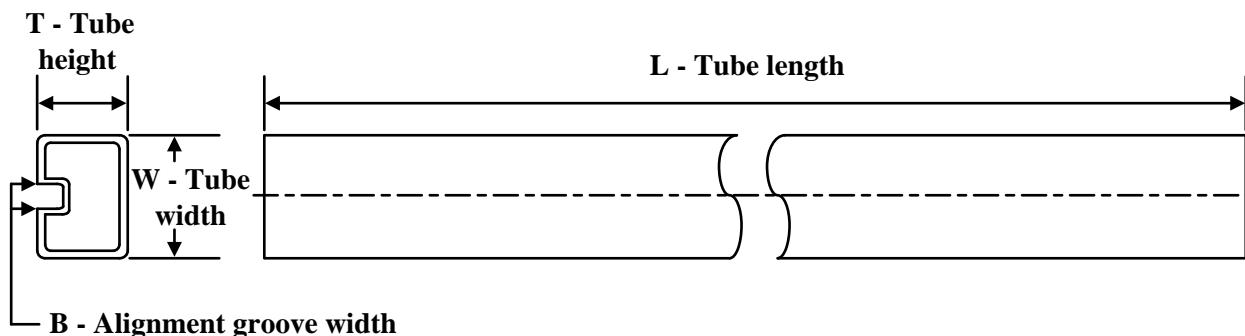

|                                            |          | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>122</b> |

## 4 デバイス比較表

| 型番       | 説明                                                           | オーディオ入力インターフェイス | パッドの位置 |

|----------|--------------------------------------------------------------|-----------------|--------|

| TAS3251  | 175W ステレオ、350W モノラル ウルトラ HD デジタル入力 クラス -D アンプ (高度な DSP 处理搭載) | デジタル            | 表      |

| TAS5782M | 30W ステレオ、60W モノラル デジタル入力 クラス -D アンプ (高度な DSP 处理搭載)           | デジタル            | 裏      |

| TPA3244  | 60W ステレオ、100W ピーク Ultra-HD パッドダウン クラス -D アンプ                 | アナログ            | 裏      |

| TPA3245  | 115W ステレオ、230W モノ Ultra-HD アナログ入力 クラス -D アンプ                 | アナログ            | 表      |

| TPA3250  | 70W ステレオ、130W ピーク Ultra-HD パッドダウン クラス -D アンプ                 | アナログ            | 裏      |

| TPA3251  | 175W ステレオ、350W モノ Ultra-HD アナログ入力電力段                         | アナログ            | 表      |

| TPA3255  | 315W ステレオ、600W モノ Ultra-HD アナログ入力 クラス -D アンプ                 | アナログ            | 表      |

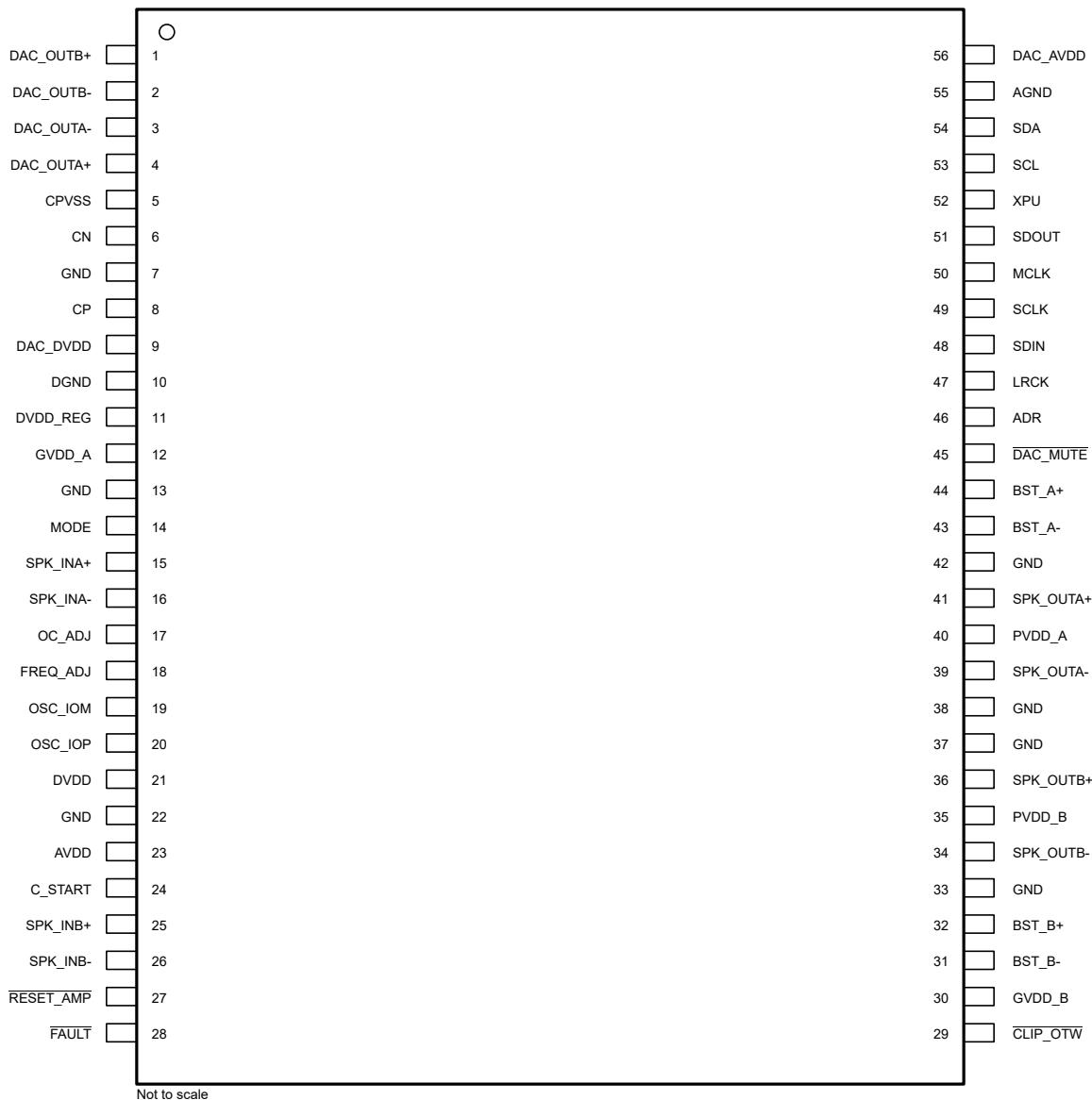

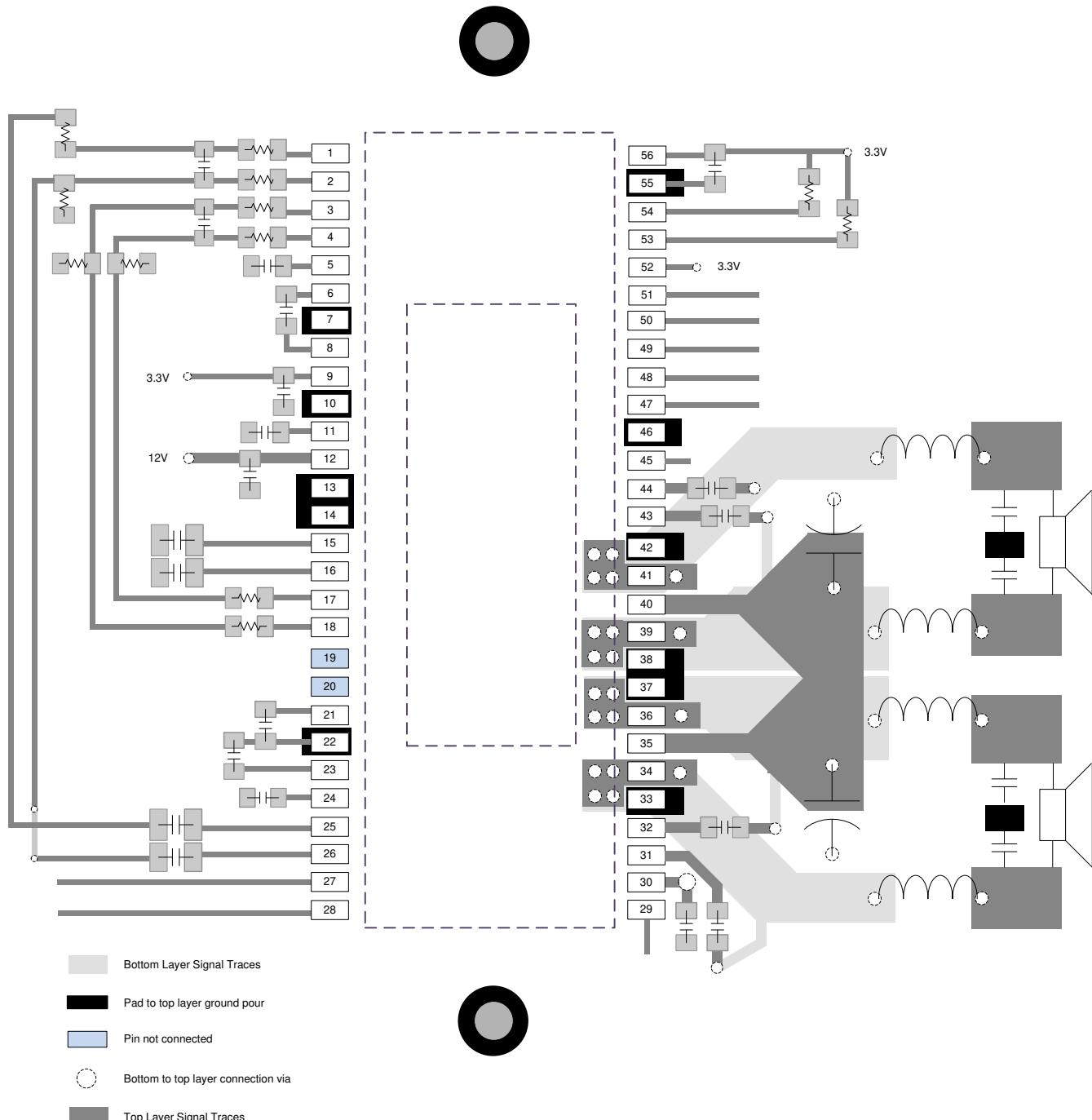

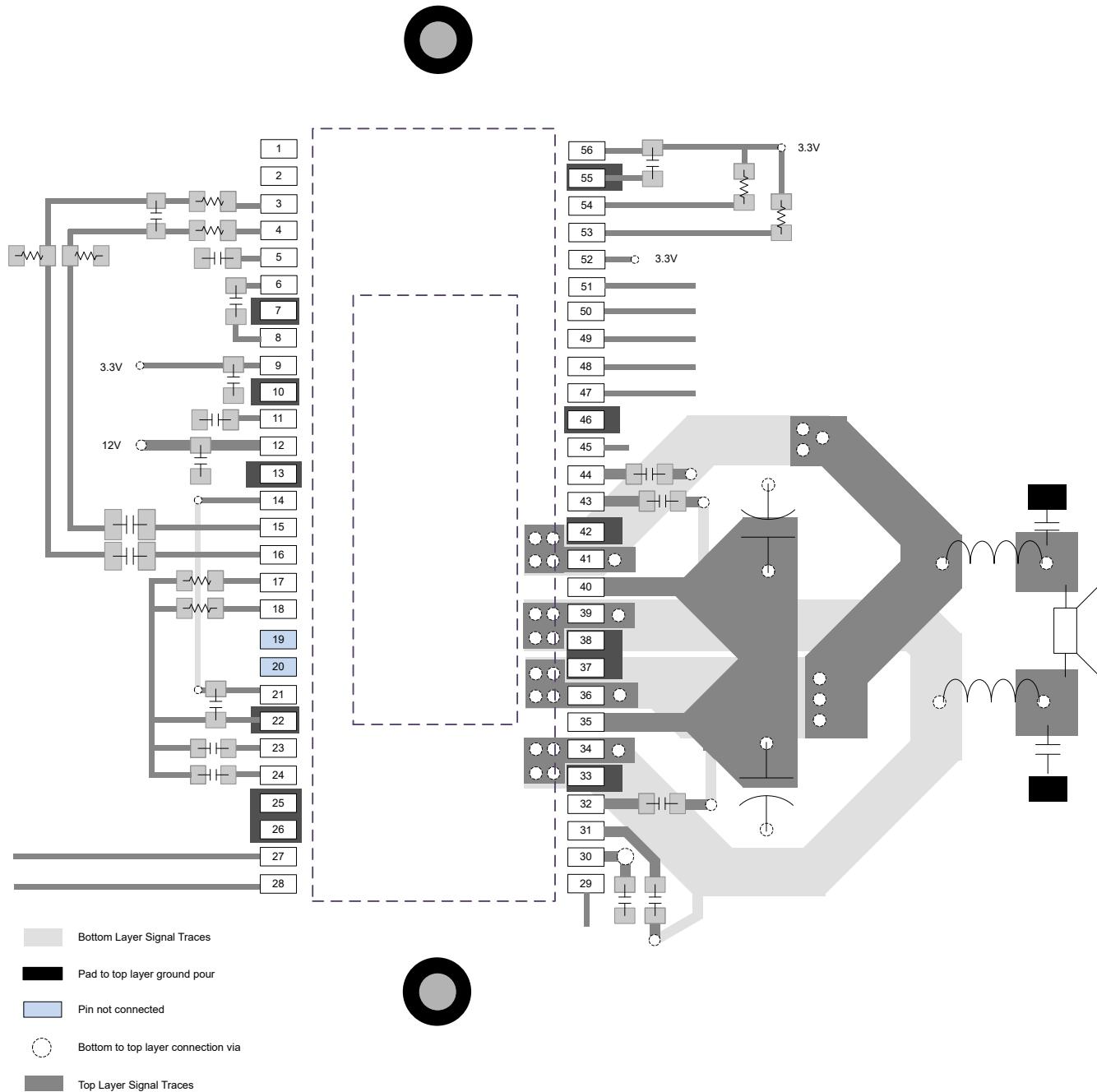

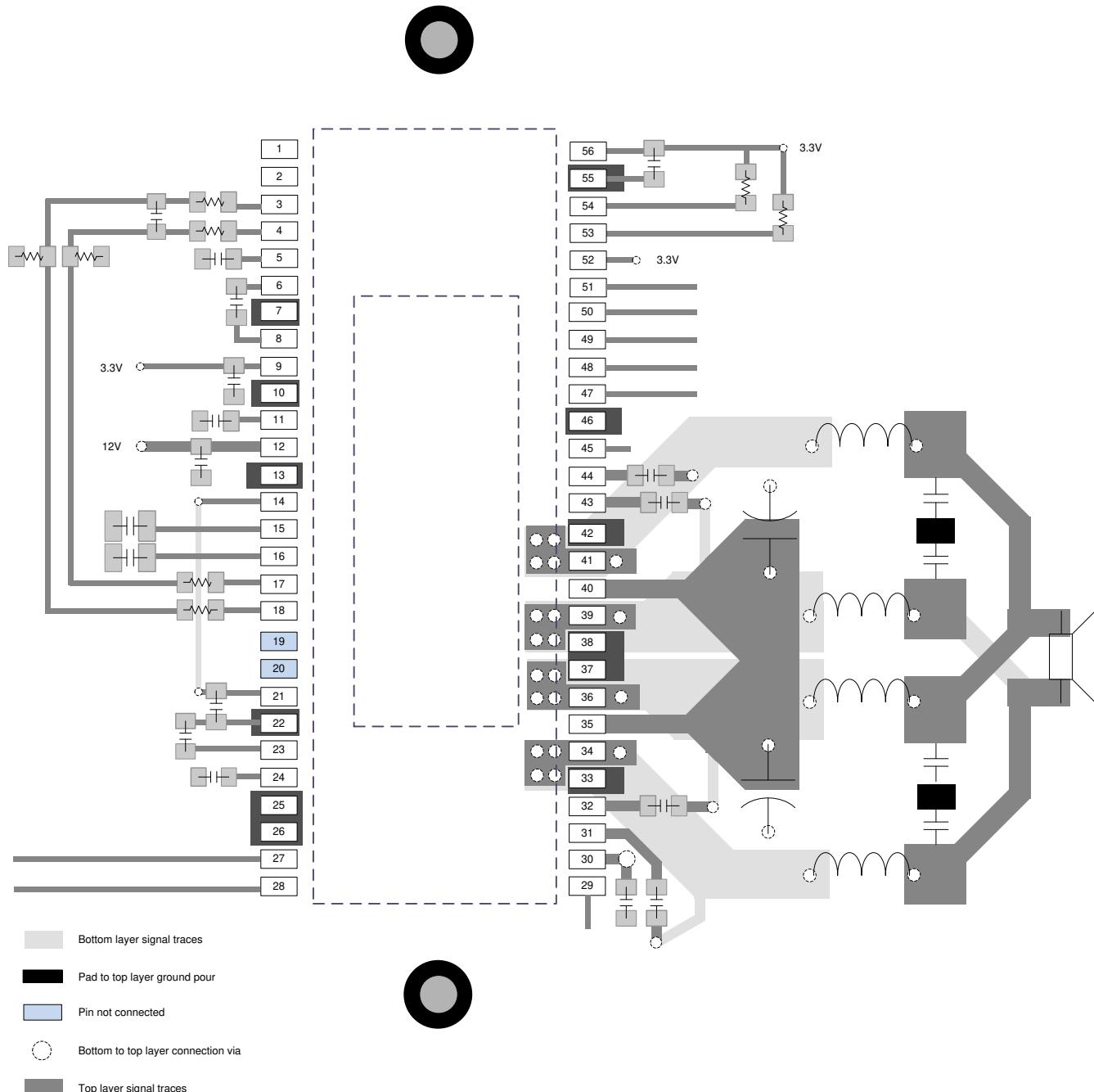

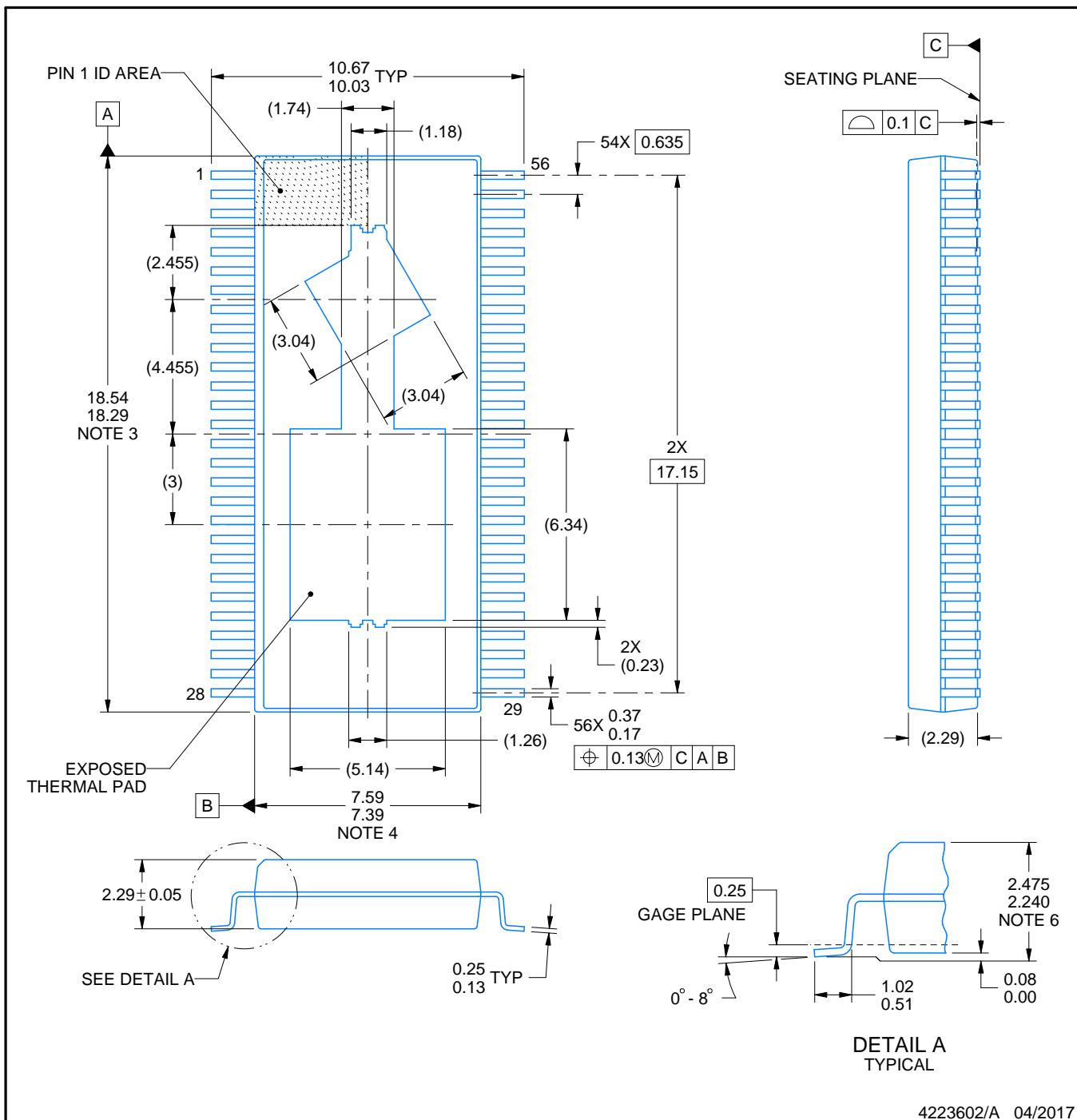

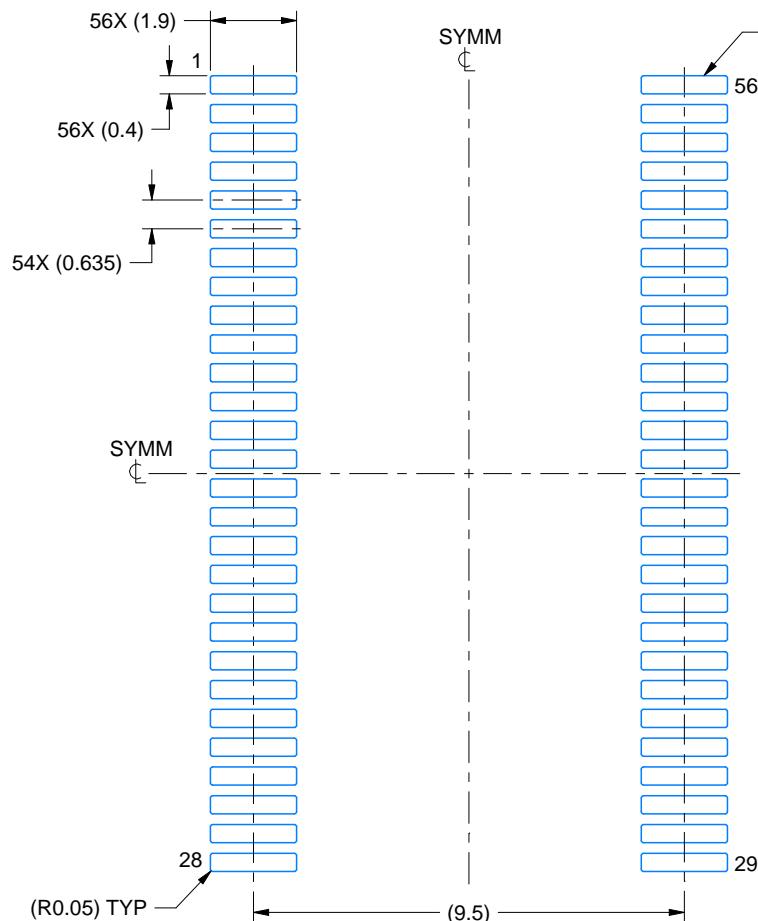

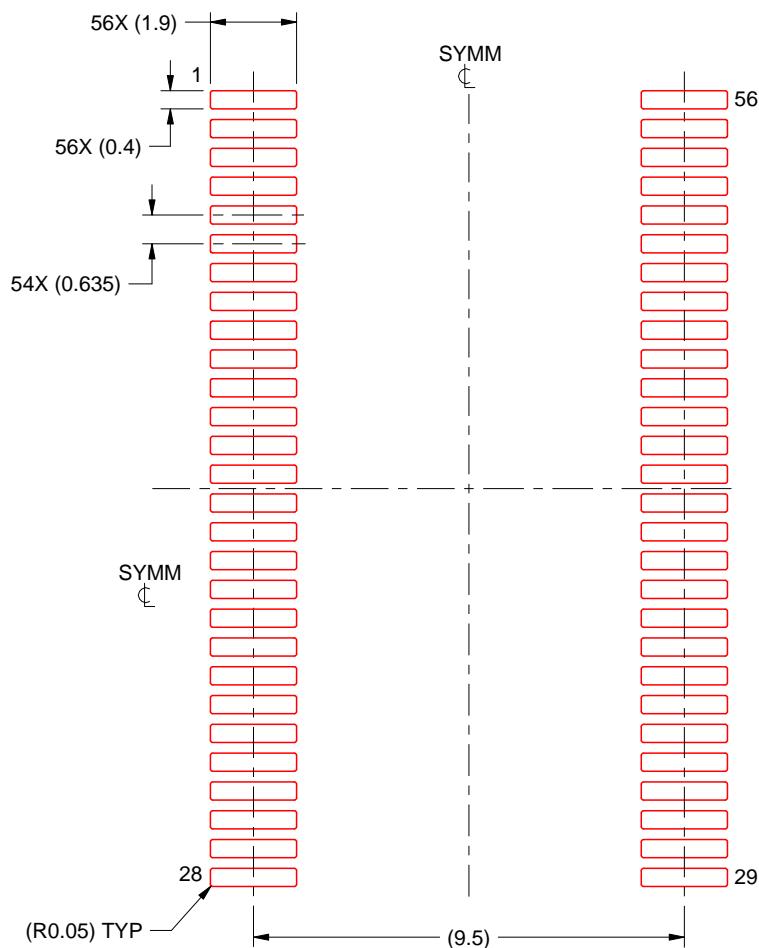

## 5 ピン構成および機能

図 5-1. DKQ パッケージ 56 ピン HSSOP PowerPAD™ 付き、上面図

表 5-1. ピンの機能

| ピン |           | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                       |

|----|-----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称        |                    |                                                                                                                                                                                                          |

| 1  | DAC_OUTB+ | O                  | 差動 DAC 出力 B+。                                                                                                                                                                                            |

| 2  | DAC_OUTB- | O                  | 差動 DAC 出力 B-。                                                                                                                                                                                            |

| 3  | DAC_OUTA- | O                  | 差動 DAC 出力 A-。                                                                                                                                                                                            |

| 4  | DAC_OUTA+ | O                  | 差動 DAC 出力 A+。                                                                                                                                                                                            |

| 5  | CPVSS     | P                  | DAC 用の -3.3V 負のチャージポンプ電源出力。1 $\mu$ F のセラミックコンデンサを GND に接続します。以下のセクションを参照します: <a href="#">電源に関する推奨事項</a>                                                                                                  |

| 6  | CN        | P                  | ラインドライバ チャージポンプで使用されるコンデンサ接続用の負のピン。CN から CP に 1 $\mu$ F のセラミックコンデンサを接続します。以下のセクションを参照します: <a href="#">電源に関する推奨事項</a>                                                                                     |

| 7  | GND       | G                  | デバイスのグランドピン。                                                                                                                                                                                             |

| 8  | CP        | P                  | ラインドライバ チャージポンプで使用されるコンデンサ接続用の正のピン。CN から CP に 1 $\mu$ F のコンデンサを接続します。以下のセクションを参照します: <a href="#">電源に関する推奨事項</a>                                                                                          |

| 9  | DAC_DVDD  | P                  | デジタルロジックおよびチャージポンプ用の DAC 電源入力。3.3V と 1 $\mu$ F のセラミックコンデンサを GND に接続します。以下のセクションを参照します: <a href="#">DAC_DVDD および DAC_AVDD 電源</a>                                                                          |

| 10 | DGND      | G                  | デジタル回路用のグランドリファレンス。このピンは、システムのグランドに接続します。                                                                                                                                                                |

| 11 | DVDD_REG  | P                  | 内部デジタル回路(1.8V)用に、DAC_DVDD 電源から生成される DAC 電圧レギュレータ出力。このピンは、本電源のフィルタ用コンデンサを接続するために用意されており、外部回路への電源供給には使用しないでください。1 $\mu$ F のセラミックコンデンサを GND に接続します。以下のセクションを参照します: <a href="#">DAC_DVDD および DAC_AVDD 電源</a> |

| 12 | GVDD_A    | P                  | アンプチャネル A 用のゲートドライブ電源入力です。12V と 0.1 $\mu$ F コンデンサを GND に接続してください。以下のセクションを参照します: <a href="#">GVDD_X 電源</a>                                                                                               |

| 13 | GND       | G                  | デバイスのグランドピン。                                                                                                                                                                                             |

| 14 | モード       | I                  | 出力構成モード選択。BTL = 0、PBTL = 1。表を参照: <a href="#">表 5-2</a>                                                                                                                                                   |

| 15 | SPK_INA+  | I                  | ハーフブリッジ A+ の入力信号。                                                                                                                                                                                        |

| 16 | SPK_INA-  | I                  | ハーフブリッジ A- の入力信号。                                                                                                                                                                                        |

| 17 | OC_ADJ    | I/O                | 過電流スレッショルドのプログラミングピン。以下のセクションを参照します: <a href="#">過負荷および短絡電流保護</a>                                                                                                                                        |

| 18 | FREQ_ADJ  | I/O                | 発振周波数プログラミングピン。以下のセクションを参照します: <a href="#">出力電力段用の発振器</a>                                                                                                                                                |

| 19 | OSC_IOM   | I/O                | PWM スイッチング発振器同期インターフェイス。オプション。未使用の場合は接続しないでください。以下のセクションを参照します: <a href="#">発振器の同期およびターゲットモード</a>                                                                                                        |

| 20 | OSC_IOP   | O                  | PWM スイッチング発振器同期インターフェイス。オプション。未使用の場合は接続しないでください。以下のセクションを参照します: <a href="#">発振器の同期およびターゲットモード</a>                                                                                                        |

| 21 | DVDD      | P                  | 内部電圧レギュレータ、アンプのデジタルセクション。1 $\mu$ F セラミックコンデンサを GND に接続します。以下のセクションを参照します: <a href="#">VDD 電源</a>                                                                                                         |

| 22 | GND       | G                  | デバイスのグランドピン。                                                                                                                                                                                             |

| 23 | AVDD      | P                  | 内部電圧レギュレータ、アンプのアナログセクション。1 $\mu$ F のセラミックコンデンサを GND に接続します。以下のセクションを参照します: <a href="#">VDD 電源</a>                                                                                                        |

| 24 | C_START   | O                  | スタートアップランプには、GND に接続された充電用コンデンサが必要です。ポップ音防止のため、10nF を GND に接続してください。セクション <a href="#">7.3.8</a> 以下のセクションを参照します:                                                                                          |

| 25 | SPK_INB+  | I                  | ハーフブリッジ B+ の入力信号。                                                                                                                                                                                        |

| 26 | SPK_INB-  | I                  | ハーフブリッジ B- の入力信号。                                                                                                                                                                                        |

| 27 | RESET_AMP | I                  | デバイスリセット、アクティブ Low。アンプのリセットとミュートに使用します。以下のセクションを参照します: <a href="#">出力電力段りセット</a>                                                                                                                         |

| 28 | FAULT     | O                  | シャットダウン信号、オープンドレイン方式、アクティブ Low。DVDD に接続された内部プルアップ抵抗。未使用の場合は接続しないでください。以下のセクションを参照します: <a href="#">デバイス出力段保護システム</a>                                                                                      |

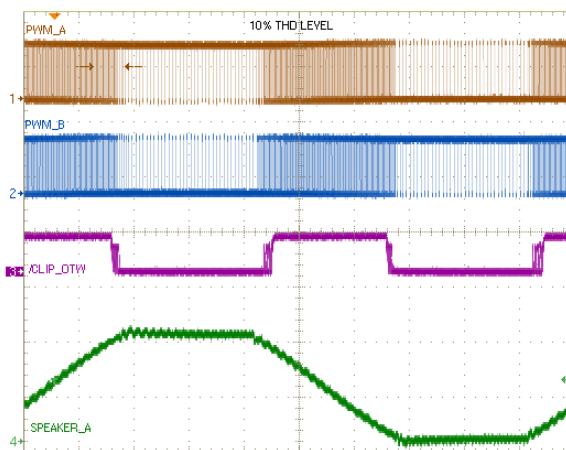

| 29 | CLIP_OTW  | O                  | クリッピング警告および過熱警告、オープンドレイン、アクティブ Low。DVDD に接続された内部プルアップ抵抗。未使用の場合は接続しないでください。以下のセクションを参照します: <a href="#">デバイス出力段保護システム</a>                                                                                  |

| 30 | GVDD_B    | P                  | アンプチャネル B 用のゲートドライブ電源入力です。12V と 0.1 $\mu$ F コンデンサを GND に接続します。以下のセクションを参照します: <a href="#">GVDD_X 電源</a>                                                                                                  |

| 31 | BST_B-    | P                  | HS ブートストラップ電源 (BST)、SPK_OUTB- への外部 0.033 $\mu$ F コンデンサ。以下のセクションを参照します: <a href="#">BST 電源</a>                                                                                                            |

| 32 | BST_B+    | P                  | HS ブートストラップ電源 (BST)、SPK_OUTB+ への外部 0.033 $\mu$ F コンデンサ。以下のセクションを参照します: <a href="#">BST 電源</a>                                                                                                            |

| 33 | GND       | G                  | デバイスのグランドピン。                                                                                                                                                                                             |

| 34 | SPK_OUTB- | O                  | 出力、ハーフブリッジ B-。                                                                                                                                                                                           |

表 5-1. ピンの機能 (続き)

| ピン |           | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                         |  |  |

|----|-----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 番号 | 名称        |                    |                                                                                                                                                                                            |  |  |

| 35 | PVDD_B    | P                  | チャネル B 用の PVDD 電源です。大容量バルクコンデンサと 1 $\mu$ F セラミック デカップリングコンデンサを GND に接続し、ピンの近くに配置します。以下のセクションを参照します： <a href="#">PVDD 電源</a>                                                                |  |  |

| 36 | SPK_OUTB+ | O                  | 出力、ハーフプリッジ B+。                                                                                                                                                                             |  |  |

| 37 | GND       | G                  | デバイスのグランドピン。                                                                                                                                                                               |  |  |

| 38 | GND       | G                  | デバイスのグランドピン。                                                                                                                                                                               |  |  |

| 39 | SPK_OUTA- | O                  | 出力、ハーフプリッジ A-。                                                                                                                                                                             |  |  |

| 40 | PVDD_A    | P                  | チャネル A 用の PVDD 電源です。大容量バルクコンデンサと 1 $\mu$ F セラミック デカップリングコンデンサを GND に接続し、ピンの近くに配置してください。以下のセクションを参照します： <a href="#">PVDD 電源</a>                                                             |  |  |

| 41 | SPK_OUTA+ | O                  | 出力、ハーフプリッジ A+。                                                                                                                                                                             |  |  |

| 42 | GND       | G                  | デバイスのグランドピン。                                                                                                                                                                               |  |  |

| 43 | BST_A-    | P                  | HS ブートストラップ電源 (BST)、SPK_OUTA- への外部 0.033 $\mu$ F コンデンサ。以下のセクションを参照します： <a href="#">BST 電源</a>                                                                                              |  |  |

| 44 | BST_A +   | P                  | HS ブートストラップ電源 (BST)、SPK_OUTA+ への外部 0.033 $\mu$ F コンデンサ。以下のセクションを参照します： <a href="#">BST 電源</a>                                                                                              |  |  |

| 45 | DAC_MUTE  | I                  | ハードウェア制御 DAC ミュート機能。本デバイスをミュートするには Low (DGND に接続) に、ミュート解除するには High (DAC_DVDD に接続) にしてください。セクション <a href="#">7.3.11.6</a> 以下のセクションを参照します：                                                  |  |  |

| 46 | ADR       | I                  | GND にプルされる場合、I <sup>2</sup> C アドレスの LSB を 0 に設定し、DAC_DVDD にプルされる場合は 1 に設定します。表を参照： <a href="#">I<sup>2</sup>C デバイスターゲットアドレス</a>                                                            |  |  |

| 47 | LRCK      | I                  | デジタル オーディオ信号用の左-右ワード (I <sup>2</sup> S) またはフレーム (TDM) 選択クロック。I <sup>2</sup> S、LJ、RJ では、これは左チャネルと右チャネルの境界に対応しています。TDM モードでは、これはフレーム同期境界に対応します。以下のセクションを参照します： <a href="#">シリアル オーディオポート</a> |  |  |

| 48 | SDIN      | I                  | オーディオ データシリアルポート、データ入力。以下のセクションを参照： <a href="#">シリアル オーディオポート</a>                                                                                                                          |  |  |

| 49 | SCLK      | I                  | シリアル データポートの入力データラインでアクティブとなるデジタル信号用のシリアル (ビット) クロック。以下のセクションを参照します： <a href="#">シリアル オーディオポート</a>                                                                                         |  |  |

| 50 | MCLK      | I                  | 内部クロック ツリーやサブ回路、ステートマシンのクロッキングに使用されるコントローラ クロック。以下のセクションを参照します： <a href="#">シリアル オーディオポート</a>                                                                                              |  |  |

| 51 | SDOUT     | I/O                | オーディオ データシリアルポート、データ出力。以下のセクションを参照します： <a href="#">SDOUT ポートおよびハードウェア制御ピン</a>                                                                                                              |  |  |

| 52 | XPU       | I                  | 外部プルアップ、ロジック レベルピン。通常動作のため、このピンは 3.3V (DAC_DVDD または DAC_AVDD) に直接接続します。                                                                                                                    |  |  |

| 53 | SCL       | I                  | I <sup>2</sup> C シリアル制御ポートクロック。以下のセクションを参照します： <a href="#">I<sup>2</sup>C 通信ポート</a>                                                                                                        |  |  |

| 54 | SDA       | I/O                | I <sup>2</sup> C シリアル制御ポートデータ。以下のセクションを参照します： <a href="#">I<sup>2</sup>C 通信ポート</a>                                                                                                         |  |  |

| 55 | AGND      | G                  | アナログ回路のグランドリファレンス。システムグランドに接続。                                                                                                                                                             |  |  |

| 56 | DAC_AVDD  | P                  | DAC 内部アナログ回路用の DAC 電源入力。3.3V と 1 $\mu$ F のセラミックコンデンサを GND に接続します。以下のセクションを参照します： <a href="#">DAC_DVDD および DAC_AVDD 電源</a>                                                                  |  |  |

|    | PowerPAD  | G                  | グランド、接地されたヒートシンクに接続します。                                                                                                                                                                    |  |  |

(1) I = 入力、O = 出力、I/O = 入出力、P = 電源、G = グランド

表 5-2. モードの選択ピン

| 出力構成     | 入力モード  | MODE ピン | SPK_INB+ ピン | SPK_INB- ピン | 説明                                                                             |

|----------|--------|---------|-------------|-------------|--------------------------------------------------------------------------------|

| 2 × BTL  | 2N + 1 | 0       | X           | X           | ステレオ BTL 出力構成                                                                  |

| 1 × PBTL | 2N + 1 | 1       | 0           | 0           | 並列 BTL 構成のプリフィルタまたはポストフィルタ。SPK_INB+ と INPUT_B- を DC ブロッキングコンデンサなしで GND に接続します。 |

**表 5-3. I<sup>2</sup>C デバイス ターゲット アドレス**

| ADR ピン |                      | 16 進 | 2 進       |

|--------|----------------------|------|-----------|

| 0      | 7 ビット アドレス           | 0x4A | 1001 010  |

|        | 7 ビット アドレス + 書き込みビット | 0x94 | 1001 0100 |

|        | 7 ビット アドレス + 読み取りビット | 0x95 | 1001 0101 |

| 1      | 7 ビット アドレス           | 0x4B | 1001 011  |

|        | 7 ビット アドレス + 書き込みビット | 0x96 | 1001 0110 |

|        | 7 ビット アドレス + 読み取りビット | 0x97 | 1001 0111 |

## 6 仕様

### 6.1 絶対最大定格

自由気流での室温 25°C (特に記述のない限り)<sup>(1)</sup>

|                 |                                                           | 最小値  | 最大値                   | 単位 |

|-----------------|-----------------------------------------------------------|------|-----------------------|----|

| 電源電圧            | PVDD_X から GND <sup>(2)</sup>                              | -0.3 | 50                    | V  |

|                 | BST_X から GVDD_X <sup>(2)</sup>                            | -0.3 | 50                    | V  |

|                 | BST_X から GND <sup>(2)</sup>                               | -0.3 | 62.5                  | V  |

|                 | VDD から GND                                                | -0.3 | 13.2                  | V  |

|                 | GVDD_X から GND <sup>(2)</sup>                              | -0.3 | 13.2                  | V  |

|                 | DVDD から GND                                               | -0.3 | 4.2                   | V  |

|                 | AVDD から GND                                               | -0.3 | 8.5                   | V  |

|                 | DAC_DVDD、DAC_AVDD                                         | -0.3 | 3.9                   | V  |

| アナログ インターフェイスピン | SPK_OUTX から GND <sup>(2)</sup>                            | -0.3 | 50                    | V  |

|                 | SPK_INX から GND                                            | -0.3 | 7                     | V  |

| デジタル インターフェイスピン | OC_ADJ、MODE、OSC_IOP、OSC_IOM、FREQ_ADJ、C_START から GND       | -0.3 | 4.2                   | V  |

|                 | RESET_AMP、FAULT、CLIP_OTW から GND                           | -0.3 | 4.2                   | V  |

|                 | 連続シンク電流 RESET_AMP、FAULT、CLIP_OTW から GND                   | 9    |                       | mA |

|                 | ADR、DAC_MUTE、LRCK、MCLK、SCL、SCLK、SDA、SDIN、SDOUT、XPU から GND | -0.5 | $V_{DAC\_DVDD} + 0.5$ | V  |

| $T_J$           | 動作接合部温度範囲、パワーダイ                                           | -40  | 165                   | °C |

|                 | 動作時接合部温度、デジタルダイ                                           | -40  | 125                   | °C |

| $T_{stg}$       | 保管温度範囲                                                    | -40  | 150                   | °C |

(1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス評価であり、このデータシートの「[セクション 6.3](#)」に示された値と等しい、またはそれを超える条件で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) これらの電圧は、あらゆる条件下においてデバイスの端子で測定された DC 電圧 + ピーク AC 波形を表します。

### 6.2 ESD 定格

|                  |                                                         | 値          | 単位 |

|------------------|---------------------------------------------------------|------------|----|

| $V_{(ESD)}$ 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | $\pm 2000$ | V  |

|                  | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | $\pm 500$  |    |

(1) JEDEC ドキュメント JEP155 には、2000V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、500V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

## 6.3 推奨動作条件

自由気流での室温 25°C (特に記述のない限り)

|                         |                                                      |                       | 最小値  | 標準値                        | 最大値                        | 単位        |

|-------------------------|------------------------------------------------------|-----------------------|------|----------------------------|----------------------------|-----------|

| PVDD_X                  | ハーフブリッジ電源                                            | DC 電源                 | 12   | 36                         | 38                         | V         |

| GVDD_X                  | ロジック レギュレータおよびゲートドライブ回路用の電源                          | DC 電源                 | 10.8 | 12                         | 13.2                       | V         |

| VDD                     | デジタル レギュレータ電源電圧                                      | DC 電源                 | 10.8 | 12                         | 13.2                       | V         |

| DAC_AVDD                | DAC 内部アナログ回路用電源。                                     | DC 電源                 | 2.9  | 3.3                        | 3.63                       | V         |

| DAC_DVDD <sup>(1)</sup> | DAC デジタル電源とチャージ ポンプ用電源                               | DC 電源                 | 2.9  | 3.3                        | 3.63                       | V         |

| $R_L(BTL)$              | 負荷インピーダンス                                            | 推奨値範囲内の出力フィルタのインダクタンス | 2.7  | 4                          |                            | $\Omega$  |

| $R_L(PBTL)$             |                                                      |                       | 1.6  | 2                          |                            |           |

| $L_{OUT}(BTL)$          | 出力フィルタのインダクタンス                                       | IOC での最小出力インダクタンス     | 5    |                            |                            | $\mu H$   |

| $L_{OUT}(PBTL)$         |                                                      |                       | 5    |                            |                            |           |

| $F_{PWM}$               | AM 干渉回避のために選択可能な PWM フレーム抵抗値許容差: 抵抗許容差 1%            | 公称                    | 575  | 600                        | 625                        | kHz       |

|                         |                                                      | AM1                   | 475  | 500                        | 525                        |           |

|                         |                                                      | AM2                   | 430  | 450                        | 470                        |           |

| $R_{(FREQ\_ADJ)}$       | PWM フレーム レート プログラミング抵抗                               | 公称、コントローラ モード         | 9.9  | 10                         | 10.1                       | $k\Omega$ |

|                         |                                                      | AM1、制御モード             | 19.8 | 20                         | 20.2                       |           |

|                         |                                                      | AM2、制御モード             | 29.7 | 30                         | 30.3                       |           |

| $C_{PVDD}$              | PVDD 近接デカップリング コンデンサ                                 |                       | 1.0  |                            |                            | $\mu F$   |

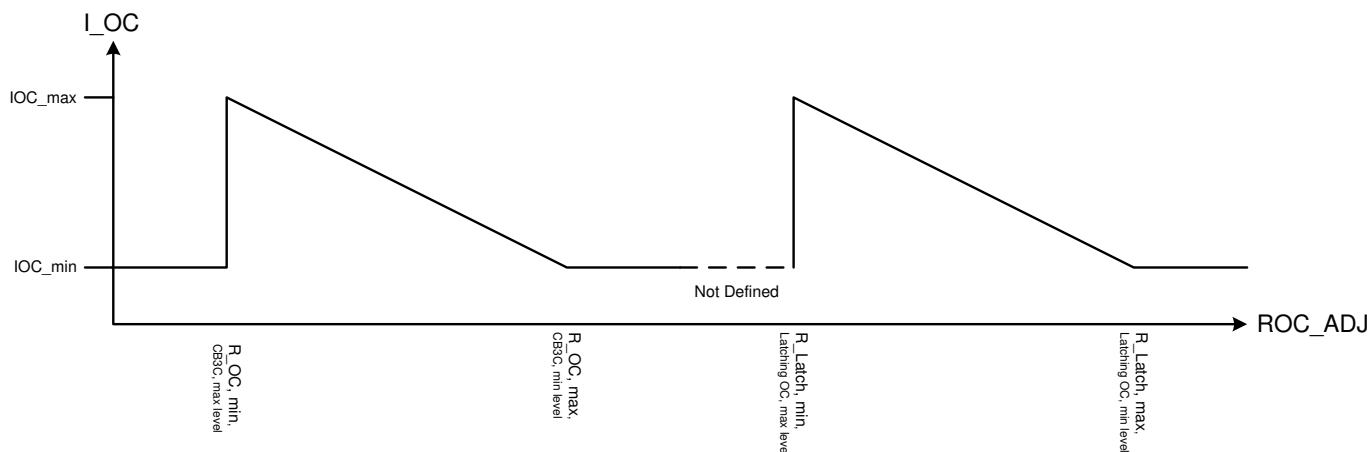

| $R_{OC}$                | 過電流プログラミング抵抗                                         | 抵抗の公差 = 5%            | 22   | 30                         |                            | $k\Omega$ |

| $R_{OC(LATCHED)}$       | 過電流プログラミング抵抗                                         | 抵抗の公差 = 5%            | 47   | 64                         |                            | $k\Omega$ |

| $V_{(FREQ\_ADJ)}$       | ターゲット モード動作用の FREQ_ADJ ピンの電圧                         | ターゲット モード             |      | 3.3                        |                            | V         |

| $V_{IH(DigIn)}$         | DAC_DVDD 基準のデジタル入力に対する入力ロジック High <sup>(1) (2)</sup> |                       |      | $0.9 \times V_{DAC\_DVDD}$ | $V_{DAC\_DVDD}$            | V         |

| $V_{IL(DigIn)}$         | DAC_DVDD 基準のデジタル入力に対する入力ロジック Low <sup>(1) (3)</sup>  |                       |      | $V_{DAC\_DVDD}$            | $0.1 \times V_{DAC\_DVDD}$ | V         |

| $T_J$                   | 接合部温度                                                |                       | 0    | 125                        |                            | °C        |

- (1) DAC\_DVDD 基準のデジタルピンには以下が含まれます: ADR、LRCK、MCLK、DAC\_MUTE、SCL、SCLK、SDA、SDIN、SDOUT、XPU。

- (2) フロントエンド (DAC および DSP) ピンは DAC\_DVDD を基準にする必要があります。電力段のデジタルピンは、DVDD を基準とする必要があります。

- (3) すべての TAS3251 のグランドピンはシステム グランドを基準にする必要があります。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> | TAS3251              |      | 単位   |  |

|----------------------|----------------------|------|------|--|

|                      | DKQ 56 ピン (HSSOP)    |      |      |  |

|                      | JEDEC 規格 4-LAYER PCB |      |      |  |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗         | 47.8 | °C/W |  |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗  | 0.3  | °C/W |  |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗         | 24.2 | °C/W |  |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ     | 0.2  | °C/W |  |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ     | 20.6 | °C/W |  |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗  | 該当なし | °C/W |  |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 アンプの電気的特性

PVDD\_X = 36V, GVDD\_X = 12V, VDD = 12V, T<sub>C</sub> (ケース温度) = 75°C, f<sub>S</sub> = 600kHz (特に記述のない限り)。

| パラメータ                              | テスト条件                               | 最小値                                                                  | 標準値    | 最大値  | 単位   |

|------------------------------------|-------------------------------------|----------------------------------------------------------------------|--------|------|------|

| <b>アンプの内部電圧レギュレータと消費電流</b>         |                                     |                                                                      |        |      |      |

| DVDD                               | 内部用電圧レギュレータ                         | VDD = 12V                                                            | 3      | 3.3  | 3.6  |

| AVDD                               | 内部用電圧レギュレータ                         | VDD = 12V                                                            |        | 7.8  | V    |

| I <sub>GVDD_A + GVDD_B + VDD</sub> | GVDD および VDD 消費電流                   | 50% デューティ サイクル                                                       | 90     |      | mA   |

|                                    |                                     | リセット モード                                                             | 19     |      | mA   |

| I <sub>PVDD_X</sub>                | PVDD アイドル電流                         | 推奨出力フィルタを使用してデューティ サイクル 50%                                          | 20     |      | mA   |

|                                    |                                     | リセット モード、スイッチングなし                                                    | 0.0048 |      | mA   |

| <b>アナログ入力</b>                      |                                     |                                                                      |        |      |      |

| R <sub>IN</sub>                    | 入力抵抗                                |                                                                      | 24     |      | kΩ   |

| V <sub>IN</sub>                    | 入力電圧の最大振幅、SPK_INx ピン                |                                                                      | 7      |      | V    |

| I <sub>IN</sub>                    | 最大入力電流、SPK_INx ピン                   |                                                                      | 1      |      | mA   |

| G                                  | 反転電圧ゲイン                             | アンプ VOUT/VIN                                                         | 20     |      | dB   |

| <b>アンプ発振器</b>                      |                                     |                                                                      |        |      |      |

| f <sub>OSC(IO+)</sub>              | 公称、コントローラ モード                       | F <sub>PWM</sub> × 6                                                 | 3.45   | 3.6  | 3.75 |

|                                    | AM1、制御モード                           | F <sub>PWM</sub> × 6                                                 | 2.85   | 3    | 3.15 |

|                                    | AM2、制御モード                           | F <sub>PWM</sub> × 6                                                 | 2.58   | 2.7  | 2.82 |

| V <sub>IH</sub>                    | High レベル入力電圧                        |                                                                      | 1.86   |      | V    |

| V <sub>IL</sub>                    | Low レベル入力電圧                         |                                                                      |        | 1.45 | V    |

| <b>出力段 MOSFET</b>                  |                                     |                                                                      |        |      |      |

| R <sub>DS(on)</sub>                | ドレイン - ソース間抵抗、ローサイド (LS)            | T <sub>J</sub> = 25°C、金属皮膜抵抗を含む、GVDD = 12V                           | 60     | 100  | mΩ   |

|                                    | ドレイン-ソース間抵抗、ハイサイド (HS)              | T <sub>J</sub> = 25°C、金属皮膜抵抗を含む、GVDD = 12V                           | 60     | 100  | mΩ   |

| <b>アンプ I/O 保護</b>                  |                                     |                                                                      |        |      |      |

| V <sub>uvp</sub> 、VDD、GVDD         | 低電圧保護制限、GVDD_X および VDD              |                                                                      | 9.5    |      | V    |

| V <sub>uvp</sub> 、VDD、GVDD、hyst    | 低電圧保護ヒステリシス、GVDD_X および VDD          |                                                                      | 0.6    |      | V    |

| OTW                                | 過熱警告、CLIP_OTW <sup>(1)</sup>        |                                                                      | 115    | 125  | 135  |

| OTW <sub>hyst</sub>                | CLIP_OTW で OTW イベントを削除するためには必要な温度低下 |                                                                      | 25     |      | °C   |

| OTE                                | 過熱エラー                               |                                                                      | 145    | 155  | 165  |

| OTE-OTW <sub>(differential)</sub>  | OTE - OTW の差分                       |                                                                      | 30     |      | °C   |

| OTE <sub>hyst</sub>                | OTE イベントをクリアするには、リセットが必要です          |                                                                      | 25     |      | °C   |

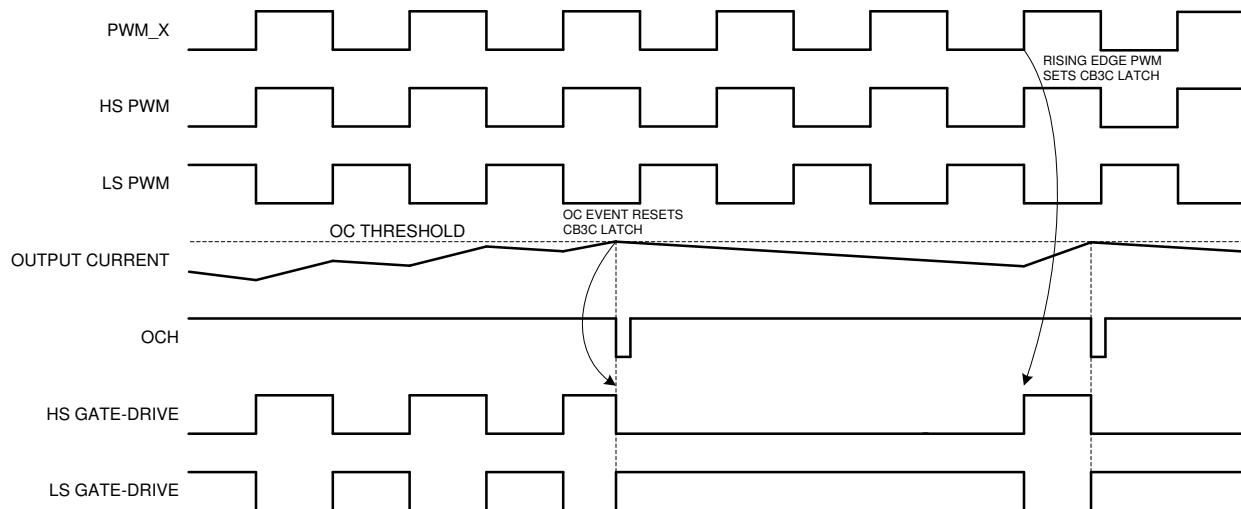

| OLPC                               | CB3C モード用過負荷保護カウンタ                  | F <sub>PWM</sub> = 600 kHz (すべての F <sub>PWM</sub> 向けに 1024 PWM サイクル) | 1.7    |      | ms   |

| I <sub>oc</sub>                    | CB3C モードの過電流制限                      | 抵抗 - プログラム可能、1Ω 負荷での公称ピーク電流、R <sub>OCP</sub> = 22kΩ                  | 14     |      | A    |

| I <sub>OC(LATCHED)</sub>           | ラッチ モードの過電流制限                       | 抵抗 - プログラム可能、1Ω 負荷でのピーク電流、R <sub>OCP</sub> = 47kΩ                    | 14     |      | A    |

| I <sub>DCspkr</sub>                | DC スピーカー保護電流のスレッショルド                | BTL の電流スレッショルドは不安定                                                   | 1.5    |      | A    |

| I <sub>OCT</sub>                   | 過電流応答時間                             | スイッチング遷移から、過電流によって状態がフリップするまでの時間                                     | 150    |      | ns   |

| I <sub>PD</sub>                    | 各ハーフブリッジの出力プルダウン電流                  | RESET がアクティブなときに接続され、ブートストラップ充電が供給されます                               | 3      |      | mA   |

## 6.5 アンプの電気的特性 (続き)

PVDD\_X = 36V、GVDD\_X = 12V、VDD = 12V、T<sub>C</sub> (ケース温度) = 75°C、f<sub>S</sub> = 600kHz (特に記述のない限り)。

| パラメータ                          | テスト条件                                       | 最小値                                | 標準値 | 最大値 | 単位   |

|--------------------------------|---------------------------------------------|------------------------------------|-----|-----|------|

| <b>アンプ静的デジタル仕様</b>             |                                             |                                    |     |     |      |

| V <sub>IH</sub>                | High レベル入力電圧                                | MODE、OSC_IOP、OSC_IOM、<br>RESET_AMP | 1.9 |     | V    |

| V <sub>IL</sub>                | Low レベル入力電圧                                 | MODE、OSC_IOP、OSC_IOM、<br>RESET_AMP |     | 0.8 | V    |

| I <sub>Ik</sub>                | 入力リーク電流                                     | MODE、OSC_IOP、OSC_IOM、<br>RESET_AMP |     | 100 | μA   |

| <b>アンプ OTW/シャットダウン (FAULT)</b> |                                             |                                    |     |     |      |

| R <sub>INT_PU</sub>            | 内部プルアップ抵抗、CLIP_OTW から<br>DVDD、FAULT から DVDD |                                    | 20  | 26  | 32   |

| V <sub>OH</sub>                | High レベル出力電圧                                | 内部プルアップ抵抗                          | 3   | 3.3 | 3.6  |

| V <sub>OL</sub>                | Low レベル出力電圧                                 | IO = 4mA                           | 200 | 500 | mV   |

| デバイスのファンアウト                    | CLIP_OTW、FAULT                              | 外部プルアップなし                          | 30  |     | デバイス |

(1) 設計により規定されています。

## 6.6 DAC の電気的特性

自由気流での室温 25°C (特に記述のない限り)

| パラメータ                       | テスト条件                                                | 最小値                                          | 標準値                             | 最大値    | 単位                   |

|-----------------------------|------------------------------------------------------|----------------------------------------------|---------------------------------|--------|----------------------|

| <b>デジタル I/O</b>             |                                                      |                                              |                                 |        |                      |

| $V_{IH1}$                   | DAC_DVDD 参照デジタル入力の入力ロジック high スレッショルド <sup>(1)</sup> |                                              | 70%                             |        | $V_{DAC\_DVDD}$      |

| $V_{IL1}$                   | DAC_DVDD 参照デジタル入力の入力ロジック low スレッショルド <sup>(1)</sup>  |                                              |                                 | 30%    | $V_{DAC\_DVDD}$      |

| $I_{IH1}$                   | DAC_DVDD 参照デジタル入力ピンの入力ロジック high 電流レベル <sup>(1)</sup> | $V_{IN(DigIn)} = V_{DAC\_DVDD}$              |                                 | 10     | $\mu A$              |

| $I_{IL1}$                   | DAC_DVDD 参照デジタル入力ピンの入力ロジック low 電流レベル <sup>(1)</sup>  | $V_{IN(DigIn)} = 0 V$                        |                                 | -10    | $\mu A$              |

| $V_{OH(DigOut)}$            | ロジック high 出力電圧レベル <sup>(1)</sup>                     | $I_{OH} = 4mA$                               | 80%                             |        | $V_{DAC\_DVDD}$      |

| $V_{OL(DigOut)}$            | 出力ロジック low 電圧レベル <sup>(1)</sup>                      | $I_{OH} = -4mA$                              |                                 | 22%    | $V_{DAC\_DVDD}$      |

| <b>I<sup>2</sup>C 制御ポート</b> |                                                      |                                              |                                 |        |                      |

| $C_L(I2C)$                  | 各 I <sup>2</sup> C ラインで許容される負荷容量                     |                                              | 400                             |        | pF                   |

| $f_{SCL(fast)}$             | SCL 周波数をサポート                                         | ウェイトなし、高速モード                                 |                                 | 400    | kHz                  |

| $f_{SCL(slow)}$             | SCL 周波数をサポート                                         | ウェイトなし、スロー モード                               |                                 | 100    | kHz                  |

| $V_{NH}$                    | 各接続デバイスの High レベルにおけるノイズ マージン (ヒステリシスを含む)            |                                              | $0.2 \times$<br>$V_{DAC\_DVDD}$ |        | V                    |

| <b>MCLK と PLL の仕様</b>       |                                                      |                                              |                                 |        |                      |

| $D_{MCLK}$                  | 許容される MCLK デューティ サイクル                                |                                              | 40%                             | 60%    |                      |

| $f_{MCLK}$                  | サポートしている MCLK 周波数                                    | 最高 50MHz                                     | 128                             | 512    | $f_S$ <sup>(2)</sup> |

| $f_{PLL}$                   | PLL 入力周波数                                            | クロック分周器は分数分周を使用し、<br>$D > 0$ 、 $P = 1$ となります | 6.7                             | 20     | MHz                  |

|                             |                                                      | クロック分周器は整数分周<br>$D = 0$ 、 $P = 1$ を使用します     | 1                               | 20     |                      |

| <b>シリアル オーディオ ポート</b>       |                                                      |                                              |                                 |        |                      |

| $t_{DLY}$                   | 必要な LRCK/FS から SCLK 立ち上がりエッジまでの遅延                    |                                              | 5                               |        | ns                   |

| $D_{SCLK}$                  | 許容される SCLK デューティ サイクル                                |                                              | 40%                             | 60%    |                      |

| $f_S$                       | サポートしている入力サンプルレート                                    |                                              | 8                               | 96     | kHz                  |

| $f_{SCLK}$                  | サポートしている SCLK 周波数                                    |                                              | 32                              | 64     | $f_S$ <sup>(2)</sup> |

| $f_{SCLK}$                  | SCLK 周波数                                             | コントローラ モードとターゲット モードのいずれかを選択                 |                                 | 24.576 | MHz                  |

(1) DAC\_DVDD 基準のデジタルピンには以下が含まれます: ADR、LRCK、MCLK、 $\overline{DAC\_MUTE}$ 、SCL、SCLK、SDA、SDIN、SDOUT、XPU。

(2)  $f_S$  の単位は、仕様が表に記載されている値に、デバイスで使用されるオーディオのサンプル レートを乗算した値であることを示します。

## 6.7 オーディオ特性 (BTL)

PCB とシステムの構成は、推奨ガイドラインに従っています。オーディオ周波数 = 1kHz, PVDD\_X = 36V, GVDD\_X = 12V, R<sub>L</sub> = 4Ω, f<sub>S</sub> = 600kHz, R<sub>OC</sub> = 22kΩ, T<sub>C</sub> = 75°C、出力フィルタ: L<sub>DEM</sub> = 10μH, C<sub>DEM</sub> = 1μF, MODE = 0, AES17 + AUX-0025 測定フィルタ (特に記述のない限り)。

| パラメータ                         | テスト条件                          | 最小値                                              | 標準値 | 最大値   | 単位 |

|-------------------------------|--------------------------------|--------------------------------------------------|-----|-------|----|

| P <sub>O</sub><br>チャネルごとの電源出力 | R <sub>L</sub> = 3Ω, 10% THD+N | 220                                              |     |       | W  |

|                               | R <sub>L</sub> = 4Ω, 10% THD+N | 175                                              |     |       |    |

|                               | R <sub>L</sub> = 3Ω, 1% THD+N  | 175                                              |     |       |    |

|                               | R <sub>L</sub> = 4Ω, 1% THD+N  | 140                                              |     |       |    |

| THD+N                         | 全高調波歪み + ノイズ                   | 1W                                               |     | 0.008 | %  |

| V <sub>n</sub>                | 出力積分ノイズ                        | A 重み付け、AES17 フィルタ、<br>入力コンデンサを接地                 |     | 95    | μV |

| V <sub>osl</sub>              | 出力オフセット電圧                      | 入力を GND に AC カップリング                              | 20  | 60    | mV |

| SNR                           | 信号対雑音比 <sup>(1)</sup>          |                                                  |     | 108   | dB |

| DNR                           | ダイナミックレンジ                      |                                                  |     | 110   | dB |

| P <sub>idle</sub>             | アイドル時の電力損失 (IPVDD_X) による電力損失   | P <sub>O</sub> = 0, 4 チャネルのスイッチング <sup>(2)</sup> |     | 0.75  | W  |

(1) SNR は、1% THD+N 出力レベルを基準として計算されています。

(2) 実際のシステムでのアイドル時の電力損失は、出力インダクタのコア損失の影響も受けます。

## 6.8 オーディオ特性 (PBTL)

PCB とシステムの構成は、推奨ガイドラインに従っています。オーディオ周波数 = 1kHz, PVDD\_X = 36V, GVDD\_X = 12V, R<sub>L</sub> = 2Ω, f<sub>S</sub> = 600kHz, R<sub>OC</sub> = 22kΩ, T<sub>C</sub> = 75°C、出力フィルタ: L<sub>DEM</sub> = 10μH, C<sub>DEM</sub> = 1μF, MODE = 1、特に記載のない限り、出力は LC フィルタ後に並列化され、AES17 + AUX-0025 測定フィルタが適用されます。

| パラメータ                         | テスト条件                          | 最小値                                              | 標準値 | 最大値   | 単位 |

|-------------------------------|--------------------------------|--------------------------------------------------|-----|-------|----|

| P <sub>O</sub><br>チャネルごとの電源出力 | R <sub>L</sub> = 2Ω, 10% THD+N | 355                                              |     |       | W  |

|                               | R <sub>L</sub> = 3Ω, 10% THD+N | 250                                              |     |       |    |

|                               | R <sub>L</sub> = 4Ω, 10% THD+N | 195                                              |     |       |    |

|                               | R <sub>L</sub> = 2Ω, 1% THD+N  | 285                                              |     |       |    |

|                               | R <sub>L</sub> = 3Ω, 1% THD+N  | 200                                              |     |       |    |

|                               | R <sub>L</sub> = 4Ω, 1% THD+N  | 155                                              |     |       |    |

| THD+N                         | 全高調波歪み + ノイズ                   | 1W                                               |     | 0.009 | %  |

| V <sub>n</sub>                | 出力積分ノイズ                        | A 重み付け、AES17 フィルタ、<br>入力コンデンサを接地                 |     | 95    | μV |

| SNR                           | 信号対雑音比 <sup>(1)</sup>          | A 重み付け                                           |     | 108   | dB |

| DNR                           | ダイナミックレンジ                      | A 重み付け                                           |     | 108   | dB |

| P <sub>idle</sub>             | アイドル時の電力損失 (IPVDD_X) による電力損失   | P <sub>O</sub> = 0, 4 チャネルのスイッチング <sup>(2)</sup> |     | 0.75  | W  |

(1) SNR は、1% THD+N 出力レベルを基準として計算されています。

(2) 実際のシステムでのアイドル時の電力損失は、出力インダクタのコア損失の影響を受けます。

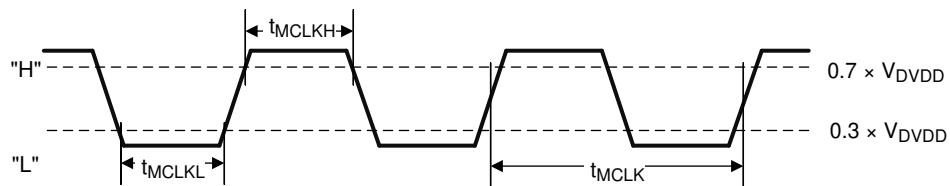

## 6.9 MCLK のタイミング

図 6-1 を参照してください。

| パラメータ       |                | 最小値 | 最大値  | 単位 |

|-------------|----------------|-----|------|----|

| $t_{MCLK}$  | MCLK 周期        | 20  | 1000 | ns |

| $t_{MCLKH}$ | MCLK パルス幅、high | 9   |      | ns |

| $t_{MCLKL}$ | MCLK パルス幅、low  | 9   |      | ns |

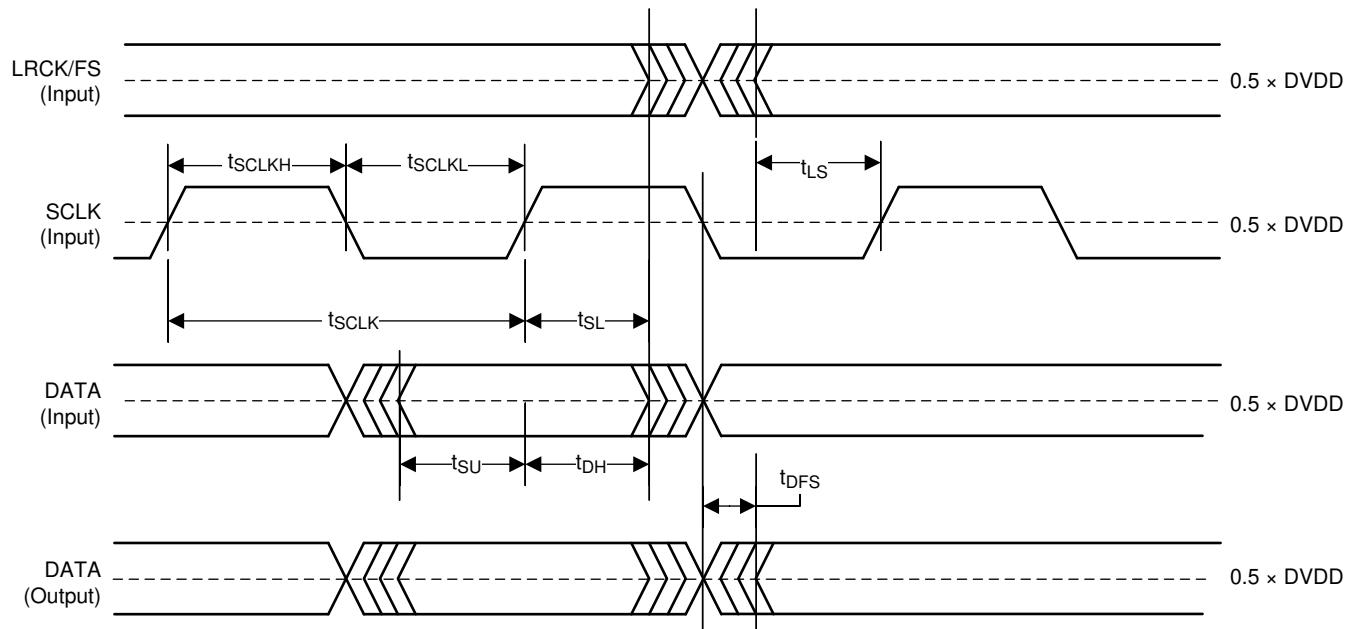

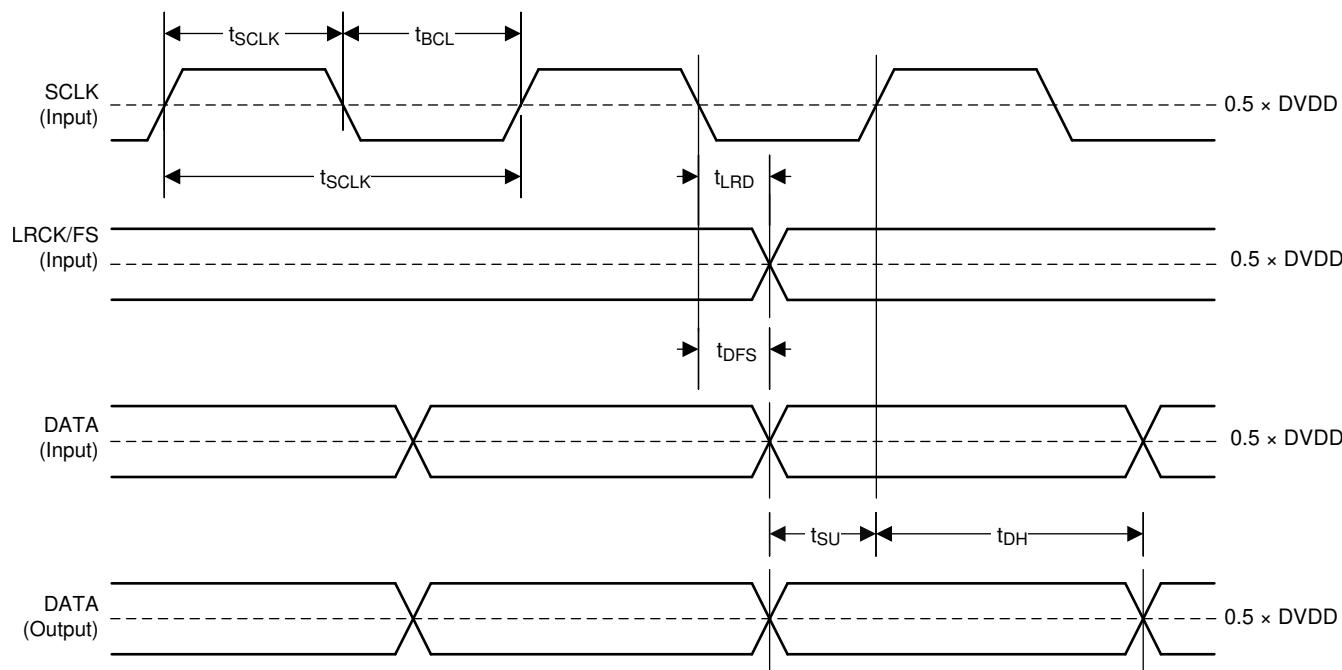

## 6.10 シリアルオーディオポートのタイミング - ターゲットモード

図 6-2 を参照してください。

| パラメータ       |                               | 最小値   | 最大値 | 単位  |

|-------------|-------------------------------|-------|-----|-----|

| $f_{SCLK}$  | SCLK 周波数                      | 1.024 |     | MHz |

| $t_{SCLK}$  | SCLK 周期                       | 40    |     | ns  |

| $t_{SCLKL}$ | SCLK パルス幅、low                 | 16    |     | ns  |

| $t_{SCLKH}$ | SCLK パルス幅、high                | 16    |     | ns  |

| $t_{SL}$    | SCLK の立ち上がりから LRCK/FS エッジまで   | 8     |     | ns  |

| $t_{LS}$    | LRCK/FS エッジから SCLK 立ち上がりエッジまで | 8     |     | ns  |

| $t_{SU}$    | データセットアップ時間、SCLK 立ち上がりエッジ前    | 8     |     | ns  |

| $t_{DH}$    | データホールド時間、SCLK 立ち上がりエッジ後      | 8     |     | ns  |

| $t_{DFS}$   | SCLK 立ち下がりエッジからのデータ遅延時間       |       | 15  | ns  |

## 6.11 シリアルオーディオポートのタイミング - コントローラモード

図 6-3 を参照してください。

| パラメータ       |                                       | 最小値 | 最大値 | 単位 |

|-------------|---------------------------------------|-----|-----|----|

| $t_{SCLK}$  | SCLK 周期                               | 40  |     | ns |

| $t_{SCLKL}$ | SCLK パルス幅、low                         | 16  |     | ns |

| $t_{SCLKH}$ | SCLK パルス幅、high                        | 16  |     | ns |

| $t_{LRD}$   | LRCK/FS の遅延時間は、SCLK の立ち下がりエッジから測定されます | -10 | 20  | ns |

| $t_{SU}$    | データセットアップ時間、SCLK 立ち上がりエッジ前            | 8   |     | ns |

| $t_{DH}$    | データホールド時間、SCLK 立ち上がりエッジ後              | 8   |     | ns |

| $t_{DFS}$   | SCLK 立ち下がりエッジからのデータ遅延時間               |     | 15  | ns |

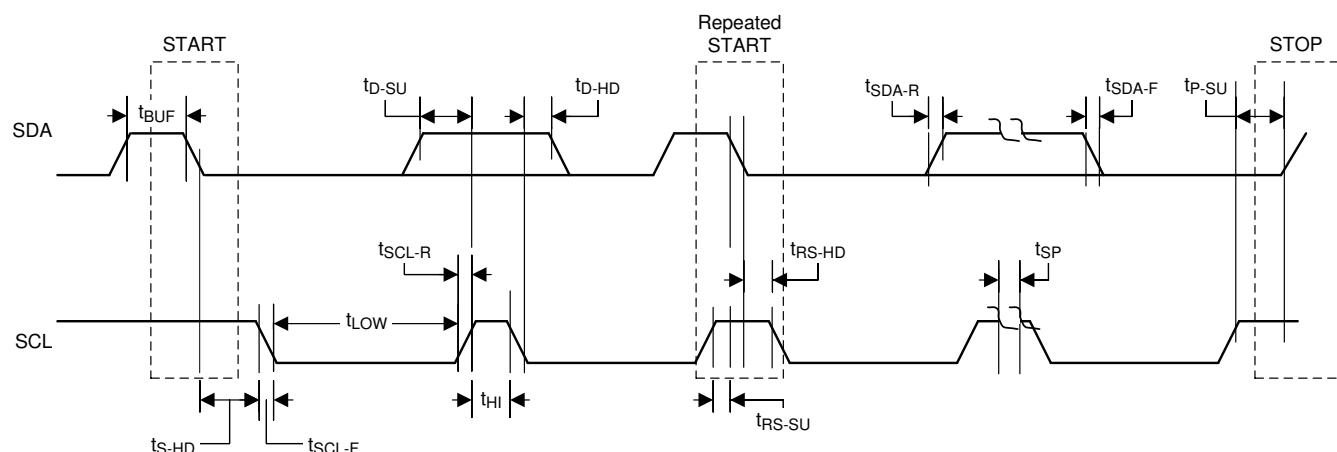

## 6.12 I<sup>2</sup>C バス タイミング - スタンダード

|              |                                              | 最小値           | 最大値  | 単位  |

|--------------|----------------------------------------------|---------------|------|-----|

| $t_{SCL}$    | SCL クロック周波数                                  |               | 400  | kHz |

| $t_{BUF}$    | STOP 条件と START 条件の間のバス フリー時間                 | 4.7           |      | μs  |

| $t_{LOW}$    | SCL クロックの Low 期間                             | 4.7           |      | μs  |

| $t_{HI}$     | SCL クロックの High 期間                            | 4             |      | μs  |

| $t_{RS-SU}$  | (反復) 開始条件のセットアップ時間                           | 4.7           |      | μs  |

| $t_{S-HD}$   | (反復) 開始条件のホールド時間                             | 4             |      | μs  |

| $t_{D-SU}$   | データ セットアップ時間                                 | 250           |      | ns  |

| $t_{D-HD}$   | データ ホールド時間                                   | 0             | 900  | ns  |

| $t_{SCL-R}$  | SCL 信号の立ち上がり時間                               | $20 + 0.1C_B$ | 1000 | ns  |

| $t_{SCL-R1}$ | START 条件の繰り返し、およびアクノリッジ ビット後の SCL 信号の立ち上がり時間 | $20 + 0.1C_B$ | 1000 | ns  |

| $t_{SCL-F}$  | SCL 信号の立ち下がり時間                               | $20 + 0.1C_B$ | 1000 | ns  |

| $t_{SDA-R}$  | SDA 信号の立ち上がり時間                               | $20 + 0.1C_B$ | 1000 | ns  |

| $t_{SDA-F}$  | SDA 信号の立ち下がり時間                               | $20 + 0.1C_B$ | 1000 | ns  |

| $t_{P-SU}$   | 停止条件のセットアップ時間                                | 4             |      | μs  |

## 6.13 I<sup>2</sup>C バス タイミング - ファスト

図 6-4 を参照してください。

|              |                                              | 最小値           | 最大値 | 単位  |

|--------------|----------------------------------------------|---------------|-----|-----|

| $t_{SCL}$    | SCL クロック周波数                                  |               | 400 | kHz |

| $t_{BUF}$    | STOP 条件と START 条件の間のバス フリー時間                 | 1.3           |     | μs  |

| $t_{LOW}$    | SCL クロックの Low 期間                             | 1.3           |     | μs  |

| $t_{HI}$     | SCL クロックの High 期間                            | 600           |     | ns  |

| $t_{RS-SU}$  | (反復) 開始条件のセットアップ時間                           | 600           |     | ns  |

| $t_{RS-HD}$  | (反復) 開始条件のホールド時間                             | 600           |     | ns  |

| $t_{D-SU}$   | データ セットアップ時間                                 | 100           |     | ns  |

| $t_{D-HD}$   | データ ホールド時間                                   | 0             | 900 | ns  |

| $t_{SCL-R}$  | SCL 信号の立ち上がり時間                               | $20 + 0.1C_B$ | 300 | ns  |

| $t_{SCL-R1}$ | START 条件の繰り返し、およびアクノリッジ ビット後の SCL 信号の立ち上がり時間 | $20 + 0.1C_B$ | 300 | ns  |

| $t_{SCL-F}$  | SCL 信号の立ち下がり時間                               | $20 + 0.1C_B$ | 300 | ns  |

| $t_{SDA-R}$  | SDA 信号の立ち上がり時間                               | $20 + 0.1C_B$ | 300 | ns  |

| $t_{SDA-F}$  | SDA 信号の立ち下がり時間                               | $20 + 0.1C_B$ | 300 | ns  |

| $t_{P-SU}$   | 停止条件のセットアップ時間                                | 600           |     | ns  |

| $t_{SP}$     | 抑制されたスパイクのパルス幅                               |               | 50  | ns  |

## 6.14 タイミング図

このセクションには、I<sup>2</sup>C および I<sup>2</sup>S/TDM のタイミング図が記載されています。

図 6-1. MCLK 入力のタイミング要件

図 6-2. ターゲット モードでの MCLK のタイミング図

図 6-3. コントローラ モードでの MCLK のタイミング図

図 6-4. I<sup>2</sup>C 通信ポート タイミング図

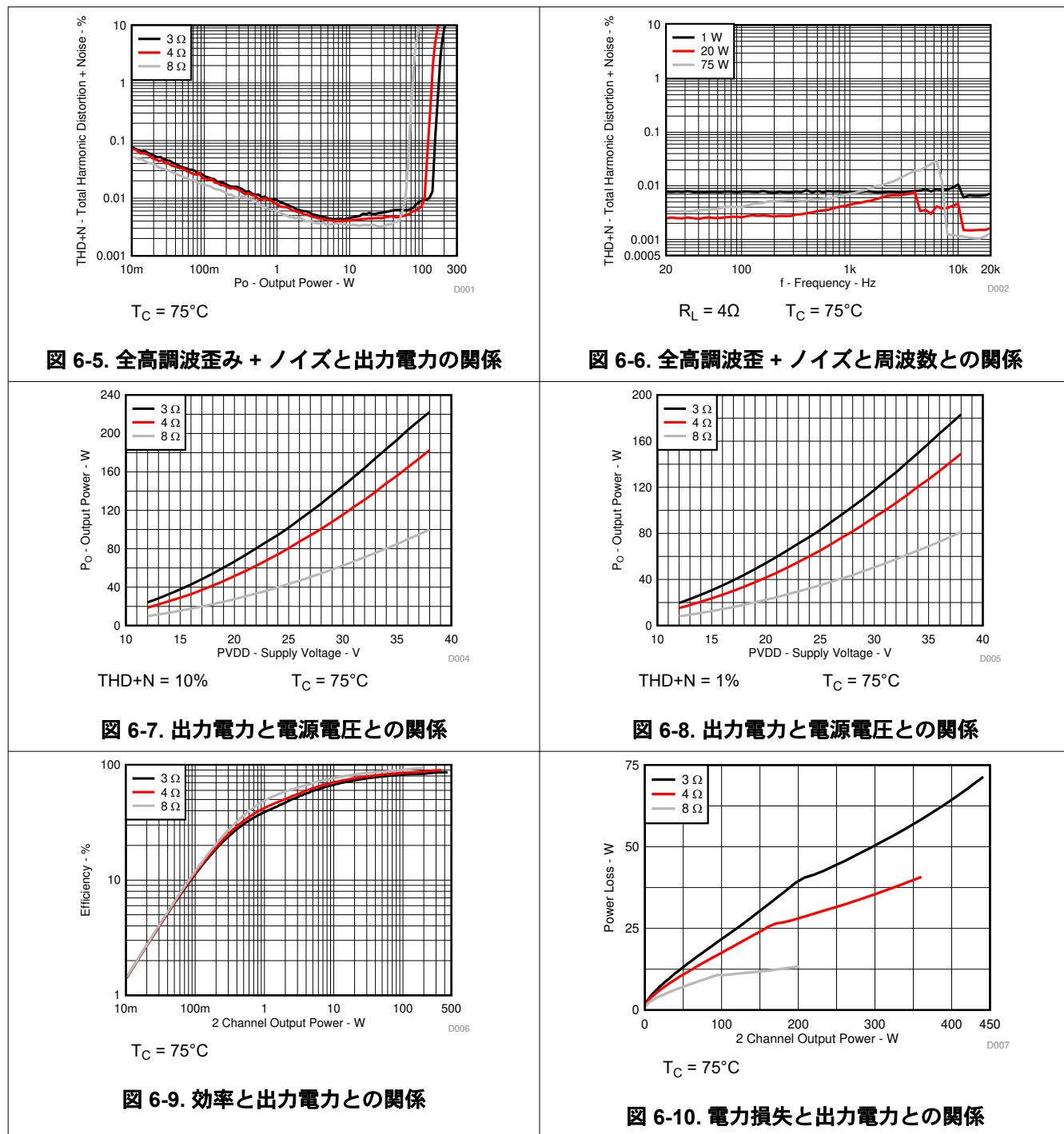

## 6.15 代表的特性

### 6.15.1 BTL の構成

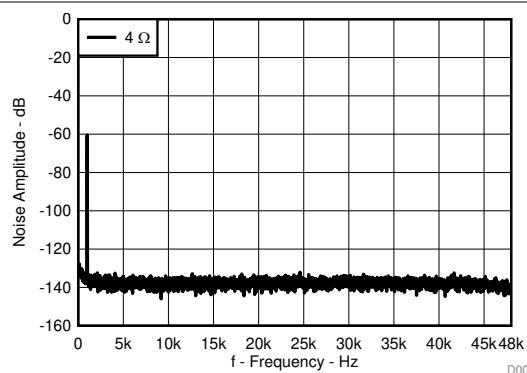

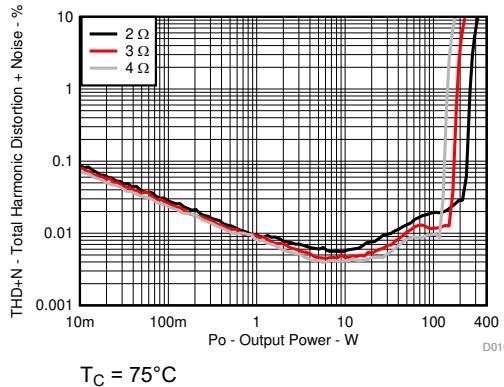

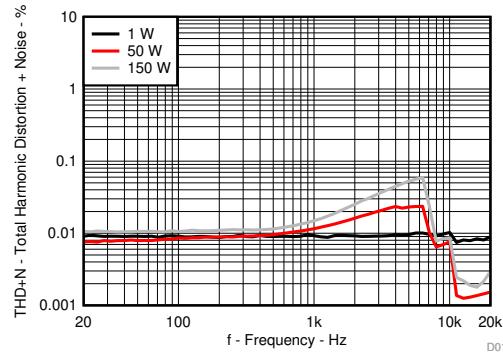

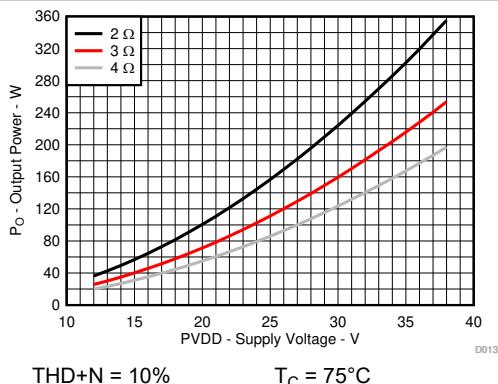

すべての測定は、オーディオ周波数 = 1kHz、PVDD\_X = 36V、GVDD\_X = 12V、 $R_L = 4\Omega$ 、 $f_s = 600\text{kHz}$ 、 $R_{OC} = 22\text{k}\Omega$ 、 $T_C = 75^\circ\text{C}$ 、出力フィルタ条件下で行われました： $L_{DEM} = 10\mu\text{H}$ 、 $C_{DEM} = 1\mu\text{F}$ 、MODE = 0、AES17 + AUX-0025 測定フィルタ (特に記述のない限り)。

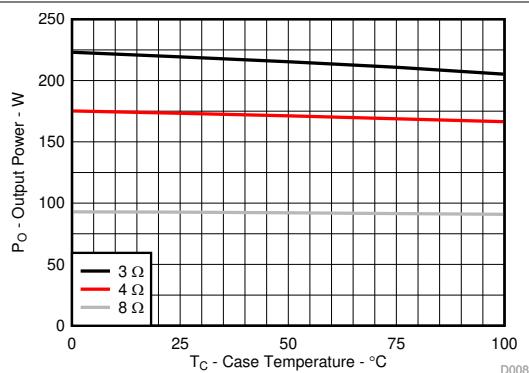

THD+N = 10%

図 6-11. 出力電力と温度との関係

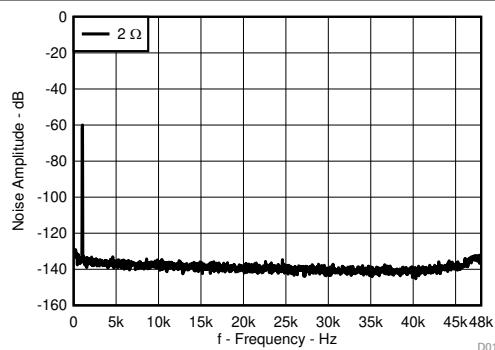

$T_C = 75^\circ\text{C}$

AUX-0025 フィル

タ

$V_{\text{REF}} = 25.46 \text{ V}$  FFT = 16384

80kHz アナライザ BW

図 6-12. ノイズ電圧と周波数との関係

### 6.15.2 PBTL の構成

すべての測定は、オーディオ周波数 = 1kHz、PVDD\_X = 36V、GVDD\_X = 12V、 $R_L = 2\Omega$ 、 $f_s = 600\text{kHz}$ 、 $R_{OC} = 22\text{k}\Omega$ 、 $T_C = 75^\circ\text{C}$ 、出力フィルタ条件下で行われました： $L_{DEM} = 10\mu\text{H}$ 、 $C_{DEM} = 1\mu\text{F}$ 、MODE = 1、特に記載のない限り、出力は LC フィルタ後に並列化され、AES17 + AUX-0025 測定フィルタが適用されます。

図 6-13. 全高調波歪み + ノイズと出力電力の関係

図 6-14. 全高調波歪み + ノイズと周波数との関係

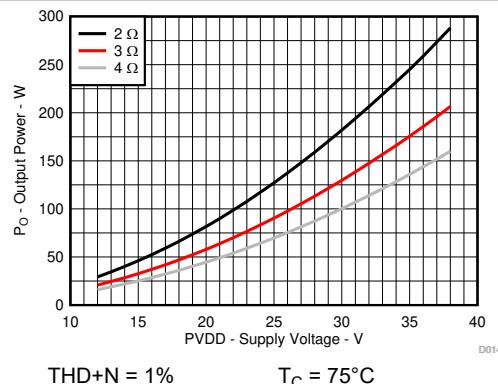

図 6-15. 出力電力と電源電圧との関係

図 6-16. 出力電力と電源電圧との関係

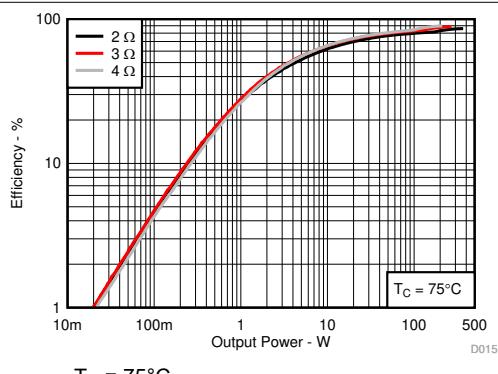

図 6-17. 効率と出力電力との関係

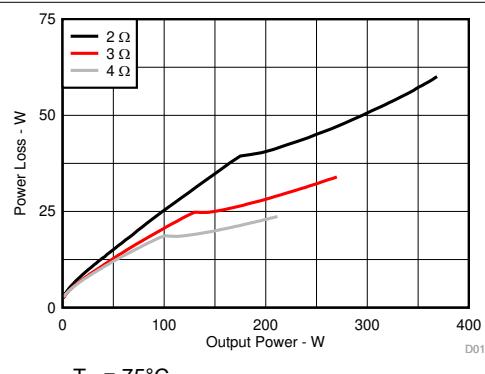

図 6-18. 電力損失と出力電力との関係

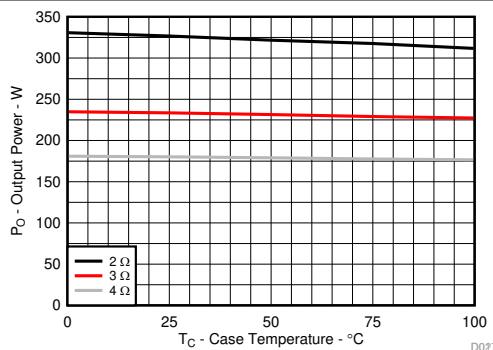

THD+N = 10%

図 6-19. 出力電力と温度との関係

$T_C = 75^\circ\text{C}$

AUX-0025 フィルタ

$V_{\text{REF}} = 25.46 \text{ V}$   $\text{FFT} = 16384$

80kHz アナライザ BW

図 6-20. ノイズ電圧と周波数との関係

## 7 詳細説明

### 7.1 概要

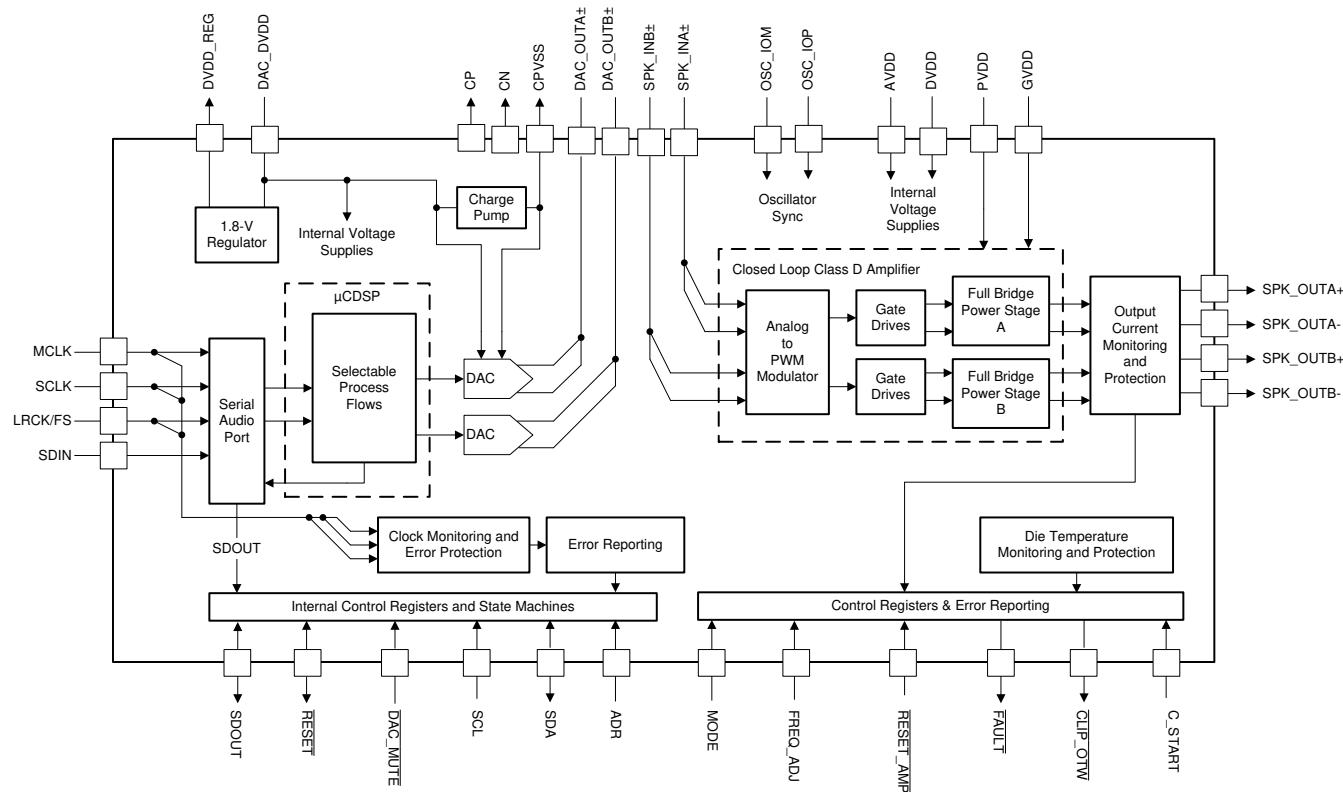

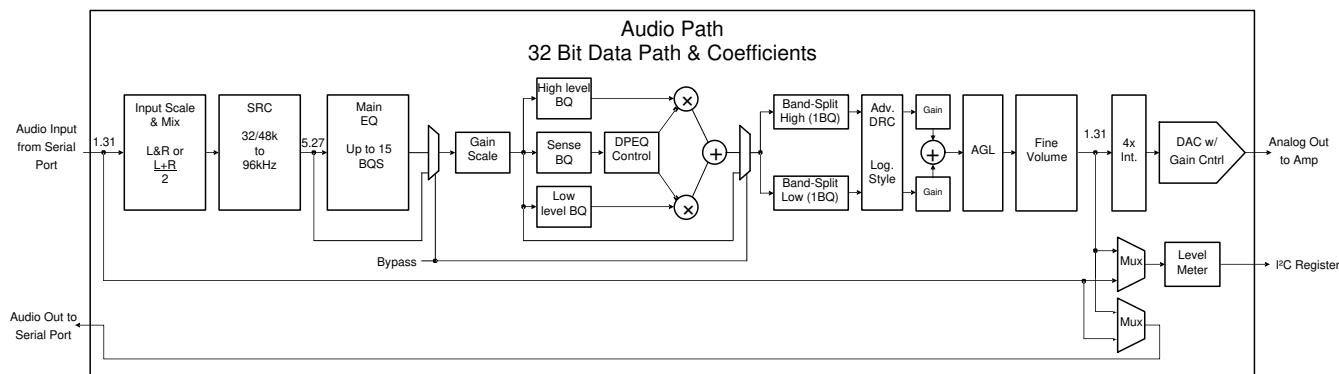

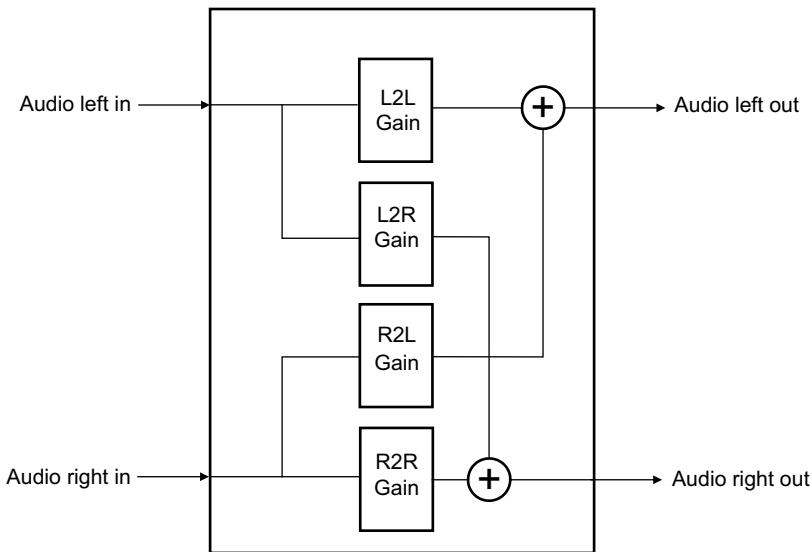

TAS3251 デバイスは、4 つの主要なビルディング ブロックを单一の統合デバイスにまとめることで、音質、柔軟性、使いやすさを最大化しています。以下のものが該当します。

- 高い柔軟性を備えたシリアル オーディオ ポート搭載の Burr-Brown ステレオ オーディオ DAC

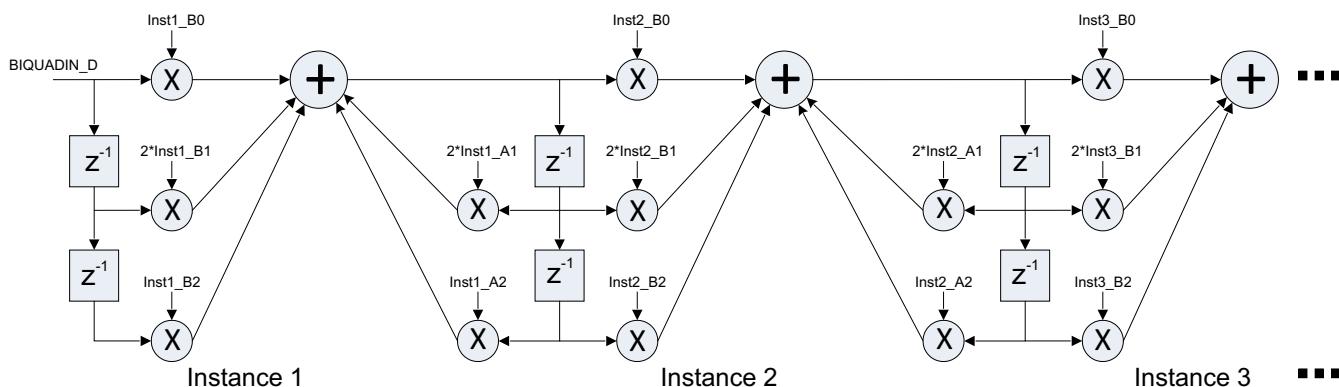

- $\mu$ CDSP - あらかじめプログラムされた DSP オーディオ処理フローを備えた TI の最新オーディオ処理コア

- ステレオまたはモノラルで動作可能な高性能、Ultra-HD 閉ループ Class-D アンプ

- デバイスとの通信および制御用の I<sup>2</sup>C 制御ポート

デバイスを正常に動作させるためには、3 つの電源が必要です。低電圧回路および DAC 用の 3.3V レール、アンプのゲート駆動用の 12V レール、そしてオーディオ アンプの出力段に電力を供給するために必要な PVDD。これらの電源の動作範囲は、[推奨動作条件](#)に示しています。

デバイスの通信および制御インターフェイスには I<sup>2</sup>C が使用されます。スピーカ アンプのフォルト出力も提供しており、過熱、過電流、または低電圧イベントの発生をシステム コントローラに通知します。

$\mu$ CDSP オーディオ プロセッsing コアは、構成可能な DSP プログラムが事前プログラミングされています。TI.com で提供されている TAS3251 アプリを備えた PurePath Console 3 ソフトウェアは、事前にプログラムされたオーディオ処理フローを制御、調整するためのツールを提供します。

### 7.2 機能ブロック図

## 7.3 機能説明

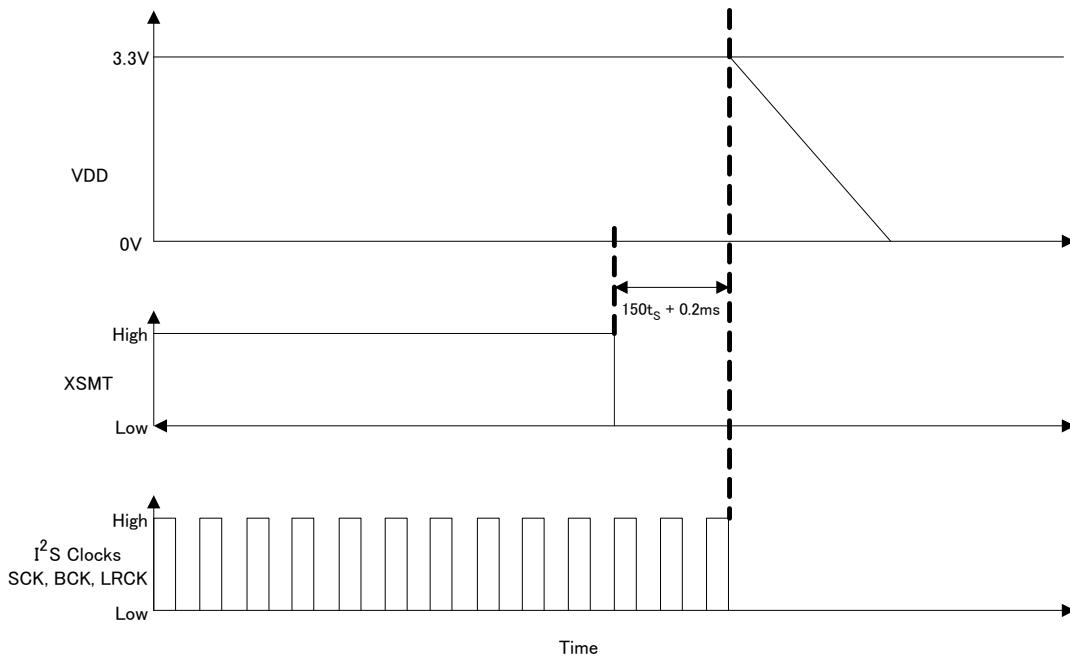

### 7.3.1 パワーオンリセット (POR) 機能

TAS3251 デバイスにはパワーオンリセット機能が含まれています。パワーオンリセット機能は、デバイスの電源投入時に、すべてのレジスタをデフォルト構成にリセットします。DVDD、AVDD、および CPVDD を駆動する低電圧電源が POR スレッショルドを超えると、デバイスはすべての内部レジスタをデフォルト値に設定し、有効な MCLK、SCLK、および LRCK/FS のトグルを約 4ms 間受信するまで、その値を保持します。トグル期間が経過すると、レジスタの内部リセットが解除され、I<sup>2</sup>C 制御ポートを使用してレジスタをプログラムできます。

### 7.3.2 デバイスの有効化

電源投入後にデバイスを有効化してオーディオを再生するには、I<sup>2</sup>C 経由で以下の値を書き込みます: book 0x00、page 0x00、register 0x02 に 0x00。次に、デバイスをイネーブルにするためのサンプルスクリプトを示します:

```

w 90 00 00 # Go to page 0

w 90 7f 00 # Go to book 0

w 90 02 00 # Enable device

```

### 7.3.3 DAC および DSP クロッキング

TAS3251 のフロントエンド (DAC および DSP) には柔軟なクロッキングシステムがあります。内部的には、デバイスを正しく機能させるために、主に関連するクロックレートで、いくつかのクロックが必要です。これらのクロックは、すべてシリアルオーディオインターフェイスから入手できます。出力段の発振器とスイッチング周波数の設定については、[出力電力段用発振器](#)セクションを参照してください。

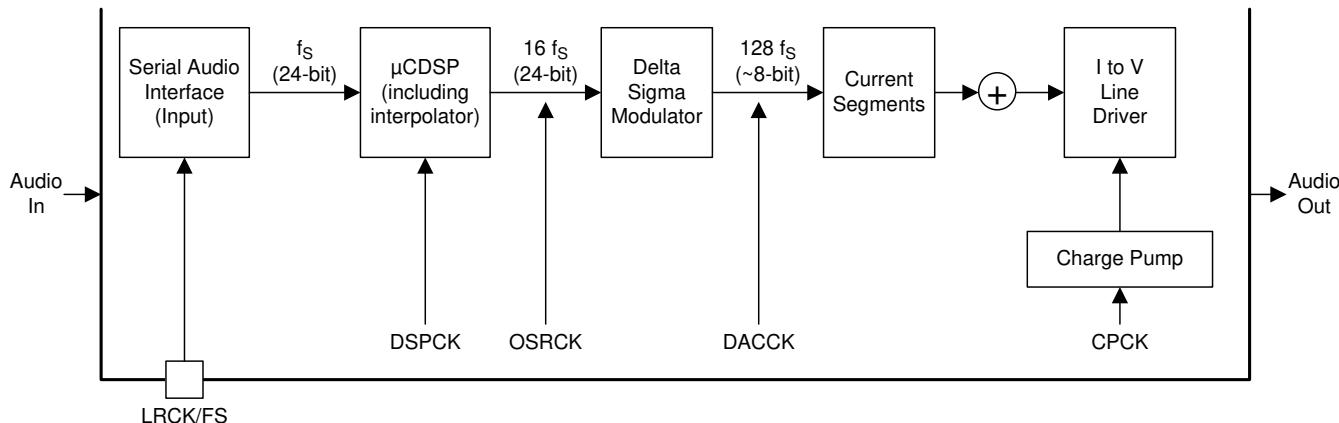

図 7-1. 各クロックのオーディオフロー

図 7-1 は、基本サンプルレート ( $f_S$ ) での基本データフローを示します。データがシリアルオーディオインターフェイスに出力されると、データの処理、補間、および  $128 \times f_S$  に変調されてから、最終的なデジタル/アナログ変換の現在のセグメントに到着します。

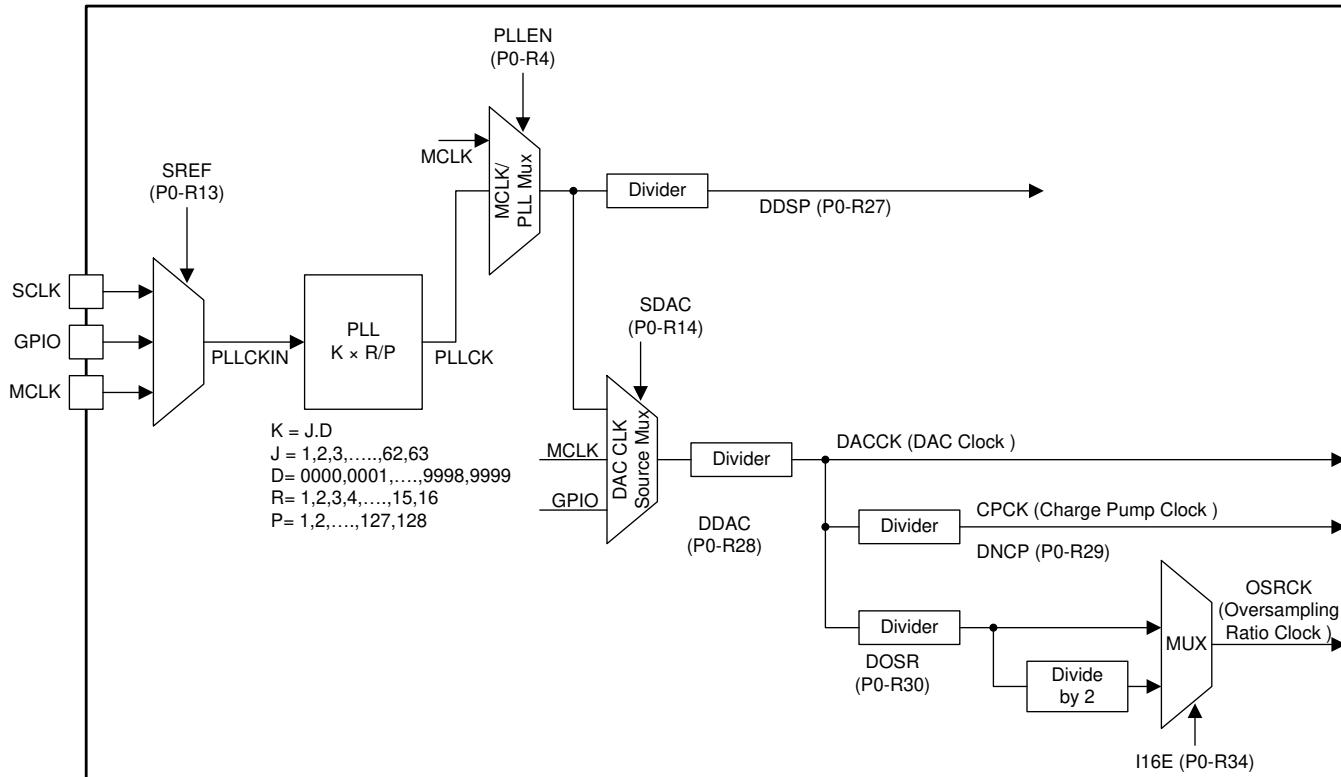

図 7-2 にクロックツリーを示します。

図 7-2. TAS3251 クロック分配ツリー

シリアルオーディオインターフェイスには、通常、以下の 4 つの接続ピンがあります。

- MCLK (システムコントローラ クロック)

- SCLK (シリアル クロックまたはビット クロック)

- LRCK/FS (左右ワード クロックおよびフレーム同期)

- SDIN (入力データ)。

- SDOUT は、外部で使用するために DSP の処理前または処理後のデータを出力するために使用できます (SDOUT ポートおよびハードウェア制御ピンセクションを参照)

このデバイスには内部 PLL があり、MCLK または SCLK のいずれかを取り込み、DSP および DAC クロックに必要な高レートのクロックを生成します。

最高のオーディオ性能が求められる場合は、SCLK および LRCK/FS とともに MCLK をデバイスに入力することが推奨されます。このデバイスは、PLL が DSP へのクロック ソースのみを供給するように構成する必要があります。その他のすべてのクロックは、入力される MCLK を分周して生成されます。MCLK を主クロック ソースとして有効にし、その他をすべて入力 MCLK の分周で生成するには、DAC CLK ソース マルチプレクサ (図 7-2 内の SDAC) を MCLK/PLL マルチプレクサの出力ではなく MCLK をソースとして使用するように設定します。

### 7.3.3.1 内部クロック エラー通知 (CLKE)

入力データ クロックでクロック エラーが検出されると、TAS3251 デバイスは内部オシレータに切り替わり、最後に正常だった値からのデータを減衰させながら DAC を駆動し続けます。このプロセスが完了すると、DAC 出力は強制的にグランドにミュートされ、Class-D PWM 出力はスイッチングを停止します。クロック エラーは B0-P0-R94 および R95 で監視できます。クロック エラー ステータス ビットはラッチなしですが、MCLK が停止した B0-P0-R95-D[4] は、読み取り時にクリアされます。

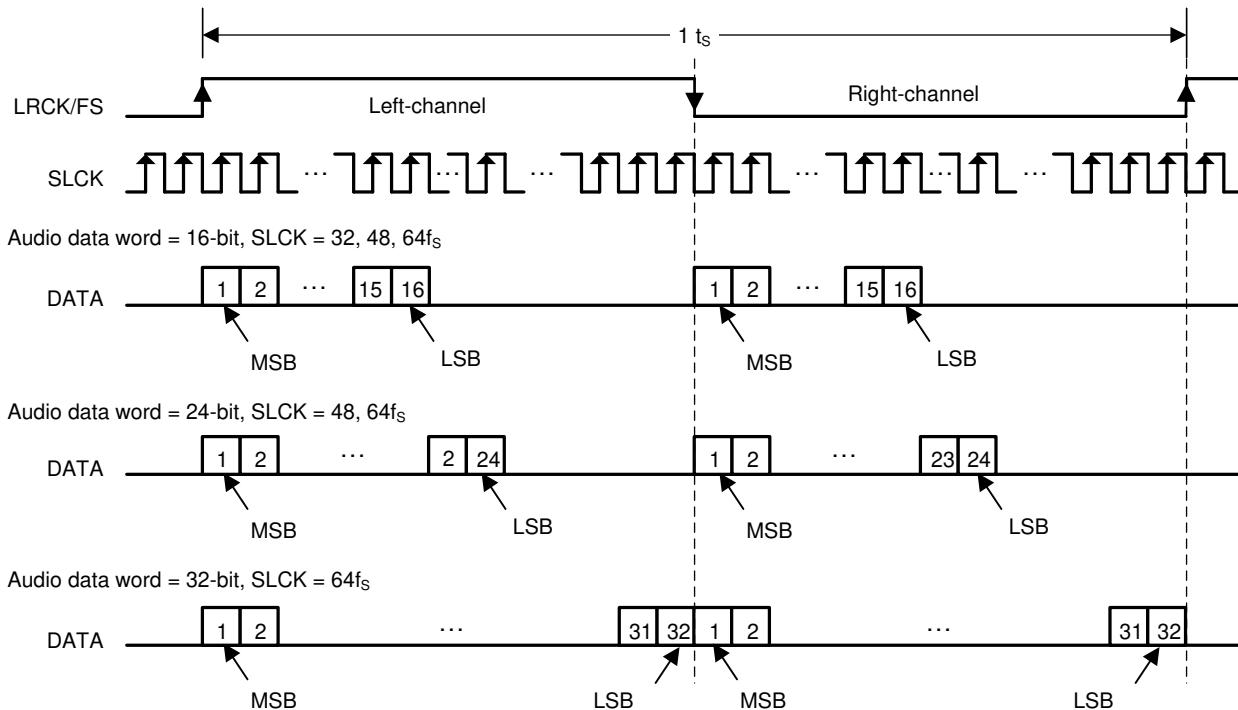

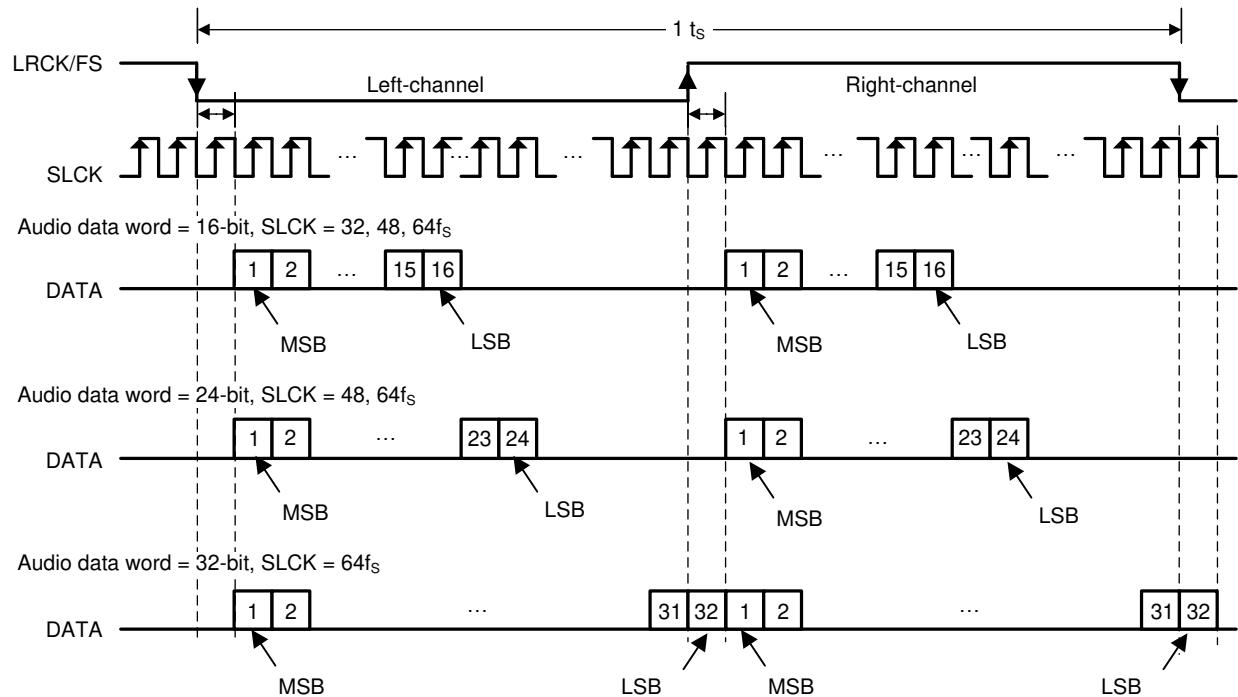

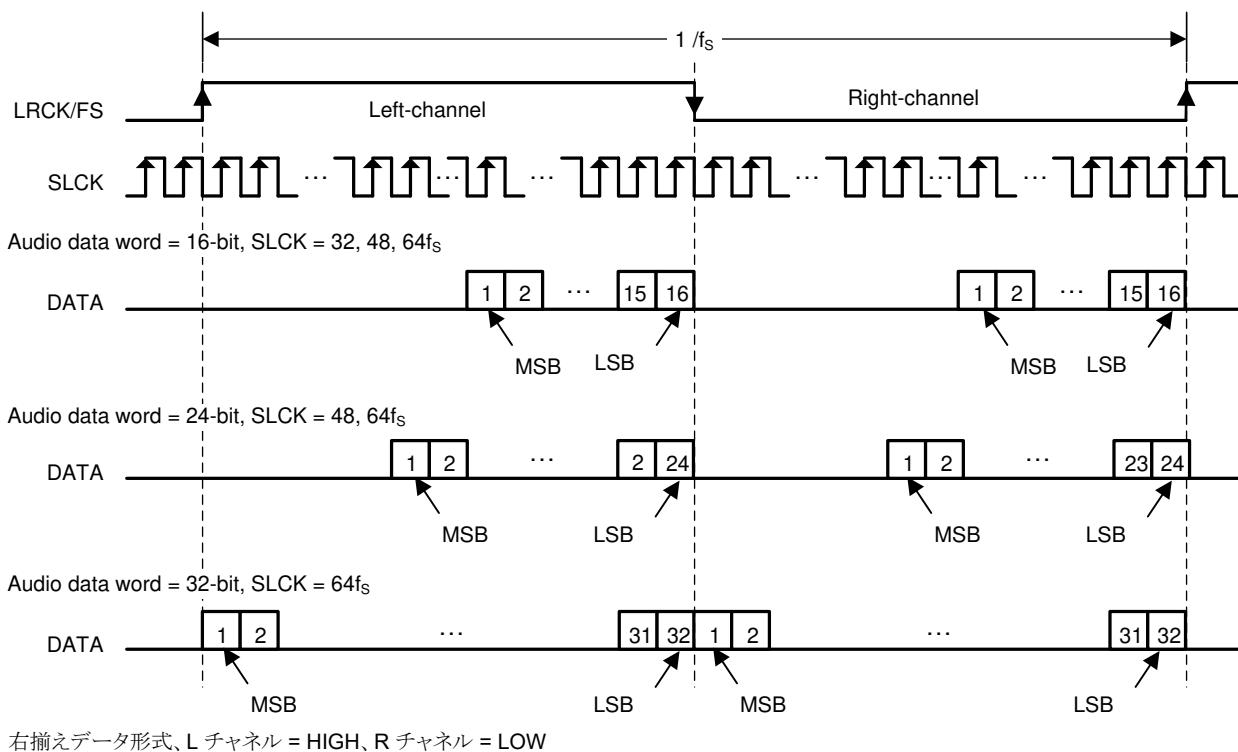

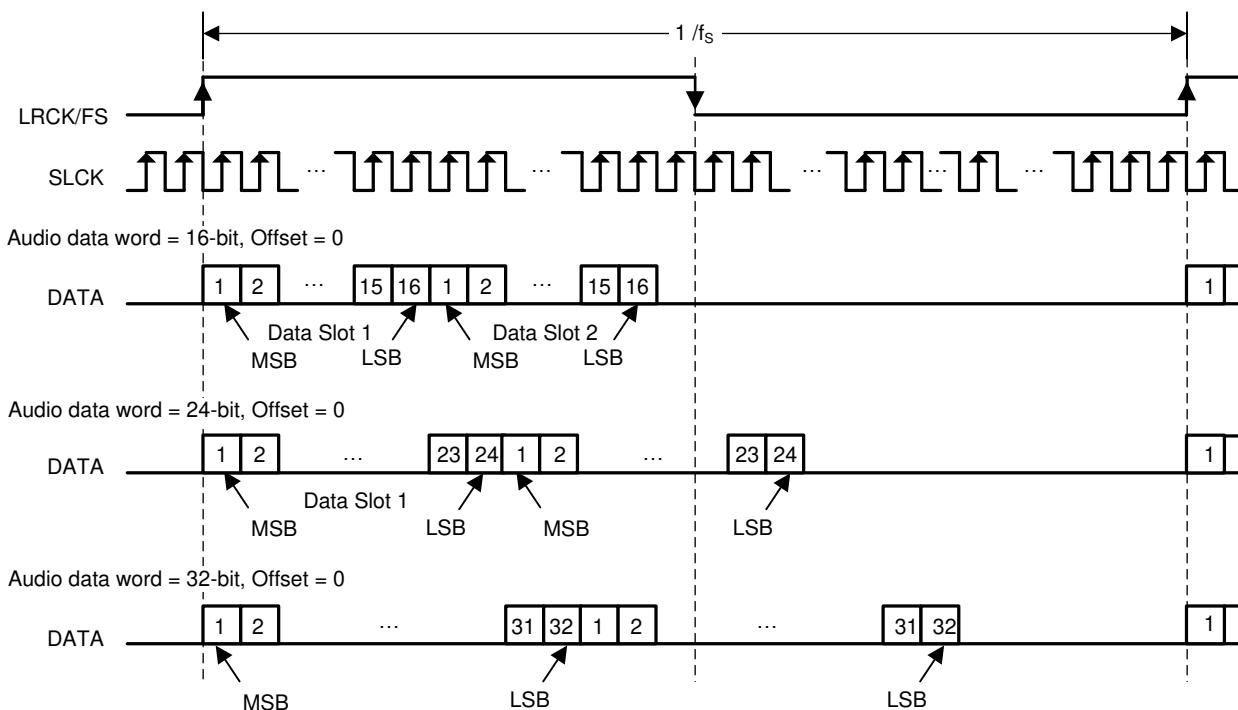

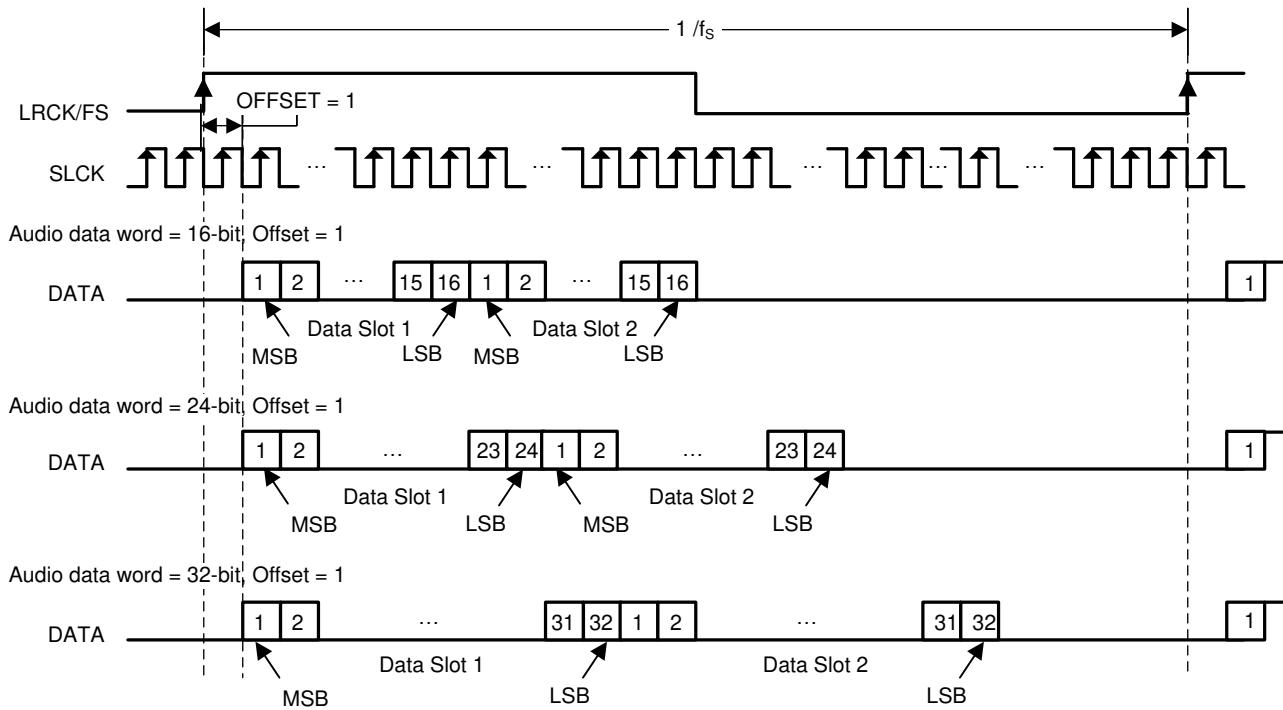

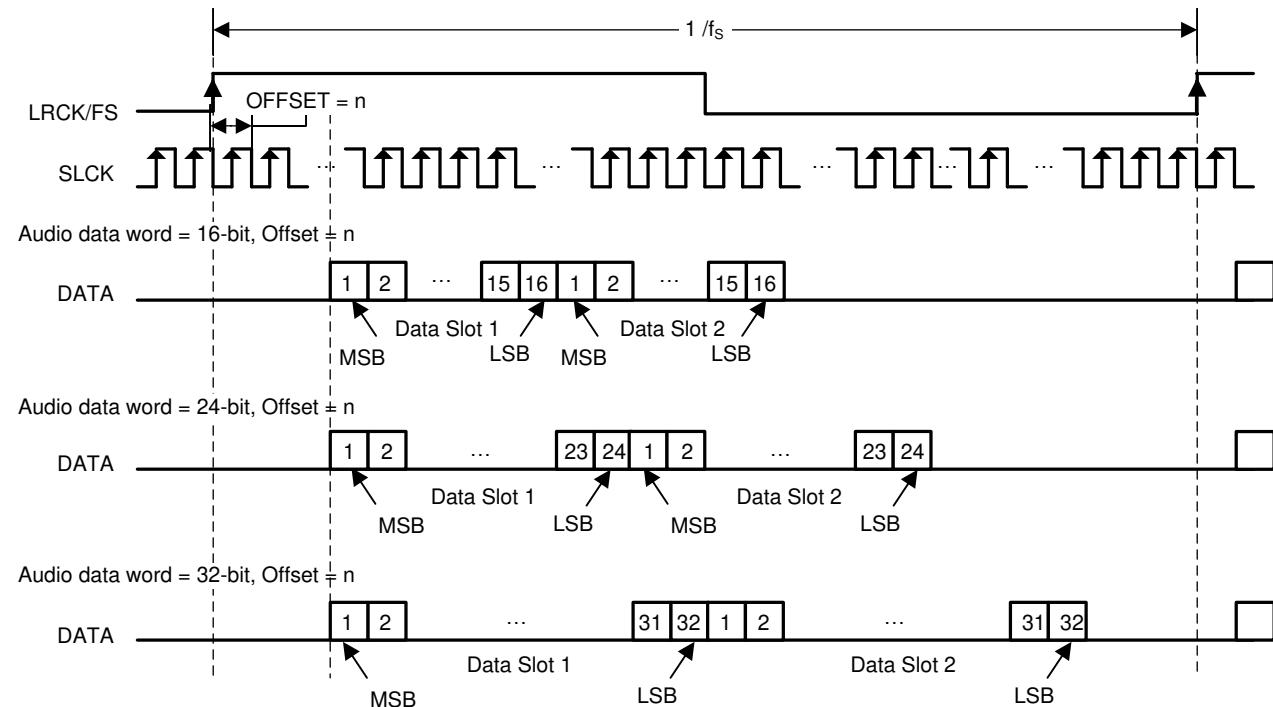

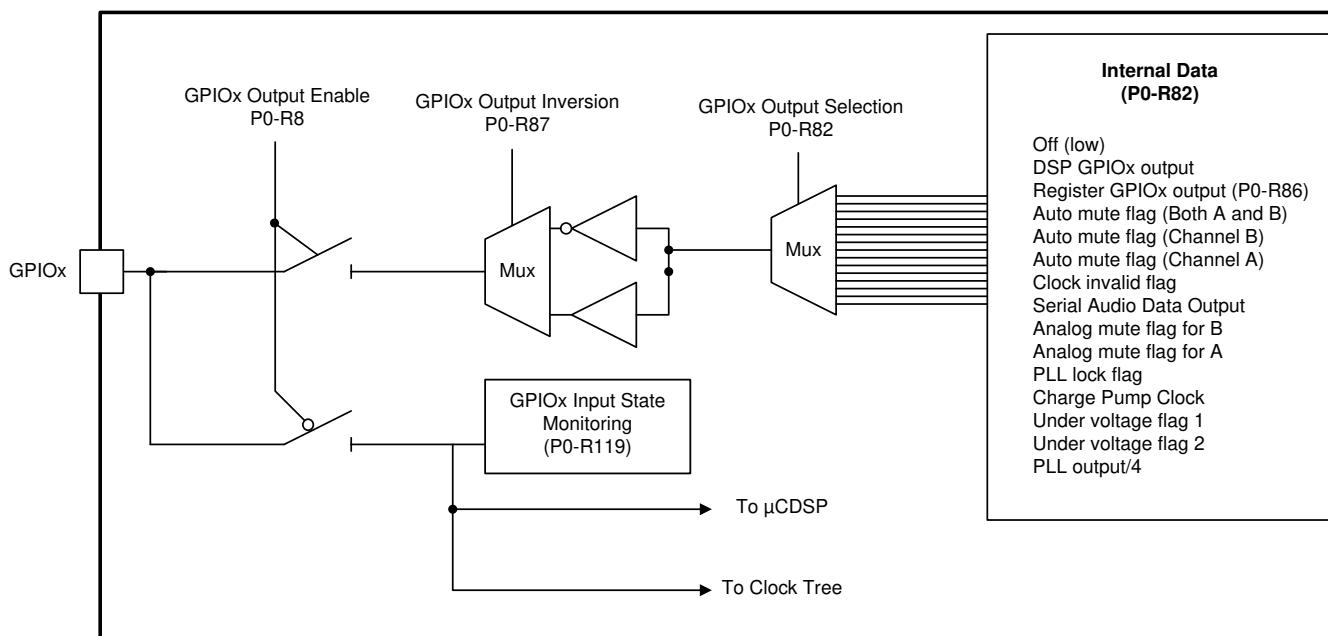

### 7.3.4 シリアルオーディオポート

#### 7.3.4.1 オーディオレートコントローラクロックからのクロックコントローラモード

コントローラモードでは、デバイスがビットクロック、左右のクロック、フレーム同期クロックを生成し、対応するピンに出力します。デバイスをコントローラモードに設定するには、まずデバイスをリセット状態にしてから、SCLKO レジスタおよびLRKO レジスタ (P0-R9) を使用します。次に、RSCLK ビットおよびRLRK ビット (P0-R12) を使用して、LRCK/FS およびSCLK の分周カウンタをリセットします。最後に、リセットを終了します。

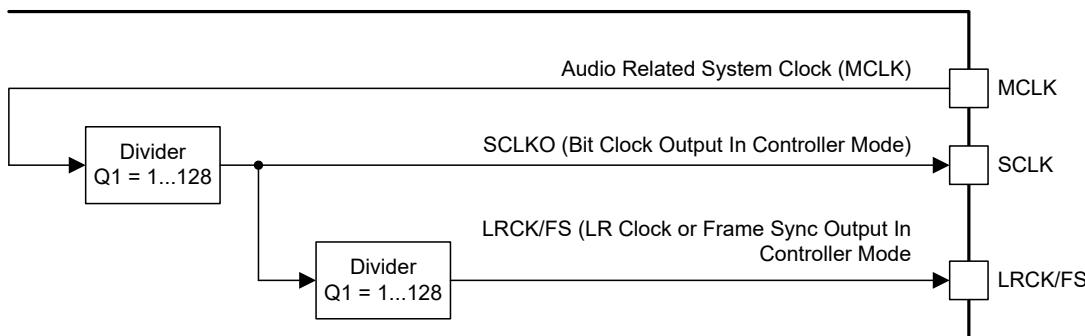

コントローラモードでのデバイスのシリアルポートクロックツリーを、図 7-3 に示します。

図 7-3. MCLK ソース コントローラモードのクロックツリーの概略図

コントローラモードでは、MCLK は入力で、SCLK および LRCK/FS は出力です。SCLK および LRCK/FS は MCLK の整数分周です。非オーディオレートのコントローラクロックソースを使用するコントローラモードでは、スタンドアロンモードで PLL を使用するために外部 GPIO が必要です。オンチッププロセッサを最大クロックレートで動作させられるように、PLL を設定する必要があります。コントローラの動作モードについては、このセクションを参照してください。

オーディオレートのコントローラクロックを使用する場合に必要なレジスタ変更には、デバイスをコントローラモードに切り替えることと、分周比を設定することが含まれます。コントローラモードでの動作例として、24.576 MHz の MCLK をコントローラクロックソースとして使用し、SCLK および LRCK/FS を整数分周して 48kHz のサンプルレートクロック出力を生成する方法があります。コントローラモードでは、デバイスの DAC セクションも PLL 出力から動作します。TAS3251 デバイスは、内部 PLL を使用しても規定されたオーディオ性能を満たすことができます。ただし、MCLK CMOS 発振器ソースを使用すると、PLL よりもジッタが小さくなります。

DAC クロック (図 7-2 の SDAC) を切り替えるには、以下のレジスタを変更する必要があります

- クロックツリー フレックスモード (P253-R63 および P253-R64)

- DAC および OSR ソースクロックレジスタ (P0~R14)。0x30 に設定します (MCLK 入力で、OSR は DAC ソースに応じて設定されます)

- DAC クロック分周器は  $16 f_S$  にする必要があります。

- $16 \times 48\text{kHz} = 768\text{kHz}$

- $24.576\text{MHz} (\text{MCLK 入力}) \div 768\text{kHz} = 32$

- したがって、レジスタ DDAC (P0-R28) の分周比は 32 に設定する必要があります。レジスタマッピングでは  $0x00 = 1$  となるため、32 は  $0x1F$  (10 進で 31) に変換する必要があります。

#### 7.3.4.2 線式動作のクロックターゲットモード (SCLK、MCLK、LRCK/FS、SDIN)

TAS3251 デバイスは、デジタル補間フィルタと高度なセグメント DAC 変調器を動作させるために、システムクロックを必要とします。システムクロックは MCLK 入力に印加され、最大 50MHz までサポートします。TAS3251 デバイスのシステムクロック検出回路は、システムクロック周波数を自動的に検出します。32 kHz, (44.1~48kHz), (88.2 ~ 96kHz) の帯域における一般的なオーディオサンプリング周波数がサポートされています。

## 注

かつての値は検出時にグループ化されます。たとえば、88.2kHz と 96kHz はダブル レートとして検出され、32kHz、44.1kHz および 48kHz はシングル レートとして検出されます。

有効なビット MCLK、SCLK、および LRCK/ FS が存在する場合、デバイスは自動的にクロック ツリーと PLL を構成し、必要に応じてミニ DSP を駆動します。

サンプリング周波数検出器は、デジタル フィルタ、デルタ シグマ変調器 (DSM)、負のチャージ ポンプ (NCP) のクロックを自動的に設定します。表 7-1 に、一般的なオーディオ サンプリング レートのシステム クロック周波数の例を示します。

1MHz ~ 50MHz の範囲で、標準的なオーディオ クロックに共通しない MCLK レートも、各種 PLL およびクロック ディバイダ レジスタを直接設定することでサポートされます。ターゲット モードでは、P0~R37 を使用して自動クロック モードを無効化する必要があります。さらに、設定中に外部クロックが一時的に利用できない場合や、デバイスのピンに入力されるクロックが無効な場合には、ユーザーがクロック エラー検出を無視するよう求められます。拡張プログラマビリティにより、このデバイスは高度なモードで動作でき、クロック コントローラとして機能し、オーディオ以外のクロックからホストシリアル ポートに LRCK/FS および SCLK を供給します（例：12MHz の設定を使用して 44.1kHz [LRCK/FS] と 2.8224MHz [SCLK] を生成）。

表 7-1 に、システム クロック入力のタイミング要件を示します。最適な性能を得るためにには、位相ジッタとノイズが小さいクロック ソースを使用します。MCLK のタイミング要件については、セクション 6.11 セクションを参照してください。

**表 7-1. オーディオ関連クロック用のシステム コントローラ クロック入力**

| サンプリング<br>周波数 | システムクロック周波数 ( $f_{MCLK}$ ) (MHz) |                    |                    |                    |                    |                    |

|---------------|----------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

|               | 64 f <sub>S</sub>                | 128 f <sub>S</sub> | 192 f <sub>S</sub> | 256 f <sub>S</sub> | 384 f <sub>S</sub> | 512 f <sub>S</sub> |

| 8kHz          | を参照してください。                       | 1.024              | 1.536              | 2.048              | 3.072              | 4.096              |

| 16kHz         |                                  | 2.048              | 3.072              | 4.096              | 6.144              | 8.192              |

| 32kHz         |                                  | 4.096              | 6.144              | 8.192              | 12.288             | 16.384             |

| 44.1kHz       |                                  | 5.6488             | 8.4672             | 11.2896            | 16.9344            | 22.5792            |

| 48kHz         |                                  | 6.144              | 9.216              | 12.288             | 18.432             | 24.576             |

| 88.2kHz       |                                  | 11.2896            | 16.9344            | 22.5792            | 33.8688            | 45.1584            |

| 96kHz         |                                  | 12.288             | 18.432             | 24.576             | 36.864             | 49.152             |

### 7.3.4.3 SCLK PLL による内部クロックを生成するクロック ターゲット モード (3 線式 PCM)

#### 7.3.4.3.1 PLL を使用したクロック生成

この TAS3251 デバイスは、図 7-2 に示すように、必要なクロックを生成するために幅広いオプションをサポートしています。

PLL のクロックには、ソース リファレンスクロックが必要です。このクロックは、入力される SCLK または MCLK をソースとしており、GPIO を使用することもできます。

PLL リファレンス クロックのソース リファレンス クロックは、P0-R13 の D[6:4] にある SRCREF 値をプログラムすることで選択されます。TAS3251 デバイスには、複数のプログラマブルなクロック分周器が搭載されており、各種のサンプリング レートを実現できます。図 7-2 を参照してください。

PLL 機能が不要な場合は、P0-R4、D[0] の PLLEN 値を 0 に設定します。この状況では、外部コントローラのクロックが必要です。

**表 7-2. PLL 構成レジスタ**

| クロック マルチプレクサ |            |                  |

|--------------|------------|------------------|

| レジスタ         | 機能         | ビット              |

| SREF         | PLL リファレンス | B0-P0-R13-D[6:4] |

| DDSP         | クロック デバイダ  | B0-P0-R27-D[6:0] |

| DSCLK        | 外部 SCLK 分周 | B0-P0-R32-D[6:0] |

表 7-2. PLL 構成レジスタ (続き)

| クロック マルチプレクサ |                |                  |

|--------------|----------------|------------------|

| レジスタ         | 機能             | ビット              |

| DLRK         | 外部 LRCK/ FS 分周 | B0-P0-R33-D[7:0] |

### 7.3.4.3.2 PLL の計算

TAS3251 デバイスには、分数乗算機能を備えたオンチップ PLL が搭載されており、デジタル信号処理ブロックが必要とするクロック周波数を生成できます。PLL のプログラマビリティにより、システムで利用可能なさまざまなクロックから動作させることができます。PLL 入力 (PLLCKIN) は 1 MHz ~ 50 MHz のクロック周波数をサポートしており、必要なサンプリングレートを高精度で生成できるようにレジスタでプログラム可能です。

デフォルトで、PLL がイネーブルになっています。PLL は、P0-R4 の D[0] に書き込むことで有効化できます。PLL が有効化されると、PLL 出力クロック PLLCK は [式 1](#) で与えられます：

$$\text{PLLCK} = \frac{\text{PLLCKIN} \times R \times J.D}{P} \quad \text{or} \quad \text{PLLCK} = \frac{\text{PLLCKIN} \times R \times K}{P} \quad (1)$$

ここで、

- $R = 1, 2, 3, 4, \dots, 15, 16$

- $J = 4, 5, 6, \dots, 63$ 、および  $D = 0000, 0001, 0002, \dots, 9999$

- $K = [J \text{ 値}]. [D \text{ 値}]$

- $P = 1, 2, 3, \dots, 15$

R, J, D, P はプログラム可能です。J は K の整数部 (小数点の左側の数値) であり、D は K の小数部 (小数点の右側の数値、精度は 4 桁を想定) です。

#### 7.3.4.3.2.1 例：

- もし  $K = 8.5$  なら、 $J = 8, D = 5000$  です

- もし  $K = 7.12$  なら、 $J = 7, D = 1200$  です。

- もし  $K = 14.03$  なら、 $J = 14, D = 0300$  です。

- もし  $K = 6.0004$  なら、 $J = 6, D = 0004$  です。

PLL をイネーブルにし、 $D = 0000$  の場合、以下の条件を満たす必要があります：

- $1\text{MHz} \leq (\text{PLLCKIN} / P) \leq 20\text{MHz}$

- $64\text{MHz} \leq (\text{PLLCKIN} \times K \times R / P) \leq 100\text{MHz}$

- $1 \leq J \leq 63$

PLL がイネーブルで  $D \neq 0000$  の場合、以下の条件を満たす必要があります：

- $6.667\text{MHz} \leq \text{PLLCKIN} / P \leq 20\text{MHz}$

- $64\text{MHz} \leq (\text{PLLCKIN} \times K \times R / P) \leq 100\text{MHz}$

- $4 \leq J \leq 11$

- $R = 1$

PLL が作動しているとき、

- $f_S = (\text{PLLCKIN} \times K \times R) / (2048 \times P)$

- N の値は、 $f_S \times N = \text{PLLCKIN} \times K \times R / P$  が許容範囲内になるように選択されます。

例: MCLK = 12MHz および  $f_S = 44.1\text{kHz}$ 、(N=2048)

$P = 1, R = 1, K = 7.5264$  を選択すると、 $J = 7, D = 5264$  となります

例: MCLK = 12MHz および  $f_S = 48\text{kHz}$ 、(N=2048)

$P = 1, R = 1, K = 8.192$  を選択すると、 $J = 8, D = 1920$  となります

値は、[表 7-3](#) のレジスタに書き込まれます。

**表 7-3. PLL レジスタ**

| デバイダ | 機能        | ビット           |

|------|-----------|---------------|

| PLLE | PLL イネーブル | P0-R4, [0]    |

| PPDV | PLL P     | P0-R20, [3:0] |

| PJDV | PLL J     | P0-R21, [5:0] |

| PDDV | PLL D     | P0-R22, [5:0] |

|      |           | P0-R23, [7:0] |

| PRDV | PLL R     | P0-R24, [3:0] |

**表 7-4. PLL 構成の推奨事項**

| 式                | 説明                                                                                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $f_S$ (kHz)      | サンプリング周波数                                                                                                                                                                                                          |

| $R_{MCLK}$       | サンプリング周波数と MCLK 周波数の比率 ( $MCLK$ 周波数 = $R_{MCLK} \times$ サンプリング周波数)                                                                                                                                                 |

| MCLK (MHz)       | MCLK 入力 (ピン 20) におけるシステムコントローラクロック周波数                                                                                                                                                                              |

| PLL VCO (MHz)    | 図 7-2 の PLLCK としての PLL VCO 周波数                                                                                                                                                                                     |

| P                | 式 1 の PLL 係数の 1 つ                                                                                                                                                                                                  |

| PLL REF (MHz)    | $MCLK/P$ によって生成される内部リファレンスクロック周波数                                                                                                                                                                                  |

| $M = K \times R$ | 式 1 に示すように、K と R から計算された最終的な PLL 乗算係数                                                                                                                                                                              |

| $K = J \cdot D$  | 式 1 の PLL 係数の 1 つ                                                                                                                                                                                                  |

| R                | 式 1 の PLL 係数の 1 つ                                                                                                                                                                                                  |

| PLL $f_S$        | $f_S$ と PLL VCO 周波数の比 (PLL VCO/ $f_S$ )                                                                                                                                                                            |

| DSP $f_S$        | 動作クロックレートと $f_S$ 間の比率 (PLL $f_S$ /NMAC)                                                                                                                                                                            |

| NMAC             | 表 7-2 のクロック分周器の値                                                                                                                                                                                                   |

| DSP CLK (MHz)    | 動作周波数は図 7-2 で DSPCK として示されています                                                                                                                                                                                     |

| MOD $f_S$        | DAC 動作クロック周波数と $f_S$ 間の比率 (PLL $f_S$ /NDAC)                                                                                                                                                                        |

| MOD f (kHz)      | DACCK としての DAC 動作周波数                                                                                                                                                                                               |

| NDAC             | 表 7-2 における DAC クロック分周値                                                                                                                                                                                             |

| DOSR             | 図 7-2 の OSRCK を生成するための、表 7-2 における OSR クロック分周値。正しく動作させるには、 $MOD f_S /DOSR = 16$ になるように DOSR を選択する必要があります。                                                                                                           |

| NCP              | NCP (負のチャージポンプ) クロック分周器値表 7-2                                                                                                                                                                                      |

| CP f             | 負のチャージポンプ クロック周波数 ( $f_S \times MOD f_S / NCP$ )                                                                                                                                                                   |

| 誤差 %             | PLL VCO/PLL $f_S$ と $f_S$ との間の誤差の割合 (ミスマッチ誤差)。<br><ul style="list-style-type: none"> <li>この値は通常 0 ですが、特に K が整数でない場合 (D が 0 でない場合) は 0 ではありません。</li> <li>TAS3251 デバイスがコントローラとして動作している場合のみ、この値をゼロ以外にできます。</li> </ul> |

上記の式は、PLL を構成するために必要なすべての係数と制御の計算方法を説明しています。表 7-5 に、コントローラクロックとしての PLL について、推奨されるクロック分周器設定を簡単に参照できます。

表 7-5. コントローラ クロックとしての PLL の推奨クロック分周器設定

| $f_s$<br>(kHz) | $R_{MCLK}$ | MCLK<br>(MHz) | PLL VCO<br>(MHz) | P | PLL<br>REF<br>(MHz) | $M = K \times R$ | $K = J \times D$ | R | PLL $f_s$ | DSP<br>$f_s$ | NMAC | DSP<br>CLK<br>(MHz) | MOD $f_s$ | MOD f<br>(kHz) | NDAC | DOSR | 誤差 % | NCP | CP f<br>(kHz) |

|----------------|------------|---------------|------------------|---|---------------------|------------------|------------------|---|-----------|--------------|------|---------------------|-----------|----------------|------|------|------|-----|---------------|

| 8              | 128        | 1.024         | 98.304           | 1 | 1.024               | 96               | 48               | 2 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 192        | 1.536         | 98.304           | 1 | 1.536               | 64               | 32               | 2 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 256        | 2.048         | 98.304           | 1 | 2.048               | 48               | 48               | 1 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 384        | 3.072         | 98.304           | 3 | 1.024               | 96               | 48               | 2 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 512        | 4.096         | 98.304           | 3 | 1.365               | 72               | 36               | 2 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 768        | 6.144         | 98.304           | 3 | 2.048               | 48               | 48               | 1 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 1024       | 8.192         | 98.304           | 3 | 2.731               | 36               | 36               | 1 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 1152       | 9.216         | 98.304           | 9 | 1.024               | 96               | 48               | 2 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 1536       | 12.288        | 98.304           | 9 | 1.365               | 72               | 36               | 2 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 2048       | 16.384        | 98.304           | 9 | 1.82                | 54               | 54               | 1 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

|                | 3072       | 24.576        | 98.304           | 9 | 2.731               | 36               | 36               | 1 | 12288     | 1024         | 12   | 8.192               | 768       | 6144           | 16   | 48   | 0    | 4   | 1536          |

| 11.025         | 128        | 1.4112        | 90.3168          | 1 | 1.411               | 64               | 32               | 2 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 192        | 2.1168        | 90.3168          | 3 | 0.706               | 128              | 32               | 4 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 256        | 2.8224        | 90.3168          | 1 | 2.822               | 32               | 32               | 1 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 384        | 4.2336        | 90.3168          | 3 | 1.411               | 64               | 32               | 2 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 512        | 5.6448        | 90.3168          | 3 | 1.882               | 48               | 48               | 1 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 768        | 8.4672        | 90.3168          | 3 | 2.822               | 32               | 32               | 1 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 1024       | 11.2896       | 90.3168          | 3 | 3.763               | 24               | 24               | 1 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 1152       | 12.7008       | 90.3168          | 9 | 1.411               | 64               | 32               | 2 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 1536       | 16.9344       | 90.3168          | 9 | 1.882               | 48               | 48               | 1 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 2048       | 22.5792       | 90.3168          | 9 | 2.509               | 36               | 36               | 1 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

|                | 3072       | 33.8688       | 90.3168          | 9 | 3.763               | 24               | 24               | 1 | 8192      | 1024         | 8    | 11.2896             | 512       | 5644.8         | 16   | 32   | 0    | 4   | 1411.2        |

| 16             | 64         | 1.024         | 98.304           | 1 | 1.024               | 96               | 48               | 2 | 6144      | 1024         | 6    | 16.384              | 384       | 6144           | 16   | 24   | 0    | 4   | 1536          |

|                | 128        | 2.048         | 98.304           | 1 | 2.048               | 48               | 48               | 1 | 6144      | 1024         | 6    | 16.384              | 384       | 6144           | 16   | 24   | 0    | 4   | 1536          |

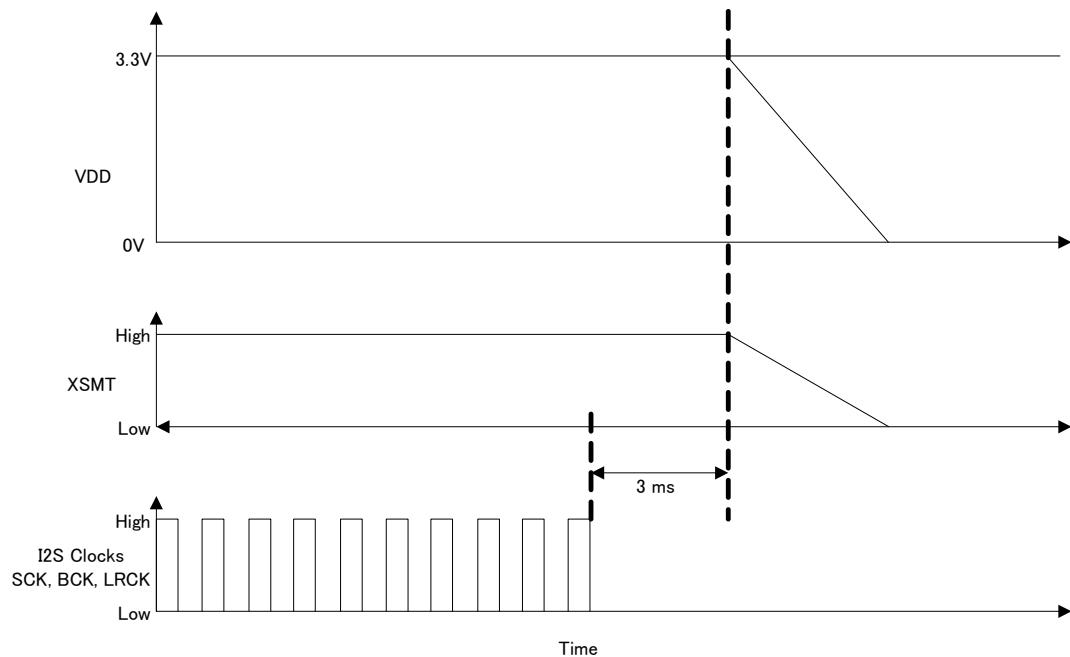

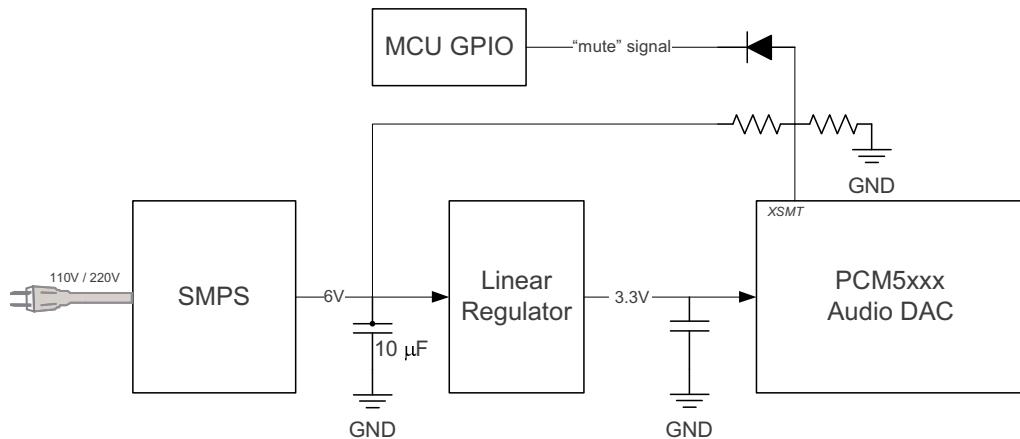

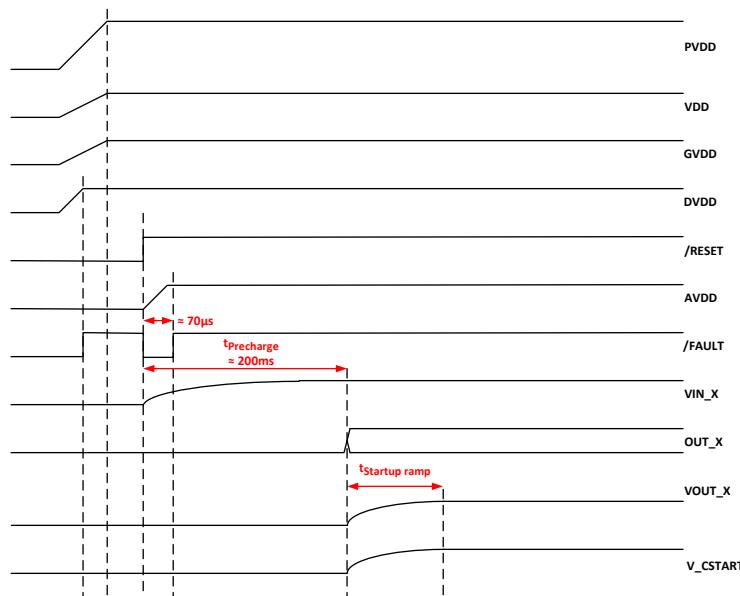

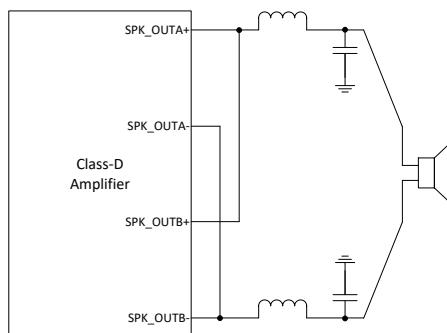

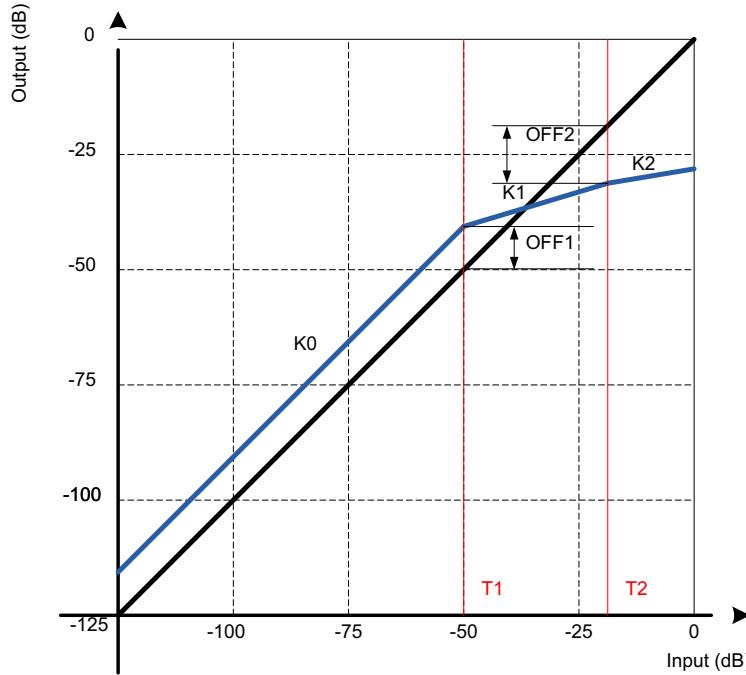

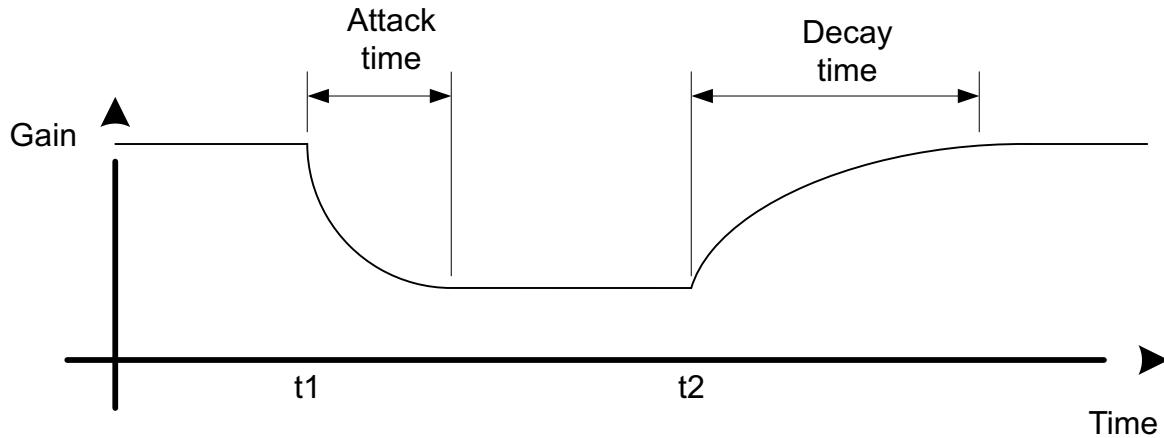

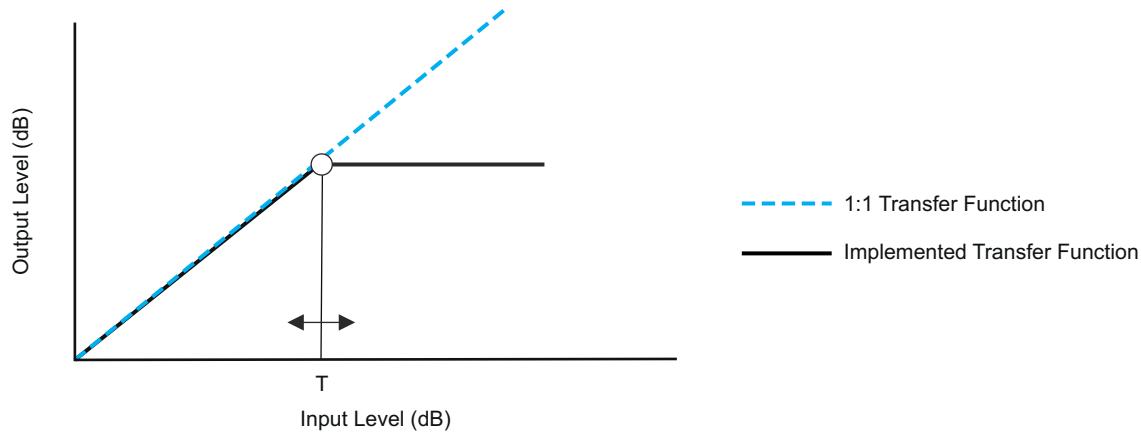

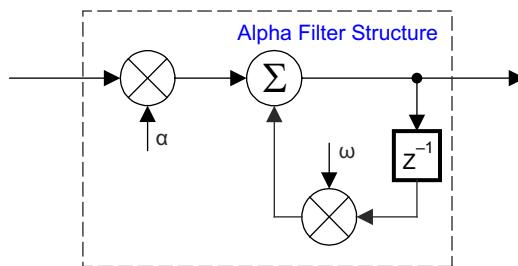

|                | 192        | 3.072         | 98.304           | 1 | 3.072               | 32               | 32               | 1 | 6144      | 1024         | 6    | 16.384              | 384       | 6144           | 16   | 24   | 0    | 4   | 1536          |