# TAS2781 24V Class-D アンプ、リアルタイムのスピーカ保護およびオーディオ処理機能内蔵

## 1 特長

主な特長

- オーディオ処理用 DSP チップを内蔵

- D 級出力段用の 24V 電源

- Y ブリッジ・マルチレベル電源アーキテクチャ

- Hybrid-Pro 外部昇圧制御アルゴリズム

- 最大 40kHz の超音波出力をサポート

出力電力:

- 1% THD+N で 25W (4Ω, 18V)

- 最大出力電力 30W、THD+N 10%

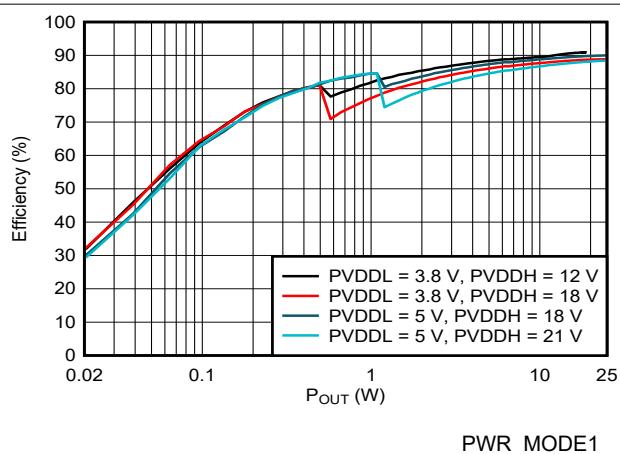

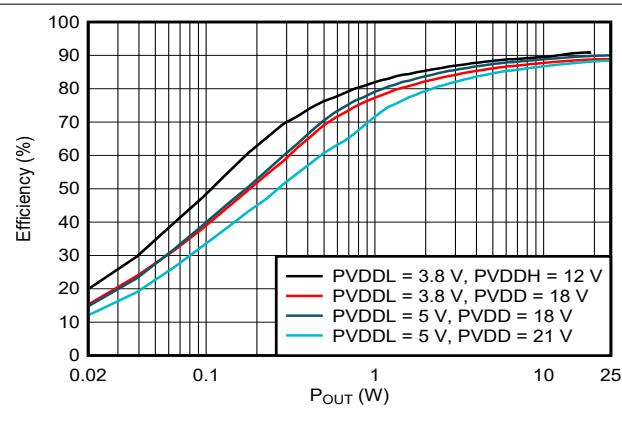

効率 (THDN 1%) と消費電力

- 1W, 4Ω, PVDDH = 12V, PVDDL = 3.8V で 82%

- 1W, 8Ω, PVDDH = 18V, PVDDL = 5V で 83%

- 1W, 4Ω, PVDDH = 18V, PVDDL = 5V で 84%

- 15W, 4Ω, PVDDH = 18V, PVDDL = 5V で 90%

- 15W, 8Ω, PVDDH = 18V, PVDDL = 5V で 93%

- ハードウェア・シャットダウン・モードで 0.5µA 未満

電源とパワー・マネージメント:

- AVDD: 1.8V

- IOVDD: 1.8V/3.3V

- PVDDL: 2.7V~5.5V

- PVDDH: 3V~24V

インターフェイスと制御:

- SDOUT によるエコー・キャンセレーション

- I<sup>2</sup>S/TDM: 32 ビット、最大 192KSPS で 8 チャネル

- I<sup>2</sup>C、Fast Mode+ または SPI

- チップ間通信バス

- 16kHz~192kHz のサンプル・レート

先進の DSP オーディオ処理:

- リアルタイムの I-V センスによるスピーカ保護

- ダイナミック・レンジ圧縮機能

- 電力リミッタによるブラウンアウト保護

- マルチチャネル・バランスシング通信

保護および EMI:

- 過電力および低バッテリ保護

- PVDDH/PVDDL 電源トラッキング・リミッタ

- 過熱および過電流保護

- サーマル・フォールドバック

- ポスト・フィルタ・フィードバックおよびスルーレート制御

## 2 アプリケーション

- ラップトップおよびデスクトップ PC

- スマート・スピーカ

- タブレットとハンドヘルド

- ワイヤレス・スピーカ

## 3 概要

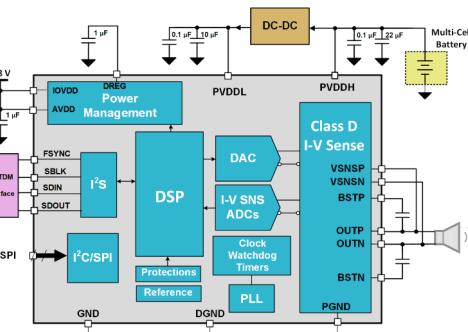

TAS2781 はモノラル、デジタル入力の Class-D オーディオ・アンプで、ラウドスピーカを高いピーク電力で効率的に駆動できるよう最適化されています。この Class-D アンプは、電源電圧 18V の場合、4Ω の負荷に 25W の連続出力を 1% 未満の THD+N で供給できます。このアンプは電圧入力範囲が広く出力電力が大きいため、バッテリでもライン電源システムでも動作できるほど多目的です。

オンチップの DSP は、テキサス・インスツルメンツの SmartAmp スピーカ保護アルゴリズムをサポートしています。スピーカ電圧および電流検出機能を内蔵しているため、ラウドスピーカをリアルタイムで監視できます。

Y ブリッジ電源アーキテクチャは、電源を内部的に選択してヘッドルームを最適化することでアンプの効率を向上させます。可変スレッショルドを備えたブラウンアウト防止方式により、電源電圧が低下した際に信号路のゲインを下げることができます。

Hybrid-Pro アルゴリズムを使用すると、外部電源を制御して効率を最適化し、バッテリ寿命を延長できます。

I<sup>2</sup>S/TDM および I<sup>2</sup>C/SPI インターフェイスにより、最大 8 個の TAS2781 デバイスが同じバスを共有できます。

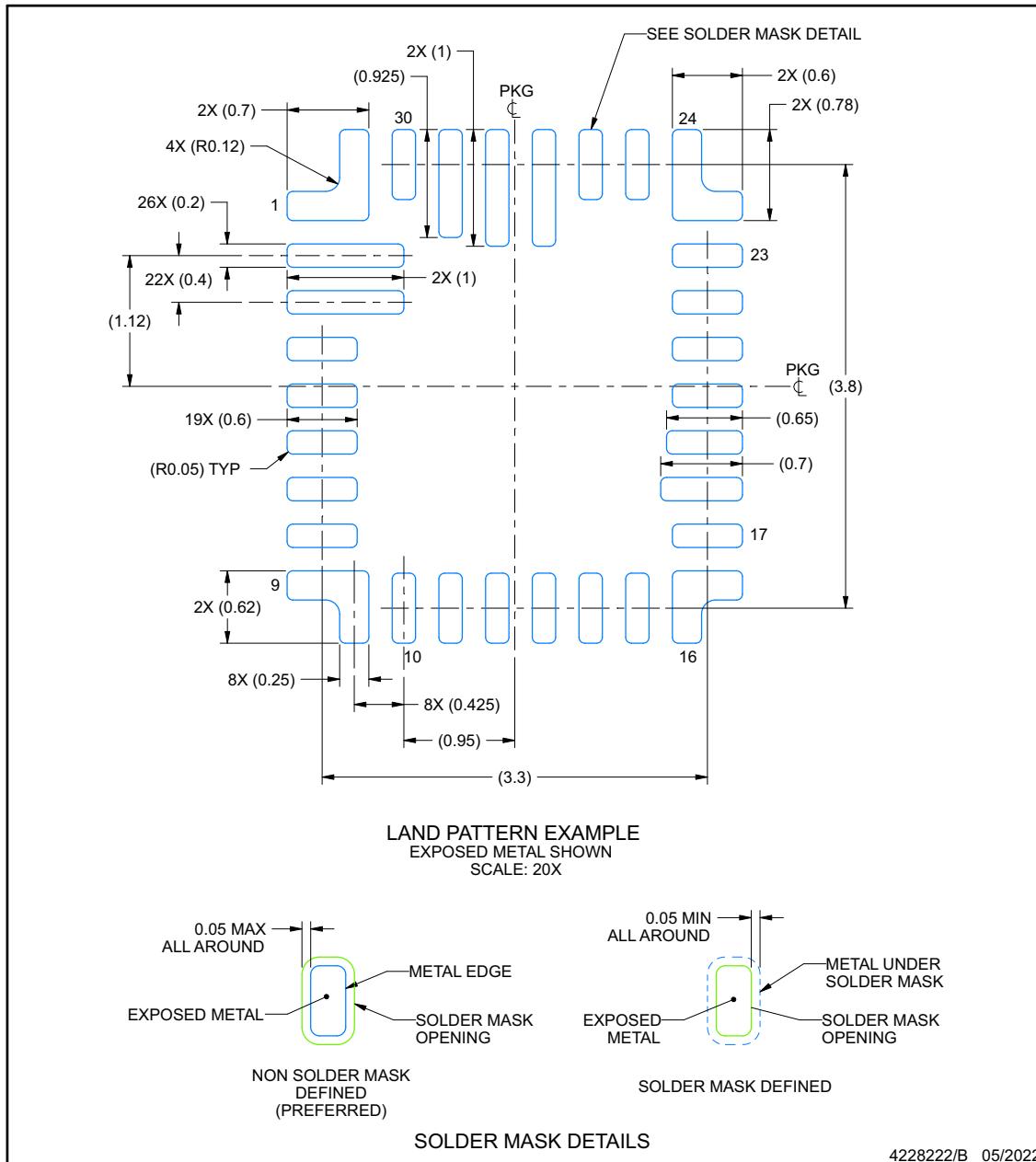

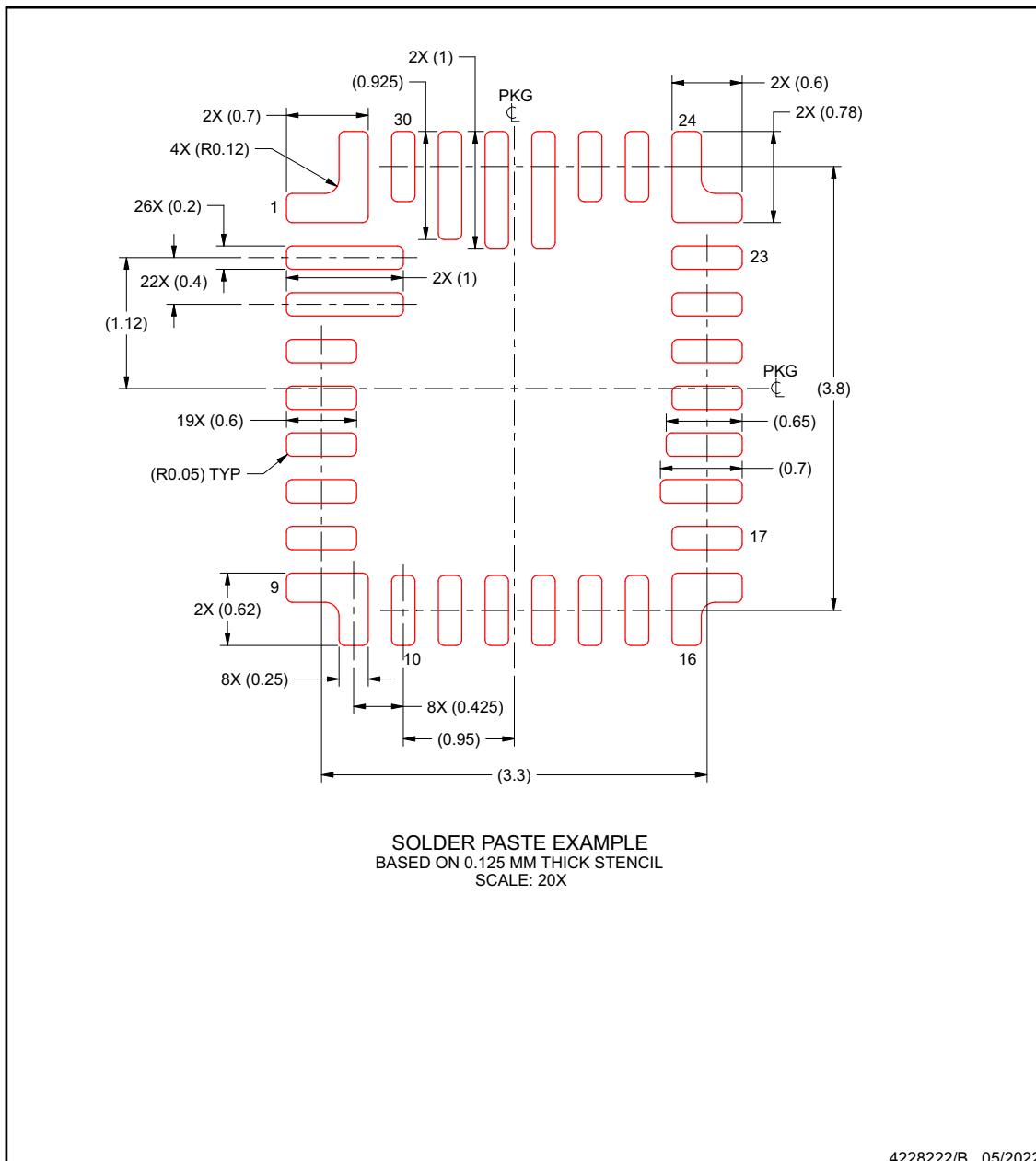

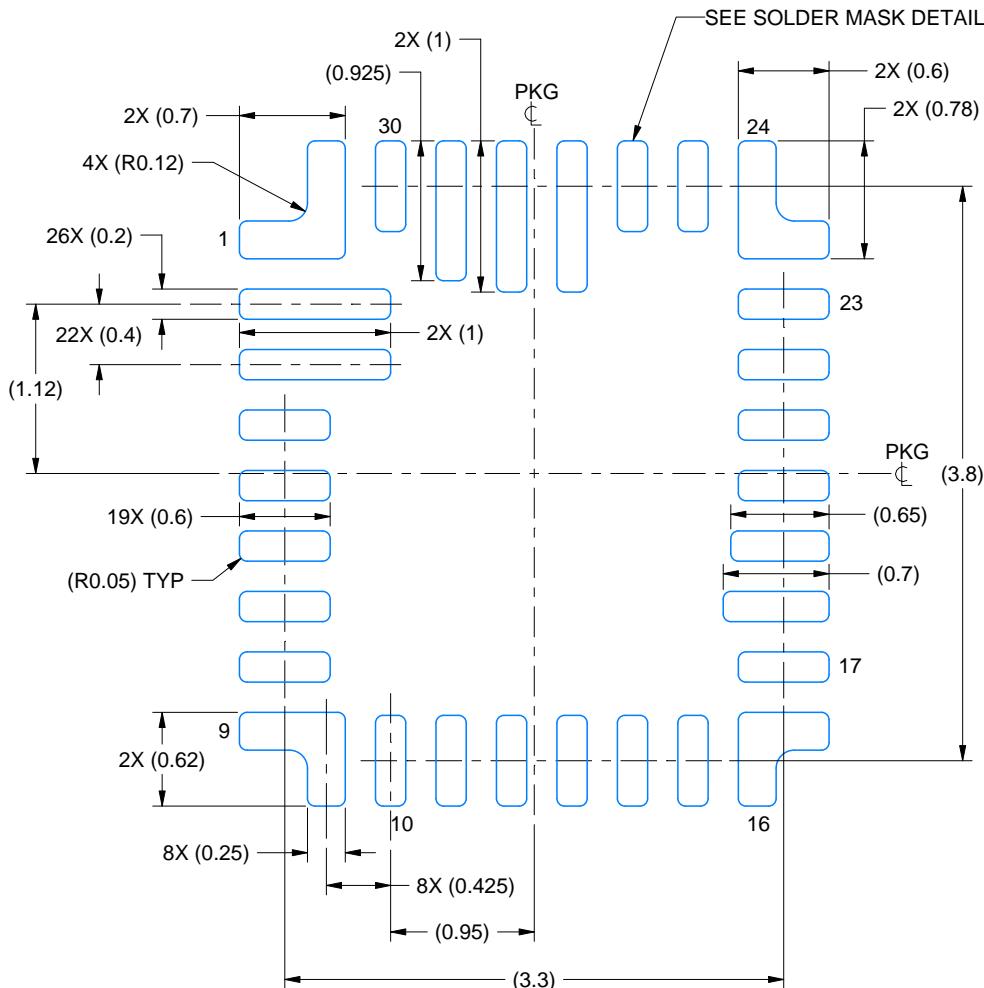

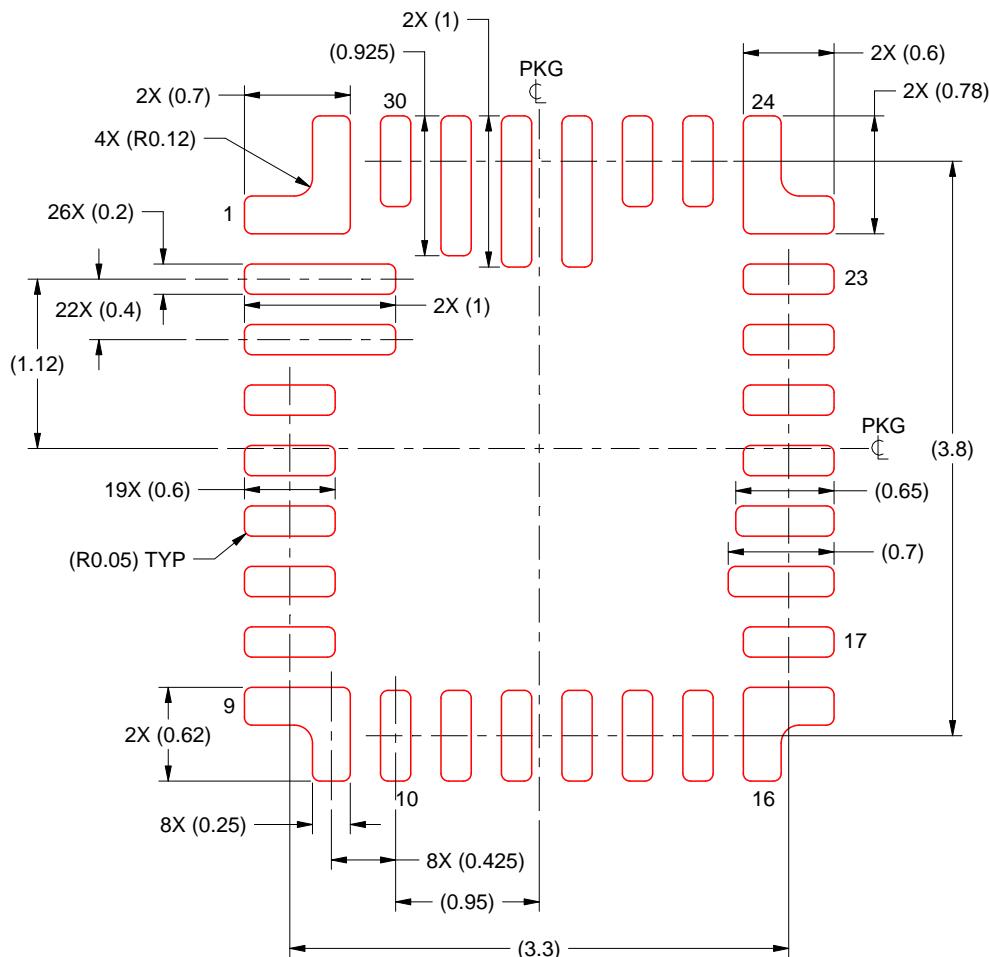

TAS2781 は、PCB の占有面積が小さい 30 ピン HR-QFN パッケージで供給されます。

## 製品情報(1)

| 部品番号    | パッケージ  | 本体サイズ(公称)   |

|---------|--------|-------------|

| TAS2781 | HR QFN | 4mm × 3.5mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

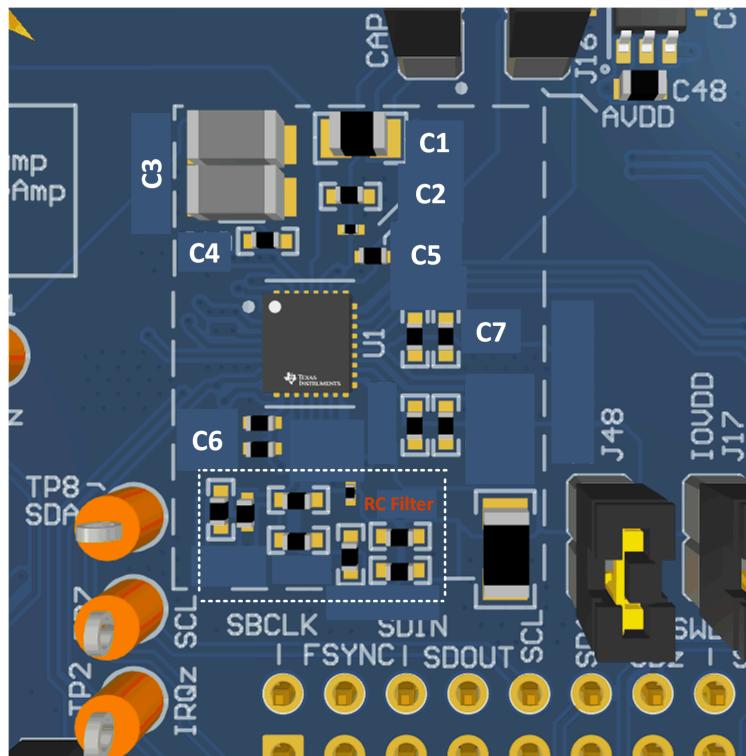

回路図

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                               |    |                                    |    |

|-------------------------------|----|------------------------------------|----|

| 1 特長                          | 1  | 8.10 SDOUT の式                      | 71 |

| 2 アプリケーション                    | 1  | 9 アプリケーションと実装                      | 72 |

| 3 概要                          | 1  | 9.1 アプリケーション情報                     | 72 |

| 4 改訂履歴                        | 2  | 9.2 代表的なアプリケーション                   | 72 |

| 5 ピン構成および機能                   | 3  | 9.3 設計要件                           | 74 |

| 6 仕様                          | 4  | 9.4 詳細な設計手順                        | 74 |

| 6.1 絶対最大定格                    | 4  | 9.5 アプリケーション曲線                     | 75 |

| 6.2 ESD 定格                    | 5  | 10 初期化セットアップ                       | 76 |

| 6.3 推奨動作条件                    | 5  | 10.1 初期デバイス構成 - 電源投入およびソフトウェア・リセット | 76 |

| 6.4 熱に関する情報                   | 5  | 10.2 初期デバイス構成 - PWR_MODE0          | 76 |

| 6.5 電気的特性                     | 6  | 10.3 初期デバイス構成 - PWR_MODE1          | 77 |

| 6.6 I <sup>2</sup> C のタイミング要件 | 11 | 10.4 初期デバイス構成 - PWR_MODE2          | 77 |

| 6.7 TDM ポートのタイミング要件           | 12 | 10.5 初期デバイス構成 - PWR_MODE3          | 78 |

| 6.8 SPI のタイミング要件              | 13 | 11 電源に関する推奨事項                      | 79 |

| 6.9 代表的特性                     | 14 | 11.1 電源モード                         | 79 |

| 7 パラメータ測定情報                   | 19 | 12 レイアウト                           | 80 |

| 8 詳細説明                        | 19 | 12.1 レイアウトのガイドライン                  | 80 |

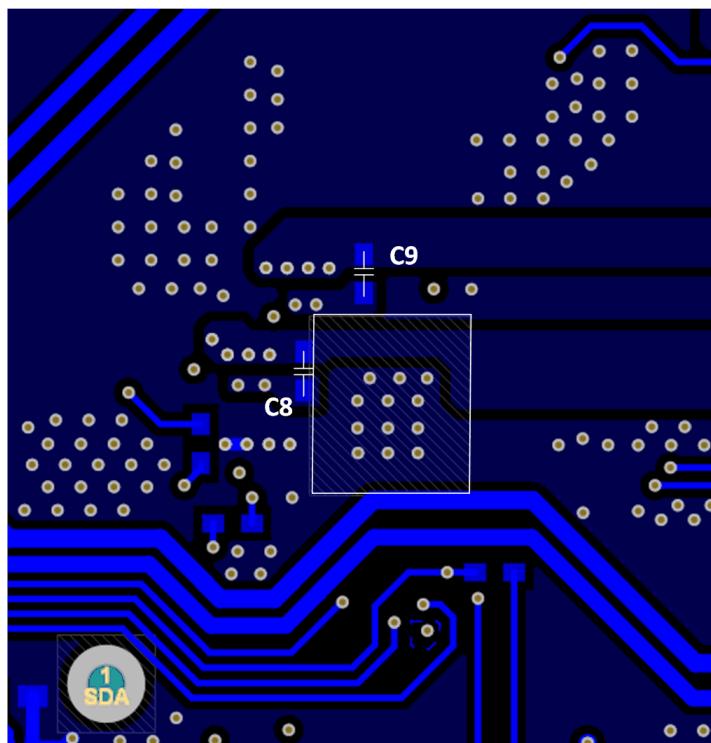

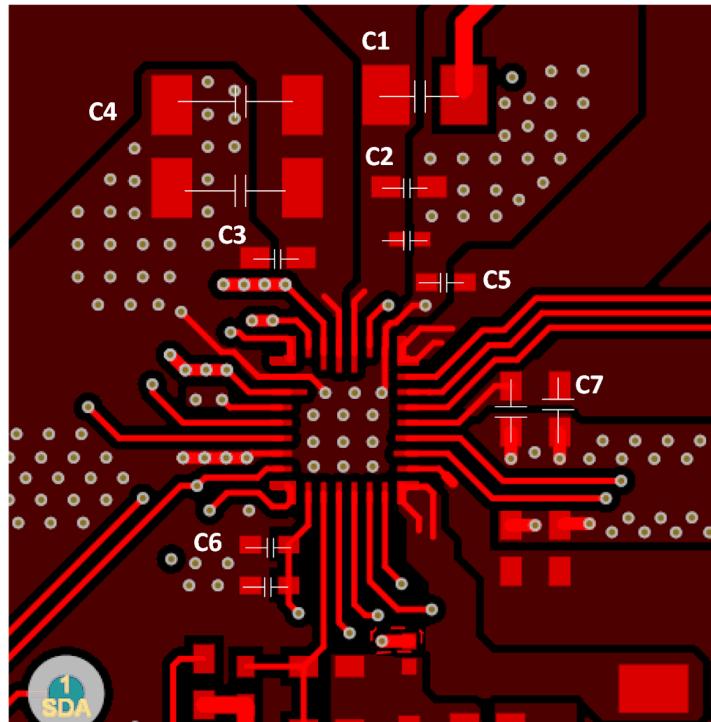

| 8.1 概要                        | 19 | 12.2 レイアウト例                        | 80 |

| 8.2 機能ブロック図                   | 20 | 13 デバイスおよびドキュメントのサポート              | 82 |

| 8.3 機能説明                      | 20 | 13.1 ドキュメントの更新通知を受け取る方法            | 82 |

| 8.4 デバイスの機能モード                | 21 | 13.2 コミュニティ・リソース                   | 82 |

| 8.5 動作モード                     | 32 | 13.3 商標                            | 82 |

| 8.6 TAS2781 のフォルトとステータス       | 34 | 14 メカニカル、パッケージ、および注文情報             | 83 |

| 8.7 電源シーケンス要件                 | 36 | 14.1 付録:パッケージ・オプション                | 84 |

| 8.8 デジタル入力プルダウン               | 36 | 14.2 テープおよびリール情報                   | 85 |

| 8.9 レジスタ・マップ                  | 36 |                                    |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (November 2022) to Revision B (July 2023) | Page |

|-------------------------------------------------------------------|------|

| • 「絶対最大定格」および「推奨動作条件」で PVDD を 24V に更新し、-20°C の温度条件の脚注を追加。         | 4    |

| • エッジ・レート・レジスタの説明を明確化。                                            | 36   |

| • フェライト・ビーズ・フィルタ用の PFFB 機能に関する推奨事項。                               | 72   |

| • 起動時のポップアップの問題を修正するために、スタートアップ構成スクリプトを追加。                        | 76   |

| Changes from Revision * (July 2022) to Revision A (November 2022) | Page |

|-------------------------------------------------------------------|------|

| • デバイスのステータスを「事前情報」から「量産データ」に変更。                                  | 1    |

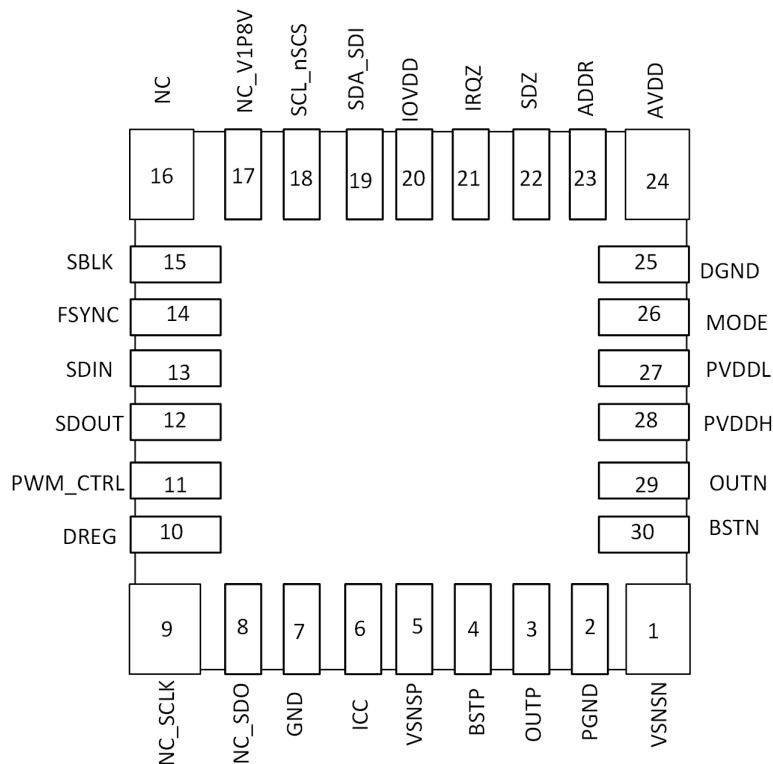

## 5 ピン構成および機能

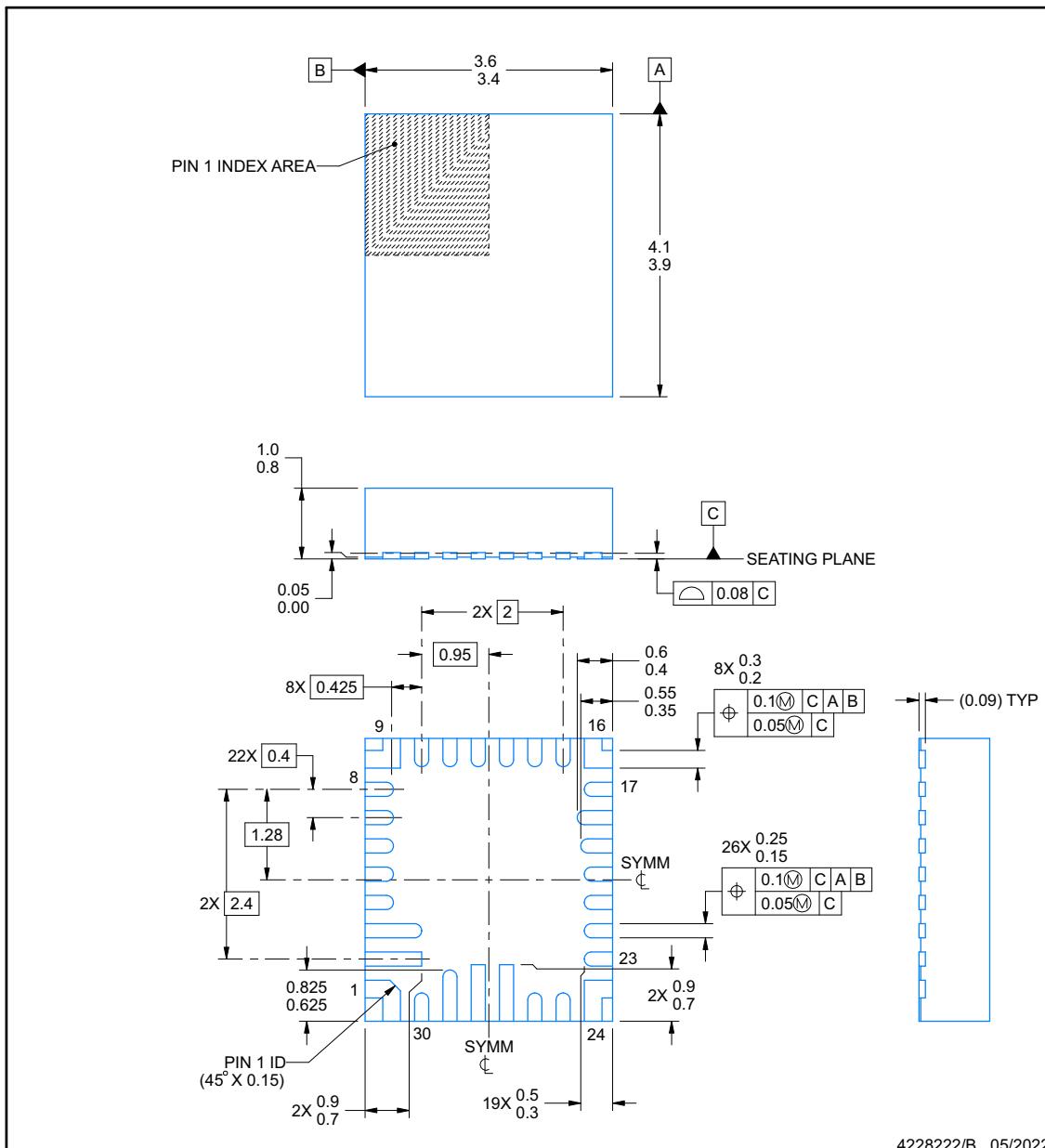

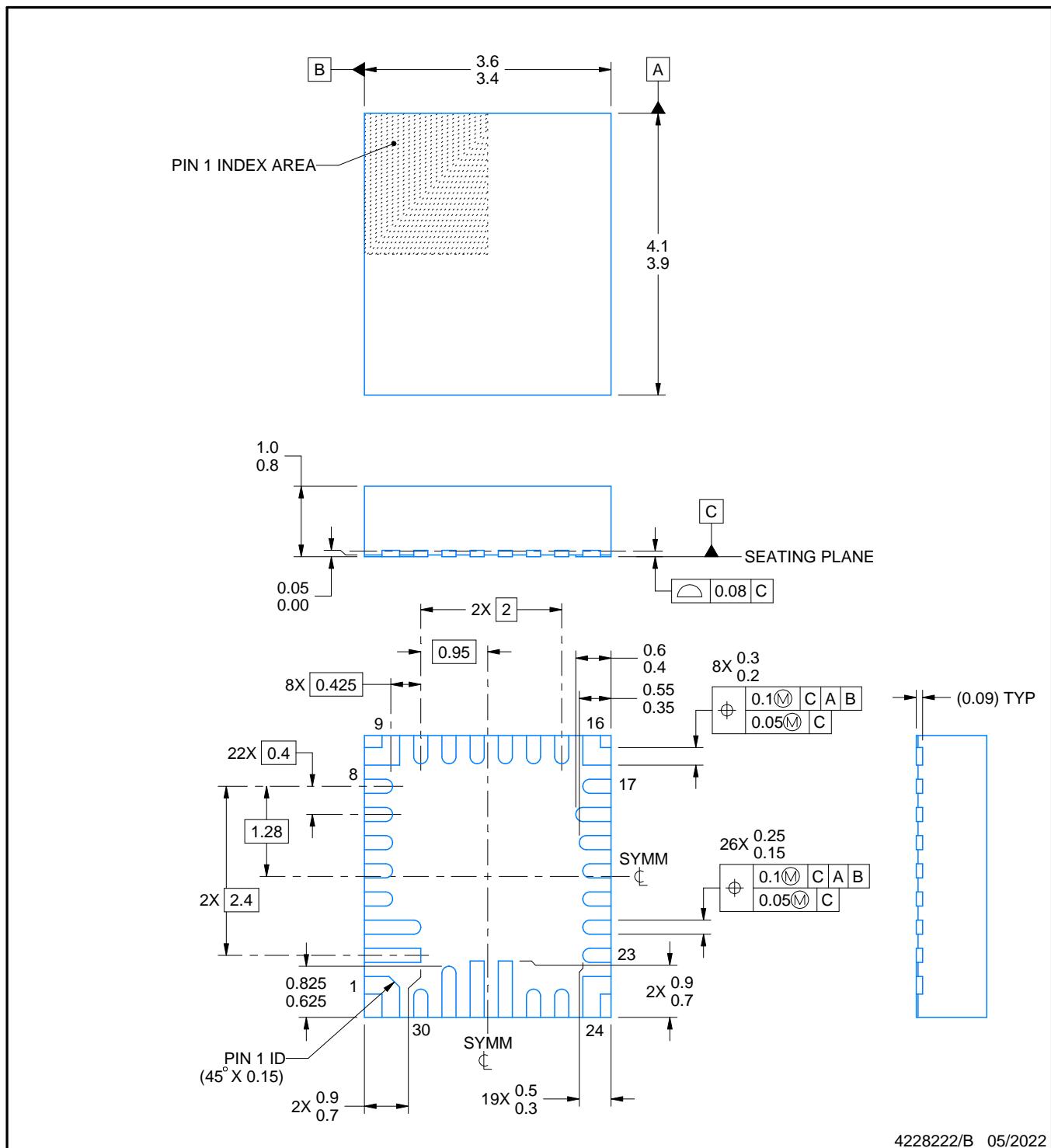

図 5-1. パッケージ 30 ピン HR-QFN 底面図

表 5-1. ピン機能

| ピン<br>名称 | I/O<br>番号 | 説明                                                                                          |

|----------|-----------|---------------------------------------------------------------------------------------------|

| ADDR     | 23        | I アドレス検出ピン。このピンの抵抗値により、I <sup>2</sup> C アドレスが選択されます。 <a href="#">セクション 8.3.2</a> を参照してください。 |

| AVDD     | 24        | P アナログ電源入力。1.8V 電源に接続し、コンデンサで GND にデカップリングします。                                              |

| BSTN     | 30        | P Class-D の負のブートストラップ。BSTN と OUTN の間にコンデンサを接続します。                                           |

| BSTP     | 4         | P Class-D の正のブートストラップ。BSTP と OUTP の間にコンデンサを接続します。                                           |

| DGND     | 25        | P デバイスのサブストレート・グランド。PCB グランド・プレーンに接続します。このピンと GND ピンの間に相互配線インダクタンスが発生しないようにします。             |

| DREG     | 10        | P デジタル・コア電圧レギュレータ出力。コンデンサを使用して GND にバイパスします。外部負荷に接続しないでください。                                |

| FSYNC    | 14        | I フレーム同期クロック。                                                                               |

| GND      | 7         | P アナログ・グランド。PCB グランド・プレーンに接続します。                                                            |

| ICC      | 6         | IO ゲイン・ライメントの送信に使用されるチップ間通信ピン。未使用時は GND に接続してください。                                          |

| IOVDD    | 20        | P デジタル IO 電源。1.8V または 3.3V の IO 電源に接続し、コンデンサで GND にデカップリングします。                              |

| IRQZ     | 21        | O オープン・ドレイン、アクティブ Low 割り込みピン。オプションの内部プルアップを使用しない場合は、抵抗を使用して IOVDD にプルアップします。                |

| MODE     | 26        | I 外部構成により、動作モードが定義されます。                                                                     |

| NC       | 16        | - GND に接続します。                                                                               |

| NC_SCLK  | 9         | I I <sup>2</sup> C モード: NC = GND に接続<br>SPI モード: クロック・ピン。                                   |

**表 5-1. ピン機能 (continued)**

| ピン<br>名称 | I/O<br>番号 | 説明                                                                                                                      |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| NC_SDO   | 8         | O I <sup>2</sup> C モード: NC = GND に接続<br>SPI モード: シリアル・データ出力ピン。                                                          |

| NC_V1P8V | 17        | P NC_V1P8V = ICC が使用されていないとき、および SPI インターフェイスが不要なときは GND に接続、<br>NC_V1P8V = ICC が使用されており、SPI インターフェイスが必要なときは 1.8V 電源に接続 |

| OUTN     | 29        | O Class-D の負出力。                                                                                                         |

| OUTP     | 3         | O Class-D の正出力。                                                                                                         |

| PGND     | 2         | P Class-D のグランド。PCB グランド・プレーンに接続します。                                                                                    |

| PVDDH    | 28        | P Class-D 電源入力。コンデンサでデカップリングします。                                                                                        |

| PVDDL    | 27        | P シングルセル・バッテリ電源入力。コンデンサでデカップリングします。                                                                                     |

| PWM_CTRL | 11        | O 外部昇圧コンバータの制御ピン。                                                                                                       |

| SBCLK    | 15        | I TDM シリアル・ビット・クロック。                                                                                                    |

| SCL_nSCS | 18        | I I <sup>2</sup> C モード: クロック・ピン。抵抗を使用して IOVDD にプルアップします。<br>SPI モード: アクティブ Low チップ・セレクト・ピン。                             |

| SDA_SDI  | 19        | IO I <sup>2</sup> C モード: データ・ピン。抵抗を使用して IOVDD にプルアップします。<br>SPI モード: シリアル・データ入力ピン。                                      |

| SDIN     | 13        | I TDM シリアル・データ入力。                                                                                                       |

| SDOUT    | 12        | IO TDM シリアル・データ出力。                                                                                                      |

| SDZ      | 22        | I アクティブ Low のハードウェア・シャットダウン。                                                                                            |

| VSNSN    | 1         | I 電圧検出の負入力。Class-D の負出力に接続するか、またはフェライト・ビーズ・フィルタの後に接続します。                                                                |

| VSNSP    | 5         | I 電圧検出の正入力。Class-D の正出力に接続するか、またはフェライト・ビーズ・フィルタの後に接続します。                                                                |

## 6 仕様

### 6.1 絶対最大定格

|                                                              |                                                                  | 最小値        | 最大値      | 単位 |

|--------------------------------------------------------------|------------------------------------------------------------------|------------|----------|----|

| 電源電圧                                                         | AVDD                                                             | -0.3       | 2        | V  |

|                                                              | IOVDD                                                            | -0.3       | 5        | V  |

|                                                              | NC_V1P8V                                                         | -0.3       | 2        | V  |

|                                                              | PVDDH                                                            | -0.3       | 26       | V  |

|                                                              | PVDDL                                                            | -0.3       | 6        | V  |

|                                                              | PVDDH - PVDDL                                                    | -0.3       | 22       | V  |

| 内部電源電圧                                                       | DREG                                                             | -0.3       | 1.5      | V  |

| IO 電圧 <sup>(1)</sup>                                         | SBLK, FSYNK, SDIN, SDOUT, IRQZ, SDA_SDI, SCL_nSCS, PWM_CTRL, SDZ | -0.3       | 5        | V  |

| IO 電圧 <sup>(1)</sup>                                         | NC_SCLK, NC_SDO, ICC, ADDR                                       | -0.3       | 2        | V  |

| 自由空気での動作温度 $T_A$ 。デバイスは高い信頼性で正しく動作しますが、一部の性能特性が低下する可能性があります。 | PVDD は 23V 以下<br>PVDD は 23V より高い                                 | -40<br>-20 | 85<br>85 | °C |

| 自由気流での性能温度 $T_P$ 。すべての性能特性を満たしています。                          |                                                                  | -20        | 70       | °C |

|                  |                 | 最小値 | 最大値 | 単位 |

|------------------|-----------------|-----|-----|----|

| 動作時の接合部温度、 $T_J$ | PVDD は 23V 以下   | -40 | 150 | °C |

|                  | PVDD は 23V より高い | -20 | 150 | °C |

| 保管温度、 $T_{stg}$  |                 | -65 | 150 | °C |

(1) すべてのデジタル入力と IO はフェイルセーフです。

## 6.2 ESD 定格

|             |       |                                                          | 値     | 単位 |

|-------------|-------|----------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | ±2000 | V  |

|             |       | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±500  |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|                      |                          |                                 | 最小値  | 公称値 | 最大値  | 単位 |

|----------------------|--------------------------|---------------------------------|------|-----|------|----|

| AVDD                 | 電源電圧                     |                                 | 1.65 | 1.8 | 1.95 | V  |

| IOVDD                | 電源電圧                     | 動作時の最低自由空気温度および最低動作接合部温度は -20°C | 3    | 3.3 | 3.6  | V  |

|                      |                          | 動作時の最低自由空気温度および最低動作接合部温度は -40°C | 1.65 | 1.8 | 1.95 |    |

| NC_V1P8V             | ICC ピンの電源電圧              |                                 | 1.65 | 1.8 | 1.95 | V  |

| PVDDH <sup>(2)</sup> | 電源電圧 (機能) <sup>(1)</sup> | 動作時の最低自由空気温度および最低動作接合部温度は -20°C | 3    | 24  | 24   | V  |

|                      |                          | 動作時の最低自由空気温度および最低動作接合部温度は -40°C | 3    | 23  | 23   |    |

|                      | 電源電圧 (性能)                | 動作時の最低自由空気温度および最低動作接合部温度は -20°C | 4.5  | 24  | 24   |    |

|                      |                          | 動作時の最低自由空気温度および最低動作接合部温度は -40°C | 4.5  | 23  | 23   |    |

| PVDDL                | 電源電圧 (機能) <sup>(1)</sup> |                                 | 2.7  | 5.5 | 5.5  | V  |

|                      | 電源電圧 (Y ブリッジがディセーブル時の性能) |                                 | 3.5  | 5.5 | 5.5  |    |

|                      | 電源電圧 (Y ブリッジがイネーブル時の性能)  |                                 | 2.7  | 5.5 | 5.5  |    |

| R <sub>SPK</sub>     | スピーカのインピーダンス             |                                 | 3.2  |     |      | Ω  |

| L <sub>SPK</sub>     | スピーカのインダクタンス             |                                 | 5    |     |      | μH |

(1) デバイスの機能は維持されますが、性能は低下します。

(2) PVDDH 電源電圧は、PVDDL-0.7V よりも高い必要があります。

## 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | HR_QFN | 単位   |

|-----------------------|---------------------|--------|------|

|                       |                     | 30 ピン  |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 44.2   | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 22.4   | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 12.3   | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性パラメータ   | 0.6    | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性パラメータ   | 12.1   | °C/W |

(1) 従来および最新の熱測定基準の詳細については、アプリケーション・レポート『半導体および IC パッケージの熱評価基準』、[SPRA953](#) を参照してください。

## 6.5 電気的特性

$T_A = 25^\circ\text{C}$ 、 $\text{PVDDH} = 18\text{V}$ 、 $\text{PVDDL} = 3.8\text{V}$ 、 $\text{AVDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega + 15\mu\text{H}$ 、 $f_{in} = 1\text{kHz}$ 、 $f_s = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ = 1、NG\_EN=0、EN\_LLSR=0、PWR\_MODE1、セクション 7 に記載されているフィルタなしの状態で測定（特に記述のない限り）。

| パラメータ                        | テスト条件                                                              | 最小値                                                                                         | 代表値                                     | 最大値                                     | 単位            |

|------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|---------------|

| <b>デジタル入出力</b>               |                                                                    |                                                                                             |                                         |                                         |               |

| $V_{IH}$                     | High レベル・デジタル入力ロジック電圧スレッショルド                                       | SBLK, FSYNC, SDIN, SCL_nSCS, SDA_SDI                                                        | $0.7 \times \text{IOVDD}$               |                                         | V             |

| $V_{IL}$                     | Low レベル・デジタル入力ロジック電圧スレッショルド                                        | SBLK, FSYNC, SDIN, SCL_nSCS, SDA_SDI                                                        |                                         | $0.3 \times \text{IOVDD}$               | V             |

| $V_{IH(\text{SDZ})}$         | High レベル・デジタル入力ロジック電圧スレッショルド                                       | SDZ                                                                                         | $0.7 \times \text{AVDD}$                |                                         | V             |

| $V_{IL(\text{SDZ})}$         | Low レベル・デジタル入力ロジック電圧スレッショルド                                        | SDZ                                                                                         |                                         | $0.3 \times \text{AVDD}$                | V             |

| $V_{IH(1\text{P}8\text{V})}$ | High レベル・デジタル入力ロジック電圧スレッショルド                                       | ICC, NC_SCLK                                                                                | $0.7 \times \text{NC\_V1P}_{8\text{V}}$ |                                         | V             |

| $V_{IL(1\text{P}8\text{V})}$ | Low レベル・デジタル入力ロジック電圧スレッショルド                                        | ICC, NC_SCLK                                                                                |                                         | $0.3 \times \text{NC\_V1P8}_{\text{V}}$ | V             |

| $V_{OH}$                     | High レベル・デジタル出力電圧                                                  | SDOUT, $I_{OH} = 100\mu\text{A}$                                                            | $\text{IOVDD} - 0.2\text{V}$            |                                         | V             |

| $V_{OL}$                     | Low レベル・デジタル出力電圧                                                   | SDOUT, $I_{OH} = 100\mu\text{A}$                                                            |                                         | 0.2                                     | V             |

| $V_{OL(\text{I}^2\text{C})}$ | Low レベル・デジタル出力電圧                                                   | SDA_SDI, $I_{OL} = -1\text{mA}$                                                             |                                         | $0.2 \times \text{IOVDD}$               | V             |

| $V_{OH(1\text{P}8\text{V})}$ | High レベル・デジタル出力電圧                                                  | NC_SDO                                                                                      | $0.8 \times \text{NC\_V1P}_{8\text{V}}$ |                                         | V             |

| $V_{OL(1\text{P}8\text{V})}$ | Low レベル・デジタル出力電圧                                                   | NC_SDO                                                                                      |                                         | $0.2 \times \text{NC\_V1P8V}$           | V             |

| $I_{IH}$                     | デジタル入力への入力ロジック High リーケージ                                          | すべてのデジタル・ピン。入力=電源レール。                                                                       | -1                                      | 1                                       | $\mu\text{A}$ |

| $I_{IL}$                     | デジタル入力への入力ロジック Low リーケージ                                           | すべてのデジタル・ピン。入力=GND。                                                                         | -1                                      | 1                                       | $\mu\text{A}$ |

| $C_{IN}$                     | デジタル入力の入力容量                                                        | すべてのデジタル・ピン                                                                                 |                                         | 5                                       | pF            |

| $R_{PD}$                     | オンにアサートされたときの IO ピンのブルダウン抵抗                                        |                                                                                             |                                         | 18                                      | k $\Omega$    |

| $R_{os}$                     | VSNS 抵抗への OUT                                                      | 負荷が切断された状態                                                                                  |                                         | 10                                      | k $\Omega$    |

| IO                           | 出力電流強度                                                             | 電源電圧より 0.4V 低く GND より 0.4V 高い値で測定。                                                          |                                         | 8                                       | mA            |

| <b>アンプ性能</b>                 |                                                                    |                                                                                             |                                         |                                         |               |

| $P_{OUT}$                    | ピーク出力電力                                                            | THD+N = 10%, PWR_MODE0 <sup>(1)</sup> , PWR_MODE1 <sup>(2)</sup>                            | 30                                      |                                         | W             |

|                              | 最大連続出力電力                                                           | THD+N = 1%, PVDDL = 5V, PWR_MODE0, PWR_MODE1                                                | 25                                      |                                         |               |

| システム効率                       | $P_{OUT} = 1\text{W}, \text{PVDDL} = 5\text{V}, \text{PWR\_MODE1}$ | $P_{OUT} = 1\text{W}, \text{PVDDL} = 5\text{V}, \text{PWR\_MODE1}$                          | 84                                      |                                         | %<br>%        |

|                              |                                                                    | $P_{OUT} = 1\text{W}, \text{PVDDL} = 5\text{V}, \text{PWR\_MODE0}$                          | 79                                      |                                         |               |

|                              |                                                                    | $P_{OUT} = 3\text{W}, \text{PVDDL} = 5\text{V}, \text{PWR\_MODE0 および PWR\_MODE1}$           | 85                                      |                                         |               |

|                              |                                                                    | $P_{OUT} = 8\text{W}, \text{PVDDL} = 5\text{V}, \text{PWR\_MODE0 および PWR\_MODE1}$           | 88                                      |                                         |               |

| THD+N                        | 全高調波歪およびノイズ                                                        | $P_{OUT} = 1\text{W}, f_{in} = 1\text{kHz}$                                                 | -84                                     |                                         | dB            |

|                              |                                                                    | $P_{OUT} = 1\text{W}, f_{in} = 6.667\text{kHz}$                                             | -84                                     |                                         |               |

| IMD                          | 相互変調歪                                                              | ITU-R, 19kHz/20kHz, 1:1: 12.5W                                                              | -83                                     |                                         | dB            |

| VN                           | アイドル・チャネル・ノイズ                                                      | A-Weighted, 20Hz~20kHz, PWR_MODE0                                                           | 42                                      |                                         | $\mu\text{V}$ |

|                              |                                                                    | A-Weighted, 20Hz~20kHz, PWR_MODE2 <sup>(3)</sup>                                            | 34                                      |                                         |               |

|                              |                                                                    | A-Weighted, 20Hz~20kHz, PWR_MODE1                                                           | 32                                      |                                         |               |

|                              | 超音波チャーブを伴うアイドル・チャネル・ノイズ (100 $\mu\text{s}$ デューティ・サイクル、25ms 周期)     | A-Weighted, 20Hz~20kHz, PWR_MODE3 <sup>(4)</sup> , 1V <sub>Peak</sub> , レジスタ 0x73 を E0h に設定 | 34                                      |                                         |               |

$T_A = 25^\circ\text{C}$ 、 $\text{PVDDH} = 18\text{V}$ 、 $\text{PVDDL} = 3.8\text{V}$ 、 $\text{AVDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega + 15\mu\text{H}$ 、 $f_{in} = 1\text{kHz}$ 、 $f_s = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ = 1、NG\_EN=0、EN\_LLSSR=0、PWR\_MODE1、セクション 7 に記載されているフィルタなしの状態で測定(特に記述のない限り)。

| パラメータ            | テスト条件                                                                                 | 最小値   | 代表値       | 最大値  | 単位  |

|------------------|---------------------------------------------------------------------------------------|-------|-----------|------|-----|

| $F_{\text{PWM}}$ | 拡散スペクトラム・モードでの平均周波数、CLASSD_SYNC=0                                                     | 384   |           |      | kHz |

|                  | 固定周波数モード、CLASSD_SYNC=0                                                                | 384   |           |      |     |

|                  | 固定周波数モード、CLASSD_SYNC=1、 $f_s = 44.1\text{kHz}$ および $88.2\text{kHz}$                   | 352.8 |           |      |     |

|                  | 固定周波数モード、CLASSD_SYNC=1、 $f_s = 48\text{kHz}$ および $96\text{kHz}$                       | 384   |           |      |     |

| $V_{os}$         | 出力オフセット電圧                                                                             | -1.3  | $\pm 0.3$ | 1.3  | mV  |

| DNR              | A-Weighted、-60dBFS                                                                    | 110   |           |      | dB  |

|                  | A-Weighted、-60dBFS、PWR_MODE2                                                          | 109   |           |      |     |

|                  | A-Weighted、-60dBFS、PWR_MODE0                                                          | 109   |           |      |     |

| SNR              | A-Weighted、1% THD+N 出力レベルを基準                                                          | 110   |           |      | dB  |

|                  | A-Weighted、1% THD+N 出力レベルを基準、PWR_MODE2 <sup>(1)</sup>                                 | 110   |           |      |     |

|                  | A-Weighted、1% THD+N 出力レベルを基準、PWR_MODE0                                                | 109   |           |      |     |

| $K_{CP}$         | クリックおよびポップ性能                                                                          | 0.8   |           |      | mV  |

|                  | フルスケール出力電圧                                                                            | 21    |           |      | dBV |

|                  | プログラム可能な最小ゲイン                                                                         | 11    |           |      | dBV |

|                  | プログラム可能な最大ゲイン                                                                         | 21    |           |      |     |

|                  | プログラム可能な出力レベルのステップ・サイズ                                                                | 0.5   |           |      | dB  |

|                  | ミュート減衰                                                                                | 108   |           |      | dB  |

|                  | チップ間群遅延                                                                               | -1    | 1         |      | μs  |

|                  | PVDDH = 18V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 217\text{Hz}$                | 118   |           |      | dB  |

|                  | PVDDH = 18V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 1\text{kHz}$                 | 110   |           |      |     |

|                  | PVDDH = 18V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 20\text{kHz}$                | 98    |           |      |     |

|                  | PVDDL = 5V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 217\text{Hz}$                 | 114   |           |      | dB  |

|                  | PVDDL = 5V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 1\text{kHz}$                  | 109   |           |      |     |

|                  | PVDDL = 5V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 20\text{kHz}$                 | 93    |           |      |     |

|                  | AVDD = 1.8V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 217\text{Hz}$                | 105   |           |      | dB  |

|                  | AVDD = 1.8V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 1\text{kHz}$                 | 103   |           |      |     |

|                  | AVDD = 1.8V + 200mV <sub>pp</sub> 、 $f_{\text{ripple}} = 20\text{kHz}$                | 88    |           |      |     |

|                  | PVDDH、217Hz、100mV <sub>pp</sub> 、入力 f = 1kHz @ 400mW                                  | -120  |           |      | dB  |

|                  | PVDDL、217Hz、100mV <sub>pp</sub> 、入力 f = 1kHz @ 400mW                                  | -120  |           |      |     |

|                  | AVDD、217Hz、100mV <sub>pp</sub> 、入力 f = 1kHz @ 400mW                                   | -80   |           |      |     |

|                  | IOVDD 217Hz、100mV <sub>pp</sub> 、入力 f = 1kHz @ 400mW                                  | -117  |           |      |     |

|                  | ソフトウェア・シャットダウンのリリースからのターンオン時間                                                         | 1.13  |           |      | ms  |

|                  | ボリューム・ランプなし                                                                           | 6.73  |           |      |     |

|                  | ソフトウェア・シャットダウンのアサートからアンプのハイ・インピーダンスまでのターンオフ時間                                         | 0.56  |           |      | ms  |

|                  | ボリューム・ランプ                                                                             | 6     |           |      |     |

|                  | ハードウェア・シャットダウンから復帰して最初の I <sup>2</sup> C コマンドまで                                       | 1     |           |      | ms  |

| SDZ タイムアウト       | HW シャットダウンの終了                                                                         | 2     | 6         | 23.8 | ms  |

|                  | $f_s = 48\text{ksps}$ 、DVC_RMP_RT[3:2]=3h (ディセーブル)。別のサンプリング・レートの場合は、 $48/f_s$ で乗算します。 | 1     |           |      | ms  |

|                  | $f_s = 48\text{ksps}$ 、DVC_RMP_RT[3:2]=0h (イネーブル)。別のサンプリング・レートの場合は、 $48/f_s$ で乗算します。  | 12.5  |           |      |     |

$T_A = 25^\circ\text{C}$ 、 $\text{PVDDH} = 18\text{V}$ 、 $\text{PVDDL} = 3.8\text{V}$ 、 $\text{AVDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega + 15\mu\text{H}$ 、 $f_{in} = 1\text{kHz}$ 、 $f_s = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ = 1、NG\_EN=0、EN\_LLSR=0、PWR\_MODE1、セクション 7 に記載されているフィルタなしの状態で測定(特に記述のない限り)。

| パラメータ                                              | テスト条件                                                    | 最小値                                                          | 代表値      | 最大値 | 単位      |

|----------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------|----------|-----|---------|

| <b>ダイ温度センサ</b>                                     |                                                          |                                                              |          |     |         |

|                                                    | 分解能                                                      | 8                                                            |          |     | ビット     |

|                                                    | 最小温度測定範囲                                                 | -40                                                          |          |     | °C      |

|                                                    | 最大温度測定範囲                                                 | 150                                                          |          |     | °C      |

|                                                    | ダイ温度分解能                                                  | 1                                                            |          |     | °C      |

|                                                    | ダイ温度精度                                                   | -5                                                           | 5        |     | °C      |

| <b>電圧モニタ</b>                                       |                                                          |                                                              |          |     |         |

|                                                    | 分解能                                                      | 12                                                           |          |     | ビット     |

|                                                    | PVDDH の測定範囲                                              | 最小レベル<br>最大レベル                                               | 2<br>23  |     | V       |

|                                                    | PVDDH の分解能                                               |                                                              | 22.5     |     | mV      |

|                                                    | PVDDH の精度                                                | $2\text{V} \leq \text{PVDDHV} \leq 23\text{V}$               | $\pm 60$ |     | mV      |

|                                                    | PVDDL の測定範囲                                              | 最小レベル<br>最大レベル                                               | 2.3<br>6 |     | V       |

|                                                    | PVDDL の分解能                                               |                                                              | 20       |     | mV      |

|                                                    | PVDDL の精度                                                | $2.3\text{V} \leq \text{PVDDL} \leq 6\text{V}$               | $\pm 20$ |     | mV      |

| <b>TDM シリアル・オーディオ・ポート</b>                          |                                                          |                                                              |          |     |         |

|                                                    | 最小 PCM サンプル・レートと FSYNC 入力周波数                             |                                                              | 14.7     |     | kHz     |

|                                                    | 最大 PCM サンプル・レートと FSYNC 入力周波数                             |                                                              | 192      |     |         |

|                                                    | 最小 SBCLK 入力周波数                                           | I <sup>2</sup> S/TDM での動作                                    | 0.512    |     | MHz     |

|                                                    | 最大 SBCLK 入力周波数                                           | I <sup>2</sup> S/TDM での動作                                    | 24.576   |     |         |

|                                                    | SBCLK の最大入力ジッタ                                           | 性能を低下させない許容範囲 40kHz 未満の RMS ジッタ                              | 0.5      |     | ns      |

|                                                    |                                                          | 性能を低下させない許容範囲 40kHz 以上の RMS ジッタ                              | 1        |     |         |

|                                                    | I <sup>2</sup> S および TDM モードにおける FSYNC 当たりの最小 SBCLK サイクル | その他の値: 24, 32, 48, 64, 96, 125, 128, 192, 250, 256, 384, 500 | 16       |     | サイクル    |

|                                                    | I <sup>2</sup> S および TDM モードにおける FSYNC 当たりの最大 SBCLK サイクル | その他の値: 24, 32, 48, 64, 96, 125, 128, 192, 250, 256, 384, 500 | 512      |     |         |

| <b>PCM 再生特性 <math>f_s \leq 48\text{kHz}</math></b> |                                                          |                                                              |          |     |         |

| $f_s$                                              | 最小サンプル・レート                                               |                                                              | 14.7     |     | kHz     |

|                                                    | 最大サンプル・レート                                               |                                                              | 48       |     |         |

|                                                    | 通過帯域周波数での交差リップル                                          |                                                              | 0.454    |     | $f_s$   |

|                                                    | 通過帯域リップル                                                 | 20Hz～LPF のカットオフ周波数                                           | -0.5     | 0.5 | dB      |

|                                                    | ストップ・バンド減衰                                               | 0.55 以上の $f_s$                                               | 60       |     | dB      |

|                                                    |                                                          | 1 以上の $f_s$                                                  | 65       |     |         |

|                                                    | 群遅延(ノイズ・ゲートを含む)                                          | DC から 0.454 $f_s$ まで、DC ブロックはディセーブル、Class-H はディセーブル          | 31       |     | $1/f_s$ |

|                                                    |                                                          | DC から 0.454 $f_s$ まで、DC ブロックはディセーブル、Class-H はイネーブル           | 221      |     |         |

| <b>PCM 再生特性 <math>f_s &gt; 48\text{kHz}</math></b> |                                                          |                                                              |          |     |         |

| $f_s$                                              | 最小サンプル・レート                                               |                                                              | 88.2     |     | kHz     |

|                                                    | 最大サンプル・レート                                               |                                                              | 192      |     |         |

$T_A = 25^\circ\text{C}$ 、 $\text{PVDDH} = 18\text{V}$ 、 $\text{PVDDL} = 3.8\text{V}$ 、 $\text{AVDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega + 15\mu\text{H}$ 、 $f_{in} = 1\text{kHz}$ 、 $f_s = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ = 1、NG\_EN=0、EN\_LLSR=0、PWR\_MODE1、セクション 7 に記載されているフィルタなしの状態で測定(特に記述のない限り)。

| パラメータ           | テスト条件                                               | 最小値  | 代表値   | 最大値 | 単位      |

|-----------------|-----------------------------------------------------|------|-------|-----|---------|

| 通過帯域リップルの周波数    | $f_s = 96\text{kHz}$                                |      | 0.437 |     | $f_s$   |

| 通過帯域 3db 周波数    | $f_s = 96\text{kHz}$                                |      | 0.459 |     | $f_s$   |

| 通過帯域リップル        | DC から LPF へのカットオフ周波数                                | -0.5 |       | 0.5 | dB      |

| ストップ・バンド減衰      | 0.56 以上の $f_s$                                      |      | 60    |     |         |

|                 | 1 以上の $f_s$                                         |      | 65    |     |         |

| 群遅延(ノイズ・ゲートを含む) | DC から $0.375 f_s$ まで、DC ブロックはディセーブル、Class-H はディセーブル |      | 51    |     | $1/f_s$ |

|                 | DC から $0.375 f_s$ まで、DC ブロックはディセーブル、Class-H はイネーブル  |      | 242   |     |         |

#### スピーカ電流センス

|       |             |                                       |      |         |

|-------|-------------|---------------------------------------|------|---------|

| 分解能   |             | 16                                    | ビット  |         |

| DNR   | ダイナミック・レンジ  | 重み付けなし、基準は 0dBFS                      | 70   | dB      |

| THD+N | 全高調波歪およびノイズ | Pout = 15W                            | -61  | dB      |

|       | フルスケール入力電流  | -6dBFS で測定。0dBFS で再スケーリング。            | 5    | A       |

|       | 差動モード・ゲイン   | Pout = 1W、40Hz - 40dBFS のパイロット・トーンを使用 | 0.98 | 1.02    |

|       | 周波数応答       | 20Hz~20kHz                            | -0.1 | 0.1     |

|       | 群遅延         |                                       | 22   | $1/f_s$ |

#### スピーカ電圧センス

|       |             |                                       |      |          |

|-------|-------------|---------------------------------------|------|----------|

| 分解能   |             | 16                                    | ビット  |          |

| DNR   | ダイナミック・レンジ  | 重み付けなし、基準は 0dBFS                      | 73   | dB       |

| THD+N | 全高調波歪およびノイズ | Pout = 15W                            | -68  | dB       |

|       | フルスケール入力電圧  |                                       | 16   | $V_{PK}$ |

|       | 差動モード・ゲイン   | Pout = 1W、40Hz - 40dBFS のパイロット・トーンを使用 | 0.98 | 1.02     |

|       | 周波数応答       | 20Hz~20kHz                            | -0.1 | 0.1      |

|       | 群遅延         |                                       | 22   | $1/f_s$  |

#### スピーカの電圧 / 電流検出比

|               |                                                                            |    |      |    |

|---------------|----------------------------------------------------------------------------|----|------|----|

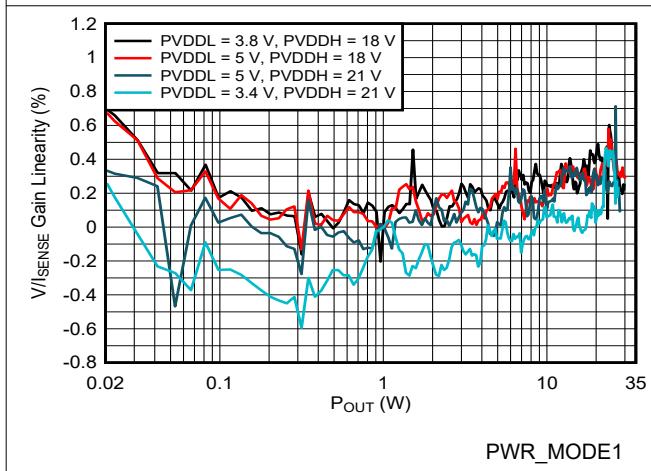

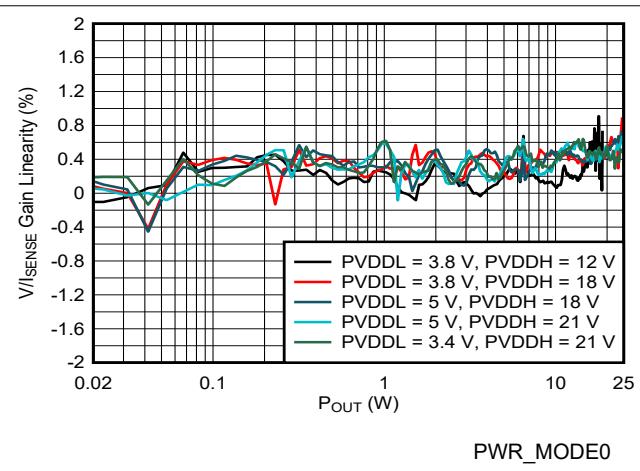

| ゲインの直線性       | Pout $\geq 40\text{mW}$ から 0.1% THD+N。40Hz、-40dBFS のパイロット・トーンを使用、PWR_MODE0 | -1 | 1    | %  |

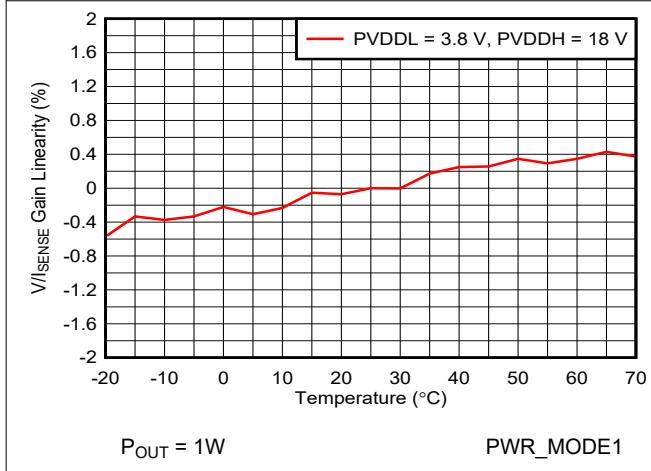

| ゲインの直線性       | Pout $\geq 80\text{mW}$ から 0.1% THD+N。40Hz、-40dBFS のパイロット・トーンを使用、PWR_MODE1 | -1 | 1    | %  |

| 温度範囲全体でのゲイン誤差 | -20°C~70°C、Pout = 1W                                                       |    | ±0.6 | %  |

| V と I の間の位相誤差 |                                                                            |    | 300  | ns |

#### 保護回路

|                            |                                    |      |               |   |

|----------------------------|------------------------------------|------|---------------|---|

| 最初のアタックに対するブラウンアウト防止リテンション | BOP_SRC = 1                        | 400  | $\mu\text{s}$ |   |

| サーマル・シャットダウン温度             |                                    | 145  | °C            |   |

| サーマル・シャットダウンの再試行           | OTE_RETRY = 1                      | 1.5  | s             |   |

| PVDDH の出力過電流制限             | 出力から出力、出力から GND、または出力から PVDDH への短絡 | 5.5  | 6.7           | A |

| PVDDL の出力過電流制限             | 出力から出力、出力から GND、または出力から PVDDL への短絡 | 2    | 2.6           | A |

| PVDDL 低電圧誤動作防止スレッショルド      | UVLO がアサートされている                    | 2    |               | V |

|                            | UVLO がアサート解除されている                  | 2.16 |               |   |

| AVDD 低電圧誤動作防止スレッショルド       | UVLO がアサートされている                    | 1.45 |               | V |

|                            | UVLO がアサート解除されている                  | 1.51 |               |   |

| IOVDD 低電圧誤動作防止スレッショルド      | UVLO がアサートされている                    | 1.13 |               | V |

|                            | UVLO がアサート解除されている                  | 1.25 |               |   |

$T_A = 25^\circ\text{C}$ 、 $\text{PVDDH} = 18\text{V}$ 、 $\text{PVDDL} = 3.8\text{V}$ 、 $\text{AVDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $R_L = 4\Omega + 15\mu\text{H}$ 、 $f_{IN} = 1\text{kHz}$ 、 $f_s = 48\text{kHz}$ 、ゲイン = 21dBV、SDZ = 1、NG\_EN=0、EN\_LLSR=0、PWR\_MODE1、セクション 7 に記載されているフィルタなしの状態で測定(特に記述のない限り)。

| パラメータ                        | テスト条件           | 最小値 | 代表値 | 最大値 | 単位 |

|------------------------------|-----------------|-----|-----|-----|----|

| PVDDL 内部 LDO 低電圧誤動作防止スレッショルド | UVLO がアサートされている |     | 4.1 |     | V  |

**Class-H コントローラ**

|                      |            |                            |      |         |

|----------------------|------------|----------------------------|------|---------|

|                      | 先読み時間      | サンプリング・レート 48kHz および 96kHz | 4.8  | ms      |

| <b>ビープ・ピン・ジェネレータ</b> |            |                            |      |         |

| $f_{IN}$             | SDZ ピン     | 入力 PWM 信号周波数               | 25.6 | 192 kHz |

| $f_{IN}$             | NC_SCLK ピン | 入力 PWM 信号周波数               | 1.6  | 12 kHz  |

**標準消費電流**

|                      |                              |                                            |       |    |

|----------------------|------------------------------|--------------------------------------------|-------|----|

| ハードウェア・シャットダウン       | SDZ = 0, PVDDH               | SDZ = 0, PVDDH                             | 0.05  | μA |

|                      |                              | SDZ = 0, PVDDL                             | 0.01  |    |

|                      |                              | SDZ = 0, AVDD                              | 0.14  |    |

|                      |                              | SDZ = 0, IOVDD                             | 0.005 |    |

| ソフトウェア・シャットダウン       | すべてのクロックが停止、PVDDH            | すべてのクロックが停止、PVDDH                          | 0.05  | μA |

|                      |                              | すべてのクロックが停止、PVDDL                          | 0.5   |    |

|                      |                              | すべてのクロックが停止、AVDD                           | 10    |    |

|                      |                              | すべてのクロックが停止、IOVDD                          | 0.52  |    |

| ノイズ・ゲート・モード          | $f_s = 48\text{kHz}$ , PVDDH | $f_s = 48\text{kHz}$ , PVDDH               | 0.012 | mA |

|                      |                              | $f_s = 48\text{kHz}$ , PVDDL               | 0.13  |    |

|                      |                              | $f_s = 48\text{kHz}$ , AVDD                | 8.2   |    |

|                      |                              | $f_s = 48\text{kHz}$ , IOVDD               | 0.01  |    |

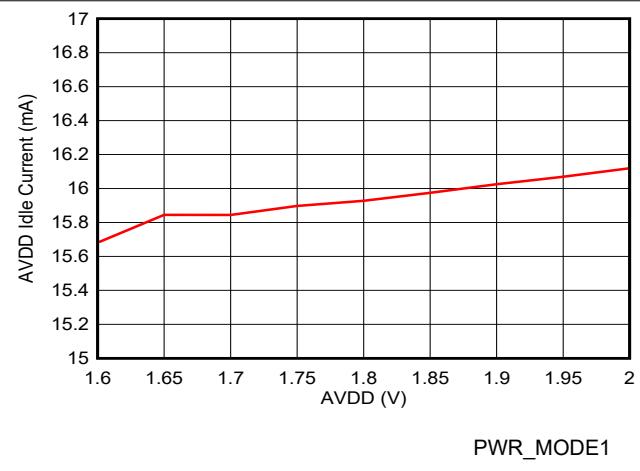

| アイドル・モード - PWR_MODE1 | $f_s = 48\text{kHz}$ , PVDDH | $f_s = 48\text{kHz}$ , PVDDH               | 0.04  | mA |

|                      |                              | $f_s = 48\text{kHz}$ , PVDDL               | 2.2   |    |

|                      |                              | $f_s = 48\text{kHz}$ , AVDD, IV センス=イネーブル  | 15.5  |    |

|                      |                              | $f_s = 48\text{kHz}$ , AVDD, IV センス=ディセーブル | 11.8  |    |

|                      |                              | $f_s = 48\text{kHz}$ , IOVDD               | 0.02  |    |

| アイドル・モード - PWR_MODE2 | $f_s = 48\text{kHz}$ , PVDDH | $f_s = 48\text{kHz}$ , PVDDH               | 3     | mA |

|                      |                              | $f_s = 48\text{kHz}$ , AVDD, IV センス=イネーブル  | 15.5  |    |

|                      |                              | $f_s = 48\text{kHz}$ , AVDD, IV センス=ディセーブル | 11.8  |    |

|                      |                              | $f_s = 48\text{kHz}$ , IOVDD               | 0.02  |    |

| アイドル・モード - PWR_MODE0 | $f_s = 48\text{kHz}$ , PVDDH | $f_s = 48\text{kHz}$ , PVDDH               | 2.3   | mA |

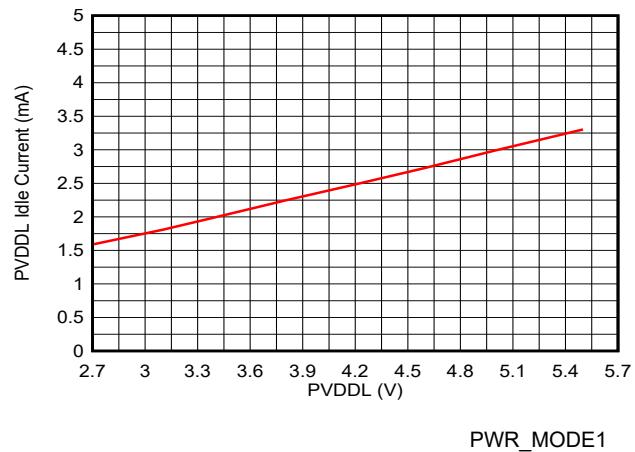

|                      |                              | $f_s = 48\text{kHz}$ , PVDDL               | 2.1   |    |

|                      |                              | $f_s = 48\text{kHz}$ , AVDD, IV センス=イネーブル  | 15.5  |    |

|                      |                              | $f_s = 48\text{kHz}$ , AVDD, IV センス=ディセーブル | 11.8  |    |

|                      |                              | $f_s = 48\text{kHz}$ , IOVDD               | 0.02  |    |

- (1) **PWR\_MODE0:** CDS\_MODE=10, PVDDL\_MODE=0

- (2) **PWR\_MODE1:** CDS\_MODE=00, PVDDL\_MODE=0

- (3) **PWR\_MODE2:** CDS\_MODE=11, PVDDL\_MODE=1

- (4) **PWR\_MODE3:** CDS\_MODE=01, PVDDL\_MODE=0

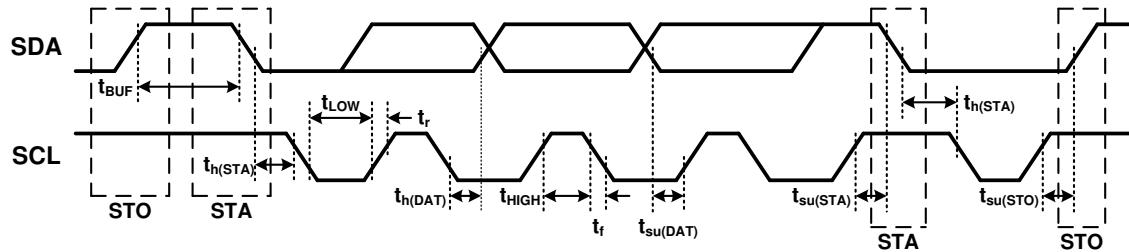

## 6.6 I<sup>2</sup>C のタイミング要件

T<sub>A</sub> = 25°C、IOVDD = 1.8V (特に記述のない限り)

|                     |                                                 | 最小値                            | 最大値  | 単位  |

|---------------------|-------------------------------------------------|--------------------------------|------|-----|

| <b>標準モード</b>        |                                                 |                                |      |     |

| f <sub>SCL</sub>    | SCL クロック周波数                                     | 0                              | 100  | kHz |

| t <sub>HD:STA</sub> | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック・パルスが生成されます。 | 4                              |      | μs  |

| t <sub>LOW</sub>    | SCL クロックの Low の時間                               | 4.7                            |      | μs  |

| t <sub>HIGH</sub>   | SCL クロックの High の時間                              | 4                              |      | μs  |

| t <sub>SU:STA</sub> | 反復開始条件のセットアップ時間                                 | 4.7                            |      | μs  |

| t <sub>HD:DAT</sub> | データ・ホールド時間:I <sup>2</sup> C バス・デバイスの場合          |                                | 3.45 | μs  |

| t <sub>SU:DAT</sub> | データ・セットアップ時間                                    | 250                            |      | ns  |

| t <sub>r</sub>      | SDA と SCL の立ち上がり時間                              |                                | 1000 | ns  |

| t <sub>f</sub>      | SDA と SCL の立ち下がり時間                              |                                | 300  | ns  |

| t <sub>SU:STO</sub> | 終了条件のセットアップ時間                                   | 4                              |      | μs  |

| t <sub>BUF</sub>    | 終了条件と開始条件の間のバス・フリー時間                            | 4.7                            |      | μs  |

| C <sub>b</sub>      | 各バス・ラインの容量性負荷                                   |                                | 400  | pF  |

| <b>Fast モード</b>     |                                                 |                                |      |     |

| f <sub>SCL</sub>    | SCL クロック周波数                                     | 0                              | 400  | kHz |

| t <sub>HD:STA</sub> | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック・パルスが生成されます。 | 0.6                            |      | μs  |

| t <sub>LOW</sub>    | SCL クロックの Low の時間                               | 1.3                            |      | μs  |

| t <sub>HIGH</sub>   | SCL クロックの High の時間                              | 0.6                            |      | μs  |

| t <sub>SU:STA</sub> | 反復開始条件のセットアップ時間                                 | 0.6                            |      | μs  |

| t <sub>HD:DAT</sub> | データ・ホールド時間:I <sup>2</sup> C バス・デバイスの場合          | 0                              | 0.9  | μs  |

| t <sub>SU:DAT</sub> | データ・セットアップ時間                                    | 100                            |      | ns  |

| t <sub>r</sub>      | SDA と SCL の立ち上がり時間                              | 20 + 0.1 × C <sub>b</sub> [pF] | 300  | ns  |

| t <sub>f</sub>      | SDA と SCL の立ち下がり時間                              | 20 + 0.1 × C <sub>b</sub> [pF] | 300  | ns  |

| t <sub>SU:STO</sub> | 終了条件のセットアップ時間                                   | 0.6                            |      | μs  |

| t <sub>BUF</sub>    | 終了条件と開始条件の間のバス・フリー時間                            | 1.3                            |      | μs  |

| C <sub>b</sub>      | 各バス・ラインに対する容量性負荷 (10pF~400pF)                   |                                | 400  | pF  |

| <b>ファスト・モード・プラス</b> |                                                 |                                |      |     |

| f <sub>SCL</sub>    | SCL クロック周波数                                     |                                | 1000 | kHz |

| t <sub>HD:STA</sub> | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック・パルスが生成されます。 | 0.26                           |      | μs  |

| t <sub>LOW</sub>    | SCL クロックの Low の時間                               | 0.5                            |      | μs  |

| t <sub>HIGH</sub>   | SCL クロックの High の時間                              | 0.26                           |      | μs  |

| t <sub>SU:STA</sub> | 反復開始条件のセットアップ時間                                 | 0.26                           |      | μs  |

| t <sub>HD:DAT</sub> | データ・ホールド時間:I <sup>2</sup> C バス・デバイスの場合          | 0                              |      | μs  |

| t <sub>SU:DAT</sub> | データ・セットアップ時間                                    | 50                             |      | ns  |

| t <sub>r</sub>      | SDA と SCL の立ち上がり時間                              |                                | 120  | ns  |

| t <sub>f</sub>      | SDA と SCL の立ち下がり時間                              |                                | 120  | ns  |

| t <sub>SU:STO</sub> | 終了条件のセットアップ時間                                   | 0.26                           |      | μs  |

| t <sub>BUF</sub>    | 終了条件と開始条件の間のバス・フリー時間                            | 0.5                            |      | μs  |

| C <sub>b</sub>      | 各バス・ラインの容量性負荷                                   |                                | 550  | pF  |

図 6-1. I<sup>2</sup>C のタイミング図

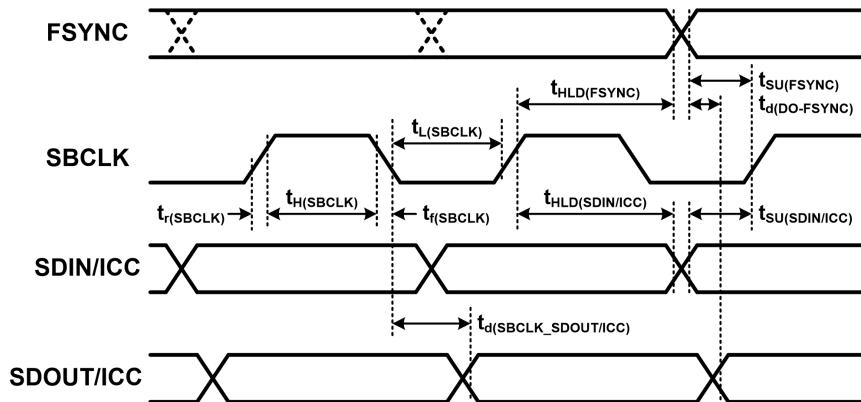

## 6.7 TDM ポートのタイミング要件

$T_A = 25^\circ\text{C}$ 、 $\text{IOVDD} = \text{NC\_V1P8V} = 1.8\text{V}$ 、すべての出力に  $20\text{pF}$  の負荷 (特に記述のない限り)

|                                |                                                                                               |  | 最小値 | 最大値 | 単位 |

|--------------------------------|-----------------------------------------------------------------------------------------------|--|-----|-----|----|

| $t_H(\text{SBCLK})$            | SBCLK の High 期間                                                                               |  | 20  |     | ns |

| $t_L(\text{SBCLK})$            | SBCLK の Low 期間                                                                                |  | 20  |     | ns |

| $t_{SU}(\text{FSYNC})$         | FSYNC セットアップ時間                                                                                |  | 8   |     | ns |

| $t_{HLD}(\text{FSYNC})$        | FSYNC のホールド時間                                                                                 |  | 8   |     | ns |

| $t_{SU}(\text{SDIN/ICC})$      | SDIN/ICC セットアップ時間                                                                             |  | 8   |     | ns |

| $t_{HLD}(\text{SDIN/ICC})$     | SDIN/ICC のホールド時間                                                                              |  | 8   |     | ns |

| $t_d(\text{SBCLK\_SDOUT/ICC})$ | SBCLK から SDOUT/ICC への遅延<br>SBCLK の 50% から SDOUT/ICC の 50%<br>まで、 $\text{IOVDD} = 1.8\text{V}$ |  |     | 30  | ns |

| $t_r(\text{SBCLK})$            | SBCLK の立ち上がり時間<br>10%~90% の立ち上がり時間                                                            |  |     | 8   | ns |

| $t_f(\text{SBCLK})$            | SBCLK の立ち下がり時間<br>90%~10% の立ち下がり時間                                                            |  |     | 8   | ns |

図 6-2. TDM と ICC のタイミング図

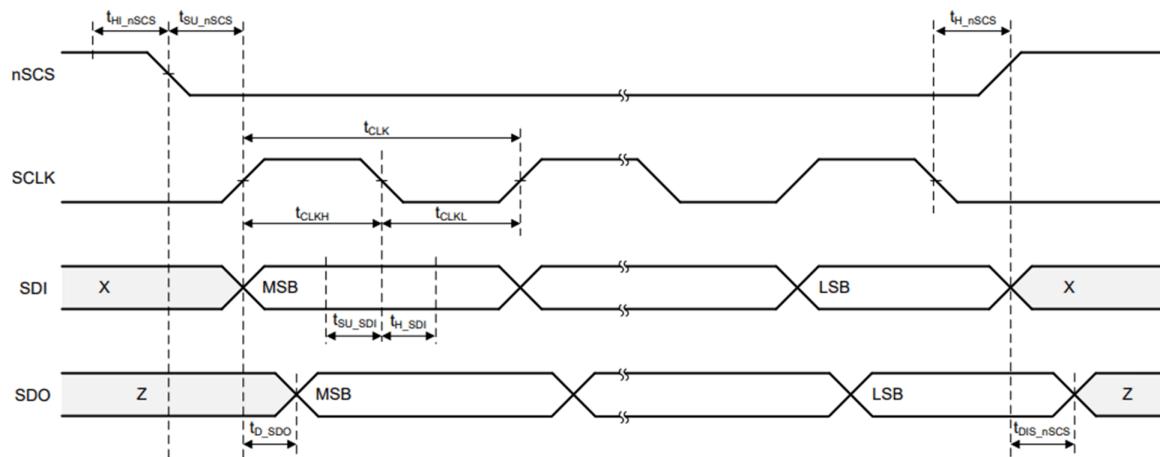

## 6.8 SPI のタイミング要件

$T_A = 25^\circ\text{C}$ , NC\_V1P8V = IOVDD = 1.8V

|                 |                               | 最小値  | 公称値 | 最大値 | 単位 |

|-----------------|-------------------------------|------|-----|-----|----|

| $t_{H\_nSCS}$   | nSCS のアクティブ Low の前の最小 High 時間 | 200  |     |     | ns |

| $t_{SU\_nSCS}$  | nSCS 入力セットアップ時間               | 60   |     |     | ns |

| $t_{H\_nSCS}$   | nSCS 入力ホールド時間                 | 60   |     |     | ns |

| $t_{CLK}$       | SCLK 周期                       | 60   |     |     | ns |

| $t_{CLKH}$      | SCL の High パルス幅               | 30   |     |     | ns |

| $t_{CLKL}$      | SCLK の Low パルス幅               | 30   |     |     | ns |

| $t_{SU\_SDI}$   | SDI 入力データのセットアップ時間            | 10.5 |     |     | ns |

| $t_{H\_SDI}$    | SDI 入力データのホールド時間              | 8    |     |     | ns |

| $t_{D\_SDO}$    | SDO データの出力遅延                  |      |     | 25  | ns |

| $t_{DIS\_nSCS}$ | nSCS ディセーブルの遅延                |      |     | 25  | ns |

図 6-3. SPI のタイミング図

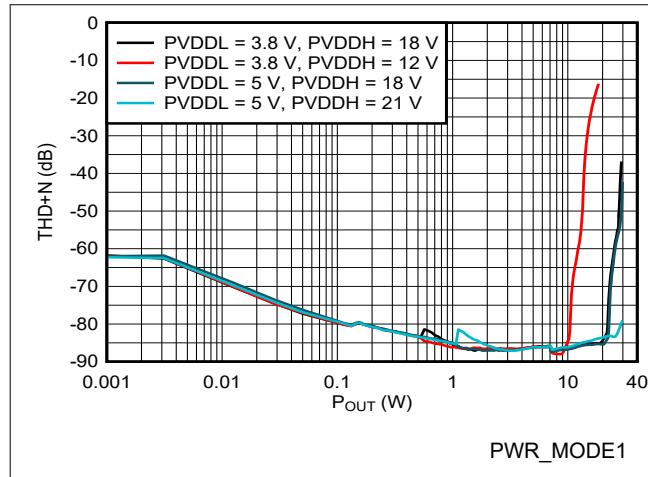

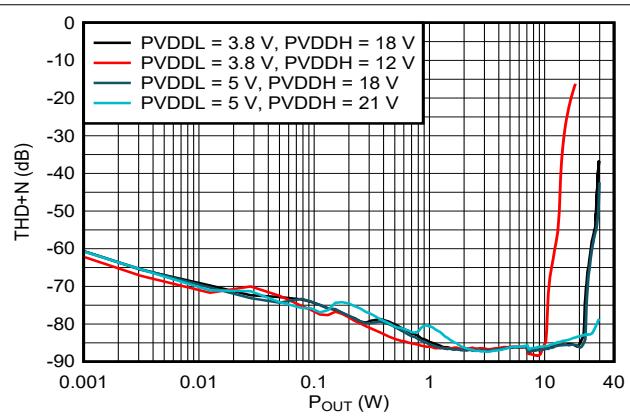

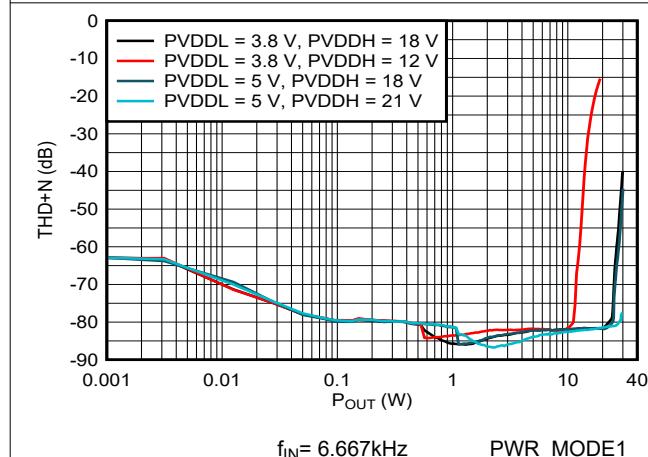

## 6.9 代表的特性

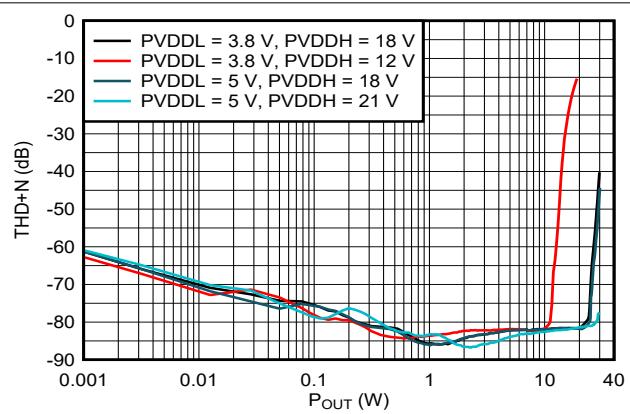

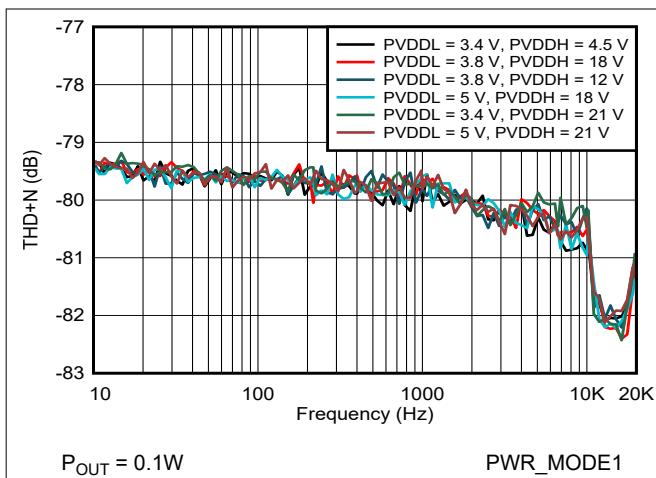

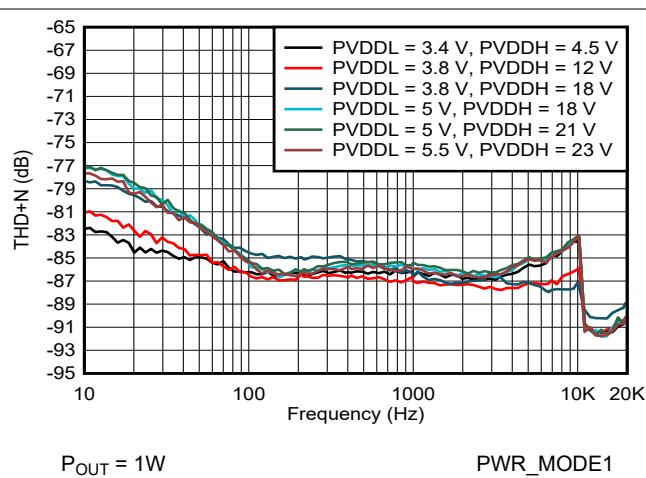

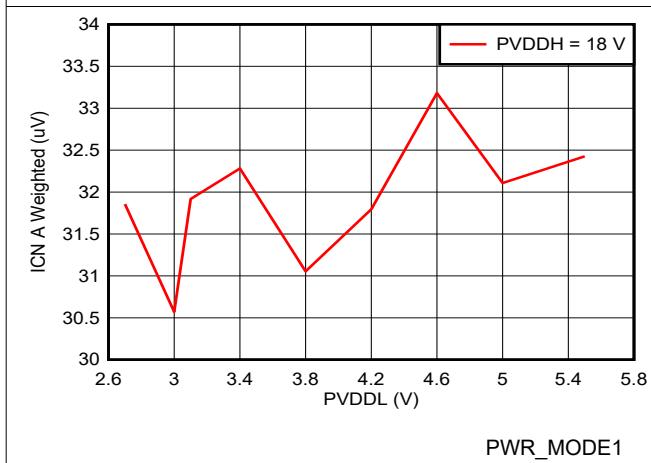

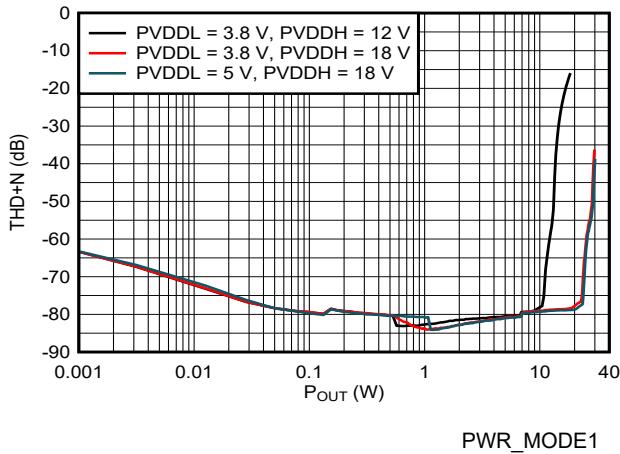

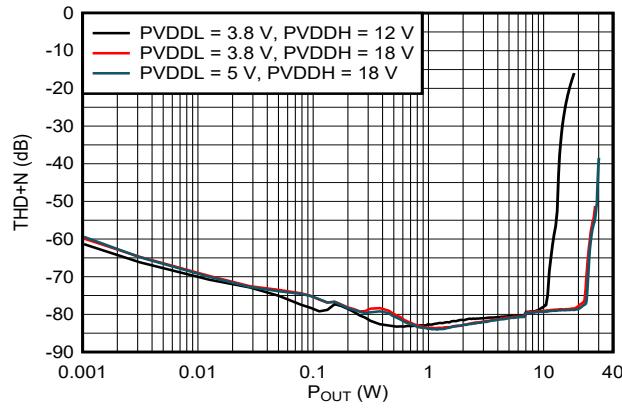

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 1.8\text{V}$ 、 $\text{IOVDD} = 1.8\text{V}$ 、 $f_s = 48\text{kHz}$ 、Class-D スイッチング周波数=384kHz、入力信号  $f_{IN} = 1\text{kHz}$  - サイン、負荷= $4\Omega + 15\mu\text{H}$  (特に記述のない限り)。

図 6-4. THD+N と出力電力との関係

図 6-5. THD+N と出力電力との関係

図 6-6. THD+N と出力電力との関係

図 6-7. THD+N と出力電力との関係

図 6-8. THD+N と周波数との関係

図 6-9. THD+N と周波数との関係

図 6-10. ICN と PVDDL との関係

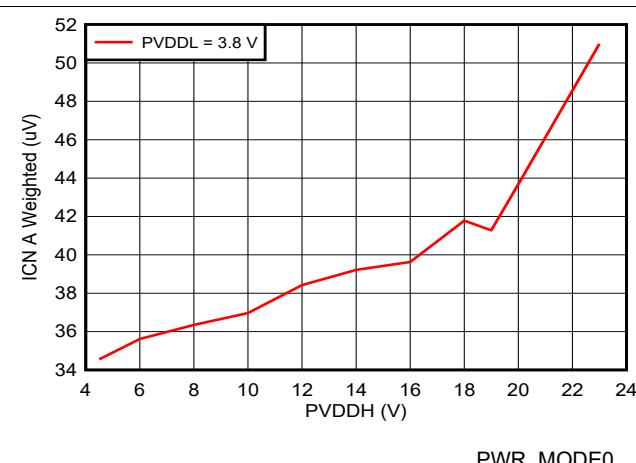

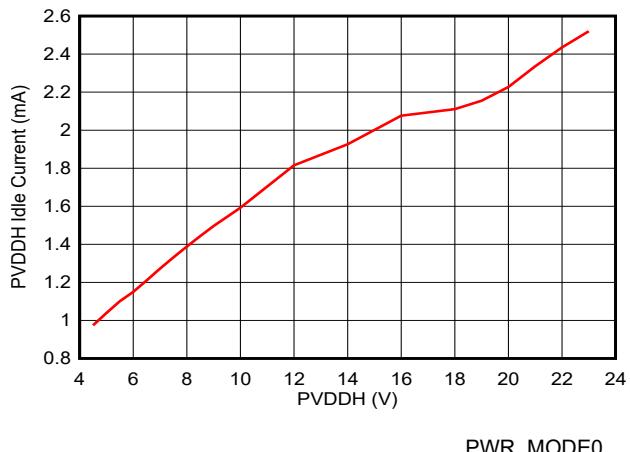

図 6-11. ICN と PVDDH との関係

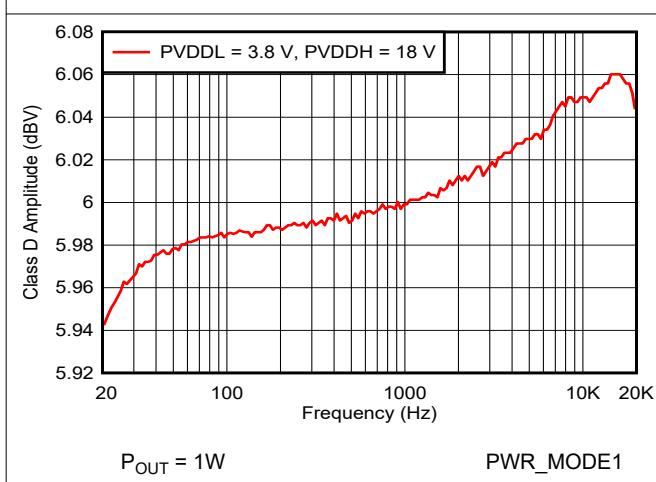

図 6-12. Class-D の振幅と周波数との関係

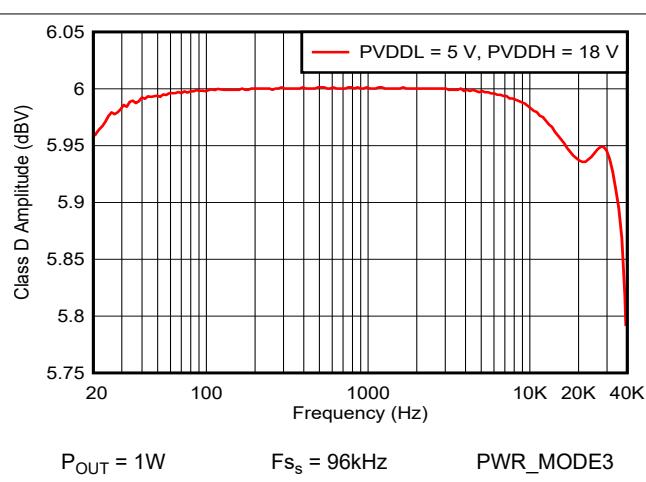

図 6-13. Class-D の振幅と周波数との関係

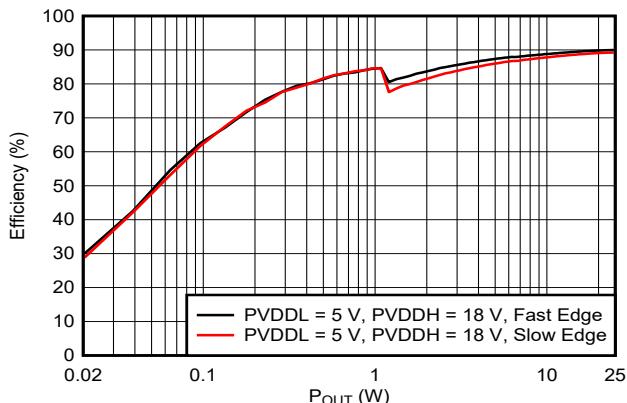

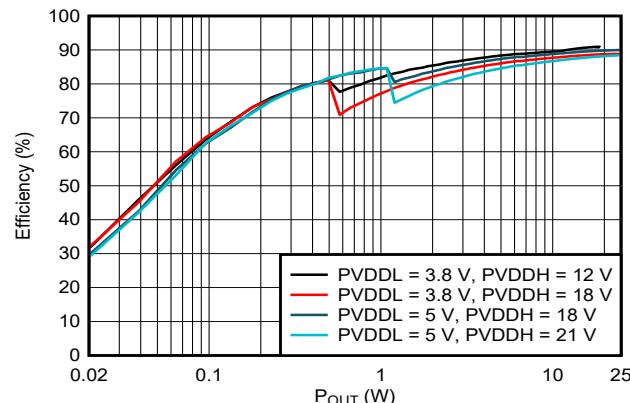

図 6-14. 効率と出力電力との関係

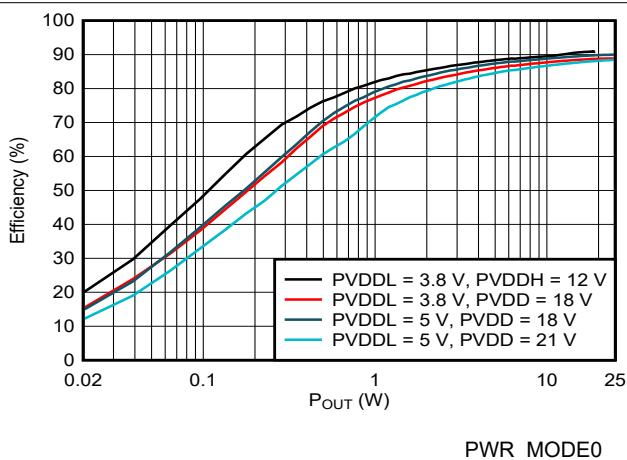

図 6-15. 効率と出力電力との関係

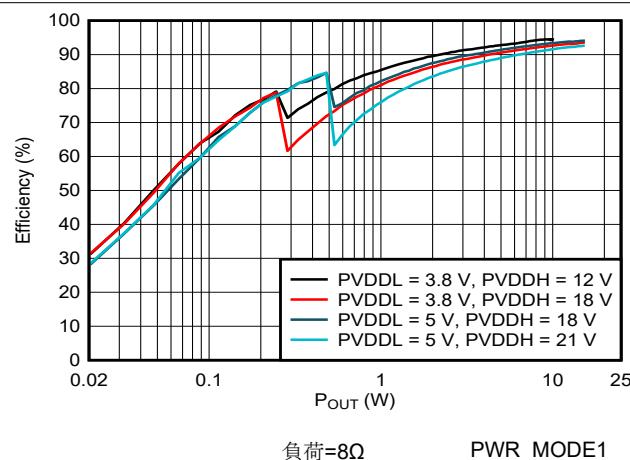

図 6-16. 効率と出力電力との関係

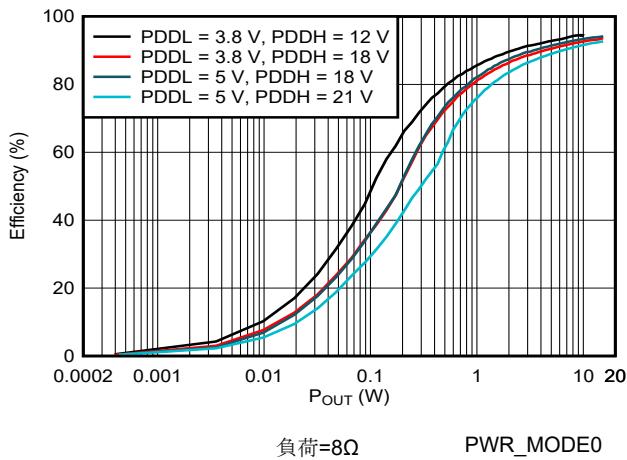

図 6-17. 効率と出力電力との関係

図 6-18. 効率と出力電力との関係

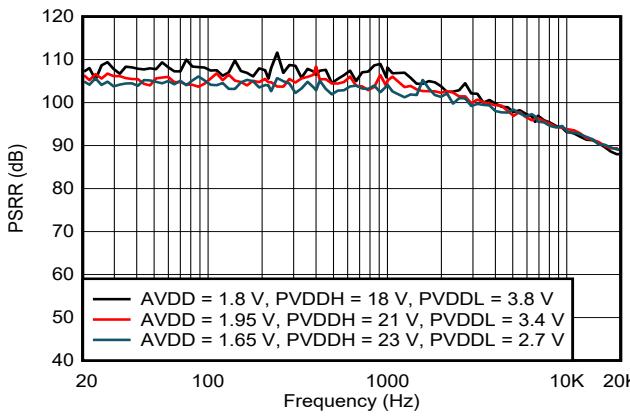

図 6-19. AVDD PSRR と周波数との関係

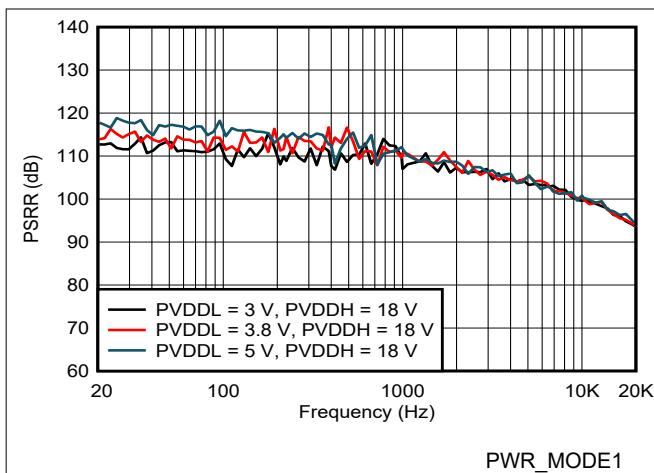

図 6-20. PVDDL PSRR と周波数との関係

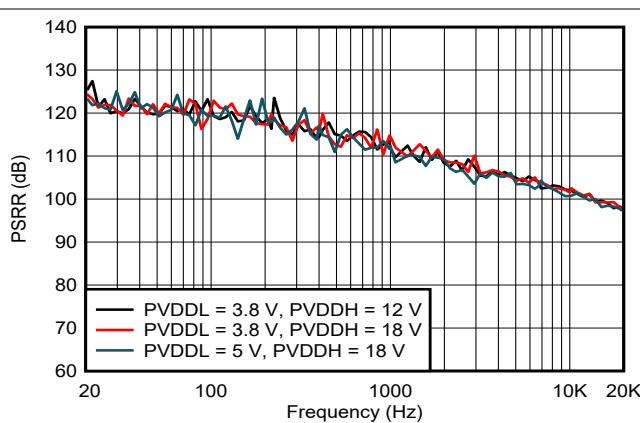

図 6-21. PVDDH PSRR と周波数との関係

図 6-22. V/I ゲインの直線性と出力電力との関係

図 6-23. V/I ゲインの直線性と出力電力との関係

P<sub>OUT</sub> = 1W

PWR\_MODE1

図 6-24. V/I ゲインの直線性と温度との関係

PWR\_MODE1

図 6-25. AVDD のアイドル電流と AVDD との関係

PWR\_MODE1

PWR\_MODE0

図 6-26. PVDDL アイドル電流と PVDDL との関係

図 6-27. PVDDH アイドル電流と PVDDH との関係

## 7 パラメータ測定情報

デバイスの標準的な特性は、ベンチ評価基板 (EVM) とオーディオ高精度アナライザを使用して測定されます。PSIA インターフェイスを使用すると、I<sup>2</sup>S インターフェイスをオーディオ高精度アナライザに直接駆動することができます。

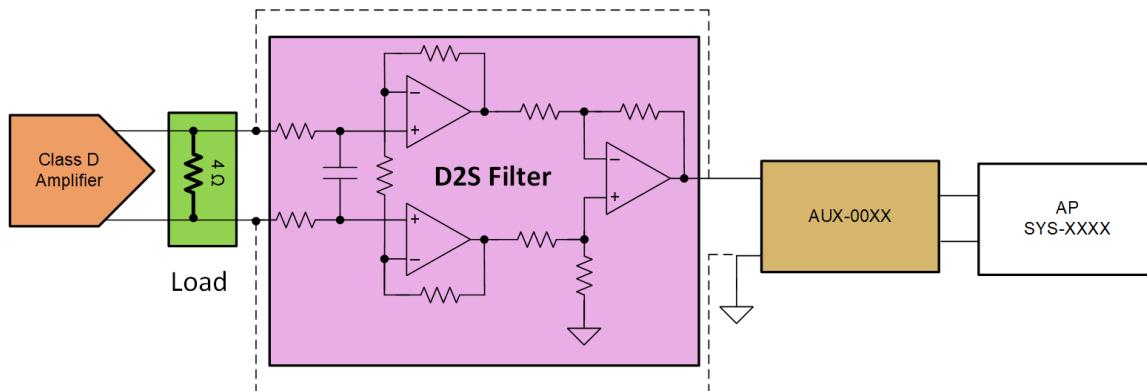

一部の測定では (THD+N、ICN、DNR など)、Class-D 出力端子は、以下に示すように差動からシングルエンドへの (D2S) フィルタを経由して、オーディオ高精度アナライザのアナログ入力に接続されます。D2S フィルタには、120kHz の 2 次パッシブ極と計測用アンプが搭載されています。D2S フィルタにより、TAS2781 の高性能 Class-D アンプは処理前の出力のフィルタリングとバッファリングを確実に行います。そのため、Class-D 出力において AUX-00XX フィルタの効果に影響を及ぼす負荷によって生じる測定誤差を防止することができます。

図 7-1. 差動からシングルエンドへの (D2S) フィルタ

## 8 詳細説明

### 8.1 概要

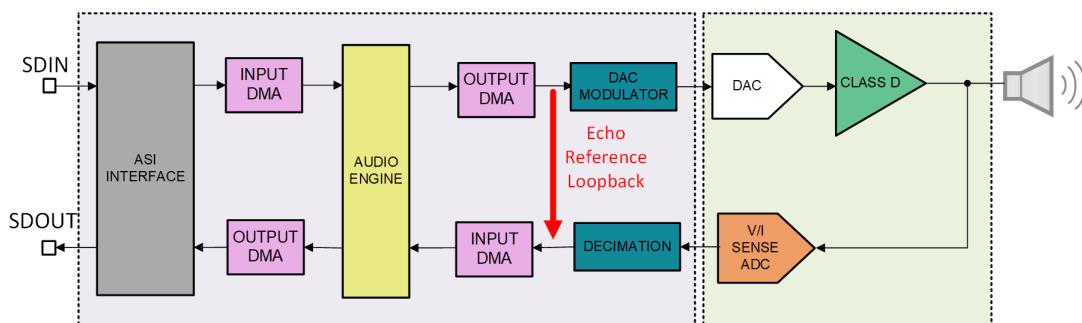

TAS2781 はモノラル・デジタル入力 Class-D アンプで、効率的なバッテリ動作と小さなソリューション・サイズが重要となるモバイル・アプリケーション向けに最適化されています。この中には、スピーカ IV (電流 / 電圧) 検出機能とブランクアウト防止付きバッテリ・キャッシング制限機能が搭載されています。このデバイスは、TDM/I<sup>2</sup>S および I<sup>2</sup>C (または SPI) インターフェイスを使用して動作します。

TAS2781 は、外部昇圧コンバータを制御してバッテリ寿命を延長する Hybrid-Pro アルゴリズムを提供します。

表 8-1. フルスケール

| 入出力信号      | フルスケール値 |

|------------|---------|

| Class-D 出力 | 21dBV   |

| 電圧モニタ      | 23V     |

| 電流検出       | 5A      |

| 電圧検出       | 16Vpk   |

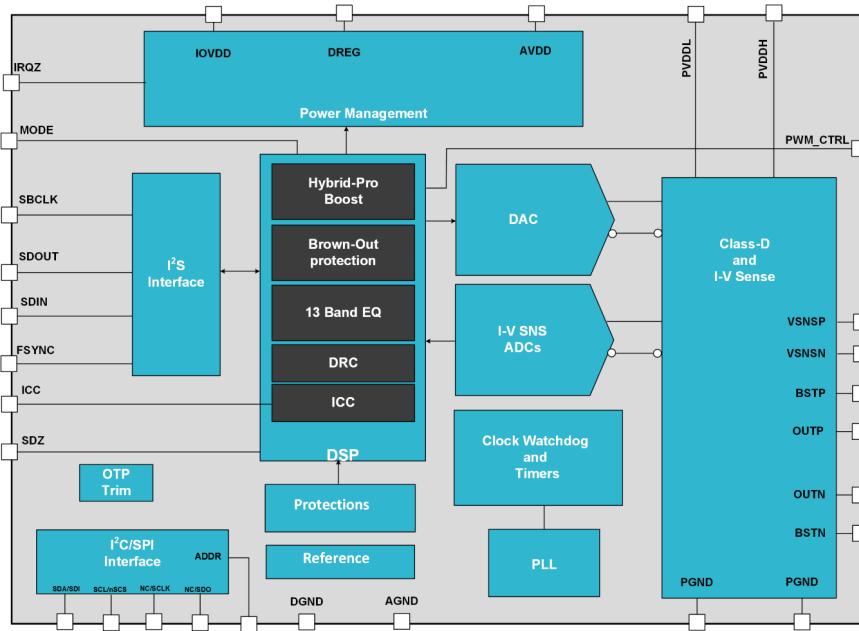

## 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 モード選択

TAS2781 には 2 つの動作モードがあり、ピン 26 (MODE) の設定に基づいて選択されます - 以下の表を参照してください。

表 8-2. TAS2781 の制御インターフェイス

| アンプ・モード  | 制御インターフェイス       | ピン 26 (MODE)      |

|----------|------------------|-------------------|

| スマート・アンプ | I <sup>2</sup> C | GND に接続           |

| スマート・アンプ | SPI              | 470Ω を GND との間に接続 |

### 8.3.2 デバイス・アドレスの選択

TAS2781 は、TDM/I<sup>2</sup>S インターフェイスを使用して動作します。オーディオ入出力は、I<sup>2</sup>S、左詰め、TDM などの形式を使用して FSYNC、SBCLK、SDIN、SDOUT ピン経由で行われます。構成とステータスは、I<sup>2</sup>C プロトコル (MODE ピンを GND に接続) か SPI プロトコル (MODE ピンを 470Ω の抵抗経由で GND に接続) を使用して提供されます。

I<sup>2</sup>C アドレス用のデバイスの構成方法を以下の表に示します。ペリフェラル・アドレスは、R/W ビットを 0 にセットし、1 ビット左にシフトして表記しています (例:{ADDR[6:0],1b0})。アドレス構成を設定するには、公差が 5% 以内の抵抗を使用する必要があります。

表 8-3. I<sup>2</sup>C アドレスの選択

| I <sup>2</sup> C アドレス | 0x70     | 0x72              | 0x74               | 0x76               | 0x78                | 0x7A              | 0x7C               | 0x7E      |

|-----------------------|----------|-------------------|--------------------|--------------------|---------------------|-------------------|--------------------|-----------|

| ADDR ピン               | GND への短絡 | 470Ω を GND との間に接続 | 470Ω を AVDD との間に接続 | 2.2kΩ を GND との間に接続 | 2.2kΩ を AVDD との間に接続 | 10kΩ を GND との間に接続 | 10kΩ を AVDD との間に接続 | AVDD への短絡 |

TAS2781 には、グローバルの 7 ビット I<sup>2</sup>C アドレス 0x80 があります。レジスタの I<sub>2</sub>C\_GLB\_EN ビットが High に設定されているとき、ADDR ピンの設定に関係なく、デバイスはこのアドレスで I<sup>2</sup>C コマンドに応答します。これにより、複数の TAS2781 デバイスを使用して、すべてのデバイスで同様の設定をプログラムする場合に、デバイス構成を迅速化することができます。複数のデバイスが I<sup>2</sup>C コマンドに応答しているため、マルチデバイスの書き込み中は I<sup>2</sup>C の ACK/NACK を使用することはできません。I<sup>2</sup>C の CRC 機能を使用して、各デバイスが I<sup>2</sup>C コマンドを正しく受信したかを確認する必要

があります。グローバル・アドレスを使用して複数のデバイスへの書き込みが完了すると、ローカル・アドレスを使用して各デバイスの I<sup>2</sup>C\_CKSUM レジスタの CRC をチェックし、適切な値が書き込まれたことを確認する必要があります。グローバル I<sup>2</sup>C アドレスをディセーブルにするには、I<sup>2</sup>C\_GBL\_EN レジスタ・ビットを使用します。SDZ ピンをリリースすると、ADDR ピンの自動サンプリングにより I<sup>2</sup>C アドレスが検出されます。さらに、電源投入後に I<sup>2</sup>C\_AD\_DET レジスタ・ビットを High に設定すると、アドレスが再検出され、ADDR ピンも再度サンプリングされます。

### 8.3.3 SPI インターフェイス

TAS2781 は、ピン 26 (MODE) が 470Ω の抵抗を経由して GND に接続されているときに使用可能な 1.8V SPI インターフェイスを実装しています。

デバイスのピン 17 (NC\_V1P8) は、1.8V 電源に接続する必要があります。

ホスト・コントローラは、CPHA = 1 と CPOL = 0 でこのモードを使用します。TAS2781 の SPI ロジック・ブロックは、SPI クロックの立ち下がりエッジで SPI 入力データをサンプリングし、SPI クロックの立ち上がりエッジで SPI 出力データを送信します。

### 8.3.4 レジスタの構成

デバイスの構成と係数は、ページとブック方式で保存されます。各ページは 128 バイト、各ブックは 256 ページで構成されています。すべてのデバイス構成レジスタはブック 0 に保存されます。これは、電源投入時とソフトウェア・リセット後のデフォルト設定です。ブックとページは、の BOOK[7:0] レジスタ・ビットと、の PAGE[7:0] レジスタ・ビットで設定できます。

#### 注

ブック 0x00、ページ 0x04、0x05、0x06、0x08、0x0A のレジスタ・ビットをプログラムするには、4 つのレジスタ (32 ビット形式) のグループ単位で行う必要があります。各バイトは 1 つの 8 ビット・レジスタに対応しており、最下位バイトはもっとも大きなレジスタ・アドレスに対応しています。たとえば、のレジスタでリミッタの最大スレッシュルドをプログラムする場合、MSB はレジスタ 0x10 で、LSB はレジスタ 0x13 です。

## 8.4 デバイスの機能モード

### 8.4.1 TDM シリアル・オーディオ・ポート

TAS2781 は、フレキシブルな TDM シリアル・オーディオ・ポートを搭載しています。このポートは、ステレオ I<sup>2</sup>S、左揃え、TDM などさまざまなフォーマットに対応するように構成することができます。モノラル・オーディオ再生は、SDIN ピンから行うことが可能です。SDOUT ピンは、PVDDL 電圧、PVDDH 電圧、ダイ温度、ステータス、エコー・キャンセレーション用のオーディオなどのストリームを送信するために使用します。

デフォルトでは、TAS2781 は PCM 再生サンプル・レート (AUTO\_RATE= 0) を自動検出します。この機能は、の AUTO\_RATE レジスタ・ビットを High にセットすることにより、ディセーブルして手動で構成することもできます。

TDM シリアル・オーディオ・ポートの有効な SBCLK 対 FSYNC 比は、のレジスタに示されています。デバイスはタイム・スロット数を自動検出するため、プログラムする必要はありません。

AUTO\_RATE レジスタ・ビットが High にセットされている場合 (TDM サンプル・レートの自動検出がディセーブル)、SAMP\_RATE[2:0] レジスタ・ビットと SBLK\_FS\_RATIO[5:0] レジスタ・ビットを使用して、PCM オーディオ・サンプル・レートを構成できます。TAS2781 は堅牢なクロック・フォルト検出エンジンを搭載しており、FSYNC が構成されているサンプル・レートに合っていない場合 (AUTO\_RATE = 1 の場合) や、SBCLK 対 FSYNC 比がサポートされていない場合に、再生パスのボリュームを自動的に低下させます (可聴アーティファクトが最小化されます)。クロックの周波数と比がどちらも有効であることが検出されると、デバイスは再生パスのボリュームを自動的に構成されている値に戻し、再生を再開します。

自動レート検出を使用すると、TDM バスで検出されたサンプリング・レートと SBCLK 対 FSYNC 比は、およびのレジスタにある読み取り専用ビット FS\_RATIO[5:0] と FS\_RATE[2:0] に通知されます。

フレームは FSYNC が High から Low、または Low から High へのいずれかの遷移で開始します (FRAME\_START レジスタ・ビットで設定)。FSYNC および SDIN は、SBCLK の立ち上がりエッジか立ち下がりエッジのいずれかを使用してサンプリングされます (RX\_EDGE レジスタ・ビットで設定)。RX\_OFF[4:0] レジスタ・ビットでは、FSYNC の遷移からタイ

ム・スロット 0 の開始までの SBCLK のサイクル数を定義します。この値は通常、左揃えフォーマットの場合は 0、I<sup>2</sup>S フォーマットの場合は 1 に設定されます。

**RX\_SLEN[1:0]** レジスタ・ビットは、RX タイム・スロットの長さを 16、24、32 (デフォルト) ビットに設定します。タイム・スロット内のオーディオ・サンプルのワード長は、**RX\_WLEN[1:0]** レジスタ・ビットで設定します。デフォルトでは、RX ポートはタイム・スロット内のオーディオ・サンプルを左揃えにしますが、**RX\_JSTF** レジスタ・ビットで右揃えに変更することも可能です。TAS2781 は、モノラルとステレオのダウンミックス再生 ( $[L+R]/2$ ) に対応しています。デフォルトでは、デバイスは I<sup>2</sup>C ベース・アドレスのオフセット (ADDR ピンで設定) と同じタイム・スロットからモノラル再生を行います。**RX\_SCFG[1:0]** レジスタ・ビットを使用すると、**RX\_SLOT\_R[3:0]** レジスタ・ビットと **RX\_SLOT\_L[3:0]** レジスタ・ビットの設定により、再生ソースを左側のタイム・スロット、右側のタイム・スロット、またはステレオ・ダウンミックスにオーバーライドすることができます。

タイム・スロットがフレーム境界を超えたときに部分的に受信するか、すべて受信するかのいずれかを選択した場合、レシーバはデジタル的にミュートされたサンプルと同等のヌル・サンプルを返します。

TDM ポートは、SDOUT ピンで、スピーカ電圧検出、スピーカ電流検出、割り込みとステータス、PVDDH 電圧、ダイ温度など多数のサンプル・ストリームを送信できます。

**SBCLK** の立ち上がりエッジか立ち下がりエッジのいずれかを使用して、SDOUT ピンでデータを送信することができます。この機能は、TX\_EDGE レジスタ・ビットをセットして構成できます。**TX\_OFF[2:0]** レジスタ・ビットは、フレーム開始時からタイム・スロット 0 の開始時までの SBCLK のサイクル数を定義します。この値は通常、左揃えフォーマットの場合は 0、I<sup>2</sup>S フォーマットの場合は 1 にプログラムされます。TDM TX は、TX\_FILL レジスタ・ビットの設定に応じて、ロジック 0 かハイ・インピーダンスのいずれかを送信できます。オプションのバス・キーパーは、すべてのデバイスがハイ・インピーダンスで駆動している場合、SDOUT ピンの状態を弱く保持します。SDOUT で必要なバス・キーパーは 1 つだけのため、この機能は TX\_KEEPEN レジスタ・ビットでディセーブルにできます。バス・キーパーは、TX\_KEEPEN レジスタ・ビットを使用して、1LSB のみバスを保持するか、常時 (永続的に) バスを保持するかを構成できます。さらに、TX\_KEEPACY レジスタ・ビットを使用して、キーパーの LSB を 1 フル・サイクルの間駆動するか、ハーフ・サイクルだけ駆動するかも設定できます。

**TX\_FILL** は、I<sup>2</sup>S バスにアンプが 1 つしかないモノラル・システムで使用されます。TX\_FILL を Low にセットしておくと、アンプに使用されないスロットにはすべて 0 が入ります。ここに記載されている TX ビットは、のレジスタにあります。

複数のデバイスが同一の I<sup>2</sup>S バス上にある場合は、ページ 0x01 の SDOUT\_HIZ レジスタが役立ちます。各デバイスは、バス上にある他のデバイスのスロット構成を認識できません。システム・レベルで SDOUT\_HIZ レジスタを、設定が正しく行われ、内部や外部の競合が発生しないよう、適切にプログラムする必要があります。

電流値と電圧値は、デフォルトでは全 16 ビットすべての測定値が送信されます。の IVMON\_EN[1:0] レジスタ・ビットを使用すると、1 スロットで 8MSB ビットだけ、または複数のスロットにまたがって 12MSB ビットの値を送信できます。ホスト・プロセッサで 24 ビットの I<sup>2</sup>S/TDM データのみを処理する場合は、特殊な 12 ビット・モードを使用します。デバイスは電圧検出スロットと電流検出スロットを 1 スロットずつオフに構成する必要があり、この結果、3 つの連続する 8 ビット・スロットが消費されます。このモードでは、デバイスは最初の 12MSB ビットを送信し、次に前のスロットで指定された 2 番目の 12MSB ビットを送信します。

タイム・スロットがフレーム境界を超えて送信されるように選択した場合、トランスマッタはフレーム境界で送信を切り捨てます。

SAR 測定 (PVDDL、PVDDH、温度) のためのタイム・スロットは SAR\_DATA\_SLOT[5:0] レジスタ・ビットで設定します。サンプル・ストリームをイネーブルにするには、SAR\_DATA\_TX レジスタ・ビットを High にセットする必要があります。スロット長は、のレジスタにある SAR\_DATA\_SL ビットによって選択します。

TDM の最後に処理されるオーディオ・スロットについては、イネーブル化や長さの設定に AUDIO\_SLOT[5:0]、AUDIO\_TX、AUDIO\_SLEN レジスタ・ビットを使用します。

スロットのステータス情報は STATUS\_SLOT[5:0] レジスタ・ビットで確認できます。STATUS\_TX レジスタ・ビットを High にセットすると、ステータス送信はイネーブルになります。

## 8.4.2 再生信号パス

### 8.4.2.1 デジタル信号プロセッサ

オンチップの低レイテンシ DSP は、テキサス・インストルメンツの SmartAmp スピーカ保護アルゴリズムに対応し、ラウドネスの最大化とともにスピーカを安全な状態に維持します。

また、DSP には Class-H アンプ向けの Band EQ、ステレオ・バランシング、超音波、外部昇圧コントローラも搭載されています。

### 8.4.2.2 ハイパス・フィルタ

オーディオ再生信号に過度な DC と低周波数の内容が含まれていると、ラウドスピーカが損傷する可能性があります。TAS2781 は、PCM 再生パスに対してこうした事象が発生することを防ぐハイパス・フィルタ (HPF) を搭載しています。HPF\_FREQ\_PB[2:0] レジスタ・ビットは、HPF のコーナー周波数を設定します。レジスタ・ビットを 3'b000 にセットすると、フィルタをバイパスさせることができます。

### 8.4.2.3 アンプの反転

TAS2781 は、OUT\_P ピンと OUT\_N ピンに非反転信号を出力します。AMP\_INV レジスタ・ビットを High に設定することにより、出力をデジタル入力値に対して反転できます。

### 8.4.2.4 デジタル・ボリューム制御およびアンプ出力レベル

オーディオ入力からスピーカ端子へのゲインは、アンプ出力レベルとデジタル・ボリューム制御 (DVC) の設定で制御します。

アンプ出力レベルの設定は、AMP\_LVL[4:0] レジスタ・ビットを使用してプログラムします。アンプのレベルは、のレジスタに示されています。デジタル・ボリューム制御 (DVC) は、デフォルトで 0dB に設定されています。このレベルは、アンプのアナログ・クリッピングにより必ずしも実現できるとは限らないため、ゲインの伝達にのみ使用してください。

式 (1) で、アンプ出力電圧を計算します：

$$V_{AMP} = INPUT + A_{DVC} + A_{AMP} \quad (1)$$

ここで

- $V_{AMP}$  は、アンプ出力電圧 (dBV) です

- INPUT は、0dBFS を基準とした場合のデジタル入力振幅を表す dB 数です

- $A_{DVC}$  は、デジタル・ボリューム制御の設定を表す dB 数です

- $A_{AMP}$  は、アンプ出力レベルの設定を表す dBV 数です

DVC は DVC\_LVL[7:0] レジスタ・ビットの設定によって、0dB~ -100dB の間で 0.5dB きざみで構成することができます。C8h より大きい設定は、ミュートと解釈されます。デジタル・ボリューム制御が変更されると、デバイスはの DVC\_SLEW[31:0] レジスタ・ビットのステータスに基づいて、ボリュームを新しい設定にランプします。のレジスタの DVC\_RMP\_RT[1:0] ビットを使用して、ボリュームのランプ制御のイネーブルとディセーブルを切り替えます。

Class-D アンプは、閉ループ・アーキテクチャを搭載しています。出力信号クリッピングのスレッシュホールドの近似値を求めるには、式 (2) を使用します。

$$V_{PK} = V_{SUP} * \frac{R_L}{R_{FET} + R_P + R_L} \quad (2)$$

ここで：

- $V_{PK}$  は、クリッピングされていない出力電圧の最大ピーク値 (V) です

- $V_{SUP}$  は、Class-D 出力段の電源です

- $R_L$  は、スピーカ負荷 ( $\Omega$ ) です

- $R_P$  は、PCB (配線、フィルタ) の寄生抵抗 ( $\Omega$ ) です

- $R_{FET}$  は、電力段の合計抵抗 (HS FET, LS FET, 検出抵抗、ボンディング、パッケージング) ( $\Omega$ ) です

PVDDL が Class-D 出力段を供給する場合、 $R_{FET}$  の標準値は  $0.5\Omega$  です。PVDDH が供給する場合、 $R_{FET}$  の標準値は  $0.25\Omega$  です。

#### 8.4.2.5 PVDDL 電源

TAS2781 は、PVDDL 電源の有無に関係なく動作可能です。PVDDL 電源を使用しない構成にした場合、PVDDH 電圧が内部 LDO と共に使用され、この電源電圧が生成されます。この場合でも、表 9-1 で推奨されているように、デカップリング・コンデンサを基板に実装する必要があります。この場合、ソフトウェア・シャットダウン・モードから遷移する前に、PVDDL\_MODE ビットを High にセットします。PVDDL 電源の動作モードの詳細については、セクション 11.1 を参照してください。

#### 8.4.2.6 Y ブリッジ

TAS2781 の Class-D 出力には Y ブリッジ構成が使用されており、再生中の効率を向上させています。内蔵の LVS () により、PVDDH 電源か PVDDL 電源を選択することができます。この機能をイネーブルにするには、PVDDH と PVDDL の両方からデバイスに電源供給されているときに CDS\_MODE[1:0] ビットを 2'b00 にセットします。Y ブリッジ・モードが構成されていない場合、クリッピングが発生することになっても、デバイスは Class-D 出力用に選択された電源のみを使用します。デバイスは、Class-D 出力への電源供給に PVDDH のみを使用して動作できます。この構成では、PVDDL への電力は外部電源から供給するか (レジスタ・ビット PVDDL\_MODE=0)、または内部 LDO で生成します (レジスタ・ビット PVDDL\_MODE[7]=1)。この場合、CDS\_MODE[7:6] ビットは 2'b10 にセットしてください。TAS2781 の Y ブリッジを PVDDL 低電力で使用した場合、アイドル状態に近い超低消費電力のときのみ PVDDL レールに切り替えることができます。これにより、アイドル状態に近いときの Class-D 出力スイングは低減し、PVDDL 電源の電流要件が制限されます。このモードにするには、CDS\_MODE[7:6] レジスタを 2'b11 にセットします。

電力モード時の動作のプログラミングの詳細については、を参照してください。

で決定された Class-D 電源に変更 (PVDDL から PVDDH) すると、スレッショルドを超える入力信号に関係した遅延が発生します。この遅延はのレジスタの CDS\_DLY[1:0] ビットでプログラムできます。

Y ブリッジ・モードの場合、PVDDH が (PVDDL + 2.5V) レベルを下回ると、Y ブリッジは電源間のスイッチングを停止して、PVDDH 電源のままになります。

#### 8.4.2.7 低電圧信号伝送 (LVS)

TAS2781 は、Class-D 出力段の Y ブリッジ構成に関連して使用されるメカニズムです。これは、オーディオ・ストリームの絶対値を監視し、適切な電源として PVDDH と PVDDL のどちらかを選択することで機能します。

信号が最初にプログラムされた LVS スレッショルドを上回ると、Class-D は PVDDH レールから供給されます。信号レベルが、LVS\_HYS[3:0] レジスタ・ビットで定義したヒステリシス時間より長く、このスレッショルドを下回った場合、Class-D 電源は PVDDL に切り替わります。信号が初期レベルに戻ると、Class-D 電源は PVDDH に戻ります。

デフォルトでは、LVS スレッショルドは PVDDL 電圧を基準にした値になるよう構成されます (LVS\_DET = 1)。スレッショルドの設定には、LVS\_RTH[3:0] レジスタ・ビットを使用します (デフォルト=0.7V)。

LVS\_DET ビットを Low にセットすると、LVS スレッショルドは LVS\_FTH[4:0] レジスタ・ビットで定義された固定値に強制されます。

LVS スレッショルドは出力信号レベルを基準とし、単位 dBFS で測定されます。

LVS 固定スレッショルドは、CDS\_MODE[1:0]=11 (セクション 11.1 の PWR\_MODE2) の場合に、レジスタ・ビット LVS\_TH\_LOW[1:0] を使用して設定できます。

#### 8.4.2.8 ノイズ・ゲート・モード

TAS2781 にはノイズ・ゲート機能が搭載されており、入力信号を監視して、に記載されている NG\_HYST\_TIME[2:0] レジスタ・ビットで設定された時間を超えて NG\_TH[1:0] ビットで設定されたスレッショルドを下回ると、Class-D をパワーダウ

します。信号がスレッショルドを上回ると、Class-D は 7 サンプル以内に再起動し、オーディオ入力インターフェイスに適用されたサンプルはその後で Class-D 出力に到達します。

ノイズ・ゲート機能をイネーブルにするには、**NG\_EN** ビットを **High** にセットします。イネーブルになると、チャネルをデバイスの処理遅延時間内に起動や停止することができ、追加で外部制御を行う必要はありません。また、**NG\_DVC\_RP** ビットを **Low** にセットすると、ノイズ・ゲート動作中にボリューム・ランプを使用することも可能です。

ノイズ・ゲートは、I<sup>2</sup>C 書き込みを追加することにより、より高分解能で構成することができます。このモードをイネーブルにするには **NGFR\_EN** ビットを使用し、高分解能に設定するには記載されている **NGFR\_LVL[23:0]** レジスタ・ビットを使用します。高分解能ヒステリシスを設定するには、とに記載されている **NGFR\_HYST[18:3]** レジスタ・ビットを使用します。

#### 8.4.2.9 電源トラッキング・リミッタ

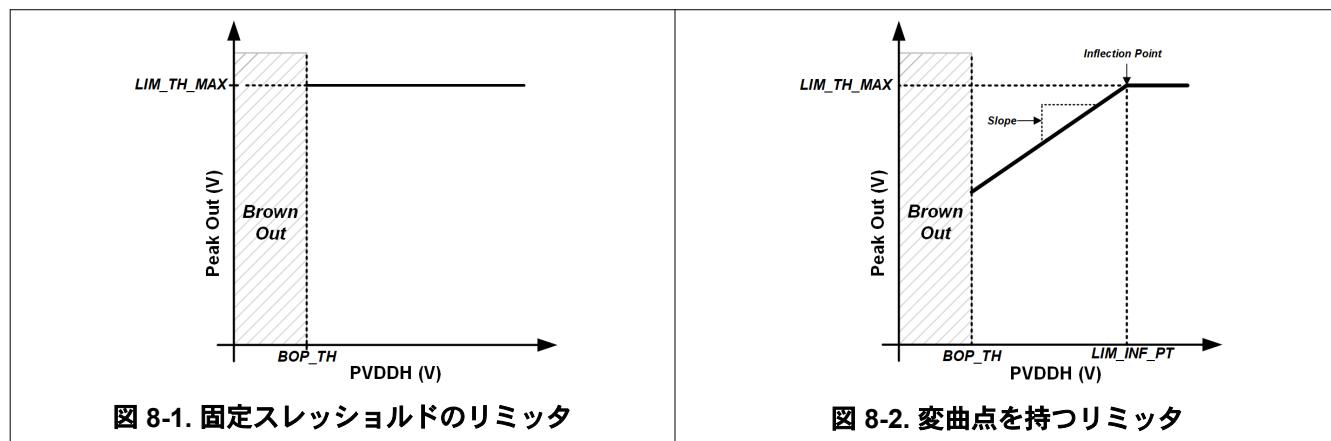

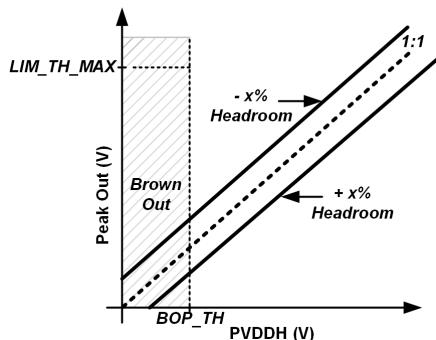

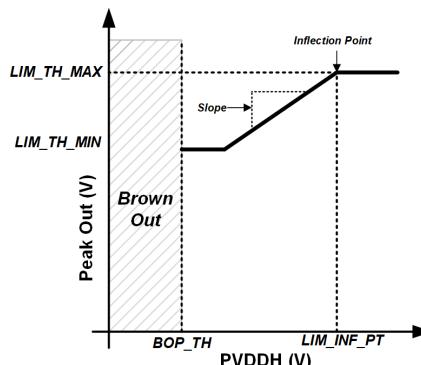

TAS2781 は PVDDH 電源電圧とオーディオ信号を監視しており、オーディオ信号のピークがプログラム可能なスレッショルドを超えるとゲインは自動的に低下します。これにより、クリッピングを防止して、充電終了時のバッテリ条件で再生時間を延ばすことができます。プログラム可能なスロープで、プログラム可能な変曲点より下まで PVDDH をトラッキングするよう、リミッタのスレッショルドを構成できます。最小スレッショルドにより、PVDDH のトラッキングからのスレッショルド低減の制限を設定します。

**LIM\_EN** レジスタ・ビットを **High** にセットすると、リミッタがイネーブルになります。

構成可能なアタック・レート、ホールド時間、リリース・レートにより、リミッタの動的応答を形成します（およびの **LIM\_ATK[3:0]**、**LIM\_HLD[2:0]**、**LIM\_RLS[3:0]** レジスタ・ビット）。

リミッタによって適用される最大減衰レベルは、の **LIM\_MAX\_AT[3:0]** レジスタ・ビットを使用して構成できます。リミッタがアタック中に最大減衰に達すると、ゲインはそれ以上低下しません。

出力信号レベルがリミッタのスレッショルドを超えると、リミッタはゲインの低下を開始します。リミッタは、PVDDH をプログラム可能な変曲点より下までトラッキングするように構成でき、最小スレッショルド値も指定できます。に、PVDDH レベルに関係なく一定レベルに制限されるように構成したリミッタを示します。この動作を実現するには、リミッタの最大スレッショルドを **LIM\_MAX\_TH[31:0]** レジスタ・ビットで目標レベルに設定します。リミッタの変曲点 (**LIM\_INF[31:0]** レジスタ・ビット) は、PVDDH の設定で許容される最小値より低く設定します。レジスタ・ビット **LIM\_MIN\_TH[31:0]** を使用して設定するリミッタの最小スレッショルドは、この使用事例ではリミッタの動作に影響を与えません。

図 8-3. 動的なスレッショルドのリミッタ

図 8-4. 変曲点と最小スレッショルドを持つリミッタ

に、最小スレッショルドなしで PVDDH をスレッショルドよりも下までトラッキングするリミッタの構成方法を示します。LIM\_MAX\_TH[31:0] レジスタ・ビットを使用して目標のスレッショルドに設定し、LIM\_INF[31:0] レジスタ・ビットを使用して目標の変曲点に設定します。この変曲点は、リミッタが PVDDH でスレッショルドの低下を開始するポイントです。LIM\_SLP[31:0] レジスタ・ビットを使用すると、PVDDH でトラッキングするリミッタの勾配を変更できます。デフォルト値の 1V/V に設定すると、PVDDH が 1V 低下するごとにスレッショルドを 1V 低下させます。必要に応じて、より急なトラッキング・スロープになるようプログラムすることができます。PVDDH をトラッキングするときに、リミッタの最小スレッショルド低下を防ぐため、LIM\_MIN\_TH[31:0] ビットは最小 PVDDH を下回るようプログラムします。

電源トラッキング・スロープのあるリミッタは、別の方で構成できます。のレジスタで LIM\_DYHDR レジスタ・ビットを 1'b1 にセットすると、LIM\_HDR[4:0] レジスタ・ビットをセットし、1V/V のスロープを使用して、ヘッドルームを電源電圧のパーセンテージとして指定できます。たとえば、-10% のヘッドルームが指定されると、ピーク出力電圧は PVDDH より 10% 高く設定されます。に示すこの使用事例では、制限は電源電圧を上回る信号に対して開始されるため、固定クリッピングが発生します。正のヘッドルーム +10% が指定されると、ピーク出力電圧は現在の PVDDH より 10% 低い値に動的に設定されます。この使用事例では、制限は電源電圧より低い信号レベルで開始されるため、クリッピングの発生を防ぎます。

PVDDH を最小スレッショルドまでだけトラッキングするリミッタを実現するには、リミッタの LIM\_MAX\_TH[31:0] と LIM\_SLP[31:0] レジスタ・ビットを前述の例のように構成します。さらに、LIM\_MIN\_TH[31:0] レジスタ・ビットを目標の最小スレッショルドに設定します。電源電圧がこの最小スレッショルドを下回ると、信号出力電圧は低下を継続しません。これは、に示すとおりです。

レジスタ・ビット LIM\_DYHDR を Low にセットすると、リミッタのメカニズムは最大 / 最小スレッショルド、変曲点、スロープの設定に応じて変わります。デフォルトでこのビットは High にセットされ、リミッタのダイナミック・ヘッドルームがイネーブルです。

#### 8.4.2.10 ブラウンアウト防止

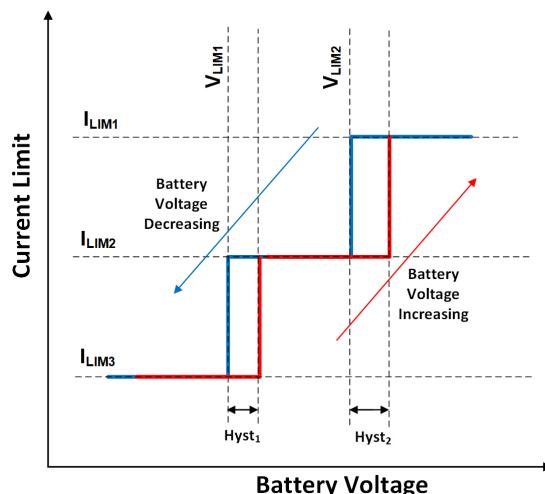

ブラウンアウト防止 (BOP) 機能は、リミッタに優先的に入力を供給することで、システムレベルでのブラウンアウトを引き起こす可能性のある充電終了時の電源電圧における過渡的なディップに対して、高速応答を生成します。電源電圧が BOP スレッショルドを下回ると、リミッタは構成可能なアタック・レートでゲインの低下を開始します。電源電圧が BOP スレッショルドを上回ると、リミッタはプログラムされたホールド時間経過後に解放を開始します。BOP 機能をイネーブルするには、BOP\_EN[0] レジスタ・ビットを High に設定します。ブラウンアウト電源ソースを設定するには、アプリケーションに応じて、BOP\_SRC レジスタ・ビットを PVDDH または PVDDL にセットします。

デフォルトでは、BOP 電源ソースは PVDDL 入力に設定されており、SAR コンバータは PVDDH および PVDDL の電圧と温度をデジタル化します。PVDDH 低電圧検出はディセーブルされます。

BOP 電源ソースが PVDDH 入力に設定されているとき、SAR ADC コンバータは PVDDH および PVDDL の電圧と温度をデジタル化します。この場合、PVDDH 低電圧検出がイネーブルされます。BOP エンジンの最初のアタックでレイテンシを低減するため、レジスタ・ビット CNV\_PVDDL を Low に設定することで、PVDDL の変換をバイパスできます。

BOP 電源ソースが PVDDL 入力に設定されているとき、SAR コンバータは PVDDH および PVDDL の電圧と温度をデジタル化します。PVDDH 低電圧検出はディセーブルされます。

BOP が機能しているとき、電源トラッキング・リミッタは一時停止します。

BOP スレッショルドを設定するには、の **BOP\_TH[31:0]** レジスタ・ビットを使用します。BOP\_MUTE ビットの設定により、電源がスレッショルドを下回ったとき、デバイスがオーディオをミュートしてシャットダウンするか、ミュートせずにオーディオ信号の減衰だけを行なうかが決定されます。

**BOPSD\_EN** レジスタ・ビットが High にセットされている場合、の **BOPSD\_TH[31:0]** レジスタ・ビットで設定したスレッショルドに到達して BOP イベントが発生すると、TAS2781 もただちにミュートしてデバイスをシャットダウンするように設定できます。このシャットダウン機能は、BOP\_MUTE が High にセットされると内部で自動的にディセーブルされます。

BOP には、プログラム可能なアタック・レート・レジスタ・ビット **BOP\_ATK[2:0]**、アタック・ステップ・サイズ・レジスタ・ビット **BOP\_ATK\_ST[1:0]**、ホールド時間レジスタ・ビット **BOP\_HLD[2:0]** が実装されています。

システムが BOP 機能を終了すると、電源トラッキング・リミッタのリリースが開始されます。リミッタがディセーブルの場合、ゲインはリミッタのリリース設定に従ってリリースされます。

ホールド時間を無限に設定するには、**BOP\_INF\_HLD** レジスタ・ビットを High にプログラムします。デバイスは、ミュート状態か SW/HW シャットダウン状態を経由して遷移する必要があります。また、レジスタ・ビット **BOP\_HLD\_CLR** を High にセットすることもできます（この場合、デバイスはホールド状態を終了し、リリースを開始します）。

**BOP\_INF\_HLD** ビットを Low にセットすると、デバイスは **BOP\_HLD[2:0]** ビットのプログラムに基いてホールド状態になります。

#### 8.4.2.11 ICC ピンとチップ間通信

TAS2781 は、ステレオ・アプリケーションでのデュアル・ゲイン・バランスングをサポートしています。1 つのデバイスは、システム内の別の 1 つのデバイスとのみペアリング可能です。

ICC ピンは、バス・キーパーで ICC バスに接続されます。ICC バッファに電力を供給するピン 17 (NC\_V1P8V) は、1.8V 電源に接続する必要があります。

SDOUT ピンをゲイン・アライメントに使用することはできません。

の **ICC\_CFG[2:0]** レジスタ・ビットで、ICC ピンの機能を構成します。

のレジスタのビットにより ICC 機能がイネーブルになり、デバイスのペアリングとゲイン送信スロットが設定されます。

この動作モードでは、16kHz と 24kHz (および 44.1kHz 相当) のサンプリング・レートはサポートされていません。

#### 8.4.2.12 Class-D 設定

##### 8.4.2.12.1 出力スルーレート制御

出力スルーレートは、に記載されているレジスタ・ビット **EDGE\_CTRL[1:0]** を使用してプログラムできます。

デフォルトでは、PVDDH 電源電圧が 20V 未満の場合、出力スルーレートは高速になり、電源および負荷に依存します。PVDDH が 20V を超えると、スルーレートは自動的に低速に変わります。

オプションとして、EMI 性能を向上させるために、**EDGE\_CTRL[1:0]** ビットを 2'b11 にセットすると、PVDDH 電源の全範囲でスルーレートを低速に設定できます。

##### 8.4.2.12.2 同期

TAS2781 の Class-D アンプは拡散スペクトラム PWM 変調に対応しており、AMP\_SS レジスタ・ビットを High にセットすることでイネーブルにできます。この機能により、システムの EMI を低減できます。

デフォルトでは、Class-D アンプのスイッチング周波数はデバイスでトリムされている内部発振器に基づいています。スイッチングをオーディオ・サンプル・レートに同期するには、**CLASSD\_SYNC** レジスタ・ビットを High にセットします。Class-D をオーディオ・サンプル・レートに同期する場合は、周波数に基づくオーディオ・サンプル・レートの 44.1kHz か 48kHz (デフォルト) に応じて **RAMP\_RATE** レジスタ・ビットを設定する必要があります。

### 8.4.3 SAR ADC

SAR ADC は、PVDDH 電圧、PVDDL 電圧、ダイ温度を監視します。この変換結果は、レジスタの読み戻し (PVDDH\_CNV[11:0]、PVDDL\_CNV[11:0]、TMP\_CNV[7:0] レジスタ・ビット) から参照可能です。PVDDH 電圧と PVDDL 電圧の変換は、リミッタとブラウンアウト防止ブロックにも使用されます。

デフォルトでは、PVDDL 変換は BOP ソースが PVDDL でも (BOP\_SRC = 0)、PVDDH (BOP\_SRC = 1) でも、PVDDH および温度とともにイネーブルになります。

ADC は、192kHz の固定サンプル・レートで、変換時間 5.2μs で実行されます。

温度は、SAR 変換 18 回ごとにサンプリングされます。温度のサンプリング・レートは約 10K サンプル / 秒です。

PVDDH および PVDDL 電圧とダイ温度は、、、およびのレジスタの式を使用して推定できます。

レジスタ・ビットの中身は、常に MSB から LSB に向かって読み出します。

SAR ADC の電圧と温度の測定値は、SDOUT ピンを経由してホストで使用することも可能です。のレジスタ・ビットを使用して、この機能をイネーブルにし、スロットを構成します。

### 8.4.4 電流と電圧 (IV) の検出

TAS2781 はスピーカ電圧と電流センスの測定機能を実現しており、ラウドスピーカの動作をリアルタイムで監視することができます。VSNSP ピンと VSNSN ピンはフェライト・ビーズ・フィルタの後に接続します (または、EMI フィルタが使用されていないなら OUTP と OUTN に直接接続します)。V センス接続を行うと、パッケージング、PCB の相互接続、またはフェライト・ビーズ・フィルタ抵抗による電圧降下誤差が排除されます。VSNS ピンの後の相互接続抵抗は補正されないため、センス接続はできる限り負荷の近くに接続してください。

電圧および電流検出の内部 ADC には、DC ブロッキング・フィルタがあります。このフィルタのカットオフ周波数は調整可能です。また、フィルタは HPF\_FREQ\_REC[2:0] レジスタ・ビットを使用してバイパスすることもできます。

| センス・ブロックと V センス・ブロックは、それぞれ ISNS\_PD および VSNS\_PD レジスタ・ビットを Low に設定してパワーアップできます。

### 8.4.5 ポスト・フィルタ・フィードバック (PFFB)

このデバイスは、外部フィルタの後にアンプ・フィードバック・ループを閉じることにより、ポスト・フィルタ・フィードバックをサポートしています。フィードバックを適用するには、デバイスの VSNSN 端子と VSNSP 端子を使用します。この機能をディセーブルにするには、PFFB\_EN レジスタ・ビットを使用します (アンプ・ループの安定性を損なう外部フィルタが実装されている場合)。PFFB がディセーブルになると、フィードバックはデバイスの OUTN ピンと OUTP ピンから内部で配線されます。

PFFB 動作モードでは、 $f_0 > 10\text{MHz}$ かつ  $f_0/Q > 2.5\text{MHz}$  の条件を満たす必要があります ( $f_0$  と  $Q$  は、外部フィルタのカットオフ周波数と品質係数です)。

### 8.4.6 サーマル・フォールドバック

TAS2781 はダイ温度を監視し、ダイ温度がスレッショルドの設定値に到達すると、自動的にオーディオ信号に制限をかけることができます。内部の DSP が各レジスタに必要な計算を行うため、この保護メカニズムを構成するためにサーマル・フォールドバック・レジスタを使用することを推奨します。

サーマル・フォールドバックをディセーブルにするには、TFB\_EN ビットを使用します。ダイ温度がの TF\_TMP\_TH[31:0] レジスタ・ビットで設定した値に達すると、この機能によりオーディオ信号は減衰を開始して、過熱によるデバイスのシャットダウンを防止します。この機能は、TFS\_SLP[31:0] レジスタ・ビットに値を設定することにより、TF\_TMP\_TH[31:0] レジスタ・ビットで設定した温度範囲でオーディオ信号を減衰します。サーマル・フォールドバック・アタックは、TF\_ATK[31:0] レジスタ・ビットを使用して設定します。最大減衰を指定するには、TF\_MAX\_ATN[31:0] レジスタ・ビットを使用します。ただし、デバイスの温度が上昇し続ける場合は、最終的にデバイスの過熱がトリガされます。減衰は TF\_HLD[31:0] レジスタ・ビットで設定したサンプル数の間保持された後、解放を開始します。

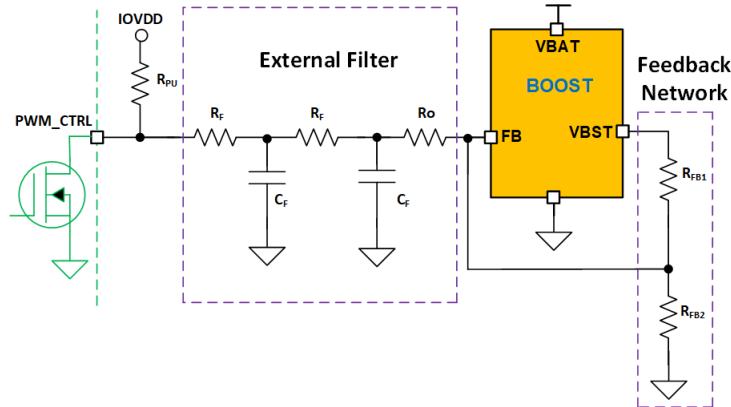

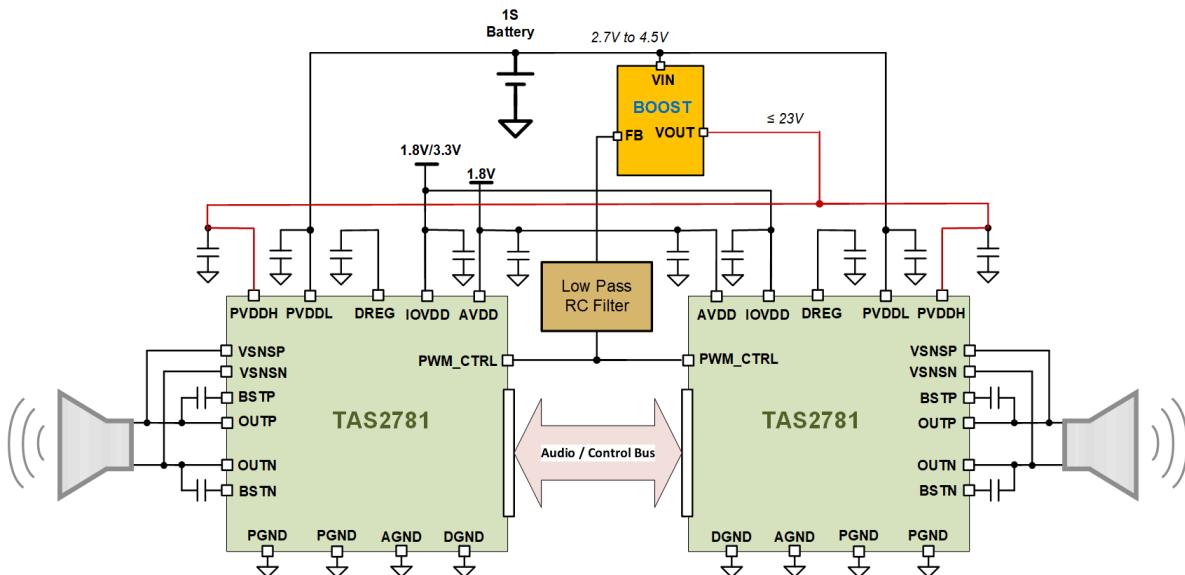

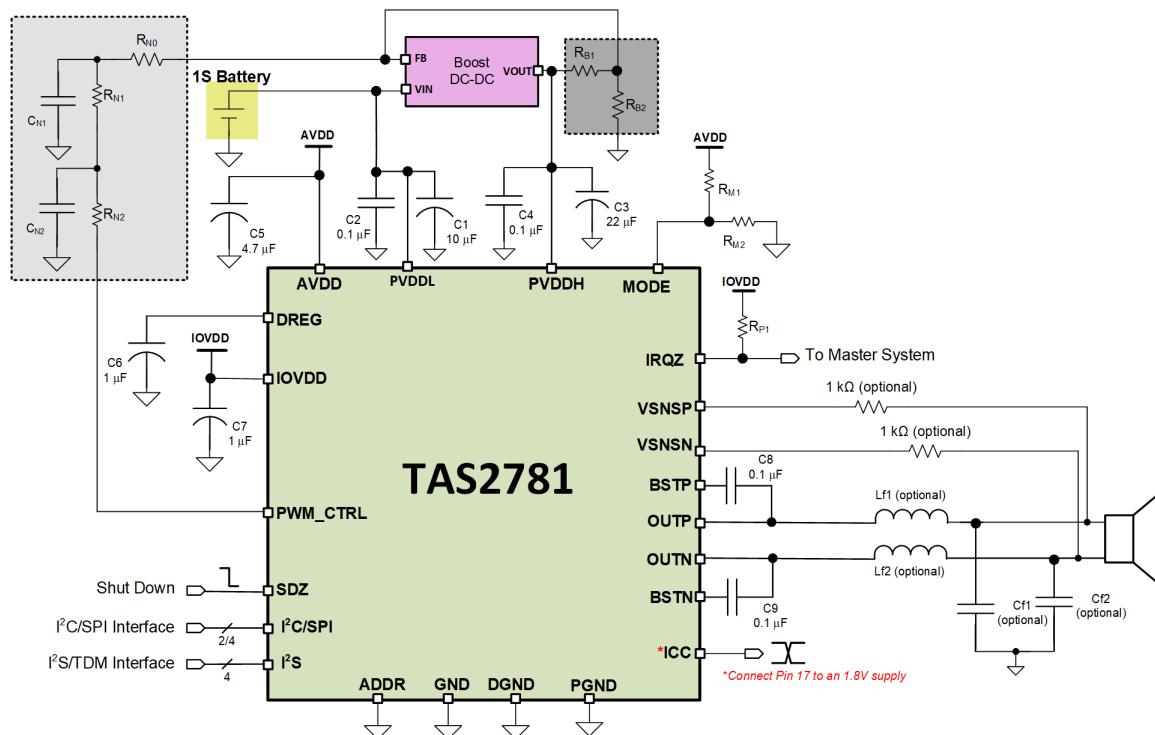

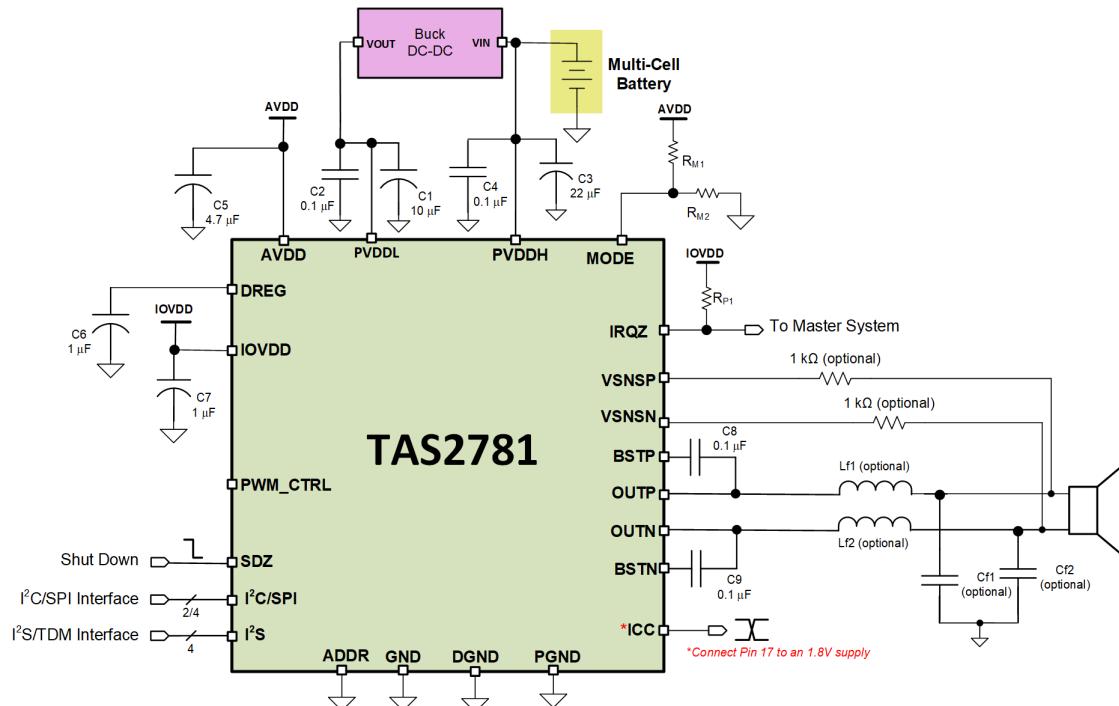

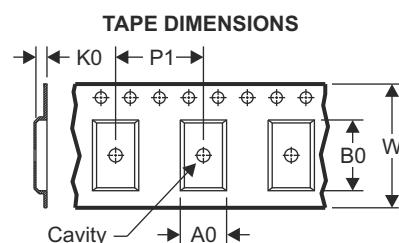

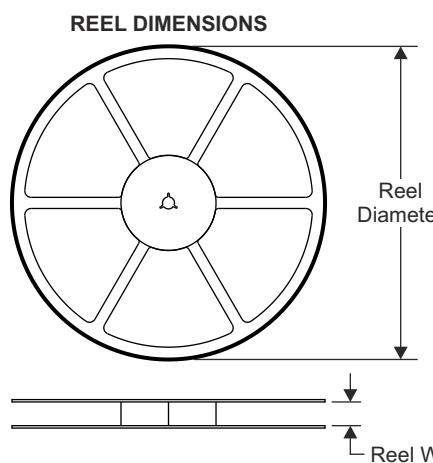

#### 8.4.7 過電力保護機能