# TAD5212-Q1 車載用高性能 ダイナミック レンジ 120dB のステレオ オーディオ DAC およびヘッドフォン/ライン ドライバ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1:  $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$

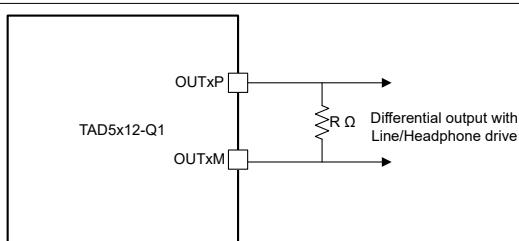

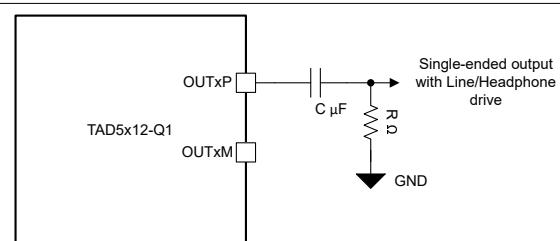

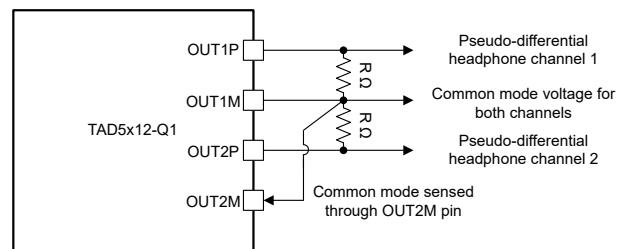

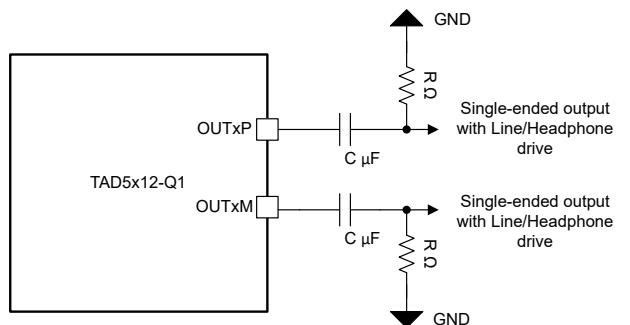

- ステレオ差動またはクアッド単一エンドの・高性能オーディオ DAC

- 性能:

- DAC から差動ライン出力までのダイナミックレンジ: 120dB

- DAC から差動ヘッドホン出力までのダイナミックレンジ: 118dB

- THD+N:  $-104\text{dB}$

- ライン出力とヘッドホン出力電圧:

- 差動、 $2V_{\text{RMS}}$  フルスケール

- 疑似差動、 $1V_{\text{RMS}}$  フルスケール

- シングルエンド、 $1V_{\text{RMS}}$  フルスケール

- DAC サンプル レート ( $f_s$ ) =  $4\text{kHz} \sim 768\text{kHz}$

- 主な特長

- アナログ入力から出力へのバイパスのパス

- 4 チャネル PDM デジタルマイクロフォン録音パス

- 入力と出力のミックス、およびマルチプレクサのオプション

- 音声アクティビティ検出

- 超音波アクティビティ検出

- 超音波信号またはトーンのジェネレータ

- バッテリおよびサーマル フォールドバック保護

- 信号歪みリミッタ

- 低レイテンシおよび超低レイテンシのフィルタオプション

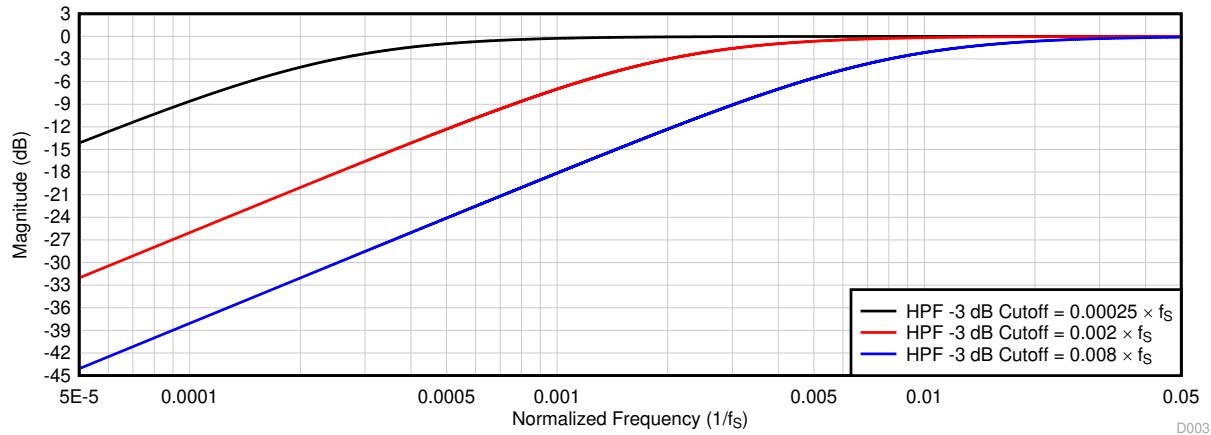

- HPF およびバイカッド フィルタをプログラム可能

- $\text{I}^2\text{C}$  および SPI 制御インターフェイス

- オーディオシリアルインターフェイス

- フォーマット: TDM,  $\text{I}^2\text{S}$ , 左揃え (LJ)

- ワード長: 16, 20, 24 または 32 ビットを選択可能

- バスコントローラおよびターゲット モード

- TDM モードのデイジーチェーン

- 柔軟なクロック供給のためのプログラム可能な PLL

- クロックとサンプル レートの自動検出

- 低消費電力モード

- 2 チャネル再生で  $11\text{mW}$  ( $1.8\text{V}$  電源)

- 単一電源動作 AVDD:  $1.8\text{V}$  または  $3.3\text{V}$

- I/O 電源動作:  $1.2\text{V}$ ,  $1.8\text{V}$  または  $3.3\text{V}$

## 2 アプリケーション

- テレマティクス制御ユニット

- 車載用ヘッド ユニット

- デジタルコックピット処理装置

- 後部座席用エンターテインメント

- 自動車向けインストルメント クラスタ

## 3 概要

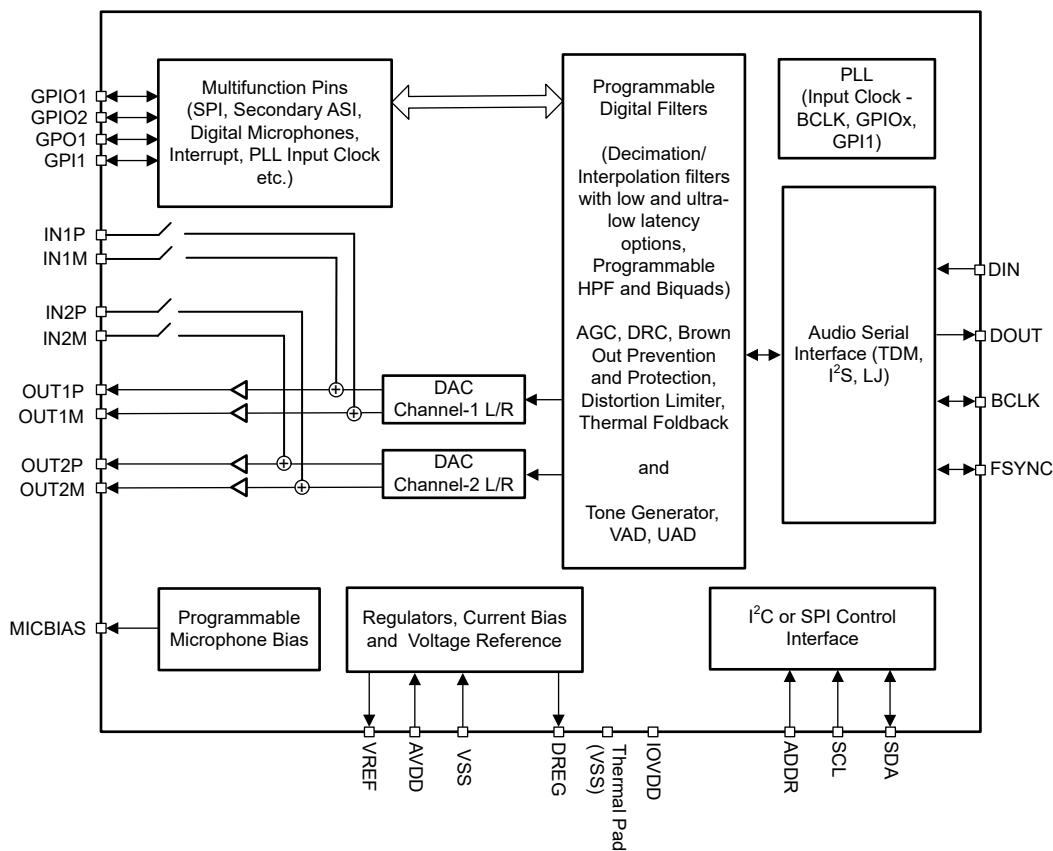

TAD5212-Q1 は車載高性能オーディオ DAC、であり、 $2V_{\text{RMS}}$  差動出力、120dB のダイナミックレンジ ステレオ チャネル、または  $1V_{\text{RMS}}$  シングルエンド出力、ダイナミックレンジが 111dB のクワッド チャネルを備えています。TAD5212-Q1 は、差動入出力とシングルエンド入出力の両方をサポートしています。DAC 出力は、ライン出力とヘッドホン負荷のいずれかに構成できます。TAD5212-Q1 は、 $16\Omega$  のヘッドホン負荷を最大  $62.5\text{mW}$  で駆動できます。TAD5212-Q1 は、プログラム可能なチャネル ゲイン、デジタル音量制御、低ジッタの位相ロック ループ (PLL)、プログラム可能なハイパス フィルタ (HPF)、プログラム可能な EQ およびバイカッド フィルタ、低レイテンシおよび超低レイテンシのフィルタ モードを内蔵しており、DAC と PDM マイクの両方のシグナル チェーンにおいて最高  $768\text{kHz}$  のサンプル レートに対応できます。TAD5212-Q1 は、アナログ入力から出力へのバイパス オプションをサポートしているほか、PDM インターフェイスを使用して最大 4 チャネルのデジタルマイクの録音もサポートしています。アナログ入力とデジタル入力からのデータをデバイス内部で混合することができます。TAD5212-Q1 は時分割多重化 (TDM)、 $\text{I}^2\text{S}$ 、左揃え (LJ) オーディオフォーマットに対応しており、 $\text{I}^2\text{C}$  または SPI で制御できます。これらの高性能な機能を搭載し、単一電源で動作するので、TAD5212-Q1 はスペースの制約が厳しいオーディオ アプリケーションに最適です。

## 製品情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ (公称) <sup>(2)</sup>                       |

|------------|----------------------|-----------------------------------------------------|

| TAD5212-Q1 | VQFN (24)            | $4\text{mm} \times 4\text{mm}$ , $0.5\text{mm}$ ピッチ |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はビンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

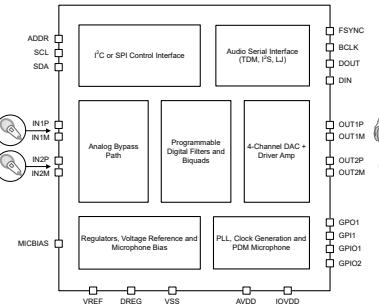

概略ブロック図

## 目次

|                                                    |          |                               |           |

|----------------------------------------------------|----------|-------------------------------|-----------|

| <b>1 特長</b>                                        | <b>1</b> | <b>6 詳細説明</b>                 | <b>22</b> |

| <b>2 アプリケーション</b>                                  | <b>1</b> | 6.1 概要                        | 22        |

| <b>3 概要</b>                                        | <b>1</b> | 6.2 機能ブロック図                   | 23        |

| <b>4 ピン構成および機能</b>                                 | <b>4</b> | 6.3 機能説明                      | 23        |

| <b>5 仕様</b>                                        | <b>6</b> | 6.4 デバイスの機能モード                | 79        |

| 5.1 絶対最大定格                                         | 6        | 6.5 プログラミング                   | 79        |

| 5.2 ESD 定格                                         | 6        | <b>7 レジスタ マップ</b>             | 85        |

| 5.3 推奨動作条件                                         | 6        | 7.1 デバイス構成レジスタ                | 85        |

| 5.4 熱に関する情報                                        | 7        | 7.2 プログラム可能な係数レジスタ            | 188       |

| 5.5 電気的特性                                          | 7        | <b>8 アプリケーションと実装</b>          | 221       |

| 5.6 タイミング要件:I <sup>2</sup> C インターフェイス              | 13       | 8.1 アプリケーション情報                | 221       |

| 5.7 スイッチング特性:I <sup>2</sup> C インターフェイス             | 14       | 8.2 代表的なアプリケーション              | 221       |

| 5.8 タイミング要件:SPI                                    | 14       | 8.3 電源に関する推奨事項                | 225       |

| 5.9 スイッチング特性:SPI                                   | 14       | 8.4 レイアウト                     | 226       |

| 5.10 タイミング要件:TDM、I <sup>2</sup> S または LJ インターフェイス  | 15       | <b>9 デバイスおよびドキュメントのサポート</b>   | 228       |

| 5.11 スイッチング特性:TDM、I <sup>2</sup> S または LJ インターフェイス | 15       | 9.1 ドキュメントのサポート               | 228       |

| 5.12 タイミング要件:PDM デジタルマイクロフォンインターフェイス               | 16       | 9.2 ドキュメントの更新通知を受け取る方法        | 228       |

| 5.13 スイッチング特性:PDM デジタルマイクロフォンインターフェイス              | 16       | 9.3 サポート・リソース                 | 228       |

| 5.14 タイミング図                                        | 17       | 9.4 商標                        | 228       |

| 5.15 代表的特性                                         | 19       | 9.5 静電気放電に関する注意事項             | 229       |

|                                                    |          | 9.6 用語集                       | 229       |

|                                                    |          | <b>10 改訂履歴</b>                | 229       |

|                                                    |          | <b>11 メカニカル、パッケージ、および注文情報</b> | 229       |

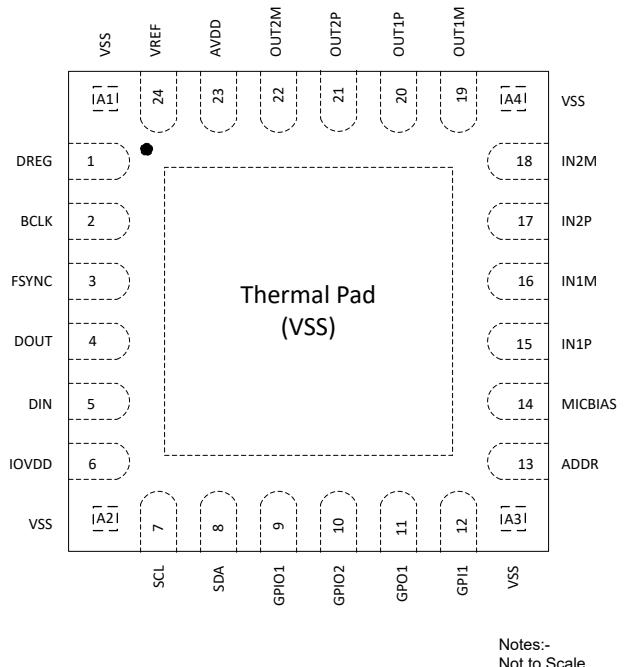

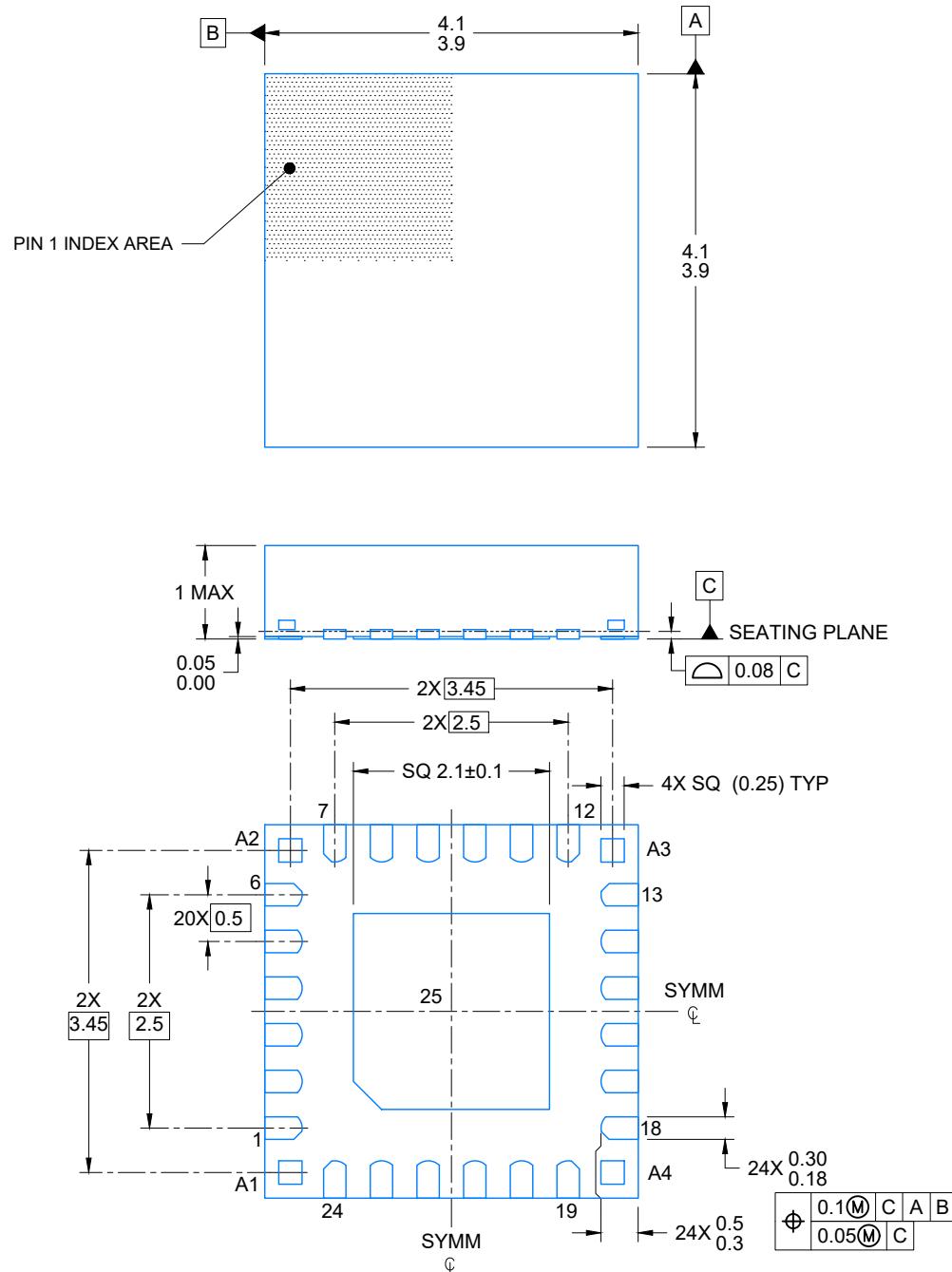

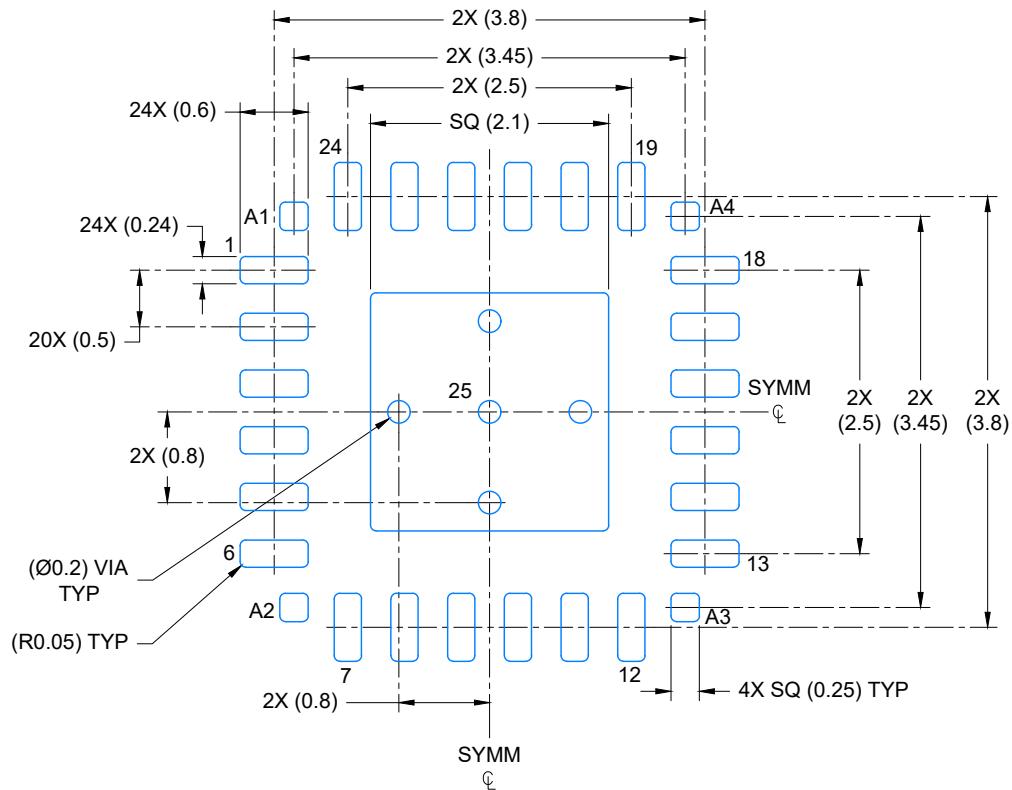

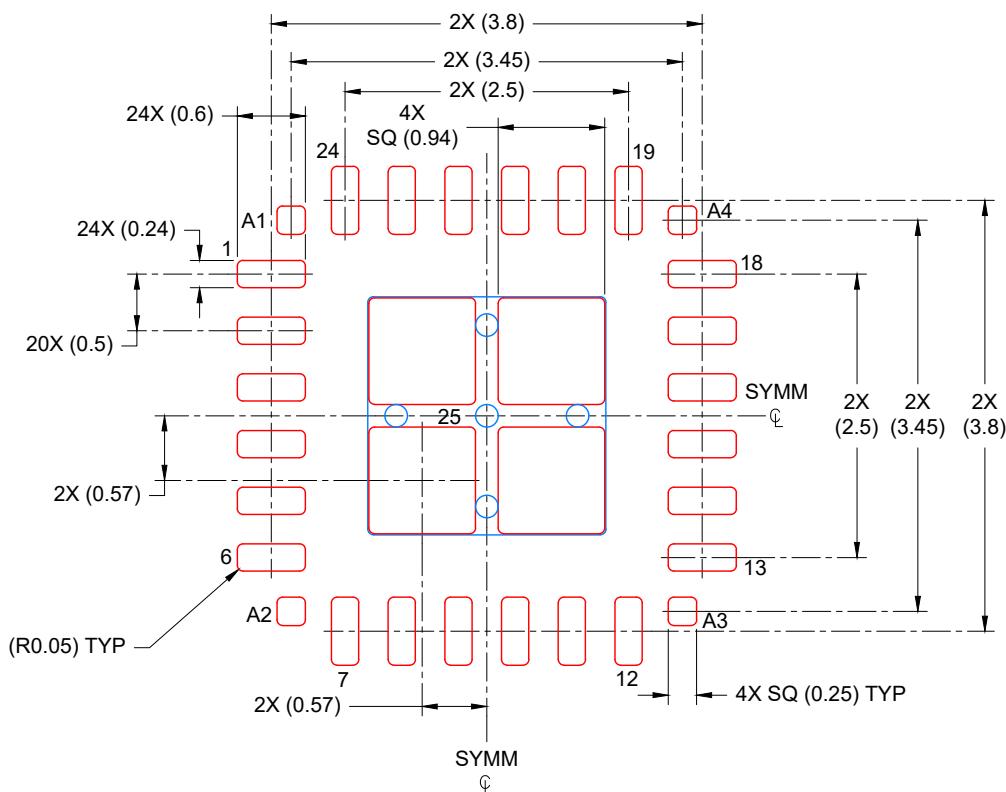

## 4 ピン構成および機能

Notes:-

Not to Scale

図 4-1. 24 ピン QFN パッケージ、露出サーマル パッドおよびコーナー ピン付き、上面図

表 4-1. ピンの機能

| ピン    |    | 種類 <sup>(1)</sup> | 説明                                                             |

|-------|----|-------------------|----------------------------------------------------------------|

| 名称    | 番号 |                   |                                                                |

| VSS   | A1 | グランド              | グランドピン。基板のグランドプレーンへ直接短絡します。                                    |

| DREG  | 1  | デジタル電源            | デジタル電源用デジタル オンチップ レギュレータ出力電圧 (1.55V、公称値)                       |

| BCLK  | 2  | デジタル I/O          | オーディオシリアル データインターフェイスのバスビットクロック                                |

| FSYNC | 3  | デジタル I/O          | オーディオシリアル データインターフェイスバスフレームの同期信号                               |

| DOUT  | 4  | デジタル I/O          | オーディオシリアル データインターフェイスバス出力                                      |

| DIN   | 5  | デジタル入力            | オーディオシリアル データインターフェイスバス入力                                      |

| IOVDD | 6  | デジタル電源            | デジタル I/O 電源 (1.2V、1.8V または 3.3V、公称値)                           |

| VSS   | A2 | グランド              | グランドピン。基板のグランドプレーンへ直接短絡します。                                    |

| SCL   | 7  | デジタル入力            | I <sup>2</sup> C 制御インターフェイス用クロック                               |

| SDA   | 8  | デジタル入力            | I <sup>2</sup> C 制御インターフェイス用データ                                |

| GPIO1 | 9  | デジタル I/O          | 汎用デジタル入出力 1 (デイジーチェーン入力、オーディオデータ出力、PLL 入力クロックソース、割り込みなど、多目的機能) |

| GPIO2 | 10 | デジタル I/O          | 汎用デジタル入出力 2 (デイジーチェーン入力、オーディオデータ出力、PLL 入力クロックソース、割り込みなど、多目的機能) |

| GPO1  | 11 | デジタル出力            | 汎用デジタル出力 1 (音声データ出力、割り込みなど多目的機能)                               |

**表 4-1. ピンの機能 (続き)**

| ピン      |          | 種類 <sup>(1)</sup> | 説明                                               |

|---------|----------|-------------------|--------------------------------------------------|

| 名称      | 番号       |                   |                                                  |

| GPI1    | 12       | デジタル<br>入力        | 汎用デジタル入力 1(デイジーチェーン入力、PLL 入力クロック ソースなど、多目的機能)    |

| VSS     | A3       | グランド              | グランド ピン。基板のグランド プレーンへ直接短絡します。                    |

| ADDR    | 13       | アナログ<br>入力        | I <sup>2</sup> C アドレス ピン                         |

| MICBIAS | 14       | アナログ              | マイク バイアス出力(最大 3V までプログラム可能な出力)                   |

| IN1P    | 15       | アナログ<br>入力        | アナログ入力 1P ピン(アナログ バイパス パス)                       |

| IN1M    | 16       | アナログ<br>入力        | アナログ入力 1M ピン(アナログ バイパス パス)                       |

| IN2P    | 17       | アナログ<br>入力        | アナログ入力 2P ピン(アナログ バイパス パス)                       |

| IN2M    | 18       | アナログ<br>入力        | アナログ入力 2M ピン(アナログ バイパス パス)                       |

| VSS     | A4       | グランド              | グランド ピン。基板のグランド プレーンへ直接短絡します。                    |

| OUT1M   | 19       | アナログ<br>出力        | アナログ出力 1M ピン                                     |

| OUT1P   | 20       | アナログ<br>出力        | アナログ出力 1P ピン                                     |

| OUT2P   | 21       | アナログ<br>出力        | アナログ出力 2P ピン                                     |

| OUT2M   | 22       | アナログ<br>出力        | アナログ出力 2M ピン                                     |

| AVDD    | 23       | アナログ<br>電源        | アナログ電源(1.8V または 3.3V、公称値)                        |

| VREF    | 24       | アナログ              | アナログ リファレンス電圧フィルタ出力                              |

| VSS     | サーマル パッド | グランド              | サーマル パッドを内部デバイスのグランドに短絡します。基板のグランド プレーンへ直接短絡します。 |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

動作環境温度範囲内(特に記載がない限り) (1)

|           |                            | 最小値  | 最大値         | 単位 |

|-----------|----------------------------|------|-------------|----|

| 電源電圧      | AVDD から VSS(サーマル パッド)      | -0.3 | 3.9         | V  |

| 電源電圧      | IOVDD から VSS(サーマル パッド)     | -0.3 | 3.9         | V  |

| グランドとの電位差 | VSS から VSS(サーマル パッド)       | -0.3 | 0.3         | V  |

| アナログ入力電圧  | アナログ入力ピン電圧から VSS(サーマル パッド) | -0.3 | 5.656       | V  |

| デジタル入力電圧  | デジタル入力ピン電圧から VSS(サーマル パッド) | -0.3 | IOVDD + 0.3 | V  |

| 温度        | 機能周囲温度、 $T_A$              | -55  | 125         | °C |

|           | 動作時周囲温度、 $T_A$             | -40  | 125         |    |

|           | 接合部、 $T_J$                 | -40  | 150         |    |

|           | 保存、 $T_{stg}$              | -65  | 150         |    |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      | 値                               | 単位    |

|-------------|------|---------------------------------|-------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 (1) | ±2000 |

| $V_{(ESD)}$ | 静電放電 | デバイス帶電モデル (CDM)、AEC Q100-011 準拠 |       |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

動作環境温度範囲内(特に記載がない限り)

|                     |                                                          | 最小値  | 公称値   | 最大値  | 単位 |

|---------------------|----------------------------------------------------------|------|-------|------|----|

| <b>電源</b>           |                                                          |      |       |      |    |

| AVDD <sup>(1)</sup> | アナログ供給電圧を VSS(サーマル パッド)に接続 - AVDD 3.3V 動作                | 3.0  | 3.3   | 3.6  | V  |

|                     | アナログ供給電圧を VSS(サーマル パッド)に接続 - AVDD 1.8V 動作 <sup>(2)</sup> | 1.65 | 1.8   | 1.95 | V  |

| IOVDD               | IO 供給電圧を VSS(サーマル パッド)に接続 - IOVDD 3.3V 動作                | 3.0  | 3.3   | 3.6  | V  |

|                     | IO 供給電圧を VSS(サーマル パッド)に接続 - IOVDD 1.8V 動作 <sup>(3)</sup> | 1.65 | 1.8   | 1.95 |    |

|                     | IO 供給電圧を VSS(サーマル パッド)に接続 - IOVDD 1.2V 動作 <sup>(3)</sup> | 1.08 | 1.2   | 1.32 |    |

| <b>入力</b>           |                                                          |      |       |      |    |

| INxx                | ラインイン バイパス経路のためのアナログ入力ピン電圧を VSS(サーマル パッド)に接続             | 0    | AVDD  | V    |    |

|                     | デジタル入力ピン電圧から VSS(サーマル パッド)                               | 0    | IOVDD | V    |    |

| ADDR                | ADDR ピン w.r.t VSS(サーマル パッド)                              | 0    | AVDD  | V    |    |

| <b>温度</b>           |                                                          |      |       |      |    |

| $T_A$               | 動作時の周囲温度                                                 | -40  | 125   | °C   |    |

動作環境温度範囲内(特に記載がない限り)

|                |                                                                                | 最小値 | 公称値                   | 最大値 | 単位  |

|----------------|--------------------------------------------------------------------------------|-----|-----------------------|-----|-----|

| <b>その他</b>     |                                                                                |     |                       |     |     |

| CCLK           | GPIOx または GPIx コントローラ モード クロック周波数(CCLK)                                        |     | 36.864 <sup>(4)</sup> |     | MHz |

| C <sub>b</sub> | I <sup>2</sup> C インターフェースの SCL および SDA バス容量は、スタンダード モードおよび ファースト モードをサポートしています |     | 400                   |     | pF  |

|                | I <sup>2</sup> C インターフェースの SCL および SDA バス容量は、ファストモード プラスをサポートします               |     | 550                   |     |     |

| C <sub>L</sub> | デジタル出力負荷容量                                                                     | 20  | 50                    |     | pF  |

- (1) VSS および VSS(サーマル パッド)。すべてのグランド ピンは一緒に接続する必要があり、電圧の差は 0.2V を超えてはなりません。

- (2) AVDD 1.8V 動作のために、AVDD\_MODE ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

- (3) IOVDD が 1.8V および 1.2V の動作の場合、IOVDD\_IO\_MODE ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

- (4) CCLK 入力の立ち上がり時間(V<sub>IL</sub> から V<sub>IH</sub>)と立ち下がり時間(V<sub>IH</sub> から V<sub>IL</sub>)は 5ns 未満である必要があります。オーディオのノイズ特性を向上させるには、低ジッタの CCLK 入力を使用する必要があります。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | TAD5212-Q1 | 単位   |

|-----------------------|-------------------|------------|------|

|                       |                   | RGE (VQFN) |      |

|                       |                   | 24 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 38.4       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 26.3       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 15.9       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.5        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 15.8       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 13.8       | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

$T_A = 25^\circ\text{C}$ 、AVDD = 3.3V、IOVDD = 3.3V、 $f_{IN} = 1\text{kHz}$  正弦波信号、 $f_S = 48\text{kHz}$ 、32 ビット オーディオ データ、BCLK =  $256 \times f_S$ 、TDM ターゲット モード、PLL オン、チャネル ゲイン = 0dB、リニア位相補間フィルタ、差動/シングルエンド構成における  $1200\Omega/600\Omega$  のラインアウト負荷、または  $32\Omega/16\Omega$  のレシーバ / ヘッドホン負荷(該当する場合)、MICBIAS は VREF に設定済み、その他はデフォルト設定とします。特に記載がない限り、20Hz~20kHz の無補正帯域幅で Audio Precision によりフィルタフリーで測定します。

| パラメータ                          | テスト条件                              | 最小値 | 公称値 | 最大値 | 単位               |

|--------------------------------|------------------------------------|-----|-----|-----|------------------|

| <b>ライン出力/ヘッドフォン再生時の DAC 性能</b> |                                    |     |     |     |                  |

| フルスケール出力電圧                     | OUTxP と OUTxM 間の差動出力、AVDD = 3.3V   | 2   |     |     | V <sub>RMS</sub> |

|                                | OUTxP と OUTxM 間の差動出力、AVDD = 1.8V   | 1   |     |     |                  |

|                                | シングルエンド出力、AVDD = 3.3V              | 1   |     |     |                  |

|                                | シングルエンド出力、AVDD = 1.8V              | 0.5 |     |     |                  |

|                                | OUTxP と OUTxM 間の疑似差動出力、AVDD = 3.3V | 1   |     |     |                  |

|                                | OUTxP と OUTxM 間の疑似差動出力、AVDD = 1.8V | 0.5 |     |     |                  |

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 3.3\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、 $f_{\text{IN}} = 1\text{kHz}$  正弦波信号、 $f_S = 48\text{kHz}$ 、32ビットオーディオデータ、 $\text{BCLK} = 256 \times f_S$ 、TDMターゲットモード、PLLオン、チャネルゲイン=0dB、リニア位相補間フィルタ、差動/シングルエンド構成における $1200\Omega/600\Omega$ のラインアウト負荷、または $32\Omega/16\Omega$ のレシーバ/ヘッドホン負荷(該当する場合)、 $\text{MICBIAS}$ は $\text{VREF}$ に設定済み、その他はデフォルト設定とします。特に記載がない限り、20Hz~20kHzの無補正帯域幅でAudio Precisionによりフィルタフリーで測定します。

| パラメータ                                  | テスト条件                                                                     | 最小値 | 公称値 | 最大値 | 単位 |

|----------------------------------------|---------------------------------------------------------------------------|-----|-----|-----|----|

| SNR<br>信号対雑音比、A特性補正 <sup>(1) (2)</sup> | 差動出力、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$                                 | 120 |     |     | dB |

|                                        | シングルエンド出力、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$                            | 111 |     |     |    |

|                                        | 疑似差動出力、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$                               | 112 |     |     |    |

|                                        | 差動出力、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$                                 | 115 |     |     |    |

|                                        | シングルエンド出力、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$                            | 105 |     |     |    |

|                                        | 疑似差動出力、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$                               | 106 |     |     |    |

|                                        | 差動出力、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$ 、パワーチューンモード <sup>(3)</sup>      | 117 |     |     |    |

|                                        | シングルエンド出力、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$ 、パワーチューンモード <sup>(3)</sup> | 104 |     |     |    |

|                                        | 疑似差動出力、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$ 、パワーチューンモード <sup>(3)</sup>    | 109 |     |     |    |

|                                        | 差動出力、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$ 、パワーチューンモード <sup>(3)</sup>      | 112 |     |     |    |

| SNR<br>信号対雑音比、A特性補正 <sup>(1) (2)</sup> | シングルエンド出力、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$ 、パワーチューンモード <sup>(3)</sup> | 100 |     |     | dB |

|                                        | 疑似差動出力、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$ 、パワーチューンモード <sup>(3)</sup>    | 104 |     |     |    |

|                                        | 差動出力、レシーバ負荷、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$                          | 118 |     |     |    |

|                                        | シングルエンド出力、ヘッドホン負荷、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$                    | 110 |     |     |    |

|                                        | 疑似差動出力、レシーバ負荷、0dBFS信号、 $\text{AVDD} = 3.3\text{V}$                        | 112 |     |     |    |

|                                        | 差動出力、レシーバ負荷、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$                          | 114 |     |     |    |

|                                        | シングルエンド出力、ヘッドホン負荷、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$                    | 105 |     |     |    |

|                                        | 疑似差動出力、レシーバ負荷、0dBFS信号、 $\text{AVDD} = 1.8\text{V}$                        | 106 |     |     |    |

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 3.3\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、 $f_{IN} = 1\text{kHz}$  正弦波信号、 $f_S = 48\text{kHz}$ 、32ビットオーディオデータ、 $\text{BCLK} = 256 \times f_S$ 、TDM ターゲットモード、PLL オン、チャネルゲイン = 0dB、リニア位相補間フィルタ、差動/シングルエンド構成における  $1200\Omega/600\Omega$  のラインアウト負荷、または  $32\Omega/16\Omega$  のレシーバ / ヘッドホン負荷(該当する場合)、 $\text{MICBIAS}$  は  $\text{VREF}$  に設定済み、その他はデフォルト設定とします。特に記載がない限り、20Hz~20kHz の無補正帯域幅で **Audio Precision** によりフィルタフリーで測定します。

| パラメータ                     | テスト条件                          | 最小値                                                                            | 公称値  | 最大値 | 単位               |

|---------------------------|--------------------------------|--------------------------------------------------------------------------------|------|-----|------------------|

| DR                        | ダイナミックレンジ、A特性補正 <sup>(2)</sup> | 差動出力、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$                                   | 120  |     | dB               |

|                           |                                | シングルエンド出力、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$                              | 111  |     |                  |

|                           |                                | 疑似差動出力、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$                                 | 112  |     |                  |

|                           |                                | 差動出力、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$                                   | 115  |     |                  |

|                           |                                | シングルエンド出力、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$                              | 105  |     |                  |

|                           |                                | 疑似差動出力、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$                                 | 107  |     |                  |

|                           |                                | 差動出力、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$ 、パワー チューン モード <sup>(3)</sup>      | 115  |     |                  |

|                           |                                | シングルエンド出力、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$ 、パワー チューン モード <sup>(3)</sup> | 104  |     |                  |

|                           |                                | 疑似差動出力、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$ 、パワー チューン モード <sup>(3)</sup>    | 109  |     |                  |

|                           |                                | 差動出力、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$ 、パワー チューン モード <sup>(3)</sup>      | 111  |     |                  |

| DR                        | ダイナミックレンジ、A特性補正 <sup>(2)</sup> | シングルエンド出力、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$ 、パワー チューン モード <sup>(3)</sup> | 100  |     | dB               |

|                           |                                | 疑似差動出力、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$ 、パワー チューン モード <sup>(3)</sup>    | 104  |     |                  |

|                           |                                | 差動出力、レシーバ負荷、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$                            | 118  |     |                  |

|                           |                                | シングルエンド出力、ヘッドフォン負荷、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$                     | 111  |     |                  |

|                           |                                | 疑似差動出力、レシーバ負荷、-60dBFS 信号、 $\text{AVDD} = 3.3\text{V}$                          | 112  |     |                  |

|                           |                                | 差動出力、レシーバ負荷、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$                            | 114  |     |                  |

| THD+N                     | 全高調波歪 <sup>(2)</sup>           | シングルエンド出力、ヘッドフォン負荷、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$                     | 105  |     | dB               |

|                           |                                | 疑似差動出力、レシーバ負荷、-60dBFS 信号、 $\text{AVDD} = 1.8\text{V}$                          | 107  |     |                  |

|                           |                                | 差動出力、-1dBFS 信号、 $\text{AVDD} = 3.3\text{V}$                                    | -104 |     |                  |

|                           |                                | 差動出力、-1dBFS 信号、 $\text{AVDD} = 1.8\text{V}$                                    | -95  |     |                  |

|                           |                                | シングルエンド出力、0dBFS 信号、ヘッドフォン負荷、 $\text{AVDD} = 3.3\text{V}$                       | -94  |     |                  |

|                           |                                | シングルエンド出力、0dBFS 信号、ヘッドフォン負荷、 $\text{AVDD} = 1.8\text{V}$                       | -94  |     |                  |

| ヘッドフォンの負荷範囲               | シングルエンド                        | 4                                                                              | 16   | 600 | $\Omega$         |

| ライン出力負荷範囲                 | シングルエンド                        | 600                                                                            |      |     | $\Omega$         |

| ヘッドフォン / ライン出力容量性負荷       | シングルエンド                        | 0                                                                              | 2    |     | nF               |

| ライン出力/ヘッドフォンアンプへのアナログバイパス |                                |                                                                                |      |     |                  |

| 入力インピーダンス                 | 入力インピーダンス                      | 入力ビン $\text{INxP}$ または $\text{INxM}$ 、 $4.4\text{k}\Omega$ の入力インピーダンス モード      | 4.4  |     | $\text{k}\Omega$ |

|                           |                                | 入力ビン $\text{INxP}$ または $\text{INxM}$ 、 $20\text{k}\Omega$ の入力インピーダンス モード       | 20   |     |                  |

|                           | シングルエンドフルスケール出力                | $\text{AVDD} = 3.3\text{V}$                                                    | 1    |     | Vrms             |

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 3.3\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、 $f_{\text{IN}} = 1\text{kHz}$  正弦波信号、 $f_S = 48\text{kHz}$ 、32ビットオーディオデータ、 $\text{BCLK} = 256 \times f_S$ 、TDM ターゲットモード、PLL オン、チャネルゲイン = 0dB、リニア位相補間フィルタ、差動/シングルエンド構成における  $1200\Omega/600\Omega$  のラインアウト負荷、または  $32\Omega/16\Omega$  のレシーバ/ヘッドホン負荷(該当する場合)、 $\text{MICBIAS}$  は  $\text{VREF}$  に設定済み、その他はデフォルト設定とします。特に記載がない限り、20Hz~20kHz の無補正帯域幅で **Audio Precision** によりフィルタフリーで測定します。

| パラメータ      | テスト条件                                | 最小値  | 公称値       | 最大値 | 単位                         |

|------------|--------------------------------------|------|-----------|-----|----------------------------|

| 差動フルスケール出力 | $\text{AVDD} = 3.3\text{V}$          |      | 2         |     | $\text{V}_{\text{rms}}$    |

|            | $\text{AVDD} = 1.8\text{V}$          |      | 1         |     | $\text{V}_{\text{rms}}$    |

| ゲイン誤差      | AC 結合入力、-6dBFS 入力                    |      | $\pm 0.1$ |     | dB                         |

| ノイズ、A 特性補正 | アイドルチャネル、AC 結合入力をグランドにショート、差動出力      |      | 3.5       |     | $\mu\text{V}_{\text{RMS}}$ |

| ノイズ、A 特性補正 | アイドルチャネル、AC 結合入力をグランドにショート、シングルエンド出力 |      | 19.7      |     | $\mu\text{V}_{\text{RMS}}$ |

| SNR        | 信号対雑音比、A 特性補正 <sup>(1) (2)</sup>     | 115  |           |     | dB                         |

| SNR        | 信号対雑音比、A 特性補正 <sup>(1) (2)</sup>     | 95   |           |     | dB                         |

| THD+N      | 全高調波歪 <sup>(2)</sup>                 | -102 |           |     | dB                         |

#### DAC チャネルの他のパラメータ

|                       |                                                                     |            |     |              |

|-----------------------|---------------------------------------------------------------------|------------|-----|--------------|

| 出力オフセット               | 0 入力、差動ライン出力                                                        | $\pm 0.5$  |     | $\text{mV}$  |

| 出力同相モード               | OUTxP および OUTxM の同相モードレベル ( $\text{AVDD} = 1.8\text{V}$ 、レジスタで構成可能) | 0.9        |     | $\text{V}$   |

|                       | OUTxP および OUTxM の同相モードレベル ( $\text{AVDD} = 3.3\text{V}$ 、レジスタで構成可能) | 1.65       |     |              |

| 同相モード誤差               | 同相モード電圧の DC 誤差                                                      | $\pm 20$   |     | $\text{mV}$  |

| 出力信号帯域幅               | 最大 192KSPS の FS レート                                                 | 0.46       |     | $\text{FS}$  |

|                       | >192KSPS                                                            | 90         |     |              |

| 入力データサンプルレート          | プログラム可能                                                             | 4          | 768 | $\text{kHz}$ |

| 入力データサンプルのワード長        | プログラム可能                                                             | 16         | 32  | ビット          |

| デジタルハイパスフィルタのカットオフ周波数 | プログラム可能な係数を持つ 1 次 IIR フィルタ、-3-dB ポイント(デフォルト設定)                      | 1          |     | Hz           |

| チャネル間絶縁               | 差動出力、非測定チャネルに -1dBFS の入力信号                                          | -134       |     | dB           |

| ゲイン誤差                 | 差動出力、-6dBFS 入力信号                                                    | $\pm 0.1$  |     | dB           |

| チャネル間ゲインのミスマッチ        | 差動出力、-6dBFS 入力信号                                                    | $\pm 0.1$  |     | dB           |

| チャネル間位相のミスマッチ         | 差動出力、-6dBFS 入力信号                                                    | $\pm 0.01$ |     | 度            |

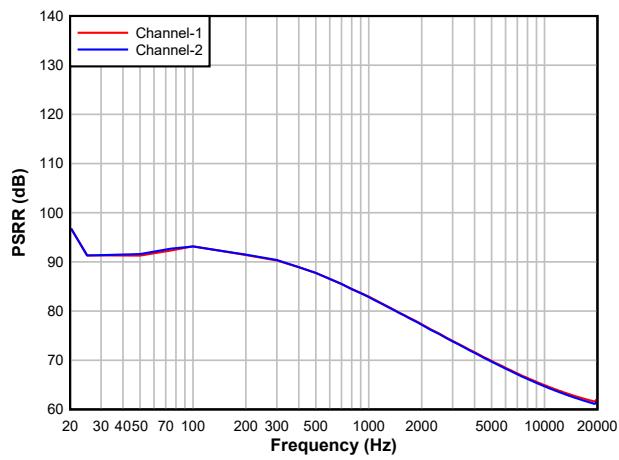

| PSRR                  | 電源除去比                                                               | 120        |     | dB           |

|                       | ミュート減衰                                                              | -130       |     | dB           |

| $P_{\text{out}}$      | 出力電力供給                                                              | 62.5       |     | $\text{mW}$  |

#### マイクバイアス

|             |                                                                            |   |  |                            |

|-------------|----------------------------------------------------------------------------|---|--|----------------------------|

| MICBIAS ノイズ | 帯域幅 = 20Hz~20kHz、A 特性補正、MICBIAS と VSS(サーマルパッド)の間に $1\mu\text{F}$ のコンデンサを接続 | 2 |  | $\mu\text{V}_{\text{RMS}}$ |

|-------------|----------------------------------------------------------------------------|---|--|----------------------------|

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 3.3\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、 $f_{\text{IN}} = 1\text{kHz}$  正弦波信号、 $f_S = 48\text{kHz}$ 、32ビットオーディオデータ、 $\text{BCLK} = 256 \times f_S$ 、TDM ターゲットモード、PLL オン、チャネルゲイン = 0dB、リニア位相補間フィルタ、差動/シングルエンド構成における  $1200\Omega/600\Omega$  のラインアウト負荷、または  $32\Omega/16\Omega$  のレシーバ/ヘッドホン負荷(該当する場合)、MICBIAS は  $\text{VREF}$  に設定済み、その他はデフォルト設定とします。特に記載がない限り、20Hz~20kHz の無補正帯域幅で Audio Precision によりフィルタフリーで測定します。

| パラメータ      | テスト条件        | 最小値 | 公称値   | 最大値 | 単位 |

|------------|--------------|-----|-------|-----|----|

| MICBIAS 電圧 | AVDD にバイパス   |     | AVDD  |     | V  |

|            | AVDD = 1.8 V |     | 1.375 |     | V  |

|            | AVDD = 3.3 V |     | 2.75  |     | V  |

**デジタル I/O**

|                 |                                    |                                                                                  |                            |                            |               |               |

|-----------------|------------------------------------|----------------------------------------------------------------------------------|----------------------------|----------------------------|---------------|---------------|

| $V_{IL}$        | Low レベル デジタル入力電圧スレッショルド            | SDA および SCL を除くすべてのデジタルピンは、<br>IOVDD が 1.8V または 1.2V で動作                         | -0.3                       | $0.35 \times \text{IOVDD}$ | V             |               |

|                 |                                    | SDA および SCL を除くすべてのデジタルピンは、<br>IOVDD 3.3V で動作                                    | -0.3                       | 0.8                        |               |               |

| $V_{IH}$        | High レベル デジタル入力電圧スレッショルド           | SDA および SCL を除くすべてのデジタルピンは、<br>IOVDD が 1.8V または 1.2V で動作                         | $0.65 \times \text{IOVDD}$ | $\text{IOVDD} + 0.3$       | V             |               |

|                 |                                    | SDA および SCL を除くすべてのデジタルピンは、<br>IOVDD 3.3V で動作                                    | 2                          | $\text{IOVDD} + 0.3$       |               |               |

| $V_{OL}$        | Low レベル デジタル出力電圧                   | SDA および SCL を除くすべてのデジタルピンにおいて、 $I_{OL} = -2\text{mA}$ 、IOVDD は 1.8V または 1.2V で動作 |                            | 0.45                       | V             |               |

|                 |                                    | SDA および SCL を除くすべてのデジタルピンにおいて、 $I_{OL} = -2\text{mA}$ 、IOVDD は 3.3V で動作          |                            | 0.4                        |               |               |

| $V_{OH}$        | High レベル デジタル出力電圧                  | SDA および SCL を除くすべてのデジタルピンにおいて、 $I_{OH} = 2\text{mA}$ 、IOVDD は 1.8V または 1.2V で動作  |                            | $\text{IOVDD} - 0.45$      | V             |               |

|                 |                                    | SDA および SCL を除くすべてのデジタルピンにおいて、 $I_{OH} = 2\text{mA}$ 、IOVDD は 3.3V で動作           | 2.4                        |                            |               |               |

| $V_{IL(I2C)}$   | Low レベル デジタル入力電圧スレッショルド            | SDA および SCL                                                                      | -0.5                       | $0.3 \times \text{IOVDD}$  | V             |               |

| $V_{IH(I2C)}$   | High レベル デジタル入力電圧スレッショルド           | SDA および SCL                                                                      |                            | $0.7 \times \text{IOVDD}$  | V             |               |

| $V_{OL1(I2C)}$  | Low レベル デジタル出力電圧                   | SDA, $I_{OL(I2C)} = -3\text{mA}$ 、IOVDD は 3.3V で動作                               |                            | 0.4                        | V             |               |

| $V_{OL2(I2C)}$  | Low レベル デジタル出力電圧                   | SDA, $I_{OL(I2C)} = -2\text{mA}$ 、IOVDD は 1.8V または 1.2V で動作                      |                            | $0.2 \times \text{IOVDD}$  | V             |               |

| $I_{OL(I2C)}$   | Low レベル デジタル出力電流                   | SDA, $V_{OL(I2C)} = 0.4\text{V}$ 、スタンダードモードまたはファーストモード                           | 3                          |                            | mA            |               |

|                 |                                    | SDA, $V_{OL(I2C)} = 0.4\text{V}$ 、ファーストモード プラス                                   | 20                         |                            |               |               |

| $I_{IL}$        | デジタル入力への入力ロジック Low リーケージ           | すべてのデジタルピン、入力 = 0V                                                               | -5                         | 0.1                        | 5             | $\mu\text{A}$ |

| $I_{IH}$        | デジタル入力への入力ロジック High リーケージ          | すべてのデジタルピン、入力 = IOVDD                                                            | -5                         | 0.1                        | 5             | $\mu\text{A}$ |

| $C_{IN}$        | デジタル入力の入力容量                        | すべてのデジタルピン                                                                       |                            | 5                          |               | pF            |

| $R_{PD}$        | デジタル I/O ピンがアサートされている場合のプルダウン抵抗    |                                                                                  |                            | 20                         |               | k $\Omega$    |

| <b>標準電源電流消費</b> |                                    |                                                                                  |                            |                            |               |               |

| $I_{AVDD}$      | スリープ モードでの消費電流(ソフトウェア シャットダウン モード) | すべてのデバイス外部クロックが停止                                                                | 9                          |                            | $\mu\text{A}$ |               |

| $I_{IOVDD}$     |                                    |                                                                                  | 1                          |                            |               |               |

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 3.3\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、 $f_{\text{IN}} = 1\text{kHz}$  正弦波信号、 $f_S = 48\text{kHz}$ 、32ビットオーディオデータ、 $\text{BCLK} = 256 \times f_S$ 、TDM ターゲットモード、PLL オン、チャネルゲイン = 0dB、リニア位相補間フィルタ、差動/シングルエンド構成における  $1200\Omega/600\Omega$  のラインアウト負荷、または  $32\Omega/16\Omega$  のレシーバ/ヘッドホン負荷(該当する場合)、MICBIAS は VREF に設定済み、その他はデフォルト設定とします。特に記載がない限り、20Hz~20kHz の無補正帯域幅で Audio Precision によりフィルタフリーで測定します。

| パラメータ              |                                                                                                       | テスト条件                                                 | 最小値 | 公称値  | 最大値 | 単位 |

|--------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|------|-----|----|

| $I_{\text{AVDD}}$  | MICBIAS オン、5mA の負荷、録音 / 再生なしの時の消費電流                                                                   | $f_S = 48\text{kHz}$ 、 $\text{BCLK} = 256 \times f_S$ |     | 1.5  |     | mA |

| $I_{\text{IOVDD}}$ |                                                                                                       |                                                       |     | 0.02 |     |    |

| $I_{\text{AVDD}}$  | DAC を使用したヘッドフォン 2 チャネル動作、MICBIAS オフ、PLL オン時の消費電流                                                      | $f_S = 16\text{kHz}$ 、 $\text{BCLK} = 512 \times f_S$ |     | 18.8 |     | mA |

| $I_{\text{IOVDD}}$ |                                                                                                       |                                                       |     | 0.02 |     |    |

| $I_{\text{AVDD}}$  | DAC を使用したヘッドフォン 2 チャネル動作、MICBIAS オフ、PLL オフ時の消費電流                                                      | $f_S = 48\text{kHz}$ 、 $\text{BCLK} = 512 \times f_S$ |     | 16   |     | mA |

| $I_{\text{IOVDD}}$ |                                                                                                       |                                                       |     | 0.04 |     |    |

| $I_{\text{AVDD}}$  | パワー チューン モード (3): DAC を使用したラインアウト 2 チャネルシングルエンド動作、MICBIAS オフ、PLL オフ、 $\text{AVDD}=1.8\text{V}$ 時の消費電流 | $f_S = 48\text{kHz}$ 、 $\text{BCLK} = 128 \times f_S$ |     | 5.6  |     | mA |

| $I_{\text{AVDD}}$  | パワー チューン モード (3): DAC を使用したラインアウト 2 チャネル動作、MICBIAS オフ、PLL オン時の消費電流                                    | $f_S = 48\text{kHz}$ 、 $\text{BCLK} = 512 \times f_S$ |     | 9.2  |     | mA |

| $I_{\text{IOVDD}}$ |                                                                                                       |                                                       |     | 0.04 |     |    |

- (1) 1kHz のフルスケール正弦波入力時の出力レベルと、ジェネレータ入力信号がない状態で入力がグラウンドにショートされている場合の出力レベルの比率、オーディオ アナライザを使用し、20Hz から 20kHz の帯域幅で A 特性補正フィルタをかけて測定します。

- (2) すべての性能測定は、20kHz のローパスフィルタを使用して行い、必要に応じて A 特性補正も使用しています。そのようなフィルタを使用しない場合、電気的特性に示されている値よりも THD+N が高く、SNR およびダイナミックレンジの読み値が低くなる可能性があります。ローパスフィルタは帯域外のノイズを除去します。これらのノイズは聴覚には影響しませんが、ダイナミック仕様値に影響を与える可能性があります。

- (3)  $\text{PWR\_TUNE\_CFG0} = 0xD4$ 、 $\text{PWR\_TUNE\_CFG1} = 0x96$ 、 $\text{PLL\_DIS} = 1'b1$ 、パワー チューン モード用

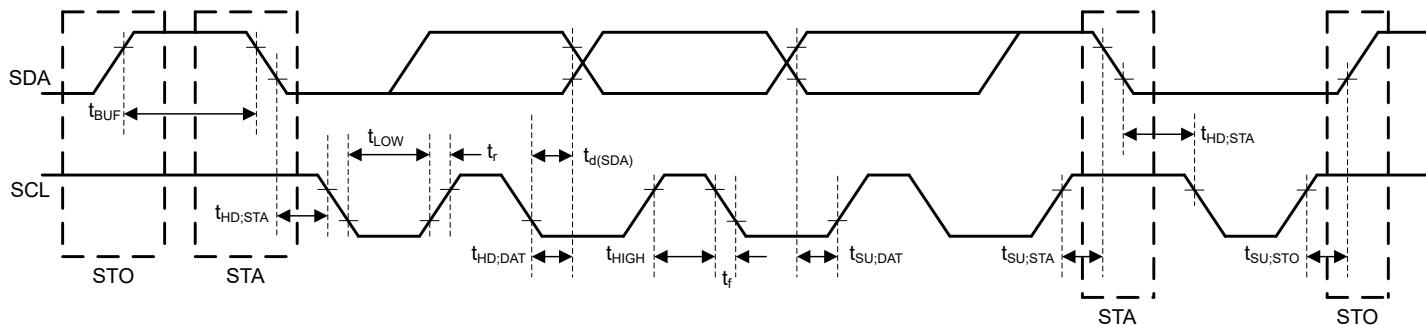

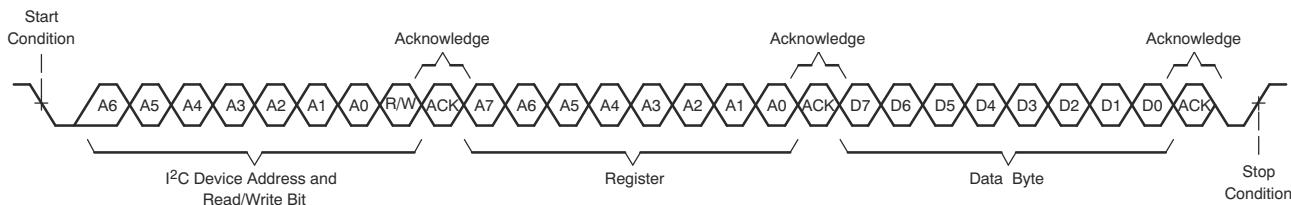

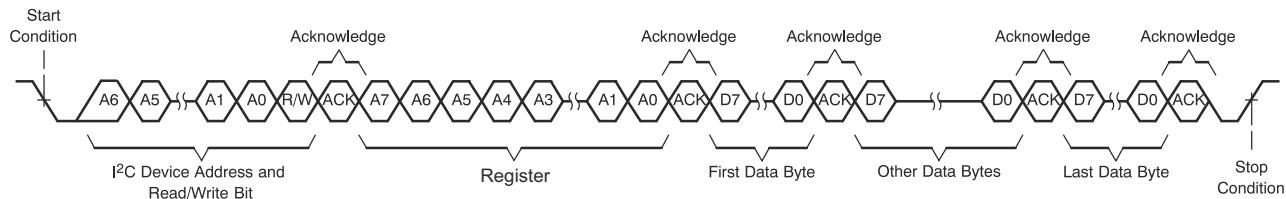

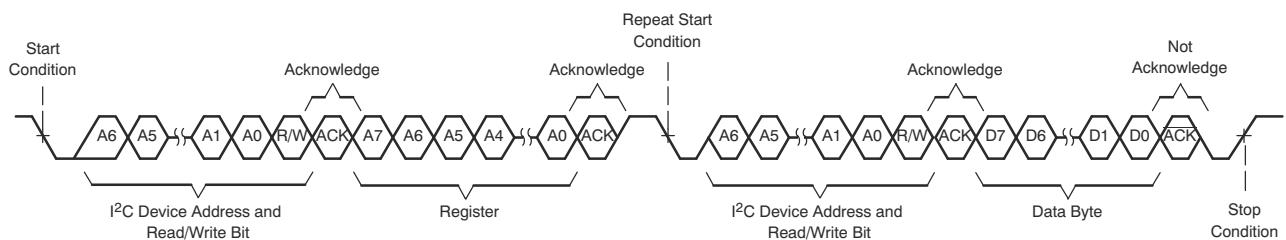

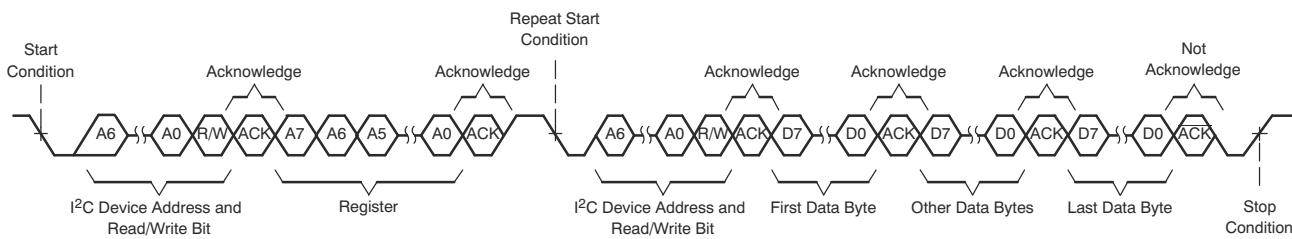

## 5.6 タイミング要件 : I<sup>2</sup>C インターフェイス

$T_A = 25^\circ\text{C}$  の場合、IOVDD は 3.3V、1.8V、または 1.2V です (特に記載がない限り)。タイミング図については図 5-1 を参照してください。IOVDD が 1.8V および 1.2V の動作の場合、IOVDD\_IO\_MODE ビットを正しく設定します。詳細については、セクション 8.3 をご参照ください。

|                     |                                                 | 最小値                       | 公称値  | 最大値  | 単位  |

|---------------------|-------------------------------------------------|---------------------------|------|------|-----|

| <b>スタンダード モード</b>   |                                                 |                           |      |      |     |

| $f_{SCL}$           | SCL クロック周波数                                     | 0                         | 100  | kHz  |     |

| $t_{HD:STA}$        | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます。 | 4                         |      |      | μs  |

| $t_{LOW}$           | SCL クロックの Low 期間                                | 4.7                       |      |      | μs  |

| $t_{HIGH}$          | SCL クロックの High 期間                               | 4                         |      |      | μs  |

| $t_{SU:STA}$        | 反復開始条件のセットアップ時間                                 | 4.7                       |      |      | μs  |

| $t_{HD:DAT}$        | データ ホールド時間                                      | 0                         | 3.45 | 3.45 | μs  |

| $t_{SU:DAT}$        | データ セットアップ時間                                    | 250                       |      |      | ns  |

| $t_r$               | SDA と SCL の立ち上がり時間                              |                           | 1000 | 1000 | ns  |

| $t_f$               | SDA と SCL の立ち下がり時間                              |                           | 300  | 300  | ns  |

| $t_{SU:STO}$        | 停止条件のセットアップ時間                                   | 4                         |      |      | μs  |

| $t_{BUF}$           | STOP 条件と START 条件の間のバス フリー時間                    | 4.7                       |      |      | μs  |

| <b>ファスト モード</b>     |                                                 |                           |      |      |     |

| $f_{SCL}$           | SCL クロック周波数                                     | 0                         | 400  | 400  | kHz |

| $t_{HD:STA}$        | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます。 | 0.6                       |      |      | μs  |

| $t_{LOW}$           | SCL クロックの Low 期間                                | 1.3                       |      |      | μs  |

| $t_{HIGH}$          | SCL クロックの High 期間                               | 0.6                       |      |      | μs  |

| $t_{SU:STA}$        | 反復開始条件のセットアップ時間                                 | 0.6                       |      |      | μs  |

| $t_{HD:DAT}$        | データ ホールド時間                                      | 0                         | 0.9  | 0.9  | μs  |

| $t_{SU:DAT}$        | データ セットアップ時間                                    | 100                       |      |      | ns  |

| $t_r$               | SDA と SCL の立ち上がり時間                              | 20                        | 300  | 300  | ns  |

| $t_f$               | SDA と SCL の立ち下がり時間                              | 20 ×<br>(IOVDD /<br>5.5V) | 300  | 300  | ns  |

| $t_{SU:STO}$        | 停止条件のセットアップ時間                                   | 0.6                       |      |      | μs  |

| $t_{BUF}$           | STOP 条件と START 条件の間のバス フリー時間                    | 1.3                       |      |      | μs  |

| <b>ファスト モード プラス</b> |                                                 |                           |      |      |     |

| $f_{SCL}$           | SCL クロック周波数                                     | 0                         | 1000 | 1000 | kHz |

| $t_{HD:STA}$        | (反復) 開始条件のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます。 | 0.26                      |      |      | μs  |

| $t_{LOW}$           | SCL クロックの Low 期間                                | 0.5                       |      |      | μs  |

| $t_{HIGH}$          | SCL クロックの High 期間                               | 0.26                      |      |      | μs  |

| $t_{SU:STA}$        | 反復開始条件のセットアップ時間                                 | 0.26                      |      |      | μs  |

| $t_{HD:DAT}$        | データ ホールド時間                                      | 0                         |      |      | μs  |

| $t_{SU:DAT}$        | データ セットアップ時間                                    | 50                        |      |      | ns  |

| $t_r$               | SDA と SCL の立ち上がり時間                              |                           | 120  | 120  | ns  |

| $t_f$               | SDA と SCL の立ち下がり時間                              | 20 ×<br>(IOVDD /<br>5.5V) | 120  | 120  | ns  |

| $t_{SU:STO}$        | 停止条件のセットアップ時間                                   | 0.26                      |      |      | μs  |

| $t_{BUF}$           | STOP 条件と START 条件の間のバス フリー時間                    | 0.5                       |      |      | μs  |

## 5.7 スイッチング特性 : I<sup>2</sup>C インターフェイス

$T_A = 25^\circ\text{C}$  の場合、IOVDD は 3.3V、1.8V、または 1.2V です (特に記載がない限り)。タイミング図については図 5-1 を参照してください。IOVDD が 1.8V および 1.2V の動作の場合、IOVDD\_IO\_MODE ビットを正しく設定します。詳細については、セクション 8.3 をご参照ください。

| パラメータ        |                  | テスト条件        | 最小値 | 標準値  | 最大値 | 単位 |

|--------------|------------------|--------------|-----|------|-----|----|

| $t_{d(SDA)}$ | SCL から SDA までの遅延 | スタンダード モード   | 200 | 1250 | ns  |    |

|              |                  | ファースト モード    | 200 | 850  | ns  |    |

|              |                  | ファスト モード プラス |     | 400  | ns  |    |

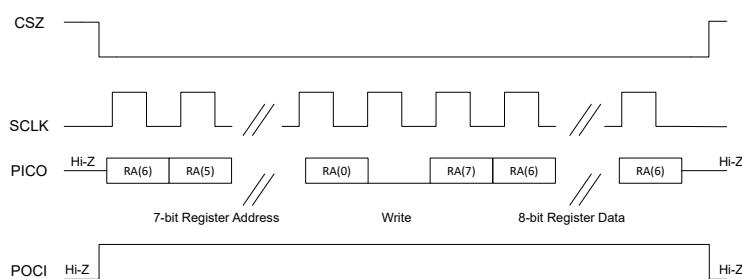

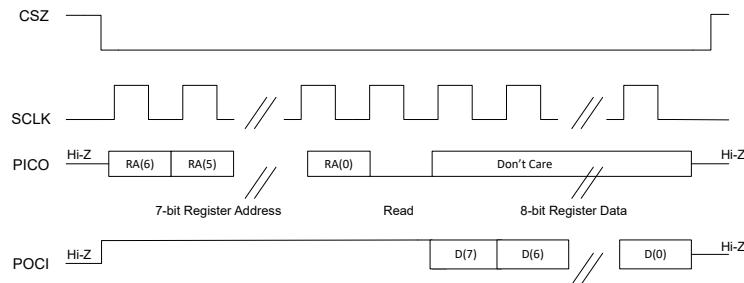

## 5.8 タイミング要件 : SPI

$T_A = 25^\circ\text{C}$ 、IOVDD = 3.3V または 1.8V、すべての出力に 20pF の負荷がかかっている場合 (特に記載がない限り)、タイミング図については図 5-2 を参照してください。IOVDD が 1.8V および 1.2V の動作の場合、IOVDD\_IO\_MODE ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

|                 |                    | 最小値              | 公称値 | 最大値 | 単位 |

|-----------------|--------------------|------------------|-----|-----|----|

| $t_{SCLK}$      | SCLK 周期            | 40               |     |     | ns |

| $t_{H(SCLK)}$   | SCLK High パルスの期間   | 18               |     |     | ns |

| $t_{L(SCLK)}$   | SCLK Low パルス持続時間   | 18               |     |     | ns |

| $t_{LEAD}$      | リードタイムをイネーブルします    | 16               |     |     | ns |

| $t_{TRAIL}$     | トレール時間をイネーブルにします   | 16               |     |     | ns |

| $t_{DSEQ}$      | シーケンシャル転送遅延        | 20               |     |     | ns |

| $t_{SU(PICO)}$  | PICO のデータ セットアップ時間 | 8                |     |     | ns |

| $t_{HLD(PICO)}$ | PICO のデータ ホールド時間   | 8                |     |     | ns |

| $t_{r(SCLK)}$   | SCLK の立ち上がり時間      | 10%~90% の立ち上がり時間 |     | 6   | ns |

| $t_{f(SCLK)}$   | SCLK の立ち下がり時間      | 90%~10% の立ち下がり時間 |     | 6   | ns |

## 5.9 スイッチング特性 : SPI

$T_A = 25^\circ\text{C}$ 、IOVDD = 3.3V または 1.8V、すべての出力に 20pF の負荷がかかっている場合 (特に記載がない限り)、タイミング図については図 5-2 を参照してください。IOVDD が 1.8V および 1.2V の動作の場合、IOVDD\_IO\_MODE ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

| パラメータ           |                    | テスト条件                                    | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------|--------------------|------------------------------------------|-----|-----|-----|----|

| $t_{a(POCI)}$   | POCI アクセス時間        | IOVDD = 1.2V                             |     | 18  | ns  |    |

|                 |                    | IOVDD = 1.8V                             |     | 18  | ns  |    |

|                 |                    | IOVDD = 3.3V                             |     | 14  |     |    |

| $t_{d(POCI)}$   | SCLK から POCI までの遅延 | SCLK の 50% から POCI の 50% まで、IOVDD = 1.2V |     | 19  | ns  |    |

|                 |                    | SCLK の 50% から POCI の 50% まで、IOVDD = 1.8V |     | 19  | ns  |    |

|                 |                    | SCLK の 50% から POCI の 50% まで、IOVDD = 3.3V |     | 15  |     |    |

| $t_{dis(POCI)}$ | POCI のディセーブル時間     | IOVDD = 1.2V                             |     | 18  | ns  |    |

|                 |                    | IOVDD = 1.8V                             |     | 18  | ns  |    |

|                 |                    | IOVDD = 3.3V                             |     | 14  |     |    |

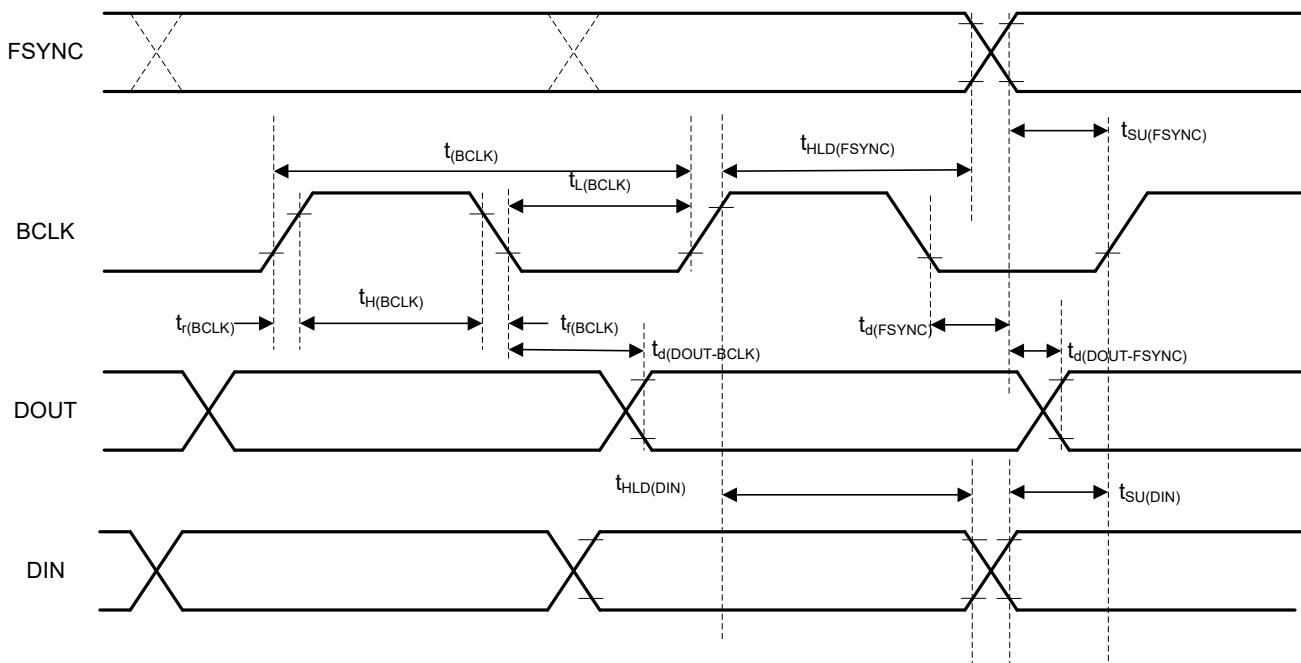

## 5.10 タイミング要件 : TDM、I<sup>2</sup>S または LJ インターフェイス

$T_A = 25^\circ\text{C}$ 、 $\text{IOVDD} = 3.3\text{V}$  または  $1.8\text{V}$  または  $1.2\text{V}$ 、すべての出力に  $20\text{pF}$  の負荷がかかっている場合(特に記載がない限り)、タイミング図については図 5-3 を参照してください。 $\text{IOVDD}$  が  $1.8\text{V}$  および  $1.2\text{V}$  の動作の場合、 $\text{IOVDD\_IO\_MODE}$  ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

|                                |                                  | 最小値              | 公称値 | 最大値 | 単位 |

|--------------------------------|----------------------------------|------------------|-----|-----|----|

| $t_{(\text{BCLK})}$            | BCLK 周期                          | 40               |     |     | ns |

| $t_{\text{H}(\text{BCLK})}$    | BCLK High パルス持続時間 <sup>(1)</sup> | 18               |     |     | ns |

| $t_{\text{L}(\text{BCLK})}$    | BCLK Low パルス持続時間 <sup>(1)</sup>  | 18               |     |     | ns |

| $t_{\text{SU}(\text{FSYNC})}$  | FSYNC のセットアップ時間                  | 8                |     |     | ns |

| $t_{\text{HLD}(\text{FSYNC})}$ | FSYNC のホールド時間                    | 8                |     |     | ns |

| $t_{\text{SU}(\text{DIN})}$    | DIN のセットアップ時間                    | 8                |     |     | ns |

| $t_{\text{HLD}(\text{DIN})}$   | DIN のホールド時間                      | 8                |     |     | ns |

| $t_{\text{r}(\text{BCLK})}$    | BCLK の立ち上がり時間                    | 10%～90% の立ち上がり時間 |     | 10  | ns |

| $t_{\text{f}(\text{BCLK})}$    | BCLK の立ち下がり時間                    | 90%～10% の立ち下がり時間 |     | 10  | ns |

(1) タイミング仕様を満たすためには、DOUT データラインがデバイスによって DOUT データを送信するために使用される BCLK エッジとは逆の BCLK エッジ極性でラッピングされる場合、BCLK の最小高 / 低パルス幅は  $25\text{ns}$  以上である必要があります。

## 5.11 スイッチング特性 : TDM、I<sup>2</sup>S または LJ インターフェイス

$T_A = 25^\circ\text{C}$ 、 $\text{IOVDD} = 3.3\text{V}$  または  $1.8\text{V}$  または  $1.2\text{V}$ 、すべての出力に  $20\text{pF}$  の負荷がかかっている場合(特に記載がない限り)、タイミング図については図 5-3 を参照してください。 $\text{IOVDD}$  が  $1.8\text{V}$  および  $1.2\text{V}$  の動作の場合、 $\text{IOVDD\_IO\_MODE}$  ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

| パラメータ                             | テスト条件                                                      | 最小値                          | 標準値 | 最大値    | 単位  |

|-----------------------------------|------------------------------------------------------------|------------------------------|-----|--------|-----|

| $t_{\text{d}(\text{DOUT-BCLK})}$  | BCLK の 50% から DOUT の 50% まで、 $\text{IOVDD} = 1.2\text{V}$  |                              |     | 18     | ns  |

|                                   | BCLK の 50% から DOUT の 50% まで、 $\text{IOVDD} = 1.8\text{V}$  |                              |     | 18     |     |

|                                   | BCLK の 50% から DOUT の 50% まで、 $\text{IOVDD} = 3.3\text{V}$  |                              |     | 14     |     |

| $t_{\text{d}(\text{DOUT-FSYNC})}$ | FSYNC の 50% から DOUT の 50% まで、 $\text{IOVDD} = 1.2\text{V}$ |                              |     | 18     | ns  |

|                                   | FSYNC の 50% から DOUT の 50% まで、 $\text{IOVDD} = 1.8\text{V}$ |                              |     | 18     |     |

|                                   | FSYNC の 50% から DOUT の 50% まで、 $\text{IOVDD} = 3.3\text{V}$ |                              |     | 14     |     |

| $f_{(\text{BCLK})}$               | BCLK 出力クロック周波数、コントローラ モード <sup>(1)</sup>                   |                              |     | 24.576 | MHz |

| $t_{\text{H}(\text{BCLK})}$       | BCLK のハイパルスの持続時間、コントローラ モード                                | $\text{IOVDD} = 1.2\text{V}$ | 14  |        | ns  |

|                                   |                                                            | $\text{IOVDD} = 1.8\text{V}$ | 14  |        |     |

|                                   |                                                            | $\text{IOVDD} = 3.3\text{V}$ | 14  |        |     |

| $t_{\text{L}(\text{BCLK})}$       | BCLK Low パルス幅、コントローラ モード                                   | $\text{IOVDD} = 1.2\text{V}$ | 14  |        | ns  |

|                                   |                                                            | $\text{IOVDD} = 1.8\text{V}$ | 14  |        |     |

|                                   |                                                            | $\text{IOVDD} = 3.3\text{V}$ | 14  |        |     |

| $t_{\text{d}(\text{FSYNC})}$      | BCLK の 50% から FSYNC の 50%、 $\text{IOVDD} = 1.2\text{V}$    |                              |     | 18     | ns  |

|                                   | BCLK の 50% から FSYNC の 50%、 $\text{IOVDD} = 1.8\text{V}$    |                              |     | 18     |     |

|                                   | BCLK の 50% から FSYNC の 50%、 $\text{IOVDD} = 3.3\text{V}$    |                              |     | 14     |     |

$T_A = 25^\circ\text{C}$ 、 $\text{IOVDD} = 3.3\text{V}$  または  $1.8\text{V}$  または  $1.2\text{V}$ 、すべての出力に  $20\text{pF}$  の負荷がかかっている場合(特に記載がない限り)、タイミング図については図 5-3 を参照してください。 $\text{IOVDD}$  が  $1.8\text{V}$  および  $1.2\text{V}$  の動作の場合、 $\text{IOVDD\_IO\_MODE}$  ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

| パラメータ              | テスト条件                                          | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------|------------------------------------------------|-----|-----|-----|----|

| $t_r(\text{BCLK})$ | 10%~90% の立ち上がり時間、 $\text{IOVDD} = 1.2\text{V}$ |     |     | 10  | ns |

|                    | 10%~90% の立ち上がり時間、 $\text{IOVDD} = 1.8\text{V}$ |     |     | 10  |    |

|                    | 10%~90% の立ち上がり時間、 $\text{IOVDD} = 3.3\text{V}$ |     |     | 10  |    |

| $t_f(\text{BCLK})$ | 90%~10% 立ち下がり時間、 $\text{IOVDD} = 1.2\text{V}$  |     |     | 8   | ns |

|                    | 90%~10% 立ち下がり時間、 $\text{IOVDD} = 1.8\text{V}$  |     |     | 8   |    |

|                    | 90%~10% 立ち下がり時間、 $\text{IOVDD} = 3.3\text{V}$  |     |     | 8   |    |

(1) タイミング仕様を満たすためには、 $\text{DOUT}$  データラインがデバイスが  $\text{DOUT}$  データを送信するために使用する  $\text{BCLK}$  エッジの極性とは反対の  $\text{BCLK}$  エッジでラッピングされる場合、 $\text{BCLK}$  出力クロック周波数は  $18.5\text{MHz}$  未満である必要があります。

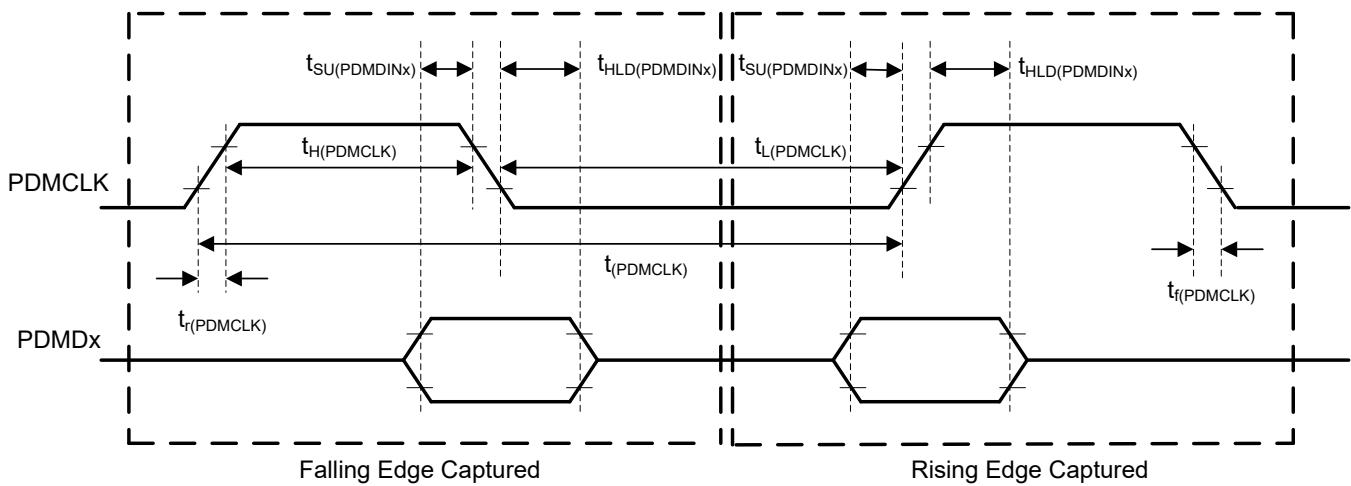

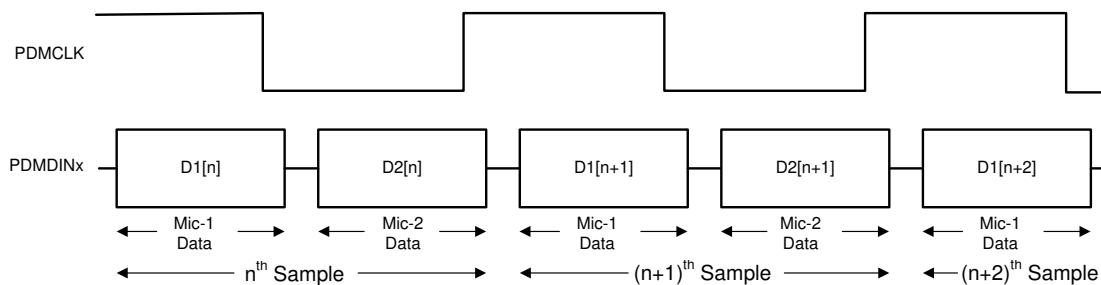

## 5.12 タイミング要件 : PDM デジタル マイクロフォン インターフェイス

$T_A = 25^\circ\text{C}$  の場合、 $\text{IOVDD}$  は  $3.3\text{V}$ 、 $1.8\text{V}$ 、または  $1.2\text{V}$  で、すべての出力に  $20\text{pF}$  の負荷がかかります(特に記載がない限り)。タイミング図については図 5-4 を参照してください。 $\text{IOVDD}$  が  $1.8\text{V}$  および  $1.2\text{V}$  の動作の場合、 $\text{IOVDD\_IO\_MODE}$  ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

|                           |                   | 最小値 | 公称値 | 最大値 | 単位 |

|---------------------------|-------------------|-----|-----|-----|----|

| $t_{SU}(\text{PDMDINx})$  | PDMDINx のセットアップ時間 | 30  |     |     | ns |

| $t_{HLD}(\text{PDMDINx})$ | PDMDINx ホールド時間    | 0   |     |     | ns |

## 5.13 スイッチング特性 : PDM デジタル マイクロフォン インターフェイス

$T_A = 25^\circ\text{C}$  の場合、 $\text{IOVDD}$  は  $3.3\text{V}$ 、 $1.8\text{V}$ 、または  $1.2\text{V}$  で、すべての出力に  $20\text{pF}$  の負荷がかかります(特に記載がない限り)。タイミング図については図 5-4 を参照してください。 $\text{IOVDD}$  が  $1.8\text{V}$  および  $1.2\text{V}$  の動作の場合、 $\text{IOVDD\_IO\_MODE}$  ビットを正しく設定してください。詳細については、セクション 8.3 をご参照ください。

| パラメータ                 | テスト条件                         | 最小値              | 標準値   | 最大値 | 単位  |

|-----------------------|-------------------------------|------------------|-------|-----|-----|

| $f_{(\text{PDMCLK})}$ | $\text{PDMCLK}$ クロック周波数       | 0.768            | 6.144 |     | MHz |

| $t_H(\text{PDMCLK})$  | $\text{PDMCLK}$ High パルスの期間   | 72               |       |     | ns  |

| $t_L(\text{PDMCLK})$  | $\text{PDMCLK}$ の Low パルス持続時間 | 72               |       |     | ns  |

| $t_r(\text{PDMCLK})$  | $\text{PDMCLK}$ の立ち上がり時間      | 10%~90% の立ち上がり時間 |       | 18  | ns  |

| $t_f(\text{PDMCLK})$  | $\text{PDMCLK}$ の立ち下がり時間      | 90%~10% の立ち下がり時間 |       | 18  | ns  |

## 5.14 タイミング図

図 5-1. I<sup>2</sup>C インターフェイス プロトコル図

図 5-2. SPI タイミング図

図 5-3. TDM (BCLK\_POL = 1)、I<sup>2</sup>S、LJ インターフェイスのタイミング図

図 5-4. PDM デジタルマイクロフォンインターフェイスのタイミング図

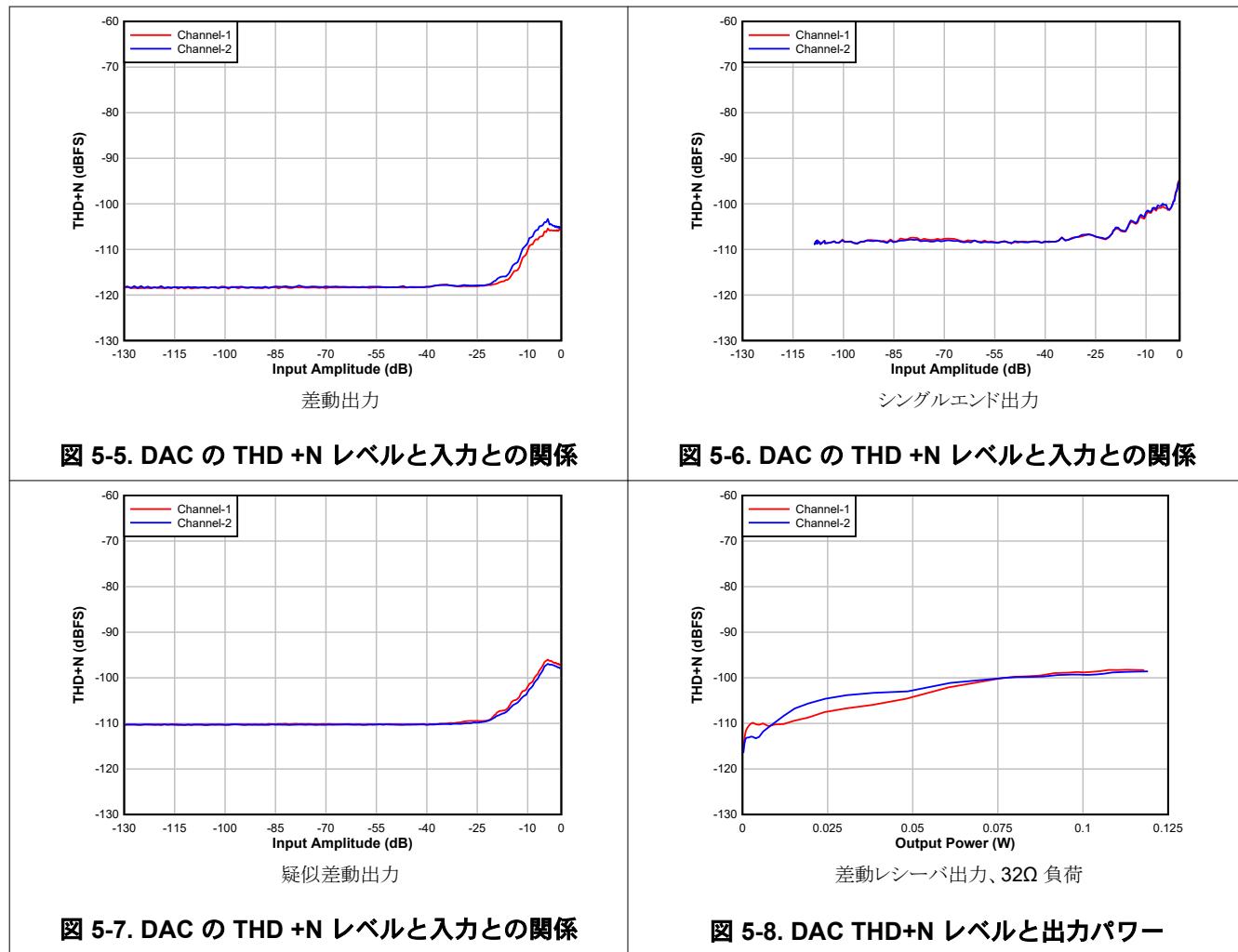

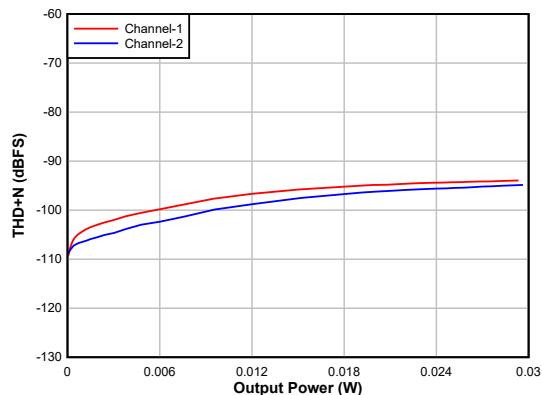

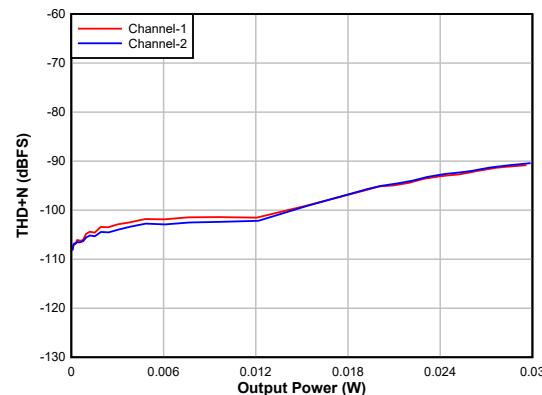

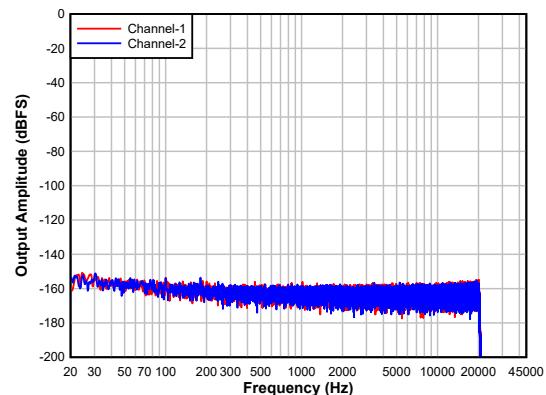

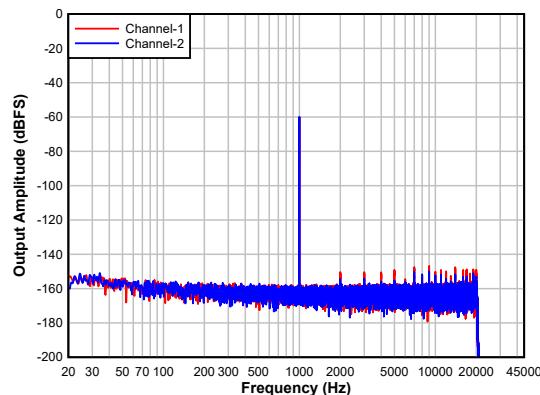

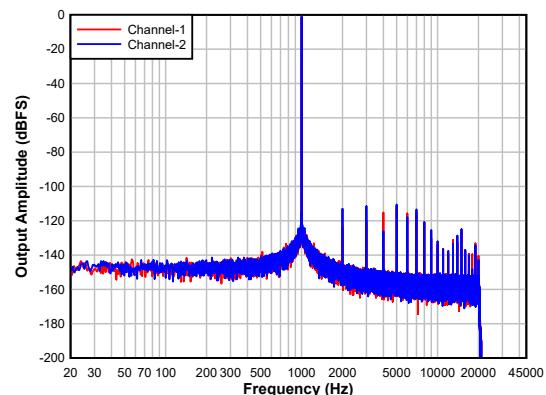

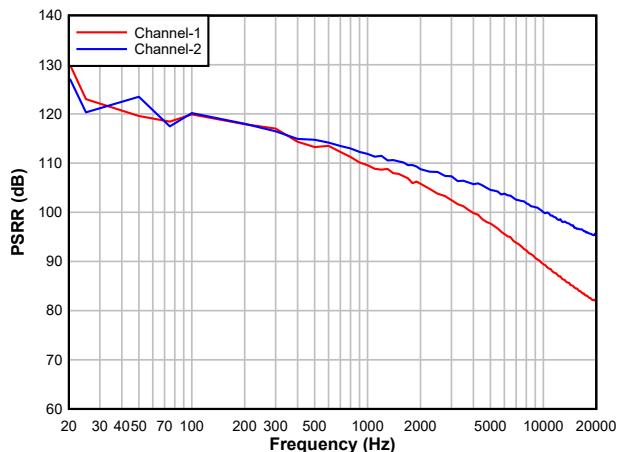

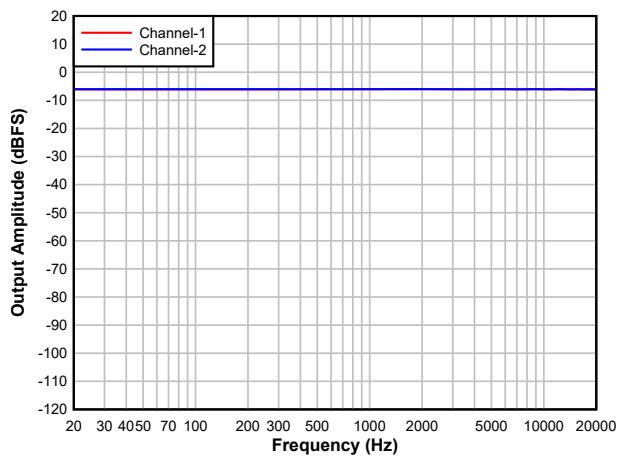

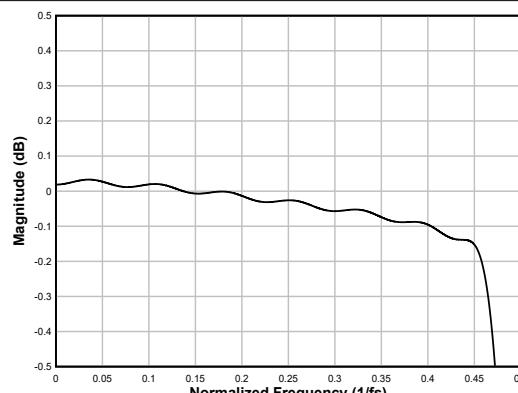

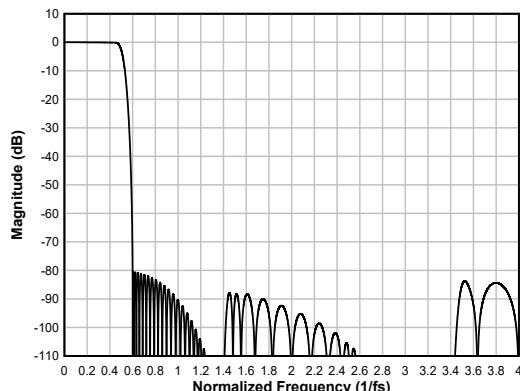

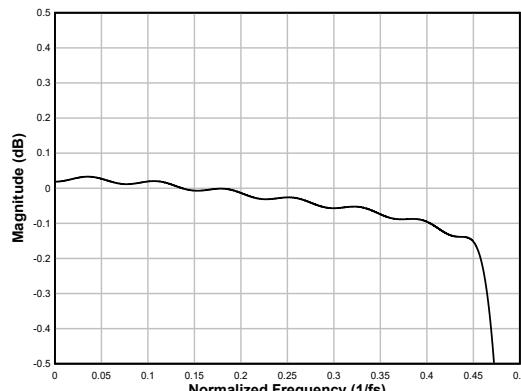

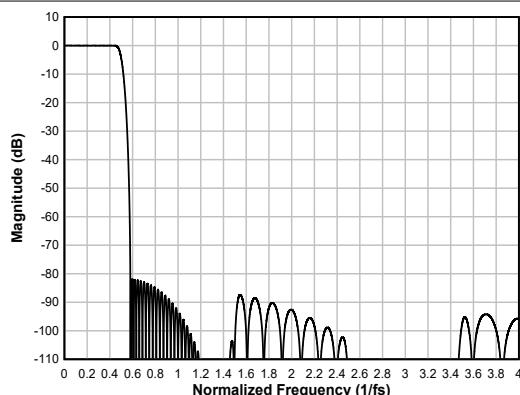

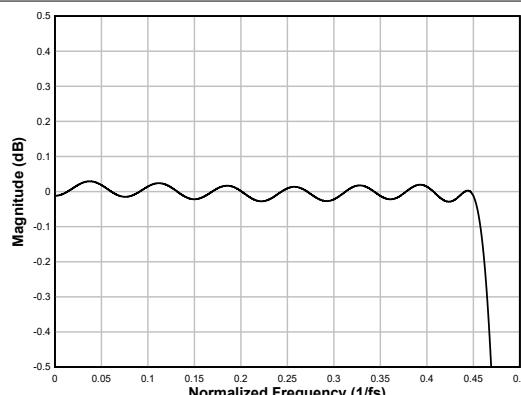

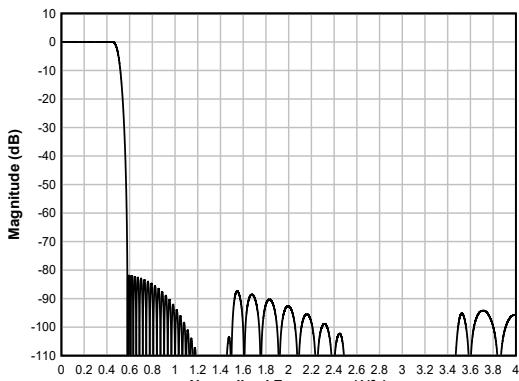

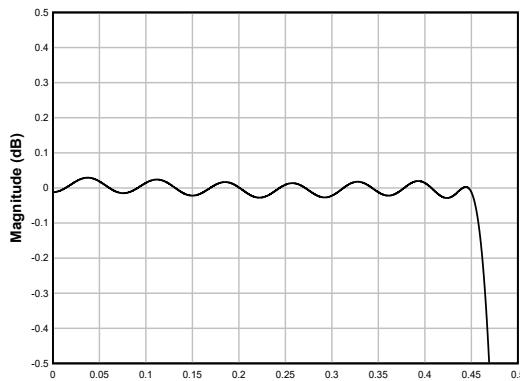

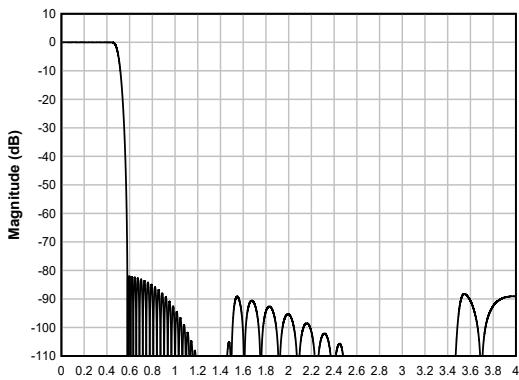

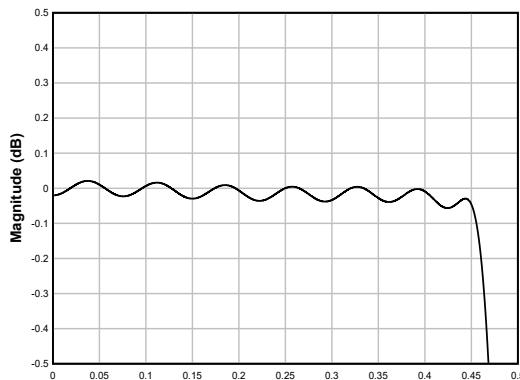

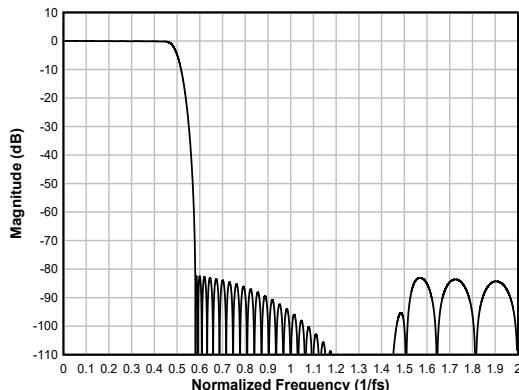

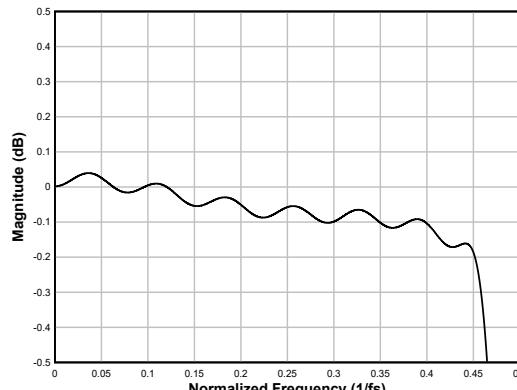

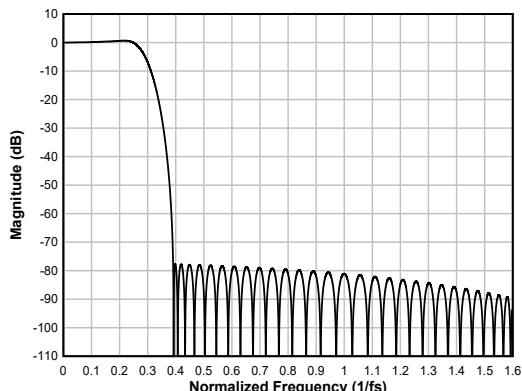

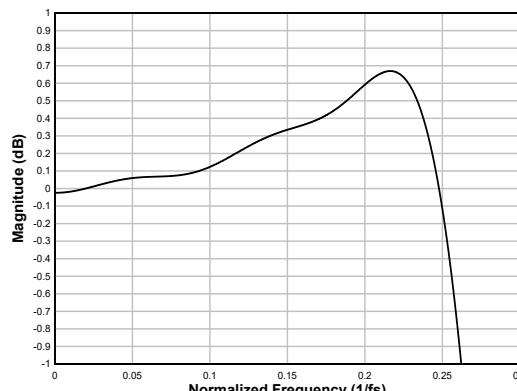

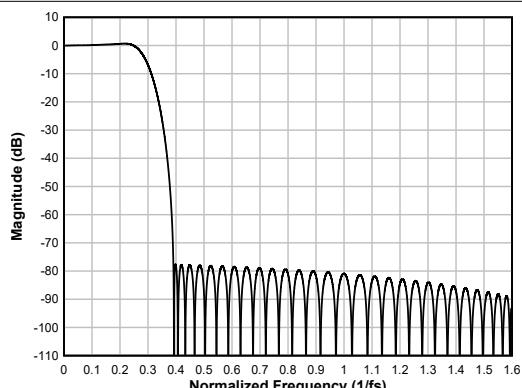

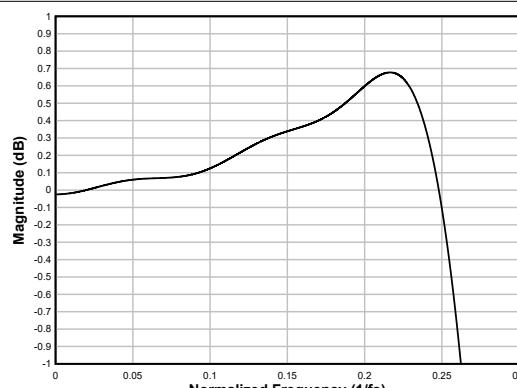

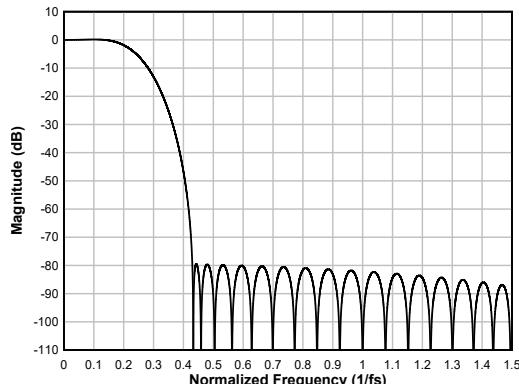

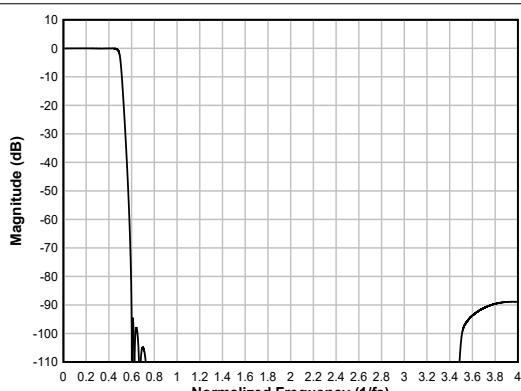

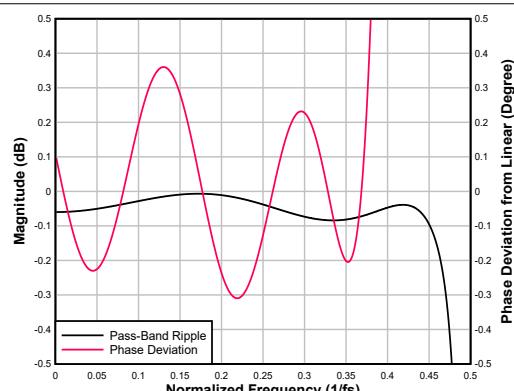

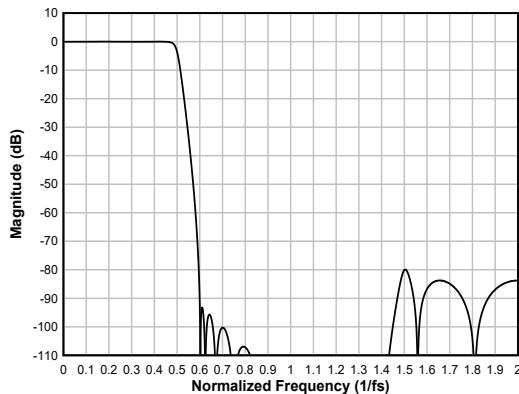

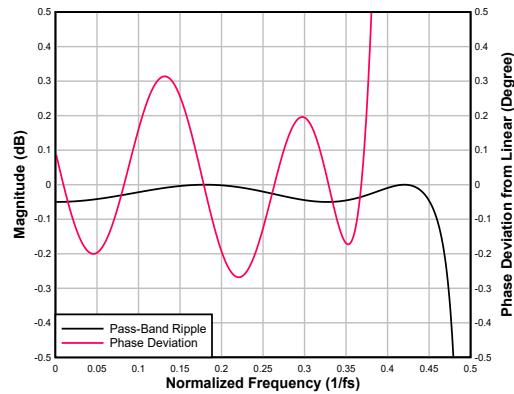

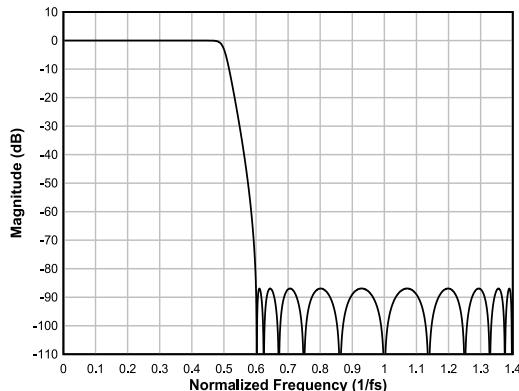

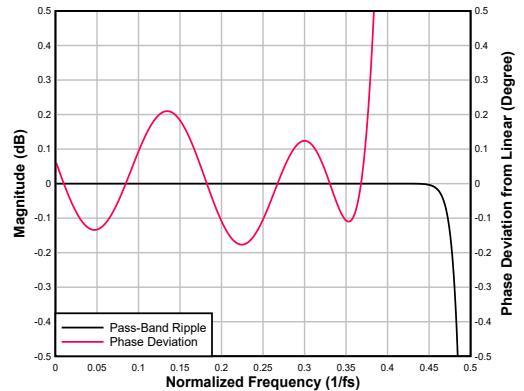

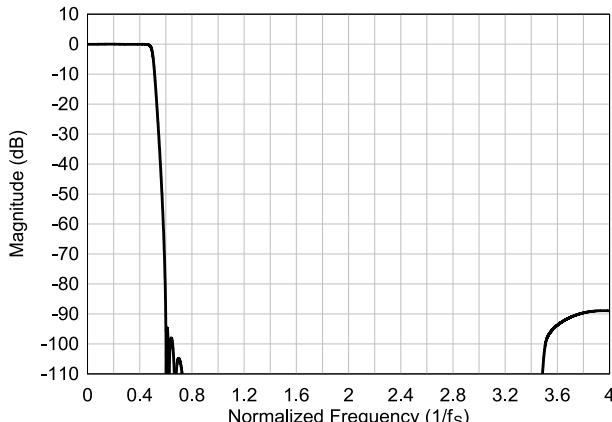

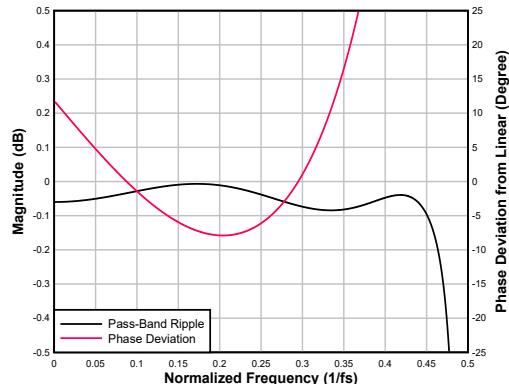

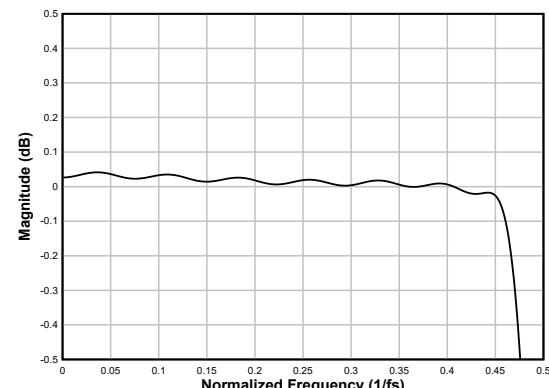

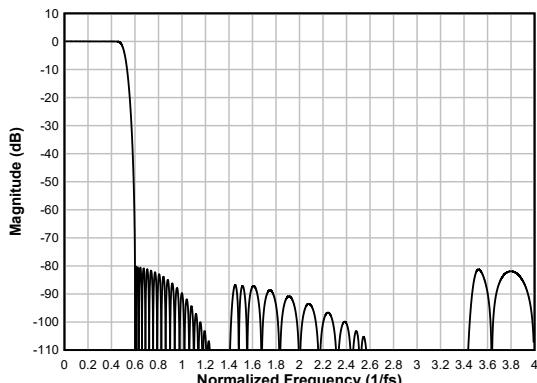

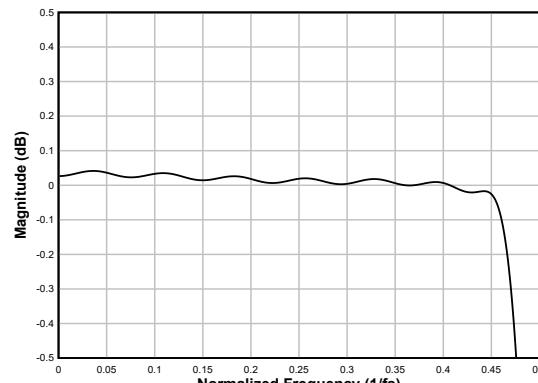

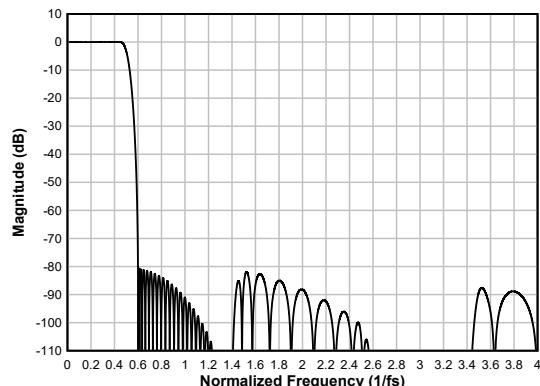

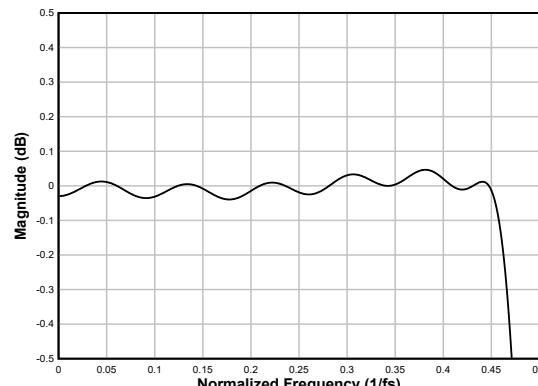

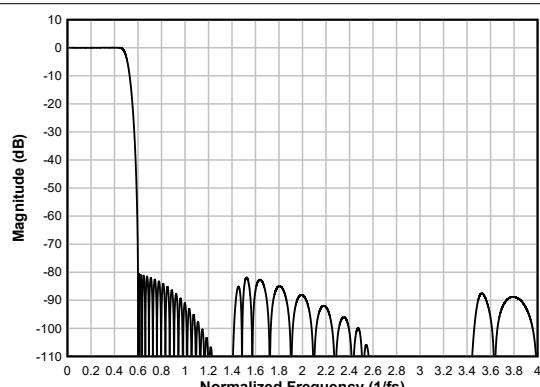

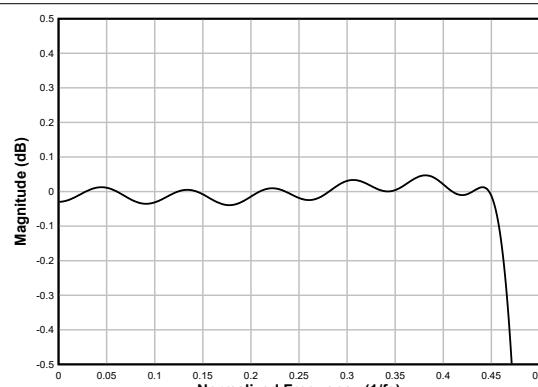

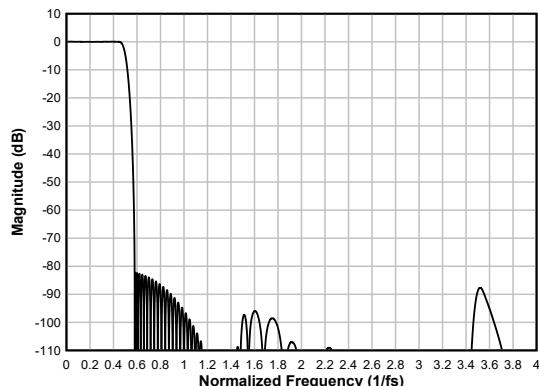

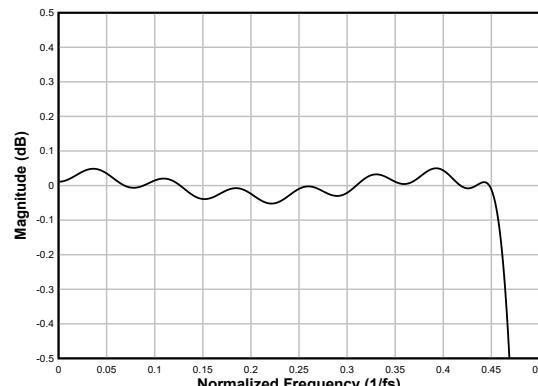

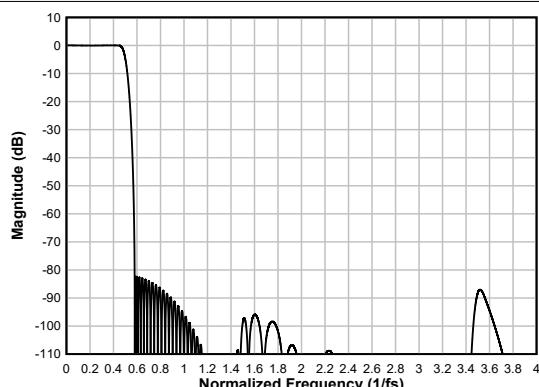

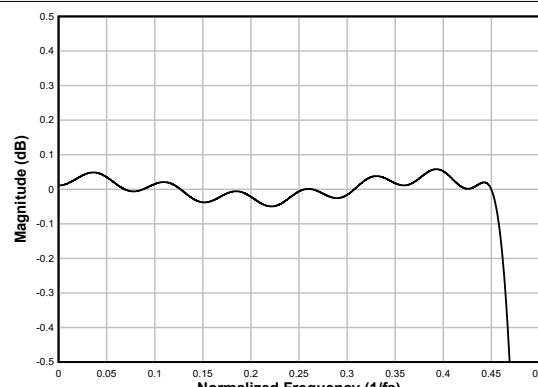

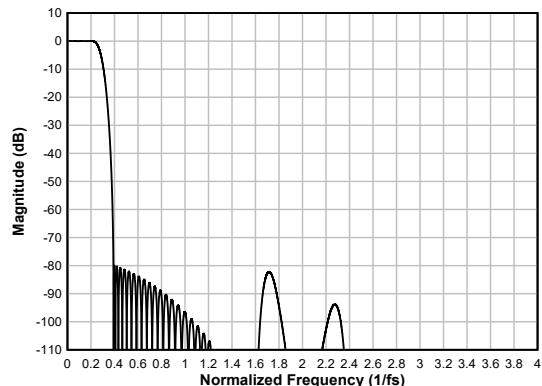

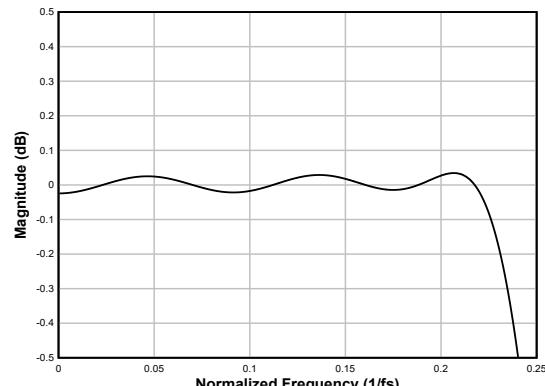

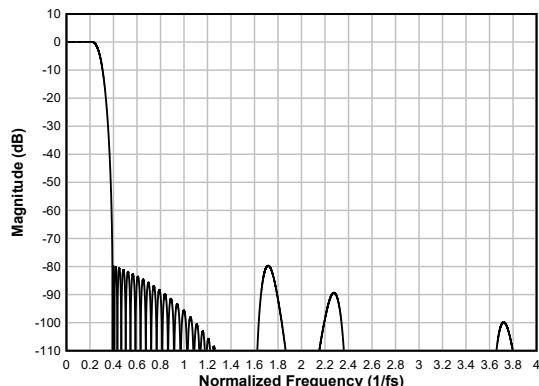

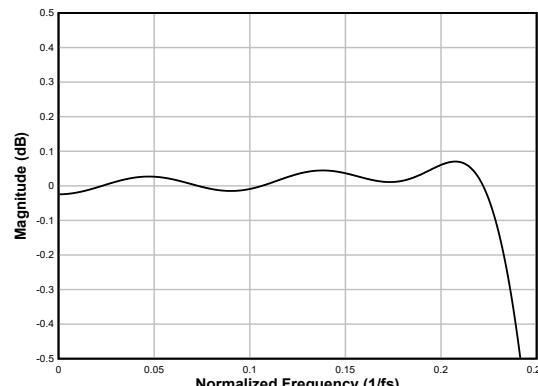

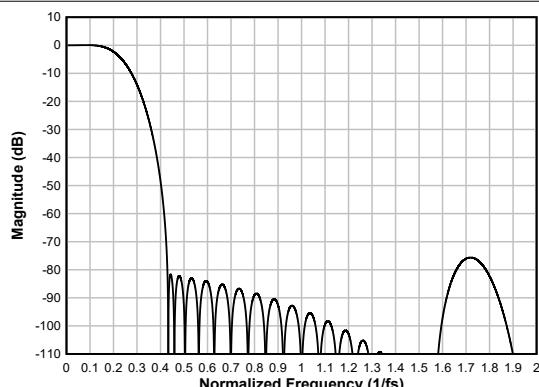

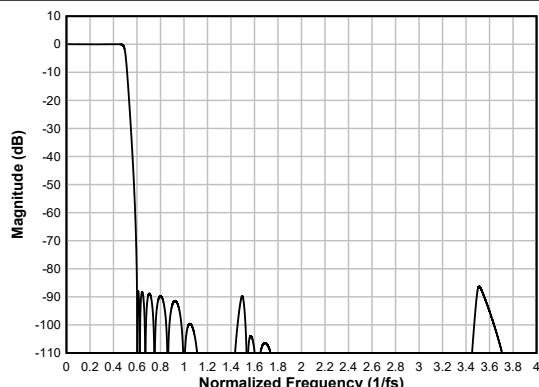

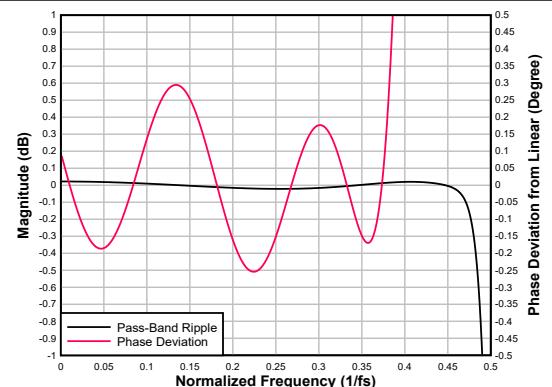

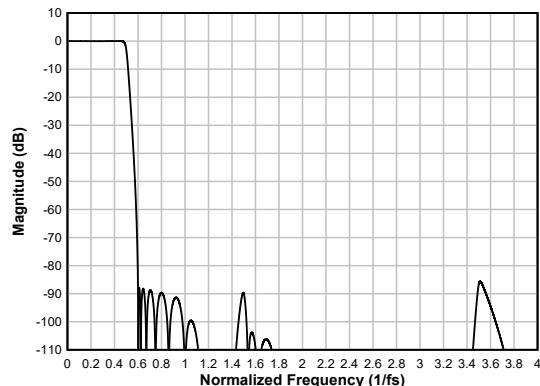

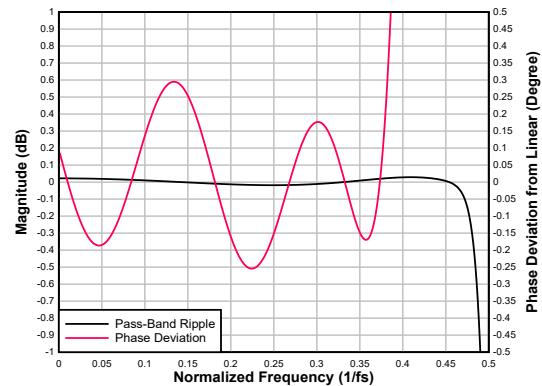

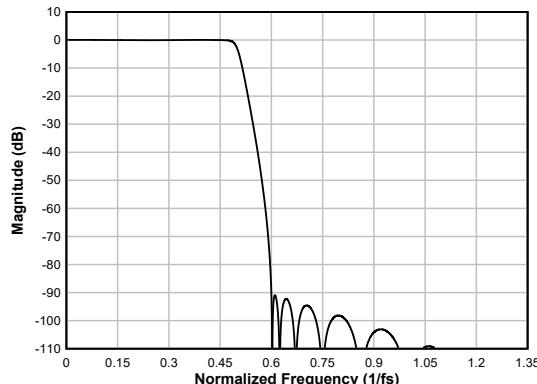

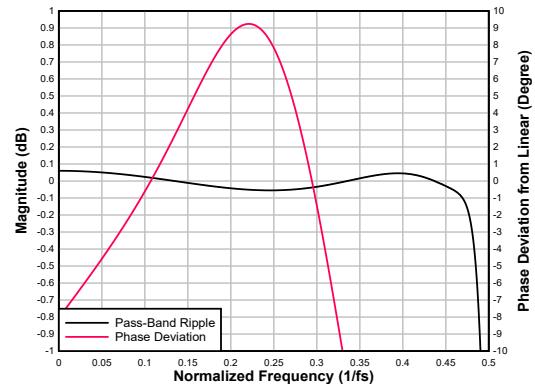

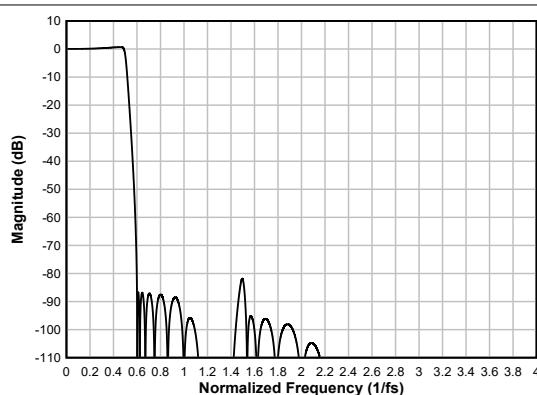

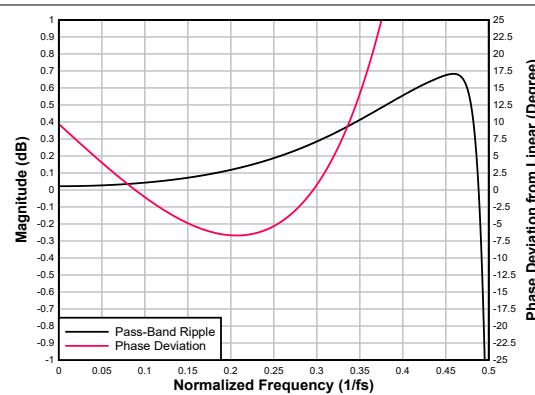

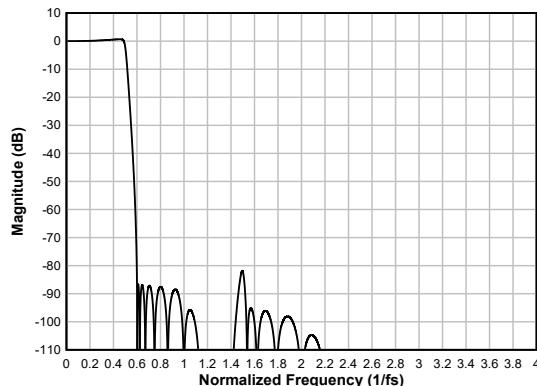

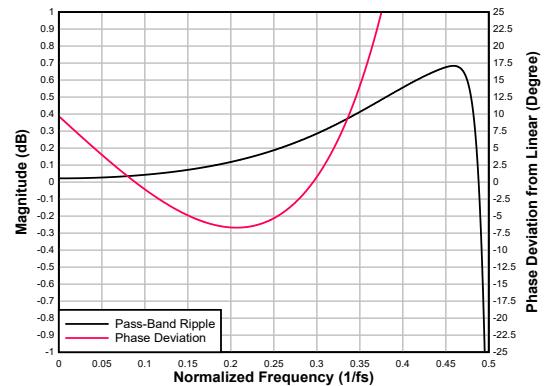

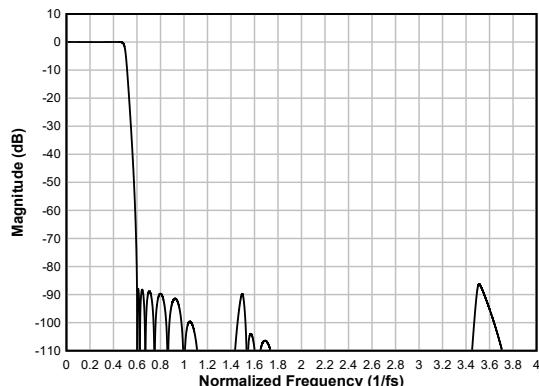

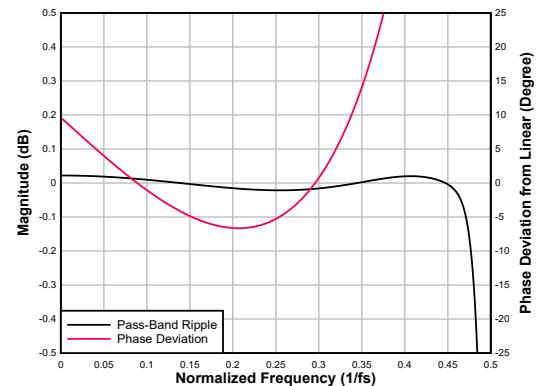

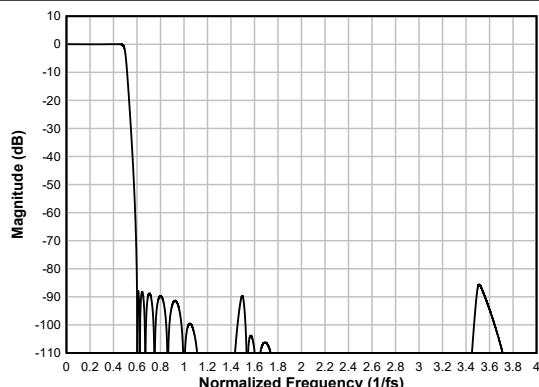

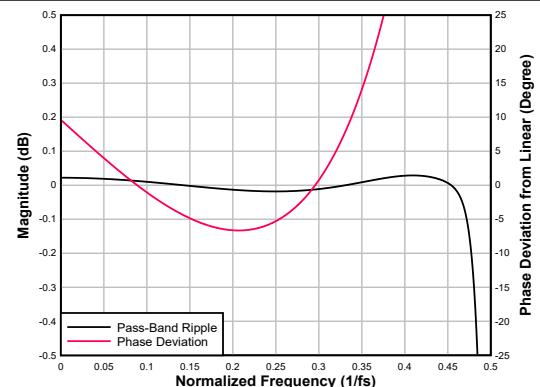

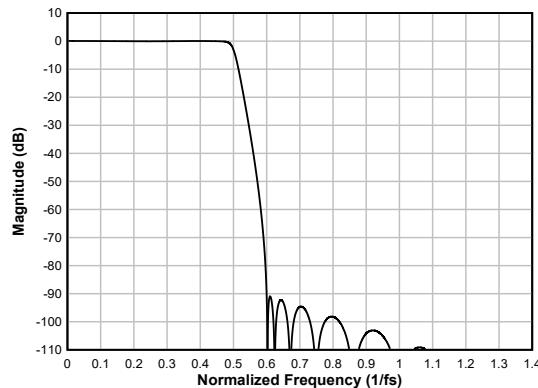

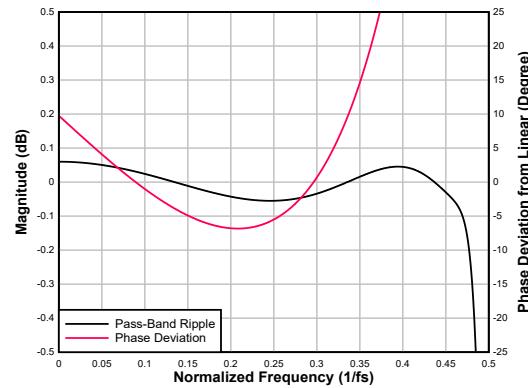

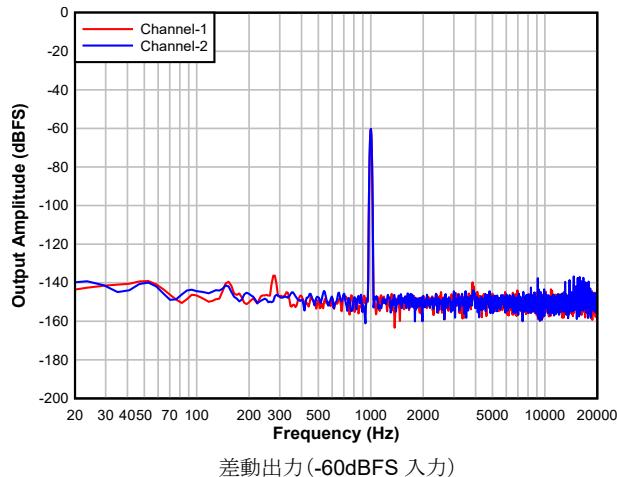

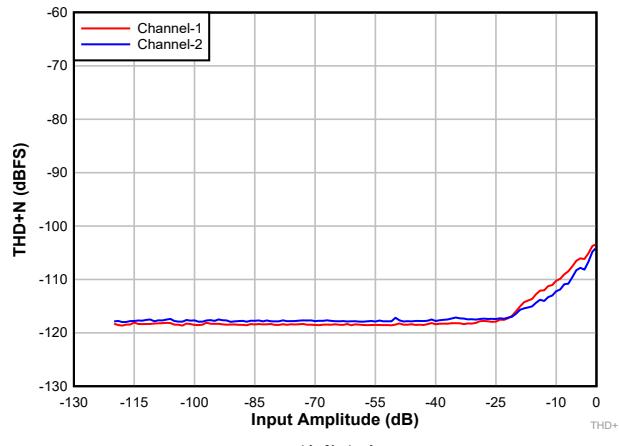

## 5.15 代表的特性

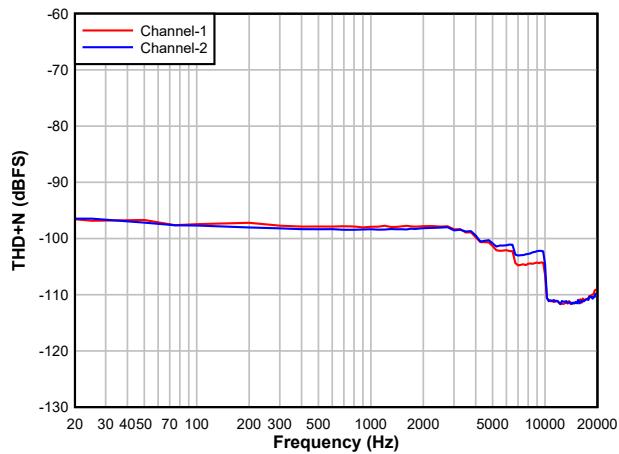

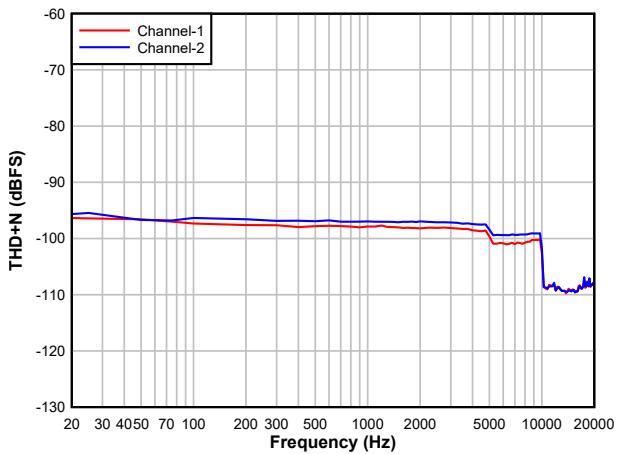

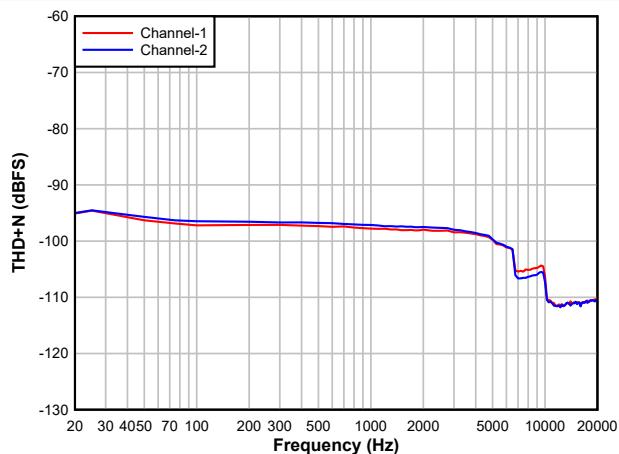

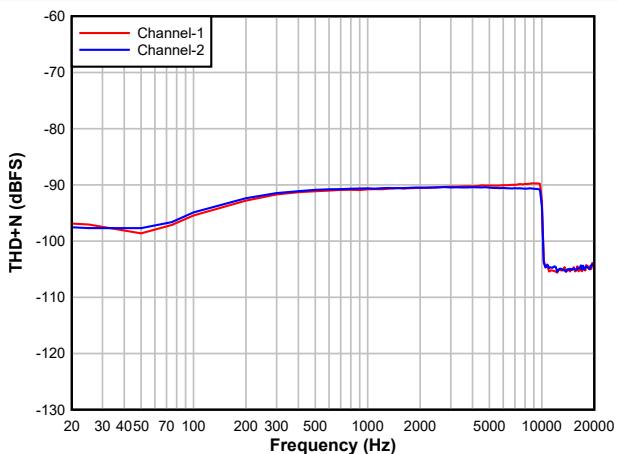

$T_A = 25^\circ\text{C}$ 、 $\text{AVDD} = 3.3\text{V}$ 、 $\text{IOVDD} = 3.3\text{V}$ 、 $f_{\text{IN}} = 1\text{kHz}$  正弦波信号、 $f_S = 48\text{kHz}$ 、32ビットオーディオデータ、 $\text{BCLK} = 256 \times f_S$ 、TDMターゲットモード、PLLオン、チャネルゲイン = 0dB、リニア位相補間フィルタ、 $1200\Omega/600\Omega$  ライン出力負荷(差動/シングルエンド構成)、または $32\Omega/16\Omega$  レシーバ/ヘッドフォン負荷(該当する場合)、その他のデフォルト構成、フィルターフリーで測定。Audio Precisionを使用し、20Hz～20kHzの非加重帯域幅で測定(特に記載がない限り)

シングルエンド ヘッドフォン出力、16Ω 負荷

図 5-9. DAC THD+N レベルと出力パワー

疑似差動ヘッドフォン出力、16Ω 負荷

図 5-10. DAC THD+N レベルと出力パワー

差動出力 (-1dBFS 入力)

図 5-11. DAC THD+N レベル対周波数

シングルエンド出力 (-1dBFS 入力)

図 5-12. DAC THD+N レベル対周波数

差動レシーバ出力、32Ω 負荷 (-1dBFS 入力)

図 5-13. DAC THD+N レベル対周波数

シングルエンド ヘッドフォン出力、16Ω 負荷 (-1dBFS 入力)

図 5-14. DAC THD+N レベル対周波数

差動出力

図 5-15. アイドルチャネル入力による DAC FFT

差動出力

図 5-16. -60dBFS 入力の DAC FFT

差動出力

図 5-17. -1dBFS 入力の DAC FFT

差動出力

図 5-18. DAC PSRR と周波数との関係

シングルエンド出力

図 5-19. DAC PSRR と周波数との関係

差動出力、-6dBFS 入力、ハイパス フィルタ (HPF) 無効

図 5-20. DAC の周波数応答

## 6 詳細説明

### 6.1 概要

TAD5212-Q1 は、スケーラブルなオーディオ コンバータ デバイス ファミリの製品です。拡張デバイス ファミリの一部である TAD5212-Q1 は、高性能、の柔軟なステレオ差動およびクワッド シングルエンド オーディオ D/A コンバータ(DAC)であり、豊富な機能を統合しています。このデバイスは、ホームシアターやエンターテイメント用スピーカー、AV レシーバー、ポータブル オーディオ機器、業務用オーディオ、マルチメディア アプリケーションなど、幅広い市場での使用を想定しています。このデバイスは、スペースに制約のある自動車用サブシステムの設計において、コスト、基板スペース、消費電力を削減する多数の機能を統合しています。パッケージ、性能、デバイス互換性のある構成レジスタにより、このデバイスはスケーラブルなシステム設計に最適です。

TAD5212-Q1 は以下に示すブロックで構成されています。

- 4 チャネル、マルチビット、高性能デルタシグマ( $\Delta\Sigma$ ) DAC

- シングルエンド、差動、または擬似差動の各オーディオ出力が構成可能

- 高度なサーマル フォールドバックと保護機能

- 高度なバッテリ ガードと歪みリミッタ

- 低ノイズのプログラム可能なマイクロフォン バイアス出力

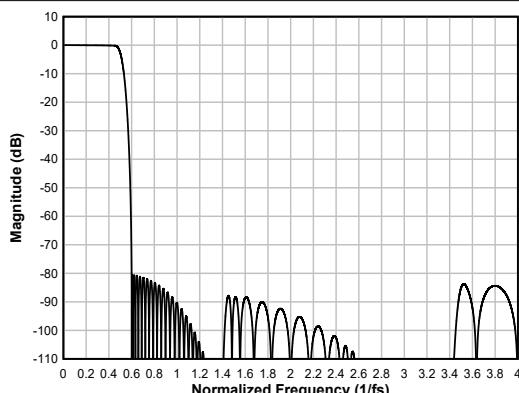

- 最大 4 つのパルス密度変調(PDM) デジタル マイクインターフェースと高性能デシメーション フィルタ

- リニア位相、低レイテンシ、超低レイテンシの応答オプションを備えた、プログラム可能なデシメーションおよび補間フィルタ

- 各録音および再生チャネルにプログラム可能なチャネルゲイン、ボリューム制御、バイカッド フィルタ

- 各記録チャンネルごとに、高分解能で位相とゲインの較正をプログラム可能

- プログラム可能なハイパス フィルタ(HPF)とデジタル チャネル リミキサーによる録音および再生チャネル

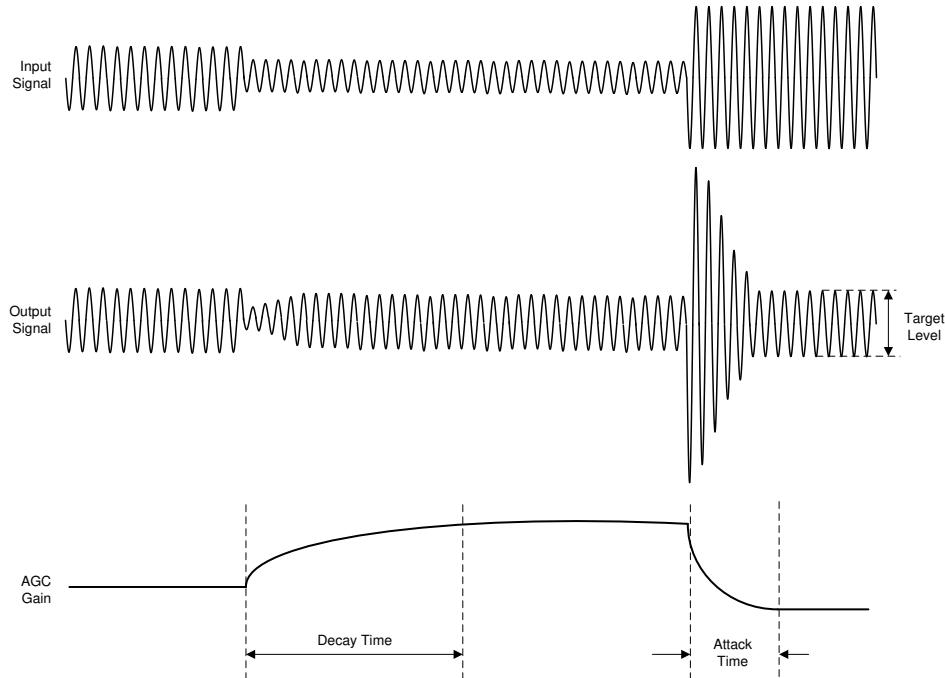

- PDM 録音チャネル用の自動利得制御(AGC)と DAC 再生チャネル用のダイナミックレンジ コントローラ(DRC)

- 独立したサンプル レートを持つデュアル I<sup>2</sup>S または TDM インターフェイス(同期)

- 同期サンプル レート コンバータ(SRC)

- 多様なシステム クロックをサポートする、低ジッタのフェーズ ロック ループ(PLL)を内蔵

- 単一電源動作をサポートするデジタルおよびアナログ電圧レギュレータを内蔵

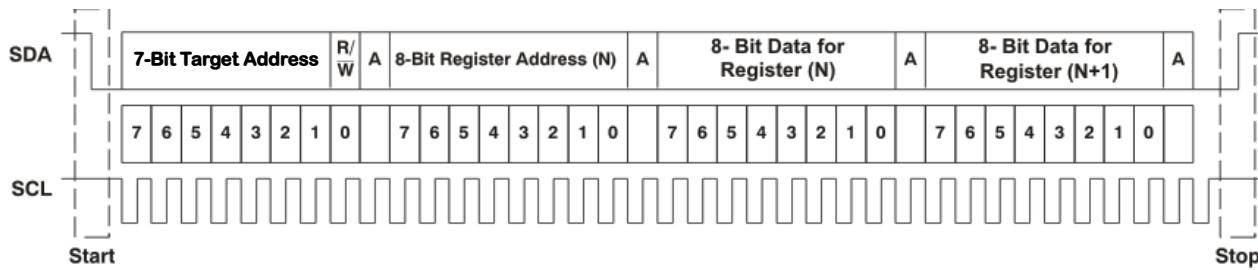

制御レジスタを構成するための TAD5212-Q1 との通信は、I<sup>2</sup>C および SPI インターフェイスを使用してサポートされています。このデバイスは、柔軟性の高いオーディオ・シリアル・インターフェイス[時分割多重化(TDM)、I<sup>2</sup>S、左揃え(LJ)]をサポートしており、システムでデバイスの間でオーディオ データをシームレスに送信できます。

TAD5212 は、複数のデバイス間で共通の TDM バスを共有することで、複数のデバイスをサポートできます。さらに、このデバイスにはデイジーチェーン機能も搭載されています。これらの機能により、高いオーディオ データ帯域幅を必要とするアプリケーションで複数のデバイスを動作させる場合、共有 TDM バスのタイミング要件と基板設計の複雑さが緩和されます。

表 6-1 に、このドキュメント全体を通して、デバイスを制御するレジスタに使用される参照用略語を示します。

表 6-1. レジスタ参照の略語

| リファレンス               | 略語           | 説明                                    | 例                                     |

|----------------------|--------------|---------------------------------------|---------------------------------------|

| ページ y、登録 z、ビット k     | Py_Rz_D[k]   | シングル データビット。レジスタの 1 ビットの値。            | ページ 1、レジスタ 36、ビット 0 = P1_R36_D[0]     |

| ページ y、レジスタ z、ビット k:m | Py_Rz_D[k:m] | データビットの範囲。データビットの範囲(含む)。              | ページ 1、レジスタ 36、ビット 3:0 = P1_R36_D[3:0] |

| ページ y、登録 z           | Py_Rz        | レジスタ全体に 1 つ。レジスタ内の 8 ビットすべてをユニットとして使用 | ページ 1、レジスタ 36 = P1_R36                |

| ページ y、レジスタ z-n       | Py_Rz-Rn     | レジスタの範囲。同じページ内のレジスタの範囲。               | ページ 1、レジスタ 36, 37, 38 = P1_R36~R38    |

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 シリアルインターフェイス

このデバイスには、制御とオーディオ データの 2 つのシリアルインターフェイスがあります。制御シリアルインターフェイスは、デバイスの構成に使用されます。オーディオ データシリアルインターフェイスは、オーディオ データをホストデバイスに送信するために使用されます。

#### 6.3.1.1 制御シリアルインターフェイス

このデバイスには、特定のシステムや用途に合わせて希望する値に設定できる構成レジスタとプログラマブル係数が含まれています。これらのレジスタには、デバイスへの I<sup>2</sup>C または SPI 通信を使用してすべてアクセスできます。詳細については、[セクション 6.5](#) と [セクション 7](#) を参照してください。

#### 6.3.1.2 オーディオシリアルインターフェイス

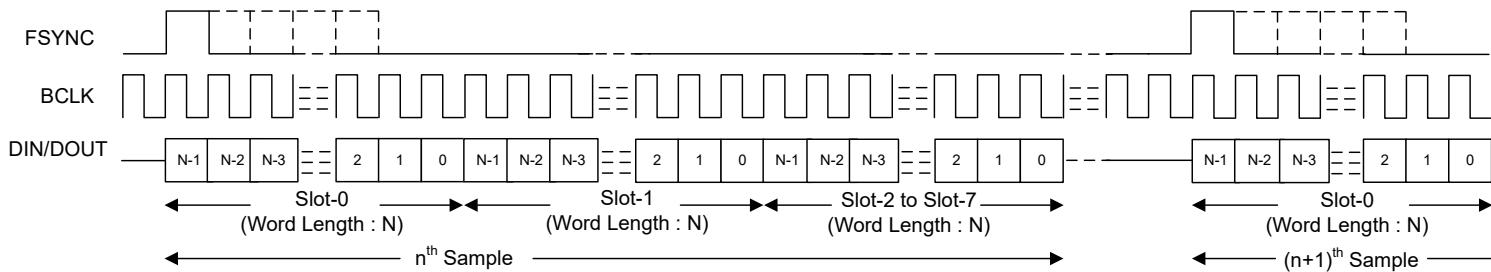

デジタルオーディオデータは、ホストプロセッサと TAD5212-Q1 の間でデジタルオーディオシリアルインターフェース (ASI) またはオーディオバスを通じて流れます。この非常に柔軟な ASI バスには、マルチチャンネル動作用の TDM モード、I<sup>2</sup>S または左揃えプロトコルフォーマットのサポート、プログラム可能なデータ長オプション、バスクロックラインのための非常に柔軟なコントローラーのターゲット設定、システム内の複数のデバイスと直接通信する能力が含まれています。

TAD5212-Q1 は、最大 2 つの ASI インターフェイスをサポートします。セカンダリ ASI クロックおよびデータピンは、GPIO を設定することで構成できます。2 つの ASI のフレーム同期は同期していかなければなりません。セカンダリ ASI の詳細については、『[TAX5X1X 同期サンプルレート変換](#)』アプリケーションレポートを参照してください。

バスプロトコル TDM、I<sup>2</sup>S、左揃え(LJ)形式は、PASI\_FORMAT[1:0]、P0\_R26\_D[7:6]レジスタビットを使用して、プライマリ ASIのために選択できます。表 6-2 と表 6-3 に示すように、これらのモードはすべて最上位ビット(MSB)ファーストのパルス符号変調(PCM)データフォーマットで、出力チャネルのデータワード長は、PASI\_WLEN[1:0]、P0\_R26\_D[5:4]レジスタビットを構成することで 16、20、24、または 32 ビットに設定可能です。

**表 6-2. プライマリ オーディオシリアルインターフェースフォーマット**

| P0_R26_D[7:6]: PASI_FORMAT[1:0] |  | プライマリ オーディオシリアルインターフェースフォーマット    |

|---------------------------------|--|----------------------------------|

| 00 (デフォルト)                      |  | 時分割多重化(TDM)モード                   |

| 01                              |  | インタ IC サウンド(I <sup>2</sup> S)モード |

| 10                              |  | 左揃え(LJ)モード                       |

| 11                              |  | 予約済み(この設定は使用しないでください)            |

**表 6-3. プライマリ オーディオシリアルインターフェースデータワード長**

| P0_R26_D[5:4]: PASI_WLEN[1:0] |  | プライマリ オーディオ出力チャネルデータワード長 |

|-------------------------------|--|--------------------------|

| 00                            |  | データワード長は 16 ビットに設定       |

| 01                            |  | データワード長は 20 ビットに設定       |

| 10                            |  | データワード長は 24 ビットに設定       |

| 11 (デフォルト)                    |  | データワード長は 32 ビットに設定       |

フレーム同期ピン(FSYNC)は、このオーディオバスプロトコルでフレームの開始を定義するために使用され、出力データサンプルレートと同じ周波数を持っています。ビットクロックピン(BCLK)は、デジタルオーディオデータをシリアルバス経由でクロックアウトするために使用されます。フレーム内のビットクロックサイクル数は、プログラムされたデータワード長を持つ複数のデバイスアクティブ出力チャネルに対応する必要があります。

フレームは、複数の時分割チャネルスロット(最大 32 個)で構成され、同じオーディオバスを共有するデバイスまたは複数のデバイスによって、すべての入力/出力チャネルのオーディオデータ伝送がオーディオバス上で完了するようになっています。このデバイスは、最大 8 つの入力チャネルと 8 つの出力チャネルをサポートしており、プライマリ ASI バス上でチャネルのオーディオデータをスロット 0 からスロット 31 まで配置するように設定できます。表 6-4 に、出力チャネル 1 スロットの設定値を示します。In I<sup>2</sup>S および LJ モードでは、セクション 6.3.1.2.2 およびセクション 6.3.1.2.3 に記載されているように、スロットは左チャネルスロットと右チャネルスロットの 2 つのセットに分割されます。

**表 6-4. 出力チャネル 1 スロット割り当て設定**

| P0_R30_D[4:0]: PASI_TX_CH1_SLOT[4:0] |  | 出力チャネル 1 のスロット割り当て                                    |

|--------------------------------------|--|-------------------------------------------------------|

| 0 0000 = 0d (デフォルト)                  |  | スロット 0 は TDM 用、または I <sup>2</sup> S、LJ 用の左チャネルスロット 0。 |

| 0 0001 = 1d                          |  | TDM の場合はスロット 1、LJ の場合は左スロット 1。                        |

| ...                                  |  | ...                                                   |

| 0 1111 = 15d                         |  | TDM の場合はスロット 15、LJ の場合は左スロット 15。                      |

| 1 0000 = 32d                         |  | TDM の場合はスロット 16、I <sup>2</sup> S、LJ の場合は右スロット 0。      |

| ...                                  |  | ...                                                   |

| 1 1110 = 30d                         |  | TDM の場合はスロット 30、LJ の場合は右スロット 14。                      |

| 1 1111 = 31d                         |  | TDM の場合はスロット 31、LJ の場合は右スロット 15。                      |

同様に、出力チャネル 2 からチャネル 8 のスロット設定は、PASI\_TX\_CH2\_SLOT\_NUM(P0\_R31\_D[4:0])から PASI\_TX\_CH8\_SLOT\_NUM(P0\_R37)レジスタを使用して行うことができ、入力チャネル 1 からチャネル 8 の設定は、PASI\_RX\_CH1\_SLOT\_NUM(P0\_R40\_D[4:0])から PASI\_RX\_CH8\_SLOT\_NUM(P0\_R47\_D[4:0])レジスタを使用して行うことができます。

スロットワード長は、デバイスに設定されたプライマリ ASI チャネルワード長と同じです。出力チャネルデータワード長は、システム内ですべてのデバイスが同じ ASI バスを共有する場合、すべての TAD5212-Q1 デバイスで同じ値に設定

する必要があります。システム内の **ASI** バスで使用可能な最大スロット数は、利用可能なバス帯域幅によって制限されます。この帯域幅は、**BCLK** 周波数、使用される出力データ サンプル レート、および設定されたチャネル データ ワード長に依存します。

このデバイスには、スロットデータ転送の開始位置をフレーム同期に対して最大 31 サイクル分、ビットクロックでオフセットする機能も含まれています。オフセットは、入力および出力データパスに対して個別に構成できます。[表 6-5](#) および [表 6-6](#) は、それぞれ送信パスと受信パスのプログラム可能なオフセット構成設定を示します。

**表 6-5. ASI スロット開始の送信に対するプログラム可能なオフセット設定**

| P0_R28_D[4:0] : PASI_TX_OFFSET[4:0] |  | スロットデータ送信開始のプログラム可能なオフセット設定                                                                                                                                |

|-------------------------------------|--|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0000 = 0d (デフォルト)                 |  | このデバイスは、オフセットなしで標準プロトコルのタイミングに従います。                                                                                                                        |

| 0 0001 = 1d                         |  | スロット開始は、標準プロトコルのタイミングと比較して、1 回の BCLK サイクル分オフセットされています。<br>I <sup>2</sup> S または LJ の場合、左チャネルと右チャネルのスロット開始は、標準プロトコルのタイミングと比較して、1 回の BCLK サイクル分オフセットされています。   |

| .....                               |  | .....                                                                                                                                                      |

| 1 1110 = 30d                        |  | スロット開始は、標準プロトコルのタイミングと比較して、30 回の BCLK サイクル分オフセットされています。<br>I <sup>2</sup> S または LJ の場合、左チャネルと右チャネルのスロット開始は、標準プロトコルのタイミングと比較して、30 回の BCLK サイクル分オフセットされています。 |

| 1 1111 = 31d                        |  | スロット開始は、標準プロトコルのタイミングと比較して、31 回の BCLK サイクル分オフセットされています。<br>I <sup>2</sup> S または LJ の場合、左チャネルと右チャネルのスロット開始は、標準プロトコルのタイミングと比較して、31 回の BCLK サイクル分オフセットされています。 |

**表 6-6. 受信のための ASI スロット開始のプログラム可能なオフセット設定**

| P0_R38_D[4:0] : PASI_RX_OFFSET[4:0] |  | スロットデータ受信開始のオフセット設定をプログラム可能                                                                                                                                |

|-------------------------------------|--|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0000 = 0d (デフォルト)                 |  | このデバイスは、オフセットなしで標準プロトコルのタイミングに従います。                                                                                                                        |

| 0 0001 = 1d                         |  | スロット開始は、標準プロトコルのタイミングと比較して、1 回の BCLK サイクル分オフセットされています。<br>I <sup>2</sup> S または LJ の場合、左チャネルと右チャネルのスロット開始は、標準プロトコルのタイミングと比較して、1 回の BCLK サイクル分オフセットされています。   |

| .....                               |  | .....                                                                                                                                                      |

| 1 1110 = 30d                        |  | スロット開始は、標準プロトコルのタイミングと比較して、30 回の BCLK サイクル分オフセットされています。<br>I <sup>2</sup> S または LJ の場合、左チャネルと右チャネルのスロット開始は、標準プロトコルのタイミングと比較して、30 回の BCLK サイクル分オフセットされています。 |

| 1 1111 = 31d                        |  | スロット開始は、標準プロトコルのタイミングと比較して、31 回の BCLK サイクル分オフセットされています。<br>I <sup>2</sup> S または LJ の場合、左チャネルと右チャネルのスロット開始は、標準プロトコルのタイミングと比較して、31 回の BCLK サイクル分オフセットされています。 |

このデバイスには、オーディオデータを転送するために使用されるフレーム同期ピン(FSYNC)の極性を反転させる機能もあり、これは標準プロトコルのタイミングで使用されるデフォルトの FSYNC 極性と比較されます。この機能は、PASI\_FSYNC\_POL(P0\_R26\_D[3])レジスタビットを使用して設定できます。同様に、このデバイスはビットクロックピン(BCLK)の極性を反転させることができます。これは PASI\_BCLK\_POL(P0\_R26\_D[2])レジスタビットを使用して設定できます。

さらに、ワードクロックとビットクロックは、コントローラモードまたはターゲットモードで独立して構成でき、さまざまなプロセッサへの柔軟な接続が可能です。ワードクロックはフレームの開始を定義するために使用され、パルス信号または正弦波信号としてプログラムされます。このクロックの周波数は、選択した DAC チャネルのサンプリング周波数の最大値に対応します。

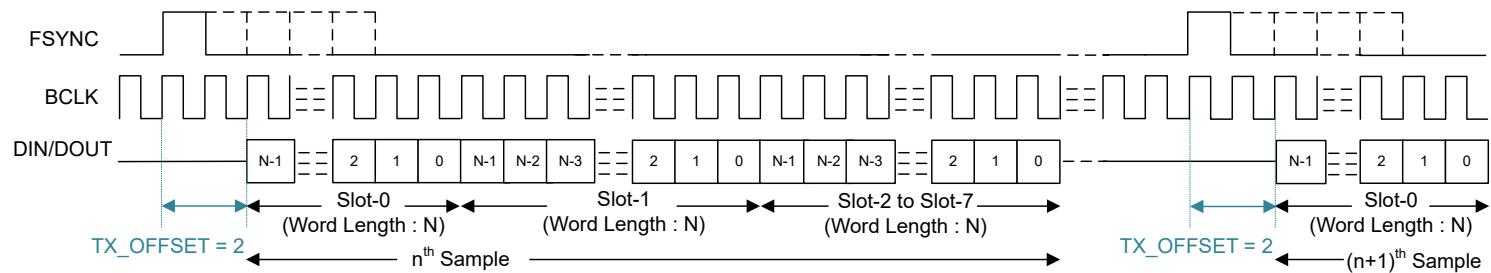

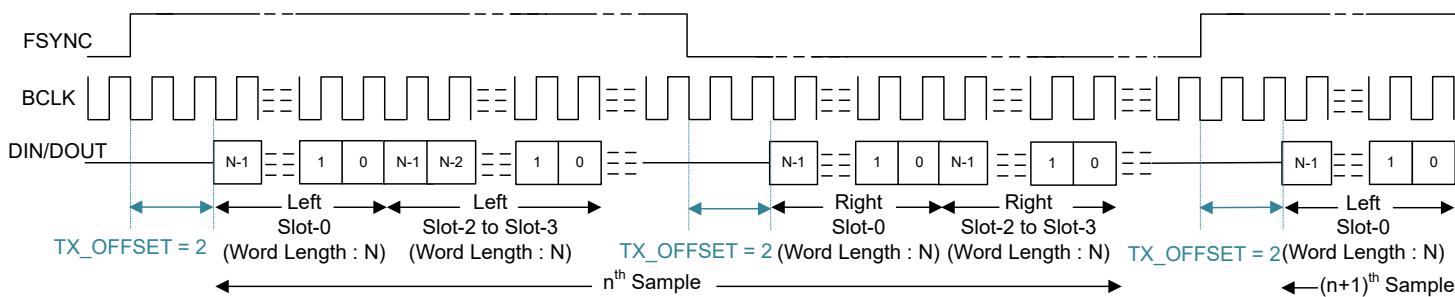

### 6.3.1.2.1 時分割多重オーディオ(TDM) インターフェイス

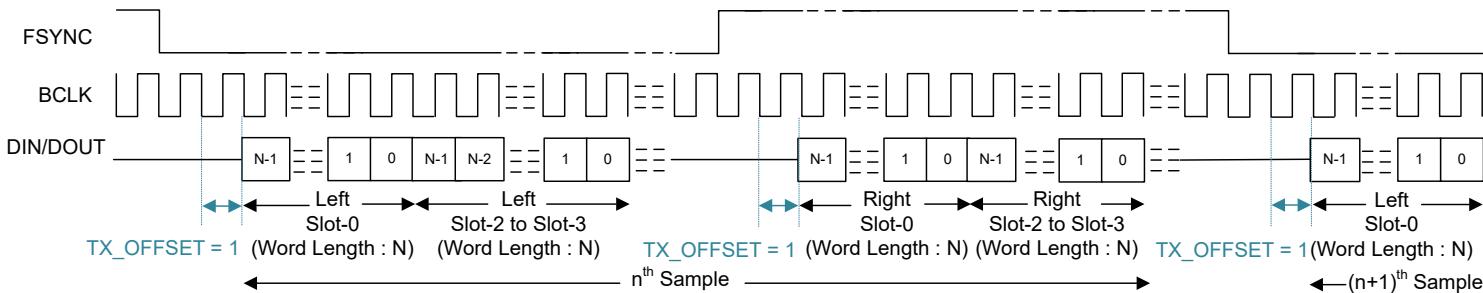

DSP モードとも呼ばれる TDM モードでは、FSYNC の立ち上がりエッジで、スロット 0 のデータから最初にデータ転送が開始されます。スロット 0 データの転送直後に、残りのスロットデータは順番に送信されます。FSYNC と各データビット(TX\_OFFSET が 0 のときのスロット 0 の MSB を除く)は、BCLK の立ち上がりエッジで送信されます。[図 6-1](#) ~ [図 6-4](#)

は送信 DOUT ラインのさまざまな構成における TDM 動作のプロトコル タイミングを示します。同じプロトコルが受信 DIN ラインにも適用できます。

図 6-1. TDM モードの標準プロトコル タイミング (PASI\_TX\_OFFSET = 0)

図 6-2. TDM モードのプロトコル タイミング (PASI\_TX\_OFFSET = 2)

図 6-3. TDM モードのプロトコル タイミング (アイドル BCLK サイクルなし、PASI\_TX\_OFFSET = 2)

図 6-4. TDM モードのプロトコル タイミング (PASI\_TX\_OFFSET = 0 および PASI\_BCLK\_POL = 1)

TDM モードでオーディオ バスを適切に動作させるには、1 フレームあたりのビット クロック数が、アクティブな出力チャネル数と出力チャネルデータのプログラムされたワード長との積以上の値である必要があります。このデバイスは、1 サイクル幅のビット クロックを使用するパルスとして FSYNC をサポートしますが、同様に複数の倍数にも対応しています。BCLK 周波数を高くして動作させるには、PASI\_TX\_OFFSET 値を 0 より高く設定した TDM モードを使用することを推奨します。

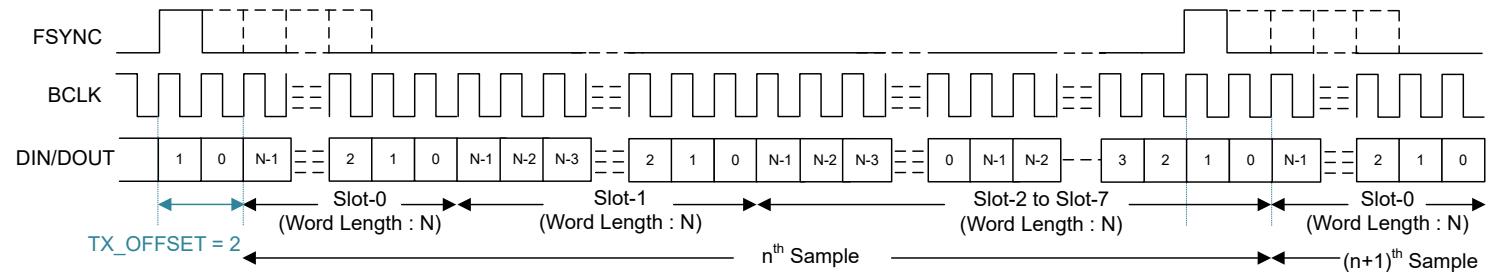

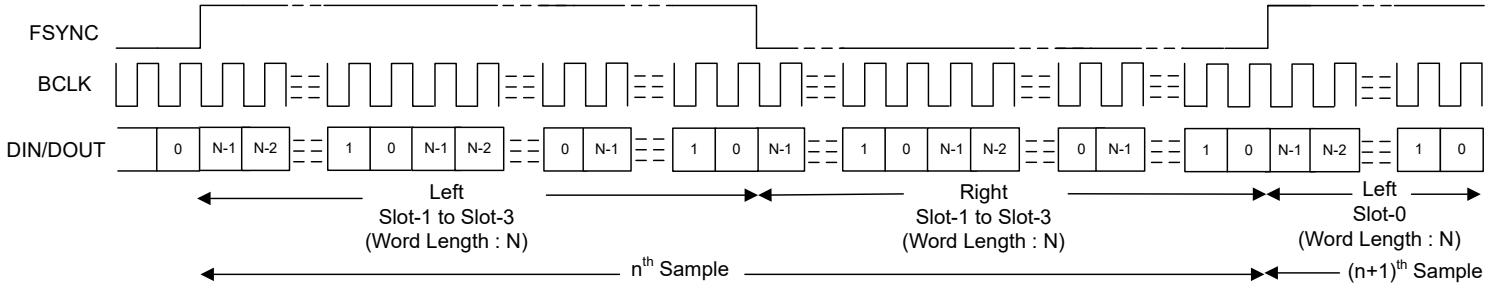

### 6.3.1.2.2 I<sup>2</sup>S (Inter IC Sound) インターフェイス

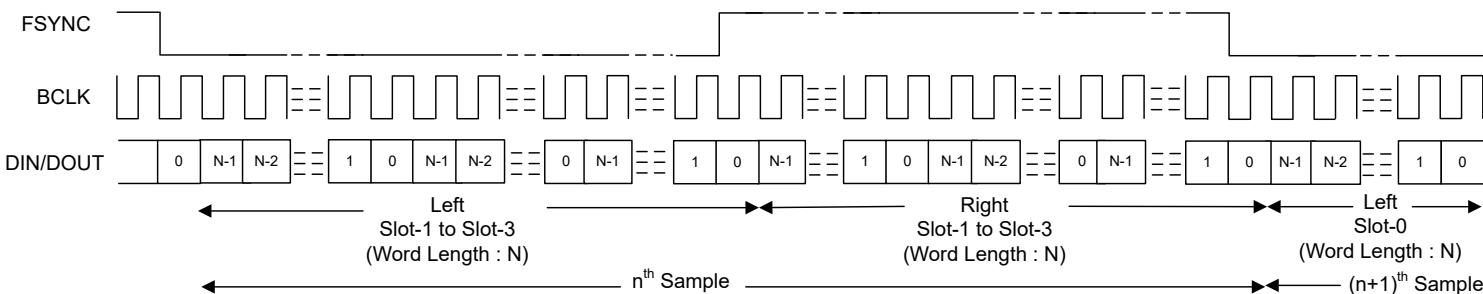

標準の I<sup>2</sup>S プロトコルは、左と右の 2 つのチャネルのみに対して定義されています。このデバイスは、同じプロトコルのタイミングをマルチチャネル動作に拡張しています。I<sup>2</sup>S モードでは、FSYNC の立ち下がりエッジの後の 2 番目のサイクルで、左スロット 0 の MSB が BCLK の立ち下がりエッジで送信されます。左スロット 0 のデータ送信が完了した直後に、残りの左スロットのデータが順番に送信されます。右スロット 0 の MSB は、FSYNC の立ち上がりエッジの後の 2 番目のサイクルで、BCLK の立ち下がりエッジで送信されます。右スロット 0 のデータ送信が完了した直後に、残りの右スロットのデータが順番に送信されます。FSYNC と各データビットは、BCLK の立ち下がりエッジで送信されます。図 6-5 ~ 図 6-8 のさまざまな構成における送信 DOUT ラインの I<sup>2</sup>S 動作に関するプロトコルタイミングを示します。同じプロトコルが受信 DIN ラインにも適用できます。

図 6-5. I<sup>2</sup>S モードの標準プロトコルのタイミング (PASI\_TX\_OFFSET = 0)

図 6-6. I<sup>2</sup>S プロトコルのタイミング (PASI\_TX\_OFFSET = 1)

図 6-7. I<sup>2</sup>S プロトコルのタイミング (アイドル BCLK サイクルなし、PASI\_TX\_OFFSET = 0)

図 6-8. I<sup>2</sup>S プロトコルのタイミング (PASI\_TX\_OFFSET = 0 および PASI\_BCLK\_POL = 1)

I<sup>2</sup>S モードでオーディオ バスを正常に動作させるためには、フレームあたりのビットクロック数が、アクティブな出力チャネル数(左および右スロットを含む)に、出力チャネル データの設定されたワード長を掛けた値以上でなければなりません。本デバイスの FSYNC のロー パルスは、アクティブな左スロット数に設定されたデータワード長を掛けた値以上の BCLK サイクル幅でなければなりません。同様に、FSYNC のハイパルスは、アクティブな右スロット数に設定されたデータワード長を掛けた値以上の BCLK サイクル幅でなければなりません。

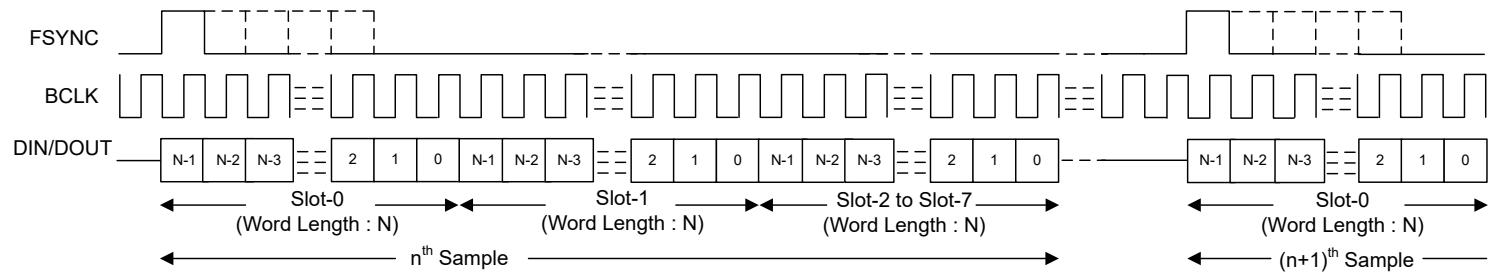

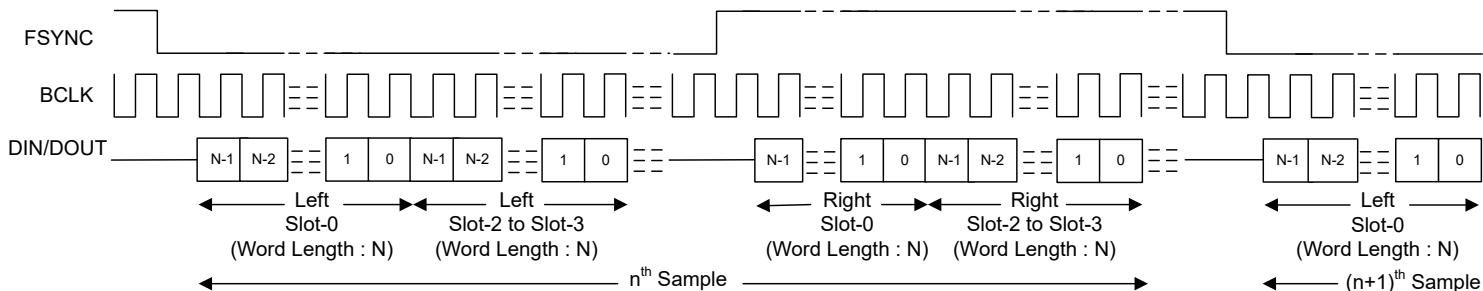

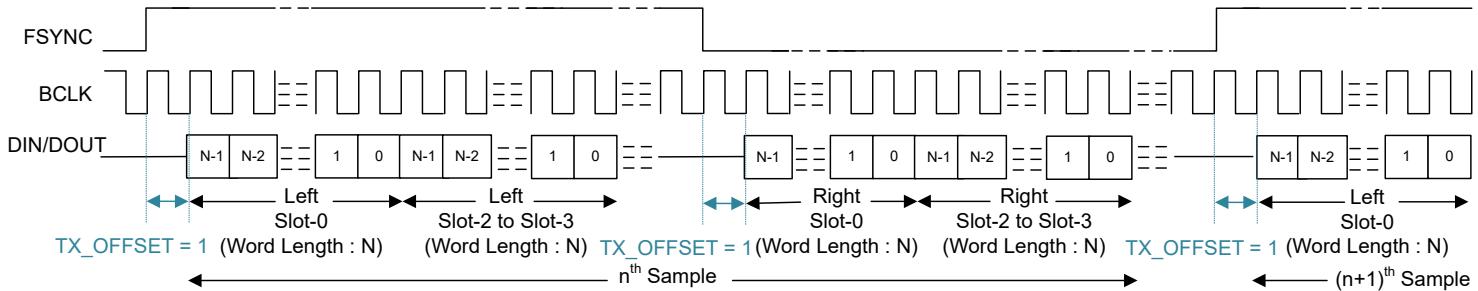

#### 6.3.1.2.3 左揃え (LJ) インターフェイス

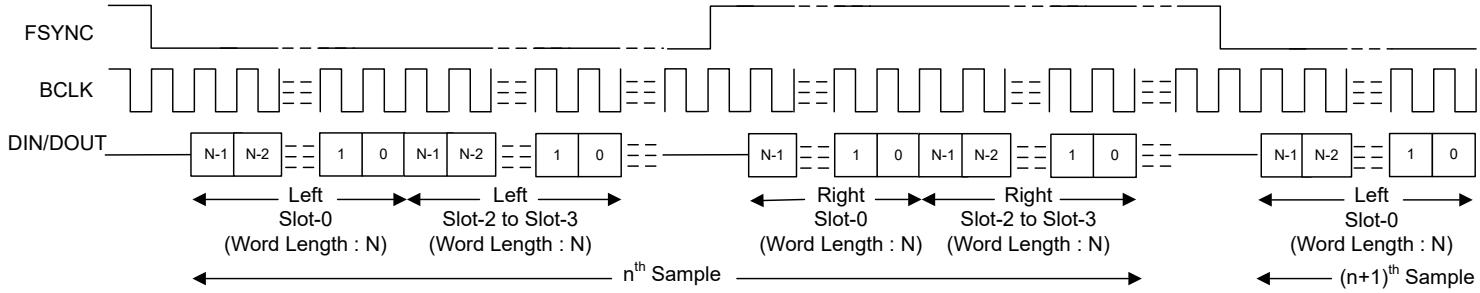

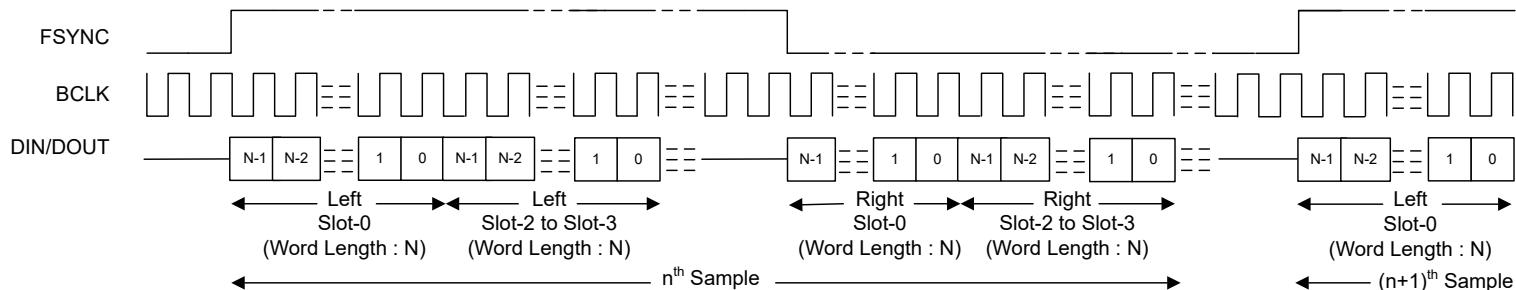

標準的な LJ プロトコルは、左と右の 2 チャネルのみに定義されています。このデバイスは、同じプロトコルのタイミングをマルチチャネル動作に拡張しています。LJ モードでは、FSYNC の立ち上がりエッジの後、左スロット 0 の MSB が同じ BCLK サイクルで送信されます。それ以降の各データビットは、BCLK の立ち下がりエッジで送信されます。左スロット 0 データ転送の直後に、残りの左スロット データが順番に送信されます。右スロット 0 の MSB は、FSYNC の立ち下がりエッジの後、同じ BCLK サイクルで送信されます。それ以降の各データビットは、BCLK の立ち下がりエッジで送信されます。右スロット 0 データ転送の直後に、残りの右スロット データが順番に送信されます。FSYNC は、BCLK の立ち下がりエッジで送信されます。図 6-9 ~ 図 6-12 は送信 DOUT ラインのさまざまな構成における LJ 動作のプロトコル タイミングを示します。同じプロトコルが受信 DIN ラインにも適用できます。

図 6-9. LJ モード標準プロトコル タイミング (TX\_OFFSET = 0)

図 6-10. LJ プロトコルのタイミング (TX\_OFFSET = 2)

図 6-11. LJ プロトコルのタイミング (アイドル BCLK サイクルなし、TX\_OFFSET = 0)

図 6-12. LJ プロトコルのタイミング (TX\_OFFSET = 1 および BCLK\_POL = 1)

LJ モードでオーディオ バスを適切に動作させるには、1 フレームあたりのビット クロック数が、アクティブな出力チャンネル数(左および右のスロットを含む)に、出力チャネル データのプログラムされたワード長を掛けた数以上である必要があります。デバイス FSYNC の高パルスは、アクティブな左スロットの数に設定されたデータ ワード長を掛けた数以上の、BCLK サイクル数分である必要があります。同様に、FSYNC の Low パルスは、アクティブな右スロットの数に設定されたデータ ワード長を掛けた数以上の BCLK サイクル数分、幅を持たせる必要があります。BCLK 周波数を高くして動作させるには、TX\_OFFSET 値を 0 より高く設定した LJ モードを使用することを推奨します。

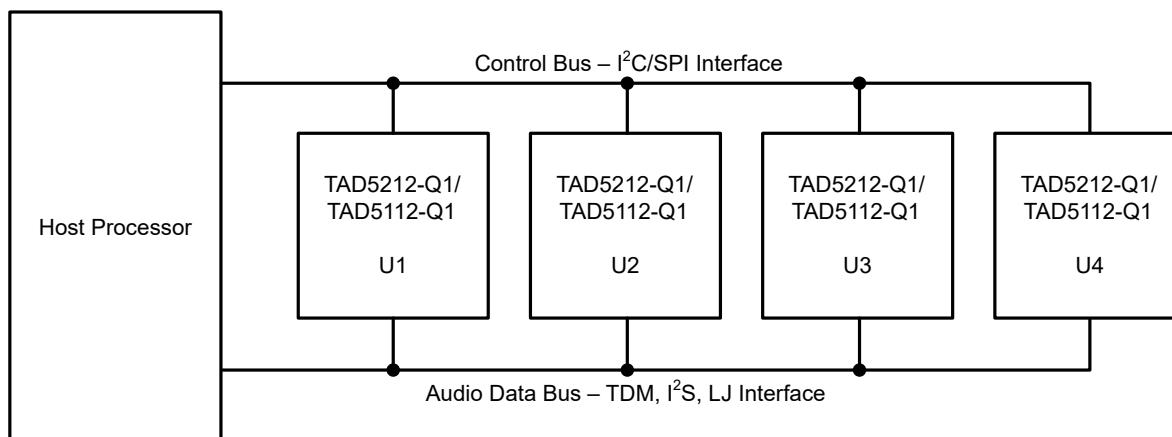

### 6.3.1.3 共有バスで複数のデバイスを使用

このデバイスは、複数の機能と柔軟なオプションを備え、单一の共通の I<sup>2</sup>C または SPI 制御バスとオーディオ シリアルインターフェイス バスを共有することで、複数の TAD5212-Q1 デバイスをシステムでシームレスに接続するために使用できます。このアーキテクチャにより、ビームフォーミング動作、電話会議、ノイズ キャンセルなどにマイクまたはスピーカ アレイを必要とするシステムに、複数のアプリケーションを適用できます。図 6-13 に、制御データ バスとオーディオ データ バスが共有されている構成内の複数の TAD5212-Q1 デバイスの図を示します。

図 6-13. 制御およびオーディオ データ バスを共有する複数の TAD5212-Q1 デバイス

TAD5212-Q1 は、共有バスを使用して複数のデバイスとのシームレスな接続と相互作用を可能にする以下の機能を備えています。

- ピンによりプログラム可能な 4 つまでの I<sup>2</sup>C ターゲットアドレスをサポート

- I<sup>2</sup>C ブロードキャストにより、すべての TAD5212-Q1 デバイスに対して同時に書き込み(またはトリガ)します

- オーディオ シリアル インターフェース用の最大 32 構成の入出力チャネル スロットをサポート

- デバイスの未使用のオーディオ データ スロット用のトライステート機能(有効化と無効化が可能)

- オーディオ バス上の最後の駆動値を保持するためのバス ホルダ機能(有効化および無効化可能)をサポート

- GPIOx、GPI1、または GPO1 ピンは、セカンダリ入出力データレーンまたはセカンダリ オーディオ シリアル インターフェースとして構成できます。

- GPIOx、GPI1、GPO1 ピンは、複数の TAD5212-Q1 デバイスのデイジーチェーン構成で使用できます

- 高速インターフェースのタイミング要件を緩和するために、BCLK サイクル 1 回のデータ ラッピング タイミングをサポート

- プライマリおよびセカンダリ オーディオ シリアル インターフェース用のプログラマブル コントローラおよびターゲット オプション

- 複数のデバイスを同期し、複数のデバイス間での同時サンプリング要件に対応できる機能

- ICGA(チャネル間ゲイン整合)機能により、デバイス間で DAC チャネル ゲインを調整します。

詳細は、[複数の TAC5x1x デバイスで共有された TDM および I<sup>2</sup>C/SPI バスアプリケーション レポート](#)をご覧ください。

### 6.3.2 フェーズロックループ(PLL) とクロック生成

このデバイスには、DAC モジュレータおよび信号処理に使用されるデジタル フィルタ エンジンに必要なすべての内部クロックを生成するスマート自動構成ブロックがあります。この構成は、オーディオ バス上の FSYNC および BCLK 信号の周波数を監視することによって行われます。

このデバイスは、さまざまなデータ サンプル レート(FSYNC 信号周波数)および BCLK と FSYNC の比率をサポートし、ホスト プログラミングなしで PLL 構成を含むすべてのクロック ディバイダを内部で構成します。[表 6-7](#) および [表 6-8](#) に、サポートされている FSYNC および BCLK 周波数を示します。

**表 6-7. サポートされる FSYNC (48kHz の倍数またはサブ倍数) および BCLK 周波数**

| BCLK 対<br>FSYNC 比 | BCLK (MHz)      |                  |                  |                  |                  |                  |                   |                   |                   |

|-------------------|-----------------|------------------|------------------|------------------|------------------|------------------|-------------------|-------------------|-------------------|

|                   | FSYNC<br>(8kHz) | FSYNC<br>(16kHz) | FSYNC<br>(24kHz) | FSYNC<br>(32kHz) | FSYNC<br>(48kHz) | FSYNC<br>(96kHz) | FSYNC<br>(192kHz) | FSYNC<br>(384kHz) | FSYNC<br>(768kHz) |

| 16                | 予約済み            | 0.256            | 0.384            | 0.512            | 0.768            | 1.536            | 3.072             | 6.144             | 12.288            |

| 24                | 予約済み            | 0.384            | 0.576            | 0.768            | 1.152            | 2.304            | 4.608             | 9.216             | 18.432            |

| 32                | 0.256           | 0.512            | 0.768            | 1.024            | 1.536            | 3.072            | 6.144             | 12.288            | 24.576            |

| 48                | 0.384           | 0.768            | 1.152            | 1.536            | 2.304            | 4.608            | 9.216             | 18.432            | 予約済み              |

| 64                | 0.512           | 1.024            | 1.536            | 2.048            | 3.072            | 6.144            | 12.288            | 24.576            | 予約済み              |

| 96                | 0.768           | 1.536            | 2.304            | 3.072            | 4.608            | 9.216            | 18.432            | 予約済み              | 予約済み              |

| 128               | 1.024           | 2.048            | 3.072            | 4.096            | 6.144            | 12.288           | 24.576            | 予約済み              | 予約済み              |

| 192               | 1.536           | 3.072            | 4.608            | 6.144            | 9.216            | 18.432           | 予約済み              | 予約済み              | 予約済み              |

| 256               | 2.048           | 4.096            | 6.144            | 8.192            | 12.288           | 24.576           | 予約済み              | 予約済み              | 予約済み              |

| 384               | 3.072           | 6.144            | 9.216            | 12.288           | 18.432           | 予約済み             | 予約済み              | 予約済み              | 予約済み              |

| 512               | 4.096           | 8.192            | 12.288           | 16.384           | 24.576           | 予約済み             | 予約済み              | 予約済み              | 予約済み              |

| 1024              | 8.192           | 16.384           | 24.576           | 予約済み             | 予約済み             | 予約済み             | 予約済み              | 予約済み              | 予約済み              |

| 2048              | 16.384          | 予約済み             | 予約済み             | 予約済み             | 予約済み             | 予約済み             | 予約済み              | 予約済み              | 予約済み              |

**表 6-8. サポートされる FSYNC (44.1kHz の倍数またはサブ倍数) および BCLK 周波数**

| BCLK 対<br>FSYNC 比 | BCLK (MHz)         |                    |                     |                    |                    |                    |                     |                     |                     |

|-------------------|--------------------|--------------------|---------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|

|                   | FSYNC<br>(7.35kHz) | FSYNC<br>(14.7kHz) | FSYNC<br>(22.05kHz) | FSYNC<br>(29.4kHz) | FSYNC<br>(44.1kHz) | FSYNC<br>(88.2kHz) | FSYNC<br>(176.4kHz) | FSYNC<br>(352.8kHz) | FSYNC<br>(705.6kHz) |

| 16                | 予約済み               | 予約済み               | 0.3528              | 0.4704             | 0.7056             | 1.4112             | 2.8224              | 5.6448              | 11.2896             |

| 24                | 予約済み               | 0.3528             | 0.5292              | 0.7056             | 1.0584             | 2.1168             | 4.2336              | 8.4672              | 16.9344             |

| 32                | 予約済み               | 0.4704             | 0.7056              | 0.9408             | 1.4112             | 2.8224             | 5.6448              | 11.2896             | 22.5792             |

| 48                | 0.3528             | 0.7056             | 1.0584              | 1.4112             | 2.1168             | 4.2336             | 8.4672              | 16.9344             | 予約済み                |

| 64                | 0.4704             | 0.9408             | 1.4112              | 1.8816             | 2.8224             | 5.6448             | 11.2896             | 22.5792             | 予約済み                |

| 96                | 0.7056             | 1.4112             | 2.1168              | 2.8224             | 4.2336             | 8.4672             | 16.9344             | 予約済み                | 予約済み                |

| 128               | 0.9408             | 1.8816             | 2.8224              | 3.7632             | 5.6448             | 11.2896            | 22.5792             | 予約済み                | 予約済み                |

| 192               | 1.4112             | 2.8224             | 4.2336              | 5.6448             | 8.4672             | 16.9344            | 予約済み                | 予約済み                | 予約済み                |

| 256               | 1.8816             | 3.7632             | 5.6448              | 7.5264             | 11.2896            | 22.5792            | 予約済み                | 予約済み                | 予約済み                |

| 384               | 2.8224             | 5.6448             | 8.4672              | 11.2896            | 16.9344            | 予約済み               | 予約済み                | 予約済み                | 予約済み                |

| 512               | 3.7632             | 7.5264             | 11.2896             | 15.0528            | 22.5792            | 予約済み               | 予約済み                | 予約済み                | 予約済み                |

| 1024              | 7.5264             | 15.0528            | 22.5792             | 予約済み               | 予約済み               | 予約済み               | 予約済み                | 予約済み                | 予約済み                |

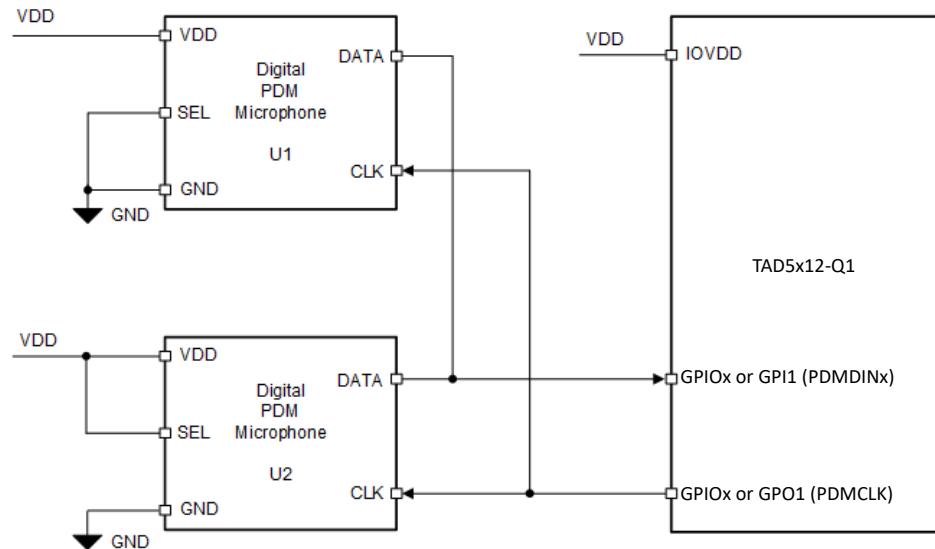

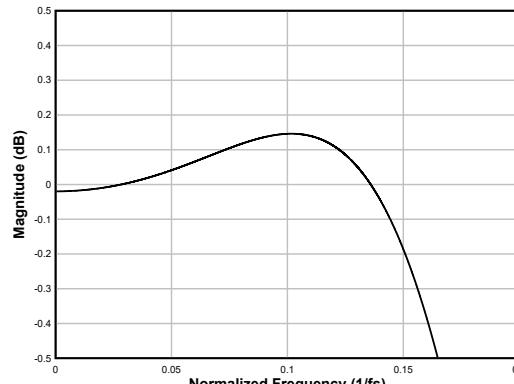

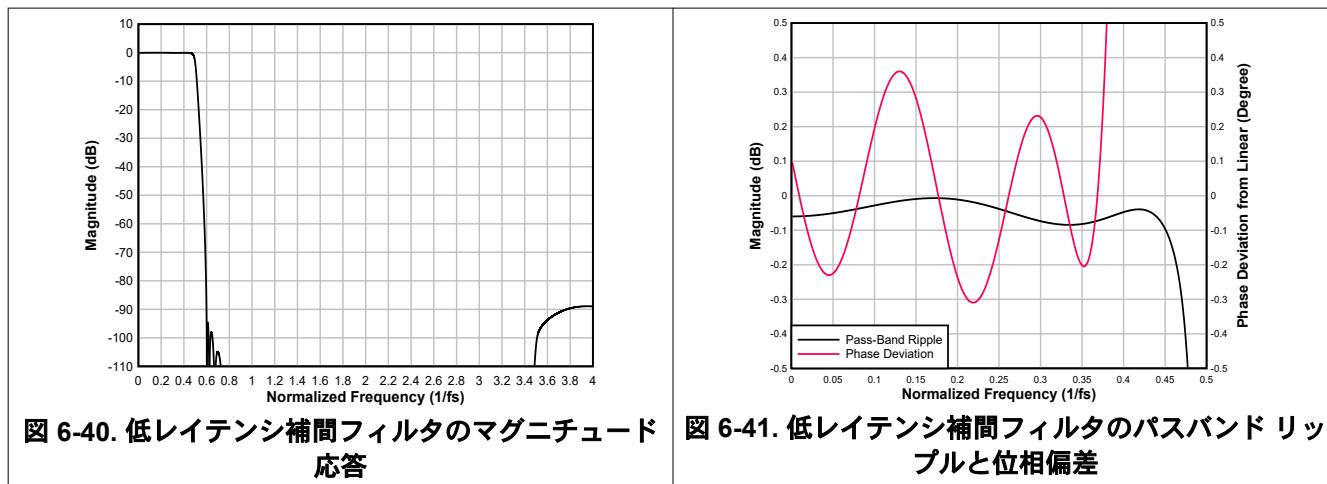

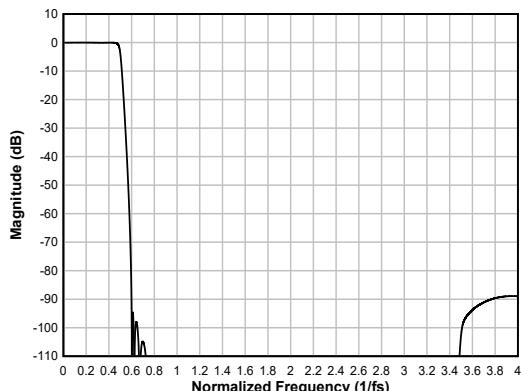

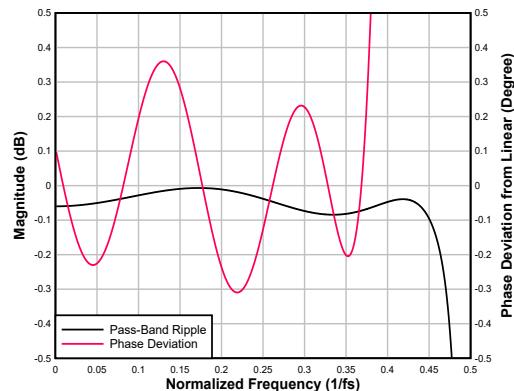

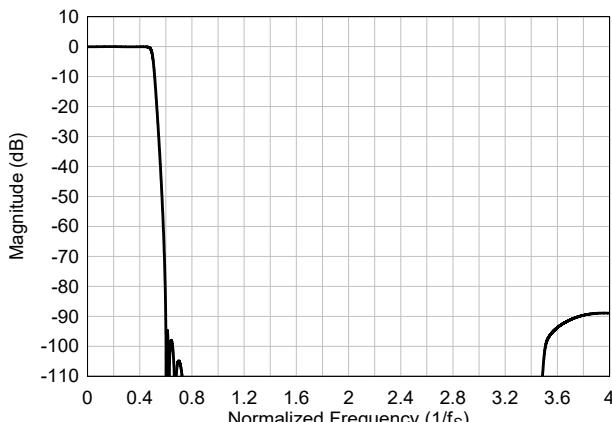

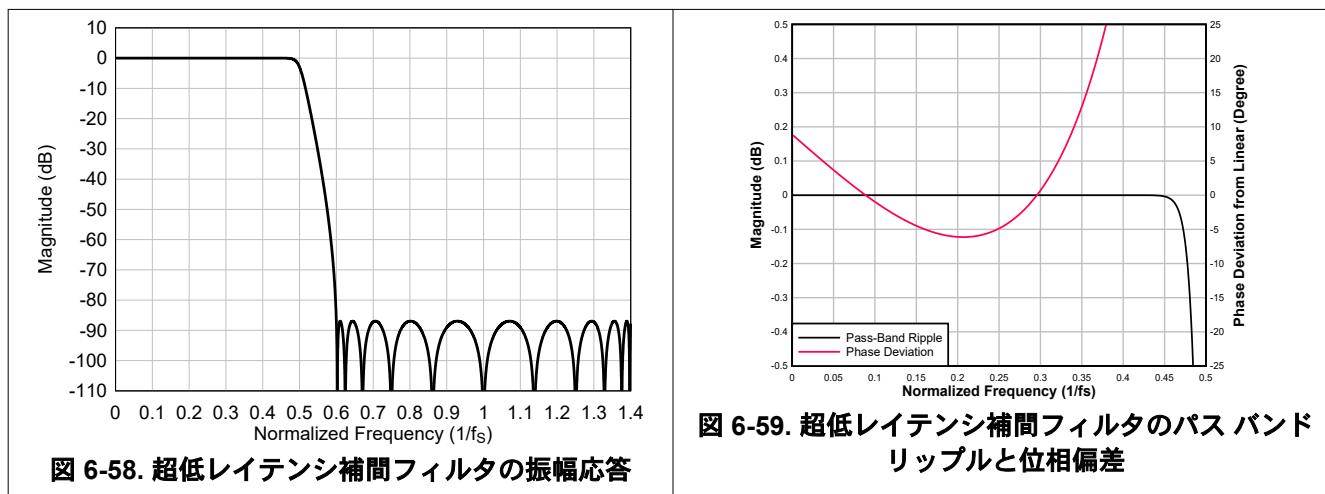

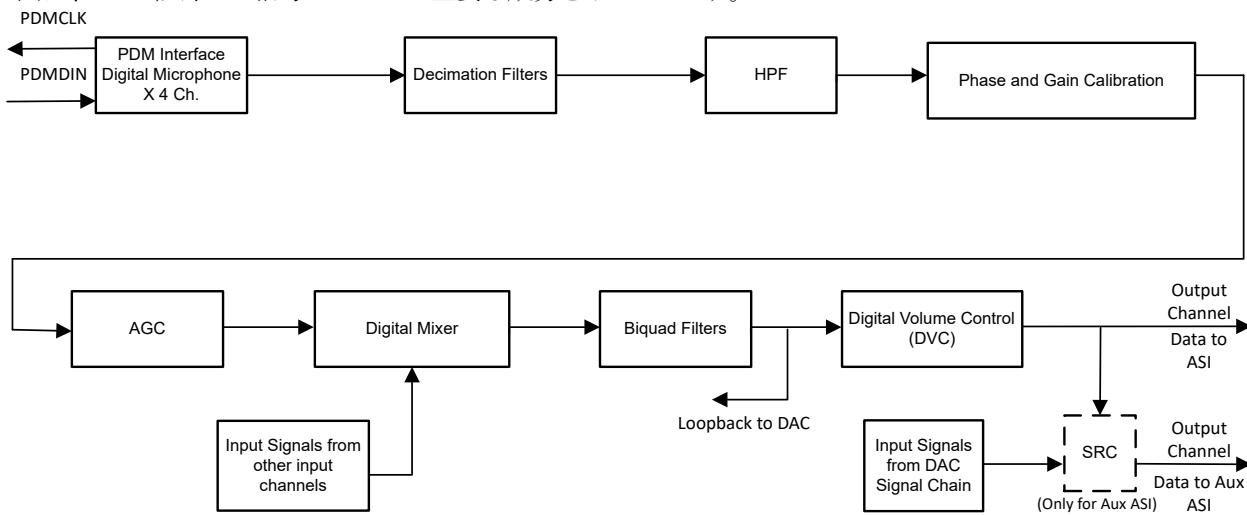

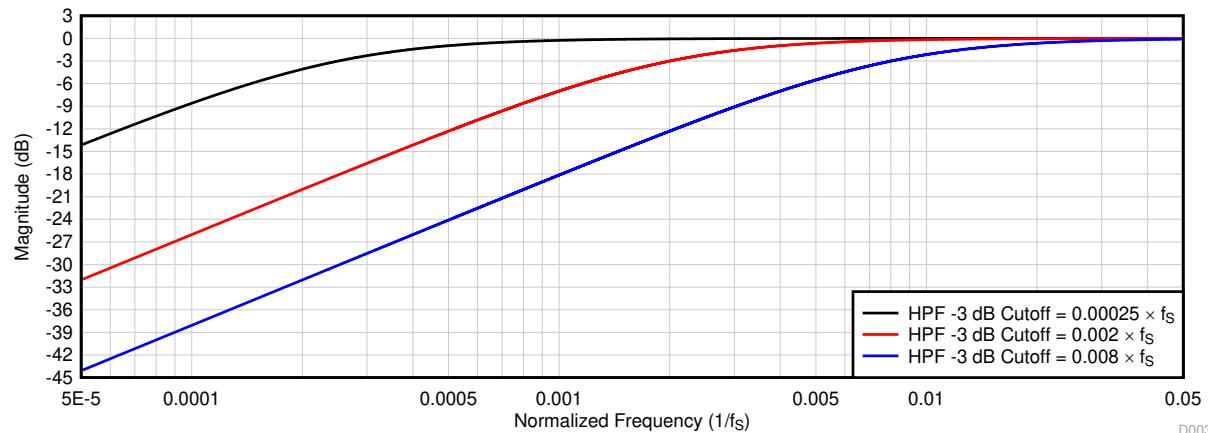

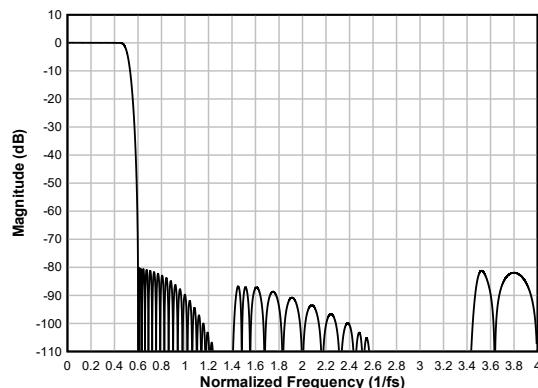

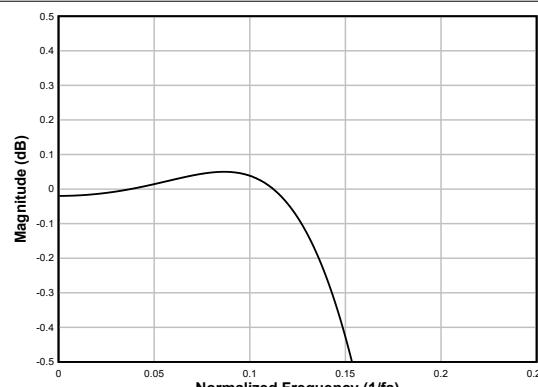

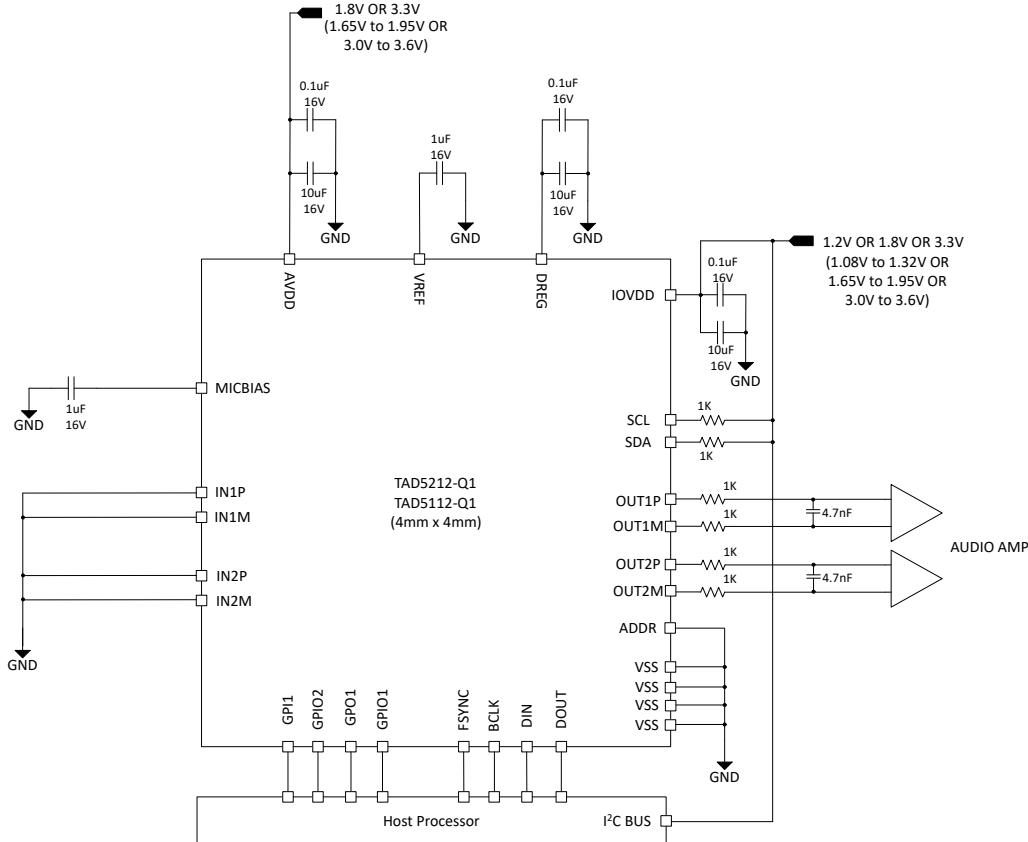

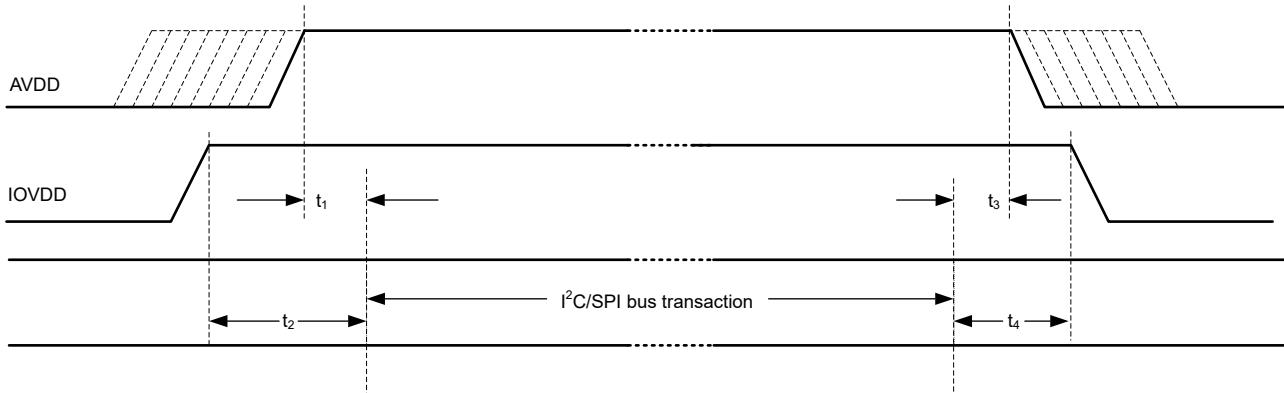

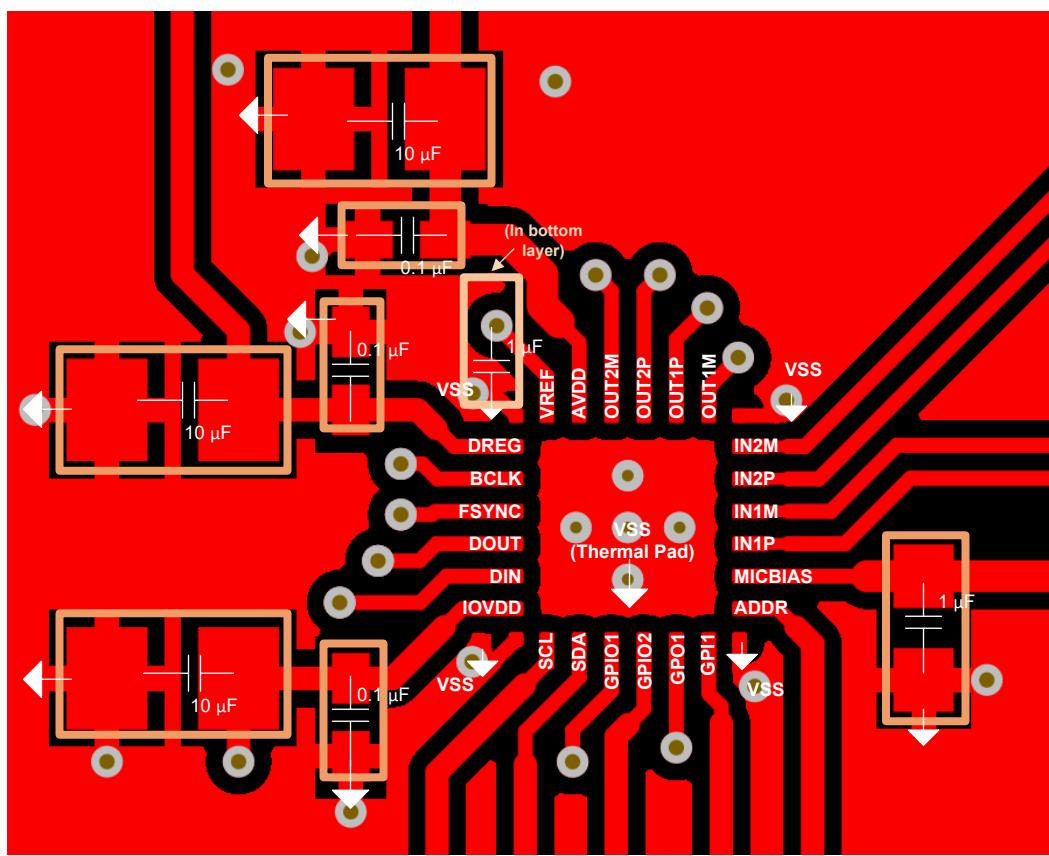

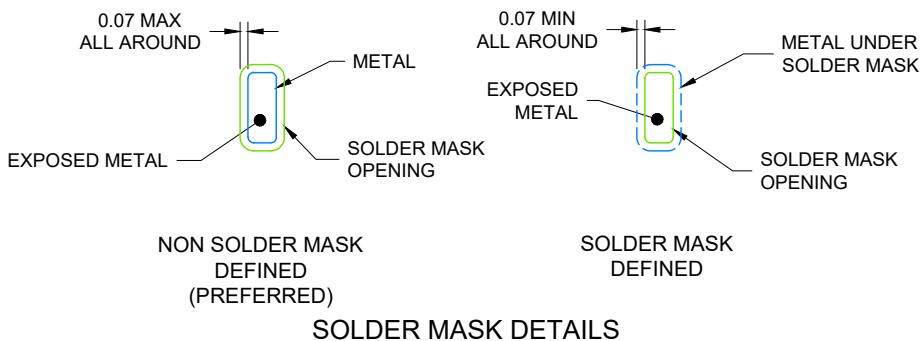

| 2048              | 15.0528            | 予約済み               | 予約済み                | 予約済み               | 予約済み               | 予約済み               | 予約済み                | 予約済み                | 予約済み                |