参考資料

SN65MLVD200A, SN65MLVD202A SN65MLVD204A, SN65MLVD205A

JAJSTP1E - DECEMBER 2003 - REVISED MARCH 2024

# SN65MLVD20xx マルチポイント LVDS ライン ドライバおよびレシーバ

## 1 特長

- 100Mbps までの信号速度、50MHz までのクロック周 波数に対応する 低電圧差動 30Ω~55Ω ラインドライバおよびレシー バ1

- Type-1 レシーバは 25mV のヒステリシス付き (SN65MLVD200A, SN65MLVD202A)

- Type-2 レシーバはオフセット (100mV) スレッショルド によりオープン回路およびアイドル バス状況を検出 (SN65MLVD204A, SN65MLVD205A)

- マルチポイントデータ交換について M-LVDS 規格 TIA/EIA-899 に適合またはそれを上回 る性能準拠またはこれを上回る

- ドライバ出力電圧の遷移時間制御による信号品質の 向上

- -1V~3.4V の同相電圧範囲により、2V のグランド ノイ ズでデータ転送が可能

- ディセーブル時または V<sub>CC</sub> ≤ 1.5V 時に バスピンが高インピーダンス

- 200Mbps のデバイスも利用可能 (SN65MLVD201、 SN65MLVD203、SN65MLVD206、SN65MLVD207)

- 8kV を超えるバスピン ESD 保護

- 利用可能なパッケージ:

- 8ピンSOIC SN65MLVD200A、SN65MLVD204A

- 14 ピン SOIC SN65MLVD202A、SN65MLVD205A

- SN65MLVD200、SN65MLVD202A、 SN65MLVD204A、SN65MLVD205A デバイスに対す る改良された代替品

SN65MLVD200A, SN65MLVD204A

# 2 アプリケーション

- 低消費電力、高速、短距離での TIA/EIA-485 の代替

- バックプレーンまたはケーブルによるマルチポイントデ ータおよびクロック転送

- 携帯電話の基地局

- 基地局用スイッチ

- ネットワークスイッチおよびルータ

## 3 概要

SN65MLVD20xx のデバイスは、最高 100Mbps の信号 速度で動作するよう最適化されたマルチポイント低電圧差 動 (M-LVDS) ラインドライバおよびレシーバです。 すべて の部品がマルチポイント低電圧差動信号伝送 (M-LVDS) 規格 TIA/EIA-899 に準拠しています。

SN65MLVD20xx のデバイスには、従来のデバイスと比較 して拡張されている機能があります。改良部分として、ドラ イバ出力のスルー レート制御により無終端スタブからの反 射を最小化し、シグナル インテグリティ(信号品質)を強化 する機能が挙げられます。さらに、バスピンに対する 8kV ESD 保護により堅牢性が向上しています。フットプリントの 定義は同じであるため、簡単なドロップイン交換によりシス テム性能のアップグレードが可能です。

これらのデバイスは、-40℃~85℃での動作が規定されて います。

#### 製品情報

| 部品番号         | パッケージ <sup>(1)</sup> | 本体サイズ (公称)              |

|--------------|----------------------|-------------------------|

| SN65MLVD200A | SOIC (8)             | 4.90 mm × 3.91 mm       |

| SN65MLVD204A | 3010 (8)             | 4.90 11111 ^ 3.91 11111 |

| SN65MLVD202A | SOIC (14)            | 8.65 mm × 3.91 mm       |

| SN65MLVD205A | 3010 (14)            | 0.05 11111 ^ 3.91 11111 |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

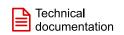

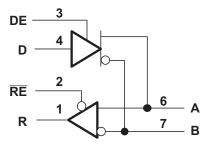

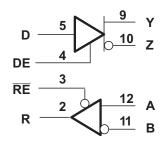

#### SN65MLVD202A, SN65MLVD205A

論理図 (正論理)

<sup>1</sup> ラインの信号速度とは、1 秒あたりの電圧遷移回数を bps (ビット/秒) で表したものです。

# 目次

| <b>1</b> 特長 1           | 8.2 機能ブロック図            | 17 |

|-------------------------|------------------------|----|

| 2 アプリケーション1             | 8.3 機能説明               | 17 |

| 3 概要1                   | 8.4 デバイスの機能モード         | 18 |

| <b>4</b> デバイス比較表3       | 9 アプリケーションと実装          | 20 |

| 5ピン構成および機能3             | 9.1 アプリケーション情報         | 20 |

| 6 仕様                    | 9.2 代表的なアプリケーション       | 20 |

| 6.1 絶対最大定格4             | 10 電源に関する推奨事項          | 24 |

| 6.2 ESD 定格4             | 11 レイアウト               | 24 |

| 6.3 推奨動作条件4             | 11.1 レイアウトのガイドライン      | 24 |

| 6.4 熱に関する情報5            | 11.2 レイアウト例            | 28 |

| 6.5 電気的特性5              | 12 デバイスおよびドキュメントのサポート  | 30 |

| 6.6 電気特性 - ドライバ5        | 12.1ドキュメントのサポート        | 30 |

| 6.7 電気特性 - レシーバ6        | 12.2ドキュメントの更新通知を受け取る方法 | 30 |

| 6.8 電気的特性 – デジタル入力および出力 | 12.3 サポート・リソース         | 30 |

| 6.9 スイッチング特性 - ドライバ7    | 12.4 商標                | 30 |

| 6.10 スイッチング特性 – レシーバ8   | 12.5 静電気放電に関する注意事項     | 30 |

| 6.11 代表的特性9             | 12.6 用語集               | 30 |

| 7 パラメータ測定情報11           | 13 改訂履歴                | 30 |

| 8 詳細説明17                | 14 メカニカル、パッケージ、および注文情報 | 31 |

| 8.1 概要17                |                        |    |

## 4 デバイス比較表

| 部品番号          | フットプリント    | レシーバのタイプ |

|---------------|------------|----------|

| SN65MLVD200AD | SN75176    | タイプ 1    |

| SM65MLVD202AD | SN75ALS180 | タイプ 1    |

| SN65MLVD204AD | SN75176    | タイプ 2    |

| SM65MLVD205AD | SN75ALS180 | タイプ 2    |

## 5 ピン構成および機能

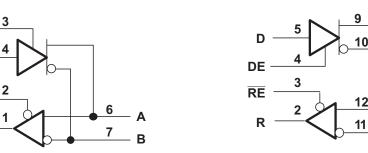

図 5-1. D パッケージ 8 ピン SOIC 上面図

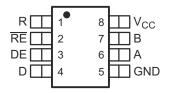

図 5-2. D パッケージ 14 ピン SOIC 上面図

表 5-1. ピンの機能

|                 | ピン     |         | פ-ייג פנ | - Da 7/6                                 |  |  |

|-----------------|--------|---------|----------|------------------------------------------|--|--|

| 名称              | SOIC-8 | SOIC-14 | タイプ      | 説明                                       |  |  |

| A               | 6      | 12      | I/O      | 差動 I/O                                   |  |  |

| В               | 7      | 11      | I/O      | 差動 I/O                                   |  |  |

| D               | 4      | 5       | I        | ドライバ入力                                   |  |  |

| DE              | 3      | 4       | I        | ドライバ イネーブル ピン: High = イネーブル、Low = ディセーブル |  |  |

| GND             | 5      | 6、7     | 電源       | 電源グランド                                   |  |  |

| NC              | _      | 1,8     | NC       | 内部接続なし                                   |  |  |

| R               | 1      | 2       | 0        | レシーバ出力                                   |  |  |

| RE              | 2      | 3       | I        | レシーバ イネーブル ピン: High = ディセーブル、Low = イネーブル |  |  |

| V <sub>CC</sub> | 8      | 13、14   | 電源       | 電源、3.3V                                  |  |  |

| Υ               | _      | 9       | I/O      | 差動 I/O                                   |  |  |

| Z               | _      | 10      | I/O      | 差動 I/O                                   |  |  |

## 6 仕様

# 6.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)(1)

|                                      |                                     | 最小値         | 最大値 | 単位 |

|--------------------------------------|-------------------------------------|-------------|-----|----|

| 電源電圧 <sup>(2)</sup> 、V <sub>CC</sub> |                                     | -0.5        | 4   | V  |

|                                      | D, DE, RE                           | -0.5        | 4   | V  |

| 入力電圧                                 | A、B (SN65MLVD200A および SN65MLVD204A) | -1.8        | 4   | V  |

| , () () (E) E                        | A、B (SN65MLVD202A、SN65MLVD205A)     | -4          | 6   | V  |

|                                      | R                                   | -0.3        | 4   | V  |

| 出力電圧範囲                               | Y, Z, A, B                          | -1.8        | 4   | V  |

| 連続消費電力                               | セクション(                              | 3.4 を参照してくた |     |    |

| 保管温度、T <sub>stg</sub> -65 150        |                                     |             | 150 | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス評価であり、データシートの「推奨動作条件」に示された値と等しい、またはそれを超える条件で本製品が正しく動作することを暗黙的に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 差動 I/O バス電圧を除くすべての電圧値は、ネットワーク グランド端子を基準にしています。

## 6.2 ESD 定格

|                    |                                                                                                                                                                                   |                                    |        |       | 単位 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------|-------|----|

|                    | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン (1)       A、B、Y、Z を除くすべてのピン (1)         お電放電       A、B、Y、Z         デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン (2)       すべてのピン | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 |        | ±4000 |    |

| V <sub>(ESD)</sub> |                                                                                                                                                                                   | ±8000                              | V      |       |    |

|                    |                                                                                                                                                                                   |                                    | すべてのピン | ±1500 |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

#### 6.3 推奨動作条件

|                   |                                              | 最小値  | 公称值 | 最大値             | 単位   |

|-------------------|----------------------------------------------|------|-----|-----------------|------|

| V <sub>CC</sub>   | 電源電圧                                         | 3    | 3.3 | 3.6             | V    |

| V <sub>IH</sub>   | High レベル入力電圧                                 | 2    |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>   | Low レベル入力電圧                                  | GND  |     | 0.8             | V    |

|                   | 任意のバス端子 $V_A$ 、 $V_B$ 、 $V_Y$ 、または $V_Z$ の電圧 | -1.4 |     | 3.8             | V    |

| V <sub>ID</sub>   | 差動入力電圧の大きさ                                   |      |     | V <sub>CC</sub> | V    |

| R <sub>L</sub>    | 差動負荷抵抗                                       | 30   | 50  |                 | Ω    |

| 1/t <sub>UI</sub> | 信号速度                                         |      |     | 100             | Mbps |

| T <sub>A</sub>    | 自由空気での動作温度                                   | -40  |     | 85              | °C   |

## 6.4 熱に関する情報

|                       |                             | SN65MLVD200A、<br>SN65MLVD204A | SN65MLVD202A、<br>SN65MLVD205A |      |

|-----------------------|-----------------------------|-------------------------------|-------------------------------|------|

|                       | <b>熱評価基準</b> <sup>(1)</sup> | D (SOIC)                      | D (SOIC)                      | 単位   |

|                       |                             | 8ピン                           | 14 ピン                         |      |

| $R_{\theta JA}$       | 接合部から周囲への熱抵抗                | 103.9                         | 78.9                          | °C/W |

| R <sub>0JC(top)</sub> | 接合部からケース (上面) への熱抵抗         | 50.6                          | 39                            | °C/W |

| $R_{\theta JB}$       | 接合部から基板への熱抵抗                | 44.5                          | 33.3                          | °C/W |

| ΨЈТ                   | 接合部から上面への特性パラメータ            | 8.1                           | 7.2                           | °C/W |

| $\Psi_{JB}$           | 接合部から基板への特性パラメータ            | 43.9                          | 33                            | °C/W |

<sup>(1)</sup> 従来および最新の熱測定基準の詳細については、アプリケーションレポート『半導体および IC パッケージの熱評価基準』(SPRA953) を参照してください。

## 6.5 電気的特性

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                   |             | Þ            | テスト条件                                                                                                              | 最小<br>値 | 標準値 (1) | 最大値 | 単位 |

|-------------------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------|---------|---------|-----|----|

|                         |             | ドライバのみ       | $V_{CC}$ で $\overline{RE}$ および $DE$ 、 $R_L = 50Ω$ 、その他はすべてオープン                                                     |         | 13      | 22  |    |

| I <sub>CC</sub> 電源電流    | <b>酒電</b> 法 | 両方ディセーブ<br>ル | $V_{CC}$ で $\overline{RE}$ 、 $0V$ で $DE$ 、 $R_L$ =無負荷、その他はすべてオープン                                                  |         | 1       | 4   | mA |

|                         | 你电机         | 両方がイネーブ<br>ル | $0V$ で $\overline{RE}$ 、 $V_{CC}$ で $DE$ 、 $R_L = 50\Omega$ 、その他はすべてオープン                                           |         | 16      | 24  |    |

|                         |             | レシーバのみ       | OV で RE、OV で DE、その他はすべてオープン                                                                                        |         | 4       | 13  |    |

| P <sub>D</sub> デバイス消費電力 |             |              | $R_L$ = $50\Omega$ 、D への入力は $50MHz$ $50\%$ デューティ サイクルの方形波、DE = High、 $\overline{RE}$ = Low、 $T_A$ = $85^{\circ}$ C |         |         | 94  | mW |

<sup>(1)</sup> 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

## 6.6 電気特性 - ドライバ

推奨動作条件範囲内 (特に記述のない限り)

|                                                  | パラメータ                 | テスト条件                     | 最小値(1) 標準値 | 最大値 | 単位 |

|--------------------------------------------------|-----------------------|---------------------------|------------|-----|----|

| V <sub>AB</sub>   また<br>は<br> V <sub>YZ</sub>    | 差動出力電圧の大きさ            | 図 7-2 を参照                 | 480        | 650 | mV |

| Δ V <sub>AB</sub>   ま<br>たは<br>Δ V <sub>YZ</sub> | ロジック状態間の差動出力電圧の大きさの変化 | N 1-2 € ØM                | -50        | 50  | mV |

| V <sub>OS(SS)</sub>                              | 定常同相出力電圧              |                           | 0.8        | 1.2 | V  |

| $\Delta V_{OS(SS)}$                              | ロジック状態間での定常同相出力電圧の変化  | 図 7-3 を参照                 | -50        | 50  | mV |

| V <sub>OS(PP)</sub>                              | ピークツーピークの同相出力電圧       |                           |            | 150 | mV |

| V <sub>Y(OC)</sub> ま<br>たは<br>V <sub>A(OC)</sub> | 最大定常断線出力電圧            | 図 7-7 を参照                 | 0          | 2.4 | ٧  |

| V <sub>Z(OC)</sub> ま<br>たは<br>V <sub>B(OC)</sub> | 最大定常断線出力電圧            | 凶 <i>I-I</i> を参照<br> <br> | 0          | 2.4 | V  |

## 6.6 電気特性 - ドライバ (続き)

推奨動作条件範囲内 (特に記述のない限り)

|                                      | パラメータ                                      | テスト条件                                                                                                | 最小値(1) 標準値(2)        | 最大値                 | 単位 |

|--------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------|---------------------|----|

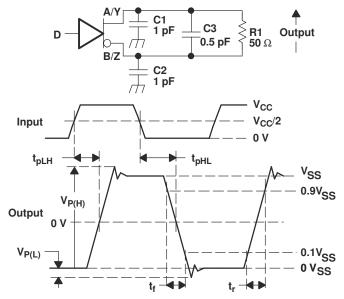

| V <sub>P(H)</sub>                    | 電圧オーバーシュート、Low レベルから High レベルへの出力          | - 図 7-5 を参照                                                                                          |                      | 1.2 V <sub>SS</sub> | V  |

| V <sub>P(L)</sub>                    | 電圧オーバーシュート、High レベルから Low レベルへの出力          | □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □                                                                | -0.2 V <sub>SS</sub> |                     | V  |

| I <sub>IH</sub>                      | High レベル入力電流 (D、DE)                        | V <sub>IH</sub> = 2V~V <sub>CC</sub>                                                                 | 0                    | 10                  | μA |

| I <sub>IL</sub>                      | Low レベル入力電流 (D、DE)                         | $V_{IL} = GND \sim 0.8V$                                                                             | 0                    | 10                  | μA |

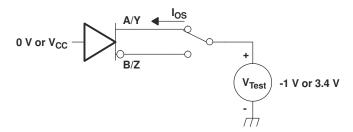

| I <sub>os</sub>                      | 差動短絡出力電流の大きさ                               | 図 6-4 を参照                                                                                            |                      | 24                  | mA |

| I <sub>OZ</sub>                      | 高インピーダンス状態の出力電流 (ドライバのみ)                   | -1.4V ≤ (V <sub>Y</sub> または V <sub>Z</sub> ) ≤ 3.8V、<br>その他の出力 = 1.2V                                | -15                  | 10                  | μА |

| I <sub>O(OFF)</sub>                  | 電源オフ出力電流                                   | -1.4V ≤ (V <sub>Y</sub> または V <sub>Z</sub> ) ≤ 3.8V、そ<br>の他の出力 = 1.2V、0V ≤ V <sub>CC</sub> ≤<br>1.5V | -10                  | 10                  | μА |

| C <sub>Y</sub> または<br>C <sub>Z</sub> | 出力容量                                       | $V_l$ = 0.4sin(30E6 $\pi$ t) + 0.5 $V$ 、 <sup>(3)</sup><br>その他の入力は 1.2 $V$ 、ドライバはディセーブル              | 3                    |                     | pF |

| C <sub>YZ</sub>                      | 差動出力容量                                     | $V_{AB} = 0.4 sin(30 E6 \pi t) V$ , $^{(3)}$<br>F = 7 / V                                            |                      | 2.5                 | pF |

| C <sub>Y/Z</sub>                     | 出力容量バランス、(C <sub>Y</sub> /C <sub>Z</sub> ) |                                                                                                      | 0.99                 | 1.01                |    |

- (1) このデータシートでは、最も小さい正 (最も大きな負の) 制限を最小として指定する代数的規約を使用します。

- (2) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (3) HP4194A インピーダンス アナライザ (または同等のもの)

## 6.7 電気特性 - レシーバ

推奨動作条件範囲内 (特に記述のない限り)

|                  | パラメータ                                               |                                                                         | テスト条件                                    | 最小<br>値 | 標準値 (1) | 最大<br>値 | 単位   |

|------------------|-----------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------|---------|---------|---------|------|

| V                | 正方向の差動入力電圧スレッショルド                                   | タイプ 1                                                                   |                                          |         |         | 50      | mV   |

| V <sub>IT+</sub> | 正万回の左動八万电圧ヘレッショルト                                   | タイプ 2                                                                   |                                          |         | •       | 150     | IIIV |

| V                | △十 <b>户</b> の光動11冊ピコン/」と                            | タイプ 1                                                                   |                                          | -50     |         |         | mV   |

| V <sub>IT-</sub> | 負方向の差動入力電圧スレッショルド                                   | タイプ 2                                                                   | - 表 7-1 と表 7-2 と図 6-9 を参照                | 50      |         |         | IIIV |

| V                | 差動入力電圧ヒステリシス (V <sub>IT+</sub> – V <sub>IT-</sub> ) | タイプ 1                                                                   |                                          |         | 25      |         | mV   |

| V <sub>HYS</sub> | 左動八刀电圧Lハノリンハ (VIT+ - VIT-)                          | タイプ 2                                                                   |                                          |         | 0       |         | ""   |

| V <sub>OH</sub>  | High レベル出力電圧 (R)                                    |                                                                         | I <sub>OH</sub> = -8 mA                  | 2.4     |         |         | V    |

| V <sub>OL</sub>  | Low レベル出力電圧 (R)                                     |                                                                         | I <sub>OL</sub> = 8 mA                   |         |         | 0.4     | V    |

| I <sub>IH</sub>  | High レベル入力電流 (RE)                                   |                                                                         | V <sub>IH</sub> = 2V~V <sub>CC</sub>     | -10     |         | 0       | μA   |

| I <sub>IL</sub>  | Low レベル入力電流 (RE)                                    |                                                                         | V <sub>IL</sub> = GND~0.8V               | -10     |         | 0       | μA   |

| I <sub>OZ</sub>  | loz 高インピーダンス出力電流 (R)                                |                                                                         | V <sub>O</sub> = 0 V または 3.6 V           | -10     |         | 15      | μA   |

| ``               |                                                     | V <sub>I</sub> = 0.4sin(30E6πt) + 0.5V <sup>(2)</sup> 、<br>その他の入力は 1.2V |                                          | 3       |         | pF      |      |

| C <sub>AB</sub>  | 差動入力容量                                              |                                                                         | $V_{AB} = 0.4 \sin(30 E6 \pi t) V^{(2)}$ |         |         | 2.5     | pF   |

| C <sub>A/B</sub> | 入力容量バランス、 $(C_A/C_B)$                               |                                                                         |                                          | 0.99    |         | 1.01    |      |

- (1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (2) HP4194A インピーダンス アナライザ (または同等のもの)

## 6.8 電気的特性 - デジタル入力および出力

推奨動作条件範囲内 (特に記述のない限り)

|                      | パラメータ                                                                    | テスト条件                                                                                               | 最小値  | 標準値 最大値 | 単位 |

|----------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|---------|----|

|                      |                                                                          | $V_A = 3.8V$ , $V_B = 1.2V$ ,                                                                       | 0    | 32      |    |

| I <sub>A</sub>       | ドライバが入力電流をディセーブルしたレシーバまたはトランシーバ                                          | V <sub>A</sub> = 0V または 2.4V、 V <sub>B</sub> = 1.2V                                                 | -20  | 20      | μΑ |

|                      |                                                                          | $V_A = -1.4 \text{ V}, \qquad V_B = 1.2 \text{V}$                                                   | -32  | 0       |    |

|                      |                                                                          | $V_B = 3.8 V_{\setminus}$ $V_A = 1.2V$                                                              | 0    | 32      |    |

| IB                   | ドライバが入力電流をディセーブルしたレシーバまたはトランシーバ                                          | $V_B = 0V$ または 2.4V、 $V_A = 1.2V$                                                                   | -20  | 20      | μΑ |

|                      |                                                                          | $V_B = -1.4 V$ , $V_A = 1.2V$                                                                       | -32  | 0       |    |

| I <sub>AB</sub>      | ドライバが差動入力電流をディセーブルしたレシー<br>バまたはトランシーバ (I <sub>A</sub> – I <sub>B</sub> ) | $V_A = V_B$ , $1.4 \le V_A \le 3.8V$                                                                | -4   | 4       | μΑ |

|                      |                                                                          | $V_A = 3.8V$ , $V_B = 1.2V$ , $0 V \le V_{CC} \le 1.5 V$                                            | 0    | 32      |    |

| I <sub>A(OFF)</sub>  | レシーバまたはトランシーバの電源オフ入力電流                                                   | $V_A = 0V$ または 2.4V、 $V_B = 1.2V$ 、 $0~V \le V_{CC} \le 1.5~V$                                      | -20  | 20      | μΑ |

|                      |                                                                          | $V_A = -1.4 \text{ V}, \qquad V_B = 1.2 \text{V}, \qquad 0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$  | -32  | 0       |    |

|                      |                                                                          | $V_B = 3.8 \text{ V}, \qquad V_A = 1.2 \text{ V}, \qquad 0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$  | 0    | 32      |    |

| I <sub>B(OFF)</sub>  | レシーバまたはトランシーバの電源オフ入力電流                                                   | $V_B = 0V$ $\sharp$ $\hbar$ $t$                                 | -20  | 20      | μΑ |

|                      |                                                                          | $V_B = -1.4 \text{ V}, \qquad V_A = 1.2 \text{ V}, \qquad 0 \text{ V} \le V_{CC} \le 1.5 \text{ V}$ | -32  | 0       |    |

| I <sub>AB(OFF)</sub> | レシーバ入力またはトランシーバの電源オフ差動入<br>力電流 (I <sub>A</sub> – I <sub>B</sub> )        | $V_A = V_B$ , $0V \le V_{CC} \le 1.5V$ , $-1.4 \le V_A \le 3.8V$                                    | -4   | 4       | μА |

| C <sub>A</sub>       | ドライバの入力容量がディセーブルされたトランシ<br>ーバ                                            | $V_A = 0.4 \sin (30 E6 \pi t) + 0.5 V^{(2)}, V_B = 1.2 V$                                           |      | 5       | pF |

| Св                   | ドライバの入力容量がディセーブルされたトランシ<br>ーバ                                            | $V_B = 0.4 \sin (30 E6 \pi t) + 0.5 V^{(2)}, V_A = 1.2 V$                                           |      | 5       | pF |

| C <sub>AB</sub>      | ドライバの差動入力容量がディセーブルされたトラ<br>ンシーバ                                          | $V_{AB} = 0.4 \sin (30 E6 \pi t) V^{(2)}$                                                           |      | 3       | pF |

| C <sub>A/B</sub>     | ドライバの入力容量バランスがディセーブルされたトランシーバ、(C <sub>A</sub> /C <sub>B</sub> )          |                                                                                                     | 0.99 | 1.01    |    |

- (1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (2) HP4194A インピーダンス アナライザ (または同等のもの)

## 6.9 スイッチング特性 – ドライバ

推奨動作条件範囲内 (特に記述のない限り)

|                       | パラメータ                                             | テスト条件                                             | 最小 値 | 標 <b>準値</b><br>(1) | 最大<br>値 | 単位 |

|-----------------------|---------------------------------------------------|---------------------------------------------------|------|--------------------|---------|----|

| t <sub>pLH</sub>      | 伝搬遅延時間、出力立ち上がり                                    |                                                   | 2    | 2.5                | 3.5     | ns |

| $t_{\text{pHL}}$      | 伝搬遅延時間、出力立ち下がり                                    |                                                   | 2    | 2.5                | 3.5     | ns |

| t <sub>r</sub>        | 差動出力信号の立ち上がり時間                                    | 図 7-5 を参照                                         | 2    | 2.6                | 3.2     | ns |

| t <sub>f</sub>        | 差動出力信号の立ち下がり時間                                    |                                                   | 2    | 2.6                | 3.2     | ns |

| t <sub>sk(p)</sub>    | パルス スキュー ( t <sub>pHL</sub> – t <sub>pLH</sub>  ) |                                                   |      | 30                 | 150     | ps |

| t <sub>sk(pp)</sub>   | 部品間スキュー(2)                                        |                                                   |      |                    | 0.9     | ns |

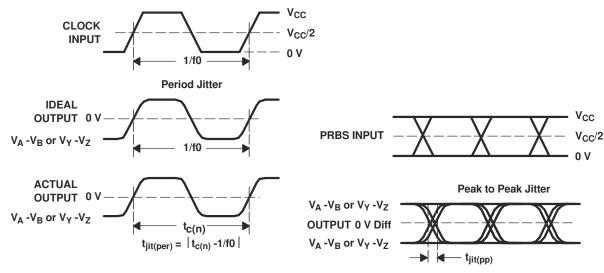

| t <sub>jit(per)</sub> | 周期ジッタ、rms (1 標準偏差) <sup>(3)</sup>                 | 50MHz クロック入力(4)                                   |      | 2                  | 3       | ps |

| t <sub>jit(pp)</sub>  | ピークツー ピーク ジッタ <sup>(3)</sup> (6)                  | 100Mbps 2 <sup>15</sup> –1 PRBS 入力 <sup>(5)</sup> |      | 55                 | 150     | ps |

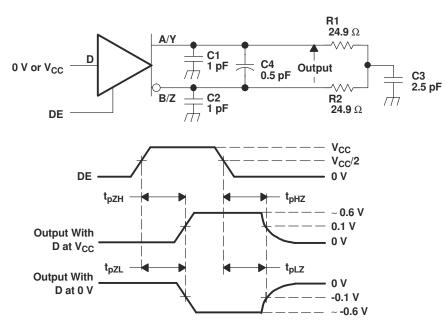

| $t_{PHZ}$             | ディセーブル時間、High レベルから高インピーダンスへの出力                   |                                                   |      | 4                  | 7       | ns |

| t <sub>PLZ</sub>      | ディセーブル時間、Low レベルから高インピーダンスへの出力                    | - 図 <b>7-6</b> を参照                                |      | 4                  | 7       | ns |

| t <sub>PZH</sub>      | イネーブル時間、高インピーダンスから High レベルへの出力                   | □□ 化参照                                            |      | 4                  | 7       | ns |

| $t_{PZL}$             | イネーブル時間、高インピーダンスから Low レベルへの出力                    |                                                   |      | 4                  | 7       | ns |

- (1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (2) 部品間スキューは、同じ V/T 条件で動作する 2 つのデバイス間の伝搬遅延の差として定義されます。

- (3) ジッタは、設計と特性によって保証されています。スティミュラスのジッタがこの数値から減算されました。

- (4)  $t_r = t_f = 0.5$ ns (10%~90%)、30K を超えるサンプルで測定。

- (5)  $t_r = t_f = 0.5$ ns (10%~90%)、100K を超えるサンプルで測定。

- (6) ピークツーピークジッタには、パルススキュー (t<sub>sk(p)</sub>) によるジッタが含まれます。

## 6.10 スイッチング特性 - レシーバ

推奨動作条件範囲内 (特に記述のない限り)

|                                                  | パラメータ                                                                                                             |                     | テスト条件                                             | 最小<br>値 | 標準値 | 最大<br>値 | 単位 |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------|---------|-----|---------|----|

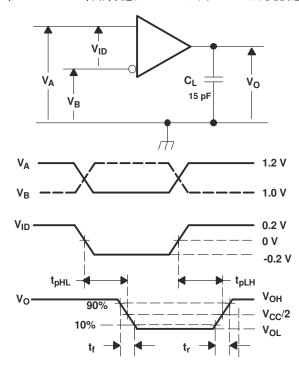

| t <sub>PLH</sub>                                 | 伝搬遅延時間、出力立ち上がり                                                                                                    |                     |                                                   | 2       | 3.6 | 6       | ns |

| t <sub>PHL</sub>                                 | 伝搬遅延時間、出力立ち下がり                                                                                                    |                     |                                                   | 2       | 3.6 | 6       | ns |

| t <sub>r</sub>                                   | 出力信号の立ち上がり時間                                                                                                      |                     |                                                   | 1       |     | 2.3     | ns |

| t <sub>f</sub>                                   | 出力信号の立ち下がり時間                                                                                                      |                     | C <sub>L</sub> = 15pF、図 7-10 を参照                  | 1       |     | 2.3     | ns |

|                                                  | $\beta / \sqrt{1}$ $\beta / \sqrt{2}$ |                     |                                                   |         | 100 | 300     | ps |

| t <sub>sk(p)</sub>                               |                                                                                                                   |                     |                                                   |         | 300 | 500     | ps |

| t <sub>sk(pp)</sub>                              | 9) 部品間スキュー(2)                                                                                                     |                     |                                                   |         |     | 1       | ns |

| t <sub>jit(per)</sub>                            | 周期ジッタ、rms (1 標準偏差) <sup>(3)</sup>                                                                                 |                     | 50MHz クロック入力 <sup>(4)</sup>                       |         | 4   | 7       | ps |

|                                                  | タイプ 1                                                                                                             |                     | 100Mbps 2 <sup>15</sup> –1 PRBS 入力 <sup>(5)</sup> |         | 200 | 700     | ps |

| t <sub>jit(pp)</sub>                             | ピークツー ピーク ジッタ <sup>(3) (6)</sup>                                                                                  | タイプ 2               | TOURIDPS 2.0—T PRBS /(/)(0)                       |         | 225 | 800     | ps |

| t <sub>PHZ</sub>                                 | ディセーブル時間、High レベルから高インピーダンスへの                                                                                     | り出力                 |                                                   |         | 6   | 10      | ns |

| t <sub>PLZ</sub> ディセーブル時間、Lowレベルから高インピーダンスへの出力   |                                                                                                                   |                     |                                                   | 6       | 10  | ns      |    |

| t <sub>PZH</sub> イネーブル時間、高インピーダンスから High レベルへの出力 |                                                                                                                   | - 図 <b>7-11</b> を参照 |                                                   | 10      | 15  | ns      |    |

| t <sub>PZL</sub>                                 | イネーブル時間、高インピーダンスから Low レベルへの                                                                                      | 出力                  |                                                   |         | 10  | 15      | ns |

- (1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (2) 部品間スキューは、同じ V/T 条件で動作する 2 つのデバイス間の伝搬遅延の差として定義されます。

- (3) ジッタは、設計と特性によって保証されています。スティミュラスのジッタがこの数値から減算されました。

- (4)  $V_{\text{ID}}$  = 200m $V_{\text{pp}}$  (MLVD200A、202A)、 $V_{\text{ID}}$  = 400m $V_{\text{pp}}$  (MLVD204A、205A)、 $V_{\text{cm}}$  = 1V、 $t_{\text{r}}$  =  $t_{\text{f}}$  = 0.5ns (10% $\sim$ 90%)、30K を超えるサンプルで測定

- (5)  $V_{ID} = 200 \text{mV}_{pp} \text{ (MLVD200A、202A)}, V_{ID} = 400 \text{mV}_{pp} \text{ (MLVD204A、205A)}, V_{cm} = 1 \text{V}, t_r = t_f = 0.5 \text{ns} (10% \sim 90\%), 100 \text{K} を超えるサンプルで測定。$

- (6) ピークツーピークジッタには、パルススキュー (t<sub>sk(p)</sub>) によるジッタが含まれます

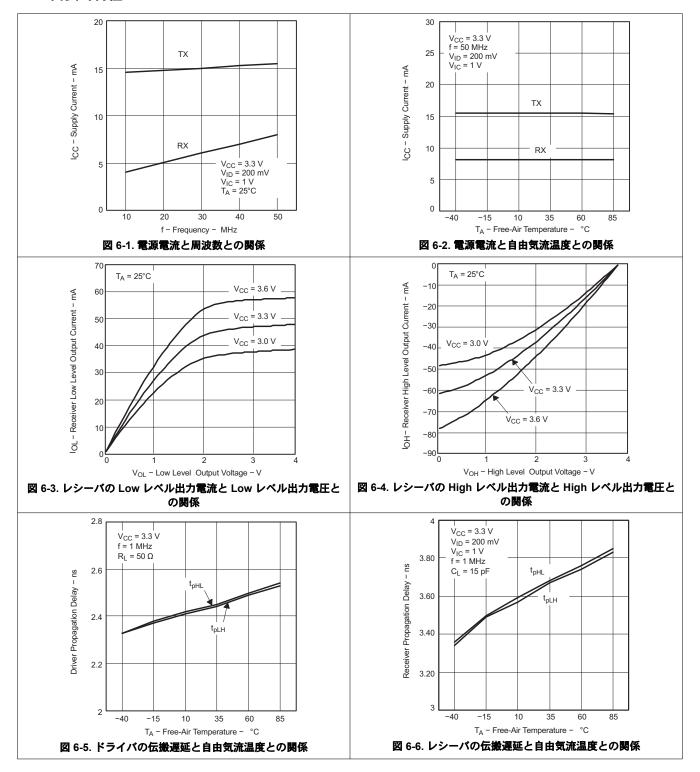

## 6.11 代表的特性

## 6.11 代表的特性 (続き)

## 7パラメータ測定情報

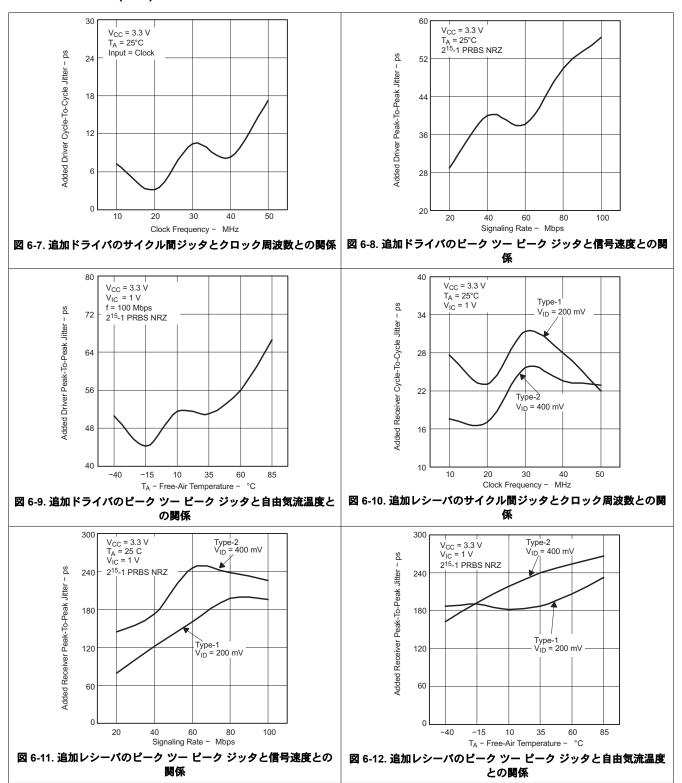

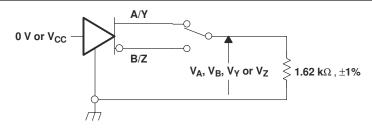

図 7-1. ドライバの電圧および電流の定義

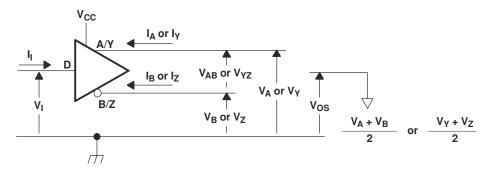

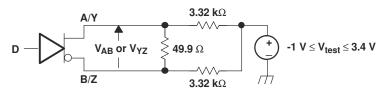

A. すべての抵抗の公差は 1% です。

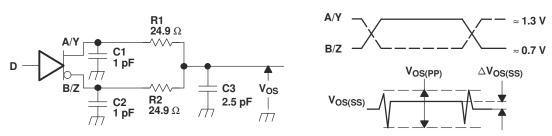

## 図 7-2. 差動出力電圧テスト回路

- A. すべての入力パルスは、t, または t, ≤ 1ns、パルス周波数 = 1MHz、デューティ サイクル = 50 ±5% の特性を持つジェネレータから供給されます。

- B. C1、C2、C3 には D.U.T. から 2cm 以内の計測機器および治具の容量が含まれ、公差は ±20% です。

- C. R1 および R2 は金属皮膜、表面実装、公差 ±1% で、D.U.T. から 2cm 以内に配置されています。

- D. V<sub>OS(PP)</sub> の測定 は、-3dB 帯域幅が 1GHz 以上のテスト機器で行います。

#### 図 7-3. ドライバの同相モード出力電圧のテスト回路と定義

図 7-4. ドライバ短絡テスト回路

- A. すべての入力パルスは、 $t_r$  または  $t_f \le 1$ ns、周波数 = 1MHz、デューティサイクル = 50 ± 5% の特性を持つジェネレータから供給されます。

- B. C1、C2、C3 には D.U.T. から 2cm 以内の計測機器および治具の容量が含まれ、公差は ±20% です。

- C. R1 は金属皮膜、表面実装、公差 1% で、D.U.T. から 2cm 以内に配置されています。

- D. 測定は、-3dB 帯域幅が 1GHz 以上のテスト機器で行います。

## 図 7-5. 差動出力信号のドライバ テスト回路、タイミング、電圧の定義

- A. すべての入力パルスは、 $t_r$  または  $t_f \le 1$ ns、周波数 = 1MHz、デューティサイクル = 50 ± 5% の特性を持つジェネレータから供給されます。

- B. C1、C2、C3、C4 には、D.U.T. から 2cm 以内の計測機器および治具の容量が含まれ、公差は ±20% です。

- C. R1 および R2 は金属皮膜、表面実装、公差 1% で、D.U.T. から 2cm 以内に配置されています。

- D. 測定は、-3dB帯域幅が1GHz以上のテスト機器で行います。

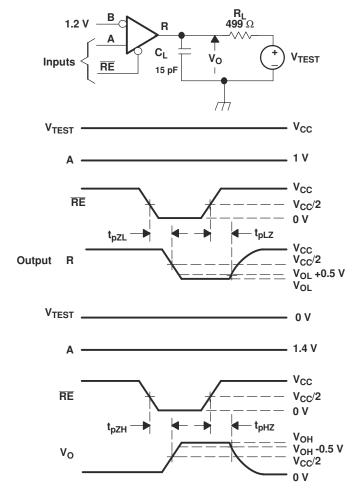

## 図 7-6. ドライバのイネーブル / ディセーブル時間回路と定義

図 7-7. 最大定常状態出力電圧

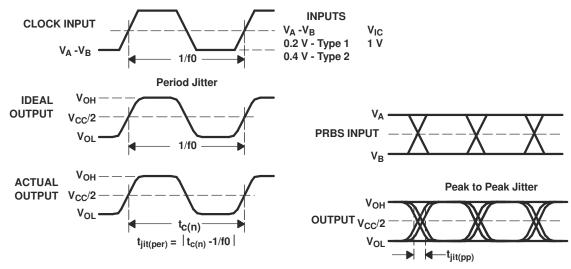

- A. すべての入力パルスは、Agilent 81250 Stimulus System から供給されます。

- B. 測定は、TDSJIT3 アプリケーション ソフトウェアを実行している TEK TDS6604 で行います。

- C. 周期ジッタは、50MHz 50 ±1% デューティ サイクルのクロック入力を使用して測定します。

- D. サイクル間ジッタは、100Mbps 2<sup>15</sup>–1 PRBS 入力を使用して測定します。

#### 図 7-8. ドライバのジッタ測定波形

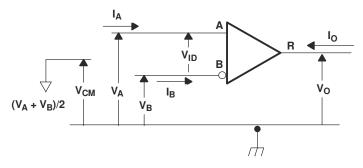

図 7-9. レシーバの電圧および電流の定義

表 7-1. Type-1 レシーバの入力スレッショルド テスト電圧

| 印加              | に関係して生じる 結果として生じる 差動入力電圧 |                 | 結果として生じる<br>同相モード入力電圧 | レシーバ<br>(1)出力 |

|-----------------|--------------------------|-----------------|-----------------------|---------------|

| V <sub>IA</sub> | V <sub>IB</sub>          | V <sub>ID</sub> | V <sub>IC</sub>       | ССШУ          |

| 2.400           | 0.000                    | 2.400           | 1.200                 | Н             |

| 0.000           | 2.400                    | -2.400          | 1.200                 | L             |

| 3.425           | 3.335                    | 0.050           | 3.4                   | Н             |

| 3.375           | 3.425                    | -0.050          | 3.4                   | L             |

| -0.975          | -1.025                   | 0.050           | -1                    | Н             |

| -1.025          | -0.975                   | -0.050          | -1                    | L             |

(1)  $H = High レベル、L = Low レベル、出力状態はレシーバがイネーブルであると仮定 (<math>\overline{RE} = L$ )

表 7-2. Type-2 レシーバの入力スレッショルド テスト電圧

| 印加電圧            |                 | 結果として生じる<br>差動入力電圧              | 結果として生じる<br>同相モード入力電圧 | レシーバ<br>出力 <sup>(1)</sup> |

|-----------------|-----------------|---------------------------------|-----------------------|---------------------------|

| V <sub>IA</sub> | V <sub>IB</sub> | V <sub>ID</sub> V <sub>IC</sub> |                       | МУЛ                       |

| 2.400           | 0.000           | 2.400                           | 1.200                 | Н                         |

| 0.000           | 2.400           | -2.400                          | 1.200                 | L                         |

| 3.475           | 3.325           | 0.150                           | 3.4                   | Н                         |

| 3.425           | 3.375           | 0.050                           | 3.4                   | L                         |

| -0.925          | -1.075          | 0.150                           | -1                    | Н                         |

| -0.975          | -1.025          | 0.050                           | -1                    | L                         |

(1)  $H = High \, \nu$ ベル、 $L = Low \, \nu$ ベル、出力状態はレシーバがイネーブルであると仮定 ( $\overline{RE} = L$ )

- A. すべての入力パルスは、 $t_r$  または  $t_f \le 1$ ns、周波数 = 1MHz、デューティサイクル = 50 ± 5% の特性を持つジェネレータから供給されます。 $C_L$  は、公差 20% の低損失セラミック表面実装コンデンサと、D.U.T. から 2cm 以内の治具容量を組み合わせたものです。

- B. 測定は、-3dB帯域幅が1GHz以上のテスト機器で行います。

#### 図 7-10. レシーバのタイミング テスト回路と波形

- A. すべての入力パルスは、 $t_r$  または  $t_f \le 1$ ns、周波数 = 1MHz、デューティサイクル = 50 ± 5% の特性を持つジェネレータから供給されます。

- B. R<sub>L</sub> は公差 1%、金属皮膜、表面実装で、D.U.T. から 2cm 以内に配置されています。

- C.  $C_L$  は、DUT から 2cm 以内の計測機器および治具の容量で、 $\pm 20\%$  です。

図 7-11. レシーバのイネーブル / ディセーブル時間テスト回路と波形

- A. すべての入力パルスは、Agilent 8304A Stimulus System から供給されます。

- B. 測定は、TDSJIT3 アプリケーション ソフトウェアを実行している TEK TDS6604 で行います。

- C. 周期ジッタは、50MHz 50 ±1% デューティ サイクルのクロック入力を使用して測定します。

- D. サイクル間ジッタは、100Mbps 2<sup>15</sup>–1 PRBS 入力を使用して測定します。

図 7-12. レシーバのジッタ測定波形

## 8 詳細説明

#### 8.1 概要

SN65MLVD20xA ファミリのデバイスは、最高 100Mbps の信号速度で動作するよう最適化されたマルチポイント低電圧 差動 (M-LVDS) ラインドライバおよびレシーバです。すべての部品がマルチポイント低電圧差動信号伝送 (M-LVDS) 規格 TIA/EIA-899 に準拠しています。これらの回路は TIA/EIA-644 規格に準拠した LVDS 対応の回路に類似しており、マルチポイント アプリケーションに対応する機能が追加されています。ドライバ出力は、最小 30Ω の負荷を供給するマルチポイント バスをサポートするように設計されており、バックボーンの伝送ラインからスタブをオフにできるように、制御された遷移時間が組み込まれています。

これらのデバイスは Type-1 および Type-2 レシーバを搭載しており、-1V~3.4V の同相範囲にわたってわずか 50mV (Type-1) または 150mV (Type-2) の差動入力電圧でバス状態を検出できます。 Type-1 レシーバは、25mV の差動入力電圧ヒステリシスにより、緩やかに変化する信号や入力の喪失による出力の発振を防止します。 Type-2 レシーバは、開路およびバス アイドルのフォルト状況で既知の出力状態を提供するためのオフセット スレッショルドを備えています。

#### 8.2 機能ブロック図

#### SN65MLVD200A, SN65MLVD204A

SN65MLVD202A, SN65MLVD205A

図 8-1. 論理図 (正論理)

#### 8.3 機能説明

#### 8.3.1 パワーオン リセット

このファミリのデバイスは、3V~3.6V の範囲の電源電圧で動作し、この範囲について規定されている性能要件をすべて満たしています。電源電圧が 1.5V を下回ると (または、電源がオンになってまだ 1.5V に達していなとき)、パワーオン リセット回路により、ドライバ出力が高インピーダンス状態に設定されます。

#### 8.3.2 ESD 保護

SN65MLVD20xA デバイスのバス端子は、 $\pm 8kV$  人体モデル (HBM) および  $\pm 8kV$  に対するオンチップ ESD 保護を備えています。

## 8.4 デバイスの機能モード

## 8.4.1 デバイス機能表

表 8-1. Type-1 レシーバ (SN65MLVD200A) (1)

| 入力                             | 出力                                                   |   |  |  |

|--------------------------------|------------------------------------------------------|---|--|--|

| $V_{ID} = V_A - V_B$           | V <sub>ID</sub> = V <sub>A</sub> – V <sub>B</sub> RE |   |  |  |

| V <sub>ID</sub> ≥ 50 mV        | L                                                    | Н |  |  |

| -50mV < V <sub>ID</sub> < 50mV | L                                                    | ? |  |  |

| V <sub>ID</sub> ≤ -50 mV       | L                                                    | L |  |  |

| X                              | Н                                                    | Z |  |  |

| X                              | オープン                                                 | Z |  |  |

(1)  $H = High \, \nu \, \langle \nu \, \rangle \, \langle \nu$

表 8-2. Type-2 レシーバ (SN65MLVD204A) <sup>(1)</sup>

| 入力                             | 出力                                                   |   |  |  |

|--------------------------------|------------------------------------------------------|---|--|--|

| $V_{ID} = V_A - V_B$           | V <sub>ID</sub> = V <sub>A</sub> - V <sub>B</sub> RE |   |  |  |

| V <sub>ID</sub> ≥ 150 mV       | L                                                    | Н |  |  |

| 50mV < V <sub>ID</sub> < 150mV | L                                                    | ? |  |  |

| V <sub>ID</sub> ≤ 50 mV        | L                                                    | L |  |  |

| X                              | Н                                                    | Z |  |  |

| X                              | オープン                                                 | Z |  |  |

(1)  $H = High \, \nu$ ベル、 $L = Low \, \nu$ ベル、Z = 高インピーダンス、<math>X =ドント ケア、? =不定

表 8-3. ドライバ (1)

| 入力   | イネーブル | 出力 |   |  |

|------|-------|----|---|--|

| D    | DE    | A  | В |  |

| L    | Н     | L  | Н |  |

| Н    | Н     | Н  | L |  |

| オープン | Н     | L  | Н |  |

| X    | オープン  | Z  | Z |  |

| X    | L     | Z  | Z |  |

(1)  $H = High \, \nu$ ベル、 $L = Low \, \nu$ ベル、Z = 高インピーダンス、<math>X = Fントケア、P = T定

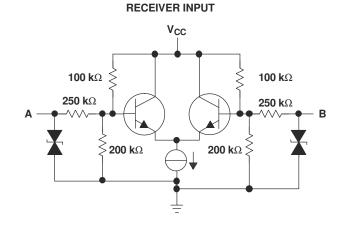

## 8.4.2 等価な入力および出力回路図

# DRIVER INPUT AND DRIVER ENABLE $V_{CC}$ $V_$

## 9アプリケーションと実装

注

以下のアプリケーションに関するセクションの情報は、テキサス・インスツルメンツの部品仕様の一部ではなく、テキサス・インスツルメンツはこれらの情報の正確性や完全性を保証しません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 9.1 アプリケーション情報

SN65MLVD20xA ファミリのデバイスは、マルチポイント ライン ドライバおよびレシーバです。これらのデバイスの機能はシンプルであると同時に非常に柔軟性が高いため、ワイヤレス ベースステーションからデスクトップ コンピュータまで、幅広い設計で使用できます。

## 9.2 代表的なアプリケーション

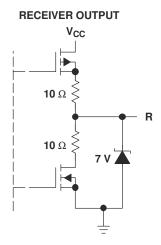

図 9-1 にマルチポイント構成を示します。マルチポイント構成では、多数のトランスミッタと多数のレシーバを 1 つの伝送ラインで相互接続できます。マルチドロップと比較した場合の主な違いは、2 つ以上のドライバが存在することです。このような状況では、ポイントツー ポイントまたはマルチドロップのシステムでは対処できない競合の問題が発生します。マルチポイント動作により、1 組の平衡な媒体ペアで双方向の半二重通信が可能になります。伝送ライン全体で各種ドライバの位置をサポートするために、伝送ラインの二重終端が必要になっています。

システム設計者が直面する主な課題は、デバイス負荷とデバイス接続 (スタブ) によって共通のバスに発生するインピーダンスの不連続性です。マルチポイントトポロジでエラーのない信号伝送を実現するには、負荷バスのインピーダンスをマッチングし、信号エッジが制御された信号ドライバを使用することが重要です。

図 9-1. マルチポイント構成

#### 9.2.1 設計要件

この設計例では、表 9-1 に記載されているパラメータを使用します。

表 9-1. 設計パラメータ

| パラメータ                | 値                          |

|----------------------|----------------------------|

| ドライバ電源電圧             | 3V∼3.6V                    |

| ドライバの入力電圧            | 0.8V~3.3V                  |

| ドライバの信号速度            | DC~100Mbps                 |

| 相互接続特性インピーダンス (差動)   | 100 Ω                      |

| 終端抵抗                 | 100 Ω                      |

| レシーバ ノード数            | 2~32                       |

| レシーバ電源電圧             | 3V∼3.6V                    |

| レシーバの入力電圧            | 0∼(V <sub>CC</sub> – 0.8)V |

| レシーバの信号速度            | DC~100Mbps                 |

| ドライバとレシーバの間のグランド シフト | ±1 V                       |

#### 9.2.2 詳細な設計手順

#### 9.2.2.1 電源電圧

SN65MLVD20xA デバイスは 1 つの電源で動作します。 SN65MLVD20xA デバイスは、最低 3V、最高 3.6V の電源で の動作をサポートしています。

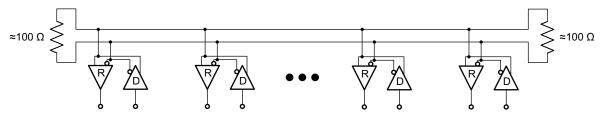

#### 9.2.2.2 電源バイパス容量

バイパス コンデンサは、パワー ディストリビューション回路で重要な役割を果たします。低周波数では、電源の端子間インピーダンスは極めて低くなっています。ただし、より高い周波数の電流が電源パターンを伝搬するため、電源でグランドへの低インピーダンス パスを維持できないことがよくあります。この欠点に対処するために、バイパス コンデンサを使用します。通常、ボード レベルで大容量のバイパス コンデンサ (10μF から 1000μF) を使用すると、kHz レンジまでの範囲で良好な成果を達成できます。リード線のサイズと長さの関係で、大きなコンデンサはスイッチング周波数で大きなインダクタンス値を持つ傾向があります。この問題を解決するには、より小型のコンデンサ (nF~μF) を IC の隣にローカルに取り付ける必要があります。

積層セラミック チップまたは表面実装コンデンサ (サイズ 0603 または 0805) は、バイパス コンデンサのリード インダクタンスが約 1nH であるため、高速環境でのリード インダクタンスを最小限に抑えます。 たとえば、リードがある標準的なコンデンサのリード インダクタンスは約 5nH です。

M-LVDS チップでローカルで使用するバイパス コンデンサの値は、Howard Johnson と Martin Graham による『High Speed Digital Design – A Handbook of Black Magic (高速デジタル設計 - ブラックマジックのハンドブック)』(1993 年) に従って 式 1 および 式 2 で決定できます。4ns の控えめな立ち上がり時間と、100mA のワーストケースの消費電流変化に、テキサス・インスツルメンツが提供するすべての M-LVDS デバイスが対応しています。この例では、最大許容電源ノイズは 100mV ですが、この値は設計で利用可能なノイズ バジェットによって異なります。

$$C_{chip} = \left(\frac{\Delta I_{Maximum Step Change Supply Current}}{\Delta V_{Maximum Power Supply Noise}}\right) \times T_{Rise Time}$$

(1)

$$C_{MLVDS} = \left(\frac{100 \text{ mA}}{100 \text{ mV}}\right) \times 4 \text{ ns} = 0.004 \text{ }\mu\text{F}$$

(2)

図 9-2 は、リード インダクタンスを低減し、基板レベルのコンデンサ (>10µF) と上記の容量値 (0.004µF) との間の中間周波数をカバーする構成を示しています。最小の容量をチップにできる限り近づけて配置します。

図 9-2. 推奨される M-LVDS バイパス コンデンサのレイアウト

#### 9.2.2.3 ドライバの入力電圧

入力段は LVTTL 信号を受け取ることができます。ドライバは約 1.4V の決定スレッショルドで動作します。

## 9.2.2.4 ドライバ出力電圧

ドライバの公称条件での定常同相モード出力電圧は 1V、差動信号は 540V です。

#### 9.2.2.5 終端抵抗

M-LVDS 通信チャネルは、2 つの抵抗性負荷で終端された伝送ラインを駆動する電流源を使用します。これらの負荷は、送信された電流をレシーバ入力の電圧に変換する役割を果たします。良好なシグナル インテグリティを確保するには、終端抵抗を伝送ラインの特性インピーダンスにマッチングする必要があります。終端抵抗がメディアの公称特性インピーダンスの 10% 以内であることを確認する必要があります。伝送ラインのインピーダンスが 100 $\Omega$  を目標としている場合、終端抵抗は  $90\Omega\sim110\Omega$  にする必要があります。通常、ライン終端抵抗は伝送ラインの終端に配置します。

#### 9.2.2.6 レシーバの入力信号

本製品の M-LVDS レシーバは M-LVDS 規格に準拠しており、バスの状態を正しく判定します。これらのデバイスは Type-1 および Type-2 レシーバを搭載しており、-1V~3.4V の同相範囲にわたってわずか 50mV の差動電圧でバス状態を検出できます。

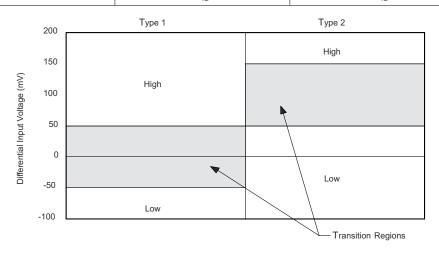

#### 9.2.2.7 レシーバ入力スレッショルド (フェイルセーフ)

M-LVDS 規格では、Type-1 レシーバと Type-2 レシーバが定義されています。Type-1 レシーバの差動入力電圧スレッショルドはほぼ 0V です。Type-2 レシーバの差動入力電圧スレッショルドは 0V からのオフセットで、これにより電圧差がないことを検出します。オフセット入力がレシーバ出力に与える影響を表 9-2 および 図 9-3 に示します。

レシーバのタイプ

出力 Low

出力 High

タイプ 1

-2.4V ≤ V<sub>ID</sub> ≤ -0.05V

0.05V ≤ V<sub>ID</sub> ≤ 2.4V

タイプ 2

-2.4V ≤ V<sub>ID</sub> ≤ 0.05V

0.1 V ≤ V<sub>ID</sub> ≤ 2.4V

表 9-2. レシーバ入力電圧スレッショルドの要件

図 9-3. 遷移領域を示すレシーバ差動入力電圧の拡大グラフ

#### 9.2.2.8 レシーバ出力信号

電源電圧が 3V~3.6V の範囲内である場合、レシーバ出力は LVTTL の出力電圧規格に準拠します。

#### 9.2.2.9 メディアの相互接続

ドライバとレシーバの間の物理的な通信チャネルには、M-LVDS 規格の要件を満たす、任意の平衡した金属導体ペアを使用できます。その重要なポイントを次に示します。メディアの相互接続には、ツイストペア、Twinax、フラットリボン ケーブル、または PCB パターンを使用できます。

相互接続の公称特性インピーダンスは  $100\Omega\sim120\Omega$  で、変動が 10% を超えないようにする必要があります ( $90\Omega\sim132\Omega$ )。

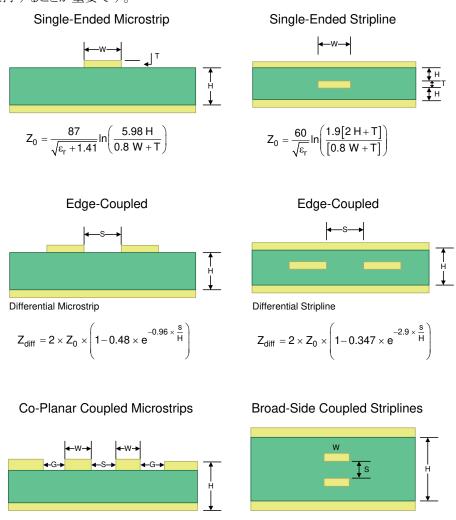

#### 9.2.2.10 PCB の伝送ライン

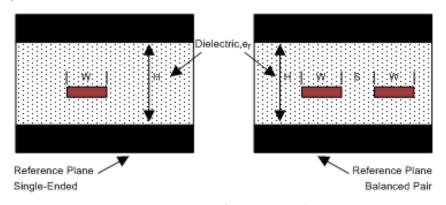

『LVDS オーナー マニュアル デザイン ガイド、第 4 版』(SNLA187) の 図 9-4 に、プリント基板 (PCB) で一般的に使用されるいくつかの伝送ライン構造を示してあります。それぞれの構造は、信号線と、その長さに沿って一様な断面を持つ帰路で構成されます。マイクロストリップは最上層 (または最下層) にある信号パターンで、グランドまたは電源プレーンの帰路から誘電体層で分離されています。ストリップラインは内層の信号パターンであり、信号パターンの上下のグランド プレーンとの間に誘電体層があります。構造の寸法と誘電体の特性によって伝送ラインの特性インピーダンスが決まります。これは制御インピーダンス伝送ラインとも呼ばれます。

2本の信号線を互いに近づけて配置すると、結合された伝送線のペアが形成されます。図 9-4 に、エッジ結合マイクロストリップ、およびエッジ結合またはブロードサイド結合ストリップラインの例を示します。差動信号によって励起される場合、結合された伝送ラインは差動ペアと呼ばれます。各ラインの特性インピーダンスを奇数モードインピーダンスと呼びます。各ラインの奇数モードインピーダンスの合計が、差動ペアの差動インピーダンスになります。パターンの寸法と誘電体の特性に加えて、2つのパターン間の間隔によって相互結合が決まり、差動インピーダンスに影響を与えます。2本のラインがすぐ隣接している場合(たとえばSがWの2倍に満たない場合)、その差動ペアは密結合差動ペアと呼ばれます。長さ方向に一定の差動インピーダンスを維持するには、パターンの幅と間隔を長さ方向で均一に保ち、2つのラインの間に良好な対称性を維持することが重要です。

図 9-4. 制御インピーダンス伝送ライン

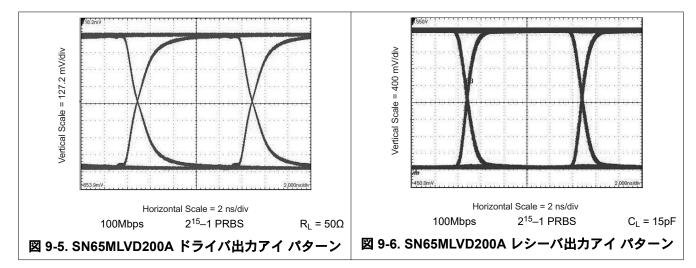

#### 9.2.3 アプリケーション曲線

## 10 電源に関する推奨事項

このデータシートに記載されている M-LVDS ドライバおよびレシーバは、1 つの電源で動作するように設計されています。ドライバとレシーバの両方が 3V~3.6V の範囲の電源電圧で動作します。代表的なアプリケーションでは、ドライバとレシーバが別々の基板上に配置されている場合も、別々の機器上に配置されている場合もあります。このような場合、それぞれの場所で個別の電源を使用する必要があります。ドライバ電源とレシーバ電源の間で想定されるグランド電位差は±1V 未満です。基板レベルおよびローカル デバイス レベルのバイパス容量を使用する必要があり、これは電源バイパス容量にカバーされています。

## 11 レイアウト

#### 11.1 レイアウトのガイドライン

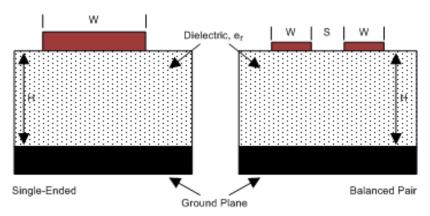

## 11.1.1 マイクロストリップとストリップラインのトポロジ

『LVDS アプリケーションおよびデータ ハンドブック』(SLLD009) に従い、プリント基板には通常、2 つの伝送ラインのオプションが用意されています。 マイクロストリップとストリップラインです。 マイクロストリップは、図 11-1 に示すように、PCB の外層のパターンです。

図 11-1. マイクロストリップのトポロジ

ストリップラインは 2 つのグランド プレーン間のパターンです (図 11-2 を参照)。ストリップラインは、基準プレーンが埋め込まれたパターンを効果的にシールドするため、放射と感受性の問題を受けにくくなります。ただし、高速伝送を考えると、2 つのプレーンを並べて使用すると、静電容量が増加します。可能であれば、M-LVDS 信号がマイクロストリップ伝送ラインを通るようにすることを推奨します。PCB パターンを使用すると、全体のノイズ バジェットと反射許容量に基づいて、 $Z_0$  に必要な公差を指定できます。脚注  $1^1$ 、 $2^2$ 、 $3^3$  に、差動およびシングルエンド パターンの  $Z_0$  および  $I_{PD}$  の式のドキュメントを示します。 $I_{PD}$  の式の

図 11-2. ストリップラインのトポロジ

#### 11.1.2 誘電体の種類と基板構造

ボードを伝搬する信号の速度によって誘電体の選択が決まります。FR-4 または同等の製品は、通常、M-LVDS 信号で使用するのに十分な性能を発揮します。TTL/CMOS 信号の立ち上がり / 立ち下がり時間が 500ps 未満であれば、Rogers™ 4350 や Nelco N4000-13 のような誘電率が 3.4 に近い材料の方がより適していることが経験的に示されています。設計者が誘電体を選択する際は、性能に影響を及ぼす可能性のある、基板構造に関連する複数のパラメータが存在します。以下に示す一連のガイドラインは、M-LVDS デバイスを使用するいくつかの設計により、実験的に策定されたものです。

- 銅の重量: 15g または ½ オンスからメッキを開始し、30g または 1 オンスにする

- 露出した回路はすべて 7.62µm または 0.0003 インチ (最小値) の半田メッキ (60/40) を行う必要がある

- スルーホールの銅めっきは 25.4µm または 0.001 インチ (最小値) である必要がある

- 高温エアレベリングによるベア銅箔上の半田マスク

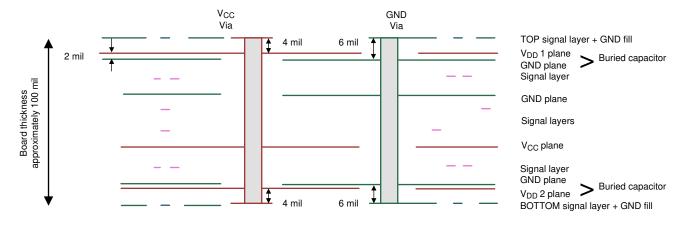

#### 11.1.3 推奨されるスタック レイアウト

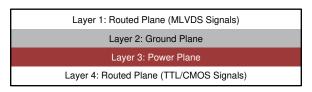

選択した誘電体と設計仕様に従って、設計者はスタックで使用するレベルの数を決定する必要があります。TTL/CMOS から M-LVDS へのクロストークを低減するには、図 11-3 に示すように、少なくとも 2 つの独立した信号プレーンを用意することを推奨します。

図 11-3. 4 層 PCB 基板

<sup>2</sup> Howard Johnson and Martin Graham. 1993. High Speed Digital Design – A Handbook of Black Magic. Prentice Hall PRT.ISBN number 013395724.

Mark I. Montrose.1996. Printed Circuit Board Design Techniques for EMC Compliance. IEEE Press. ISBN number 0780311310.

<sup>4</sup> Clyde F. Coombs. 1995. Printed Circuits Handbook. McGraw Hill. ISBN number 0070127549.

#### 注

2 層と 3 層の間隔は 127μm (0.005 インチ) である必要があります。電源プレーンとグランド プレーンの緊密 な結合を維持することで、増加した容量は過渡信号に対するバイパスとして機能します。

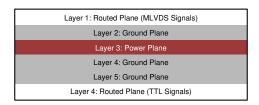

最も一般的なスタック構成の1つは、図11-4に示す6層基板です。

図 11-4.6層 PCB 基板

この具体的な構成では、少なくとも 1 つのグランド プレーンを使用して、各信号層を電源プレーンから絶縁できます。その結果、シグナル インテグリティは向上しますが、製造にはコストがかかります。レイアウト設計者が信号層 1 および 6 のグランド プレーンへのリファレンスを確保することに加えて、信号層と基準プレーンの間の距離を柔軟に変更できるため、6 層基板の使用が推奨されます。

#### 11.1.4 パターン間の分離

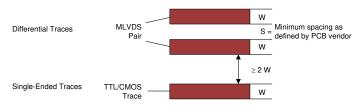

パターンの間隔はいくつかの要因に依存しますが、通常は許容される結合の量によって実際の間隔が決まります。低ノイズ結合では、電磁場の打ち消しを活用するために、M-LVDS リンクの差動ペアが密接に結合していることが必要です。これらのパターンは 100Ω 差動で、

この要件に最も適した方法で結合する必要があります。さらに、差動ペアは平衡を保つために同じ電気的長さを持つ必要があり、これにより、スキューと信号反射の問題を最小限に抑えることができます。

隣接するシングルエンド パターンが 2 つある場合、3W のルールを使用する必要があります。このルールでは、2 つのパターン間の距離は、1 つのパターンの幅の 2 倍、またはパターンの中心からパターンの中心まで測定した幅の 3 倍を超える必要があります。このように分離を増やすことで、クロストークの可能性が実質的に減少します。 隣接する M-LVDS 差動ペア間の分離にも、パターンがエッジ結合かブロードサイド結合かにかかわらず、同じルールを適用する必要があります。

図 11-5. シングルエンドおよび差動パターンの 3W ルール (上面図)

オートルータを使用する場合は、クロストークや信号反射に影響するすべての要因を考慮しているとは限らないため、注意が必要です。たとえば、信号路の不連続性を防ぐために、90°の急な角を避けることが最善です。45°の角を連続して使用すると、反射を最小限に抑える傾向があります。

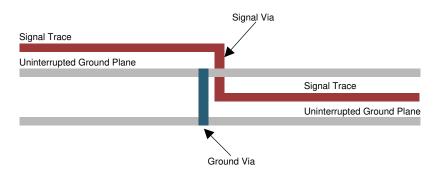

#### 11.1.5 クロストークおよびグランド バウンスの最小化

クロストークを低減するには、高周波電流の帰路を、発生元のパターンにできるだけ近い場所に配置することが重要です。通常、グランドプレーンでこれを実現できます。リターン電流は常に最小のインダクタンスのパスを選択するため、元のパターンのすぐ下に戻る可能性が最も高く、クロストークを最小化できます。電流ループの面積を小さくすると、クロストークの可能性も低くなります。パターンをできる限り短くし、その下に連続したグランドプレーンを配置することで、放射される電磁界強度を最小化できます。グランドプレーンが不連続だと帰路のインダクタンスが増加するため、回避する必要があります。

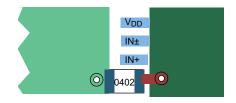

## 11.1.6 デカップリング

高速デバイスの各電源リードまたはグランド リードは、低インダクタンスのパスを経由して PCB に接続する必要があります。最良の結果を得るには、1 つ以上のビアを使用して電源ピンまたはグランド ピンを近くのプレーンに接続します。パターンのインダクタンスの増加を避けるため、ビアをピンのすぐ隣に配置するのが理想的です。電源プレーンを基板の最上面に近づけて配置すると、実効ビアの長さと、それに関連するインダクタンスが減少します。

Typical 12-Layer PCB

#### 図 11-6. 低インダクタンスで大容量の電源接続

バイパス コンデンサは V<sub>DD</sub> ピンの近くに配置する必要があります。角の近くやパッケージの下に配置することで、ループ 面積を最小限に抑えることができます。これにより、増加した容量の有効な周波数範囲が拡張されます。コンデンサのボ ディインダクタンスを最小化するため、小型のコンデンサ (0402 や 0201、または X7R 表面実装コンデンサなど)を使用 する必要があります。各バイパス コンデンサは、図 11-7(a) に示すように、コンデンサのパッドに接するビア経由で、電源 およびグランド プレーンに接続されます。

サイズ 0402 の X7R 表面実装コンデンサのボディインダクタンスは約 0.5nH です。30MHz を上回る程度の周波数では、X7R コンデンサは低インピーダンスのインダクタとして動作します。動作周波数範囲を数百 MHz に拡張するため、一般的に 100pF、1nF、 $0.03\mu F$ 、 $0.1\mu F$  などの値のコンデンサの配列を並列に使用します。最も効果的なバイパスコンデンサは、 $2\sim3$ mil の間隔で、電源とグランドの層を挟んで形成できます。FR4 誘電体を 2mil で使用した場合、PCB 1 平方インチあたり約 500pF になります。

多くの高速デバイスでは、パッケージの裏面で低インダクタンスの GND 接続が提供されています。このセンター パッドは、ビアのアレイを介してグランド プレーンに接続する必要があります。ビア アレイにより、グランドへの実効インダクタンスが減少し、小型面実装 (SMT) パッケージの放熱性能が向上します。パッド接続の周囲にビアを配置することで、適切な熱の拡散と、可能な限り低いダイ温度を確保できます。2 つの GND プレーンを使用して高性能デバイスを PCB の反対側に配置すると(図 9-4 を参照)、熱伝達のための複数の経路が形成されます。

多くの場合、PCB の熱に関する問題は、あるデバイスが別のデバイスに熱を加えることで発生し、その結果、局所的な温度が非常に高くなります。熱伝達のための複数の経路がこの可能性を最小限に抑えます。多くの場合、放熱にとって非常に重要な GND パッドは、図 11-8(b) に示すようにパッド間の間隔が不十分なため、最適なデカップリング レイアウトを実現できません。この現象が発生した場合、ボードの裏面にデカップリング コンデンサを配置することで、追加のインダクタンスを最小限に抑えることができます。

V<sub>DD</sub> ビアは、十分な半田マスク領域を確保しながら、デバイスのピンにできる限り近づけて配置することが重要です。ビアをオープンのままにすると、ハンダがパッドからビア バレルに流れる可能性があり、半田接続が不十分になります。

## 図 11-7. デカップリング コンデンサの標準レイアウト (a)

図 11-8. デカップリング コンデンサの標準レイアウト (b)

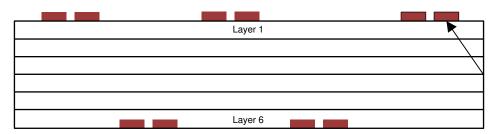

## 11.2 レイアウト例

クロストークの可能性を最小限に抑えるため、個々のパターンの幅の少なくとも 2 倍または 3 倍の間隔で、シングルエンドのパターンと差動ペアを分離する必要があります。立ち上がり時間または立ち下がり時間の波長より短い間隔で並列に配線されるシングルエンドのパターンでは、通常、クロストークは無視できるほど小さくなります。クロストークを低減するため、長い並列配線の場合は信号路間の間隔を増やします。図 11-9 に示すように、基板の面積が限られている場合、配線パターンレイアウトを交互に配置することにはメリットがあります。

図 11-9. 交互パターンのレイアウト

この構成では、異なる層に交互の信号パターンが配置されるため、パターン間の水平間隔は個々のパターンの幅の 2 倍または 3 倍未満にできます。グランド信号路の連続性を確保するため、図 11-10 に示すように、すべての信号ビアに隣接するグランドビアを配置することを推奨します。

#### 注

ビアを使用すると追加の容量が発生します。たとえば、代表的なビアには、FR4 で ½pF~1pF の容量増加効果があります。

図 11-10. グランド ビアの位置 (側面図)

デバイスのグランド ピンを PCB のグランド プレーンに短く低インピーダンスで接続すると、グランド バウンスが低減されます。グランド プレーンの穴や切り欠きがリターン電流のループ面積を増やすような不連続性を形成する場合、電流のリターン パスに悪影響を及ぼす可能性があります。

EMI の問題を最小限に抑えるため、パターンの下に不連続が生じることを避け (穴、スリットなど)、パターンをできるだけ短くすることを推奨します。機能を混在させるのではなく、類似の機能を同じ領域にすべて配置してボードを適切にゾーニングすることは、感受性の問題を低減するのに役立ちます。

# 12 デバイスおよびドキュメントのサポート 12.1 ドキュメントのサポート

#### 12.1.1 関連資料

関連資料については、以下を参照してください。

- 『M-LVDS (TIA/EIA-899) 入門』(SLLA108)

- 『LVDS アプリケーションおよびデータ ハンドブック』(SLLD009)

- 『LVDS オーナー マニュアル デザイン ガイド、第 4 版』(SNLA187)

- 『半導体および IC パッケージの熱評価基準』(SPRA953)

- Howard Johnson and Martin Graham. 1993. High Speed Digital Design A Handbook of Black Magic. Prentice Hall PRT.ISBN number 013395724.

- Mark I. Montrose. 1996. Printed Circuit Board Design Techniques for EMC Compliance. IEEE Press. ISBN number 0780311310.

- Clyde F. Coombs. 1995. Printed Circuits Handbook. McGraw Hill. ISBN number 0070127549.

## 12.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

#### 12.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 12.4 商標

Rogers<sup>™</sup> is a trademark of Rogers Corporation.

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 12.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 12.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

#### 13 改訂履歷

#### Changes from Revision D (December 2015) to Revision E (March 2024)

Page

| Changes from Revision C (September 2015) to Revision D (Decer                                                                                                                                        | mber 2015) Page                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| <ul><li>「特長」のリスト項目「±8kV IEC 61000-4-2 接触放電に適合」を削除</li></ul>                                                                                                                                          | 1                                                                          |

| Changes from Revision B (June 2015) to Revision C (August 201                                                                                                                                        | 5)                                                                         |

| <ul> <li>表 8-1 および表 8-2 から行「開路」を冗長として削除</li> </ul>                                                                                                                                                   | 18                                                                         |

| • 表 8-2 の「V <sub>ID</sub> ≥ 50mV」を「V <sub>ID</sub> ≥ 150mV」に変更                                                                                                                                       | 18                                                                         |

|                                                                                                                                                                                                      | 18                                                                         |

| <u> </u>                                                                                                                                                                                             |                                                                            |

| Changes from Revision A (December 2003) to Revision B (June 2                                                                                                                                        |                                                                            |

| Changes from Revision A (December 2003) to Revision B (June 2 「ピン構成および機能」セクション、「ESD 定格」表、「機能説明」セクショ                                                                                                  | 2 <b>015)</b> Page<br>ン、「デバイスの機能モード」セクション、「アプ                              |

| <ul> <li>Changes from Revision A (December 2003) to Revision B (June 2</li> <li>「ピン構成および機能」セクション、「ESD 定格」表、「機能説明」セクショリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レ</li> </ul>                                 | <b>Page</b> ン、「デバイスの機能モード」セクション、「アプ<br>イアウト」セクション、「デバイスおよびドキュメ             |

| Changes from Revision A (December 2003) to Revision B (June 2 「ピン構成および機能」セクション、「ESD 定格」表、「機能説明」セクショリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レントのサポート」セクション、「メカニカル、パッケージ、および注文情報」、                          | 2015) Page<br>ン、「デバイスの機能モード」セクション、「アプ<br>ィイアウト」セクション、「デバイスおよびドキュメ<br>セクション |

| Changes from Revision A (December 2003) to Revision B (June 2 「ピン構成および機能」セクション、「ESD 定格」表、「機能説明」セクショリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レントのサポート」セクション、「メカニカル、パッケージ、および注文情報」・ SN65MLVD204B をデータシートから削除 | <b>Page</b> ン、「デバイスの機能モード」セクション、「アプ ィイアウト」セクション、「デバイスおよびドキュメ セクション         |

| Changes from Revision A (December 2003) to Revision B (June 2 「ピン構成および機能」セクション、「ESD 定格」表、「機能説明」セクショリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レントのサポート」セクション、「メカニカル、パッケージ、および注文情報」、                          | <b>Page</b> ン、「デバイスの機能モード」セクション、「アプ ィイアウト」セクション、「デバイスおよびドキュメ セクション         |

| Changes from Revision A (December 2003) to Revision B (June 2 「ピン構成および機能」セクション、「ESD 定格」表、「機能説明」セクショリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レントのサポート」セクション、「メカニカル、パッケージ、および注文情報」・ SN65MLVD204B をデータシートから削除 | 2015) Page ン、「デバイスの機能モード」セクション、「アプ アイアウト」セクション、「デバイスおよびドキュメ セクション          |

# 14 メカニカル、パッケージ、および注文情報

Changes from Revision \* (December 2003) to Revision A (December 2003)

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側のナビゲーションリンクを参照してください。

• 図 **7-11** から重複する注記を削除.......11

**Page**

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated www.ti.com

17-Jun-2025

#### **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| SN65MLVD200AD         | Active     | Production    | SOIC (D)   8   | 75   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF200A           |

| SN65MLVD200AD.B       | Active     | Production    | SOIC (D)   8   | 75   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF200A           |

| SN65MLVD200ADG4       | Active     | Production    | SOIC (D)   8   | 75   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF200A           |

| SN65MLVD200ADR        | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF200A           |

| SN65MLVD200ADR.B      | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF200A           |

| SN65MLVD200ADRG4      | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF200A           |

| SN65MLVD202AD         | Active     | Production    | SOIC (D)   14  | 50   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD202A         |

| SN65MLVD202AD.B       | Active     | Production    | SOIC (D)   14  | 50   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD202A         |

| SN65MLVD202ADG4       | Active     | Production    | SOIC (D)   14  | 50   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD202A         |

| SN65MLVD202ADG4.B     | Active     | Production    | SOIC (D)   14  | 50   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD202A         |

| SN65MLVD202ADR        | Active     | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD202A         |

| SN65MLVD202ADR.B      | Active     | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD202A         |

| SN65MLVD204AD         | Active     | Production    | SOIC (D)   8   | 75   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF204A           |

| SN65MLVD204AD.B       | Active     | Production    | SOIC (D)   8   | 75   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF204A           |

| SN65MLVD204ADG4       | Active     | Production    | SOIC (D)   8   | 75   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF204A           |

| SN65MLVD204ADR        | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF204A           |

| SN65MLVD204ADR.B      | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF204A           |

| SN65MLVD204ADR1G4     | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF204A           |

| SN65MLVD204ADR1G4.B   | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MF204A           |

| SN65MLVD205AD         | Active     | Production    | SOIC (D)   14  | 50   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD205A         |

| SN65MLVD205AD.B       | Active     | Production    | SOIC (D)   14  | 50   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD205A         |

| SN65MLVD205ADG4       | Active     | Production    | SOIC (D)   14  | 50   TUBE             | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD205A         |

| SN65MLVD205ADR        | Active     | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD205A         |

| SN65MLVD205ADR.B      | Active     | Production    | SOIC (D)   14  | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | MLVD205A         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

## PACKAGE OPTION ADDENDUM

www.ti.com 17-Jun-2025

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

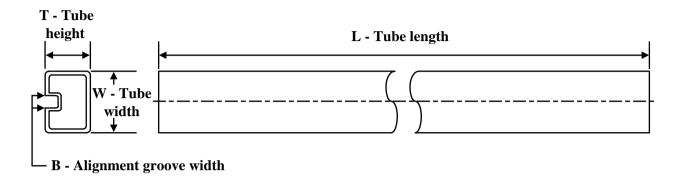

**PACKAGE MATERIALS INFORMATION**

www.ti.com 18-Jun-2025

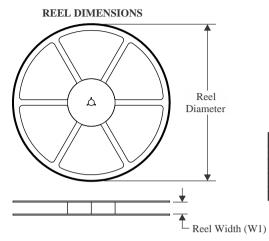

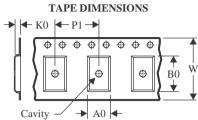

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

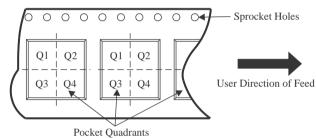

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65MLVD200ADR    | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| SN65MLVD202ADR    | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| SN65MLVD204ADR    | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| SN65MLVD204ADR1G4 | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| SN65MLVD205ADR    | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

www.ti.com 18-Jun-2025

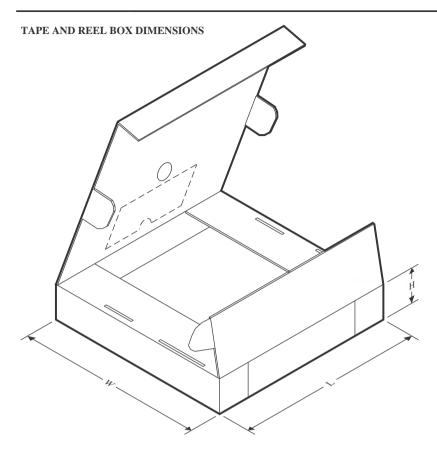

#### \*All dimensions are nominal

| 7 til dillionorio di o momina |              |                 |      |      |             |            |             |

|-------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| SN65MLVD200ADR                | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| SN65MLVD202ADR                | SOIC         | D               | 14   | 2500 | 353.0       | 353.0      | 32.0        |

| SN65MLVD204ADR                | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| SN65MLVD204ADR1G4             | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| SN65MLVD205ADR                | SOIC         | D               | 14   | 2500 | 353.0       | 353.0      | 32.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 18-Jun-2025

## **TUBE**

\*All dimensions are nominal

| Device            | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| SN65MLVD200AD     | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD200AD.B   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD200ADG4   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD202AD     | D            | SOIC         | 14   | 50  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD202AD.B   | D            | SOIC         | 14   | 50  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD202ADG4   | D            | SOIC         | 14   | 50  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD202ADG4.B | D            | SOIC         | 14   | 50  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD204AD     | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD204AD.B   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD204ADG4   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD205AD     | D            | SOIC         | 14   | 50  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD205AD.B   | D            | SOIC         | 14   | 50  | 507    | 8      | 3940   | 4.32   |

| SN65MLVD205ADG4   | D            | SOIC         | 14   | 50  | 507    | 8      | 3940   | 4.32   |

#### NOTES:

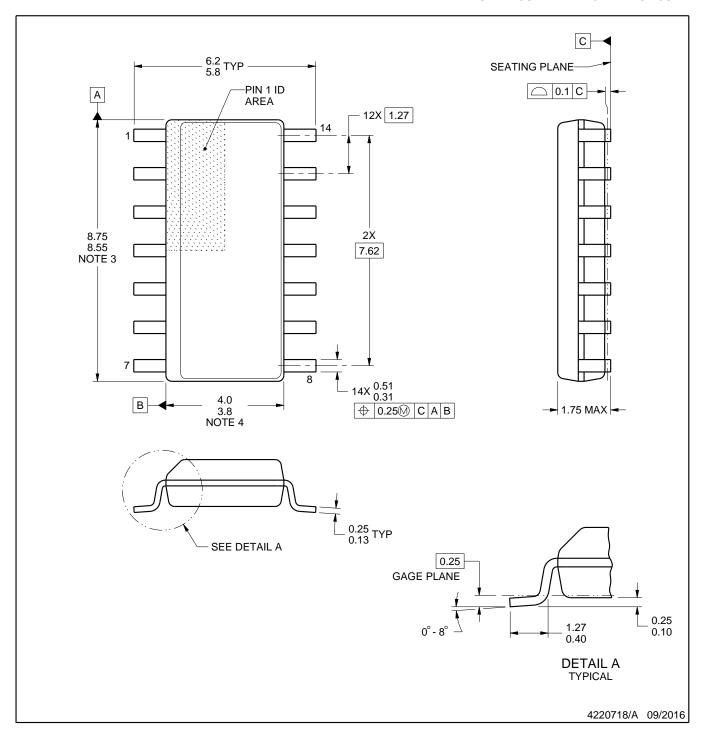

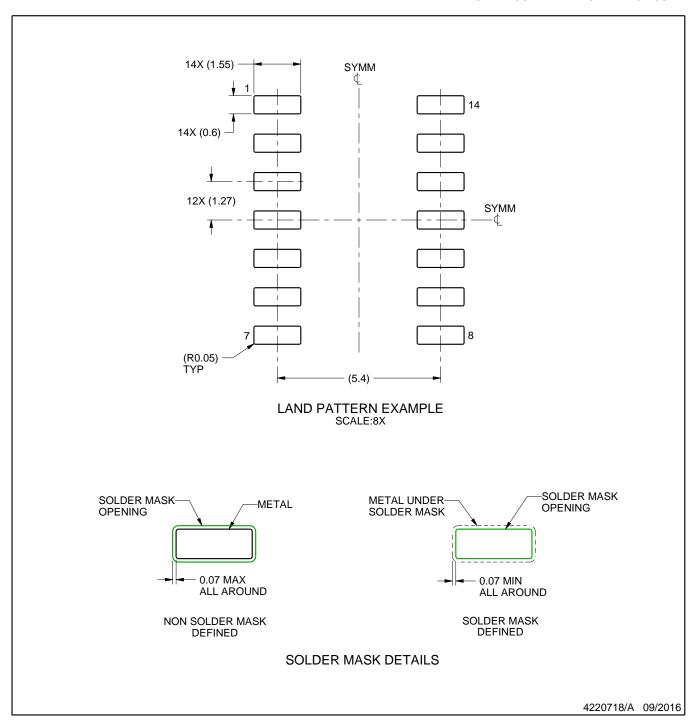

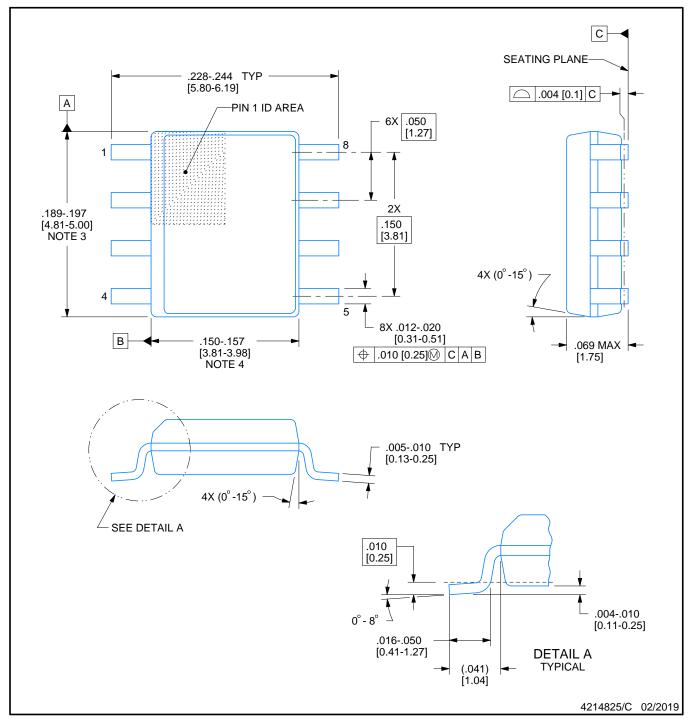

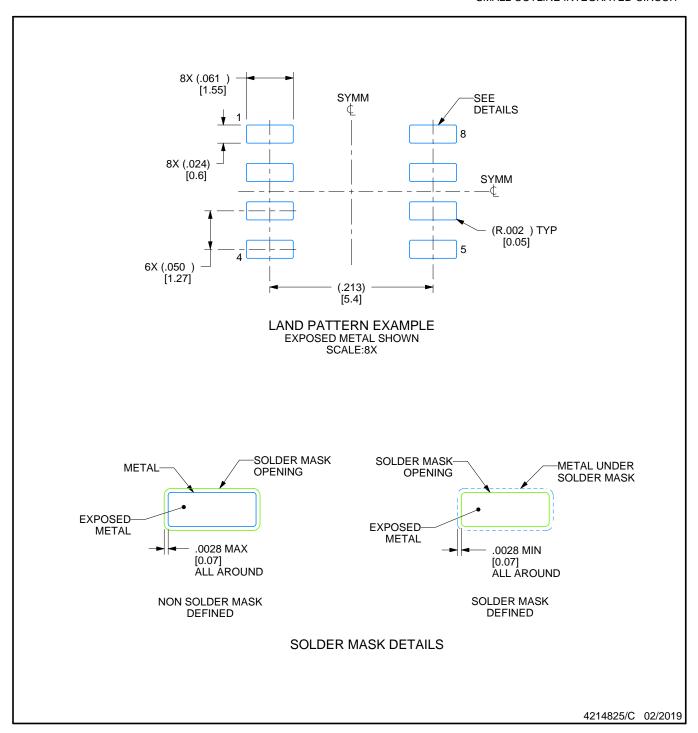

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

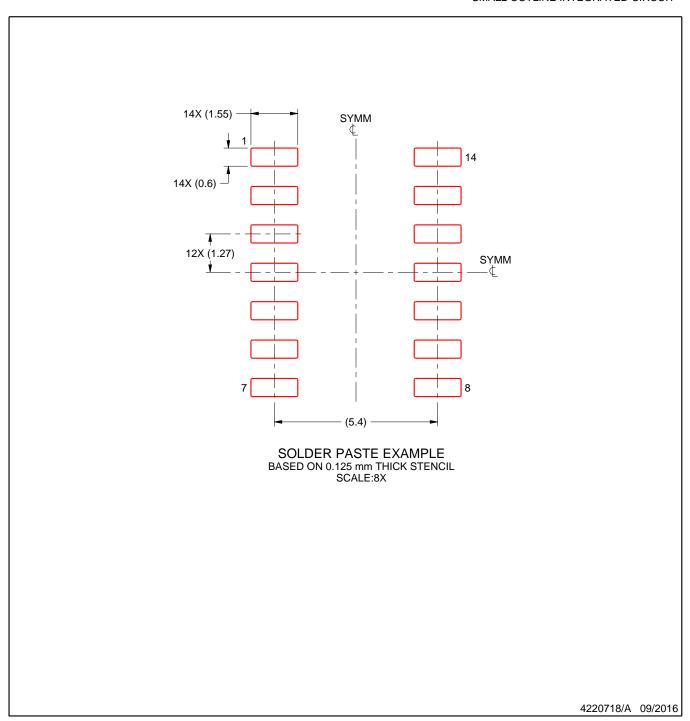

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated