SN65MLVD040 JAJST94A - FEBRUARY 2010 - REVISED MARCH 2024

# SN65MLVD040 4 チャネル、半二重 M-LVDS ライン トランシーバ

#### 1 特長

低電圧の差動 30Ω~55Ω ラインドライバおよびレシ ーバにより最高 **250Mbps** までの信号速度に対応<sup>(1)</sup>。

125MHz のクロック周波数

- マルチポイント データ交換について M-LVDS 標準 TIA/EIA-899 準拠またはこれを上回る

- ドライバ出力電圧の遷移時間制御による信号品質の

- -1V~3.4V の同相電圧範囲により、2V のグランド ノイ ズでデータ転送が可能

- ドライバ ディセーブル時または  $V_{CC} \le 1.5V$  時にバス ピンが高インピーダンス

- ドライバおよびレシーバごとに独立のイネーブル

- 強化 ESD 保護機能: すべてのピンで 7kV HBM

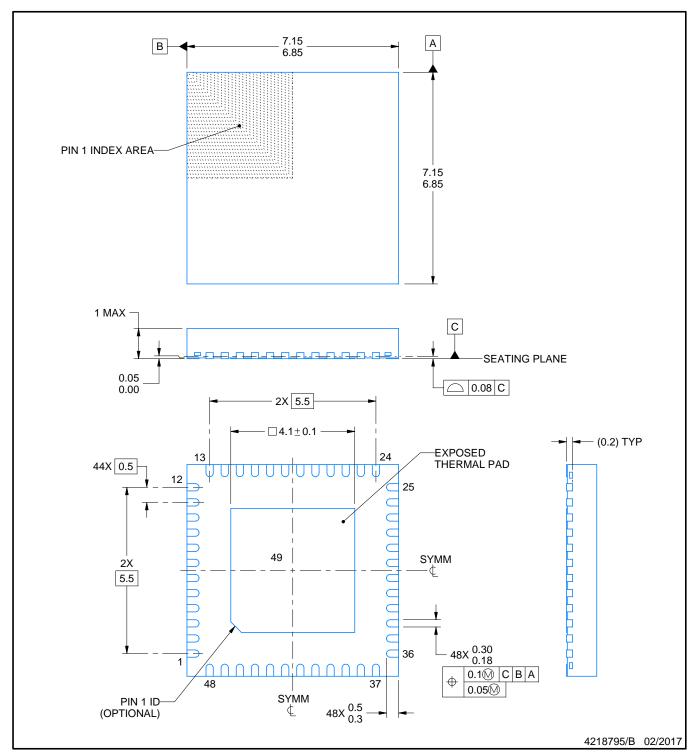

- 48ピン7X7QFN (RGZ)

- M-LVDS バスの電源オン/オフ時のグリッチ フリー

# 2 アプリケーション

- バックプレーンとケーブルを介した 並列マルチポイントデータおよびクロック伝送

- 低消費電力、高速、短距離での TIA/EIA-485 の代替

- 携帯電話の基地局

- 基地局用スイッチ

- ネットワーク スイッチおよびルータ

ラインの信号レートとは、1 秒あたりの電圧遷移回数を bps (ビット/ 秒)単位で表したものです。

### 3 概要

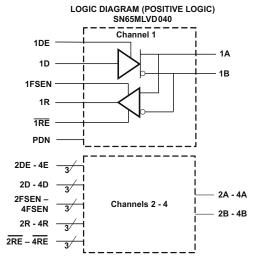

SN65MLVD040 は、TIA/EIA-899 (M-LVDS) 規格に完 全準拠してマルチポイント低電圧差動信号を送受信する ための 4 つの半二重トランシーバを備えており、最高 250Mbps の信号速度で動作するよう最適化されていま す。ドライバ出力は、最小 30 Ω の負荷を供給するマルチ ポイントバスをサポートするように設計されており、バック プレーンの伝送ラインからスタブをオフにできるように、制 御された遷移時間が組み込まれています。

M-LVDS 規格では、Type-1 および Type-2 という 2 種類 のレシーバが定義されています。Type-1 レシーバは、ゼ ロを中心とするスレッショルドで、25mV のヒステリシスを設 けて、入力が失われた場合の出力発振を防止します。 Type-2 レシーバは、オフセット スレッショルドを使用してフ ェイルセーフを実装しています。xFSEN ピンを使用して、 各チャネルの Type-1 および Type-2 レシーバを選択しま す。さらに、ドライバの立ち上がり時間と立ち下がり時間は 1ns~2ns であり、M-LVDS 規格に準拠して 250Mbps で の動作を実現すると同時に、バス上にスタブも備えていま す。レシーバ出力はスルーレート制御されているため、大 きな電流サージに伴う EMI およびクロストークの影響を低 減できます。 M-LVDS 規格ではバス上に 32 のノードを接 続でき、低い同相モードを許容できる場合や、より速い信 号速度が必要な場合に、RS-485 の高速な代替となりま

ドライバ ロジック入力とレシーバ ロジック出力は、一部のト ランシーバ デザインのように互いに接続されるのではな く、個別のピンに配置されています。ドライバには個別のイ ネーブル (DE) があり、レシーバ (RE) も同様です。このよ うにロジック入力、ロジック出力、イネーブル ピンを個別に 配置することで、listen-while-talking 動作が可能になりま す。これらのデバイスは、-40℃~85℃での動作が規定さ れています。

パッケージ情報

| <u> </u>        | ~ ~ IIV IN           |                 |

|-----------------|----------------------|-----------------|

| 部品番号            | パッケージ <sup>(1)</sup> | パッケージ サイズ       |

| SN65MLVD040RGZR | VQFN (RGZ)           | 7 x 7、0.5mm ピッチ |

| SN65MLVD040RGZT | VQFN (RGZ)           | 7 x 7、0.5mm ピッチ |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

# 目次

| 1 特長                | 1 | 5.11 代表的特性             | 10              |

|---------------------|---|------------------------|-----------------|

| 2 アプリケーション          |   | 6 パラメータ測定情報            |                 |

| 3 概要                | 1 | 6.1 等価な入力および出力回路図      | <u>2</u> 2      |

| 4 ピン構成および機能         | 2 | 7 アプリケーションと実装          |                 |

| 5 仕様                | 4 | 7.1 アプリケーション情報         | 23              |

| 5.1 絶対最大定格          | 4 | 8 デバイスおよびドキュメントのサポート   | 26              |

| 5.2 推奨動作条件          | 4 | 8.1ドキュメントのサポート         | 26              |

| 5.3 熱特性             | 4 | 8.2ドキュメントの更新通知を受け取る方法  | 26              |

| 5.4 パッケージ定格消費電力     | 4 | 8.3 サポート・リソース          | 26              |

| 5.5 デバイスの電気的特性      | 5 | 8.4 商標                 | 26              |

| 5.6 ドライバの電気的特性      | 5 | 8.5 静電気放電に関する注意事項      | 26              |

| 5.7 レシーバの電気的特性      | 6 | 8.6 用語集                | 26              |

| 5.8 バス入力および出力の電気的特性 | 6 | 9 改訂履歴                 | <mark>26</mark> |

| 5.9 ドライバ スイッチング特性   | 8 | 10 メカニカル、パッケージ、および注文情報 | 26              |

| 5.10 レシーバのスイッチング特性  | 9 |                        |                 |

|                     |   |                        |                 |

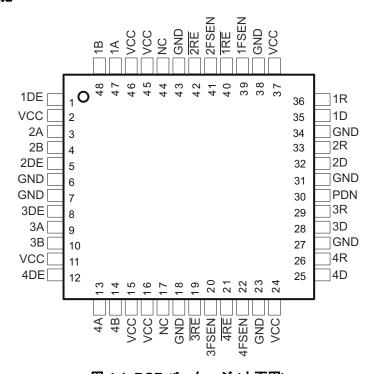

# 4 ピン構成および機能

図 4-1. RGZ パッケージ (上面図)

# 表 4-1. ピンの機能

|       | ピン          | I/O    | 説明                |

|-------|-------------|--------|-------------------|

| 名称    | 番号          | 1/0    | होटा <del>।</del> |

| 1D-4D | 35、32、28、25 | I      | ドライバ用データ入力        |

| 1R–4R | 36、33、29、26 | 0      | レシーバ用データ出力        |

| 1A-4A | 47、3、9、13   | バス I/O | M-LVDS バスの非反転入出力  |

| 1B-4B | 48、4、10、14  | バス 1/0 | M-LVDS バスの反転入出力   |

Product Folder Links: SN65MLVD040

### 表 4-1. ピンの機能 (続き)

|                 | ピン                           | I/O | 3X aq                                                                                                                                                                                    |

|-----------------|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称              | 番号                           | 1/0 | 説明                                                                                                                                                                                       |

| GND             | 6、7、18、23、27、31、34、<br>38、43 |     | 回路グランド。 すべての GND ピンは、グランドに接続する必要があります。                                                                                                                                                   |

| V <sub>CC</sub> | 2、11、15、16、24、37、45、<br>46   |     | 電源電圧。すべての VCC ピンは、電源に接続する必要があります。                                                                                                                                                        |

| TRE- 4RE        | 40、42、19、21                  | I   | レシーバ イネーブル、アクティブ Low、個別のレシーバをイネーブル。このピンをフローティングのままにすると、内部でこのピンは論理 High にプルアップされます。                                                                                                       |

| 1DE-4DE         | 1、5、8、12                     | I   | ドライバ イネーブル、アクティブ High、個別にドライバをイネーブル。このピンをフローティングのままにすると、内部でこのピンは論理 Low にプルダウンされます。                                                                                                       |

| 1FSEN-4FSEN     | 39、41、20、22                  | I   | フェイルセーフ イネーブル ピン。このピンをフローティングのままにすると、内部でこの ピンは論理 High にプルアップされます。 このピンにより、それぞれのチャネルの Type 2 レシーバがイネーブルになります。 $xFSEN = L \rightarrow Type 1$ レシーバ入力 $xFSEN = H \rightarrow Type 2$ レシーバ入力 |

| PDN             | 30                           | I   | パワー ダウン ピン。このピンをフローティングのままにすると、内部でこのピンは論理<br>Low にプルダウンされます。<br>PDN が High のとき、デバイスは電源オンになります。<br>PDN が Low のとき、デバイスは他のすべての制御を無効にし、電源オフになります。<br>すべての出力は Hi-Z です。                        |

| NC              | 17                           |     | 接続なし                                                                                                                                                                                     |

| NC              | 44                           |     | 接続なし。TI内部テストピン。このピンは未接続にしておかなくてはなりません。                                                                                                                                                   |

| PowerPAD™       | -                            |     | GND に接続                                                                                                                                                                                  |

# 表 4-2. デバイス機能表

| レシーバ                             |     |      |      |              |       |   | ドライバ  |      |       |   |

|----------------------------------|-----|------|------|--------------|-------|---|-------|------|-------|---|

| 入力(1)                            |     |      |      | レシーバのタ<br>イプ | 出力(1) |   | 入力(1) |      | 出力(1) |   |

| $V_{ID} = V_A - V_B$             | PDN | FSEN | RE   |              | R     |   | D     | DE   | Α     | В |

| V <sub>ID</sub> > 35mV           | Н   | L    | L    | タイプ 1        | Н     |   | L     | Н    | L     | Н |

| –35mV ≤ V <sub>ID</sub> ≤ 35mV   | Н   | L    | L    | タイプ 1        | ?     | 1 | Н     | Н    | Н     | L |

| V <sub>ID</sub> < 35 mV          | Н   | L    | L    | タイプ 1        | L     |   | オープン  | Н    | L     | Н |

|                                  | •   | 1    | '    | '            | 1     | 1 | Х     | オープン | Z     | Z |

| V <sub>ID</sub> > 135 mV         | Н   | Н    | L    | タイプ 2        | Н     | ] | Х     | L    | Z     | Z |

| 65 mV ≤ V <sub>ID</sub> ≤ 135 mV | Н   | Н    | L    | タイプ 2        | ?     | 1 |       |      |       |   |

| V <sub>ID</sub> < 65 mV          | Н   | Н    | L    | タイプ 2        | L     |   |       |      |       |   |

| 開路                               | Н   | L    | L    | タイプ 1        | ?     |   |       |      |       |   |

| 開路                               | Н   | Н    | L    | タイプ 2        | L     |   |       |      |       |   |

| X                                | Н   | Х    | Н    | Х            | Z     | - |       |      |       |   |

| X                                | Н   | Х    | オープン | Х            | Z     | 1 |       |      |       |   |

| X                                | L   | Х    | Х    | Х            | Z     | 1 |       |      |       |   |

(1)  $H = High \, \nu$ ベル、 $L = Low \, \nu$ ベル、Z = 高インピーダンス、<math>X =ドント ケア、? =不定

# 5 仕様

### 5.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)(1)

|                                        |                      |                                                                                                             | SN65MLVD040       |  |

|----------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------|-------------------|--|

| 電源電圧範囲 <sup>(2)</sup> 、V <sub>CC</sub> |                      |                                                                                                             | -0.5 V $\sim$ 4 V |  |

| 入力電圧範囲                                 | D, DE, RE, FSEN      |                                                                                                             | -0.5 V $\sim$ 4 V |  |

| 八月电圧                                   | A, B                 | , B                                                                                                         |                   |  |

| 山土帝正然岡                                 | R                    | R                                                                                                           |                   |  |

| 出力電圧範囲                                 | A または B              | -0.5 V ~ -0.5 V ~ -0.5 V ~ -1.8 V ~ | -1.8 V ∼ 4 V      |  |

| <b>数最与社</b> 委                          | 人体モデル <sup>(3)</sup> | すべてのピン                                                                                                      | ±7 kV             |  |

| 静電気放電                                  | デバイス帯電モデル (4)        | すべてのピン                                                                                                      | ±1500 V           |  |

| 保管温度範囲                                 |                      |                                                                                                             | -65°C∼150°C       |  |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値と等しい、またはそれを超える条件で本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 差動 I/O バス電圧を除くすべての電圧値は、ネットワーク グランド端子を基準にしています。

- (3) JEDEC 規格 22、テスト方法 A114-E に従ってテスト済み。 GND と VCC の共通接続に対してバス ピンにストレスを印加

- (4) JEDEC 規格 22、テスト方法 C101-D に従ってテスト済み。

### 5.2 推奨動作条件

|                 |                                               | 最小値  | 公称值 | 最大値             | 単位 |

|-----------------|-----------------------------------------------|------|-----|-----------------|----|

| V <sub>CC</sub> | 電源電圧                                          | 3    | 3.3 | 3.6             | V  |

| V <sub>IH</sub> | High レベル入力電圧                                  | 2    |     | V <sub>CC</sub> | V  |

| V <sub>IL</sub> | Low レベル入力電圧                                   | GND  |     | 0.8             | V  |

|                 | 任意のバス端子での電圧 V <sub>A</sub> または V <sub>B</sub> | -1.4 |     | 3.8             | V  |

| V <sub>ID</sub> | 差動入力電圧の大きさ                                    | 0.05 |     | V <sub>CC</sub> | V  |

| T <sub>A</sub>  | 自由空気での動作温度                                    | -40  |     | 85              | °C |

|                 | 最大接合部温度                                       |      |     | 140             | °C |

#### 5.3 熱特性

|                 | パラメータ                              | テスト条件                                                                                | 最小値 | 代表値  | 最大値 | 単位   |

|-----------------|------------------------------------|--------------------------------------------------------------------------------------|-----|------|-----|------|

| $R_{\theta JB}$ | 接合部から基板への熱抵抗                       |                                                                                      |     | 9    |     | °C/W |

| $R_{\theta JC}$ | 接合部からケースへの熱抵抗                      |                                                                                      |     | 20   |     | °C/W |

| $R_{\theta JP}$ | 接合部からパッドへの熱抵抗                      |                                                                                      |     | 1.37 |     | °C/W |

| P <sub>D</sub>  | デバイスの電力散逸 (詳細については<br>「代表的な曲線」を参照) | 0V で RE、0V で DE、C <sub>L</sub> = 15pF、V <sub>ID</sub> = 400mW、<br>125MHz、その他はすべてオープン |     |      | 382 | mW   |

#### 5.4 パッケージ定格消費電力

| パッケージ | PCB JEDEC<br>規格       | T <sub>A</sub> ≦25℃ の<br>電力定格 | T <sub>A</sub> = 25℃ を<br>超える場合のディレーティング<br>係数 <sup>(1)</sup> | T <sub>A</sub> ≦85℃ の<br>電力定格 |

|-------|-----------------------|-------------------------------|---------------------------------------------------------------|-------------------------------|

| RGZ   | Low-K (2)             | 1298 mW                       | 12.98 mW/°C                                                   | 519 mW                        |

| RGZ   | High-K <sup>(3)</sup> | 3448 mW                       | 34.48 mW/°C                                                   | 1379 mW                       |

- (1) これは、ボードに取り付けられ、エアフローがないときの、接合部から周囲への熱抵抗の逆数です。

- (2) EIA/JESD51-3 の Low-K 熱評価基準の定義に従います。

- (3) EIA/JESD51-7 の High-K 熱評価基準の定義に従います。

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: SN65MLVD040

# 5.5 デバイスの電気的特性

推奨動作条件範囲内 (特に記述のない限り)

|     | パ                          | ラメータ     | テスト条件                                                                                                                | 最小値 | 標 <b>準値</b> | 最大値 | 単位 |

|-----|----------------------------|----------|----------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|----|

|     |                            | ドライバのみ   | $V_{CC}$ で $\overline{RE}$ および $DE$ 、 $R_L$ = $50\Omega$ 、 $125MHz$ 、<br>その他はすべてオープン                                 |     |             | 76  |    |

|     |                            | 両方ディセーブル | V <sub>CC</sub> で RE、0V で DE、R <sub>L</sub> =無負荷、<br>125MHz、その他はすべてオープン                                              |     |             | 10  |    |

| Icc | 電源電流                       | 両方がイネーブル | $0V$ で $\overline{RE}$ 、 $V_{CC}$ で $DE$ 、 $R_L = 50\Omega$ 、 $C_L = 15pF$ 、その他はすべてオープン、 $125MHz$ 、外部 $RX$ スティミュラスなし |     |             | 165 | mA |

|     |                            | レシーバのみ   | $0V$ で $\overline{RE}$ 、 $0V$ で $DE$ 、 $C_L$ = $15pF$ 、 $V_{ID}$ = $400mV$ 、 $125MHz$ 、その他はすべてオープン                   |     |             | 100 |    |

|     | パワー ダウン<br>(Power<br>down) | PDN = L  |                                                                                                                      |     |             | 5   | mA |

(1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

## 5.6 ドライバの電気的特性

推奨動作条件範囲内 (特に記述のない限り)

|                     | パラメータ                                      | テスト条件                                     | 最小值(1)               | 標準値 | 最大値                 | 単位 |

|---------------------|--------------------------------------------|-------------------------------------------|----------------------|-----|---------------------|----|

| V <sub>AB</sub>     | 差動出力電圧の大きさ (A、B)                           |                                           | 480                  |     | 650                 | mV |

| Δ V <sub>AB</sub>   | ロジック状態間<br>の差動出力電圧の大きさの変化 (A、B)            | 図 6-2 を参照                                 | -50                  |     | 50                  | mV |

| V <sub>OS(SS)</sub> | 定常同相モード出力電圧 (A、B)                          |                                           | 0.7                  |     | 1.1                 | V  |

| $\Delta V_{OS(SS)}$ | ロジック状態間での定常同相モード出力電圧<br>の変化 (A、B)          | 図 6-3 を参照                                 | -50                  |     | 50                  | mV |

| V <sub>OS(PP)</sub> | ピークツー ピークの同相モード出力電圧 (A、B)                  |                                           |                      |     | 150                 | mV |

| V <sub>A(OC)</sub>  | 最大定常断線出力電圧 (A、B)                           | - 図 6-7 を参照                               | 0                    |     | 2.4                 | V  |

| V <sub>B(OC)</sub>  | 最大定常断線出力電圧 (A、B)                           | 図 0-7 を参照                                 | 0                    |     | 2.4                 | V  |

| V <sub>P(H)</sub>   | 電圧オーバーシュート、Low レベルから High<br>レベルへの出力 (A、B) | ₩ C E ナ.☆ ₩                               |                      |     | 1.2 V <sub>SS</sub> | V  |

| V <sub>P(L)</sub>   | 電圧オーバーシュート、High レベルから Low<br>レベルへの出力 (A、B) | - 図 6-5 を参照                               | -0.2 V <sub>SS</sub> |     |                     | V  |

| I <sub>IH</sub>     | High レベル入力電流 (D、DE)                        | V <sub>IH</sub> = 2V~V <sub>CC</sub>      |                      |     | 10                  | μA |

| I <sub>IL</sub>     | Low レベル入力電流 (D、DE)                         | V <sub>IL</sub> = GND~0.8V                |                      |     | 10                  | μA |

| I <sub>OS</sub>     | 差動短絡出力電流の大きさ (A、B)                         | 図 6-4 を参照                                 |                      |     | 24                  | mA |

| Cı                  | 入力容量 (D、DE)                                | $V_I = 0.4 \sin(30E6\pi t) + 0.5 V^{(3)}$ |                      | 5   |                     | pF |

- (1) このデータシートでは、最も小さい正 (最も大きな負)の制限を最小として指定する代数的規約を使用します。

- (2) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (3) HP4194A インピーダンス アナライザ (または同等のもの)

### 5.7 レシーバの電気的特性

推奨動作条件範囲内 (特に記述のない限り)

|                  | パラメータ                                                         |       | テスト条件                                   | 最小值 | 標準値 <sup>(1)</sup> | 最大值 | 単位   |

|------------------|---------------------------------------------------------------|-------|-----------------------------------------|-----|--------------------|-----|------|

| V <sub>IT+</sub> | 正方向の差動入力電圧スレッショルド                                             | タイプ 1 |                                         |     |                    | 35  | mV   |

| VIT+             | (A、B)                                                         | タイプ 2 |                                         |     |                    | 135 | IIIV |

| V                | 負方向の差動入力電圧スレッショルド                                             | タイプ 1 | 表 6-1 および 表 6-2 を                       | -35 |                    |     | mV   |

| V <sub>IT</sub>  | (A、B)                                                         | タイプ 2 | 参照                                      | 65  |                    |     | 1110 |

| V <sub>HYS</sub> | 差動入力電圧ヒステリシス (V <sub>IT+</sub> – V <sub>IT-</sub> )<br>(A, B) | タイプ 1 |                                         |     | 25                 |     | mV   |

| VHYS             |                                                               | タイプ 2 |                                         |     | 0                  |     | IIIV |

| V <sub>OH</sub>  | High レベル出力電圧 (R)                                              |       | I <sub>OH</sub> = -8 mA                 | 2.4 |                    |     | V    |

| V <sub>OL</sub>  | Low レベル出力電圧 (R)                                               |       | I <sub>OL</sub> = 8 mA                  |     |                    | 0.4 | V    |

| I <sub>IH</sub>  | High レベル入力電流 (RE)                                             |       | $V_{IH} = 2V \sim V_{CC}$               | -10 |                    |     | μΑ   |

| I <sub>IL</sub>  | Low レベル入力電流 (RE)                                              |       | $V_{IL} = GND \sim 0.8V$                | -10 |                    |     | μΑ   |

| I <sub>OZ</sub>  | 高インピーダンス出力電流 <b>(R)</b>                                       |       | V <sub>O</sub> = 0V または V <sub>CC</sub> | -10 |                    | 15  | μΑ   |

<sup>(1)</sup> 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

# 5.8 バス入力および出力の電気的特性

推奨動作条件範囲内 (特に記述のない限り)

|                      | パラメータ                                                                              |                                        | テスト条件                          |                               | 最小値 巷 | 票準値 (1) 最大値 | 単位 |

|----------------------|------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|-------------------------------|-------|-------------|----|

|                      |                                                                                    | V <sub>A</sub> = 3.8V,                 | V <sub>B</sub> = 1.2V          |                               |       | 32          |    |

| I <sub>A</sub>       | セーブルしたレシーバまた<br>はトランシーバ                                                            | V <sub>A</sub> = -1.4 V,               | V <sub>B</sub> = 1.2V          |                               | -32   |             | μΑ |

|                      | ドライバが入力電流をディ                                                                       | V <sub>B</sub> = 3.8 V,                | V <sub>A</sub> = 1.2V          |                               |       | 32          |    |

| I <sub>B</sub>       | セーブルしたレシーバまた<br>はトランシーバ                                                            | V <sub>B</sub> = -1.4 V,               | V <sub>A</sub> = 1.2V          |                               | -32   |             | μΑ |

| I <sub>AB</sub>      | ドライバが差動入力電流<br>をディセーブルしたレシー<br>バまたはトランシーバ<br>(I <sub>A</sub> - I <sub>B</sub> )    | V <sub>A</sub> = V <sub>B</sub> ,      | 1.4 ≤ V <sub>A</sub> ≤ 3.8     | V                             | -4    | 4           | μΑ |

|                      | レシーバまたはトランシー                                                                       | V <sub>A</sub> = 3.8V,                 | V <sub>B</sub> = 1.2V,         | 0V ≤ V <sub>CC</sub> ≤ 1.5V   |       | 32          |    |

| I <sub>A(OFF)</sub>  | バの電源オフ入力電流                                                                         | V <sub>A</sub> = -1.4 V,               | V <sub>B</sub> = 1.2V,         | 0V ≤ V <sub>CC</sub> ≤ 1.5V   | -32   |             | μΑ |

| 1                    | レシーバまたはトランシー                                                                       | V <sub>B</sub> = 3.8 V,                | V <sub>A</sub> = 1.2 V,        | 0 V ≤ V <sub>CC</sub> ≤ 1.5 V |       | 32          | μA |

| I <sub>B(OFF)</sub>  | バの電源オフ入力電流                                                                         | V <sub>B</sub> = -1.4 V,               | V <sub>A</sub> = 1.2 V,        | 0 V ≤ V <sub>CC</sub> ≤ 1.5 V | -32   |             | μΛ |

| I <sub>AB(OFF)</sub> | レシーバ入力またはトラン<br>シーバの電源オフ差動入<br>力電流<br>(I <sub>A(off)</sub> – I <sub>B(off)</sub> ) | $V_A = V_B$ , $0 \text{ V} \le V_{CO}$ | <sub>C</sub> ≤ 1.5 V、–1.4 ≤ V, | λ ≤ 3.8 V                     | -4    | 4           | μΑ |

| C <sub>A</sub>       | ドライバの入力容量<br>がディセーブルされたトラ<br>ンシーバ                                                  | V <sub>A</sub> = 0.4 sin (30E6         | 6πt) + 0.5V <sup>(2)</sup> ,   | V <sub>B</sub> = 1.2V         |       | 5           | pF |

| СВ                   | ドライバの入力容量<br>がディセーブルされたトラ<br>ンシーバ                                                  | V <sub>B</sub> = 0.4 sin (30E6         | 6πt) + 0.5V <sup>(2)</sup> ,   | V <sub>A</sub> = 1.2V         |       | 5           | pF |

| C <sub>AB</sub>      | ドライバの差動入力容量<br>がディセーブルされたトラ<br>ンシーバ                                                | V <sub>AB</sub> = 0.4 sin (30E         | -6πt)V <sup>(2)</sup>          |                               |       | 3           | pF |

| C <sub>A/B</sub>     | ドライバの入力容量<br>バランスがディセーブルさ<br>れたトランシーバ、<br>(C <sub>A</sub> /C <sub>B</sub> )        |                                        |                                |                               | 0.99  | 1.01        |    |

(1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

Copyright © 2024 Texas Instruments Incorporated

(2) HP4194A インピーダンス アナライザ (または同等のもの)

Product Folder Links: SN65MLVD040

# 5.9 ドライバ スイッチング特性

推奨動作条件範囲内 (特に記述のない限り)

|                       | パラメータ                                             | テスト条件                                                           | 最小値 | 標準値 <sup>(1)</sup> | 最大値 | 単位 |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------------|-----|--------------------|-----|----|

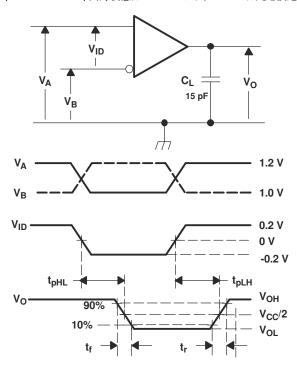

| t <sub>pLH</sub>      | 伝搬遅延時間、出力立ち上がり                                    |                                                                 | 1.3 | 1.9                | 2.4 | ns |

| t <sub>pHL</sub>      | 伝搬遅延時間、出力立ち下がり                                    |                                                                 | 1.3 | 1.9                | 2.4 | ns |

| t <sub>r</sub>        | 差動出力信号の立ち上がり時間                                    |                                                                 | 0.9 |                    | 2   | ns |

| t <sub>f</sub>        | 差動出力信号の立ち下がり時間                                    | 図 6-5 を参照                                                       | 0.9 |                    | 2.2 | ns |

| t <sub>sk(o)</sub>    | 出力スキュー                                            |                                                                 |     |                    | 200 | ps |

| t <sub>sk(p)</sub>    | パルス スキュー ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) |                                                                 |     |                    | 150 | ps |

| t <sub>sk(pp)</sub>   | 部品間スキュー(2)                                        |                                                                 |     |                    | 300 | ps |

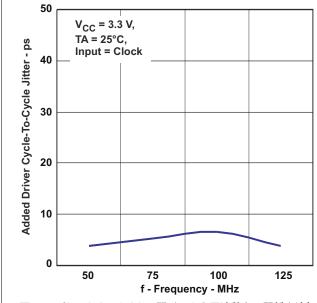

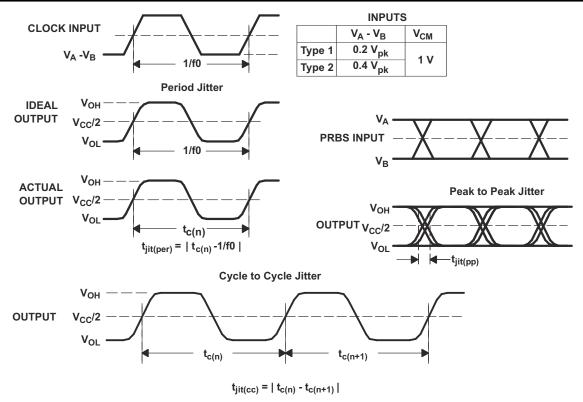

| t <sub>jit(per)</sub> | 周期ジッタ、rms (1 標準偏差) <sup>(3)</sup>                 | すべてのチャネルのスイッチング、                                                |     |                    | 2   | ps |

| t <sub>jit(c-c)</sub> | サイクル間ジッタ、rms <sup>(3)</sup>                       | 125MHz クロック入力 <sup>(4)</sup> 、図 6-8 を参<br>照                     |     |                    | 9   | ps |

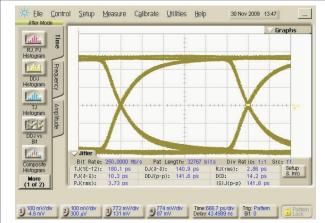

| t <sub>jit(det)</sub> | 確定的ジッタ(3)                                         | すべてのチャネルがスイッチング、                                                |     |                    | 290 | ps |

| t <sub>jit(r)</sub>   | ランダム ジッタ <sup>(3)</sup>                           | 250Mbps 2 <sup>15</sup> –1 PRBS 入力 <sup>(4)</sup> 、図<br>6-8 を参照 |     |                    | 4   | ps |

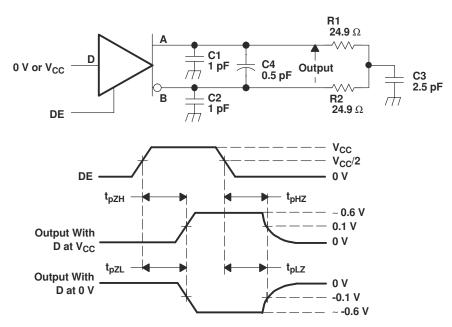

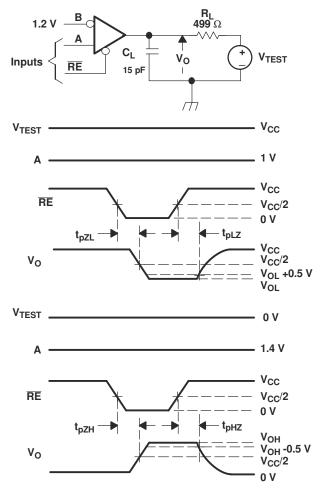

| t <sub>PZH</sub>      | イネーブル時間、高インピーダンスから High レベルへの出力                   |                                                                 |     |                    | 7   | ns |

| t <sub>PZL</sub>      | イネーブル時間、高インピーダンスから <b>Low</b> レベルへの出力             | - 図 6-6 を参照                                                     |     |                    | 7   | ns |

| t <sub>PHZ</sub>      | ディセーブル時間、High レベルから<br>高インピーダンスへの出力               |                                                                 |     |                    | 7   | ns |

| t <sub>PLZ</sub>      | ディセーブル時間、Low レベルから高<br>インピーダンスへの出力                |                                                                 |     |                    | 7   | ns |

- (1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (2) t<sub>sk(pp)</sub> は、2 つのデバイスが同じ電源電圧、同じ温度で動作し、パッケージとテスト回路が同一である場合の、両方のデバイスの指定された任意の端子間の伝搬遅延時間の差です。

- (3) ジッタは、設計と特性によって保証されています。スティミュラスのジッタがこの数値から減算されました。

- (4)  $t_r = t_f = 0.5$ ns (10% to 90%)

Copyright © 2024 Texas Instruments Incorporated

English Data Sheet: SLLS902

# 5.10 レシーバのスイッチング特性

推奨動作条件範囲内 (特に記述のない限り)

|                       | パラメータ                                             |                                     | テスト条件                                                                                   | 最小值 | 標準値 (1) | 最大値  | 単位 |

|-----------------------|---------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------|-----|---------|------|----|

| t <sub>pLH</sub>      | 伝搬遅延時間、出力立ち上がり                                    |                                     |                                                                                         | 2.5 | 4.5     | 6    | ns |

| t <sub>pHL</sub>      | 伝搬遅延時間、出力立ち下がり                                    |                                     | 2.5                                                                                     | 4.5 | 6       | ns   |    |

| t <sub>r</sub>        | 出力信号の立ち上がり時間                                      |                                     |                                                                                         | 1.4 |         | 2.35 | ns |

| t <sub>f</sub>        | 出力信号の立ち下がり時間                                      |                                     | 0 - 45*5 図 0 40 た                                                                       | 1.4 |         | 2.35 | ns |

| t <sub>sk(o)</sub>    | 出力スキュー                                            |                                     | - C <sub>L</sub> = 15pF、図 6-10 を参照                                                      |     |         | 350  | ps |

|                       | 31777 (IL L I)                                    | タイプ 1                               |                                                                                         |     | 35      | 210  |    |

| t <sub>sk(p)</sub>    | パルス スキュー ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) | タイプ 2                               |                                                                                         |     | 150     | 470  | ps |

| t <sub>sk(pp)</sub>   | 部品間スキュー(2)                                        |                                     |                                                                                         |     |         | 800  | ps |

| t <sub>jit(per)</sub> | 周期ジッタ、rms (1 標準偏差) <sup>(3)</sup>                 | 周期ジッタ、rms (1 標準偏差) <sup>(3)</sup>   |                                                                                         |     |         | 6    | ps |

| t <sub>jit(c-c)</sub> | サイクル間ジッタ、rms <sup>(3)</sup>                       |                                     | 「グ、125MHz クロック入力 <sup>(4)</sup> 、図<br>  <mark>6-12</mark> を参照                           |     |         | 13   | ps |

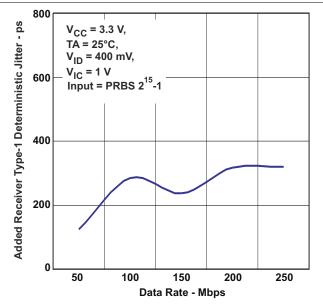

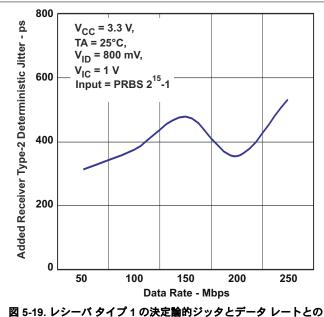

|                       | 76 + 16 × 6(2)                                    | タイプ 1                               |                                                                                         |     |         | 800  | ps |

| t <sub>jit(det)</sub> | 確定的ジッタ <sup>(3)</sup>                             | タイプ 2                               | すべてのチャネルがスイッチン<br>- グ、250Mbps 2 <sup>15</sup> -1 PRBS 入<br>カ <sup>(4)</sup> 、図 6-12 を参照 |     |         | 945  | ps |

|                       | - 18 1 18 1 (2)                                   | タイプ 1                               |                                                                                         |     |         | 9    | ps |

| t <sub>jit(r)</sub>   | ランダム ジッタ <sup>(3)</sup>                           | タイプ 2                               |                                                                                         |     |         | 8    | ps |

| t <sub>PZH</sub>      | イネーブル時間、高インピーダン<br>の出力                            | イネーブル時間、高インピーダンスから High レベルへ<br>の出力 |                                                                                         |     |         | 15   | ns |

| t <sub>PZL</sub>      | イネーブル時間、高インピーダン<br>の出力                            | C _ 15pF   図 C 11 大会 図              |                                                                                         |     | 15      | ns   |    |

| t <sub>PHZ</sub>      | ディセーブル時間、High レベル<br>への出力                         | - C <sub>L</sub> = 15pF、図 6-11 を参照  |                                                                                         |     | 10      | ns   |    |

| t <sub>PLZ</sub>      | ディセーブル時間、Low レベル<br>への出力                          | から高インピーダンス                          |                                                                                         |     |         | 10   | ns |

- (1) 標準値はすべて 25℃で、3.3V の電源電圧を使用します。

- (2) t<sub>sk(pp)</sub> は、2 つのデバイスが同じ電源電圧、同じ温度で動作し、パッケージとテスト回路が同一である場合の、両方のデバイスの指定された任意の端子間の伝搬遅延時間の時間差です。

- (3) ジッタは、設計と特性によって保証されています。スティミュラスのジッタがこの数値から減算されました。

- (4)  $t_r = t_f = 0.5 \text{ns} (10\% \sim 90\%)$

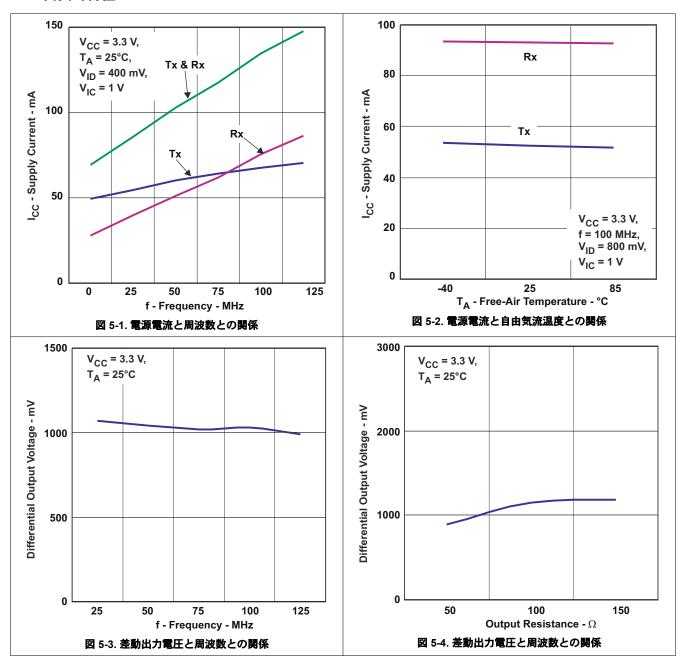

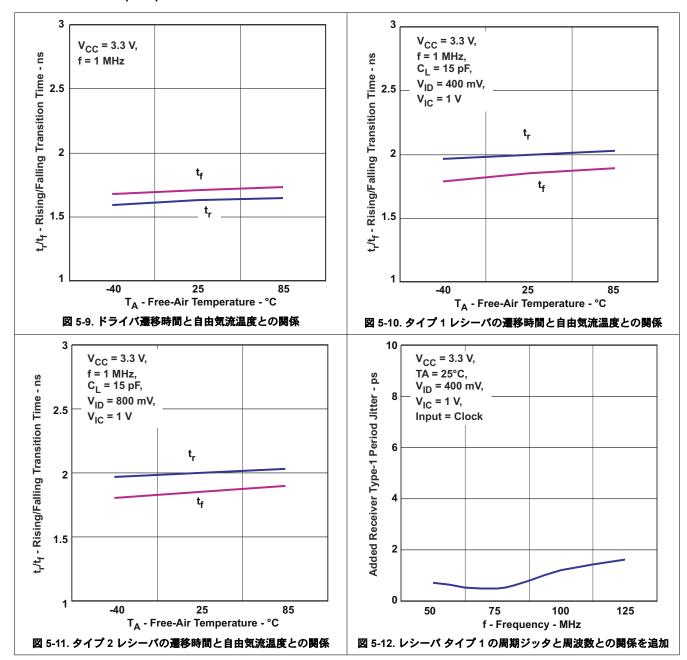

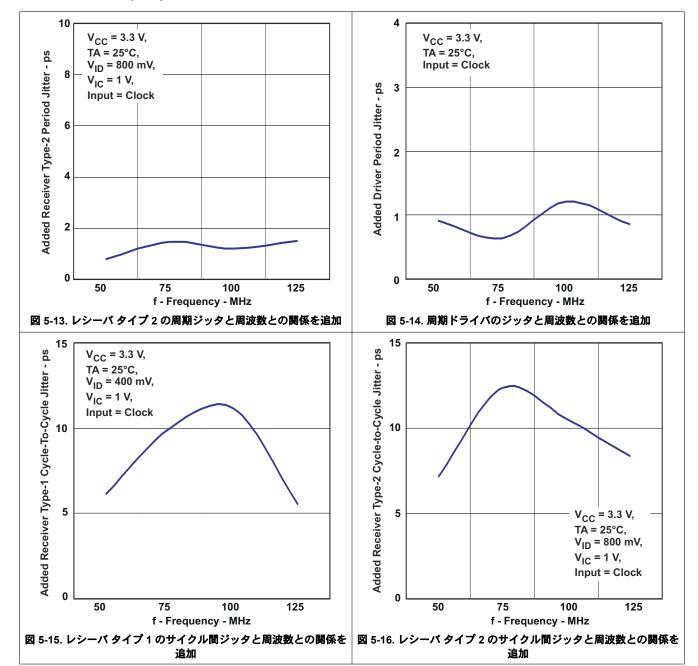

# 5.11 代表的特性

11

Product Folder Links: SN65MLVD040

English Data Sheet: SLLS902

図 5-17. ドライパのサイクル間ジッタと周波数との関係を追加

図 5-18. レシーバ タイプ 1 の決定論的ジッタとデータ レートとの 関係を追加

関係を追加

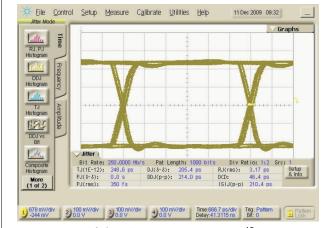

図 5-20. ドライバ出力アイ パターン 250Mbps、2<sup>15</sup>-1 PRBS、V<sub>CC</sub> = 3.3V

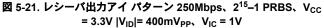

図 5-22. レシーバ出力アイ パターン 250Mbps、2<sup>15</sup>–1 PRBS、V<sub>CC</sub> = 3.3V |V<sub>ID</sub>|= 800 mV<sub>PP</sub>、V<sub>IC</sub> = 1V

15

Product Folder Links: SN65MLVD040

# 6パラメータ測定情報

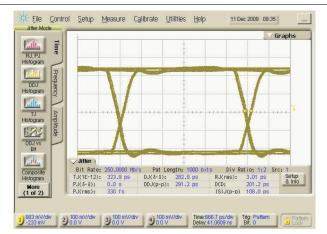

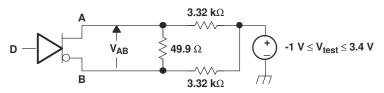

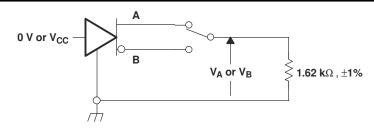

図 6-1. ドライバ電圧および電流の定義

すべての抵抗の公差は1%です。

### 図 6-2. 差動出力電圧テスト回路

- A. すべての入力パルスは、 $t_r$  または  $t_r \le 1$ ns、パルス周波数 = 1 MHz、デューティ サイクル = 50 ±5% の特性を持つジェネレータから供給されます。

- B. C1、C2、C3 には D.U.T. から 2cm 以内の計測機器および治具の容量が含まれ、公差は ±20% です。

- C. R1 および R2 は金属皮膜、表面実装、公差 ±1% で、D.U.T. から 2cm 以内に配置されています。

- D. V<sub>OS(PP)</sub> の測定 は、-3dB 帯域幅が 1GHz 以上のテスト機器で行います。

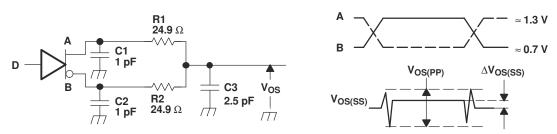

#### 図 6-3. ドライバの同相モード出力電圧のテスト回路と定義

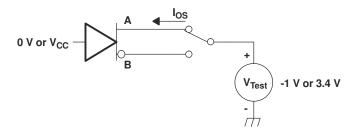

図 6-4. ドライバ短絡テスト回路

Product Folder Links: SN65MLVD040

資料に関するフィードバック (ご意見やお問い合わせ) を送信 Copyright © 2024 ™

- A. すべての入力パルスは、 $t_r$  または  $t_f \leq 1$ ns、周波数 1MHz、デューティサイクル 50 ±5%の特性を持つジェネレータから供給されます。

- B. C1、C2、C3 には D.U.T. から 2cm 以内の計測機器および治具の容量が含まれ、公差は ±20% です。

- C. R1 は金属皮膜、表面実装、1% 公差で、D.U.T. から 2cm 以内に配置されています。

- D. 測定は、-3dB 帯域幅が 1GHz 以上のテスト機器で行います。

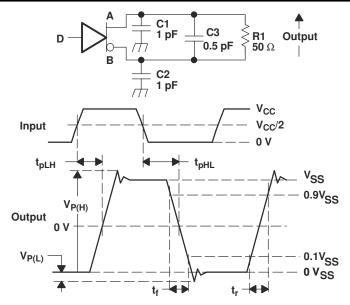

### 図 6-5. 差動出力信号のドライバ テスト回路、タイミング、電圧の定義

- A. すべての入力パルスは、 $t_i$  または  $t_f \le 1$ ns、周波数 1MHz、デューティサイクル 50  $\pm 5$ %の特性を持つジェネレータから供給されます。

- B. C1、C2、C3、C4 には、D.U.T. から 2cm 以内の計測機器および治具の容量が含まれ、公差は ±20% です。

- C. R1 および R2 は金属皮膜、表面実装、1% 公差で、D.U.T. から 2cm 以内に配置されています。

- D. 測定は、-3dB 帯域幅が 1GHz 以上のテスト機器で行います。

# 図 6-6. ドライバのイネーブル / ディセーブル時間回路と定義

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

17

図 6-7. 最大定常状態出力電圧

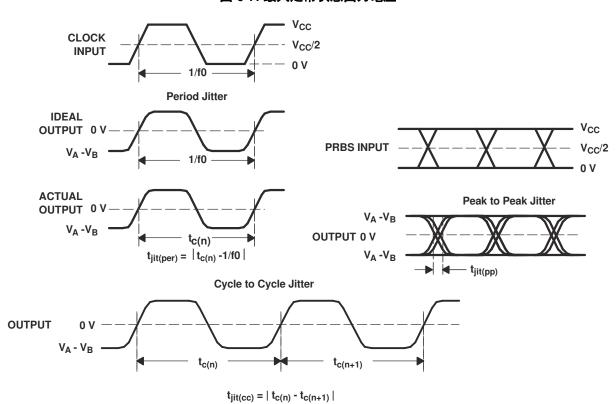

- A. すべての入力パルスは、プラグイン E4832A を備えた Agilent 81250 Parallel BERT Stimulus System から供給されます。

- B. サイクル間測定は、TDSJIT3 アプリケーション ソフトウェアを実行している TEK TDS6604 で行います。

- C. 他のすべてのジッタ測定は、Agilent Infiniium DCA-J 86100C Digital Communications Analyzer で行います。

- D. 周期ジッタとサイクル間ジッタは、125MHz 50 ±1% デューティ サイクルのクロック入力を使用して測定します。75K を超えるサンプルで測定。

- E. 確定的ジッタとランダム ジッタは、250Mbps 2<sup>15</sup>-1 PRBS 入力を使用して測定します。BER = 10<sup>-12</sup> 超で測定

### 図 6-8. ドライバのジッタ測定波形

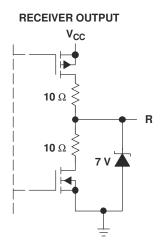

図 6-9. レシーバの電圧および電流の定義

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

| 表 6-1. Type-1 | レシーバの入力スレ | /ッショルド テスト電圧 |

|---------------|-----------|--------------|

|---------------|-----------|--------------|

|        |                 | <b>3</b> • • • • • • • • • • • • • • • • • • • |                       |                           |

|--------|-----------------|------------------------------------------------|-----------------------|---------------------------|

| 印加     | 電圧              | 結果として生じる差動<br>入力電圧                             | 結果として生じる同相<br>モード入力電圧 | レシーバ<br>出力 <sup>(1)</sup> |

| VIA    | V <sub>IB</sub> | V <sub>ID</sub>                                | V <sub>IC</sub>       | ЩЛ                        |

| 2.400  | 0.000           | 2.400                                          | 1.200                 | Н                         |

| 0.000  | 2.400           | -2.400                                         | 1.200                 | L                         |

| 3.400  | 3.365           | 0.035                                          | 3.3825                | Н                         |

| 3.365  | 3.400           | -0.035                                         | 3.3825                | L                         |

| -0.965 | -1              | 0.035                                          | -0.9825               | Н                         |

| -1     | -0.965          | -0.035                                         | -0.9825               | L                         |

|        |                 |                                                |                       |                           |

(1)  $H = High \, \nu$ ベル、 $L = Low \, \nu$ ベル、出力状態はレシーバがイネーブルであると仮定 ( $\overline{RE} = L$ )

表 6-2. Type-2 レシーバの入力スレッショルド テスト電圧

|                 |                 | <b>7</b> 1         |                       |                           |

|-----------------|-----------------|--------------------|-----------------------|---------------------------|

| 印加              | 電圧              | 結果として生じる差動<br>入力電圧 | 結果として生じる同相<br>モード入力電圧 | レシーバ<br>出力 <sup>(1)</sup> |

| V <sub>IA</sub> | V <sub>IB</sub> | V <sub>ID</sub>    | V <sub>IC</sub>       | ЩУЛ                       |

| 2.400           | 0.000           | 2.400              | 1.200                 | Н                         |

| 0.000           | 2.400           | -2.400             | 1.200                 | L                         |

| 3.400           | 3.265           | 0.135              | 3.3325                | Н                         |

| 3.4000          | 3.335           | 0.065              | 3.3675                | L                         |

| -0.865          | -1              | 0.135              | -0.9325               | Н                         |

| -0.935          | -1              | 0.065              | -0.9675               | L                         |

(1)  $H = High \, \nu$ ベル、 $L = Low \, \nu$ ベル、出力状態はレシーバがイネーブルであると仮定 ( $\overline{RE} = L$ )

- A. すべての入力パルスは、 $t_r$  または  $t_f \leq 1$ ns、周波数 1MHz、デューティサイクル 50 ±5%の特性を持つジェネレータから供給されます。 $C_L$  は、公差 20% の低損失セラミック表面実装コンデンサと、D.U.T. から 2cm 以内の治具容量を組み合わせたものです。

- B. 測定は、-3dB帯域幅が1GHz以上のテスト機器で行います。

#### 図 6-10. レシーバのタイミング テスト回路と波形

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

19

- A. すべての入力パルスは、 $t_f$  または  $t_f \le 1$ ns、周波数 = 1 MHz、デューティ サイクル = 50 ± 5% の特性を持つジェネレータによって供給されます。

- B. R<sub>L</sub> は公差 1%、金属皮膜、表面実装で、D.U.T. から 2cm 以内に配置されています。

- C.  $C_L$  は、DUT から 2cm 以内の計測機器および治具の容量で、 $\pm 20\%$  です。測定は、-3dB 帯域幅が 1GHz 以上のテスト機器で行います。

図 6-11. レシーバのイネーブル / ディセーブル時間テスト回路と波形

- A. すべての入力パルスは、プラグイン E4832A を備えた Agilent 81250 Parallel BERT Stimulus System から供給されます。

- B. サイクル間測定は、TDSJIT3 アプリケーション ソフトウェアを実行している TEK TDS6604 で行います。

- C. 他のすべてのジッタ測定は、Agilent Infiniium DCA-J 86100C Digital Communications Analyzer で行います。

- D. 周期ジッタとサイクル間ジッタは、125MHz 50 ±1% デューティ サイクルのクロック入力を使用して測定します。75K を超えるサンプルで測定。

- E. 確定的ジッタとランダム ジッタは、250Mbps  $2^{15}$ –1 PRBS 入力を使用して測定します。BER =  $10^{-12}$  超で測定

図 6-12. レシーバのジッタ測定波形

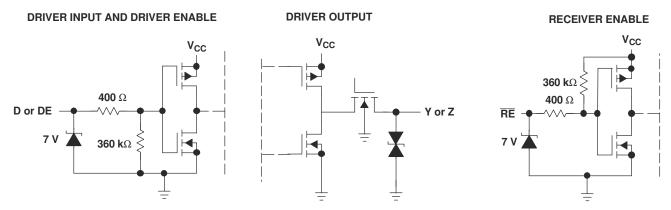

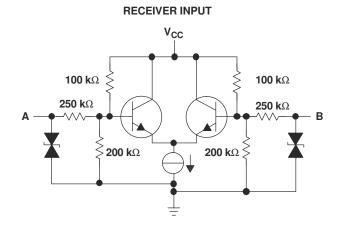

# 6.1 等価な入力および出力回路図

# 7アプリケーションと実装

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

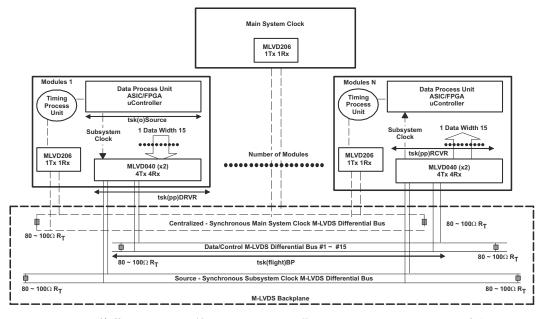

#### 7.1.1 ソース同期システム クロック (SSSC)

同期システムでデータを送信するには、集中型同期システム クロック (CSSC) とソース同期システム クロック (SSSC) の2 つの方法があります。CSSC システムは、中央のソースからのクロック信号を使用して、異なるモジュール間でのデータ 転送を同期します。CSSC システムの主要な要件は、データの送受信が 1 クロック サイクルで完了することです。最大動作周波数は、有効なデータの送受信が保証される最短クロック サイクルの逆数です。SSSC システムは、クロック信号と データ信号を一緒に送信して、伝送メディア、バックプレーン、またはケーブルでのフライトタイムを削減することで、より高い動作周波数を実現します。SSSC システムでは、最大動作周波数は、クロックとデータの間に存在する場合がある累積スキューによって制限されます。CSSC とは異なり、バックプレーン上のデータのフライトタイムの絶対値が動作周波数を制限することはありません。

SN65MLVD082 は、ソース同期システム クロック (SSSC) 動作をサポートするために、データとクロックとのインターフェイスを実現するよう設計できます。最大 250Mbps のデータ転送と、最大 125MHz のクロック周波数の転送が規定されています。図 7-1 に、M-LVDS トランシーバでサポートされる SSSC アーキテクチャの例を示します。SN65MLVD206 はシングル チャネルトランシーバであり、モジュール間でメイン システム クロックを送信します。その後、リタイミング ユニットがメイン システム クロックに適用され、サブシステムの同期処理用のローカル クロックを生成します。システム動作データ (または制御) とサブシステム クロック信号は、モジュール 1 上のマイクロプロセッサ、FPGA、ASIC などのデータ処理ユニットから生成され、SN65MLVD082 経由でスレーブ モジュールに送信されます。このような設計構成は、バックプレーンを経由し、より高い SSSC サブシステム クロック周波数でパラレル制御データを送信する際には一般的です。サブシステムのクロック周波数を、データ処理ユニットの動作周波数と整合させて、複数のユニット間でデータ転送を同期させます。

図 7-1. 差動 M-LVDS を使用したソース同期システム クロック分配の実行

Product Folder Links: SN65MLVD040

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

23

透過モードでの最大 SSSC 周波数は、式1で計算できます。

$$f_{\text{max(clk)}} < 1/[t_{\text{sk(o)Source}} + t_{\text{sk(pp)DRVR}} + t_{\text{sk(flight)BP}} + t_{\text{sk(pp)RCVR}}$$

$$\tag{1}$$

この例では、レシーバ側のセットアップ時間とホールド時間は、データ処理ユニット、FPGA、または ASIC によって決定されます。データがトランシーバのみを通過することを考慮すると、以下のデータを使用した場合、一般的な計算結果は 238 MHz となります。

$\mathbf{t}_{\mathsf{sk(o)Source}}$  = 2ns - データ処理ユニットの出力スキュー、データビットまたはクロックおよびデータビット間の任意のスキュ

$t_{sk(pp)DRVR}$  = 0.6ns - SN65MLVD040 のドライバ部品間スキュー

t<sub>sk(flight)BP</sub> = 0.4ns - データとクロックとの間のバックプレーン伝搬遅延のスキュー

t<sub>sk(pp)RCVR</sub> = 1ns - SN65MLVD040 のレシーバ部品間スキュー

上記で計算した最大動作速度 238MHz は、データとクロックのスキューのみに基づいて決定されています。最大動作速度を計算するときのもう 1 つの重要な考慮事項は、出力遷移時間です。遷移時間制限された動作速度は 式 2 で計算されます。

$$f = 45\% \times \frac{1}{2 \times t_{transition}}$$

(2)

SN65MLVD040 の標準遷移時間である 1.4ns を使用すると、遷移時間制限された動作周波数 170 MHz をサポートできます。

SN65MLVD040 は、SSSC の高い動作周波数を保証できることに加えて、他の M-LVDS バストランシーバが実現できる利点も提供します。

- 低電圧差動レシーバを使用した同相ノイズキャンセル機能による、堅牢なシステム動作

- 差動信号に起因する EMI 放射ノイズが小さく、バックプレーン経由のシグナル インテグリティが向上

- シングル終端の伝送ラインは、設計と実装が容易

- アクティブ モードとアイドル モードの両方で消費電力が低いため、各モジュールの熱の問題を最小限に抑えることが 可能

高密度バックプレーン設計では、システム全体の性能を向上させるうえで、これらの利点が重要になります。

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

#### 7.1.1.1 活線挿抜 / グリッチのない電源オン / オフ

テキサス・インスツルメンツが提供する SN65MLVD040 ファミリ製品は、電源オンまたは電源オフ時にデバイスの M-LVDS 出力がオンになるのを防止するグリッチ フリーの電源オン / オフ機能を備えています。デバイスが M-LVDS マルチポイント バスに物理的に接続され、Vcc が上昇している場合、活線挿抜アプリケーションではこれは特に重要です。

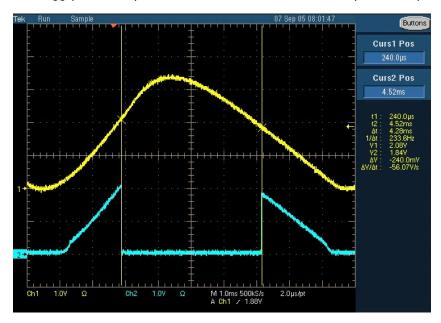

これらのデバイスの M-LVDS インターフェイスは電源オン / オフ時にグリッチがありませんが、レシーバの出力構造はそうではありません。図 7-2 に、V<sub>CC</sub> (チャネル 1) が上昇したときのレシーバ出力ピン R (チャネル 2) の性能を示します。

図 7-2. M-LVDS レシーバ出力:V<sub>CC</sub> (チャネル 1)、R ピン (チャネル 2)

R ピンのグリッチは、RE 電圧に依存しません。このグリッチによるあらゆる複雑な現象や問題は、電源シーケンスまたは Vcc が定常状態値に達するまで動作を中断するシステム要件で解消します。

25

Product Folder Links: SN65MLVD040

# 8 デバイスおよびドキュメントのサポート

テキサス・インスツルメンツでは、幅広い開発ツールを提供しています。デバイスの性能の評価、コードの生成、ソリューションの開発を行うためのツールとソフトウェアを以下で紹介します。

#### 8.1 ドキュメントのサポート

#### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 8.4 商標

PowerPAD<sup>™</sup> and テキサス・インスツルメンツ E2E<sup>™</sup> are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

#### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 8.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

#### 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Changes from Revision \* (Febuary 2010) to Revision A (March 2024)

Page

### 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報はそのデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側のナビゲーションをご覧ください。

かせ) を送信 Copyright © 2024 Texas Instruments Incorporated Product Folder Links: SN65MLVD040

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated www.ti.com 7-Oct-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                 |              |              |

| SN65MLVD040RGZR       | Active | Production    | VQFN (RGZ)   48 | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 85    | MLVD040      |

| SN65MLVD040RGZR.B     | Active | Production    | VQFN (RGZ)   48 | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 85    | MLVD040      |

| SN65MLVD040RGZT       | Active | Production    | VQFN (RGZ)   48 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 85    | MLVD040      |

| SN65MLVD040RGZT.B     | Active | Production    | VQFN (RGZ)   48 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 85    | MLVD040      |

| SN65MLVD040RGZTG4     | Active | Production    | VQFN (RGZ)   48 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 85    | MLVD040      |

| SN65MLVD040RGZTG4.B   | Active | Production    | VQFN (RGZ)   48 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 85    | MLVD040      |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 7-Oct-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

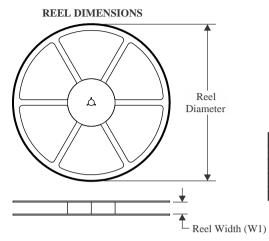

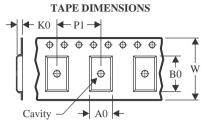

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

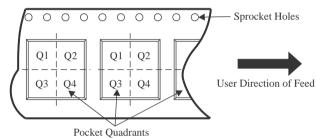

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65MLVD040RGZR   | VQFN            | RGZ                | 48 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

| SN65MLVD040RGZT   | VQFN            | RGZ                | 48 | 250  | 180.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

| SN65MLVD040RGZTG4 | VQFN            | RGZ                | 48 | 250  | 180.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

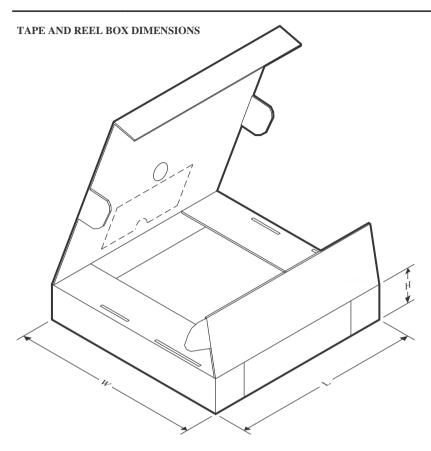

www.ti.com 24-Jul-2025

### \*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65MLVD040RGZR   | VQFN         | RGZ             | 48   | 2500 | 353.0       | 353.0      | 32.0        |

| SN65MLVD040RGZT   | VQFN         | RGZ             | 48   | 250  | 213.0       | 191.0      | 35.0        |

| SN65MLVD040RGZTG4 | VQFN         | RGZ             | 48   | 250  | 213.0       | 191.0      | 35.0        |

7 x 7, 0.5 mm pitch

PLASTIC QUADFLAT PACK- NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224671/A

PLASTIC QUAD FLATPACK - NO LEAD

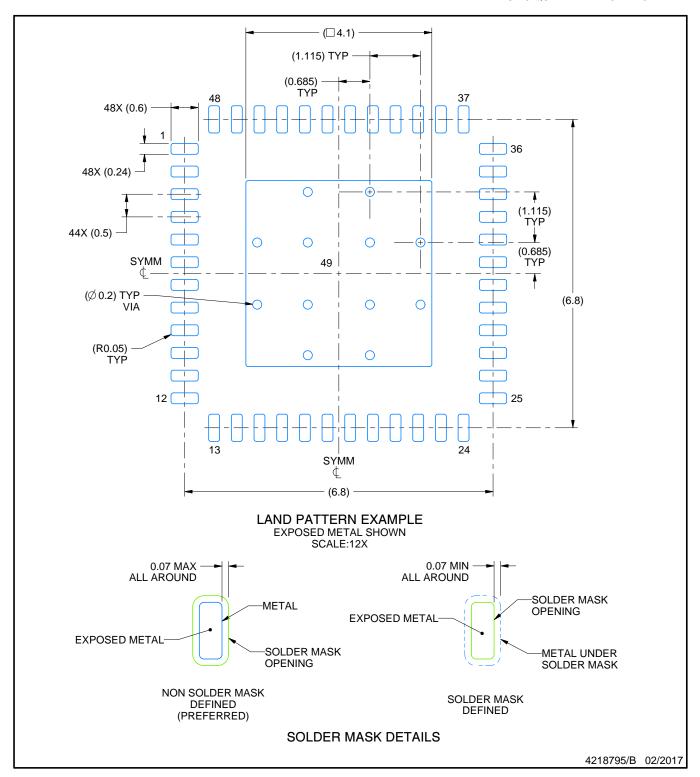

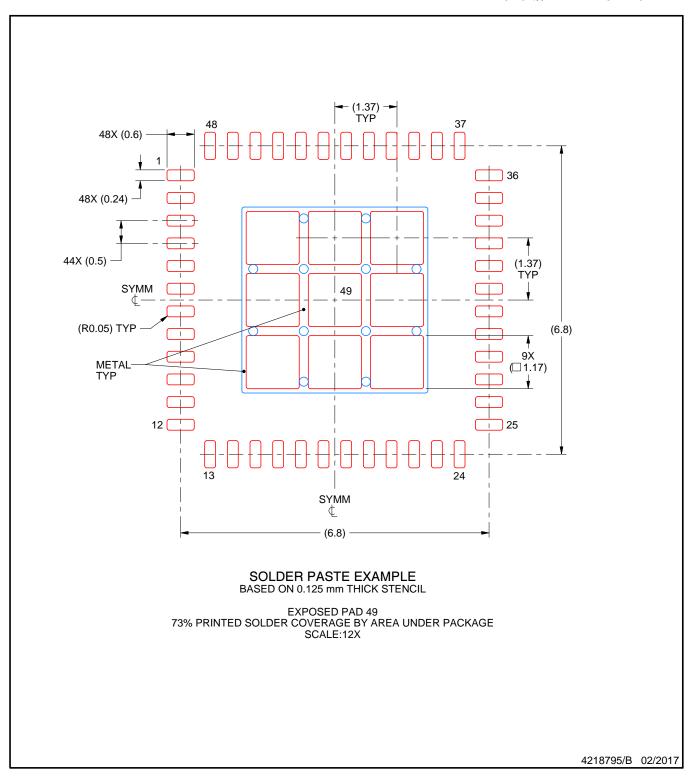

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated