JAJSPU8F - JUNE 2004 - REVISED FEBRUARY 2023

# SN65HVD485E、半二重、RS-485 トランシーバ

# 1 特長

- バス・ピンの ESD 保護: 最大 15kV

- 1/2 の単位負荷で、バス上に最大 64 のノード

- バス・オープン・フェイルセーフ・レシーバ

- グリッチの発生しないパワーアップ / パワーダウン・バス 入出力

- 小型の VSSOP-8 パッケージで利用可能

- TIA/EIA-485A 規格の要件に適合またはそれを上回る

- 業界標準の SN75176 フットプリント

# 2 アプリケーション

- モータ制御

- 電力インバータ

- 産業用オートメーション

- ビル・オートメーション・ネットワーク

- 産業用プロセス制御

- バッテリ駆動のアプリケーション

- 通信機器

## 3 概要

SN65HVD485E デバイスは、RS-485 データ・バス・ネット ワーク用に設計された半二重トランシーバです。5V 電源 で動作し、TIA/EIA-485A 規格に完全準拠しています。こ のデバイスは、長いツイストペア・ケーブルを使用して最大 10Mbps のデータ転送に適しており、負荷を除外して、通 常 2mA 未満の非常に低い電源電流で動作するように設 計されています。デバイスが非アクティブ・シャットダウン・ モードのとき、消費電流は 1mA を下回ります。

このデバイスは同相範囲が広く ESD 保護レベルが高い ため、電気インバータ、テレコム・ラックのステータス/コマ ンド信号、ケーブル接続シャーシ・インターコネクト、ノイズ 耐性が重要な産業用オートメーション・ネットワークなど、 要求の厳しいアプリケーションに適しています。 SN65HVD485E デバイスのフットプリントは、SN75176 デ バイスの業界標準のフットプリントと一致しています。パワ ー・オン・リセット回路は、電源電圧が安定するまで出力を 高インピーダンス状態に維持します。サーマル・シャットダ ウン機能は、システムのフォルト状態による損傷からデバイ スを保護します。SN65HVD485E デバイスは、-40°C~ 85℃で動作が規定されています。

#### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|-------------|----------------------|-----------------|

|             | SOIC (8)             | 4.91mm × 3.90mm |

| SN65HVD485E | VSSOP (8)            | 3.00mm × 3.00mm |

|             | PDIP (8)             | 9.81mm × 6.35mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

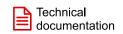

代表的なアプリケーション回路図

## **Table of Contents**

| 1 特長                                                                                             | 1        | 8 Detailed Description                                | 13              |

|--------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------|-----------------|

| 2 アプリケーション                                                                                       |          | 8.1 Overview                                          |                 |

| 3 概要                                                                                             |          | 8.2 Functional Block Diagram                          | 13              |

| 4 Revision History                                                                               |          | 8.3 Feature Description                               | 13              |

| 5 Device Comparison Table                                                                        | 3        | 8.4 Device Functional Modes                           | 13              |

| 6 Pin Configuration and Functions                                                                | 3        | 9 Application and Implementation                      |                 |

| 7 Specifications                                                                                 |          | 9.1 Application Information                           | 15              |

| 7.1 Absolute Maximum Ratings                                                                     |          | 9.2 Typical Application                               |                 |

| 7.2 ESD Ratings                                                                                  |          | 9.3 Power Supply Recommendations                      |                 |

| 7.3 Recommended Operating Conditions                                                             |          | 9.4 Layout                                            |                 |

| 7.4 Thermal Information                                                                          | 5        | 10 Device and Documentation Support                   |                 |

| 7.5 Electrical Characteristics: Driver                                                           |          | 10.1 Device Support                                   |                 |

| 7.6 Electrical Characteristics: Receiver                                                         | 6        | 10.2 Documentation Support                            |                 |

| 7.7 Power Dissipation Characteristics                                                            |          | 10.3 サポート・リソース                                        | 21              |

| 7.8 Supply Current                                                                               |          | 10.4 Trademarks                                       |                 |

| 7.9 Switching Characteristics: Driver                                                            |          | 10.5 静電気放電に関する注意事項                                    | 21              |

| 7.10 Switching Characteristics: Receiver                                                         |          | 10.6 用語集                                              |                 |

| 7.11 Dissipation Ratings                                                                         |          | 11 Mechanical, Packaging, and Orderable               |                 |

| 7.12 Typical Characteristics                                                                     |          | Information                                           | <mark>21</mark> |

| 4 Revision History<br>資料番号末尾の英字は改訂を表しています。その<br>Changes from Revision E (November 2015)          |          |                                                       | Paga            |

| <ul> <li>Changed the values in the Thermal Information</li> </ul>                                |          |                                                       | Page5           |

| Changes from Revision D (July 2015) to Re  Changed 3.3 V To: 5 V at pin V <sub>CC</sub> in ⊠ 9-4 |          |                                                       | Page            |

| Changes from Revision C (March 2007) to I                                                        |          |                                                       | Page            |

| 装」セクション、「電源に関する推奨事項」セクション、「電源に関する推奨事項」セクション、「電源に関する推奨事項」セクション、「電源に関する推奨事項」を                      | ション、「レイ) | 「デバイスの機能モード」セクション、「アプリケー<br>アウト」セクション、「デバイスおよびドキュメントの | サポート」           |

|                                                                                                  |          | ウションを追加                                               |                 |

|                                                                                                  |          |                                                       |                 |

| <ul> <li>Changed Thermal Information table</li> </ul>                                            |          |                                                       | 5               |

Added Power Dissipation Characteristics table......6

Product Folder Links: SN65HVD485E

# **5 Device Comparison Table**

## **Improved Replacement for Devices**

| PART NUMBER | REPLACE WITH | BENEFITS                                                                                                                                                                    |

|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADM485      | SN65HVD485E  | Better ESD protection (±15 kV versus unspecified) Faster signaling rate (10 Mbps versus 5 Mbps) More nodes on a bus (64 versus 32) Wider power supply tolerance (10% vs 5%) |

| SP485E      | SN65HVD485E  | More nodes on a bus (64 versus 32)<br>Wider power supply tolerance (10% versus 5%)                                                                                          |

| LMS485E     | SN65HVD485E  | Higher signaling rate (10 Mbps versus 2.5 Mbps) More nodes on a bus (64 versus 32) Wider power supply tolerance (10% versus 5%)                                             |

| DS485       | SN65HVD485E  | Higher signaling rate (10 Mbps versus 2.5 Mbps) Better ESD (±15 kV versus ±2 kV) More nodes on a bus (64 versus 32) Wider power supply tolerance (10% versus 5%)            |

| LTC485      | SN65HVD485E  | Better ESD (±15 kV versus ±2 kV) Wider power supply tolerance (10% versus 5%)                                                                                               |

| MAX485E     | SN65HVD485E  | Higher signaling rate (10 Mbps versus 2.5 Mbps) More nodes on a bus (64 versus 32) Wider power supply tolerance (10% versus 5%)                                             |

| ST485E      | SN65HVD485E  | Higher signaling rate (10 Mbps versus 5 Mbps) Wider power supply tolerance (10% versus 5%)                                                                                  |

| ISL8485E    | SN65HVD485E  | More nodes on a bus (64 versus 32) Faster signaling rate (10 Mbps versus 5 Mbps)                                                                                            |

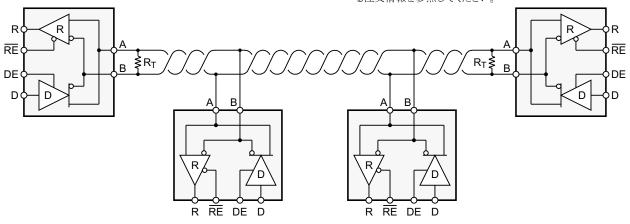

# **6 Pin Configuration and Functions**

図 6-1. D, DGK, P Packages, 8-Pin SOIC, VSSOP, PDIP (Top View)

表 6-1. Pin Functions

| PIN             |     | TYPE                | DESCRIPTION                                          |

|-----------------|-----|---------------------|------------------------------------------------------|

| NAME            | NO. | 1175                | DESCRIPTION                                          |

| Α               | 6   | Bus input/output    | Driver output or receiver input (complementary to B) |

| В               | 7   | Bus input/output    | Driver output or receiver input (complementary to A) |

| D               | 4   | Digital input       | Driver data input                                    |

| DE              | 3   | Digital input       | Driver enable, active high                           |

| GND             | 5   | Reference potential | Local device ground                                  |

| R               | 1   | Digital input       | Receive data output                                  |

| RE              | 2   | Digital input       | Receiver enable, active low                          |

| V <sub>CC</sub> | 8   | Supply              | 4.5-V to 5.5-V supply                                |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                  |                                                                           | MIN                 | MAX                   | UNIT |

|------------------|---------------------------------------------------------------------------|---------------------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage                                                            | -0.5                | 7                     | V    |

|                  | Voltage range at A or B                                                   | -9                  | 14                    | V    |

|                  | Voltage range at any logic pin                                            | -0.3                | V <sub>CC</sub> + 0.3 | V    |

|                  | Receiver output current                                                   | -24                 | 24                    | mA   |

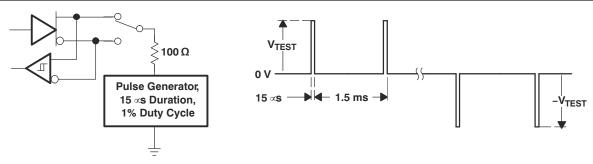

|                  | Voltage input range, transient pulse, A and B, through 100 Ω (see 🗵 8-13) | -50                 | 50                    | V    |

| $T_{J}$          | Junction temperature                                                      | 170                 | 170                   | °C   |

|                  | Continuous total power dissipation                                        | Refer to セクション 7.11 |                       |      |

| T <sub>stg</sub> | Storage temperature                                                       | -65                 | 130                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under セクション 7.3 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                                                  |                                                                                |          | VALUE | UNIT |

|--------------------|--------------------------------------------------|--------------------------------------------------------------------------------|----------|-------|------|

|                    | Trainan body model (Tibiti), per Alton Lob Albed | Bus pins and GND                                                               | ±15000   |       |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge                       | JS-001 <sup>(1)</sup>                                                          | All pins | ±4000 | V    |

| u                  |                                                  | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |          | ±1000 |      |

<sup>1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                   |                                    | ,                                                             | MIN | NOM | MAX             | UNIT |

|-------------------|------------------------------------|---------------------------------------------------------------|-----|-----|-----------------|------|

| V <sub>CC</sub>   | Supply voltage                     |                                                               | 4.5 |     | 5.5             | V    |

| VI                | Input voltage at any bu            | Input voltage at any bus terminal (separately or common mode) |     |     | 12              | V    |

| V <sub>IH</sub>   | High-level input voltage           | High-level input voltage (D, DE, or RE inputs)                |     |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>   | Low-level input voltage            | (D, DE, or RE inputs)                                         | 0   |     | 0.8             | V    |

| V <sub>ID</sub>   | Differential input voltag          | е                                                             | -12 |     | 12              | V    |

|                   | Outroot sums at                    | Driver                                                        | -60 |     | 60              | mA   |

| I <sub>O</sub>    | Output current                     | Receiver                                                      | -8  |     | 8               | ША   |

| R <sub>L</sub>    | Differential load resista          | nce                                                           | 54  | 60  |                 | Ω    |

| 1/t <sub>UI</sub> | Signaling rate                     |                                                               | 0   |     | 10              | Mbps |

| T <sub>A</sub>    | Operating free-air temp            | perature                                                      | -40 |     | 85              | °C   |

| TJ                | Junction temperature <sup>(2</sup> |                                                               | -40 |     | 130             | °C   |

<sup>(1)</sup> The algebraic convention, in which the least positive (most negative) limit is designated as minimum, is used in this data sheet.

<sup>(2)</sup> All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> See セクション 7.4 for information on maintenance of this specification for the DGK package.

#### 7.4 Thermal Information

|                       |                                                       | SN65HVD485E |                |             |      |

|-----------------------|-------------------------------------------------------|-------------|----------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                         | D<br>(SOIC) | DGK<br>(VSSOP) | P<br>(PDIP) | UNIT |

|                       |                                                       | 8 PINS      | 8 PINS         | 8 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance <sup>(2)</sup> | 116.7       | 137.8          | 84.3        | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance             | 56.3        | 31.2           | 65.4        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                  | 63.4        | 71.7           | 62.1        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter            | 8.8         | 0.6            | 31.3        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter          | 62.6        | 70.5           | 60.4        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

#### 7.5 Electrical Characteristics: Driver

over recommended operating conditions (unless otherwise noted)

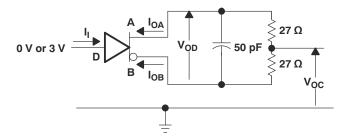

|                     | PARAMETER                                          | TEST CONDITIONS                              | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|---------------------|----------------------------------------------------|----------------------------------------------|------|--------------------|-----|------|

|                     |                                                    | I <sub>O</sub> = 0, No load                  | 3    | 4.3                |     |      |

| V <sub>OD</sub>     | Differential output voltage                        | R <sub>L</sub> = 54 W (see ⊠ 8-1)            | 1.5  | 2.3                |     | V    |

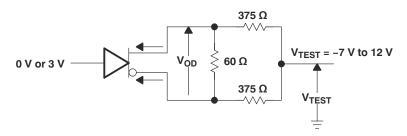

|                     |                                                    | V <sub>TEST</sub> = -7 V to 12 V (see ⊠ 8-2) | 1.5  |                    |     |      |

| Δ V <sub>OD</sub>   | Change in magnitude of differential output voltage | See ⊠ 8-1 and ⊠ 8-2                          | -0.2 | 0                  | 0.2 | V    |

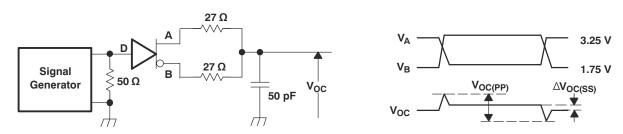

| V <sub>OC(SS)</sub> | Steady-state common-mode output voltage            | See 図 8-3                                    | 1    | 2.6                | 3   | V    |

| $\Delta V_{OC(SS)}$ | Change in steady-state common-mode output voltage  |                                              | -0.1 | 0                  | 0.1 | V    |

| V <sub>OC(PP)</sub> | Common-mode output voltage                         | See 図 8-3                                    |      | 500                |     | mV   |

| I <sub>OZ</sub>     | High-impedance output current                      | See receiver input currents                  |      |                    |     | μA   |

| I <sub>I</sub>      | Input current                                      | D, DE                                        | -100 |                    | 100 | μΑ   |

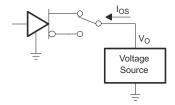

| I <sub>OS</sub>     | Short-circuit output current                       | -7 V ≤ V <sub>O</sub> ≤ 12 V (see ⊠ 8-7)     | -250 |                    | 250 | mA   |

<sup>(1)</sup> All typical values are at 25°C and with a 5-V supply.

<sup>(2)</sup> See the Package Thermal Characterization Methodologies application note (SZZA003) for an explanation of this parameter.

## 7.6 Electrical Characteristics: Receiver

over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                                 | TEST CONDITIONS                                               | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|-------------------|-----------------------------------------------------------|---------------------------------------------------------------|------|--------------------|-----|------|

| V <sub>IT+</sub>  | Positive-going input threshold voltage                    | I <sub>O</sub> = -8 mA                                        |      | -85                | -10 | mV   |

| V <sub>IT</sub>   | Negative-going input threshold voltage                    | I <sub>O</sub> = 8 mA                                         | -200 | -115               |     | mV   |

| V <sub>hys</sub>  | Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT-</sub> ) |                                                               |      | 30                 |     | mV   |

| V <sub>OH</sub>   | High-level output voltage                                 | V <sub>ID</sub> = 200 mV, I <sub>OH</sub> = −8 mA (see ⊠ 8-8) | 4    | 4.6                |     | V    |

| V <sub>OL</sub>   | Low-level output voltage                                  | V <sub>ID</sub> = –200 mV, I <sub>OH</sub> = 8 mA (see 図 8-8) |      | 0.15               | 0.4 | V    |

| I <sub>OZ</sub>   | High-impedance-state output current                       | $V_O = 0$ to $V_{CC}$ , $\overline{RE} = V_{CC}$              | -1   |                    | 1   | μA   |

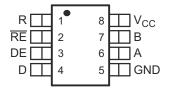

|                   |                                                           | V <sub>IH</sub> = 12 V, V <sub>CC</sub> = 5 V                 |      |                    | 0.5 |      |

|                   | Bus input current                                         | V <sub>IH</sub> = 12 V, V <sub>CC</sub> = 0                   |      |                    | 0.5 | mA   |

| I <sub>1</sub>    | bus input current                                         | V <sub>IH</sub> = -7 V, V <sub>CC</sub> = 5 V                 | -0.4 |                    |     | ША   |

|                   |                                                           | $V_{IH} = -7 \text{ V, } V_{CC} = 0$                          | -0.4 |                    |     |      |

| I <sub>IH</sub>   | High-level input current ( RE)                            | V <sub>IH</sub> = 2 V                                         | -60  | -30                |     | μA   |

| I <sub>IL</sub>   | Low-level input current ( RE)                             | V <sub>IL</sub> = 0.8 V                                       | -60  | -30                |     | μA   |

| C <sub>diff</sub> | Differential input capacitance                            | V <sub>I</sub> = 0.4 sin (4E6πt) + 0.5 V, DE at 0 V           |      | 7                  |     | pF   |

<sup>(1)</sup> All typical values are at 25°C and with a 5-V supply.

# 7.7 Power Dissipation Characteristics

|                    | PARAMETER                              | TEST CONDITIONS                                                                                   | MIN | TYP | MAX | UNIT |

|--------------------|----------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>(AVG)</sub> | Average power dissipation              | $R_L$ = 54 Ω, Input to D is a 10 Mbps 50% duty cycle square wave $V_{CC}$ at 5.5 V, $T_J$ = 130°C |     |     | 219 | mW   |

| T <sub>SD</sub>    | Thermal shut-down junction temperature |                                                                                                   |     | 165 |     | °C   |

Product Folder Links: SN65HVD485E

## 7.8 Supply Current

over recommended operating conditions (unless otherwise noted)

| PARAMETER TEST CONDITIONS |                              | MIN                                  | TYP <sup>(1)</sup>                         | MAX | UNIT |   |    |

|---------------------------|------------------------------|--------------------------------------|--------------------------------------------|-----|------|---|----|

| 1                         | Driver and receiver enabled  | D at V <sub>CC</sub> or open or 0 V, | DE at V <sub>CC</sub> , RE at 0 V, No load |     |      | 2 | mA |

| ICC                       | Driver and receiver disabled | D at V <sub>CC</sub> or open,        | DE at 0 V, RE at V <sub>CC</sub>           |     |      | 1 | mA |

<sup>(1)</sup> All typical values are at 25°C and with a 5-V supply.

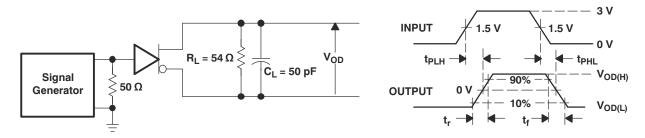

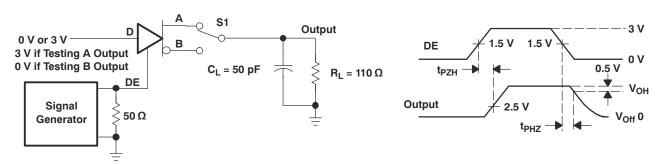

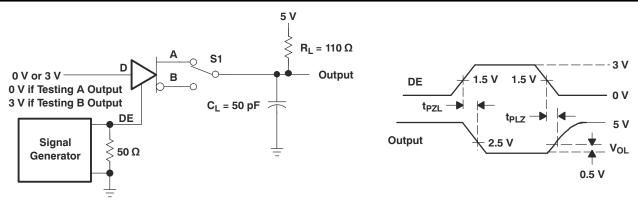

## 7.9 Switching Characteristics: Driver

over recommended operating conditions (unless otherwise noted)

|                        | PARAMETER                                                   | TEST CONDITIONS                                      | MIN | TYP | MAX  | UNIT |

|------------------------|-------------------------------------------------------------|------------------------------------------------------|-----|-----|------|------|

| t <sub>PLH</sub>       | Propagation delay time, low-to-high-level output            |                                                      |     |     | 30   | ns   |

| t <sub>PHL</sub>       | Propagation delay time, high-to-low-level output            |                                                      |     |     | 30   | ns   |

| t <sub>r</sub>         | Differential output signal rise time                        | $R_L$ = 54 Ω, $C_L$ = 50 pF (see $\boxtimes$ 8-4)    |     |     | 25   | ns   |

| t <sub>f</sub>         | Differential output signal fall time                        |                                                      |     |     | 25   | ns   |

| t <sub>sk(p)</sub>     | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  )         |                                                      |     |     | 5    | ns   |

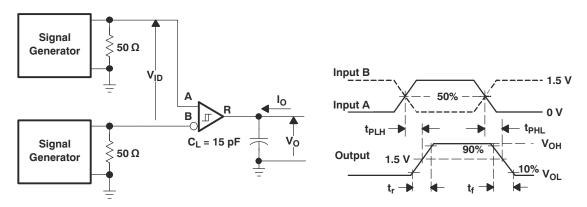

| t <sub>PZH</sub>       | Propagation delay time, high-impedance-to-high-level output | R <sub>1</sub> = 110 Ω, RE at 0 V (see ⊠ 8-5)        |     |     | 150  | ns   |

| t <sub>PHZ</sub>       | Propagation delay time, high-level-to-high-impedance output | - 110 Ω, RE at 0 V (See 🗵 0-3)                       |     |     | 100  | ns   |

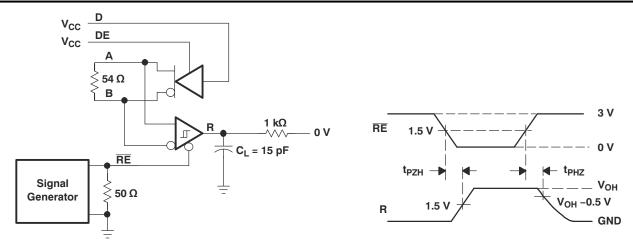

| t <sub>PZL</sub>       | Propagation delay time, high-impedance-to-low-level output  | R <sub>1</sub> = 110 Ω, RE at 0 V (see ⊠ 8-6)        |     |     | 150  | ns   |

| t <sub>PLZ</sub>       | Propagation delay time, low-level-to-high-impedance output  | $R_L = 110 \Omega$ , RE at 0 V (see $\boxtimes$ 8-6) |     |     | 100  | ns   |

| t <sub>PZH(SHN)</sub>  | Propagation delay time, shutdown-to-high-level output       | R <sub>L</sub> = 110 Ω, RE at VCC (see ⊠ 8-5)        |     |     | 2600 | ns   |

| t <sub>PZL(SHDN)</sub> | Propagation delay time, shutdown-to-low-level output        | R <sub>L</sub> = 110 Ω, RE at VCC (see 🗵 8-6)        |     |     | 2600 | ns   |

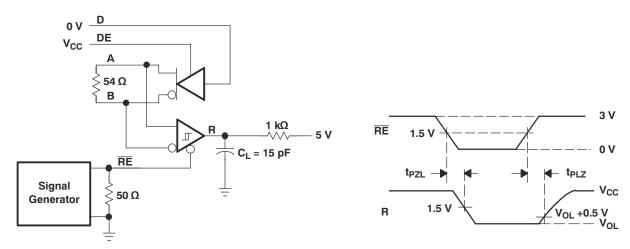

## 7.10 Switching Characteristics: Receiver

over recommended operating conditions (unless otherwise noted)

|                        | PARAMETER                                             | TEST CONDITIONS                                                            | MIN | TYP | MAX  | UNIT |

|------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>PLH</sub>       | Propagation delay time, low-to-high-level output      |                                                                            |     |     | 200  | ns   |

| t <sub>PHL</sub>       | Propagation delay time, high-to-low-level output      | 7, 45,44,45,46,45,5                                                        |     |     | 200  | ns   |

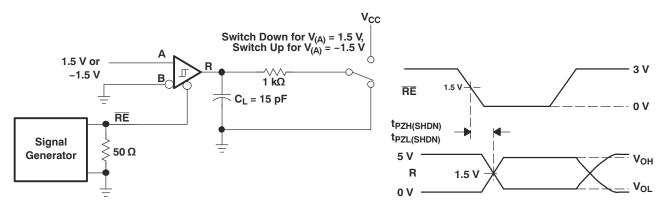

| t <sub>sk(p)</sub>     | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  )   | V <sub>ID</sub> = -1.5 V to 1.5 V, C <sub>L</sub> = 15 pF<br>_ (see 図 8-9) |     | 6   |      | ns   |

| t <sub>r</sub>         | Output signal rise time                               | (655 12 5 5)                                                               |     |     | 3    | ns   |

| t <sub>f</sub>         | Output signal fall time                               |                                                                            |     |     | 3    | ns   |

| t <sub>PZH</sub>       | Output enable time to high level                      |                                                                            |     |     | 50   | ns   |

| t <sub>PZL</sub>       | Output enable time to low level                       | C <sub>L</sub> = 15 pF, DE at 3 V,                                         |     |     | 50   | ns   |

| t <sub>PHZ</sub>       | Output enable time from high level                    | (see 図 8-10 and 図 8-11)                                                    |     |     | 50   | ns   |

| t <sub>PLZ</sub>       | Output enable time from low level                     |                                                                            |     |     | 50   | ns   |

| t <sub>PZH(SHDN)</sub> | Propagation delay time, shutdown-to-high-level output | C <sub>L</sub> = 15 pF, DE at 0 V,                                         |     |     | 3500 | ns   |

| t <sub>PZL(SHDN)</sub> | Propagation delay time, shutdown-to-low-level output  | (see ⊠ 8-12)                                                               |     |     | 3500 | ns   |

English Data Sheet: SLLS612

## 7.11 Dissipation Ratings

| PACKAGE <sup>(1)</sup> | JEDEC BOARD<br>MODEL         | T <sub>A</sub> < 25°C<br>POWER RATING | DERATING FACTOR <sup>(2)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|------------------------|------------------------------|---------------------------------------|---------------------------------------------------------------|---------------------------------------|---------------------------------------|

| D                      | Low k <sup>(3)</sup>         | 507 mW                                | 4.82 mW/°C                                                    | 289 mW                                | 217 mW                                |

| (SIOC)                 | (SIOC) High k <sup>(3)</sup> |                                       | 7.85 mW/°C                                                    | 471 mW                                | 353 mW                                |

| P<br>(PDIP)            | Low k <sup>(3)</sup>         | 686 mW                                | 6.53 mW/°C                                                    | 392 mW                                | 294 mW                                |

| DGK                    | Low k <sup>(3)</sup>         | 394 mW                                | 3.76 mW/°C                                                    | 255 mW                                | 169 mW                                |

| (VSSOP)                | High k <sup>(4)</sup>        | 583 mW                                | 5.55 mW/°C                                                    | 333 mW                                | 250 mW                                |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (2) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

- (3) In accordance with the low-k thermal metric definitions of EIA/JESD51-3.

- (4) In accordance with the high-k thermal metric definitions of EIA/JESDS1-7.

## 7.12 Typical Characteristics

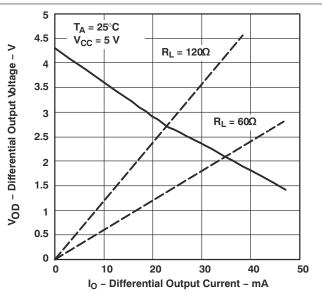

図 7-2. Driver Differential Output Voltage vs Differential Output

Current

## **Parameter Measurement Information**

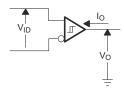

図 8-1. Driver Test Circuit, V<sub>OD</sub> and V<sub>OC</sub> Without Common-Mode Loading

図 8-2. Driver Test Circuit, V<sub>OD</sub> With Common-Mode Loading

図 8-3. Driver V<sub>OC</sub> Test Circuit and Waveforms

図 8-4. Driver Switching Test Circuit and Waveforms

☑ 8-5. Driver Enable/Disable Test Circuit and Waveforms, High Output

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

図 8-6. Driver Enable/Disable Test Circuit and Waveforms, Low Output

図 8-7. Driver Short-Circuit Test

**図** 8-8. Receiver Parameter Definitions

図 8-9. Receiver Switching Test Circuit and Waveforms

図 8-10. Receiver Enable/Disable Test Circuit and Waveforms, Data Output High

図 8-11. Receiver Enable/Disable Test Circuit and Waveforms, Data Output Low

図 8-12. Receiver Enable From Shutdown Test Circuit and Waveforms

図 8-13. Test Circuit and Waveforms, Transient Over-Voltage Test

English Data Sheet: SLLS612

## 8 Detailed Description

#### 8.1 Overview

The SN65HVD485E device is a half-duplex RS-485 transceiver suitable for data transmission at rates up to 10 Mbps over controlled-impedance transmission media (such as twisted-pair cabling). Up to 64 units of the SN65HVD485E device can share a common RS-485 bus due to the low bus-input currents of the device. The device also features a high degree of ESD protection and low standby current consumption of 1 mA (maximum).

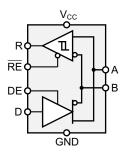

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

The SN65HVD485E device provides internal biasing of the receiver input thresholds for open-circuit, bus-idle, or short-circuit failsafe conditions. It features a typical hysteresis of 30 mV to improve noise immunity. Internal ESD protection circuits protect the transceiver bus terminals against ±15-kV Human Body Model (HBM) electrostatic discharges.

#### 8.4 Device Functional Modes

When the driver enable pin (DE) is logic high, the differential outputs A and B follow the logic states at data input D. A logic high at D causes A to turn high and B to turn low. In this case, the differential output voltage defined as  $V_{OD} = V_A - V_B$  is positive. When D is low, the output states reverse, B turns high, A is low, and  $V_{OD}$  is negative.

When DE is low, both outputs turn high impedance. In this condition, the logic state at D is irrelevant. The DE pin has an internal pulldown resistor to ground; thus when left open, the driver is disabled (high impedance) by default. The D pin has an internal pullup resistor to VCC; thus when left open while the driver is enabled, output A turns high and B turns low.

| INPUT | ENABLE | OUT | PUTS | FUNCTION                           |

|-------|--------|-----|------|------------------------------------|

| D     | DE     | Α   | В    | TONOTION                           |

| Н     | Н      | Н   | L    | Actively drive bus High            |

| L     | Н      | L   | Н    | Actively drive bus Low             |

| Х     | L      | Z   | Z    | Driver disabled                    |

| X     | OPEN   | Z   | Z    | Driver disabled by default         |

| OPEN  | Н      | Н   | L    | Actively drive bus high by default |

表 8-1. Driver Function Table

When the receiver enable pin ( $\overline{RE}$ ) is logic low, the receiver is enabled. When the differential input voltage defined as  $V_{ID} = V_A - V_B$  is positive and higher than the positive input threshold ( $V_{IT+}$ ) the receiver output (R) turns high. When  $V_{ID}$  is negative and lower than the negative input threshold ( $V_{IT-}$ ), the receiver output (R) turns low. If  $V_{ID}$  is between  $V_{IT+}$  and  $V_{IT-}$ , the output is indeterminate.

When  $\overline{RE}$  is logic high or left open, the receiver output is high impedance and the magnitude and polarity of  $V_{ID}$  are irrelevant. Internal biasing of the receiver inputs causes the output to go failsafe high when the transceiver is disconnected from the bus (open-circuit), the bus lines are shorted (short-circuit), or the bus is not actively driven (idle bus).

#### 表 8-2. Receiver Function Table

| DIFFERENTIAL INPUT V <sub>ID</sub> = V <sub>A</sub> - V <sub>B</sub> | ENABLE<br>RE | OUTPUT<br>R | FUNCTION                     |

|----------------------------------------------------------------------|--------------|-------------|------------------------------|

| V <sub>IT+</sub> < V <sub>ID</sub>                                   | L            | Н           | Receive valid bus High       |

| $V_{IT-} < V_{ID} < V_{IT+}$                                         | L            | ?           | Indeterminate bus state      |

| V <sub>ID</sub> < V <sub>IT</sub>                                    | L            | L           | Receive valid bus Low        |

| X                                                                    | Н            | Z           | Receiver disabled            |

| X                                                                    | OPEN         | Z           | Receiver disabled by default |

| Open-circuit bus                                                     | L            | Н           | Fail-safe high output        |

| Short-circuit bus                                                    | L            | Н           | Fail-safe high output        |

| Idle (terminated) bus                                                | L            | Н           | Fail-safe high output        |

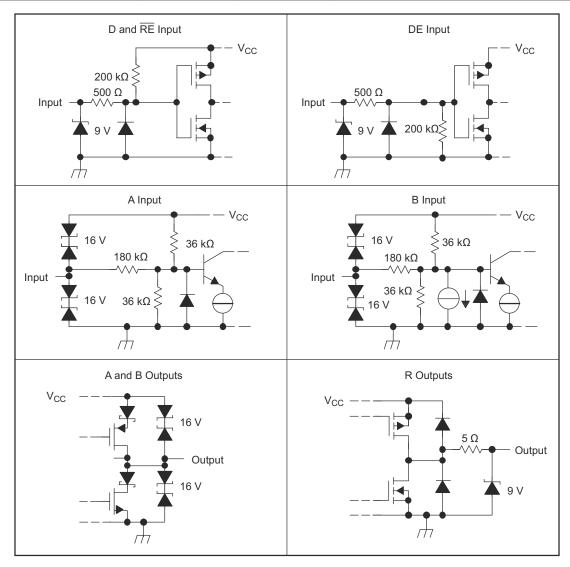

図 8-1. Equivalent Input and Output Schematic Diagrams

# 9 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 Application Information

The SN65HVD485E device is a half-duplex RS-485 transceiver commonly used for asynchronous data transmissions. The driver and receiver enable pins allow for configuration of different operating modes.

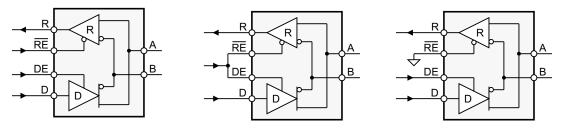

図 9-1. Half-Duplex Transceiver Configurations

Using independent enable lines provides the most flexible control as it allows for the driver and the receiver to be turned on and off individually. While this configuration requires two control lines, it allows for selective listening into the bus traffic whether the driver is transmitting data or not.

Combining the enable signals simplifies the interface to the controller by forming a single direction-control signal. In this configuration, the transceiver operates as a driver when the direction-control line is high and as a receiver when the direction-control line is low.

Additionally, only one line is required when connecting the receiver-enable input to ground and controlling only the driver-enable input. In this configuration, a node receives the data from the bus, receives the data it sends, and can verify that the correct data has been transmitted.

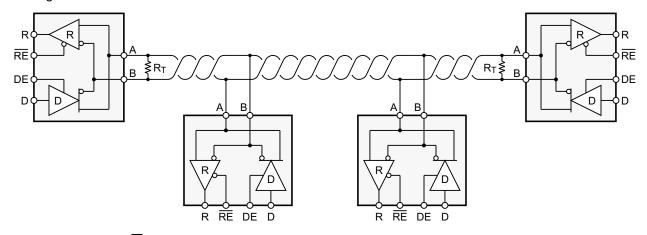

#### 9.2 Typical Application

An RS-485 bus consists of multiple transceivers connecting in parallel to a bus cable. To eliminate line reflections, each cable end is terminated with a termination resistor ( $R_T$ ) whose value matches the characteristic impedance ( $Z_0$ ) of the cable. This method, known as parallel termination, allows for higher data rates over longer cable length.

図 9-2. Typical RS-485 Network With Half-Duplex Transceivers

#### 9.2.1 Design Requirements

RS-485 is a robust electrical standard suitable for long-distance networking that can be used in a wide range of applications with varying requirements such as distance, data rate, and number of nodes.

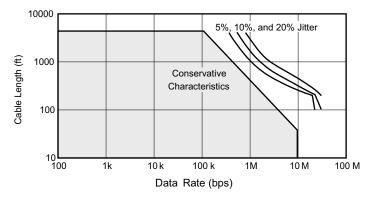

#### 9.2.1.1 Data Rate and Bus Length

There is an inverse relationship between data rate and bus length: the higher the data rate, the shorter the cable length, and conversely the lower the data rate, the longer the cable can be without introducing data errors. While most RS-485 systems use data rates between 10 kbps and 100 kbps, some applications require data rates up to 250 kbps at distances of 4000 feet and longer. Longer distances are possible by allowing for small signal jitter of up to 5 or 10%.

図 9-3. Cable Length vs Data Rate Characteristic

### 9.2.1.2 Stub Length

When connecting a node to the bus, the distance between the transceiver inputs and the cable trunk, known as the stub, must be as short as possible. Stubs present a nonterminated piece of bus line that can introduce reflections as the length of the stub increases. As a general guideline, the electrical length, or round-trip delay, of a stub must be less than one-tenth of the rise time of the driver; thus giving a maximum physical stub length as shown in  $\pm 1$ .

$$L_{stub} \le 0.1 \times t_r \times v \times c \tag{1}$$

#### where

- t<sub>r</sub> is the 10/90 rise time of the driver

- c is the speed of light  $(3 \times 10^8 \text{ m/s})$

- v is the signal velocity of the cable or trace as a factor of c

#### 9.2.1.3 Bus Loading

The RS-485 standard specifies that a compliant driver must be able to drive 32-unit loads (UL), where 1-unit load represents a load impedance of approximately 12 k $\Omega$ . Because the SN65HVD485E device is a ½ UL transceiver, it is possible to connect up to 64 receivers to the bus.

#### 9.2.1.4 Receiver Failsafe

The differential receiver of the SN65HVD485E device is failsafe to invalid bus states caused by the following:

- Open bus conditions such as a disconnected connector

- · Shorted bus conditions such as cable damage shorting the twisted pair together

- Idle bus conditions that occur when no driver on the bus is actively driving

In any of these cases, the differential receiver outputs a failsafe logic-high state so that the output of the receiver is not indeterminate.

English Data Sheet: SLLS612

Receiver failsafe is accomplished by offsetting the receiver thresholds such that the *input indeterminate* range does not include zero volts differential. To comply with the RS-422 and RS-485 standards, the receiver output must output a high when the differential input  $V_{ID}$  is more positive than 200 mV, and it must output a Low when  $V_{ID}$  is more negative than -200 mV. The receiver parameters that determine the failsafe performance are  $V_{IT+}$ ,  $V_{IT-}$ , and  $V_{hys}$  (the separation between  $V_{IT+}$  and  $V_{IT-}$ ). As shown in the TDIST > 7.6 table, differential signals more negative than -200 mV cause a low receiver output, and differential signals more positive than 200 mV cause a high receiver output.

When the differential input signal is close to zero, it is still above the  $V_{IT+}$  threshold, and the receiver output is High. Only when the differential input is more than  $V_{hys}$  below  $V_{IT+}$  does the receiver output transition to a Low state. Therefore, the noise immunity of the receiver inputs during bus fault conditions includes the receiver hysteresis value ( $V_{hys}$ ) as well as the value of  $V_{IT+}$ .

### 9.2.2 Detailed Design Procedure

To protect bus nodes against high-energy transients, the implementation of external transient protection devices is necessary.

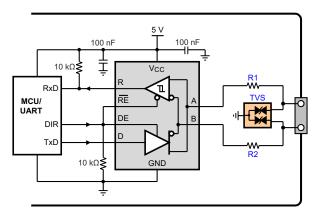

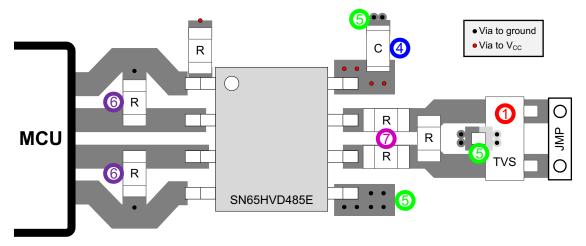

図 9-4. Transient Protection Against ESD, EFT, and Surge Transients

図 9-4 suggests a protection circuit against 10-kV ESD (IEC 61000-4-2), 4-kV EFT (IEC 61000-4-4), and 1-kV surge (IEC 61000-4-5) transients. 表 9-1 shows the associated bill of materials.

| DEVICE | FUNCTION                                 | ORDER NUMBER       | MANUFACTURER |

|--------|------------------------------------------|--------------------|--------------|

| XCVR   | 5-V, 10-Mbps RS-485<br>transceiver       | SN65HVD485E        | TI           |

| R1, R2 | 10-Ω, pulse-proof thick-film resistor    | CRCW0603010RJNEAHP | Vishay       |

| TVS    | Bidirectional 400-W transient suppressor | CDSOT23-SM712      | Bourns       |

表 9-1. Bill of Materials

#### 9.2.2.1 Power Usage in an RS-485 Transceiver

Power consumption is a concern in many applications. Power supply current is delivered to the bus load and to the transceiver circuitry. For a typical RS-485 bus configuration, the load that an active driver must drive consists of all of the receiving nodes plus the termination resistors at each end of the bus.

The load presented by the receiving nodes depends on the input impedance of the receiver. The TIA/EIA-485-A standard defines a unit load as allowing up to 1 mA. With up to 32 unit loads allowed on the bus, the total current supplied to all receivers can be as high as 32 mA. The SN65HVD485E device is rated as a ½ unit load device, so up to 64 can be connected on one bus.

The current in the termination resistors depends on the differential bus voltage. The standard requires active drivers to produce at least 1.5 V of differential signal. For a bus terminated with one standard  $120-\Omega$  resistor at

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

each end, this sums to 25-mA differential output current whenever the bus is active. Typically, the SN65HVD485E device can drive more than 25 mA to a  $60-\Omega$  load, which results in a differential output voltage higher than the minimum required by the standard (see  $\boxtimes$  7-2).

Supply current increases with signaling rate primarily because of the totem pole outputs of the driver. When these outputs change state, there is a moment when both the high-side and low-side output transistors are conducting, which creates a short spike in the supply current. As the frequency of state changes increases, more power is used.

#### 9.2.3 Application Curve

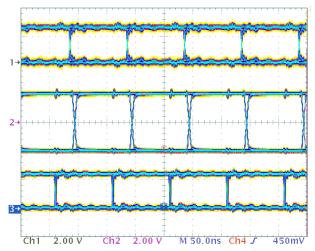

図 9-5. SN65HVD485E Single-Ended Input (Top), Differential Output (Middle), and Single-Ended Output (Bottom) at 10 MHz

#### 9.3 Power Supply Recommendations

To ensure reliable operation at all data rates and supply voltages, each supply must be decoupled with a 100-nF ceramic capacitor located as close as possible to the supply pins. This helps to reduce supply voltage ripple present on the outputs of switched-mode power supplies and also helps to compensate for the resistance and inductance of the PCB power planes.

English Data Sheet: SLLS612

#### 9.4 Layout

#### 9.4.1 Layout Guidelines

Robust and reliable bus-node design often requires the use of external transient-protection devices to protect against EFT and surge transients that may occur in industrial environments. Because these transients have a wide frequency bandwidth (from approximately 3 MHz to 3 GHz), high-frequency layout techniques must be applied during PCB design.

- 1. Place the protection circuitry close to the bus connector to prevent noise transients from entering the board.

- 2. Use V<sub>CC</sub> and ground planes to provide low-inductance power distribution. High-frequency currents tend to follow the path of least inductance and not the path of least resistance.

- 3. Design the protection components into the direction of the signal path. Do not force the transient currents to divert from the signal path to reach the protection device.

- 4. Apply 100-nF to 220-nF bypass capacitors as close as possible to the V<sub>CC</sub> pins of transceiver, UART, or controller ICs on the board.

- 5. Use at least two vias for V<sub>CC</sub> and ground connections of bypass capacitors and protection devices to minimize effective via inductance.

- 6. Use 1-k $\Omega$  to 10-k $\Omega$  pullup or pulldown resistors for enable lines to limit noise currents in these lines during transient events.

- 7. Insert series pulse-proof resistors into the A and B bus lines if the TVS clamping voltage is higher than the specified maximum voltage of the transceiver bus terminals. These resistors limit the residual clamping current into the transceiver and prevent it from latching up.

- 8. While pure TVS protection is sufficient for surge transients up to 1 kV, higher transients require metal-oxide varistors (MOVs), which reduces the transients to a few hundred volts of clamping voltage and transient blocking units (TBUs) that limit transient current to less than 1 mA.

## 9.4.2 Layout Example

図 9-6. Layout Example

## 10 Device and Documentation Support

## 10.1 Device Support

#### 10.1.1 Device Nomenclature

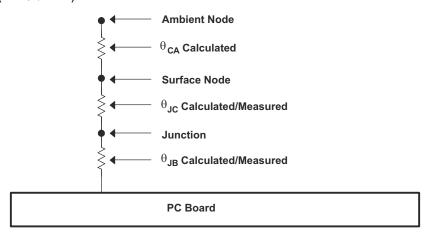

#### 10.1.1.1 Thermal Characteristics of IC Packages

$\theta_{JA}$  (Junction-to-Ambient Thermal Resistance) is defined as the difference in junction temperature to ambient temperature divided by the operating power

$\theta_{JA}$  is NOT a constant and is a strong function of

- the PCB design (50% variation)

- altitude (20% variation)

- device power (5% variation)

$\theta_{JA}$  can be used to compare the thermal performance of packages if the specific test conditions are defined and used. Standardized testing includes specification of PCB construction, test chamber volume, sensor locations, and the thermal characteristics of holding fixtures.  $\theta_{JA}$  is often misused when it is used to calculate junction temperatures for other installations.

TI uses two test PCBs as defined by JEDEC specifications. The low-k board gives average in-use condition thermal performance and consists of a single trace layer 25 mm long and 2-oz thick copper. The high-k board gives best case in-use condition and consists of two 1-oz buried power planes with a single trace layer 25 mm long with 2-oz thick copper. A 4% to 50% difference in  $\theta_{JA}$  can be measured between these two test cards

$\theta_{JC}$  (Junction-to-Case Thermal Resistance) is defined as difference in junction temperature to case divided by the operating power. It is measured by putting the mounted package up against a copper block cold plate to force heat to flow from die, through the mold compound into the copper block.

$\theta_{JC}$  is a useful thermal characteristic when a heatsink is applied to package. It is NOT a useful characteristic to predict junction temperature as it provides pessimistic numbers if the case temperature is measured in a non-standard system and junction temperatures are backed out. It can be used with  $\theta_{JB}$  in 1-dimensional thermal simulation of a package system.

$\theta_{JB}$  (Junction-to-Board Thermal Resistance) is defined to be the difference in the junction temperature and the PCB temperature at the center of the package (closest to the die) when the PCB is clamped in a cold-plate structure.  $\theta_{JB}$  is only defined for the high-k test card.

$\theta_{JB}$  provides an overall thermal resistance between the die and the PCB. It includes a bit of the PCB thermal resistance (especially for BGA's with thermal balls) and can be used for simple 1-dimensional network analysis of package system (see  $\boxtimes$  10-1).

図 10-1. Thermal Resistance

Product Folder Links: SN65HVD485E

## 10.2 Documentation Support

#### 10.2.1 Related Documentation

For related documentation see the following:

SZZA003, Package Thermal Characterization Methodologies

•

#### 10.3 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 10.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 10.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (0)  | (4)                           | (5)                        |              | (0)          |

| SN65HVD485EDGKR       | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | (NWH, NWJ)   |

| SN65HVD485EDGKR.A     | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 85    | (NWH, NWJ)   |

| SN65HVD485EDR         | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | VP485        |

| SN65HVD485EDR.A       | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | VP485        |

| SN65HVD485EDRG4       | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | VP485        |

| SN65HVD485EP          | Active | Production    | PDIP (P)   8    | 50   TUBE             | Yes  | NIPDAU                        | N/A for Pkg Type           | -40 to 85    | 65HVD485     |

| SN65HVD485EP.A        | Active | Production    | PDIP (P)   8    | 50   TUBE             | Yes  | NIPDAU                        | N/A for Pkg Type           | -40 to 85    | 65HVD485     |

| SN65HVD485EPE4        | Active | Production    | PDIP (P)   8    | 50   TUBE             | Yes  | NIPDAU                        | N/A for Pkg Type           | -40 to 85    | 65HVD485     |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Nov-2025

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-Jun-2025

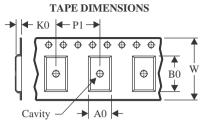

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

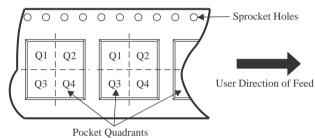

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65HVD485EDGKR | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.25       | 3.35       | 1.25       | 8.0        | 12.0      | Q1               |

| SN65HVD485EDR   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 11-Jun-2025

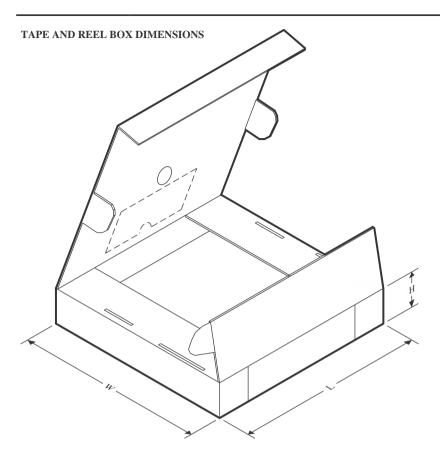

### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65HVD485EDGKR | VSSOP        | DGK             | 8    | 2500 | 366.0       | 364.0      | 50.0        |

| SN65HVD485EDR   | SOIC         | D               | 8    | 2500 | 340.5       | 336.1      | 25.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-Jun-2025

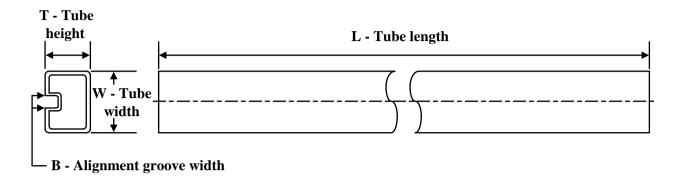

## **TUBE**

\*All dimensions are nominal

| Device         | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| SN65HVD485EP   | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| SN65HVD485EP.A | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| SN65HVD485EPE4 | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

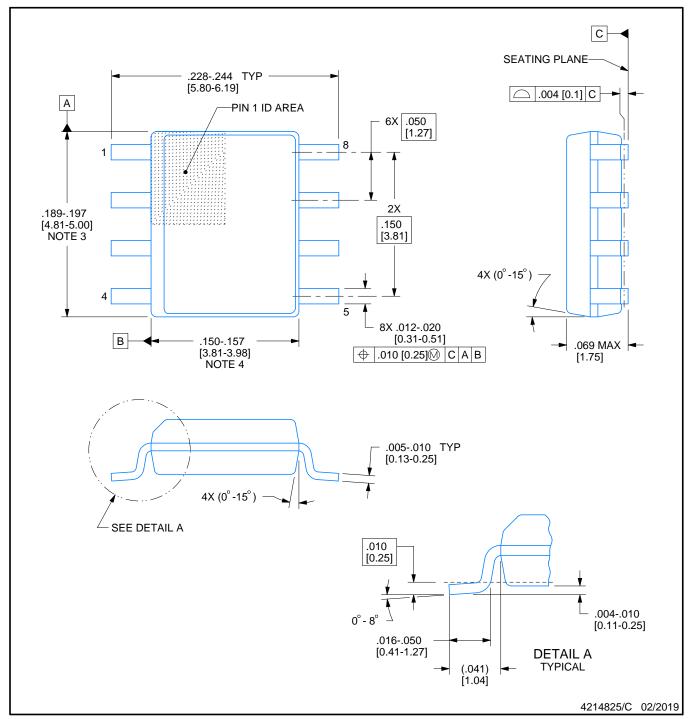

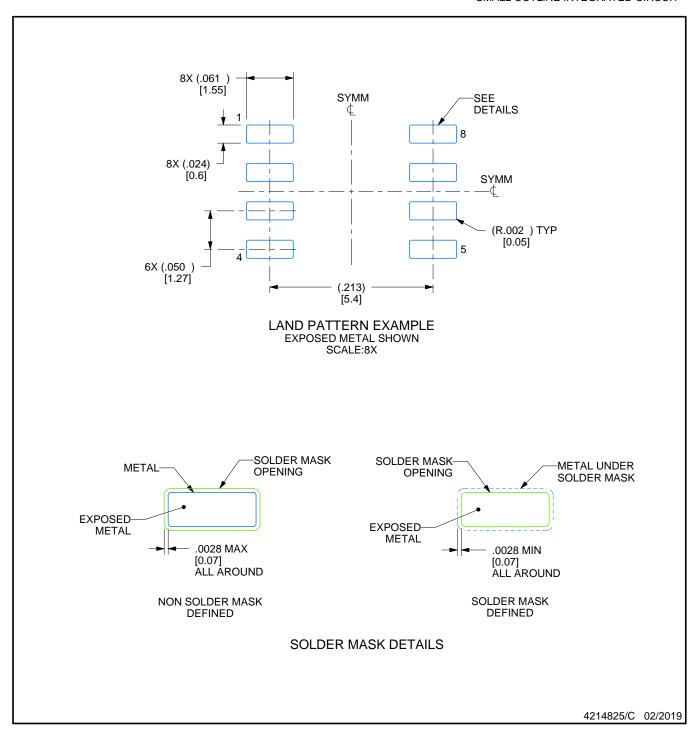

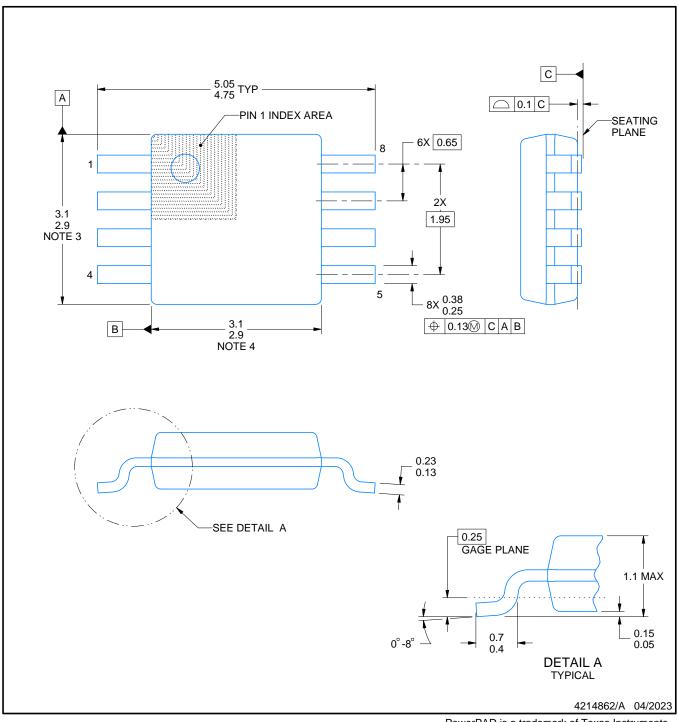

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

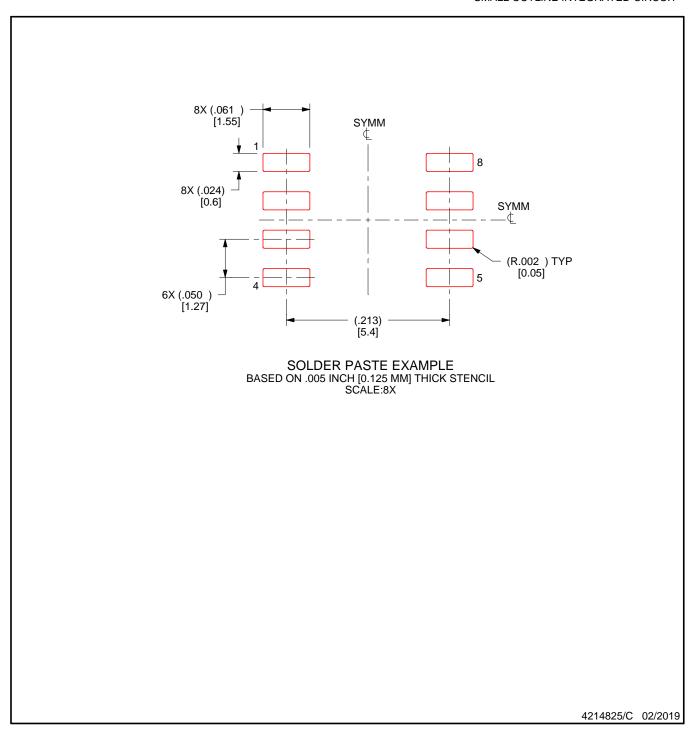

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

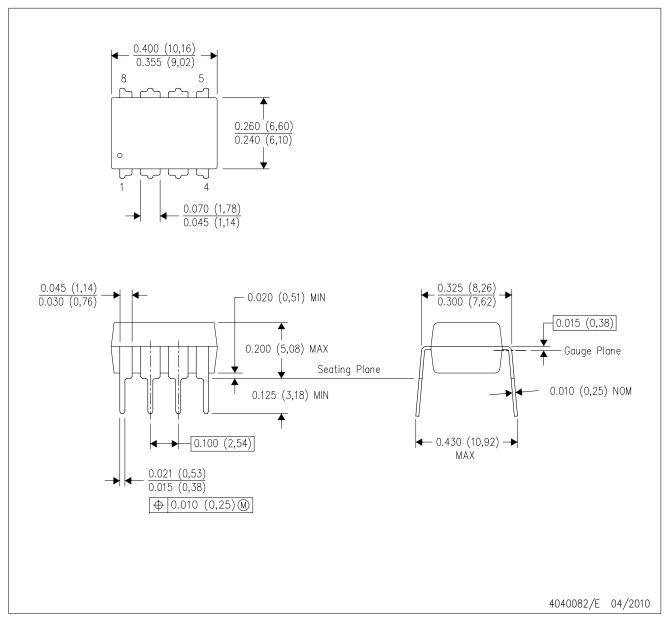

# P (R-PDIP-T8)

# PLASTIC DUAL-IN-LINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

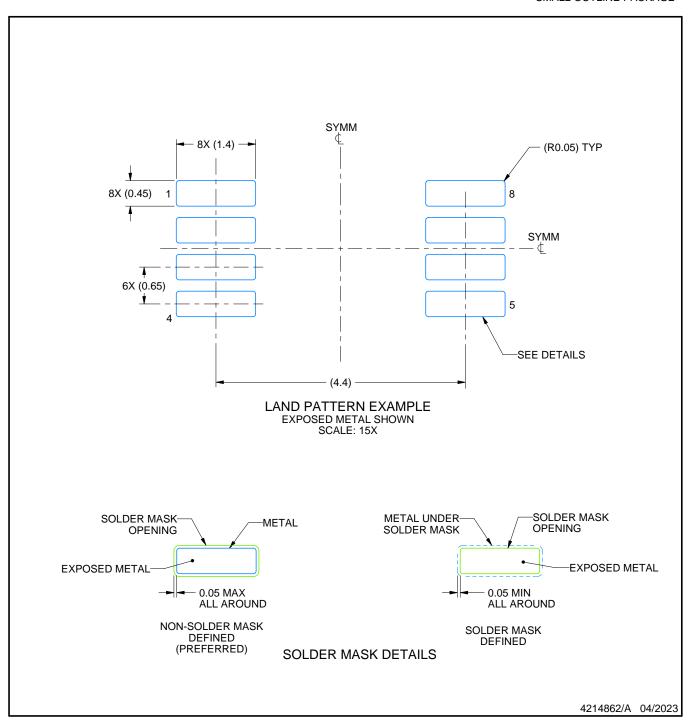

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

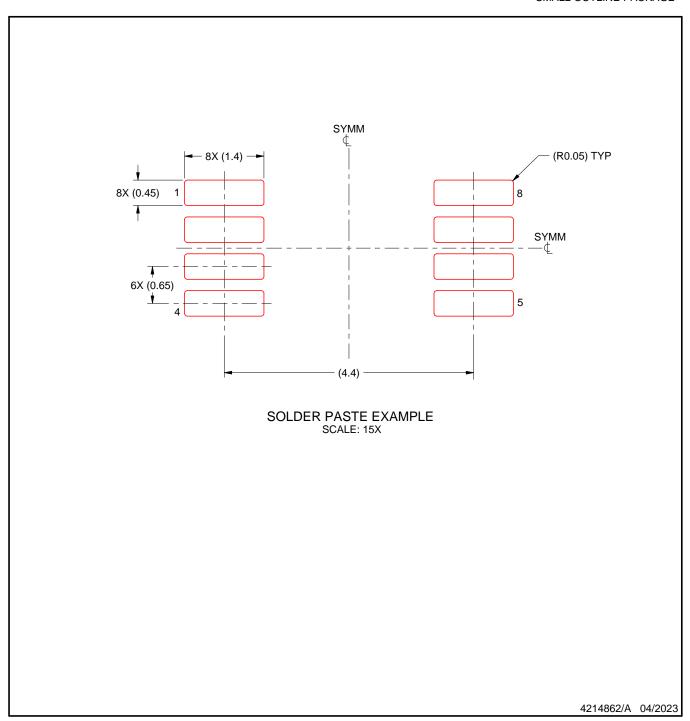

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日: 2025 年 10 月