SN6505A, SN6505B JAJSGI2I – SEPTEMBER 2015 – REVISED AUGUST 2023

# SN6505x 絶縁電源用、低ノイズ、1A 変圧器ドライバ

# 1 特長

- トランス用のプッシュプル・ドライバ

- 幅広い入力電圧範囲:2.25V~5.5V

- 高い出力駆動能力:5V 電源で 1A

- 低い R<sub>ON</sub>:4.5V 電源で最大値 0.25Ω

- 非常に低い EMI

- スペクトラム拡散クロック

- 高精度内部発振器のオプション: 160kHz (SN6505A) および 420kHz (SN6505B)

- 外部クロック入力により複数のデバイスを同期

- スルー・レート制御

- 1.7A の電流制限

- 低シャットダウン電流:1µA 未満

- サーマル・シャットダウン

- 幅広い温度範囲:-55℃~125℃

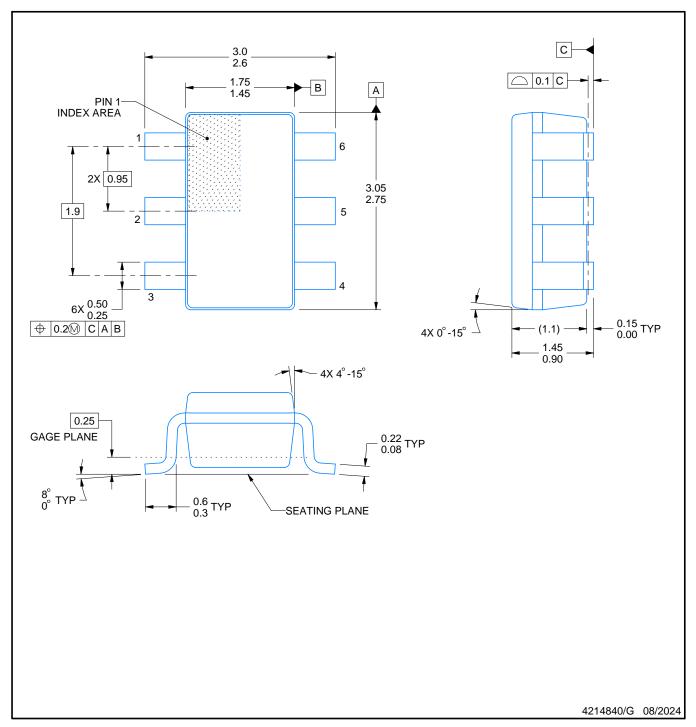

- 小型の 6 ピン SOT23 (DBV) パッケージ

- ソフトスタートにより突入電流を低減

# 2 アプリケーション

- CAN、RS-485、RS-422、RS-232、SPI、I2C、低消費 電力 LAN 用の絶縁電源

- 低ノイズの絶縁 USB 電源

- プロセス制御

- 電気通信用電源

- 無線用電源

- 分散電源

- 医療機器

- 高精度の計器

- 低ノイズのフィラメント用電源

# 3 概要

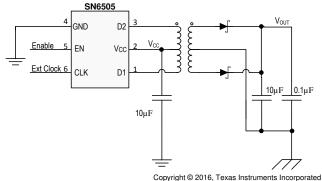

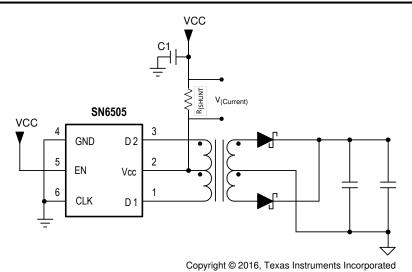

SN6505x は低ノイズ、低 EMI のプッシュプル変圧器ドライバで、小型の絶縁電源に特化して設計されています。低背のセンター・タップ付き変圧器を 2.25V~

5V の DC 電源で駆動できます。出力スイッチ電圧のスル ーレート制御と、スペクトラム拡散クロック (SSC) により、非 常に低いノイズと EMI を実現しています。 SN6505x は、 発振器と、それに続くゲート・ドライブ回路とで構成され、 ゲート・ドライブ回路はグランドを基準とする N チャネル電 源スイッチを駆動するための補完出力信号を供給します。 このデバイスには、重負荷時のスタートアップを保証する ため、2 つの 1A パワー MOSFET スイッチが内蔵されて います。スイッチャの高調波を正しく配置するため、または 複数の変圧器ドライバを使用して動作する場合に、スイッ チング・クロックを外部から供給することもできます。内部保 護機能として、1.7A の電流制限、低電圧誤動作防止、サ ーマル・シャットダウン、Break-Before-Make 回路が搭載 されています。SN6505x にはソフトスタート機能が搭載さ れており、大容量の負荷コンデンサに対して電源投入す る際に過大な突入電流の発生を防止します。SN6505A には、放射の最小化を必要とするアプリケーション向けに 160kHz の内部発振器が搭載されています。これに対し て、SN6505B には、高効率とサイズの小さい変圧器を必 要とするアプリケーション向けに 420kHz の内部発振器が 搭載されています。 SN6505x は、小型の 6 ピン SOT23/DBV パッケージで供給されます。このデバイス は、-55℃~125℃の温度範囲で動作が特性付けされて います。

## 製品情報

|         | 40KHH IFI TIX  |                        |  |

|---------|----------------|------------------------|--|

| 部品番号    | パッケージ          | 本体サイズ (公称)             |  |

| SN6505A | SOT23 (6 ピン)   | 2.90mm × 1.60mm        |  |

| SN6505B | 30123 (0 L > ) | 2.9011111 × 1.00111111 |  |

,

#### 概略回路図

# **Table of Contents**

| 1 特長                                        | 1               | 8.3 Feature Description                                               |      |

|---------------------------------------------|-----------------|-----------------------------------------------------------------------|------|

| 2 アプリケーション                                  | 1               | 8.4 Device Functional Modes                                           |      |

| 3 概要                                        | 1               | 9 Application and Implementation                                      |      |

| 4 Revision History                          |                 | 9.1 Application Information                                           |      |

| 5 Pin Configuration and Functions           |                 | 9.2 Typical Application                                               |      |

| 6 Specifications                            | 4               | 10 Power Supply Recommendations                                       |      |

| 6.1 Absolute Maximum Ratings                | 4               | 11 Layout                                                             | 34   |

| 6.2 ESD Ratings                             |                 | 11.1 Layout Guidelines                                                |      |

| 6.3 Recommended Operating Conditions        |                 | 11.2 Layout Example                                                   |      |

| 6.4 Thermal Information                     |                 | 12 Device and Documentation Support                                   |      |

| 6.5 Electrical Characteristics              |                 | 12.1 Device Support                                                   |      |

| 6.6 Timing Requirements                     |                 | 12.2 Documentation Support                                            |      |

| 6.7 Typical Characteristics, SN6505A        |                 | 12.3 Related Links                                                    |      |

| 6.8 Typical Characteristics, SN6505B        |                 | 12.4 Receiving Notification of Documentation 12.5 Community Resources |      |

| 7 Parameter Measurement Information         |                 | 12.6 Trademarks                                                       |      |

| 8 Detailed Description                      |                 | 13 Mechanical, Packaging, and Orderable                               | 55   |

| 8.1 Overview8.2 Functional Block Diagram    |                 | Information                                                           | 35   |

| 4 Revision History                          |                 |                                                                       |      |

| Changes from Revision H (July 2019) to Rev  | vision I (      | August 2023)                                                          | Page |

| • セクション 6.8, added new graphs               |                 |                                                                       | 9    |

| • Added new transformers to 表 9-3           |                 |                                                                       | 28   |

| Changes from Revision G (November 2018)     |                 |                                                                       |      |

| • Added HCT-SM-1.3-8-2 transformer to 表 9   | -3              |                                                                       | 28   |

| • Added EPC3668G-LF transformer to 表 9-3    | table           |                                                                       | 28   |

|                                             |                 |                                                                       |      |

|                                             |                 |                                                                       |      |

| Changes from Revision F (September 2016)    | to Revis        | sion G (November 2018)                                                | Page |

| <ul><li>ドキュメント全体を通して編集上の修正と変更を</li></ul>    | <br>シ実施         |                                                                       | 1    |

|                                             |                 | section                                                               |      |

| ·                                           |                 | 9.2.2.1 section                                                       |      |

| ·                                           |                 |                                                                       |      |

|                                             |                 | 40 in セクション 9.2.2.3 section                                           |      |

|                                             |                 | for SN6505B in セクション 9.2.2.5.1 section and                            |      |

|                                             |                 | I <sub>D-max</sub> values and updated 式 11 in セクション 9                 |      |

|                                             |                 | DER NO. 750313638 and 750313626 in 表 9-3                              |      |

| •                                           |                 |                                                                       |      |

|                                             |                 |                                                                       |      |

| Changed the Electrostatic Discharge Caution | on statem       | ent                                                                   | 35   |

| Changes from Revision E (August 2016) to    |                 | ·····                                                                 | Page |

| Changed text From: "connected as possible   | ∍" To: "cor<br> | nnected as close as possible" in セクション 10 .                           | 33   |

| Changes from Revision D (August 2016) to    | Revision        | E (August 2016)                                                       | Page |

| • Changed 表 9-3, and added Note 1           |                 |                                                                       | 28   |

| Changes from Revision C (August 2016) to Revision D (August 2016)           | Page |

|-----------------------------------------------------------------------------|------|

| • セクション 6.7, added 図 6-1 and 図 6-2 back into the datasheet                  | 7    |

| • セクション 6.7, added 図 6-9 to 図 6-47 back into the datasheet                  | 7    |

| • セクション 6.8, added 図 6-11 and 図 6-12 back into the data sheet               | 9    |

| • セクション 6.8, added 図 6-45 and 図 6-46 back into the data sheet               | 9    |

| • Changed 表 9-3                                                             | 28   |

| Changes from Revision B (February 2016) to Revision C (August 2016)         | Page |

| • Changed the セクション 6.7 section                                             | 7    |

| • Added the セクション 6.8 section                                               |      |

| • Changed 表 9-3                                                             |      |

| Changes from Revision A (October 2015) to Revision B (February 2016)        | Page |

| • Changed the セクション 6.4 table From: 16 Pin DW (SOIC) To: 6 Pin DBV (SOT-23) | 4    |

| Changes from Revision * (September 2015) to Revision A (October 2015)       | Page |

| <ul><li>製品リリース</li></ul>                                                    | 1    |

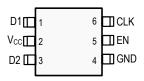

# **5 Pin Configuration and Functions**

図 5-1. DBV Package SOT-23 (6 Pin) Top View

表 5-1. Pin Functions

|                 | PIN |                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                          |

|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | TYPE                                                                                                                                                                                                         | DESCRIPTION                                                                                                                                                                                                          |

| D1              | 1   | 0                                                                                                                                                                                                            | Open drain output of the first power MOSFETs. Typically connected to the outer terminals of the center tap transformer. Because large currents flow through these pins, their external traces should be kept short.  |

| V <sub>CC</sub> | 2   | P This is the device supply pin. It should be bypassed with a 4.7 µF or greater, low ESR capaci<br>When V <sub>CC</sub> ≤ 2.25 V, an internal undervoltage lockout circuit trips and turns both outputs off. |                                                                                                                                                                                                                      |

| D2              | 3   | 0                                                                                                                                                                                                            | Open drain output of the second power MOSFETs. Typically connected to the outer terminals of the center tap transformer. Because large currents flow through these pins, their external traces should be kept short. |

| GND             | 4   | Р                                                                                                                                                                                                            | GND is connected to the source of the power MOSFET switches via an internal sense circuit. Because large currents flow through it, the GND terminals must be connected to a low-inductance quality ground plane.     |

| EN              | 5   | ı                                                                                                                                                                                                            | The EN pin turns the device on or off. Grounding or leaving this pin floating disables all internal circuitry. If unused this pin should be tied directly to $V_{CC}$ .                                              |

| CLK             | 6   | ı                                                                                                                                                                                                            | This pin is used to run the device with external clock. Internally it is pulled down to GND. If valid clock is not detected on this pin, the device shifts automatically to internal clock.                          |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>. All typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC} = 5$  V.

|                                      |                                           | MIN  | MAX                  | UNIT |

|--------------------------------------|-------------------------------------------|------|----------------------|------|

| Supply voltage (2)                   | V <sub>CC</sub>                           | -0.5 | 6                    | V    |

| Voltage                              | EN, CLK                                   | -0.5 | $V_{CC} + 0.5^{(3)}$ |      |

| Output switch voltage                | D1, D2                                    |      | 16                   | V    |

| Peak output switch current           | I <sub>(D1)Pk</sub> , I <sub>(D2)Pk</sub> |      | 2.4                  | А    |

| Junction temperature, T <sub>J</sub> |                                           | -55  | 150                  | °C   |

| Storage temperature range            | , T <sub>stg</sub>                        | -65  | 150                  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under セクション 6.3 is not implied. Exposure to absolute-maximum-rated conditions for extended periods affects device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±6000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

|                                   |                                      |                                  | MIN  | TYP | MAX  | UNIT |

|-----------------------------------|--------------------------------------|----------------------------------|------|-----|------|------|

| V <sub>CC</sub>                   | Supply voltage                       |                                  | 2.25 |     | 5.5  | V    |

|                                   | Output switch current - Primary side | 2.25 V < V <sub>CC</sub> < 2.8 V |      |     | 0.75 | ۸    |

| I <sub>D1</sub> , I <sub>D2</sub> | Output switch current - Filmary side | 2.8 V < V <sub>CC</sub> < 5.5 V  |      |     | 1    | ^    |

| T <sub>A</sub>                    | Ambient temperature                  |                                  | -55  |     | 125  | °C   |

## 6.4 Thermal Information

|                         | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT-23) | UNIT |

|-------------------------|----------------------------------------------|--------------|------|

|                         |                                              | 6 PINS       |      |

| $R_{\theta JA}$         | Junction-to-ambient thermal resistance       | 137.7        | °C/W |

| R <sub>0JC(top)</sub>   | Junction-to-case (top) thermal resistance    | 57.7         | °C/W |

| $R_{\theta JB}$         | Junction-to-board thermal resistance         | 46.0         | °C/W |

| Ψ <sub>JT</sub>         | Junction-to-top characterization parameter   | 13.4         | °C/W |

| ΨЈВ                     | Junction-to-board characterization parameter | 44.9         | °C/W |

| $R_{\theta JC(bottom)}$ | Junction-to-case(bottom) thermal resistance  | N/A          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>2)</sup> All voltage values except differential I/O bus voltages are with respect to the local ground terminal (GND) and are peak voltage values.

<sup>(3)</sup> Maximum voltage of 6V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.5 Electrical Characteristics**

over full-range of recommended operating conditions, unless otherwise noted. All typical values are at  $T_A$  = 25°C,  $V_{CC}$  = 5 V.

|                                              | PARAMETER                                                 | TEST CONDITIONS                                              | MIN  | TYP  | MAX  | UNIT            |

|----------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|------|------|------|-----------------|

| VOLTAGE S                                    | UPPLY                                                     |                                                              |      | ·    |      |                 |

| 1                                            | Supply Current (2.8 V < V <sub>C C</sub> < 5.5) (SN6505A) | R <sub>L</sub> = 50 Ω                                        |      | 1    | 1.4  | mA              |

| I <sub>(Vcc)</sub>                           | Supply Current (2.8 V < V <sub>C C</sub> < 5.5) (SN6505B) | R <sub>L</sub> = 50 Ω                                        |      | 1.56 | 2.3  | mA              |

| I <sub>IH</sub>                              | Leakage Current on EN and CLK pin                         | EN / CLK = V <sub>CC</sub>                                   |      | 10   | 20   | μΑ              |

| I <sub>DIS</sub>                             | V <sub>CC</sub> current for EN = 0                        |                                                              |      | 0.1  |      | μΑ              |

| I <sub>LKG(D1)</sub><br>I <sub>LKG(D2)</sub> | Leakage Current on D1,D2 for EN=0                         | Voltage of D1,D2 = V <sub>CC</sub>                           |      | 0.1  |      | μΑ              |

| V <sub>CC+ (UVLO)</sub>                      | Positive-going UVLO threshold                             |                                                              |      |      | 2.25 | V               |

| V <sub>CC- (UVLO)</sub>                      | Negative-going UVLO threshold                             |                                                              | 1.7  |      |      | V               |

| V <sub>HYS (UVLO1)</sub>                     | UVLO threshold hysteresis                                 |                                                              |      | 0.3  |      | V               |

| V <sub>IN(ON)</sub>                          | EN, CLK pin logic high threshold                          |                                                              |      |      | 0.7  | V <sub>CC</sub> |

| V <sub>IN(OFF)</sub>                         | EN, CLK pin logic low threshold                           |                                                              | 0.3  |      |      | $V_{CC}$        |

| V <sub>IN(HYS)</sub>                         | EN, CLK pin threshold hysteresis                          |                                                              |      | 0.2  |      | V <sub>CC</sub> |

| CLK                                          |                                                           |                                                              |      |      |      |                 |

| Г                                            | D1, D2 average switching Frequency (SN6505A)              | $R_L$ = 50 Ω to $V_{CC}$ ; Refer to $\boxtimes$ 7-3          | 138  | 160  | 203  | Khz             |

| F <sub>SW</sub>                              | D1, D2 average switching Frequency (SN6505B)              | $R_L$ = 50 Ω to $V_{CC}$ ; Refer to $\boxtimes$ 7-3.         | 363  | 424  | 517  | kHz             |

| _                                            | External clock frequency on CLK pin (SN6505A)             |                                                              | 100  |      | 600  | kHz             |

| F <sub>(EXT)</sub>                           | External clock frequency on CLK pin (SN6505B)             |                                                              | 100  |      | 1600 | kHz             |

| OUTPUT ST                                    | AGE                                                       |                                                              |      |      |      |                 |

| DMM                                          | Average ON time mismatch between D1 and D2                | R <sub>L</sub> = 50 Ω                                        |      | 0%   |      |                 |

|                                              |                                                           | V <sub>CC</sub> = 4.5 V, ID1,ID2 = 1 A                       |      | 0.16 | 0.25 | Ω               |

| R <sub>(ON)</sub>                            | Output switch on resistance                               | V <sub>CC</sub> = 2.8 V, ID1,ID2 = 1 A                       |      | 0.19 | 0.31 | Ω               |

|                                              |                                                           | V <sub>CC</sub> = 2.25 V, ID1,ID2 = 0.5 A                    |      | 0.21 | 0.45 | Ω               |

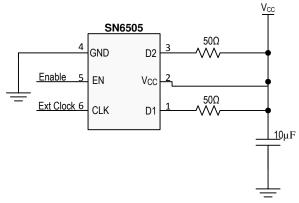

| V <sub>(SLEW)</sub>                          | Voltage slew rates on D1 and D2 for SN6505A               | $R_L$ = 50 Ω to $V_{CC}$ ; Refer to $\boxtimes$ 7-3          |      | 48   |      | V/µs            |

| I <sub>(SLEW)</sub>                          | Current slew rates at D1 and D2 for SN6505A               | $R_L$ = 5 Ω through transformer;<br>Refer to $\boxtimes$ 7-4 |      | 11   |      | A/µs            |

| V <sub>(SLEWHF)</sub>                        | Voltage slew rates on D1 and D2 for SN6505B               | $R_L$ = 50 Ω to $V_{CC}$ ; Refer to $\boxtimes$ 7-3          |      | 152  |      | V/µs            |

| I <sub>(SLEWHF)</sub>                        | Current slew rates at D1 and D2 for SN6505B               | R <sub>L</sub> = 5 Ω through transformer;<br>Refer to ⊠ 7-4  |      | 41   |      | A/µs            |

| 1                                            | Current clamp limit (2.8 V < V <sub>CC</sub> < 5.5V )     |                                                              | 1.42 | 1.75 | 2.15 | Α               |

| I <sub>LIM</sub>                             | Current clamp limit (2.25 V < V <sub>CC</sub> < 2.8 V)    |                                                              | 0.65 |      | 1.85 | Α               |

| THERMAL S                                    | SHUT DOWN                                                 | 1                                                            | 1    |      | l    |                 |

| T <sub>SD+</sub>                             | T <sub>SD</sub> turn on temperature                       |                                                              | 154  | 168  | 181  | °C              |

| T <sub>SD-</sub>                             | T <sub>SD</sub> turn off temperature                      |                                                              | 135  | 150  | 166  | °C              |

| T <sub>SD-</sub>                             | T <sub>SD</sub> hysteresis                                |                                                              | 13   | 17   |      | °C              |

|                                              | 1                                                         | I .                                                          | 1    |      |      |                 |

# **6.6 Timing Requirements**

|                       |                                        |                                                                                                                            | MIN | NOM  | MAX | UNIT |

|-----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| CLK                   |                                        | ,                                                                                                                          |     |      |     |      |

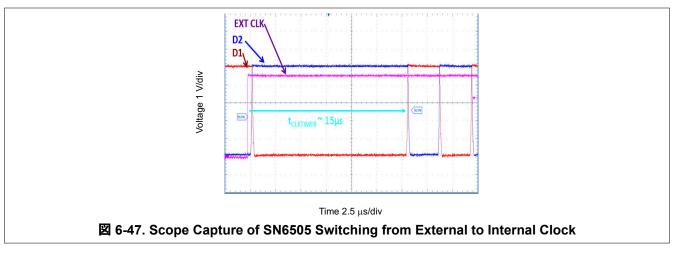

| t <sub>CLKTIMER</sub> | Duration after which device such clock | vitches to internal clock in case of invalid external                                                                      | 10  |      | 25  | μs   |

| OUTPUT                | STAGE                                  | ,                                                                                                                          |     |      | -   |      |

|                       | Break-before-make time (SN6505A)       | Measured as voltage with R <sub>L</sub> = 50 $\Omega$ to V <sub>CC</sub> , Refer to $\boxtimes$ 7-3                        |     | 115  |     | ns   |

| t <sub>BBM</sub>      | Break-before-make time (SN6505B)       | Measured as voltage with R <sub>L</sub> = 50 $\Omega$ to V <sub>CC</sub> , Refer to $\boxtimes$ 7-3                        |     | 90   |     | ns   |

| SOFT-STA              | ART                                    |                                                                                                                            |     |      | 1   |      |

| t <sub>SS</sub>       | Soft-start time                        | 10% to 90% transition time on V <sub>OUT</sub> With transformer C <sub>LOAD</sub> = 40 $\mu$ F R <sub>L</sub> = 5 $\Omega$ | 1   | 4.25 | 8   | ms   |

| t <sub>SSdelay</sub>  | Soft-start time delay                  | From power up to 90% transition time on $V_{OUT}$ With transformer $C_{LOAD}$ = 40 $\mu F$ $R_L$ = 5 $\Omega$              | 3.5 | 8.5  | 18  | ms   |

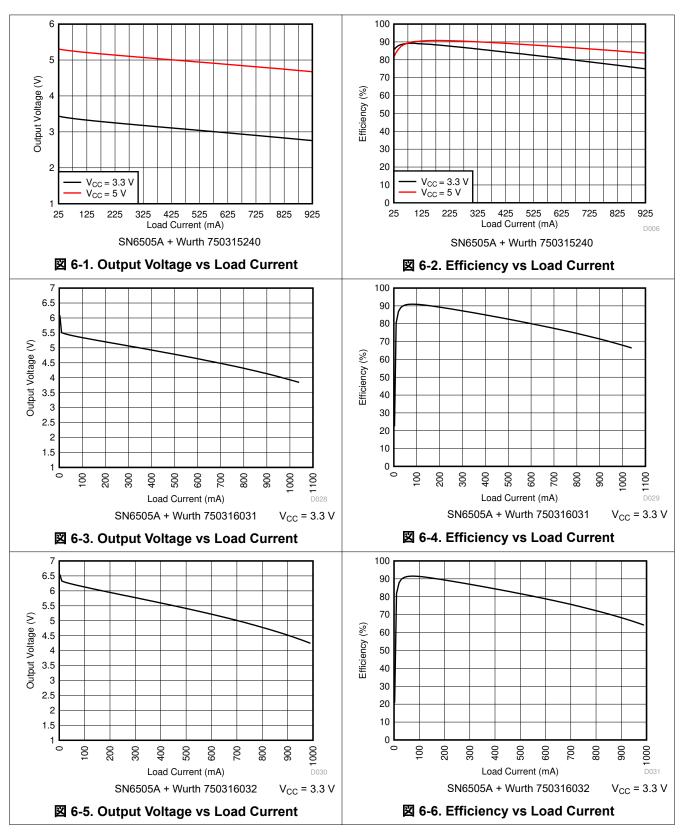

# 6.7 Typical Characteristics, SN6505A

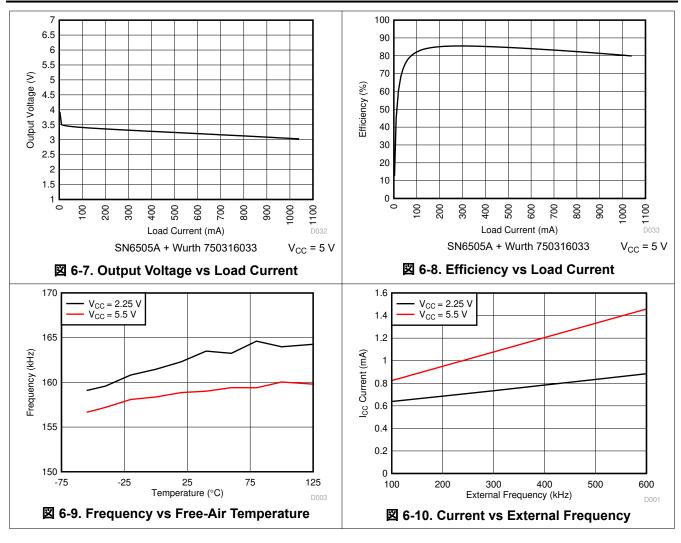

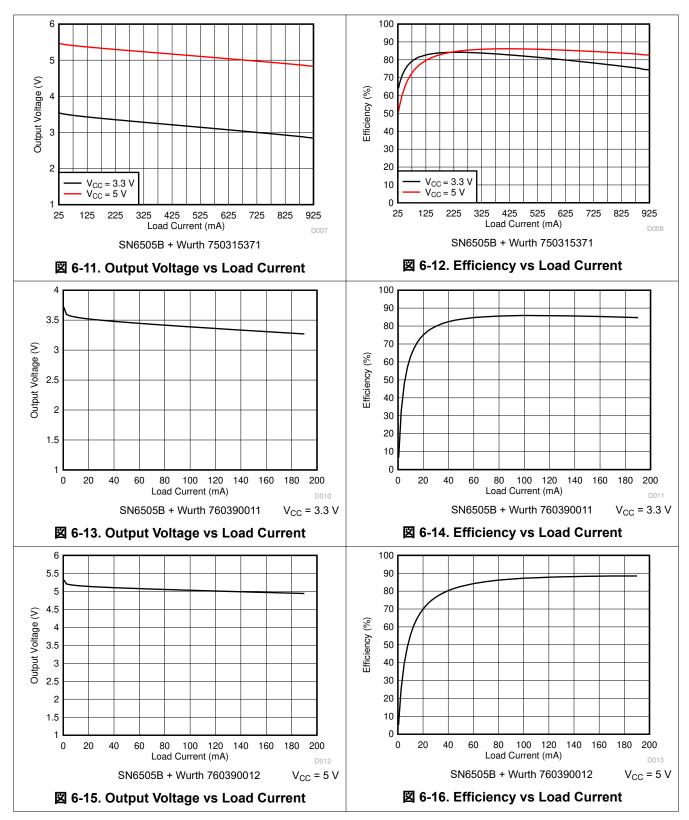

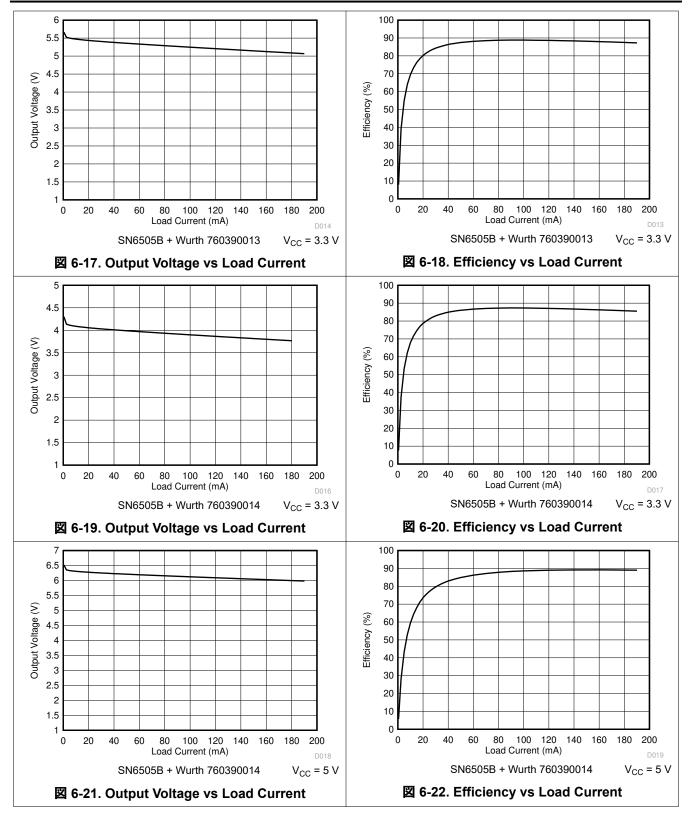

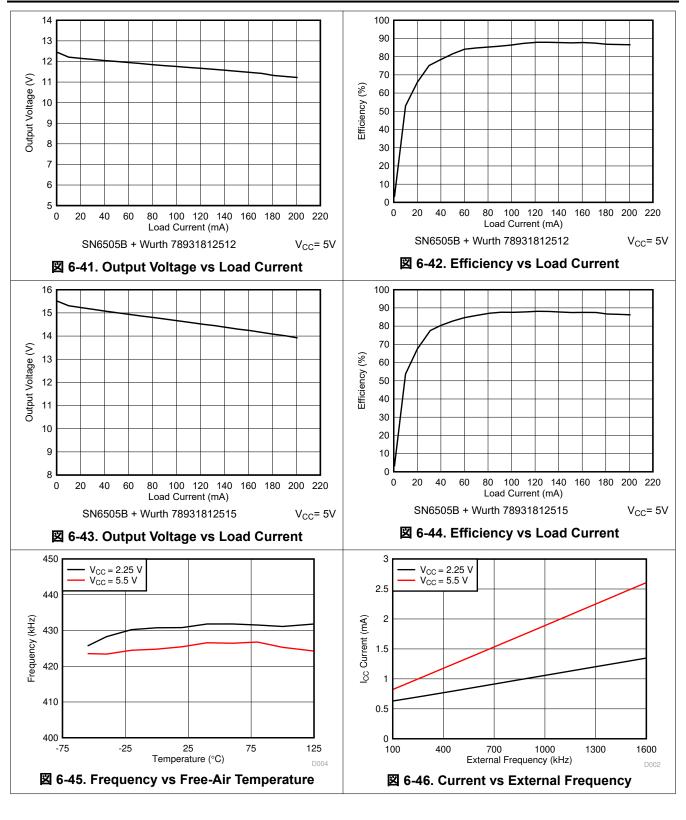

# 6.8 Typical Characteristics, SN6505B

# 7 Parameter Measurement Information

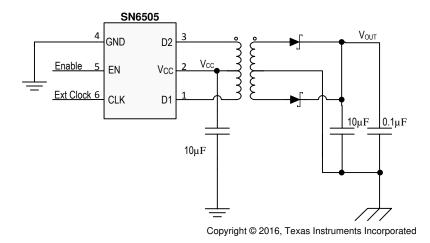

図 7-1. Measurement Circuit for Unregulated Output (TP1)

図 7-2. Timing Diagram

Copyright © 2016, Texas Instruments Incorporated

図 7-3. Test Circuit for F<sub>SW</sub>, V<sub>(slew)</sub>, t<sub>BBM</sub>

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

図 7-4. I<sub>(slew)</sub> Test Setup

# **8 Detailed Description**

## 8.1 Overview

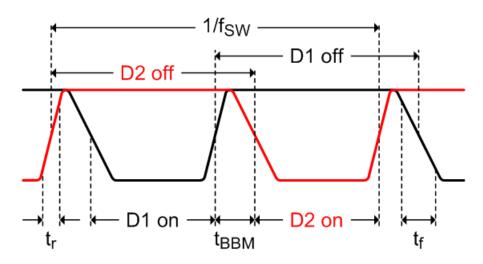

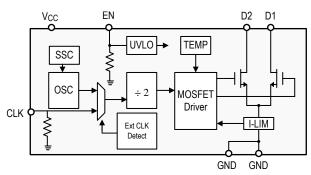

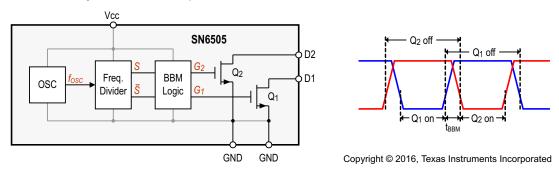

The SN6505 is a transformer driver designed for low-cost, small form-factor, isolated DC/DC converters utilizing the push-pull topology. The device includes an oscillator that feeds a gate-drive circuit. The gate-drive, comprising a frequency divider and a break-before-make (BBM) logic, provides two complementary output signals which alternately turn the two output transistors on and off.

The output frequency of the oscillator is divided down by two . A subsequent break-before-make logic inserts a dead-time between the high-pulses of the two signals. Before either one of the gates can assume logic high, the BBM logic ensures a short time period during which both signals are low and both transistors are high-impedance. This short period, is required to avoid shorting out both ends of the primary. The resulting output signals, present the gate-drive signals for the output transistors.

## 8.2 Functional Block Diagram

## 8.3 Feature Description

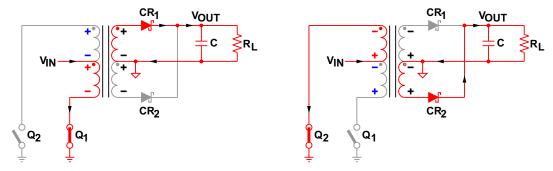

## 8.3.1 Push-Pull Converter

Push-pull converters require transformers with center-taps to transfer power from the primary to the secondary (see  $\boxtimes$  8-1).

図 8-1. Switching Cycles of a Push-Pull Converter

When  $Q_1$  conducts,  $V_{IN}$  drives a current through the lower half of the primary to ground, thus creating a negative voltage potential at the lower primary end with regards to the  $V_{IN}$  potential at the center-tap.

At the same time the voltage across the upper half of the primary is such that the upper primary end is positive with regards to the center-tap in order to maintain the previously established current flow through  $Q_2$ , which now has turned high-impedance. The two voltage sources, each of which equaling  $V_{IN}$ , appear in series and cause a voltage potential at the open end of the primary of  $2 \times V_{IN}$  with regards to ground.

Per dot convention the same voltage polarities that occur at the primary also occur at the secondary. The positive potential of the upper secondary end therefore forward biases diode  $CR_1$ . The secondary current starting from the upper secondary end flows through  $CR_1$ , charges capacitor C, and returns through the load impedance  $R_L$  back to the center-tap.

When  $Q_2$  conducts,  $Q_1$  goes high-impedance and the voltage polarities at the primary and secondary reverse. Now the lower end of the primary presents the open end with a  $2 \times V_{IN}$  potential against ground. In this case  $CR_2$  is forward biased while  $CR_1$  is reverse biased and current flows from the lower secondary end through  $CR_2$ , charging the capacitor and returning through the load to the center-tap.

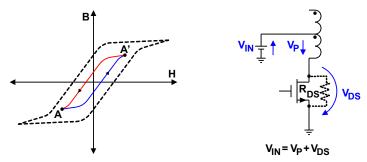

## 8.3.2 Core Magnetization

図 8-2. Core Magnetization and Self-Regulation Through Positive Temperature Coefficient of R<sub>DS(on)</sub>

This volt-seconds (V-t) product is important as it determines the core magnetization during each switching cycle. If the V-t products of both phases are not identical, an imbalance in flux density swing results with an offset from the origin of the B-H curve. If balance is not restored, the offset increases with each following cycle and the transformer slowly creeps toward the saturation region.

#### 8.4 Device Functional Modes

The functional modes of the device are divided into start-up, operating, and off-mode.

## 8.4.1 Start-Up Mode

When the supply voltage at  $V_{CC}$  ramps up to 2.25 V , the internal oscillator starts operating . The output stage begins switching but the amplitude of the drain signals at D1 and D2 has not reached its full maximum yet.

#### 8.4.1.1 Soft-Start

SN6505A and SN6505B devices support soft-start feature. Upon power up or when EN pin transitions from Low to High, the gate drive of the output power-MOSFET is gradually increased over a period of time from 0 V to  $V_{CC}$ . Soft-start prevents high inrush current from  $V_{CC}$  while charging large secondary side decoupling capacitors, and also prevents overshoot in secondary voltage during power-up.

## 8.4.2 Operating Mode

When the device supply has reached its nominal value ±10% the oscillator is fully operating. However variations over supply voltage and operating temperature can vary the switching frequencies at D1 and D2.

#### 8.4.3 Shutdown-Mode

The device has a dedicated enable pin to put the device in very low power mode to save power when not in use. Enable pin has an internal pull down resistor which keeps device disabled when not driven. When disabled or when  $V_{CC}$  is < 1.7 V, both drain outputs, D1 and D2, are tri-stated.

## 8.4.4 Spread Spectrum Clocking

Radiated emissions is an important concern in high current switching power supplies. SN6505 addresses this by modulating its internal clock in such a way that the emitting energy is spread over multiple frequency bins. This Spread Spectrum clocking feature greatly improves the emissions performance of the entire power supply block and hence relieves the system designer from one major concern in isolated power supply design.

## 8.4.5 External Clock Mode

The SN6505 has a CLK pin which can be used to synchronize the device with system clock and in turn with other SN6505 devices so that the system can control the exact switching frequency of the device. The Rising edge of the CLK is used to divide a clock by two and used to drive the gates.  $\boxtimes$  9-2 shows the timing diagram for the same. The device also has external clock fail safe feature which automatically switches the device to the internal clock if a valid input clock is not present for long (t<sub>CLKTIMER</sub>). The in-built emissions reduction scheme of Spread Spectrum clocking is disabled when external clock is present.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 9.1 Application Information

The SN6505 is a transformer driver designed for low-cost, small form-factor, isolated DC/DC converters using the push-pull topology. The device includes an oscillator that feeds a gate-drive circuit. The gate-drive, comprising a frequency divider and a break-before-make (BBM) logic, provides two complementary output signals which alternately turn the two output transistors on and off.

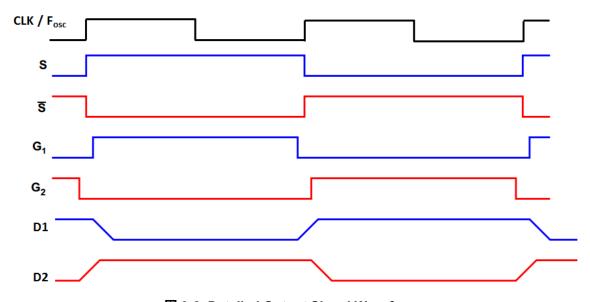

図 9-1. Block Diagram and Output Timing With Break-Before-Make Action

The output frequency of the oscillator is divided down by an asynchronous divider that provides two complementary output signals, S and  $\overline{S}$ , with a 50% duty cycle. A subsequent break-before-make logic inserts a dead-time between the high-pulses of the two signals. The resulting output signals,  $G_1$  and  $G_2$ , present the gate-drive signals for the output transistors  $Q_1$  and  $Q_2$ . As shown in  $\mathbb{Z}$  9-2, before either one of the gates can assume logic high, there must be a short time period during which both signals are low and both transistors are high-impedance. This short period, known as break-before-make time, is required to avoid shorting out both ends of the primary.

図 9-2. Detailed Output Signal Waveforms

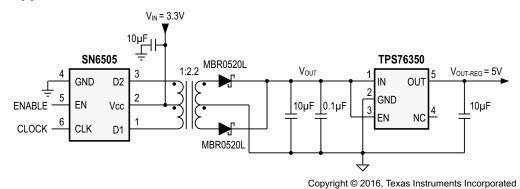

# 9.2 Typical Application

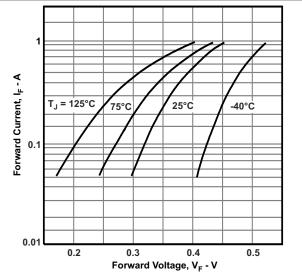

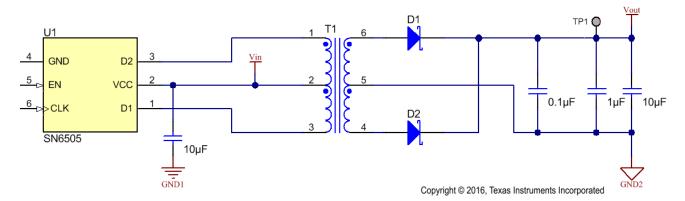

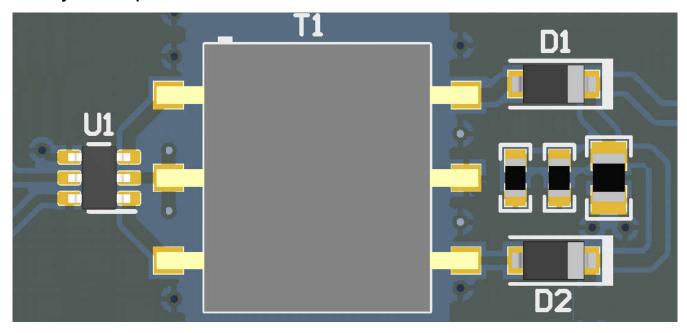

図 9-3. Typical Application Schematic

# 9.2.1 Design Requirements

For this design example, use the parameters listed in 表 9-1 as design parameters.

| <b></b>              |               |  |  |  |

|----------------------|---------------|--|--|--|

| DESIGN PARAMETER     | EXAMPLE VALUE |  |  |  |

| Input voltage range  | 3.3 V ± 3%    |  |  |  |

| Output voltage       | 5 V           |  |  |  |

| Maximum load current | 100 mA        |  |  |  |

表 9-1. Design Parameters

## 9.2.2 Detailed Design Procedure

The following recommendations on components selection focus on the design of an efficient push-pull converter with high current drive capability. Contrary to popular belief, the output voltage of the unregulated converter output drops significantly over a wide range in load current. The characteristic curve in  $\boxtimes$  6-11 and  $\boxtimes$  6-11 for example, shows that the difference between  $V_{OUT}$  at minimum load and  $V_{OUT}$  at maximum load exceeds a transceiver's supply range. Therefore, in order to provide a stable, load independent supply while maintaining maximum possible efficiency the implementation of a low dropout regulator (LDO) is strongly advised.

The final converter circuit is shown in  $\boxtimes$  9-8. The measured  $V_{OUT}$  and efficiency characteristics for the regulated and unregulated outputs are shown in  $\boxtimes$  6-2 and  $\boxtimes$  6-12.

# 9.2.2.1 Drive Capability

The transformer driver is designed for low-power push-pull converters with input and output voltages in the range of 2.25 V to 5.5 V. While converter designs with higher output voltages are possible, care must be taken that higher turns ratios don't lead to primary currents that exceed the specified current limits of the device.

## 9.2.2.2 LDO Selection

The minimum requirements for a suitable low dropout regulator are:

- Its current drive capability should slightly exceed the specified load current of the application to prevent the LDO from dropping out of regulation. Therefore, for a load current of 600 mA, choose a 600 mA to 750 mA LDO. While regulators with higher drive capabilities are acceptable, they also usually possess higher dropout voltages that will reduce overall converter efficiency.

- The internal dropout voltage, V<sub>DO</sub>, at the specified load current should be as low as possible to maintain

efficiency. For a low-cost 750 mA LDO, a V<sub>DO</sub> of 600 mV at 750 mA is common. Be aware; however, that this

lower value is usually specified at room temperature and can increase by a factor of 2 over temperature,

which in turn will raise the required minimum input voltage.

- The required minimum input voltage preventing the regulator from dropping out of line regulation is given with:

$$V_{l-min} = V_{DO-max} + V_{O-max}$$

(1)

This means in order to determine  $V_I$  for worst-case condition, the user must take the maximum values for  $V_{DO}$  and  $V_O$  specified in the LDO data sheet for rated output current (that is, 600 mA) and add them together. Also specify that the output voltage of the push-pull rectifier at the specified load current is equal or higher than  $V_{I-min}$ . If it is not, the LDO will lose line-regulation and any variations at the input passes straight through to the output. Hence, below  $V_{I-min}$  the output voltage follows the input and the regulator behaves like a simple conductor

• The maximum regulator input voltage must be higher than the rectifier output under no-load. Under this condition there is no secondary current reflected back to the primary, thus making the voltage drop across R<sub>DS-on</sub> negligible and allowing the entire converter input voltage to drop across the primary. At this point, the secondary reaches its maximum voltage of

$$V_{S-max} = V_{IN-max} \times n \tag{2}$$

with  $V_{IN-max}$  as the maximum converter input voltage and n as the transformer turns ratio. Thus to prevent the LDO from damage the maximum regulator input voltage must be higher than  $V_{S-max}$ . 表 9-2 lists the maximum secondary voltages for various turns ratios commonly applied in push-pull converters.

表 9-2. Required Maximum LDO Input Voltages for Various Push-Pull Configurations

|                                             | PUSH-PULL CONVERTER     |             |                        |                        |  |  |

|---------------------------------------------|-------------------------|-------------|------------------------|------------------------|--|--|

| CONFIGURATION                               | V <sub>IN-max</sub> [V] | TURNS-RATIO | V <sub>S-max</sub> [V] | V <sub>I-max</sub> [V] |  |  |

| 3.3 V <sub>IN</sub> to 3.3 V <sub>OUT</sub> | 3.6                     | 1.5 ± 3%    | 5.6                    | 6 to 10                |  |  |

| 3.3 V <sub>IN</sub> to 5 V <sub>OUT</sub>   | 3.6                     | 2.2 ± 3%    | 8.2                    | 10                     |  |  |

| 5 V <sub>IN</sub> to 5 V <sub>OUT</sub>     | 5.5                     | 1.5 ± 3%    | 8.5                    | 10                     |  |  |

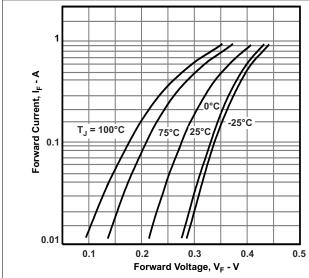

#### 9.2.2.3 Diode Selection

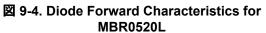

A rectifier diode should always possess low-forward voltage to provide as much voltage to the converter output as possible. When used in high-frequency switching applications, such as the SN6505 however, the diode must also possess a short recovery time. Schottky diodes meet both requirements and are therefore strongly recommended in push-pull converter designs. A good choice for low-volt applications and ambient temperatures of up to 85°C is the low-cost Schottky rectifier MBR0520L with a typical forward voltage of 275 mV at 100-mA forward current. For higher output voltages such as ±10 V and above use the MBR0530 which provides a higher DC blocking voltage of 30 V.

Lab measurements have shown that at temperatures higher than 100°C the leakage currents of the above Schottky diodes increase significantly. This can cause thermal runaway leading to the collapse of the rectifier output voltage. Therefore, for ambient temperatures higher than 85°C use low-leakage Schottky diodes, such as RB168MM-40.

図 9-5. Diode Forward Characteristics MBR0530

#### 9.2.2.4 Capacitor Selection

The capacitors in the converter circuit in 🗵 9-8 are multi-layer ceramic chip (MLCC) capacitors.

As with all high speed CMOS ICs, the device requires a bypass capacitor in the range of 10 nF to 100 nF.

The input bulk capacitor at the center-tap of the primary supports large currents into the primary during the fast switching transients. For minimum ripple make this capacitor 1  $\mu$ F to 10  $\mu$ F. In a 2-layer PCB design with a dedicated ground plane, place this capacitor close to the primary center-tap to minimize trace inductance. In a 4-layer board design with low-inductance reference planes for ground and  $V_{IN}$ , the capacitor can be placed at the supply entrance of the board. To ensure low-inductance paths use two vias in parallel for each connection to a reference plane or to the primary center-tap.

The bulk capacitor at the rectifier output smooths the output voltage. Make this capacitor 1 µF to 10 µF.

The small capacitor at the regulator input is not necessarily required. However, good analog design practice suggests, using a small value of 47 nF to 100 nF improves the regulator's transient response and noise rejection.

The LDO output capacitor buffers the regulated output for the subsequent isolator and transceiver circuitry. The choice of output capacitor depends on the LDO stability requirements specified in the data sheet. However, in most cases, a low-ESR ceramic capacitor in the range of 4.7  $\mu$ F to 10  $\mu$ F will satisfy these requirements.

#### 9.2.2.5 Transformer Selection

#### 9.2.2.5.1 V-t Product Calculation

To prevent a transformer from saturation its V-t product must be greater than the maximum V-t product applied by the device. The maximum voltage delivered by the device is the nominal converter input plus 10%. The maximum time this voltage is applied to the primary is half the period of the lowest frequency at the specified input voltage. Therefore, the transformer's minimum V-t product is determined through:

$$Vt_{min} \ge V_{IN-max} \times \frac{T_{max}}{2} = \frac{V_{IN-max}}{2 \times f_{min}}$$

(3)

Taking an example of  $f_{min}$  as 138 kHz for SN6505A and 363 kHZ for SN6505B with a 5 V supply,  $\not \lesssim$  3 yields the minimum V-t products of:

$$Vt_{min} \geq \frac{5.5 \text{ V}}{2 \times 138 \text{ kHz}} = 20 \text{ V}\mu\text{s} \qquad \text{for SN6505A, and}$$

$$Vt_{min} \geq \frac{5.5 \text{ V}}{2 \times 363 \text{ kHz}} = 7.6 \text{ V}\mu\text{s} \quad \text{for SN6505B applications.} \tag{4}$$

Common V-t values for low-power center-tapped transformers range from 22 V $\mu$ s to 150 V $\mu$ s with typical footprints of 10 mm x 12 mm. However, transformers specifically designed for PCMCIA applications provide as little as 11 V $\mu$ s and come with a significantly reduced footprint of 6 mm x 6 mm only.

While Vt-wise all of these transformers can be driven by the device, other important factors such as isolation voltage, transformer wattage, and turns ratio must be considered before making the final decision.

## 9.2.2.5.2 Turns Ratio Estimate

Assume the rectifier diodes and linear regulator has been selected. Also, it has been determined that the transformer chosen must have a V-t product of at least 11 Vµs. However, before searching the manufacturer web sites for a suitable transformer, the user still needs to know its minimum turns ratio that allows the push-pull converter to operate flawlessly over the specified current and temperature range. This minimum transformation ratio is expressed through the ratio of minimum secondary to minimum primary voltage multiplied by a correction factor that takes the transformer's typical efficiency of 97% into account:

$$V_{P-min} = V_{IN-min} - V_{DS-max}$$

(5)

$V_{S-min}$  must be large enough to allow for a maximum voltage drop,  $V_{F-max}$ , across the rectifier diode and still provide sufficient input voltage for the regulator to remain in regulation. From the  $\frac{\cancel{\text{tops}}}{\cancel{\text{const}}}$  9.2.2.2 section, this minimum input voltage is known and by adding  $V_{F-max}$  gives the minimum secondary voltage with:

$$V_{S-min} = V_{F-max} + V_{DO-max} + V_{O-max}$$

$$V_{IN} \stackrel{\downarrow}{\downarrow} V_{P}$$

$$V_{DS} \stackrel{\downarrow}{\downarrow} R_{DS}$$

$$(6)$$

図 9-6. Establishing the Required Minimum Turns Ratio Through  $N_{min}$  = 1.031 ×  $V_{S-min}$  /  $V_{P-min}$

Then calculating the available minimum primary voltage,  $V_{P-min}$ , involves subtracting the maximum possible drain-source voltage of the device,  $V_{DS-max}$ , from the minimum converter input voltage  $V_{IN-min}$ :

$$V_{P-min} = V_{IN-min} - V_{DS-max}$$

$$(7)$$

$V_{DS-max}$  however, is the product of the maximum  $R_{DS(on)}$  and  $I_D$  values for a given supply specified in the data sheet:

$$V_{DS-max} = R_{DS-max} \times I_{Dmax}$$

(8)

Then inserting 式 8 into 式 7 yields:

$$V_{P-min} = V_{IN-min} - R_{DS-max} \times I_{Dmax}$$

(9)

and inserting 式 9 and 式 6 into 式 5 provides the minimum turns ration with:

$$n_{min} = 1.031 \times \frac{V_{F-max} + V_{DO-max} + V_{O-max}}{V_{IN-min} - R_{DS-max} \times I_{D-max}}$$

$$(10)$$

## Example:

For a 3.3  $V_{IN}$  to 5  $V_{OUT}$  converter using the rectifier diode MBR0520L and the 5 V LDO, the data sheet values taken for a load current of 600 mA and a maximum temperature of 85°C are  $V_{F-max}$  = 0.2 V,  $V_{DO-max}$  = 0.5 V, and  $V_{O-max}$  = 5.1 V.

Then assuming that the converter input voltage is taken from a 3.3 V controller supply with a maximum  $\pm 2\%$  accuracy makes  $V_{IN-min}$  = 3.234 V. Finally the maximum values for drain-source resistance and drain current at 3.3 V are taken from the data sheet with  $R_{DS-max}$  = 0.31  $\Omega$  and  $I_{D-max}$  = 1 A.

Inserting the values above into 式 10 yields a minimum turns ratio of:

$$n_{min} = 1.031 \times \frac{0.2 \text{ V} + 0.5 \text{ V} + 5.1 \text{ V}}{3.234 \text{ V} - 0.31 \Omega \times 1 \text{ A}} = 2.05$$

(11)

Most commercially available transformers for 3-to-5 V push-pull converters offer turns ratios between 2.0 and 2.3 with a common tolerance of ±3%.

#### 9.2.2.5.3 Recommended Transformers

Depending on the application, use the minimum configuration in 🗵 9-7 or standard configuration in 🗵 9-8.

図 9-7. Unregulated Output for Low-Current Loads With Wide Supply Range

図 9-8. Regulated Output for Stable Supplies and High Current Loads

The Wurth Electronics Midcom isolation transformers in  $\frac{1}{2}$  9-3 are optimized designs for the device, providing high efficiency and small form factor at low-cost.

The 1:1.1 and 1:1.7 turns-ratios are designed for logic applications with wide supply rails and low load currents. These applications operate without LDO, thus achieving further cost-reduction.

Product Folder Links: SN6505A SN6505B

# 表 9-3. Recommended Isolation Transformers Optimized for the Device

| TURNS<br>RATIO | V × T<br>(Vµs) | ISOLATION<br>(V <sub>RMS</sub> ) | DIMENSIONS<br>(mm)                                                                                                                                                     | APPLICATION                                                                            | LDO <sup>(1)</sup> | ORDER NO.      | MANUFACTURER        |

|----------------|----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------|----------------|---------------------|

| 1:1.1 ±2%      | 7              |                                  |                                                                                                                                                                        | 3.3 V → 3.3 V, 100mA, SN6505B<br>Refer to ☑ 6-13 and ☑ 6-14                            |                    | 760390011      |                     |

| 1:1.1 ±2%      |                |                                  |                                                                                                                                                                        | 5 V → 5 V, 100mA, SN6505B<br>Refer to 図 6-15 and 図 6-16                                | No                 | 760390012      |                     |

| 1:1.7 ±2%      |                |                                  |                                                                                                                                                                        | 3.3 V → 5 V, 100mA, SN6505B<br>Refer to 図 6-17 and 図 6-18                              |                    | 760390013      |                     |

| 1:1.3 ±2%      | 11             |                                  | 6.73 x 10.05 x 4.19                                                                                                                                                    | 3.3 V → 3.3 V, 100mA, SN6505B<br>Refer to ⊠ 6-19 and ⊠ 6-20                            |                    | 760390014      |                     |

| 1:1.3 ±2%      |                |                                  |                                                                                                                                                                        | 5 V → 5 V, 100mA, SN6505B<br>Refer to 図 6-21 and 図 6-22                                |                    | 760390014      |                     |

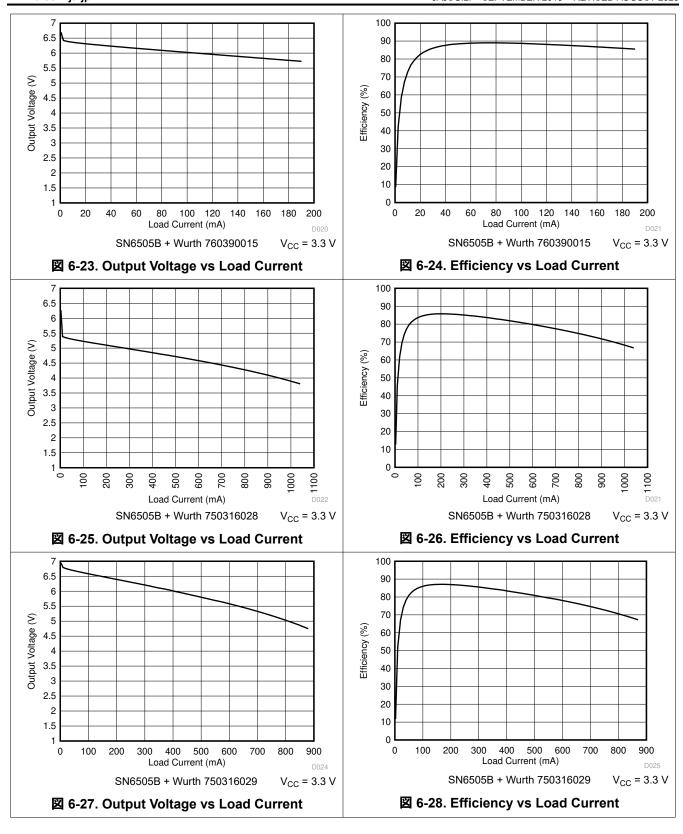

| 1:2.1 ±2%      |                | 2500                             |                                                                                                                                                                        | 3.3 V → 5 V, 100mA, SN6505B<br>Refer to ⊠ 6-23 and ⊠ 6-24                              | Yes                | 760390015      |                     |

| 1.23:1 ±2%     |                |                                  |                                                                                                                                                                        | 5 V → 3.3 V, 100mA, SN6505B                                                            |                    | 750313710      |                     |

| 1:1.7 ±2%      | 8.9            |                                  |                                                                                                                                                                        | 3.3 V → 3.3 V, 1A, SN6505B<br>Refer to ⊠ 6-25 and ⊠ 6-26                               |                    | 750316028      |                     |

| 1:2.1 ±2%      | 0.5            |                                  |                                                                                                                                                                        | 3.3 V → 5 V, 1A, SN6505B<br>Refer to 図 6-27 and 図 6-28                                 |                    | 750316029      |                     |

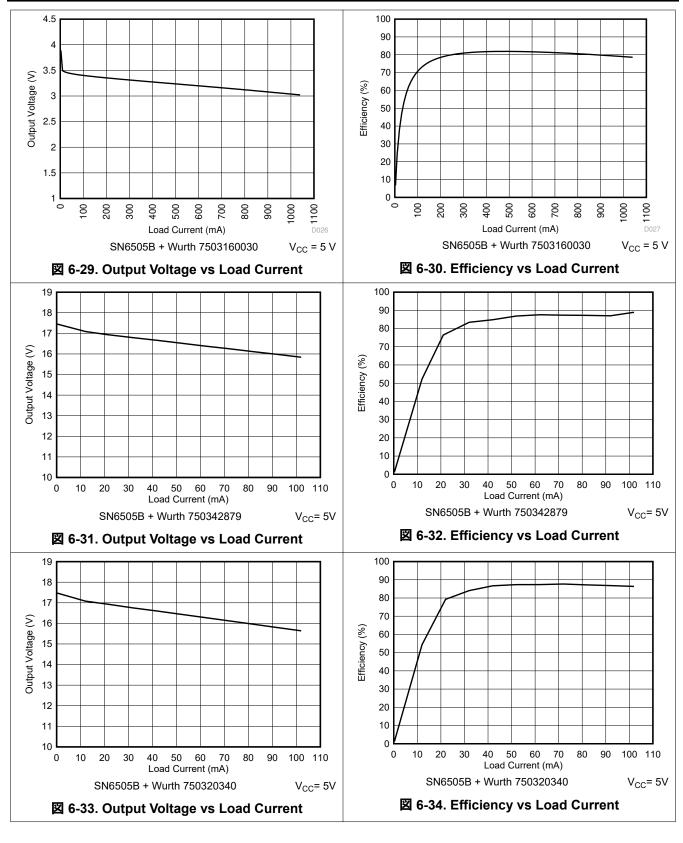

| 1.3:1 ±2%      | 10.8           |                                  | 8.3 x 12.6 x 4.1                                                                                                                                                       | 5 V → 3.3 V, 1A, SN6505B<br>Refer to 図 6-29 and 図 6-30                                 |                    | 750316030      |                     |

| 1:1.1 ±2%      | 8.6            |                                  |                                                                                                                                                                        | 3.3 V → 3.3 V , 1A , SN6505B<br>5 V → 5 V , 1A , SN6505B<br>Refer to ⊠ 6-11 and ⊠ 6-12 | No                 | 750315371      |                     |

| 1:1.1 ±2%      |                |                                  |                                                                                                                                                                        | 3.3 V → 3.3 V, 100mA, SN6505B                                                          |                    | 750313734      |                     |

| 1:1.1 ±2%      |                |                                  |                                                                                                                                                                        | 5 V → 5 V, 100mA, SN6505B                                                              | 1                  | 750313734      |                     |

| 1:1.7 ±2%      |                |                                  |                                                                                                                                                                        | 3.3 V → 5 V, 100mA, SN6505B                                                            | 1                  | 750313769      |                     |

| 1:1.3 ±2%      | 11             |                                  | 9.14 x 12.7 x 7.37                                                                                                                                                     | 3.3~V  ightarrow 3.3~V, 100mA, SN6505B 5 V $ ightarrow 5~V$ , 100mA, SN6505B           | Yes                | 750313638      |                     |

| 1:2.1 ±2%      |                |                                  | 12.32 x 15.41 x 11.05                                                                                                                                                  | 3.3 V → 5 V, 100mA, SN6505B                                                            |                    | 750313626      |                     |

| 1.3:1 ±2%      |                |                                  |                                                                                                                                                                        | 5 V → 3.3 V, 100mA , SN6505B                                                           | No                 | 750313638      | Wurth Electronics / |

| 1:1.75 ±2%     | 41             |                                  |                                                                                                                                                                        | 3.3 V → 3.3 V, 1A, SN6505A<br>Refer to 図 6-3 and 図 6-4                                 | Yes                | 750316031      | Midcom              |

| 1:2 ±2%        | 41             | 5000                             |                                                                                                                                                                        | 3.3 V → 5 V, 1A, SN6505A<br>Refer to 図 6-5 and 図 6-6                                   |                    | 750316032      |                     |

| 1.3:1 ±2%      | 42             |                                  |                                                                                                                                                                        | 5.0 V → 3.3 V, 1A, SN6505A<br>Refer to 図 6-7 and 図 6-8                                 |                    | 750316033      |                     |

| 1:1.1 ±2%      | 23             |                                  | 3.3 V → 3.3 V, 1A, SN6505A 5 V → 5 V, 1A, SN6505A Refer to 図 6-1 and 図 6-2  9.14 x 12.95 x 7.62  3.3 V → 3.3 V, 1A, SN6505A Ferror or |                                                                                        | 750315240          |                |                     |

| 1:3.5 ±2%      | - 9            |                                  |                                                                                                                                                                        |                                                                                        | 750342879          |                |                     |

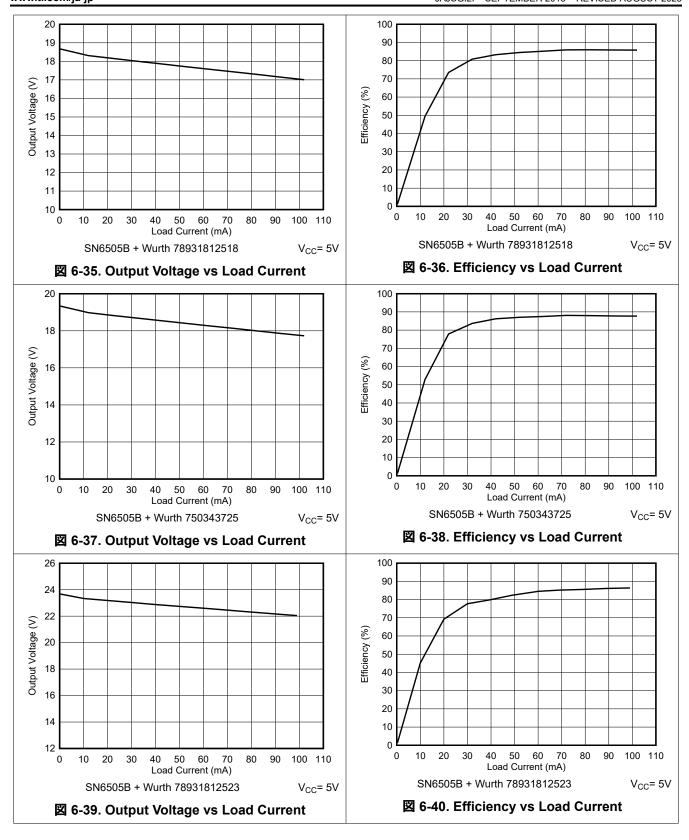

| 1:3.9 ±2%      |                |                                  | 9.17 x 12.7 x 7.62                                                                                                                                                     | 5V → 19.5 V, 100mA,SN6505B<br>Refer to ⊠ 6-33, and ⊠ 6-34                              |                    | 750343725      |                     |

| 1:3.75 ±2%     |                |                                  |                                                                                                                                                                        | 5V → 18.75 V, 100mA,SN6505B<br>Refer to ☑ 6-35, and ☑ 6-35                             | No                 | 78931812518    |                     |

| 1:4.75 ±2%     |                | 2500                             |                                                                                                                                                                        | 5V → 23.75V, 100mA,SN6505B<br>Refer to ☑ 6-37, and ☑ 6-38                              |                    | 78931812523    |                     |

| 1:2.5 ±2%      | 9.5            | 2500                             | 8.3 x 12.6 x 4.1                                                                                                                                                       | 5V → 12.5V, 200mA,SN6505B<br>Refer to ☑ 6-39, and ☑ 6-40                               |                    | 78931812512    |                     |

| 1:3.13 ±2%     |                |                                  |                                                                                                                                                                        | 5V → 15.65V, 200mA,SN6505B<br>Refer to 図 6-41, and 図 6-42                              |                    | 78931812515    |                     |

| 1:3.5 ±2%      | 16             | 6000                             | 9.14 x 12.7 x 7.62                                                                                                                                                     | 5V → 17.5V, 100mA,SN6505B<br>Refer to ⊠ 6-43, and ⊠ 6-44                               |                    | 750320340      |                     |

| 1:1.3 ±3%      | 11             | 5000                             | 10.4 x 12.2 x 6.1                                                                                                                                                      | 3.3 V → 3.3 V, 300mA, SN6505B<br>5 V → 5 V, 300mA , SN6505B                            | No                 | HCT-SM-1.3-8-2 | Bourns              |

# 表 9-3. Recommended Isolation Transformers Optimized for the Device (continued)

| TURNS<br>RATIO | V × T<br>(Vµs) | ISOLATION<br>(V <sub>RMS</sub> ) | DIMENSIONS<br>(mm) | APPLICATION                                                                        |     | ORDER NO.   | MANUFACTURER    |

|----------------|----------------|----------------------------------|--------------------|------------------------------------------------------------------------------------|-----|-------------|-----------------|

| 1:1.1 ±2%      | 9.2            | 2500                             | 7.01 x 11 x 4.19   | $3.3~V \rightarrow 3.3~V$ , 150mA, SN6505B $5~V \rightarrow 5~V$ , 150mA , SN6505B | No  | EPC3668G-LF | PCA Electronics |

| 1:1.5 ±3%      | 34.4           | 2500                             | 10 x 12.07 x 5.97  | 3.3 V → 3.3 V, 1A, SN6505A/B<br>5 V → 5 V, 1A , SN6505A/B                          | Yes | DA2303-AL   | Coilcraft       |

| 1:2.2 ±3%      | 21.5           | 2500                             | 10 x 12.07 x 5.97  | 3.3 V → 5 V, 1A, SN6505A/B                                                         |     | DA2304-AL   |                 |

<sup>(1)</sup> For configurations with LDO, a higher voltage than the required output voltage is generated, to allow for LDO drop-out. Figures show the voltage and efficiency at the LDO input.

## 9.2.3 Application Curves

See the  $\forall D \forall \exists V$  6.7 and  $\forall D \forall \exists V$  6.8 for application curves with transformers optimized for the device, providing high efficiency and small form factor at low-cost.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 9.2.4 System Examples

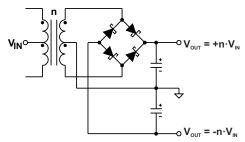

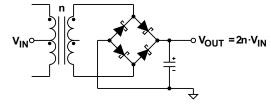

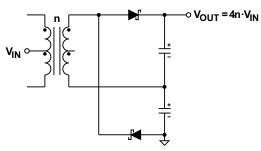

# 9.2.4.1 Higher Output Voltage Designs

The device can drive push-pull converters that provide high output voltages of up to 30 V, or bipolar outputs of up to ±15 V. Using commercially available center-tapped transformers, with their rather low turns ratios of 0.8 to 5, requires different rectifier topologies to achieve high output voltages.

9-9 to

9-11 show some of these topologies together with their respective open-circuit output voltages.

図 9-10. Bridge Rectifier Without Center-Tapped Secondary Performs Voltage Doubling

# 図 9-9. Bridge Rectifier With Center-Tapped Secondary Enables Bipolar Outputs

図 9-11. Half-Wave Rectifier Without Centered Ground and Center-Tapped Secondary Performs Voltage Doubling Twice, Hence Quadrupling V<sub>IN</sub>

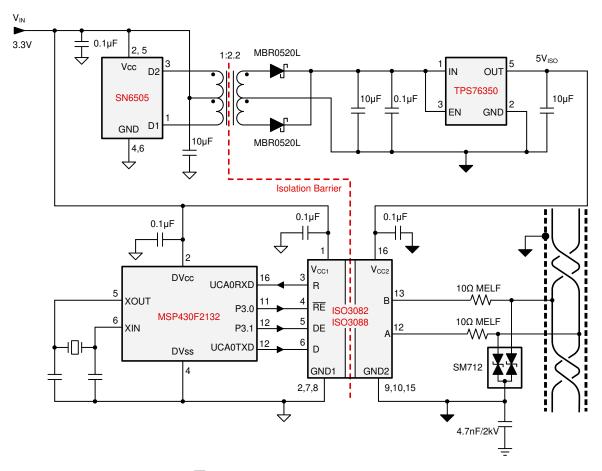

## 9.2.4.2 Application Circuits

The following application circuits are shown for a 3.3 V input supply commonly taken from the local, regulated microcontroller supply. For 5 V input voltages requiring different turn ratios refer to the transformer manufacturers and their web sites listed in 表 9-4.

表 9-4. Transformer Manufacturers

| MANUFACTURER                 | MORE INFORMATION               |

|------------------------------|--------------------------------|

| Coilcraft Inc.               | http://www.coilcraft.com       |

| Halo-Electronics Inc.        | http://www.haloelectronics.com |

| Murata Power Solutions       | http://www.murata-ps.com       |

| Wurth Electronics Midcom Inc | http://www.midcom-inc.com      |

図 9-12. Isolated RS-485 Interface

# 10 Power Supply Recommendations

The device is designed to operate from an input voltage supply range between 2.5 V and 5 V nominal. This input supply must be regulated within  $\pm 10\%$ . If the input supply is located more than a few inches from the device, a 0.1  $\mu$ F by-pass capacitor should be connected as close as possible to the device  $V_{CC}$  pin and a 10  $\mu$ F capacitor should be connected close to the transformer center-tap pin.

# 11 Layout

# 11.1 Layout Guidelines

- The V<sub>IN</sub> pin must be buffered to ground with a low-ESR ceramic bypass-capacitor. The recommended capacitor value can range from 1 μF to 10 μF. The capacitor must have a voltage rating of 10 V minimum and a X5R or X7R dielectric.

- The optimum placement is closest to the V<sub>IN</sub> and GND pins at the board entrance to minimize the loop area formed by the bypass-capacitor connection, the V<sub>IN</sub> terminal, and the GND pin. See ☑ 11-1 for a PCB layout example.

- The connections between the device D1 and D2 pins and the transformer primary endings, and the

connection of the device V<sub>CC</sub> pin and the transformer center-tap must be as close as possible for minimum

trace inductance.

- The connection of the device V<sub>CC</sub> pin and the transformer center-tap must be buffered to ground with a low-ESR ceramic bypass-capacitor. The recommended capacitor value can range from 1μF to 10 μF. The capacitor must have a voltage rating of 16 V minimum and a X5R or X7R dielectric.

- The device GND pins must be tied to the PCB ground plane using two vias for minimum inductance.

- The ground connections of the capacitors and the ground plane should use two vias for minimum inductance.

- The rectifier diodes should be Schottky diodes with low forward voltage in the 10 mA to 100 mA current range to maximize efficiency.

- The  $V_{OUT}$  pin must be buffered to ISO-Ground with a low-ESR ceramic bypass-capacitor. The recommended capacitor value can range from 1µF to 10 µF. The capacitor must have a voltage rating of 16 V minimum and a X5R or X7R dielectric.

## 11.2 Layout Example

図 11-1. Layout Example of a 2-Layer Board

# 12 Device and Documentation Support

# 12.1 Device Support

# **12.2 Documentation Support**

#### 12.2.1 Related Documentation

For related documentation see the following:

- · Texas Instruments, Digital Isolator Design Guide

- Texas Instruments, Isolation Glossary

- Texas Instruments, How to Isolate Signal and Power in Isolated CAN Systems TI TechNote

- Texas Instruments, Small Form-Factor Reinforced Isolated IGBT Gate Drive Reference Design for 3-Phase Inverter TI Design

#### 12.3 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to order now.

| 表 | 12-1 | I. Re | lated | Links |

|---|------|-------|-------|-------|

|---|------|-------|-------|-------|

| PARTS   | PRODUCT FOLDER   ORDER NOW |            | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |  |

|---------|----------------------------|------------|---------------------|---------------------|---------------------|--|

| SN6505A | Click here                 | Click here | Click here          | Click here          | Click here          |  |

| SN6505B | Click here                 | Click here | Click here          | Click here          | Click here          |  |

# 12.4 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

# 12.5 Community Resources

## 12.6 Trademarks

すべての商標は、それぞれの所有者に帰属します。

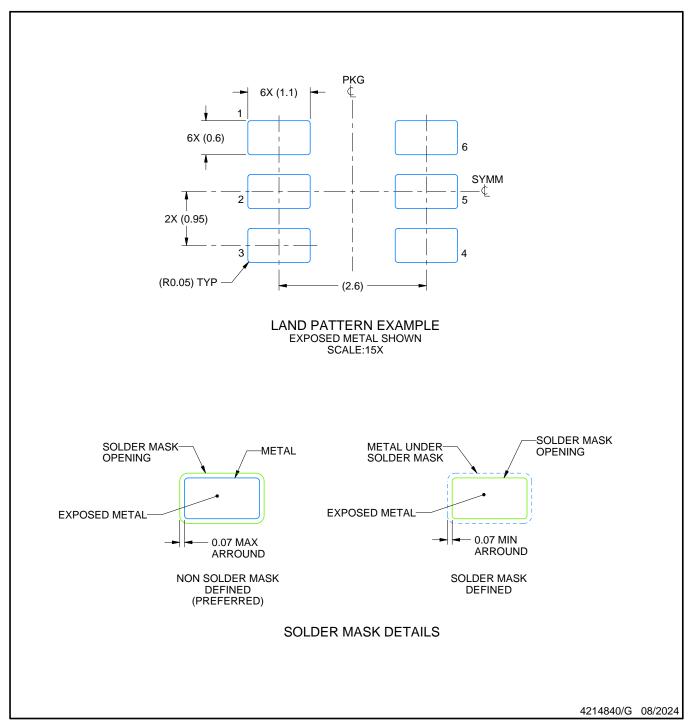

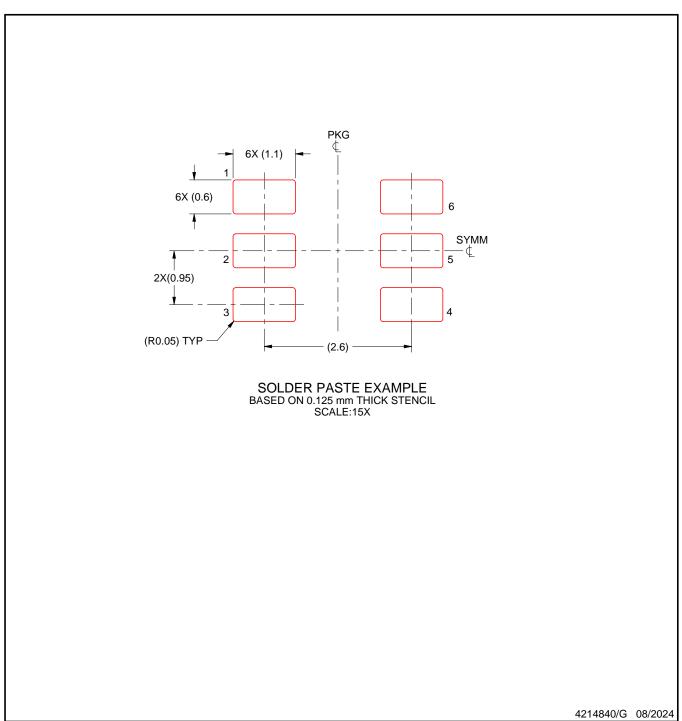

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

www.ti.com 24-Jul-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                |              |              |

| SN6505ADBVR           | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650A, 65AQ) |

| SN6505ADBVR.A         | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650A, 65AQ) |

| SN6505ADBVR.B         | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | -    | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650A, 65AQ) |

| SN6505ADBVT           | Active | Production    | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650A, 65AQ) |

| SN6505ADBVT.A         | Active | Production    | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650A, 65AQ) |

| SN6505BDBVR           | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650B, 65BQ) |

| SN6505BDBVR.A         | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650B, 65BQ) |

| SN6505BDBVR.B         | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | -    | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650B, 65BQ) |

| SN6505BDBVRG4         | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | 65BQ         |

| SN6505BDBVRG4.A       | Active | Production    | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | 65BQ         |

| SN6505BDBVT           | Active | Production    | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650B, 65BQ) |

| SN6505BDBVT.A         | Active | Production    | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650B, 65BQ) |

| SN6505BDBVT.B         | Active | Production    | SOT-23 (DBV)   6 | 250   SMALL T&R       | -    | NIPDAU        | Level-1-260C-UNLIM | -55 to 125   | (650B, 65BQ) |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# PACKAGE OPTION ADDENDUM

www.ti.com 24-Jul-2025

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF SN6505A, SN6505B:

Automotive: SN6505A-Q1, SN6505B-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 18-Jun-2025

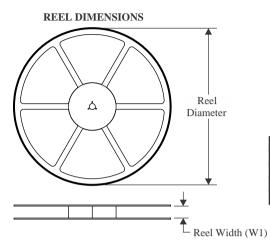

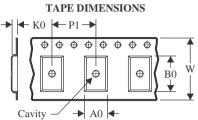

# TAPE AND REEL INFORMATION

|    | -                                                         |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

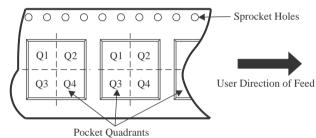

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN6505ADBVR   | SOT-23          | DBV                | 6 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| SN6505ADBVT   | SOT-23          | DBV                | 6 | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| SN6505BDBVR   | SOT-23          | DBV                | 6 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| SN6505BDBVRG4 | SOT-23          | DBV                | 6 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| SN6505BDBVT   | SOT-23          | DBV                | 6 | 250  | 178.0                    | 9.0                      | 3.23       | 3.17       | 1.37       | 4.0        | 8.0       | Q3               |

| SN6505BDBVT   | SOT-23          | DBV                | 6 | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

www.ti.com 18-Jun-2025

# \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN6505ADBVR   | SOT-23       | DBV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| SN6505ADBVT   | SOT-23       | DBV             | 6    | 250  | 210.0       | 185.0      | 35.0        |

| SN6505BDBVR   | SOT-23       | DBV             | 6    | 3000 | 210.0       | 185.0      | 35.0        |