## RM48L952 16/32 ビット RISC フラッシュ・マイコン

### 1. RM48L952 16/32 ビット RISC フラッシュ・マイコン

#### 1.1 機能

- セーフティクリティカル・アプリケーションに適した高性能マイコン

- ロックステップで動作するデュアル CPU

- フラッシュおよび RAM インターフェイスの ECC

- CPU／オンチップ RAM 用ビルトイン・セルフテスト

- エラー・ピンを搭載したエラー・シグナリング・モジュール

- 電圧およびクロック・モニタリング

- ARM® Cortex™ - R4F 32 ビット RISC CPU

- 8 ステージ・パイプラインによる効率的な 1.66 DMIPS/MHz

- 単精度/倍精度の FPU

- 12 リージョンのメモリ・プロテクション・ユニット

- サード・パーティ・サポートのオープン・アーキテクチャ

- 動作条件

- 最大 220 MHz のシステム・クロック

- コア電源電圧(VCC) : 公称 1.2 V

- 入出力電源電圧(VCCIO) : 公称 3.3 V

- 内蔵メモリ

- ECC 付きの 3 MB プログラム・フラッシュ

- ECC 付きの 256 KB RAM

- EEPROM エミュレーション用 64 KB フラッシュ

- 16 ビット外部メモリ・インターフェイス

- 共通プラットフォーム・アーキテクチャ

- ファミリ間で一貫したメモリ・マップ

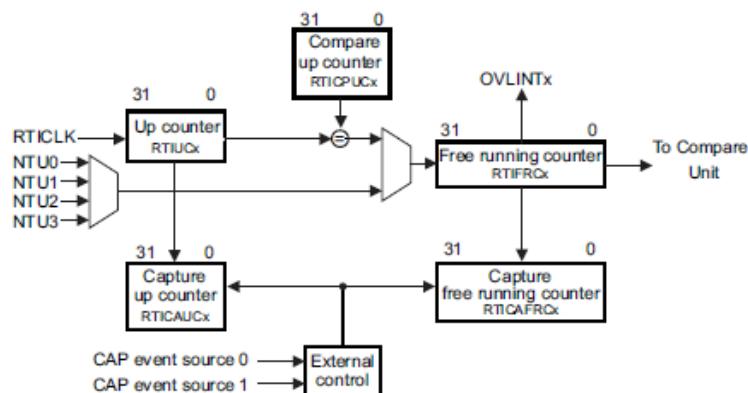

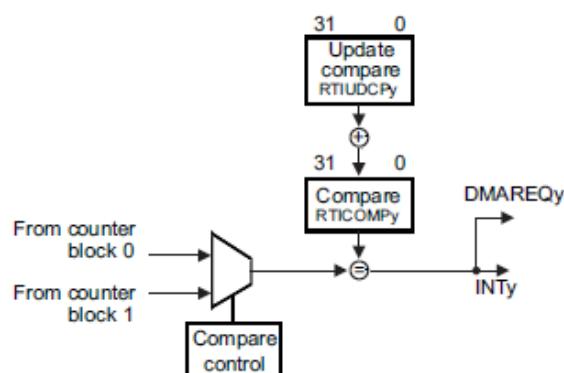

- リアルタイム割り込みタイマ(RTI)OS タイマ

- 96 チャネル・ベクタ割り込みモジュール(VIM)

- 2 チャネル巡回冗長検査(CRC)

- ダイレクト・メモリ・アクセス(DMA)コントローラ

- 16 チャネルおよび 32 コントロール・パケット

- コントロール・パケット RAM のパリティ保護

- 専用 MPU によって保護される DMA アクセス

- スリップ検出機能を内蔵した周波数変調フェーズ・ロック・ループ回路(FMPPLL)

- 独立した非変調 PLL

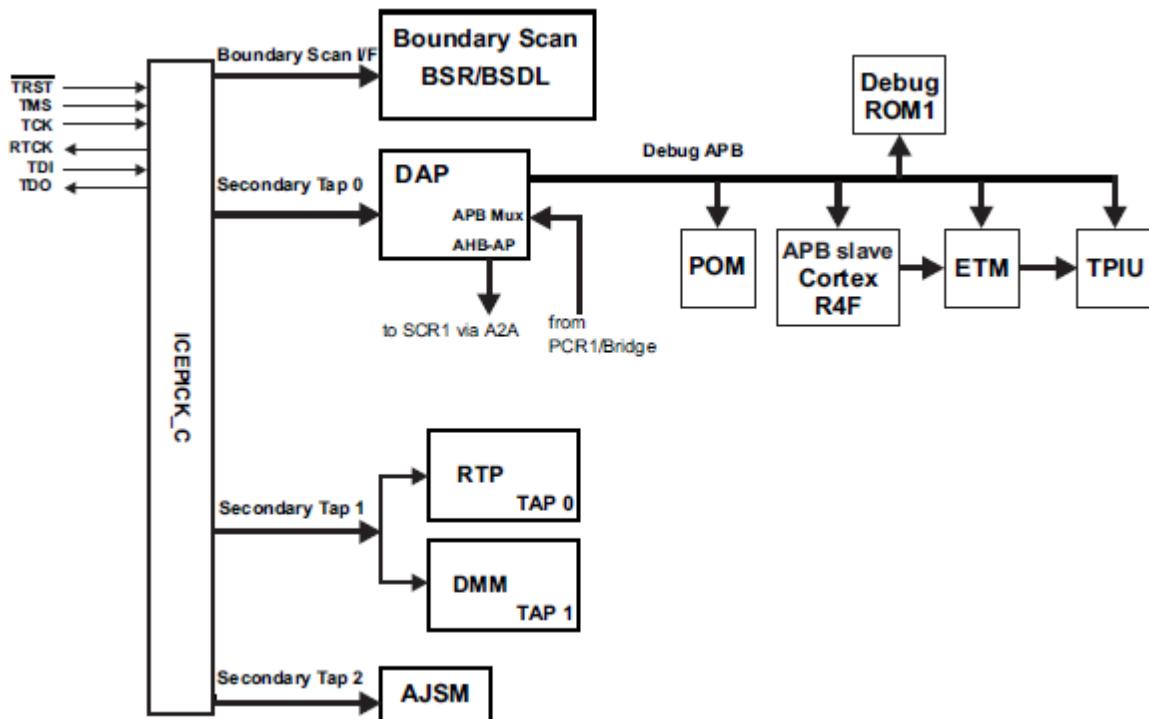

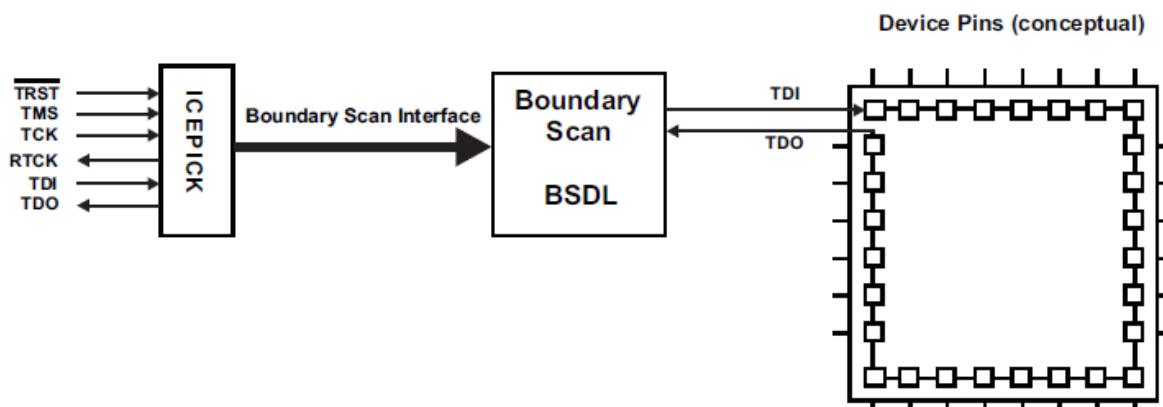

- IEEE 1149.1 JTAG、バウンダリ・スキャンおよび ARM CoreSight コンポーネント

- JTAG セキュリティ・モジュール

- トレースおよびキャリブレーション機能

- 組み込みトレース・マクロセル(ETM-R4)

- Data Modification Module (DMM)

- RAM トレース・ポート(RTP)

- パラメータ・オーバーレイ・モジュール(POM)

- 複数の通信インターフェイス

- 10/100 Mbps イーサネット MAC(EMAC)

- IEEE 802.3 準拠(3.3 V 入出力のみ)

- MII および MDIO のサポート

- USB

- 2 ポート USB 仕様、リビジョン 2.0 準拠のホスト・コントローラ、USB リリース 1.0 の OHCI 仕様準拠

- USB 仕様リビジョン 2.0 および 1.1 準拠の、フルスピード USB デバイス × 1

- CAN コントローラ(DCAN) × 3

- パリティ保護付きのメールボックス × 64

- CAN プロトコル、バージョン 2.0B への準拠

- I2C (Inter-Integrated Circuit)

- マルチバッファ・シリアル・ペリフェラル・インターフェイス(MibSPI) × 3

- 128 ワード、それぞれにパリティ保護付き

- 標準シリアル・ペリフェラル・インターフェイス(SPI) × 2

- ローカル相互接続ネットワーク・インターフェイス(LIN)コントローラ

- LIN プロトコル・バージョン 2.1 に準拠

- 標準シリアル通信インターフェイス(SCI)

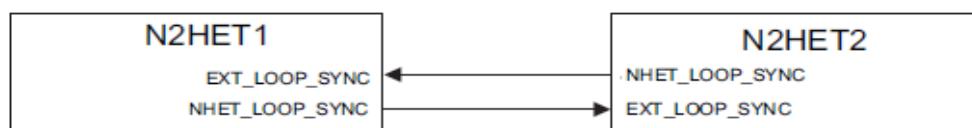

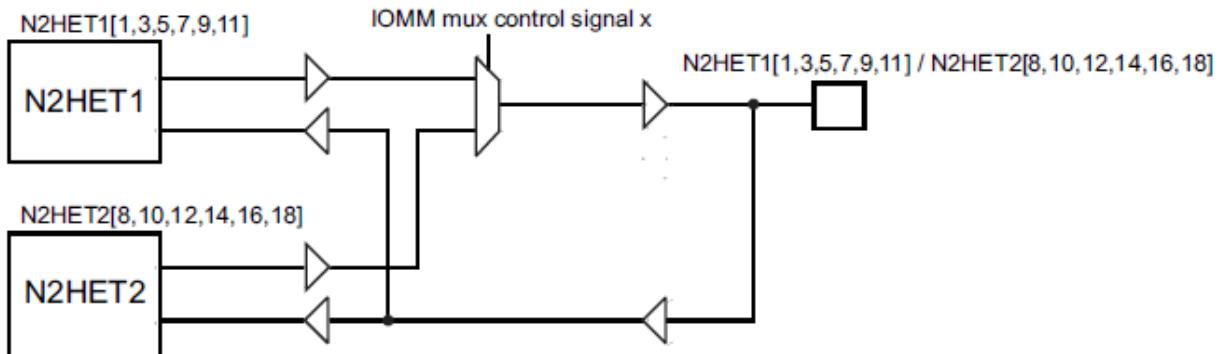

- ハイエンド・タイマー・モジュール(N2HET) × 2

- N2HET1:32 のプログラマブルなチャネル

- N2HET2:20 のプログラマブルなチャネル

- パリティ保護付きの 160 ワードの命令 RAM

- それぞれにハードウェア・アンギル・ジェネレータが付属

- N2HET(HTU)ごとに専用の転送ユニット

- 10/12 ビット・マルチバッファ ADC モジュール × 2

- ADC1: 24 チャネル

- ADC2: 16 チャネル

- 共有チャネル × 16

- パリティ保護付きのリザルト・バッファ × 64

- パッケージ

- 144 ピン・クワッド・フラットパック(PQE)[緑]

- 337 ボール・グリッド・アレイ(ZWT)[緑]

テキサス・インスツルメンツ半導体製品の入手の可否、標準的な保証、およびクリティカルなアプリケーションでの使い方とその免責事項に関する重要な通知は本データシートの最後に記載しております。

## 1.2 アプリケーション

- 産業用セーフティ・アプリケーション

- 産業オートメーション

- セーフティ PLC(プログラマブル・ロジック・コントローラ)

- 発電および配電

- タービンおよび風車

- エレベーターおよびエスカレーター

- 医療分野

- 換気装置

- 除細動器

- 輸液ポンプおよびインスリン・ポンプ

- 放射線治療

- ロボット外科手術

### 1.3 説明

RM48L952 は、セーフティ・システム向けの高性能マイコン・ファミリです。このセーフティ・アーキテクチャには、ロックステップで動作するデュアル CPU、CPU およびメモリ用ビルトイン・セルフテスト(BIST)ロジック、フラッシュとデータ SRAM の両方に搭載された ECC、ペリフェラル・メモリのパリティ、ペリフェラル IO のループ・バック機能などの特徴があります。

RM48L952 は、ARM® Cortex™-R4F 浮動小数点 CPU を内蔵しています。これは、最大 220 MHz、最大 365 DMIPS で動作可能な構成を持ち、高効率の 1.66 DMIPS/MHz を実現します。このデバイスはリトルエンディアン[LE32]形式をサポートしています。

RM48L952 は、1 ビットの誤り訂正と 2 ビットの誤り検出機能を持つ、3 MB のフラッシュ・メモリおよび 256 KB のデータ RAM を内蔵しています。このデバイスのフラッシュ・メモリは、64 ビット幅のデータ・バス・インターフェイスを持ち電気的に消去、プログラムが可能な不揮発性のメモリが実装されています。このフラッシュは、すべての読み取り、プログラム、消去などの操作を 3.3 V 電源入力(入出力電源と同じレベル)で実行します。パイプライン・モードでは、フラッシュは、最大 220 MHz のシステム・クロック周波数で動作します。この SRAM は、バイト単位、ハーフワード単位、ワード・モードでの單一サイクル読み取り/書き込みアクセスをサポートしています。

RM48L952 デバイスは、リアルタイム制御アプリケーションのためのペリフェラルを搭載しています。これには、最大 44 個の IO 端子を持つ 2 個の Next Generation High End Timer(N2HET)タイミング・コプロセッサ、最大 24 の入力をサポートする 12 ビット・アナログ/デジタル・コンバータも含まれます。

N2HET は、リアルタイム・アプリケーションに対応する洗練されたタイミング機能を搭載した先進のインテリジェント・タイマです。このタイマは、専用のタイマ・マイクロマシンや付属の入出力ポートを持ち、縮小した命令セットで、ソフトウェア制御されるようになっています。N2HET は、パルス幅変調された出力、キャプチャ/コンペア入力、汎用入出力で使用することができます。複数のセンサ情報や、複雑で正確な時間パルスを持つドライブ・アクチュエータが必要なアプリケーションに最適です。ハイエンド・タイマ転送ユニット(HET-TU)では、DMA タイプのトランザクションを実行して、N2HET データをメイン・メモリとの間で転送することができます。HET-TU には、メモリ・プロテクション・ユニット(MPU)が組み込まれています。

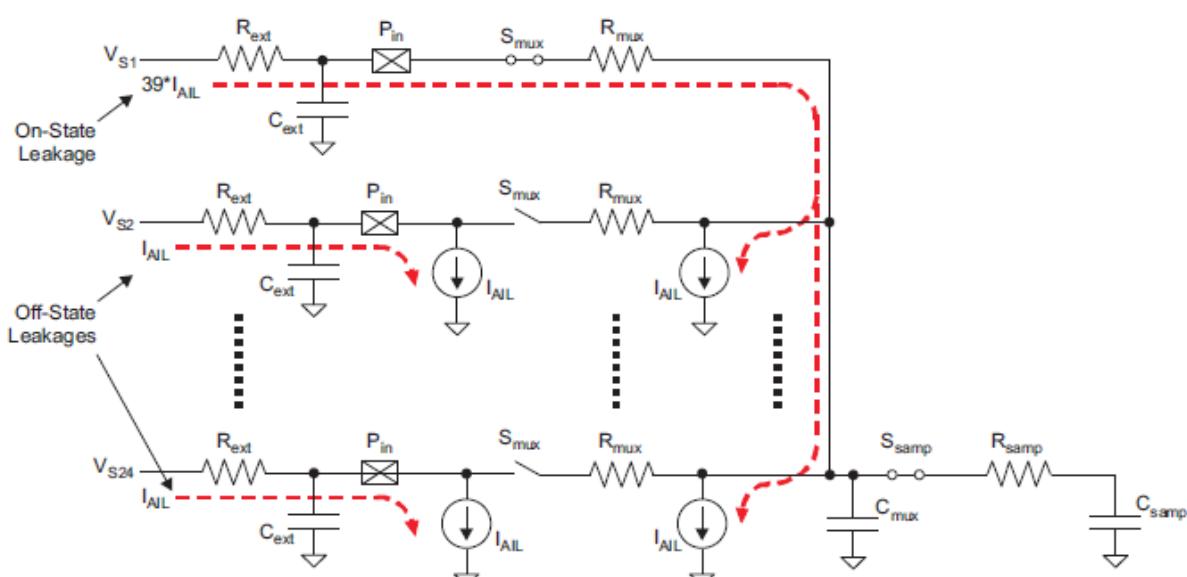

このデバイスは、2 個の 12 ビット分解能 MibADC を搭載しており、全部で 24 チャネル、それぞれにパリティ保護された 64 ワードのバッファ RAM を備えています。MibADC の各チャネルは、個別に変換できる他、ソフトウェアにより連続変換シーケンスごとにグループ化することもできます。16 のチャネルは、2 個の MibADC で共有されます。3 つの独立したグループ分けがあります。それぞれのシーケンスは、トリガによる单一変換あるいは連続変換することができます。

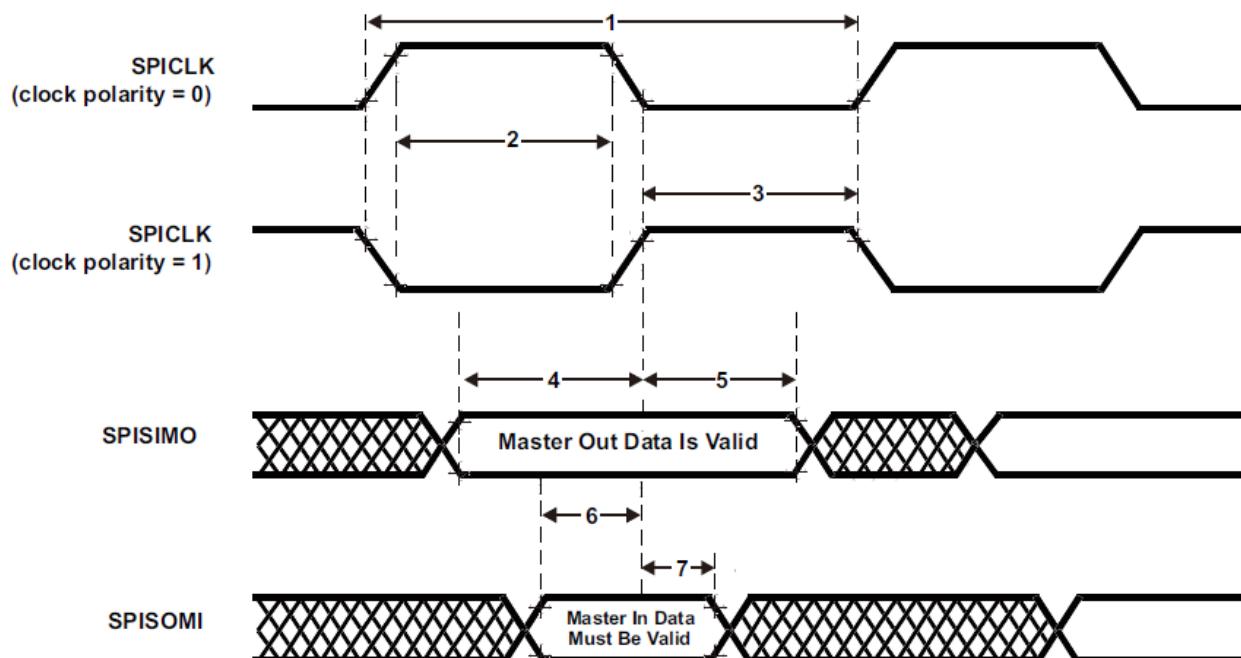

このデバイスは、3 つの MibSPI、最大 2 つの SPI、1 つの LIN、1 つの SCI、3 つの DCAN、1 つの I<sup>2</sup>C、1 つのイーサネット、1 つの USB モジュールのように、複数の通信インターフェイスを搭載しています。SPI は、シフトレジスタ・タイプのデバイスとの高速な通信のための簡便なシリアル通信を提供します。LIN では、Local Interconnect Standard 2.0 をサポートし、標準の Non-Return-to-Zero(NRZ) 形式を使用した全二重の UART として使用することができます。DCAN では、CAN 2.0B プロトコル規格をサポートし、最大 1 メガビット/秒(Mbps) の堅牢な通信速度で分散リアルタイム制御を効率的にサポートするシリアルのマルチマスター通信プロトコルを使用します。DCAN は、信頼性の高いシリアル通信や多重配線が必要な、ノイズの多い厳しい環境(たとえば自動車や工業分野など)で動作するアプリケーションに適しています。イーサネット・モジュールでは、MII および MDIO インターフェイスをサポートしています。USB モジュールは、2 ポート USB ホスト・コントローラと USB デバイス・コントローラを搭載しています。

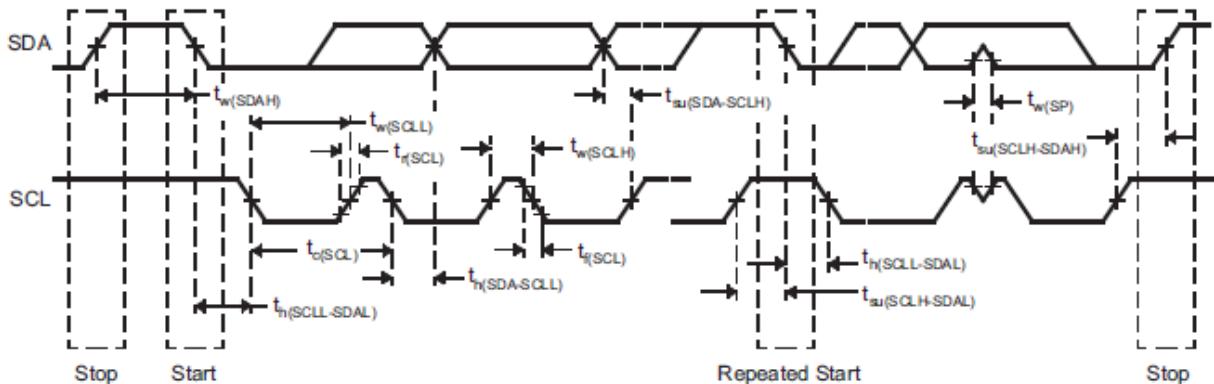

I<sup>2</sup>C モジュールは、I<sup>2</sup>C シリアル・バスによる、マイコンと I<sup>2</sup>C 互換デバイス間のインターフェイスを搭載したマルチマスター通信モジュールです。I<sup>2</sup>C では、100 Kbps と 400 Kbps の両方の速度をサポートしています。

---

周波数変調フェーズ・ロック・ループ(FMPLL)・クロック・モジュールは、内部利用目的で使用され、外部周波数基準を高い周波数に遙倍します。FMPLL では、7つのクロック・ソース入力の1つをグローバル・クロック・モジュール(GCM)に供給します。GCM モジュールでは、使用可能なクロック・ソースとデバイス・クロック・ドメイン間のマッピングを管理します。

このデバイスは、外部クロック・プリスケーラ(ECP)モジュールも搭載しており、これをイネーブルにすると、連続外部クロック出力を ECLK ピン/ボールに出力します。ECLK 周波数は、ペリフェラル・インターフェイス・クロック(VCLK)をプログラムされた比率で分周されたものです。この低周波数出力は、デバイスの動作周波数のインジケータとして外部でモニタすることができます。

ダイレクト・メモリ・アクセス・コントローラ(DMA)は 16 のチャネル、32 のコントロール・パケットを搭載しており、メモリはパリティ保護されています。DMA にはメモリ・プロテクション・ユニット(MPU)が組み込まれており、誤った転送からメモリを保護します。

エラー・シグナリング・モジュール(ESM)は、すべてのデバイス・エラーをモニタし、障害が検出されたときに割り込みまたは外部エラー・ピン/ボールのトリガを行うかどうか決定します。nERROR は、マイコンの障害条件のインジケータとして外部でモニタすることができます。

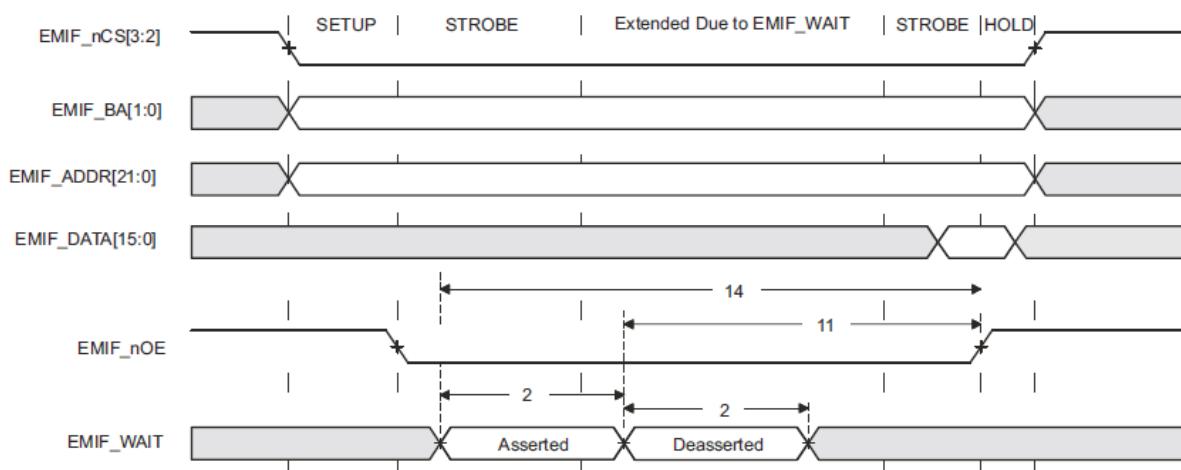

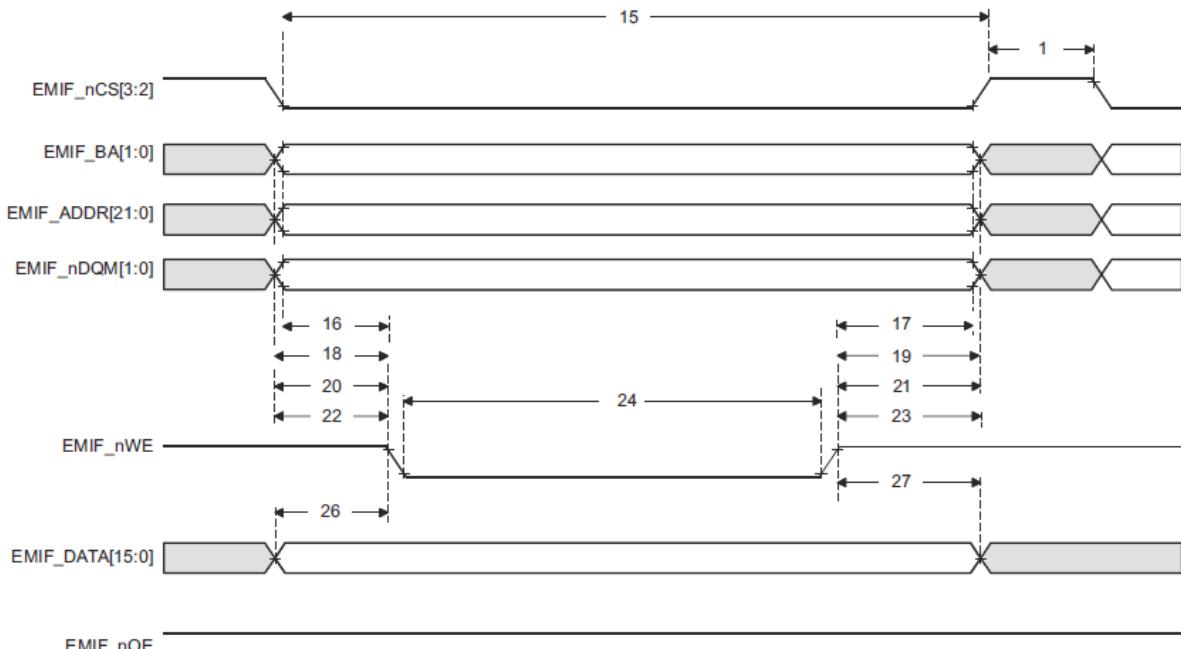

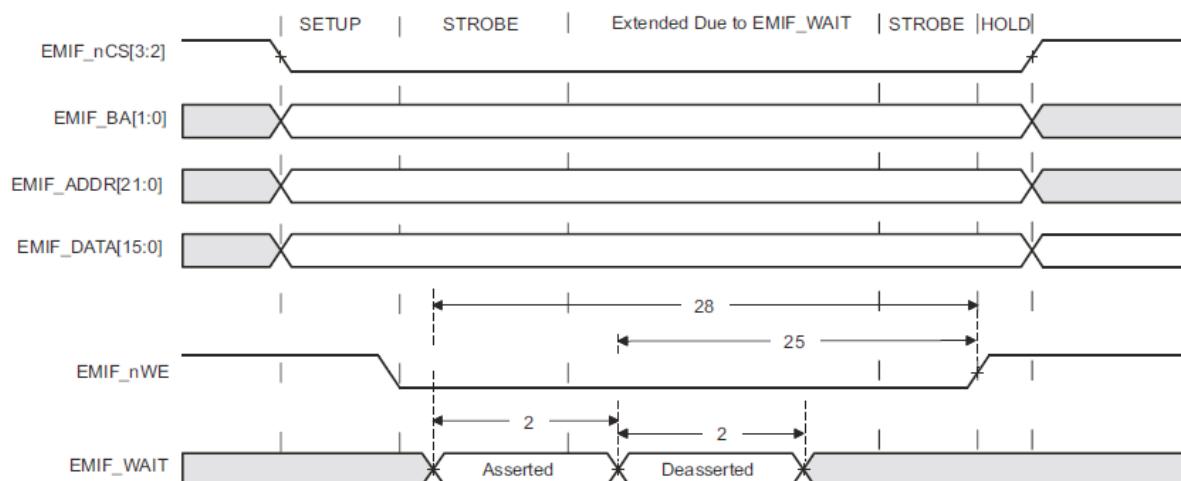

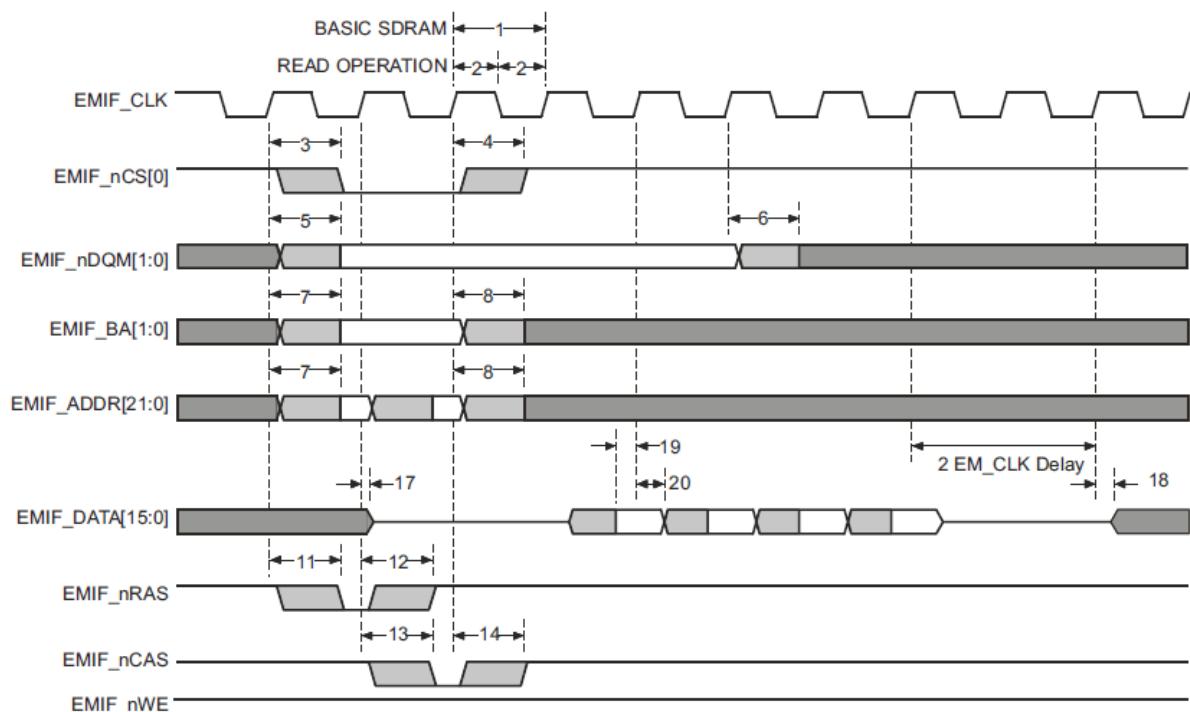

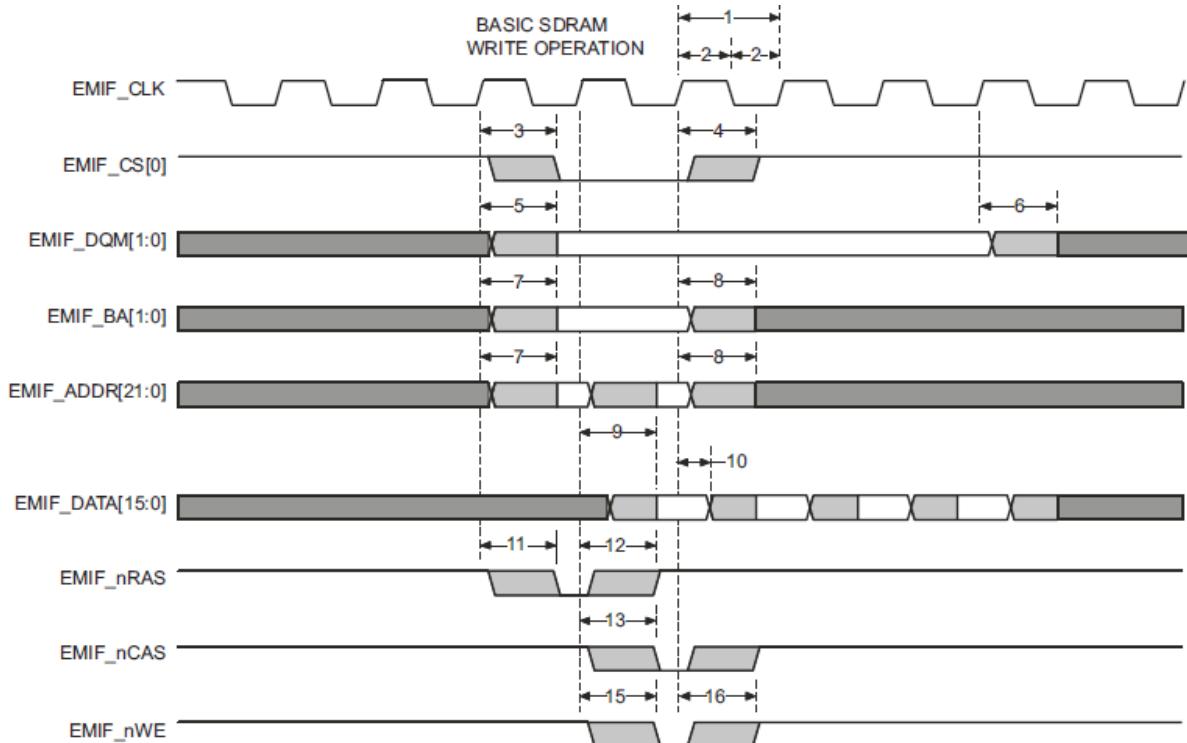

外部メモリ・インターフェイス(EMIF)では、非同期および同期メモリまたは他のスレーブ・デバイスにメモリ拡張を行います。

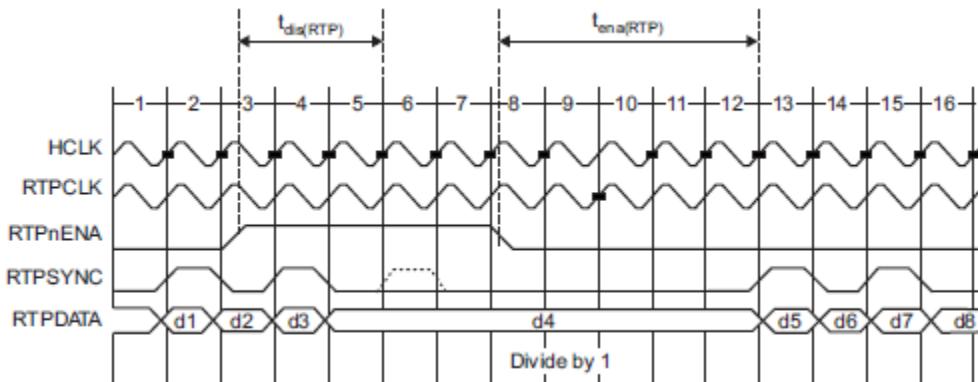

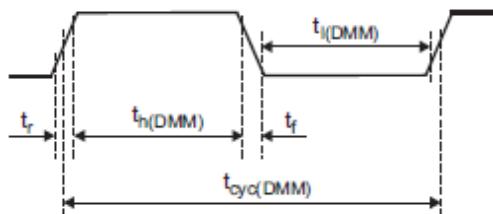

アプリケーション・コードのデバッグ機能を強化するために、いくつかのインターフェイスが実装されています。ビルトインの ARM Cortex-R4F CoreSight デバッグ機能に加え、外部トレース・マクロセル(ETM)でも、プログラム実行の命令トレースやデータ・トレースを行うことができます。計測の目的で、CPU または他のマスターによる RAM およびペリフェラルへのアクセスを高速トレースできるようにするため、RAM トレース・ポート・モジュール(RTP)が実装されています。Data Modification Module(DMM)には、外部データをデバイス・メモリに書き込む機能があります。RTP も DMM も、アプリケーション・コードのプログラム実行時間への影響は皆無か、たとえあっても最小レベルです。パラメータ・オーバーレイ・モジュール(POM)は、フラッシュ・アクセスを内部メモリや EMIF に経路変更できるため、フラッシュでのパラメータ更新の際に必要になる再プログラム手順を回避することができます。

RM48L952 は、セーフティ機能や広範囲の通信および制御ペリフェラルを内蔵しているため、セーフティクリティカルの必要性がある高性能リアルタイム制御アプリケーションにとって理想的なソリューションを提供します。

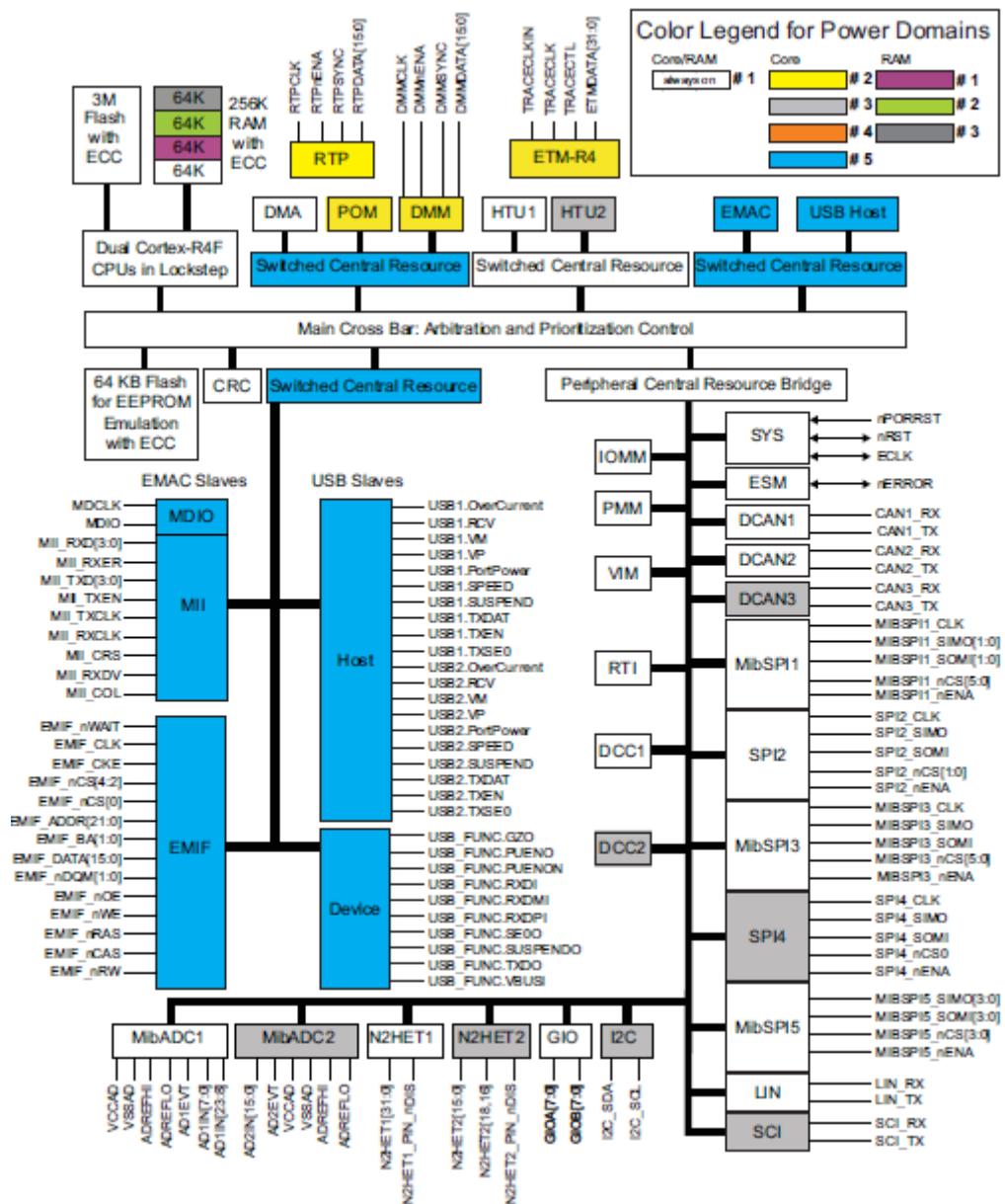

## 1.4 機能ブロック図

図 1-1 機能ブロック図

|                                                   |            |

|---------------------------------------------------|------------|

| <b>1. RM48L952 16/32 ビット RISC フラッシュ・マイコン.....</b> | <b>1</b>   |

| 1.1 機能 .....                                      | 1          |

| 1.2 アプリケーション .....                                | 2          |

| 1.3 説明 .....                                      | 3          |

| 1.4 機能ブロック図 .....                                 | 5          |

| <b>2. デバイス・パッケージおよび端子機能 .....</b>                 | <b>7</b>   |

| 2.1 PGE QFP パッケージ・ピンアウト(144 ピン) .....             | 7          |

| 2.2 ZWT BGA パッケージ・ボールマップ(337 ボール・グリッド・アレイ) .....  | 8          |

| 2.3 端子機能 .....                                    | 9          |

| <b>3. デバイス動作条件 .....</b>                          | <b>39</b>  |

| 3.1 動作フリー・エア温度範囲での絶対最大定格 <sup>(1)</sup> .....     | 39         |

| 3.2 デバイス推奨動作条件 <sup>(1)</sup> .....               | 39         |

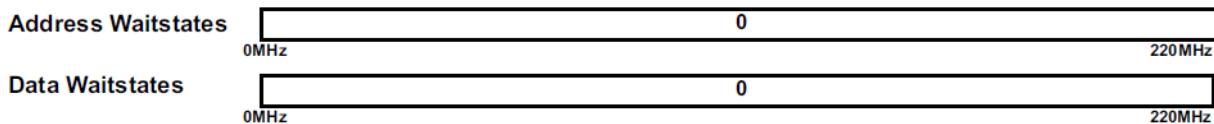

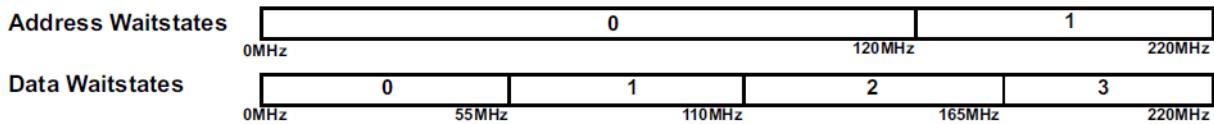

| 3.3 クロック・ドメインに対する、推奨動作条件でのスイッチング特性 .....          | 40         |

| 3.4 必要なウェイト・ステート .....                            | 40         |

| 3.5 推奨動作条件での消費電力 .....                            | 41         |

| 3.6 推奨動作条件での入出力電気特性 <sup>(1)</sup> .....          | 42         |

| 3.7 出力バッファ・ドライブ強度 .....                           | 43         |

| 3.8 入力タイミング .....                                 | 44         |

| 3.9 出力タイミング .....                                 | 44         |

| 3.10 低 EMI 出力バッファ .....                           | 46         |

| <b>4. システム情報および電気的特性.....</b>                     | <b>47</b>  |

| 4.1 デバイスのパワー・ドメイン .....                           | 47         |

| 4.2 電圧モニタの特性 .....                                | 48         |

| 4.3 電源シーケンスおよびパワーオン・リセット .....                    | 49         |

| 4.4 ウオーム・リセット(nRST) .....                         | 51         |

| 4.5 ARM® Cortex-R4F™ CPU の情報 .....                | 52         |

| 4.6 クロック .....                                    | 56         |

| 4.7 クロック・モニタリング .....                             | 64         |

| 4.8 グリッチ・フィルタ .....                               | 67         |

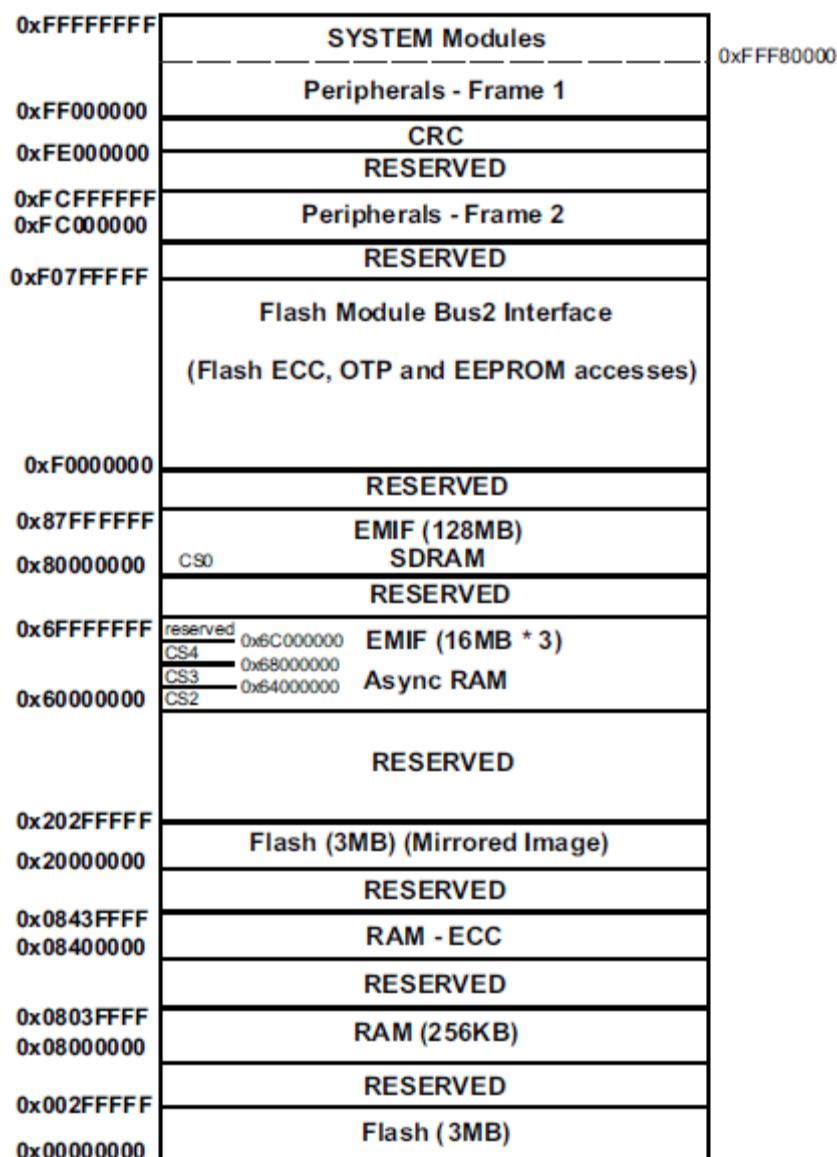

| 4.9 デバイスのメモリ・マップ .....                            | 68         |

| 4.10 フラッシュ・メモリ .....                              | 75         |

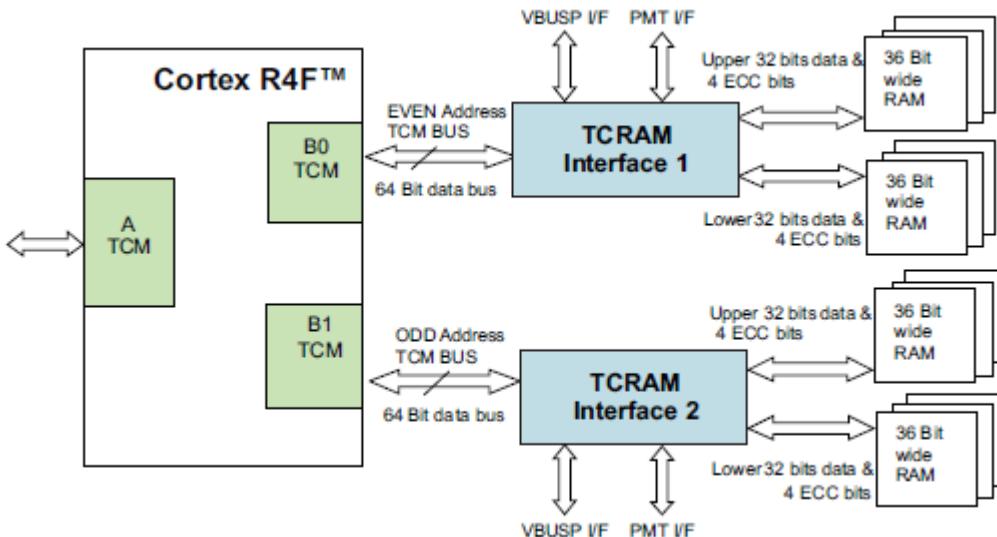

| 4.11 密接合メモリ RAM インターフェイス・モジュール 78                 |            |

| 4.12 ペリフェラル RAM へのアクセスに対するパリティ保護 .....            | 79         |

| 4.13 オンチップ SRAM の初期化およびテスト .....                  | 80         |

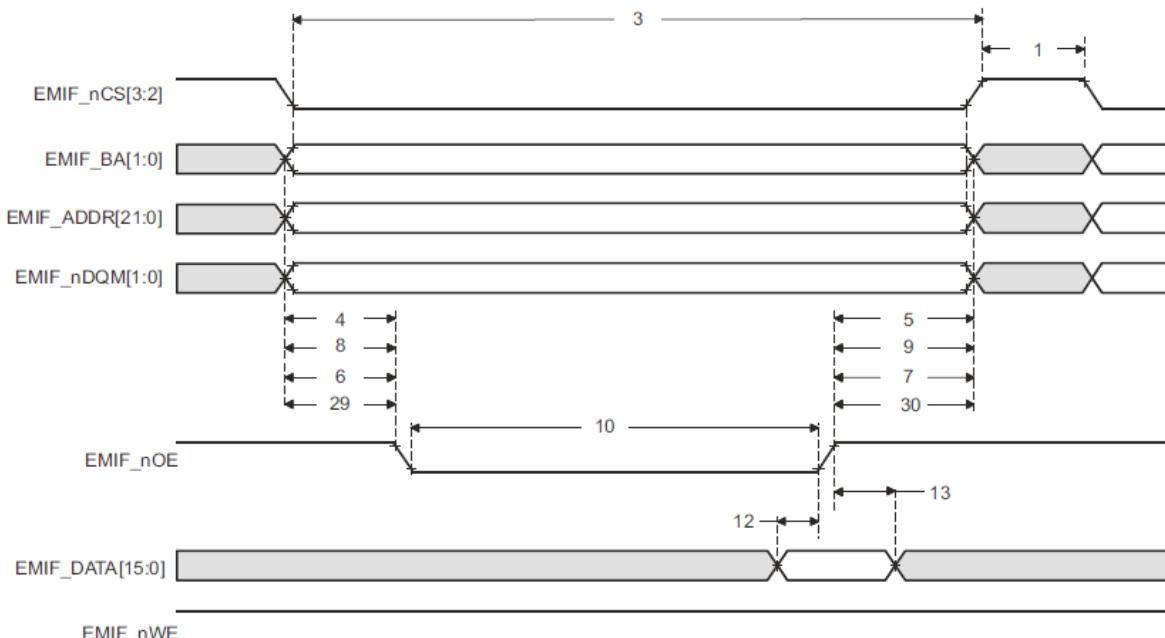

| 4.14 外部メモリ・インターフェイス(EMIF) .....                   | 83         |

| 4.15 ベクタ割り込みマネージャー .....                          | 91         |

| 4.16 DMA コントローラ .....                             | 94         |

| 4.17 リアルタイム割り込みモジュール .....                        | 96         |

| 4.18 エラー・シグナリング・モジュール .....                       | 98         |

| 4.19 リセット/アポート/エラー・ソース .....                      | 102        |

| 4.20 デジタル・ウインドウ・ウォッチドッグ .....                     | 104        |

| 4.21 デバッグ・サブシステム .....                            | 105        |

| <b>5. ペリフェラルの情報および電気的特性 .....</b>                 | <b>114</b> |

| 5.1 ペリフェラルの凡例 .....                               | 114        |

| 5.2 マルチバッファ・12 ビット A/D コンバータ .....                | 115        |

| 5.3 汎用入出力 .....                                   | 123        |

| 5.4 エンハンスド・ハイエンド・タイマ(N2HET) .....                 | 124        |

| 5.5 コントローラ・エリア・ネットワーク(DCAN) .....                 | 129        |

| 5.6 ローカル相互接続ネットワーク・インターフェイス (LIN) .....           | 130        |

| 5.7 シリアル通信インターフェイス(SCI) .....                     | 131        |

| 5.8 I2C (Inter-Integrated Circuit) .....          | 132        |

| 5.9 マルチバッファ/標準シリアル・ペリフェラル・インターフェイス .....          | 135        |

| 5.10 イーサネットメディア・アクセス・コントローラ .....                 | 147        |

| 5.11 ユニバーサル・シリアル・バス・コントローラ .....                  | 149        |

| <b>6. デバイスおよびドキュメンテーション・サポート .....</b>            | <b>150</b> |

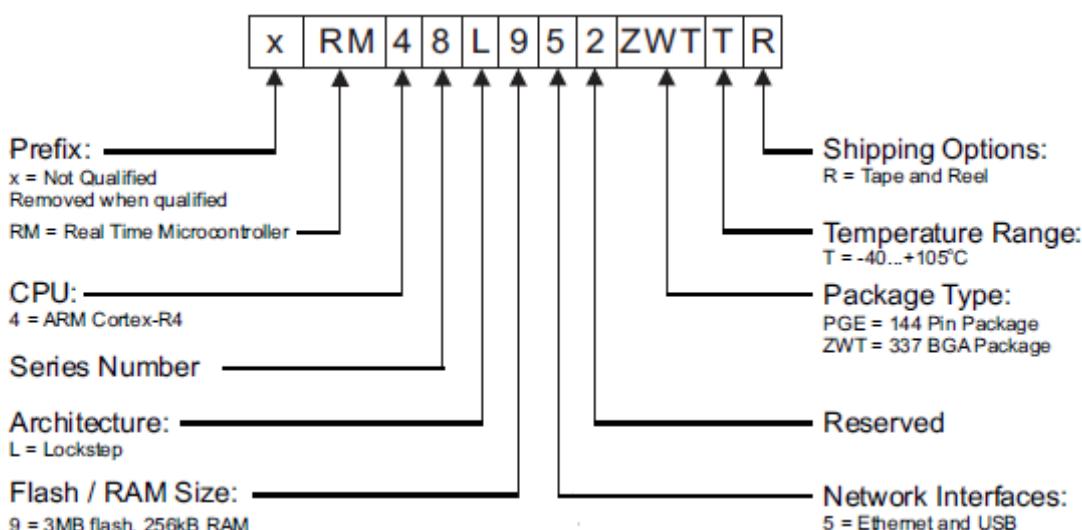

| 6.1 デバイスおよび開発サポート・ツールの命名体系 .....                  | 150        |

| 6.2 注文用部品番号 .....                                 | 150        |

| 6.3 デバイスの識別 .....                                 | 151        |

| 6.4 改訂履歴 .....                                    | 152        |

| <b>7. メカニカル・データ .....</b>                         | <b>153</b> |

| 7.1 温度データ .....                                   | 153        |

| 7.2 パッケージ情報 .....                                 | 153        |

## 2. デバイス・パッケージおよび端子機能

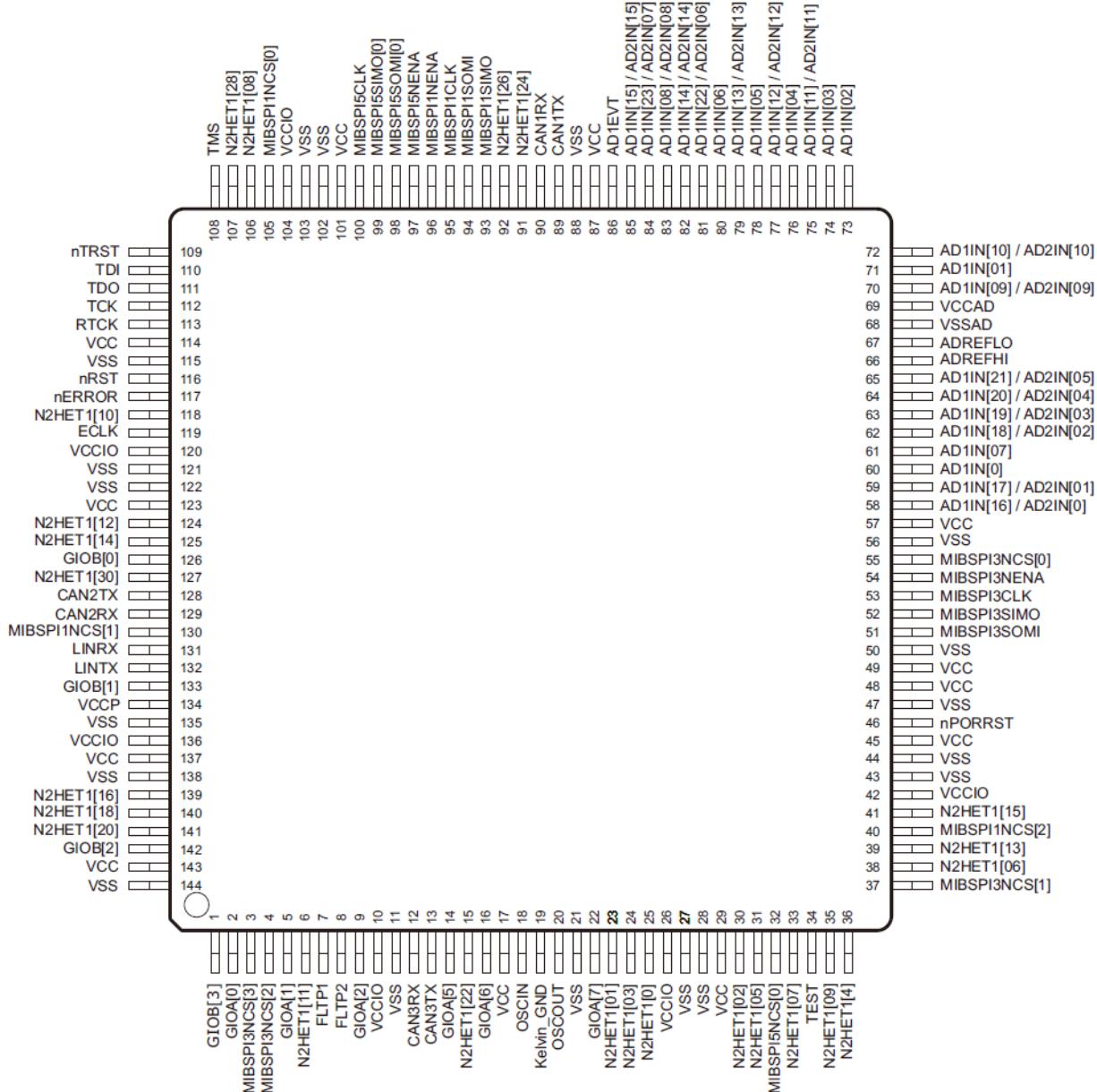

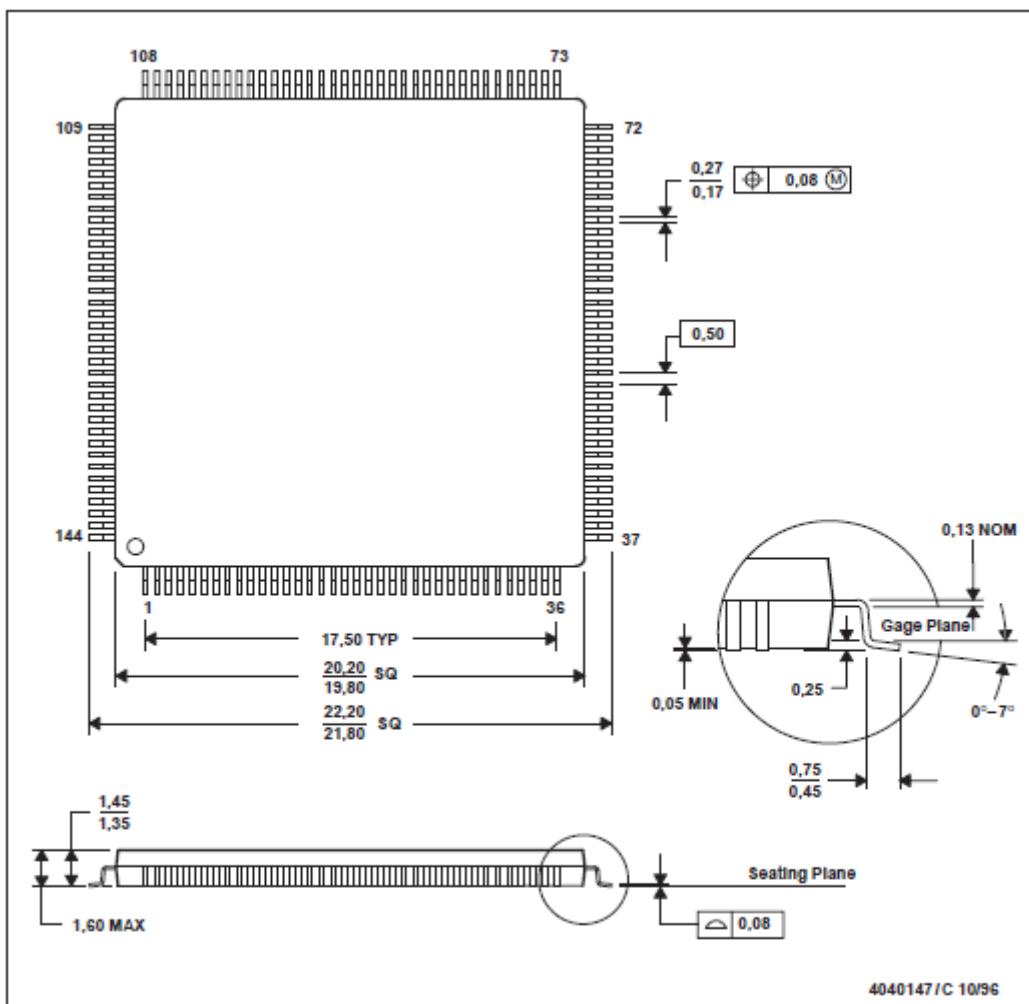

## 2.1 PGE QFP パッケージ・ピンアウト (144 ピン)

図 2-1 PGE QFP パッケージ・ピンアウト(144 ピン)

注：ピンには多重機能を持つものもあります。上の図ではデフォルト機能のみを示しています。

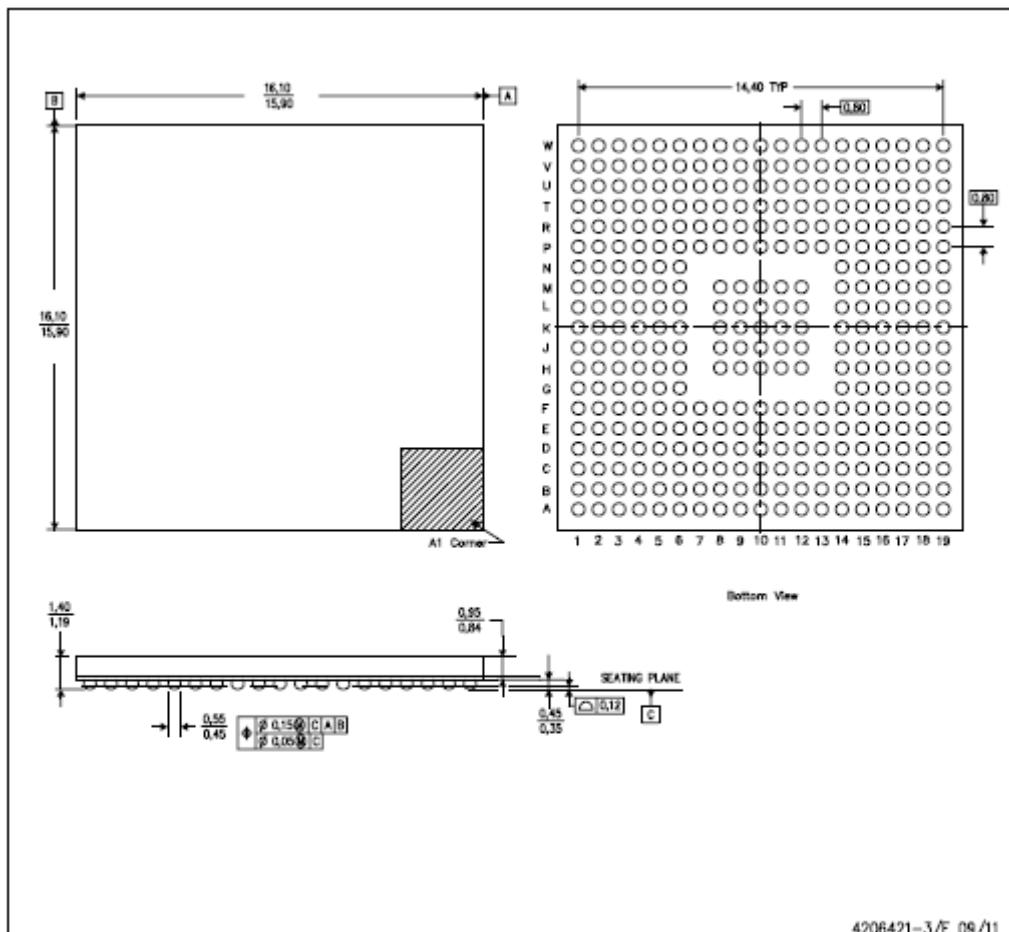

## 2.2 ZWT BGA パッケージ・ポールマップ (337 ポール・グリッド・アレイ)

|     | A           | B              | C              | D             | E               | F              | G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | H               | J               | K            | L            | M            | N            | P                     | R                     | T                     | U                     | V                     | W              |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

|-----|-------------|----------------|----------------|---------------|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------|--------------|--------------|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------|------------------|----------------|-----------------------|----------------------|--------------|----|

| 19  | VSS         | VSS            | TMS            | N2HET1 [10]   | MIBSPI5 NCS[0]  | MIBSPI1 SIMO   | MIBSPI1 NENA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MIBSPI5 CLK     | MIBSPI5 SIMO[0] | N2HET1 [28]  | DMM_DATA[0]  | CAN3RX       | AD1EVT       | AD1IN[15] / AD2IN[15] | AD1IN[22] / AD2IN[06] | AD1IN [06]            | AD1IN[11] / AD2IN[11] | VSSAD                 | VSSAD          | 19    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 18  | VSS         | TCK            | TDO            | nTRST         | N2HET1 [08]     | MIBSPI1 CLK    | MIBSPI1 SOMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MIBSPI5 NENA    | MIBSPI5 SOMI[0] | N2HET1 [0]   | DMM_DATA[1]  | CAN3TX       | NC           | AD1IN[08] / AD2IN[08] | AD1IN[14] / AD2IN[14] | AD1IN[13] / AD2IN[13] | AD1IN [04]            | AD1IN [02]            | VSSAD          | VSSAD | 18  |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 17  | TDI         | RST            | EMIF_ADDR[21]  | EMIF_nWE      | MIBSPI5 SOMI[1] | DMM_CLK        | MIBSPI5 SIMO[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIBSPI5 SIMO[2] | N2HET1 [31]     | EMIF_nCS[3]  | EMIF_nCS[2]  | EMIF_nCS[0]  | NC           | AD1IN [05]            | AD1IN [03]            | AD1IN[10] / AD2IN[10] | AD1IN [01]            | AD1IN[09] / AD2IN[09] | 17             |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 16  | RTCK        | NC             | EMIF_ADDR[20]  | EMIF_BA[1]    | MIBSPI5 SIMO[1] | DMM_NENA       | MIBSPI5 SOMI[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIBSPI5 SOMI[2] | DMM_SYNC        | NC           | NC           | NC           | NC           | AD1IN[23] / AD2IN[07] | AD1IN[12] / AD2IN[12] | AD1IN[19] / AD2IN[03] | ADREFLO               | VSSAD                 | 16             |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 15  | NC          | NC             | EMIF_ADDR[19]  | EMIF_ADDR[18] | ETM DATA[06]    | ETM DATA[05]   | ETM DATA[04]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ETM DATA[03]    | ETM DATA[02]    | ETM DATA[16] | ETM DATA[17] | ETM DATA[18] | ETM DATA[19] | NC                    | NC                    | AD1IN[21] / AD2IN[05] | AD1IN[20] / AD2IN[04] | ADREFHI               | VCCAD          | 15    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 14  | N2HET1 [26] | nERROR         | EMIF_ADDR[17]  | EMIF_ADDR[16] | ETM DATA[07]    | VCCIO          | VCCIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VCC             | VCC             | VCCIO        | VCCIO        | VCCIO        | VCCIO        | NC                    | NC                    | AD1IN[18] / AD2IN[02] | AD1IN [07]            | AD1IN [0]             | 14             |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 13  | N2HET1 [17] | N2HET1 [19]    | EMIF_ADDR[15]  | NC            | ETM DATA[12]    | VCCIO          | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VCC</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VCC</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> </table> |                 |                 |              |              |              |              |                       |                       |                       |                       |                       | VSS            | VSS   | VCC | VSS | VCC | VSS | VSS | VSS | VCC | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCCIO   | ETM DATA[01]     | NC             | AD1IN[17] / AD2IN[01] | AD1IN[16] / AD2IN[0] | NC           | 13 |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VCC | VSS         | VSS            | VSS            | VCC           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 12  | ECLK        | N2HET1 [04]    | EMIF_ADDR[14]  | NC            | ETM DATA[13]    | VCCIO          | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VCC</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VCC</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> </table> |                 |                 |              |              |              |              |                       |                       |                       |                       |                       | VSS            | VSS   | VCC | VSS | VCC | VSS | VSS | VSS | VCC | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCCIO   | ETM DATA[0]      | MIBSPI5 NCS[3] | NC                    | NC                   | NC           | 12 |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VCC | VSS         | VSS            | VSS            | VCC           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 11  | N2HET1 [14] | N2HET1 [30]    | EMIF_ADDR[13]  | NC            | ETM DATA[14]    | VCCIO          | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VCC</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VCC</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> </table> |                 |                 |              |              |              |              |                       |                       |                       |                       |                       | VSS            | VSS   | VSS | VSS | VSS | VSS | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VSS | VCC | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCCPPLL | ETM TRACE CTL    | NC             | NC                    | NC                   | NC           | 11 |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VCC | VSS         | VSS            | VSS            | VCC           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 10  | CAN1TX      | CAN1RX         | EMIF_ADDR[12]  | NC            | ETM DATA[15]    | VCC            | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr><td>VCC</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VCC</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VCC</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> </table> |                 |                 |              |              |              |              |                       |                       |                       |                       |                       | VCC            | VSS   | VSS | VSS | VSS | VSS | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VSS | VCC | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCC     | ETM TRACE CLKOUT | NC             | NC                    | MIBSPI3 NCS[0]       | GIOB[3]      | 10 |

| VCC | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VCC | VSS         | VSS            | VSS            | VCC           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 9   | N2HET1 [27] | NC             | EMIF_ADDR[11]  | NC            | ETM DATA[08]    | VCC            | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VCC</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VCC</td></tr> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> </table> |                 |                 |              |              |              |              |                       |                       |                       |                       |                       | VSS            | VSS   | VSS | VSS | VSS | VSS | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VSS | VCC | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCCIO   | ETM TRACE CLKIN  | NC             | NC                    | MIBSPI3 CLK          | MIBSPI3 NENA | 9  |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VCC | VSS         | VSS            | VSS            | VCC           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 8   | NC          | NC             | EMIF_ADDR[10]  | NC            | ETM DATA[09]    | VCCP           | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VCC</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> </table> |                 |                 |              |              |              |              |                       |                       |                       |                       |                       | VSS            | VSS   | VSS | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCC | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCCIO   | ETM DATA[31]     | NC             | NC                    | MIBSPI3 SOMI         | MIBSPI3 SIMO | 8  |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VCC | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 7   | LINRX       | LINTX          | EMIF_ADDR[9]   | NC            | ETM DATA[10]    | VCCIO          | <table border="1" style="margin-left: auto; margin-right: auto;"> <tr><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VCC</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VCC</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> <tr><td>VSS</td><td>VSS</td><td>VCC</td><td>VSS</td><td>VSS</td></tr> </table> |                 |                 |              |              |              |              |                       |                       |                       |                       |                       | VSS            | VSS   | VSS | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCC | VSS | VCC | VSS | VCC | VSS | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VSS | VSS | VCC | VSS | VSS | VCCIO   | ETM DATA[30]     | NC             | NC                    | N2HET1 [09]          | nPORRST      | 7  |

| VSS | VSS         | VSS            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VCC | VSS         | VCC            | VSS            | VCC           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| VSS | VSS         | VCC            | VSS            | VSS           |                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |              |              |              |              |                       |                       |                       |                       |                       |                |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 6   | GIOA[4]     | MIBSPI5 NCS[1] | EMIF_ADDR[8]   | NC            | ETM DATA[11]    | VCCIO          | VCCIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VCCIO           | VCC             | VCC          | VCCIO        | VCCIO        | VCCIO        | ETM DATA[29]          | ETM DATA[29]          | NC                    | NC                    | N2HET1 [05]           | MIBSPI5 NCS[2] | 6     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 5   | GIOA[0]     | GIOA[5]        | EMIF_ADDR[7]   | EMIF_ADDR[1]  | ETM DATA[20]    | ETM DATA[21]   | ETM DATA[22]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FLTP2           | FLTP1           | ETM DATA[23] | ETM DATA[24] | ETM DATA[25] | ETM DATA[26] | ETM DATA[27]          | ETM DATA[28]          | NC                    | NC                    | MIBSPI3 NCS[1]        | N2HET1 [02]    | 5     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

| 4   | N2HET1 [16] | N2HET1 [12]    | EMIF_ADDR[6]   | EMIF_ADDR[0]  | NC              | NC             | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N2HET1 [21]     | N2HET1 [23]     | NC           | NC           | NC           | NC           | NC                    | EMIF_nCAS             | NC                    | NC                    | NC                    | NC             | 4     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |

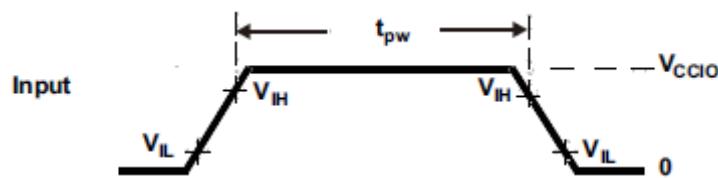

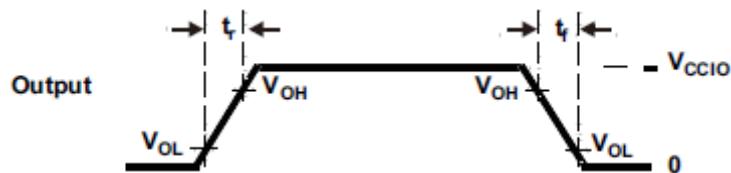

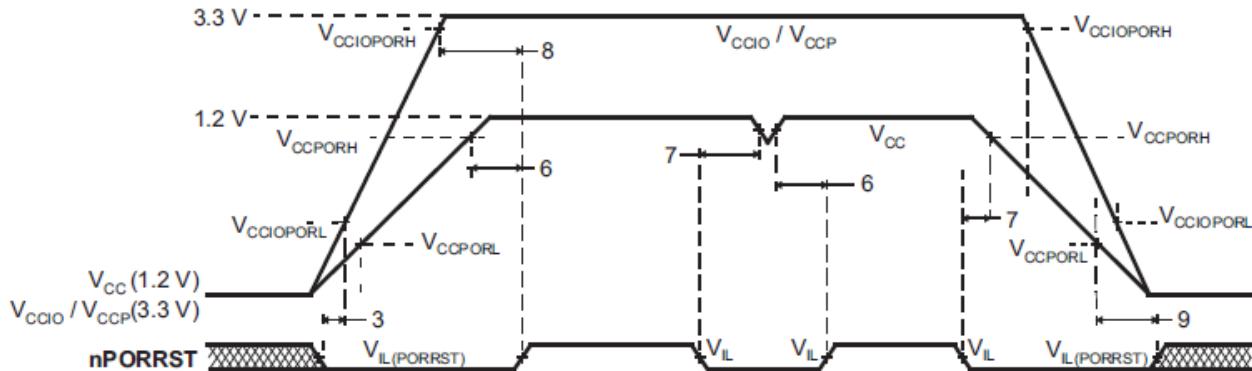

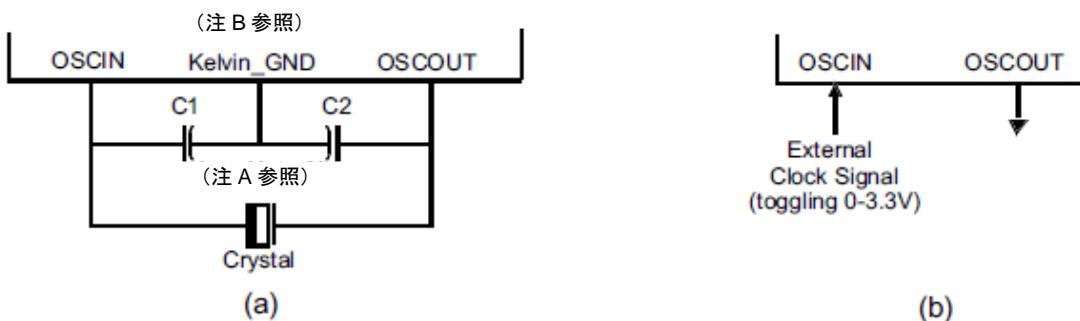

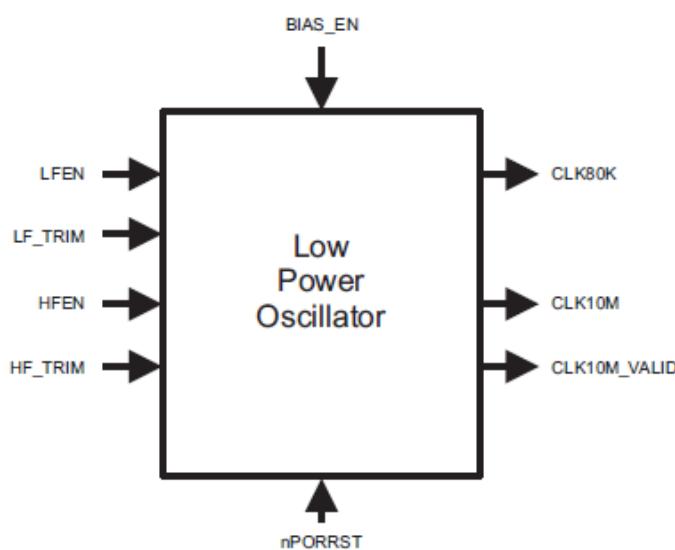

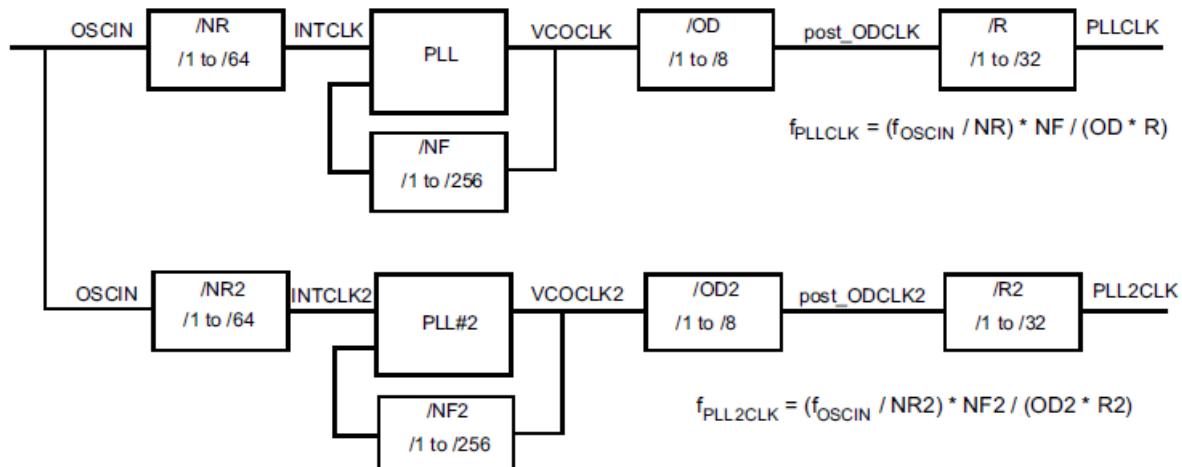

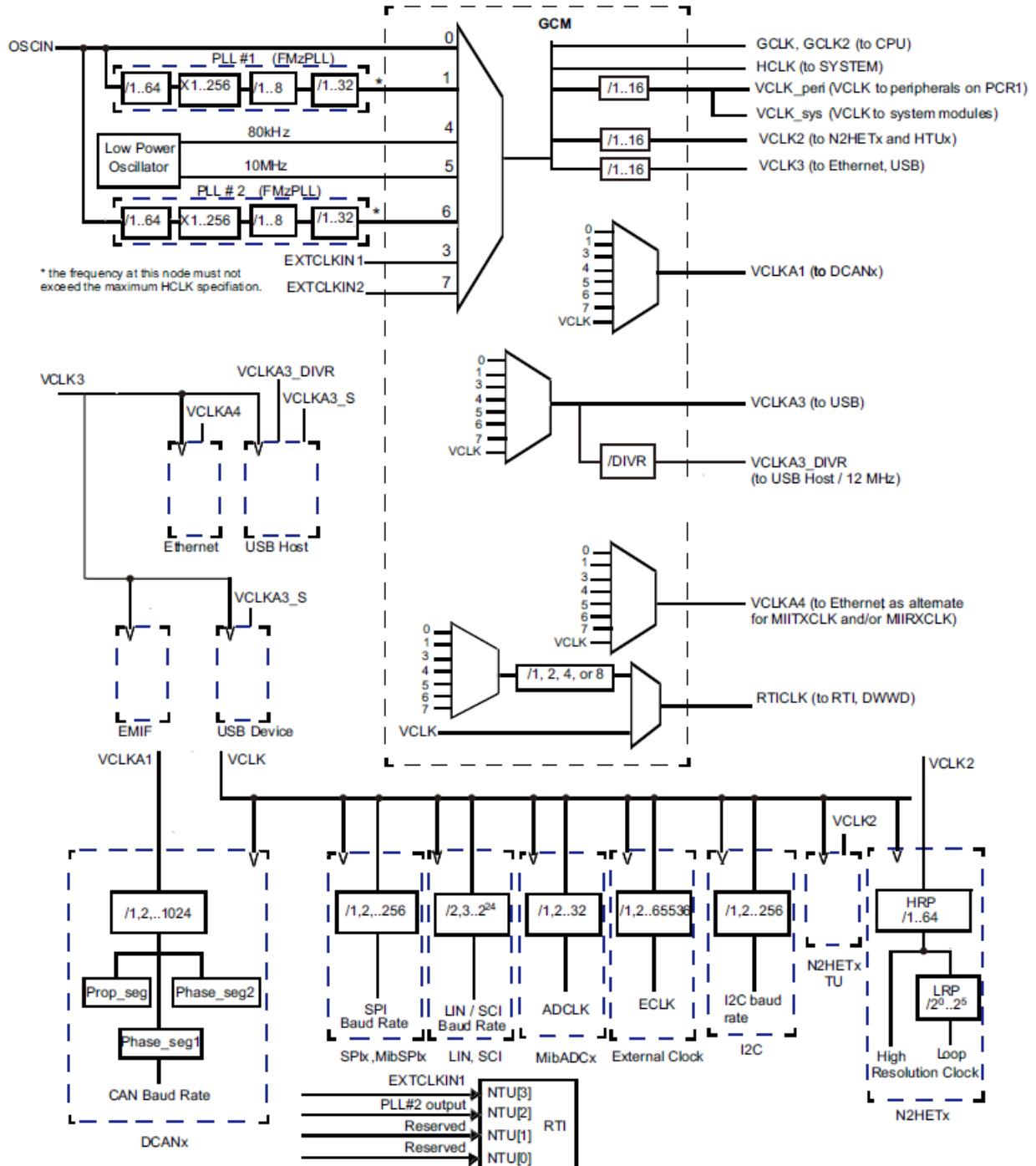

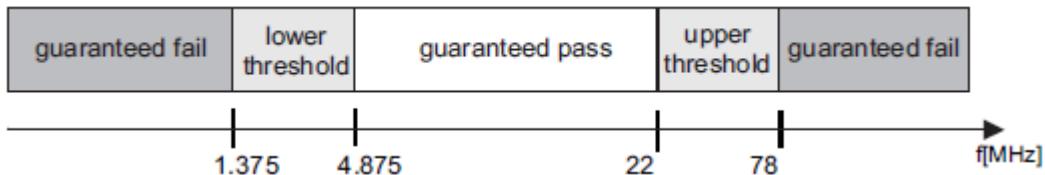

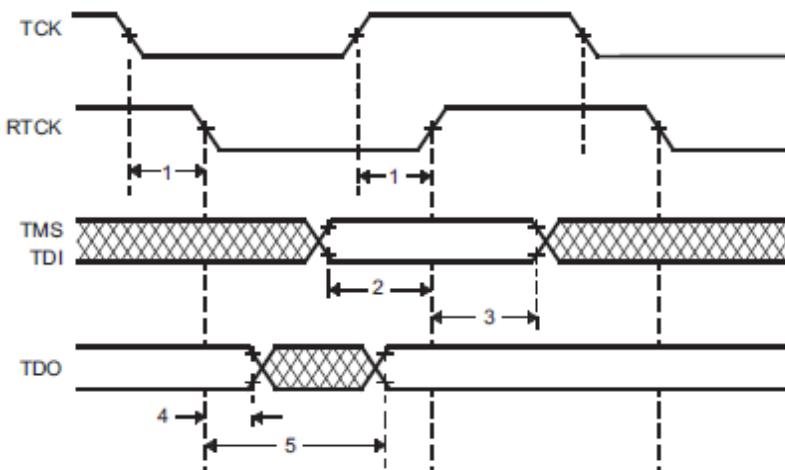

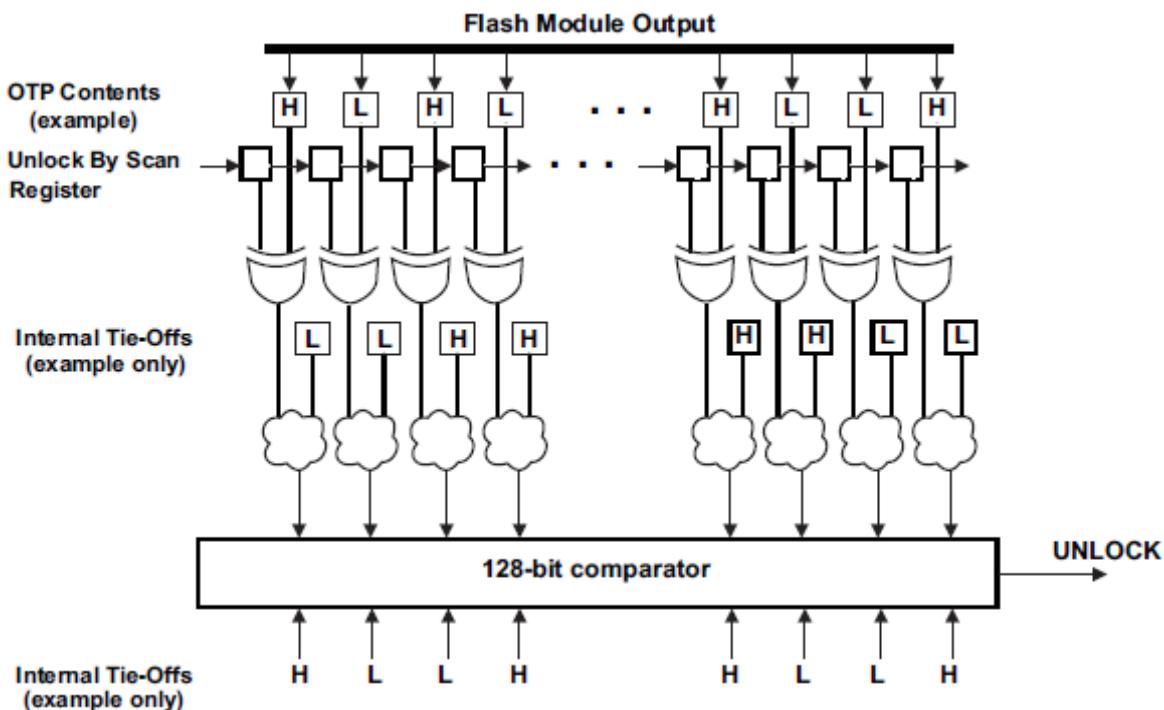

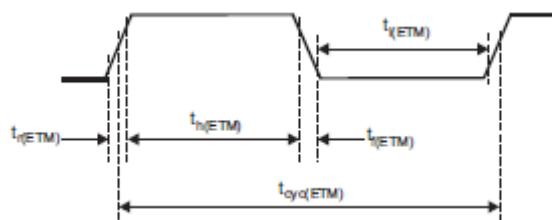

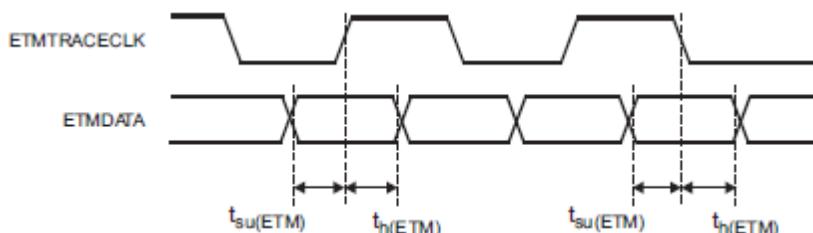

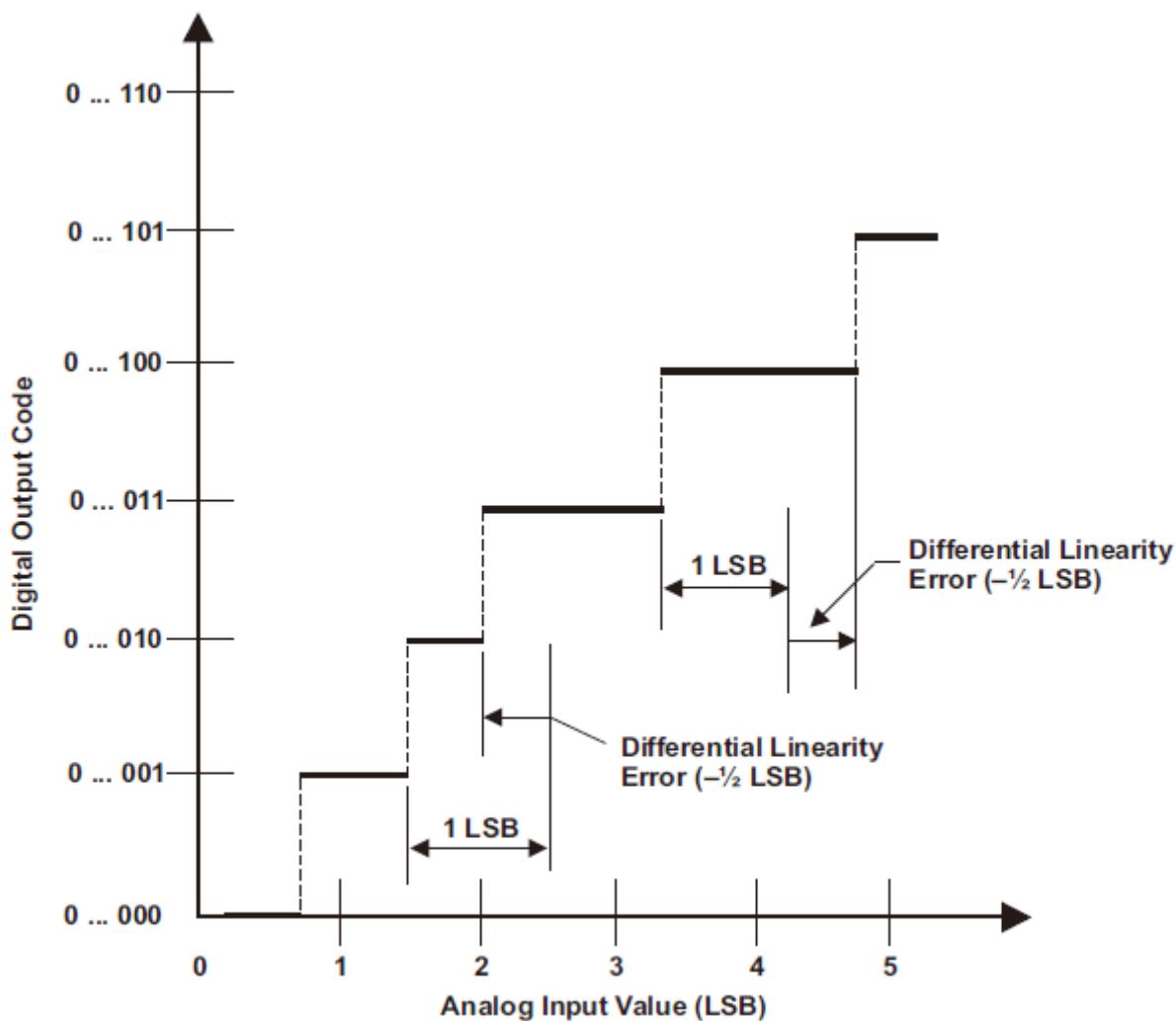

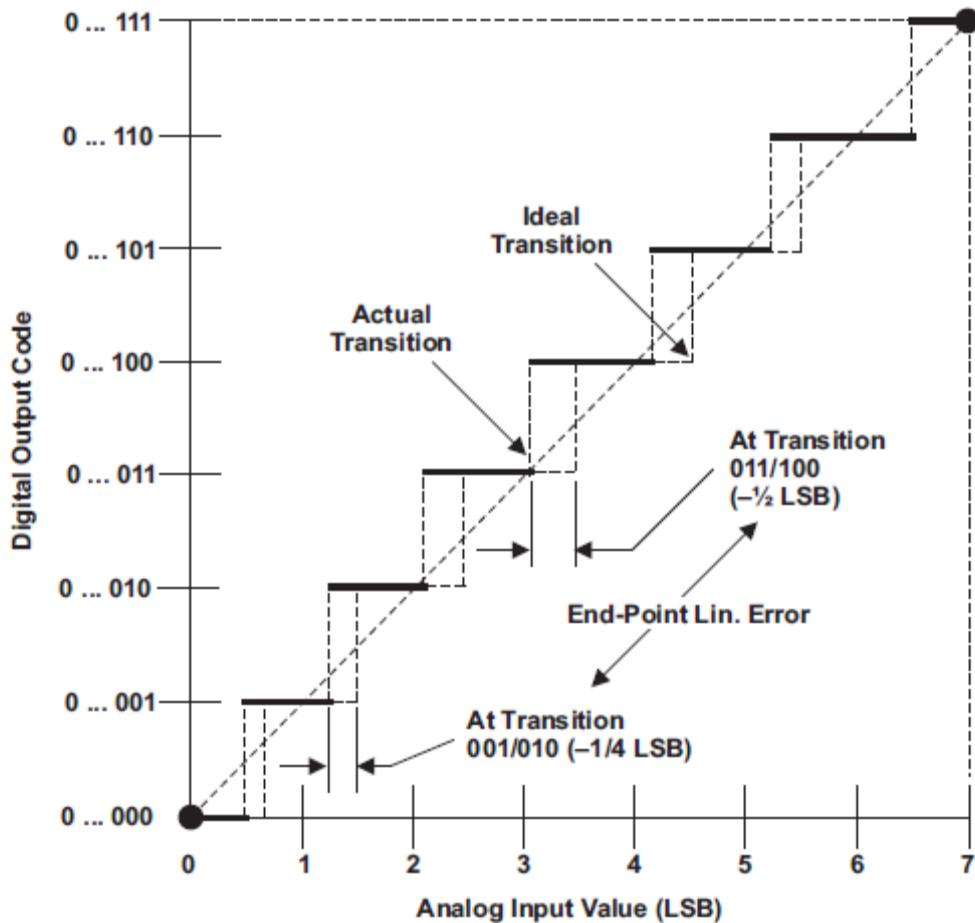

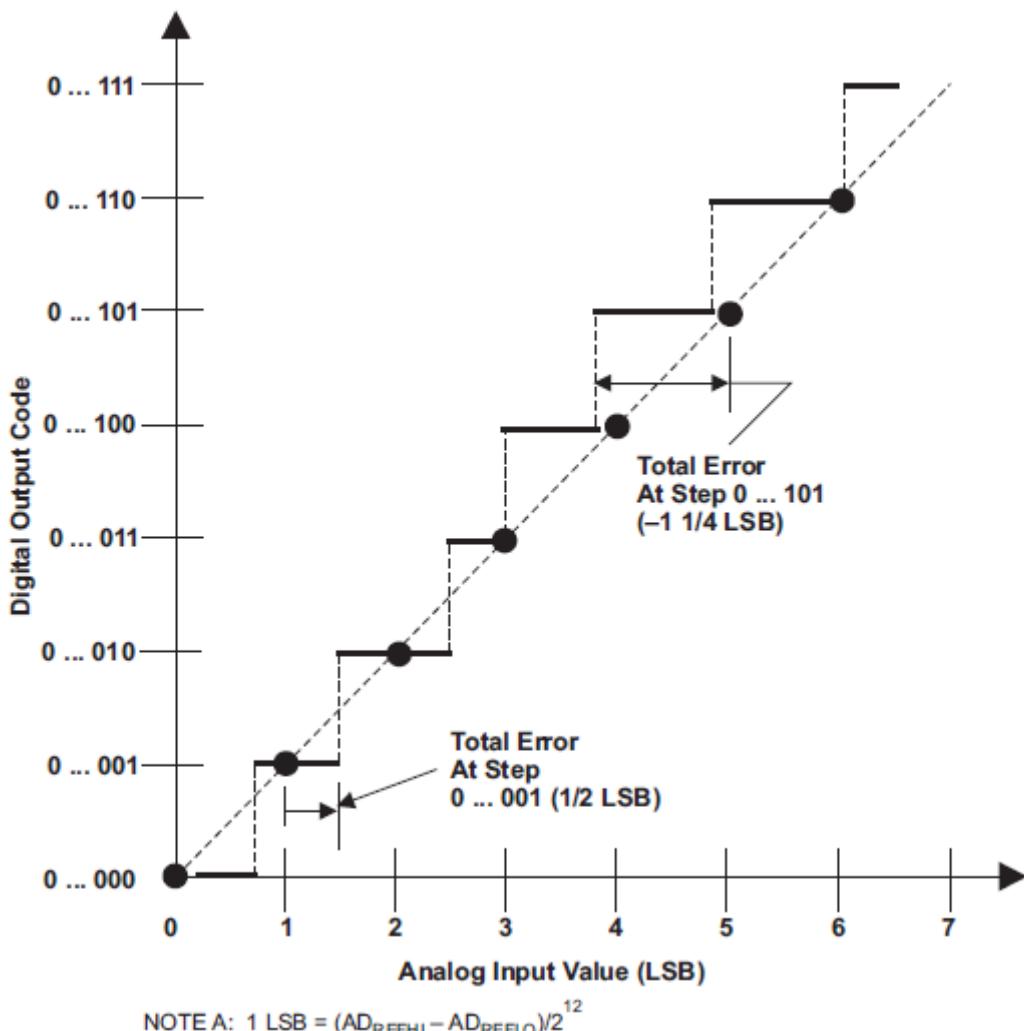

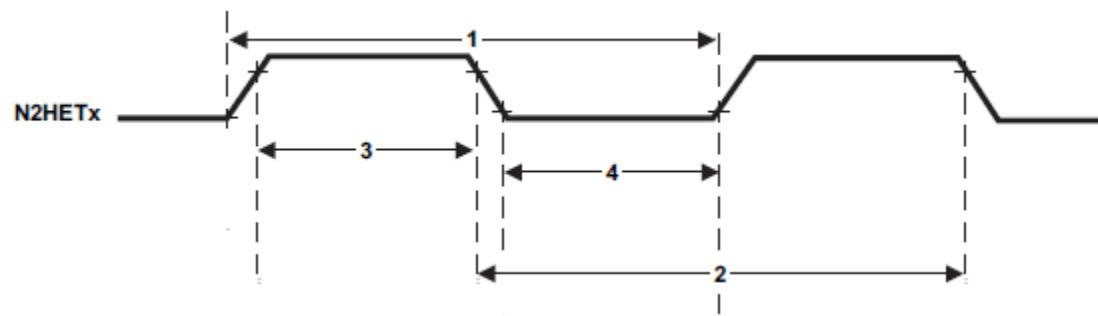

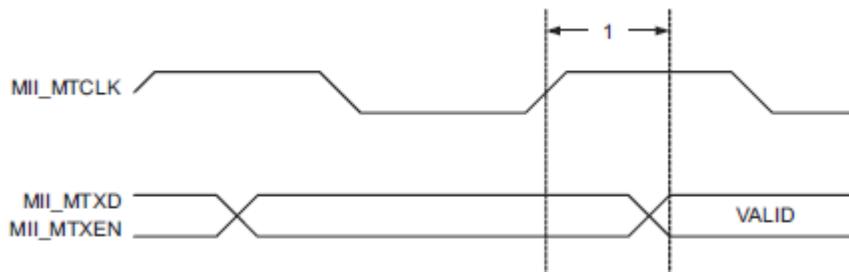

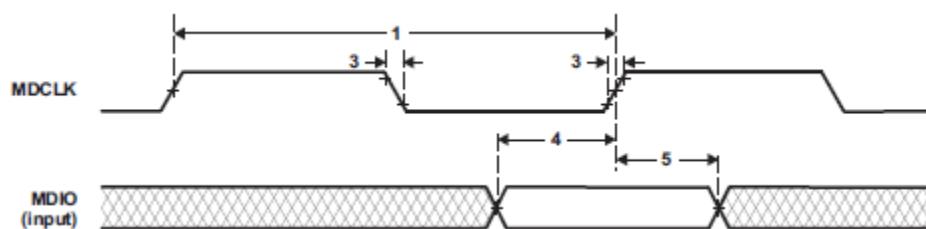

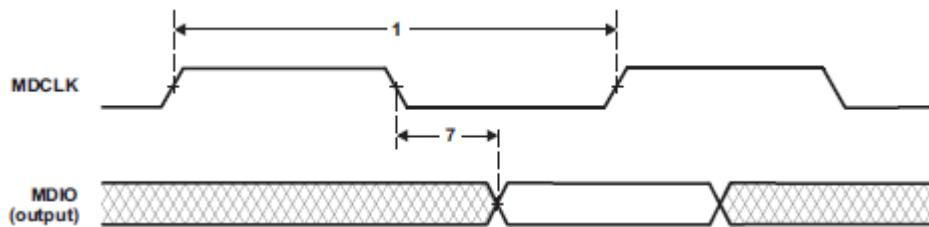

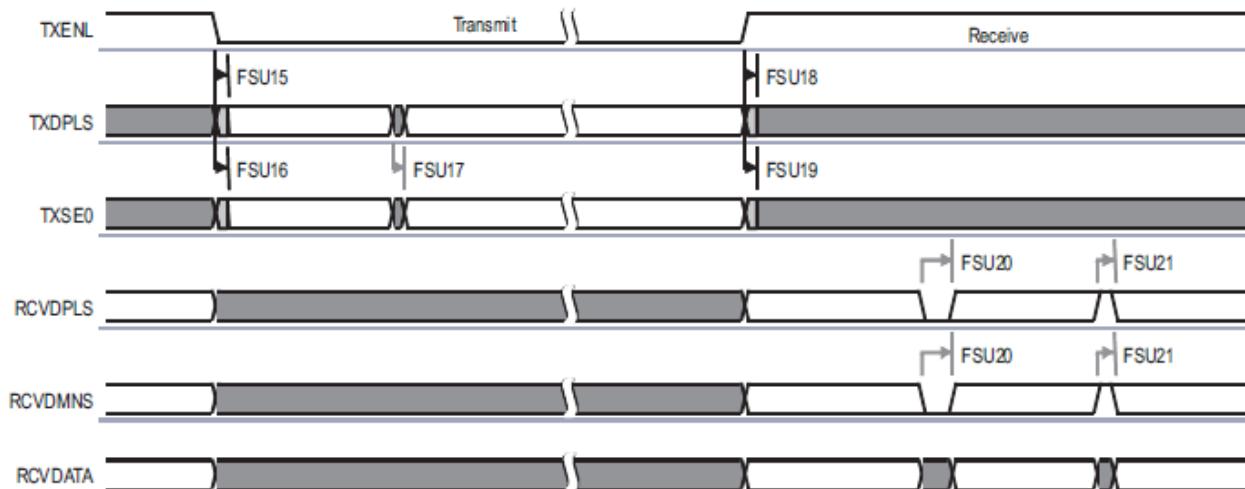

| 3   | N2HET1 [29] | N2HET1 [22]    | MIBSPI3 NCS[3] | SPI2_NENA     | N2HET1 [11]     | MIBSPI1 NCS[1] | MIBSPI1 NCS[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GIOA[6]         | MIBSPI1 NCS[3]  | EMIF_CLK     | EMIF_CKE     | NH2ET1 [25]  | SPI2_NCS[0]  | EMIF_nWAIT            | EMIF_nRAS             | NC                    | NC                    | NC                    | N2HET1 [06]    | 3     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |         |                  |                |                       |                      |              |    |