# PGA460 超音波信号プロセッサおよびトランスデューサ・ドライバ

## 1 特長

- 超音波センシング用の完全に統合されたソリューション

- 電流制限を設定可能な相補的なローサイド・ドライバ、トランス・ベースおよび直接駆動トポロジのトランスデューサ励起をサポート

- 単一のトランスデューサでバースト/リスンの両方を行うか、または、トランスデューサのペアを使用し、1つをバースト、もう1つをリスン動作に使用

- 低ノイズのレシーバ、6ポイントの時変ゲイン(32~90dB)をプログラム可能で、エコー・エンベロープ検出用の DSP (BPF、復調) を内蔵

- 物体検出のための 12 ポイントの時変スレッシュルドについて 2 つのプリセット

- タイマにより複数のエコー距離と期間を測定

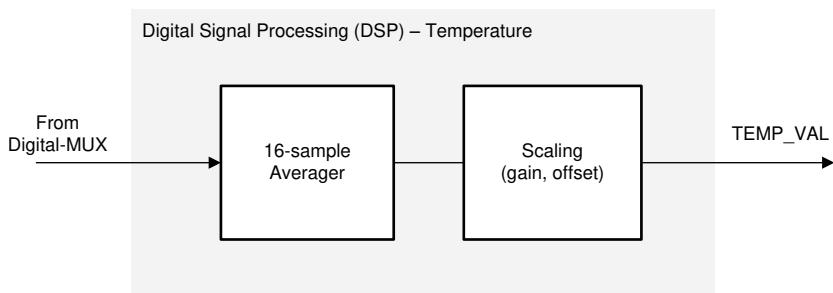

- 温度センサ内蔵

- 時間記録による 11m までの物体検出

- 128 バイトの RAM によるエコー記録

- 42 バイトのユーザー EEPROM に構成を保存して高速に初期化

- 1 線式高電圧の時間コマンド・インターフェイスまたは USART 非同期インターフェイス

- CMOS レベル USART インターフェイス

- センサ診断(減衰周波数および時間、励起電圧)、電源、およびトランシーバ診断

## 2 アプリケーション

- 超音波レーダー

- 物体の距離と位置の検出

- 存在および近接検出

- ドローンおよびロボットの着地補助および障害物検出

- 人感センサおよびモーション・センサ

## 3 概要

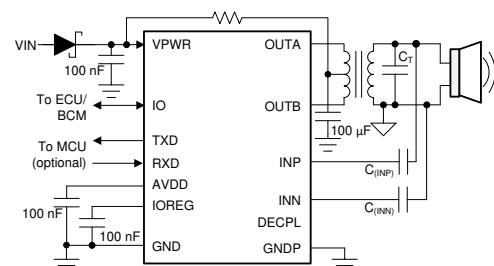

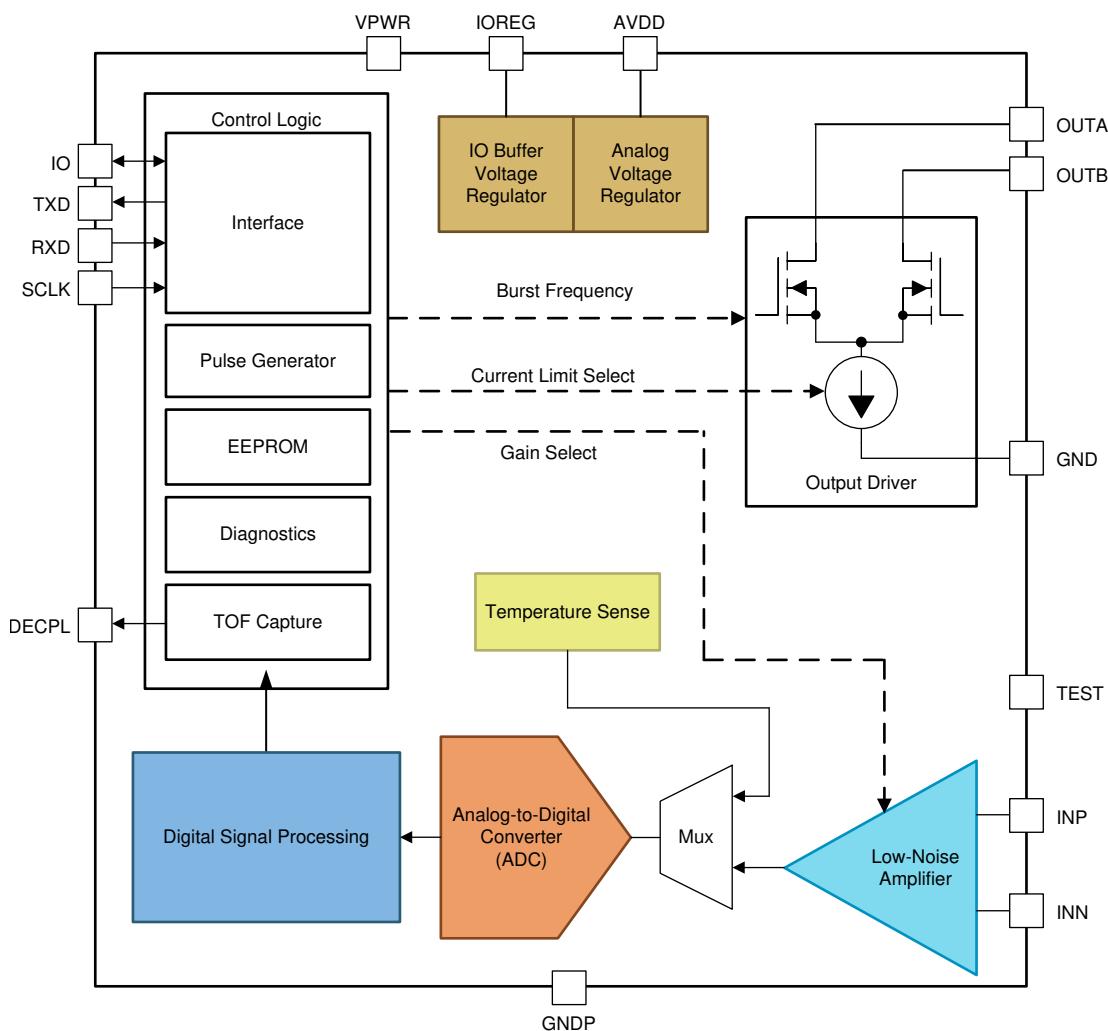

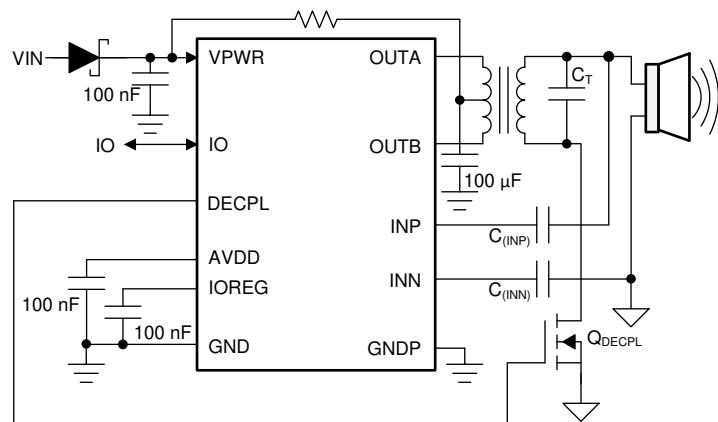

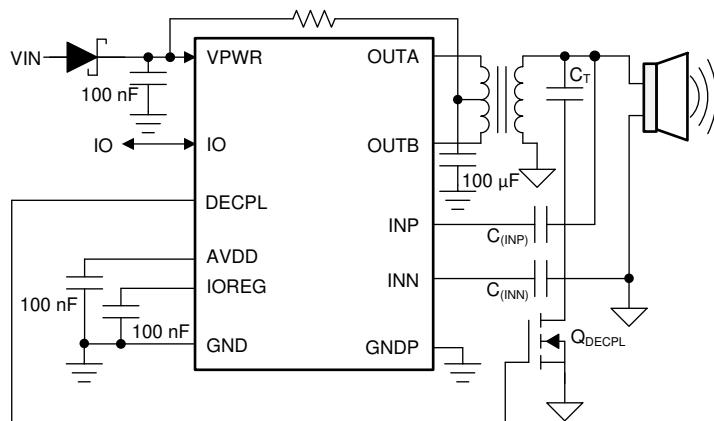

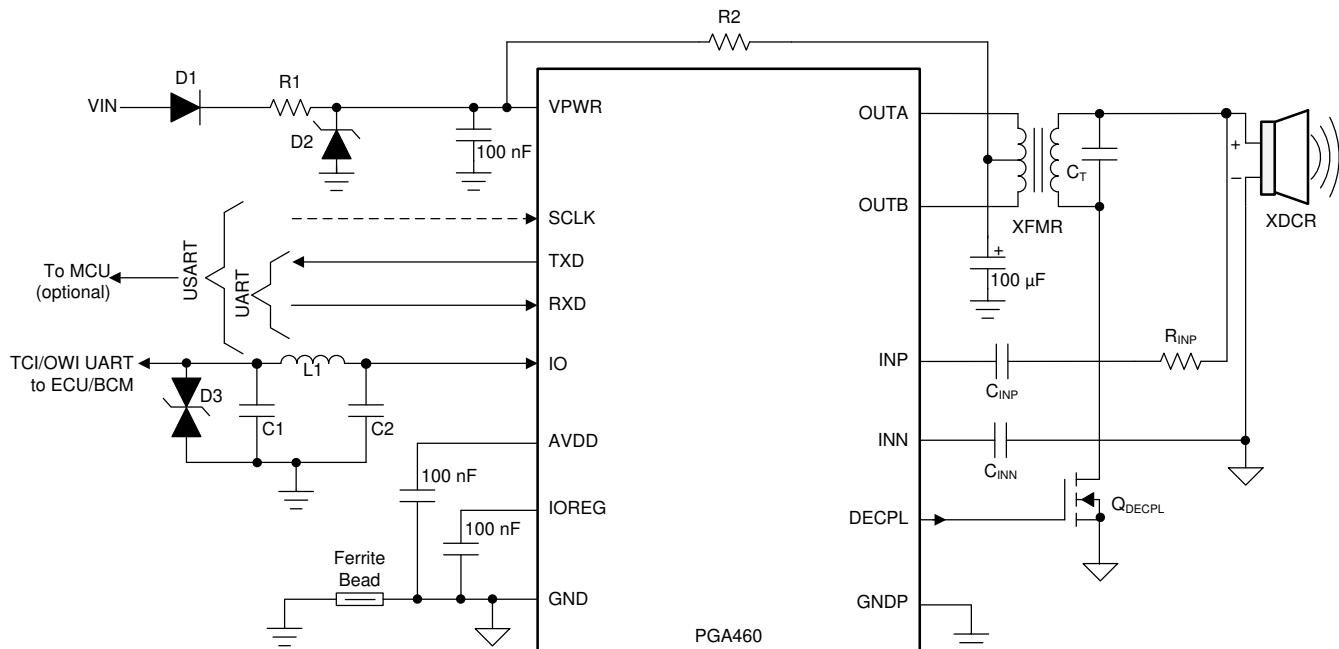

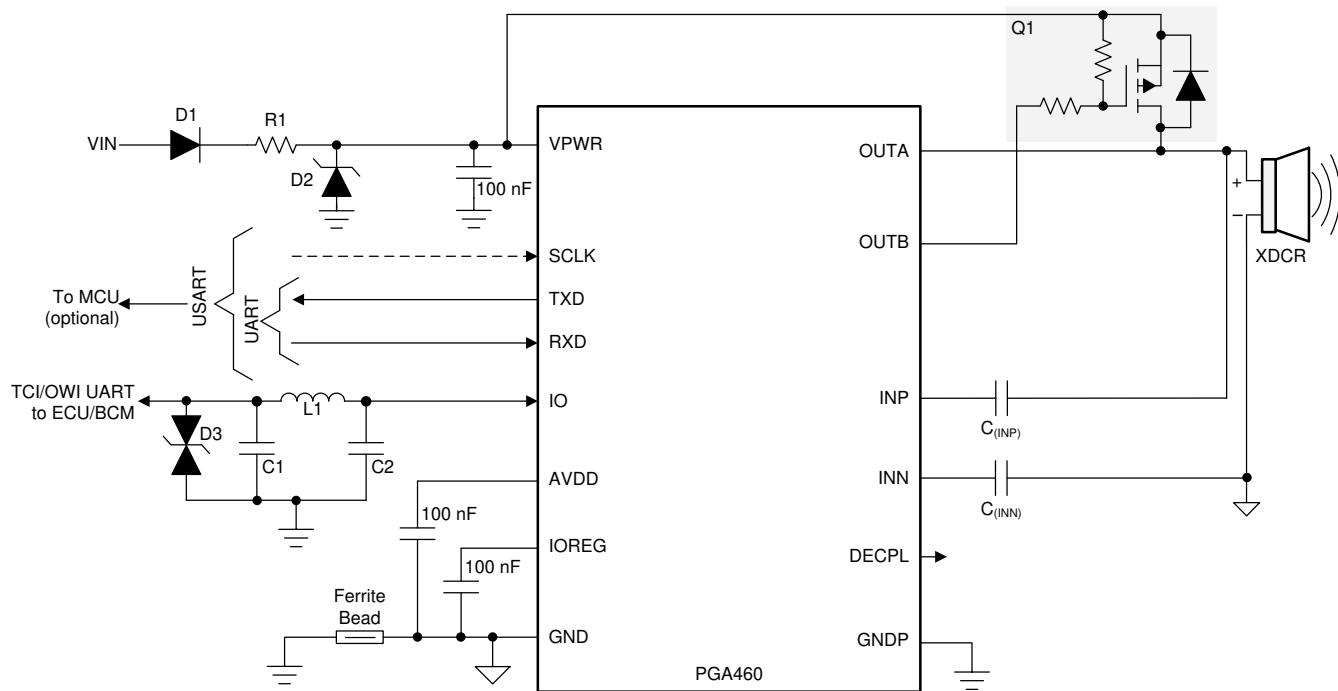

PGA460 デバイスは、高度に統合されたシステム・オン・チップの超音波トランスデューサ・ドライバおよび信号コンディショナで、高度な DSP コアが搭載されています。このデバイスには相補的なローサイド・ドライバ・ペアが搭載されており、昇圧型トランスを使用するトランス・ベースのトポロジ、または外付けのハイサイド FET を使用する直接駆動トポロジでトランスデューサを駆動できます。このデバイスは、反射されたエコー信号を受信してコンディショニングし、信頼性の高い物体検出を行えます。この機能はアナログ・フロントエンド (AFE) を使用して実現されており、低ノイズのアンプと、ADC へ信号を供給する後続のプログラム可能な時変ゲイン段から構成されています。デジタル化された信号は DSP コアで処理され、時変スレッシュルドを使用して近距離と遠距離の物体検出が行われます。

外部コントローラとの主な通信は、IO ピン上の時間コマンド・インターフェイス (TCI) または 1 線式の USART 非同期インターフェイス、または RXD および TXD ピン上の CMOS レベル USART インターフェイスにより行われます。PGA460 を使用しないときは、静止電流が非常に低い低消費電力モードに移行でき、通信インターフェイス上のコマンドでウェークアップ可能です。

また、PGA460 にはオンチップのシステム診断機能が内蔵されており、バースト時のトランスデューサ電圧、トランスデューサの周波数と減衰時間を監視して、励起の整合性についての情報を取得し、電源側およびトランシーバ側の過電圧、低電圧、過電流、短絡状況の診断を行います。

### パッケージ情報 (1)

| 部品番号   | パッケージ      | 本体サイズ (公称)      |

|--------|------------|-----------------|

| PGA460 | TSSOP (16) | 5.00mm × 4.40mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

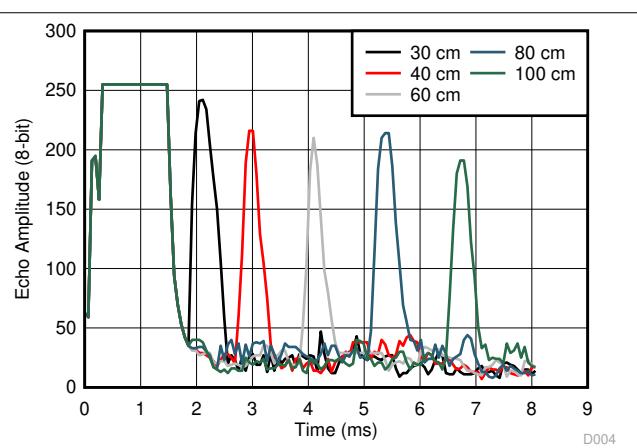

代表的なアプリケーション図 (トランス駆動)

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                   |   |                        |     |

|-------------------|---|------------------------|-----|

| 1 特長              | 1 | 6.16 代表的な特性            | 9   |

| 2 アプリケーション        | 1 | 7 詳細説明                 | 10  |

| 3 概要              | 1 | 7.1 概要                 | 10  |

| 4 改訂履歴            | 2 | 7.2 機能ブロック図            | 11  |

| 5 ピン構成および機能       | 4 | 7.3 機能説明               | 11  |

| 6 仕様              | 5 | 7.4 デバイスの機能モード         | 50  |

| 6.1 絶対最大定格        | 5 | 7.5 プログラミング            | 50  |

| 6.2 ESD 定格        | 5 | 7.6 レジスタ・マップ           | 53  |

| 6.3 推奨動作条件        | 5 | 8 アプリケーションと実装          | 103 |

| 6.4 熱に関する情報       | 6 | 8.1 アプリケーション情報         | 103 |

| 6.5 内部電源レギュレータの特性 | 6 | 8.2 代表的なアプリケーション       | 103 |

| 6.6 トランジスタ・ドライバ特性 | 6 | 8.3 電源に関する推奨事項         | 109 |

| 6.7 トランジスタ・レシーバ特性 | 7 | 8.4 レイアウト              | 109 |

| 6.8 A/D コンバータの特性  | 7 | 9 デバイスおよびドキュメントのサポート   | 111 |

| 6.9 デジタル信号処理特性    | 7 | 9.1 ドキュメントのサポート        | 111 |

| 6.10 温度センサの特性     | 7 | 9.2 ドキュメントの更新通知を受け取る方法 | 111 |

| 6.11 高電圧 I/O 特性   | 8 | 9.3 サポート・リソース          | 111 |

| 6.12 デジタル I/O 特性  | 8 | 9.4 商標                 | 111 |

| 6.13 EEPROM の特性   | 8 | 9.5 静電気放電に関する注意事項      | 111 |

| 6.14 タイミング要件      | 8 | 9.6 用語集                | 111 |

| 6.15 スイッチング特性     | 9 | 10 メカニカル、パッケージ、および注文情報 | 111 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (January 2019) to Revision C (February 2023) | Page |

|----------------------------------------------------------------------|------|

| • 文書全体にわたって表、図、相互参照の採番方法を更新                                          | 1    |

| • SPI に言及している場合、すべての旧式の用語をコントローラおよびペリフェラルに変更                         | 1    |

| • 表のタイトルを「デバイス情報」から「パッケージ情報」に変更                                      | 1    |

| • 「電源に関する推奨事項」および「レイアウト」セクションを「アプリケーションと実装」セクションに移動                  | 109  |

| Changes from Revision A (August 2017) to Revision B (January 2019)                                                                    | Page |

|---------------------------------------------------------------------------------------------------------------------------------------|------|

| • 出力ドライバを正しく接地するための機能ブロック図の GND および GNDP ピンの記号を変更                                                                                     | 11   |

| • 表 7-3 の注を更新                                                                                                                         | 34   |

| • 以下の文を追加。USART 同期モードは、チップセレクトなしのシリアル・ペリフェラル・インターフェイス (SPI) と同じです。アドレス指定は 3 ビットの UART_ADDR 値によって処理され、1 つのバスで最大 8 つのデバイスをイネーブルにできるからです | 39   |

| • 注を追加。温度測定のサンプルおよび変換時間には、温度測定コマンドを発行してから少なくとも 100us が必要です。温度の値を適切に更新できるように、この期間中は他のコマンドを送信しないでください                                   | 47   |

| Changes from Revision * (April 2017) to Revision A (August 2017) | Page |

|------------------------------------------------------------------|------|

| • 「構成 / ステータス・コマンド」セクションにゼロ・パディング情報を探加                           | 27   |

| • USART インターフェイスのパラメータ・テキストを「1 ストップ・ビット」から「2 ストップ・ビット」に変更        | 31   |

| • フィールド間待機時間のテキストを「オプション」から「1 ストップ・ビットで必須」に変更                    | 31   |

| • 文を追加。SYNC フィールド (0x55) は、チェックサム計算の対象に含まれていません                  | 34   |

| • コンテンツを更新し、表 7-3 に注を追加                                          | 34   |

| • 文を追加。診断フィールドは、ペリフェラルによって生成されるチェックサム計算に含まれます                    | 38   |

| • サブセクション「USART 同期モードによるダイレクト・データ・バースト」を追加                       | 43   |

| • 式 8 を追加                                                        | 47   |

---

|                                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • 文を追加。これには、すべてのスレッショルド・タイミングとレベル値が含まれます。.....                                                                                             | 50  |

| • 「 <i>UART</i> および <i>USART</i> 通信の例」のコンテンツを更新.....                                                                                       | 53  |

| • 表 8-2 のコンテンツを更新.....                                                                                                                     | 104 |

| • 「アプリケーション曲線」にコンテンツを追加.....                                                                                                               | 107 |

| • 「直接駆動 (トランスレス) 方式」に内容を追加し、 $XDCR_{\text{Negative}}$ および $C_{\text{INN}}$ に GND ノードが存在するように 図 8-6 を変更.....                                | 108 |

| • 「概要」のテキストを TDK EPCOS B78416A2232A03 トランス、muRata MA40H1S-R トランスデューサから Fairchild FDC6506P p-チャネル MOSFET、muRata MA40H1S-R トランスデューサに変更。..... | 109 |

---

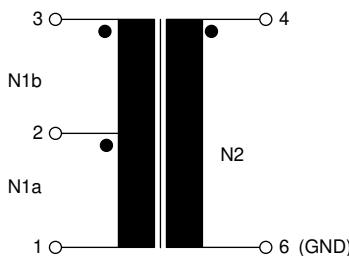

## 5 ピン構成および機能

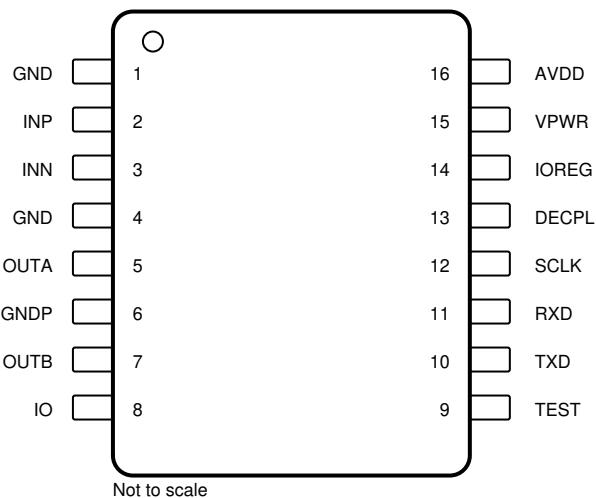

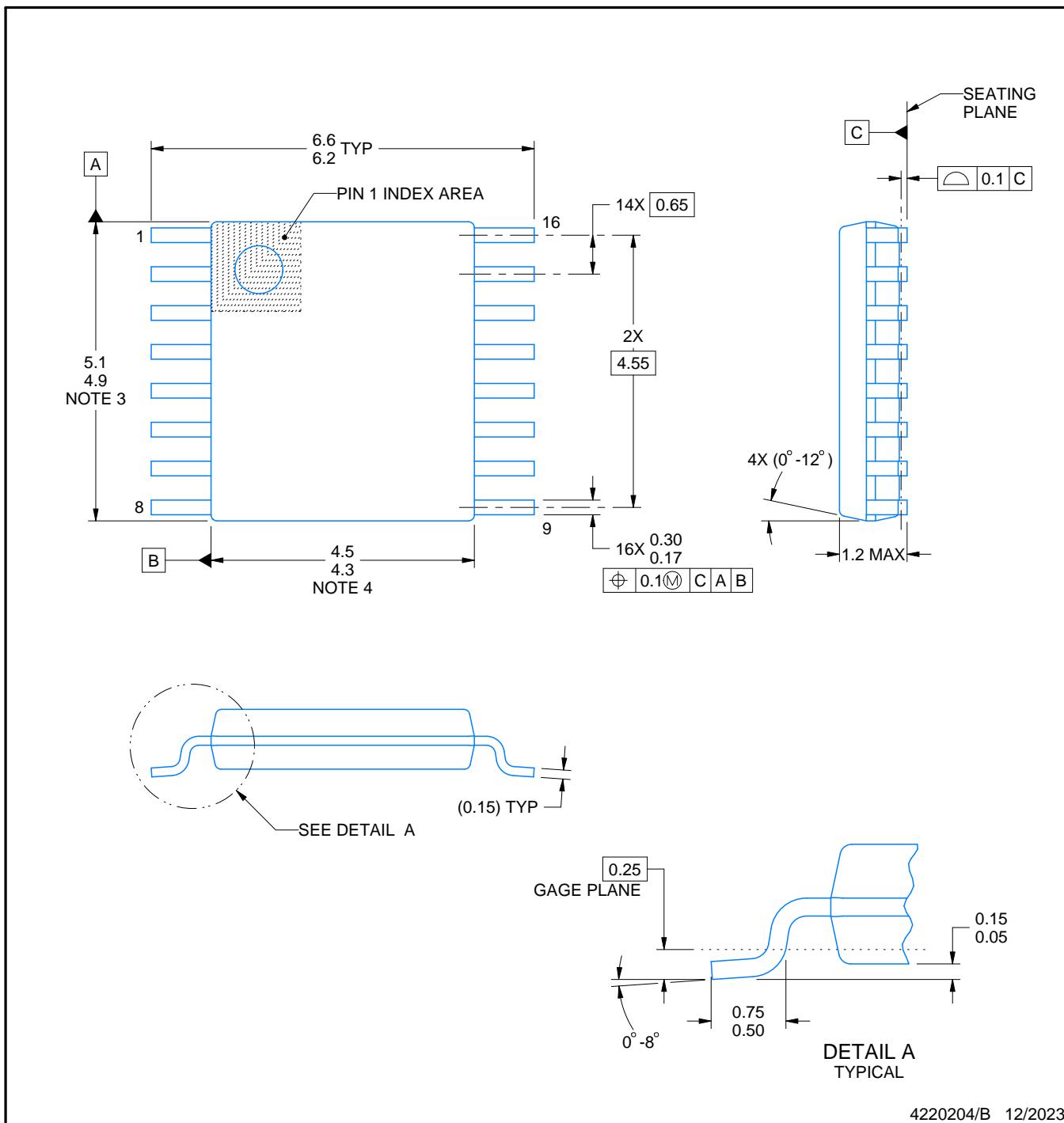

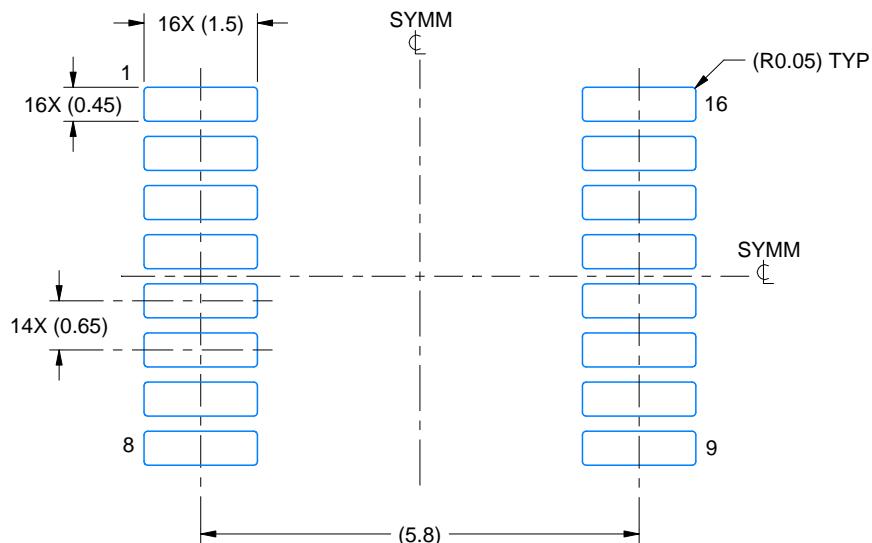

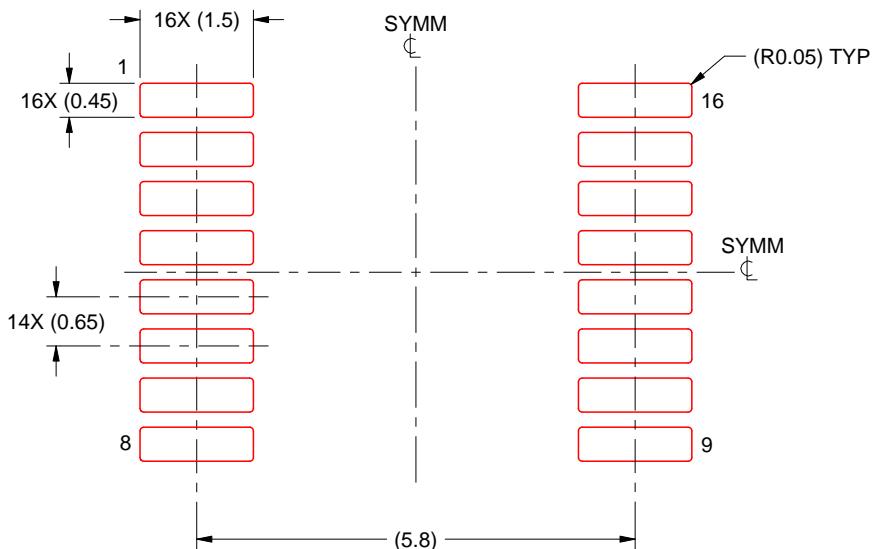

図 5-1. PW パッケージ 16 ピン TSSOP 上面図

表 5-1. ピン機能

| ピン |       | タイプ <sup>(1)</sup> | 説明                         |

|----|-------|--------------------|----------------------------|

| 番号 | 名称    |                    |                            |

| 1  | GND   | P                  | グランド                       |

| 2  | INP   | I                  | 正のトランズデューサ受信               |

| 3  | INN   | I                  | 負のトランズデューサ受信               |

| 4  | GND   | P                  | グランド                       |

| 5  | OUTA  | O                  | トランズデューサ・ドライバ出力 A          |

| 6  | GNDP  | P                  | 電源グランド                     |

| 7  | OUTB  | O                  | トランズデューサ・ドライバ出力 B          |

| 8  | IO    | I/O                | 時間コマンド・インターフェイスのデータ入力および出力 |

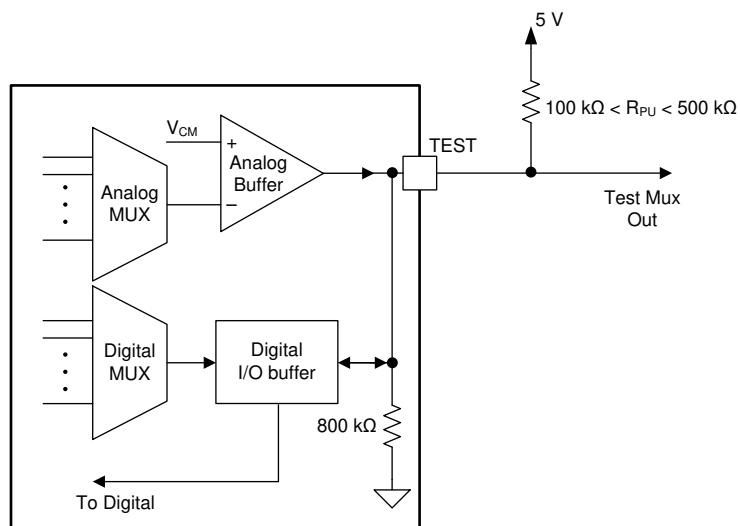

| 9  | TEST  | I/O                | テスト出力ピン                    |

| 10 | TXD   | O                  | USART インターフェイス送信           |

| 11 | RXD   | I                  | USART インターフェイス受信           |

| 12 | SCLK  | I                  | USART 同期モード・クロック入力         |

| 13 | DECPL | O                  | デカッピング・トランジスタのゲート・ドライブ     |

| 14 | IOREG | P                  | I/O バッファ電圧レギュレータ・コンデンサ     |

| 15 | VPWR  | P                  | 電源電圧                       |

| 16 | AVDD  | P                  | アナログ電圧レギュレータ・コンデンサ         |

(1) I = 入力、O = 出力、I/O = 入力および出力、P = 電源

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                       |                         | 最小値  | 最大値 | 単位 |

|-----------------------|-------------------------|------|-----|----|

| 入力電圧                  | VPWR                    | -0.3 | 30  | V  |

|                       | IO                      | -0.3 | 30  |    |

|                       | INP, INN                | -0.3 | 2   |    |

|                       | TEST, SCLK, RXD         | -0.3 | 5.5 |    |

| 出力電圧                  | AVDD                    | -0.3 | 2   | V  |

|                       | IOREG, DECPL, TEST, TXD | -0.3 | 5.5 |    |

|                       | OUTA, OUTB              | -0.3 | 30  |    |

| グランド電圧                | GNDP, GND               | -0.3 | 0.3 | V  |

| シンク電流                 | OUTA, OUTB              |      | 500 | mA |

| 動作時接合部温度              |                         | -40  | 125 | °C |

| 保存温度、T <sub>stg</sub> |                         | -40  | 125 | °C |

- (1) 絶対最大定格の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                          |                                                          |                       | 値     | 単位 |

|--------------------------|----------------------------------------------------------|-----------------------|-------|----|

| V <sub>(ESD)</sub> 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     |                       | ±2000 | V  |

|                          | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | コーナー・ピン (1, 8, 9, 16) | ±750  |    |

|                          |                                                          | その他すべてのピン             | ±500  |    |

|                          | IEC 61000-4-2 接触放電                                       | IO ピン                 | ±8000 |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

(2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)。

|                                       |                       | 最小値              | 最大値  | 単位                 |

|---------------------------------------|-----------------------|------------------|------|--------------------|

| V <sub>VPWR_XF</sub> トランジスト・トポロジの電源入力 |                       | 6                | 15   | V                  |

| V <sub>VPWR_DD</sub> 直接駆動トポロジの電源入力    |                       | 6                | 28   | V                  |

| V <sub>IO</sub>                       | IO ピン                 | IO               | -0.1 | V <sub>PWR</sub>   |

| V <sub>INx</sub>                      | トランジスト・デューサ受信入力       | INP, INN         | -0.1 | 0.9                |

| V <sub>DIG_IO</sub>                   | デジタル I/O 電源ピン         | RXD, TEST, SCLK  | -0.1 | V <sub>IOREG</sub> |

| V <sub>GND</sub>                      | グランド・ピン               | GNDP, GND        | -0.1 | 0.1                |

| I <sub>LPM</sub>                      | V <sub>PWR</sub> 入力電流 | ロー・パワー・モード・イネーブル | 500  | μA                 |

| I <sub>BURST</sub>                    |                       | 超音波バースト時         | 500  | mA                 |

| T <sub>A</sub>                        | 自由気流での動作温度            |                  | -40  | 105                |

| T <sub>J</sub>                        | 動作時接合部温度              |                  | -40  | 125                |

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                    | PGA460 | 単位   |

|-----------------------------|--------------------|--------|------|

| PW (TSSOP)                  |                    |        |      |

| 16 ピン                       |                    |        |      |

| $R_{\theta JA}$             | 接合部から周囲への热抵抗       | 96.1   | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への热抵抗  | 24.6   | °C/W |

| $R_{\theta JB}$             | 接合部から基板への热抵抗       | 42     | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への热特性パラメータ  | 0.8    | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性評価パラメータ | 41.3   | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体およびICパッケージの热評価基準』アプリケーション・レポートを参照してください。

## 6.5 内部電源レギュレータの特性

| パラメータ                                                       | テスト条件                                                                                 | 最小値  | 標準値  | 最大値  | 単位 |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|----|

| $V_{AVDD}$ 内部アナログ電源電圧                                       | $I_{AVDD} = 5\text{mA}$                                                               | 1.74 | 1.8  | 1.9  | V  |

| $I_{VPWR\_RX\_ONL}$ リスン・オンリー・モード時の VPWR ピンからの供給電流。          | $V_{VPWR} = 14\text{V}$ 、バーストなし、リスン・オンリーがアクティブ                                        |      | 12   |      | mA |

| $V_{IOREG\_33}$<br>$V_{IOREG\_50}$ デジタル IO 電源電圧             | 電源投入時 $V_{TEST} = 0\text{V}$ 、 $I_{IOREG} = 2\text{mA}$                               | 2.95 | 3.3  | 3.65 | V  |

|                                                             | 電源投入時 $V_{TEST} \geq 2\text{V}$ 、 $I_{IOREG} = 2\text{mA}$ 、 $V_{VPWR} > 7.5\text{V}$ | 4.45 | 5    | 5.65 |    |

| $I_{LIM\_AVDD}$ AVDD 電流制限                                   | AVDD はグランドへ短絡                                                                         | 40   | 150  |      | mA |

| $I_{LIM\_IOREG}$ IOREG 電流制限                                 | IOREG はグランドへ短絡                                                                        | 10   | 50   |      | mA |

| $V_{OV\_AVDD}$ AVDD 過電圧スレッショルド                              |                                                                                       | 1.95 | 2.3  |      | V  |

| $V_{UV\_AVDD}$ AVDD 低電圧スレッショルド                              |                                                                                       | 1.29 | 1.53 |      | V  |

| $V_{OV\_IOREG\_33}$ IOREG 過電圧スレッショルド                        | 電源投入時 $V_{TEST} = 0\text{V}$                                                          | 3.6  | 4.6  |      | V  |

| $V_{UV\_IOREG\_33}$<br>$V_{UV\_IOREG\_50}$ IOREG 低電圧スレッショルド | 電源投入時 $V_{TEST} = 0\text{V}$                                                          | 2.57 | 2.9  |      | V  |

|                                                             | 電源投入時 $V_{TEST} \geq 2\text{V}$                                                       | 3.8  | 4.5  |      |    |

| $V_{OV\_VPWR}$ VPWR 過電圧スレッショルド                              | $VPWR\_OV\_TH = 0x0$                                                                  | 11   | 12.3 | 15   | V  |

|                                                             | $VPWR\_OV\_TH = 0x1$                                                                  | 16   | 17.7 | 21   |    |

|                                                             | $VPWR\_OV\_TH = 0x2$                                                                  | 21.5 | 22.8 | 27   |    |

|                                                             | $VPWR\_OV\_TH = 0x3$                                                                  | 27   | 28.3 | 31   |    |

| $V_{UV\_VPWR}$ VPWR 低電圧スレッショルド                              |                                                                                       | 5.25 | 6    |      | V  |

| $t_{ON\_REG}$ AVDD および IOREG パワーアップ時間                       | $V_{VPWR} = 6\text{V}$                                                                |      | 10   |      | ms |

## 6.6 トランジスタ・ドライバ特性

| パラメータ                                | テスト条件                                                                                  | 最小値 | 標準値 | 最大値 | 単位            |

|--------------------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $V_{CLAMP\_DRV}$ ドライバのクランプ電圧         | ドライバはオフ                                                                                | 30  |     |     | V             |

| $I_{PULSE\_MAX\_DRV}$ 最大ドライバ・パルス電流   | $V_{OUTA}, V_{OUTB} = 6\text{V}$ : $f_{SW} = 30\text{kHz}$ , $T_A = 105^\circ\text{C}$ |     | 500 |     | mA            |

| $RDSON_{DRV}$ MOSFET オン抵抗            | $I_{DRAIN} = 500\text{mA}$ : $T_A = 105^\circ\text{C}$ , $DIS\_CL = 1$                 |     | 4.8 | 8   | $\Omega$      |

| $E_{DIS\_BURST}$ バースト中に消費されるエネルギー    |                                                                                        |     | 6.4 |     | $\text{mJ}$   |

| $I_{LEAK\_DRV}$ リーク電流                | $V_{OUTA}, V_{OUTB} = 14\text{V}$                                                      | -1  | 1   |     | $\mu\text{A}$ |

| $I_{CLAMP\_DRV\_0}$ 最小コード設定の電流クランプ範囲 | $V_{VPWR} > 7\text{V}$ , $CURR\_LIM1 = CURR\_LIM2 = 0$                                 | 15  | 50  | 75  | mA            |

| パラメータ                                                       |               | テスト条件                                                      | 最小値 | 標準値 | 最大値 | 単位  |

|-------------------------------------------------------------|---------------|------------------------------------------------------------|-----|-----|-----|-----|

| I <sub>CLAMP_DRV_63</sub> 最大コード設定からの電流クランプ範囲                |               | V <sub>VPWR</sub> > 7V、<br>CURRE_LIM1 =<br>CURRE_LIM2 = 63 | 450 | 500 | 570 | mA  |

| I <sub>STEP_SIZE_CLAMP_DRV</sub> ステップ・サイズ (前のステップの電流値からの変化) |               |                                                            | 5.2 | 7.2 | 9.2 | mA  |

| f <sub>SW_LOW</sub>                                         | 設定可能スイッチング周波数 | FREQ_SHIFT = 0                                             | 30  | 80  |     | kHz |

| f <sub>SW_HIGH</sub>                                        |               | FREQ_SHIFT = 1                                             | 180 | 480 |     |     |

## 6.7 トランステューサ・レシーバ特性

| パラメータ                                      |               | テスト条件                                                                                               | 最小値   | 標準値  | 最大値 | 単位          |

|--------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------|-------|------|-----|-------------|

| GAIN <sub>RNG_TOT_RCV</sub> レシーバの合計増幅ゲイン範囲 |               | F <sub>SW</sub> = F <sub>SW_LOW</sub> 、<br>F <sub>SW_HIGH</sub> 、T <sub>A</sub> = -40°C ~<br>+105°C | 32    | 90   |     | dB          |

| GAIN <sub>RNG_RCV</sub> レシーバの増幅ゲイン         |               | AFE_GAIN_RNG = 0x03                                                                                 | 32    | 64   |     |             |

|                                            |               | AFE_GAIN_RNG = 0x02                                                                                 | 46    | 78   |     |             |

|                                            |               | AFE_GAIN_RNG = 0x01                                                                                 | 52    | 84   |     |             |

|                                            |               | AFE_GAIN_RNG = 0x00                                                                                 | 58    | 90   |     |             |

| GAIN <sub>NSTEP_RCV</sub>                  | ゲイン調整ステップ     |                                                                                                     | 64    |      |     |             |

| GAIN <sub>STEP_SIZE_RCV</sub>              | ゲイン調整ステップ・サイズ |                                                                                                     | 0.2   | 0.5  | 0.8 | dB          |

| GAIN <sub>THRM_DRFT_RCV</sub>              | ゲイン温度ドリフト     | F <sub>SW</sub> = 30kHz, T <sub>A</sub> = -40°C<br>~+105°C、ゲイン =<br>58.5dB                          | -3.5% | 3.5% |     |             |

| Z <sub>INP_RCV</sub>                       | 入力インピーダンス     | F <sub>SW</sub> = 80kHz                                                                             | 300   |      |     | kΩ          |

| N <sub>RCV</sub>                           | ノイズ・フロア       | F <sub>SW</sub> = 58kHz, T <sub>A</sub> =<br>105°C, BW = 4kHz                                       | 7     |      |     | nV/sqrt(Hz) |

## 6.8 A/D コンバータの特性

| パラメータ                |          | テスト条件 | 最小値 | 標準値               | 最大値 | 単位  |

|----------------------|----------|-------|-----|-------------------|-----|-----|

| V <sub>INP_ADC</sub> | 入力電圧範囲   |       | 0   | V <sub>AVDD</sub> |     | V   |

| V <sub>REF_ADC</sub> | 電圧リファレンス |       |     | V <sub>AVDD</sub> |     |     |

| N <sub>ADC</sub>     | 分解能      |       | 12  |                   |     | ビット |

| t <sub>CONV</sub>    | 変換時間     |       | 1   |                   |     | μs  |

## 6.9 デジタル信号処理特性

| パラメータ                         |                      | テスト条件       | 最小値 | 標準値 | 最大値 | 単位  |

|-------------------------------|----------------------|-------------|-----|-----|-----|-----|

| FREQ <sub>CENTER_BPF</sub>    | バンドパス・フィルタの中心周波数     | ドライバ周波数に正規化 | 1   |     |     |     |

| BW <sub>BPF</sub>             | バンドパス・フィルタの帯域幅       |             | 2   | 8   |     | kHz |

| N <sub>BPF</sub>              | バンドパス・フィルタの調整可能なステップ |             | 4   |     |     |     |

| FREQ <sub>STEP_SIZE_BPF</sub> | バンドパス・フィルタのステップ・サイズ  |             | 2   |     |     | kHz |

| FREQ <sub>CUTOFF_LPF</sub>    | ローパス・フィルタのカットオフ周波数   |             | 1   | 4   |     | kHz |

| N <sub>LPF</sub>              | ローパス・フィルタの調整可能なステップ  |             | 4   |     |     |     |

| FREQ <sub>STEP_SIZE_LPF</sub> | ローパス・フィルタのステップ・サイズ   |             | 1   |     |     | kHz |

## 6.10 温度センサの特性

| パラメータ                    |          | テスト条件 | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------------|----------|-------|-----|-----|-----|----|

| T <sub>RANGE_SENSE</sub> | 温度センサの範囲 |       | -40 | 125 |     | °C |

| パラメータ                  | テスト条件                                                   | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------|---------------------------------------------------------|-----|-----|-----|----|

| $T_{ACC\_SENSE}$ 距離の精度 | $VPWR = 12V$ 、<br>$TEMP\_GAIN = 0$ 、<br>$TEMP\_OFF = 0$ |     | 5   |     | °C |

## 6.11 高電圧 I/O 特性

| パラメータ                           | テスト条件                  | 最小値                   | 標準値                 | 最大値 | 単位 |

|---------------------------------|------------------------|-----------------------|---------------------|-----|----|

| $V_{IH\_IO}$ 高電圧 IO 入力 HIGH レベル | IO ピン                  | $0.6 \times V_{VPWR}$ |                     |     | V  |

| $V_{IL\_IO}$ 高電圧 IO 入力 LOW レベル  | IO ピン                  | $0.4 \times V_{VPWR}$ |                     |     | V  |

| $V_{HYS\_IO}$ 高電圧入力ヒステリシス       | IO ピン                  | $0.05 \times VPWR$    | $0.175 \times VPWR$ |     | V  |

| $V_{OL\_IO}$ 高電圧 IO 出力 LOW レベル  | IO ピン、 $I_{IO} = 10mA$ |                       | 2                   |     | V  |

| $R_{PU\_IO}$ 高電圧 IO プルアップ抵抗     | IO ピン                  | 4                     | 10                  | 16  | kΩ |

| $I_{LIM\_IO}$ 高電圧 IO の電流制限      | VPWR への短絡              | 40                    |                     | 250 | mA |

## 6.12 デジタル I/O 特性

| パラメータ                           | テスト条件                                                                                        | 最小値                      | 標準値                      | 最大値 | 単位  |    |

|---------------------------------|----------------------------------------------------------------------------------------------|--------------------------|--------------------------|-----|-----|----|

| $V_{IH\_DIGIO}$ デジタル入力 HIGH レベル | $RX$ および SCLK ピン、<br>$V_{IOREG} = V_{IOREG\_33} / V_{IOREG\_50}$                             | $0.7 \times V_{IOR\_EG}$ |                          |     | V   |    |

| $V_{IL\_DIGIO}$ デジタル入力 LOW レベル  | $RX$ および SCLK ピン、<br>$V_{IOREG} = V_{IOREG\_33} / V_{IOREG\_50}$                             |                          | $0.3 \times V_{IOR\_EG}$ |     | V   |    |

| $V_{HYS\_DIGIO}$ デジタル入力ヒステリシス   | $RX$ および SCLK ピン                                                                             | 100                      |                          |     | mV  |    |

| $V_{OH\_DIGIO}$ デジタル出力 HIGH レベル | $DECPL$ および TX ピン、 $I_{DECPL} / I_{TX} = -2mA$ 、 $V_{IOREG} = V_{IOREG\_33} / V_{IOREG\_50}$ | $V_{IOREG} - 0.2$        |                          |     | V   |    |

| $V_{OL\_DIGIO}$ デジタル出力 LOW レベル  | $DECPL$ および TX ピン、 $I_{DECPL} / I_{TX} = 2mA$                                                |                          | 0.2                      |     | V   |    |

| $R_{PU\_DIGIO\_RX}$             | $IOREG$ に対するデジタル入力プルアップ抵抗                                                                    | 90                       | 100                      | 160 | kΩ  |    |

| $R_{PU\_DIGIO\_SC\_LK}$         | デジタル入力プルダウン抵抗                                                                                | SCLK ピン                  | 80                       | 100 | 130 | kΩ |

## 6.13 EEPROM の特性

| パラメータ                          | テスト条件               | 最小値 | 標準値  | 最大値 | 単位  |

|--------------------------------|---------------------|-----|------|-----|-----|

| $Bytes_{EE}$ EEPROM メモリのサイズ    | アプリケーションおよびデバイス内部   | 64  |      |     | バイト |

| $t_{RET\_EE}$ EEPROM データ保持期間   | $T_A = 105^\circ C$ |     | 10   |     | 年   |

| $CyclBURN_{EE}$ EEPROM の書き込み回数 |                     |     | 1000 |     | 回   |

| $t_{PROG\_EE}$ EEPROM のプログラム時間 |                     |     | 600  |     | ms  |

## 6.14 タイミング要件

|                        |                             | 最小  | 公称値  | 最大値  | 単位 |

|------------------------|-----------------------------|-----|------|------|----|

| <b>時間コマンド・インターフェイス</b> |                             |     |      |      |    |

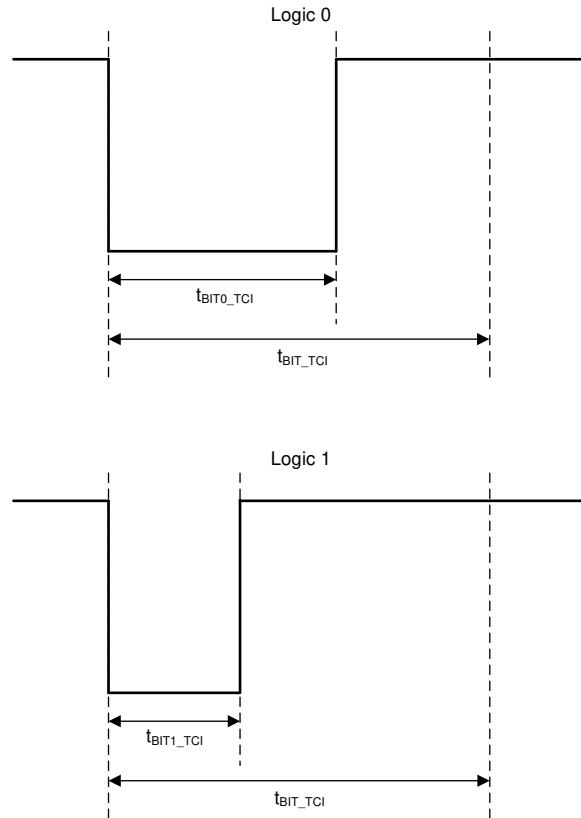

| $t_{BIT\_TCI}$         | ビット周期                       | 225 | 300  | 375  | μs |

| $t_{BIT0\_TCI}$        | 論理 0 ビット長                   | 150 | 200  | 250  | μs |

| $t_{BIT1\_TCI}$        | 論理 1 ビット長                   | 75  | 100  | 125  | μs |

| $t_{BLP1\_TCI}$        | バースト / リスン (プリセット 1) コマンド期間 | 328 | 400  | 472  | μs |

| $t_{BLP2\_TCI}$        | バースト / リスン (プリセット 2) コマンド期間 | 920 | 1010 | 1100 | μs |

|                          |                           | 最小   | 公称値   | 最大値  | 単位 |

|--------------------------|---------------------------|------|-------|------|----|

| $t_{LP1\_TCI}$           | リスン・オンリー (プリセット 1) コマンド期間 | 697  | 780   | 863  | μs |

| $t_{LP2\_TCI}$           | リスン・オンリー (プリセット 2) コマンド期間 | 503  | 580   | 657  | μs |

| $t_{CFG\_TCI}$           | デバイス構成コマンド期間              | 1170 | 1270  | 1370 | μs |

| $t_{TEMP\_TCI}$          | 温度測定コマンド期間                | 1440 | 1550  | 1660 | μs |

| $t_{NOISE\_TCI}$         | ノイズ・レベル測定コマンド期間           | 2070 | 2200  | 2340 | μs |

| $T_{DT\_TCI}$            | コマンド処理デッドタイム              | 75   | 100   | 125  | μs |

| <b>USART 非同期インターフェイス</b> |                           |      |       |      |    |

| $t_{BIT\_UART}$          | 19.2kbps での論理ビット長         | 45.5 | 52.08 | 58.6 | μs |

| $t_{BITF\_UART}$         | 115.2kbps での論理ビット長        | 7.6  | 8.68  | 9.76 | μs |

| <b>USART 同期インターフェイス</b>  |                           |      |       |      |    |

| $t_{BIT\_USART}$         | 8Mbps での論理ビット長            | 55   | 125   |      | ns |

## 6.15 スイッチング特性

| パラメータ             | テスト条件                     | 最小値 | 標準値  | 最大値  | 単位    |

|-------------------|---------------------------|-----|------|------|-------|

| $f_{CORE\_CLK}$   | コア周波数 <sup>(1)</sup>      |     | 15.5 | 16   | 16.5  |

| $ACC_{CORE\_CLK}$ | コア周波数の精度 <sup>(2)</sup>   |     | -4%  | 4%   |       |

| $Baud_{UART}$     | USART 非同期インターフェイスのボーレート   |     | 2.4  | 19.2 | 131.5 |

| $Baud_{USART}$    | USART インターフェイス同期モードのボーレート |     |      | 8    | Mbps  |

(1) 室温 (25°C)

(2) 動作温度範囲内 (-40°C~105°C)

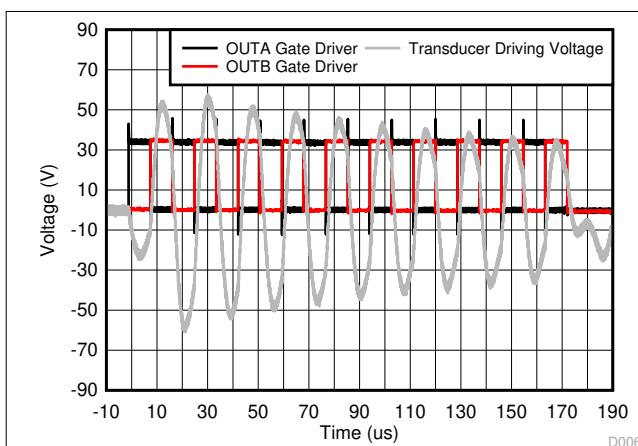

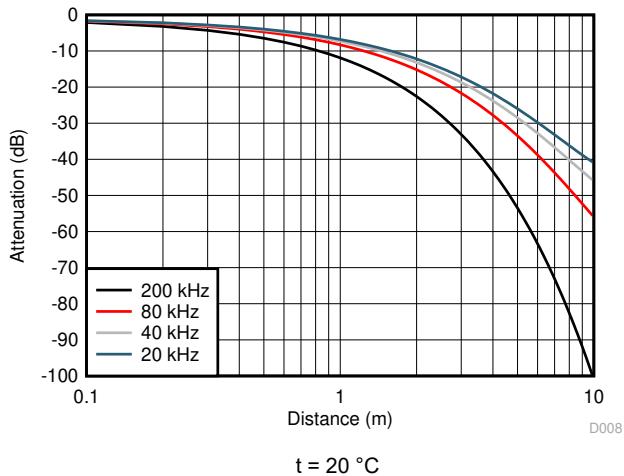

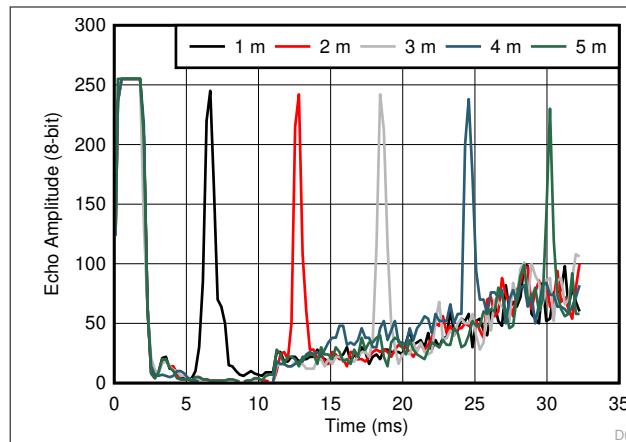

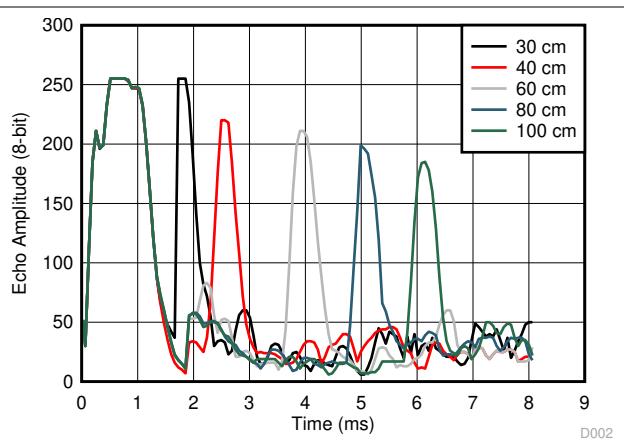

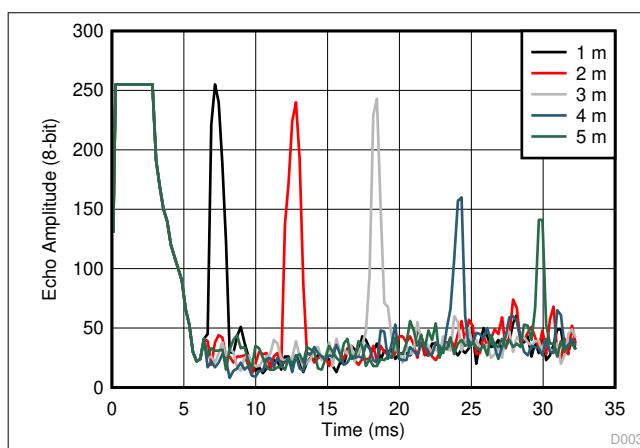

## 6.16 代表的な特性

10 パルス、400mA の電流制限、58.6kHz の駆動周波数

TDK EPCOS B78416A2232A003 トランス

muRata MA58MF14-7N トランスデューサ

OUTA /B ゲート・ドライバは 10 倍に拡大されています

図 6-1. ドライバ段とその結果としてのトランスデューサ動作

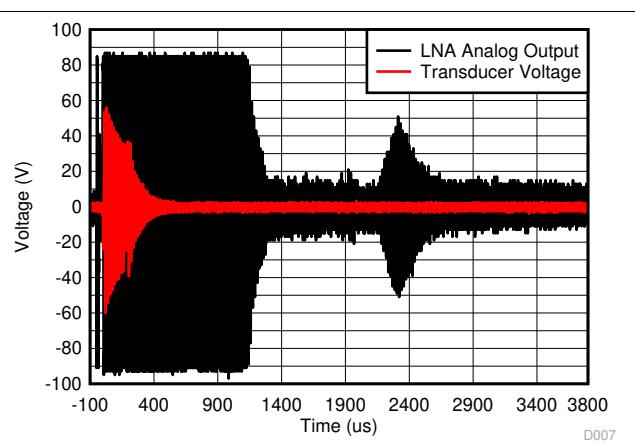

TDK EPCOS B78416A2232A003 トランス

muRata MA58MF14-7N トランスデューサ

LNA アナログ出力はスケーリングおよびシフトされています。実際の信号は 100 分の 1 で、コモン・モードは 0.9V シフト・アップされています

図 6-2. LNA 後のレシーバ AFE 出力、物体位置 35cm

## 7 詳細説明

### 7.1 概要

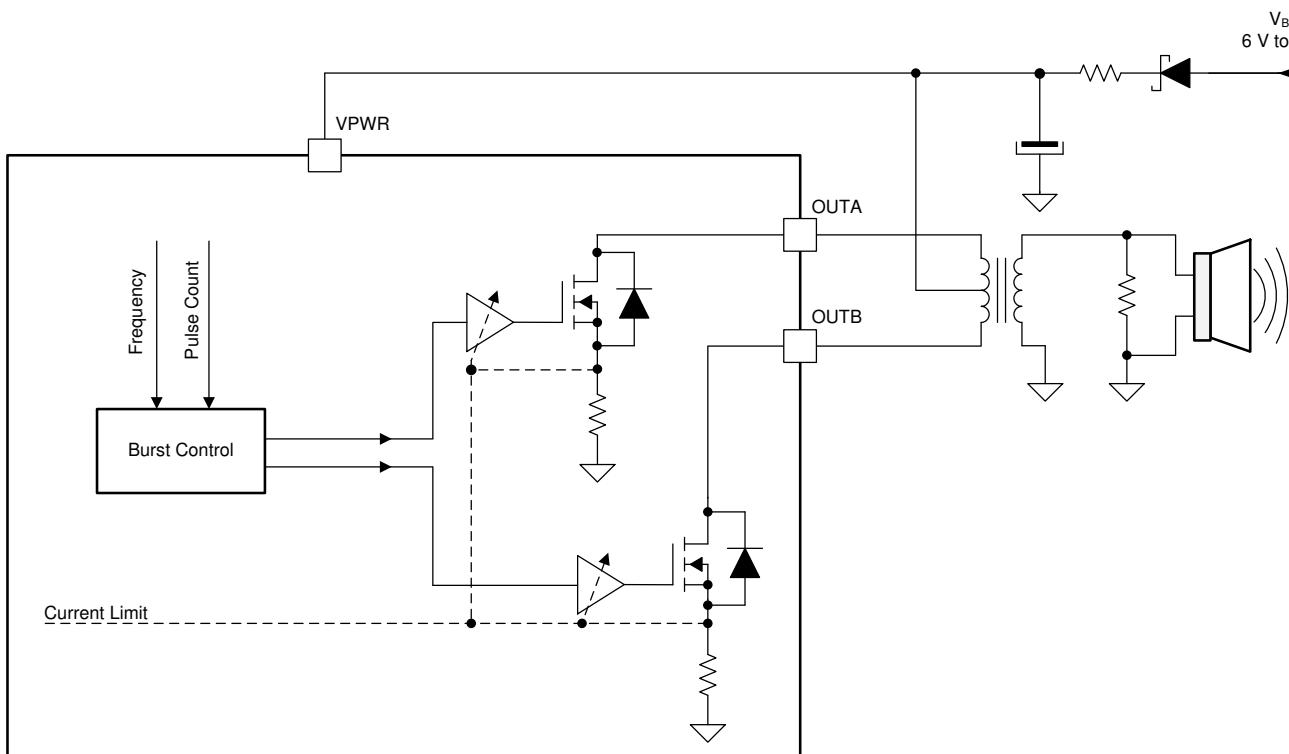

PGA460 デバイスは、物体または距離センシング用の超音波センシング用のシグナル・コンディショニングおよびトランスデューサ・ドライバ・デバイスです。出力ドライバは、センター・タップ・トランスを駆動して超音波トランスデューサに対して大きい励起電圧を生成できる相補的なローサイド・ドライバで構成されており、その結果、目的の音圧レベル (SPL) が生成されます。出力ドライバは、外部 **FET** を使って、トランスなしで直接駆動モードで使用するように構成することもできます。出力ドライバには、トランスを効率的に駆動するために、設定可能な電流制限が実装されています。また、さまざまなトランスデューサに対応できるように、バースト周波数およびバースト長を設定できます。

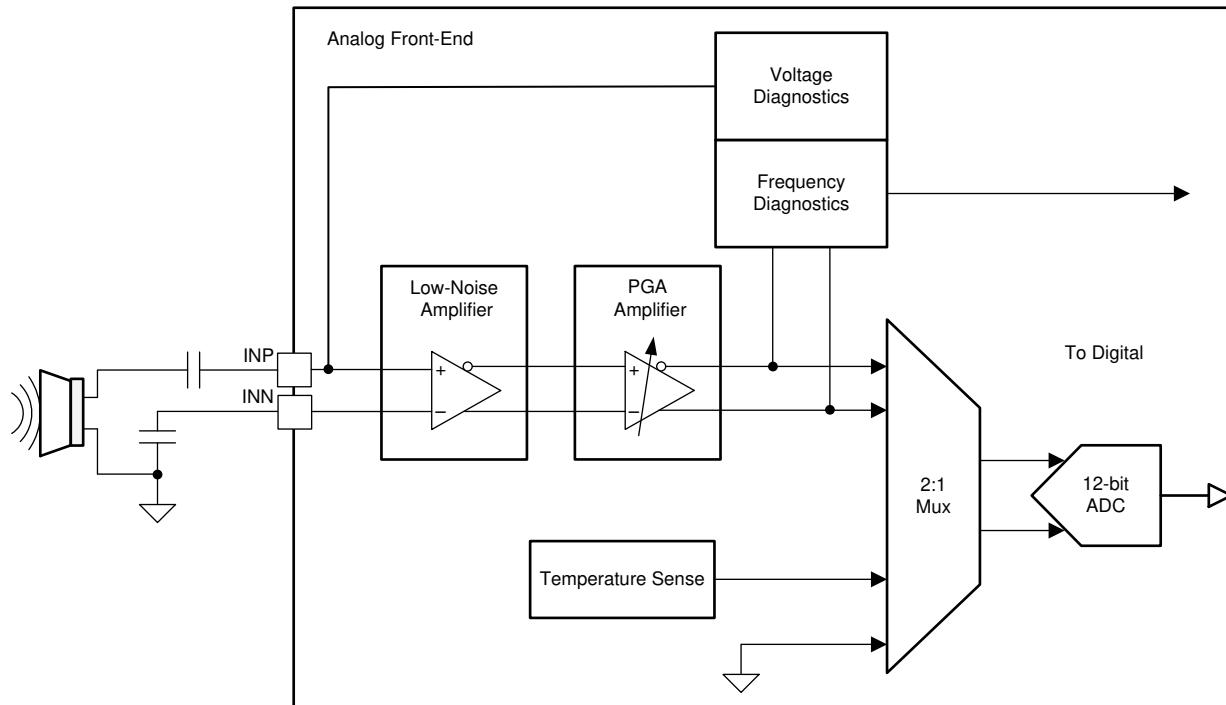

アナログ・フロントエンド (AFE) は、トランスデューサから受信したエコーを検出し、それを増幅して正しい物体検出を行うことができます。AFE には低ノイズ・アンプが実装されており、それに続いて時変ゲイン・アンプが実装されているため、さまざまな距離にある物体からの信号をそれに応じて増幅できます。この実装により、同じ記録において近距離の物体と遠距離の物体の両方に対して、ADC の最大ダイナミック・レンジを使用できます。組込み温度センサを使って、温度変化に応じてシグナル・コンディショナを較正できます。デジタル信号処理パスは、受信したエコーをさらにフィルタ処理し、時変スレッショルドを使って物体を正確に検出します。バーストおよびスレッショルドについて 2 つのプリセットを利用可能なので、複数のバーストの間でデバイスを構成するために必要な時間を節約し、検出サイクルを短縮できます。ほとんどの構成パラメータは不揮発性メモリに保存されているため、迅速な起動が可能で、初期化にかかる時間を短縮できます。

PGA460 デバイスには、コントローラと通信するための複数の IO プロトコルがあります。このデバイスは、VPWR 基準の IO ピンにおいて、時間コマンド・インターフェイスおよび 1 線式 UART を提供します。また、TXD、RXD、SCLK ピンで、同期および非同期の USART を提供します。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 電源ブロック

PGA460 デバイスは、複数の内部レギュレータを内部回路の電源として使用します。アナログ電圧レギュレータ (AVDD) には、100nF の外付けコンデンサが必要です。電源ブロックは、高精度の電圧リファレンス、電流バイアス、および内部クロックを生成します。追加のレギュレータ (IOREG) によって、USART ピン (RXD, TXD, SCLK)、DECPL ピン、TEST ピンの電源電圧が生成されて、デジタル機能が利用できます。AVDD および IOREG レギュレータは、外部負荷をサポートすることを意図していません。外部コンデンサは、関連するピン (AVDD および IOREG) のできるだけ近くに配置することを推奨します。VPWR ピンに電圧が印加されると、PGA460 デバイスはパワーアップを開始します。内部パワーオン・リセット (POR) は、すべてのレギュレータ電源がレギュレーション状態になり、かつ、内部クロックが動作すると解除されます。低消費電力モードでは、IOREG レギュレータはオンになっていますが、他のレギュレータはシャットダウンして電力を節約します。

### 7.3.2 バースト生成

PGA460 デバイスでは、FREQ および P1\_PULSE / P2\_PULSE レジスタを構成することによって、バーストの周波数およびパルス数をプログラム可能です。

式 1 を使用して、30kHz～80kHz の範囲でバースト周波数を計算します (FREQ\_SHIFT ビットを 0 に設定)。

$$f_{(DRV)} = 0.2 \text{ kHz} \times f + 30 \text{ kHz} \quad (1)$$

ここで、

- $f$  は、FREQUENCY レジスタで定義されている 0 ~ 200 の周波数です。

出力段の実際の駆動周波数は、コア・クロック周波数から 式 1 および 式 2 を使って得られます。

$$n = \frac{f_{(CORE\_CLK)}}{f_{(DRV)}} \quad (2)$$

ここで、

- $n$  は、メイン発振器の  $f_{(CORE\_CLK)}$  を分周する比率です。

PULSE\_P1 および PULSE\_P2 レジスタの範囲は、0～31 です。M の値を 0 より大きい値に設定すると、OUTA および OUTB 出力に M 個のパルス・ペアが生成されます。

#### 7.3.2.1 センタータップ・トランスの使用

PGA460 デバイスは、電流制限モードで動作する相補的なローサイド FET を経由して、OUTA ピンおよび OUTB ピンに接続されたセンター・タップ・トランスの 1 次側を励起することによって、効率的なバースト発生を実現します。バーストの周波数は 30kHz～80kHz であり、電流制限は 50mA～500mA です。バーストの周波数、トランスの 1 次側電流の電流制限、バースト・パルスの数は、FREQUENCY、CURRENT\_LIM\_P1、CURRENT\_LIM\_P12、PULL\_P1、および PULL\_P2 パラメータを使って制御できます。

図 7-1 に、エコー発生の機能ブロック図を示します。

Copyright © 2017, Texas Instruments Incorporated

図 7-1. エコー発生ブロック図

### 7.3.2.2 直接駆動

相補的なローサイド・ドライバを外部 PMOS FET と組み合わせて使用すると、シングルエンドの直接励起によりトランジスタを駆動できます。この構成では、電流制限機能を無効にすることで、内部 FET を RDSON モードで使用できます。そのためには、CURRENT\_LIM\_P1 レジスタの DIS\_CL ビットを設定します。

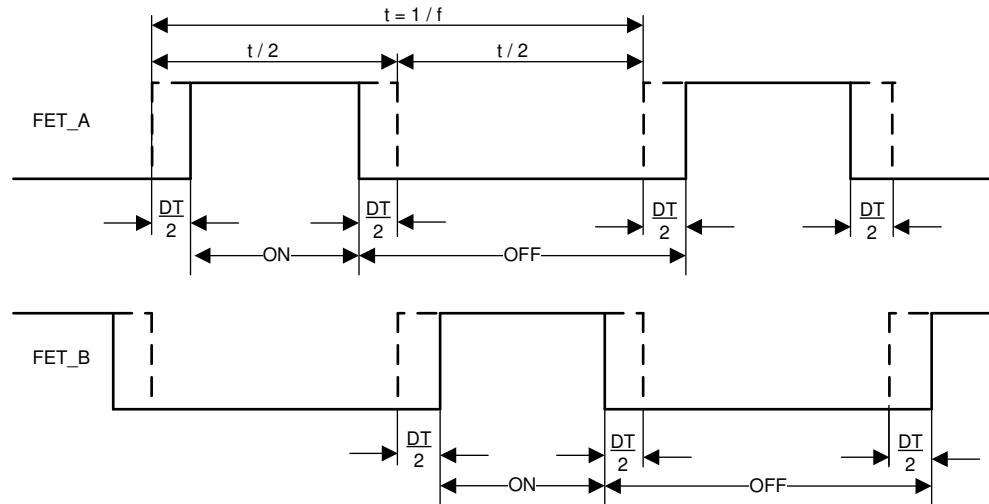

このモードでは、PULL\_DT ビットを構成することによって追加のデッドタイム機能を使用して、外部 PMOS FET と内部ローサイド FET との間の貫通電流を除去できます。ローサイド FET のバースト・サイクル期間は変わりませんが、非アクティベーション時間はデッドタイムの設定値によって短縮されます。この状況を 図 7-2 に示します。

図 7-2. エコー生成のデッドタイム調整

### 7.3.2.3 その他の構成

P1\_PULSE ビットまたは P2\_PULSE ビットのいずれかが 0 に設定されている場合、OUTA 出力のみがパルスを生成し、OUTB 出力は、この期間中、高インピーダンス状態を維持します。この構成を使用して、短距離のみを検出する必要がある場合に出力電圧を低減します。

#### 注

- より高い周波数をサポートするため、デバイスには、CURRE\_LIM\_P1 レジスタの FREQ\_SHIFT ビットを設定することによって、バースト周波数範囲をシフトアップするオプションがあります。このビットが設定されている場合、バースト周波数は、FREQUENCY レジスタで選択されるバースト周波数の 6 倍になります。このビットが設定されているとき、バースト周波数の範囲は 180kHz~480kHz、ステップは約 1.2kHz です。

- 最大デッドタイム設定は、バースト期間を  $t$  とすると、 $t/8$  以下にする必要があります。

### 7.3.3 アナログ・フロントエンド

図 7-3 に示す PGA460 デバイスのアナログ・フロントエンド (AFE) は、物体から反射されたエコーを受信し、増幅して、エコー検出のためのデジタル信号処理 (DSP) データ・パスに送ります。受信したエコー信号の振幅は変動する可能性があるため (近くにある物体では mV 単位、遠くにある物体では  $\mu$ V 単位)、最初の AFE 段は、あらかじめ決められた固定ゲインで非常に低いノイズの平衡アンプであり、それに続いて、32dB~90dB の可変ゲイン段アンプが設けられています。増幅されたエコー信号は、12 ビットの A/D コンバータ (ADC) によってデジタル信号に変換され、DSP 处理ブロックに供給されて、さらに評価およびタイム・オブ・フライト測定が行われます。

PGA460 AFE は、エコー記録プロセスのバーストおよび減衰段において、センシング素子 (トランシスデューサ) を監視するためのシステム診断機能を実装しています。これは、トランシスデューサ・ノードで得られる最大電圧とトランシスデューサ・ノードでの発振周波数を測定する方法を使っています。この診断の詳細については、「[システム診断](#)」セクションを参照してください。

Copyright © 2017, Texas Instruments Incorporated

図 7-3. アナログ・フロントエンド

AFE の可変ゲイン・アンプには時変ゲイン機能が実装されており、ユーザーはさまざまな静的ゲインを設定できます。また、エコー・リスン・プロセス（エコー記録時間）のゲイン・プロファイルも指定できます。この機能により、ADC を飽和させずに、さまざまな距離にある物体からのエコー信号を均一に増幅できます。たとえば、最初は、近い物体のために低いゲインをプログラムしておいて、その後、記録時間中にゲインを増加させて、非常に小さいエコー信号を発生する遠くの物体を検出することができます。この機能は、高精度のタイム・オブ・フライト測定のために、ADC 変換後にすべての距離にわたって十分な SNR を達成するのに役立ちます。

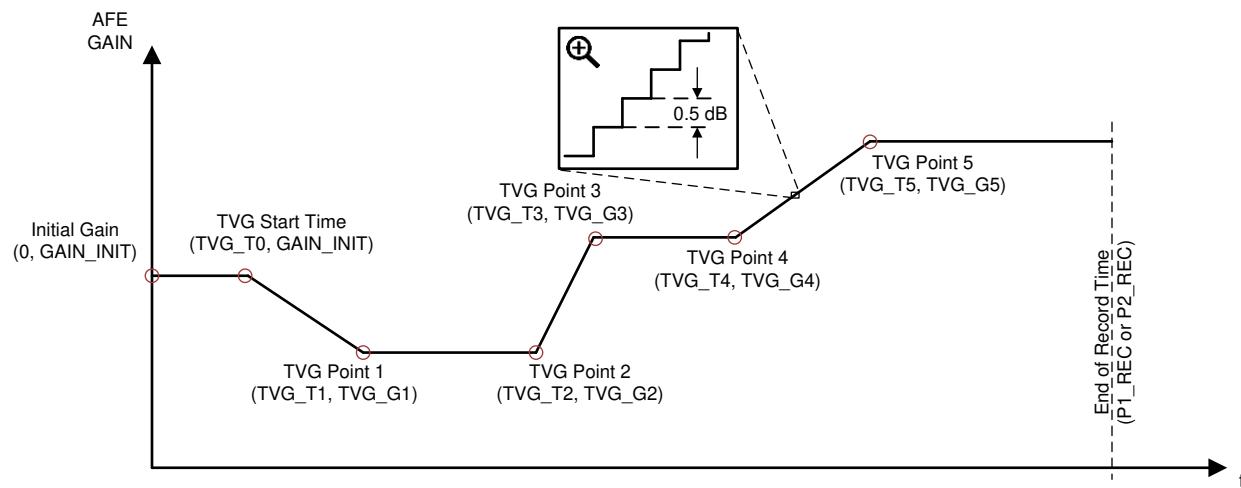

時変ゲイン・パラメータは、EEPROM メモリに保存され、以下に示す特性があります。

- 初期固定ゲイン・パラメータ、**GAIN\_INIT**。

- TVGAIN0 レジスタに保存される、時変ゲイン開始時の値。

- TVGAIN0～TVGAIN6 レジスタに配置された、ゲインが変化する 5 つの交点の配列。

図 7-4 に、時変ゲインのプロット例を示します。

図 7-4. 時変ゲインの割り当て例

TVG の開始時間は、絶対時間で表されており、以後のすべての TVG ポイント時間 (TVG\_Tx パラメータ) は、現在と前のポイントとの時間差として表されます。すべてのゲイン値は、dB 単位の絶対ゲイン値で表されており、相互の関連はありません。TVG ポイント 5 (TVG\_G5) の最終ゲイン設定は、エコー記録時間が終了するまで一定に維持されます。時変ゲインの割り当ては、両方のプリセットで同じです。2 つの TVG ポイント間のゲインは、線形補間方式を使って計算します。AFE のゲイン分解能は標準値 0.5dB です。

#### 注

記録中に時変ゲインを変更した場合、その変更は次の記録サイクルから適用されます。TVGAIN[0:6] レジスタが 0x00 にプログラムされている場合、PGA460 デバイスの時変ゲイン機能がディセーブルされ、INIT\_GAIN レジスタで定義された固定ゲインが適用されます。この場合、INIT\_GAIN レジスタを変更すると、記録中に AFE のゲインが変更されます。

時変ゲインのオフセットは、DECPL\_TEMP レジスタの 2 つの AFE\_GAIN\_RNG ビットによって制御されます。レジスタ・マップセクションで定義されている 4 つの各設定について、そのオフセットに加算するゲインを 0～32dB の範囲で変更できます。

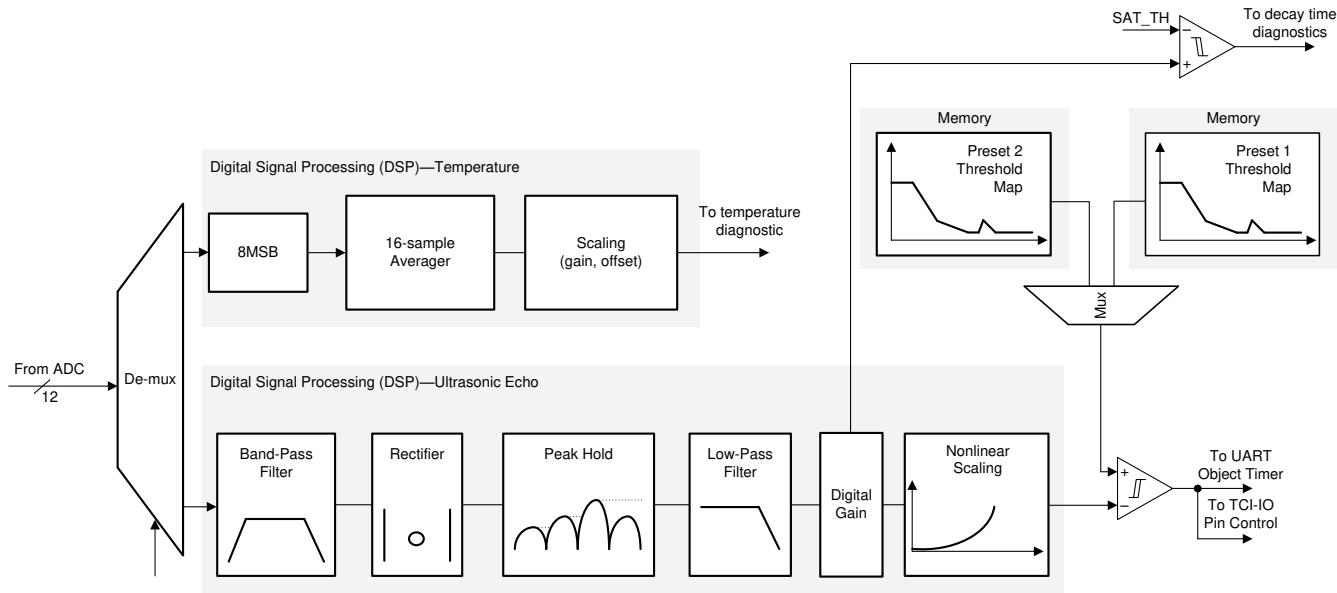

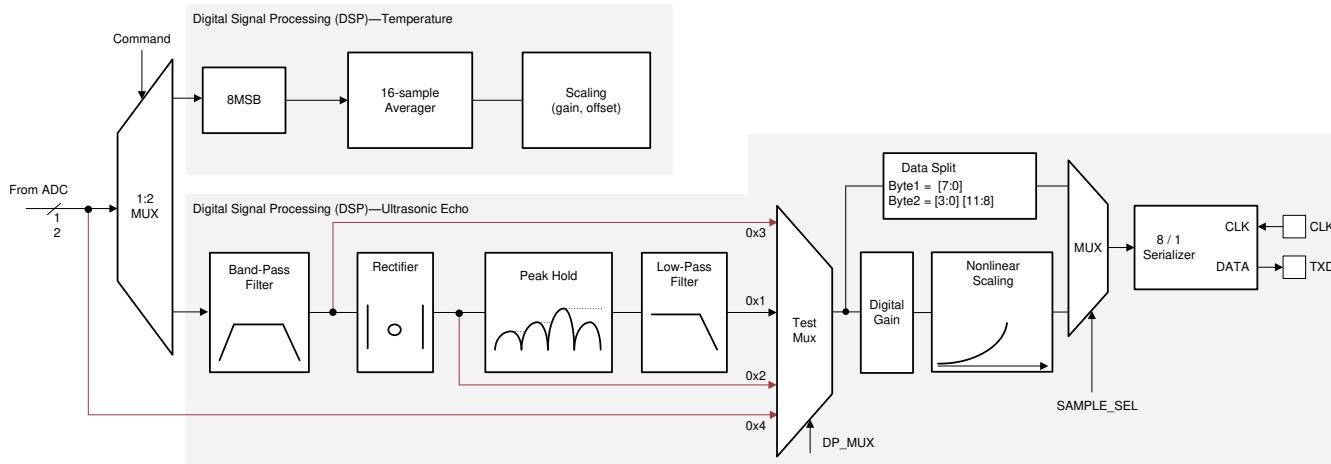

#### 7.3.4 デジタル・シグナル・プロセッサ

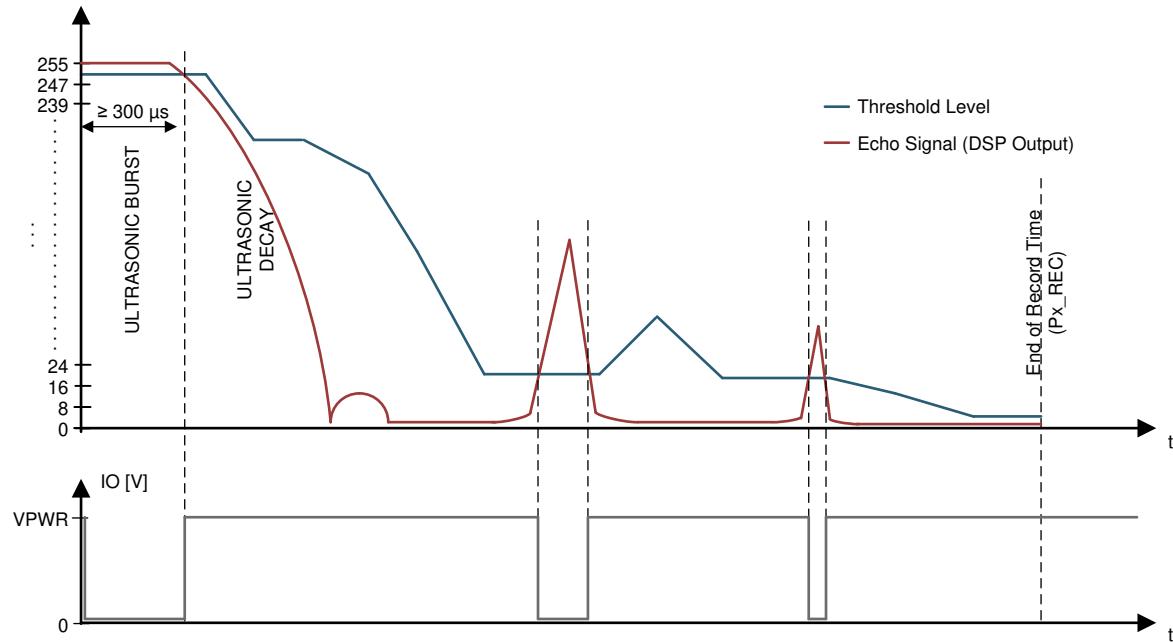

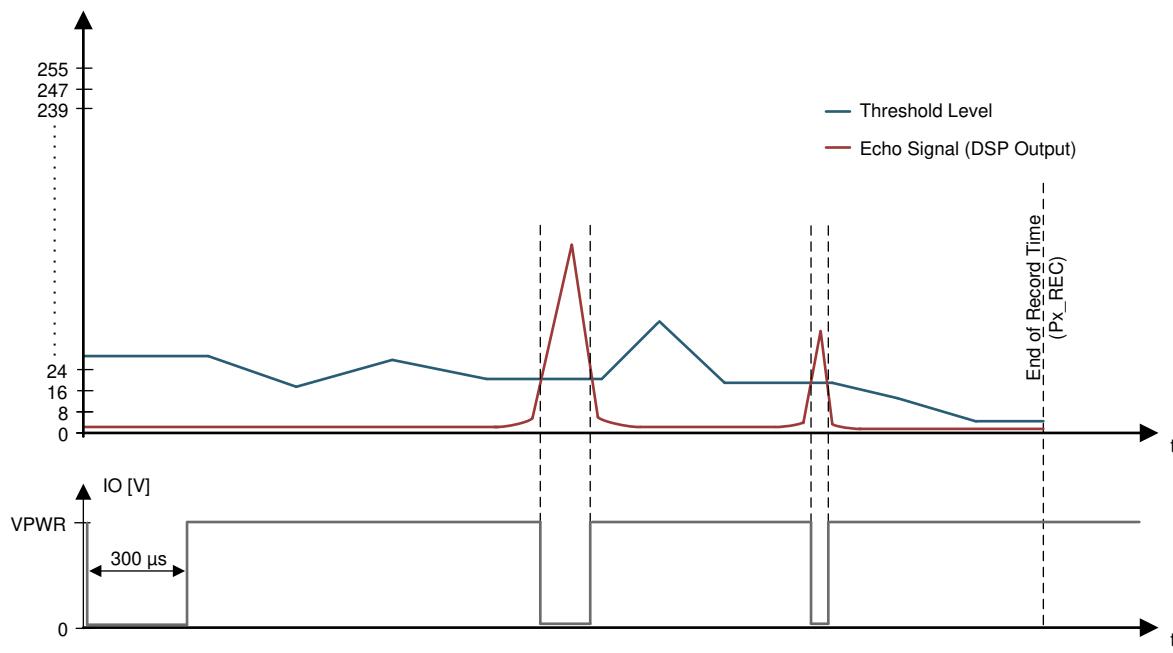

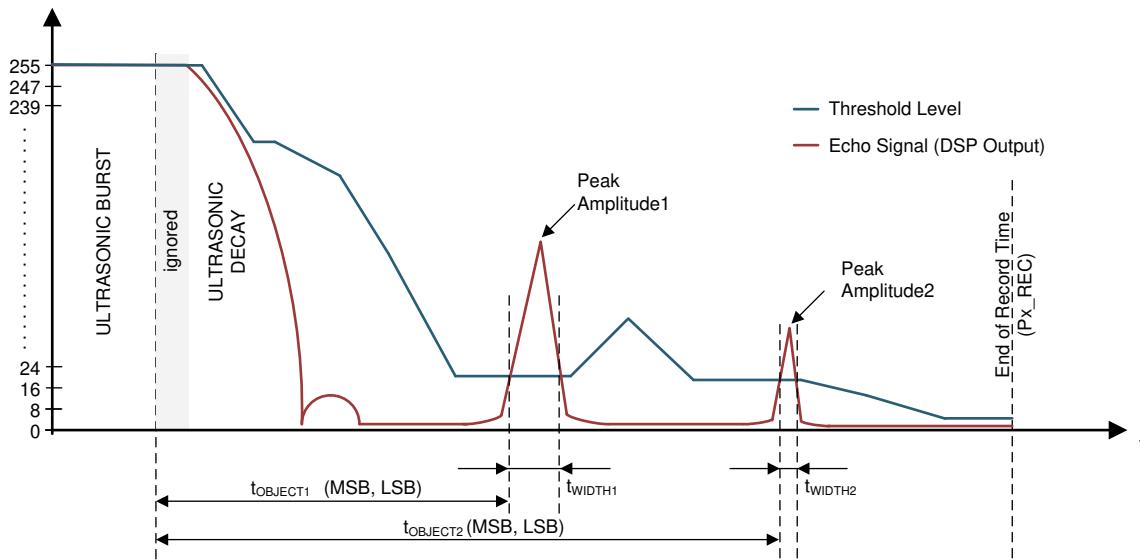

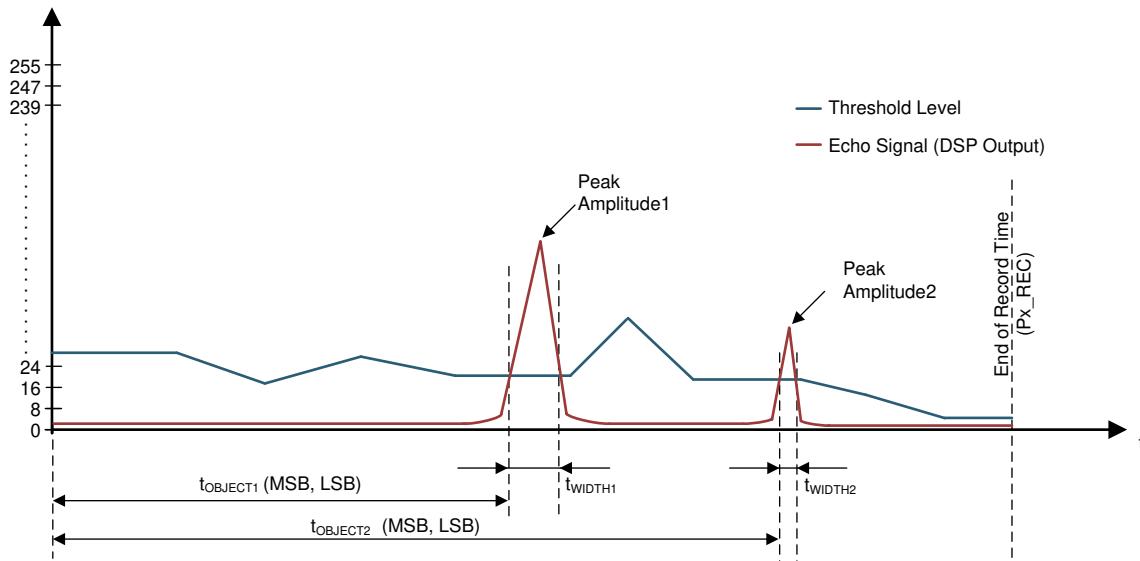

PGA460 デバイスの DSP ブロックは、ADC からのデジタル・データを処理してエコーのピーク・プロファイルを抽出します。その後、DSP の出力とプログラミングされたスレッショルドとを比較して、物体距離計算のためのタイム・オブ・フライト（飛行時間）を測定します。

図 7-5 に、DSP のデータ・パスを示します。また、コンパレータの出力は、デッドタイム・レジスタの THR\_CMP\_DEGLTCH[7:4] ビットによってデグリッヂ (グリッヂ除去) できます。

図 7-5. DSP データ・パス

#### 7.3.4.1 超音波エコー - バンドパス・フィルタ

超音波エコー信号は、超音波トランスデューサの駆動周波数と同じキャリア周波数を持つ振幅変調信号です。DSP バンドパス・フィルタ・ブロックを使用すると、観測対象の周波数帯域外の周波数をフィルタで除外できるため、超音波エコー信号に影響を及ぼすノイズの量を減らすことができます。

フィルタの中心周波数は、FREQ ビットで設定された駆動周波数に基づいて自動的に調整されます。また、INIT\_GAIN EEPROM レジスタの BPF\_BW ビットを設定することにより、フィルタの帯域幅を 2kHz 刻みで 2kHz~8kHz に調整できます。

このバンドパス・フィルタは、2 次バターワース IIR タイプ・フィルタです。電源投入時に、PGA460 デバイスは係数を計算し、それらを BPF\_A2\_xSB、BPF\_A3\_xSB、および BPF\_B1\_xSB レジスタに入れます。ユーザーは、これらのレジスタを上書きして、フィルタを再構成できます。ただし、FREQ または BPF\_BW ビットが変更された場合、係数計算シーケンスが再実行され、デバイスはこれらのレジスタを再書き込みします。FREQ\_SHIFT ビットが 1 (80~480kHz の駆動周波数範囲) に設定されている場合、PGA460 デバイスは、バンドパス・フィルタ係数を自動的に計算しません。この場合には、MCU は、UART または USART インターフェイス経由でこれらの値を書き込む必要があります。

#### 7.3.4.2 超音波エコー - 整流器、ピーク・ホールド、ローパス・フィルタ、データ選択

整流器、ピーク抽出機能、ローパス・フィルタの DSP ブロックは、エコー信号を復調すると同時に、ベースバンド表現を出力して、プログラムされたレッシュホールドと比較します。これらのブロックの定義は、次の通りです。

**整流器** 入力信号の振幅は正と負の両方になる可能性があるため、このブロックは入力信号の絶対値を出力します。

**ピーク・ホールド** このブロックは、ローパス・フィルタが信号のピーク振幅を検出するために必要な一定時間にわたって、整流された信号のピーク値を保持します。

**ローパス・フィルタ (LPF)** このブロックは、エコー信号からノイズの影響を除去します。LPF は、1 次 IIR タイプ・フィルタとして実現されています。ユーザーは、CURR\_LIM\_P2 レジスタの LPF\_CO ビットを設定することによって、カットオフ周波数を 1kHz ステップで 1kHz~4kHz に設定できます。

電源投入時に、PGA460 デバイスはフィルタ係数の値を計算して、各係数を LPF\_A2\_xSB および LPF\_B1\_xSB レジスタに入れます。ユーザーは、これらのレジスタの値を上書きしてフィルタを再構成できます。このとき、PGA460 デバイス

は何も操作を行いません。ただし、LPF\_CO ビットが変更された場合には、係数計算シーケンスを再実行する必要があり、デバイスがこれらのレジスタを再構成します。

### 7.3.4.3 超音波エコー - 非線形スケーリング

DSP データ・パスの非線形スケーリング・ブロックは、エコー信号の指数関数スケーリング（デジタル非線形増幅）を行い、より高い SNR を実現します。この機能は、遠い距離にある物体を検出する際に、エコー信号の振幅が非常に減衰してノイズ・フロアに近い場合に役立ちます。

非線形スケーリング・ブロックは、以下のアルゴリズムを実行します。

```

if (t < Time_Offset)

Output = Input;

else

Output = (Input - Noise_Level)Scale_Exponent;           (3)

```

ここで、

- $t$  は現在の記録時間です。

- $Time\_Offset$  (時間オフセット) は、 $SCALE\_N$  パラメータによって設定され、**超音波エコー - スレッショルド・データの割り当て** セクションで定義されている TH9、TH10、TH11、TH12 のいずれかの時点を選択するために使用されます。

- $Scale\_Exponent$  (スケール指数) は、非線形の指数 (1.5 または 2) であり、 $SCALE\_K$  ビットによって定義されます。

- $Noise\_Level$  (ノイズレベル) は、1 LSB ステップ、0~31 の範囲でユーザーが設定したノイズ・レベルであり、 $NOISE\_LVL$  ビットによって定義されます。

$SCALE\_N$ 、 $SCALE\_K$  および  $NOISE\_LVL$  ビットは、**DSP\_SCALE** レジスタの EEPROM パラメータです。

#### 注

非線形スケーリング・ブロックは、プリセット 1 およびプリセット 2 に適用できます。

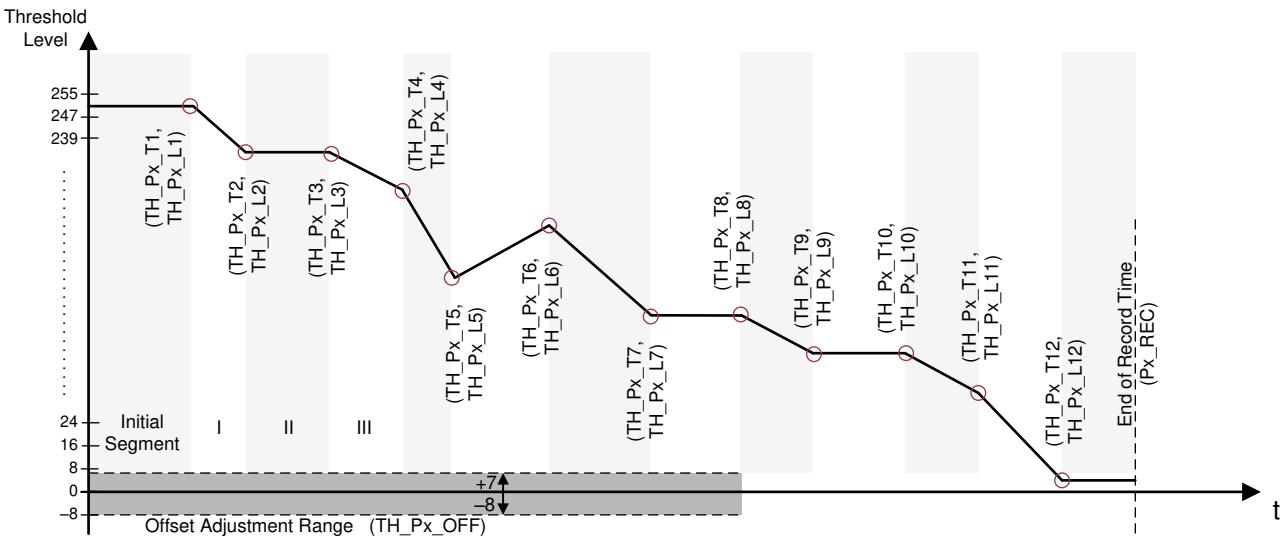

### 7.3.4.4 超音波エコー - スレッショルド・データの割り当て

PGA460 スレッショルドの割り当ては、2 つのプリセットで構成されています。プリセット 1 およびプリセット 2 です。これらのプリセットは、いずれもスレッショルド・セグメントを割り当てるための独立したメモリ・マップを備えています。PGA460 デバイスは、各プリセットに対して最大 12 のスレッショルド・セグメントをサポートします。そのスレッショルド・セグメント・ポイント (TSP) は、プリセット 1 については **P1\_THR\_[0:15]** レジスタ、プリセット 2 については **P2\_THR\_[0:15]** レジスタで定義されています。

図 7-6 に、スレッショルドの割り当て例を示します。

図 7-6. スレッショルドの割り当て例

図 7-6 に示すように、各 TSP は (時間、レベル) という形式で記述され、Px はプリセット番号 (プリセット 1 の場合は P1、プリセット 2 の場合は P2) です。さらに、初期セグメント時間パラメータ (TH\_Px\_T1) の値だけが絶対時間で表され、それ以降のすべての TSP 時間 (TH\_Px\_Tx パラメータ) は、前の TSP の絶対時間値と現在の TSP の絶対時間値との間の差分として表されます。各 TSP のレベル値 (TH\_Px\_Lx パラメータ) は、すべて絶対 LSB レベルの値で表され、互いに関連がありません。任意の時点での TSP レベルのスレッショルド値は、PGA460 デバイスによって、2 つの隣接するスレッショルド・セグメント・ポイント間の線形補間関数として決定されます。

図 7-6 に示すように、最初のセグメントの開始に達するまでの初期セグメントのスレッショルド値は、TH\_Px\_L1 パラメータによって決定される一定のスレッショルド値となっています。また、Px\_REC パラメータで定義された記録終了時間に達するまでの 12 番目のセグメントのスレッショルドは、TH\_Px\_L12 パラメータによって決定される一定のスレッショルド値となっています。

TH\_Px\_L1～TH\_Px\_L8 のスレッショルド・パラメータは 5 ビット幅であり、TH\_Px\_L9～TH\_Px\_L12 のパラメータは 8 ビット幅です。このようなサイズになっているので、メモリ領域を節約すると同時に、長距離の弱いエコー信号でノイズが存在する場合でも高い分解能で検出することができ、すべての TSP にわたって検出範囲を一定に保っています。TH\_Px\_L1～TH\_Px\_L8 の分解能は 8 LSB であるため、短距離検出に対するスレッショルド割り当てを微調整するようにスレッショルド・オフセットを定義できます。

#### 注

- オフセット加算後の TSP の計算値が負になる場合は、線形補間の前に 0 にクランプされるため、スレッショルド曲線の勾配が予想される値から外れます。

- プリセット 1 およびプリセット 2 のスレッショルド割り当てパラメータは、CRC 計算アルゴリズムによって保護されています (式 6)。

- 電源投入時または低消費電力モードからのウェークアップ時には、すべてのスレッショルド・レジスタ (Px\_THR\_XX) とスレッショルド CRC レジスタ (THR\_CRC) がデフォルト値に初期化されないので、CRC エラーが発生して THR\_CRC\_ERR ビットが 1 に設定されます。これによって、構成が正しくロードされていないことを MCU に通知します。スレッショルド・レジスタへ書き込むと、CRC 計算が再実行されて、エラー・ビットが更新されます。

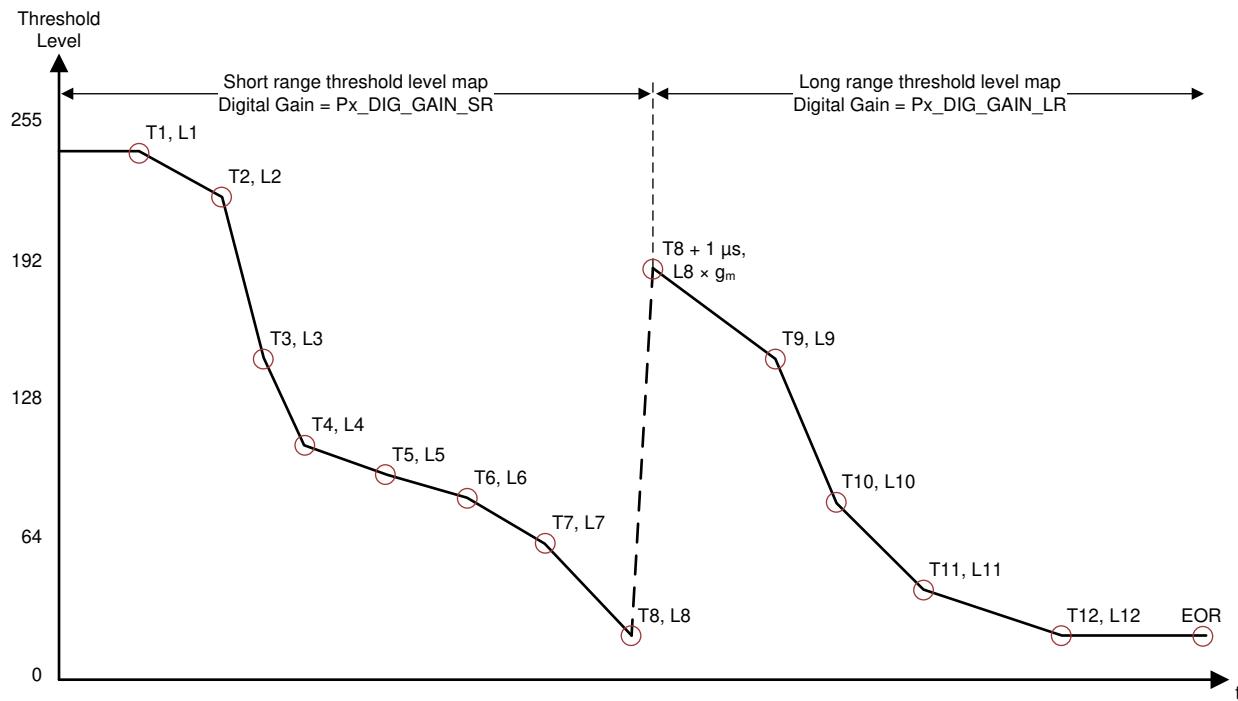

#### 7.3.4.5 デジタル・ゲイン

ローパス・フィルタ後のデジタル・ゲイン機能が実装されているので、スレッショルド値を小さくせずに受信エコーの SNR を向上できます。このゲインは、バンドパスおよびローパス・フィルタの後に適用されるため、デジタル・ゲインは帯域外ノイ

ズを増幅しません。このゲイン機能は、地面反射などの誤検出を抑制し、より高い精度でより遠くにある物体を検出するのに役立ちます。

デジタル・ゲイン範囲には、短距離 (SR) と長距離 (LR) の 2 つの設定があります。SR および LR のゲイン・レベルは、プリセット 1 およびプリセット 2 のために個別に `Px_GAIN_CTRL` レジスタで、それぞれ `Px_DIG_GAIN_SR` および `Px_DIG_GAIN_LR` パラメータを使って設定されます。LR ゲインは、`Px_DIG_GAIN_LR_ST` パラメータで設定されたスレッショルド・レベル・ポイントから、記録期間の終了まで適用されます。SR ゲインは、時間ゼロから選択した LR スレッショルド・レベル・ポイントの開始まで適用されます。

デジタル・ゲインが適用される時点でのエコーの誤検出を防止するために、定義されたスレッショルドも変更されます(図 7-7 を参照)。ここでは、スレッショルド・レベルのポイント 9 から LR ゲインを適用します。LR ゲインがスレッショルド・レベル 8 の SR ゲインと異なる場合、スレッショルド・レベル 8 に、LR ゲインと SR ゲインの比 (`DIG_GAIN_LR`/`DIG_GAIN_SR`) を乗算します。この比率は、SR スレッショルド・レベル 9 のポイントの終了後  $1\mu\text{s}$  の時点で使われます。これによりスレッショルド・レベルに不連続性が生じますが、エコー信号も同じゲイン比でスケーリングされるため、物体検出に影響はありません(誤ったスレッショルド交差は防止されます)。このポイントの後、リニア補間方式を使用して、スレッショルド・レベルを次の設定スレッショルド・レベル(以下の例ではポイント 9)に変化させます。スレッショルド・レベルは、デジタル・ゲインおよび LR ゲインと SR ゲインの比率を考慮して調整する必要があります。

図 7-7. `DIG_GAIN_LR_ST` = [00] TH9 の例

### 7.3.5 システム診断

PGA460 デバイスのシステム診断機能は、バースト中のトランシーバー素子の特性評価と、システム全体のステータスの判定に役立ちます。提供されている情報を使って、システムは、トランシーバーの故障、ドライバ回路の故障(使用する場合はトランシスの故障も)、システムに対する環境的影響(氷、泥、雪など)、トランシーバーの動作を損なう物体(たとえばトランシーバーに加えられた圧力)などを検出できます。

PGA460 デバイスには、システムの故障検出に使用できる情報を提供するシステム診断機能が 3 種類実装されています。これらの診断機能を以下に示します。

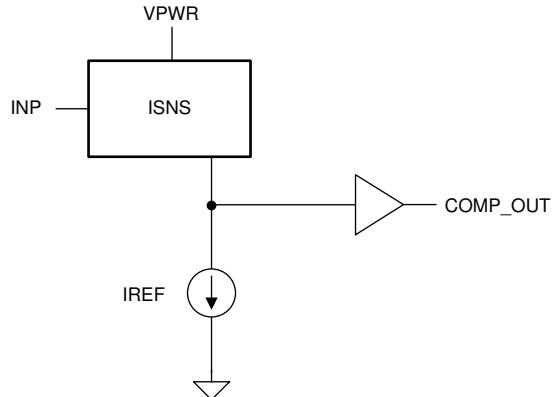

**電圧診断** 電圧診断機能は、バースト / リスン実行コマンドを実行したときのみ、`INP` ピンを流れる電流を監視することができます。特定のバースト周波数でのトランシーバー励起電圧により、`INP` ピンに電流が発生し、図 7-8 に示すように、電流コンパレータを使ってリファレンス電流と比較します。励起電流が、`FVOLT_DEC` レジスタ

の **FVOLT\_ERR\_TH** で設定されたスレッショルド・レベルを超えると、電流コンパレータの出力が **HIGH** になります。これは、目的の励起電圧レベルで正常なバーストが発生したことを意味します。測定は、バースト段の始動から約 **50μs** 後に開始され、バースト段の終了時に終了します。この診断測定の結果は、[インターフェイスの説明](#) セクションで説明しているように、**IO** 時間コマンドまたは **UART** インターフェイスのステータス・フレームで通知されます。

図 7-8. 電圧診断のブロック図

$$V_{(\text{diag})} \cong 3.25E^{-3} \times \text{FVOLT_ERR_TH}[2:0] \times \left( R_{(\text{INP})} + \frac{1}{6.28 \times f_{(\text{burst})} \times C_{(\text{INP})}} \right) \quad (4)$$

ここで、

- **FVOLT\_ERR\_TH[2:0]** は、000b が 1、111b が 8 に対応しています。

- $f_{(\text{burst})}$  は、バースト周波数を kHz 単位で表したものです。

- $C_{(\text{INP})}$  は、**INP** ピンの入力容量です。

- $R_{(\text{INP})}$  は、EMI および ESD の堅牢性を確保するために使用するオプションの抵抗です (図 8-1 を参照)。

#### 注

バーストが発生する前には、コンパレータの出力が **LOW** になっていることが想定されます。出力が **HIGH** に固着した場合、その状態が検出され、診断失敗フラグが設定されます

**トランステューサの周波数測定** 記録期間の減衰段において、トランステューサ・ノードの周波数測定を実行して、トランスとトランステューサのマッチングの性能と適切な調整を検証します。

トランステューサの周波数を測定するには、スタート・パラメータ **FDIAG\_START**、ウィンドウ長パラメータ **FDIAG\_LEN** を EEPROM メモリに定義します。スタート・パラメータ **FDIAG\_START** は、バースト時間終了を基準として、周波数測定を開始する時間を定義します。診断ウィンドウ長パラメータ **FDIAG\_LEN** は、キャプチャされた信号期間を基準として、診断ウィンドウの時間幅を設定します。パラメータ構成の簡単な例を説明します。

1. **FDIAG\_START = 2, FDIAG\_LEN = 1** と仮定します。レジスタ・マップ セクションを参照すると、これらの EEPROM パラメータの開始時間は、バースト終了から  $200\mu s$ 、ウィンドウ長は、3 信号周期となります。動作周波数が **58kHz** と仮定すると、信号周期は  $17.24\mu s$  であるので、バースト終了から  $200\mu s + 3 \times 17.24\mu s = 251.72\mu s$  の時点での診断が終了します。

2. 測定ウィンドウ内でキャプチャされた周波数情報は平均化され、500ns の時間ベースのカウンタ値として表されます。信号周波数は、式 5 を使って計算できます。

$$f = 1 / (FDIAG_VAL \times 500e-09) \quad (5)$$

ここで、

- **FDIAG\_VAL** は、いずれかのデバイス・インターフェイスを使って抽出できる値です。

3. 周波数診断測定が完了する前に、指定された数の物体が検出された場合、周波数測定結果は保存されません。これは、事前に定義した診断パラメータおよび近距離物体検出のスレッショルドを設定することで管理できます。

PGA460 デバイスには、この他に周波数エラー機能が実装されており、測定されたトランスデューサの周波数が、**FDIAG\_ERR\_TH** スレッショルド・パラメータで設定された制限値を超えていることを示します。この機能の結果は、IO 時間コマンドまたは **UART** インターフェイスのステータス・フレームで通知されます。トランスデューサ周波数エラー通知の詳細については、「[インターフェイスの説明](#)」セクションを参照してください。

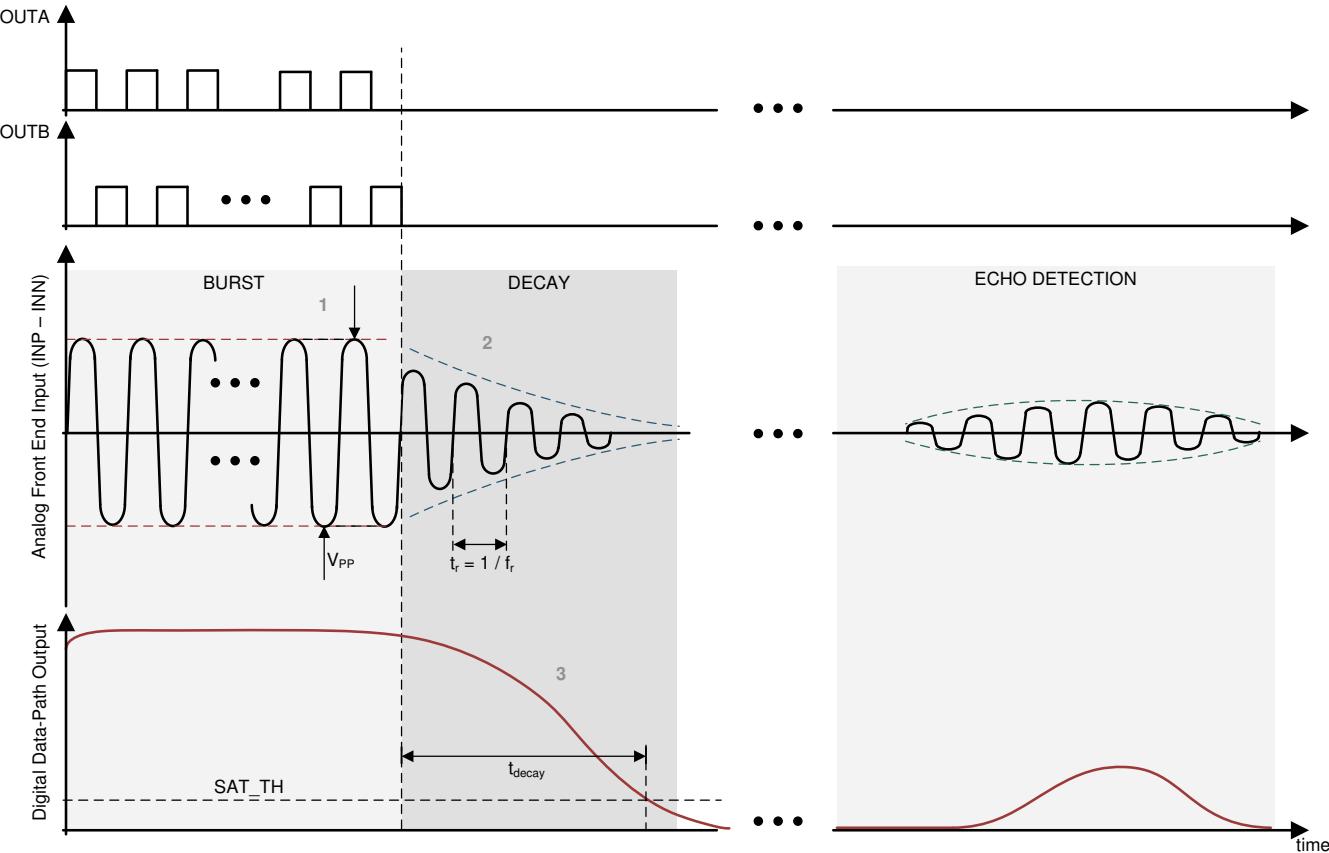

**減衰時間** 記録期間の減衰段では、トランスデューサ減衰時間測定を実行して、トランスデューサが正常に動作していることを確認できます。この診断機能とトランスデューサ周波数測定機能の組み合わせは、超音波トランスデューサに対する外部的な妨害を検出するために、超音波システムで一般的に使用されます。

減衰期間は、デジタル・データ・バスの出力で測定されます。バースト段が終了すると同時に測定を開始し、エコー・レベルが、**SAT\_TH** パラメータによって **EEPROM** で定義されている飽和スレッショルド・レベルを超えている間、減衰時間が測定されます。得られた結果は、いずれかの **PGA460** インターフェイスを使って抽出でき、その値は **16μs** 刻みの時間で表されます。測定された減衰時間が **4ms** を超える場合、抽出される値は **0xFF** となります。

**ノイズ・レベル測定** **PGA460** デバイスに実装されているもう 1 つのシステム診断は、ノイズレベル測定診断です。この機能の目的は、付近にある他の超音波システムによって発生する周囲のノイズを評価して外乱を判定すること、および遠距離にある物体を検出するときのノイズ・フロア・レベルを評価することです。

ノイズレベルの測定中、**PGA460** デバイスは、リスン・オンリー (プリセット 2) コマンドを実行します (コマンドの詳細については、[インターフェイスの説明](#) セクションを参照)。ここではバーストは実行されず、記録期間だけが開始されて **8.192ms** 続きます。この記録期間中、デジタル・データ・バスの出力で収集されたデータは平均化され、それぞれが **4096** サンプルを含んでいる 2 つのグループになります。ノイズ・レベル測定機能を実行して測定される最終的なノイズ・レベルは、この 2 つのグループのうち高い方の平均値になります。この値が、最終的なノイズレベル測定値として通知されます。

### 注

ノイズレベル測定プロセス中、非線形スケーリング・ブロックは、常に無効になります (スケール・ファクタ **EEPROM** の **SCAL\_K** ビットが 0、**NOISE\_LVL** ビットが 0 の状態)。

図 7-9 に、物体検出記録サイクル全体の例として、**PGA460** デバイスに実装されているシステム診断を示します。図 7-9 の数字 1、2、3 は、それぞれ電圧診断、トランスデューサ周波数、減衰期間の測定値を示しています。

図 7-9. システム診断の例

### 7.3.5.1 デバイス内部診断

PGA460 は、過電圧 (OV)、低電圧 (UV)、過電流 (OC)、サーマル・シャットダウンに対する内部診断機能も備えています。

OV、UV、サーマル・シャットダウン状態は、`DEV_STAT1` レジスタのステータス・ビットで通知されます。OC 保護はデバイス内蔵レギュレータに実装されていますが、この保護の影響は通知されません。正常な動作と誤トリガ防止のため、すべての電気的診断は 25 $\mu$ s のグリッチ除去を通過した後、サーマル・シャットダウン診断は 50 $\mu$ s のグリッチ除去を通過した後で、通知されます。

**仕様** に、内部レギュレータの OV および UV 保護スレッショルドを示します。�ルトが検出されると、対応するステータス・ビットが設定され、インターフェイスの読み取り時にクリアされます (読み取り時クリア・タイプ)。VPWR ピンの入力デバイス電源は、固定の UV スレッショルド・レベルと可変の OV スレッショルド・レベル (VPWR\_OV\_TH) が定義されており、出力ドライバはディセーブルになりますが、デバイスはアクティブ状態を維持します。この機能により、ドライバに損傷を与えることなく、高電圧入力での消費電力を制御できます。VPWR\_UV フラグが検出されると、現在実行中の TCI コマンドはすべて完了し、低電圧状態が解消されるまで新しい TCI コマンドは実行されません。この機能は、ピン (RxD、TxD、IO) に関係なく、USART 通信には適用できません。

サーマル・シャットダウン保護診断機能は、ローサイド・ドライバの FET の温度を監視します。サーマル・シャットダウン・イベントが発生した場合、PGA460 デバイスは、出力ドライバをディセーブルします。サーマル・シャットダウン条件が解消されると、出力ドライバを再度イネーブルにします。サーマル・シャットダウンから回復した後、サーマル・シャットダウン・ステータス・ビットが設定され、処置が実行されたことをユーザーに通知します。

### 注

VPWR ピンの電圧が 5V 未満の場合、デジタル・コアがリセットされる可能性があるため、デバイスの性能は保証されません。レジスタ・マップの揮発性メモリ・セクションに保存されている設定はすべてクリアされます。

#### 7.3.6 インターフェイスの説明

PGA460 デバイスには 2 つの通信インターフェイスが搭載されており、それぞれにピンが割り当てられています。時間コマンド・インターフェイスは、オープン・ドレイン出力構造の IO ピンに接続されており、内部の  $10\text{k}\Omega$  プルアップ抵抗によりバッテリ・レベルの電圧で通信できます。非同期 UART インターフェイスは、IO ピンで通信でき、RXD および TXD ピンにも接続されています。3 つ目のインターフェイス・オプションは、RXD ピンと TXD ピンでのみ利用可能な同期 USART インターフェイスを使用することです。この通信は、シリアル・クロック入力に SCLK ピンを使用し、最高速のデータ・レート・モードです。RXD および TXD ピンでの USART 通信は、[TEST ピンの機能](#) セクションで説明しているように、構成されている IOREG 電圧に応じて、3.3V または 5V の CMOS レベルで利用できます。

### 注

システムにおいて時間コマンド・インターフェイスと UART インターフェイスの両方を同時に使用する可能性は低いため、PGA460 デバイスは、IO ピン・トランシーバをディセーブルにして電力を維持できます。そのためには、IO\_IF\_SEL ビットを 0 にし、IO\_DIS ビットを 1 にする必要があります。このビットは、RXD および TXD ピン経由でのみ通信が可能な IO ピン・トランシーバを直ちにディセーブルにします。IO\_DIS ビットを 0 に戻しても、IO インターフェイスは再イネーブルされません。IO\_DIS ビットが意図せずに設定された場合、PGA460 デバイスはパワー・サイクル時に IO インターフェイスを回復できます (IO\_DIS ビットを 0 にリセット)。ただし、このビットの値が EEPROM にプログラムされている場合、デバイスは、電源投入時、常に EEPROM でプログラムされた値に従います。

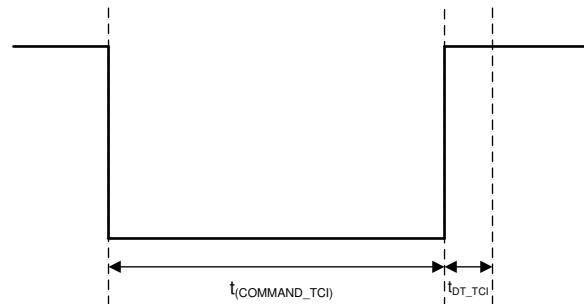

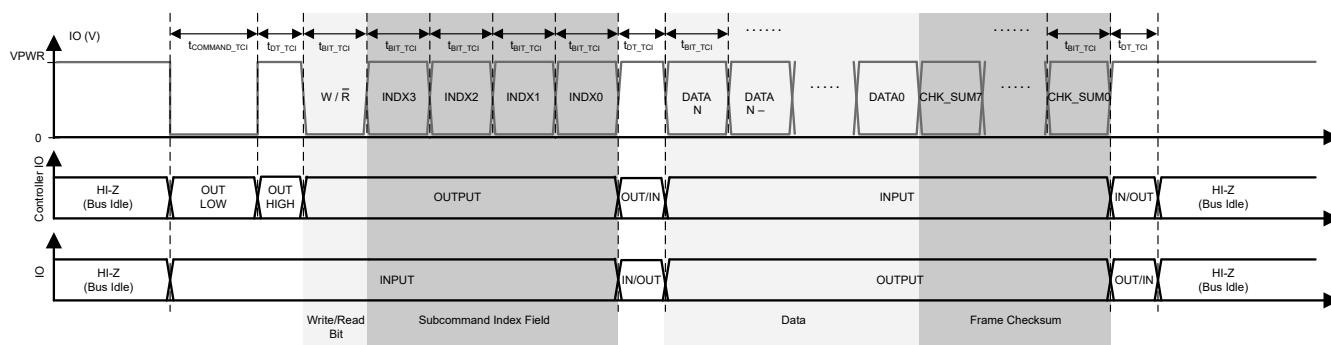

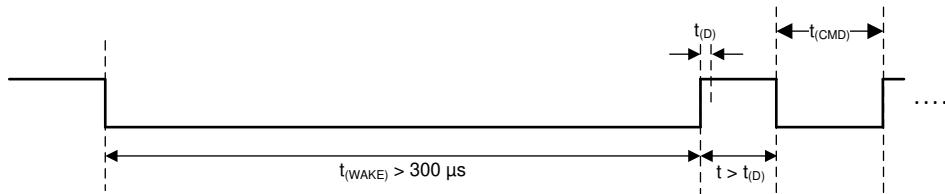

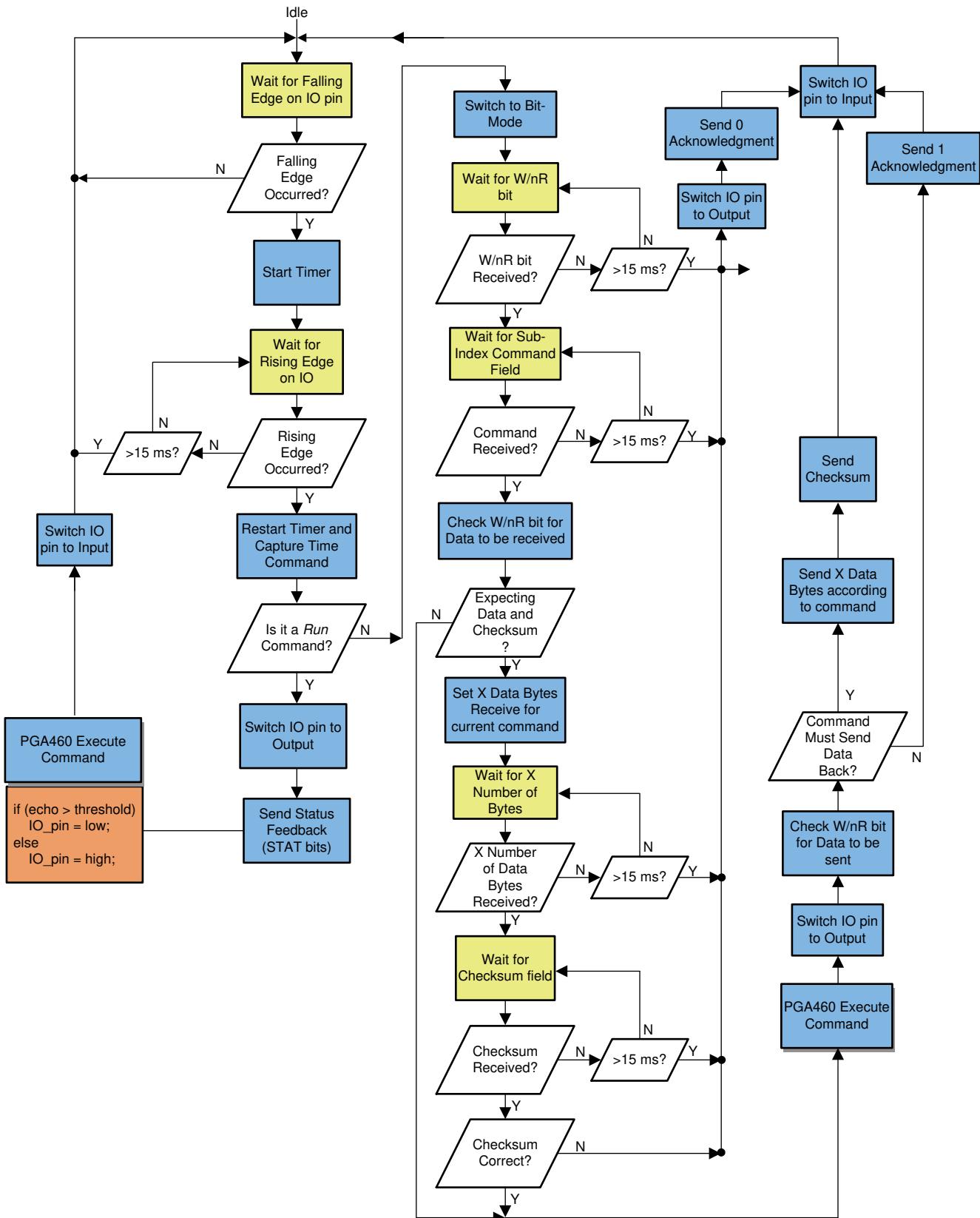

##### 7.3.6.1 時間コマンド・インターフェイス

時間コマンド・インターフェイスは、IO ピンに接続された通信インターフェイスです。インターフェイスがアイドル状態のときの IO ピンのデフォルト状態は、HIGH (VPWR にプルアップ) です。ピン通信は双方向であり、コマンドを受信すると、PGA460 デバイスは IO ピンをアクティブに駆動し、IO ピンの状態を変更することで応答を提供します。特定のコマンドについてコマンドまたはデータを送信している間に、時間コマンド・インターフェイスが 15ms を超える期間にわたって LOW または HIGH にスタックしたままになった場合、PGA460 通信はリセットされ、コントローラからの新しいコマンド通信を受信するのを待ちます。

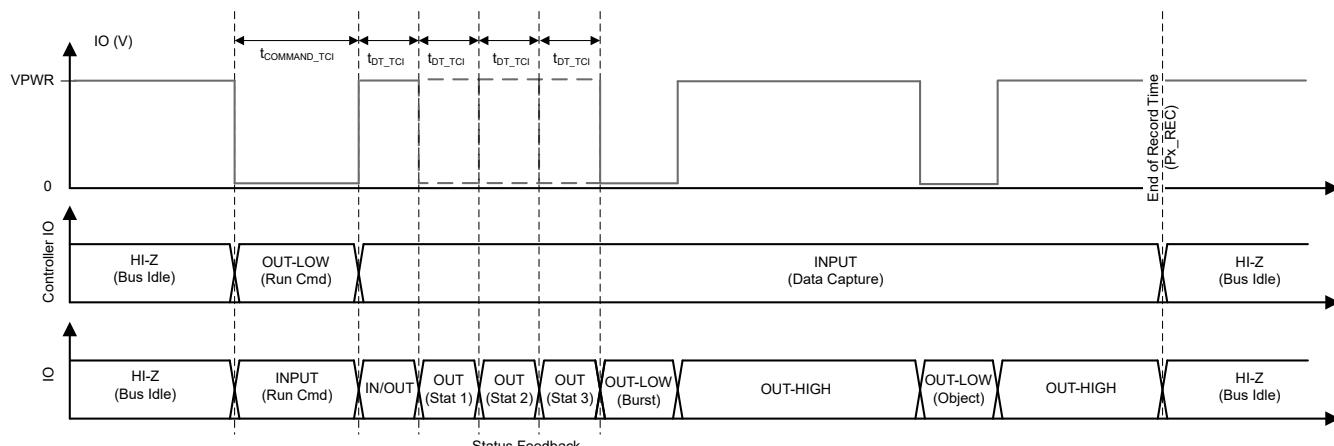

時間コマンド・インターフェイスには、5 つの時間コマンドがあり、4 つは実行コマンド、1 つは構成 / ステータス・コマンドに分類されます。仕様 セクションで定義されているように、 $t_{BIT0\_TCI}$  の期間にわたって IO ピンを LOW にすることによって論理 0 が送信され、 $t_{BIT1\_TCI}$  の期間にわたって IO ピンを LOW にすることによって論理 1 が送信されます。図 7-10 および 図 7-11 に、デバイスの時間コマンドのタイミングおよびロジック・ビットのタイミングに関する一般的なタイミング図を示します。 $t_{DT\_TCI}$  デッドタイムは、PGA460 デバイスが受信したコマンドを処理し、IO ピンの状態を入力から出力に変更するために定義されています。

図 7-10. 時間コマンド・インターフェイスのコマンドのタイミング

図 7-11. 時間コマンド・インターフェイスのピットのタイミング

#### 7.3.6.1.1 実行コマンド

実行コマンドは、デバイスのランタイム動作に使われるものであり、PGA460 デバイスの通常動作サイクル中に最も多く使用されます。これらのデバイス・コマンドは、[仕様](#) セクションで定義されているように、指定された期間にわたって IO ピンを LOW にすることで指定されます。以下に示すものが、実行コマンドに分類されます。

**バースト/リスン (プリセット 1)** デバイスは、P1\_PULSE 個のパルスを使って CURR\_LIM1 電流制限設定により超音波バーストを送信し、P1\_REC の値で定義された記録期間で物体検出を実行します。物体検出の処理中、P1\_THR\_xx スレッショルド・マップを使用して信号を比較します。このコマンドでは、非線形スケーリング DSP 機能を使用できます。

**バースト/リスン (プリセット 2)** デバイスは、P2\_PULSE 個のパルスを使って CURR\_LIM2 電流制限設定により超音波バーストを送信し、P2\_REC の値で定義された記録期間で物体検出を実行します。物体検出の処理中、P2\_THR\_xx スレッショルド・マップを使用して信号を比較します。このコマンドでは、非線形スケーリング DSP 機能を使用できます。

**リスン・オンリー (プリセット 1)** デバイスは、超音波バーストを送信しませんが、P1\_REC の値で定義された記録期間で物体検出のみを実行します。物体検出の処理中、P1\_THR\_xx スレッショルド・マップを使用して信号を比較します。このコマンドでは、非線形スケーリング DSP 機能を使用できます。

**リスン・オンリー (プリセット 2)** デバイスは、超音波バーストを送信しませんが、P2\_REC の値で定義された記録期間で物体検出のみを実行します。物体検出の処理中、P2\_THR\_xx スレッショルド・マップを使用して信号を比較します。このコマンドでは、非線形スケーリング DSP 機能を使用できます。

図 7-12 に、IO ピン実行コマンドの通信プロセスを示します。

図 7-12. 時間コマンド・インターフェイス実行コマンドの実行

PGA460 デバイスのステータス・フィールドは実行コマンドに組み込まれており、IO バスのデッドタイムを延長することによってコントローラに通知されます。デッドタイムは、3 つのステータス・ビット STAT[1:3] を示すために最大  $3 \times t_{(DT\_TCI)}$  までさらに延長できます。表 7-1 に、割り当てられた診断機能および各ステータス・ビットの優先順位を示します。

表 7-1. 時間コマンド・インターフェイスのステータス・ビットの説明

| ステータス・ビット | 優先順位  | 概要                                                         |

|-----------|-------|------------------------------------------------------------|

| STAT 1    | 1 (低) | スレッショルド設定未初期化エラー                                           |

| STAT 2    | 2     | 周波数診断エラー<br>電圧診断エラー                                        |

| STAT 3    | 3 (高) | パワーアップ時の自動 EEPROM CRC エラー<br>ユーザーによる EEPROM ダウンロード CRC エラー |

表 7-1 に示すように、STAT3 ビットは最も高い優先度を持っています。STAT3 エラー状態が存在する場合、デッドタイムは  $3 \times t_{(DT\_TCI)}$  にまで延長されます。このとき、STAT2 または STAT1 のいずれかのエラー状態が存在する場合には、これらの条件は STAT3 エラー状態の優先度が高いことによって却下されます。同様に、STAT1 条件は STAT2 エラー条件によって却下されます。この場合、デッドタイムは  $2 \times t_{(DT\_TCI)}$  にまで延長されます。STAT3 および STAT2 のすべてのエラー条件がクリアされると、STAT1 条件によってデッドタイムが  $t_{(DT\_TCI)}$  だけ延長されます。

ステータス・ビットの機能は、次のように説明できます。

**STAT 1** 2 つのプリセット・スレッショルド・レジスタ・グループが両方とも初期化されていない場合、このステータス・ビットは 1 に設定されます。TCI 通信チャネル経由で受信した実行コマンドは、どちらかのプリセット・スレッショルド・レジスタ・グループがプログラムされるまで実行されません。

**STAT 2** 以下のいずれかが発生すると、このステータス・ビットは 1 に設定されます。

- システム診断 セクションで周波数診断について説明されている測定周波数の値が、EEPROM メモリの FDIAG\_ERR\_TH パラメータで定義されているデルタ値よりも大きいまたは小さい場合 (これは周波数診断エラーとみなされます)。

- システム診断 セクションでトランシスデューサ電圧測定について説明されている測定電圧値が、EEPROM メモリの FVOLT\_ERR\_TH パラメータで指定されているレベルよりも低い場合。

**STAT 3** TCI 通信チャネル経由で受信した実行コマンドは、EE CRC エラーが修正されるまで実行されません。ユーザーは、EEPROM にマップされたいずれかのレジスタに書き込んでエラーをクリアできます。

ユーザーは、自動または手動で発生した次の EEPROM ダウンロード動作でエラーが発生しないようにするため、EEPROM を再プログラムする必要があります。

デバイスが実行コマンドを受信すると、物体検出を示すための最終的な DSP 出力に応じて、IO ピンが PGA460 デバイスによってアクティブに駆動されます。任意の時点で、処理されたエコー信号がその時点のスレッショルドを超えた場合は、IO ピンが **LOW (GND、強いプルダウン)** になります。それ以外の場合は、内部の  $10\text{k}\Omega$  (弱いプルアップ) 抵抗によって IO ピンがプルアップされます。記録時間が  $\text{Px\_REC}$  パラメータで定義された記録終了時間に達すると、IO ピンが解放され (入力としてプルアップ)、デバイスは、次のコマンドの受け入れ準備完了になっています。図 7-13 に、IO ピンの物体検出機能を示します。デバイスはバースト中は IO ピンを **LOW** にして、その後、解放することによって MCU に対して記録時間枠の基準を提供します。基準時間、プログラムされたバーストの持続時間、およびその後の検出された各物体による立ち下がりエッジを把握することで、コントローラまたは MCU は、物体の距離を計算できます。

図 7-13. バースト / リスン時間コマンドによる IO ピン物体検出信号

図 7-14. リスン・オンリー時間コマンドによる IO ピン物体検出信号

PGA460 デバイスは、実行コマンドを受信してから  $t_{(DT\_TCI)}$  の時間が経過した後、IO ピンを強制的に **LOW** にします。これは、記録期間の開始を示します。このプロセスは、タイム・オブ・フライト測定を開始するための基準エッジをコントローラに提供するとともに、PGA460 デバイスがステータス (STAT) ビットの応答を記録サイクルの情報から分離するためでもあります。一般に、低い周波数範囲でバースト期間が経過した後にリンクギングが発生すると、AFE は飽和し、IO ピンが  $300\mu\text{s}$  以上にわたって **LOW** になります。より高い周波数でのバーストもしくはリスン・オンリー・コマンドの場合、または超音波バーストによる飽和が指定されたスレッショルドよりも高い値にならない場合 ([図 7-14](#) を参照) には、最小パルス幅は  $300\mu\text{s}$  です。特定のフィルタ設定およびグリッヂ除去設定において、この  $300\mu\text{s}$  の期間が経過した直後に、偽の物体が検出される可能性があります。

#### 7.3.6.1.2 構成 / ステータス・コマンド

構成 / ステータス・コマンドは、以下の目的で使用します。

- PGA460 内部パラメータ構成

- 時変ゲインとスレッショルドの設定

- EEPROM のプログラミング

- 診断と温度測定

- エコー・データ・ダンプ機能

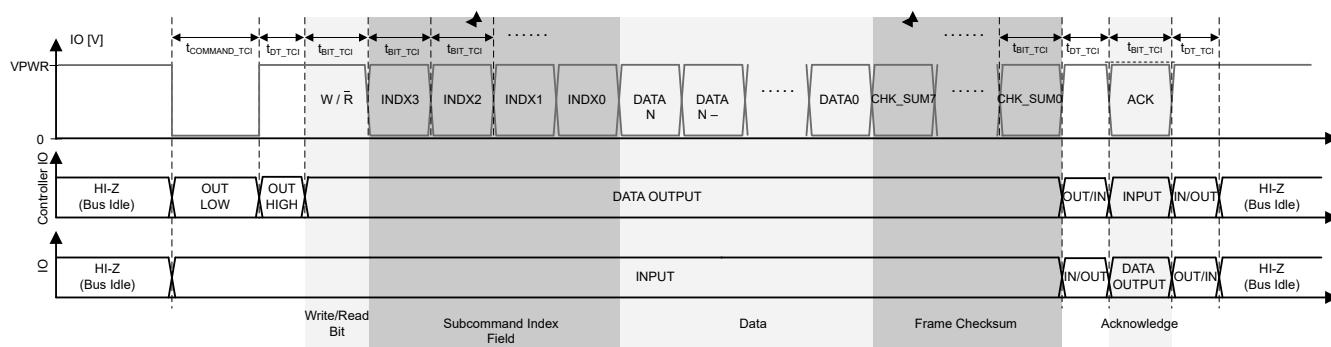

構成 / ステータス・コマンドが発行される場合には、残りのデータは、ビット的な通信を使って転送されます。このデータには、論理 1 と論理 0 がエンコードされています (図 7-11 を参照)。図 7-15 および 図 7-16 に、構成 / ステータス・コマンドの全体を示します。

図 7-15. 時間コマンド・インターフェイスの構成 / ステータス・コマンド書き込み

図 7-16. 時間コマンド・インターフェイスの構成 / ステータス・コマンドー読み取り

ここに示すように、それぞれの構成 / ステータス・コマンド・フレームは、サブコマンド・フィールド、データ・フィールド、フレーム・チェックサムという 3 つのデータ・セグメントで構成されています。サブコマンドは、4 ビットのインデックス・フィールドによって定義されており、順序が決まっています。それぞれのサブコマンドごとに、フレームのデータ・セグメントにおけるデータ長が異なる可能性があります。表 7-2 に、すべての PGA460 サブコマンドをインデックス順に示します。

表 7-2. 時間コマンド・インターフェイス・サブコマンドの説明<sup>(4)</sup>

| インデックス | 説明                                                      | データ長 (ビット) | アクセス | EE |

|--------|---------------------------------------------------------|------------|------|----|

| 0      | 温度の値                                                    | 8          | R    | N  |

| 1      | トランസデューサの周波数診断値                                         | 8          | R    | N  |

|        | 減衰時間の診断値                                                | 8          |      |    |

|        | ノイズ・レベルの診断値                                             | 8          |      |    |

| 2      | ドライバ周波数 (FREQ)                                          | 8          | R/W  | Y  |

| 3      | プリセット 1 バースト・パルス数 (P1_PULSE)                            | 5          | R/W  | Y  |

|        | プリセット 2 バースト・パルス数 (P2_PULSE)                            | 5          |      |    |

|        | スレッショルド・コンパレータ・デグリッチ (THR_CMP_DEG)                      | 4          |      |    |

|        | バースト・パルスのデッドタイム (PULSE_DT)                              | 4          |      |    |

| 4      | プリセット 1 記録時間の長さ (P1_REC)                                | 4          | R/W  | Y  |

|        | プリセット 2 記録時間の長さ (P2_REC)                                | 4          |      |    |

| 5      | プリセット 1 スレッショルド割り当て (P1_THR_0~P1_THR_15) <sup>(1)</sup> | 124        | R/W  | N  |

| 6      | プリセット 2 スレッショルド割り当て (P2_THR_0~P2_THR_15) <sup>(1)</sup> | 124        | R/W  | N  |

| 7      | バンドパス・フィルタ帯域幅 (BPF_BW)                                  | 2          | R/W  | Y  |

|        | 初期 AFE ゲイン (GAIN_INIT)                                  | 6          |      |    |

|        | ローパス・フィルタのカットオフ周波数 (LPF_CO)                             | 2          |      |    |

|        | 非線形スケーリング・ノイズ・レベル (NOISE_LVL)                           | 5          |      |    |

|        | 非線形スケーリング指数 (SCALE_K)                                   | 1          |      |    |

|        | 非線形スケーリング時間オフセット (SCALE_N)                              | 2          |      |    |

|        | 温度スケール・ゲイン (TEMP_GAIN)                                  | 4          |      |    |

|        | 温度スケール・オフセット (TEMP_OFF)                                 | 4          |      |    |

|        | P1 デジタル・ゲイン開始スレッショルド (P1_DIG_GAIN_LR_ST)                | 2          |      |    |

|        | P1 デジタル長距離ゲイン (P1_DIG_GAIN_LR)                          | 3          |      |    |

|        | P1 デジタル短距離ゲイン (P1_DIG_GAIN_SR)                          | 3          |      |    |

|        | P2 デジタル・ゲイン開始スレッショルド (P2_DIG_GAIN_LR_ST)                | 2          |      |    |

|        | P2 デジタル長距離ゲイン (P2_DIG_GAIN_LR)                          | 3          |      |    |

|        | P2 デジタル短距離ゲイン (P2_DIG_GAIN_SR)                          | 3          |      |    |

| 8      | 時変ゲイン割り当て (TV_GAIN0~TV_GAIN6)                           | 56         | R/W  | Y  |

| 9      | ユーザー・データ・メモリ (USER_1~USER_20)                           | 160        | R/W  | Y  |

**表 7-2. 時間コマンド・インターフェイス・サブコマンドの説明<sup>(4)</sup> (continued)**

| インデックス | 説明                                              | データ長 (ビット) | アクセス | EE  |

|--------|-------------------------------------------------|------------|------|-----|

| 10     | 周波数診断ウィンドウ長 (FDIAG_LEN)                         | 4          | 46   | R/W |

|        | 周波数診断開始時間 (FDIAG_START)                         | 4          |      |     |

|        | 周波数診断エラー時間スレッショルド (FDIAG_ERR_TH)                | 3          |      |     |

|        | 飽和診断レベル (SAT_TH)                                | 4          |      |     |

|        | P1 非線形スケーリング (P1_NLS_EN)                        | 1          |      |     |

|        | P2 非線形スケーリング (P2_NLS_EN)                        | 1          |      |     |

|        | 電源過電圧シャットダウン・スレッショルド (VPWR_OV_TH)               | 2          |      |     |

|        | スリープ・モード・タイマ (LPM_TMR)                          | 2          |      |     |

|        | 電圧診断スレッショルド (FVOLT_ERR_TH)                      | 3          |      |     |

|        | AFE ゲイン範囲 (AFE_GAIN_RNG)                        | 2          |      |     |

|        | 低消費電力モード・イネーブル (LPM_EN)                         | 1          |      |     |

|        | 時間および温度のデカップリング選択 (DECPL_TEMP_SEL)              | 1          |      |     |

|        | 時間および温度のデカップリング値 (DECPL_T)                      | 4          |      |     |

|        | 電流制限ディセーブル (DIS_CL)                             | 1          |      |     |

| 11     | 予約済み                                            | 1          | 8    | R/W |

|        | プリセット 1 ドライバ電流制限 (CURRENT_LIM1)                 | 6          |      |     |

|        | プリセット 2 ドライバ電流制限 (CURRENT_LIM2)                 | 6          |      |     |

|        | エコー・データ・ダンプ・イネーブル (DATADUMP_EN)                 | 1          |      |     |

|        | EEPROM プログラミング・パスワード (0xD)                      | 4          |      |     |

|        | EEPROM プログラミング成功 (EE_PRGM_OK)                   | 1          |      |     |

|        | EEPROM 再ロード (EE_RLOAD)                          | 1          |      |     |

|        | EEPROM プログラム (EE_PRGM)                          | 1          |      |     |

| 12     | エコー・データ・ダンプ値 <sup>(2)</sup>                     | 1024       | R    | N   |

| 13     | EEPROM ユーザー・パルク・コマンド (0x00~0x2B) <sup>(3)</sup> | 352        | R/W  | Y   |

| 14     | 予約済み                                            |            |      |     |

| 15     | EEPROM CRC 値 (EE_CRC)<br>THR_CRC 値 (THR_CC)     | 16         | R    | Y   |

(1) スレッショルド・レベルのオフセット・パラメータ (TH\_Px\_OFF) を含みます。

(2) エコー・ダンプ・メモリは、128 サンプル、8 ビット/サンプルの配列です。

(3) インデックス 13 については、バイト 0x2B は読み取り専用です。インデックス 13 書き込みコマンドを送信する場合、バイト 2B のデータ・フィールドは、EE\_CRC 値に影響を与えません。

(4) この表で使用されている略語 (たとえば、CURRENT\_LIM1) は、[レジスタ・マップ](#) セクションで使用されている略語と同じです。

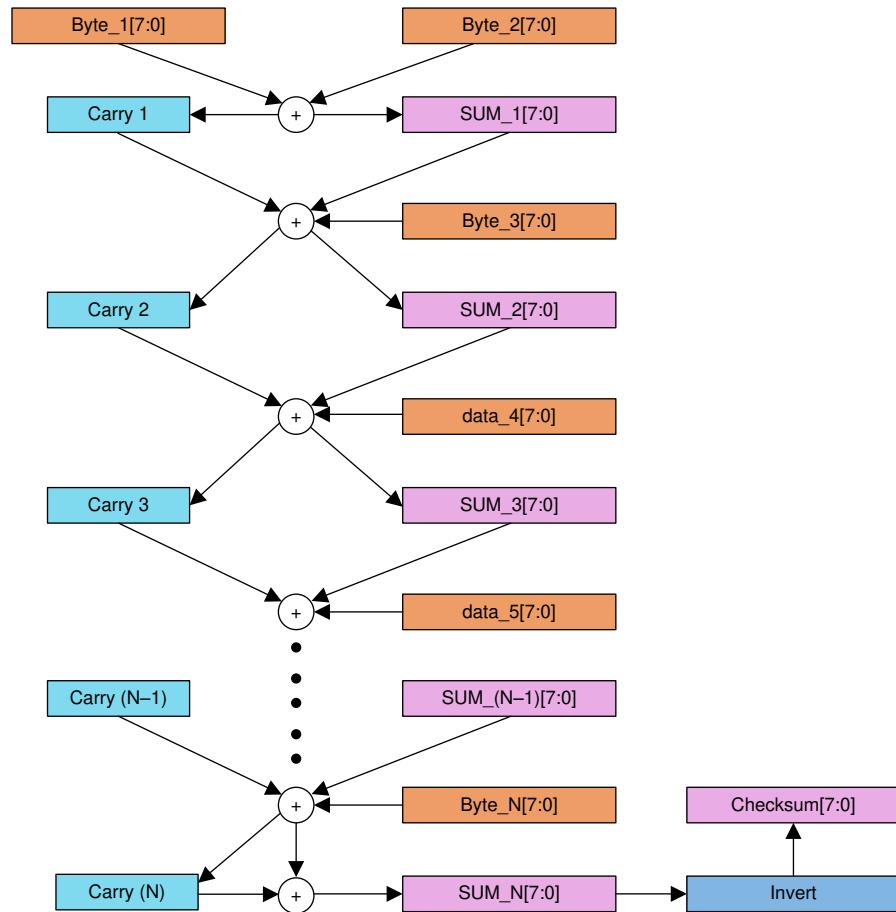

フレーム・チェックサム値は、コントローラ・デバイスでもペリフェラル・デバイスでも生成され、データ・フィールドの後に追加されます。この値は、フレーム内のすべてのビットに対するキャリオーバー (桁上がり) を伴う 8 ビット合計を反転したものです。チェックサム計算は、最上位ビット (MSB) からバイト単位で実行されます。この MSB は、PGA460 書き込み動作時には読み取り-書き込み (R/W) ビットであり、PGA460 読み取り動作時にはデータ・フィールドの MSB です。チェックサム・フィールドの計算対象となるビット数が 8 の倍数でない場合、最も近い 8 の倍数になるまで、後にゼロ・パディング (ゼロ埋め) してチェックサム演算を行います。ゼロ・パディングは、チェックサム計算にのみ必要とされるものです。ゼロ・パディングのビットは、IO-TCI インターフェイス経由で実際には送信しないでください。

次の例は、サブコマンド・インデックス 7 (42 データ・ビット) の PGA460 書き込み動作を示すフレーム・チェックサム計算の 1 つの例です。

- チェックサム生成対象の合計ビット数: 1 R/W ビット、4 ビット・インデックス値、42 ビット・データ値。合計ビット数は 47 です。

- チェックサムはバイト単位で計算されるため、6 フル・バイトを実現するために、末尾に 1 個のゼロが追加されます。

- 図 7-17 に、加算によるチェックサム計算を示します。

次の例は、サブコマンド・インデックス 8 の PGA460 読み取り動作を示すフレーム・チェックサム計算の 2 番目の例です。

- PGA460 デバイスによるチェックサム生成対象の合計ビット数: 56 ビット・データ値 + 8 コマンド・ビット。合計ビット数は 64 です。

- 8 コマンド・ビットは、4 ゼロ・ビット + インデックス[3:0] = 8 コマンド・ビットであり、チェックサム計算で使用される最初のバイトです。

- ビット数がすでに 56 であり、すなわち 7 バイトであるため、後続のゼロは追加されません。

- 図 7-17 に、加算によるチェックサム計算を示します。

図 7-17. チェックサム計算

さらに、PGA460 デバイスは、PGA460 書き込み動作が発行されたときに、正しいデータ転送が行われたことを示すアクノリッジ・ビット応答を実装しています。この場合、構成 / ステータス・コマンドの期間が正しく検出されないと、PGA460 デバイスは、アクノリッジ・ビットを発行します。構成 / ステータス・コマンドの期間が正しく検出されたにもかかわらず、転送されたフレームのチェックサムが正しくない場合、PGA460 デバイスは、論理 0 アクノリッジを送信します。構成 / ステータス・コマンドの期間が正しく検出されて、チェックサム値が正しいチェックサムと一致した場合、PGA460 デバイスは、論理 1 アクノリッジを送信します。

ビット的な通信を実施しているとき (PGA460 が構成 / ステータス・コマンドをアクティブに処理中) に、ビット・ストリームが別の時間コマンド (実行または構成のいずれか) によって中断されると、PGA460 デバイスは、このイベントをビット時間イベントとしてデコードします。この場合、元の構成 / ステータス・コマンドの実行は、タイムアウト・エラー・イベントに達するまで継続されます。または、連続データ転送の場合には、誤って転送されたフレームが PGA460 フレーム・チェックサムによって無効になります。ビット・ストリームが有効であるが想定よりも長い場合、PGA460 は、正しく転送されたフレームに基づいて実行し、残りのビット・ストリームは無視されます。

PGA460 アイドル状態のとき、パルス持続時間がいづれかのコマンドの制限値を外れた時間コマンドを受信した場合、この条件は無視されて、PGA460 デバイスは、有効な時間コマンドを受信するまでアイドル状態を維持します。この場合、PGA460 は、論理 0 アクノリッジを返しません。

### 7.3.6.2 USART インターフェイス

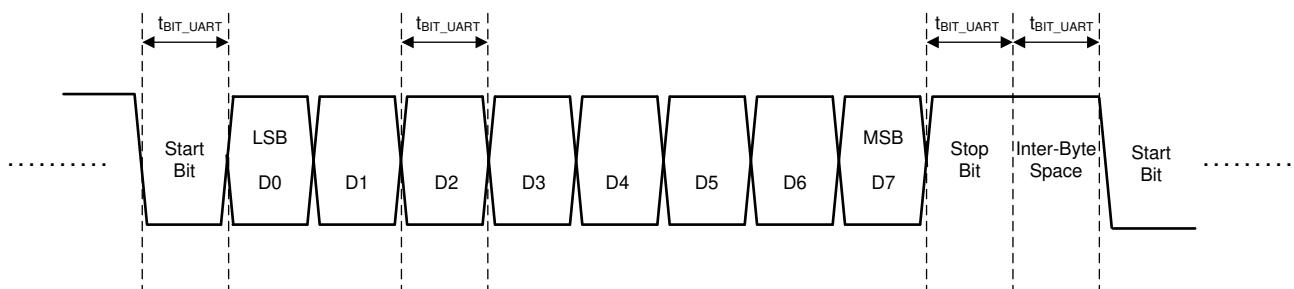

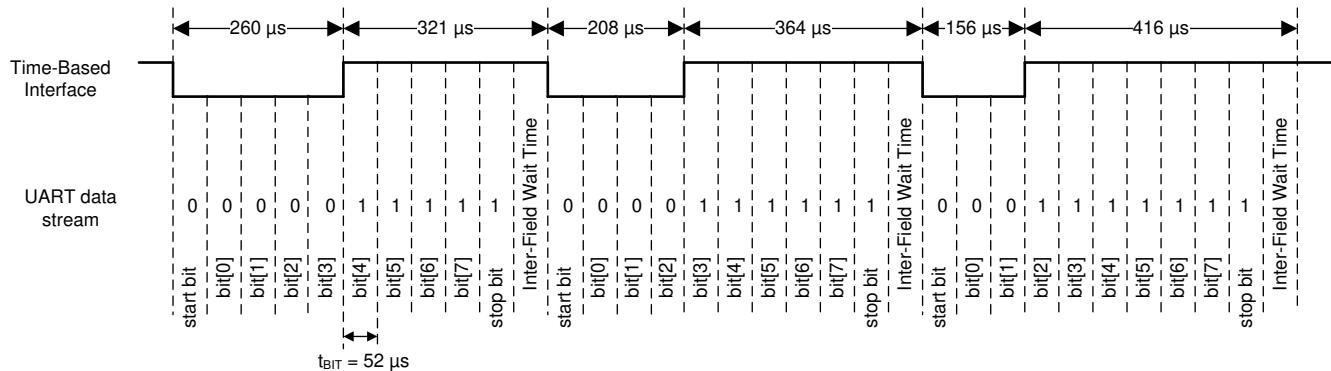

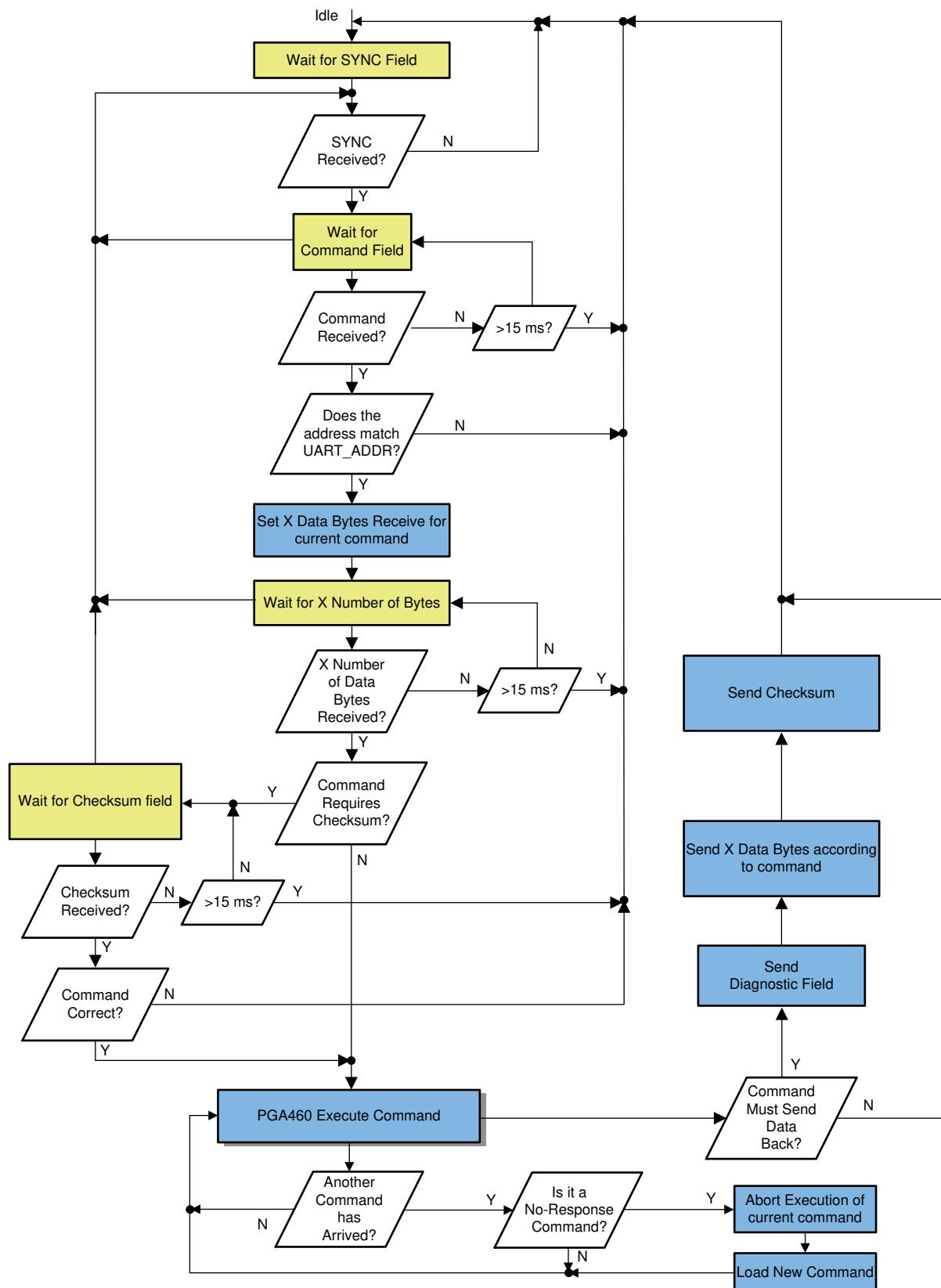

#### 7.3.6.2.1 USART 非同期モード

PGA460 デバイスには、USART デジタル通信インターフェイスが搭載されています。USART の主な機能は、USART アクセスが可能なすべてのアドレスに対して、書き込みおよび読み出しを可能にすることです。この機能には、PGA460 デバイス上のほとんどの EEPROM レジスタおよび RAM レジスタ・メモリへのアクセスが含まれます。USART 非同期モード (UART) デジタル通信は、PGA460 がペリフェラル・デバイスのみとなるコントローラ・ペリフェラル通信リンクです。コントローラは、データ送信の開始と終了を設定します。コントローラからコマンドが発行されるまで、ペリフェラルはコントローラにデータを送信しません。UART インターフェイスの論理 1 の値は、リセシシブ値 (RXD ピンの弱いプルアップ) として定義されます。UART インターフェイスの論理 0 の値は、ドミナント値 (RXD ピンの強いプルダウン) として定義されます。

PGA460 の UART 非同期モード・インターフェイスは、2400bps～115200bps のデータ・レートで動作するように設計されており、コントローラによって生成される同期フィールドに基づいてデータ・レートが自動的に検出されます。UART インターフェイスの動作に関連するその他のパラメータには、次のものがあります。

- 2400bps～115200bps のボーレート、自動検出 (前述のとおり)

- 8 データ・ビット

- 1 スタート・ビット

- 2 ストップ・ビット

- パリティ・ビットなし

- フロー制御なし

- フィールド間の待機時間 (1 ストップ・ビット必要)

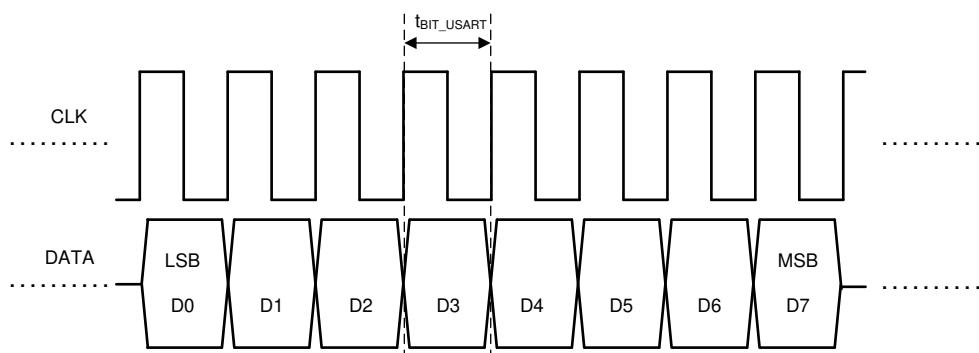

図 7-18. USART 非同期インターフェイスのビット・タイミング

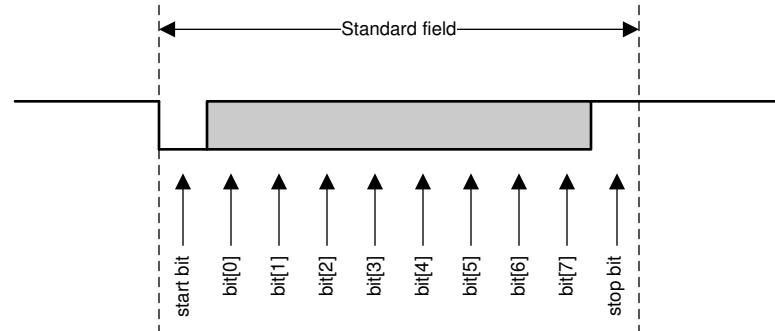

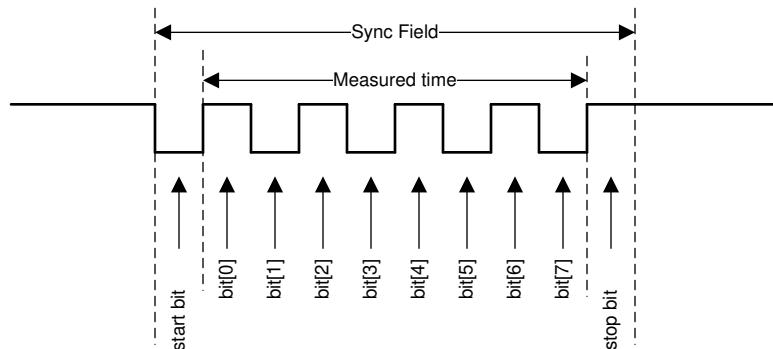

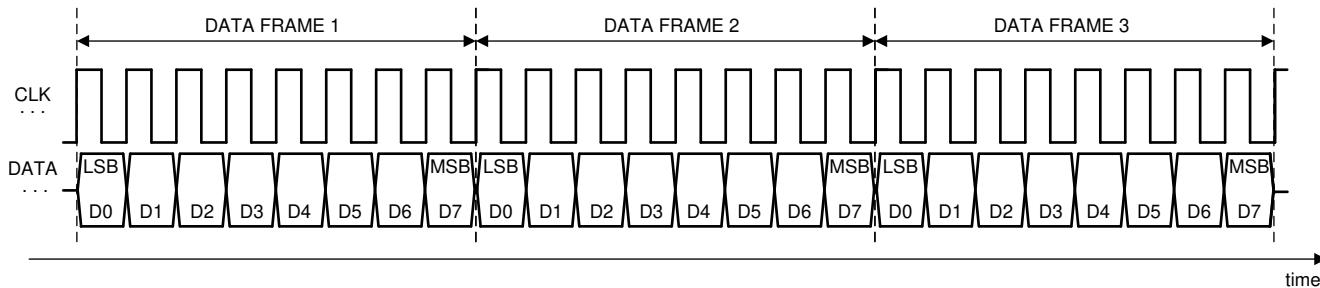

図 7-18 に、USART 非同期モードのビット・タイミングを示します。データおよび制御は、いずれもリトル・エンディアン形式です。データは、バイトサイズのパケットで UART を通って伝送されます。パケット・フィールドの最初のビットは、スタート・ビット (ドミナント) です。フィールドの次の 8 ビットは、UART レシーバで処理されるデータビットです。フィールドの最後のビットは、ストップ・ビットです。情報の組み合わせバイトと、スタート・ビットおよびストップ・ビットによって、UART フィールドが構成されます。図 7-19 に、UART インターフェイス・フィールドの標準的なフィールド構造を示します。

図 7-19. UART インターフェイス・パケット・フィールド

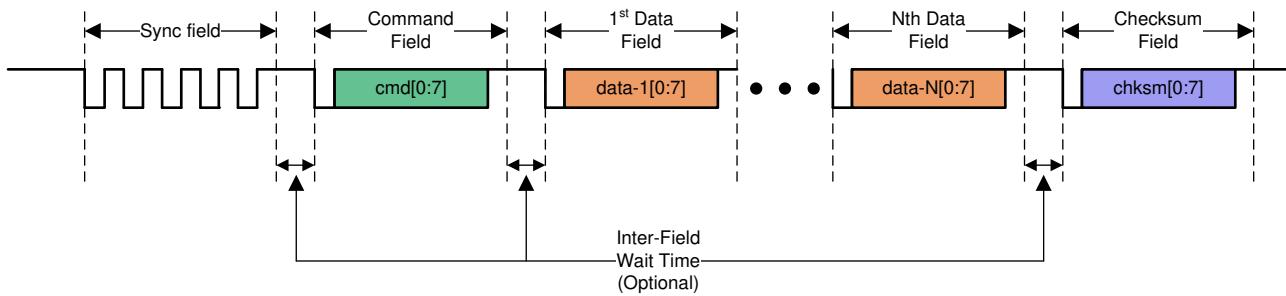

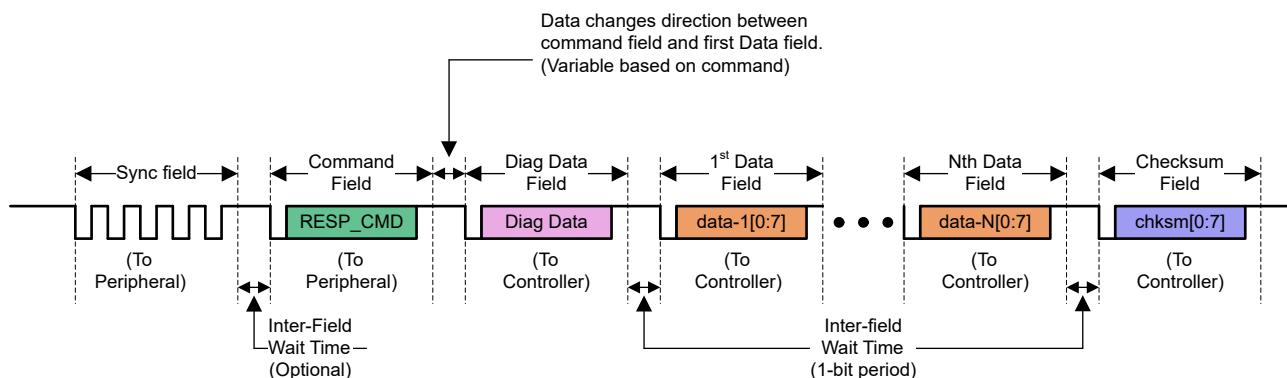

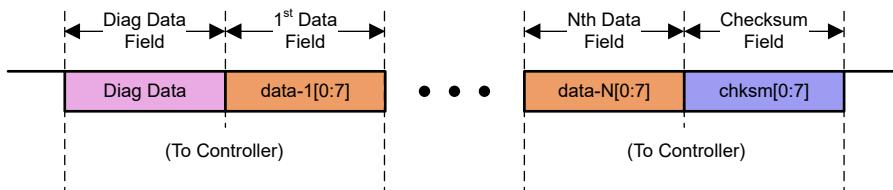

フィールドのグループにより、伝送フレームが構成されます。伝送フレームは、UART インターフェイス上で 1 つの伝送動作を完了するために必要なフィールドで構成されます。図 7-20 に、伝送フレーム内のデータ送信動作の構造を示します。

図 7-20. UART インターフェイスの伝送フレーム

それぞれの伝送フレームには、同期フィールドとコマンド・フィールドが必要で、その後にいくつかのデータ・フィールドが続きます。同期フィールドとコマンド・フィールドは、常にコントローラから送信されます。データ・フィールドは、コマンド・フィールドに指定されているコマンドに応じて、コントローラまたはペリフェラルのいずれかにより送信されます。コマンド・フィールドによって、データ・フィールドの移動方向 (コントローラからペリフェラルへ、またはペリフェラルからコントローラへ) が決まります。伝送されるデータ・フィールドの数も、コマンド・フィールドのコマンドによって決まります。フィールド間待機時間は 1 ビットの長さで、ペリフェラルまたはコントローラが受信したデータを処理するために、または、コマンド・フィールドの送信後にデータの方向を変更してペリフェラルがコントローラにデータを送信する場合に必要です。コントローラおよびペリフェラルの信号ドライバが方向を変更するために、時間を確保する必要があります。UART が論理 0 または論理 1 の状態で 15ms を超えてアイドルのまま維持されると、PGA460 の通信はリセットされ、コントローラから次のデータ伝送の同期フィールドが送られるのを待ちます。

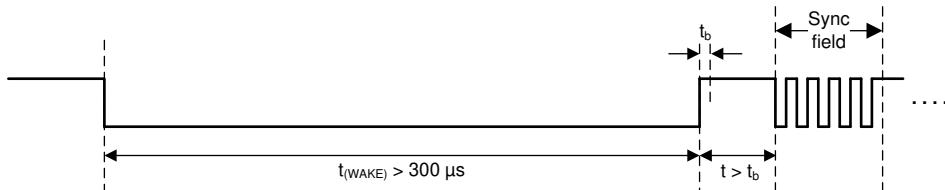

### 7.3.6.2.1.1 同期フィールド

同期フィールドは、マスタから伝送されるすべてのフレームについて、最初のフィールドです。PGA460 デバイスは、同期フィールドを使って、コントローラが送信するフレームの正しいボーレートを確認します。このビット幅は、マスタにより伝送される以後のフィールドすべてを正確に受信するために使用します。ビット幅は、コントローラから送信されるデータの 1 つのビットを構成する、内部発振器クロック周期の数として定義されます。このビット幅は、同期フィールド・データの長さ全体でペリフェラル発振器のクロック数をカウントし、8 で除算することで測定されます。図 7-21 に、同期フィールドの形式を示します。

図 7-21. UART 同期フィールド

スタート・ビットとストップ・ビットを含めて、連続した同期フィールド・ビットを測定し、比較することによって、有効な同期フィールドが PGA460 デバイスに送信されているかどうかを判定します。同期フィールドで連続するいずれかの 2 ビットについて、ビット幅の差異が  $\pm 25\%$  を超える場合、PGA460 デバイスは、UART フレームの以後の部分を無視します。すなわち、PGA460 デバイスは、その UART メッセージに反応しません。

#### 7.3.6.2.1.2 コマンド・フィールド

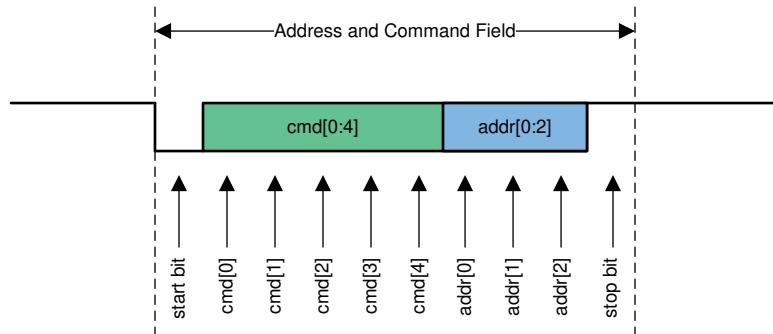

コマンド・フィールドは、マスターから送信される各フレームの中で 2 番目のフィールドです。コマンド・フィールドには、特定の PGA460 デバイスへ伝送されるデータについて、デバイスがそのデータをどのように扱うべきか、そのデータをどこへ送信すべきかという命令が収容されています。コマンド・フィールドでは、読み取り操作で、データをコントローラへ送り返すように PGA460 デバイスへ指示することもできます。伝送されるデータ・フィールドの数も、コマンド・フィールドのコマンドにより決定されます。図 7-22 は、コマンド・フィールドのフォーマットを示したものです。

図 7-22. UART コマンド・フィールド

PGA460 デバイスでは、コマンド・フィールドの最後の 3 ビットは UART アドレス情報用に予約されています。コマンド・フィールドのアドレス情報は、UART アドレスが書き込まれている EEPROM メモリの UART\_ADDR パラメータと比較されます。コマンド・フィールドを受信すると、PGA460 デバイスは、自己のアドレスが受信アドレスと一致しているかどうかを確認します。一致している場合、デバイスは受信したコマンドを実行します。アドレスが一致しない場合、デバイスは受信フレームを無視します。通信効率を向上させるため、共通のブロードキャスト・コマンドが定義されています。これは、コマンド・フィールドのアドレスに関係なく PGA460 デバイスが実行するものです。これらのコマンドおよびすべての UART コマンドについては、表 7-3 を参照してください。

#### 注

PGA460 デバイスの出荷時にあらかじめ書き込まれているアドレスは 0 です。

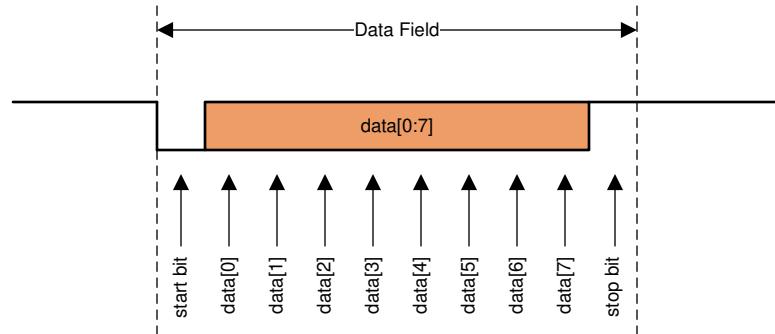

#### 7.3.6.2.1.3 データ・フィールド

コントローラが伝送フレームのコマンド・フィールドを送信した後、ゼロ個以上のデータ・フィールドが PGA460 デバイスへ(書き込み動作の場合)またはコントローラへ(読み出し動作の場合)送信されます。データ・フィールドには、生のメモリ・

データまたはコマンドに関連するパラメータが入ります。データのフォーマットは、コマンド・フィールドのコマンドにより決定されます。図 7-23 は、データ・フィールドの代表的なフォーマットを示したものです。

図 7-23. UART データ・フィールド

#### 7.3.6.2.1.4 チェックサム・フィールド

チェックサム・フィールドは、各 UART フレームの最後のフィールドとして送信されます。チェックサムは、すべてのデータ・フィールドとコマンド・フィールド (コントローラのみのコマンド・フィールド) をキャリー (桁上がり) 付きでバイト加算した結果を反転した値です。コントローラから PGA460 への転送では、チェックサム・フィールドはコントローラによって計算され、PGA460 デバイスによってチェックされます。PGA460 からコントローラへの転送では、PGA460 デバイスがチェックサムを生成し、コントローラがその整合性を検証します。チェックサムのフォーマットは、データ・フィールドと同じであり、チェックサムを計算する手順については [時間コマンド・インターフェイス](#)セクションで説明します。UART インターフェイスは、バイトを基準としたインターフェイスであるため、チェックサムの計算プロセスでゼロ・パディングは発生しません。

コントローラがチェックサム・フィールドを計算するときには、UART コマンド・フィールドから計算が開始され、それに続いて、現在の通信フレームの一部として送信されるすべての UART データ・フィールドが計算の対象となります。PGA460 デバイスがチェックサム・フィールドを計算する場合、その計算には、診断データ・フィールド ([診断フィールド](#) セクションを参照) と、現在のフレーム内のすべての UART データ・フィールドが含まれます。SYNC フィールド (0x55) は、チェックサム計算の対象に含まれていません。

#### 7.3.6.2.1.5 PGA460 UART コマンド

表 7-3 に、PGA460 UART コマンドの一覧を示します。

##### 注

誤ったコマンド、誤ったバイト数、誤ったデータ・バイト値など、何らかのコマンドが PGA460 デバイスで不適切に受信された場合、PGA460 デバイスは受信したコマンドを実行しません。また、[診断フィールド](#) セクションで説明されている Error\_Status[4] ビットを設定します。

表 7-3. UART インターフェイスのコマンド・リスト

| CMD[4:0]      | コマンド名                | PGA460 応答 | C から P へのデータ・バイト数 | コントローラ (C) からペリフェラル (P) へのデータ・バイトの説明 | P から C へのデータ・バイト数 | ペリフェラル (P) からコントローラ (C) へのデータ・バイトの説明 |

|---------------|----------------------|-----------|-------------------|--------------------------------------|-------------------|--------------------------------------|

| <b>单一アドレス</b> |                      |           |                   |                                      |                   |                                      |

| 0             | バーストおよびリスン (プリセット 1) | なし        | 1                 | バイト 1:N - 検出する物体の数<br>(有効範囲は 1 ~ 8)  | 0                 |                                      |

| 1             | バーストおよびリスン (プリセット 2) | なし        | 1                 |                                      | 0                 |                                      |

| 2             | リスン・オンリー (プリセット 1)   | なし        | 1                 |                                      | 0                 |                                      |

| 3             | リスン・オンリー (プリセット 2)   | なし        | 1                 |                                      | 0                 |                                      |

**表 7-3. UART インターフェイスのコマンド・リスト (continued)**

| <b>CMD[4:<br/>0]</b> | コマンド名                              | <b>PGA460<br/>応答</b> | <b>C から P へ<br/>の<br/>データ・バイ<br/>ト数</b> | コントローラ (C) からペリフェラ<br>ル (P) へのデータ<br>バイトの説明                     | <b>P から C へ<br/>の<br/>データ・バイ<br/>ト数</b> | ペリフェラル (P) からコントローラ<br>(C) へのデータ<br>バイトの説明                                                                                                                                                                                                   |

|----------------------|------------------------------------|----------------------|-----------------------------------------|-----------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                    | 温度およびノイズレベル測定                      | なし                   | 1                                       | バイト 1:0 - 温度測定<br>1 - ノイズ測定<br>2~255 - 未使用                      | 0                                       |                                                                                                                                                                                                                                              |

| 5                    | 超音波測定結果 <sup>(4) (5)</sup>         | あり                   | 0                                       |                                                                 | 4 × N                                   | バイト 1~バイト 2: 物体 1 のタイ<br>ム・オブ・フライト (μs) (MSB, LSB)<br>バイト 3: 物体 1 の幅<br>バイト 4: 物体 1 のピーク振幅<br>.<br>.<br>バイト (3 × N - 3)~バイト (3 × N -<br>2): 物体 N のタイム・オブ・フライト<br>(μs) (MSB, LSB)<br>バイト (4 × N - 1): 物体 N の幅<br>バイト (4 × N): 物体 N のピーク振<br>幅 |

| 6                    | 温度およびノイズ・レベル<br>の結果                | あり                   | 0                                       |                                                                 | 2                                       | バイト 1: 温度の値<br>バイト 2: ノイズ・レベルの値                                                                                                                                                                                                              |

| 7                    | トランスマルチキャストのエコー・<br>データ・ダンプ        | あり                   | 0                                       |                                                                 | 128                                     | バイト 1~バイト 128: エコー・デー<br>タ・ダンプ (128 サンプルの配列)                                                                                                                                                                                                 |

| 8                    | システム診断 <sup>(3)</sup>              | あり                   | 0                                       |                                                                 | 2                                       | バイト 1: トランスマルチキャスト周波数<br>バイト 2: 減衰時間                                                                                                                                                                                                         |

| 9                    | レジスタ読み出し                           | あり                   | 1                                       | バイト 1: レジスタ・アドレス                                                | 1                                       | バイト 1: レジスタ・データ                                                                                                                                                                                                                              |

| 10                   | レジスタ書き込み <sup>(2)</sup>            | なし                   | 2                                       | バイト 1: レジスタ・アドレス<br>バイト 2: レジスタ・データ                             | 0                                       |                                                                                                                                                                                                                                              |

| 11                   | EEPROM バルク読み取り                     | あり                   | 0                                       |                                                                 | 43                                      | バイト 1: USER_DATA1 データ<br>.<br>.<br>バイト 43: P2_GAIN_CTRL デー<br>タ                                                                                                                                                                              |

| 12                   | EEPROM バルク書き込み <sup>(1)</sup>      | なし                   | 43                                      | バイト 1: USER_DATA1 データ<br>.<br>.<br>バイト 43: P2_GAIN_CTRL デ<br>ータ | 0                                       |                                                                                                                                                                                                                                              |

| 13                   | 時変ゲインのバルク読み<br>取り                  | あり                   | 0                                       |                                                                 | 7                                       | バイト 1~バイト 6: TVGAIN0~<br>TVGAIN6 データ                                                                                                                                                                                                         |

| 14                   | 時変ゲインのバルク書き込<br>み <sup>(1)</sup>   | なし                   | 7                                       | バイト 1~バイト 6: TVGAIN0~<br>TVGAIN6 データ                            | 0                                       |                                                                                                                                                                                                                                              |

| 15                   | スレッショルドのバルク読み<br>取り                | あり                   | 0                                       |                                                                 | 32                                      | バイト 1~バイト 32: P1_THR_0~<br>P2_THR_15 データ                                                                                                                                                                                                     |

| 16                   | スレッショルドのバルク書き<br>込み <sup>(1)</sup> | なし                   | 32                                      | バイト 1~バイト 28: 1_THR_0<br>~2_THR_15 データ                          | 0                                       |                                                                                                                                                                                                                                              |

| プロードキャスト             |                                    |                      |                                         |                                                                 |                                         |                                                                                                                                                                                                                                              |

| 17                   | バーストおよびリスン (プリ<br>セット 1)           | なし                   | 1                                       | バイト 1:N - 検出する物体の数<br>(有効範囲は 1 ~ 8)                             | 0                                       |                                                                                                                                                                                                                                              |

| 18                   | バーストおよびリスン (プリ<br>セット 2)           | なし                   | 1                                       |                                                                 | 0                                       |                                                                                                                                                                                                                                              |

| 19                   | リスン・オンリー (プリセット<br>1)              | なし                   | 1                                       |                                                                 | 0                                       |                                                                                                                                                                                                                                              |

| 20                   | リスン・オンリー (プリセット<br>2)              | なし                   | 1                                       |                                                                 | 0                                       |                                                                                                                                                                                                                                              |

表 7-3. UART インターフェイスのコマンド・リスト (continued)

| CMD[4:0] | コマンド名                         | PGA460<br>応答 | C から P へ<br>の<br>データ・バイ<br>ト数 | コントローラ (C) からペリフェラ<br>ル (P) へのデータ<br>バイトの説明              | P から C へ<br>の<br>データ・バイ<br>ト数 | ペリフェラル (P) からコントローラ<br>(C) へのデータ<br>バイトの説明 |

|----------|-------------------------------|--------------|-------------------------------|----------------------------------------------------------|-------------------------------|--------------------------------------------|

| 21       | 温度およびノイズレベル測定                 | なし           | 1                             | バイト 1:0 - 温度測定<br>1 - ノイズ測定<br>2~255 - 未使用               | 0                             |                                            |

| 22       | レジスタ書き込み <sup>(2)</sup>       | なし           | 2                             | バイト 1:レジスタ・アドレス<br>バイト 2:レジスタ・データ                        | 0                             |                                            |

| 23       | EEPROM バルク書き込み <sup>(1)</sup> | なし           | 43                            | バイト 1:USER_DATA1 データ<br>.<br>バイト 43:P2_GAIN_CTRL デ<br>ータ | 0                             |                                            |

| 24       | 時変ゲインのバルク書き込み <sup>(1)</sup>  | なし           | 7                             | バイト 1~バイト 6:TVGAIN0~<br>TVGAIN6 データ                      | 0                             |                                            |

| 25       | スレッショルドのバルク書き込み               | なし           | 32                            | バイト 1~バイト 32:1_THR_0<br>~2_THR_15                        | 0                             |                                            |

| 26~31    | 予約済み                          | なし           |                               |                                                          |                               |                                            |

- (1) コマンド 12、14、16、23、24、25 の場合: 50 $\mu$ s 待ってから、読み取りコマンドを発行してください。

- (2) コマンド 10 および 22 の場合: INIT\_GAIN、TVG、THR、P1\_GAIN\_CTRL または P2\_GAIN\_CTRL に書き込んだ後は、60 $\mu$ s 待ってから読み取りを行ってください。それ以外の場合は、3.3 $\mu$ s 待ってから他の機能を実施してください。

- (3) 実行コマンドの前にコマンド 8 を発行した場合、読み出されるデータの値は無効です。

- (4) エコー・データ・ダンプ・ビットがイネーブルの間にコマンド 5 を実行した場合、読み出されるデータの値は、無効または古いものです。この状態では、エコー・データ・ダンプ・メモリにデータが収集されるだけです。または、バーストおよびリスン・コマンドもしくはリスン・オンリー・コマンドによってスレッショルド・コンパレータを使用できます。

- (5) 物体のタイムオブフライ (μs 単位) をメートル単位の距離に変換する式は次のとおりです。距離(m) = [音速 × (MSB<<8 + LSB) ÷ 2 × 1μs]。バーストおよびリスンの精度を向上させるには、最初に計算された距離に、追加のバースト・オフセットを加算します。距離バースト・オフセット (m) = [音速 × (パルス / 周波数) ÷ 2]。一般的に、音速は、室温で 343m/s と想定されます。周囲温度に応じて、音速を調整します。音速 = 331m/s + (0.6m/s/°C × 温度 (°C))

### 7.3.6.2.1.6 UART の動作

#### 7.3.6.2.1.6.1 無応答動作

UART インターフェイスでの無応答動作は、かなり単純です。コマンド・フィールドは、動作のアドレスとコマンドを指定します。その後にデータ・バイトがある場合は、そのバイトを PGA460 デバイスに格納します。送信されるデータ・バイトの数は、UART コマンドによってあらかじめ決まっています。フレームの最後のフィールドは、コントローラによって生成されるチェックサム・フィールドです。図 7-24 に、メモリ・レジスタの書き込み動作の例を示します (コマンド 10)。

図 7-24. UART 無応答の例

### 注

UART インターフェイスに無応答コマンドが到着したときに、別の無応答コマンドを処理している途中であった場合、または PGA460 デバイスが機能を実行しているビジー状態であった場合には、前のコマンドは中止され、新しいコマンドが直ちに処理されます。コマンド 0～コマンド 4 またはコマンド 17～コマンド 21 のいずれかを以前に受信して、PGA460 デバイスが記録期間の処理中であるときに UART で他のコマンドを受信した場合、この処理は特に重要です。この場合、PGA460 デバイスは前のコマンドを中止して現在の記録期間を終了させ、新しいコマンドを処理するサイクルを開始します。

#### 7.3.6.2.1.6.2 応答動作(レジスタ読み取りを除くすべて)

PGA460 UART インターフェイスの応答動作は、コントローラが応答要求を送信することで開始されます。応答要求を PGA460 デバイスが受信した後、UART は、そのコマンドで要求されている適切なデータで応答します。応答動作では、コントローラはチェックサム・フィールドを生成せず、PGA460 が生成します。

### 注

データの方向が変化すること(コントローラから PGA460 へ、その後 PGA460 からコントローラへ)、および PGA460 デバイスが応答するのに要する処理時間があることにより、応答要求と PGA460 の UART の応答との間に 1 ビット分の応答遅延時間が発生します。

図 7-25 に、PGA460 応答動作の例を示します。

図 7-25. UART 応答の例

#### 7.3.6.2.1.6.3 応答動作(レジスタ読み取り)

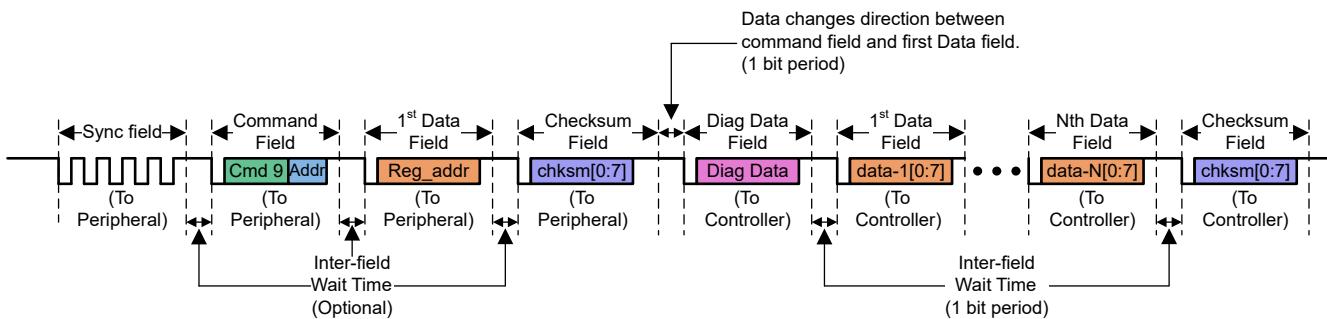

レジスタ読み取りコマンドでは、コントローラが PGA460 メモリ内のレジスタ・アドレスを指定する必要があるため、別のフレーム・タイプが定義されています。まず、コントローラが SYNC およびコマンド・フィールドを発行します。次に、コントローラ・フレームの中で 1 バイトだけのフィールドとしてメモリ・レジスタ・アドレスを発行し、最後のフィールドとしてコントローラ・チェックサムを発行します。コントローラからペリフェラルへの転送後、PGA460 デバイスは、標準の PGA460 応答動作フレームで応答します。この動作を 図 7-26 に示します。

図 7-26. UART レジスタ読み取り応答の例

## 注

UART インターフェイスに応答コマンドが到着したときに、別の無応答コマンドを処理している途中であった場合、または PGA460 デバイスが機能を実行しているビジー状態であった場合には、PGA460 デバイスは、エラー・ステータスが 0 となっている診断フィールド（[診断フィールド](#) セクションを参照）で応答します。これは、デバイスが機能を実行しているビジー状態であることを示します。応答コマンドが到着したときに、PGA460 が別の応答コマンドを処理している途中であった場合、PGA460 デバイスは、前の応答コマンドの処理が完了するまで、新しい応答コマンドを無視します。

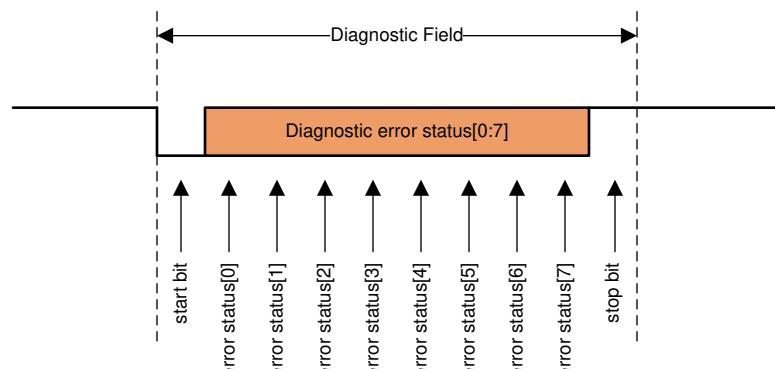

## 7.3.6.2.1.7 診断フィールド

[応答動作（レジスタ読み取り）](#) セクションで説明しているように、PGA460 デバイスは、診断データ・フィールドから応答送信を開始します。このフィールドには、UART 通信エラー・ビットが含まれています。特定のビットが 1 に設定されている場合、対応する通信エラーが、直前の応答動作と現在の応答動作の間に発生した可能性があります。応答動作を実行した後、通信エラー・ビットはクリアされます。診断フィールドは、ペリフェラルによって生成されるチェックサム計算に含まれます。[図 7-27](#) に、診断データ・フィールドを示します。

図 7-27. UART 診断データ・フィールド

[表 7-4](#) に、診断データのエラー・ステータス・ビットを示します。

診断フィールドのエラー・ステータス [7:6] ビットは、01b に設定されているため、ペリフェラルから送信されるビット時間を簡単に測定できます。さらにエラー・ステータスが必要な場合は、これらのビット位置を使用して追加のエラー・ステータスを送信できます。

表 7-4. UART 診断データの説明

| ビット           | UART_DIAG = 0 | UART_DIAG = 1   |

|---------------|---------------|-----------------|

| エラー・ステータス [0] |               | PGA460 デバイス・ビジー |

**表 7-4. UART 診断データの説明 (continued)**