Documents So

JAJSFD2A-MAY 2018-REVISED JUNE 2018

# OPA521 2.5A狭帯域ライン・ドライバ

## 1 特長

- 対応プロトコル:

- CENELECの周波数帯A、B、C、D

- ARIB STD-T84, FCC

- FSK、SFSK、NB-OFDM

- 標準への準拠

- EN50065-1, -2, -3, -7

- FCC, Part 15

- ARIB STD-T84

- 規格

- G3、PRIME、P1901.2、ITU-G.hnem

- 熱および過電流保護機能を内蔵したライン・ドライバ

- 静止電流をピンで選択可能

- スタンバイ・モードで58µA (標準値)

- CENELECの周波数帯A、B、C、Dで51mA (標準値)

- FCC、ARIB STD-T84で78mA (標準値)

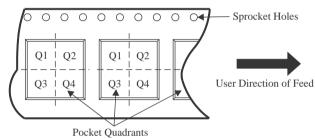

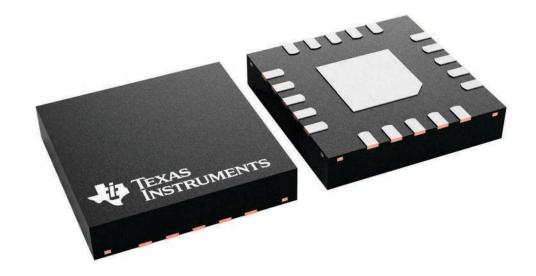

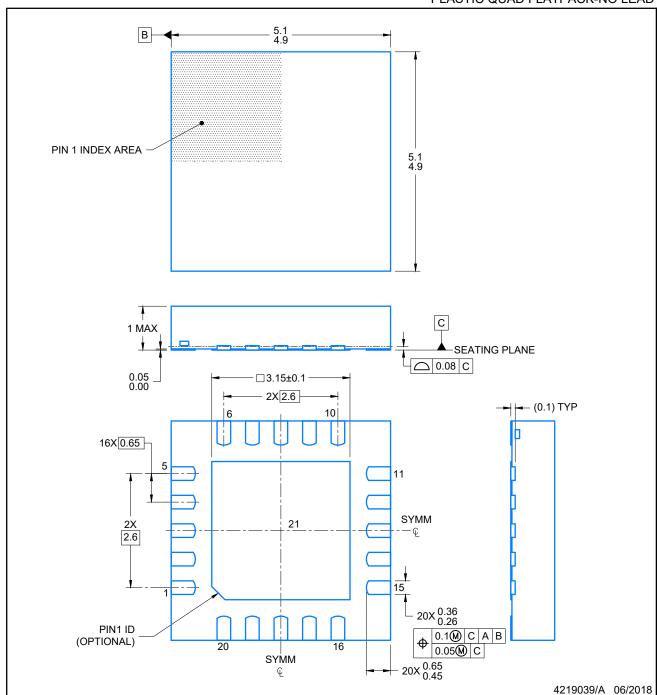

- パッケージ: 5mm×5mmの20ピンVQFN

- 動作時接合部温度範囲:

T<sub>A</sub>=-40℃~+125℃

## 2 アプリケーション

- 電力品質測定器

- 商用ネットワークとサーバーのPSU (電源)

- 照明

- ソーラー・アーク保護

- 集中型インバータ

## 3 概要

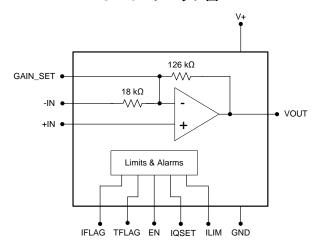

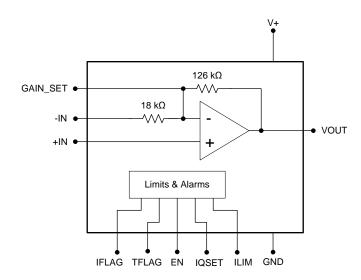

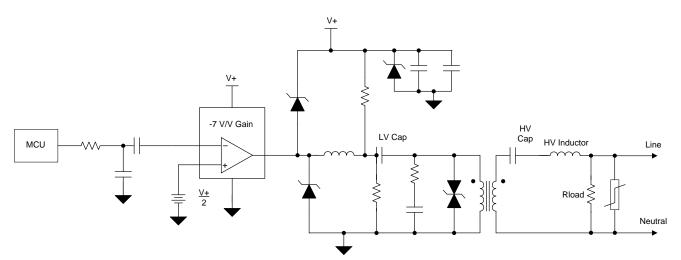

OPA521は、CENELECの周波数帯A、B、C、D、および ARIB STD-T84、FCC Part 15の電力線通信(PLC)伝導 エミッション要件を満たしたライン・ドライバ・パワー・アンプ であり、無効負荷への最大2.5Aの大電流、低インピーダンスのラインを駆動できます。内部保護構造が最適化されているため、外付けの保護部品を最小限に抑え、コスト効果およびスペース効率の高いシステムを実現できます。

OPA521は、3.8MHzの帯域幅で-7V/Vの閉ループ・ゲインを提供します。またモノリシックな集積回路により、電力線通信機器で高い信頼性を実現します。

OPA521ライン・ドライバは、 $7V\sim24V$ の単一電源で動作し、標準的な負荷電流( $I_{OUT}=2.5A$  (最大値))では、広い出力振幅により公称24V電源で $10V_{PP}$ の能力が得られます。

過熱および短絡条件に対する保護機能を備えており、異常検出フラグにより、電流および熱の限度値を示します。 シャットダウン・ピンも用意されているため、低消費電力状態に移行して、消費電流を58µA (標準値)に抑えることができます。

OPA521は表面実装の5mm $\times 5$ mm $\times 20$ ピンVQFN (RGW)パッケージで供給されます。-40 $^{\circ}$  $^{\circ}$  $^{\circ}$  拡張産業用接合部温度範囲で動作可能です。

#### 製品情報(1)

| 型番     | パッケージ     | 本体サイズ(公称)     |

|--------|-----------|---------------|

| OPA521 | VQFN (20) | 5.00mm×5.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

#### OPA521ブロック図

# 目次

| 1 | 特長1                                            |    | 7.4 Device Functional Modes    | 12 |

|---|------------------------------------------------|----|--------------------------------|----|

| 2 | アプリケーション1                                      | 8  | Application and Implementation | 13 |

| 3 | 概要 1                                           |    | 8.1 Application Information    | 13 |

| 4 | 改訂履歴                                           |    | 8.2 Typical Application        | 13 |

| 5 | Pin Configuration and Functions3               | 9  | Power Supply Recommendations   | 18 |

| 6 | Specifications4                                | 10 | Layout                         | 21 |

| • | 6.1 Absolute Maximum Ratings                   |    | 10.1 Layout Guidelines         | 21 |

|   | 6.2 ESD Ratings                                |    | 10.2 Layout Example            | 23 |

|   | 6.3 Recommended Operating Conditions 4         | 11 | デバイスおよびドキュメントのサポート             | 24 |

|   | 6.4 Thermal Information                        |    | 11.1 デバイス・サポート                 | 24 |

|   | 6.5 Electrical Characteristics                 |    | 11.2 ドキュメントのサポート               | 24 |

|   | 6.6 Electrical Characteristics: Digital        |    | 11.3 ドキュメントの更新通知を受け取る方法        | 24 |

|   | 6.7 Electrical Characteristics: Power Supply 6 |    | 11.4 コミュニティ・リソース               | 24 |

|   | 6.8 Typical Characteristics                    |    | 11.5 商標                        | 24 |

| 7 | Detailed Description                           |    | 11.6 静電気放電に関する注意事項             | 24 |

|   | 7.1 Overview                                   |    | 11.7 Glossary                  |    |

|   | 7.2 Functional Block Diagram 11                | 12 | メカニカル、パッケージ、および注文情報            | 24 |

|   | 7.3 Feature Description                        |    |                                |    |

|   |                                                |    |                                |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 20 | 018年5月発行のものから更新    | Page |

|----|--------------------|------|

| •  | 生産データを用いたデータシートの初版 | 1    |

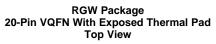

# 5 Pin Configuration and Functions

NC - no internal connection

## **Pin Functions**

| PIN         |                      | 1/0 | DECORPORA                                                                                                                                                         |  |

|-------------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.                  | I/O | DESCRIPTION                                                                                                                                                       |  |

| EN          | 11                   | 1   | Enables the amplifier (active high, high enables the OPA521)                                                                                                      |  |

| GAIN_SET    | 8                    | 1   | Connect an external resistor to Gain_Set and -IN to increase the gain beyond -7 V/V                                                                               |  |

| GND         | 16, 17               | _   | Ground                                                                                                                                                            |  |

| IFLAG       | 13                   | 0   | Current limit warning flag (open-drain, active high, high signifies current limit condition)                                                                      |  |

| ILIM        | 12                   | I   | Resistor programmable current limit                                                                                                                               |  |

| +IN         | 9                    | 1   | Non-inverting input (connect to a voltage equal to (V+)/2)                                                                                                        |  |

| -IN         | 7                    | 1   | Inverting input for closed loop gain = -7 V/V                                                                                                                     |  |

| IQSET       | 15                   | I   | Quiescent current select (active high, high configures the OPA521 to operate in FCC/ARIB bands, low configures the OPA521 to operate in CENELEC Bands A, B, C, D) |  |

| NC          | 2, 3, 4, 5, 6,<br>10 | _   | No internal connection                                                                                                                                            |  |

| TFLAG       | 14                   | 0   | Thermal limit warning flag (open-drain, active high, high signifies thermal limit condition)                                                                      |  |

| V+          | 1, 20                | _   | Positive power supply                                                                                                                                             |  |

| VOUT        | 18. 19               | 0   | Output                                                                                                                                                            |  |

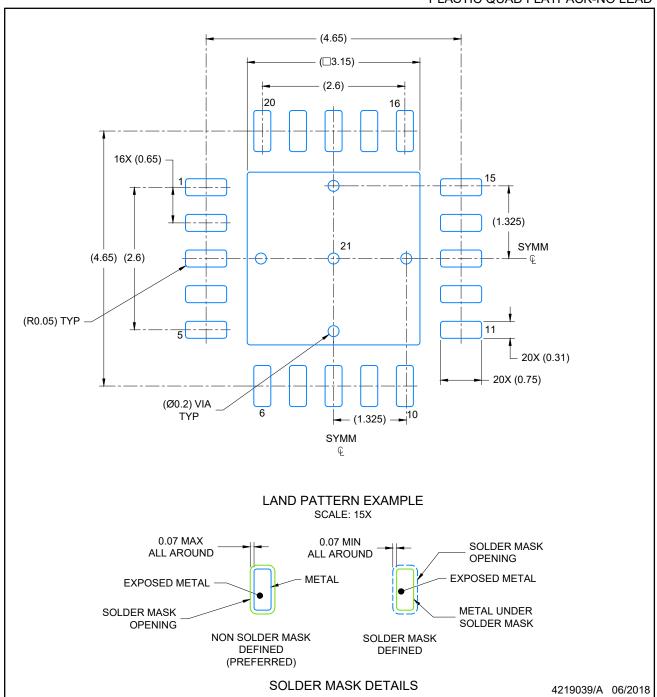

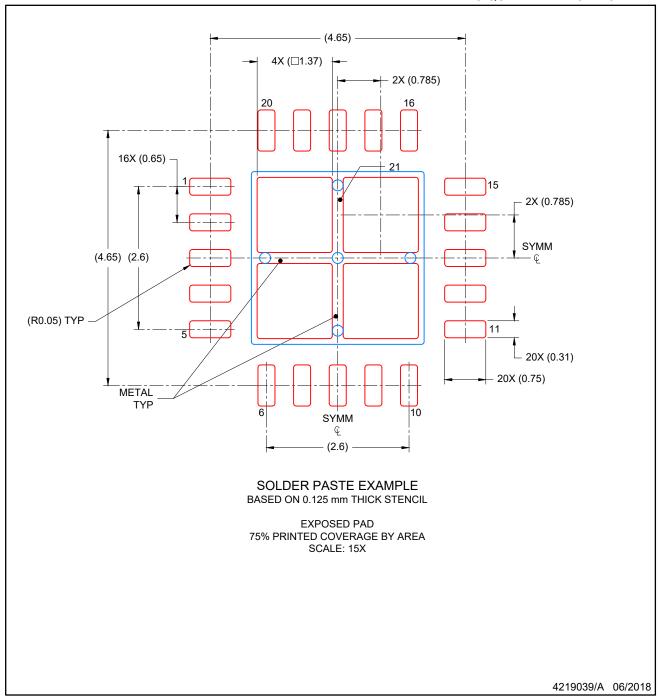

| Thermal pad |                      |     | Must be soldered to PCB and connected to GND                                                                                                                      |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       |                        |                          | MIN         | MAX        | UNIT |

|---------------------------------------|------------------------|--------------------------|-------------|------------|------|

| Supply voltage, V+                    |                        | Pins 1, 20               |             | 26         | V    |

|                                       | Voltage <sup>(2)</sup> | Pins 7, 8, 9, 12         | -0.4        | (V+) + 0.4 | V    |

| Signal input pins                     | voltage (=/            | Pins 11, 15              | -0.4        | 3.3        | V    |

| Current <sup>(2)</sup>                |                        | Pins 7, 8, 9, 11, 12, 15 |             | ±10        | mA   |

|                                       | Voltage                | Pins 18, 19              | -0.4        | (V+) + 0.4 | V    |

| Signal output terminals               |                        | Pins 13, 14              | -0.4        | 3.3        | V    |

| Current; short-circuit to GND         |                        | Pins 13, 14, 18, 19      | Con         | tinuous    |      |

| Operating junction temperature (3)    |                        |                          | -40         | 125        | °C   |

| Storage temperature, T <sub>stg</sub> |                        |                          | <b>–</b> 55 | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                 |                          |                                                                                | VALUE | UNIT |

|-----------------|--------------------------|--------------------------------------------------------------------------------|-------|------|

| \/              |                          | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1500 | V    |

| V <sub>(E</sub> | <sup>SD)</sup> discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                   | MIN | NOM MAX | UNIT |

|-----------------------------------|-----|---------|------|

| Supply voltage, V+                | 7   | 24      | ٧    |

| Output current, DC <sup>(1)</sup> |     | 1.9     | Α    |

| Operating junction temperature    | -40 | 125     | °C   |

<sup>(1)</sup> Under safe operating conditions. See Power Amplifier Stress and Power Handling Limitations safe operating area (SOA) information.

#### 6.4 Thermal Information

|                        |                                              | OPA521    |      |

|------------------------|----------------------------------------------|-----------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RGW (QFN) | UNIT |

|                        |                                              | 20 PINS   |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 33.0      | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 24.4      | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 12.7      | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.3       | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 12.7      | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 3.4       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.4 V beyond the supply rails should be current limited to 10 mA or less.

<sup>(3)</sup> The device automatically goes into shutdown above +140°C junction temperature

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics

At T<sub>CASE</sub> = 25°C, V+ = 15 V, IN+ = (V+) / 2, R<sub>LOAD</sub> = 50  $\Omega$  unless otherwise noted.

|                | PARAMETER                  |                     | TEST CONDITIONS                                        | MIN           | TYP                | MAX                     | UNIT          |

|----------------|----------------------------|---------------------|--------------------------------------------------------|---------------|--------------------|-------------------------|---------------|

| NOISE          |                            |                     |                                                        |               |                    |                         |               |

|                |                            | CEN-A               | 35 kHz to 95 kHz                                       |               | 45                 |                         | $\mu V_{RMS}$ |

|                | -                          | CEN-B               | 95 kHz to 125 kHz                                      |               | 32                 |                         | $\mu V_{RMS}$ |

|                |                            | CEN-C               | 125 kHz to 140 kHz                                     |               | 23                 |                         | $\mu V_{RMS}$ |

|                | Integrated output noise    | CEN-D               | 140 kHz to 148 kHz                                     |               | 16.5               |                         | $\mu V_{RMS}$ |

|                |                            | ARIB STD-T84        | 35 kHz to 420 kHz                                      |               | 114                |                         | $\mu V_{RMS}$ |

|                |                            | FCC-LOW             | 35 kHz to 125 kHz                                      |               | 55                 |                         | $\mu V_{RMS}$ |

|                |                            | G3-FCC              | 150 kHz to 490 kHz                                     |               | 107                |                         | $\mu V_{RMS}$ |

| INPUT          |                            | 1                   |                                                        | T.            |                    |                         |               |

|                | Input voltage rang         | e, IN-              | For linear operation, +IN = V+/2                       | (GND + 0.4)/7 |                    | (V+ -<br>0.4)/7         | V             |

|                | Input impedance            |                     |                                                        |               | 18                 |                         | kΩ            |

| FREQUE         | NCY RESPONSE               |                     |                                                        |               |                    |                         |               |

| BW             | Bandwidth                  |                     | I <sub>LOAD</sub> = 0 mA                               |               | 3.82               |                         | MHz           |

| SR             | Slew rate                  |                     | V+ = 24 V, V <sub>OUT</sub> = 20-V step                |               | 75                 |                         | V/µs          |

|                | Full-power bandw           | idth                | V+ = 24 V, V <sub>OUT</sub> = 15 V <sub>PP</sub>       |               | 800                |                         | kHz           |

| DODD           |                            |                     | RTI, DC                                                | 80            | 94                 |                         | ID            |

| PSRR           | Power-supply reje          | ction ratio         | RTI, DC to f = 50 kHz                                  |               | See Typical Curves |                         | dB            |

| OUTPUT         | Ī                          |                     |                                                        |               |                    |                         |               |

|                |                            | - V                 | I <sub>O</sub> = 200-mA sourcing, 1-ms pulse           |               |                    | 0.5                     | V             |

| \ /            | Voltage output swing       | From V+             | I <sub>O</sub> = 1.5-A sourcing, 1-ms pulse            |               |                    | 2.25                    | V             |

| V <sub>O</sub> |                            | From GND            | I <sub>O</sub> = 200 mA sinking, 1-ms pulse            |               |                    | 0.5                     | V             |

|                |                            |                     | I <sub>O</sub> = 1.5-A sinking, 1-ms pulse             |               |                    | 1.5                     | V             |

|                | Max continuous current, DC |                     | ILIM (pin 12) connected to ground                      | See Reco      | ommended (         | Operating<br>conditions | А             |

|                | Output resistance          |                     | I <sub>O</sub> = 1.9 A, f = 500 kHz                    |               | 0.1                |                         | Ω             |

|                | Disabled output in         | npedance            | f = 100 kHz                                            | 1-            | 45    125          |                         | kΩ    pF      |

|                | Max output current         | Resistor-selectable | ILIM (pin 12) connected to ground                      |               | 2.5                |                         | Α             |

| GAIN           |                            | •                   |                                                        | *             |                    | •                       |               |

| G              | Nominal gain               |                     | V <sub>OUT</sub> /V <sub>IN</sub>                      |               | -7                 | _                       | V/V           |

| G <sub>E</sub> | Gain error                 |                     | $T_{J} = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | -2%           | 0.1%               | 2%                      |               |

|                | Gain error drift           |                     | $T_{J} = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |               | ±5                 |                         | ppm/°C        |

| THERMA         | AL SHUTDOWN                |                     |                                                        |               |                    |                         |               |

|                | Junction temperat          | ure at shutdown     |                                                        |               | 140                |                         | °C            |

|                | Hysteresis                 |                     |                                                        |               | 10                 |                         | °C            |

| <u></u>        | Return to normal           | operation           |                                                        |               | 130                |                         | °C            |

# 6.6 Electrical Characteristics: Digital

At T<sub>CASE</sub> = 25°C, V+ = 15 V, IN+ = (V+) / 2, R<sub>LOAD</sub> = 50  $\Omega$  unless otherwise noted.

| PARAMETE                                                      | R                                                                                                                                                                                                                                                                                                                                     | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN                                                                                                                                                                                                                                    | TYP                                                                                                                                                                                                                   | MAX                                                                                                                                                                                                                                                                | UNIT          |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| INPUTS (ENABLE, IQSE                                          | ET)                                                                                                                                                                                                                                                                                                                                   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u>'</u>                                                                                                                                                                                                                               |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    |               |

| Leakage input current                                         |                                                                                                                                                                                                                                                                                                                                       | GND ≤ V <sub>IN</sub> ≤ 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1                                                                                                                                                                                                                                     | 0.01                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                  | μA            |

| High-level input voltage                                      |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                     | 3.3                                                                                                                                                                                                                                                                | V             |

| Low-level input voltage                                       | е                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GND                                                                                                                                                                                                                                    |                                                                                                                                                                                                                       | 0.8                                                                                                                                                                                                                                                                | V             |

| EN pin function                                               | EN pin high                                                                                                                                                                                                                                                                                                                           | 2 < EN < 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                        | Devid                                                                                                                                                                                                                 | ce in norma                                                                                                                                                                                                                                                        | al operation  |

| (active high)                                                 | EN pin low                                                                                                                                                                                                                                                                                                                            | EN < 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | Device in                                                                                                                                                                                                                                                          | n shutdown    |

| IQSET pin function (active high) IQSET pin high IQSET pin low |                                                                                                                                                                                                                                                                                                                                       | IQSET > 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Device in I                                                                                                                                                                                                                            | Device in FCC/ARIB mode (I <sub>Q</sub> = 78 mA                                                                                                                                                                       |                                                                                                                                                                                                                                                                    |               |

|                                                               |                                                                                                                                                                                                                                                                                                                                       | IQSET < 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Device in (                                                                                                                                                                                                                            | Device in CENELEC mode (I <sub>Q</sub> = 51 mA (ty                                                                                                                                                                    |                                                                                                                                                                                                                                                                    |               |

| OUTPUTS (TFLAG, IFLA                                          | AG)                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>'</u>                                                                                                                                                                                                                               |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    |               |

| High-level output curre                                       | ent                                                                                                                                                                                                                                                                                                                                   | V <sub>OH</sub> = 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                  | μA            |

| Low-level output volta                                        | ge                                                                                                                                                                                                                                                                                                                                    | I <sub>OL</sub> = 4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | 0.4                                                                                                                                                                                                                                                                | V             |

| Low-level output curre                                        | ent                                                                                                                                                                                                                                                                                                                                   | V <sub>OL</sub> = 400 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                                                                                                      |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    | mA            |

| TFLAG (active high,                                           | TFLAG pin high                                                                                                                                                                                                                                                                                                                        | TFLAG sink high < 1 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Device is in thermal                                                                                                                                                                                                                   |                                                                                                                                                                                                                       | al shutdown                                                                                                                                                                                                                                                        |               |

| open-drain)                                                   | TFLAG pin low                                                                                                                                                                                                                                                                                                                         | TFLAG < 0.4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                        | Device is no                                                                                                                                                                                                          | t in therma                                                                                                                                                                                                                                                        | al shutdown   |

| IFLAG (active high,                                           | IFLAG pin high                                                                                                                                                                                                                                                                                                                        | IFLAG sink high < 1 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                        | De                                                                                                                                                                                                                    | evice is in o                                                                                                                                                                                                                                                      | current limit |

| open-drain) IFLAG pin low                                     |                                                                                                                                                                                                                                                                                                                                       | IFLAG < 0.4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Device is not in current                                                                                                                                                                                                               |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    | current limit |

| OWN MODE TIMING                                               |                                                                                                                                                                                                                                                                                                                                       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    |               |

| Enable time                                                   |                                                                                                                                                                                                                                                                                                                                       | SD pin transitions from low to high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                        | 3                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                    | ms            |

| Disable time                                                  |                                                                                                                                                                                                                                                                                                                                       | SD pin transitions from high to low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                    | ms            |

|                                                               | Leakage input current High-level input voltage Low-level input voltage EN pin function (active high)  IQSET pin function (active high)  OUTPUTS (TFLAG, IFLAG) High-level output curred Low-level output curred Low-level output curred TFLAG (active high, open-drain)  IFLAG (active high, open-drain)  IWN MODE TIMING Enable time | Leakage input current High-level input voltage Low-level input voltage  EN pin function (active high)  IQSET pin function (active high)  OUTPUTS (TFLAG, IFLAG)  High-level output current Low-level output voltage Low-level output current TFLAG (active high, open-drain)  IFLAG pin high TFLAG pin high TFLAG pin high TFLAG pin high TFLAG pin low  IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low IFLAG pin low | INPUTS (ENABLE, IQSET)         Leakage input current       GND ≤ V <sub>IN</sub> ≤ 3.3         High-level input voltage       EN pin function (active high)         EN pin function (active high)       EN pin high       2 < EN < 3.3 | INPUTS (ENABLE, IQSET)         Leakage input current       GND ≤ V <sub>IN</sub> ≤ 3.3       −1         High-level input voltage       GND         EN pin function (active high)       EN pin high       2 < EN < 3.3 | INPUTS (ENABLE, IQSET)         Leakage input current       GND ≤ V <sub>IN</sub> ≤ 3.3       −1 0.01         High-level input voltage       2         Low-level input voltage       GND         EN pin function (active high)       EN pin high       2 < EN < 3.3 |               |

# 6.7 Electrical Characteristics: Power Supply

At  $T_{CASE} = 25^{\circ}C$ , V+ = 15 V, IN+ = (V+) / 2,  $R_{LOAD} = 50 \Omega$  unless otherwise noted.

| 07.02                               | <u> </u>                  | TT = (VT) / Z, REDAD = 30 32 differs of the wise flotes |     |     |     |      |

|-------------------------------------|---------------------------|---------------------------------------------------------|-----|-----|-----|------|

|                                     | PARAMETER TEST CONDITIONS |                                                         | MIN | TYP | MAX | UNIT |

| OPERATI                             | OPERATING SUPPLY RANGE    |                                                         |     |     |     |      |

| V+                                  | Power amplifier           |                                                         | 7   | 15  | 24  | V    |

| QUIESCENT CURRENT (ENABLE pin high) |                           |                                                         |     |     |     |      |

| 1                                   | FCC/ARIB mode             | I <sub>O</sub> = 0 A, IQSET pin high                    | 64  | 78  | 88  | mA   |

| IQ                                  | CENELEC mode              | I <sub>O</sub> = 0 A, IQSET pin low                     | 41  | 51  | 61  | mA   |

| SHUTDOWN (ENABLE pin low)           |                           |                                                         |     |     |     |      |

| EN                                  | Power amplifier           | EN pin low                                              |     | 58  | 130 | μA   |

|                                     | ` '                       | EN pin low                                              |     | 58  |     | 130  |

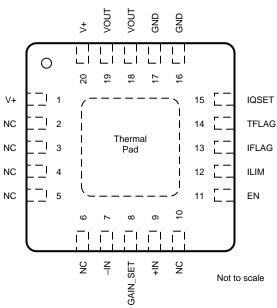

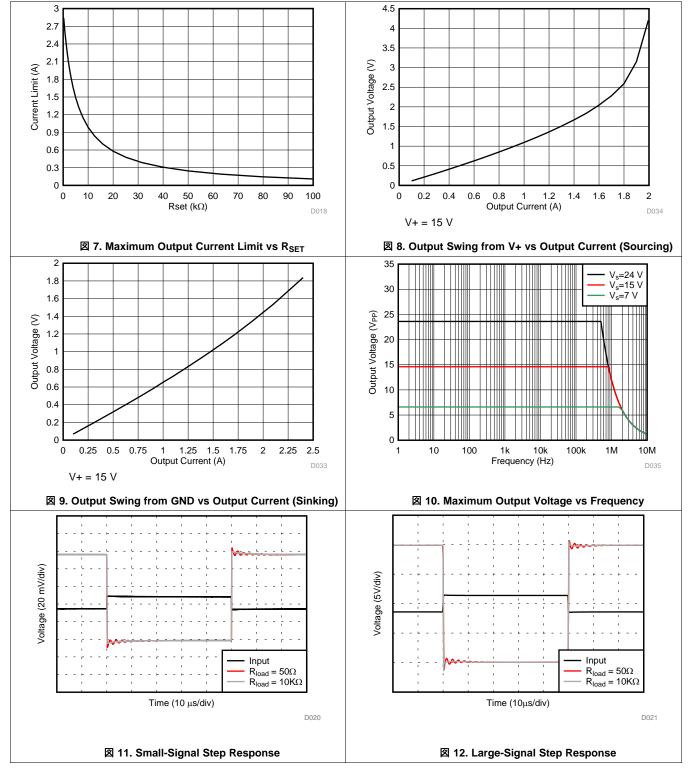

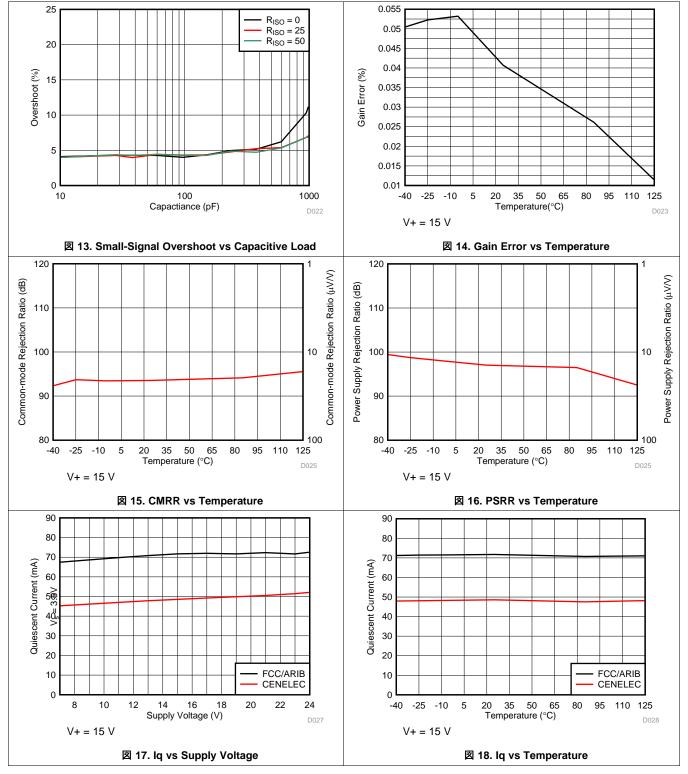

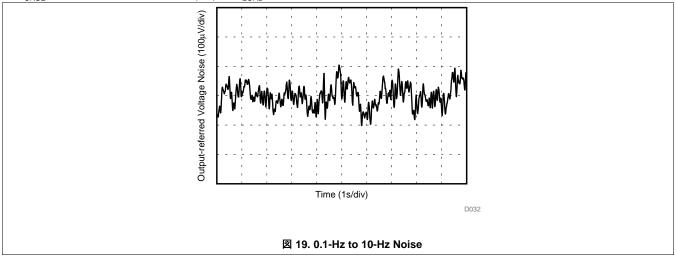

# 6.8 Typical Characteristics

At  $T_{CASE}$  = +25°C, V+ = 24 V, IN+ = (V+)/2,  $R_{LOAD}$  = 50  $\Omega$  unless otherwise noted.

## **Typical Characteristics (continued)**

At  $T_{CASE}$  = +25°C, V+ = 24 V, IN+ = (V+)/2,  $R_{LOAD}$  = 50  $\Omega$  unless otherwise noted.

## **Typical Characteristics (continued)**

At  $T_{CASE}$  = +25°C, V+ = 24 V, IN+ = (V+)/2,  $R_{LOAD}$  = 50  $\Omega$  unless otherwise noted.

# **Typical Characteristics (continued)**

At T<sub>CASE</sub> = +25°C, V+ = 24 V, IN+ = (V+)/2, R<sub>LOAD</sub> = 50  $\Omega$  unless otherwise noted.

## 7 Detailed Description

#### 7.1 Overview

The OPA521 is a power amplifier (PA) designed for power-line communication (PLC) applications. The device features a fixed gain of -7 V/V, low-pass filter response, excellent linearity and low distortion through the bandwidth. The amplifier operates with 7-V to 24-V supplies, and can deliver up to  $\pm 1.9$  A of continuous current from  $-40^{\circ}$ C to  $\pm 1.25^{\circ}$ C.

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

The OPA521 offers an optional output current limit (ILIM), quiescent current (IQSET) selection pins, and a device enable pin. The IFLAG output alarm pin indicates an output current warning and the TFLAG alarm triggers when the internal temperature of the device forces the devices to shut down.

#### 7.3.1 IQSET Pin

This pin sets the operating band of the amplifier by adjusting the quiescent current.

- IQSET > 2 V sets the device to operate in the FCC or ARIB bands

- IQSET < 0.8 V sets the device to operate in the CENELEC bands</li>

#### 7.3.2 EN Pin

When the transmitter is not in use, the output is disabled and placed in a high-impedance state when the EN pin decreases. For typical operation, connect the EN pin to 3.3 V. In disabled mode, the entire device draws 58  $\mu$ A (typical) of current.

## 7.3.3 ILIM Pin Current Limiting

The ILIM pin (pin 12) provides a resistor-programmable output current limit.  $\boxtimes$  6 shows the typical current limit for a given external R<sub>SET</sub> resistor attached to this pin.

Several typical target values and the approximate corresponding R<sub>SET</sub> are provided in 表 1.

## 表 1. Typical Current Limit and R<sub>SET</sub> Values

| CURRENT LIMIT (A) | R <sub>SET</sub> (approximate, kΩ) |  |  |

|-------------------|------------------------------------|--|--|

| Maximum Output    | Grounded                           |  |  |

| 1                 | 10                                 |  |  |

| 0.5               | 25                                 |  |  |

#### 7.3.4 IFLAG and TFLAG Pins

The IFLAG and TFLAG pins are active-high, open-drain outputs that indicate if the OPA521 is in current or thermal limit. Connect these pins to 3.3 V through pullup resistors (for example 10 k $\Omega$ ).

The maximum output current from the power amplifier is programmed with the external I<sub>LIM</sub> resistor that is connected between ILIM (pin 12) and ground. IFLAG is set if the amplifier goes to a current limit state if a fault condition occurs. This causes the power amplifier to source or sink more current than the programmed limit value. IFLAG exhibits transient pulses under typical operation. An IFLAG true state for greater than 100 ms is a definite indication of a fault current condition.

The device contains internal thermal shutdown protection circuitry that automatically disables the output stage if the junction temperature exceeds 140°C. The device thermal shutdown protection circuitry lets the amplifier typical normal operation only when the junction temperature falls below 130°C. The TFLAG is active when the device is in thermal shut down mode.

#### 7.4 Device Functional Modes

The OPA521 operates from a single power rail from 7 V to 24 V. The gain is fixed at -7 V/V and can increase with an external resistor that is connected to the GAIN\_SET and -IN pins.

# 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

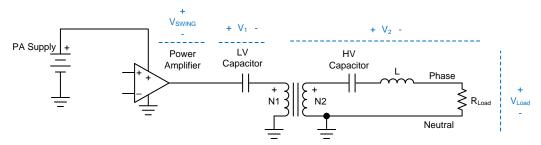

The application circuit shown in 20 is an AC mains-line driver over 40-kHz-to-90-kHz utility band and is based around the European standard (EN56065–1) describing utility and consumer applications. This example shows a possible implementation for differential transmission on the mains line. This applications circuit is designed around the requirements of a domestic electricity meter operating over a utility band of 40 kHz to 90 kHz.

## 8.2 Typical Application

The impedance of the mains network at these signaling frequencies is relatively low (< 1  $\Omega$  to 30  $\Omega$ ). This circuit has been designed to drive a 2- $\Omega$  mains line over the 40-kHz-to-90-kHz bandwidth. The signaling impedance of the mains network fluctuates as different loads are switched on during the day or over a season and it is influenced by many factors such as:

- Localized loading from appliances connected to the mains supply near to the connection of the communication equipment; for example, heavy loads such as cookers and immersion heaters and reactive loads such as EMC filters and power factor corrections.

- Distributed loading from consumers connected to the same mains cable, where their collective loading reduces the mains signaling impedance during times of peak electricity consumption; for example, meal times.

- Network parameters; for example, transmission properties of cables and the impedance characteristics of distribution transformers and other system elements.

With such a diversity of factors, the signaling environment fluctuates enormously, irregularly, and can differ greatly from one installation to another. Design the signaling system for reliable communications over a wide range of mains impedances and signaling conditions. Consequently, the transmitter must be able to drive sufficient signal into the mains network under these loading conditions.

The OPA521 amplifier has 1.9-A output drive capability with short-circuit protection; hence, it adequately copes with the high current demands required for implementing mains signaling systems.

図 20. OPA521 Interface to the AC Mains

## Typical Application (continued)

#### 8.2.1 Design Requirements

The primary subsystems of a power-line communication mains-line driver system include the line coupling circuit, circuit protection, and power supply. The following sections detail the design of each.

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Interfacing the OPA521 to the AC Mains

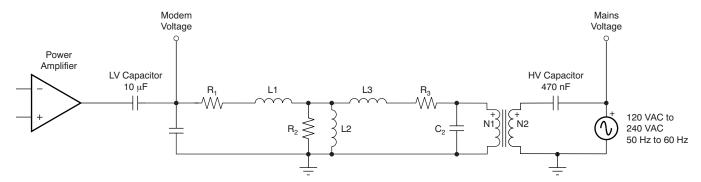

The line coupling circuit is one of the most critical segments of a power-line modem. The line coupling circuit has two primary functions: first, to prevent the high voltage, low frequency of the mains (commonly 50 Hz or 60 Hz) from damaging the low-voltage modem circuitry; and second, as the name implies, to couple the modem signal to and from the ac mains.

#### 8.2.2.1.1 Low-Voltage Capacitor

The low-voltage capacitor (LV Cap) couples the time-varying components of the power amplifier output signal into the line coupling transformer. The LV Cap must have a large enough capacitance to appear as a low impedance throughout the signal band of interest; 10-µF is a common value for signals in the range of 35 kHz to 150 kHz. The voltage rating of the LV cap should be sufficient to withstand the clamping voltage of the TVS diode (that is, the transient voltage suppressor (see Circuit Protection more information) operating under surge conditions. Generally, this limit must be equal to the power amplifier supply voltage or slightly higher.

#### 8.2.2.1.2 High-Voltage Capacitor

The high-voltage capacitor (HV Cap) blocks the low-frequency mains voltage by forming a voltage divider with the winding inductance of the line coupling transformer. In many applications, a maximum reactive power (VA limit) on the HV Cap may be required. To meet this requirement, the HV Cap value is calculated by 式 1.

$$HV_{CAP} = \frac{VA_{LIMIT}}{V_{AC^2} \times 2 \pi \times f}$$

(1)

For a 240-VAC, 50-Hz application with a 10-VA limit, the maximum value for the HV Cap is shown in 式 2.

$$HV_{CAP} \le \frac{10}{240^2 \times 2 \pi \times f} = 550 \text{ nF}$$

(2)

A 470-nF capacitor is frequently used in these types of applications. A metallized polypropylene electromagnetic interference and radio frequency interference (EMI/RFI) suppression capacitor is recommended because of the low loss factor associated with the dielectric, which results in minimal internal self-heating. Operating the capacitor at approximately 80% of its ac-rated voltage ensures a long component operating life. See Circuit Protection of this document for additional discussion on selecting the correct HV Cap value to withstand impulses on the mains.

#### 8.2.2.1.3 Inductor

The inductor that is connected in series with the HV Cap is required when driving low line impedances and the HV Cap is restricted to approximately 470 nF for the reasons previously stated. In applications that operate in the CENELEC A band, the impedance of the 470-nF capacitance at 40 kHz is approximately 8.5  $\Omega$ . If the application requires the ability to drive a 2- $\Omega$  load, for example, this series impedance is restrictive. Adding the series inductor can mitigate this effect. To properly select the value of the inductance, the operating frequency range of the system must be known. A common example would be the PRIME frequency band, which is approximately 40 kHz to 90 kHz. Selecting the HV Cap and inductor to have a resonant frequency in the center of the frequency band is recommended, and results in a series inductor value of 12.8  $\mu$ H and HV Cap value of 470 nF. The inductor must be sized to be capable of withstanding the maximum load current without saturation, using this  $\vec{x}$  3 as a guideline.

$$L = \frac{1}{\left(HV_{CAP} \times 2 \pi \times f\right)^2}$$

(3)

## **Typical Application (continued)**

#### 8.2.2.1.4 Line Coupling Transformer

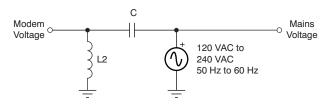

Most power-line communication transformers are compact, with turns ratios between 1:1 and 4:1, low leakage inductance, and approximately 1-mH of winding inductance. It is the voltage divider formed by the HV Cap and winding inductance that divides down the ac mains voltage and reduces it to negligible levels at the modem output. 2 21 shows the equivalent circuit formed with the HV Cap and the line coupling transformer.

図 21. Voltage Divider with HV Cap and Transformer Equivalent Circuit

#### Where:

- 1. R1 is the series dc resistance of the primary winding

- 2. R2 is the shunt resistance reflecting losses in the core

- 3. R3 is the series dc resistance of the secondary winding, reflected to the primary side

- 4. L1 is the primary leakage inductance

- 5. L2 is the open circuit inductance of the primary winding

- 6. L3 is the secondary leakage inductance reflected to the primary side

- 7. C1 is the self-capacitance of the primary winding

- 8. C2 is the self-capacitance of the secondary winding reflected to the primary side

For the purposes of analysis, this circuit can be simplified as shown in 22.

HVCap reflected to the primary side

図 22. Simplified AC Mains Voltage Divider

#### Where:

- 1. L2 = OCL of the transformer primary

- 2. C = HV Cap reflected to the primary side

In a typical line coupling circuit the ac mains voltage injected into the modem is approximately 20 mVPP.

Determining the optimal turns ratio (N1/N2) for the power-line communication transformer is simple, and based on the principle of using the maximum output swing capability of the power amplifier together with the maximum output current capability of the power amplifier to achieve maximum power transfer efficiency into the load. Assuming the power-supply voltage and target load impedance are known, the turns ratio is determined as shown in Figure 17, and calculated with Equation 11 and Equation 12.

## Typical Application (continued)

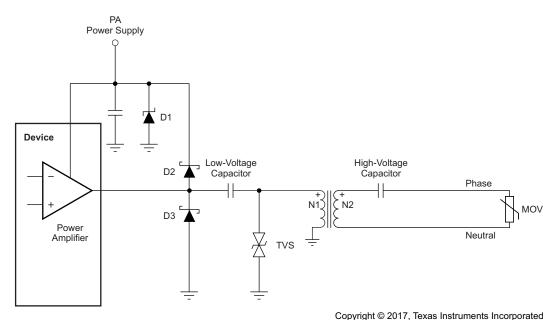

#### 8.2.2.2 Circuit Protection

Power-line communications are often located in operating environments that are harsh for electrical components connected to the ac line. Noise or surges from electrical anomalies (such as lightning, capacitor bank switching, inductive switching, or other grid fault conditions) can damage high-performance integrated circuits if proper protection is not provided. The OPA521, however, can survive even the harshest conditions by using a variety of techniques to protect the device. Layout the protection circuitry in order to dissipate as much of the electrical disturbance as possible with a multilayer approach using metal-oxide varistors (MOVs), transient voltage suppression diodes (TVSs), Schottky diodes, and a Zener diode. These components dissipate the electrical disturbance before the anomaly reaches the device. shows the recommended strategy for transient overvoltage protection.

図 23. Transient Overvoltage Protection for OPA521

Note that the high-voltage coupling capacitor must be able to withstand pulses up to the clamping protection provided by the MOV. A metalized polypropylene capacitor, such as the 474MKP275KA from Illinois Capacitor, is rated for 50 Hz to 60 Hz and 250 VAC to 310 VAC, and can withstand 24 impulses of 2.5 kV. 表 2 lists several recommended transient protection components.

表 2. Recommended Transient Protection Components

| COMPONENT | DESCRIPTION                   | MANUFACTURER            | MFR PART NO (OR EQUIVALENT) |  |  |

|-----------|-------------------------------|-------------------------|-----------------------------|--|--|

| D1        | Zener diode                   | Diodes, Inc.            | 1SMB59xxB                   |  |  |

| D2, D3    | Schottky diode                | Diodes, Inc.            | 1N5819HW                    |  |  |

| TVS       | Transient voltage suppressor  | Diodec<br>Semiconductor | P6SMBJxxC                   |  |  |

| MOV       | Varistor (for 120 VAC, 60 Hz) | LittleFuse              | TMOV20RP140E                |  |  |

| MOV       | Varistor (for 240 VAC, 50 Hz) | LittleFuse              | TMOV20RP300E                |  |  |

| HV Cap    | High-voltage capacitor        | Illinois Capacitor, Inc | 474MKP275KA                 |  |  |

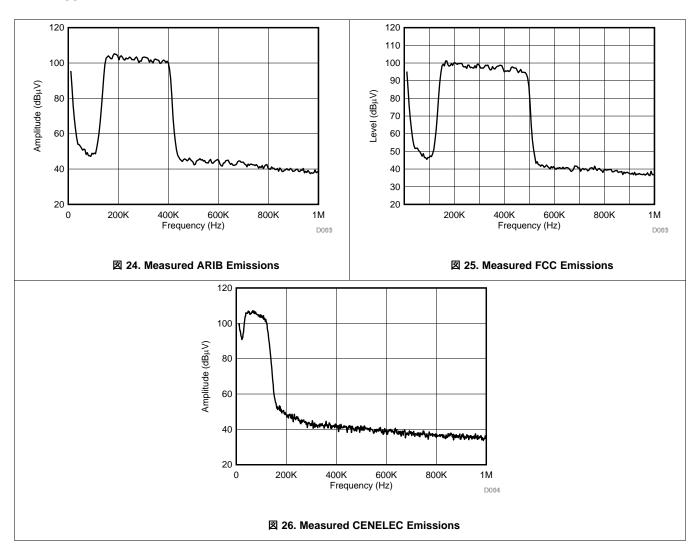

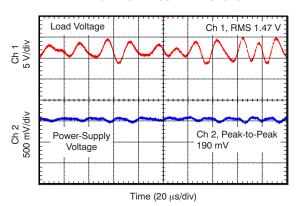

## 8.2.3 Application Curves

## 9 Power Supply Recommendations

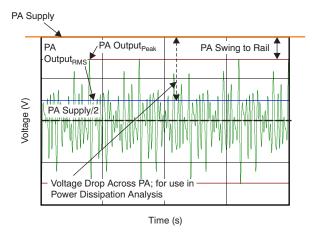

Determining the power-supply requirements requires only a straightforward analysis. The desired load voltage, load impedance, and available power-supply voltage or desired transformer ratio are all the parameters that must be known. In many power-line communication applications, such as PRIME, it is required to drive a 1-V<sub>RMS</sub> signal into a 2- $\Omega$  load. Using 27, calculate the minimum power-supply voltage required by adding the peak-to-peak load voltage; the voltage dropped across the HV Cap and inductor, V2; the voltage dropped across the LV Cap, V1; and twice the output swing to rail limit of the power amplifier, VSWING. For FSK and SFSK systems, the peak to average ratio is  $\sqrt{2}$ , while for OFDM systems this ratio is approximately 3:1.

図 27. Typical Line Coupling Circuit

These ratios must be considered when performing calculations that relate the RMS voltages and peak voltages during an analysis. Choosing a large value for the LV Cap results in the voltage drop (V1) becoming negligible in most circumstances. The losses in the transformer are also negligible, even at high load currents, if the proper transformer with a low DCR is used. For FSK and SFSK systems, the voltage drop across the HV Cap and inductor, V2, is also usually negligible; in OFDM systems, because of the wider operating bandwidth, voltage drop V2 can be ignored and accounted for by using a 1.5x multiplier on the load voltage as an approximation.

注

This approximation is only valid with a load impedance of 2  $\Omega$  for PRIME and G3. Voltage drop V2 becomes negligible with increasing load impedance. These assumptions greatly simplify the analysis.

| PARAMETER           | FSK OR SFSK | PRIME OR G3 OFDM | UNIT       |

|---------------------|-------------|------------------|------------|

| Frequency range     | 63 to 74    | 35 to 95         | kHz        |

| $R_{LOAD}$          | 2           | 2                | Ω          |

| $V_{LOAD}$          | 1           | 1                | $V_{RMS}$  |

| $V_{LOAD}$          | 1.414       | 3                | $V_{PEAK}$ |

| $V_{LOAD}$          | 2.828       | 6                | $V_{PP}$   |

| OFDM multiplier     | _           | 1.5              | _          |

| $V_{SWING}$         | 2           | 2                | V          |

| Turns ration, N1/N2 | 1.5         | 1.5              | _          |

| PA supply           | 8.25        | 17.5             | V          |

表 3. Power-Supply Requirements

表 3 summarizes the power-supply requirements for various power-line communication systems.

#### Example:

For PRIME or G3 using an OFDM signal with a 2- $\Omega$  load and 1-V<sub>RMS</sub>load voltage:

$PA_{Supply} = V_{LOAD} \times OFDM Multiplier \times Turns Ration + (2 \times V_{SWING})$

$PA_{Supply} = 6 V \times 1.5 \times 1.5 + (2 \times 2 V)$

$PA_{Supply} = 17.5 V$

Power consumption

Calculating the power dissipation in the load and in OPA521 also requires some direct calculations. The desired load voltage, load impedance, available power-supply voltage, and the transformer ratio are the only parameters required. In many power-line communication applications, such as PRIME, it is required to drive a 1-VRMS signal into a  $2-\Omega$  load. The power dissipation in the power amplifier is determined by calculating the RMS value of the OPA521's output current, and the voltage difference between the power amplifier supply and RMS value of the output voltage. These two values are multiplied, and the quiescent power of the power amplifier is added.

The power in the load is given as 式 4 shows.

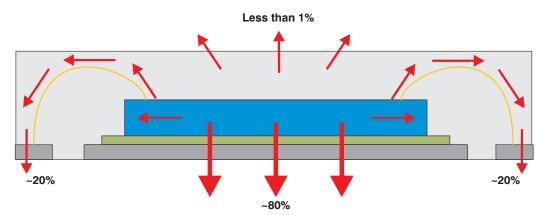

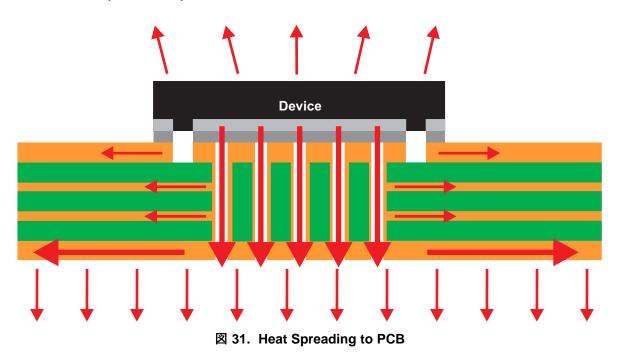

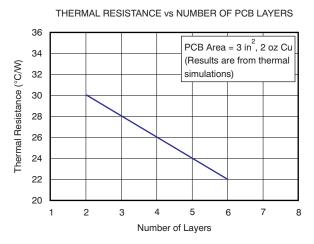

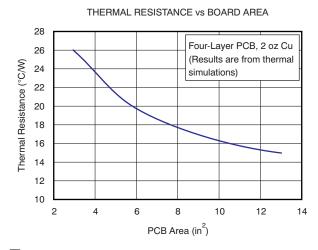

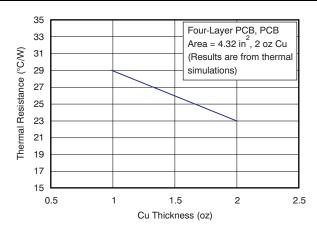

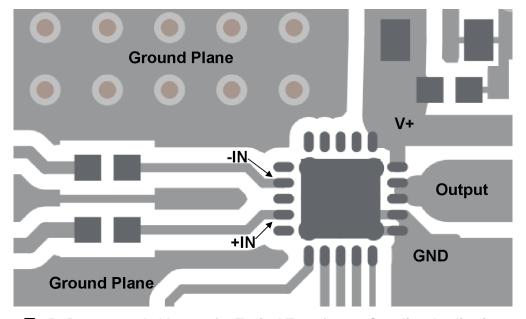

PA output voltage (RMS) =