## OPA180, OPA2180, OPA4180

JAJSFN7E -NOVEMBER 2011-REVISED JUNE 2018

# OPAx180 ドリフト係数0.1μV/℃、低ノイズ、 レール・ツー・レール出力、36V、ゼロ・ドリフト・オペアンプ

#### 1 特長

低いオフセット電圧: 75μV (最大値)

ゼロ・ドリフト: 0.1μV/℃

• 低ノイズ: 10nV/√Hz

• 非常に低い1/fノイズ

非常に優れたDC精度

PSRR: 126dB

- CMRR: 114dB

- オープン・ループ・ゲイン(A<sub>OL</sub>): 120dB

静止電流: 525μA (最大値)

• 広い電源電圧範囲: ±2V~±18V

レール・ツー・レール出力: 入力に負のレールも含む

低いバイアス電流: 250pA (標準値)

• RFIフィルタ付きの入力

MicroSizeパッケージ

#### 2 アプリケーション

- ブリッジ・アンプ

- 歪みゲージ

- 試験用機器

- トランスデューサ・アプリケーション

- 温度測定

- 電子計測器

- 医療用計測機器

- 抵抗熱検出器

- 高精度アクティブ・フィルタ

#### 3 概要

OPA180、OPA2180、OPA4180オペアンプは、TI独自のゼロ・ドリフト技法を使用して、低いオフセット電圧(75μV)と、時間や温度に対してほぼゼロのドリフト係数を同時に実現しています。これらの小型、高精度、低静止電流オペアンプは、高い入力インピーダンスと、レールから18mV以内のレール・ツー・レール出力を提供します。入力同相範囲には、負のレールも含まれます。4V~36V(±2V~±18V)の範囲の単一またはデュアル電源を使用できます。

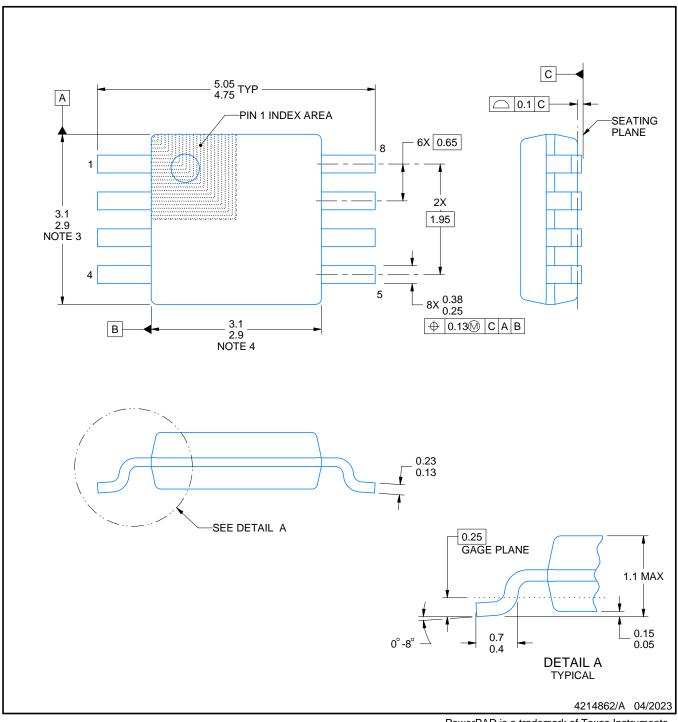

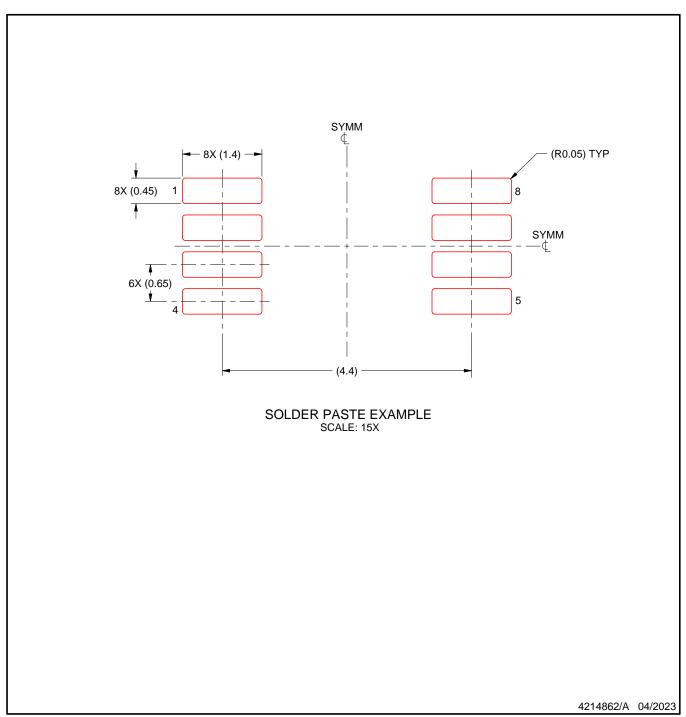

デュアル・チャネル・バージョンは、は、VSSOP-8パッケージとSOIC-8パッケージで供給されます。 クワッド・チャネル・バージョンは、SOIC-14およびTSSOP-14パッケージで供給されます。 シングルおよびクワッド・パッケージ製品(OPA180とOPA4180)は-40℃~+125℃で、デュアル・パッケージ製品(OPA2180)は-40℃~+105℃で動作が規定されています。

#### 製品情報(1)

| 型番        | パッケージ          | 本体サイズ(公称)     |  |  |  |  |

|-----------|----------------|---------------|--|--|--|--|

|           | SOT-23 (5)     | 1.60mm×2.90mm |  |  |  |  |

| OPA180    | VSSOP、MSOP (8) | 3.00mm×3.00mm |  |  |  |  |

|           | SOIC (8)       | 4.90mm×3.91mm |  |  |  |  |

| OPA2180   | VSSOP、MSOP (8) | 3.00mm×3.00mm |  |  |  |  |

| OPA2160   | SOIC (8)       | 4.90mm×3.91mm |  |  |  |  |

| ODA 44.80 | TSSOP (14)     | 5.00mm×4.40mm |  |  |  |  |

| OPA4180   | SOIC (14)      | 8.65mm×3.91mm |  |  |  |  |

(1) 提供されているすべてのパッケージについては、このデータシート の末尾にある注文情報を参照してください。

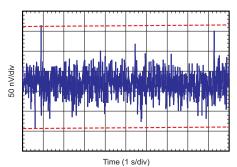

低ノイズ (ピーク・ツー・ピークのノイズ = 250nV)

#### 目次

|   |                                                                                                                             | •  |                                |    |

|---|-----------------------------------------------------------------------------------------------------------------------------|----|--------------------------------|----|

| 1 | 特長1                                                                                                                         |    | 8.1 Overview                   | 17 |

| 2 | アプリケーション1                                                                                                                   |    | 8.2 Functional Block Diagram   | 17 |

| 3 | 概要1                                                                                                                         |    | 8.3 Feature Description        | 18 |

| 4 | 改訂履歴                                                                                                                        |    | 8.4 Device Functional Modes    | 20 |

| 5 | Device Comparison Table 4                                                                                                   | 9  | Application and Implementation | 21 |

| 6 | Pin Configuration and Functions 5                                                                                           |    | 9.1 Application Information    | 21 |

| - | _                                                                                                                           |    | 9.2 Typical Applications       | 21 |

| 7 | Specifications8                                                                                                             | 10 | Power Supply Recommendations   | 25 |

|   | 7.1 Absolute Maximum Ratings 8                                                                                              | 11 | Layout                         |    |

|   | 7.2 ESD Ratings                                                                                                             |    | 11.1 Layout Guidelines         |    |

|   | 7.3 Recommended Operating Conditions                                                                                        |    | 11.2 Layout Example            |    |

|   | 7.4 Thermal Information: OPA180                                                                                             | 12 | デバイスおよびドキュメントのサポート             |    |

|   | 7.5 Thermal Information: OPA2180                                                                                            | 12 | 12.1 関連リンク                     |    |

|   | 7.6 Thermal Information: OPA41809                                                                                           |    | 12.2 商標                        |    |

|   | 7.7 Electrical Characteristics: $V_S = \pm 2 \text{ V to } \pm 18 \text{ V } (V_S = \pm 2 \text{ V to } \pm 18 \text{ V })$ |    |                                |    |

|   | 4 V to 36 V)                                                                                                                |    | 12.3 静電気放電に関する注意事項             |    |

|   | 7.8 Typical Characteristics: Table of Graphs 12                                                                             |    | 12.4 Glossary                  |    |

|   | 7.9 Typical Characteristics                                                                                                 | 13 | メカニカル、パッケージ、および注文情報            | 27 |

| 8 | Detailed Description 17                                                                                                     |    |                                |    |

|   |                                                                                                                             |    |                                |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Revision D (May 2014) から Revision E に変更

Page

| • | 「概要」セクションで、OPA180とOPA4180の動作温度を「-40℃~+105℃」から「-40℃~+125℃」に 変更                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Added storage temperature parameter as the last row in the Absolute Maximum Ratings table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| • | Changed maximum operating temperature value from 105°C to 125°C in Absolute Maximum Ratings table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| • | Changed maximum operating temperature value from 105°C to 125°C in Recommended Operating Conditions table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| • | Changed input offset voltage drift temperature range from $T_A = -40^{\circ}\text{C}$ to $105^{\circ}\text{C}$ to $T_A = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • | Changed power supply rejection ratio temperature range from $T_A = -40$ °C to $105$ °C to $T_A = -40$ °C to $+125$ °C in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| • | Changed OPA180 input bias current temperature range from $T_A = -40^{\circ}\text{C}$ to $105^{\circ}\text{C}$ to $T_A = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| • | Added minimum OPA2180 input bias current value of 18 nA in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • | Added minimum OPA180 input bias current value of 18 nA in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| • | Changed OPA180 input offset current temperature range from $T_A = -40^{\circ}\text{C}$ to $105^{\circ}\text{C}$ to $T_A = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| • | Added minimum OPA2180 input offset current value of 6 nA in <i>Electrical Characteristics</i> table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| • | Added minimum OPA180 input offset current value of 6 nA in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • | Changed common-mode rejection ratio temperature range from $T_A = -40^{\circ}\text{C}$ to $105^{\circ}\text{C}$ to $T_A = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| • | Changed open-loop voltage gain temperature range from $T_A = -40^{\circ}\text{C}$ to $105^{\circ}\text{C}$ to $T_A = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ in <i>Electrical Characteristics</i> table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| • | Changed voltage output swing from rail temperature range from $T_A = -40^{\circ}\text{C}$ to $105^{\circ}\text{C}$ to $T_A = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ in Electrical Characteristics table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • | Changed quiescent current temperature range from T <sub>A</sub> = -40°C to 105°C to T <sub>A</sub> = -40°C to +125°C in <i>Electrical Characteristics</i> table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 変更 operating temperature from "-40°C to +105°C" to " -40°C to +125°C" in <i>Feature Description</i> section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • | 変更 operating temperature from "-40°C to +105°C" to " -40°C to +125°C" in <i>Power Supply Recommendations</i> section 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | Several and Complete and the second s |

## 改訂履歴 (continued)

| Revision C (December 2012) から Revision D に変更                                                                            | Page            |

|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| • 最新のデータシート標準に合わせてフォーマットを変更、「デバイスの機能モード」セクション、「アプリケー:<br>ション、「電源に関する推奨事項」セクションを追加、既存のセクションを移動                           |                 |

| • OPA180をドキュメントに追加                                                                                                      | 1               |

| ● 製品情報の表を追加                                                                                                             | 1               |

| Deleted Package Information table                                                                                       | 5               |

| OPA180 pinout drawings                                                                                                  | 5               |

| Added Pin Functions table                                                                                               | 5               |

| Added Pin Functions table                                                                                               | 6               |

| Added Pin Functions table                                                                                               | 7               |

| Added Recommended Operating Conditions table                                                                            | 8               |

| Added Thermal Information: OPA180 table                                                                                 | 9               |

| <ul> <li>Changed Offset Voltage, Long-term stability parameter typical specification in Electrical Character</li> </ul> | ristics table10 |

| Changed last sentence of EMI Rejection section                                                                          | 18              |

| Revision B (December 2011) から Revision C に変更                                                                            | Page            |

| <ul><li>製品ステータスを混在ステータスから量産データへ変更</li></ul>                                                                             | 1               |

| • OPA4180のステータスを量産データへ変更                                                                                                |                 |

| Added package marking to OPA2180 VSSOP-8 row in Package Information table                                               | 5               |

| Deleted ordering number and transport media columns from Package Information table                                      |                 |

| • Changed Input Bias Current section in Electrical Characteristics (V <sub>S</sub> = +4 V to +36 V) table               | 10              |

| Revision A (November 2011) から Revision B に変更                                                                            | Page            |

| Changed footnote 1 of Electrical Characteristics table                                                                  | 10              |

| Updated 図 7                                                                                                             | 13              |

# 5 Device Comparison Table

Table 1. Zero-Drift Amplifier Portfolio

| VERSION | PRODUCT               | OFFSET VOLTAGE<br>(μV) | OFFSET VOLTAGE DRIFT<br>(μV/°C) | BANDWIDTH<br>(MHz) |

|---------|-----------------------|------------------------|---------------------------------|--------------------|

|         | OPA188(4 V to 36 V)   | 25                     | 0.085                           | 2                  |

|         | OPA180 (4 V to 36 V)  | 75                     | 0.35                            | 2                  |

| Single  | OPA333 (5 V)          | 10                     | 0.05                            | 0.35               |

|         | OPA378 (5 V)          | 50                     | 0.25                            | 0.9                |

|         | OPA735 (12 V)         | 5                      | 0.05                            | 1.6                |

|         | OPA2188 (4 V to 36 V) | 25                     | 0.085                           | 2                  |

|         | OPA2180 (4 V to 36 V) | 75                     | 0.35                            | 2                  |

| Dual    | OPA2333 (5 V)         | 10                     | 0.05                            | 0.35               |

|         | OPA2378 (5 V)         | 50                     | 0.25                            | 0.9                |

|         | OPA2735 (12 V)        | 5                      | 0.05                            | 1.6                |

|         | OPA4188 (4 V to 36 V) | 25                     | 0.085                           | 2                  |

| Quad    | OPA4180 (4 V to 36 V) | 75                     | 0.35                            | 2                  |

|         | OPA4330 (5 V)         | 50                     | 0.25                            | 0.35               |

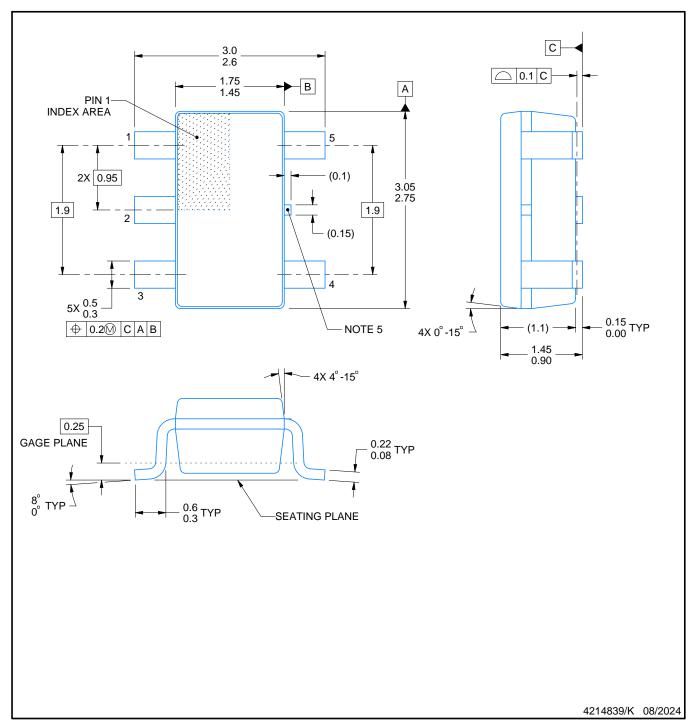

# 6 Pin Configuration and Functions

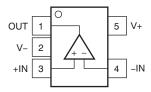

#### OPA180 DBV Package 5-Pin SOT-23 (Top View)

#### **Pin Functions**

| PIN  |     | 1/0 | DESCRIPTION                                             |

|------|-----|-----|---------------------------------------------------------|

| NAME | NO. | I/O | DESCRIPTION                                             |

| -IN  | 4   | 1   | Inverting input                                         |

| +IN  | 3   | 1   | Noninverting input                                      |

| OUT  | 1   | 0   | Output                                                  |

| V-   | 2   | _   | Negative supply or ground (for single-supply operation) |

| V+   | 5   | _   | Positive supply or ground (for single-supply operation) |

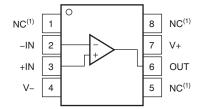

#### OPA180 D, DGK Packages 8-Pin SO, MSOP Top View

#### (1) NC- no internal connection

#### **Pin Functions: OPA180**

| PIN  |         | DESCRIPTION           |  |

|------|---------|-----------------------|--|

| NAME | NO.     | DESCRIPTION           |  |

| -IN  | 2       | Inverting input       |  |

| +IN  | 3       | Noninverting input    |  |

| NC   | 1, 5, 8 | No connection         |  |

| OUT  | 6       | Output                |  |

| V-   | 4       | Negative power supply |  |

| V+   | 7       | Positive power supply |  |

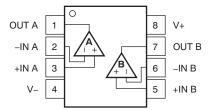

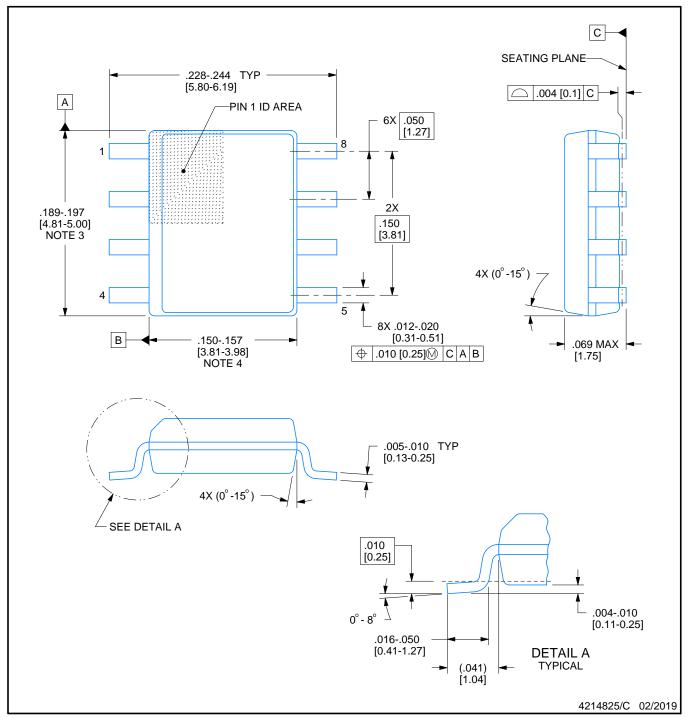

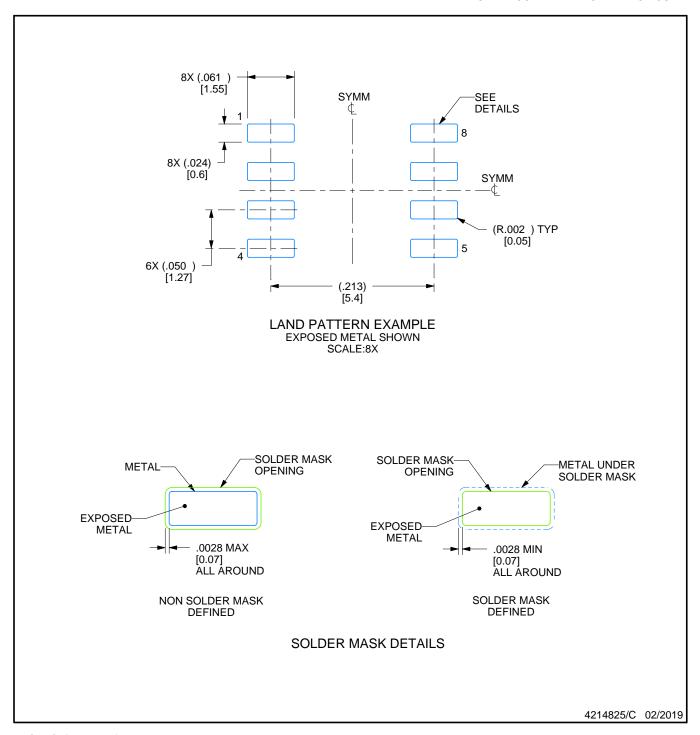

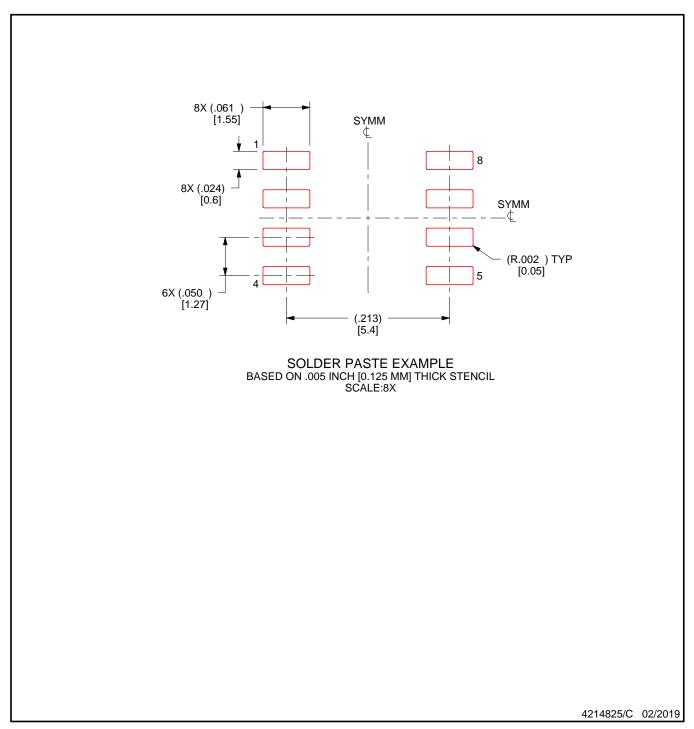

#### OPA2180 D, DGK Packages 8-Pin SOIC, VSSOP Top View

#### **Pin Functions: OPA2180**

| PIN   |     | DESCRIPTION                   |  |

|-------|-----|-------------------------------|--|

| NAME  | NO. | DESCRIPTION                   |  |

| −IN A | 2   | Inverting input, channel A    |  |

| +IN A | 3   | Noninverting input, channel A |  |

| –IN B | 6   | nverting input, channel B     |  |

| +IN B | 5   | Noninverting input, channel B |  |

| OUT A | 1   | Output, channel A             |  |

| OUT B | 7   | Output, channel B             |  |

| V-    | 4   | Negative power supply         |  |

| V+    | 8   | Positive power supply         |  |

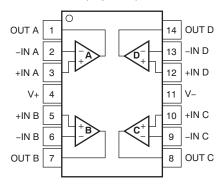

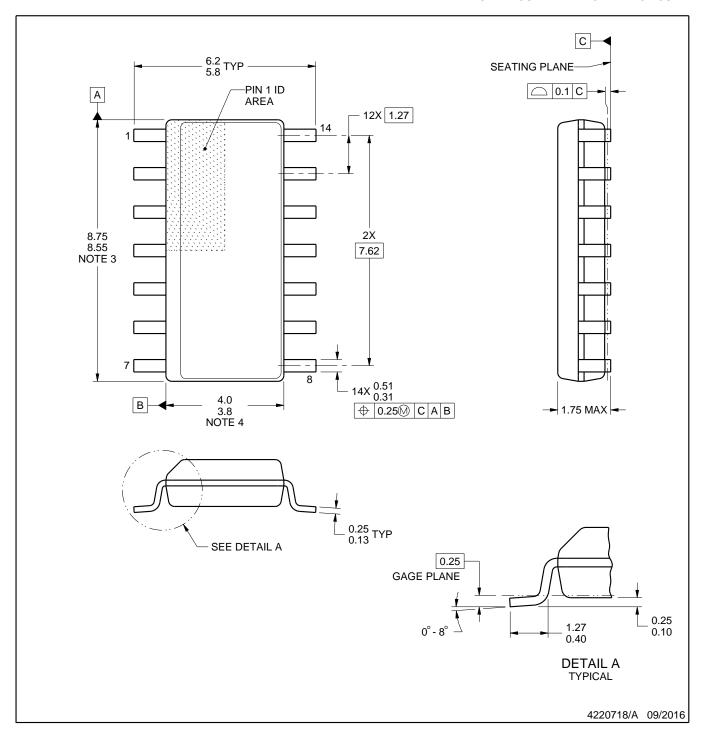

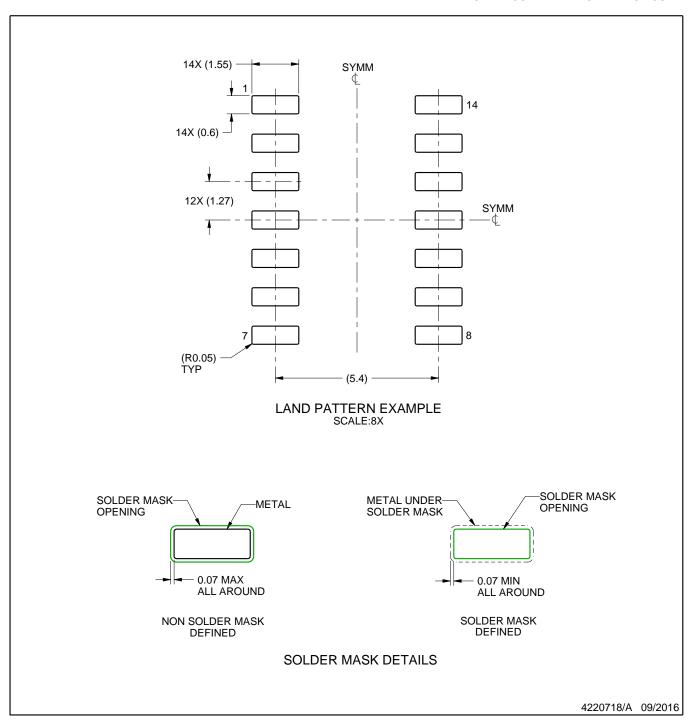

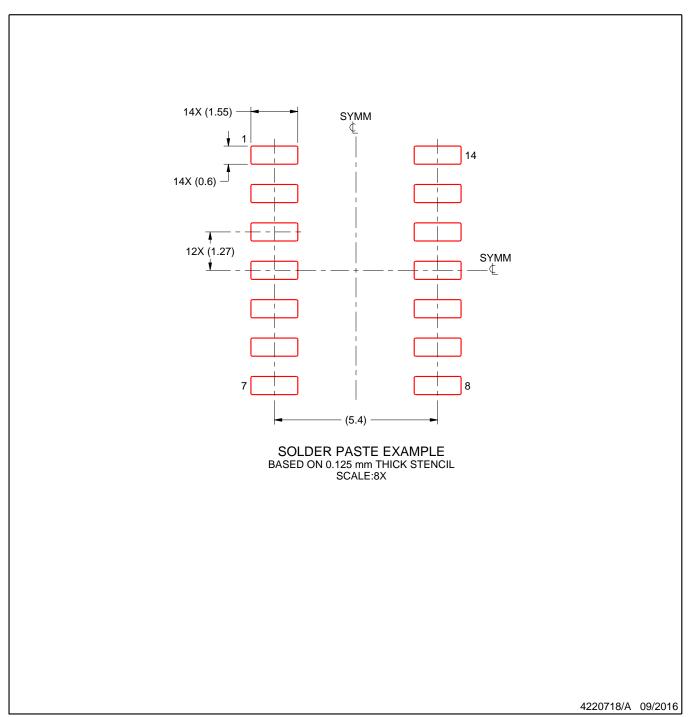

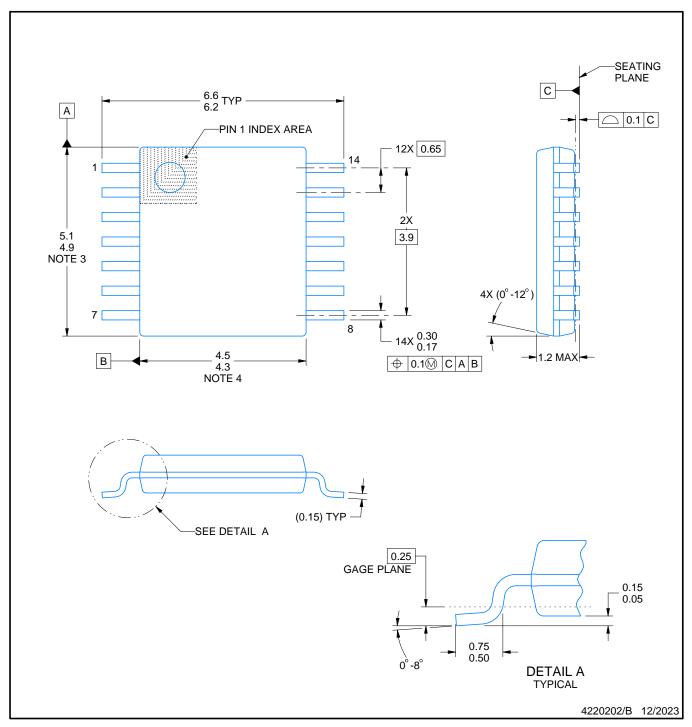

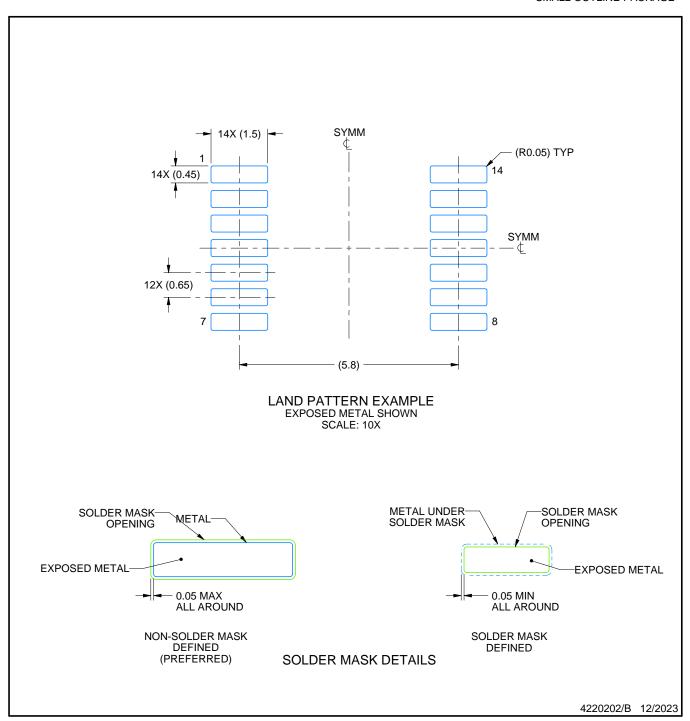

#### OPA4180 D, PW Packages 14-Pin SOIC, TSSOP (Top View)

#### **Pin Functions: OPA4180**

|       | PIN | DESCRIPTION                                             |  |

|-------|-----|---------------------------------------------------------|--|

| NAME  | NO. | DESCRIPTION                                             |  |

| −IN A | 2   | Inverting input, channel A                              |  |

| +IN A | 3   | Noninverting input, channel A                           |  |

| –IN B | 6   | Inverting input, channel B                              |  |

| +IN B | 5   | Noninverting input, channel B                           |  |

| –IN C | 9   | Inverting input, channel C                              |  |

| +IN C | 10  | Noninverting input, channel C                           |  |

| –IN D | 13  | Inverting input, channel D                              |  |

| +IN D | 12  | Noninverting input, channel D                           |  |

| OUT A | 1   | Output, channel A                                       |  |

| OUT B | 7   | Output, channel B                                       |  |

| OUT C | 8   | Output, channel C                                       |  |

| OUT D | 14  | Output, channel D                                       |  |

| V-    | 11  | Negative supply or ground (for single-supply operation) |  |

| V+    | 4   | Positive supply or ground (for single-supply operation) |  |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                          |                                     | MIN        | MAX                         | UNIT |

|------------------|--------------------------|-------------------------------------|------------|-----------------------------|------|

|                  | Supply voltage           |                                     |            | ±20, ±40<br>(single-supply) | V    |

|                  | Signal input terminals   | Voltage                             | (V-) - 0.5 | (V+) + 0.5                  | V    |

|                  | Signal input terminals   | Current                             |            | ±10                         | mA   |

|                  | Output short-circuit (2) | Output short-circuit <sup>(2)</sup> |            |                             |      |

|                  | Operating temperature    |                                     | -55        | 125                         | °C   |

| TJ               | Junction temperature     |                                     |            | 150                         | °C   |

| T <sub>stg</sub> | Storage temperature      |                                     | -65        | 150                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                          |                                                                               | MIN  | MAX | UNIT |

|--------------------|--------------------------|-------------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>   | Storage temperature rang | e                                                                             | -65  | 150 | °C   |

| V                  | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | -1.5 | 1.5 | 147  |

| V <sub>(ESD)</sub> |                          | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -1   | 1   | - kV |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted),  $R_L = 10 \text{ k}\Omega$  connected to  $V_S / 2$ , and  $V_{COM} = V_{OUT} = V_S / 2$ , (unless otherwise noted)

|                              |                | MIN   | NOM | MAX | UNIT |

|------------------------------|----------------|-------|-----|-----|------|

| Supply voltage [(V+) – (V–)] | Single-supply  | 4.5   |     | 36  | V    |

|                              | Bipolar-supply | ±2.25 |     | ±18 | V    |

| Operating temperature        |                | -40   |     | 125 | °C   |

<sup>(2)</sup> Short-circuit to ground, one amplifier per package.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information: OPA180

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DBV (SOT-23) | DGK (MSOP) | UNIT |

|----------------------|----------------------------------------------|----------|--------------|------------|------|

|                      |                                              | 8 PINS   | 5 PINS       | 8 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 115.8    | 158.8        | 180.4      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case(top) thermal resistance     | 60.1     | 60.7         | 67.9       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 56.4     | 44.8         | 102.1      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 12.8     | 1.6          | 10.4       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 55.9     | 4.2          | 100.3      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case(bottom) thermal resistance  | N/A      | N/A          | N/A        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Thermal Information: OPA2180

|                      |                                              | OP/      |            |      |

|----------------------|----------------------------------------------|----------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGK (MSOP) | UNIT |

|                      |                                              | 8 PINS   | 8 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 111      | 159.3      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 54.9     | 37.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 51.7     | 48.5       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 9.3      | 1.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 51.1     | 77.1       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A      | N/A        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.6 Thermal Information: OPA4180

|                      |                                              | OPA4180  |            |      |  |  |

|----------------------|----------------------------------------------|----------|------------|------|--|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | PW (TSSOP) | UNIT |  |  |

|                      |                                              | 14 PINS  | 14 PINS    |      |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 93.2     | 106.9      | °C/W |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 51.8     | 24.4       | °C/W |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 49.4     | 59.3       | °C/W |  |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 13.5     | 0.6        | °C/W |  |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 42.2     | 54.3       | °C/W |  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A      | N/A        | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.7 Electrical Characteristics: $V_S = \pm 2 \text{ V to } \pm 18 \text{ V (}V_S = 4 \text{ V to } 36 \text{ V)}$

at T\_A = 25°C, R\_L = 10 k $\Omega$  connected to V\_S / 2, and V\_COM = V\_OUT = V\_S / 2, unless otherwise noted.

|                      | PARAMETER                   |         | CONDITIONS                                                                                                      | MIN | TYP              | MAX        | UNIT                     |

|----------------------|-----------------------------|---------|-----------------------------------------------------------------------------------------------------------------|-----|------------------|------------|--------------------------|

| OFFSET \             | /OLTAGE                     |         |                                                                                                                 |     |                  |            |                          |

| V <sub>IO</sub>      | Input offset voltage        |         |                                                                                                                 |     | 15               | 75         | μV                       |

| dV <sub>IO</sub> /dT | Input offset voltage drift  |         | $T_A = -40$ °C to +125°C                                                                                        |     | 0.1              | 0.35       | μV/°C                    |

| DCDD                 | Dawar aumah, raia atian ra  | lia.    | V <sub>S</sub> = 4 V to 36 V,<br>V <sub>CM</sub> = V <sub>S</sub> / 2                                           |     | 0.1              | 0.5        | μV/V                     |

| PSRR                 | Power supply rejection ra   | lio     | $T_A = -40$ °C to +125°C,<br>$V_S = 4$ V to 36 V, $V_{CM} = V_S$ / 2                                            |     |                  | 0.5        | μV/V                     |

|                      | Long-term stability         |         |                                                                                                                 |     | 4 <sup>(1)</sup> |            | μV                       |

|                      | Channel separation, DC      |         |                                                                                                                 |     | 1                |            | μV/V                     |

| INPUT BIA            | AS CURRENT                  |         |                                                                                                                 |     |                  |            |                          |

|                      |                             |         | OPA2180                                                                                                         |     | ±0.25            | ±1         | nA                       |

|                      | In most bing assument       |         | OPA2180: $T_A = -40^{\circ}\text{C}$ to +105°C                                                                  | 18  |                  | ±5         | nA                       |

| I <sub>IB</sub>      | Input bias current          |         | OPA180, OPA4180                                                                                                 |     | ±0.25            | ±1.7       | nA                       |

|                      |                             |         | OPA180, OPA4180: T <sub>A</sub> = -40°C to +125°C                                                               | 18  |                  | ±6         | nA                       |

|                      |                             |         | OPA2180                                                                                                         |     | ±0.5             | ±2         | nA                       |

|                      |                             |         | OPA2180: $T_A = -40^{\circ}\text{C}$ to +105°C                                                                  | 6   |                  | ±2.5       | nA                       |

| I <sub>IO</sub>      | Input offset current        |         | OPA180, OPA4180                                                                                                 |     |                  | ±3.4       | nA                       |

|                      |                             |         | OPA180, OPA4180: T <sub>A</sub> = -40°C to +125°C                                                               | 6   |                  | ±3         | nA                       |

| NOISE                |                             |         | , ,                                                                                                             |     |                  |            |                          |

|                      | Input voltage noise         |         | f = 0.1 Hz to 10 Hz                                                                                             |     | 0.25             |            | $\mu V_{PP}$             |

| e <sub>n</sub>       | Input voltage noise density |         | f = 1  kHz                                                                                                      |     | 10               |            | nV/√ <del>Hz</del>       |

| in                   | Input current noise density |         | f = 1  kHz                                                                                                      |     | 10               |            | fA/√ <del>Hz</del>       |

|                      | LTAGE RANGE                 | ,       | 3                                                                                                               |     |                  |            |                          |

| V <sub>CM</sub>      | Common-mode voltage ra      | ange    |                                                                                                                 | V-  |                  | (V+) - 1.5 | V                        |

| CIVI                 |                             | - J-    | (V–) < V <sub>CM</sub> < (V+) – 1.5 V                                                                           | 104 | 114              | ( / -      | dB                       |

| CMRR                 | Common-mode rejection       | ratio   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C},$<br>$(V-) + 0.5 \text{ V} < V_{CM} < (V+) - 1.5 \text{ V}$ | 100 | 104              |            | dB                       |

| INPUT IM             | PEDANCE                     |         |                                                                                                                 | +   |                  |            |                          |

| Z <sub>id</sub>      | Differential                |         |                                                                                                                 |     | 100    6         |            | MΩ    pF                 |

| z <sub>ic</sub>      | Common-mode                 |         |                                                                                                                 |     | 6    9.5         |            | 10 <sup>12</sup> Ω    pF |

| OPEN-LO              |                             |         |                                                                                                                 |     | - 11             |            |                          |

|                      | <u></u>                     |         | $(V-) + 500 \text{ mV} < V_0 < (V+) - 500 \text{ mV}$<br>$R_L = 10 \text{ k}\Omega$                             | 110 | 120              |            | dB                       |

| A <sub>OL</sub>      | Open-loop voltage gain      |         | $T_A = -40$ °C to +125 °C (V-) + 500 mV < V <sub>O</sub> < (V+) - 500 mV, R <sub>L</sub> = 10 kΩ                | 104 | 114              |            | dB                       |

| FREQUEN              | NCY RESPONSE                |         |                                                                                                                 |     |                  |            | ·                        |

| GBW                  | Gain bandwidth product      |         |                                                                                                                 |     | 2                |            | MHz                      |

| SR                   | Slew rate                   |         | G = 1                                                                                                           |     | 0.8              |            | V/μs                     |

|                      | 0.1%                        |         | $V_S = \pm 18 \text{ V}, G = 1, 10\text{-V step}$ 22                                                            |     |                  | μS         |                          |

| t <sub>s</sub>       | Settling time               | 0.01%   | V <sub>S</sub> = ±18 V, G = 1, 10-V step                                                                        |     | 30               |            | μS                       |

| t <sub>or</sub>      | Overload recovery time      | 1       | $V_{IN} \times G = V_{S}$                                                                                       |     | 1                |            | μS                       |

| THD+N                | Total harmonic distortion   | + noise | $f = 1 \text{ kHz}, G = 1, V_{OUT} = 1 V_{RMS}$                                                                 |     | 0.0001%          |            | •                        |

<sup>(1) 1000-</sup>hour life test at 125°C demonstrated randomly distributed variation in the range of measurement limits, or approximately 4  $\mu$ V.

# Electrical Characteristics: $V_S = \pm 2 \text{ V to } \pm 18 \text{ V (V}_S = 4 \text{ V to } 36 \text{ V)}$ (continued)

at  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$  connected to  $V_S$  / 2, and  $V_{COM}$  =  $V_{OUT}$  =  $V_S$  / 2, unless otherwise noted.

|                   | PARAMETER                         | CONDITIONS                                             | MIN       | TYP | MAX        | UNIT |  |  |  |  |

|-------------------|-----------------------------------|--------------------------------------------------------|-----------|-----|------------|------|--|--|--|--|

| OUTPUT            | •                                 |                                                        |           |     |            |      |  |  |  |  |

|                   |                                   | No load                                                |           | 8   | 18         | mV   |  |  |  |  |

|                   | Voltage output swing from rail    | $R_L = 10 \text{ k}\Omega$                             |           | 250 | 300        | mV   |  |  |  |  |

|                   | vollage output swing from fair    | $T_A = -40$ °C to +125°C<br>$R_L = 10 \text{ k}\Omega$ |           | 325 | 360        | mV   |  |  |  |  |

| Ios               | Short-circuit current             |                                                        |           | ±18 |            | mA   |  |  |  |  |

| r <sub>o</sub>    | Output resistance (open loop)     | $f = 2 \text{ MHz}, I_{O} = 0 \text{ mA}$              |           | 120 |            | Ω    |  |  |  |  |

| C <sub>LOAD</sub> | Capacitive load drive             |                                                        |           | 1   |            | nF   |  |  |  |  |

| POWER             | SUPPLY                            |                                                        |           |     |            |      |  |  |  |  |

| Vs                | Operating voltage range           |                                                        | ±2 (or 4) | ±   | 18 (or 36) | V    |  |  |  |  |

|                   |                                   |                                                        |           | 450 | 525        | μА   |  |  |  |  |

| IQ                | Quiescent current (per amplifier) | $T_A = -40$ °C to +125°C<br>$I_O = 0$ mA               |           |     | 600        | μА   |  |  |  |  |

| TEMPER            | TEMPERATURE                       |                                                        |           |     |            |      |  |  |  |  |

|                   | Specified range                   |                                                        | -40       |     | 105        | °C   |  |  |  |  |

|                   | Operating range                   |                                                        | -40       |     | 105        | °C   |  |  |  |  |

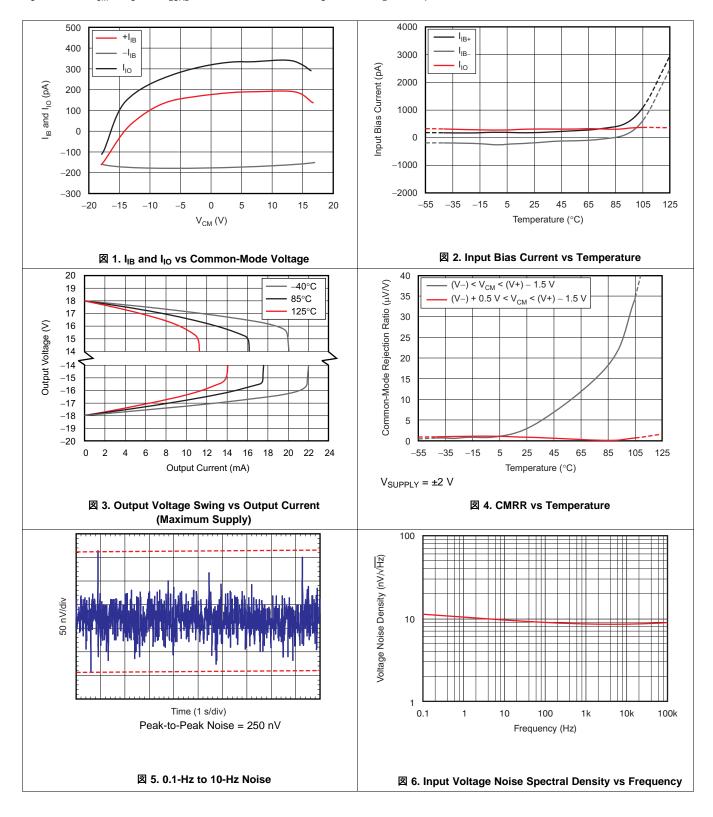

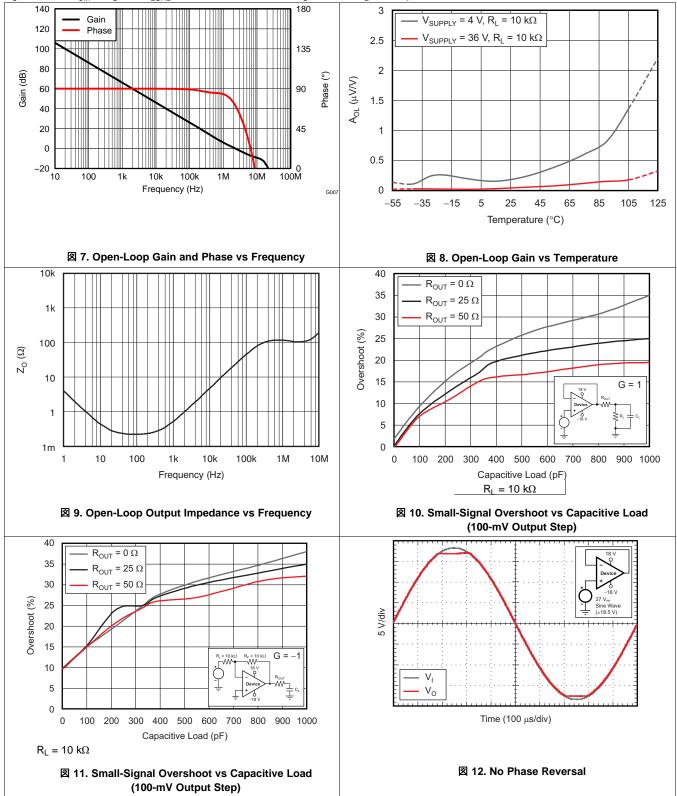

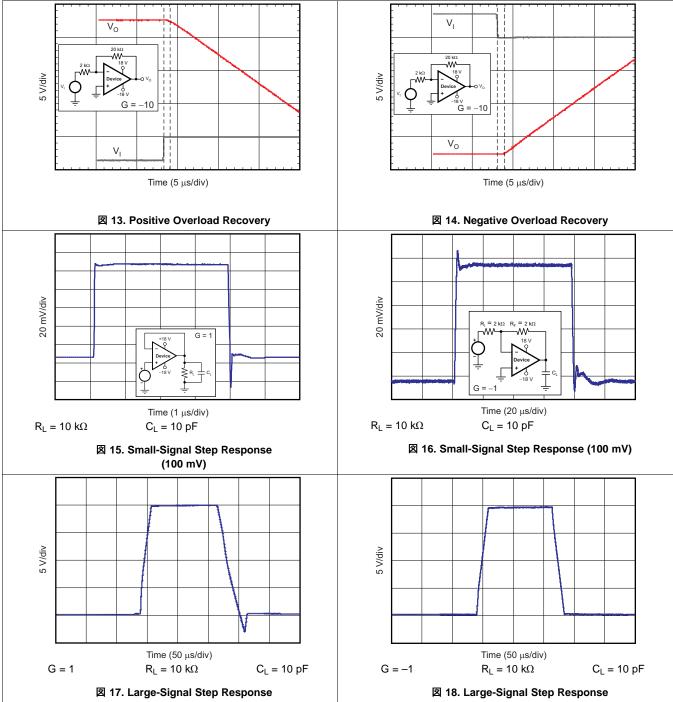

## 7.8 Typical Characteristics: Table of Graphs

## 表 2. Characteristic Performance Measurements

| DESCRIPTION                                                    | FIGURE     |

|----------------------------------------------------------------|------------|

| I <sub>B</sub> and I <sub>OS</sub> vs Common-Mode Voltage      | 図 1        |

| Input Bias Current vs Temperature                              | ⊠ 2        |

| Output Voltage Swing vs Output Current (Maximum Supply)        | ⊠ 3        |

| CMRR vs Temperature                                            | ☑ 4        |

| 0.1-Hz to 10-Hz Noise                                          | 図 5        |

| Input Voltage Noise Spectral Density vs Frequency              | 図 6        |

| Open-Loop Gain and Phase vs Frequency                          | 図 7        |

| Open-Loop Gain vs Temperature                                  | 図 8        |

| Open-Loop Output Impedance vs Frequency                        | 図 9        |

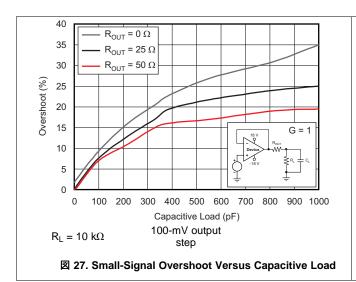

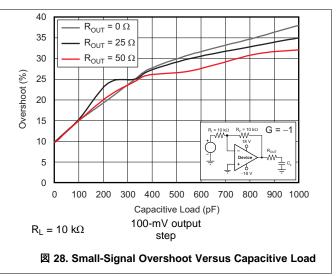

| Small-Signal Overshoot vs Capacitive Load (100-mV Output Step) | 図 10, 図 11 |

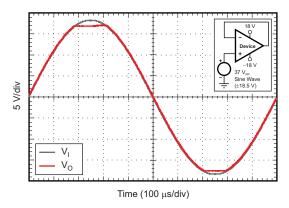

| No Phase Reversal                                              | 図 12       |

| Positive Overload Recovery                                     | 図 13       |

| Negative Overload Recovery                                     | 図 14       |

| Small-Signal Step Response (100 mV)                            | 図 15, 図 16 |

| Large-Signal Step Response                                     | 図 17, 図 18 |

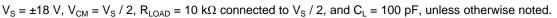

| Large-Signal Settling Time (10-V Positive Step)                | 図 19       |

| Large-Signal Settling Time (10-V Negative Step)                | 図 20       |

| Short-Circuit Current vs Temperature                           | 図 21       |

| Maximum Output Voltage vs Frequency                            | 図 22       |

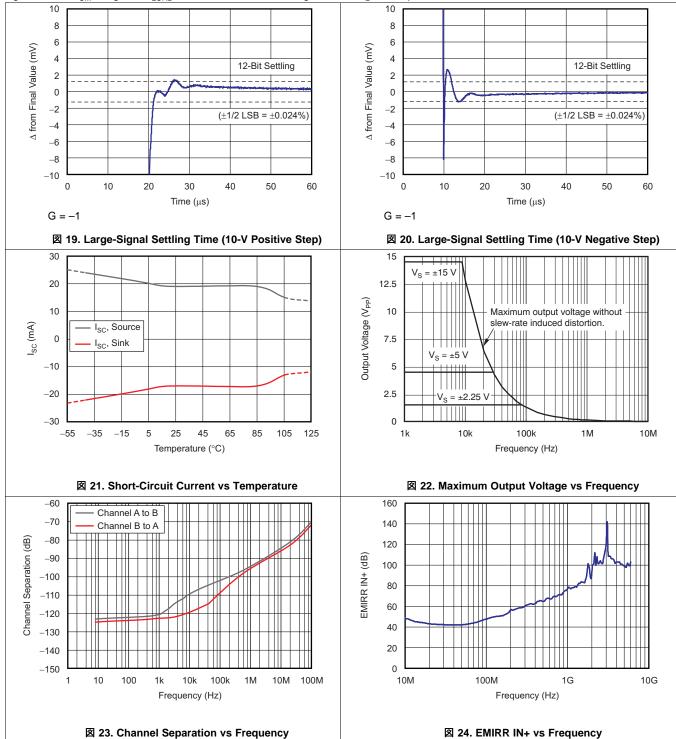

| Channel Separation vs Frequency                                | ☑ 23       |

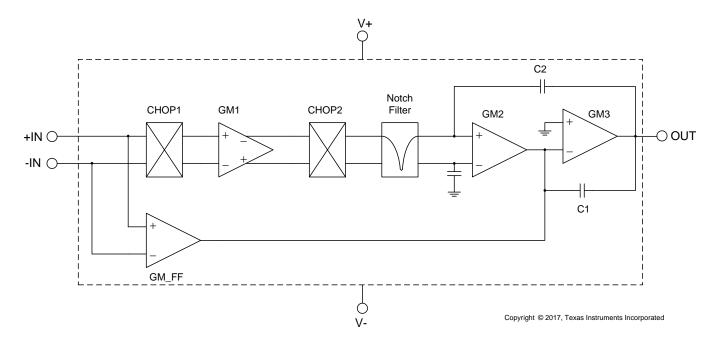

| EMIRR IN+ vs Frequency                                         | 図 24       |

#### 7.9 Typical Characteristics

$V_S$  = ±18 V,  $V_{CM}$  =  $V_S$  / 2,  $R_{LOAD}$  = 10 k $\Omega$  connected to  $V_S$  / 2, and  $C_L$  = 100 pF, unless otherwise noted.

# TEXAS INSTRUMENTS

#### **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

$V_S$  = ±18 V,  $V_{CM}$  =  $V_S$  / 2,  $R_{LOAD}$  = 10 k $\Omega$  connected to  $V_S$  / 2, and  $C_L$  = 100 pF, unless otherwise noted.

# TEXAS INSTRUMENTS

#### **Typical Characteristics (continued)**

#### 8 Detailed Description

#### 8.1 Overview

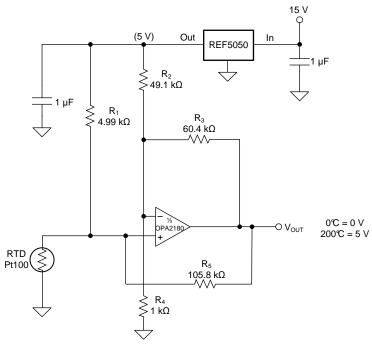

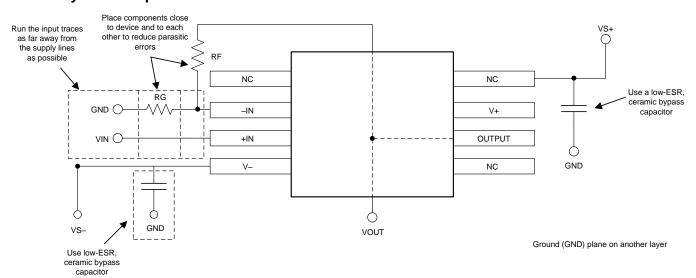

The OPAx180 family of operational amplifiers combine precision offset and drift with excellent overall performance, making them designed for many precision applications. The precision offset drift of only 0.1  $\mu$ V/°C provides stability over the entire temperature range. In addition, the devices offer excellent overall performance with high CMRR, PSRR, and A<sub>OL</sub>. As with all amplifiers, applications with noisy or high-impedance power supplies require decoupling capacitors close to the device pins. In most cases, 0.1- $\mu$ F capacitors are adequate.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Operating Characteristics

The OPAx180 family of amplifiers is specified for operation from 4 V to 36 V (±2 V to ±18 V). Many of the specifications apply from -40°C to +125°C. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in the *Typical Characteristics*.

#### 8.3.2 EMI Rejection

The OPAx180 family uses integrated electromagnetic interference (EMI) filtering to reduce the effects of EMI interference from sources such as wireless communications and densely populated boards with a mix of analog signal chain and digital components. EMI immunity can improve with circuit design techniques; the OPAx180 family benefits from these design improvements. Texas Instruments has developed the ability to accurately measure and quantify the immunity of an operational amplifier over a broad frequency spectrum extending from 10 MHz to 6 GHz. 25 shows the results of this testing on the OPAx180 family. For more detailed information, see the EMI Rejection Ratio of Operational Amplifiers application report, available for download from www.ti.com.

図 25. OPAx180 EMIRR Testing

#### 8.3.3 Phase-Reversal Protection

The OPAx180 family has an internal phase-reversal protection. Many op amps exhibit a phase reversal when the input is driven beyond the linear common-mode range. This condition is most often encountered in noninverting circuits when the input is driven beyond the specified common-mode voltage range, causing the output to reverse into the opposite rail. The input of the OPAx180 prevents phase reversal with excessive common-mode voltage. Instead, the output limits into the appropriate rail. This performance is shown in 26.

図 26. No Phase Reversal

#### **Feature Description (continued)**

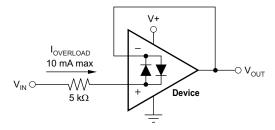

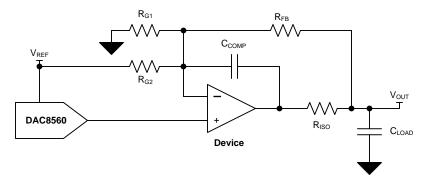

#### 8.3.4 Capacitive Load and Stability