## OPAx277 高精度オペアンプ

### 1 特長

- 非常に小さいオフセット電圧:  $10\mu V$

- 非常に低いドリフト:  $0.1\mu V/C$

- 高いオープン・ループ・ゲイン:  $134dB$

- 高い同相信号除去比:  $140dB$

- 高い電源電圧変動除去比:  $130dB$

- 低いバイアス電流:  $1nA$  (最大値)

- 広い電源電圧範囲:  $\pm 2V \sim \pm 18V$

- 低い静止電流:  $800\mu A$  (アンプ 1 個あたり)

- シングル、デュアル、クワッドの各バージョン

- OP-07, OP-77, OP-177 の代替

- $\pm 40V$  の過電圧保護で同様の性能を得るには、**OPA2206** を参照

### 2 アプリケーション

- アナログ入力モジュール

- 重量計

- 温度トランスマッタ

- 圧力トランスマッタ

- データ・アクイジション (DAQ)

- 実験室およびフィールド計測

- バッテリ試験装置

### 3 概要

OPAx277 シリーズの高精度オペアンプは、業界標準の OP-177 に代わる製品です。OPAx277 デバイスは、ノイズを改善、出力電圧スイングを拡大、半分の静止電流で 2 倍の速度を実現します。非常に低いオフセット電圧およびドリフト、低いバイアス電流、高い同相除去比、高い電源電圧変動除去比という特長があります。

OPAx277 は  $\pm 2 \sim \pm 18V$  の電源で動作し、非常に優れた性能を発揮します。ほとんどのオペアンプは 1 つの電源電圧でのみ動作が規定されているのに対して、OPAx277 シリーズは複数の実アプリケーション向けに規定されており、 $\pm 5V$  (10V)  $\sim \pm 15V$  (30V) の電源電圧範囲に対して単一の制限が適用されます。アンプが規定された制限までスイングしても、高い性能が維持されます。初期オフセット電圧 (最大  $\pm 20\mu V$ ) は非常に低いため、ユーザーによる調整は通常必要ありません。ただし、シングル・バージョン (OPA277) では、特別なアプリケーション用に外部トリム・ピンが提供されます。

OPAx277 オペアンプは簡単に使用でき、一部のオペアンプに見られる位相反転や過負荷の問題は発生しません。これらのデバイスはユニティ・ゲイン安定で、広い範囲の負荷状況にわたって優れた動的動作を実現します。デュアルおよびクワッド・バージョンは完全に独立した回路を使用しているため、オーバードライブまたは過負荷時でも、クロストークが最小限に抑えられ、相互作用が発生しません。

### 製品情報

| 部品番号               | パッケージ <sup>(1)</sup> | 本体サイズ (公称)       |

|--------------------|----------------------|------------------|

| OPA277、<br>OPA2277 | D (SOIC, 8)          | 3.91mm × 4.90mm  |

|                    | DRM (VSON, 8)        | 4.00mm × 4.00mm  |

|                    | P (PDIP, 8)          | 6.35mm × 9.81mm  |

| OPA4277            | D (SOIC, 14)         | 3.91mm × 8.65mm  |

|                    | P (PDIP, 14)         | 6.35mm × 19.30mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照くださいますようお願いいたします。

## 目次

|                           |           |                                     |           |

|---------------------------|-----------|-------------------------------------|-----------|

| <b>1 特長</b>               | <b>1</b>  | 7.3 機能説明.....                       | <b>14</b> |

| <b>2 アプリケーション</b>         | <b>1</b>  | 7.4 デバイスの機能モード.....                 | <b>17</b> |

| <b>3 概要</b>               | <b>1</b>  | <b>8 アプリケーションと実装</b> .....          | <b>18</b> |

| <b>4 改訂履歴</b>             | <b>2</b>  | 8.1 アプリケーション情報.....                 | <b>18</b> |

| <b>5 ピン構成および機能</b>        | <b>3</b>  | 8.2 代表的なアプリケーション.....               | <b>18</b> |

| <b>6 仕様</b>               | <b>6</b>  | 8.3 電源に関する推奨事項.....                 | <b>20</b> |

| 6.1 絶対最大定格.....           | 6         | 8.4 レイアウト.....                      | 21        |

| 6.2 ESD 定格.....           | 6         | <b>9 デバイスおよびドキュメントのサポート</b> .....   | <b>23</b> |

| 6.3 推奨動作条件.....           | 6         | 9.1 デバイスのサポート.....                  | 23        |

| 6.4 熱に関する情報: OPA277.....  | 7         | 9.2 ドキュメントのサポート.....                | 24        |

| 6.5 熱に関する情報: OPA2277..... | 7         | 9.3 ドキュメントの更新通知を受け取る方法.....         | 24        |

| 6.6 熱に関する情報: OPA4277..... | 7         | 9.4 サポート・リソース.....                  | 24        |

| 6.7 電気的特性.....            | 8         | 9.5 商標.....                         | 24        |

| 6.8 代表的特性.....            | 10        | 9.6 静電気放電に関する注意事項.....              | 24        |

| <b>7 詳細説明</b>             | <b>14</b> | 9.7 用語集.....                        | <b>24</b> |

| 7.1 概要.....               | 14        | <b>10 メカニカル、パッケージ、および注文情報</b> ..... | <b>24</b> |

| 7.2 機能ブロック図.....          | 14        |                                     |           |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision B (April 2015) to Revision C (February 2023)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • 文書全体にわたって表、図、相互参照の採番方法を更新.....                                          | 1           |

| • アプリケーションの箇条書き項目にリンクを追加.....                                             | 1           |

| • シングル、デュアル、クワッドの各バージョンで同一仕様に関するテキストを削除.....                              | 1           |

| • オフセット・トリム・ピンの種類を「入力」から「—」に変更.....                                       | 3           |

| • 「OPA2277 のピン機能」表で「DFN」を「DRM (VSON)」に変更.....                             | 3           |

| • 「絶対最大定格」表に、入力ピンの電流制限 10mA の注を追加.....                                    | 6           |

| • 「絶対最大定格」表から動作温度を削除.....                                                 | 6           |

| • 「絶対最大定格」表からリード温度を削除.....                                                | 6           |

| • OPA2277 および OPA4277 SOIC パッケージの「熱に関する情報」の値を変更。.....                     | 7           |

| • 「電気的特性」のヘッダーにテスト条件を追加.....                                              | 8           |

| • 読みやすさのために「電気的特性」のフォーマットを変更.....                                         | 8           |

| • 「電気的特性」の入力オフセット電圧と時間の関係を長期ドリフトに変更.....                                  | 8           |

| • 入力バイアス電流のテスト条件を温度範囲全体の仕様と分離するよう変更.....                                  | 8           |

| • 開ループ・ゲイン・パラメータの冗長行を削除.....                                              | 8           |

| • 整合性のため $C_{LOAD}$ を $C_L$ に変更.....                                      | 8           |

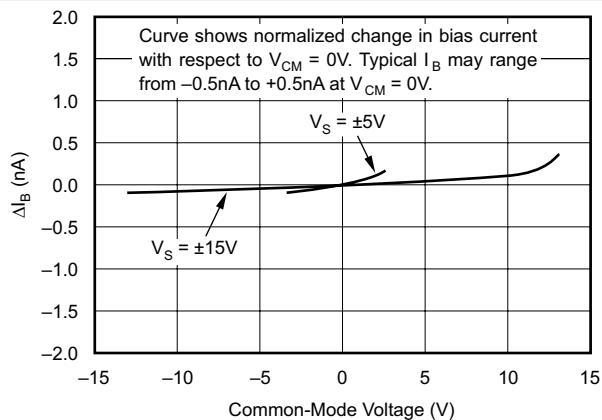

| • 図 6-14「入力バイアス電流と同相電圧との関係」を変更し、注の誤字を訂正.....                              | 10          |

| • 「DFN パッケージ」を「DRM パッケージ (8 ピン VSON)」に変更.....                             | 21          |

| • 「DFN パッケージ」を「DRM パッケージ」に変更し、「8 ピン VSON」を追加.....                         | 21          |

| • 「開発サポート」セクションを変更し、更新されたリンクとリソースを表示.....                                 | 23          |

| <b>Changes from Revision A (April 2005) to Revision B (April 2015)</b>                                                                                    | <b>Page</b> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • 「ESD 定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加。..... | 1           |

## 5 ピン構成および機能

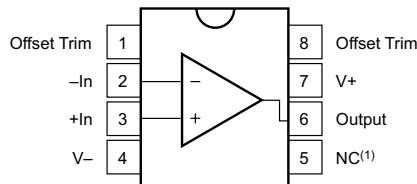

図 5-1. OPA277 P パッケージ、8 ピン PDIP および D パッケージ、8 ピン SOIC (上面図)

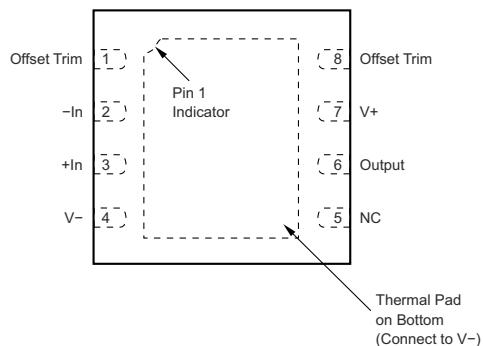

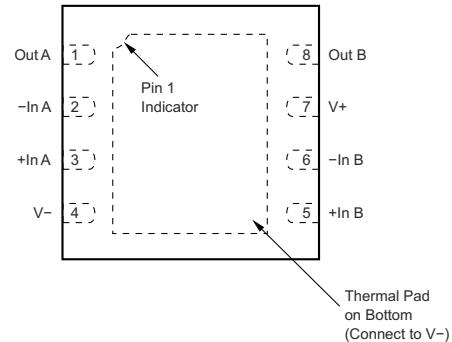

図 5-2. OPA277 DRM パッケージ、8 ピン VSON (上面図)

表 5-1. ピンの機能 : OPA277

| ピン        |    | 種類 | 説明                                |

|-----------|----|----|-----------------------------------|

| 名称        | 番号 |    |                                   |

| -In       | 2  | 入力 | 反転入力                              |

| +In       | 3  | 入力 | 非反転入力                             |

| NC        | 5  | —  | 内部接続なし (フローティングのままで可)             |

| オフセット・トリム | 1  | —  | 入力オフセット電圧トリム (使用しない場合はフローティングのまま) |

| オフセット・トリム | 8  | —  | 入力オフセット電圧トリム (使用しない場合はフローティングのまま) |

| 出力        | 6  | 出力 | 出力                                |

| V-        | 4  | —  | 負 (最低) 電源                         |

| V+        | 7  | —  | 正 (最高) 電源                         |

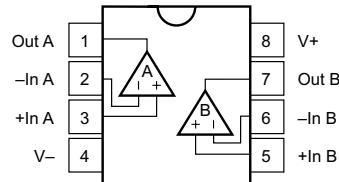

図 5-3. OPA2277 P パッケージ、8 ピン PDIP および D パッケージ、8 ピン SOIC (上面図)

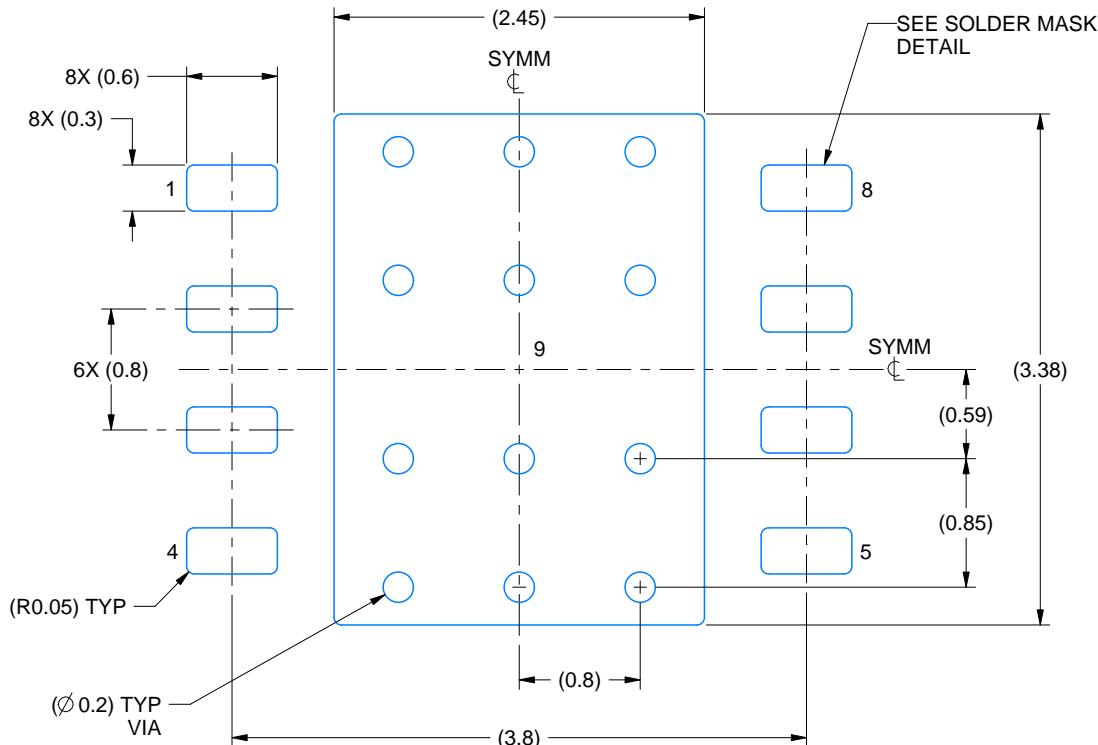

図 5-4. OPA2277 DRM パッケージ、8 ピン VSON (上面図)

表 5-2. ピンの機能 : OPA2277

| ピン    |                   |            | 種類 | 説明           |

|-------|-------------------|------------|----|--------------|

| 名称    | D (SOIC)、P (PDIP) | DRM (VSON) |    |              |

| -In A | 2                 | 2          | 入力 | 反転入力、チャネル A  |

| -In B | 6                 | 6          | 入力 | 反転入力、チャネル B  |

| +In A | 3                 | 3          | 入力 | 非反転入力、チャネル A |

| +In B | 5                 | 5          | 入力 | 非反転入力、チャネル B |

| Out A | 1                 | 1          | 出力 | 出力チャネル A     |

| Out B | 7                 | 8          | 出力 | 出力チャネル B     |

| V-    | 4                 | 4          | —  | 負(最低)電源      |

| V+    | 8                 | 7          | —  | 正(最高)電源      |

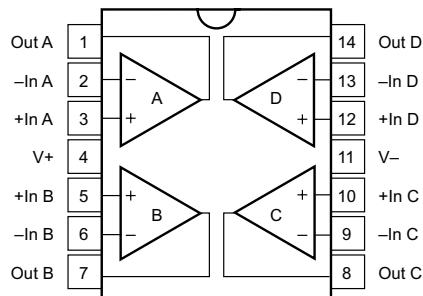

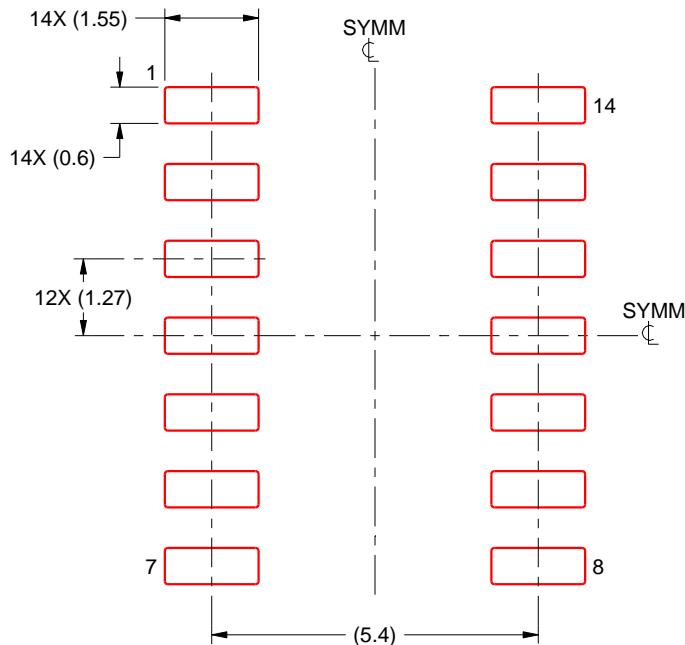

図 5-5. OPA4277 P パッケージ、14 ピン PDIP および D パッケージ、14 ピン SOIC (上面図)

表 5-3. ピンの機能 : OPA4277

| ピン    |    | 種類 | 説明           |

|-------|----|----|--------------|

| 名称    | 番号 |    |              |

| -In A | 2  | 入力 | 反転入力、チャネル A  |

| -In B | 6  | 入力 | 反転入力、チャネル B  |

| -In C | 9  | 入力 | 反転入力、チャネル C  |

| -In D | 13 | 入力 | 反転入力、チャネル D  |

| +In A | 3  | 入力 | 非反転入力、チャネル A |

| +In B | 5  | 入力 | 非反転入力、チャネル B |

| +In C | 10 | 入力 | 非反転入力、チャネル C |

| +In D | 12 | 入力 | 非反転入力、チャネル D |

| Out A | 1  | 出力 | 出力チャネル A     |

| Out B | 7  | 出力 | 出力チャネル B     |

| Out C | 8  | 出力 | 出力チャネル C     |

| Out D | 14 | 出力 | 出力チャネル D     |

| V+    | 4  | —  | 正(最高)電源      |

| V-    | 11 | —  | 負(最低)電源      |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|           |                           | 最小値          | 最大値          | 単位 |

|-----------|---------------------------|--------------|--------------|----|

| $V_S$     | 電源電圧、 $V_S = (V+) - (V-)$ |              | 36           | V  |

|           | 入力電圧 <sup>(2)</sup>       | $(V-) - 0.7$ | $(V+) + 0.7$ | V  |

| $I_{SC}$  | 出力短絡 <sup>(3)</sup>       |              | 連続           |    |

| $T_J$     | 接合部温度                     |              | 150          | °C |

| $T_{STG}$ | 保管温度                      | -55          | 125          | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このような条件や、「推奨動作条件」に記載されている条件を超える条件でデバイスが機能するということを意味するわけではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 電源レールを超えて 0.7V 以上スイングする入力信号は、電流を 10mA 以下に抑える必要があります。

- (3) グランドへの短絡、1 パッケージ当たり 1 アンプ。

### 6.2 ESD 定格

|             |       |                                                        | 値     | 単位 |

|-------------|-------|--------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>   | ±2000 | V  |

|             |       | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | ±500  | V  |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|       |                           |      | 最小値 | 公称値 | 最大値 | 単位 |

|-------|---------------------------|------|-----|-----|-----|----|

| $V_S$ | 電源電圧、 $V_S = (V+) - (V-)$ | 単一電源 | 4   | 30  | 36  | V  |

|       |                           | 2 電源 | ±2  | ±15 | ±18 |    |

| $T_A$ | 周囲温度                      |      | -40 |     | 85  | °C |

## 6.4 热に関する情報 : OPA277

| 热評価基準 <sup>(1)</sup>  |                   | OPA277   |            |          | 単位   |

|-----------------------|-------------------|----------|------------|----------|------|

|                       |                   | D (SOIC) | DRM (VSON) | P (PDIP) |      |

|                       |                   | 8 ピン     | 8 ピン       | 8 ピン     |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 110.1    | 40.7       | 49.2     | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 52.2     | 41.3       | 39.4     | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 52.3     | 16.7       | 26.4     | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性パラメータ | 10.4     | 0.6        | 15.4     | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性パラメータ | 51.5     | 16.9       | 26.3     | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(下面)への熱抵抗 | 該当なし     | 3.3        | 該当なし     | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.5 热に関する情報 : OPA2277

| 热評価基準 <sup>(1)</sup>  |                   | OPA2277  |            |          | 単位   |

|-----------------------|-------------------|----------|------------|----------|------|

|                       |                   | D (SOIC) | DRM (VSON) | P (PDIP) |      |

|                       |                   | 8 ピン     | 8 ピン       | 8 ピン     |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 126.9    | 39.3       | 47.2     | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 67.1     | 36.9       | 36.0     | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 70.3     | 15.4       | 24.4     | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性パラメータ | 18.8     | 0.4        | 13.4     | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性パラメータ | 69.5     | 15.6       | 24.3     | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(下面)への熱抵抗 | 該当なし     | 2.2        | 該当なし     | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.6 热に関する情報 : OPA4277

| 热評価基準 <sup>(1)</sup>  |                   | OPA4277  |          | 単位   |

|-----------------------|-------------------|----------|----------|------|

|                       |                   | D (SOIC) | P (PDIP) |      |

|                       |                   | 14 ピン    | 14 ピン    |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 86.5     | 66.3     | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 38.5     | 20.5     | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 43.5     | 26.8     | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性パラメータ | 7.4      | 2.1      | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性パラメータ | 42.9     | 26.2     | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(下面)への熱抵抗 | 該当なし     | 該当なし     | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.7 電気的特性

$T_A = 25^\circ\text{C}$ ,  $V_S = 10\text{V} \sim 30\text{V}$ ,  $V_{CM} = V_{OUT} = V_S/2$ ,  $R_L = 2\text{k}\Omega$  を  $V_S/2$  に接続 (特に記述のない限り)

| パラメータ                       | テスト条件         | 最小値                                                                                                     | 標準値                  | 最大値               | 単位                                   |  |

|-----------------------------|---------------|---------------------------------------------------------------------------------------------------------|----------------------|-------------------|--------------------------------------|--|

| <b>オフセット電圧</b>              |               |                                                                                                         |                      |                   |                                      |  |

| $V_{OS}$                    | 入力オフセット電圧     | OPA277P, U                                                                                              | $\pm 10$             | $\pm 20$          | $\mu\text{V}$                        |  |

|                             |               | OPA2277P, U                                                                                             | $\pm 10$             | $\pm 25$          |                                      |  |

|                             |               | OPAx277PA, UA                                                                                           | $\pm 20$             | $\pm 50$          |                                      |  |

|                             |               | OPAx277AIDRM                                                                                            | $\pm 35$             | $\pm 100$         |                                      |  |

|                             |               | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                        | OPA277P, U           | $\pm 30$          |                                      |  |

|                             |               |                                                                                                         | OPA2277P, U          | $\pm 50$          |                                      |  |

|                             |               |                                                                                                         | OPAx277PA, UA        | $\pm 100$         |                                      |  |

|                             |               |                                                                                                         | OPAx277AIDRM         | $\pm 165$         |                                      |  |

| $dV_{OS}/dT$                | 入力オフセット電圧ドリフト | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                        | OPA277P, U           | $\pm 0.1$         | $\pm 0.15$                           |  |

|                             |               |                                                                                                         | OPA2277P, U          | $\pm 0.1$         | $\pm 0.25$                           |  |

|                             |               |                                                                                                         | OPAx277AIDRM, PA, UA | $\pm 0.15$        | $\pm 1$                              |  |

| 長期ドリフト                      |               |                                                                                                         |                      | 0.2               | $\mu\text{V}/\text{mo}$              |  |

| PSRR                        | 電源電圧変動除去比     | $V_S = \pm 2\text{V} \sim \pm 18\text{V}$                                                               | OPAx277P, U          | $\pm 0.3$         | $\pm 0.5$                            |  |

|                             |               |                                                                                                         | OPAx277AIDRM, PA, UA | $\pm 0.3$         | $\pm 1$                              |  |

|                             |               | $V_S = \pm 2\text{V} \sim \pm 18\text{V}$ ,<br>$T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$         | OPAx277P, U          | $\pm 0.5$         | $\pm 1$                              |  |

|                             |               |                                                                                                         | OPAx277AIDRM, PA, UA | $\pm 0.5$         | $\pm 1$                              |  |

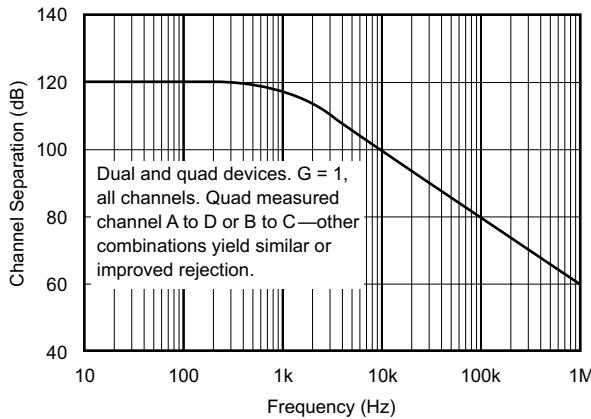

| チャネル・セパレーション<br>(デュアル、クワッド) |               | dc                                                                                                      |                      | 0.1               | $\mu\text{V}/\text{V}$               |  |

| <b>入力バイアス電流</b>             |               |                                                                                                         |                      |                   |                                      |  |

| $I_B$                       | 入力バイアス電流      | OPAx277P, U                                                                                             |                      | $\pm 0.5$         | $\pm 1$                              |  |

|                             |               |                                                                                                         |                      | $\pm 0.5$         | $\pm 2.8$                            |  |

|                             |               | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                        | OPAx277P, U          | $\pm 2$           | $\text{nA}$                          |  |

|                             |               |                                                                                                         | OPAx277AIDRM, PA, UA | $\pm 4$           |                                      |  |

| $I_{OS}$                    | 入力オフセット電流     | OPAx277P, U                                                                                             |                      | $\pm 0.5$         | $\pm 1$                              |  |

|                             |               |                                                                                                         |                      | $\pm 0.5$         | $\pm 2.8$                            |  |

|                             |               | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                        | OPAx277P, U          | $\pm 2$           | $\text{nA}$                          |  |

|                             |               |                                                                                                         | OPAx277AIDRM, PA, UA | $\pm 4$           |                                      |  |

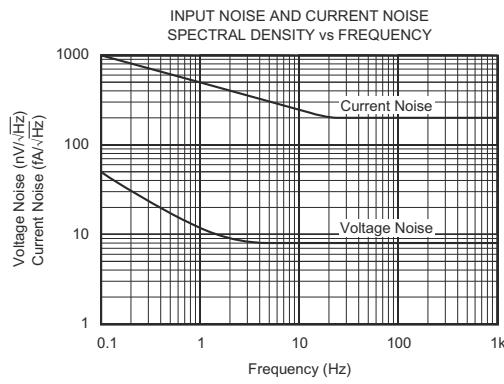

| <b>ノイズ</b>                  |               |                                                                                                         |                      |                   |                                      |  |

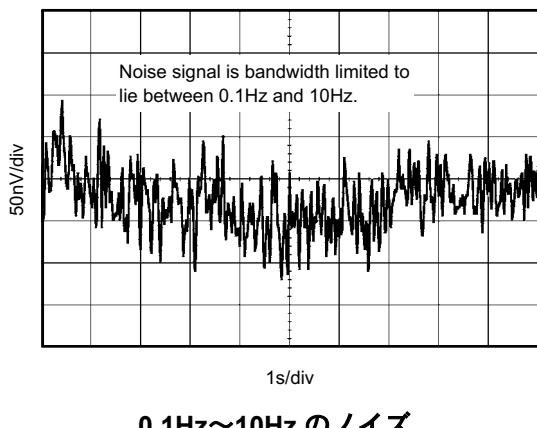

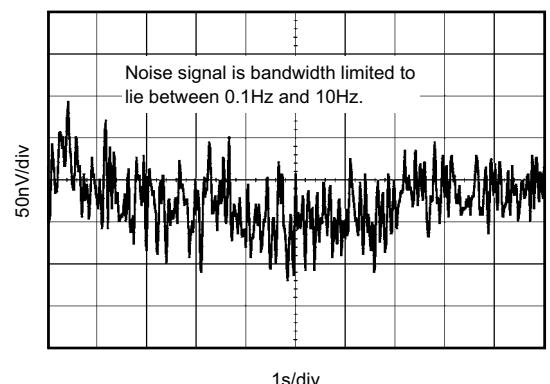

|                             | 入力電圧ノイズ       | $f = 0.1\text{Hz} \sim 10\text{Hz}$                                                                     |                      | 0.22              | $\mu\text{V}_{PP}$                   |  |

| $e_n$                       | 入力電圧ノイズ密度     | $f = 10\text{Hz}$                                                                                       |                      | 12                | $\text{nV}/\sqrt{\text{Hz}}$         |  |

|                             |               | $f = 100\text{Hz}$                                                                                      |                      | 8                 |                                      |  |

|                             |               | $f = 1\text{kHz}$                                                                                       |                      | 8                 |                                      |  |

|                             |               | $f = 10\text{kHz}$                                                                                      |                      | 8                 |                                      |  |

| $i_n$                       | 入力電流ノイズ密度     | $f = 1\text{kHz}$                                                                                       |                      | 0.2               | $\text{pA}/\sqrt{\text{Hz}}$         |  |

| <b>入力電圧</b>                 |               |                                                                                                         |                      |                   |                                      |  |

| $V_{CM}$                    | 同相電圧範囲        |                                                                                                         | $(V-) + 2$           | $(V+) - 2$        | $\text{V}$                           |  |

| CMRR                        | 同相信号除去比       | $V_{CM} = (V-) + 2\text{V} \sim (V+) - 2\text{V}$                                                       | OPAx277P, U          | 130               | 140                                  |  |

|                             |               |                                                                                                         | OPAx277AIDRM, PA, UA | 115               | 140                                  |  |

|                             |               | $V_{CM} = (V-) + 2\text{V} \sim (V+) - 2\text{V}$ ,<br>$T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ | OPAx277P, U          | 128               | $\text{dB}$                          |  |

|                             |               |                                                                                                         | OPAx277AIDRM, PA, UA | 115               |                                      |  |

| <b>入力インピーダンス</b>            |               |                                                                                                         |                      |                   |                                      |  |

| $Z_{ID}$                    | 差動            |                                                                                                         |                      | $100 \parallel 3$ | $\text{M}\Omega \parallel \text{pF}$ |  |

| $Z_{IC}$                    | 同相            | $V_{CM} = (V-) + 2\text{V} \sim (V+) - 2\text{V}$                                                       |                      | $250 \parallel 3$ | $\text{G}\Omega \parallel \text{pF}$ |  |

## 6.7 電気的特性 (continued)

$T_A = 25^\circ\text{C}$ ,  $V_S = 10\text{V} \sim 30\text{V}$ ,  $V_{CM} = V_{OUT} = V_S/2$ ,  $R_L = 2\text{k}\Omega$  を  $V_S/2$  に接続 (特に記述のない限り)

| パラメータ           | テスト条件         |                                                                                  | 最小値                                              | 標準値          | 最大値        | 単位        |  |

|-----------------|---------------|----------------------------------------------------------------------------------|--------------------------------------------------|--------------|------------|-----------|--|

| <b>開ループ・ゲイン</b> |               |                                                                                  |                                                  |              |            |           |  |

| $A_{OL}$        | 開ループ電圧ゲイン     | $V_O = (V-) + 0.5\text{V} \sim (V+) - 1.2\text{V}$ ,<br>$R_L = 10\text{k}\Omega$ |                                                  | 140          | dB         |           |  |

|                 |               | $V_O = (V-) + 1.5\text{V} \sim (V+) - 1.5\text{V}$ ,<br>$R_L = 2\text{k}\Omega$  | 126                                              | 134          |            |           |  |

|                 |               | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                 | 126                                              |              |            |           |  |

| <b>周波数応答</b>    |               |                                                                                  |                                                  |              |            |           |  |

| GBW             | ゲイン帯域幅積       |                                                                                  |                                                  | 1            | MHz        |           |  |

| SR              | スルーレート        |                                                                                  |                                                  | 0.8          | V/ $\mu$ s |           |  |

| $t_s$           | セトリング・タイム     | $V_S = \pm 15\text{V}$ , $G = 1$ , $10\text{V}$ ステップ                             | 0.1% まで                                          | 14           | $\mu$ s    |           |  |

|                 |               |                                                                                  | 0.01% まで                                         | 16           |            |           |  |

| $t_{OR}$        | 過負荷復帰時間       | $V_{IN} \times G = V_S$                                                          |                                                  |              | 3          | $\mu$ s   |  |

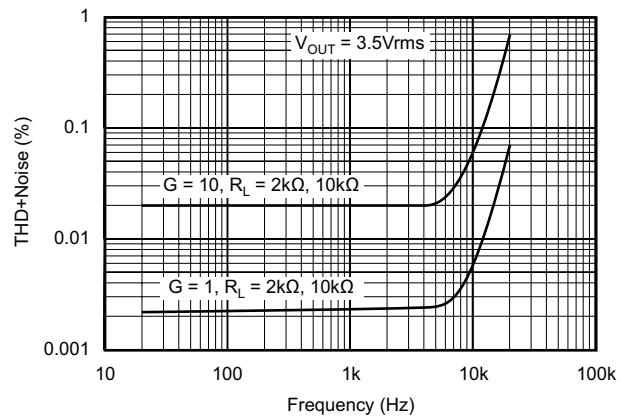

| THD+N           | 全高調波歪 + ノイズ   | $G = 1$ , $f = 1\text{kHz}$ , $V_O = 3.5\text{V}_{RMS}$                          |                                                  |              | 0.002%     |           |  |

| <b>出力</b>       |               |                                                                                  |                                                  |              |            |           |  |

| $V_O$           | 電圧出力          | $R_L = 10\text{k}\Omega$                                                         | $(V-) + 0.5$                                     | $(V+) - 1.2$ | V          |           |  |

|                 |               |                                                                                  | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ | $(V-) + 0.5$ |            |           |  |

|                 |               | $R_L = 2\text{k}\Omega$                                                          | $(V-) + 1.5$                                     | $(V+) - 1.5$ |            |           |  |

|                 |               |                                                                                  | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ | $(V-) + 1.5$ |            |           |  |

| $I_{SC}$        | 短絡電流          |                                                                                  |                                                  | $\pm 35$     | mA         |           |  |

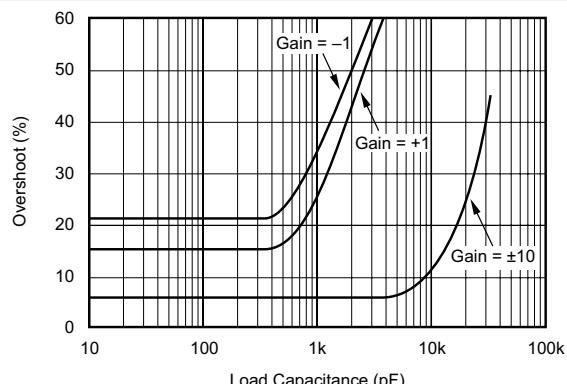

| $C_L$           | 容量性負荷駆動能力     |                                                                                  |                                                  | 「代表的特性」を参照   |            |           |  |

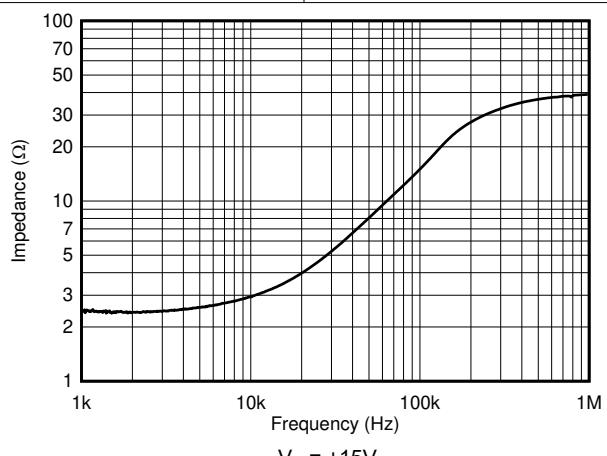

| $Z_O$           | 開ループ出力インピーダンス | $f = 1\text{MHz}$                                                                |                                                  |              | 40         | $\Omega$  |  |

| <b>電源</b>       |               |                                                                                  |                                                  |              |            |           |  |

| $I_Q$           | アンプごとの静止電流    | $I_O = 0\text{A}$                                                                |                                                  |              | $\pm 790$  | $\pm 825$ |  |

|                 |               |                                                                                  | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$ |              |            | $\pm 900$ |  |

|                 |               |                                                                                  |                                                  |              | $\mu$ A    |           |  |

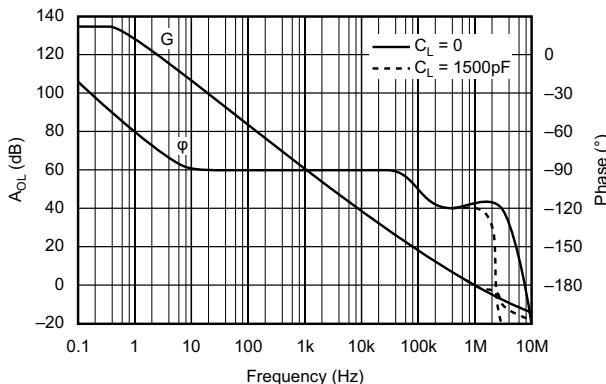

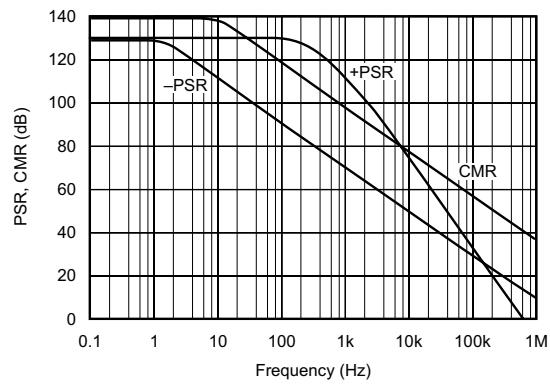

## 6.8 代表的特性

$T_A = 25^\circ\text{C}$ ,  $V_S = \pm 15\text{V}$ ,  $R_L = 2\text{k}\Omega$  (特に記述のない限り)。

図 6-1. 開ループ・ゲインおよび位相と周波数との関係

図 6-2. 電源および同相除去比と周波数との関係

図 6-3. 入力ノイズおよび電流のノイズ・スペクトラム密度と周波数との関係

図 6-4. 入力ノイズ電圧と時間との関係

図 6-5. チャネル・セパレーションと周波数との関係

図 6-6. 全高調波歪 + ノイズと周波数との関係

## 6.8 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 15\text{V}$ 、 $R_L = 2\text{k}\Omega$  (特に記述のない限り)。

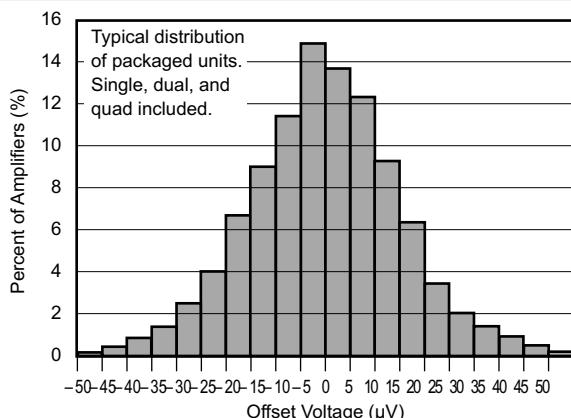

図 6-7. オフセット電圧の製品分布

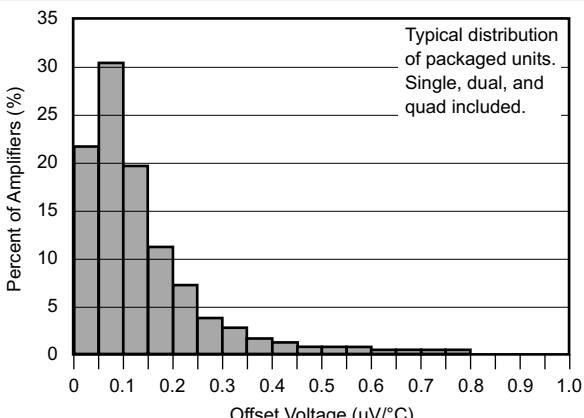

図 6-8. オフセット電圧ドリフトの製品分布

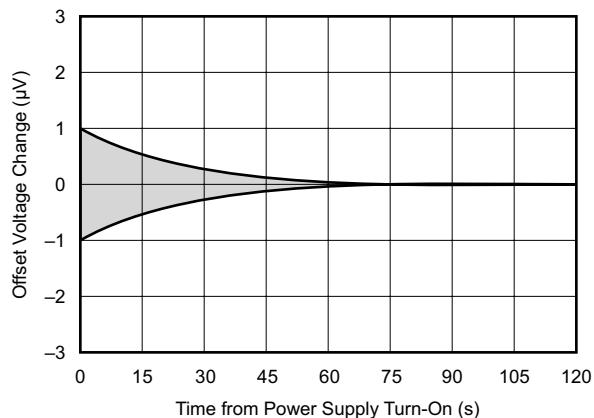

図 6-9. ウォームアップ時のオフセット電圧ドリフト

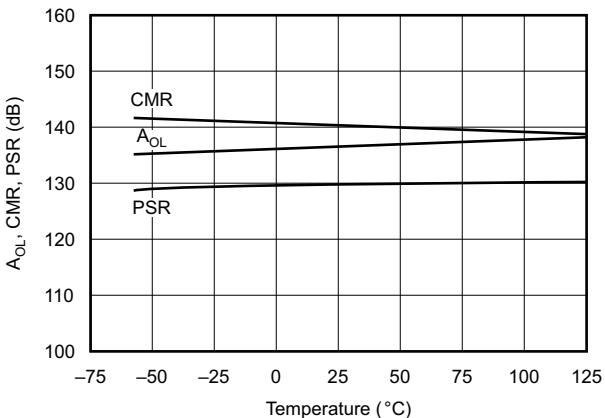

図 6-10. A<sub>OL</sub>、CMR、PSR と温度との関係

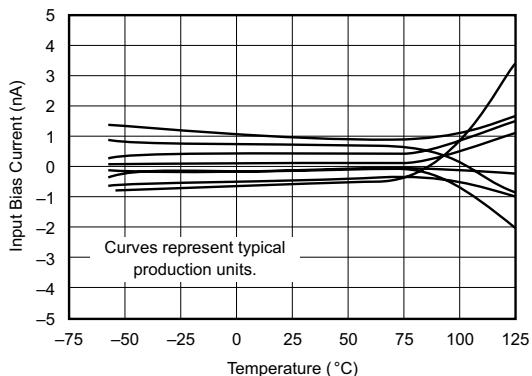

図 6-11. 入力バイアス電流と温度との関係

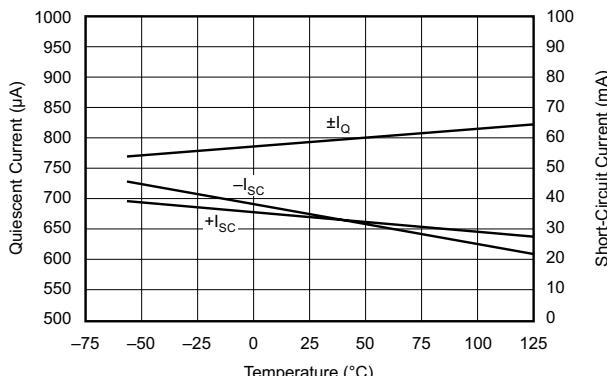

図 6-12. 静止電流および短絡電流と温度との関係

## 6.8 代表的特性 (continued)

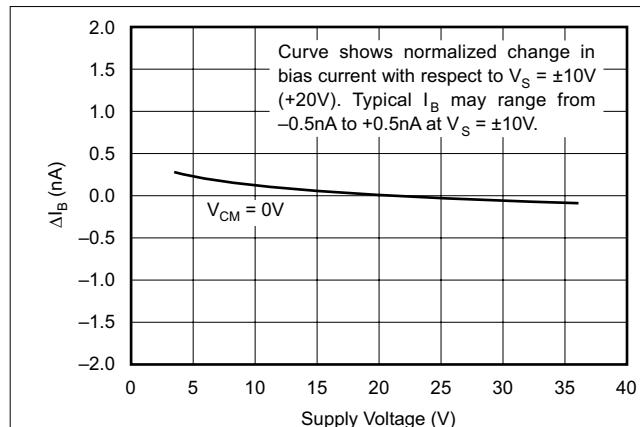

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 15\text{V}$ 、 $R_L = 2\text{k}\Omega$  (特に記述のない限り)。

図 6-13. 入力バイアス電流の変化と電源電圧との関係

図 6-14. 入力バイアス電流の変化と同相電圧との関係

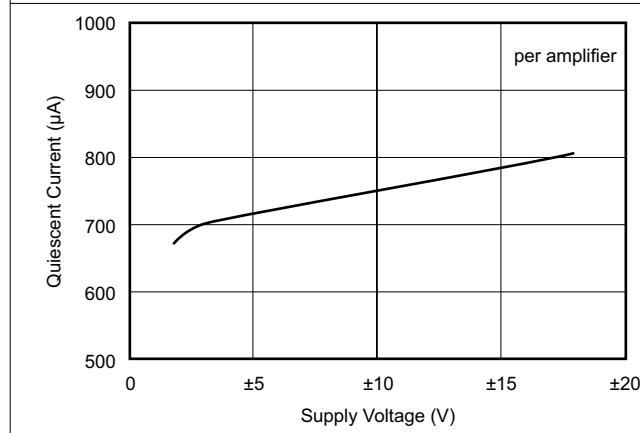

図 6-15. 静止電流と電源電圧との関係

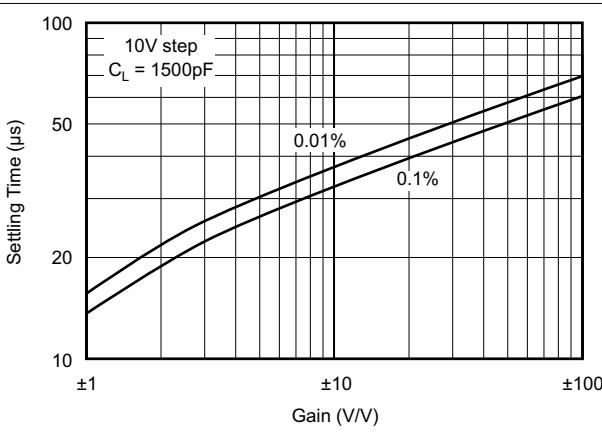

図 6-16. セトリング・タイムと閉ループ・ゲインとの関係

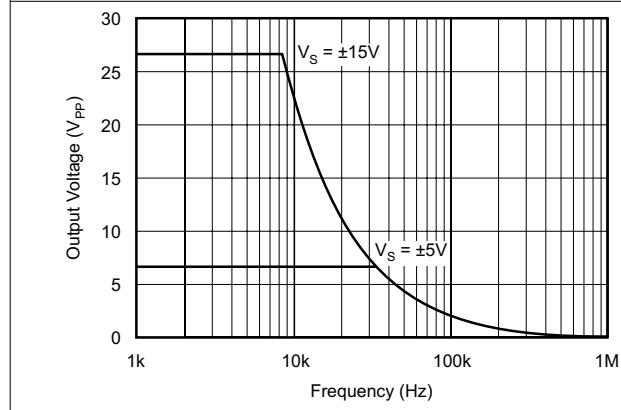

図 6-17. 最大出力電圧と周波数との関係

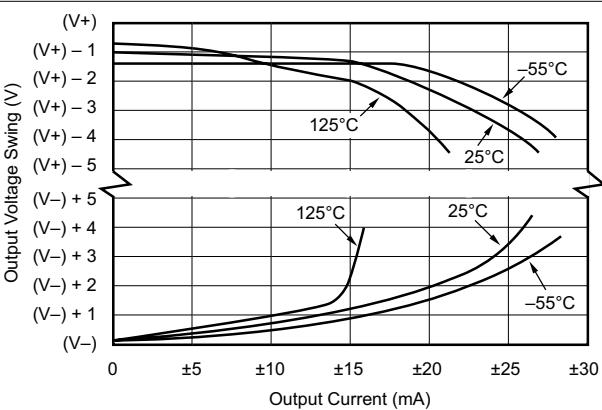

図 6-18. 出力電圧スイングと出力電流との関係

## 6.8 代表的特性 (continued)

$T_A = 25^\circ\text{C}$ ,  $V_S = \pm 15\text{V}$ ,  $R_L = 2\text{k}\Omega$  (特に記述のない限り)。

図 6-19. 小信号のオーバーシュートと負荷容量との関係

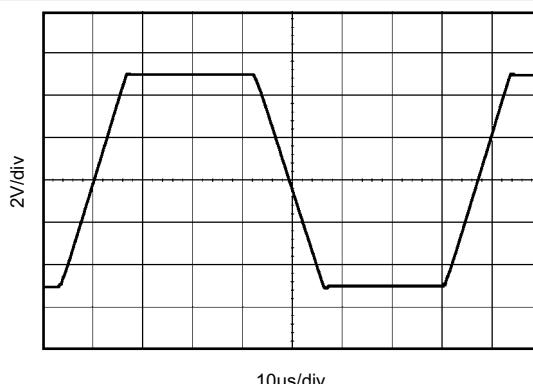

$G = 1$ ,  $C_L = 1500\text{pF}$ ,  $V_S = \pm 15\text{V}$

図 6-20. 大信号ステップ応答

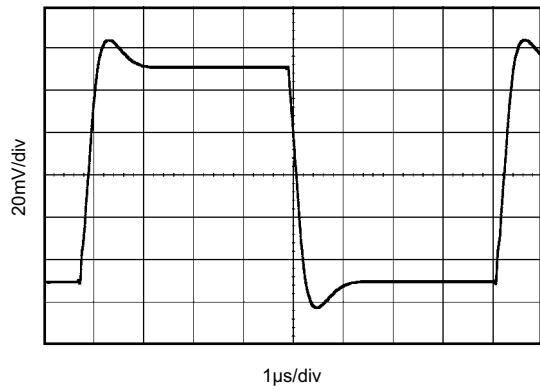

$G = 1$ ,  $C_L = 0$ ,  $V_S = \pm 15\text{V}$

図 6-21. 小信号ステップ応答

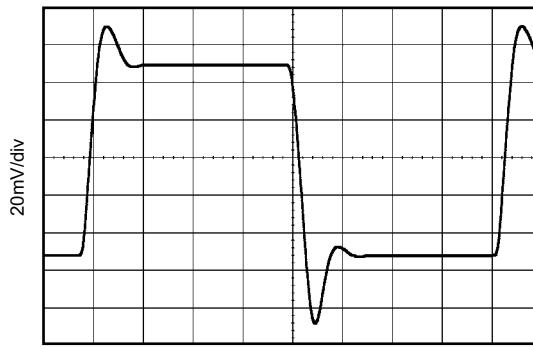

$G = 1$ ,  $C_L = 1500\text{pF}$ ,  $V_S = \pm 15\text{V}$

図 6-22. 小信号ステップ応答

$V_S = \pm 15\text{V}$

図 6-23. 開ループ出力インピーダンス

## 7 詳細説明

### 7.1 概要

OPAx277 シリーズ高精度オペアンプは、業界標準の OP-177 に代わる製品です。これらのデバイスは、ノイズの改善、出力電圧スイングの拡大、および半分の静止電流で 2 倍の速度を実現します。非常に低い入力オフセット電圧およびドリフト、低いバイアス電流、高い同相除去比、高い電源電圧除去比といった特長があります。

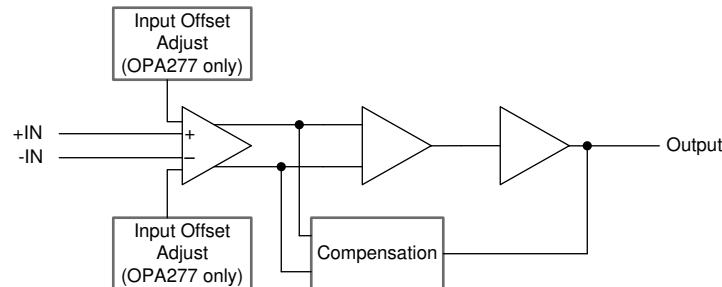

### 7.2 機能ブロック図

### 7.3 機能説明

OPAx277 シリーズはユニティ・ゲイン安定で、予期しない出力位相反転が発生しないため、幅広いアプリケーションで簡単に使用できます。ノイズが多い、またはインピーダンスが高い電源によるアプリケーションでは、デバイスのピンの近くにデカップリング・コンデンサが必要です。通常は、 $0.1\mu\text{F}$  のコンデンサが適しています。

OPAx277 シリーズはオフセット電圧とドリフトが低くなっています。最高の性能を実現するには、回路レイアウトと機械的条件を最適化してください。オフセット電圧とドリフトは、オペアンプ入力の小さな熱電気電位によって低下する可能性があります。異なる金属を接続すると熱電位が発生し、OPAx277 シリーズの最終的な性能が低下する可能性があります。これらの熱電位を相殺するには、両方の入力ピンで熱電位が等しいことを確認します。

- 2 つの入力ピンへの接続部の熱量を同量に保つ

- 重要な入力回路からできるだけ離れた場所に熱源を配置する

- オペアンプおよび入力回路を、冷却ファンなどの空気流から遮蔽する

#### 7.3.1 動作電圧

OPAx277 シリーズのオペアンプは、 $\pm 2\text{V} \sim \pm 18\text{V}$  の電源で動作し、優れた性能を発揮します。ほとんどのオペアンプは 1 つの電源電圧でのみ動作が規定されているのに対して、OPAx277 シリーズは複数の実アプリケーションに対応して規定されており、 $\pm 5 \sim \pm 15\text{V}$  の電源電圧範囲に対して単一の制限が適用されます。この単一の制限により、 $V_S = \pm 10\text{V}$  で動作している場合は、 $\pm 15\text{V}$  電源を使用している場合と同じ仕様の性能を得ることができます。さらに、主要なパラメータは、 $-40^\circ\text{C} \sim +85^\circ\text{C}$  の規定温度範囲で動作が規定されています。ほとんどの動作は、 $\pm 2\text{V} \sim \pm 18\text{V}$  の全動作電圧範囲で変化しません。動作電圧または温度によって大きく変動するパラメータを、[セクション 6.8](#) に示します。

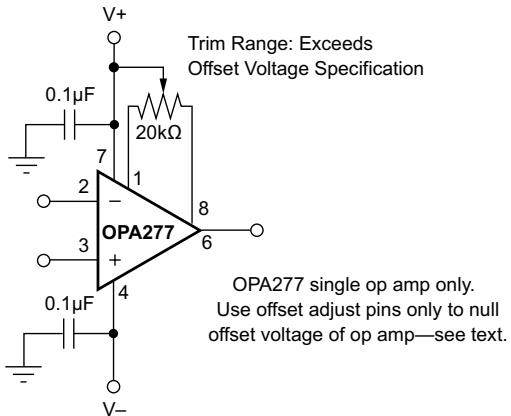

#### 7.3.2 オフセット電圧調整

OPAx277 シリーズは、オフセット電圧とドリフトを低く抑えるためにレーザ・トリミングされているので、ほとんどの回路は外部調整を必要としません。ただし、OPA277 の場合、ピン 1 とピン 8 にオフセット電圧トリム接続があります。[図 7-1](#) に、ポテンショメータを接続してオフセット電圧を調整する方法を示します。この調整は、オペアンプのオフセットをゼロにするためにのみ使用してください。システム内の他の場所で作成されたオフセットを補正するためにこの調整を使用しないでください。追加の温度ドリフトが発生する可能性があります。

図 7-1. OPA277 オフセット電圧トリム回路

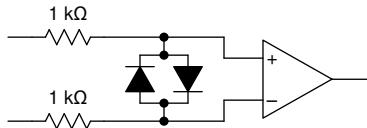

### 7.3.3 入力保護

OPAx277 デバイスの入力は、 $1\text{k}\Omega$  の直列入力抵抗とダイオード・クランプで保護されています。入力は、 $\pm 30\text{V}$  の差動入力に損傷なしで耐えることができます。保護ダイオードは、入力がオーバードライブされたときに導通します。この伝導電流はユニティ・ゲイン安定を利用するアプリケーションのスルーライン動作に悪影響を及ぼす可能性がありますが、オペアンプに損傷を与えることはありません。

図 7-2. OPAx277 入力保護

### 7.3.4 入力バイアス電流のキャンセル

OPAx277 シリーズの入力段のベース電流は、同等で逆のキャンセル回路によって内部的に補償されます。結果として得られる入力バイアス電流は、入力段のベース電流とキャンセル電流の差になります。この残留入力バイアス電流は、正にも負にもなる可能性があります。

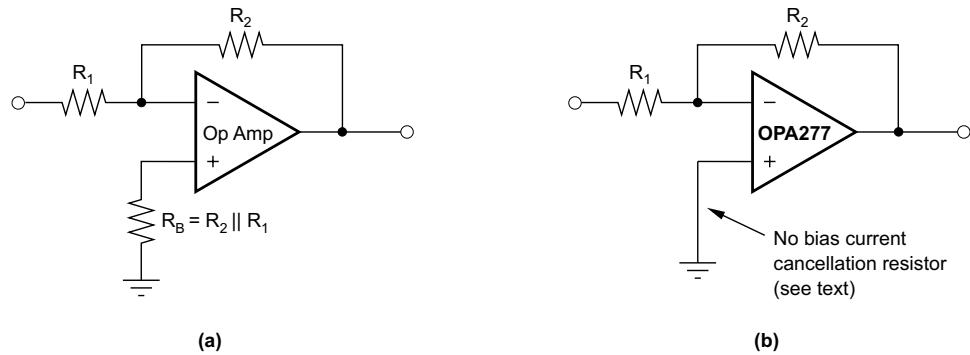

この方法でバイアス電流がキャンセルされると、入力バイアス電流と入力オフセット電流はほぼ同じ大きさになります。その結果、他のオペアンプでよく見られるバイアス電流キャンセル抵抗が不要になります。図 7-3 は、外付けバイアス電流キャンセル抵抗を備えた従来のオペアンプと、外付けバイアス電流キャンセル抵抗を使用しない OPA277 の比較を示しています。入力バイアス電流誤差をキャンセルするために抵抗を追加すると、実際にはオフセット電圧とノイズが増加する可能性があります。

図 7-3. 入力バイアス電流のキャンセル

### 7.3.5 EMI 除去比 (EMIRR)

電磁干渉 (EMI) 除去比 (EMIRR) は、オペアンプの EMI 耐性を表します。多くのオペアンプに共通する悪影響は、RF 信号の整流によるオフセット電圧の変化です。EMI によるオフセットのこの変化をより効率的に除去できるオペアンプは、EMIRR がより高く、デシベル値によって定量化されます。EMIRR の測定はさまざまな方法で実行できますが、このレポートでは特に、RF 信号がオペアンプの非反転入力ピンに印加されたときの EMIRR 性能を説明する EMIRR IN+ について記載しています。一般に、以下の 3 つの理由により、非反転入力のみが EMIRR でテストされます。

1. オペアンプの入力ピンは、EMI への感受性が最も高いことが知られており、通常は電源ピンまたは出力ピンよりも RF 信号の整流に適しています。

2. 非反転および反転オペアンプ入力は、対称的な物理レイアウトを採用しており、EMIRR 性能がほぼ一致しています。

3. 非反転入力端子をプリント基板 (PCB) 上で絶縁できるため、他のピンよりも非反転ピンの方が EMIRR を簡単に測定できます。この絶縁により、他の部品や PCB 配線の接続からの複雑な相互作用を発生させることなく、RF 信号を非反転入力端子に直接印加できます。

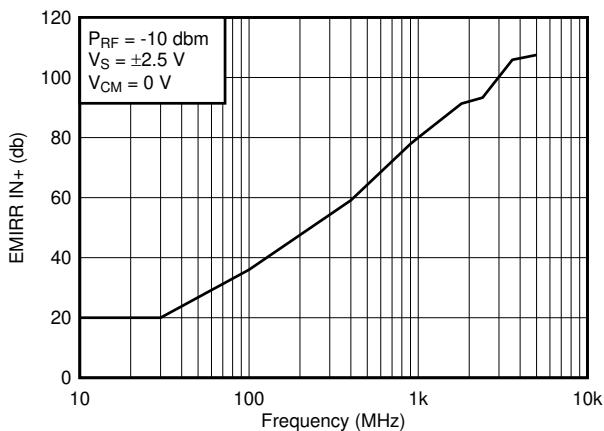

EMIRR IN+ の定義およびテスト方法の詳細については、『オペアンプの EMI 除去率』アプリケーション・ノートを参照してください。このアプリケーション・ノートは、[www.ti.com](http://www.ti.com) からダウンロードできます。図 7-4 に、OPA277 の EMIRR IN+ を周波数に対してプロットしたものを示します。

図 7-4. OPA277 の EMIRR IN+ と周波数との関係

利用可能な場合、すべてのデュアルおよびクワッド・オペアンプ・デバイスのバージョンが、ほぼ同等の EMIRR +IN 性能を持ちます。OPA277 のユニティ・ゲイン帯域幅は 1MHz です。EMIRR 性能がこの周波数を下回る場合は、オペアンプの帯域幅内に干渉する信号が存在していることを示しています。

実際のアプリケーションで一般的に発生する、特定の周波数における OPA277 の EMIRR IN+ 値を、表 7-1 に示します。表 7-1 に示すアプリケーションは、表に示す特定の周波数を中心として、またはその周波数の付近で動作させることができます。この情報は、これらの種類のアプリケーションを使用する設計者、または産業、科学、医療 (ISM) 無線帯域などの幅広いソースから RF 干渉に遭遇する可能性の高い他の分野で作業する設計者にとって特に重要です。

**表 7-1. 特定周波数における OPA277 の EMIRR IN+**

| 周波数    | アプリケーション / 割り当て                                         | EMIRR IN+ |

|--------|---------------------------------------------------------|-----------|

| 400MHz | モバイル無線、モバイルの衛星と宇宙での運用、気象、レーダー、UHF                       | 59.1dB    |

| 900MHz | GSM、無線通信ナビゲーション GPS (最大 1.6GHz)、ISM、航空モバイル、UHF          | 77.9dB    |

| 1.8GHz | GSM、モバイル・パーソナル広帯域通信、衛星、L バンド                            | 91.3dB    |

| 2.4GHz | 802.11b/g/n、Bluetooth®、モバイル・パーソナル通信、ISM、アマチュア無線衛星、S バンド | 93.3dB    |

| 3.6GHz | 無線測位、航空通信ナビゲーション、衛星、モバイル、S バンド                          | 105.9dB   |

| 5.0GHz | 802.11a/n、航空通信ナビゲーション、モバイル通信、宇宙衛星運用、C バンド               | 107.5dB   |

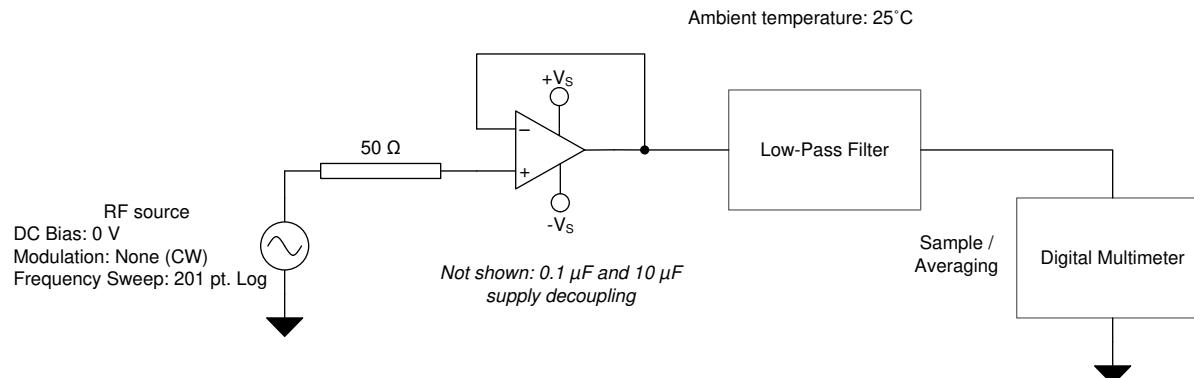

### 7.3.5.1 EMIRR IN+ のテスト構成

図 7-5 に、EMIRR IN+ をテストするための回路構成を示します。伝送ラインを使用して、RF ソースをオペアンプの非反転入力端子に接続します。オペアンプはユニティ・ゲイン・バッファ・トポロジで構成され、出力はローパス・フィルタ (LPF) とデジタル・マルチメータ (DMM) に接続されています。オペアンプの入力でインピーダンスの大きなミスマッチが発生すると、電圧が反射しますが、この影響は EMIRR IN+ を決定するときに特性化され、考慮されます。結果として得られた DC オフセット電圧は、マルチメータによってサンプリングおよび測定されます。LPF はマルチメータの精度に干渉する可能性のある残留 RF 信号からマルチメータを絶縁します。詳細については、『オペアンプの EMI 除去率』アプリケーション・ノートを参照してください。

**図 7-5. EMIRR IN+ テスト構成の回路図**

### 7.4 デバイスの機能モード

OPAx277 には単一機能モードがあり、電源電圧が 4V ( $\pm 2V$ ) を上回ると動作します。OPAx277 の最大電源電圧は 36V ( $\pm 18V$ ) です。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

OPAx277 ファミリは DC 精度と AC 性能が非常に優れています。これらのデバイスは、最高 36V の電源レールで動作し、超低オフセット電圧、オフセット電圧ドリフトに加えて、1MHz の帯域幅と、高い容量性負荷駆動を実現しています。OPAx277 は、上記の特長を持つ、高電圧の産業用アプリケーションに適した、堅牢な高性能オペアンプです。

### 8.2 代表的なアプリケーション

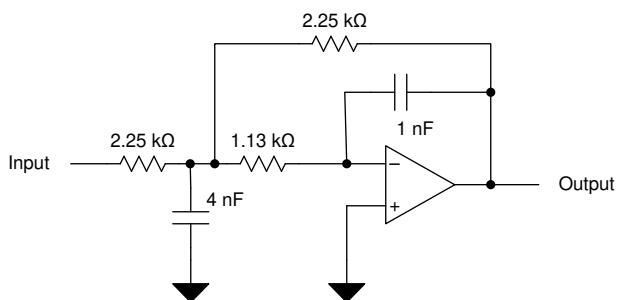

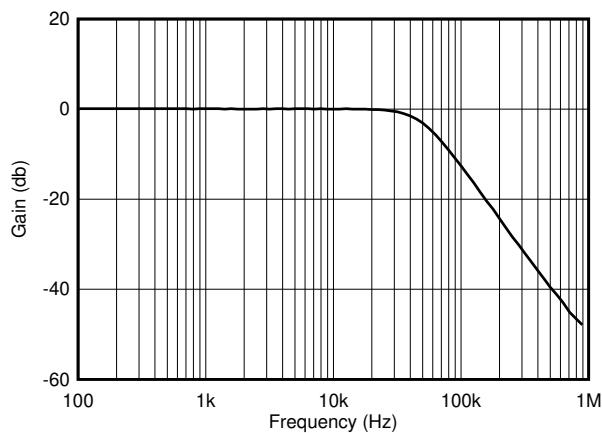

#### 8.2.1.2 次ローパス・フィルタ

図 8-1.2 次ローパス・フィルタ

##### 8.2.1.1 設計要件

- ゲイン = 1V/V

- ローパス・カットオフ周波数 = 50kHz

- 40dB/dec のフィルタ応答

- ゲインと周波数応答の間で、ゲインのピークが 3dB 未満に維持されます

##### 8.2.1.2 詳細な設計手順

フィルタ設計ツールは単純で強力な、使いやすいアクティブ・フィルタ設計プログラムです。フィルタ設計ツールを使用すると、テキサス・インスツルメンツ製オペアンプや、テキサス・インスツルメンツのベンダ・パートナーが提供するパッシブ・コンポーネントを使用して、最適なフィルタを設計できます。

フィルタ設計ツールは、[設計ツールとシミュレーション Web](#) サイトから Web 対応ツールとして利用でき、包括的な多段アクティブ・フィルタ・ソリューションをわずか数分で設計、最適化、シミュレーションできます。

### 8.2.1.3 アプリケーション曲線

図 8-2. OPA277、2 次、50kHz、ローパス・フィルタ

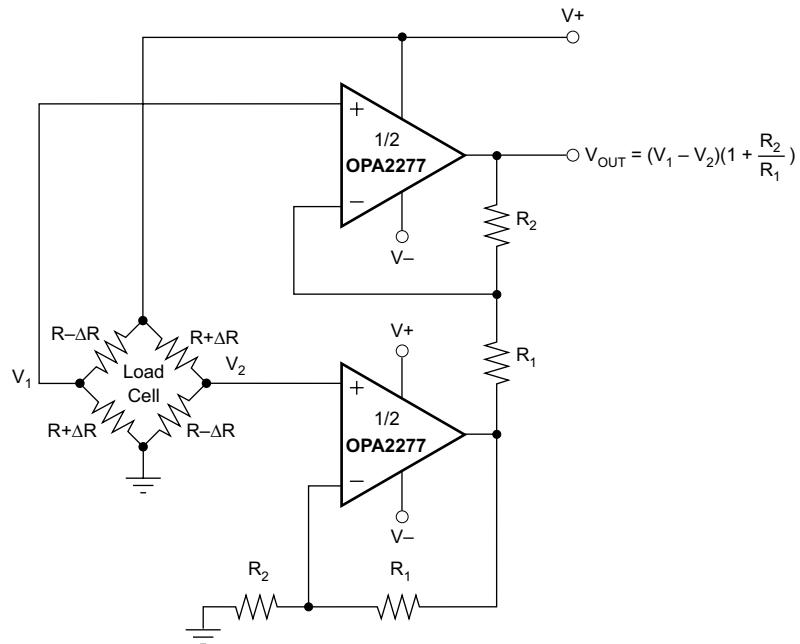

### 8.2.2 ロード・セル・アンプ

For integrated solution see:

INA126, INA2126 (dual)

INA125 (on-board reference)

INA122 (single-supply)

図 8-3. ロード・セル・アンプ

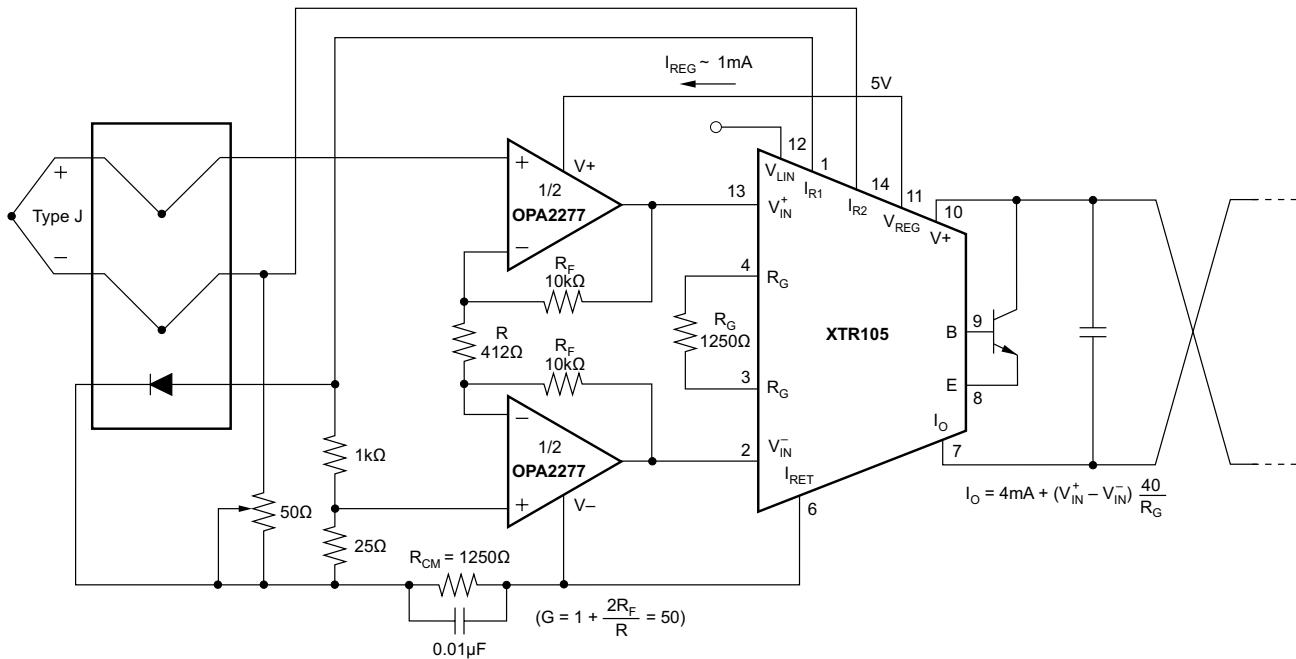

### 8.2.3 ダイオードの冷接点補償を使用した熱電対の低オフセット、低ドリフト・ループ測定

図 8-4. ダイオードの冷接点補償を使用した熱電対の低オフセット、低ドリフト・ループ測定

### 8.3 電源に関する推奨事項

OPAx277 は 4V～36V ( $\pm 2V \sim \pm 18V$ ) で動作が規定されており、多くの仕様は  $-40^{\circ}C \sim 85^{\circ}C$  で適用されます。動作電圧または温度に関して大きな変動を示す可能性があるパラメータについては、[セクション 6.8](#) を参照してください。

#### 注意

電源電圧が 36V を超えると、デバイスに恒久的な損傷を与える可能性があります。[セクション 6.1](#) を参照してください。

電源ピンの近くに  $0.1\mu F$  のバイパス・コンデンサを配置すると、ノイズの多い電源や高インピーダンスの電源から混入する誤差を低減できます。バイパス・コンデンサの配置の詳細については、[セクション 8.4.1](#) を参照してください。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

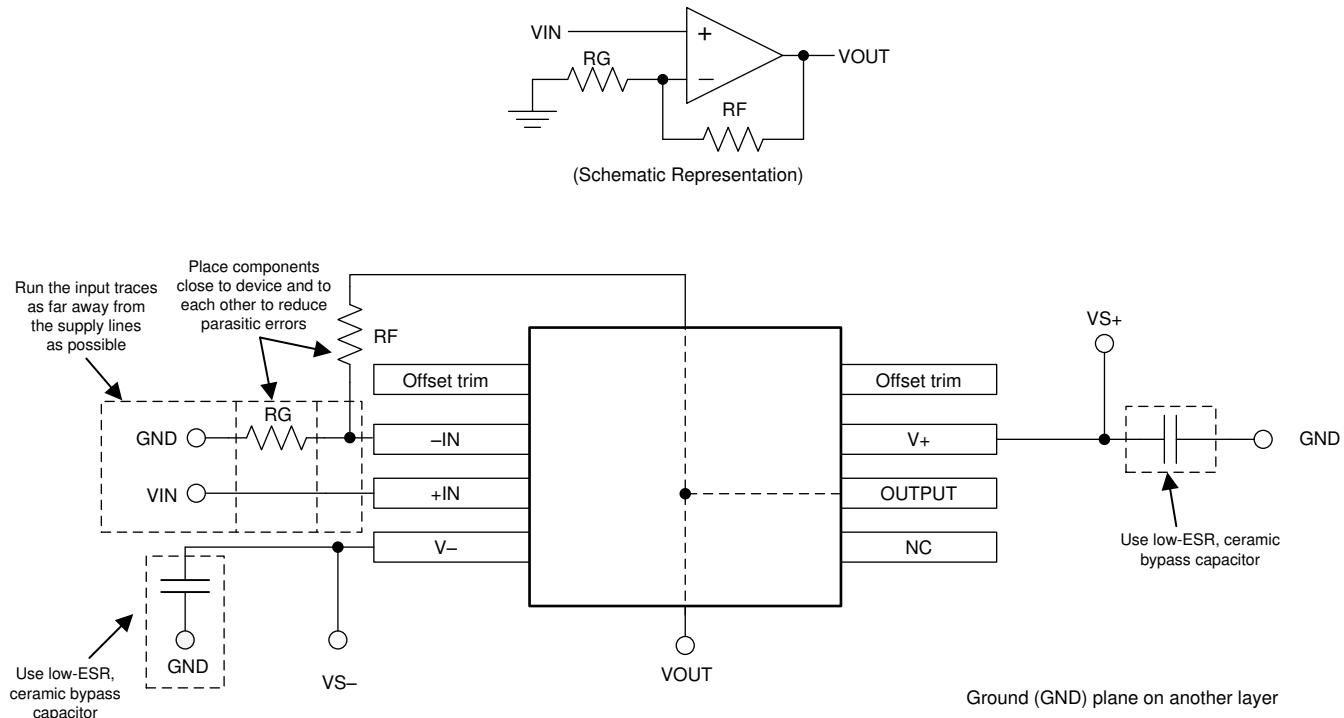

デバイスで最高の動作性能を実現するには、以下の適切な PCB レイアウト手法を使用してください。

- ノイズが回路全体の電源ピンとオペアンプ自体を経由して、アナログ回路に伝播することがあります。バイパス・コンデンサは、アナログ回路に対してローカルに低インピーダンスの電源を供給し、結合ノイズを低減するために使用されます。

- 各電源ピンとグランドとの間に、低 ESR の  $0.1\mu\text{F}$  セラミック・バイパス・コンデンサを接続し、可能な限りデバイスの近くに配置します。単一電源アプリケーションの場合は、V+ からグランドに対して 1 つのバイパス・コンデンサを接続します。

- 回路のアナログ部とデジタル部のグランド配線を分離することは、ノイズを抑制する最も簡単かつ効果的な方法の 1 つです。通常、多層 PCB のうち 1 つ以上の層はグランド・プレーン専用です。グランド・プレーンは熱の分散に役立つとともに、EMI ノイズを拾う可能性を低減します。グランド電流の流れに注意して、デジタル・グランドとアナログ・グランドを物理的に確実に分離するようにします。

- 寄生カップリングを低減するには、入力配線を電源配線または出力配線からできるだけ離して配置します。これらの配線を分離しておけない場合、敏感な配線をノイズの多い配線と平行にするよりは、垂直に交差させる方がはるかに良い結果が得られます。

- 外付け部品は、可能な限りデバイスに近く配置します。セクション 8.4.2 に示すように、寄生容量を最小限に抑えるため、RF と RG は反転入力の近くに配置します。

- 入力配線は、できる限り短くします。入力配線は、回路の最も敏感な部分であることに常に注意してください。

- 重要な配線の周囲に、駆動される低インピーダンスのガード・リングを配置することを検討します。ガード・リングを使用すると、付近に存在する、さまざまな電位の配線からのリーク電流を大幅に低減できます。

- 最高の性能を実現するため、基板組み立ての後で PCB を清掃することを推奨します。

- 高精度の集積回路は、プラスチック・パッケージへの湿気の侵入により性能が変化する場合があります。PCB を水で洗浄してから、PCB アセンブリをベーキングして、清掃プロセス中にデバイスのパッケージに取り込まれた水分を除去することを推奨します。ほとんどの場合、清掃後に  $85^\circ\text{C}$  で 30 分間の低温ベーキングを行えば十分です。

- DRM パッケージ(8 ピン VSON)のみ:リードフレームのダイ・パッドを、PCB の熱パッドに半田付けします。このデータシートの末尾に掲載されたパッケージ図面には、パッケージとパッドの物理的寸法が記載されています。

- DRM パッケージ(8 ピン VSON)のみ:露出パッドを半田付けすると、温度サイクル、キープッシュ、パッケージ切断、および類似のボード・レベル・テスト中のボード・レベルの信頼性が大幅に向上了します。低消費電力のアプリケーションでも、露出したパッドは必ず PCB に半田付けして、構造上の完全性と長期的な信頼性を確保する必要があります。

#### 8.4.1.1 DRM パッケージ(8 ピン VSON)

OPAx277 シリーズは DRM パッケージ (8 ピン VSON とも呼ばれます) を使用しています。これはリードレス・パッケージで、パッケージ底面の 2 つの面のみに接触します。このニアチップスケールのパッケージにより、ボードの面積が最大化され、露出したパッドによって熱特性と電気的特性が向上します。

DRM パッケージは物理的に小さく、配線領域も小さくなっています。さらに、SOIC や VSSOP などの一般的に使用される他のパッケージと整合性のあるピン配列になっており、熱特性や電気的寄生が改善されています。また、外部にリードがないため、リード曲がりの問題も解消されます。

DRM パッケージは、標準的なプリント基板 (PCB) のアセンブリ技法を使用して容易に実装できます。『QFN/SON の PCB 実装』および『クワッド・フラットパック・リード端子なしロジック・パッケージ』のアプリケーション・ノートを参照してください。どちらも、[www.ti.com](http://www.ti.com) からダウンロードできます。

パッケージ底部に露出したリード端子を持つダイ・パッドは、V- に接続します。

### 8.4.2 レイアウト例

図 8-5. OPA277 非反転構成のレイアウト例

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイスのサポート

#### 9.1.1 開発サポート

##### 9.1.1.1 PSpice® for TI

PSpice® for TI は、アナログ回路の性能評価に役立つ設計およびシミュレーション環境です。レイアウトと製造に移る前に、サブシステムの設計とプロトタイプ・ソリューションを作成することで、開発コストを削減し、市場投入までの期間を短縮できます。

##### 9.1.1.2 TINA-TI™ シミュレーション・ソフトウェア(無償ダウンロード)

TINA-TI™ シミュレーション・ソフトウェアは、SPICE エンジンをベースにした単純かつ強力な、使いやすい回路シミュレーション・プログラムです。TINA-TI シミュレーション・ソフトウェアは、TINA™ ソフトウェアのすべての機能を持つ無償バージョンで、パッシブ・モデルとアクティブ・モデルに加えて、マクロモデルのライブラリがプリロードされています。TINA-TI シミュレーション・ソフトウェアには、SPICE の標準的な DC 解析、過渡解析、周波数ドメイン解析などの全機能に加え、追加の設計機能が搭載されています。

TINA-TI シミュレーション・ソフトウェアは [設計ツールとシミュレーション Web ページ](#)から無料でダウンロードでき、ユーザーが結果をさまざまな方法でフォーマットできる、広範な後処理機能を備えています。仮想計測器により、入力波形を選択し、回路ノード、電圧、および波形をプローブして、動的なクリック・スタート・ツールを作成できます。

#### 注

これらのファイルを使用するには、TINA ソフトウェアまたは TINA-TI ソフトウェアがインストールされている必要があります。TINA-TI™ ソフトウェア・フォルダから、無償の TINA-TI シミュレーション・ソフトウェアをダウンロードしてください。

##### 9.1.1.3 DIP アダプタ評価基板

DIP アダプタ評価基板は、オペアンプの迅速なプロトタイプ製作とテストを可能にする評価基板です。小型の表面実装デバイスとのインターフェイスを迅速、容易、低成本で実現します。付属の Samtec 端子ストリップか、直接配線により既存の回路へサポートされているオペアンプを接続します。DIP アダプタ評価基板キットは、以下の業界標準パッケージをサポートしています。D または U (SOIC-8)、PW (TSSOP-8)、DGK (VSSOP-8)、DBV (SOT-23-6、SOT-23-5、および SOT-23-3)、DCK (SC70-6 および SC70-5)、および DRL (SOT563-6)。

##### 9.1.1.4 DIYAMP-EVM

DIYAMP-EVM は、実際のアンプ回路を提供する独自の評価基板 (EVM) であり、設計コンセプトの迅速な評価とシミュレーションの検証を実現します。この評価基板は、3 つの業界標準パッケージ (SC70、SOT23、SOIC) で供給されており、シングル / デュアル電源向けに、アンプ、フィルタ、安定性補償、コンパレータの各構成など、12 の一般的なアンプ構成が可能です。

##### 9.1.1.5 TI のリファレンス・デザイン

TI のリファレンス・デザインは、TI の高精度アナログ・アプリケーション専門家により作成されたアナログ・ソリューションです。TI のリファレンス・デザインは、動作原理、部品の選択、シミュレーション、完全な PCB 回路図およびレイアウト、部品表、測定済みの性能を提供します。TI のリファレンス・デザインは、<http://www.ti.com/ww/en/analog/precision-designs/> からオンラインで入手できます。

##### 9.1.1.6 フィルタ設計ツール

フィルタ設計ツールは単純で強力な、使いやすいアクティブ・フィルタ設計プログラムです。フィルタ設計ツールを使用すると、TI のベンダー・パートナーからの TI 製オペアンプやパッシブ・コンポーネントを使用して、最適なフィルタ設計を作成できます。

フィルタ設計ツールは、[設計ツールとシミュレーション Web ページ](#)から Web 対応ツールとして利用でき、包括的な複数段アクティブ・フィルタ・ソリューションをわずか数分で設計、最適化、シミュレーションできます。

## 9.2 ドキュメントのサポート

### 9.2.1 関連資料

関連資料については、以下のアプリケーション・レポートおよび出版物を参照してください（[www.ti.com](http://www.ti.com) からダウンロードできます）。

- テキサス・インスツルメンツ、『QFN/SON の PCB 実装』

- テキサス・インスツルメンツ、『クワッド・フラットパック・リード端子なしロジック・パッケージ』

- テキサス・インスツルメンツ、『オペアンプの EMI 除去率』

## 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 9.4 サポート・リソース

[TI E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。[TI の使用条件](#)を参照してください。

## 9.5 商標

TINA-TI™ and TI E2E™ are trademarks of Texas Instruments.

TINA™ is a trademark of DesignSoft, Inc.

Bluetooth® is a registered trademark of Bluetooth SIG, Inc.

PSpice® is a registered trademark of Cadence Design Systems, Inc.

すべての商標は、それぞれの所有者に帰属します。

## 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number         | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-------------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">OPA2277AIDRMT</a> | Active        | Production           | VSON (DRM)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -            | BHZ                 |

| OPA2277AIDRMT.B               | Active        | Production           | VSON (DRM)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | BHZ                 |

| OPA2277AIDRMT1G4              | Active        | Production           | VSON (DRM)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | BHZ                 |

| OPA2277AIDRMT1G4.B            | Active        | Production           | VSON (DRM)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | BHZ                 |

| <a href="#">OPA2277P</a>      | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -            | OPA2277P            |

| OPA2277P.B                    | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | OPA2277P            |

| <a href="#">OPA2277PA</a>     | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -            | OPA2277PA           |

| OPA2277PA.B                   | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | OPA2277PA           |

| <a href="#">OPA2277U</a>      | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI   Nipdau                     | Level-3-260C-168 HR               | -            | OPA2277U            |

| OPA2277U.B                    | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | OPA2277U            |

| <a href="#">OPA2277U/2K5</a>  | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-3-260C-168 HR               | -40 to 85    | OPA2277U            |

| OPA2277U/2K5.B                | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | OPA2277U            |

| <a href="#">OPA2277UA</a>     | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI   Nipdau                     | Level-3-260C-168 HR               | -40 to 85    | OPA2277UA           |

| OPA2277UA.B                   | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | OPA2277UA           |

| <a href="#">OPA2277UA/2K5</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | OPA2277UA           |

| OPA2277UA/2K5.B               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | OPA2277UA           |

| OPA2277UA1G4                  | Active        | Production           | SOIC (D)   8   | 75   TUBE             | -           | Call TI                              | Call TI                           | -40 to 85    | OPA2277UA           |

| <a href="#">OPA277AIDRMR</a>  | Active        | Production           | VSON (DRM)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -            | NSS                 |

| OPA277AIDRMR.A                | Active        | Production           | VSON (DRM)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | NSS                 |

| Orderable part number        | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|------------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">OPA277AIDRMT</a> | Active        | Production           | VSON (DRM)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -            | NSS                 |

| OPA277AIDRMT.A               | Active        | Production           | VSON (DRM)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | NSS                 |

| <a href="#">OPA277P</a>      | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | Call TI                              | N/A for Pkg Type                  | -            | OPA277P             |

| OPA277P.A                    | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | Call TI                              | N/A for Pkg Type                  | -40 to 85    | OPA277P             |

| <a href="#">OPA277PA</a>     | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | Call TI                              | N/A for Pkg Type                  | -            | OPA277P A           |

| OPA277PA.A                   | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | Call TI                              | N/A for Pkg Type                  | -40 to 85    | OPA277P A           |

| OPA277PAG4                   | Active        | Production           | PDIP (P)   8   | 50   TUBE             | Yes         | Call TI                              | N/A for Pkg Type                  | See OPA277PA | OPA277P A           |

| <a href="#">OPA277U</a>      | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI   Nipdau                     | Level-3-260C-168 HR               | -            | OPA 277U            |

| OPA277U.B                    | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | OPA 277U            |

| <a href="#">OPA277U/2K5</a>  | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-3-260C-168 HR               | -            | OPA 277U            |

| OPA277U/2K5.B                | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | OPA 277U            |

| <a href="#">OPA277UA</a>     | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI   Nipdau                     | Level-3-260C-168 HR               | -40 to 85    | OPA 277U A          |

| OPA277UA.B                   | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | OPA 277U A          |

| <a href="#">OPA277UA/2K5</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | OPA 277U A          |

| OPA277UA/2K5.B               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 85    | OPA 277U A          |

| OPA277UA/2K51G4              | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 85    | OPA 277U A          |

| OPA277UAG4                   | Active        | Production           | SOIC (D)   8   | 75   TUBE             | -           | Call TI                              | Call TI                           | -40 to 85    |                     |

| <a href="#">OPA4277PA</a>    | Active        | Production           | PDIP (N)   14  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -            | OPA4277PA           |

| Orderable part number         | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-------------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| OPA4277PA.A                   | Active        | Production           | PDIP (N)   14  | 25   TUBE             | Yes         | NIPDAU                               | N/A for Pkg Type                  | -40 to 85    | OPA4277PA           |

| <a href="#">OPA4277UA</a>     | Active        | Production           | SOIC (D)   14  | 50   TUBE             | Yes         | NIPDAU   NIPDAUAG                    | Level-3-260C-168 HR               | -40 to 85    | OPA4277UA           |

| OPA4277UA.B                   | Active        | Production           | SOIC (D)   14  | 50   TUBE             | -           | Call TI                              | Call TI                           | -40 to 85    |                     |

| <a href="#">OPA4277UA/2K5</a> | Active        | Production           | SOIC (D)   14  | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG                    | Level-3-260C-168 HR               | -40 to 85    | OPA4277UA           |

| OPA4277UA/2K5.B               | Active        | Production           | SOIC (D)   14  | 2500   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 85    |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF OPA2277, OPA4277 :**

- Enhanced Product : [OPA2277-EP](#), [OPA4277-EP](#)

- Space : [OPA4277-SP](#)

NOTE: Qualified Version Definitions:

- Enhanced Product - Supports Defense, Aerospace and Medical Applications

- Space - Radiation tolerant, ceramic packaging and qualified for use in Space-based application

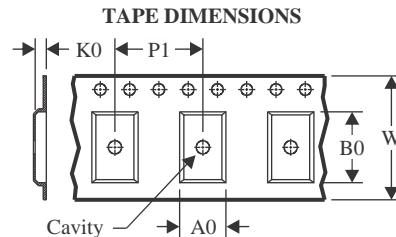

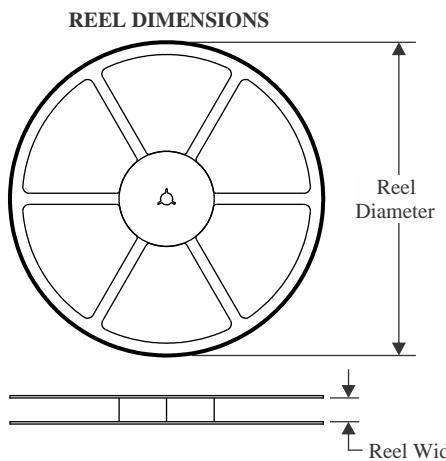

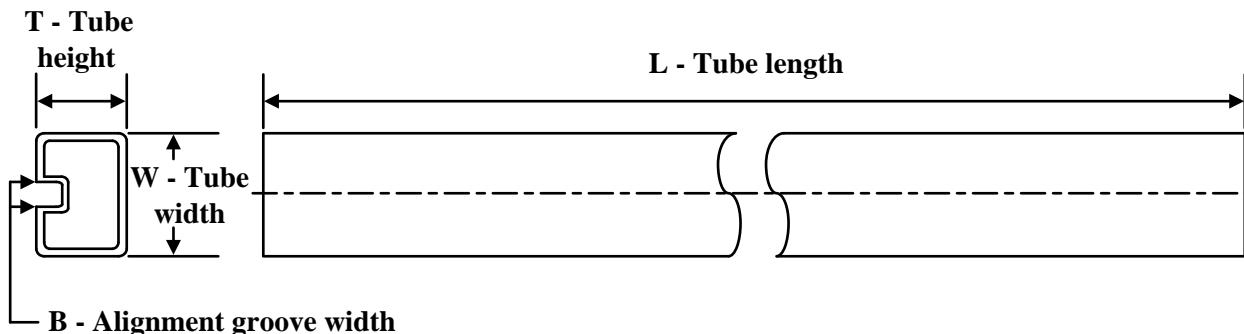

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

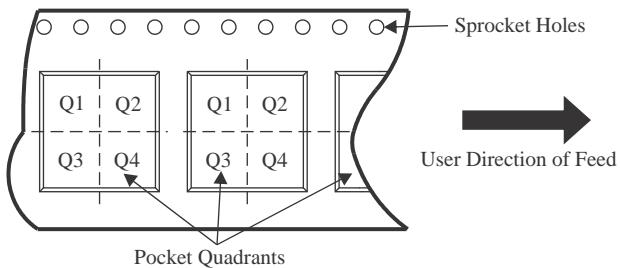

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| OPA2277AIDRMT    | VSON         | DRM             | 8    | 250  | 180.0              | 12.4               | 4.25    | 4.25    | 1.15    | 8.0     | 12.0   | Q2            |

| OPA2277AIDRMT1G4 | VSON         | DRM             | 8    | 250  | 180.0              | 12.4               | 4.25    | 4.25    | 1.15    | 8.0     | 12.0   | Q2            |

| OPA2277U/2K5     | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA2277UA/2K5    | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA277AIDRMR     | VSON         | DRM             | 8    | 3000 | 330.0              | 12.4               | 4.25    | 4.25    | 1.15    | 8.0     | 12.0   | Q2            |

| OPA277AIDRMT     | VSON         | DRM             | 8    | 250  | 180.0              | 12.4               | 4.25    | 4.25    | 1.15    | 8.0     | 12.0   | Q2            |

| OPA277U/2K5      | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA277UA/2K5     | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA4277UA/2K5    | SOIC         | D               | 14   | 2500 | 330.0              | 16.4               | 6.5     | 9.0     | 2.1     | 8.0     | 16.0   | Q1            |

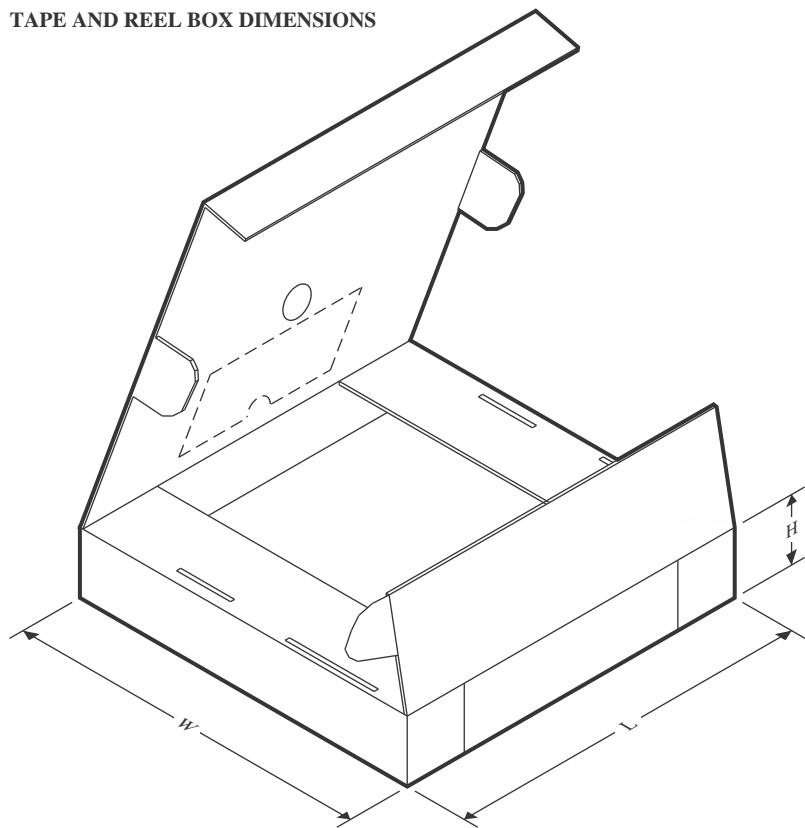

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA2277AIDRMT    | VSON         | DRM             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| OPA2277AIDRMT1G4 | VSON         | DRM             | 8    | 250  | 210.0       | 185.0      | 35.0        |

| OPA2277U/2K5     | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA2277UA/2K5    | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA277AIDRMR     | VSON         | DRM             | 8    | 3000 | 353.0       | 353.0      | 32.0        |

| OPA277AIDRMT     | VSON         | DRM             | 8    | 250  | 213.0       | 191.0      | 35.0        |

| OPA277U/2K5      | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA277UA/2K5     | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA4277UA/2K5    | SOIC         | D               | 14   | 2500 | 353.0       | 353.0      | 32.0        |

## TUBE

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| OPA2277P    | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA2277P.B  | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA2277PA   | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA2277PA.B | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA2277U    | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA2277U.B  | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA2277UA   | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA2277UA.B | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA277P     | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA277P.A   | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA277PA    | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA277PA.A  | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA277PAG4  | P            | PDIP         | 8    | 50  | 506    | 13.97  | 11230        | 4.32   |

| OPA277U     | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA277U.B   | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA277UA    | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA277UA.B  | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA4277PA   | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230        | 4.32   |

| OPA4277PA.A | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230        | 4.32   |

| OPA4277UA   | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940         | 4.32   |

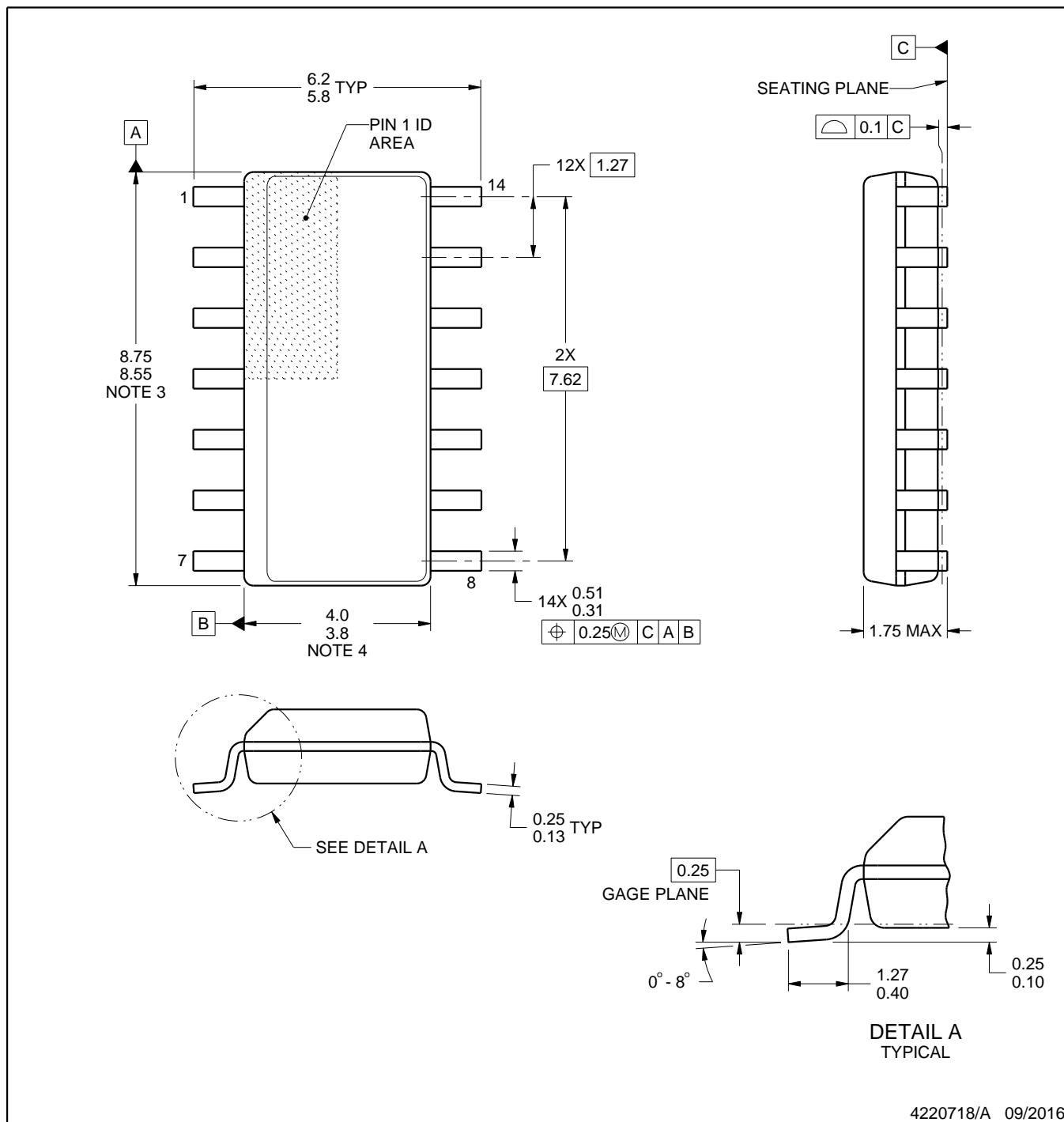

# PACKAGE OUTLINE

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4220718/A 09/2016

## NOTES:

1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

5. Reference JEDEC registration MS-012, variation AB.

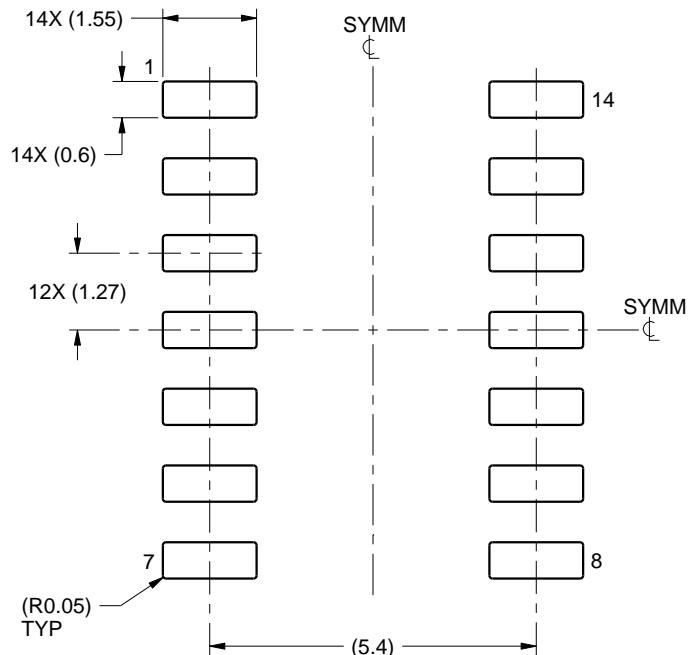

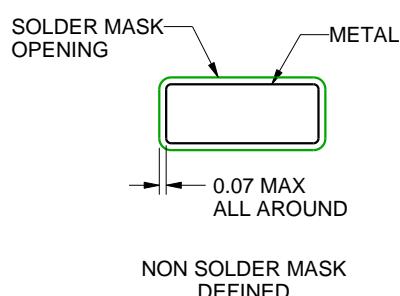

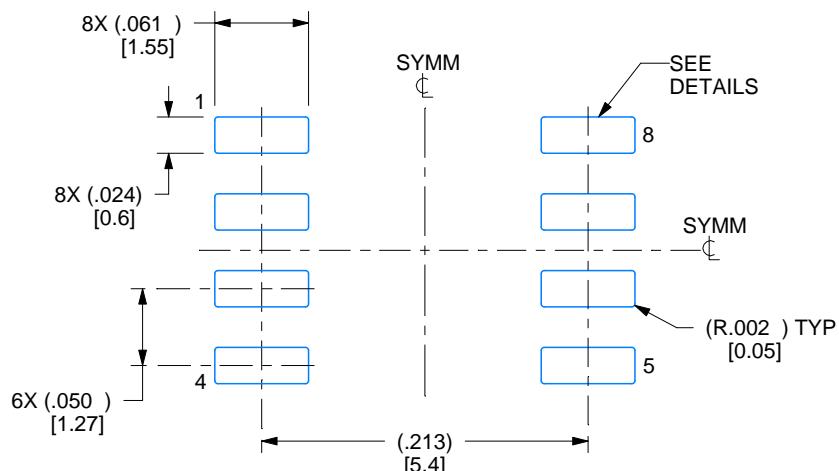

# EXAMPLE BOARD LAYOUT

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

SCALE:8X

SOLDER MASK DETAILS

4220718/A 09/2016

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

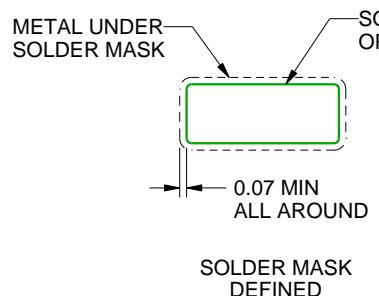

# EXAMPLE STENCIL DESIGN

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:8X

4220718/A 09/2016

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

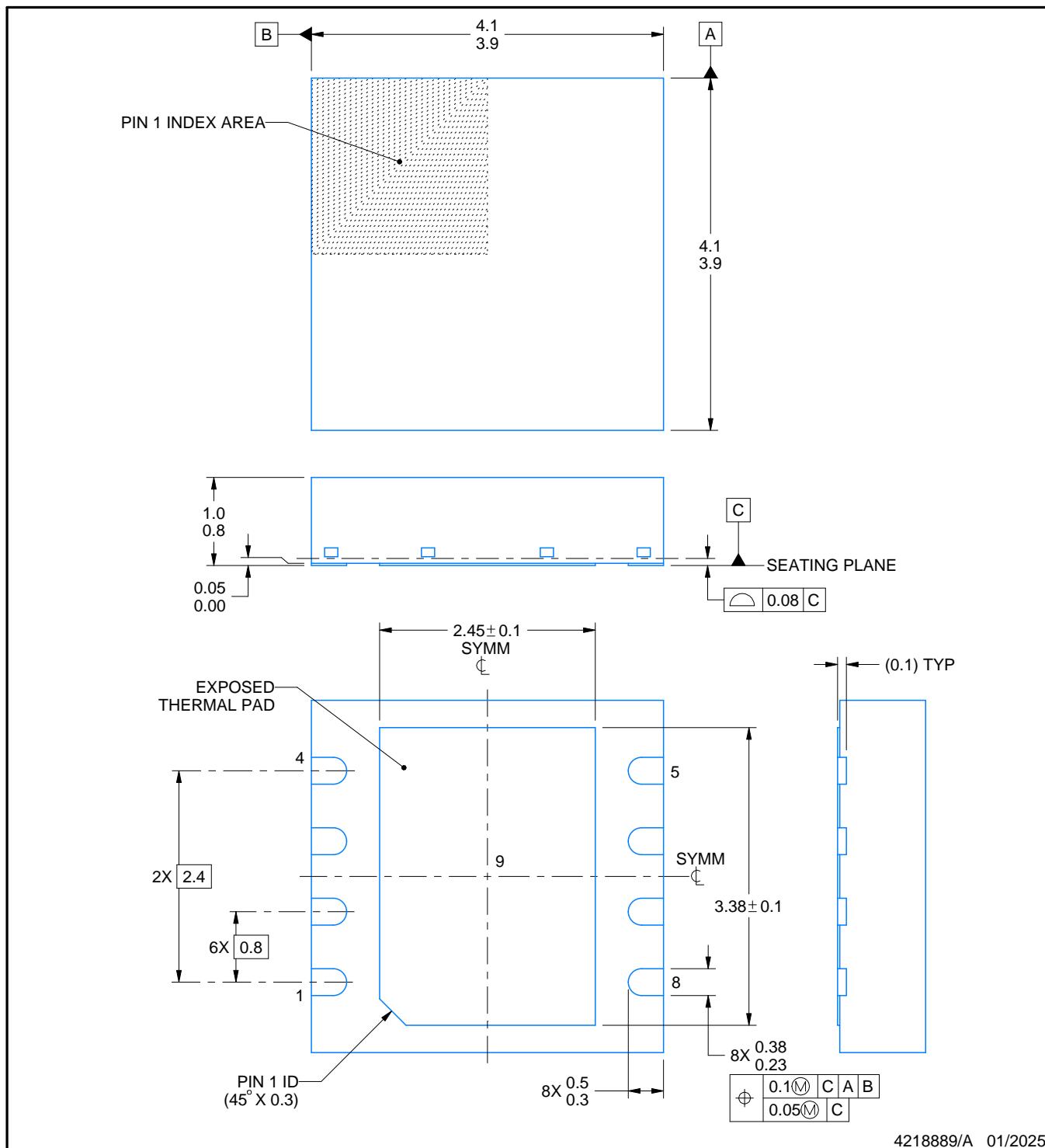

# PACKAGE OUTLINE

**DRM0008A**

**VSON - 1 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

4218889/A 01/2025

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

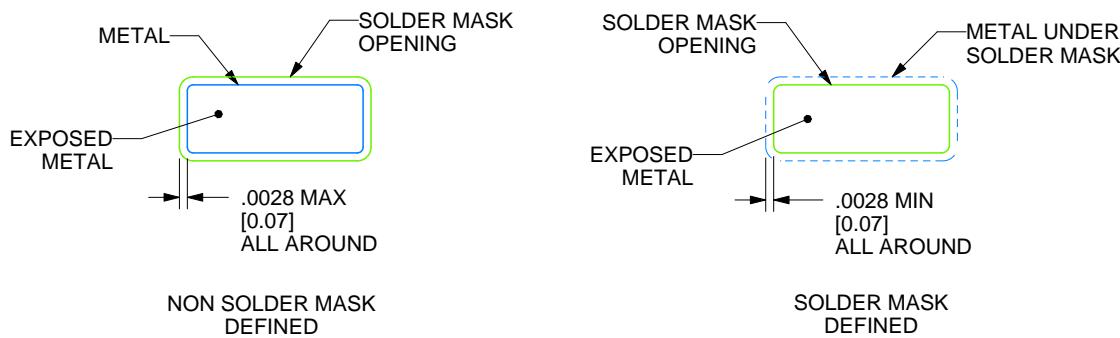

# EXAMPLE BOARD LAYOUT

DRM0008A

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 20X

SOLDER MASK DETAILS

4218889/A 01/2025

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

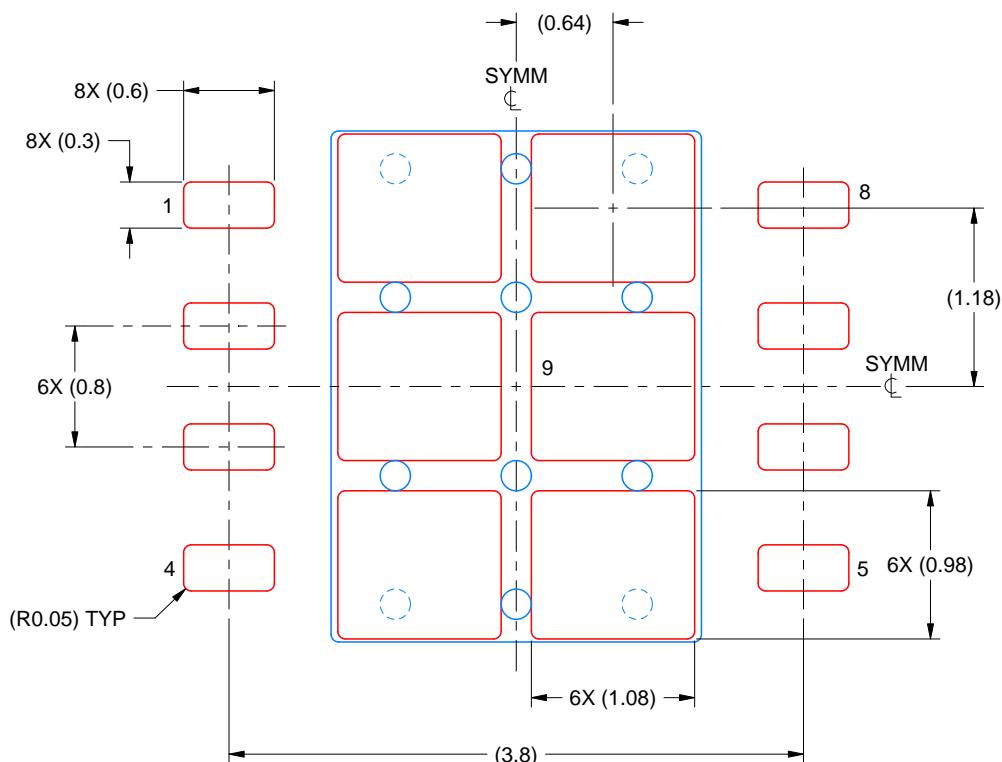

# EXAMPLE STENCIL DESIGN

DRM0008A

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 MM THICK STENCIL

SCALE: 20X

EXPOSED PAD 9

77% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

4218889/A 01/2025

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

D0008A

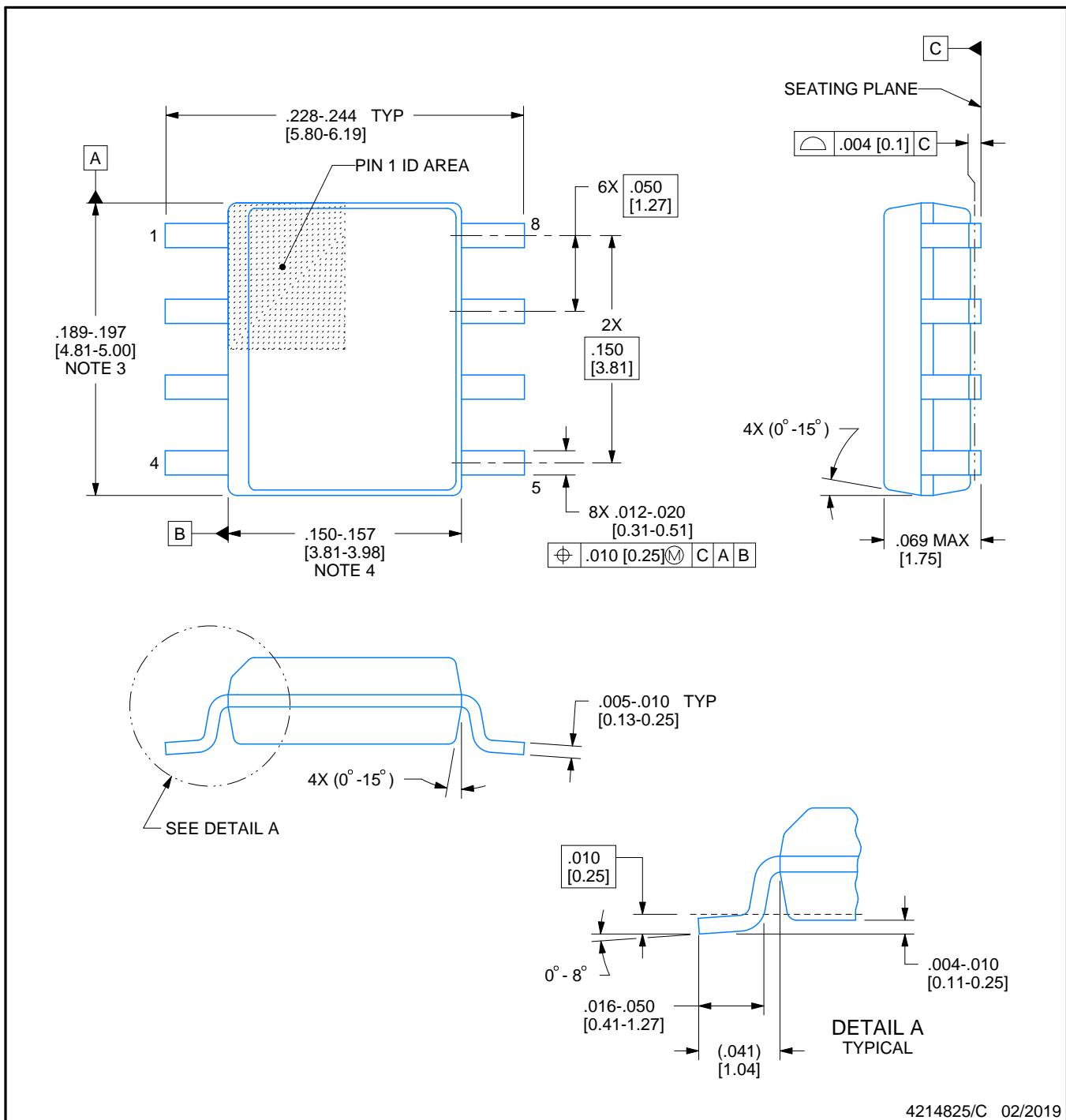

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

### NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- Reference JEDEC registration MS-012, variation AA.

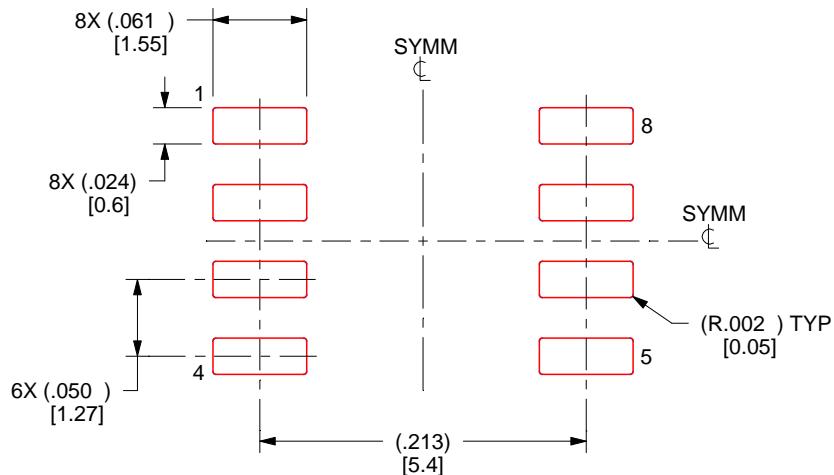

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

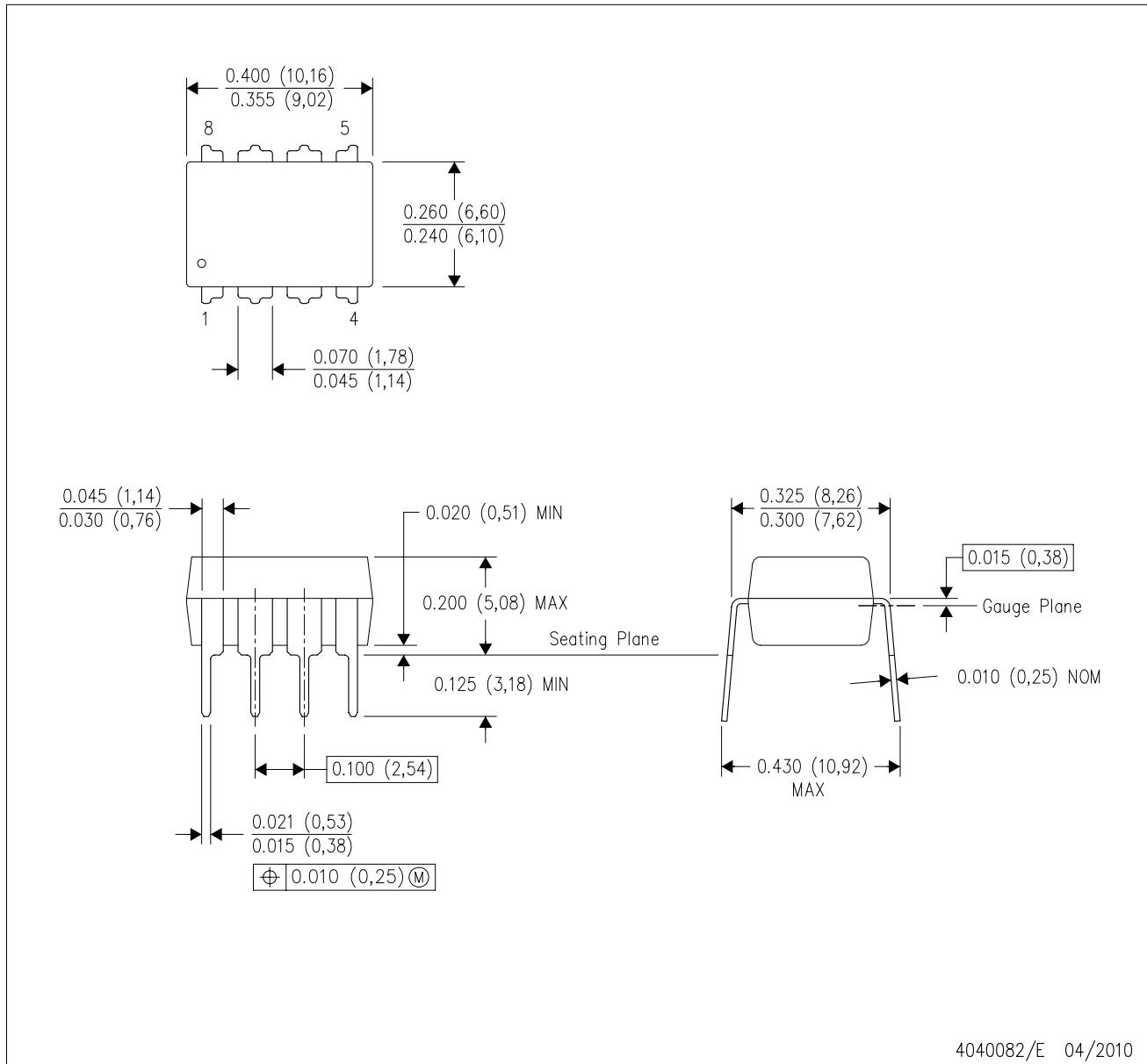

## MECHANICAL DATA

P (R-PDIP-T8)

PLASTIC DUAL-IN-LINE PACKAGE

4040082/E 04/2010

- NOTES:

- All linear dimensions are in inches (millimeters).

- This drawing is subject to change without notice.

- Falls within JEDEC MS-001 variation BA.

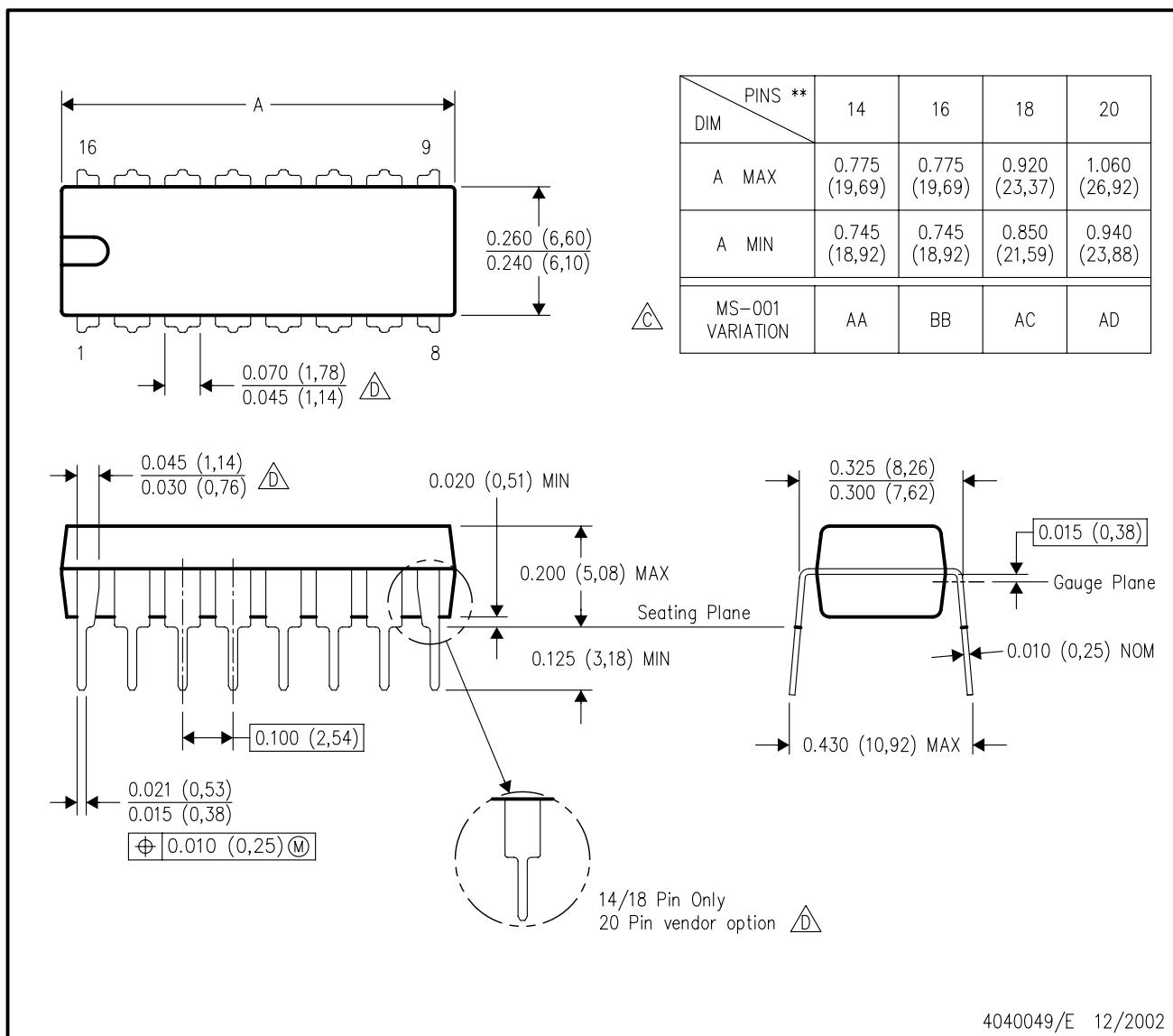

## N (R-PDIP-T\*\*)

16 PINS SHOWN

## PLASTIC DUAL-IN-LINE PACKAGE

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月