## 単一電源、10MHz、レール・ツー・レール出力、低ノイズ、JETアンプ

### 特 長

- 低消費電流 : 2.3mA(最大)

- 低オフセット・ドリフト : 10 $\mu$ V/°C(最大)

- 低い入力バイアス電流 : 20pA(最大)

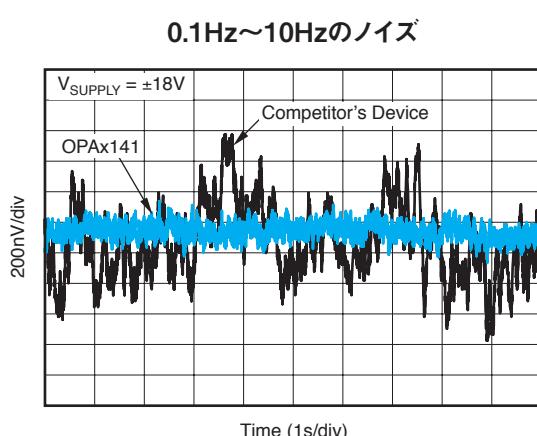

- 非常に小さい1/fノイズ : 250nV<sub>PP</sub>

- 低ノイズ : 6.5nV/ $\sqrt{\text{Hz}}$

- 広帯域幅 : 10MHz

- スルーレート : 20V/ $\mu$ s

- V-を含む入力電圧範囲

- レール・ツー・レール出力

- 単一電源動作 : 4.5V~36V

- デュアル電源動作 :  $\pm 2.25\text{V}$ ~ $\pm 18\text{V}$

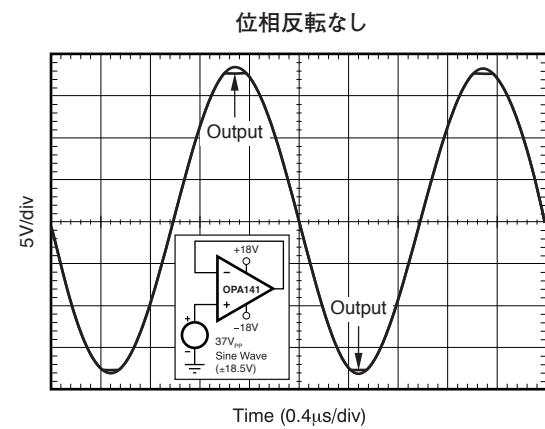

- 位相反転なし

- MSOP-8、TSSOPパッケージ

### アプリケーション

- バッテリ駆動機器

- 産業用制御

- 医療用計測機器

- フォトダイオード・アンプ

- アクティブ・フィルタ

- データ収集システム

- ポータブル・オーディオ

- 自動テスト・システム

### 概 要

OPA141、OPA2141、およびOPA4141アンプ・ファミリーは、優れたドリフト性能と低い入力バイアス電流を特徴とした低電力JFET入力アンプのシリーズです。レール・ツー・レールの出力スイングと、V-を含む入力範囲により、JFETアンプの低ノイズ特性を活かしながら、現在の高精度な単一電源A/Dコンバータ(ADC)およびD/Aコンバータ(DAC)へのインターフェイスが可能です。

OPA141は、10MHzのユニティ・ゲイン帯域幅と20V/ $\mu$ sのスルーレートを実現しながら、わずか1.8mA(typ)の静止電流しか消費しません。このデバイスは、単一の4.5~36V電源またはデュアル $\pm 2.25\text{V}$ ~ $\pm 18\text{V}$ 電源で動作します。

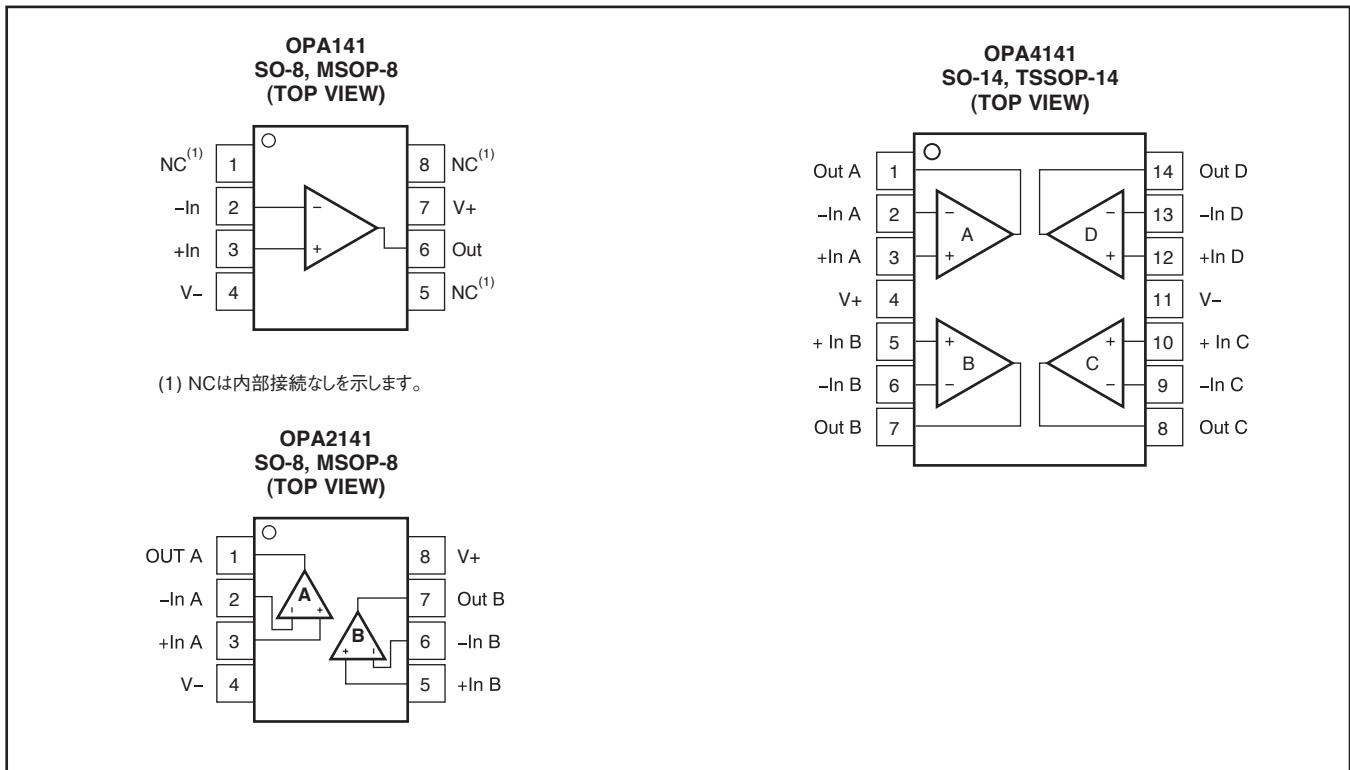

いずれの製品も-40°C~+125°Cの温度範囲で仕様が完全に規定され、最も厳しい環境での使用に対応しています。OPA141(シングル)およびOPA2141(デュアル)は、MSOP-8とSO-8の両方のパッケージで供給され、OPA4141(クアッド)はSO-14およびTSSOP-14パッケージで供給されます。

### 関連製品

| 特 長                                                 | 製品名    |

|-----------------------------------------------------|--------|

| 高精度、低電力、10MHz、FET入力、産業用オペアンプ                        | OPA140 |

| 2.2nV/ $\sqrt{\text{Hz}}$ 、低電力、36Vオペアンプ、SOT-23パッケージ | OPA209 |

| 低ノイズ、高精度、JFET入力オペアンプ                                | OPA827 |

| 低ノイズ、低IQ、高精度オペアンプ                                   | OPA376 |

| 高速、FET入力オペアンプ                                       | OPA132 |

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

### 絶対最大定格<sup>(1)</sup>

動作温度範囲内(特に記述のない限り)

|                      |                   | 値                      | 単位 |

|----------------------|-------------------|------------------------|----|

| 電源電圧                 |                   | $\pm 20$               | V  |

| 信号入力端子               | 電圧 <sup>(2)</sup> | (V-) -0.5 to (V+) +0.5 | V  |

|                      | 電流 <sup>(2)</sup> | $\pm 10$               | mA |

| 出力短絡 <sup>(3)</sup>  |                   | 連続                     |    |

| 動作温度、T <sub>A</sub>  |                   | -55 to +150            | °C |

| 保存温度、T <sub>A</sub>  |                   | -65 to +150            | °C |

| 接合部温度、T <sub>J</sub> |                   | +150                   | °C |

| ESD定格                | ESD定格 人体モデル(HBM)  | 2000                   | V  |

|                      | デバイス帯電モデル (CDM)   | 500                    | V  |

(1) 絶対最大定格以上のストレスが加わると、永続的な損傷を製品に与えることがあります。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。これはストレスの定格のみについて示してあり、このデータ・シートに示された値を超える状態での本製品の機能動作は含まれていません。

(2) 入力端子は、電源レールにダイオード・クランプされています。電源レールから0.5V以上スイング可能な入力信号は、10mA以下に電流制限する必要があります。

(3) V<sub>S</sub>/2(対称なデュアル電源構成でのグランド)への短絡、パッケージあたり1つのアンプ。

### パッケージ情報<sup>(1)</sup>

| 製品名     | パッケージ - リード | パッケージ・コード | パッケージ捺印  |

|---------|-------------|-----------|----------|

| OPA141  | SO-8        | D         | O141A    |

|         | MSOP-8      | DGK       | 141      |

| OPA2141 | SO-8        | D         | O2141A   |

|         | MSOP-8      | DGK       | 2141     |

| OPA4141 | TSSOP-14    | PW        | O4141A   |

|         | SO-14       | D         | O4141AG4 |

(1) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録：パッケージ・オプション」を参照するか、www.ti.comでデバイスの製品フォルダをご覧ください。

## 熱特性について

| 熱特性                   |                                | OPA141,<br>OPA2141 | OPA141,<br>OPA2141        | 単位   |

|-----------------------|--------------------------------|--------------------|---------------------------|------|

|                       |                                | D (SO)             | DGK (MSOP) <sup>(1)</sup> |      |

|                       |                                | 8                  | 8                         |      |

| $\theta_{JA}$         | 接合部・周囲間熱抵抗 <sup>(2)</sup>      | 160                | 180                       | °C/W |

| $\theta_{JC(top)}$    | 接合部・ケース(上面)間熱抵抗 <sup>(3)</sup> | 75                 | 55                        |      |

| $\theta_{JB}$         | 接合部・基板間熱抵抗 <sup>(4)</sup>      | 60                 | 130                       |      |

| $\Psi_{JT}$           | 接合部・上面間特性パラメータ <sup>(5)</sup>  | 9                  | n/a                       |      |

| $\Psi_{JB}$           | 接合部・底面間特性パラメータ <sup>(6)</sup>  | 50                 | 120                       |      |

| $\theta_{JC(bottom)}$ | 接合部・ケース(底面)間熱抵抗 <sup>(7)</sup> | n/a                | n/a                       |      |

- (1) 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

- (2) 自然状態での接合部・周囲間熱抵抗は、JESD51-2aに記載の環境で、JESD51-7に規定されたJEDEC標準High-K基板上のシミュレーションによって求められます。

- (3) 接合部・ケース(上面)間の熱抵抗は、パッケージ上面での冷却板試験のシミュレーションによって求められます。指定のJEDEC標準試験はありませんが、類似した内容がANSI SEMI規格のG30-88で参照できます。

- (4) 接合部・基板間の熱抵抗は、JESD51-8の規定に従い、PCB温度を制御するリング型冷却板測定器を用いた環境でのシミュレーションによって求められます。

- (5) 接合部・上面間の特性化パラメータ $\Psi_{JT}$ は、実システムでのデバイスの接合部温度を見積るために使用され、JESD51-2a(セクション6および7)に規定される手順を用いて $\theta_{JA}$ を求めるシミュレーション・データから抽出されます。

- (6) 接合部・基板間の特性化パラメータ $\Psi_{JB}$ は、実システムでのデバイスの接合部温度を見積るために使用され、JESD51-2a(セクション6および7)に規定される手順を用いて $\theta_{JA}$ を求めるシミュレーション・データから抽出されます。

- (7) 接合部・ケース(底面)間の熱抵抗は、露出したパッド(PowerPAD)上での冷却板試験のシミュレーションによって求められます。指定のJEDEC標準試験はありませんが、類似した内容がANSI SEMI規格のG30-88で参照できます。

## 熱特性について

| 熱特性                   | OPA4141                        | OPA4141                   | 単位  |

|-----------------------|--------------------------------|---------------------------|-----|

|                       | D (SO)                         | PW (TSSOP) <sup>(1)</sup> |     |

|                       | 14                             | 14                        |     |

| $\theta_{JA}$         | 接合部・周囲間熱抵抗 <sup>(2)</sup>      | 97                        | 135 |

| $\theta_{JC(top)}$    | 接合部・ケース(上面)間熱抵抗 <sup>(3)</sup> | 56                        | 45  |

| $\theta_{JB}$         | 接合部・基板間熱抵抗 <sup>(4)</sup>      | 53                        | 66  |

| $\Psi_{JT}$           | 接合部・上面間特性パラメータ <sup>(5)</sup>  | 19                        | n/a |

| $\Psi_{JB}$           | 接合部・底面間特性パラメータ <sup>(6)</sup>  | 46                        | 60  |

| $\theta_{JC(bottom)}$ | 接合部・ケース(底面)間熱抵抗 <sup>(7)</sup> | n/a                       | n/a |

- (1) 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

- (2) 自然状態での接合部・周囲間熱抵抗は、JESD51-2aに記載の環境で、JESD51-7に規定されたJEDEC標準High-K基板上のシミュレーションによって求められます。

- (3) 接合部・ケース(上面)間の熱抵抗は、パッケージ上面での冷却板試験のシミュレーションによって求められます。指定のJEDEC標準試験はありませんが、類似した内容がANSI SEMI規格のG30-88で参照できます。

- (4) 接合部・基板間の熱抵抗は、JESD51-8の規定に従い、PCB温度を制御するリング型冷却板測定器を用いた環境でのシミュレーションによって求められます。

- (5) 接合部・上面間の特性化パラメータ $\psi_{JT}$ は、実システムでのデバイスの接合部温度を見積もるために使用され、JESD51-2a(セクション6および7)に規定される手順を用いて $\theta_{JA}$ を求めるシミュレーション・データから抽出されます。

- (6) 接合部・基板間の特性化パラメータ $\psi_{JB}$ は、実システムでのデバイスの接合部温度を見積もるために使用され、JESD51-2a(セクション6および7)に規定される手順を用いて $\theta_{JA}$ を求めるシミュレーション・データから抽出されます。

- (7) 接合部・ケース(底面)間の熱抵抗は、露出したパッド(PowerPAD)上での冷却板試験のシミュレーションによって求められます。指定のJEDEC標準試験はありませんが、類似した内容がANSI SEMI規格のG30-88で参照できます。

**電気的特性 :  $V_S = +4.5V \sim +36V, \pm 2.25V \sim \pm 18V$**

太字の制限は、仕様温度範囲  $T_A = -40^{\circ}C \sim +125^{\circ}C$  にわたって適用されます。

$T_A = +25^{\circ}C, R_L = 2k\Omega$  を電源中点に接続、 $V_{CM} = V_{OUT}$  = 電源中点 (特に記述のない限り)

| パラメータ                        | テスト条件        | OPA141, OPA2141, OPA4141                                      |           |                       | 単位                        |

|------------------------------|--------------|---------------------------------------------------------------|-----------|-----------------------|---------------------------|

|                              |              | MIN                                                           | TYP       | MAX                   |                           |

| オフセット電圧                      |              |                                                               |           |                       |                           |

| オフセット電圧、RTI                  | $V_{OS}$     | $V_S = \pm 18V$                                               |           | $\pm 1$               | $\pm 3.5$ mV              |

| 対温度                          |              | $V_S = \pm 18V$                                               |           |                       | $\pm 4.3$ mV              |

| ドリフト                         | $dV_{OS}/dT$ | $V_S = \pm 18V$                                               |           | $\pm 2$               | $\pm 10$ $\mu V^{\circ}C$ |

| 対電源電圧                        | PSRR         | $V_S = \pm 2.25V \text{ to } \pm 18V$                         |           | $\pm 0.14$            | $\pm 2$ $\mu V/V$         |

| 対温度                          |              | $V_S = \pm 2.25V \text{ to } \pm 18V$                         |           |                       | $\pm 4$ $\mu V/V$         |

| 入力バイアス電流                     |              |                                                               |           |                       |                           |

| 入力バイアス電流                     | $I_B$        |                                                               |           | $\pm 2$               | $\pm 20$ pA               |

| 対温度                          |              |                                                               |           | $\pm 5$               | nA                        |

| 入力オフセット電流                    | $I_{OS}$     |                                                               |           | $\pm 2$               | $\pm 20$ pA               |

| 対温度                          |              |                                                               |           | $\pm 1$               | nA                        |

| ノイズ                          |              |                                                               |           |                       |                           |

| 入力電圧ノイズ                      |              |                                                               |           |                       |                           |

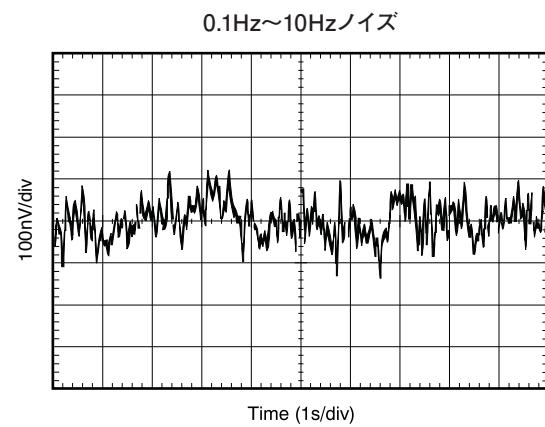

| $f = 0.1Hz \text{ to } 10Hz$ |              |                                                               |           | 250                   | $nV_{PP}$                 |

| $f = 0.1Hz \text{ to } 10Hz$ |              |                                                               |           | 42                    | $nVRMS$                   |

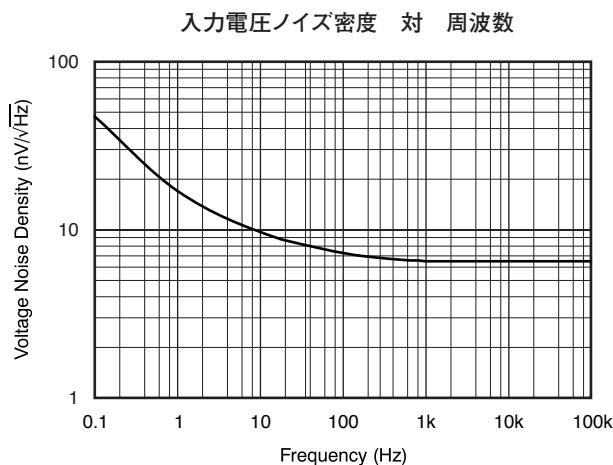

| 入力電圧ノイズ密度                    | $e_n$        |                                                               |           |                       |                           |

| $f = 10Hz$                   |              |                                                               |           | 12                    | $nV/\sqrt{Hz}$            |

| $f = 100Hz$                  |              |                                                               |           | 6.5                   | $nV/\sqrt{Hz}$            |

| $f = 1kHz$                   |              |                                                               |           | 6.5                   | $nV/\sqrt{Hz}$            |

| 入力電流ノイズ密度                    | $i_n$        |                                                               |           |                       |                           |

| $f = 1kHz$                   |              |                                                               |           | 0.8                   | $fA/\sqrt{Hz}$            |

| 入力電圧範囲                       |              |                                                               |           |                       |                           |

| 同相モード電圧範囲                    | $V_{CM}$     |                                                               | (V-) -0.1 |                       | (V+) -3.5 V               |

| 同相モード除去比                     | CMRR         | $V_S = \pm 18V, V_{CM} = (V-) -0.1V \text{ to } (V+) - 3.5V$  | 120       | 126                   |                           |

| 対温度                          |              | $V_S = \pm 18V, V_{CM} = (V-) -0.1V \text{ to } (V+) - 3.5V$  | 120       |                       |                           |

| 入力インピーダンス                    |              |                                                               |           |                       |                           |

| 差動                           |              |                                                               |           | $10^{13} \parallel 8$ | $\Omega \parallel pF$     |

| 同相モード                        |              | $V_{CM} = (V-) -0.1V \text{ to } (V+) -3.5V$                  |           | $10^{13} \parallel 6$ | $\Omega \parallel pF$     |

| 開ループ・ゲイン                     |              |                                                               |           |                       |                           |

| 開ループ電圧ゲイン                    | $A_{OL}$     | $V_O = (V-) + 0.35V \text{ to } (V+) - 0.35V, R_L = 2k\Omega$ | 114       | 126                   |                           |

| 対温度                          |              | $V_O = (V-) + 0.35V \text{ to } (V+) - 0.35V, R_L = 2k\Omega$ | 108       |                       |                           |

| 周波数応答                        |              |                                                               |           |                       |                           |

| ゲイン・帯域幅積                     | BW           |                                                               |           | 10                    | MHz                       |

| スルーレート                       |              |                                                               |           | 20                    | $V/\mu s$                 |

| セトリング・タイム、12ビット(0.024)       |              |                                                               |           | 880                   | ns                        |

| THD+N                        |              | $1kHz, G = 1, V_O = 3.5V_{RMS}$                               |           | 0.00005               | %                         |

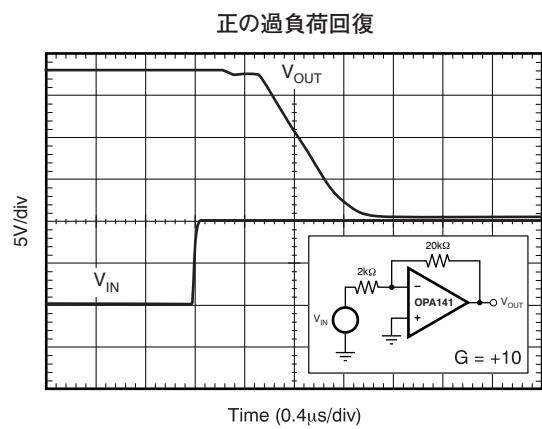

| 過負荷回復時間                      |              |                                                               |           | 600                   | ns                        |

**電気的特性 :  $V_S = +4.5V \sim +36V$ ,  $\pm 2.25V \sim \pm 18V$**

太字の制限は、仕様温度範囲  $T_A = -40^{\circ}C \sim +125^{\circ}C$  にわたって適用されます。

$T_A = +25^{\circ}C$ ,  $R_L = 2k\Omega$  を電源中点に接続、 $V_{CM} = V_{OUT}$  = 電源中点 (特に記述のない限り)

| パラメータ         | テスト条件      | OPA141, OPA2141, OPA4141        |              |      | 単位          |

|---------------|------------|---------------------------------|--------------|------|-------------|

|               |            | MIN                             | _TYP         | MAX  |             |

| 出力            |            |                                 |              |      |             |

| 出力電圧          | $V_O$      | $R_L = 10k\Omega$               | (V-) + 0.2   |      | (V+) - 0.2  |

|               |            | $R_L = 2k\Omega$                | (V-) + 0.35  |      | (V+) - 0.35 |

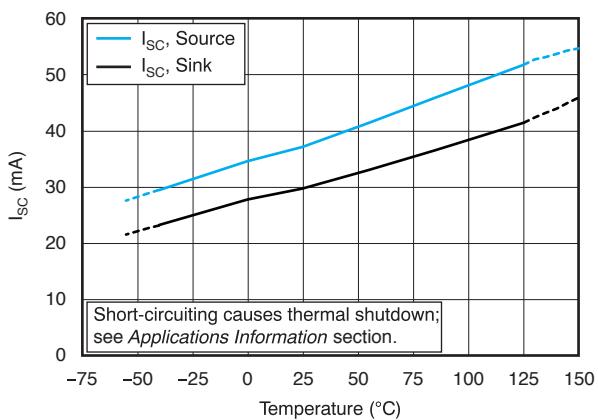

| 短絡電流          | $I_{SC}$   | ソース                             |              | +36  | mA          |

|               |            | シンク                             |              | -30  | mA          |

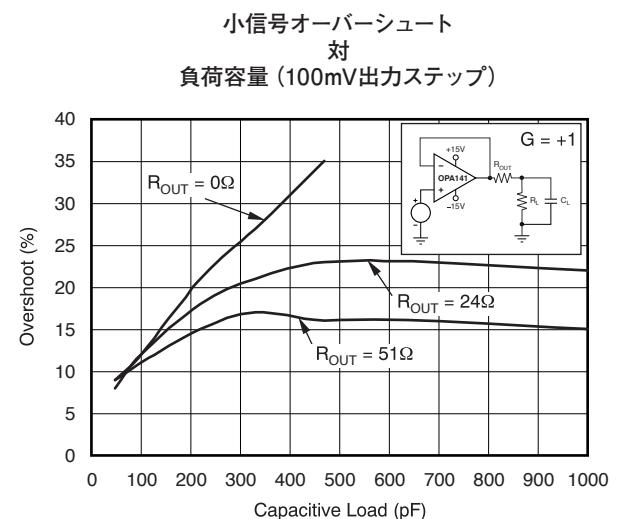

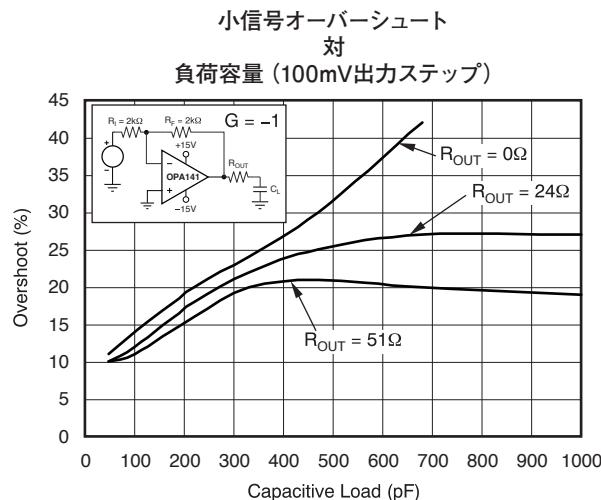

| 容量性負荷駆動       | $C_{LOAD}$ |                                 | 図19および図20を参照 |      |             |

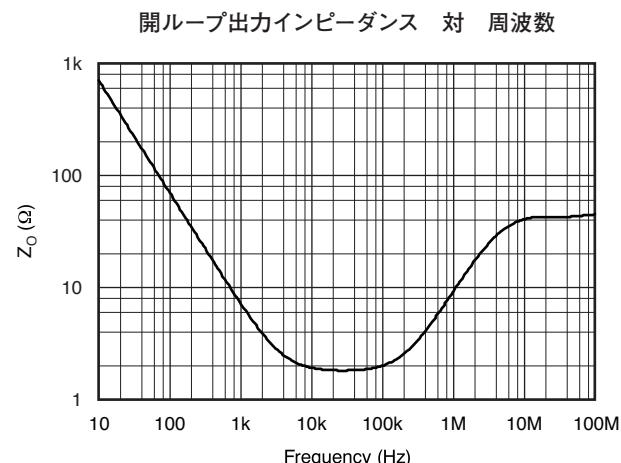

| 開ループ出力インピーダンス | $R_O$      | $f = 1MHz$ , $I_O = 0$ (図18を参照) |              | 10   | $\Omega$    |

| 電源            |            |                                 |              |      |             |

| 仕様電圧範囲        | $V_S$      |                                 | $\pm 2.25$   |      | $\pm 18$    |

| 静止電流(アンプ毎)    | $I_Q$      | $I_O = 0mA$                     |              | 1.8  | 2.3         |

| 対温度           |            |                                 |              |      | 3.1         |

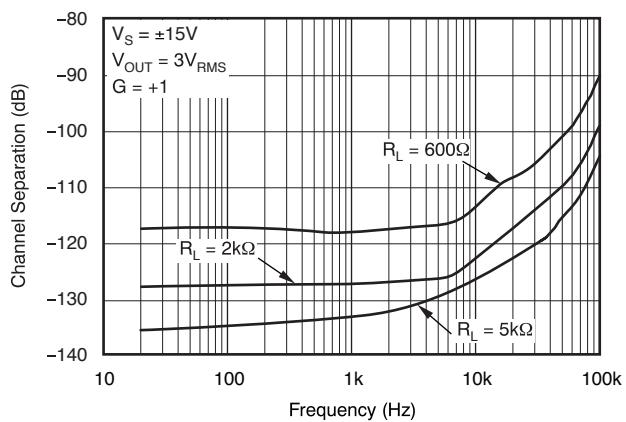

| チャネル間分離       |            |                                 |              |      |             |

| チャネル間分離       |            | DC時                             |              | 0.02 | $\mu V/V$   |

|               |            | 100kHz時                         |              | 10   | $\mu V/V$   |

| 温度範囲          |            |                                 |              |      |             |

| 仕様範囲          |            |                                 | -40          |      | +125        |

| 動作範囲          |            |                                 | -55          |      | +150        |

|               |            |                                 |              |      | $^{\circ}C$ |

## ピン配置

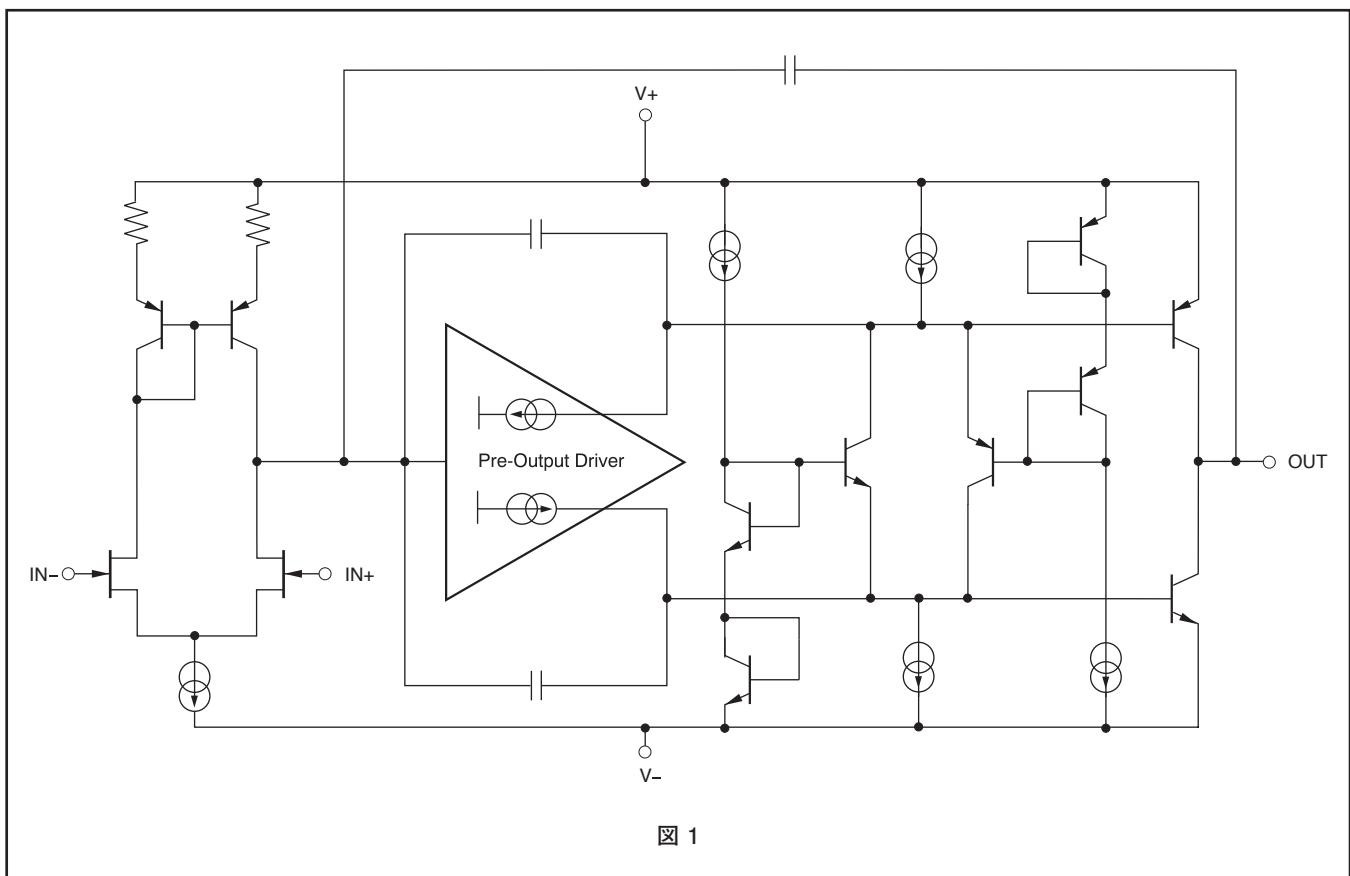

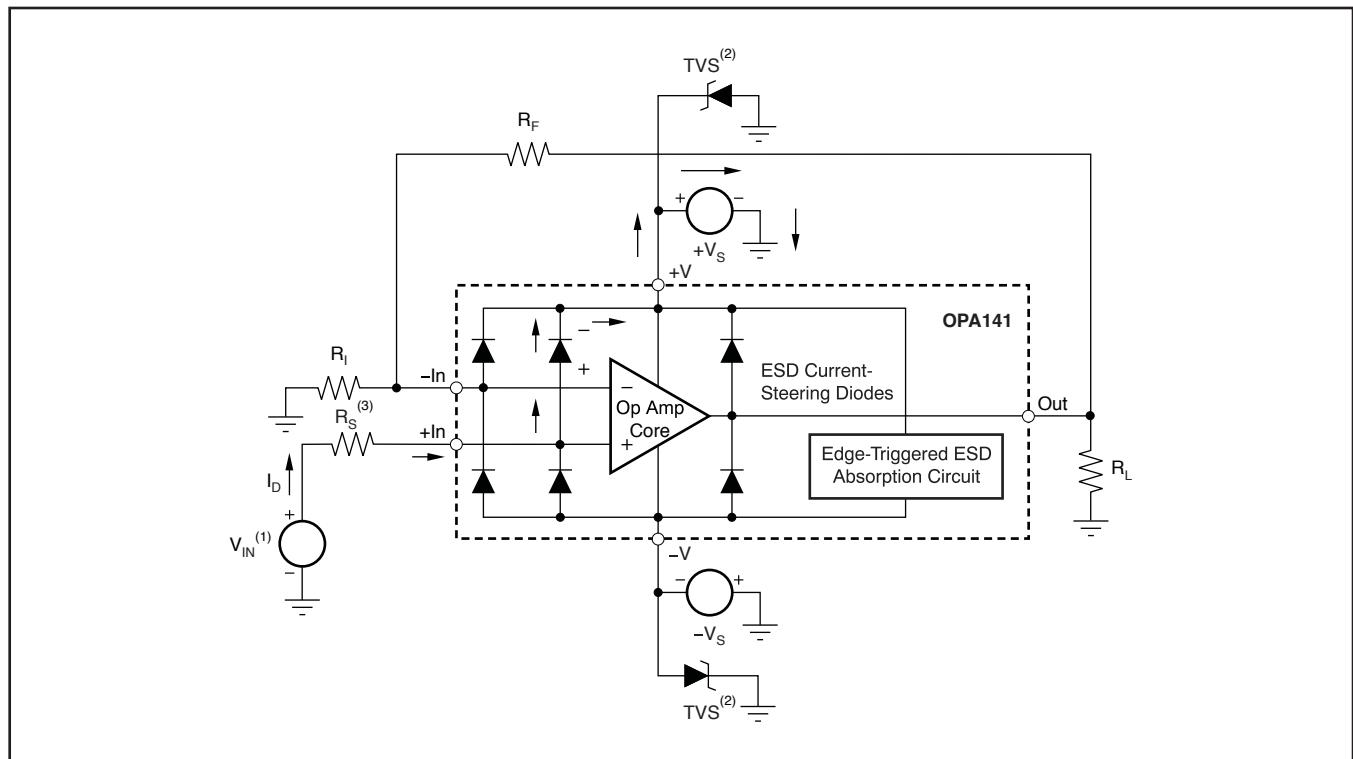

## ブロック概略図

図 1

## 標準的特性一覧

### グラフ一覧

| 説明                             | 図   |

|--------------------------------|-----|

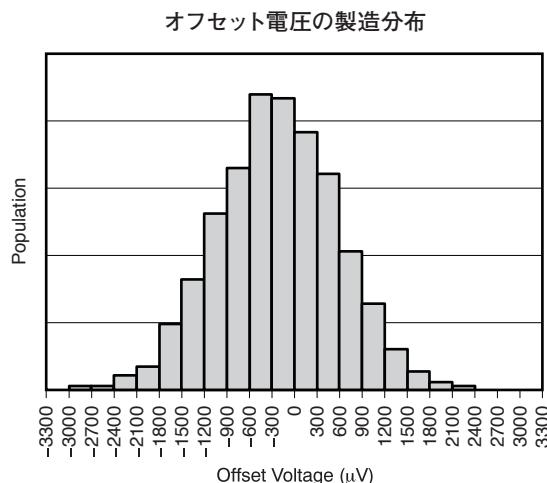

| オフセット電圧の製造分布                   | 図2  |

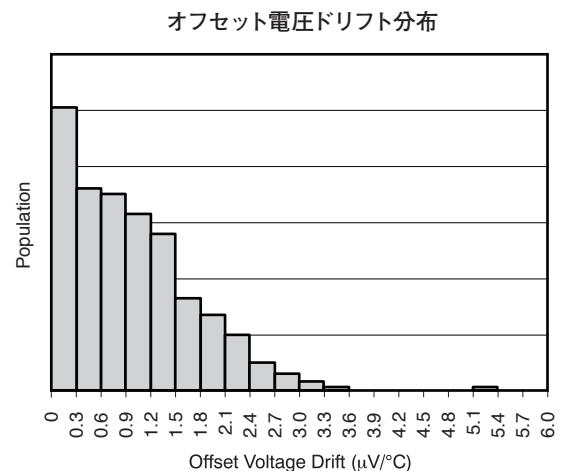

| オフセット電圧ドリフト分布                  | 図3  |

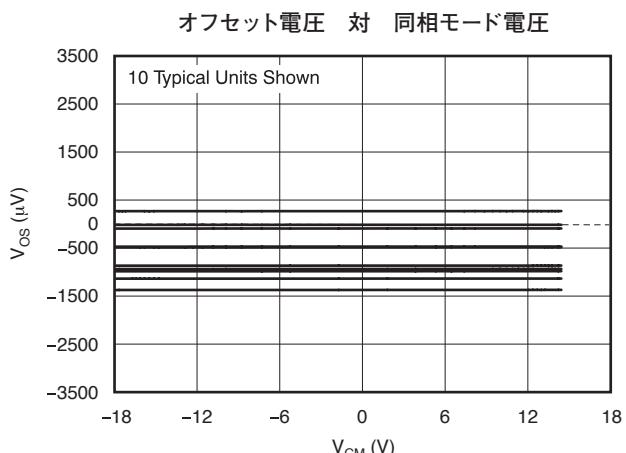

| オフセット電圧 対 同相モード電圧(最大電源電圧)      | 図4  |

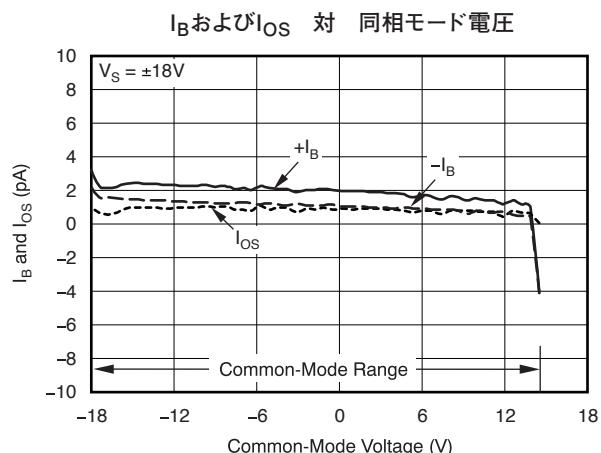

| $I_B$ および $I_{OS}$ 対 同相モード電圧   | 図5  |

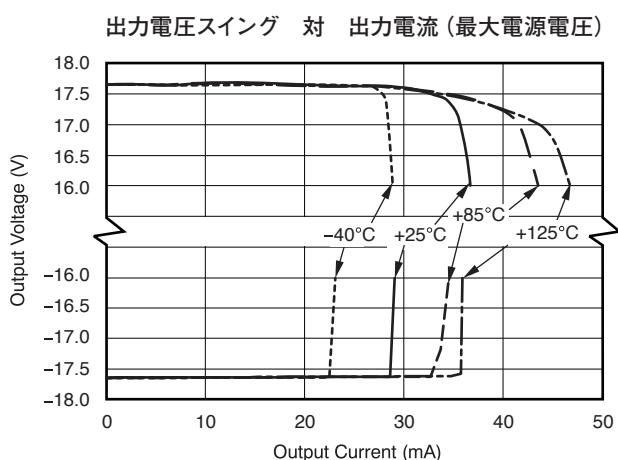

| 出力電圧スイング 対 出力電流                | 図6  |

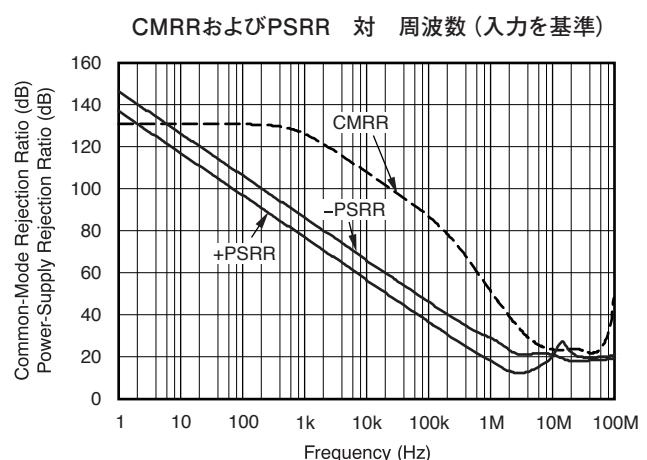

| CMRRおよびPSRR 対 周波数(RTI)         | 図7  |

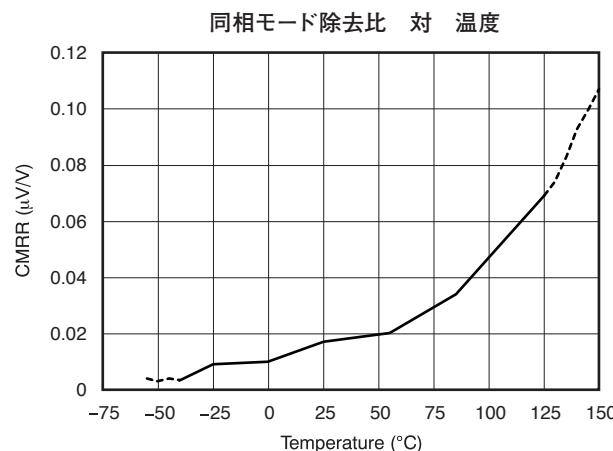

| 同相モード除去比 対 温度                  | 図8  |

| 0.1Hz～10Hzのノイズ                 | 図9  |

| 入力電圧ノイズ密度 対 周波数                | 図10 |

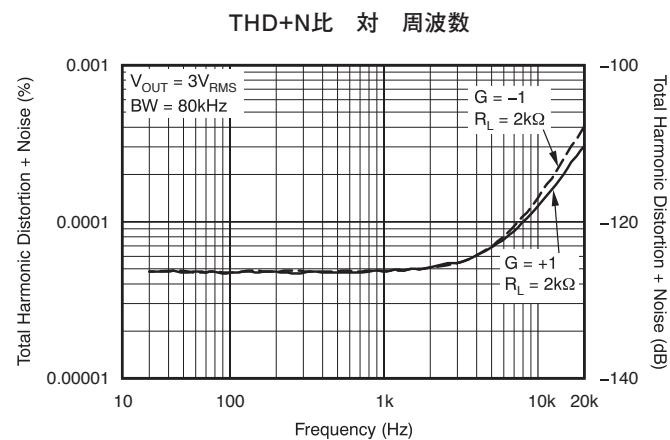

| THD+N比 対 周波数(80kHz AP帯域幅)      | 図11 |

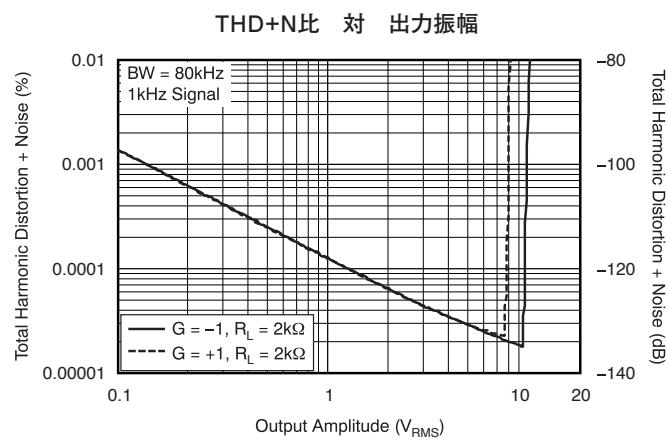

| THD+N比 対 出力振幅                  | 図12 |

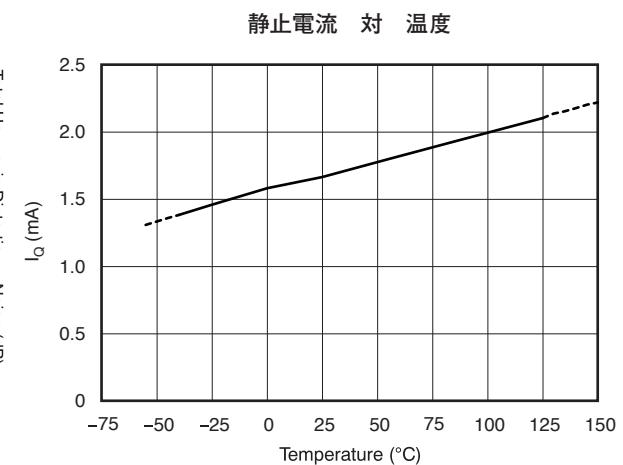

| 静止電流 対 温度                      | 図13 |

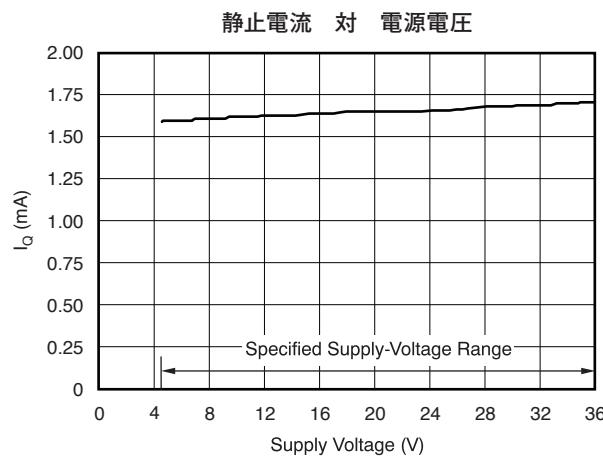

| 静止電流 対 電源電圧                    | 図14 |

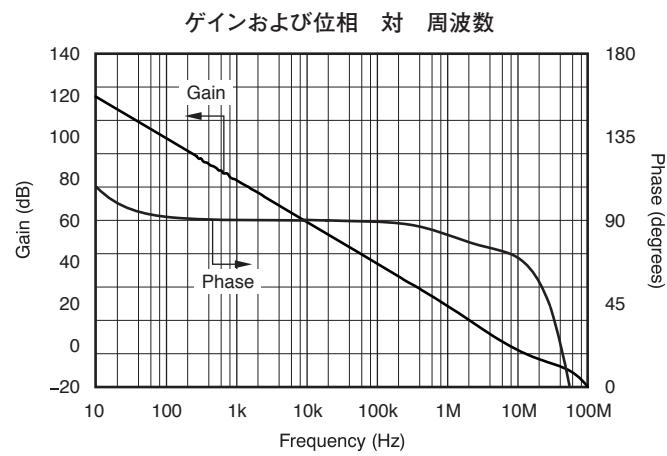

| ゲインおよび位相 対 周波数                 | 図15 |

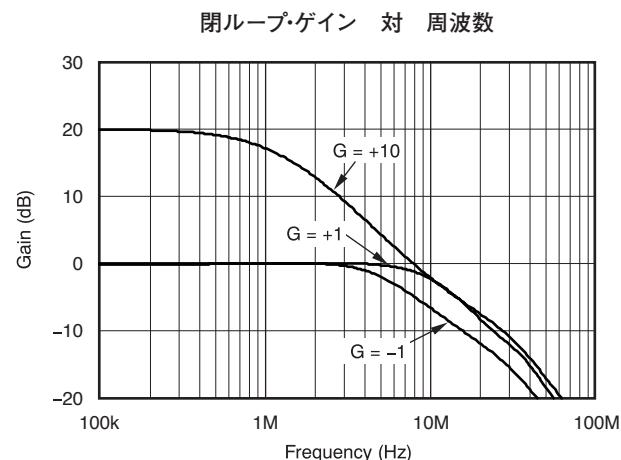

| 閉ループ・ゲイン 対 周波数                 | 図16 |

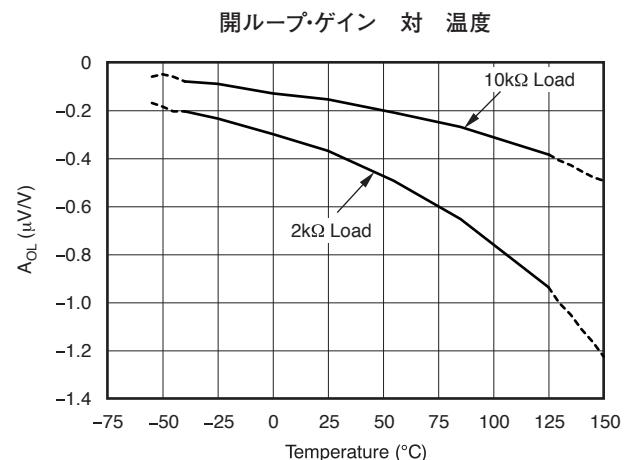

| 開ループ・ゲイン 対 温度                  | 図17 |

| 開ループ出力インピーダンス 対 周波数            | 図18 |

| 小信号オーバーシュート 対 負荷容量( $G = +1$ ) | 図19 |

| 小信号オーバーシュート 対 負荷容量( $G = -1$ ) | 図20 |

| 位相反転なし                         | 図21 |

| 正の過負荷回復                        | 図22 |

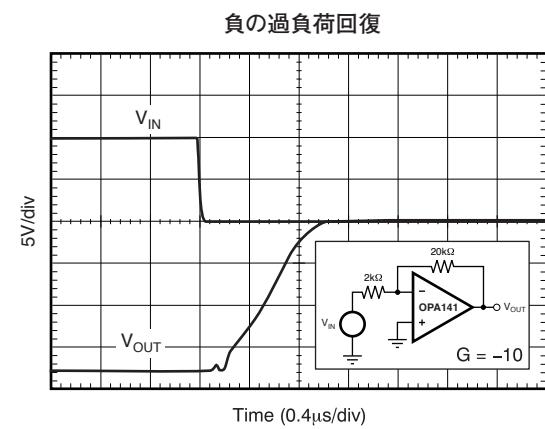

| 負の過負荷回復                        | 図23 |

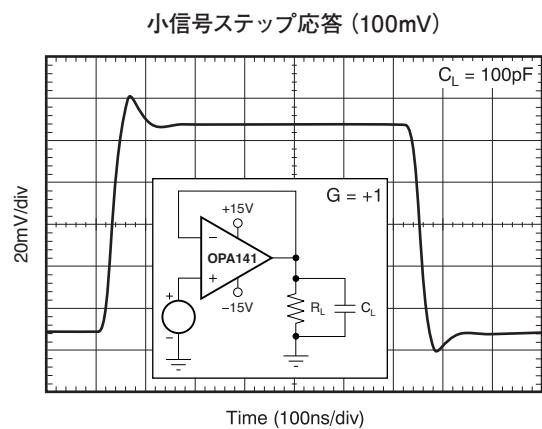

| 小信号ステップ応答( $G = +1$ )          | 図24 |

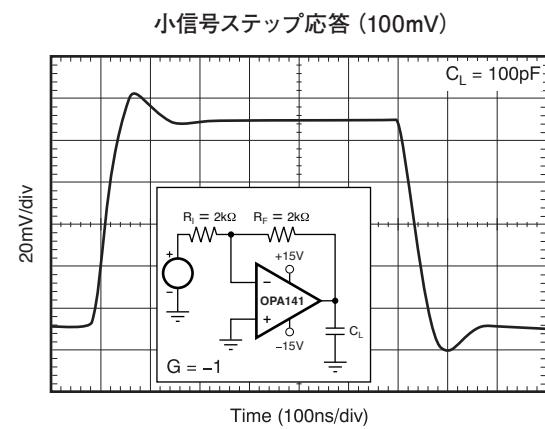

| 小信号ステップ応答( $G = -1$ )          | 図25 |

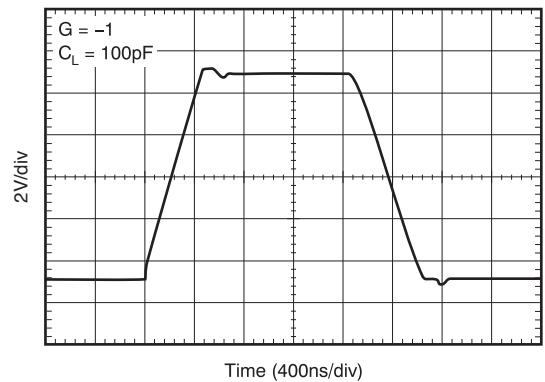

| 大信号ステップ応答( $G = +1$ )          | 図26 |

| 大信号ステップ応答( $G = -1$ )          | 図27 |

| 短絡電流 対 温度                      | 図28 |

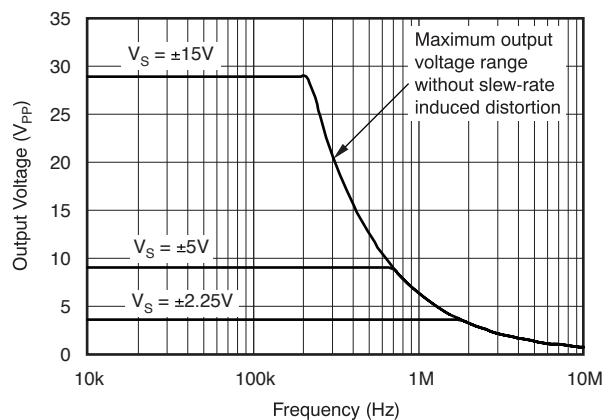

| 最大出力電圧 対 周波数                   | 図29 |

| チャネル間分離 対 周波数                  | 図30 |

表 1. 特性測定図

## 代表的特性

$T_A = +25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $R_L = 2\text{k}\Omega$ を電源中点に接続、 $V_{CM} = V_{OUT}$  = 電源中点 (特に記述のない限り)

図 2

図 3

図 4

図 5

図 6

図 7

## 代表的特性

$T_A = +25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $R_L = 2\text{k}\Omega$ を電源中点に接続、 $V_{CM} = V_{OUT} = \text{電源中点}$ （特に記述のない限り）

図 8

図 9

図 10

図 11

図 12

図 13

## 代表的特性

$T_A = +25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $R_L = 2\text{k}\Omega$ を電源中点に接続、 $V_{CM} = V_{OUT} = \text{電源中点}$ （特に記述のない限り）

図 14

図 15

図 16

図 17

図 18

図 19

## 代表的特性

$T_A = +25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $R_L = 2\text{k}\Omega$ を電源中点に接続、 $V_{CM} = V_{OUT} = \text{電源中点}$ （特に記述のない限り）

図 20

図 21

図 22

図 23

図 24

図 25

## 代表的特性

$T_A = +25^\circ\text{C}$ 、 $V_S = \pm 18\text{V}$ 、 $R_L = 2\text{k}\Omega$ を電源中点に接続、 $V_{CM} = V_{OUT} =$  電源中点 (特に記述のない限り)

大信号ステップ応答

図 26

大信号ステップ応答

図 27

短絡電流 対 温度

図 28

最大出力電圧 対 周波数

図 29

チャネル分離 対 周波数

図 30

## アプリケーション情報

OPA141、OPA2141、およびOPA4141は、ユニティ・ゲインで安定なオペアンプであり、ノイズ、入力バイアス電流、入力オフセット電圧が非常に低いという特徴があります。ノイズの多い電源や高インピーダンスの電源を使用するアプリケーションでは、デバイス・ピンの近くにデカッピング・コンデンサを配置する必要があります。ほとんどの場合は、 $0.1\mu\text{F}$ のコンデンサで十分です。図1に、OPA141の概略回路図を示しています。

## 動作電圧

OPA141、OPA2141、およびOPA4141シリーズのオペアンプは、単一電源またはデュアル電源により、 $V_S = +4.5\text{V}(\pm 2.25\text{V}) \sim V_S = +36\text{V}(\pm 18\text{V})$ の動作範囲で使用できます。これらのデバイスには、対称電源は必要なく、最小電源電圧として $+4.5\text{V}(\pm 2.25\text{V})$ を必要とするだけです。 $V_S$ が $\pm 3.5\text{V}$ 未満の場合、同相モード入力範囲には電源中点が含まれません。 $+40\text{V}$ を超える電源電圧は、デバイスに永久的な損傷を与える可能性があります。「絶対最大定格」の表を参照してください。主要なパラメータは、動作温度範囲 $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ で規定されています。電源電圧または温度範囲に対して変化する主なパラメータは、このデータ・シートの「標準的特性」に示されています。

## 容量性負荷と安定性

OPAx141のダイナミック特性は、一般的なゲイン、負荷、および動作条件に対して最適化されています。低い閉ループ・ゲインと高い容量性負荷の組み合わせでは、アンプの位相余裕が減り、ゲインのピーキングや発振が生じる可能性があります。したがって、大きな容量性負荷は出力から分離する必要があります。この分離を行う最も簡単な方法は、出力と直列に小さな抵抗(例えば、 $R_{\text{OUT}} = 50\Omega$ )を追加することです。

図19および図20は、 $R_{\text{OUT}}$ のいくつかの値に対する小信号オーバーシュート対容量性負荷のグラフを示しています。また、分析手法およびアプリケーション回路の詳細については、TIのアプリケーション・ブリテンAB-028(文献番号SBOA015、TIのWebサイトからダウンロード可能)を参照してください。

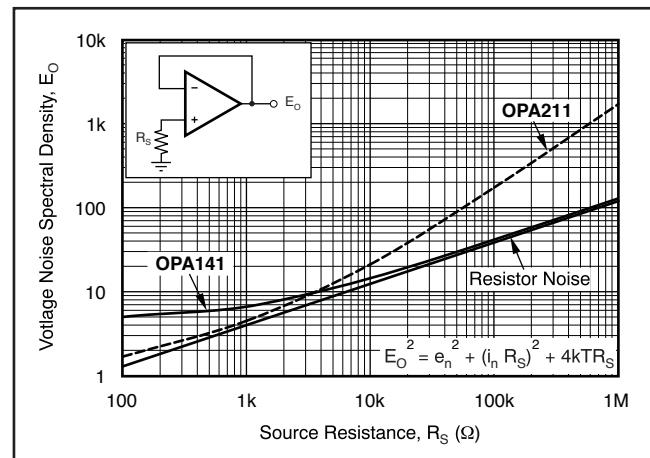

## ノイズ特性

図31に、オペアンプがユニティ・ゲイン構成のときの、ソース・インピーダンスの変化に対するすべてのサーキットノイズを示します(帰還抵抗回路は使用していないため、追加のノイズ成分はありません)。OPA141およびOPA211のすべてのサーキットノイズの計算値が示されています。オペアンプ自体は、電圧ノイズ成分と電流ノイズ成分の両方に寄与します。一般に、電圧ノイズは、オフセット電圧の時間によって変化する成分としてモデル化されます。電流ノイズは、入力バイアス電流の時間によって変化する成分としてモデル化され、ソース抵抗によってノイズの電圧成分を生成します。したがって、あるアプリケーションに対して最小ノイズとなるオペアンプは、ソース・インピーダンスによって異なります。ソース・インピーダンスが低い場合、電流ノイズは無視でき、電圧ノイズが一般に支配的です。OPA141、OPA2141、およびOPA4141ファミリーは、オペアンプのFET入力により、電圧ノイズが低く、電流ノイズは極

めて低くなっています。その結果、OPAx141シリーズは、実用的なソース・インピーダンスに対して電流ノイズ成分を無視できるため、ソース・インピーダンスの高いアプリケーション向けに優れた選択肢となります。

図31の式は、以下のパラメータを使用したすべてのサーキットノイズの計算を示しています。

- $e_n$  = 電圧ノイズ

- $I_n$  = 電流ノイズ

- $R_S$  = ソース・インピーダンス

- $k = \text{ボルツマン定数} = 1.38 \times 10^{-23} \text{ J/K}$

- $T = \text{温度 (ケルビン, K)}$

ノイズの計算の詳細については、「基本的なノイズ計算」を参照してください。

図 31. ユニティ・ゲイン・バッファ構成でのOPA141およびOPA211のノイズ特性

## 基本的なノイズ計算

低ノイズ回路の設計では、すべてのノイズ発生源を注意深く分析する必要があります。多くの場合は、外部のノイズ発生源が優勢となります。オペアンプ全体のノイズ特性に対するソース抵抗の影響を考慮してください。回路の合計ノイズは、すべてのノイズ成分の二乗和平方根となります。

ソース・インピーダンスの抵抗部分によって、抵抗の平方根に比例した熱ノイズが発生します。この関係は図31に示されています。ソース・インピーダンスは通常は固定です。したがって、オペアンプと帰還抵抗は、合計ノイズに対するそれぞれの寄与が最小となるように選択します。

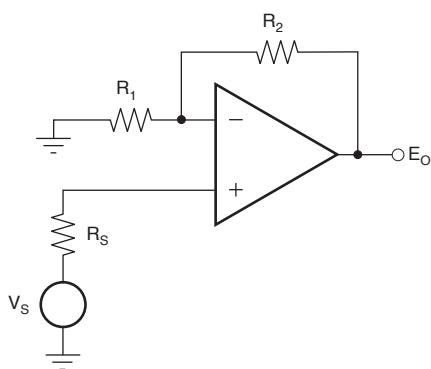

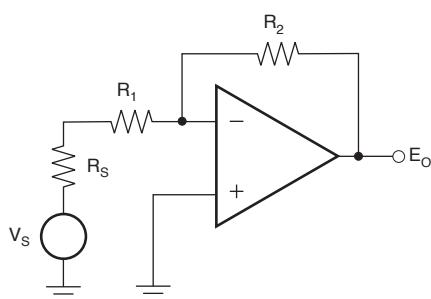

図32は、オペアンプ回路の非反転(A)および反転(B)ゲイン構成を示しています。ゲインを持つ回路構成では、帰還抵抗もノイズに寄与します。一般には、オペアンプの電流ノイズが帰還抵抗に作用して、追加のノイズ成分が生成されます。ただし、OPAx141では電流ノイズが極めて低いため、電流ノイズ成分は無視できます。

一般に、帰還抵抗の値は、これらのノイズ源を無視できるように選択されます。低インピーダンスの帰還抵抗はアンプの出力の負荷となることに注意してください。図では、両方の構成に対して合計ノイズの式が示されています。

### A) Noise in Noninverting Gain Configuration

Noise at the output:

$$E_o^2 = \left(1 + \frac{R_2}{R_1}\right)^2 e_n^2 + \left(\frac{R_2}{R_1}\right)^2 e_1^2 + e_2^2 + \left(1 + \frac{R_2}{R_1}\right)^2 e_s^2$$

Where  $e_s = \sqrt{4kTR_s}$  = thermal noise of  $R_s$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

### B) Noise in Inverting Gain Configuration

Noise at the output:

$$E_o^2 = \left(1 + \frac{R_2}{R_1 + R_s}\right)^2 e_n^2 + \left(\frac{R_2}{R_1 + R_s}\right)^2 e_1^2 + e_2^2 + \left(\frac{R_2}{R_1 + R_s}\right)^2 e_s^2$$

Where  $e_s = \sqrt{4kTR_s}$  = thermal noise of  $R_s$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

図 32. ゲイン構成のノイズの計算

OPAx141シリーズのオペアンプでは、1kHzで $e_n = 6.5nV/\sqrt{Hz}$ となります。

## 位相反転保護

OPA141、OPA2141、およびOPA4141ファミリーには、位相反転保護機能が内蔵されています。多くのFETおよびバイポーラ入力オペアンプでは、入力が線形同相モード範囲を超えて駆動されたときに、位相の反転が発生します。この状態は、非反転回路で、入力が指定された同相モード電圧範囲を超えて駆動され、出力が反対側のレールへと反転した場合に、最もよく見られます。OPA141、OPA2141、およびOPA4141の入力回路は、過度の同相モード電圧による位相の反転を防ぎ、出力を適切なレールへと制限します（図21を参照）。

を超えない限り、より低い負荷抵抗を使用できます。出力電流が13mAを超えると、デバイスの短絡電流保護回路が作動する場合があります。

高い電源電圧で動作すると、内部の消費電力が増加します。OPA141、OPA2141、およびOPA4141シリーズのデバイスでは、銅のリードフレーム構造を使用することにより、従来の材質と比較して放熱性能が向上しています。また、プリント基板（PCB）のレイアウトによっても、接合部温度の上昇幅を抑えることができます。広い銅パターンは、追加のヒートシンクとして機能するため、放熱を助けます。ソケットを使用する代わりにデバイスをPCBに直接半田付けすることで、温度上昇をさらに小さく抑えることができます。

出力電流は内部保護回路によって制限されていますが、デバイスの1つまたは複数のチャネルが誤って短絡された場合には、過度の温度上昇が生じる可能性があります。例えば、出力が電源中点に短絡された場合、標準36mAの短絡電流により、±18Vの電源で内部消費電力が600mWを超えます。

MSOP-8パッケージのデュアル製品OPA2141（熱抵抗 $\theta_{JA} = 180^\circ\text{C}/\text{W}$ ）では、両方のチャネルが短絡された場合、この消費電力によってダイ温度が周囲温度を220°C上回ります。このような温度上昇が生じると、デバイスの動作寿命が大きく短縮されます。

過度の温度上昇を防ぐために、OPAx141シリーズは内部に過熱シャットダウン回路を備え、ダイ温度が+180°Cを超えるとデバイスがシャットダウンされます。この過熱シャットダウン回路が作動すると、15°Cの内蔵ヒステリシスにより、ダイ温度が約+165°Cに低下

## 出力電流制限

OPAx141シリーズの出力電流は、内部回路によって+36mA/-30mA（ソース/シンク）に制限され、出力が誤って短絡された場合にデバイスを保護します。図28に示されるように、この短絡電流は温度によって変化します。

## 消費電力および過熱保護

OPAx141シリーズのオペアンプは、仕様温度範囲全体にわたり、最大±18Vの電源電圧で2kΩの負荷を駆動できます。単一電源構成で、負荷が負電源電圧に接続されている場合は、+36Vの電源電圧で最小負荷抵抗が2.8kΩとなります。電源電圧がそれより低い場合（単一電源または対称電源）には、出力電流が13mA

するまでデバイスは再起動されません。

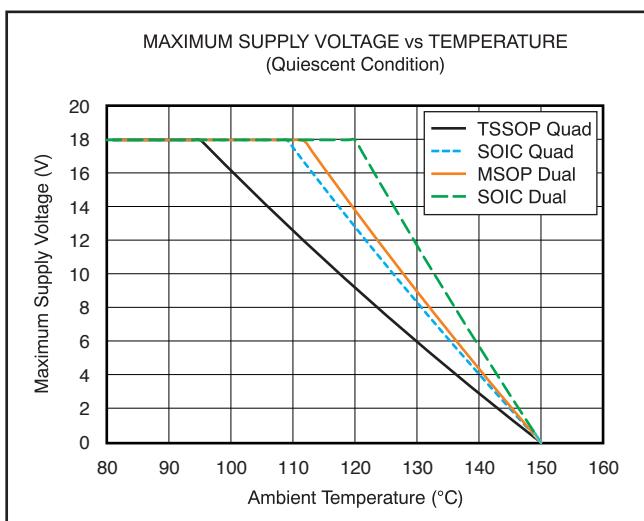

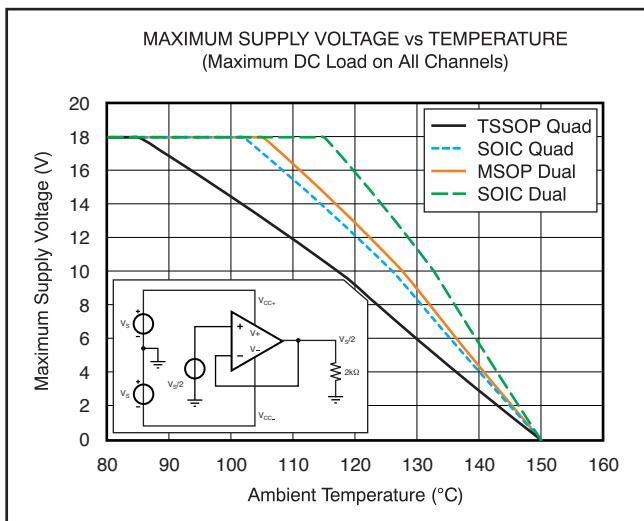

最大動作電圧、最大動作温度、負荷、およびパッケージ・タイプの組み合わせにも、追加の配慮が必要です。図33および図34に、OPA2141(デュアル製品)およびOPA4141(クアッド製品)を評価するときの実際的な考慮事項をいくつか示しています。

例として、OPA4141では、温度に対する最大合計静止電流が12.4mA(3.1mA/チャネル)です。TSSOP-14パッケージの標準熱抵抗は135°C/Wです。このパラメータは、動作の信頼性確保のために接合部温度を150°C以下とする必要があるため、電源電圧を下げるか、または接合部温度が150°Cを超えないよう周囲温度を低く保つ必要があることを意味します。図33では、この条件を各種のパッケージ・タイプについて示しています。さらに、出力の抵抗性負荷によって消費電力が増加し、自己発熱も大きくなるため、最大電源電圧または動作温度を決定する際には、その点も考慮に入れる必要があります。その目的のため、図34では、ワースト・ケースDC負荷の2kΩに対して、最大電源電圧対温度の特性を示しています。

図33. 最大電源電圧 対 温度 (OPA2141およびOPA4141)、

静止状態

図34. 最大電源電圧 対 温度 (OPA2141およびOPA4141)、

最大DC負荷

## 電気的オーバーストレス

電気的なオーバーストレスに対するオペアンプの耐性に関して、設計者から質問されることがあります。それらの質問は、デバイスの入力について言及する傾向にあります。電源電圧ピンや出力ピンも関わってくる可能性があります。それらの異なるピン機能にはそれぞれ、個別の半導体製造プロセスや、ピンに接続される回路に固有のブレーカダウン電圧特性によって決定される、電気的ストレス制限があります。また、これらの回路には静電放電(ESD)保護が内蔵され、製品の組み立て前および組み立て中の偶発的なESDから回路を保護しています。

この基本的なESD回路について、また、この回路と電気的オーバーストレス状態との関連について、よく理解しておくと役に立ちます。図35に、OPA141xシリーズに内蔵されるESD回路を示します(点線の領域内)。ESD保護回路では、入力ピンと出力ピンからいくつかの電流ステアリング・ダイオードが内部電源ラインに接続され、電源ラインにはオペアンプ内部のESD吸収デバイスが接続されています。この保護回路は、通常の回路動作中は機能しないように設計されています。

ESDが発生すると、短い時間の高電圧パルスが生成され、これは半導体デバイス内で放電しながら、短い時間の高電流パルスへと変換されます。ESD保護回路は、オペアンプのコアの周りに電流パスを設けることで、その損傷を防ぐように設計されています。保護回路によって吸収されるエネルギーは、熱として放散されます。

アンプ・デバイスの2本以上のピン間でESD電圧が生じた場合、1つまたは複数のステアリング・ダイオードに電流が流れます。電流が流れる経路に応じて、吸収デバイスが機能します。吸収デバイスには、トリガとなるスレッショルド電圧があり、これはOPA141xの通常動作電圧より高く、デバイスのブレーカダウン電圧レベルよりも低い値です。このスレッショルドを超えた場合には、吸収デバイスがすばやく機能して、電源レール間の電圧を安全なレベルにクランプします。

オペアンプを図35に示すような回路に接続する場合には、ESD保護回路は機能せず、アプリケーション回路の動作に関与しないよう設計されています。ただし、印加電圧があるピンの動作電圧範囲を超えるような状況が発生する可能性があります。そのような状況が発生した場合には、内部ESD保護回路の一部がオンにバイアスされて、電流を導通するおそれがあります。そのような電流はステアリング・ダイオードのパスを流れますが、吸収デバイスが機能することはまれです。

図35は、入力電圧 $V_{IN}$ が正電源電圧( $+V_S$ )を500mV以上上回る場合の例を示しています。このような状況で回路に起こることの多くは、電源特性に依存します。 $+V_S$ が電流をシンクできる場合は、上側の入力ステアリング・ダイオードの1つが導通し、電流を $+V_S$ へと流します。 $V_{IN}$ が高くなると、極めて高いレベルの電流が流れる可能性があります。そのため、データシートの仕様では、アプリケーションで入力電流を10mAに制限することを推奨しています。

電源が電流をシンクできない場合は、 $V_{IN}$ が電流をオペアンプへとソースし始め、正電源電圧としての役割を引き継ぐ可能性があります。この場合、オペアンプの絶対最大定格を超えるレベルにまで電圧が上昇する危険があります。

また、電源 $+V_S$ および $-V_S$ の一方または両方が $0V$ のときに入力信号が印加されるとどうなるのか、という質問もよく受けます。

これもやはり、 $0V$ 、または入力信号振幅より低いレベルでの電源特性に依存します。電源が高インピーダンスとして見える場合は、入力ソースから電流ステアリング・ダイオードを通してオペアンプの電源電流が供給される可能性があります。この状態は通常のバイアス状態ではなく、アンプはほとんどの場合、正常に動作しません。電源が低インピーダンスの場合は、ステアリング・ダイオードを流れる電流が非常に高くなる可能性があります。電流レベルは、入力ソースの電流供給能力、および入力パス上の抵抗に依存します。

電源がこの電流を吸収する能力が不確かである場合は、図35に示すように、電源ピンに外部ツェナー・ダイオードを追加します。ツェナー電圧は、ダイオードが通常動作中にオンにならないような値を選択する必要があります。

その一方で、電源ピンが安全動作電源電圧レベルを超えて上昇し始めた場合にツェナー・ダイオードが導通するよう、十分低い値である必要があります。

図 35. 等価内部ESD回路、および標準回路アプリケーションとの関係

(1)  $V_{IN} = +V_S + 500mV$

(2) TVS:  $+V_{S(max)} > V_{TVSBR(Min)} > +V_S$

(3) 推奨値は約 $1k\Omega$

# パッケージ情報

## 製品情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login)            |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|----------------------------------------|

| OPA141AID        | ACTIVE                | SOIC         | D               | 8    | 75          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Request Free Samples                   |

| OPA141AIDGKR     | ACTIVE                | MSOP         | DGK             | 8    | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Purchase Samples                       |

| OPA141AIDGKT     | ACTIVE                | MSOP         | DGK             | 8    | 250         | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Request Free Samples                   |

| OPA141AIDR       | ACTIVE                | SOIC         | D               | 8    | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Purchase Samples                       |

| OPA2141AID       | ACTIVE                | SOIC         | D               | 8    | 75          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Request Free Samples                   |

| OPA2141AIDGKR    | ACTIVE                | MSOP         | DGK             | 8    | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Purchase Samples                       |

| OPA2141AIDGKT    | ACTIVE                | MSOP         | DGK             | 8    | 250         | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Request Free Samples                   |

| OPA2141AIDR      | ACTIVE                | SOIC         | D               | 8    | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Contact TI Distributor or Sales Office |

| OPA4141AID       | ACTIVE                | SOIC         | D               | 14   | 50          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Request Free Samples                   |

| OPA4141AIDR      | ACTIVE                | SOIC         | D               | 14   | 2500        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Purchase Samples                       |

| OPA4141AIPW      | ACTIVE                | TSSOP        | PW              | 14   | 90          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Request Free Samples                   |

| OPA4141AIPWR     | ACTIVE                | TSSOP        | PW              | 14   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          | Purchase Samples                       |

<sup>(1)</sup> マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TIによりデバイスの生産が中止されました。

<sup>(2)</sup> エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free(RoHS)、Pb-Free(RoHS Expert) および Green(RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent>でご確認ください。

TBD : Pb-Free/Green変換プランが策定されていません。

Pb-Free(RoHS) : TIにおける "Lead-Free" または "Pb-Free" (鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free(RoHS Exempt) : この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free(RoHS)と考えられます。

Green(RoHS & no Sb/Br) : TIにおける "Green" は、"Pb-Free" (RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

<sup>(3)</sup> MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

**重要な情報および免責事項:** このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパートの購入価格の合計金額を超える責任は負いかねます。

## パッケージ・マテリアル情報

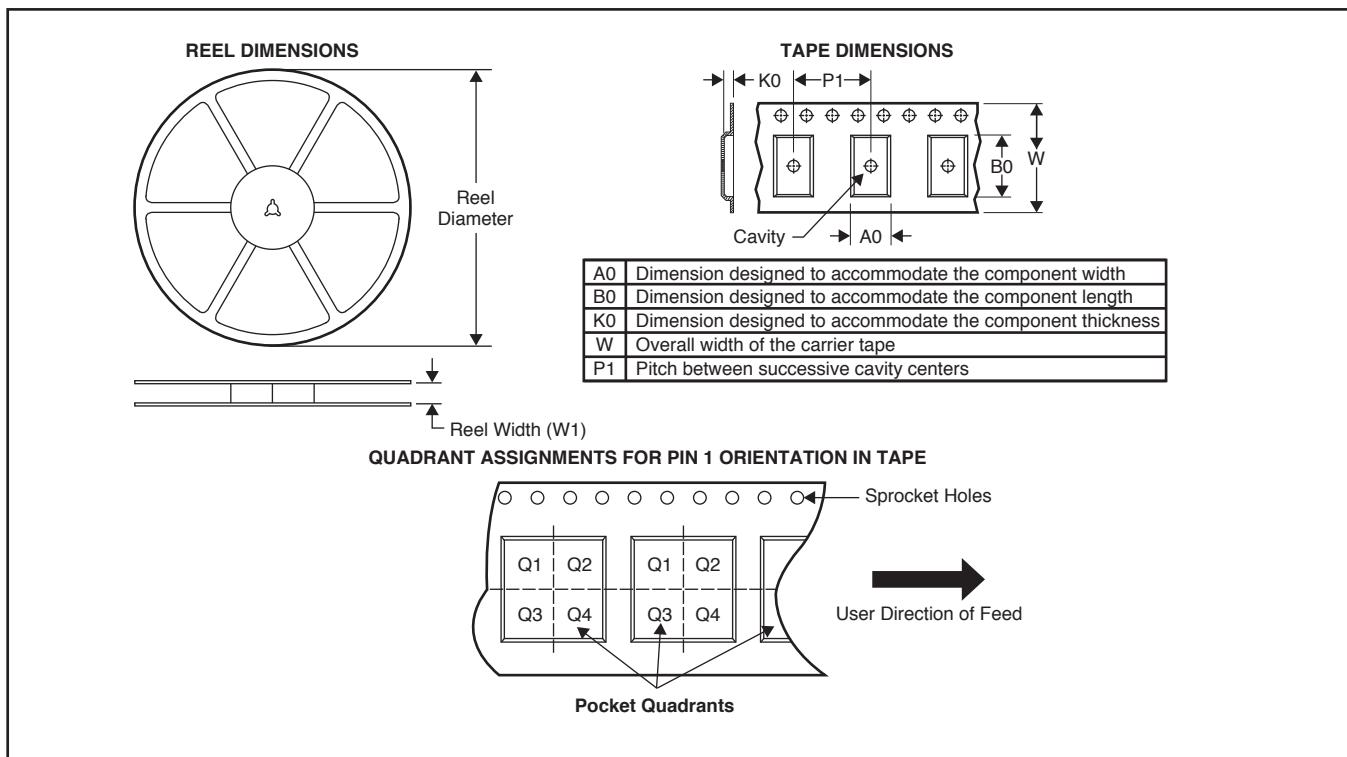

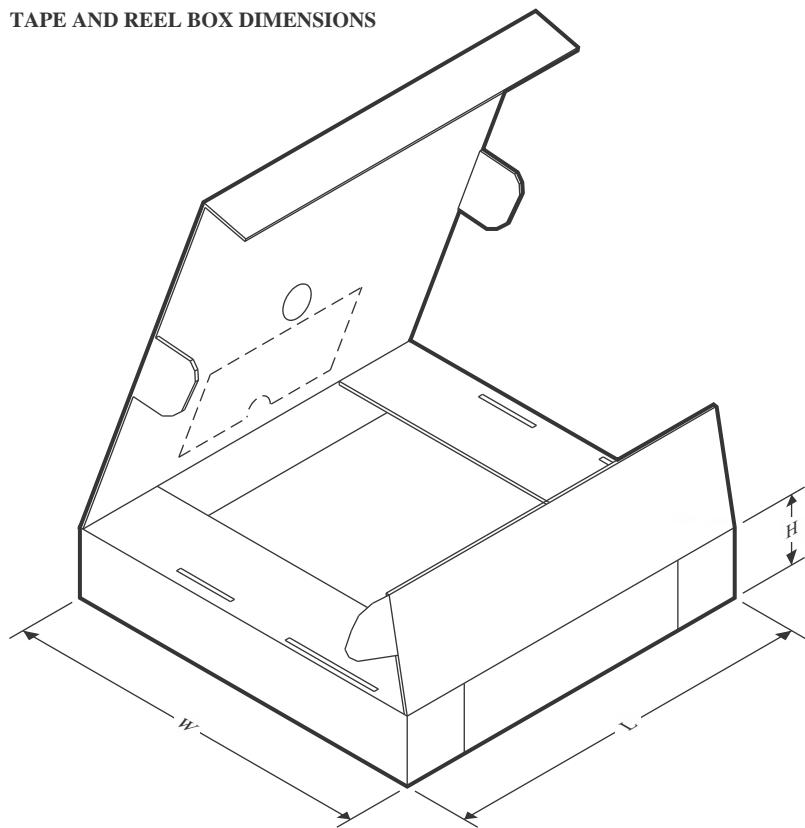

### テープおよびリール・ボックス情報

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| OPA141AIDGKR  | MSOP         | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA141AIDGKT  | MSOP         | DGK             | 8    | 250  | 180.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA141AIDR    | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA2141AIDGKR | MSOP         | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA2141AIDGKT | MSOP         | DGK             | 8    | 250  | 180.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA2141AIDR   | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA4141AIPWR  | TSSOP        | PW              | 14   | 2000 | 330.0              | 16.4               | 6.5     | 9.0     | 2.1     | 8.0     | 16.0   | Q1            |

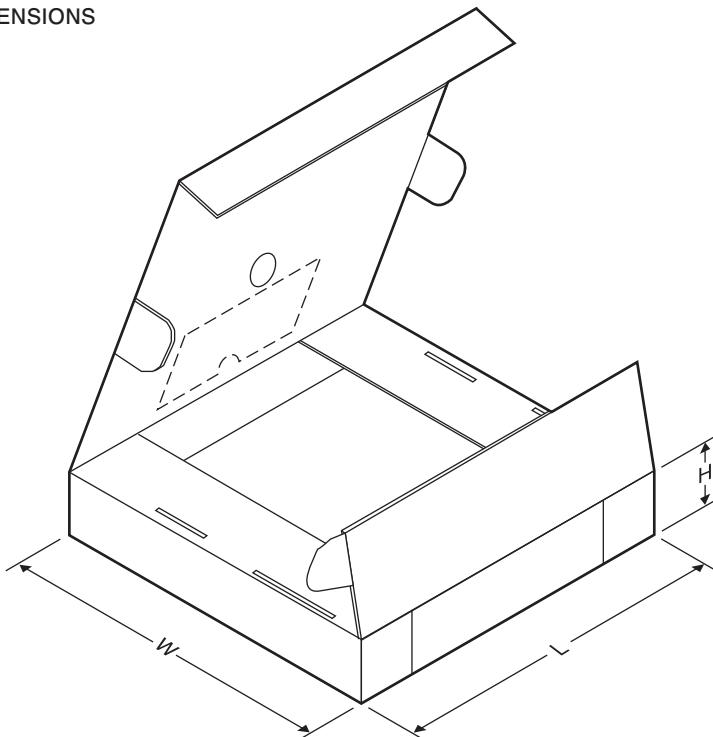

## パッケージ・マテリアル情報

TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA141AIDGKR  | MSOP         | DGK             | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| OPA141AIDGKT  | MSOP         | DGK             | 8    | 250  | 190.5       | 212.7      | 31.8        |

| OPA141AIDR    | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| OPA2141AIDGKR | MSOP         | DGK             | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| OPA2141AIDGKT | MSOP         | DGK             | 8    | 250  | 190.5       | 212.7      | 31.8        |

| OPA2141AIDR   | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| OPA4141AIDR   | SOIC         | D               | 14   | 2500 | 346.0       | 346.0      | 33.0        |

| OPA4141AIPWR  | TSSOP        | PW              | 14   | 2000 | 346.0       | 346.0      | 29.0        |

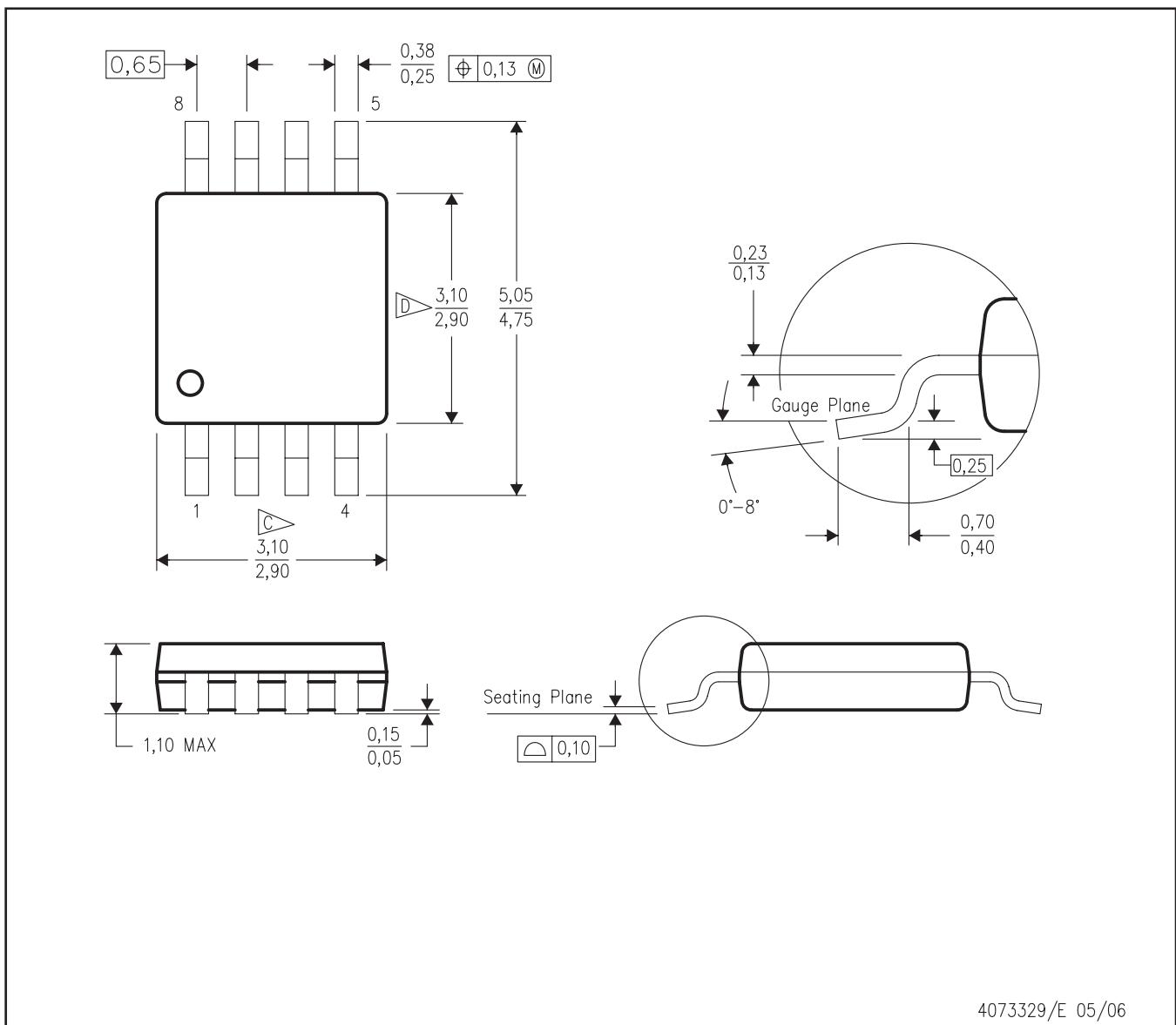

# メカニカル・データ

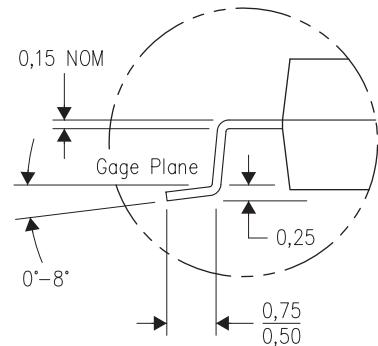

DGK(S-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

注: A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

△ ボディ寸法には、0.15mmを超えるモールド・フラッシュや突起は含まれません。

△ ボディ幅には、インターリード・フラッシュは含まれません。インターリード・フラッシュは、片側で0.17(0.43mm)を超えることはありません。

E JEDEC MO-187 バージョンAAに適合しています。

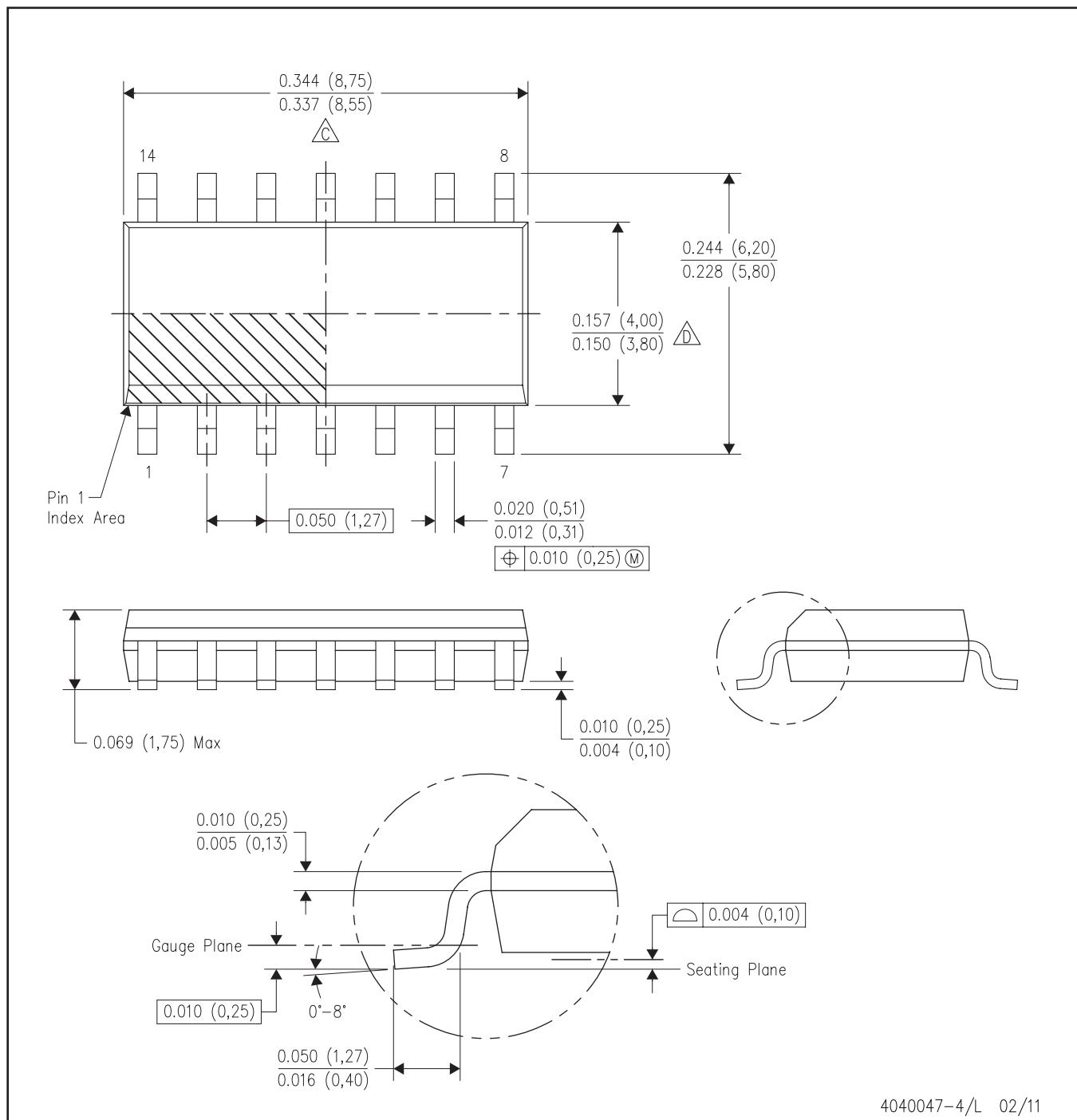

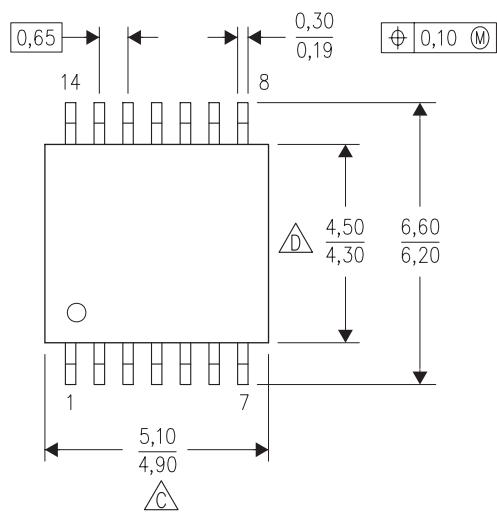

# メカニカル・データ

D(R-PDSO-G14)

PLASTIC SMALL OUTLINE

4040047-4/L 02/11

注: A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

△ ボディ寸法には、0.15mmを超えるモールド・フラッシュや突起は含まれません。

△ ボディ幅には、インターリード・フラッシュは含まれません。インターリード・フラッシュは、片側で0.17(0.43mm)を超えることはありません。

E JEDEC MS-012 バージョンABに適合しています。

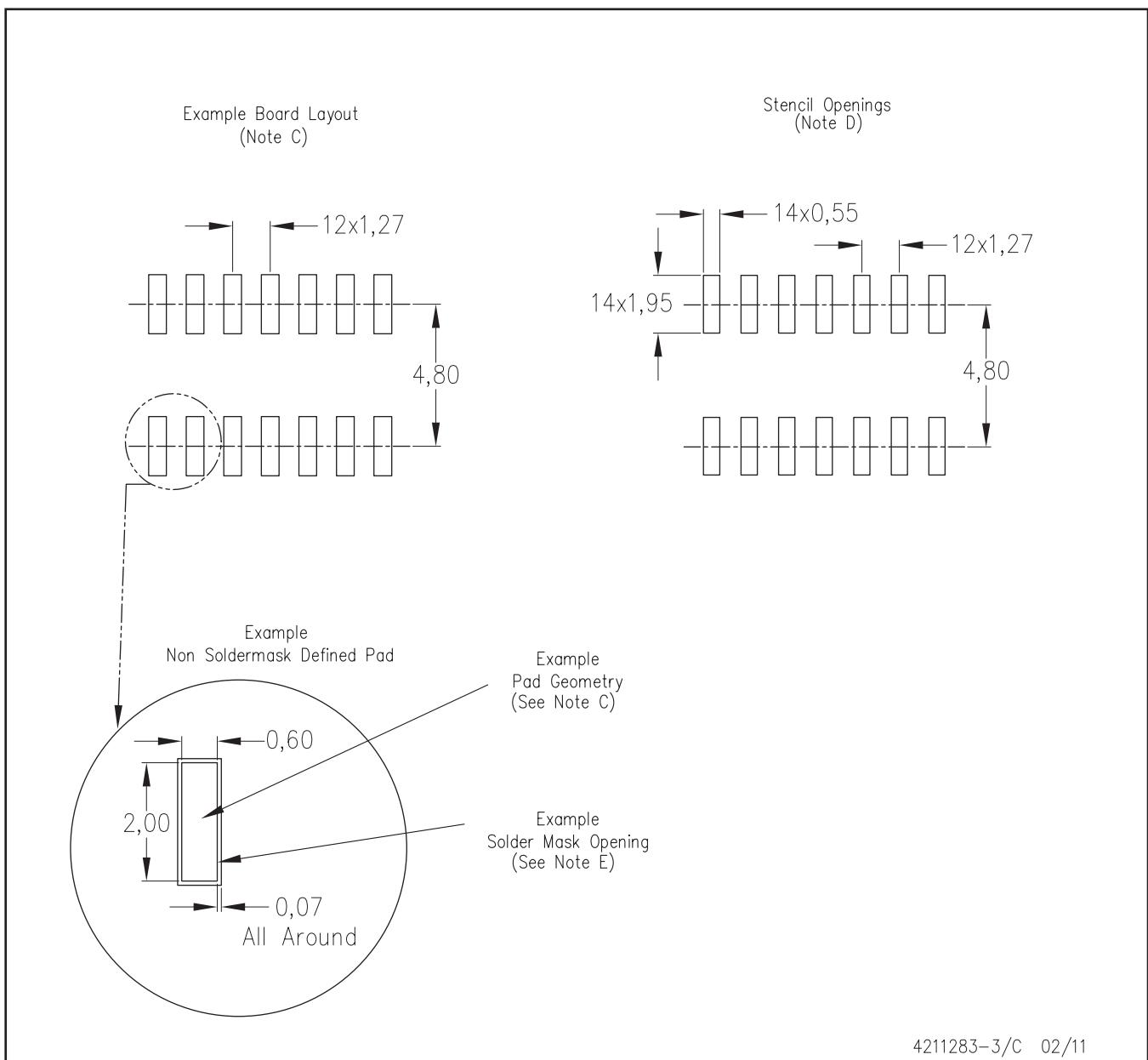

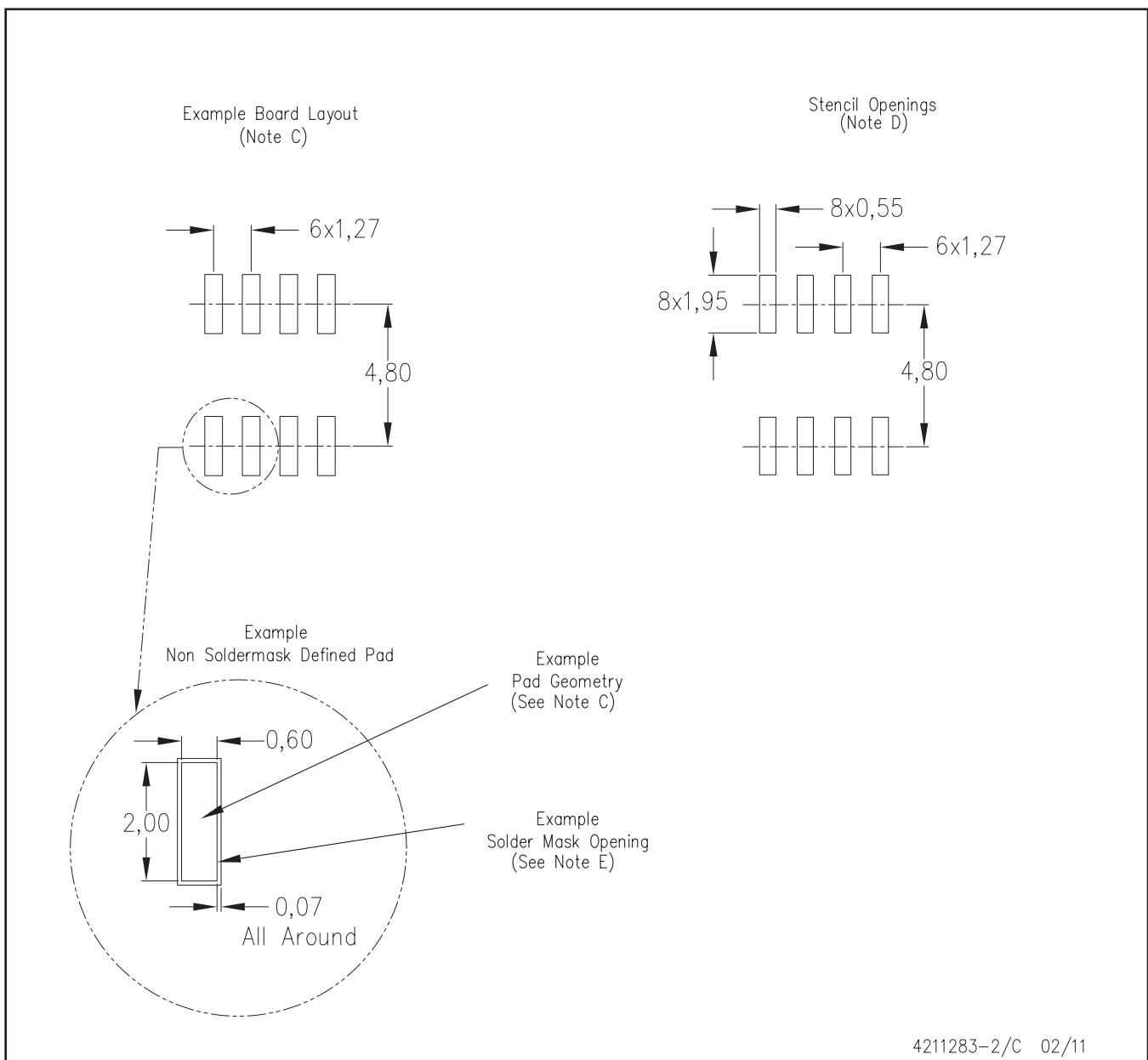

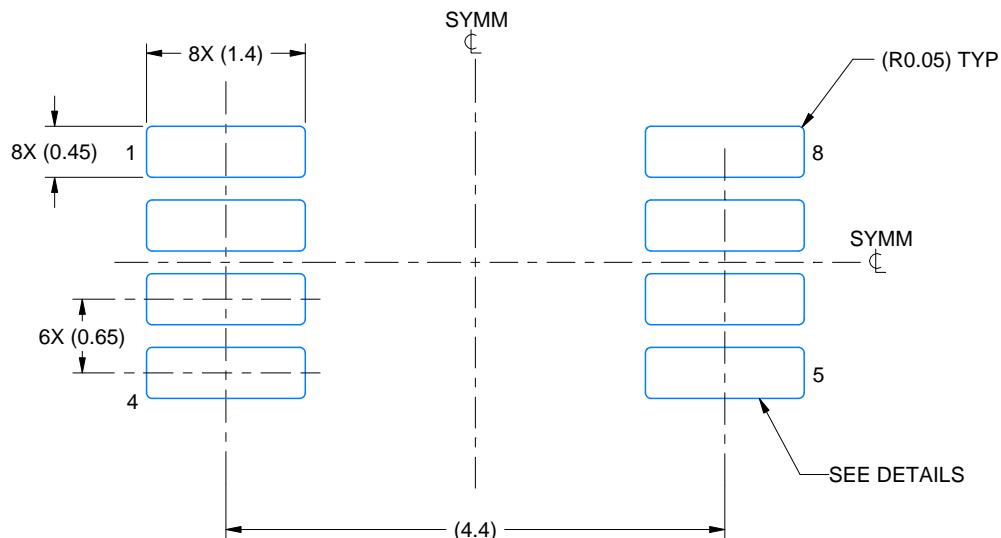

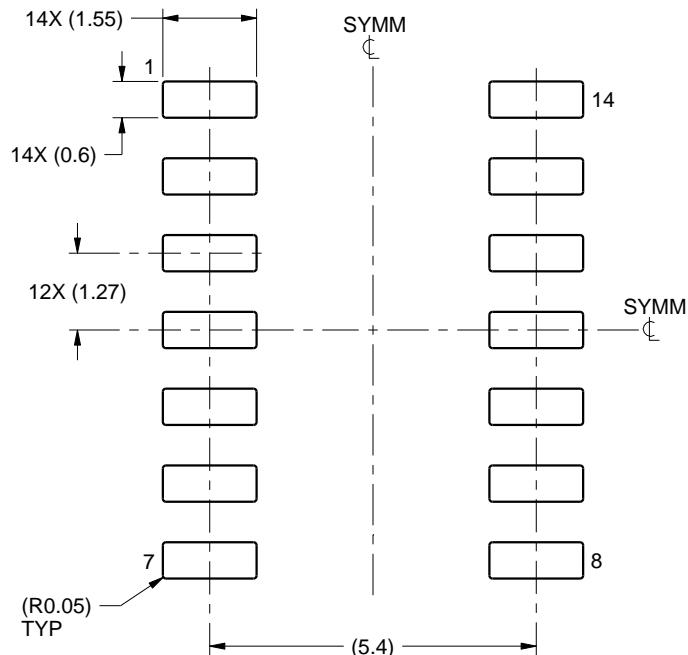

# ランド・パターン

D(R-PDSO-G14)

PLASTIC SMALL OUTLINE

4211283-3/C 02/11

- 注: A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 代替設計については、資料IPC-7351を推奨します。

D. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

# メカニカル・データ

PW(R-PDSO-G14)

PLASTIC SMALL OUTLINE

4040064-3/G 02/11

注: A. 全ての線寸法の単位はミリメートルです。寸法/公差はASME Y14.5M-1994によります。

B. 図は予告なく変更することがあります。

ボディ寸法には、0.15mmを超えるモールド・フラッシュや突起は含まれません。

ボディ幅には、インターリード・フラッシュは含まれません。インターリード・フラッシュは、片側で0.17(0.43mm)を超えることはありません。

E. JEDEC MO-153に準拠

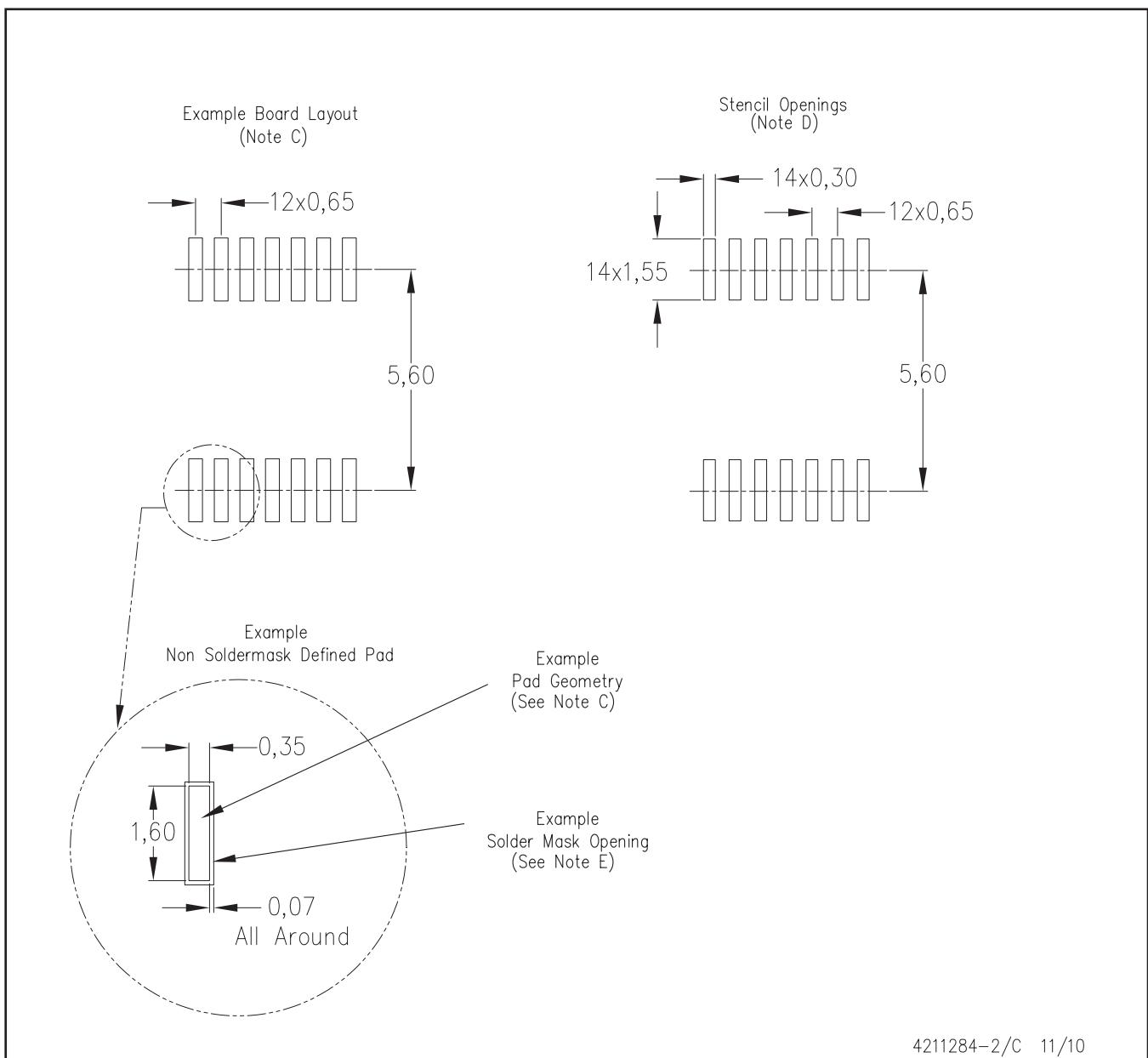

# ランド・パターン

PW(R-PDSO-G14)

PLASTIC SMALL OUTLINE

4211284-2/C 11/10

- 注: A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 代替設計については、資料IPC-7351を推奨します。

D. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

## メカニカル・データ

D(R-PDSO-G8)

## PLASTIC SMALL OUTLINE

注：A. 全ての線寸法の単位はミリメートルです。寸法/公差はASME Y14.5M-1994によります。

B. 図は予告なく変更することがあります。

ボディ寸法には、0.15mmを超えるモールド・フラッシュや突起は含まれません。

Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0.43) each side.

E. JEDEC MS-012 バージョンAAに適合しています。

# ランド・パターン

D(R-PDSO-G8)

PLASTIC SMALL OUTLINE

4211283-2/C 02/11

- 注: A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 代替設計については、資料IPC-7351を推奨します。

D. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基板組み立て拠点にお問い合わせください。

**PACKAGING INFORMATION**

| Orderable part number         | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-------------------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">OPA141AID</a>     | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O141A               |

| OPA141AID.B                   | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O141A               |

| <a href="#">OPA141AIDGKR</a>  | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug<br>  Nipdau        | Level-2-260C-1 YEAR               | -40 to 125   | 141                 |

| OPA141AIDGKR.B                | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 141                 |

| OPA141AIDGKRG4                | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 141                 |

| OPA141AIDGKRG4.B              | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 141                 |

| <a href="#">OPA141AIDGKT</a>  | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI   Nipdaug<br>  Nipdau        | Level-2-260C-1 YEAR               | -40 to 125   | 141                 |

| OPA141AIDGKT.B                | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 141                 |

| <a href="#">OPA141AIDR</a>    | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O141A               |

| OPA141AIDR.B                  | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O141A               |

| OPA141AIDRG4                  | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O141A               |

| OPA141AIDRG4.B                | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O141A               |

| <a href="#">OPA2141AID</a>    | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O2141A              |

| OPA2141AID.B                  | Active        | Production           | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O2141A              |

| <a href="#">OPA2141AIDGKR</a> | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdaug<br>  Nipdau        | Level-2-260C-1 YEAR               | -40 to 125   | 2141                |

| OPA2141AIDGKR.B               | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2141                |

| OPA2141AIDGKRG4               | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2141                |

| OPA2141AIDGKRG4.B             | Active        | Production           | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2141                |

| <a href="#">OPA2141AIDGKT</a> | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI   Nipdaug<br>  Nipdau        | Level-2-260C-1 YEAR               | -40 to 125   | 2141                |

| OPA2141AIDGKT.B               | Active        | Production           | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 2141                |

| <a href="#">OPA2141AIDR</a>   | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O2141A              |

| OPA2141AIDR.B                 | Active        | Production           | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O2141A              |

| <a href="#">OPA4141AID</a>    | Active        | Production           | SOIC (D)   14   | 50   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AID.B                  | Active        | Production           | SOIC (D)   14   | 50   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIDG4                  | Active        | Production           | SOIC (D)   14   | 50   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIDG4.B                | Active        | Production           | SOIC (D)   14   | 50   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| OPA4141AIDR           | Active        | Production           | SOIC (D)   14   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIDR.B         | Active        | Production           | SOIC (D)   14   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIPW           | Active        | Production           | TSSOP (PW)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIPW.B         | Active        | Production           | TSSOP (PW)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIPWG4         | Active        | Production           | TSSOP (PW)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIPWG4.B       | Active        | Production           | TSSOP (PW)   14 | 90   TUBE             | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIPWR          | Active        | Production           | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

| OPA4141AIPWR.B        | Active        | Production           | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | O4141A              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

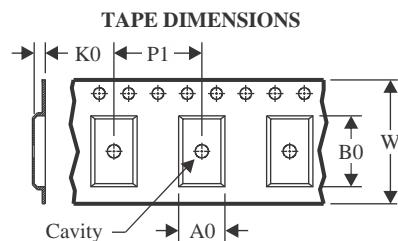

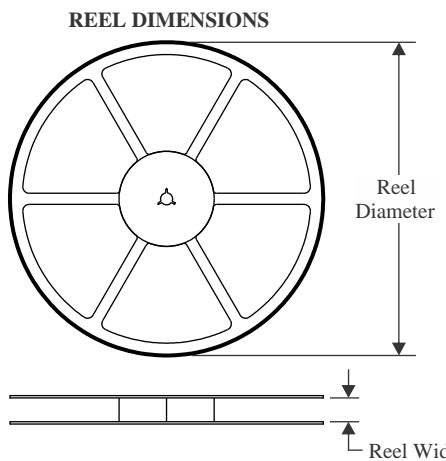

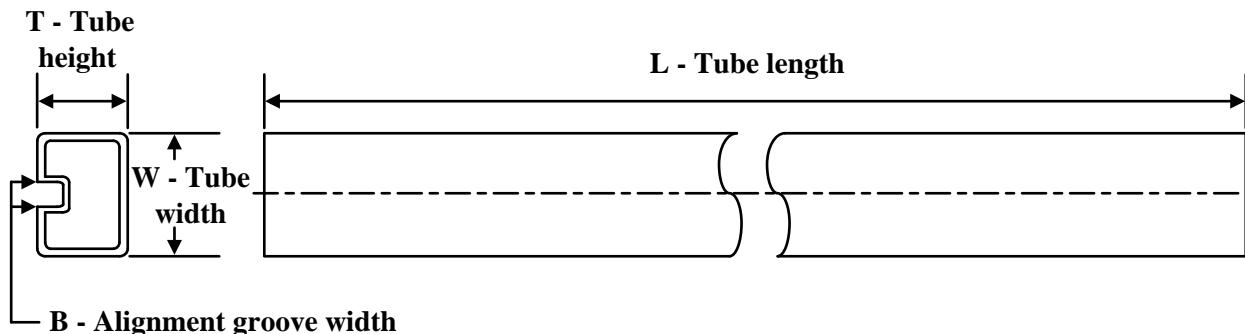

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

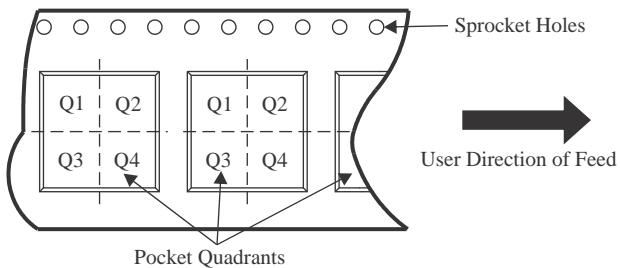

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| OPA141AIDGKR    | VSSOP        | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA141AIDGKRG4  | VSSOP        | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA141AIDGKT    | VSSOP        | DGK             | 8    | 250  | 180.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA141AIDR      | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA141AIDRG4    | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA2141AIDGKR   | VSSOP        | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA2141AIDGKRG4 | VSSOP        | DGK             | 8    | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA2141AIDGKT   | VSSOP        | DGK             | 8    | 250  | 180.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| OPA2141AIDR     | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| OPA4141AIDR     | SOIC         | D               | 14   | 2500 | 330.0              | 16.4               | 6.5     | 9.0     | 2.1     | 8.0     | 16.0   | Q1            |

| OPA4141AIPWR    | TSSOP        | PW              | 14   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA141AIDGKR    | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA141AIDGKRG4  | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA141AIDGKT    | VSSOP        | DGK             | 8    | 250  | 213.0       | 191.0      | 35.0        |

| OPA141AIDR      | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA141AIDRG4    | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA2141AIDGKR   | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA2141AIDGKRG4 | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA2141AIDGKT   | VSSOP        | DGK             | 8    | 250  | 213.0       | 191.0      | 35.0        |

| OPA2141AIDR     | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| OPA4141AIDR     | SOIC         | D               | 14   | 2500 | 353.0       | 353.0      | 32.0        |

| OPA4141AIPWR    | TSSOP        | PW              | 14   | 2000 | 353.0       | 353.0      | 32.0        |

**TUBE**

\*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| OPA141AID       | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA141AID.B     | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA2141AID      | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA2141AID.B    | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940         | 4.32   |

| OPA4141AID      | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940         | 4.32   |

| OPA4141AID.B    | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940         | 4.32   |

| OPA4141AIDG4    | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940         | 4.32   |

| OPA4141AIDG4.B  | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940         | 4.32   |

| OPA4141AIPW     | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250         | 2.8    |

| OPA4141AIPW.B   | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250         | 2.8    |

| OPA4141AIPWG4   | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250         | 2.8    |

| OPA4141AIPWG4.B | PW           | TSSOP        | 14   | 90  | 508    | 8.5    | 3250         | 2.8    |

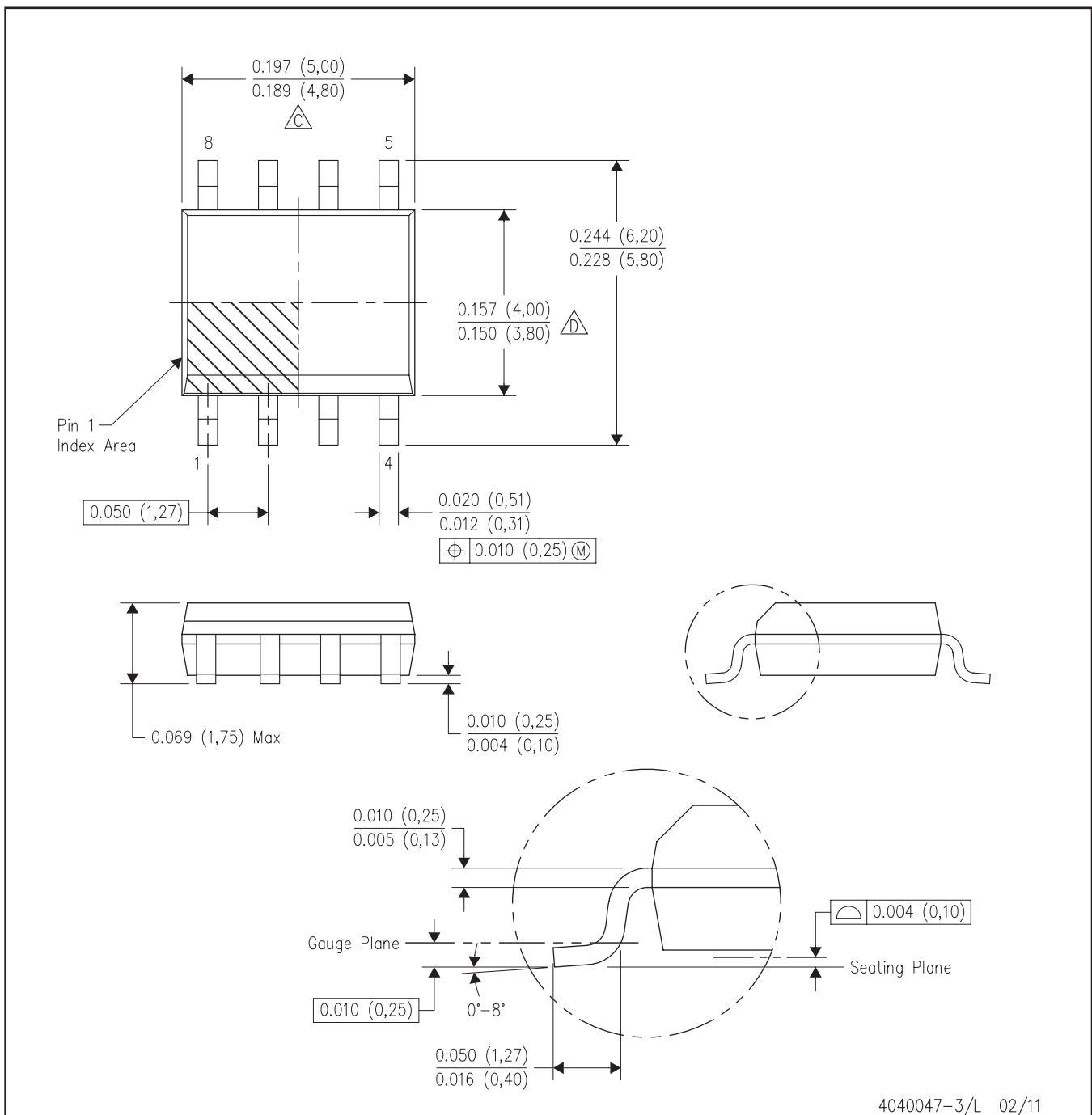

D0008A

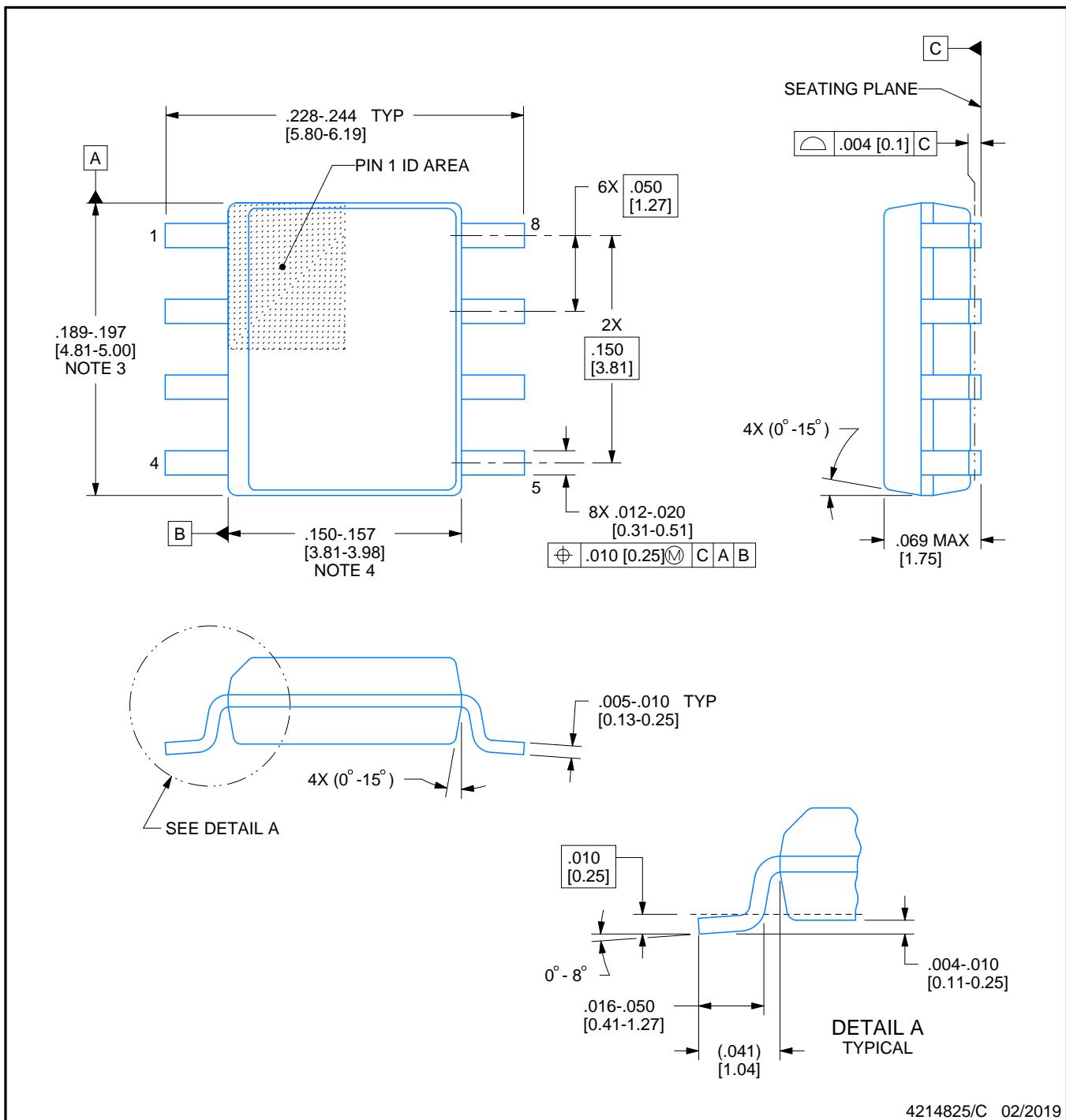

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

### NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- Reference JEDEC registration MS-012, variation AA.

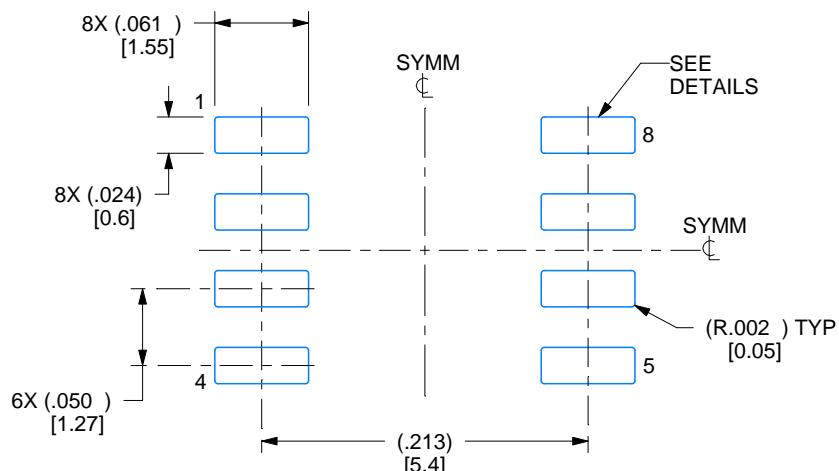

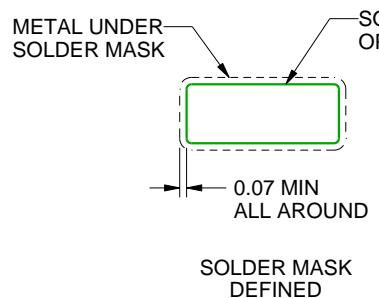

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

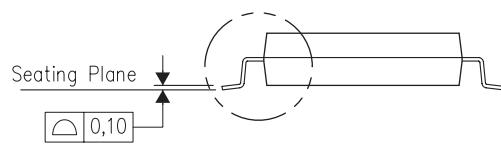

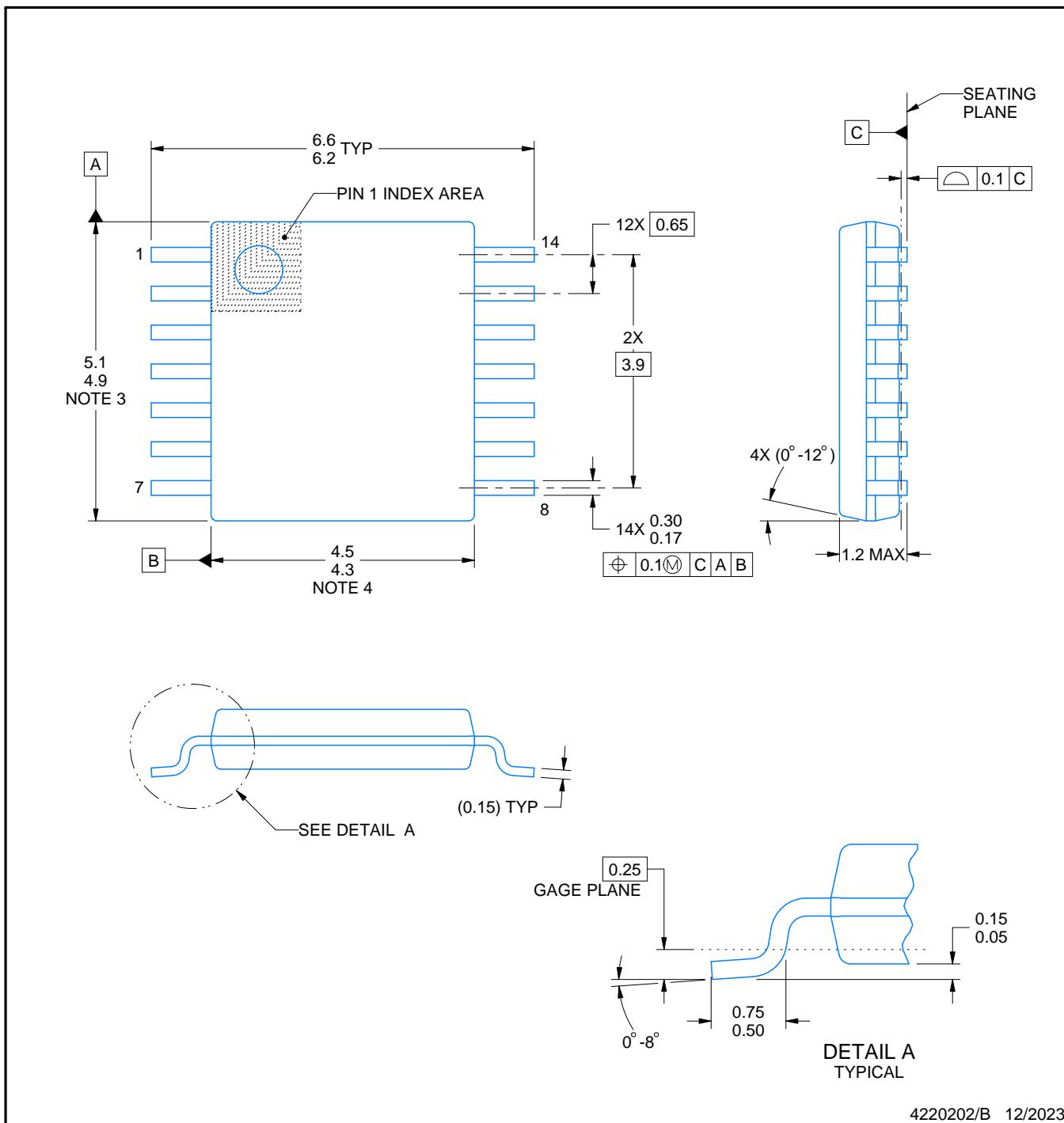

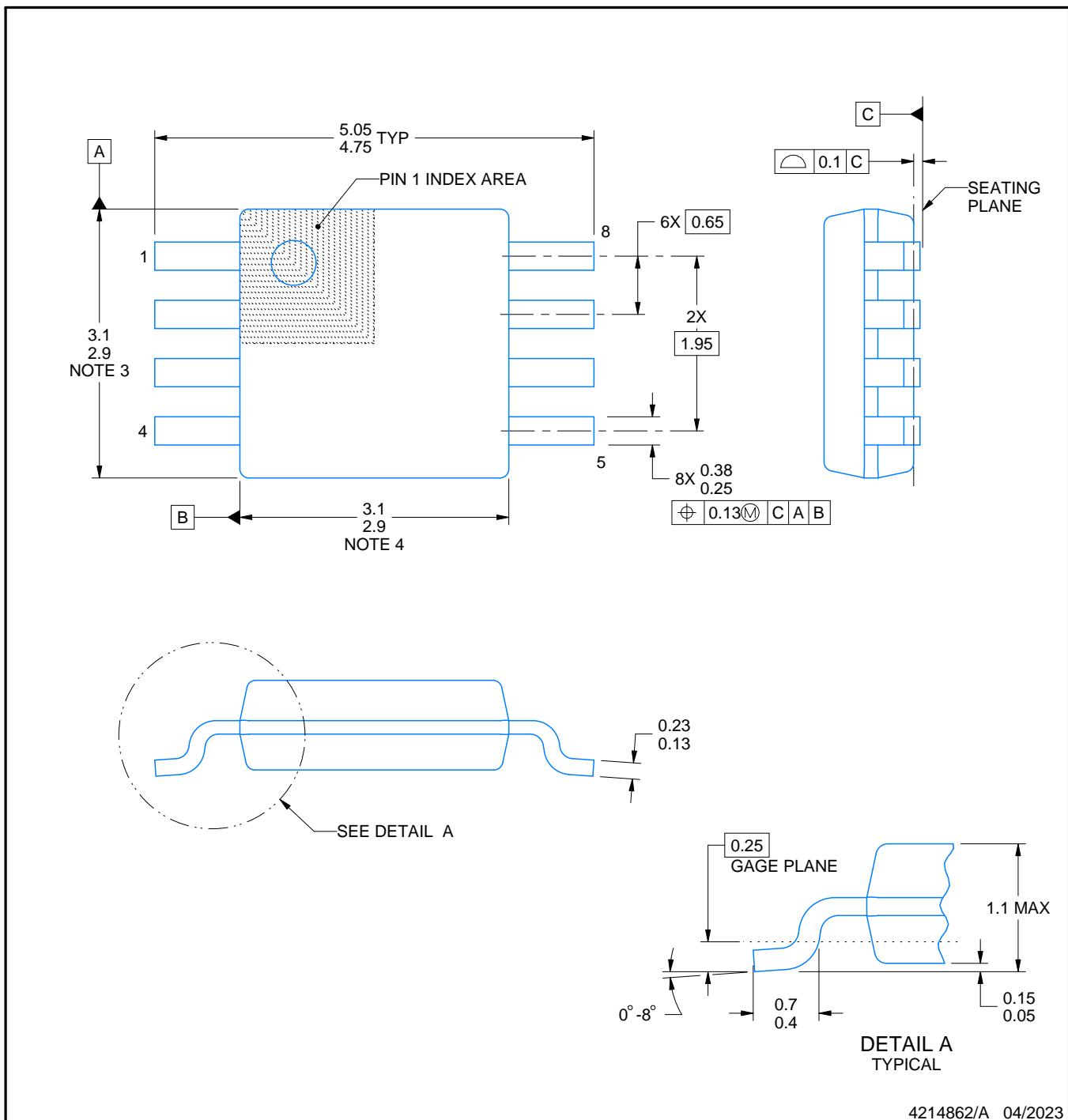

# PACKAGE OUTLINE

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- Reference JEDEC registration MO-153.

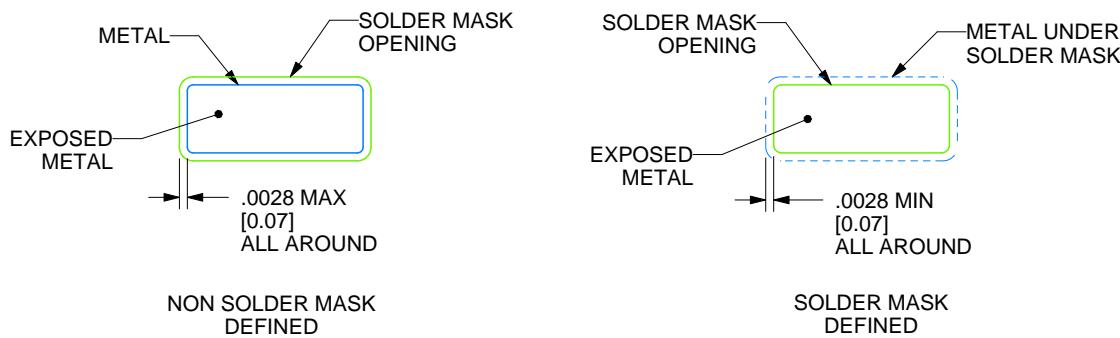

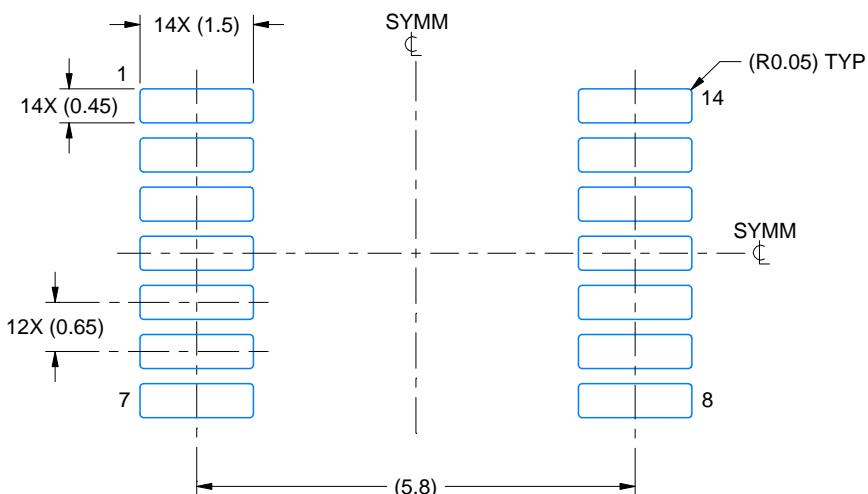

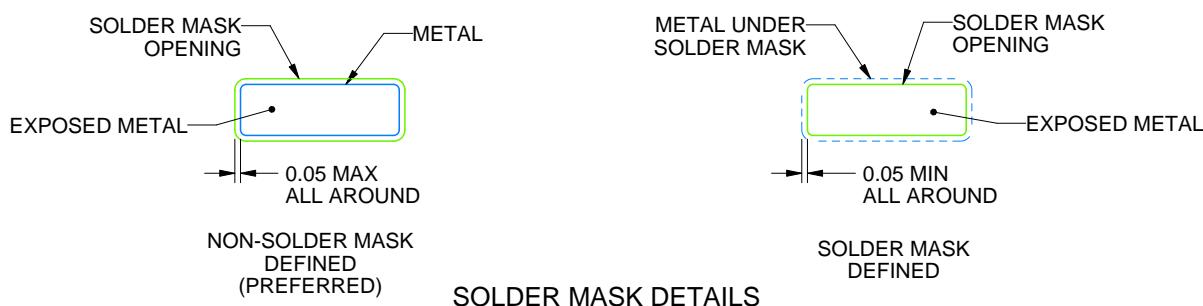

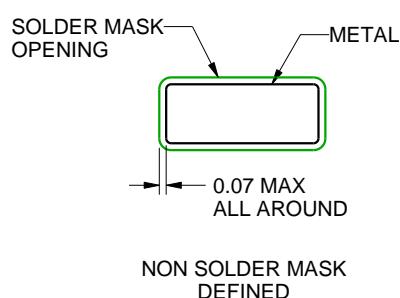

# EXAMPLE BOARD LAYOUT

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

4220202/B 12/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

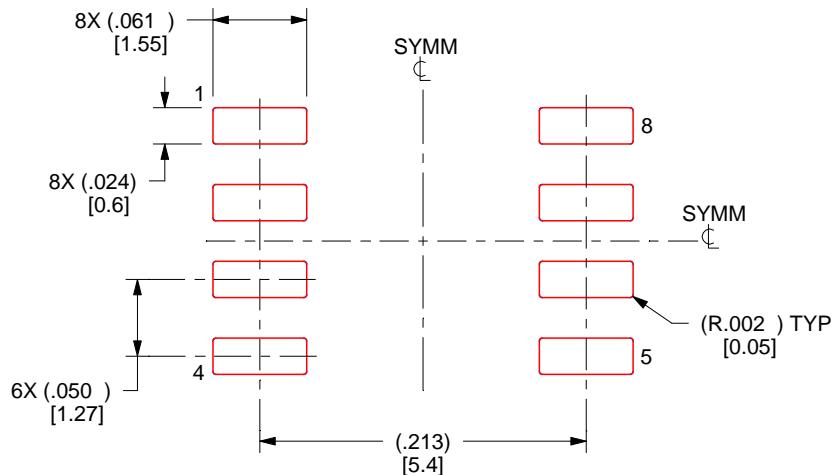

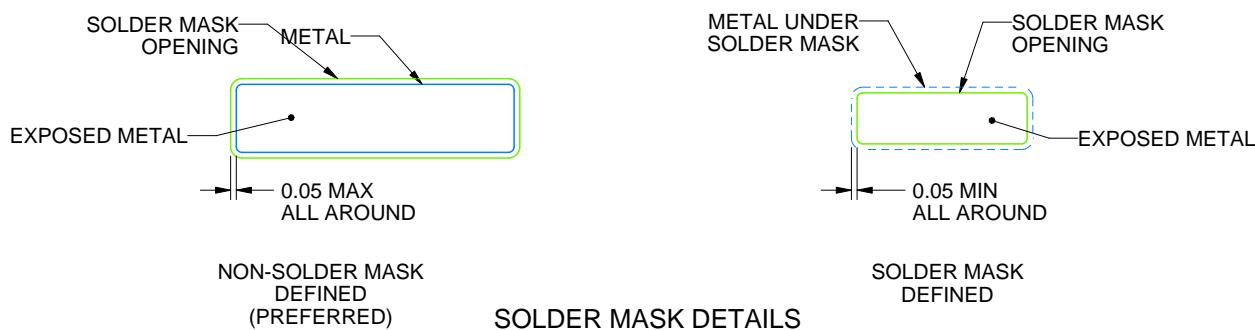

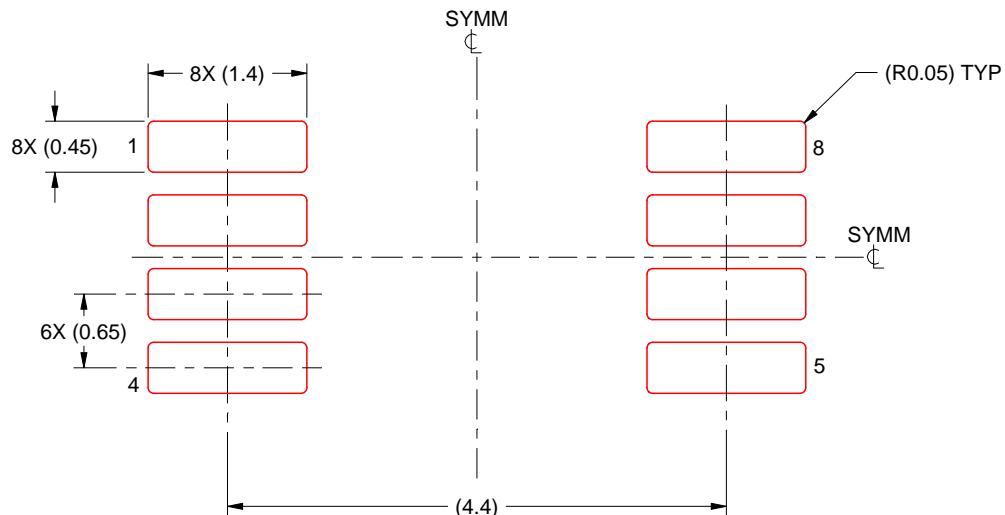

# EXAMPLE STENCIL DESIGN

PW0014A

TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 10X

4220202/B 12/2023

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

DGK0008A

# PACKAGE OUTLINE

VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MO-187.

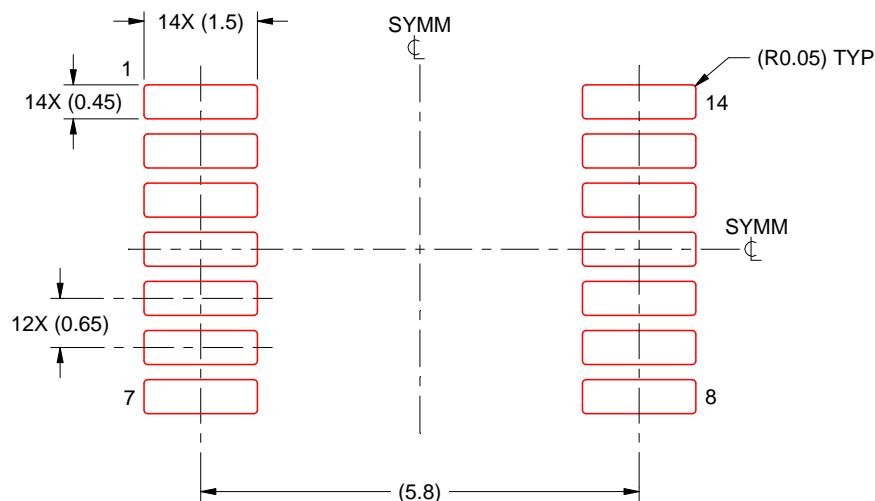

# EXAMPLE BOARD LAYOUT

DGK0008A

™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 15X

4214862/A 04/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

9. Size of metal pad may vary due to creepage requirement.

# EXAMPLE STENCIL DESIGN

DGK0008A

™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

SCALE: 15X

4214862/A 04/2023

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

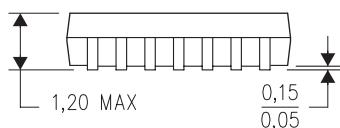

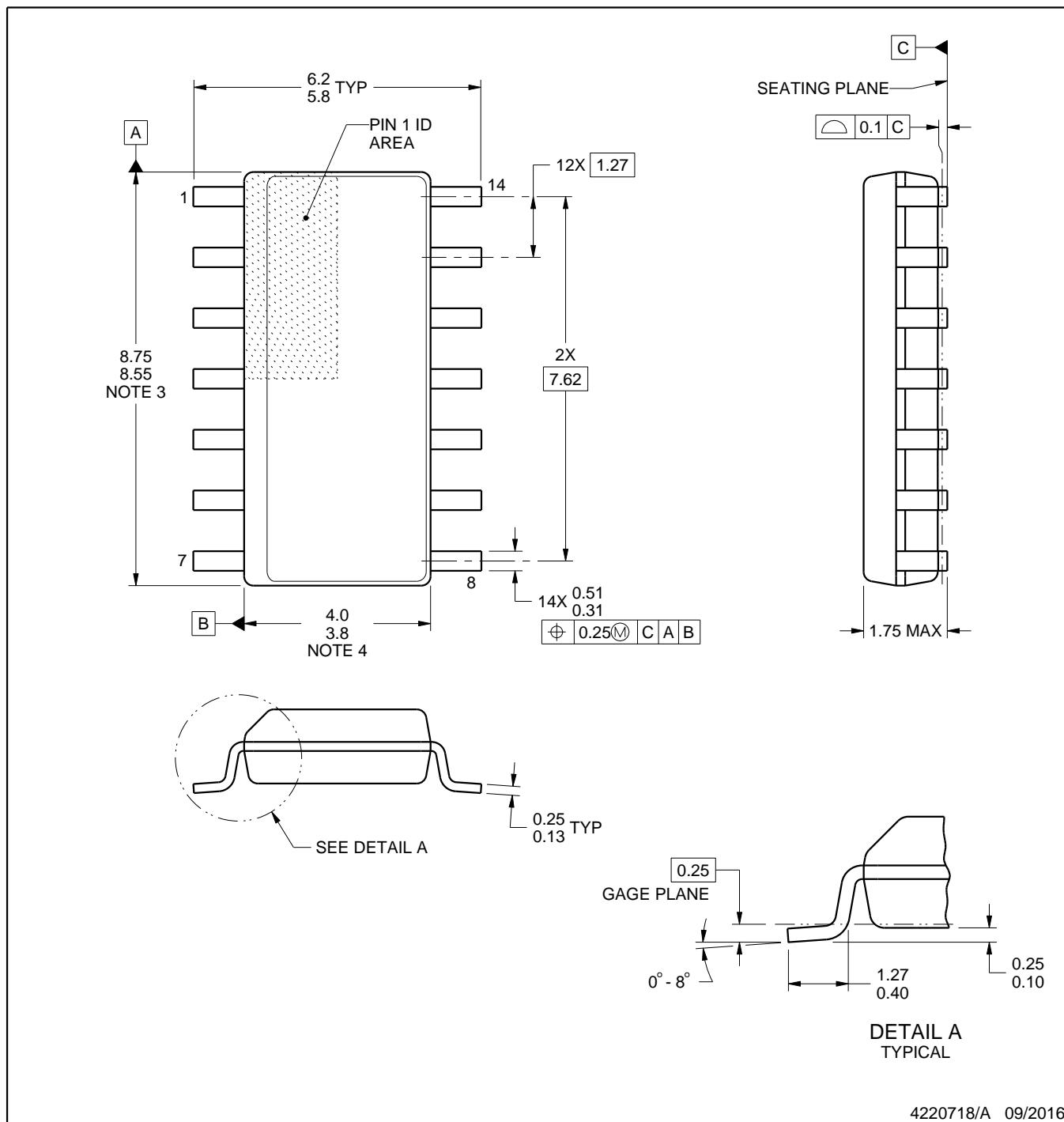

# PACKAGE OUTLINE

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES:

- All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

- This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- Reference JEDEC registration MS-012, variation AB.

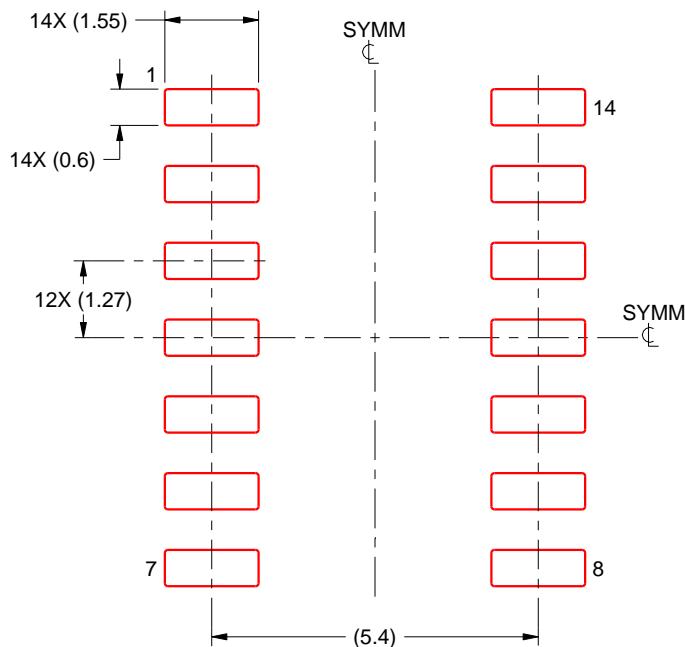

# EXAMPLE BOARD LAYOUT

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

SCALE:8X

SOLDER MASK DETAILS

4220718/A 09/2016

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# EXAMPLE STENCIL DESIGN

D0014A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:8X

4220718/A 09/2016

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月