#### **OPA1662, OPA1664** INSTRUMENTS JAJSVW9A - DECEMBER 2011 - REVISED DECEMBER 2024

# OPA166x 低消費電力、低ノイズおよび低歪、バイポーラ入力、SoundPlus™ ーディオ オペアンプ

## 1 特長

- 低ノイズ:1kHz で 3.3nV/√Hz

- 低歪:1kHz 時に 0.00006%

- 小さい静止電流: 1.5mA (チャネルあたり)

- スルーレート: 17V/μs

- 広いゲイン帯域幅:22MHz (G = +1)

- ユニティゲイン安定

- レールツーレール出力

- 広い電源電圧範囲: ±1.5V~±18V または 3V~36V

- デュアルおよびクワッドのバージョンで供給

- 小型のパッケージ デュアル:SOIC-8、VSSOP-8 クワッド:SOIC-14、TSSOP-14

## 2 アプリケーション

- USB および FireWire オーディオ システム

- アナログ/デジタルミキサ

- ポータブル レコーディング システム

- オーディオ エフェクト プロセッサ

- ハイエンド A/V レシーバ

- ハイエンド DVD および Blu-Ray™ プレーヤ

- ハイエンドカーオーディオ

### 3 概要

デュアル OPA1662 およびクワッド OPA1664 (OPA166x) バイポーラ入力 SoundPlus™ オーディオ オペアンプ シリ ーズは、3.3nV/√Hz の低ノイズ密度と 0.00006% (1kHz 時) の超低歪みを実現しています。 OPA166x オペアンプ シリーズは、2kΩ の負荷で 600mV 以内のレール ツー レ ール出力が可能なため、ヘッドルームが増大し、ダイナミ ックレンジが最大化されます。これらのデバイスは、 ±30mA の高い出力駆動能力も持っています。

これらのデバイスは ±1.5V~±18V または 3V~36V の非 常に広い範囲の電源電圧において、チャネルごとにわず か 1.5mA の消費電流で動作します。 OPA166x オペアン プは、ユニティゲインにおいて安定であり、幅広い負荷条 件にわたって優れた動的挙動を示します。

これらのデバイスは完全に独立した回路を使用しているた め、オーバードライブまたは過負荷時でも、クロストークが 最小限に抑えられ、チャネル間干渉が発生しません。

**OPA166x** は、-40℃~+85℃で動作が規定されていま す。

### 製品情報

| 製品名     | チャネル数 | パッケージ <sup>(1)</sup> |

|---------|-------|----------------------|

| OPA1662 | デュアル  | D (SOIC, 8)          |

|         |       | DGK (VSSOP, 8)       |

| OPA1664 | クワッド  | D (SOIC、14)          |

| OFA1004 |       | PW (TSSOP, 14)       |

(1) 詳細については、セクション 9 を参照してください。

## **Table of Contents**

| 8   |

|-----|

| 15  |

| 15  |

| 21  |

| .22 |

| 22  |

| 22  |

| 22  |

| 22  |

| 22  |

| 22  |

| 22  |

|     |

## **4 Pin Configurations**

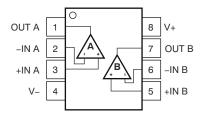

図 4-1. OPA1662: D and DGK Packages, SOIC-8 and VSSOP-8 (Top View)

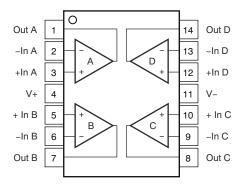

図 4-2. OPA1664: D and PW Packages, SOIC-14 and TSSOP-14 (Top View)

English Data Sheet: SBOS489

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted). (1)

|                  |                                                   | MIN         | MAX        | UNIT |

|------------------|---------------------------------------------------|-------------|------------|------|

| Vs               | Supply voltage, $V_S = (V+) - (V-)$               |             | 40         | V    |

|                  | Input voltage                                     | (V-) - 0.5  | (V+) + 0.5 | V    |

|                  | Input current (all pins except power-supply pins) |             | ±10        | mA   |

|                  | Output short-circuit <sup>(2)</sup>               | Continuous  |            |      |

| T <sub>A</sub>   | Operating temperature                             | <b>–</b> 55 | 125        | °C   |

| TJ               | Junction temperature                              |             | 150        | °C   |

| T <sub>stg</sub> | Storage temperature                               | -65         | 150        | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | 2000  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 1000  | V    |

|                    |                         | Machine model (MM)                                                             | 200   |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                             | MIN NOM | MAX | UNIT |

|----------------|-----------------------------|---------|-----|------|

| Vs             | Supply voltage, (V+) – (V–) | ±1.5    | ±18 | V    |

| T <sub>A</sub> | Ambient temperature         | -40     | 85  | °C   |

Short-circuit to V<sub>S</sub>/2 (ground in symmetrical dual supply setups), one amplifier per package.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 5.4 Thermal Information: OPA1662

|                    |                                              |          | OPA1662     |       |  |

|--------------------|----------------------------------------------|----------|-------------|-------|--|

|                    | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGK (VSSOP) | UNITS |  |

|                    |                                              | 8 PINS   | 8 PINS      |       |  |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 156.3    | 225.4       | °C/W  |  |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 85.5     | 78.8        | °C/W  |  |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 64.9     | 110.5       | °C/W  |  |

| ΨЈТ                | Junction-to-top characterization parameter   | 33.8     | 14.6        | °C/W  |  |

| ΨЈВ                | Junction-to-board characterization parameter | 64.3     | 108.5       | °C/W  |  |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | N/A      | N/A         | °C/W  |  |

<sup>(1)</sup> For information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 5.5 Thermal Information: OPA1664

|                     |                                              | OPA      |            |       |

|---------------------|----------------------------------------------|----------|------------|-------|

|                     | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | PW (TSSOP) | UNITS |

|                     |                                              | 14 PINS  | 14 PINS    |       |

| $R_{\theta JA}$     | Junction-to-ambient thermal resistance       | 78.6     | 125.8      | °C/W  |

| R <sub>θJCtop</sub> | Junction-to-case (top) thermal resistance    | 37.0     | 45.2       | °C/W  |

| $R_{\theta JB}$     | Junction-to-board thermal resistance         | 24.9     | 57.5       | °C/W  |

| ΨЈТ                 | Junction-to-top characterization parameter   | 9.7      | 5.5        | °C/W  |

| $\Psi_{JB}$         | Junction-to-board characterization parameter | 24.6     | 56.7       | °C/W  |

| R <sub>θJCbot</sub> | Junction-to-case (bottom) thermal resistance | N/A      | N/A        | °C/W  |

<sup>(1)</sup> For information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

4

Product Folder Links: OPA1662 OPA1664

## 5.6 Electrical Characteristics: $V_S = \pm 15V$

at  $T_A$  = 25°C and  $R_L$  = 2k $\Omega$ , and  $V_{CM}$  =  $V_{OUT}$  = mid-supply (unless otherwise noted)

|                   | PARAMETER                            |                                  | TEST CONDITIONS                                           | MIN        | TYP               | MAX       | UNIT               |  |

|-------------------|--------------------------------------|----------------------------------|-----------------------------------------------------------|------------|-------------------|-----------|--------------------|--|

| AUDIO I           | PERFORMANCE                          |                                  |                                                           |            |                   |           |                    |  |

| THD+N             | Total harmonic distortion + noise    | G = +1 f = 1kl                   | Hz \/_ = 3\/                                              |            | 0.00006           |           | %                  |  |

| 1110.11           | Total Harmonic distortion : Holse    | G = 11, 1 = 1Ki                  | $G = +1, f = 1kHz, V_O = 3V_{RMS}$                        |            | -124              |           | dB                 |  |

|                   |                                      | SMPTE/DIN two-tone, 4:1          |                                                           |            | 0.00004           |           | %                  |  |

|                   |                                      |                                  | (60Hz and 7kHz)                                           |            | -128              |           | dB                 |  |

|                   | Interned distantian                  | G = +1,                          | DIM 30                                                    |            | 0.00004           |           | %                  |  |

| IMD               | Intermodulation distortion           | $V_O = 3V_{RMS}$                 | (3kHz square wave and 15kHz sine wave)                    |            | -128              |           | dB                 |  |

|                   |                                      |                                  | CCIF twin-tone                                            |            | 0.00004           |           | %                  |  |

|                   |                                      |                                  | (19kHz and 20kHz)                                         |            | -128              |           | dB                 |  |

| FREQUE            | ENCY RESPONSE                        |                                  |                                                           |            |                   |           |                    |  |

| GBW               | Gain-bandwidth product               | G = +1                           |                                                           |            | 22                |           | MHz                |  |

| SR                | Slew rate                            | G = -1                           |                                                           |            | 17                |           | V/µs               |  |

|                   | Full power bandwidth <sup>(1)</sup>  | V <sub>O</sub> = 1V <sub>P</sub> |                                                           |            | 2.7               |           | MHz                |  |

|                   | Overload recovery time               | G = -10                          |                                                           |            | 1                 |           | μs                 |  |

|                   | Channel separation (dual and quad)   | f = 1kHz                         |                                                           |            | -120              |           | dB                 |  |

| NOISE             | 1                                    | 1                                |                                                           |            |                   | -         |                    |  |

| e <sub>n</sub>    | Input voltage noise                  | f = 20Hz to 20                   | kHz                                                       |            | 2.8               |           | μV <sub>PP</sub>   |  |

|                   | Innut valtage paige density          | f = 1kHz                         |                                                           |            | 3.3               |           | nV/√ <del>Hz</del> |  |

|                   | Input voltage noise density          | f = 100Hz                        |                                                           |            | 5                 |           | ΠV/√ HZ            |  |

|                   | land a second a single day site.     | f = 1kHz                         |                                                           |            | 1                 |           | • • • • •          |  |

| l <sub>n</sub>    | Input current noise density          | f = 100Hz                        |                                                           |            | 2                 |           | pA/√ <del>Hz</del> |  |

| OFFSET            | VOLTAGE                              | •                                |                                                           |            |                   |           |                    |  |

| Vos               | Input offset voltage                 | V <sub>S</sub> = ±1.5V to        | ±18V                                                      |            | ±0.5              | ±1.5      | mV                 |  |

| V OS              | Input offset voltage                 | $V_{S} = \pm 1.5 V \text{ to}$   | $\pm$ 18V, T <sub>A</sub> = -40°C to +85°C <sup>(2)</sup> |            | 2                 | 8         | μV/°C              |  |

| PSRR              | Power-supply rejection ratio         | $V_{S} = \pm 1.5 V \text{ to}$   | ±18V                                                      |            | 1                 | 3         | μV/V               |  |

| INPUT E           | BIAS CURRENT                         |                                  |                                                           |            |                   |           |                    |  |

| I <sub>B</sub>    | Input bias current                   | V <sub>CM</sub> = 0V             |                                                           |            | 600               | 1200      | nA                 |  |

| Ios               | Input offset current                 | V <sub>CM</sub> = 0V             |                                                           |            | ±25               | ±100      | nA                 |  |

| INPUT V           | /OLTAGE                              |                                  |                                                           |            |                   |           |                    |  |

| $V_{CM}$          | Common-mode voltage                  |                                  |                                                           | (V-) + 0.5 |                   | (V+) – 1  | V                  |  |

| CMRR              | Common-mode rejection ratio          |                                  |                                                           | 106        | 114               |           | dB                 |  |

| INPUT II          | MPEDANCE                             |                                  |                                                           |            |                   |           |                    |  |

|                   | Differential                         |                                  |                                                           |            | 170    2          |           | kΩ    pF           |  |

|                   | Common-mode                          |                                  |                                                           |            | 600    2.5        |           | MΩ    pF           |  |

| OPEN-L            | OOP GAIN                             |                                  |                                                           |            |                   |           |                    |  |

| A <sub>OL</sub>   | Open-loop voltage gain               | (V−) + 0.6V ≤                    | $V_0 \le (V+) - 0.6V, R_L = 2k\Omega$                     | 106        | 114               |           | dB                 |  |

| OUTPUT            | Т                                    |                                  |                                                           |            |                   |           |                    |  |

| V <sub>OUT</sub>  | Output voltage                       | $R_L = 2k\Omega$                 |                                                           | (V-) + 0.6 | (                 | V+) - 0.6 | V                  |  |

| I <sub>OUT</sub>  | Output current                       |                                  |                                                           | See Typica | l Characteristics | 3         | mA                 |  |

| Z <sub>O</sub>    | Open-loop output impedance           |                                  |                                                           | See Typica | l Characteristics | 5         | Ω                  |  |

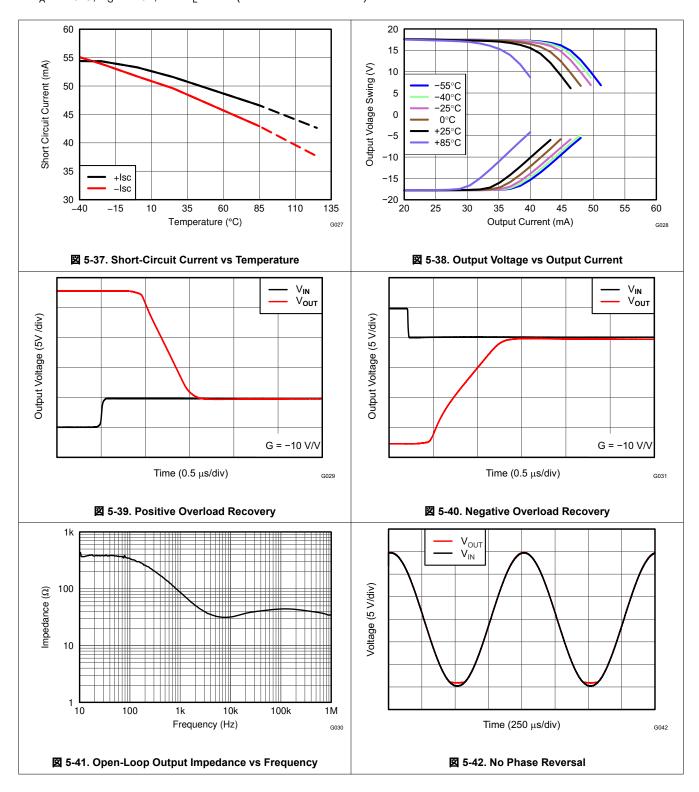

| I <sub>SC</sub>   | Short-circuit current <sup>(3)</sup> |                                  |                                                           |            | ±50               |           | mA                 |  |

| C <sub>LOAD</sub> | Capacitive load drive                |                                  |                                                           |            | 200               |           | pF                 |  |

| POWER             | SUPPLY                               |                                  |                                                           |            |                   |           |                    |  |

| 1-                | Quiescent current                    | I <sub>OUT</sub> = 0A            |                                                           |            | 1.5               | 1.8       | mA                 |  |

| IQ                | (per channel)                        | OUT - UA                         | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}^{(2)}$ |            |                   | 2         | ША                 |  |

Full-power bandwidth = SR / ( $2\pi \times V_P$ ), where SR = slew rate. Specified by design and characterization.

(3) One channel at a time.

## 5.7 Electrical Characteristics: $V_S = 5V$

at  $T_A$  = 25°C and  $R_L$  = 2k $\Omega$ , and  $V_{CM}$  =  $V_{OUT}$  = mid-supply (unless otherwise noted)

|                   | PARAMETER                             |                              | TEST CONDITIONS                                           | MIN                         | TYP             | MAX       | UNIT             |  |

|-------------------|---------------------------------------|------------------------------|-----------------------------------------------------------|-----------------------------|-----------------|-----------|------------------|--|

| AUDIO I           | PERFORMANCE                           |                              |                                                           |                             |                 |           |                  |  |

| THD+N             | Total harmonic distortion + noise     | G = +1 f = 1kl               | Hz, V <sub>O</sub> = 3V <sub>RMS</sub>                    |                             | 0.0001          |           | %                |  |

|                   | Total Harmonic distortion - Holse     | ,, i. i.i. i., i.o. o rains  |                                                           |                             | -120            |           | dB               |  |

|                   |                                       |                              | SMPTE/DIN two-tone, 4:1                                   |                             | 0.00004         |           | %                |  |

|                   |                                       |                              | (60Hz and 7kHz)                                           |                             | -128            |           | dB               |  |

| IMD               | Intermodulation distortion            | G = +1,                      | DIM 30<br>(3kHz square wave and                           |                             | 0.00004         |           | %                |  |

| טואוו             | intermodulation distortion            | $V_O = 3V_{RMS}$             | 15kHz sine wave)                                          |                             | -128            |           | dB               |  |

|                   |                                       |                              | CCIF twin-tone                                            |                             | 0.00004         |           | %                |  |

|                   |                                       |                              | (19kHz and 20kHz)                                         |                             | -128            |           | dB               |  |

| FREQUE            | ENCY RESPONSE                         |                              |                                                           |                             |                 |           |                  |  |

| GBW               | Gain-bandwidth product                | G = +1                       |                                                           |                             | 20              |           | MHz              |  |

| SR                | Slew rate                             | G = -1                       |                                                           |                             | 13              |           | V/µs             |  |

|                   | Full power bandwidth <sup>(1)</sup>   | $V_O = 1V_P$                 |                                                           |                             | 2               |           | MHz              |  |

|                   | Overload recovery time                | G = -10                      |                                                           |                             | 1               |           | μs               |  |

|                   | Channel separation (dual and quad)    | f = 1kHz                     |                                                           |                             | -120            |           | dB               |  |

| NOISE             | •                                     | •                            |                                                           |                             |                 |           |                  |  |

| e <sub>n</sub>    | Input voltage noise                   | f = 20Hz to 20               | kHz                                                       |                             | 3.3             |           | μV <sub>PP</sub> |  |

|                   | land to the second of the             | f = 1kHz                     |                                                           |                             | 3.3             |           | >//-/ TI         |  |

|                   | Input voltage noise density           | f = 100Hz                    |                                                           |                             | 5               |           | nV/√ Hz          |  |

|                   |                                       | f = 1kHz                     |                                                           |                             | 1               |           |                  |  |

| l <sub>n</sub>    | Input current noise density f = 100H: |                              | 00Hz                                                      |                             | 2               |           | — pA/√ Hz        |  |

| OFFSET            | VOLTAGE                               |                              |                                                           |                             |                 |           |                  |  |

| .,                | land off a book as                    | V <sub>S</sub> = ±1.5V to    | ±18V                                                      |                             | ±0.5            | ±1.5      | mV               |  |

| Vos               | Input offset voltage                  | V <sub>S</sub> = ±1.5V to    | $\pm 18V$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C^{(2)}$  |                             | 2               | 8         | μV/°C            |  |

| PSRR              | Power-supply rejection ratio          | $V_S = \pm 1.5 V \text{ to}$ | ±18V                                                      |                             | 1               | 3         | μV/V             |  |

| INPUT E           | BIAS CURRENT                          | •                            |                                                           |                             |                 |           |                  |  |

| l <sub>B</sub>    | Input bias current                    | V <sub>CM</sub> = 0V         |                                                           |                             | 600             | 1200      | nA               |  |

| los               | Input offset current                  | V <sub>CM</sub> = 0V         |                                                           |                             | ±25             | ±100      | nA               |  |

| INPUT V           | /OLTAGE                               | •                            |                                                           |                             |                 |           |                  |  |

| V <sub>CM</sub>   | Common-mode voltage                   |                              |                                                           | (V-) + 0.5                  |                 | (V+) – 1  | V                |  |

| CMRR              | Common-mode rejection ratio           |                              |                                                           | 86                          | 100             |           | dB               |  |

| NPUT II           | MPEDANCE                              | •                            |                                                           |                             |                 |           |                  |  |

|                   | Differential                          |                              |                                                           |                             | 170    2        |           | kΩ    pF         |  |

|                   | Common-mode                           |                              |                                                           | 6                           | 800    2.5      |           | MΩ    pF         |  |

| OPEN-L            | OOP GAIN                              | •                            |                                                           |                             |                 | <u>'</u>  |                  |  |

| A <sub>OL</sub>   | Open-loop voltage gain                | (V–) + 0.6V ≤ V              | $V_0 \le (V+) - 0.6V, R_L = 2k\Omega$                     | 90                          | 100             |           | dB               |  |

| OUTPU             | τ                                     | •                            |                                                           |                             |                 | <u> </u>  |                  |  |

| Vout              | Output voltage                        | $R_L = 2k\Omega$             |                                                           | (V-) + 0.6                  | (               | V+) - 0.6 | V                |  |

| OUT               | Output current                        |                              |                                                           | See Typical                 | Characteristics | 3         | mA               |  |

| Z <sub>O</sub>    | Open-loop output impedance            |                              |                                                           | See Typical Characteristics |                 | Ω         |                  |  |

| sc                | Short-circuit current <sup>(3)</sup>  |                              |                                                           |                             | ±40             |           | mA               |  |

| C <sub>LOAD</sub> | Capacitive load drive                 |                              |                                                           |                             | 200             |           | pF               |  |

| POWER             | SUPPLY                                | 1                            |                                                           | -                           |                 |           |                  |  |

|                   | Quiescent current                     |                              |                                                           |                             | 1.4             | 1.7       |                  |  |

| ΙQ                | (per channel)                         | I <sub>OUT</sub> = 0A        | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}^{(2)}$ |                             |                 | 2         | mA               |  |

(1) Full-power bandwidth = SR /  $(2\pi \times V_P)$ , where SR = slew rate.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

- (2) Specified by design and characterization.

- One channel at a time. (3)

Product Folder Links: OPA1662 OPA1664

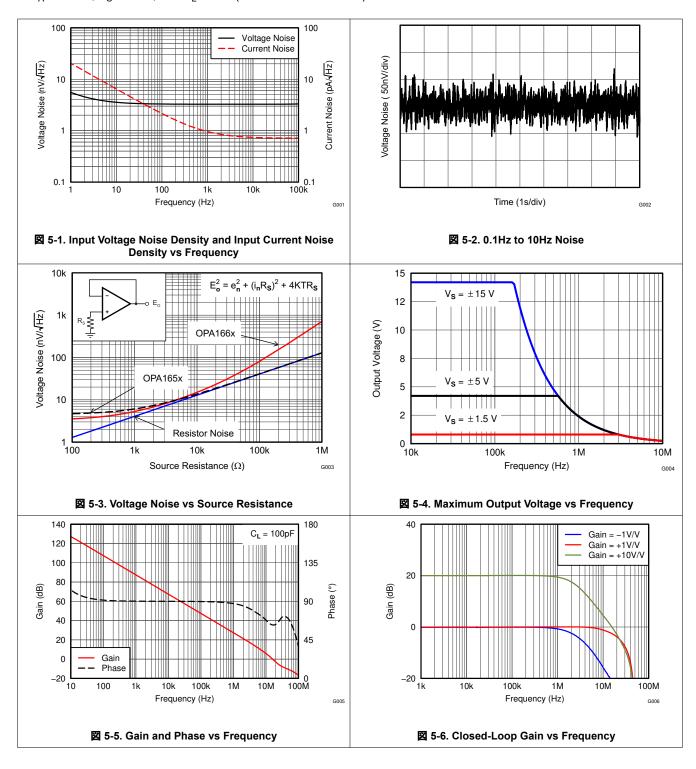

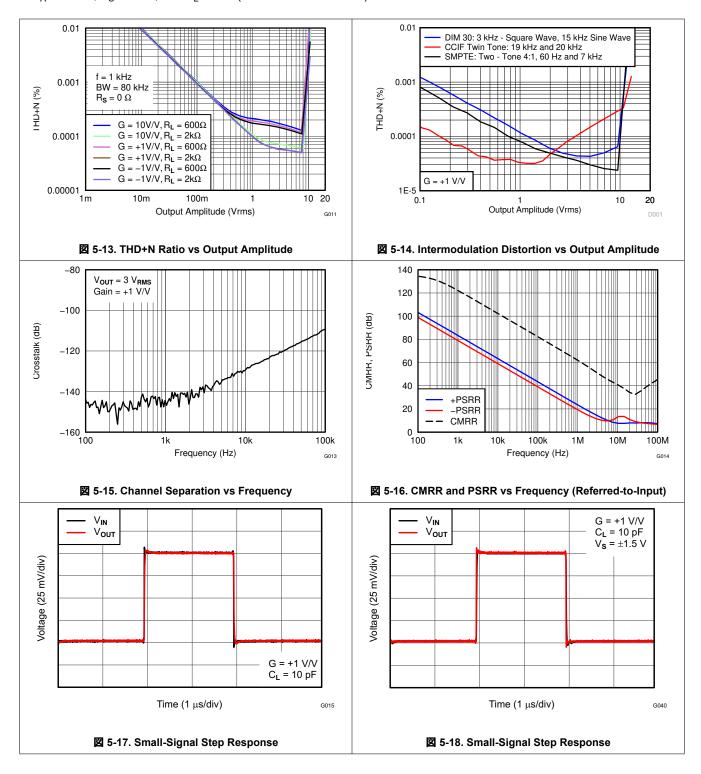

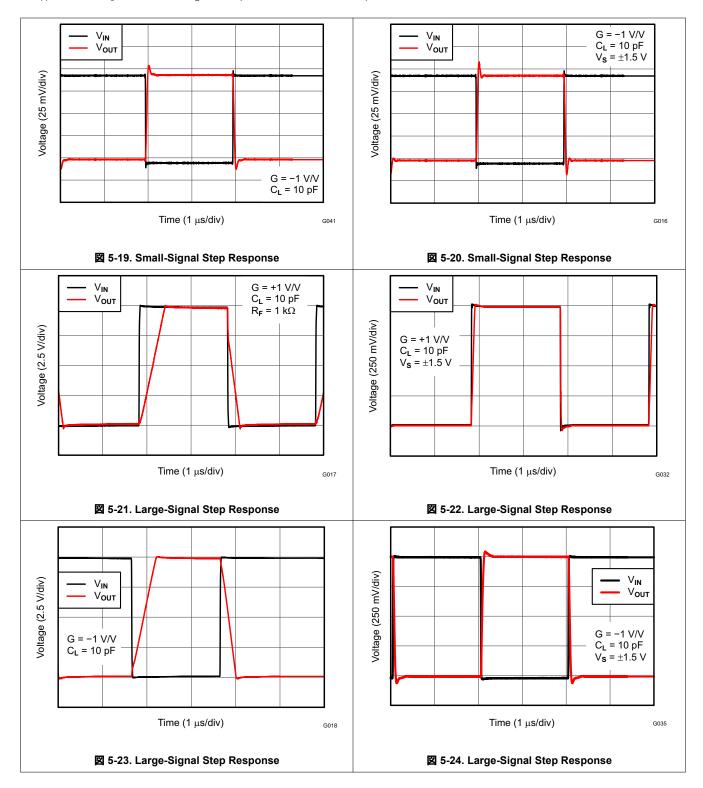

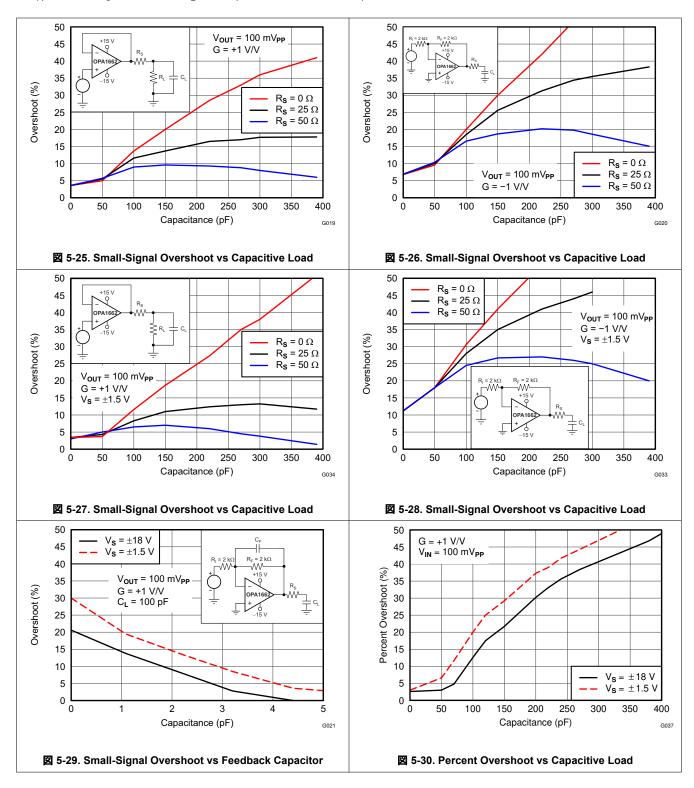

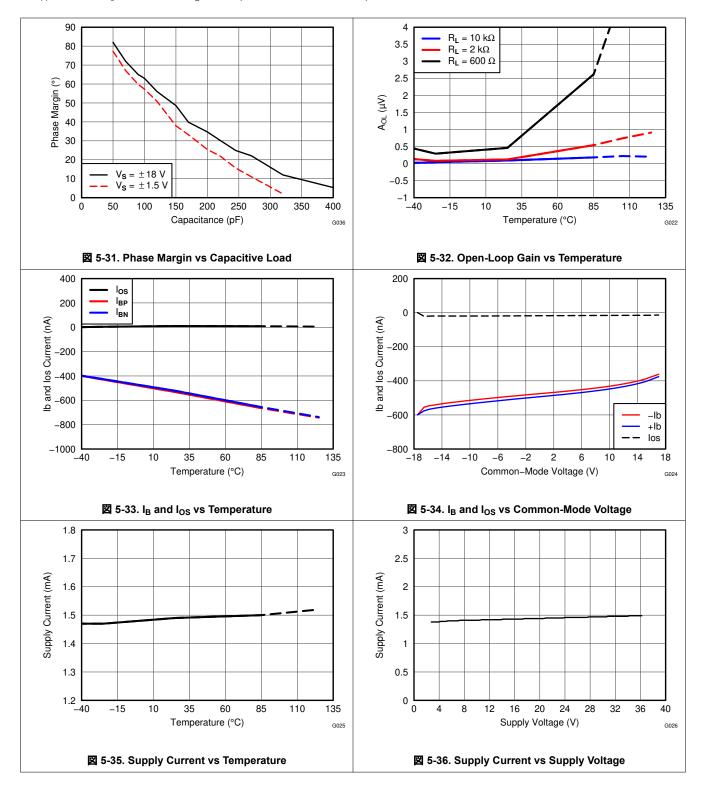

## **5.8 Typical Characteristics**

## 6 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## **6.1 Application Information**

The OPA166x are unity-gain stable, precision dual and quad op amps with very low noise. Applications with noisy or high-impedance power supplies require decoupling capacitors close to the device pins. In most cases, 0.1µF capacitors are adequate.

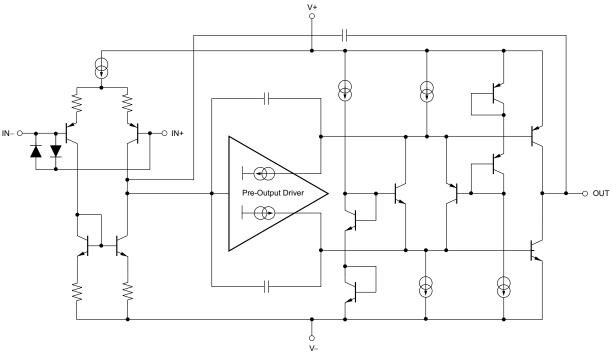

6-1 shows a simplified schematic of the OPA166x (one channel shown).

#### 6.1.1 Operating Voltage

The OPA166x series op amps operate from ±1.5V to ±18V supplies while maintaining excellent performance. The OPA166x series can operate with as little as 3V between the supplies and with up to 36V between the supplies. However, some applications do not require equal positive and negative output voltage swing. With the OPA166x series, power-supply voltages do not need to be equal. For example, set the positive supply to 25V with the negative supply at –5V.

In all cases, the common-mode voltage must be maintained within the specified range. In addition, key parameters are specified over the specified temperature range of  $T_A = -40$ °C to +85°C. Parameters that vary significantly with operating voltage or temperature are shown in the Typical Characteristics.

Copyright © 2016, Texas Instruments Incorporated

図 6-1. OPA166x Simplified Schematic

English Data Sheet: SBOS489

#### 6.1.2 Input Protection

図 6-2. Pulsed Operation

#### 6.1.3 Noise Performance

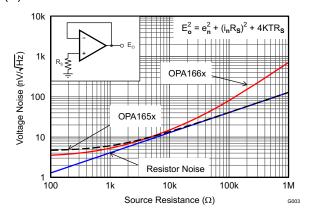

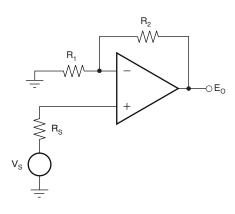

☑ 6-3 shows the total circuit noise for varying source impedance values with the op amp in a unity-gain configuration (no feedback resistor network, and therefore no additional noise contributions).

The OPA166x (GBW = 22MHz, G = +1) is shown with total circuit noise calculated. The op amp contributes both a voltage noise component and a current noise component. The voltage noise is commonly modeled as a time-varying component of the offset voltage. The current noise is modeled as the time-varying component of the input bias current and reacts with the source resistance to create a voltage component of noise. Therefore, the lowest noise op amp for a given application depends on the source impedance. For low source impedance, current noise is negligible, and voltage noise generally dominates. The low voltage noise of the OPA166x series op amps makes them a better choice for low source impedances of less than  $1k\Omega$ .

The equation in 🗵 6-3 shows the calculation of the total circuit noise, with these parameters:

- e<sub>n</sub> = Voltage noise

- i<sub>n</sub> = Current noise

- R<sub>S</sub> = Source impedance

- k = Boltzmann's constant = 1.38 × 10<sup>-23</sup> J/K

- T = Temperature in kelvins (K)

図 6-3. Noise Performance of the OPA166x in Unity-Gain Buffer Configuration

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

#### 6.1.4 Basic Noise Calculations

Design of low-noise op amp circuits requires careful consideration of a variety of possible noise contributors: noise from the signal source, noise generated in the op amp, and noise from the feedback network resistors. The total noise of the circuit is the root-sum-square combination of all noise components.

The resistive portion of the source impedance produces thermal noise proportional to the square root of the resistance.

6-3 plots this equation. The source impedance is usually fixed; consequently, select the op amp and the feedback resistors to minimize the respective contributions to the total noise.

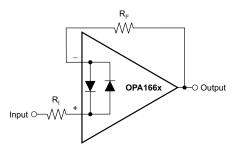

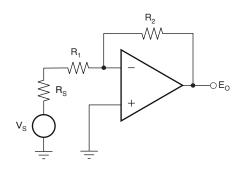

☑ 6-4 illustrates both inverting and noninverting op amp circuit configurations with gain. In circuit configurations with gain, the feedback network resistors also contribute noise. The current noise of the op amp reacts with the feedback resistors to create additional noise components. The feedback resistor values can generally be chosen to make these noise sources negligible. The equations for total noise are shown for both configurations.

#### A) Noise in Noninverting Gain Configuration

Noise at the output:

$$E_0^2 = \left[1 + \frac{R_2}{R_1}\right]^2 e_n^2 + \left[\frac{R_2}{R_1}\right]^2 e_1^2 + e_2^2 + \left[1 + \frac{R_2}{R_1}\right]^2 e_s^2$$

Where

$$e_S = \sqrt{4kTR_S}$$

= thermal noise of  $R_S$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

#### B) Noise in Inverting Gain Configuration

Noise at the output:

$$E_{O}^{2} = \left[1 + \frac{R_{2}}{R_{1} + R_{S}}\right]^{2} e_{n}^{2} + \left[\frac{R_{2}}{R_{1} + R_{S}}\right]^{2} e_{1}^{2} + e_{2}^{2} + \left[\frac{R_{2}}{R_{1} + R_{S}}\right]^{2} e_{s}^{2}$$

Where

$$e_S = \sqrt{4kTR_S}$$

= thermal noise of  $R_S$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

For the OPA166x series of op amps at 1kHz,  $e_n = 3.3 \text{nV}/\sqrt{\text{Hz}}$ .

図 6-4. Noise Calculation in Gain Configurations

English Data Sheet: SBOS489

#### 6.1.5 Total Harmonic Distortion Measurements

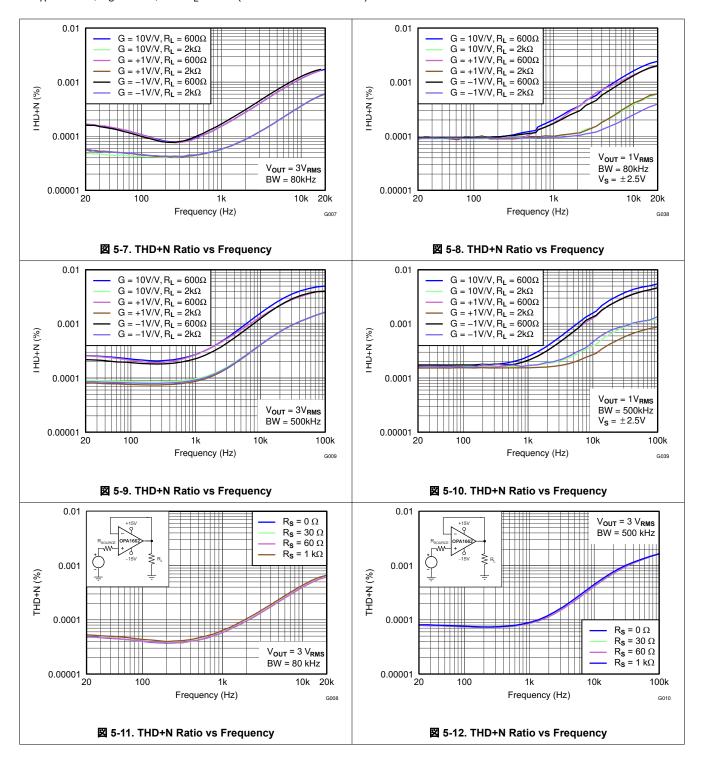

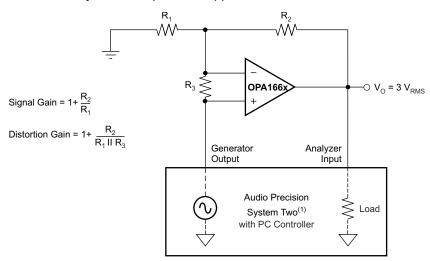

The OPA166x series op amps have excellent distortion characteristics. THD + noise is below 0.0006% (G = +1,  $V_O = 3V_{RMS}$ , BW = 80kHz) throughout the audio frequency range, 20Hz to 20kHz, with a  $2k\Omega$  load (see  $\boxtimes$  5-7 for characteristic performance).

The distortion produced by the OPA166x series op amps is below the measurement limit of many commercially available distortion analyzers. However, a special test circuit (such as 🗵 6-5 shows) can be used to extend the measurement capabilities.

Op amp distortion is considered an internal error source that is referred to the input.  $\boxtimes$  6-5 shows a circuit that causes the op amp distortion to be gained up (refer to the table in  $\boxtimes$  6-5 for the distortion gain factor for various signal gains). The addition of  $R_3$  to the otherwise standard non-inverting amplifier configuration alters the feedback factor or noise gain of the circuit. The closed-loop gain is unchanged, but the feedback available for error correction is reduced by the distortion gain factor, thus extending the resolution by the same amount. Note that the input signal and load applied to the op amp are the same as with conventional feedback without  $R_3$ . The value of  $R_3$  must be kept small to minimize the effect on the distortion measurements.

The validity of this technique can be verified by duplicating measurements at high gain and/or high frequency where the distortion is within the measurement capability of the test equipment. Measurements for this data sheet were made with an Audio Precision System Two distortion/noise analyzer, which greatly simplifies such repetitive measurements. The measurement technique can, however, be performed with manual distortion measurement instruments.

#### 6.1.6 Capacitive Loads

The dynamic characteristics of the OPA1662 and OPA1664 have been optimized for commonly encountered gains, loads, and operating conditions. The combination of low closed-loop gain and high capacitive loads decreases the phase margin of the amplifier and can lead to gain peaking or oscillations. As a result, heavier capacitive loads must be isolated from the output. The simplest way to achieve this isolation is to add a small resistor ( $R_S$  equal to  $50\Omega$ , for example) in series with the output.

This small series resistor also prevents excess power dissipation if the output of the device becomes shorted.

5-25 illustrates a graph of *Small-Signal Overshoot vs Capacitive Load* for several values of R<sub>S</sub>. Also, refer to Applications Bulletin AB-028 (literature number SBOA015, available for download from the TI web site) for details of analysis techniques and application circuits.

| SIGNAL<br>GAIN | DISTORTION<br>GAIN | R <sub>1</sub> | $R_2$                   | $R_3$  |

|----------------|--------------------|----------------|-------------------------|--------|

| +1             | 101                | 8              | 1 kΩ                    | 10 Ω   |

| -1             | 101                | 4.99 kΩ        | $4.99~\mathrm{k}\Omega$ | 49.9 Ω |

| +10            | 110                | 549 Ω          | $4.99~\mathrm{k}\Omega$ | 49.9 Ω |

(1) For measurement bandwidth, see <a>\overline{\mathbb{Z}}</a> 5-7 through <a>\overline{\mathbb{Z}}</a> 5-12.

図 6-5. Distortion Test Circuit

### 6.1.7 Power Dissipation

The OPA1662 and OPA1664 series op amps are capable of driving  $2k\Omega$  loads with a power-supply voltage up to  $\pm 18V$  and full operating temperature range. Internal power dissipation increases when operating at high supply voltages. Copper leadframe construction used in the OPA166x series op amps improves heat dissipation compared to conventional materials. Circuit board layout can also help minimize junction temperature rise. Wide copper traces help dissipate the heat by acting as an additional heat sink. Temperature rise can be further minimized by soldering the devices to the circuit board rather than using a socket.

#### 6.1.8 Electrical Overstress

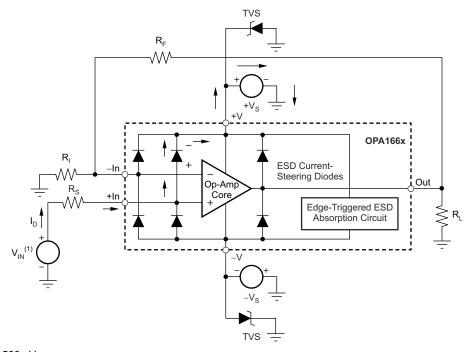

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but can involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits to protect them from accidental ESD events both before and during product assembly.

A good understanding of this basic ESD circuitry and the relevance to an electrical overstress event is important.

6-6 illustrates the ESD circuits contained in the OPA166x (indicated by the dashed line area). The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power-supply lines, where the diodes meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

An ESD event produces a short duration, high-voltage pulse that is transformed into a short duration, high-current pulse when discharging through a semiconductor device. The ESD protection circuits are designed to provide a current path around the operational amplifier core to prevent the amplifier from being damaged. The energy absorbed by the protection circuitry is then dissipated as heat.

When an ESD voltage develops across two or more of the amplifier device pins, current flows through one or more of the steering diodes. Depending on the path that the current takes, the absorption device can activate. The absorption device internal to the OPA166x triggers when a fast ESD voltage pulse is impressed across the supply pins. Once triggered, the ESD cell quickly activates, clamping the ESD pulse to a safe voltage level.

When the operational amplifier connects into a circuit such as that illustrated in 🗵 6-6, the ESD protection components are intended to remain inactive and not become involved in the application circuit operation. However, circumstances can arise where an applied voltage exceeds the operating voltage range of a given pin. During this condition, there is a risk that some of the internal ESD protection circuits can be biased on, and conduct current. Any such current flow occurs through steering diode paths and rarely involves the absorption device.

$\boxtimes$  6-6 depicts a specific example where the input voltage,  $V_{IN}$ , exceeds the positive supply voltage (+V<sub>S</sub>) by 500mV or more. Much of what happens in the circuit depends on the supply characteristics. If +V<sub>S</sub> can sink the current, one of the upper input steering diodes conducts and directs current to +V<sub>S</sub>. Excessively high current levels can flow with increasingly higher V<sub>IN</sub>. As a result, the data sheet specifications recommend that applications limit the input current to 10mA.

If the supply is not capable of sinking the current,  $V_{IN}$  can begin sourcing current to the operational amplifier, and then take over as the source of positive supply voltage. The danger in this case is that the voltage can rise to levels that exceed the operational amplifier absolute maximum ratings. In extreme but rare cases, the absorption device triggers on while  $+V_S$  and  $-V_S$  are applied. If this event happens, a direct current path is established between the  $+V_S$  and  $-V_S$  supplies. The power dissipation of the absorption device is quickly exceeded, and the extreme internal heating destroys the operational amplifier.

Another common question involves what happens to the amplifier if an input signal is applied to the input while the power supplies  $+V_S$  and/or  $-V_S$  are at 0V. This also depends on the supply characteristic while at 0V, or at a level below the input signal amplitude. If the supplies appear as high impedance, then the operational amplifier supply current can be supplied by the input source via the current steering diodes. This state is not a normal bias

English Data Sheet: SBOS489

condition; the amplifier does not operate normally. If the supplies are low impedance, then the current through the steering diodes can become quite high. The current level depends on the ability of the input source to deliver current, and any resistance in the input path.

If there is an uncertainty about the ability of the supply to absorb this current, external zener diodes can be added to the supply pins as shown in  $\boxtimes$  6-6.

The zener voltage must be selected such that the diode does not turn on during normal operation. However, the zener voltage must be low enough so that the zener diode conducts if the supply pin begins to rise above the safe operating supply voltage level.

(1)  $V_{IN} = +V_S + 500$ mV.

図 6-6. Equivalent Internal ESD Circuitry and the Relation to a Typical Circuit Application (Single Channel Shown)

## **6.2 Typical Application**

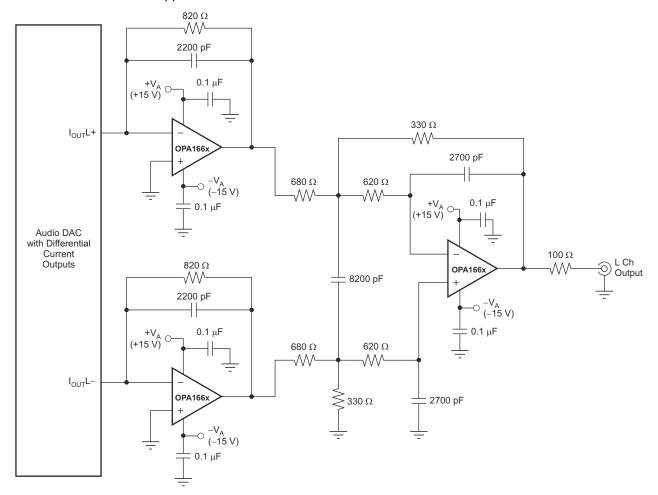

図 6-7. Audio DAC I/V Converter and Output Filter

## 7 Device and Documentation Support

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

## 7.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 7.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 7.3 Trademarks

Blu-Ray<sup>™</sup> is a trademark of Blu-Ray Disc Association. SoundPlus<sup>™</sup> is a trademark of Texas Instruments Incorporated. テキサス・インスツルメンツ E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

### 7.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 7.5 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

### 8 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | hanges from Revision * (December 2011) to Revision A (December 2024)         | Page |

|---|------------------------------------------------------------------------------|------|

| • | ドキュメント全体にわたって表、図、相互参照の採番方法を更新                                                | 1    |

| • | 「仕様」、「ESD 定格」、「推奨動作条件」、「アプリケーションと実装」、「代表的なアプリケーション」、「デバイスお                   | よびド  |

|   | キュメントのサポート」、「改訂履歴」、「メカニカル、パッケージ、および注文情報」の各セクションを追加                           | 1    |

| • | Updated table note 1 in Absolute Maximum Ratings                             | 3    |

| • | Changed junction temperature from 200°C to 150°C in Absolute Maximum Ratings | 3    |

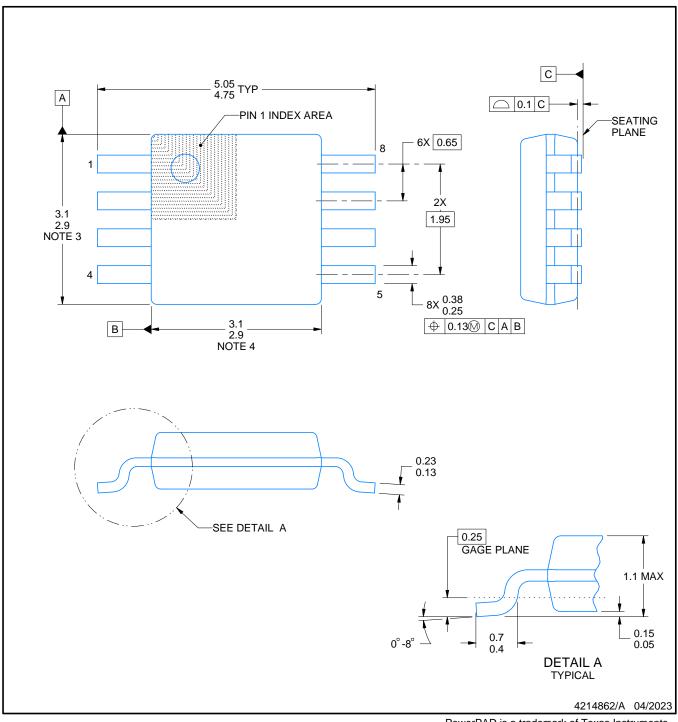

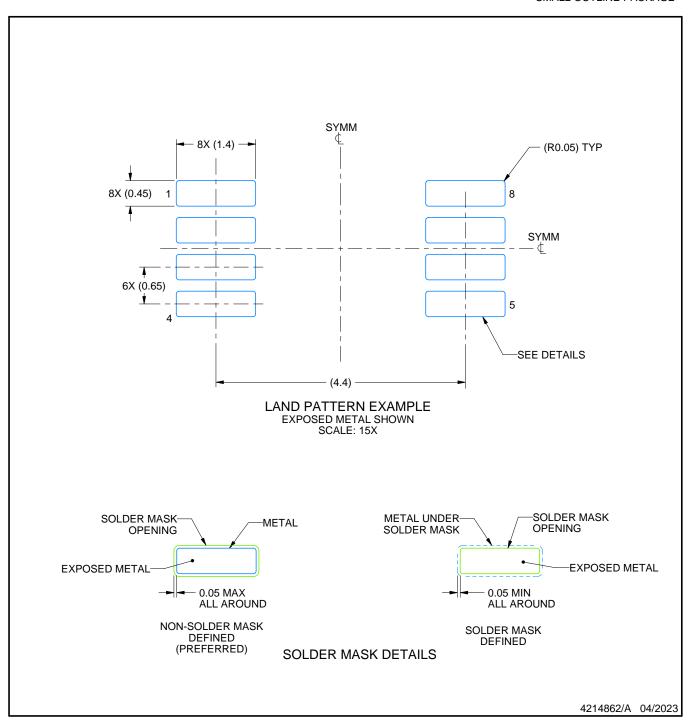

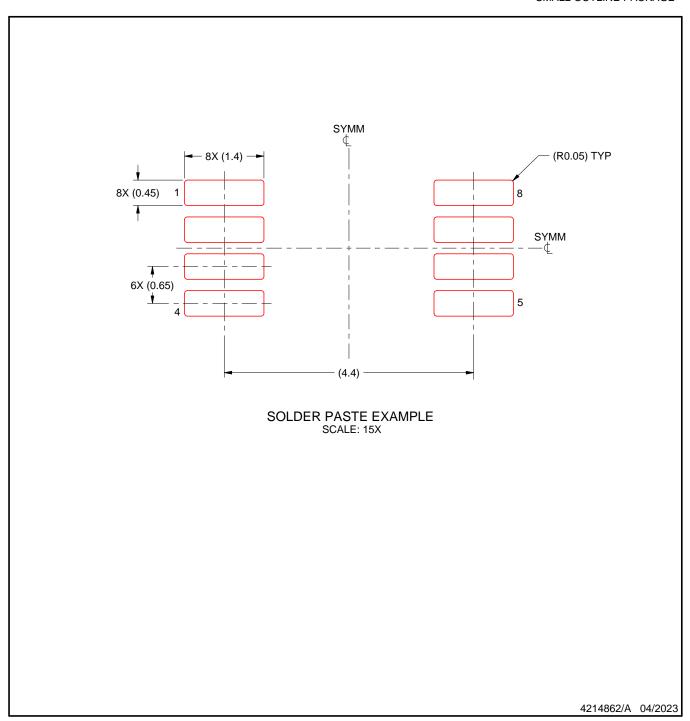

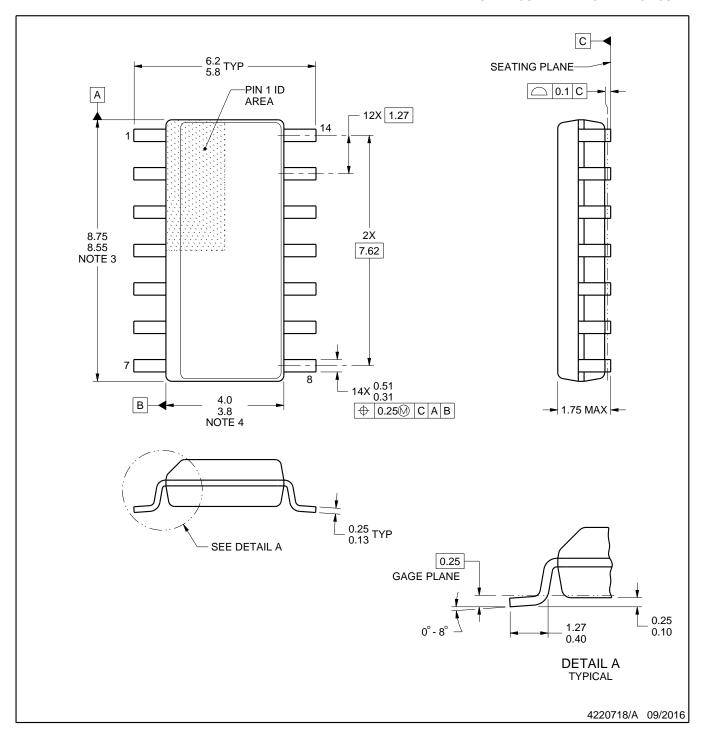

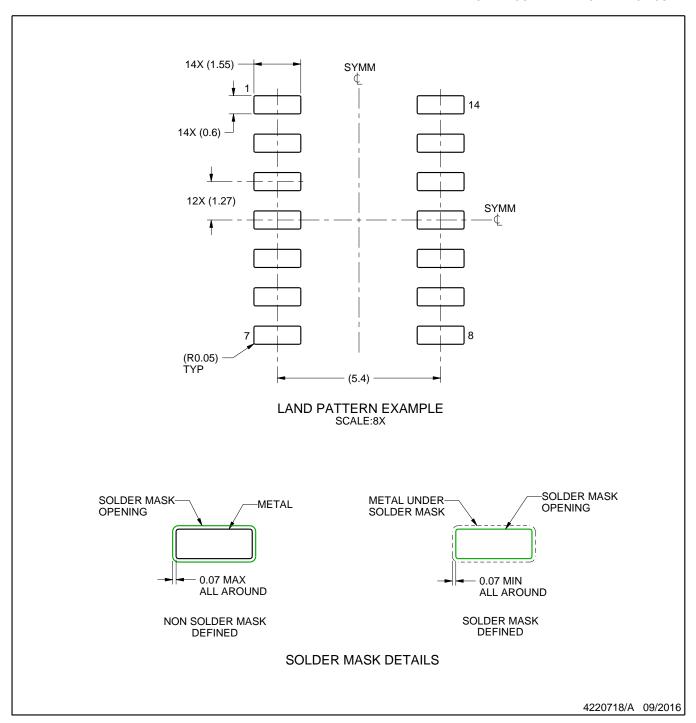

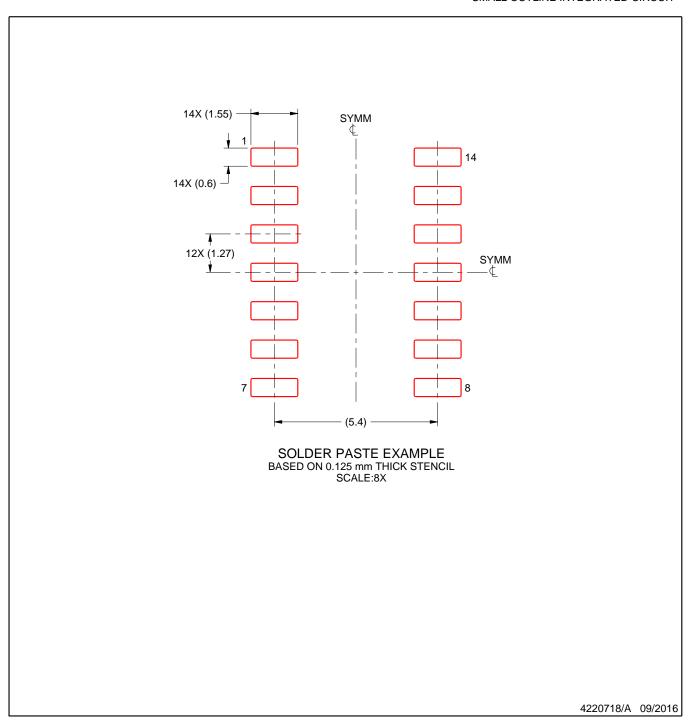

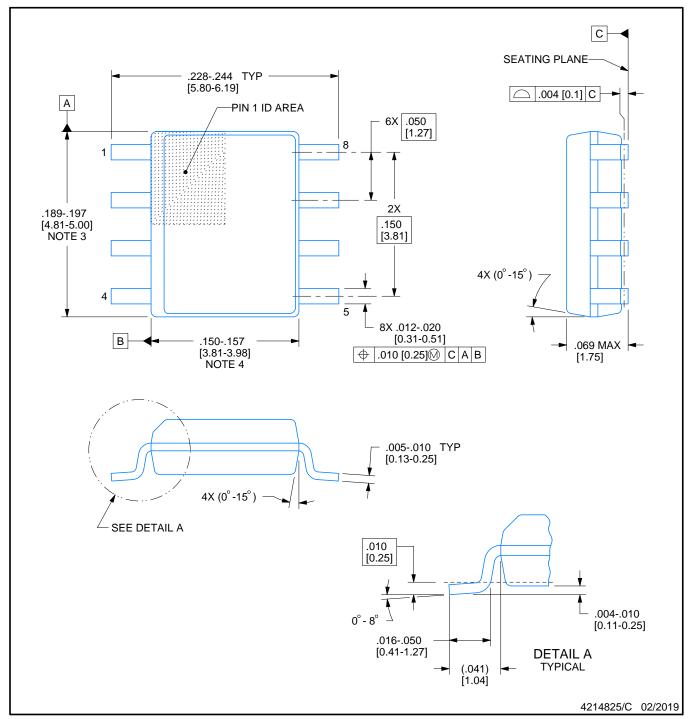

## 9 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

資料に関するフィードバック (ご意見やお問い合わせ) を送信 Copyright © 2025 Texas Instruments Incorporated

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

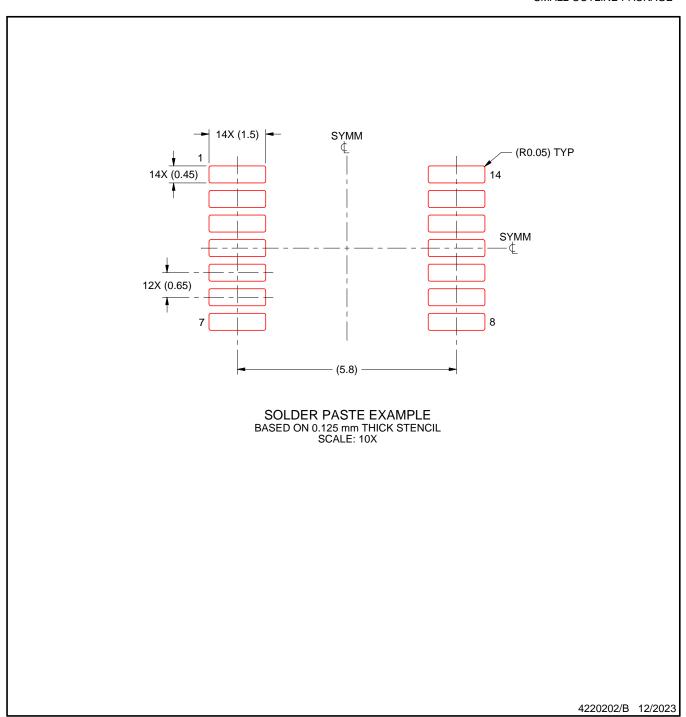

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

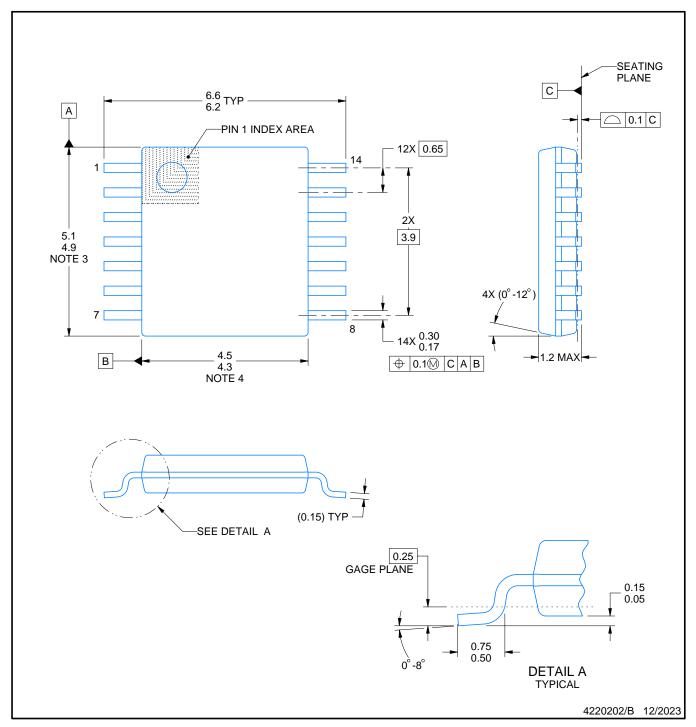

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm, per side.

- 5. Reference JEDEC registration MS-012, variation AB.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

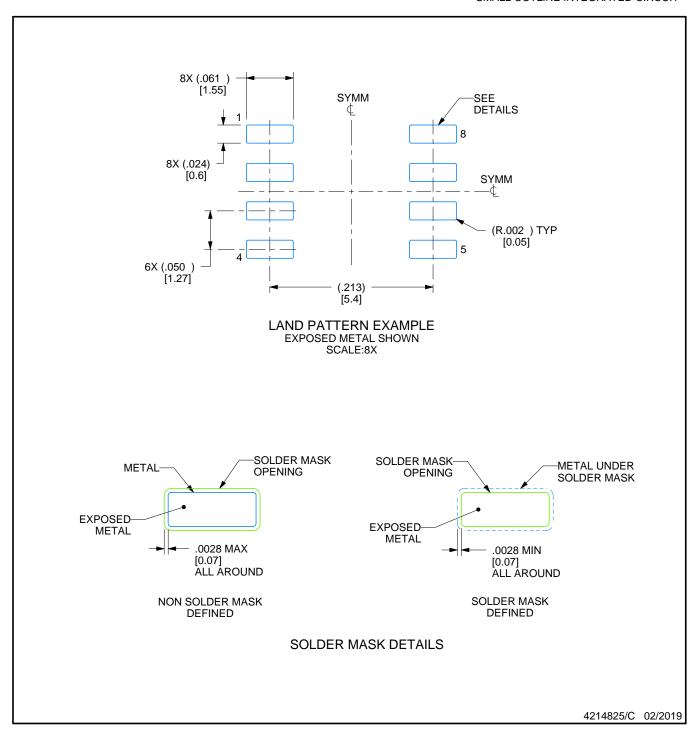

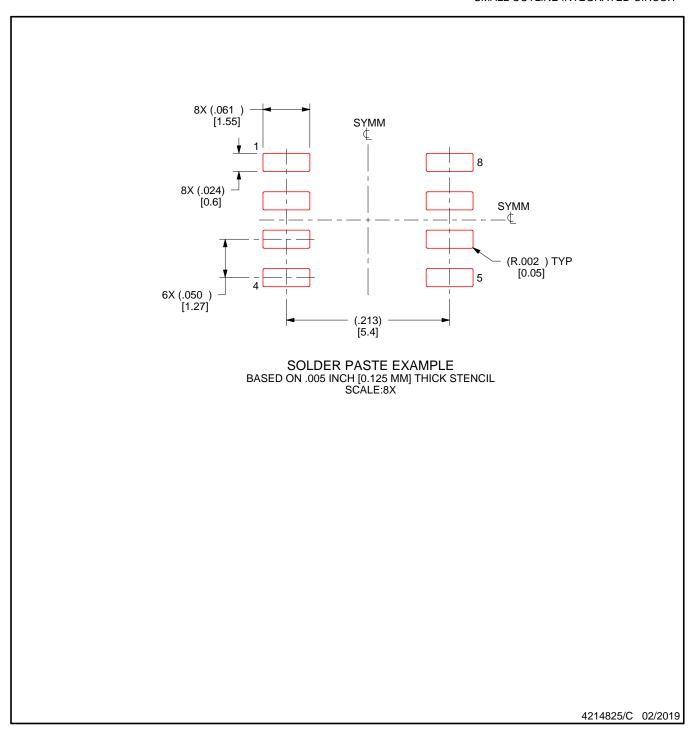

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

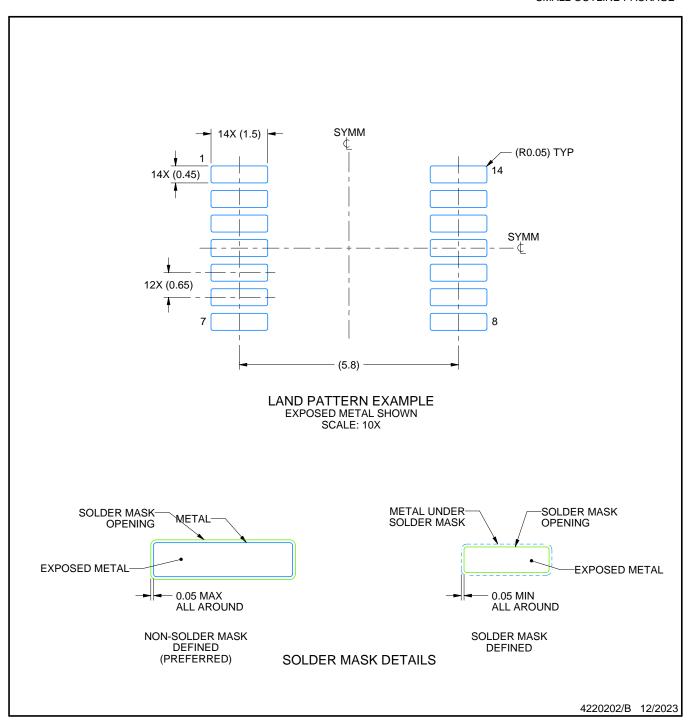

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated