- 低電源電圧範囲: 1.8 V ~ 3.6 V

- 超低消費電力:

- アクティブ・モード: 200  $\mu$ A (1 MHz, 2.2 V)

- スタンバイ・モード: 0.7  $\mu$ A

- オフ・モード (RAM データ保持): 0.1  $\mu$ A

- 5 つのパワー・セーブ・モード

- スタンバイ・モードからのウェークアップは 6  $\mu$ s 以下

- 周波数ロック・ループ (FLL+)

- 16 ビット RISC アーキテクチャ、

125 ns インストラクション・サイクル・タイム

- 水、熱、及びガスの残量測定のためのスキャン

IF (インターフェース)

- 16 ビット タイマ\_A (3 つのキャプチャ/コンペア・

レジスタ付き)

- 16 ビット タイマ\_A (5 つのキャプチャ/コンペア・

レジスタ付き)

- 96 セグメント LCD ドライバ内蔵

- オン・チップ・コンパレータ

- シリアル・オンボード・プログラミング、

外部プログラミング電圧不要、

セキュリティ・ヒューズによるプログラム可能な

コード保護

- ブラウンアウト検出 (BOR)

- 検出レベル可変 電源電圧監視/モニタ

- ブートストラップ・ローダ (フラッシュ・デバイス)

- ファミリ製品:

- MSP430FW423:

8KB + 256B フラッシュ・メモリ、

256B RAM

- MSP430FW425:

16KB + 256B フラッシュ・メモリ、

512B RAM

- MSP430FW427:

32KB + 256B フラッシュ・メモリ、

1KB RAM

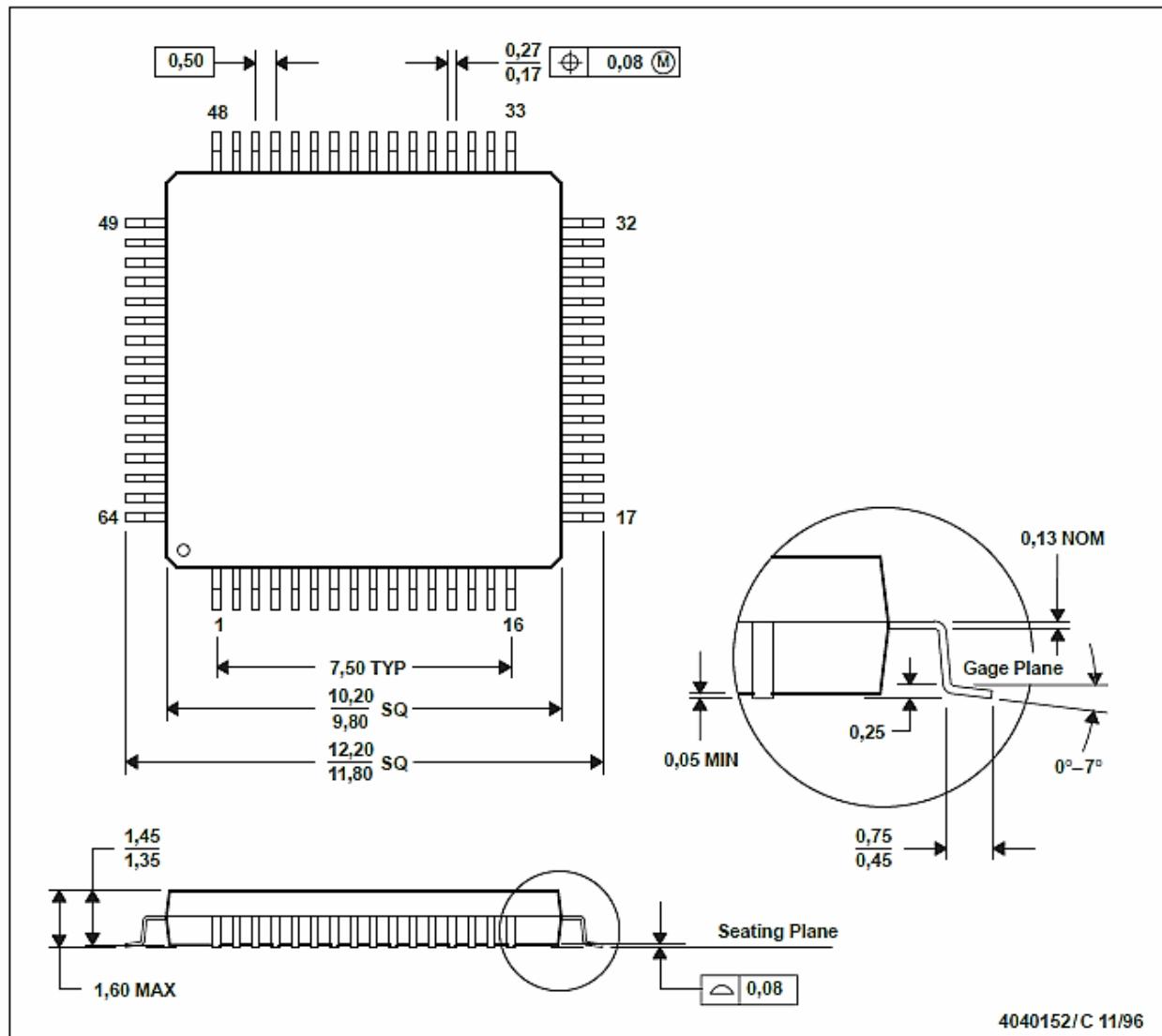

- 64 ピン QFP パッケージ

- モジュールの詳細は、MSP430x4xx ファミリ ユーザーズ・ガイド 資料番号 SLAU141 (日本語版)、

SLAU056 (英語版) を参照して下さい。

## 概要

テキサス・インスツルメンツの超低消費電力マイクロコントローラ MSP430 ファミリは、色々なアプリケーションのための異なる種類のペリフェラルデバイスで構成されています。5つの低消費電力モードを持ったアーキテクチャは、携帯型計測機器アプリケーションのバッテリ寿命を延ばすために最適化されています。デバイスには、パワフルな 16 ビット RISC CPU、16 ビット・レジスタ、及び最大コード効率のためのコンスタント・ジェネレータが搭載されています。デジタル・コントロール・オシレータ (DCO) により、低消費電力モードからアクティブ・モードへのウェイクアップが 6  $\mu$ s 以内で行われます。

MSP430xW42x シリーズは、2 つの 16 ビット・タイマ、コンパレータ、96 LCD セグメント・ドライブ機能、スキャン・インターフェース、及び 48 I/O 端子を搭載したマイクロコントローラ構成となっています。

標準的なアプリケーションとしては、アナログ信号を取得し、デジタル値に変換し、データを処理し、ホスト・システムへ送信するセンサ・システムがあります。コンパレータ及びタイマにより、ガス、熱、及び水用メータ、工業用メータ、カウンタ・アプリケーション、ハンド・ヘルド・メータ等に理想的な構成となります。

## 製品オプション

| T <sub>A</sub> | パッケージ・デバイス                                         |

|----------------|----------------------------------------------------|

|                | プラスチック 64 ピン QFP<br>(PM)                           |

| -40°C ~ 85°C   | MSP430FW423IPM<br>MSP430FW425IPM<br>MSP430FW427IPM |

テキサス・インスツルメンツの半導体製品の供給状況、標準保証、及び重大用途における使用に関しては、重要なご注意がこのデータ・シートの終わりに掲載されていますので、ご参照下さい。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本 TI) が英文から和文へ翻訳して作成したもので、資料によっては正規英語版資料の更新に対応していないものがあります。日本 TI による和文資料は、あくまでも TI 正規英語版をご理解頂くための補助的参考資料としてご使用下さい。製品のご検討及びご採用にあたりましては、必ず正規英語版の最新資料をご確認下さい。TI 及び日本 TI は、正規英語版にて更新の情報を提供しているにも関わらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

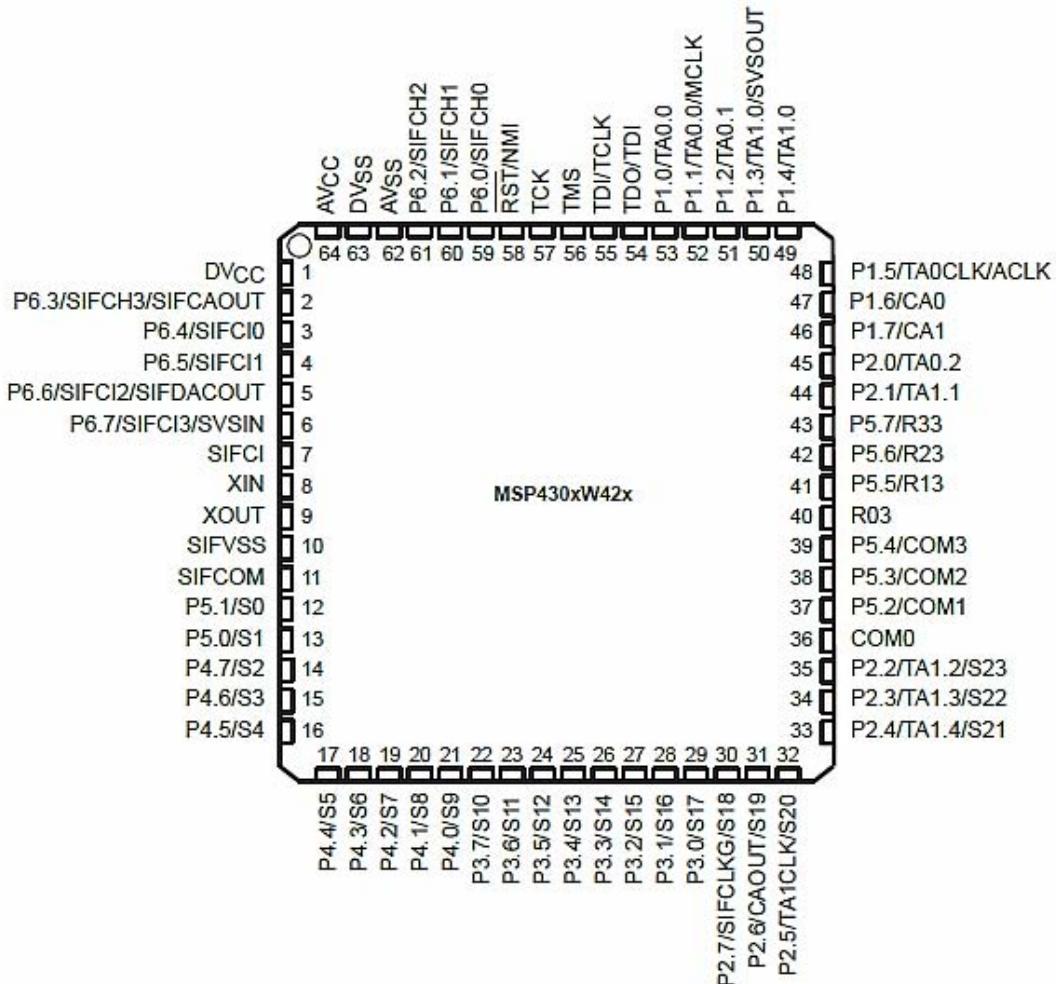

## ピン配置、MSP430xW42x

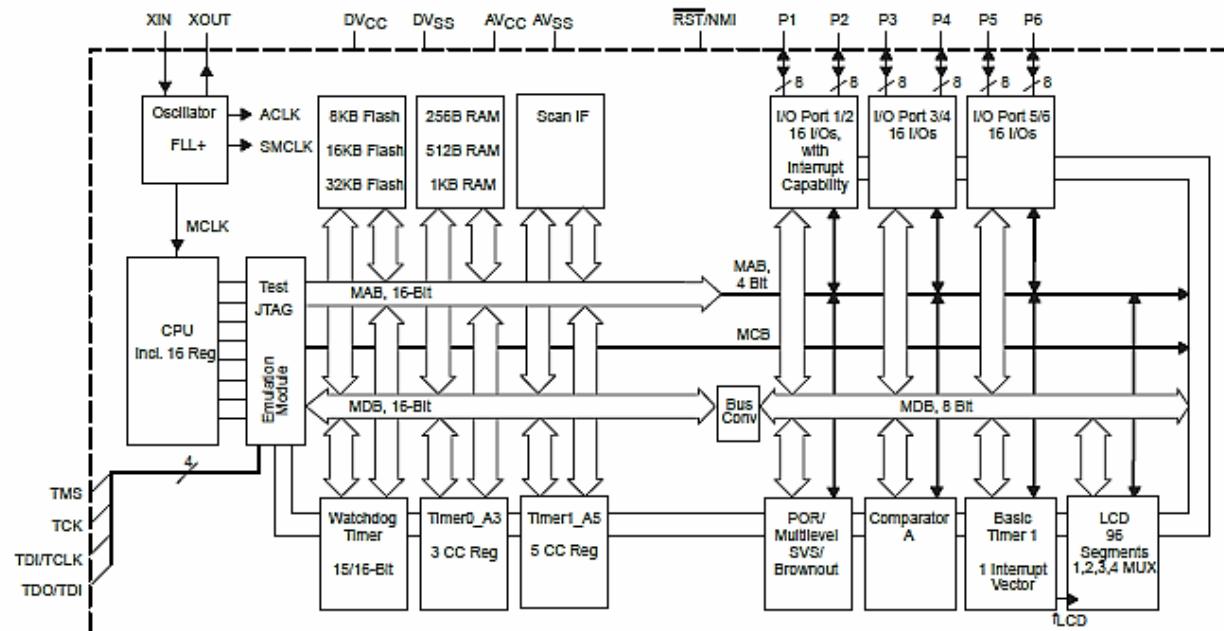

## 機能ブロック図

## 端子機能表

## MSP430xW42x

| 端子名<br>前<br>番号    | I/O | 機能                                                                                                                                                                     |

|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AV <sub>cc</sub>  | 64  | アナログ電源電圧（正端子）。電源電圧監視回路（SVS）、プラウンアウト、オシレータ、FLL+、コンパレータ_A、スキャン IF AFE、ポート 6、及び LCD 抵抗ディバイダ回路に電源を供給します。DV <sub>cc</sub> より前にパワー・アップしてはいけません。                              |

| AV <sub>ss</sub>  | 62  | アナログ電源電圧（負端子）。電源電圧監視回路（SVS）、プラウンアウト、オシレータ、FLL+、コンパレータ_A、スキャン IF AFE、ポート 6、及び LCD 抵抗ディバイダ回路に電源を供給します。外部で DV <sub>ss</sub> に接続しなければなりません。内部で DV <sub>ss</sub> に接続されています。 |

| DV <sub>cc</sub>  | 1   | デジタル電源電圧（正端子）                                                                                                                                                          |

| DV <sub>ss</sub>  | 63  | デジタル電源電圧（負端子）                                                                                                                                                          |

| SIFVSS            | 10  | スキャン IF AFE 基準電源電圧                                                                                                                                                     |

| P1.0/TA0.0        | 53  | 汎用デジタル I/O / タイマ0_A、キャプチャ : CCI0A 入力、コンペア : Out0 出力 / BSL 送信                                                                                                           |

| P1.1/TA0.0/MCLK   | 52  | 汎用デジタル I/O / タイマ0_A、キャプチャ : CCI0B 入力 / MCLK 出力 / BSL 受信<br>(注) TA0.0 は入力のみ                                                                                             |

| P1.2/TA0.1        | 51  | 汎用デジタル I/O / タイマ0_A、キャプチャ : CCI1A 入力、コンペア : Out1 出力                                                                                                                    |

| P1.3/TA1.0/SVSOUT | 50  | 汎用デジタル I/O / タイマ1_A、キャプチャ : CCI0B 入力 / SVS : 電源電圧監視コンパレータの出力 (注) TA1.0 は入力のみ                                                                                           |

| P1.4/TA1.0        | 49  | 汎用デジタル I/O / タイマ1_A、キャプチャ : CCI0A 入力、コンペア : Out0 出力                                                                                                                    |

| P1.5/TA0CLK/ACLK  | 48  | 汎用デジタル I/O / タイマ0_A クロック入力 / ACLK 出力                                                                                                                                   |

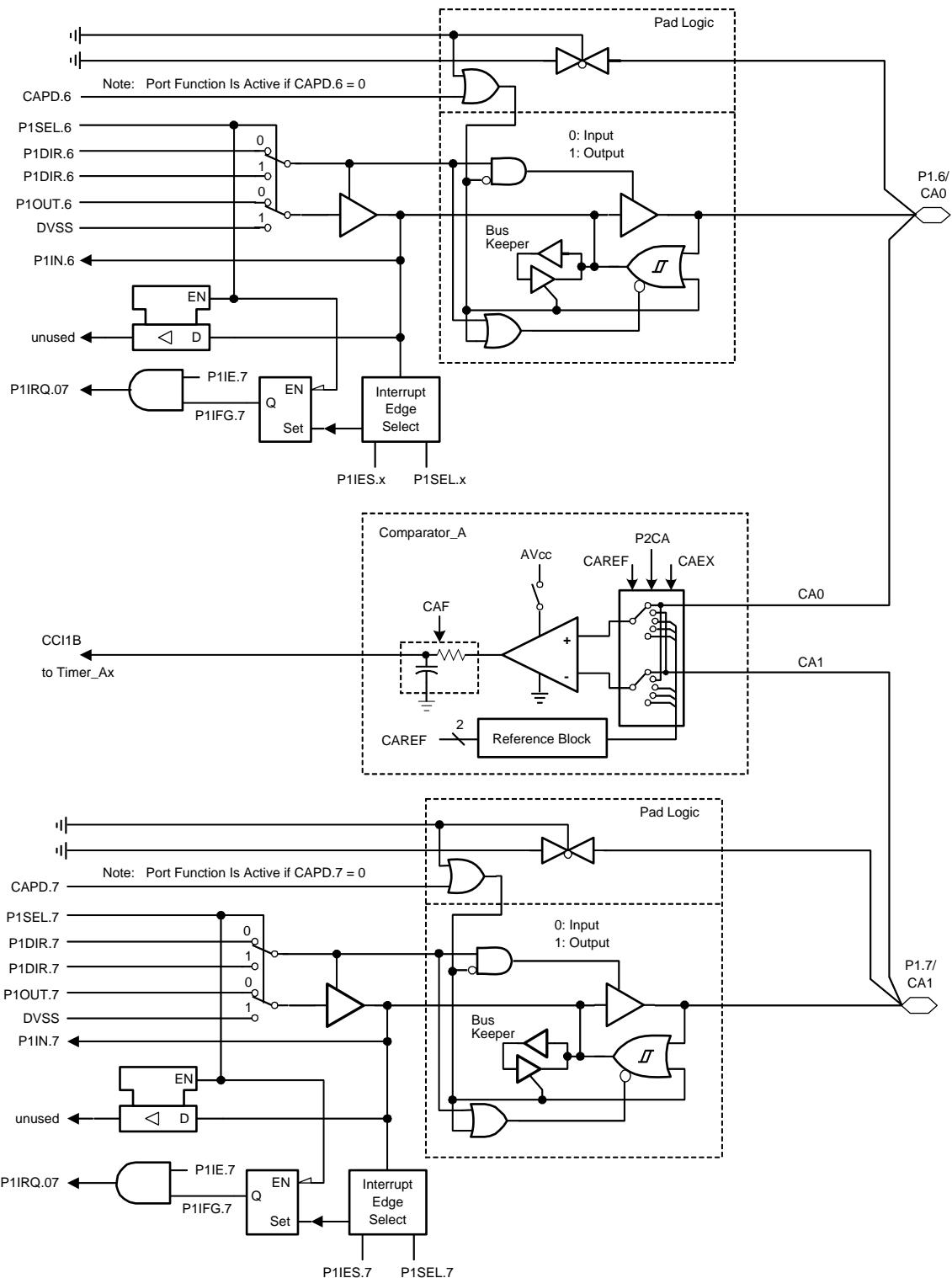

| P1.6/CA0          | 47  | 汎用デジタル I/O / コンパレータ_A 入力                                                                                                                                               |

| P1.7/CA1          | 46  | 汎用デジタル I/O / コンパレータ_A 入力                                                                                                                                               |

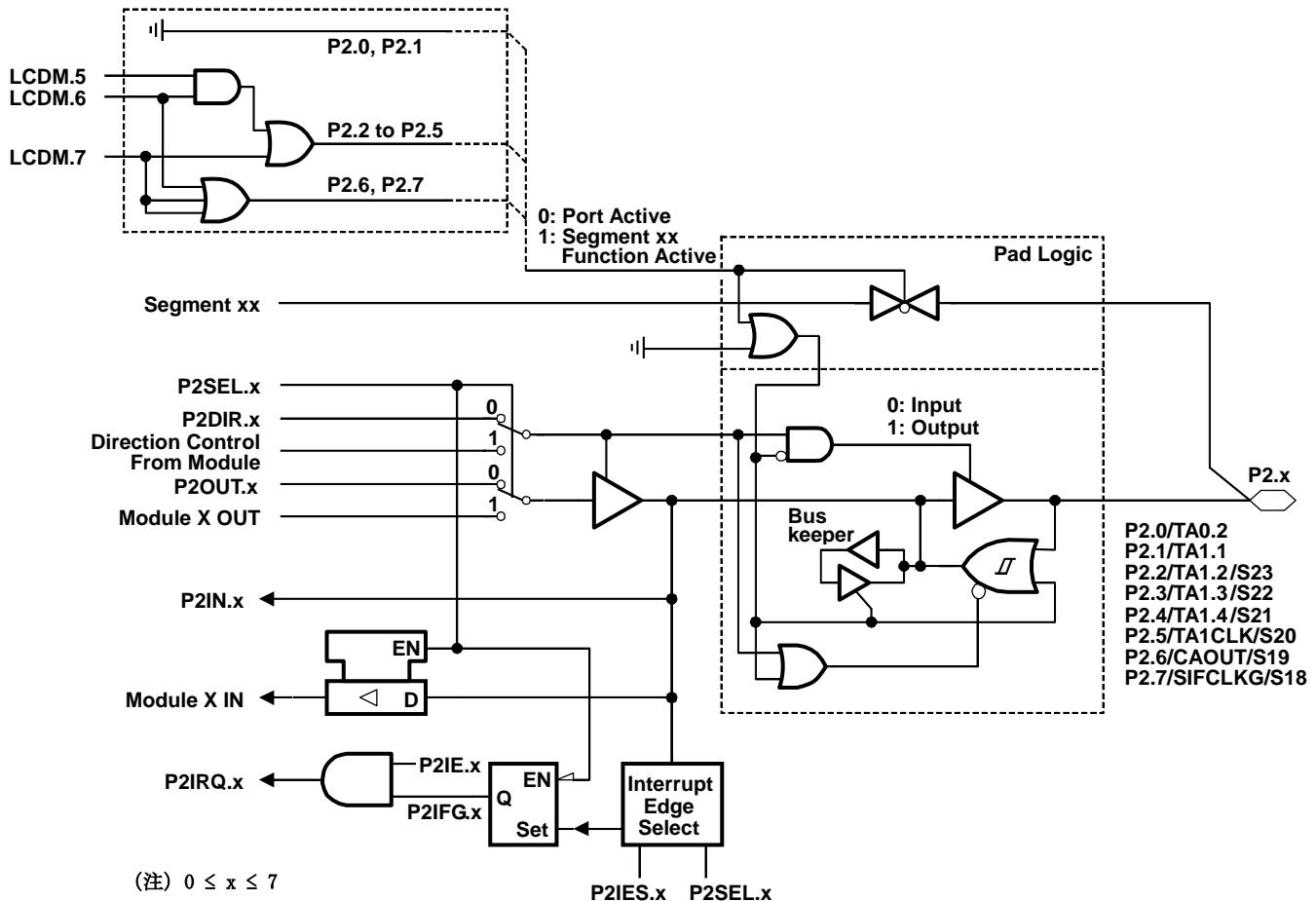

| P2.0/TA0.2        | 45  | 汎用デジタル I/O / タイマ0_A、キャプチャ : CCI2A 入力、コンペア : Out2 出力                                                                                                                    |

| P2.1/TA1.1        | 44  | 汎用デジタル I/O / タイマ0_A、キャプチャ : CCI1A 入力、コンペア : Out1 出力                                                                                                                    |

| P2.2/TA1.2/S23    | 35  | 汎用デジタル I/O / タイマ1_A、キャプチャ : CCI2A 入力、コンペア : Out2 出力 / LCD セグメント出力 23 (注)                                                                                               |

| P2.3/TA1.3/S22    | 34  | 汎用デジタル I/O / タイマ1_A、キャプチャ : CCI3A 入力、コンペア : Out3 出力 / LCD セグメント出力 22 (注)                                                                                               |

| P2.4/TA1.4/S21    | 33  | 汎用デジタル I/O / タイマ1_A、キャプチャ : CCI4A 入力、コンペア : Out4 出力 / LCD セグメント出力 21 (注)                                                                                               |

| P2.5/TA1CLK/S20   | 32  | 汎用デジタル I/O / タイマ1_A クロック入力 / LCD セグメント出力 20 (注)                                                                                                                        |

| P2.6/CAOUT/S19    | 31  | 汎用デジタル I/O / コンパレータ_A 出力 / LCD セグメント出力 19 (注)                                                                                                                          |

| P2.7/SIFCLKG/S18  | 30  | 汎用デジタル I/O / スキャン IF、内部クロック発生器からの SIFCLKG 信号 / LCD セグメント出力 18 (注)                                                                                                      |

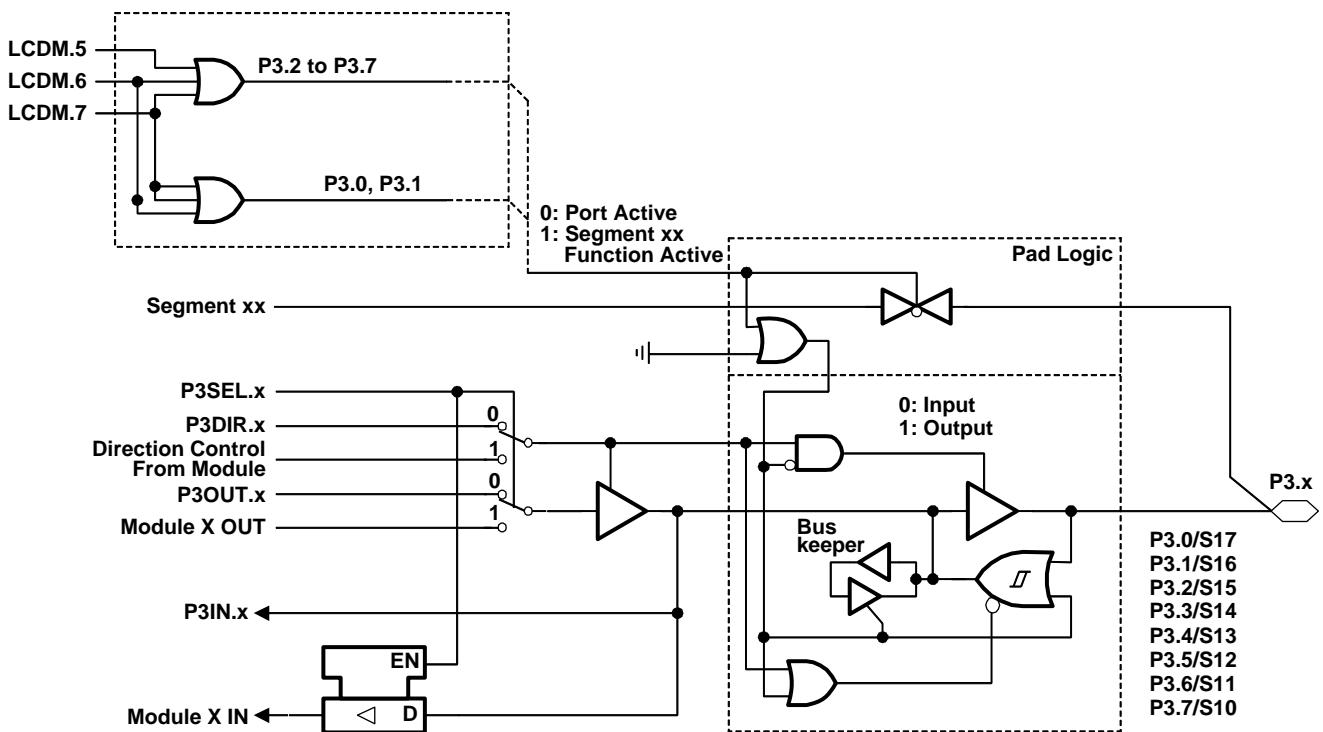

| P3.0/S17          | 29  | 汎用デジタル I/O / LCD セグメント出力 17 (注)                                                                                                                                        |

| P3.1/S16          | 28  | 汎用デジタル I/O / LCD セグメント出力 16 (注)                                                                                                                                        |

| P3.2/S15          | 27  | 汎用デジタル I/O / LCD セグメント出力 15 (注)                                                                                                                                        |

| P3.3/S14          | 26  | 汎用デジタル I/O / LCD セグメント出力 14 (注)                                                                                                                                        |

| P3.4/S13          | 25  | 汎用デジタル I/O / LCD セグメント出力 13 (注)                                                                                                                                        |

| P3.5/S12          | 24  | 汎用デジタル I/O / LCD セグメント出力 12 (注)                                                                                                                                        |

| P3.6/S11          | 23  | 汎用デジタル I/O / LCD セグメント出力 11 (注)                                                                                                                                        |

| P3.7/S10          | 22  | 汎用デジタル I/O / LCD セグメント出力 10 (注)                                                                                                                                        |

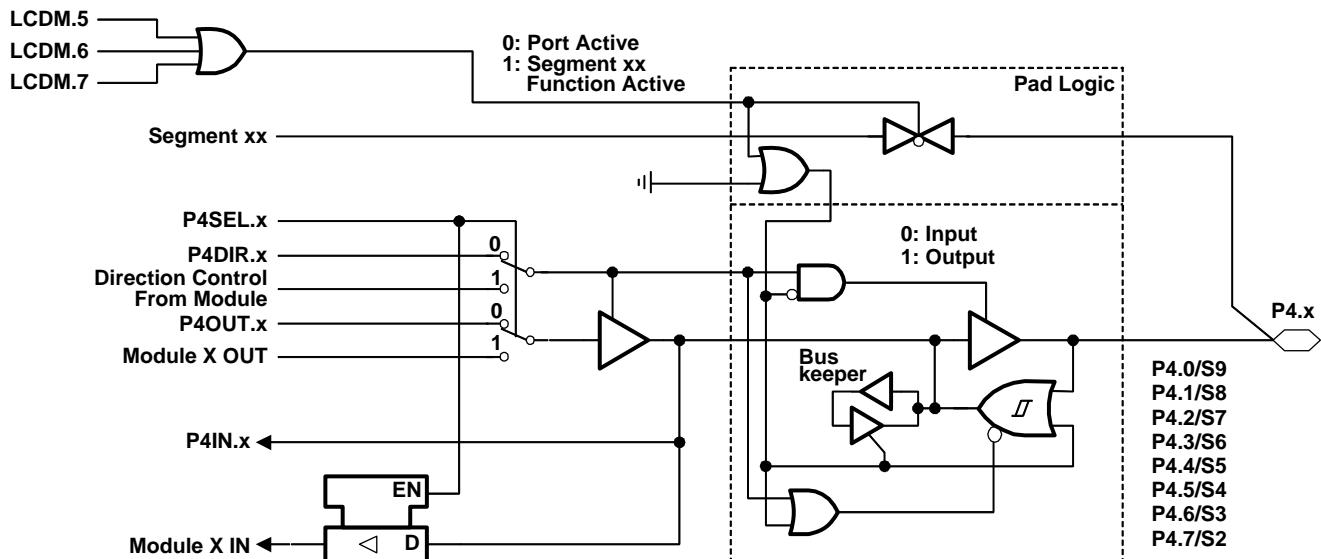

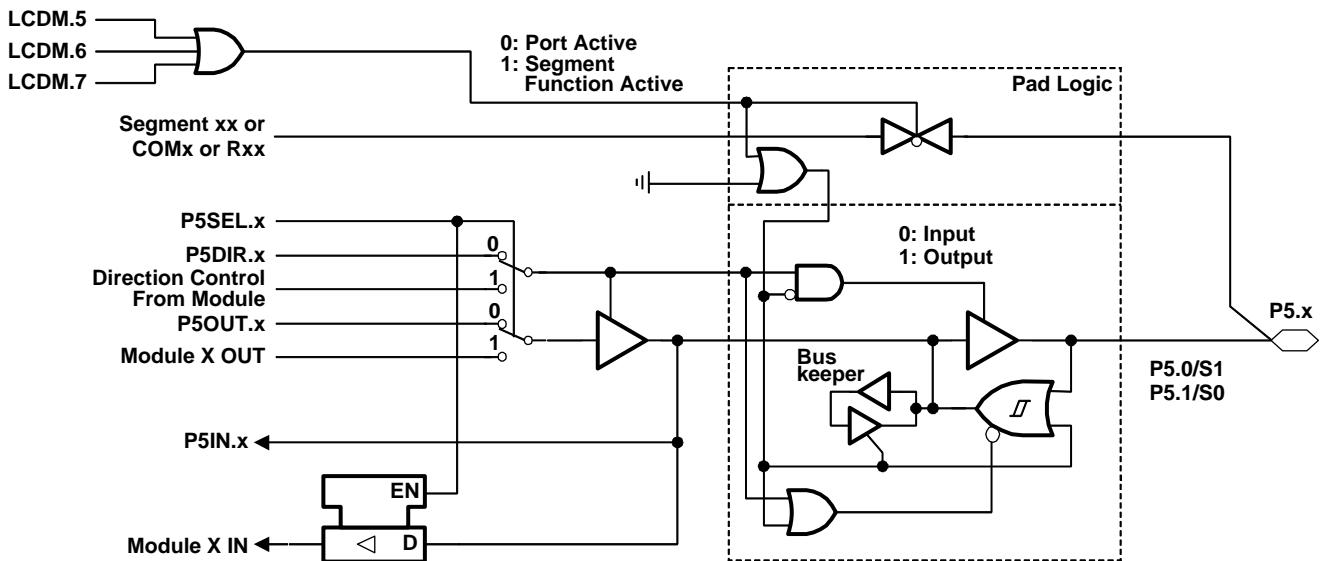

(注) 使用可能な LCD モジュールの制御ビット (PxSEL ビットではなく) が設定された時、LCD 機能は自動的に選択されます。

端子機能表

MSP430xW42x (続き)

| 端子<br>名前                  | 番号 | I/O | 機能                                                           |

|---------------------------|----|-----|--------------------------------------------------------------|

| P4.0/S9                   | 21 | I/O | 汎用デジタル I/O / LCD セグメント出力 9 (注)                               |

| P4.1/S8                   | 20 | I/O | 汎用デジタル I/O / LCD セグメント出力 8 (注)                               |

| P4.2/S7                   | 19 | I/O | 汎用デジタル I/O / LCD セグメント出力 7 (注)                               |

| P4.3/S6                   | 18 | I/O | 汎用デジタル I/O / LCD セグメント出力 6 (注)                               |

| P4.4/S5                   | 17 | I/O | 汎用デジタル I/O / LCD セグメント出力 5 (注)                               |

| P4.5/S4                   | 16 | I/O | 汎用デジタル I/O / LCD セグメント出力 4 (注)                               |

| P4.6/S3                   | 15 | I/O | 汎用デジタル I/O / LCD セグメント出力 3 (注)                               |

| P4.7/S2                   | 14 | I/O | 汎用デジタル I/O / LCD セグメント出力 2 (注)                               |

| P5.0/S1                   | 13 | I/O | 汎用デジタル I/O / LCD セグメント出力 1 (注)                               |

| P5.1/S0                   | 12 | I/O | 汎用デジタル I/O / LCD セグメント出力 0 (注)                               |

| COM0                      | 36 | 0   | コモン出力、COM0 ~ 3 は LCD バックプレーンのために使用されます。                      |

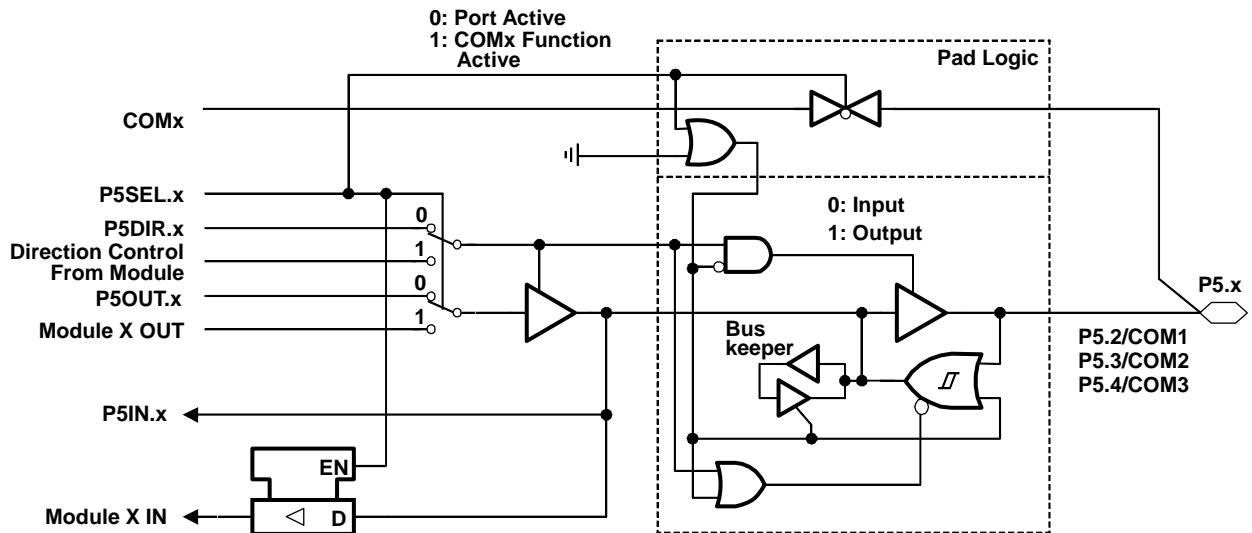

| P5.2/COM1                 | 37 | I/O | 汎用デジタル I/O / コモン出力、COM0 ~ 3 は LCD バックプレーンのために使用されます。         |

| P5.3/COM2                 | 38 | I/O | 汎用デジタル I/O / コモン出力、COM0 ~ 3 は LCD バックプレーンのために使用されます。         |

| P5.4/COM3                 | 39 | I/O | 汎用デジタル I/O / コモン出力、COM0 ~ 3 は LCD バックプレーンのために使用されます。         |

| R03                       | 40 | I   | 正側から 4 番目 (最低レベル) のアナログ LCD レベル(V5) の入力ポート                   |

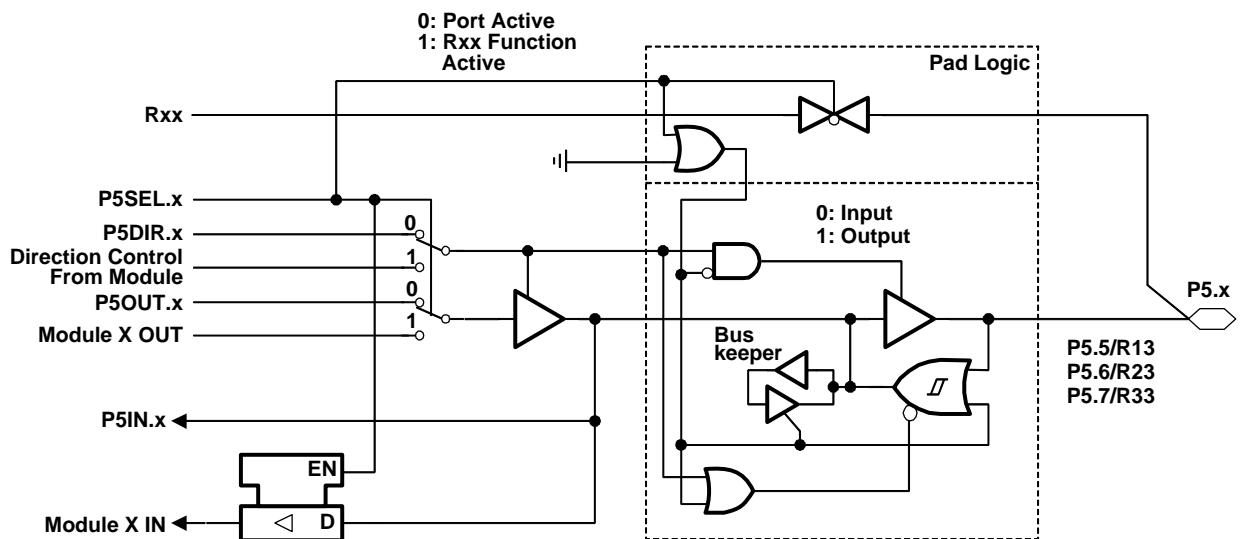

| P5.5/R13                  | 41 | I/O | 汎用デジタル I/O / 正側から 3 番目のアナログ LCD レベル(V4 又は V3) の入力ポート         |

| P5.6/R23                  | 42 | I/O | 汎用デジタル I/O / 正側から 2 番目のアナログ LCD レベル(V2) の入力ポート               |

| P5.7/R33                  | 43 | I/O | 汎用デジタル I/O / 最も正側のアナログ LCD レベル(V1) の出力ポート                    |

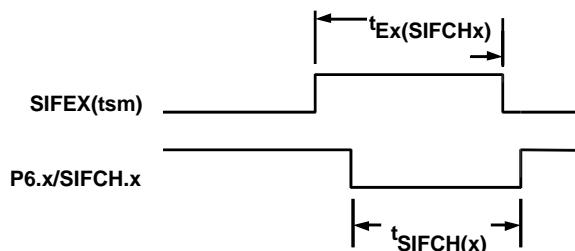

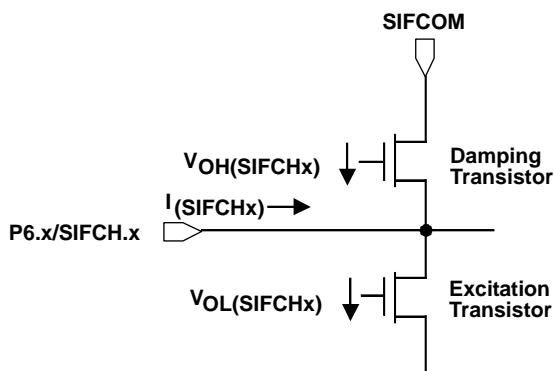

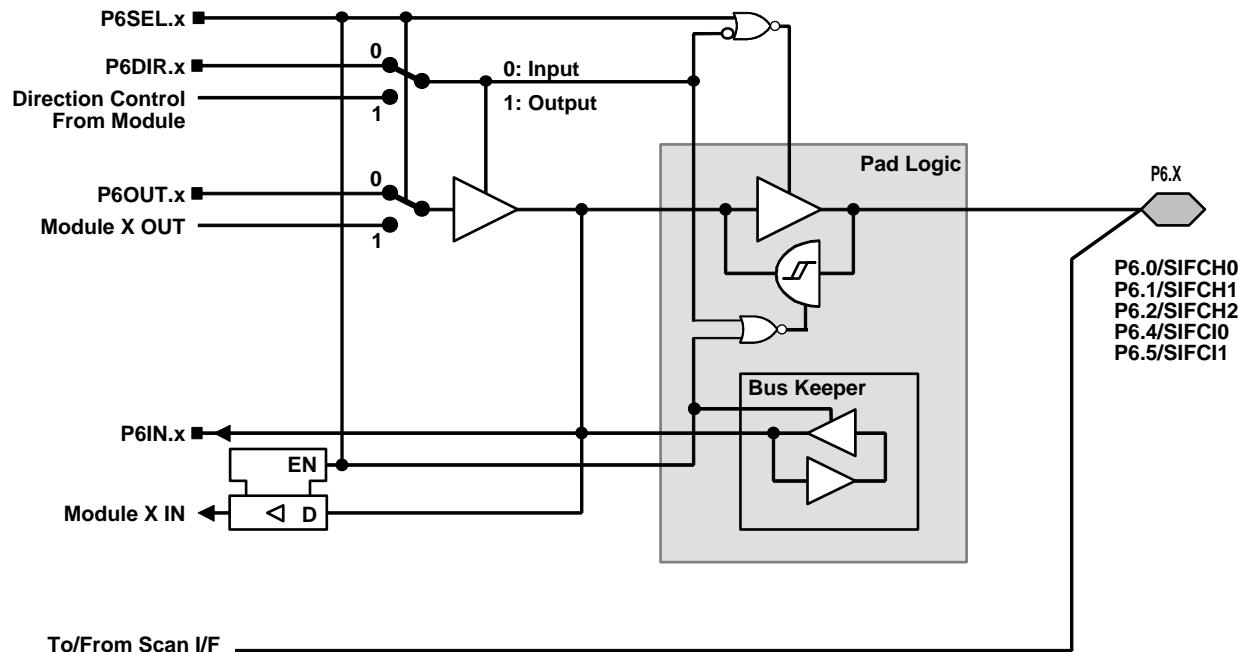

| P6.0/SIFCH0               | 59 | I/O | 汎用デジタル I/O / スキャン IF、チャネル 0 センサ励起出力及び信号入力                    |

| P6.1/SIFCH1               | 60 | I/O | 汎用デジタル I/O / スキャン IF、チャネル 1 センサ励起出力及び信号入力                    |

| P6.2/SIFCH2               | 61 | I/O | 汎用デジタル I/O / スキャン IF、チャネル 2 センサ励起出力及び信号入力                    |

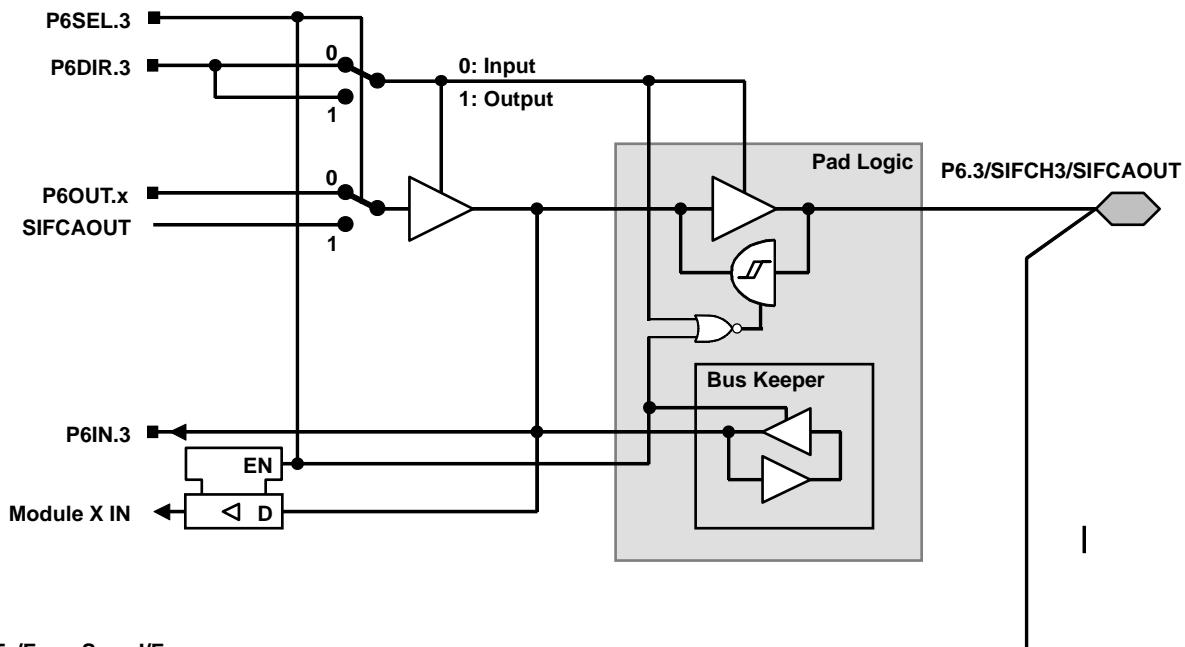

| P6.3/SIFCH3/<br>SIFCAOUT  | 2  | I/O | 汎用デジタル I/O / スキャン IF、チャネル 3 センサ励起出力及び信号入力 / スキャン IF コンパレータ出力 |

| P6.4/SIFCI0               | 3  | I/O | 汎用デジタル I/O / スキャン IF、コンパレータへのチャネル 0 信号入力                     |

| P6.5/SIFCI1               | 4  | I/O | 汎用デジタル I/O / スキャン IF、コンパレータへのチャネル 1 信号入力                     |

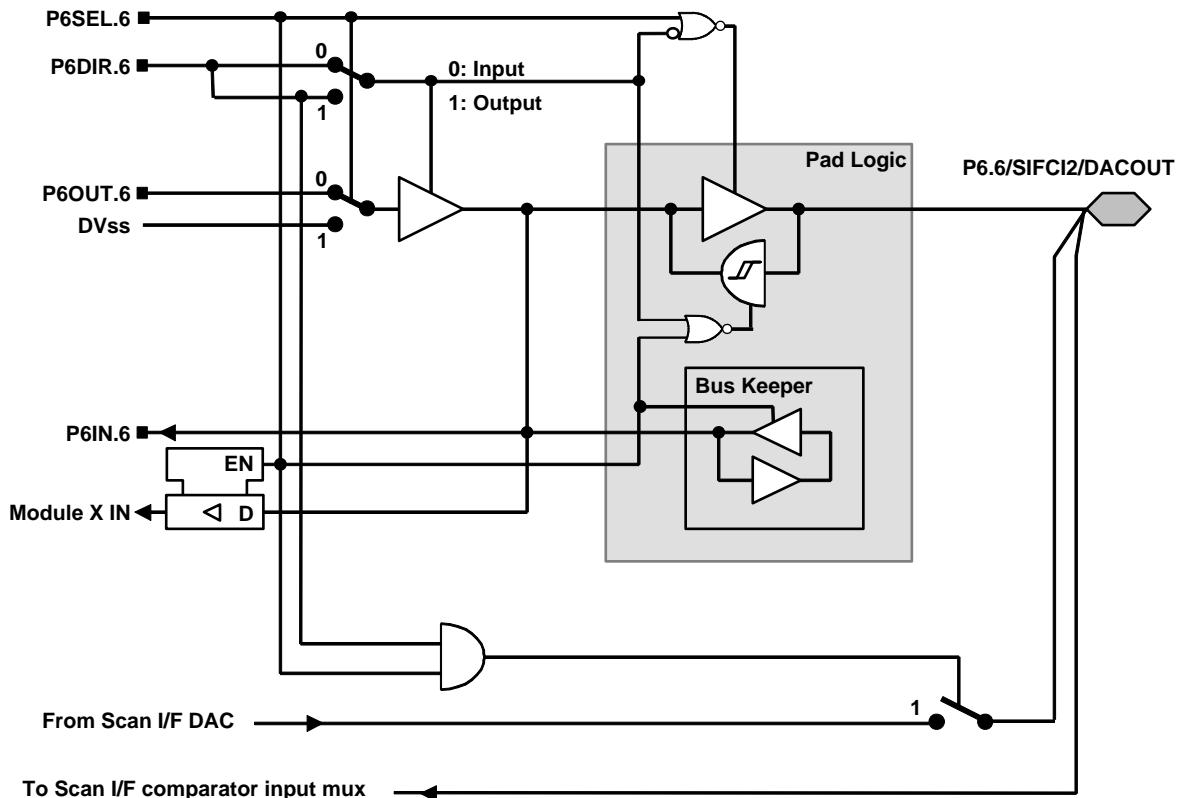

| P6.6/SIFCI2/<br>SIFDACOUT | 5  | I/O | 汎用デジタル I/O / スキャン IF、コンパレータへのチャネル 2 信号入力 / 10 ビット DAC 出力     |

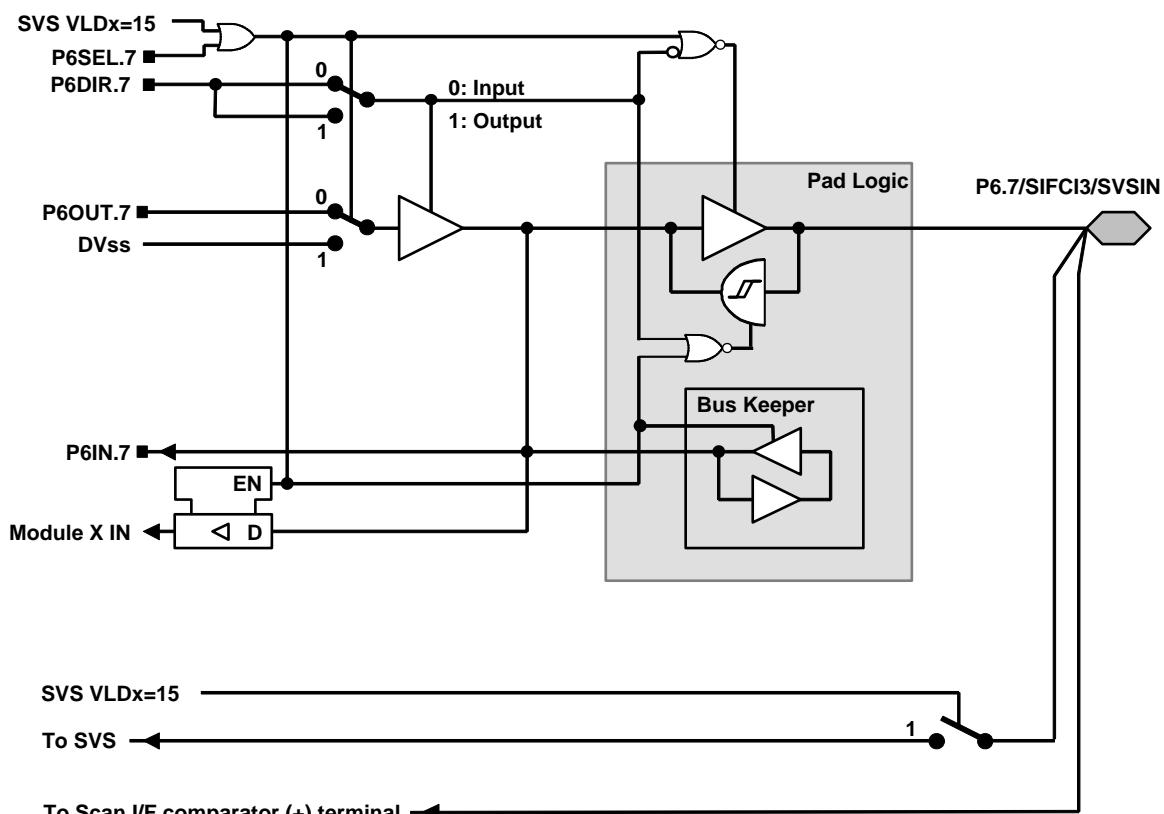

| P6.7/SIFCI3/<br>SVSIN     | 6  | I/O | 汎用デジタル I/O / スキャン IF、コンパレータへのチャネル 3 信号入力 / SVS、アナログ入力        |

| SIFCI                     | 7  | I   | コンパレータへのスキャン IF 入力                                           |

| SIFCOM                    | 11 | 0   | スキャン IF センサ用コモン終端                                            |

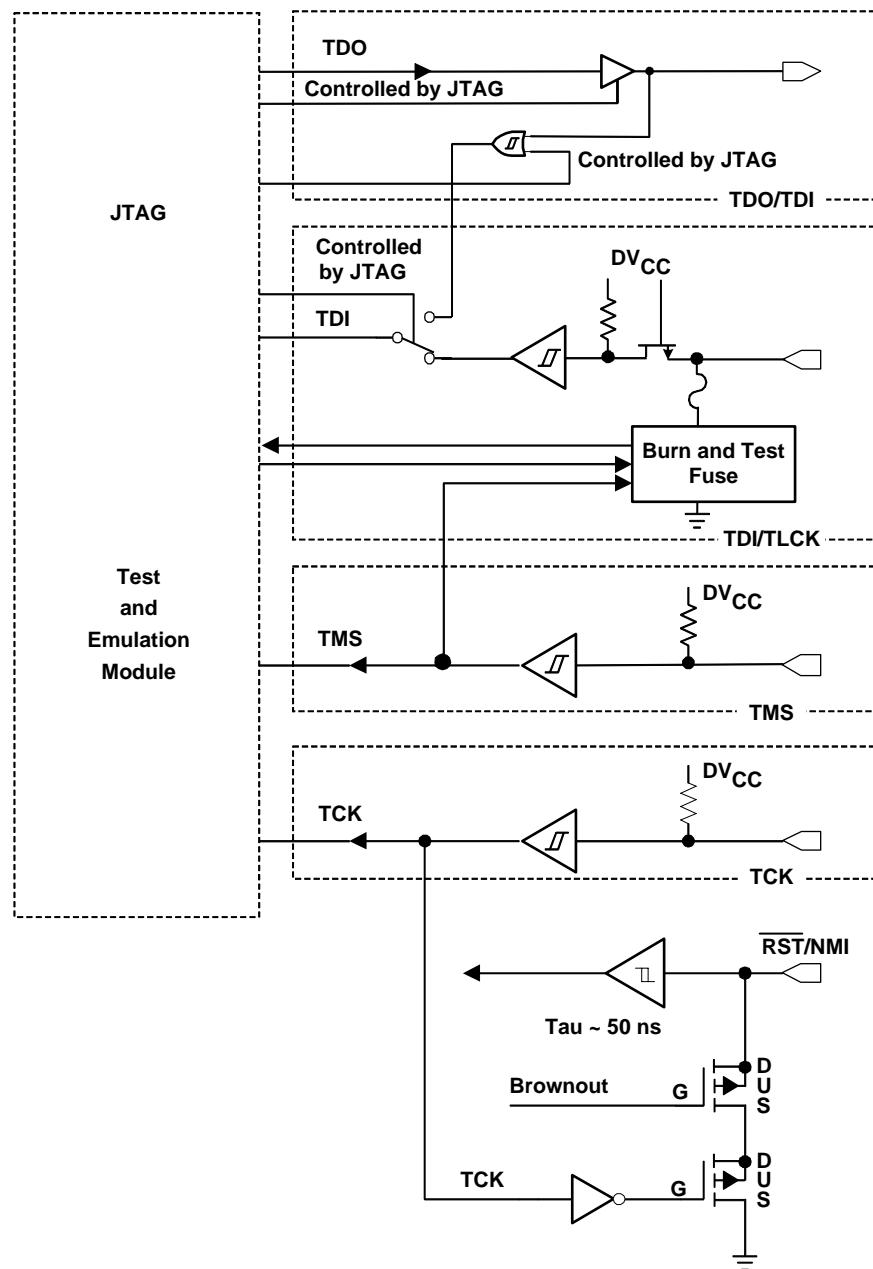

| RST/NMI                   | 58 | I   | リセット入力又はマスク不可能な割り込み入力ポート                                     |

| TCK                       | 57 | I   | テスト・クロック入力。TCK は、デバイス・プログラミング及びテストのためのクロック入力ポートです。           |

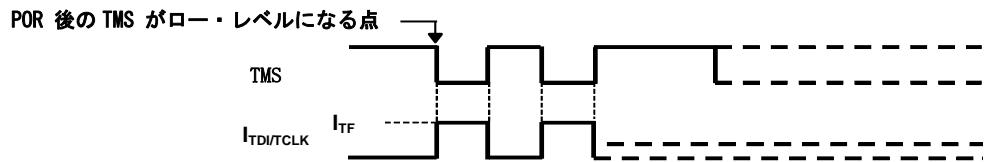

| TDI/TCLK                  | 55 | I   | テスト・データ入力又はテスト・クロック入力。デバイス保護ヒューズが、TDI/TCLK に接続されています。        |

| TDO/TDI                   | 54 | I/O | テスト・データ出力ポート。TDO/TDI データ出力又はプログラミング・データ入力端子                  |

| TMS                       | 56 | I   | テスト・モード選択入力。TMS は、デバイス・プログラミング及びテストのための入力ポートとして使用します。        |

| XIN                       | 8  | I   | クリスタル・オシレータ XT1 の入力。標準又は時計用クリスタルが接続できます。                     |

| XOUT                      | 9  | 0   | クリスタル・オシレータ XT1 の出力端子                                        |

(注 1) 使用可能な LCD モジュールの制御ビット (PxSEL ビットではなく) が設定された時、LCD 機能は自動的に選択されます。

## 概要説明

## CPU

MSP430 CPU には、アプリケーションに適した 16 ビット RISC アーキテクチャを搭載しています。プログラム・フロー・インストラクション以外のすべての動作は、ソース・オペランドのための 7 つのアドレッシング・モード及びデステイネーション・オペランドのための 4 つのアドレッシング・モードと共にレジスタ・オペレーションとして実行されます。

CPU は、命令実行時間を短縮する 16 個のレジスタを内蔵しています。レジスタ間のオペレーション実行時間は、CPU クロックの 1 サイクルです。

レジスタの内の 4 個 (R0~R3) は、それぞれプログラム・カウンタ、スタック・ポインタ、ステータス・レジスタ、及びコンスタント・ジェネレータ (定数発生回路) として割り当てられています。残りのレジスタは、汎用レジスタです。

ペリフェラルは、データ、アドレス、及びコントロール・バスを使って CPU に接続され、すべての命令によって取り扱うことができます。

## 命令セット

命令セットは 3 つのフォーマット及び 7 つのアドレス・モードを持った 51 の命令からなります。各々の命令は、ワード及びバイト データに基づいて実行することができます。表 1 は命令フォーマットの 3 つのタイプの例を示します。表 2 にアドレス・モードを示します。

|               |           |

|---------------|-----------|

| プログラム・カウンタ    | PC/R0     |

| スタック・ポインタ     | SP/R1     |

| ステータス・レジスタ    | SR/CG1/R2 |

| コンスタント・ジェネレータ | CG2/R3    |

| 汎用レジスタ        | R4        |

| 汎用レジスタ        | R5        |

| 汎用レジスタ        | R6        |

| 汎用レジスタ        | R7        |

| 汎用レジスタ        | R8        |

| 汎用レジスタ        | R9        |

| 汎用レジスタ        | R10       |

| 汎用レジスタ        | R11       |

| 汎用レジスタ        | R12       |

| 汎用レジスタ        | R13       |

| 汎用レジスタ        | R14       |

| 汎用レジスタ        | R15       |

表 1. 命令ワード・フォーマット

|                            |              |                       |

|----------------------------|--------------|-----------------------|

| デュアル・オペランド (ソース-デスティネーション) | 例、ADD R4, R5 | R4 + R5 → R5          |

| シングル・オペランド (デスティネーションのみ)   | 例、CALL R8    | PC → (TOS), R8 → PC   |

| 相対ジャンプ (無条件/条件付き)          | 例、JNE        | Jump-on-equal bit = 0 |

表 2 アドレス・モード

| アドレス・モード       | S | D | 構文               | 例                 | 動作                            |

|----------------|---|---|------------------|-------------------|-------------------------------|

| レジスタ           | ● | ● | MOV Rs, Rd       | MOV R10, R11      | R10 → R11                     |

| インデックス         | ● | ● | MOV X(Rn), Y(Rm) | MOV 2(R5), 6(R6)  | M(2+R5) → M(6+R6)             |

| シンボリック (PC 対応) | ● | ● | MOV EDE, TONI    |                   | M(EDE) → M(TONI)              |

| 絶対             | ● | ● | MOV &MEM, &TCDAT |                   | M(MEM) → M(TCDAT)             |

| 間接             | ● |   | MOV @Rn, Y(Rm)   | MOV @R10, Tab(R6) | M(R10) → M(Tab+R6)            |

| 間接 (自動インクリメント) | ● |   | MOV @Rn+, Rm     | MOV @R10+, R11    | M(R10) → R11<br>R10 + 2 → R10 |

| 即時             | ● |   | MOV #X, TONI     | MOV #45, TONI     | #45 → M(TONI)                 |

(注) S = ソース、D = デスティネーション

## 動作モード

MSP430 には、1 つのアクティブ・モードと、ソフトウェアで選択可能な 5 つの低消費電力動作モードがあります。割り込みイベントにより、デバイスを 5 つの低消費電力モードのどれからでもウェークアップすることができ、要求に応え、そして、割り込みプログラムから戻るのに伴って低消費電力モードに戻ることができます。以下の 6 つの動作モードを、ソフトウェアによって構成することができます：

- アクティブ・モード AM；

- すべてのクロックはアクティブ

- 低消費電力モード 0 (LPM0)；

- CPU はディスエーブル

- ACLK 及び SMCLK はアクティブのまま。MCLK はモジュールで使用できます。

- FLL+ ループ制御はアクティブのまま

- 低消費電力モード 1 (LPM1)；

- CPU はディスエーブル

- ACLK 及び SMCLK はアクティブのまま。MCLK はモジュールで使用できます。

- FLL+ ループ制御はディスエーブル

- 低消費電力モード 2 (LPM2)；

- CPU はディスエーブル

- MCLK、FLL+ ループ制御、及び DCOCLK はディスエーブル

- DCO の DC 発生回路はイネーブルのまま

- ACLK はアクティブのまま

- 低消費電力モード 3 (LPM3)；

- CPU はディスエーブル

- MCLK、FLL+ ループ制御、及び DCOCLK はディスエーブル

- DCO の DC 発生回路はディスエーブル

- ACLK はアクティブのまま

- 低消費電力モード 4 (LPM4)；

- CPU はディスエーブル

- ACLK はディスエーブル

- MCLK、FLL+ ループ制御、及び DCOCLK はディスエーブル

- DCO の DC 発生回路はディスエーブル

- クリスタル・オシレータは停止

## 割り込みベクタ アドレス

割り込みベクタ及びパワーアップの開始アドレスは、ROM のアドレス範囲 0FFFFh ~ OFFE0h に位置します。ベクタは、適切な割り込み処理命令シーケンスの 16 ビット アドレスを含みます。

| 割り込みソース                                   | 割り込みフラグ                                                       | システム割り込み                                  | ワードアドレス | 優先順位     |

|-------------------------------------------|---------------------------------------------------------------|-------------------------------------------|---------|----------|

| パワー・アップ<br>外部リセット<br>ウォッチドッグ<br>フラッシュ・メモリ | WDTIFG<br>KEYV<br>(注 1)                                       | リセット                                      | 0FFEh   | 15 (最上位) |

| NMI<br>オシレータ障害<br>フラッシュ・メモリ・アクセス違反        | NMIIFG<br>OFIFG<br>ACCVIFG<br>(注 1, 3)                        | マスク可能 (不可能)<br>マスク可能 (不可能)<br>マスク可能 (不可能) | 0FFFCCh | 14       |

| タイマ 1_A5                                  | TA1CCR0 CCIFG (注 2)                                           | マスク可能                                     | 0FFFAh  | 13       |

| タイマ 1_A5                                  | TA1CCR1 CCIFG ~<br>TA1CCR4 CCIFG,<br>TA1CTL TAIFG<br>(注 1, 2) | マスク可能                                     | 0FFF8h  | 12       |

| コンパレータ_A                                  | CMPAIFG                                                       | マスク可能                                     | 0FFF6h  | 11       |

| ウォッチドッグ・タイマ                               | WDTIFG                                                        | マスク可能                                     | 0FFF4h  | 10       |

| スキャン IF                                   | SIFIFG0 ~ SIFIFG6<br>(注 1)                                    | マスク可能                                     | 0FFF2h  | 9        |

|                                           |                                                               |                                           | 0FFF0h  | 8        |

|                                           |                                                               |                                           | 0FFEEh  | 7        |

| タイマ 0_A3                                  | TA0CCR0 CCIFG (注 2)                                           | マスク可能                                     | 0FFECh  | 6        |

| タイマ 0_A3                                  | TA0CCR1 CCIFG,<br>TA0CCR2 CCIFG,<br>TA0CTL TAIFG<br>(注 1, 2)  | マスク可能                                     | 0FFEAh  | 5        |

| I/O ポート P1<br>(8 つのフラグ)                   | P1IFG.0 ~ P1IFG.7<br>(注 1, 2)                                 | マスク可能                                     | 0FFE8h  | 4        |

|                                           |                                                               |                                           | 0FFE6h  | 3        |

|                                           |                                                               |                                           | 0FFE4h  | 2        |

| I/O ポート P2<br>(8 つのフラグ)                   | P2IFG.0 ~ P2IFG.7<br>(注 1, 2)                                 | マスク可能                                     | 0FFE2h  | 1        |

| Basic Timer1                              | BTIFG                                                         | マスク可能                                     | 0FFE0h  | 0 (最下位)  |

(注 1) 複数のソース・フラグ

(注 2) 割り込みフラグはモジュールの中にあります。

(注 3) マスク可能 (不可能) : 個々の割り込みイネーブル・ビットにより、割り込みイベントをディスエーブルにすることができます。しかし、汎用割り込みイネーブルでは、それをディスエーブルにすることはできません。

## スペシャル・ファンクション・レジスター

大部分の割り込み及びモジュール・イネーブル・ビットは、最下位アドレス空間に集約されています。機能が割り当てられていないスペシャル・ファンクション・レジスタは、実際のデバイスにも内蔵されておりません。これによって、容易にソフトウェアによりアクセス可能です。

## 割り込みイネーブル 1、2

| アドレス | 7 | 6 | 5      | 4     | 3 | 2 | 1    | 0     |

|------|---|---|--------|-------|---|---|------|-------|

| 00h  |   |   | ACCVIE | NMIIE |   |   | OFIE | WDTIE |

|      |   |   | rw-0   | rw-0  |   |   | rw-0 | rw-0  |

| アドレス | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|------|---|---|---|---|---|---|---|

| 01h  | BTIE |   |   |   |   |   |   |   |

|      | rw=0 |   |   |   |   |   |   |   |

WDTIE: ウオッチドッグ・タイマ割り込みイネーブル。ウォッチドッグ・モードが選択された場合はインアクティブとなります。ウォッチドッグ・タイマがインターバル・タイマ・モードとして構成された場合はアクティブとなります。

OFIE: オシレータ障害割り込みイネーブル

NMITE：マスク不可能な割り込みイネーブル

ACCVIE: フラッシュ・アクセス違反割り込みイネーブル

BTIE: Basic Timer1 割り込みイネーブル

### 割り込みフラグ・レジスタ 1, 2

| アドレス | 7    | 6 | 5 | 4      | 3    | 2 | 1      | 0      |

|------|------|---|---|--------|------|---|--------|--------|

| 02h  |      |   |   | NMIIFG |      |   | OFIFG  | WDTIFG |

|      | rw-0 |   |   |        | rw-1 |   | rw-(0) |        |

| アドレス | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|-----------|---|---|---|---|---|---|---|

| 03h  | BTIFG     |   |   |   |   |   |   |   |

|      | 1111 0000 |   |   |   |   |   |   |   |

WDTIFG : ウオッチドッグ・タイマ・オーバーフロー (ウォッチドッグ・モード時) 又はセキュリティ・キー違反でセットされます。Vcc パワー・アップ又はリセット・モードでの RST/NMI 端子のリセット条件でリセットされます。

OEFIG : オシレータ障害でフラグがセットされます。

NMT IEG : RST/NMT 端子によってセットされます。

BTIEG : Basic Timer1 割り込みフラグ

## モジュール・イネーブル・レジスター 1, 2

説明 : `rw` : ビットは、読み出し及び書き込みをすることができます。

rw-0, 1 : ビットは読み出し及び書き込みをすることができます。PUCによりリセット又はセットされます。

**rw-(0,1) :** ビットは読み出し及び書き込みをすることができます。PORによりリセット又はセットされます。

デバイスには、SER ビットが存在します。

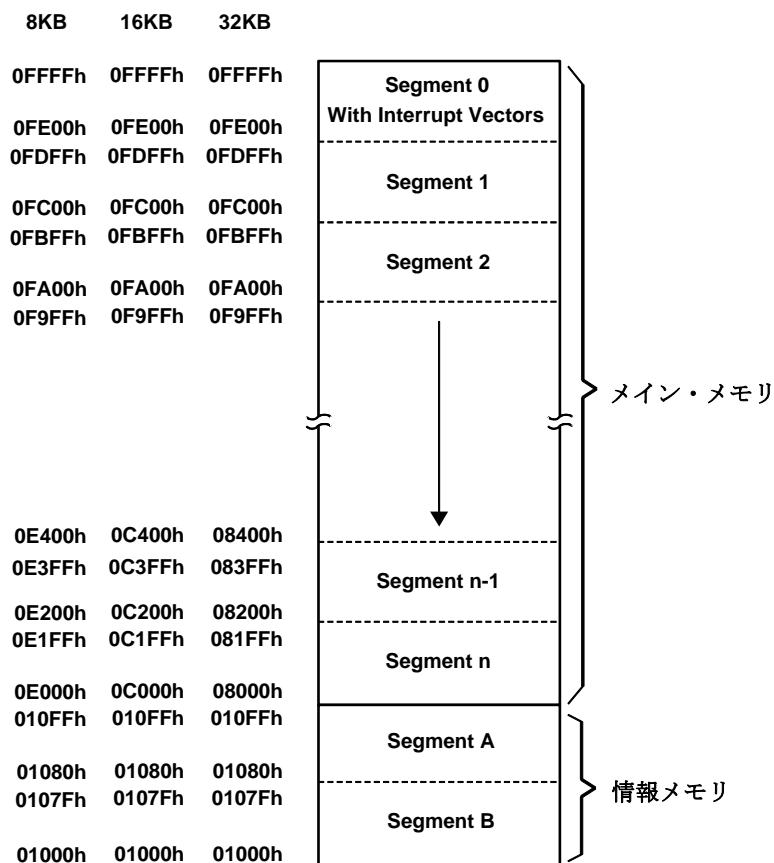

## メモリ構成

|                                    |                              | MSP430FW423                               | MSP430FW425                                | MSP430FW427                                |

|------------------------------------|------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|

| メモリ<br>割り込みベクタ<br>コード・メモリ<br>情報メモリ | サイズ<br>フラッシュ<br>フラッシュ        | 8KB<br>0FFFFh - 0FFE0h<br>0FFFFh - 0E000h | 16KB<br>0FFFFh - 0FFE0h<br>0FFFFh - 0C000h | 32KB<br>0FFFFh - 0FFE0h<br>0FFFFh - 08000h |

|                                    | サイズ                          | 256 バイト<br>010FFh - 01000h                | 256 バイト<br>010FFh - 01000h                 | 256 バイト<br>010FFh - 01000h                 |

|                                    | サイズ                          | 1KB<br>0FFFh - 0C00h                      | 1KB<br>0FFFh - 0C00h                       | 1KB<br>0FFFh - 0C00h                       |

| 起動メモリ<br>RAM                       | サイズ                          | 256 バイト<br>02FFh - 0200h                  | 512 バイト<br>03FFh - 0200h                   | 1KB<br>05FFh - 0200h                       |

|                                    | 16 ビット<br>8 ビット<br>8 ビット SFR | 01FFh - 0100h<br>0FFh - 010h<br>0Fh - 00h | 01FFh - 0100h<br>0FFh - 010h<br>0Fh - 00h  | 01FFh - 0100h<br>0FFh - 010h<br>0Fh - 00h  |

## ブートストラップ・ローダ (BSL)

MSP430 ブートストラップ・ローダ (BSL) により、ユーザーは UART シリアル・インターフェースを使用してフラッシュ・メモリ又は RAM をプログラムすることができます。BSL を経由した MSP430 メモリへのアクセスは、ユーザーによって定義されたパスワードにより保護されています。BSL 及びその実施方法の詳細は、アプリケーション・レポート *MSP430 ブートストラップ・ローダの特徴* “*Features of the MSP430 Bootstrap Loader*” (資料番号 SLAA089) を参照して下さい。

| BSL 機能 | PM パッケージ端子 |

|--------|------------|

| データ送信  | 53 - P1.0  |

| データ受信  | 52 - P1.1  |

## フラッシュ・メモリ

フラッシュ・メモリは、JTAG ポート、ブートストラップ・ローダ、又は CPU によるイン・システムによりプログラムすることができます。CPU はフラッシュ・メモリに対して、1 バイト及び 1 ワードの書き込みを行うことができます。フラッシュ・メモリは、以下の特徴を持っています。:

- フラッシュ・メモリは、n セグメントのメイン・メモリ及び 2 つのセグメントのそれぞれ 128 バイトの情報メモリ (A と B) を持っています。メイン・メモリのそれぞれのセグメントのサイズは、512 バイトです。

- セグメント 0 ~ n は 1 ステップで消去が可能です。あるいは、それぞれのセグメントは個々に消去も可能です。

- セグメント A と B は、個々に又はセグメント 0 ~ n のグループとして消去することができます。セグメント A と B は、情報メモリとも呼ばれます。

- 新しいデバイスでは、数バイトを情報メモリにプログラムしておくことがあります。(製造時のテストのため) ユーザーは、最初に使用する前に情報メモリの消去を実行しなければなりません。

## フラッシュ・メモリ (続き)

## ペリフェラル

ペリフェラルは、データ、アドレス、及びコントロール バスを通して CPU に接続され、すべての命令を使って取り扱うことができます。モジュールの詳細は、*MSP430x4xx ファミリ ユーザーズ・ガイド* 資料番号 SLAU141 (日本語版)、SLAU056 (英語版) を参照して下さい。

## オシレータ及びシステム・クロック

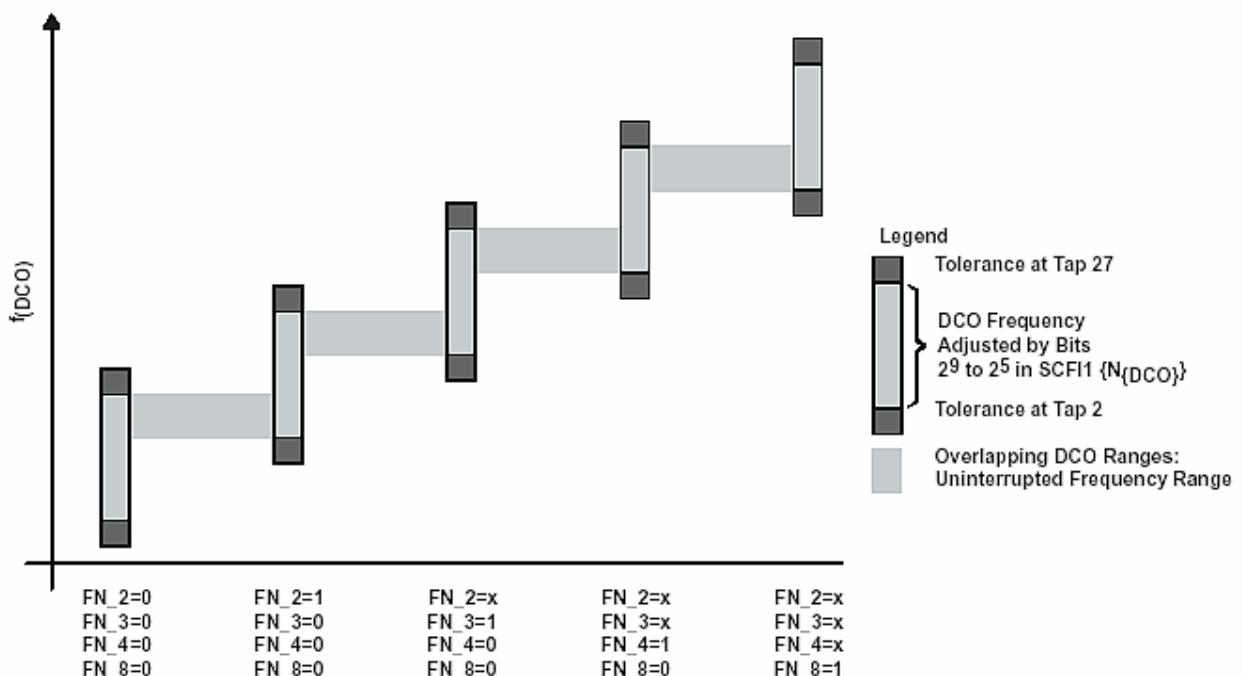

MSP430xW42x ファミリ・デバイスのクロック・システムは、32768 Hz の時計用クリスタル・オシレータ、内部デジタル制御オシレータ (DCO)、及び高周波クリスタル・オシレータのサポートを含む FLL+ モジュールで構成されます。FLL+ クロック・モジュールは、安いシステム・コストと低消費電力の必要条件を満たすように設計されています。FLL+ は、デジタル周波数同期ループ (FLL) がデジタル変換装置と共に、DCO 周波数を時計用クリスタル発振周波数のプログラム可能な倍数に安定させることを特徴としています。内部 DCO は、高速ターン・オン・クロック・ソースを提供し、6  $\mu$ s 以内に安定します。FLL+ モジュールは以下のクロック信号を供給します：

- 補助クロック (ACLK) : 32768 Hz の時計用クリスタル又は高周波クリスタルから供給

- メイン・クロック (MCLK) : CPU によって使用されるシステム・クロック

- サブ・メイン・クロック (SMCLK) : ペリフェラル・モジュールによって使用されるサブ・システム・クロック

- ACLK/n : ACLK、ACLK/2、ACLK/4、又は ACLK/8 のパッファ出力

## ブラウンアウト、電源電圧監視

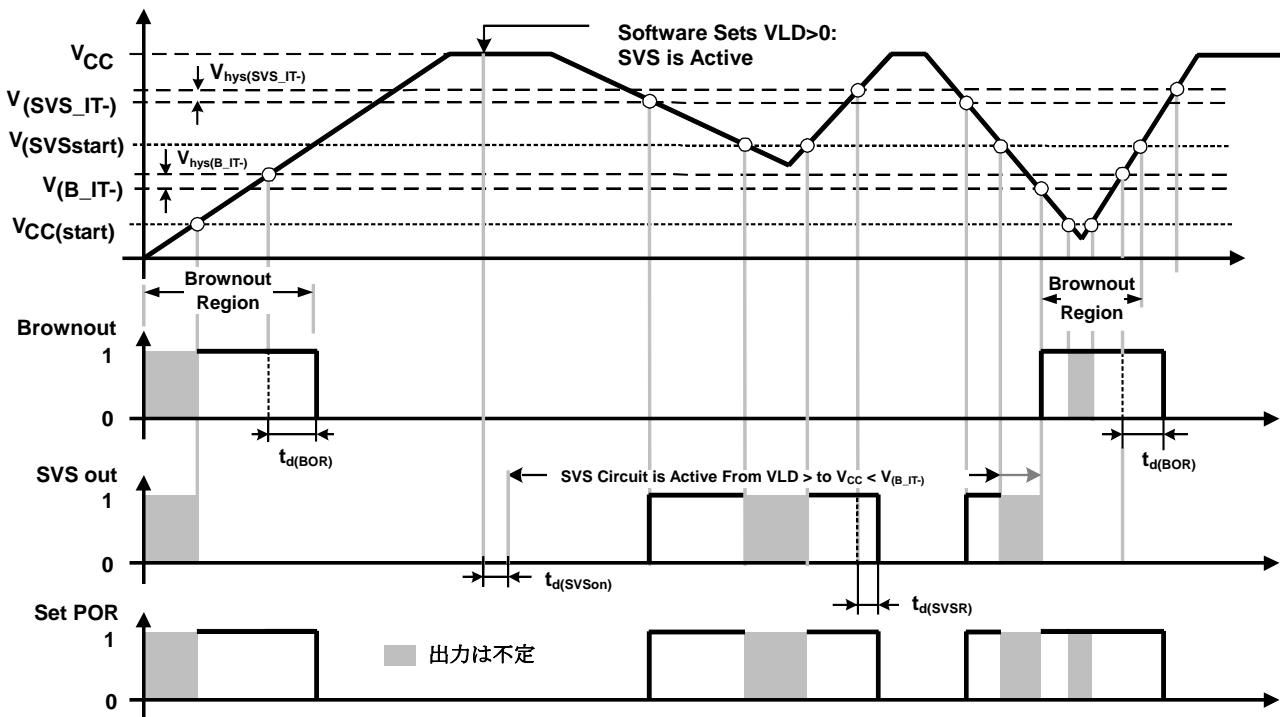

ブラウンアウト回路は、パワー・オン及びパワー・オフ時にデバイスに適切な内部リセット信号を供給するため内蔵されています。電源電圧監視回路 (SVS) は、電源電圧がユーザーが設定したレベル以下に下がっているかどうかを検出し、電源電圧の監視（デバイスは自動的にリセットされます）と電源電圧のモニタ (SVM、デバイスは自動的にリセットされません）の両方を行います。

CPU は、ブラウンアウト回路がデバイス・リセットを指示した後、コード実行を開始します。しかし、その時点では  $V_{cc}$  は  $V_{cc}(\min)$  に到達していないかもしれません。ユーザーは、 $V_{cc}$  が  $V_{cc}(\min)$  に到達するまでは、デフォルトの FLL+ 設定が変わらないようにしなければなりません。もし必要ならば、いつ  $V_{cc}$  が  $V_{cc}(\min)$  に到達したかを知るのに電源電圧監視回路を使用することもできます。

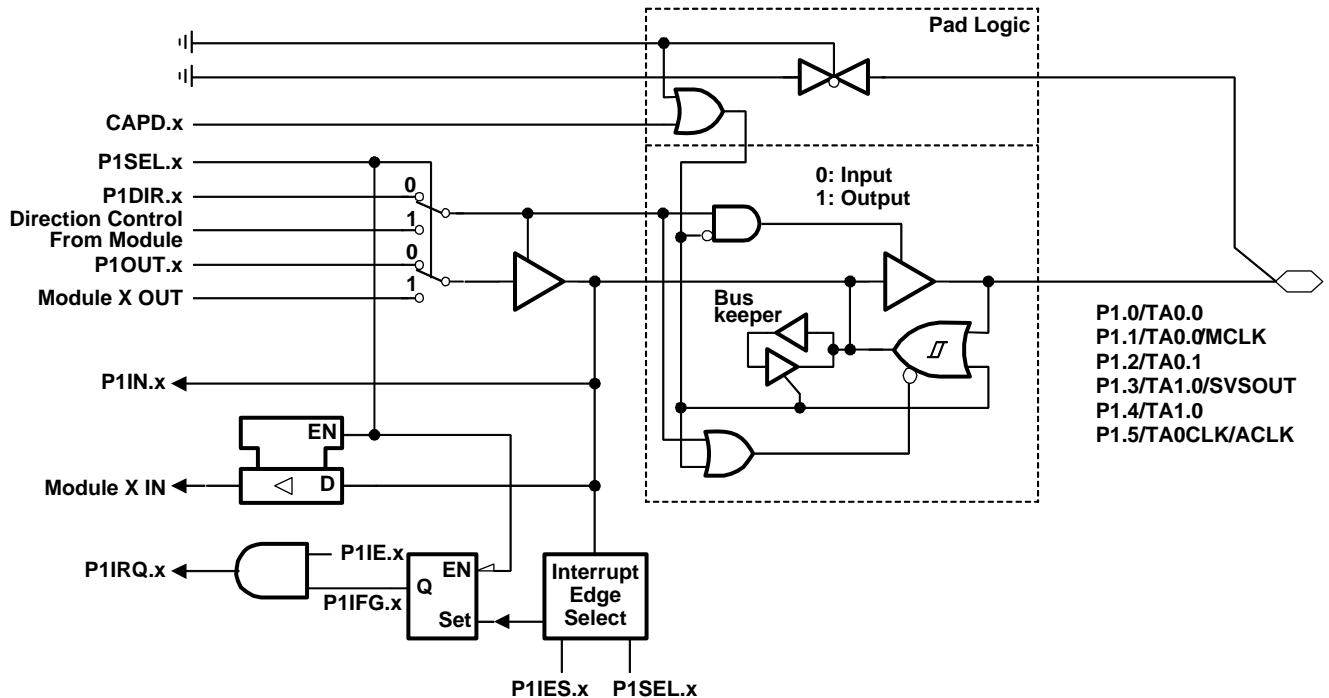

## デジタル I/O

6 つの 8 ビット I/O ポート内蔵：ポート P1 ~ P6

- すべての個々の I/O ビットは、独立してプログラム可能です。

- 入力、出力、及び割り込み条件のどんな組み合わせでも可能です。

- ポート P1 及びポート P2 のすべての 8 ビットはエッジ選択可能な割り込み入力に設定可能です。

- ポート・コントロール・レジスタへの読み出し/書き込みアクセスは、すべての命令により可能です。

## Basic Timer1

Basic Timer1 は、2 つの独立した 8 ビット タイマを持ち、16 ビット タイマ/カウンタを構成するためにカスケードにすることもできます。両方のタイマは、ソフトウェアによって読み出し/書き込みができます。Basic Timer1 は、周期的な割り込み及び LCD モジュールのためのクロックを生成するために使用することができます。

## LCD ドライブ

LCD ドライバは、液晶ディスプレイを駆動するために必要なセグメント及びコモン信号を生成します。LCD コントローラは、セグメント・ドライブ情報を持つために専用のデータ・メモリを持っています。コモン及びセグメント信号は、モードによる定義に従って生成されます。スタティック、2MUX、3MUX、及び 4MUX LCD が、このペリフェラルでサポートされます。

## ウォッチドッグ・タイマ

ウォッチドッグ・タイマ (WDT) モジュールの主な機能は、ソフトウェア障害が起こった後、制御されたシステム再開を行うことです。設定された時間間隔が経過すると、システム・リセットが生成されます。ウォッチドッグ機能が必要でないアプリケーションでは、モジュールはインターバル・タイマとして設定することができ、設定された時間間隔で割り込みを発生することができます。

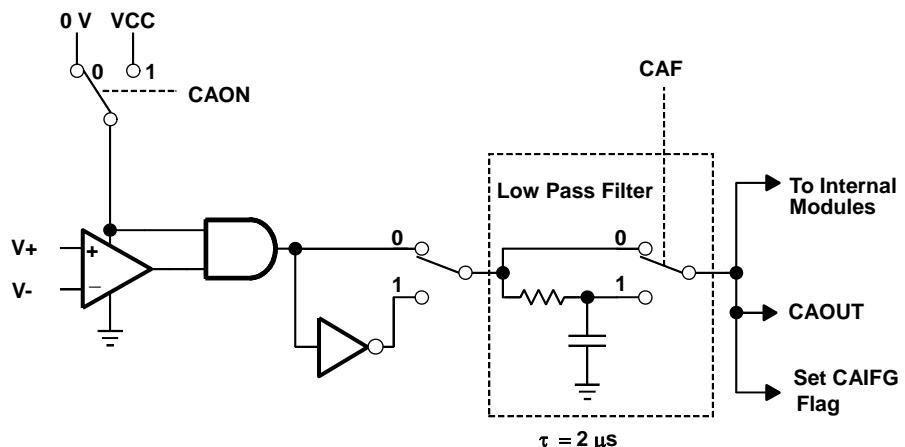

## コンパレータ\_A

コンパレータ\_A モジュールの基本的な機能は、高精度スロープ A/D 変換、バッテリ電圧監視、及び外部アナログ信号のモニタを行うことです。

## スキャン IF

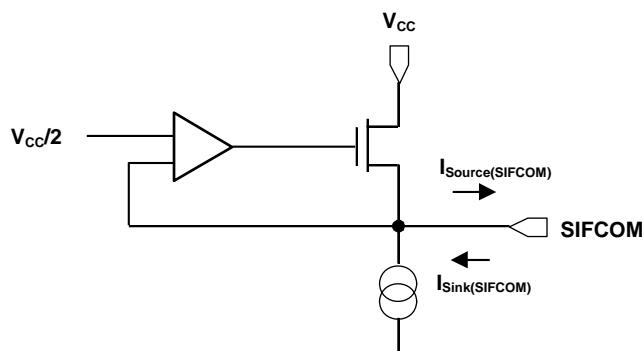

スキャン IF は、直線的動作又は回転動作を測定するために使用され、GMR センサのような LC 及び抵抗センサをサポートします。スキャン IF は  $V_{cc}/2$  発生器、コンパレータ、及び 10 ビット DAC を内蔵し、4 つまでのセンサをサポートします。

### タイマ0\_A3

タイマ0\_A3 は、3つのキャプチャ/コンペア・レジスタ付きの 16 ビット・タイマ/カウンタです。タイマ0\_A3 により、複数のキャプチャ/コンペア、PWM 出力、及びインターバル・タイミングを利用することができます。タイマ0\_A3 にも、拡張割り込みの機能があります。割り込みは、オーバーフロー状態のカウンタから、及びキャプチャ/コンペア・レジスタのそれぞれから生成されることがあります。

| タイマ0_A3 信号の接続 |                  |                 |                |               |           |

|---------------|------------------|-----------------|----------------|---------------|-----------|

| 入力端子番号        | デバイス入力<br>信号     | モジュール入力名        | モジュール・<br>ブロック | モジュール出力<br>信号 | 出力端子番号    |

| 48 - P1.5     | TA0CLK           | TACLK           | タイマ            | NA            |           |

|               | ACLK             | ACLK            |                |               |           |

|               | SMCLK            | SMCLK           |                |               |           |

|               | TA0CLK           | INCLK           |                |               |           |

| 53 - P1.0     | TA0.0            | CCI0A           | CCR0           | TA0.0         | 53 - P1.0 |

| 52 - P1.1     | TA0.0            | CCI0B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

| 51 - P1.2     | TA0.1            | CCI1A           | CCR1           | TA0.1         | 51 - P1.2 |

|               | CAOUT (内部)       | CCI1B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

| 45 - P2.0     | TA0.2            | CCI2A           | CCR2           | TA0.2         | 45 - P2.0 |

|               | ACLK (内部)        | CCI2B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

## タイマ1\_A5

タイマ1\_A5 は、5つのキャプチャ/コンペア・レジスタ付きの 16 ビット・タイマ/カウンタです。タイマ1\_A5 により、複数のキャプチャ/コンペア、PWM 出力、及びインターバル・タイミングを利用することができます。タイマ1\_A5 にも、拡張割り込みの機能があります。割り込みは、オーバーフロー状態のカウンタから、及びキャプチャ/コンペア・レジスタのそれぞれから生成されることがあります。

| タイマ1_A5 信号の接続 |                  |                 |                |               |           |

|---------------|------------------|-----------------|----------------|---------------|-----------|

| 入力端子番号        | デバイス入力<br>信号     | モジュール入力名        | モジュール・<br>ブロック | モジュール出力<br>信号 | 出力端子番号    |

| 32 - P2.5     | TA1CLK           | TACLK           | タイマ            | NA            |           |

|               | ACLK             | ACLK            |                |               |           |

|               | SMCLK            | SMCLK           |                |               |           |

|               | TA1CLK           | INCLK           |                |               |           |

| 49 - P1.4     | TA1.0            | CCI0A           | CCR0           | TA1.0         | 49 - P1.4 |

|               | TA1.0            | CCI0B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

| 44 - P2.1     | TA1.1            | CCI1A           | CCR1           | TA1.1         | 44 - P2.1 |

|               | CAOUT (内部)       | CCI1B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

| 35 - P2.2     | TA1.2            | CCI2A           | CCR2           | TA1.2         | 35 - P2.2 |

|               | SIFO0 信号 (内部)    | CCI2B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

| 34 - P2.3     | TA1.3            | CCI3A           | CCR3           | TA1.3         | 34 - P2.3 |

|               | SIFO1 信号 (内部)    | CCI3B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

| 33 - P2.4     | TA1.4            | CCI4A           | CCR4           | TA1.4         | 33 - P2.4 |

|               | SIFO2 信号 (内部)    | CCI4B           |                |               |           |

|               | DV <sub>ss</sub> | GND             |                |               |           |

|               | DV <sub>cc</sub> | V <sub>cc</sub> |                |               |           |

ペリフェラル・ファイル・マップ

| ワード・アクセスによるペリフェラル |                                                                                                                                                                                                                                                                                               |                                                                                                                                            |                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| ウォッチドッグ           | ウォッチドッグ・タイマ制御                                                                                                                                                                                                                                                                                 | WDTCTL                                                                                                                                     | 0120h                                                                                                                                                 |

| タイマ1_A5           | タイマ1_A 割り込みベクタ<br>タイマ1_A 制御<br>キャプチャ/コンペア制御 0<br>キャプチャ/コンペア制御 1<br>キャプチャ/コンペア制御 2<br>キャプチャ/コンペア制御 3<br>キャプチャ/コンペア制御 4<br>予約されています<br>予約されています<br>タイマ1_A レジスタ<br>キャプチャ/コンペア・レジスタ 0<br>キャプチャ/コンペア・レジスタ 1<br>キャプチャ/コンペア・レジスタ 2<br>キャプチャ/コンペア・レジスタ 3<br>キャプチャ/コンペア・レジスタ 4<br>予約されています<br>予約されています | TA1IV<br>TA1CTL<br>TA1CCTL0<br>TA1CCTL1<br>TA1CCTL2<br>TA1CCTL3<br>TA1CCTL4<br>TA1R<br>TA1CCR0<br>TA1CCR1<br>TA1CCR2<br>TA1CCR3<br>TA1CCR4 | 011Eh<br>0180h<br>0182h<br>0184h<br>0186h<br>0188h<br>018Ah<br>018Ch<br>018Eh<br>0190h<br>0192h<br>0194h<br>0196h<br>0198h<br>019Ah<br>019Ch<br>019Eh |

| タイマ0_A3           | タイマ0_A 割り込みベクタ<br>タイマ0_A 制御<br>キャプチャ/コンペア制御 0<br>キャプチャ/コンペア制御 1<br>キャプチャ/コンペア制御 2<br>予約されています<br>予約されています<br>予約されています<br>予約されています<br>タイマ0_A レジスタ<br>キャプチャ/コンペア・レジスタ 0<br>キャプチャ/コンペア・レジスタ 1<br>キャプチャ/コンペア・レジスタ 2<br>予約されています<br>予約されています<br>予約されています<br>予約されています                               | TA0IV<br>TA0CTL0<br>TA0CCTL0<br>TA0CCTL1<br>TA0CCTL2<br>TA0R<br>TA0CCR0<br>TA0CCR1<br>TA0CCR2                                              | 012Eh<br>0160h<br>0162h<br>0164h<br>0166h<br>0168h<br>016Ah<br>016Ch<br>016Eh<br>0170h<br>0172h<br>0174h<br>0176h<br>0178h<br>017Ah<br>017Ch<br>017Eh |

| フラッシュ             | フラッシュ制御 3<br>フラッシュ制御 2<br>フラッシュ制御 1                                                                                                                                                                                                                                                           | FCTL3<br>FCTL2<br>FCTL1                                                                                                                    | 012Ch<br>012Ah<br>0128h                                                                                                                               |

## ペリフェラル・ファイル・マップ (続き)

| ワード・アクセスによるペリフェラル (続き) |                                                                                                                                                                                                                                        |                                                                                                                                               |                                                                                                                    |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| スキャン IF                | SIF タイミング・ステート・マシン 23<br>:<br>SIF タイミング・ステート・マシン 0<br>SIF DAC レジスタ 7<br>:<br>SIF DAC レジスタ 0<br>SIF 制御レジスタ 5<br>SIF 制御レジスタ 4<br>SIF 制御レジスタ 3<br>SIF 制御レジスタ 2<br>SIF 制御レジスタ 1<br>SIF プロセシング・ステート・マシン・ベクタ<br>SIF カウンタ CNT1/2<br>予約されています。 | SIFTSM23<br>:<br>SIFTSM0<br>SIFDACR7<br>:<br>SIFDACR0<br>SIFCTL5<br>SIFCTL4<br>SIFCTL3<br>SIFCTL2<br>SIFCTL1<br>SIFPSMV<br>SIFCNT<br>SIFDEBUG | 01FEh<br>:<br>01D0h<br>01CEh<br>:<br>01C0h<br>01BEh<br>01BCh<br>01BAh<br>01B8h<br>01B6h<br>01B4h<br>01B2h<br>01B0h |

| バイト・アクセスによるペリフェラル      |                                                                                                                                                                                                                                        |                                                                                                                                               |                                                                                                                    |

| LCD                    | LCD メモリ 20<br>:<br>LCD メモリ 16<br>LCD メモリ 15<br>:<br>LCD メモリ 1<br>LCD 制御及びモード                                                                                                                                                           | LCDM20<br>:<br>LCDM16<br>LCDM15<br>:<br>LCDM1<br>LCDCTL                                                                                       | 0A4h<br>:<br>0A0h<br>09Fh<br>:<br>091h<br>090h                                                                     |

| コンパレータ_A               | コンパレータ_A ポート・ディスエーブル<br>コンパレータ_A 制御 2<br>コンパレータ_A 制御 1                                                                                                                                                                                 | CAPD<br>CACTL2<br>CACTL1                                                                                                                      | 05Bh<br>05Ah<br>059h                                                                                               |

| プラウンアウト、SVS            | SVS 制御レジスタ                                                                                                                                                                                                                             | SVSCTL                                                                                                                                        | 056h                                                                                                               |

| FLL+ クロック              | FLL+ 制御 1<br>FLL+ 制御 0<br>システム・クロック周波数制御<br>システム・クロック周波数積分器<br>システム・クロック周波数積分器                                                                                                                                                         | FLL_CTL1<br>FLL_CTL0<br>SCFQCTL<br>SCFI1<br>SCFI0                                                                                             | 054h<br>053h<br>052h<br>051h<br>050h                                                                               |

| Basic Timer1           | BT カウンタ 2<br>BT カウンタ 1<br>BT 制御                                                                                                                                                                                                        | BTcnt2<br>BTcnt1<br>BTCTL                                                                                                                     | 047h<br>046h<br>040h                                                                                               |

ペリフェラル・ファイル・マップ (続き)

| ペイト・アクセスによるペリフェラル (続き) |                                                                                                                  |                                                           |                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|

| ポート P6                 | ポート P6 選択<br>ポート P6 方向<br>ポート P6 出力<br>ポート P6 入力                                                                 | P6SEL<br>P6DIR<br>P6OUT<br>P6IN                           | 037h<br>036h<br>035h<br>034h                         |

| ポート P5                 | ポート P5 選択<br>ポート P5 方向<br>ポート P5 出力<br>ポート P5 入力                                                                 | P5SEL<br>P5DIR<br>P5OUT<br>P5IN                           | 033h<br>032h<br>031h<br>030h                         |

| ポート P4                 | ポート P4 選択<br>ポート P4 方向<br>ポート P4 出力<br>ポート P4 入力                                                                 | P4SEL<br>P4DIR<br>P4OUT<br>P4IN                           | 01Fh<br>01Eh<br>01Dh<br>01Ch                         |

| ポート P3                 | ポート P3 選択<br>ポート P3 方向<br>ポート P3 出力<br>ポート P3 入力                                                                 | P3SEL<br>P3DIR<br>P3OUT<br>P3IN                           | 01Bh<br>01Ah<br>019h<br>018h                         |

| ポート P2                 | ポート P2 選択<br>ポート P2 割り込みイネーブル<br>ポート P2 割り込み - エッジ選択<br>ポート P2 割り込みフラグ<br>ポート P2 方向<br>ポート P2 出力<br>ポート P2 入力    | P2SEL<br>P2IE<br>P2IES<br>P2IFG<br>P2DIR<br>P2OUT<br>P2IN | 02Eh<br>02Dh<br>02Ch<br>02Bh<br>02Ah<br>029h<br>028h |

| ポート P1                 | ポート P1 選択<br>ポート P1 割り込みイネーブル<br>ポート P1 割り込み - エッジ選択<br>ポート P1 割り込みフラグ<br>ポート P1 方向<br>ポート P1 出力<br>ポート P1 入力    | P1SEL<br>P1IE<br>P1IES<br>P1IFG<br>P1DIR<br>P1OUT<br>P1IN | 026h<br>025h<br>024h<br>023h<br>022h<br>021h<br>020h |

| スペシャル・ファンクション          | SFR モジュール・イネーブル 2<br>SFR モジュール・イネーブル 1<br>SFR 割り込みフラグ 2<br>SFR 割り込みフラグ 1<br>SFR 割り込み・イネーブル 2<br>SFR 割り込み・イネーブル 1 | ME2<br>ME1<br>IFG2<br>IFG1<br>IE2<br>IE1                  | 005h<br>004h<br>003h<br>002h<br>001h<br>000h         |

絶対最大定格 †

|                                |             |                       |           |

|--------------------------------|-------------|-----------------------|-----------|

| 印加電圧 ( $V_{cc} \sim V_{ss}$ 間) | .....       | -0.3 ~ 4.1            | V         |

| 印加電圧 (全端子) (注)                 | .....       | -0.3 ~ $V_{cc} + 0.3$ | V         |

| ダイオード電流 (全端子)                  | .....       | ±2                    | mA        |

| 保存温度範囲                         | 未プログラムのデバイス | $T_{stg}$             | -55 ~ 150 |

| 保存温度範囲                         | プログラム済みデバイス | $T_{stg}$             | -40 ~ 85  |

†絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これは、ストレスの定格のみについて示しており、この仕様書の「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(注) すべての電圧は  $V_{ss}$  を基準とします。JTAG ヒューズ切断電圧  $V_{FB}$  は、絶対最大定格を越えても構いません。JTAG ヒューズを切断する時、TDI/TCLK 端子に電圧が印加されます。

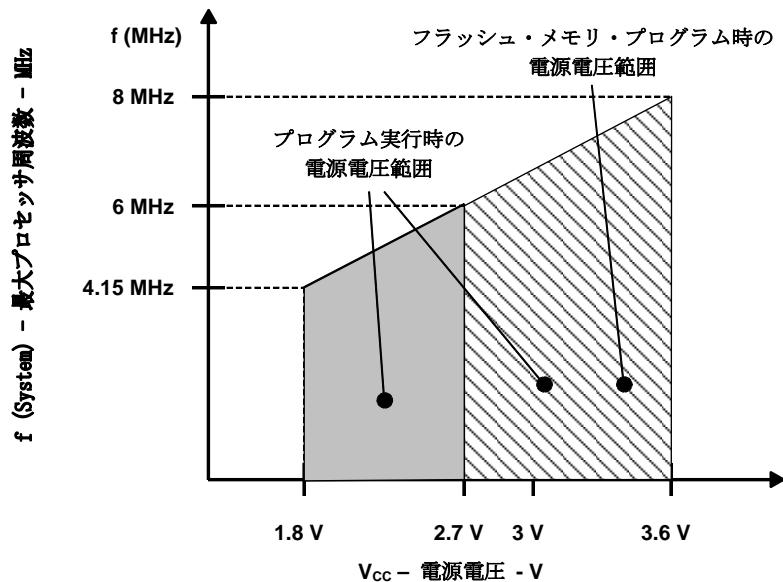

## 推奨動作条件

| 項目                                                                             |                     | 最小          | 標準    | 最大   | 単位  |

|--------------------------------------------------------------------------------|---------------------|-------------|-------|------|-----|

| 電源電圧 (プログラム実行時)、SVS はディスエーブル、<br>$V_{cc}$ ( $AV_{cc} = DV_{cc} = V_{cc}$ )     | MSP430xW42x         | 1.8         |       | 3.6  | V   |

| 電源電圧 (プログラム実行時)、SVS はイネーブル (注 1)、<br>$V_{cc}$ ( $AV_{cc} = DV_{cc} = V_{cc}$ ) | MSP430xW42x         | 2.2         |       | 3.6  | V   |

| 電源電圧 (フラッシュ・メモリ・プログラム時)、<br>$V_{cc}$ ( $AV_{cc} = DV_{cc} = V_{cc}$ )          | MSP430FW42x         | 2.7         |       | 3.6  | V   |

| 電源電圧、 $V_{ss}$ ( $AV_{ss} = DV_{ss} = V_{ss}$ )                                |                     | 0           |       | 0    | V   |

| 動作周囲温度、 $T_A$                                                                  | MSP430xW42x         | -40         |       | 85   | °C  |

| LFXT1 クリスタル周波数、 $f_{(LFXT1)}$<br>(注 2)                                         | LF 選択時、XTS_FLL = 0  | 時計用クリスタル    | 32768 |      | Hz  |

|                                                                                | XT1 選択時、XTS_FLL = 1 | セラミック・レゾネータ | 450   | 8000 | kHz |

|                                                                                | XT1 選択時、XTS_FLL = 1 | クリスタル       | 1000  | 8000 |     |

| プロセッサ周波数 (MCLK 信号)、 $f_{(System)}$                                             | $V_{cc} = 1.8$ V    | DC          | 4.15  |      | MHz |

|                                                                                | $V_{cc} = 3.6$ V    | DC          | 8     |      |     |

(注 1) 最小動作電源電圧は、電源電圧を下降させて POR がアクティブとなるトリップ・ポイントで定義します。POR は、電源電圧が最小電源電圧 + SVS 回路のヒステリシスより上昇するとインアクティブとなります。

(注 2) LF モードでは、LFXT1 オシレータには時計用クリスタルが必要です。XT1 モードでは、LFXT1 にはセラミック・レゾネータ又はクリスタルが使用できます。

推奨動作周囲温度における電気的特性（特記無き場合）

電源電流 ( $AV_{CC} + DV_{CC}$ ) (外部電流を除く) (注 1)

| 項目                                                                                                                                                       | 測定条件                                            | 最小                     | 標準   | 最大  | 単位            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|------|-----|---------------|

| $I_{(AM)}$<br>アクティブ・モード<br>$f_{(MCLK)} = f_{(SMCLK)} = 1$ MHz、<br>$f_{(ACLK)} = 32,768$ Hz、XTS_FLL = 0<br>(FW42x: フラッシュ・メモリのプログラムを実行)                    | $T_A = -40^\circ\text{C} \sim 85^\circ\text{C}$ | $V_{CC} = 2.2$ V       | 200  | 250 | $\mu\text{A}$ |

|                                                                                                                                                          |                                                 | $V_{CC} = 3$ V         | 300  | 350 |               |

| $I_{(LPM0)}$<br>ロー・パワー・モード (LPM0)<br>$f_{(MCLK)} = f_{(SMCLK)} = 1$ MHz、<br>$f_{(ACLK)} = 32,768$ Hz、XTS_FLL = 0、<br>$FN\_8 = FN\_4 = FN\_3 = FN\_2 = 0$ | $T_A = -40^\circ\text{C} \sim 85^\circ\text{C}$ | $V_{CC} = 2.2$ V       | 57   | 70  | $\mu\text{A}$ |

|                                                                                                                                                          |                                                 | $V_{CC} = 3$ V         | 92   | 100 |               |

| $I_{(LPM2)}$<br>ロー・パワー・モード (LPM2)                                                                                                                        | $T_A = -40^\circ\text{C} \sim 85^\circ\text{C}$ | $V_{CC} = 2.2$ V       | 11   | 14  | $\mu\text{A}$ |

|                                                                                                                                                          |                                                 | $V_{CC} = 3$ V         | 17   | 22  |               |

| $I_{(LPM3)}$<br>ロー・パワー・モード (LPM3)<br>(注 2)                                                                                                               | $T_A = -40^\circ\text{C}$                       | $V_{CC} = 2.2$ V       | 0.95 | 1.4 | $\mu\text{A}$ |

|                                                                                                                                                          | $T_A = -10^\circ\text{C}$                       |                        | 0.8  | 1.3 |               |

|                                                                                                                                                          | $T_A = 25^\circ\text{C}$                        |                        | 0.7  | 1.2 |               |

|                                                                                                                                                          | $T_A = 60^\circ\text{C}$                        |                        | 0.95 | 1.4 |               |

|                                                                                                                                                          | $T_A = 85^\circ\text{C}$                        |                        | 1.6  | 2.3 |               |

|                                                                                                                                                          | $T_A = -40^\circ\text{C}$                       | $V_{CC} = 3$ V         | 1.1  | 1.7 |               |

|                                                                                                                                                          | $T_A = -10^\circ\text{C}$                       |                        | 1    | 1.6 |               |

|                                                                                                                                                          | $T_A = 25^\circ\text{C}$                        |                        | 0.9  | 1.5 |               |

|                                                                                                                                                          | $T_A = 60^\circ\text{C}$                        |                        | 1.1  | 1.7 |               |

|                                                                                                                                                          | $T_A = 85^\circ\text{C}$                        |                        | 2    | 2.6 |               |

| $I_{(LPM4)}$<br>ロー・パワー・モード (LPM4)                                                                                                                        | $T_A = -40^\circ\text{C}$                       | $V_{CC} = 2.2$ V / 3 V | 0.1  | 0.5 | $\mu\text{A}$ |

|                                                                                                                                                          | $T_A = 25^\circ\text{C}$                        |                        | 0.1  | 0.5 |               |

|                                                                                                                                                          | $T_A = 85^\circ\text{C}$                        |                        | 0.8  | 2.5 |               |

(注 1) すべての入力は、0 V 又は  $V_{CC}$  に接続します。出力にはソース電流、シンク電流を流しません。消費電流は、Basic Timer1 及び LCD はアクティブ (ACLK を選択した状態) にして測定します。

コンパレータ\_A 及び SVS モジュールの消費電流は、各セクションで規定されています。

(注 2) LPM3 電流は、KDS 大真空 DT-38 (6 pF) クリスタルを使用して評価されています。

アクティブ・モードのシステム周波数 対 消費電流、F バージョン

$$I_{(AM)} = I_{(AM) [1 \text{ MHz}]} \times f_{(\text{System})} [\text{MHz}]$$

アクティブ・モードの電源電圧 対 消費電流、F バージョン

$$I_{(AM)} = I_{(AM) [3 \text{ V}]} + 140 \text{ } \mu\text{A/V} \times (V_{CC} - 3 \text{ V})$$

## 推奨動作周囲温度における電気的特性（特記無き場合）（続き）

シユミット・トリガ入力（ポート P1、P2、P3、P4、P5、及び P6； $\bar{RST}/NMI$ ； JTAG：TCK、TMS、TDI/TCLK）

| 項目                                           | $V_{CC}$ | 最小   | 標準 | 最大  | 単位 |

|----------------------------------------------|----------|------|----|-----|----|

| $V_{IT+}$ 立ち上がり入力スレッショルド電圧                   | 2.2 V    | 1.1  |    | 1.5 | V  |

|                                              | 3 V      | 1.5  |    | 1.9 |    |

| $V_{IT-}$ 立ち下がり入力スレッショルド電圧                   | 2.2 V    | 0.4  |    | 0.9 | V  |

|                                              | 3 V      | 0.9  |    | 1.3 |    |

| $V_{HYS}$ 入力電圧ヒステリシス ( $V_{IT+} - V_{IT-}$ ) | 2.2 V    | 0.3  |    | 1.1 | V  |

|                                              | 3 V      | 0.45 |    | 1   |    |

## 入力 Px.x、TAX.x

| 項目                                     | 測定条件                                        | $V_{CC}$  | 最小  | 標準 | 最大 | 単位    |

|----------------------------------------|---------------------------------------------|-----------|-----|----|----|-------|

| $t_{(int)}$ 外部割り込みタイミング                | ポート P1、P2: P1.x ~ P2.x、割り込みフラグ用外部トリガ信号（注 1） | 2.2 V/3 V | 1.5 |    |    | cycle |

|                                        |                                             | 2.2 V     | 62  |    |    | ns    |

|                                        |                                             | 3 V       | 50  |    |    |       |

| $t_{(cap)}$ タイマ_A、キャプチャ・タイミング          | TAX.x                                       | 2.2 V     | 62  |    |    | ns    |

|                                        |                                             | 3 V       | 50  |    |    |       |

| $f_{(TAext)}$ タイマ_A、外部から端子に印加するクロック周波数 | TAXCLK、INCLK $t_{(H)} = t_{(L)}$            | 2.2 V     |     | 8  |    | MHz   |

|                                        |                                             | 3 V       |     | 10 |    |       |

| $f_{(TAint)}$ タイマ_A クロック周波数            | SMCLK 又は ACLK 信号選択時                         | 2.2 V     |     | 8  |    | MHz   |

|                                        |                                             | 3 V       |     | 10 |    |       |

（注 1） 外部信号は、最小  $t_{(int)}$  サイクル及び時間のパラメータが適合するたび毎に割り込みフラグをセットします。トリガ信号が  $t_{(int)}$  より短い場合にもセットされることがあります。フラグを確実にセットするためには、サイクル及びタイミング仕様の両方を満足しなければなりません。 $t_{(int)}$  は MCLK サイクルで測定します。

## リーク電流（注 1）

| 項目              | 測定条件                            | $V_{CC}$  | 最小 | 標準 | 最大       | 単位 |

|-----------------|---------------------------------|-----------|----|----|----------|----|

| $I_{1kg(P1.x)}$ | リーク電流 ポート P1 $V_{(P1.x)}$ （注 2） | 2.2 V/3 V |    |    | $\pm 50$ | nA |

|                 | ポート P6 $V_{(P6.x)}$ （注 2）       |           |    |    | $\pm 50$ |    |

（注 1） 特記無き場合、リーク電流は対応する端子に  $V_{SS}$  又は  $V_{CC}$  を印加して測定します。

（注 2） ポート端子は入力となるように選択しなければなりません。

推奨動作周囲温度における電気的特性 (特記無き場合) (続き)

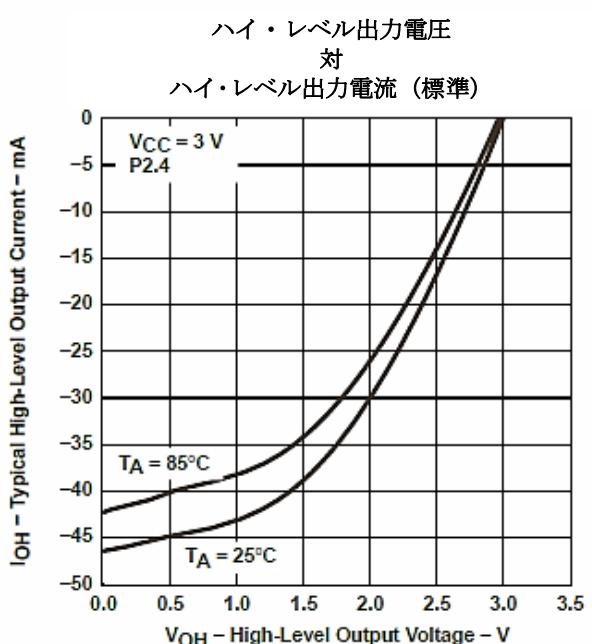

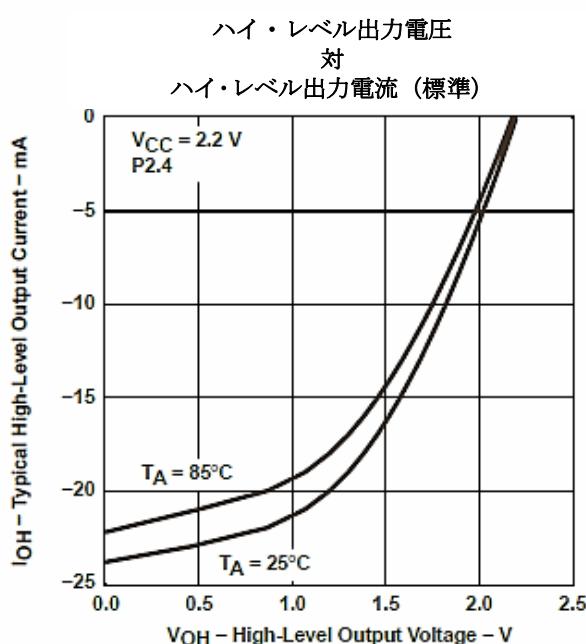

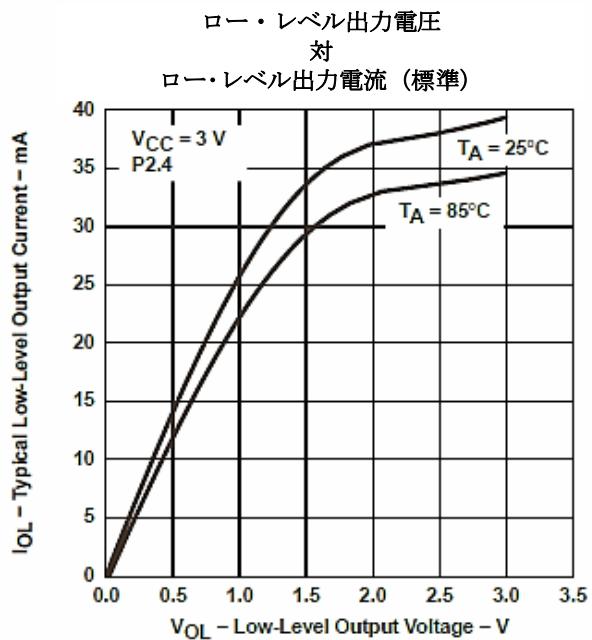

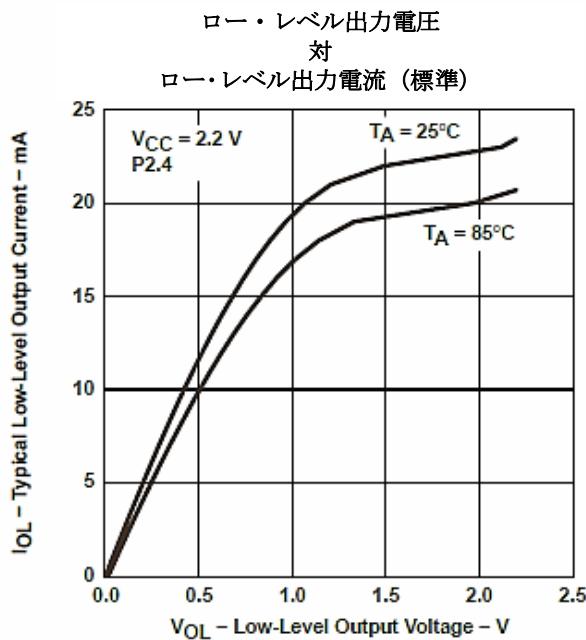

出力 (ポート P1、P2、P3、P4、P5、及び P6)

| 項目       |            | 測定条件                                                               | 最小              | 標準       | 最大              | 単位 |

|----------|------------|--------------------------------------------------------------------|-----------------|----------|-----------------|----|

| $V_{OH}$ | ハイ・レベル出力電圧 | $I_{OH(max)} = -1.5 \text{ mA}$ , $V_{CC} = 2.2 \text{ V}$ , (注 1) | $V_{CC} - 0.25$ |          | $V_{CC}$        | V  |

|          |            | $I_{OH(max)} = -6 \text{ mA}$ , $V_{CC} = 2.2 \text{ V}$ , (注 2)   | $V_{CC} - 0.6$  |          | $V_{CC}$        |    |

|          |            | $I_{OH(max)} = -1.5 \text{ mA}$ , $V_{CC} = 3 \text{ V}$ , (注 1)   | $V_{CC} - 0.25$ |          | $V_{CC}$        |    |

|          |            | $I_{OH(max)} = -6 \text{ mA}$ , $V_{CC} = 3 \text{ V}$ , (注 2)     | $V_{CC} - 0.6$  |          | $V_{CC}$        |    |

| $V_{OL}$ | ロー・レベル出力電圧 | $I_{OL(max)} = 1.5 \text{ mA}$ , $V_{CC} = 2.2 \text{ V}$ , (注 1)  |                 | $V_{SS}$ | $V_{SS} + 0.25$ | V  |

|          |            | $I_{OL(max)} = 6 \text{ mA}$ , $V_{CC} = 2.2 \text{ V}$ , (注 2)    |                 | $V_{SS}$ | $V_{SS} + 0.6$  |    |

|          |            | $I_{OL(max)} = 1.5 \text{ mA}$ , $V_{CC} = 3 \text{ V}$ , (注 1)    |                 | $V_{SS}$ | $V_{SS} + 0.25$ |    |

|          |            | $I_{OL(max)} = 6 \text{ mA}$ , $V_{CC} = 3 \text{ V}$ , (注 2)      |                 | $V_{SS}$ | $V_{SS} + 0.6$  |    |

(注 1) 全出力の最大電流  $I_{OH(max)}$  と  $I_{OL(max)}$  の合計は、規定の最大電圧降下を保持するため  $\pm 12 \text{ mA}$  を越えてはいけません。

(注 2) 全出力の最大電流  $I_{OH(max)}$  と  $I_{OL(max)}$  の合計は、規定の最大電圧降下を保持するため  $\pm 24 \text{ mA}$  を越えてはいけません。

出力周波数

| 項目                                          |                                                          | 測定条件                                                                                   | 最小                               | 標準             | 最大             | 単位  |

|---------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------|----------------|----------------|-----|

| $f_{Px,y}$                                  | Px, y 出力周波数<br>( $1 \leq x \leq 6$ 、 $0 \leq y \leq 7$ ) | $C_L = 20 \text{ pF}$ ,<br>$I_L = \pm 1.5 \text{ mA}$                                  | $V_{CC} = 2.2 \text{ V}$         | DC             | 10             | MHz |

|                                             |                                                          |                                                                                        | $V_{CC} = 3 \text{ V}$           | DC             | 12             |     |

| $f_{ACLK}$ ,<br>$f_{MCLK}$ ,<br>$f_{SMCLK}$ | P1.1/TA0.0/MCLK,<br>P1.5/TAOCLK/ACLK                     | $C_L = 20 \text{ pF}$                                                                  | $V_{CC} = 2.2 \text{ V}$         |                | 8              | MHz |

|                                             |                                                          |                                                                                        | $V_{CC} = 3 \text{ V}$           |                | 12             |     |

| $t_{x_{dc}}$                                | 出力周波数デューティ比                                              | P1.5/TAOCLK/ACLK,<br>$C_L = 20 \text{ pF}$ ,<br>$V_{CC} = 2.2 \text{ V} / 3 \text{ V}$ | $f_{ACLK} = f_{LFXT1} = f_{XT1}$ | 40%            | 60%            |     |

|                                             |                                                          |                                                                                        | $f_{ACLK} = f_{LFXT1} = f_{LF}$  | 30%            | 70%            |     |

|                                             |                                                          |                                                                                        | $f_{ACLK} = f_{LFXT1/n}$         |                | 50%            |     |

|                                             |                                                          | P1.1/TAO.0/MCLK,<br>$C_L = 20 \text{ pF}$ ,<br>$V_{CC} = 2.2 \text{ V} / 3 \text{ V}$  | $f_{MCLK} = f_{LFXT1/n}$         | 50% -<br>15 ns | 50% +<br>15 ns |     |

|                                             |                                                          |                                                                                        | $f_{MCLK} = f_{DCOCLK}$          | 50% -<br>15 ns | 50% +<br>15 ns |     |

## 推奨動作周囲温度における電気的特性（特記無き場合）（続き）

## 出力（ポート P1、P2、P3、P4、P5、及び P6）（続き）

（注）同時に 1 出力のみ負荷をかけます。

推奨動作周囲温度における電気的特性（特記無き場合）（続き）

ウェークアップ (LPM3)

| 項目          |      | 測定条件        |                      | 最小 | 標準 | 最大 | 単位      |

|-------------|------|-------------|----------------------|----|----|----|---------|

| $t_d(LPM3)$ | 遅延時間 | $f = 1$ MHz | $V_{CC} = 2.2$ V/3 V | 6  |    |    | $\mu$ s |

|             |      | $f = 2$ MHz |                      | 6  |    |    |         |

|             |      | $f = 3$ MHz |                      | 6  |    |    |         |

RAM (注 1)

| 項目             |  | 測定条件                  |  | 最小  | 標準 | 最大 | 単位 |

|----------------|--|-----------------------|--|-----|----|----|----|

| VRAMh RAM 保持電圧 |  | CPU 停止 (HALT) 時 (注 1) |  | 1.6 |    |    | V  |

(注 1) このパラメータは、プログラム・メモリ RAM のデータが保持される時の最小電源電圧を定義します。この電源電圧の条件ではプログラムを実行させないで下さい。

LCD

| 項目                    |                 | 測定条件                                 |                                                          | 最小                                    | 標準 | 最大               | 単位 |

|-----------------------|-----------------|--------------------------------------|----------------------------------------------------------|---------------------------------------|----|------------------|----|

| $V_{(33)}$            | アナログ電圧          | P5. 7/R33 の電圧                        | $V_{CC} = 3$ V                                           | 2.5                                   |    | $V_{CC} + 0.2$   | V  |

| $V_{(23)}$            |                 | P5. 6/R23 の電圧                        |                                                          | $(V_{33}-V_{03}) \times 2/3 + V_{03}$ |    |                  |    |

| $V_{(13)}$            |                 | P5. 5/R13 の電圧                        |                                                          | $(V_{33}-V_{03}) \times 1/3 + V_{03}$ |    |                  |    |

| $V_{(33)} - V_{(03)}$ |                 | R33/R03 の電圧                          |                                                          | 2.5                                   |    | $V_{CC} + 0.2$   |    |

| $I_{(R03)}$           | 入力リーク電流         | $R03 = V_{SS}$                       | 全セグメント出力<br>ライン及びコモン<br>出力ラインは無負<br>荷、<br>$V_{CC} = 3$ V |                                       |    | $\pm 20$         | nA |

| $I_{(R13)}$           |                 | $P5. 5/R13 = V_{CC}/3$               |                                                          |                                       |    | $\pm 20$         |    |

| $I_{(R23)}$           |                 | $P5. 6/R23 = 2 \times V_{CC}/3$      |                                                          |                                       |    | $\pm 20$         |    |

| $V_{(Sxx0)}$          | セグメント・ライン<br>電圧 | $I_{(Sxx)} = -3 \mu A, V_{CC} = 3$ V | $V_{(03)}$                                               |                                       |    | $V_{(03)} - 0.1$ | V  |

| $V_{(Sxx1)}$          |                 |                                      | $V_{(13)}$                                               |                                       |    | $V_{(13)} - 0.1$ |    |

| $V_{(Sxx2)}$          |                 |                                      | $V_{(23)}$                                               |                                       |    | $V_{(23)} - 0.1$ |    |

| $V_{(Sxx3)}$          |                 |                                      | $V_{(33)}$                                               |                                       |    | $V_{(33)} + 0.1$ |    |

## 推奨動作周囲温度における電気的特性（特記無き場合）（続き）

## コンパレータ\_A（注1）

| 項目                                                                              | 測定条件                                                        | 最小                          | 標準   | 最大                  | 単位   |

|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------|------|---------------------|------|

| I <sub>(cc)</sub>                                                               | V <sub>cc</sub> = 2.2 V                                     | 25                          | 40   |                     | μA   |

|                                                                                 | V <sub>cc</sub> = 3 V                                       | 45                          | 60   |                     |      |

| I <sub>(RefLadder/RefDiode)</sub>                                               | V <sub>cc</sub> = 2.2 V                                     | 30                          | 50   |                     | μA   |

|                                                                                 | V <sub>cc</sub> = 3 V                                       | 45                          | 71   |                     |      |

| V <sub>(Ref025)</sub><br>Voltage @ 0.25 V <sub>CC</sub> node<br>V <sub>CC</sub> | PCA0 = 1、CARSEL = 1、CAREF = 1、<br>P1.6/CA0 及び P1.7/CA1 は無負荷 | V <sub>cc</sub> = 2.2 V/3 V | 0.23 | 0.24                | 0.25 |

| V <sub>(Ref050)</sub><br>Voltage @ 0.5 V <sub>CC</sub> node<br>V <sub>CC</sub>  | PCA0 = 1、CARSEL = 1、CAREF = 2、<br>P1.6/CA0 及び P1.7/CA1 は無負荷 | V <sub>cc</sub> = 2.2 V/3 V | 0.47 | 0.48                | 0.5  |

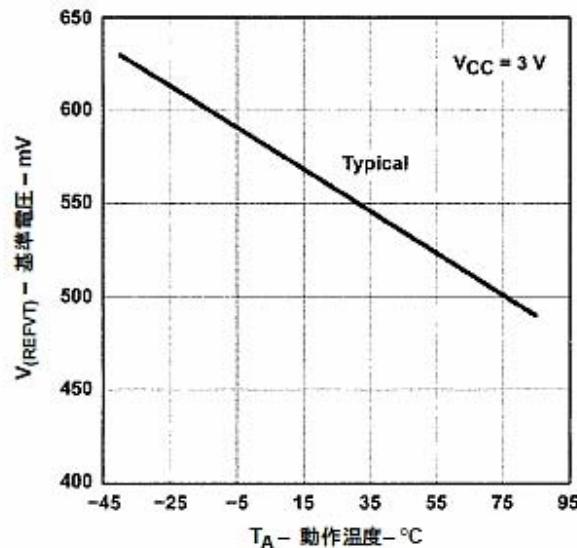

| V <sub>(RefVT)</sub><br>(図 6、7 参照)                                              | V <sub>cc</sub> = 2.2 V                                     | 390                         | 480  | 540                 | mV   |

|                                                                                 | V <sub>cc</sub> = 3 V                                       | 400                         | 490  | 550                 |      |

| V <sub>(IC)</sub><br>同相入力電圧範囲                                                   | CAON = 1                                                    | V <sub>cc</sub> = 2.2 V/3 V | 0    | V <sub>cc</sub> - 1 | V    |

| V <sub>(offset)</sub><br>オフセット電圧                                                | (注2)                                                        | V <sub>cc</sub> = 2.2 V/3 V | -30  | 30                  | mV   |

| V <sub>hys</sub><br>入力ヒステリシス                                                    | CAON = 1                                                    | V <sub>cc</sub> = 2.2 V/3 V | 0    | 0.7                 | 1.4  |

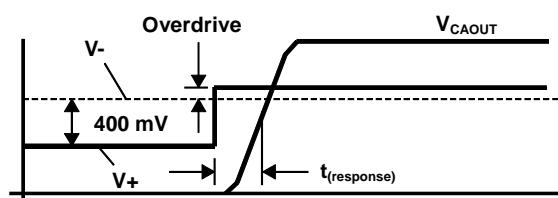

| t <sub>(response LH)</sub>                                                      | T <sub>A</sub> = 25°C、オーバードライブ 10 mV、<br>フィルタなし: CAF = 0    | V <sub>cc</sub> = 2.2 V     | 130  | 210                 | 300  |

|                                                                                 |                                                             | V <sub>cc</sub> = 3 V       | 80   | 150                 | 240  |

| t <sub>(response HL)</sub>                                                      | T <sub>A</sub> = 25°C、オーバードライブ 10 mV、<br>フィルタ付き: CAF = 1    | V <sub>cc</sub> = 2.2 V     | 1.4  | 1.9                 | 3.4  |

|                                                                                 |                                                             | V <sub>cc</sub> = 3 V       | 0.9  | 1.5                 | 2.6  |

|                                                                                 | T <sub>A</sub> = 25°C、オーバードライブ 10 mV、<br>フィルタなし: CAF = 0    | V <sub>cc</sub> = 2.2 V     | 130  | 210                 | 300  |

|                                                                                 |                                                             | V <sub>cc</sub> = 3 V       | 80   | 150                 | 240  |

|                                                                                 | T <sub>A</sub> = 25°C、オーバードライブ 10 mV、<br>フィルタ付き: CAF = 1    | V <sub>cc</sub> = 2.2 V     | 1.4  | 1.9                 | 3.4  |

|                                                                                 |                                                             | V <sub>cc</sub> = 3 V       | 0.9  | 1.5                 | 2.6  |

(注1) コンパレータ\_A 端子のリーク電流は、I<sub>1kg(P1.x)</sub> 規格と同じです。

(注2) 入力オフセット電圧は、連続して測定する毎に CAEX ビットを使ってコンパレータ\_A 入力を反転させることにより、キャンセルすることができます。2 つの連続した測定値を加算します。

推奨動作周囲温度における電気的特性（特記無き場合）（続き）

代表特性

図 6. 温度対  $V_{(RefVT)}$ 、 $V_{CC} = 3$  V

図 7. 温度対  $V_{(RefVT)}$ 、 $V_{CC} = 2.2$  V

図 8. コンパレータ\_A モジュール ブロック図

図 9. オーバードライブの定義

## 推奨動作周囲温度における電気的特性（特記無き場合）（続き）

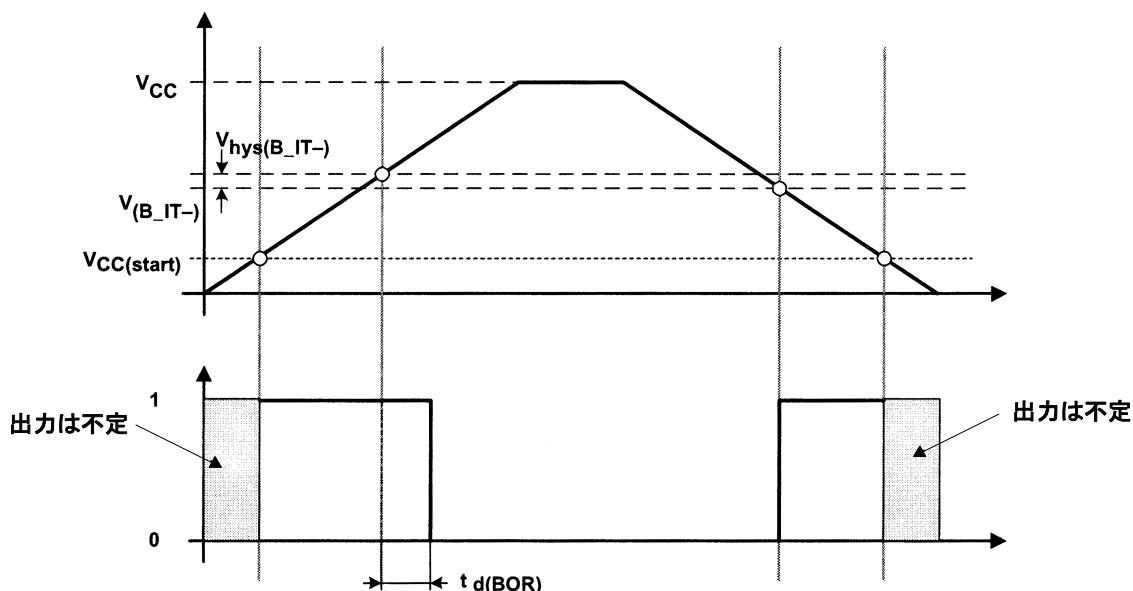

## POR/ブラウンアウト、リセット（注 1、2）

| 項目               | 測定条件    | 最小                                                                                 | 標準                  | 最大   | 単位            |

|------------------|---------|------------------------------------------------------------------------------------|---------------------|------|---------------|

| $t_{d(BOR)}$     | ブラウンアウト |                                                                                    |                     | 2000 | $\mu\text{s}$ |

| $V_{CC(start)}$  |         | $dV_{CC}/dt \leq 3 \text{ V/s}$ （図 10 参照）                                          | 0.7 x $V_{(B\_IT)}$ |      | V             |

| $V_{(B\_IT)}$    |         | $dV_{CC}/dt \leq 3 \text{ V/s}$ （図 10、11、12 参照）                                    |                     | 1.71 | V             |

| $V_{hys(B\_IT)}$ |         | $dV_{CC}/dt \leq 3 \text{ V/s}$ （図 10 参照）                                          | 70                  | 130  | 180           |

| $t_{(reset)}$    |         | 内部でリセットを受け付けるための $\overline{RST}/NMI$ 入力パルス幅、 $V_{CC} = 2.2 \text{ V}/3 \text{ V}$ | 2                   |      | $\mu\text{s}$ |

（注 1） ブラウンアウト・モジュールの消費電流は、 $I_{CC}$  に含まれています。電圧レベル  $V_{(B\_IT)} + V_{hys(B\_IT)}$   $\leq 1.8 \text{ V}$  とします。

（注 2） パワーアップ時は、CPU は  $V_{CC} = V_{(B\_IT)} + V_{hys(B\_IT)}$  となった後  $t_{d(BOR)}$  経過後にコードの実行を開始します。デフォルトの FLL+ の設定は、 $V_{CC} \geq V_{CC(min)}$  となるまで変えてはいけません。 $V_{CC(min)}$  は、使用する動作周波数における最小電源電圧を表します。ブラウンアウト/SVS 回路の詳細は、MSP430x4xx ファミリー ユーザーズ・ガイド SLAU141（日本語版）、SLAU056（英語版）を参照して下さい。

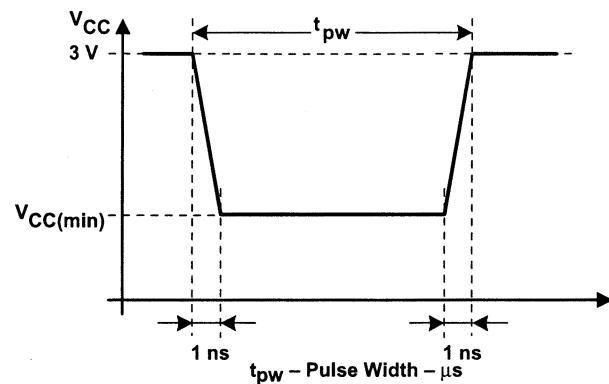

図 10. 電源電圧 対 POR/ブラウンアウト リセット (BOR)

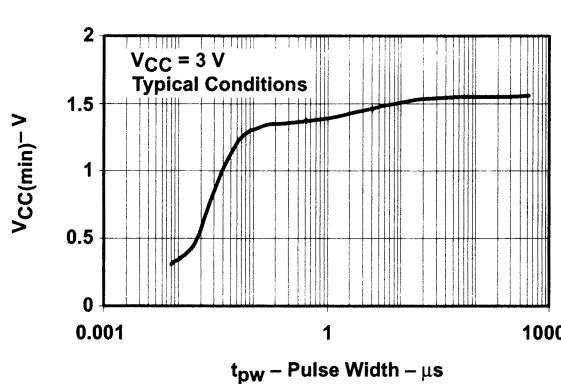

図 11. POR/ブラウンアウト信号を生成するための  $V_{CC(min)}$  レベル (矩形波電圧降下)

推奨動作周囲温度における電気的特性（特記無き場合）（続き）

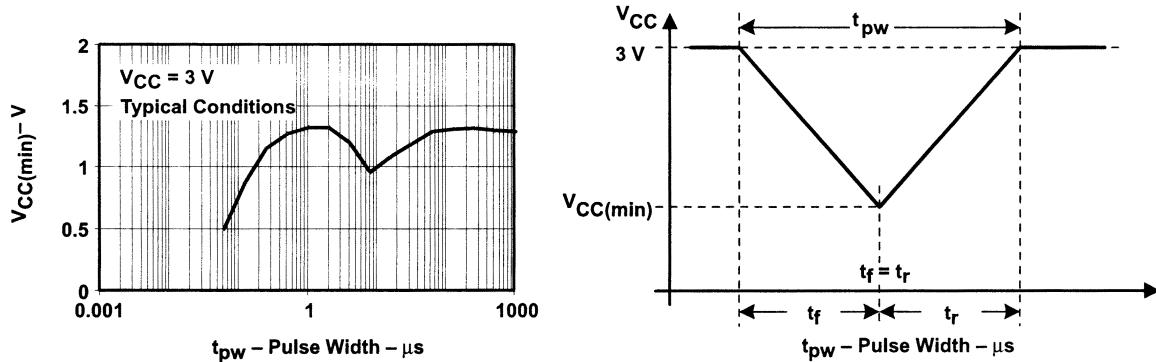

図 12. POR/プルアップ信号を生成するための  $V_{CC(min)}$  レベル（三角波電圧降下）

SVS（電源電圧監視／モニタ）（注 1、2）

| 記号                         | 測定条件                                                      | 最小                            | 標準                            | 最大             | 単位            |

|----------------------------|-----------------------------------------------------------|-------------------------------|-------------------------------|----------------|---------------|

| $t_d(SVS)$                 | $dV_{CC}/dt > 30 \text{ V/ms}$ (図 13 参照)                  | 5                             | 150                           |                | $\mu\text{s}$ |

|                            | $dV_{CC}/dt \leq 30 \text{ V/ms}$                         |                               | 2000                          |                |               |

| $t_d(SVSon)$               | SVSon、VLD = 0 ~ VLD ≠ 0 ヘスイッチ、 $V_{CC} = 3 \text{ V}$     | 20                            | 150                           |                | $\mu\text{s}$ |

| $t_{settle}$               | $VLD \neq 0 \ddagger$                                     |                               |                               | 12             | $\mu\text{s}$ |

| $V_{(SVSstart)}$           | $VLD \neq 0, V_{CC}/dt \leq 3 \text{ V/s}$ (図 13 参照)      |                               | 1.55                          | 1.7            | $\text{V}$    |

| $V_{(SVS\_IT-)}(SVS\_IT-)$ | $V_{CC}/dt \leq 3 \text{ V/s}$ (図 13 参照)                  | 70                            | 120                           | 155            | $\text{mV}$   |

|                            | $VLD = 1$                                                 | $V_{(SVS\_IT-)} \times 0.004$ | $V_{(SVS\_IT-)} \times 0.008$ |                |               |

|                            | $VLD = 2 \dots 14$                                        |                               |                               |                |               |

| $V_{(SVS\_IT-)}$           | $V_{CC}/dt \leq 3 \text{ V/s}$ (図 13 参照)、SVSIN に印加される外部電圧 | 4.4                           |                               | 10.4           | $\text{V}$    |

|                            | $VLD = 1$                                                 | 1.8                           | 1.9                           | 2.05           |               |

|                            | $VLD = 2$                                                 | 1.94                          | 2.1                           | 2.25           |               |

|                            | $VLD = 3$                                                 | 2.05                          | 2.2                           | 2.37           |               |

|                            | $VLD = 4$                                                 | 2.14                          | 2.3                           | 2.48           |               |

|                            | $VLD = 5$                                                 | 2.24                          | 2.4                           | 2.6            |               |

|                            | $VLD = 6$                                                 | 2.33                          | 2.5                           | 2.71           |               |

|                            | $VLD = 7$                                                 | 2.46                          | 2.65                          | 2.86           |               |

|                            | $VLD = 8$                                                 | 2.58                          | 2.8                           | 3              |               |

|                            | $VLD = 9$                                                 | 2.69                          | 2.9                           | 3.13           |               |

|                            | $VLD = 10$                                                | 2.83                          | 3.05                          | 3.29           |               |

|                            | $VLD = 11$                                                | 2.94                          | 3.2                           | 3.42           |               |

|                            | $VLD = 12$                                                | 3.11                          | 3.35                          | 3.61 $\dagger$ |               |

|                            | $VLD = 13$                                                | 3.24                          | 3.5                           | 3.76 $\dagger$ |               |

|                            | $VLD = 14$                                                | 3.43                          | 3.7 $\dagger$                 | 3.99 $\dagger$ |               |

| $I_{CC(SVS)}$<br>(注 1)     | $VLD \neq 0, V_{CC} = 2.2 \text{ V}/3 \text{ V}$          |                               | 10                            | 15             | $\mu\text{A}$ |

$\dagger$  推奨動作電圧範囲は 3.6 V に制限されます。

$\ddagger$  セトリング時間  $t_{settle}$  は、 $VLD \neq 0$  から 2 ~ 15 の間の違った値にスイッチした後、コンパレータ出力が安定したレベルになるのに必要な時間です。オーバードライブ  $> 50 \text{ mV}$  と仮定します。

(注 1) SVS モジュールの消費電流は  $ICC$  の値に含まれていません。

(注 2) SVS は、パワーアップ時はアクティブになりません。

## 推奨動作周囲温度における電気的特性（特記無き場合）（続き）

図 13. 電源電圧 対 SVS リセット (SVSR)

図 14. SVS 信号を生成するための  $V_{CC(min)}$  レベル（矩形波電圧及び三角波電圧降下）

推奨動作周囲温度における電気的特性（特記無き場合）（続き）

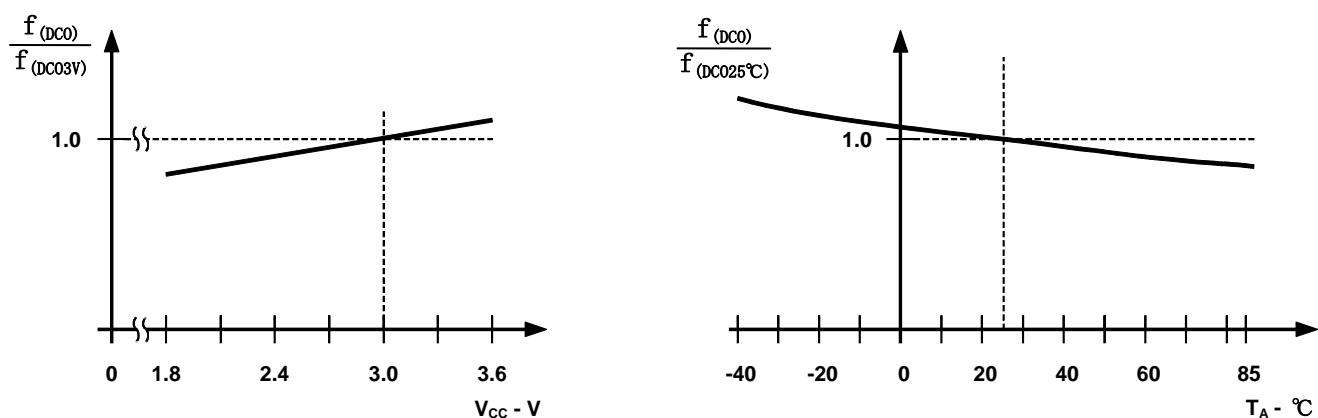

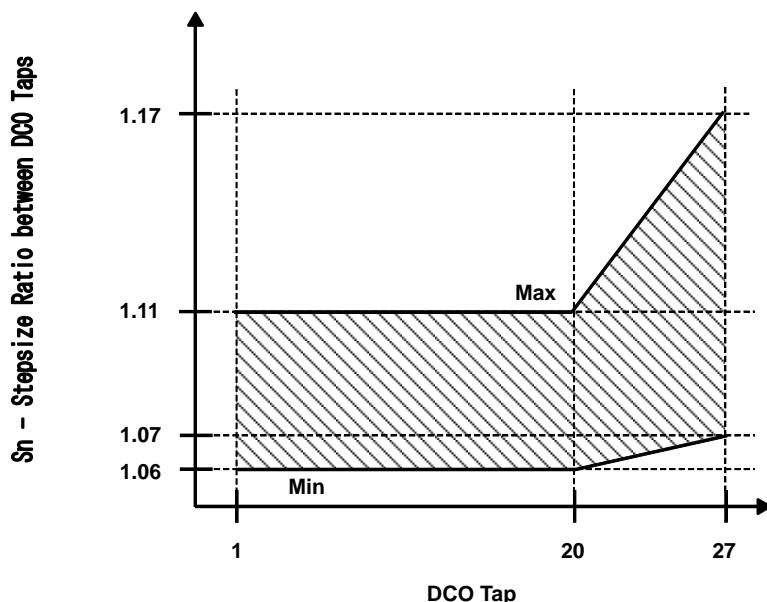

DCO

| 項目                    | 測定条件                                                                                                                    | V <sub>CC</sub> | 最小   | 標準   | 最大   | 単位   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------|------|

| f <sub>(DCOCLK)</sub> | N <sub>(DCO)</sub> = 01E0h、FN_8 = FN_4 = FN_3 = FN_2 = 0、D = 2、DCOPLUS = 0                                              | 2.2 V/3 V       |      | 1    |      | MHz  |

| f <sub>(DCO)</sub>    | FN_8 = FN_4 = FN_3 = FN_2 = 0 ; DCOPLUS = 1                                                                             | 2.2 V           | 0.3  | 0.65 | 1.25 | MHz  |

|                       |                                                                                                                         | 3 V             | 0.3  | 0.7  | 1.3  |      |

| f <sub>(DCO27)</sub>  | FN_8 = FN_4 = FN_3 = FN_2 = 0 ; DCOPLUS = 1 (注 1)                                                                       | 2.2 V           | 2.5  | 5.6  | 10.5 | MHz  |

|                       |                                                                                                                         | 3 V             | 2.7  | 6.1  | 11.3 |      |

| f <sub>(DCO2)</sub>   | FN_8 = FN_4 = FN_3 = 0、FN_2 = 1; DCOPLUS = 1                                                                            | 2.2 V           | 0.7  | 1.3  | 2.3  | MHz  |

|                       |                                                                                                                         | 3 V             | 0.8  | 1.5  | 2.5  |      |

| f <sub>(DCO27)</sub>  | FN_8 = FN_4 = FN_3 = 0、FN_2 = 1; DCOPLUS = 1 (注 1)                                                                      | 2.2 V           | 5.7  | 10.8 | 18   | MHz  |

|                       |                                                                                                                         | 3 V             | 6.5  | 12.1 | 20   |      |

| f <sub>(DCO2)</sub>   | FN_8 = FN_4 = 0、FN_3 = 1、FN_2 = x; DCOPLUS = 1                                                                          | 2.2 V           | 1.2  | 2    | 3    | MHz  |

|                       |                                                                                                                         | 3 V             | 1.3  | 2.2  | 3.5  |      |

| f <sub>(DCO27)</sub>  | FN_8 = FN_4 = 0、FN_3 = 1、FN_2 = x; DCOPLUS = 1 (注 1)                                                                    | 2.2 V           | 9    | 15.5 | 25   | MHz  |

|                       |                                                                                                                         | 3 V             | 10.3 | 17.9 | 28.5 |      |

| f <sub>(DCO2)</sub>   | FN_8 = 0、FN_4 = 1、FN_3 = FN_2 = x; DCOPLUS = 1                                                                          | 2.2 V           | 1.8  | 2.8  | 4.2  | MHz  |

|                       |                                                                                                                         | 3 V             | 2.1  | 3.4  | 5.2  |      |

| f <sub>(DCO27)</sub>  | FN_8 = 0、FN_4 = 1、FN_3 = FN_2 = x; DCOPLUS = 1 (注 1)                                                                    | 2.2 V           | 13.5 | 21.5 | 33   | MHz  |

|                       |                                                                                                                         | 3 V             | 16   | 26.6 | 41   |      |