# MCT8329A 高速センサレス台形波制御の3相 BLDC ゲート・ドライバ

## 1 特長

- センサレス・モーター制御アルゴリズムを統合した3相 BLDC モーター・ドライバ

- コード・フリーの高速台形波制御

- 最大 3kHz (電気的周波数) をサポート

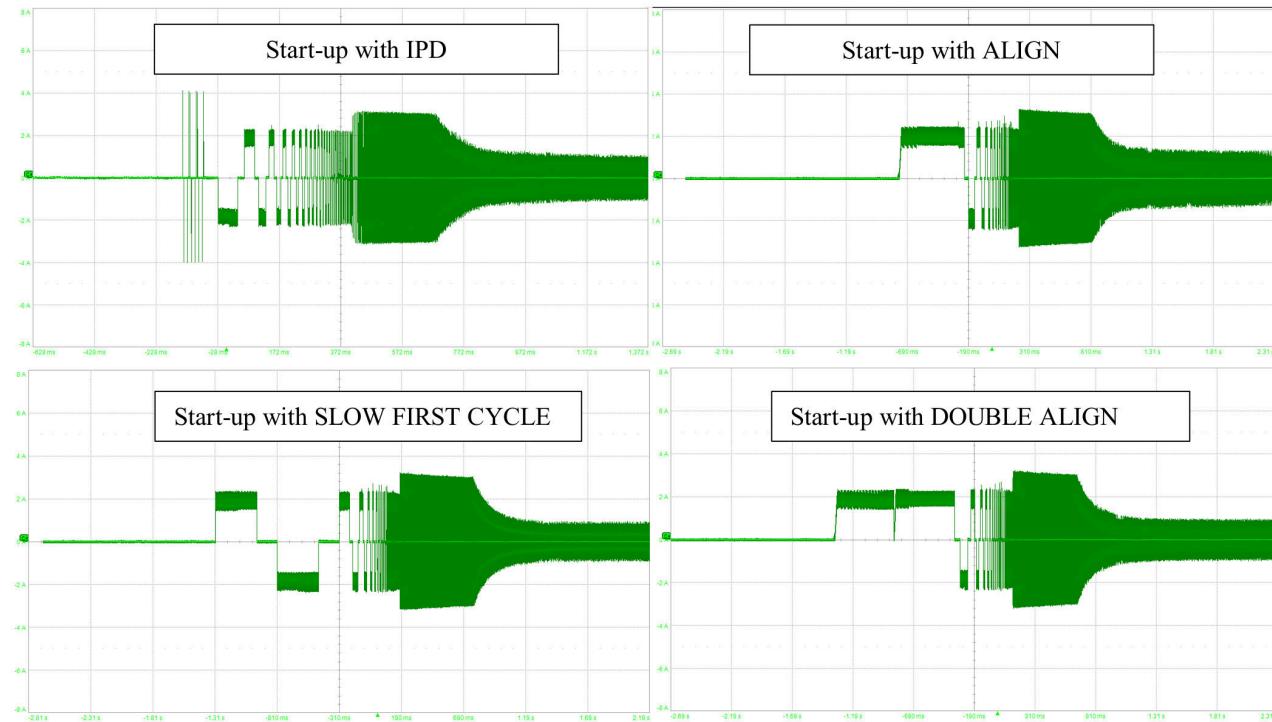

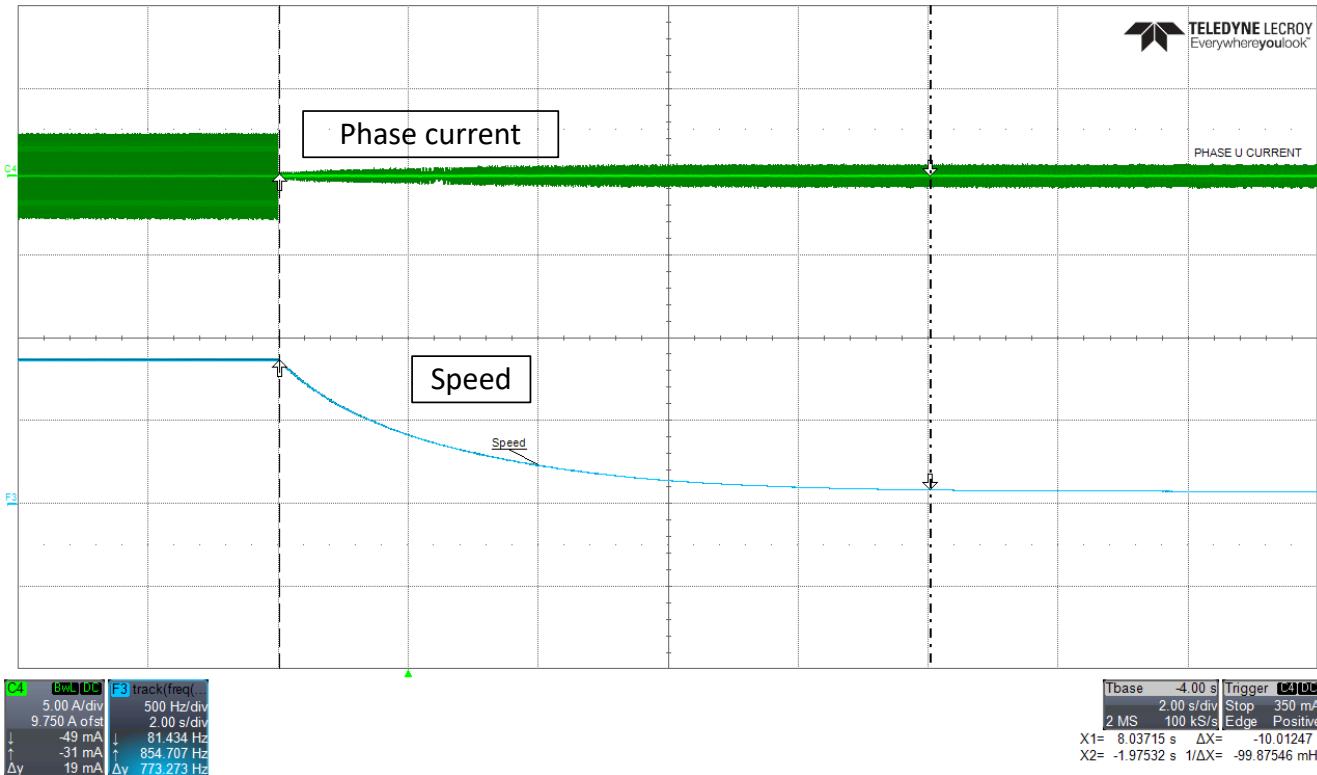

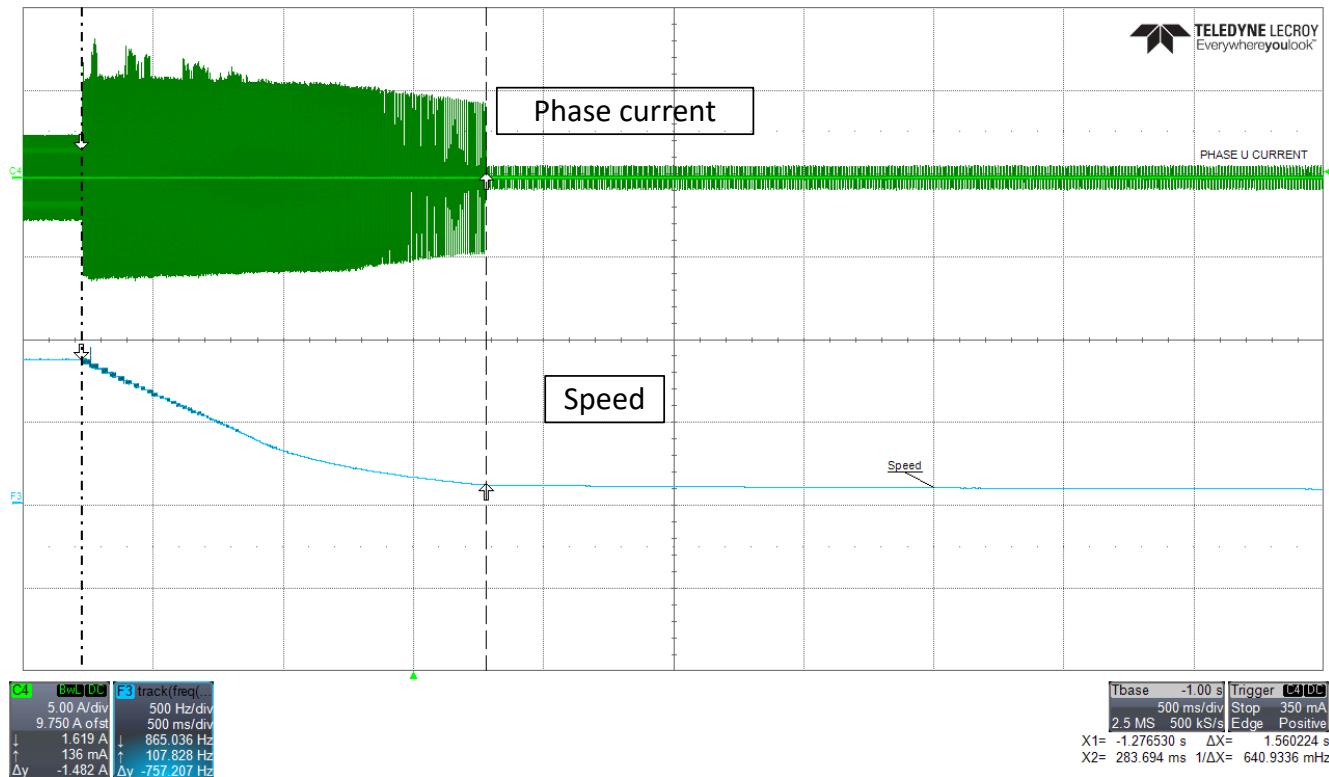

- 非常に高速なスタートアップ時間 (50ms 未満)

- 迅速な減速 (150ms 未満)

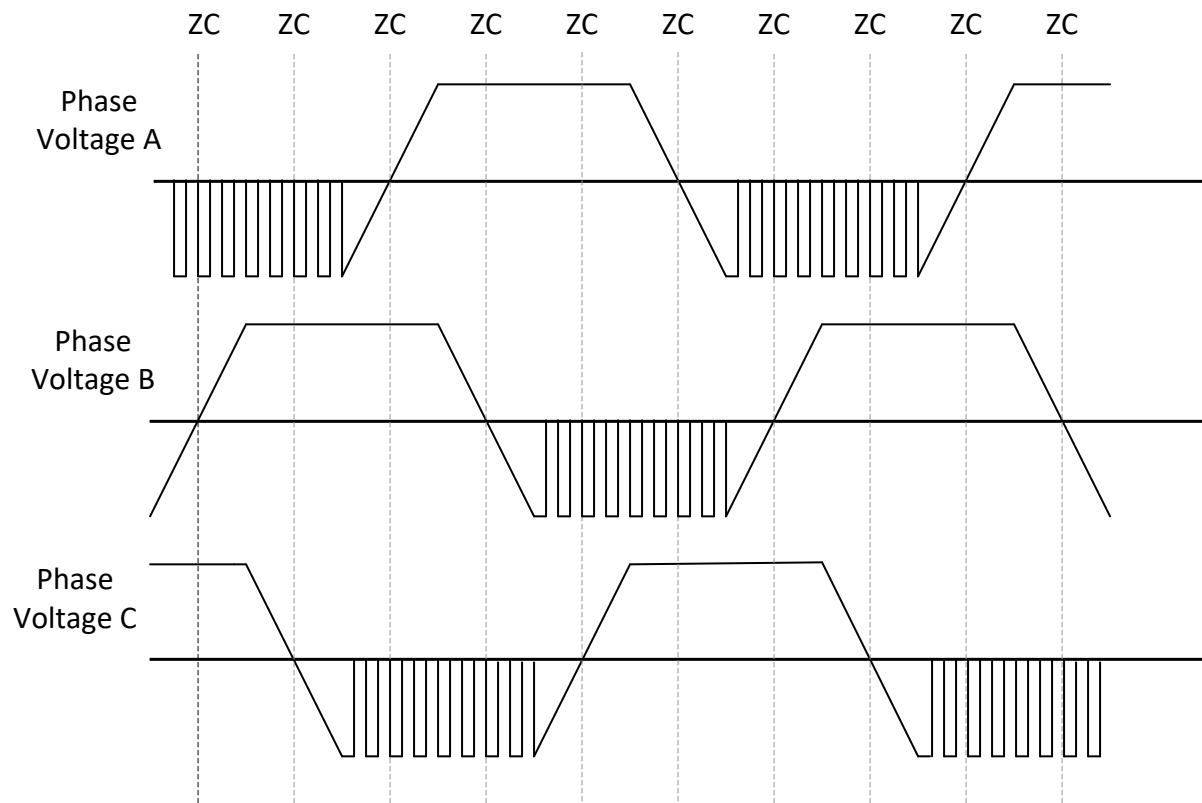

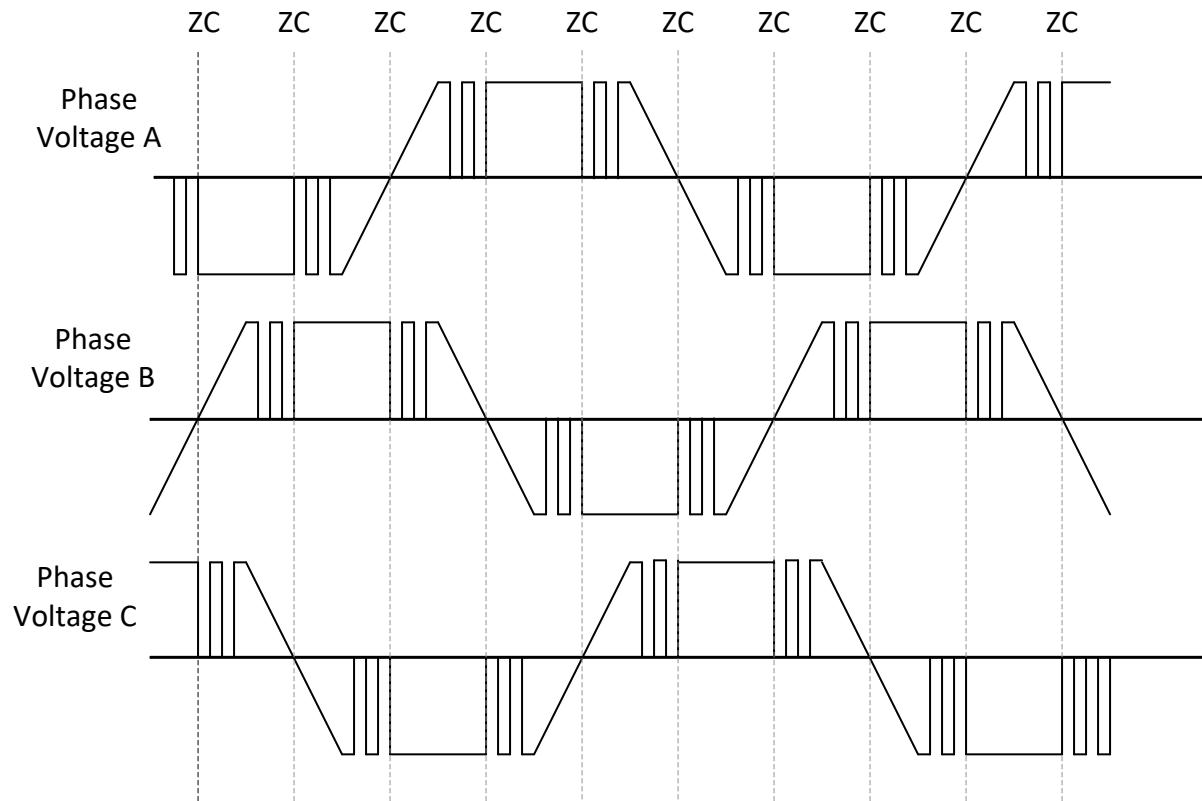

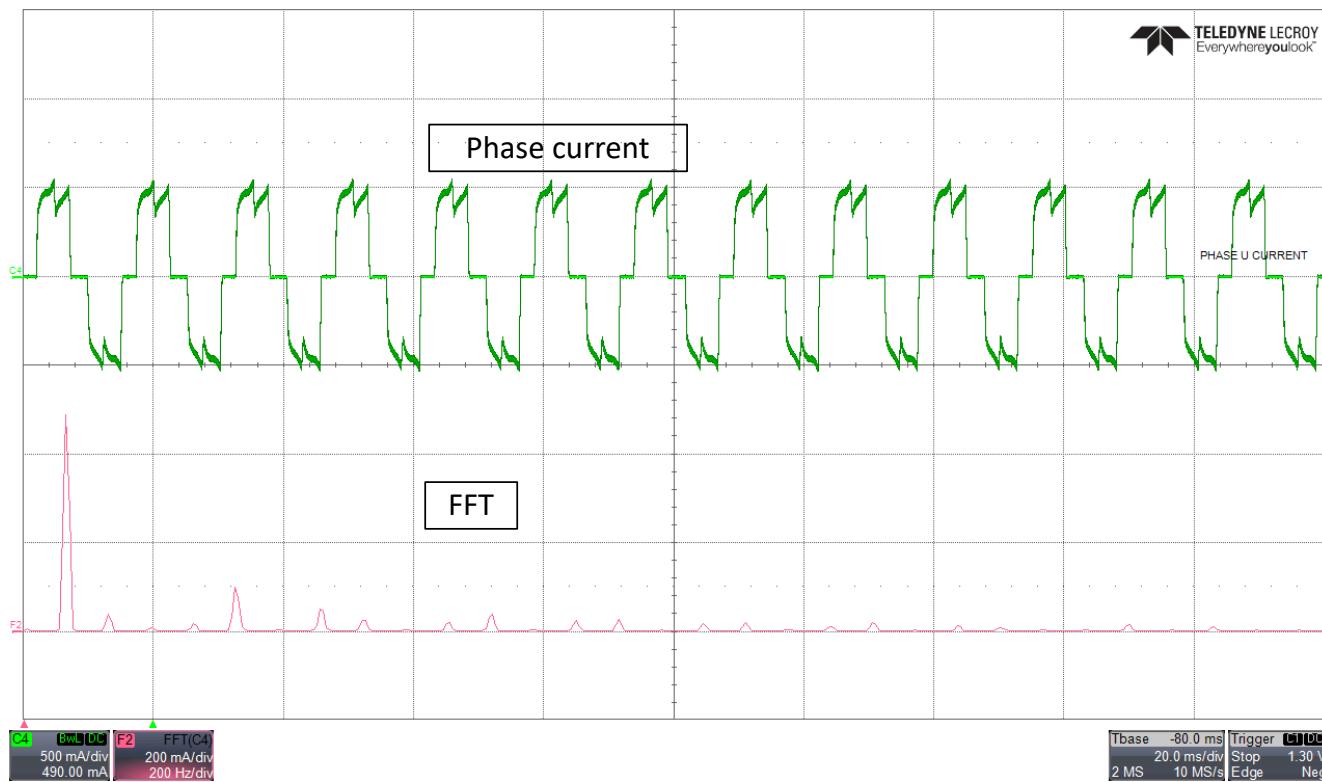

- 音響性能を向上する 120° または 150° 変調をサポート

- 順方向および逆方向の巻線のサポート

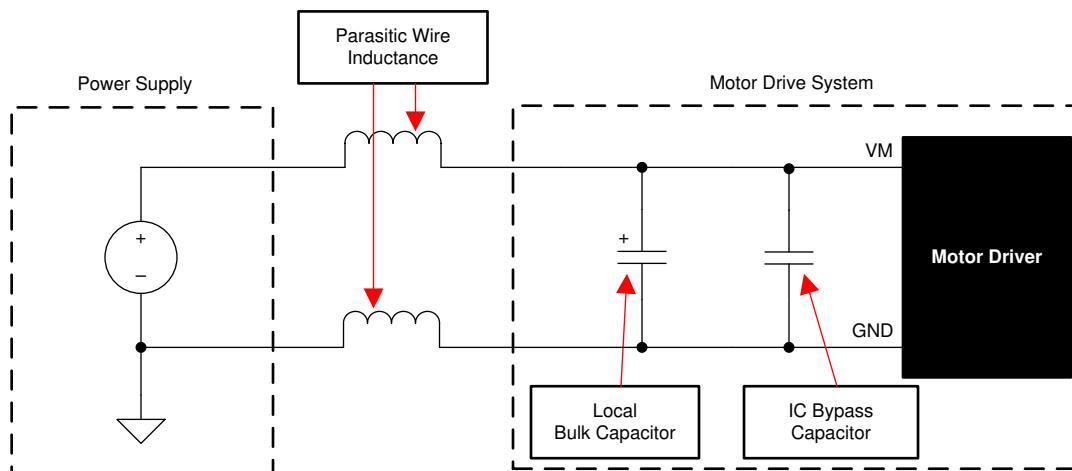

- アナログ、PWM、周波数、または I<sup>2</sup>C ベースの制御入力

- モーターのスタートアップと停止のオプションを構成可能

- オプションの閉ループ速度または電力制御、開ループ電圧制御

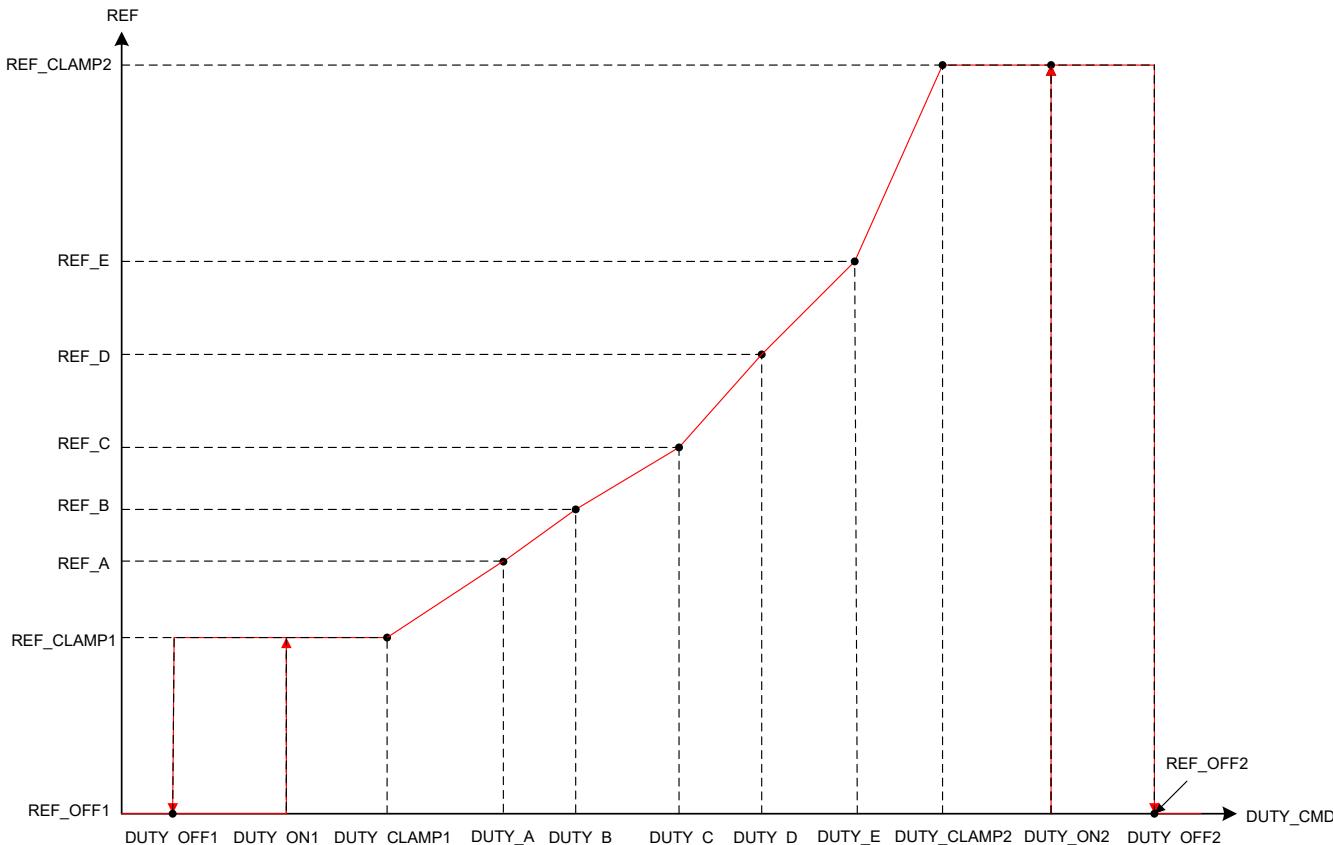

- 構成可能な 5 点リファレンス・プロファイルをサポート

- 電圧サージ防止の保護機能により過電圧を防止

- DACOUT を使用した可変監視

- 65V 三相ハーフブリッジ・ゲート・ドライバ

- 3 個のハイサイドおよび 3 個のローサイド N チャネル MOSFET を駆動、動作電圧 4.5~60V

- 100% の PWM デューティ・サイクルをサポート

- ブートストラップ・ベースのゲート・ドライバ・アキテクチャ

- 最大ピーカー・ソース / シンク電流: 1A/2A

- 電流検出アンプを内蔵

- 可変ゲイン (5, 10, 20, 40V/V)

- 低消費電力スリープ・モード

- $V_{VM} = 24V$ 、 $T_A = 25^\circ C$  で  $5\mu A$  (最大値)

- 速度ループの精度: 内部クロックの場合に 3% 未満

- 最大 100kHz の PWM 周波数をサポート

- VREG に接続された AVDD で、高精度 LDO (AVDD)  $3.3V \pm 3\%$ 、50mA をサポート

- 独立したドライバ・シャットダウン・パス (DRVOFF)

- スペクトラム拡散により EMI を軽減

- 一連の内蔵保護機能

- 電源低電圧誤動作防止 (UVLO)

- モーター・ロック検出 (3 つの異なる種類)

- 過電流保護 (OCP)

- サーマル・シャットダウン (TSD)

- フォルト状況表示ピン (nFAULT)

- I<sup>2</sup>C インターフェイスによるフォルト診断 (オプション)

## 2 アプリケーション

- プラシレス DC (BLDC) モーター・モジュール

- コードレス掃除機

- HVAC プロヴおよび換気装置

- 電気器具のファンとポンプ

- コードレスの庭園機器および電動工具、芝刈り機

## 3 概要

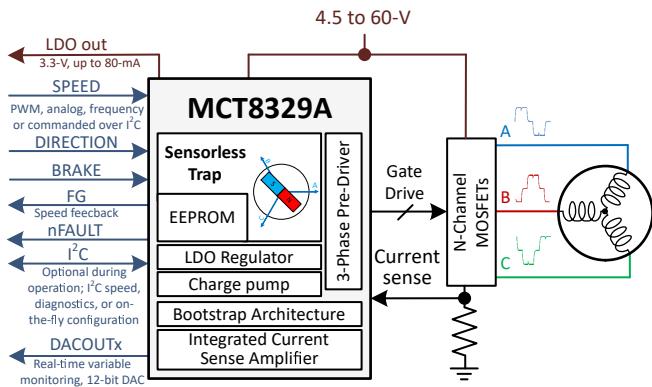

MCT8329A は、3 相プラシレス DC モーターの高速動作、または非常に高速な起動時間を必要とするアプリケーションに向けた、コード不要のシングルチップ・センサレス台形波ソリューションです。このデバイスには 3 つのハーフ・ブリッジ・ゲート・ドライバがあり、それぞれがハイサイドとローサイドの N チャネル・パワー MOSFET を駆動できます。このデバイスは、内部のチャージ・ポンプを使用して適切なゲート駆動電圧を生成し、ブートストラップ回路を使用してハイサイド MOSFET を強化します。100% デューティ・サイクルをサポートするためにトリクル・チャージ・ポンプを備えています。このゲート・ドライブのアキテクチャは、最大でソース (供給) 1A、シンク (吸い込み) 2A のピーカー・ゲート駆動電流をサポートします。MCT8329A は単一電源で動作でき、4.5V~60V の広い入力電源電圧範囲に対応します。

センサレス台形波制御は、モーターのスタートアップ動作から閉ループ動作まで、不揮発性 EEPROM (MCT8329A1I) のレジスタ設定を使用して細かく構成可能で、構成後はデバイスをスタンダードで動作できます。単一の外部シャント抵抗をサポートする内蔵電流センシング・アンプを使用して、モーター電流を検出します。デバイスは、PWM 入力、アナログ電圧、可変周波数の方形波、I<sup>2</sup>C コマンドによって速度コマンドを受信します。MCT8329A は、デバイス、モーター、システムをフォルト・イベントから保護するための多くの保護機能を内蔵しています。

### デバイス情報 (1)

| 部品番号           | パッケージ     | 本体サイズ (公称)      |

|----------------|-----------|-----------------|

| MCT8329A1IREER | VQFN (36) | 5.00mm × 4.00mm |

- (1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

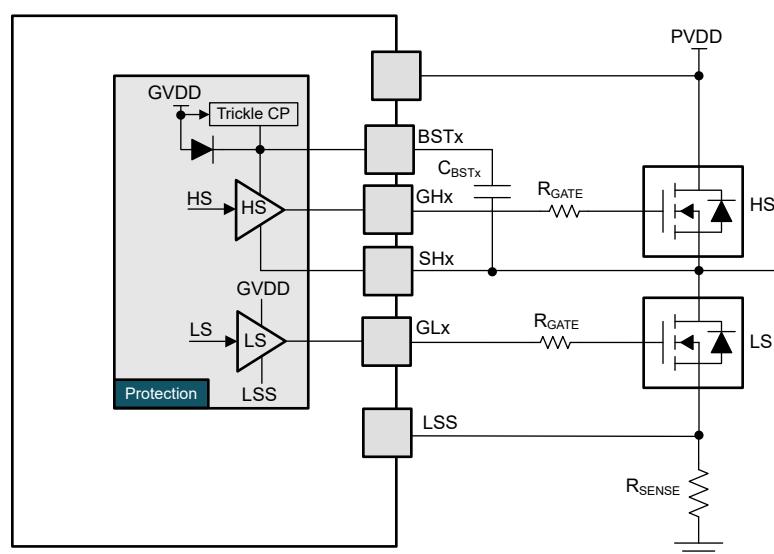

簡略回路図

## 目次

|                                             |           |                                            |            |

|---------------------------------------------|-----------|--------------------------------------------|------------|

| <b>1 特長</b>                                 | <b>1</b>  | 7.6 EEPROM アクセスと I <sup>2</sup> C インターフェイス | <b>73</b>  |

| <b>2 アプリケーション</b>                           | <b>1</b>  | 7.7 EEPROM (不揮発性) レジスタ・マップ                 | <b>79</b>  |

| <b>3 概要</b>                                 | <b>1</b>  | 7.8 RAM (揮発性) レジスタ・マップ                     | <b>131</b> |

| <b>4 改訂履歴</b>                               | <b>3</b>  | <b>8 アプリケーションと実装</b>                       | <b>149</b> |

| <b>5 ピン構成および機能</b>                          | <b>4</b>  | 8.1 アプリケーション情報                             | <b>149</b> |

| <b>6 仕様</b>                                 | <b>7</b>  | 8.2 代表的なアプリケーション                           | <b>149</b> |

| 6.1 絶対最大定格                                  | 7         | <b>9 電源に関する推奨事項</b>                        | <b>162</b> |

| 6.2 ESD 定格 (通信機器)                           | 8         | 9.1 バルク容量                                  | <b>162</b> |

| 6.3 推奨動作条件                                  | 9         | <b>10 レイアウト</b>                            | <b>163</b> |

| 6.4 熱に関する情報 (1 パッケージ)                       | 9         | 10.1 レイアウトのガイドライン                          | <b>163</b> |

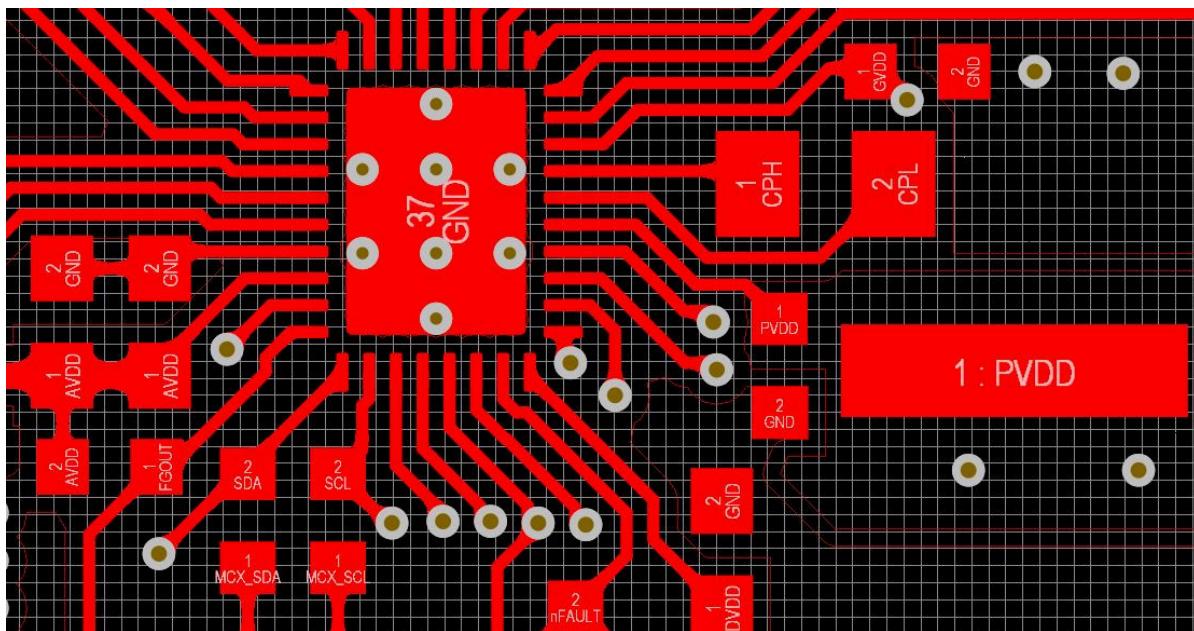

| 6.5 電気的特性                                   | 10        | 10.2 レイアウト例                                | <b>164</b> |

| 6.6 スタンダード・モードとファースト・モードの SDA および SCL バスの特性 | 17        | 10.3 熱に関する注意事項                             | <b>165</b> |

| 6.7 代表的な特性                                  | 19        | <b>11 デバイスおよびドキュメントのサポート</b>               | <b>166</b> |

| <b>7 詳細説明</b>                               | <b>20</b> | 11.1 ドキュメントのサポート                           | <b>166</b> |

| 7.1 概要                                      | 20        | 11.2 サポート・リソース                             | <b>166</b> |

| 7.2 機能ブロック図                                 | 21        | 11.3 商標                                    | <b>166</b> |

| 7.3 機能説明                                    | 22        | 11.4 静電気放電に関する注意事項                         | <b>166</b> |

| 7.4 デバイスの機能モード                              | 69        | 11.5 用語集                                   | <b>166</b> |

| 7.5 外部インターフェイス                              | 70        | <b>12 メカニカル、パッケージ、および注文情報</b>              | <b>166</b> |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付           | リビジョン | 注: |

|--------------|-------|----|

| January 2023 | *     | 初版 |

## 5 ピン構成および機能

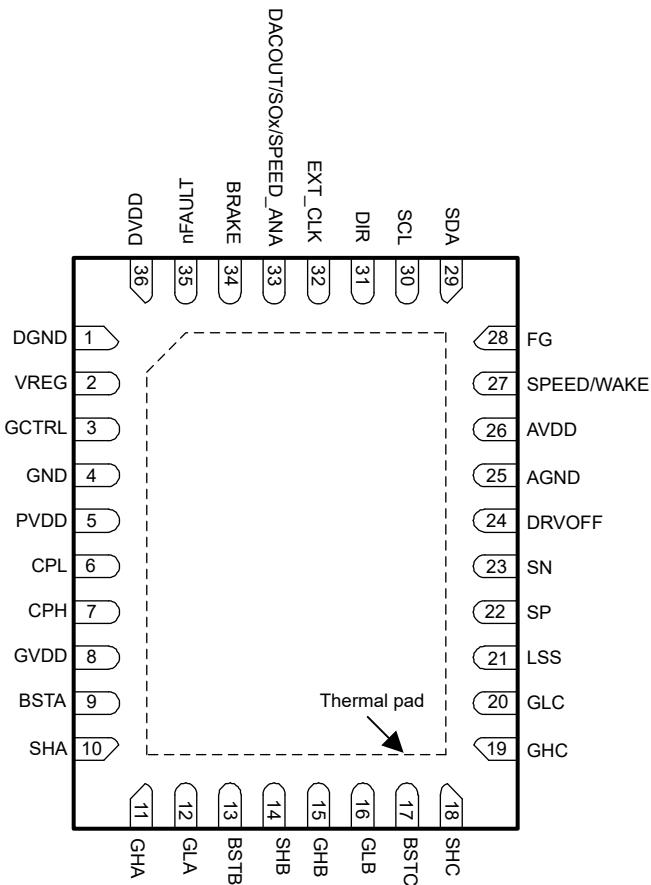

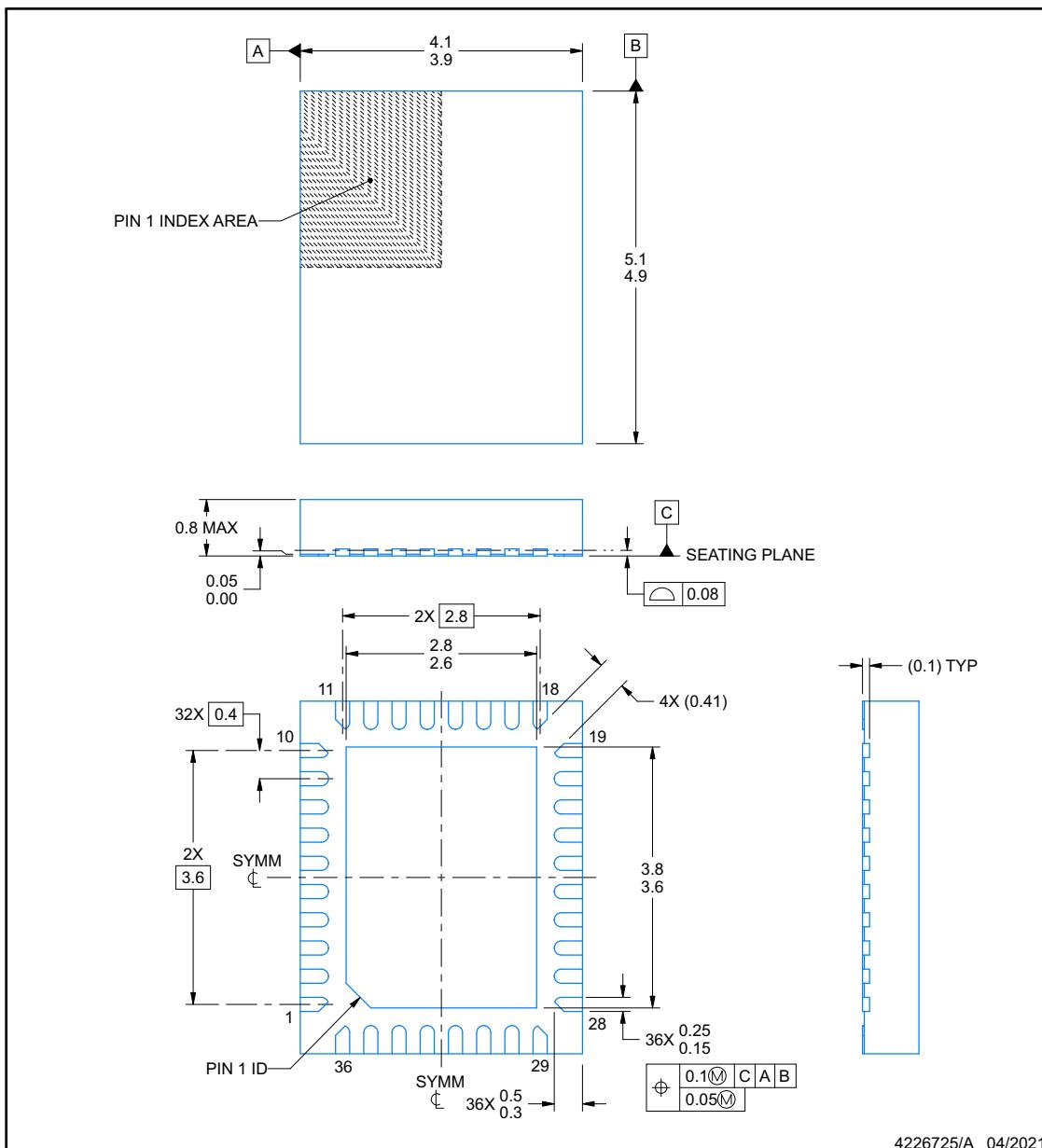

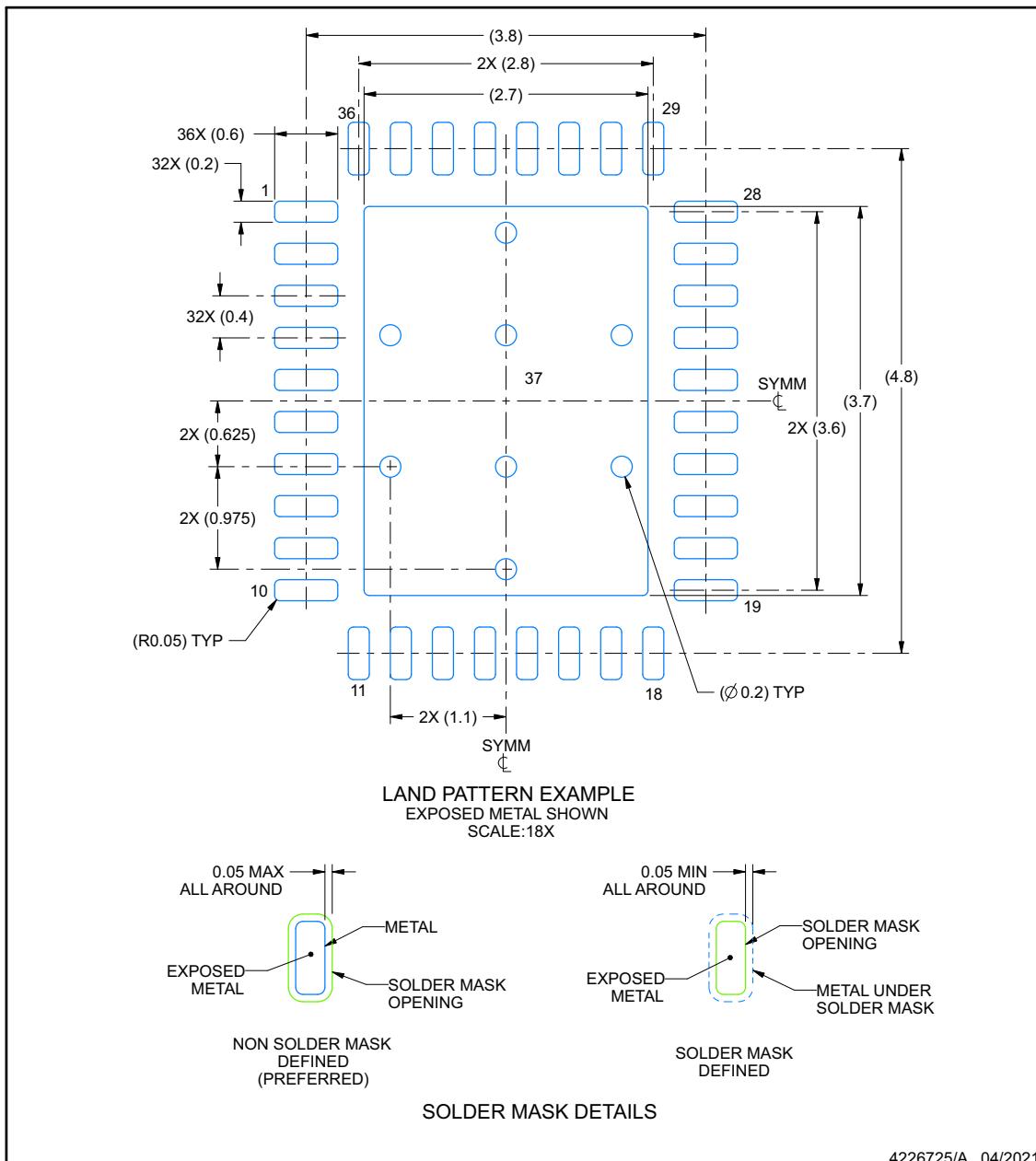

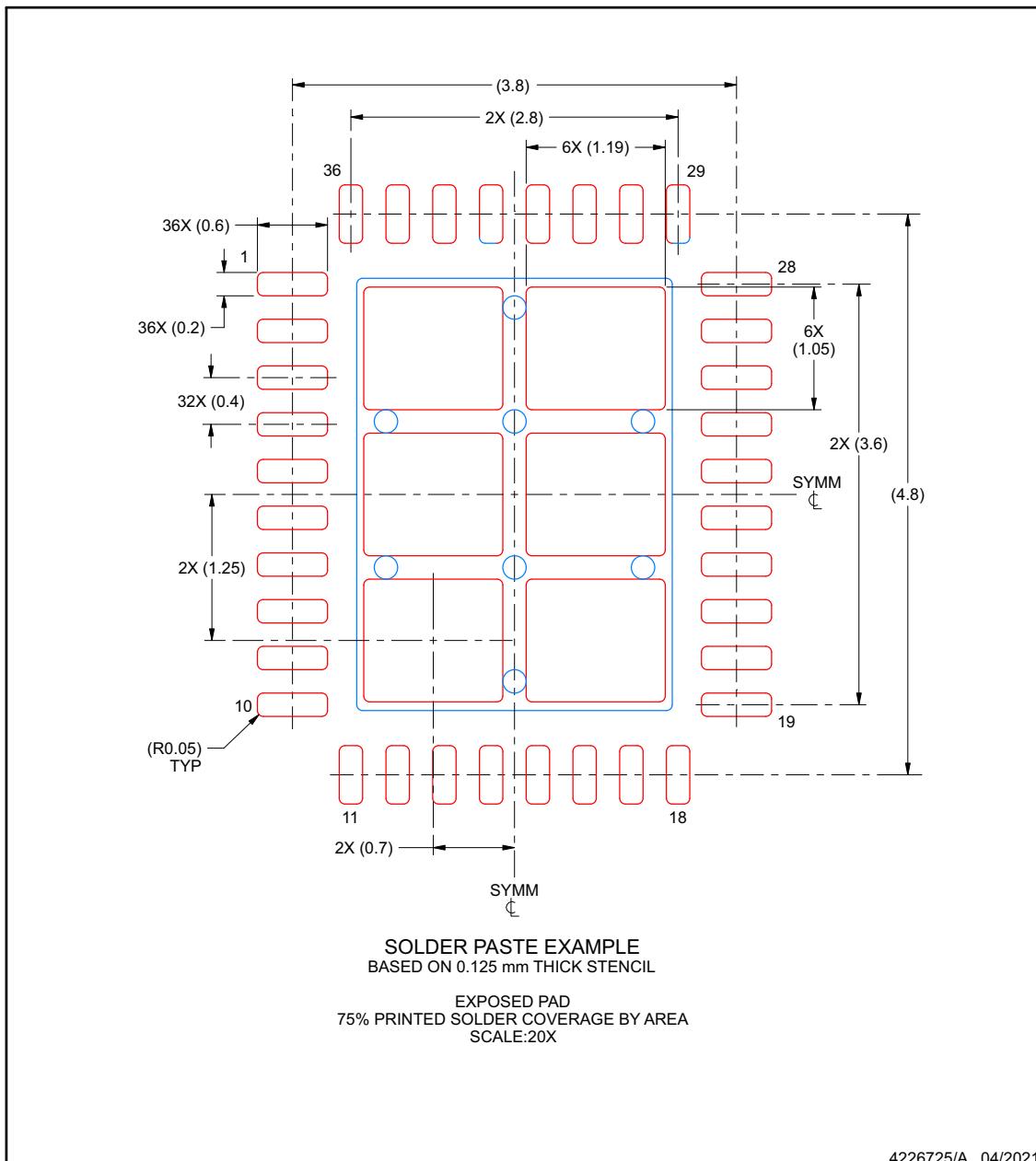

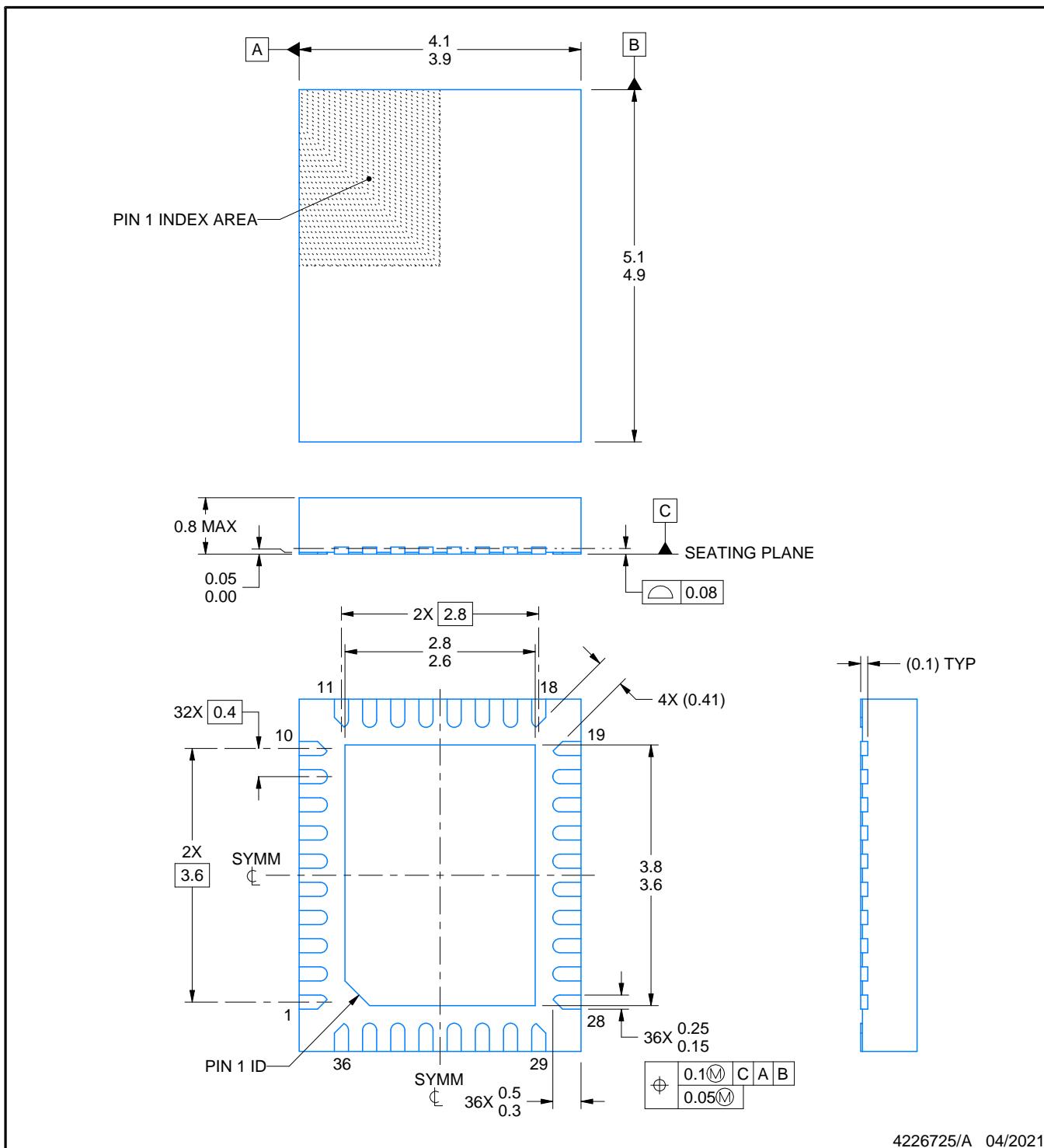

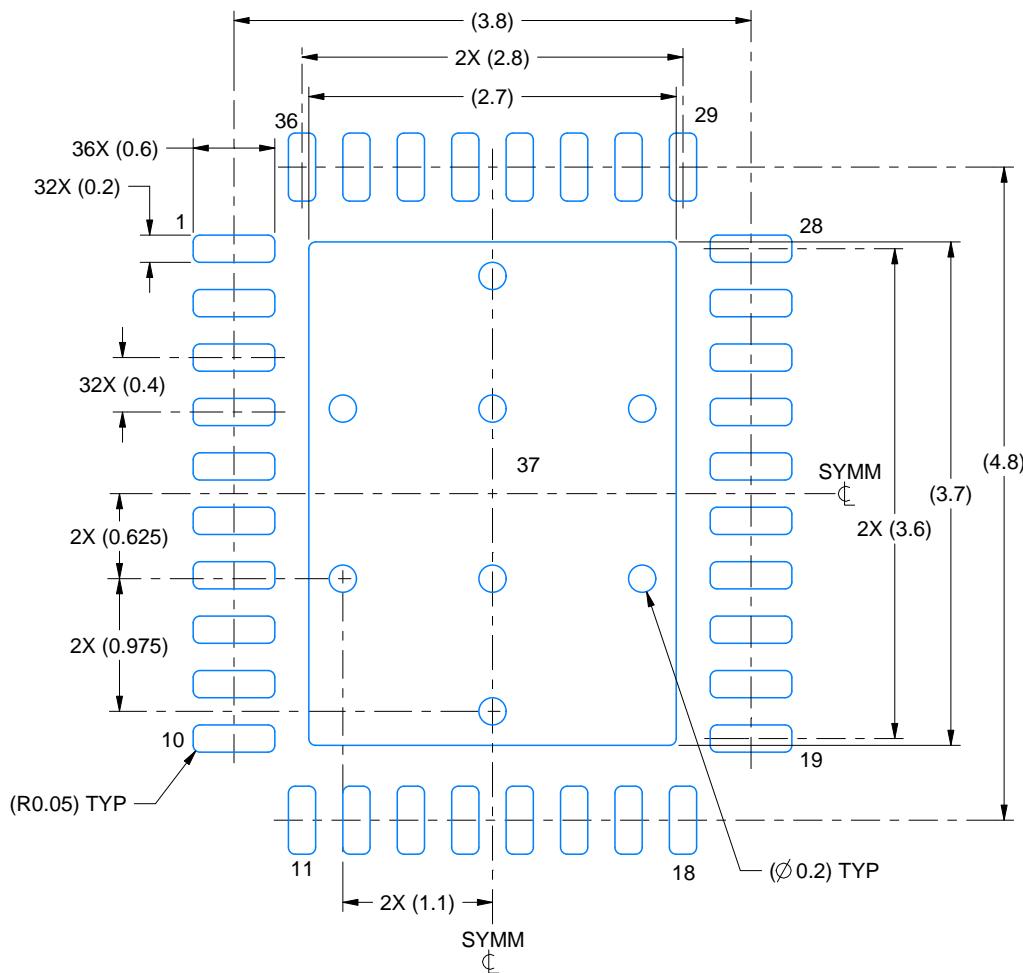

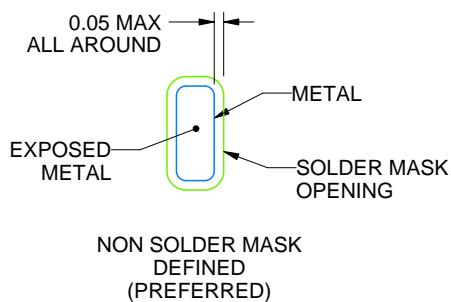

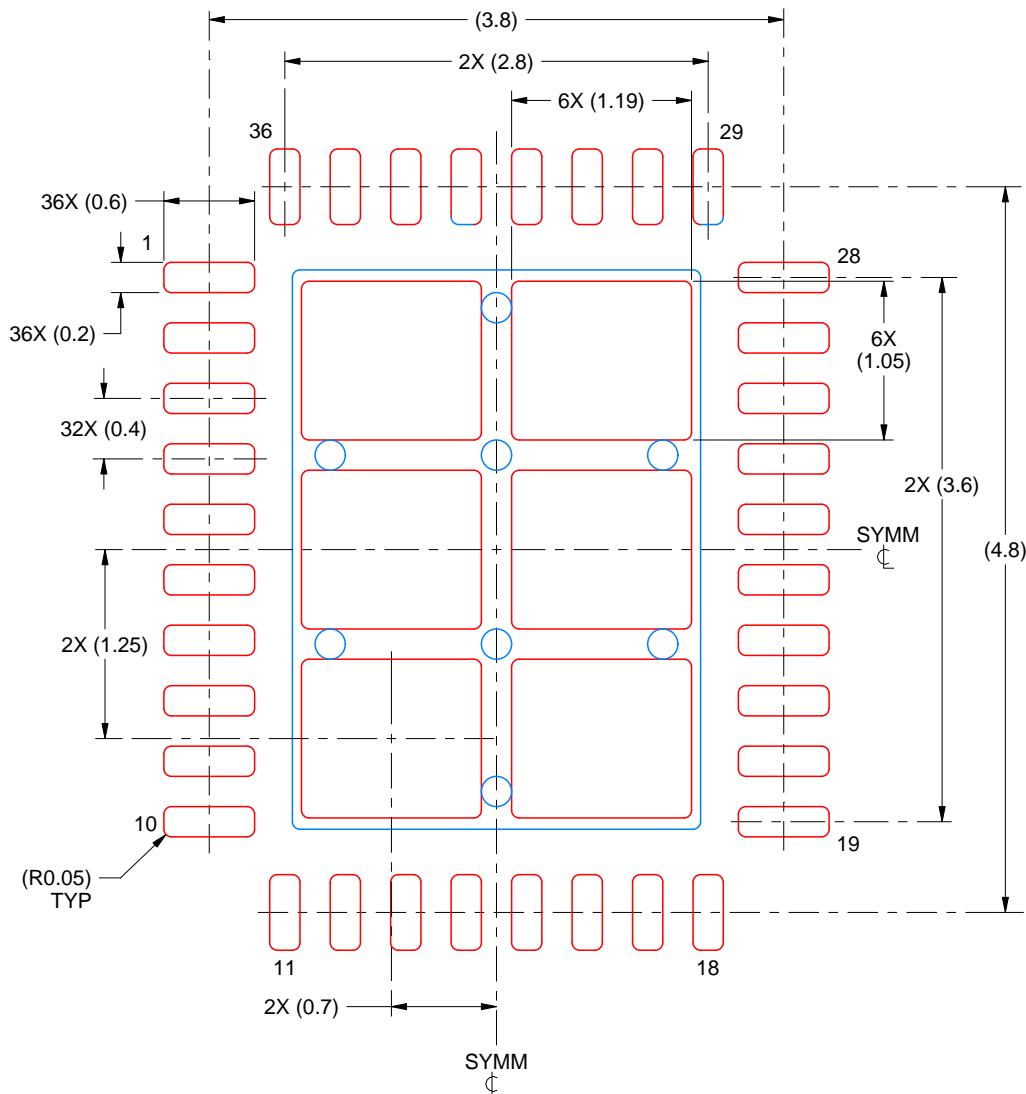

図 5-1. MCT8329A1 36 ピン VQFN (露出サーマル・パッド付き) 上面図

表 5-1. ピン機能

| ピン    | 36 ピン・パッケージ | タイプ (1) | 説明                                                                                                                                                                                 |

|-------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | MCT8329A1I  |         |                                                                                                                                                                                    |

| AGND  | 25          | GND     | デバイスのアナログ・グランド。                                                                                                                                                                    |

| AVDD  | 26          | PWR     | 3.3V レギュレータ出力。X5R または X7R、0.1 $\mu$ F、6.3V セラミック・コンデンサを AVDD ピンと AGND ピンの間に接続します。このレギュレータは、最大 50mA の電流を外部に供給できます (AVDD が VREG に短絡されている場合)。コンデンサの電圧定格を、ピンの通常動作電圧の 2 倍以上とすることを推奨します。 |

| BRAKE | 34          | I       | High → モーターにブレーキをかける。<br>Low → 通常動作<br>使用しない場合、10k $\Omega$ の抵抗を介して GND に接続します。                                                                                                    |

| BSTA  | 9           | O       | ブートストラップ出力ピン。X5R または X7R、1 $\mu$ F、25V セラミック・コンデンサを BSTA ピンと SHA ピンの間に接続します。                                                                                                       |

| BSTB  | 13          | O       | ブートストラップ出力ピン。X5R または X7R、1 $\mu$ F、25V セラミック・コンデンサを BSTB ピンと SHB ピンの間に接続します。                                                                                                       |

| BSTC  | 17          | O       | ブートストラップ出力ピン。X5R または X7R、1 $\mu$ F、25V セラミック・コンデンサを BSTC ピンと SHC ピンの間に接続します。                                                                                                       |

| CPH   | 7           | PWR     | チャージ・ポンプのスイッチング・ノード。X5R または X7R、PVDD 定格セラミック・コンデンサを CPH ピンと CPL ピンの間に接続します。コンデンサの電圧定格を、ピンの通常動作電圧の 2 倍以上とすることを推奨します。                                                                |

| CPL   | 6           | PWR     |                                                                                                                                                                                    |

**表 5-1. ピン機能 (continued)**

| ピン<br>名称                         | 36 ピン・パッケージ<br>MCT8329A1I | タイプ <sup>(1)</sup> | 説明                                                                                                                                                               |

|----------------------------------|---------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DACOUT/S<br>Ox/<br>SPEED_AN<br>A | 33                        | I/O                | 多目的ピン。DAC 出力、電流検出アンプ出力、アナログ・リファレンス(速度、電力、電圧)入力のいずれかとして構成できます。                                                                                                    |

| DGND                             | 1                         | GND                | デバイス・デジタル・グランド                                                                                                                                                   |

| DIR                              | 31                        | I                  | モーターの回転方向。<br>Low の場合、位相駆動シーケンスは OUT A → OUT B → OUT C<br>High の場合、位相駆動シーケンスは OUT A → OUT C → OUT B<br>使用しない場合、10kΩ の抵抗を介して GND に接続します。                          |

| DRVOFF                           | 24                        | I                  | 独立したドライバ・シャットダウン・パス。DRVOFF を High にプルすると、ゲート・ドライバをシャットダウン状態にすることで、すべての外部 MOSFET がターンオフされます。この信号は、デジタルおよび制御コアをバイパスおよびオーバーライドします。                                  |

| DVDD                             | 36                        | PWR                | 1.5V 内部レギュレータ出力。X5R または X7R、1μF、6.3V セラミック・コンデンサを DVDD ピンと DGND ピンの間に接続します。                                                                                      |

| EXT_CLK                          | 32                        | I                  | 外部クロック基準モードの外部クロック基準入力。                                                                                                                                          |

| FG                               | 28                        | O                  | モーター速度インジケータ出力。オープン・ドレイン出力には、1.8V～5V への外部プルアップ抵抗が必要です。そのピン機能を使わない場合でも、外部プルアップ抵抗を接続する必要があります。                                                                     |

| GCTRL                            | 3                         | O                  | VREG ピンを介してデジタル・サブシステムに電流を供給するためのレギュレータとして使用される外部 MOSFET のゲート制御。この機能は、デバイス内部の消費電力を低減するのに役立ちます。                                                                   |

| GHA                              | 11                        | O                  | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                                                                    |

| GHB                              | 15                        | O                  | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                                                                    |

| GHC                              | 19                        | O                  | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                                                                    |

| GLA                              | 12                        | O                  | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                                                                    |

| GLB                              | 16                        | O                  | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                                                                    |

| GLC                              | 20                        | O                  | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                                                                    |

| GND                              | 4                         | GND                | デバイスの電源グランド                                                                                                                                                      |

| GVDD                             | 8                         | PWR                | ゲート・ドライバの電源出力。X5R または X7R、10μF 以上の 30V 定格セラミック・ローカル・コンデンサを GVDD ピンと GND ピンの間に接続します。C <sub>BS1x</sub> の 10 倍を上回る容量値と、ピンの通常動作電圧の 2 倍以上の電圧定格を推奨します。                 |

| LSS                              | 21                        | PWR                | ローサイド・ソース・ピン。外部ローサイド MOSFET のすべてのソースをここに接続します。このピンはローサイド・ゲート・ドライバのシンク・パスであり、ローサイド MOSFET の VDS 電圧と VSEN_OCP 電圧を監視するための入力として機能します。                                |

| nFAULT                           | 35                        | O                  | フォルト・インジケータ。このピンは、フォルト条件によってロジック Low にプルされます。オープン・ドレイン出力には、1.8V～5V への外部プルアップ抵抗が必要です。そのピン機能を使わない場合でも、外部プルアップ抵抗を接続する必要があります。                                       |

| PVDD                             | 5                         | PWR                | ゲート・ドライバの電源入力。ブリッジ電源に接続します。X5R または X7R、0.1μF、PVDD の 2 倍を超える定格のセラミック・コンデンサと 10μF を超えるローカル・コンデンサを PVDD ピンと GND ピンの間に接続します。コンデンサの電圧定格を、ピンの通常動作電圧の 2 倍以上とすることを推奨します。 |

| SCL                              | 30                        | I                  | I <sup>2</sup> C クロック入力                                                                                                                                          |

| SDA                              | 29                        | I/O                | I <sup>2</sup> C データ・ライン                                                                                                                                         |

| SHA                              | 10                        | I/O                | ハイサイド・ソース・ピン。ハイサイド・パワー MOSFET のソースに接続します。このピンは VDS 監視用入力であり、ハイサイド・ゲート・ドライバのシンクのための出力です。                                                                          |

| SHB                              | 14                        | I/O                | ハイサイド・ソース・ピン。ハイサイド・パワー MOSFET のソースに接続します。このピンは VDS 監視用入力であり、ハイサイド・ゲート・ドライバのシンクのための出力です。                                                                          |

| SHC                              | 18                        | I/O                | ハイサイド・ソース・ピン。ハイサイド・パワー MOSFET のソースに接続します。このピンは VDS 監視用入力であり、ハイサイド・ゲート・ドライバのシンクのための出力です。                                                                          |

表 5-1. ピン機能 (continued)

| ピン<br>名称       | 36 ピン・パッケージ<br>MCT8329A1I | タイプ <sup>(1)</sup> | 説明                                                                                                                     |

|----------------|---------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|

| SN             | 23                        | I                  | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                                                                                         |

| SP             | 22                        | I                  | ローサイド電流シャント・アンプ入力。ローサイド・パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                                                           |

| SPEED/<br>WAKE | 27                        | I                  | マルチファンクション入力。<br>デバイス・スリープ / ウェーク入力。<br>デバイス速度入力。アナログ、PWM、周波数方式のリファレンス (速度、電力、電圧) 入力をサポートしています。                        |

| VREG           | 2                         | PWR                | 内部 DVDD LDO の電圧レギュレータ入力電源。AVDD または外部 3~5.5V に接続します。X5R または X7R、0.1 $\mu$ F、6.3V セラミック・コンデンサを VREG ピンと DGND ピンの間に接続します。 |

| 放熱パッド          | -                         | PWR                | GND に接続する必要があります。                                                                                                      |

(1) I = 入力、O = 出力、GND = グランド・ピン、PWR = 電源、NC = 未接続

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                                         |                                                                               | 最小値    | 最大値        | 単位 |

|-----------------------------------------|-------------------------------------------------------------------------------|--------|------------|----|

| 電源ピン電圧                                  | PVDD                                                                          | -0.3   | 65         | V  |

| ブートストラップ・ピン電圧                           | BSTx                                                                          | -0.3   | 80         | V  |

| ブートストラップ・ピン電圧                           | SHx を基準とした BSTx                                                               | -0.3   | 20         | V  |

| ブートストラップ・ピン電圧                           | GHx を基準とした BSTx                                                               | -0.3   | 20         | V  |

| チャージ・ポンプ・ピン電圧                           | CPL, CPH                                                                      | -0.3   | $V_{GVDD}$ | V  |

| グランド・ピン間の電圧差                            | GND, DGND, AGND                                                               | -0.3   | 0.3        | V  |

| 電圧レギュレータ・ピン電圧 (VREG)                    | VREG                                                                          | -0.3   | 6          | V  |

| ゲート制御ピン電圧 (GCTRL)                       | GCTRL                                                                         | -0.3   | 7          | V  |

| ゲート・ドライバ・レギュレータ・ピン電圧                    | GVDD                                                                          | -0.3   | 20         | V  |

| デジタル・レギュレータ・ピン電圧                        | DVDD                                                                          | -0.3   | 1.7        | V  |

| アナログ・レギュレータ・ピン電圧                        | AVDD                                                                          | -0.3   | 4          | V  |

| ロジック・ピン電圧                               | BRAKE, DRVOFF, DIR, EXT_CLK,<br>SCL, SDA, SPEED/WAKE,<br>DACOUT/SOx/SPEED_ANA | -0.3   | 6          | V  |

| オーブン・ドレイン・ピン出力電圧                        | nFAULT, FG                                                                    | -0.3   | 6          | V  |

| ハイサイド・ゲート駆動ピン電圧                         | GHx                                                                           | -8     | 80         | V  |

| 過渡 500ns ハイサイド・ゲート駆動ピン電圧                | GHx                                                                           | -10    | 80         | V  |

| ハイサイド・ゲート駆動ピン電圧                         | SHx を基準とした GHx                                                                | -0.3   | 20         | V  |

| ハイサイド・ソース・ピン電圧                          | SHx                                                                           | -8     | 70         | V  |

| 過渡 500ns ハイサイド・ソース・ピン電圧                 | SHx                                                                           | -10    | 72         | V  |

| ローサイド・ゲート駆動ピン電圧                         | LSS を基準とした GLx                                                                | -0.3   | 20         | V  |

| 過渡 500ns ローサイド・ゲート駆動ピン電圧 <sup>(2)</sup> | LSS を基準とした GLx                                                                | -1     | 20         | V  |

| ローサイド・ゲート駆動ピン電圧                         | GVDD を基準とした GLx                                                               |        | 0.3        | V  |

| 過渡 500ns ローサイド・ゲート駆動ピン電圧                | GVDD を基準とした GLx                                                               |        | 1          | V  |

| ローサイド・ソース検出ピン電圧                         | LSS                                                                           | -1     | 1          | V  |

| 過渡 500ns ローサイド・ソース検出ピン電圧                | LSS                                                                           | -10    | 8          | V  |

| ゲート駆動電流                                 | GHx, GLx                                                                      | 内部的に制限 | 内部的に制限     | A  |

| シャント・アンプ入力ピン電圧                          | SN, SP                                                                        | -1     | 1          | V  |

| 過渡 500ns シャント・アンプ入力ピン電圧                 | SN, SP                                                                        | -10    | 8          | V  |

| 周囲温度、 $T_A$                             |                                                                               | -40    | 125        | °C |

| 接合部温度、 $T_J$                            |                                                                               | -40    | 150        | °C |

| 保管温度、 $T_{stg}$                         |                                                                               | -65    | 150        | °C |

- (1) 絶対最大定格の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) GLx - LSS が負である場合、500ns の間、最大 5A に耐えます。

## 6.2 ESD 定格 (通信機器)

|             |       |                                             | 値          | 単位 |

|-------------|-------|---------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 (1)   | $\pm 2000$ | V  |

|             |       | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 (2) | $\pm 750$  |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                  |                                 |                                                   | 最小値 | 公称値     | 最大値     | 単位   |

|------------------|---------------------------------|---------------------------------------------------|-----|---------|---------|------|

| $V_{PVDD}$       | 電源電圧                            | PVDD                                              | 4.5 | 60      | 60      | V    |

| $V_{PVDD\_RAMP}$ | 電源投入時の電源電圧ランプ・レート               | PVDD                                              |     | 30      | 30      | V/us |

| $V_{BST}$        | $SH_x$ を基準とするブートストラップ・ピンの電圧     | SPEED/WAKE = High、出力はスイッチング                       | 4   | 20      | 20      | V    |

| $I_{AVDD}$ (1)   | レギュレータの外部負荷電流 (AVDD を VREG に接続) | AVDD                                              |     | 50      | 50      | mA   |

| $I_{TRICKLE}$    | トリクル・チャージ・ポンプの外部負荷電流            | BSTx                                              |     | 2       | 2       | μA   |

| $V_{VREG}$       | VGEG ピンの電圧                      | VREG                                              | 2.2 | 5.5     | 5.5     | V    |

| $V_{IN}$         | ロジック入力電圧                        | BRAKE, DRVOFF, DIR, EXT_CLK, SPEED/WAKE, SDA, SCL | 0   | 5.5     | 5.5     | V    |

| $f_{PWM}$        | PWM 周波数                         |                                                   | 0   | 100     | 100     | kHz  |

| $V_{OD}$         | オープン・ドレイン・プルアップ電圧               | FG, nFAULT                                        |     | 5.5     | 5.5     | V    |

| $I_{OD}$         | オープン・ドレイン出力電流                   | nFAULT                                            |     | -10     | -10     | mA   |

| $I_{GS}$ (1)     | 総平均ゲート駆動電流 (ローサイドとハイサイドを合わせて)   | $I_{GHx}, I_{GLx}$                                |     | 30      | 30      | mA   |

| $V_{SHSL}$       | $SH_x$ ピンのスルーレート                |                                                   |     | 4       | 4       | V/ns |

| $C_{BOOT}$       | BSTx と $SH_x$ との間のコンデンサ         |                                                   |     | 4.7 (2) | 4.7 (2) | μF   |

| $C_{GVDD}$       | GVDD と GND との間のコンデンサ            |                                                   |     |         | 130     | μF   |

| $T_A$            | 動作時周囲温度                         |                                                   | -40 | -40     | 125     | °C   |

| $T_J$            | 動作時接合部温度                        |                                                   | -40 | -40     | 150     | °C   |

(1) 消費電力および温度の制限に従う必要があります。

(2)  $C_{BSTx} > 4.7\mu F$  については、ブート・ダイオード (DBOOT) を流れる電流を制限する必要があります。

## 6.4 热に関する情報 (1 パッケージ)

| 熱評価基準 (1)            | MCT8329A            |      | 単位   |  |

|----------------------|---------------------|------|------|--|

|                      | REE (VQFN)          |      |      |  |

|                      | 36                  |      |      |  |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 37.7 | °C/W |  |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 23.3 | °C/W |  |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 16   | °C/W |  |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 3.8  | °C/W |  |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 16   | °C/W |  |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 5    | °C/W |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.5 電気的特性

4.5V  $\leq$   $V_{PVDD}$   $\leq$  60V, -40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{PVDD} = 24\text{V}$  が適用されます。

| パラメータ                                           | テスト条件                         | 最小値                                                                                                                                                                          | 標準値                   | 最大値  | 単位            |               |

|-------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|---------------|---------------|

| <b>電源 (PVDD, GVDD, AVDD, DVDD, VREG, GCTRL)</b> |                               |                                                                                                                                                                              |                       |      |               |               |

| $I_{PVDDQ}$                                     | PVDD スリープ・モード電流               | $V_{PVDD} = 24\text{V}$ 、 $V_{SPEED/WAKE} = 0$ 、 $T_A = 25^\circ\text{C}$ 、AVDD を VREG に接続                                                                                   | 3                     | 5    | $\mu\text{A}$ |               |

|                                                 |                               | $V_{SPEED/WAKE} = 0$ 、 $T_A = 125^\circ\text{C}$ 、AVDD を VREG に接続                                                                                                            | 3.5                   | 6    | $\mu\text{A}$ |               |

| $I_{PVDDS}$                                     | PVDD スタンバイ・モード電流              | $V_{PVDD} = 24\text{V}$ 、 $V_{SPEED/WAKE} < V_{EN\_SB}$ 、 $DRVOFF = \text{Low}$ 、 $T_A = 25^\circ\text{C}$ 、AVDD を VREG に接続                                                  | 25                    | 28   | $\text{mA}$   |               |

|                                                 |                               | $V_{SPEED/WAKE} < V_{EN\_SB}$ 、 $DRVOFF = \text{Low}$ 、AVDD を VREG に接続                                                                                                       | 25                    | 28   | $\text{mA}$   |               |

| $I_{PVDD}$                                      | PVDD アクティブ・モード電流              | $V_{PVDD} = 24\text{V}$ 、 $V_{SPEED/WAKE} > V_{EX\_SL}$ 、 $PWM\_FREQ\_OUT = 10000\text{b}$ (25kHz)、 $T_J = 25^\circ\text{C}$ 、FET もモーターも未接続、AVDD を VREG に接続                  | 28                    | 30   | $\text{mA}$   |               |

|                                                 |                               | $V_{PVDD} = 24\text{V}$ 、 $V_{SPEED/WAKE} > V_{EX\_SL}$ 、 $PWM\_FREQ\_OUT = 10000\text{b}$ (25kHz)、FET もモーターも未接続、AVDD を VREG に接続                                             | 28                    | 30   | $\text{mA}$   |               |

|                                                 |                               | $V_{PVDD} = 8\text{V}$ 、 $V_{SPEED/WAKE} > V_{EX\_SL}$ 、 $PWM\_FREQ\_OUT = 10000\text{b}$ (25kHz)、 $T_J = 25^\circ\text{C}$ 、FET もモーターも未接続、AVDD は VREG に未接続、VREG = 3.3V (外部) | 8.5                   | 14.1 | $\text{mA}$   |               |

|                                                 |                               | $V_{PVDD} = 24\text{V}$ 、 $V_{SPEED/WAKE} > V_{EX\_SL}$ 、 $PWM\_FREQ\_OUT = 10000\text{b}$ (25kHz)、FET もモーターも未接続、AVDD は VREG に未接続、VREG = 3.3V (外部)                           | 8.5                   | 11.1 | $\text{mA}$   |               |

| $I_{VREG}$                                      | VREG ピン・アクティブ・モード電流           | $V_{SPEED/WAKE} > V_{EX\_SL}$ 、 $PWM\_FREQ\_OUT = 10000\text{b}$ (25kHz)、VREG を AVDD に接続                                                                                     |                       | 25   | $\text{mA}$   |               |

| $IL_{BSx}$                                      | ブートストラップ・ピンのリーク電流             | $V_{BSTR} = V_{SHx} = 60\text{V}$ 、 $V_{GVDD} = 0\text{V}$ 、 $V_{SPEED/WAKE} = \text{Low}$                                                                                   | 5                     | 10   | $\mu\text{A}$ |               |

| $IL_{BS\_TRAN}$                                 | ブートストラップ・ピンのアクティブ・モードの過渡リーク電流 | $GLx = GHx = 20\text{kHz}$ でスイッチング、FET 未接続                                                                                                                                   | 60                    | 115  | 300           | $\mu\text{A}$ |

| $V_{GVDD\_RT}$                                  | GVDD ゲート・ドライバ・レギュレータ電圧 (室温)   | $V_{PVDD} \geq 40\text{V}$ 、 $I_{GS} = 10\text{mA}$ 、 $T_J = 25^\circ\text{C}$                                                                                               | 11.8                  | 13   | 15            | V             |

|                                                 |                               | $22\text{V} \leq V_{PVDD} \leq 40\text{V}$ 、 $I_{GS} = 30\text{mA}$ 、 $T_J = 25^\circ\text{C}$                                                                               | 11.8                  | 13   | 15            | V             |

|                                                 |                               | $8\text{V} \leq V_{PVDD} \leq 22\text{V}$ 、 $I_{GS} = 30\text{mA}$ 、 $T_J = 25^\circ\text{C}$                                                                                | 11.8                  | 13   | 15            | V             |

|                                                 |                               | $6.75\text{V} \leq V_{PVDD} \leq 8\text{V}$ 、 $I_{GS} = 10\text{mA}$ 、 $T_J = 25^\circ\text{C}$                                                                              | 11.8                  | 13   | 14.5          | V             |

|                                                 |                               | $4.5\text{V} \leq V_{PVDD} \leq 6.75\text{V}$ 、 $I_{GS} = 10\text{mA}$ 、 $T_J = 25^\circ\text{C}$                                                                            | $V_{PVDD} - 1$<br>2 * |      | 13.5          | V             |

4.5V  $\leq V_{PVDD} \leq 60V$ , -40°C  $\leq T_J \leq 150^{\circ}C$  (特に記述のない限り)。標準値には  $T_A = 25^{\circ}C$ 、 $V_{PVDD} = 24V$  が適用されます。

| パラメータ          |                         | テスト条件                                                                     | 最小値   | 標準値              | 最大値  | 単位 |

|----------------|-------------------------|---------------------------------------------------------------------------|-------|------------------|------|----|

| $V_{GVDD}$     | GVDD ゲート・ドライバ・レギュレータ電圧  | $V_{PVDD} \geq 40V$ , $I_{GS} = 10mA$                                     | 11.5  | 15.5             | 15.5 | V  |

|                |                         | $22V \leq V_{PVDD} \leq 40V$ , $I_{GS} = 30mA$                            | 11.5  | 15.5             | 15.5 | V  |

|                |                         | $8V \leq V_{PVDD} \leq 22V$ , $I_{GS} = 30mA$                             | 11.5  | 15.5             | 15.5 | V  |

|                |                         | $6.75V \leq V_{PVDD} \leq 8V$ , $I_{GS} = 10mA$                           | 11.5  | 14.5             | 14.5 | V  |

|                |                         | $4.5V \leq V_{PVDD} \leq 6.75V$ , $I_{GS} = 10mA$                         | 2 *   | $V_{PVDD} - 1.4$ | 13.5 | V  |

| $V_{AVDD\_RT}$ | AVDD アナログ・レギュレータ電圧 (室温) | $V_{PVDD} \geq 6V$ , $0mA \leq I_{AVDD} \leq 30mA$ , $T_J = 25^{\circ}C$  | 3.26  | 3.3              | 3.33 | V  |

|                |                         | $V_{PVDD} \geq 6V$ , $30mA \leq I_{AVDD} \leq 80mA$ , $T_J = 25^{\circ}C$ | 3.2   | 3.3              | 3.4  | V  |

|                |                         | $V_{PVDD} \geq 6V$ , $0mA \leq I_{AVDD} \leq 50mA$ , $T_J = 25^{\circ}C$  | 3.13  | 3.3              | 3.46 | V  |

| $V_{DVDD}$     | デジタル・レギュレータ電圧           | $V_{REG} = 3.3V$                                                          | 1.4   | 1.55             | 1.65 | V  |

| $V_{AVDD}$     | AVDD アナログ・レギュレータ電圧      | $V_{PVDD} \geq 6V$ , $0mA \leq I_{AVDD} \leq 80mA$                        | 3.2   | 3.3              | 3.4  | V  |

|                |                         | $V_{PVDD} \geq 6V$ , $0mA \leq I_{AVDD} \leq 50mA$                        | 3.125 | 3.3              | 3.5  | V  |

| $V_{GCTRL}$    | ゲート制御電圧                 | $V_{PVDD} > 4.5V$                                                         | 4.9   | 5.7              | 6.5  | V  |

#### ゲート・ドライバ (GHx, GLx, SHx, SLx)

|                      |                                                  |                                                 |      |       |      |           |

|----------------------|--------------------------------------------------|-------------------------------------------------|------|-------|------|-----------|

| $V_{GSHx\_LO}$       | ハイサイド・ゲート駆動の Low レベル電圧                           | $I_{GHx} = -100mA$ , $V_{GVDD} = 12V$ , FET 未接続 | 0.05 | 0.11  | 0.24 | V         |

| $V_{GSHx\_HI}$       | ハイサイド・ゲート駆動の High レベル電圧 ( $V_{BSTx} - V_{GHx}$ ) | $I_{GHx} = 100mA$ , $V_{GVDD} = 12V$ , FET 未接続  | 0.28 | 0.44  | 0.82 | V         |

| $V_{GSLx\_LO}$       | ローサイド・ゲート駆動の Low レベル電圧                           | $I_{GLx} = -100mA$ , $V_{GVDD} = 12V$ , FET 未接続 | 0.05 | 0.11  | 0.27 | V         |

| $V_{GSLx\_HI}$       | ローサイド・ゲート駆動の High レベル電圧 ( $V_{GVDD} - V_{GLx}$ ) | $I_{GLx} = 100mA$ , $V_{GVDD} = 12V$ , FET 未接続  | 0.28 | 0.44  | 0.82 | V         |

| $R_{DS(ON)\_PU\_HS}$ | ハイサイド・プルアップ・スイッチ抵抗                               | $I_{GHx} = 100mA$ , $V_{GVDD} = 12V$            | 2.7  | 4.5   | 8.4  | $\Omega$  |

| $R_{DS(ON)\_PD\_HS}$ | ハイサイド・プルダウン・スイッチ抵抗                               | $I_{GHx} = 100mA$ , $V_{GVDD} = 12V$            | 0.5  | 1.1   | 2.4  | $\Omega$  |

| $R_{DS(ON)\_PU\_LS}$ | ローサイド・プルアップ・スイッチ抵抗                               | $I_{GLx} = 100mA$ , $V_{GVDD} = 12V$            | 2.7  | 4.5   | 8.3  | $\Omega$  |

| $R_{DS(ON)\_PD\_LS}$ | ローサイド・プルダウン・スイッチ抵抗                               | $I_{GLx} = 100mA$ , $V_{GVDD} = 12V$            | 0.5  | 1.1   | 2.8  | $\Omega$  |

| $I_{DRIVEP\_HS}$     | ハイサイド・ピーク・ソース・ゲート電流                              | $V_{GSHx} = 12V$                                | 550  | 1,000 | 1575 | mA        |

| $I_{DRIVEN\_HS}$     | ハイサイド・ピーク・シンク・ゲート電流                              | $V_{GSHx} = 0V$                                 | 1150 | 2000  | 2675 | mA        |

| $I_{DRIVEP\_LS}$     | ローサイド・ピーク・ソース・ゲート電流                              | $V_{GSLx} = 12V$                                | 550  | 1000  | 1575 | mA        |

| $I_{DRIVEN\_LS}$     | ローサイド・ピーク・シンク・ゲート電流                              | $V_{GSLx} = 0V$                                 | 1150 | 2000  | 2675 | mA        |

| $R_{PD\_LS}$         | ローサイド・パッシブ・プルダウン                                 | GLx から LSS                                      | 80   | 100   | 120  | $k\Omega$ |

| $R_{PDPA\_HS}$       | ハイサイド・セミアクティブ・プルダウン                              | GHx から SHx, $V_{GSHx} = 2V$                     | 8    | 10    | 12.5 | $k\Omega$ |

#### ブートストラップ・ダイオード

|             |                                                        |                               |     |     |   |          |

|-------------|--------------------------------------------------------|-------------------------------|-----|-----|---|----------|

| $V_{BOOTD}$ | ブートストラップ・ダイオードの順方向電圧                                   | $I_{BOOT} = 100\mu A$         |     | 0.8 | V |          |

|             |                                                        | $I_{BOOT} = 100mA$            |     | 1.6 | V |          |

| $R_{BOOTD}$ | ブートストラップの動的抵抗 ( $\Delta V_{BOOTD} / \Delta I_{BOOT}$ ) | $I_{BOOT} = 100mA$ および $50mA$ | 4.5 | 5.5 | 9 | $\Omega$ |

#### ロジック・レベル入力 (BRAKE, DIR, EXT\_CLK, SCL, SDA, SPEED/WAKE)

|          |               |                     |  |                 |   |

|----------|---------------|---------------------|--|-----------------|---|

| $V_{IL}$ | 入力ロジック Low 電圧 | $AVDD = 3\sim 3.6V$ |  | $0.25^* / AVDD$ | V |

|----------|---------------|---------------------|--|-----------------|---|

4.5V  $\leq$  V<sub>PVDD</sub>  $\leq$  60V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C (特に記述のない限り)。標準値には T<sub>A</sub> = 25°C、V<sub>PVDD</sub> = 24V が適用されます。

| パラメータ                          |                | テスト条件                    | 最小値    | 標準値  | 最大値  | 単位 |

|--------------------------------|----------------|--------------------------|--------|------|------|----|

| V <sub>IH</sub>                | 入力ロジック High 電圧 | AVDD = 3~3.6V            | 0.65 * | AVDD |      | V  |

| V <sub>HYS</sub>               | 入力ヒステリシス       |                          | 50     | 500  | 800  | mV |

| I <sub>IL</sub>                | 入力ロジック Low 電流  | AVDD = 3~3.6V            | -0.15  |      | 0.15 | μA |

| I <sub>IH</sub>                | 入力ロジック High 電流 | AVDD = 3~3.6V            | -0.3   |      | 0.1  | μA |

| R <sub>PD_SPEED</sub>          | 入力プルダウン抵抗      | SPEED/WAKE ピンから GND に対して | 0.6    | 1    | 1.4  | MΩ |

| <b>ロジック・レベル入力 (DRVOFF)</b>     |                |                          |        |      |      |    |

| V <sub>IL</sub>                | 入力ロジック Low 電圧  |                          |        | 0.8  |      | V  |

| V <sub>IH</sub>                | 入力ロジック High 電圧 |                          | 2.2    |      |      | V  |

| V <sub>HYS</sub>               | 入力ヒステリシス       |                          | 200    | 400  | 650  | mV |

| I <sub>IL</sub>                | 入力ロジック Low 電流  | ピン電圧 = 0V                | -1     | 0    | 1    | μA |

| I <sub>IH</sub>                | 入力ロジック High 電流 | ピン電圧 = 5V                | 7      | 20   | 35   | μA |

| R <sub>PD_DRVOFF</sub>         | 入力プルダウン抵抗      | DRVOFF から GND に対して       | 100    | 200  | 300  | kΩ |

| <b>オープン・ドレイン出力 (nFAULT、FG)</b> |                |                          |        |      |      |    |

| V <sub>OL</sub>                | 出力ロジック Low 電圧  | I <sub>OD</sub> = -5mA   |        | 0.4  |      | V  |

| I <sub>OZ</sub>                | 出力ロジック High 電流 | V <sub>OD</sub> = 3.3V   | 0      | 0.5  |      | μA |

| <b>SPEED 入力 - アナログ・モード</b>     |                |                          |        |      |      |    |

| V <sub>ANA_FS</sub>            | アナログ・フルスピード電圧  |                          | 2.95   | 3    | 3.05 | V  |

| V <sub>ANA_RES</sub>           | アナログ電圧分解能      |                          |        | 732  |      | μV |

4.5V  $\leq V_{PVDD} \leq 60V$ 、-40°C  $\leq T_J \leq 150°C$  (特に記述のない限り)。標準値には  $T_A = 25°C$ 、 $V_{PVDD} = 24V$  が適用されます。

| パラメータ                     | テスト条件     | 最小値                                  | 標準値  | 最大値  | 単位      |

|---------------------------|-----------|--------------------------------------|------|------|---------|

| <b>SPEED 入力 - PWM モード</b> |           |                                      |      |      |         |

| $f_{PWM}$                 | PWM 入力周波数 |                                      | 0.01 | 95   | kHz     |

| Res <sub>PWM</sub>        | PWM 入力分解能 | $f_{PWM} = 0.01 \sim 0.35\text{kHz}$ | 11   | 12   | 13 ビット  |

|                           |           | $f_{PWM} = 0.35 \sim 2\text{kHz}$    | 12   | 13   | 14 ビット  |

|                           |           | $f_{PWM} = 2 \sim 3.5\text{kHz}$     | 11   | 11.5 | 12 ビット  |

|                           |           | $f_{PWM} = 3.5 \sim 7\text{kHz}$     | 13   | 13.5 | 14 ビット  |

|                           |           | $f_{PWM} = 7 \sim 14\text{kHz}$      | 12   | 12.5 | 13 ビット  |

|                           |           | $f_{PWM} = 14 \sim 29.2\text{kHz}$   | 11   | 11.5 | 12 ビット  |

|                           |           | $f_{PWM} = 29.3 \sim 60\text{kHz}$   | 10   | 10.5 | 11 ビット  |

|                           |           | $f_{PWM} = 60 \sim 95\text{kHz}$     | 8    | 9    | 10 ビット数 |

**SPEED 入力 - 周波数モード**

|                 |             |                  |   |       |    |

|-----------------|-------------|------------------|---|-------|----|

| $f_{PWM\_FREQ}$ | PWM 入力周波数範囲 | デューティ・サイクル = 50% | 3 | 32767 | Hz |

|-----------------|-------------|------------------|---|-------|----|

**スリープ・モード**

|                       |                                      |                                                                                                            |     |    |                   |

|-----------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------|-----|----|-------------------|

| $V_{EN\_SL}$          | スリープ・モードに移行するためのアナログ電圧               | $SPD\_CTRL\_MODE = 00b$ (アナログ・モード)                                                                         |     | 40 | mV                |

| $V_{EX\_SL}$          | スリープ・モードを終了するためのアナログ電圧               |                                                                                                            | 2.6 |    | V                 |

| $t_{DET\_ANA}$        | SPEED/WAKE ピンでウェークアップ信号を検出するために必要な時間 | $SPD\_CTRL\_MODE = 00b$ (アナログ・モード)、 $V_{SPEED/WAKE} > V_{EX\_SL}$                                          | 0.5 | 1  | 1.5 $\mu\text{s}$ |

| $t_{WAKE}$            | スリープ・モードからのウェークアップ時間                 | $V_{SPEED/WAKE} > V_{EX\_SL}$ から DVDD 電圧利用可能まで、 $SPD\_CTRL\_MODE = 00b$ (アナログ・モード)                         |     | 3  | 5 ms              |

| $t_{EX\_SL\_DR\_ANA}$ | スリープ・モードから復帰後、モーターを駆動するために必要な時間      | $SPD\_CTRL\_MODE = 00b$ (アナログ・モード)<br>$V_{SPEED/WAKE} > V_{EX\_SL}$ 、ISD 検出は無効化                            |     | 30 | ms                |

| $t_{DET\_PWM}$        | SPEED ピンでウェークアップ信号を検出するために必要な時間      | $SPD\_CTRL\_MODE = 01b$ (PWM モード) または 11b (周波数モード)、 $V_{SPEED/WAKE} > V_{IH}$                              | 0.5 | 1  | 1.5 $\mu\text{s}$ |

| $t_{WAKE\_PWM}$       | スリープ・モードからのウェークアップ時間                 | $V_{SPEED/WAKE} > V_{IH}$ から DVDD 電圧利用可能かつ nFault 解放まで、 $SPD\_CTRL\_MODE = 01b$ (PWM モード) または 11b (周波数モード) |     | 3  | 5 ms              |

| $t_{EX\_SL\_DR\_PWM}$ | スリープ状態から復帰後、モーターを駆動するために必要な時間        | $SPD\_CTRL\_MODE = 01b$ (PWM モード)<br>$V_{SPEED/WAKE} > V_{IH}$ 、ISD 検出は無効化                                 |     | 30 | ms                |

| $t_{DET\_SL\_ANA}$    | スリープ・コマンドを検出するために必要な時間               | $SPD\_CTRL\_MODE = 00b$ (アナログ・モード)<br>$V_{SPEED/WAKE} < V_{EN\_SL}$ 、 $SLEEP\_TIME = 00b$ または 01b          | 0.5 | 1  | 2 ms              |

4.5V  $\leq$   $V_{PVDD}$   $\leq$  60V, -40°C  $\leq$   $T_J$   $\leq$  150°C (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ 、 $V_{PVDD} = 24\text{V}$  が適用されます。

| パラメータ              | テスト条件                                                                                                                                                                          | 最小値                                                                                    | 標準値  | 最大値   | 単位 |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-------|----|

| $t_{DET\_SL\_PWM}$ | SPD_CTRL_MODE = 01b (PWM モード) または 11b (周波数モード)、 $V_{SPEED}/WAKE < V_{IL}$ (PWM モードおよび周波数モード)、 $SLEEP\_TIME = 00b$                                                              | 0.035                                                                                  | 0.05 | 0.065 | ms |

|                    | SPD_CTRL_MODE = 01b (PWM モード) または 11b (周波数モード)、 $V_{SPEED}/WAKE < V_{IL}$ (PWM モードおよび周波数モード)、 $SLEEP\_TIME = 01b$                                                              | 0.14                                                                                   | 0.2  | 0.26  | ms |

|                    | SPD_CTRL_MODE = 01b (PWM モード) または 11b (周波数モード) または 00b (アナログ・モード)、 $V_{SPEED}/WAKE < V_{IL}$ (PWM モードおよび周波数モード)、 $V_{SPEED}/WAKE < V_{EN\_SL}$ (アナログ・モード)、 $SLEEP\_TIME = 10b$ | 14                                                                                     | 20   | 26    | ms |

|                    | SPD_CTRL_MODE = 01b (PWM モード) または 11b (周波数モード) または 00b (アナログ・モード)、 $V_{SPEED}/WAKE < V_{IL}$ (PWM モードおよび周波数モード)、 $V_{SPEED}/WAKE < V_{EN\_SL}$ (アナログ・モード)、 $SLEEP\_TIME = 11b$ | 140                                                                                    | 200  | 260   | ms |

| $t_{EN\_SL}$       | スリープ・コマンドの検出後、モーターの駆動を停止するために必要な時間                                                                                                                                             | $V_{SPEED}/WAKE < V_{EN\_SL}$ (アナログ・モード) または $V_{SPEED}/WAKE < V_{IL}$ (PWM および周波数モード) | 1    | 2     | ms |

4.5V  $\leq V_{PVDD} \leq 60V$ 、-40°C  $\leq T_J \leq 150°C$  (特に記述のない限り)。標準値には  $T_A = 25°C$ 、 $V_{PVDD} = 24V$  が適用されます。

| パラメータ                 | テスト条件                                                                     | 最小値                                                                                                       | 標準値   | 最大値  | 単位    |    |

|-----------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|-------|----|

| <b>スタンバイ・モード</b>      |                                                                           |                                                                                                           |       |      |       |    |

| $t_{EX\_SB\_DR\_ANA}$ | スタンバイ・モードを終了した後、モーターを駆動するために必要な時間<br>$V_{SPEED} > V_{EN\_SB}$ 、ISD 検出は無効化 |                                                                                                           |       | 6    | ms    |    |

| $t_{EX\_SB\_DR\_PWM}$ | スタンバイ・モードを終了した後、モーターを駆動するために必要な時間                                         |                                                                                                           |       | 6    | ms    |    |

| $t_{DET\_SB\_ANA}$    | スタンバイ・モードを検出するために必要な時間<br>$V_{SPEED} < V_{EN\_SB}$                        | 0.5                                                                                                       | 1     | 2    | ms    |    |

| $t_{EN\_SB\_PWM}$     | スタンバイ・コマンドを検出するために必要な時間                                                   | SPD_CTRL_MODE = 00b (アナログ・モード)<br>$V_{SPEED} < V_{IL}$ 、SLEEP_TIME = 00b                                  | 0.035 | 0.05 | 0.065 | ms |

|                       |                                                                           | SPD_CTRL_MODE = 01b (PWM モード)<br>または 11b (周波数モード)、<br>$V_{SPEED} < V_{IL}$ 、SLEEP_TIME = 01b              | 0.14  | 0.2  | 0.26  | ms |

|                       |                                                                           | SPD_CTRL_MODE = 01b (PWM モード)<br>または 11b (周波数モード)、<br>$V_{SPEED} < V_{IL}$ 、SLEEP_TIME = 10b              | 14    | 20   | 26    | ms |

|                       |                                                                           | SPD_CTRL_MODE = 01b (PWM モード)<br>または 11b (周波数モード)、<br>$V_{SPEED} < V_{IL}$ 、SLEEP_TIME = 11b              | 140   | 200  | 260   | ms |

| $t_{EN\_SB\_DIG}$     | スタンバイ・モードを検出するために必要な時間                                                    | SPD_CTRL_MODE = 10b (I2C モード)、<br>SPEED_CMD = 0                                                           | 1     | 2    | ms    |    |

| $t_{EN\_SB}$          | スタンバイ・コマンドの検出後、モーターの駆動を停止するために必要な時間                                       | $V_{SPEED} < V_{EN\_SL}$ (アナログ・モード) または<br>$V_{SPEED} < V_{IL}$ (PWM モード) または<br>SPEED コマンド = 0 (I2C モード) | 1     | 2    | ms    |    |

**発振器**

|              |          |                          |       |      |     |

|--------------|----------|--------------------------|-------|------|-----|

| $SL_{ACC}$   | 速度ループの精度 | $T_J = -25 \sim 125°C$ 。 | -2.25 | 2.25 | %   |

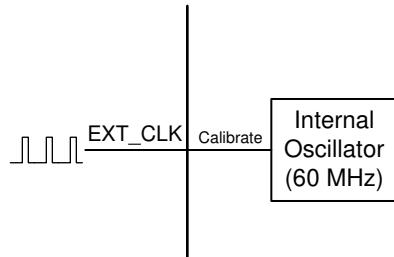

| $f_{OSCREF}$ | 外部クロック基準 | EXT_CLK_CONFIG = 000b    | 8     |      | kHz |

|              |          | EXT_CLK_CONFIG = 001b    | 16    |      | kHz |

|              |          | EXT_CLK_CONFIG = 010b    | 32    |      | kHz |

|              |          | EXT_CLK_CONFIG = 011b    | 64    |      | kHz |

|              |          | EXT_CLK_CONFIG = 100b    | 128   |      | kHz |

|              |          | EXT_CLK_CONFIG = 101b    | 256   |      | kHz |

|              |          | EXT_CLK_CONFIG = 110b    | 512   |      | kHz |

|              |          | EXT_CLK_CONFIG = 111b    | 1024  |      | kHz |

**保護回路**

|                       |                                 |                       |      |      |      |    |

|-----------------------|---------------------------------|-----------------------|------|------|------|----|

| $V_{VREG\_UVLO}$      | レギュレータ入力の低電圧誤動作防止 (VREG-UVLO)   | 電源立ち上がり               | 1.8  | 1.9  | 2    | V  |

|                       |                                 | 電源立ち下がり               | 1.7  | 1.8  | 1.9  | V  |

| $V_{VREG\_UVLO\_HYS}$ | レギュレータ UVLO ヒステリシス              | 立ち上がりから立ち下がりへのスレッショルド | 30   | 100  | 160  | mV |

| $t_{VREG\_UVLO\_DEG}$ | レギュレータ UVLO グリッチ除去時間            |                       |      | 5    |      | μs |

| $V_{DVDD\_UVLO}$      | デジタル・レギュレータ低電圧誤動作防止 (DVDD-UVLO) | 電源立ち上がり               | 1.2  | 1.25 | 1.32 | V  |

| $V_{DVDD\_UVLO}$      | デジタル・レギュレータ低電圧誤動作防止 (DVDD-UVLO) | 電源立ち下がり               | 1.25 | 1.35 | 1.45 | V  |

| $V_{PVDD\_UV}$        | PVDD 低電圧誤動作防止スレッショルド            | $V_{PVDD}$ の立ち上がり     | 4.3  | 4.4  | 4.5  | V  |

|                       |                                 | $V_{PVDD}$ の立ち下がり     | 4    | 4.1  | 4.25 |    |

4.5V  $\leq V_{PVDD} \leq 60V$ 、-40°C  $\leq T_J \leq 150°C$  (特に記述のない限り)。標準値には  $T_A = 25°C$ 、 $V_{PVDD} = 24V$  が適用されます。

| パラメータ                | テスト条件                                  | 最小値                                      | 標準値  | 最大値  | 単位   |

|----------------------|----------------------------------------|------------------------------------------|------|------|------|

| $V_{PVDD\_UV\_HYS}$  | PVDD 低電圧誤動作防止ヒステリシス                    | 立ち上がりから立ち下がりへのスレッショルド                    | 225  | 265  | 325  |

| $t_{PVDD\_UV\_DG}$   | PVDD 低電圧グリッチ除去時間                       |                                          | 10   | 20   | 30   |

| $V_{AVDD\_POR}$      | AVDD 電源 POR スレッショルド                    | AVDD の立ち上がり                              | 2.7  | 2.85 | 3.0  |

|                      |                                        | AVDD の立ち下がり                              | 2.5  | 2.65 | 2.8  |

| $V_{AVDD\_POR\_HYS}$ | AVDD POR ヒステリシス                        | 立ち上がりから立ち下がりへのスレッショルド                    | 170  | 200  | 250  |

| $t_{AVDD\_POR\_DG}$  | AVDD POR グリッチ除去時間                      |                                          | 7    | 12   | 22   |

| $V_{GVDD\_UV}$       | GVDD 低電圧スレッショルド                        | $V_{GVDD}$ の立ち上がり                        | 7.3  | 7.5  | 7.8  |

|                      |                                        | $V_{GVDD}$ の立ち下がり                        | 6.4  | 6.7  | 6.9  |

| $V_{GVDD\_UV\_HYS}$  | GVDD 低電圧ヒステリシス                         | 立ち上がりから立ち下がりへのスレッショルド                    | 800  | 900  | 1000 |

| $t_{GVDD\_UV\_DG}$   | GVDD 低電圧グリッチ除去時間                       |                                          | 5    | 10   | 15   |

| $V_{BST\_UV}$        | ブートストラップ低電圧スレッショルド                     | $V_{BSTx} - V_{SHx}$ 、 $V_{BSTx}$ の立ち上がり | 3.9  | 4.45 | 5    |

|                      |                                        | $V_{BSTx} - V_{SHx}$ 、 $V_{BSTx}$ の立ち下がり | 3.7  | 4.2  | 4.8  |

| $V_{BST\_UV\_HYS}$   | ブートストラップ低電圧ヒステリシス                      | 立ち上がりから立ち下がりへのスレッショルド                    | 150  | 220  | 285  |

| $t_{BST\_UV\_DG}$    | ブートストラップ低電圧グリッチ除去時間                    |                                          | 2    | 4    | 6    |

| $V_{DS\_LVL}$        | $V_{DS}$ 過電流保護スレッショルド・リファレンス           | SEL_VDS_LVL = 0000                       | 0.04 | 0.06 | 0.08 |

|                      |                                        | SEL_VDS_LVL = 0001                       | 0.09 | 0.12 | 0.15 |

|                      |                                        | SEL_VDS_LVL = 0010                       | 0.14 | 0.18 | 0.23 |

|                      |                                        | SEL_VDS_LVL = 0011                       | 0.19 | 0.24 | 0.29 |

|                      |                                        | SEL_VDS_LVL = 0100                       | 0.23 | 0.3  | 0.37 |

|                      |                                        | SEL_VDS_LVL = 0101                       | 0.3  | 0.36 | 0.43 |

|                      |                                        | SEL_VDS_LVL = 0110                       | 0.35 | 0.42 | 0.5  |

|                      |                                        | SEL_VDS_LVL = 0111                       | 0.4  | 0.48 | 0.56 |

|                      |                                        | SEL_VDS_LVL = 1000                       | 0.5  | 0.6  | 0.7  |

|                      |                                        | SEL_VDS_LVL = 1001                       | 0.65 | 0.8  | 0.9  |

|                      |                                        | SEL_VDS_LVL = 1010                       | 0.85 | 1    | 1.15 |

|                      |                                        | SEL_VDS_LVL = 1011                       | 1    | 1.2  | 1.34 |

|                      |                                        | SEL_VDS_LVL = 1100                       | 1.2  | 1.4  | 1.58 |

|                      |                                        | SEL_VDS_LVL = 1101                       | 1.4  | 1.6  | 1.78 |

|                      |                                        | SEL_VDS_LVL = 1110                       | 1.6  | 1.8  | 2    |

|                      |                                        | SEL_VDS_LVL = 1111                       | 1.7  | 2    | 2.2  |

| $V_{SENSE\_LVL}$     | $V_{SENSE}$ 過電流保護スレッショルド               | LSS から GND ピン = 0.5V                     | 0.48 | 0.5  | 0.52 |

| $t_{DS\_BLK}$        | $V_{DS}$ 過電流保護ブランギング時間                 |                                          | 0.5  | 1    | 2.7  |

| $t_{DS\_DG}$         | $V_{DS}$ および $V_{SENSE}$ 過電流保護グリッチ除去時間 |                                          | 1.5  | 3    | 5    |

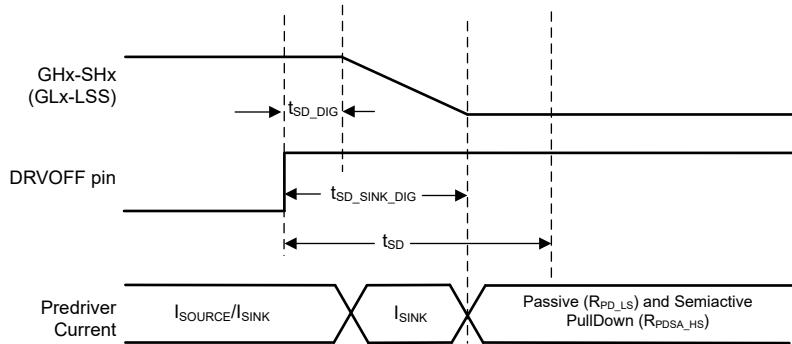

| $t_{SD\_SINK\_DIG}$  | DRV0FF ピーク・シンク電流の継続時間                  |                                          | 3    | 5    | 7    |

| $t_{SD\_DIG}$        | DRV0FF デジタル・シャットダウン遅延                  |                                          | 0.5  | 1.5  | 2.2  |

| $t_{SD}$             | DRV0FF アナログ・シャットダウン遅延                  |                                          | 7    | 14   | 21   |

| $T_{OTSD}$           | 過熱シャットダウン温度                            | $T_J$ 立ち上がり:                             | 160  | 170  | 187  |

| $T_{HYS}$            | サーマル・シャットダウン・ヒステリシス                    |                                          | 16   | 20   | 23   |

| $I^2C$ シリアル・インターフェイス |                                        |                                          |      |      |      |

4.5V  $\leq V_{PVDD} \leq 60V$ 、-40°C  $\leq T_J \leq 150°C$  (特に記述のない限り)。標準値には  $T_A = 25°C$ 、 $V_{PVDD} = 24V$  が適用されます。

| パラメータ          | テスト条件                                                    | 最小値                    | 標準値            | 最大値           | 単位 |

|----------------|----------------------------------------------------------|------------------------|----------------|---------------|----|

| $V_{I2C\_L}$   | Low レベル入力電圧                                              |                        | -0.5           | 0.3 *<br>AVDD | V  |

| $V_{I2C\_H}$   | High レベル入力電圧                                             |                        | 0.7 *<br>AVDD  | 5.5           | V  |

| $V_{I2C\_HYS}$ | ヒステリシス                                                   |                        | 0.05 *<br>AVDD |               | V  |

| $V_{I2C\_OL}$  | Low レベル出力電圧                                              | オープン・ドレイン (2mA のシンク電流) | 0              | 0.4           | V  |

| $I_{I2C\_OL}$  | Low レベル出力電流                                              | $V_{I2C\_OL} = 0.6V$   |                | 6             | mA |

| $I_{I2C\_IL}$  | SDA と SCL の入力電流                                          |                        | -10 (1)        | 10 (1)        | μA |

| $C_i$          | SDA と SCL の容量                                            |                        |                | 10            | pF |

| $t_{of}$       | 出力立ち下がり時間 ( $V_{I2C\_H}$ (min) から $V_{I2C\_L}$ (max) まで) | スタンダード・モード             |                | 250 (2)       | ns |

|                |                                                          | ファースト・モード              |                | 250 (2)       | ns |

| $t_{SP}$       | 入力フィルタにより抑制されるスパイクのパルス幅                                  | ファースト・モード              | 0              | 50(3)         | ns |

#### EEPROM

|             |           |                        |      |       |      |   |

|-------------|-----------|------------------------|------|-------|------|---|

| $EE_{Prog}$ | プログラミング電圧 |                        | 1.35 | 1.5   | 1.65 | V |

| $EE_{RET}$  | 保持        | $T_A = 25°C$           |      | 100   |      | 年 |

|             |           | $T_J = -40 \sim 150°C$ |      | 10    |      | 年 |

| $EE_{END}$  | 耐久性       | $T_J = -40 \sim 150°C$ |      | 1000  |      | 回 |

|             |           | $T_J = -40 \sim 85°C$  |      | 20000 |      | 回 |

(1) AVDD がオフの場合、I/O ピンが SDA および SCL ラインを妨げないようにする必要があります。

(2) SDA および SCL バス・ラインの  $t_f$  の最大値 (300ns) は、出力段の  $t_{of}$  の最大値の規定値 (250ns) より大きいです。そのため、SDA/SCL ピンと SDA/SCL バス・ラインとの間に直列保護抵抗 ( $R_s$ ) を接続しても、 $t_f$  の最大値の規定値を超えません。

(3) SDA および SCL 入力の入力フィルタは 50ns 未満のノイズ・スパイクを抑制します。

## 6.6 スタンダード・モードとファースト・モードの SDA および SCL バスの特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ             | テスト条件                                     | 最小値                            | 公称値   | 最大値      | 単位  |

|-------------------|-------------------------------------------|--------------------------------|-------|----------|-----|

| <b>スタンダード・モード</b> |                                           |                                |       |          |     |

| $f_{SCL}$         | SCL クロック周波数                               |                                | 0     | 100      | kHz |

| $t_{HD\_STA}$     | (繰り返し) START 条件のホールド時間                    | この時間が経過すると、最初のクロック・パルスが生成されます。 | 4     |          | μs  |

| $t_{LOW}$         | SCL クロックの Low の時間                         |                                | 4.7   |          | μs  |

| $t_{HIGH}$        | SCL クロックの High の時間                        |                                | 4     |          | μs  |

| $t_{SU\_STA}$     | 繰り返し START 条件のセットアップ時間                    |                                | 4.7   |          | μs  |

| $t_{HD\_DAT}$     | データ・ホールド時間 (1)                            | I2C バス・デバイス                    | 0 (2) | (3)      | μs  |

| $t_{SU\_DAT}$     | データ・セットアップ時間                              |                                | 250   |          | ns  |

| $t_r$             | SDA 信号と SCL 信号の両方の立ち上がり時間                 |                                |       | 1000     | ns  |

| $t_f$             | SDA 信号と SCL 信号の両方の立ち下がり時間 (2) (5) (6) (7) |                                |       | 300      | ns  |

| $t_{SU\_STO}$     | STOP 条件のセットアップ時間                          |                                | 4     |          | μs  |

| $t_{BUF}$         | STOP 条件と START 条件の間のバス解放時間                |                                | 4.7   |          | μs  |

| $C_b$             | 各バス・ラインの容量性負荷 (8)                         |                                |       | 400      | pF  |

| $t_{VD\_DAT}$     | データ有効時間 (9)                               |                                |       | 3.45 (3) | μs  |

| $t_{VD\_ACK}$     | データ有効アクリッジ時間 (10)                         |                                |       | 3.45 (3) | μs  |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ            | テスト条件                                     | 最小値                            | 公称値                      | 最大値     | 単位  |

|------------------|-------------------------------------------|--------------------------------|--------------------------|---------|-----|

| $V_{nL}$         | Low レベルでのノイズ・マージン                         | 接続された各デバイスに対して (ヒステリシスを含む)     | 0.1 *<br>AVDD            |         | V   |

| $V_{nh}$         | High レベルでのノイズ・マージン                        | 接続された各デバイスに対して (ヒステリシスを含む)     | 0.2 *<br>AVDD            |         | V   |

| <b>ファースト・モード</b> |                                           |                                |                          |         |     |

| $f_{SCL}$        | SCL クロック周波数                               |                                | 0                        | 400     | kHz |

| $t_{HD\_STA}$    | (繰り返し) START 条件のホールド時間                    | この時間が経過すると、最初のクロック・パルスが生成されます。 | 0.6                      |         | μs  |

| $t_{LOW}$        | SCL クロックの Low の時間                         |                                | 1.3                      |         | μs  |

| $t_{HIGH}$       | SCL クロックの High の時間                        |                                | 0.6                      |         | μs  |

| $t_{SU\_STA}$    | 繰り返し START 条件のセットアップ時間                    |                                | 0.6                      |         | μs  |

| $t_{HD\_DAT}$    | データ・ホールド時間 (1)                            |                                | 0 (2)                    | (3)     | μs  |

| $t_{SU\_DAT}$    | データ・セットアップ時間                              |                                | 100 (4)                  |         | ns  |

| $t_r$            | SDA 信号と SCL 信号の両方の立ち上がり時間                 |                                | 20                       | 300     | ns  |

| $t_f$            | SDA 信号と SCL 信号の両方の立ち下がり時間 (2) (5) (6) (7) |                                | 20 x<br>(AVDD /<br>5.5V) | 300     | ns  |

| $t_{SU\_STO}$    | STOP 条件のセットアップ時間                          |                                | 0.6                      |         | μs  |

| $t_{BUF}$        | STOP 条件と START 条件の間のバス解放時間                |                                | 1.3                      |         | μs  |

| $C_b$            | 各バス・ラインの容量性負荷 (8)                         |                                |                          | 400     | pF  |

| $t_{VD\_DAT}$    | データ有効時間 (9)                               |                                |                          | 0.9 (3) | μs  |

| $t_{VD\_ACK}$    | データ有効アノリッジ時間 (10)                         |                                |                          | 0.9 (3) | μs  |

| $V_{nL}$         | Low レベルでのノイズ・マージン                         | 接続された各デバイスに対して (ヒステリシスを含む)     | 0.1 *<br>AVDD            |         | V   |

| $V_{nh}$         | High レベルでのノイズ・マージン                        | 接続された各デバイスに対して (ヒステリシスを含む)     | 0.2 *<br>AVDD            |         | V   |

- (1)  $t_{HD\_DAT}$  は、SCL の立ち下がりエッジから測定されたデータ・ホールド時間であり、送信中のデータとアノリッジに適用されます。

- (2) SCL 信号の立ち下がりエッジの未定義領域をブリッジするため、デバイスは SDA 信号のために (SCL 信号の  $V_{IH(min)}$  を基準として) 300ns 以上のホールド時間を内部的に確保する必要があります。

- (3)  $t_{HD\_DAT}$  の最大値は、スタンダード・モードで 3.45μs、ファースト・モードで 0.9μs ですが、 $t_{VD\_DAT}$  と  $t_{VD\_ACK}$  の大きい方より遷移時間の分だけ小さくする必要があります。この最大値を満たす必要があるのは、SCL 信号の Low 期間 ( $t_{LOW}$ ) を本デバイスがストレッチ (延長) しない場合に限られます。クロックが SCL をストレッチした場合、クロックが解放されるときからセットアップ時間の分だけ前に、データが有効になっている必要があります。

- (4) ファースト・モード I2C バス・デバイスは、スタンダード・モード I2C バス・システムでも使えますが、その場合、 $t_{SU\_DAT}$  250ns の要件を満たす必要があります。本デバイスが SCL 信号の Low 期間をストレッチしない場合、これは自動的に当てはまります。そのようなデバイスが SCL 信号の Low 期間を延長する場合、SCL ラインが解放されるときより 1250ns ( $t_r(max) + t_{SU\_DAT} = 1000ns + 250ns$ ) だけ前に、次のデータ・ビットを SDA ラインに出力する必要があります (スタンダード・モード I2C バス仕様に従って)。アノリッジのタイミングもこのセットアップ時間を満たす必要があります。

- (5) HS モード・デバイスと混在させる場合、より速い立ち下がり時間 (表 10 を参照) が許容されます。

- (6) SDA および SCL バス・ラインの立ち下がり時間 ( $t_f$ ) の最大値は 300ns と規定されています。SDA 出力段の立ち下がり時間 ( $t_f$ ) の最大値は 250ns と規定されています。そのため、SDA/SCL ピンと SDA/SCL バス・ラインとの間に直列保護抵抗 ( $R_s$ ) を接続しても、 $t_f$  の最大値の規定値を超えません。

- (7) ファースト・モード・プラスでは、出力段とバス・タイミングの立ち下がり時間が同じに規定されています。直列抵抗を使用する場合、バスのタイミングを検討する際に設計者はこのことを見込む必要があります。

- (8) 許容される最大バス容量は、そのアプリケーションの実際の動作電圧および周波数に応じて、規定値と異なる場合があります。

- (9)  $t_{VD\_DAT}$  = データ信号が必要とする SCL Low から SDA 出力 (High または Low、どちらか長い方) までの時間。

- (10)  $t_{VD\_ACK}$  = アノリッジ信号が必要とする SCL Low から SDA 出力 (High または Low、どちらか長い方) までの時間。

## 6.7 代表的な特性

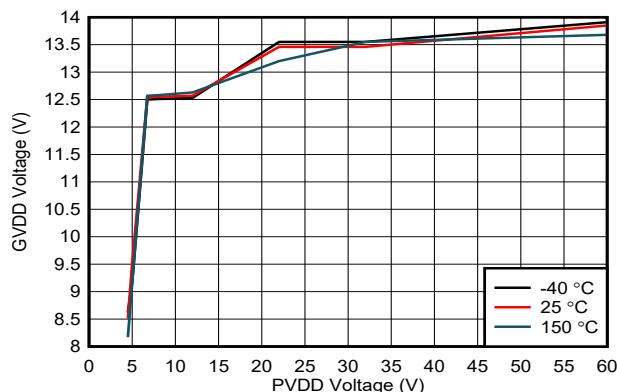

図 6-1. GVDD 電圧と PVDD 電圧との関係

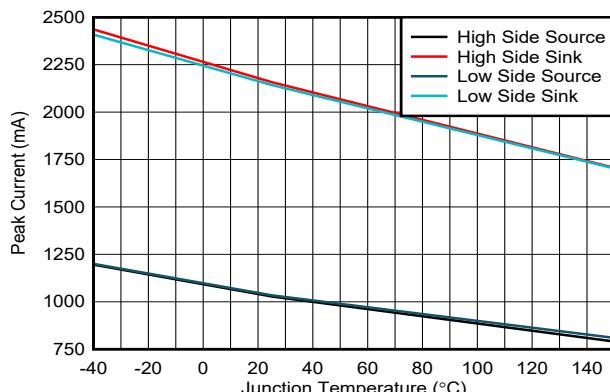

図 6-2. ドライバ・ピーク電流と接合部温度との関係

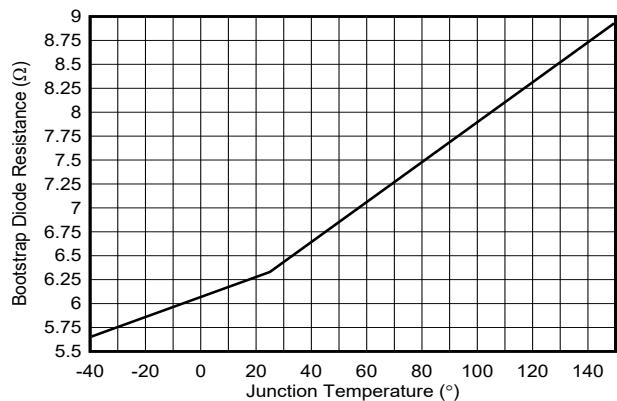

図 6-3. ブートストラップ・ダイオード抵抗と接合部温度との関係

図 6-4. ブートストラップ・ダイオード順方向電圧降下と接合部温度との関係

## 7 詳細説明

### 7.1 概要

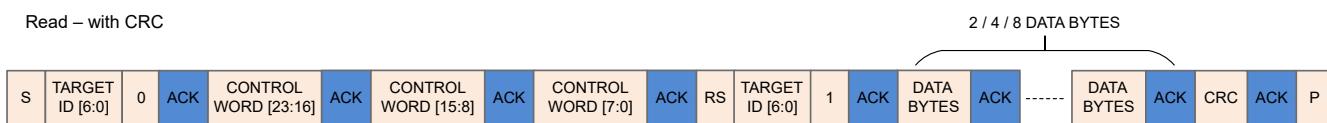

MCT8329A は、ブラシレス DC モーターの高速動作 (最大 3kHz の電気的速度) または超高速起動時間 (50ms 未満) を必要とするアプリケーション向けに、内蔵 3 相ゲート・ドライバによるコード作成不要のセンサレス台形制御ソリューションを提供します。

このデバイスには、3 つのハーフ・ブリッジ・ゲート・ドライバがあり、それぞれがハイサイドとローサイドの N チャネル・パワー MOSFET を駆動できます。モーター電流は、内蔵の電流検出アンプ (外付けローサイド検出抵抗が必要) を使用して検出されます。本デバイスは、本デバイスに必要な電圧レールを生成し、また外部回路に電力を供給できる LDO を内蔵しています。

センサレス台形制御は、モーター起動動作から閉ループ動作まで、レジスタ設定によって詳細に設定できます。これらのレジスタ設定は不揮発性 EEPROM に保存されるため (MCT8329A1I)、設定後は本デバイスをスタンドアロンで動作させることができます。MCT8329A1I では高度な監視が可能です。1 つの 12 ビット DAC を使って、アルゴリズム内の任意の変数をアナログ出力として表示および監視できます。この機能により、速度ループとモーター加速を効率的に調整できます。本デバイスは、PWM 入力、アナログ電圧、周波数入力、I<sup>2</sup>C コマンドによって速度コマンドを受信します。

内蔵保護機能には、電源低電圧誤動作防止 (PVDD\_UVLO)、レギュレータ低電圧誤動作防止 (GVDD\_UV)、ブーストラップ電圧低電圧誤動作防止 (BST\_UV)、VDS 過電流保護 (OCP)、検出抵抗過電流保護 (SEN\_OCP)、モーター・ロック検出、過熱シャットダウン (OTSD) が含まれます。�ルト・イベントは nFAULT ピンにより通知され、ステータス・レジスタで詳細な�ルト情報を取得できます。

標準の I<sup>2</sup>C を使うと、デバイスの各種設定と�ルト診断情報の読み出しを外部コントローラから簡単に行うことができます。

MCT8329A デバイスは、0.4mm ピン・ピッチの VQFN 表面実装パッケージで供給されます。この VQFN パッケージのサイズは 5mm × 4mm です。

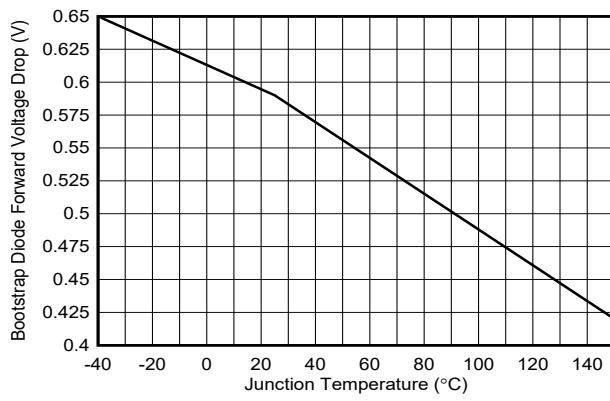

## 7.2 機能ブロック図

図 7-1. MCT8329A の機能ブロック図

## 7.3 機能説明

表 7-1 に、ドライバの外付け部品の推奨値を示します。

表 7-1. MCT8329A の外付け部品

| 部品           | ピン 1       | ピン 2   | 推奨事項                                                                                                                    |

|--------------|------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| $C_{PVDD1}$  | PVDD       | PGND   | X5R または X7R、0.1 $\mu$ F、PVDD の 2 倍を超える定格のコンデンサ                                                                          |

| $C_{PVDD2}$  | PVDD       | PGND   | 10 $\mu$ F 以上、PVDD の 2 倍を超える定格のバルク・コンデンサ                                                                                |

| $C_{CP}$     | CPH        | CPL    | X5R または X7R、470nF、PVDD 定格コンデンサ                                                                                          |

| $C_{AVDD}$   | AVDD       | AGND   | X5R または X7R、1 $\mu$ F 以上、6.3V コンデンサ                                                                                     |

| $C_{GVDD}$   | GVDD       | GND    | X5R または X7R、10 $\mu$ F 以上、30V 定格コンデンサ                                                                                   |

| $C_{DVDD}$   | DVDD       | GND    | X5R または X7R、1 $\mu$ F、4V 以上。DVDD が出力電圧を正確に制御するには、コンデンサは、動作温度範囲全体にわたって、1.5V で 0.6 $\mu$ F～1.3 $\mu$ F の実効的な容量を持つ必要があります。 |

| $C_{VREG}$   | VREG       | GND    | X5R または X7R、1 $\mu$ F 以上、10V コンデンサ                                                                                      |

| $C_{BSTx}$   | BSTx       | SHx    | X5R または X7R、1 $\mu$ F (標準値)、25V 定格コンデンサ                                                                                 |

| $R_{nFAULT}$ | 1.8～5V の電源 | nFAULT | 5.1k $\Omega$ 、プルアップ抵抗                                                                                                  |

| $R_{FG}$     | 1.8～5V の電源 | FG     | 5.1k $\Omega$ 、プルアップ抵抗                                                                                                  |

| $R_{SDA}$    | 1.8～5V の電源 | SDA    | 5.1k $\Omega$ 、プルアップ抵抗                                                                                                  |

| $R_{SCL}$    | 1.8～5V の電源 | SCL    | 5.1k $\Omega$ 、プルアップ抵抗                                                                                                  |

| $R_{BRAKE}$  | BRAKE      | GND    | BRAKE ピンを使用する場合、ノイズ耐性を向上させるため、任意で 100k $\Omega$ 未満の抵抗を使用できます。                                                           |

| $R_{DIR}$    | DIR        | GND    | DIR ピンを使用する場合、ノイズ耐性を向上させるため、任意で 100k $\Omega$ 未満の抵抗を使用できます。                                                             |

### 注

FG および nFAULT ピンの場合、そのピン機能を使わない場合でも、外部プルアップ抵抗を接続する必要があります。プルアップに外部電源を使う場合、本デバイスがアクティブ状態になる前に、FG および nFAULT ピンは High にプルアップされる必要があります。

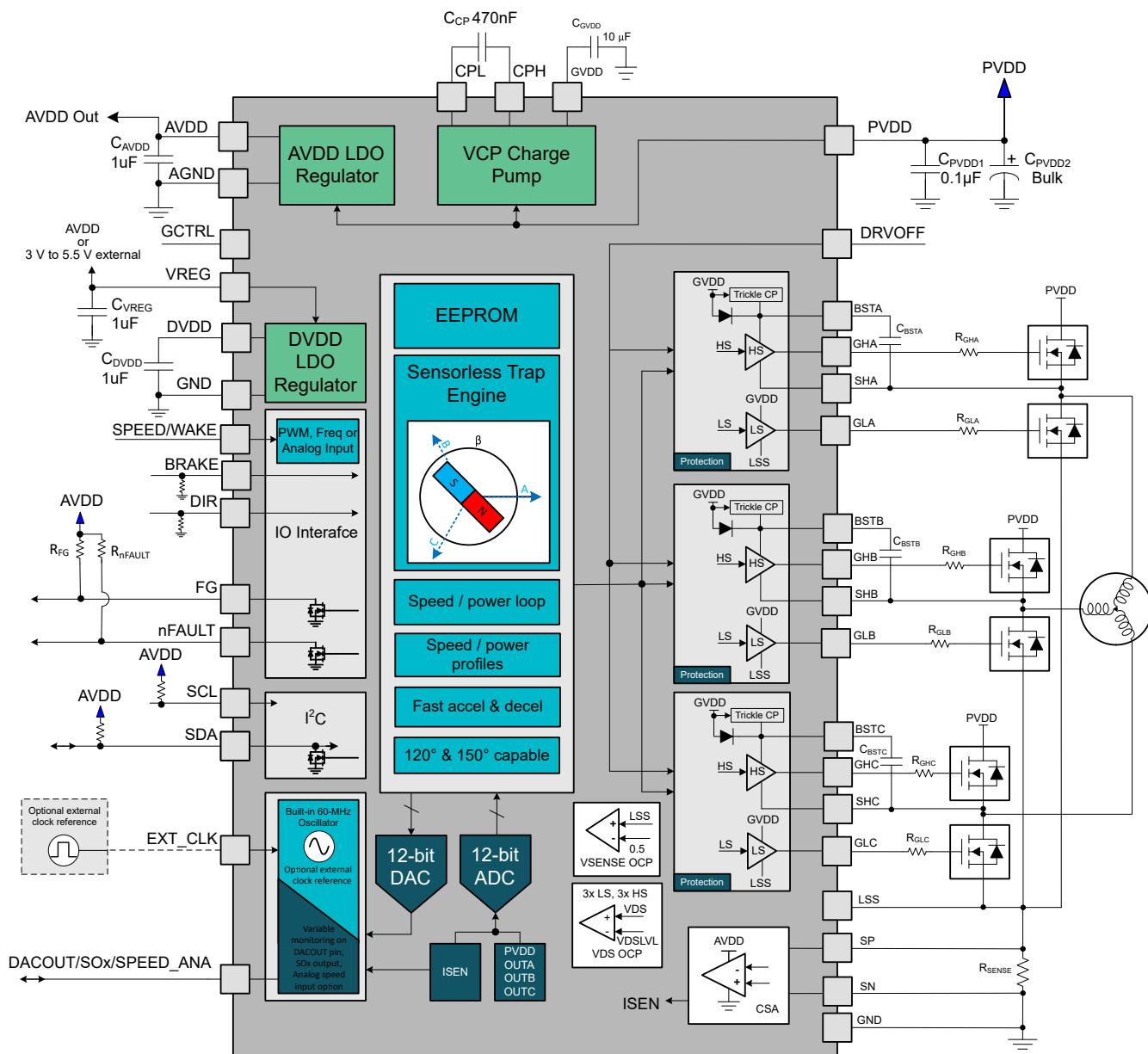

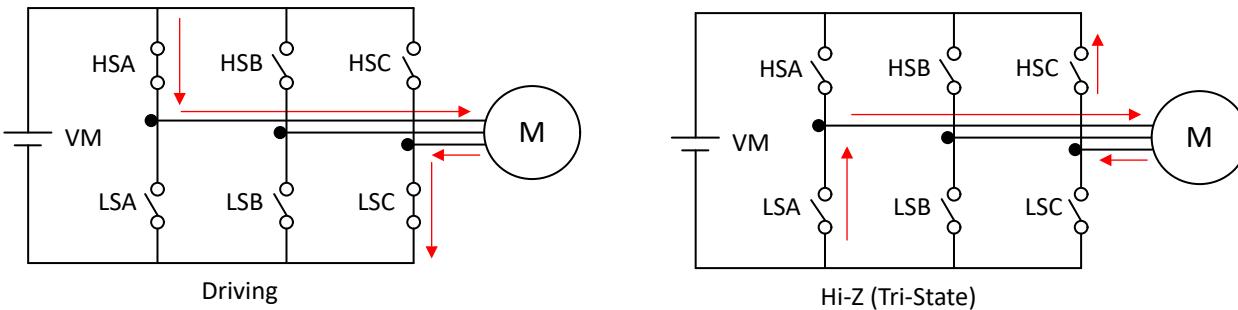

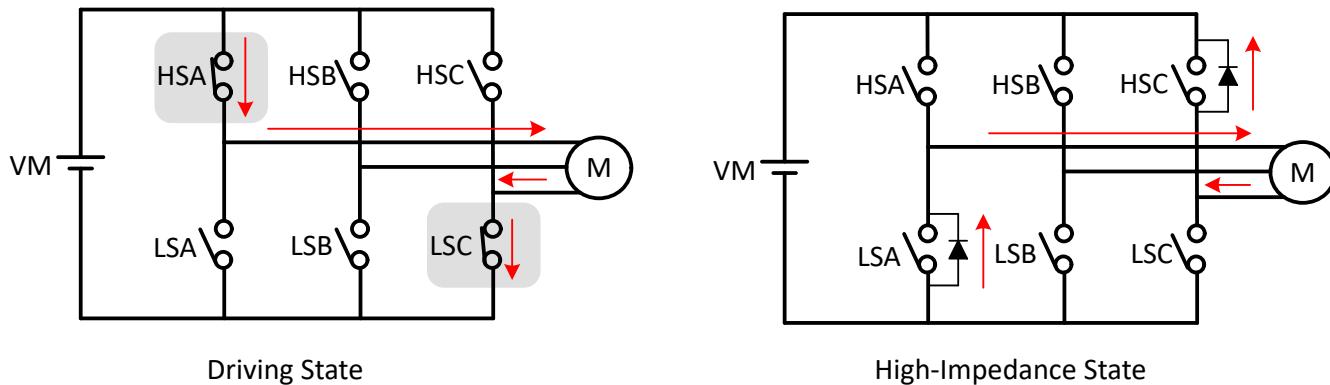

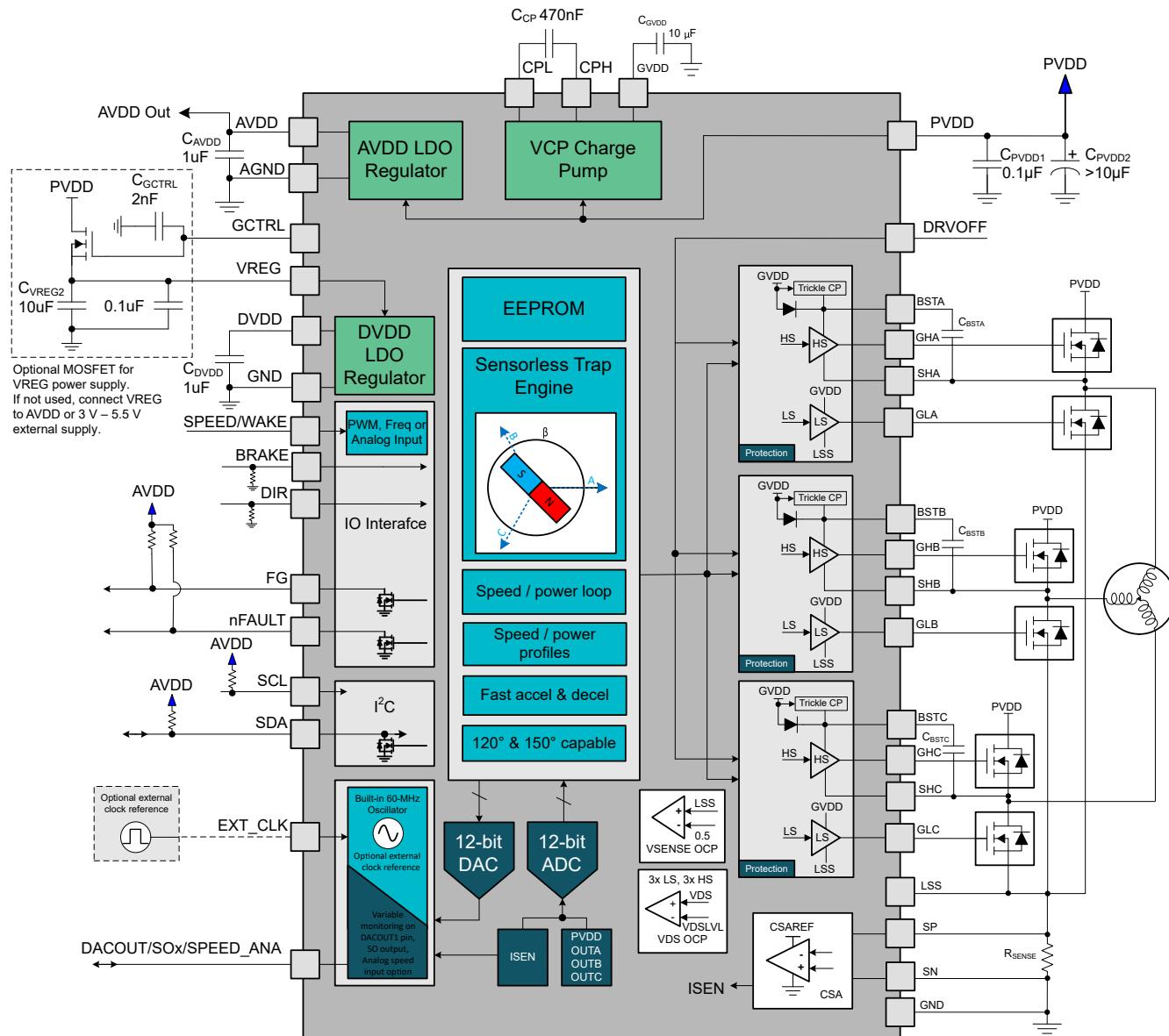

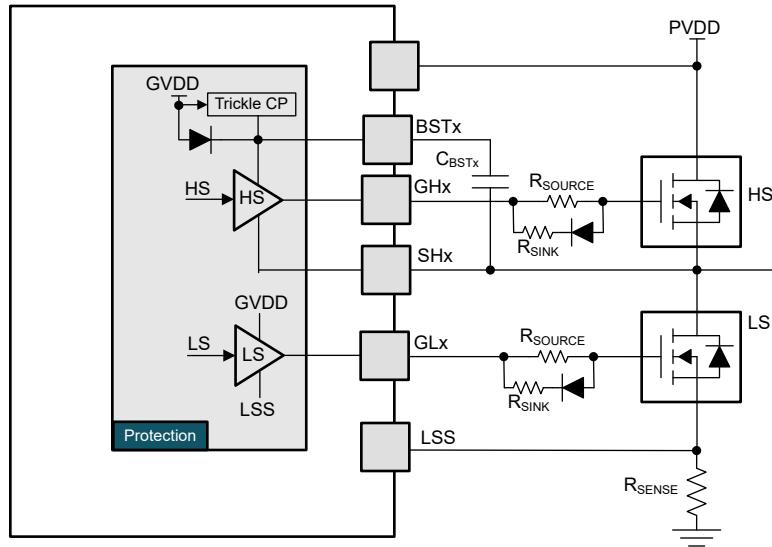

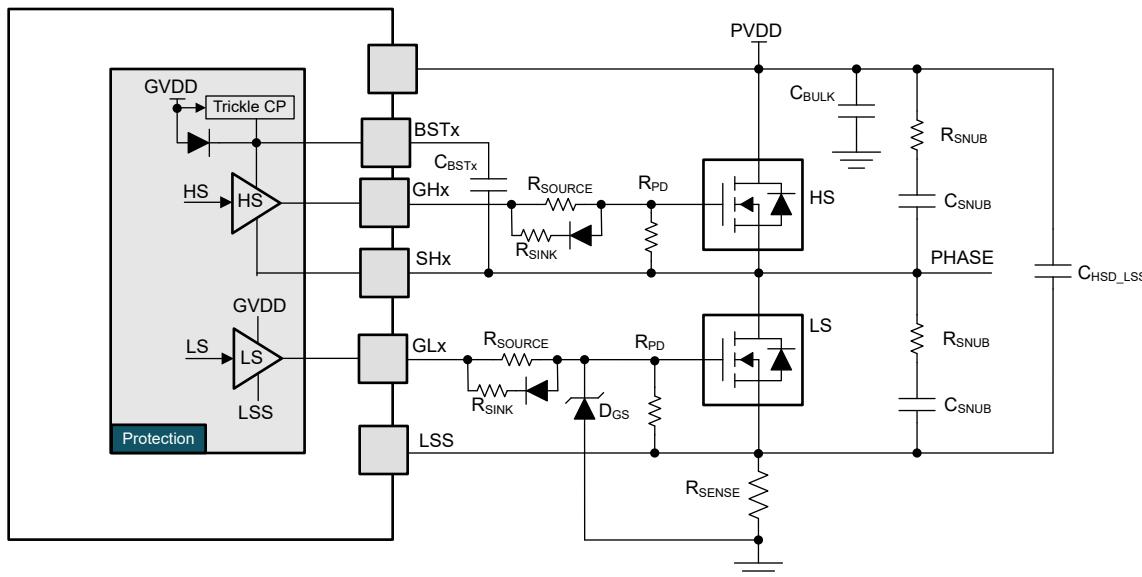

### 7.3.1 3 相 BLDC ゲート・ドライバ

MCT8329A デバイスは 3 つのハーフ・ブリッジ・ゲート・ドライバを内蔵しており、それぞれがハイサイドとローサイドの N チャネル・パワー MOSFET を駆動できます。広い動作電圧範囲にわたって適切なゲート・バイアス電圧を供給する GVDD を生成するため、チャージ・ポンプが使われます。ローサイド・ゲート出力は GVDD から直接駆動されるのに対して、ハイサイド・ゲート出力はダイオード内蔵ブートストラップ回路を使って駆動されます。また、内部トリクル・チャージ・ポンプは 100% デューティ・サイクル動作をサポートしています。

### 7.3.2 ゲート駆動アーキテクチャ

本ドライバ・デバイスは、ハイサイドとローサイド両方のドライバに対して、相補型のプッシュプル・トポロジが使用されています。このトポロジにより、外部 MOSFET ゲートのプルアップとプルダウンが両方とも強化できます。ローサイド・ゲート・ドライバには、GVDD レギュレータ電源から直接電力が供給されます。ハイサイド・ゲート・ドライバ用には、ブートストラップ・ダイオードとブートストラップ・コンデンサを使ってフローティング・ハイサイド・ゲート電源電圧を生成します。ブートストラップ・ダイオードは内蔵されており、BSTx ピンに外付けのブートストラップ・コンデンサを使います。100% デューティ・サイクル制御をサポートするため、トリクル・チャージ・ポンプが本デバイスに内蔵されています。ドライバと外部 MOSFET のリーキー電流による電圧降下を防止するため、トリクル・チャージ・ポンプが BSTx ノードに接続されています。

スリープ状態中または電源が切り離された際に外部 MOSFET がターンオンするのを防止するため、ハイサイド・ゲート・ドライバはセミアクティブ・プルダウンを備えており、ローサイド・ゲートはパッシブ・プルダウンを備えています。

図 7-2. ゲート・ドライバのブロック図

### 7.3.2.1 デッドタイムによるクロス導通の防止

MCT8329A は、各ハーフ・ブリッジの外部 MOSFET の両方が同時にオンに切り換わるのを防止するため、ハイサイドとローサイドの PWM 信号の間にデジタル・デッドタイムを挿入する機能を備えています。デジタル・デッドタイムは、EEPROM レジスタ `DIG_DEAD_TIME` を設定することで、50ns～1000ns の範囲で調整できます。

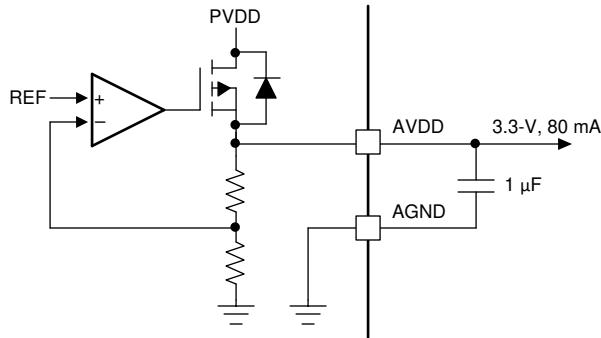

### 7.3.3 AVDD リニア電圧レギュレータ

MCT8329A には 3.3V、80mA のリニア・レギュレータが内蔵されており、外部回路から使用できます。VREG が AVDD に接続されている場合、外部回路が使用できるのはわずか 50mA です。LDO の出力は 3.3V に固定されています。このレギュレータは、低消費電力 MCU や、必要な電源電流が小さいその他の回路に電源電圧を供給できます。AVDD レギュレータの出力は、X5R または X7R、1 $\mu$ F、6.3V のセラミック・コンデンサを使用して AVDD ピンの近くで AGND ピンにバイパスする必要があります。

図 7-3. AVDD リニア・レギュレータのブロック図

AVDD リニア・レギュレータが本デバイス内で消費する電力は、次の式 1 のように計算できます。

$$P = (V_{PVDD} - V_{AVDD}) \times I_{AVDD} \quad (1)$$

たとえば、24V の  $V_{PVDD}$  で、AVDD から 20mA の電流が流れると、消費電力は式 2 のようになります。

$$P = (24 \text{ V} - 3.3 \text{ V}) \times 20 \text{ mA} = 414 \text{ mW} \quad (2)$$

### 7.3.4 DVDD 電圧レギュレータ

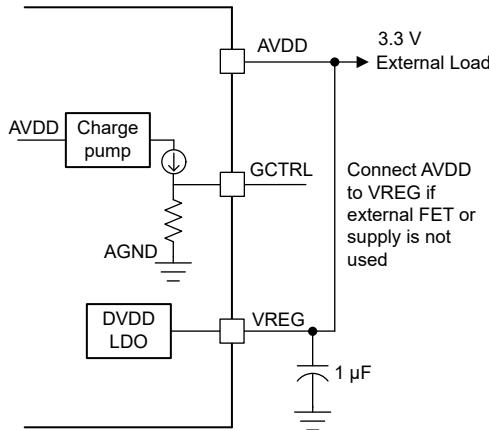

VREG ピンは、内蔵 DVDD 電圧レギュレータの電源入力として使用されます。VREG ピンに電源電圧を供給するために各種の方法 (外部の 3V~5.5V 電源 (30mA ソース) を使用、AVDD を VREG に接続、GCTRL ピンによって外部 MOSFET を制御) を選択できます。

#### 7.3.4.1 AVDD から VREG への電力供給

外部 MOSFET レギュレータも外部電源も使用しない場合、AVDD を VREG ピンに接続します (図 7-4 を参照)。このモードでは、DVDD に接続されたデジタル回路に、AVDD を使って電力が供給されます。このモードでは、外部負荷に供給できる AVDD 電流能力は 50mA に減少します。

図 7-4. AVDD から VREG への電力供給

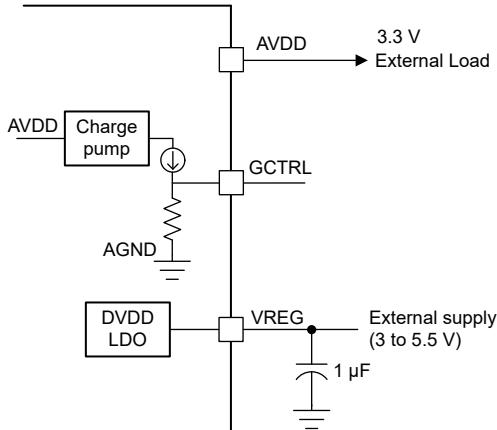

#### 7.3.4.2 VREG 用の外部電源

MCT8329A は、外部電源電圧を VREG ピンに接続するための機能を備えています (図 7-5 を参照)。このモードでは、GCTRL ピンをフローティングのままにし、外部レギュレータを VREG ピンに接続する必要があります。DVDD に電力を供給するために外部 MOSFET または外部電源を使用する場合、AVDD がサポートする最大外部負荷は 80mA です。

図 7-5. VREG 用の外部電源

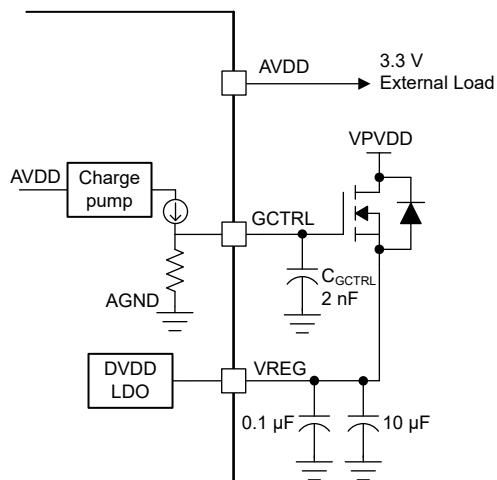

#### 7.3.4.3 VREG 電源用外部 MOSFET

MCT8329A は、レギュレータとして機能し、VREG ピンを使って内部デジタル回路に電力を供給するために使用できる外部 MOSFET を駆動する機能を備えています (セクション 7.3.4.3 を参照)。この場合、VREG を AVDD にも外部 3.3V/5V 電源にも接続しないでください。外部 MOSFET を接続すると、熱的課題を抱える使用事例のために、MCT8329A 内の消費電力を低減し、電力損失を外部 MOSFET に移転できます。

外部 MOSFET の  $V_{GS(th)}$  は、動作条件全体にわたって VREG 電圧が確実に 2.2V~5.5V の間になるように選択する必要があります。アプリケーションの設計例の計算については、セクション 8.2.3 を参照してください。起動時間 ( $t_{EX\_SL\_DR\_ANA}$  (アナログ入力) または  $t_{EX\_SL\_DR\_PWM}$  (PWM 入力)) の規定を満たすため、外部 MOSFET の入力容量は 2nF 未満とする必要があります。

注

GCTRL ピンはハイ・インピーダンス・ノード ( $> 1M\Omega$ ) であり、外部 MOSFET ゲートと  $C_{GCTRL}$  以外の外部負荷をこのピンに接続しないでください。GCTRL ピン (と GND との間) に外部負荷を接続すると、GCTRL ピンと VREG ピンの電圧が低下します。

図 7-6. VREG 用の外部 MOSFET 電圧レギュレータ

#### 7.3.5 ローサイド電流検出アンプ

MCT8329A は、ローサイド・シャント抵抗を使った電流測定のための高性能ローサイド電流検出アンプを内蔵しています。ローサイド電流測定は、MCT8329A の各種制御機能および保護のために使用されます。この電流検出アンプは、

EEPROM 設定によりゲイン (5V/V、10V/V、20V/V、40V/V) を設定できます。この電流検出アンプは、EEPROM ビット (VREF\_SEL) を設定することで、ローサイド・シャント抵抗を流れる双方向または単方向の電流を検出できます。

双方向電流検出モードでは、MCT8329A は、両方向の電流測定の分解能を最大限に高めるため、 $V_{REF}/2$  のコモンモード電圧を内部で生成します。 $V_{REF}$  は、内部で生成される基準電圧 (標準値は 3V) です。

双方向電流検出モードにおいて、SP と SN の間に接続されたシャント抵抗 ( $R_{SENSE}$ ) の値を設計するには、式 3 を使います。ここで、ローサイド・シングル・シャントを流れる電流を  $I$ 、EEPROM ビットを設定することで選択された電流検出アンプ・ゲインを CSA\_GAIN とします。

$$R_{SENSE} = \frac{V_{SO} - \frac{V_{REF}}{2}}{CSA\_GAIN \times I} \quad (3)$$

単方向電流検出モードでは、MCT8329A は、SP から SN への方向の電流測定の分解能を最大限に高めるため、 $V_{REF}/8$  のコモンモード電圧を内部で生成します。

単方向電流検出モードにおいて、SP と SN の間に接続されたシャント抵抗 ( $R_{SENSE}$ ) を流れる電流の値を計算するには、式 4 を使います。

$$R_{SENSE} = \frac{V_{SO} - \frac{V_{REF}}{8}}{CSA\_GAIN \times I} \quad (4)$$

### 注

単方向および双方向電流検出モードにおいて、ローサイド・シングル・シャント抵抗電流 ( $I$ ) と選択されたゲイン (CSA\_GAIN) での動作範囲にわたって、電流検出アンプの出力電圧 ( $V_{SO}$ ) が 0.25V と 3V の間に制限されるようにシャント抵抗 ( $R_{SENSE}$ ) の値を設計することを推奨します。 $I^2R_{SENSE}$  損失に基づき、十分なマージンを確保した上でシャント抵抗の電力定格を適切に選択します。

## 7.3.6 デバイス・インターフェイス・モード

MCT8329A デバイス・ファミリは、柔軟性と単純性のどちらに適した最終アプリケーションの設計にも使えるように、I<sup>2</sup>C インターフェイスをサポートしています。I<sup>2</sup>C インターフェイスに加えて、本デバイスは FG、nFAULT、DIR、BRAKE、SPEED/WAKE、DACOUT/SOx/SPEED\_ANA、EXT\_CLK、DRVOFF などの I/O ピンをサポートしています。

### 7.3.6.1 インターフェイス・制御と監視

#### モーター制御および I/O 信号

- **BRAKE**: BRAKE ピンが「High」に駆動されると、MCT8329A はブレーキ状態に移行します。このブレーキ状態の間、ローサイド・ブレーキ (ローサイド・ブレーキを参照) が実行されます。MCT8329A は、ブレーキ状態に移行する前に、BRAKE\_DUTY\_THRESHOLD で定義された値まで出力速度を下げます。BRAKE が「High」に駆動されている限り、MCT8329A はブレーキ状態にとどまります。BRAKE ピン入力は、I<sup>2</sup>C インターフェイスを介して BRAKE\_INPUT を設定することで上書きできます。

- **DIR**: DIR ピンはモーターの回転方向を決定します。「High」に駆動すると、シーケンスは OUTA → OUTC → OUTB となり、「Low」に駆動すると、シーケンスは OUTA → OUTB → OUTC となります。DIR ピン入力は、I<sup>2</sup>C インターフェイスを介して DIR\_INPUT を設定することで上書きできます。

- **DRVOFF**: DRVOFF ピンを「High」に駆動すると、MCT8329A はゲート・ドライバをプルダウン状態にすることで、すべての外部 MOSFET をターンオフします。DRVOFF を「Low」に駆動すると、モーターを再始動させる場合と同様に、MCT8329A は通常の動作状態に戻ります。DRVOFF は、本デバイスがスリープ・モードにもスタンバイ・モードにも移行する原因にはなりません (デジタル・コアはアクティブに維持されます)。スリープまたはスタンバイ状態の開始と終了は SPEED/WAKE ピンによって制御されます。

- **SPEED/WAKE**: SPEED/WAKE ピンは、モーター速度 (または電力または電圧) を制御し、MCT8329A をスリープ・モードから復帰させるために使われます。SPEED/WAKE ピンは、PWM、周波数、アナログ制御入力信号を入力するように設定できます。このピンはスリープおよびスタンバイ・モードの開始と終了に使われます (表 7-3 を参照)。

- **DACOUT/SOx/SPEED\_ANA**: DACOUT/SOx/SPEED\_ANA ピンは多重化された機能を備えており、このピンは DACOUT 出力ピン、電流検出アンプの出力ピン、速度 (または電力または開ループ電圧) 制御アナログ入力ピンとして構成できます。DACOUT/SOx/SPEED\_ANA ピンを DACOUT として構成すると、本デバイスはアルゴリズム変数、速度などを監視できます ([セクション 7.5.2](#) を参照)。DACOUT/SOx/SPEED\_ANA ピンを SOx として構成すると、本デバイスは内蔵電流センス・アンプ出力 ( $V_{SOx}$ ) を監視できます。DACOUT/SOx/SPEED\_ANA ピンを SPEED\_ANA として構成すると、ユーザーは DACOUT/SOx/SPEED\_ANA ピンを使って速度、電力、電圧のアナログ制御入力を与えることができます。その場合、独立した速度またはスタンバイ制御入力ピンとして SPEED/WAKE ピンを使用できます。このピン機能は、EEPROM レジスタ・ビット **DAC\_SOX\_ANA\_CONFIG** によって設定できます。

- **EXT\_CLK**: EXT\_CLK ピンは、外部クロック基準を供給するために使えます。その場合、内部クロックは外部クロックを使って較正されます。

- **FG**: FG ピンは、モーター速度に比例するパルスを出力します ([セクション 7.3.19](#) を参照)。

- **nFAULT**: nFAULT ピンは、デバイスまたはモーター動作のフォルト・ステータスを示します。

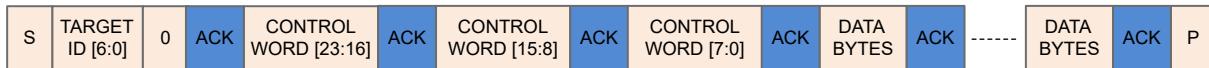

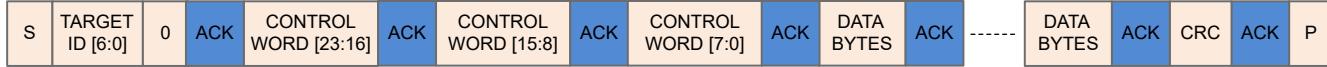

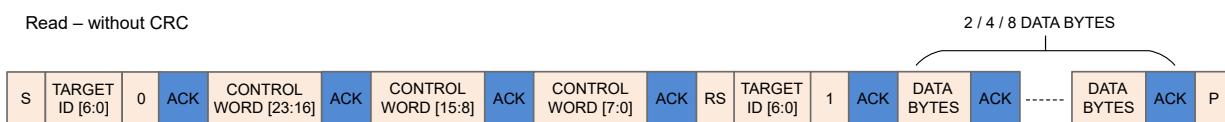

### 7.3.6.2 I<sup>2</sup>C インターフェイス

MCT8329A は、それによって外部コントローラがデータを送受信できる I<sup>2</sup>C シリアル通信インターフェイスをサポートしています。この I<sup>2</sup>C インターフェイスにより、外部コントローラは EEPROM を設定し、フォルトとモーターの状態の詳しい情報を読み出すことができます。I<sup>2</sup>C バスは、以下に説明するような、SCL および SDA ピンを使用する 2 線式インターフェイスです。

- SCL ピンはクロック信号入力です。

- SDA ピンはデータ入力および出力です。

### 7.3.7 モーター制御入力オプション

MCT8329A は、モーターを制御するための 3 つの方法を備えています。

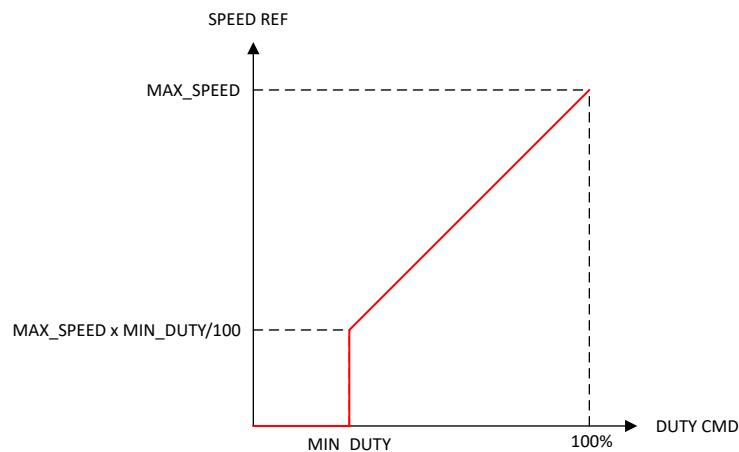

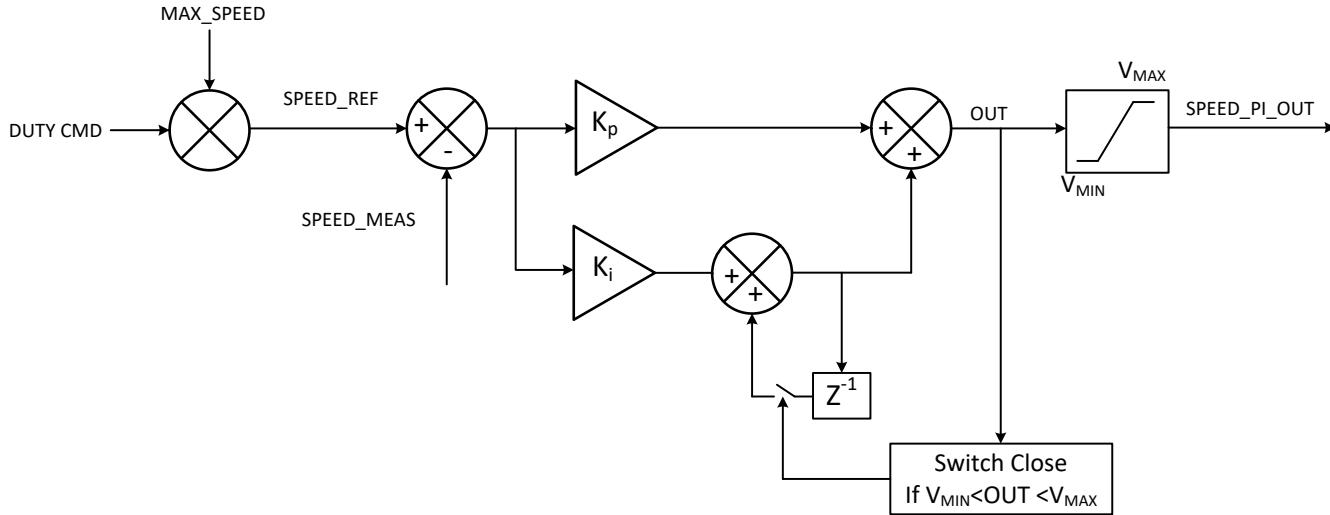

1. 速度制御: 速度制御モードでは、入力リファレンスに応じた閉ループ PI 制御を使ってモーター速度が制御されます。

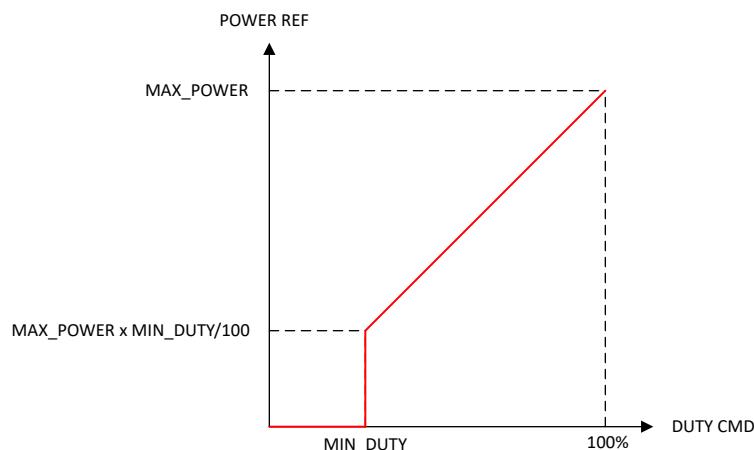

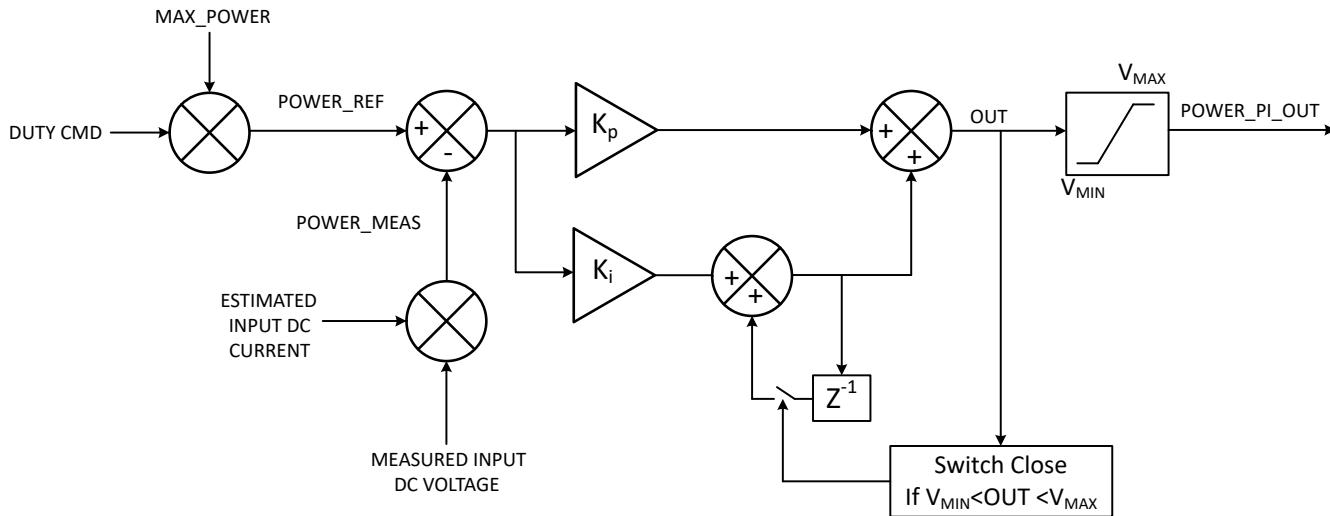

2. 電力制御: 電力制御モードでは、入力リファレンスに応じた閉ループ PI 制御を使ってインバータ出力段の DC 入力電力が制御されます。

3. 電圧制御: 電圧制御モードでは、入力リファレンスに応じてモーターの印加電圧が制御されます。

MCT8329A は、モーターのリファレンス入力を直接制御するための 4 つの方法を備えています。リファレンスの制御方法は **SPD\_CTRL\_MODE** によって設定されます。

リファレンス (速度、電力、電圧) 入力コマンドは、次の 4 つの方法のいずれかで制御できます。

- SPEED/WAKE ピンの PWM 入力信号のデューティ・サイクルを変化させることで制御

- SPEED/WAKE ピンの周波数を変化させることで制御

- SPEED/WAKE ピンまたは DACOUT/SOx/SPEED\_ANA ピンのアナログ入力信号の振幅を変化させることで制御

- SPEED\_CTRL を設定することで、I<sup>2</sup>C を介して制御

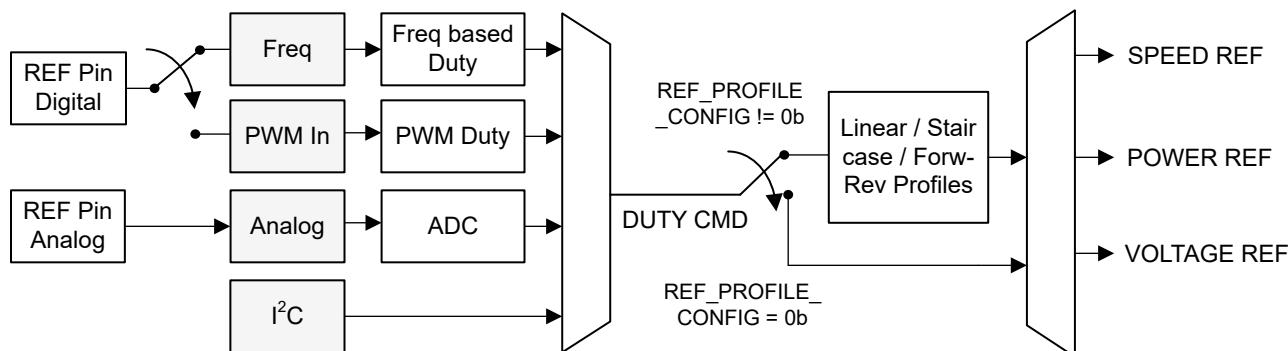

図 7-7. リファレンス入力コマンドの多重化

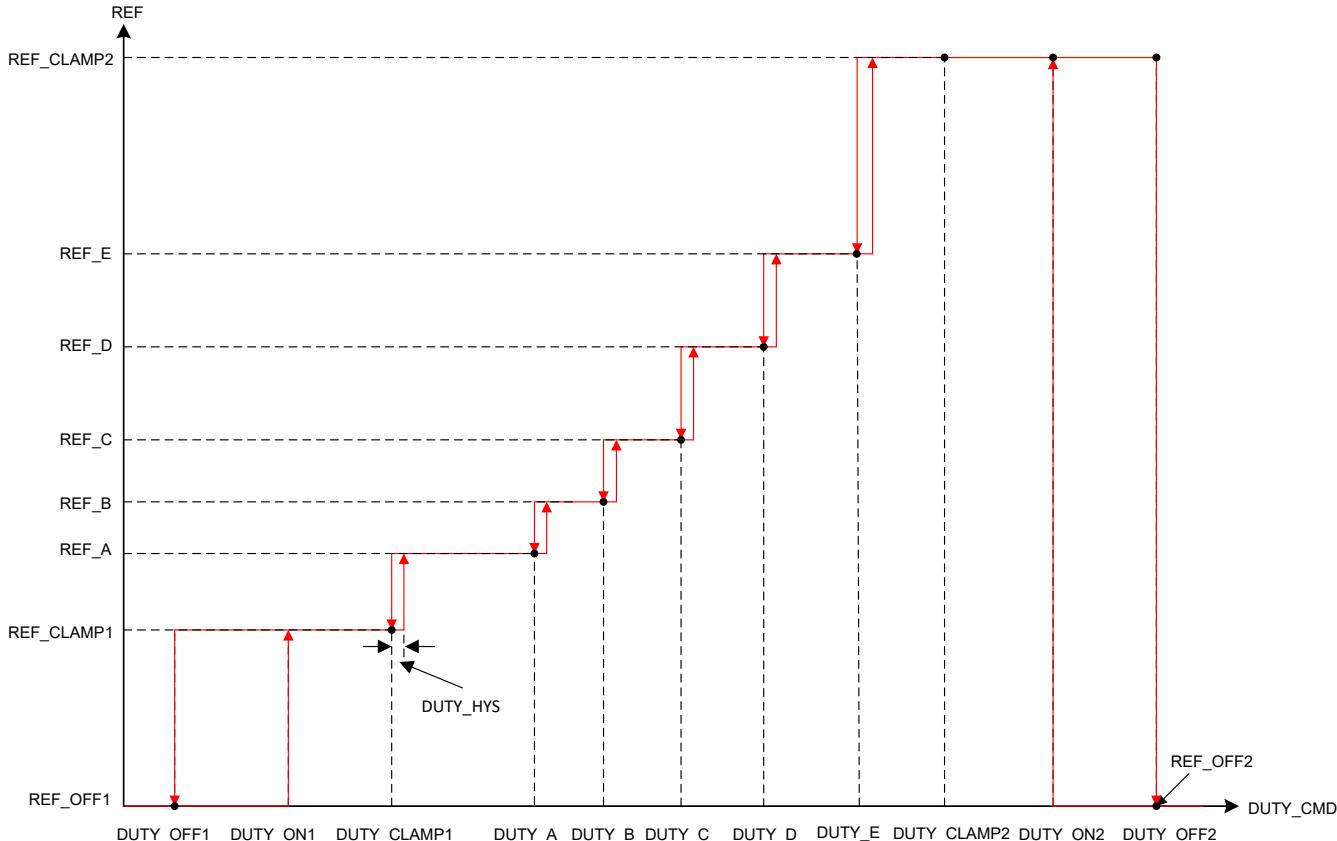

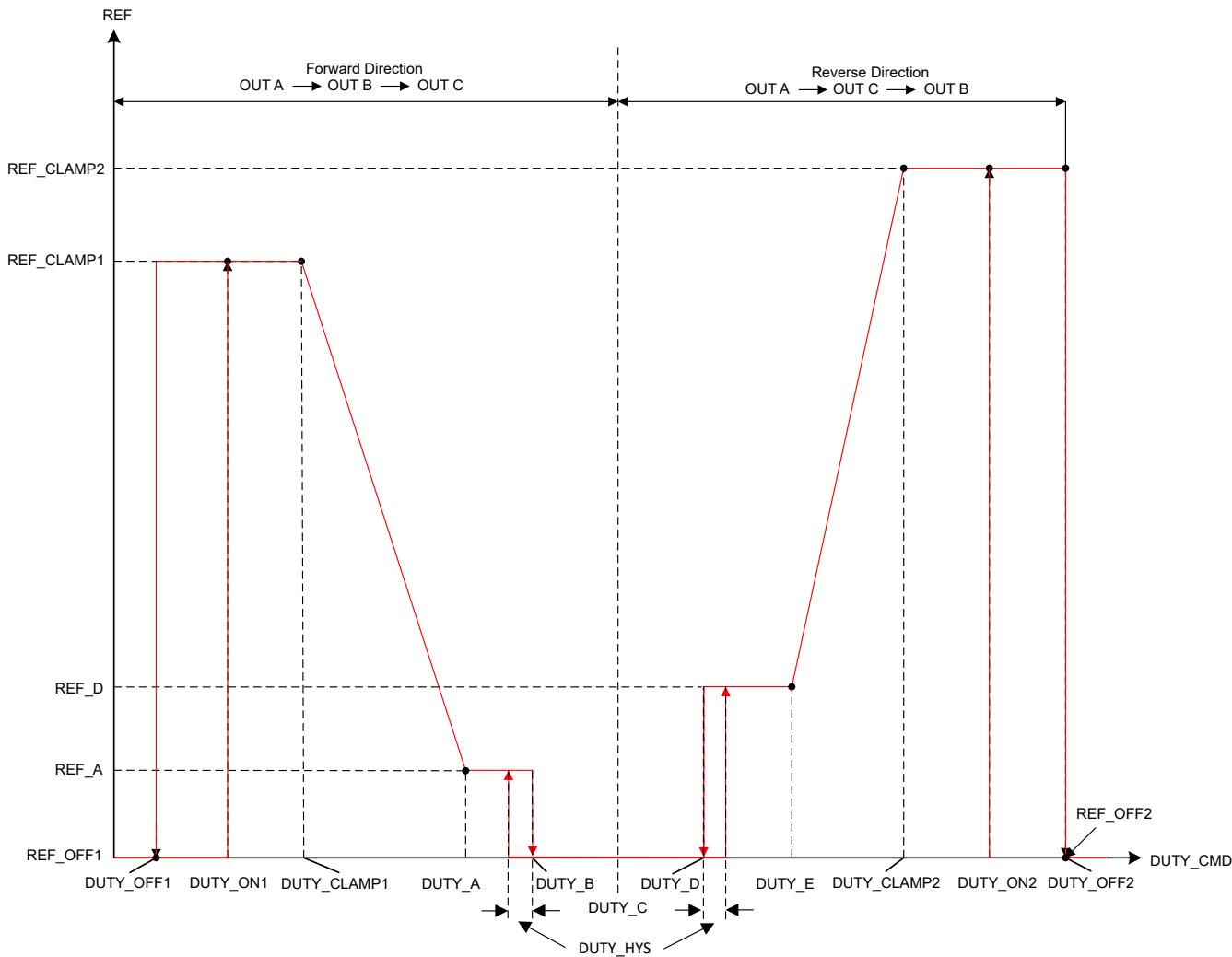

図 7-7 に、リファレンス (SPEED/WAKE または DACOUT/SOx/SPEED\_ANA) ピン入力 (または I<sup>2</sup>C による入力) から出力リファレンスまでの信号路を示します。リファレンス・ピンの最大分解能の値を DUTY CMD として使って、速度、電力、電圧リファレンスを求めるすることができます。速度、電力、電圧リファレンスを求める前に、各種プロファイル (リニア、階段、双方向) を挿入することもできます。その選択は、REF\_PROFILE\_CONFIG を設定することで行うことができます。

#### 7.3.7.1 アナログ・モードのモーター制御

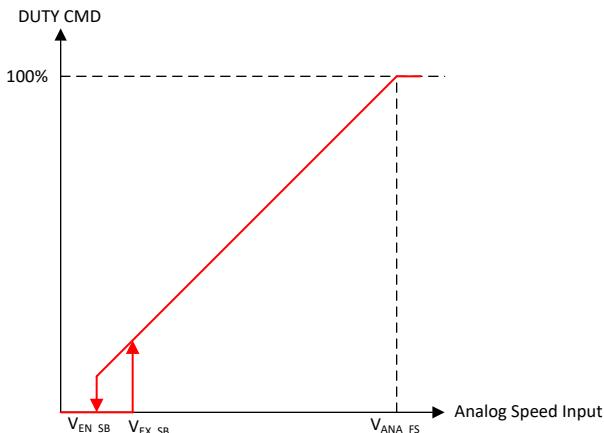

アナログ入力方式のモーター制御は、SPD\_CTRL\_MODE を 00b に設定することで有効化できます。このモードでは、デューティ・コマンド (DUTY CMD) は、SPEED/WAKE ピンのアナログ電圧入力 ( $V_{SPEED}$ ) または DACOUT/SOx/SPEED\_ANA ピン (DAC\_SOX\_ANA\_CONFIG によって設定可能)  $V_{SPEED}$  によって変化します。 $0 < V_{SPEED} < V_{EN\_SB}$  の場合、DUTY CMD は 0 に設定され、モーターは停止します。 $V_{EN\_SB} < V_{SPEED} < V_{ANA\_FS}$  の場合、DUTY CMD は  $V_{SPEED}$  に対して直線的に変化します (図 7-8 を参照)。 $V_{SPEED} > V_{ANA\_FS}$  の場合、DUTY CMD は 100% にクランプされます。

アナログ制御入力として DACOUT/SOx/SPEED\_ANA ピンを使用すると、スリープまたはスタンバイの開始 / 終了を制御するために SLEEP/WAKE ピンを独立して使用できます (表 7-3 を参照)。

図 7-8. アナログ・モード速度制御

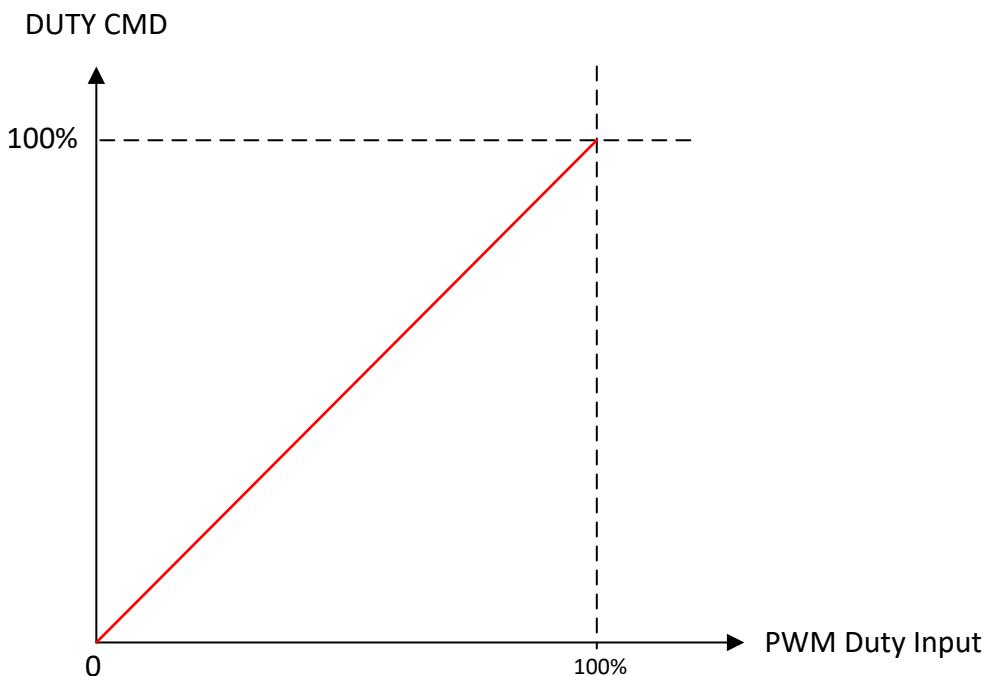

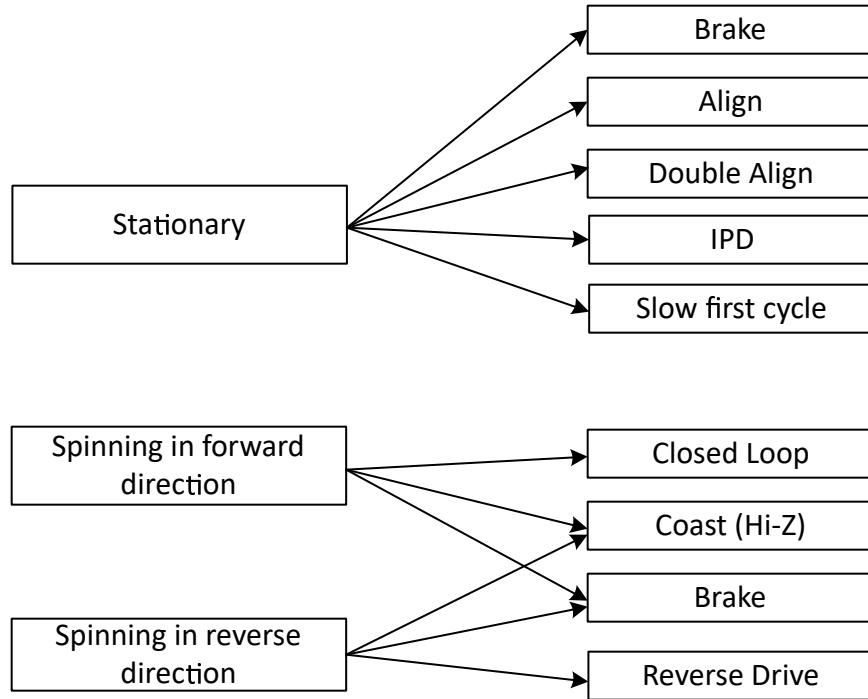

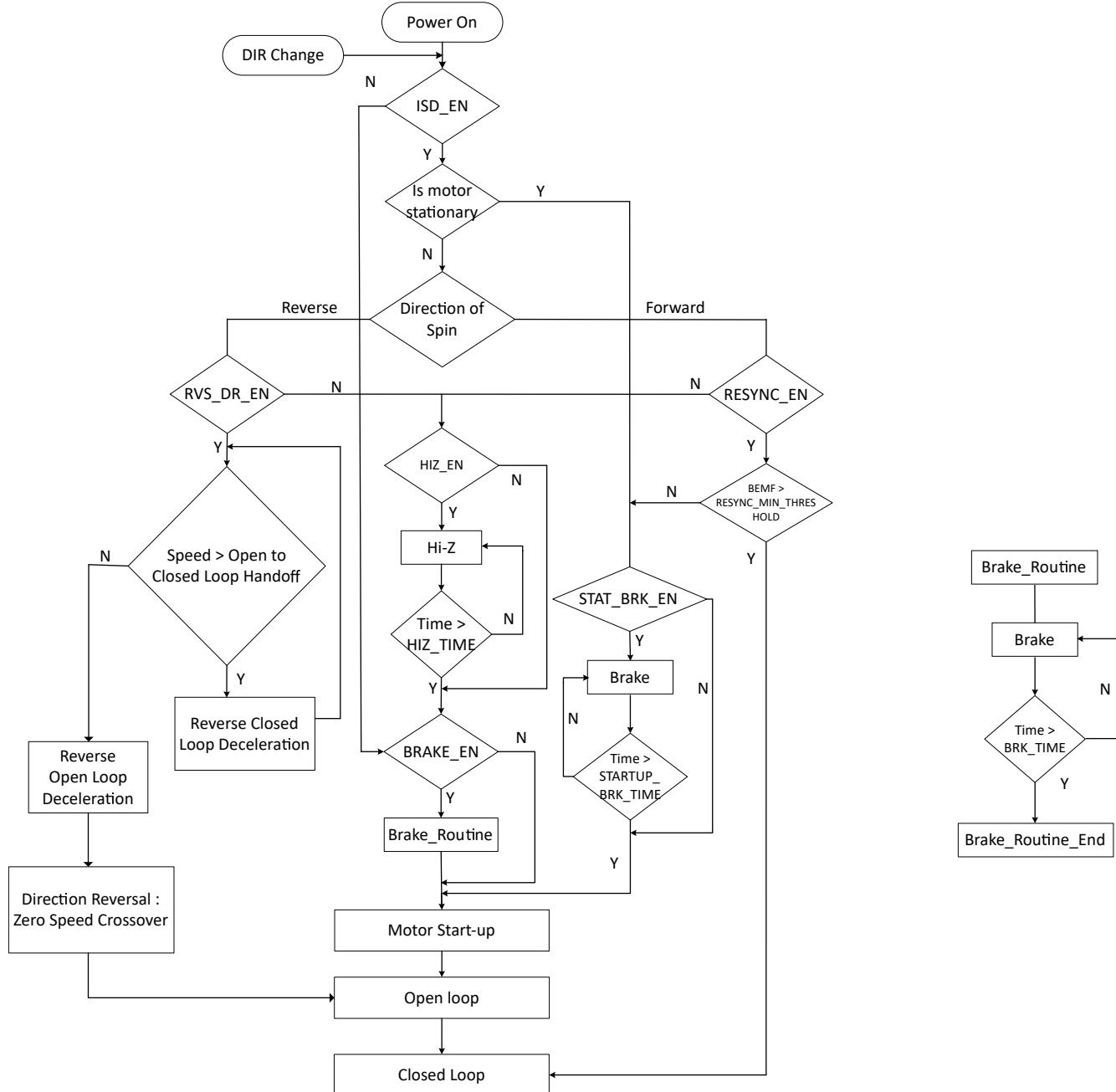

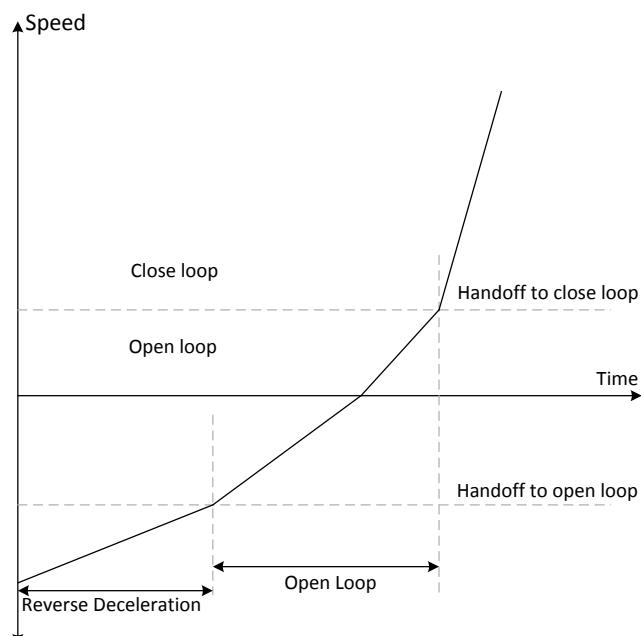

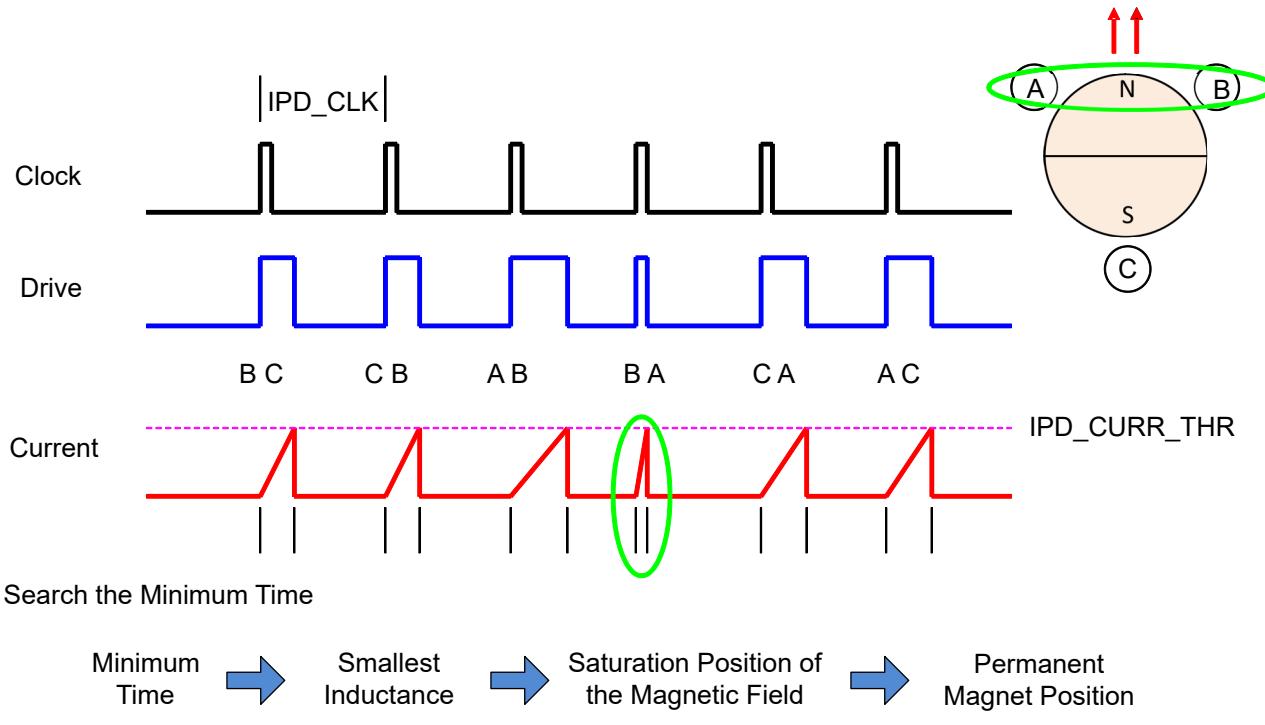

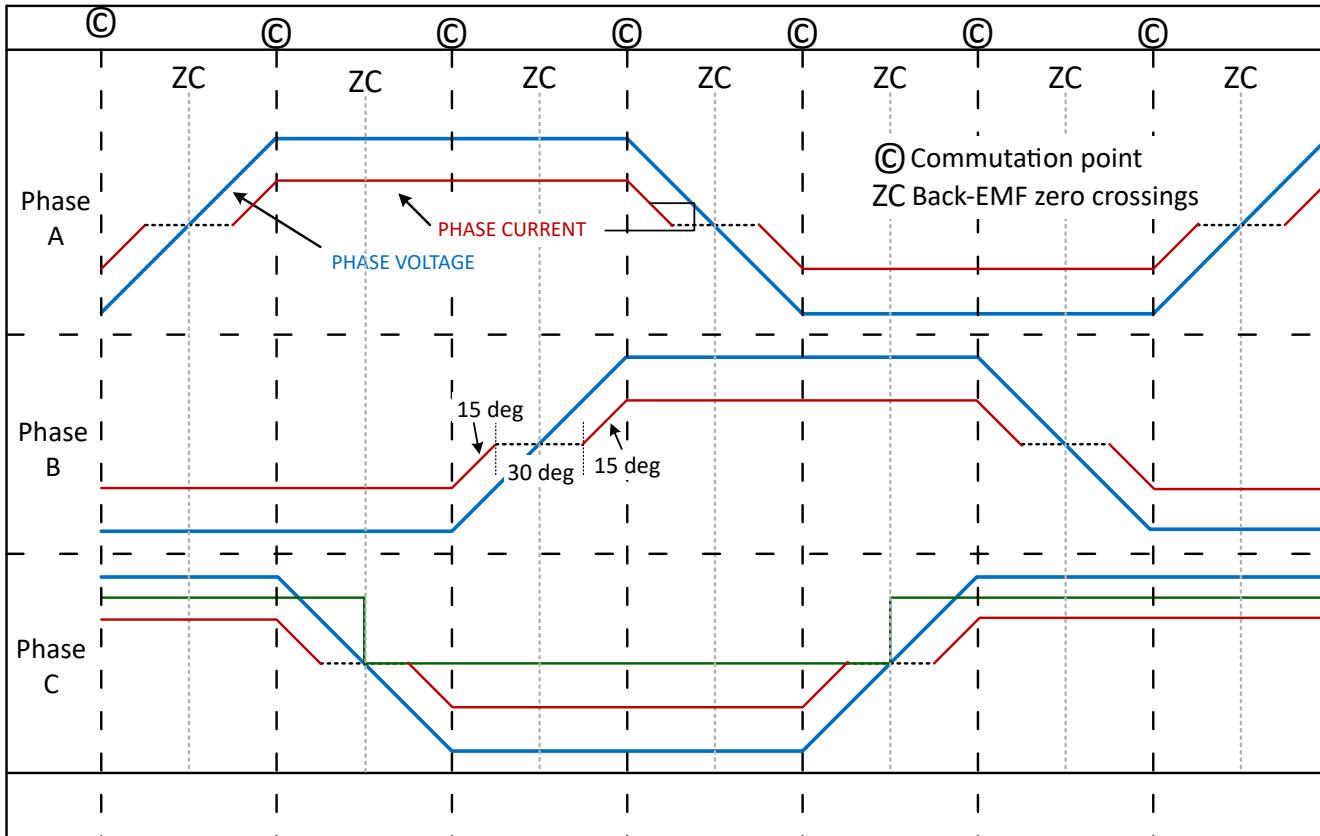

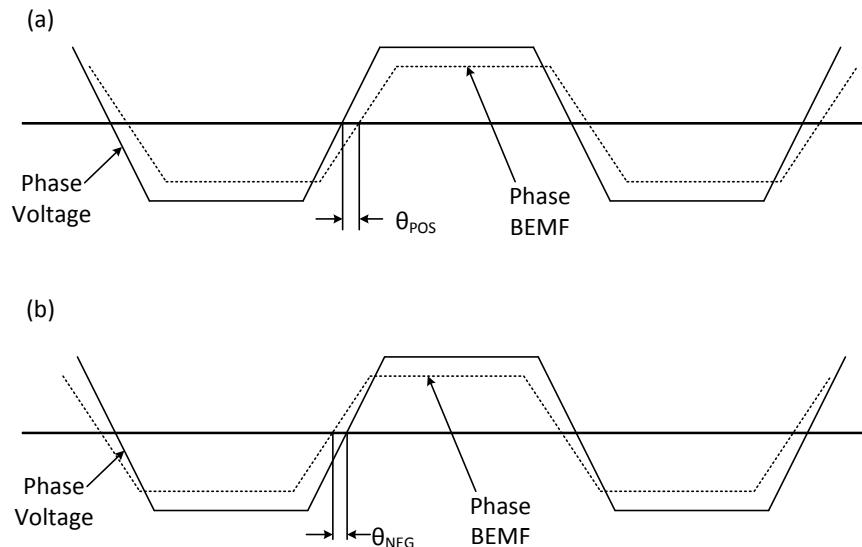

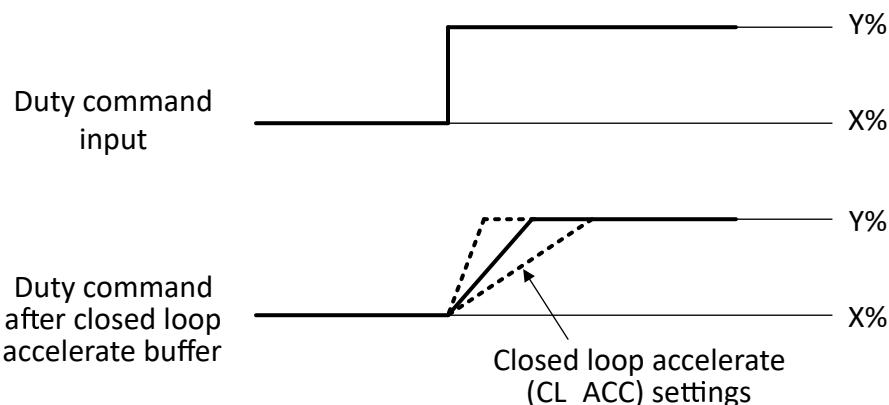

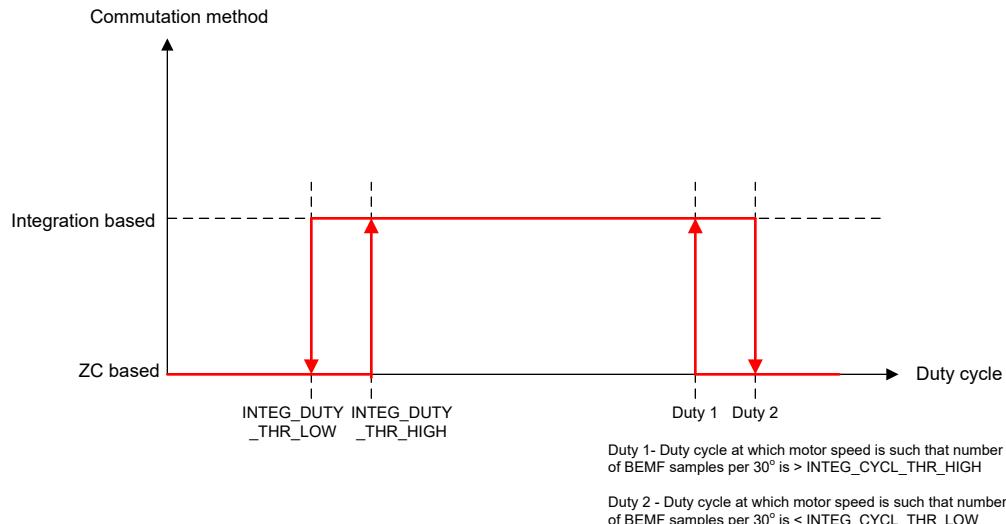

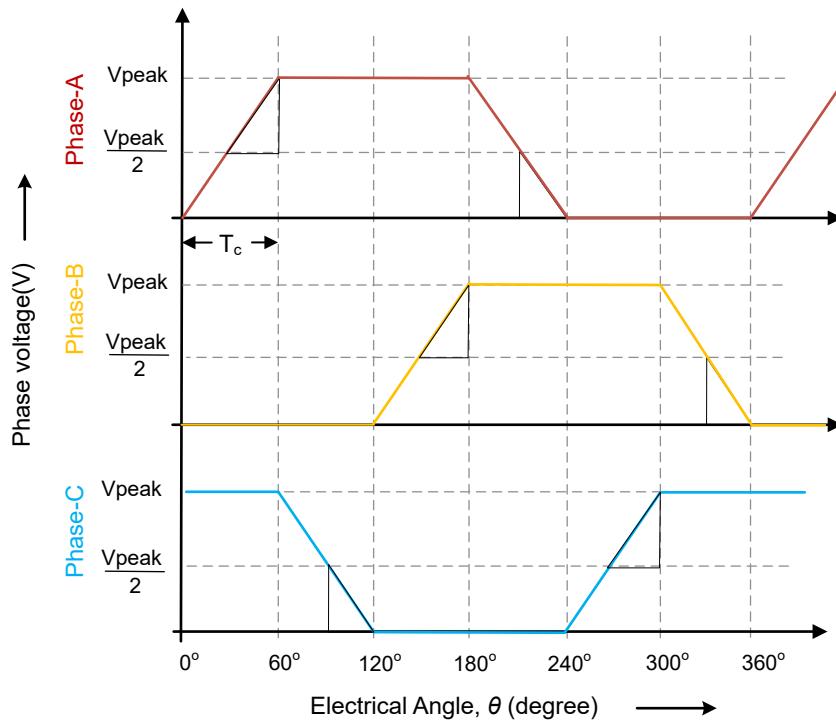

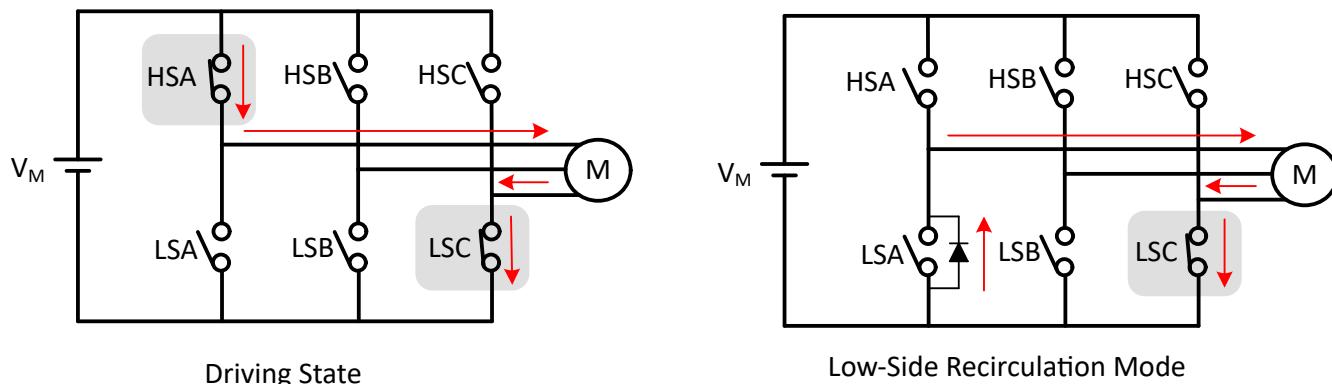

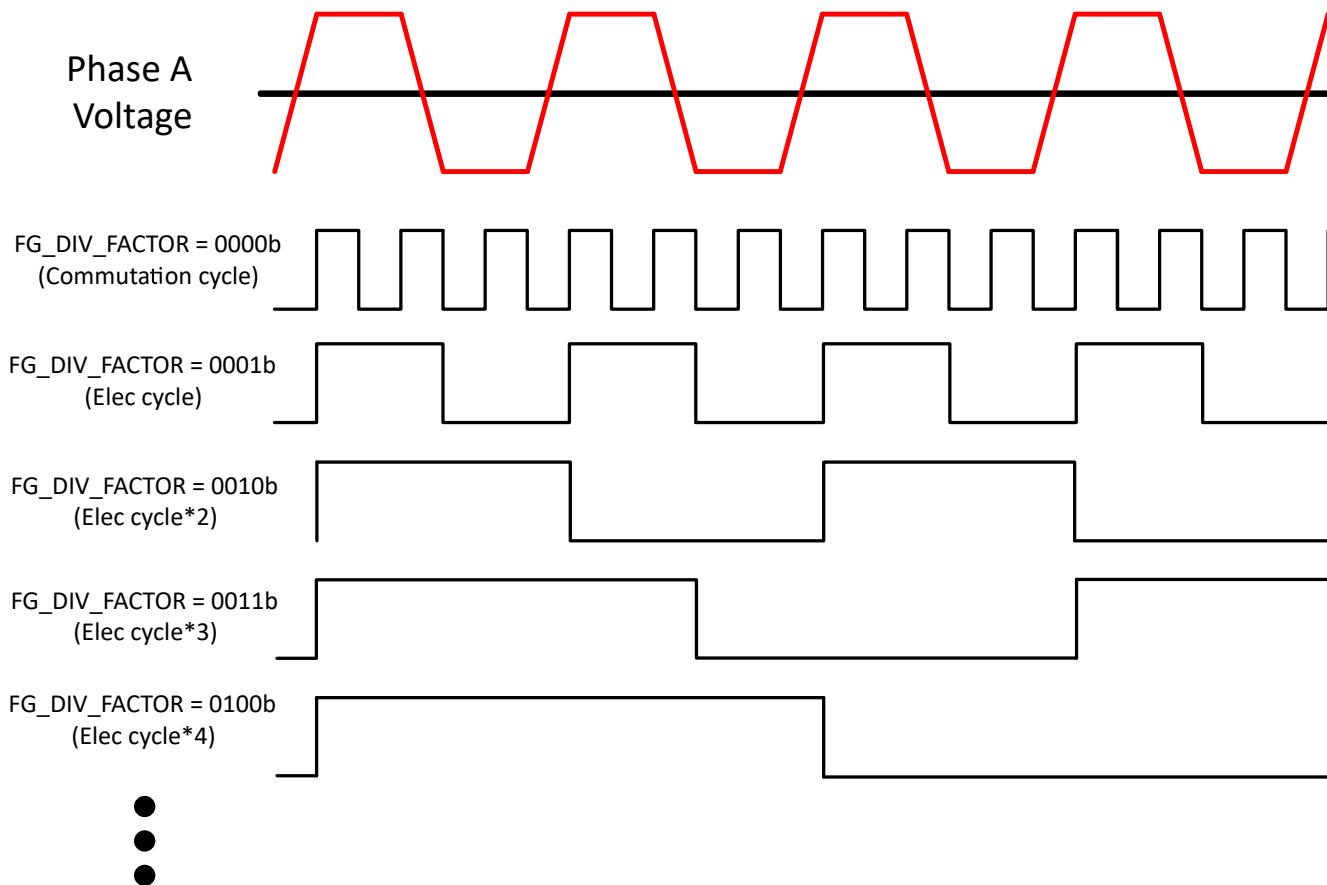

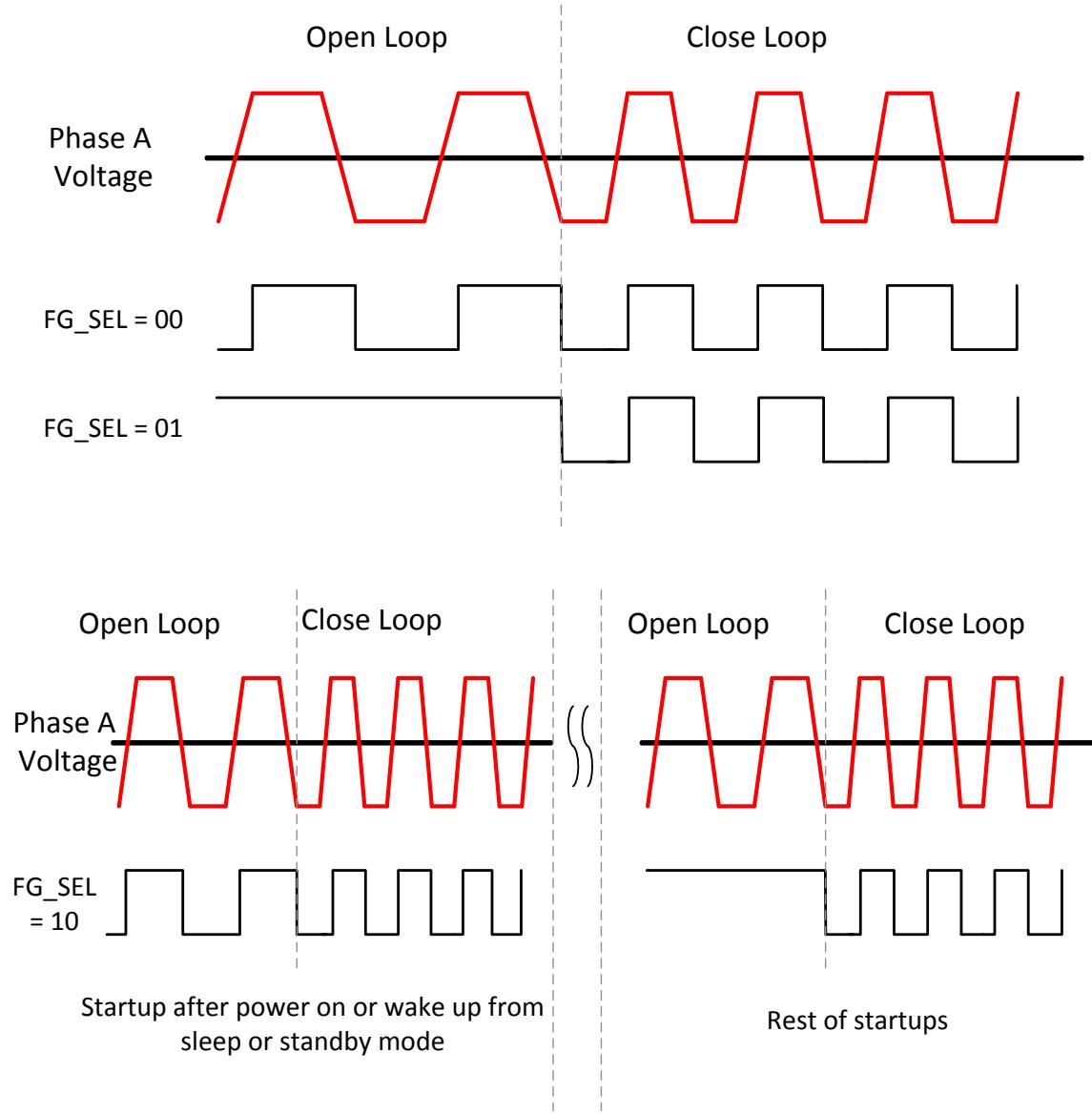

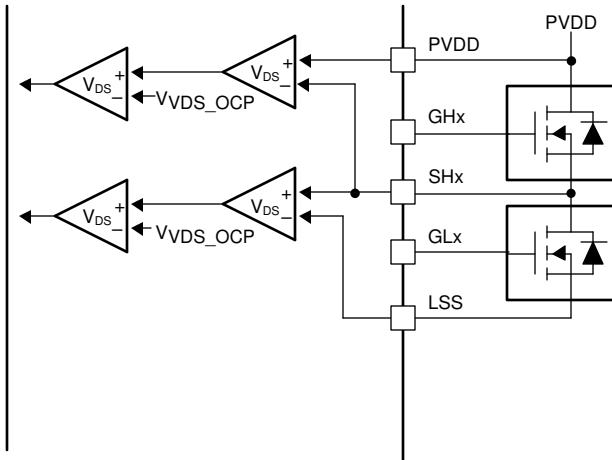

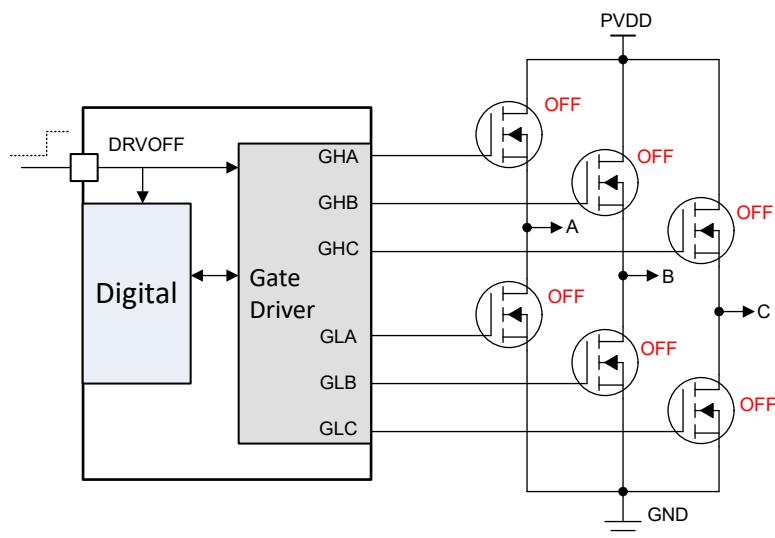

#### 7.3.7.2 PWM モード・モーター制御