# LP8772x-Q1 ミリ波レーダー センサ向け、3 個の降圧コンバータ、1 個のリニアレギュレータ、1 個のロードスイッチ

## 1 特長

- 以下の結果で AEC-Q100 認定済み :

- デバイス温度グレード 1 : 動作時周囲温度範囲 : -40°C ~ +125°C

- 機能安全に準拠したデバイス

- 機能安全アプリケーション向けに開発

- ASIL-Bまでの ISO 26262 機能安全システム設計に役立つ資料

- 降圧、LDO、ロードスイッチ出力、入力電源過電圧 / 低電圧監視

- Q&A ウォッチドッグ

- レベルまたは PWM エラー信号モニタ (ESM)

- ABIST および CRC

- 入力電圧 : 公称 3.3V (3V ~ 4V の範囲)

- 高効率、低ノイズ、高周波の 3 つの降圧 DC/DC コンバータ :

- 出力電圧 : 0.8V、0.82V、0.9V ~ 1.9V、20mV 刻みの出力電圧による

- 最大出力電流 : 3.5A

- スイッチング周波数 : 4.4MHz、8.8MHz、17.6MHz

- 600mA リニアレギュレータ、バイパス / ロードスイッチモード付き (LDO\_LS1)

- 入力電圧、LDO モード : 1.2V ~ 4V

- 出力電圧 : 0.6V ~ 3.4V、50mV 刻みの出力電圧による

- 入力電圧、バイパス / ロードスイッチモード : 1.6V ~ 3.4V

- 400mA ロードスイッチ (LS2)

- 入力電圧範囲 : 1.6V ~ 3.6V

- オン抵抗 3.3V 入力、200mA : 7.5mΩ (代表値)

- 出力短絡および過負荷保護

- I2C インターフェイスを介したレギュレータ出力の動的電圧スケーリング (DVS)

- 入力過電圧保護 (OVP) および低電圧誤動作防止 (UVLO)

- LDO\_LS1 および LS2 出力と共有される 2 つの汎用電圧モニタ

- 過熱警告および保護

- 標準、ファーストモード、ファーストモード+、オプションの I2C アドレス選択をサポートする I2C インターフェイス

## 2 アプリケーション

- 衛星レーダー

- 短距離と中距離のコーナー レーダー

- 超短距離レーダー

- 長距離フロント レーダー

- 低リップル、低ノイズのアプリケーション

## 3 概要

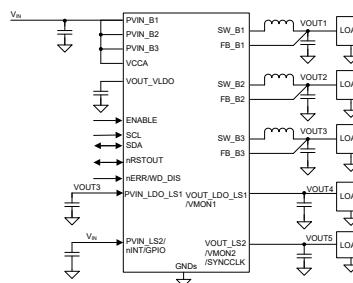

LP8772x-Q1 デバイスは、車載用および産業用のさまざまなレーダー アプリケーションで使用する AWR、IWR、他の MMIC (ミリ波 IC) のパワー マネージメント要件を満たすよう設計しています。このデバイスは、3 個の降圧 DC/DC コンバータ、1 個の LDO レギュレータ、1 個の ロードスイッチを搭載しています。この LDO は外部から電力を供給され、イーサネット デバイスやシステム内にある他のデバイスへの電力供給を目的としています。ロードスイッチは、センサがスリープ モードになっているときに 3.3V の IO 電源を供給停止する設計を採用しています。このデバイスは、I2C 通信インターフェイスとイネーブル信号を使用して制御します。

低ノイズ降圧 DC/DC コンバータは、工場出荷時にプログラミングされた 17.6MHz、8.8MHz、または 4.4MHz のスイッチング周波数をサポートしています。高いスイッチング周波数と、広い周波数範囲にわたる低ノイズにより、LDO フリーの電源ソリューションを実現し、ソリューションコストの削減と放熱性能の向上に貢献します。スイッチングクロックは強制的に PWM モードに設定されて優れた RF 性能を実現しているほか、外部クロックと同期することもできます。LP8772x-Q1 は、リモート電圧センシングに対応しており、レギュレータ出力とポイントオブ ポート (POL) との間の IR 降下を補償して出力電圧の精度を高めることができます。

## パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|------------|----------------------|-------------------------|

| LP8772x-Q1 | RAG (VQFN-HR, 24)    | 4.00mm × 4.00mm         |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンも含まれます。

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.comで必ず最新の英語版をご参照くださいますようお願いいたします。

## Table of Contents

|                                         |   |                                                        |   |

|-----------------------------------------|---|--------------------------------------------------------|---|

| 1 特長.....                               | 1 | 6.2 ドキュメントの更新通知を受け取る方法.....                            | 7 |

| 2 アプリケーション.....                         | 1 | 6.3 サポート・リソース.....                                     | 7 |

| 3 概要.....                               | 1 | 6.4 Trademarks.....                                    | 7 |

| 4 概要(続き).....                           | 3 | 6.5 静電気放電に関する注意事項.....                                 | 7 |

| 5 Pin Configuration and Functions.....  | 4 | 6.6 用語集.....                                           | 7 |

| 5.1 Digital Signal Descriptions.....    | 6 | 7 Revision History.....                                | 7 |

| 6 Device and Documentation Support..... | 7 | 8 Mechanical, Packaging, and Orderable Information.... | 7 |

| 6.1 Documentation Support.....          | 7 |                                                        |   |

## 4 概要 (続き)

LP8772x-Q1 デバイスは、プログラム可能なスタートアップとシャットダウンの遅延、および ENABLE 信号に同期したシーケンスをサポートしています。これらのシーケンスには、外部レギュレータ、ロードスイッチ、プロセッサリセットを制御するための GPO 信号も含めることができます。デバイスのデフォルト設定は、工場で不揮発性メモリ (NVM) / ワンタイムプログラマブル (OTP) メモリにプログラマされているため、ユーザーはデバイスのデフォルトの NVM/OTP 設定を変更できません。このデバイスは、出力スルーレートを制御し、デバイスのスタートアップ時に出力電圧のオーバーシュートおよび突入電流を最小化します。

LP8772x-Q1 ファミリのデバイスは、注文可能な型番体系である **LP8772xyzRAGRQ1** に従います。ここで、

### LP8772xyzRAGRQ1

Q1: Automotive AEC-Q100 Qualified

R: Tape and Reel (3000 units/reel) (other shipping options may be included in future. This field is not specific to device NVM or functional safety features)

A: package designator

z: Device NVM ID (01, 02...etc. TI\_NVM\_ID set by TI)

y = Buck regulators switching frequency set in the device NVM

o 1 : 17.6 MHz

o 2 : 8.8 MHz

o 3 : 4.4 MHz

x = Output rails configuration in the device NVM

o 5: 3 buck regulators, LDO\_LS1 regulator, LS2 load switch

o 4: 3 buck regulators, LDO\_LS1 regulator

o 3: 3 buck regulators

o 2: reserved for future use

o 1: reserved for future use

LP8772: device family and base part number

## 5 Pin Configuration and Functions

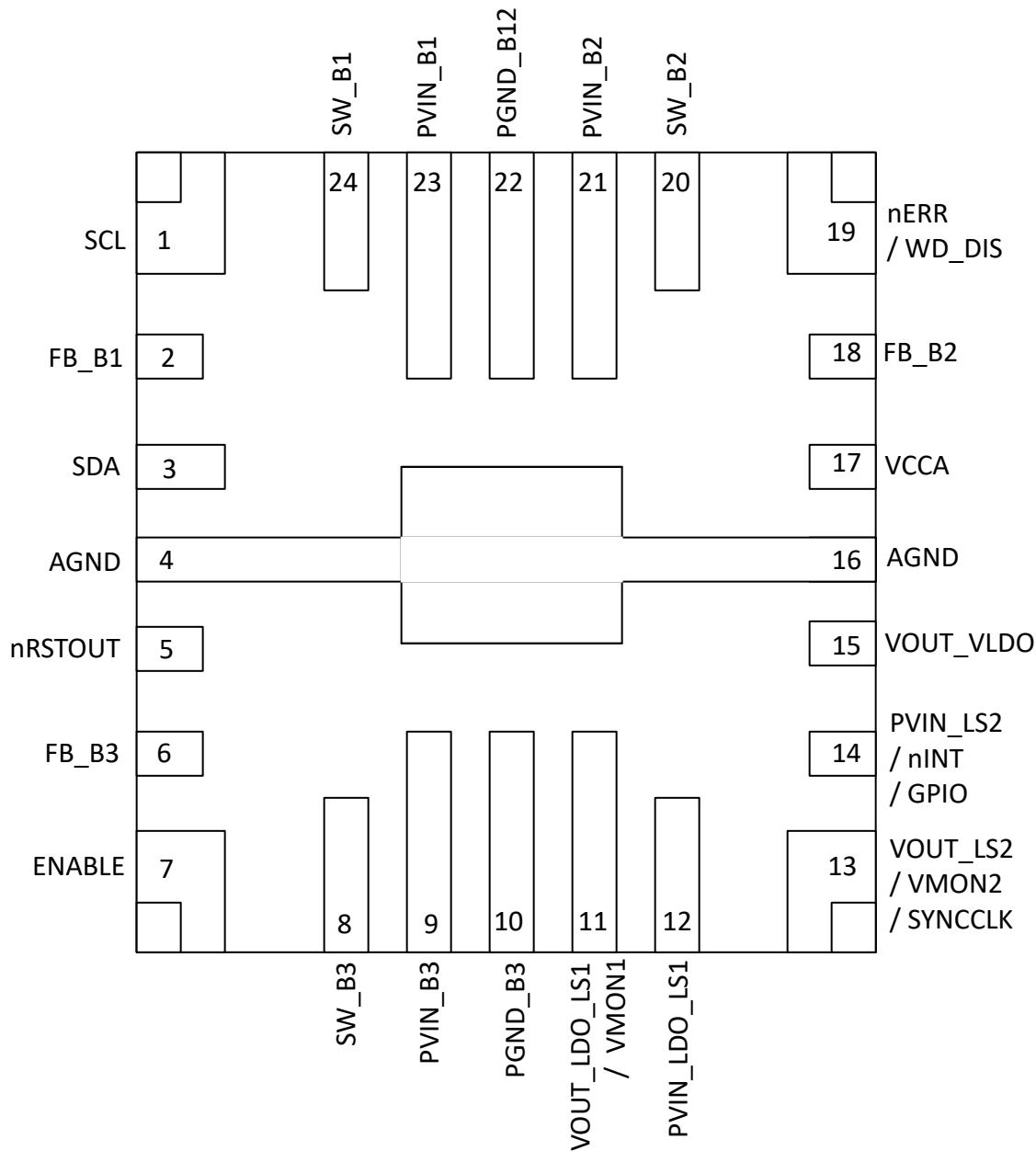

図 5-1. Package 24-Pin VQFN-HR Top View

表 5-1. Pin Functions

| NO. | NAME    | I/O   | TYPE    | DESCRIPTION                                                 |  |  |  |  |  | CONNECTION IF NOT USED |

|-----|---------|-------|---------|-------------------------------------------------------------|--|--|--|--|--|------------------------|

| 1   | SCL     | I     | Digital | I2C interface serial clock (external pull up).              |  |  |  |  |  | VCCA                   |

| 2   | FB_B1   | —     | Analog  | Output voltage feedback for BUCK1.                          |  |  |  |  |  | GND                    |

| 3   | SDA     | I / O | Digital | I2C interface bidirectional serial data (external pull up). |  |  |  |  |  | VCCA                   |

| 4   | AGND    | —     | Ground  | Ground.                                                     |  |  |  |  |  | Ground                 |

| 5   | nRSTOUT | O     | Digital | Reset output.                                               |  |  |  |  |  | Floating               |

| 6   | FB_B3   | —     | Analog  | Output voltage feedback for BUCK3.                          |  |  |  |  |  | Ground                 |

**表 5-1. Pin Functions (続き)**

| <b>PIN</b> |                        | <b>I/O</b> | <b>TYPE</b> | <b>DESCRIPTION</b>                                                                                                                                                                            | <b>CONNECTION IF NOT USED</b> |

|------------|------------------------|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| <b>NO.</b> | <b>NAME</b>            |            |             |                                                                                                                                                                                               |                               |

| 7          | ENABLE                 | I          | Digital     | Programmable ENABLE signal.                                                                                                                                                                   | Not applicable                |

| 8          | SW_B3                  | —          | Analog      | BUCK3 switch node.                                                                                                                                                                            | Floating                      |

| 9          | PVIN_B3                | —          | Power       | Power input for BUCK3. The separate power pins PVIN_Bxx are not connected together internally – PVIN_Bxx and VCCA pins must be connected together in the application and be locally bypassed. | PMIC input supply             |

| 10         | PGND_B3                | —          | Ground      | Power ground for BUCK3.                                                                                                                                                                       | Ground                        |

| 11         | VOUT_LDO_LS1/VMON1     | —          | Power       | Output voltage of LDO_LS1                                                                                                                                                                     | Floating                      |

|            |                        | —          | Analog      | Alternative programmable function: Voltage monitoring input                                                                                                                                   | GND                           |

| 12         | PVIN_LDO_LS1           | —          | Power       | Input voltage of LDO_LS1                                                                                                                                                                      | VCCA                          |

| 13         | VOUT_LS2/VMON2/SYNCCLK | —          | Power       | Output of Load Switch 2                                                                                                                                                                       | GND                           |

|            |                        | —          | Analog      | Alternative programmable function: Voltage monitoring input                                                                                                                                   | GND                           |

|            |                        | I          | Digital     | Alternative programmable function: External clock input.                                                                                                                                      | GND                           |

| 14         | PVIN_LS2/nINT/GPIO     | —          | Power       | Input supply for Load Switch 2                                                                                                                                                                | Ground                        |

|            |                        | O          | Digital     | Alternative programmable function: Interrupt output for System MCU                                                                                                                            | Floating                      |

|            |                        | I/O        | Digital     | Alternative programmable function (output): General purpose output. Alternative programmable function (input): I2C address selection through external pull-up / pull-down                     | Floating                      |

| 15         | VOUT_VLDO              | —          | Power       | Internal LDO regulator filter node. LDO is used for internal purposes.                                                                                                                        | -                             |

| 16         | AGND                   | —          | Ground      | Ground.                                                                                                                                                                                       | Ground                        |

| 17         | VCCA                   | —          | Power       | Supply voltage for internal LDO. VCCA and PVIN_Bxx pins must be connected together in the application and be locally bypassed.                                                                | System supply                 |

| 18         | FB_B2                  | —          | Analog      | Output voltage feedback for BUCK2.                                                                                                                                                            | Ground                        |

| 19         | nERR/WD_DIS            | I          | Digital     | Primary function: System MCU Error Monitoring Input.                                                                                                                                          | Ground                        |

|            |                        | I          | Digital     | Alternative programmable function: Watchdog Disable Input.                                                                                                                                    | Ground                        |

| 20         | SW_B2                  | —          | Analog      | BUCK2 switch node.                                                                                                                                                                            | Floating                      |

| 21         | PVIN_B2                | —          | Power       | Power input for BUCK2. The separate power pins PVIN_Bxx are not connected together internally – PVIN_Bxx and VCCA pins must be connected together in the application and be locally bypassed. | System supply                 |

| 22         | PGND_B12               | —          | Ground      | Power ground for BUCK1 and BUCK2.                                                                                                                                                             | Ground                        |

| 23         | PVIN_B1                | —          | Power       | Power input for BUCK1. The separate power pins PVIN_Bxx are not connected together internally – PVIN_Bxx and VCCA pins must be connected together in the application and be locally bypassed. | System supply                 |

| 24         | SW_B1                  | —          | Analog      | BUCK1 switch node.                                                                                                                                                                            | Floating                      |

## 5.1 Digital Signal Descriptions

表 5-2. Input Signal Descriptions

| PIN NAME                  | POWER DOMAIN<br>(recommended max) | INTERNAL PU/PD   | DEGLITCH TIME              |

|---------------------------|-----------------------------------|------------------|----------------------------|

| nERR                      | VCCA                              | 10 kΩ PU to VCCA | 15 µs                      |

| WD_DIS                    | VCCA                              | -                | 30 µs                      |

| SCL                       | VCCA                              | -                | -                          |

| SDA                       | VCCA                              | -                | -                          |

| VMON1                     | VCCA                              | -                | LDO_LS1_VMON1_DEGLITCH_SEL |

| VMON2                     | VCCA                              | -                | LS2_VMON2_DEGLITCH_SEL     |

| SYNCLK                    | VCCA                              | 400 kΩ PD to GND | -                          |

| ENABLE                    | VCCA                              | 400 kΩ PD to GND | 8 µs                       |

| GPIO (I2C Address select) | VCCA                              | -                | 8 µs                       |

ENABLE input is always functional when VCCA is at the valid level. Other input buffers are disabled until the valid VCCA supply is present and the device startup has progressed to a certain state. The input buffers are enabled after the OTP is read.

表 5-3. Output Signal Descriptions

| PIN NAME | POWER DOMAIN | PIN MODE | OUTPUT TYPE                                          | INTERNAL PU/PD                                                                                        |

|----------|--------------|----------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| SDA      | VCCA         | -        |                                                      | -                                                                                                     |

| nRSTOUT  | VCCA         | -        | Open-drain or push-pull<br>Active low or active high | In OD mode 10 kΩ programmable PU to VCCA when output driven high. PU disabled when output driven low. |

| nINT/GPO | VCCA         | -        | Open-drain or push-pull<br>Active low or active high | In OD mode 10 kΩ programmable PU to VCCA when output driven high. PU disabled when output driven low. |

## 6 Device and Documentation Support

### 6.1 Documentation Support

#### 6.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

#### 6.3 サポート・リソース

[テキサス・インスツルメンツ E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

#### 6.4 Trademarks

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 6.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 6.6 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 7 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2023 | *        | Initial Release |

## 8 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins     | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LP87725101RAGRQ1      | Active        | Production           | VQFN-HR (RAG)   24 | 5000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | LP8772<br>5101-Q1   |

| LP87725101RAGRQ1.A    | Active        | Production           | VQFN-HR (RAG)   24 | 5000   LARGE T&R      | Yes         | SN                                   | Level-2-260C-1 YEAR               | -40 to 125   | LP8772<br>5101-Q1   |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月