# LP5899 LP589x デバイス ファミリ向け、 SPI 互換接続機能

## 1 特長

- 動作電圧  $V_{CC}$  範囲: 2.5V ~ 5.5V

- SPI ペリフェラル

- 最大 20MHz のデータ転送レート

- 1 つのコントローラで複数のペリフェラルをサポート

- 連続クロックシリアルインターフェイス (CCSI) コントローラおよびペリフェラル

- 最大 20MHz のデータ転送レート

- EMI 耐性を強化できるプログラマブルなクロックジッタ

- 診断

- オープンドレインの FAULT ピン

- SPI 通信喪失検出

- SPI 通信用 CRC

- CCSI のデータ整合性

- データが利用可能かどうかを確認するためのデータレディ割り込み

## 2 アプリケーション

- LP5890 および LP5891 のための SPI 互換接続機能

## 3 説明

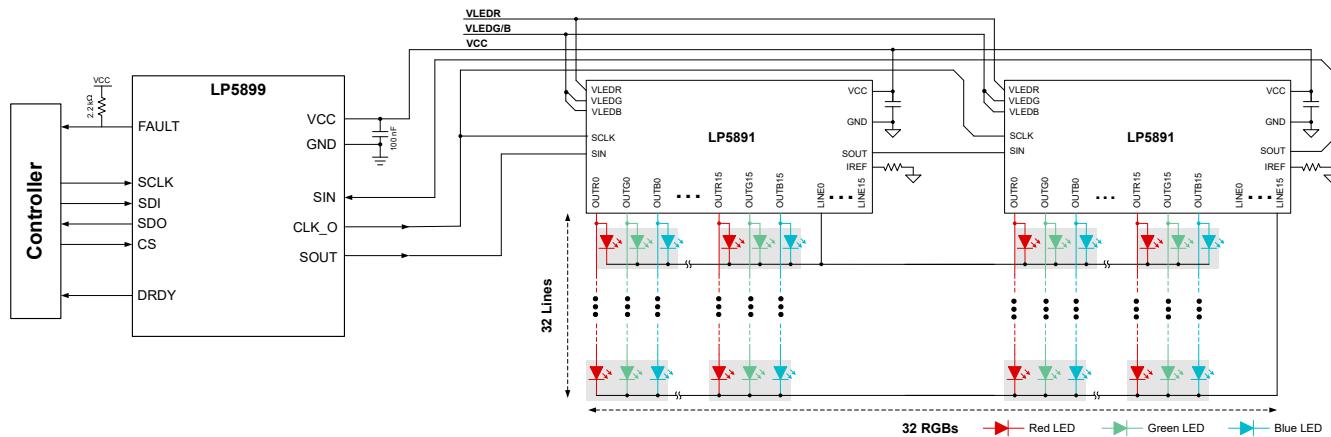

LP5899 SPI 互換接続機能を使うと、標準 SPI コントローラを使用して、LP589x デバイス ファミリを制御できます。本デバイスには、LP589x デバイス ファミリが必要とする連続クロックを生成するための内部発振器が備わっています。EMI 耐性を強化するため、連続クロックにジッタを付加できます。送信データは、CCSI インターフェイスのタイミング要件を維持するため、連続クロックに合わせて調整されます。

LP5899 には、LP589x のデイジーチェーンと LP5899 内部の両方の�オルトの報告機能が内蔵されています。レジスタと VSYNC コマンドの、LP589x デイジーチェーンへのデータ転送は、LP5899 によって CRC 保護されます。また、データラインは固着障害に対して LP5899 によって保護されます。

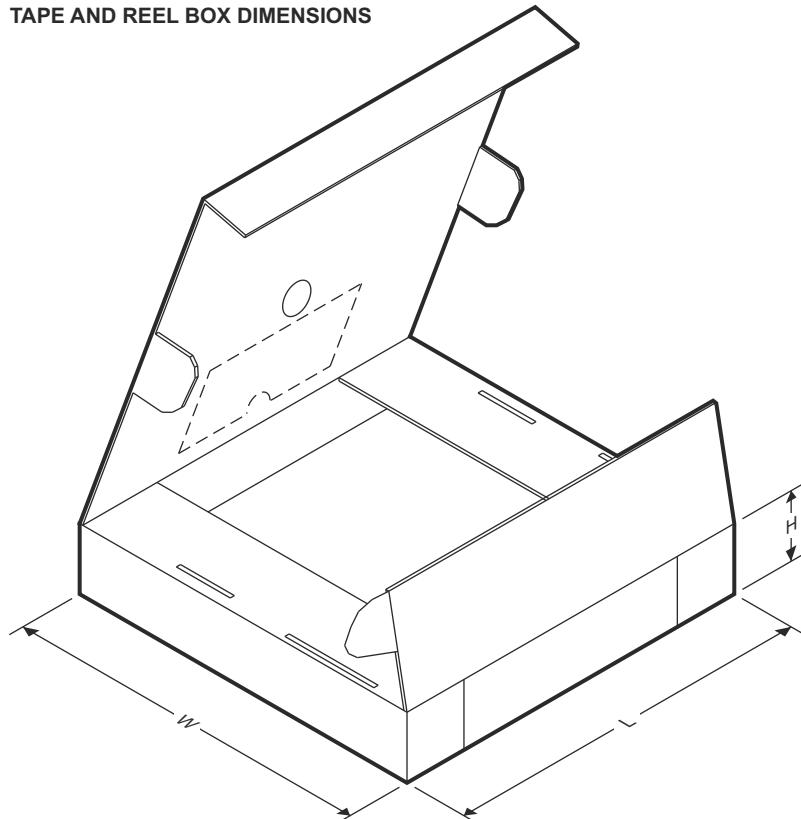

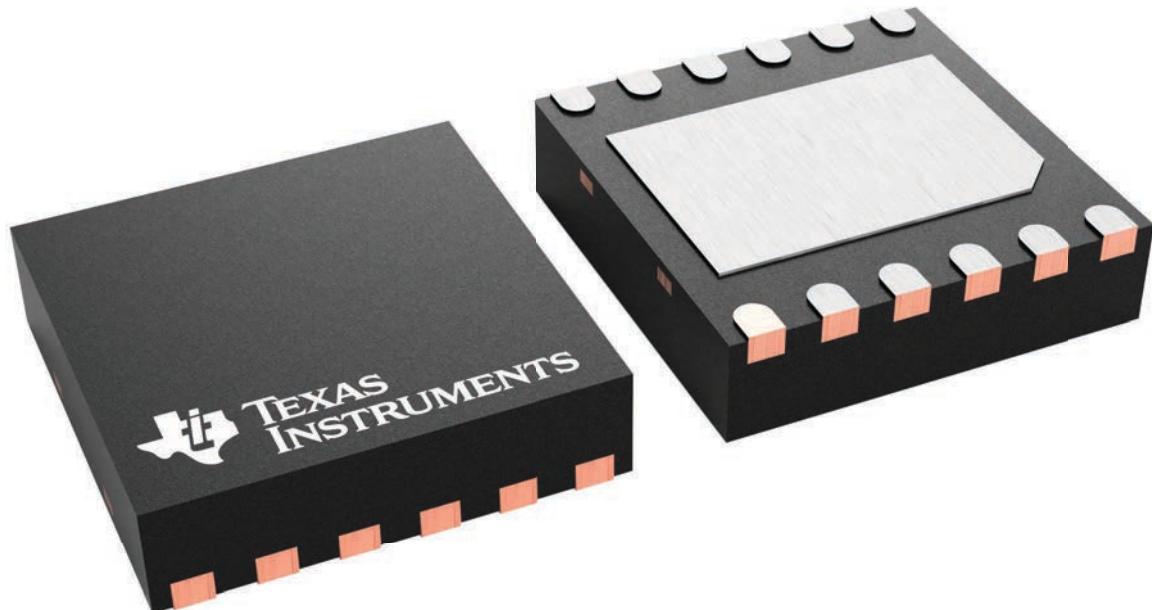

### パッケージ情報

| 部品番号   | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|--------|----------------------|--------------------------|

| LP5899 | DYY (SOT-23-THN, 14) | 4.2mm × 3.26mm           |

|        | DRR (WSON, 12)       | 3mm × 3mm                |

(1) 詳細については、[セクション 12](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

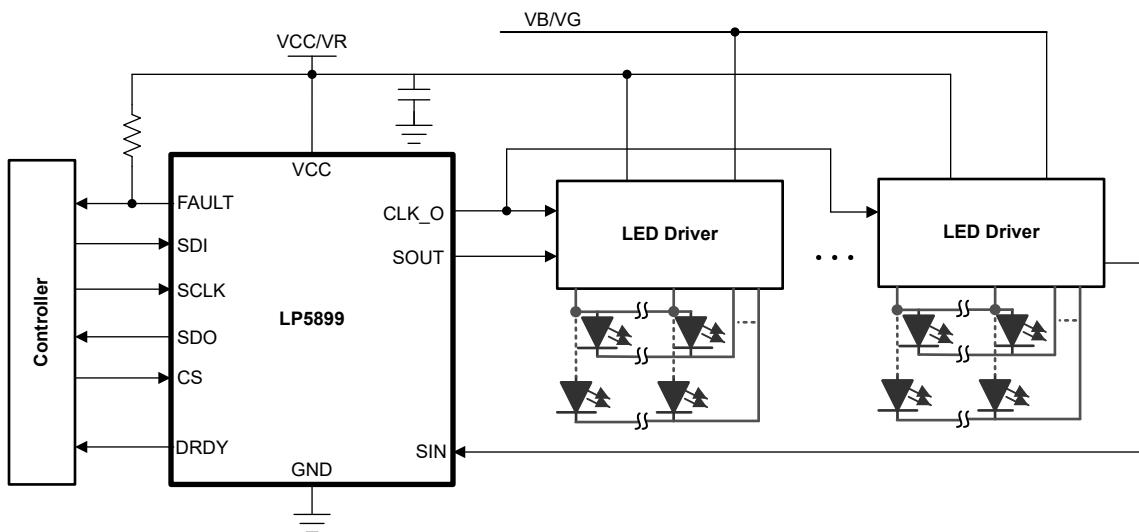

代表的なアプリケーションの図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSHF4](#)

## 目次

|              |    |                         |    |

|--------------|----|-------------------------|----|

| 1 特長         | 1  | 7.4 デバイスの機能モード          | 22 |

| 2 アプリケーション   | 1  | 7.5 プログラミング             | 23 |

| 3 説明         | 1  | 8 デバイスのレジスタ             | 33 |

| 4 デバイス比較表    | 3  | 9 アプリケーションと実装           | 46 |

| 5 ピン構成および機能  | 3  | 9.1 アプリケーション情報          | 46 |

| 6 仕様         | 4  | 9.2 代表的なアプリケーション        | 46 |

| 6.1 絶対最大定格   | 4  | 9.3 電源に関する推奨事項          | 50 |

| 6.2 ESD 定格   | 4  | 9.4 レイアウト               | 50 |

| 6.3 熱に関する情報  | 4  | 10 デバイスおよびドキュメントのサポート   | 52 |

| 6.4 推奨動作条件   | 4  | 10.1 ドキュメントの更新通知を受け取る方法 | 52 |

| 6.5 電気的特性    | 5  | 10.2 サポート・リソース          | 52 |

| 6.6 タイミング要件  | 6  | 10.3 商標                 | 52 |

| 6.7 スイッチング特性 | 6  | 10.4 静電気放電に関する注意事項      | 52 |

| 6.8 タイミング図   | 7  | 10.5 用語集                | 52 |

| 6.9 代表的特性    | 8  | 11 改訂履歴                 | 52 |

| 7 詳細説明       | 9  | 12 メカニカル、パッケージ、および注文情報  | 52 |

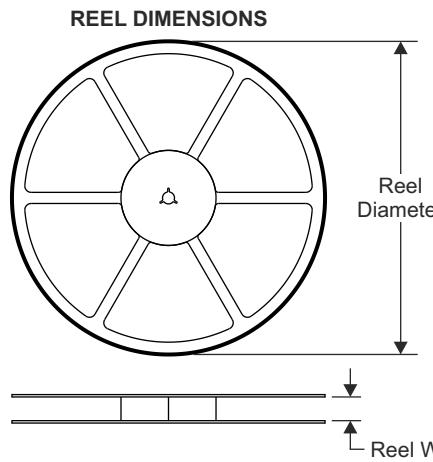

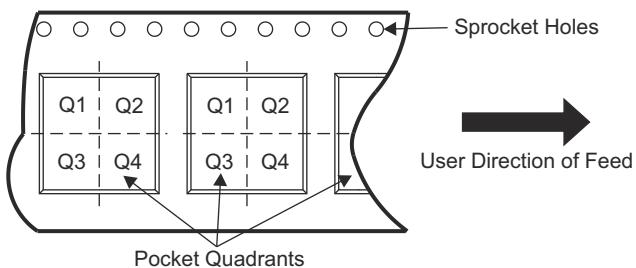

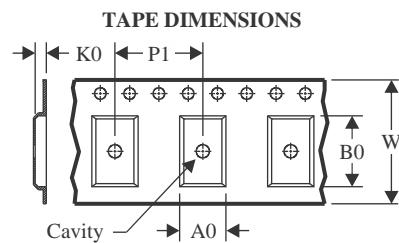

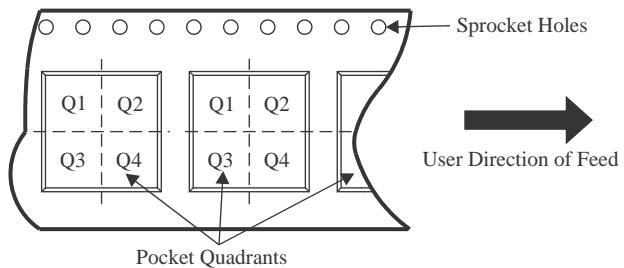

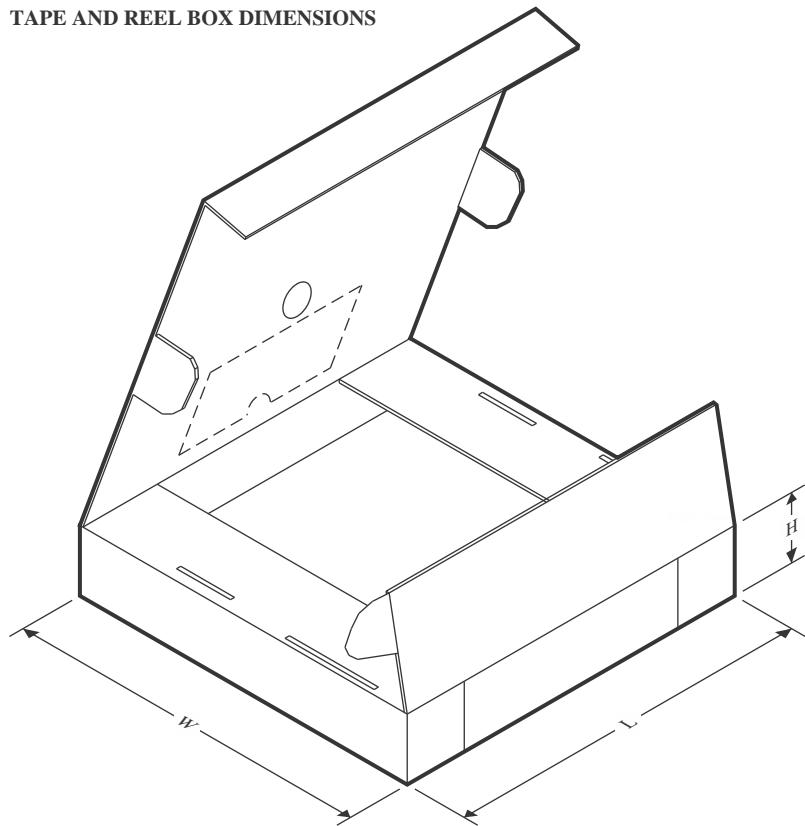

| 7.1 概要       | 9  | 12.1 テープおよびリール情報        | 53 |

| 7.2 機能ブロック図  | 9  | 12.2 メカニカル データ          | 55 |

| 7.3 機能説明     | 10 |                         |    |

## 4 デバイス比較表

| 部品番号   | 材料         | パッケージ           |

|--------|------------|-----------------|

| LP5899 | LP5899DYYR | SOT-23-THN (14) |

|        | LP5899DRRR | WSON (12)       |

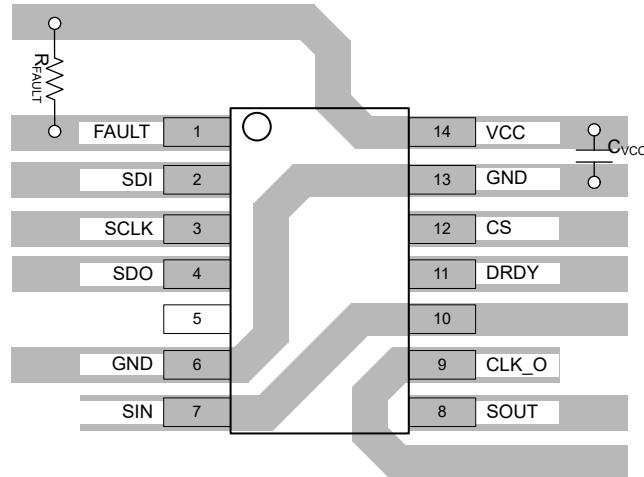

## 5 ピン構成および機能

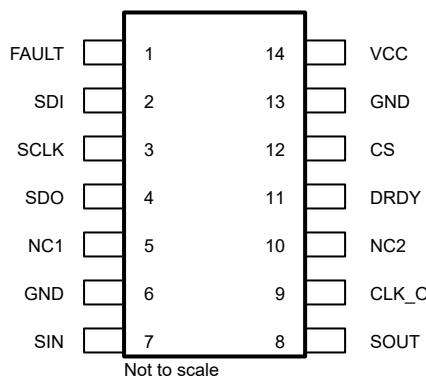

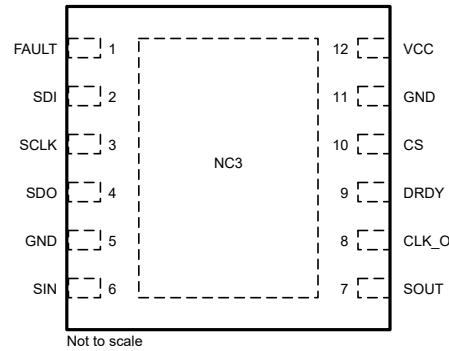

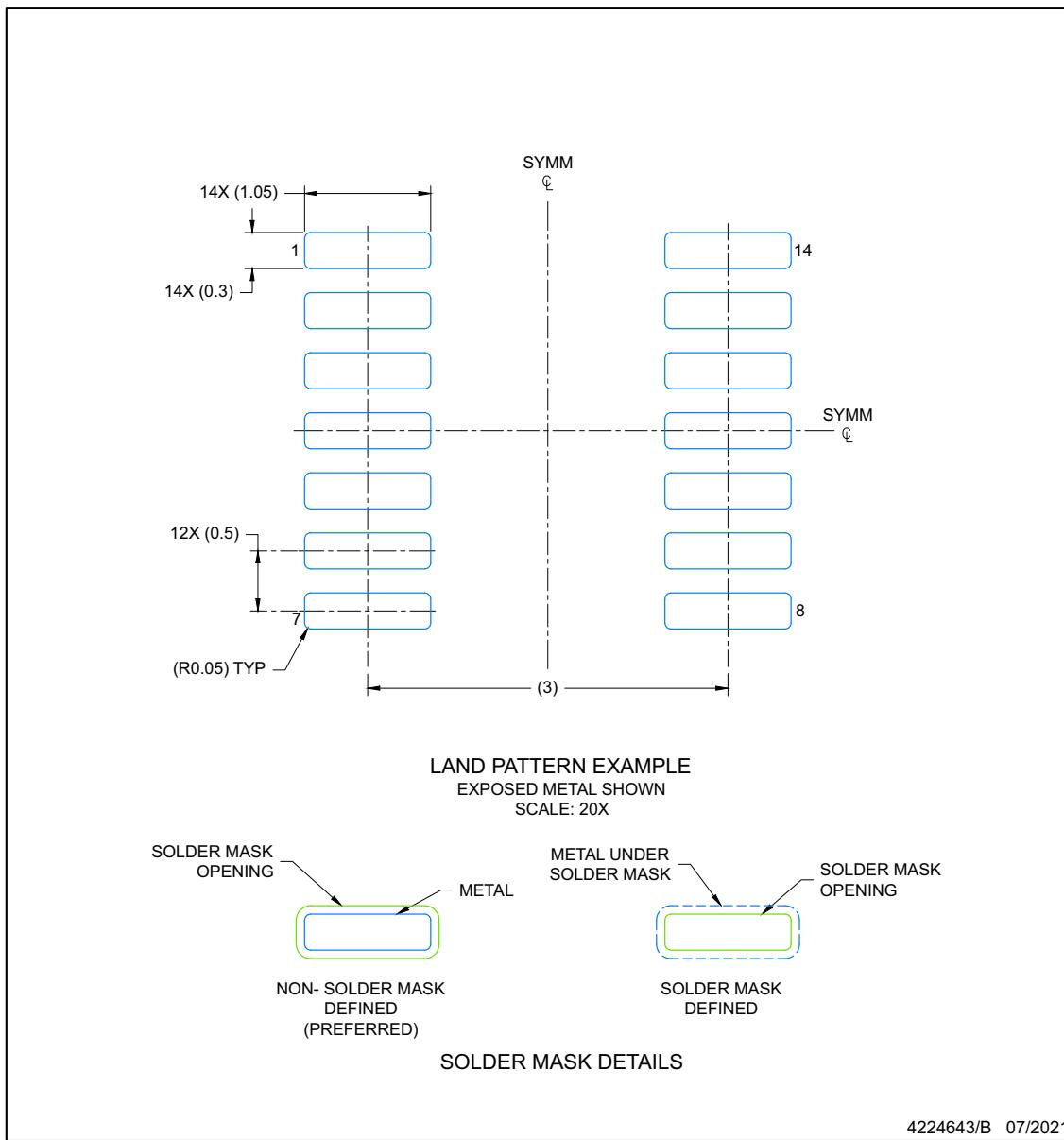

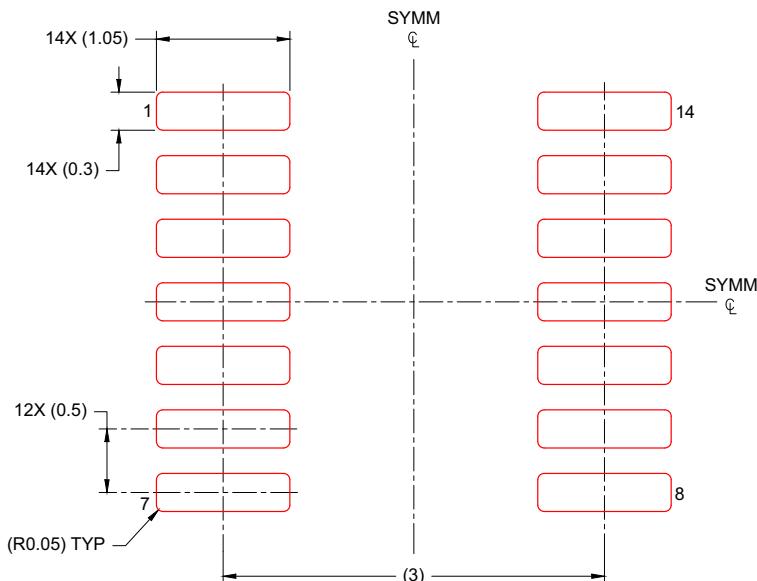

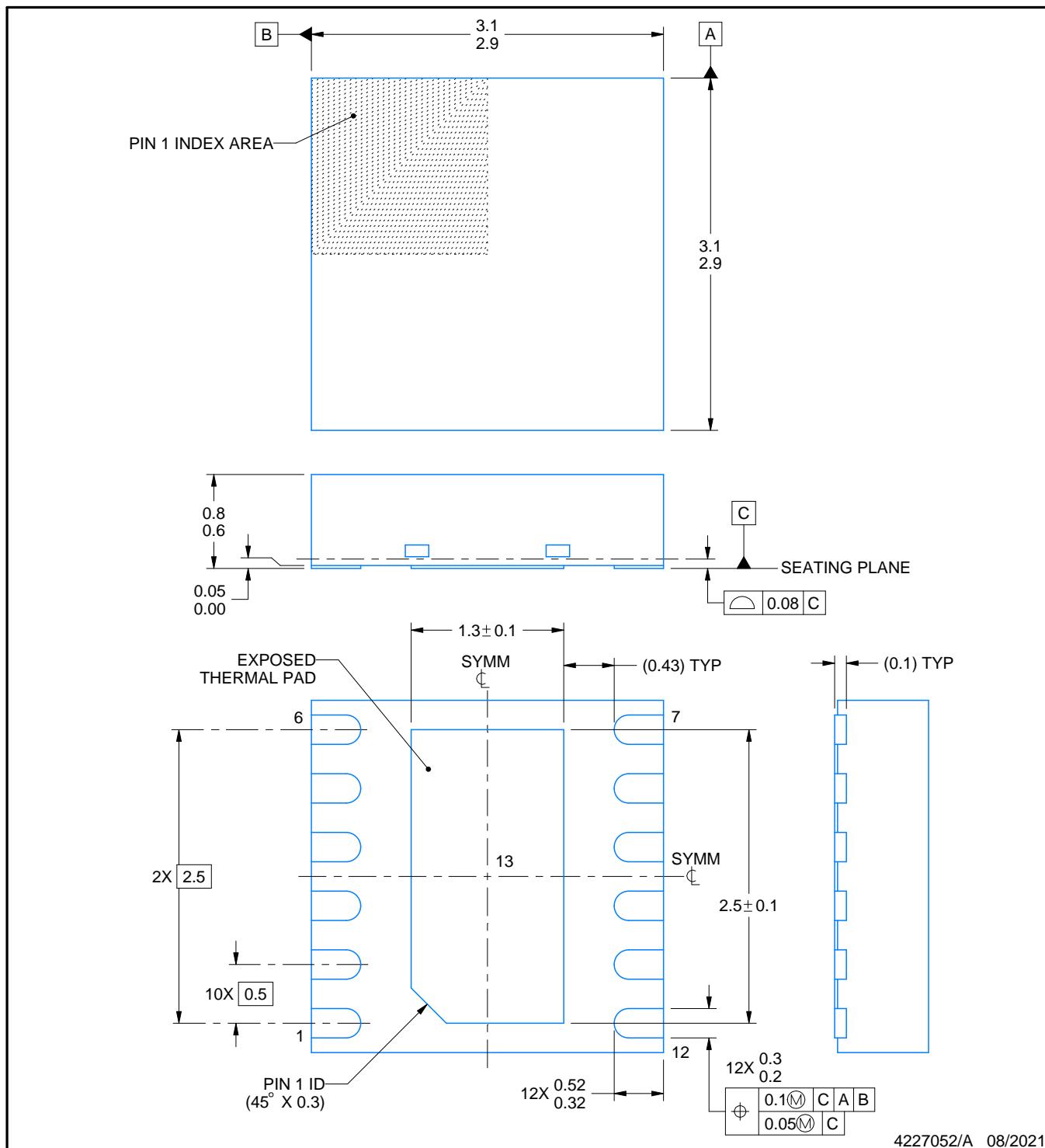

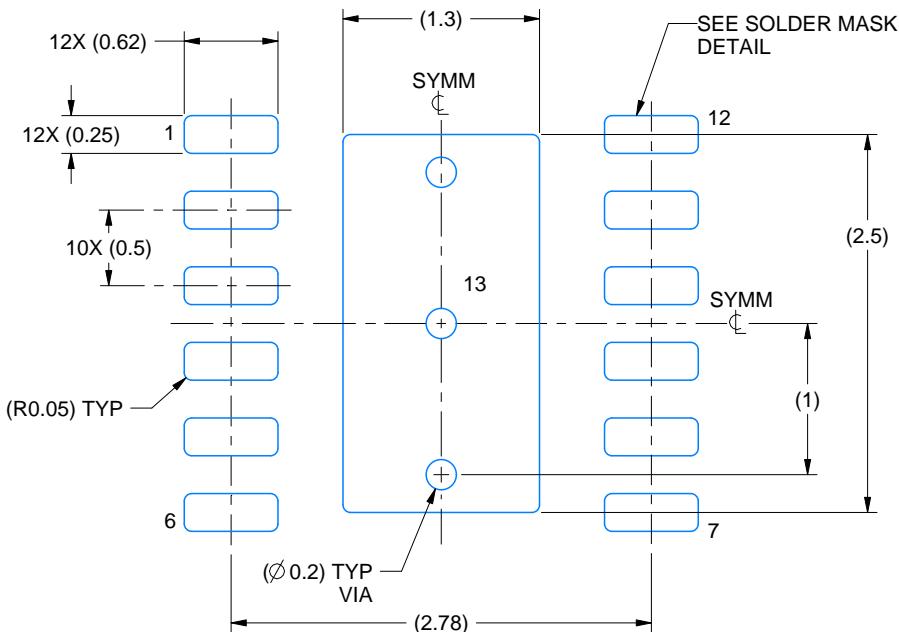

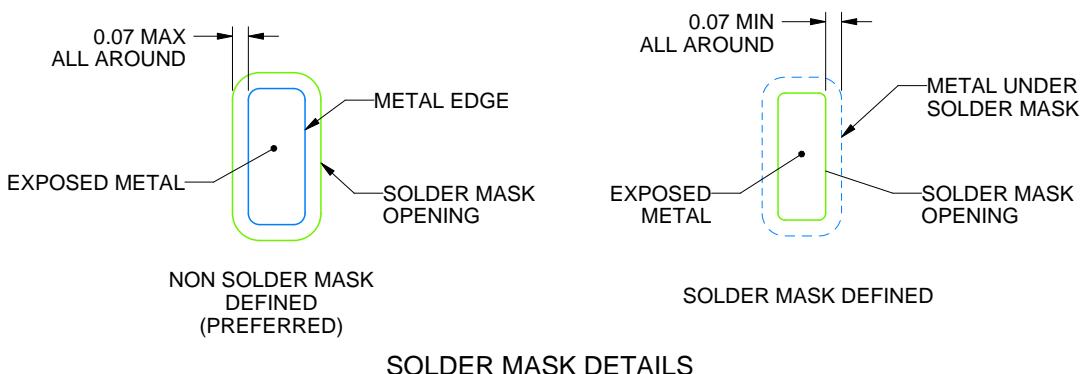

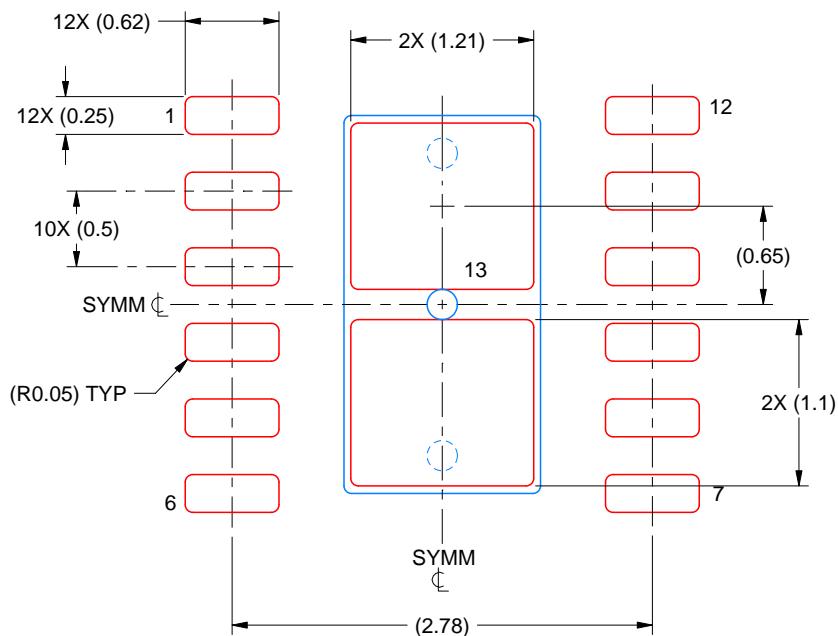

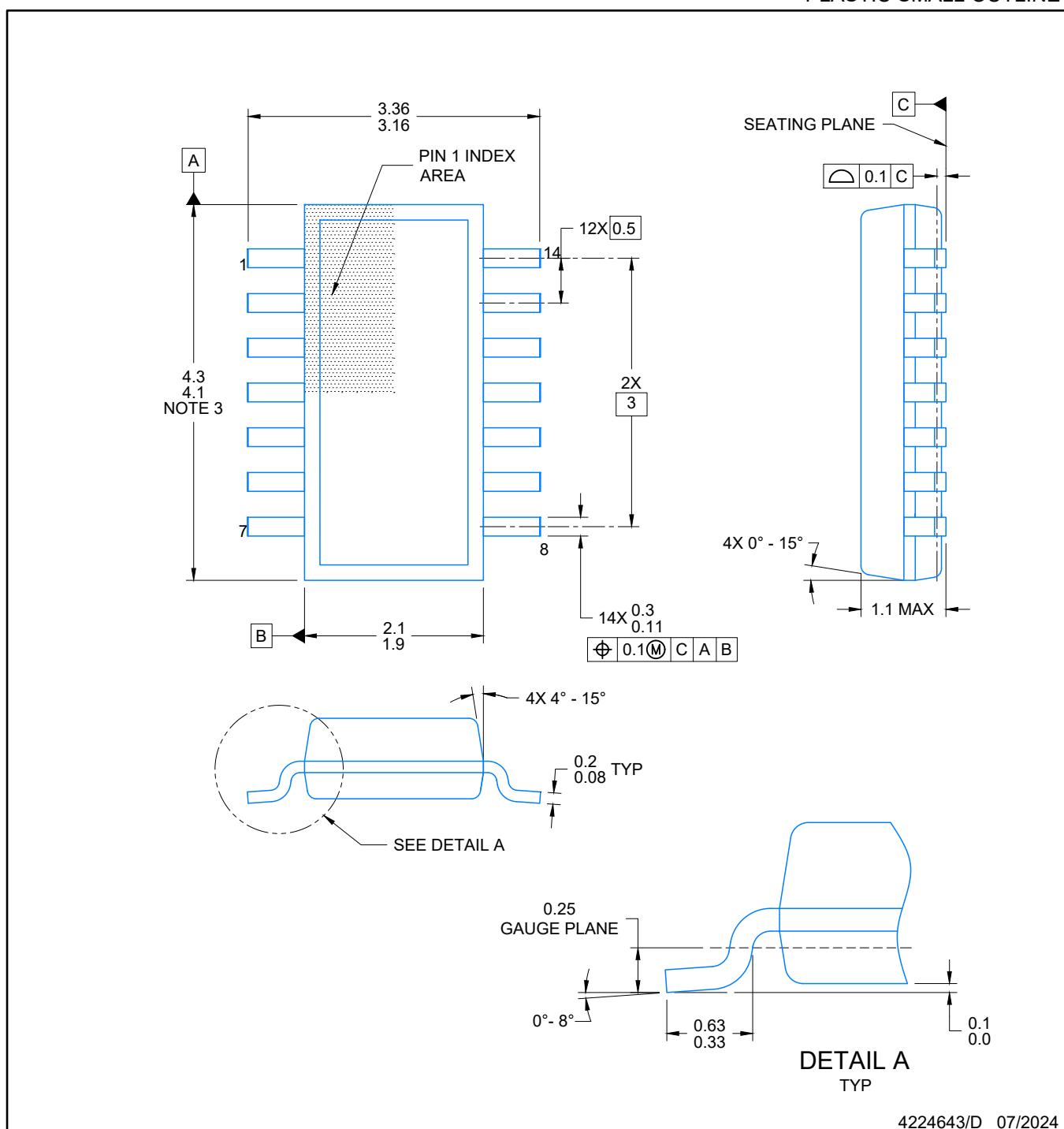

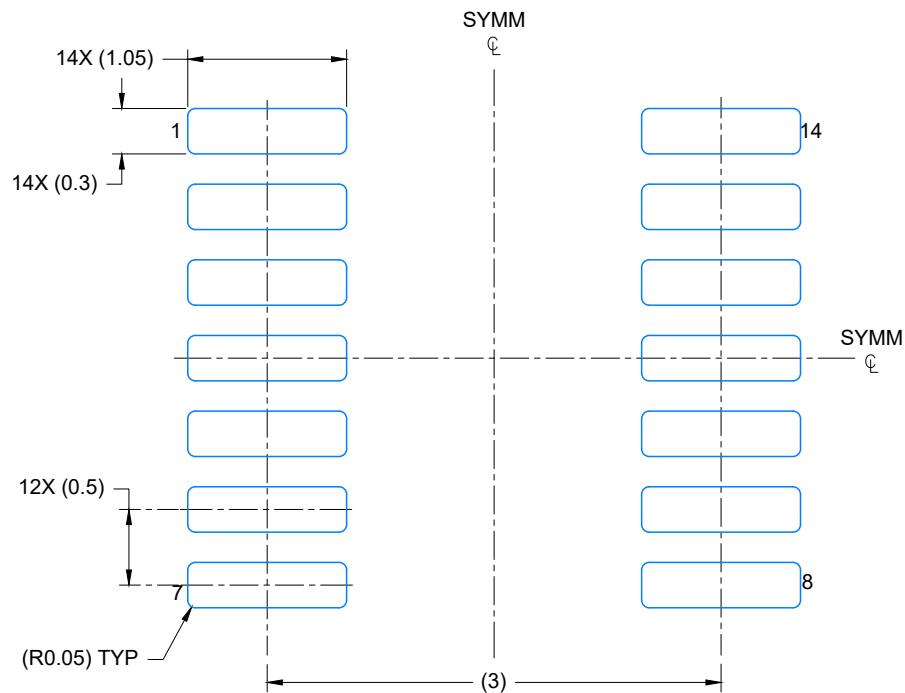

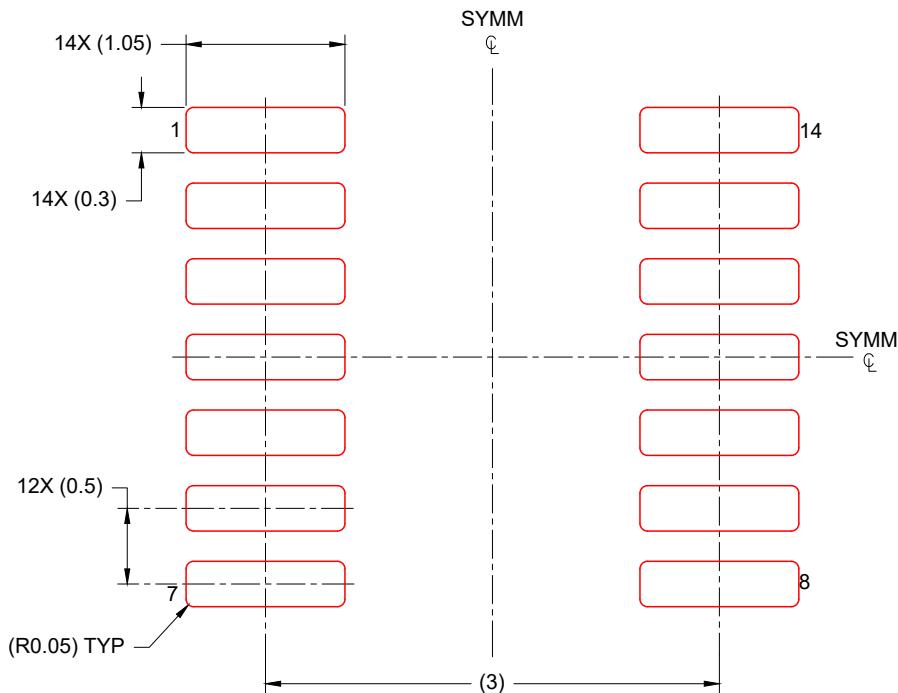

図 5-1. LP5899 DYY パッケージ 14 ピン SOT-23-THN

上面図

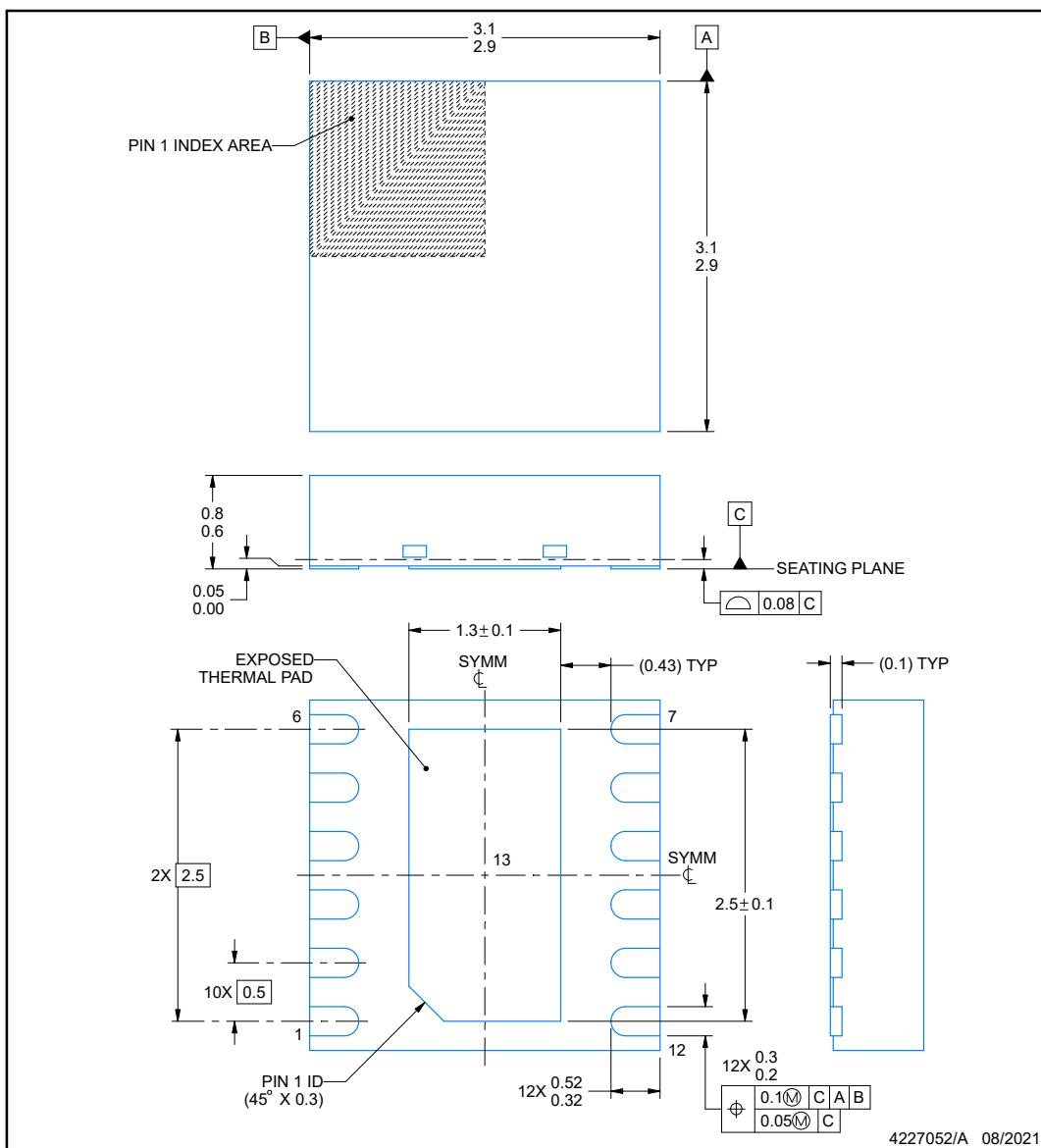

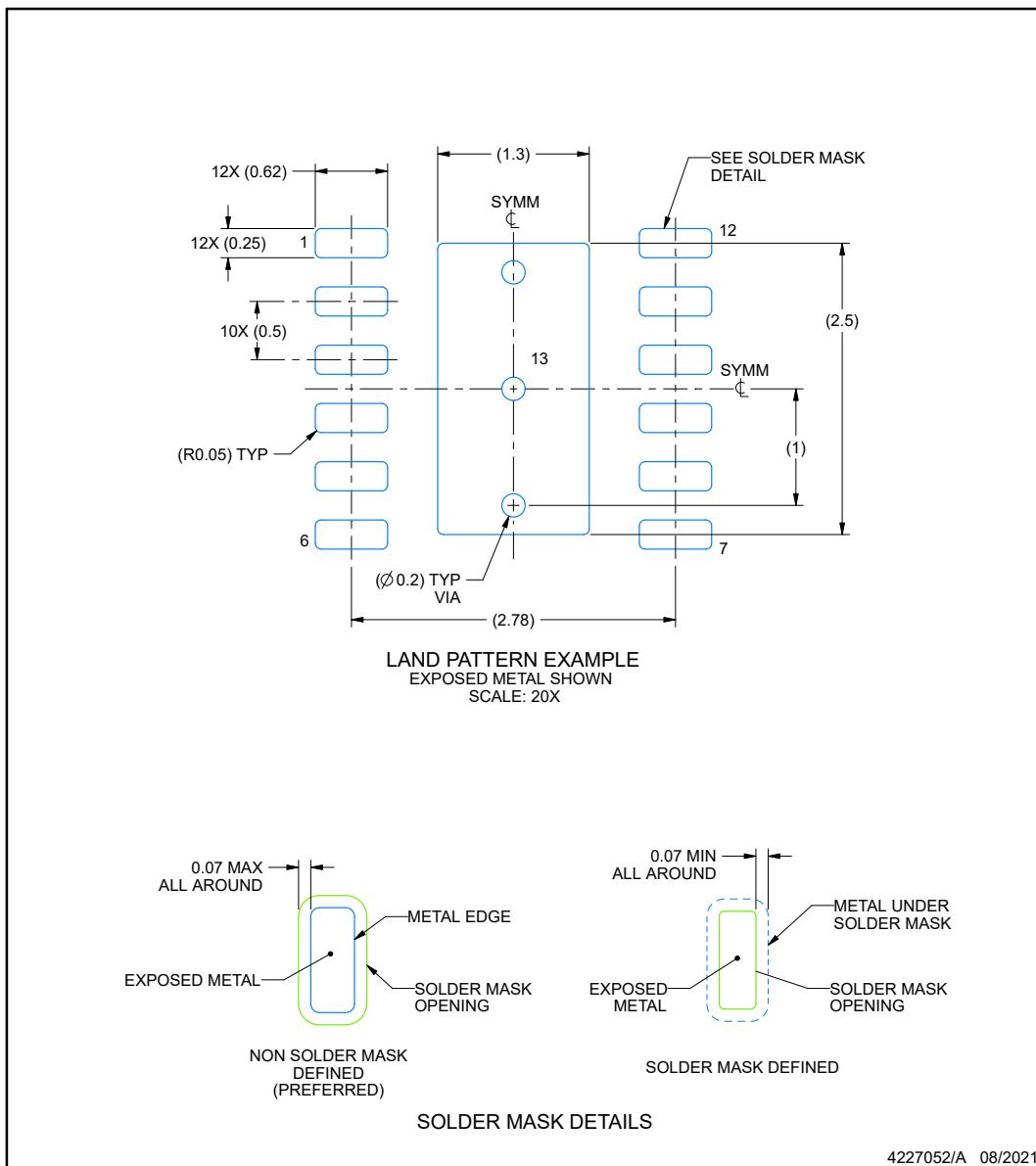

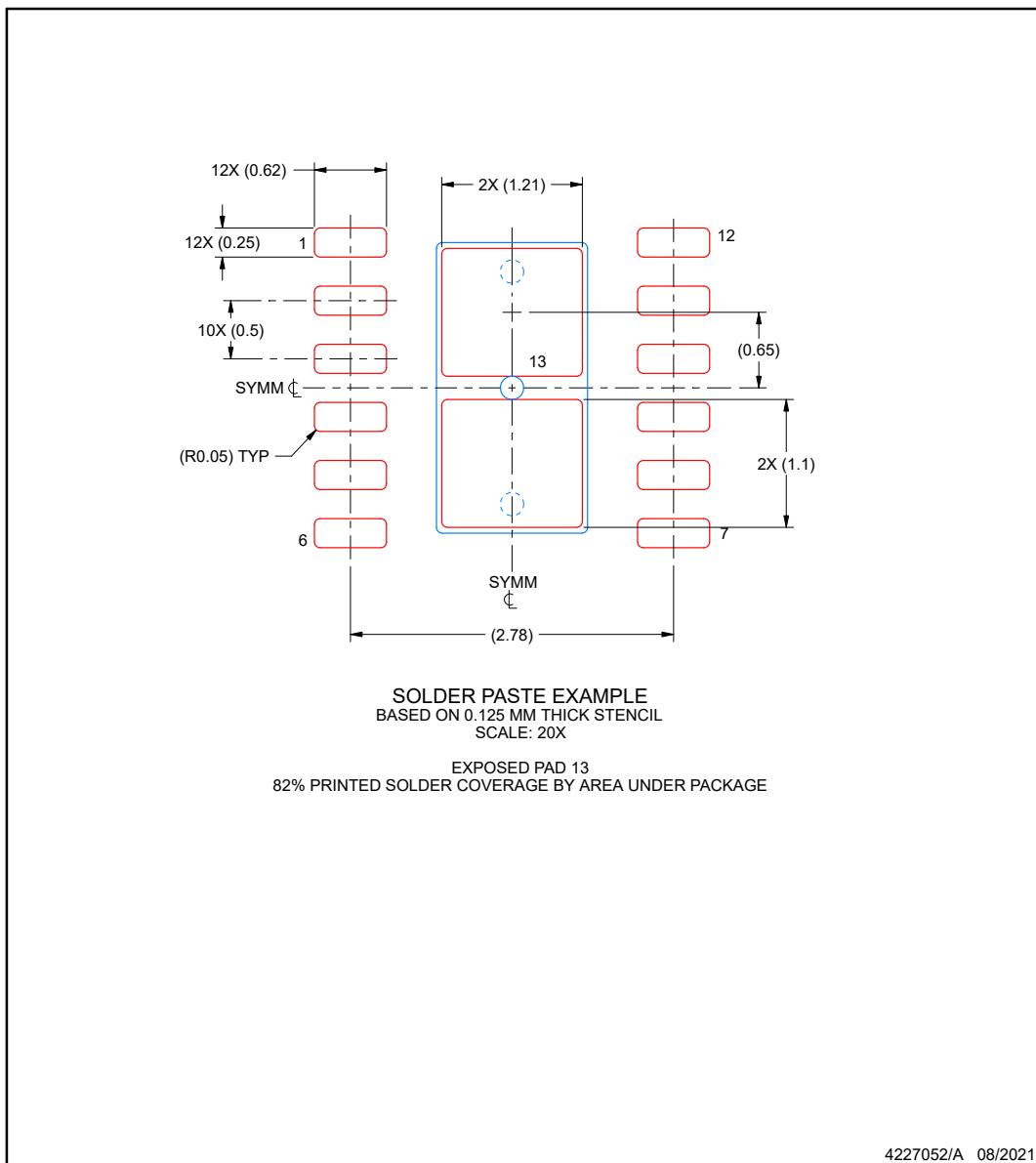

図 5-2. LP5899 DRR パッケージ 12 ピン WSON (露出

サーマルパッド付き) 上面図

表 5-1. ピンの機能

| 名称    | DYY 番号 | DRR 番号  | 種類 <sup>(1)</sup> | 説明                                   |

|-------|--------|---------|-------------------|--------------------------------------|

| FAULT | 1      | 1       | O                 | FAULT通知ピン                            |

| SDI   | 2      | 2       | I                 | SPIシリアルデータ入力                         |

| SCLK  | 3      | 3       | I                 | SPIシリアルクロック入力                        |

| SDO   | 4      | 4       | O                 | SPIシリアルデータ出力                         |

| NC1   | 5      | -       | NC                | 接続なし。信号の配線に使用できます。                   |

| GND   | 6      | 5       | G                 | グランドピン(グランドに接続する必要があります。)            |

| SIN   | 7      | 6       | I                 | CCSIシリアルデータ入力                        |

| SOUT  | 8      | 7       | O                 | CCSIシリアルデータ出力                        |

| CLK_O | 9      | 8       | O                 | CCSIシリアルクロック出力                       |

| NC2   | 10     | -       | NC                | 接続なし。信号の配線に使用できます。                   |

| DRDY  | 11     | 9       | O                 | データレディ割り込み                           |

| CS    | 12     | 10      | I                 | SPIチップセレクト                           |

| GND   | 13     | 11      | G                 | グランドピン(グランドに接続する必要があります。)            |

| VCC   | 14     | 12      | P                 | VCC電源入力                              |

| NC3   | -      | 露出パッド付き | NC                | 接続なし。グランドを除くすべての信号から電気的に絶縁する必要があります。 |

(1) I = 入力、O = 出力、G = グランド、P = 電源、NC = 未接続。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                  |                     | 最小値  | 最大値       | 単位 |

|------------------|---------------------|------|-----------|----|

| ピンの電圧            | VCC                 | -0.3 | 6         | V  |

|                  | SDI、SCLK、CS、SIN     | -0.3 | VCC + 0.3 | V  |

|                  | SDO、DRDY、SOUT、CLK_O | -0.3 | VCC + 0.3 | V  |

|                  | フォルト                | -0.3 | 6         | V  |

| T <sub>J</sub>   | 接合部温度               | -40  | 150       | °C |

| T <sub>stg</sub> | 保存温度                | -55  | 150       | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |      |                                                          | 値     | 単位 |

|--------------------|------|----------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001<br>に準拠 <sup>(1)</sup> | ±4000 | V  |

|                    |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±1000 |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | DRR (SON) | DYY (SOT) | 単位   |

|-----------------------|---------------------|-----------|-----------|------|

|                       |                     | 12 ピン     | 14 ピン     |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 66.6      | 127.7     | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 57.1      | 58.9      | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 37.1      | 54.6      | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 2.3       | 3.2       | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 36.9      | 54.1      | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 12.7      |           | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

### 6.4 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                               | 最小値 | 公称値 | 最大値             | 単位  |

|-------------------|-------------------------------|-----|-----|-----------------|-----|

| V <sub>CC</sub>   | 電源電圧                          | 2.5 |     | 5.5             | V   |

| ピンの電圧             | SDI、SCLK、CS、SIN               | 0   |     | V <sub>CC</sub> | V   |

|                   | SDO、DRDY、SOUT、CLK_O           | 0   |     | V <sub>CC</sub> | V   |

|                   | フォルト                          | 0   |     | V <sub>CC</sub> | V   |

| f <sub>SCLK</sub> | SPI クロック周波数                   |     |     | 20              | MHz |

| C <sub>VCC</sub>  | V <sub>CC</sub> デカップリング コンデンサ | 100 |     |                 | nF  |

自由気流での動作温度範囲内 (特に記述のない限り)

|                |      | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|------|-----|-----|-----|----|

| T <sub>A</sub> | 周囲温度 | -40 |     | 85  | °C |

## 6.5 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)、 $2.5V < V_{CC} < 5.5V$

| パラメータ                  |                                       | テスト条件                                                 | 最小値       | 標準値  | 最大値  | 単位  |

|------------------------|---------------------------------------|-------------------------------------------------------|-----------|------|------|-----|

| <b>入力電源</b>            |                                       |                                                       |           |      |      |     |

| V <sub>CC</sub>        | デバイス電源電圧                              |                                                       |           | 5.5  |      | V   |

| V <sub>UVR</sub>       | 低電圧再起動                                | V <sub>CC</sub> 立ち上がり                                 |           | 2.3  |      | V   |

| V <sub>UVF</sub>       | 低電圧シャットダウン                            | V <sub>CC</sub> 立ち下がり                                 | 2         |      |      | V   |

| V <sub>UV,HYS</sub>    | 低電圧シャットダウン、ヒステリシス                     |                                                       | 0.12      |      |      | V   |

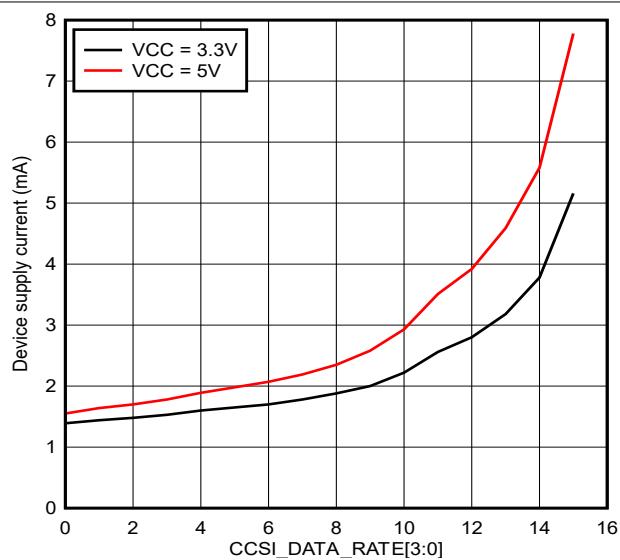

| I <sub>CC</sub>        | デバイス電源電流                              | V <sub>CC</sub> = 3.3V, CCSI_DATA_RATE[3:0] = 4b'1110 | 3.6       |      |      | mA  |

| <b>発振器</b>             |                                       |                                                       |           |      |      |     |

| f <sub>osc</sub>       | 内部発振器周波数                              |                                                       | -3%       | 40   | 3%   | MHz |

| t <sub>WD,OSC</sub>    | 内部発振器ウォッチドッグ                          |                                                       | 0.66      | 1.45 | 2.48 | μs  |

| <b>デジタル IO</b>         |                                       |                                                       |           |      |      |     |

| V <sub>IH</sub>        | High レベル入力電圧 (SCLK, SDI, CS, SIN)     |                                                       | 1.05      |      |      | V   |

| V <sub>IL</sub>        | Low レベル入力電圧 (SCLK, SDI, CS, SIN)      |                                                       | 0.45      |      |      | V   |

| V <sub>OH</sub>        | High レベル出力電圧 (SOUT, CLK_O, SDO, DRDY) | I <sub>OH</sub> = -3mA                                | VCC - 0.4 | VCC  |      | V   |

| V <sub>OL</sub>        | Low レベル出力電圧 (SOUT, CLK_O, SDO, DRDY)  | I <sub>OL</sub> = 3mA                                 |           | 0.4  |      | V   |

| I <sub>LOGIC</sub>     | ロジック ピン電流 (SCLK, SDI, CS, SIN)        | SCLK/SDI/CS/SIN = V <sub>CC</sub> または GND             | -1        | 1    |      | μA  |

| <b>フォルト</b>            |                                       |                                                       |           |      |      |     |

| I <sub>PD,FAULT</sub>  | FAULT プルダウン電流能力                       | V <sub>FAULT</sub> = 0.4V                             | 22        | 59   |      | mA  |

| I <sub>LKG,FAULT</sub> | FAULT のリーケ電流                          |                                                       |           | 1    |      | μA  |

| V <sub>OH,FAULT</sub>  | High レベル出力電圧 (FAULT)                  | 外部プルアップ抵抗経由で FAULT ピンに印加される電圧                         |           | VCC  |      | V   |

| V <sub>OL,FAULT</sub>  | Low レベル出力電圧 (FAULT)                   | I <sub>OL</sub> = 3mA、外付けプルアップ抵抗により制限する必要あり           |           | 0.4  |      | V   |

| <b>診断</b>              |                                       |                                                       |           |      |      |     |

| t <sub>WD,SIN</sub>    | SIN ウォッチドッグ                           |                                                       | 5         |      |      | ms  |

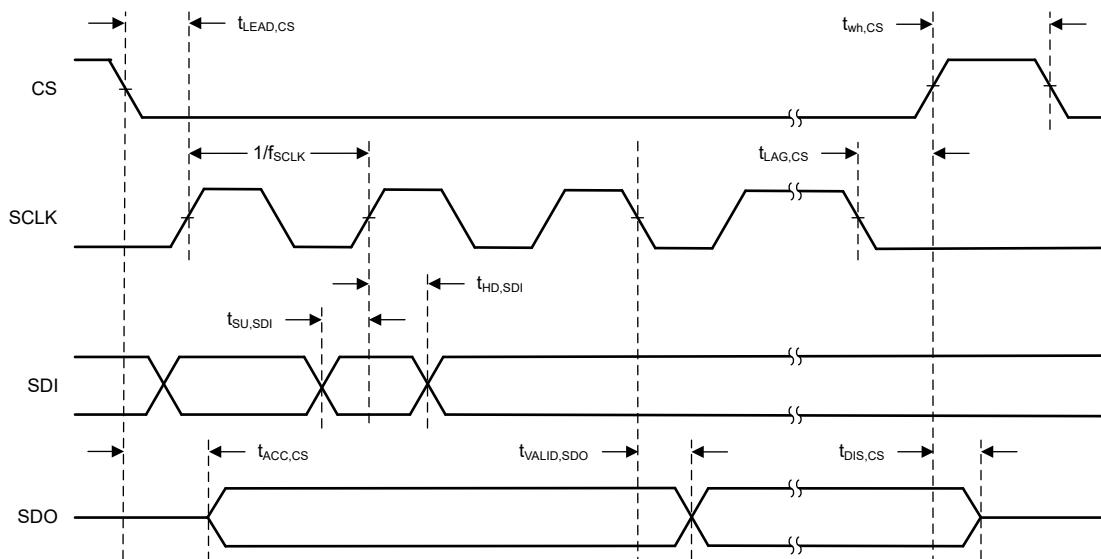

## 6.6 タイミング要件

| パラメータ             |                                        | テスト条件 | 最小値 | 公称値 | 最大値 | 単位  |

|-------------------|----------------------------------------|-------|-----|-----|-----|-----|

| $f_{SCLK,NORMAL}$ | NORMAL 状態での SCLK クロック周波数               |       |     | 20  |     | MHz |

| $t_{SCLK,INIT}$   | INIT 状態での SCLK クロック周波数                 |       |     | 5   |     | MHz |

| $t_{LEAD,CS}$     | 遅延時間、CS 立ち下がりエッジから最初の SCLK 立ち上がりエッジまで  |       | 15  |     |     | ns  |

| $t_{LAG,CS}$      | 遅延時間、最後の SCLK 立ち下がりエッジから CS 立ち上がりエッジまで |       | 5   |     |     | ns  |

| $t_{SU,SDI}$      | SCLK 立ち上がりエッジまでの SDI 入力データセットアップ時間     |       | 10  |     |     | ns  |

| $t_{HD,SDI}$      | SCLK 立ち上がりエッジ後の SDI 入力データホールド時間        |       | 5   |     |     | ns  |

| $t_{wh,CS}$       | パルス幅、CS high                           |       | 40  |     |     | ns  |

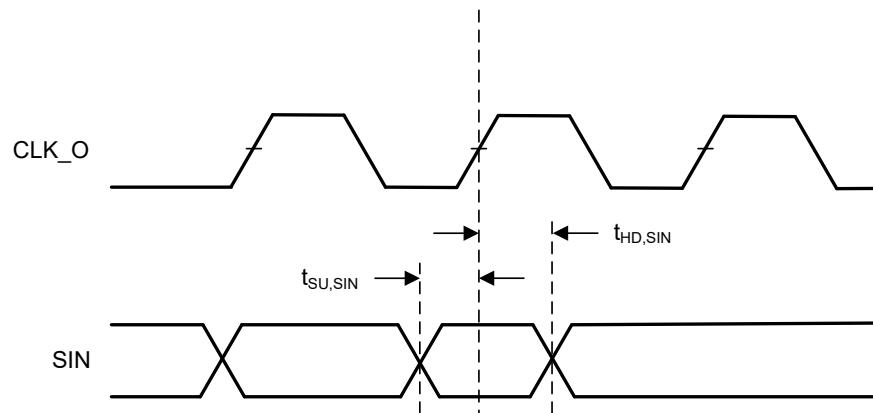

| $t_{SU,SIN}$      | CLK_O 立ち上がりエッジまでの SIN 入力データセットアップ時間    |       | 10  |     |     | ns  |

| $t_{HD,SIN}$      | CLK_O 立ち上がりエッジ後の SIN 入力データホールド時間       |       | 2   |     |     | ns  |

## 6.7 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ           |                                                           | テスト条件                                 | 最小値    | 標準値  | 最大値 | 単位  |

|-----------------|-----------------------------------------------------------|---------------------------------------|--------|------|-----|-----|

| $t_{ACC,CS}$    | 伝搬遅延時間、CS 立ち下がりエッジから SDO 駆動まで                             |                                       |        | 50   |     | ns  |

| $t_{DIS,CS}$    | 伝搬遅延時間、CS 立ち上がりエッジから SDO 高インピーダンスまで                       |                                       |        | 75   |     | ns  |

| $t_{VALID,SDO}$ | 伝搬遅延時間、SCLK 立ち下がりエッジから有効な新しい SDO まで                       |                                       |        | 22   |     | ns  |

| $DC_{CLK\_O}$   | デューティ サイクル CLK_O                                          | CCSI_DATA_RATE[3:0] = 4b'1110         | 33.33% |      |     |     |

|                 |                                                           | CCSI_DATA_RATE[3:0] = 4b'1100         | 40%    |      |     |     |

|                 |                                                           | CCSI_DATA_RATE[3:0] = その他             | 50%    |      |     |     |

| $t_{r,SOUT}$    | 立ち上がり時間 (SOUT) - $V_{CC}$ の 10%~ $V_{CC}$ の 90% まで        | $V_{CC} = 3.3V$ 、 $C_{SOUT} = 30pF$   | 2      | 10   |     | ns  |

| $t_{f,SOUT}$    | 立ち下がり時間 (SOUT) - $V_{CC}$ の 90%~ $V_{CC}$ の 10% まで        | $V_{CC} = 3.3V$ 、 $C_{SOUT} = 30pF$   | 2      | 10   |     | ns  |

| $f_{CLK\_O}$    | CLK_O 出力周波数。出力電圧は、指定されたトグル周波数で 10% 以上、90% $V_{CC}$ に達します。 | $V_{CC} = 3.3V$ 、 $C_{CLK\_O} = 30pF$ |        | 20.6 |     | MHz |

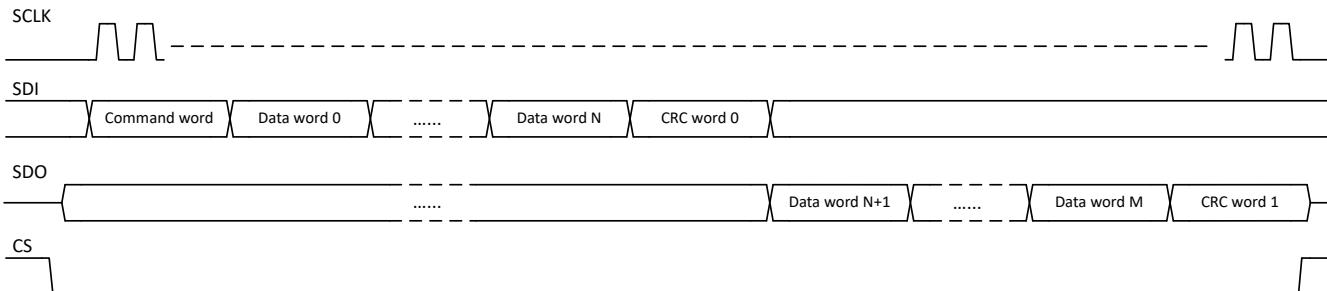

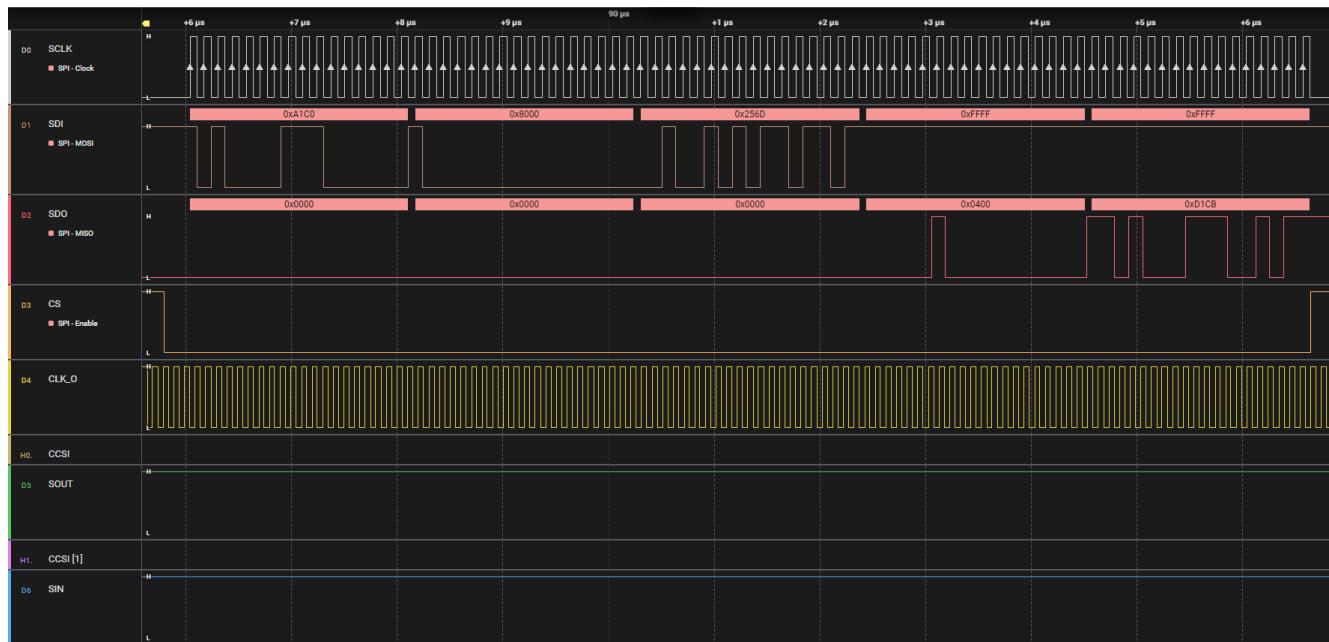

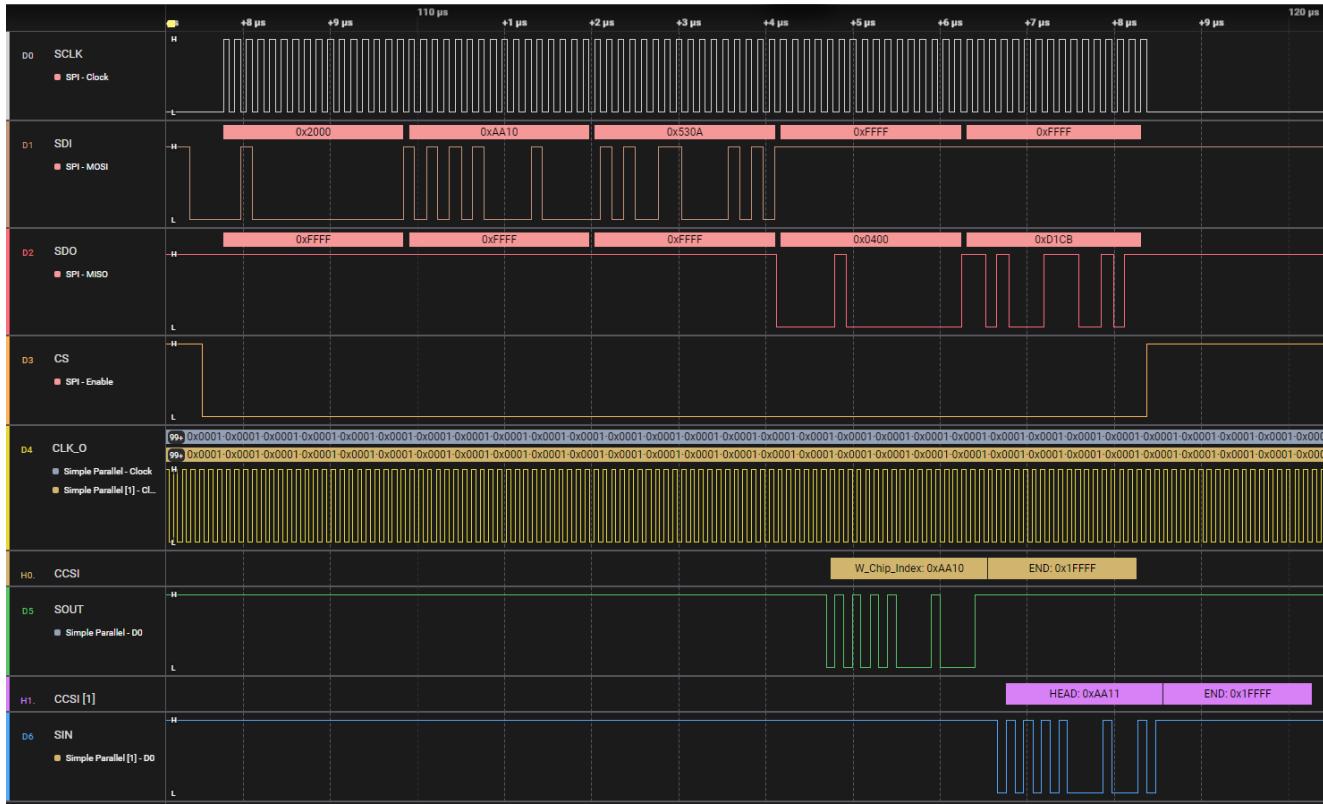

## 6.8 タイミング図

図 6-1. SPI ペリフェラルのタイミング図

図 6-2. CCSI ペリフェラルのタイミング図

## 6.9 代表的特性

特に記述のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{CC} = 3.3\text{V}$

図 6-3. デバイス電源電流と CCSI\_DATA\_RATE との関係

## 7 詳細説明

### 7.1 概要

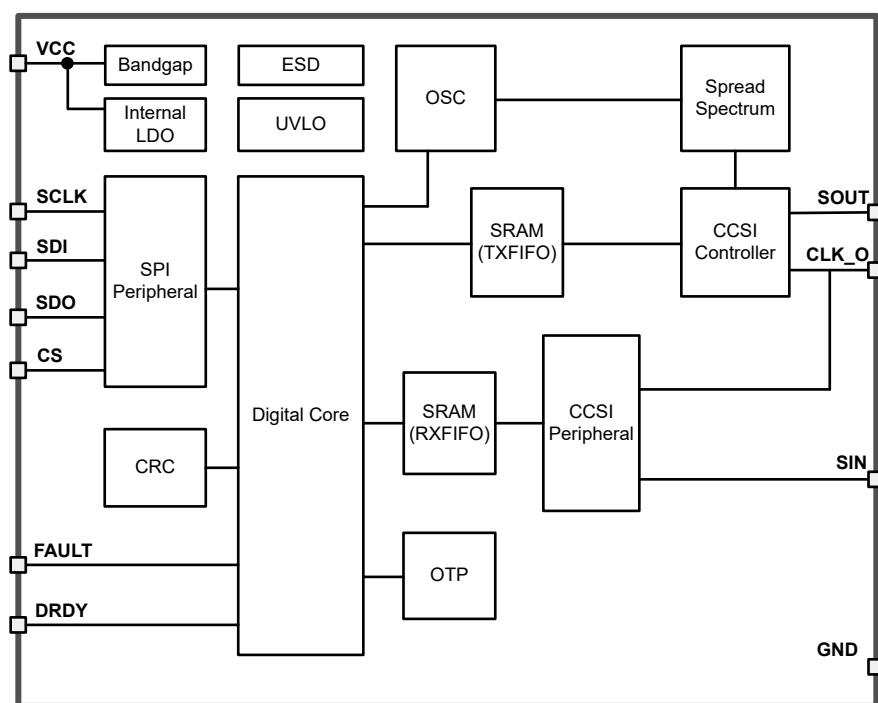

LP5899 は、SPI と連続クロック シリアル インターフェイス (CCSI) 間の SPI 互換接続を提供します。本デバイスは、LP589x ファミリのカスケード接続された LED ドライバを任意の数だけ駆動できます。カスケード接続されたデバイスの最大数は、LED ドライバによって制限されます。

LP5899 は、内部発振器とクロック分周器を使用して、CCSI にプログラム可能な連続クロック周波数を提供します。SPI ペリフェラルによって受信されたデータワードは、連続クロックに整合された状態で CCSI コントローラによって転送されます。CCSI ペリフェラルによって受信されたデータワードは、LP5899 によって保存され、SPI を使用してコントローラによって読み取られます。連続クロックには、EMI 放射を低減するために、プログラマブル疑似ランダム ジッタ (スペクトラム拡散) 機能が組み込まれています。

LP5899 は、SPI ペリフェラルによって受信されたデータワードを転送する際に、必要なスタートビットと検査ビットを自動的に挿入します。CCSI ペリフェラルによって受信されたデータワードについて、LP5899 は検査ビットを自動的に分析し、エラーが検出されると通知します。データワードが SPI で読み取るために格納されるとき、スタートビットと検査ビットはデータ文字列から取り除かれます。

LP5899 は、SPI ペリフェラルによって受信されたデータワードを転送する際に、必要な END バイトを自動的に挿入し、異なる SPI コマンドが異なる CCSI コマンドとして認識されるようにします。データワードが SPI で読み取るために格納されるとき、END バイトはデータ文字列から取り除かれます。

### 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 内部発振器およびクロック

#### 7.3.1.1 システム クロック

LP5899 は、デバイスに対する 40MHz システム クロックを提供する内部発振器を内蔵しています。システム クロックは、デジタル ロジックの動作に使用できます。

内部発振器ウォッチドッグ

POR が完了した後に、内部発振器ウォッチドッグ タイマ ( $t_{WD,osc}$ ) は自動的に有効になります。内部発振器が  $t_{WD,osc}$  より長い間トグルを停止すると、ウォッチドッグがタイムアウトし、発振器が再びトグルを開始するまでロジックをリセット (POR) 状態に保持します。内部発振器は、システム クロックとして使用されます。

#### 7.3.1.2 連続クロック シリアル インターフェイス (CCSI) クロック

CCSI コントローラがデータを送信するためのクロックは、システム クロックから生成されます。LED ドライバのデイジーチェーンで目的のクロック周波数を実現するために、16 の分周器オプション (CCSICTRL レジスタの CCSI\_DATA\_RATE) が利用可能です。

CCSI クロックはプログラマブル デジタル スペクトラム拡散によって変調され、システム レベルの EMI 性能を向上させることができます。CCSICTRL レジスタの CCSI\_SS\_CLKO フィールドによって、スペクトラム拡散が有効かどうかが決まります。CCSI\_DATA\_RATE \* CCSI\_SS\_CLKO \* 2 が 120kBit/s より小さい場合、変調周波数 30kHz が使用されます。それ以外の場合、変調周波数は 120kHz です。CCSICTRL レジスタの CCSI\_DATA\_RATE が 4b'1111 または 4b'1110 に設定されている場合、スペクトラム拡散を有効にすることは推奨されません。

#### 7.3.2 連続クロック シリアル インターフェイス (CCSI)

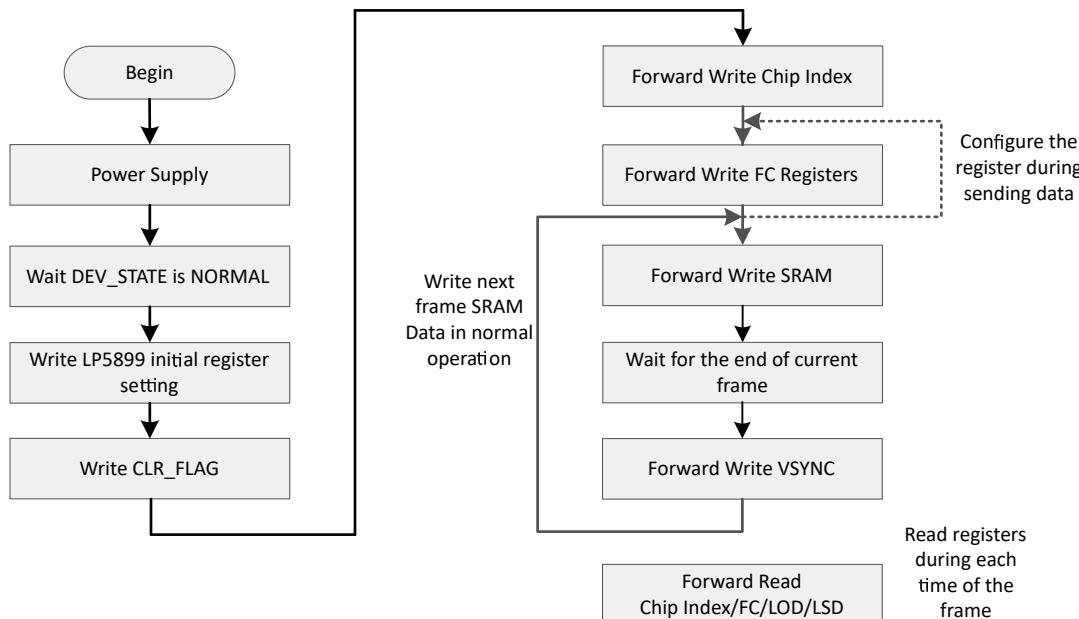

連続クロックシリーズ インターフェイス (CCSI) を使用すると、CCSI コントローラと CCSI ペリフェラル間のデイジーチェーンで接続されている LED ドライバのプログラマブルな機能とレジスタにアクセスできます。CCSI コントローラでは、シリアル データ出力 (SOUT) とシリアル クロック出力 (CLK\_O) を使用します。CCSI コントローラが送信していないとき、SOUT はロジック HIGH に設定され、CLK\_O はアクティブで連続的な状態を維持します。連続クロックは、デバイスの電源投入後に開始されます。CCSI コントローラによる送信を開始するには、デバイスが NORMAL 状態になっており、FLAG\_POR フラグがクリアされている必要があります。

CCSI ペリフェラルは、シリアル データ入力 (SIN) の 1 線で構成されています。データは、CLK\_O と同じクロック ソースを使用してシフト インされます。

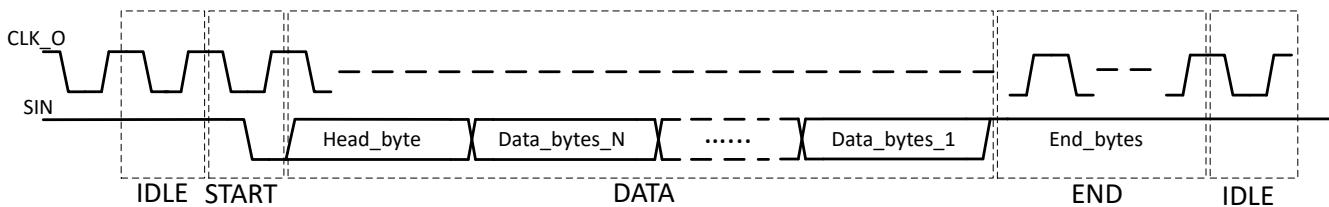

### 7.3.2.1 コマンドフォーマット

コマンドフォーマットは、CCSI ペリフェラルの視点から見た場合のものです。図 7-1 に、コマンド送信のフォーマットを定義します。1 つのコマンドには 3 つの状態があります。

- **IDEL:CLK\_O** は常にアクティブで連続的に動作しています。SIN は常に HIGH です。

- **START:SIN** は IDLE 状態の後に HIGH から LOW に変わります。

- **DATA:**

- **Head\_byte:** コマンド識別子には、1 つの 16 ビットデータと 1 つの検査ビットが含まれています。

- **Data\_bytes\_N-1:** 各データバイトには  $3 \times 17$  ビットデータが含まれ、各 17 ビットのデータは 1 つの 16 ビットデータワードと 1 つの検査ビットで構成されています。

- **END:** デバイスは、SIN の連続した 18 ビットの HIGH を認識してから、IDLE 状態に戻ります。

- **CHECK BIT:** 検査ビット(17 番目のビット)の値は、連続した 18 ビットの HIGH を回避するため (END と区別するため)、16 番目のビット値の NOT となります。

IDLE 状態は必要なく、次のコマンドの START 状態を現在のコマンドの END 状態に接続できることを意味します。

図 7-1. コマンドフォーマット

### 7.3.2.2 コマンドの認識および同期化

2 つの異なる CCSI コマンドを別々のコマンドとして認識できるようにするには、コマンド間に少なくとも 1 つの END バイトが必要です。LP5899 は、1 つの SPI コマンドからの全データが送信された後、自動的に 1 つの END バイトを挿入します。ただし、特定の CCSI コマンドの場合、LED ドライバはデータストリームにデータを追加します。この場合、CCSI ペリフェラルが 2 つの CCSI コマンドを区別するには、送信中の 1 つの END バイトでは不十分です。十分な END バイトがないと、CCSI コントローラと CCSI ペリフェラルは同期を失います。同期化は、いくつかのアクションに必要なものです。たとえば、受信データを RXFIFO に格納する必要があるかどうか、または受信データに対して CRC を計算し、送信データに対する CRC と比較する必要があるかどうかを決める場合などに必要です。同期が失われた場合、SPI コマンド SOFTRESET\_CRC を使用して CCSI コントローラと CCSI ペリフェラルの同期を戻すことができます。SPI コントローラは、追加の END バイトを挿入する専用の SPI コマンドを使用することで、CCSI コマンド間に十分な END バイトがあるようにして同期を維持します。

### 7.3.2.3 CCSI コマンド キュー

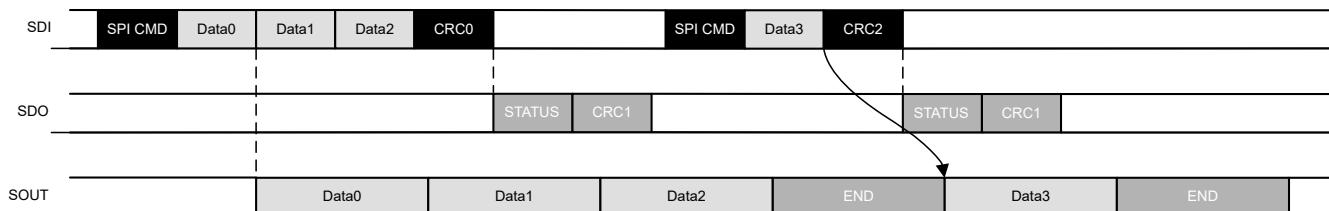

CCSI コントローラは、複数の SPI コマンドをキューイングできる機能を備えています。つまり、CCSI コントローラがまだ送信中であるときに、SPI ペリフェラルによって新しい SPI 転送コマンドが受信可能であることを意味します。この新しいコマンドは、古いコマンドの送信が終了すると自動的に送信されます。図 7-2 に、例を示します。この図では、すべてのデータワードは 16 ビットです。つまり、ロックの幅が大きいほどクロック周波数は低くなることを意味しています。この例では、CCSI 周波数が SPI 周波数より低くなっています。

図 7-2. CCSI コマンドのキューイングの例

### 7.3.2.4 CCSI のスタート ビットと検査ビットの挿入と除去

LP5899 は、CCSI に必要なスタートビットと検査ビットを自動的に挿入および削除します。つまり、コントローラによって送信されたときに、これらのビットを SPI データワードに挿入する必要はありません。さらに、SPI を使用してデータを読み取る際には、スタートビットと検査ビットは取り除かれます。これにより、標準の 16 ビット SPI データワードが得られます。図 7-3 に、その例を示します。本書の残りの部分では、スタートビットと検査ビットは明示的に示されません。

図 7-3. スタート ビットと検査ビットの挿入と除去の例

### 7.3.3 FIFO

LP5899 は、送信 FIFO と受信 FIFO の両方を搭載しています。FIFO の名前は、連続クロック シリアル インターフェイス (CCSI) の視点から見た場合のものです。つまり、送信 FIFO (TXFIFO) とは、SPI ペリフェラルによって受信され、CCSI コントローラによって送信されるデータです。受信 FIFO (RXFIFO) は、CCSI ペリフェラルによって受信されたデータであり、SPI ペリフェラル経由でコントローラによって読み取り可能です。

どちらの FIFO も、16 ビット幅の先入れ先出しメモリ バッファです。FIFO は、データが SPI クロック ドメインと CCSI クロック ドメインの間でクロスする間のタイミング要件を満たすために、データ ワードの格納に使用されます。TXFIFO は、SPI クロック ドメインから CCSI クロック ドメインへのクロスオーバー中にデータを保持します。RXFIFO は、CCSI クロック ドメインから SPI クロック ドメインへのクロスオーバー中に、データを保持します。

SPI クロック ドメインが CCSI クロック ドメインよりも高い周波数で動作する場合、TXFIFO は、CCSI コントローラによってまだ送信されていない、SPI ペリフェラルによってすでに受信されたデータを格納します。カウンタ (TXFFST) は、TXFIFO に現在格納されているワード数を追跡します。SPI ペリフェラルが CCSI コントローラよりも高いクロック周波数で動作する例を、図 7-4 に示します。この図では、すべてのデータ ワードは 16 ビットです。つまり、ブロックの幅が大きいほどクロック周波数は低くなることを意味しています。

| SDI    | SPI CMD | Data0 | Data1 | Data2 | Data3 | CRC   |   |       |   |

|--------|---------|-------|-------|-------|-------|-------|---|-------|---|

|        |         |       |       |       |       |       |   |       |   |

| TXFFST | 0       | 1     | 0     | 1     | 2     | 1     | 2 | 1     | 0 |

| SOUT   |         | Data0 |       | Data1 |       | Data2 |   | Data3 |   |

図 7-4. CCSI コントローラより高い周波数で動作する SPI ペリフェラルの例

SPI ペリフェラルが CCSI コントローラよりも低いクロック周波数で動作する場合、CCSI コントローラによる送信が開始される前に、TXFIFO は最初に SPI ペリフェラルによって受信された多数のデータ ワードを格納するために使用されます。この方法に従うことで、データ ワードが SPI ペリフェラルによってまだ受信されていないため、CCSI のデータ ストリームは連続クロックを停止させることなく、連続させることができます。図 7-5 に、この状況の例を示します。

| SDI    | SPI CMD | Data0 | Data1 | Data2 | Data3 | CRC   |       |       |   |

|--------|---------|-------|-------|-------|-------|-------|-------|-------|---|

|        |         |       |       |       |       |       |       |       |   |

| TXFFST | 0       |       | 1     | 2     | 3     | 2     | 1     | 1     | 0 |

| SOUT   |         |       |       |       | Data0 | Data1 | Data2 | Data3 |   |

図 7-5. CCSI コントローラより低い周波数で動作する SPI ペリフェラルの例

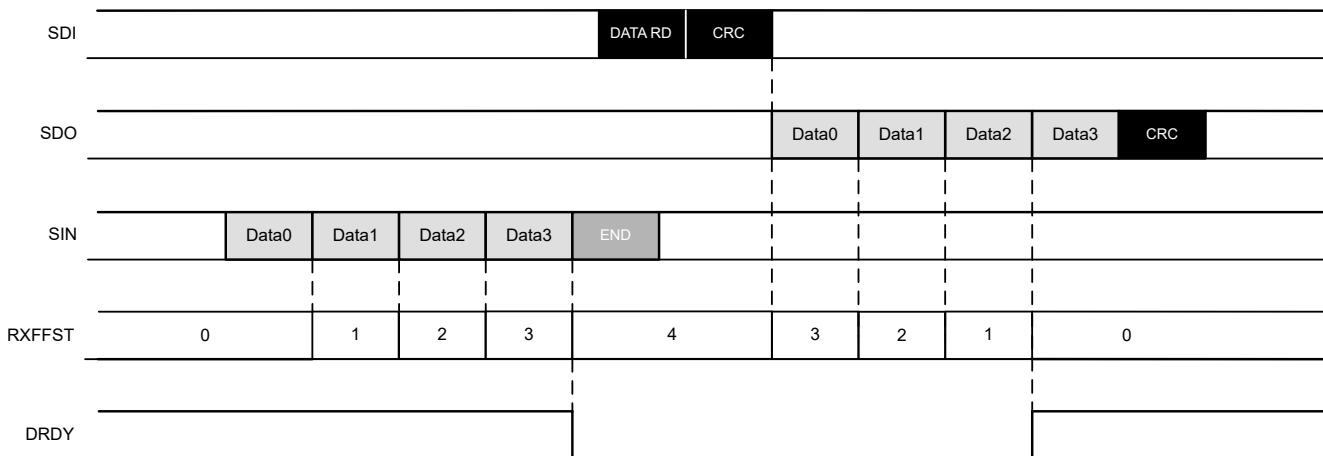

RXFIFO の場合、CCSI ペリフェラルはデータを受信して、RXFIFO に格納します。SPI ペリフェラルは RXFIFO からデータを読み取り、SPI コントローラに送信します。また、RXFIFO には、現在格納されているデータ ワードの数を追跡するためのカウンタ (RXFFST) が存在します。

END バイトが受信されると、格納は停止します。END バイトは RXFIFO では格納されません。また、START ビットと CHECK ビットは格納されません。

### 7.3.3.1 FIFO レベルおよびデータ レディ (DRDY) 割り込み

TXFIFO レベル (TXFFLVL) は、SPI CRC に依存しない SPI 転送コマンドに対する CCSi コントローラの送信開始を制御します。FIFO レベルを正しく設定すると、FIFO のオーバーフローとアンダーフローを防止できます。この設定は、SPI クロック周波数と CCSi クロック周波数の差、SPI ペリフェラルに供給されるクロックの精度、CCSi コントローラのクロックの精度、転送されるデータの最大長によって異なります。

RXFIFO レベル (RXFFLVL) は、データ レディ (DRDY) 割り込みを制御します。RXFIFO のデータ ワード数が RXFFLVL を上回ると、DRDY ピンはロジック Low になります。この DRDY ピンは、RXFIFO にワードがなくなるまで ロジック Low のままであります。RXFFLVL 設定は、転送されるデータの最大長が CCSi ペリフェラルによって受信されるデータ ワードの最大数に置き換えられることを除き、TXFFLVL と同じ依存関係を持ちます。図 7-6 に、DRDY ピンの動作の例を示します。

図 7-6. RXFFLVL レジスタが 3 に設定された状態の DRDY ピンの例

DRDY ピンは、END バイトが検出され、RXFIFO のワード数がまだ RXFFLVL に達していない場合にもロジック Low になります。

### 7.3.3.2 FIFO クリアランス

実行中の CCSi 送信を停止するには、TXFFLVL レジスタの TXFFCLR ビットで TXFIFO をクリアできます。これにより、TXFIFO カウンタ (TXFFST) が 0 にリセットされます。キュー内のすべてのコマンドがクリアされます。CCSi コントローラは、自動的に END バイトを挿入し、LED ドライバをリセットします。CCSi ペリフェラルは通常どおり動作し続けます。TXFFCLR ビットは自動的に 0 に戻ります。

RXFIFO のデータは、RXFFLVL レジスタの RXFFCLR ビットでクリアできます。これにより、RXFIFO カウンタ (RXFFST) が 0 にリセットされます。CCSi ペリフェラルが RXFIFO に格納する必要のあるデータを受信している場合、このコマンドに対して格納が停止されます。CCSi ペリフェラルによって受信された次の CCSi コマンドは、SPI コマンドの元の要求に基づいて処理されます。CCSi コントローラは通常どおり動作し続けます。RXFFCLR ビットは自動的に 0 に戻ります。

## 7.3.4 診断

LP5899 には、デバイスの内部診断と外部診断があります。デバイスは障害を検出し、FAULT ピンとステータス レジスタを介してステータスを通知します。デバイスを正常な動作状態にするためには、SPI コントローラがアクションを起こす必要があります。�ルトは、STATUS レジスタに CLR\_FLAG ビットを書き込むことでクリアできます。このビットでクリアできないのは、OTP CRC エラーと FAILSAFE 状態のフラグのみです。CLR\_FLAG ビットは自動的に 0 に戻ります。�ルトが残っている場合、次の検出の後にエラー フラグが設定されます。

### 7.3.4.1 低電圧誤動作防止

VCC 電圧が UVLO スレッショルドを下回ると、デバイスは電源が供給されていない状態になります。電圧が回復すると、デバイスは、FLAG\_POR と FLAG\_ERR が 1 に設定された状態で、自動的に初期化状態に切り替わります。SPI コントローラは、CLR\_FLAG レジスタに 1 を書き込むことでフラグをクリアできます。

### 7.3.4.2 発振器�ルト診断

POR が完了した後に、内部クロック ウオッチドッグ タイマ ( $t_{WD,osc}$ ) は自動的に有効になります。内部発振器が  $t_{WD,osc}$  より長い時間トグルを停止すると、ウォッチドッグがタイムアウトし、FAULT ピンが Low になります。�ルトがラッチされ、発振器が再びトグルを開始すると、FLAG\_OSC と FLAG\_ERR が 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。

### 7.3.4.3 SPI 通信喪失

LP5899 は、内部ウォッチドッグ タイマで SPI の通信を監視しています。デバイスは、通信喪失の間に有効な SPI コマンドを受信することを想定しています。デバイスが NORMAL 状態に移行すると、タイマはカウントを開始します。有効な SPI コマンドが検出されると、タイマはリセットされます。ウォッチドッグタイマがオーバーフローすると、デバイスは自動的に FAILSAFE 状態に切り替わり、DEV\_STATE を 0x3 に、FLAG\_ERR を 1 に設定します。SPI コントローラは LP5899 にアクセスし、DEVCTRL レジスタの EXIT\_FS に 1 を書き込むことで、通信が回復したときにデバイスを NORMAL 状態に戻すことができます。ウォッチドッグ タイマは、SPICTRL レジスタの 2 ビットフィールド SPI\_WDT\_CFG でプログラム可能です。SPI\_WDT\_CFG を 0x3 に設定してウォッチドッグ タイマを無効にすると、デバイスが自動的に FAILSAFE 状態に移行するのを防ぐことができます。

### 7.3.4.4 SPI 通信エラー

#### 7.3.4.4.1 リセット タイマー

LP5899 は、内部 SPI リセット タイマで SPI の通信を監視しています。SPI コマンドが開始されるとタイマが起動し、デバイスはタイマがオーバーフローする前にコマンド全体（データの読み取りを含む）が完了することを想定しています。タイマは、デバイスが SPI コマンド ワードの検出を試みているときに、SCLK ピンの最初のクロック パルス（CS ピンがアクティブ 状態）からカウントを開始します。タイマは、デバイスが次の SPI コマンド ワードの待機を開始するとリセットされます。ウォッチドッグ タイマがオーバーフローすると、SPI ペリフェラルはリセットされ、次の SPI コマンド ワードの受信待機を始めます。さらに、FLAG\_SPI\_TIMEOUT、FLAG\_SPI、FLAG\_ERR が 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。SPI リセット タイマは、SPICTRL レジスタの 4 ビット フィールド SPI\_RST\_TIMEOUT\_CFG でプログラム可能です。テキサス・インスツルメンツでは、CS ピンが常にアクティブ 状態に保たれている場合、このタイマを有効にすることを推奨しています。

#### 7.3.4.4.2 チップセレクト (CS) リセット

SPI ペリフェラルは、CS ピンをロジック High にすることでリセットされます。これは通常、SPI コマンドがすべて完了し、SPI ペリフェラルが次のコマンドを待機しているときに実行されます。SPI ペリフェラルが SPI コマンド ワードを受信した後、コマンド全体が受信される前に CS ピンが High になると、FLAG\_SPI\_CS、FLAG\_SPI、FLAG\_ERR が 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。

#### 7.3.4.4.3 CRC 順差

CRC ワードは、LP5899 が SPI コントローラからすべてのワードを正しく受信したことを確認するために、SPI コントローラ が送信するコマンドの最後のワードです。SPI コントローラは、SPI コマンド ワードとデータ ワードを含むすべてのワードの CRC 値を計算する必要があります。LP5899 はすべてのワードを受信し、CRC ワードを計算して、計算された CRC ワードを受信された CRC ワードと比較します。2 つの CRC ワードが一致しない場合、LP5899 は FLAG\_SPI\_CRC と FLAG\_ERR を 1 に設定します。受信されたコマンドに応じて、LP5899 はコマンドを無視するか、コマンドの処理を継続します。SPI コントローラはデバイスにアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。2 つの異なる CRC アルゴリズムがサポートされています。デフォルトのアルゴリズムは CCITT-FALSE です。これは、REG\_WR SPI コマンドを使用して CRC-16/XMODEM アルゴリズムに変更できます。CRC アルゴリズムを変更すると、次の SPI コマンドから新しいアルゴリズムが使用されます。

#### 7.3.4.4.4 レジスタ書き込みエラー

CCSI コントローラが送信中または CCSI ペリフェラルが受信中は、CCSICTRL レジスタへの書き込みは禁止されています。これにより、CLK\_O の連続クロック出力は、SOUT で送信され SIN で受信されるデータと一致した状態を維持します。CCSI コントローラや CCSI ペリフェラルの動作中に CCSICTRL レジスタへの書き込みを試みると、デバイスは自動的にこれを検出し、FLAG\_CCSI\_REG\_WRITE を 1 に設定します。SPI コントローラはデバイスにアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。

#### 7.3.4.5 CCSI 通信喪失

##### 7.3.4.5.1 SIN 固着診断

CCSI ペリフェラルのデータ入力 (SIN) ピンは監視されています。CCSI コントローラが送信を開始（SOUT ピンがロジック High から Low に遷移）した後、タイマはカウントを開始します。タイマがオーバーフローする前（5 ミリ秒後）に SIN ピンでトグルが検出されなかった場合、FLAG\_CCSI\_SIN、FLAG\_CCSI、FLAG\_ERR は 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。

FLAG\_CCSI\_SIN が設定されると、CCSI コントローラと CCSI ペリフェラルは同期を失う可能性が高くなります。そのため、テキサス・インスツルメンツでは、このフラグが設定された後で SOFTRESET コマンドの実行を推奨しています。

#### 7.3.4.6 CCSI 通信エラー

CCSI ペリフェラルは、受信データの診断を行います。検査ビットの検出は、受信されたすべてのデータに対してチェックされます。データ整合性は、CCSI コントローラによって送信されたデータを追加または変更していない CCSI コマンドに対してのみチェックされます。

#### 7.3.4.6.1 CHECK ビット エラー

各 CCSI データ バイトの CHECK (17 番目) ビットは、16 番目のビットの NOT である必要があります。CHECK ビットが 16 番目のビットと同じである場合、FLAG\_CCSI\_CHECK\_BIT、FLAG\_CCSI、FLAG\_ERR が 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。CCSI ペリフェラルは現在の CCSI コマンドの受信を停止し、END バイトが受信されるまで待機します。その後、CCSI ペリフェラルは、エラー フラグのステータスとは無関係に正常に動作します。

#### 7.3.4.6.2 データ整合性診断

CCSI コントローラによって送信されるデータは、LED ドライバのデイジーチェーン内で変更または拡張されないので、LP5899 デバイスによって CRC で保護されます。CCSI コマンドの送信された全ワードに対して、CRC 値が計算されます。CCSI ペリフェラルによってコマンドが受信されると、受信された全ワードについて別の CRC が計算されます。送信されたワードに対する CRC が受信されたワードに対する CRC と一致しない場合、FLAG\_CCSI\_CRC、FLAG\_CCSI、FLAG\_ERR が 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。

SPI コマンドが FWD (コマンド 0x2~0x7) で始まると、SPI コマンドの最初のデータ ワードがチェックされます。このワードが FC0~FC15 (0xAA00~0xAA0F) または VSYNC (0xAA0F) CCSI 書き込みコマンドと一致すると、データ整合性診断が実行されます。

このエラー フラグが連続してトリガされると、CCSI コントローラと CCSI ペリフェラルは同期を失う可能性が高くなります。この場合、テキサス・インスツルメンツでは、SOFTRESET コマンドの実行を推奨しています。

#### 7.3.4.6.3 CCSI コマンド キュー オーバーフロー

LP5899 は、CCSI コントローラによって送信されるコマンドまたは CCSI ペリフェラルによって受信が予想されるコマンドがキュー内に多過ぎる場合、検出を行います。コマンド キューが満杯のときに SPI ペリフェラルによって新しい CCSI コマンドが受信されると、FLAG\_CCSI\_CMD\_QUEUE\_OVF、FLAG\_CCSI、FLAG\_ERR が 1 に設定されます。さらに、CCSI コマンド キューと TXFIFO は、TXFFCLR と同じ方法でクリアされます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。新しい CCSI コマンドを格納し、CCSI コントローラが送信を開始できるようにするには、エラー フラグをクリアする必要があります。

FLAG\_CCSI\_CMD\_QUEUE\_OVF が設定されると、CCSI コントローラと CCSI ペリフェラルは同期を失う可能性が高くなります。そのため、テキサス・インスツルメンツでは、このフラグが設定された後で SOFTRESET コマンドの実行を推奨しています。

#### 7.3.4.7 FIFO 診断

TXFIFO と RXFIFO はどちらも、オーバーフロー診断とアンダーフロー診断を備えています。以下のセクションでは、これらをより詳細に説明します。

##### 7.3.4.7.1 TXFIFO オーバーフロー

TXFIFO が満杯になり (TXFFST = 0x1FF)、TXFIFO に格納されなければならない新しいデータ ワードが SPI ペリフェラルによって受信されると、FLAG\_TXFFOVF、FLAG\_TXFF、FLAG\_ERR が 1 に設定されます。さらに、TXFIFO は TXFFCLR と同じ方法でクリアされます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。新しい CCSI データ ワードを TXFIFO に格納し、CCSI コントローラが送信を開始できるようにするには、エラー フラグをクリアする必要があります。

##### 7.3.4.7.2 TXFIFO アンダーフロー

FIFO が空 (TXFFST = 0x0) の場合、CCSI コントローラが TXFIFO から新しいワードの読み取りを試みると、FLAG\_TXFFUVF、FLAG\_TXFF、FLAG\_ERR が 1 に設定されます。CCSI コントローラによる実行中の送信が停止されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。新しい CCSI データ ワードを TXFIFO に格納し、CCSI コントローラが送信を開始できるようにするには、エラー フラグをクリアする必要があります。

#### 7.3.4.7.3 TXFIFO シングル エラー検出 (SED)

TXFIFO は、パリティ ビットで保護されます。TXFIFO からの読み取り動作中にシングル ビット エラーが検出されると、FLAG\_TXFFSED、FLAG\_RXFF、FLAG\_ERR が 1 に設定されます。CCSI コントローラによる実行中の送信が停止されます。ただし、TXFIFO は自動的にはクリアされません。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。新しい CCSI データ ワードを TXFIFO に格納し、CCSI コントローラが送信を開始できるようにするには、エラー フラグをクリアする必要があります。

#### 7.3.4.7.4 RXFIFO オーバーフロー

RXFIFO が満杯になり (RXFFST = 0x0FF)、RXFIFO に格納されなければならない新しいデータ ワードが CCSI ペリフェラルによって受信されると、FLAG\_RXFFOVF、FLAG\_RXFF、FLAG\_ERR が 1 に設定されます。RXFIFO はクリアされないため、SPI コントローラからデータにアクセスできます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。CCSI ペリフェラルは、エラー フラグがクリアされた後でのみ、RXFIFO への新しいデータの格納を開始できます。格納は、FWD\_RD\_END または FWD\_RD\_END\_CRC の SPI コマンドから受信された最初の CCSI head\_byte から開始されます。

#### 7.3.4.7.5 RXFIFO アンダーフロー

RXFIFO が空 (RXFFST = 0x0) の場合、SPI ペリフェラルが RXFIFO から新しいデータ ワードの読み取りを試みると、FLAG\_RXFFUVF、FLAG\_RXFF、FLAG\_ERR が 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。CCSI ペリフェラルは、エラー フラグがクリアされた後でのみ、RXFIFO への新しいデータの格納を開始できます。格納は、FWD\_RD\_END または FWD\_RD\_END\_CRC の SPI コマンドから受信された最初の CCSI head\_byte から開始されます。

#### 7.3.4.7.6 RXFIFO シングル エラー検出 (SED)

RXFIFO は、パリティ ビットで保護されます。RXFIFO からの読み取り動作中にシングル ビット エラーが検出されると、FLAG\_RXFFSED、FLAG\_RXFF、FLAG\_ERR が 1 に設定されます。SPI コントローラは LP5899 にアクセスし、CLR\_FLAG に 1 を書き込むことでフラグをクリアできます。

#### 7.3.4.8 OTP CRC エラー

内部 OTP は、多項式  $X^8 + X^2 + X + 1$  に基づく 8 ビット CRC で保護されています。デバイスが起動すると OTP が読み取られ、読み取られた CRC は、読み取られた全 OTP バイトに対して計算された CRC と比較されます。CRC が一致しない場合、FLAG\_OTP\_CRC および FLAG\_ERR は 1 に設定されます。このフラグは、SPI コントローラでクリアすることはできません。デバイスは初期化状態のままで、VCC をパワーダウンし再度アップするだけで、OTP の読み取りを再開できます。

### 7.3.4.9 フォルトマスク

LP5899 には、マスク レジスタを使ったフォルト マスク機能があります。本デバイスでは、フォルト タイプ別のフォルト マスクが可能です。フォルト マスクは、診断機能を無効にするのではなく、FLAG\_ERR レジスタと FAULT 出力へのフォルト 通知を行わないようにするだけです。下表に、各フォルト マスク レジスタの詳細な説明を示します。

| フォルト検出         | マスク ビット                 | フラグ名                                                     | FAULT ピン |

|----------------|-------------------------|----------------------------------------------------------|----------|

| SPI CRC エラー    | MASK_SPI_CRC = 1        | FLAG_SPI_CRC = 1<br>FLAG_ERR = 0                         | 何も起こらない  |

|                | MASK_SPI_CRC = 0        | FLAG_SPI_CRC = 1<br>FLAG_ERR = 1                         | 常時プルダウン  |

| SIN 固着エラー      | MASK_CCSI_SIN = 1       | FLAG_CCSI_SIN = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 0       | 何も起こらない  |

|                | MASK_CCSI_SIN = 0       | FLAG_CCSI_CC = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 1        | 常時プルダウン  |

| CCSI 検査ビット エラー | MASK_CCSI_CHECK_BIT = 1 | FLAG_CCSI_CHECK_BIT = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 0 | 何も起こらない  |

|                | MASK_CCSI_CHECK_BIT = 0 | FLAG_CCSI_CHECK_BIT = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 1 | 常時プルダウン  |

| CCSI CRC エラー   | MASK_CCSI_CRC = 1       | FLAG_CCSI_CRC = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 0       | 何も起こらない  |

|                | MASK_CCSI_CRC = 0       | FLAG_CCSI_CRC = 1<br>FLAG_CCSI = 1<br>FLAG_ERR = 1       | 常時プルダウン  |

### 7.3.4.10 診断表

表 7-1. 診断表

| フォルトタイプ                | 検出基準                                                               | 条件                                                              | フォルト検出時の動作                                 | フォルト出力                                               | フォルトピン          |

|------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------|------------------------------------------------------|-----------------|

| VCC UVLO               | $V_{CC} < V_{UVF}$                                                 |                                                                 | デバイスが電源が供給されていない状態に切り替わる                   | FLAG_POR<br>FLAG_ERR                                 | 常時プルダウン         |

| 発振器エラー                 | $t_{WD,OSC}$ オーバーフロー                                               |                                                                 | 何も起こらない                                    | FLAG_OSC<br>FLAG_ERR                                 | 常時プルダウン         |

| SPI 通信喪失フォルト           | $t_{SPI\_WDT}$ オーバーフロー                                             |                                                                 | デバイスが FAILSAFE 状態に移行する                     | DEV_STATE = FAILSAFE<br>FLAG_ERR                     | 常時プルダウン         |

| SPI コマンド タイムアウト フォルト   | $t_{SPI\_RST\_TIMEOUT}$ オーバーフロー                                    |                                                                 | SPI ロジックをリセットする                            | FLAG_SPI_TIMEOUT<br>FLAG_SPI<br>FLAG_ERR             | 常時プルダウン         |

| SPI チップ セレクト (CS) フォルト | SPI コマンドの途中で CS ピンが High になる                                       |                                                                 | SPI ロジックをリセットする                            | FLAG_SPI_CS<br>FLAG_SPI<br>FLAG_ERR                  | 常時プルダウン         |

| SPI CRC エラー            | 計算された CRC と受信された CRC が異なる                                          |                                                                 | 何も起こらない                                    | FLAG_SPI_CRC<br>FLAG_ERR (マスク可能)                     | 常時プルダウン (マスク可能) |

| レジスタ書き込みエラー            | CCSICTRL が CCSI コントローラ / ベリフェラル動作中に書き込まれる                          |                                                                 | 何も起こらない                                    | FLAG_SPI_REG_WRITE                                   | 何も起こらない         |

| SIN 固着エラー              | $t_{WD,SIN}$ オーバーフロー                                               |                                                                 | 何も起こらない                                    | FLAG_CCSI_SIN<br>FLAG_CCSI<br>FLAG_ERR (マスク可能)       | 常時プルダウン (マスク可能) |

| CCSI 検査ビット エラー         | 検査ビットが 16 番目のビット値の反転ではない                                           |                                                                 | 何も起こらない                                    | FLAG_CCSI_CHECK_BIT<br>FLAG_CCSI<br>FLAG_ERR (マスク可能) | 常時プルダウン (マスク可能) |

| CCSI CRC エラー           | CCSI の SOUT Head_bytes と Data_bytes_N が SIN で受信された CRC 値とは異なる結果である | Head_bytes = VSYNC (0xAA0F)<br>または<br>FCx に書き込み (0xAA00~0xAA0F) | 何も起こらない                                    | FLAG_CCSI_CRC<br>FLAG_CCSI<br>FLAG_ERR (マスク可能)       | 常時プルダウン (マスク可能) |

| CCSI コマンド キュー オーバーフロー  | コマンド キューが満杯になりかつ SPI が新しい CCSI コマンドを受信している                         |                                                                 | CCSI コントローラが停止し (実行中の場合)、TXFFST が 0 に設定される | FLAG_CCSI_CMD_QUEUE_OVF<br>FLAG_CCSI<br>FLAG_ERR     | 常時プルダウン         |

| TXFIFO オーバーフロー         | TXFFST = 511<br>かつ<br>SPI データワードを格納する必要がある                         | SPI コマンドタイプが FWD で始まっている                                        | CCSI コントローラが停止し (実行中の場合)、TXFFST が 0 に設定される | FLAG_TXFFOVF<br>FLAG_TXFF<br>FLAG_ERR                | 常時プルダウン         |

表 7-1. 診断表 (続き)

| フォルトタイプ           | 検出基準                                             | 条件                              | フォルト検出時の動作                     | フォルト出力                                | フォルトピン  |

|-------------------|--------------------------------------------------|---------------------------------|--------------------------------|---------------------------------------|---------|

| TXFIFO アンダーフロー    | TXFFST = 0<br>かつ<br>CCSI コントローラが新しいワードの送信を要求している |                                 | CCSI コントローラが停止する               | FLAG_TXFFUVF<br>FLAG_TXFF<br>FLAG_ERR | 常時プルダウン |

| TXFIFO シングル エラー検出 | CCSI コントローラが新しいワードの送信を要求し、TXFIFO パリティ エラーが発生した   |                                 | CCSI コントローラが停止する               | FLAG_TXFFSED<br>FLAG_TXFF<br>FLAG_ERR | 常時プルダウン |

| RXFIFO オーバーフロー    | RXFFST = 255<br>かつ<br>CCSI データ ワードを格納する必要がある     |                                 | CCSI ペリフェラルが RXFIFO にワードを格納しない | FLAG_RXFFOVF<br>FLAG_RXFF<br>FLAG_ERR | 常時プルダウン |

| RXFIFO アンダーフロー    | RXFFST = 0<br>かつ<br>SPI ペリフェラルが新しいワードの送信を要求している  | SPI コマンド タイプが DATA_READ で始まっている | CCSI ペリフェラルが RXFIFO にワードを格納しない | FLAG_RXFFUVF<br>FLAG_RXFF<br>FLAG_ERR | 常時プルダウン |

| RXFIFO シングル エラー検出 | SPI ペリフェラルが新しいワードの送信を要求し、RXFIFO パリティ エラーが発生した    | SPI コマンド タイプが DATA_READ で始まっている | 何も起こらない                        | FLAG_RXFFSED<br>FLAG_RXFF<br>FLAG_ERR | 常時プルダウン |

| OTP CRC エラー       | CALC_OTPCRC が異なる OTPCRC である                      |                                 | 何も起こらない                        | FLAG_OTP_CRC<br>FLAG_ERR              | 常時プルダウン |

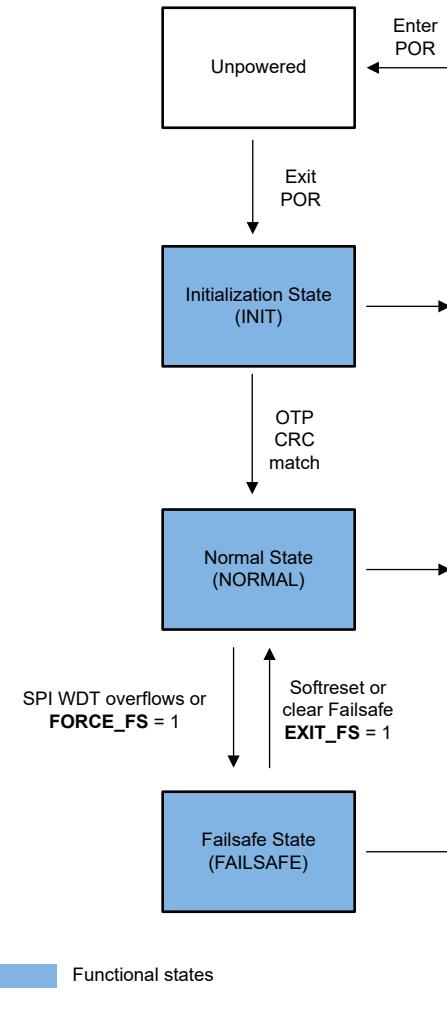

## 7.4 デバイスの機能モード

図 7-7. デバイスの機能モード

### 7.4.1 電源なし

VCC が UVLO スレッショルドを下回っている限り、デバイスは POR 状態に維持されます。すべてのレジスタがリセット状態に維持されます。VCC がその他の状態で UVLO スレッショルドを下回ると、デバイスは直ちに POR 状態に維持されます。

### 7.4.2 初期化状態

VCC が UVLO スレッショルドを上回ると、デバイスは初期化状態に移行します。この状態では SPI ペリフェラルは有効ですが、サポートされている最大周波数は NORMAL 状態より低くなります。CCSI コントローラの連続クロックは有効ですが、送信が開始できるのは NORMAL 状態でのみになります。また、OTP が読み取られ、読み取られた CRC が、読み取られたすべての OTP バイトの計算された CRC と比較されます。CRC が一致すると、OTP レジスタが更新され、デバイスは NORMAL 状態に移行します。

### 7.4.3 NORMAL 状態

CCSI コントローラによる送信を可能にするには、FLAG\_POR がクリアされる必要があります。通信ウォッチドッグ タイマが有効で、通信がないためにタイマがタイムアウトすると、デバイスは FAILSAFE 状態に移行します。また、DEVCTRL レジスタの FORCE\_FS ビットを 1 に設定することで、NORMAL 状態のときはいつでも、デバイスを強制的に FAILSAFE 状態にすることもできます。FORCE\_FS ビットは自動的に 0 に戻ります。

### 7.4.4 FAILSAFE 状態

デバイスが FAILSAFE 状態に移行すると、TXFFCLR ビットが設定されて、実行中の CCSI 送信が停止します。

FAILSAFE 状態に移行すると、SPI ペリフェラルは最初にリセットされます。その後、SPI ペリフェラルはデバイスとの通信が可能な状態に維持されます。ただし、CCSI コントローラと CCSI ペリフェラルの制御はできません。つまり、SPI コマンドが FWD で始まるとき、データは無視され、TXFIFO に格納されないことを意味します。

DEVCTRL レジスタの EXIT\_FS ビットを 1 にセットすることで、デバイスを FAILSAFE 状態から NORMAL 状態に移行することができます。EXIT\_FS ビットは自動的に 0 に戻ります。SOFTRESET\_CRC SPI コマンドを送信することでデバイスを NORMAL 状態にする方法もあります。

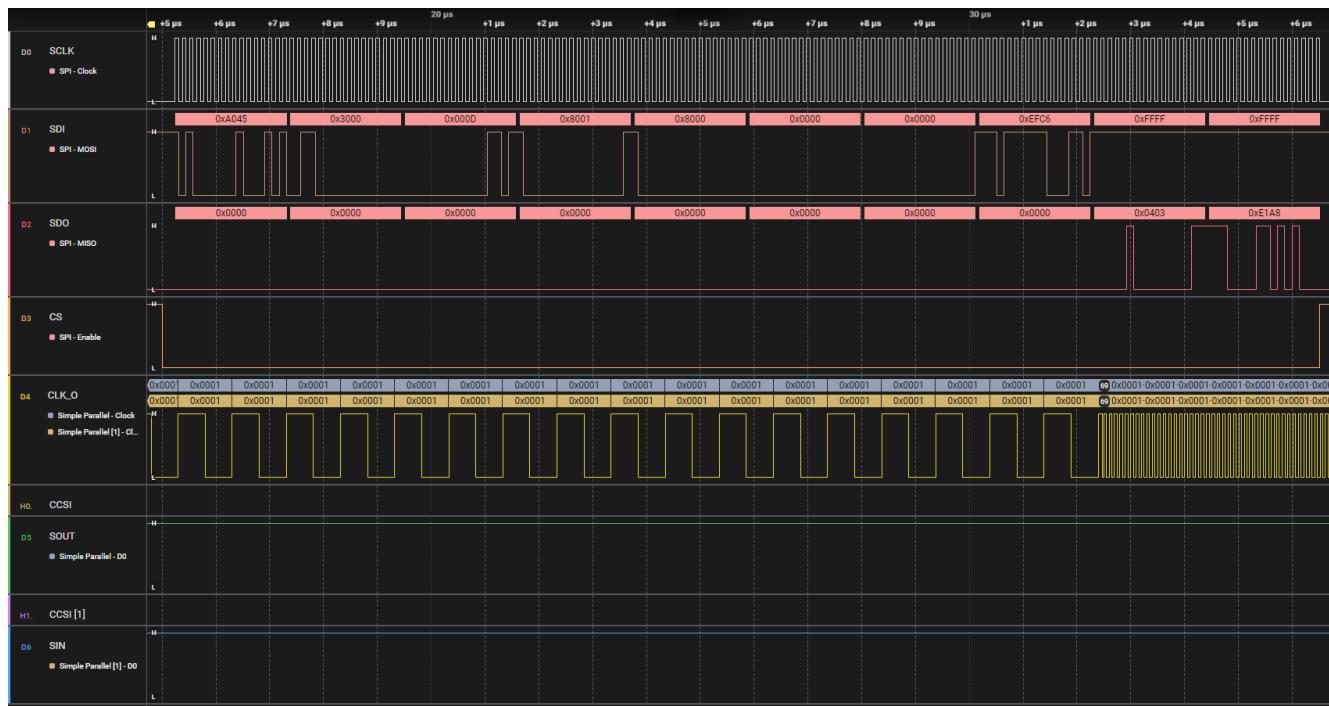

## 7.5 プログラミング

LP5899 は、高速な同期シリアル入出力 (I/O) ポートであるシリアル ペリフェラル インターフェイス (SPI) のペリフェラルを搭載しており、外部から供給されるクロック レートに基づいて、16 ビット長のシリアル ビットストリームをデバイスにシフトインおよびシフトアウトできます。デバイスにシフトインされたビットストリームにより、プログラマブルな機能とレジスタにアクセスできます。4 本の信号線から構成されるインターフェイスになります。

- シリアル データ入力 (SDI)

- シリアル データ出力 (SDO)

- シリアル クロック (SCLK)

- チップ セレクト (CS)

### 7.5.1 SPI データの有効性

SDI 線のデータは、SCLK 線の立ち上がりエッジで安定している必要があります。SDO のデータは、SCLK 線の立ち下がりエッジでシフト アウトします。SDO は、SPICTRL レジスタの SPI\_SDO\_DIS ビットを使用して強制的に無効にできます。これは、単一の SPI バスで複数の LP5899 デバイスに同じコマンドがブロードキャストされる場合に便利です。デバイスにデータがシフトされない場合、SCLK 線はロジック Low である必要があります。

### 7.5.2 チップ セレクト (CS) および SPI リセット制御

CS 信号は、スプリアス クロック パルスやデータ パルスをゲート処理する能力を備えています。CS 上の HIGH ロジック信号は、ペリフェラルがデータを受信するのをブロックします。これにより、SPI ペリフェラルがコントローラとの同期を失うことを防止できます。テキサス・インスツルメンツでは、CS を常にアクティブ状態にすることは推奨していません。

SPI ペリフェラルがコントローラとの同期を失うことがあれば、CS に HIGH ロジック信号を供給することで、ビット カウンタを含む SPI ペリフェラルをリセットします。別の方法として、SCLK を停止し、SPICTRL レジスタの SPI\_RST\_TIMEOUT\_CFG フィールドの設定よりも長い時間待機することができます。このタイムアウトは、SPI ペリフェラルがコマンド ワードを待機している際の SCLK の最初の立ち上がりクロック エッジからカウントを開始します。

### 7.5.3 SPI コマンドフォーマット

図 7-8 と表 7-2 に、SPI コマンドの送信フォーマットの定義を示します。各 SPI コマンドには複数の 16 ビットワードが含まれています。ワードのタイプは次のとおりです。

- **コマンドワード:**コマンドワードには、常にコマンドタイプの識別子が含まれます。タイプに応じて、コマンドワードには以下も含まれます。

- 書き込みまたは読み取り対象の開始アドレス。フィールド アドレス = 0 の場合はアドレス 0x00 を意味します。

- 送信される、または読み取りが予想されるデータの長さ。長さフィールドが opt で始まる場合はデータはオプションです。したがって、opt\_data\_length = 0 は 0 データワードを意味します。opt で始まらないフィールドの場合、data\_length = 0 は 1 データワードを意味します。

- データ転送時に付加される追加の END バイト数。extra\_end\_bytes フィールド = 0 は、追加の END バイト 0 を意味します。1 つの SPI コマンドで最大 127 の追加 END バイトを付加できます。

- 固定データ (SOFTRESET\_CRC コマンドの場合)

- **データワード:**コマンドタイプに応じて、転送が必要なデータ (0~N)、デバイスに書き込まれたレジスタデータ (0~N)、デバイスから読み取られたレジスタデータ (N+1~M)、RXFIFO から読み取られたデータ (N+1~M) になります。

- **CRCワード:**各コマンドには、次の 2 つの異なる CRC ワードが含まれます。

- SPI コントローラによって生成された CRC ワード。この CRC は、SPI コマンドワードとすべての送信データワード (0~N) に対して計算されています。

- SPI ペリフェラルによって生成された CRC ワード。この CRC は、返されたすべてのデータワード (N+1~M) に対して計算されています。

2 つの異なる CRC アルゴリズムがサポートされています。デフォルトのアルゴリズムは CCITT-FALSE です。これは、REG\_WR コマンドを使用して CRC-16/XMODEM アルゴリズムに変更できます。CRC アルゴリズムを変更すると、次の SPI コマンドから新しいアルゴリズムが使用されます。どちらのアルゴリズムも、多項式  $X^{16} + X^{12} + X^5 + 1$  に基づいています。

図 7-8. SPI コマンド フォーマット

**表 7-2. SPI コマンドの詳細**

| コマンド タイプ       | コマンド ワード   |                      |                  |                  |                      |     |                  |   |   |   |   | データ ワード | CRC ワード                   |                           |      |                                   |     |

|----------------|------------|----------------------|------------------|------------------|----------------------|-----|------------------|---|---|---|---|---------|---------------------------|---------------------------|------|-----------------------------------|-----|

|                | CMD[15:12] | 11                   | 10               | 9                | 8                    | 7   | 6                | 5 | 4 | 3 | 2 | 1       | 0                         |                           |      |                                   |     |

| FWD_WR_CRC     | 0x2        | 0x0                  | data_length[8:0] |                  |                      |     |                  |   |   |   |   |         |                           | データ ワード 0-<br>data_length | CRC  |                                   |     |

| FWD_WR         | 0x3        | data_length[11:0]    |                  |                  |                      |     |                  |   |   |   |   |         | データ ワード 0-<br>data_length | CRC                       |      |                                   |     |

| FWD_WR_END_CRC | 0x4        | opt_data_length[4:0] |                  |                  | extra_end_bytes[6:0] |     |                  |   |   |   |   |         |                           |                           |      | データ ワード 0-<br>(opt_data_length-1) | CRC |

| FWD_WR_END     | 0x5        | opt_data_length[4:0] |                  |                  | extra_end_bytes[6:0] |     |                  |   |   |   |   |         |                           |                           |      | データ ワード 0-<br>(opt_data_length-1) | CRC |

| FWD_RD_END_CRC | 0x6        | data_length[4:0]     |                  |                  | extra_end_bytes[6:0] |     |                  |   |   |   |   |         |                           |                           |      | データ ワード 0-<br>data_length         | CRC |

| FWD_RD_END     | 0x7        | data_length[4:0]     |                  |                  | extra_end_bytes[6:0] |     |                  |   |   |   |   |         |                           |                           |      | データ ワード 0-<br>data_length         | CRC |

| DATA_RD_CRC    | 0x8        | 0x0                  |                  | data_length[7:0] |                      |     |                  |   |   |   |   |         |                           |                           | 該当なし | CRC                               |     |

| DATA_RD        | 0x9        | 0x0                  |                  | data_length[7:0] |                      |     |                  |   |   |   |   |         |                           |                           | 該当なし | CRC                               |     |

| REG_WR_CRC     | 0xA        | 0x0                  | address[3:0]     |                  |                      | 0x0 | data_length[3:0] |   |   |   |   |         |                           | データ ワード 0-<br>data_length | CRC  |                                   |     |

| REG_WR         | 0xB        | 0x0                  | address[3:0]     |                  |                      | 0x0 | data_length[3:0] |   |   |   |   |         |                           | データ ワード 0-<br>data_length | CRC  |                                   |     |

| REG_RD_CRC     | 0xC        | 0x0                  | address[3:0]     |                  |                      | 0x0 | data_length[3:0] |   |   |   |   |         |                           | 該当なし                      | CRC  |                                   |     |

| REG_RD         | 0xD        | 0x0                  | address[3:0]     |                  |                      | 0x0 | data_length[3:0] |   |   |   |   |         |                           | 該当なし                      | CRC  |                                   |     |

| SOFTRESET_CRC  | 0xE        | 0x1E1                |                  |                  |                      |     |                  |   |   |   |   |         | 該当なし                      | CRC                       |      |                                   |     |

### 7.5.4 SPI コマンドの詳細

SOFTRESET\_CRC を除いて、各コマンドには 2 つのバージョンがあります。タイプ名の末尾に CRC を含まないバージョンは、CRC 値が正しくない場合でも常に実行されます。タイプ名の末尾に CRC を含むバージョンは、受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致する場合にのみ実行されます。

FWD で始まるコマンドは、CCSI コントローラによって受信されたデータワードを転送します。データ長が 0 より大きい限り、CCSI コントローラは自動的に 1 つのスタートビット、検査ビット、および 1 つの END バイトを挿入します。したがって、1 つの SPI コマンドの SPI データワードは、最初の SPI データワードの前に 1 つのスタートビットがあり、各データワードの後に 1 つの検査ビットがあり、最後の SPI データワードの後に 1 つの END バイトがある CCSI コマンドとみなされます。

REG で始まるコマンドは、LP5899 デバイスのレジスタの書き込みと読み取りに使用されます。DATA\_RD コマンドは、RXFIFO に格納されているデータを返します。

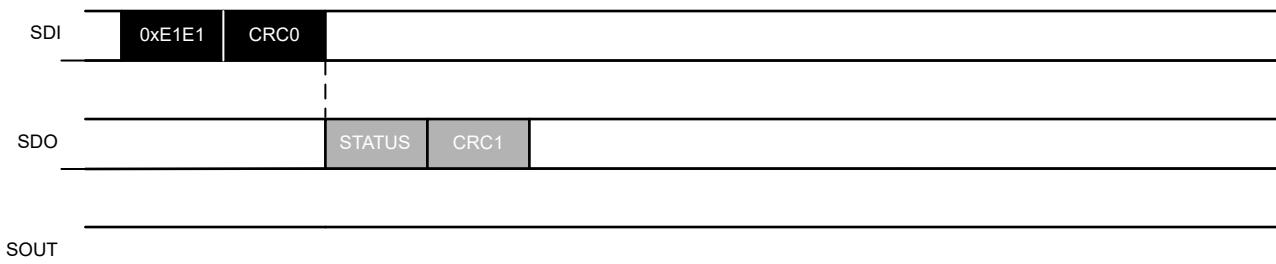

FWD、REG\_WR、SOFTRESET\_CRC で始まるコマンドは、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。この アクノリッジ (受信確認) は、SPICTRL レジスタの SPI\_ACK\_DIS ビットで無効にできます。アクノリッジ (受信確認) が無効にされている間に SOFTRESET\_CRC を実行する場合は、注意が必要です。この場合、テキサス・インスツルメンツでは、次のコマンドを送信する前に、少なくとも 1 つの SPI ワードの待機を推奨しています。

LP5899 デバイスが SDO ピンでデータをコントローラに返すたびに、コントローラはデータをシフトアウトするのに十分なクロック パルスを SCLK ピンに供給する必要があります。テキサス・インスツルメンツでは、クロック パルスを供給してデータをシフトアウトする間、SDI ピンをロジック HIGH に維持することを推奨しています。

**FWD\_WR\_CRC (CRC 書き込みコマンドの転送)**

[SPI コマンド表](#)を参照してください。

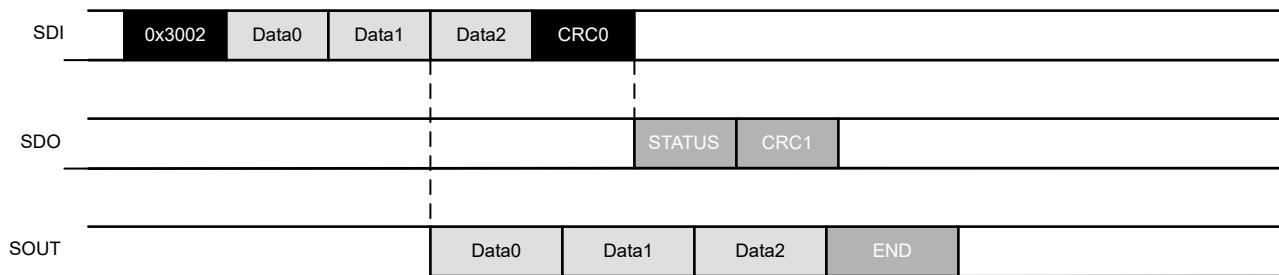

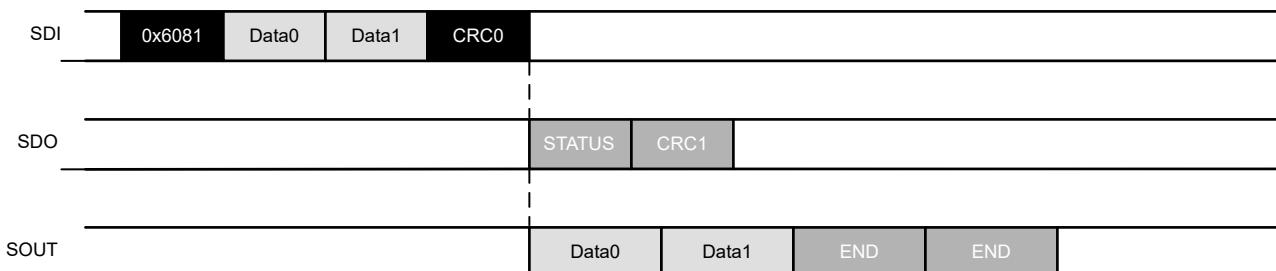

FWD\_WR\_CRC コマンドは、デバイス内の CCSI コントローラによってデータワードを送信するために使用されます。SPI ペリフェラルによって受信されたすべてのデータワードは、TXFIFO に格納されます。受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致した場合にのみ、CCSI コントローラは送信を開始します。これは、TXFFLVL がこの送信の開始には影響しないことを意味しています。SPI コントローラは、データ長が TXFIFO のサイズよりも短いことに注意する必要があります。この SPI コマンドは、最大 512 のデータワードをサポートし、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。図 7-9 に、2 つのデータワードを転送する FWD\_WR\_CRC コマンドの例を示します。

図 7-9. FWD\_WR\_CRC コマンドの例

### FWD\_WR (書き込みコマンドの転送)

[SPI コマンド表](#)を参照してください。

FWD\_WR コマンドは、デバイス内の CCSI コントローラによってデータワードを送信するために使用されます。SPI ペリフェラルによって受信されたすべてのデータワードは、TXFIFO に格納されます。次の条件が 1 つ以上満たされると、CCSI コントローラは送信を開始します。

- TXFIFO に格納されたワード数が TXFFLVL に達する

- SPI コマンドのデータワードをすべて受信した

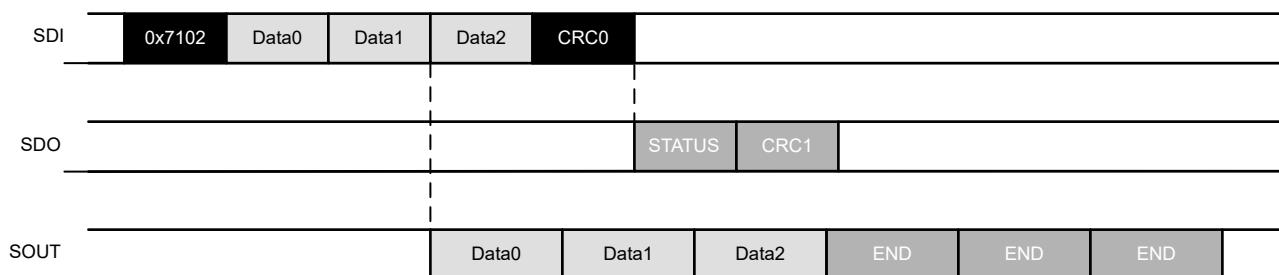

これは、CRC がこの送信の開始に影響しないことを意味しています。受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致しない場合、FAULT ピン (マスクされていない場合) は Low になり、FLAG\_SPI\_CRC フラグが設定されます。この SPI コマンドは、最大 4096 のデータワードをサポートし、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。図 7-10 に、TXFFLVL が 2 つのデータワードに設定された状態で 3 つのワードを転送する FWD\_WR コマンドの例を示します。

図 7-10. FWD\_WR コマンドの例

### FWD\_WR\_END\_CRC (END バイトを含む CRC 書き込みコマンドの転送)

[SPI コマンド表](#)を参照してください。

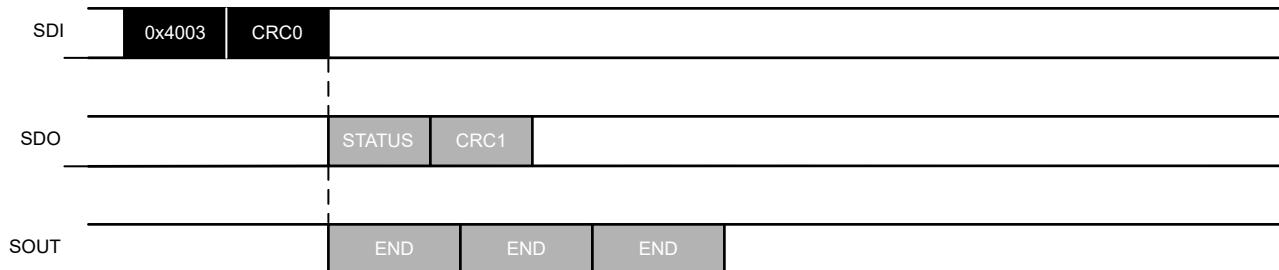

FWD\_WR\_END\_CRC コマンドは、デバイス内の CCSI コントローラによってデータワードを送信するために使用されます。SPI ペリフェラルによって受信されたすべてのデータワードは、TXFIFO に格納されます。受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致した場合にのみ、CCSI コントローラは送信を開始します。これは、TXFFLVL がこの送信の開始には影響しないことを意味しています。データワードがすべて CCSi コントローラによって送信された後、指定された数の追加の END バイトが付加されます。データワードの送信と追加の END バイトの送信は、2 つの別々の CCSI コマンドとみなされます。この SPI コマンドは、最大 31 のデータワードをサポートし、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。図 7-11 に、0 データワード (つまり 1 つの END バイトを挿入しない) と 3 つの追加の END バイトを転送する FWD\_WR\_END\_CRC コマンドの例を示します。

図 7-11. FWD\_WR\_END\_CRC コマンドの例

### FWD\_WR\_END (END バイトを含む書き込みコマンドの転送)

[SPI コマンド表](#)を参照してください。

FWD\_WR\_END コマンドは、デバイス内の CCSi コントローラによってデータワードを送信するために使用されます。SPI ペリフェラルによって受信されたすべてのデータワードは、TXFIFO に格納されます。次の条件が 1 つ以上満たされると、CCSi コントローラは送信を開始します。

- TXFIFO に格納されたワード数が TXFFLVL に達する

- SPI コマンドのデータワードをすべて受信した

これは、CRC がこの送信の開始に影響しないことを意味しています。受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致しない場合、FAULT ピン（マスクされていない場合）は Low になり、FLAG\_SPI\_CRC フラグが設定されます。データワードがすべて CCSi コントローラによって送信された後、指定された数の追加の END バイトが付加されます。データワードの送信と追加の END バイトの送信は、2 つの別々の CCSi コマンドとみなされます。この SPI コマンドは、最大 31 のデータワードをサポートし、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。図 7-12 に、2 つのデータワードと 1 つの追加の END バイトを転送する FWD\_WR\_END コマンドの例を示します。この例では、TXFFLVL が 2 ワード以上に設定されています。

図 7-12. FWD\_WR\_END コマンドの例

### FWD\_RD\_END\_CRC (END バイトを含む CRC 読み取りコマンドの転送)

[SPI コマンド表](#)を参照してください。

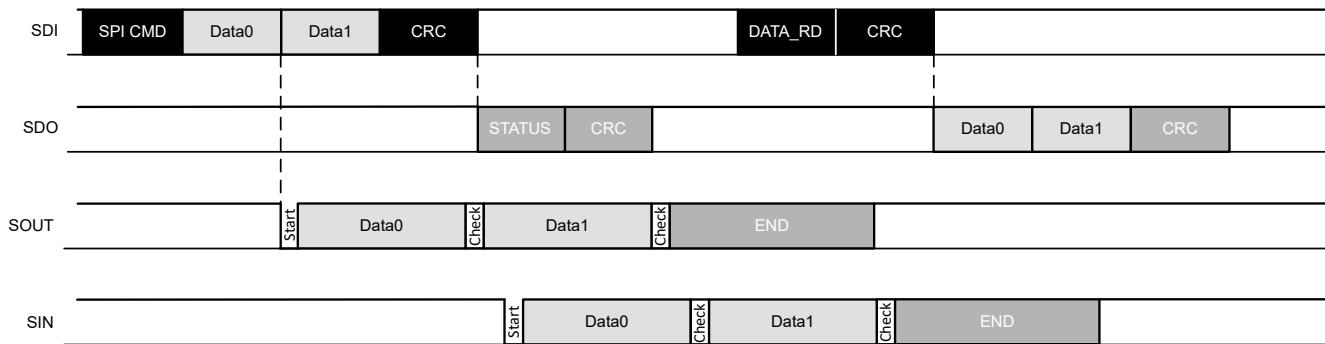

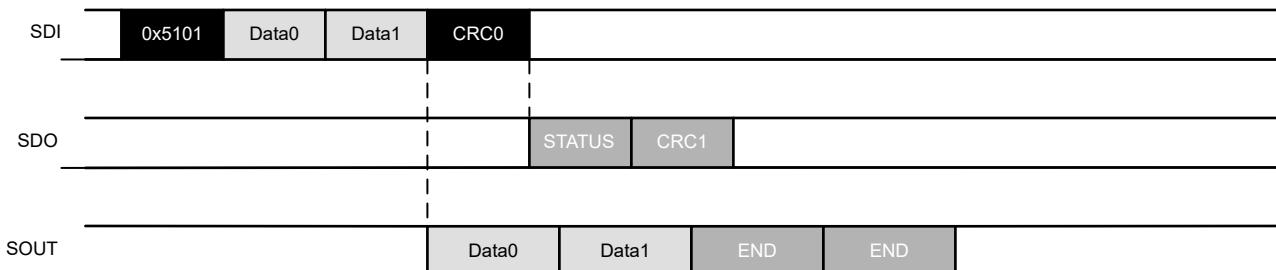

FWD\_RD\_END\_CRC コマンドは、デバイス内の CCSi コントローラによってデータワードを送信するために使用されます。SPI ペリフェラルによって受信されたすべてのデータワードは、TXFIFO に格納されます。受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致した場合にのみ、CCSi コントローラは送信を開始します。これは、TXFFLVL がこの送信の開始には影響しないことを意味しています。データワードがすべて CCSi コントローラによって送信された後、指定された数の追加の END バイトが付加されます。データワードの送信と追加の END バイトの送信は、2 つの別々の CCSi コマンドとみなされます。このコマンドで CCSi ペリフェラルによって受信されたすべてのデータワードは、RXFIFO に格納されます。この SPI コマンドは、最大 32 のデータワードをサポートし、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。図 7-13 に、2 つのデータワードと 1 つの追加の END バイトを転送する FWD\_RD\_END\_CRC コマンドの例を示します。

図 7-13. FWD\_RD\_END\_CRC コマンドの例

### FWD\_RD\_END (END バイトを含む読み取りコマンドの転送)

[SPI コマンド表](#)を参照してください。

FWD\_RD\_END コマンドは、デバイス内の CCS1 コントローラによってデータワードを送信するために使用されます。SPI ペリフェラルによって受信されたすべてのデータワードは、TXFIFO に格納されます。次の条件が 1 つ以上満たされたら、CCS1 コントローラは送信を開始します。

- TXFIFO に格納されたワード数が TXFFLVL に達する

- SPI コマンドのデータワードをすべて受信した

これは、CRC がこの送信の開始に影響しないことを意味しています。受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致しない場合、FAULT ピン (マスクされていない場合) は Low になり、FLAG\_SPI\_CRC フラグが設定されます。データワードがすべて CCS1 コントローラによって送信された後、指定された数の追加の END バイトが付加されます。データワードの送信と追加の END バイトの送信は、2 つの別々の CCS1 コマンドとみなされます。このコマンドで CCS1 ペリフェラルによって受信されたすべてのデータワードは、RXFIFO に格納されます。この SPI コマンドは、最大 32 のデータワードをサポートし、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。図 7-14 に、TXFFLVL が 2 つのデータワードに設定された状態の 3 つのデータワードおよび 2 つの追加の END バイトを転送する FWD\_RD\_END コマンドの例を示します。

図 7-14. FWD\_RD\_END コマンドの例

### DATA\_RD\_CRC (CRC データ読み取りコマンド)

[SPI コマンド表](#)を参照してください。

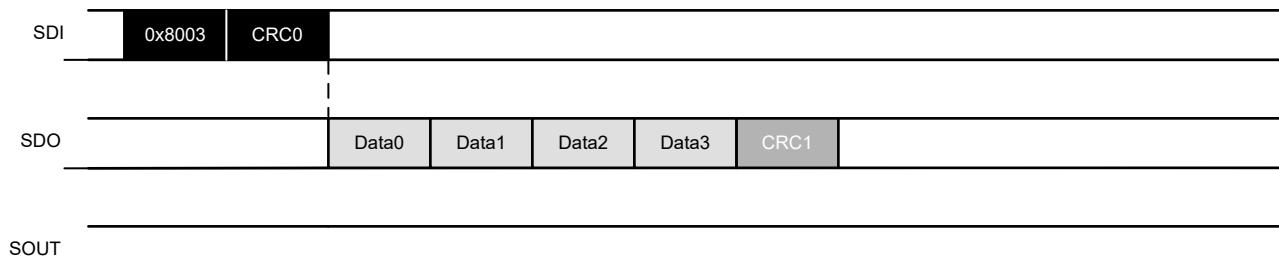

DATA\_RD\_CRC コマンドは、RXFIFO からデータワードを読み取るために使用されます。受信された CRC がコマンドワードに対して計算された CRC と一致している場合のみ、デバイスは要求された数のデータワードと、データワードに対して計算された CRC を返します。CRC が失敗すると、SDO はロジック HIGH に維持されます。フィールド data\_length が 0 の場合、RXFFST レジスタのフィールド RXFFST が 0 の後に RXFFLVL レジスタの RXFFCLR ビットを書き込みます。図 7-15 に、4 つのデータワードを要求する DATA\_RD\_CRC コマンドの例を示します。

図 7-15. DATA\_RD\_CRC コマンドの例

### DATA\_RD (データ読み取りコマンド)

[SPI コマンド表](#)を参照してください。

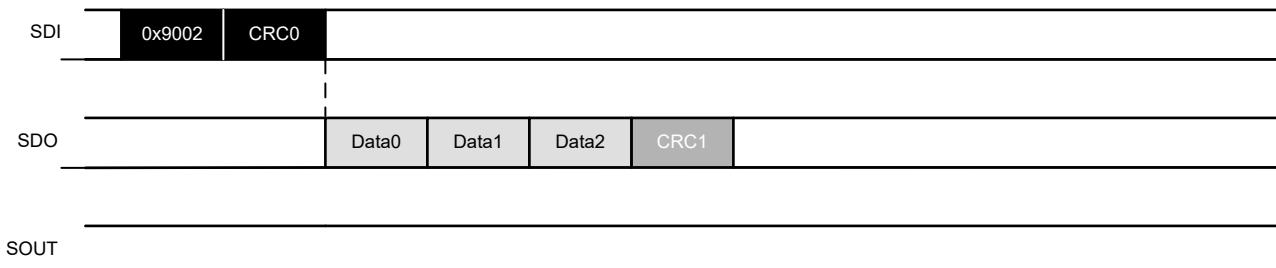

DATA\_RD コマンドは、RXFIFO からデータワードを読み取るために使用されます。受信された CRC がコマンドワードに対して計算された CRC と一致しない場合でも、デバイスは要求された数のデータワードと、データワードに対して計算された CRC を返します。受信された CRC がコマンドワードに対して計算された CRC と一致しない場合、FAULT ピン (マスクされていない場合) は Low になり、FLAG\_SPI\_CRC フラグが設定されます。フィールド data\_length が 0 の場合、RXFFST レジスタのフィールド RXFFST が 0 の後に RXFFLVL レジスタの RXFFCLR ビットを書き込みます。[図 7-16](#) に、3 つのデータワードを要求する DATA\_RD コマンドの例を示します。

**図 7-16. DATA\_RD コマンドの例**

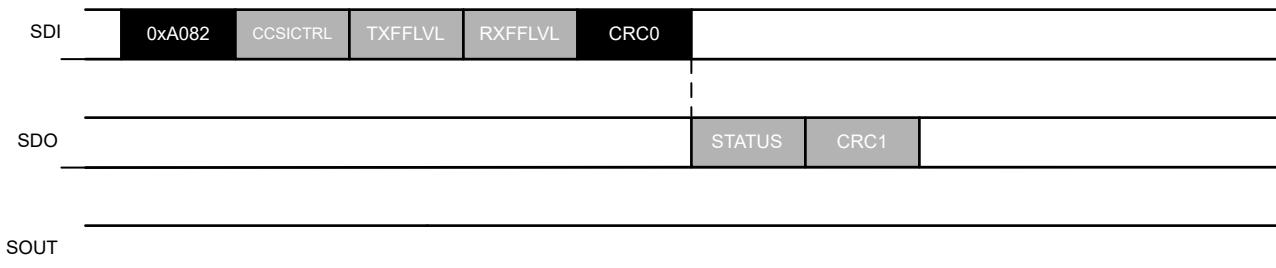

### REG\_WR\_CRC (CRC レジスタ書き込みコマンド)

[SPI コマンド表](#)を参照してください。

REG\_WR\_CRC コマンドは、LP5899 デバイスの内部レジスタに書き込むために使用されます。このコマンドには、最初に書き込まれるレジスタのアドレスを示すフィールドが含まれています。SPI ペリフェラルによって受信されたすべてのデータワードは、シャドウ レジスタに格納されます。受信された CRC がコマンドワードとデータワードに対して計算された CRC と一致した場合にのみ、レジスタが更新されます。このコマンドは、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。[図 7-17](#) に、3 つのレジスタを書き込む REG\_WR\_CRC コマンドの例を示します。

**図 7-17. REG\_WR\_CRC コマンドの例**

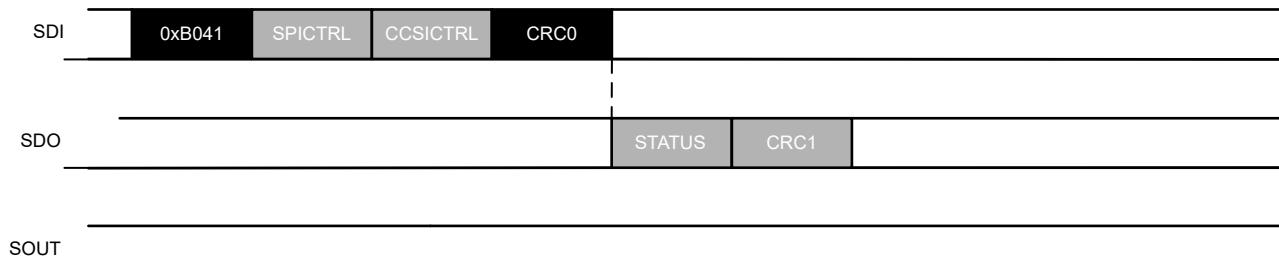

**REG\_WR (レジスタ書き込みコマンド)**

[SPI コマンド表](#)を参照してください。

REG\_WR コマンドは、LP5899 デバイスの内部レジスタに書き込むために使用されます。このコマンドには、最初に書き込まれるレジスタのアドレスを示すフィールドが含まれています。SPI ペリフェラルによって受信されたすべてのデータワードは、レジスタに直接書き込まれます。これは、CRC がレジスタの書き込みに影響しないことを意味しています。受信された CRC がコマンド ワードに対して計算された CRC と一致しない場合、FAULT ピン (マスクされていない場合) は Low になり、FLAG\_SPI\_CRC フラグが設定されます。このコマンドは、STATUS レジスタと STATUS レジスタに対して計算された CRC を返します。図 7-18 に、2 つのレジスタを書き込む REG\_WR\_CRC コマンドの例を示します。

**図 7-18. REG\_WR コマンドの例**

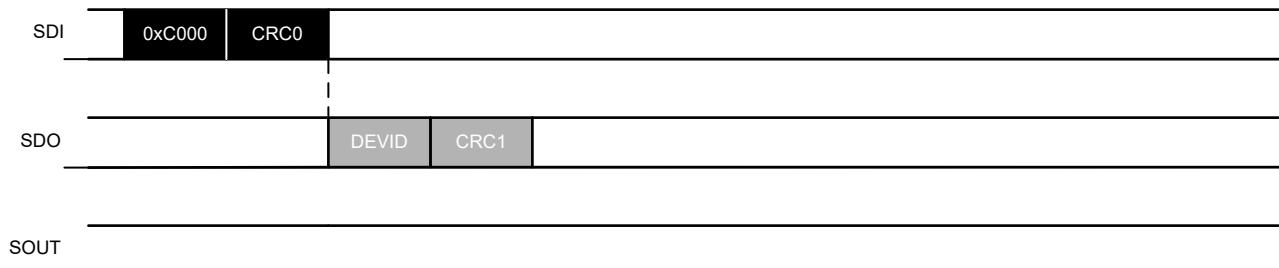

**REG\_RD\_CRC (CRC レジスタ読み取りコマンド)**

[SPI コマンド表](#)を参照してください。

REG\_RD\_CRC コマンドは、LP5899 デバイスの内部レジスタを読み取るために使用されます。このコマンドには、最初に読み取られるレジスタのアドレスを示すフィールドが含まれています。受信された CRC がコマンド ワードに対して計算された CRC と一致している場合のみ、デバイスは要求された数のレジスタ ワードと、レジスタ ワードに対して計算された CRC を返します。CRC が失敗すると、SDO はロジック HIGH に維持されます。図 7-19 に、1 つのレジスタを読み取る REG\_RD\_CRC コマンドの例を示します。

**図 7-19. REG\_RD\_CRC コマンドの例**

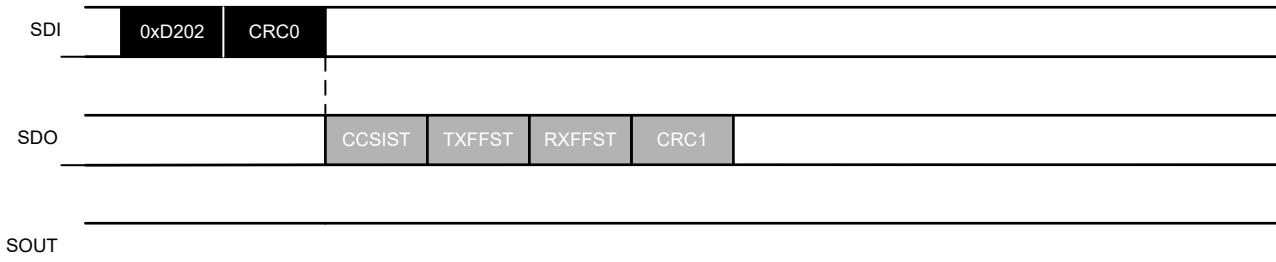

## REG\_RD (レジスタ読み取りコマンド)

[SPI コマンド表](#)を参照してください。

REG\_RD コマンドは、LP5899 デバイスの内部レジスタを読み取るために使用されます。このコマンドには、最初に読み取られるレジスタのアドレスを示すフィールドが含まれています。受信された CRC がコマンド ワードに対して計算された CRC と一致しない場合でも、デバイスは要求された数のレジスタワードと、レジスタ ワードに対して計算された CRC を返します。受信された CRC がコマンド ワードに対して計算された CRC と一致しない場合、FAULT ピン (マスクされていない場合) は Low になり、FLAG\_SPI\_CRC フラグが設定されます。図 7-20 に、3 つのレジスタを読み取る REG\_RD コマンドの例を示します。

図 7-20. REG\_RD コマンドの例

## SOFTRESET\_CRC (SOFTRESET\_CRC コマンド)

[SPI コマンド表](#)を参照してください。

SOFTRESET\_CRC コマンドは、すべての内部レジスタをデフォルト値にリセットし、CCSI コントローラと CCSI ペリフェラルを同期させるために使用されます。このコマンドは、次の場合に実行されます。

- 受信された CRC がコマンド ワードに対して計算された CRC と一致している

- CCSI コントローラが送信していない

CCITT-FALSE アルゴリズムを使用した SOFTRESET\_CRC コマンドの CRC 値は 0xD383 で、CRC-16/XMODEM アルゴリズムを使用した場合の CRC 値は 0xCE8C です。

すべての内部レジスタがリセットされると、それまでに設定されていたフォルト フラグのほとんどがクリアされます。FLAG\_POR と FLAG\_ERR のみが HIGH にリセットされます。さらに、RXFIFO に格納されたすべてのデータにアクセスできなくなります。CCSI ペリフェラルによってまだ受信されていない CCSI コマンドが LED デイジーチェーン内にある場合、CCSI コントローラと CCSI ペリフェラル間の同期のために計算された CRC 値がクリアされているため、CCSI CRC 診断をチェックできなくなります。テキサス・インスツルメンツでは、SOFTRESET\_CRC コマンドを送信した後、デイジーチェーン内の LED ドライバの数と同じ数の END バイトを送信することを推奨しています。これにより、すでに送信されている CCSI コマンドがすべてクリアされ、同期が維持されます。デバイスが FAILSAFE モードの場合、SOFTRESET\_CRC コマンドはデバイスを NORMAL モードに移行させます。失敗した SOFTRESET\_CRC コマンドが、STATUS レジスタの FLAG\_SRST ビットに記録されます。図 7-21 に、SOFTRESET\_CRC コマンドの例を示します。

図 7-21. SOFTRESET\_CRC コマンドの例

## 8 デバイスのレジスタ

デバイスのレジスタの概要表 に、デバイスのレジスタ用のメモリ マップト レジスタを示します。デバイスのレジスタの概要表に記載されていないすべてのレジスタ オフセット アドレスは予約領域と見なされ、レジスタの内容は変更しないでください。

**表 8-1. デバイスのレジスタの概要表**

| アドレス | 略称       | 説明                              | セクション      |

|------|----------|---------------------------------|------------|

| 0x0  | DEVID    | デバイス識別情報                        | セクション 8.1  |

| 0x1  | SPICTRL  | SPI の制御                         | セクション 8.2  |

| 0x2  | CCSICTRL | 連続クロック シリアル インターフェイス (CCSI) の制御 | セクション 8.3  |

| 0x3  | TXFFLVL  | 送信 FIFO レベルの制御                  | セクション 8.4  |

| 0x4  | RXFFLVL  | 受信 FIFO レベルの制御                  | セクション 8.5  |

| 0x5  | DEVCTRL  | デバイスの制御レジスタ                     | セクション 8.6  |

| 0x6  | DIAGMASK | 診断マスク                           | セクション 8.7  |

| 0x7  | STATUS   | グローバル デバイス ステータス                | セクション 8.8  |

| 0x8  | IFST     | インターフェイス ステータスの詳細               | セクション 8.9  |

| 0x9  | TXFFST   | 送信 FIFO ステータスの詳細                | セクション 8.10 |

| 0xA  | RXFFST   | 受信 FIFO ステータスの詳細                | セクション 8.11 |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 8-2 このセクションでアクセス タイプに使用しているコードを示します。

**表 8-2. デバイスのアクセス タイプ コード**

| アクセス タイプ      | コード     | 説明               |

|---------------|---------|------------------|

| 読み取りタイプ       |         |                  |

| R             | R       | 読み出し             |

| 書き込みタイプ       |         |                  |

| W             | W       | 書き込み             |

| W1C           | W<br>1C | 書き込み<br>1 でクリア   |

| リセットまたはデフォルト値 |         |                  |

| -n            |         | リセット後の値またはデフォルト値 |

## 8.1 DEVID レジスタ (アドレス = 0x0) [リセット = 0xED99]

図 8-1 に DEVID を示し、表 8-3 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

図 8-1. DEVID レジスタ

|          |    |    |    |    |    |   |   |

|----------|----|----|----|----|----|---|---|

| 15       | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| DEVID    |    |    |    |    |    |   |   |

| R-0xED99 |    |    |    |    |    |   |   |

| 7        | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

| DEVID    |    |    |    |    |    |   |   |

| R-0xED99 |    |    |    |    |    |   |   |

表 8-3. DEVID レジスタ フィールドの説明

| ピット  | フィールド | タイプ | リセット   | 説明       |

|------|-------|-----|--------|----------|

| 15-0 | DEVID | R   | 0xED99 | デバイス識別情報 |

## 8.2 SPICTRL レジスタ (アドレス = 0x1) [リセット = 0x00A0]

図 8-2 に SPICTRL を示し、表 8-4 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

**図 8-2. SPICTRL レジスタ**

| 15                  | 14          | 13      | 12   | 11      | 10          | 9           | 8           |

|---------------------|-------------|---------|------|---------|-------------|-------------|-------------|

| 予約済み                | SPI_WDT_CFG |         | 予約済み |         |             |             |             |

| R/W-0x0             |             | R/W-0x0 |      |         |             | R/W-0x0     |             |

| 7                   | 6           | 5       | 4    | 3       | 2           | 1           | 0           |

| SPI_RST_TIMEOUT_CFG |             |         |      | 予約済み    | SPI_CRC_ALG | SPI_SDO_DIS | SPI_ACK_DIS |

| R/W-0xA             |             |         |      | R/W-0x0 | R/W-0x0     | R/W-0x0     | R/W-0x0     |

**表 8-4. SPICTRL レジスタ フィールドの説明**

| ビット   | フィールド               | タイプ | リセット | 説明                                                                                                                                                                                                                                                                |

|-------|---------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-14 | 予約済み                | R/W | 0x0  | 予約済み                                                                                                                                                                                                                                                              |

| 13-12 | SPI_WDT_CFG         | R/W | 0x0  | FAILSAFE 状態に移行するための SPI のウォッチドッグ<br>0x0 = 40ms<br>0x1 = 20ms<br>0x2 = 10ms<br>0x3 = 無効                                                                                                                                                                            |

| 11-8  | 予約済み                | R/W | 0x0  | 予約済み                                                                                                                                                                                                                                                              |

| 7-4   | SPI_RST_TIMEOUT_CFG | R/W | 0xA  | タイムアウト後に SPI をリセットするための SCLK のウォッチドッグ<br>0x0 = 無効<br>0x1 = 500us<br>0x2 = 1ms<br>0x3 = 2ms<br>0x4 = 3ms<br>0x5 = 4ms<br>0x6 = 5ms<br>0x7 = 10ms<br>0x8 = 15ms<br>0x9 = 20ms<br>0xA = 30ms<br>0xB = 40ms<br>0xC = 50ms<br>0xD = 85ms<br>0xE = 100ms<br>0xF = 200ms |

| 3     | 予約済み                | R/W | 0x0  | 予約済み                                                                                                                                                                                                                                                              |

| 2     | SPI_CRC_ALG         | R/W | 0x0  | SPI 通信に使用される CRC アルゴリズム<br>0x0 = CCITT-FALSE を使用<br>0x1 = CRC-16/XMODEM を使用                                                                                                                                                                                       |

| 1     | SPI_SDO_DIS         | R/W | 0x0  | SPI SDO 用ビットを無効化<br>0x0 = CS が Low のとき SDO を駆動<br>0x1 = SDO は常に高インピーダンス                                                                                                                                                                                           |

| 0     | SPI_ACK_DIS         | R/W | 0x0  | STATUS レジスタの SPI 自動応答用ビットを無効化<br>0x0 = 自動応答が有効<br>0x1 = 自動応答が無効                                                                                                                                                                                                   |

### 8.3 CCSICTRL レジスタ (アドレス = 0x2) [リセット = 0x0000]

図 8-3 に CCSICTRL を示し、表 8-5 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

図 8-3. CCSICTRL レジスタ

|         |    |    |    |    |    |                |   |

|---------|----|----|----|----|----|----------------|---|

| 15      | 14 | 13 | 12 | 11 | 10 | 9              | 8 |

| 予約済み    |    |    |    |    |    | CCSI_SS_CLKO   |   |

| R/W-0x0 |    |    |    |    |    | R/W-0x0        |   |

| 7       | 6  | 5  | 4  | 3  | 2  | 1              | 0 |

| 予約済み    |    |    |    |    |    | CCSI_DATA_RATE |   |

| R/W-0x0 |    |    |    |    |    | R/W-0x0        |   |

表 8-5. CCSICTRL レジスタ フィールドの説明

| ビット   | フィールド          | タイプ | リセット | 説明                                                                                                                                                                                                                                                                                                                        |

|-------|----------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-10 | 予約済み           | R/W | 0x0  | 予約済み                                                                                                                                                                                                                                                                                                                      |

| 9-8   | CCSI_SS_CLKO   | R/W | 0x0  | CLK_O ピンの拡散スペクトラム設定<br>0x0 = 無効<br>0x1 = 2%<br>0x2 = 4%<br>0x3 = 8%                                                                                                                                                                                                                                                       |

| 7-4   | 予約済み           | R/W | 0x0  | 予約済み                                                                                                                                                                                                                                                                                                                      |

| 3-0   | CCSI_DATA_RATE | R/W | 0x0  | CCSI のデータレート<br>0x0 = 1Mbit/s<br>0x1 = 1.25Mbit/s<br>0x2 = 1.43Mbit/s<br>0x3 = 1.67Mbit/s<br>0x4 = 2Mbit/s<br>0x5 = 2.22Mbit/s<br>0x6 = 2.5Mbit/s<br>0x7 = 2.86Mbit/s<br>0x8 = 3.33Mbit/s<br>0x9 = 4Mbit/s<br>0xA = 5Mbit/s<br>0xB = 6.67Mbit/s<br>0xC = 8Mbit/s<br>0xD = 10Mbit/s<br>0xE = 13.33Mbit/s<br>0xF = 20Mbit/s |

#### 8.4 TXFFLVL レジスタ (アドレス = 0x3) [リセット = 0x01FF]

図 8-4 に TXFFLVL を示し、表 8-6 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

**図 8-4. TXFFLVL レジスタ**

| 15        | 14 | 13 | 12      | 11        | 10 | 9 | 8         |

|-----------|----|----|---------|-----------|----|---|-----------|

| TXFFCLR   |    |    |         | 予約済み      |    |   | TXFFLVL   |

| R/W1C-0x0 |    |    |         | R/W-0x0   |    |   | R/W-0x1FF |

| 7         | 6  | 5  | 4       | 3         | 2  | 1 | 0         |

|           |    |    | TXFFLVL |           |    |   |           |

|           |    |    |         | R/W-0x1FF |    |   |           |

**表 8-6. TXFFLVL レジスタ フィールドの説明**

| ピット  | フィールド   | タイプ   | リセット  | 説明                                                    |

|------|---------|-------|-------|-------------------------------------------------------|

| 15   | TXFFCLR | R/W1C | 0x0   | 送信 FIFO のすべてのデータをクリア                                  |

| 14-9 | 予約済み    | R/W   | 0x0   | 予約済み                                                  |

| 8-0  | TXFFLVL | R/W   | 0x1FF | CCSI で送信を開始するための TX FIFO レベル (ワード単位、0x0 は 1 ワードを意味する) |

## 8.5 RXFFLVL レジスタ (アドレス = 0x4) [リセット = 0x00FF]

図 8-5 に RXFFLVL を示し、表 8-7 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

図 8-5. RXFFLVL レジスタ

| 15        | 14 | 13 | 12       | 11      | 10 | 9 | 8 |

|-----------|----|----|----------|---------|----|---|---|

| RXFFCLR   |    |    |          | 予約済み    |    |   |   |

| R/W1C-0x0 |    |    |          | R/W-0x0 |    |   |   |

| 7         | 6  | 5  | 4        | 3       | 2  | 1 | 0 |

|           |    |    | RXFFLVL  |         |    |   |   |

|           |    |    | R/W-0xFF |         |    |   |   |

表 8-7. RXFFLVL レジスタ フィールドの説明

| ピット  | フィールド   | タイプ   | リセット | 説明                                                            |

|------|---------|-------|------|---------------------------------------------------------------|

| 15   | RXFFCLR | R/W1C | 0x0  | 受信 FIFO のすべてのデータをクリア                                          |

| 14-8 | 予約済み    | R/W   | 0x0  | 予約済み                                                          |

| 7-0  | RXFFLVL | R/W   | 0xFF | ワード数を超えたときに DRDY ピンをプルダウンする RX FIFO レベル<br>(0x0 は 1 ワードを意味する) |

## 8.6 DEVCTRL レジスタ (アドレス = 0x5) [リセット = 0x0000]

図 8-6 に DEVCTRL を示し、表 8-8 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

**図 8-6. DEVCTRL レジスタ**

|         |    |    |    |           |         |   |           |

|---------|----|----|----|-----------|---------|---|-----------|

| 15      | 14 | 13 | 12 | 11        | 10      | 9 | 8         |

| 予約済み    |    |    |    |           |         |   |           |

| R/W-0x0 |    |    |    |           |         |   |           |

| 7       | 6  | 5  | 4  | 3         | 2       | 1 | 0         |

| 予約済み    |    |    |    | FORCE_FS  | 予約済み    |   | EXIT_FS   |

| R/W-0x0 |    |    |    | R/W1C-0x0 | R/W-0x0 |   | R/W1C-0x0 |

**表 8-8. DEVCTRL レジスタ フィールドの説明**

| ピット  | フィールド    | タイプ   | リセット | 説明                                                                                        |

|------|----------|-------|------|-------------------------------------------------------------------------------------------|

| 15-3 | 予約済み     | R/W   | 0x0  | 予約済み                                                                                      |

| 2    | FORCE_FS | R/W1C | 0x0  | デバイスの NORMAL 状態から FAILSAFE 状態への切り替え<br>0x0 = 現在の状態を維持する。<br>0x1 = デバイスを FAILSAFE 状態に移行する。 |

| 1    | 予約済み     | R/W   | 0x0  | 予約済み                                                                                      |

| 0    | EXIT_FS  | R/W1C | 0x0  | デバイスを FAILSAFE モードから NORMAL に移行する                                                         |

## 8.7 DIAGMASK レジスタ (アドレス = 0x6) [リセット = 0x0000]

図 8-7 に DIAGMASK を示し、表 8-9 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

図 8-7. DIAGMASK レジスタ

| 15      | 14 | 13 | 12 | 11                  | 10      | 9             | 8             |

|---------|----|----|----|---------------------|---------|---------------|---------------|

| 予約済み    |    |    |    | MASK_CCSI_CHECK_BIT | 予約済み    | MASK_CCSI_CRC | MASK_CCSI_SIN |

| R/W-0x0 |    |    |    | R/W-0x0             | R/W-0x0 | R/W-0x0       | R/W-0x0       |

| 7       | 6  | 5  | 4  | 3                   | 2       | 1             | 0             |

| 予約済み    |    |    |    |                     |         | MASK_SPI_CRC  |               |

|         |    |    |    | R/W-0x0             |         |               | R/W-0x0       |

表 8-9. DIAGMASK レジスタ フィールドの説明

| ビット   | フィールド               | タイプ | リセット | 説明                                                                                          |

|-------|---------------------|-----|------|---------------------------------------------------------------------------------------------|

| 15-12 | 予約済み                | R/W | 0x0  | 予約済み                                                                                        |

| 11    | MASK_CCSI_CHECK_BIT | R/W | 0x0  | CCSI 検査ビット フォルトをマスクして FLAG_ERR を設定し、FAULT ピンをプルダウンする。<br>0x0 = フォルト通知が有効<br>0x1 = フォルト通知が無効 |

| 10    | 予約済み                | R/W | 0x0  | 予約済み                                                                                        |

| 9     | MASK_CCSI_CRC       | R/W | 0x0  | CCSI CRC フォルトをマスクして FLAG_ERR を設定し、FAULT ピンをプルダウンする。<br>0x0 = フォルト通知が有効<br>0x1 = フォルト通知が無効   |

| 8     | MASK_CCSI_SIN       | R/W | 0x0  | CCSI SIN 固着フォルトをマスクして FLAG_ERR を設定し、FAULT ピンをプルダウンする。<br>0x0 = フォルト通知が有効<br>0x1 = フォルト通知が無効 |

| 7-1   | 予約済み                | R/W | 0x0  | 予約済み                                                                                        |

| 0     | MASK_SPI_CRC        | R/W | 0x0  | SPI CRC フォルトをマスクして FLAG_ERR を設定し、FAULT ピンをプルダウンする。<br>0x0 = フォルト通知が有効<br>0x1 = フォルト通知が無効    |

## 8.8 STATUS レジスタ (アドレス = 0x7) [リセット = 0x0403]

図 8-8 に STATUS を示し、表 8-10 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

**図 8-8. ステータス レジスタ**

| 15                 | 14           | 13        | 12           | 11        | 10       | 9         | 8        |

|--------------------|--------------|-----------|--------------|-----------|----------|-----------|----------|

| CLR_FLAG           | FLAG_CCSI    | 予約済み      | FLAG_TXFF    | FLAG_RXFF | DRDYST   | FLAG_SRST | FLAG_SPI |

| R/W1C-0x0          | R-0x0        | R-0x0     | R-0x0        | R-0x0     | R-0x1    | R-0x0     | R-0x0    |

| 7                  | 6            | 5         | 4            | 3         | 2        | 1         | 0        |

| FLAG_SPI_REG_WRITE | FLAG_SPI_CRC | DEV_STATE | FLAG OTP_CRC | FLAG_OSC  | FLAG_POR | FLAG_ERR  |          |

| R-0x0              | R-0x0        | R-0x0     | R-0x0        | R-0x0     | R-0x1    | R-0x1     |          |

**表 8-10. STATUS レジスタ フィールドの説明**

| ビット | フィールド              | タイプ   | リセット | 説明                                                                                                                               |

|-----|--------------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------|

| 15  | CLR_FLAG           | R/W1C | 0x0  | すべてのフラグをクリアする書き込み<br>0x0 = フラグをクリアしない。<br>0x1 = すべてのフラグをクリアする。                                                                   |

| 14  | FLAG_CCSI          | R     | 0x0  | CCSI エラー フラグ<br>0x0 = デバイス エラーは検出されなかった。<br>0x1 = デバイス エラーが検出された。詳細については IFST を参照。                                               |

| 13  | 予約済み               | R     | 0x0  | 予約済み                                                                                                                             |

| 12  | FLAG_TXFF          | R     | 0x0  | 送信 FIFO エラーの検出<br>0x0 = 送信 FIFO エラーは検出されなかった。<br>0x1 = 送信 FIFO エラーが検出された。詳細については TXFFST を参照。                                     |

| 11  | FLAG_RXFF          | R     | 0x0  | 受信 FIFO エラーの検出<br>0x0 = 受信 FIFO エラーは検出されなかった。<br>0x1 = 受信 FIFO エラーが検出された。詳細については RXFFST を参照。                                     |

| 10  | DRDYST             | R     | 0x1  | DRDY ピンのステータス<br>0x0 = DRDY ピンはロジック Low<br>0x1 = DRDY ピンはロジック High                                                               |

| 9   | FLAG_SRST          | R     | 0x0  | 正常に実行されなかった SOFTRESET。CCSI の送信中は SOFTRESET は実行できない。<br>0x0 = SOFTRESET エラーは検出されなかった。<br>0x1 = SOFTRESET エラーが検出された。               |

| 8   | FLAG_SPI           | R     | 0x0  | SPI エラー フラグ<br>0x0 = デバイス エラーは検出されなかった。<br>0x1 = デバイス エラーが検出された。詳細については IFST を参照。                                                |

| 7   | FLAG_SPI_REG_WRITE | R     | 0x0  | 正常に実行されなかった SPI レジスタ書き込みコマンド。CCSI の送受信中は CCSICTRL の書き込みはできない。<br>0x0 = SPI レジスタ書き込みエラーは検出されなかった。<br>0x1 = SPI レジスタ書き込みエラーが検出された。 |

| 6   | FLAG_SPI_CRC       | R     | 0x0  | SPI 通信の CRC エラーが検出された。<br>0x0 = CRC エラーは検出されなかった。<br>0x1 = CRC エラーが検出された。                                                        |

| 5-4 | DEV_STATE          | R     | 0x0  | デバイスの状態<br>0x0 = デバイスは NORMAL 状態<br>0x1 = デバイスは INIT 状態<br>0x2 = デバイスは INIT 状態<br>0x3 = デバイスは FAILSAFE 状態                        |

表 8-10. STATUS レジスタ フィールドの説明 (続き)

| ピット | フィールド        | タイプ | リセット | 説明                                                                                   |

|-----|--------------|-----|------|--------------------------------------------------------------------------------------|

| 3   | FLAG OTP_CRC | R   | 0x0  | OTP CRC エラーの検出<br>0x0 = OTP CRC エラーは検出されなかった。<br>0x1 = OTP CRC エラーが検出された。            |

| 2   | FLAG_OSC     | R   | 0x0  | 発振器の範囲外検出<br>0x0 = 発振器エラーは検出されなかった。<br>0x1 = 発振器エラーが検出された。                           |

| 1   | FLAG_POR     | R   | 0x1  | パワーオンリセットフラグ<br>0x0 = POR はトリガされていない。<br>0x1 = デバイスが POR をトリガした。                     |

| 0   | FLAG_ERR     | R   | 0x1  | グローバル エラー フラグ。これは FAULT ピンの反転ステータス。<br>0x0 = エラーは検出されなかった。<br>0x1 = 1 つ以上のエラーが検出された。 |

## 8.9 IFST レジスタ (アドレス = 0x8) [リセット = 0x0000]

図 8-9 に IFST を示し、表 8-11 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

図 8-9. IFST レジスタ

| 15    | 14 | 13                      | 12                  | 11    | 10 | 9             | 8                |

|-------|----|-------------------------|---------------------|-------|----|---------------|------------------|

| 予約済み  |    |                         |                     |       |    | FLAG_SPI_CS   | FLAG_SPI_TIMEOUT |

| R-0x0 |    |                         |                     |       |    | R-0x0         | R-0x0            |

| 7     | 6  | 5                       | 4                   | 3     | 2  | 1             | 0                |

| 予約済み  |    | FLAG_CCSI_CMD_QUEUE_OVF | FLAG_CCSI_CHECK_BIT | 予約済み  |    | FLAG_CCSI_CRC | FLAG_CCSI_SIN    |

| R-0x0 |    | R-0x0                   | R-0x0               | R-0x0 |    | R-0x0         | R-0x0            |

表 8-11. IFST レジスタ フィールドの説明

| ビット   | フィールド                   | タイプ | リセット | 説明                                                                                                                   |

|-------|-------------------------|-----|------|----------------------------------------------------------------------------------------------------------------------|

| 15-10 | 予約済み                    | R   | 0x0  | 予約済み                                                                                                                 |

| 9     | FLAG_SPI_CS             | R   | 0x0  | コマンド受信の途中で SPI チップ セレクト ビンが High になった。<br>0x0 = CS エラーは検出されなかった。<br>0x1 = CS エラーが検出された。                              |

| 8     | FLAG_SPI_TIMEOUT        | R   | 0x0  | SPI タイムアウト エラーが検出された。<br>SPI_RST_TIMEOUT_CFG が有効なときのみ設定される。<br>0x0 = SPI タイムアウトが検出されなかった。<br>0x1 = SPI タイムアウトが検出された。 |

| 7-5   | 予約済み                    | R   | 0x0  | 予約済み                                                                                                                 |

| 4     | FLAG_CCSI_CMD_QUEUE_OVF | R   | 0x0  | CCSI コマンド キュー オーバーフロー エラーが検出された。<br>0x0 = オーバーフロー エラーは検出されなかった。<br>0x1 = オーバーフロー エラーが検出された。                          |

| 3     | FLAG_CCSI_CHECK_BIT     | R   | 0x0  | CCSI 受信データに CCSI 検査ビット エラーが検出された。<br>0x0 = 検査ビット エラーは検出されなかった。<br>0x1 = 検査ビット エラーが検出された。                             |

| 2     | 予約済み                    | R   | 0x0  | 予約済み                                                                                                                 |

| 1     | FLAG_CCSI_CRC           | R   | 0x0  | CCSI データに CRC エラーが検出された。<br>0x0 = CRC エラーは検出されなかった。<br>0x1 = CRC エラーが検出された。                                          |

| 0     | FLAG_CCSI_SIN           | R   | 0x0  | SIN のトグル欠落<br>0x0 = SIN のトグル欠落エラーは検出されなかった。<br>0x1 = SIN のトグル欠落エラーが検出された。                                            |

## 8.10 TXFFST レジスタ (アドレス = 0x9) [リセット = 0x0000]

図 8-10 に TXFFST を示し、表 8-12 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

図 8-10. TXFFST レジスタ

| 15           | 14           | 13           | 12     | 11    | 10 | 9 | 8      |

|--------------|--------------|--------------|--------|-------|----|---|--------|

| FLAG_TXFFOVF | FLAG_TXFFUVF | FLAG_TXFFSED |        | 予約済み  |    |   | TXFFST |

| R-0x0        | R-0x0        | R-0x0        |        | R-0x0 |    |   | R-0x0  |

| 7            | 6            | 5            | 4      | 3     | 2  | 1 | 0      |

|              |              |              | TXFFST |       |    |   |        |

|              |              |              |        | R-0x0 |    |   |        |

表 8-12. TXFFST レジスタ フィールドの説明

| ビット  | フィールド        | タイプ | リセット | 説明                                                                                                                                                                          |

|------|--------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | FLAG_TXFFOVF | R   | 0x0  | 送信 FIFO のオーバーフロー エラー                                                                                                                                                        |

| 14   | FLAG_TXFFUVF | R   | 0x0  | 送信 FIFO のアンダーフロー エラー                                                                                                                                                        |

| 13   | FLAG_TXFFSED | R   | 0x0  | 送信 FIFO のシングル エラー検出                                                                                                                                                         |

| 12-9 | 予約済み         | R   | 0x0  | 予約済み                                                                                                                                                                        |

| 8-0  | TXFFST       | R   | 0x0  | TX FIFO ステータス<br>0x0 = 送信 FIFO が空<br>0x1 = 送信 FIFO に 1 ワードある。<br>0x2 = 送信 FIFO に 2 ワードある。<br>...<br>0x1FE = 送信 FIFO に 510 ワードある。<br>0x1FF = 送信 FIFO に 511 ワードまたは 512 ワードある。 |

### 8.11 RXFFST レジスタ (アドレス = 0xA) [リセット = 0x0000]

図 8-11 に RXFFST を示し、表 8-13 でその説明を示します。

デバイスのレジスタの概要表 を参照してください。

**図 8-11. RXFFST レジスタ**

| 15           | 14           | 13           | 12 | 11    | 10 | 9 | 8 |

|--------------|--------------|--------------|----|-------|----|---|---|

| FLAG_RXFFOVF | FLAG_RXFFUVF | FLAG_RXFFSED |    | 予約済み  |    |   |   |

| R-0x0        | R-0x0        | R-0x0        |    | R-0x0 |    |   |   |

| 7            | 6            | 5            | 4  | 3     | 2  | 1 | 0 |

| RXFFST       |              |              |    |       |    |   |   |

| R-0x0        |              |              |    |       |    |   |   |