# LMX1860-SEP 宇宙グレード、低ノイズ、高周波 JESD204B/C バッファ / マルチ プライヤ/デバイダ

### 1 特長

- VID #V62/24630

- 総照射線量耐性: 30krad (ELDRS フリー)

- シングル イベント ラッチアップ (SEL) 耐性: 最大 43MeV-cm<sup>2</sup>/mg

- シングル イベント機能割り込み (SEFI) 耐性: 最大 43MeV-cm<sup>2</sup>/mg

- 300MHz から 15GHz までの周波数に対応するクロッ ク バッファ

- 超低ノイズ

- ノイズ フロア (6GHz 出力):-159dBc/Hz

- 6GHz 出力時の 36fs の追加ジッタ (100Hz~f<sub>CLK</sub>)

- 5fs の追加ジッタ (100Hz~100MHz)

- 対応する SYSREF 出力を備えた 4 つの高周波クロッ

- 共有分周比は 1 (バイパス)、2、3、4、5、および 7

- 共有プログラマブル乗算器 x2、x3、および x4

- SPI なしでデバイスを構成するためのピン モード オプ ションをサポート

- LOGICLK 出力、対応する SYSREF 出力付き

- 個別の分周バンク上

- 1、2、4 プリデバイダ

- 1 (バイパス)、2、…、1023 ポストディバイダ

- 8 つのプログラム可能な出力電力レベル

- 同期された SYSREF クロック出力

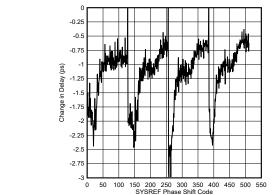

- 508 遅延ステップの調整は、12.8GHz でそれぞれ 2.5ps 未満

- ジェネレータモードとリピータモード

- SYSREFREQ ピンのウィンドウ処理機能によりタイ ミングを最適化します

- すべてのデバイダおよび複数のデバイスに対する SYNC 機能

- 2.5V の動作電圧

- -55°C~125°Cの動作温度

- 高信頼性

- 管理されたベースライン

- 単一のアセンブリ/テスト施設

- 単一の製造施設

- 長期にわたる製品ライフ サイクル

- 製品のトレーサビリティ

## 2 アプリケーション

- レーダー画像処理ペイロード

- 通信ペイロード

- コマンドとデータの処理

- データコンバータのクロック供給

- クロック分配 / 乗算 / 除算

## 3 説明

LMX1860-SEP は、高周波、超低ジッタ、SYSREF 出力 を備えたバッファ、デバイダ、マルチプレクサです。このデ バイスは、超低ノイズのリファレンス クロック ソースと組み 合わせると、特にサンプリングが 3GHz を超える場合に、 データコンバータのクロック供給用の模範的な設計になり ます。4 つの各高周波クロック出力と、追加の LOGICLK 出力は、SYSREF 出力クロック信号と組み合わせられま す。JESD インターフェイスの SYSREF 信号は、内部で 生成するか、入力として渡されて、デバイスクロックに再度 クロックされます。このデバイスは、SYSREF 出力をディセ ーブルにすることで、マルチチャネル、低スキュー、超低ノ イズの局所発振器信号を複数のミキサに分配できます。

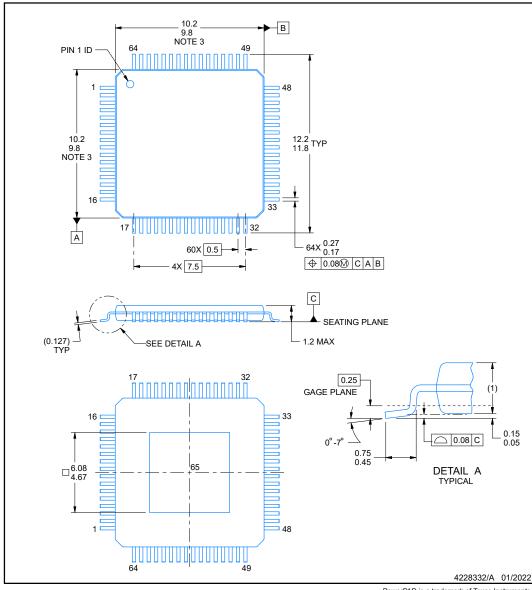

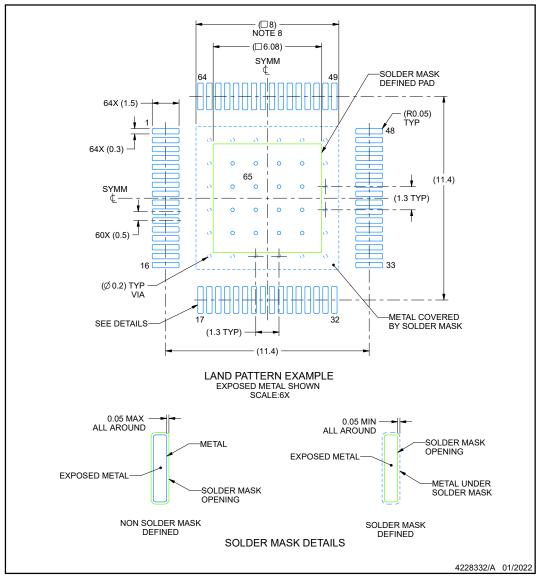

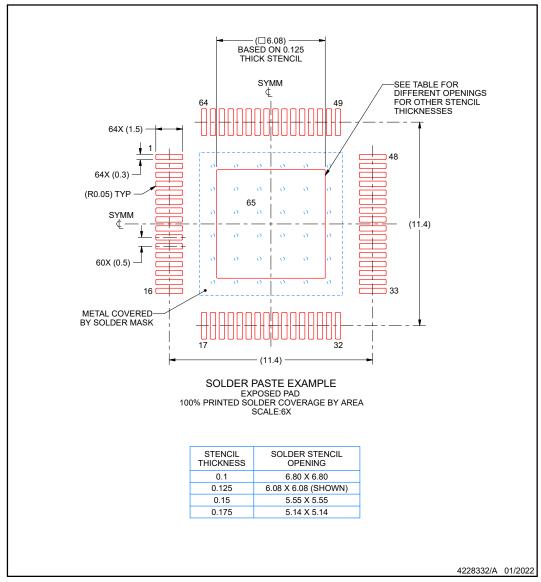

#### パッケージ情報

| 部品番号               | タイプ              | パッケージ (1)  | パッケージ サイズ<br>(2) |

|--------------------|------------------|------------|------------------|

| LMX1860PA<br>P/EM  | エンジニアリング<br>サンプル | PAP        | 10.00mm ×        |

| LMX1860MP<br>APSEP | 放射線耐性強化<br>の保証   | (HTQFP、64) | 10.00mm          |

- 供給されているすべてのパッケージについては、セクション 10 を

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

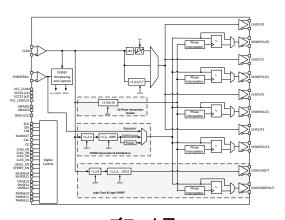

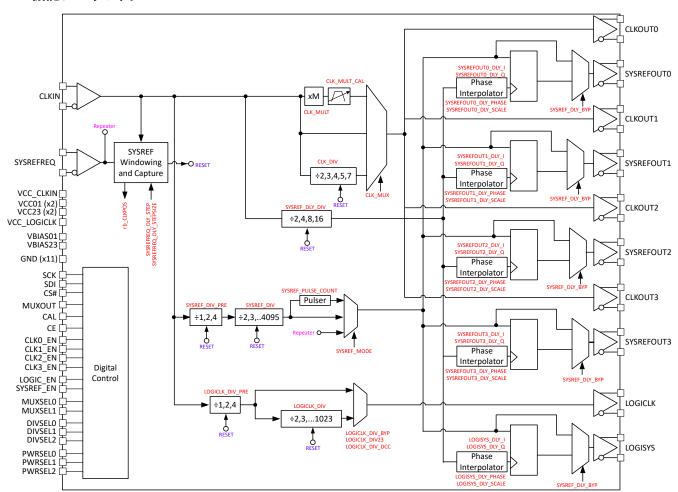

ブロック図

## 目次

| 1 特長 1        | 6.4 デバイスの機能モード構成       | 29 |

|---------------|------------------------|----|

| 2 アプリケーション1   | 7 アプリケーションと実装          | 32 |

| 3 説明 1        | 7.1 アプリケーション情報         | 32 |

| 4 ピン構成および機能3  | 7.2 代表的なアプリケーション       | 35 |

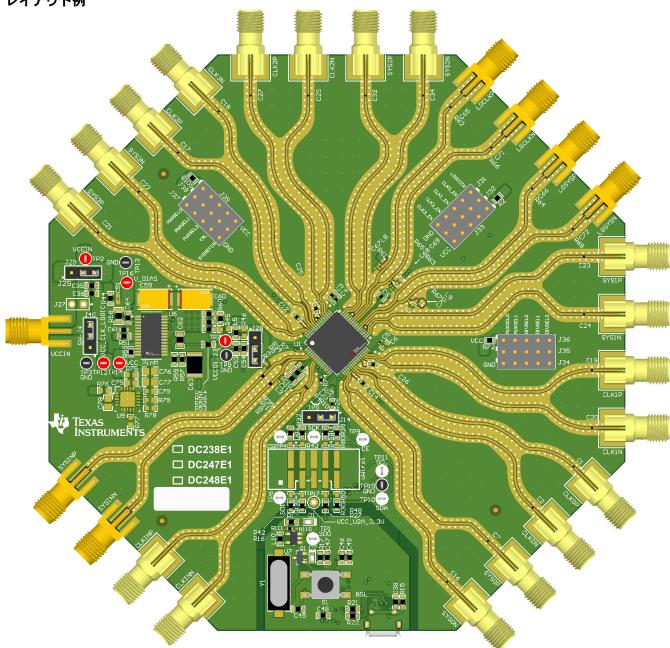

| 5 仕様7         | 7.3 レイアウト              |    |

| 5.1 絶対最大定格7   | 7.4 電源に関する推奨事項         |    |

| 5.2 ESD 定格    | 7.5 レジスタ マップ           | 41 |

| 5.3 推奨動作条件7   | 8 デバイスおよびドキュメントのサポート   | 65 |

| 5.4 熱に関する情報7  | 8.1 デバイス サポート          | 65 |

| 5.5 電気的特性8    | 8.2ドキュメントのサポート         | 65 |

| 5.6 タイミング要件10 | 8.3ドキュメントの更新通知を受け取る方法  | 65 |

| 5.7 タイミング図10  | 8.4 サポート・リソース          | 65 |

| 5.8 代表的特性11   | 8.5 商標                 | 65 |

| 6 詳細説明15      | 8.6 静電気放電に関する注意事項      | 65 |

| 6.1 概要15      | 8.7 用語集                | 65 |

| 6.2 機能ブロック図16 | 9 改訂履歴                 | 65 |

| 6.3 機能説明17    | 10 メカニカル、パッケージ、および注文情報 | 66 |

|               |                        |    |

English Data Sheet: SNAS883

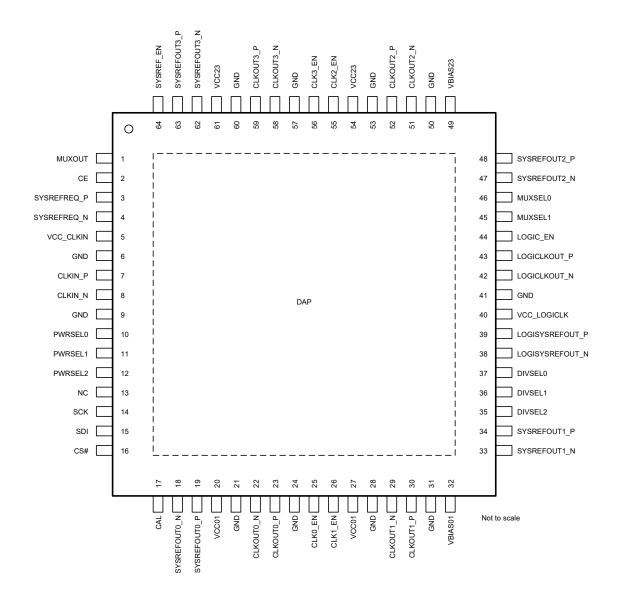

## 4 ピン構成および機能

図 4-1. PAP0064E パッケージ 64 ピン HTQFP 上面図

表 4-1. ピンの機能

| 番号 | 名称          | タイプ <sup>(1)</sup> | 説明                                                                                                                  |  |  |

|----|-------------|--------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| 1  | MUXOUT      | 0                  | 多重化ピンのシリアル データ読み戻し (SDO) および乗算器のロック ステータス。                                                                          |  |  |

| 2  | CE          | I                  | チップのイネーブル                                                                                                           |  |  |

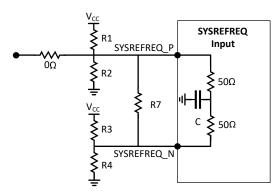

| 3  | SYSREFREQ_P |                    | JESD204B/C サポート用の差動 SYSREF 要求入力。内部の 50Ω AC 結合を内部同相電圧または GND へのコンデンサ。1.2V ~ 2V の同相電圧を直接受け入れる AC および DC 結合をサポートしています。 |  |  |

## 表 4-1. ピンの機能 (続き)

| 番号 | 名称           | タイプ <sup>(1)</sup> | 説明                                                                                                                                 |  |  |

|----|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4  | SYSREFREQ_N  | ı                  | JESD204B/C サポート用の差動 SYSREF 要求入力。内部の $50\Omega$ AC 結合を内部同相電圧または GND へのコンデンサ。 $1.2V\sim 2V$ の同相電圧を直接受け入れる AC および DC 結合をサポートしています。    |  |  |

| 5  | VCC_CLKIN    | PWR                | 2.5V 電源に接続します。より大きいコンデンサ (通常は 1µF や 10µF) と並列にピンの近くにシャント RF 広帯域コンデンサ (通常は 0.1µF 以下) を配置することを推奨します。大容量コンデンサは、ピンから離れた場所に配置できます。      |  |  |

| 6  | GND          | GND                | これらのピンはグランドに接続します                                                                                                                  |  |  |

| 7  | CLKIN_P      |                    | 差動リファレンス入力クロック。内部で 50Ω 終端。入力周波数に適したコンデンサ                                                                                           |  |  |

| 8  | CLKIN_N      | I                  | (通常は 0.1μF 以下) と AC 結合します。シングルエンドを使用する場合は、未使用のピンをグランドに AC 結合した 50Ω の抵抗で終端します。                                                      |  |  |

| 9  | GND          | GND                | これらのピンはグランドに接続します                                                                                                                  |  |  |

| 10 | PWRSEL0      | I                  | ピンモードで出力電力レベルを選択します。                                                                                                               |  |  |

| 11 | PWRSEL1      | I                  | ピンモードで出力電力レベルを選択します。                                                                                                               |  |  |

| 12 | PWRSEL2      | I                  | ピンモードで出力電力レベルを選択します。                                                                                                               |  |  |

| 13 | NC           | NC                 | 接続なし (1kΩ 抵抗でグランドに接続)                                                                                                              |  |  |

| 14 | SCK          | I                  | SPI クロック。高インピーダンスの CMOS 入力。最大 3.3V を受け入れます。                                                                                        |  |  |

| 15 | SDI          | I                  | SPI データ入力。高インピーダンスの CMOS 入力。最大 3.3V を受け入れます。                                                                                       |  |  |

| 16 | CS#          | 1                  | SPI チップ セレクト。 高インピーダンスの CMOS 入力。 最大 3.3V を受け入れます。                                                                                  |  |  |

| 17 | CAL          | I                  | 乗算器 モードで使用されるキャリブレーション ピン。                                                                                                         |  |  |

| 18 | SYSREFOUT0_N | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。0.6V ~ 2V の グラマブル同相電圧で AC および DC 結合をサポートします。 JESD204B/C サポート向けの差動 SYSREF CML 出力ペア、0.6V ~ 2V の |  |  |

| 19 | SYSREFOUT0_P | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。0.6V ~ 2V のグラマブル同相電圧で AC および DC 結合をサポートします。                                                   |  |  |

| 20 | VCC01        | PWR                | 2.5V 電源に接続します。より大きいコンデンサ (通常は 1µF や 10µF)と並列にピンの近くにシャント RF 広帯域コンデンサ (通常は 0.1µF 以下)を配置することを推奨します。大容量コンデンサは、ピンから少し離れた場所に配置できます。      |  |  |

| 21 | GND          | GND                | これらのピンはグランドに接続します                                                                                                                  |  |  |

| 22 | CLKOUT0_N    | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                       |  |  |

| 23 | CLKOUT0_P    | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                       |  |  |

| 24 | GND          | GND                | これらのピンはグランドに接続します                                                                                                                  |  |  |

| 25 | CLK0_EN      | I                  | 個別出力チャネルを有効化/無効化します。                                                                                                               |  |  |

| 26 | CLK1_EN      | I                  | 個別出力チャネルを有効化/無効化します。                                                                                                               |  |  |

| 27 | VCC01        | PWR                | 2.5V 電源に接続します。より大きいコンデンサ (通常は 1µF や 10µF)と並列にピンの近くにシャント RF 広帯域コンデンサ (通常は 0.1µF 以下)を配置することを推奨します。大容量コンデンサは、ピンから少し離れた場所に配置できます。      |  |  |

| 28 | GND          | GND                | これらのピンはグランドに接続します                                                                                                                  |  |  |

| 29 | CLKOUT1_N    | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                       |  |  |

| 30 | CLKOUT1_P    | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                       |  |  |

| 31 | GND          | GND                | これらのピンはグランドに接続します                                                                                                                  |  |  |

| 32 | VBIAS01      | ВҮР                | このピンは 10nF のコンデンサで GND にバイパスすることで、乗算器 モードで最適なノイズ性能を実現します。                                                                          |  |  |

| 33 | SYSREFOUT1_N | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。 $0.6V\sim 2V$ のプログラマブル同相電圧で AC および DC 結合をサポートします。                                            |  |  |

## 表 4-1. ピンの機能 (続き)

| 番号 | 名称              | タイプ <sup>(1)</sup> | 説明                                                                                                                               |

|----|-----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 34 | SYSREFOUT1_P    | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。 $0.6V\sim 2V$ のプログラマブル同相電圧で AC および DC 結合をサポートします。                                          |

| 35 | DIVSEL2         | ı                  | ピン構成では、分周器または乗算器 モードでの分周器の値または乗算器の値を 選択します。                                                                                      |

| 36 | DIVSEL1         | I                  | ピン構成では、分周器または乗算器 モードでの分周器の値または乗算器の値を 選択します。                                                                                      |

| 37 | DIVSEL0         | I                  | ピン構成では、分周器または乗算器 モードでの分周器の値または乗算器の値を 選択します。                                                                                      |

| 38 | LOGISYSREFOUT_N | 0                  | 差動クロック出力ペア。 CML または LVDS 形式を選択可能。 プログラム可能な同相電圧。                                                                                  |

| 39 | LOGISYSREFOUT_P | 0                  | 差動クロック出力ペア。 CML または LVDS 形式を選択可能。 プログラム可能な同相電圧。                                                                                  |

| 40 | VCC_LOGICLK     | PWR                | 2.5V 電源に接続します。より大きいコンデンサ (通常は 1µF や 10µF) と並列にピンの近くにシャント RF 広帯域コンデンサ (通常は 0.1µF 以下) を配置することを推奨します。 大容量コンデンサは、ピンから少し離れた場所に配置できます。 |

| 41 | GND             | GND                | これらのピンはグランドに接続します                                                                                                                |

| 42 | LOGICLKOUT_N    | 0                  | 差動クロック出力ペア。 CML または LVDS 形式を選択可能。 プログラム可能な同相電圧。                                                                                  |

| 43 | LOGICLKOUT_P    | 0                  | 差動クロック出力ペア。 CML または LVDS 形式を選択可能。 プログラム可能な同相電圧。                                                                                  |

| 44 | LOGIC_EN        | I                  | ピンモードでの論理チャネルのイネーブル/ディスエーブル。                                                                                                     |

| 45 | MUXSEL1         | I                  | ピンモード構成で動作モードバッファ、分周器、または乗算器を選択します。                                                                                              |

| 46 | MUXSEL0         | I                  | ピン モード構成で動作モード バッファ、分周器、または乗算器を選択します。                                                                                            |

| 47 | SYSREFOUT2_N    | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。 $0.6V\sim 2V$ のプログラマブル同相電圧で AC および DC 結合をサポートします。                                          |

| 48 | SYSREFOUT2_P    | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。 $0.6V\sim 2V$ のプログラマブル同相電圧で AC および DC 結合をサポートします。                                          |

| 49 | VBIAS23         | ВҮР                | 乗算器 モードで最適なノイズ性能を得るため、10μF および 0.1μF コンデンサを使用してこのピンを GND にバイパスします。                                                               |

| 50 | GND             | GND                | これらのピンはグランドに接続します                                                                                                                |

| 51 | CLKOUT2_N       | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                     |

| 52 | CLKOUT2_P       | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                     |

| 53 | GND             | GND                | これらのピンはグランドに接続します                                                                                                                |

| 54 | VCC23           | PWR                | 2.5V 電源に接続します。より大きいコンデンサ (通常は 1µF や 10µF) と並列にピンの近くにシャント RF 広帯域コンデンサ (通常は 0.1µF 以下) を配置することを推奨します。 大容量コンデンサは、ピンから少し離れた場所に配置できます。 |

| 55 | CLK2_EN         | I                  | 個別出力チャネルを有効化/無効化します。                                                                                                             |

| 56 | CLK3_EN         | I                  | 個別出力チャネルを有効化/無効化します。                                                                                                             |

| 57 | GND             | GND                | これらのピンはグランドに接続します                                                                                                                |

| 58 | CLKOUT3_N       | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                     |

| 59 | CLKOUT3_P       | 0                  | 差動クロック出力ペア。各ピンはオープン コレクタ出力で、50Ω 抵抗を内部的に内蔵し、出力スイングをプログラム可能です。 AC カップリングが必要です。                                                     |

| 60 | GND             | GND                | これらのピンはグランドに接続します                                                                                                                |

| 61 | VCC23           | PWR                | 2.5V 電源に接続します。より大きいコンデンサ (通常は 1µF や 10µF) と並列にピンの近くにシャント RF 広帯域コンデンサ (通常は 0.1µF 以下) を配置することを推奨します。大容量コンデンサは、ピンから少し離れた場所に配置できます。  |

## 表 4-1. ピンの機能 (続き)

| ZV : II ZV IV MAID (INC.) |              |                    |                                                                                         |  |  |

|---------------------------|--------------|--------------------|-----------------------------------------------------------------------------------------|--|--|

| 番号                        | 名称           | タイプ <sup>(1)</sup> | 説明                                                                                      |  |  |

| 62                        | SYSREFOUT3_N | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。 $0.6V\sim 2V$ のプログラマブル同相電圧で AC および DC 結合をサポートします。 |  |  |

| 63                        | SYSREFOUT3_P | 0                  | JESD204B/C サポート向けの差動 SYSREF CML 出力ペア。 $0.6V\sim 2V$ のプログラマブル同相電圧で AC および DC 結合をサポートします。 |  |  |

| 64                        | SYSREF_EN    | I                  | ピン モード構成で、SYSREF セクションをイネーブル/ディセーブルします。                                                 |  |  |

| DAP                       | DAP          | GND                | パッドを接地します。                                                                              |  |  |

(1) I =入力、O =出力、GND =グランド、PWR =電源、BYP =バイパス

## 5 仕様

## 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) (1)

|                  |                       | 最小値  | 最大値                   | 単位  |

|------------------|-----------------------|------|-----------------------|-----|

| V <sub>CC</sub>  | 電源電圧                  | -0.3 | 2.75                  | V   |

| V <sub>IN</sub>  | DC 入力電圧 (SCK、SDI、CSB) | GND  | 3.6                   | V   |

| V <sub>IN</sub>  | DC 入力電圧範囲 (SYSREFREQ) | GND  | V <sub>CC</sub> + 0.3 | V   |

| V <sub>IN</sub>  | AC 入力電圧 (CLKIN)       |      | 2.1                   | Vpp |

| TJ               | 接合部温度                 |      | 150                   | °C  |

| T <sub>stg</sub> | 保存温度                  | -65  | 150                   | °C  |

<sup>(1) 「</sup>絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

## 5.2 ESD 定格

|        |      |                                                                  | 値     | 単位       |

|--------|------|------------------------------------------------------------------|-------|----------|

| V      | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | ±2500 | V        |

| V(ESD) |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±250  | <b>V</b> |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                 |       | 最小值 | 公称值 | 最大値 | 単位 |

|-----------------|-------|-----|-----|-----|----|

| V <sub>CC</sub> | 電源電圧  | 2.4 | 2.5 | 2.6 | V  |

| T <sub>C</sub>  | ケース温度 | -55 |     | 125 | °C |

## 5.4 熱に関する情報

| <b>≠</b> 2 □          | (c(top) 接合部からケース (上面) への熱抵抗 接合部から基板への熱抵抗 接合部から上面への特性パラメータ 接合部から基板への特性パラメータ | PAP (HTQFP) | 単位   |

|-----------------------|----------------------------------------------------------------------------|-------------|------|

| 記号                    | サーマルマナイッグい                                                                 | 64 ピン       | 単位   |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗                                                               | 21.7        | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗                                                        | 9.1         | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗                                                               | 7.3         | °C/W |

| $\Psi_{JT}$           | 接合部から上面への特性パラメータ                                                           | 0.1         | °C/W |

| $\Psi_{JB}$           | 接合部から基板への特性パラメータ                                                           | 7.2         | °C/W |

| R <sub>0JC(bot)</sub> | 接合部からケース (底面) への熱抵抗                                                        | 0.6         | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

2.4V  $\leq$  V<sub>CC</sub>  $\leq$  2.6V、-55°C  $\leq$  T<sub>C</sub>  $\leq$  +125°C。標準値は V<sub>CC</sub> = 2.5V、25°C でのものです (特に記述のない限り)。

|                       | パラメータ                | テス                           | 卜条件                                                        | 最小値  | 標準値  | 最大値                                                                                      | 単位  |  |

|-----------------------|----------------------|------------------------------|------------------------------------------------------------|------|------|------------------------------------------------------------------------------------------|-----|--|

| 消費電流                  |                      |                              |                                                            |      |      |                                                                                          |     |  |

|                       |                      | 電源投入、すべての出                   | 力と SYSREF がオン                                              |      | 1050 |                                                                                          |     |  |

| I <sub>CC</sub>       | 消費電流 <sup>(1)</sup>  | 電源オン、すべての出<br>SYSREF がオフ     | 電源オン、すべての出力がオン、すべての<br>SYSREF がオフ                          |      | 600  |                                                                                          | mA  |  |

|                       |                      | 電源オン、すべての出力と SYSREF はオフ      |                                                            |      | 265  |                                                                                          |     |  |

|                       |                      | 電源オフ(2)                      |                                                            |      | 11   |                                                                                          |     |  |

| SYSREF                | 1                    | ,                            |                                                            |      |      | '                                                                                        |     |  |

| £                     | CVCDEE II + EI II ** | ジェネレータ モード                   |                                                            |      |      | 200                                                                                      | MHz |  |

| f <sub>SYSREF</sub>   | SYSREF 出力周波数         | リピータ モード                     |                                                            |      |      | 100                                                                                      | MHz |  |

| Δt                    | SYSREF 遅延ステップ サイズ    | f <sub>CLKIN</sub> = 12.8GHz |                                                            |      | 3    |                                                                                          | ps  |  |

|                       |                      | SYSREFOUT                    |                                                            |      | 45   |                                                                                          | ps  |  |

| t <sub>RISE</sub>     | 立ち上がり時間 (20% から 80%) | LOGISYSREFOUT                | CML                                                        |      | 120  |                                                                                          | ps  |  |

|                       |                      | EGGIOTOIXEI GGT              | LVDS                                                       |      | 120  |                                                                                          | ps  |  |

|                       |                      | SYSREFOUT                    |                                                            |      | 45   |                                                                                          | ps  |  |

| t <sub>FALL</sub>     | 立ち下がり時間 (20% ~ 80%)  | LOGISYSREFOUT                | CML                                                        |      | 120  | 200<br>100<br>100<br>2<br>2<br>2<br>2<br>2<br>2<br>15 <sup>(3)</sup><br>10<br>6.4<br>800 | ps  |  |

|                       |                      |                              | LVDS                                                       |      | 120  |                                                                                          | ps  |  |

|                       |                      | SYSREFOUT                    |                                                            |      | 0.85 |                                                                                          | Vpp |  |

| $V_{OD}$              | 差動出力電圧               | LOGISYSREFOUT                | CML                                                        |      | 0.4  |                                                                                          | Vp  |  |

|                       |                      |                              | LVDS                                                       |      | 0.4  |                                                                                          | Vp  |  |

| V <sub>SYSREFCM</sub> | 同相電圧                 | SYSREFOUT                    | CML<br>SYSREFOUTx_PW<br>R = 4<br>100Ω 差動負荷                 |      | 0.8  |                                                                                          | V   |  |

| SYSREFRE              | <br>:Q ピン            | I                            |                                                            |      |      |                                                                                          |     |  |

| V <sub>SYSREFIN</sub> | 電圧入力範囲               | AC 差動電圧                      |                                                            | 0.8  |      | 2                                                                                        | Vpp |  |

| V <sub>CM</sub>       | 入力同相モード              | 差動 100Ω 終端、DC 外部に設定          | 結合                                                         | 1.2  | 1.3  | 2                                                                                        | V   |  |

| クロック入力                |                      |                              |                                                            |      |      |                                                                                          |     |  |

| f <sub>IN</sub>       | 入力周波数                | バッファモードのみ                    |                                                            | 0.3  |      | 15 <sup>(3)</sup>                                                                        | GHz |  |

| P <sub>IN</sub> /     | 入力電力                 | CLKIN_P または CLK<br>ド電源       | IN_N でのシングルエン                                              | 0    |      | 10                                                                                       | dBm |  |

| クロック出力                |                      |                              |                                                            |      |      | <u>"</u>                                                                                 |     |  |

| f <sub>OUT</sub>      | 出力周波数                | 2 分周                         |                                                            | 0.15 |      | 6.4                                                                                      |     |  |

| f <sub>OUT</sub>      | 出力周波数                | バッファモード                      |                                                            | 0.3  |      | 15 <sup>(3)</sup>                                                                        | GHz |  |

| f <sub>OUT</sub>      | 出力周波数                | x2、x3、x4                     |                                                            | 3.2  |      | 6.4                                                                                      |     |  |

| f <sub>OUT</sub>      | 出力周波数                | LOGICLK 出力                   |                                                            | 1    |      | 800                                                                                      | MHz |  |

| t <sub>CAL</sub>      | キャリブレーション時間          | 乗算器のキャリブレーミョン時間              | f <sub>IN</sub> = 3.2GHz, x2<br>f <sub>SMCLK</sub> = 28MHz |      | 750  |                                                                                          | μs  |  |

|                       |                      |                              | f <sub>CLKLOUT</sub> = 6GHz<br>OUTx_PWR = 7                |      | 6    |                                                                                          |     |  |

| Роит                  | 出力電力                 | シングル エンド                     | f <sub>CLKLOUT</sub> = 12.8GHz<br>OUTx_PWR = 7             |      | 0    |                                                                                          | dBm |  |

|                       |                      |                              | f <sub>CLKLOUT</sub> = 15GHz<br>OUTx_PWR = 7               |      | -3   |                                                                                          |     |  |

| t <sub>RISE</sub>     | 立ち上がり時間 (20% から 80%) | f <sub>CLKOUT</sub> = 300MHz | •                                                          |      | 45   |                                                                                          | ps  |  |

2.4V  $\leq$  V<sub>CC</sub>  $\leq$  2.6V、-55°C  $\leq$  T<sub>C</sub>  $\leq$  +125°C。標準値は V<sub>CC</sub> = 2.5V、25°Cでのものです (特に記述のない限り)。

|                       | パラメータ                                 | テス                                             | 条件                                         | 最小値       | 標準値      | 最大値     | 単位      |  |

|-----------------------|---------------------------------------|------------------------------------------------|--------------------------------------------|-----------|----------|---------|---------|--|

| t <sub>FALL</sub>     | 立ち下がり時間 (20% ~ 80%)                   | f <sub>CLKOUT</sub> = 300MHz                   |                                            |           | 45       |         | ps      |  |

| t <sub>MUTE</sub>     | 出力ミュート時間                              | OE ピンの立ち下がりエッジ                                 |                                            |           |          | 30      | μs      |  |

| t <sub>UNMUTE</sub>   | 出力のミュート解除時間                           | OE ピンの立ち上がりエ<br>ッジ                             |                                            |           |          | 30      | μs      |  |

| 伝搬遅延と                 | スキュー                                  |                                                |                                            |           |          |         |         |  |

| t <sub>SKEW</sub>     | 複数の出力間のスキューの大きさ                       | T <sub>A</sub> = -55°C ~ +125°C                |                                            |           | 2.5      | 10      | ps      |  |

| Δt <sub>DLY</sub> /ΔT | 温度による伝搬遅延の変動                          | バッファ モード                                       |                                            | 0.02      | 0.06     | 0.1     | ps/C    |  |

|                       |                                       | バッファ モード                                       |                                            |           | 180      |         |         |  |

| t <sub>DLY</sub>      | 伝搬遅延                                  | デバイダ モード                                       | T <sub>A</sub> = 25°C                      |           | 182      |         | ps      |  |

|                       |                                       | 乗算器 モード                                        | 乗算器 モード                                    |           | 185      |         |         |  |

| ノイズ、ジッ                |                                       |                                                |                                            |           |          |         |         |  |

|                       |                                       |                                                | バッファ モード                                   |           | 5        |         |         |  |

|                       | /// / / / / / / / / / / / / / / / / / | 付加ジッタ。12kHz ~                                  | X2 乗算器                                     |           | 16       |         |         |  |

| J <sub>CKx</sub>      | 付加ジッタ                                 | 100Mhz の積分帯域<br>幅。                             | X3 乗算器                                     |           | 21       |         | fs, rms |  |

|                       |                                       | тро                                            | X4 乗算器                                     |           | 26       |         |         |  |

| フリッカー                 | 1/f フリッカー ノイズ                         | スルーレート > 8V/ns、 $f_{CLK} = 6GHz$               | バッファ モード                                   |           | -155     |         | dBc/Hz  |  |

|                       |                                       |                                                | バッファ モード                                   |           | -159     |         |         |  |

| NFL                   | ノイズ フロア                               | f <sub>OUT</sub> = 6GHz, f <sub>Offset</sub> = | 2 分周                                       |           | -158.5   |         | dBc/Hz  |  |

|                       |                                       | 100MHz                                         | 乗算器 (x2、x3、x4)                             |           | -159.5   |         |         |  |

|                       | 117707                                | LOGICLIK III//                                 | CML                                        |           | -150.5   | 4D -    | 15 // 1 |  |

|                       | ノイズ フロア                               |                                                | LVDS                                       |           | -151.5   |         | dBc/Hz  |  |

|                       |                                       | f <sub>OUT</sub> = 6GHz (差動)、/                 | ベッファ モード                                   |           | -25      |         |         |  |

| H2                    | 2 次高調波                                | f <sub>OUT</sub> = 6GHz (シングル                  | f <sub>OUT</sub> = 6GHz (シングルエンド)、バッファ モード |           | -13      |         | dBc     |  |

|                       |                                       | f <sub>OUT</sub> = 6GHz、シングル                   | ・エンド、2 分周                                  |           | -16      |         |         |  |

| H1/2                  |                                       |                                                | x2 (f <sub>SPUR</sub> = 3GHz)              |           | -40      |         | dDo     |  |

| H1/3                  | 入力クロックのリーク スプリアス                      | F <sub>OUT</sub> = 6GHz (シング<br>ルエンド)          | x3 (f <sub>SPUR</sub> = 2GHz)              |           | -50      |         | dBc     |  |

| H1/4                  |                                       | ,,,,,                                          | x4 (f <sub>SPUR</sub> = 1.5GHz)            |           | -54      |         | dBc     |  |

| I <sub>SPUR</sub>     | LOGICLK から CLKOUT へ                   | f <sub>SPUR</sub> = 300MHz (差動                 | 1)                                         |           | -70      |         | dBc     |  |

| デジタル イ                | ンターフェイス (SCK、SDI、CS#、MU)              | KOUT, CLKx_EN, MUXSE                           | Lx, PWRSELx, DIVSE                         | Lx, LOGIC | _EN、SYSF | REF_EN、 | CAL、CE) |  |

|                       | High レベル入力電圧                          | SCK, SDI, CS#                                  |                                            | 1.4       |          | 3.3     | V       |  |

| V <sub>IH</sub>       | High レベル入力電圧                          | CLKx_EN、MUXSELx<br>DIVSELx、LOGIC_EN<br>CAL、CE  |                                            | 1.4       |          | 3.3     | ٧       |  |

|                       | Low レベル入力電圧                           | SCK, SDI, CS#                                  |                                            | 0         |          | 0.4     | V       |  |

| V <sub>IL</sub>       | Low レベル入力電圧                           | CLKx_EN、MUXSELx<br>DIVSELx、LOGIC_EN<br>CAL、CE  |                                            | 0         |          | 0.4     | ٧       |  |

|                       | High レベル入力電流                          | SCK, SDI, CS#                                  |                                            | -42       | ,        | 42      | μΑ      |  |

| I <sub>IH</sub>       | High レベル入力電流                          | CLKx_EN、MUXSELx<br>DIVSELx、LOGIC_EN<br>CAL、CE  |                                            | -42       |          | 42      | μΑ      |  |

2.4V ≦ V<sub>CC</sub> ≦ 2.6V、-55°C ≦ T<sub>C</sub> ≦ +125°C。標準値は V<sub>CC</sub> = 2.5V、25°Cでのものです (特に記述のない限り)。

|                 | パラメータ テスト条件  |                                                             | 最小値                   | 標準値 最大値 | 単位   |    |

|-----------------|--------------|-------------------------------------------------------------|-----------------------|---------|------|----|

|                 | Low レベル入力電流  | SCK, SDI, CS#                                               |                       | -25     | 25   | μΑ |

| I <sub>IL</sub> | Low レベル入力電流  | CLKx_EN、MUXSELx、PWRSELx、 DIVSELx、LOGIC_EN、SYSREF_EN、 CAL、CE |                       | -25     | 25   | μΑ |

| Vall            | High レベル出力電圧 | - MUXOUT                                                    | I <sub>OH</sub> = 5mA | 1.4     | 2.2  | V  |

| V <sub>OH</sub> | High レベル出力電圧 | I <sub>OH</sub> = 0.1mA                                     |                       | 2.2     | 2.5  | V  |

| V <sub>OL</sub> | Low レベル出力電圧  | MUXOUT                                                      | I <sub>OL</sub> = 5mA |         | 0.45 | V  |

- (1) 特に記述のない限り、f<sub>CLKIN</sub> = 6GHz、CLK\_MUX = バッファ、すべてのクロックは OUTx\_PWR = 7、SYSREFREQ\_MODE = 1 でオンになります

- (2) パワーダウン モードの場合。

- (3) 最大 12.8Ghz の周波数で動作する同期、デバイダ、SYSREF、SYSREF のウィンドウ処理をサポート。

## 5.6 タイミング要件

|                  |                         | 最小値 | 公称值 | 最大値 | 単位  |

|------------------|-------------------------|-----|-----|-----|-----|

| タイミング            | 要件                      |     |     |     |     |

| f <sub>SPI</sub> | SPI 読み出し書き込み速度          |     |     | 2   | MHz |

| t <sub>CE</sub>  | クロックからイネーブル low 時間      | 20  |     |     | ns  |

| t <sub>CS</sub>  | クロックからデータまでの待機時間        | 20  |     |     | ns  |

| t <sub>CH</sub>  | クロックからデータまでのホールド時間      | 20  |     |     | ns  |

| t <sub>CWH</sub> | クロック パルス幅 high          | 100 |     |     | ns  |

| t <sub>CWL</sub> | クロック パルス幅 low           | 100 |     |     | ns  |

| t <sub>CES</sub> | クロック セットアップ時間をイネーブル     | 20  |     |     | ns  |

| t <sub>EWH</sub> | パルス幅 high をイネーブル        | 50  |     |     | ns  |

| t <sub>CD</sub>  | 立ち下がりクロックエッジからデータ待ち時間まで | 0   |     | 100 | ns  |

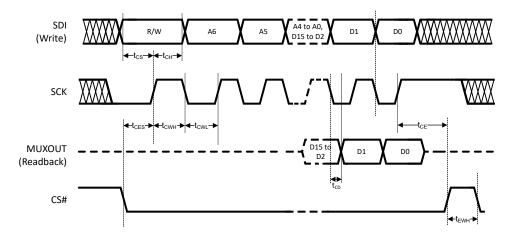

## 5.7 タイミング図

図 5-1. シリアル データ入力のタイミング図

SPI に書き込む場合、他にも次のような考慮事項があります。

- R/W ビットを 0 に設定する必要があります。

- SDI ピンのデータは、SCK ピンの各立ち上がりエッジでシフトレジスタに取り込まれます。

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

- データをクロックするには、CS# を low に保持する必要があります。CS# が high に保持されている場合、デバイスは クロックパルスを無視します。

- このデバイスの推奨 SPI 設定は、CPOL = 0 および CPHA = 0 です。

- SCK ラインと SDI ラインがデバイス間で共有されている場合は、クロック供給しないデバイスについて CS# ラインを high に保持することを推奨します。

SPI 読み戻しには、他にもいくつかの考慮事項があります。

- R/W ビットを 1 に設定する必要があります。

- MUXOUT ピンは、トランザクションのアドレス部分にとって常に low です。

- MUXOUT のデータは、SCK の立ち下がりエッジでクロック アウトします。 つまり、 読み戻しデータは、クロックの立ち下がりエッジ後に MUXOUT ピン t<sub>CD</sub> で利用可能です。

- SDI ラインの遷移のデータ部分は、常に無視されます。

- MUXOUT ピンは、読み戻しトランザクションの完了後に自動的に tri 状態になることはありません。SPI バスの読み戻しピンを他のデバイスと共有する場合は、デバイスからのすべての読み戻しトランザクションが完了した後で MUXOUT\_EN を 0 に設定して、手動で MUXOUT ピンを tri 状態にし、他のデバイスが読み戻しラインを制御できるようにします。

- R/W ビットについても、読み戻される値は必ずしも書き込まれる値ではなく、プログラムされた値やピンの状態など他の要因が考慮された内部デバイス状態です。

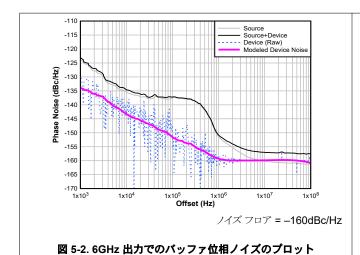

### 5.8 代表的特性

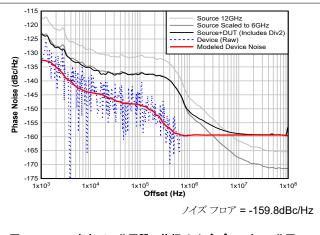

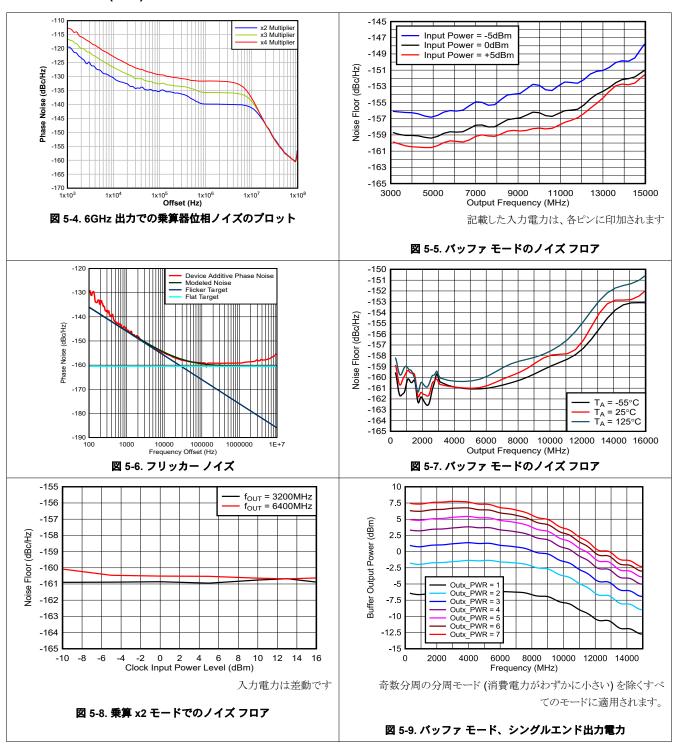

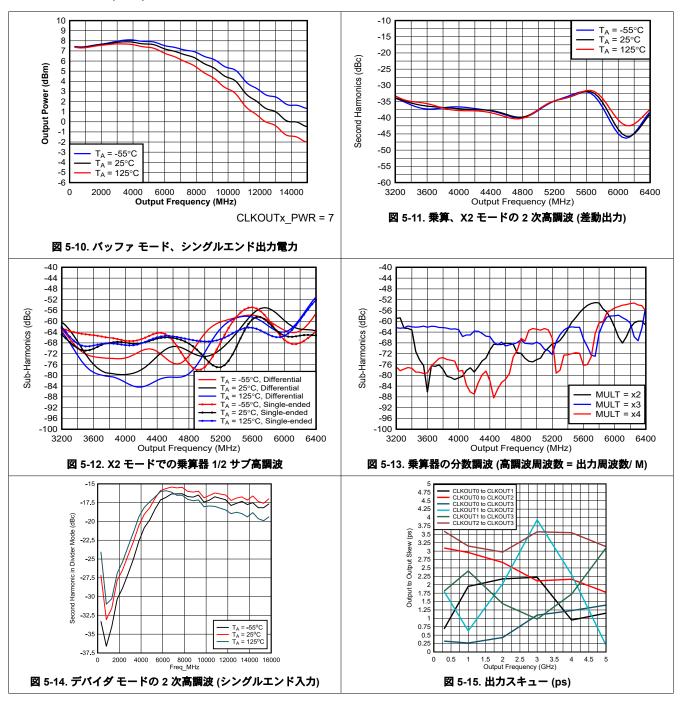

それ以外の場合は、次の条件が想定されます。 温度 = 25°C、 $V_{CC}$  = 2.5V、OUTx\_PWR = 5、CLKIN は各ピンで 8dBm で差動駆動。 使用する信号源は、 超低ノイズオプション B711 の Rohde & Schwarz® SMA100B です。

図 5-3. 6GHz 出力での分周器の位相ノイズ プロット (2 分周)

## 5.8 代表的特性 (続き)

## 5.8 代表的特性 (続き)

English Data Sheet: SNAS883

## 5.8 代表的特性 (続き)

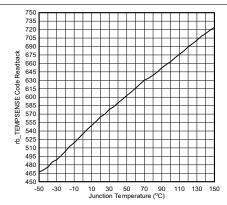

図 5-16. SYSREF デルタ遅延とコードとの関係

接合部温度 = 周囲温度になるようにパワーダウン モードで測定。

#### 図 5-17. 温度センサの読み戻し

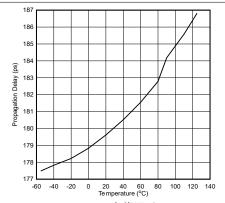

図 5-18. 伝搬遅延

図 5-19. チャネル イネーブル設定時間

図 5-20. チャネル ディセーブル設定時間

## 6 詳細説明

#### 6.1 概要

このデバイスには 4 つのメインクロック出力と、別の LOGICLK 出力があります。メイン クロック出力は、すべて同じ周波数です。この周波数は、入力クロックと同じ、分周、または乗算を行うことができます。これらのクロック出力には、プログラム可能な電力レベルがあります。LOGICLK の出力周波数は独立しており、通常は他の 4 つのメイン クロックよりも低い周波数で、プログラマブル出力形式 (CML および LVDS)と電力レベルを備えています。

SYSRE は、SYSREFREQ ピンから入力を繰り返すか、内部で生成できます。SYSREF の内部ウィンドウ機能により、デバイスの内部タイミングを調整して、CLKIN 入力を基準とした SYSREFREQ 入力のセットアップ時間とホールド時間を最適化できます。この機能では、SYSREF エッジと次の立ち上がりクロック エッジとの間の遅延が整合していると仮定しています。5 つの出力にはそれぞれ、個別の遅延とプログラム可能な同相を持つ対応する SYSREF 出力があります。LOGISYSREF 出力の場合、出力フォーマットは CML または LVDS としてプログラムできます。

#### 6.1.1 分周器および乗数の範囲

MAIN および LOGICLK 出力を入力クロックの分周値にできる分周器があります。メイン クロック出力には乗算器もあります。これに加えて、デバイダはジェネレータ モードの SYSREF 生成および遅延ブロックの生成に使用されます。

| 女 0-1. 月内前のより未致り毛田 |               |             |               |                                  |  |  |  |

|--------------------|---------------|-------------|---------------|----------------------------------|--|--|--|

| カテゴリ               |               |             | RANGE         | 備考                               |  |  |  |

|                    | ,             | <b>バッファ</b> |               |                                  |  |  |  |

| メイン クロック           | デバイダ          |             | 2、3、4、5 および7  | 奇数分周 (1 を除く) のデューティ サイクルは 50% です |  |  |  |

|                    | 乗算器           |             | 2, 3, 4       |                                  |  |  |  |

| LOGICLK            | 分周            | プレデバイド      | 1, 2, 4       | TotalDivide = PreDivide×Divide   |  |  |  |

| LOGICER            |               | 分周          | 1, 2, 3, 1023 | 奇数分周 (1 を除く) のデューティ サイクルは 50% です |  |  |  |

|                    | 周波数生成の        | プレデバイド      | 1.2、4         | SYSREF 生成のためにクロックを分周します。         |  |  |  |

| SYSREF             | 分周            | 分周          | 2, 3, 4, 4095 | TotalDivide = PreDivide          |  |  |  |

|                    | 遅延生成のた<br>め分周 | 分周          | 2, 4, 8, 16   | この分周値は位相補間用で、入力周波数に応じて設定されます。    |  |  |  |

表 6-1. 分周器および乗数の範囲

## 6.2 機能ブロック図

図 6-1. 機能ブロック図

#### 6.3 機能説明

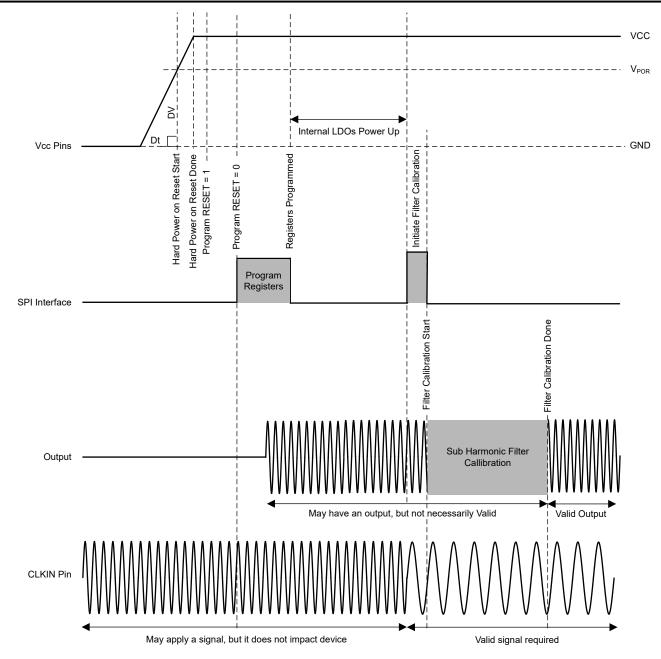

#### 6.3.1 パワーオン リセット

デバイスの電源を投入すると、パワーオン リセット (POR) により、すべてのレジスタがデフォルト状態にリセットされ、すべてのステート マシンおよび分周器がリセットされます。パワーオン RESET 状態では、すべての SYSREF 出力がディセーブルされ、すべての分周器がバイパスされて、デバイスは 4 出力バッファとして動作します。他のレジスタをプログラムする前に、電源レールの約 100μs の後を待ち、このリセットが完了したことを確認します。デバイス クロックが存在しないときにパワーオン リセットが発生した場合、デバイスは適切に機能しますが、入力クロックが挿入された後に電流が変化します。

SPI バス に RESET = 1 を書き込み、ソフトウェア パワーオン リセットを実行することも可能であり、一般的に適切な方法です。ユーザーが他のレジスタに書き込むと、リセット ビットは自動的にクリアされます。 SPI バスを使用すると、これらの状態を目的の設定にオーバーライドできます。

デバイスには自動パワー オンリセットがありますが、特に強い入力クロック信号が存在する場合には、さまざまな電源ピンのさまざまなランプ レートの影響を受ける可能性があります。そのため、POR 後にソフトウェア リセットを行うことを推奨します。これは、RESET = 1 をプログラムすることで実行できます。リセット ビットは、他のレジスタをプログラムすることでも、0 にリセットすることでもクリアできます。許容される最大 SPI バス速度でも、ソフトウェア リセット イベントは次の SPI 書き込みより前に必ず完了します。

#### 6.3.2 温度センサ

接合部温度は、特性評価などの目的で、または温度に基づいて調整を行うために読み戻すことができます。このような調整には、CLKOUTx\_PWR を調整して出力電力をより安定させたり、温度による伝搬遅延の変化を補償するために外部またはデジタル遅延を使用することが含まれます。

接合部温度は一般に、デバイスの出力と他の機能による消費電力により、周囲温度よりも高くなります。式 1 に、コード読み戻しと接合部温度との関係を示します。

Temperature =

$$0.65 \times \text{Code} - 351$$

(1)

式 1 は、低速、公称、高速コーナー ロット (合計 9 パーツ) から作成された 3 つのデバイスから作成された最適なライン に基づいています。 ベストフィットの線で予測される温度からの実際の温度のワーストケースの変動は 13°C で、20 のコードで機能します。

#### 6.3.3 クロック出力

このデバイスには、共通の周波数を共有する 4 つのメイン出力クロックがあります。この中には、追加の低周波数 LOGICLK 出力は含まれていません。

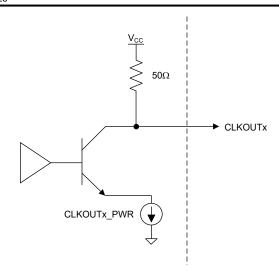

#### 6.3.3.1 クロック出力バッファ

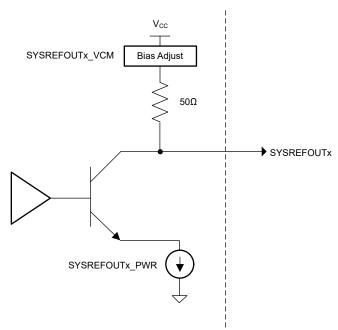

出力バッファの形式は、CMLと同様の、プルアップ抵抗が内蔵されたオープンコレクタです。

図 6-2. CLKOUT 出力パッファ

CLKOUTx\_EN ビットは、出力バッファをイネーブルすることができます。バッファの出力電力は、CLKOUTx\_PWR フィールドで個別に設定可能です。ただし、これらのフィールドは出力バッファのみを制御し、このバッファを駆動する内部チャネルパスは制御しません。パス全体をパワーダウンするには、CHx\_EN ビットをディセーブルにします。

| CHx_EN | 内部チャネル パス | CLKOUTx_EN | CLKOUTx_PWR | 出力バッファ |  |  |

|--------|-----------|------------|-------------|--------|--|--|

| 0      | 電源オフ      | ドントケア      | ドントケア       | 電源オフ   |  |  |

|        |           | 0          | ドントケア       | 電源オフ   |  |  |

|        | 電源オン      | 4          | 0           | 最小     |  |  |

| 1      |           |            | 1           |        |  |  |

|        |           |            |             |        |  |  |

|        |           |            | 7           | 最大     |  |  |

表 6-2. クロック出力電力

#### 6.3.3.2 クロック MUX

4 つのメイン クロックは同じ周波数である必要がありますが、この周波数は、バイパス、乗算、または分周できます。これは、CLK\_MUX ワードによって決定されます。

CLK\_MUX

オプション

サポートされている値

0

バッファ モード

+1 (バイパス)

1

デバイダ モード

+2、3、4、5、および 7

2

乗算器 モード

x2、x3、x4

表 6-3. クロック MUX

#### 6.3.3.3 クロック分周比

CLK\_MUX を 2、3、4、5、7 分周値に設定します。これは CLK\_DIV ワードによって設定されます。クロック分周器を使用しているとき、入力周波数を変更する場合には、CLK\_DIV\_RST ビットを 1 から 0 に切り替えなければなりません。

CLK\_DIV

分周

デューティサイクル

0

予約済み

該当なし

1

2

50%

2

3

33%

3

4

50%

表 6-4. クロック分周比

## 表 6-4. クロック分周比 (続き)

| CLK_DIV | 分周   | デューティ サイクル |

|---------|------|------------|

| 4       | 5    | 40%        |

| 5       | 予約済み | 該当なし       |

| 6       | 7    | 43%        |

| 7       | 予約済み | 該当なし       |

#### 6.3.3.4 クロック 乗算器

#### 6.3.3.4.1 クロック 乗算器に関する一般情報

クロック 乗算器を使用して、入力クロック周波数を x2、x3、または x4 の係数で乗算します。乗算値は、CLK\_MULT フィールドによって設定されます。乗算器は PLL ベースで、内蔵 VCO が含まれるため、乗算器にはステート マシン クロックがあり、キャリブレーションを必要とし、ロック検出機能があります。

#### 6.3.3.4.2 クロック 乗算器のステート マシン クロック

ステート マシン クロック周波数 (f<sub>SMCLK</sub>) は、入力クロック周波数をプログラムされた分周値で分周することで得られます。 乗算器のキャリブレーションとロック検出にも、ステート マシンのクロックも必要です。

#### 6.3.3.4.2.1 ステート マシン クロック

ステートマシンクロックは、すべての動作モード (バッファ、分周器、乗算器) で有効化する必要があります。このデバイスではパワーオンリセットのデフォルト設定値 SMCLK\_EN = 1 があり、このフィールドを他の状態に変更することはできません。SMCLK\_EN の状態はレジスタ R2[5] ビットで読み戻すことができます。本デバイスを適切に構成するには、CLKIN ピンに入力クロックを印加する必要があります。

ステートマシンのクロックは 30MHz 未満にする必要があり、周波数は次のようになります。

$f_{SMCLK} = f_{CLKIN} / (SMCLK_DIV_PRE \times SMCLK_DIV)$

#### 6.3.3.4.3 クロック 乗算器のキャリブレーション

最適な位相ノイズを得るために、乗算器の VCO は周波数範囲をさまざまなバンドおよびコアに分割し、バンドおよびコア ごとに最適化された振幅設定を持っています。このため、最初の使用時、または周波数を変更したときに、キャリブレーション ルーチンを実行して、コア、周波数帯域、および振幅の正しい設定を決定する必要があります。キャリブレーションを 実行するために、RO レジスタを有効な入力信号でプログラムします。信頼性の高い乗算器 キャリブレーションを実現する には、ステート マシンのクロック周波数を SPI 書き込み速度の 2 倍以上、30MHz 以下にする必要があります。 CLK\_MUX モードを変更した場合、または乗算器を初めてキャリブレーションする場合は常に、キャリブレーション時間が 5ms 程度大幅に長くなります。

#### 6.3.3.4.4 クロック 乗算器のロック検出

乗算器のロック検出ステータスは、rb\_LOCK\_DETECT フィールドまたは MUXOUT ピンから読み出すことができます。ロック検出が正しく動作するには、ステートマシンのクロックが動作している必要があります。

#### 6.3.3.4.5 ウォッチドッグ タイマ

ウォッチドッグ機能は、VCO キャリブレーション時の放射線によって、乗算器 モードで VCO キャリブレーションが失敗する場合に使用されます。ウォッチドッグ タイマは VCO キャリブレーション中に動作します。VCO のキャリブレーションが完了する前にこのタイマが実行されると、VCO のキャリブレーションが再開始されます。ウォッチドッグ タイマ動作中は、ステートマシン クロックをイネーブルにする必要があります。

#### 6.3.4 LOGICLK 出力

LOGICLK 出力は、FPGA などの低周波数クロックを使用するデバイスの駆動に使用できます。LOGICLK 出力は、プログラマブルな出力形式と、それに対応する SYSREF 出力を備えています。

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

## 6.3.4.1 LOGICLK 出力フォーマット

LOGICLK 出力フォーマットは、LVDS および CML モードにプログラムできます。フォーマットによっては、同相モードをプログラム可能、または外部部品が必要になる場合があります (表 6-5 を参照)。

| 表 6. | .5 L | OGICI | K のフォー | マット | とプロパティ |

|------|------|-------|--------|-----|--------|

|      |      |       |        |     |        |

| LOGICLKOUT_FMT | フォーマット | 外付け部品必要                            | 出力レベル                       | 同相モード                           |

|----------------|--------|------------------------------------|-----------------------------|---------------------------------|

| 0              | LVDS   | なし                                 | 固定                          | LOGICLKOUT_VCM によりプログラ<br>ム可能です |

| 2              | CML    | プルアップ抵抗<br>50Ω を V <sub>CC</sub> へ | LOGICLKOUT_PWR によりプログラム可能です | プログラム不可                         |

### 6.3.4.2 LOGICLK\_DIV\_PRE および LOGICLK\_DIV デバイダ

LOGICLK の出力には、LOGICLK\_DIV\_PRE デバイダと LOGICLK\_DIV デバイダを使用します。LOGICLK\_DIV\_PRE デバイダは、LOGICLK\_DIV デバイダへの入力が 3.2GHz 以下であることを確認するために、周波数を分周するために必要です。LOGICLK\_DIV が偶数でなく、バイパスされていない場合、デューティ サイクルは50% ではありません。両方の LOGICLK デバイダは SYNC 機能によって同期されるため、複数のデバイス間で同期が可能です。デバイダ LOGICLK\_DIV\_PRE および LOGICLK\_DIV のデフォルト分周値はそれぞれ 4 と 32 です。

表 6-6. N デバイダの最小制限

| f <sub>CLKIN</sub> (MHz)             | LOGICLK_DIV_PRE | LOGICLK_DIV   | 合計分周範囲                                     |

|--------------------------------------|-----------------|---------------|--------------------------------------------|

| f <sub>CLKIN</sub> ≤ 3.2GHz          | ÷1, 2, 4        | ÷1, 2, 3,1023 | [1, 2,1023]<br>[2, 4,2046]<br>[4, 8, 4092] |

| 3.2GHz < f <sub>CLKIN</sub> ≤ 6.4GHz | ÷2, 4           | ÷1, 2, 3,1023 | [4,2046]<br>[4, 8, 4092]                   |

| f <sub>CLKIN</sub> > 6.4GHz          | ÷4              | 1, 2, 3,1023  | [8, 4092]                                  |

#### **6.3.5 SYSREF**

SYSREF により、メインまたは LOGICLK 出力にリクロックされる低周波数の JESD204B/C 準拠信号を生成できます。 CLKOUT 出力と SYSREF 出力の間の遅延は、ソフトウェアで調整できます。 SYSREF 出力は、内部の SYSREF 分周器を使用するジェネレータとして、または SYSREFREQ ピンの信号を複製するリピータとして構成できます。メインクロックと LOGICLK 出力の両方の SYSREF ジェネレータは同じです。

表 6-7. SYSREF モード

| SYSREF_MODE | 説明                                                                                                                                                                                                                                      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | <b>ジェネレータ モード</b> 内部ジェネレータにより、SYSREF パルスの連続ストリームが生成されます。SYSREFREQ ピンまたは SYSREFREQ_FORCE ビットを使用すると、チャネルから SYSREF 分圧器をゲートして、SYSREF 分周器の同期を 中断せずにノイズ絶縁を向上させることができます。SYSREF 出力を出力するには、SYSREFREQ ピンまたは SYSREFREQ_FORCE ビットが high である必要があります。 |

| 1           | <b>パルサ</b> 内部ジェネレータは、SYSREFREQ ピンの立ち上がりエッジの後、または SYSREFREQ_FORCE ビットを 0 から 1 に変更した後 (SYSREFREQ ピンが強制的に low 状態になったと仮定)、SYSREF_PULSE_CNT によって設定される 1 ~ 16 パルスのバーストを生成します。                                                                 |

| 2           | <b>反復モード</b> SYSREFREQ ピンの入力はクロック出力にリクロックされ、SYSREF_DLY_BYP フィールドに従って遅延してから、 SYSREFOUT 出力ピンに送信されます。                                                                                                                                      |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

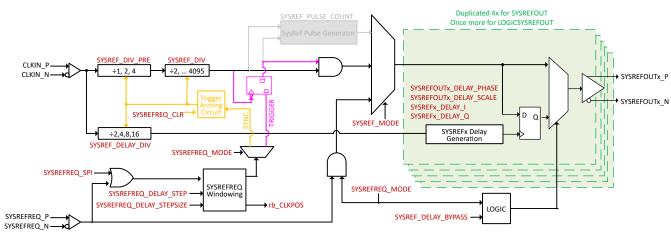

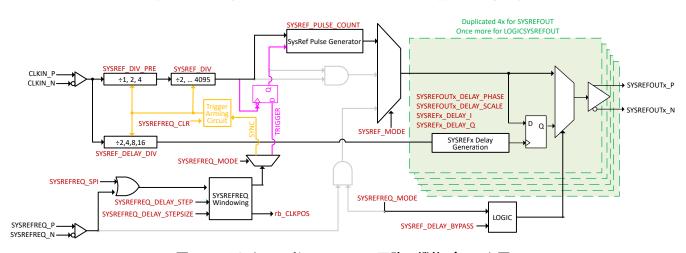

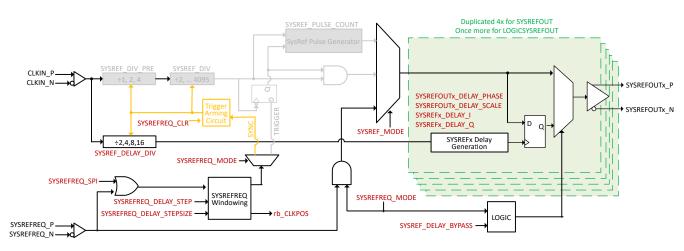

図 6-3. ジェネレータ モードの SYSREF 回路の機能ブロック図

図 6-4. パルサ モードの SYSREF 回路の機能ブロック図

図 6-5. リピータ モードの SYSREF 回路の機能ブロック図

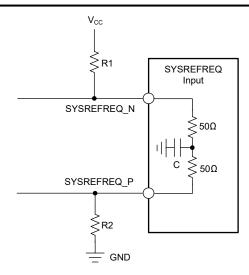

SYSREFREQ\_FORCE ビットによって制御される SYSREF 出力 (パルサ) と SYNC を動作させるには、SYSREFREQ ピンを外部的に low ロジック状態に設定します。 たとえば、SYSREFREQ\_N ピンが SYSREFREQ\_P ピンよりも高いレベル (400mV) であり、入力同相電圧の要件を維持していることを確認します。

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ) を送信

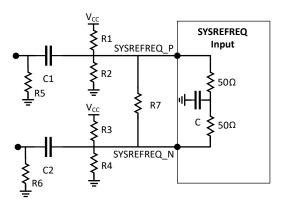

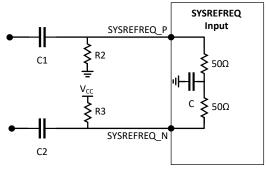

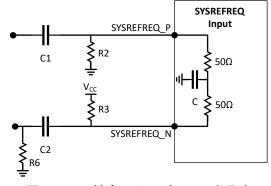

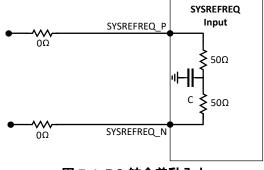

図 6-6. SYSREFREQ ピンのロジック low セットアップ

例えば、VCC が 2.5V のときに最小 400mV の電圧差を維持するには、 $100\Omega$  を流れる電流が 4mA です。この例では、SYSREFREQ\_P ピンを 1.4V DC のままにし、SYSREFREQ\_N ピンで R2 を 350 $\Omega$ 、R1 を 1.8V で 175 $\Omega$  に設定します。

#### 6.3.5.1 SYSREF 出力パッファ

#### 6.3.5.1.1 メイン クロック用の SYSREF 出力パッファ (SYSREFOUT)

クロック出力チャネル内の SYSREF 出力は、クロック出力バッファと同じ出力バッファ構造を持ち、同相電圧を調整する 回路が追加されています。 SYSREF 出力は、SYSREFOUTx\_VCM フィールドで調整できる同相電圧付きの CML 出力と、SYSREFOUTx\_PWR フィールドで設定できる出力レベルです。 このリファレンス デザインにより DC 結合が可能になります。 CLKOUT 出力には調整可能な同相電圧がないため、最適なノイズ性能を得るには AC 結合が必要であることに注意します。

図 6-7. SYSREF 出力バッファ

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

同相電圧と出力電力は相互に関連しており、 $100\Omega$  の差動負荷があり、グランドへの DC パスがないと仮定してシミュレーションできます。同相電圧と出力は、表 6-8 に示すように相互関係しています。長期的な信頼性の場合、 $V_{CM} - V_{OD}/2 \ge 0.5V$  is required.に注意してください

表 6-8. シングルエンド電圧 (V<sub>OD</sub>) と同相電圧 (V<sub>CM</sub>)

| SYSREFOUT_PWR | 確認:<br>V <sub>CM</sub> - V <sub>OL</sub> /2 ≥ 0.5V? | SYSREFOUT_VCM | V <sub>OD</sub> | V <sub>CM</sub> |

|---------------|-----------------------------------------------------|---------------|-----------------|-----------------|

|               |                                                     | 0             | 0.27            | 1.09            |

| 0             |                                                     | 1             | 0.27            | 1.22            |

|               |                                                     | 2             | 0.28            | 1.37            |

|               |                                                     | 3             | 0.28            | 1.54            |

|               |                                                     | 4             | 0.29            | 1.69            |

|               |                                                     | 5             | 0.29            | 1.83            |

|               |                                                     | 6             | 0.29            | 2.00            |

|               | <del>/</del> +±. ₹.√15.4€                           | 7             | 0.29            | 2.16            |

|               | 有効な状態                                               | 0             | 0.32            | 0.79            |

|               |                                                     | 1             | 0.33            | 0.95            |

|               |                                                     | 2             | 0.33            | 1.12            |

| 4             |                                                     | 3             | 0.34            | 1.33            |

| 1             |                                                     | 4             | 0.35            | 1.51            |

|               |                                                     | 5             | 0.35            | 1.69            |

|               |                                                     | 6             | 0.36            | 1.89            |

|               |                                                     | 7             | 0.37            | 2.08            |

|               | for +1 3, 11, 445                                   | 0             | 0.37            | 0.52            |

|               | 無効な状態                                               | 1             | 0.38            | 0.68            |

|               | 有効な状態                                               | 2             | 0.39            | 0.89            |

| 2             |                                                     | 3             | 0.40            | 1.12            |

| 2             |                                                     | 4             | 0.41            | 1.34            |

|               |                                                     | 5             | 0.42            | 1.54            |

|               |                                                     | 6             | 0.43            | 1.78            |

|               |                                                     | 7             | 0.44            | 2.01            |

|               | 無効な状態                                               | 0             | 0.39            | 0.43            |

|               |                                                     | 1             | 0.42            | 0.50            |

|               |                                                     | 2             | 0.45            | 0.66            |

| 2             |                                                     | 3             | 0.46            | 0.93            |

| 3             |                                                     | 4             | 0.47            | 1.17            |

|               | 有効な状態                                               | 5             | 0.48            | 1.41            |

|               |                                                     | 6             | 0.49            | 1.68            |

|               |                                                     | 7             | 0.51            | 1.93            |

|               |                                                     | 0             | 0.40            | 0.40            |

|               | <b>御されよい小台</b>                                      | 1             | 0.43            | 0.44            |

|               | 無効な状態                                               | 2             | 0.48            | 0.52            |

| 4             |                                                     | 3             | 0.51            | 0.73            |

| 4             |                                                     | 4             | 0.52            | 1.00            |

|               | جلتا رازرن المتمث                                   | 5             | 0.54            | 1.27            |

|               | 有効な状態                                               | 6             | 0.55            | 1.57            |

|               |                                                     | 7             | 0.57            | 1.86            |

## 表 6-8. シングルエンド電圧 (Von) と同相電圧 (VcM) (続き)

| SYSREFOUT_PWR | 確認:<br>V <sub>CM</sub> - V <sub>OL</sub> /2 ≥ 0.5V? | SYSREFOUT_VCM | V <sub>OD</sub> | V <sub>CM</sub> |

|---------------|-----------------------------------------------------|---------------|-----------------|-----------------|

|               |                                                     | 0             | 0.40            | 0.38            |

|               | 何さない人                                               | 1             | 0.44            | 0.42            |

|               | 無効な状態                                               | 2             | 0.49            | 0.47            |

| 5             |                                                     | 3             | 0.55            | 0.59            |

| 5             |                                                     | 4             | 0.58            | 0.85            |

|               | 大学が作品                                               | 5             | 0.59            | 1.14            |

|               | 有効な状態                                               | 6             | 0.62            | 1.48            |

|               |                                                     | 7             | 0.63            | 1.79            |

|               | 無効な状態                                               | 0             | 0.40            | 0.36            |

|               |                                                     | 1             | 0.44            | 0.39            |

|               |                                                     | 2             | 0.49            | 0.45            |

| 6             |                                                     | 3             | 0.57            | 0.54            |

| 0             |                                                     | 4             | 0.63            | 0.70            |

|               | 有効な状態                                               | 5             | 0.65            | 1.01            |

|               |                                                     | 6             | 0.67            | 1.38            |

|               |                                                     | 7             | 0.70            | 1.73            |

|               |                                                     | 0             | 0.40            | 0.35            |

|               |                                                     | 1             | 0.44            | 0.38            |

|               | 無効な状態                                               | 2             | 0.50            | 0.43            |

| 7             |                                                     | 3             | 0.58            | 0.51            |

| 1             |                                                     | 4             | 0.66            | 0.62            |

|               |                                                     | 5             | 0.70            | 0.89            |

|               | 有効な状態                                               | 6             | 0.73            | 1.29            |

|               |                                                     | 7             | 0.76            | 1.66            |

#### 6.3.5.1.2 LOGICLK の SYSREF 出力バッファ

LOGISYSREFOUT 出力は、LVDS と CML の 2 つのフォーマットをサポートしています。LOGISYSREFOUT\_EN は出力バッファをイネーブルにし、LOGISYSREF\_FMT はその形式を設定します。LVDS モードにより同相をプログラムでき、CML は外部コンポーネントを必要とし、CML は出力電力をプログラム可能です (表 6-9 を参照)。

#### 表 6-9. LOGISYSREFOUT 出力バッファの構成

| LOGISYSREFOUT_E<br>N | LOGISYSREF_FMT | LOGISYSREF フォーマット | 外部規制が必要です                          | 出力電力                      | 出力同相モード                                                             |  |

|----------------------|----------------|-------------------|------------------------------------|---------------------------|---------------------------------------------------------------------|--|

| 0                    |                |                   | 電源オフ                               |                           |                                                                     |  |

|                      | 0              | LVDS              | なし                                 | 固定                        | LOGISYSREF_VCM<br>でプログラム可能                                          |  |

|                      | 1              | 予約済み              |                                    |                           |                                                                     |  |

| 1                    | 2              | CML               | プルアップ抵抗<br>50Ω を V <sub>CC</sub> へ | LOGISYSREF_PWR<br>で制御されます | LOGISYSREF_VCM<br>は影響を与えません<br>が、この変更は<br>LOGISYSREF_PWR<br>で行われます。 |  |

|                      | 3              |                   | 予約                                 | 済み                        |                                                                     |  |

#### 6.3.5.2 SYSREF の周波数および遅延の生成

ジェネレータ モードでの SYSREF 出力の周波数には、SYSREF\_DIV 分周器の入力が 3.2GHz を超えないことを確認 するために SYSREF DIV PRE デバイダが必要です。

表 6-10. SYSREF\_DIV\_PRE セットアップ

| f <sub>CLKIN</sub>                   | SYSREF_DIV_PRE  | 合計 SYSRE 分周範囲     |

|--------------------------------------|-----------------|-------------------|

| 3.2GHz 以下                            | ÷1、2、または 4      | ÷2, 3, 4,16380    |

| 3.2GHz < f <sub>CLKIN</sub> ≤ 6.4GHz | ÷2 または <b>4</b> | ÷4, 6, 8, 16380   |

| f <sub>CLKIN</sub> > 6.4GHz          | ÷4              | ÷8, 12, 16, 16380 |

遅延の場合、入力クロック周波数を SYSREF\_DLY\_DIV で除算して、 $f_{\text{INTERPOLATOR}}$  が生成されます。表 6-11 に示すように、範囲が制限されています。また、SYSREF\_DLY\_BYP = 0 または 2 (ジェネレータ モードで遅延発生) で、SYSREF\_MODE = 0 または 1 (ジェネレータ モード) の場合、SYSREF 出力周波数は位相補間器周波数の倍数である必要があることにも注意してください。

finterpolator % fsysref = 0.

表 6-11. SYSREF 遅延設定

| f <sub>CLKIN</sub>                    | SYSREF_DLY_DIV | SYSREFx_DLY_SCALE | finterpolator                             |

|---------------------------------------|----------------|-------------------|-------------------------------------------|

| 6.4GHz < f <sub>CLKIN</sub> ≤ 12.8GHz | 16             | 0                 | $0.4 \mathrm{GHz} \sim 0.8 \mathrm{GHz}$  |

| 3.2GHz < f <sub>CLKIN</sub> ≤ 6.4GHz  | 8              | 0                 | $0.4 	ext{GHz} \sim 0.8 	ext{GHz}$        |

| 1.6GHz < f <sub>CLKIN</sub> ≤ 3.2GHz  | 4              | 0                 | 0.4GHz ∼ 0.8GHz                           |

| 0.8GHz < f <sub>CLKIN</sub> ≤ 1.6GHz  | 2              | 0                 | $0.4 	ext{GHz} \sim 0.8 	ext{GHz}$        |

| 0.4GHz < f <sub>CLKIN</sub> ≤ 0.8GHz  | 2              | 1                 | $0.2 	ext{GHz} \sim 0.4 	ext{GHz}$        |

| 0.3GHz < f <sub>CLKIN</sub> ≤ 0.4GHz  | 2              | 2                 | $0.15 \mathrm{GHz} \sim 0.2 \mathrm{GHz}$ |

最大遅延は位相補間法周期と等しく、4×127 = 508 の異なる遅延ステップがあります。式 2 を使用し、各ステップのサイズを計算します。

DelayStepSize =

$$1/(f_{INTERPOLATOR} \times 508)$$

= SYSREF DLY DIV  $/(f_{CLKIN} \times 508)$  (2)

合計遅延を計算するには、式3を使用します。

表 6-12 に、各遅延のステップ数を示します。

表 6-12. ステップ数の計算

| SYSREFx_DLY_PHASE | ステップ番号              |

|-------------------|---------------------|

| 3                 | 127 - SYSREFx_DLY_I |

| 2                 | 254 - SYSREFx_DLY_Q |

| 0                 | 381 - SYSREFx_DLY_I |

| 1                 | 508 - SYSREFx_DLY_Q |

SYSREF\_DLY\_BYP フィールドは、SYSREF 生成出力の遅延パスとリピータ モードのバイパス信号を選択します。 SYSREF\_MODE が連続モードまたはパルサ モードに設定されている場合、SYSREF\_DLY\_BYP をジェネレータ モードに設定することを推奨します。 SYSREF\_MODE がリピータ モードに設定されている場合、SYSREF\_DLY\_BYP をバイパス モードに設定することを推奨します。

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

### 6.3.5.3 SYSREFREQ ピンと SYSREFREQ\_force フィールド

SYSREFREQ ピンは多目的であり、同期、SYSREF 要求、SYSREF ウィンドウ処理に使用できます。これらのピンは DC または AC 結合にすることができ、 $50\Omega$  のシングルエンド終端を個別に持ち、同相信号をプログラム可能です。

これらのピンに加えて、SYSREFREQ\_force フィールドは 1 に設定することで、これらのピンを強制的に High にするのと同じ効果をエミュレートでき、場合によってはハードウェアを簡素化できます。

#### 6.3.5.3.1 SYSREFREQ ピン同相電圧

SYSREFREQ\_P ピンと SYSREFREQ\_N ピンは、AC 結合と DC 結合のどちらでも駆動できます。AC 結合を駆動する場合、SYSREFREQ\_VCM ビットを使用して同相電圧を調整できます。

表 6-13. SYSREFREQ ピン同相電圧

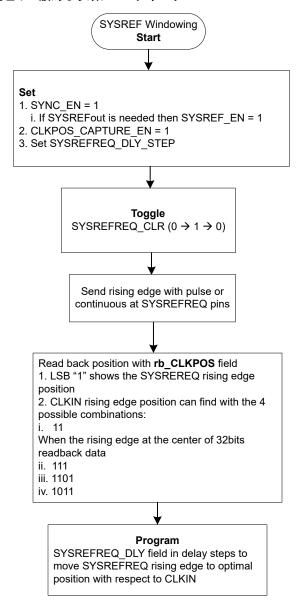

#### 6.3.5.3.2 SYSREFREQ ウィンドウ処理機能

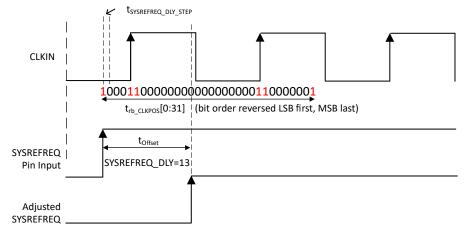

SYSREF ウィンドウ処理を使用して SYSREFREQ ピンと CLKIN ピンの間のタイミングを内部で較正し、セットアップおよびホールドのタイミングを最適化します。また、SYSREF のウィンドウ処理により、SYSREFREQ と CLKIN のパスとの間のミスマッチをトリミングできます。この機能を使用するには、SYSREFREQ の立ち上がりエッジから CLKIN の立ち上がりエッジまでのタイミングが一致している必要があります。SYSREFREQ の立ち上がりエッジから CLKIN の立ち上がりエッジまでのタイミングは、RB\_CLKPOS フィールドで追跡できます。CLKIN ピンの立ち上がりエッジとのタイミングが見つかると、SYSREFREQ の立ち上がりエッジを SYSREFREQ\_DLY フィールドと SYSREF\_DLY\_STEP フィールドを使用して内部で調整し、セットアップおよびホールドタイミングを最適化できます。

図 6-8. SYSREFREQ 内部タイミング調整

Copyright © 2025 Texas Instruments Incorporated

English Data Sheet: SNAS883

## 6.3.5.3.2.1 SYSREF ウィンドウ処理の一般的な手順フローチャート

図 6-9. SYSREF ウィンドウ処理のフローチャート

表 6-14. SYSREFREQ\_DLY\_STEP

| 入力周波数                                | 推奨される<br>SYSREFREQ_DLY_STEP | 遅延 (ps) |

|--------------------------------------|-----------------------------|---------|

| 1.4GHz < f <sub>CLKIN</sub> ≤ 2.7GHz | 0                           | 22.25   |

| 2.4GHz < f <sub>CLKIN</sub> ≤ 4.7GHz | 1                           | 13      |

| 3.1GHz < f <sub>CLKIN</sub> ≤ 5.7GHz | 2                           | 10.5    |

| f <sub>CLKIN</sub> ≥ 4.5GHz          | 3                           | 7.75    |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

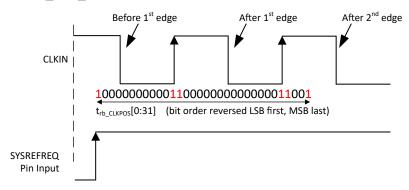

## 6.3.5.3.2.2 遅延生成機能 (リタイム) 付きの SYSREFREQ リピータ モード

遅延イネーブルの SYSREF リピータ モードは、LMX から LMX へのファンアウト デバイスでは、IQ 生成のさまざまなエッジで SYSREFout をリタイミング することで実現できます。このリタイミングは、SYSREF\_DLY\_DIV 値に基づき、CLKIN 入力と SYSREFREQ 入力の間の遅延マージンを持つことができます。

表 6-15 に、SYSREF ウィンドウ処理の合計遅延マージンと各種の SYSREF 設定との関係を示します。

| 次 6-13. グレーグ ヒード (の ) クイムの 3 T S NEF 世 旧 嗣 並 |                    |                |                       |                       |               |               |

|----------------------------------------------|--------------------|----------------|-----------------------|-----------------------|---------------|---------------|

| SYSREF_DLY_DI<br>V                           | 同期中に選択され<br>た位置コード | 最大マージンのエッ<br>ジ | CLKIN サイクルの<br>合計マージン | SYSREFx_DLY_P<br>HASE | SYSREFx_DLY_Q | SYSREFx_DLY_i |

|                                              | 1番目のエッジより前         | I              | -1、+1                 | "11"                  | 0             | 127           |

| /2                                           | 1番目のエッジの後          | QZ             | -1、+1                 | "01"                  | 127           | 0             |

|                                              | 2番目のエッジの後          | lz             | -1、+1                 | "00"                  | 0             | 127           |

|                                              | 1番目のエッジより前         | QZ             | -2、+2                 | "01"                  | 127           | 0             |

| /4                                           | 1番目のエッジの後          | lz             | -2、+2                 | "00"                  | 0             | 127           |

|                                              | 2番目のエッジの後          | Q              | -2、+2                 | "10"                  | 127           | 0             |

|                                              | 1番目のエッジより前         | QZ             | -5、+3                 | "01"                  | 127           | 0             |

| /8                                           | 1番目のエッジの後          | QZ             | -4、+4                 | "01"                  | 127           | 0             |

|                                              | 2番目のエッジの後          | QZ             | -3、+5                 | "01"                  | 127           | 0             |

|                                              | 1番目のエッジより前         | I              | -9、+7                 | "11"                  | 0             | 127           |

| /16                                          | 1番目のエッジの後          | I              | -8、+8                 | "11"                  | 0             | 127           |

|                                              | 2番目のエッジの後          | ı              | -7、+9                 | "11"                  | 0             | 127           |

表 6-15. リピータ モードでのリタイムの SYSREF 位相調整設定

複数のデバイスで SYSREF\_DLY\_DIV を同期するために、初期フェーズで SYSREF ウィンドウ処理を実行するには、リピータ リタイム モードが必要です。ユーザーは後で、同期に選択したエッジの SYSREFx\_DLY\_PHASE、SYSREF\_DLY\_Q、SYSREFx\_DLY\_I の設定を選択できます。

図 6-10. 同期するエッジ位置を選択する SYSREF ウィンドウ処理

この構成では、デバイスを SYSREF\_MODE R17[1:0] の値「2」(リピータ モード) に設定し、SYSREF\_DLY\_BPY R72[1:0] の値「2」(すべてのモードで有効) に設定する必要があります。

Copyright © 2025 Texas Instruments Incorporated

#### 6.3.5.3.2.3 SYSREF ウィンドウ処理に関するその他のガイダンス

- SYSREFREQ ピンは、3/f<sub>CLKIN</sub> + 1.6ns の最小時間にわたって high に保持する必要があり、この時間の後でのみ rb CLKPOS フィールドが有効になります。

- ユーザーが rb\_CLKPOS レジスタから複数の有効な SYSREFREQ\_DLY 値を推測して、セットアップ時間およびホールド時間違反を回避します。温度による変動を最小限に抑えるため、有効な最小の SYSREFREQ\_DLY を選択することをお勧めします。

- SYSREF ウィンドウ処理後にセットアップおよびホールド時間を最適化するようにプログラムされた SYSREFREQ\_DLY によって内部 SYSREFREQ が調整されますが、SYSREFREQ\_DLY は SYSREF ウィンドウ 読み取りコードの移動を示しません。SYSREF ウィンドウ処理では、常にピンでの信号が評価されます。

#### 6.3.5.3.2.4 グリッチのない出力

- リクエスト モードからウィンドウ モードに切り替えて、リクエスト モードに戻るときは、SYSREFRE Q ピンで同じ状態を 維持します。たとえば、ウィンドウ モードが開始されたときに SYSREFREQ ピンが high (または low) になる場合、 CLKPOS\_CAPTURE\_EN をプログラムする前に、ウィンドウモードの終了後にピンの状態を再度 high (または low) にするようにしてください。

- または同期モードから切り替えるときは、SYSREFREQ ピンを low に設定する必要があります。

#### 6.3.5.3.2.5 SYNC 機能を使用する場合

- 75 入力クロック サイクルごとに 1 つの SYSREFREQ ピンの立ち上がりエッジのみが許可されます

- SYSREFREQ は6クロックサイクル以上にわたって high に維持する必要があります

#### 6.3.5.3.3 同期機能

SYNC 機能を使用すると、ユーザー は CLK\_DIV、LOGICLK\_DIV、LOGICLK\_DIV\_PRE、SYSREF\_DIV、SYSREF\_DIV\_PRE、SYSREF\_DLY\_DIV デバイダを同期して、電源サイクル間で位相オフセットを一貫させることができます。これにより、ユーザーは複数のデバイスを同期できます。この同期分周器は、ソフトウェアではなく SYSREFREQ ピン経由でのみ実行できます。

## 6.4 デバイスの機能モード構成

本デバイスは、高周波クロック バッファ モード、分周器モード、または逓倍器モードに構成できます。各モードを機能させるには、以下のレジスタ設定が必要です。

表 6-16. デバイスの機能モードの設定

| レジスタ アドレス | ビット | フィールド                 | 機能                                 | バッファ                                                        | デバイダ                                                                | 乗算器                                          |

|-----------|-----|-----------------------|------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|

| R25       | 2:0 | CLK_MUX               | モードを選択します                          | 1                                                           | 2                                                                   | 3                                            |

| R25       | 5:3 | CLK_DIV /<br>CLK_MULT | 除算値または乗算<br>値を選択します                | X                                                           | CLK_DIV<br>0x1 = ÷2<br>0x2 = ÷3<br>0x3 = ÷4<br>0x4 = ÷5<br>0x6 = ÷7 | CLK_MULT<br>0x2 = ×2<br>0x3 = ×3<br>0x4 = ×4 |

| R2        | 5   | SMCLK_EN              | ステート マシン クロック ジェネレータを<br>イネーブルにします | 1                                                           |                                                                     |                                              |

| R2        | 9:6 | SMCLK_DIV_PRE         | 2                                  | ステート マシン クロックのプリクロック分周器<br>0x2 = +2<br>0x4 = +4<br>0x8 = +8 |                                                                     |                                              |

Product Folder Links: LMX1860-SEP

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

#### 表 6-16. デバイスの機能モードの設定 (続き)

| レジスタ アドレス | ビット | フィールド              | 機能                           | バッファ                                                                                                                                | デバイダ               | 乗算器                                 |

|-----------|-----|--------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------|

| R3        | 2:0 | SMCLK_DIV          | ステートマシンのクロック分周器を設定します        | さらに<br>出力周波数を維持す<br>ある必要があります。<br>0x0 = ÷1<br>0x1 = ÷2<br>0x2 = ÷4<br>0x3 = ÷8<br>0x4 = ÷16<br>0x5 = ÷32<br>0x6 = ÷64<br>0x7 = ÷128 | -<br>-るには、SMCLK ディ | 、<br>ベイダは ≤30Mhz で                  |

| R0        | すべて | 乗算器一のキャリブ<br>レーション | PLL ベースの乗算<br>器をキャリブレーションします | х                                                                                                                                   | x                  | キャリブレーション<br>乗算器ーのために<br>R0 を書き込みます |

#### 6.4.1 ピン モード制御

このデバイスは、デバイス モード選択、分周器および乗算器値の選択、出力電力制御、およびチャネル出力制御 (ON/ OFF) のプログラムに使用できるピン モードをサポートしています。ピンモード動作中にピンでロジック状態を変更するには、ステートマシン (SM) クロックをイネーブルにする必要があります。

### 6.4.1.1 チップ イネーブル (CE)

チップ イネーブル ピンは、デバイスをイネーブルおよびはディセーブルにするために使用されます。 **CE** ピンが **high (1)** のとき、チップ イネーブルは **SPI** 経由で制御できます。

### 表 6-17. チップ イネーブル制御

| CE ロジック | デバイス ステータス | SPI オーバーライド制御 |

|---------|------------|---------------|

| 0       | 無効         | なし            |

| 1       | イネーブル      | あり            |

#### 6.4.1.2 出力チャネル制御

各チャネル出力は、CLKx\_EN ピンにより制御されます。このピンは、特定のチャネル出力の CLKOUT と SYSREFOUT をイネーブルまたはディセーブルにします。

#### 表 6-18. 出力チャネル制御の選択

| CLKx_EN | チャネルの出力状態       | SPI オーバーライド制御 |

|---------|-----------------|---------------|

| 0       | チャネル出力がディセーブルです | なし            |

| 1       | チャネル出力をイネーブルします | あり            |

#### 6.4.1.3 ロジック出力制御

ロジック出力ピンは、ロジッククロックとロジック SYSREF 出力をイネーブル/ディセーブルにできます。

#### 表 6-19. ロジック出力イネーブル

| LOGIC_EN | ロジック出力状態       | SPI オーバーライド制御 |

|----------|----------------|---------------|

| 0        | ディスエーブル ロジック出力 | なし            |

| 1        | イネーブル ロジック出力   | あり            |

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

#### 6.4.1.4 SYSREF の出力制御

SYSREF\_EN ピンは、SYSREF セクションをイネーブルおよびディセーブルにできます。

#### 表 6-20. SYSREF 回路イネーブル

| SYSREF_EN | SYSREF 回路 | SPI オーバーライド制御 |

|-----------|-----------|---------------|

| 0         | 無効        | なし            |

| 1         | イネーブル     | あり            |

#### 6.4.1.5 デバイス モード選択

バッファ モード、分周器モード、乗算器 モードなどのデバイス機能は、MUXSELx ピンの設定で選択します。

### 表 6-21. デバイス動作モード選択

| MUXSEL1 | MUXSEL0 | モード選択    |

|---------|---------|----------|

| 0       | 0       | SPI 制御   |

| 0       | 1       | バッファ モード |

| 1       | 0       | デバイダ モード |

| 1       | 1       | 乗算器 モード  |

#### 6.4.1.6 分割器または乗算器値の選択

MUXSELx ピン ロジックにより動作モード (分周器モードまたは乗算器モード) を選択した後で、分周器の値または乗算器の値は DIVSELx ピン ロジックによって選択されます。

#### 表 6-22. 分割器または乗算器値の選択

| 女。ここの日か田の人にの木井田庫で入びが、 |         |         |        |        |

|-----------------------|---------|---------|--------|--------|

| DIVSEL2               | DIVSEL1 | DIVSEL0 | 分周器の値  | 乗数の値   |

| 0                     | 0       | 0       | SPI 制御 | SPI 制御 |

| 0                     | 0       | 1       | 2      | х      |

| 0                     | 1       | 0       | 3      | 2      |

| 0                     | 1       | 1       | 4      | 3      |

| 1                     | 0       | 0       | 5      | 4      |

| 1                     | 0       | 1       | 予約済み   | х      |

| 1                     | 1       | 0       | 7      | х      |

| 1                     | 1       | 1       | 予約済み   | х      |

#### 6.4.1.7 キャリブレーション制御ピン

乗算器 モードで動作している間、PLL ベースの乗算器は周波数ロックのキャリブレーションを必要とし、CAL ピンを low から high に遷移させるとキャリブレーションが開始されます。

#### 表 6-23. CAL ピン ロジック

| CAL   | キャリブレーション状態     |

|-------|-----------------|

| 0     | SPI 制御キャリブレーション |

| 0 → 1 | キャリブレーションを開始します |

### 6.4.1.8 出力電力制御

すべてのチャネルの出力電力は PWRSELx ピンで制御されます。

#### 表 6-24. チャネル出力電力制御

| PWRSEL2 | PWRSEL1 | PWRSEL0 | 出力電力    |

|---------|---------|---------|---------|

| 0       | 0       | 0       | SPI 制御  |

| 0       | 0       | 1       | 最小の出力電力 |

| 0       | 1       | 0       | -       |

| 0       | 1       | 1       | -       |

| 1       | 0       | 0       | -       |

| 1       | 0       | 1       | -       |

| 1       | 1       | 0       | -       |

| 1       | 1       | 1       | 最大出力電力  |

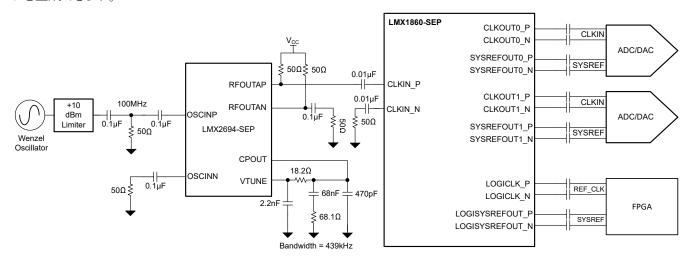

## 7アプリケーションと実装

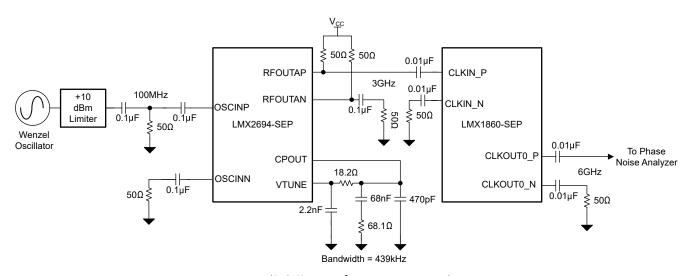

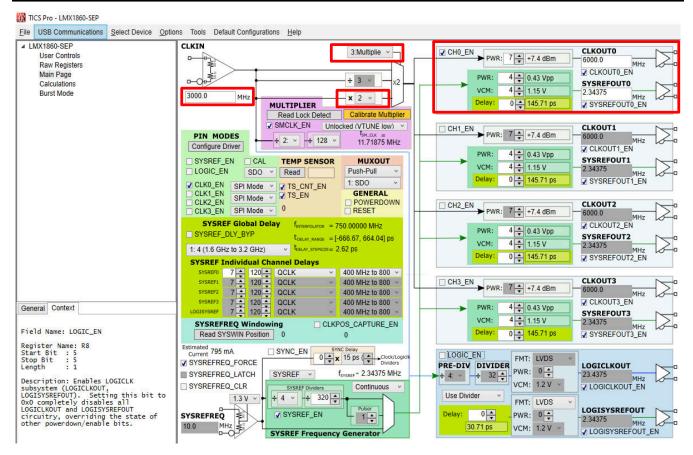

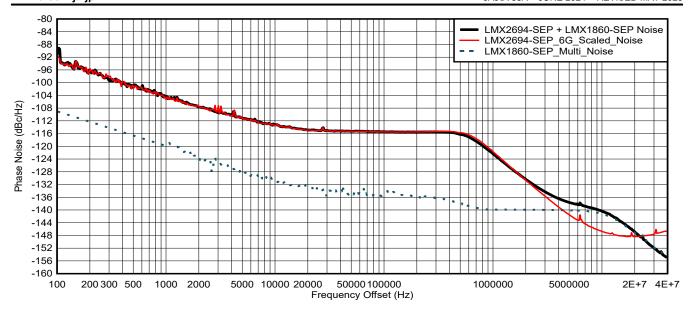

注