LMX1204 JAJSMF0B - JULY 2021 - REVISED FEBRUARY 2024

# LMX1204 低ノイズ、高周波 JESD バッファ / 逓倍器 / 分周器

## 1 特長

- 出力周波数:300MHz~12.8GHz

- 超低ノイズ

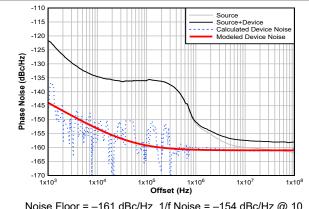

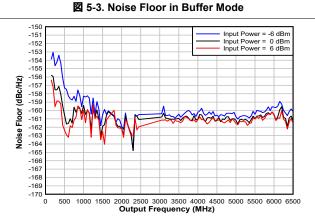

- ノイズ フロア (6GHz 出力):-161dBc/Hz

- 1/f ノイズ (6GHz 出力、10kHz オフセッ 卜):-154dBc/Hz

- ジッタ (12kHz~20MHz):5fS

- 付加ジッタ (DC~f<sub>CLK</sub>):<30fs

- 対応する SYSREF 出力を備えた 4 つの高周波クロッ

- ÷1 (バッファ モード)、÷2、3、4、5、6、7、8 をサポ ートする共有デバイダ

- ×1 (フィルタ モード)、×2、×3、×4 をサポートする共 有 PLL ベースのマルチプライヤ

- LOGICLK 出力と対応する SYSREF 出力

- 個別の分周バンク上

- +1、2、4 プリデバイダ

- ÷1 (バイパス)、2、...、1023 ポストデバイダ

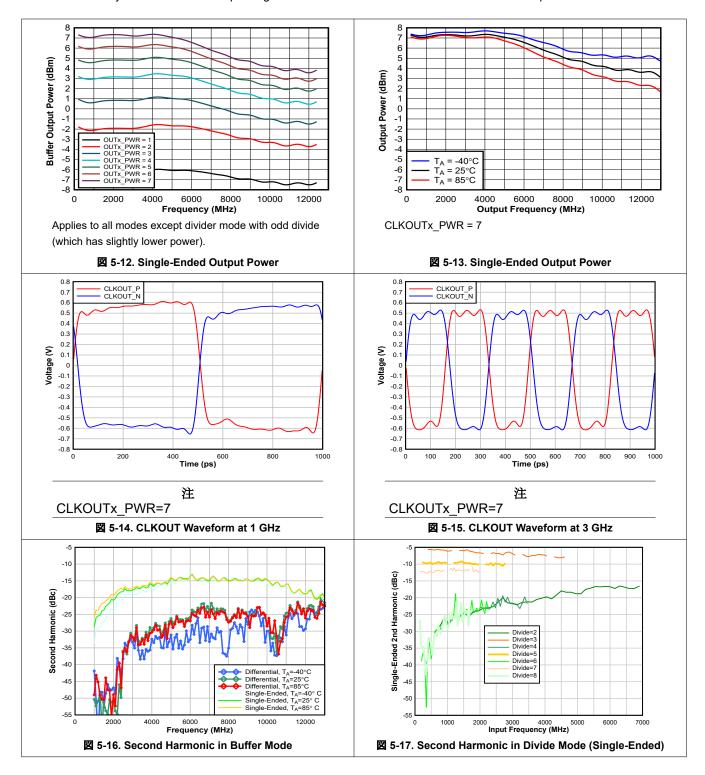

- 8 つのプログラム可能な出力電力レベル

- 同期された SYSREF クロック出力

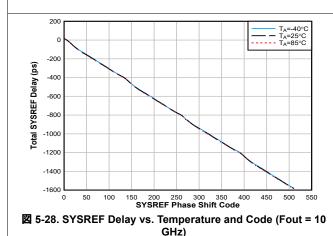

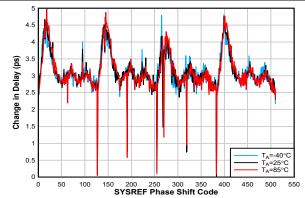

- 508 遅延ステップの調整は、12.8GHz でそれぞれ 2.5ps 未満

- ジェネレータモードとリピータモード

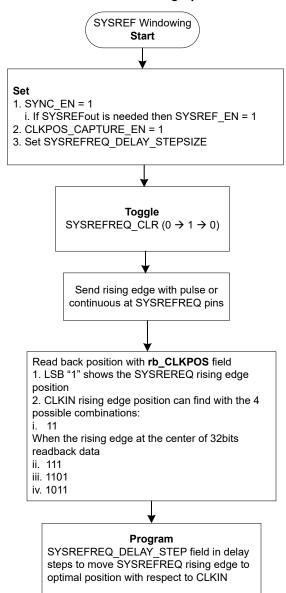

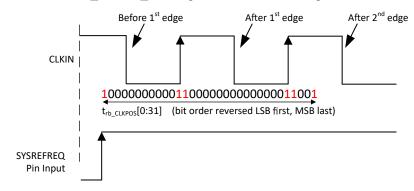

- SYSREFREQ ピンのウィンドウ処理機能によりタイ ミングを最適化します

- すべてのデバイダおよび複数のデバイスに対する SYNC 機能

- 2.5V の動作電圧

- 動作温度:-40℃~85℃

# 2 アプリケーション

- 試験 & 測定:

- オシロスコープ

- ワイヤレス機器テスター

- 広帯域デジタイザ

- 航空宇宙 & 防衛:

- レーダー

- 電子戦

- シーカー フロントエンド

- 軍需品

- フェーズドアレイアンテナ/ビームフォーミング

- 汎用:

- データコンバータのクロック供給

- クロック バッファの分配 / 分周

## 3 概要

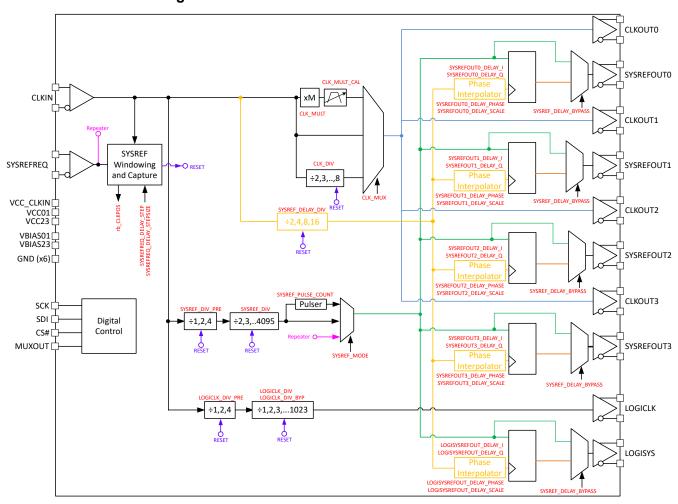

このデバイスは高い周波数に対応し、ジッタが非常に小さ いため、信号対雑音比の劣化なく、高精度クロック、高周 波データコンバータを容易に実現できます。4 つの高周 波クロック出力のそれぞれと、より大きな分周器範囲を持 つ追加の LOGICLK 出力は、SYSREF 出力クロック信号 と対になります。JESD インターフェイスの SYSREF 信号 は、内部で生成するか、入力として渡されて、デバイスク ロックに再度クロックされます。データコンバータのクロック 供給アプリケーションでは、クロックのジッタをデータコン バータのアパーチャ ジッタよりも小さくすることが重要で す。4 つより多いデータ コンバータにクロックを供給する必 要があるアプリケーションでは、複数のデバイスを使用し て、必要なすべての高周波クロックと SYSREF 信号を分 配する、さまざまなカスケード接続アーキテクチャを開発で きます。このデバイスはジッタが小さくノイズフロアが低い ため、超低ノイズのリファレンスクロックソースと組み合わ せると、特にサンプリングが 3GHz を超える場合に、デー タコンバータのクロック供給用の模範的な選択肢になりま す。

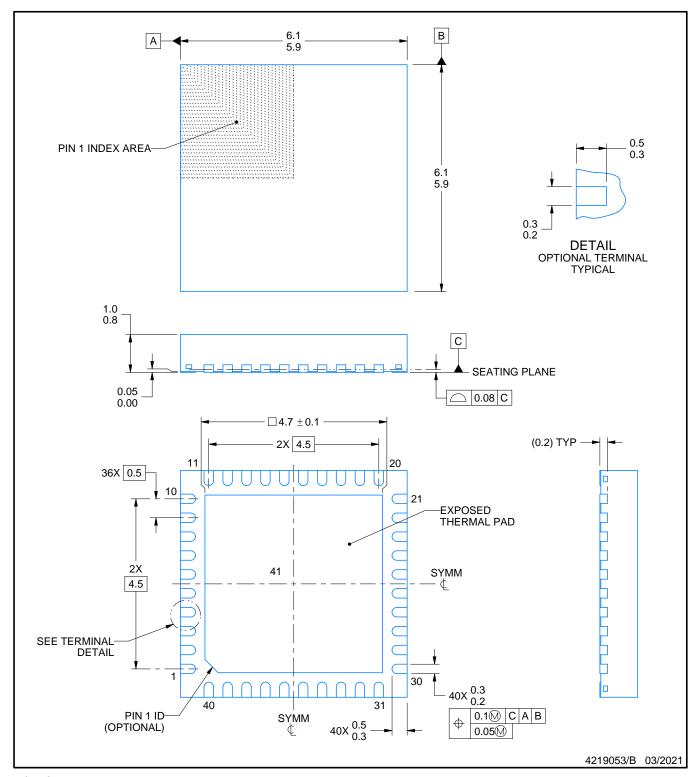

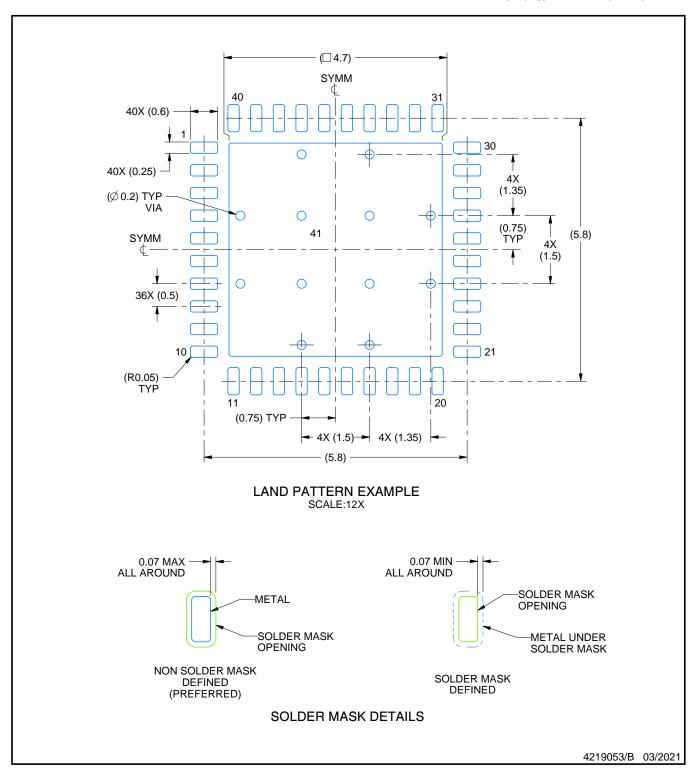

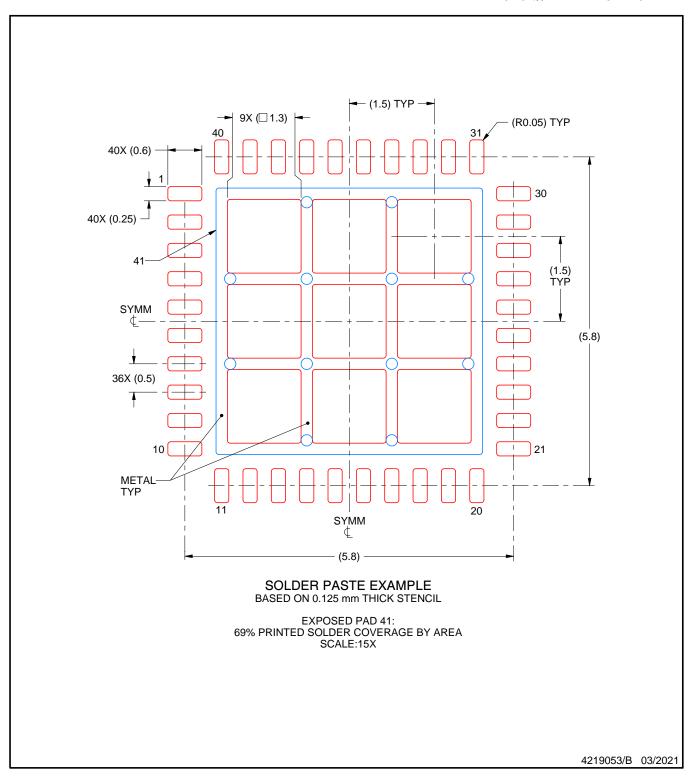

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |  |  |

|---------|----------------------|--------------------------|--|--|

| LMX1204 | RHA (VQFN, 40)       | 6.00mm × 6.00mm          |  |  |

- 詳細については、セクション 11 を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

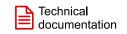

ブロック図

## **Table of Contents**

| <b>1</b> 特長 1                         | 7 Register Map                          | 31 |

|---------------------------------------|-----------------------------------------|----|

| <b>2</b> アプリケーション1                    | 7.1 LMX1204 Registers                   | 33 |

| 3 概要1                                 | 8 Application and Implementation        |    |

| 4 Pin Configuration and Functions3    | 8.1 Application Information             |    |

| 5 Specifications5                     | 8.2 Typical Application                 |    |

| 5.1 Absolute Maximum Ratings5         | 8.3 Power Supply Recommendations        | 62 |

| 5.2 ESD Ratings5                      | 8.4 Layout                              |    |

| 5.3 Recommended Operating Conditions5 | 9 Device and Documentation Support      | 64 |

| 5.4 Thermal Information5              | 9.1 Device Support                      |    |

| 5.5 Electrical Characteristics6       | 9.2 Documentation Support               | 64 |

| 5.6 Timing Requirements8              | 9.3ドキュメントの更新通知を受け取る方法                   | 64 |

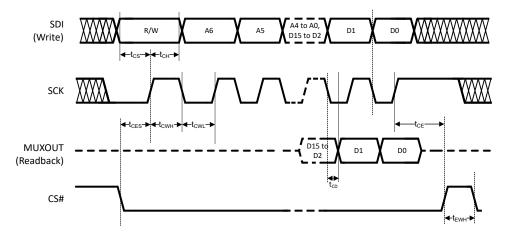

| 5.7 Timing Diagram8                   | 9.4 サポート・リソース                           | 64 |

| 5.8 Typical Characteristics9          | 9.5 Trademarks                          | 64 |

| 6 Detailed Description15              | 9.6 静電気放電に関する注意事項                       | 64 |

| 6.1 Overview                          | 9.7 用語集                                 | 64 |

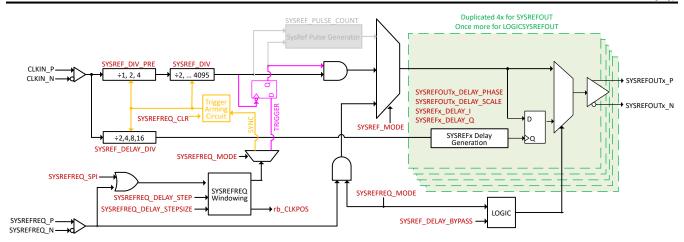

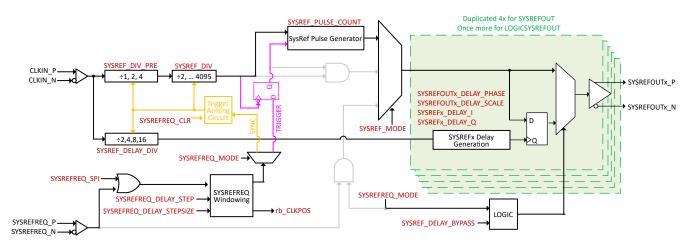

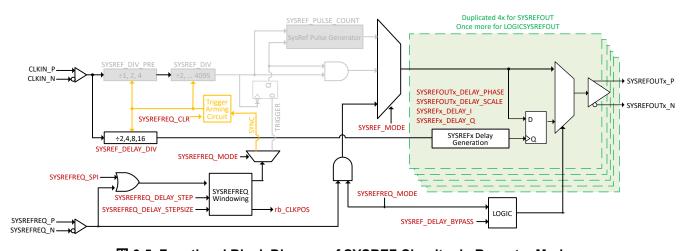

| 6.2 Functional Block Diagram16        | 10 Revision History                     |    |

| 6.3 Feature Description17             | 11 Mechanical, Packaging, and Orderable |    |

| 6.4 Device Functional Modes30         | Information                             | 65 |

|                                       |                                         |    |

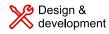

# **4 Pin Configuration and Functions**

図 4-1. RHA Package 40-Pin VQFN Top View

3

## 表 4-1. Pin Functions

| BIAS01 20 BYP If not using the multiplier, this pin can be left open. If using the multiplier, bypass this pin to GND with a 10-nf capacitor for optimal noise performance.  BIAS23 31 BYP BYP  BIAS23 31 BYP  BIAS24 31 BYP  BIAS25 31 BYP  BIAS25 31 BYP  BIAS25 31 BYP  BIAS25 31 BYP  BIAS26 31 BYP  BIAS26 31 BYP  BIAS26 31 BYP  BIAS26 31 BYP  BIAS27 31 BYP  BIAS27 31 BYP  BIAS28 3  | NAME            | NO.              | TYPE <sup>(1)</sup> | -1. PIN FUNCTIONS DESCRIPTION                                                |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|---------------------|------------------------------------------------------------------------------|--|--|

| bypass this jin to GND with a 10-in-Capacitor for optimal noise performance.  If not using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using single-ended, the trainiate unused side with a 10-in-Capacitor for optimal noise performance.  If not using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier appears to the input frequency (typically 0.1 µF or smaller). If using single-ended, terminate unused side with a series AC-coupling capacitor 30-Ω resistor to GND.  If not using the multiplier, this pin can be left open. If using the multiplier, left capacitor for optimal noise performance.  If not using the multiplier, this pin can be left open. If using the multiplier, this pin can be left open. If using the multiplier is using single-ended, the trainate unused side with a series AC-coupling capacitor 30-Ω resistor to GND.  In the pin in the pin pin series of GND.  In the pin in an open-collector output with internally integrated 50-Ω resistor with programmable output swing. AC output pairs. Each pin is an open-collector output with internally integrated 50-Ω resistor with programmable output swing. AC output pairs and pen-collector output with internally integrated 50-Ω resistor to GND.  In the pin internal 50-Ω termination. AC-coupling with pin internal 50-Ω to pin                                                                                                                                                                                             |                 |                  |                     |                                                                              |  |  |

| BIAS23   Signature   Signat    | BIAS01          | 20               | BYP                 | bypass this pin to GND with a 10-nF capacitor for optimal noise performance. |  |  |

| CLKINI_P   6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BIAS23          | 31               | ВҮР                 | bypass this pin to GND with a 10-µF and 0.1-µF capacitor for optimal noise   |  |  |

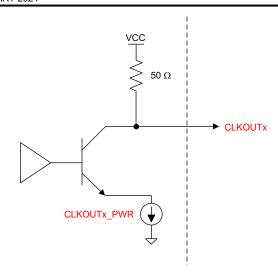

| CLKINI_P       6       I       using single-ended, terminate unused side with a series AC-coupling capacitor 50-Ω resistor to GND.         CLKOUTO_N       15       capacitor 50-Ω resistor to GND.         CLKOUTI_N       19       cut of the coupling capacitor 50-Ω resistor to GND.         CLKOUT2_N       32       differential clock output pairs. Each pin is an open-collector output with internally integrated 50-Ω resistor with programmable output swing. AC coupling required.         CLKOUT3_N       36       differential clock output pairs. Each pin is an open-collector output with internally integrated 50-Ω resistor with programmable output swing. AC coupling required.         CLKOUT3_N       36       differential clock output pairs. Each pin is an open-collector output with internally integrated 50-Ω resistor with programmable output swing. AC coupling required.         CLKOUT3_N       36       differential clock output pairs.       Cond output pairs.       Selectable CML, LVDS, or LVPECL format.       Programmable common-mode voltage.       Programmable common-mode voltage.       Differential clock output pair. Selectable CML, LVDS, or LVPECL format.       Programmable common-mode voltage.       Differential cond output pair. Selectable CML, LVDS, or LVPECL format.       Programmable common-mode voltage.       Differential cond output pairs.       Selectable CML, LVDS, or LVPECL format.       Programmable common-mode voltage.       Differential cond outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLKIN_N         | 7                |                     |                                                                              |  |  |

| CLKOUTO_P         14           CLKOUT1_N         19           CLKOUT1_P         18           CLKOUT2_N         32           CLKOUT2_P         33           CLKOUT3_N         36           CLKOUT3_N         36           CLKOUT3_P         37           CS#         10         I         SPI chip select. High impedance CMOS input. Accepts up to 3.3 V.           DAP         DAP         GND         5.13,17,26,34,38         GND         5.13,17,26,34,38         GOND           LOGICLKOUT_N         27         28         O         Differential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.           LOGISYSREFOUT_N         23         O         Differential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.           MUXOUT         1         O         Multiplexed pin serial data readback and lock status of the multiplier.           SCK         8         1         SPI clock. High impedance CMOS input. Accepts up to 3.3 V.           SPI         9         1         SPI clock. High impedance CMOS input. Accepts up to 3.3 V.           SYSREFREQ_N         3         SPI clock. High impedance CMOS input. Accepts up to 3.3 V.           SYSREFOUT0_N         12         SPI clock. High impedanc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLKIN_P         | 6                | I                   | using single-ended, terminate unused side with a series AC-coupling          |  |  |

| CLKOUT1_N CLKOUT1_P CLKOUT2_N CLKOUT2_P CLKOUT3_N SOBOR CLKOUT3_P CS# 10 DAP GND S13,17,26,34,38 LOGICLKOUT_P 28 LOGICLKOUT_P 28 LOGICLKOUT_P 29 LOGISYSREFOUT_N SCK 8 1 1 0 0 Multiplexed pin serial data readback and lock status of the multiplier.  SCK 8 1 1 SPI clock. High impedance CMOS input. Accepts up to 3.3 V. Differential clock output pairs. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.  LOGICLKOUT_P 10 LOGISYSREFOUT_N 11 SCK 11 SCK 12 SUBJECTED SINCE SYSREFOUT_D 11 SYSREFOUT_D 12 SYSREFOUT_D 12 SYSREFOUT_D 13 SYSREFOUT_D 14 SYSREFOUT_D 15 SYSREFOUT_D 16 SYSREFOUT_D 17 SYSREFOUT_D 18 SYSREFOUT_D 19 SYSREFOUT_D 11 SYSREFOUT_  | CLKOUT0_N       | 15               |                     |                                                                              |  |  |

| CLKOUT1_P 18 CLKOUT2_N 32 CLKOUT2_P 33 CLKOUT3_P 36 CLKOUT3_P 37 CS# 10 1 SPI chip select. High impedance CMOS input. Accepts up to 3.3 V. DAP DAP GND 5,13,17,26,34,38 CLGICKOUT_P 28 CLGICKOUT_P 29 CLGICKOUT_P 20 CLGICKOUT_P 20 CLGICKOUT_P 21 CLGICKOUT_P 21 CLGICKOUT_P 22 CLGICKOUT_P 24 CLGICKOUT_P 25 CLGICKOUT_P 26 CLGICKOUT_P 27 CLOGICKOUT_P 28 CLGICKOUT_P 29 CLGICKOUT_P 29 CLGICKOUT_P 29 CLGICKOUT_P 20 CLGICKOUT_P 20 CLGICKOUT_P 21 CLGICKOUT_P 21 CLGICKOUT_P 21 CLGICKOUT_P 21 CLGICKOUT_P 21 CLGICKOUT_P 22 CLGICKOUT_P 24 CLCICKOUT_P 25 CLCICKOUT_P 26 CLCICKOUT_P 26 CLCICKOUT_P 27 CLCICKOUT_P 28 CLCICKOUT_P 29 CLCICKOUT_P 20 CLCICKOUT_P 20 CLCICKOUT_P 20 CLCICKOUT_P 21 CL | CLKOUT0_P       | 14               |                     |                                                                              |  |  |

| CLKOUT2_N 32 CLKOUT3_N 36 CLKOUT3_N 36 CLKOUT3_P 37 CS# 10 I SPI chip select. High impedance CMOS input. Accepts up to 3.3 V. DAP DAP DAP 6ND 71 COGICLKOUT_N 27 COGICLKOUT_N 28 COGICLKOUT_P 28 COGICLKOUT_P 28 COGICLKOUT_P 29 COGICLKOUT_P 24 COGICLKOUT_P 24 COGICLKOUT_P 24 COGICLKOUT_P 24 COGICLKOUT_P 24 COGICLKOUT_P 24 COGICLKOUT_P 25 COGICLKOUT_P 26 COGICLKOUT_P 27 COGICLKOUT_P 26 COGICLKOUT_P 27 COGICLKOUT_P 27 COGICLKOUT_P 28 COGICLKOUT_P 29 COGICLKOUT_P 30 COGICLKOUT_P  | CLKOUT1_N       | 19               |                     |                                                                              |  |  |

| CLKOUT2_N         32           CLKOUT3_N         36           CLKOUT3_P         37           CS#         10         I         SPI chip select. High impedance CMOS input. Accepts up to 3.3 V.           DAP         DAP         GND         5,13,17,26,34,38         Ground these pins.           LOGICLKOUT_N         27         O         Differential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.           LOGISYSREFOUT_N         23         O         Differential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.           MUXOUT         1         O         Multiplexed pin serial data readback and lock status of the multiplier.           SCK         8         I         SPI clock. High impedance CMOS input. Accepts up to 3.3 V.           SYSREFREQ_N         3         I         SPI clock. High impedance CMOS input. Accepts up to 3.3 V.           SYSREFOUT_N         2         Differential SYSREF request input for JESD204B support. Internal 50-Q AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.           SYSREFOUT_N         21         O         Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.           SYSREFOUT_N         29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLKOUT1_P       | 18               | 0                   |                                                                              |  |  |

| CLKOUT2_P         33           CLKOUT3_N         36           CLKOUT3_P         37           CS#         10         I         SPI chip select. High impedance CMOS input. Accepts up to 3.3 V.           DAP         DAP         DAP         GND         5,13,17,26,34,38         GND         Ground these pins.           LOGICLKOUT_N         27         28         Differential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.           LOGISYSREFOUT_N         23         0         Differential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.           LOGISYSREFOUT_P         24         0         Differential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.           MUXOUT         1         0         Multiplexed pin serial data readback and lock status of the multiplier.           SCK         8         1         SPI clock. High impedance CMOS input. Accepts up to 3.3 V.           SYSREFREQ_N         3         3         1         SPI data input. High impedance CMOS input. Accepts up to 3.3 V.           SYSREFOUT_N         3         2         Differential SYSREF request input for JESD204B support. Internal 50-Ω Accepts up to 3.2 V.           SYSREFOUT_N         11         SYSREFOUT_N         20         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CLKOUT2_N       | 32               | U                   |                                                                              |  |  |

| CLKOUT3_P 37  CS# 10 1 I SPI chip select. High impedance CMOS input. Accepts up to 3.3 V.  DAP DAP  GND 5,13,17,26,34,38  LOGICLKOUT_N 27  LOGICLKOUT_P 28  LOGISYSREFOUT_N 23  LOGISYSREFOUT_P 24  MUXOUT 1 0 Multiplexed pin serial data readback and lock status of the multiplier.  SCK 8 I SPI clock. High impedance CMOS input. Accepts up to 3.3 V.  SYSREFREQ_N 3 SYSREFOUT_N 3 SYSREFOUT_N 2 SYSREFOUT_N 2 SYSREFOUT_N 3 SYSR | CLKOUT2_P       | 33               |                     |                                                                              |  |  |

| CS# 10 I SPI chip select. High impedance CMOS input. Accepts up to 3.3 V.  DAP DAP GND 5,13,17,26,34,38 COBD STILL COGICLKOUT_N 27 COBD STILL COGICLKOUT_N 27 COBD STILL COGICLKOUT_N 28 COBD STILL COGICLKOUT_N 29 COBD STILL COGICLKOUT_N 20 COBD STILL COGICLK 20 COBD STILL COGICLK 20 COBD STILL COGICLK 25 COBD STILL COGICLK 20 COBD STILL COGICLK 25 COBD STILL COGICL COGICLK 25 COBD STILL COGICLK 25 COBD STILL COGICL COGICL COGICLK 25 COBD STILL COGICL COG | CLKOUT3_N       | 36               |                     |                                                                              |  |  |

| DAP DAP GND 5,13,17,26,34,38 LOGICLKOUT_N 27 LOGICLKOUT_P 28 LOGISYSREFOUT_N 23 LOGISYSREFOUT_P 24  MUXOUT 1 0 Multiplexed pin serial data readback and lock status of the multiplier.  SCK 8 I SPI clock. High impedance CMOS input. Accepts up to 3.3 V.  SYSREFREQ_N 3 I SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  SYSREFREQ_P 2 I Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  SYSREFOUT_N 22 SYSREFOUT_N 29 SYSREFOUT_N 29 SYSREFOUT_N 29 SYSREFOUT_N 39   | CLKOUT3_P       | 37               |                     |                                                                              |  |  |

| GND 5,13,17,26,34,38  LOGICLKOUT_N 27  LOGICLKOUT_P 28  LOGISYSREFOUT_N 23  LOGISYSREFOUT_P 24  MUXOUT 1 0 Multiplexed pin serial data readback and lock status of the multiplier.  SCK 8 I SPI clock. High impedance CMOS input. Accepts up to 3.3 V.  SYSREFREQ_N 3 I SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  SYSREFOUT_D 2 I Differential SYSREF request input for JESD204B support. Internal 50-0 AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  SYSREFOUT_D 2 I Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  SYSREFOUT_D 30  SYSREFOUT_D 20  SYSREFOUT_D 30  SYSREFOUT_D 40  SYSREFOUT_D 30  SYSREFOUT_D 40  SYSREFOUT_D 40  SYSREFOUT_D 40  SYSREFOUT_D 50  SYSREFOUT_D | CS#             | 10               | I                   | SPI chip select. High impedance CMOS input. Accepts up to 3.3 V.             |  |  |

| GND 5,13,17,26,34,38  LOGICLKOUT_N 27  LOGICLKOUT_P 28  LOGISYSREFOUT_N 23  LOGISYSREFOUT_P 24  MUXOUT 1 0 Multiplexed pin serial data readback and lock status of the multiplier.  SCK 8 I SPI clock. High impedance CMOS input. Accepts up to 3.3 V.  SYSREFREQ_N 3 Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  SYSREFOUTO_N 12  SYSREFOUTO_N 12  SYSREFOUTO_N 12  SYSREFOUTO_N 22  SYSREFOUTO_N 22  SYSREFOUTO_N 22  SYSREFOUTO_N 22  SYSREFOUTO_N 30  SYSREFOUTO  | DAP             | DAP              | OND                 | 0 111                                                                        |  |  |

| LOGICLKOUT_P28Programmable common-mode voltage.LOGISYSREFOUT_N23ODifferential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.MUXOUT1OMultiplexed pin serial data readback and lock status of the multiplier.SCK8ISPI clock. High impedance CMOS input. Accepts up to 3.3 V.SDI9ISPI data input. High impedance CMOS input. Accepts up to 3.3 V.SYSREFREQ_N3Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.SYSREFOUTO_N1222SYSREFOUTI_N22Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT2_N29Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT3_N39SYSREFOUT3_P40VCC_CLKIN4VCC_LOGICLK25VCC0116  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GND             | 5,13,17,26,34,38 | GND                 | Ground these pins.                                                           |  |  |

| LOGICLKOUT_P28Programmable common-mode voltage.LOGISYSREFOUT_N23ODifferential clock output pair. Selectable CML, LVDS, or LVPECL format. Programmable common-mode voltage.MUXOUT1OMultiplexed pin serial data readback and lock status of the multiplier.SCK8ISPI clock. High impedance CMOS input. Accepts up to 3.3 V.SDI9ISPI data input. High impedance CMOS input. Accepts up to 3.3 V.SYSREFREQ_N3Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.SYSREFOUTO_N12Differential SYSREF cML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT1_N22Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT2_N29Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT3_N39SYSREFOUT3_P40VCC_CLKIN4VCC_LOGICLK25VCC0116  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LOGICLKOUT_N    | 27               |                     | Differential clock output pair. Selectable CML, LVDS, or LVPECL format.      |  |  |

| Deficiential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts. SYSREFOUT2_P 30 SYSREFOUT3_P 40 VCC_CLKIN VCC01 16  MUXOUT 1 O Multiplexed pin serial data readback and lock status of the multiplier.  SPI ode data input. High impedance CMOS input. Accepts up to 3.3 V.  SPI clock. High impedance CMOS input. Accepts up to 3.3 V.  SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  SYSREFOUT2_P 30  SYSREFOUT3_P 40  VCC_CLKIN 4  VCC_LOGICLK 25  VCC01 16  PWR  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LOGICLKOUT_P    | 28               | O                   |                                                                              |  |  |

| LOGISYSREFOUT_P24Programmable common-mode voltage.MUXOUT1OMultiplexed pin serial data readback and lock status of the multiplier.SCK8ISPI clock. High impedance CMOS input. Accepts up to 3.3 V.SDI9ISPI data input. High impedance CMOS input. Accepts up to 3.3 V.SYSREFREQ_N3JDifferential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.SYSREFOUT0_N11SYSREFOUT1_N22SYSREFOUT1_N22Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT2_N29Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT3_N39Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT3_N39Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.SYSREFOUT3_N39SYSREFOUT3_N39SYSREFOUT3_P40Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LOGISYSREFOUT_N | 23               |                     | Differential clock output pair. Selectable CML, LVDS, or LVPECL format.      |  |  |

| SCK SDI SPI clock. High impedance CMOS input. Accepts up to 3.3 V. SPI data input. High impedance CMOS input. Accepts up to 3.3 V. SYSREFREQ_N SYSREFREQ_P 2 Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  SYSREFOUTO_N SYSREFOUTO_P 11 SYSREFOUT1_N 22 SYSREFOUT1_P 21 SYSREFOUT2_N SYSREFOUT2_P 30 SYSREFOUT3_N SYSREFOUT3_P 40  VCC_CLKIN 4 VCC_LOGICLK Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LOGISYSREFOUT_P | 24               | O                   |                                                                              |  |  |

| SDI 9 I SPI data input. High impedance CMOS input. Accepts up to 3.3 V.  SYSREFREQ_N 3 Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  SYSREFOUT0_N 12 SYSREFOUT1_N 22 SYSREFOUT1_P 21 SYSREFOUT2_N 29 SYSREFOUT2_P 30 SYSREFOUT3_N 39 SYSREFOUT3_P 40  VCC_CLKIN 4 VCC_LOGICLK 25 VCC01 16  I SPI data input. High impedance CMOS input. Accepts up to 3.3 V. Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MUXOUT          | 1                | 0                   | Multiplexed pin serial data readback and lock status of the multiplier.      |  |  |

| SYSREFREQ_N  SYSREFREQ_P  2  Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  SYSREFOUT0_P  SYSREFOUT1_N  SYSREFOUT1_P  SYSREFOUT2_N  SYSREFOUT2_P  SYSREFOUT3_N  SYSREFOUT3_P  VCC_CLKIN  VCC_LOGICLK  VCC01  Differential SYSREF request input for JESD204B support. Internal 50-Ω AC coupled to internal common-mode voltage or capacitor to GND. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SCK             | 8                | I                   | SPI clock. High impedance CMOS input. Accepts up to 3.3 V.                   |  |  |

| SYSREFREQ_P  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SDI             | 9                | 1                   | SPI data input. High impedance CMOS input. Accepts up to 3.3 V.              |  |  |

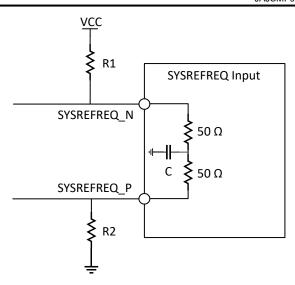

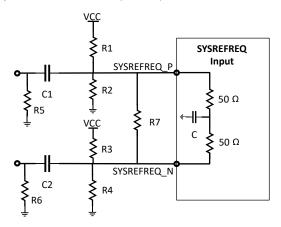

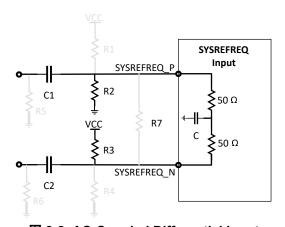

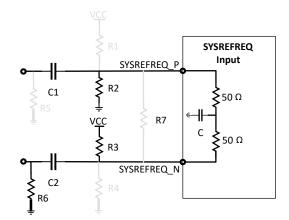

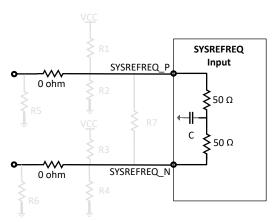

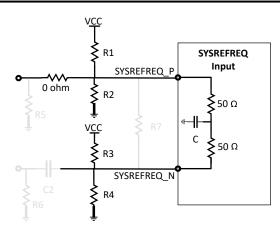

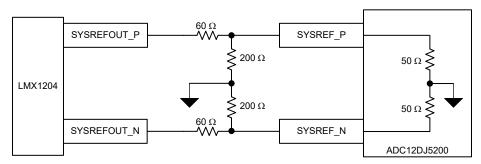

| SYSREFREQ_P  2 and DC coupling which can directly accept a common mode voltage of 1.2 to 2 V.  SYSREFOUTO_N  SYSREFOUTO_P  SYSREFOUT1_N  SYSREFOUT1_P  SYSREFOUT2_N  SYSREFOUT2_P  SYSREFOUT3_N  SYSREFOUT3_P  VCC_CLKIN  VCC_LOGICLK  VCCO1  16  Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 µF or smaller) close to the pin in parallel with larger capacitors (typically 1 µF and 10 µF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SYSREFREQ_N     | 3                |                     |                                                                              |  |  |

| SYSREFOUT1_N SYSREFOUT1_P SYSREFOUT2_N SYSREFOUT2_P SYSREFOUT3_N SYSREFOUT3_P VCC_LCGICLK VCC01  SYSREFOUT5 S  | SYSREFREQ_P     | 2                | I                   | and DC coupling which can directly accept a common mode voltage of 1.2 to    |  |  |

| SYSREFOUT1_N  SYSREFOUT1_P  SYSREFOUT2_N  SYSREFOUT2_P  SYSREFOUT3_N  SYSREFOUT3_P  VCC_CLKIN  VCC_LOGICLK  VCC01  Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SYSREFOUT0_N    | 12               |                     |                                                                              |  |  |

| SYSREFOUT1_P  SYSREFOUT2_N  SYSREFOUT2_P  SYSREFOUT3_N  SYSREFOUT3_P  VCC_CLKIN  VCC_LOGICLK  VCC01  Differential SYSREF CML output pairs for JESD204B support. Supports AC and DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 µF or smaller) close to the pin in parallel with larger capacitors (typically 1 µF and 10 µF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SYSREFOUT0_P    | 11               |                     |                                                                              |  |  |

| SYSREFOUT2_N SYSREFOUT3_P SYSREFOUT3_P VCC_LCGICLK VCC01 SYSREFOUT5_N  | SYSREFOUT1_N    | 22               |                     |                                                                              |  |  |

| SYSREFOUT2_N 29 SYSREFOUT3_N 39 SYSREFOUT3_P 40 VCC_CLKIN 4 VCC_LOGICLK 25 VCC01 16  And DC coupling with programmable common-mode voltage of 0.6 to 2 volts.  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 µF or smaller) close to the pin in parallel with larger capacitors (typically 1 µF and 10 µF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SYSREFOUT1_P    | 21               |                     | Differential SYSREF CML output pairs for JESD204B support. Supports AC       |  |  |

| SYSREFOUT3_N 39  SYSREFOUT3_P 40  VCC_CLKIN 4  VCC_LOGICLK 25  VCC01 16  PWR Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 µF or smaller) close to the pin in parallel with larger capacitors (typically 1 µF and 10 µF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SYSREFOUT2_N    | 29               | O                   |                                                                              |  |  |

| SYSREFOUT3_P 40  VCC_CLKIN 4  VCC_LOGICLK 25  VCC01 16  Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SYSREFOUT2_P    | 30               |                     |                                                                              |  |  |

| VCC_CLKIN       4         VCC_LOGICLK       25         VCC01       16         PWR       Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SYSREFOUT3_N    | 39               |                     |                                                                              |  |  |

| VCC_LOGICLK25Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor<br>(typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors<br>(typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SYSREFOUT3_P    | 40               |                     |                                                                              |  |  |

| VCC_LOGICLK25Connect to a 2.5-V supply. Recommend a shunt high frequency capacitor<br>(typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors<br>(typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VCC_CLKIN       | 4                |                     |                                                                              |  |  |

| VCC01 16 (typically 0.1 μF or smaller) close to the pin in parallel with larger capacitors (typically 1 μF and 10 μF) farther away.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | 25               |                     |                                                                              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 16               | PWR                 |                                                                              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VCC23           | 35               |                     | (2) [                                                                        |  |  |

(1) I = Input, O = Output, GND = Ground, PWR = Power, BYP = Bypass

Copyright © 2024 Texas Instruments Incorporated

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                  | MIN  | MAX                   | UNIT |

|------------------|----------------------------------|------|-----------------------|------|

| $V_{DD}$         | Power supply voltage             | -0.3 | 2.75                  | V    |

| V <sub>IN</sub>  | DC Input Voltage (SCK, SDI, CSB) | GND  | 3.6                   | V    |

| V <sub>IN</sub>  | DC Input Voltage (SYSREFREQ)     | GND  | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IN</sub>  | AC Input Voltage (CLKIN)         |      | $V_{DD}$              | Vpp  |

| T <sub>J</sub>   | Junction temperature             |      | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature              | -65  | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|  |        |                          |                                                                                          | VALUE | UNIT |

|--|--------|--------------------------|------------------------------------------------------------------------------------------|-------|------|

|  | .,     | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2500 | V    |

|  | V(ESD) | Electrostatic discriarge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                 |                      | MIN | NOM | MAX | UNIT |

|-----------------|----------------------|-----|-----|-----|------|

| V <sub>DD</sub> | Supply voltage       | 2.4 | 2.5 | 2.6 | V    |

| T <sub>A</sub>  | Ambient temperature  | -40 |     | 85  | °C   |

| TJ              | Junction temperature |     |     | 125 | °C   |

### 5.4 Thermal Information

|                       |                                              | VALUE      |      |

|-----------------------|----------------------------------------------|------------|------|

| SYMBOL                | THERMAL METRIC (1)                           | RHA (VQFN) | UNIT |

|                       |                                              | 40 Pins    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 24.8       | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 13.0       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.9        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 6.9        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.5        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

## **5.5 Electrical Characteristics**

|                       | PARAMETER                        | TEST CO                                  | NDITIONS                                                     | MIN  | TYP  | MAX  | UNIT |

|-----------------------|----------------------------------|------------------------------------------|--------------------------------------------------------------|------|------|------|------|

| Current Co            | onsumption                       | 1                                        |                                                              |      |      |      |      |

|                       |                                  | Powered up, all outpu                    | its and SYSREF on                                            |      | 1050 |      |      |

|                       |                                  | Powered up, all outpu                    | its on, all SYSREF off                                       |      | 600  |      |      |

| I <sub>CC</sub>       | Supply Current (1)               | Powered up, all outpu                    | its and SYSREF off                                           |      | 265  |      | mA   |

|                       |                                  | Powered down <sup>(2)</sup>              |                                                              |      | 11   |      |      |

| SYSREF                |                                  |                                          |                                                              |      |      |      |      |

| _                     | T                                | Generator mode                           |                                                              |      |      | 200  | MHz  |

| f <sub>SYSREF</sub>   | SYSREF output frequency          | Repeater mode                            |                                                              |      |      | 100  | MHz  |

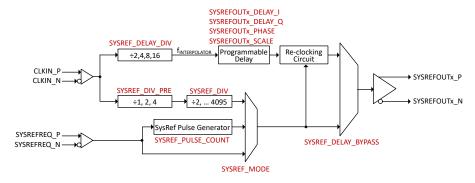

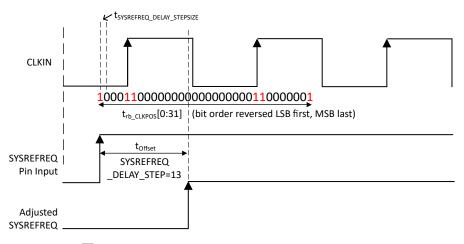

| Δt                    | SYSREF delay step size           | f <sub>CLKIN</sub> = 12.8 GHz            |                                                              |      | 3    |      | ps   |

|                       |                                  | SYSREFOUT                                |                                                              |      | 45   |      | ps   |

|                       |                                  |                                          | CML                                                          |      | 120  |      | ps   |

| t <sub>RISE</sub>     | Rise time (20% to 80%)           | LOGISYSREFOUT                            | LVDS                                                         |      | 120  |      | ps   |

|                       |                                  |                                          | LVPECL                                                       |      | 230  |      | ps   |

|                       |                                  | SYSREFOUT                                |                                                              |      | 45   |      | ps   |

|                       |                                  |                                          | CML                                                          |      | 120  |      | ps   |

| t <sub>FALL</sub>     | Fall time (20% to 80%)           | 20% to 80%) LOGISYSREFOUT                | LVDS                                                         |      | 120  |      | ps   |

|                       |                                  |                                          | LVPECL                                                       |      | 170  |      | ps   |

|                       |                                  | SYSREFOUT                                |                                                              |      | 0.85 |      | Vpp  |

|                       | Differential output voltage      |                                          | CML                                                          |      | 0.4  |      | Vp   |

| $V_{OD}$              |                                  | LOGISYSREFOUT                            | LVDS                                                         |      | 0.4  |      | Vp   |

|                       |                                  |                                          | LVPECL                                                       |      | 0.8  |      | Vp   |

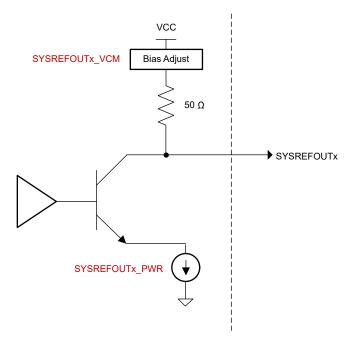

| V <sub>SYSREFCM</sub> | Common mode voltage              | SYSREFOUT                                | CML<br>SYSREFOUTx_PW<br>R=4<br>100 Ω Differential<br>Load    |      | 0.8  |      | V    |

| SYSREFRE              | Q Pins                           |                                          |                                                              |      |      |      |      |

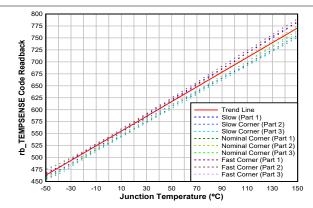

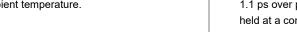

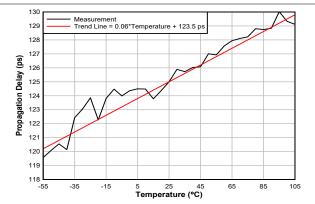

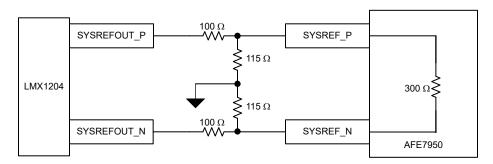

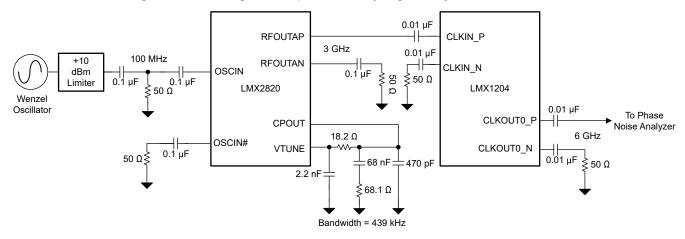

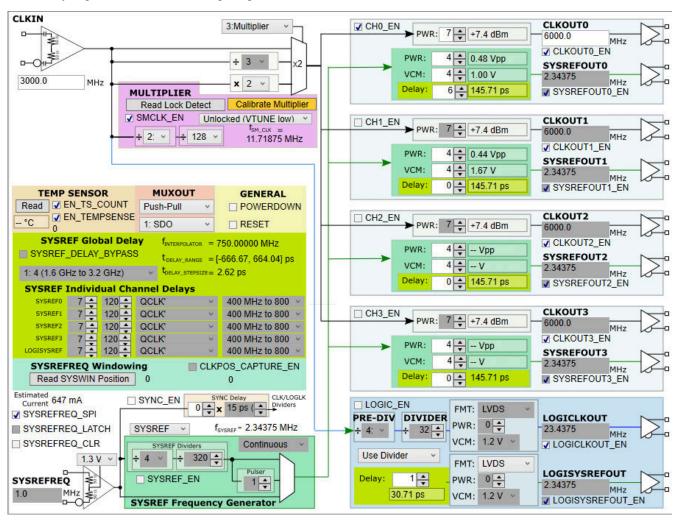

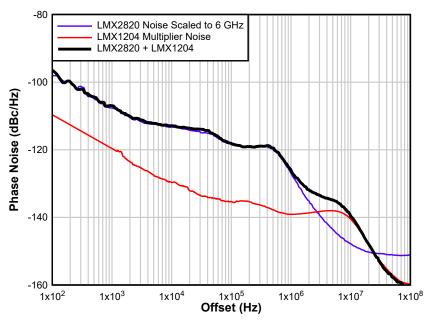

| V <sub>SYSREFIN</sub> | Voltage input range              | AC differential voltage                  | Э                                                            | 0.8  |      | 2    | Vpp  |