## LMR36520 SIMPLE SWITCHER® 4.2V ~ 65V、2A 同期整流降圧コンバータ

### 1 特長

- 信頼性が高く堅牢なアプリケーション向けに設計

- 最大 70V の過渡入力に対する保護

- 保護機能: サーマルシャットダウン、入力低電圧誤動作防止、サイクル単位の電流制限、ヒップ短絡保護

- スケーラブルな産業用電源に対応した設計

- 次の製品とピン互換:

- LMR36510 (65V、1A)

- LMR33610、LMR33620、LMR33630、LMR33640 (36V、1A、2A、3A、または4A)

- 補償機能を内蔵していることが、設計サイズの小型化、コストの削減、設計の複雑さの低減に貢献

- 400kHz 周波数

- 広い変換範囲

- 入力電圧範囲: 4.2V ~ 65V

- 出力電圧範囲: 1V から  $V_{IN}$  の 95% まで

- 負荷スペクトル全体で低消費電力

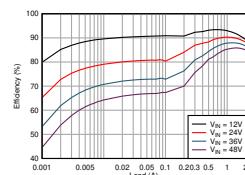

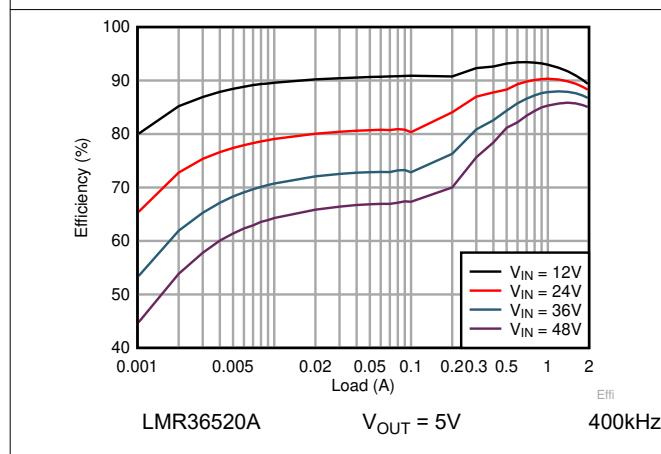

- 90% の効率: 24V<sub>IN</sub>、5V<sub>OUT</sub>、1A、400kHz 時

- PFM モードでの軽負荷効率の向上

- 低い動作時静止電流: 26μA

- フィルタおよび遅延リリース付きのパワー グッド出力

### 2 アプリケーション

- IP ネットワーク カメラ

- アナログ セキュリティ カメラ

- HVAC (空調) バルブおよびアクチュエータの制御

- AC ドライブとサーボ ドライブの制御モジュール

- アナログ入力モジュールと混在 IO モジュール

- $V_{IN}$  が広い汎用電源

効率と出力電流との関係  $V_{OUT} = 5V$ 、400kHz

### 3 説明

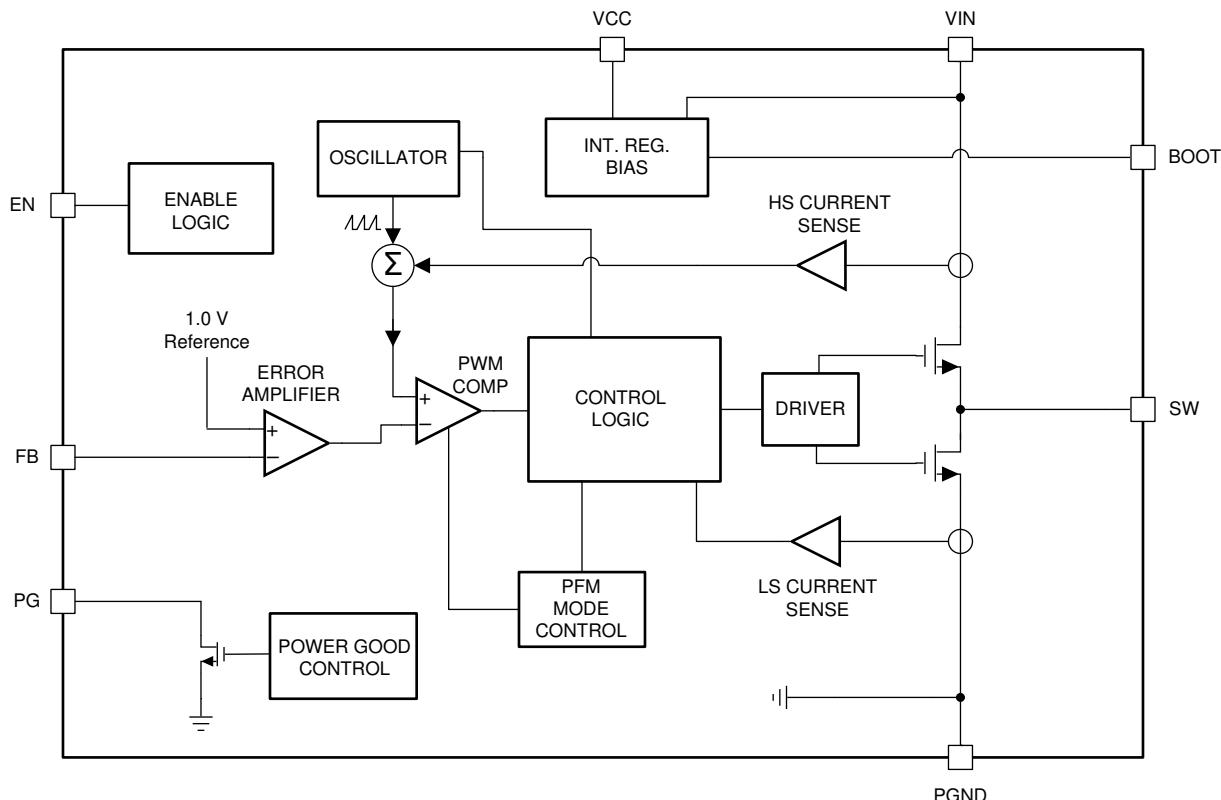

LMR36520 レギュレータは、使いやすい同期整流降圧 DC/DC SIMPLE SWITCHER パワー コンバータです。ハイサイドとローサイドのパワー MOSFET が内蔵されており、4.2V ~ 65V の広い入力電圧範囲にわたって最大 2A の出力電流を供給できます。最大 70V の過渡耐性により、過電圧から保護したり IEC 61000-4-5 のサージ耐性要件を満たしたりするために必要な設計作業やコストが軽減されます。

LMR36520 はピーク電流モード制御を採用し、卓越した効率と出力電圧精度を実現しています。高精度インエーブルを使って幅広い入力電圧と直接接続でき、またデバイスのスタートアップとシャットダウンを精密に制御できるため、設計の柔軟性を高めることができます。パワー グッド フラグと内蔵のフィルタ処理および遅延により、システムの実際の状態を示すことができ、外部スーパーバイザが不要になります。

高度な統合と内部補償により、多くの外付け部品が不要で、PCB レイアウトが単純になるようにピン配置が設計されています。デバイスの豊富な機能セットは、広範な最終製品を簡単に実装できるように設計されています。LMR36520 は LMR36510 (65V、1A) および LMR33610、LMR33620、LMR33630、LMR33640 (36V、1A、2A、3A、4A) とピン互換であり、最新の SIMPLE SWITCHER パワー コンバータ ファミリを構成しています。この互換性により入力電圧範囲の広いコンバータの使いやすさと拡張性が向上し、基板レイアウトの変更を必要とせずに、さまざまな一般的な定格電圧電流に対応します。結果として、全体的なコスト、設計の労力、開発期間を最適化できます。

LMR36520 は、8 ピンの HSOIC パッケージで供給されます。

#### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| LMR36520 | DDA (HSOIC, 8)       | 4.9mm × 6mm              |

(1) 詳細については、セクション 11 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

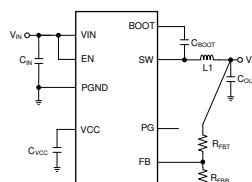

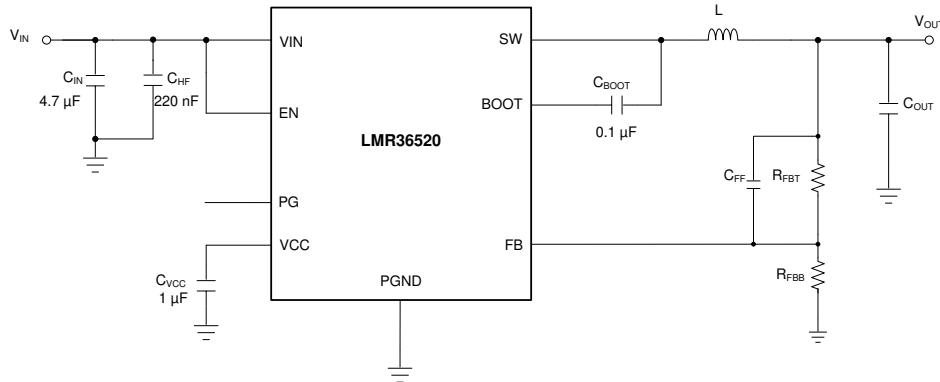

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SNVSBF0

## 目次

|                 |    |                        |    |

|-----------------|----|------------------------|----|

| 1 特長            | 1  | 7.4 デバイスの機能モード         | 14 |

| 2 アプリケーション      | 1  | 8 アプリケーションと実装          | 17 |

| 3 説明            | 1  | 8.1 アプリケーション情報         | 17 |

| 4 デバイス比較表       | 3  | 8.2 代表的なアプリケーション       | 17 |

| 5 ピン構成および機能     | 4  | 8.3 設計のベスト プラクティス      | 26 |

| 6 仕様            | 5  | 8.4 電源に関する推奨事項         | 27 |

| 6.1 絶対最大定格      | 5  | 8.5 レイアウト              | 27 |

| 6.2 ESD Ratings | 5  | 9 デバイスおよびドキュメントのサポート   | 30 |

| 6.3 推奨動作条件      | 5  | 9.1 デバイス サポート          | 30 |

| 6.4 熱に関する情報     | 6  | 9.2 ドキュメントのサポート        | 30 |

| 6.5 電気的特性       | 6  | 9.3 ドキュメントの更新通知を受け取る方法 | 30 |

| 6.6 タイミング要件     | 7  | 9.4 サポート・リソース          | 30 |

| 6.7 スイッチング特性    | 7  | 9.5 商標                 | 30 |

| 6.8 システム特性      | 8  | 9.6 静電気放電に関する注意事項      | 31 |

| 6.9 代表的特性       | 9  | 9.7 用語集                | 31 |

| 7 詳細説明          | 10 | 10 改訂履歴                | 31 |

| 7.1 概要          | 10 | 11 メカニカル、パッケージ、および注文情報 | 31 |

| 7.2 機能ブロック図     | 10 | 11.1 テープおよびリール情報       | 31 |

| 7.3 機能説明        | 10 |                        |    |

## 4 デバイス比較表

| 発注用製品型番        | CURRENT | FPWM | f <sub>SW</sub> |

|----------------|---------|------|-----------------|

| LMR36520ADDAR  | 2A      | なし   | 400kHz          |

| LMR36520FADDAR | 2A      | あり   | 400kHz          |

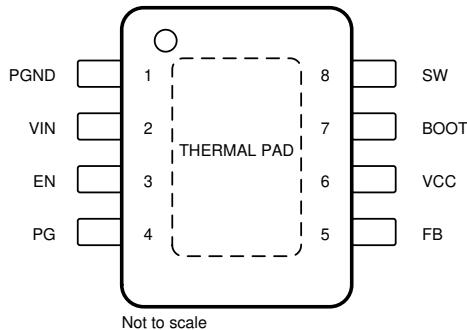

## 5 ピン構成および機能

図 5-1. 8 ピン HSOIC DDA パッケージ (上面図)

表 5-1. ピンの機能

| ピン   |          | タイプ | 説明                                                                                                                                  |

|------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号       |     |                                                                                                                                     |

| PGND | 1        | G   | 電源およびアナログ グランドピン。短く幅の広いトレースを使用してバイパスコンデンサに接続します。内部リファレンスおよびロジック用のグランドリファレンスです。すべての電気的バラメータは、このピンを基準に測定されます。                         |

| VIN  | 2        | P   | レギュレータへの入力電源。高品質のバイパスコンデンサまたはコンデンサをこのピンと PGND に直接接続します。                                                                             |

| EN   | 3        | A   | レギュレータへのイネーブル入力。High = オン、Low = オフ。VIN に直接接続可能。フローティングにしないでください。                                                                    |

| PG   | 4        | A   | オープンドレインのパワー グッド フラグ出力。電流制限抵抗を介して、このピンを適切な電圧源に接続します。High = パワー OK、Low = フォルト。EN = Low のとき、このフラグは low にプルされます。使用しない場合は、フローティングにできます。 |

| FB   | 5        | A   | レギュレータへの帰還入力。帰還電圧分圧回路のタップポイントに接続します。フローティングにはしないでください。接続しないでください。                                                                   |

| VCC  | 6        | P   | 内部 5V LDO 出力。内部制御回路への電源として使用されます。外部負荷に接続しないでください。パワーグッド フラグのロジック電源として使用できます。このピンと PGND との間に高品質の 1 $\mu$ F コンデンサを接続します。              |

| BOOT | 7        | P   | 内部ハイサイドドライバのブートストラップ電源電圧。このピンと SW ピンとの間に高品質の 100nF コンデンサを接続します。                                                                     |

| SW   | 8        | P   | レギュレータのスイッチ ノード。パワー インダクタに接続します。                                                                                                    |

| PAD  | サーマル パッド | 熱   | デバイスの主要な放熱パス。グランド プレーンに直接熱的に接続する必要があります。PAD は電気的相互接続を意図していません。電気的特性は指定されていません。                                                      |

A = アナログ、P = 電源、G = グランド

## 6 仕様

### 6.1 絶対最大定格

接合部温度  $-40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  の範囲において (特に記述のない限り)<sup>(1)</sup>

|                 |                         | 最小値  | 最大値  | 単位                 |

|-----------------|-------------------------|------|------|--------------------|

| 入力電圧            | VIN から PGND へ           | -0.3 | 70   | V                  |

| 入力電圧            | EN から PGND              | -0.3 | 70.3 | V                  |

| 入力電圧            | FB から PGND              | -0.3 | 5.5  | V                  |

| 入力電圧            | PG から PGND              | -0.3 | 20   | V                  |

| 出力電圧            | SW～PGND                 | -0.3 | 70.3 | V                  |

| 出力電圧            | SW から PGND (過渡 10ns 未満) | -3.5 | 70   | V                  |

| 出力電圧            | SW に対する CBOOT           | -0.3 | 5.5  | V                  |

| 出力電圧            | VCC から PGND へ           | -0.3 | 5.5  | V                  |

| 接合部温度 $T_J$     |                         | -40  | 150  | $^{\circ}\text{C}$ |

| 保管温度、 $T_{stg}$ |                         | -65  | 150  | $^{\circ}\text{C}$ |

(1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、「推奨動作条件」に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 6.2 ESD Ratings

|             |      |                                                              | 値                       | 単位 |

|-------------|------|--------------------------------------------------------------|-------------------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM) <sup>(1)</sup><br>デバイス帶電モデル (CDM) <sup>(2)</sup> | $\pm 2500$<br>$\pm 750$ | V  |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  において (特に記述のない限り)<sup>(1)</sup>

|      |                           | 最小値 | 最大値 | 単位 |

|------|---------------------------|-----|-----|----|

| 入力電圧 | VIN から PGND へ             | 4.2 | 65  | V  |

|      | EN から PGND <sup>(2)</sup> | 0   | 65  | V  |

|      | PG から PGND <sup>(2)</sup> | 0   | 18  | V  |

| 出力電圧 | $V_{\text{OUT}}$          | 1   | 28  | V  |

| 出力電流 | $I_{\text{OUT}}$          | 0   | 2   | A  |

(1) 推奨動作条件は本デバイスが機能する条件を示していますが、特定の性能限界を指定するものではありません。指定される仕様については、「電気的特性」を参照してください。

(2) このピンの電圧は、VIN ピンの電圧が 0.3V 以上超えないようにする必要があります。

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                   | LMR36520    | 単位   |

|----------------------|-------------------|-------------|------|

|                      |                   | DDA (HSOIC) |      |

|                      |                   | 8 ピン        |      |

| $R_{\theta JA}$      | 接合部から周囲への热抵抗      | 42.9        | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への热抵抗 | 54          | °C/W |

| $R_{\theta JB}$      | 接合部から基板への热抵抗      | 13.6        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 4.3         | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 13.8        | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への热抵抗 | 4.3         | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体およびIC パッケージの热評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

特に記述のない限り、各制限値は動作時の接合部温度 ( $T_J$ ) 範囲 (-40°C ~ +125°C) にわたって適用されます。最小値および最大値<sup>(1)</sup>は、試験、設計、および統計的相關に基づいて規定されています。標準値は  $T_J = 25^\circ\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。  $V_{IN} = 24\text{V}$ 。

| パラメータ                   |                                  | テスト条件                                   | 最小値   | 標準値   | 最大値   | 単位 |

|-------------------------|----------------------------------|-----------------------------------------|-------|-------|-------|----|

| <b>電源電圧 (VIN ピン)</b>    |                                  |                                         |       |       |       |    |

| $I_{Q-nonSW}$           | 動作静止電流 (スイッチングなし) <sup>(2)</sup> | $V_{EN} = 3.3\text{V}$ (PFM バリエントのみ)    | 26    | 36    |       | μA |

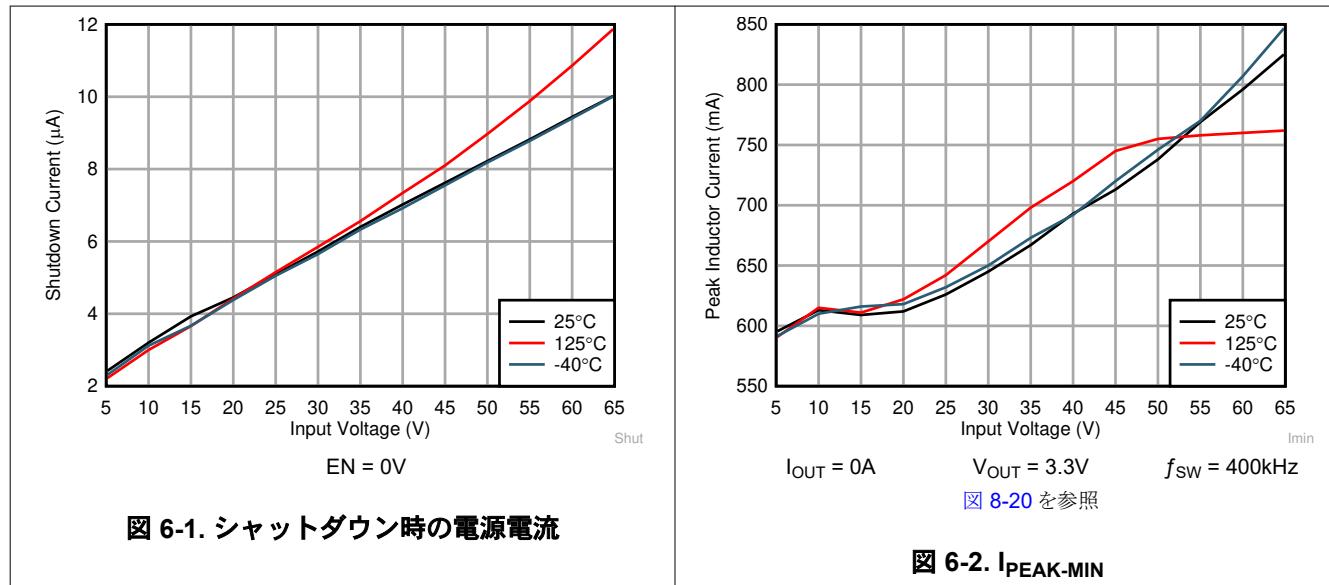

| $I_{SD}$                | シャットダウン時の静止電流 (VIN ピンで測定)        | $V_{EN} = 0\text{V}$                    |       | 5.3   |       | μA |

| <b>イネーブル (EN ピン)</b>    |                                  |                                         |       |       |       |    |

| $V_{EN-VCC-H}$          | $V_{CC}$ 出力のイネーブル入力 High レベル     | $V_{ENABLE}$ 立ち上がり                      |       | 1.14  |       | V  |

| $V_{EN-VCC-L}$          | $V_{CC}$ 出力のイネーブル入力 Low レベル      | $V_{ENABLE}$ 立ち下がり                      | 0.3   |       |       | V  |

| $V_{EN-VOUT-H}$         | $V_{OUT}$ のイネーブル入力 High レベル      | $V_{ENABLE}$ 立ち上がり                      | 1.157 | 1.231 | 1.3   | V  |

| $V_{EN-VOUT-HYS}$       | $V_{OUT}$ のイネーブル入力ヒステリシス         | $V_{ENABLE-H}$ の下のヒステリシス、立ち下がり          |       | 110   |       | mV |

| $I_{LKG-EN}$            | イネーブル入力リーク電流                     | $V_{EN} = 3.3\text{V}$                  |       | 2.7   |       | nA |

| <b>内部 LDO (VCC ピン)</b>  |                                  |                                         |       |       |       |    |

| $V_{CC}$                | 内部 $V_{CC}$ 電圧                   | $6\text{V} \leq V_{IN} \leq 65\text{V}$ | 4.75  | 5     | 5.25  | V  |

| $V_{CC-UVLO-Rising}$    | 内部 $V_{CC}$ 低電圧誤動作防止             | $V_{CC}$ 立ち上がり                          | 3.6   | 3.8   | 4.0   | V  |

| $V_{CC-UVLO-Falling}$   | 内部 $V_{CC}$ 低電圧誤動作防止             | $V_{CC}$ 立ち下がり                          | 3.1   | 3.3   | 3.5   | V  |

| <b>電圧リファレンス (FB ピン)</b> |                                  |                                         |       |       |       |    |

| $V_{FB}$                | 帰還電圧                             |                                         | 0.985 | 1     | 1.015 | V  |

| $I_{LKG-FB}$            | フィードバックリリーク電流                    | $FB = 1\text{V}$                        |       | 2.1   |       | nA |

| <b>電流制限およびヒップ</b>       |                                  |                                         |       |       |       |    |

| $I_{SC}$                | ハイサイド電流制限 <sup>(3)</sup>         |                                         | 2.4   | 3     | 3.6   | A  |

| $I_{LS-LIMIT}$          | ローサイド電流制限 <sup>(3)</sup>         |                                         | 1.8   | 2.3   | 2.8   | A  |

| $I_{L-ZC}$              | ゼロクロス検出のスレッショルド                  | PFM バリエントのみ                             |       | 0.04  |       | A  |

| $I_{PEAK-MIN}$          | 最小インダクタピーク電流 <sup>(3)</sup>      |                                         |       | 0.59  |       | A  |

| $I_{L-NEG}$             | 負の電流制限 <sup>(3)</sup>            | FPWM バリエントのみ                            |       | -1.7  |       | A  |

## 6.5 電気的特性 (続き)

特に記述のない限り、各制限値は動作時の接合部温度 ( $T_J$ ) 範囲 (-40°C ~ +125°C) にわたって適用されます。最小値および最大値 (1) は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^\circ\text{C}$  における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 24\text{V}$ 。

| パラメータ                    |                                | テスト条件                   | 最小値  | 標準値  | 最大値  | 単位               |

|--------------------------|--------------------------------|-------------------------|------|------|------|------------------|

| <b>パワーグッド (PGOOD ピン)</b> |                                |                         |      |      |      |                  |

| $V_{PG-HIGH-UP}$         | パワーグッドの上側スレッショルド - 立ち上がり       | % of FB voltage         | 105% | 107% | 110% |                  |

| $V_{PG-LOW-DN}$          | パワーグッドの下側スレッショルド - 立ち下がり       | % of FB voltage         | 90%  | 93%  | 95%  |                  |

| $V_{PG-HYS}$             | パワーグッド ヒステリシス (立ち上がり、および立ち下がり) | % of FB voltage         |      | 1.5% |      |                  |

| $V_{PG-VALID}$           | 正常なパワーグッド機能のための最小入力電圧          |                         |      | 2    |      | V                |

| $R_{PG}$                 | パワーグッドのオン抵抗                    | $V_{EN} = 2.5\text{V}$  | 80   | 165  |      | $\Omega$         |

| $R_{PG}$                 | パワーグッドのオン抵抗                    | $V_{EN} = 0\text{V}$    | 35   | 90   |      | $\Omega$         |

| <b>MOSFETS</b>           |                                |                         |      |      |      |                  |

| $R_{DS-ON-HS}$           | 下限側 MOSFET オン抵抗                | $I_{OUT} = 0.5\text{A}$ | 245  | 465  |      | $\text{m}\Omega$ |

| $R_{DS-ON-LS}$           | 上限側 MOSFET オン抵抗                | $I_{OUT} = 0.5\text{A}$ | 165  | 310  |      | $\text{m}\Omega$ |

- (1) 最小および最大の制限値は 25°C で 100% 製造テスト済みです。全動作温度範囲における制限値は、統計的品質管理 (SQC) 手法を使って相関により検証しています。

これらの制限値を使って、平均出検品質限界 (AOQL) を計算しています。

- (2) これは、デバイスの開ループが使用する電流です。この値は、レギュレーション中にシステムに流れ込む入力電流の合計を示すものではありません。

- (3) この表の電流制限値は、開ループでテスト済みであり、量産時に使用されます。これらの値は、閉ループ アプリケーションで見られるものとは異なる場合があります。

## 6.6 タイミング要件

特に記述のない限り、各制限値は動作時の接合部温度 ( $T_J$ ) 範囲 (-40°C ~ +125°C) にわたって適用されます。最小値および最大値 (1) は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^\circ\text{C}$  における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 24\text{V}$ 。

|               |             | 最小値 | 公称値 | 最大値 | 単位            |

|---------------|-------------|-----|-----|-----|---------------|

| $t_{ON-MIN}$  | 最小スイッチ オン時間 |     | 92  |     | ns            |

| $t_{OFF-MIN}$ | 最小スイッチ オフ時間 |     | 80  | 102 | ns            |

| $t_{ON-MAX}$  | 最大スイッチ オン時間 |     | 7   | 12  | $\mu\text{s}$ |

| $t_{SS}$      | 内部ソフトスタート時間 | 3   | 4.5 | 6   | ms            |

- (1) 最小および最大の制限値は 25°C で 100% 製造テスト済みです。全動作温度範囲における制限値は、統計的品質管理 (SQC) 手法を使って相関により検証しています。

これらの制限値を使って、平均出検品質限界 (AOQL) を計算しています。

## 6.7 スイッチング特性

$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $V_{IN} = 24\text{V}$  (特に記述のない限り)

| パラメータ      |           | テスト条件        | 最小値 | 標準値 | 最大値 | 単位  |

|------------|-----------|--------------|-----|-----|-----|-----|

| <b>発振器</b> |           |              |     |     |     |     |

| $F_{osc}$  | 内部発振器の周波数 | 400kHz バリエント | 340 | 400 | 460 | kHz |

## 6.8 システム特性

以下の仕様は、標準的なアプリケーション回路に適用され、コンポーネントの公称値が設定されています。「代表値 (TYP)」列の仕様は、 $T_J = 25^\circ\text{C}$  にのみ適用されます。最小値および最大値列の仕様は、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  の温度範囲での標準的な部品の場合に適用されます。これらの仕様は、製造試験では規定されていません。

| パラメータ        | テスト条件                            | 最小値                                                                                                                 | 標準値   | 最大値  | 単位               |

|--------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|------|------------------|

| $V_{IN}$     | 動作時入力電圧範囲                        |                                                                                                                     | 4.2   | 65   | V                |

| $V_{OUT}$    | 可変出力電圧レギュレーション <sup>(1)</sup>    | PFM動作                                                                                                               | -1.5% | 2.5% |                  |

| $V_{OUT}$    | 可変出力電圧レギュレーション <sup>(1)</sup>    | FPWM動作                                                                                                              | -1.5% | 1.5% |                  |

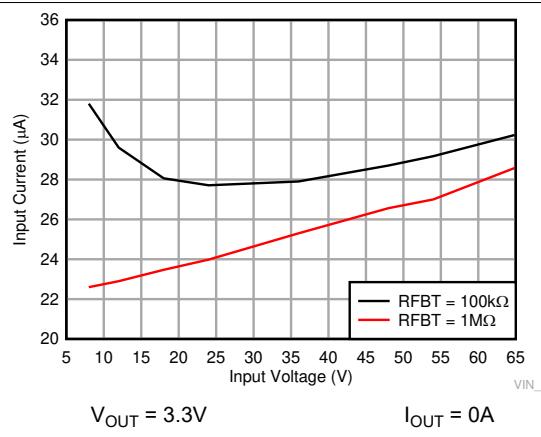

| $I_{SUPPLY}$ | レギュレーション時の入力電源電流                 | $V_{IN} = 24\text{V}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、<br>$R_{FBT} = 1\text{M}\Omega$ 、PFM バリエント |       | 26   | $\mu\text{A}$    |

| $D_{MAX}$    | 最大スイッチ デューティ サイクル <sup>(2)</sup> |                                                                                                                     | 98%   |      |                  |

| $V_{HC}$     | 短絡ヒップモードのトリップに必要な FB ピン電圧        |                                                                                                                     | 0.4   |      | V                |

| $t_D$        | スイッチ電圧デッドタイム                     |                                                                                                                     | 2     |      | ns               |

| $T_{SD}$     | サーマル シャットダウン温度                   | シャットダウン温度                                                                                                           | 170   |      | $^\circ\text{C}$ |

| $T_{SD}$     | サーマル シャットダウン温度                   | 復帰温度                                                                                                                | 158   |      | $^\circ\text{C}$ |

(1) 全負荷時、 $V_{IN} = 24\text{V}$ 、 $I_{OUT} = 0\text{A}$  における  $V_{OUT}$  の公称出力電圧値からの偏差

(2) ドロップアウト時にはスイッチング周波数が低下し、実効デューティ サイクルが増加します。最小周波数は、およそ以下に示す値でクランプされます。 $F_{MIN} = 1 / (t_{ON-MAX} + t_{OFF-MIN})$ 。 $D_{MAX} = t_{ON-MAX} / (t_{ON-MAX} + t_{OFF-MIN})$ 。

## 6.9 代表的特性

特記のない限り、次の条件が適用されます。 $T_A = 25^\circ\text{C}$ 、および  $V_{IN} = 24\text{V}$ 。

## 7 詳細説明

### 7.1 概要

LMR36520 は、さまざまな産業用アプリケーション向けに設計された同期整流ピーク電流モード降圧レギュレータです。このレギュレータは、負荷に応じて PFM モードと PWM モードを自動的に切り替えます。負荷が大きい場合、このデバイスは PWM モードで一定のスイッチング周波数で動作します。軽負荷時には、ダイオード エミュレーションによる PFM モードに変更され、DCM が可能になります。これにより、入力供給電流が低減され、高い効率が維持されます。このデバイスはループ補償機能を内蔵しているため、設計時間を短縮でき、外部補償式のレギュレータに比べて必要な外付け部品が少なくて済みます。

### 7.2 機能ブロック図

### 7.3 機能説明

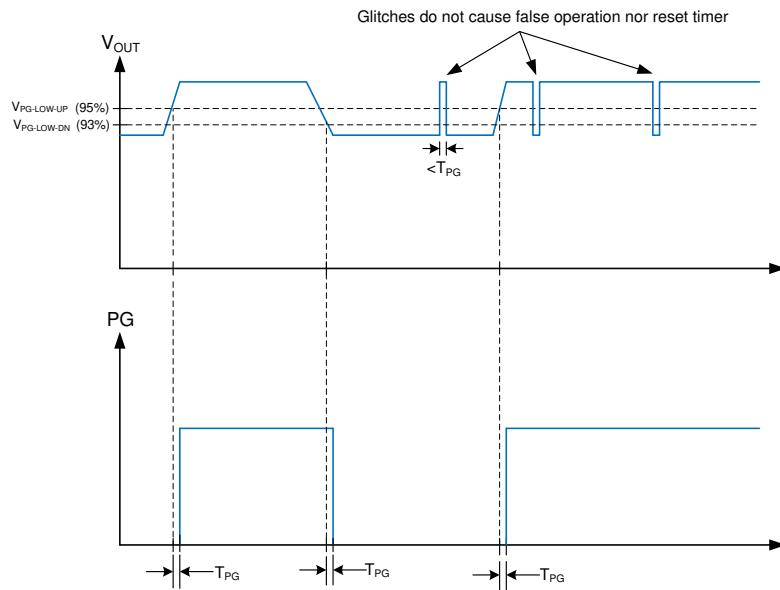

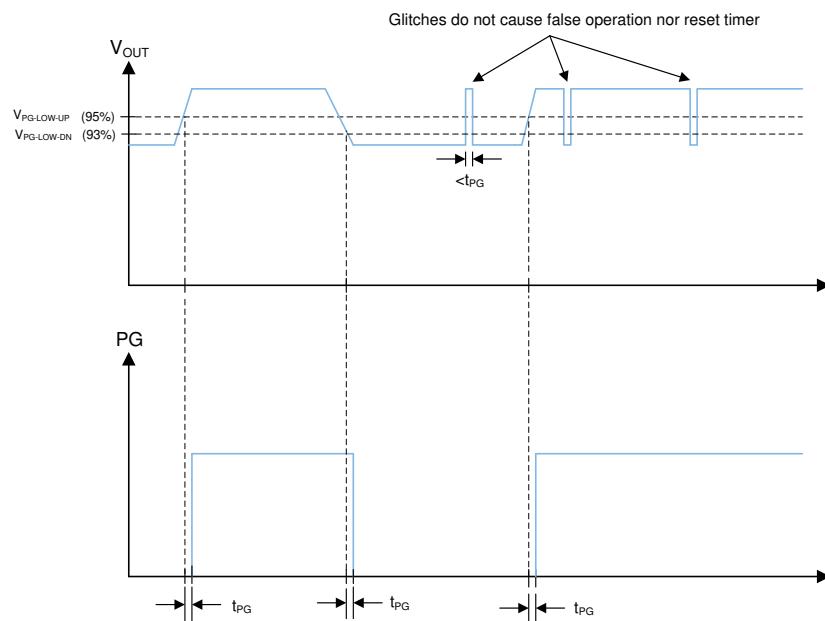

#### 7.3.1 パワー グッド フラグの出力

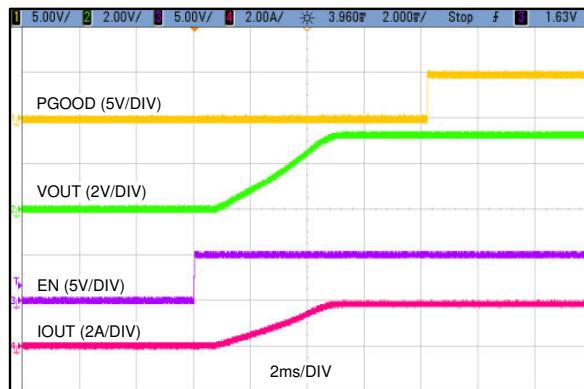

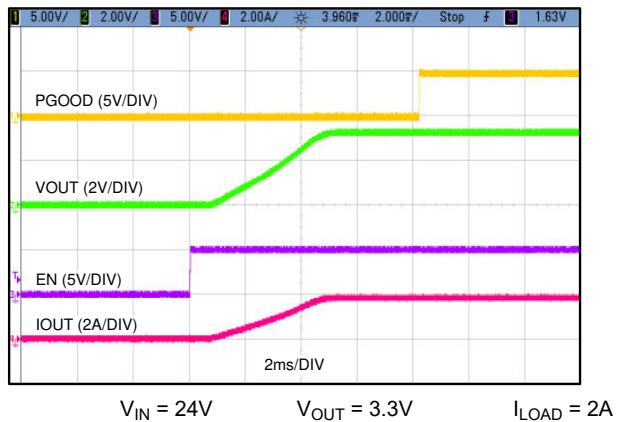

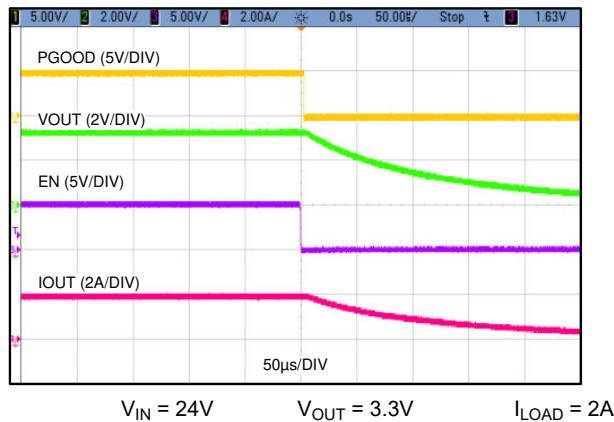

LMR36520 デバイスのパワー グッド フラグ出力機能 (PG 出力ピン) を使用すると、出力電圧が規定範囲外になったときにシステムマイクロプロセッサをリセットできます。通常の起動中だけでなく、フォルト条件 (電流制限、サーマル シャットダウンなど) の際も、このオープンドレイン出力は **Low** に維持されます。グリッチ フィルタは、出力電圧の短時間の変動 (ラインおよび負荷過渡時など) に対するフラグの誤動作を防止します。 $t_{PG}$  よりも短い出力電圧変動では、パワー グッド フラグは立ちません。**図 7-1** および **図 7-2** に、パワー グッド動作を分かりやすく図示します。最初の電源投入時には、EN がアサートされてからパワー グッド フラグが **High** になるまでに約 4ms (標準値) の遅延が挿入されることにご注意ください。この遅延は起動時にのみ発生し、パワー グッド機能の通常動作中は発生しません。

パワー グッド出力はオープンドレインの NMOS で構成されており、外付けプルアップ抵抗を適切なロジック電源へ接続する必要があります。パワー グッド出力は、必要に応じて適切な抵抗を介して VCC または  $V_{OUT}$  にプルアップすることができます。この機能が不要な場合は、PG ピンをグランドに接続しなければなりません。EN が **Low** にプルされると、フラグ出力も **Low** に強制されます。EN が **Low** の場合、入力電圧が 2V 以上 (標準値) である限り、パワー グッドは有効です。このピンに流れ込む電流は、4mA 以下に制限します。

図 7-1. 静的パワー グッド動作

図 7-2. パワー グッドのタイミング動作

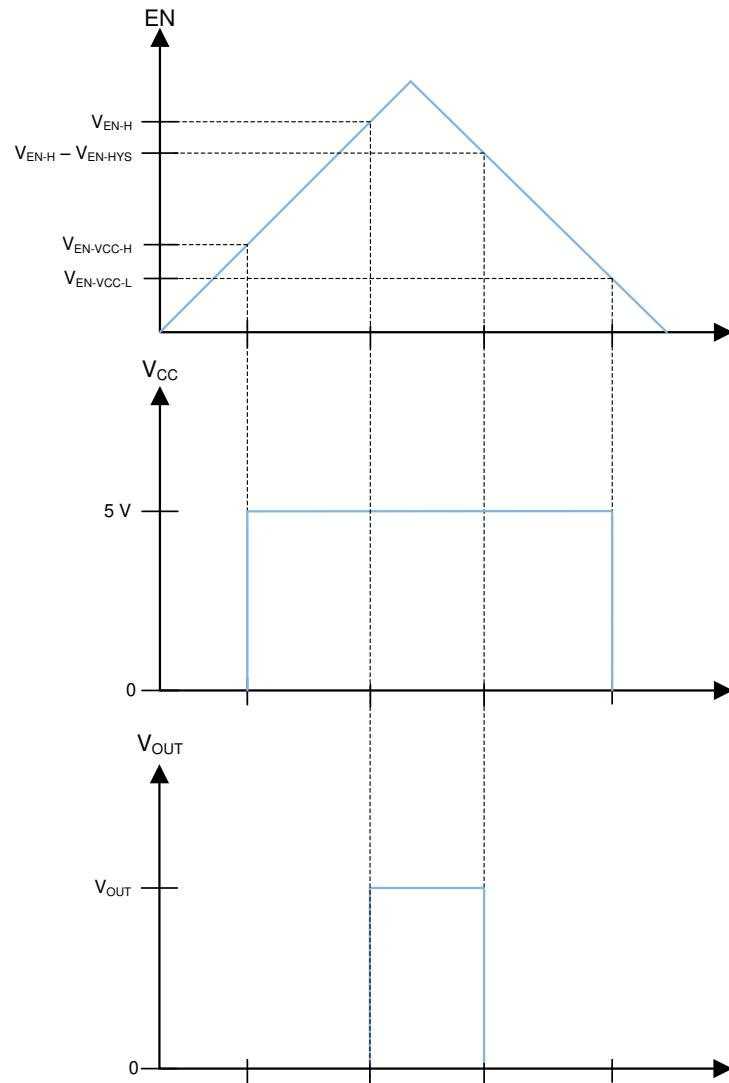

### 7.3.2 イネーブルおよびスタートアップ

起動とシャットダウンは、EN 入力により制御されます。この入力には高精度のスレッショルドが搭載されており、外付け分割電圧を使用して可変の入力 UVLO を行えます（[セクション 8.2.1.2.9](#) セクションを参照）。 $V_{EN-VCC\_H}$  以上の電圧を印加すると、デバイスはスタンバイモードに移行し、内部 VCC に電力を供給しますが、出力電圧は生成しません。EN 電圧を  $V_{EN-H}$  に上げると、本デバイスが完全にイネーブルされ、本デバイスは起動モードに移行し、ソフトスタート期間を開始できます。EN 入力が  $V_{EN-H}$  を  $V_{EN-HYS}$  下回ると、レギュレータは動作を停止し、スタンバイモードに移行します。EN 電圧が  $V_{EN-VCC-L}$  を下回ると、デバイスはシャットダウンします。[図 7-3](#) にこの動作を示します。この機能が必要ない場合は、EN 入力を VIN に直接接続できます。この入力をフローティングにすることはできません。各種の EN スレッショルドの値については、[電気的特性表](#)を参照してください。

LMR36520 は、レギュレータの起動中の出力電圧のオーバーシュートと大きな突入電流を防止するため、基準電圧を使ったソフトスタートを採用しています。

図 7-3. 高精度イネーブルの動作

図 7-4. 標準的なスタートアップ動作  $V_{IN} = 24V$ 、 $V_{OUT} = 5V$ 、 $I_{OUT} = 2A$

### 7.3.3 電流制限と短絡

LMR36520 は、通常の過負荷と短絡保護のためのバレー電流制限機能を内蔵しています。さらに、ピーク電流制限回路により、ハイサイド パワー MOSFET が過剰な電流から保護されています。過負荷にはサイクル単位の電流制限が使用され、短絡にはヒップ モードが使用されます。最後に、ローサイド パワー MOSFET にゼロ電流検出器を使用して、軽負荷時にダイオード エミュレーションを実装します (セクション 9.7 を参照)。

過負荷時、ローサイド電流制限  $I_{LIMIT}$  によって LMR36520 が供給できる最大負荷電流が決まります。ローサイド スイッチがオンになると、インダクタ電流は減少し始めます。電流が次のターンオン サイクルの前に  $I_{LIMIT}$  を下回ることがなければ、そのサイクルはスキップされ、ローサイド MOSFET はオンのままになり、電流が  $I_{LIMIT}$  を下回るまでオンのままとなります。これは、より標準的なピーク電流制限とは少し異なりますが、この結果、負荷電流の最大値は 式 1 のとおりになります。

$$I_{OUT|_{max}} = I_{LIMIT} + \frac{(V_{IN} - V_{OUT})}{2 \cdot f_{SW} \cdot L} \cdot \frac{V_{OUT}}{V_{IN}} \quad (1)$$

ここで、

- $f_{SW}$  = スイッチング周波数

- $L$  = インダクタの値

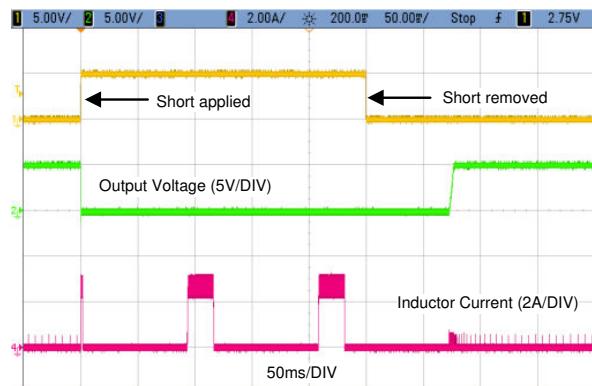

電流制限中に短絡が発生して FB 入力の電圧が約 0.4V を下回ると、本デバイスはヒップ モードに入ります。このモードでは、本デバイスは  $t_{HC}$  または約 94ms の間スイッチングを停止し、その後、ソフトスタートを使って通常の再起動を行います。短絡状態が続く場合、本デバイスは電流制限内で約 20ms (標準値) 動作した後、再度シャットダウンします。このサイクルは短絡状態が続く限り繰り返されます。この動作モードでは、出力で激しい短絡状態が発生したときのデバイスの温度上昇が減少します。もちろん、ヒップ モードでは出力電流が大幅に低下します。出力短絡が解除され、ヒップ 遅延時間が経過すると、出力電圧は正常に回復します。

ピーク インダクタ電流が  $I_{SC}$  に達すると、ハイサイド電流制限がトリップします。これはサイクル単位の電流制限であり、周波数や負荷電流のフォールドバックは発生しません。これは、ハイサイド MOSFET を過剰な電流から保護することを目的としています。高入力電圧などの一部の条件では、この電流制限がローサイド保護の前にトリップする可能性があります。この条件で、 $I_{SC}$  は最大出力電流を決定します。 $I_{SC}$  がデューティサイクルによって変化することにご注意ください。

図 7-5. 短絡過渡と回復

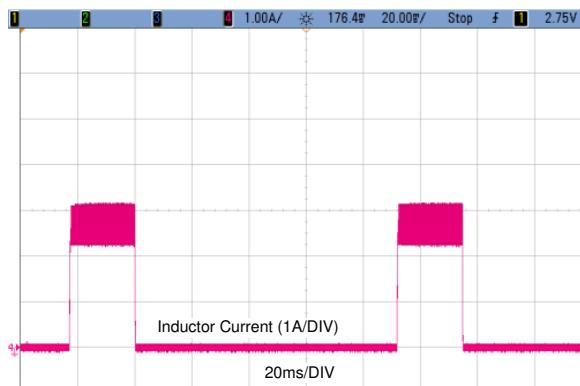

図 7-6. 短絡モードでのインダクタ電流バースト

### 7.3.4 低電圧誤動作防止とサーマルシャットダウン

LMR36520 は、内部 LDO (VCC ピン) の出力に低電圧誤動作防止機能を内蔵しています。VCC が約 3.7V に達すると、デバイスは EN 信号を受信して起動する準備ができる状態になります。VCC が 3V を下回ると、EN の状態に関係なくデバイスはシャットダウンします。これらの遷移中に LDO はドロップアウト状態にあるため、上記の値は遷移中の入力電圧レベルを大まかに表します。

サーマルシャットダウン機能は、過度の接合部温度からレギュレータを保護するために搭載されています。接合部温度が 170°C 付近に達すると、デバイスはシャットダウンし、温度が 158°C 付近に低下すると再起動します。安全な動作を確保するため、サーマルシャットダウン中にデバイスが短絡状態にならないようにしてください。

## 7.4 デバイスの機能モード

### 7.4.1 自動モード

自動モードでは、負荷の変化に応じて、デバイスは PWM と PFM を切り替えます。負荷が小さいとき、レギュレータは PFM で動作します。負荷が大きくなると、モードは PWM に切り替わります。

PWM では、レギュレータは定周波数、電流モード、フル同期整流コンバータとして動作し、PWM を使って出力電圧を安定化します。このモードで動作しているときには、一定の周波数でスイッチングし、デューティサイクルを変調して負荷への電力を制御することにより、出力電圧を安定化します。これにより、優れたラインおよび負荷レギュレーションと、低い出力電圧リップルを実現します。

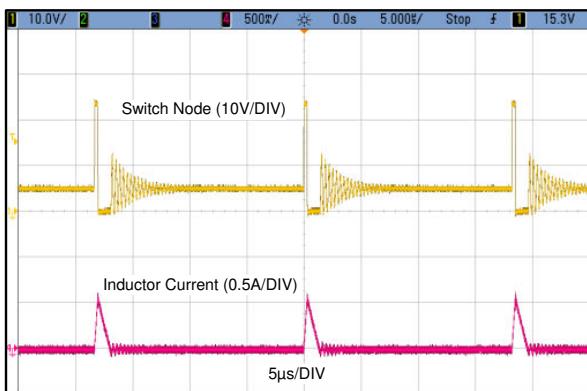

PFM では、1つまたは複数のパルスのバーストによってハイサイド MOSFET がオンになり、負荷にエネルギーを供給します。バースト期間は、インダクタ電流が  $I_{PEAK-MIN}$  に達するまでに要する時間に依存します。このバーストの周波数を調整して出力を安定化するとともに、ダイオードエミュレーションを使って効率を最大化します (セクション 9.7 を参照)。このモードでは、少しの負荷で出力電圧を制御するために必要な入力消費電流の総量を削減することにより、軽負荷の効率を高めることができます。出力電圧リップルの増大およびスイッチング周波数の変動とのトレードオフにより、軽負荷時に非常に良好な効率を実現します。また、軽負荷時には出力電圧がわずかに上昇します。実際のスイッチング周波数と出力電圧リップルは、入力電圧、出力電圧、負荷によって変わります。

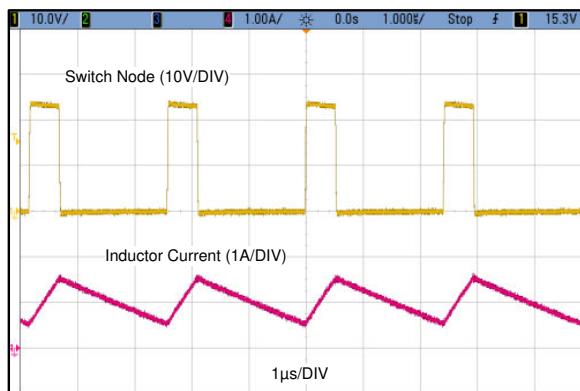

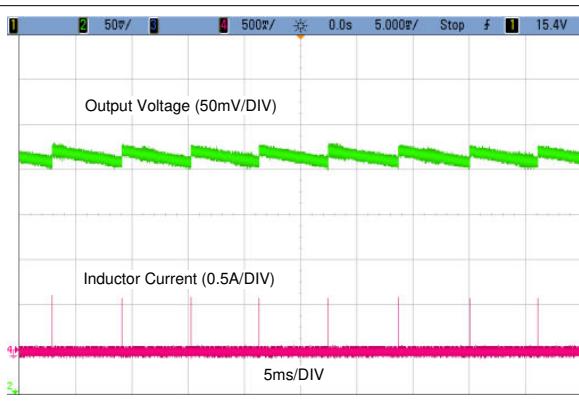

図 7-7. 標準的な PFM スイッチング波形  $V_{IN} = 24V$ 、

$V_{OUT} = 5V$ 、 $I_{OUT} = 50mA$

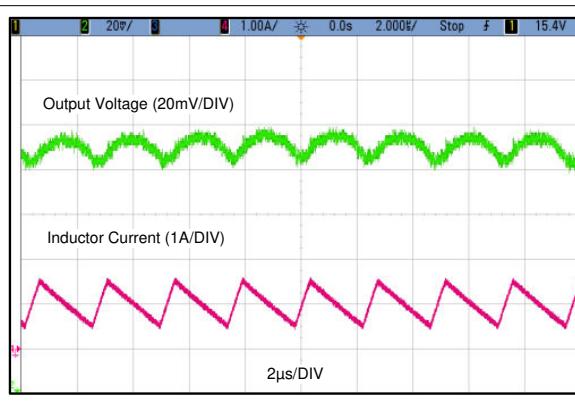

図 7-8. 標準的な PWM スイッチング波形  $V_{IN} = 24V$ 、

$V_{OUT} = 5V$ 、 $I_{OUT} = 1A$ 、 $f_s = 400kHz$

#### 7.4.2 強制 PWM 動作

以下の選択されたバリアントは、軽負荷時の効率よりも一定の周波数動作が重要な場合に備えた工場オプションです。

表 7-1. LMR36520 無負荷時固定周波数で動作するデバイス バリアント

| 発注用製品型番        | 出力電流 | FPWM | $f_{SW}$ |

|----------------|------|------|----------|

| LMR36520FADDAR | 2A   | あり   | 400kHz   |

FPWM 動作では、ダイオード エミュレーション機能がオフになります。これは、軽負荷時にデバイスが CCM に維持されることを意味します。デバイスがレギュレーションを維持するためにオン時間またはオフ時間を保証された最小値よりも短くする必要がある条件下では、レギュレーションに必要な実効デューティ サイクルを維持するために周波数が低下します。これは、入力および出力電圧比が非常に高く、かつ非常に低い場合に発生します。FPWM モードでは、インダクタを流れる逆電流が制限されるため、レギュレータの出力からレギュレータの入力に電力が流れることができます。FPWM モードでは、自動モードよりも軽負荷の場合、より大きな電流がインダクタを通過することに注意します。負荷が十分に重いため CCM 動作が必要になると、FPWM モードはレギュレータの動作に重大な影響はもたらしません。

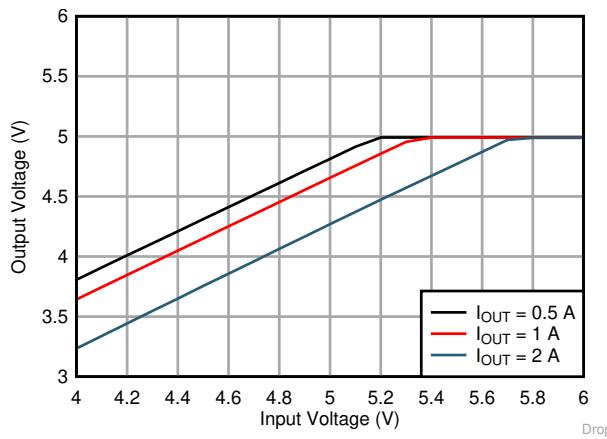

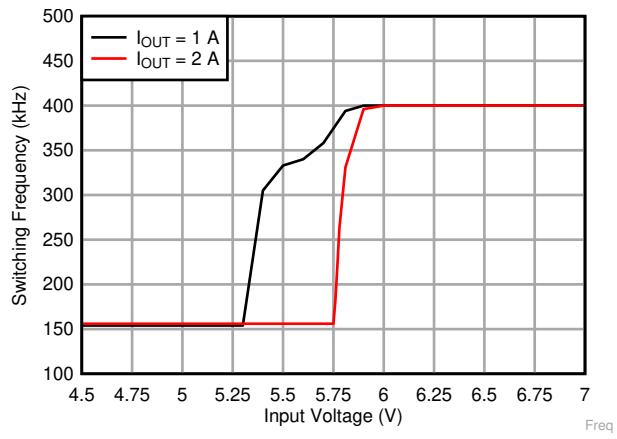

#### 7.4.3 ドロップアウト

降圧レギュレータのドロップアウト性能は、パワー MOSFET の  $D_{SON}$ 、インダクタの DC 抵抗、コントローラが実現できる最大デューティ サイクルの影響を受けます。入力電圧が出力電圧まで低下すると、ハイサイド MOSFET のオフ時間が最小値に近づき始めます。このポイントを超えると、スイッチングが不安定になり、出力電圧が安定化範囲外になる可能性があります。この問題を回避するため、LMR36520 は、スイッチング周波数を自動的に低下させて有効なデューティ サイクルを増加させ、安定化を維持します。このデータシートでは、ドロップアウト電圧は、出力が公称値の 1% 低下したときの入力電圧と出力電圧の差として定義されます。この状況では、スイッチング周波数は最小値である約 140kHz まで低下しています。ドロップアウト モードでは、0.4V の短絡検出スレッショルドはアクティブにならないことに注意してください。

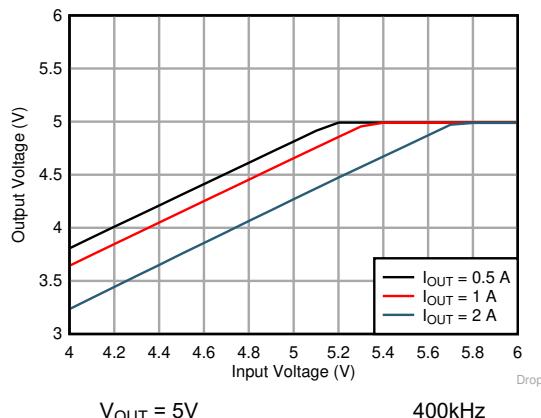

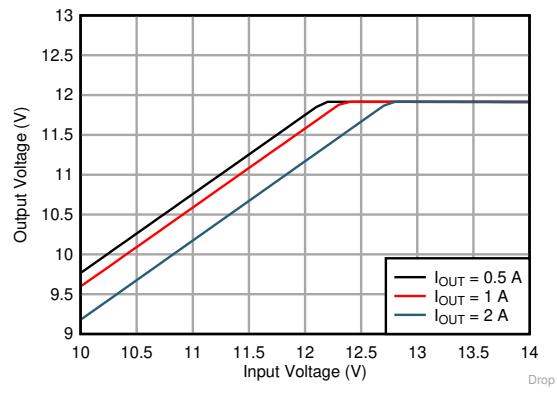

図 7-9. 全体のドロップアウト特性  $V_{OUT} = 5V$ 図 7-10. 周波数ドロップアウト特性  $f_{SW} = 400\text{kHz}$

#### 7.4.4 最小スイッチオン時間

すべてのスイッチングレギュレータには、制御回路に関連する固有の遅延とブランディング時間によって決まる、制御可能なオン時間の最小値があります。これにより、スイッチのデューティサイクルには最小値があるので、変換比にも最小値があります。この制約は、入力電圧が高く出力電圧が低いときに発生します。制御可能な最小デューティサイクルを延長できるように、LMR36520は最小オン時間制限に達するとスイッチング周波数を自動的に低下させます。このようにして、コンバータは、最大入力電圧におけるプログラム可能な最小出力電圧を安定化できます。与えられた出力電圧に対して、周波数フォールドバックが発生する前の入力電圧の概略推定値を式2に示します。入力電圧が高くなると、出力電圧を安定化するためにスイッチオン時間(デューティサイクル)が短くなります。オン時間が制限値に達すると、スイッチング周波数は低下しますが、オン時間は固定されたままです。

$$V_{IN} \leq \frac{V_{OUT}}{t_{ON} \cdot f_{SW}} \quad (2)$$

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LMR36520 降圧 DC/DC コンバータは、2A の最大出力電流で、高い DC 電圧を低い DC 電圧に変換するために使われることが一般的です。以下に示す設計手順を使って LMR36520 の部品を選択できます。

### 注

以下のアプリケーション情報に記載されているすべての容量値は、特に記述のない限り実効値を指しています。実効値は、定格値や銘板値ではなく、DC バイアスおよび温度における実際の容量として定義されます。X7R 以上の誘電体を使用した、高品質で低 ESR のセラミックコンデンサを全体にわたって使用してください。値の大きいセラミックコンデンサは、すべて、通常の許容誤差と温度効果に加えて、電圧係数が大きくなります。DC バイアスを印加すると、静電容量は大幅に低下します。この点については、ケース サイズが大きく、より高い電圧定格のものが望ましいです。これらの影響を軽減するために、複数のコンデンサを並列に使用すれば、最小実効静電容量を必要な値まで大きくすることができます。これにより、個別のコンデンサの RMS 電流要件も緩和されます。実効静電容量の最小値を確保するため、コンデンサ バンクのバイアスおよび温度変動を慎重に検討する必要があります。

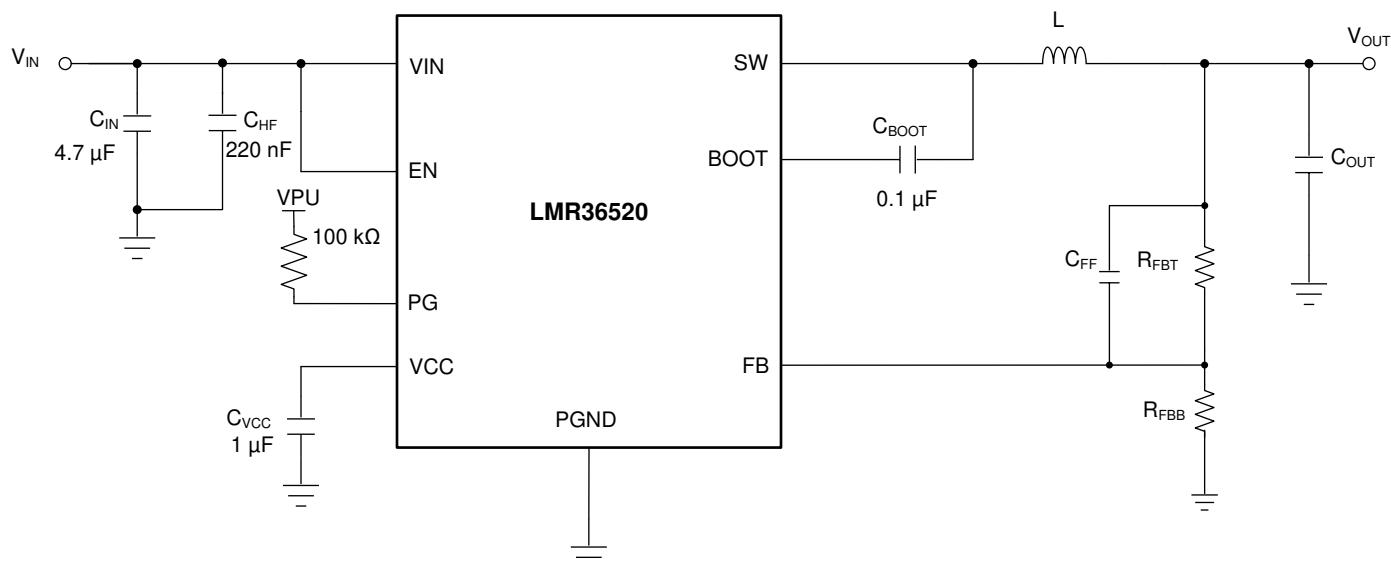

### 8.2 代表的なアプリケーション

に、LMR36520 の代表的なアプリケーション回路を示します。本デバイスは、幅広い外付け部品とシステム パラメータで機能するように設計されています。しかし内部補償は、特定の範囲の外付けインダクタンスおよび出力容量に対して最適化されています。クイック スタート ガイドとして、図 8-1 に最も一般的な出力電圧範囲に対する代表的な部品値を示しています。

図 8-1. アプリケーション回路例

表 8-1. 外付け部品の代表的な値

| $f_{sw}$<br>(kHz) | $V_{OUT}$ (V) | $L$ ( $\mu$ H) | 公称 $C_{OUT}$ (定格容量)<br>(1) | 最小 $C_{OUT}$ (定格容量)<br>(2) | $R_{FBT}$ ( $\Omega$ ) | $R_{FBB}$ ( $\Omega$ ) | $C_{IN}$                    | $C_{FF}$ |

|-------------------|---------------|----------------|----------------------------|----------------------------|------------------------|------------------------|-----------------------------|----------|

| 400               | 3.3           | 6.8            | $3 \times 22\mu$ F         | $3 \times 22\mu$ F         | 100k                   | 43.2k                  | $2 \times 4.7\mu$ F + 220nF | なし       |

| 400               | 5             | 10             | $2 \times 22\mu$ F         | $2 \times 22\mu$ F         | 100k                   | 24.9k                  | $2 \times 4.7\mu$ F + 220nF | なし       |

| 400               | 12            | 33             | $4 \times 10\mu$ F         | $4 \times 10\mu$ F         | 100k                   | 9.09k                  | $2 \times 4.7\mu$ F + 220nF | なし       |

(1) 0 ~ 100% 定格負荷範囲で卓越した負荷過渡特性を実現するように最適化されています。

(2) サイズに制約のある最終アプリケーション向けに最適化されています。

## 8.2.1 設計 1：低消費電力 24V、2A 降圧コンバータ

### 8.2.1.1 設計要件

以下に、代表的な 5V または 3.3V アプリケーションの要件の例を示します。入力電圧は、説明のためにのみここに記載しています。動作時入力電圧範囲については、[セクション 6](#) を参照してください。

表 8-2. 詳細設計パラメータ

| 設計パラメータ           | 数値の例                                     |

|-------------------|------------------------------------------|

| 入力電圧              | 12V ~ 24V の定常状態、4.2V ~ 60V の過渡           |

| 出力電圧              | 5V                                       |

| 最大出力電流            | 0A ~ 2A                                  |

| スイッチング周波数         | 400kHz                                   |

| 0-A 負荷での消費電流      | クリティカル: バッテリドレン低減するために、低消費電流を確保することが必要です |

| 0-A 負荷時のスイッチング周波数 | 重要ではない: 高負荷時の固定周波数動作が必要です                |

表 8-3. 設計 1 の部品リスト

| $V_{OUT}$ | FREQUENCY | $R_{FBB}$      | $C_{OUT}$          | $L$         | U1       |

|-----------|-----------|----------------|--------------------|-------------|----------|

| 5V        | 400kHz    | 24.9k $\Omega$ | $2 \times 22\mu$ F | 10 $\mu$ H  | LMR36520 |

| 3.3V      | 400kHz    | 43.2k $\Omega$ | $3 \times 22\mu$ F | 6.8 $\mu$ H | LMR36520 |

### 8.2.1.2 詳細な設計手順

以下の設計手順は、[図 8-1](#) と [表 8-2](#) に適用されます。

#### 8.2.1.2.1 スイッチング周波数の選択

スイッチング周波数の選択は、変換効率と設計全体のサイズとのトレードオフとなります。LMR36520 のスイッチング周波数は IC 内部に固定されているため、この設計では 400kHz の値が使用されます。

#### 8.2.1.2.2 出力電圧の設定

LMR36520 の出力電圧は、分圧抵抗回路を使用して外部で調整可能です。推奨される出力電圧範囲は、[「推奨動作条件」](#) に記載されています。分圧回路は  $R_{FBT}$  と  $R_{FBB}$  で構成され、出力電圧とコンバータの間のループを閉じています。コンバータは、FB ピン電圧を内部基準電圧 ( $V_{REF}$ ) と同じ電圧に保持することで、出力電圧をレギュレートします。分圧器の抵抗値は、ノイズの過剰な混入と出力の過剰な負荷との折り合いを付けることで決定します。抵抗値を小さくすると、ノイズの影響は小さくなりますが、軽負荷時の効率も低下します。 $R_{FBT}$  の推奨値は 100k $\Omega$  (最大値は 1M $\Omega$ ) です。 $R_{FBT}$  に 1M $\Omega$  を選択する場合、この抵抗の両端にフィードフォワードコンデンサを接続し、十分なループ位相マージンを確保する必要があります ([セクション 8.2.1.2.8](#) セクションを参照)。 $R_{FBT}$  を選択した後、[式 3](#) を使用して  $R_{FBB}$  を選択します。 $V_{REF}$  は公称 1V です。

$$R_{FBB} = \frac{R_{FBT}}{\left[ \frac{V_{OUT}}{V_{REF}} - 1 \right]} \quad (3)$$

この 5V の例では、値は次のとおりです。 $R_{FBT} = 100\text{k}\Omega$ 、および  $R_{FBB} = 24.9\text{k}\Omega$

### 8.2.1.2.3 インダクタの選択

インダクタを選択するためのパラメータはインダクタンスと飽和電流です。目的のピーク ツー ピーク インダクタ リップル電流がデバイスの最大出力電流定格の 20%~40% の範囲に収まるように、インダクタを選択します。経験上、インダクタのリップル電流の最適な値は最大負荷電流の 30% であることがわかっています。このデバイスで利用可能な最大電流よりも最大負荷電流の方がはるかに小さいアプリケーションの場合でも、リップル電流を選択する際はデバイスの最大電流を使用してください。[式 4](#) を使用して、インダクタンスの値を決定することができます。定数  $K$  はインダクタ電流リップルのパーセンテージです。この設計では  $K = 0.4$  を使用します。入力電圧が 24V の場合、 $L = 12.37\mu\text{H}$  のインダクタンスが求められます。 $10\mu\text{H}$  の標準値が選択されます。

$$L = \frac{(V_{IN} - V_{OUT})}{f_{SW} \cdot K \cdot I_{OUT\max}} \cdot \frac{V_{OUT}}{V_{IN}} \quad (4)$$

理想的には、インダクタの飽和電流定格は、ハイサイド スイッチの電流制限値  $I_{SC}$  以上にする必要があります。こうすることで、出力の短絡中でもインダクタが飽和しないようにします。インダクタのコア材が飽和すると、インダクタンスは非常に小さい値に低下し、インダクタ電流は急増します。バレー電流制限値  $I_{LIMIT}$  は、電流が暴走しづらいように設計されているといえ、インダクタが飽和することで電流値が急増する可能性があります。これは部品の損傷につながる可能性があります。したがって、インダクタを飽和させないようにしてください。フェライト コア材を採用したインダクタは飽和特性が非常に急峻ですが、コア損失は通常、圧粉コアよりも小さいです。圧粉コアは穏やかな飽和特性を示すため、インダクタの電流定格をある程度緩和できます。しかし、約 1MHz を上回る周波数では、コア損失が増加します。いずれにしても、インダクタの飽和電流がデバイスのローサイド電流制限値 ( $I_{LIMIT}$ ) よりも小さくならないようにする必要があります。分数調波発振を防止するため、インダクタンス値が[式 5](#) で与えられる値よりも小さくならないようにする必要があります。

$$L_{MIN} \geq M \cdot \frac{V_{OUT}}{f_{SW}} \quad (5)$$

ここで、

- $L_{min}$  = 最小インダクタンス (H)

- $M = 0.42$

- $f_{SW}$  = スイッチング周波数 (Hz)

### 8.2.1.2.4 出力コンデンサの選択

出力コンデンサの値、およびそれぞれの ESR により、出力電圧リップルと負荷過渡性能が決まります。出力コンデンサ バンクは通常、出力電圧リップルではなく負荷過渡要件によって制限されます。[式 6](#) を使用して、合計出力容量の下限と、指定された負荷過渡を満たすのに必要な ESR の上限を推定できます。

$$C_{OUT} \geq \frac{\Delta I_{OUT}}{f_{SW} \cdot \Delta V_{OUT} \cdot K} \cdot \left[ (1-D) \cdot (1+K) + \frac{K^2}{12} \cdot (2-D) \right]$$

$$ESR \leq \frac{(2+K) \cdot \Delta V_{OUT}}{2 \cdot \Delta I_{OUT} \left[ 1+K + \frac{K^2}{12} \cdot \left( 1 + \frac{1}{(1-D)} \right) \right]} \quad (6)$$

$$D = \frac{V_{OUT}}{V_{IN}}$$

ここで、

- $\Delta V_{OUT}$  = 出力電圧過渡

- $\Delta I_{OUT}$  = 出力電流過渡

- $K$  = セクション 8.2.1.2.3 からのリップル係数

出力コンデンサと ESR を計算した後、式 7 を使用して出力電圧リップルをチェックすることができます。

$$V_r \approx \Delta I_L \cdot \sqrt{ESR^2 + \frac{1}{(8 \cdot f_{SW} \cdot C_{OUT})^2}} \quad (7)$$

ここで、

- $V_r$  = ピークツー ピークの出力電圧リップル

出力コンデンサと ESR は、負荷過渡と出力リップルの両方の要件を満たすように調整できます。

実際には、過渡応答とループ位相マージンに最も影響を与えるのは出力コンデンサです。負荷過渡テストおよびボード線図は、特定の設計を検証する最善の方法であり、アプリケーションを量産に移行する前に必ず完了する必要があります。必要な出力キャパシタンスに加えて、出力に小さなセラミックコンデンサを配置すると、高周波ノイズを低減するのに役立ちます。小さいケース サイズで  $1nF \sim 100nF$  の範囲のセラミックコンデンサは、インダクタや基板の寄生成分に起因する出力のスパイクを低減するのに非常に役立ちます。

合計出力容量の最大値は、設計値の約 10 倍、または  $1000\mu F$  のどちらか小さい方に制限します。出力容量の値が大きいと、レギュレータのスタートアップ動作やループの安定性に悪影響を及ぼす可能性があります。ここに記載した値よりも大きい値を使用する必要がある場合、全負荷でのスタートアップおよびループ安定性を慎重に検討する必要があります。

### 8.2.1.2.5 入力コンデンサの選択

セラミック入力コンデンサは、レギュレータに低インピーダンスソースを供給するだけでなく、リップル電流を供給して、他の回路からスイッチングノイズを絶縁します。LMR36520 の入力には、少なくとも  $4.7\mu F$  のセラミックキャパシタンスが必要です。これは、少なくともアプリケーションが必要とする最大入力電圧を定格とする必要があり、可能であれば、最大入力電圧の 2 倍が推奨されます。この容量を増やすことで、入力電圧リップルを低減し、負荷過渡時の入力電圧を維持できます。また、小さいケース サイズ  $220nF$  のセラミックコンデンサを入力に使用し、レギュレータのできるだけ近くに配置する必要があります。これにより、デバイス内部に制御回路のための高周波バイパスができます。この例では、 $1 \times 4.7\mu F$ 、 $100V$ 、 $X7R$  (またはそれ以上) のセラミックコンデンサを選択しています。また、 $220nF$  コンデンサも、 $X7R$  誘電体を使用した  $100V$  定格品とする必要があります。

多くの場合、入力にセラミックと並列に電解コンデンサを使用することが推奨されます。これは、長い配線またはパターンを使って入力電源をレギュレータに接続する場合に特に当てはまります。このコンデンサに中程度の ESR を持つコンデンサを使うことは、長い電源配線によって生じる入力電源のリギングを減衰させるのに有効です。この追加コンデンサの使用は、インピーダンスの非常に高い入力電源によって生じる電圧低下の防止にも有効です。

入力スイッチング電流のほとんどは、セラミック入力コンデンサを流れます。この電流の RMS 近似値は 式 8 から計算でき、メーカーの最大定格に照らしてチェックする必要があります。

$$I_{RMS} \approx \frac{I_{OUT}}{2} \quad (8)$$

### 8.2.1.2.6 $C_{BOOT}$

LMR36520 では、BOOT ピンと SW ピンの間にブートストラップコンデンサを接続する必要があります。このコンデンサは、パワー MOSFET のゲートドライバに電力を供給するために使用するエネルギーを蓄積します。 $16V$  以上の  $100nF$  高品質セラミックコンデンサが必要です。

### 8.2.1.2.7 VCC

VCC ピンは、レギュレータの制御回路に電力を供給するために使用される内部 LDO の出力です。この出力を正常に動作させるには、 $1\mu F$ 、 $16V$  のセラミックコンデンサを VCC と GND との間に接続する必要があります。一般に、この出力を負荷として外部回路を接続できません。ただし、この出力は、パワー グッド機能のプルアップに電力を供給するために使

えます（[セクション 7.3.1 セクションを参照](#)）。この場合、 $10\text{k}\Omega \sim 100\text{k}\Omega$  の範囲の値が適しています。VCC の公称出力電圧は 5V です。

#### 8.2.1.2.8 $C_{FF}$ の選択

場合によっては、 $R_{FBT}$  の両端にフィードフォワード コンデンサを接続して、負荷過渡応答やループ位相マージンを改善できます。この方法は  $100\text{k}\Omega$  より大きい  $R_{FBT}$  を使用する場合に特に有効です。 $R_{FBT}$  の値が大きいと、FB ピンの寄生容量との組み合わせにより、小さな信号極が形成されてループの安定性に影響を与える可能性があります。 $C_{FF}$  は、この影響を緩和するのに役立ちます。[式 9](#) を使用して、 $C_{FF}$  の値を推定できます。[式 9](#) で求めた値を出発点として、より小さい値の  $C_{FF}$  コンデンサを使って利点が得られるかどうかを判定します。[内部的に補正されるフィードフォワード コンデンサを持つ DC-DC コンバータの過渡応答の最適化アプリケーション レポート](#)は、フィードフォワード コンデンサの実験に役立ちます。

$$C_{FF} < \frac{V_{OUT} \cdot C_{OUT}}{120 \cdot R_{FBT} \cdot \sqrt{\frac{V_{REF}}{V_{OUT}}}} \quad (9)$$

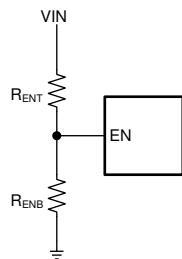

#### 8.2.1.2.9 外部 UVLO

場合によっては、本デバイスが内部的に備えているものとは異なる入力 UVLO レベルが必要とされることがあります。これは、[図 8-2](#) に示す回路を使うことで実現できます。本デバイスがオンする入力電圧を  $V_{ON}$ 、そしてオフする入力電圧を  $V_{OFF}$  と呼びます。最初に、 $R_{ENB}$  の値を  $10\text{k}\Omega \sim 100\text{k}\Omega$  の範囲で選択し、次に[式 10](#) を使って  $R_{ENT}$  と  $V_{OFF}$  を計算します。

図 8-2. 外部 UVLO アプリケーション用のセットアップ

$$R_{ENT} = \left( \frac{V_{ON}}{V_{EN-H}} - 1 \right) \cdot R_{ENB}$$

$$V_{OFF} = V_{ON} \cdot \left( 1 - \frac{V_{EN-HYS}}{V_{EN}} \right) \quad (10)$$

ここで、

- $V_{ON} = V_{IN}$  のターンオン電圧

- $V_{OFF} = V_{IN}$  のターンオフ電圧

#### 8.2.1.2.10 最大周囲温度

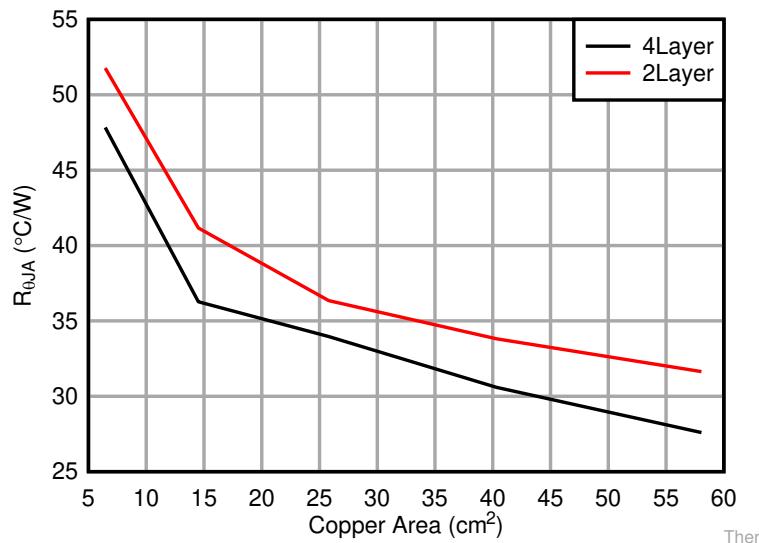

他の電源変換デバイスと同様に、LMR36520 は動作時に内部で電力を消費します。この消費電力の影響により、コンバータの内部温度が周囲温度よりも高くなります。内部ダイ温度 ( $T_J$ ) は、周囲温度、電力損失、デバイスと PCB の組み合わせの実効熱抵抗  $R_{\theta JA}$  の関数です。LMR36520 の最大内部ダイ温度は  $150^\circ\text{C}$  に制限する必要があります。これにより、デバイスの最大消費電力(つまり負荷電流)が制限されます。[式 11](#) に、重要なパラメータ間の関係を示します。周囲温度 ( $T_A$ ) が高いほど、また、 $R_{\theta JA}$  が大きいほど、利用可能な最大出力電流が低減されます。コンバータの効率は、このデ

一タシートに示す曲線を使用して推定できます。いずれかの曲線に目的の動作条件が見つからない場合は、補間によって効率を推定できます。または、目的のアプリケーション要件に合わせて EVM を調整し、効率を直接測定することもできます。 $R_{\theta JA}$  の正確な値を推定するのは、より困難です。『半導体および IC パッケージの熱評価基準』アプリケーション レポートで述べているように、「熱に関する情報」に記載されている値は、設計目的には有効ではなく、アプリケーションの熱性能の推定に使用してはなりません。この表に報告されている値は、実際のアプリケーションではめったに見られない特定の一連の条件で測定されたものです。

$$I_{OUT}|_{MAX} = \frac{(T_J - T_A)}{R_{\theta JA}} \cdot \frac{\eta}{(1-\eta)} \cdot \frac{1}{V_{OUT}} \quad (11)$$

ここで、

- $\eta$  = 効率

実効  $R_{\theta JA}$  は重要なパラメータであり、以下のような多くの要因に依存します。

- 消費電力

- 空気温度 / フロー

- PCB 面積

- 銅箔ヒートシンク面積

- パッケージの下にあるサーマル リビアの数

- 隣接する部品の配置

図 8-3 に、銅基板面積に対する  $R_{\theta JA}$  の代表例を示します。このグラフに記載されているデータは、説明のみを目的としており、特定のアプリケーションにおける実際の性能は、上記のすべての要因に依存することに注意してください。

図 8-3.  $R_{\theta JA}$  と銅基板面積との関係

最適な PCB 設計および特定のアプリケーション環境における  $R_{\theta JA}$  を推定するためのガイドとして、以下の資料を使用してください。

- 『過去ではなく、現在の識見による熱設計』アプリケーション レポート

- 『半導体および IC パッケージの熱評価基準』アプリケーション レポート

- 『LM43603 および LM43602 を使用した簡単な熱設計』アプリケーション レポート

- 『新しい熱評価基準の解説』アプリケーション レポート

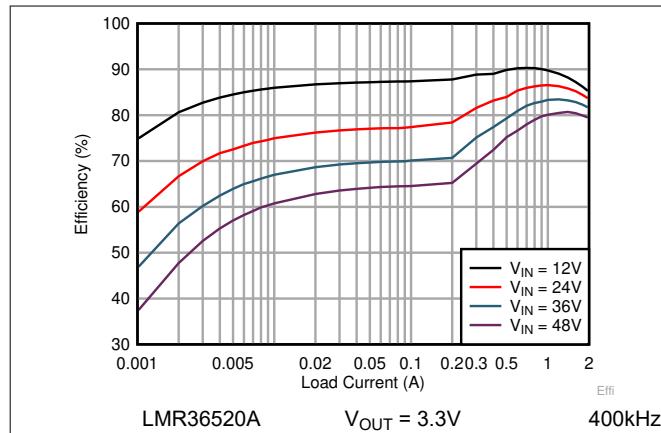

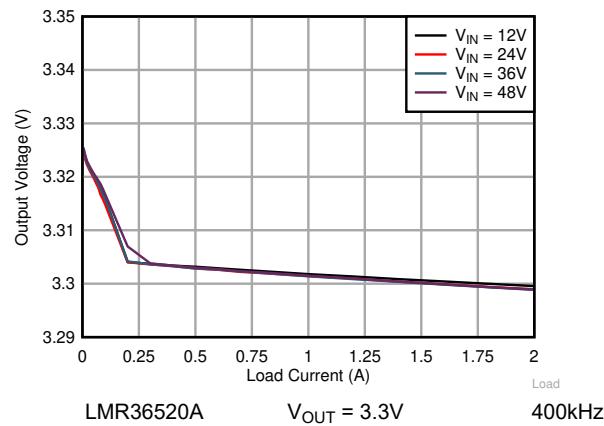

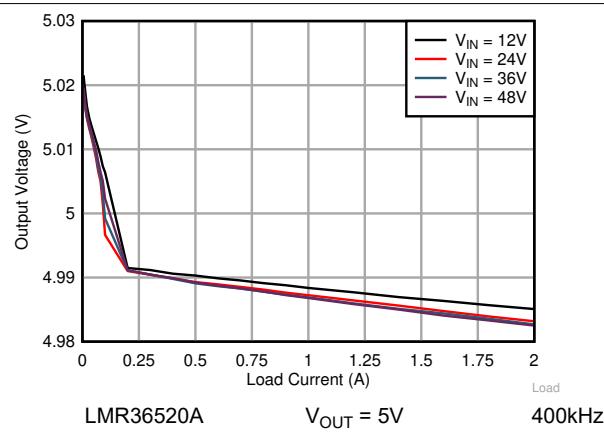

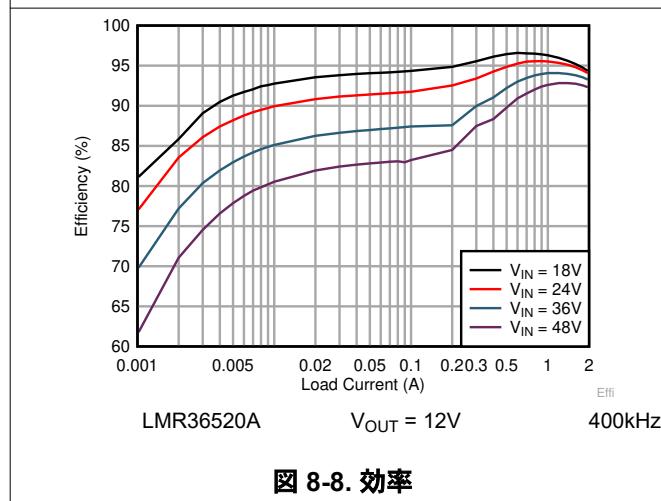

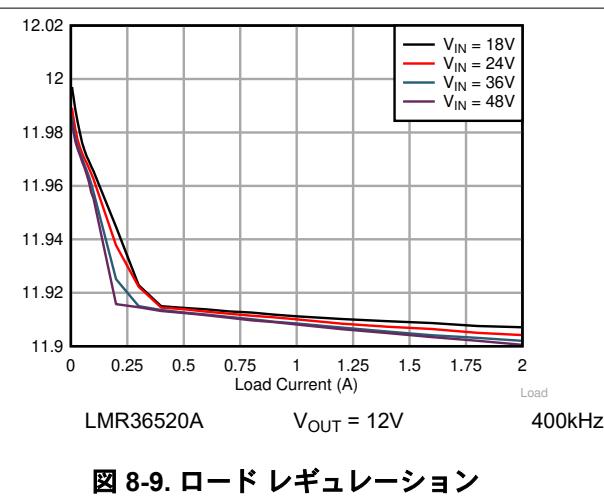

### 8.2.1.3 アプリケーション曲線

特に記述のない限り、次の条件が適用されます。 $V_{IN} = 24V$ 、 $T_A = 25^\circ C$ 。図 8-20 は、表 8-4 からの適切な BOM を含む回路を示しています。

図 8-4. 効率

図 8-5. ロード レギュレーション

図 8-6. 効率

図 8-7. ロード レギュレーション

図 8-8. 効率

図 8-9. ロード レギュレーション

図 8-10. ドロップアウト特性

図 8-11. ドロップアウト特性

図 8-12. 入力電源電流

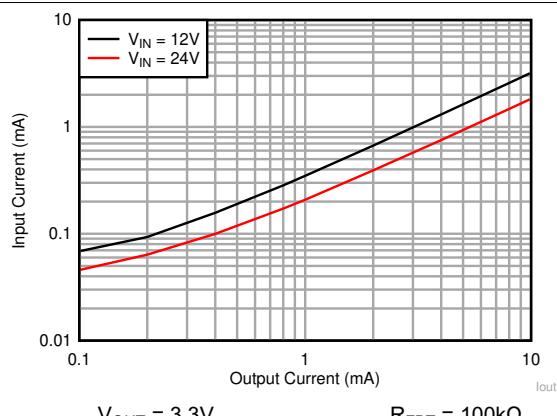

図 8-13. 入力電源電流と負荷電流との関係

図 8-14. イネーブルスタートアップ波形

図 8-15. イネーブルシャットダウン波形

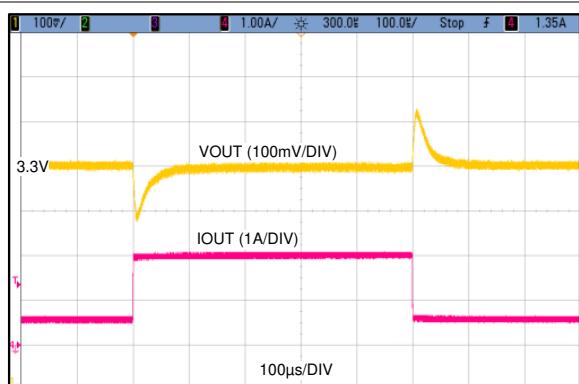

$V_{OUT} = 3.3V$        $400kHz$        $I_{LOAD} = 0.5A - 2A$

スルーレート = 1A/

μs

図 8-16. 負荷過渡

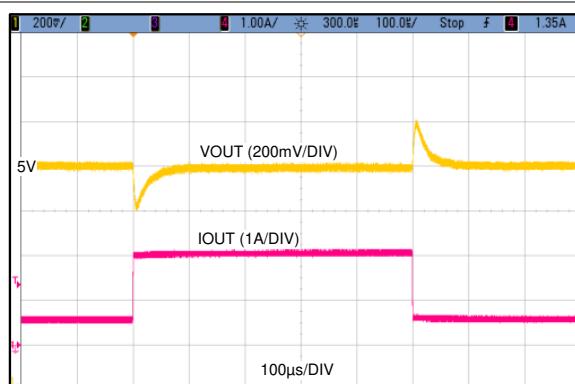

$V_{OUT} = 5V$        $400kHz$        $I_{LOAD} = 0.5A - 2A$

スルーレート = 1A/

μs

図 8-17. 負荷過渡

$V_{IN} = 24V$        $V_{OUT} = 5V$        $I_{LOAD} = 0A$

図 8-18. 無負荷時での出力リップル

$V_{IN} = 24V$        $V_{OUT} = 5V$        $I_{LOAD} = 1A$

図 8-19. 1A 時の出力リップル

図 8-20. 代表的なアプリケーションの特性曲線で使われた回路

表 8-4. 代表的なアプリケーションの特性曲線で使われた BOM

| V <sub>OUT</sub> | FREQUENCY | L              | C <sub>OUT</sub> | R <sub>FBT</sub> | R <sub>FBB</sub> | C <sub>FF</sub> | IC        |

|------------------|-----------|----------------|------------------|------------------|------------------|-----------------|-----------|

| 3.3V             | 400kHz    | 6.8μH, 29.45mΩ | 3 x 22μF, 25V    | 46.4kΩ           | 20.0kΩ           | なし              | LMR36520A |

| 5V               | 400kHz    | 10μH, 29.82mΩ  | 2 x 22μF, 25V    | 34.0kΩ + 46.4kΩ  | 20.0kΩ           | なし              | LMR36520A |

| 12V              | 400kHz    | 33μH, 57mΩ     | 3 x 22μF, 25V    | 100kΩ            | 9.09kΩ           | なし              | LMR36520A |

### 8.3 設計のベスト プラクティス

- EN 入力をフローティングにしないでください。

- 出力電圧が入力電圧を超えないように、またグランドを下回らないようにしてください。

- [熱に関する情報](#)の表に記載されている熱データをアプリケーションの設計に使用しないでください。

## 8.4 電源に関する推奨事項

入力電源の特性は、このデータシートに記載されている [セクション 6](#) に適合している必要があります。また、入力電源は、負荷時のレギュレータに必要な入力電流を供給できる必要があります。平均入力電流は、[式 12](#) を使って見積もることができます。

$$I_{IN} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta} \quad (12)$$

ここで、

- $\eta$  は効率です。

レギュレータを長いワイヤや PCB パターンで入力電源に接続している場合は、良好な性能を実現するために特別な注意が必要です。入力ケーブルの寄生インダクタンスと抵抗は、レギュレータの動作に悪影響を及ぼすおそれがあります。寄生インダクタンスは、低 ESR セラミック入力コンデンサとの組み合わせによって不足減衰共振回路を形成し、レギュレータへの入力での過電圧過渡の原因となる可能性があります。寄生抵抗は、出力に負荷過渡が加わった際に、VIN ピンの電圧が低下する原因となる可能性があります。アプリケーションが最小入力電圧に近い値で動作している場合、この低下によってレギュレータが瞬間的にシャットダウンし、リセットされる可能性があります。この種の問題を解決する最善策は、入力電源からレギュレータまでの距離を短くして、セラミック入力コンデンサと並列にアルミニウムまたはタンタルの入力コンデンサを使用することです。この種のコンデンサの ESR は比較的低いため、入力共振回路の減衰およびオーバーシュートの低減に役立ちます。通常、 $20\mu F \sim 100\mu F$  の値は入力のダンピングに十分であり、大きな負荷過渡中も入力電圧を安定した状態に保持できます。

システムに関するその他の考慮事項として、レギュレータの前に入力フィルタが使われる場合があります。入力フィルタは、注意深く設計しないと、不安定性につながる可能性があり、上述の現象の一因ともなり得ます。[『AN-2162 DC/DC コンバータ向け伝導 EMI の簡単な成功事例』ユーザーガイド](#) では、スイッチングレギュレータの入力フィルタを設計する際に役立つ提案を紹介しています。

場合によっては、コンバータの入力に過渡電圧サプレッサ (TVS) が使われています。この素子の種類には、スナップバック特性を持つもの (サイリスタ型) があります。このタイプの特性を持つデバイスの使用は推奨しません。このタイプの TVS が作動すると、クランプ電圧は非常に低い値に低下します。この電圧がレギュレータの出力電圧よりも低い場合、出力コンデンサは本デバイスを通して放電し、入力に戻します。この制御されない電流は、デバイスに損傷を与える可能性があります。

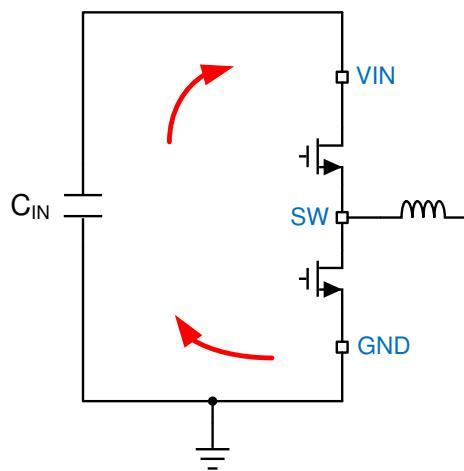

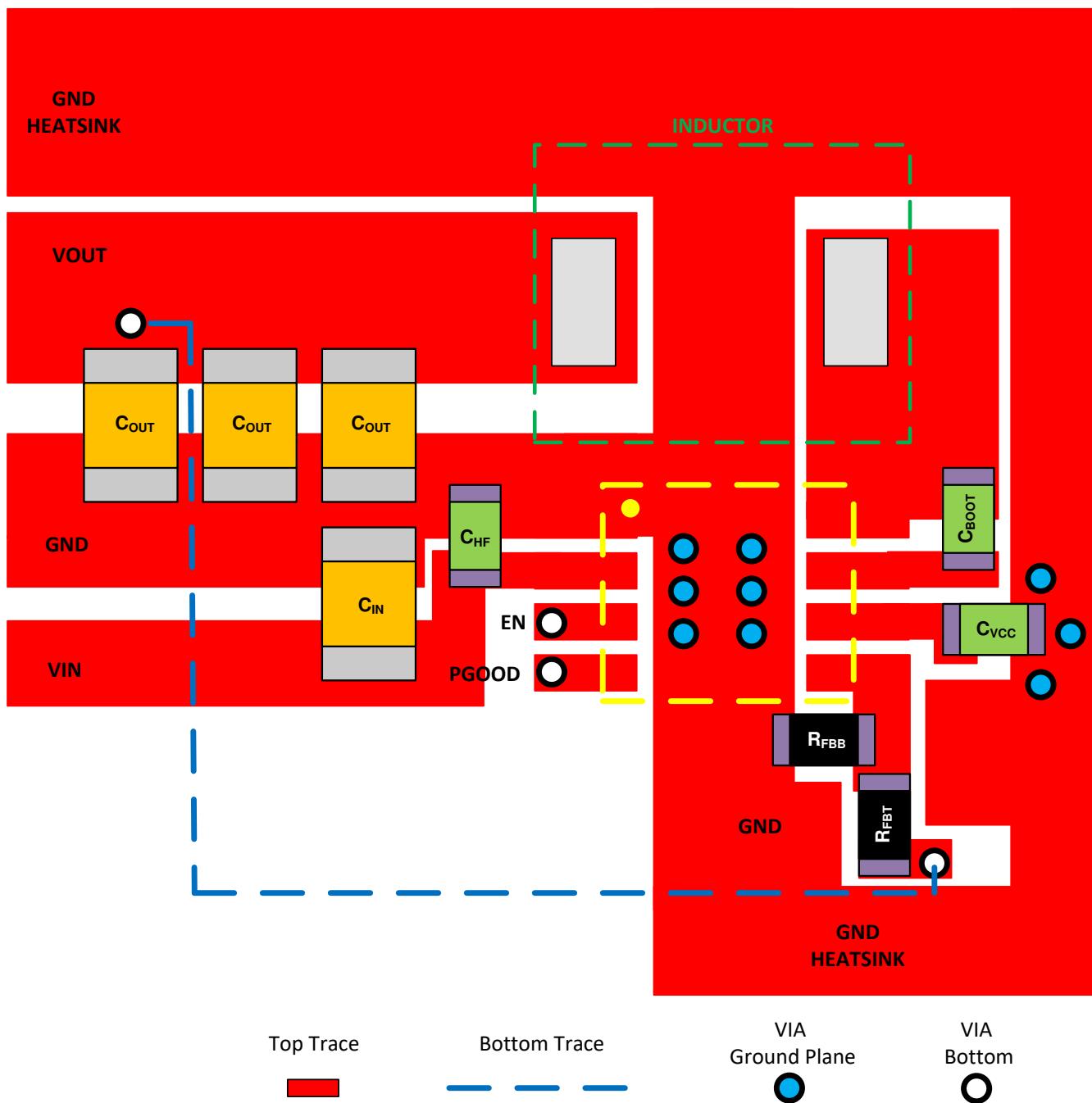

## 8.5 レイアウト

### 8.5.1 レイアウトのガイドライン

DC/DC コンバータの PCB レイアウトは、最適な設計性能を実現するために重要です。PCB レイアウトが不適切な場合、適正な回路図設計の動作の妨げとなる可能性があります。コンバータが適切にレギュレートしている場合でも、PCB レイアウトが不適切では、堅牢な設計と量産できない設計という違いが生じる可能性があります。さらに、レギュレータの EMI 性能は、PCB レイアウトの影響を大きく受けます。降圧コンバータにおける PCB の最も重要な機能は、入力コンデンサと電源グランドによって形成されるループです ([図 8-21](#) を参照)。このループには、パターンのインダクタンスに応答して大きな過渡電圧を発生させる可能性がある大きな過渡電流が流れます。これらの望ましくない過渡電圧は、コンバータの正常な動作を妨げます。このことから、寄生インダクタンスを低減するため、このループ内のパターンは広く短くする必要があります、ループの面積はできる限り小さくする必要があります。[図 8-22](#) は、LMR36520 の重要な部品の推奨レイアウトを示しています。

1. 入力コンデンサは、VIN および GND ピンにできる限り近づけて配置してください。VIN および GND ピンは隣接しているため、入力コンデンサを簡単に配置できます。

2. VCC のバイパスコンデンサは、VCC ピンの近くに配置します。このコンデンサは、本デバイスの近くに配置し、短く広いパターンで VCC および GND ピンに配線する必要があります。

3. C<sub>BOOT</sub> コンデンサには広いパターンを使用します。C<sub>BOOT</sub> コンデンサは、デバイスのできる限り近くに、BOOT および SW ピンに短くて幅の広いパターンで配置します。SW ピンは N/C ピンに配線し、これを使って BOOT コンデンサを SW に接続します。

4. 帰還分圧器は、本デバイスの **FB** ピンのできるだけ近くに配置します。 $R_{FBB}$ 、 $R_{FBT}$ 、 $C_{FF}$  は、使用する場合、本デバイスに物理的に近付けて配置します。**FB** および **GND** への接続は、短くする必要があり、かつ本デバイスのそれらのピンに近付ける必要があります。**V<sub>OUT</sub>** への接続は、多少長くなつてもかまいません。ただし、この後者のパターンは、レギュレータの帰還経路に静電容量結合する可能性があるすべてのノイズ源 (**SW** ノードなど) の近くには配線しないでください。

5. 内層の 1 つを使って、少なくとも 1 つのグランドプレーンを配置します。このプレーンは、ノイズシールドと放熱経路として機能します。

6. **V<sub>IN</sub>**、**V<sub>OUT</sub>**、**GND** には広いパターンを使います。コンバータの入力または出力経路でのすべての電圧降下を低減し、効率を最大化するため、これらの配線はできるだけ広くかつ真っすぐにする必要があります。

7. 適切なヒートシンクのために十分な PCB 領域を確保します。セクション 8.2.1.2.10 セクションで述べているように、最大負荷電流と周囲温度に応じて、 $R_{\theta JA}$  を低く抑えるには十分な銅面積を使用する必要があります。PCB の上層と下層は 2 オンス銅箔とし、最低でも 1 オンス以上とする必要があります。PCB 設計に複数の銅層を使用している場合は (推奨設計)、これらのサーマルビアも内部層の熱拡散グランドプレーンに接続することができます。

8. スイッチングする領域は小さく保ちます。**SW** ピンをインダクタに接続する銅箔領域は、できるだけ短くかつ広くします。同時に、放射 EMI を低減するため、このノードの総面積を最小化する必要があります。

その他の重要なガイドラインについては、以下の PCB レイアウト資料を参照してください。

- ・『スイッチング電源のレイアウトのガイドライン』アプリケーションレポート

- ・『Simple Switcher PCB レイアウト ガイドライン』アプリケーションレポート

- ・『独自電源の構築 - レイアウトの考慮事項』セミナー

- ・『LM4360x および LM4600x による低放射 EMI レイアウトの簡単な設計』アプリケーションレポート

図 8-21. 高速エッジを持つ電流ループ

#### 8.5.1.1 グランドと熱に関する考慮事項

前述のように、テキサス・インスツルメンツでは、中間層の 1 つをソリッド グランドプレーンとして使用することを推奨しています。グランドプレーンは敏感な回路やパターンのシールドとして機能するだけでなく、制御回路の低ノイズ基準電位を提供します。バイパスコンデンサの隣にあるビアを使用して、PGND ピンをグランドプレーンに接続します。PGND ピンは、ローサイド MOSFET スイッチのソースに直接接続し、入力および出力コンデンサのグランドにも直接接続します。PGND にはスイッチング周波数におけるノイズが含まれており、負荷変動により戻ってくる場合があります。PGND パターンは、VIN および SW パターンと同様に、グランドプレーンの片方に固定する必要があります。グランドプレーンのもう片方はノイズが非常に少ないと想定し、ノイズの影響を受けやすい配線に使用します。

システムのグランドプレーンでは、効率の高い放熱のために、レイヤの上下に出来る限り多くの銅を使用します。4 つの層の銅厚が上からそれぞれ 2 オンス、1 オンス、1 オンス、2 オンスとなっている 4 層基板を使用します。十分な厚さの銅箔と適切なレイアウトを備えた 4 層基板は、低インピーダンスの電流導通、適切なシールド効果、低熱抵抗を実現します。

### 8.5.2 レイアウト例

図 8-22. レイアウト例

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 開発サポート

- DC/DC コンバータのパッケージとピン配置設計により車載 EMI 性能を向上させる方法に関するブログ

- 降圧コンバータ機能の概要:UVLO、イネーブル、ソフトスタート、パワーグッドに関するトレーニングビデオ

- 降圧コンバータの概要:モード遷移について理解するためのトレーニングビデオ

- 降圧コンバータの概要:最小オン時間と最小オフ時間の動作に関するトレーニングビデオ

- 降圧コンバータの概要:静止電流の仕様について理解するためのトレーニングビデオ

- DC/DC コンバータでの熱性能とソリューション サイズ縮小とのトレードオフに関するトレーニングビデオ

- Hot Rod パッケージでの EMI の低減とソリューション サイズの縮小に関するトレーニングビデオ

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『高性能、低 EMI、車載用電源の設計』アプリケーションレポート

- テキサス・インスツルメンツ、『Simple Switcher PCB レイアウト ガイドライン』アプリケーションレポート

- テキサス・インスツルメンツ、『独自電源の構築 - レイアウトの考慮事項』セミナー

- テキサス・インスツルメンツ、『LM4360x および LM4600x による低放射 EMI レイアウトの簡単な設計』レポート

- テキサス・インスツルメンツ、『半導体および IC パッケージの熱評価基準』アプリケーションレポート

- テキサス・インスツルメンツ、『LM43603 および LM43602 を使用した簡単な熱設計』アプリケーションレポート

- テキサス・インスツルメンツ、『AN-2162 DC/DC コンバータからの伝導 EMI への簡単な対処方法』ユーザーズガイド

- テキサス・インスツルメンツ、『過去ではなく、現在の識見による熱設計』アプリケーションレポート

- テキサス・インスツルメンツ、『半導体および IC パッケージの熱評価基準』アプリケーションレポート

- テキサス・インスツルメンツ、『LM43603 および LM43602 を使用した簡単な熱設計』アプリケーションレポート

- テキサス・インスツルメンツ、『新しい熱評価基準の解説』アプリケーションレポート

- テキサス・インスツルメンツ、『フィードフォワードコンデンサ付き内部補正 DC-DC コンバータの過渡応答の最適化』アプリケーションレポート

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

SIMPLE SWITCHER® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお奨めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from Revision B (April 2020) to Revision C (November 2025)

Page

- ドキュメント全体にわたって表、図、相互参照の採番方法を更新..... 1

### Changes from Revision A (February 2020) to Revision B (April 2020)

Page

- 「デバイス比較表」から入手可能状況列を削除 ..... 3

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

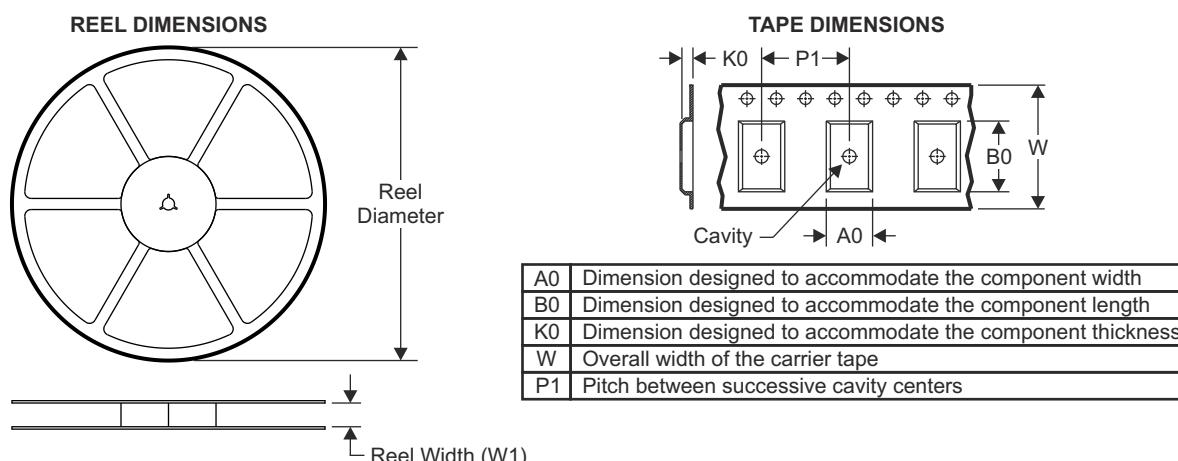

### 11.1 テープおよびリール情報

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス           | パッケージ<br>タイプ   | パッケージ<br>図 | ピン | SPQ  | リール<br>直径 (mm) | リール<br>幅 W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | ピン 1 の<br>象限 |

|----------------|----------------|------------|----|------|----------------|------------------|------------|------------|------------|------------|-----------|--------------|

| LMR36520ADDAR  | SO<br>PowerPAD | DDA        | 8  | 2500 | 330            | 12.4             | 6.4        | 5.2        | 2.1        | 8          | 12        | Q1           |

| LMR36520FADDAR | SO<br>PowerPAD | DDA        | 8  | 2500 | 330            | 12.4             | 6.4        | 5.2        | 2.1        | 8          | 12        | Q1           |

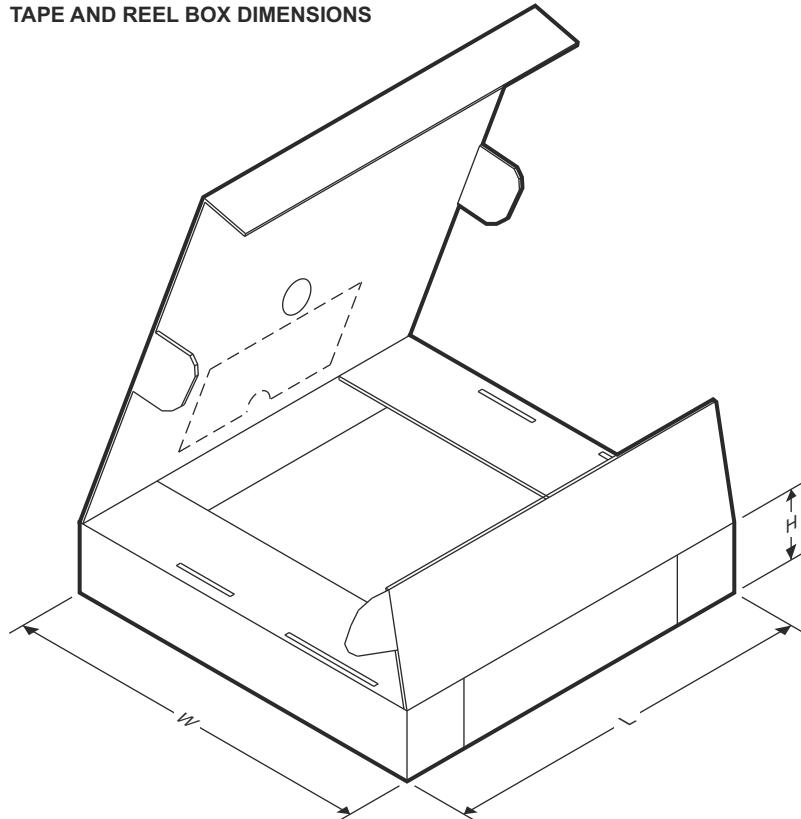

## TAPE AND REEL BOX DIMENSIONS

| デバイス           | パッケージ<br>タイプ | パッケージ<br>図 | ピン | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|----------------|--------------|------------|----|------|---------|--------|---------|

| LMR36520ADDAR  | SO PowerPAD  | DDA        | 8  | 2500 | 353     | 353    | 36      |

| LMR36520FADDAR | SO PowerPAD  | DDA        | 8  | 2500 | 353     | 353    | 36      |

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMR36520ADDR          | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG                    | Level-2-260C-1 YEAR               | -40 to 125   | 36520A              |

| LMR36520ADDR.A        | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 36520A              |

| LMR36520ADDARG4       | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 36520A              |

| LMR36520ADDARG4.A     | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 36520A              |

| LMR36520FADDR         | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG                    | Level-2-260C-1 YEAR               | -40 to 125   | 36520F              |

| LMR36520FADDR.A       | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 36520F              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

---

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

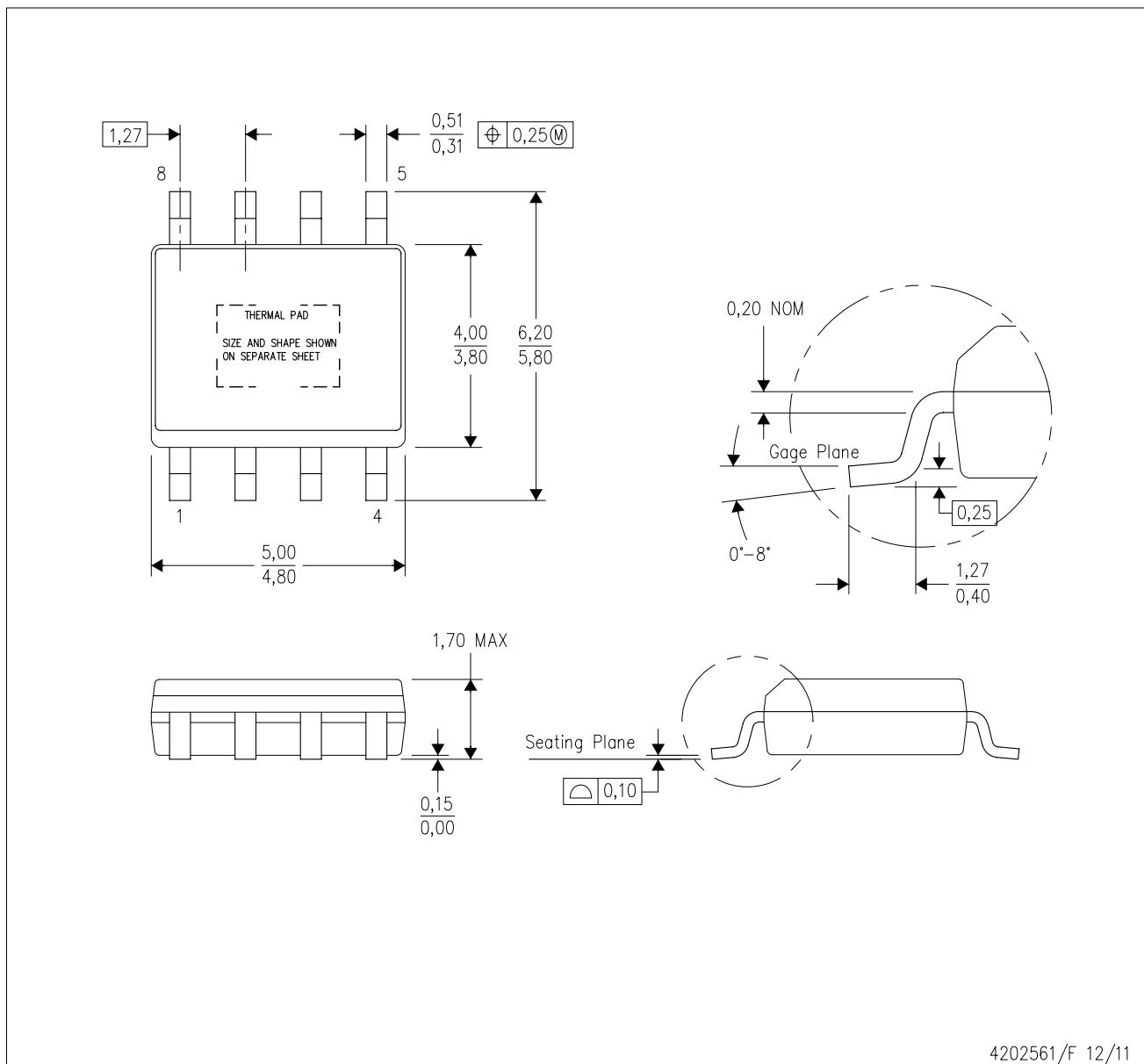

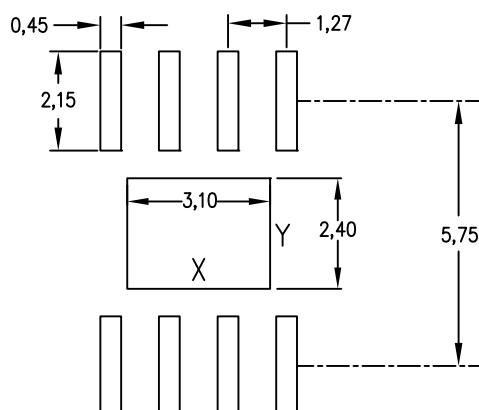

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL-OUTLINE

4202561/F 12/11

- NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. This package complies to JEDEC MS-012 variation BA

PowerPAD is a trademark of Texas Instruments.

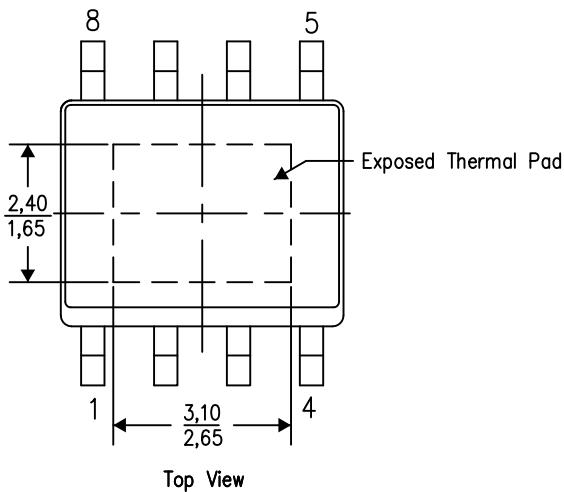

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL OUTLINE

## THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206322-6/L 05/12

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

## DDA (R-PDSO-G8)

## PowerPAD™ PLASTIC SMALL OUTLINE

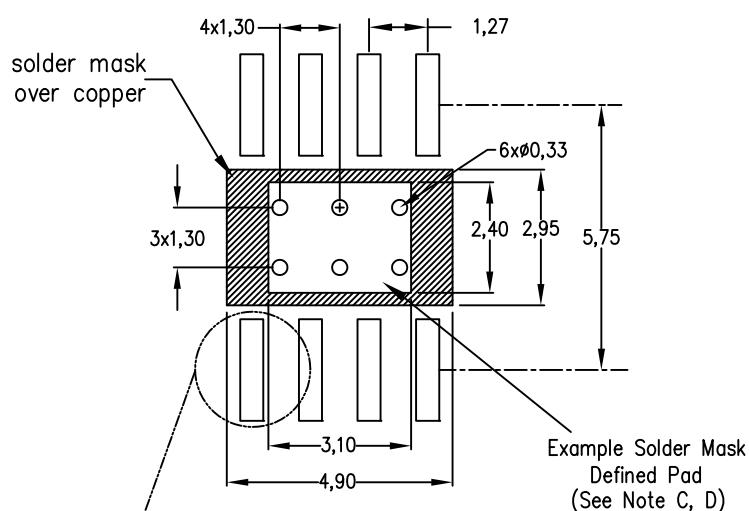

Example Board Layout

Via pattern and copper pad size

may vary depending on layout constraints

### Non Solder Mask Defined Pad

0,127mm Thick Stencil Design Example

Reference table below for other

solder stencil thicknesses

(Note E)

| Center  | Power Pad | Solder | Stencil | Opening |

|---------|-----------|--------|---------|---------|

| Stencil | Thickness | X      | Y       |         |

|         | 0.1mm     | 3.3    | 2.6     |         |

|         | 0.127mm   | 3.1    | 2.4     |         |

|         | 0.152mm   | 2.9    | 2.2     |         |

|         | 0.178mm   | 2.8    | 2.1     |         |

4208951-6/D 04/12

- NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments.

DDA0008B

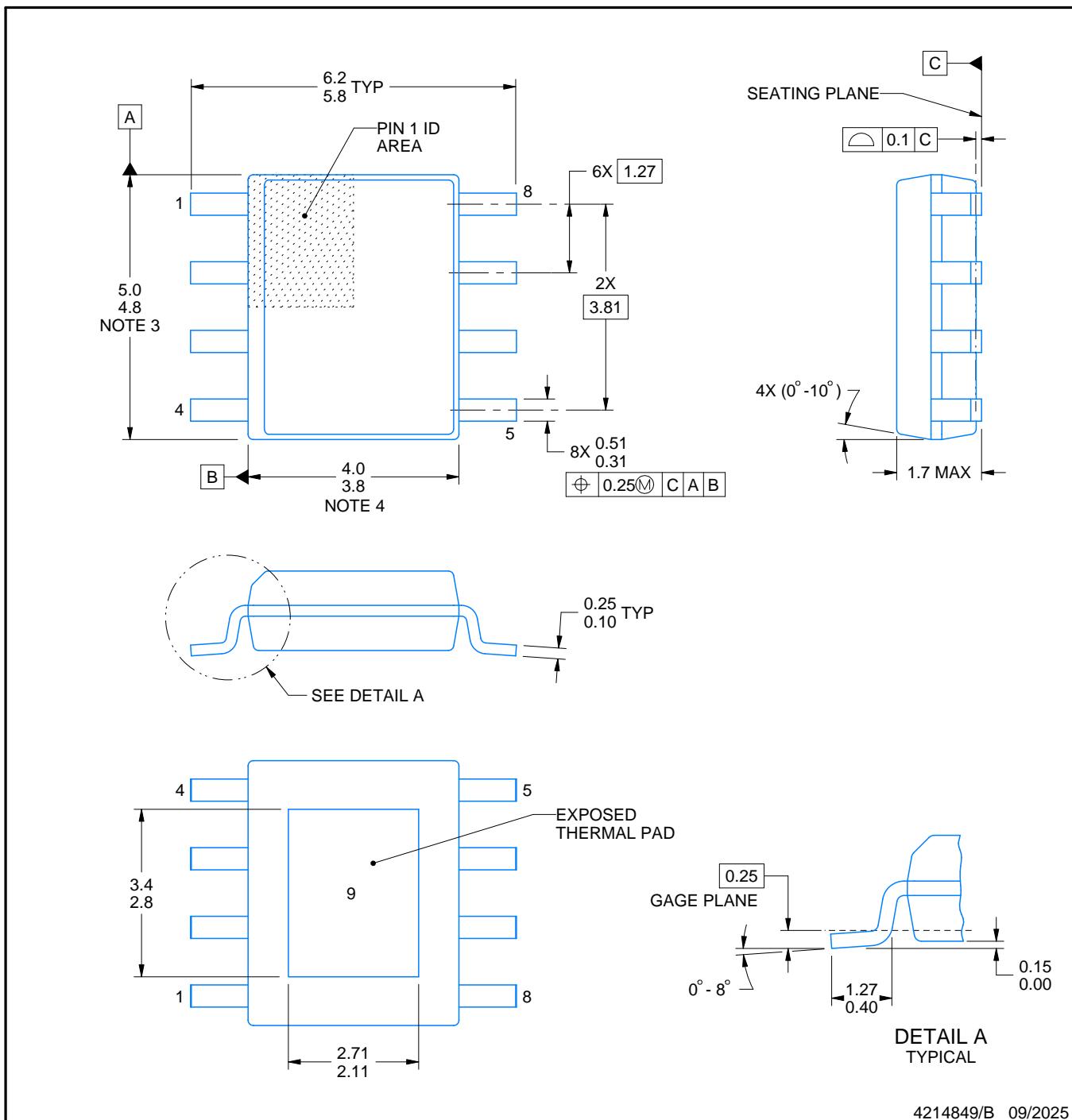

# PACKAGE OUTLINE

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

4214849/B 09/2025

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MS-012.

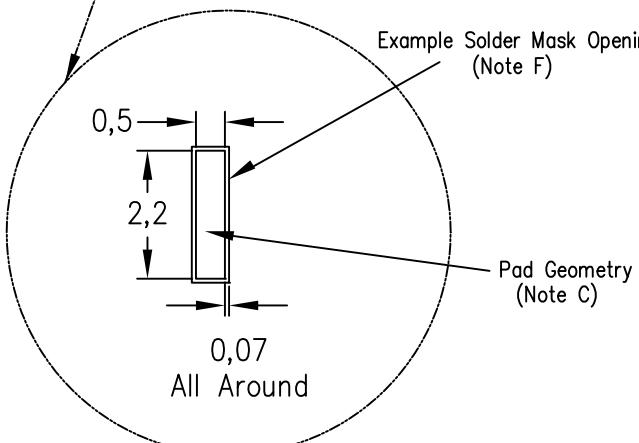

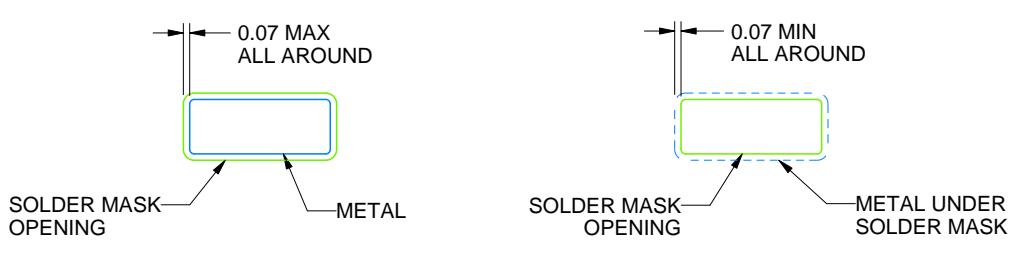

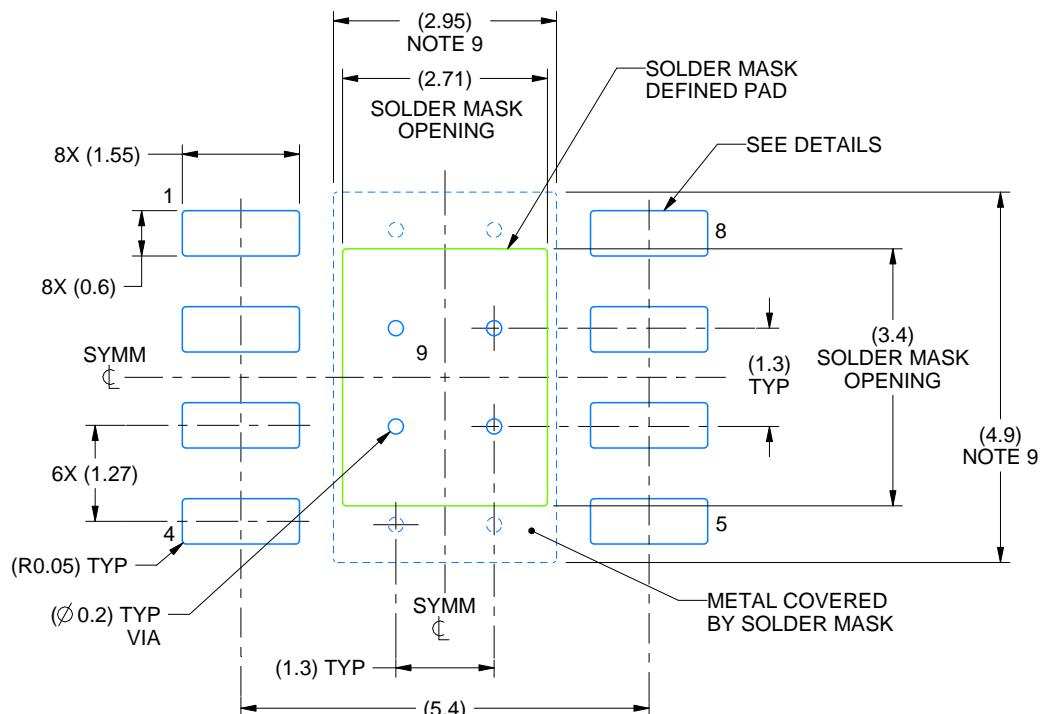

# EXAMPLE BOARD LAYOUT

DDA0008B

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

SOLDER MASK DETAILS

PADS 1-8

4214849/B 09/2025

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

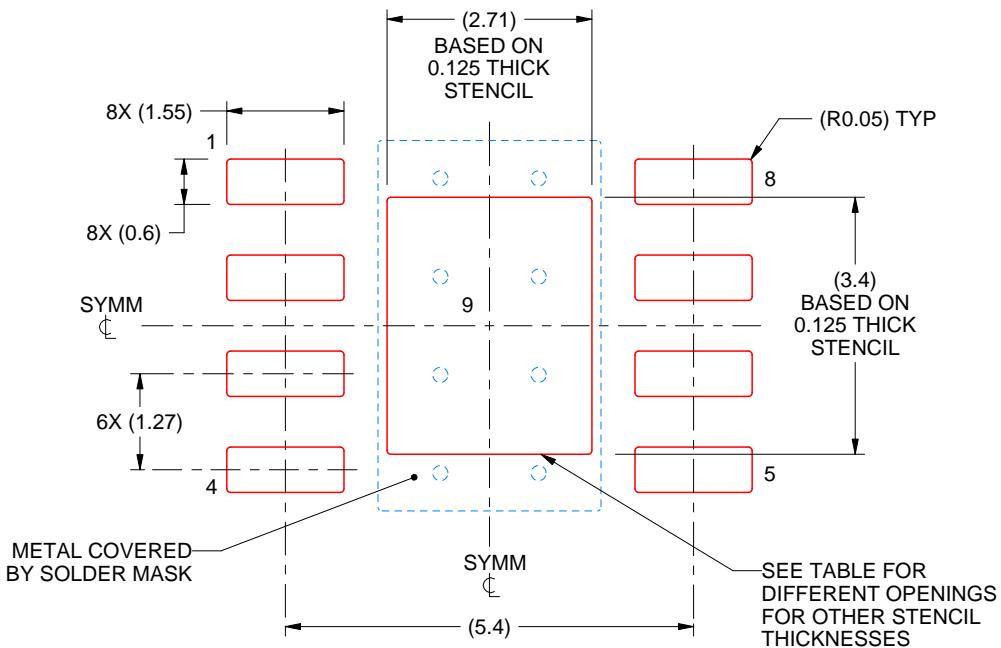

# EXAMPLE STENCIL DESIGN

DDA0008B

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 3.03 X 3.80            |

| 0.125             | 2.71 X 3.40 (SHOWN)    |

| 0.150             | 2.47 X 3.10            |

| 0.175             | 2.29 X 2.87            |

4214849/B 09/2025

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月