# LMQ61460 3V ~ 36V、6A 同期 ZEN 2 整流降圧コンバータ

## 1 特長

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可能

- ZEN 2 スイッチャ

- HotRod™ パッケージによりスイッチ ノード リンギングを最小化

- 内部バイパス コンデンサにより EMI を低減

- 並列入力バスにより寄生インダクタンスを最小化

- スペクトラム拡散によりピーク エミッショを削減

- スイッチ ノードの立ち上がり時間を調整可能

- 堅牢なアプリケーション向け

- 42V 過渡に対応

- 4A 負荷での 0.4V ドロップアウト (代表値)

- あらゆる負荷で高効率の電力変換

- 無負荷電流: 7µA (13.5V<sub>IN</sub>、3.3V<sub>OUT</sub>)

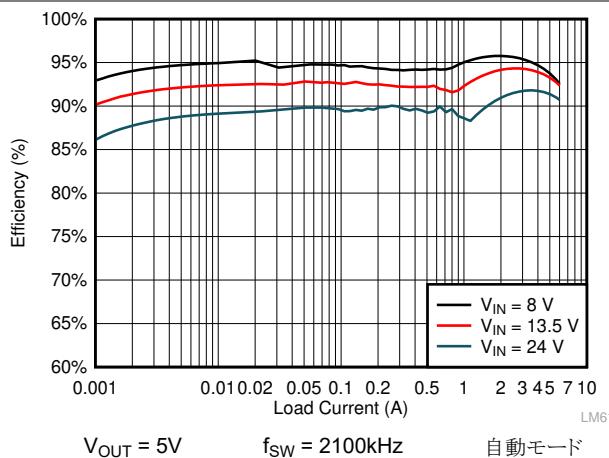

- PFM 効率: 90% (1mA、13.5V<sub>IN</sub>、5V<sub>OUT</sub>)

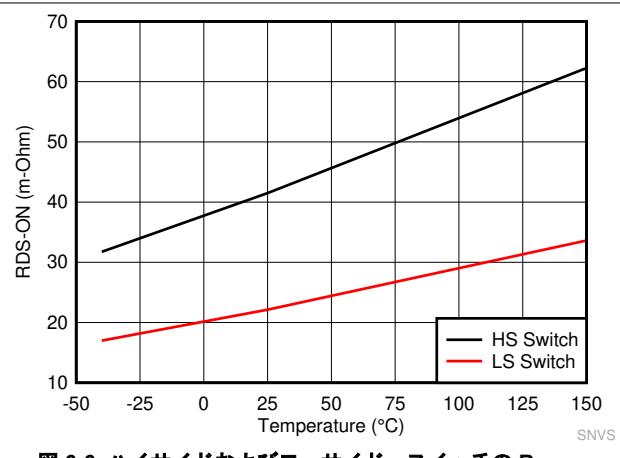

- 低い MOSFET ON 抵抗

- $R_{DS\_ON\_HS} = 41\text{m}\Omega$  (代表値)

- $R_{DS\_ON\_LS} = 21\text{m}\Omega$  (代表値)

- 外部バイアス オプションによる効率向上

- 次の製品とピン互換:

- LM61460 (36V、6A)

- TPSM63606 モジュールを使用して開発期間を短縮

## 2 アプリケーション

- USB Type-C

- 産業用ロボット: CPU ボード

- 産業用 PC: シングル・ボード・コンピュータ

- 試験および計測機器

- $V_{IN}$  範囲の広い汎用の降圧アプリケーション

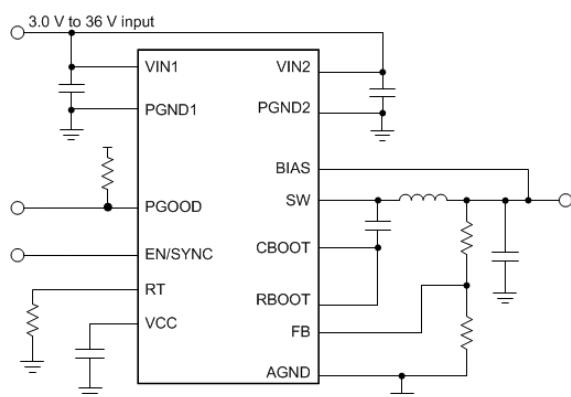

概略回路図

## 3 説明

LMQ61460 は、バイパス コンデンサを内蔵した高性能 DC/DC 同期整流降圧コンバータです。ハイサイドおよびローサイド MOSFET を内蔵しており、3.0V~36V という広い入力電圧範囲にわたって最大 6A の出力電流を供給できます。42V 許容であるため、入力サージ保護設計が簡単です。このデバイスは、ドロップアウトからのソフト回復を実装しているため、出力のオーバーシュートを除去できます。

ZEN 2 スイッチャ技術を搭載した LMQ61460 は、特に EMI を最小限に抑えるように設計されています。このデバイスは、疑似ランダム スペクトラム拡散機能、内蔵バイパス コンデンサ、SW ノード立ち上がり時間調整機能、スイッチ ノードのリンギングが小さい低 EMI の VQFN-HR パッケージ、使いやすく最適化されたピン配置を採用しています。スイッチング周波数は、ノイズの影響を受けやすい周波数帯を避けるため、200kHz~2.2MHz の範囲で同期できます。また、効率向上のために低い動作周波数を選択することも、設計小型化のために高い動作周波数を選択することも可能です。

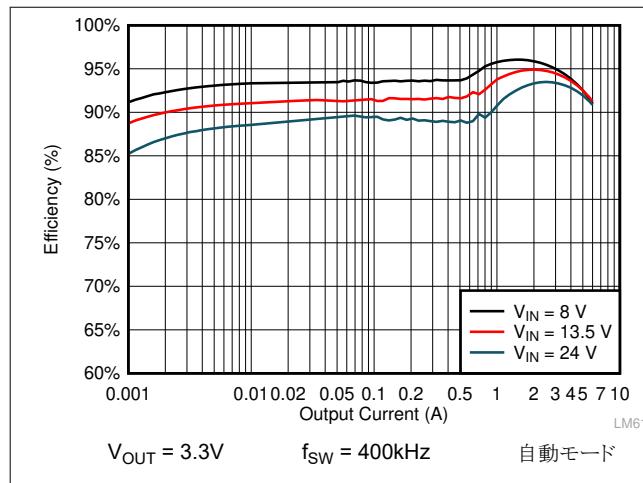

自動モードでは、軽負荷動作時の周波数フォールドバックが可能であり、わずか 7µA (標準値) の無負荷時消費電流と、軽負荷時の効率向上を実現できます。PWM モードと PFM モードの間のシームレスな移行、非常に小さな MOSFET ON 抵抗、外部バイアス入力により、負荷範囲全体にわたって非常に優れた効率が得られます。

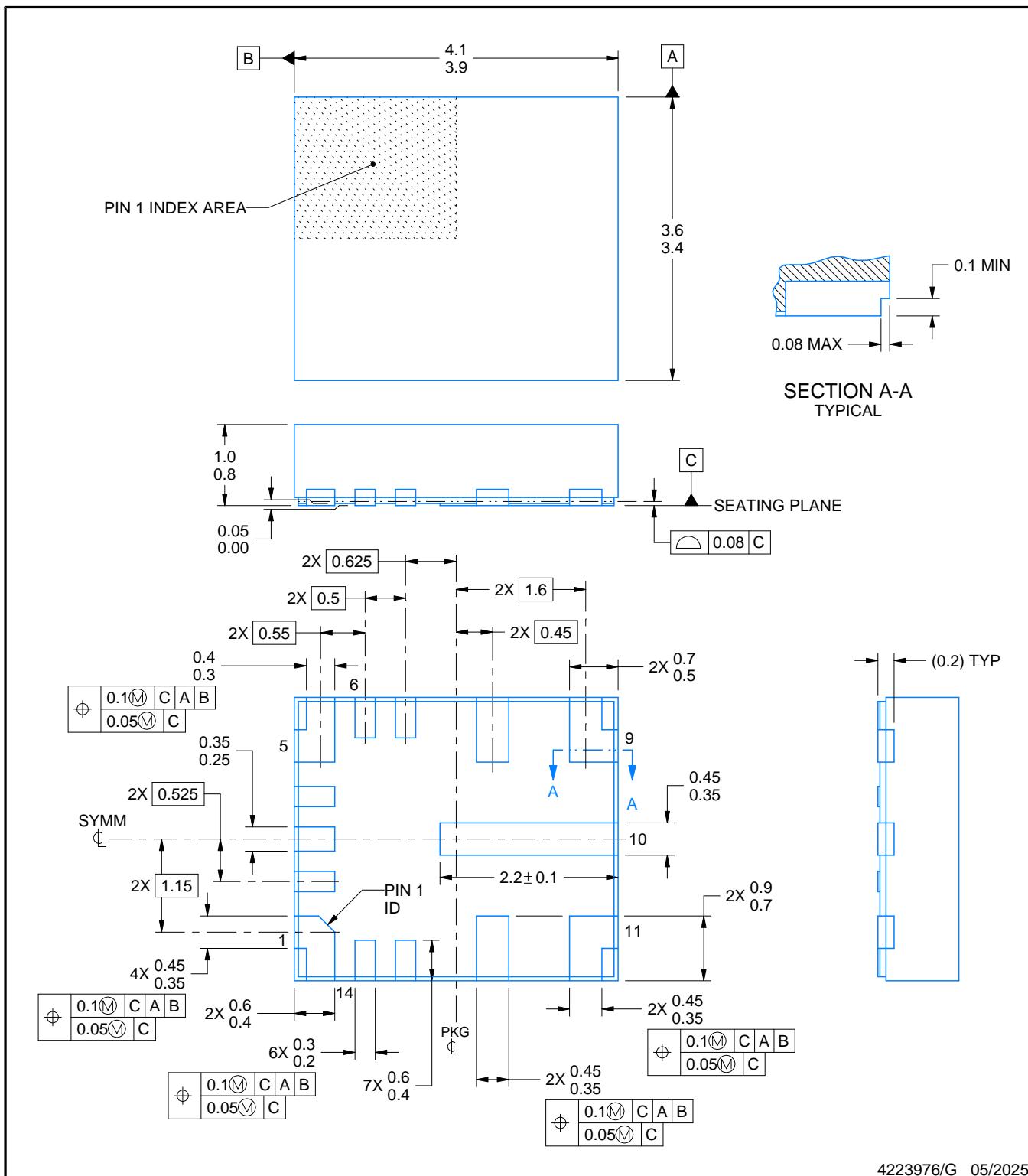

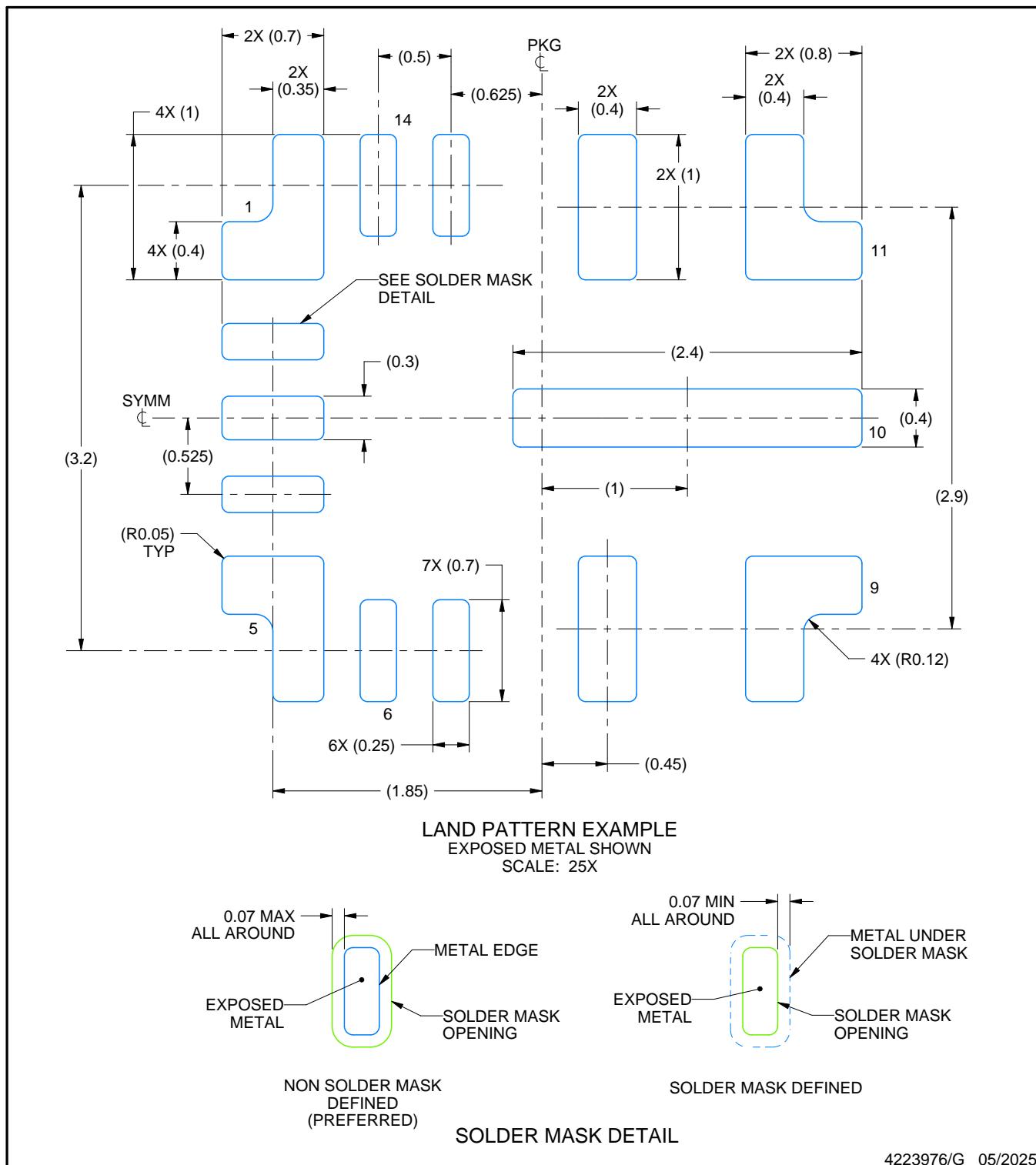

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| LMQ61460 | RJR (VQFN-HR、14)     | 4.00mm × 3.50mm          |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合にピンも含まれます。

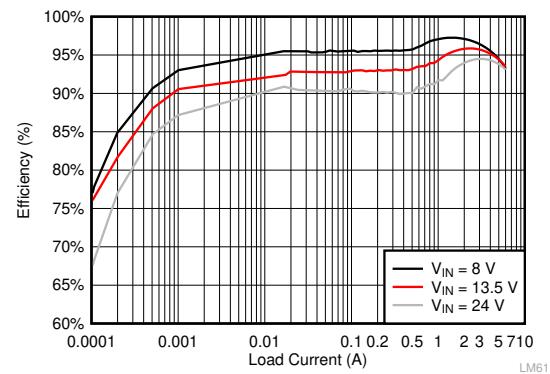

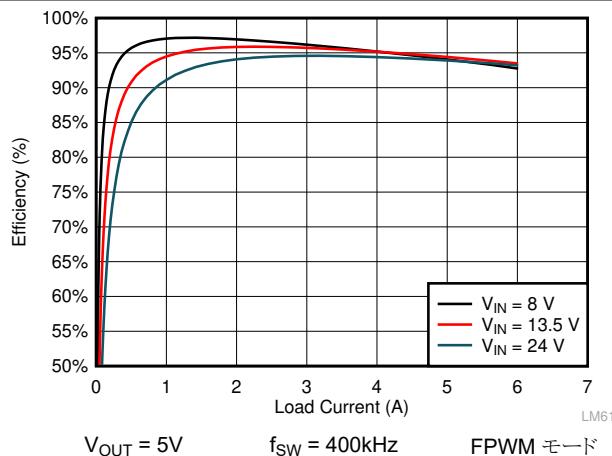

効率 :  $V_{OUT} = 5\text{V}$ 、 $f_{SW} = 400\text{kHz}$

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                        |    |

|-------------|----|------------------------|----|

| 1 特長        | 1  | 7.3 機能説明               | 15 |

| 2 アプリケーション  | 1  | 7.4 デバイスの機能モード         | 24 |

| 3 説明        | 1  | 8 アプリケーションと実装          | 30 |

| 4 デバイス比較表   | 3  | 8.1 アプリケーション情報         | 30 |

| 5 ピン構成および機能 | 4  | 8.2 代表的なアプリケーション       | 30 |

| 6 仕様        | 5  | 8.3 電源に関する推奨事項         | 47 |

| 6.1 絶対最大定格  | 5  | 8.4 レイアウト              | 48 |

| 6.2 ESD 定格  | 5  | 9 デバイスおよびドキュメントのサポート   | 51 |

| 6.3 推奨動作条件  | 5  | 9.1 ドキュメントのサポート        | 51 |

| 6.4 熱に関する情報 | 6  | 9.2 ドキュメントの更新通知を受け取る方法 | 51 |

| 6.5 電気的特性   | 6  | 9.3 サポート・リソース          | 51 |

| 6.6 タイミング特性 | 8  | 9.4 商標                 | 51 |

| 6.7 システム特性  | 9  | 9.5 静電気放電に関する注意事項      | 51 |

| 6.8 代表的特性   | 11 | 9.6 用語集                | 51 |

| 7 詳細説明      | 13 | 10 改訂履歴                | 51 |

| 7.1 概要      | 13 | 11 メカニカル、パッケージ、および注文情報 | 52 |

| 7.2 機能ブロック図 | 14 |                        |    |

## 4 デバイス比較表

| デバイス     | 発注用製品型番         | 参照先の部品番号    | 軽負荷時のモード | スペクトラム拡散 | 出力電圧 | スイッチング周波数 |

|----------|-----------------|-------------|----------|----------|------|-----------|

| LMQ61460 | LMQ61460AASRJRT | LMQ61460AAS | 自動モード    | あり       | 可変   | 可変        |

## 5 ピン構成および機能

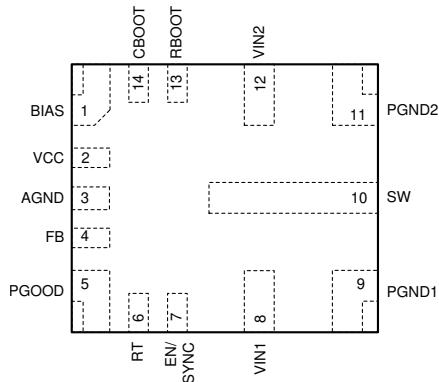

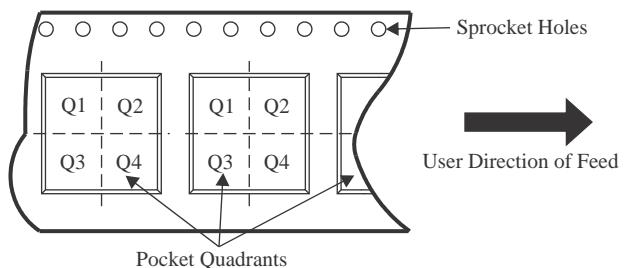

図 5-1. RJR パッケージ 14 ピン VQFN-HR 上面図

表 5-1. ピンの機能

| ピン      |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                      |

|---------|----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号 |                    |                                                                                                                                                                                                                                                                                                                         |

| BIAS    | 1  | P                  | 内部 LDO への入力。効率を向上させるため、出力電圧点に接続します。ノイズ耐性を向上させるには、このピンとグランドとの間に高品質の $0.1\mu\text{F}$ ~ $1\mu\text{F}$ コンデンサを任意で接続します。出力電圧が $12\text{V}$ より高い場合、このピンをグランドに接続します。                                                                                                                                                          |

| VCC     | 2  | O                  | 内部 LDO 出力。内部制御回路への電源として使用されます。いずれの外部負荷にも接続しないでください。このピンと AGND との間に高品質の $1\mu\text{F}$ コンデンサを接続します。                                                                                                                                                                                                                      |

| AGND    | 3  | G                  | 内部回路用のアナログ グランド。帰還と VCC は、このピンを基準に測定されます。PCB 上の PGND1 と PGND2 の両方に AGND を接続する必要があります。                                                                                                                                                                                                                                   |

| FB      | 4  | I                  | 内部制御ループへの出力電圧帰還入力。出力電圧を調整する場合、帰還分圧器のタップ点に接続します。フローティング状態にすることも、グランドに接続することもしないでください。                                                                                                                                                                                                                                    |

| PGOOD   | 5  | O                  | オープンドレインのパワー グッド ステータス出力。電流制限抵抗を介して、このピンを適切な電圧源にプルアップします。High = パワー OK, Low = フォルト。EN = Low, $V_{IN} > 1\text{V}$ のとき、PGOOD 出力は Low になります。このピンを使用しない場合、オープンにしてもグランドに接続してもかまいません。                                                                                                                                        |

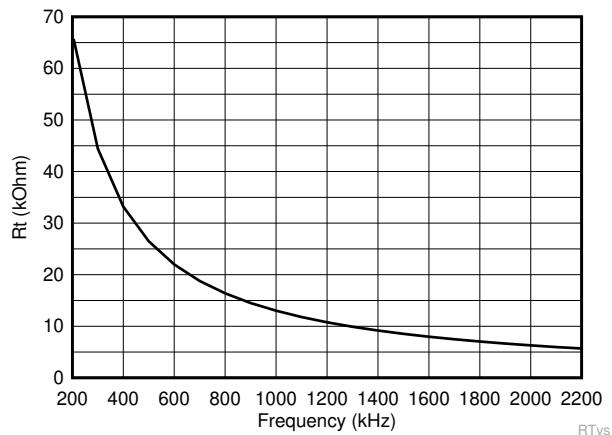

| RT      | 6  | I/O                | スイッチング周波数を $200\text{kHz}$ ~ $2200\text{kHz}$ に設定するため、 $5.76\text{k}\Omega$ ~ $66.5\text{k}\Omega$ の値の抵抗を介してこのピンをグランドに接続します。フローティング状態にすることも、グランドに接続することもしないでください。                                                                                                                                                       |

| EN/SYNC | 7  | I                  | 高精度イネーブル入力。High = オン, Low = オフ。VIN に接続できます。高精度イネーブルを使うと、このピンを調整可能な UVLO として使用できます。セクション 8 を参照してください。フローティングにはしないでください。EN/SYNC は同期入力ピンとしても機能します。本デバイスのスイッチング周波数をシステム クロックに同期させるために使います。外部クロックの立ち上がりエッジでトリガれます。コンデンサを使って、このピンに同期信号を AC 結合することができます。外部クロックに同期した場合、本デバイスは強制 PWM で動作し、PFM 軽負荷効率モードを無効化します。セクション 7 を参照してください。 |

| VIN1    | 8  | P                  | コンバータへの入力電源。このピンと PGND1 との間に高品質のバイパスコンデンサを接続します。VIN2 と低インピーダンスで接続する必要があります。                                                                                                                                                                                                                                             |

| PGND1   | 9  | G                  | 内部ローサイド MOSFET への電源グランド。システム グランドに接続。PGND2 と低インピーダンスで接続する必要があります。このピンと VIN1 との間に高品質のバイパスコンデンサを接続します。                                                                                                                                                                                                                    |

| SW      | 10 | O                  | コンバータのスイッチ ノード。出力インダクタに接続します。                                                                                                                                                                                                                                                                                           |

| PGND2   | 11 | G                  | 内部ローサイド MOSFET への電源グランド。システム グランドに接続。PGND1 と低インピーダンスで接続する必要があります。このピンと VIN2 との間に高品質のバイパスコンデンサを接続します。                                                                                                                                                                                                                    |

| VIN2    | 12 | P                  | コンバータへの入力電源。このピンと PGND2 との間に高品質のバイパスコンデンサを接続します。VIN1 と低インピーダンスで接続する必要があります。                                                                                                                                                                                                                                             |

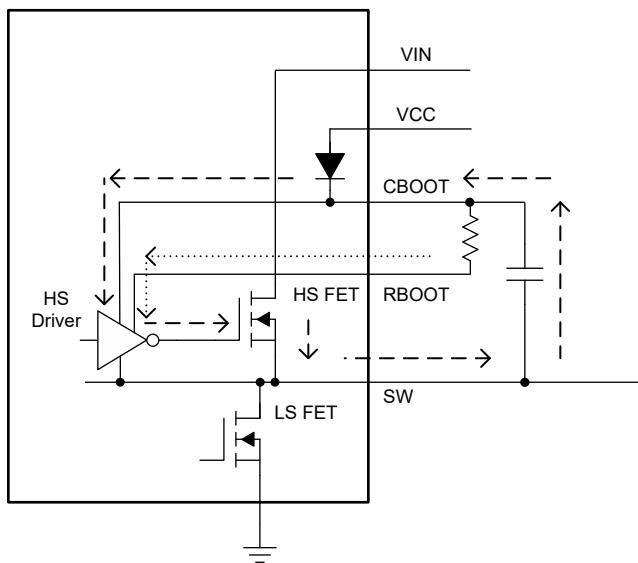

| RBOOT   | 13 | I/O                | 抵抗を介して CBOOT に接続します。この抵抗値は $0\Omega$ ~オープンの範囲内である必要があります、SW ノードの立ち上がり時間で決定します。                                                                                                                                                                                                                                          |

| CBOOT   | 14 | I/O                | ハイサイド ドライバの上側電源レール。SW と CBOOT との間に $100\text{nF}$ のコンデンサを接続します。内部ダイオードは VCC に接続されており、SW ノードが Low の間、CBOOT が充電されます。                                                                                                                                                                                                      |

(1) I = 入力、O = 出力、P = 電源、G = グランド

## 6 仕様

### 6.1 絶対最大定格

接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ において (特に記述のない限り) <sup>(1)</sup>

| パラメータ            |                                   | 最小値  | 最大値                   | 単位 |

|------------------|-----------------------------------|------|-----------------------|----|

| 入力電圧             | 「AGND、PGND」に対する「VIN1、VIN2」        | -0.3 | 42                    | V  |

|                  | SW に対する RBOOT                     | -0.3 | 5.5                   |    |

|                  | SW に対する CBOOT                     | -0.3 | 5.5                   |    |

|                  | 「AGND、PGND」に対する BIAS              | -0.3 | 16                    |    |

|                  | 「AGND、PGND」に対する EN/SYNC           | -0.3 | 42                    |    |

|                  | 「AGND、PGND」に対する RT                | -0.3 | 5.5                   |    |

|                  | 「AGND、PGND」に対する FB                | -0.3 | 16                    |    |

|                  | 「AGND、PGND」に対する PGOOD             | 0    | 20                    |    |

|                  | AGND に対する PGND <sup>(3)</sup>     | -1   | 2                     |    |

| 出力電圧             | 「AGND、PGND」に対する SW <sup>(2)</sup> | -0.3 | $V_{\text{IN}} + 0.3$ | V  |

|                  | 「AGND、PGND」に対する VCC               | -0.3 | 5.5                   |    |

| 電流               | PGOOD シンク電流 <sup>(4)</sup>        |      | 10                    | mA |

| $T_J$            | 接合部温度                             | -40  | 150                   | °C |

| $T_{\text{stg}}$ | 保存温度                              | -40  | 150                   | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) このピンには、GND より 2V 低い値から  $V_{\text{IN}}$  より 2V 高い値までの電圧を最大 200ns の間 (デューティ・サイクルは 0.01% 以下) 印加できます。

- (3) この仕様は、100ns 以下の持続時間の電圧に適用されます。D.C. 電圧は、 $\pm 0.3\text{V}$  の範囲内である必要があります。

- (4) ピンの電圧定格を超えないようにしてください。

### 6.2 ESD 定格

|                    |       |                                | 最小値   | 最大値  | 単位 |

|--------------------|-------|--------------------------------|-------|------|----|

| $V_{(\text{ESD})}$ | 静電気放電 | 人体モデル (HBM) <sup>(1)</sup>     | -2000 | 2000 | V  |

|                    |       | デバイス帶電モデル (CDM) <sup>(2)</sup> | -500  | 500  |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ において (特に記述のない限り) <sup>(1)</sup>

|       |                                       | 最小値 | 公称値                         | 最大値  | 単位  |

|-------|---------------------------------------|-----|-----------------------------|------|-----|

| 入力電圧  | 入力電圧範囲 (起動後)                          | 3   |                             | 36   | V   |

| 出力電圧  | 可変バージョンの出力電圧範囲 <sup>(2)</sup>         | 1   | $0.95 \times V_{\text{IN}}$ |      | V   |

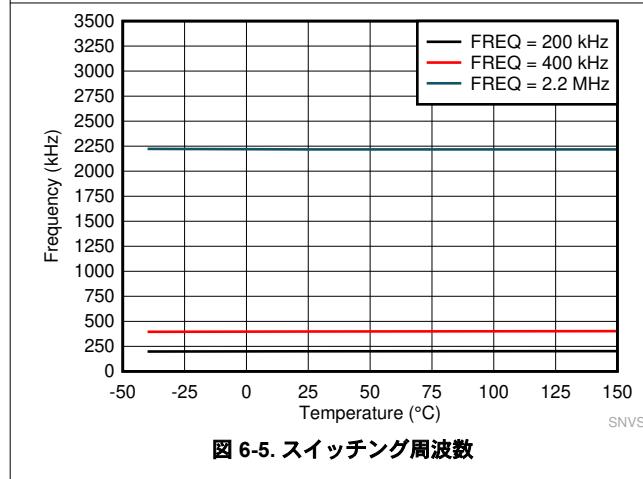

| 周波数   | 周波数調整範囲                               | 200 |                             | 2200 | kHz |

| 同期周波数 | 同期周波数範囲                               | 200 |                             | 2200 | kHz |

| 負荷電流  | 出力 DC 電流範囲 <sup>(3)</sup>             | 0   |                             | 6    | A   |

| 温度    | 動作時の接合部温度 ( $T_J$ ) 範囲 <sup>(4)</sup> | -40 |                             | 150  | °C  |

- (1) 推奨動作条件は本デバイスが機能する条件を示していますが、特定の性能限界を保証するものではありません。適合する仕様については「電気的特性」表を参照してください。

- (2) いかなる条件下でも、出力電圧は 0V を下回ることはできません。

- (3) 高いスイッチング周波数と高い周囲温度のどちらかまたはその両方で動作している場合、最大連続 DC 電流はディレーティングされる場合があります。詳細については、「アプリケーションと実装」セクションを参照してください。

- (4) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が  $125^{\circ}\text{C}$ を超えると、動作寿命が短くなります。

## 6.4 热に関する情報

この表に示す  $R_{\theta JA}$  の値は、その他のパッケージとの比較のためにのみに有効であり、設計目的では使用できません。これらの値は JESD 51-7 に従って計算されており、4 層 JEDEC 基板上でシミュレーションされています。これらは、実際のアプリケーションで得られた性能を表すものではありません。たとえば 4 層 PCB を使うと、 $R_{\theta JA} = 25^{\circ}\text{C}/\text{W}$  が達成可能です。設計情報については、「最大周囲温度と出力電流との関係」を参照してください。

| 热評価基準 (1) (2)               |                   | LMQ61460  | 単位   |

|-----------------------------|-------------------|-----------|------|

|                             |                   | RJR (QFN) |      |

|                             |                   | 14 ピン     |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗      | 59        | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 19        | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 19.2      | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 1.4       | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 19        | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗 | —         | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーション・レポートを参照してください。

(2) この表に示す  $R_{\theta JA}$  の値は、その他のパッケージとの比較のためにのみに有効であり、設計目的では使用できません。これらの値は JESD 51-7 に従って計算されており、4 層 JEDEC 基板上でシミュレーションされています。これらは、実際のアプリケーションで得られた性能を表すものではありません。

## 6.5 電気的特性

制限値は、接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ において適用されます(特に記述のない限り)。最小値および最大値の制限値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 。 $VIN1$  ( $VIN2$  と短絡) =  $V_{IN}$ 。 $V_{OUT}$  はコンバータの出力電圧です。

| パラメータ                | テスト条件                                                             | 最小値                                             | 標準値   | 最大値  | 単位            |

|----------------------|-------------------------------------------------------------------|-------------------------------------------------|-------|------|---------------|

| <b>電源電圧および電流</b>     |                                                                   |                                                 |       |      |               |

| $V_{IN\_OPERATE}$    | 入力動作電圧 (3)                                                        | 起動するために必要な電圧                                    | 3.95  | V    |               |

|                      |                                                                   | 動作開始後                                           | 3.0   |      |               |

| $V_{IN\_OPERATE\_H}$ | ヒステリシス (3)                                                        |                                                 | 1     | V    |               |

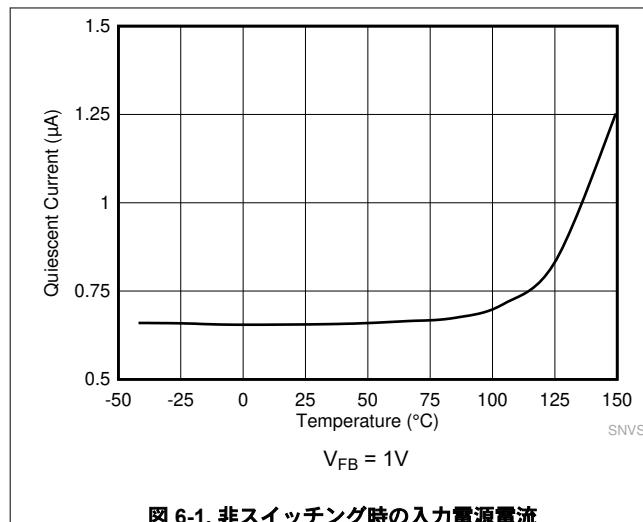

| $I_Q$                | 動作時の静止電流(スイッチングなし)。 $VIN$ ピンで測定 (1)                               | $V_{FB} = +5\%$ 、 $V_{BIAS} = 5\text{V}$        | 0.6   | 6    | $\mu\text{A}$ |

| $I_{BIAS}$           | $BIAS$ ピンに流れ込む電流(スイッチングなし、 $T_J = 125^{\circ}\text{C}$ での最大値) (1) | $V_{FB} = +5\%$ 、 $V_{BIAS} = 5\text{V}$ 、自動モード | 24    | 31.2 | $\mu\text{A}$ |

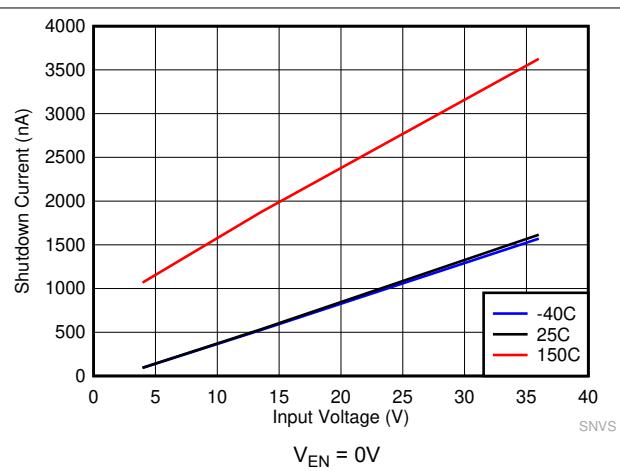

| $I_{SD}$             | シャットダウン時の静止電流( $VIN$ ピンで測定)                                       | $EN = 0\text{V}$ 、 $T_J = 25^{\circ}\text{C}$   | 0.6   | 6    | $\mu\text{A}$ |

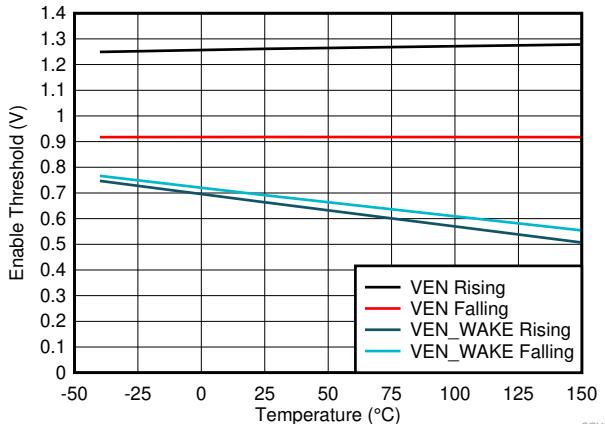

| <b>イネーブル</b>         |                                                                   |                                                 |       |      |               |

| $V_{EN}$             | イネーブル入力スレッショルド電圧 - 立ち上がり                                          |                                                 | 1.263 | V    |               |

| $V_{EN-ACC}$         | イネーブル入力スレッショルド電圧 - 標準値からの立ち上がりの偏差                                 |                                                 | -8.1% |      |               |

| $V_{EN-HYST}$        | イネーブル・スレッショルドのヒステリシス( $V_{EN}$ (標準値) のパーセンテージで表示)                 |                                                 | 24%   | 28%  | 32%           |

| $V_{EN-WAKE}$        | イネーブル・ウェークアップ・スレッショルド                                             |                                                 | 0.4   | V    |               |

| $I_{EN}$             | イネーブル・ピンの入力電流                                                     | $V_{IN} = EN = 13.5\text{V}$                    | 2.3   |      |               |

| $V_{EN\_SYNC}$       | $EN/SYNC$ ピンを使った同期に必要なエッジの高さ                                      | 立ち上がり / 立ち下がり時間: 30ns 未満                        |       | 2.4  | V             |

| <b>LDO - VCC</b>     |                                                                   |                                                 |       |      |               |

## 6.5 電気的特性 (続き)

制限値は、接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ において適用されます (特に記述のない限り)。最小値および最大値の制限値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 。 $VIN1$  ( $VIN2$  と短絡) =  $V_{IN}$ 。 $V_{OUT}$  はコンバータの出力電圧です。

| パラメータ                |                                                  | テスト条件                                                                         | 最小値  | 標準値   | 最大値   | 単位               |

|----------------------|--------------------------------------------------|-------------------------------------------------------------------------------|------|-------|-------|------------------|

| $V_{CC}$             | 内部 $V_{CC}$ 電圧                                   | $V_{BIAS} > 3.4\text{V}$ 、CCM 動作 <sup>(3)</sup>                               |      | 3.3   |       | V                |

|                      |                                                  | $V_{BIAS} = 3.1\text{V}$ 、非スイッチング                                             |      | 3.1   |       |                  |

| $V_{CC\_UVLO}$       | 内部 $V_{CC}$ 入力低電圧誤動作防止                           | $V_{CC}$ 立ち上がり低電圧スレッショルド                                                      |      | 3.6   |       | V                |

| $V_{CC\_UVLO\_HYST}$ | 内部 $V_{CC}$ 入力低電圧誤動作防止                           | $V_{CC\_UVLO}$ の下側のヒステリシス                                                     |      | 1.1   |       | V                |

| 帰還                   |                                                  |                                                                               |      |       |       |                  |

| $V_{FB\_acc}$        | 5V、3.3V、可変 (1V FB) バージョンの基準電圧の初期精度               | $V_{IN} = 3.3\text{V} \sim 36\text{V}$ 、 $T_J = 25^{\circ}\text{C}$ 、FPWM モード | -1%  |       | 1%    |                  |

| $I_{FB}$             | FB から AGND への入力電流                                | 可変バージョンのみ、FB = 1V                                                             |      | 10    |       | nA               |

| 発振器                  |                                                  |                                                                               |      |       |       |                  |

| $f_{ADJ}$            | $R_T$ または SYNC で調整可能な最小周波数                       | $RT = 66.5\text{k}\Omega$                                                     | 0.18 | 0.2   | 0.22  | MHz              |

|                      | $R_T$ または SYNC で調整可能な周波数 (400kHz の設定を使用)         | $RT = 33.2\text{k}\Omega$                                                     | 0.36 | 0.4   | 0.44  | MHz              |

|                      | $R_T$ または SYNC で調整可能な最大周波数                       | $RT = 5.76\text{k}\Omega$                                                     | 1.98 | 2.2   | 2.42  | MHz              |

| MOSFET               |                                                  |                                                                               |      |       |       |                  |

| $R_{DS(ON)\_HS}$     | パワー・スイッチの ON 抵抗                                  | ハイサイド MOSFET の $R_{DS(ON)}$                                                   |      | 41    | 82    | $\text{m}\Omega$ |

| $R_{DS(ON)\_LS}$     | パワー・スイッチの ON 抵抗                                  | ローサイド MOSFET の $R_{DS(ON)}$                                                   |      | 21    | 45    | $\text{m}\Omega$ |

| $V_{BOOT\_UVLO}$     | ハイサイド・スイッチがオフになる CBOOT ピンの電圧 (SW 基準)             |                                                                               |      | 2.1   |       | V                |

| 電流制限                 |                                                  |                                                                               |      |       |       |                  |

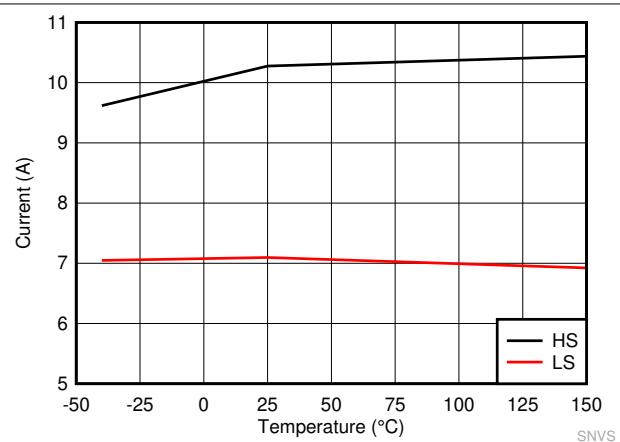

| $I_{L\text{-}HS}$    | ハイサイド・スイッチ電流制限値 <sup>(2)</sup>                   | デューティ・サイクルを 0% に近付ける                                                          | 8.9  | 10.3  | 11.5  | A                |

| $I_{L\text{-}LS}$    | ローサイド・スイッチ電流制限値                                  |                                                                               | 6.1  | 7.1   | 8.1   | A                |

| $I_{L\text{-}ZC}$    | ゼロクロスの電流制限値。正の電流の方向は、SW ピンから流れ出す電流の方向です。         | 自動モード、静的測定                                                                    |      | 0.25  |       | A                |

| $I_{L\text{-}NEG}$   | 負電流制限 FPWM および同期モード。正の電流の方向は、SW ピンから流れ出す電流の方向です。 | FPWM 動作                                                                       |      | -3    |       | A                |

| $I_{PK\_MIN\_0}$     | 自動モードでの最小ピーク・コマンドおよびデバイス電流定格                     | パルス幅 < 100ns                                                                  |      | 25%   |       |                  |

| $I_{PK\_MIN\_100}$   | 自動モードでの最小ピーク・コマンドおよびデバイス電流定格                     | パルス幅 > 1 $\mu\text{s}$                                                        |      | 12.5% |       |                  |

| $V_{HICCUP}$         | レギュレートされる前の FB 電圧に対する FB 電圧の比率                   | ソフトスタート中以外                                                                    |      | 40%   |       |                  |

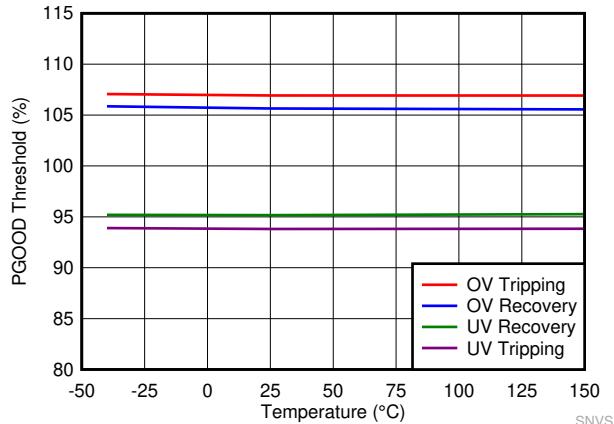

| パワー・グッド              |                                                  |                                                                               |      |       |       |                  |

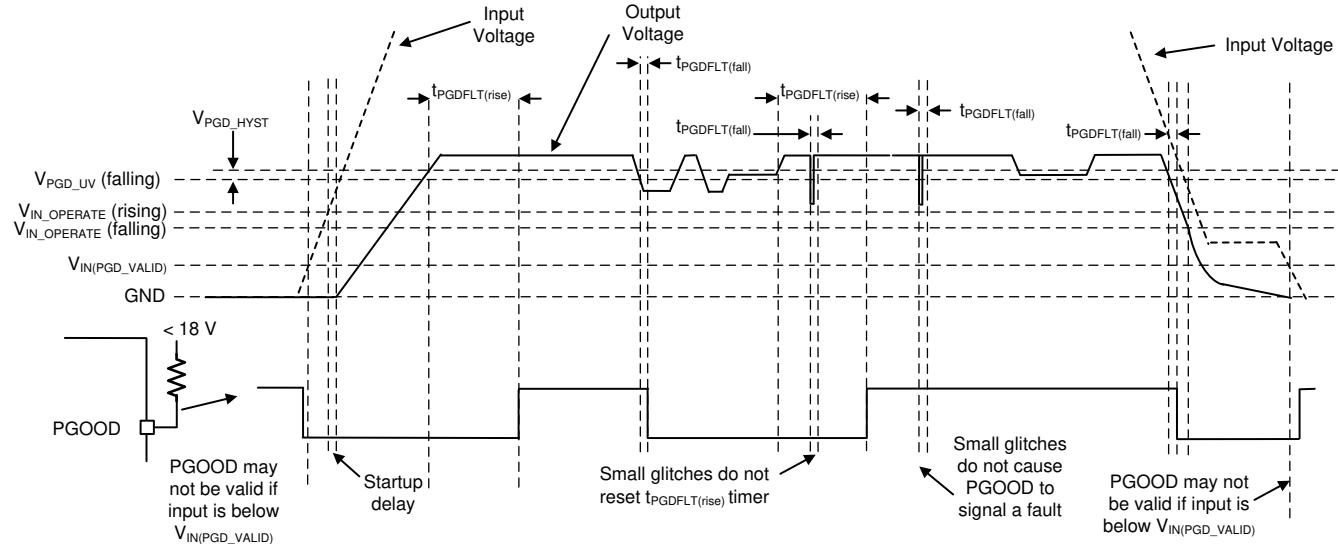

| $PGD_{OV}$           | PGOOD の上限 - 立ち上がり                                | $V_{OUT}$ 設定の %                                                               | 105% | 107%  | 110%  |                  |

| $PGD_{UV}$           | PGOOD の下限 - 立ち下がり                                | $V_{OUT}$ 設定の %                                                               | 92%  | 94%   | 96.5% |                  |

| $PGD_{HYST}$         | PGOOD の上限 (立ち上がりおよび立ち下がり)                        | $V_{OUT}$ 設定の %                                                               |      | 1.3%  |       |                  |

| $V_{IN(PGD\_VALID)}$ | PGOOD が適切に機能するための入力電圧                            |                                                                               | 1.0  |       |       | V                |

## 6.5 電気的特性 (続き)

制限値は、接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ において適用されます (特に記述のない限り)。最小値および最大値の制限値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 。 $VIN1$  ( $VIN2$  と短絡) =  $V_{IN}$ 。 $V_{OUT}$  はコンバータの出力電圧です。

| パラメータ          |                                         | テスト条件                                                                | 最小値 | 標準値 | 最大値      | 単位       |

|----------------|-----------------------------------------|----------------------------------------------------------------------|-----|-----|----------|----------|

| $V_{PGD(LOW)}$ | Low レベル PGOOD 機能出力電圧                    | PGOOD ピンに $46\mu\text{A}$ のプルアップを接続、 $V_{IN} = 1.0\text{V}$ 、EN = 0V |     |     | 0.4      | V        |

|                |                                         | PGOOD ピンに $1\text{mA}$ のプルアップを接続、 $V_{IN} = 13.5\text{V}$ 、EN = 0V   |     |     | 0.4      |          |

|                |                                         | PGOOD ピンに $2\text{mA}$ のプルアップを接続、 $V_{IN} = 13.5\text{V}$ 、EN = 3.3V |     |     | 0.4      |          |

| $R_{PGD}$      | PGOOD 出力の $R_{DS(ON)}$                  | PGOOD ピンに $1\text{mA}$ のプルアップを接続、EN = 0V                             | 17  | 40  | $\Omega$ | $\Omega$ |

|                |                                         | PGOOD ピンに $1\text{mA}$ のプルアップを接続、EN = 3.3V                           | 40  | 90  | $\Omega$ |          |

| $I_{OV}$       | 過電圧条件での SW ノードのプルダウン電流                  |                                                                      |     | 0.5 |          | mA       |

| サーマル・シャットダウン   |                                         |                                                                      |     |     |          |          |

| $T_{SD\_R}$    | サーマル・シャットダウン立ち上がりスレッショルド <sup>(3)</sup> |                                                                      | 158 | 168 | 180      | °C       |

| $T_{SD\_HYST}$ | サーマル・シャットダウン・ヒステリシス <sup>(3)</sup>      |                                                                      |     | 10  |          | °C       |

- (1) これは、スイッチングなし、開ループ、「公称値 + 5%」に FB をプルするという条件で、本デバイスが使用する電流です。この電流は、レギュレーション中にシステムに流れ込む入力電流の合計を示すものではありません。詳細については、「システム特性」とセクション 7.3.14 を参照してください。

- (2) ハイサイド電流制限値はデューティ・サイクルの関数です。ハイサイド電流制限値は、小さいデューティ・サイクルで大きく、大きいデューティ・サイクルで小さくなります。

- (3) パラメータは、設計、統計分析、相関パラメータの製造試験によって規定されています。

## 6.6 タイミング特性

制限値は、接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ において適用されます (特に記述のない限り)。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 。

| パラメータ          |                                                 | テスト条件                                                                 | 最小値 | 標準値 | 最大値 | 単位 |

|----------------|-------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|----|

| スイッチ・ノード       |                                                 |                                                                       |     |     |     |    |

| $t_{ON\_MIN}$  | HS スイッチの最小オン時間                                  | $V_{IN} = 20\text{V}$ 、 $I_{OUT} = 2\text{A}$ 、RBOOT は CBOOT と短絡      |     | 55  | 70  | ns |

| $t_{ON\_MAX}$  | HS スイッチの最大オン時間                                  |                                                                       |     | 9   |     | μs |

| $t_{OFF\_MIN}$ | LS スイッチの最小オン時間                                  | $V_{IN} = 4.0\text{V}$ 、 $I_{OUT} = 1\text{A}$ 、RBOOT は CBOOT と短絡     |     | 65  | 85  | ns |

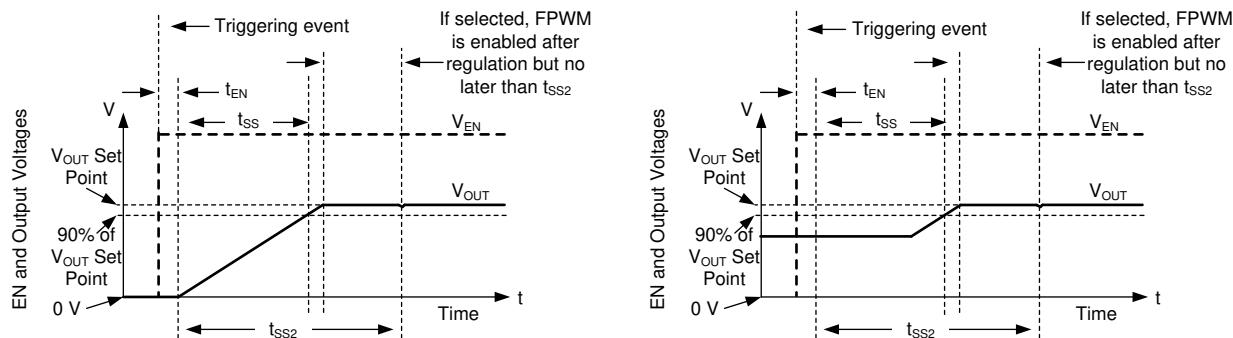

| $t_{SS}$       | 最初の SW パルスから $V_{REF}$ が設定点の 90% に達するまでの時間      | $V_{IN} \geq 4.2\text{V}$                                             | 3.5 | 5   | 7   | ms |

| $t_{SS2}$      | 最初の SW パルスから FPWM 誤動作防止解除までの時間 (出力がレギュートされない場合) | $V_{IN} \geq 4.2\text{V}$                                             | 9.5 | 13  | 17  | ms |

| $t_w$          | 短絡待機時間 (「ヒップ」時間)                                |                                                                       |     | 80  |     | ms |

| イネーブル          |                                                 |                                                                       |     |     |     |    |

| $t_{EN}$       | ターンオン遅延 <sup>(1)</sup>                          | $C_{VCC} = 1\mu\text{F}$ 、EN High から最初の SW パルスまでの時間 (出力が 0V から開始する場合) |     | 0.7 |     | ms |

制限値は、接合部の動作時推奨温度である  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ において適用されます (特に記述のない限り)。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 。

| パラメータ              | テスト条件                               | 最小値 | 標準値 | 最大値 | 単位            |

|--------------------|-------------------------------------|-----|-----|-----|---------------|

| $t_B$              | 立ち上がりまたは立ち下がりエッジの後の EN のブランディング (1) | 4   | 28  |     | $\mu\text{s}$ |

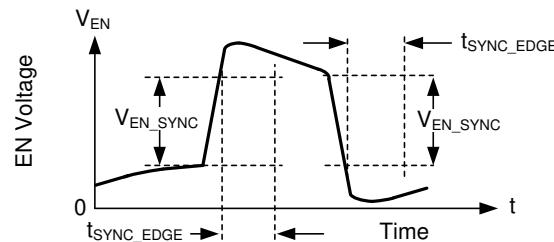

| $t_{SYNC\_EDGE}$   | エッジ認識のためのエッジ後のイネーブル同期信号のホールド時間      | 100 |     |     | $\text{ns}$   |

| <b>パワー・グッド</b>     |                                     |     |     |     |               |

| $t_{PGDFLT(rise)}$ | PGOOD High 信号までの遅延時間                | 1.5 | 2   | 2.5 | $\text{ms}$   |

| $t_{PGDFLT(fall)}$ | PGOOD 機能のグリッチ・フィルタ時定数               | 120 |     |     | $\mu\text{s}$ |

(1) パラメータは、設計、統計分析、相関パラメータの製造試験によって規定されています。出荷時のテストは行っていません。

## 6.7 システム特性

以下の値は、代表的なアプリケーション回路の部品の値が使用されるという前提で、設計によって規定されています。特に記述のない限り、各制限値は接合部温度範囲 ( $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ ) にわたって適用されます。最小値および最大値は、試験、設計、統計的相関を使って求められています。標準値は  $T_J = 25^{\circ}\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 。 $V_{IN1}$  ( $V_{IN2}$  と短絡) =  $V_{IN}$ 。 $V_{OUT}$  は出力設定値。これらのパラメータについては、出荷時のテストは行っていません。

| パラメータ                 | テスト条件                                                          | 最小値                                                                                                       | 標準値  | 最大値 | 単位            |

|-----------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|-----|---------------|

| <b>効率</b>             |                                                                |                                                                                                           |      |     |               |

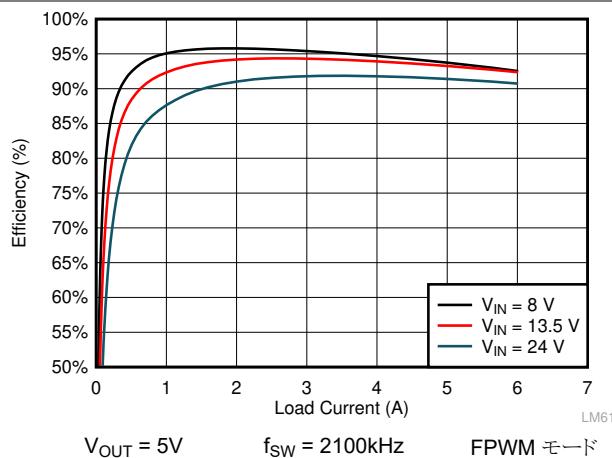

| $\eta_{5V\_2p1MHz}$   | 2.1MHz (標準値) での効率                                              | $V_{OUT} = 5\text{V}$ 、 $I_{OUT} = 4\text{A}$ 、 $R_{BOOT} = 0\Omega$                                      | 93%  |     |               |

|                       |                                                                | $V_{OUT} = 5\text{V}$ 、 $I_{OUT} = 100\mu\text{A}$ 、 $R_{BOOT} = 0\Omega$ 、 $R_{FBT} = 1\text{M}\Omega$   | 73%  |     |               |

| $\eta_{3p3V\_2p1MHz}$ | 2.1MHz (標準値) での効率                                              | $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 4\text{A}$ 、 $R_{BOOT} = 0\Omega$                                    | 91%  |     |               |

|                       |                                                                | $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 100\mu\text{A}$ 、 $R_{BOOT} = 0\Omega$ 、 $R_{FBT} = 1\text{M}\Omega$ | 71%  |     |               |

| $\eta_{5V\_400kHz}$   | 400kHz (標準値) での効率                                              | $V_{OUT} = 5\text{V}$ 、 $I_{OUT} = 4\text{A}$ 、 $R_{BOOT} = 0\Omega$                                      | 95%  |     |               |

|                       |                                                                | $V_{OUT} = 5\text{V}$ 、 $I_{OUT} = 100\mu\text{A}$ 、 $R_{BOOT} = 0\Omega$ 、 $R_{FBT} = 1\text{M}\Omega$   | 76%  |     |               |

| <b>動作範囲</b>           |                                                                |                                                                                                           |      |     |               |

| $V_{VIN\_MIN1}$       | 起動後、軽負荷時に完全に機能するための $V_{IN}$                                   | $V_{OUT}$ を $3.3\text{V}$ に設定                                                                             | 3.0  |     | $\text{V}$    |

| $V_{VIN\_MIN2}$       | 起動後、最大定格負荷の 100% 時に完全に機能するための $V_{IN}$                         | $V_{OUT}$ を $3.3\text{V}$ に設定                                                                             | 3.95 |     | $\text{V}$    |

| $I_{Q-VIN}$           | 動作時静止電流 (1)                                                    | $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、自動モード、 $R_{FBT} = 1\text{M}\Omega$                       | 7    |     | $\mu\text{A}$ |

|                       |                                                                | $V_{OUT} = 5\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、自動モード、 $R_{FBT} = 1\text{M}\Omega$                         | 10   |     |               |

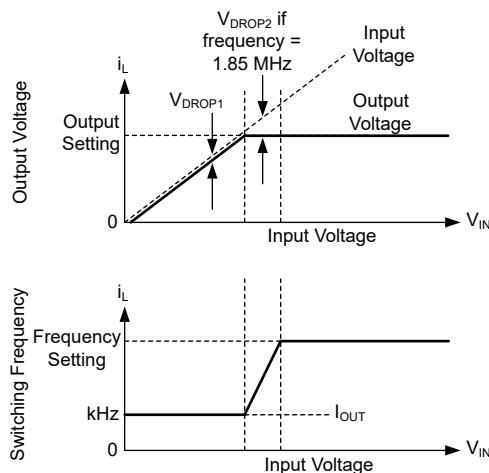

| $V_{DROP1}$           | インダクタの DCR 電圧降下を起こさず、レギュレーション精度を維持するための入力と出力との電圧差              | $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 4\text{A}$ 、-3% の出力精度 ( $25^{\circ}\text{C}$ )                       | 0.4  |     | $\text{V}$    |

|                       |                                                                | $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 4\text{A}$ 、-3% の出力精度 ( $125^{\circ}\text{C}$ )                      | 0.55 |     |               |

| $V_{DROP2}$           | DCR 電圧降下を起こさず、 $f_{SW} \geq 1.85\text{MHz}$ を維持するための入力と出力との電圧差 | $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 4\text{A}$ 、-3% のレギュレーション精度 ( $25^{\circ}\text{C}$ )                 | 0.8  |     | $\text{V}$    |

|                       |                                                                | $V_{OUT} = 3.3\text{V}$ 、 $I_{OUT} = 4\text{A}$ 、-3% のレギュレーション精度 ( $125^{\circ}\text{C}$ )                | 1.2  |     |               |

| $D_{MAX}$             | 最大デューティ・サイクル                                                   | $f_{SW} = 1.85\text{MHz}$                                                                                 | 87%  |     |               |

|                       |                                                                | 周波数フォールドバック中                                                                                              | 98%  |     |               |

以下の値は、代表的なアプリケーション回路の部品の値が使用されるという前提で、設計によって規定されています。特に記述のない限り、各制限値は接合部温度範囲 (-40°C ~ +150°C) にわたって適用されます。最小値および最大値は、試験、設計、統計的相関を使って求められています。標準値は  $T_J = 25^\circ\text{C}$  における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 。 $V_{IN1}$  ( $V_{IN2}$  と短絡) =  $V_{IN}$ 。 $V_{OUT}$  は出力設定値。これらのパラメータについては、出荷時のテストは行っていません。

| パラメータ        |                | テスト条件                                                      | 最小値 | 標準値  | 最大値 | 単位 |

|--------------|----------------|------------------------------------------------------------|-----|------|-----|----|

| <b>RBOOT</b> |                |                                                            |     |      |     |    |

| $t_{RISE}$   | SW ノードの立ち上がり時間 | $R_{BOOT} = 0\Omega$ , $I_{OUT} = 2\text{A}$ (10% ~ 80%)   |     | 2.15 |     | ns |

|              |                | $R_{BOOT} = 100\Omega$ , $I_{OUT} = 2\text{A}$ (10% ~ 80%) |     | 2.7  |     | ns |

(1) この仕様の意味と計算方法については、詳細説明を参照してください。

## 6.8 代表的特性

特に記述のない限り、 $V_{IN} = 13.5V$ 、 $f_{SW} = 400\text{kHz}$  です。

図 6-1. 非スイッチング時の入力電源電流

図 6-2. シャットダウン時の電源電流

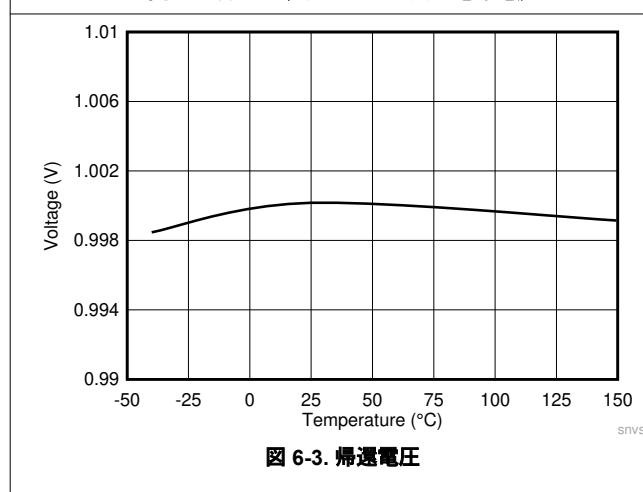

図 6-3. 帰還電圧

図 6-4. LMQ61460 のハイサイドおよびローサイド電流制限

図 6-5. スイッチング周波数

図 6-6. ハイサイドおよびローサイド・スイッチの  $R_{DS\_ON}$

## 6.8 代表的特性 (続き)

特に記述のない限り、 $V_{IN} = 13.5V$ 、 $f_{SW} = 400\text{kHz}$  です。

図 6-7. イネーブル・スレッショルド

図 6-8. PGOOD スレッショルド

## 7 詳細説明

### 7.1 概要

LMQ61460 は、幅広い産業用アプリケーション向けに設計された同期整流ピーク電流モード降圧レギュレータです。本レギュレータは、400kHz (AM 帯域より下) と 2.1MHz (AM 帯域より上) を含む幅広いスイッチング周波数で動作できます。このデバイスは幅広い変換比で動作します。最小オン時間または最小オフ時間が目的の変換比に対応しない場合、周波数が自動的に下がるため、動作周波数を高く設定した状態で入力電圧過渡が発生しても、出力電圧レギュレーションを維持できます。

本デバイスは低 EMI を考慮して設計されており、AM 帯域より上および下での動作のために最適化されています。

- HotRod パッケージによりスイッチ ノード リンギングを最小化

- 並列入力パスにより寄生インダクタンスを最小化

- 内部バイパス コンデンサにより EMI を低減

- スペクトラム拡散によりピーク エミッションを削減

- SW ノードの立ち上がり時間を調整可能

これらの機能を組み合わせることで、シールドとその他の高価な EMI 軽減対策を不要にできます。

このデバイスは、要求の厳しい高性能産業用環境で動作しながら、最終製品のコストとサイズが最小化されるように設計されています。LMQ61460 は、200kHz~2.2MHz の範囲で動作するように、RT ピンを使って設定できます。2.1MHz で動作させることで、小型の受動部品を使用できます。最新の電流制限機能により、および 6A レギュレータ用に最適化されたインダクタを使用できます。また、このデバイスは無負荷時の消費電流が小さく、バッテリ直結型の常時オン アプリケーションに最適です。また、シャットダウン電流が小さく、最大動作電圧が高いため、外部負荷スイッチと入力過渡保護をなくすこともできます。システムコストをさらに低減するため、先進の PGOOD 出力が備わっており、大抵、外部リセットまたは監視デバイスを使わずに済みます。

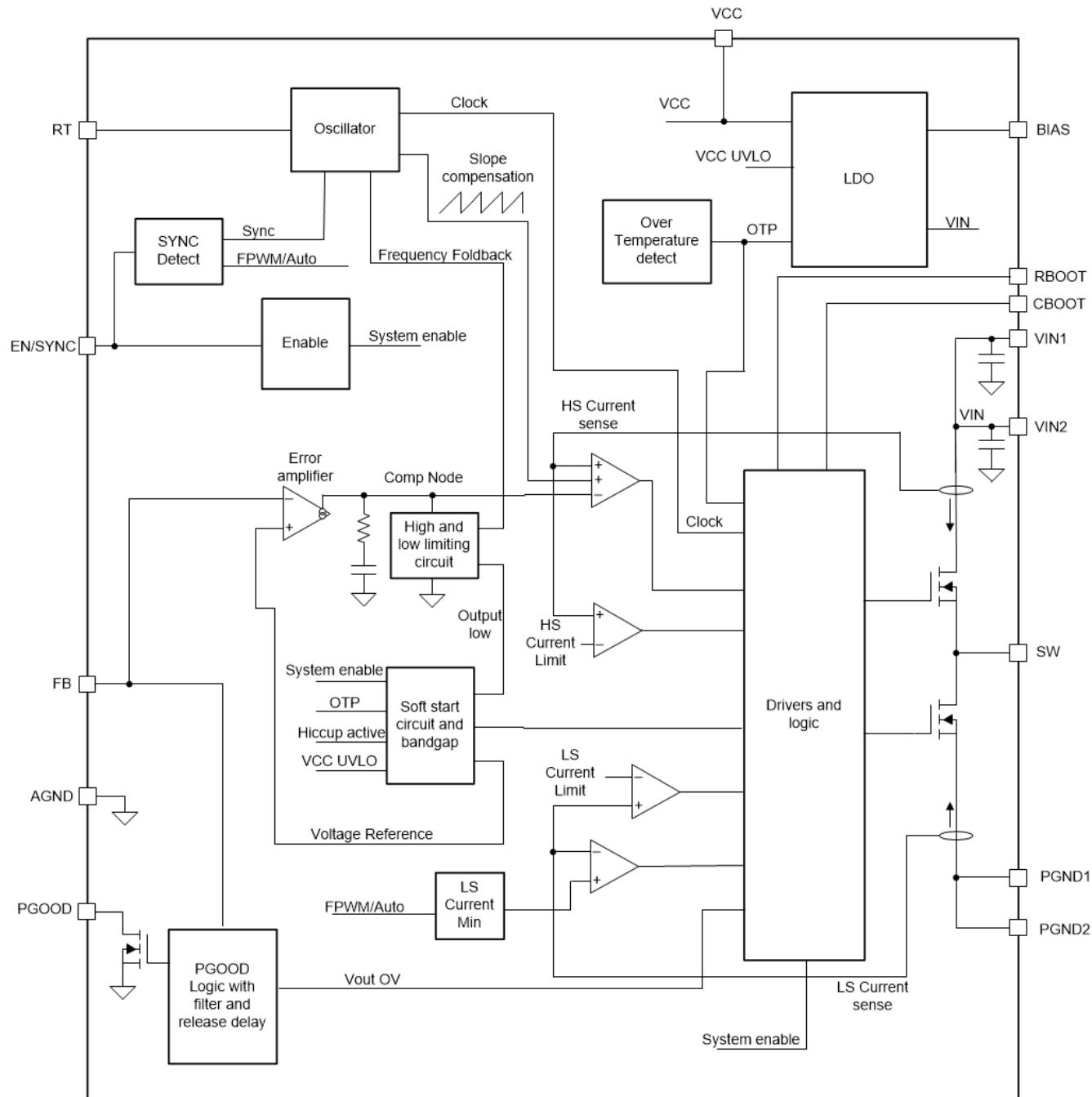

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 EN/SYNC による有効化と $V_{IN}$ UVLO

起動とシャットダウンは、EN/SYNC 入力と  $V_{IN}$  UVLO により制御されます。本デバイスをシャットダウン モードにするには、 $V_{EN\_WAKE}$  (4V) より低い電圧を EN ピンに印加します。シャットダウン モードでは、静止電流は  $0.6\mu A$  (標準値) に低下します。 $V_{EN\_WAKE}$  より高くかつ  $V_{EN}$  より低い電圧では、VCC がアクティブになり、SW ノードは非アクティブになります。EN 電圧が  $V_{EN}$  を上回ると、入力電圧が 3V を超えている場合、本チップは通常スイッチングを開始します。

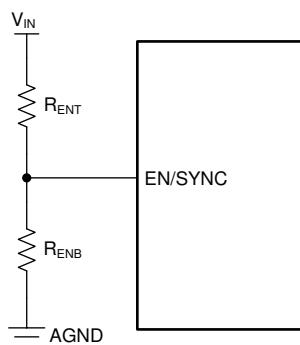

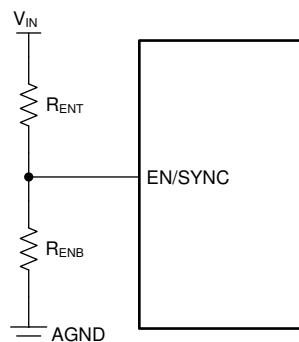

EN/SYNC ピンはフローティングのままにすることはできません。この動作を可能にする最も簡単な方法は、EN/SYNC ピンを  $V_{IN}$  に接続することです。これにより、 $V_{IN}$  によって内部 VCC が UVLO レベルよりも高く駆動されると本デバイスは自動的に起動できます。しかし多くのアプリケーションでは、イネーブル分圧回路 (図 7-1) を採用することで恩恵を受けることができます。これにより、高精度の入力低電圧誤動作防止 (UVLO) を実現できるためです。UVLO は、シーケンシング、長い入力ケーブルと組み合わせて使った場合の本デバイスの再トリガの防止、バッテリ電源の過放電の発生頻度低減のために使用できます。高精度イネーブル スレッショルド ( $V_{EN}$ ) の許容誤差は 8.1% であることに注意します。再トリガを防止するには、ヒステリシスが十分な大きさである必要があります。その他の IC の外部ロジック出力で EN/SYNC ピンを駆動して、システム電源のシーケンシングを行うこともできます。

図 7-1. EN ピンを使った  $V_{IN}$  同期

抵抗値は、式 1 を使用して計算できます。

$$R_{ENB} = R_{ENT} \cdot \frac{V_{EN}}{V_{ON} - V_{EN}} \quad (1)$$

ここで、

- $V_{ON}$  は、設計対象の回路の起動入力電圧 (標準値) の目標値です。

EN ピンは外部同期クロック入力としても使用できるために注意してください。クロックのエッジが検出されると、イネーブルロジックにブランкиング時間 ( $t_B$ ) が適用されます。ブランкиング時間内のロジックの変化はすべて無視されます。本デバイスがシャットダウン モード中の場合、ブランкиング時間は適用されません。ブランкиング時間は  $4\mu s$  から  $28\mu s$  の範囲です。出力を実質的に無効化するには、EN/SYNC 入力を  $28\mu s$  より長い間 Low に維持する必要があります。

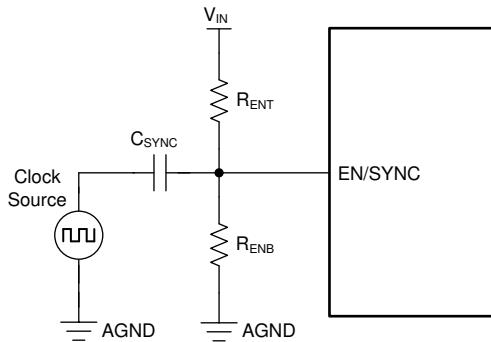

### 7.3.2 EN/SYNC ピンによる同期

LMQ61460 では、FREQ/SYNC ピンを使って内部発振器を外部クロックに同期させることができます。クロックの立ち上がりエッジを EN ピンに AC 結合することで、内部発振器を同期させることができます (図 7-2 を参照)。 $R_{ENT}$  と  $R_{ENB}$  の並列合成値を約  $100k\Omega$  にすることを推奨します。 $R_{ENT}$  は同期のために必要ですが、 $R_{ENB}$  は未実装にしておくことがで

きます。スイッチング動作は、200kHz～2.2MHz の外部クロックと同期することができます。外部クロックは、適切な起動シーケンスが行われるように、起動前に必ずオフにします。

図 7-2. EN ピンを使用した同期のための代表的な実装

図 7-3 に示すように、内部同期パルス検出器をトリップさせるには、EN ピンの AC 結合電圧エッジが SYNC 振幅スレッショルド ( $V_{EN\_SYNC\_MIN}$ ) を上回る必要があります。また、EN/SYNC の最小立ち上がりおよび立ち下がりパルス幅は、 $t_{SYNC\_EDGE(MIN)}$  より長くかつプランギング時間 ( $t_B$ ) より短い必要があります。1nF のコンデンサ ( $C_{SYNC}$ ) で結合された 3.3V 以上の振幅のパルス信号を使うことを推奨します。

図 7-3. 代表的な SYNC/EN 波形

有効な同期信号が 2048 サイクルにわたって印加されると、印加された信号の周波数に向かってクロック周波数が急激に変化します。また、使用中のデバイスがスペクトラム拡散機能を備えている場合、有効な同期信号はスペクトラム拡散に優先し (スペクトラム拡散をオフにし)、クロックは印加されたクロック周波数に切り替わります。

### 7.3.3 可変スイッチング周波数

本デバイスの RT ピンと AGND の間に接続された抵抗は、動作周波数を設定するために使われます。抵抗値を求めるには、式 2 を使います。または図 7-4 を参照します。推奨範囲外の抵抗値を使うと本デバイスがシャットダウンする場合があることに注意します。シャットダウンすることで、RT ピンがグランドに短絡している場合またはオープンのままである場合の意図しない動作を防止します。強制的に同期させる目的で、このピンにパルス信号を印加することはしないでください。同期が必要な場合、セクション 7.3.2 を参照してください。

$$R_{RT} (\text{k}\Omega) = (1 / f_{SW} (\text{kHz}) - 3.3 \times 10^{-5}) \times 1.346 \times 10^4 \quad (2)$$

図 7-4. クロック周波数の設定

### 7.3.4 クロックのロック

有効な同期信号が検出された後、クロック ロック手順が開始されます。LMQ61460 デバイスは、EN/SYNC ピンを通してこの信号を受信します。約 2048 パルスの後、クロック周波数は、出力を変動させることなく、同期信号の周波数へのスムーズな遷移を完了します。周波数は、突然に調整されるとはいえ、そのクロック サイクルは、デフォルトの周波数で動作する際のクロック サイクルと同期周波数で動作する際のクロック サイクルとの間の長さになるように、位相が維持されることに注意します。そのため、長すぎるパルスまたは短すぎるパルスは除去されます。周波数が調整された後、立ち上がり同期エッジが立ち上がり SW ノードパルスと対応するように、数 10 サイクルかけて位相が調整されます。図 7-5 を参照。

図 7-5. 同期プロセス

### 7.3.5 PGOOD 出力動作

ディスクリートのリセット デバイスを置き換えるために PGOOD 機能が実装されているため、部品点数とコストを低減できます。帰還電圧が、規定された PGOOD レッショルド (図 6-8 を参照) の外に出ると、PGOOD ピンの電圧は Low に遷移します。この遷移は、電流制限中、サーマル シャットダウン中、ディスエーブル中、通常の起動中に発生する可能性があります。グリッチ フィルタは、出力電圧の短時間の変動 (ラインおよび負荷過渡時など) に対するフラグの誤動作を防止します。 $t_{PGDFLT\_FALL}$  よりも短い出力電圧変動では、パワー グッド フラグは立ちません。図 7-6 に、パワー グッド動作の詳細を示します。

パワー グッド出力はオープン ドレインの NMOS で構成されており、適切なロジック電源または  $V_{OUT}$  に接続した外付け プルアップ抵抗が必要です。EN が Low にプルされると、フラグ出力も Low に強制されます。EN が Low の場合、入力電圧が 1V 以上 (標準値) である限り、パワー グッドは有効です。

図 7-6. PGOOD のタイミング図 (OV イベントを除く)

表 7-1. PGOOD がフォルトを通知 (Low をプル) する条件

| フォルト条件の開始                                                            | フォルト条件の終了 (その後、PGOOD 出力が解放される前に $t_{PGDFLT(rise)}$ が経過する必要があります。) (1)                                                                      |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{OUT} < V_{OUT-target} \times PGD_{UV}$ かつ $t > t_{PGDFLT(fall)}$ | 出力電圧がレギュレートされている。<br>$V_{OUT-target} \times (PGD_{UV} + PGD_{HYST}) < V_{OUT} < V_{OUT-target} \times (PGD_{OV} - PGD_{HYST})$ (図 6-8 を参照) |

| $V_{OUT} > V_{OUT-target} \times PGD_{OV}$ かつ $t > t_{PGDFLT(fall)}$ | 出力電圧がレギュレートされている。                                                                                                                          |

| $T_J > T_{SD\_R}$                                                    | $T_J < T_{SD\_F}$ かつ「出力電圧がレギュレートされている」                                                                                                     |

| $EN < V_{EN}$ (立ち下がり)                                                | $EN > V_{EN}$ (立ち上がり) かつ「出力電圧がレギュレートされている」                                                                                                 |

| $V_{CC} < V_{CC\_UVLO} - V_{CC\_UVLO\_HYST}$                         | $V_{CC} > V_{CC\_UVLO}$ かつ「出力電圧がレギュレートされている」                                                                                               |

(1) 追加の動作チェックとして、ソフトスタート中 PGOOD は Low に維持されます。その期間は、最大出力電圧に達したときと初期化から  $t_{SS2}$  が経過したときのどちらか早い方までと定義されています。

### 7.3.6 内部LDO、VCC UVLO、BIAS 入力

VCC ピンは、本デバイスの制御回路に電力を供給するために使用される内部 LDO の出力です。公称出力は 3V～3.3V です。BIAS ピンは内部 LDO への入力です。入力電源電流をできるだけ小さくするため、この入力を  $V_{OUT}$  に接続することもできます。BIAS 電圧が 3.1V 未満の場合、VIN1 と VIN2 は内部 LDO に直接電力を供給します。

不適切な動作を防止するため、VCC には、内部電圧が低すぎる場合にスイッチングを止める UVLO が備わっています。セクション 6.5 の  $V_{CC\_UVLO}$  と  $V_{CC\_UVLO\_HYST}$  を参照してください。これらの UVLO 値と LDO ドロップアウトを使って  $V_{IN\_OPERATE}$  と  $V_{IN\_OPERATE\_H}$  の最小値を求めるに注意します。

### 7.3.7 ブートストラップ電圧と $V_{CBOOT-UVLO}$ (CBOOT ピン)

ハイサイド (HS) スイッチのドライバには、 $V_{IN}$  より高いバイアスが必要です。CBOOT と SW の間に接続されたコンデンサ ( $C_{BOOT}$ ) は、CBOOT ピンの電圧を SW + VCC に昇圧するチャージ・ポンプとして機能します。外付け部品点数を最小化するため、本デバイスのダイにはブート・ダイオードが内蔵されています。定格 10V 以上の 100nF コンデンサを使うことを推奨します。 $V_{BOOT\_UVLO}$  スレッショルド (標準値 2.1V) は、適切な HS スイッチ動作を維持するように設計されています。 $C_{BOOT}$  コンデンサの電圧が  $V_{BOOT\_UVLO}$  を下回ると、本デバイスは HS スイッチをオンしようとする前にローサイド・スイッチをオンすることで充電シーケンスを開始します。

### 7.3.8 調整可能な SW ノードのスルーレート

効率の観点から EMI を最適化できるように、ハイサイド FET のドライバの駆動強度を電源投入時に抵抗で選択できるように本デバイスは設計されています。図 7-7 を参照してください。RBOOT ピンに流れ込む電流 (点線のループ) の大きさに応じて拡大された電流が CBOOT から流れ込みます (破線)。この電流は、ハイサイド・パワー MOSFET をオンさせるために使われます。

図 7-7. RBOOT の機能を示す概略回路図

RBOOT を CBOOT に短絡させると、立ち上がり時間が非常に短くなります。その結果、SW ノードの高調波は 150MHz 超まで「ロール・オフ」しません。100Ω のブート抵抗は約 2.7ns の SW ノード立ち上がり時間に相当するため、この 100Ω のブート抵抗によって SW ノードのオーバーシュートは実質的に解消されます。立ち上がり時間を遅くすることで、ほとんどの条件下で SW ノードの高調波のエネルギーを 100MHz 付近でロール・オフさせることができます。高調波をロール・オフさせることで、多くのアプリケーションでシールドとコモン・モード・チョークを不要にできます。入力電圧の増加と共に立ち上がり時間が増加することに注意します。また、RBOOT 抵抗の増加と共に蓄積電荷に起因するノイズは大幅に低減されます。スイッチングのスルーレートを下げるとき、効率も下がります。

### 7.3.9 スペクトラム拡散

スペクトラム拡散は工場オプションです。そのデバイスでスペクトラム拡散が利用できるかどうかを確認するには、セクション 4 を参照してください。スペクトラム拡散の目的は、一定の周波数で動作する代わりに、特定の周波数のピーク放射をより広い範囲の周波数に拡散することで、これらのピーク放射を除去することです。本デバイスが含まれるほとんどのシステムでは、スイッチング周波数の最初の数個の高調波からの低い周波数の伝導エミッションは、簡単にフィルタで除去できます。設計でより難しいことは、FM 帯域に妨害を与えるより高い高調波での放射の低減です。これらの高調波はしばしば、スイッチ・ノードとインダクタの周囲の電界によって環境と結合します。FM および TV 帯域にわたってエネルギーを滑らかに拡散でき、しかも本デバイスのスイッチング周波数未満の分数調波放射を制限するのに十分な小ささである  $\pm 2\%$  の周波数拡散を本デバイスは採用しています。本デバイスのスイッチング周波数でのピーク放射の低減量はわずか (1dB 未満) ですが、FM 帯域内のピークは通常 6dB 以上低減されます。

本デバイスは、線形帰還シフト・レジスタ (LFSR) を使ったサイクル間周波数ホッピング方式を採用しています。このインテリジェント疑似ランダム・ジェネレータは、出力リップルを制限するためにサイクル間の周波数変化を制限します。疑似ランダム・パターンは、オーディオ帯域よりも低い 1.5Hz 未満で繰り返されます。

スペクトラム拡散は、本デバイスのクロックが本来の周波数で自走している間のみ利用できます。以下の条件はすべてスペクトラム拡散に優先し、スペクトラム拡散はオフになります。

- ドロップアウト中にクロック速度が低下した。

- 自動モードで軽負荷時にクロック速度が低下した。FPWM モードでは、無負荷でもスペクトラム拡散は作動します。

- 出力電圧に対する入力電圧の比が高く、本デバイスが最小オン時間で動作している。内部クロックは低速化され、スペクトラム拡散は無効化されます。セクション 6.6 を参照してください。

- クロックが外部クロックに同期している。

### 7.3.10 ソフトスタートとドロップアウトからの回復

本デバイスは、起動中の出力電圧のオーバーシュートと大きな突入電流を防止するため、基準電圧を使ったソフトスタートを採用しています。ソフトスタートは、以下のいずれかの条件によってトリガされます。

- 本 IC の VIN ピンに電力が供給され、UVLO が解除された。

- 本デバイスをオンにするために EN が使われた。

- ヒップ待機期間から回復した。

- 過熱保護によるシャットダウンから回復した。

ソフトスタートがトリガされた後、本 IC は以下の動作を実行します。

- 出力電圧を制御するために本 IC が使用する基準電圧が、ゆっくりと上昇する。その結果、出力電圧が  $t_{SS}$  の時間でかけて目的の値の 90% に達します。

- 動作モードが自動に設定され、ダイオード エミュレーションを有効化する。これにより、電圧がすでに出力されている場合、出力を Low にすることなく起動できます。

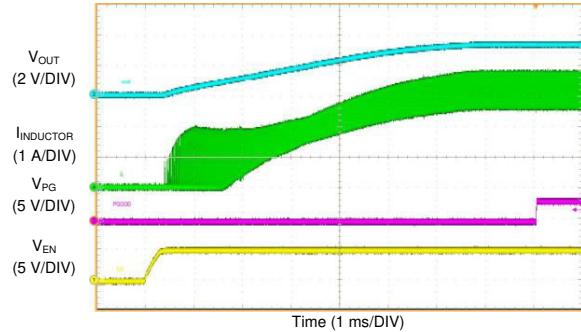

これらの動作を組み合わせることで、突入電流を制限しながら起動でき、また、起動時に、電流制限値に近い電流を生じさせる大きな出力コンデンサと重い負荷条件を、ヒップをトリガすることなく使用できます。図 7-8 を参照してください。

ソフトスタートは、出力電圧が 0V から始まる場合 (左側の図) とすでに電圧が出力されている場合 (右側の図) の両方で動作します。どちらの場合も出力電圧は、ソフトスタート開始から  $t_{SS}$  後、目標値との誤差が 10% 以内の範囲に達する必要があります。ソフトスタート中、FPWM とヒップは無効化されます。出力がレギュレーションに達した時点と  $t_{SS2}$  が経過した時点のどちらか早い方で、ヒップと FPWM は両方とも有効化されます。

図 7-8. ソフトスタート動作

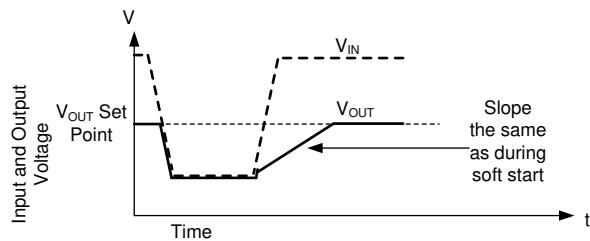

出力電圧の低下が数 % を超えると常に、出力電圧はゆっくり上昇します。この条件はドロップアウトからの回復と呼ばれ、ソフトスタートとは以下の 3 つの重要な点で異なります。

- 基準電圧は、現在の出力電圧を実現するために必要な値よりも約 1% 高い値に設定される。

- 出力電圧がその設定点の 0.4 倍未満である場合、ヒップが許可される。ドロップアウト レギュレーション自体の間、ヒップは禁止されることに注意します。

- ドロップアウトからの回復中、FPWM モードが許可される。外部電源によって出力電圧が突然プルアップされた場合、本デバイスは出力をプルダウンする場合があります。

ドロップアウトからの回復と呼ばれているにもかかわらず、出力電圧が設定点よりも数 % 低くなると常に、この機能が作動します。これは主に、以下の条件で発生します。

- ドロップアウト: 目的の出力電圧を生成するのに十分な入力電圧がない場合

- 過電流:ヒップをトリガするほどの大きさではない過電流イベントが発生した場合

出力電圧の低下が、高負荷と低入力電圧のどちらによるものであっても、出力がその設定点を下回る原因となっている条件が解消され次第、起動時と同じ速度で出力は上昇します。ドロップアウトが原因でヒップがトリガされなかつたとしても、128 クロック サイクル以上にわたって出力電圧が出力設定点の 0.4 倍を下回った場合、原則として、回復中にヒップがトリガされます。

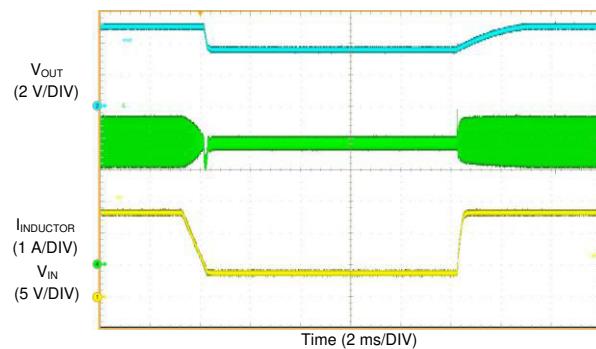

図 7-9. ドロップアウトからの回復

図 7-10. ドロップアウトからの回復 ( $V_{OUT} = 5V$ 、 $I_{OUT} = 4A$ 、 $V_{IN} = 13.5V \rightarrow 4V \rightarrow 13.5V$ )

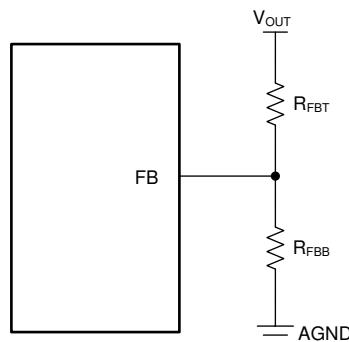

### 7.3.11 出力電圧設定

出力電圧と FB ピンとの間の帰還抵抗分圧回路を使用して出力電圧レベルを設定します。図 7-11 を参照してください。

図 7-11. 可変バージョンの出力電圧の設定

本デバイスでは、帰還 (FB) ピン用に 1V の基準電圧を使用しています。FB ピンの電圧は、基準電圧と同じになるように内部コントローラによって制御されます。その結果、抵抗分圧器の比によって出力電圧レベルが設定されます。式 3 を使

用して、目的の出力電圧と与えられた  $R_{FBT}$  に対応する  $R_{FBB}$  を決定できます。通常、 $R_{FBT}$  は  $10\text{k}\Omega \sim 1\text{M}\Omega$  です。 $R_{FBT}$  として  $100\text{k}\Omega$  を推奨します。 $1\text{M}\Omega$  に比べてノイズ耐性を向上させることができ、より小さい抵抗値に比べて消費電流を低減できます。

$$R_{FBB} = \frac{R_{FBT}}{V_{OUT} - 1}$$

(3)

また、過渡応答を最適化するため、フィードフォワード コンデンサ ( $C_{FF}$ ) を  $R_{FBT}$  と並列に接続する必要がある場合があります。

### 7.3.12 過電流および短絡保護

このデバイスは、ハイサイド MOSFET とローサイド MOSFET の両方でサイクル毎に電流を制限することで、過電流状態から保護されます。

ハイサイド MOSFET 過電流保護機能は、ピーク電流のモード制御の性質を利用して実装されています。HS スイッチ電流は、短いプランギング時間の後に HS がオンになると検出されます。スイッチング サイクルごとに、固定電流設定点と、電圧レギュレーション ループ出力からスロープ補償を引いた値のどちらか小さい方と HS スイッチ電流が比較されます。電圧ループには最大値があり、スロープ補償はデューティ サイクルに対応して大きくなるため、デューティ サイクルが 35% より大きい場合、デューティ サイクルが大きくなると HS 電流制限値は下がります。

LS スイッチがオンになると、スイッチ電流もセンスされ、監視されます。ローサイド素子は、ハイサイド素子と同様に、電圧制御ループのローサイド電流制限の指示に従ってオフになります。LS スイッチ電流がスイッチング サイクルの終わりに  $I_{LS\_Limit}$  を上回っている場合、そのスイッチング サイクルは、LS 電流が制限値を下回るまで延長されます。LS 電流が制限値を下回った時点で LS スイッチはオフになり、HS 素子が最後にオンになってから 1 クロック周期以上が経過しなければ、HS スイッチは再度オンになります。

図 7-12. 電流制限波形

電流波形は  $I_{L-HS}$  と  $I_{L-LS}$  の間の値をとるため、最大出力電流はこれらの 2 つの値の平均値に非常に近い値になります。出力電圧がゼロに近づくにつれて、ヒステリシス制御が使われ、電流は増加しなくなります。

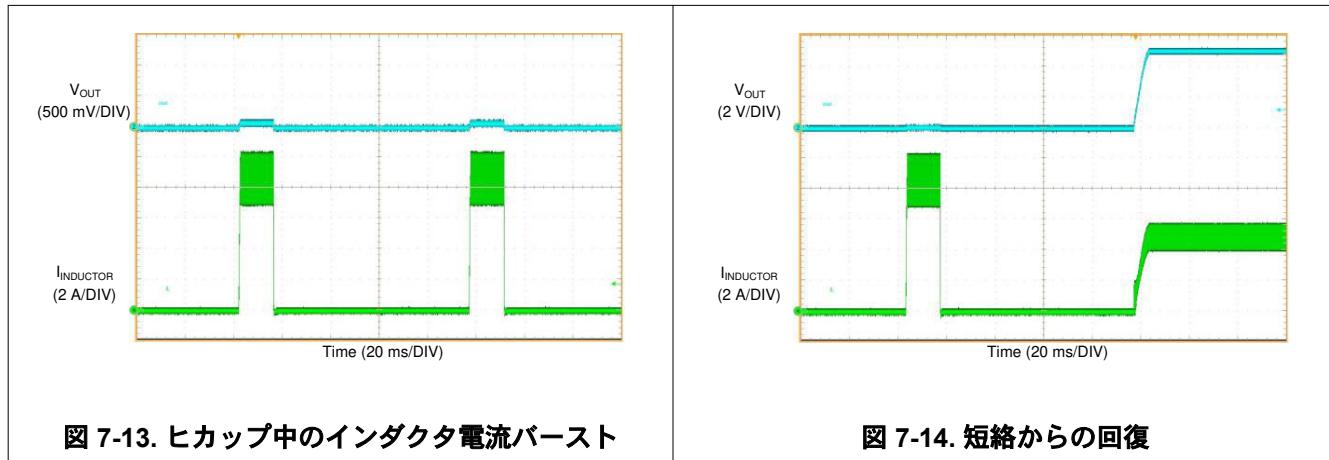

負荷が非常に重く、128 連続スイッチング サイクルの間、以下の条件を満たされた場合、本デバイスはヒップ過電流保護を使用します。

- 出力電圧が、出力電圧設定点の約 0.4 倍を下回っている。

- ソフトスタートが開始されてから、 $t_{SS2}$  以上経過した (セクション 7.3.10 を参照)。

- 本デバイスがドロップアウト (デューティ サイクルが最小オフ時間によって制御されている状態) で動作していない。

ヒップ モードに入ると、本デバイスはシャットダウンし、 $t_W$  後にソフトスタートを試みます。ヒップ モードは、過酷な過電流条件と短絡の際に本デバイスの消費電力を低減するのに役立ちます。図 7-13 を参照してください。

過負荷が解消されると、本デバイスはソフトスタート中であるかのように回復します。図 7-14 を参照してください。

### 7.3.13 サーマル・シャットダウン

サーマル・シャットダウンは、本 IC の接合部温度が  $165^{\circ}\text{C}$  (標準値) を超えると内部スイッチをオフにすることで、接合部温度が極端に上がるのを防止します。サーマル・シャットダウンは  $158^{\circ}\text{C}$  未満ではトリガされません。サーマル・シャットダウンが作動した後、ヒステリシスにより、接合部温度が約  $155^{\circ}\text{C}$  に低下するまで本デバイスのスイッチングが止められます。接合部温度が  $155^{\circ}\text{C}$  (標準値) を下回ると、本デバイスはソフトスタートを試みます。

高い接合部温度に起因して本デバイスがシャットダウンされるとはいって、電力は  $\text{VCC}$  に供給され続けます。高い接合部温度のせいで本デバイスが無効化されると同時に、 $\text{VCC}$  の短絡による過熱を防止するため、 $\text{VCC}$  に電力を供給する LDO の電流制限値が低減されます。サーマル・シャットダウン中、 $\text{VCC}$  の電流制限値は数ミリアンペアに低減されます。

### 7.3.14 入力電源電流

本デバイスは、軽負荷をレギュレートする際に入力電源電流が非常に小さくなるように設計されています。これは、内部回路の多くに、出力から電力を供給することで実現されています。BIAS ピンは、制御回路の大部分に電力を供給する LDO への入力です。BIAS 入力ピンをレギュレータの出力に接続することで、出力から少量の電流が BIAS ピンに流れ込みます。この電流により、入力の電流が  $V_{OUT}/V_{IN}$  の比で減少します。

$$I_{Q\_VIN} = I_Q + I_{EN} + (I_{BIAS} + I_{div}) \frac{\text{Output Voltage}}{\eta_{eff} \times \text{Input Voltage}} \quad (4)$$

ここで

- $I_{Q\_VIN}$  は、動作 (スイッチング) 中の降圧コンバータが無負荷時に消費する電流です。

- $I_Q$  は、 $V_{IN}$  端子から流れ込む電流です (セクション 6.5 の  $I_Q$  を参照)。

- $I_{EN}$  は、EN 端子に流れ込む電流です。EN が  $VIN$  に接続されている場合、この電流を含めます (セクション 6.5 の  $I_{EN}$  を参照)。5V 未満の電圧に接続した場合、この電流は非常に小さい値に下がることに注意します。

- $I_{BIAS}$  は、BIAS 入力に流れ込むバイアス電流です (セクション 6.5 の  $I_{BIAS}$  を参照)。

- $I_{div}$  は、出力電圧を設定するために使用される帰還分圧器に流れる電流です。

- $\eta_{eff}$  は、降圧コンバータの入力電流から  $I_{Q\_VIN}$  を除いた場合の降圧コンバータの軽負荷効率です。 $\eta_{eff} = 0.8$  は、通常動作条件で使用できる安全な値です。

## 7.4 デバイスの機能モード

### 7.4.1 シャットダウン・モード

EN ピンは、本デバイスの電気的オン / オフ制御に使用できます。EN ピンの電圧が 0.4V を下回ると、コンバータと内部 LDO の両方が電圧を出力しなくなり、本デバイスはシャットダウン・モードに入ります。シャットダウン・モードでは、静止電流が 0.6µA (標準値) まで低下します。

### 7.4.2 スタンバイ・モード

内部 LDO の EN スレッショルドは、コンバータの出力よりも低い値です。EN ピンの電圧が 1.1V (最大値) より高く、かつ出力電圧の高精度イネーブル・スレッショルドより低い場合、内部 LDO は VCC 電圧を 3.3V (標準値) にレギュレートします。VCC がその UVLO を上回ると、高精度イネーブル回路がオンになります。EN ピンの電圧が高精度イネーブル・スレッショルドを上回らない限り、SW ノードの内部パワー MOSFET はオフのままで。本デバイスは UVLO 保護も採用しています。VCC 電圧が UVLO レベルを下回ると、コンバータの出力はオフになります。

### 7.4.3 アクティブ・モード

EN ピンの電圧が  $V_{EN}$  を上回っており、かつ  $V_{IN}$  が  $V_{IN\_OPERATE}$  を満たすのに十分高く、かつその他のフォルト条件が存在しない場合は常に、本デバイスはアクティブ・モードに入ります。この動作を可能にする最も簡単な方法は、EN ピンを  $V_{IN}$  に接続することです。これにより、印加された入力電圧が最小  $V_{IN\_OPERATE}$  を超えると自動的に起動できます。

アクティブ・モードでは、負荷電流、入力電圧、出力電圧に応じて、本デバイスは次の 6 つのモードのいずれかになります。

- 連続導通モード (CCM)。負荷電流がインダクタ・リップル電流の 1/2 より大きいときには、固定周波数の連続導通モードになります。

- 自動モード - 軽負荷動作: パルス周波数変調 (PFM) (非常に軽い負荷でスイッチング周波数が低下した場合)

- FPWM モード - 軽負荷動作: 不連続導通モード (DCM) (負荷電流がインダクタ・リップル電流の 1/2 未満である場合)

- 最小オン時間: 入力電圧が高くかつ出力電圧が低い場合に、レギュレーションを維持するため、スイッチング周波数が低下します。

- ドロップアウト・モード: 電圧低下を最小限に抑えるため、スイッチング周波数が低下します。

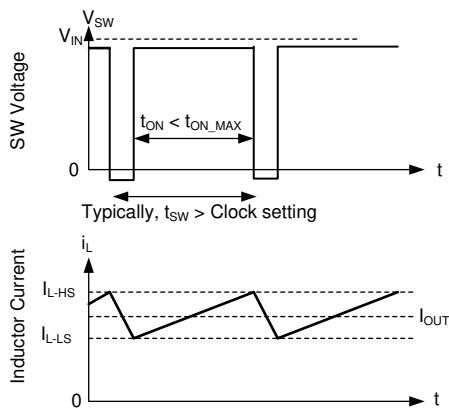

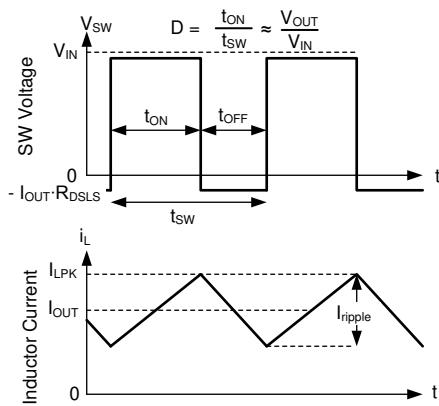

#### 7.4.3.1 CCM モード

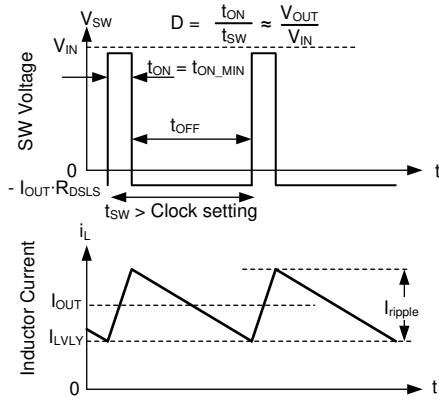

本デバイスの以下の動作の説明は、セクション 7.2 と以下の波形 (図 7-15) を参照しています。CCM では、本デバイスは、内蔵ハイサイド (HS) およびローサイド (LS) NMOS スイッチを各種デューティ・サイクル (D) でオンにすることで、出力電圧のレギュレーションを実現します。HS スイッチのオン時間の間、SW ピンの電圧 ( $V_{SW}$ ) は  $V_{IN}$  の付近までスイングし、インダクタ電流 ( $i_L$ ) は線形的な傾きで増加します。HS スイッチは、制御ロジックによってオフにされます。HS スイッチのオフ時間 ( $t_{OFF}$ ) の間、LS スイッチはオンにされます。インダクタ電流は LS スイッチを通して放電され、LS スイッチの両端の電圧降下によって  $V_{SW}$  をグランドの下まで強制的にスイングさせます。一定の出力電圧を維持するため、コンバータ・ループはデューティ・サイクルを調整します。D は、HS スイッチのオン時間をスイッチング周期で割った値として次のように定義されます。

$$D = t_{ON} / t_{SW} \quad (5)$$

損失が無視される理想的な降圧コンバータでは、次のように D は出力電圧に比例し、入力電圧に反比例します。

$$D = V_{OUT} / V_{IN} \quad (6)$$

図 7-15. 連続モード (CCM) における SW 電圧とインダクタ電流の波形

#### 7.4.3.2 自動モード – 軽負荷動作

軽負荷時、本デバイスは 2 種類の動作を行うことができます。自動モード動作と呼ばれる動作を使うと、負荷が重い際の通常電流モードと高効率の軽負荷動作との間を継ぎ目なく移行できます。FPWM モードと呼ばれるもう 1 つの動作では、無負荷時でも最大周波数が維持されます。本デバイスがどちらのモードで動作するかは、採用された工場オプションの種類で決まります (セクション 4 を参照)。周波数を外部信号に同期させる場合、すべてのデバイスは FPWM モードで動作することに注意します。

自動モードでは、定格最大出力電流の約 1/10 未満の負荷の場合、本デバイスでは軽負荷動作が使われます。軽負荷動作では、効率を向上させるため次の 2 つの手法が使われます。

- DCM 動作が可能なダイオード・エミュレーション

- 周波数低減

これら 2 つの機能は、同時に動作することで非常に優れた軽負荷動作を実現しますが、互いに独立して動作することに注意します。

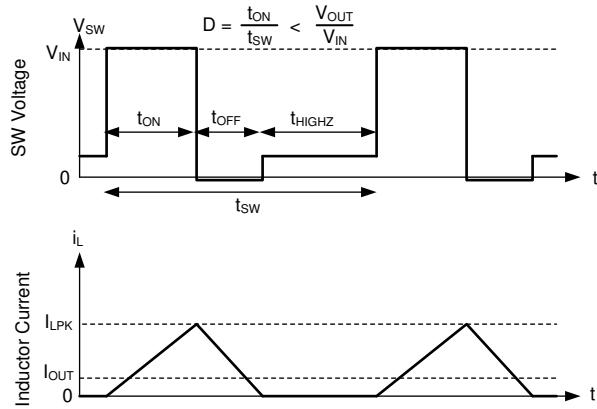

#### 7.4.3.2.1 ダイオード エミュレーション

ダイオード エミュレーションは、インダクタを流れる逆電流を防止します。固定ピーク インダクタ電流の場合、レギュレートするために周波数をより低くする必要があります。ダイオード エミュレーションは、周波数が下がった際のリップル電流も制限します。固定ピーク電流では、出力電流がゼロに向かって低下するにつれて、レギュレーションを維持するために周波数をゼロに近い値まで下げる必要があります。

自動モードでは、SW ノード電流がゼロに近づくとローサイド素子はオフになります。その結果、出力電流が CCM で発生する可能性があるインダクタリップルの  $1/2$  未満になると、本部品は DCM で動作します。これは、ダイオードエミュレーションが機能しているということと等価です。

**図 7-16. PFM 動作**

自動モードでは、本デバイスは最小ピークインダクタ電流設定値を持っています。入力電圧を一定にした状態で、電流値が下がると、オン時間は一定になります。その後、周波数を調整することで、レギュレーションが達成されます。この動作モードを PFM モード レギュレーションと呼びます。

#### 7.4.3.2.2 周波数低減

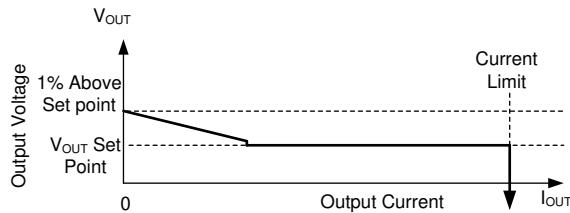

本デバイスは、出力電圧が高くなると常に周波数を下げます。この機能は、内部信号 Comp が Low でありかつ FB のレギュレーション設定点と FB に印加される電圧との間にオフセットが存在する場合、常に有効化されます。結果的に、自動モードでの軽負荷の間、通常動作の場合よりも出力インピーダンスが大きくなります。本デバイスが完全に無負荷である場合、出力電圧は約 1% 高くなるはずです。

自動モードでは、本デバイスの出力電流が定格電流の約  $1/10$  を下回ると、降圧コンバータが完全に無負荷になった際に出力電圧が 1% 高くなるように出力抵抗が増大します。

**図 7-17. 定常状態の出力電圧と自動モードの出力電流との関係**

PFM 動作では、PFM 検出回路を動作させるために、出力電圧に小さな正の DC オフセットが必要となります。PFM の周波数が低いほど、 $V_{OUT}$  に必要な DC オフセットは大きくなります。 $V_{OUT}$  での DC オフセットが許容できない場合、 $V_{OUT}$  に接続したダミー負荷または FPWM モードを使うことで、このオフセットを低減または除去できます。

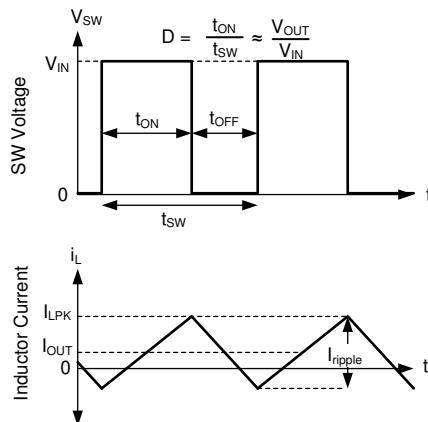

#### 7.4.3.3 FPWM モード - 軽負荷動作

自動モード動作と同様に、軽負荷動作時の FPWM モード動作は工場オプションとして選択されます。

FPWM モードでは、軽負荷時に周波数が維持されます。周波数を維持するため、インダクタを流れる逆電流が制限されます。逆電流制限回路により、逆電流が制限されます。逆電流制限値については、[セクション 6.5](#) を参照してください。

FPWM モードでは、 $i_{OUT}$  が  $i_{ripple}$  の半分未満でも連続導通 (CCM) が可能です。

図 7-18. FPWM モード動作

デバイスの種類にかかわらず、FPWM モードでは、軽負荷時であっても最小オン時間を指示できるほど出力電圧が高ければ、依然として周波数を低減できるため、出力をプルアップする必要があるフォルト中も良好に動作できます。

#### 7.4.3.4 最小オン時間 (高入力電圧) での動作

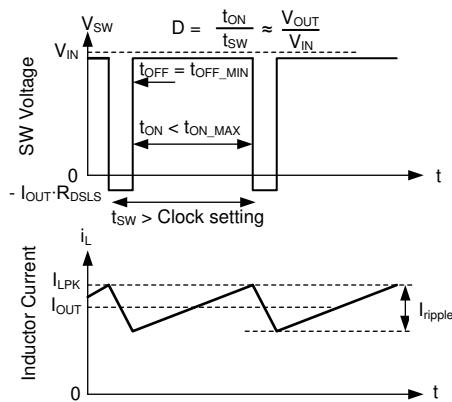

出力電圧に対する入力電圧の比が要求するオン時間が、与えられたクロック設定のチップの最小オン時間より短い場合でも、本デバイスは出力電圧をレギュレートし続けます。これは、バレー電流制御を使用して実現されます。補償回路は常に最大ピーカーインダクタ電流と最大バレーインダクタ電流の両方を指示します。何らかの理由でバレー電流を超過した場合、補償回路によって決定された値をバレー電流が下回るまで、クロックサイクルは延長されます。コンバータが電流制限動作をしていない場合、最大バレー電流はピーカーインダクタ電流よりも高く設定され、ピーカー電流のみを使ったレギュレーションに失敗しない限りバレー制御が使われることがないようにしています。出力電圧に対する入力電圧の比が高すぎる場合、補償回路が指示したピーカー値を超える電流が流れたとしても、出力電圧をレギュレートするのに十分な速さではハイサイド素子をオフにすることはできません。結果的に、補償回路はピーカー電流とバレー電流の両方を小さくします。補償回路によって十分小さい電流が選択されると、バレー電流は、補償回路が指示した電流に一致します。これらの条件では、ローサイド素子がオンに維持され、目的のバレー電流をインダクタ電流が下回るまで、次のクロックサイクルは開始されません。オン時間は最小値に固定されているため、このタイプの動作は、COT 制御方式を採用したデバイスの動作と似ています (図 7-19 を参照)。

バレー制御モードでは、ピーク インダクタ電流ではなく、最小インダクタ電流が制御されます。

図 7-19. バレー電流モード動作

#### 7.4.3.5 ドロップアウト

ドロップアウト動作とは、必要なデューティサイクルを達成するために周波数を下げ、入力電圧に対する出力電圧の比を任意の値に制御することです。与えられたクロック周波数において、デューティサイクルは最小オフ時間によって制限されます。この制限値に達した後、仮にクロック周波数が維持される場合、出力電圧は低下します。本デバイスは、出力電圧が下がるのを許容するのではなく、クロックサイクルが終わっても必要なピークインダクタ電流が達成されるまでオン時間を延長します。必要なピークインダクタ電流に達すると、または設定済みの最大オン時間 ( $t_{ON\_MAX}$  約 9 $\mu$ s) が経過すると、クロックは新しいサイクルを開始できます。その結果、最小オフ時間の存在に起因して、選択されたクロック周波数において必要なデューティサイクルが達成できない場合、レギュレーションを維持するために周波数が低下します。オン時間 ( $t_{ON\_MAX}$ ) を使っても出力電圧をレギュレートできないほど入力電圧が低い場合、出力電圧は入力電圧よりもわずかに ( $V_{DROP1}$ ) 低い値に下がります。ドロップアウトからの回復の詳細については、図 7-9 を参照してください。

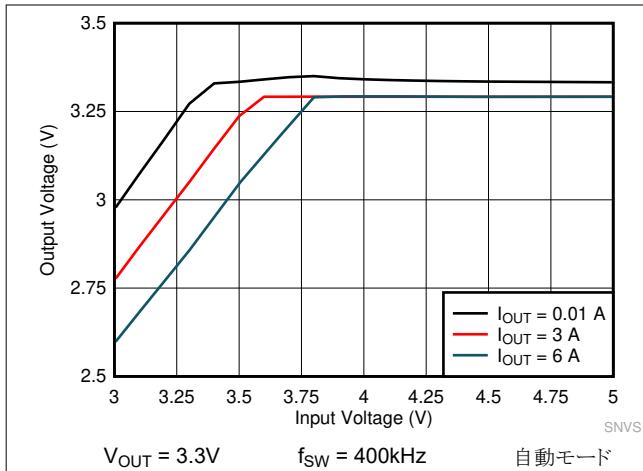

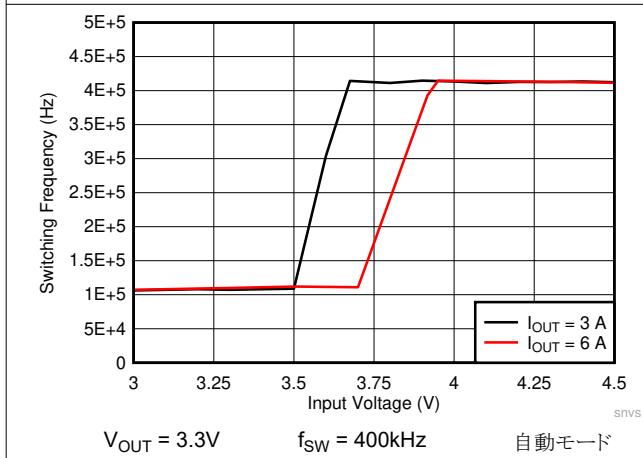

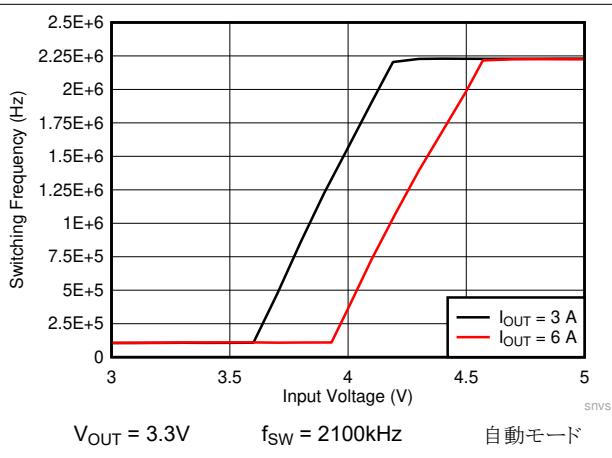

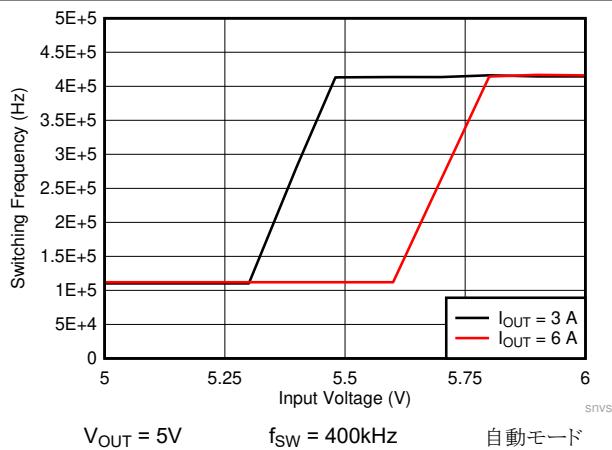

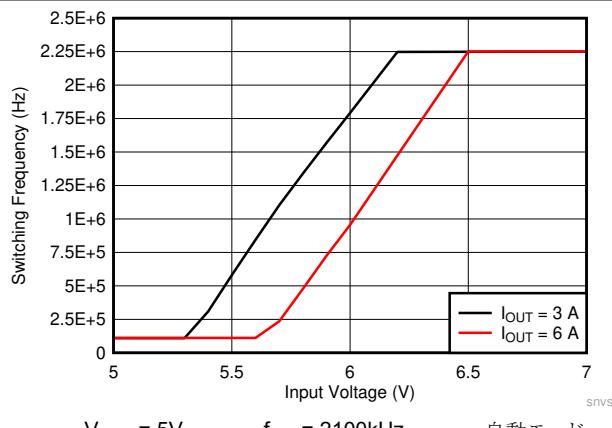

出力電圧および周波数と入力電圧との関係: 入力電圧と出力電圧設定値との差がほとんどない場合、本 IC はレギュレーションを維持するために周波数を下げます。入力電圧が低すぎて、約 110kHz で目的の出力電圧を供給できない場合、入力電圧は出力電圧に追従します。

図 7-20. ドロップアウト時の周波数と出力電圧

ドロップアウト中のスイッチング波形。インダクタ電流は、目的のピーク値に達するのに通常のクロックよりも長い時間を要します。その結果、周波数は低下します。この周波数の低下は  $t_{ON\_MAX}$  によって制限されます。

図 7-21. ドロップアウト波形

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

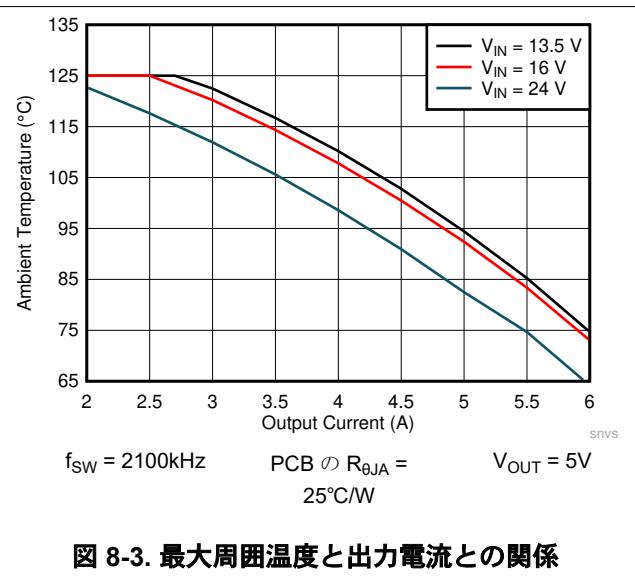

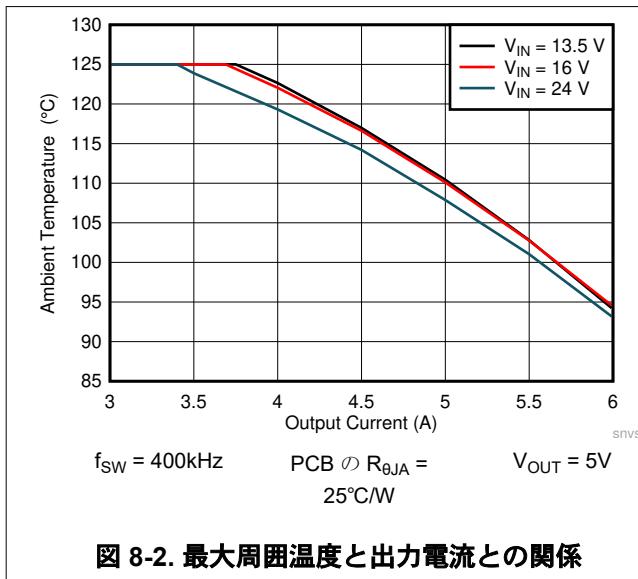

LMQ61460 降圧 DC/DC コンバータは通常、DC 電圧をより低い DC 電圧 (最大出力電流 6A) に変換するために使用されます。4 層基板に実装した LMQ61460 を 400kHz で使用する場合、本デバイスは約 95°C の周囲温度まで連続 6A の負荷に耐えられます。周囲温度が 105°C であり、周波数が 2.1MHz に設定されている場合、電流を 4A に制限する必要があります。「最大周囲温度と出力電流との関係」を参照してください。LMQ61460 の部品を選択する際には、次の設計手順を使用します。

### 8.2 代表的なアプリケーション

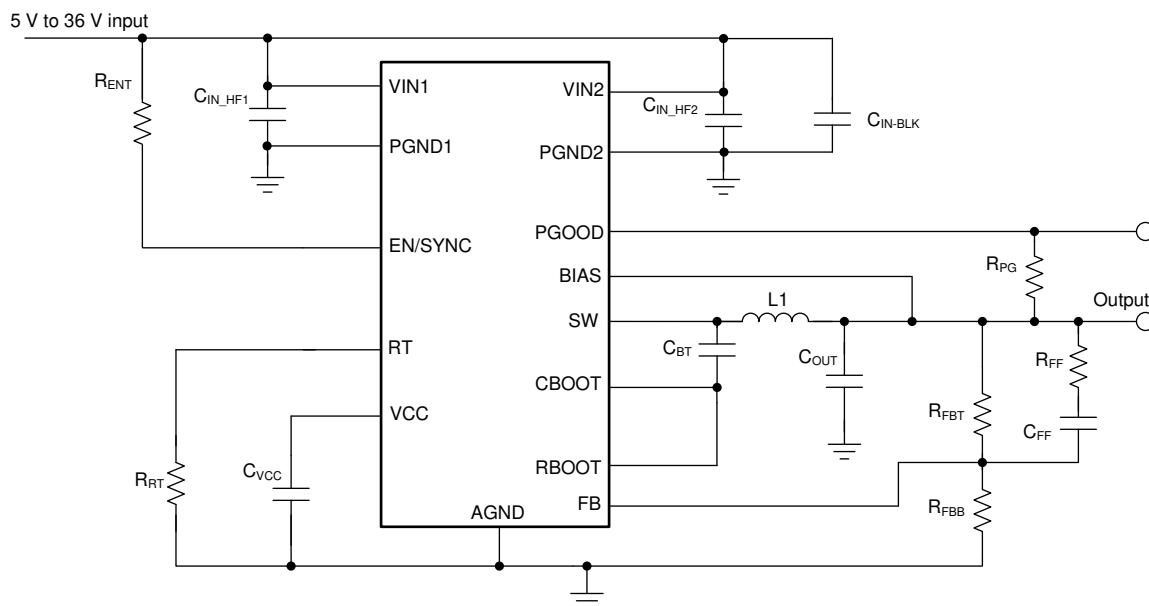

図 8-1 に、本デバイスの代表的なアプリケーション回路を示します。本デバイスは、幅広い外付け部品とシステム・パラメータで機能するように設計されています。しかし内部補償は、特定の範囲の外付けインダクタンスおよび出力容量に対して最適化されています。クイック・スタート・ガイドとして、表 8-2 では一般的な構成の代表的な部品の値が提供されています。

図 8-1. アプリケーション回路例

#### 8.2.1 設計要件

表 8-1 に、詳細設計手順のパラメータ例を示します。

表 8-1. 詳細設計パラメータ

| 設計パラメータ                        | 値の例            |

|--------------------------------|----------------|

| 入力電圧                           | 13.5V (5V~36V) |

| 固定スイッチング周波数 ( $f_{SW}$ ) の入力電圧 | 8V~18V         |

| 出力電圧                           | 5V             |

| 最大出力電流                         | 0A~6A          |

**表 8-1. 詳細設計パラメータ (続き)**

| 設計パラメータ   | 値の例    |

|-----------|--------|

| スイッチング周波数 | 400kHz |

**表 8-2. 外付け部品の代表的な値**

| $f_{SW}$<br>(kHz) | $V_{OUT}$ (V) | $L1$ ( $\mu$ H) | $C_{OUT}$ (定格)           | $R_{FBT}$<br>(k $\Omega$ ) | $R_{FBB}$<br>(k $\Omega$ ) | $C_{BOOT}$<br>( $\mu$ F) | $R_{BOOT}$<br>( $\Omega$ ) | $C_{VCC}$<br>( $\mu$ F) | $C_{FF}$ (pF) | $R_{FF}$ (k $\Omega$ ) |

|-------------------|---------------|-----------------|--------------------------|----------------------------|----------------------------|--------------------------|----------------------------|-------------------------|---------------|------------------------|

| 2100              | 3.3           | 1               | $3 \times 22\mu$ F セラミック | 100                        | 43.2                       | 0.1                      | 0                          | 1                       | 10            | 1                      |

| 400               | 3.3           | 4.7             | $3 \times 47\mu$ F セラミック | 100                        | 43.2                       | 0.1                      | 0                          | 1                       | 4.7           | 1                      |

| 2100              | 5             | 1.5             | $2 \times 22\mu$ F セラミック | 100                        | 24.9                       | 0.1                      | 0                          | 1                       | 22            | 1                      |

| 400               | 5             | 4.7             | $2 \times 47\mu$ F セラミック | 100                        | 24.9                       | 0.1                      | 0                          | 1                       | 22            | 1                      |

## 8.2.2 詳細な設計手順

以下の設計手順は、図 8-1 と表 8-1 に適用されます。

### 8.2.2.1 スイッチング周波数の選択

スイッチング周波数の選択は、変換効率とソリューション全体のサイズとのトレードオフとなります。スイッチング周波数を低くすると、スイッチング損失は減少し、一般的にシステム効率が高くなります。一方、スイッチング周波数を高くすると、より小型のインダクタと出力コンデンサを使用できるようになりますため、よりコンパクトな設計が可能となります。

動作周波数を選択する場合、最も重要な考慮事項は熱的な制約です。この制約は通常、周波数の選択において最も重要なです。400kHz で動作する回路については図 8-2 を、2.1MHz で動作する回路については図 8-3 を参照してください。これらの曲線は、与えられた周囲温度と与えられたこれらのスイッチング周波数でサポートできる出力電流の大きさを示しています。消費電力はレイアウトの影響を受けるため、これらの曲線は適切な出発点であるとしても、すべての設計の熱抵抗は、図 8-2 と図 8-3 を作成するために使われた推定値とは異なることに注意します。最大温度定格は、基板面積が約 100mm x 80mm である LMQ61460EVM に基づいています。銅箔面積を拡大することまたは冷却を導入することで実効的な  $R_{\theta JA}$  を低減しない限り、周囲温度が 105°C、スイッチング周波数が 2.1MHz に設定されている場合、負荷電流は通常 4A に制限されます。

その他の 2 つの考慮事項は、本デバイスがその周波数設定を維持する必要がある最大入力電圧と最小入力電圧です。本デバイスは、最小オン時間または最小オフ時間によって通常はレギュレーションが妨げられる条件下でその周波数を調整するため、これらの制約は、固定周波数動作を必要とする入力電圧に対してのみ重要です。

高い入力電圧でのフォールドバックを望まない場合、次の式 7 を使用します。

$$f_{SW} \leq \frac{V_{OUT}}{V_{IN}(MAX2) \cdot t_{ON\_MIN}(MAX)} \quad (7)$$

低い入力電圧でのフォールドバックが問題となる場合、次の式 8 を使用します。

$$f_{SW} \leq \frac{V_{INeff}(MIN2) - V_{OUT}}{V_{INeff}(MIN2) \cdot t_{OFF\_MIN}(MAX)} \quad (8)$$

ここで

- $V_{INeff}(MIN2) = V_{IN}(MIN2) - I_{OUT}(MAX) \times (R_{DS(ON)}(MAX) + DCR(MAX))$

- $DCR(MAX)$  はインダクタの DCR の最大値です。

$t_{OFF\_MIN}(MAX)$  と  $R_{DS(ON)\_HS}(MAX)$  については、セクション 6.5 を参照してください。

4 つ目の制約は本 IC の定格周波数範囲です。セクション 6.5 の  $f_{ADJ}$  を参照してください。周波数を選択する際には、前述のすべての制約（熱、 $V_{IN}(MAX2)$ 、 $V_{IN}(MIN2)$ 、デバイス特有の周波数範囲）を考慮する必要があります。

多くのアプリケーションでは、AM 帯域を回避する必要があります。これらのアプリケーションでは、AM 帯域よりも低い 400kHz と、AM 帯域よりも高い 2.1MHz のどちらかの動作周波数が使われる傾向があります。この例では、400kHz を選択しています。

### 8.2.2.2 出力電圧の設定

本デバイスの出力電圧は、分圧抵抗回路を使用して外部で調整可能です。推奨出力電圧の範囲については、セクション 6.3 を参照してください。分圧回路は  $R_{FBT}$  と  $R_{FBB}$  で構成され、出力電圧とコンバータの間のループを閉じています。コンバータは、FB ピン電圧を内部基準電圧 ( $V_{REF}$ ) と同じ電圧に保持することで、出力電圧をレギュレートします。分圧器の抵抗値は、ノイズの過剰な混入と出力の過剰な負荷との折り合いを付けることで決定します。抵抗値を小さくすると、ノイズの影響は小さくなりますが、軽負荷時の効率も低下します。 $R_{FBT}$  の推奨値は 100kΩ（最大値は 1MΩ）です。 $R_{FBT}$  に 1MΩ を選択する場合、この抵抗の両端にフィードフォワード・コンデンサを接続し、十分なループ位相マージンを確保する必要があります（セクション 8.2.2.10 を参照）。 $R_{FBT}$  を選択した後、式 3 を使用して  $R_{FBB}$  を選択します。 $V_{REF}$  は公称 1V です。この 5V の例では、 $R_{FBT} = 100k\Omega$ 、 $R_{FBB} = 24.9k\Omega$  を選択しています。

### 8.2.2.3 インダクタの選択

インダクタを選択するためのパラメータはインダクタンスと飽和電流です。目的のピーク・ツー・ピーク・インダクタ・リップル電流がデバイスの最大出力電流定格の 20%～40% の範囲に収まるように、インダクタを選択します。経験上、インダクタ・リップル電流の最適値は、固定入力電圧を使うシステムでは最大負荷電流の 30%、可変入力電圧（自動車の 12V バッテリなど）を使うシステムでは最大負荷電流の 25% です。本デバイスから利用可能な最大電流よりも、最大負荷電流がはるかに小さいアプリケーションのリップル電流を選択する場合でも、依然として本デバイスの最大電流を利用する必要があります。式 9 を使用して、インダクタンスの値を決定することができます。定数  $K$  はインダクタ電流リップルのパーセンテージです。この例では、 $K = 0.25$  を選択し、約 5.25μH のインダクタンスを求めました。最も近い標準値である 4.7μH を選択しました。

$$L = \frac{V_{IN} - V_{OUT}}{f_{SW} \cdot K \cdot I_{OUT}(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \quad (9)$$

インダクタの飽和電流定格は、ハイサイド・スイッチの電流制限値 ( $I_{L-HS}$ ) 以上にする必要があります（セクション 6.5 を参照）。こうすることで、出力の短絡中でもインダクタが飽和しないようにします。インダクタのコア材が飽和すると、インダクタンスは非常に小さい値に低下し、インダクタ電流は急増します。バレー電流制限値 ( $I_{L-LS}$ ) は、電流が暴走しづらいように設計されているとはいえ、インダクタが飽和することで電流値が急増する可能性があります。これは部品の損傷につながる

可能性があります。インダクタを飽和させないでください。フェライト・コア材を採用したインダクタは飽和特性が非常に急峻ですが、コア損失は通常、圧粉コアよりも小さいです。圧粉コアは穏やかな飽和特性を示すため、インダクタの電流定格がある程度緩和できます。しかし、通常 1MHz を上回る周波数では、コア損失が増加します。いずれにしても、インダクタの飽和電流は、デバイスのハイサイド電流制限値 ( $I_{L-HS}$ 、[セクション 6.5](#) を参照) よりも小さくしないようにします。分数調波発振を防止するため、[式 10](#) で与えられる値よりインダクタンス値を小さくしないようにします。最大インダクタンスは、電流モード制御を正しく行うために必要な最小電流リップルによって制限されます。目安として、インダクタの最小リップル電流は、公称条件でのデバイスの最大定格電流の約 10% 以上とする必要があります。

$$L \geq 0.32 \cdot \frac{V_{OUT}}{f_{SW}} \quad (10)$$

[式 10](#) では、ドロップアウトに近い入力電圧またはドロップアウトに入った入力電圧でこの設計が動作するものと仮定しています。この設計の最小動作電圧が、デューティ・サイクルを 50% 未満に制限するのに十分なほど高い場合、[式 10](#) の代わりに[式 11](#) を使用できます。

$$L \geq 0.2 \cdot \frac{V_{OUT}}{f_{SW}} \quad (11)$$

[式 9](#)～[式 11](#) を使用して計算した最小インダクタンスより大きいインダクタを選択すると、出力リップルを抑制するために必要とされる出力容量は減少しますが、大きな負荷過渡を制御するためにより大きな出力容量が必要とされることに注意します。[セクション 8.2.2.4](#) を参照してください。

#### 8.2.2.4 出力コンデンサの選択

出力コンデンサの値、およびその ESR により、出力電圧リップルと負荷過渡性能が決まります。出力コンデンサは通常、出力電圧リップルではなく負荷過渡要件によって決定されます。[表 8-3](#) を使うと、複数の一般的なアプリケーションに適した出力コンデンサと  $C_{FF}$  を選択できます。1kΩ の  $R_{FF}$  を  $C_{FF}$  と直列に接続する必要があることに注意します。この例では、優れた過渡性能を実現するため、出力コンデンサとして 2 × 47μF のセラミック・コンデンサを、 $C_{FF}$  として 22pF のコンデンサを使用しています。

**表 8-3. 出力セラミック・コンデンサと  $C_{FF}$  の推奨値**

| 周波数    | 過渡性能      | 3.3V 出力   |          | 5V 出力     |          |

|--------|-----------|-----------|----------|-----------|----------|

|        |           | セラミック出力容量 | $C_{FF}$ | セラミック出力容量 | $C_{FF}$ |

| 2.1MHz | 最小        | 3 × 22μF  | 10pF     | 2 × 22μF  | 22pF     |

| 2.1MHz | より優れた過渡性能 | 2 × 47μF  | 33pF     | 3 × 22μF  | 33pF     |

| 400kHz | 最小        | 3 × 47μF  | 4.7pF    | 2 × 47μF  | 10pF     |

| 400kHz | より優れた過渡性能 | 4 × 47μF  | 33pF     | 3 × 47μF  | 33pF     |

セラミック容量を最小化するために、最小限のセラミック容量と並列に低 ESR の電解コンデンサを使用できます。出力電解コンデンサを使用した設計の出発点として、電解コンデンサを使用する場合の出力セラミック容量 ( $C_{FF}$ ) の推奨値を[表 8-4](#) に示します。

**表 8-4. 電解コンデンサ、セラミック・コンデンサ、 $C_{FF}$  の推奨値**

| 周波数    | 過渡性能      | 3.3V 出力                               |          | 5V 出力                                 |          |

|--------|-----------|---------------------------------------|----------|---------------------------------------|----------|

|        |           | $C_{OUT}$                             | $C_{FF}$ | $C_{OUT}$                             | $C_{FF}$ |

| 400kHz | 最小        | 2 × 47μF のセラミック + 1 × 470μF、100mΩ の電解 | 10pF     | 3 × 22μF のセラミック + 1 × 470μF、100mΩ の電解 | 10pF     |

| 400kHz | より優れた過渡性能 | 3 × 47μF のセラミック + 2 × 280μF、100mΩ の電解 | 33pF     | 4 × 22μF のセラミック + 1 × 560μF、100mΩ の電解 | 22pF     |

ほとんどのセラミック・コンデンサの実効的な容量は、表示されたそのコンデンサの定格値よりもはるかに小さい値です。選択されたすべてのコンデンサの初期精度、温度ディレーティング、電圧ディレーティングを必ず確認します。表 8-3 と表 8-4 は、16V、X7R コンデンサの代表的なディレーティングを仮定して作成されています。より低い電圧、非車載グレード、より低い温度の定格のコンデンサを使う場合、表に記載されているコンデンサよりも大きいコンデンサが必要になる可能性があります。

#### 8.2.2.5 入力コンデンサの選択

セラミック入力コンデンサは、コンバータに低インピーダンス・ソースを供給するだけでなく、リップル電流を供給して、他の回路からスイッチング・ノイズを絶縁します。本デバイスの入力には  $10\mu\text{F}$  以上のセラミック・コンデンサが必要です。このコンデンサの定格は、アプリケーションが必要とする最大入力電圧以上 (できれば最大入力電圧の 2 倍) である必要があります。この容量を増やすことで、入力電圧リップルを低減し、負荷過渡時の入力電圧を維持できます。また、各入力 / グラウンド・ピン・ペア (VIN1/PGND1、VIN2/PGND2) に、コンバータと直接隣接して、小型の  $100\text{nF}$  セラミック・コンデンサを使用する必要があります。これにより、本デバイス内の制御回路のための高周波バイパスを実現します。これらのコンデンサは SW ノードのリンクも抑制します。これにより、SW ノードに生じる最大電圧と EMI を低減します。また、これらの 2 つの  $100\text{nF}$  コンデンサも、X7R 以上の性能の誘電体を使用した  $50\text{V}$  定格品とする必要があります。VQFN-HR (RJR) パッケージ品は、パッケージの両側に 2 つの入力電圧ピンと 2 つの電源グラウンド・ピンを備えており、入力コンデンサを分割して、内部パワー MOSFET に対して最適に配置することができるため、入力のバイパスの効果を高めることができます。この例では、2 つの  $4.7\mu\text{F}$  セラミック・コンデンサと 2 つの  $100\text{nF}$  セラミック・コンデンサを、各 VIN/PGND 位置に 1 つずつ配置しています。パッケージの片側に 1 つの  $10\mu\text{F}$  を配置することもできます。

多くの場合、入力に、セラミックと並列に電解コンデンサを配置することが望ましくかつ必要です。これは、長い配線またはパターンを使って入力電源をコンバータに接続する場合に特に当てはまります。このコンデンサに中程度の ESR を持つコンデンサを使うことは、長い電源配線によって生じる入力電源のリンクを減衰させるのに有効です。この追加のコンデンサの使用は、インピーダンスが非常に高い入力電源によって生じる瞬間的な電圧低下の防止にも有効です。

入力スイッチング電流のほとんどは、セラミック入力コンデンサを流れます。この電流の最も厳しい条件の RMS 近似値は、式 12 から計算でき、メーカーの最大定格に照らしてチェックする必要があります。

$$I_{\text{RMS}} \approx \frac{I_{\text{OUT}}}{2} \quad (12)$$

#### 8.2.2.6 ブート・コンデンサ

本デバイスでは、CBOOT ピンと SW ピンの間にブートストラップ・コンデンサを接続する必要があります。このコンデンサは、ハイサイド・パワー MOSFET のゲート・ドライバに電力を供給するために使用するエネルギーを蓄積します。 $100\text{nF}$ 、 $10\text{V}$  以上の高品質 (X7R) セラミック・コンデンサが必要です。

#### 8.2.2.7 ブート抵抗

ブート抵抗は、CBOOT ピンと RBOOT ピンの間に接続できます。設計するアプリケーションの EMI が特に重要でない限り、これらの 2 つのピンを短絡できます。これらのピンの間に  $100\Omega$  の抵抗を接続すると、オーバーシュートが除去されます。 $0\Omega$  であっても、入力コンデンサが正しく配置されている限り、オーバーシュートとリンクは最小限 (2V 未満) です。 $100\Omega$  のブート抵抗は、約  $2.7\text{ns}$  の SW ノード立ち上がり時間に相当し、 $2\text{MHz}$  で効率を約 0.5% 低下させます。効率を最大化するため、この例では  $0\Omega$  を選択します。ほとんどの状況下で、 $100\Omega$  を上回る RBOOT 抵抗値を選択することは望ましくありません。結果として得られる EMI の改善量が、効率のさらなる低下に見合うほど大きくないためです。

#### 8.2.2.8 VCC

VCC ピンは、コンバータの制御回路に電力を供給するために使用される内部 LDO の出力です。この出力を正常に動作させるには、 $1\mu\text{F}$ 、 $16\text{V}$  のセラミック コンデンサを VCC と AGND との間に接続する必要があります。通常、いかなる外部回路によっても、この出力に負荷をかけることは避けます。ただし、この出力は、パワー グッド機能のプルアップに電力を供給するために使えます (セクション 7.3.5 を参照)。この場合、 $100\text{k}\Omega$  の値のプルアップ抵抗が適しています。

$V_{EN\_WAKE} < EN < V_{EN}$  の場合、VCC は High に維持されることに注意します。VCC の公称出力電圧は 3.3V です。この出力をグランドまたはその他の外部電圧に短絡しないでください。

### 8.2.2.9 BIAS

この設計では  $V_{OUT} = 5V$  であるため、LDO の電力損失を低減するために BIAS ピンを  $V_{OUT}$  に接続します。入力電圧の代わりに、出力電圧が LDO 電流を供給するようになります。節約される電力は  $I_{LDO} \times (V_{IN} - V_{OUT})$  です。 $V_{IN} \gg V_{OUT}$  であり、かつより高い周波数で動作する場合、省電力はより重要です。 $V_{OUT}$  のノイズと過渡が BIAS に結合しないように、 $V_{OUT}$  と BIAS の間に  $1\Omega \sim 10\Omega$  の直列抵抗を追加できます。ノイズをフィルタするため、BIAS ピンの近くに  $1\mu F$  以上の値のバイパス・コンデンサを追加できます。BIAS ピンの最大許容電圧は 16V であることに注意します。

### 8.2.2.10 $C_{FF}$ と $R_{FF}$ の選択

フィードフォワードコンデンサ ( $C_{FF}$ ) は、低 ESR の出力コンデンサを使った回路の位相マージンと過渡応答を改善するために使います。このコンデンサは、回路の出力から IC の FB ノードに直接ノイズを導く可能性があるため、 $1k\Omega$  の抵抗 ( $R_{FF}$ ) を  $C_{FF}$  と直列に配置する必要があります。出力コンデンサの ESR ゼロが 200kHz 未満である場合、 $C_{FF}$  を使用しないでください。

出力電圧が 2.5V 未満である場合、 $C_{FF}$  はほとんど影響を及ぼさないため省略できます。出力電圧が 14V を超える場合、高い周波数でゲインが大きくなりすぎるため、 $C_{FF}$  を使用しないでください。

### 8.2.2.11 外部 UVLO

場合によっては、本デバイスが内部的に備えているものとは異なる入力 UVLO レベルが必要とされることがあります。これは、図 8-4 に示す回路を使うことで実現できます。本デバイスがオンする入力電圧を  $V_{ON}$ 、オフする入力電圧を  $V_{OFF}$  と呼びます。最初に、 $R_{ENT}$  の値を  $10k\Omega \sim 100k\Omega$  の範囲で選択し、次に、式 14 を使って  $R_{ENT}$  と  $V_{OFF}$  を計算します。 $R_{ENT}$  は通常、この分圧器に流す必要がある電流の大きさに基づいて設定されます。 $R_{ENT}$  は、式 13 を使用して計算できます。

$$R_{ENT} = \frac{V_{EN} \cdot V_{IN}}{I_{DIVIDER} \cdot V_{ON}} \quad (13)$$

図 8-4. EN を使った UVLO

$$R_{ENT} = \left( \frac{V_{ON}}{V_{EN}} - 1 \right) \cdot R_{ENB}$$

$$V_{OFF} = V_{ON} \cdot (1 - V_{EN-HYST})$$

(14)

ここで

- $V_{ON}$  は  $V_{IN}$  のターンオン電圧、

- $V_{OFF}$  は  $V_{IN}$  のターンオフ電圧、

- $I_{DIVIDER}$  は分圧器の電流です。

### 8.2.3 アプリケーション曲線

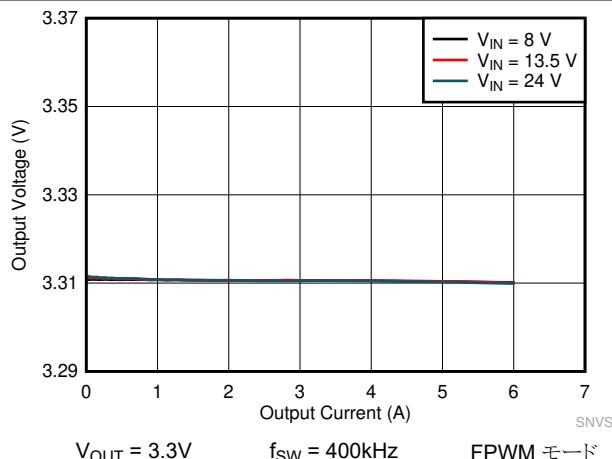

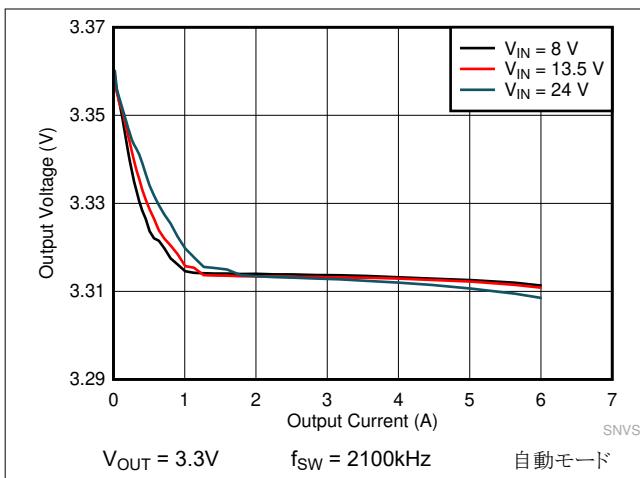

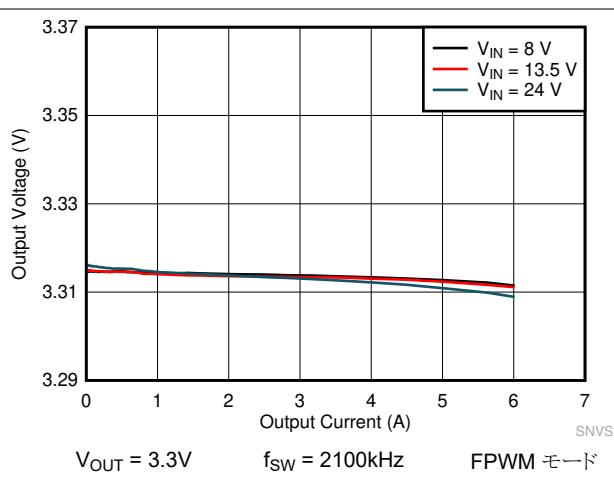

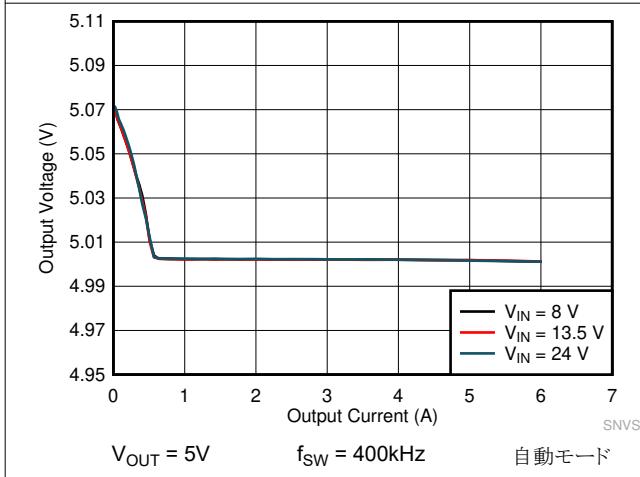

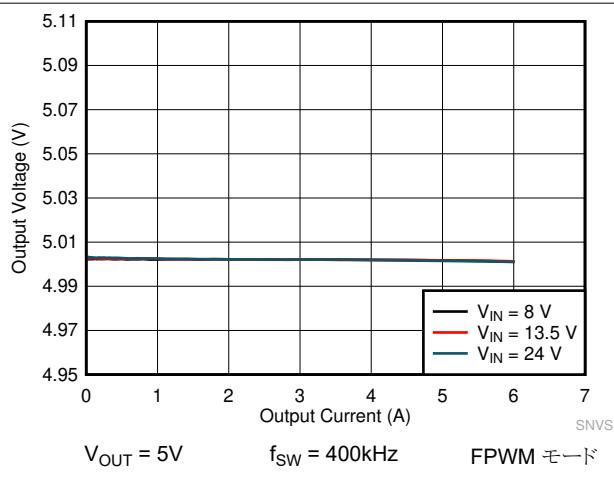

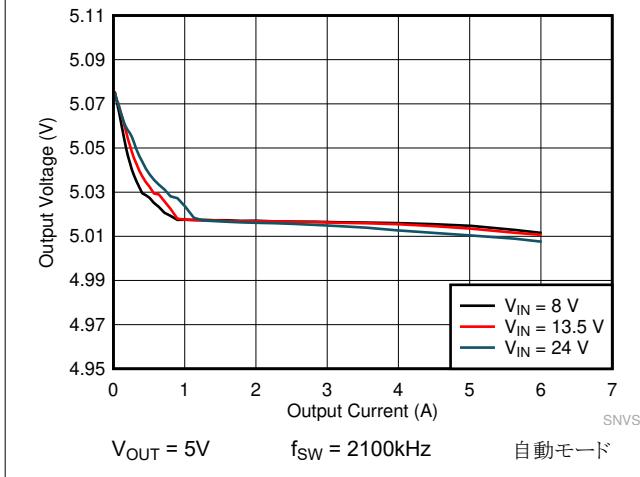

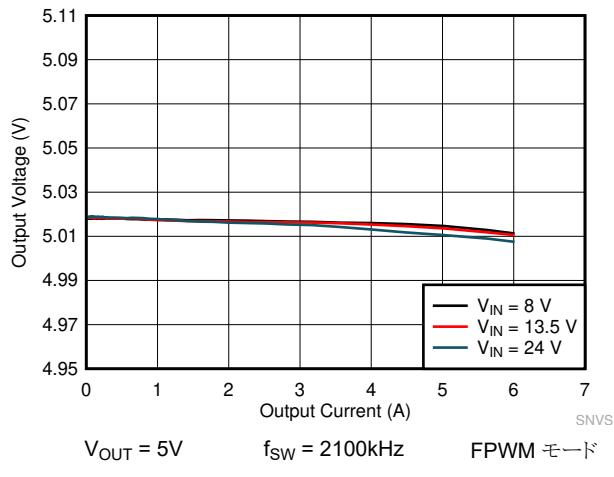

特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5V$ 、 $T_A = 25^\circ\text{C}$ 。回路を図 8-1 に示します。それにふさわしい BOM を表 8-5 に示します。

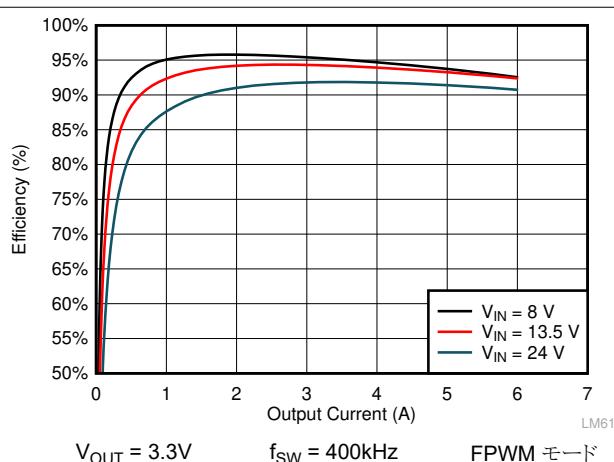

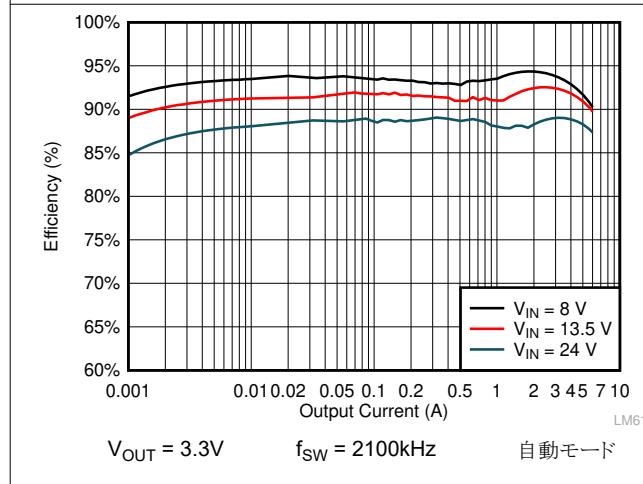

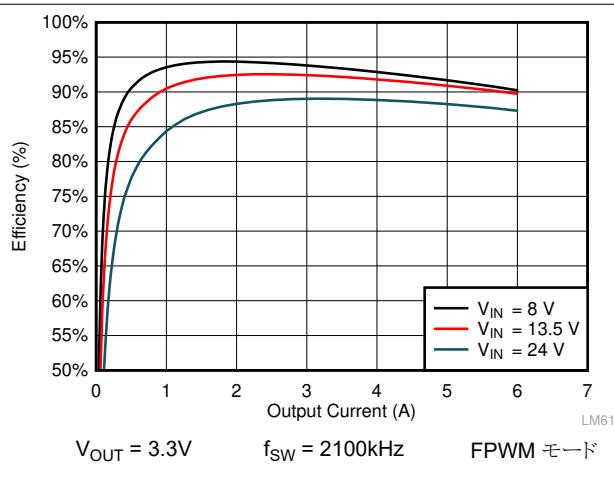

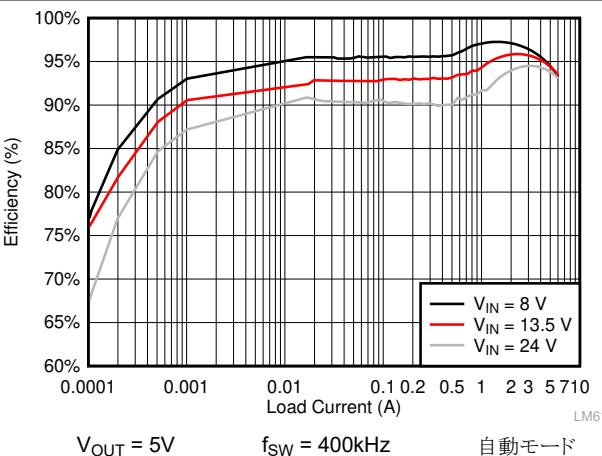

図 8-5. LMQ61460 の効率

図 8-6. LMQ61460 の効率

図 8-7. LMQ61460 の効率

図 8-8. LMQ61460 の効率

図 8-9. LMQ61460 の効率

図 8-10. LMQ61460 の効率

図 8-11. LMQ61460 の効率

図 8-12. LMQ61460 の効率

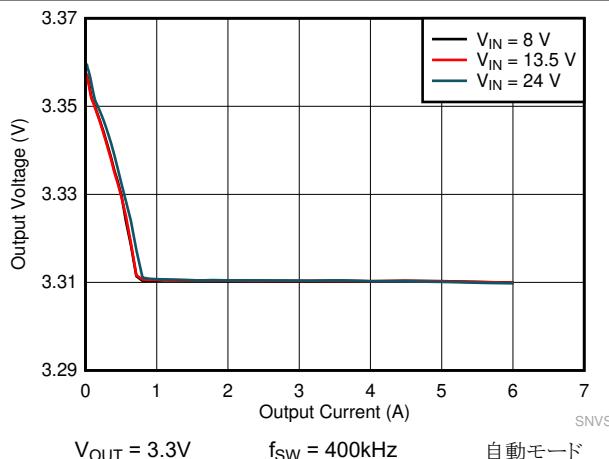

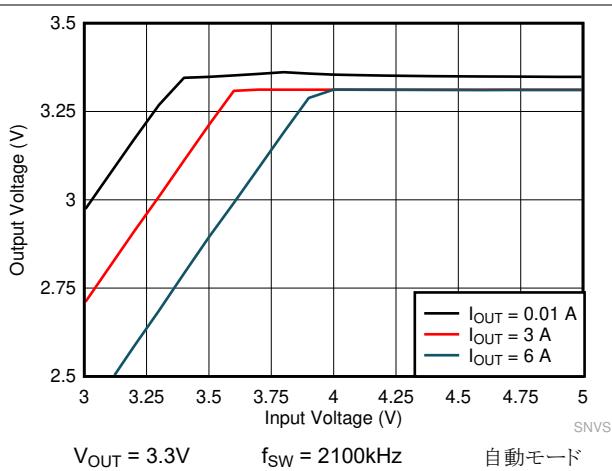

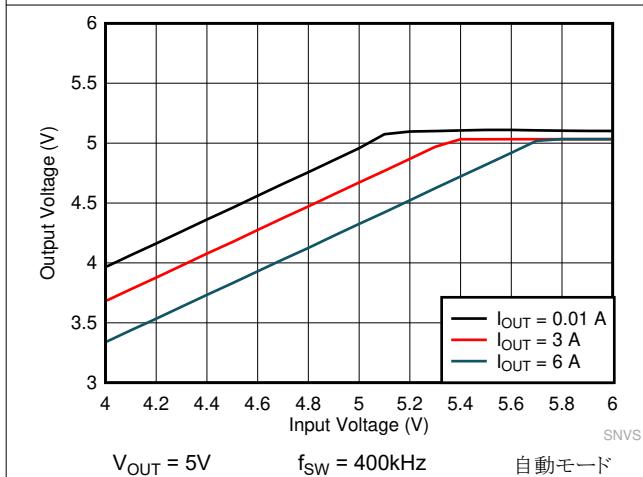

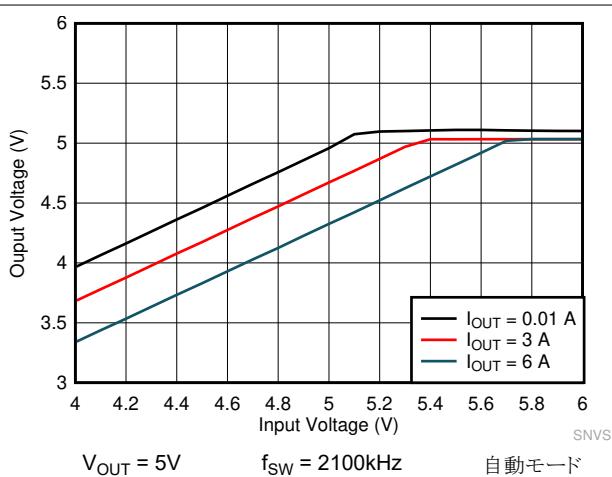

図 8-13. LMQ61460 の負荷およびライン レギュレーション

図 8-14. LMQ61460 の負荷およびライン レギュレーション

図 8-15. LMQ61460 の負荷およびライン レギュレーション

図 8-16. LMQ61460 の負荷およびライン レギュレーション

図 8-17. LMQ61460 の負荷およびライン レギュレーション

図 8-18. LMQ61460 の負荷およびライン レギュレーション

図 8-19. LMQ61460 の負荷およびライン レギュレーション

図 8-20. LMQ61460 の負荷およびライン レギュレーション

図 8-21. LMQ61460 のドロップアウト曲線

図 8-22. LMQ61460 のドロップアウト曲線

図 8-23. LMQ61460 のドロップアウト曲線

図 8-24. LMQ61460 のドロップアウト曲線

図 8-25. LMQ61460 の周波数ドロップアウト曲線

図 8-26. LMQ61460 の周波数ドロップアウト曲線

図 8-27. LMQ61460 の周波数ドロップアウト曲線

図 8-28. LMQ61460 の周波数ドロップアウト曲線

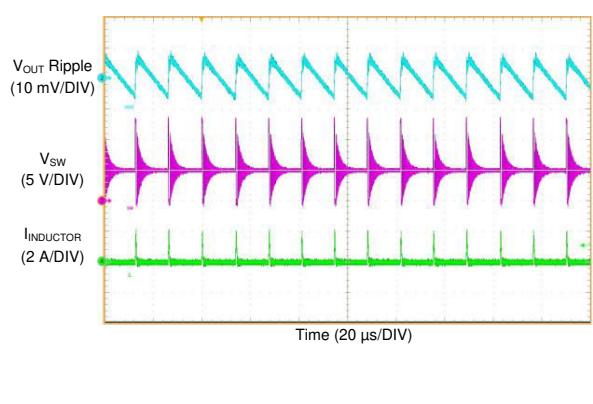

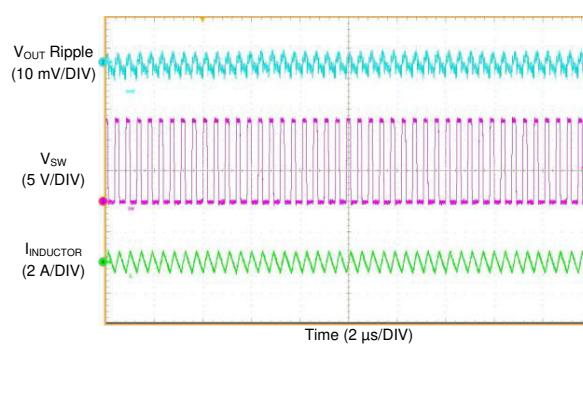

図 8-29. LMQ61460 のスイッチング波形と  $V_{OUT}$  リップル

図 8-30. LMQ61460 のスイッチング波形と  $V_{OUT}$  リップル

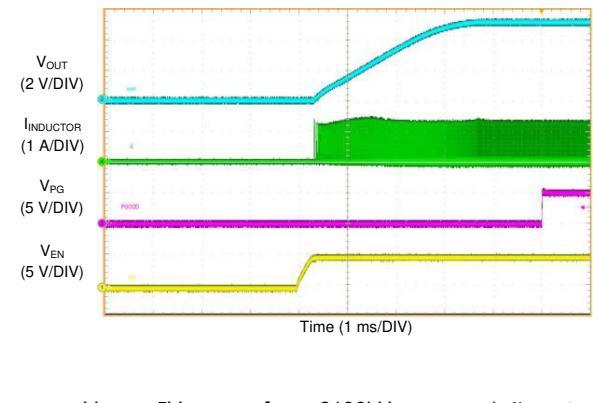

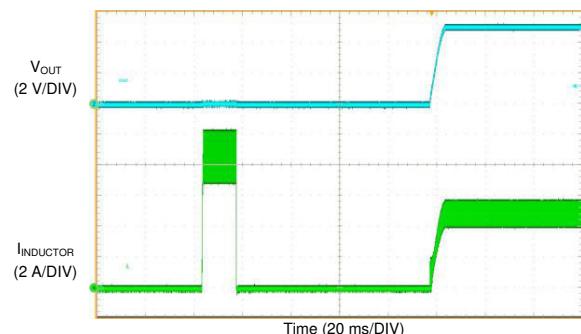

図 8-31. LMQ61460 の起動 (50-mA 負荷)

図 8-32. LMQ61460 の起動 (50-mA 負荷)

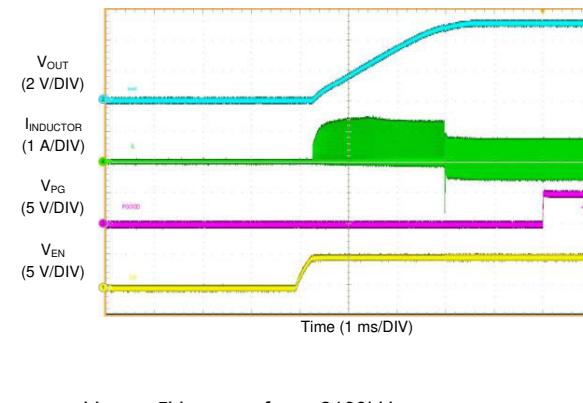

$V_{OUT} = 3.3V$     $f_{SW} = 2100\text{kHz}$    FPWM モード

$I_{OUT} = 3.25A$     $V_{IN} = 13.5V$

図 8-33. LMQ61460 の起動 (3.25A 負荷)

$V_{OUT} = 5V$     $f_{SW} = 2100\text{kHz}$    FPWM モード

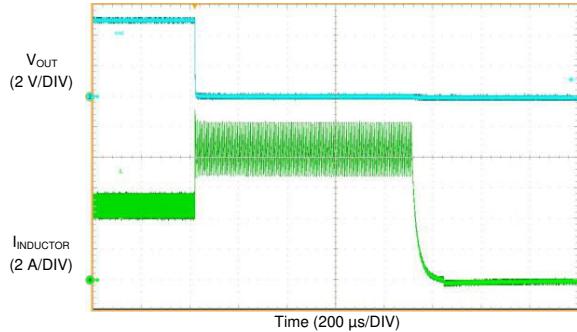

$I_{OUT} = 5A \rightarrow$  短絡    $V_{IN} = 13.5V$

図 8-34. LMQ61460 の短絡保護

$V_{OUT} = 5V$     $f_{SW} = 2100\text{kHz}$    FPWM モード

$I_{OUT} = \text{短絡} \rightarrow 5A$     $V_{IN} = 13.5V$

図 8-35. LMQ61460 の短絡からの回復

$V_{OUT} = 5V$     $f_{SW} = 2100\text{kHz}$    FPWM モード

$I_{OUT} = \text{短絡}$     $V_{IN} = 13.5V$

図 8-36. LMQ61460 の短絡性能

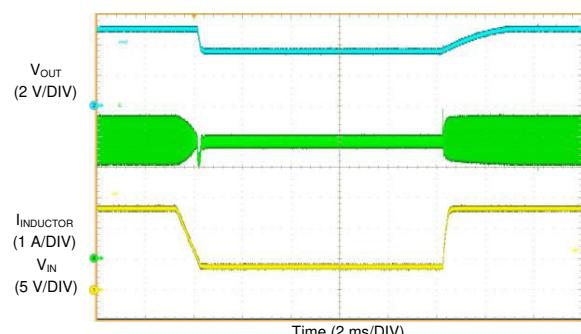

$V_{OUT} = 5V$     $f_{SW} = 2100\text{kHz}$    FPWM モード

$I_{OUT} = 4A$     $V_{IN} = 13.5V \rightarrow 4V \rightarrow 13.5V$

図 8-37. LMQ61460 のドロップアウトからの正常な回復

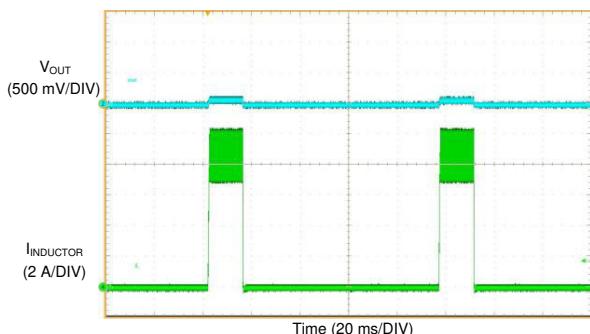

$V_{OUT} = 5V$     $f_{SW} = 400\text{kHz}$    自動モード

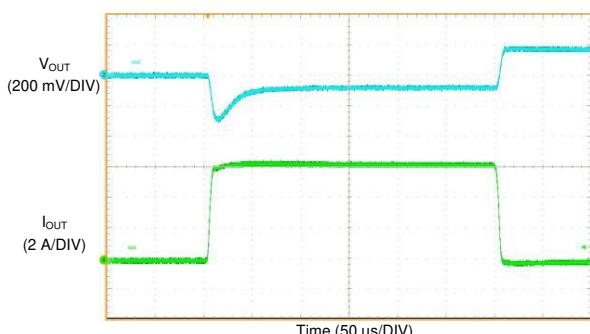

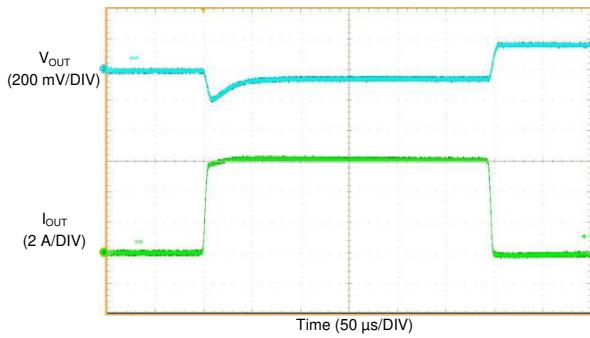

$I_{OUT} = 0A \rightarrow 6A \rightarrow 0A$     $V_{IN} = 13.5V$     $T_R = T_F = 6\mu\text{s}$

図 8-38. LMQ61460 の負荷過渡応答

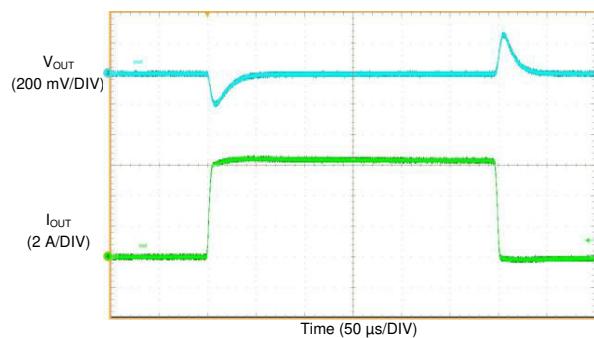

$V_{OUT} = 5V$        $f_{SW} = 400\text{kHz}$       FPWM モード

$I_{OUT} = 0A \rightarrow 6A \rightarrow 0A$        $V_{IN} = 13.5V$        $T_R = T_F = 6\mu\text{s}$

図 8-39. LMQ61460 の負荷過渡応答

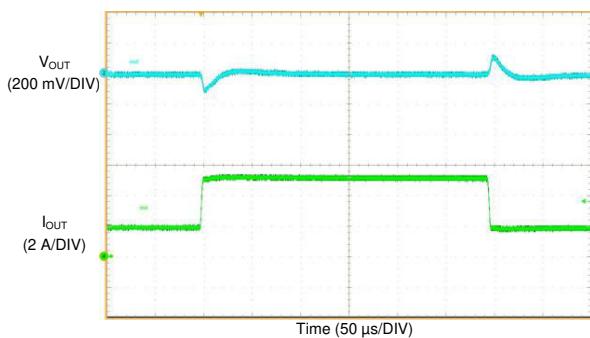

$V_{OUT} = 5V$        $f_{SW} = 400\text{kHz}$       自動モード

$I_{OUT} = 2A \rightarrow 5A \rightarrow 2A$        $V_{IN} = 13.5V$        $T_R = T_F = 3\mu\text{s}$

図 8-40. LMQ61460 の負荷過渡応答

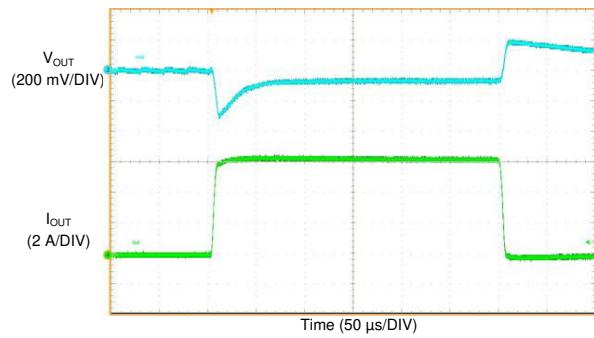

$V_{OUT} = 5V$        $f_{SW} = 400\text{kHz}$       自動モード

$I_{OUT} = 50\text{mA} \rightarrow 6A \rightarrow 50\text{mA}$        $V_{IN} = 13.5V$        $T_R = T_F = 6\mu\text{s}$

図 8-41. LMQ61460 の負荷過渡応答

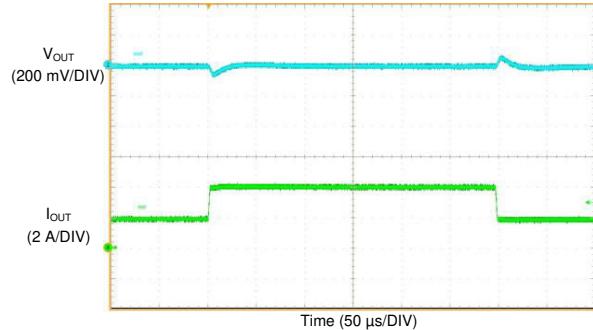

$V_{OUT} = 3.3V$        $f_{SW} = 400\text{kHz}$       自動モード

$I_{OUT} = 0A \rightarrow 6A \rightarrow 0A$        $V_{IN} = 13.5V$        $T_R = T_F = 6\mu\text{s}$

図 8-42. LMQ61460 の負荷過渡応答

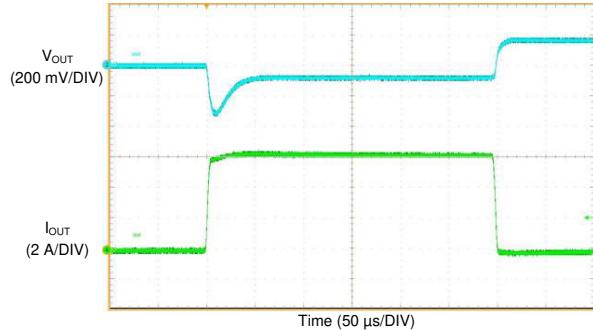

$V_{OUT} = 3.3V$        $f_{SW} = 400\text{kHz}$       自動モード

$I_{OUT} = 2A \rightarrow 4A \rightarrow$        $V_{IN} = 13.5V$        $T_R = T_F = 2\mu\text{s}$

$0A$

図 8-43. LMQ61460 の負荷過渡応答

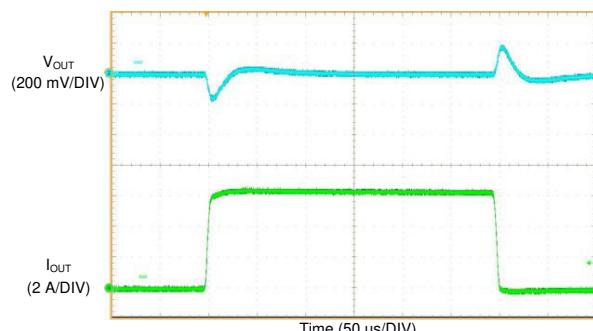

$V_{OUT} = 5V$        $f_{SW} = 2100\text{kHz}$       自動モード

$I_{OUT} = 0A \rightarrow 6A \rightarrow$        $V_{IN} = 13.5V$        $T_R = T_F = 6\mu\text{s}$

$0A$

図 8-44. LMQ61460 の負荷過渡応答

$V_{OUT} = 5V$        $f_{SW} = 2100\text{kHz}$       FPWM モード

$I_{OUT} = 0A \rightarrow 6A \rightarrow$        $V_{IN} = 13.5V$        $T_R = T_F = 6\mu\text{s}$

$0A$

図 8-45. LMQ61460 の負荷過渡応答

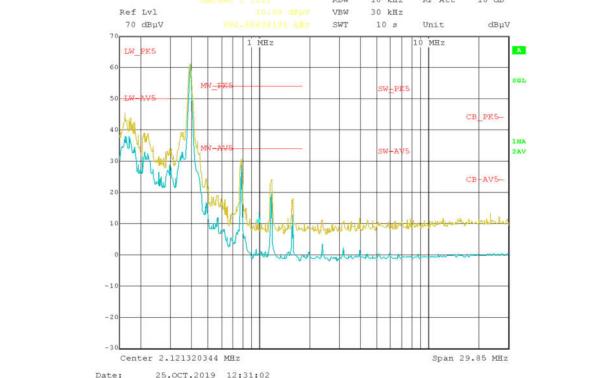

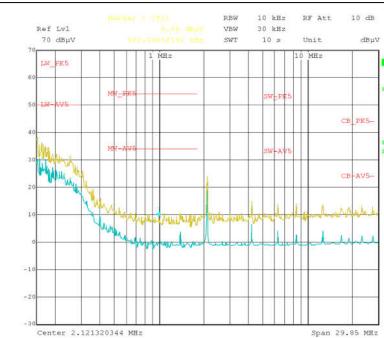

$f_{SW} = 400\text{kHz}$        $V_{OUT} = 5V$        $I_{OUT} = 5A$

測定周波数: 150kHz ~ 30MHz

図 8-46. 伝導 EMI と CISPR25 制限値との関係 (黄: ピーク信号、青: 平均信号)

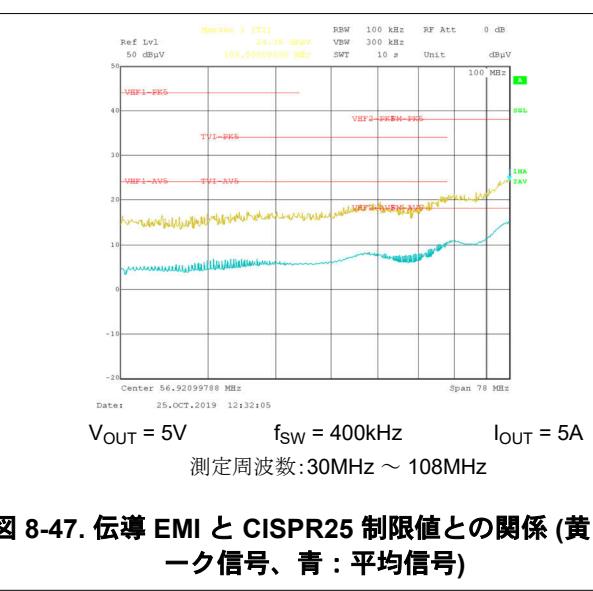

$V_{OUT} = 5V$        $f_{SW} = 400\text{kHz}$        $I_{OUT} = 5A$

測定周波数: 30MHz ~ 108MHz

図 8-47. 伝導 EMI と CISPR25 制限値との関係 (黄: ピーク信号、青: 平均信号)

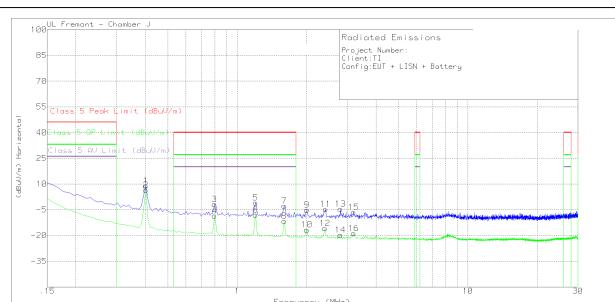

$V_{OUT} = 5V$        $f_{SW} = 400\text{kHz}$        $I_{OUT} = 5A$

測定周波数: 150kHz ~ 30MHz

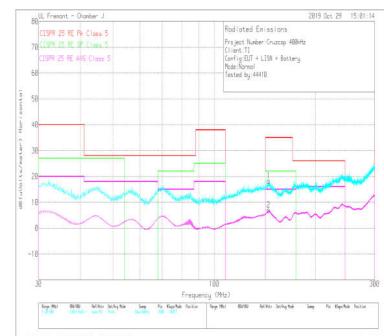

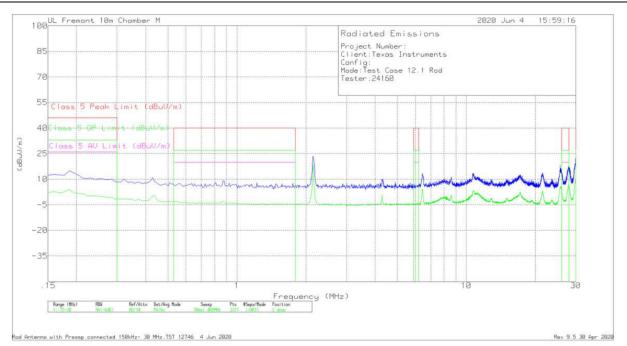

図 8-48. 放射 EMI (ロッド) と CISPR25 制限値との関係

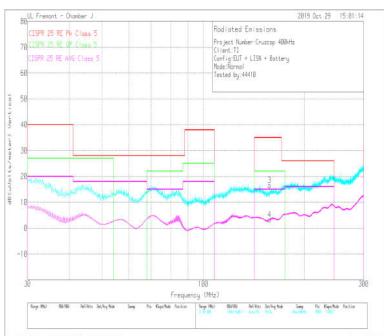

$V_{OUT} = 5V$     $f_{sw} = 400\text{kHz}$     $I_{OUT} = 5A$

測定周波数: 30MHz ~ 300MHz

図 8-49. 放射 EMI (バイコニカル、垂直) と CISPR25 制限値との関係

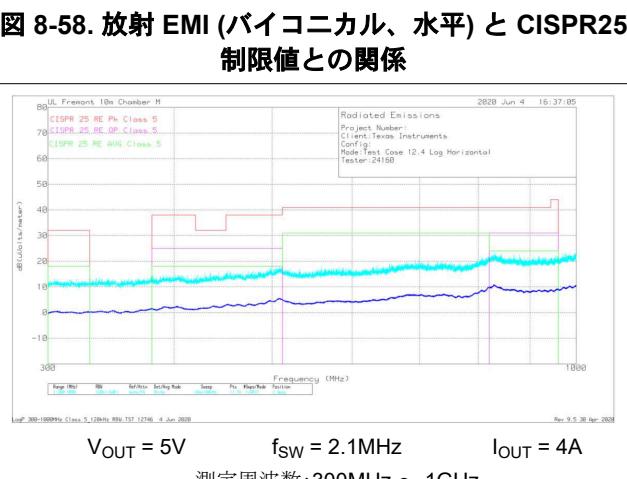

$V_{OUT} = 5V$     $f_{sw} = 400\text{kHz}$     $I_{OUT} = 5A$

測定周波数: 30MHz ~ 300MHz

図 8-50. 放射 EMI (バイコニカル、水平) と CISPR25 制限値との関係

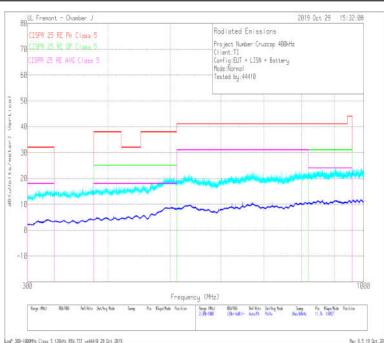

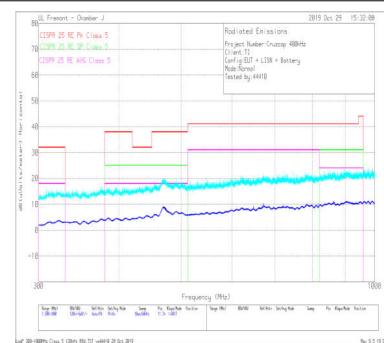

$V_{OUT} = 5V$     $f_{sw} = 400\text{kHz}$     $I_{OUT} = 5A$

測定周波数: 300MHz ~ 1GHz

図 8-51. 放射 EMI (ログペリ、垂直) と CISPR25 制限値との関係

$V_{OUT} = 5V$     $f_{sw} = 400\text{kHz}$     $I_{OUT} = 5A$

測定周波数: 300MHz ~ 1GHz

図 8-52. 放射 EMI (ログペリ、水平) と CISPR25 制限値との関係

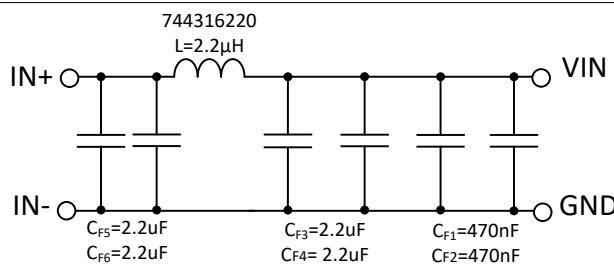

図 8-53. 推奨入力 EMI フィルタ

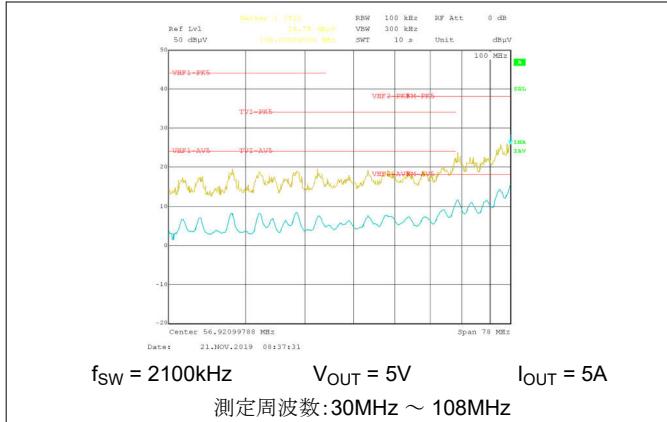

$f_{sw} = 2100\text{kHz}$     $V_{OUT} = 5V$     $I_{OUT} = 5A$

測定周波数: 150kHz ~ 30MHz

図 8-54. 伝導 EMI と CISPR25 制限値との関係 (黄: ピーク信号、青: 平均信号)

図 8-55. 伝導 EMI と CISPR25 制限値との関係 (黄: ピーク信号、青: 平均信号)

図 8-56. 放射 EMI (ロッド) と CISPR25 制限値との関係

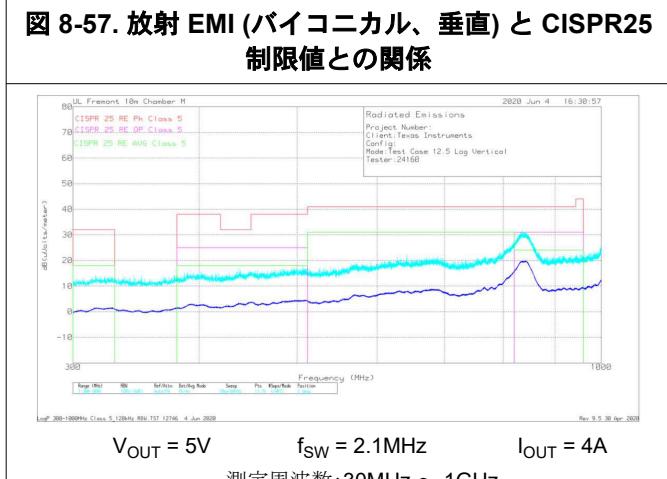

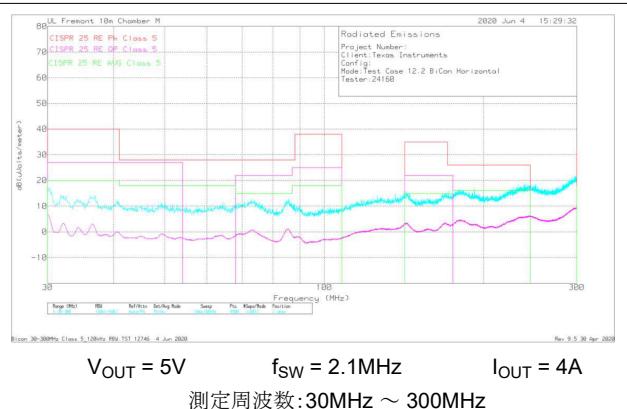

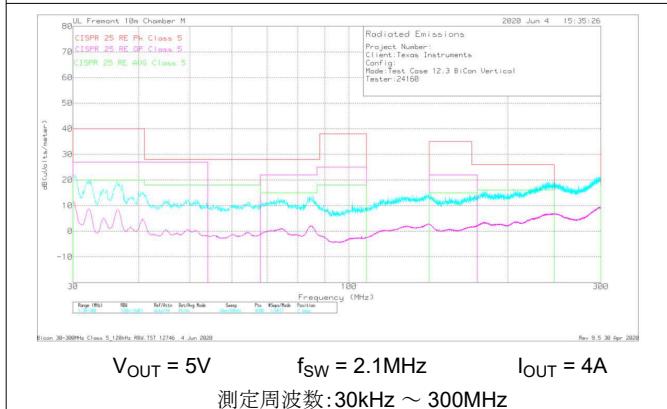

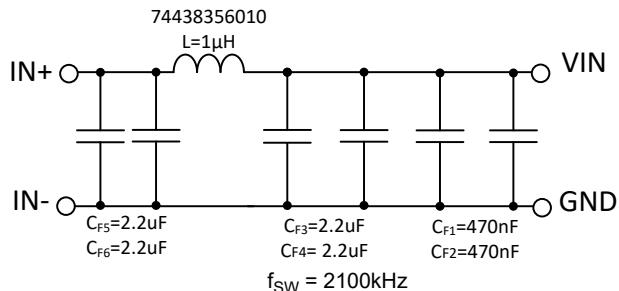

図 8-61. 推奨入力 EMI フィルタ

表 8-5. 代表的なアプリケーションの特性曲線で使われた BOM

| V <sub>OUT</sub> | 周波数     | R <sub>FBB</sub> | C <sub>OUT</sub> | C <sub>IN</sub> + C <sub>HF</sub> | L                   | C <sub>FF</sub> |

|------------------|---------|------------------|------------------|-----------------------------------|---------------------|-----------------|

| 3.3V             | 400kHz  | 43.2kΩ           | 6 × 22μF         | 2 × 4.7μF + 2 × 100nF             | 4.7μH (XHMI6060)    |                 |

| 3.3V             | 2100kHz | 43.2kΩ           | 3 × 22μF         | 2 × 4.7μF + 2 × 100nF             | 1.5μH (MAPI 4020HT) | 22pF            |

| 5V               | 400kHz  | 24.9kΩ           | 4 × 22μF         | 2 × 4.7μF + 2 × 100nF             | 4.7μH (XHMI6060)    |                 |

| 5V               | 2100kHz | 24.9kΩ           | 2 × 22μF         | 2 × 4.7μF + 2 × 100nF             | 1.5μH (MAPI 4020HT) | 22pF            |

### 8.3 電源に関する推奨事項

入力電源の特性は、このデータシートの「[絶対最大定格](#)」と「[推奨動作条件](#)」に適合している必要があります。また、入力電源は、負荷時のコンバータに必要な入力電流を供給できる必要があります。平均入力電流は、[式 15](#) を使って見積もることができます。

$$I_{IN} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta} \quad (15)$$

ここで

- $\eta$  は効率です。

コンバータを長いワイヤや PCB パターンで入力電源に接続している場合は、良好な性能を実現するために特別な注意が必要です。入力ケーブルの寄生インダクタンスと抵抗は、コンバータの動作に悪影響を及ぼすおそれがあります。寄生インダクタンスは、低 ESR セラミック入力コンデンサと組み合わせることで不足減衰共振回路を形成し、コンバータへの入力での過電圧過渡または UVLO のトリップの原因となる可能性があります。寄生抵抗は、出力に負荷過渡が加わった際に、VIN ピンの電圧が低下する原因となる可能性があります。アプリケーションが最小入力電圧に近い値で動作している場合、この低下によってコンバータが瞬間にシャットダウンし、リセットされる可能性があります。この種の問題を解決する最善策は、入力電源からコンバータまでの距離を短くして、セラミック入力コンデンサと並列にアルミニウム入力コンデンサを使用することです。中程度の ESR を持つこのタイプのコンデンサを使うことは、入力共振回路の振動を減衰させ、入力のすべてのオーバーシュートまたはアンダーシュートを低減するのに有効です。通常、20μF～100μF の値は入力のダンピングに十分であり、大きな負荷過渡中も入力電圧を安定した状態に保持できます。

一部の例では、コンバータの入力に過渡電圧サプレッサ (TVS) が使われています。この素子の種類には、スナップバック特性を持つもの (サイリスタ型) があります。このタイプの特性を持つ素子の使用は推奨しません。このタイプの TVS が作動すると、クランプ電圧は非常に低い値に低下します。コンバータの出力電圧よりもこの電圧が低い場合、出力コンデンサは本デバイスを通して入力に向かって放電します。この制御されない電流は、TVS に損傷を与え、大きな入力過渡を引き起こす可能性があります。

入力電圧は、出力電圧を下回ることはできません。この状況（入力短絡テストなど）では、出力コンデンサは、本デバイスの VIN ピンと SW ピンの間に形成された内部寄生ダイオードを通じて放電されます。この状況では電流は制御できなくなる可能性があり、デバイスが損傷するおそれがあります。このシナリオが想定される場合は、入力電源と出力の間にショットキー・ダイオードを使用してください。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

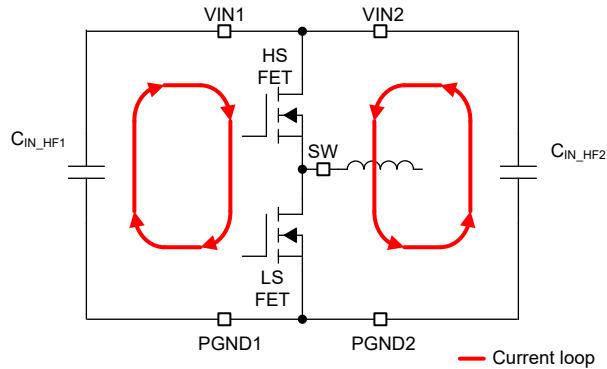

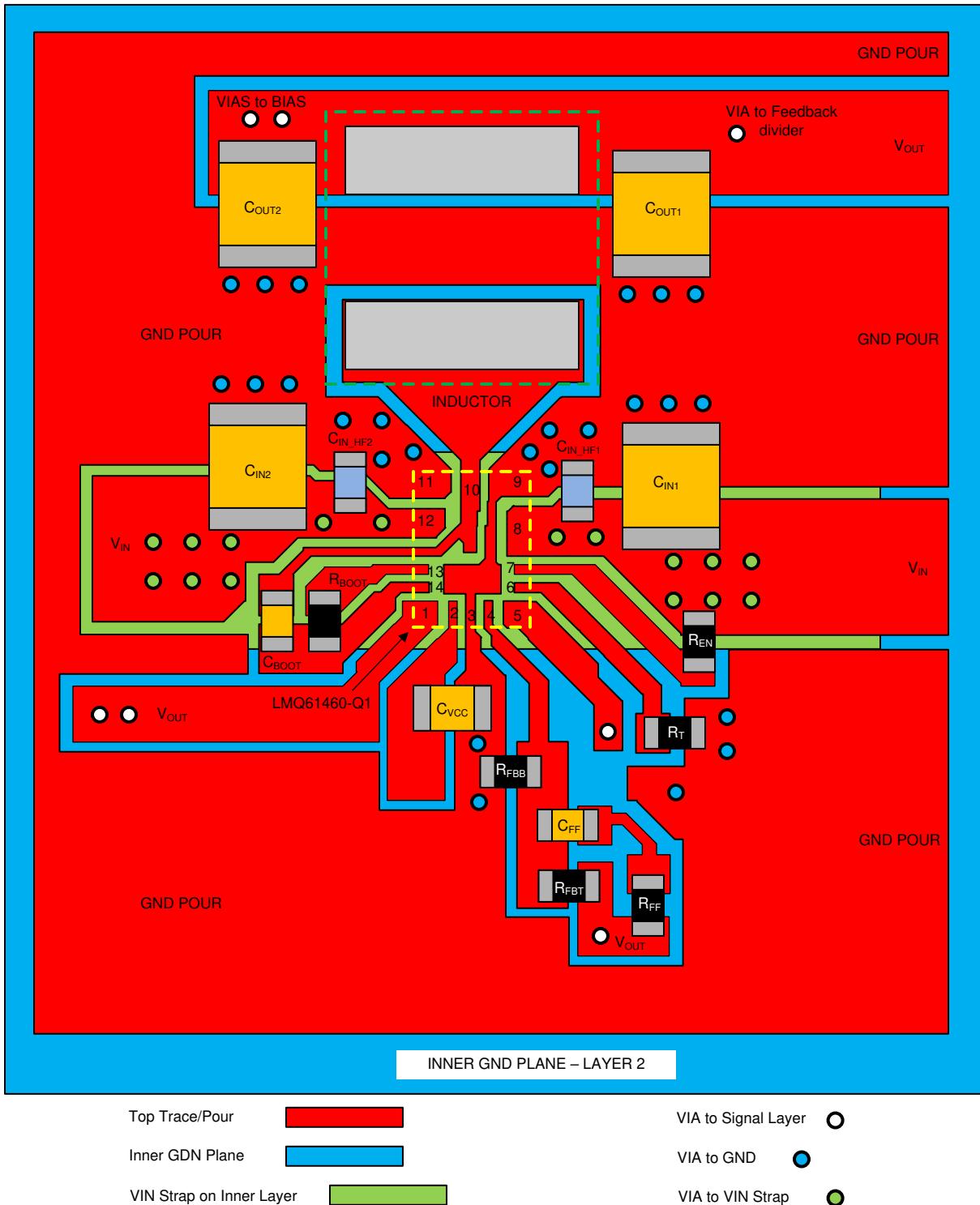

すべての DC/DC コンバータの PCB レイアウトは、最適な設計性能を実現するために重要です。PCB レイアウトが不適切な場合、適正な回路図設計の動作の妨げとなる可能性があります。コンバータが適切にレギュレートしている場合でも、PCB レイアウトが不適切では、堅牢な設計と量産できない設計という違いが生じる可能性があります。さらに、コンバータの EMI 性能は、PCB レイアウトに大きく依存します。降圧コンバータにおける PCB の最も重要な機能は、入力コンデンサと電源グランドによって形成されるループです（図 8-62 を参照）。このループには、パターンのインダクタンスに応答して大きな過渡電圧を発生させる可能性がある大きな過渡電流が流れます。これらの望ましくない過渡電圧は、コンバータの正常な動作を妨げます。このことから、寄生インダクタンスを低減するため、このループ内のパターンは広く短くする必要があります、ループの面積はできる限り小さくする必要があります。図 8-63 に、本デバイスの回路の重要な部品の推奨レイアウトを示します。

- 入力コンデンサは、入力ピン・ペア（VIN1/PGND1、VIN2/PGND2）のできるだけ近くに配置します。ピンのペアはそれぞれ隣接しているため、入力コンデンサを簡単に配置できます。VQFN-HR パッケージ品では、パッケージのどちらの側にも 2 つの VIN/PGND ペアがあるため、対称にレイアウトすることで、スイッチング・ノイズと EMI 生成を最小限に抑えることができます。下位層で広い VIN プレーンを使用して、両方の VIN ペアをまとめて入力電源に接続します。

- VCC のバイパス・コンデンサは、VCC ピンと AGND ピンの近くに配置します。このコンデンサは、短く広いパターンで VCC および AGND ピンに配線する必要があります。

- CBOOT コンデンサには広いパターンを使用します。CBOOT コンデンサは、デバイスのできる限り近くに、CBOOT および SW ピンに短く広いパターンで配置します。VIN2 ピンと RBOOT ピンの間の隙間を通して本デバイスの下に SW 接続を配線することで、SW ノードの露出面積を減らすことが重要です。RBOOT 抵抗を使用する場合、CBOOT ピンと RBOOT ピンのできるだけ近くに配置します。高い効率が必要な場合、RBOOT ピンと CBOOT ピンを短絡できます。この短絡は、RBOOT ピンと CBOOT ピンのできるだけ近くに配置する必要があります。

- 帰還分圧器は、本デバイスの FB ピンのできるだけ近くに配置します。R<sub>FBB</sub>、R<sub>FBT</sub>、C<sub>FF</sub> は、（使用する場合、）本デバイスに物理的に近付けて配置します。R<sub>FBB</sub> を経由した FB と AGND への接続は、短くする必要があり、かつ本デバイスのそれらのピンに近付ける必要があります。V<sub>OUT</sub> への接続は、多少長くてもかまいません。ただし、この後者のパターンは、コンバータの帰還経路に静電容量結合する可能性があるすべてのノイズ源（SW ノードなど）の近くには配線しないでください。

- PCB の第 2 層はグランド・プレーンにする必要があります。このプレーンは、ノイズ・シールドと放熱経路として機能します。第 2 層をすることで、入力ループ内の入力循環電流が囲む面積を低減させ、インダクタンスを低減できます。

- V<sub>IN</sub>、V<sub>OUT</sub>、GND には広いパターンを使います。コンバータの入力または出力経路でのすべての電圧降下を低減し、効率を最大化するため、これらの配線はできるだけ広くかつ真っすぐにする必要があります。

- 適切なヒートシンクのために十分な PCB 領域を確保します。最大負荷電流と周囲温度に見合った低 R<sub>θJA</sub> を実現するため、十分な銅領域を確保してください。PCB 層の上部と下部は 2 オンス銅箔とし、最低でも 1 オンス以上とします。PCB 設計に複数の銅層を使用している場合は（推奨設計）、サーマル・ビアも内部層の熱拡散グランド・プレーンに接続することができます。このデバイスのパッケージは、すべてのピンで放熱されます。ノイズに配慮して面積を最小化する必要がある場合を除き、すべてのピンに幅広パターンを使う必要があります。

- スイッチングする領域は、小さく保ちます。SW ピンをインダクタに接続する銅箔領域は、できるだけ短くかつ広くします。同時に、放射 EMI を低減するため、このノードの総面積を最小化する必要があります。

図 8-62. 入力電流ループ

#### 8.4.1.1 グランドと熱に関する考慮事項

前述のように、テキサス・インスツルメンツでは、中間層の 1 つをソリッド・グランド・プレーンとして使用することを推奨しています。グランド・プレーンは、ノイズの影響を受けやすい回路とパターンにシールドを提供します。また、制御回路に対して、低ノイズのリファレンス電位も提供します。AGND および PGND ピンは、バイパス・コンデンサの隣にあるビアを使用して、グランド・プレーンに接続する必要があります。PGND ピンは、ローサイド MOSFET スイッチのソースに直接接続し、入力および出力コンデンサのグランドにも直接接続します。PGND にはスイッチング周波数におけるノイズが含まれており、負荷変動により戻ってくる場合があります。PGND パターンは、VIN および SW パターンと同様に、グランド・プレーンの片方に固定する必要があります。グランド・プレーンのもう片方はノイズが非常に少ないため、ノイズの影響を受けやすい配線に使用します。

グランドと  $V_{IN}$  の近くに配置したビアを使用して、システムのグランド・プレーンまたは  $V_{IN}$  ストラップ (どちらも熱を放散します) に接続することで、適切なデバイス・ヒートシンクを形成することを推奨します。システムのグランド・プレーンでは、効率の高い放熱のために、レイヤの上下に出来る限り多くの銅を使用します。4 つの層の銅厚が上からそれぞれ 2 オンス、1 オンス、1 オンス、2 オンスとなっている 4 層基板を使用します。十分な厚さの銅箔と適切なレイアウトを備えた 4 層基板は、低インピーダンスの電流導通、適切なシールド効果、低熱抵抗を実現します。

### 8.4.2 レイアウト例

図 8-63. レイアウト例

## 9 デバイスおよびドキュメントのサポート

### 9.1 ドキュメントのサポート

#### 9.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『高性能、低EMI、車載用電源の設計』アプリケーションレポート

- テキサス・インスツルメンツ、『車載用デュアル USB Type-C 充電ポート用 30W 電源』テストレポート

- テキサス・インスツルメンツ、『EMI Filter Components and Their Nonidealities for Automotive DC/DC Regulators』*Analog Design Journal*

- テキサス・インスツルメンツ、『AN-2020 過去ではなく、現在の議見による熱設計』アプリケーションレポート

- テキサス・インスツルメンツ、『放熱性能の向上を目的とした TPS54424/TPS54824 の HotRod QFN パッケージのレイアウトの最適化』アプリケーションレポート

- テキサス・インスツルメンツ、『AN-2162 DC-DC コンバータからの伝導EMIへの簡単な対処方法』アプリケーションレポート