SNOSC63B-FEBRUARY 2012-REVISED DECEMBER 2014

LMP8646

# **LMP8646 Precision Current Limiter**

#### **Features**

- Provides Circuit Protection and Current Limiting

- Single Supply Operation

- -2-V to 76-V Common-Mode Voltage Range

- Variable Gain Set by External Resistor

- Adjustable Bandwidth Set by External Capacitor

- **Buffered Output**

- 3% Output Accuracy Achievable at V<sub>SENSE</sub> = 100

- **Key Specifications:**

- Supply Voltage Range 2.7 V to 12 V

- Output Current (Source) 0 to 5 mA

- Gain Accuracy 2.0% (max)

- Transconductance 200 μA/V

- Offset ±1 mV (Maximum)

- Quiescent Current 380 μA

- Input Bias 12 µA (Typical)

- PSRR 85 dB

- CMRR 95 dB

- Temperature Range -40°C to 125°C

- 6-Pin SOT Package

# 2 Applications

- High-Side and Low-Side Current Limit

- Circuit Fault Protection

- Battery and Supercap Charging

- LED Constant Current Drive

- **Power Management**

# 3 Description

The LMP8646 is a precision current limiter used to improve the current limit accuracy of any switching or linear regulator with an available feedback node.

The LMP8646 accepts input signals with a commonmode voltage ranging from -2 V to 76 V. It has a variable gain which is used to adjust the sense current. The gain is configured with a single external resistor, R<sub>G</sub>, providing a high level of flexibility and accuracy up to 2%. The adjustable bandwidth, which allows the device to be used with a variety of applications, is configurable with a single external capacitor in parallel with R<sub>G</sub>. In addition, the output is buffered in order to provide a low output impedance.

The LMP8646 is an ideal choice for industrial, automotive, telecommunications, and consumer applications where circuit protection and improved precision systems are required. The LMP8646 is available in a 6-pin SOT package and can operate at temperature range of -40°C to 125°C.

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| LMP8646     | SOT (6) | 2.90 mm × 1.60 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

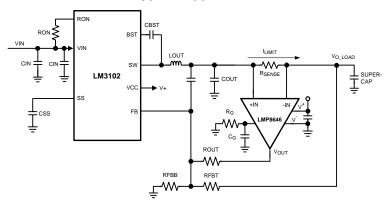

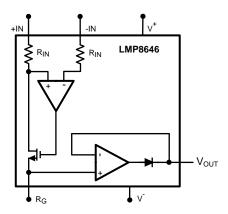

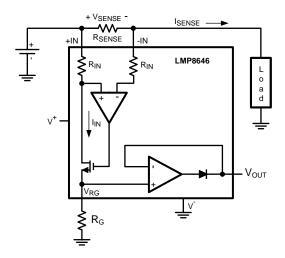

#### **Typical Application**

#### **Table of Contents**

| 1 | Features 1                                                        |             | ctional Block Diagram                |    |

|---|-------------------------------------------------------------------|-------------|--------------------------------------|----|

| 2 | Applications 1                                                    | 7.3 Feat    | ure Description                      | 13 |

| 3 | Description 1                                                     | 7.4 Devi    | ce Functional Modes                  | 15 |

| 4 | Revision History2                                                 | 8 Applicati | ion and Implementation               | 17 |

| 5 | Pin Configuration and Functions                                   | 8.1 Appl    | ication Information                  | 17 |

| 6 | Specifications                                                    | 8.2 Typi    | cal Applications                     | 17 |

| U | 6.1 Absolute Maximum Ratings                                      | 9 Power S   | upply Recommendations                | 23 |

|   | 6.2 ESD Ratings                                                   | 10 Layout   |                                      | 23 |

|   | 6.3 Recommended Operating Conditions                              |             | out Guidelines                       |    |

|   | 6.4 Thermal Information                                           |             | out Example                          |    |

|   | 6.5 Electrical Characteristics: 2.7 V                             |             | and Documentation Support            |    |

|   | 6.6 Electrical Characteristics: 5 V                               |             | demarks                              |    |

|   | 6.7 Electrical Characteristics: 12 V                              | 11.2 Ele    | ctrostatic Discharge Caution         | 24 |

|   | 6.8 Typical Characteristics                                       |             | ossary                               |    |

| 7 | Detailed Description         13           7.1 Overview         13 |             | cal, Packaging, and Orderable<br>ion | 24 |

|   |                                                                   |             |                                      |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision A (March 2013) to Revision B

Page

Added Pin Configuration and Functions section, Handling Rating table, Feature Description section, Device

Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout

section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information

section

Changes from Original (March 2013) to Revision A

Page

Submit Documentation Feedback

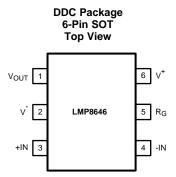

# **5 Pin Configuration and Functions**

**Pin Functions**

| PIN              |     | DESCRIPTION                                                                                                                            |

|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO. | DESCRIPTION                                                                                                                            |

| V <sub>OUT</sub> | 1   | Single-Ended Output Voltage                                                                                                            |

| V-               | 2   | Negative Supply Voltage. This pin should be connected to ground.                                                                       |

| +IN              | 3   | Positive Input                                                                                                                         |

| -IN              | 4   | Negative Input                                                                                                                         |

| $R_{G}$          | 5   | External Gain Resistor. An external capacitance (C <sub>G</sub> ) may be added in parallel with R <sub>G</sub> to limit the bandwidth. |

| V <sup>+</sup>   | 6   | Positive Supply Voltage                                                                                                                |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(1)

|                                          | MIN | MAX            | UNIT |

|------------------------------------------|-----|----------------|------|

| Supply Voltage ( $V_S = V^+ - V^-$ )     |     | 13.2           | V    |

| Differential voltage +IN- (-IN)          |     | 6              | V    |

| Voltage at pins +IN, -IN                 | -6  | 80             | V    |

| Voltage at R <sub>G</sub> pin            |     | 13.2           | V    |

| Voltage at OUT pin                       | V-  | V <sup>+</sup> | V    |

| Junction Temperature <sup>(2)</sup>      |     | 150            | °C   |

| Storage temperature range                | -65 | 150            | °C   |

| For soldering specifications see SNOA549 |     |                |      |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics: 2.7 V tables.

- (2) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>J(MAX)</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation P<sub>DMAX</sub> = (T<sub>J(MAX)</sub> T<sub>A</sub>)/ θ<sub>JA</sub> or the number given in Absolute Maximum Ratings, whichever is lower.

6.2 ESD Ratings

|                                            |                                                                     |                              |       | VALUE      | UNIT |

|--------------------------------------------|---------------------------------------------------------------------|------------------------------|-------|------------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 (1)           | Pins +IN and -IN             | ±4000 |            |      |

|                                            | ANSI/ESDA/JEDEC JS-001(1)                                           | All pins except +IN and - IN | ±2000 | \ <u>\</u> |      |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) |                              | ±1250 | V          |      |

|                                            |                                                                     | Machine model                |       | ±250       |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

|                                      | MIN | MAX | UNIT |

|--------------------------------------|-----|-----|------|

| Supply Voltage ( $V_S = V^+ - V^-$ ) | 2.7 | 12  | V    |

| Temperature Range <sup>(1)</sup>     | -40 | 125 | V    |

<sup>(1)</sup> The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>J(MAX)</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation P<sub>DMAX</sub> = (T<sub>J(MAX)</sub> - T<sub>A</sub>)/ θ<sub>JA</sub> or the number given in Absolute Maximum Ratings, whichever is lower.

# 6.4 Thermal Information

|                                                         | LMP8646 |      |

|---------------------------------------------------------|---------|------|

| THERMAL METRIC <sup>(1)</sup>                           | DDC     | UNIT |

|                                                         | 6 PINS  |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 96      | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics: 2.7 V

Unless otherwise specified, all limits ensured for at  $T_A = 25^{\circ}$ C,  $V_S = (V^+ - V^-) = (2.7 \text{ V} - 0 \text{ V}) = 2.7 \text{ V}$ ,  $-2 \text{ V} < V_{CM} < 76 \text{ V}$ ,  $R_G = 10^{\circ}$ 25 kΩ,  $R_1 = 10 kΩ.$  (1)

|                     | PARAMETER                              | TEST CONDITIONS                                                                                          | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT    |  |

|---------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|---------|--|

| V <sub>OFFSET</sub> | Input Offset Voltage                   | V <sub>CM</sub> = 2.1 V                                                                                  | -1                 |                    | 1                  | \/      |  |

|                     |                                        | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                          | -1.7               |                    | 1.7                | mV      |  |

| TCV <sub>OS</sub>   | Input Offset Voltage Drift (4)(5)      | V <sub>CM</sub> = 2.1 V                                                                                  |                    |                    | 7                  | μV/°C   |  |

| I <sub>B</sub>      | Input Bias Current <sup>(6)</sup>      | V <sub>CM</sub> = 2.1 V                                                                                  |                    | 12                 | 20                 | μА      |  |

| e <sub>ni</sub>     | Input Voltage Noise <sup>(5)</sup>     | $f > 10 \text{ kHz}, R_G = 5 \text{ k}\Omega$                                                            |                    | 120                |                    | nV/√Hz  |  |

| V <sub>SENSE</sub>  | Max Input Sense Voltage (5)            | $V_{CM} = 12 \text{ V}, R_G = 5 \text{ k}\Omega$                                                         |                    |                    | 600                | mV      |  |

| Gain A <sub>V</sub> | Adjustable Gain Setting <sup>(5)</sup> | V <sub>CM</sub> = 12 V                                                                                   | 1                  |                    | 100                | V/V     |  |

| Gm                  | Transconductance = 1/R <sub>IN</sub>   | V <sub>CM</sub> = 2.1 V                                                                                  |                    | 200                |                    | μA/V    |  |

|                     | A                                      | V <sub>CM</sub> = 2.1 V                                                                                  | -2%                |                    | 2%                 |         |  |

|                     | Accuracy                               | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                          | -3.4%              |                    | 3.4%               |         |  |

|                     | Gm drift <sup>(5)</sup>                | -40°C to 125°C, V <sub>CM</sub> = 2.1 V                                                                  |                    |                    | 140                | ppm /°C |  |

| PSRR                | Power Supply Rejection Ratio           | V <sub>CM</sub> = 2.1 V, 2.7 V < V <sup>+</sup> < 12 V                                                   | 85                 |                    |                    | dB      |  |

| CMRR                | Occasion Made Balantine Batin          | 2.1 V < V <sub>CM</sub> < 76 V                                                                           | 95                 |                    |                    | 40      |  |

|                     | Common-Mode Rejection Ratio            | -2 V <v<sub>CM &lt; 2.1 V</v<sub>                                                                        | 55                 |                    |                    | dB      |  |

| SR                  | Slew Rate <sup>(7)(5)</sup>            | $V_{CM}$ = 5 V, $C_{G}$ = 4 pF, $V_{SENSE}$ from 25 mV to 175 mV, $C_{L}$ = 30 pF, $R_{L}$ = 1M $\Omega$ |                    | 0.5                |                    | V/µs    |  |

| Is                  | Supply Current                         | V <sub>CM</sub> = 2.1 V                                                                                  |                    | 380                | 610                |         |  |

|                     |                                        | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                          |                    |                    | 807                |         |  |

|                     |                                        | $V_{CM} = -2 \text{ V}$                                                                                  |                    | 2000               | 2500               | uA      |  |

|                     |                                        | $V_{CM} = -2 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                           |                    |                    | 2700               |         |  |

| V <sub>OUT</sub>    | Maximum Output Voltage                 | $V_{CM} = 2.1 \text{ V}, R_G = 500 \text{ k}\Omega$                                                      | 1.1                |                    |                    | V       |  |

|                     | Minimum Output Voltage                 | V <sub>CM</sub> = 2.1 V                                                                                  |                    |                    | 20                 | mV      |  |

|                     | Maximum Output Voltage                 | $VS = V_{CM} = 3.3 \text{ V}, R_G = 500 \text{ k}\Omega$                                                 | 1.6                |                    |                    | V       |  |

|                     | Minimum Output Voltage                 | $VS = V_{CM} = 3.3 \text{ V}, R_G = 500 \text{ k}\Omega$                                                 |                    |                    | 22                 | mV      |  |

| I <sub>OUT</sub>    | Output current <sup>(5)</sup>          | Sourcing, $V_{OUT}$ = 600 mV, $R_{G}$ = 150 k $\Omega$                                                   |                    | 5                  |                    | mA      |  |

| C <sub>LOAD</sub>   | Max Output Capacitance Load (5)        |                                                                                                          |                    | 30                 |                    | pF      |  |

Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No assurance of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

All limits are specified by testing, design, or statistical analysis.

Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

Offset voltage temperature drift is determined by dividing the change in Vos at the temperature extremes by the total temperature

This parameter is specified by design and/or characterization and is not tested in production.

Positive Bias Current corresponds to current flowing into the device.

The number specified is the average of rising and falling slew rates and measured at 90% to 10%.

#### 6.6 Electrical Characteristics: 5 V

Unless otherwise specified, all limits ensured for at  $T_A = 25^{\circ}C$ ,  $V_S = V^+ - V^-$ ,  $V^+ = 5$  V,  $V^- = 0$  V, -2 V  $< V_{CM} < 76$  V,  $R_0 = 25$  k $\Omega$ ,  $R_1 = 10 \text{ k}\Omega.^{(1)}$

|                         | PARAMETER                              | TEST CONDITIONS                                                                                           | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT               |

|-------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|

| V <sub>OFFSET</sub>     | Input Offset Voltage                   | V <sub>CM</sub> = 2.1 V                                                                                   | -1                 |                    | 1                  | >/                 |

|                         |                                        | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                           | -1.7               |                    | 1.7                | mV                 |

| TCV <sub>OS</sub>       | Input Offset Voltage Drift (4) (5)     | V <sub>CM</sub> = 2.1 V                                                                                   |                    |                    | 7                  | μV/°C              |

| $I_{B}$                 | Input Bias Current <sup>(6)</sup>      | V <sub>CM</sub> = 2.1 V                                                                                   |                    | 12.5               | 22                 | μА                 |

| e <sub>ni</sub>         | Input Voltage Noise (5)                | $f > 10 \text{ kHz}, R_G = 5 \text{ k}\Omega$                                                             |                    | 120                |                    | nV/√ <del>Hz</del> |

| V <sub>SENSE(MAX)</sub> | Max Input Sense Voltage (5)            | $V_{CM}$ = 12 V, $R_G$ = 5 k $\Omega$                                                                     |                    | 600                |                    | mV                 |

| Gain A <sub>V</sub>     | Adjustable Gain Setting <sup>(5)</sup> | V <sub>CM</sub> = 12 V                                                                                    | 1                  |                    | 100                | V/V                |

| Gm                      | Transconductance = 1/R <sub>IN</sub>   | V <sub>CM</sub> = 2.1 V                                                                                   |                    | 200                |                    | μA/V               |

|                         | Accuracy                               | V <sub>CM</sub> = 2.1 V                                                                                   | -2%                |                    | 2%                 |                    |

|                         |                                        | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                           | -3.4%              |                    | 3.4%               |                    |

|                         | Gm drift <sup>(5)</sup>                | -40°C to 125°C, V <sub>CM</sub> = 2.1 V                                                                   |                    |                    | 140                | ppm /°C            |

| PSRR                    | Power Supply Rejection Ratio           | $V_{CM} = 2.1 \text{ V}, 2.7 \text{ V} < V^{+} < 12 \text{ V},$                                           | 85                 |                    |                    | dB                 |

| CMRR                    | Common-Mode Rejection Ratio            | 2.1 V <v<sub>CM &lt; 76 V</v<sub>                                                                         | 95                 |                    |                    | dB                 |

|                         |                                        | -2 V < V <sub>CM</sub> < 2.1 V                                                                            | 55                 |                    |                    | uБ                 |

| SR                      | Slew Rate <sup>(7)(5)</sup>            | $V_{CM}$ = 5 V, $C_{G}$ = 4 pF, $V_{SENSE}$ from 100 mV to 500 mV, $C_{L}$ = 30 pF, $R_{L}$ = 1M $\Omega$ |                    | 0.5                |                    | V/µs               |

| Is                      | Supply Current                         | V <sub>CM</sub> = 2.1 V                                                                                   |                    | 450                | 660                |                    |

|                         |                                        | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                           |                    |                    | 939                |                    |

|                         |                                        | $V_{CM} = -2 V$                                                                                           |                    | 2100               | 2800               | uA                 |

|                         |                                        | $V_{CM} = -2 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                            |                    |                    | 3030               |                    |

| V <sub>OUT</sub>        | Maximum Output Voltage                 | $V_{CM} = 5 \text{ V}, R_G = 500 \text{ k}\Omega$                                                         | 3.3                |                    |                    | V                  |

|                         | Minimum Output Voltage                 | V <sub>CM</sub> = 2.1 V                                                                                   |                    |                    | 22                 | mV                 |

| I <sub>OUT</sub>        | Output current <sup>(5)</sup>          | Sourcing, $V_{OUT}$ = 1.65 V, $R_G$ = 150 k $\Omega$                                                      |                    | 5                  |                    | mA                 |

| C <sub>LOAD</sub>       | Max Output Capacitance Load (5)        |                                                                                                           |                    | 30                 |                    | pF                 |

<sup>(1)</sup> Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No assurance of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

All limits are specified by testing, design, or statistical analysis.

Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and

Submit Documentation Feedback

Copyright © 2012-2014, Texas Instruments Incorporated

will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

Offset voltage temperature drift is determined by dividing the change in Vos at the temperature extremes by the total temperature

This parameter is specified by design and/or characterization and is not tested in production.

Positive Bias Current corresponds to current flowing into the device.

The number specified is the average of rising and falling slew rates and measured at 90% to 10%.

#### 6.7 Electrical Characteristics: 12 V

Unless otherwise specified, all limits ensured for at  $T_A = 25$ °C,  $V_S = V^+ - V^-$ ,  $V^+ = 12$  V,  $V^- = 0$  V,  $V^- =$  $k\Omega$ ,  $R_L = 10 \ k\Omega$ . (1)

|                         | PARAMETER                                    | TEST CONDITIONS                                                                                           | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT    |

|-------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|---------|

| V <sub>OFFSET</sub>     | Input Offset Voltage                         | V <sub>CM</sub> = 2.1 V                                                                                   | -1                 |                    | 1                  | >/      |

|                         |                                              | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                           | -1.7               |                    | 1.7                | mV      |

| TCV <sub>OS</sub>       | Input Offset Voltage Drift <sup>(4)(5)</sup> | V <sub>CM</sub> = 2.1 V                                                                                   |                    |                    | 7                  | μV/°C   |

| I <sub>B</sub>          | Input Bias Current <sup>(6)</sup>            | V <sub>CM</sub> = 2.1 V                                                                                   |                    | 13                 | 23                 | μА      |

| e <sub>ni</sub>         | Input Voltage Noise <sup>(5)</sup>           | $f > 10 \text{ kHz}, R_G = 5 \text{ k}\Omega$                                                             |                    | 120                |                    | nV/√Hz  |

| V <sub>SENSE(MAX)</sub> | Max Input Sense Voltage (5)                  | $V_{CM}$ =12 V, $R_G$ = 5 k $\Omega$                                                                      |                    | 600                |                    | mV      |

| Gain A <sub>V</sub>     | Adjustable Gain Setting <sup>(5)</sup>       | V <sub>CM</sub> = 12 V                                                                                    | 1                  |                    | 100                | V/V     |

| Gm                      | Transconductance = 1/R <sub>IN</sub>         | V <sub>CM</sub> = 2.1 V                                                                                   |                    | 200                |                    | μA/V    |

|                         | Accuracy                                     | V <sub>CM</sub> = 2.1 V                                                                                   | -2%                |                    | 2%                 |         |

|                         |                                              | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                           | -3.4%              |                    | 3.4%               |         |

|                         | Gm drift <sup>(5)</sup>                      | -40°C to 125°C, V <sub>CM</sub> =2.1 V                                                                    |                    |                    | 140                | ppm /°C |

| PSRR                    | Power Supply Rejection Ratio                 | V <sub>CM</sub> = 2.1 V, 2.7 V < V <sup>+</sup> < 12 V                                                    | 85                 |                    |                    | dB      |

| CMRR                    | Common-Mode Rejection Ratio                  | 2.1 V < V <sub>CM</sub> < 76 V                                                                            | 95                 |                    |                    | dB      |

|                         |                                              | $-2 \text{ V} < \text{V}_{CM} < 2.1 \text{ V}$                                                            | 55                 |                    |                    | uБ      |

| SR                      | Slew Rate <sup>(7)(5)</sup>                  | $V_{CM}$ = 5 V, $C_{G}$ = 4 pF, $V_{SENSE}$ from 100 mV to 500 mV, $C_{L}$ = 30 pF, $R_{L}$ =1 M $\Omega$ |                    | 0.6                |                    | V/µs    |

| Is                      | Supply Current                               | V <sub>CM</sub> = 2.1 V                                                                                   |                    | 555                | 845                |         |

|                         |                                              | $V_{CM} = 2.1 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                           |                    |                    | 1123               |         |

|                         |                                              | $V_{CM} = -2 V$                                                                                           |                    | 2200               | 2900               | uA      |

|                         |                                              | $_{CM} = -2 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$               |                    |                    | 3110               |         |

| V <sub>OUT</sub>        | Maximum Output Voltage                       | $V_{CM}$ = 12 V, $R_G$ = 500 k $\Omega$ ,                                                                 | 10                 |                    |                    | V       |

|                         | Minimum Output Voltage                       | V <sub>CM</sub> = 2.1 V                                                                                   |                    |                    | 24                 | mV      |

| I <sub>OUT</sub>        | Output current (5)                           | Sourcing, $V_{OUT}$ = 5.25 V, $R_{G}$ = 150 k $\Omega$                                                    |                    | 5                  |                    | mA      |

| C <sub>LOAD</sub>       | Max Output Capacitance Load (5)              |                                                                                                           |                    | 30                 |                    | pF      |

<sup>(1)</sup> Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No assurance of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

All limits are specified by testing, design, or statistical analysis.

Typical values represent the most likely parametric norm at the time of characterization. Actual typical values may vary over time and

will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

Offset voltage temperature drift is determined by dividing the change in Vos at the temperature extremes by the total temperature

This parameter is specified by design and/or characterization and is not tested in production.

Positive Bias Current corresponds to current flowing into the device.

The number specified is the average of rising and falling slew rates and measured at 90% to 10%.

# TEXAS INSTRUMENTS

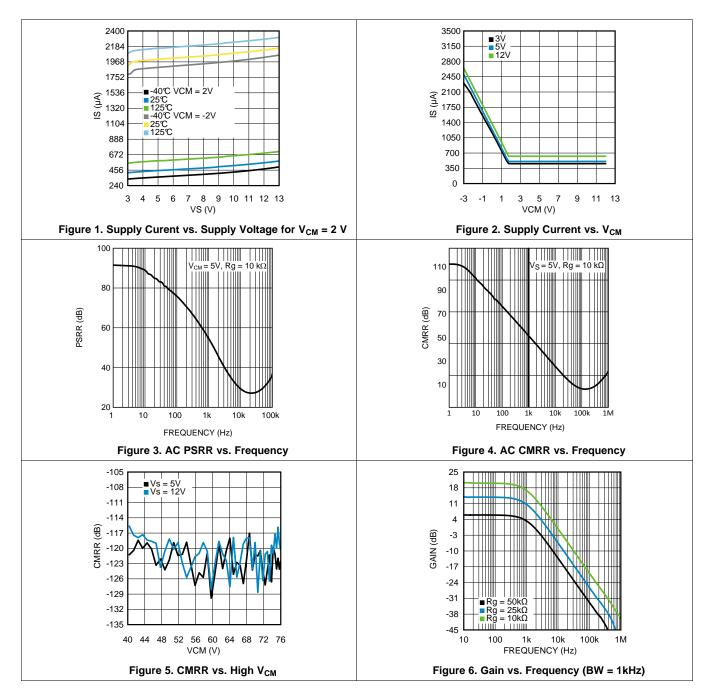

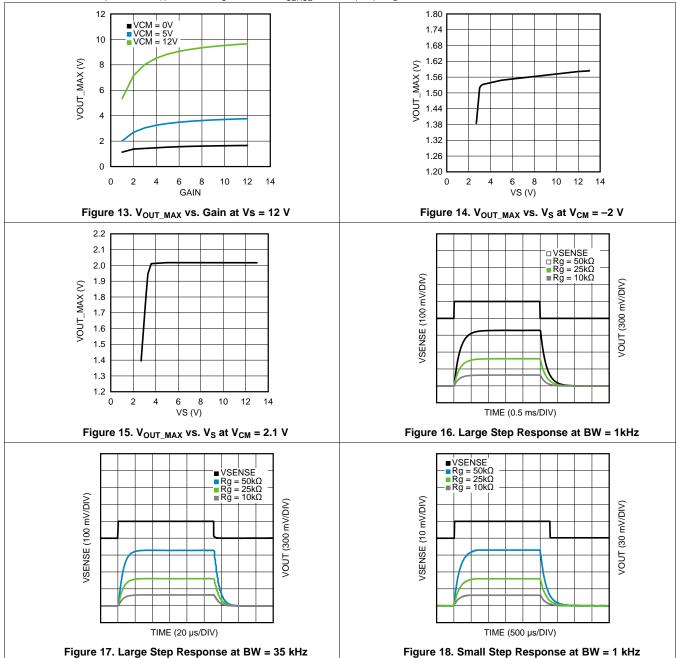

# 6.8 Typical Characteristics

Unless otherwise specified:  $T_A$  = 25°C,  $V_S$ =  $V^+$  -  $V^-$ ,  $V_{SENSE}$ = +IN - (-IN),  $R_L$  = 10 k $\Omega$ .

Submit Documentation Feedback

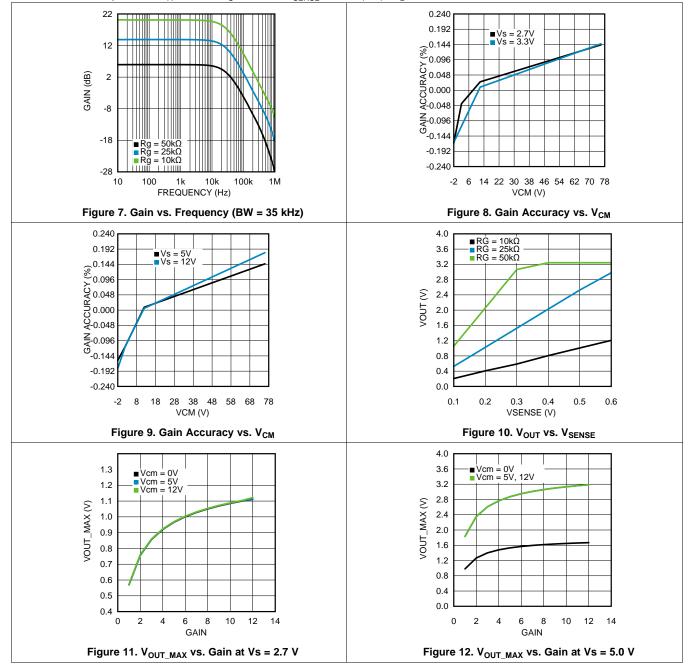

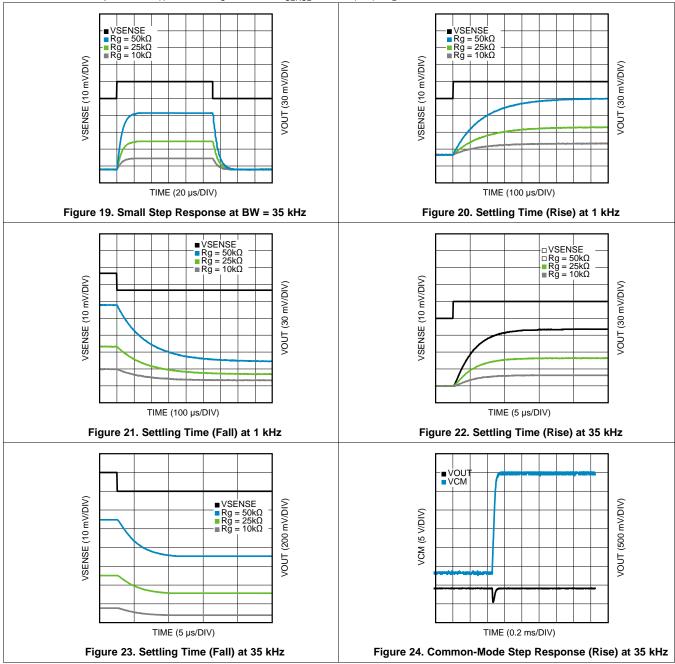

# **Typical Characteristics (continued)**

Unless otherwise specified:  $T_A = 25^{\circ}C$ ,  $V_S = V^+ - V^-$ ,  $V_{SENSE} = +IN - (-IN)$ ,  $R_L = 10 \text{ k}\Omega$ .

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Unless otherwise specified:  $T_A = 25^{\circ}C$ ,  $V_S = V^+ - V^-$ ,  $V_{SENSE} = +IN - (-IN)$ ,  $R_L = 10 \text{ k}\Omega$ .

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

# **Typical Characteristics (continued)**

Unless otherwise specified:  $T_A = 25$ °C,  $V_S = V^+ - V^-$ ,  $V_{SENSE} = +IN - (-IN)$ ,  $R_L = 10 \text{ k}\Omega$ .

Product Folder Links: LMP8646

Copyright © 2012-2014, Texas Instruments Incorporated

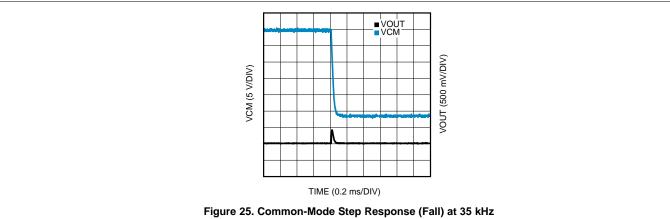

# **Typical Characteristics (continued)**

Unless otherwise specified:  $T_A = 25^{\circ}C$ ,  $V_S = V^+ - V^-$ ,  $V_{SENSE} = +IN - (-IN)$ ,  $R_L = 10 \text{ k}\Omega$ .

# 7 Detailed Description

#### 7.1 Overview

The LMP8646 is a single-supply precision current limiter with variable gain selected through an external resistor ( $R_G$ ) and a variable bandwidth selected through an external capacitor ( $C_G$ ) in parallel with  $R_G$ . Its common-mode of operation is -2 V to 76 V, and the LMP8646 has an buffered output to provide a low-output impedance. More details of the LMP8646's functional description can be seen in the following subsections.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

#### 7.3.1 Theory of Operation

As seen from Figure 26, the sense current flowing through  $R_{SENSE}$  develops a voltage drop equal to  $V_{SENSE}$ . The high impedance inputs of the amplifier does not conduct this current and the high open-loop gain of the sense amplifier forces its noninverting input to the same voltage as the inverting input. In this way the voltage drop across  $R_{IN}$  matches  $V_{SENSE}$ . The current  $I_{IN}$  flowing through  $R_{IN}$  has the following equation:

$$I_{IN} = V_{SENSE} / R_{IN} = R_{SENSE} * I_{SENSE} / R_{IN}$$

where

•

$$R_{IN} = 1/Gm = 1/(200 \mu A/V) = 5 kOhm$$

(1)

$I_{IN}$  flows entirely across the external gain resistor  $R_G$  to develop a voltage drop equal to:  $V_{RG} = I_{IN} * R_G = (V_{SENSE}/R_{IN}) * R_G = [(R_{SENSE} * I_{SENSE}) / R_{IN}] * R_G$ (2)

This voltage is buffered and showed at the output with a very low impedance allowing a very easy interface of the LMP8646 with the feedback of many voltage regulators. This output voltage has the following equation:

$$V_{OUT} = V_{RG} = [(R_{SENSE}^* I_{SENSE}) / R_{IN}]^* R_G$$

(3)

$$V_{OUT} = V_{SENSE}^* R_G / R_{IN}$$

(4)

$$V_{OUT} = V_{SENSE}^* R_G / (5 \text{ kOhm})$$

(5)

V<sub>OUT</sub> = V<sub>SENSE</sub>\* Gain

Copyright © 2012-2014, Texas Instruments Incorporated

where

• Gain =

$$R_G/R_{IN}$$

(6)

# Feature Description (continued)

Figure 26. Current Monitor

#### 7.3.1.1 Maximum Output Voltage, V<sub>OUT MAX</sub>

The maximum output voltage,  $V_{OUT\ MAX}$ , depends on the supply voltage,  $V_S = V^+ - V^-$ , and on the common-mode voltage,  $V_{CM} = (+IN + -IN) / 2$ .

The following subsections show three cases to calculate for  $V_{\text{OUT MAX}}$ .

#### 7.3.1.1.1 Case 1: $-2 \text{ V} < \text{V}_{CM} < 1.8 \text{ V}$ , and $\text{V}_{S} > 2.7 \text{ V}$

If  $V_S \ge 5 V$ , then  $V_{OUT\ MAX} = 1.3\ V$ . Else if Vs = 2.7 V, then  $V_{OUT\ MAX} = 1.1\ V$ .

#### 7.3.1.1.2 Case 2: 1.8 V < $V_{CM}$ < $V_{S}$ , and $V_{S}$ > 3.3 V

In this case,  $V_X$  is a fixed value that depends on the supply voltage.  $V_X$  has the following values:

If  $V_S = 12 \text{ V}$ , then  $V_X = 10 \text{ V}$ . Else if  $V_S = 5 \text{ V}$ , then  $V_X = 3.3 \text{ V}$ . Else if  $V_S = 2.7 \text{ V}$ , then  $V_X = 1.1 \text{ V}$ . If  $V_X \le (V_{CM} - V_{SENSE} - 0.25)$ , then  $V_{OUT\ MAX} = V_X$ . Else,  $V_{OUT\ MAX} = (V_{CM} - V_{SENSE} - 0.25).$

For example, if  $V_{CM} = 4 \text{ V}$ ,  $V_S = 5 \text{ V}$  (and thus  $V_X = 3.3 \text{ V}$ ),  $V_{SENSE} = 0.1 \text{ V}$ , then  $V_{OUT\_MAX} = 3.3 \text{ V}$  because 3.3 V  $\leq$  (4 - 0.1 - 0.25).

# 7.3.1.1.3 Case 3: $V_{CM} > V_{S}$ , and $V_{S} > 2.7 V$

If  $V_S = 12 \text{ V}$ , then  $V_{OUT\ MAX} = 10 \text{ V}$ . Else if  $V_S = 5 \text{ V}$ , then  $V_{OUT\ MAX} = 3.3 \text{ V}$ . Else if  $V_S = 2.7 \text{ V}$ , then  $V_{OUT\ MAX} = 1.1 \text{ V}$ .

#### 7.4 Device Functional Modes

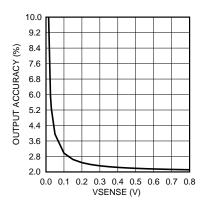

#### 7.4.1 Output Accuracy

The output accuracy is the device error contributed by the LMP8646 based on its offset and gain errors. The LMP8646 output accuracy has the following equations:

Output Accuracy =

$$\left| \frac{V_{OUT\_THEO} - V_{OUT\_CAL}}{V_{OUT\_THEO}} \right| \times 100(\%)$$

where  $V_{OUT\_THEO} = (V_{SENSE}) \times \frac{R_G}{1/Gm}$

and  $V_{OUT\_CALC} = \frac{(V_{SENSE} + V_{OFFSET}) \times R_G}{1/[Gm (1 + Gm\_Accuracy)]}$

Output Accuracy Equations (7)

For example, assume  $V_{SENSE} = 100 \text{ mV}$ ,  $R_G = 10 \text{ kOhm}$ , and it is known that  $V_{OFFSET} = 1 \text{ mV}$  and  $Gm\_Accuracy = 2\%$  (Electrical Characteristics Table), then the output accuracy can be calculated as:

$$V_{OUT\_THEO} = (100 \text{ mV}) \times \frac{10 \text{ k}\Omega}{1/(200\mu)} = 0.2 \text{V}$$

$$V_{OUT\_CALC} = \frac{(100 \text{ mV} + 1 \text{ mV}) \times 10 \text{ k}\Omega}{1/[200\mu (1 + 2/100)]} = 0.20604 \text{V}$$

$$Output \text{ Accuracy} = \left| \frac{0.2 \text{V} - 0.20604 \text{V}}{0.2 \text{V}} \right| \times 100 = 3.02\%$$

$$Output \text{ Accuracy Example} \tag{8}$$

In fact, as  $V_{\text{SENSE}}$  decreases, the output accuracy worsens as seen in Figure 27. These equations provide a valuable tool to estimate how the LMP8646 affects the overall system performance. Knowing this information allows the system designer to pick the appropriate external resistances ( $R_{\text{SENSE}}$  and  $R_{\text{G}}$ ) to adjust for the tolerable system error. Examples of this tolerable system error can be seen in the next sections.

Figure 27. Output Accuracy vs. V<sub>SENSE</sub>

# 7.4.2 Selection of the Sense Resistor, R<sub>SENSE</sub>

The accuracy of the current measurement also depends on the value of the shunt resistor  $R_{\text{SENSE}}$ . Its value depends on the application and is a compromise between small-signal accuracy and maximum permissible voltage loss in the load line.

$R_{SENSE}$  is directly proportional to  $V_{SENSE}$  through the equation  $R_{SENSE} = (V_{SENSE}) / (I_{SENSE})$ . If  $V_{SENSE}$  is small, then there is a smaller voltage loss in the load line, but the output accuracy is worse because the LMP8646 offset error will contribute more. Therefore, high values of  $R_{SENSE}$  provide better output accuracy by minimizing the effects of offset, while low values of  $R_{SENSE}$  minimize the voltage loss in the load line. For most applications, best performance is obtained with an  $R_{SENSE}$  value that provides a  $V_{SENSE}$  of 100 mV to 200 mV.

# **Device Functional Modes (continued)**

# 7.4.2.1 R<sub>SENSE</sub> Consideration for System Error

The output accuracy described in the previous section talks about the error contributed just by the LMP8646. The system error, however, consists of the errors contributed by the LMP8646 as well as other external resistors such as  $R_{SENSE}$  and  $R_{G}$ . Let's rewrite the output accuracy equation for the system error assuming that  $R_{SENSE}$  is non-ideal and  $R_{G}$  is ideal. This equation can be seen as:

$$System \ Error = \left| \frac{V_{OUT\_THEO} - V_{OUT\_CAL}}{V_{OUT\_THEO}} \right| \times 100(\%)$$

$$where \ V_{OUT\_THEO} = (R_{SENSE} \times I_{SENSE}) \times \frac{R_G}{1/Gm}$$

$$and \ V_{OUT\_CALC} = \frac{[R_{SENSE} (1 + Tolerance) \times I_{SENSE} + V_{OFFSET}] \times R_G}{1/[Gm \ (1 + Gm\_Accuracy)]}$$

$$System \ Error \ Example \ Assuming \ R_{SENSE} \ is \ Non-ideal \ and \ R_G \ is \ Ideal$$

$$(9)$$

Continuing from the previous output accuracy example, we can calculate for the system error assuming that  $R_{SENSE} = 100$  mOhm (with 1% tolerance),  $I_{SENSE} = 1$ A, and  $R_{G} = 10$  kOhm. From the Electrical Characteristics Table, it is also known that  $V_{OFFSET} = 1$  mV and  $Gm_{Accuracy} = 2$ %.

$$V_{OUT\_THEO} = (100 \text{ m}\Omega \text{ x 1A}) \text{ x } \frac{10 \text{ k}\Omega}{1/(200\mu)} = 0.2 \text{V}$$

$$V_{OUT\_CALC} = \frac{[100 \text{ m}\Omega (1+1/100) \text{ x 1A} + 1 \text{mV}] \text{ x 10 k}\Omega}{1/[200\mu (1+2/100)]} = 0.20808 \text{V}$$

$$System \ \text{Error} = \left| \frac{0.2 \text{V} \cdot 0.20808 \text{V}}{0.2 \text{V}} \right| \text{ x 100} = 4.04\%$$

$$System \ \text{Error} \ \text{Example Assuming RSENSE is Non-ideal and RG is Ideal}$$

Because an  $R_{SENSE}$  tolerance will increase the system error, we recommend selecting an  $R_{SENSE}$  resistor with low tolerance.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LMP8646 can be driven by many different regulators with a feedback pin and connected to many different types of loads such as capacititve and resistive. The following sections gives three typical applications of the LMP8646.

# 8.2 Typical Applications

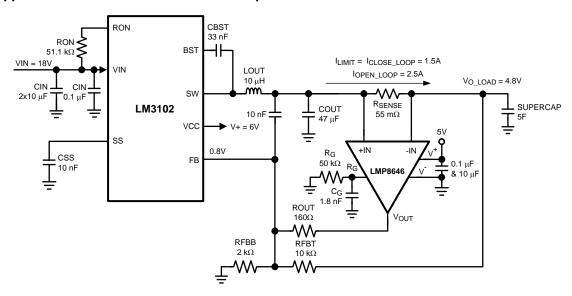

#### 8.2.1 Application #1: Current Limiter With a Capacitive Load

Figure 28. SuperCap Application With LM3102 Regulator

#### 8.2.1.1 Design Requirements

A supercap application requires a very high capacitive load to be charged. This example assumes the output capacitor is 5F with a limited sense current at 1.5A. The LM3102 will provide the current to charge the supercap, and the LMP8646 will monitor this current to make sure it does not exceed the desired 1.5A value.

#### 8.2.1.2 Detailed Design Procedure

To limit the capacitor current, first connect the LMP8646 output to the feedback pin of the LM3102, as shown in Figure 28. This feedback voltage at the FB pin is compared to a 0.8V internal reference. Any voltage above this 0.8V means the output current is above the desired value of 1.5A, and the LM3102 will reduce its output current to maintain the desired 0.8V at the FB pin.

The following steps show the design procedures for this supercap application. In summary, the steps consist of selecting the components for the voltage regulator, integrating the LMP8646 and selecting the proper values for its gain, bandwidth, and output resistor, and adjusting these components to yield the desired performance.

#### Step 1: Choose the components for the Regulator.

Refer to the LM3102 evaluation board application note (AN-1646) to select the appropriate components for the LM3102 voltage regulator.

# Step 2: Choose the sense resistor, R<sub>SENSE</sub>

R<sub>SENSE</sub> sets the voltage V<sub>SENSE</sub> between +IN and -IN and has the following equation:

$$R_{SENSE} = V_{OUT} / \left[ (I_{LIMIT}) * (R_G / 5kOhm) \right]$$

(11)

In general, R<sub>SENSE</sub> depends on the output voltage, limit current, and gain. Refer to section *Selection of the Sense Resistor*, R<sub>SENSE</sub> to choose the appropriate R<sub>SENSE</sub> value; this example uses 55 mOhm.

#### Step 3: Choose the gain resistor, R<sub>G</sub>, for LMP8646

$R_G$  is chosen from the limited sense current. As stated,  $V_{OUT}$  = ( $R_{SENSE}$  \*  $I_{LIMIT}$ ) \* ( $R_G$  / 5kOhm). Since  $V_{OUT}$  =  $V_{FB}$  = 0.8V, the limited sense current is 1.5A, and  $R_{SENSE}$  is 55 mOhm,  $R_G$  can be calculated as:

$$R_{G} = (V_{OUT} * 5 \text{ kOhm}) / (R_{SENSE} * I_{LIMIT})$$

$$(12)$$

$$R_G = (0.8 * 5 \text{ kOhm}) / (55 \text{ mOhm} * 1.5\text{A}) = 50 \text{ kOhm (approximate)}$$

(13)

# Step 4: Choose the Bandwidth Capacitance, C<sub>G</sub>.

The product of  $C_G$  and  $R_G$  determines the bandwidth for the LMP8646. Refer to the Typical Performance Characteristics plots to see the range for the LMP8646 bandwidth and gain. Since each application is very unique, the LMP8646 bandwidth capacitance,  $C_G$ , needs to be adjusted to fit the appropriate application.

Bench data has been collected for the supercap application with the LM3102 regulator, and we found that this application works best for a bandwidth of 500 Hz to 3 kHz. Operating outside of this recommended bandwidth range might create an undesirable load current ringing. We recommend choosing a bandwidth that is in the middle of this range and using the equation  $C_G = 1/(2*pi*R_G*Bandwidth)$  to find  $C_G$ . For example, if the bandwidth is 1.75 kHz and  $R_G$  is 50 kOhm, then  $C_G$  is approximately 1.8 nF. After this selection, capture the plot for  $I_{LIMIT}$  and adjust  $C_G$  until a desired load current plot is obtained.

#### Step 5: Calculate the Output Accuracy and Tolerable System Error

Since the LMP8646 is a precision current limiter, the output current accuracy is extremely important. This accuracy is affected by the system error contributed by the LMP8646 device error and other errors contributed by external resistances, such as  $R_{\text{SENSE}}$  and  $R_{\text{G}}$ .

In this application,  $V_{SENSE} = I_{LIMIT} * R_{SENSE} = 1.5A * 55$  mOhm = 0.0825V, and  $R_G = 50$  kOhm. From the Electrical Characteristics Table, it is known that  $V_{OFFSET} = 1$  mV and Gm\_Accuracy = 2%. Using the equations shown in Equation 8, the output accuracy can be calculated as 3.24%.

After figuring out the LMP8646 output accuracy, choose a tolerable system error or the output current accuracy that is bigger than the LMP8646 output accuracy. This tolerable system error will be labeled as  $I_{ERROR}$ , and it has the equation  $I_{ERROR} = (I_{MAX} - I_{LIMIT})/I_{MAX}$  (%). In this example, we will choose an  $I_{ERROR}$  of 5%, which will be used to calculate for ROUT shown in the next step.

#### Step 6: Choose the output resistor, ROUT

At start-up, the capacitor is not charged yet and thus the output voltage of the LM3102 is very small. Therefore, at start-up, the output current is at its maximum ( $I_{MAX}$ ). When the output voltage is at its nominal, then the output current will settle to the desired limited value. Because a large current error is not desired, ROUT needs to be chosen to stabilize the loop with minimal initial start-up current error. Follow the equations and example below to choose the appropriate value for ROUT to minimize this initial error.

As discussed in step 4, the allowable  $I_{ERROR}$  is 5%, where  $I_{ERROR} = (I_{MAX} - I_{LIMIT})/I_{MAX}$  (%). Therefore, the maximum allowable current is calculated as:  $I_{MAX} = I_{LIMIT}$  (1+  $I_{ERROR}$ ) = 1.5A \* (1 + 5/100) = 1.575 A.

Next, use Equation 14 below to calculate for ROUT:

$$ROUT = \underbrace{\frac{(I_{MAX} * R_{SENSE} * Gain - V_{FB})}{V_{FB}}}_{RFBB} - \underbrace{\frac{(V_{O\_REG\_MIN} - V_{FB})}{RFBT}}$$

(14)

For example, assume the minimum LM3102 output voltage,  $V_{O\_REG\_MIN}$ , is 0.6V, then ROUT can be calculated as ROUT = [1.575A \* 55 mOhm \* (49.9k / 5k) - 0.8] / [ (0.8 / 2k) - (0.6 - 0.8) / 10k] = 153.6 Ohm.

Populate ROUT with a resistor that is as close as possible to 153.6 Ohm (this application uses 160 Ohm). If the limited sense current has a gain error and is not 1.5A at any point in time, then adjust this ROUT value to obtain the desired limit current.

We recommend that the value for ROUT is at least 50 Ohm.

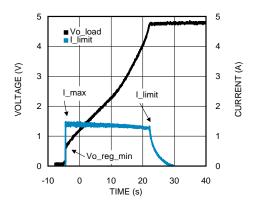

#### Step 7: Adjusting Components

Capture the output current and output voltage plots and adjust the components as necessary. The most common components to adjust are  $C_G$  to decrease the current ripple and ROUT to get a low current error. An example output current and voltage plot can be seen in Figure 29.

## 8.2.1.3 Application Curve

Figure 29. SuperCap Application With LM3102 Regulator Plot

# 8.2.2 Application #2: Current Limiter With a Resistive Load

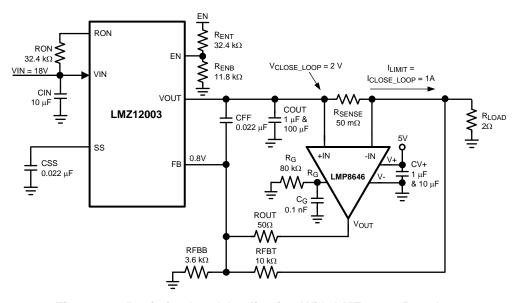

Figure 30. Resistive Load Application With LMZ12003 Regulator

#### 8.2.2.1 Design Requirements

This subsection describes the design process for a resistive load application with the LMZ12003 voltage regulator as seen in Figure 30. To see the current limiting capability of the LMP8646, the open-loop current must be greater than the close-loop current. An open-loop occurs when the LMP8646 output is not connected the LMZ12003's feedback pin. For this example, we will let the open-loop current to be 1.5A and the close-loop current, I<sub>LIMIT</sub>, to be 1A.

#### 8.2.2.2 Detailed Design Procedure

#### Step 1: Choose the components for the Regulator.

Refer to the LMZ12003 application note (AN-2031) to select the appropriate components for the LMZ12003.

# Step 2: Choose the sense resistor, R<sub>SENSE</sub>

R<sub>SENSE</sub> sets the voltage V<sub>SENSE</sub> between +IN and -IN and has the following equation:

$$R_{SENSE} = V_{OUT} / [(I_{LIMIT}) * (R_G / 5kOhm)]$$

(15)

In general,  $R_{SENSE}$  depends on the output voltage, limit current, and gain. Refer to section *Selection of the Sense Resistor*,  $R_{SENSE}$  to choose the appropriate  $R_{SENSE}$  value; this example uses 50 mOhm.

# Step 3: Choose the gain resistor, R<sub>G</sub>, for LMP8646

$R_G$  is chosen from  $I_{LIMIT}$ . As stated,  $V_{OUT}$  = ( $R_{SENSE}$  \*  $I_{LIMIT}$ ) \* ( $R_G$  / 5kOhm). Since  $V_{OUT}$  =  $V_{FB}$  = 0.8V,  $I_{LIMIT}$  = 1A, and  $R_{SENSE}$  = 50 mOhm ,  $R_G$  can be calculated as:

$$R_{G} = (V_{OUT} * 5 \text{ kOhm}) / (R_{SENSE} * I_{LIMIT})$$

$$(16)$$

$$R_G = (0.8 * 5 \text{ kOhm}) / (50 \text{ mOhm} * 1A) = 80 \text{ kOhm}$$

(17)

# Step 4: Choose the Bandwidth Capacitance, C<sub>G</sub>.

The product of  $C_G$  and  $R_G$  determines the bandwidth for the LMP8646. Refer to the Typical Performance Characteristics plots to see the range for the LMP8646 bandwidth and gain. Since each application is very unique, the LMP8646 bandwidth capacitance,  $C_G$ , needs to be adjusted to fit the appropriate application.

Bench data has been collected for this resistive load application with the LMZ12003 regulator, and we found that this application works best for a bandwidth of 2 kHz to 30 kHz. Operating anything less than this recommended bandwidth might prevent the LMP8646 from quickly limiting the current. We recommend choosing a bandwidth that is in the middle of this range and using the equation:  $C_G = 1/(2*pi*R_G*Bandwidth)$  to find  $C_G$  (this example uses a  $C_G$  value of 0.1nF). After this selection, capture the load current plot and adjust  $C_G$  until a desired output current plot is obtained.

#### Step 5: Choose the output resistor, ROUT, for the LMP8646

ROUT plays a very small role in the overall system performance for the resistive load application. ROUT was important in the supercap application because it affects the initial current error. Because current is directly proportional to voltage for a resistive load, the output current is not large at start-up. The bigger the ROUT, the longer it takes for the output voltage to reach its final value. We recommend that the value for ROUT is at least 50 Ohm, which is the chosen value for this example.

#### **Step 6: Adjusting Components**

Capture the output current and output voltage plots and adjust the components as necessary. The most common component to adjust is  $C_G$  for the bandwidth. An example of the output current and voltage plot can be seen in Figure 31.

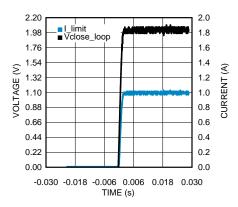

#### 8.2.2.3 Application Curve

Figure 31. Plot for the Resistive Load Application With LMZ12003 Regulator Plot

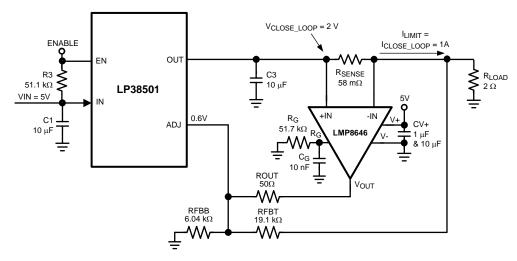

# 8.2.3 Application #3: Current Limiter With a Low-Dropout Regulator and Resistive Load

Figure 32. Resistive Load Application With LP38501 Regulator

## 8.2.3.1 Design Requirements

This next example is the same as the last example, except that the regulator is now a low-dropout regulator, the LP38501, as seen in Figure 32. For this example, we will let the open-loop current to be 1.25A and the close-loop current, I<sub>LIMIT</sub>, to be 1A.

#### 8.2.3.2 Detailed Design Procedure

#### Step 1: Choose the components for the Regulator.

Refer to the LP38501 application note (AN-1830) to select the appropriate components for the LP38501.

# Step 2: Choose the sense resistor, R<sub>SENSE</sub>

$R_{\text{SENSE}}$  sets the voltage  $V_{\text{SENSE}}$  between +IN and -IN and has the following equation:

$$R_{SENSE} = V_{OUT} / [(I_{LIMIT}) * (R_G / 5kOhm)]$$

(18)

In general,  $R_{SENSE}$  depends on the output voltage, limit current, and gain. Refer to section *Selection of the Sense Resistor*,  $R_{SENSE}$  to choose the appropriate  $R_{SENSE}$  value; this example uses 58 mOhm.

#### Step 3: Choose the gain resistor, R<sub>G</sub>, for LMP8646

$R_G$  is chosen from  $I_{LIMIT}$ . As stated,  $V_{OUT} = (R_{SENSE} * I_{LIMIT}) * (R_G / 5kOhm)$ . Since  $V_{OUT} = ADJ = 0.6V$ ,  $I_{LIMIT} = 1A$ , and  $R_{SENSE} = 58$  mOhm ,  $R_G$  can be calculated as:

$$R_{G} = (V_{OUT} * 5 \text{ kOhm}) / (R_{SENSE} * I_{LIMIT})$$

$$(19)$$

$$R_G = (0.6 * 5 \text{ kOhm}) / (58 \text{ mOhm} * 1A) = 51.7 \text{ kOhm}$$

(20)

#### Step 4: Choose the Bandwidth Capacitance, C<sub>G</sub>.

The product of  $C_G$  and  $R_G$  determines the bandwidth for the LMP8646. Refer to the Typical Performance Characteristics plots to see the range for the LMP8646 bandwidth and gain. Since each application is very unique, the LMP8646 bandwidth capacitance,  $C_G$ , needs to be adjusted to fit the appropriate application.

Bench data has been collected for this resistive load application with the LP38501 regulator, and we found that this application works best for a bandwidth of 50 Hz to 300 Hz. Operating anything larger than this recommended bandwidth might prevent the LMP8646 from quickly limiting the current. We recommend choosing a bandwidth that is in the middle of this range and using the equation:  $C_G = 1/(2*pi*R_G*Bandwidth)$  to find  $C_G$  (this example uses a  $C_G$  value of 10 nF). After this selection, capture the plot for  $I_{SENSE}$  and adjust  $C_G$  until a desired sense current plot is obtained.

#### Step 5: Choose the output resistor, ROUT, for the LMP8646

ROUT plays a very small role in the overall system performance for the resistive load application. ROUT was important in the supercap application because it affects the initial current error. Because current is directly proportional to voltage for a resistive load, the output current is not large at start-up. The bigger the ROUT, the longer it takes for the output voltage to reach its final value. We recommend that the value for ROUT is at least 50 Ohm, which is the value we used for this example.

### **Step 6: Adjusting Components**

Capture the output current and output voltage plots and adjust the components as necessary. The most common component to adjust is  $C_G$  for the bandwidth. An example plot of the output current and voltage can be seen in Figure 33.

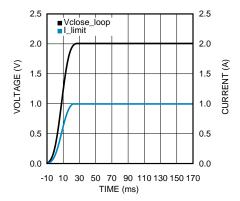

#### 8.2.3.3 Application Curve

Figure 33. Plot for the Resistive Load Application With the LP38501 LDO Regulator

# 9 Power Supply Recommendations

Source V+ with an external voltage as recommended in the electrical characteristics table. It is recommended to place a 100nF ceramic bypass capacitor to ground as close to possible to the V+ pin. In addition, an electrolytic or tantalum capacitor of  $10\mu F$  is recommended. The bulk capacitor does not need to be in close vicinity with the LMP8646 and could be close to the voltage source terminals or at the output of the voltage regulator powering the LMP8646.

# 10 Layout

#### 10.1 Layout Guidelines

- In a 4-layer board design, the recommended layer stack order from top to bottom is: signal, power, ground, and signal

- Bypass capacitors should be placed in close proximity to the V+ pin

- The trace for pins +IN and -IN should be big enough to handle the current running through it.

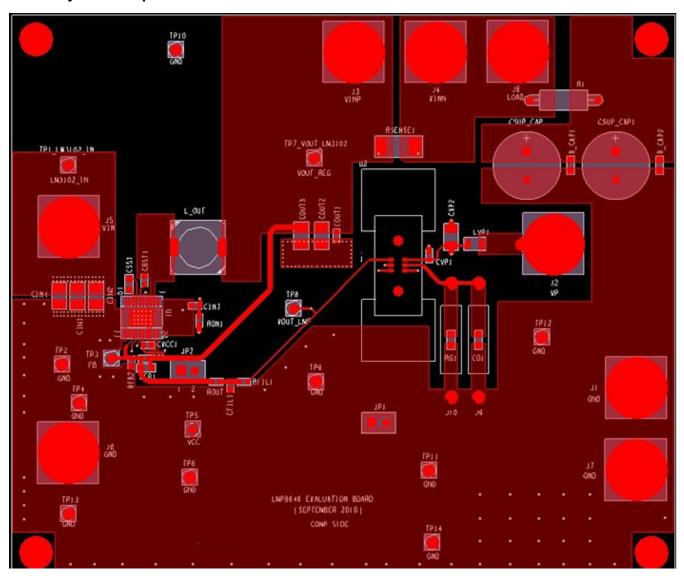

# 10.2 Layout Example

Figure 34. LMP8646 Evaluation Board Layout

Product Folder Links: LMP8646

Submit Documentation Feedback

# 11 Device and Documentation Support

#### 11.1 Trademarks

All trademarks are the property of their respective owners.

#### 11.2 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 11.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: LMP8646

Copyright © 2012-2014, Texas Instruments Incorporated

www.ti.com

14-Jul-2025

#### **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins            | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|---------------------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       |        |               |                           |                       |      | (4)                           | (5)                        |              |              |

| LMP8646MK/NOPB        | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 1000   SMALL T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MK/NOPB.A      | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 1000   SMALL T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MK/NOPB.B      | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 1000   SMALL T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKE/NOPB       | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKE/NOPB.A     | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKE/NOPB.B     | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKX/G4         | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKX/G4.A       | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKX/G4.B       | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKX/NOPB       | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKX/NOPB.A     | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

| LMP8646MKX/NOPB.B     | Active | Production    | SOT-23-<br>THIN (DDC)   6 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | AK7A         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

# PACKAGE OPTION ADDENDUM

www.ti.com 14-Jul-2025

(4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

(5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

(6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

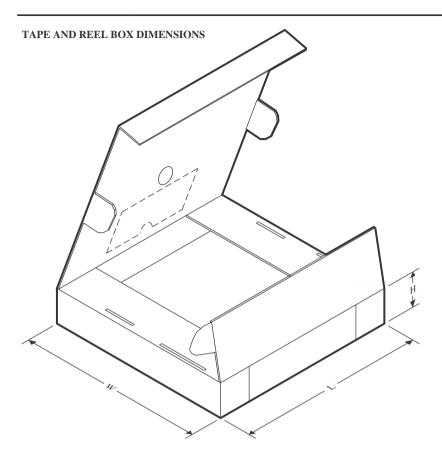

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 15-Jul-2025

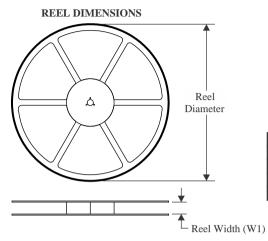

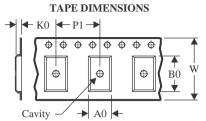

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

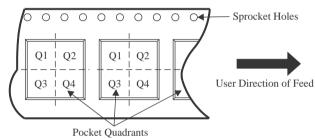

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMP8646MK/NOPB  | SOT-23-<br>THIN | DDC                | 6 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMP8646MKE/NOPB | SOT-23-<br>THIN | DDC                | 6 | 250  | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMP8646MKX/G4   | SOT-23-<br>THIN | DDC                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMP8646MKX/NOPB | SOT-23-<br>THIN | DDC                | 6 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

www.ti.com 15-Jul-2025

## \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMP8646MK/NOPB  | SOT-23-THIN  | DDC             | 6    | 1000 | 208.0       | 191.0      | 35.0        |

| LMP8646MKE/NOPB | SOT-23-THIN  | DDC             | 6    | 250  | 208.0       | 191.0      | 35.0        |

| LMP8646MKX/G4   | SOT-23-THIN  | DDC             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

| LMP8646MKX/NOPB | SOT-23-THIN  | DDC             | 6    | 3000 | 208.0       | 191.0      | 35.0        |

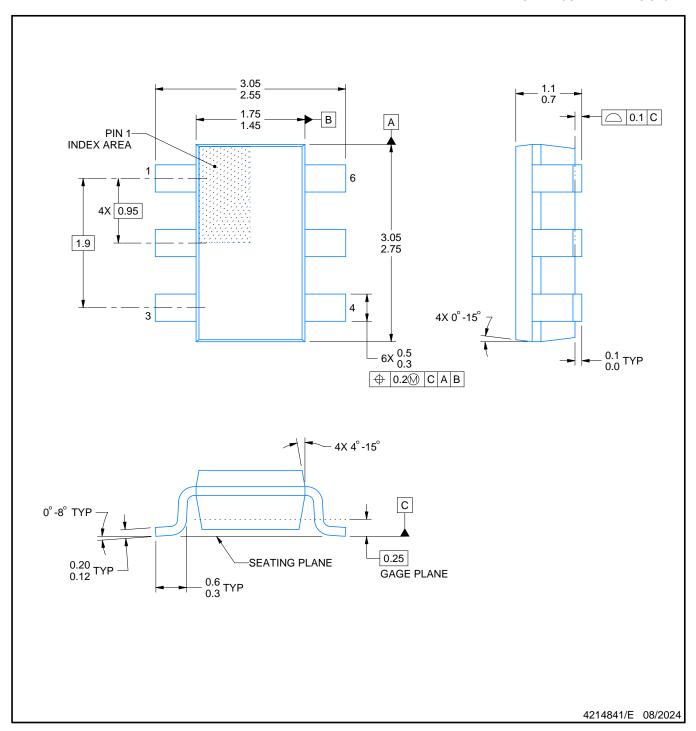

SMALL OUTLINE TRANSISTOR

# NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC MO-193.

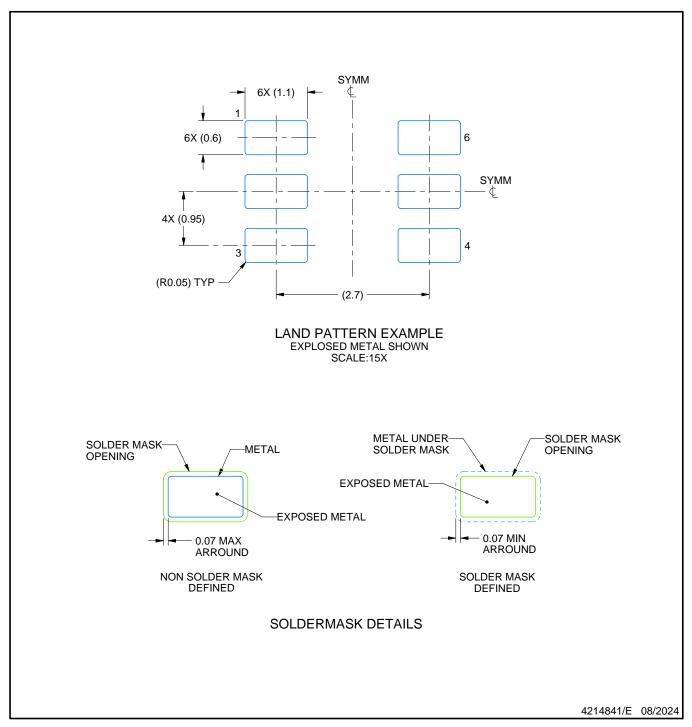

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 4. Publication IPC-7351 may have alternate designs.

- 5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

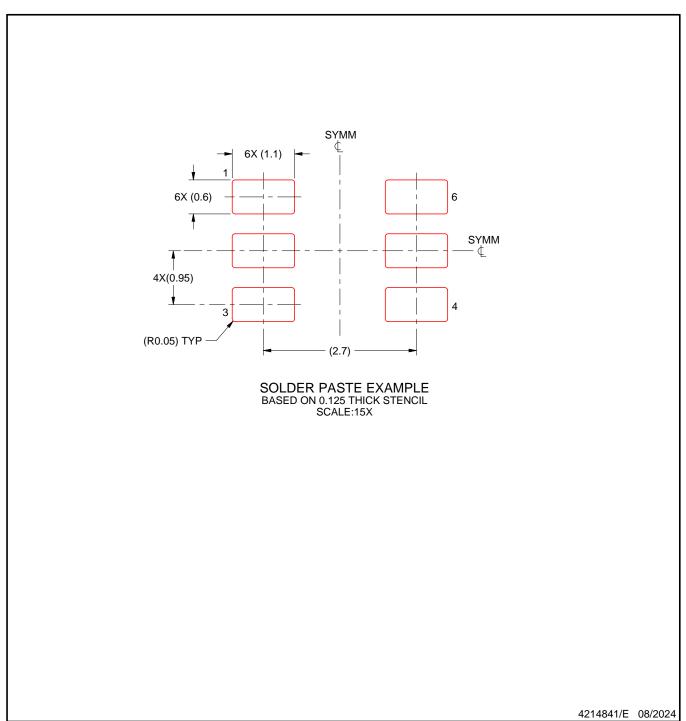

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated