# LMKDB11xx PCIe 第1世代～第7世代対応 超低ジッタ LP-HCSL クロックバッファ ファミリ

## 1 特長

- LP-HCSL クロック バッファおよびクロック マルチプレクサ(以下に対応):

- PCIe Gen 1～Gen 7

- CC(共通クロック) および IR(独立リファレンス) PCIe アーキテクチャ

- SSC あり/なしの入力クロック

- DB2000QL 準拠:

- すべてのデバイスが DB2000QL 仕様に適合

- LMKDB1120 は、DB2000QL とピン互換

- 非常に小さい追加ジッタ:

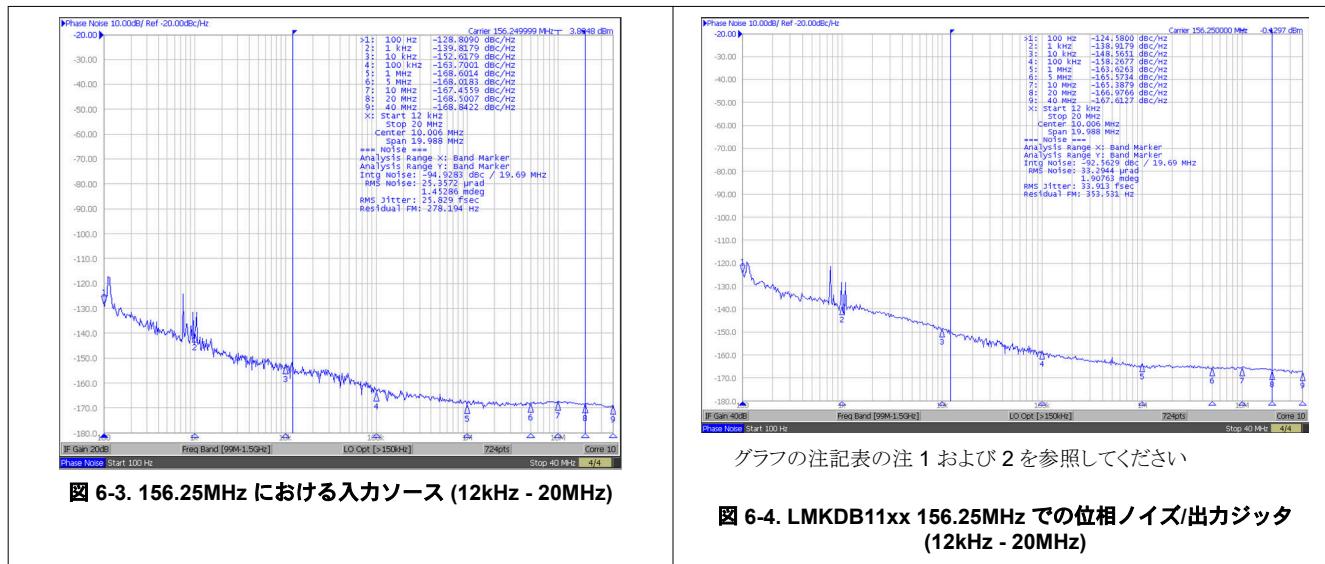

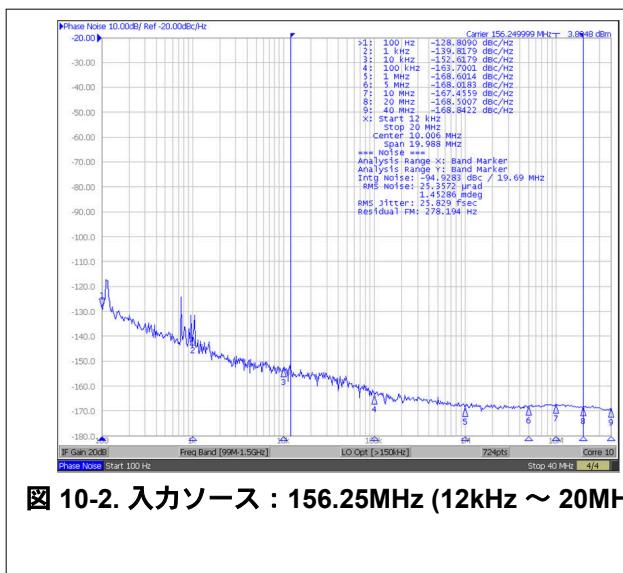

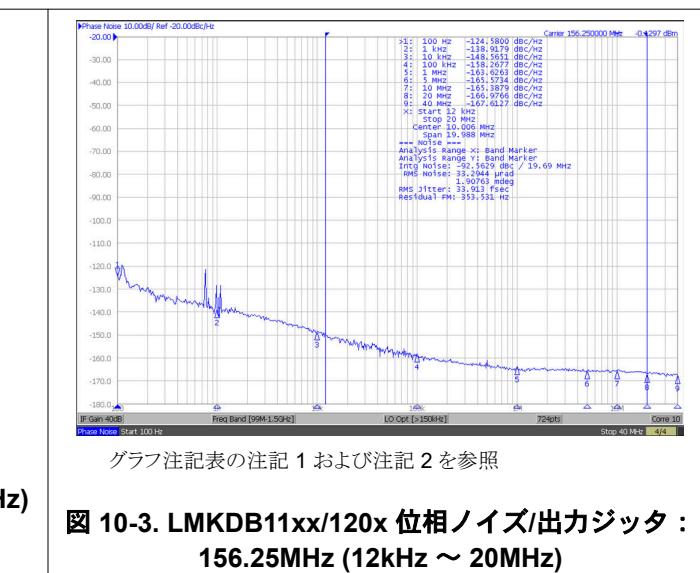

- 156.25MHz 時の 12kHz～20MHz に対する RMS 追加ジッタ: 31fs 以下

- PCIe Gen 4 の追加ジッタ: 13fs 以下

- PCIe Gen 5 の追加ジッタ: 5fs 以下

- PCIe Gen 6 の追加ジッタ: 3fs 以下

- PCIe Gen 7 の追加ジッタ: 2.1fs 以下

- フェイルセーフ入力

- フェイルセーフ出力 (LMKDB1120FS, LMKDB1108FS, LMKDB1104FS のみ)

- 柔軟な電源投入シーケンス

- 自動出力ディスエーブル

- 個別出力イネーブル

- SBI(サイドバンドインターフェイス)による高速出力のイネーブル/ディセーブル

- LOS(信号損失)入力検出

- 出力インピーダンス: 85Ω または 100Ω

- 電源: 1.8V/3.3V±10%

- 周囲温度範囲: -40°C～105°C

## 2 アプリケーション

- 高性能コンピューティング

- サーバー マザーボード

- NIC/SmartNIC

- ハードウェア アクセラレータ

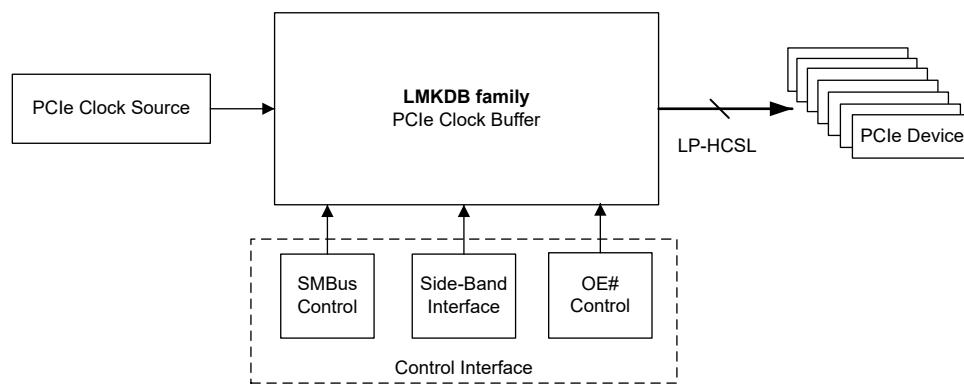

## 3 説明

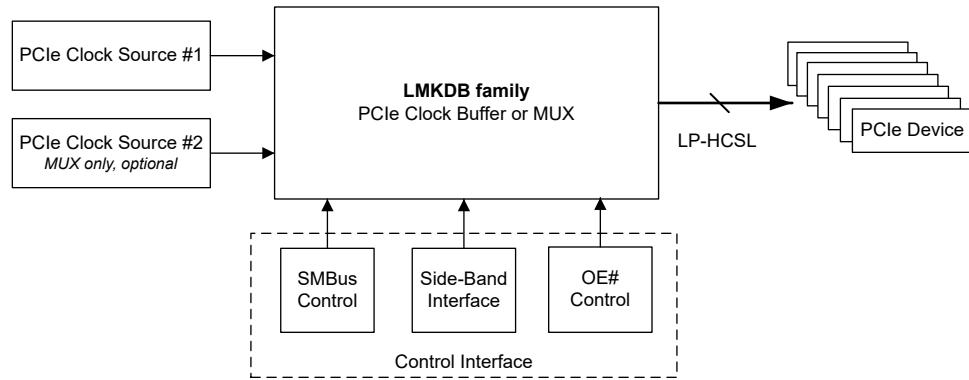

LMKDB デバイスは、PCIe Gen 1 から Gen 7 に対応し、DB2000QL に準拠した、極めて低ジッタの LP-HCSL バッファ ファミリです。このデバイスは、柔軟なパワーアップ シーケンス、フェイルセーフ入力、フェイルセーフ出力、各出力における個別の有効/無効ピン、入力信号ロス (LOS) 検出および自動出力無効化機能、さらに優れた電源ノイズ除去性能を備えています。

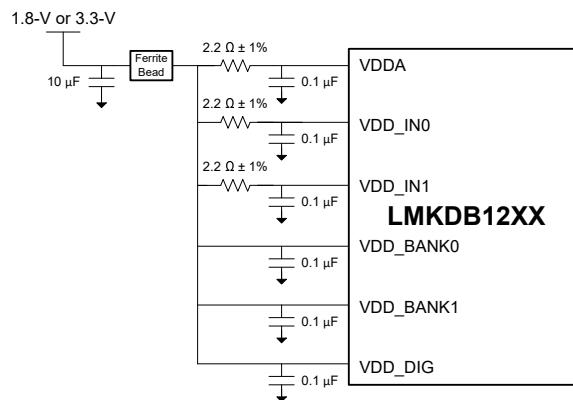

1.8V と 3.3V の両方の電源電圧に対応しています。LMKDB1120 の場合、1.8V 電源を使用すると、3.3V に比べて 250mW の電力を節減できます。

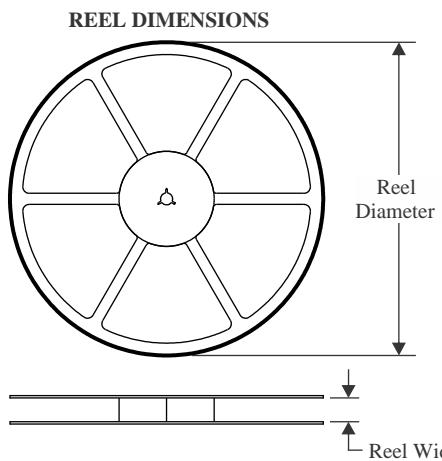

### パッケージ情報

| 部品番号                       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------------------------|----------------------|--------------------------|

| LMKDB1120 /<br>LMKDB1120FS | NPP (TLGA, 80)       | 6mm × 6mm                |

| LMKDB1108 /<br>LMKDB1108FS | RKP (VQFN, 40)       | 5mm × 5mm                |

| LMKDB1104 /<br>LMKDB1104FS | REX (VQFN, 28)       | 4mm × 4mm                |

| LMKDB1102                  | REY (VQFN, 20)       | 3mm × 3mm                |

(1) 供給されているすべてのパッケージについては、[セクション 13](#) を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンを含みます。

## 目次

|                    |    |                                    |    |

|--------------------|----|------------------------------------|----|

| 1 特長               | 1  | 8.4 デバイスの機能モード                     | 35 |

| 2 アプリケーション         | 1  | 9 レジスタ マップ                         | 39 |

| 3 説明               | 1  | 9.1 LMKDB1120 および LMKDB1120FS レジスタ | 39 |

| 4 デバイスの比較          | 3  | 9.2 LMKDB1108 および LMKDB1108FS レジスタ | 51 |

| 5 ピン構成および機能        | 4  | 9.3 LMKDB1104 および LMKDB1104FS レジスタ | 61 |

| 6 仕様               | 16 | 10 アプリケーションと実装                     | 70 |

| 6.1 絶対最大定格         | 16 | 10.1 アプリケーション情報                    | 70 |

| 6.2 ESD 定格         | 16 | 10.2 代表的なアプリケーション                  | 70 |

| 6.3 推奨動作条件         | 16 | 10.3 電源に関する推奨事項                    | 72 |

| 6.4 熱情報            | 16 | 10.4 レイアウト                         | 73 |

| 6.5 電気的特性          | 17 | 11 デバイスおよびドキュメントのサポート              | 75 |

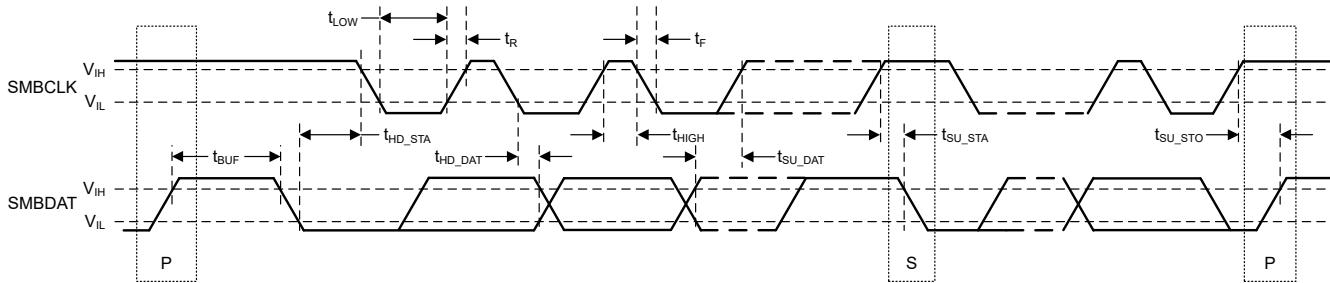

| 6.6 SMBus のタイミング要件 | 25 | 11.1 ドキュメントのサポート                   | 75 |

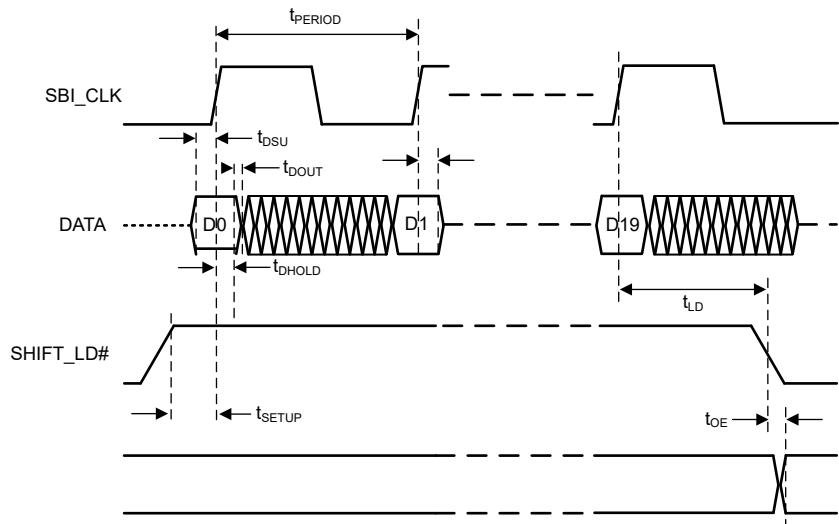

| 6.7 SBI のタイミング要件   | 25 | 11.2 ドキュメントの更新通知を受け取る方法            | 75 |

| 6.8 タイミング図         | 26 | 11.3 サポート・リソース                     | 75 |

| 6.9 代表的特性          | 27 | 11.4 商標                            | 75 |

| 7 パラメータ測定情報        | 27 | 11.5 静電気放電に関する注意事項                 | 75 |

| 8 詳細説明             | 29 | 11.6 用語集                           | 75 |

| 8.1 概要             | 29 | 12 改訂履歴                            | 75 |

| 8.2 機能ブロック図        | 29 | 13 メカニカル、パッケージ、および注文情報             | 77 |

| 8.3 機能説明           | 30 |                                    |    |

## 4 デバイスの比較

**表 4-1. デバイスの比較**

| 部品番号                         | タイプ     | 入力 | 出力 | 出力インピーダンス          | 特長              |

|------------------------------|---------|----|----|--------------------|-----------------|

| LMKDB1120Z85                 | バッファ    | 1  | 20 | 85 Ω               | すべての入力フェイルセーフ   |

| LMKDB1120FS85                | バッファ    | 1  | 20 | 85 Ω               | すべての入出力はフェイルセーフ |

| LMKDB1120Z100                | バッファ    | 1  | 20 | 100 Ω              | すべての入力フェイルセーフ   |

| LMKDB1116Z85 <sup>(1)</sup>  | バッファ    | 1  | 16 | 85 Ω               | すべての入力フェイルセーフ   |

| LMKDB1116Z100 <sup>(1)</sup> | バッファ    | 1  | 16 | 100 Ω              | すべての入力フェイルセーフ   |

| LMKDB1113Z85 <sup>(1)</sup>  | バッファ    | 1  | 13 | 85 Ω               | すべての入力フェイルセーフ   |

| LMKDB1113Z100 <sup>(1)</sup> | バッファ    | 1  | 13 | 100 Ω              | すべての入力フェイルセーフ   |

| LMKDB1112Z85 <sup>(1)</sup>  | バッファ    | 1  | 12 | 85 Ω               | すべての入力フェイルセーフ   |

| LMKDB1112Z100 <sup>(1)</sup> | バッファ    | 1  | 12 | 100 Ω              | すべての入力フェイルセーフ   |

| LMKDB1108Z85                 | バッファ    | 1  | 8  | 85 Ω               | すべての入力フェイルセーフ   |

| LMKDB1108FS85                | バッファ    | 1  | 8  | 85 Ω               | すべての入出力はフェイルセーフ |

| LMKDB1108Z100                | バッファ    | 1  | 8  | 100 Ω              | すべての入力フェイルセーフ   |

| LMKDB1104Z85                 | バッファ    | 1  | 4  | 85 Ω               | すべての入力フェイルセーフ   |

| LMKDB1104FS85                | バッファ    | 1  | 4  | 85 Ω               | すべての入出力はフェイルセーフ |

| LMKDB1104Z100                | バッファ    | 1  | 4  | 100 Ω              | すべての入力フェイルセーフ   |

| LMKDB1102                    | バッファ    | 1  | 2  | 85Ω または 100Ω を選択可能 | すべての入力フェイルセーフ   |

| LMKDB1216 <sup>(1)</sup>     | マルチブレクサ | 2  | 16 | 85Ω または 100Ω を選択可能 | すべての入力フェイルセーフ   |

| LMKDB1208 <sup>(1)</sup>     | マルチブレクサ | 2  | 8  | 85Ω または 100Ω を選択可能 | すべての入力フェイルセーフ   |

| LMKDB1204                    | マルチブレクサ | 2  | 4  | 85Ω または 100Ω を選択可能 | すべての入力フェイルセーフ   |

| LMKDB1202                    | マルチブレクサ | 2  | 2  | 85Ω または 100Ω を選択可能 | すべての入力フェイルセーフ   |

(1) プレビュー版のみ。詳細についてはテキサス・インスツルメンツまでお問い合わせください。

## 5 ピン構成および機能

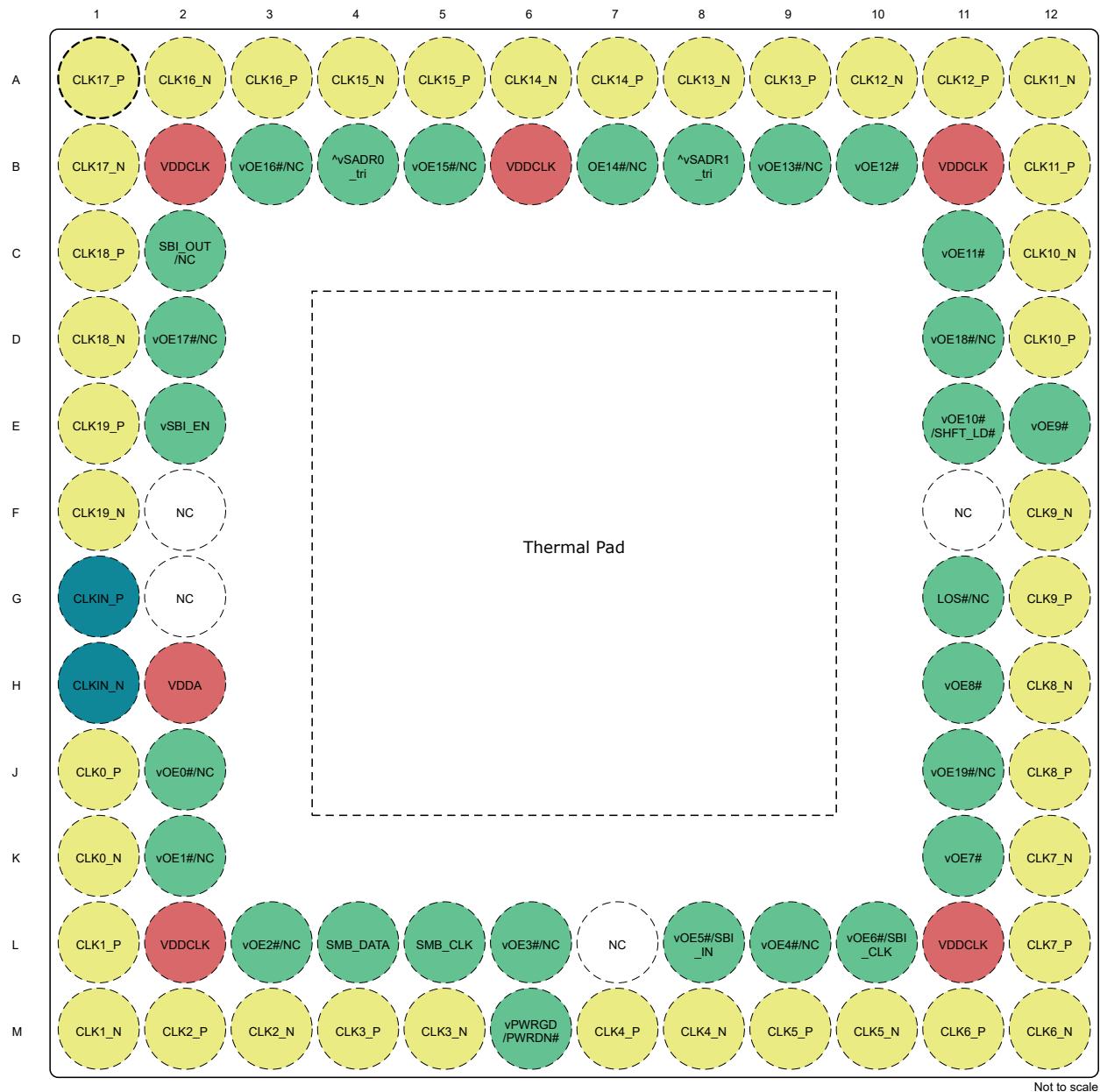

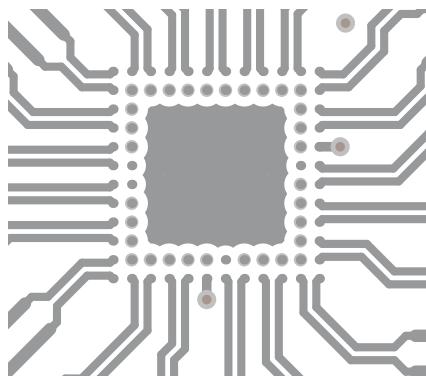

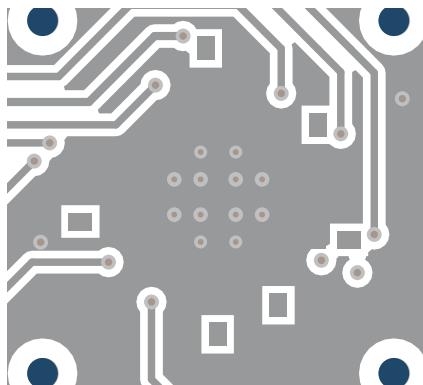

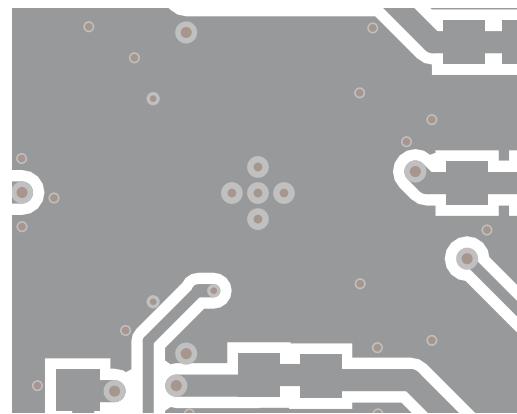

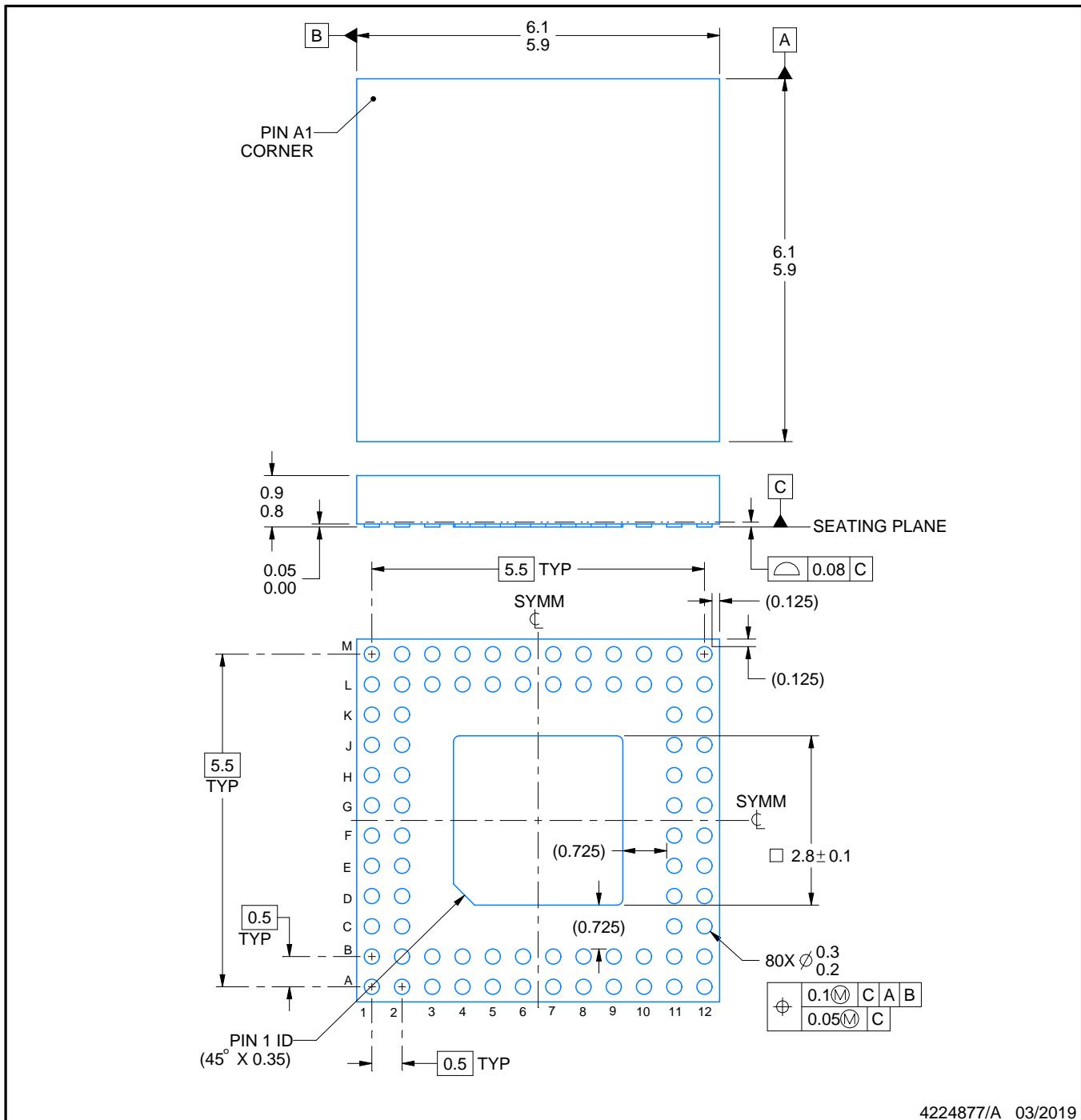

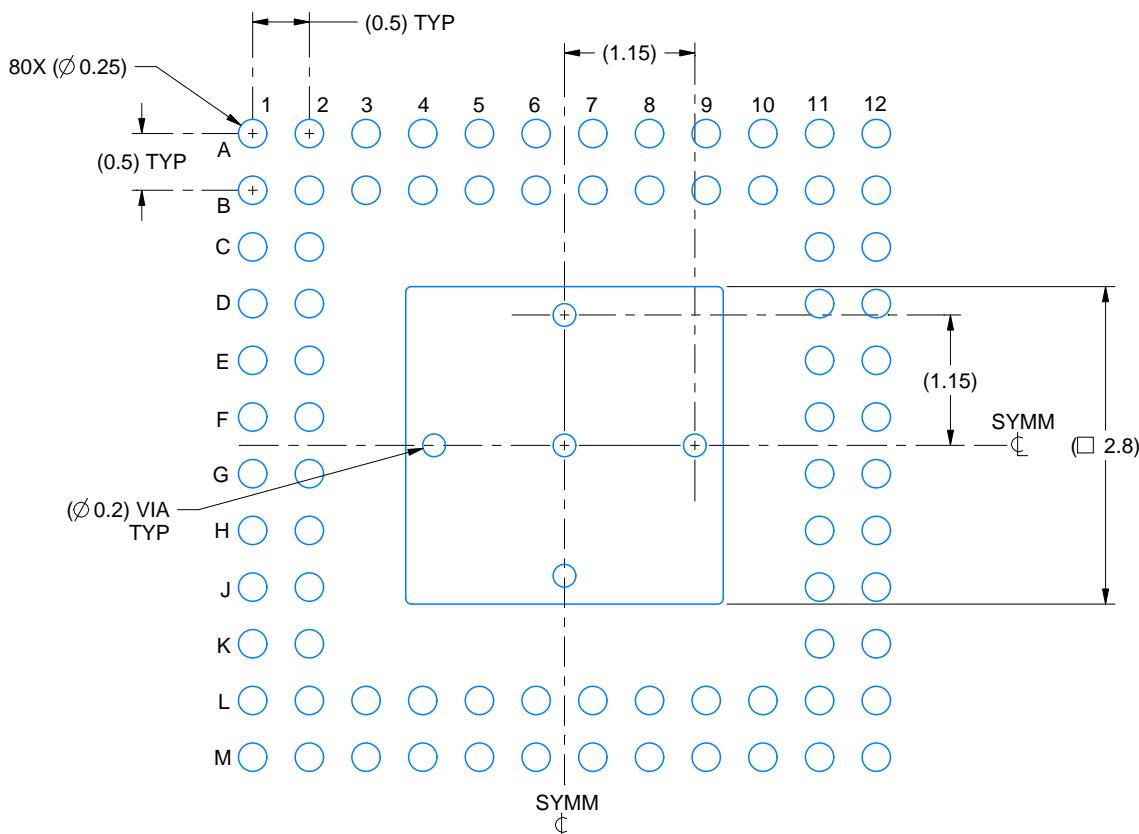

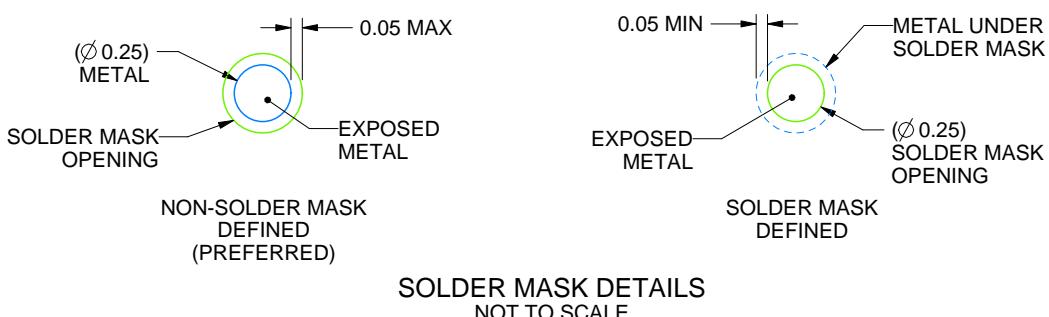

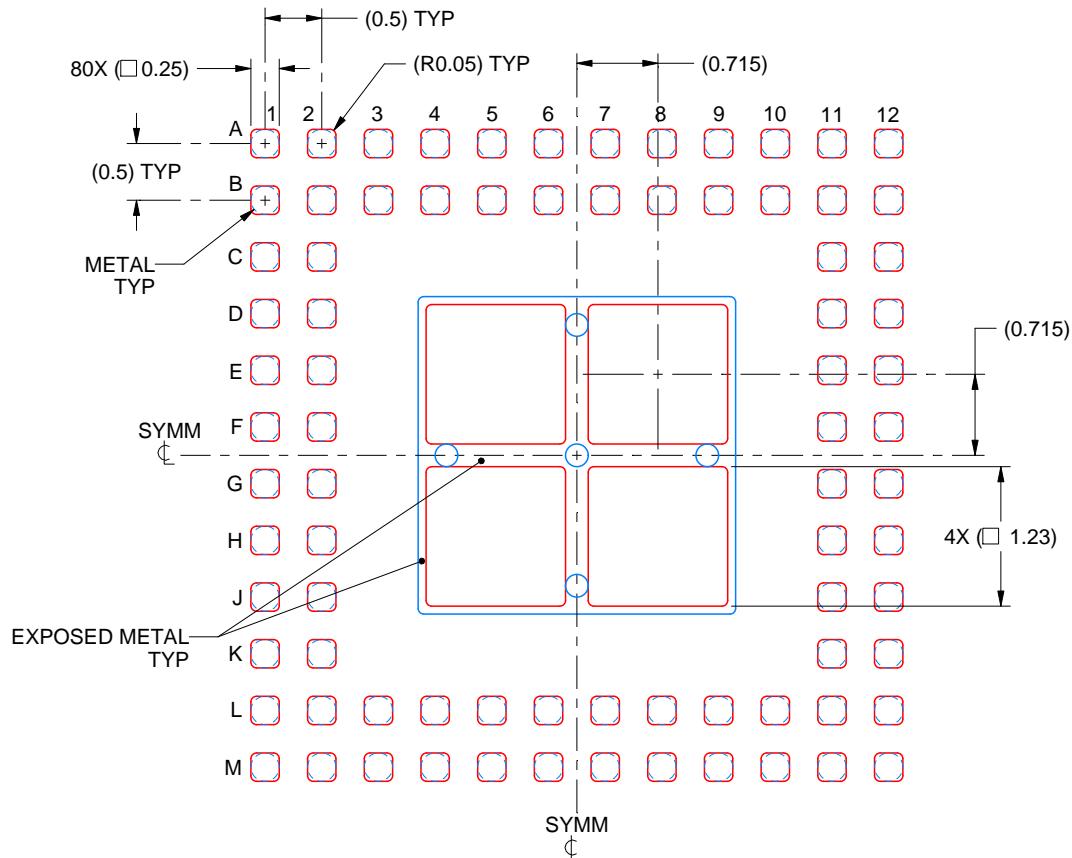

図 5-1. LMKDB1120 および LMKDB1120FS 6mm × 6mm NPP パッケージ 80 ピン TLLGA 上面図

| 凡例     |              |        |

|--------|--------------|--------|

| クロック入力 | クロック出力       | 電源     |

| GND    | ロジック制御/ステータス | 内部接続なし |

表 5-1. LMKDB1120 および LMKDB1120FS のピンの機能

| ピン                    |    | 種類 <sup>(1)</sup> | 説明 |

|-----------------------|----|-------------------|----|

| 名称 <sup>(2) (3)</sup> | 番号 |                   |    |

| クロック入力                |    |                   |    |

**表 5-1. LMKDB1120 および LMKDB1120FS のピンの機能 (続き)**

| ピン                    |     | 種類 <sup>(1)</sup> | 説明                                     |

|-----------------------|-----|-------------------|----------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号  |                   |                                        |

| CLKIN_P               | G1  | I                 |                                        |

| CLKIN_N               | H1  | I                 | 差動クロック入力。                              |

| クロック出力                |     |                   |                                        |

| CLK0_P                | J1  | O                 | LP-HCSL 差動クロック出力 0。未使用の場合は接続しないでください。  |

| CLK0_N                | K1  | O                 |                                        |

| CLK1_P                | L1  | O                 | LP-HCSL 差動クロック出力 1。未使用の場合は接続しないでください。  |

| CLK1_N                | M1  | O                 |                                        |

| CLK2_P                | M2  | O                 | LP-HCSL 差動クロック出力 2。未使用の場合は接続しないでください。  |

| CLK2_N                | M3  | O                 |                                        |

| CLK3_P                | M4  | O                 | LP-HCSL 差動クロック出力 3。未使用の場合は接続しないでください。  |

| CLK3_N                | M5  | O                 |                                        |

| CLK4_P                | M7  | O                 | LP-HCSL 差動クロック出力 4。未使用の場合は接続しないでください。  |

| CLK4_N                | M8  | O                 |                                        |

| CLK5_P                | M9  | O                 | LP-HCSL 差動クロック出力 5。未使用の場合は接続しないでください。  |

| CLK5_N                | M10 | O                 |                                        |

| CLK6_P                | M11 | O                 | LP-HCSL 差動クロック出力 6。未使用の場合は接続しないでください。  |

| CLK6_N                | M12 | O                 |                                        |

| CLK7_P                | L12 | O                 | LP-HCSL 差動クロック出力 7。未使用の場合は接続しないでください。  |

| CLK7_N                | K12 | O                 |                                        |

| CLK8_P                | J12 | O                 | LP-HCSL 差動クロック出力 8。未使用の場合は接続しないでください。  |

| CLK8_N                | H12 | O                 |                                        |

| CLK9_P                | G12 | O                 | LP-HCSL 差動クロック出力 9。未使用の場合は接続しないでください。  |

| CLK9_N                | F12 | O                 |                                        |

| CLK10_P               | D12 | O                 | LP-HCSL 差動クロック出力 10。未使用の場合は接続しないでください。 |

| CLK10_N               | C12 | O                 |                                        |

| CLK11_P               | B12 | O                 | LP-HCSL 差動クロック出力 11。未使用の場合は接続しないでください。 |

| CLK11_N               | A12 | O                 |                                        |

| CLK12_P               | A11 | O                 | LP-HCSL 差動クロック出力 12。未使用の場合は接続しないでください。 |

| CLK12_N               | A10 | O                 |                                        |

| CLK13_P               | A9  | O                 | LP-HCSL 差動クロック出力 13。未使用の場合は接続しないでください。 |

| CLK13_N               | A8  | O                 |                                        |

| CLK14_P               | A7  | O                 | LP-HCSL 差動クロック出力 14。未使用の場合は接続しないでください。 |

| CLK14_N               | A6  | O                 |                                        |

| CLK15_P               | A5  | O                 | LP-HCSL 差動クロック出力 15。未使用の場合は接続しないでください。 |

| CLK15_N               | A4  | O                 |                                        |

| CLK16_P               | A3  | O                 | LP-HCSL 差動クロック出力 16。未使用の場合は接続しないでください。 |

| CLK16_N               | A2  | O                 |                                        |

| CLK17_P               | A1  | O                 | LP-HCSL 差動クロック出力 17。未使用の場合は接続しないでください。 |

| CLK17_N               | B1  | O                 |                                        |

| CLK18_P               | C1  | O                 | LP-HCSL 差動クロック出力 18。未使用の場合は接続しないでください。 |

| CLK18_N               | D1  | O                 |                                        |

| CLK19_P               | E1  | O                 | LP-HCSL 差動クロック出力 19。未使用の場合は接続しないでください。 |

| CLK19_N               | F1  | O                 |                                        |

| 電源                    |     |                   |                                        |

表 5-1. LMKDB1120 および LMKDB1120FS のピンの機能 (続き)

| ピン                    |                      | 種類 <sup>(1)</sup> | 説明                                                                                                                                                      |

|-----------------------|----------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号                   |                   |                                                                                                                                                         |

| VDAA                  | H2                   | P                 | アナログ電源。追加の電源フィルタリングを推奨。詳しくは、セクション 10.3 を参照してください。                                                                                                       |

| VDDCLK                | B2, B6, B11, L2, L11 | P                 | 出力電源                                                                                                                                                    |

| サーマル パッド (GND)        | パッド                  | G                 | デバイス グランド、サーマル パッド。                                                                                                                                     |

| ロジック制御/ステータス          |                      |                   |                                                                                                                                                         |

| vOE0#/NC              | J2                   | I                 | CLK0 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                     |

| vOE1#/NC              | K2                   | I                 | CLK1 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                     |

| vOE2#/NC              | L3                   | I                 | CLK2 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                     |

| vOE3#/NC              | L6                   | I                 | CLK3 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                     |

| vOE4#/NC              | L9                   | I                 | CLK4 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                     |

| vOE5#/SBI_IN          | L8                   | I                 | CLK5 を制御するアクティブ Low 入力または SBI データ入力ピン。SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。<br>OE モード: 0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI データ入力。                          |

| vOE6#/SBI_CLK         | L10                  | I                 | CLK6 を制御するアクティブ Low 入力または SBI クロック入力ピン。SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。<br>OE モード: 0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI クロック入力。                        |

| vOE7#                 | K11                  | I                 | CLK7 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                  |

| vOE8#                 | H11                  | I                 | CLK8 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                  |

| vOE9#                 | E12                  | I                 | CLK9 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                  |

| vOE10#/SHFT_LD#       | E11                  | I                 | CLK10 を制御するアクティブ Low 入力または SBI アクティブ Low シフトレジスタ ロードピン。SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。<br>OE モード: 0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI シフトレジスタ ロード入力。 |

| vOE11#                | C11                  | I                 | CLK11 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                 |

| vOE12#                | B10                  | I                 | CLK12 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                 |

| vOE13#/NC             | B9                   | I                 | CLK13 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                    |

**表 5-1. LMKDB1120 および LMKDB1120FS のピンの機能 (続き)**

| ピン                    |                  | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                    |

|-----------------------|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号               |                   |                                                                                                                                                                                                                                                       |

| OE14#/NC              | B7               | I                 | CLK14 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                  |

| vOE15#/NC             | B5               | I                 | CLK15 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                  |

| vOE16#/NC             | B3               | I                 | CLK16 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                  |

| vOE17#/NC             | D2               | I                 | CLK17 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                  |

| vOE18#/NC             | D11              | I                 | CLK18 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                  |

| vOE19#/NC             | J11              | I                 | CLK19 を制御するアクティブ Low 入力。内部プルダウン抵抗。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                  |

| SBI_OUT/NC            | C2               | O                 | SBI データ出力ピン/未接続。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。                                                                                                                                                                                         |

| vPWRGD/PWRDN#         | M6               | I                 | パワー グッド/パワー ダウン アクティブ Low。多機能入力ピン。内部プルアップ抵抗。<br>最初の Low から High への遷移時に、デバイスを起動するパワー グッド ピンとして機能する<br>その後の Low/High 遷移時には、デバイスをパワーダウン モードに入るまたは解除するための パ<br>ワー ダウン アクティブ Low ピンとして機能します。<br>Low = パワーダウンモード<br>High = 通常動作モード                          |

| vSBI_EN               | E2               | I                 | SBI イネーブル。内部プルダウン抵抗。パワーアップ後はこのピンの状態を変更しないでください。<br>パワーアップ時に Low の場合 = SBI インターフェイスは無効です。ピン L8、L10、および E11 は<br>OE ピンとして機能します。パワーアップ時に High の場合 = SBI インターフェイスは有効です。<br>ピン L8、L10、および E11 は SBI インターフェイス ピンとして機能します。SMBus およびその他<br>の OE ピンは引き続き動作します。 |

| ^vSADR1_tri           | B8               | I                 | SMBus アドレス 3 レベル入力ピン。内部プルアップおよびプルダウン抵抗を内蔵しています。                                                                                                                                                                                                       |

| ^vSADR0_tri           | B4               | I                 | SMBus アドレス 3 レベル入力ピン。内部プルアップおよびプルダウン抵抗を内蔵しています。                                                                                                                                                                                                       |

| LOS#/NC               | G11              | O                 | 入力クロック信号喪失アクトティブ Low/未接続。オープンドレイン。外部プルアップ抵抗が必要で<br>す。DB2000QL のピン配置に合わせるために、このピンは未接続のままにすることができます。<br>Low = 無効な入力クロック。<br>High = 有効な入力クロック。                                                                                                           |

| SMB_DATA              | L4               | I/O               | SMBus データ。外部プルアップ抵抗が必要です。未使用の場合は接続しないでください。                                                                                                                                                                                                           |

| SMB_CLK               | L5               | I                 | SMBus クロック。外部プルアップ抵抗が必要です。未使用の場合は接続しないでください。                                                                                                                                                                                                          |

| NC                    | F2、F11、G2、<br>L7 | NC                | 未接続。                                                                                                                                                                                                                                                  |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源、NC = 未接続

(2) 「^」プレフィックスが付いたピンは内部プルアップ抵抗を内蔵しています。「v」プレフィックスが付いたピンは内部プルダウン抵抗を内蔵していま

す。「^v」プレフィックスが付いたピンは内部プルアップ抵抗と内部プルダウン抵抗の両方を内蔵しており、ピンが未接続の場合は中間レベルが選

択されます。「^v」プレフィックスが付いたピンは、選択された機能に応じて内部プルアップまたはプルダウン抵抗を内蔵しています。

(3) 「#」記号はアクトティブ Low を示します。

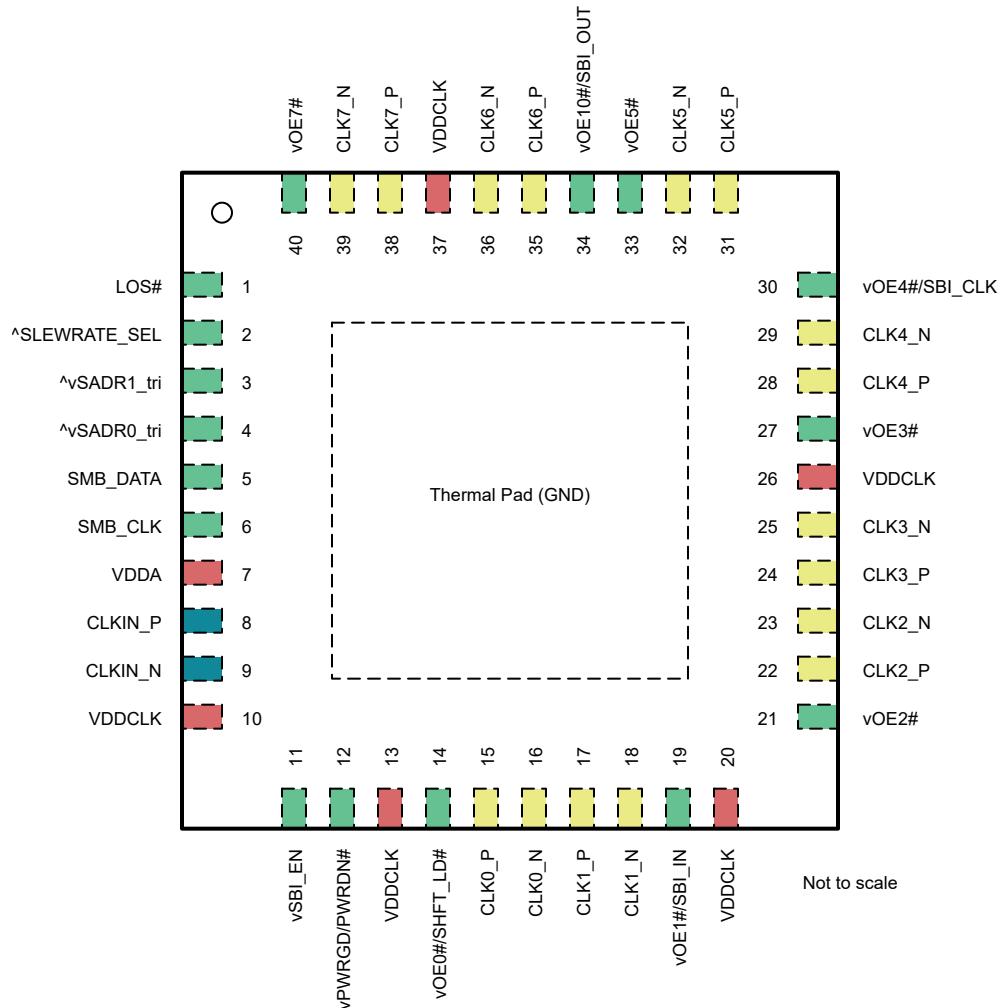

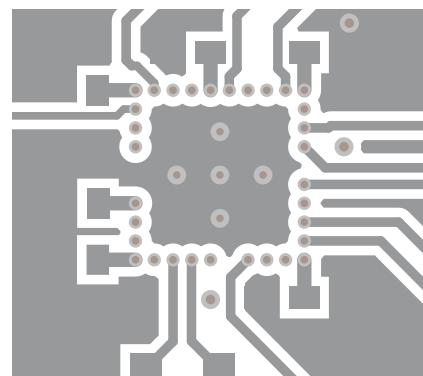

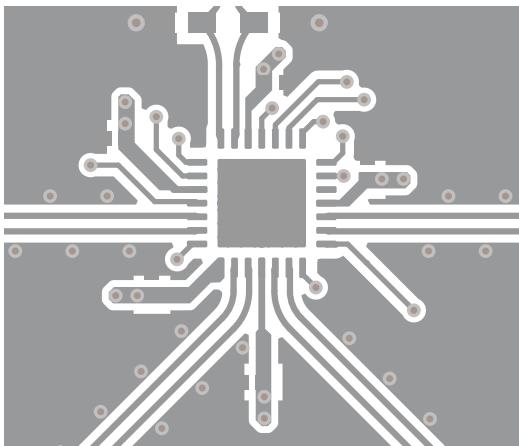

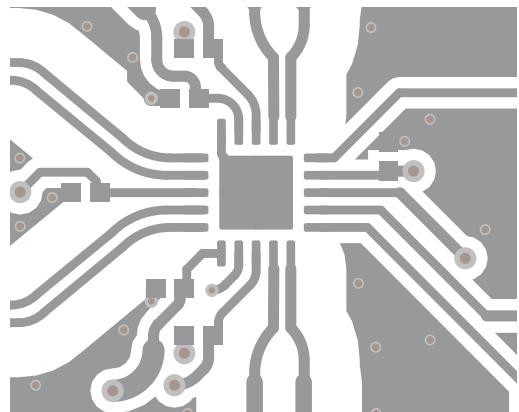

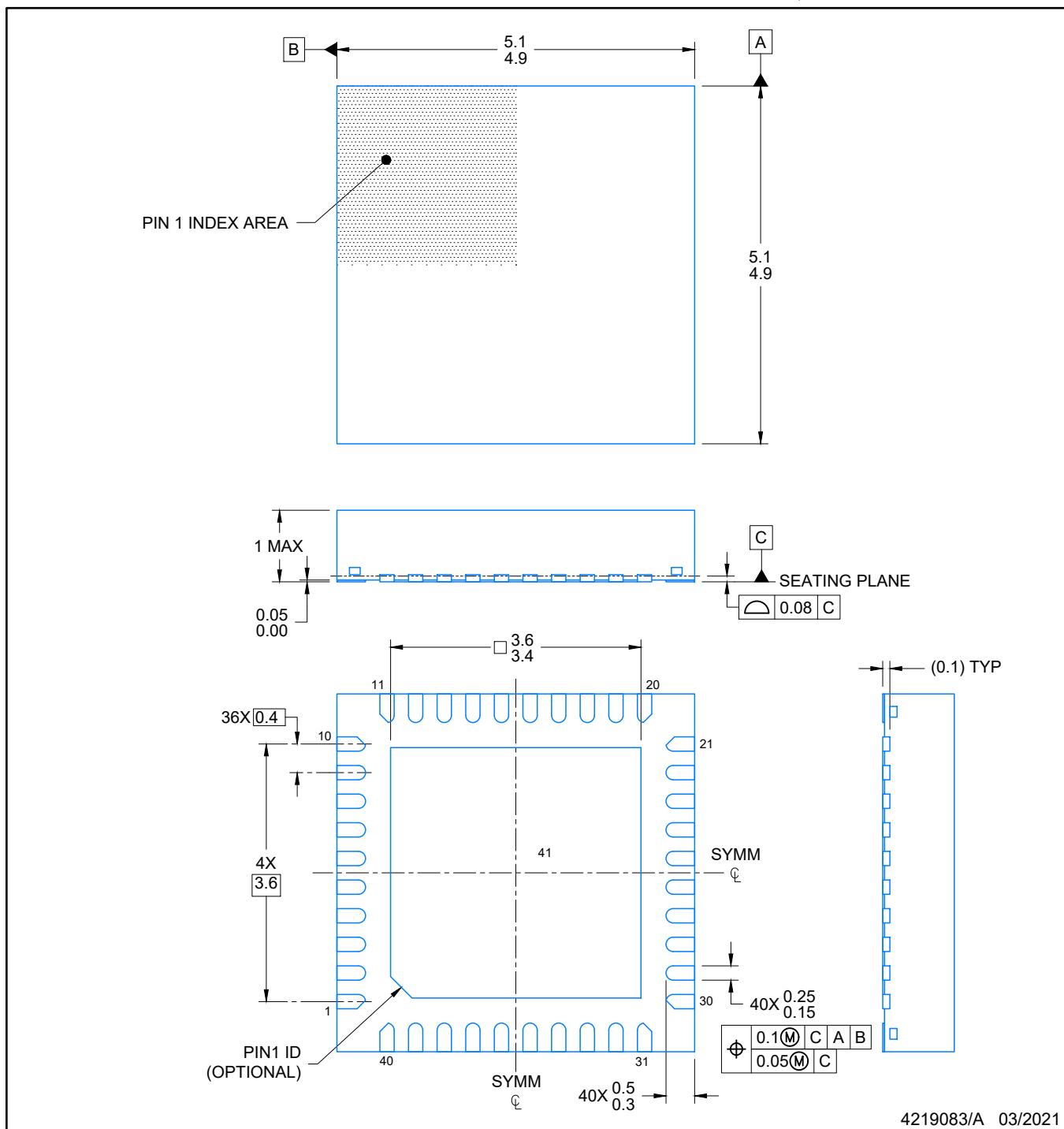

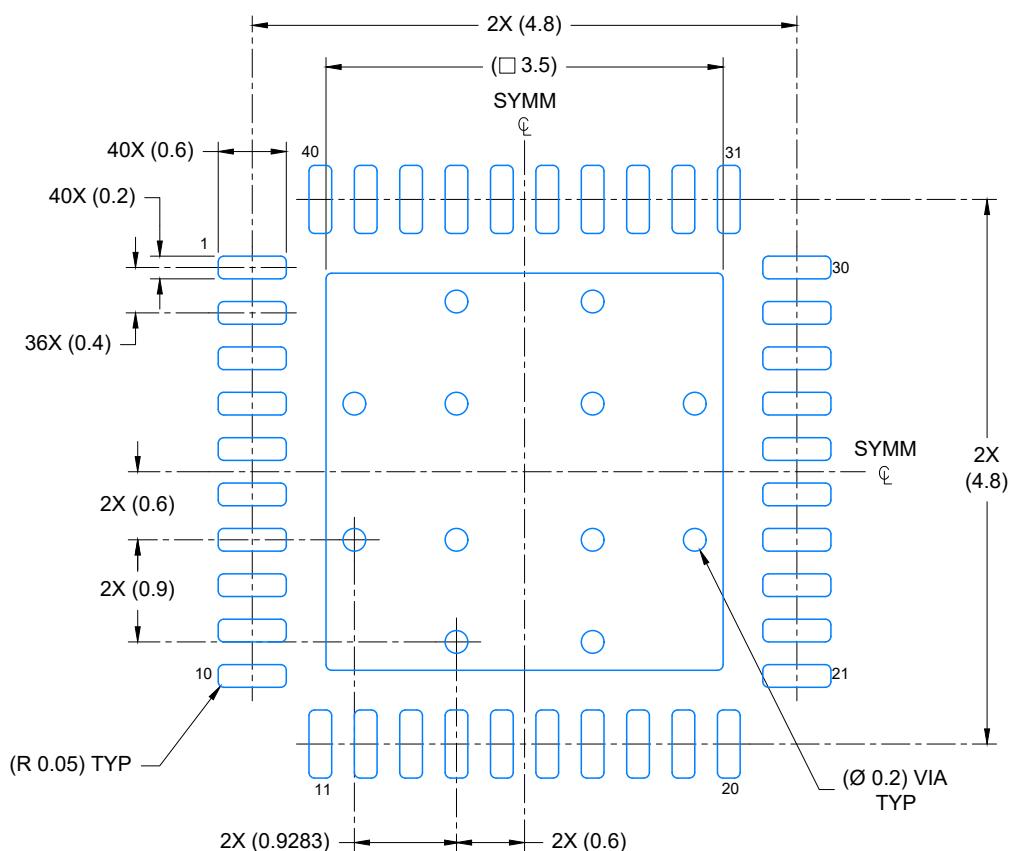

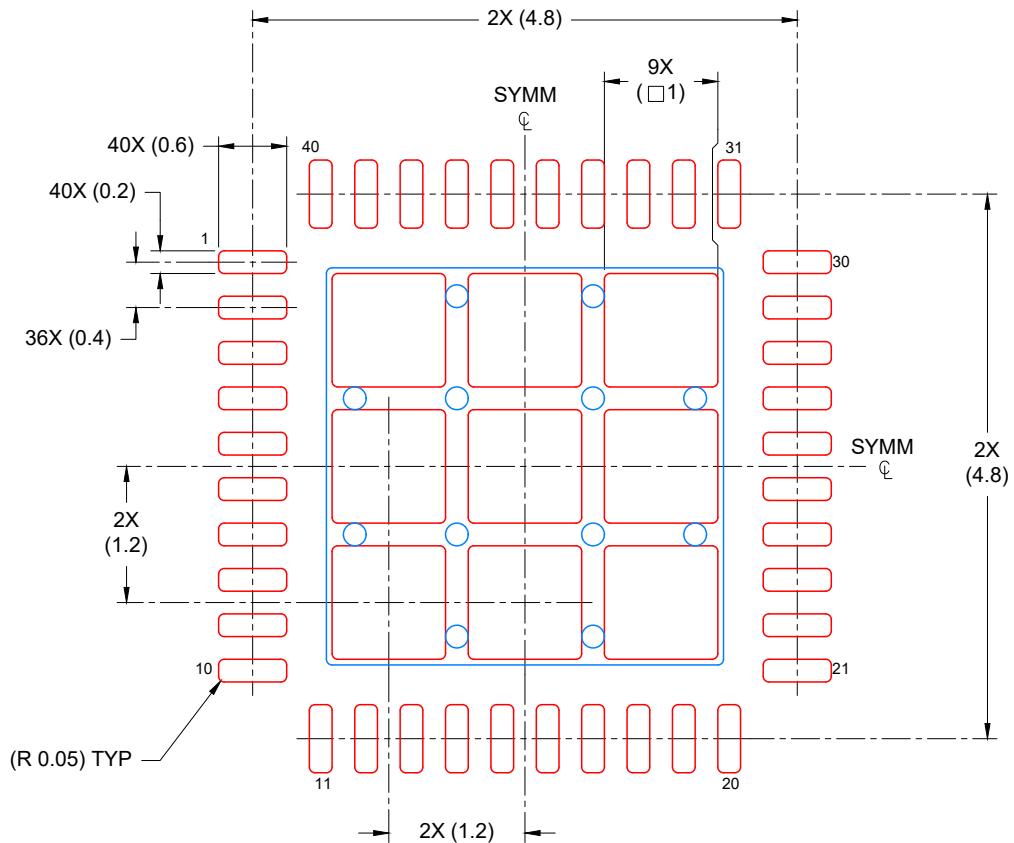

図 5-2. LMKDB1108 および LMKDB1108FS 5mm × 5mm VQFN パッケージ 40 ピン 上面図

| 凡例     |              |        |

|--------|--------------|--------|

| クロック入力 | クロック出力       | 電源     |

| GND    | ロジック制御/ステータス | 内部接続なし |

表 5-2. LMKDB1108 および LMKDB1108FS のピンの機能

| ピン                    | 種類 <sup>(1)</sup> | 説明 |                                       |

|-----------------------|-------------------|----|---------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号                |    |                                       |

| クロック入力                |                   |    |                                       |

| CLKIN_P               | 8                 | I  | 差動クロック入力。                             |

| CLKIN_N               | 9                 | I  |                                       |

| クロック出力                |                   |    |                                       |

| CLK0_P                | 15                | O  | LP-HCSL 差動クロック出力 0。未使用の場合は接続しないでください。 |

| CLK0_N                | 16                | O  |                                       |

| CLK1_P                | 17                | O  | LP-HCSL 差動クロック出力 1。未使用の場合は接続しないでください。 |

| CLK1_N                | 18                | O  |                                       |

| CLK2_P                | 22                | O  | LP-HCSL 差動クロック出力 2。未使用の場合は接続しないでください。 |

| CLK2_N                | 23                | O  |                                       |

**表 5-2. LMKDB1108 および LMKDB1108FS のピンの機能 (続き)**

| ピン                    |                     | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                      |

|-----------------------|---------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号                  |                   |                                                                                                                                                                                                                         |

| CLK3_P                | 24                  | O                 | LP-HCSL 差動クロック出力 3。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK3_N                | 25                  | O                 | LP-HCSL 差動クロック出力 3。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK4_P                | 28                  | O                 | LP-HCSL 差動クロック出力 4。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK4_N                | 29                  | O                 | LP-HCSL 差動クロック出力 4。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK5_P                | 31                  | O                 | LP-HCSL 差動クロック出力 5。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK5_N                | 32                  | O                 | LP-HCSL 差動クロック出力 5。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK6_P                | 35                  | O                 | LP-HCSL 差動クロック出力 6。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK6_N                | 36                  | O                 | LP-HCSL 差動クロック出力 6。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK7_P                | 38                  | O                 | LP-HCSL 差動クロック出力 7。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| CLK7_N                | 39                  | O                 | LP-HCSL 差動クロック出力 7。未使用の場合は接続しないでください。                                                                                                                                                                                   |

| 電源                    |                     |                   |                                                                                                                                                                                                                         |

| VDDA                  | 7                   | P                 | アナログ電源。追加の電源フィルタリングを推奨。詳しくは、 <a href="#">セクション 10.3</a> を参照してください。                                                                                                                                                      |

| VDDCLK                | 10, 13, 20, 26, 37、 | P                 | 出力電源                                                                                                                                                                                                                    |

| サーマル パッド (GND)        | パッド                 | G                 | デバイス グランド、サーマル パッド。                                                                                                                                                                                                     |

| ロジック制御/ステータス          |                     |                   |                                                                                                                                                                                                                         |

| vOE0#/SHFT_LD#        | 14                  | I                 | CLK0 を制御するアクティブ Low 入力または SBI アクティブ Low シフトレジスタ ロード ピン SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。OE モード:0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI ラッチ レジスタ入力。                                                                         |

| vOE1#/SBI_IN          | 19                  | I                 | CLK1 を制御するアクティブ Low 入力または SBI データ入力ピン。SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。OE モード:0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI データ入力。                                                                                               |

| vOE2#                 | 21                  | I                 | CLK2 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                                  |

| vOE3#                 | 27                  | I                 | CLK3 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                                  |

| vOE4#/SBI_CLK         | 30                  | I                 | CLK4 を制御するアクティブ Low 入力または SBI クロック入力ピン SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。OE モード:0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI クロック入力。                                                                                             |

| vOE5#                 | 33                  | I                 | CLK5 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                                  |

| vOE10#/SBI_OUT        | 34                  | I または O           | CLK6 を制御するアクティブ Low 入力または SBI データ出力ピン内部プルダウン抵抗。SBI_EN ピンがこのピンの機能を制御する。<br>OE モード:0 = 有効出力、1 = 無効出力。<br>SBI モード:SBI シフトレジスタ データ出力。                                                                                       |

| vOE7#                 | 40                  | I                 | CLK7 を制御するアクティブ Low 入力。内部プルダウン抵抗。<br>0 = 出力有効、1 = 出力無効                                                                                                                                                                  |

| vPWRGD/PWRDN#         | 12                  | I                 | パワー グッド/パワー ダウン アクティブ Low。多機能入力ピン。内部プルダウン抵抗。<br>最初の Low から High への遷移時に、デバイスを起動するパワー グッド ピンとして機能する<br>その後の Low/High 遷移時には、デバイスをパワーダウン モードに入るまたは解除するためのパワー ダウン アクティブ Low ピンとして機能します。<br>Low = パワーダウンモード<br>High = 通常動作モード |

表 5-2. LMKDB1108 および LMKDB1108FS のピンの機能 (続き)

| ピン                    |    | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                   |

|-----------------------|----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号 |                   |                                                                                                                                                                                                                                                      |

| vSBI_EN               | 11 | I                 | SBI イネーブル。内部プルダウン抵抗。パワーアップ後はこのピンの状態を変更しないでください。<br>パワーアップ時に Low の場合 = SBI インターフェイスは無効です。ピン 20, 32, 48、および 55 は OE ピンとして機能します。<br>パワーアップ時に High の場合 = SBI インターフェイスは有効です。ピン 20, 32, 48、および 55 は SBI インターフェイス ピンとして機能します。SMBus およびその他の OE ピンは引き続き動作します。 |

| ^vSADDR1_tri          | 3  | I                 | SMBus アドレス 3 レベル入力ピン。内部プルアップおよびプルダウン抵抗を内蔵しています。                                                                                                                                                                                                      |

| ^vSADDR0_tri          | 4  | I                 | SMBus アドレス 3 レベル入力ピン。内部プルアップおよびプルダウン抵抗を内蔵しています。                                                                                                                                                                                                      |

| ^SLEWRATE_SEL         | 2  | I                 | LP-HCSL 差動クロック出力のスルーレート選択ピン。内部プルアップ抵抗。<br>Low = 低速スルーレート。<br>High = 高速スルーレート。                                                                                                                                                                        |

| LOS#                  | 1  | O                 | 入力クロック信号喪失アクティブ Low/未接続。オープンドレイン。外部プルアップ抵抗が必要です。<br>Low = 無効な入力クロック。<br>High = 有効な入力クロック。                                                                                                                                                            |

| SMB_DATA              | 5  | I/O               | SMBus データ。外部プルアップ抵抗が必要です。未使用の場合は接続しないでください。                                                                                                                                                                                                          |

| SMB_CLK               | 6  | I                 | SMBus クロック。外部プルアップ抵抗が必要です。未使用の場合は接続しないでください。                                                                                                                                                                                                         |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源、NC = 未接続

(2) 「^」プレフィックスが付いたピンは内部プルアップ抵抗を内蔵しています。「v」プレフィックスが付いたピンは内部プルダウン抵抗を内蔵しています。「^v」プレフィックスが付いたピンは内部プルアップ抵抗と内部プルダウン抵抗の両方を内蔵しており、ピンが未接続の場合は中間レベルが選択されます。

(3) 「#」記号はアクティブ Low を示します。

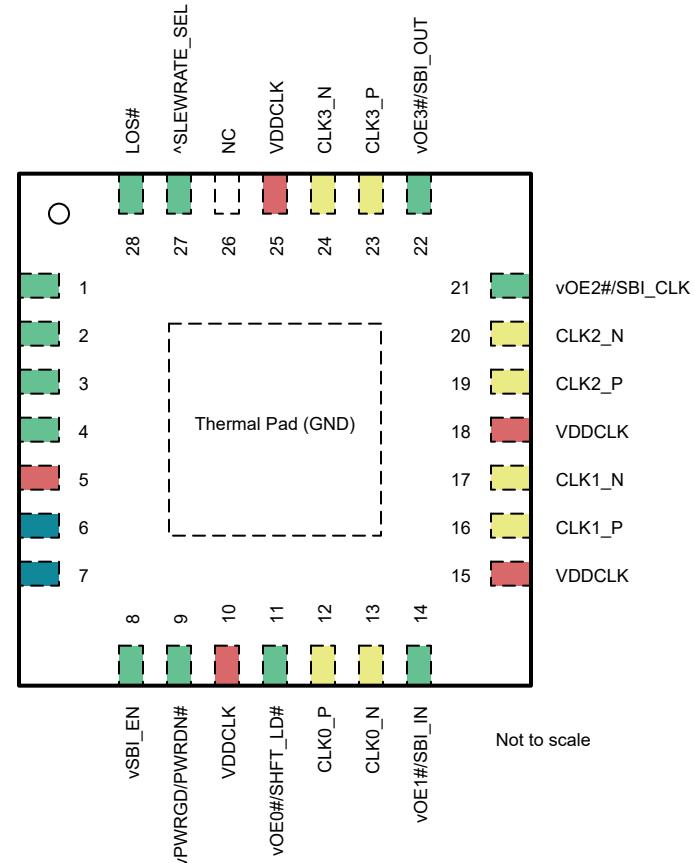

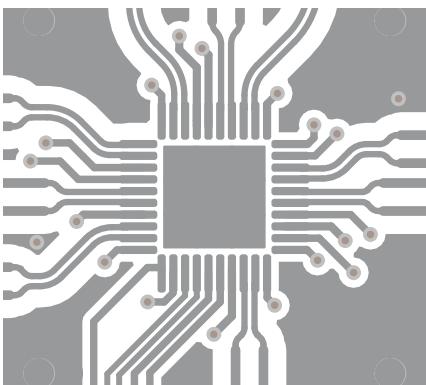

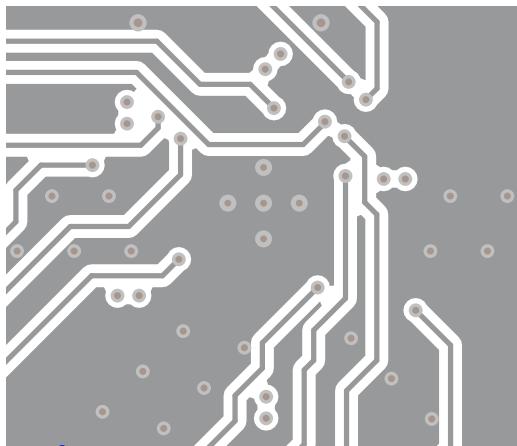

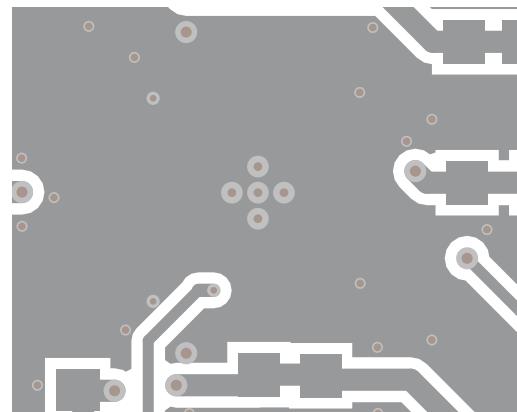

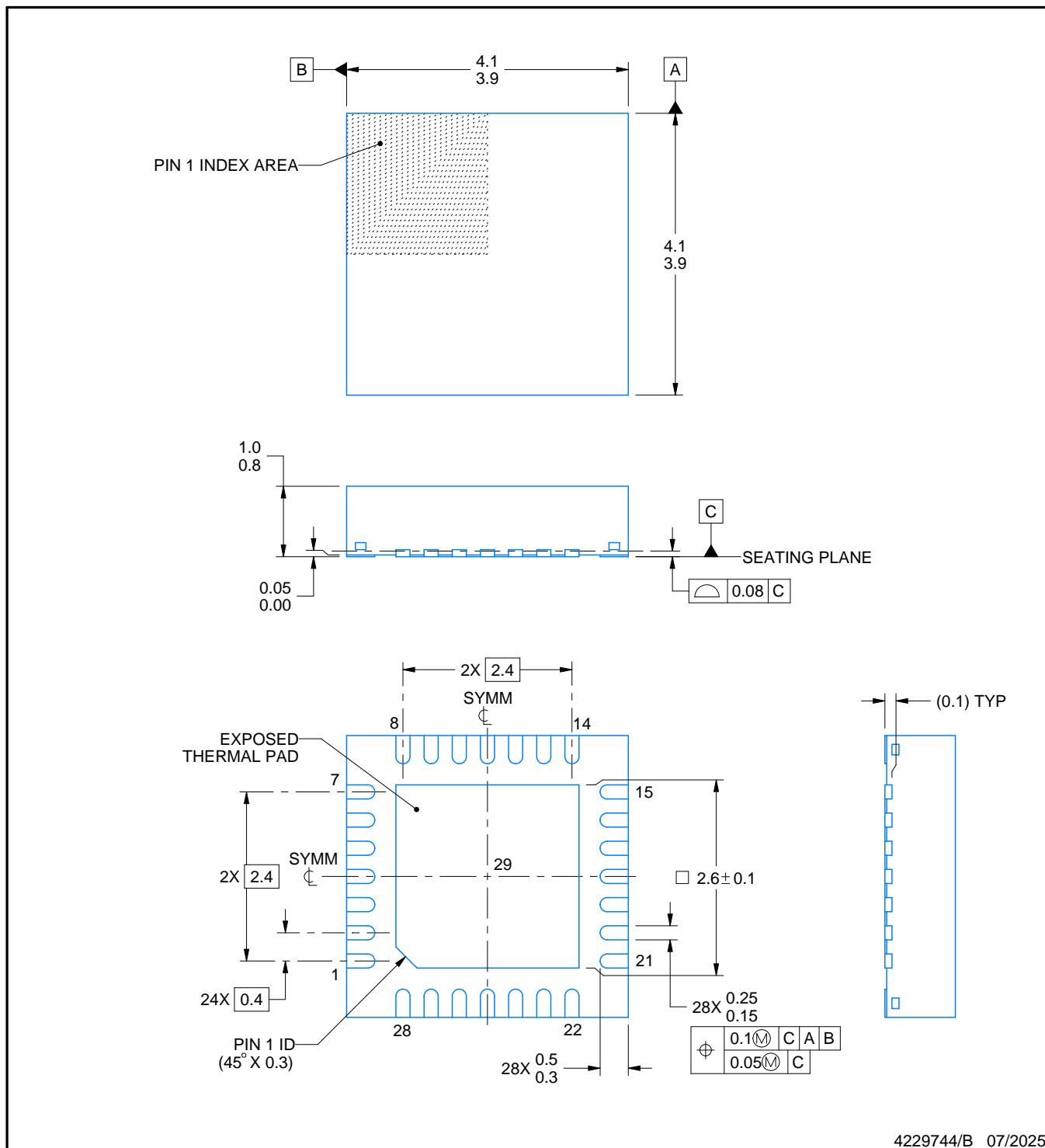

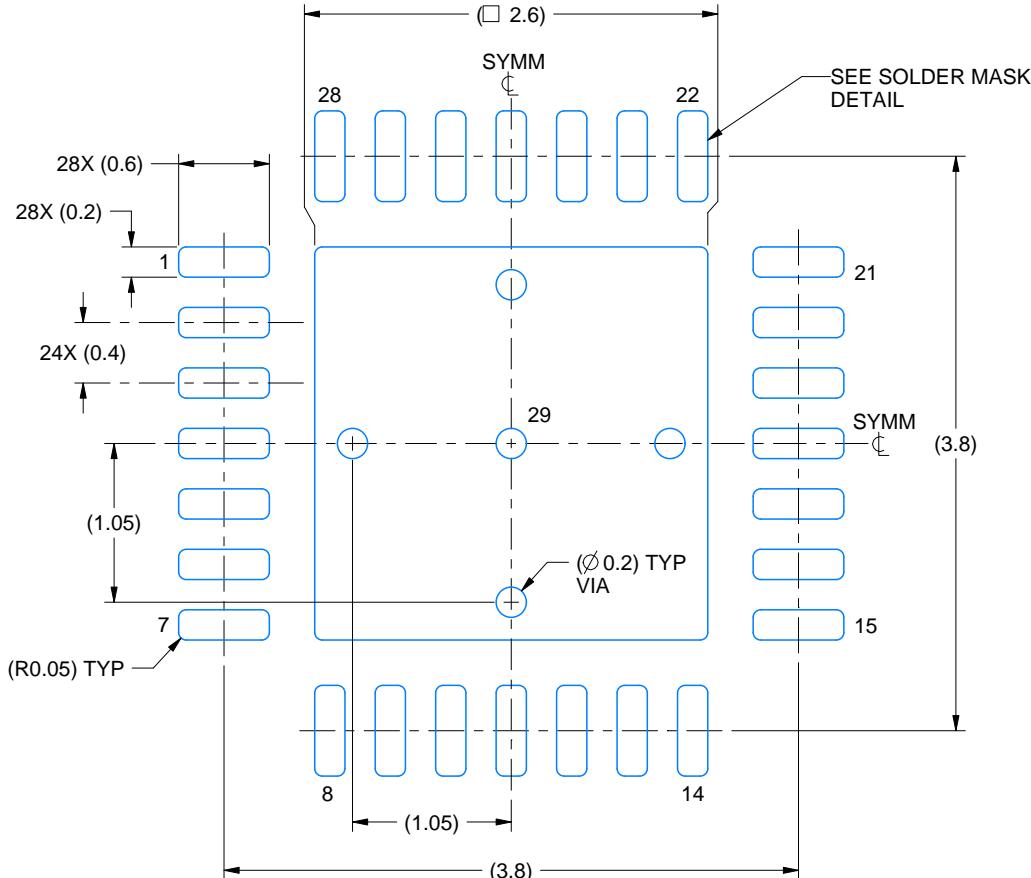

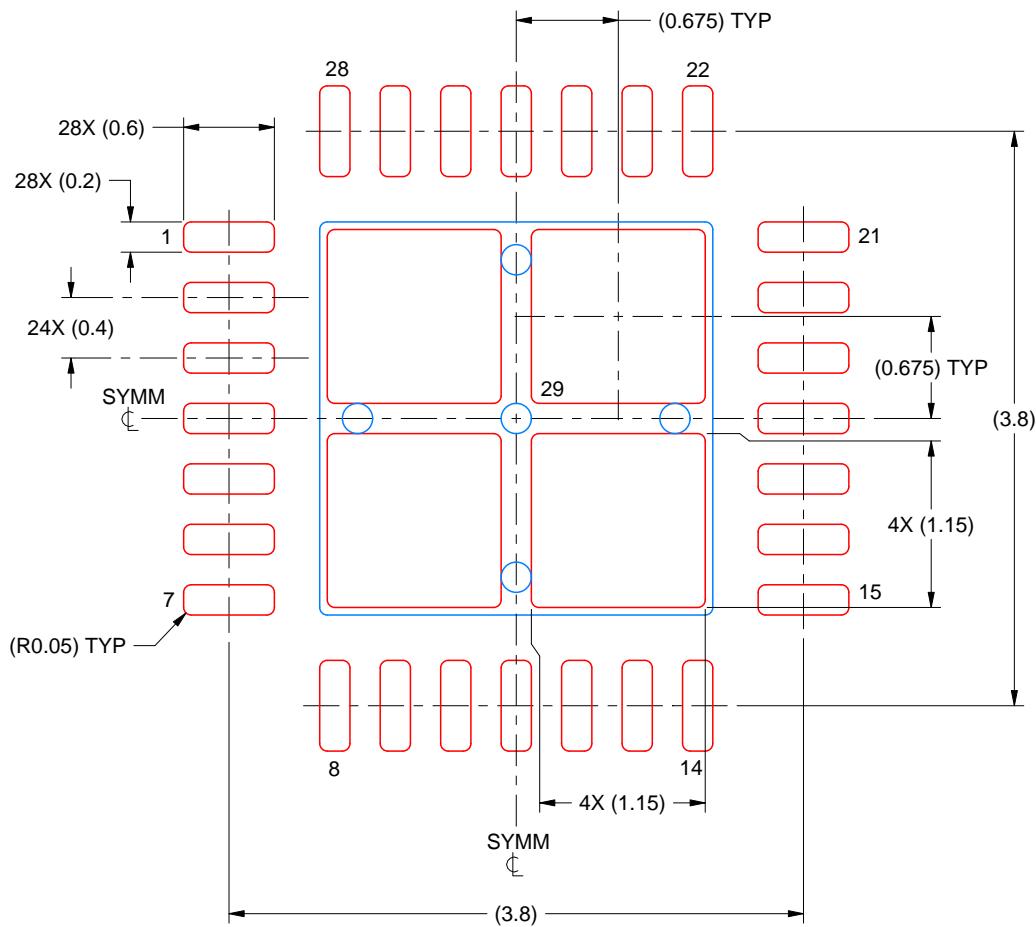

図 5-3. LMKDB1104 および LMKDB1104FS 4mm × 4mm VQFN パッケージ 28 ピン 上面図

| 凡例     |              |        |

|--------|--------------|--------|

| クロック入力 | クロック出力       | 電源     |

| GND    | ロジック制御/ステータス | 内部接続なし |

表 5-3. LMKDB1104 および LMKDB1104FS のピンの機能

| ピン                    | 種類 <sup>(1)</sup> | 説明 |                                                   |

|-----------------------|-------------------|----|---------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号                |    |                                                   |

| クロック入力                |                   |    |                                                   |

| CLKIN_P               | 6                 | I  |                                                   |

| CLKIN_N               | 7                 | I  | 差動クロック入力。                                         |

| クロック出力                |                   |    |                                                   |

| CLK0_P                | 12                | O  | LP-HCSL 差動クロック出力 0。未使用の場合は接続しないでください。             |

| CLK0_N                | 13                | O  |                                                   |

| CLK1_P                | 16                | O  | LP-HCSL 差動クロック出力 1。未使用の場合は接続しないでください。             |

| CLK1_N                | 17                | O  |                                                   |

| CLK2_P                | 19                | O  | LP-HCSL 差動クロック出力 2。未使用の場合は接続しないでください。             |

| CLK2_N                | 20                | O  |                                                   |

| CLK3_P                | 23                | O  | LP-HCSL 差動クロック出力 3。未使用の場合は接続しないでください。             |

| CLK3_N                | 24                | O  |                                                   |

| 電源                    |                   |    |                                                   |

| VDDA                  | 5                 | P  | アナログ電源。追加の電源フィルタリングを推奨。詳しくは、セクション 10.3 を参照してください。 |

表 5-3. LMKDB1104 および LMKDB1104FS のピンの機能 (続き)

| ピン                    |                | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                   |

|-----------------------|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号             |                   |                                                                                                                                                                                                                                                      |

| VDDCLK                | 10, 15, 18, 25 | P                 | 出力電源                                                                                                                                                                                                                                                 |

| サーマル パッド (GND)        | パッド            | G                 | デバイス グランド、サーマル パッド。                                                                                                                                                                                                                                  |

| ロジック制御/ステータス          |                |                   |                                                                                                                                                                                                                                                      |

| vOE0#/SHFT_LD#        | 11             | I                 | CLK0 を制御するアクティブ Low 入力または SBI アクティブ Low シフトレジスタ ロード ピン SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。OE モード:0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI ラッチ レジスタ入力。                                                                                                      |

| vOE1#/SBI_IN          | 14             | I                 | CLK1 を制御するアクティブ Low 入力または SBI データ入力ピン。SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。OE モード:0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI データ入力。                                                                                                                            |

| vOE2#/SBI_CLK         | 21             | I                 | CLK2 を制御するアクティブ Low 入力または SBI クロック入力ピン SBI_EN ピンがこのピンの機能を制御する。内部プルダウン抵抗。OE モード:0 = 有効出力、1 = 無効出力。<br>サイドバンド モード:SBI クロック入力。                                                                                                                          |

| vOE3#/SBI_OUT         | 22             | I または O           | CLK3 を制御するアクティブ Low 入力または SBI データ出力ピン 内部プルダウン抵抗。SBI_EN ピンがこのピンの機能を制御する。<br>OE モード:0 = 有効出力、1 = 無効出力。<br>SBI モード:SBI シフトレジスタ データ出力。                                                                                                                   |

| vPWRGD/PWRDN#         | 9              | I                 | パワー グッド/パワー ダウン アクティブ Low。多機能入力ピン。内部プルダウン抵抗。<br>最初の Low から High への遷移時に、デバイスを起動する パワー グッド ピンとして機能する<br>その後の Low/High 遷移時には、デバイスをパワーダウン モードに入るまたは解除するための パワー ダウン アクティブ Low ピンとして機能します。<br>Low = パワーダウンモード<br>High = 通常動作モード                            |

| vSBI_EN               | 8              | I                 | SBI イネーブル。内部プルダウン抵抗。パワーアップ後はこのピンの状態を変更しないでください。<br>パワーアップ時に Low の場合 = SBI インターフェイスは無効です。ピン 20, 32, 48、および 55 は OE ピンとして機能します。<br>パワーアップ時に High の場合 = SBI インターフェイスは有効です。ピン 20, 32, 48、および 55 は SBI インターフェイス ピンとして機能します。SMBus およびその他の OE ピンは引き続き動作します。 |

| ^vSADR1_tri           | 1              | I                 | SMBus アドレス 3 レベル入力ピン。内部プルアップおよびプルダウン抵抗を内蔵しています。                                                                                                                                                                                                      |

| ^vSADR0_tri           | 2              | I                 | SMBus アドレス 3 レベル入力ピン。内部プルアップおよびプルダウン抵抗を内蔵しています。                                                                                                                                                                                                      |

| ^SLEWRATE_SEL         | 27             | I                 | LP-HCSL 差動クロック出力のスルーレート選択ピン。内部プルアップ抵抗。<br>Low = 低速スルーレート。<br>High = 高速スルーレート。                                                                                                                                                                        |

| LOS#                  | 28             | O                 | 入力クロック信号喪失アクティブ Low/未接続。オープンドレイン。外部プルアップ抵抗が必要です。<br>Low = 無効な入力クロック。<br>High = 有効な入力クロック。                                                                                                                                                            |

| SMB_DATA              | 3              | I/O               | SMBus データ。外部プルアップ抵抗が必要です。未使用の場合は接続しないでください。                                                                                                                                                                                                          |

| SMB_CLK               | 4              | I                 | SMBus クロック。外部プルアップ抵抗が必要です。未使用の場合は接続しないでください。                                                                                                                                                                                                         |

| NC                    | 26             | NC                | 未接続。                                                                                                                                                                                                                                                 |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源、NC = 未接続

(2) 「^」プレフィックスが付いたピンは内部プルアップ抵抗を内蔵しています。「v」プレフィックスが付いたピンは内部プルダウン抵抗を内蔵しています。「^v」プレフィックスが付いたピンは内部プルアップ抵抗と内部プルダウン抵抗の両方を内蔵しており、ピンが未接続の場合は中間レベルが選択されます。

- (3) 「#」記号はアクティブ Low を示します。

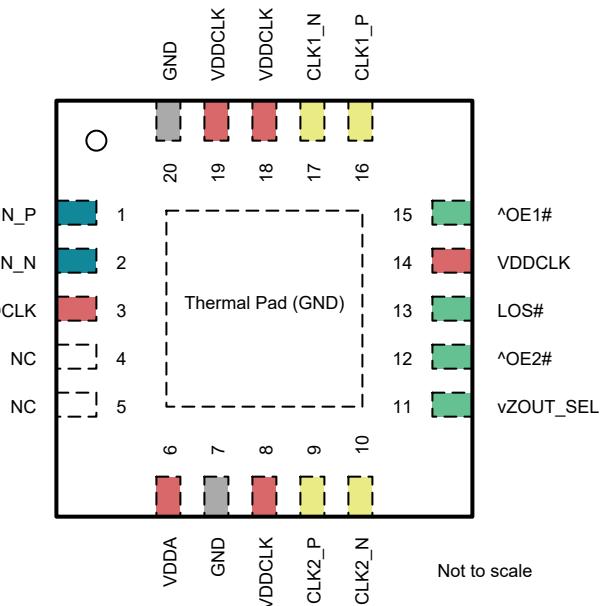

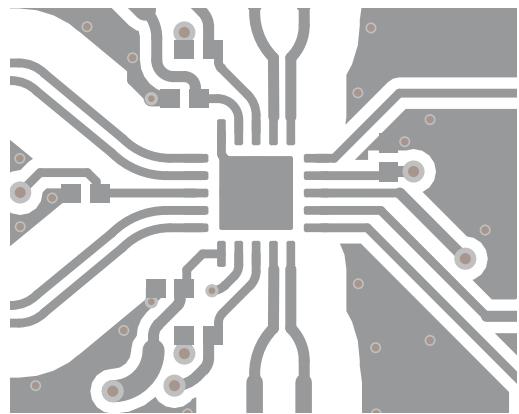

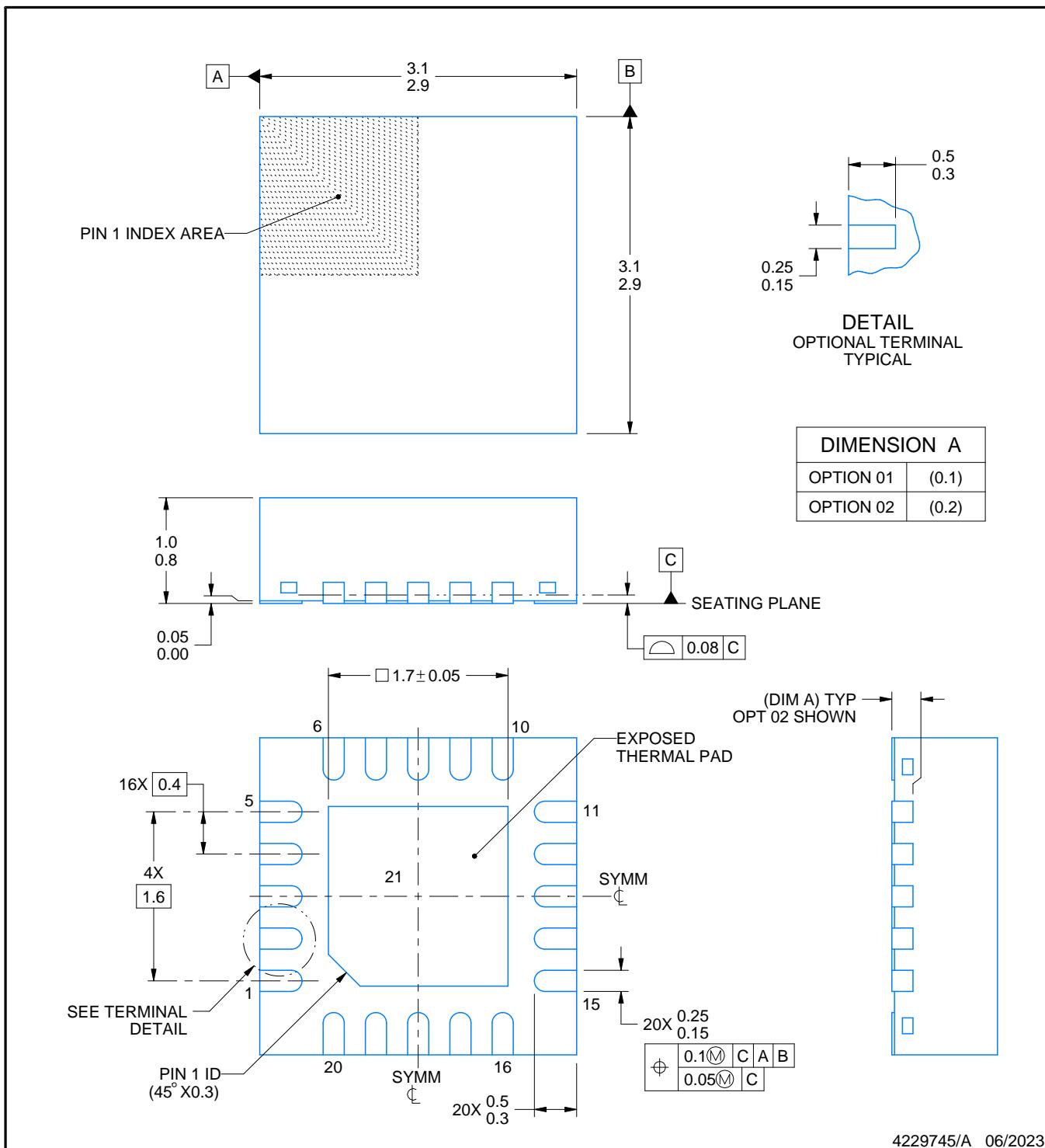

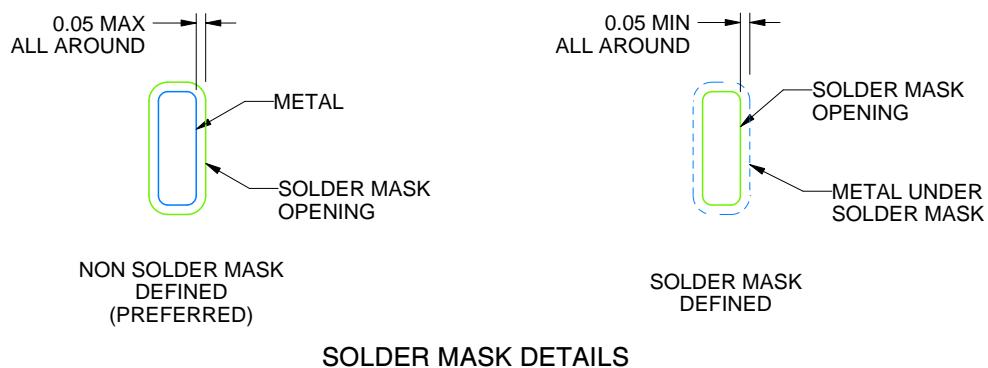

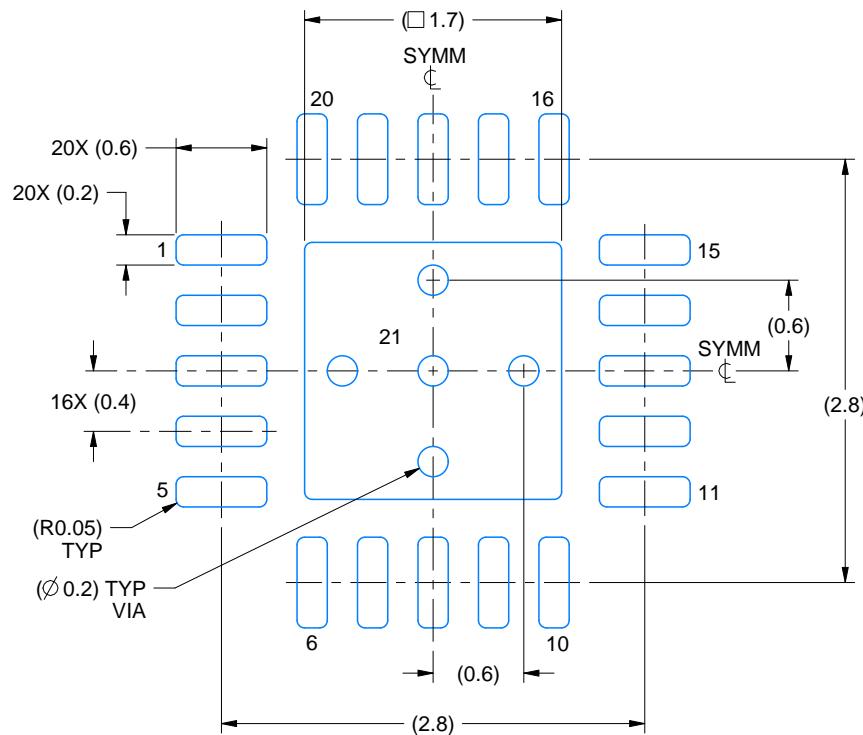

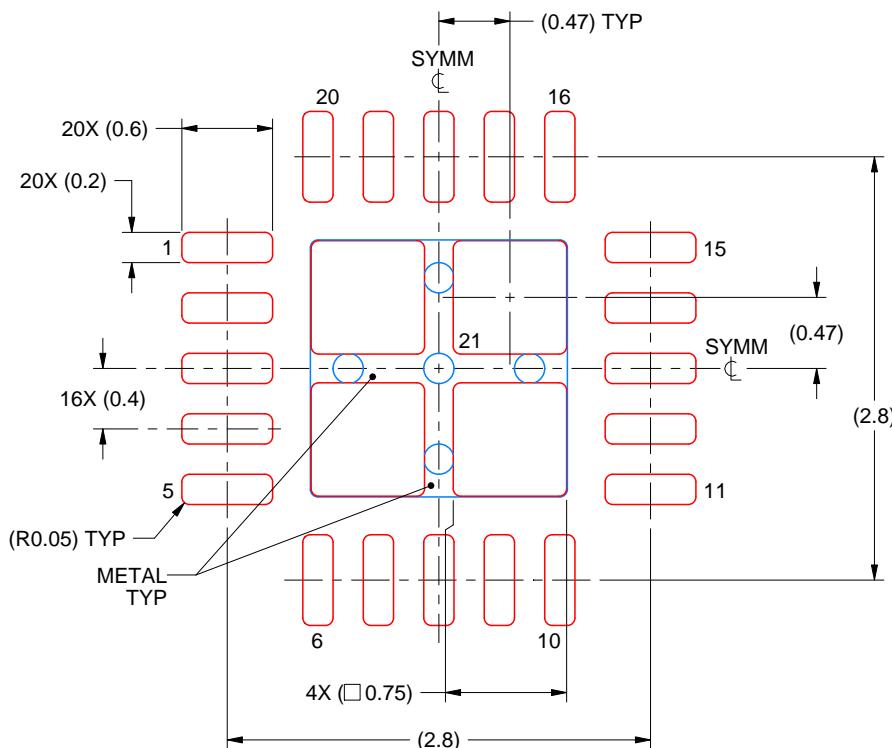

図 5-4. LMKDB1102 3mm × 3mm VQFN パッケージ 20 ピン 上面図

| 凡例     |              |        |

|--------|--------------|--------|

| クロック入力 | クロック出力       | 電源     |

| GND    | ロジック制御/ステータス | 内部接続なし |

表 5-4. LMKDB1102 のピンの機能

| ピン                    | 種類 <sup>(1)</sup> | 説明 |                                                        |

|-----------------------|-------------------|----|--------------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号                |    |                                                        |

| クロック入力                |                   |    |                                                        |

| CLKIN_P               | 1                 | I  | 差動クロック入力。                                              |

| CLKIN_N               | 2                 | I  |                                                        |

| クロック出力                |                   |    |                                                        |

| CLK1_P                | 16                | O  | LP-HCSL 差動クロック出力 1。未使用の場合は接続しないでください。                  |

| CLK1_N                | 17                | O  |                                                        |

| CLK2_P                | 9                 | O  | LP-HCSL 差動クロック出力 2。未使用の場合は接続しないでください。                  |

| CLK2_N                | 10                | O  |                                                        |

| 電源                    |                   |    |                                                        |

| VDDA                  | 6                 | P  | アナログ電源。追加の電源フィルタリングを推奨。詳しくは、セクション 10.3 を参照してください。      |

| VDDCLK                | 3、8、14、18、19      | P  | 出力電源                                                   |

| GND                   | 7、20              | G  | デバイス グランド、サーマル パッド。                                    |

| サーマル パッド (GND)        | パッド               | G  | デバイス グランド、サーマル パッド。                                    |

| ロジック制御/ステータス          |                   |    |                                                        |

| ^OE1#                 | 15                | I  | CLK1 を制御するアクティブ Low 入力。内部プルアップ抵抗。<br>0 = 出力有効、1 = 出力無効 |

**表 5-4. LMKDB1102 のピンの機能 (続き)**

| ピン                    |     | 種類 <sup>(1)</sup> | 説明                                                                                        |

|-----------------------|-----|-------------------|-------------------------------------------------------------------------------------------|

| 名称 <sup>(2) (3)</sup> | 番号  |                   |                                                                                           |

| ^OE2#                 | 12  | I                 | CLK2 を制御するアクティブ Low 入力。内部プルアップ抵抗。<br>0 = 出力有効、1 = 出力無効                                    |

| LOS#                  | 13  | O                 | 入力クロック信号喪失アクティブ Low/未接続。オーブンドレイン。外部プルアップ抵抗が必要です。<br>Low = 無効な入力クロック。<br>High = 有効な入力クロック。 |

| vZOUT_SEL             | 11  | I                 | LP-HCSL 差動クロック出力のインピーダンス選択。内部プルダウン抵抗。<br>Low = 85Ω。<br>High = 100Ω。                       |

| NC                    | 4、5 | NC                | 未接続。                                                                                      |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源、NC = 未接続

(2) 「^」プレフィックスが付いたピンは内部プルアップ抵抗を内蔵しています。「v」プレフィックスが付いたピンは内部プルダウン抵抗を内蔵しています。「^v」プレフィックスが付いたピンは内部プルアップ抵抗と内部プルダウン抵抗の両方を内蔵しており、ピンが未接続の場合は中間レベルが選択されます。

(3) 「#」記号はアクティブ Low を示します。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|           |                                | 最小値  | 最大値  | 単位 |

|-----------|--------------------------------|------|------|----|

| $V_{DDX}$ | 任意の VDD ピンの供給電圧                | -0.3 | 3.63 | V  |

| $V_{IN}$  | CLKIN およびデジタル入力ピンの入力電圧         | -0.3 | 3.63 | V  |

| $I_{OUT}$ | 出力電流 - 連続 (CLKOUT)             |      | 30   | mA |

|           | 出力電流 - 連続 (SMB_DATA, SBI_OUT)  |      | 25   | mA |

|           | 出力電流 - サージ (CLKOUT)            |      | 60   | mA |

|           | 出力電流 - サージ (SMB_DATA, SBI_OUT) |      | 50   | mA |

| $T_S$     | 保存温度                           | -65  | 150  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|             |      |                                                          | 値          | 単位 |

|-------------|------|----------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠 <sup>(1)</sup>    | $\pm 2000$ | V  |

|             |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | $\pm 500$  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|            |                        |  | 最小値  | 公称値 | 最大値  | 単位 |

|------------|------------------------|--|------|-----|------|----|

| $T_J$      | 接合部温度                  |  |      | 125 |      | °C |

| $T_A$      | 周囲温度                   |  | -40  | 105 |      | °C |

| $V_{DD}$   | 電源電圧                   |  | 2.97 | 3.3 | 3.6  | V  |

|            |                        |  | 1.71 | 1.8 | 1.89 | V  |

| $V_{IN}$   | CLKIN およびデジタル入力ピンの入力電圧 |  | -0.3 | 3.6 |      | V  |

| $t_{ramp}$ | 電源立ち上げ時間               |  | 0.05 |     | 5    | ms |

### 6.4 熱情報

| パッケージ          | ピン | 熱評価基準 <sup>(1)</sup> |                |           |          |          |                | 単位   |

|----------------|----|----------------------|----------------|-----------|----------|----------|----------------|------|

|                |    | $R_{θJA}$            | $R_{θJC(top)}$ | $R_{θJB}$ | $Ψ_{JT}$ | $Ψ_{JB}$ | $R_{θJC(bot)}$ |      |

| NPP0080 (TLGA) | 80 | 33.1                 | 31.9           | 16.2      | 0.5      | 16.0     | 1.8            | °C/W |

| RKP0040 (VQFN) | 40 | 33.6                 | 24.6           | 13.8      | 0.4      | 13.7     | 4.2            | °C/W |

| REX0028 (VQFN) | 28 | 44.2                 | 36.8           | 20.6      | 0.9      | 20.6     | 5.9            | °C/W |

| REY0020 (VQFN) | 20 | 46.4                 | 50.4           | 20.3      | 1.1      | 20.3     | 6.5            | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                               | テスト条件                          | 最小値                                                                   | 標準値   | 最大値  | 単位    |   |

|-------------------------------------|--------------------------------|-----------------------------------------------------------------------|-------|------|-------|---|

| <b>クロック入力の要件</b>                    |                                |                                                                       |       |      |       |   |

| $V_{IN, cross}$                     | クロック入力クロッシング ポイントの電圧           | 100                                                                   | 1400  | 1400 | mV    |   |

| $DC_{IN}$                           | クロック入力デューティ サイクル               | 45                                                                    | 55    | 55   | %     |   |

| $V_{IN}$                            | 差動クロック入力振幅 (差動ピーク・ピーク電圧の半分)    | 200                                                                   | 2000  | 2000 | mV    |   |

|                                     | $f_0 \leq 300\text{MHz}$       | 250                                                                   | 2000  | 2000 | mV    |   |

| $dV_{IN}/dt$                        | クロックの入力スルーレート                  | 差動波形の -150mV から +150mV までを基準に測定                                       | 0.6   |      | V/ns  |   |

| <b>クロック出力の特性 - 100MHz 85Ω PCIe</b>  |                                |                                                                       |       |      |       |   |

| $V_{OH,AC}$                         | 出力電圧 High                      | DB2000QL AC テスト負荷 <sup>(6)</sup>                                      | 670   | 820  | mV    |   |

| $V_{OL,AC}$                         | 出力電圧 Low                       |                                                                       | -100  | 100  | mV    |   |

| $V_{max,AC}$                        | 出力最大電圧 (オーバーシュートを含む)           |                                                                       | 670   | 920  | mV    |   |

| $V_{min,AC}$                        | 出力最小電圧 (アンダーシュートを含む)           |                                                                       | -100  | 100  | mV    |   |

| $V_{OH,DC}$                         | DC テスト負荷時の出力高電圧                | DB2000QL DC テスト負荷 <sup>(2)</sup>                                      | 225   | 270  | mV    |   |

| $V_{OL,DC}$                         | DC テスト負荷時の出力低電圧                |                                                                       | 10    | 150  | mV    |   |

| $V_{ovs,DC}$                        | DC テスト負荷時の出力オーバーシュート電圧         |                                                                       |       | 75   | mV    |   |

| $V_{uds,DC}$                        | DC テスト負荷時の出力アンダーシュート電圧         |                                                                       | -75   |      | mV    |   |

| $Z_{diff}$                          | 差動出力インピーダンス                    | $V_{OL}/V_{OH}$ にて測定、 $V_{DD} = 3.3\text{V}$                          | 80.75 | 85   | 89.25 | Ω |

|                                     |                                | $V_{OL}/V_{OH}$ にて測定、 $V_{DD} = 1.8\text{V}$                          | 81    | 85   | 90    | Ω |

| $Z_{diff-crossing}$                 | 差動出力インピーダンス - クロッシング           | 遷移中に測定                                                                | 68    | 85   | 102   | Ω |

| $dV/dt$                             | 出力スルーレート                       | 差動波形の -150mV から +150mV までを基準に測定します。最小スルーレート <sup>(6) (7)</sup>        | 1.5   | 2.2  | V/ns  |   |

|                                     |                                | 差動波形の -150mV から +150mV までを基準に測定します。低速スルーレート <sup>(6) (7)</sup>        | 1.8   | 2.6  | V/ns  |   |

|                                     |                                | 差動波形の -150mV から +150mV までを基準に測定します。高スルーレート (デフォルト) <sup>(6) (7)</sup> | 2     | 2.9  | V/ns  |   |

|                                     |                                | 差動波形の -150mV から +150mV までを基準に測定します。最大スルーレート <sup>(6) (7)</sup>        | 2.4   | 4    | V/ns  |   |

| $\Delta dV/dt$                      | 立ち上がりエッジレートと立ち下がりエッジレートの一一致    | DB2000QL AC テスト負荷 <sup>(6)</sup>                                      |       | 10   | %     |   |

| $DCD$                               | デューティ サイクルの歪み                  | 差動波形上で測定します。入力デューティ サイクル = 50% <sup>(6)</sup>                         | -1    | 1    | %     |   |

| $V_{cross,AC}$                      | 絶対交差点電圧                        | DB2000QL AC テスト負荷 <sup>(6)</sup>                                      | 250   | 550  | mV    |   |

| $V_{cross,DC}$                      | 絶対交差点電圧                        | DB2000QL DC テスト負荷 <sup>(2)</sup>                                      | 130   | 200  | mV    |   |

| $\Delta V_{cross,A_C}$              | クロック エッジ全体における $V_{cross}$ の変動 | DB2000QL AC テスト負荷 <sup>(6)</sup>                                      |       | 140  | mV    |   |

| $\Delta V_{cross-DC}$               | クロック エッジ全体における $V_{cross}$ の変動 | DB2000QL DC テスト負荷 <sup>(2)</sup>                                      |       | 35   | mV    |   |

| $ V_{RB} $                          | PCIe で定義されるリンクギング バック電圧の絶対値    | DB2000QL AC テスト負荷 <sup>(6)</sup>                                      | 100   |      | mV    |   |

| $t_{stable}$                        | $V_{RB}$ が許容されるまでの時間           | DB2000QL AC テスト負荷 <sup>(6)</sup>                                      | 500   |      | ps    |   |

| <b>クロック出力の特性 - 100MHz 100Ω PCIe</b> |                                |                                                                       |       |      |       |   |

| $V_{max}$                           | オーバーシュートを含む出力電圧 High           | PCIe AC テスト負荷 <sup>(1)</sup>                                          | 670   | 920  | mV    |   |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ              |                               | テスト条件                                                          | 最小値  | 標準値 | 最大値 | 単位       |

|--------------------|-------------------------------|----------------------------------------------------------------|------|-----|-----|----------|

| $V_{min}$          | アンダーシュートを含む出力低電圧              | PCIe AC テスト負荷 <sup>(1)</sup>                                   | -100 | 100 | 100 | mV       |

| $V_{OH}$           | 出力電圧 High                     | PCIe AC テスト負荷 <sup>(1)</sup>                                   | 670  | 820 | 820 | mV       |

| $V_{OL}$           | 出力電圧 Low                      | PCIe AC テスト負荷 <sup>(1)</sup>                                   | -100 | 100 | 100 | mV       |

| $Z_{diff}$         | 差動出力 DC インピーダンス               | $V_{DD} = 3.3V$                                                | 95   | 100 | 105 | $\Omega$ |

|                    |                               | $V_{DD} = 1.8V$                                                | 95   | 100 | 105 | $\Omega$ |

| $dV/dt$            | 出力スルーレート                      | 差動波形の -150mV から +150mV までを基準に測定します。最小スルーレート <sup>(1) (7)</sup> | 1.5  | 2.2 | 2.2 | V/ns     |

|                    |                               | 差動波形の -150mV から +150mV までを基準に測定します。低速スルーレート <sup>(1) (7)</sup> | 1.8  | 2.6 | 2.6 | V/ns     |

|                    |                               | 差動波形の -150mV から +150mV までを基準に測定します。高速スルーレート <sup>(1) (7)</sup> | 2    | 2.9 | 2.9 | V/ns     |

|                    |                               | 差動波形の -150mV から +150mV までを基準に測定します。最大スルーレート <sup>(1) (7)</sup> | 2.4  | 4   | 4   | V/ns     |

| $\Delta dV/dt$     | 立ち上がりエッジレートと立ち下がりエッジレートの一一致   | PCIe AC テスト負荷 <sup>(1)</sup>                                   |      | 10  | 10  | %        |

| DCD                | デューティサイクルの歪み                  | 差動波形上で測定します。入力デューティサイクル = 50% <sup>(1)</sup>                   | -1   | 1   | 1   | %        |

| $V_{cross}$        | 絶対交差点電圧                       | PCIe AC テスト負荷 <sup>(1)</sup>                                   | 250  | 550 | 550 | mV       |

| $\Delta V_{cross}$ | クロックエッジ全体における $V_{cross}$ の変動 | PCIe AC テスト負荷 <sup>(1)</sup>                                   |      | 140 | 140 | mV       |

| $ V_{RB} $         | PCIe で定義されるリンクギングバック電圧の絶対値    | PCIe AC テスト負荷 <sup>(1)</sup>                                   | 100  |     |     | mV       |

| $t_{stable}$       | $V_{RB}$ が許容されるまでの時間          | PCIe AC テスト負荷 <sup>(1)</sup>                                   | 500  |     |     | ps       |

### クロック出力の特性 - 非 PCIe

|            |                               |                                                              |      |     |    |

|------------|-------------------------------|--------------------------------------------------------------|------|-----|----|

| $V_{OH}$   | 出力電圧 High                     | 出力スイングを 800mV に設定。 $f_0 = 156.25MHz$ または $312.5MHz$          | 720  | 880 | mV |

| $V_{OL}$   | 出力電圧 Low                      |                                                              | -120 | 120 | mV |

| $V_{OH}$   | 出力電圧 High                     | 出力スイングを 900mV に設定。 $f_0 = 156.25MHz$ または $312.5MHz$          | 780  | 980 | mV |

| $V_{OL}$   | 出力電圧 Low                      |                                                              | -120 | 120 | mV |

| $t_R, t_F$ | シングルエンド波形の立上り/立下り時間 (20%~80%) | 出力スイングを 800mV に設定。最速スルーレート。 $f_0 = 156.25MHz$ または $312.5MHz$ |      | 340 | ps |

|            |                               | 出力スイングを 900mV に設定。最速スルーレート。 $f_0 = 156.25MHz$ または $312.5MHz$ |      | 370 | ps |

| DCD        | デューティサイクルの歪み                  | 入力デューティサイクル = 50%                                            | -1   | 1   | %  |

### クロック出力の特性 - 100MHz 85Ω PCIe (LMKDB1120FS, LMKDB1108FS, LMKDB1104FS)

|              |                        |                                       |       |     |       |          |

|--------------|------------------------|---------------------------------------|-------|-----|-------|----------|

| $V_{OH,AC}$  | 出力電圧 High              | DB2000QL AC テスト負荷 <sup>(6)</sup>      | 670   | 820 | mV    |          |

| $V_{OL,AC}$  | 出力電圧 Low               |                                       | -100  | 100 | mV    |          |

| $V_{max,AC}$ | 出力最大電圧 (オーバーシュートを含む)   |                                       | 670   | 920 | mV    |          |

| $V_{min,AC}$ | 出力最小電圧 (アンダーシュートを含む)   |                                       | -100  | 100 | mV    |          |

| $V_{OH,DC}$  | DC テスト負荷時の出力高電圧        | DB2000QL DC テスト負荷 <sup>(2)</sup>      | 225   | 270 | mV    |          |

| $V_{OL,DC}$  | DC テスト負荷時の出力低電圧        |                                       | 10    | 150 | mV    |          |

| $V_{ovs,DC}$ | DC テスト負荷時の出力オーバーシュート電圧 |                                       |       | 75  | mV    |          |

| $V_{uds,DC}$ | DC テスト負荷時の出力アンダーシュート電圧 |                                       | -75   |     | mV    |          |

| $Z_{diff}$   | 差動出力インピーダンス            | $V_{OL}/V_{OH}$ にて測定、 $V_{DD} = 3.3V$ | 80.75 | 85  | 89.25 | $\Omega$ |

|              |                        | $V_{OL}/V_{OH}$ にて測定、 $V_{DD} = 1.8V$ | 81    | 85  | 90    | $\Omega$ |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                                      |                                       | テスト条件                                                                                                                       | 最小値   | 標準値   | 最大値   | 単位            |

|------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------|

| $Z_{\text{diff}}$                                          | 差動出力インピーダンス                           | $V_{\text{OL}}/V_{\text{OH}}$ にて測定、 $V_{\text{DD}} = 3.3\text{ V}$ , $T_{\text{A}} = 0^\circ\text{C}$ ~ $105^\circ\text{C}$ | 80.75 | 85    | 89.25 | $\Omega$      |

|                                                            |                                       | $V_{\text{OL}}/V_{\text{OH}}$ にて測定、 $V_{\text{DD}} = 1.8\text{ V}$ , $T_{\text{A}} = 0^\circ\text{C}$ ~ $105^\circ\text{C}$ | 81    | 85    | 90    | $\Omega$      |

| $Z_{\text{diff}}$                                          | 差動出力インピーダンス                           | 最小スイング、 $V_{\text{DD}} = 3.3\text{V}$                                                                                       | 80    | 88.5  |       | $\Omega$      |

| $Z_{\text{diff}}$                                          | 差動出力インピーダンス                           | 最大スイング、 $V_{\text{DD}} = 3.3\text{V}$                                                                                       | 86.5  | 106.5 |       | $\Omega$      |

| $Z_{\text{diff}}$                                          | 差動出力インピーダンス                           | 最小スイング、 $V_{\text{DD}} = 1.8\text{V}$                                                                                       | 80    | 89    |       | $\Omega$      |

| $Z_{\text{diff}}$                                          | 差動出力インピーダンス                           | 最大スイング、 $V_{\text{DD}} = 1.8\text{V}$                                                                                       | 88    | 112.5 |       | $\Omega$      |

| $Z_{\text{diff-crossing}}$                                 | 差動出力インピーダンス - クロッシング                  | 遷移中に測定                                                                                                                      | 68    | 85    | 102   | $\Omega$      |

| $dV/dt$                                                    | 出力スルーレート                              | 最小スイング。デフォルトのスルーレートの設定                                                                                                      | 2.4   | 2.85  |       | $\text{V/ns}$ |

| $dV/dt$                                                    | 出力スルーレート                              | 最大スイング。デフォルトのスルーレートの設定                                                                                                      | 3.5   | 4.8   |       | $\text{V/ns}$ |

| $dV/dt$                                                    | 出力スルーレート                              | 差動波形の $-150\text{mV}$ から $+150\text{mV}$ までを基準に測定します。最小スルーレート <sup>(6) (7)</sup>                                            | 1.3   | 2.2   |       | $\text{V/ns}$ |

|                                                            |                                       | 差動波形の $-150\text{mV}$ から $+150\text{mV}$ までを基準に測定します。低速スルーレート <sup>(6) (7)</sup>                                            | 2.5   | 3     |       | $\text{V/ns}$ |

|                                                            |                                       | 差動波形の $-150\text{mV}$ から $+150\text{mV}$ までを基準に測定します。高スルーレート (デフォルト) <sup>(6) (7)</sup>                                     | 3     | 3.5   |       | $\text{V/ns}$ |

|                                                            |                                       | 差動波形の $-150\text{mV}$ から $+150\text{mV}$ までを基準に測定します。最大スルーレート <sup>(6) (7)</sup>                                            | 2.4   | 4     |       | $\text{V/ns}$ |

| $\Delta dV/dt$                                             | 立ち上がりエッジレートと立ち下がりエッジレートの一一致           | DB2000QL AC テスト負荷 <sup>(6)</sup>                                                                                            |       | 10    |       | %             |

| DCD                                                        | デューティ サイクルの歪み                         | 差動波形上で測定します。入力デューティ サイクル = 50% <sup>(6)</sup>                                                                               | -1    | 1     |       | %             |

| $V_{\text{cross,AC}}$                                      | 絶対交差点電圧                               | DB2000QL AC テスト負荷 <sup>(6)</sup>                                                                                            | 250   | 550   |       | $\text{mV}$   |

| $V_{\text{cross,DC}}$                                      | 絶対交差点電圧                               | DB2000QL DC テスト負荷 <sup>(2)</sup>                                                                                            | 130   | 200   |       | $\text{mV}$   |

| $\Delta V_{\text{cross,A}}$<br>$C$                         | クロック エッジ全体における $V_{\text{cross}}$ の変動 | DB2000QL AC テスト負荷 <sup>(6)</sup>                                                                                            |       | 140   |       | $\text{mV}$   |

| $\Delta V_{\text{cross-DC}}$                               | クロック エッジ全体における $V_{\text{cross}}$ の変動 | DB2000QL DC テスト負荷 <sup>(2)</sup>                                                                                            |       | 35    |       | $\text{mV}$   |

| $ V_{\text{RB}} $                                          | PCIe で定義されるリンクギング バック電圧の絶対値           | DB2000QL AC テスト負荷 <sup>(6)</sup>                                                                                            | 100   |       |       | $\text{mV}$   |

| $V_{\text{RB}}$                                            | DB800ZL で定義されるリンクギング バック電圧            | DB2000QL AC テスト負荷 <sup>(6)</sup>                                                                                            | -200  | 200   |       | $\text{mV}$   |

| $t_{\text{stable}}$                                        | $V_{\text{RB}}$ が許容されるまでの時間           | DB2000QL AC テスト負荷 <sup>(6)</sup>                                                                                            | 500   |       |       | $\text{ps}$   |

| クロック出力の特性 - 非 PCIe (LMKDB1120FS, LMKDB1108FS, LMKDB1104FS) |                                       |                                                                                                                             |       |       |       |               |

| $V_{\text{OH}}$                                            | 出力電圧 High                             | 出力スイングを $800\text{mV}$ に設定。 $f_0 = 156.25\text{MHz}$ または $312.5\text{MHz}$                                                  | 720   | 890   |       | $\text{mV}$   |

| $V_{\text{OL}}$                                            | 出力電圧 Low                              |                                                                                                                             | -120  | 120   |       | $\text{mV}$   |

| $V_{\text{OH}}$                                            | 出力電圧 High                             | 出力スイングを $900\text{mV}$ に設定。 $f_0 = 156.25\text{MHz}$ または $312.5\text{MHz}$                                                  | 780   | 980   |       | $\text{mV}$   |

| $V_{\text{OL}}$                                            | 出力電圧 Low                              |                                                                                                                             | -120  | 120   |       | $\text{mV}$   |

| $t_{\text{R}}, t_{\text{F}}$                               | シングルエンド波形の立上り/立下り時間 (20%~80%)         | 出力スイングを $800\text{mV}$ に設定。最速スルーレート。 $f_0 = 156.25\text{MHz}$ または $312.5\text{MHz}$                                         |       | 402   |       | $\text{ps}$   |

|                                                            |                                       | 出力スイングを $900\text{mV}$ に設定。最速スルーレート。 $f_0 = 156.25\text{MHz}$ または $312.5\text{MHz}$                                         |       | 419   |       | $\text{ps}$   |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                     |                   | テスト条件                                                                                                                                                   | 最小値     | 標準値        | 最大値  | 単位  |

|---------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|------|-----|

| DCD                       | デューティサイクルの歪み      | 入力デューティサイクル = 50%                                                                                                                                       | -1      | 1          | 1    | %   |

| 周波数およびタイミング特性             |                   |                                                                                                                                                         |         |            |      |     |

| $f_0$                     | 動作周波数             | 自動出力無効化機能が無効<br>自動出力無効化機能が有効                                                                                                                            | 1<br>25 | 400<br>400 | 400  | MHz |

| $t_{\text{startup}}$      | 起動時間              | コールドスタート。VDD が有効 (最終 VDD の 90%) になってから出力クロックが安定するまでの測定値 <sup>(3)</sup> 。VDD が有効になる前に入力クロックが供給される。<br>PWRGD_PWRDN# ピンを VDD に接続、 $f_0 \geq 100\text{MHz}$ | 0.4     | ms         | 0.4  | ms  |

|                           |                   | コールドスタート。VDD が有効 (最終 VDD の 90%) になってから出力クロックが安定するまでの測定値 <sup>(3)</sup> 。VDD が有効になる前に入力クロックが供給される。<br>PWRGD_PWRDN# ピンを VDD に接続、 $f_0 < 100\text{MHz}$    | 0.8     | ms         | 0.8  | ms  |

| $t_{\text{stable}}$       | クロック安定時間          | VDD が安定しています。PWRGD アサートから <sup>(4)</sup> 出力クロックが安定するまでの測定値、 $f_0 \geq 100\text{MHz}$ <sup>(3)</sup>                                                     | 0.4     | ms         | 0.4  | ms  |

|                           |                   | VDD が安定しています。PWRGD アサートから <sup>(4)</sup> 出力クロックが安定するまでの測定値、 $f_0 < 100\text{MHz}$ <sup>(3)</sup>                                                        | 0.8     | ms         | 0.8  | ms  |

| $t_{\text{PD}\#}$         | パワーダウン デアサート時間    | PWRDN# デアサートから <sup>(4)</sup> 出力クロックが安定するまでの測定値、 $f_0 \geq 100\text{MHz}$ <sup>(3)</sup>                                                                | 0.15    | ms         | 0.15 | ms  |

|                           |                   | PWRDN# デアサートから <sup>(4)</sup> 出力クロックが安定するまでの測定値、 $f_0 < 100\text{MHz}$ <sup>(3)</sup>                                                                   | 0.5     | ms         | 0.5  | ms  |

| $t_{\text{OE}}$           | 出力イネーブル/ディスエーブル時間 | OE アサート/デアサート <sup>(4)</sup> から出力クロックの開始/停止までの経過時間                                                                                                      | 4       | 10         | 10   | clk |

| $t_{\text{LOS-assert}}$   | LOS# アサート時間       | 入力クロックの喪失から LOS# アサートまでの経過時間、 $f_0 < 100\text{MHz}$                                                                                                     | 120     | ns         | 120  | ns  |

|                           |                   | 入力クロックの喪失から LOS# アサートまでの経過時間、 $f_0 \geq 100\text{MHz}$                                                                                                  | 120     | ns         | 120  | ns  |

| $t_{\text{LOS-deassert}}$ | LOS# デアサート時間      | 入力クロックの検出から LOS# デアサートまでの経過時間、 $f_0 < 100\text{MHz}$                                                                                                    | 340     | ns         | 340  | ns  |

|                           |                   | 入力クロック検出から LOS# デアサートまでの経過時間、 $f_0 \geq 100\text{MHz}$                                                                                                  | 105     | ns         | 105  | ns  |

| $t_{\text{AOD}}$          | 自動の出力ディスエーブル時間    | LOS# アサートから出力無効化 (両出力が Low/Low) までの経過時間、 $f_0 < 100\text{MHz}$                                                                                          | 0.07    | ns         | 0.07 | ns  |

|                           |                   | LOS# アサートから出力無効化 (両出力が Low/Low) までの経過時間、 $f_0 \geq 100\text{MHz}$                                                                                       | 0.07    | ns         | 0.07 | ns  |

| $t_{\text{AOE}}$          | 自動の出力イネーブル時間      | LOS# デアサートから出力クロックが安定するまでの経過時間。 $f_0 < 100\text{MHz}$ <sup>(3)</sup>                                                                                    | 115     | ns         | 115  | ns  |

|                           |                   | LOS# デアサートから出力クロックが安定するまでの経過時間、 $f_0 \geq 100\text{MHz}$ <sup>(3)</sup>                                                                                 | 22      | ns         | 22   | ns  |

| $t_{\text{switch}}$       | 時間の切り替え           | 2つの 100MHz 入力クロック間の切り替え (マルチプレクサのみ)                                                                                                                     | 70      | ns         | 70   | ns  |

| スキーおよびディレイ特性              |                   |                                                                                                                                                         |         |            |      |     |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ           |                     | テスト条件                                                       | 最小値 | 標準値   | 最大値   | 単位 |

|-----------------|---------------------|-------------------------------------------------------------|-----|-------|-------|----|

| $t_{skew}$      | 出力間スキー              | 同一バンク                                                       |     | 50    | ps    |    |

|                 |                     | バンクに関係なく                                                    |     | 50    | ps    |    |

|                 | 部品間スキー              |                                                             |     | 330   | ps    |    |

| $t_{PD}$        | 入出力間遅延              |                                                             |     | 1     | ns    |    |

| $\Delta t_{PD}$ | 入出力間遅延の変動           | 単一デバイスにおける温度および電圧条件                                         |     | 1.7   | ps/°C |    |

| <b>ジッタ特性</b>    |                     |                                                             |     |       |       |    |

| $J_{PCle1-CC}$  | PCIe Gen 1 の CC ジッタ | シングル クロック入力。入力スルーレート $\geq 3.5V/ns$ 。差動入力スイング $\geq 1600mV$ |     | 442.5 | fs    |    |

| $J_{PCle2-CC}$  | PCIe Gen 2 の CC ジッタ |                                                             |     | 39    | fs    |    |

| $J_{PCle3-CC}$  | PCIe Gen 3 の CC ジッタ |                                                             |     | 12.3  | fs    |    |

| $J_{PCle4-CC}$  | PCIe Gen 4 の CC ジッタ |                                                             |     | 12.3  | fs    |    |

| $J_{PCle5-CC}$  | PCIe Gen 5 の CC ジッタ |                                                             |     | 4.9   | fs    |    |

| $J_{PCle6-CC}$  | PCIe Gen 6 の CC ジッタ |                                                             |     | 3     | fs    |    |

| $J_{PCle7-CC}$  | PCIe Gen 7 の CC ジッタ |                                                             |     | 2.1   | fs    |    |

| $J_{PCle2-IR}$  | PCIe Gen 2 の IR ジッタ |                                                             |     | 33.8  | fs    |    |

| $J_{PCle3-IR}$  | PCIe Gen 3 の IR ジッタ |                                                             |     | 14.1  | fs    |    |

| $J_{PCle4-IR}$  | PCIe Gen 4 の IR ジッタ |                                                             |     | 14.5  | fs    |    |

| $J_{PCle5-IR}$  | PCIe Gen 5 の IR ジッタ |                                                             |     | 3.9   | fs    |    |

| $J_{PCle6-IR}$  | PCIe Gen 6 の IR ジッタ |                                                             |     | 3     | fs    |    |

| $J_{PCle7-IR}$  | PCIe Gen 7 の IR ジッタ |                                                             |     | 2.1   | fs    |    |

| $J_{PCle1-CC}$  | PCIe Gen 1 の CC ジッタ | シングル クロック入力。入力スルーレート $\geq 1.5V/ns$ 。差動入力スイング $\geq 800mV$  |     | 583.2 | fs    |    |

| $J_{PCle2-CC}$  | PCIe Gen 2 の CC ジッタ |                                                             |     | 51.3  | fs    |    |

| $J_{PCle3-CC}$  | PCIe Gen 3 の CC ジッタ |                                                             |     | 16    | fs    |    |

| $J_{PCle4-CC}$  | PCIe Gen 4 の CC ジッタ |                                                             |     | 16    | fs    |    |

| $J_{PCle5-CC}$  | PCIe Gen 5 の CC ジッタ |                                                             |     | 6.4   | fs    |    |

| $J_{PCle6-CC}$  | PCIe Gen 6 の CC ジッタ |                                                             |     | 3.9   | fs    |    |

| $J_{PCle7-CC}$  | PCIe Gen 7 の CC ジッタ |                                                             |     | 2.8   | fs    |    |

| $J_{PCle2-IR}$  | PCIe Gen 2 の IR ジッタ |                                                             |     | 41.9  | fs    |    |

| $J_{PCle3-IR}$  | PCIe Gen 3 の IR ジッタ |                                                             |     | 18.3  | fs    |    |

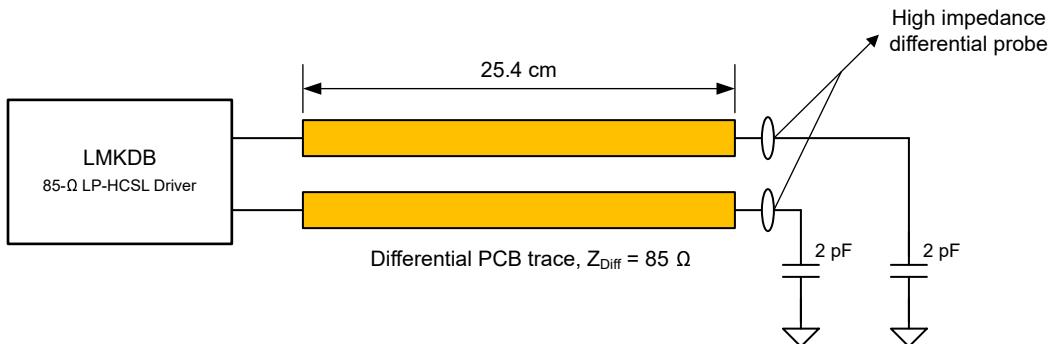

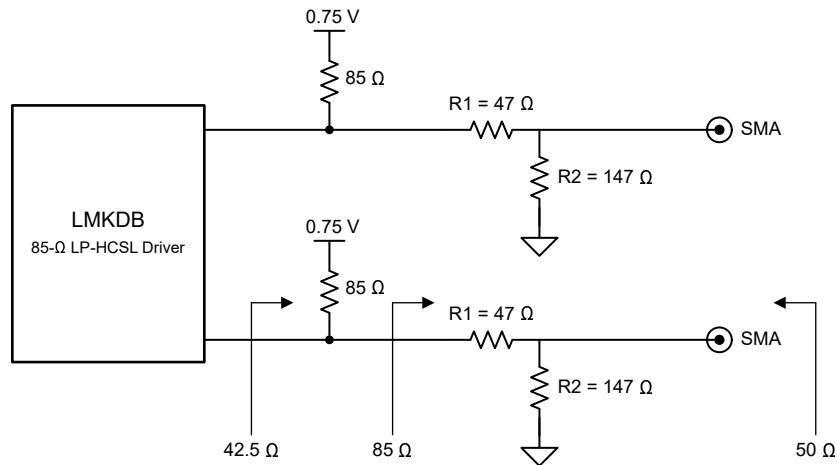

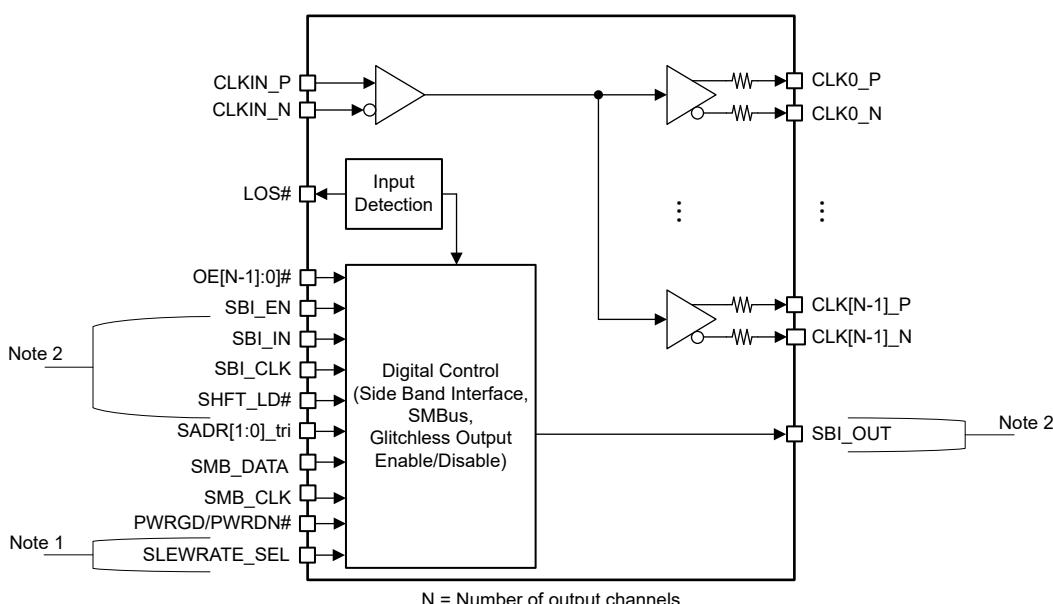

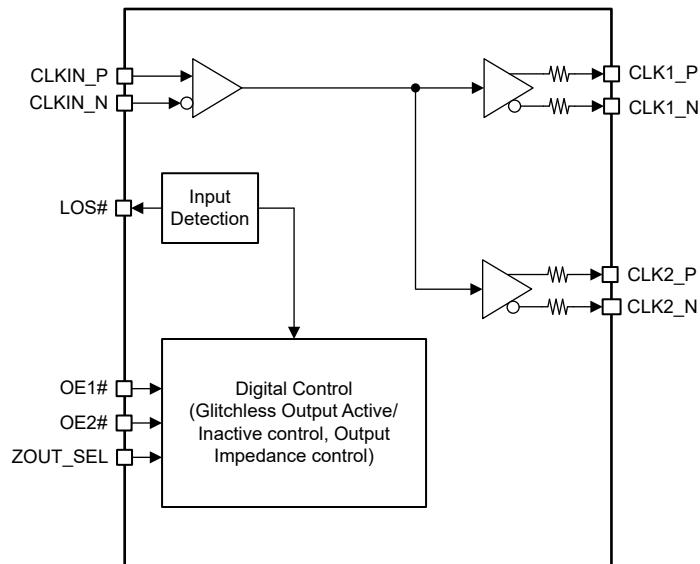

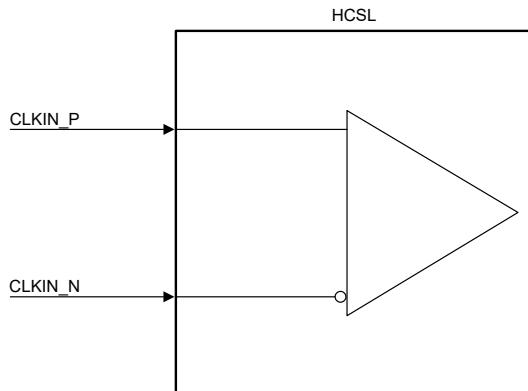

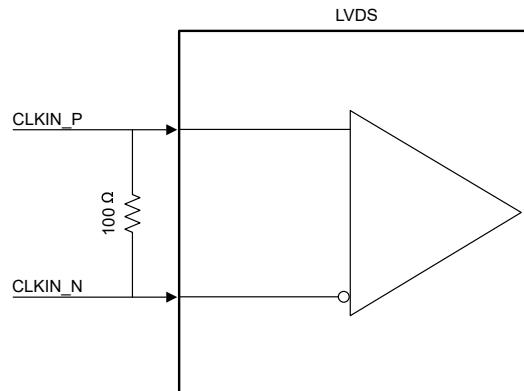

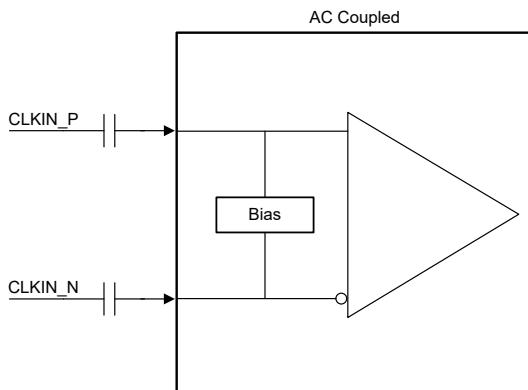

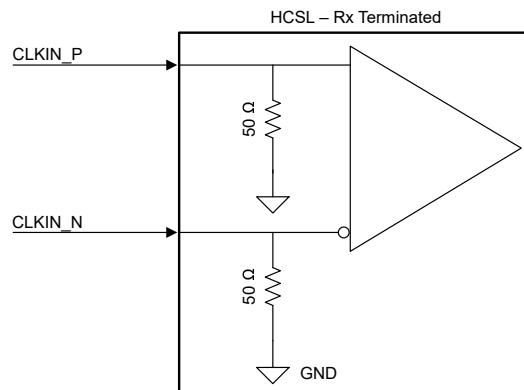

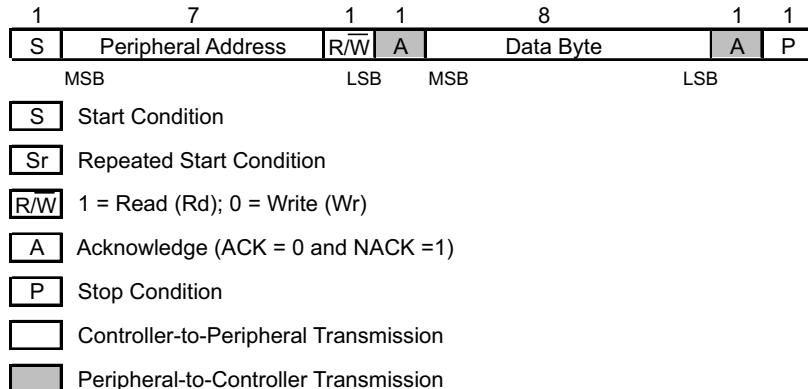

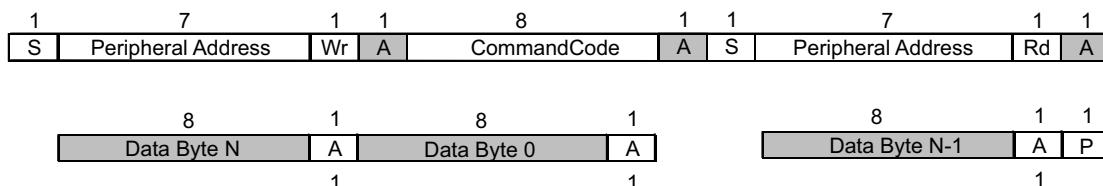

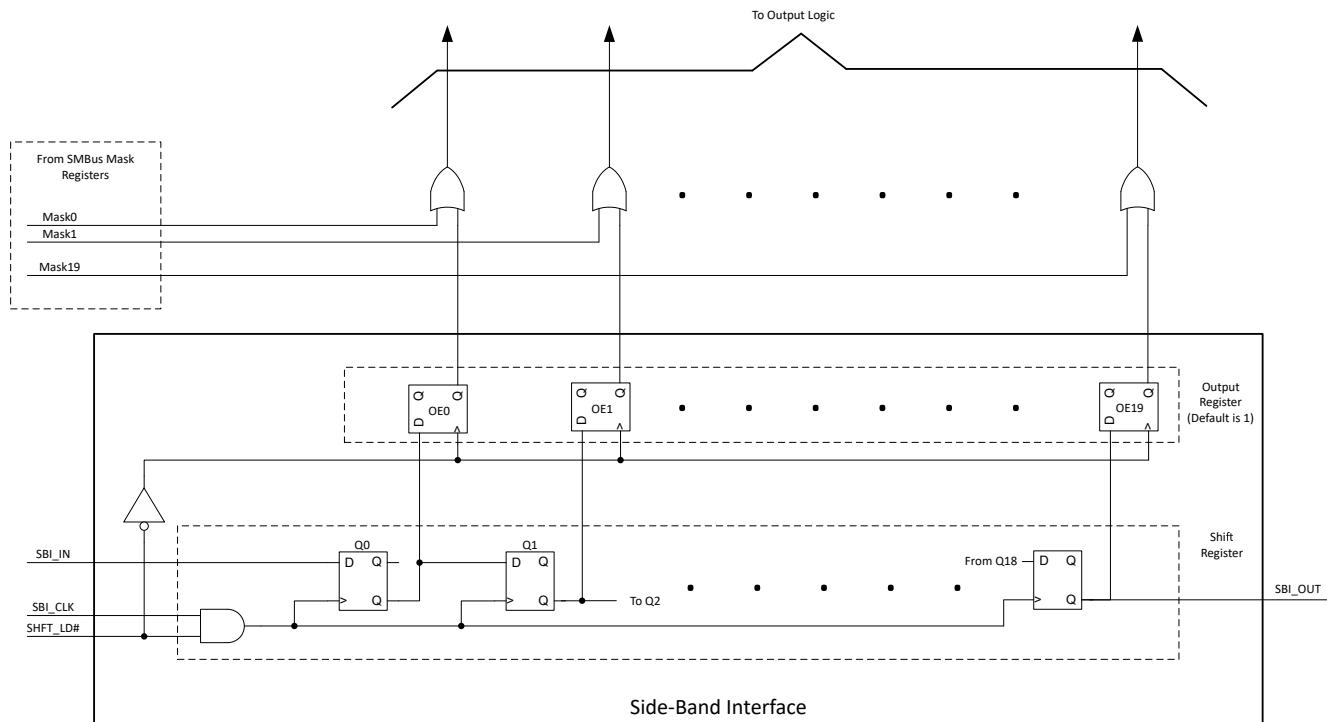

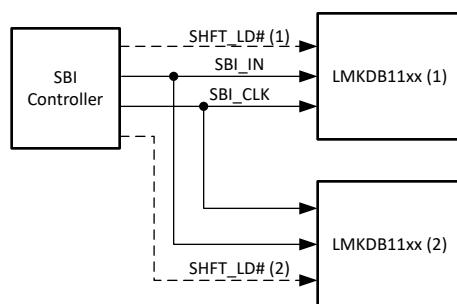

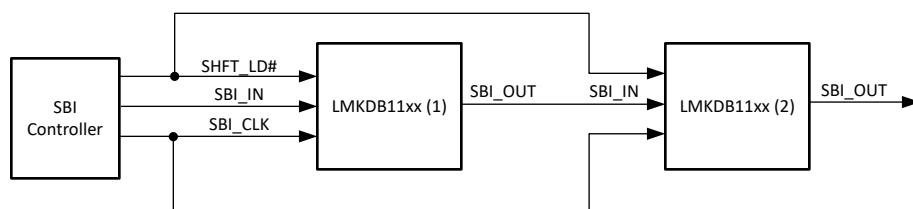

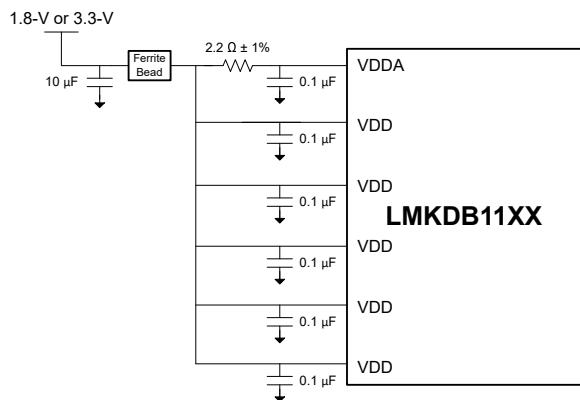

| $J_{PCle4-IR}$  | PCIe Gen 4 の IR ジッタ |                                                             |     | 18.9  | fs    |    |