# LMK5B12212 BAW VCO 搭載 イーサネットベースのネットワークアプリケーション用、1 DPLL、2 APLL、2 入力、12 出力、ネットワークシンクロナイザ

## 1 特長

- 超低ジッタ BAW VCO ベースのイーサネットクロック

- 4MHz 1 次ハイパスフィルタ (HPF) を使用した 625MHz で 13fs の RMS ジッタ (標準値)

- 4MHz 1 次 HPF を使用した 312.5MHz で 24fs の RMS ジッタ (標準値)

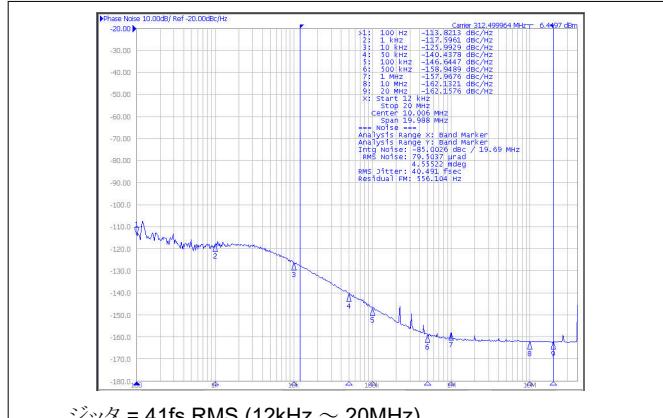

- 312.5MHz での RMS ジッタ 42fs (標準値) / 60fs (最大値)

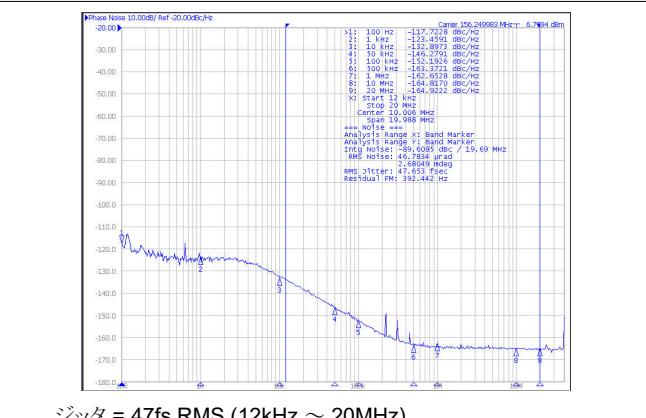

- 156.25MHz での RMS ジッタ 47fs (標準値) / 65fs (最大値)

- 2 つのアナログ位相ロックループ (APLL) による 1 つの高性能デジタル位相ロックループ (DPLL)

- 1mHz~4kHz にプログラム可能な DPLL ループフィルタの帯域幅

- 1ppt 未満の DCO 周波数調整ステップサイズ

- 2 差動またはシングルエンド DPLL 入力

- 入力周波数: 1Hz (1PPS) ~ 800MHz

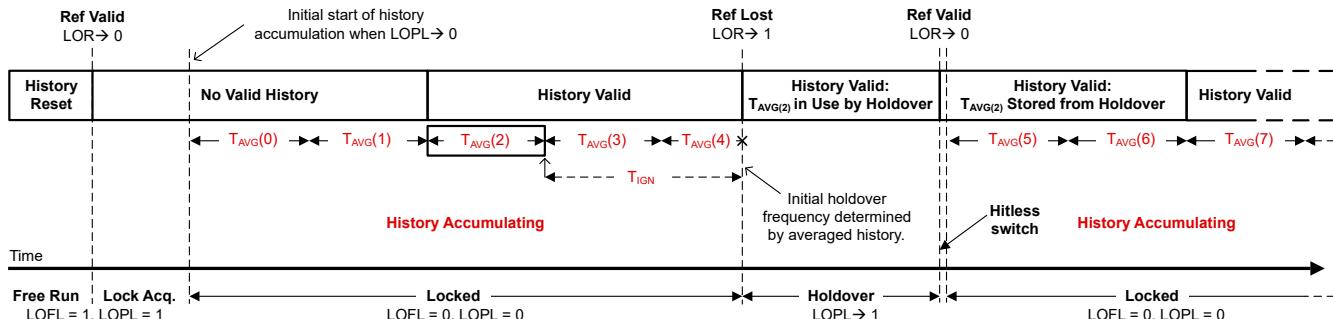

- デジタルホールドオーバー および ヒットレススイッチング

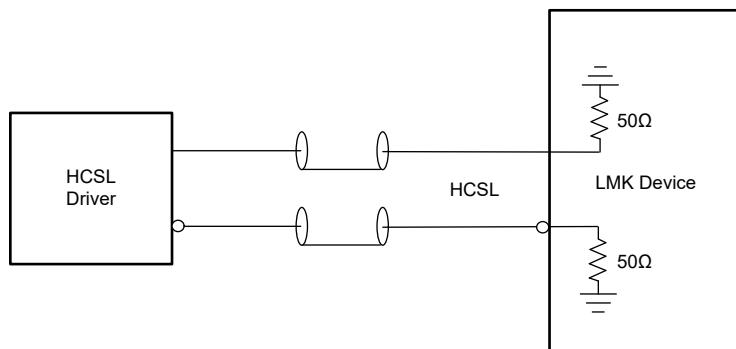

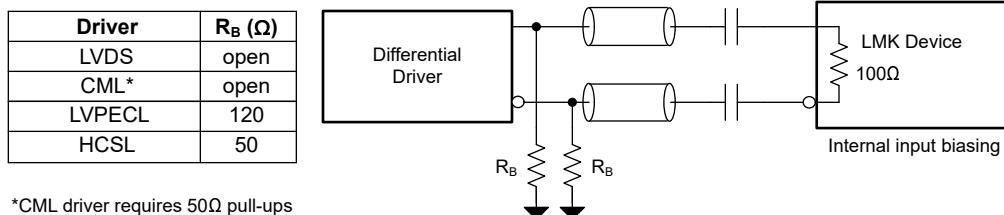

- プログラム可能な HSDS、AC-LVPECL、LVDS、HSCL 形式による、12 の差動出力

- 最大 16 つの合計周波数出力 (OUT0\_P/N、OUT1\_P/N、GPIO1、GPIO2 の 6 つの LVCMOS 周波数出力と、OUT2\_P/N から OUT11\_P/N までの 10 つの差動出力で構成した場合)

- プログラム可能なスイングおよび同相モードによる 1Hz (1PPS)~1250MHz の出力周波数

- PCIe Gen 1~6 準拠

- I<sup>2</sup>C または 3 線式 / 4 線式 SPI

## 2 アプリケーション

- 有線ネットワーク

- データセンター間 / データセンター内相互接続

- タイミングカード、ラインカード、固定カード (ピザボックス)

- SyncE (G.8262)、SONET/SDH (Stratum 3/3E、G.813、GR-1244、GR-253)、IEEE 1588 PTP センダリクロック

- 112G/224G PAM-4 SerDes 用ジッタクリーニング、ワンド減衰、基準クロック生成

- 100G~800G データセンター スイッチ、コアルータ、エッジルータ、WLAN

- データセンターおよびエンタープライズコンピューティング

- スマートネットワークインターフェイスカード (NIC)

- 光伝送ネットワーク (OTN G.709)

- ブロードバンド固定回線アクセス

- 産業用

- 試験および測定機器

- 医療用画像処理

## 3 説明

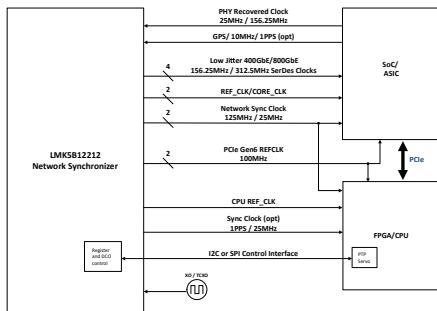

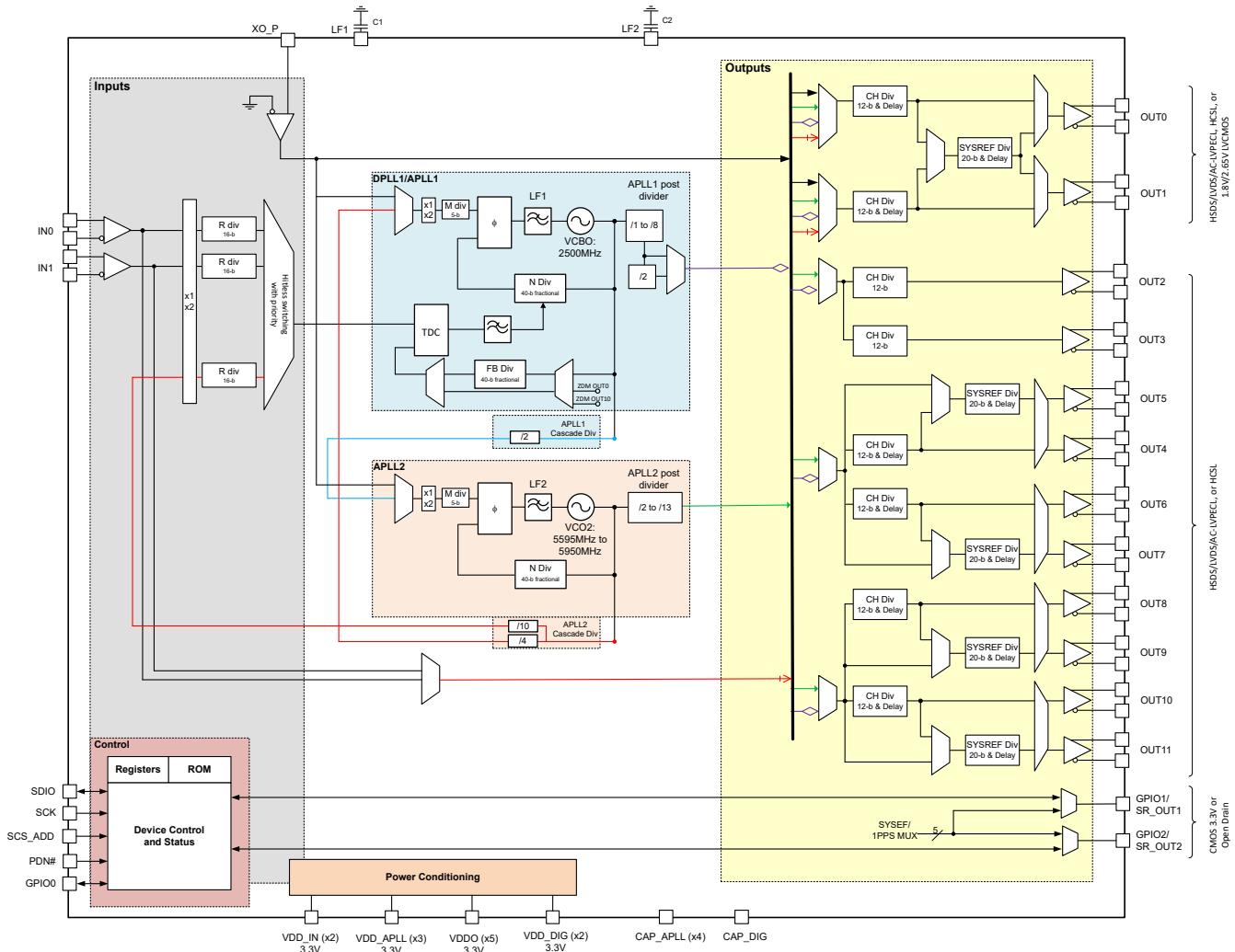

LMK5B12212 は、タイミング精度が 5ns 未満 (クラス D) のイーサネットベースのネットワーキング アプリケーションの厳しい要件を満たすように設計された、高性能ネットワークシンクロナイザおよびジッタクリーナです。

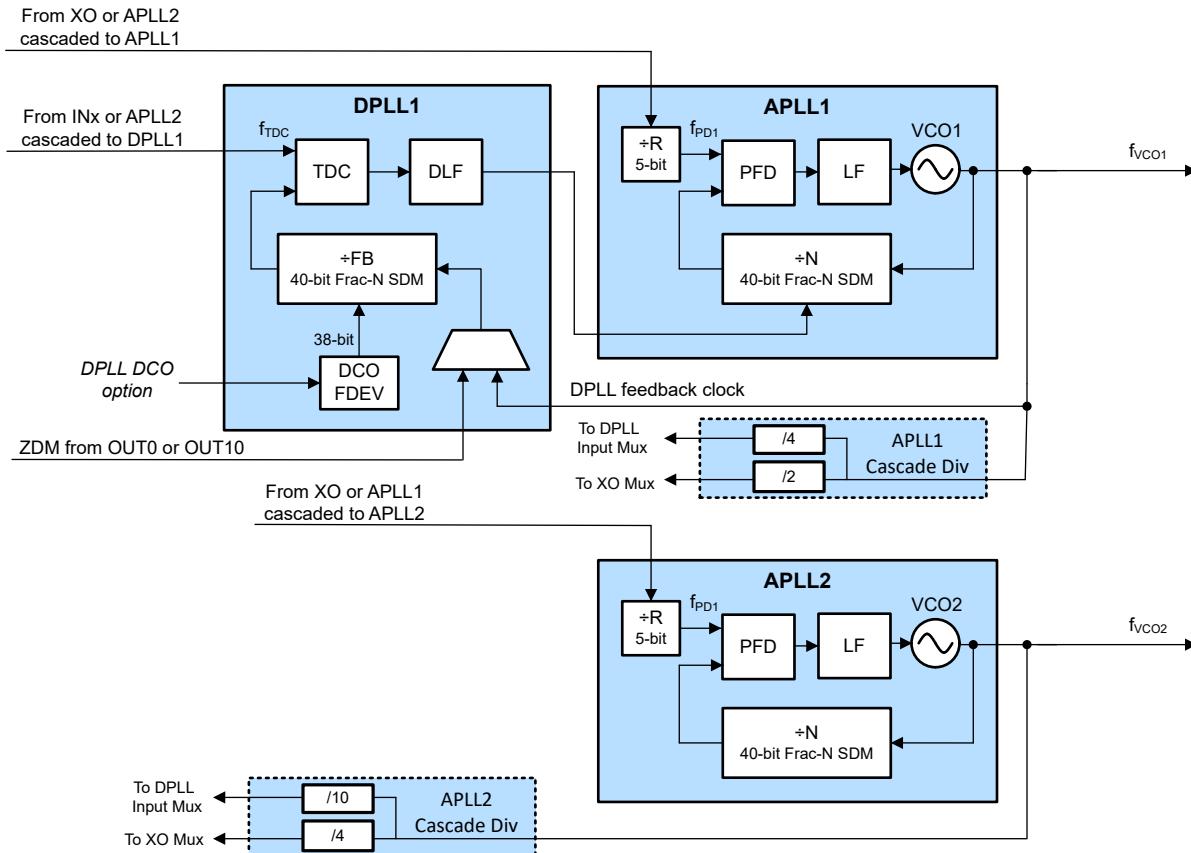

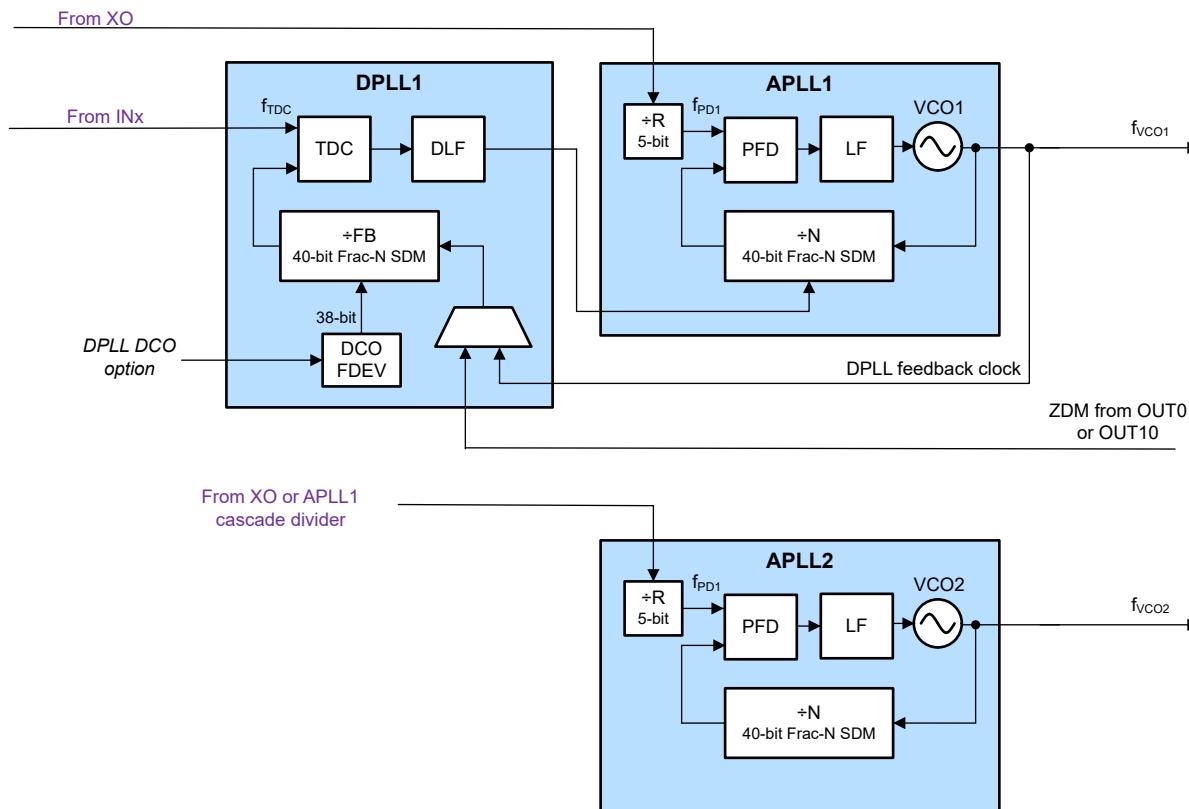

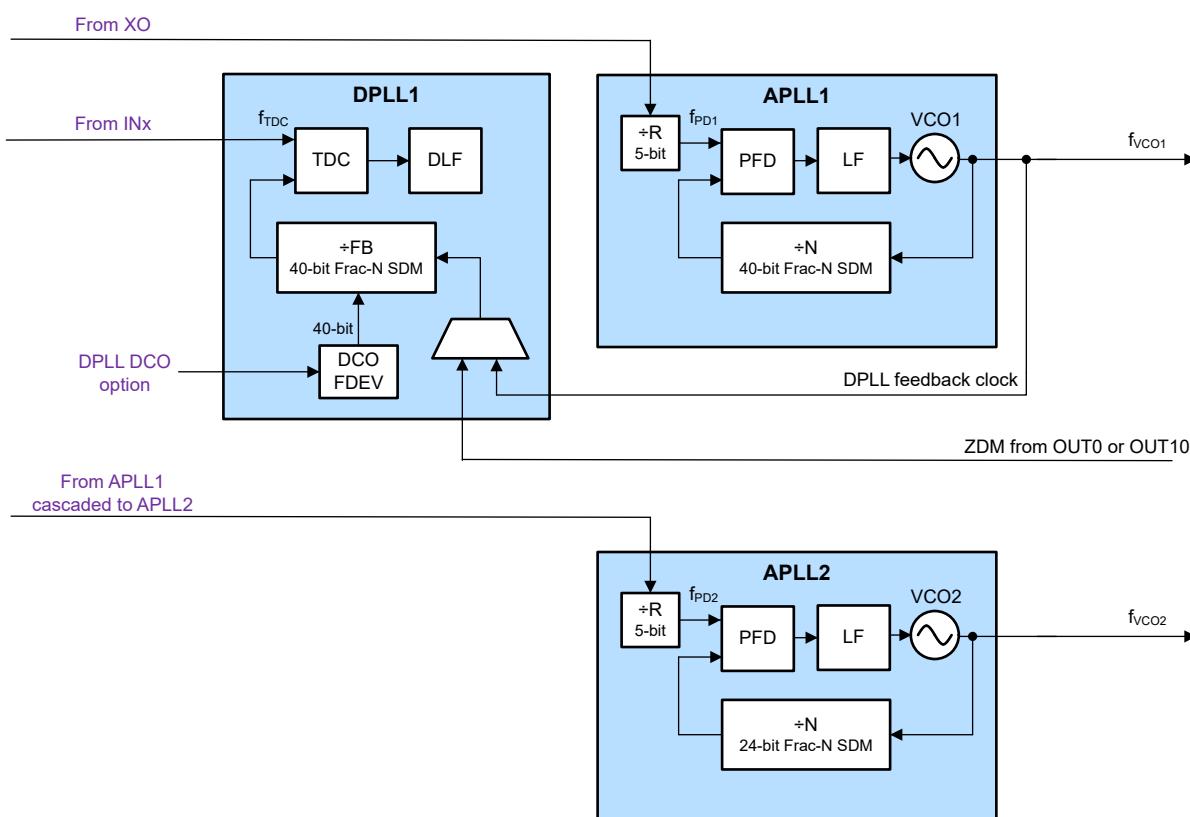

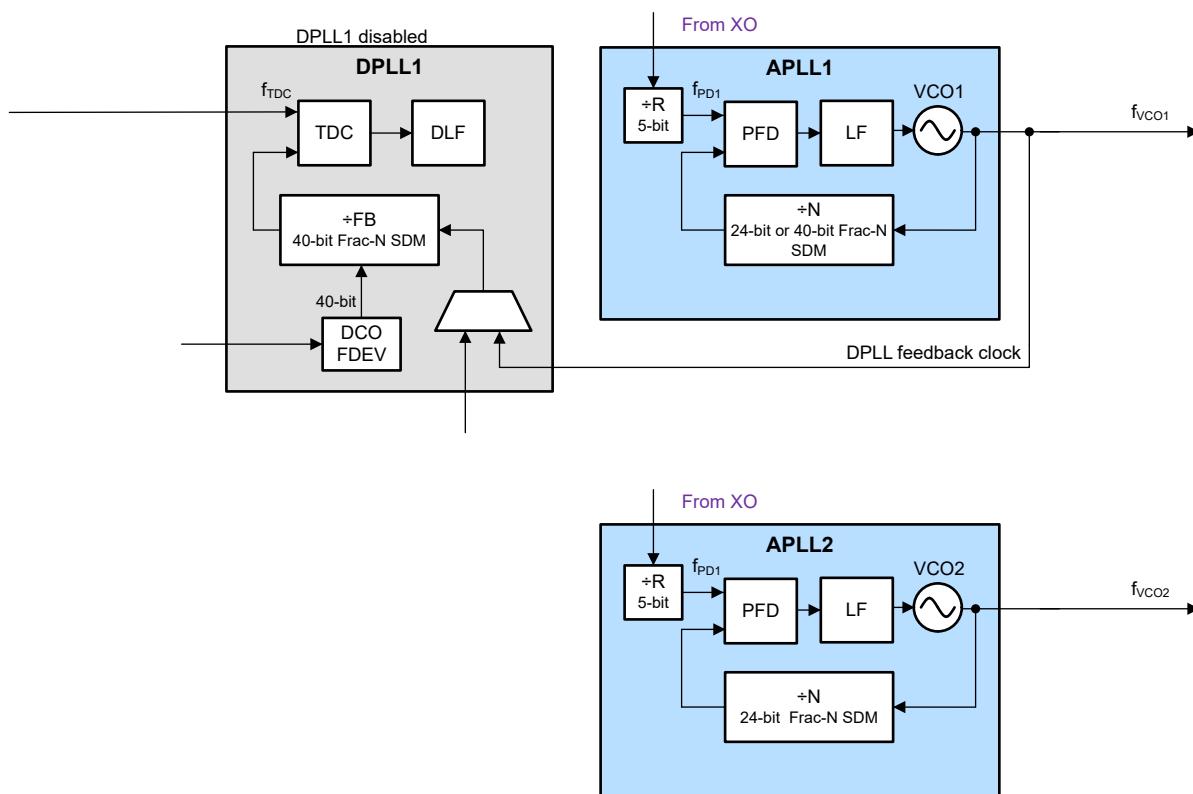

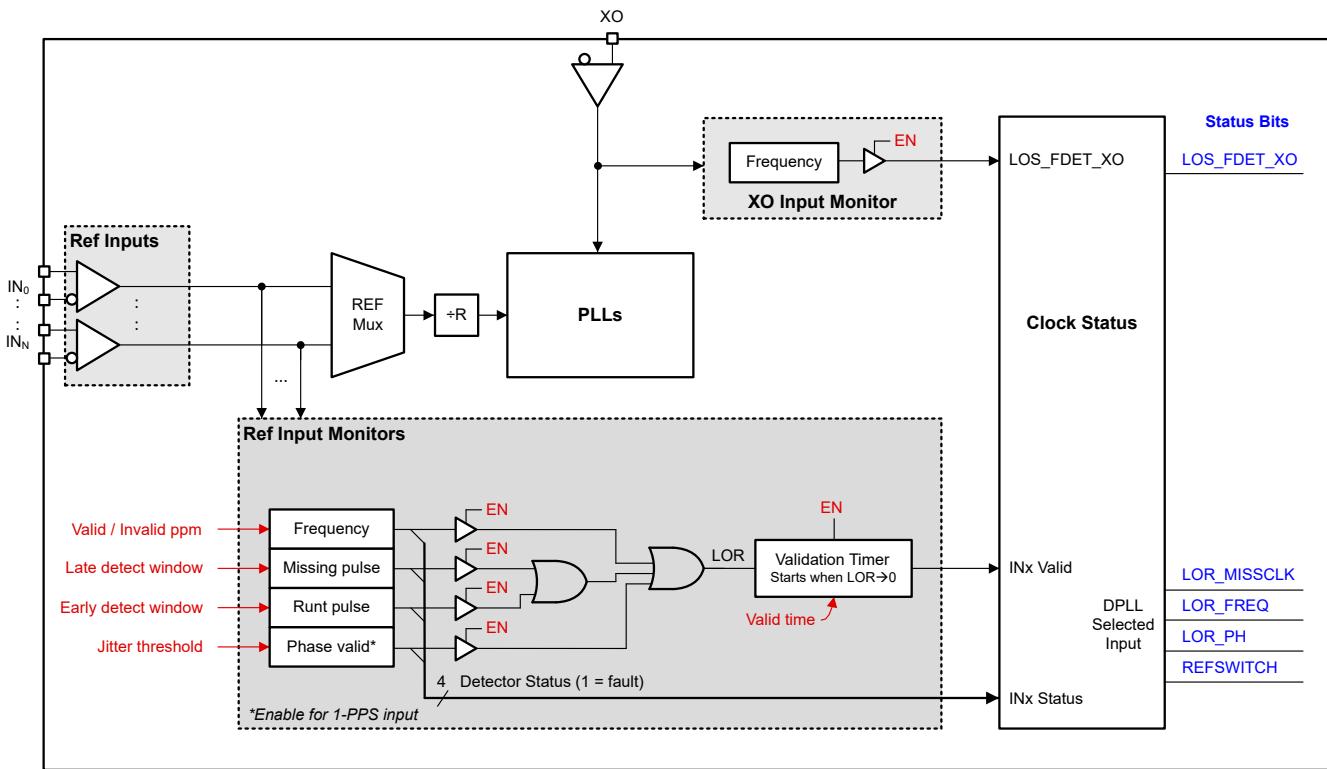

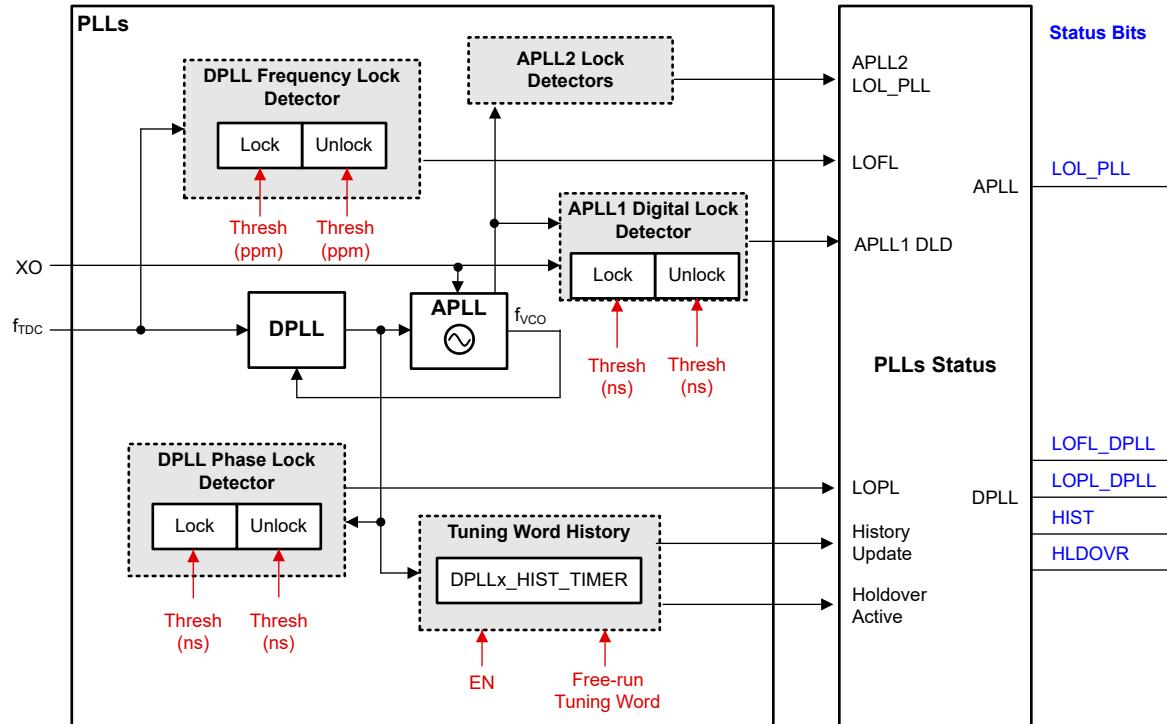

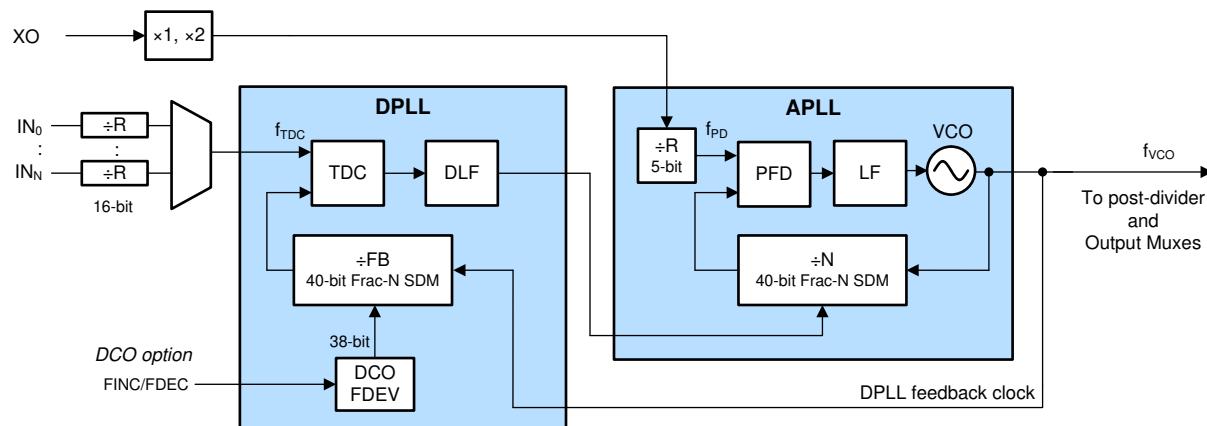

ネットワークシンクロナイザは、ループ帯域幅 (LBW) がプログラム可能で外部ループフィルタを使用しないヒットレススイッチングとジッタ減衰を実現するために、DPLL を内蔵しており、最大限の柔軟性と使いやすさを備えています。DPLL は、提供されたリファレンス入力に対して内蔵 APLL の位相をロックします。

APLL1 は、TI 独自のバルク音響波 (BAW) 技術を用いた超高性能 PLL (BAW APLL) を搭載しており、DPLL のリファレンス入力周波数やジッタ特性に関係なく、42fs (代表値)/60fs (最大値) の RMS ジッタで 312.5MHz の出力クロックを生成できます。APLL2 には、2 番目の周波数および/または同期ドメインのオプションがあります。

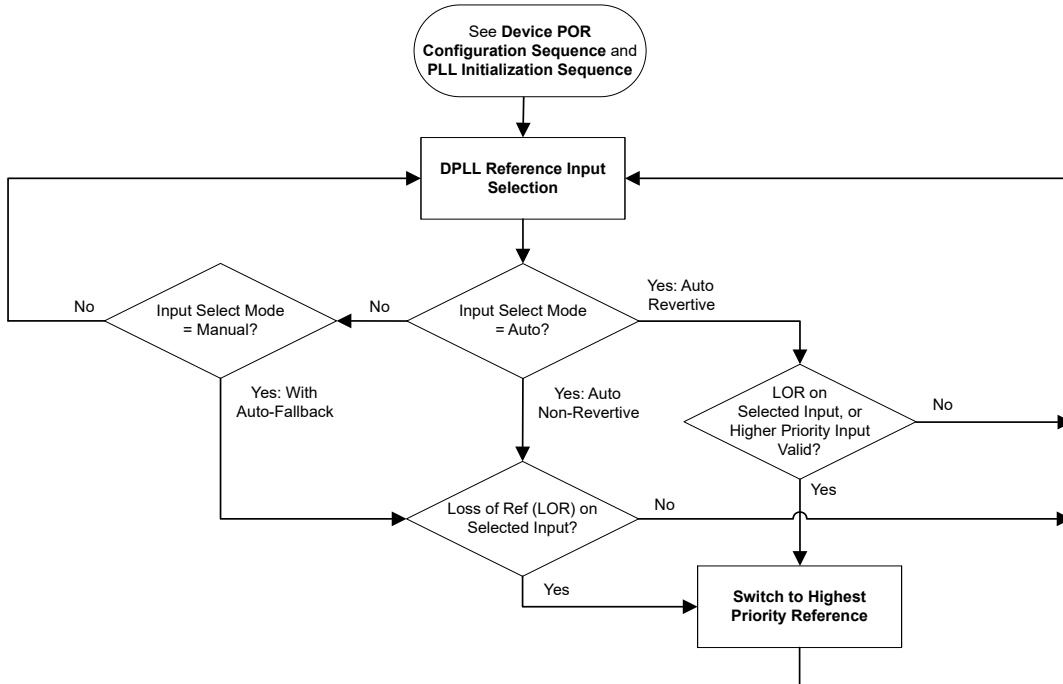

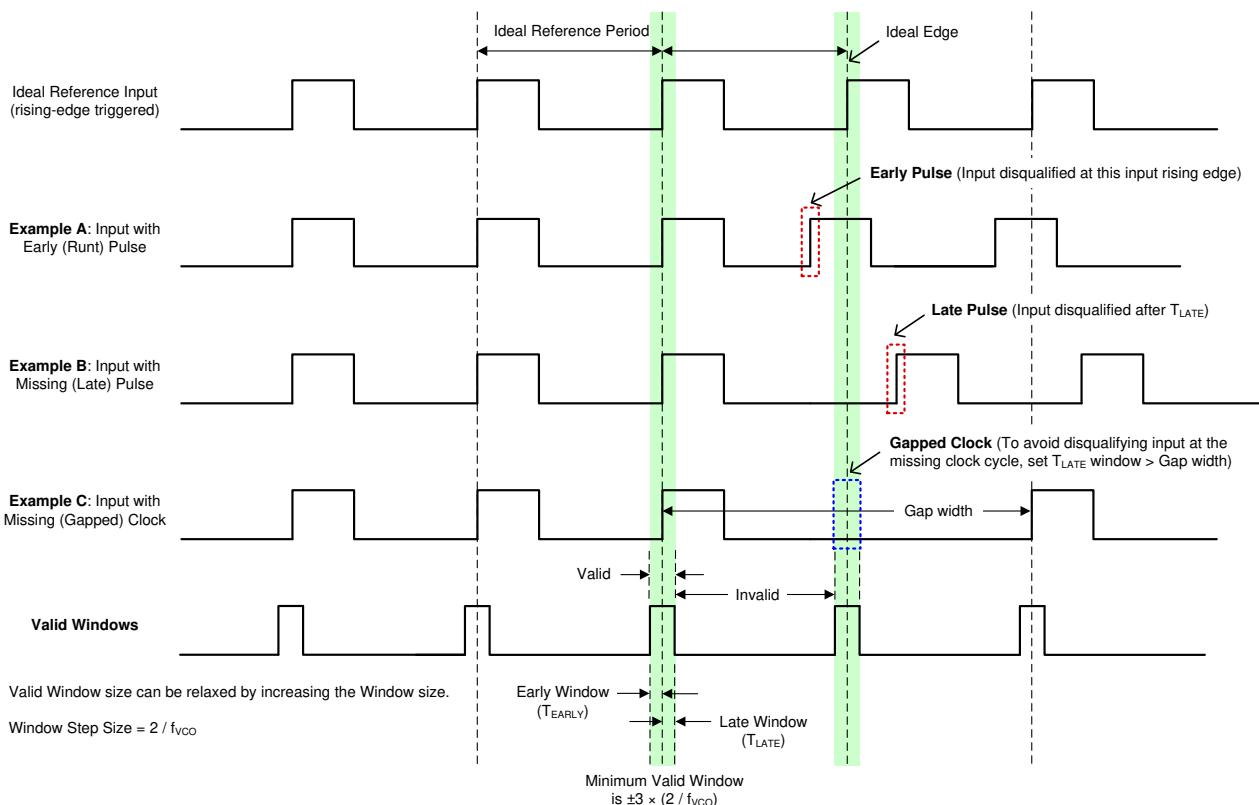

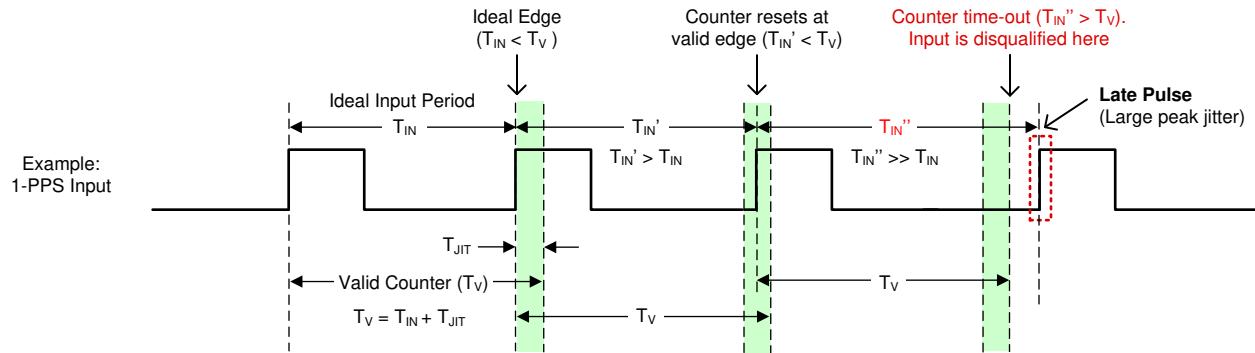

リファレンス検証回路は、DPLL 基準クロックを監視し、スイッチオーバーイベントを検出すると入力間でヒットレススイッチングを実行します。ゼロ遅延モード (ZDM) と位相キャンセルを有効にすることで、入力と出力の位相関係を制御できます。

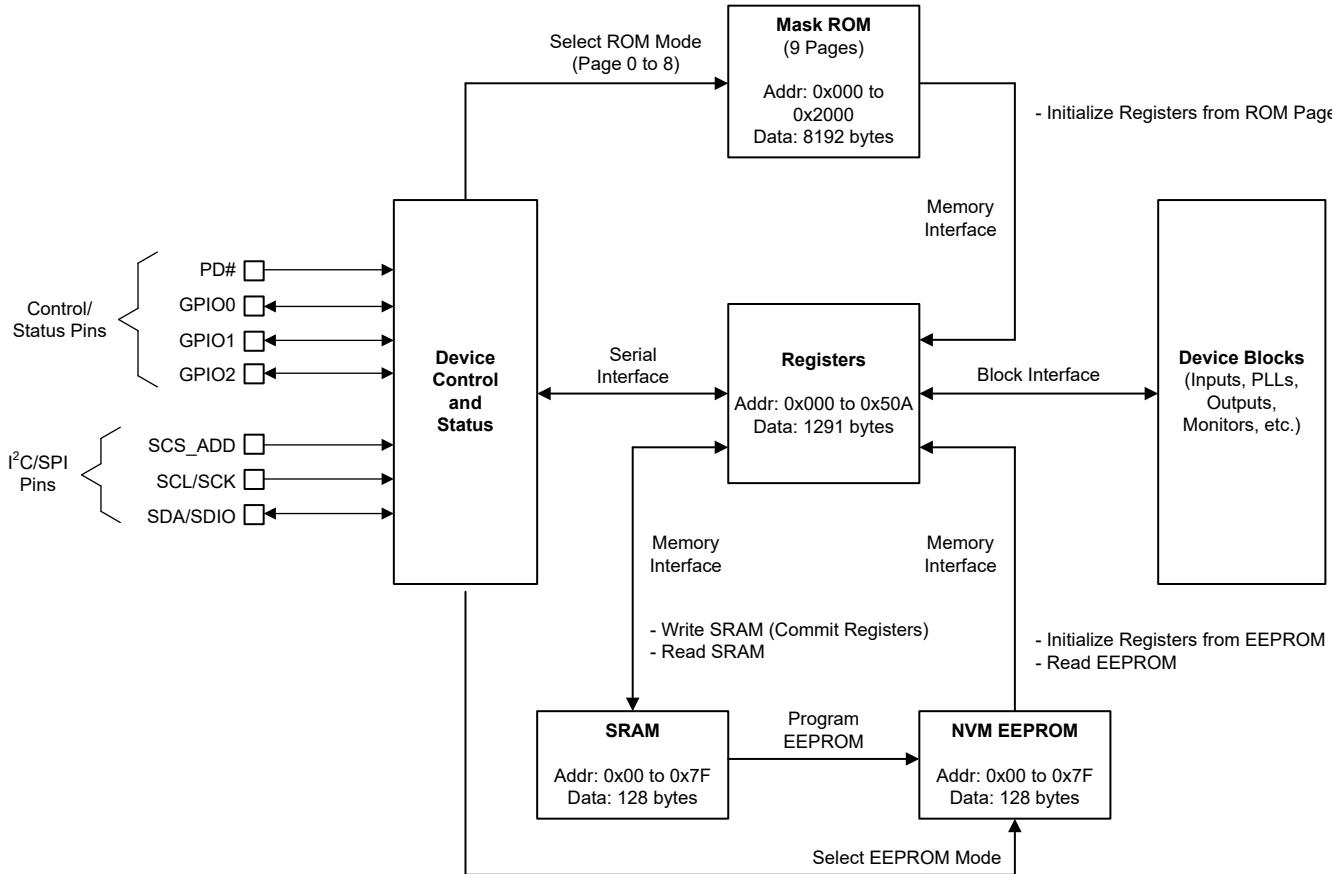

本デバイスは、I<sup>2</sup>C または SPI インターフェイスを介して完全にプログラム可能です。内蔵 EEPROM を使用して、システムの起動クロックをカスタマイズできます。また、このデバイスには出荷時デフォルトの ROM プロファイルもフォールバックオプションとして用意されています。

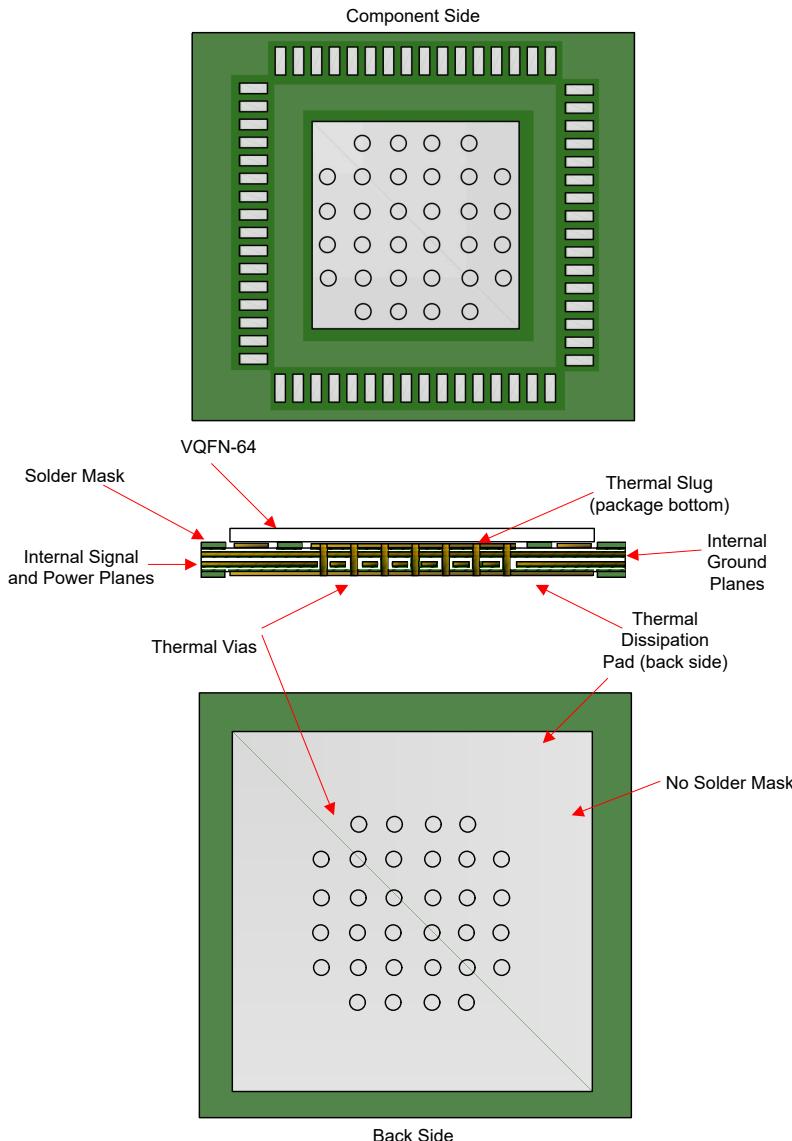

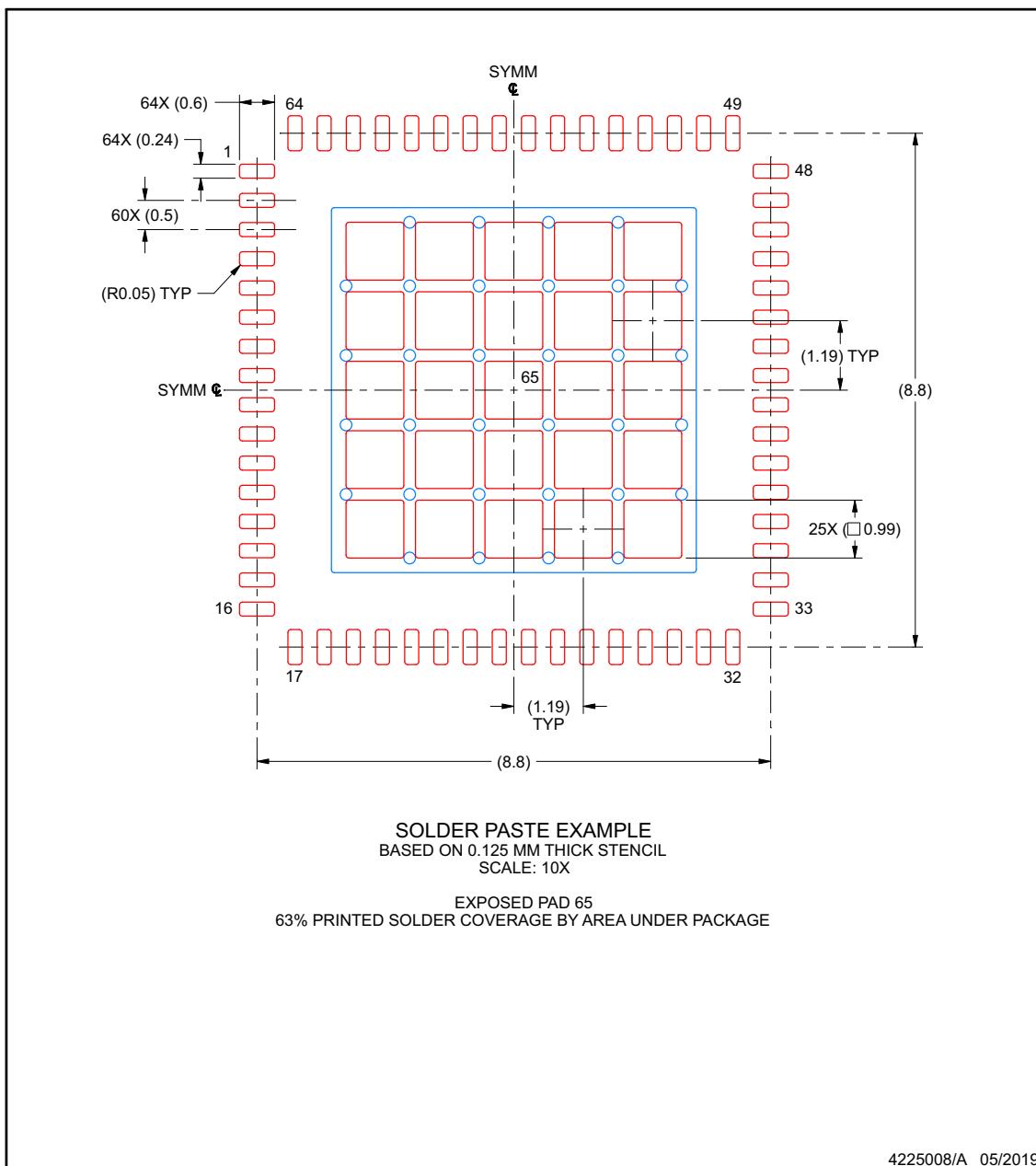

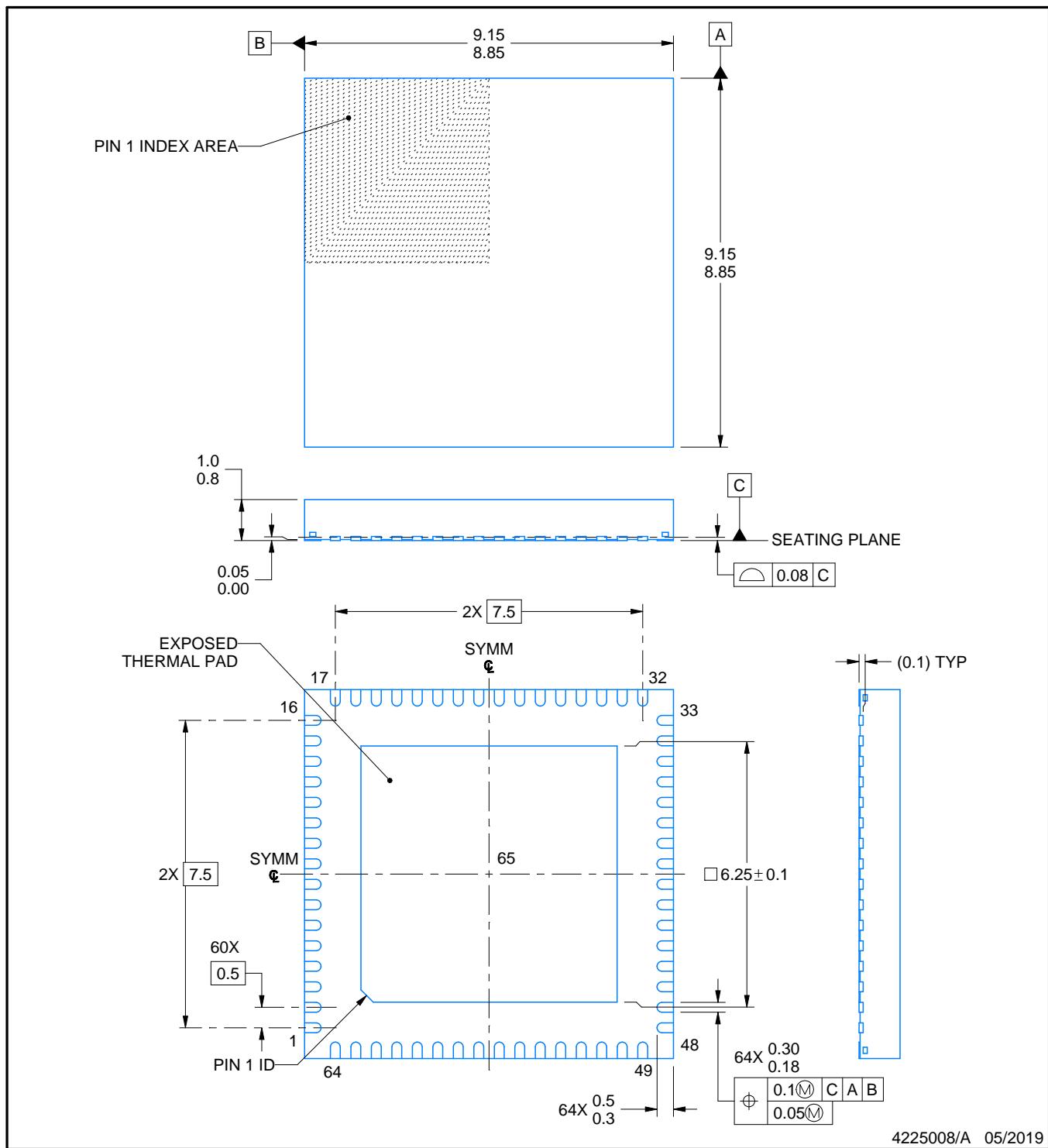

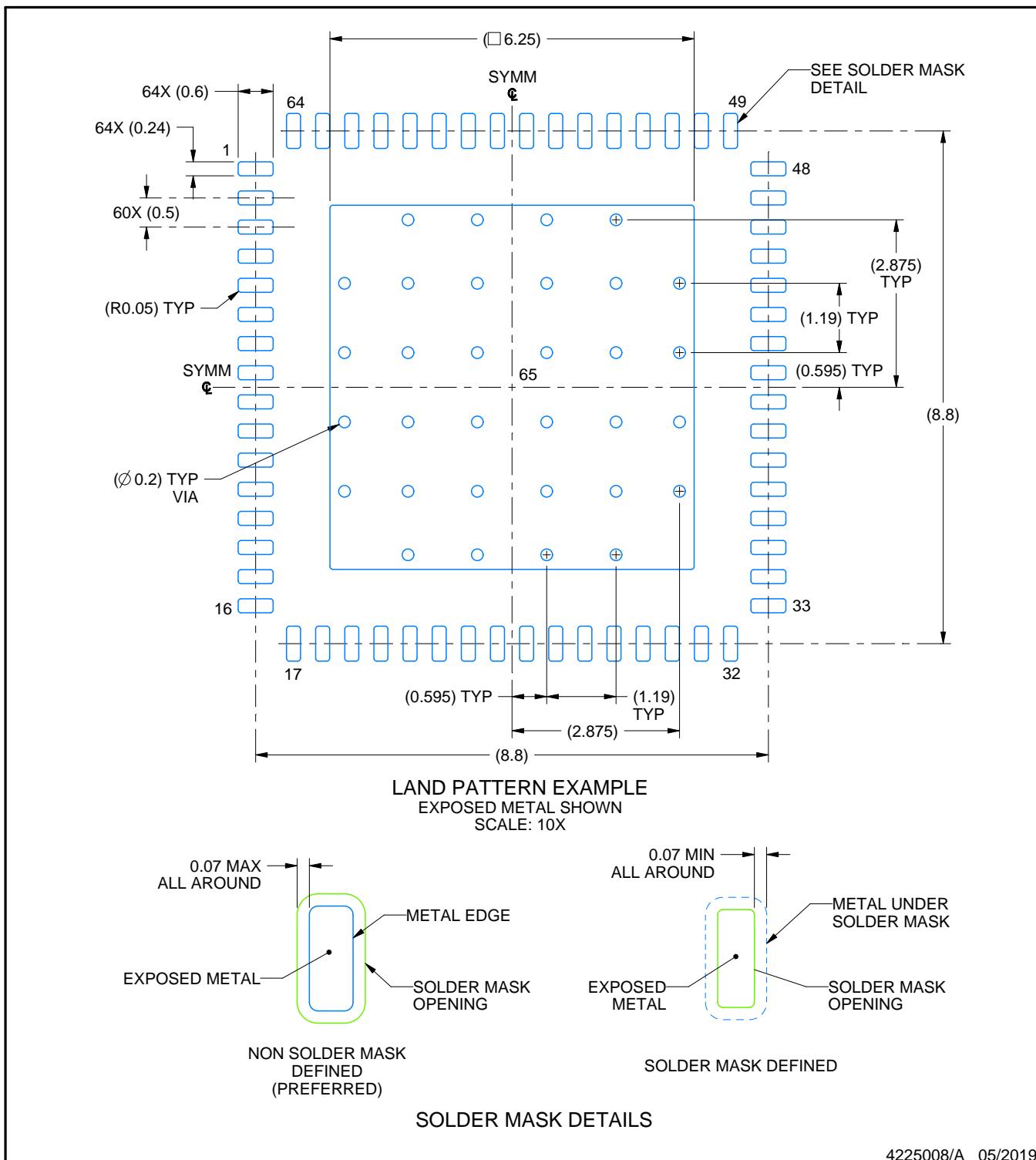

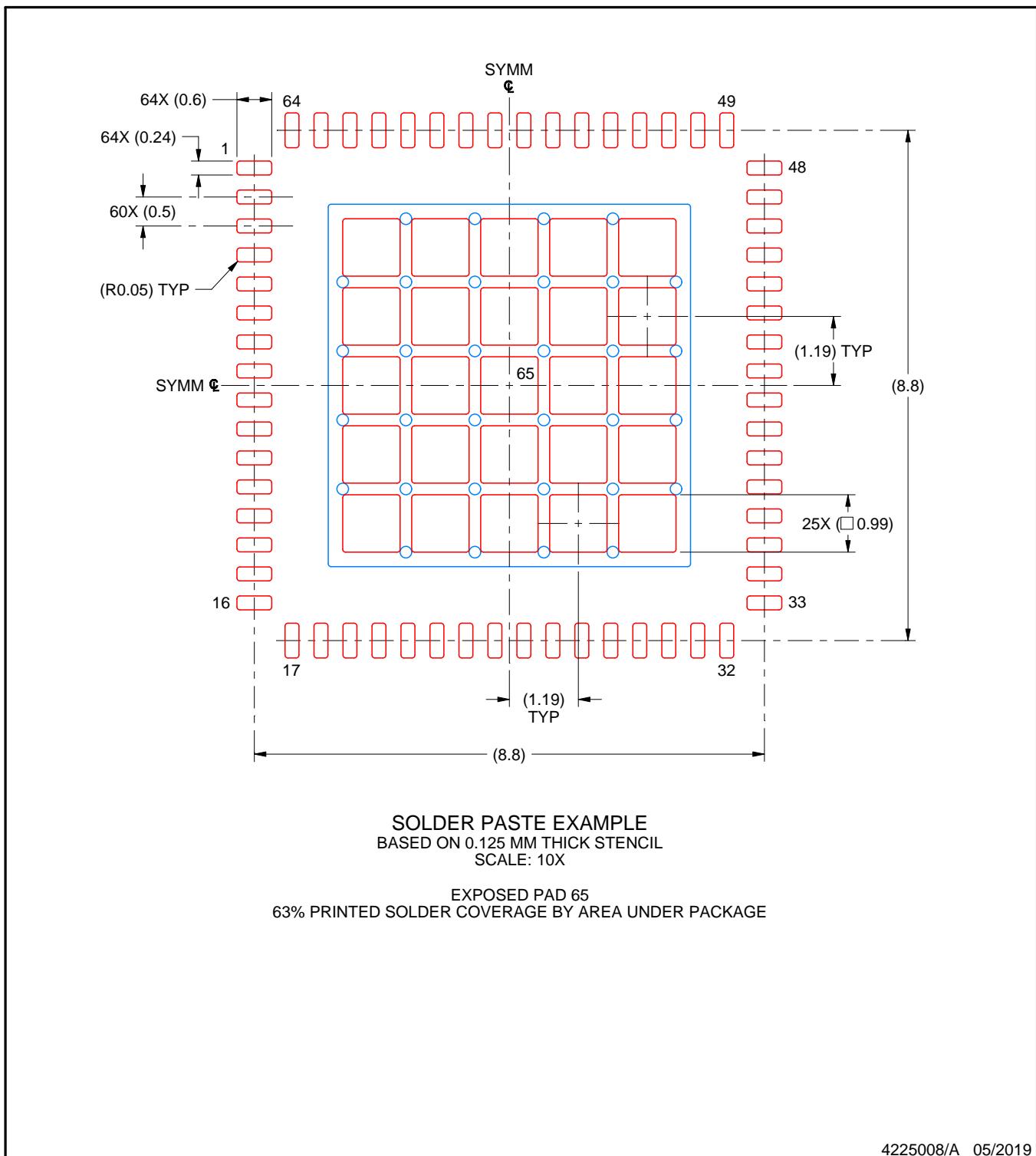

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| LMK5B12212 | VQFN (64)            | 9.00mm × 9.00mm          |

- (1) 供給されているすべてのパッケージについては、セクション 12 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

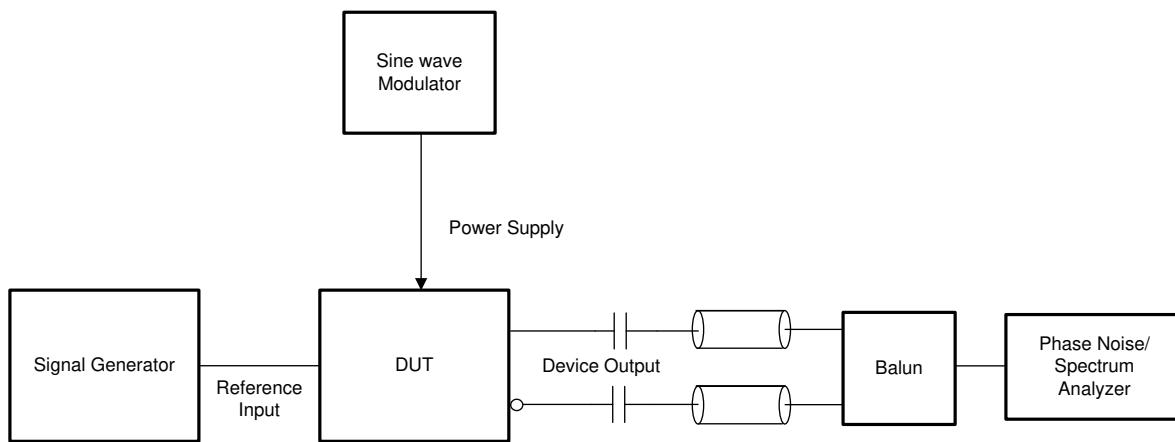

LMK5B12212 代表的なシステム ブロック図

## 目次

|                  |    |                         |    |

|------------------|----|-------------------------|----|

| 1 特長             | 1  | 8.2 機能ブロック図             | 29 |

| 2 アプリケーション       | 1  | 8.3 機能説明                | 33 |

| 3 説明             | 1  | 8.4 デバイスの機能モード          | 63 |

| 4 デバイスの比較        | 4  | 9 アプリケーションと実装           | 80 |

| 5 ピン構成および機能      | 5  | 9.1 アプリケーション情報          | 80 |

| 6 仕様             | 8  | 9.2 代表的なアプリケーション        | 84 |

| 6.1 絶対最大定格       | 8  | 9.3 設計のベスト プラクティス       | 89 |

| 6.2 ESD 定格       | 8  | 9.4 電源に関する推奨事項          | 89 |

| 6.3 推奨動作条件       | 8  | 9.5 レイアウト               | 90 |

| 6.4 熱に関する情報      | 9  | 10 デバイスおよびドキュメントのサポート   | 93 |

| 6.5 電気的特性        | 9  | 10.1 ドキュメントのサポート        | 93 |

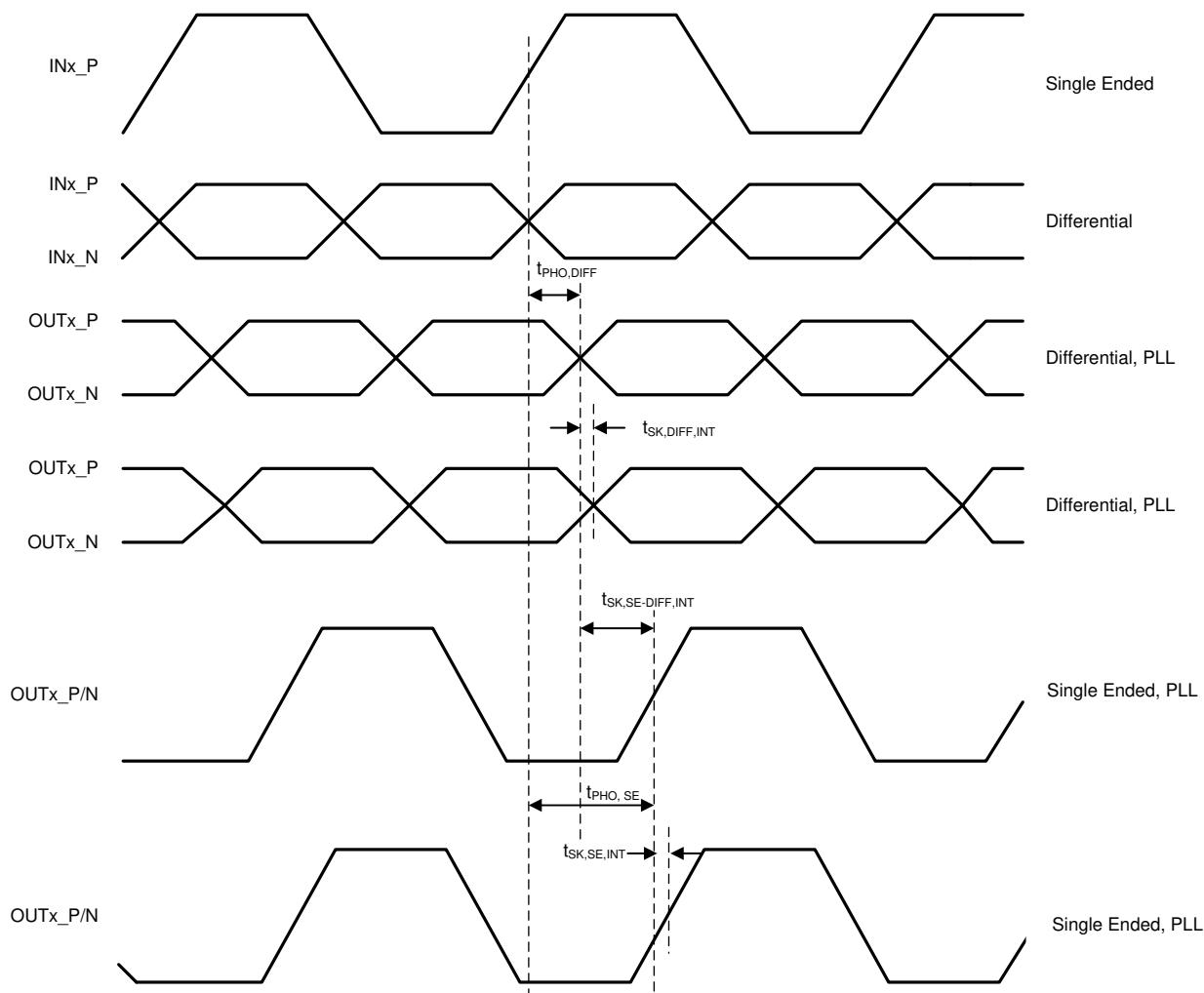

| 6.6 タイミング図       | 19 | 10.2 ドキュメントの更新通知を受け取る方法 | 93 |

| 6.7 代表的特性        | 22 | 10.3 サポート・リソース          | 94 |

| 7 パラメータ測定情報      | 25 | 10.4 商標                 | 94 |

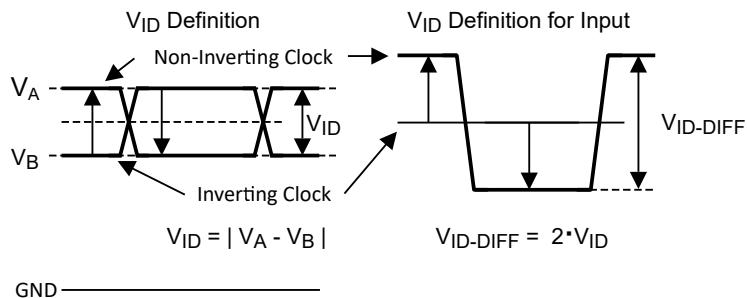

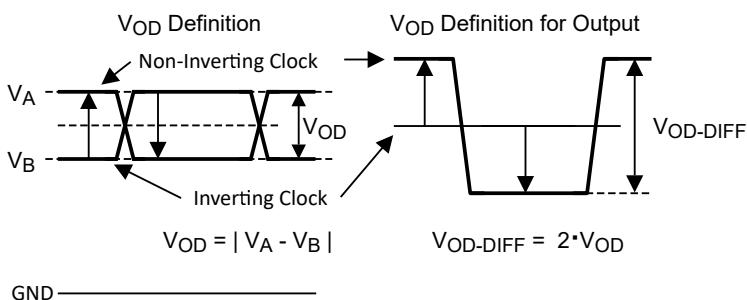

| 7.1 差動電圧測定に関する用語 | 25 | 10.5 用語集                | 94 |

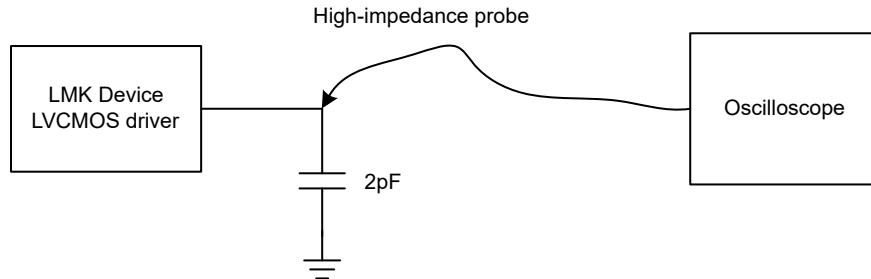

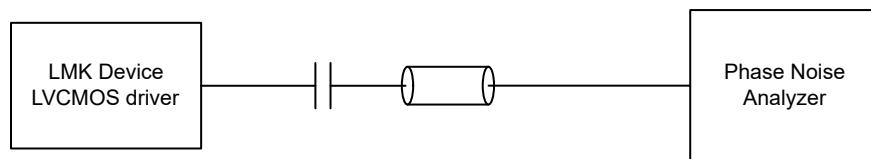

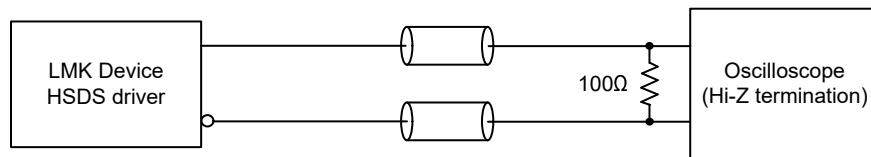

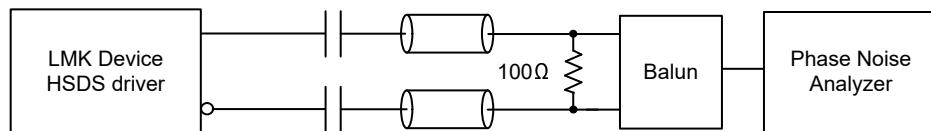

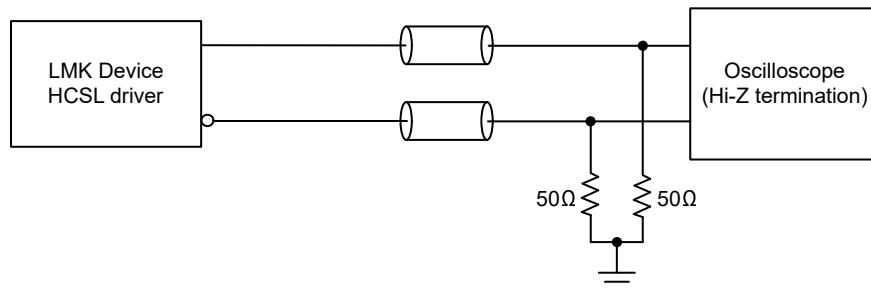

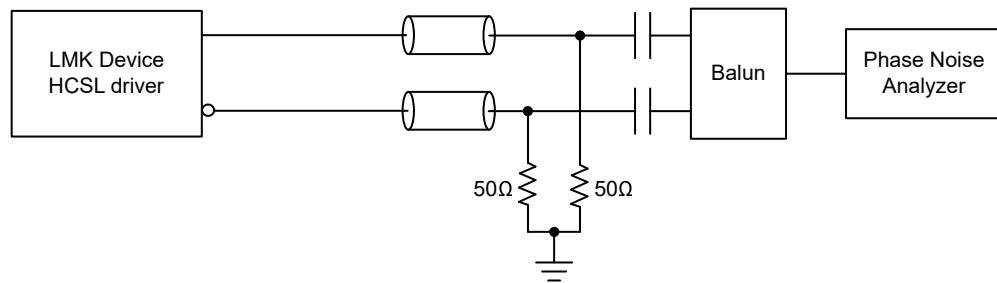

| 7.2 出力クロックのテスト構成 | 26 | 10.6 静電気放電に関する注意事項      | 94 |

| 8 詳細説明           | 28 | 11 改訂履歴                 | 94 |

| 8.1 概要           | 28 | 12 メカニカル、パッケージ、および注文情報  | 94 |

## 4 デバイスの比較

表 4-1. デバイス比較表

| 新しい部品番号     | IN | OUT | DPLL | APLL | VCBO 周波数[MHz] |

|-------------|----|-----|------|------|---------------|

| LMK5C33216A | 2  | 16  | 3    | 3    | 2457.6        |

| LMK5C33414A | 4  | 14  | 3    | 3    | 2457.6        |

| LMK5C22212A | 2  | 12  | 2    | 2    | 2457.6        |

| LMK5B33216  | 2  | 16  | 3    | 3    | 2500          |

| LMK5B33414  | 4  | 14  | 3    | 3    | 2500          |

| LMK5B12212  | 2  | 12  | 1    | 2    | 2500          |

## 5 ピン構成および機能

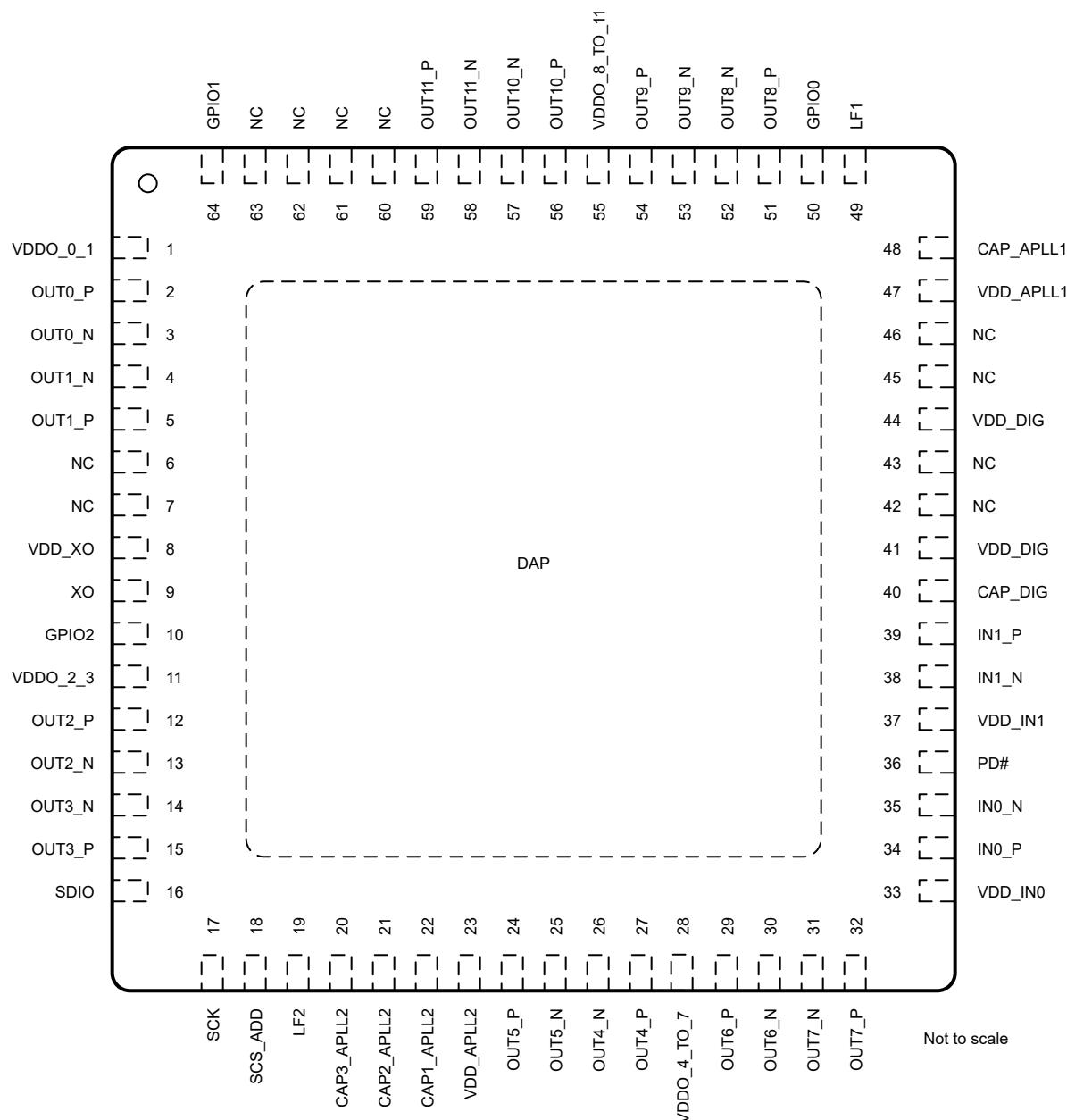

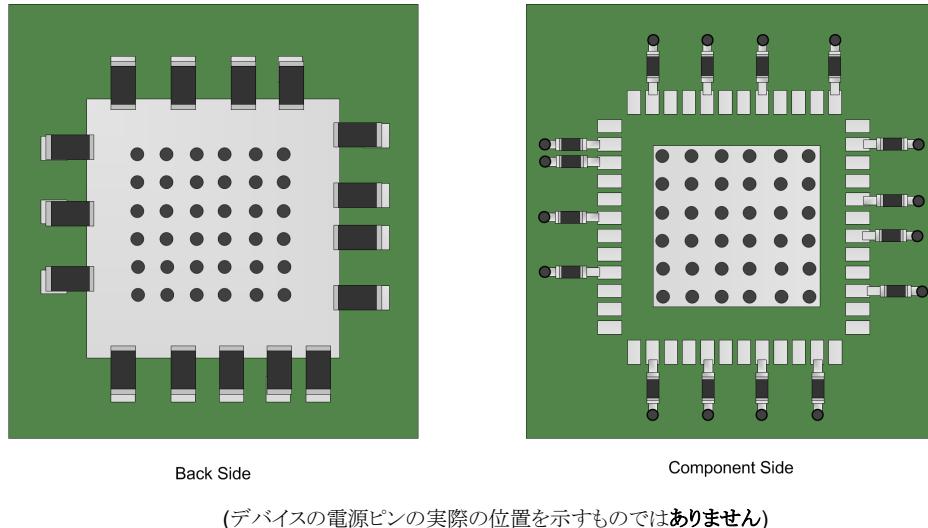

図 5-1. LMK5B12212 RGC パッケージ、64 ピン VQFN 上面図

表 5-1. LMK5B12212 ピンの機能

| 名称        | 番号 | タイプ <sup>(1)</sup> | 説明                                                            |

|-----------|----|--------------------|---------------------------------------------------------------|

| <b>電源</b> |    |                    |                                                               |

| VDDO_0_1  | 1  | P                  | OUT0 および OUT1 の電源。電源に接続します。フローティングのままにしたり、GND に接続したりしないでください。 |

| VDD_XO    | 8  | P                  | XO の電源。電源に接続します。フローティングのままにしたり、GND に接続したりしないでください。            |

| VDDO_2_3  | 11 | P                  | OUT2 および OUT3 の電源。電源に接続します。フローティングのままにしたり、GND に接続したりしないでください。 |

表 5-1. LMK5B12212 ピンの機能 (続き)

| ピン           | 番号   | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                |

|--------------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           |      |                    |                                                                                                                                                                                                                   |

| VDD_APLL2    | 23   | P                  | APLL2 の電源                                                                                                                                                                                                         |

| VDDO_4_To_7  | 28   | P                  | OUT4 から OUT7 までの電源                                                                                                                                                                                                |

| VDD_IN0      | 33   | P                  | IN0 DPLL リファレンスの電源                                                                                                                                                                                                |

| VDD_IN1      | 37   | P                  | IN1 DPLL リファレンスの電源                                                                                                                                                                                                |

| VDD_DIG      | 41   | P                  | デジタルの電源                                                                                                                                                                                                           |

| VDD_DIG      | 44   | p                  | デジタルの電源。通常はピン 41 に接続されます。                                                                                                                                                                                         |

| VDD_APLL1    | 47   | P                  | APLL1 の電源。電源に接続します。フローティングのままにしたり、GND に接続したりしないでください。                                                                                                                                                             |

| VDDO_8_TO_11 | 55   | P                  | OUT8 から OUT11 までの電源。                                                                                                                                                                                              |

| DAP          | 該当なし | G                  | グランド                                                                                                                                                                                                              |

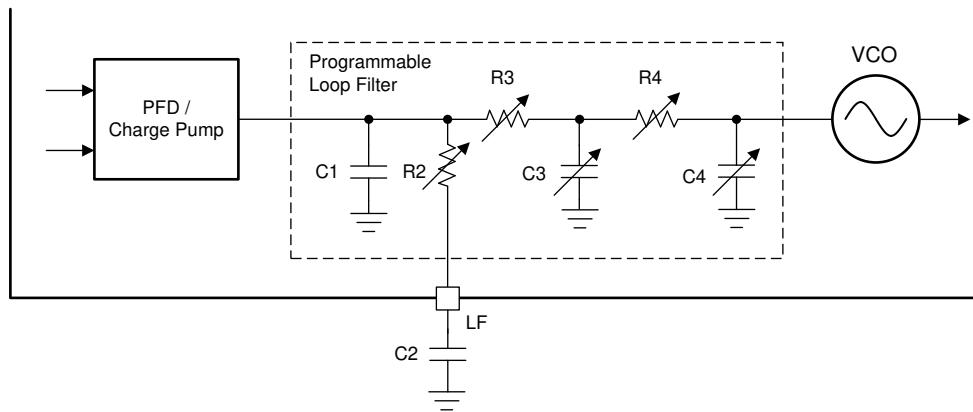

| LF2          | 19   | A                  | APLL2 (100nF) 用の外部ループ フィルタ用コンデンサは、詳細については <a href="#">APLL のループ フィルタ (LF1, LF2)</a> を参照してください。                                                                                                                    |

| CAP3_APLL2   | 20   | A                  | APLL2 VCO に対する内部バイアス用のバイパス コンデンサ (10μF)                                                                                                                                                                           |

| CAP2_APLL2   | 21   | A                  | APLL2 VCO に対する内部バイアス用のバイパス コンデンサ (10μF)                                                                                                                                                                           |

| CAP1_APLL2   | 22   | A                  | APLL2 VCO 用 LDO バイパス コンデンサ (10μF)                                                                                                                                                                                 |

| CAP_DIG      | 40   | A                  | デジタル コア ロジック用 LDO バイパス コンデンサ (100nF)                                                                                                                                                                              |

| CAP_APLL1    | 48   | A                  | APLL1 用の内部バイアス バイパス コンデンサ (10μF)                                                                                                                                                                                  |

| LF1          | 49   | A                  | APLL1 (470nF) 用の外部ループ フィルタ用コンデンサは、詳細については <a href="#">APLL のループ フィルタ (LF1, LF2)</a> を参照してください。                                                                                                                    |

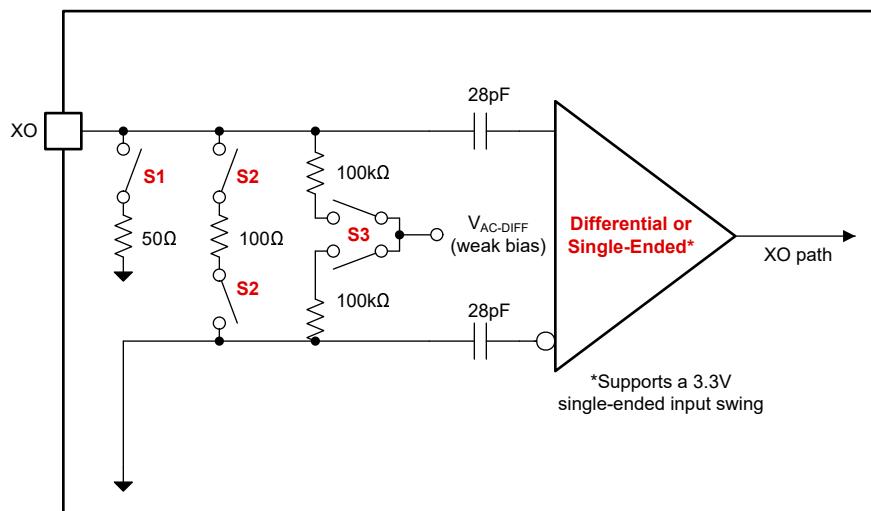

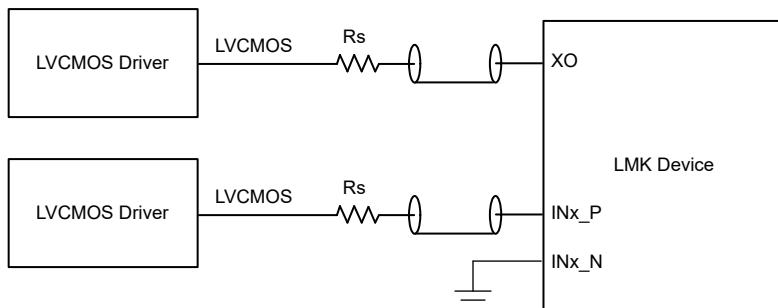

| XO           | 9    | I                  | XO/TCXO/OCXO 入力ピン。内部 XO 入力終端の構成については <a href="#">発振器入力 (XO)</a> を参照してください。                                                                                                                                        |

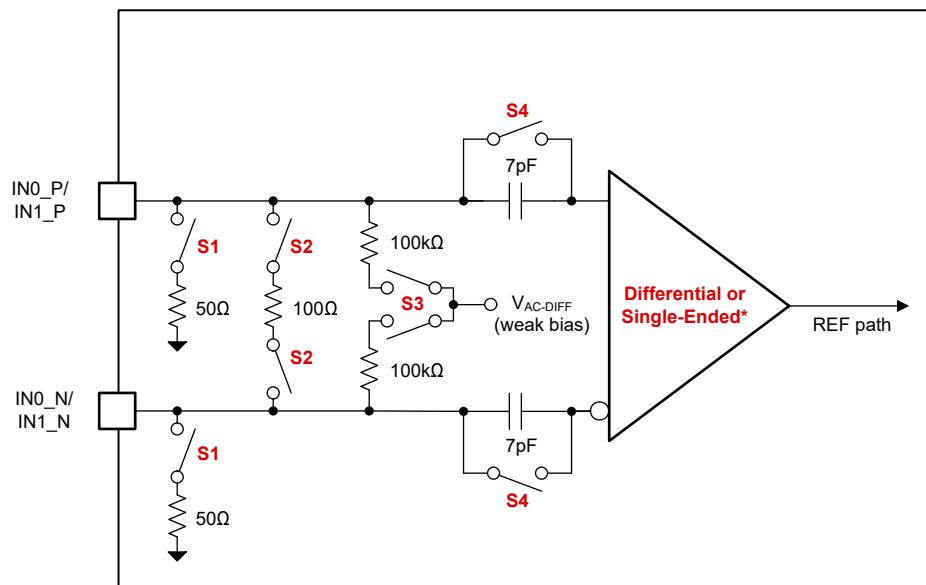

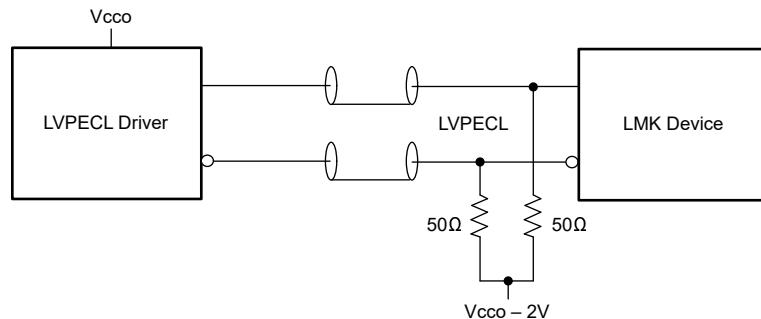

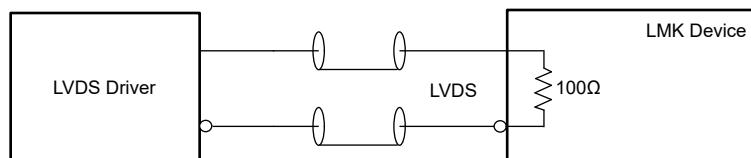

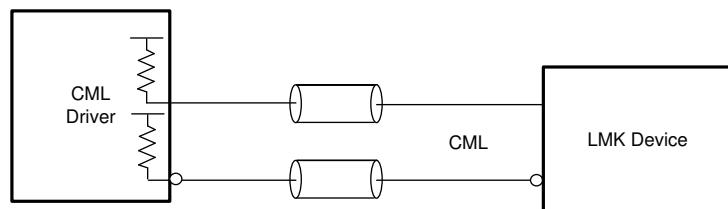

| IN0_P        | 34   | I                  | DPLLx へのリファレンス入力、または OUT0 または OUT1 にバッファされます。内部リファレンス入力終端の設定については、 <a href="#">リファレンス入力</a> を参照してください。                                                                                                            |

| IN0_N        | 35   | I                  |                                                                                                                                                                                                                   |

| IN1_P        | 39   | I                  | DPLLx へのリファレンス入力、または OUT0 または OUT1 にバッファされます。内部リファレンス入力終端の設定については、 <a href="#">リファレンス入力</a> を参照してください。                                                                                                            |

| IN1_N        | 38   | I                  |                                                                                                                                                                                                                   |

| OUT0_P       | 2    | O                  | クロック出力 0。DPLL リファレンス入力、XO、またはすべての VCO ポスト分周器からのソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS、HCSL、1.8V LVCMOS、2.65V LVCMOS のいずれかです。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT0_N       | 3    | O                  |                                                                                                                                                                                                                   |

| OUT1_N       | 4    | O                  | クロック出力 1。DPLL リファレンス入力、XO、またはすべての VCO ポスト分周器からのソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS、HCSL、1.8V LVCMOS、2.65V LVCMOS のいずれかです。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT1_P       | 5    | O                  |                                                                                                                                                                                                                   |

| OUT2_P       | 12   | O                  | クロック出力 2。APLL1 と APLL2 から生成されたソース。プログラム可能な形式:AC-LVPECL、LVDS、HSDS、HCSL または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。                                                                                |

| OUT2_N       | 13   | O                  |                                                                                                                                                                                                                   |

| OUT3_N       | 14   | O                  | クロック出力 3。APLL1 と APLL2 から生成されたソース。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。                                                                                     |

| OUT3_P       | 15   | O                  |                                                                                                                                                                                                                   |

| OUT4_P       | 26   | O                  | クロック出力 4。APLL1 または APLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。                                             |

| OUT4_N       | 27   | O                  |                                                                                                                                                                                                                   |

| OUT5_P       | 24   | O                  | クロック出力 5。APLL1 または APLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。                                             |

| OUT5_N       | 25   | O                  |                                                                                                                                                                                                                   |

| OUT6_P       | 29   | O                  | クロック出力 6。APLL1 または APLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。                                             |

| OUT6_N       | 30   | O                  |                                                                                                                                                                                                                   |

**表 5-1. LMK5B12212 ピンの機能 (続き)**

| ピン<br>名称               | 番号 | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                      |

|------------------------|----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT7_N                 | 31 | O                  | クロック出力 7。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。  |

| OUT7_P                 | 32 | O                  | クロック出力 8。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。  |

| OUT8_P                 | 51 | O                  | クロック出力 9。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。  |

| OUT8_N                 | 52 | O                  | クロック出力 10。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT9_N                 | 53 | O                  | クロック出力 11。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT9_P                 | 54 | O                  | クロック出力 12。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT10_P                | 56 | O                  | クロック出力 13。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT10_N                | 57 | O                  | クロック出力 14。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT11_N                | 58 | O                  | クロック出力 15。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| OUT11_P                | 59 | O                  | クロック出力 16。APLL1 または APPLL2 から生成されたソース。 <a href="#">SYSREF/1-PPS</a> 出力をサポート。プログラム可能な形式:AC-LVPECL、LVDS、HSDS または HCSL。出力の設定と終端の詳細については、 <a href="#">クロック出力</a> を参照してください。 |

| GPIO2 <sup>(2)</sup>   | 10 | I/O、S              | POR: <a href="#">ROM ページの選択</a><br>通常動作:を参照してください GPIO 入出力                                                                                                              |

| SDIO <sup>(3)</sup>    | 16 | I/O                | SPI または I <sup>2</sup> C データ (SDA)                                                                                                                                      |

| SCK <sup>(3)</sup>     | 17 | I                  | SPI または I <sup>2</sup> C クロック (SCL)                                                                                                                                     |

| SCS_ADD <sup>(2)</sup> | 18 | I、S                | POR:I <sup>2</sup> C アドレス セレクト ( <a href="#">GPIO1 および SCS_ADD 機能</a> および I <sup>2</sup> C シリアル インターフェイス)<br>通常動作:を参照してください SPI チップ セレクト (2 状態)                         |

| PD#                    | 36 | I                  | デバイスの電源オフ (アクティブ Low)、V <sub>CC</sub> への内部 200kΩ ブルアップ                                                                                                                  |

| GPIO0 <sup>(2)</sup>   | 50 | I/O、S              | POR: <a href="#">ROM ページの選択</a><br>通常動作:を参照してください GPIO 入出力                                                                                                              |

| GPIO1 <sup>(2)</sup>   | 64 | I/O、S              | POR: <a href="#">GPIO1 および SCS_ADD 機能</a><br>通常動作:を参照してください GPIO 入出力                                                                                                    |

| NC                     | 6  | -                  | 接続なし。フローティングのままにし、GND に接続しないでください。                                                                                                                                      |

| NC                     | 7  | -                  |                                                                                                                                                                         |

| NC                     | 60 | -                  |                                                                                                                                                                         |

| NC                     | 61 | -                  |                                                                                                                                                                         |

| NC                     | 62 | -                  |                                                                                                                                                                         |

| NC                     | 63 | -                  |                                                                                                                                                                         |

| NC                     | 42 | -                  | 接続なし。フローティングのままにするか、GND に接続します。                                                                                                                                         |

| NC                     | 43 | -                  |                                                                                                                                                                         |

| NC                     | 45 | -                  |                                                                                                                                                                         |

| NC                     | 46 | -                  |                                                                                                                                                                         |

(1) P = 電源、G = グランド、I = 入力、O = 出力、I/O = 入力または出力、A = アナログ、S = 構成。

(2) 電源ランプ中または PD GND# が Low の場合、3 レベルモードが有効の場合:555kΩ から V<sub>CC</sub> へ、201kΩ から GND への内部デバイダ。2 レベル入力モードが有効化されている場合:GND に内部 408kΩ ブルダウン。

(3) 内部 2.6V LDO への 670kΩ ブルアップ。

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                        |                      | 最小値  | 最大値      | 単位 |

|------------------------|----------------------|------|----------|----|

| VDD <sup>(2)</sup>     | コア電源電圧               | -0.3 | 3.6      | V  |

| VDDO <sup>(3)</sup>    | 出力電源電圧               | -0.3 | 3.6      | V  |

| V <sub>IN</sub>        | クロックおよびロジック入力の入力電圧範囲 | -0.3 | VDD+0.3  | V  |

| V <sub>OUT_LOGIC</sub> | ロジック出力の出力電圧範囲        | -0.3 | VDD+0.3  | V  |

| V <sub>OUT</sub>       | クロック出力の出力電圧範囲        | -0.3 | VDDO+0.3 | V  |

| T <sub>j</sub>         | 接合部温度                |      | 150      | °C |

| T <sub>stg</sub>       | 保管温度範囲               | -65  | 150      | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

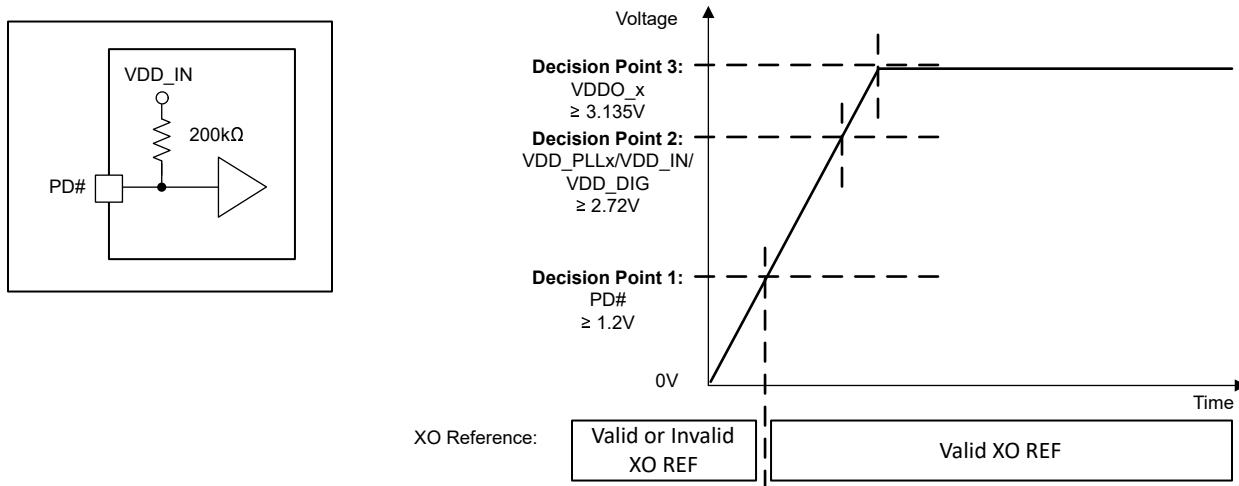

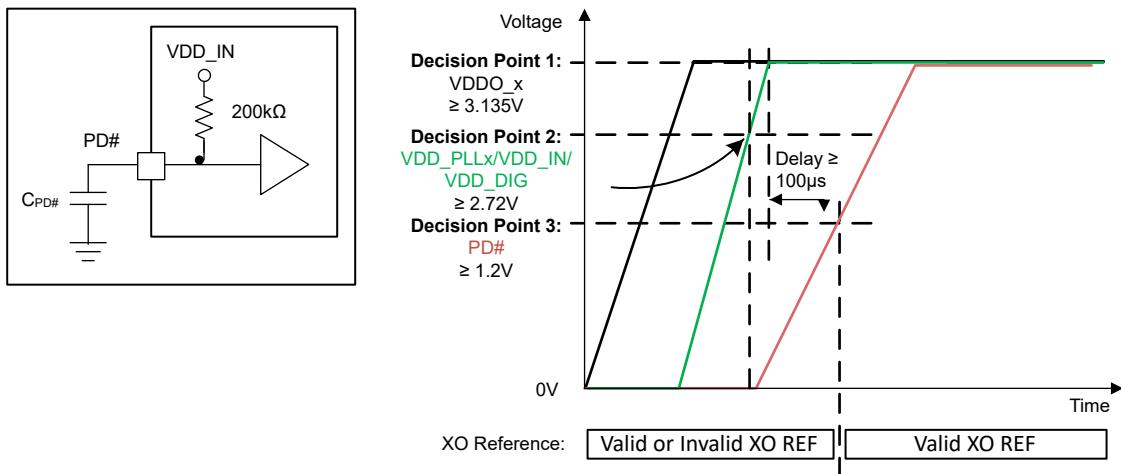

- (2) VDD はすべてのコア電源ピンまたは電圧を指します。PD# が High に引き上げられて内部パワーオンリセット (POR) がトリガされる前に、すべての VDD コア電源をオンにする必要があります。

- (3) VDDO はすべての出力電源ピンまたは電圧を指します。VDDO\_X は、特定の出力チャネルの出力電源を表します。ここで、X はチャネル インデックスを表します。

### 6.2 ESD 定格

|                    |      |                                                                  | 値     | 単位 |

|--------------------|------|------------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | ±2000 | V  |

|                    |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±750  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|                        |                                     | 最小値   | 公称値  | 最大値   | 単位 |

|------------------------|-------------------------------------|-------|------|-------|----|

| VDD <sup>(1)</sup>     | コア電源電圧                              | 3.135 | 3.3  | 3.465 | V  |

| VDDO_X <sup>(2)</sup>  | 出力電源電圧 <sup>(3)</sup>               | 3.135 | 3.3  | 3.465 | V  |

| VDD <sub>OD</sub>      | オープンドレイン出力の出力電圧範囲                   |       | 1.71 | 3.465 | V  |

| T <sub>A</sub>         | 動作時周囲温度範囲                           | -40   |      | 85    | °C |

| T <sub>J</sub>         | 接合部温度                               |       |      | 135   | °C |

| T <sub>CONT-LOCK</sub> | 全温度範囲に対して連続ロック - VCO の再キャリブレーションは不要 |       |      | 125   | °C |

| t <sub>VDD</sub>       | 電源ランプ時間 <sup>(4)</sup>              | 0.01  |      | 100   | ms |

- (1) VDD はすべてのコア電源ピンまたは電圧を指します。内部パワーオンリセット (POR) の前に、すべての VDD コア電源をオンにする必要があります。

- (2) VDDO はすべての出力電源ピンまたは電圧を指します。VDDO\_X は、特定の出力チャネルの出力電源を表します。ここで、X はチャネル インデックスを表します。

- (3) CMOS 出力電圧レベルは、1.8V または 2.65V をサポートする CMOS 出力 LDO の内部プログラミングによって決定されます。

- (4) 内部パワーオンリセットが適切に行われるために、VDD が 2.7V を超えて単調に上昇するのにかかる時間。より遅い、または単調ではない VDD ランプの場合は、VDD 電圧が有効になるまで PD# を低く維持します。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1) (2) (3)</sup> |                   | LMK5B12212 | 単位   |

|------------------------------|-------------------|------------|------|

|                              |                   | RGC (VQFN) |      |

|                              |                   | 64 ピン      |      |

| $R_{\theta JA}$              | 接合部から周囲への熱抵抗      | 21.8       | °C/W |

| $R_{\theta JC(top)}$         | 接合部からケース(上面)への熱抵抗 | 11.1       | °C/W |

| $R_{\theta JB}$              | 接合部から基板への熱抵抗      | 6.5        | °C/W |

| $R_{\theta JC(bot)}$         | 接合部からケース(底面)への熱抵抗 | 0.8        | °C/W |

| $\Psi_{JT}$                  | 接合部から上面への特性パラメータ  | 0.3        | °C/W |

| $\Psi_{JB}$                  | 接合部から基板への特性パラメータ  | 6.3        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、[半導体およびIC パッケージの熱評価基準](#)アプリケーション ノートを参照してください。

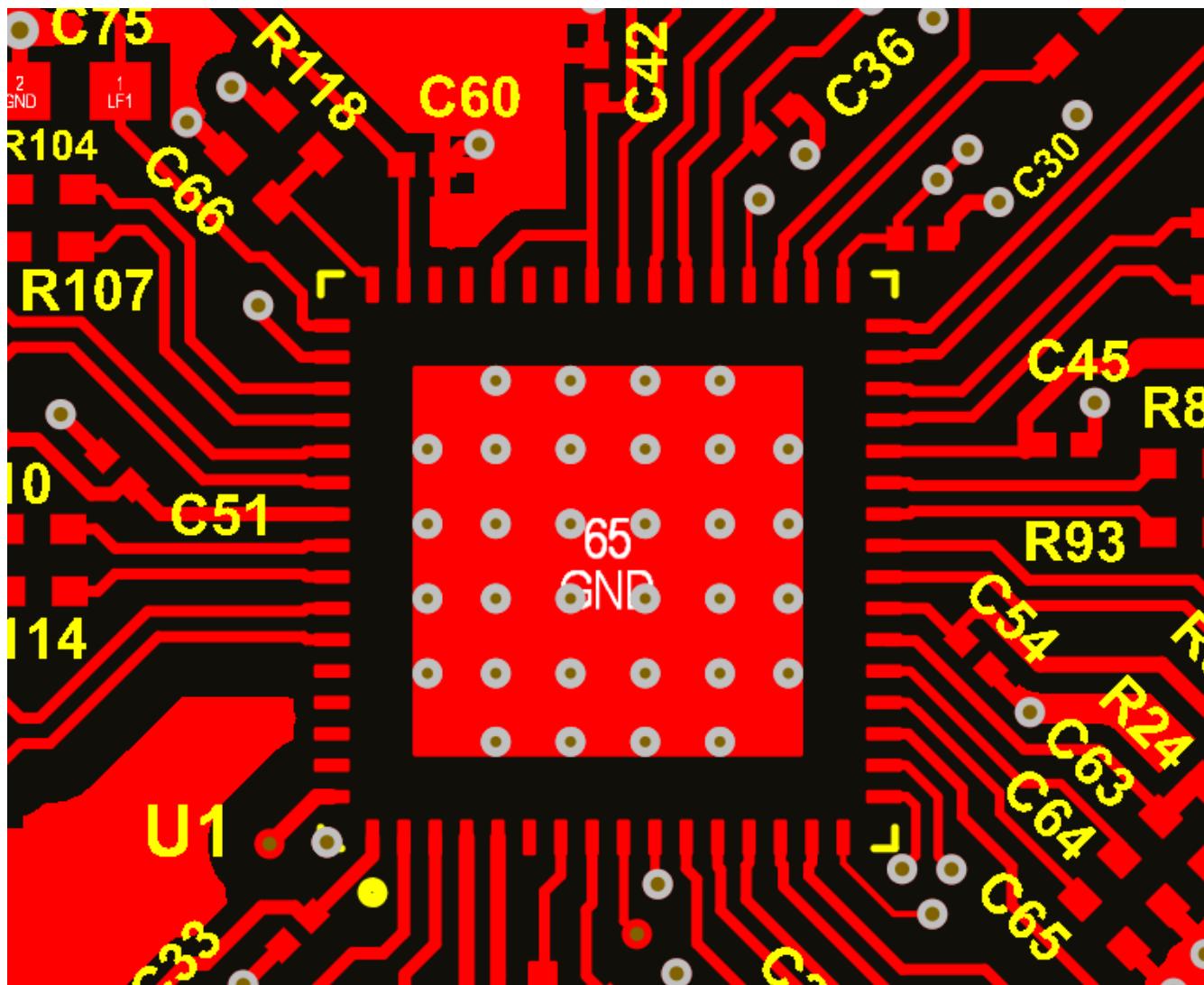

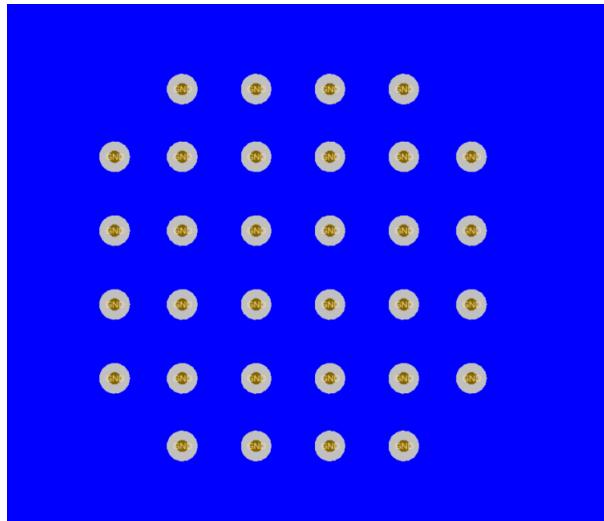

(2) 熱情報は、49 個のサーマルピア (7mm × 7mm パターン、0.3mm のホール) を備えた 10 層 200mm × 250mm ボードに基づいています。

(3)  $\Psi_{JB}$  を使用すると、システム設計者はファインゲージ熱電対を使用してボード温度 ( $T_{PCB}$ ) を測定し、デバイスの接合部温度  $T_J = T_{PCB} + (\Psi_{JB} \times$  電力) を逆計算できます。 $\Psi_{JB}$  の測定は JESD51-6 で定義されています。

## 6.5 電気的特性

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ             | テスト条件                          | 最小値                                                                               | 標準値 | 最大値 | 単位 |

|-------------------|--------------------------------|-----------------------------------------------------------------------------------|-----|-----|----|

| <b>消費電流特性</b>     |                                |                                                                                   |     |     |    |

| $I_{DD\_TOT}$     | 指定された構成での総消費電流                 | OUT0 ~ OUT11 LVDS 出力までの 156.25MHz、BAW APLL ポストデバイダ = 8、チャネルデバイダおよび APLL2 は無効。     | 650 |     | mA |

|                   |                                | OUT0 ~ OUT11 までの 156.25MHz HSDS 出力、BAW APLL ポストデバイダはバイパスされ、チャネルデバイダは有効、APLL2 は無効。 | 800 |     | mA |

| $I_{DD-XO}$       | XO 入力電流消費                      | XO                                                                                | 3.5 |     | mA |

| $I_{DD-XO2X}$     | XO ダブルあたりの消費電流                 | XO ダブル <sup>(1)</sup>                                                             | 0.3 |     | mA |

| $I_{DD-INX}$      | DPLL リファレンス入力ブロックあたりのコア電流消費    | IN0                                                                               | 3.6 |     | mA |

|                   |                                | IN1                                                                               | 3.1 |     | mA |

| $I_{DD-DPLL}$     | DPLL あたりの電流消費                  | DPLL <sup>(2)</sup>                                                               | 55  |     | mA |

| $I_{DD-APLL2}$    | APLL2 電流消費                     | APLL2                                                                             | 160 |     | mA |

| $I_{DD-APLL1}$    | APLL1 電流消費                     | APLL1                                                                             | 120 |     | mA |

| $I_{DD-ANA}$      | アナログ バイアス電流消費                  | VDD_XO 電源ピンから供給されるアナログ回路。デバイスが有効のときは常にオン。                                         | 42  |     | mA |

| $I_{DD-DIG}$      | デジタル制御電流消費                     | デバイスが有効のとき、VDD_DIG 電源ピンからのデジタル制御回路は常にオン。                                          | 34  |     | mA |

| $I_{DDO\_CHDIV}$  | チャネル デバイダ ブロックあたりの電流消費         | 12 ビット チャネル デバイダ                                                                  | 20  |     | mA |

| $I_{DDO-1PPSDIV}$ | 1PPS/SYSREF デバイダ ブロックあたりの電流消費  | 20 ビットの 1PPS/SYSREF デバイダ                                                          | 12  |     | mA |

| $I_{DDO-DELAY}$   | 1PPS/SYSREF アナログ遅延ブロックあたりの電流消費 | アナログ遅延機能有効                                                                        | 10  |     | mA |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ          |                     | テスト条件                                                             | 最小値                        | 標準値  | 最大値 | 単位 |

|----------------|---------------------|-------------------------------------------------------------------|----------------------------|------|-----|----|

| $I_{DDO-HSDS}$ | 出力ドライバごとの HSDS 電流消費 | HSDS バッファ ( $V_{cm}$ レベル = s1、 $I_{OUT} = 4mA$ 、 $100\Omega$ 終端)  |                            | 19   |     | mA |

|                |                     | HSDS バッファ ( $V_{cm}$ レベル = s1、 $I_{OUT} = 7mA$ 、 $100\Omega$ 終端)  |                            | 22   |     | mA |

|                |                     | HSDS バッファ ( $V_{cm}$ レベル = s1、 $I_{OUT} = 10mA$ 、 $100\Omega$ 終端) |                            | 25   |     | mA |

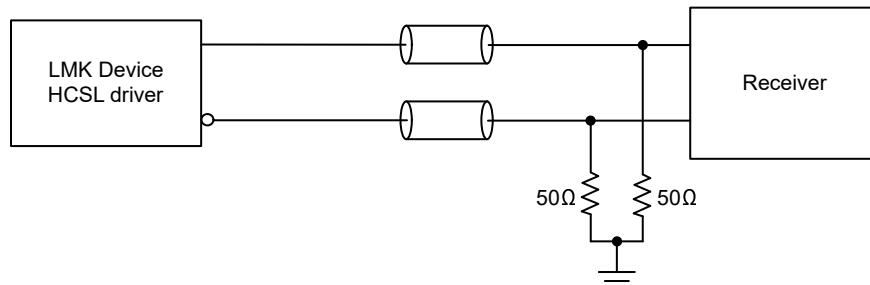

| $I_{DDO-HCSL}$ | 出力ドライバごとの HCSL 電流消費 |                                                                   | HCSL 出力 (片側 $50\Omega$ 終端) | 30.5 |     | mA |

| $I_{DD\_PD}$   | パワーダウン電流消費          |                                                                   | デバイスのパワーダウン、PD # = Low     | 90   | 110 | mA |

## リファレンス入力特性 (INx)

|                  |                   |                                                                              |        |           |          |

|------------------|-------------------|------------------------------------------------------------------------------|--------|-----------|----------|

| $f_{IN}$         | INx 周波数範囲         | シングル エンド入力                                                                   | 0.5E-6 | 200       | MHz      |

|                  |                   | 差動入力                                                                         | 5      | 800       |          |

| $V_{IH}$         | シングルエンド入力 High 電圧 | DC 結合入力モード (3)                                                               | 1.2    | VDD + 0.3 | V        |

| $V_{IL}$         | シングルエンド入力 Low 電圧  |                                                                              |        | 0.5       | V        |

| $V_{IN-SE-PP}$   | シングルエンド入力電圧スイング   | AC 結合入力モード (4)                                                               | 0.4    | 2         | $V_{pp}$ |

| $V_{IN-DIFF-PP}$ | 差動入力電圧スイング        | AC 結合または DC 結合の入力 (5)                                                        | 0.4    | 2         | $V_{pp}$ |

| $V_{ICM}$        | 入力共通モード           | DC 結合差動入力 (6)                                                                | 0.1    | 2         | V        |

| $dV/dt$          | 入力スルーレート          | シングル エンド入力                                                                   | 0.2    | 0.5       | V/ns     |

|                  |                   | 差動入力                                                                         | 0.2    | 0.5       | V/ns     |

| IDC              | 入力クロック デューティ サイクル | 非 1PPS 信号                                                                    | 40     | 60        | %        |

| $t_{PULSE-1PPS}$ | 入力用 1PPS パルス幅     | 1PPS またはパルス信号                                                                | 100    |           | ns       |

| $I_{IN-DC}$      | DC の入力リーケ電流       | シングル ピン INx_P または INx_N、 $50\Omega$ および $100\Omega$ 内部終端は無効、AC 結合モードは有効または無効 | -350   | 350       | $\mu A$  |

| $C_{IN}$         | 入力容量              | シングルエンド、各ピン                                                                  |        | 2         | pF       |

## XO/TCXO 入力特性 (XO)

|             |                   |                                                   |      |           |          |

|-------------|-------------------|---------------------------------------------------|------|-----------|----------|

| $f_{CLK}$   | XO 入力周波数範囲(7)     |                                                   | 10   | 156.25    | MHz      |

| $V_{IH}$    | LVC MOS 高入力電圧     | DC 結合入力モード (8)                                    | 1.4  | VDD + 0.3 | V        |

| $V_{IL}$    | LVC MOS 入力低電圧     |                                                   |      | 0.8       | V        |

| $V_{IN-SE}$ | シングルエンド入力電圧スイング   | AC 結合入力モード (9)                                    | 0.4  | VDD + 0.3 | $V_{pp}$ |

| $dV/dt$     | 入力スルーレート          |                                                   | 0.2  | 0.5       | V/ns     |

| IDC         | 入力デューティ サイクル      |                                                   | 40   | 60        | %        |

| $I_{IN-DC}$ | DC の入力リーケ電流       | シングル ピン XO_P、 $50\Omega$ および $100\Omega$ の内部終端は無効 | -350 | 350       | $\mu A$  |

| $C_{IN}$    | 各ピンの入力容量          |                                                   |      | 1         | pF       |

| $C_{EXT}$   | 外部 AC カップリング キャップ |                                                   |      | 10        | nF       |

## APLL/VCO 特性

|                      |                |                                          |         |      |             |

|----------------------|----------------|------------------------------------------|---------|------|-------------|

| $f_{PFD}$            | PFD 周波数範囲      | BAW APLL 分周フィードバック デバイダ                  |         | 110  | MHz         |

|                      |                | APLL2 分周フィードバック デバイダ                     |         | 125  | MHz         |

| $f_{VCO2}$           | VCO2 周波数範囲     |                                          | 5595    | 5950 | MHz         |

| $f_{VCBO}$           | VCBO 周波数範囲     |                                          | 2499.75 | 2500 | 2500.25 MHz |

| $t_{APLL2-LOCK}$     | APLL2 ロック時間    | ソフトリセットまたはハードリセットと安定した APLL2 出力までの時間。    |         | 350  | 460 ms      |

| $t_{BAW\ APPL-LOCK}$ | BAW APLL ロック時間 | ソフトリセットまたはハードリセットと安定した BAW APLL 出力までの時間。 |         | 12.5 | 13 ms       |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                   |                        | テスト条件                                                                                               | 最小値                 | 標準値  | 最大値   | 単位   |

|-------------------------|------------------------|-----------------------------------------------------------------------------------------------------|---------------------|------|-------|------|

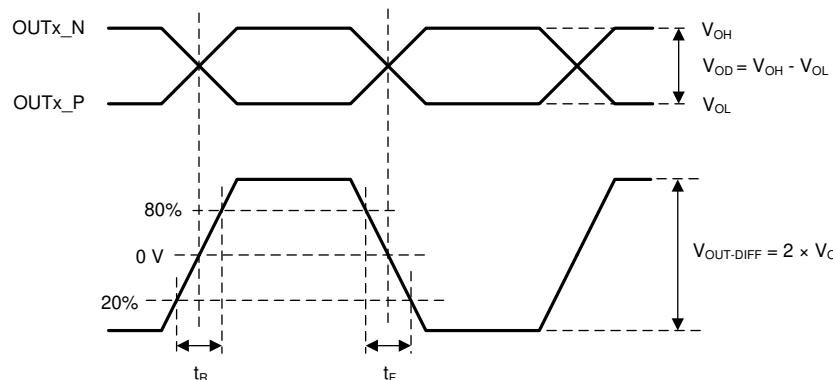

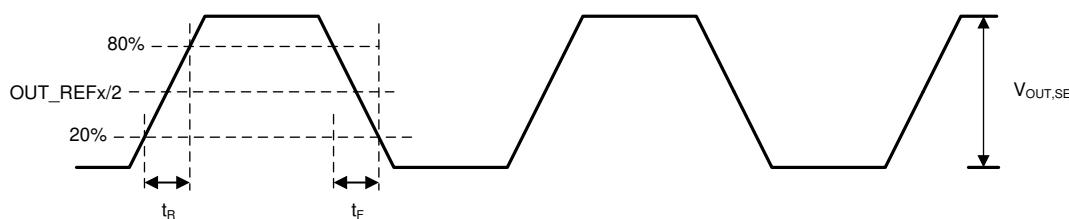

| <b>HSDS 出力特性 (OUTx)</b> |                        |                                                                                                     |                     |      |       |      |

| $f_{OUT}$               | 出力周波数範囲                |                                                                                                     | 1E-6                |      | 1250  | MHz  |

| $V_{OUT-DIFF}$          | 差動出力スイング               |                                                                                                     | 2× $V_{OD-HSDS}$    |      |       | mVpp |

| $V_{OD-HSDS}$           | HSDS 出力電圧スイング          | $f_{out} < 100MHz, I_{out} = 4mA$                                                                   | 350                 | 400  | 440   | mV   |

|                         |                        | $f_{out} < 100MHz, I_{out} = 7mA$                                                                   | 625                 | 700  | 750   | mV   |

|                         |                        | $f_{out} < 100MHz, I_{out} = 10mA$                                                                  | 900                 | 975  | 1050  | mV   |

|                         |                        | $100MHz \leq f_{out} \leq 325MHz, I_{out} = 4mA$                                                    | 335                 | 400  | 445   | mV   |

|                         |                        | $100MHz \leq f_{out} \leq 325MHz, I_{out} = 5mA$                                                    | 425                 | 500  | 575   | mV   |

|                         |                        | $100MHz \leq f_{out} \leq 325MHz, I_{out} = 6mA$                                                    | 510                 | 600  | 690   | mV   |

|                         |                        | $100MHz \leq f_{out} \leq 325MHz, I_{out} = 7mA$                                                    | 595                 | 700  | 805   | mV   |

|                         |                        | $100MHz \leq f_{out} \leq 325MHz, I_{out} = 8mA$                                                    | 680                 | 800  | 920   | mV   |

|                         |                        | $100MHz \leq f_{out} \leq 325MHz, I_{out} = 9mA$                                                    | 765                 | 900  | 1035  | mV   |

|                         |                        | $100MHz \leq f_{out} \leq 325MHz, I_{out} = 10mA$                                                   | 850                 | 1000 | 1150  | mV   |

|                         |                        | $325MHz < f_{out} \leq 800MHz, I_{out} = 4mA$                                                       | 300                 | 350  | 400   | mV   |

|                         |                        | $325MHz < f_{out} \leq 800MHz, I_{out} = 7mA$                                                       | 580                 | 640  | 700   | mV   |

|                         |                        | $325MHz < f_{out} \leq 800MHz, I_{out} = 10mA$                                                      | 800                 | 865  | 940   | mV   |

|                         |                        | $800MHz < f_{out} \leq 1250MHz, I_{out} = 4mA$                                                      | 235                 | 320  | 400   | mV   |

|                         |                        | $800MHz < f_{out} \leq 1250MHz, I_{out} = 7mA$                                                      | 480                 | 625  | 740   | mV   |

|                         |                        | $800MHz < f_{out} \leq 1250MHz, I_{out} = 10mA$                                                     | 600                 | 800  | 1000  | mV   |

| $V_{OH}$                | 出力電圧 High              |                                                                                                     | $V_{OL} + V_{OD}$   |      |       | mVpp |

| $V_{OL}$                | 出力電圧 Low               | VCM レベル = s1                                                                                        | 50                  | 150  | 250   | mV   |

|                         |                        | VCM レベル = s2+3                                                                                      | 300                 | 470  | 720   | mV   |

| $V_{CM}$                | 出力同相電圧                 | VCM レベル = s1 または s2+3                                                                               | $V_{OL} + V_{OD}/2$ |      |       | V    |

|                         |                        | VCM レベル = s2、 $I_{out} = 4mA$                                                                       | 0.6                 | 0.7  | 0.8   | V    |

|                         |                        | VCM レベル = s3、 $I_{out} = 4mA$                                                                       | 1.125               | 1.25 | 1.375 | V    |

| $t_{SKEW}$              | 出力スキュー <sup>(13)</sup> | 同じ APPLL、同じポスト・デバイダとチャネル・デバイダの値、同じバンク                                                               |                     |      | 50    | ps   |

|                         |                        | バンク間は、同じ APPLL、同じポスト・デバイダとチャネル・デバイダの値                                                               |                     |      | 80    | ps   |

| $t_R/t_F$               | 立ち上がり / 立ち下がり時間        | $f_{OUT} < 100MHz, 20\% \sim 80\%, OUT\_x\_CAP\_EN = 0, C_L = 2pF$                                  | 200                 | 250  | 350   | ps   |

|                         |                        | $100MHz \leq f_{OUT} \leq 325MHz, 20\% \sim 80\%, I_{out} \geq 8mA, OUT\_x\_CAP\_EN = 0, C_L = 2pF$ | 165                 | 225  | 260   | ps   |

|                         |                        | $100MHz \leq f_{OUT} \leq 325MHz, 20\% \sim 80\%, OUT\_x\_CAP\_EN = 0, C_L = 2pF$                   | 175                 | 230  | 300   | ps   |

|                         |                        | $325MHz < f_{OUT} \leq 800MHz, 20\% \sim 80\%, OUT\_x\_CAP\_EN = 0, C_L = 2pF$                      | 150                 | 215  | 285   | ps   |

|                         |                        | $800MHz < f_{OUT} \leq 1250MHz, 20\% \sim 80\%, OUT\_x\_CAP\_EN = 0, C_L = 2pF$                     | 120                 | 205  | 250   | ps   |

| ODC                     | 出力デューティ サイクル           |                                                                                                     | 48                  |      | 52    | %    |

| <b>HCSL 出力特性 (OUTx)</b> |                        |                                                                                                     |                     |      |       |      |

| $f_{OUT}$               | 出力周波数範囲                | HSCL 出力モード                                                                                          | 25                  | 100  | 650   | MHz  |

| $V_{OL}$                | 出力電圧 Low               |                                                                                                     | -150                | 0    | 150   | mV   |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ               |                        | テスト条件                                                   | 最小値  | 標準値 | 最大値  | 単位 |

|---------------------|------------------------|---------------------------------------------------------|------|-----|------|----|

| V <sub>OH</sub>     | 出力電圧 High              |                                                         | 600  | 750 | 900  | mV |

| V <sub>MIN</sub>    | 出力電圧 (最小値)             | アンダーシュートを含む                                             | -300 | 0   | 150  | mV |

| V <sub>MAX</sub>    | 出力電圧 (最大)              | オーバーシュートを含む                                             | 600  | 750 | 1150 | mV |

| dV/dt               | 差動出力スルーレート             | 中心点の周囲 ±150mV、<br>OUT_x_CAP_EN = 1、C <sub>L</sub> = 2pF | 2    | 4   | V/ns |    |

| dV/dt               | 差動出力スルーレート             | 中心点の周囲 ±150mV、<br>OUT_x_CAP_EN = 0、C <sub>L</sub> = 2pF | 3    | 5   | V/ns |    |

| t <sub>SKew</sub>   | 出力スキュー <sup>(13)</sup> | 同じ APLL、同じポスト・デバイダとチャネル・デバイダの値、同じバンク                    |      | 50  |      | ps |

|                     |                        | バンク間は、同じ APLL、同じポスト・デバイダとチャネル・デバイダの値                    |      | 80  |      | ps |

| V <sub>CROSS</sub>  | 絶対電圧交差ポイント             | f <sub>OUT</sub> = 100MHz                               | 300  | 500 |      | mV |

| ΔV <sub>CROSS</sub> | 電圧交差ポイントの変動            | f <sub>OUT</sub> = 100MHz                               |      | 75  |      | mV |

| ODC                 | 出力デューティ サイクル           |                                                         | 45   | 55  |      | %  |

#### 1.8V LVC MOS 出力特性 (OUT0、OUT1)

|                   |                   |                                                                                      |      |     |     |

|-------------------|-------------------|--------------------------------------------------------------------------------------|------|-----|-----|

| f <sub>OUT</sub>  | 出力周波数範囲           |                                                                                      | 1E-6 | 200 | MHz |

| V <sub>OH</sub>   | 出力 HIGH 電圧        | I <sub>OH</sub> = -2mA                                                               | 1.5  |     | V   |

| V <sub>OL</sub>   | 出力 LOW 電圧         | I <sub>OL</sub> = 2mA                                                                |      | 0.2 | V   |

| t <sub>R/tF</sub> | 出力立ち上がり / 立ち下がり時間 | 20%~80%                                                                              |      | 150 | ps  |

| t <sub>SK</sub>   | 出力間スキュー           | 同じ極性、同じ APLL ポスト デバイダおよび出力デバイダの値を持つ OUT0_P、OUT0_N、OUT1_P、OUT1_N。同じ極性と出力タイプ (LVC MOS) |      | 60  | ps  |

|                   |                   | 同じ APLL、同じポスト デバイダと出力 デバイダの値。LVC MOS 出力と差動出力間のスキュー                                   | 0.7  | 1   | 1.3 |

| ODC               | 出力デューティ サイクル      |                                                                                      | 45   | 55  | %   |

| R <sub>OUT</sub>  | 出力インピーダンス         |                                                                                      | 54   | 64  | 75  |

#### 2.65V LVC MOS 出力特性 (OUT0、OUT1)

|                     |                                              |                                                                                     |      |      |        |

|---------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------|------|--------|

| f <sub>OUT</sub>    | 出力周波数範囲                                      |                                                                                     | 1E-6 | 200  | MHz    |

| V <sub>OH</sub>     | 出力 HIGH 電圧                                   | I <sub>OH</sub> = -2mA                                                              | 2.3  |      | V      |

| V <sub>OL</sub>     | 出力 LOW 電圧                                    | I <sub>OL</sub> = 2mA                                                               |      | 0.2  | V      |

| t <sub>R/tF</sub>   | 出力立ち上がり / 立ち下がり時間                            | 20%~80%                                                                             |      | 150  | ps     |

| t <sub>SK</sub>     | 出力間スキュー                                      | 同じ極性、同じ APLL ポスト デバイダおよび出力デバイダの値を持つ OUT_P、OUT0_N、OUT1_P、OUT1_N。同じ極性と出力タイプ (LVC MOS) |      | 60   | ps     |

|                     |                                              | 同じ APLL、同じポスト デバイダと出力 デバイダの値。LVC MOS 出力と差動出力間のスキュー                                  | 0.7  | 1.0  | 1.3    |

| PN <sub>FLOOR</sub> | 出力位相ノイズ フロア<br>(f <sub>OFFSET</sub> > 10MHz) | 25MHz                                                                               |      | -155 | dBc/Hz |

| ODC                 | 出力デューティ サイクル                                 |                                                                                     | 45   | 55   | %      |

| R <sub>OUT</sub>    | 出力インピーダンス                                    |                                                                                     | 40   | 50   | 65     |

#### 3.3V LVC MOS GPIO クロック 出力特性 (GPIO0、GPIO1、GPIO2)

|                  |            |                       |  |     |     |

|------------------|------------|-----------------------|--|-----|-----|

| f <sub>OUT</sub> | 最高出力周波数    | GPIO1、GPIO2           |  | 25  | MHz |

| V <sub>OH</sub>  | 出力 HIGH 電圧 | I <sub>OH</sub> = 2mA |  | 2.4 | V   |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                          |                                            | テスト条件                                                                                                 | 最小値  | 標準値 | 最大値 | 単位 |

|--------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------|------|-----|-----|----|

| V <sub>OL</sub>                | 出力 LOW 電圧                                  | I <sub>OL</sub> = 2mA                                                                                 |      |     | 0.4 | V  |

| I <sub>IH</sub>                | 入力 High 電流                                 | V <sub>IN</sub> = V <sub>DD</sub>                                                                     |      |     | 100 | μA |

| I <sub>IL</sub>                | 出力 LOW 電流                                  | V <sub>IN</sub> = 0V                                                                                  | -100 |     |     | μA |

| t <sub>R</sub> /t <sub>F</sub> | 出力立ち上がり / 立ち下がり時間                          | 20% ~ 80%、1kΩ ~ GND                                                                                   | 0.5  | 1.3 | 2.6 | ns |

| t <sub>SK</sub>                | 出力間スキュー                                    | OUT0_P、OUT0_N、OUT1_P、OUT1_N CMOS 出力と比較した GPIO1、GPIO2 出力スキュー。<br>GPIOx_SEL = 115<br>fout = 100kHz      |      | 7.5 | 11  | ns |

| ODC                            | 出力デューティ サイクル                               |                                                                                                       | 45   | 55  |     | %  |

| R <sub>OUT</sub>               | 出力インピーダンス                                  |                                                                                                       | 35   | 42  | 50  | Ω  |

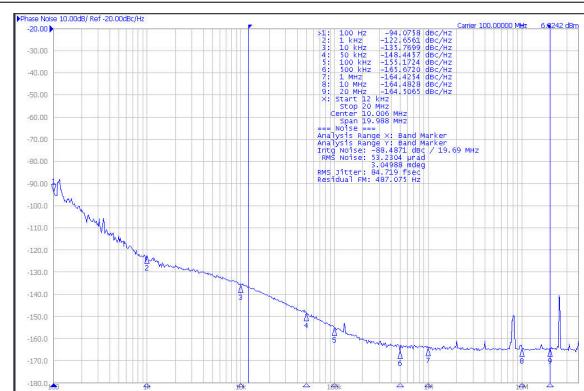

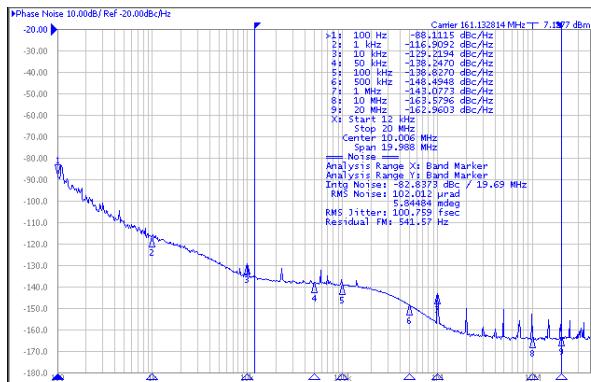

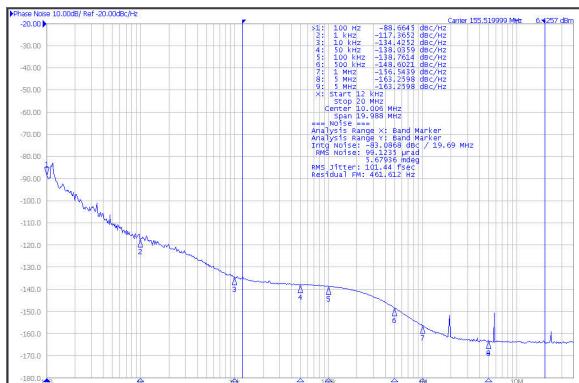

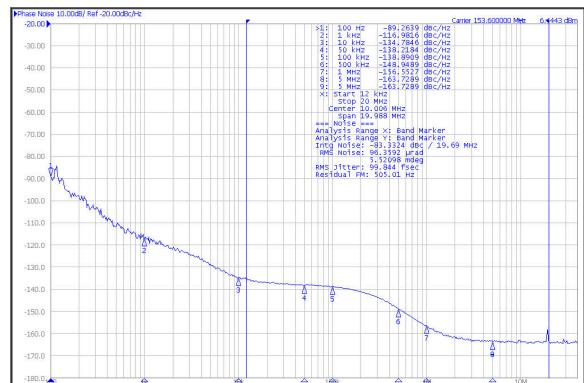

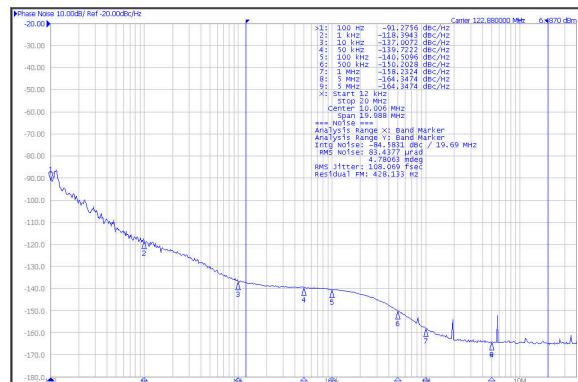

| <b>PLL 出力クロックノイズ特性</b>         |                                            |                                                                                                       |      |     |     |    |

| RJ <sub>BAW APLL</sub>         | BAW APLL 出力に対する、12kHz ~ 20MHz の積分型 RMS ジッタ | XO = 48MHz、f <sub>out</sub> = 625MHz、HSDS 出力、すべての VOD レベル、すべての出力が有効、4MHz HPF フィルタ適用 <sup>(18)</sup>   |      | 13  |     | fs |

| RJ <sub>BAW APLL</sub>         | BAW APLL 出力に対する、12kHz ~ 20MHz の積分型 RMS ジッタ | XO = 48MHz、f <sub>out</sub> = 312.5MHz、HSDS 出力 VOD ≥ 800mV、すべての出力が有効、4MHz HPF フィルタ適用 <sup>(18)</sup>  |      | 24  |     | fs |

| RJ <sub>BAW APLL</sub>         | BAW APLL 出力に対する、12kHz ~ 20MHz の積分型 RMS ジッタ | XO = 48MHz、f <sub>out</sub> = 156.25MHz、HSDS 出力 VOD ≥ 800mV、すべての出力が有効、4MHz HPF フィルタ適用 <sup>(18)</sup> |      | 30  |     | fs |

| RJ <sub>BAW APLL</sub>         | BAW APLL 出力に対する、12kHz ~ 20MHz の積分型 RMS ジッタ | XO = 48MHz、fout = 1250MHz、ポスト デバイダ P1 <sub>APLL1</sub> = 2、HSDS 出力 VOD ≥ 800mV <sup>(10)</sup>        |      |     | 45  | fs |

|                                |                                            | XO = 48MHz、fout = 625MHz、ポスト デバイダ P1 <sub>APLL1</sub> = 4、HSDS 出力 VOD ≥ 800mV <sup>(10)</sup>         |      | 35  | 50  | fs |

|                                |                                            | XO = 48MHz、fout = 500MHz、ポスト デバイダ P1 <sub>APLL1</sub> = 5、HSDS 出力 VOD ≥ 800mV <sup>(10)</sup>         |      |     | 50  | fs |

|                                |                                            | XO = 48MHz、fout = 312.5MHz、ポスト デバイダ P1 <sub>APLL1</sub> = 8、HSDS 出力 VOD ≥ 800mV <sup>(10)</sup>       |      | 42  | 60  | fs |

|                                |                                            | XO = 48MHz、fout = 156.25MHz、ポスト デバイダ P1 <sub>APLL1</sub> = 16、HSDS 出力 VOD ≥ 800mV <sup>(10)</sup>     |      | 47  | 65  | fs |

|                                |                                            | XO = 48MHz、fout = 156.25MHz、バイパス ポスト デバイダ P1 <sub>APLL1</sub> = 1、HSDS 出力 VOD ≥ 800mV <sup>(11)</sup> |      | 55  | 73  | fs |

|                                |                                            | XO = 48MHz、f <sub>out</sub> = 312.5MHz、HSDS 出力、すべての VOD レベル                                           |      | 50  | 80  | fs |

|                                |                                            | XO = 48MHz、f <sub>out</sub> = 312.5MHz、HSDS 出力、すべての VOD レベル                                           |      | 50  | 80  | fs |

|                                |                                            | XO = 48MHz、f <sub>out</sub> = 156.25MHz、HSDS 出力、すべての VOD レベル                                          |      | 60  | 90  | fs |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                      |                                         | テスト条件                                                                                                                                                                                                                                                                          | 最小値 | 標準値  | 最大値 | 単位     |

|----------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

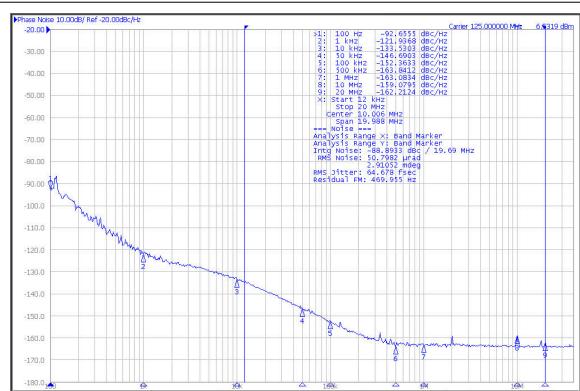

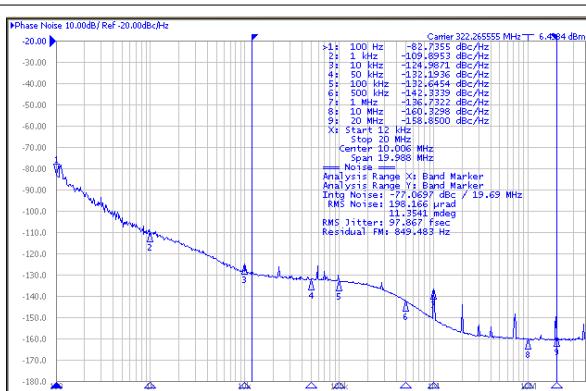

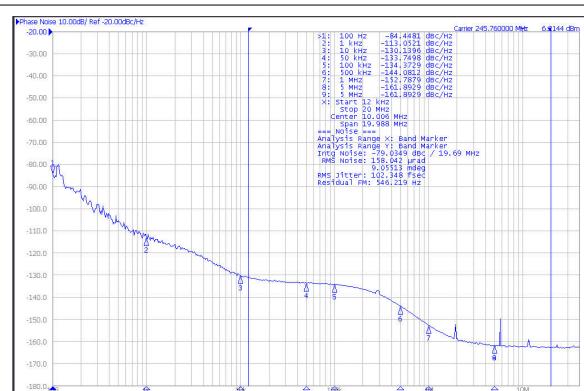

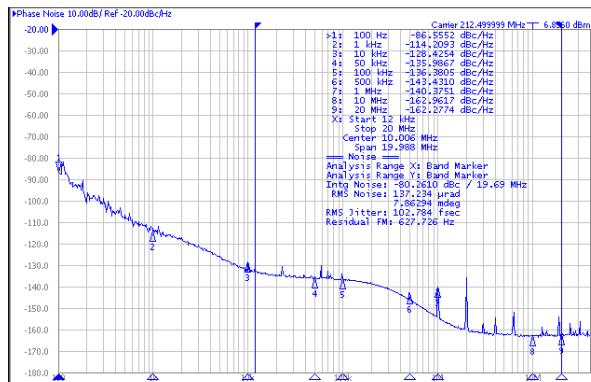

| RJ <sub>APLL2</sub>        | APLL2 出力に対する、12kHz ~ 20MHz の積分型 RMS ジッタ | XO = 48MHz, f <sub>out</sub> = 161.1328125MHz または 322.265625MHz (VCO2 = 5800.78125MHz)、または APPLL2 から 212.5MHz (VCO2 = 5950MHz)。 HSDS 出力、OUT4、OUT5、OUT6、OUT7 からの VOD ≥ 800mV。他のすべての出力バンクの BAW APPLL 出力からの 156.25MHz。                                                            |     | 110  | 150 | fs     |

|                            |                                         | XO = 48MHz, f <sub>out</sub> = 153.6MHz (VCO2 = 5836.8MHz)、155.52MHz (VCO2 = 5598.72MHz)、174.703084MHz (VCO2 = 5765.2MHz)、または 184.32MHz (VCO2 = 5898.24MHz) (APPLL2 から)。 HSDS 出力、OUT4、OUT5、OUT6、OUT7 または OUT2 および OUT3 からの VOD ≥ 800mV。他のすべての出力バンクの BAW APPLL 出力からの 156.25MHz。 |     | 110  | 150 | fs     |

|                            |                                         | XO = 48MHz, f <sub>out</sub> = 156.25MHz または 125MHz (VCO2 = 5625MHz)、または APPLL2 から 100MHz (VCO2 = 5600MHz)。 HSDS 出力、OUT4、OUT5、OUT6、OUT7 または OUT2 および OUT3 からの VOD ≥ 800mV。他のすべての出力バンクの BAW APPLL 出力からの 156.25MHz。                                                              |     | 110  | 150 | fs     |

|                            |                                         | XO = 48MHz, f <sub>out</sub> = 245.76MHz または APPLL2 から 122.88MHz (VCO2 = 5898.24MHz)。 HSDS 出力、OUT4、OUT5、OUT6、OUT7 または OUT2 および OUT3 からの VOD ≥ 800mV。他のすべての出力バンクの BAW APPLL 出力からの 156.25MHz。                                                                                    |     | 110  | 150 | fs     |

| PSNR <sub>VDDO_0_1</sub>   | 電源ノイズ除去 VDD_0_1                         | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -105 |     | dBc    |

| PSNR <sub>VDDO_2_3</sub>   | 電源ノイズ除去 VDD_2_3                         | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -105 |     | dBc    |

| PSNR <sub>VDDO_4_7</sub>   | 電源ノイズ除去 VDDO_4_7                        | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -110 |     | dBc    |

| PSNR <sub>VDDO_8_11</sub>  | 電源ノイズ除去 VDDO_8_11                       | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -110 |     | dBc    |

| PSNR <sub>VDD_XO</sub>     | 電源ノイズ除去 VDD_XO                          | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -100 |     | dBc    |

| PSNR <sub>VDD_APOLL2</sub> | 電源ノイズ除去 VDD_APOLL2                      | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -105 |     | dBc    |

| PSNR <sub>VDD_APOLL1</sub> | 電源ノイズ除去 VDD_APOLL1                      | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -105 |     | dBc    |

| PSNR <sub>VDD_DIG</sub>    | 電源ノイズ除去 VDD_DIG                         | VCC=3.3V, V <sub>N</sub> =50mVpp, HSDS、LVDS、または AC-LVPECL 出力。 <sup>(12)</sup>                                                                                                                                                                                                  |     | -120 |     | dBc    |

| <b>PCIe ジッタ特性</b>          |                                         |                                                                                                                                                                                                                                                                                |     |      |     |        |

| J <sub>PCIE-Gen1-CC</sub>  | PCIe Gen 1 (2.5 GT/s) 共通クロックのジッタ        | APLL2 または APPLL1 出力、3 倍のノイズ折りたたみ                                                                                                                                                                                                                                               |     | 0.8  | 5   | ps p-p |

| J <sub>PCIE-Gen2-CC</sub>  | PCIe Gen 2 (5.0 GT/s) 共通クロック ジッタ        | APLL2 または APPLL1 出力、3 倍のノイズ折りたたみ                                                                                                                                                                                                                                               |     | 85   | 250 | fs RMS |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                     |                                | テスト条件                                                                                                             | 最小値   | 標準値  | 最大値    | 単位 |

|---------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|------|--------|----|

| J <sub>PCIe-Gen3-CC</sub> | PCIe Gen 3 (8 GT/s) 共通クロックジッタ  | APLL2 または APLL1 出力、3 倍のノイズ折りたたみ                                                                                   | 25    | 100  | fs RMS |    |

| J <sub>PCIe-Gen4-CC</sub> | PCIe Gen 4 (16 GT/s) 共通クロックジッタ | APLL2 または APLL1 出力、3 倍のノイズ折りたたみ                                                                                   | 25    | 100  | fs RMS |    |

| J <sub>PCIe-Gen5-CC</sub> | PCIe Gen 5 (64 GT/s) 共通クロックジッタ | APLL2 または APLL1 出力、3 倍のノイズ折りたたみ                                                                                   | 9     | 50   | fs RMS |    |

| J <sub>PCIe-Gen6-CC</sub> | PCIe Gen 6 (32 GT/s) 共通クロックジッタ | APLL2 または APLL1 出力、3 倍のノイズ折りたたみ                                                                                   | 6     | 40   | fs RMS |    |

| <b>DPLL の特性</b>           |                                |                                                                                                                   |       |      |        |    |

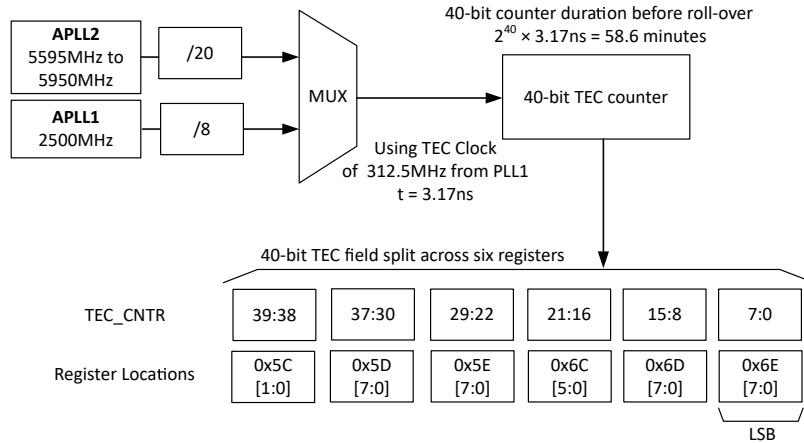

| f <sub>TDC</sub>          | DPLLx の TDC レート範囲              |                                                                                                                   | 1E-6  | 26   | MHz    |    |

| dφ/dt                     | スイッチオーバー中の位相スルーブ               | プログラマブルな範囲                                                                                                        | 695   |      | ns/s   |    |

| DPLL-BW                   | DPLL ループ帯域幅                    | プログラム可能なループ帯域幅 <sup>(17)</sup>                                                                                    | 1E-3  | 4000 | Hz     |    |

| J <sub>PK</sub>           | DPLL 閉ループ ジッタのピーク              |                                                                                                                   | 0.1   |      | dB     |    |

| J <sub>TOL</sub>          | ジッタの許容範囲                       | G.8262 Options 1 と 2 に準拠。ジッタ変調 = 10Hz, 25.78152Gbps ラインレート                                                        | 6455  |      | UI p-p |    |

| <b>DCO の特性</b>            |                                |                                                                                                                   |       |      |        |    |

| f <sub>DCO-DPLL</sub>     | DCO DCO の周波数チューニング範囲           | DPLLx                                                                                                             | -200  | 200  | ppm    |    |

| f <sub>DCO-APLL</sub>     | DCO 周波数のチューニング範囲               | ホールドオーバー状態の BAW APLL または APLL のみの動作。                                                                              | -200  | 200  | ppm    |    |

|                           |                                | APLL2、は、ホールドオーバー状態または APLL 単独動作モードでも動作可能。                                                                         | -1000 | 1000 | ppm    |    |

| <b>ゼロ遅延モード (ZDM) 特性</b>   |                                |                                                                                                                   |       |      |        |    |

| f <sub>OUT-ZDM</sub>      | ZDM を有効にした場合の出力周波数範囲           | DPLL1:OUT0 または OUT10                                                                                              | 1E-6  | 1250 | MHz    |    |

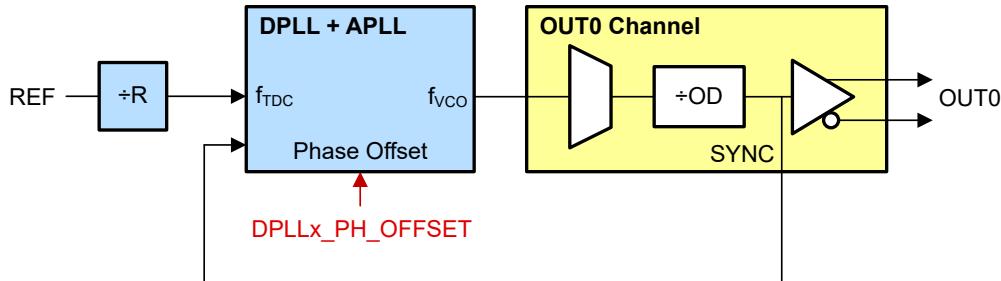

| t <sub>DLY-ZDM</sub>      | ZDM を有効にした場合の入力から出力への伝播遅延      | OUT0, f <sub>IN</sub> ≤ f <sub>TDC_MAX</sub> , f <sub>OUT</sub> ≤ f <sub>TDC_MAX</sub> , DPLLx_PH_OFFSET = 172500 | 150   |      | ps     |    |

| t <sub>DLY-VAR-ZDM</sub>  | ZDM を有効にした場合の入力から出力への伝播遅延の変化   | OUT0, f <sub>IN</sub> ≤ f <sub>TDC_MAX</sub> , f <sub>OUT</sub> ≤ f <sub>TDC_MAX</sub> , DPLLx_PH_OFFSET = 0      | 65    |      | ±ps    |    |

| <b>1PPS れふえレンズ特性</b>      |                                |                                                                                                                   |       |      |        |    |

| t <sub>DPLL_FL</sub>      | 1PPS リファレンスによる DPLL 周波数ロック時間   | XO = 48Mhz、初期誤差 = ±25pb、-180° ≤ Θ ≤ 180°。DPLL LBW = 10MHz、周波数ロック Δf <sub>out</sub> ≤ ±4.6ppm                      | 5     | 6    | s      |    |

| t <sub>DPLL_PL</sub>      | 1PPS リファレンスによる DPLL フェーズのロック時間 | XO = 48Mhz、初期誤差 = ±25pb、-180° ≤ Θ ≤ 180°。DPLL LBW = 10MHz、DPLL LBW = 10Mhz、フェーズロック ≤ ±100ns                       | 34    | 38   | s      |    |

| <b>ピットレス スイッチング特性</b>     |                                |                                                                                                                   |       |      |        |    |

| t <sub>HIT</sub>          | スイッチオーバー中の位相遷移                 | INx = 1Hz, INy = 1Hz、周波数はロック。INx と INy の相対位相オフセット- 180° ≤ Θ ≤ 180°。DPLL LBW = 10MHz。                              | 4     |      | ± ps   |    |

|                           |                                | INx = 8kHz, INy = 8kHz、周波数はロック。INx と INy の相対位相オフセット- 180° ≤ Θ ≤ 180°。DPLL LBW = 1Hz                               | 19    |      | ± ps   |    |

|                           |                                | Nx = 25MHz, INy = 25MHz、周波数はロックされています。INx と INy の相対位相オフセット- 180° ≤ Θ ≤ 180°。DPLL LBW = 1Hz                        | 1.8   |      | ± ps   |    |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ               |                                | テスト条件                                                                                                                                                 | 最小値                     | 標準値   | 最大値 | 単位        |

|---------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|-----|-----------|

| $f_{HIT}$           | スイッチオーバー中の周波数遷移                | INx = 1Hz, INy = 1Hz、周波数はロック。<br>INx と INy の相対位相オフセット-<br>$180^\circ \leq \Theta \leq 180^\circ$ 。DPLL LBW = 10mHz                                    |                         | 0.85  |     | $\pm ppb$ |

|                     |                                | INx = 8kHz, INy = 8kHz、周波数はロック。<br>INx と INy の相対位相オフセット-<br>$180^\circ \leq \Theta \leq 180^\circ$ 。DPLL LBW = 1Hz                                    |                         | 0.45  |     | $\pm ppb$ |

|                     |                                | INx = 25MHz, INy = 25MHz、周波数は<br>ロック。INx と INy の相対位相オフセット-<br>$180^\circ \leq \Theta \leq 180^\circ$ 。DPLL LBW = 1Hz                                  |                         | 0.63  |     | $\pm ppb$ |

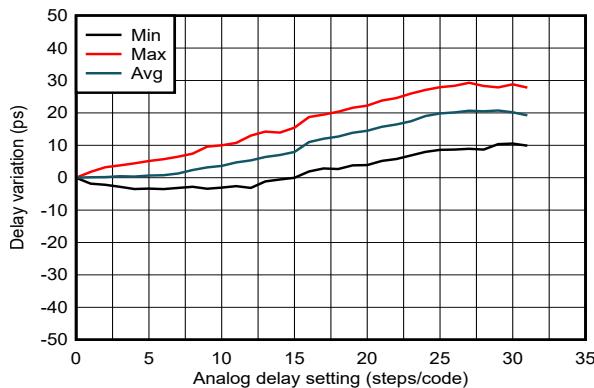

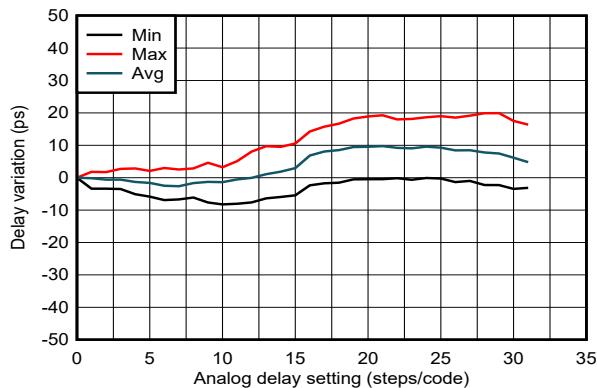

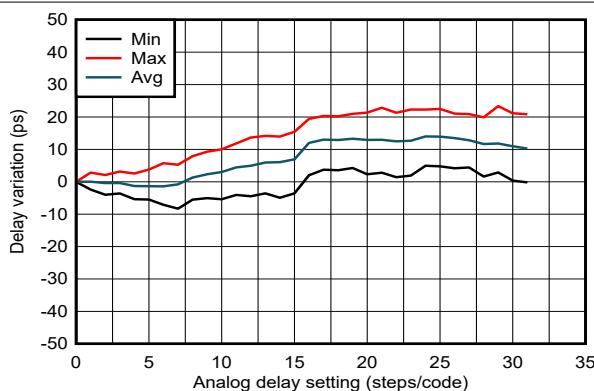

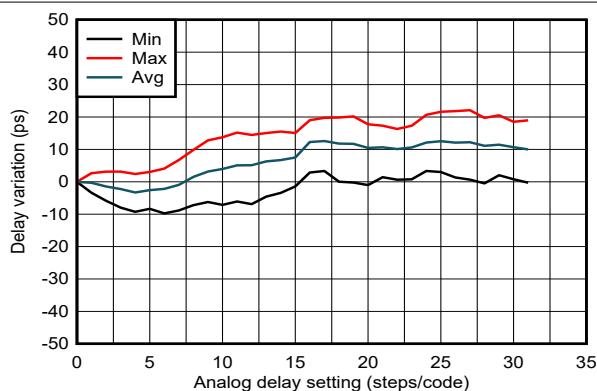

| プログラム可能出力遅延特性       |                                |                                                                                                                                                       |                         |       |     |           |

| $t_{ANA-DLY}$       | アナログ遅延のステップサイズ <sup>(14)</sup> | BAW APLL = 2500.0MHz VCO ポスト デバイダ = 2, 0.5x 範囲スケール、1Hz ≤ OUTx ≤ 156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 2                                            |                         | 12.9  |     | ps        |

|                     |                                | BAW APLL = 2500.0MHz、VCO ポスト<br>デバイダ = 1, 2x 範囲スケール、1Hz ≤<br>OUTx ≤ 156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 5                                        |                         | 25.8  |     | ps        |

|                     |                                | APLL2 = 5625.0MHz、VCO ポスト デバ<br>イダ = 3, 1x 範囲スケール、1Hz ≤ OUTx<br>≤ 156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 3                                          |                         | 17.2  |     | ps        |

|                     |                                | APLL2 = 5625.0MHz、VCO ポスト デバ<br>イダ = 4, 1x 範囲; 1Hz ≤ OUTx ≤<br>156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 4                                             |                         | 22.9  |     | ps        |

| $t_{ANA-DLY-ERR}$   | アナログ遅延ステップサイズ誤差                | BAW APLL = 2500.0MHz、VCO ポスト<br>デバイダ = 2, 0.5x 範囲スケール、1Hz ≤<br>OUTx ≤ 156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 2                                      | -6.5                    | 6.5   |     | ps        |

|                     |                                | BAW APLL = 2500.0MHz、VCO ポスト<br>デバイダ = 1, 2x 範囲スケール、1Hz ≤<br>OUTx ≤ 156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 5                                        | -12.9                   | 12.9  |     | ps        |

|                     |                                | APLL2 = 5625.0MHz、VCO ポスト デバ<br>イダ = 3, 1x 範囲スケール、1Hz ≤ OUTx<br>≤ 156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 3                                          | -8.6                    | 8.6   |     | ps        |

|                     |                                | APLL2 = 5625.0MHz、VCO ポスト デバ<br>イダ = 4, 1x 範囲; 1Hz ≤ OUTx ≤<br>156.25MHz,<br>ANA_DELAY_LINEARITY_CODE = 4                                             | -11.45                  | 11.45 |     | ps        |

| $t_{ANA-DLY-RANGE}$ | アナログ遅延範囲                       |                                                                                                                                                       | $31 \times t_{ANA-DLY}$ |       |     | ps        |

| $t_{ANA-DLY-ACC}$   | アナログ遅延の精度                      | アナログ遅延範囲全体にわたる任意設定<br>$N = 0 \sim 31$ のアナログ遅延の絶対精度。<br>期待値に対する実際の値の最悪ケースの<br>誤差 $N \times t_{ANA-DLY-STEP}$ for<br>ANA_DELAY_LINEARITY_CODE = 3, 4, 5 | -25                     | 25    |     | ps        |

| $t_{ANA-DLY-LIN}$   | アナログ遅延の直線性 <sup>(15)</sup>     | ANA_DELAY_LINEARITY_CODE = 2                                                                                                                          | 333                     | 450   |     | ps        |

|                     |                                | ANA_DELAY_LINEARITY_CODE = 3                                                                                                                          | 450                     | 600   |     | ps        |

|                     |                                | ANA_DELAY_LINEARITY_CODE = 4                                                                                                                          | 600                     | 750   |     | ps        |

|                     |                                | ANA_DELAY_LINEARITY_CODE = 5                                                                                                                          | 750                     | 1050  |     | ps        |

推奨動作条件範囲内 (特に記述のない限り)

| パラメータ                                                                      |                                                                 | テスト条件                                 | 最小値 | 標準値  | 最大値 | 単位  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|-----|------|-----|-----|

| $t_{DIG-DLY}$                                                              | デジタル遅延のステップサイズ                                                  | VCO ポスト デバイダ周波数出力 = 2500MHz、ハーフステップ設定 |     | 200  |     | ps  |

|                                                                            |                                                                 | VCO ポスト デバイダ周波数出力 = 1250MHz、フルステップ設定  |     | 800  |     | ps  |

| <b>3 レベル ロジック入力特性 (GPIO0, GPIO1, GPIO2, SCS_ADD)</b>                       |                                                                 |                                       |     |      |     |     |

| $V_{IH}$                                                                   | 入力 High 電圧                                                      |                                       | 1.4 |      |     | V   |

| $V_{IM}$                                                                   | 入力 MID 電圧                                                       |                                       | 0.6 | 0.95 |     | V   |

| $V_{IL}$                                                                   | 入力 MID 電圧自己バイアス                                                 | 内部バイアスと PD# が Low にプルされた入力フローティング     | 0.7 | 0.9  |     | V   |

| $R_{IM-PD}$                                                                | MID レベルの自己バイアス用の内部プルダウン抵抗 <sup>(16)</sup>                       |                                       | 145 | 163  | 180 | kΩ  |

| $R_{IM-PU}$                                                                | 中間レベルの自己バイアス用の内部プルアップ <sup>(16)</sup>                           |                                       | 470 | 526  | 580 | kΩ  |

| $V_{IL}$                                                                   | 入力 Low 電圧                                                       |                                       |     | 0.4  |     | V   |

| $I_{IH}$                                                                   | 入力 High 電流                                                      | $V_{IH} = VDD$                        | -40 | 40   |     | μA  |

| $I_{IL}$                                                                   | 入力 Low 電流                                                       | $V_{IL} = GND$                        | -40 | 40   |     | μA  |

| $C_{IN}$                                                                   | 入力容量                                                            |                                       |     | 2    |     | pF  |

| <b>2 レベルロジック入力特性 (PD#, SCK, SDIO, SCS_ADD, 電源投入後の GPIO0, GPIO1, GPIO2)</b> |                                                                 |                                       |     |      |     |     |

| $V_{IH}$                                                                   | 入力 High 電圧                                                      |                                       | 1.2 |      |     | V   |

| $V_{IL}$                                                                   | 入力 Low 電圧                                                       |                                       |     | 0.4  |     | V   |

| $I_{IH}$                                                                   | 入力 High 電流                                                      | $V_{IH} = VDD$ (PD# を除く)              | -40 | 40   |     | μA  |

| $I_{IL}$                                                                   | 入力 Low 電流                                                       | $V_{IL} = GND$ (PD# を除く)              | -40 | 40   |     | μA  |

| $I_{IH}$                                                                   | 入力 High 電流                                                      | $V_{IH} = VDD$ 、PD# (内部 200kΩ プルアップ)  | -57 | 24   |     | μA  |

| $I_{IL}$                                                                   | 入力 Low 電流                                                       | $V_{IL} = GND$ 、PD# (内部 200kΩ プルアップ)  | -57 | 24   |     | μA  |

| $t_{WIDTH}$                                                                | GPIO SYNC、SYSREF 要求、TEC トリガ、DPLL 入力選択、FDEV トリガ、FDEV_dir の入力パルス幅 | モノトニック エッジ                            | 200 |      |     | ns  |

| $C_{IN}$                                                                   | 入力容量                                                            |                                       |     | 2    |     | pF  |

| <b>ロジック出力特性 (GPIO0, GPIO1, GPIO2, SDIO)</b>                                |                                                                 |                                       |     |      |     |     |

| $V_{OH}$                                                                   | 出力 HIGH 電圧                                                      | $I_{OH} = 1mA$                        | 2.4 |      |     | V   |

| $V_{OL}$                                                                   | 出力 LOW 電圧                                                       | $I_{OL} = 1mA$                        |     | 0.4  |     | V   |

| $t_R/t_F$                                                                  | 出力立ち上がり / 立ち下がり時間                                               | 20% ~ 80%、LVC MOS モード、1kΩ から GND へ    |     | 500  |     | ps  |

| <b>オープンドレイン出力 (GPIO0, GPIO1, GPIO2, SDA)</b>                               |                                                                 |                                       |     |      |     |     |

| $V_{OL}$                                                                   | 出力 Low レベル                                                      | $I_{OL} = 3mA$                        |     | 0.3  |     | V   |

|                                                                            |                                                                 | $I_{OL} = 6mA$                        |     | 0.6  |     | V   |

| $I_{OH}$                                                                   | 出力リーコンデンサー電流                                                    |                                       | -15 | 15   |     | μA  |

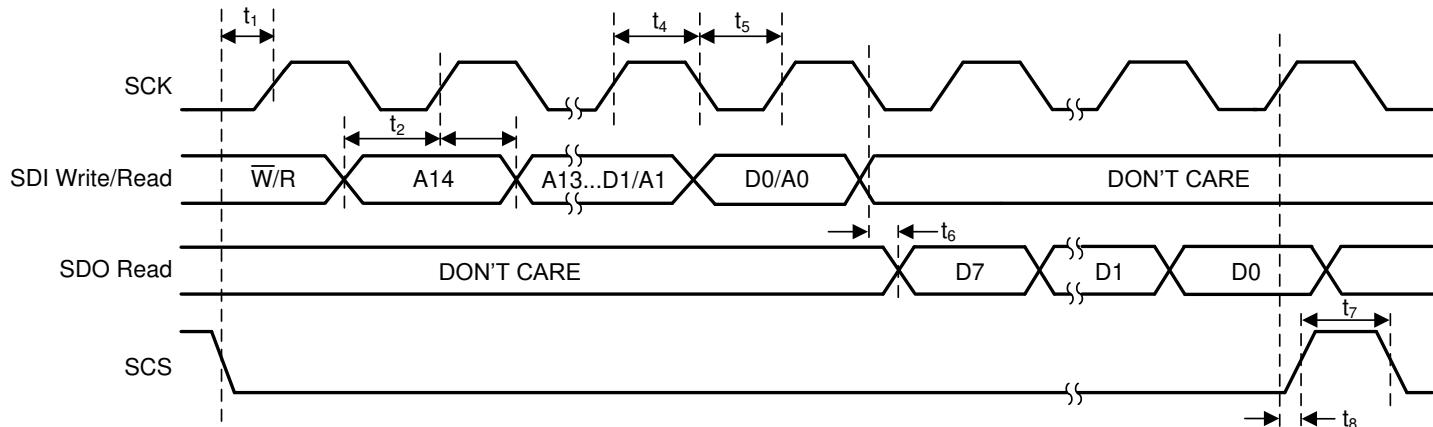

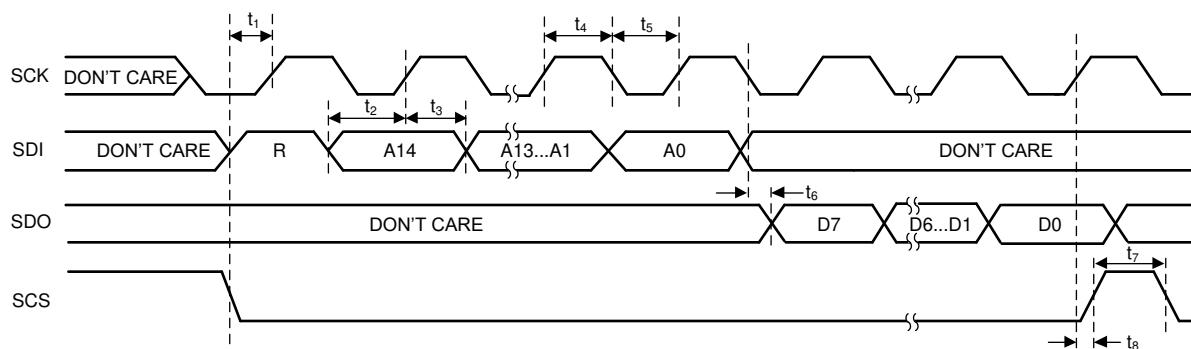

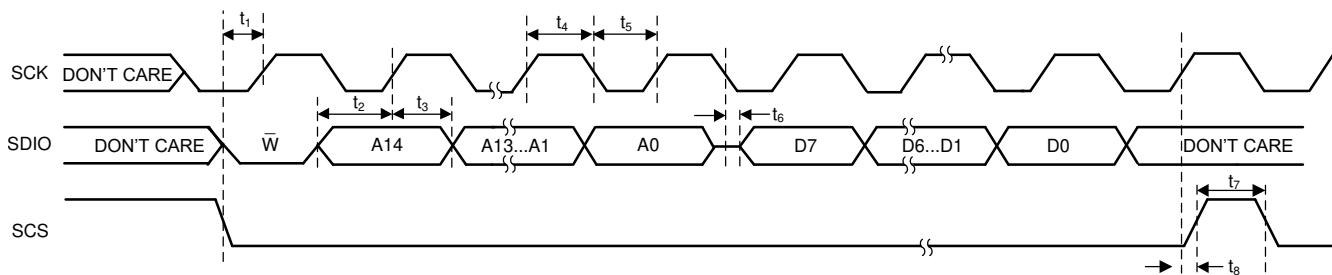

| <b>SPI タイミング要件 (SDIO, SCK, SCS_ADD)</b>                                    |                                                                 |                                       |     |      |     |     |

| $f_{SCK}$                                                                  | SPI クロック レート                                                    |                                       |     | 20   |     | MHz |

|                                                                            | SPI クロック レート、SRAM の読み取りおよび書き込み動作中                               |                                       |     | 5    | 10  | MHz |

| $t_1$                                                                      | SCS から SCK までのセットアップ時間 (通信サイクル開始)                               |                                       |     | 10   |     | ns  |

## 推奨動作条件範囲内 (特に記述のない限り)

| パラメータ |                                   | テスト条件 | 最小値 | 標準値 | 最大値 | 単位 |

|-------|-----------------------------------|-------|-----|-----|-----|----|

| $t_2$ | SDI から SCK までのセットアップ時間            |       | 10  |     |     | ns |

| $t_3$ | SDI から SCK までのホールド時間              |       | 10  |     |     | ns |

| $t_4$ | SCK High 時間                       |       | 25  |     |     | ns |

| $t_5$ | SCK Low 時間                        |       | 25  |     |     | ns |

| $t_6$ | SCK から SDO への有効なリードバック データ        |       |     | 20  |     | ns |

| $t_7$ | SCS パルス幅                          |       | 20  |     |     | ns |

| $t_8$ | SCK から SCS までのセットアップ時間 (通信サイクル終了) |       | 10  |     |     | ns |

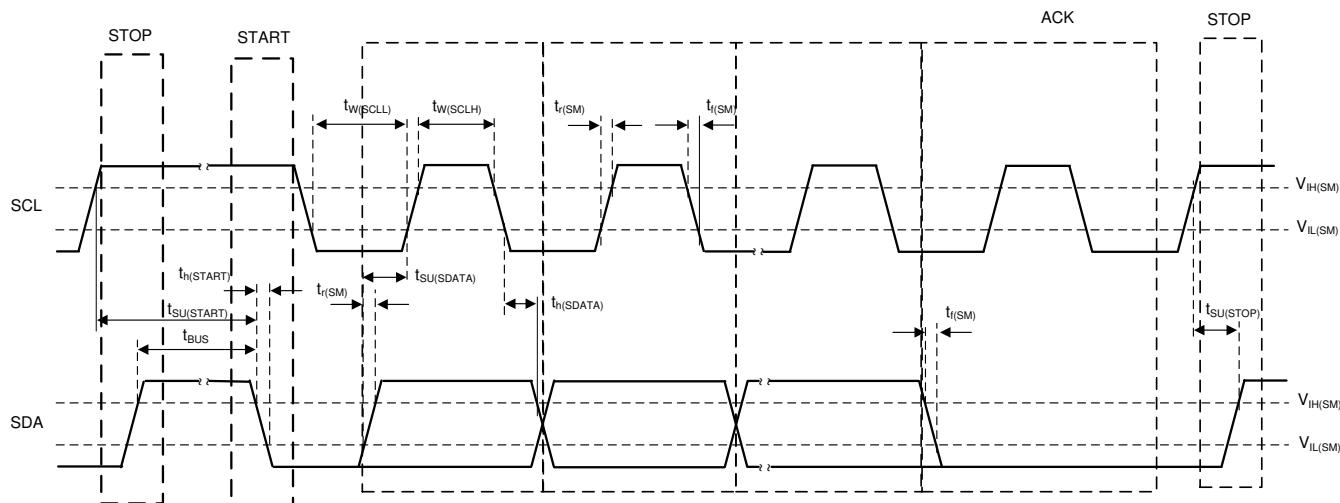

**I<sup>2</sup>C タイミング要件 (SDA、SCL)**

|                 |                       |                                 |     |     |         |

|-----------------|-----------------------|---------------------------------|-----|-----|---------|

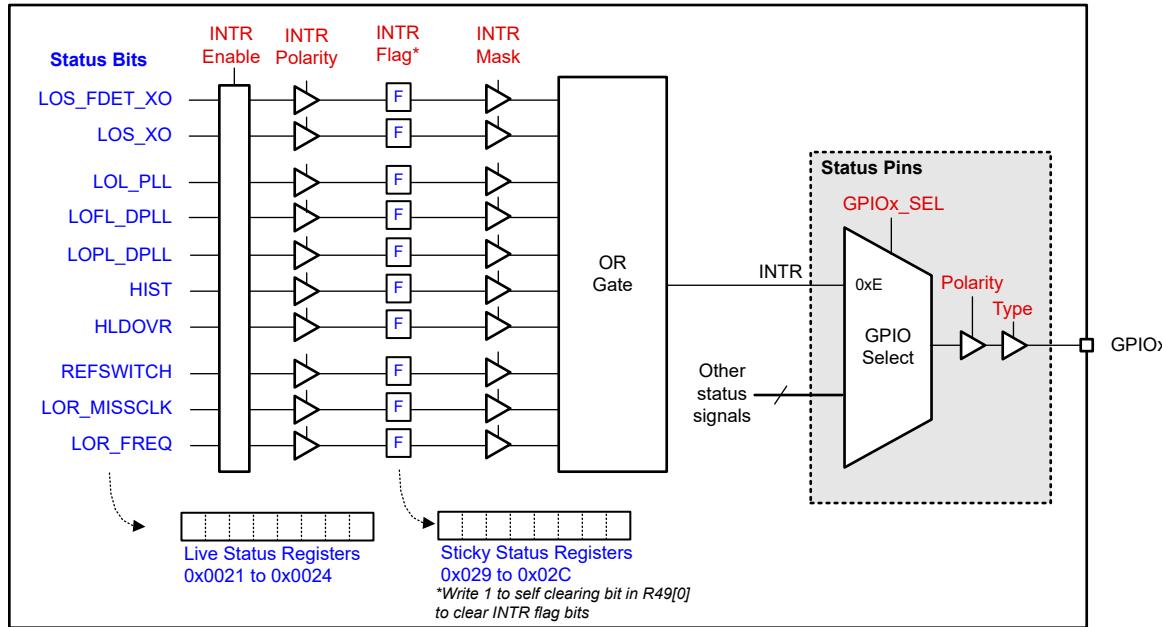

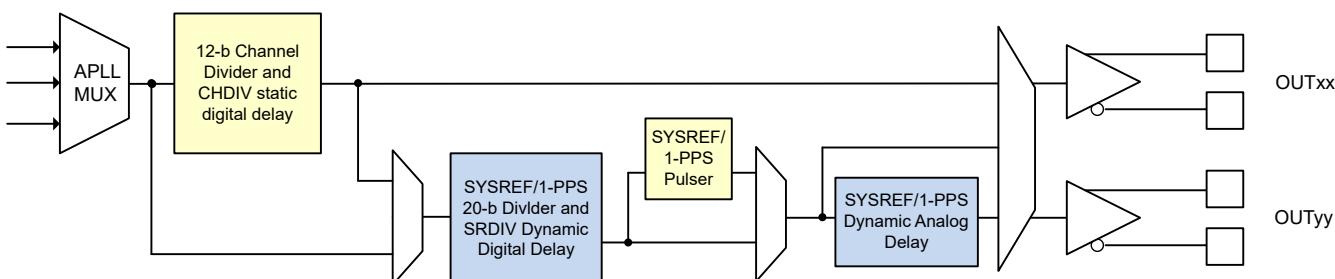

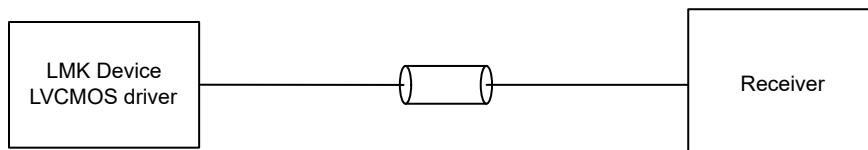

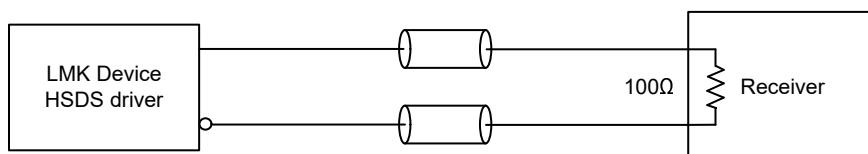

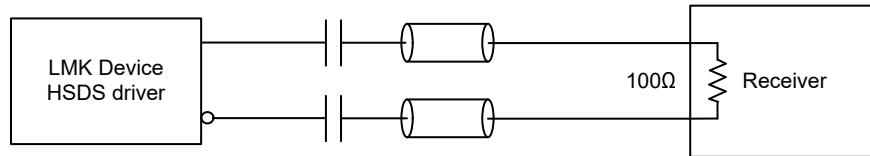

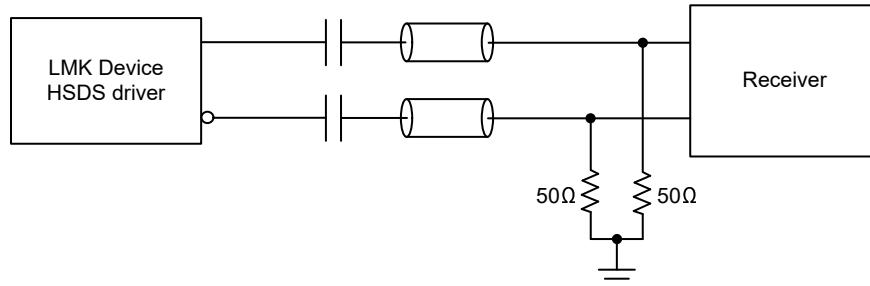

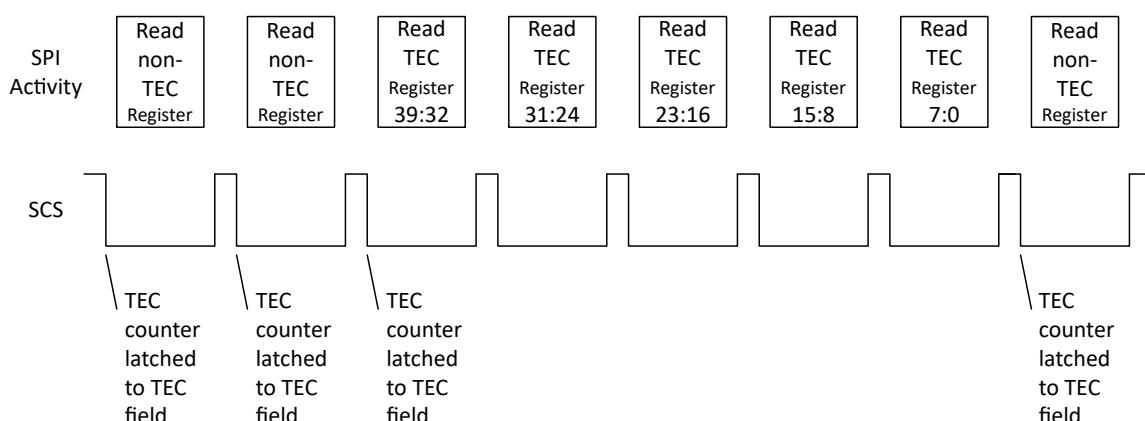

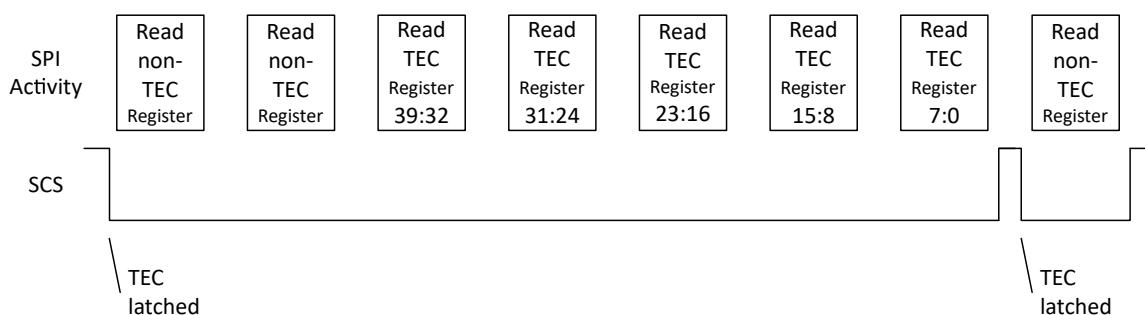

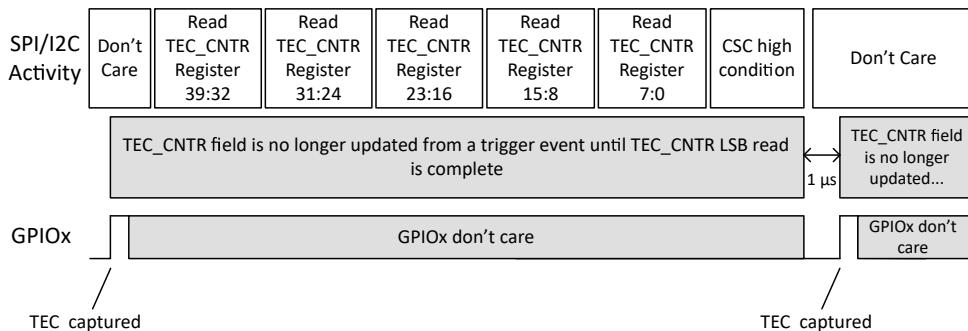

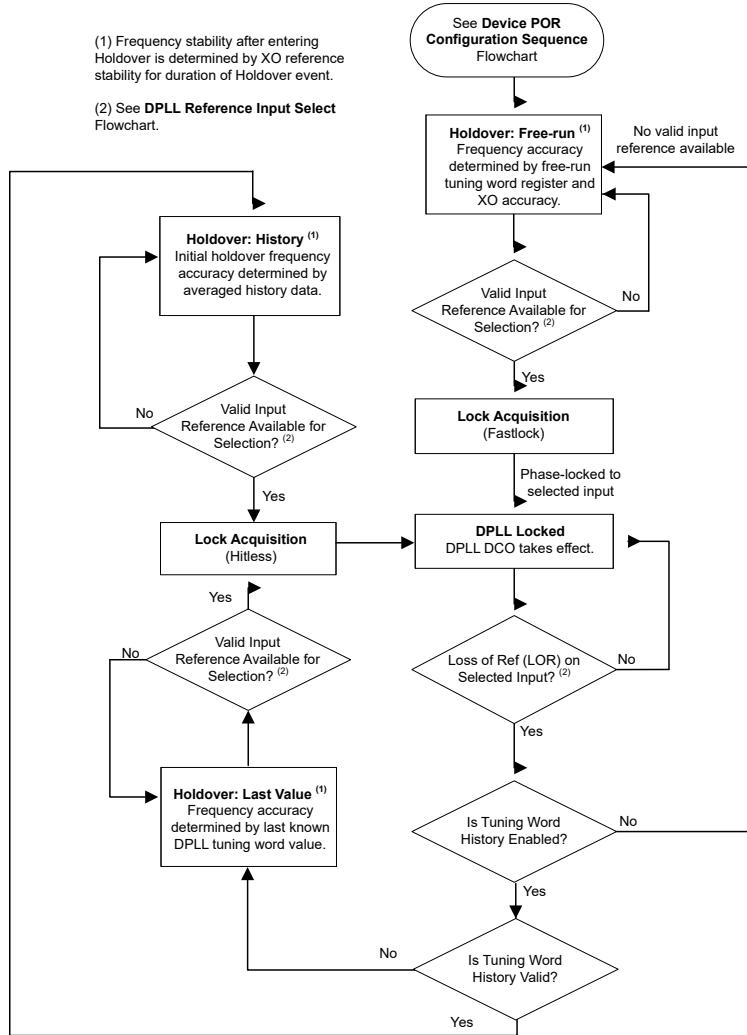

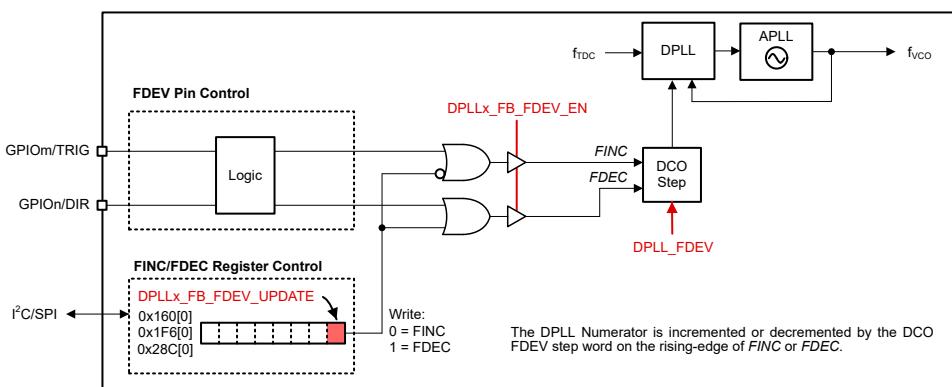

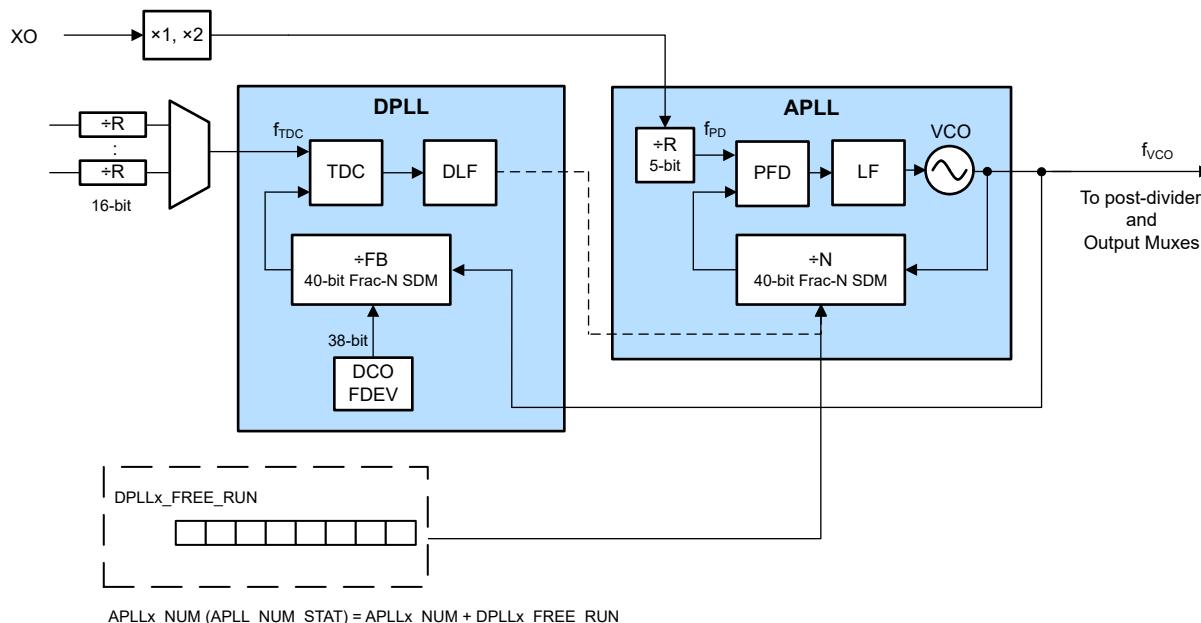

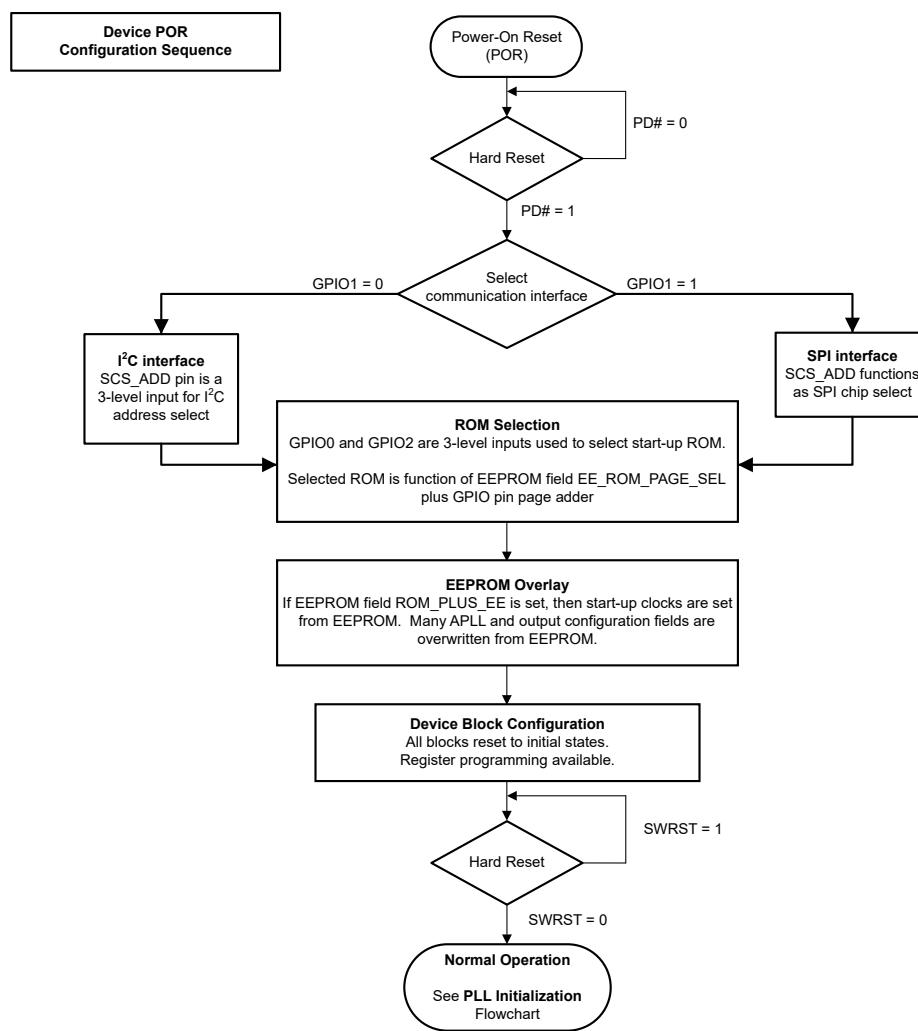

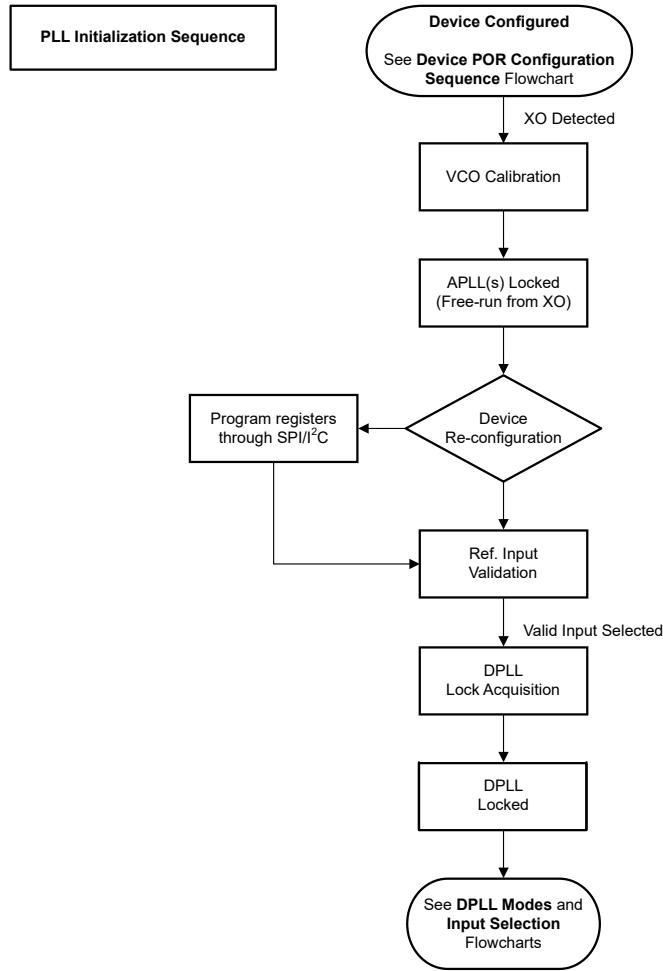

| $V_{IH}$        | 入力 High 電圧            |                                 | 1.2 |     | V       |